3D (three-dimensional) NAND memory and manufacturing method thereof

A manufacturing method and memory technology, applied in the field of semiconductors, can solve the problems of difficult through-holes, long signal transmission paths, unstable signal transmission, etc., and achieve the effects of reducing parasitic parameters, strengthening control capabilities, and increasing cut-off frequency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] In order to make the above objects, features and advantages of the present invention more comprehensible, specific implementations of the present invention will be described in detail below in conjunction with the accompanying drawings.

[0046] In the following description, numerous specific details are set forth in order to provide a thorough understanding of the present invention. However, the present invention can be implemented in many other ways different from those described here, and those skilled in the art can make similar extensions without violating the connotation of the present invention, so the present invention is not limited by the specific implementations disclosed below.

[0047] Circuit structure of 3D NAND memory

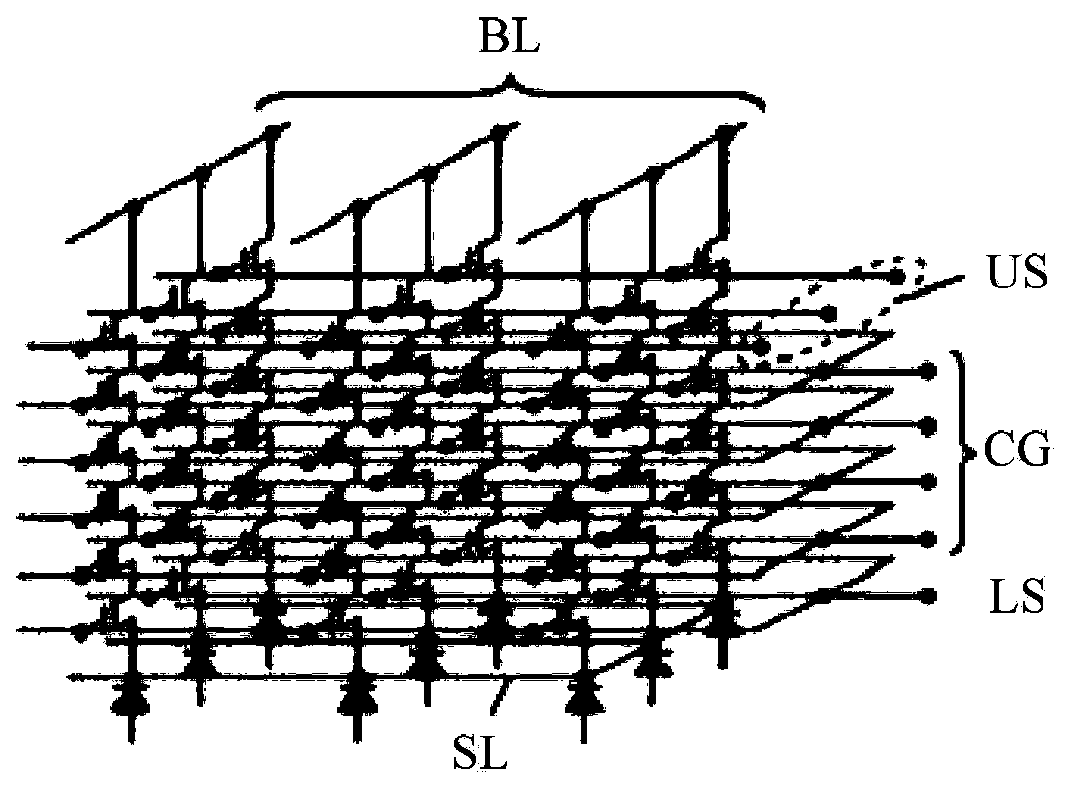

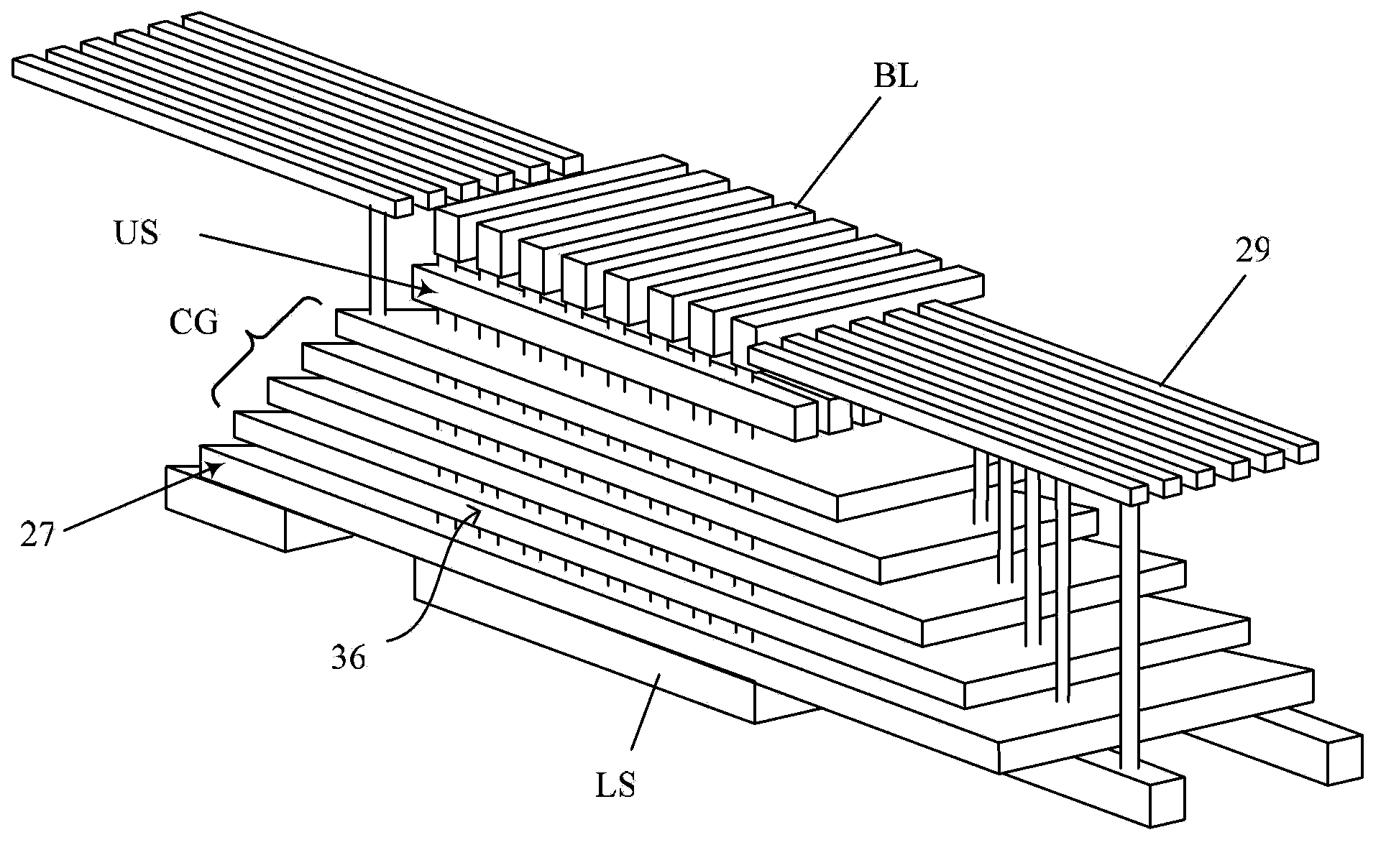

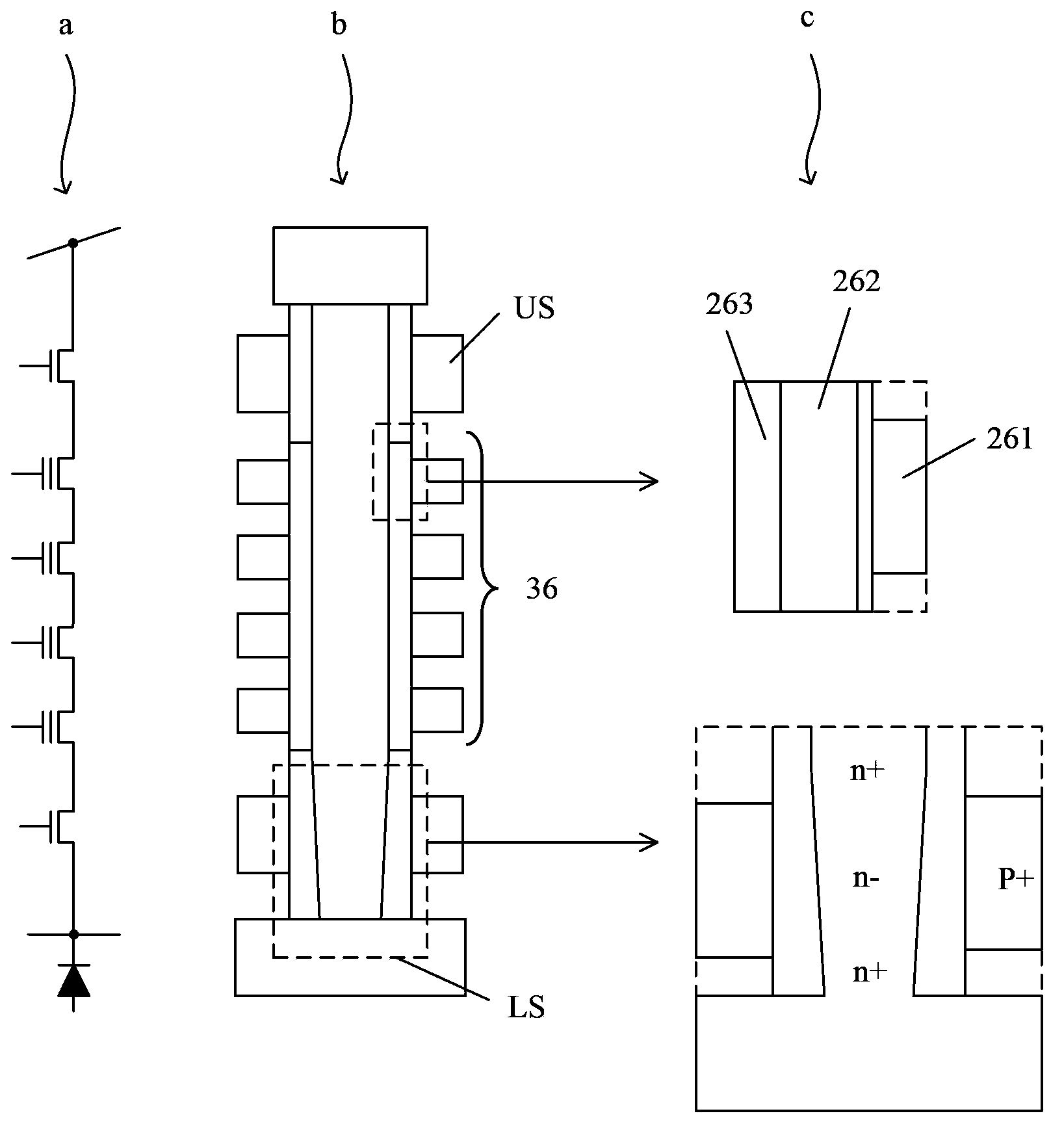

[0048] Such as Figure 7 Shown is a schematic circuit diagram of an embodiment of the 3D NAND memory of the present invention. The 3D NAND memory of the present invention retains the original memory array (Memory anay) of the 3D NAND ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More