Symmetric integrated stacked transformer

An integrated layer and transformer technology, applied in the direction of electric solid-state devices, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problems of induction coil asymmetry, low resonance frequency, large parasitic capacitance and parasitic resistance, etc., to achieve gain and bandwidth The effect of improving and improving the quality factor and high magnetic induction coefficient

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] In order to deepen the understanding of the present invention, the present invention will be described in further detail below in conjunction with the examples and accompanying drawings. The examples are only used to explain the present invention, and do not constitute regulations on the protection scope of the present invention.

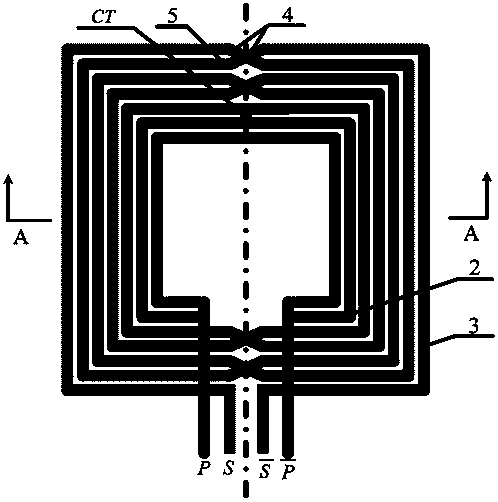

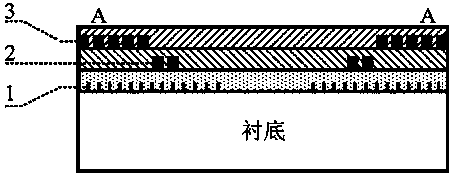

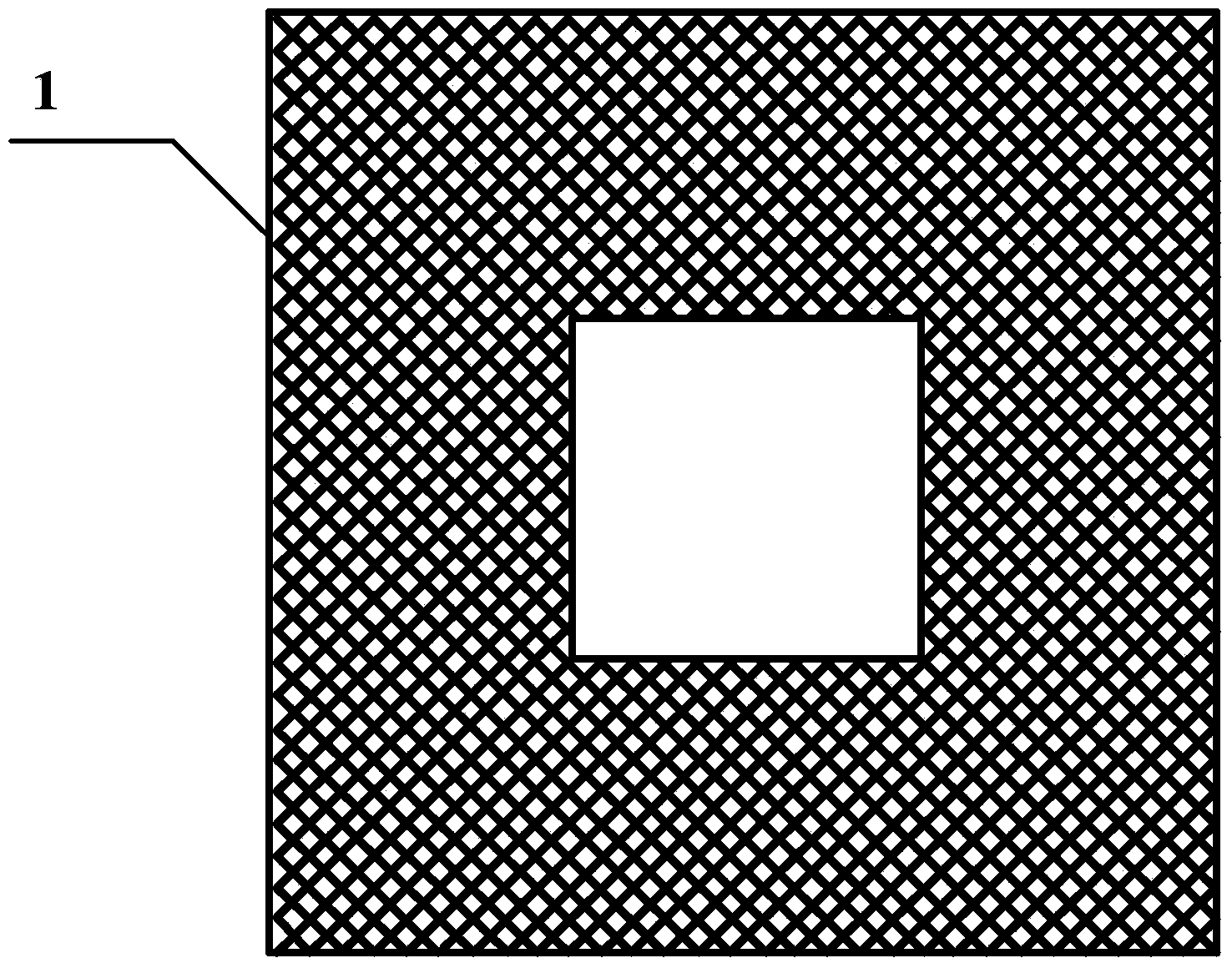

[0025] Such as figure 1 , figure 2 with image 3 As shown, a symmetrical integrated laminated transformer consists of a substrate, the first to third layers of dielectrics arranged on the substrate from bottom to top, and the shield grid 1 and the second layer respectively placed in the first layer of dielectric The primary coil 2 in the layer medium and the secondary coil 3 in the third layer medium. Wherein, the substrate is 100 μm gallium arsenide GaAs, and three layers of dielectrics are arranged on the substrate, wherein the first layer of dielectrics is silicon tetranitride Si 3 N 4 , the second dielectric layer is silicon dioxide ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More