Field-effect transistor and manufacturing method thereof

A technology for field effect transistors and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., and can solve the problems of increasing parasitic parameters of parasitic capacitance and affecting MOSFET performance and reliability, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

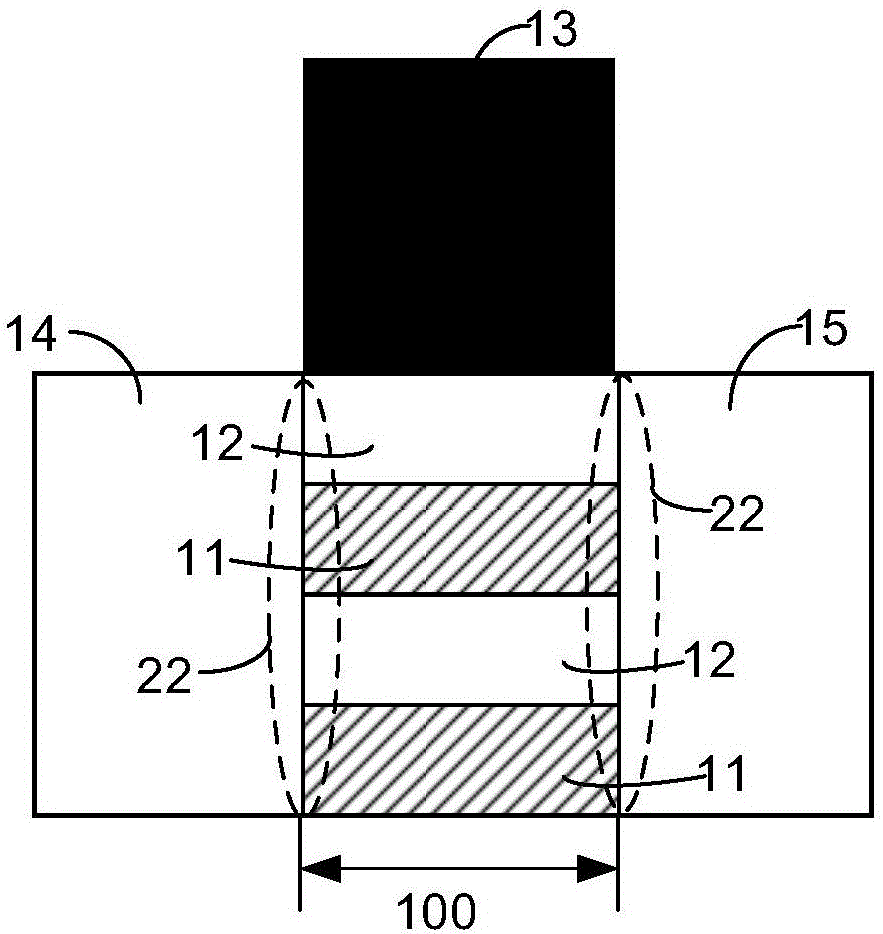

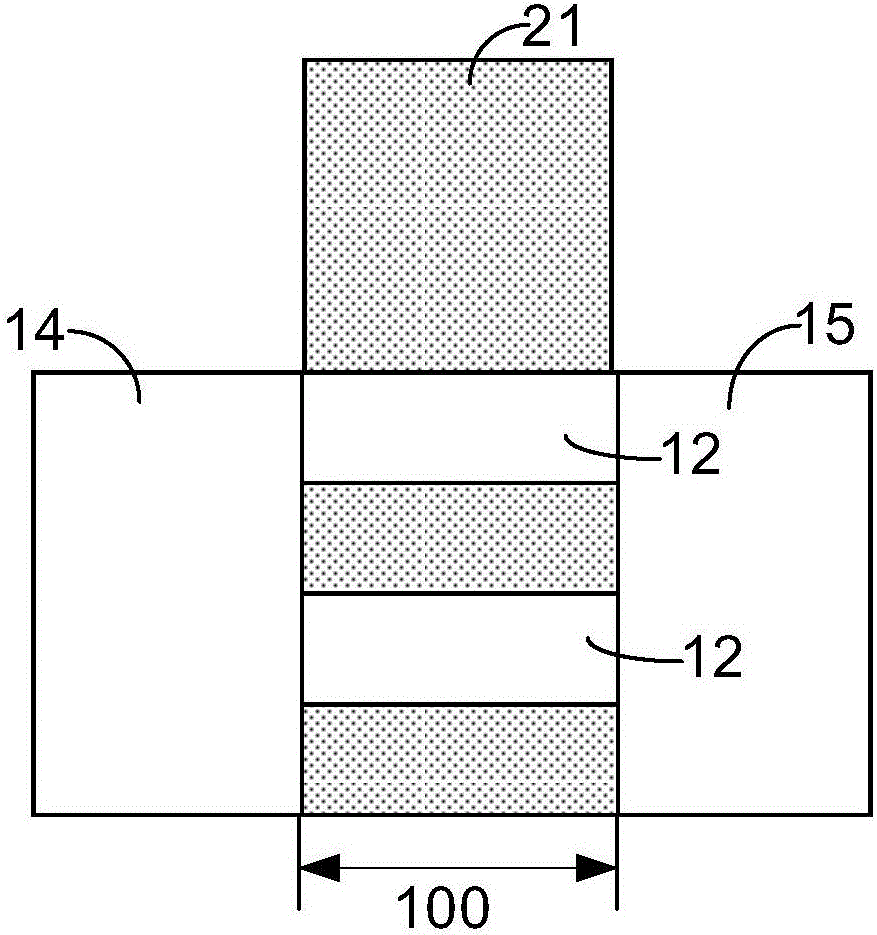

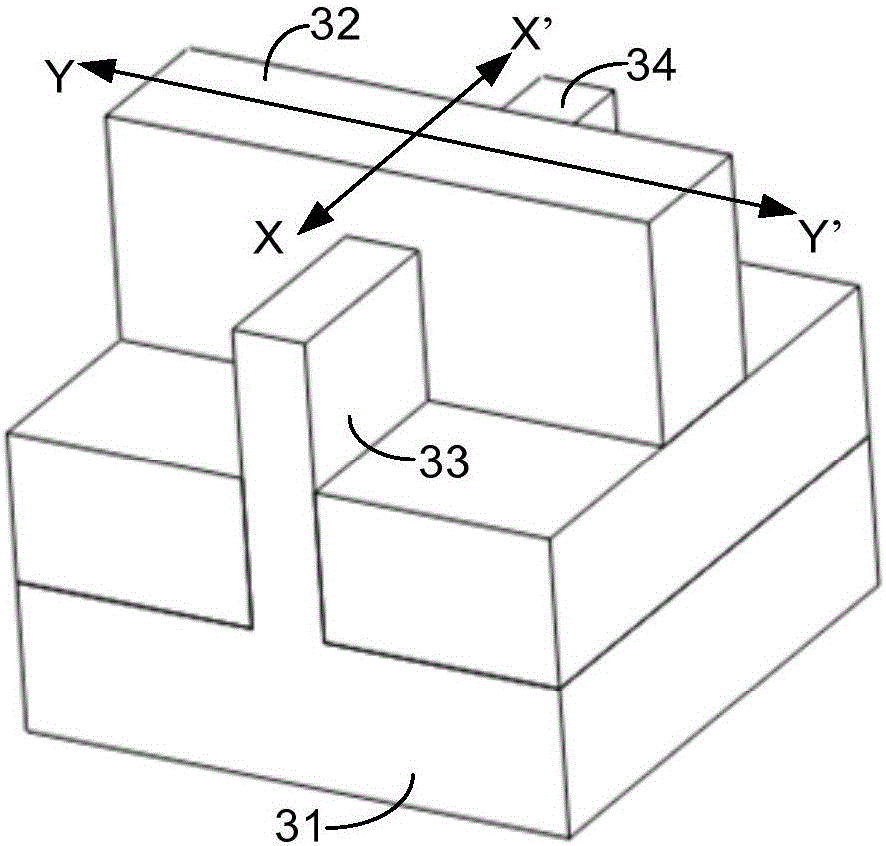

[0036] The technical solutions in the embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some of the embodiments of the present invention, not all of them.

[0037] An embodiment of the present invention provides a field-effect transistor, which can be a MOSFET, for example, a stacked gate-all-around nanowire transistor (Stacked Gate-All-Around Nanowire Transistor), a fin field-effect transistor (Fin Field-Effect Transistor) , FinFET), etc., may also be a tunneling field effect transistor (TFET, Tunneling Field Effect Transistor), etc., which is not limited in this embodiment of the present invention.

[0038] In addition, in order to provide a field effect transistor and its manufacturing method for the convenience of explaining the embodiments of the present invention, firstly, each cross-sectional direction of the field ...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More