Novel lamination structure of multilayer high-speed PCB and signal via-hole optimization method

A stacked structure, signal via technology, applied in the reduction of crosstalk/noise/electromagnetic interference (, circuit devices, conductive pattern layout details, etc., can solve the problem of signal via impedance discontinuity, etc., to achieve good service product design , The effect of improving SI performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0032] The invention provides a novel multi-layer high-speed PCB laminate design and proposes a multi-layer high-speed PCB signal via optimization method with wide applicability on the basis of the laminate.

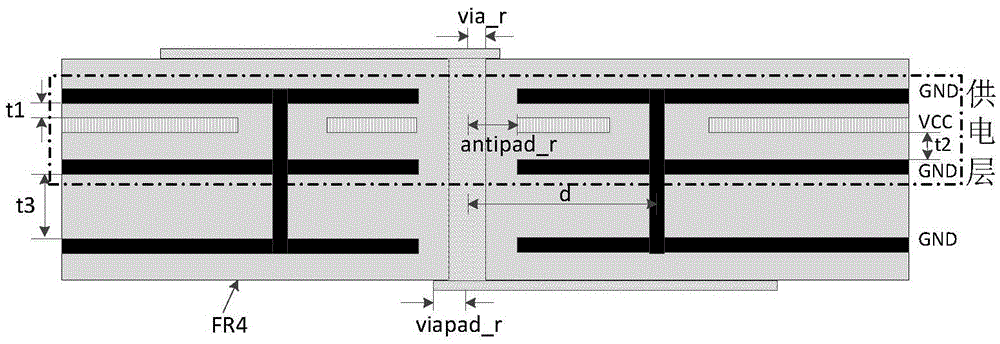

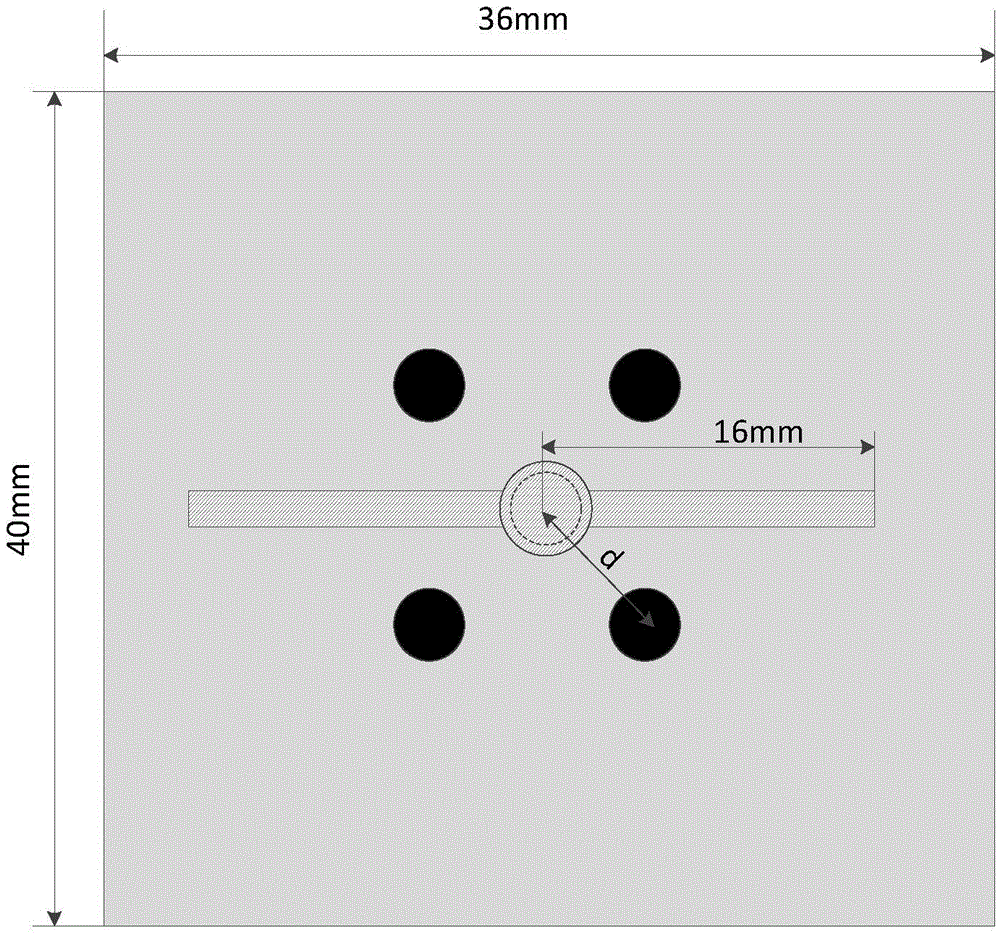

[0033] The main feature of the high-speed multi-layer PCB stacking scheme provided by the present invention is that all power planes are only used for power supply, each power plane is sandwiched by two ground planes with a thin medium, and all signal layers are separated by ground planes , so that each signal layer has a good reference plane, and four short-circuit holes (ground holes) are evenly placed around the signal via hole to provide a low-impedance return path for the signal via hole.

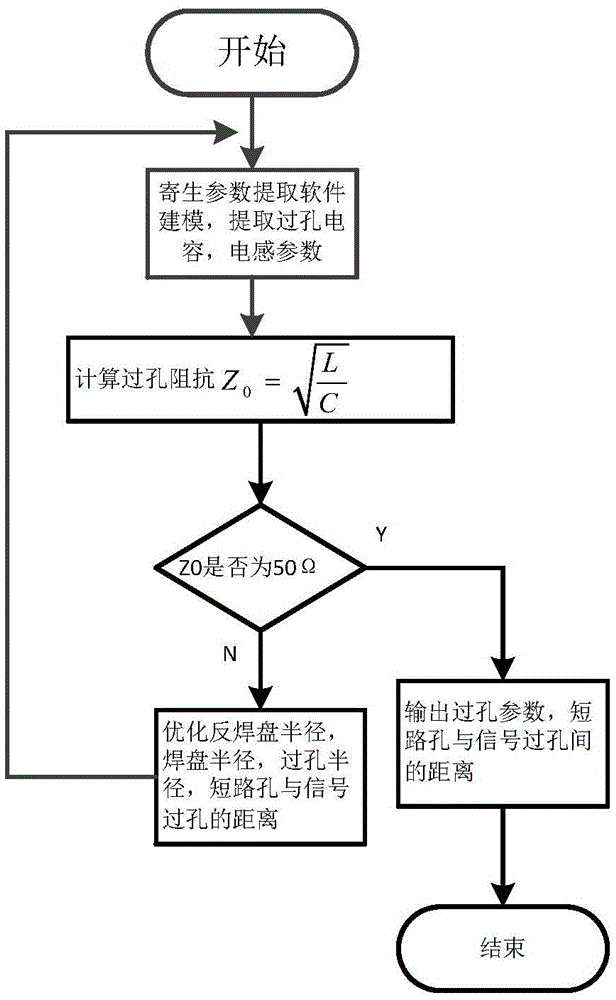

[0034] On the basis of this stack, by optimizing the parameters such as pad radius, via hole radius, anti-pad radius, and the distance from the short-circuit hole to the signal via hole, a performance optimization scheme for signal vias is proposed through repeated iterative optim...

Embodiment 2

[0040] The schematic diagram of the laminate of the multilayer high-speed PCB proposed in this embodiment is as follows: figure 1 , 2 As shown, place four short-circuit holes (ground holes) evenly around the signal via hole. figure 1 The lamination thicknesses in are respectively: t1=0.05mm, t2=0.1mm, t3=1mm. First, follow the figure 1 The stackup schematic is shown as well as Figure 4 The size of the top view is shown to establish a three-dimensional parasitic parameter extraction model. The size of the PCB in the established three-dimensional parasitic parameter extraction model is: 18mm*20mm, and the length of the microstrip line is: 1mm. Set the solution frequency to 5GHz, repeatedly optimize parameters such as pad radius, via hole radius, anti-pad radius, distance from short-circuit hole to signal via hole, and iteratively optimize, according to the characteristic impedance calculation formula Calculate impedance. After actual calculation and optimization, on the b...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Radius | aaaaa | aaaaa |

| Radius | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More