Signal acquisition device of memory bus

A signal acquisition and memory bus technology, applied in the field of high-performance computing, can solve the problems of low versatility, difficulty, high-speed oscilloscopes and logic analyzers, etc., to improve the acquisition effect, high input impedance, and reduce interference. Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

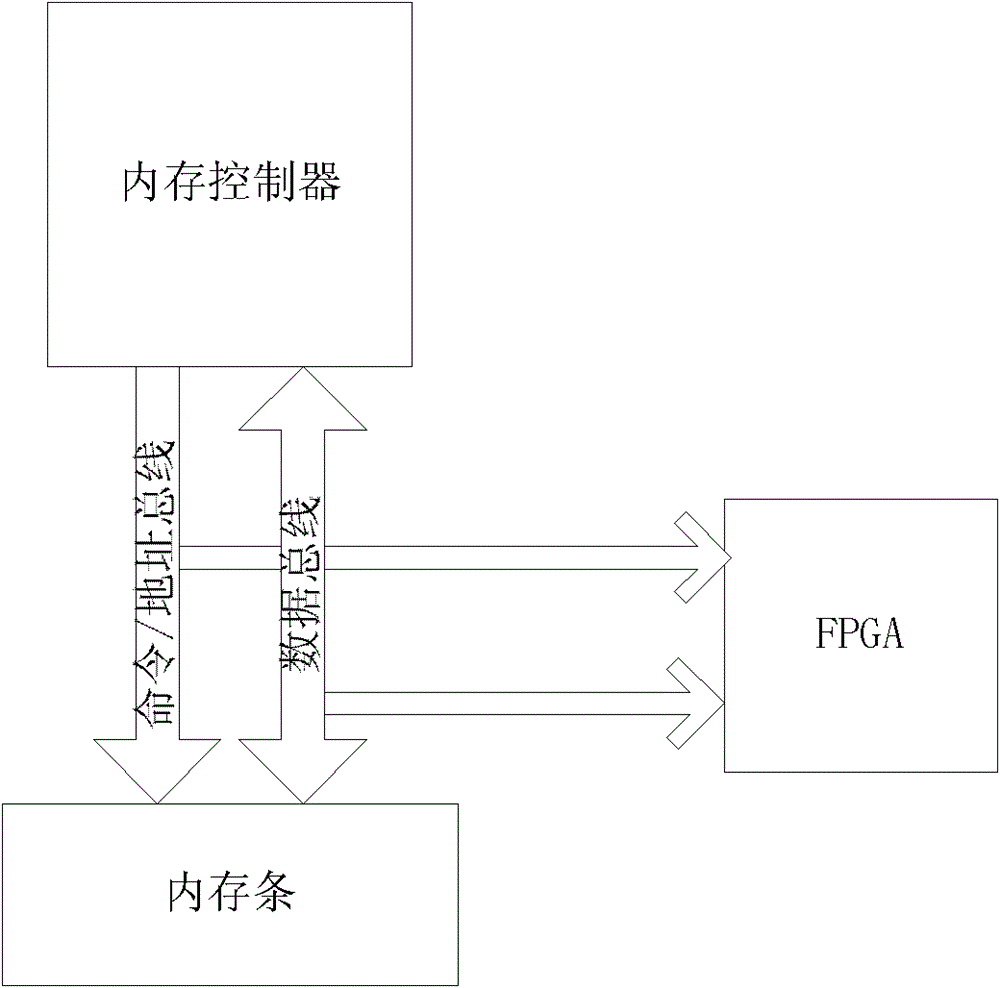

Problems solved by technology

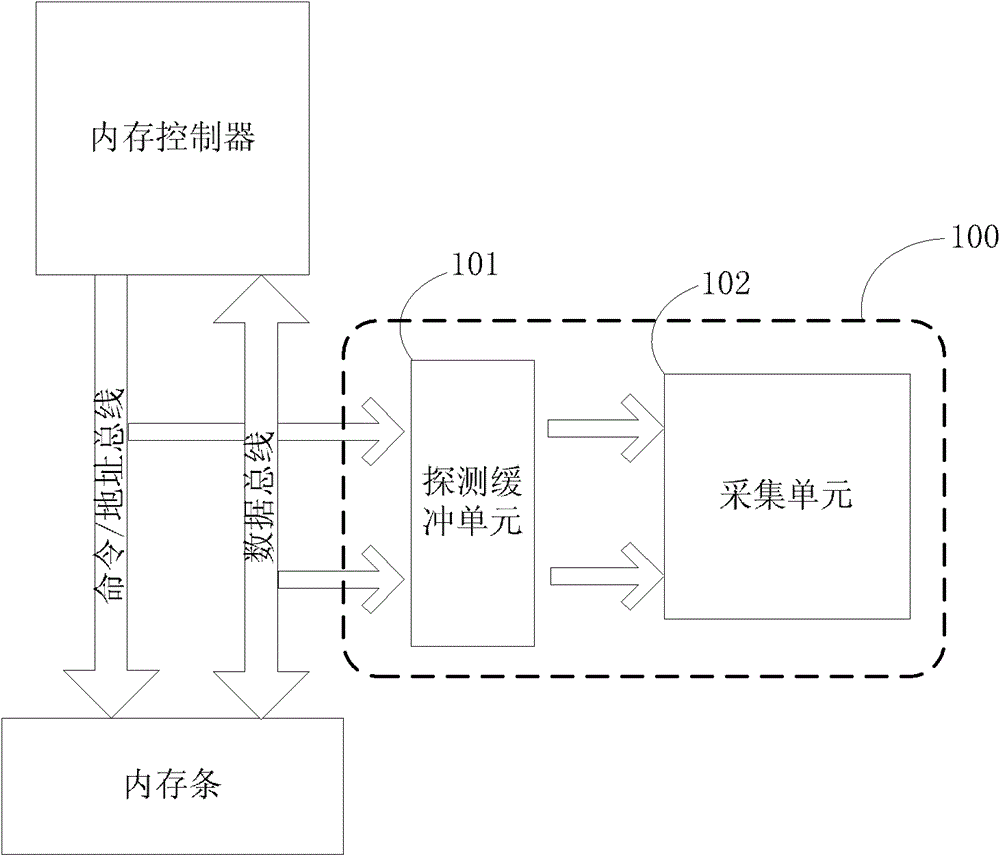

Method used

Image

Examples

Embodiment Construction

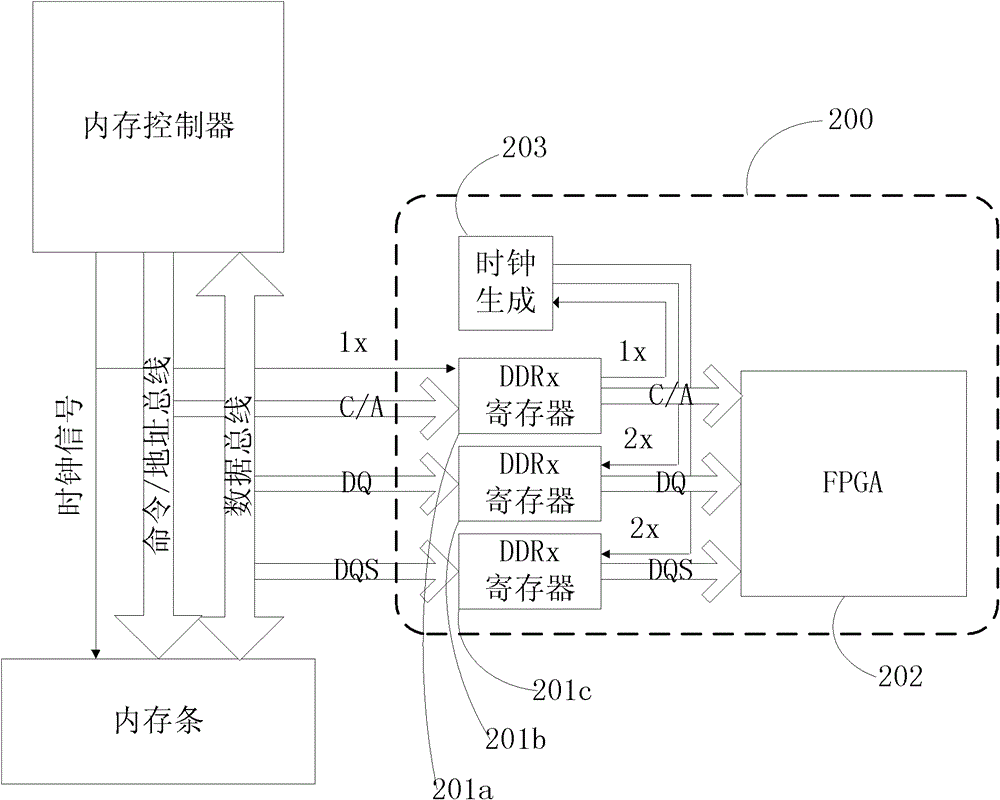

[0027] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

[0028] DDRx registers and memory buffers are two special chips currently used in server memory sticks, which are used to reduce the electrical load of the memory stick itself; among them: DDRx registers are used to produce RDIMM (Registered Dual In-line Memory Module, dual in-line memory module with registers) In-line memory module), which buffers and forwards the commands and address signals sent by the memory controller to the memory particles on the memory module; the memory buffer is used to produce LRDIMM (Load-Reduced Dual In-line Memory Module, low-load dual-row DDRx register), it can also buffer the bidire...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More