Multilayer interconnection structure of wafer level package, manufacturing method and application

A technology of wafer-level packaging and multilayer interconnection, which is applied in semiconductor/solid-state device manufacturing, electrical components, electric solid-state devices, etc., can solve problems such as large parasitic effects and large losses, and reduce parasitic effects and losses, reduce Loss, the effect of increasing packing density and production efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] Embodiments of the present invention will be further specifically described below with reference to the accompanying drawings in order to fully demonstrate the advantages and positive effects of the present invention. The scope of the present invention is not limited to the following examples.

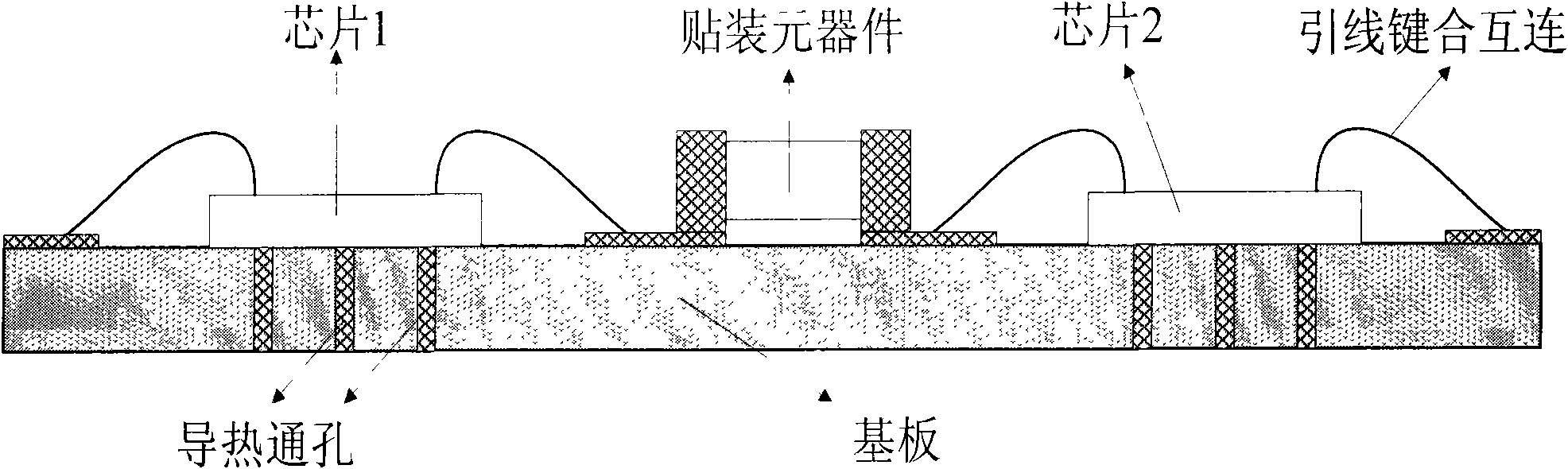

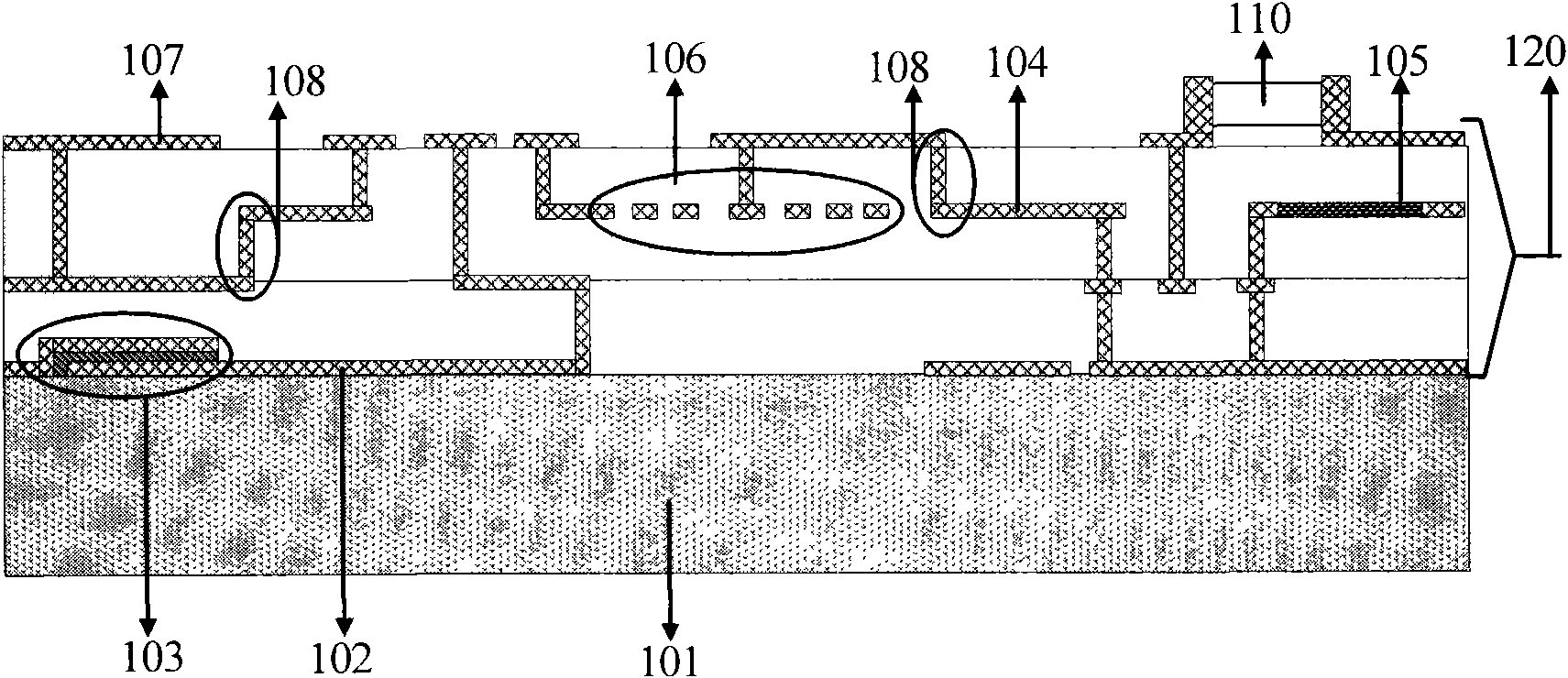

[0033] Such as figure 2 Shown is a microwave multi-chip module wafer-level packaging structure according to an embodiment of the present invention. The multi-layer interconnection structure 120 based on the silicon substrate 101 is embedded with interconnection transmission lines 104 , ground layer 102 and various passive components, such as capacitors 103 , resistors 105 , inductors 106 , and miniature antennas 107 . Metal interconnects (eg, transmission lines 104 and vertical interconnect vias 108 ) and passive components within the multilayer interconnect structure are implemented by low-cost electroplating processes. The metal thickness is generally 1-5 microns, which can...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More