Semiconductor rectifier device and manufacturing method thereof

A technology of rectifier devices and manufacturing methods, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve problems such as unreasonable distribution and large area of vertical MOS tubes, and achieve improved junction characteristics and reduced Parasitic effect, effect of increasing cell density

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

[0066] Embodiment 1: a semiconductor rectifier device,

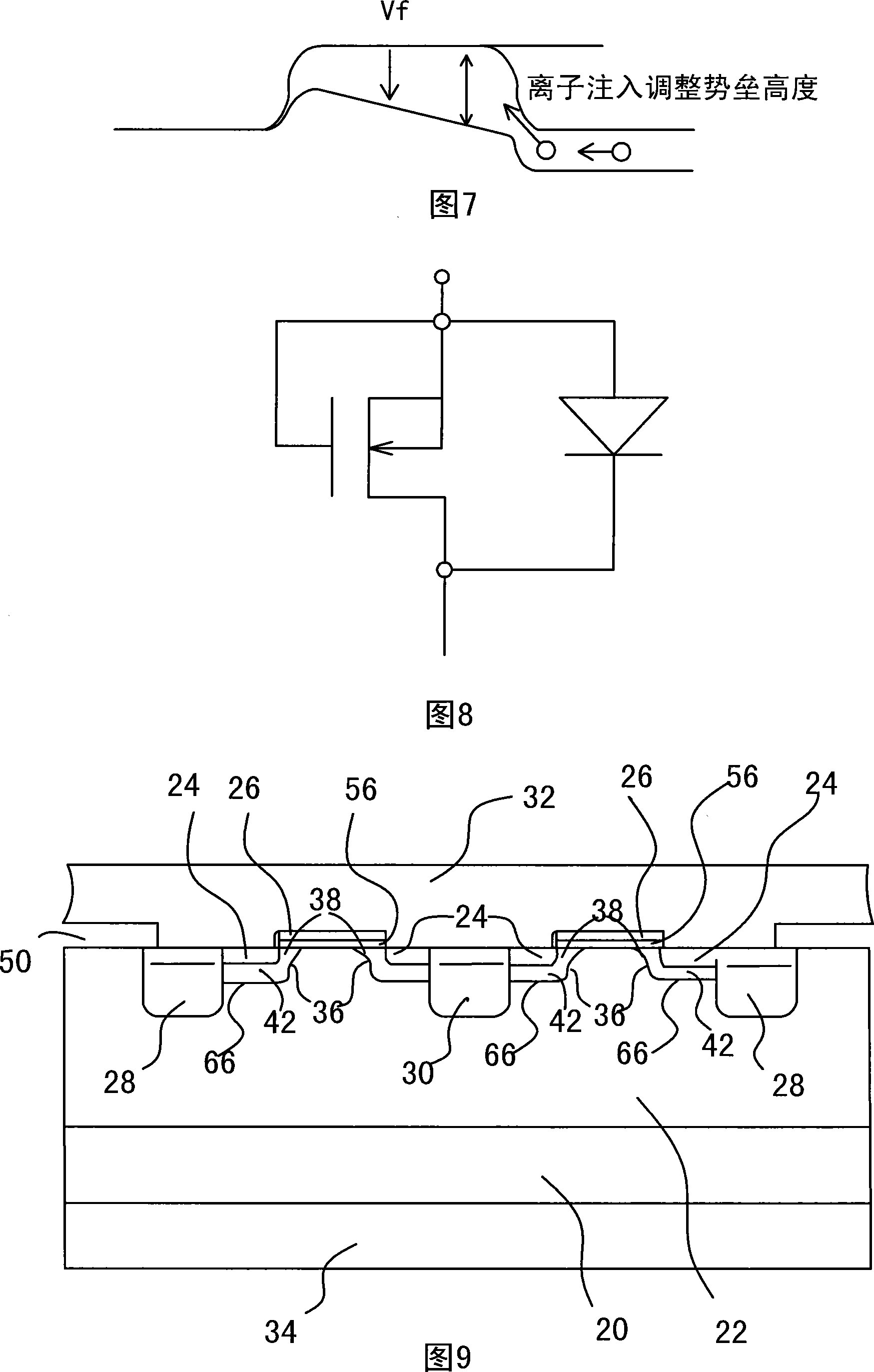

[0067] As shown in FIG. 10 , on a top view plane, the active region of the semiconductor rectifier device is composed of various rectification units arranged and various protection diodes 1 arranged. Each rectifier unit is connected in parallel through upper and lower electrodes to form a whole, wherein each rectifier unit is formed by adjacent combination of PN junction region 66 and vertical semiconductor MOS transistor region 3 . A guard ring 28 is provided around the active area.

[0068] As shown in FIG. 11 , in cross-section, the PN junction region 66 is composed of an upper electrode 32, a second P-diffusion region 42, an N-epitaxial layer 22, an N+ substrate layer 20 and a lower electrode 34 from top to bottom, wherein , the second P-diffusion region 42 and the N-epitaxial layer 22 form the PN junction region.

[0069] As shown in Figure 11, on the cross-section, the vertical semiconductor MOS transistor region...

Embodiment 2

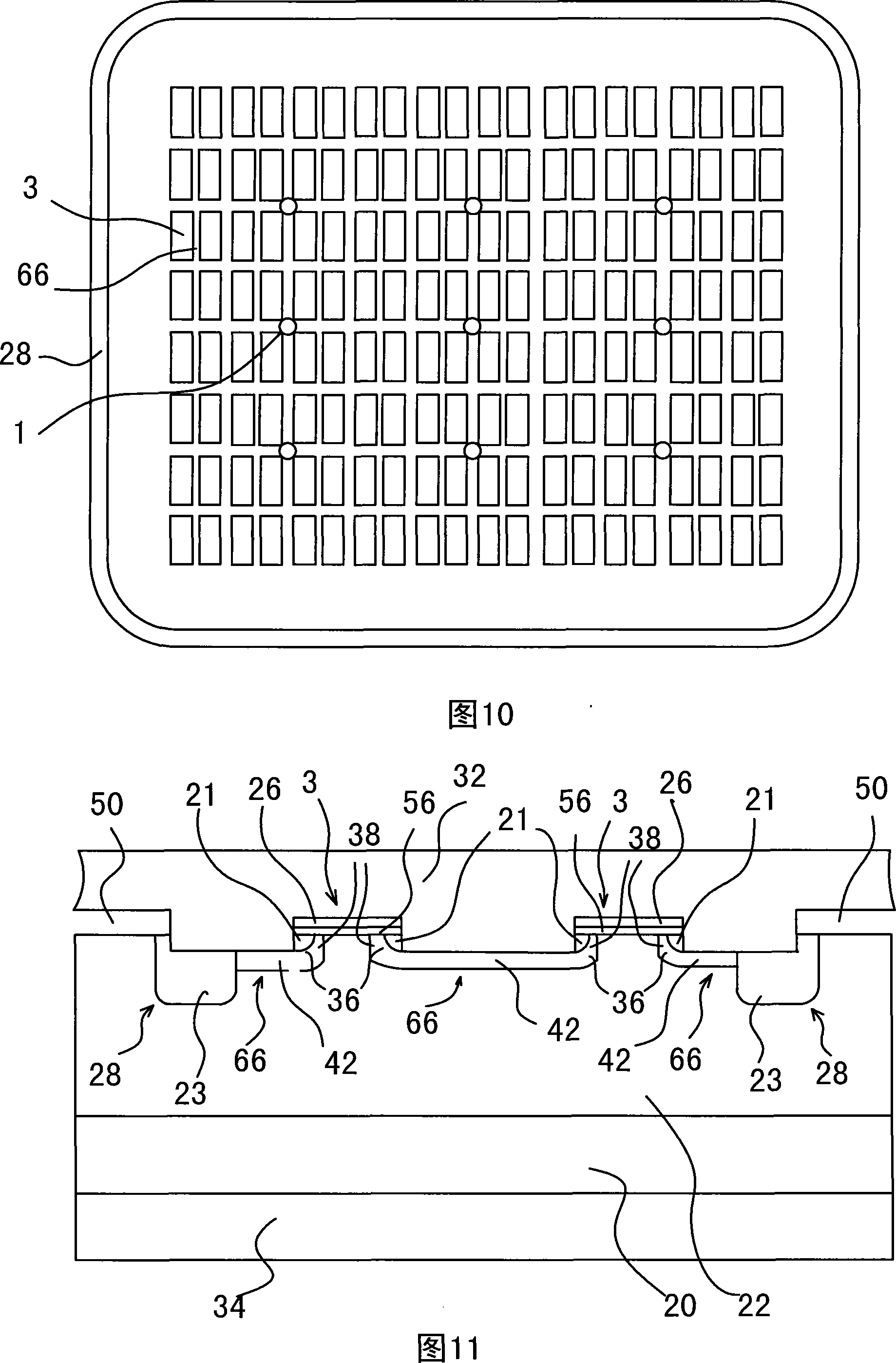

[0073] Embodiment two: a manufacturing method of a semiconductor rectifier device, comprising the following process steps:

[0074] FIG. 12 is a schematic diagram of the manufacturing process of a rectifier device, showing growth of the first silicon oxide layer / photolithography etching of the first P- diffusion region / B+ implantation. Concrete process steps are:

[0075] a) Providing an N-type doped semiconductor silicon wafer having two opposite main surfaces. Wherein, the first main surface refers to the front side of the semiconductor silicon wafer having an N- epitaxial layer, and the second main surface refers to the back side of the semiconductor silicon wafer having an N+ substrate layer.

[0076] b) growing a first silicon oxide layer 25 on the first main surface.

[0077] c) Forming the etching mask pattern of the first P-diffusion region 23 in the first photolithography.

[0078] d) Etching the first silicon oxide layer 25 to open the window of the first P-diffus...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More