Patents

Literature

306results about "Computing operation arrangements" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

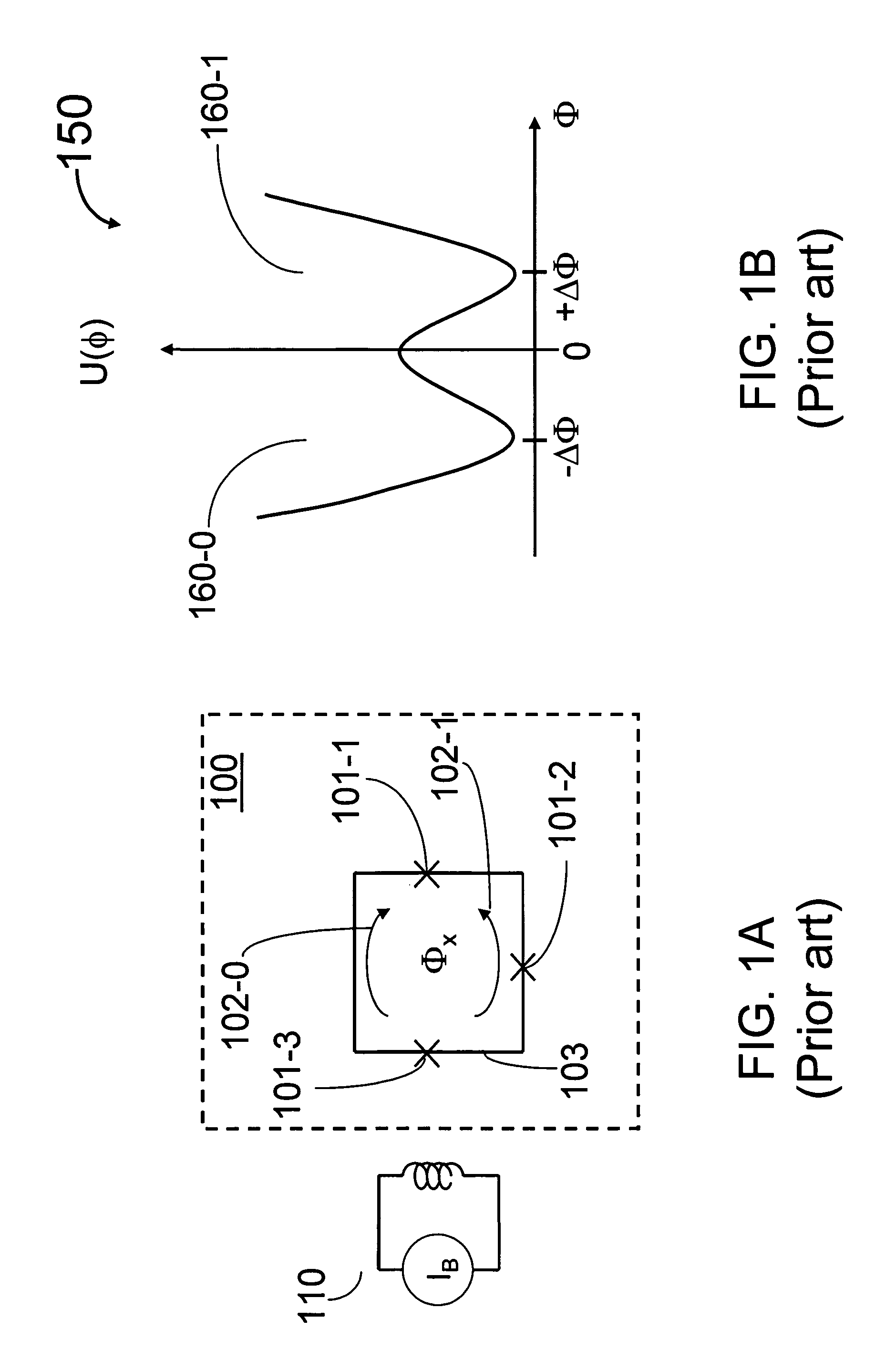

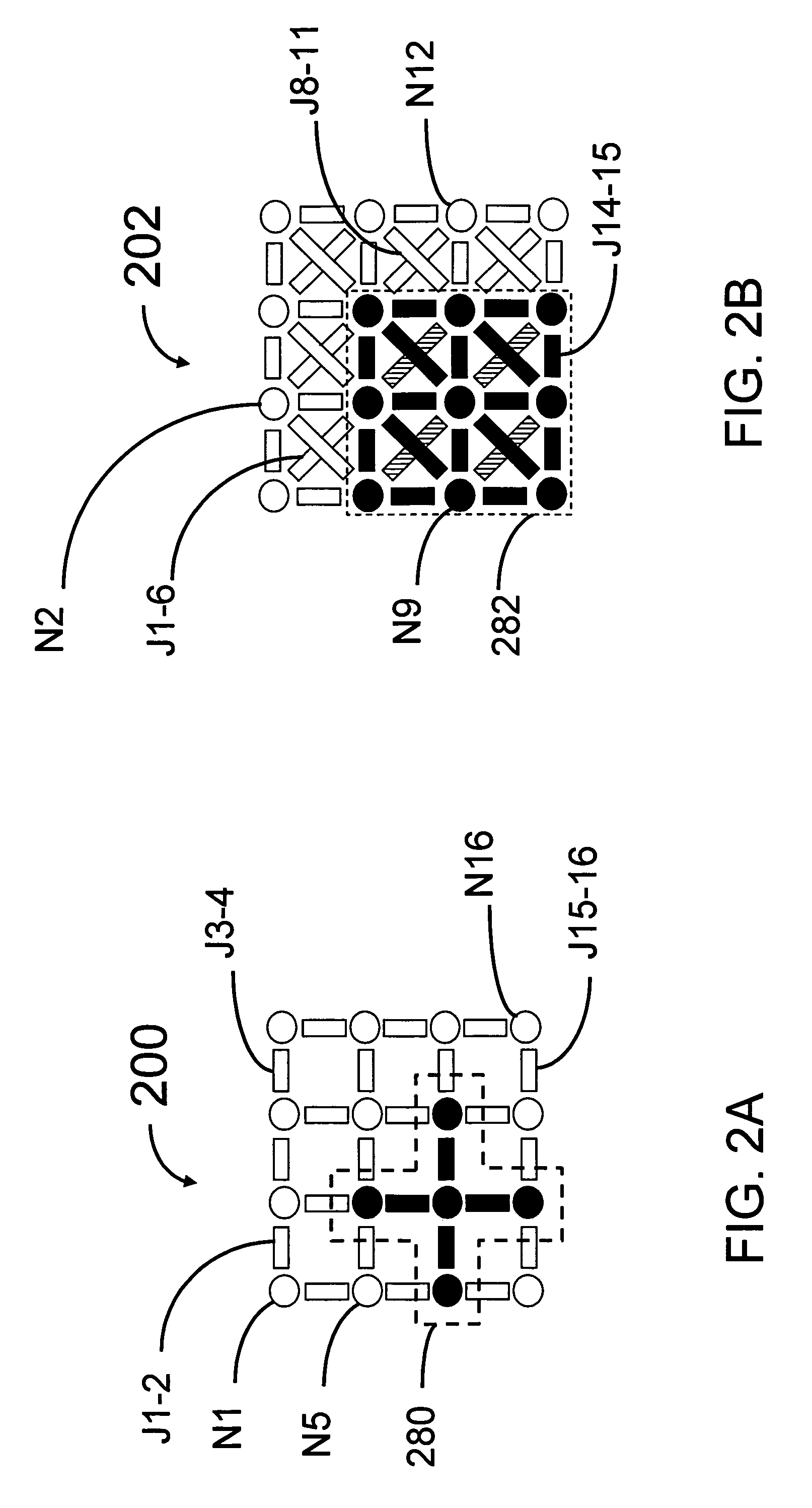

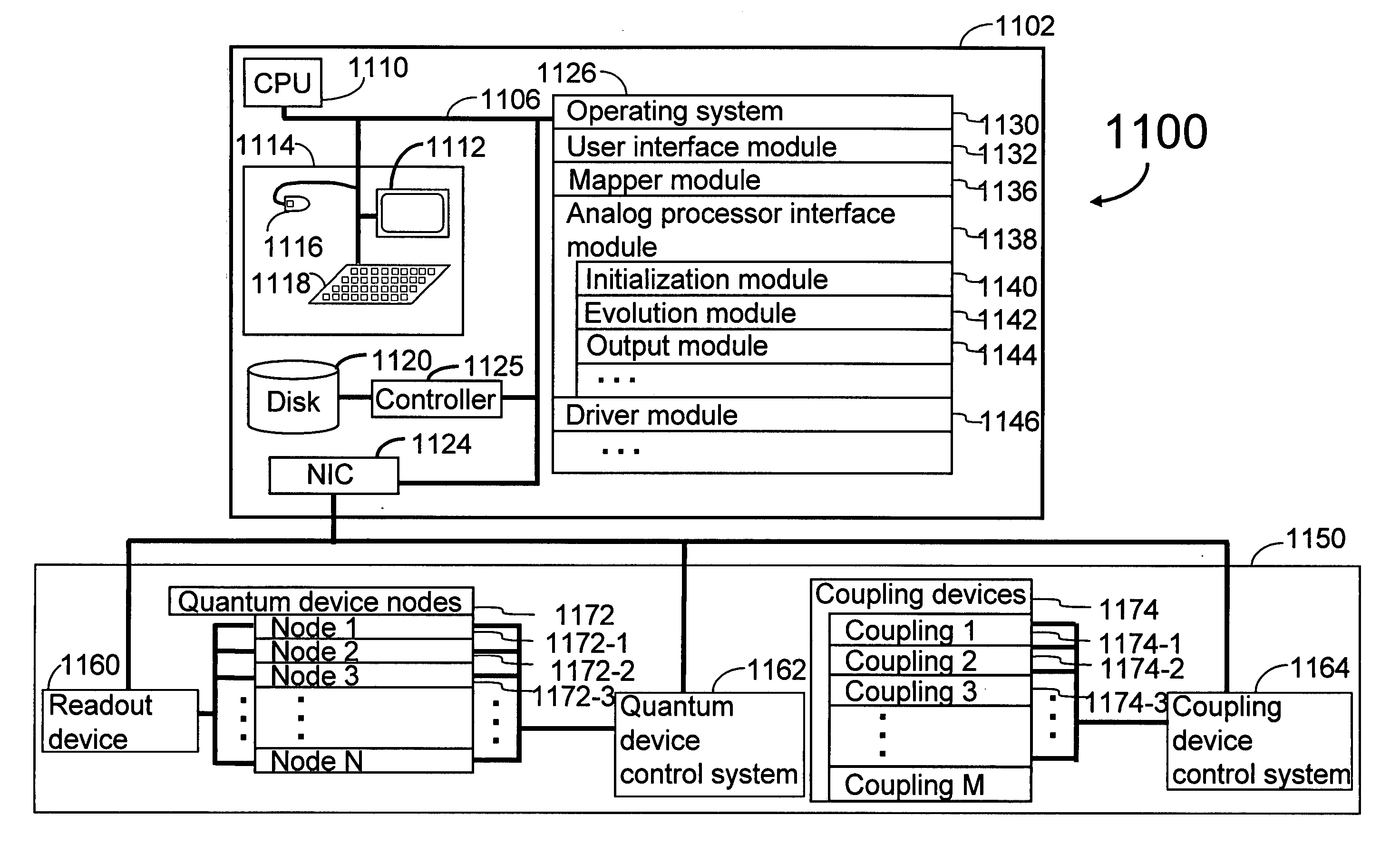

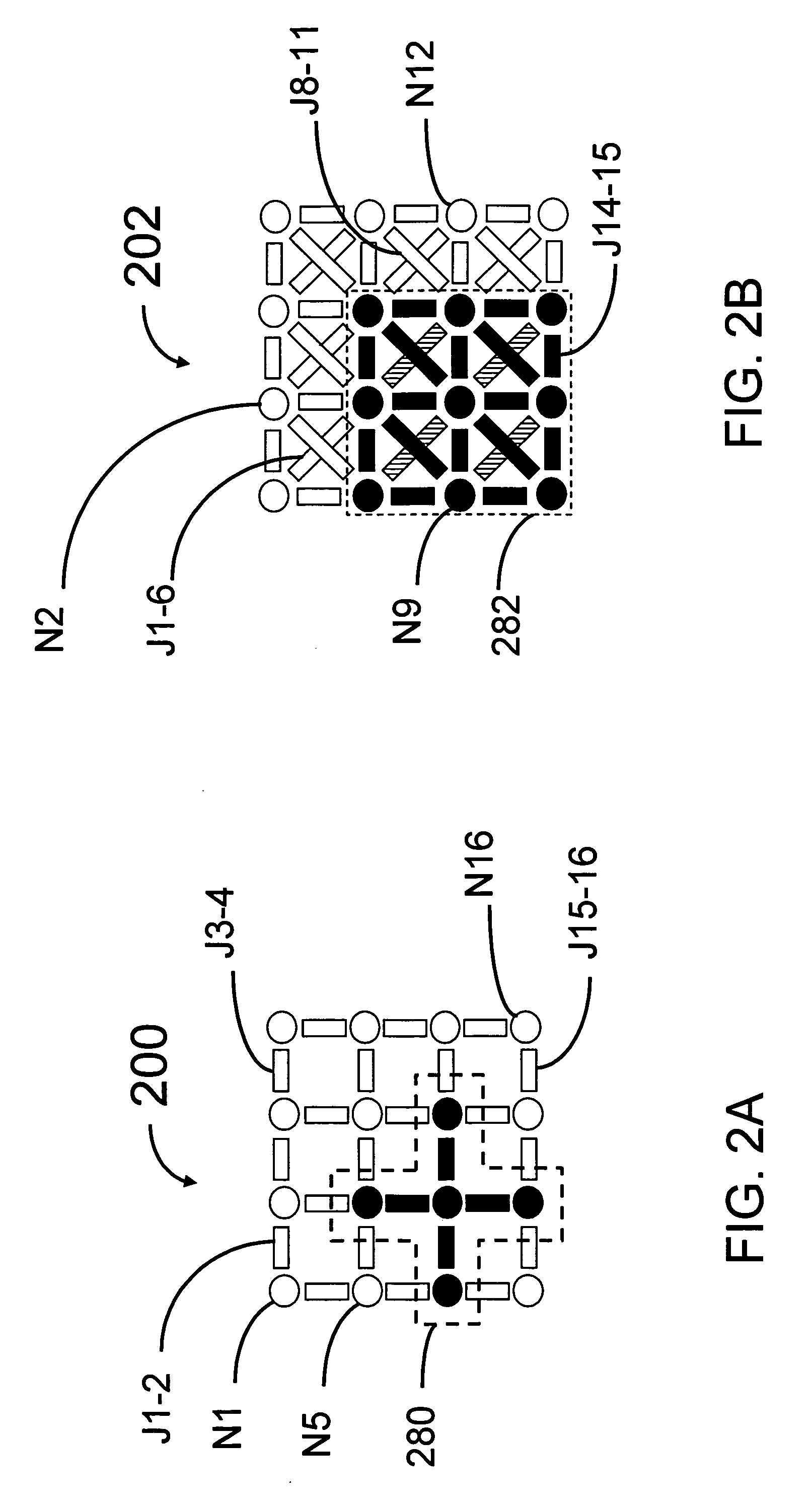

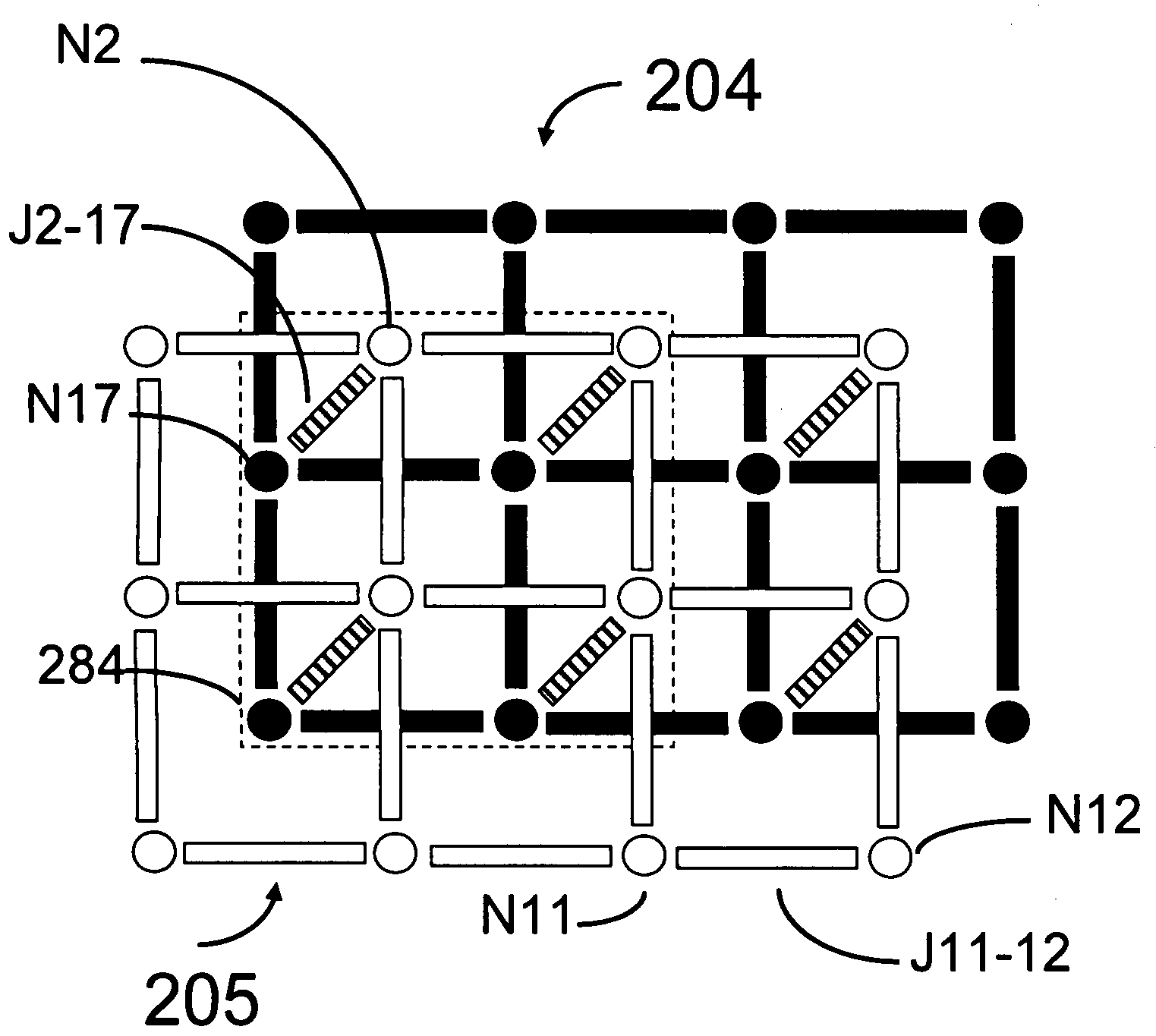

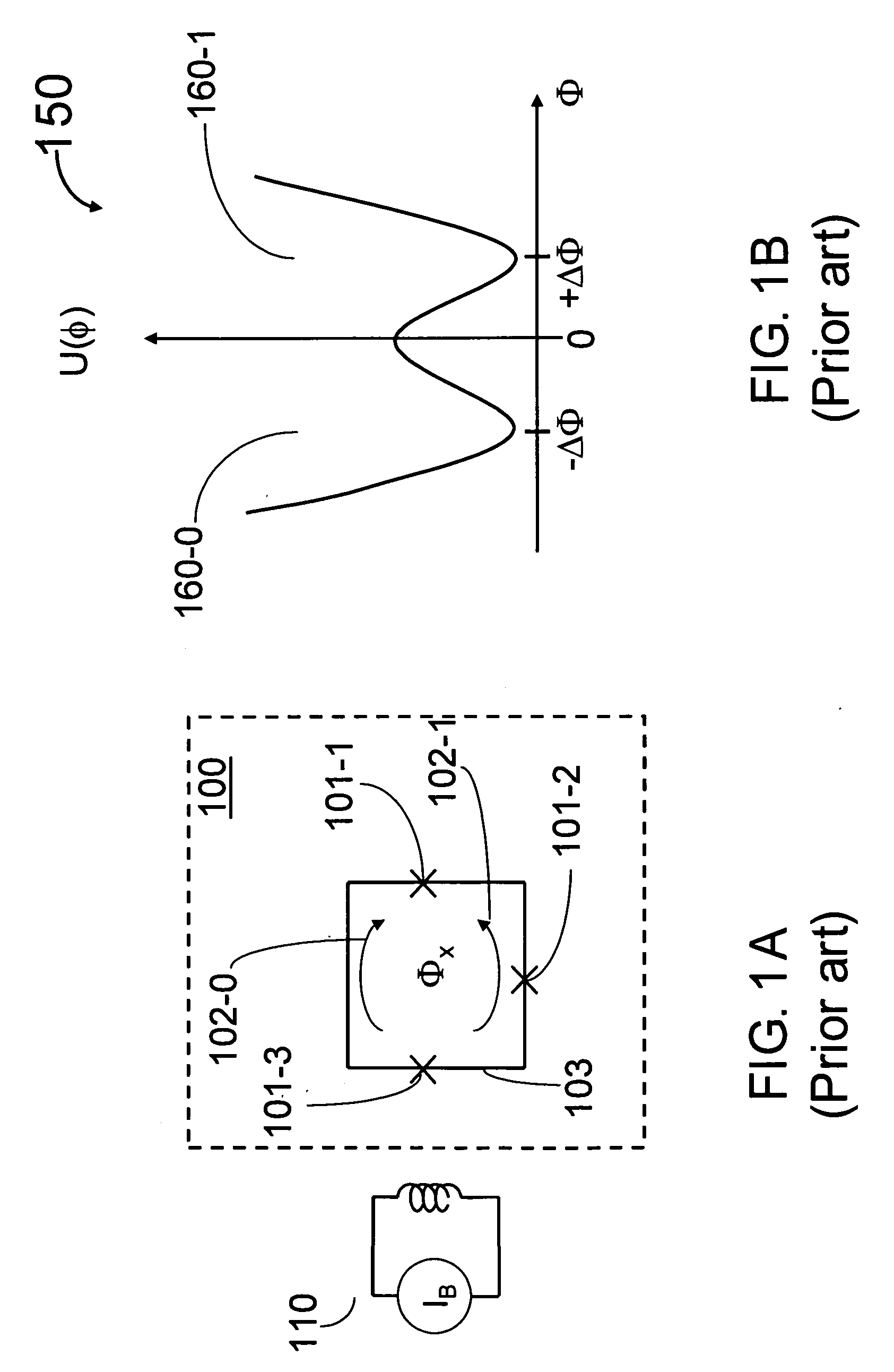

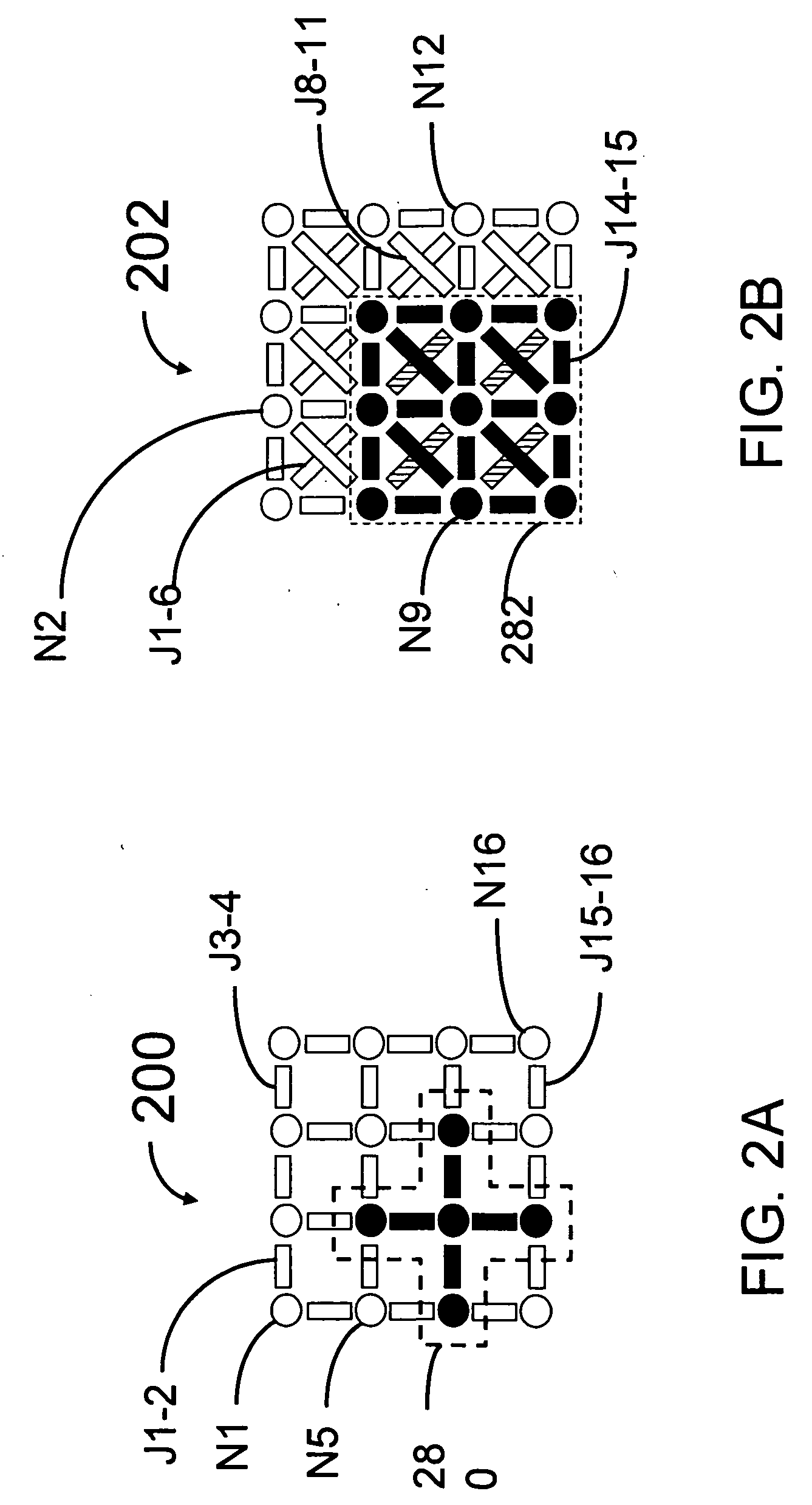

Analog processor comprising quantum devices

Owner:D WAVE SYSTEMS INC

Analog processor comprising quantum devices

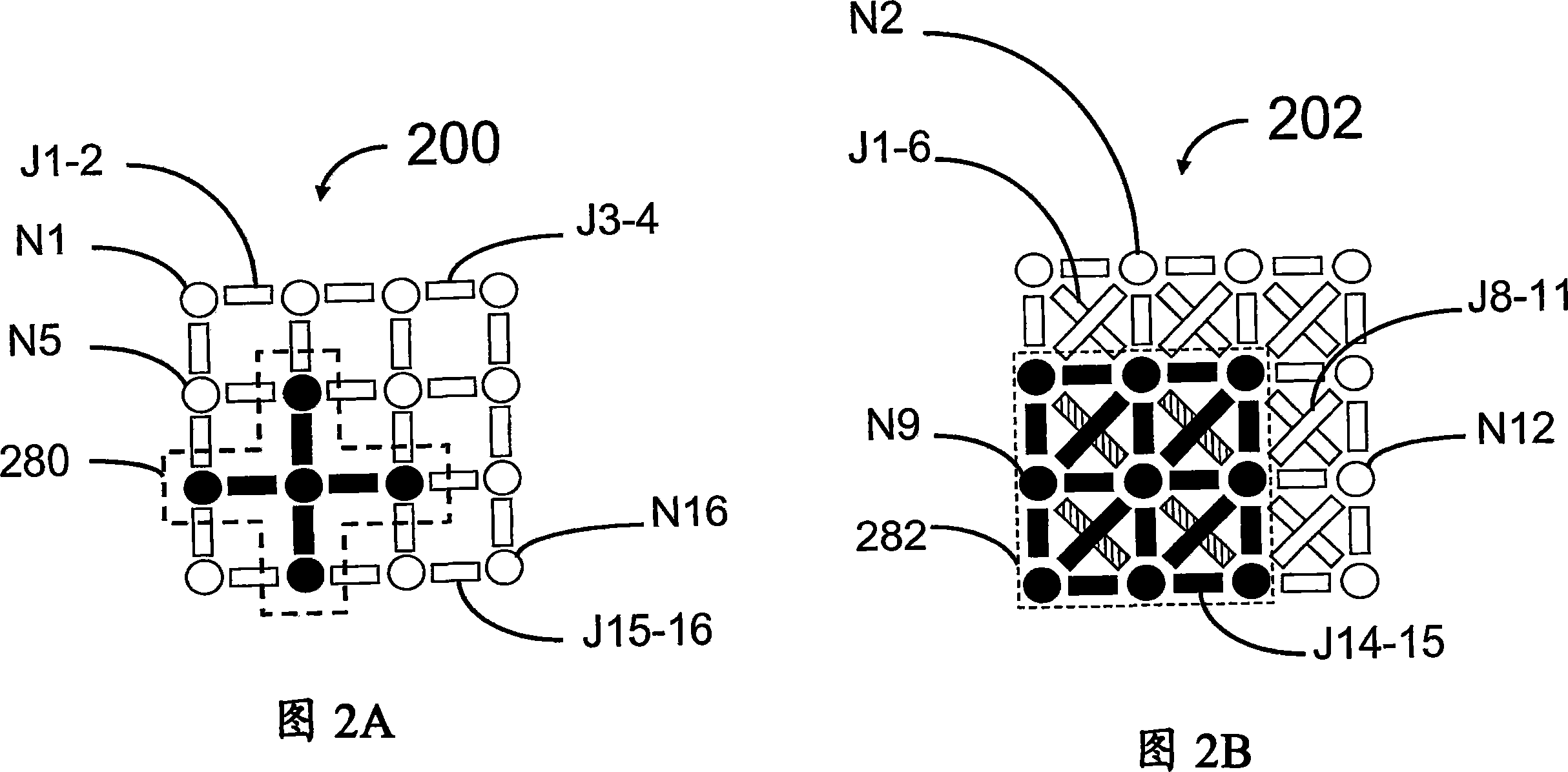

Analog processors for solving various computational problems are provided. Such analog processors comprise a plurality of quantum devices, arranged in a lattice, together with a plurality of coupling devices. The analog processors further comprise bias control systems each configured to apply a local effective bias on a corresponding quantum device. A set of coupling devices in the plurality of coupling devices is configured to couple nearest-neighbor quantum devices in the lattice. Another set of coupling devices is configured to couple next-nearest neighbor quantum devices. The analog processors further comprise a plurality of coupling control systems each configured to tune the coupling value of a corresponding coupling device in the plurality of coupling devices to a coupling. Such quantum processors further comprise a set of readout devices each configured to measure the information from a corresponding quantum device in the plurality of quantum devices.

Owner:D WAVE SYSTEMS INC

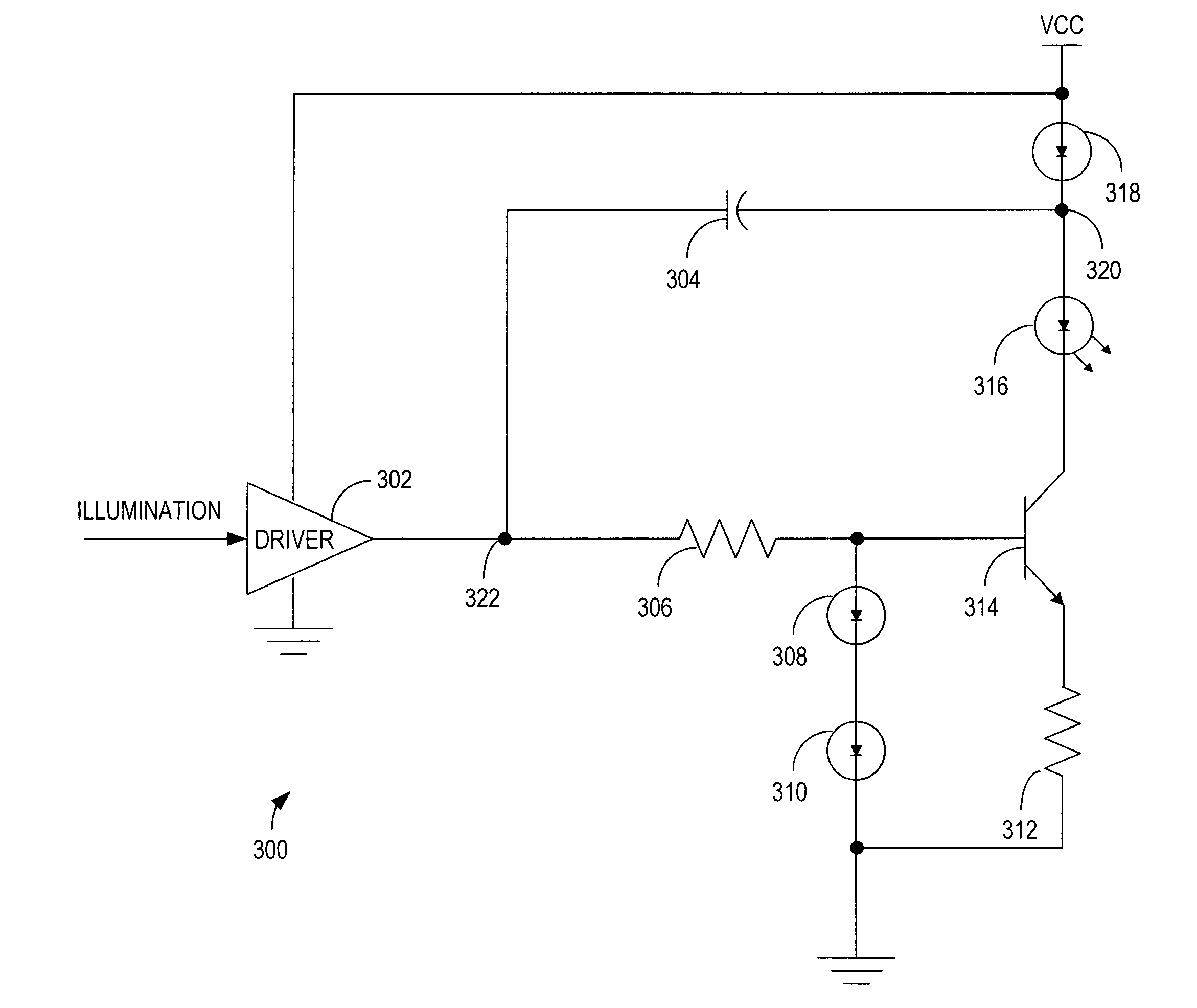

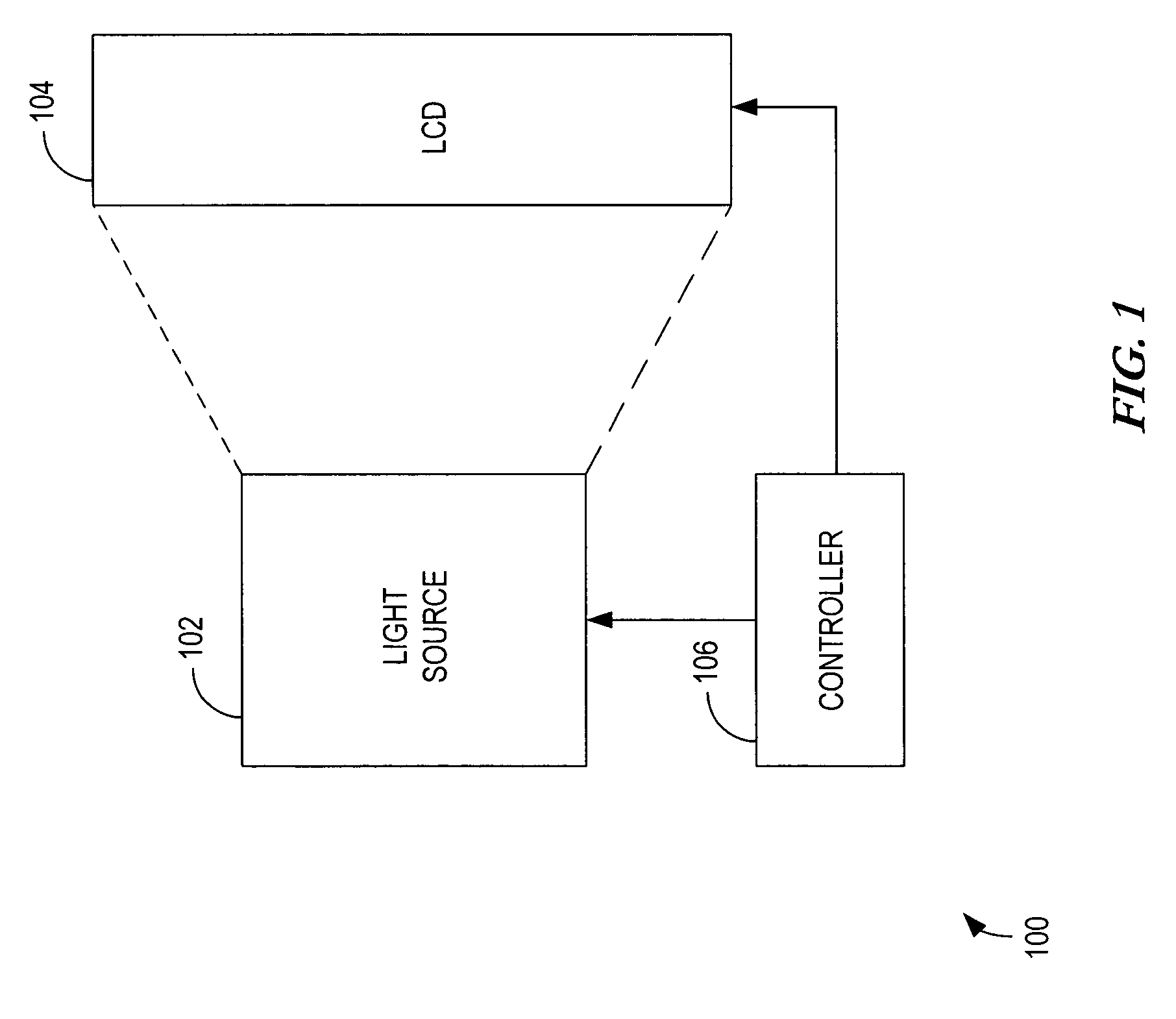

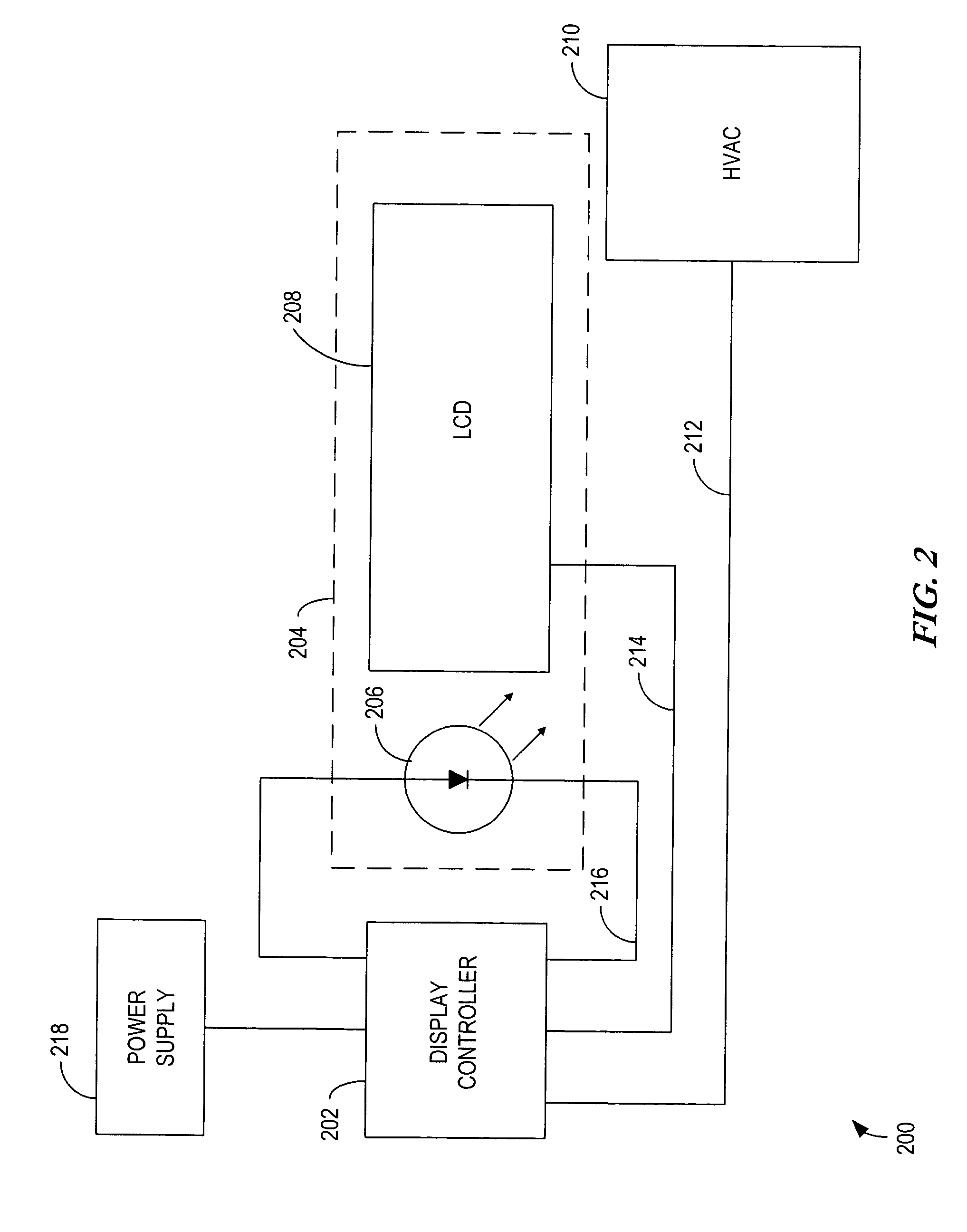

System, apparatus, and method for driving light emitting diodes in low voltage circuits

InactiveUS6995518B2Electrical apparatusStatic indicating devicesLow voltage circuitsLight-emitting diode

A system, apparatus, and method for allowing LED operation in circuits operating with power supply levels that are below the forward voltage limits of the LED. A first level of a modulated voltage signal is applied to charge a voltage increasing component in a first phase of operation. A second level of the modulated voltage signal is then summed with the voltage stored across the voltage increasing component to provide adequate forward potential across Light Emitting Diode (LED) for illumination. The second level of modulated voltage is also used to provide a source of constant forward current to be conducted by LED when in its luminescent state.

Owner:ADEMCO INC

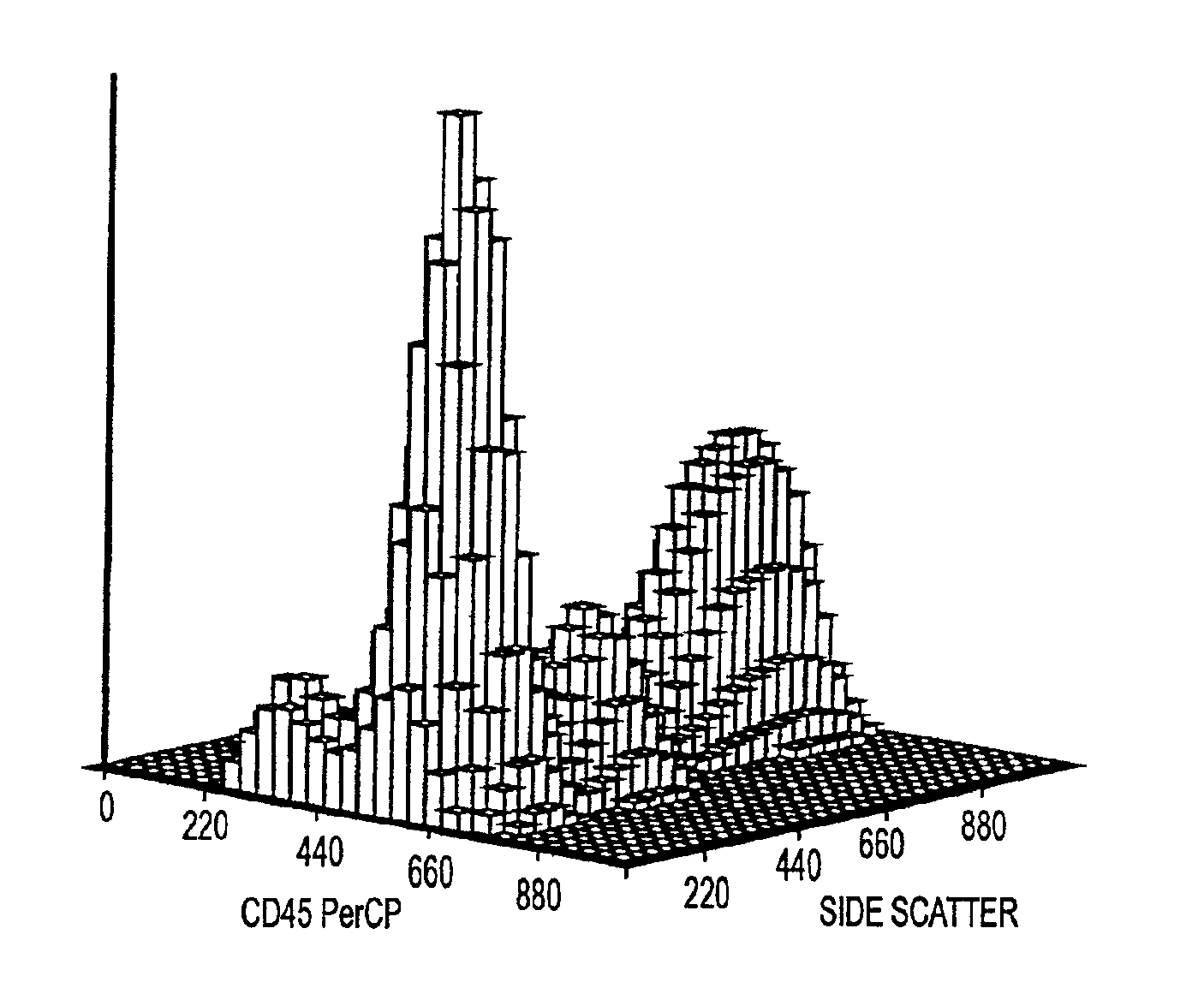

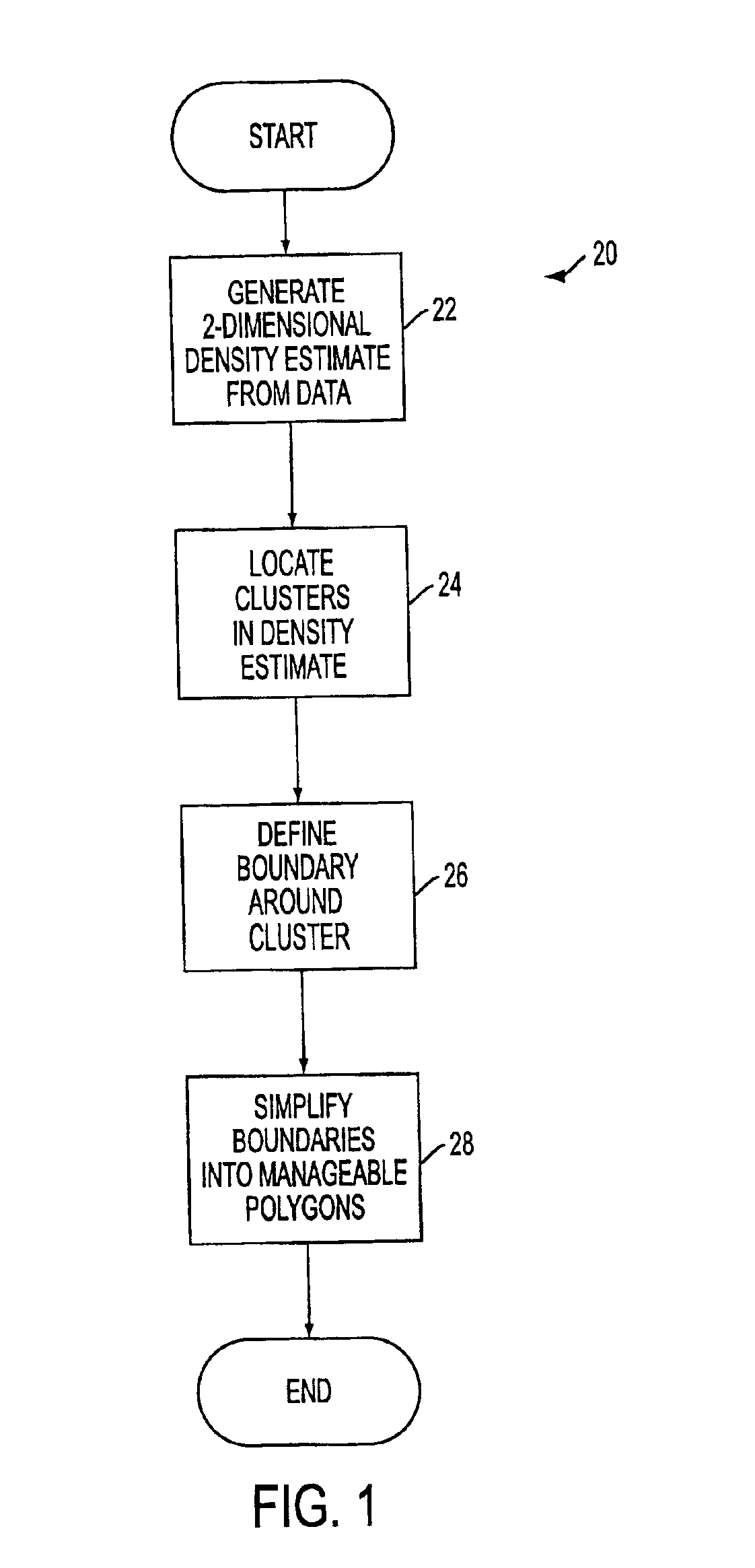

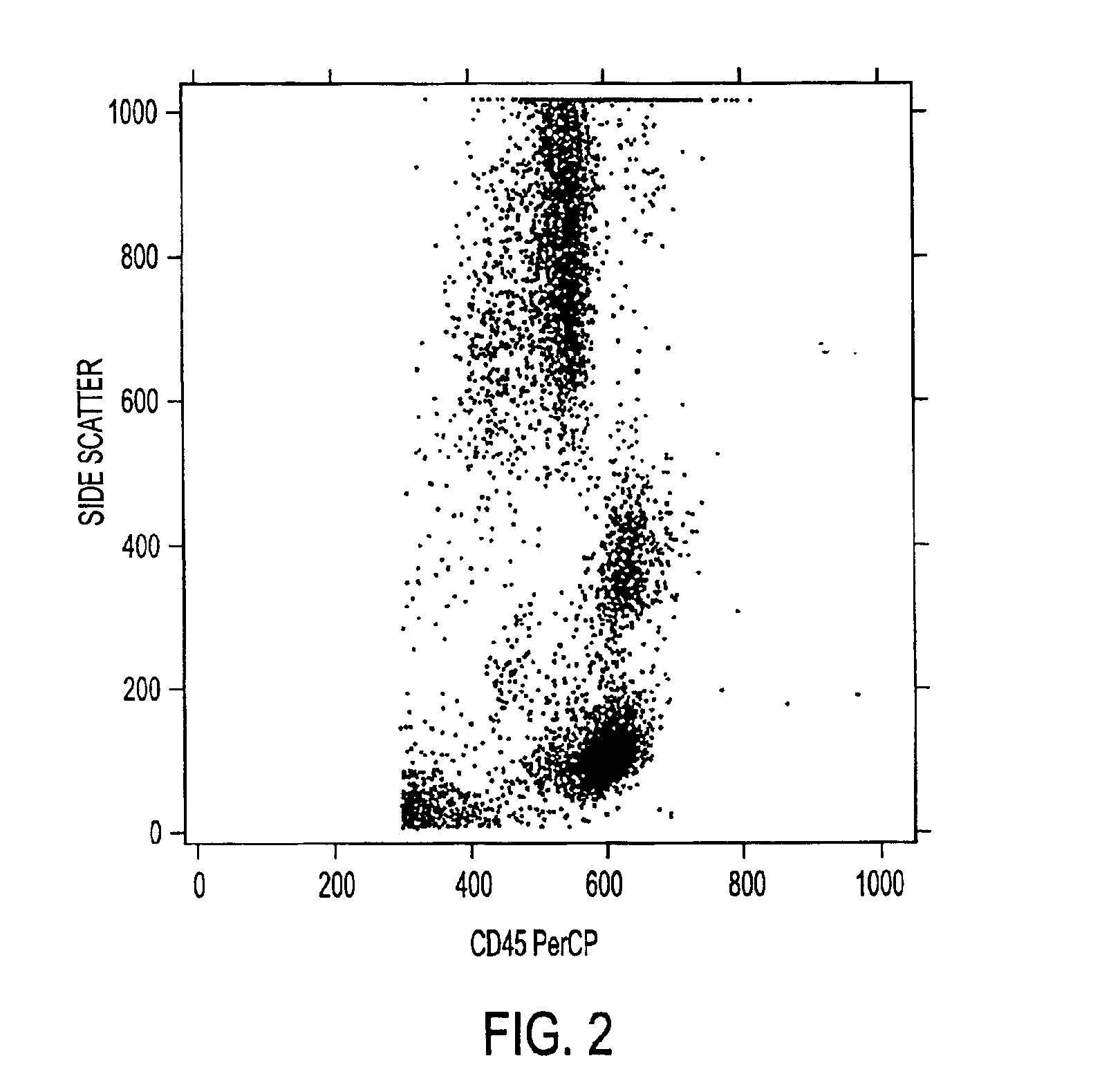

System for identifying clusters in scatter plots using smoothed polygons with optimal boundaries

InactiveUS6944338B2Ease of batch processingEasy to processScattering properties measurementsCharacter and pattern recognitionComputer scienceHistogram

An apparatus and method for identifying clusters in two-dimensional data by generating a two-dimensional histogram characterized by a grid of bins, determining a density estimate based on the bins, and identifying at least one cluster in the data. A smoothed density estimate is generated using a Gaussian kernel estimator algorithm. Clusters are identified by locating peaks and valleys in the density estimate (e.g., by comparing slope of adjacent bins). Boundaries (e.g., polygons) around clusters are identified using bins after bins are identified as being associated with a cluster. Boundaries can be simplified (e.g., by reducing the number of vertices in a polygon) to facilitate data manipulation.

Owner:BECTON DICKINSON & CO

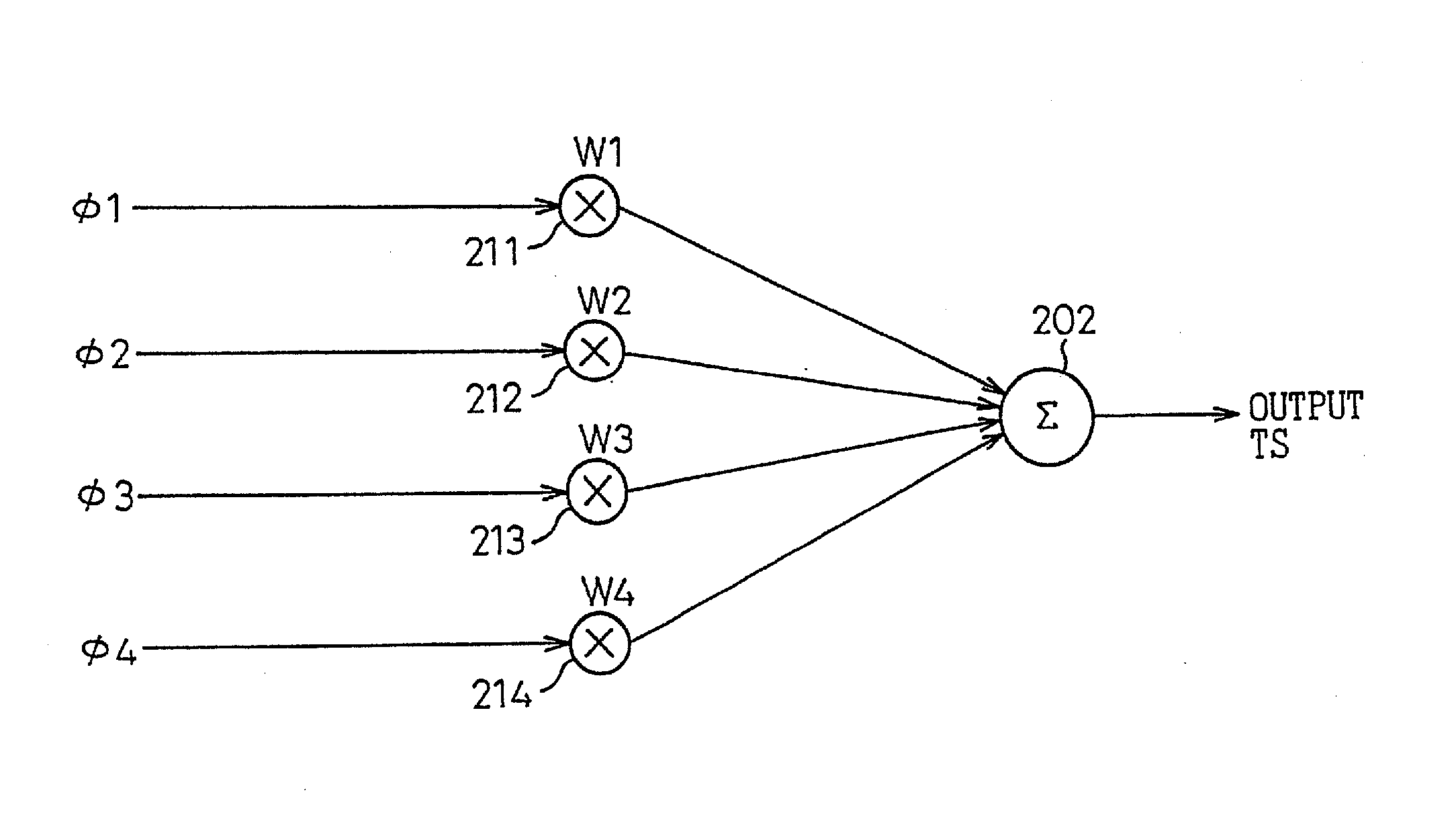

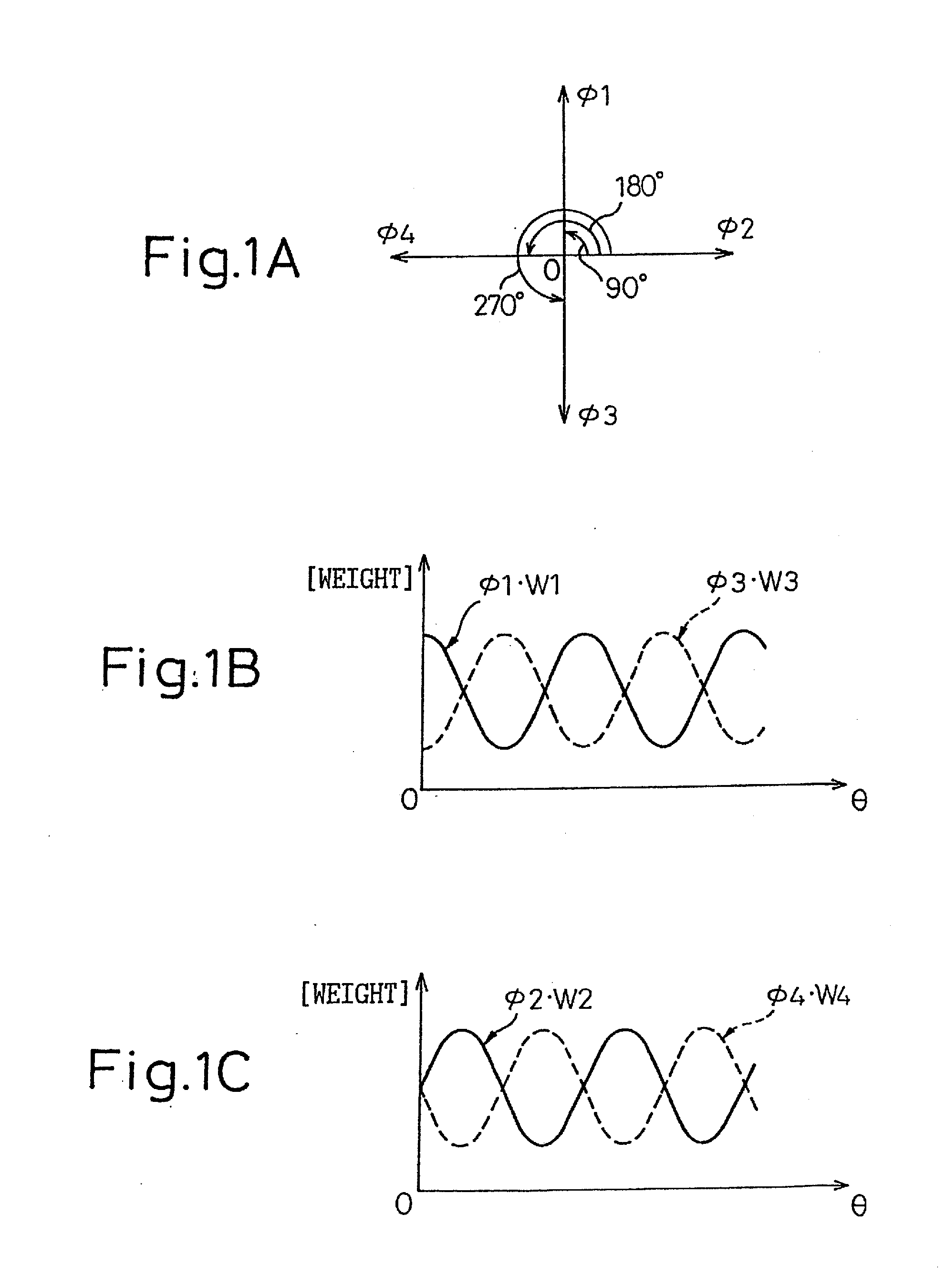

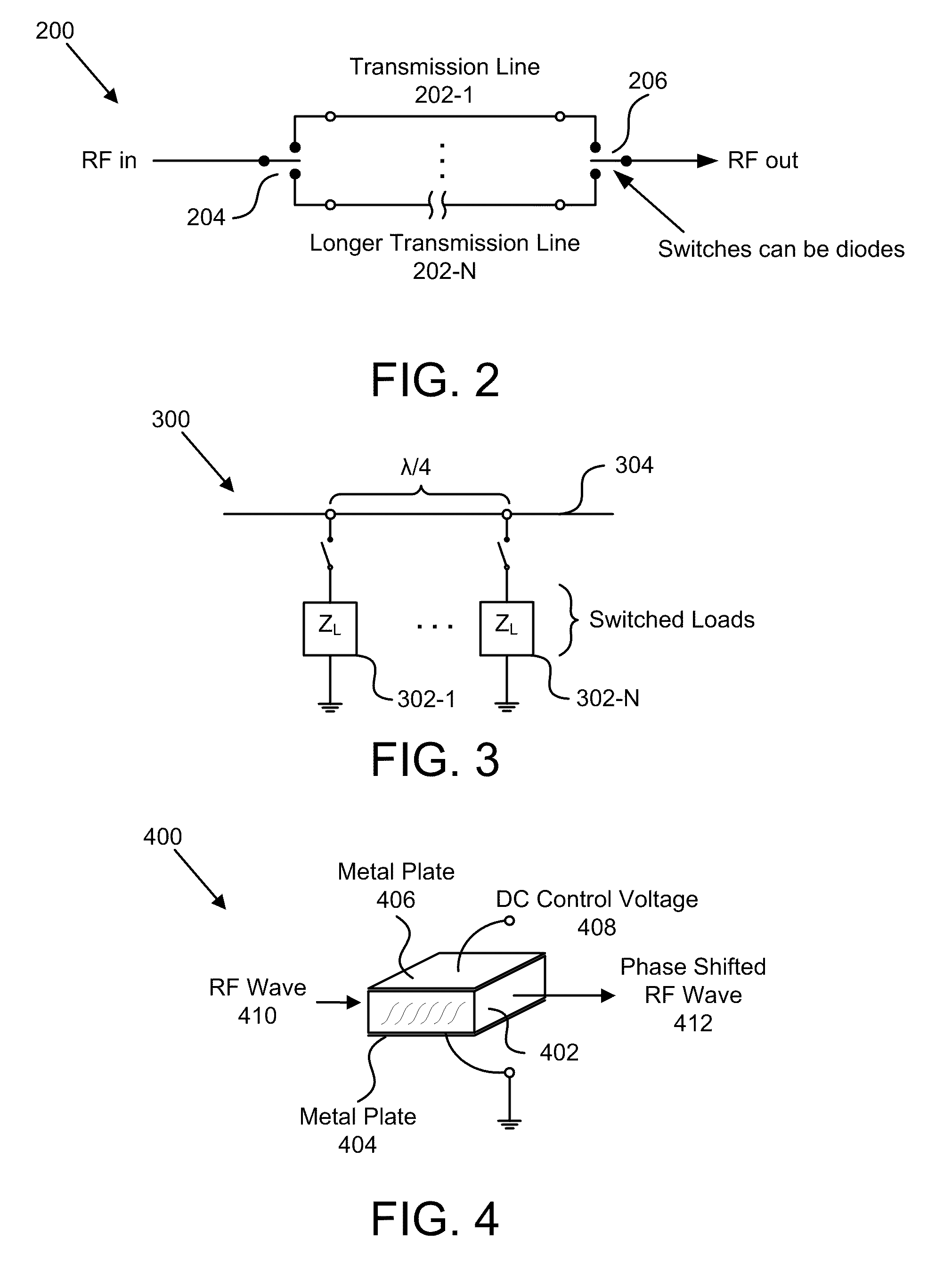

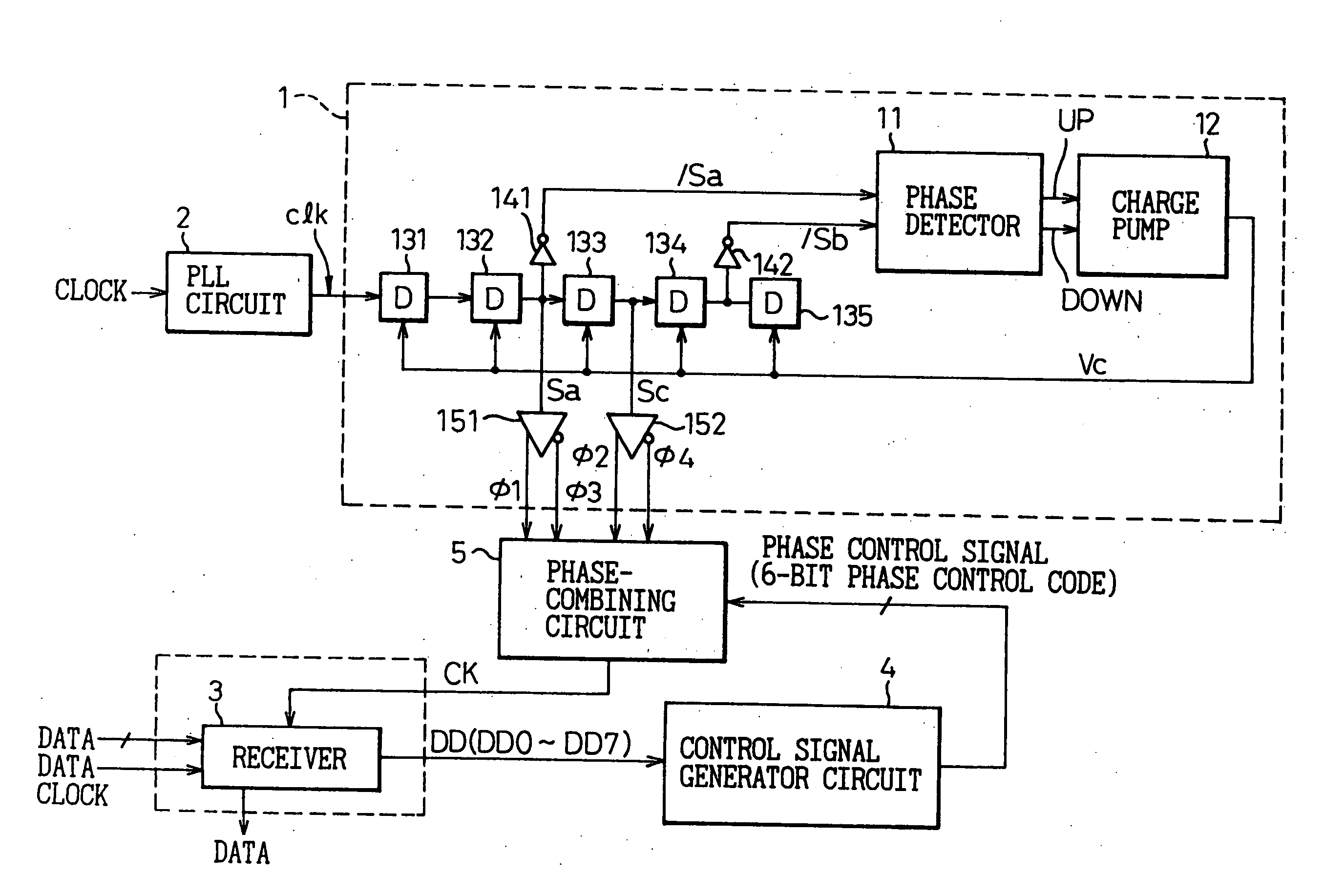

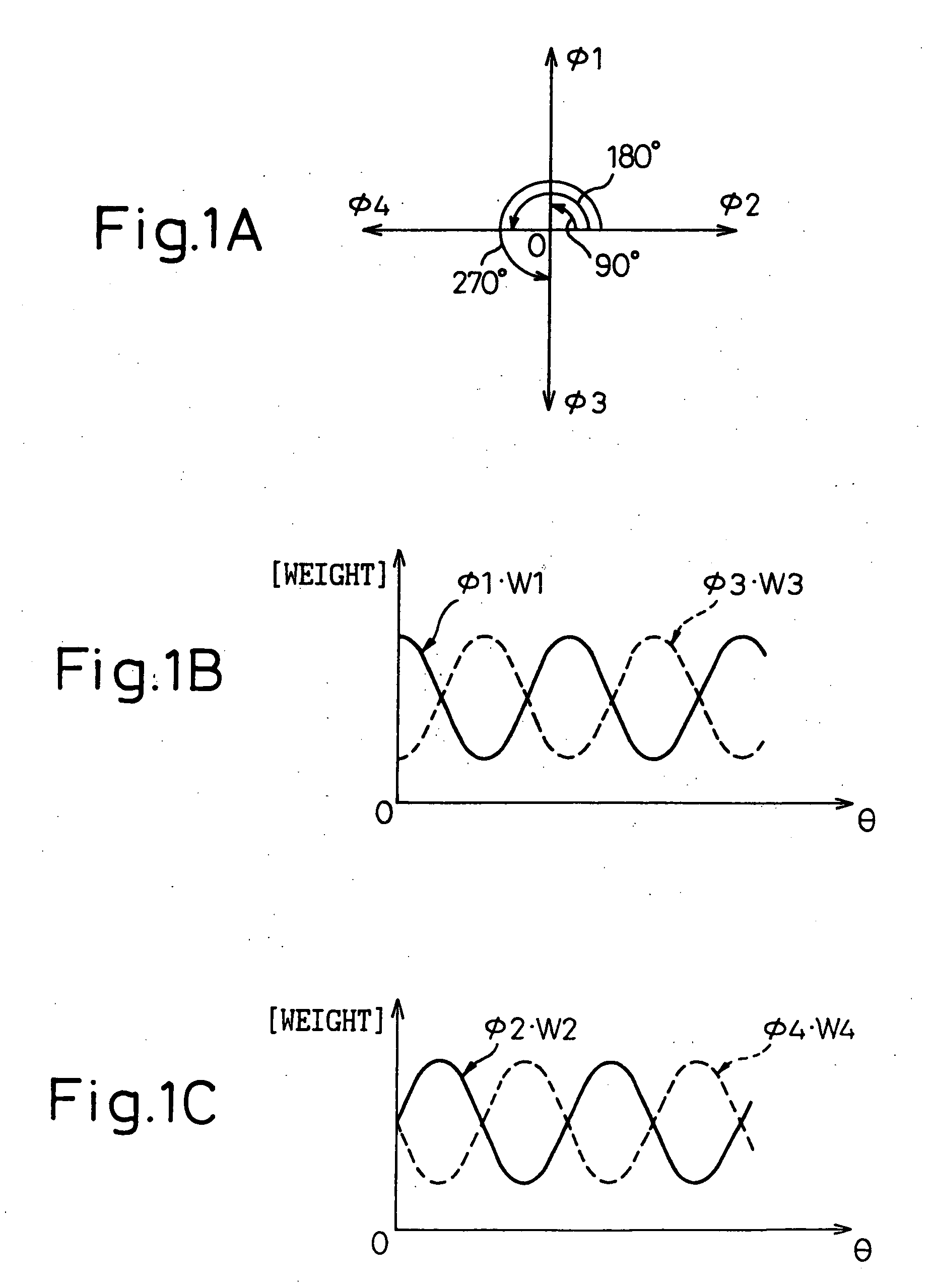

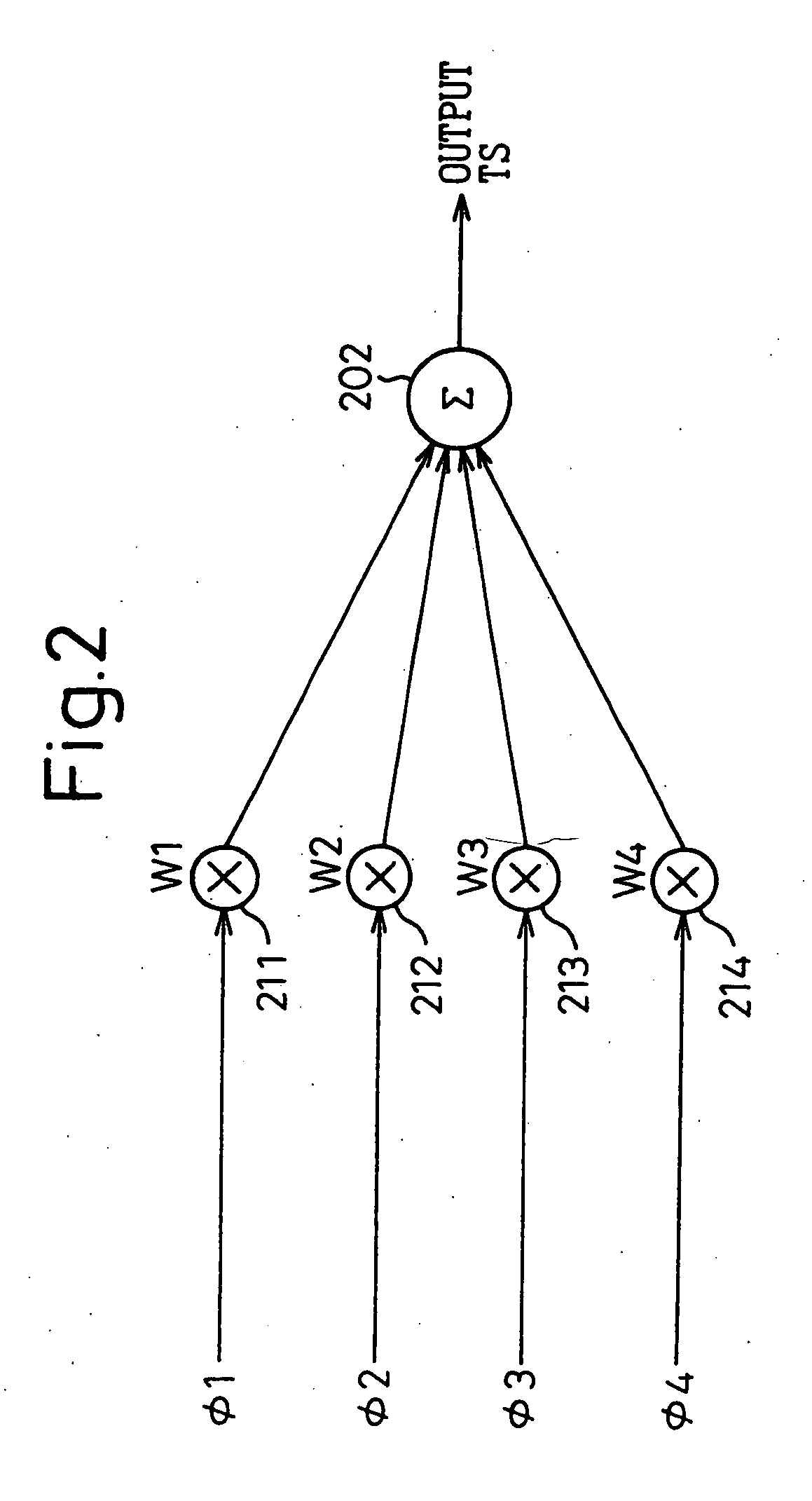

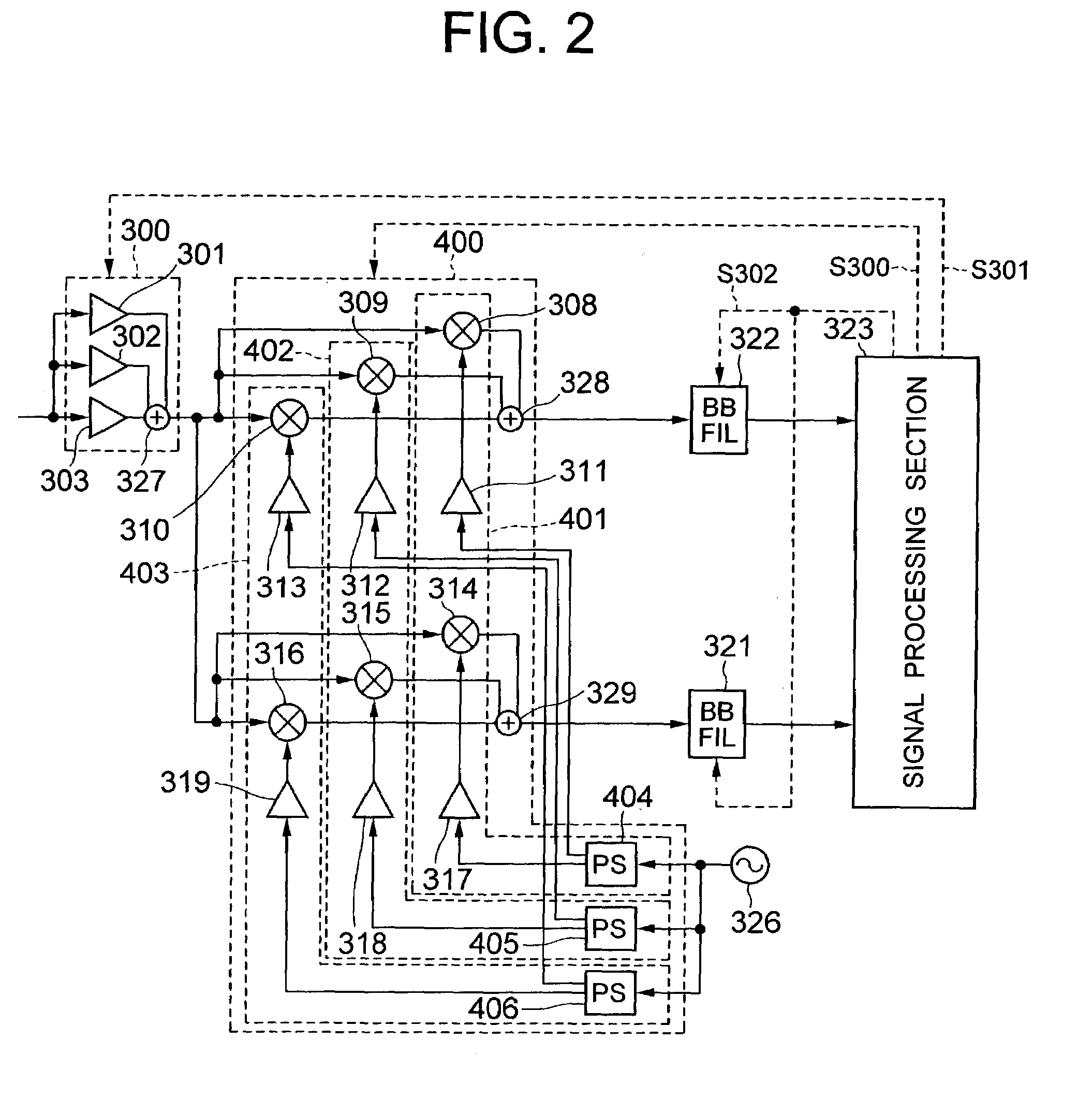

Phase-combining circuit and timing signal generator circuit for carrying out a high-speed signal transmission

InactiveUS20130314142A1Simple structureError minimizationPulse automatic controlSingle output arrangementsControl signalPhase control

A phase-combining circuit for combining cyclic timing waveforms that have been phase-controlled by control signals based on three or more input signals of different phases, has a weight signal generating circuit and a weighting circuit. The weight signal generating circuit generates weights according to the control signals, and the weighting circuit gives the weights to the respective input signals, with a positive or negative polarity for each one signal.

Owner:FUJITSU LTD

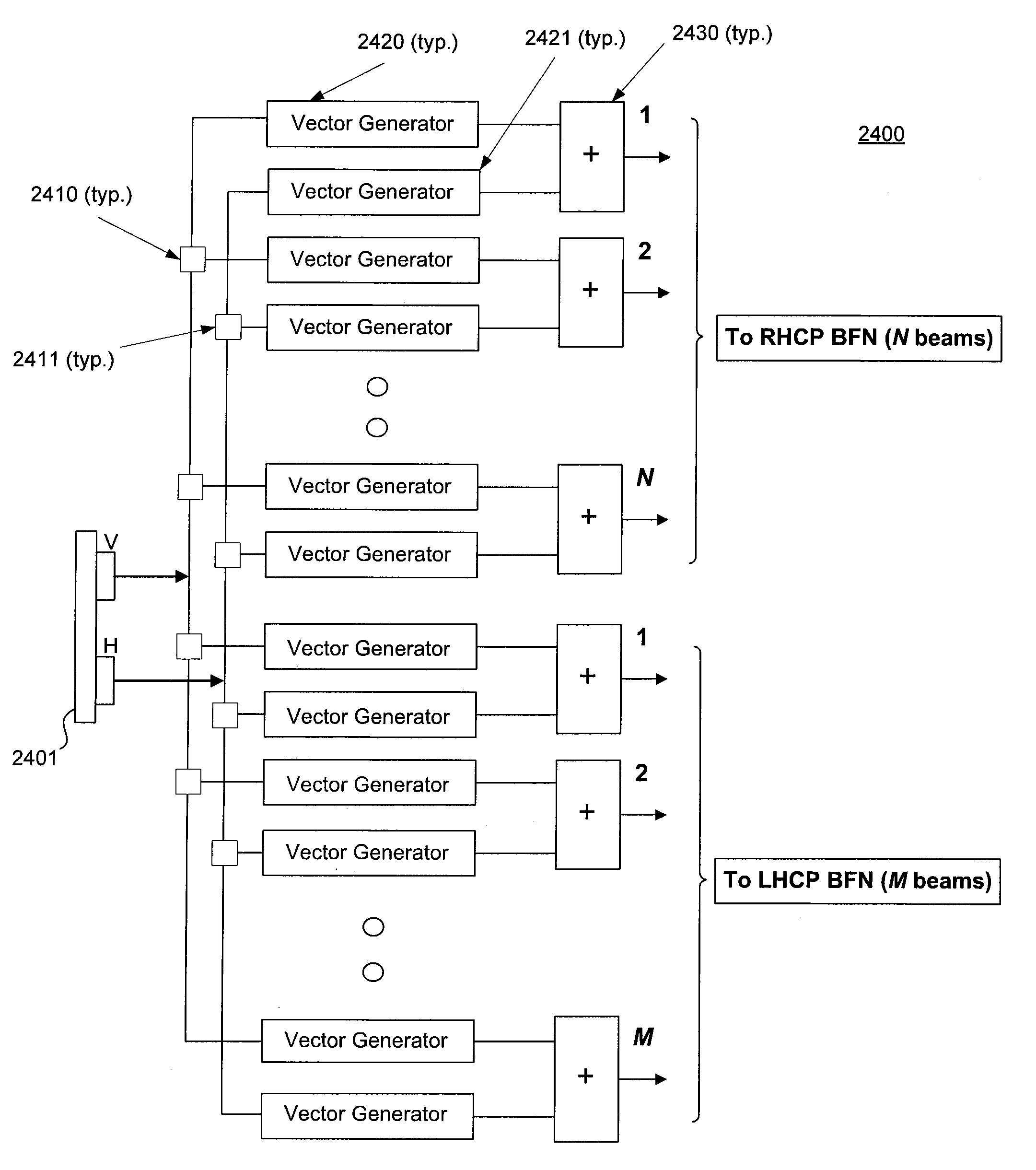

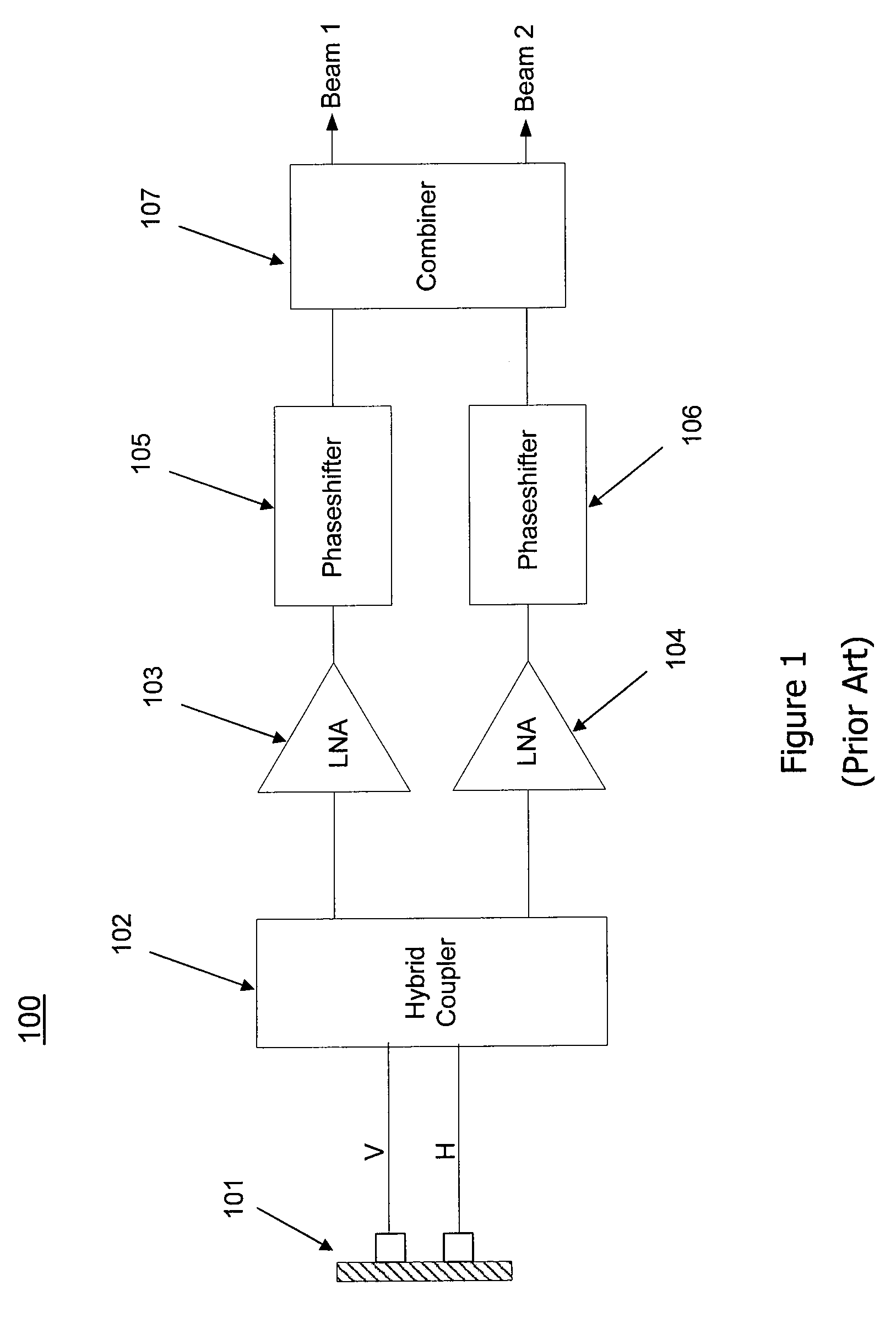

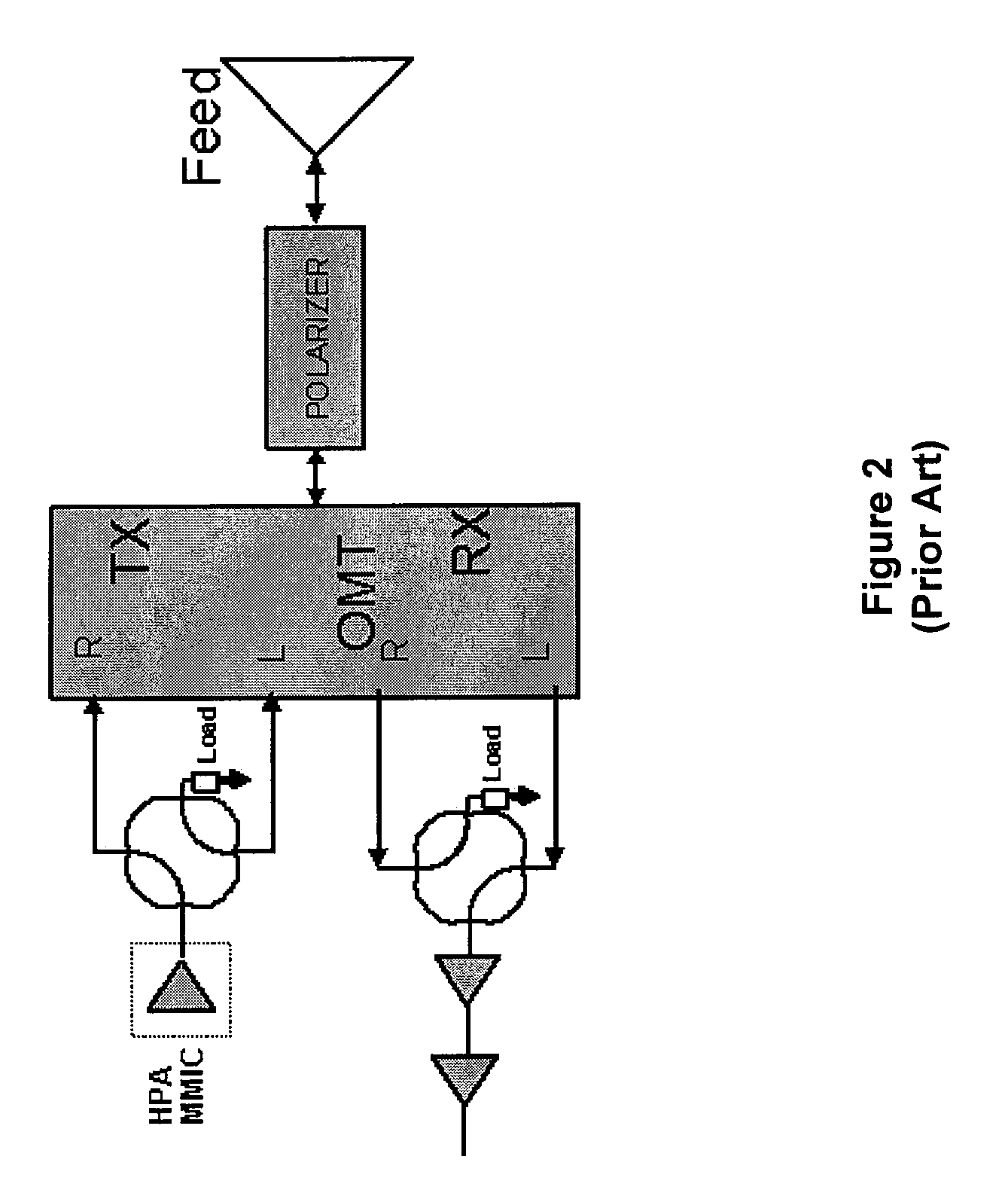

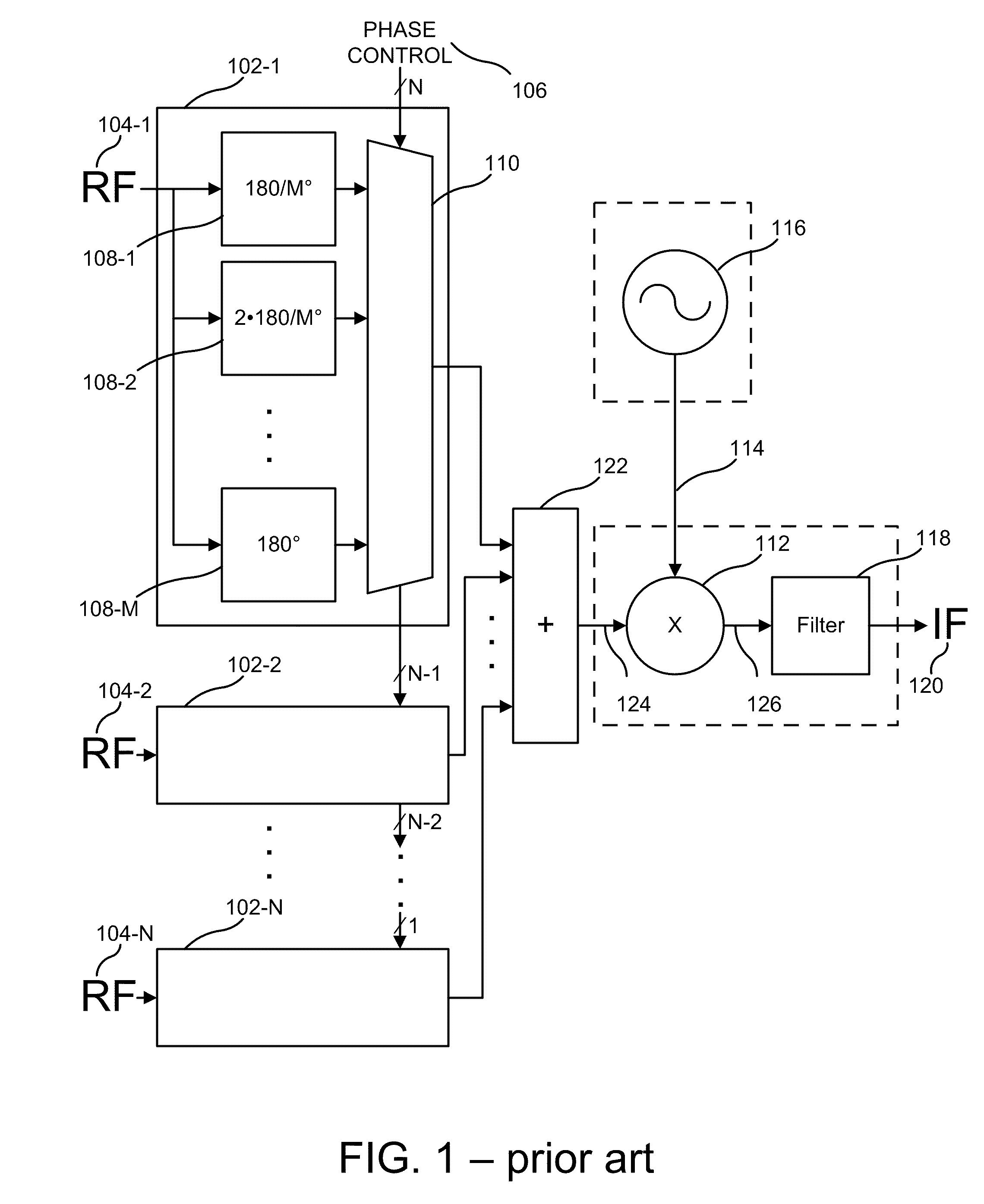

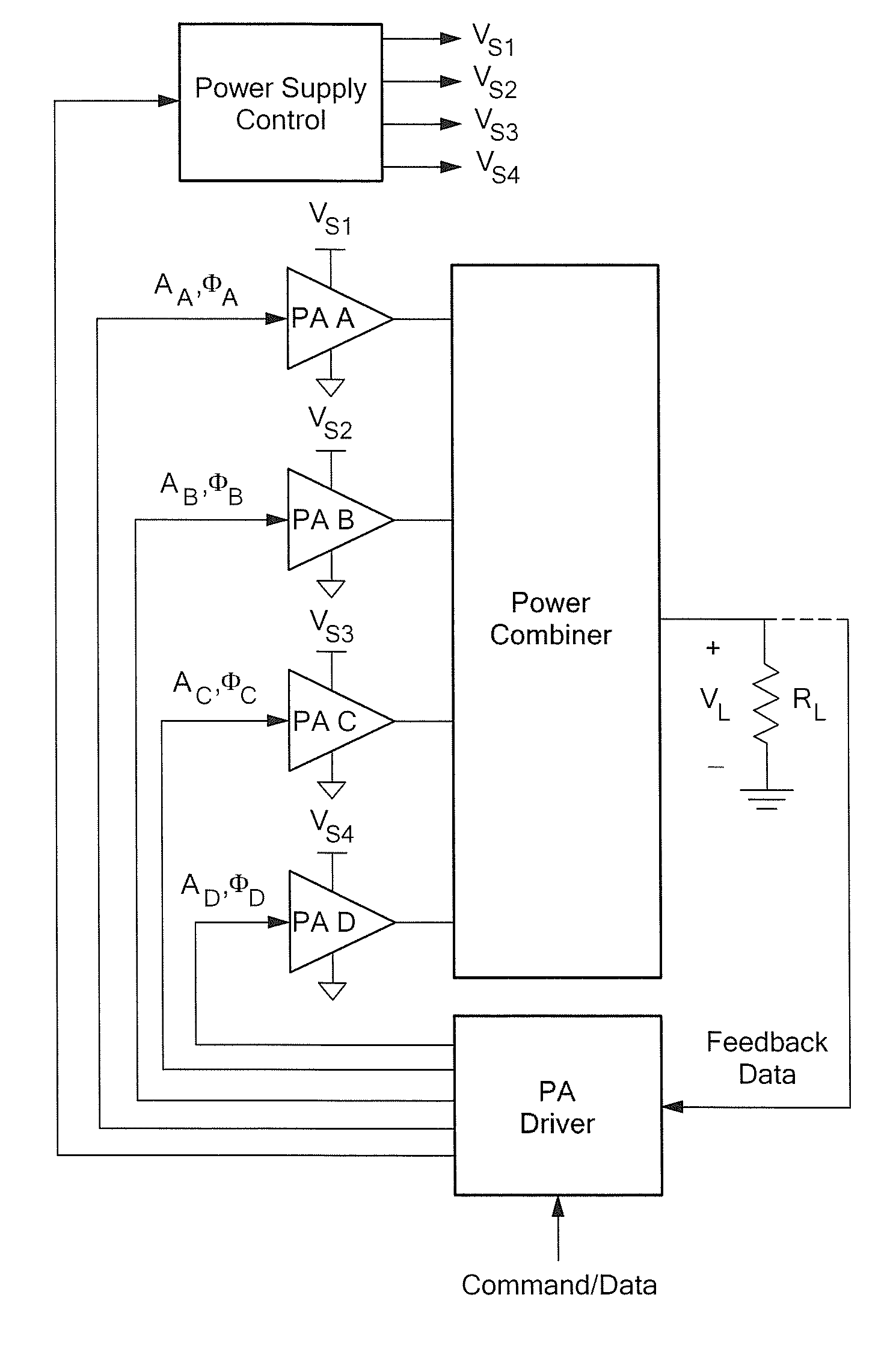

Multi-beam active phased array architecture

ActiveUS20100261440A1Increase flexibilityIncrease system capacityActive element networkComputing operation arrangementsAntenna polarizationBeam steering

In an exemplary embodiment, a phased array antenna comprises multiple subcircuits in communication with multiple radiating elements. The radio frequency signals are adjusted for both polarization control and beam steering. In a receive embodiment, multiple RF signals are received and combined into at least one receive beam output. In a transmit embodiment, at least one transmit beam input is divided and transmitted through multiple radiating elements. In an exemplary embodiment, the phased array antenna provides multi-beam formation over multiple operating frequency bands. The wideband nature of the active components allows for operation over multiple frequency bands simultaneously. Furthermore, the antenna polarization may be static or dynamically controlled at the subarray or radiating element level.

Owner:VIASAT INC

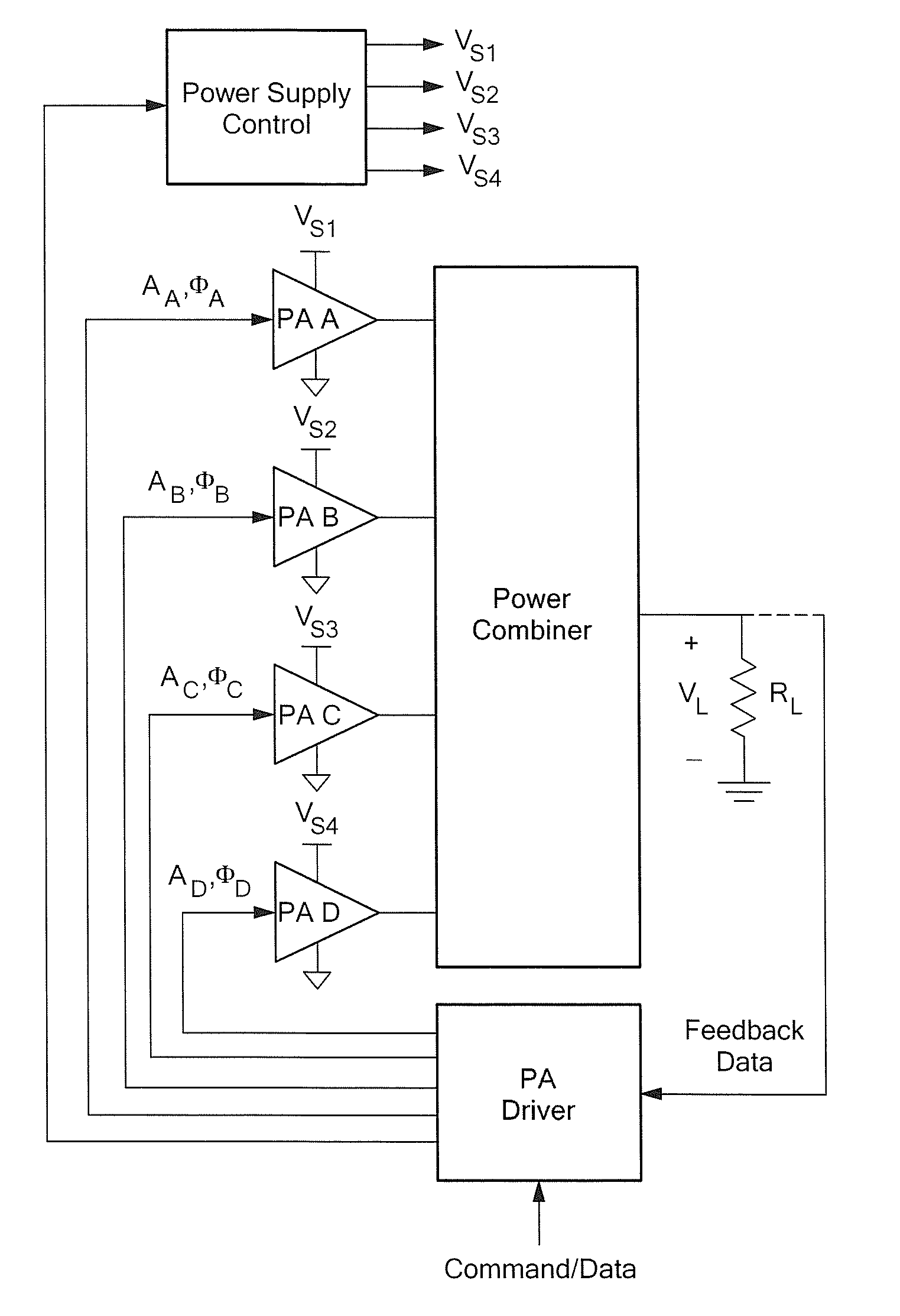

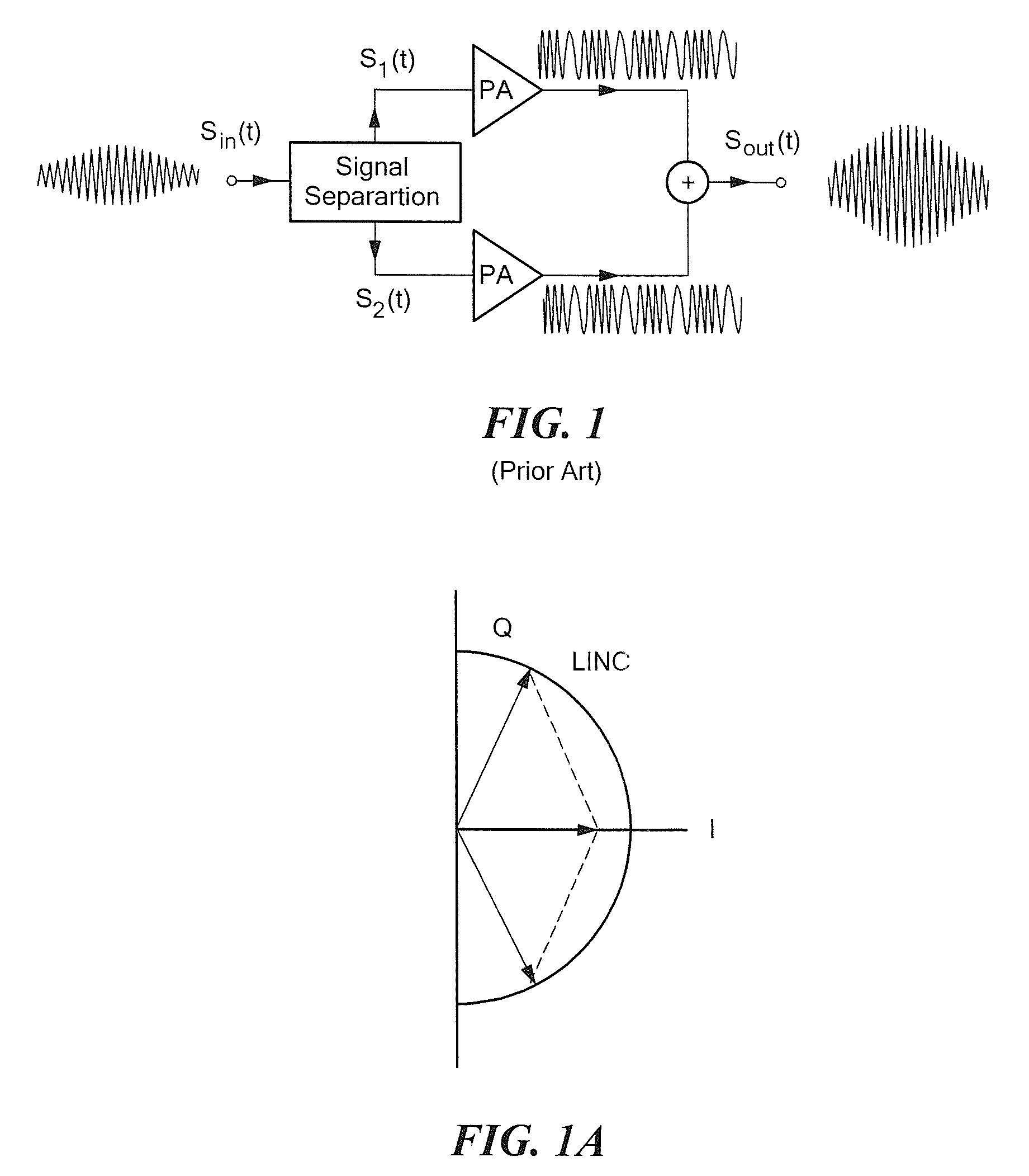

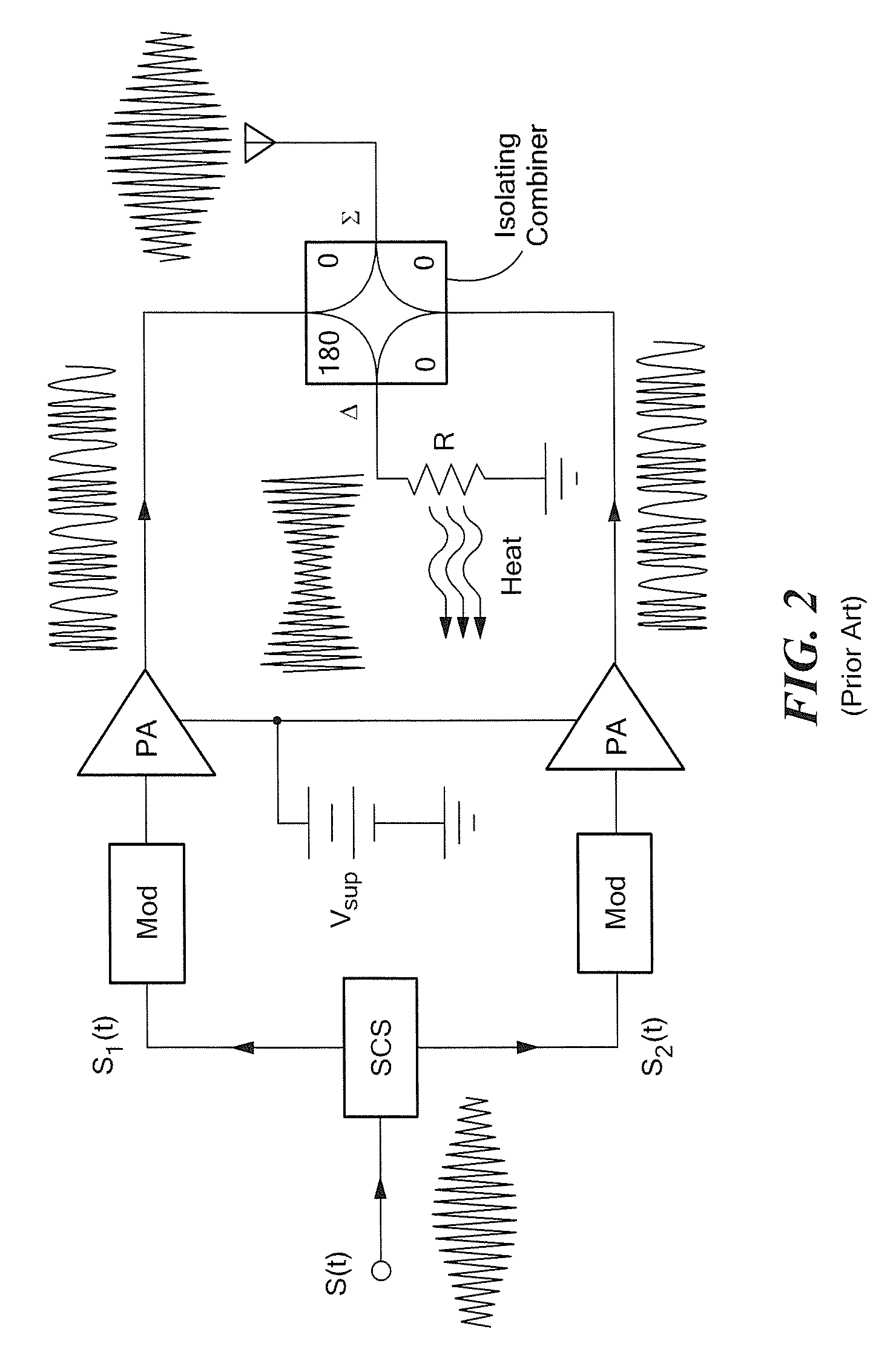

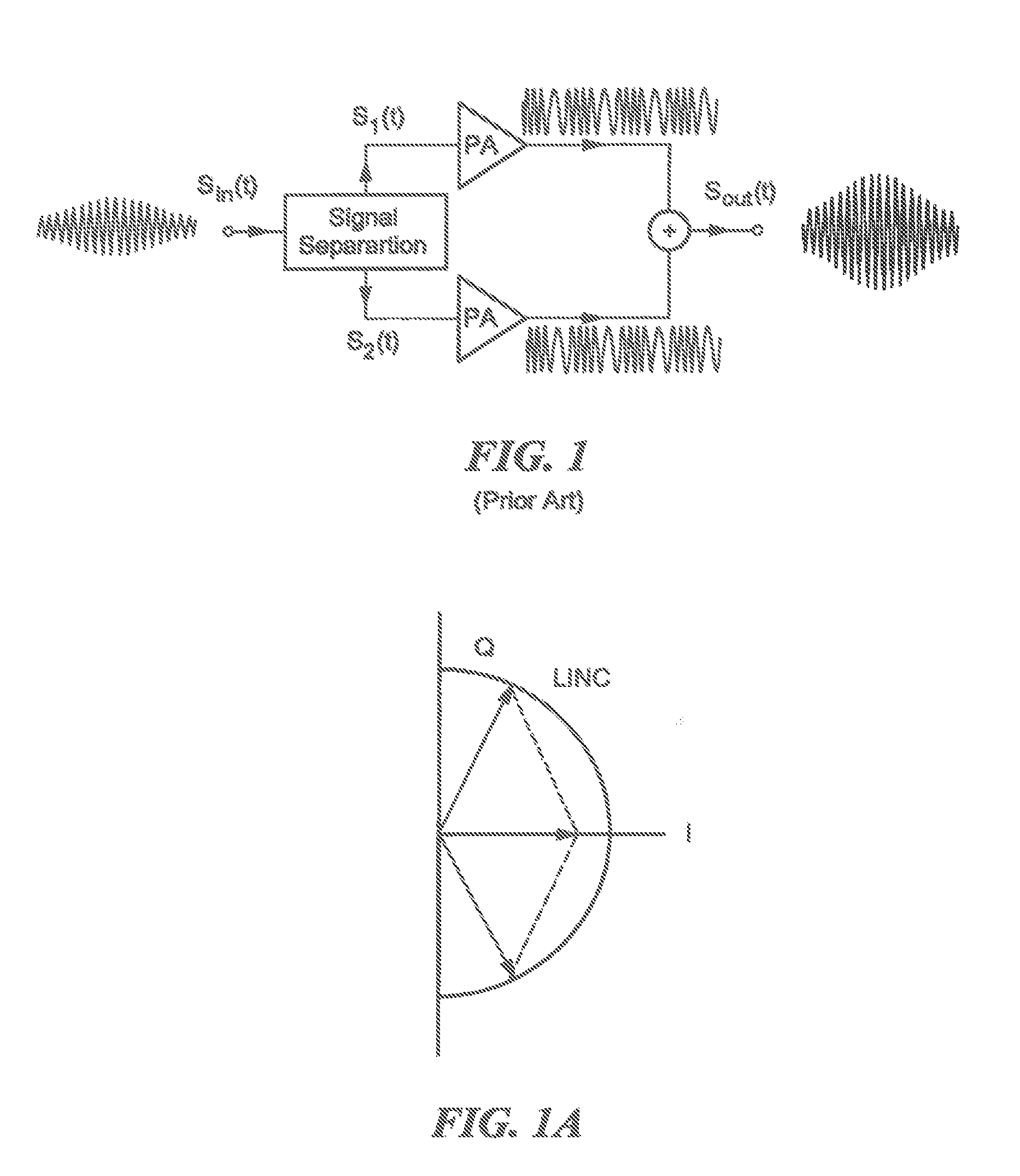

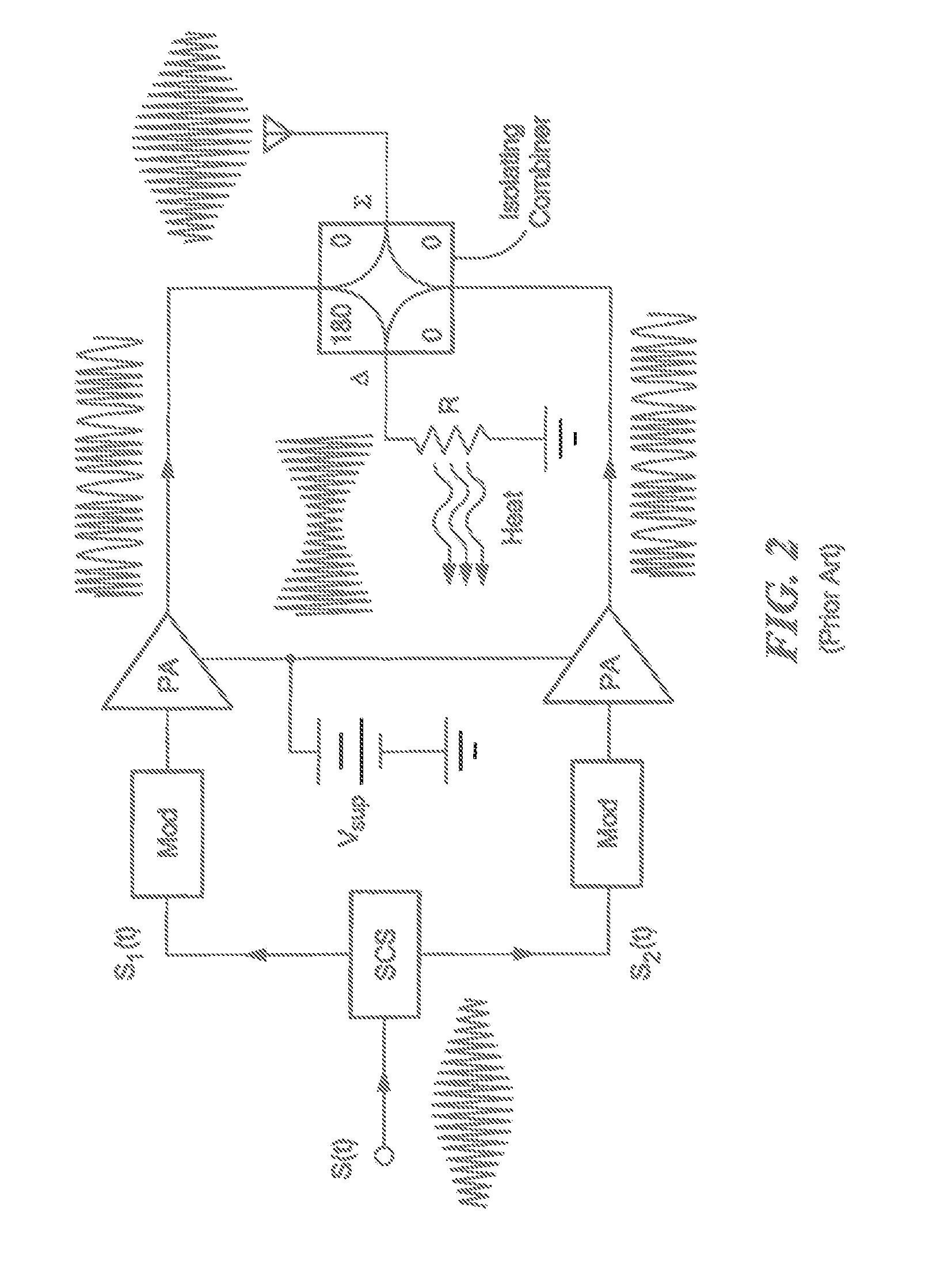

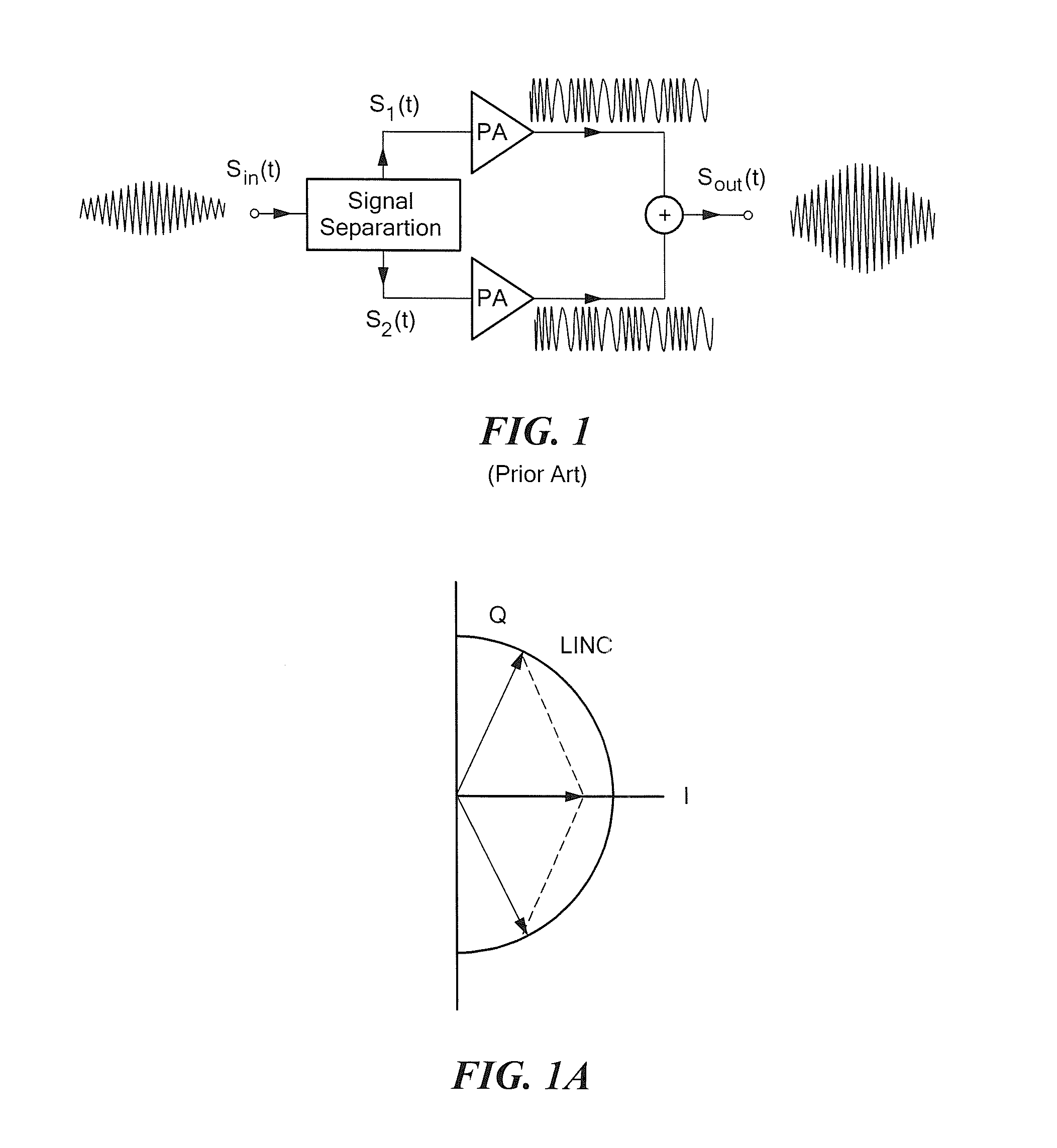

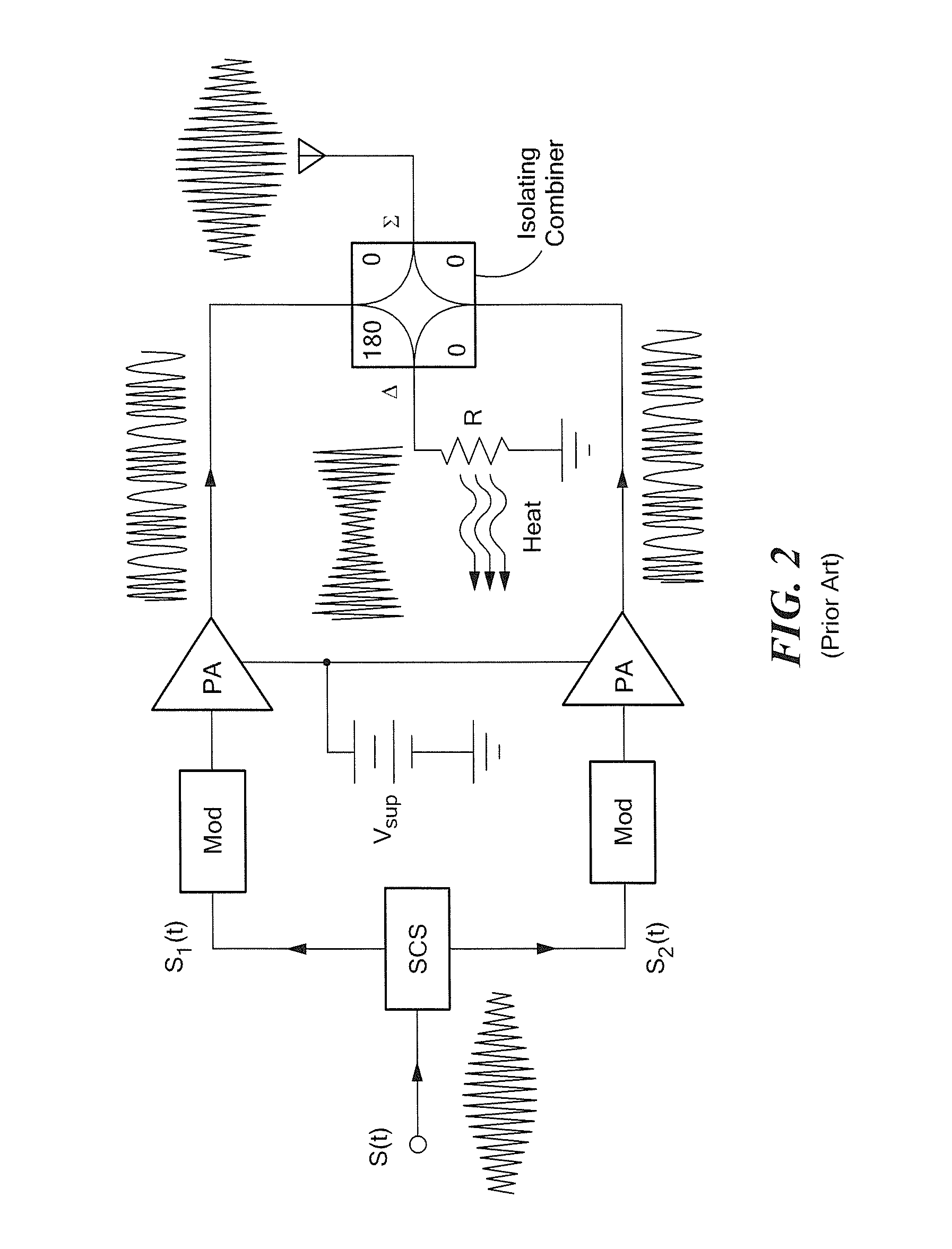

Radio-frequency (RF) amplifier circuits and related techniques

ActiveUS8451053B2Reduce lossesSmall output powerAmplifier combinationsComputing operation arrangementsEngineeringLinear amplification

Owner:MASSACHUSETTS INST OF TECH

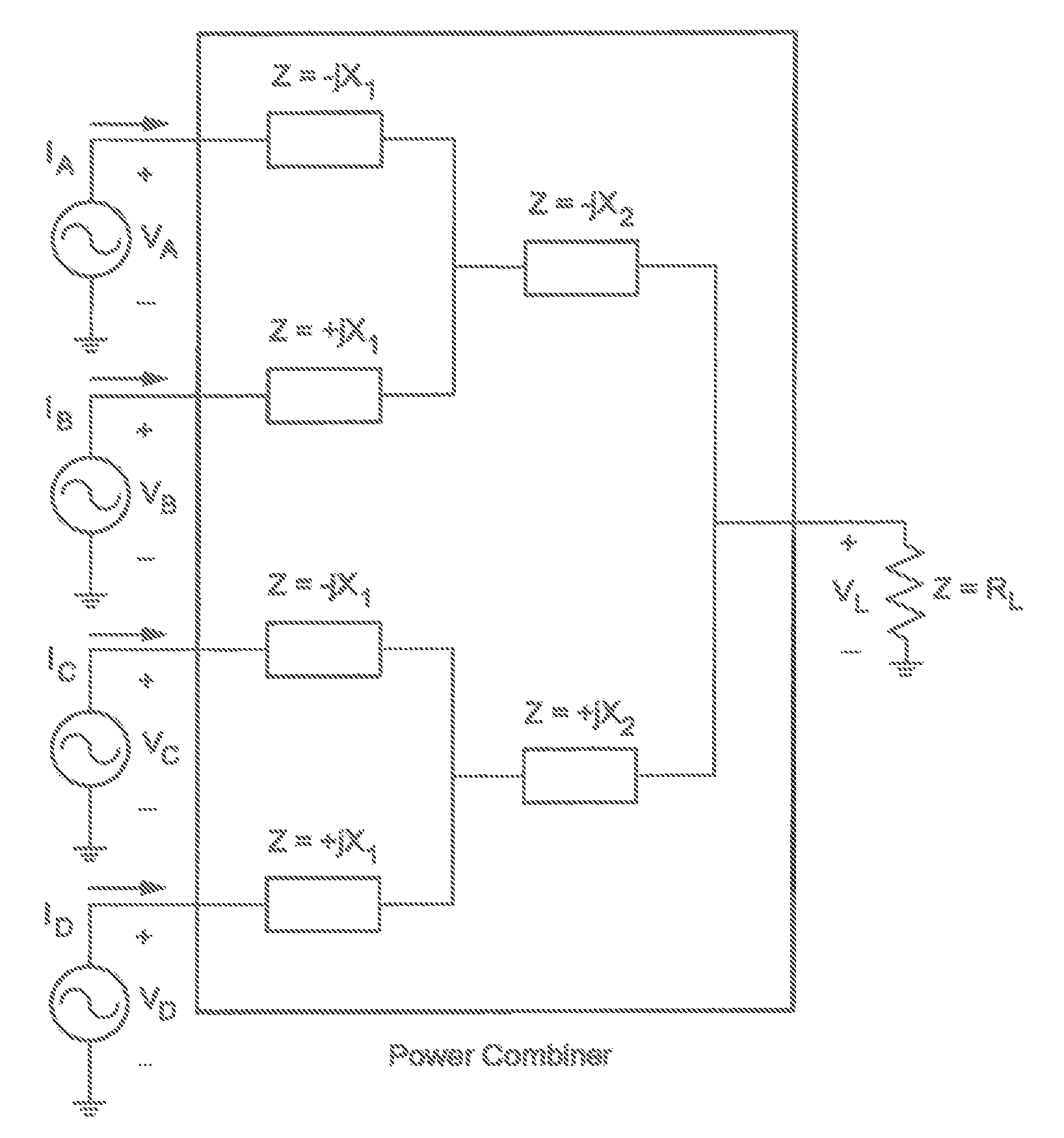

Multiway Lossless Power Combining and Outphasing Incorporating Transmission Lines

ActiveUS20130241625A1Reduce lossesSmall output powerHigh frequency amplifiersAmplifier combinationsLinear amplificationLinearity

A power combining and outphasing system and related techniques for simultaneously providing both wide-bandwidth linear amplification and high average efficiency is described. Providing linear amplification encompasses the ability to dynamically control an RF output power level over a wide range while still operating over a wide frequency bandwidth. The system and techniques described herein also operate to maintain high efficiency across a wide range of output power levels, such that a high average efficiency can be achieved for highly modulated output waveforms.

Owner:MASSACHUSETTS INST OF TECH

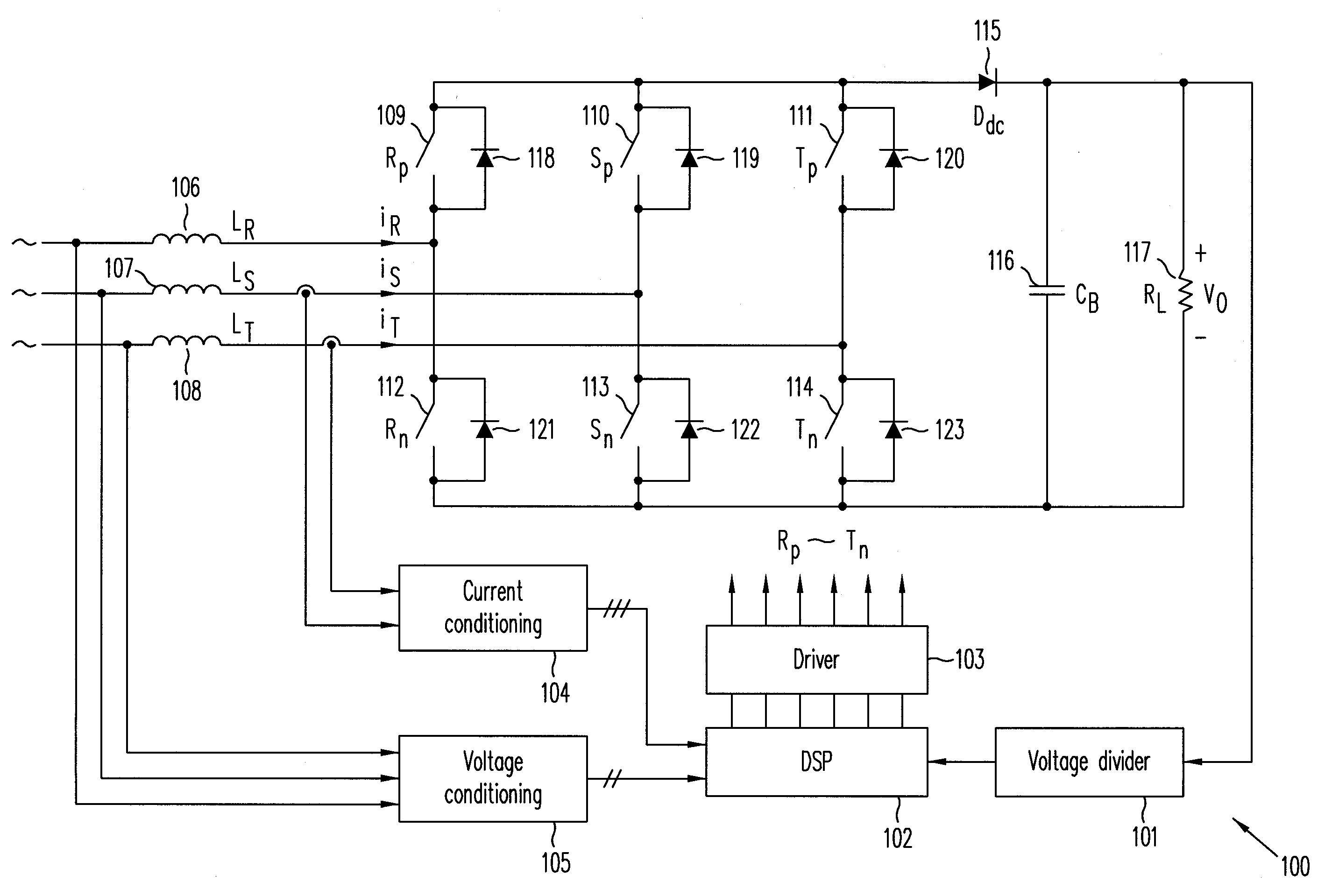

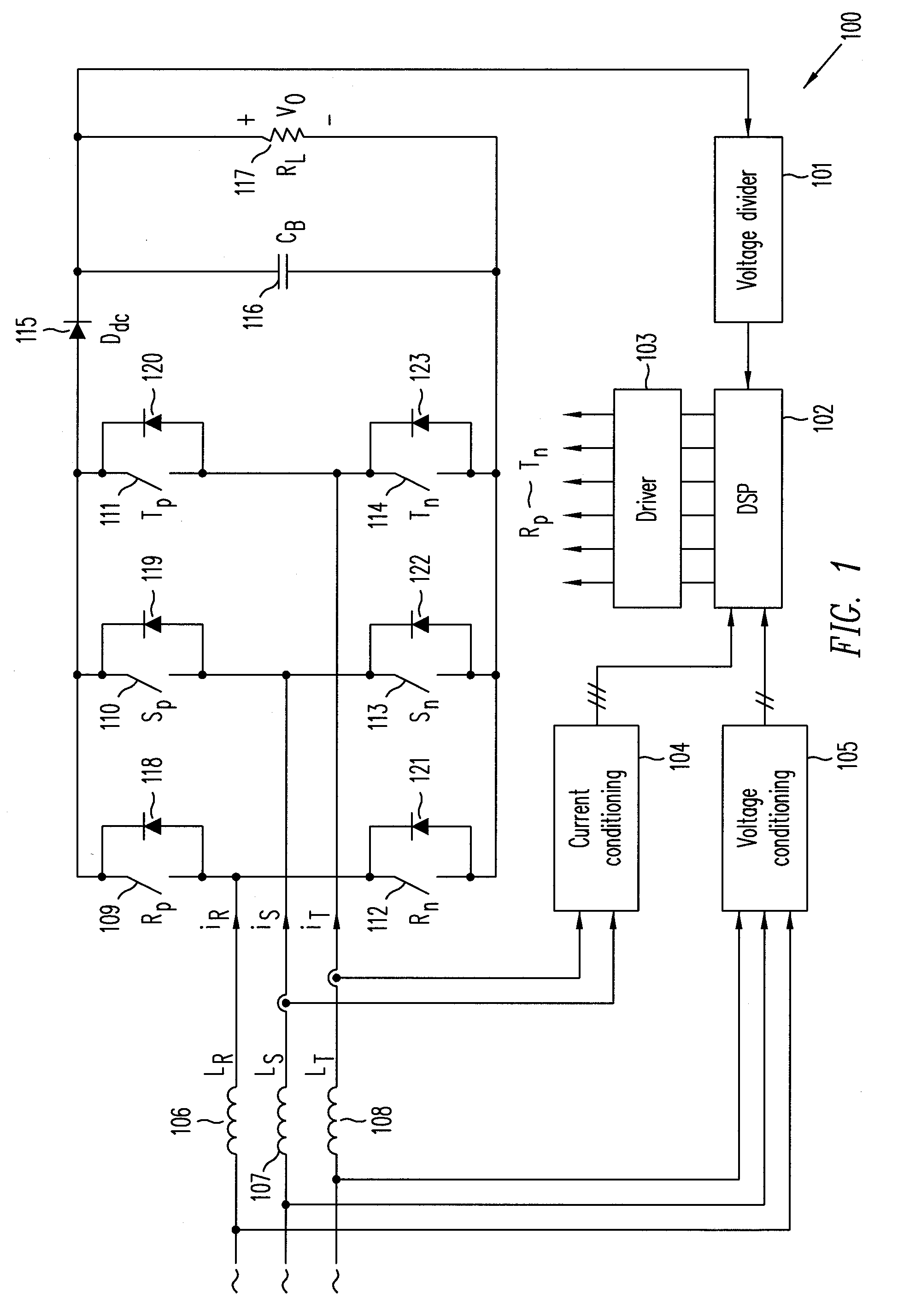

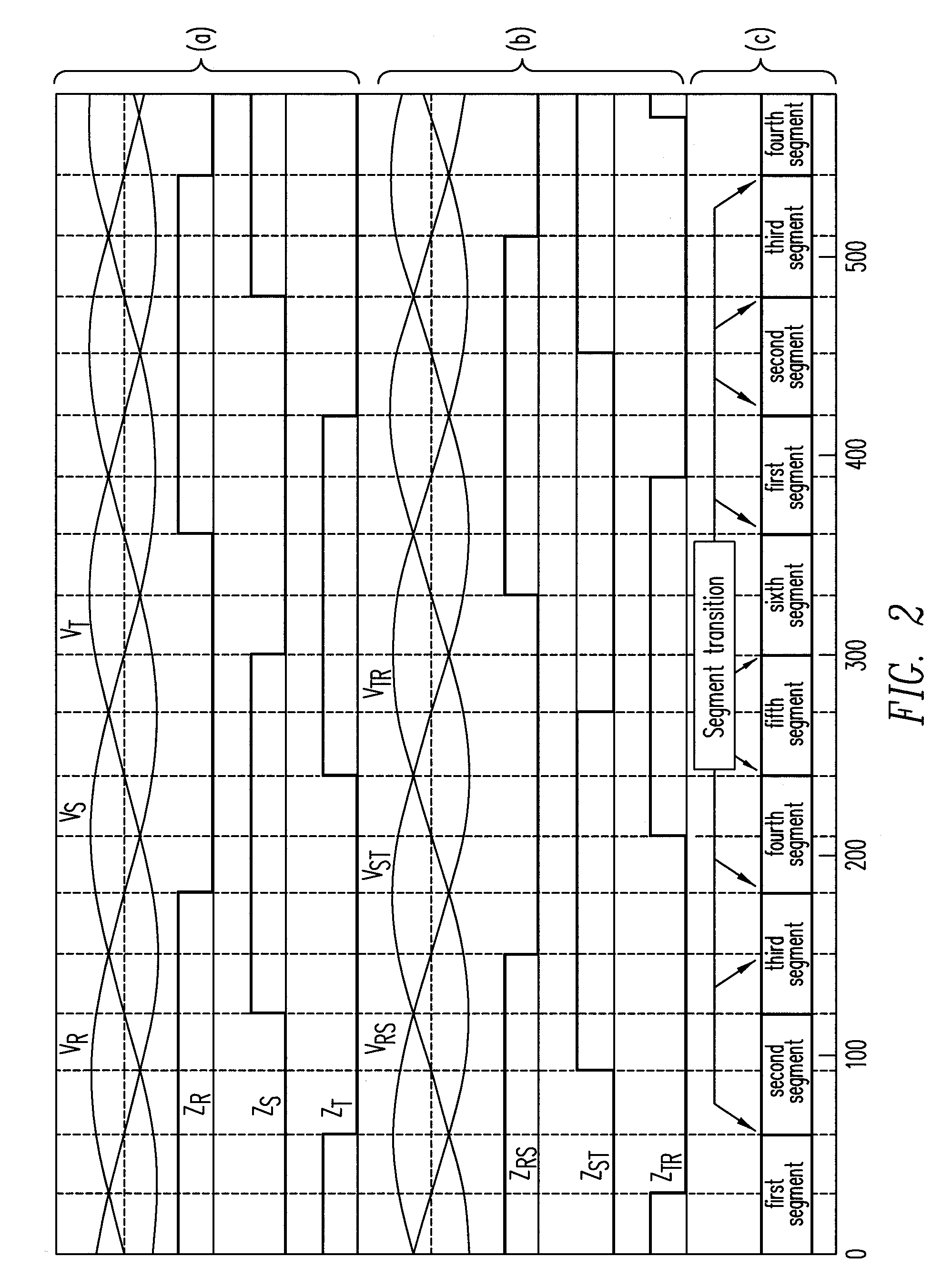

Digitally controlled three-phase pfc rectifier

ActiveUS20090122582A1Simple and practical methodPractical and convenientAc-dc conversion without reversalEfficient power electronics conversionThree-phaseInductor

A robust decoder generates an output state from input signals related to the line-voltage signals of a three-phase power system, using a segment identification method based on zero-crossings derived from line-voltage difference signals. The robust decoder includes a basic decoder that provides a current output state based on the input signals, a state table that provides a presumed previous state based on the current output state of the basic decoder, a binary feed back loop including a state element for storing a previous output state, and a selector for providing the output state based on the stored previous output state and the presumed previous state. The robust decoder may be implemented as hardware or software in a digital power converter. Such a digital power converter may include boost inductors each receiving an input line voltage signal from the three-phase power system to provide phase voltage signals, switches receiving the phase voltage signals to provide an intermediate voltage signal, the plurality of switches each being control by a driving signal, an output circuit coupled to the intermediate voltage signal to provide a rectified output voltage signal for digital power converter, and a digital control circuit receiving the input line voltages and the output voltage signal, the digital control circuit generating the driving signals to control the switches. The switches may be configured according to a state machine.

Owner:DELTA ELECTRONICS INC

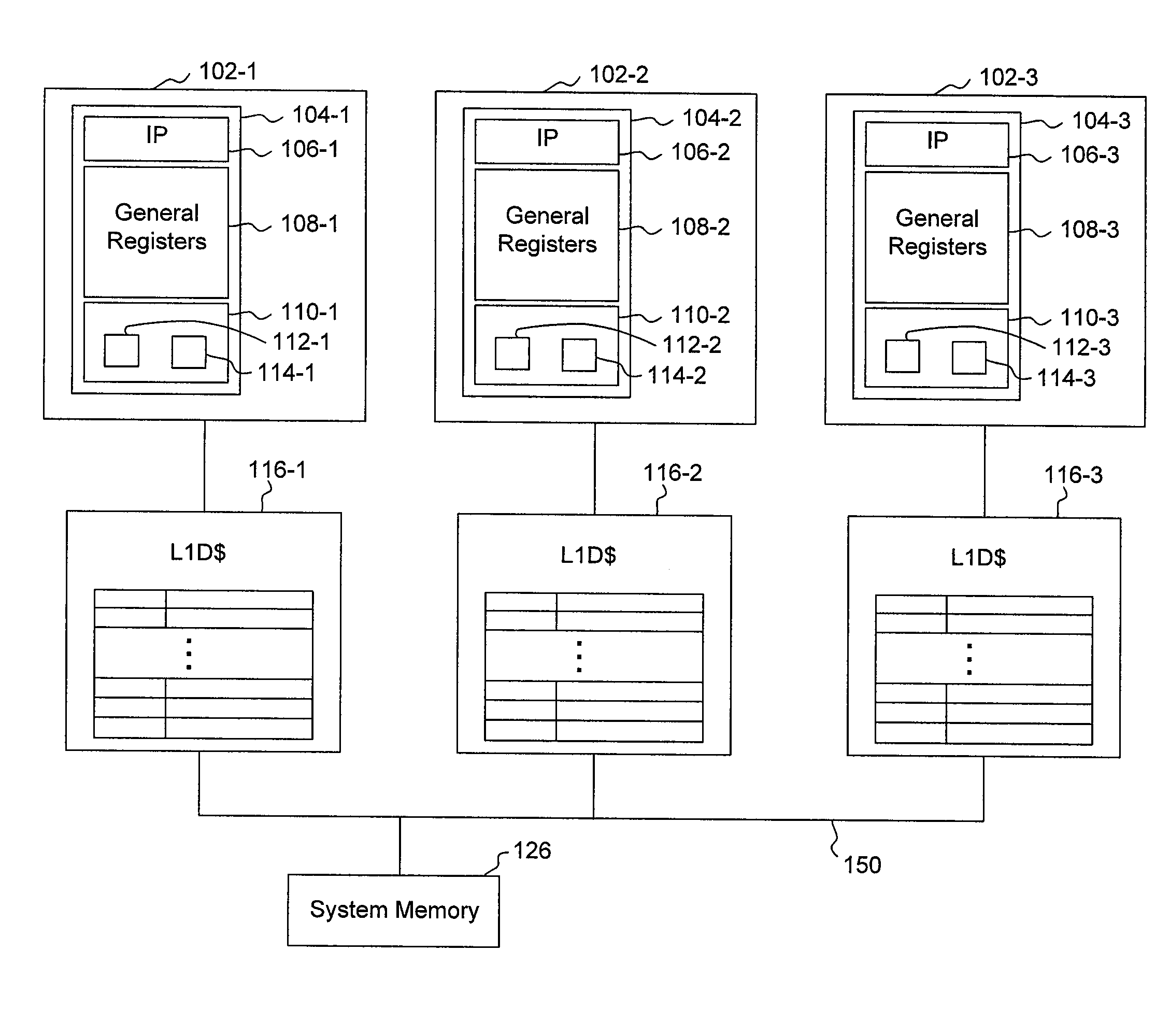

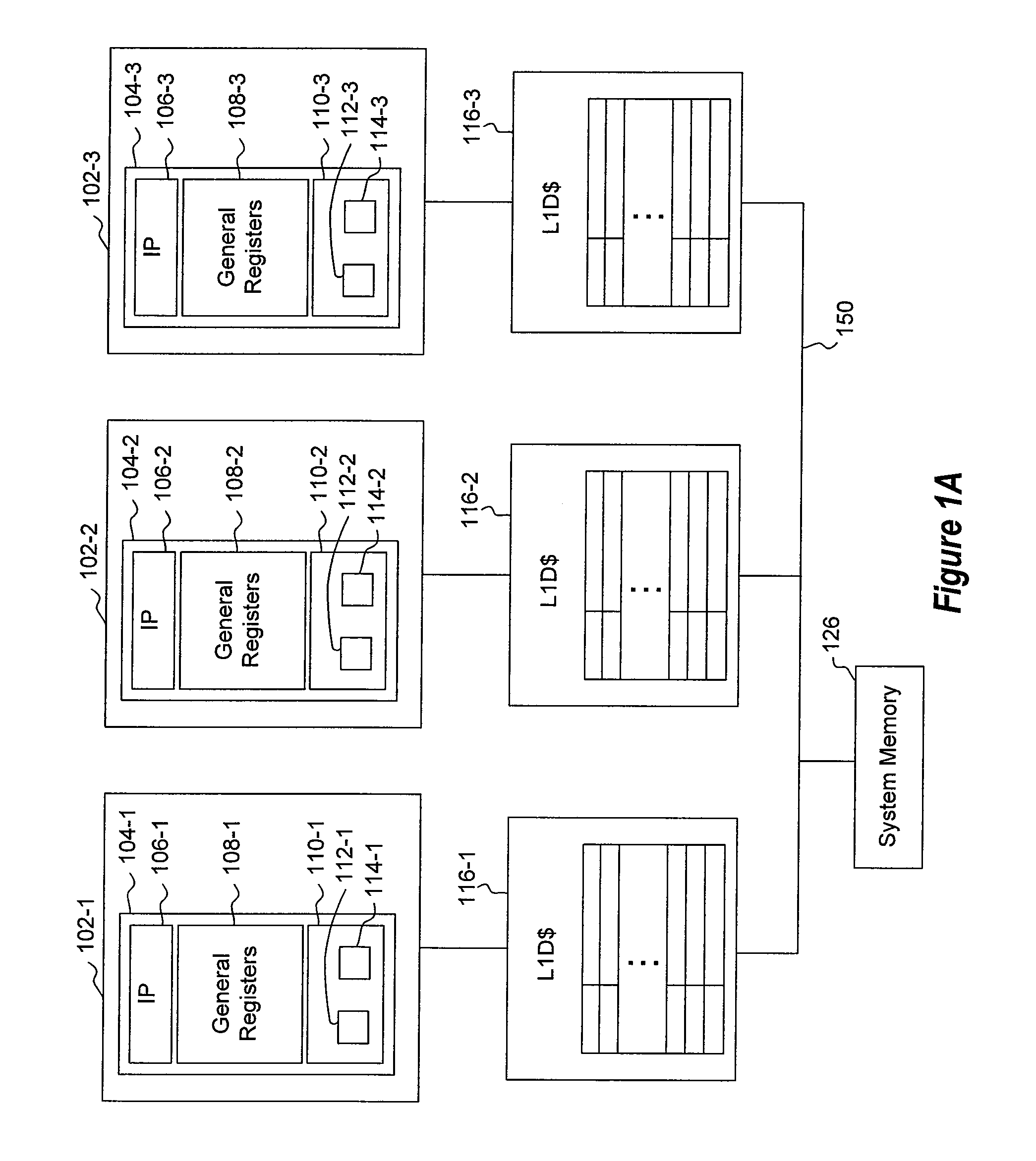

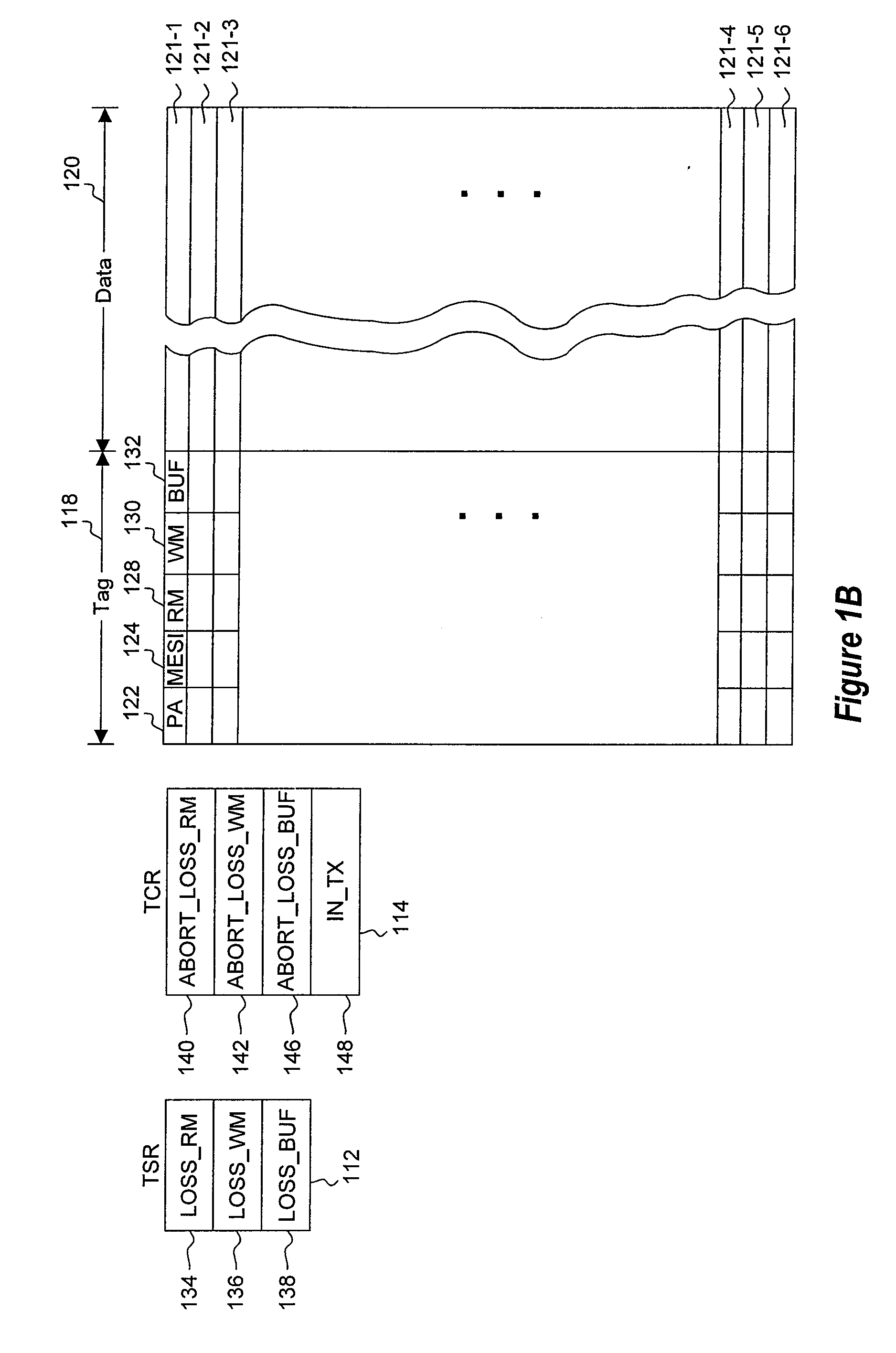

Efficient garbage collection and exception handling in a hardware accelerated transactional memory system

ActiveUS20110145304A1Memory adressing/allocation/relocationComputing operation arrangementsComputer hardwareMarshalling

Handling garbage collection and exceptions in hardware assisted transactions. Embodiments are practiced in a computing environment including a hardware assisted transaction system. Embodiments includes acts for writing to a card table outside of a transaction; handling garbage collection compaction occurring when a hardware transaction is active by using a common global variable and instructing one or more agents to write to the common global variable any time an operation is performed which may change an object's virtual address; acts for managing a thread-local allocation context; acts for handling exceptions while in a hardware assisted transaction. A method includes beginning a hardware assisted transaction, raising an exception while in the hardware assisted transaction, including creating an exception object, determining that the transaction should be rolled back, and as a result of determining that the transaction should be rolled back, marshaling the exception object out of the hardware assisted transaction.

Owner:MICROSOFT TECH LICENSING LLC

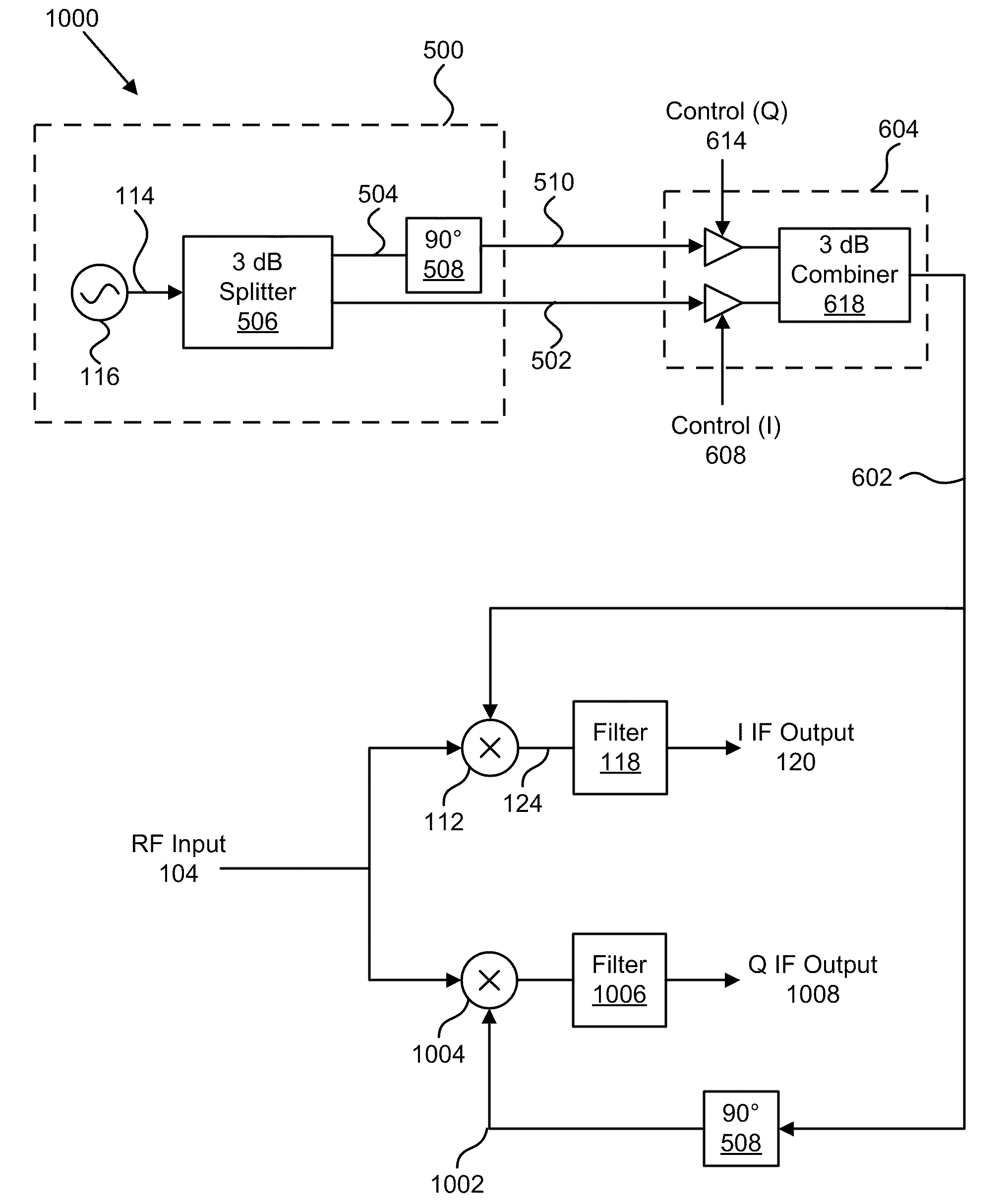

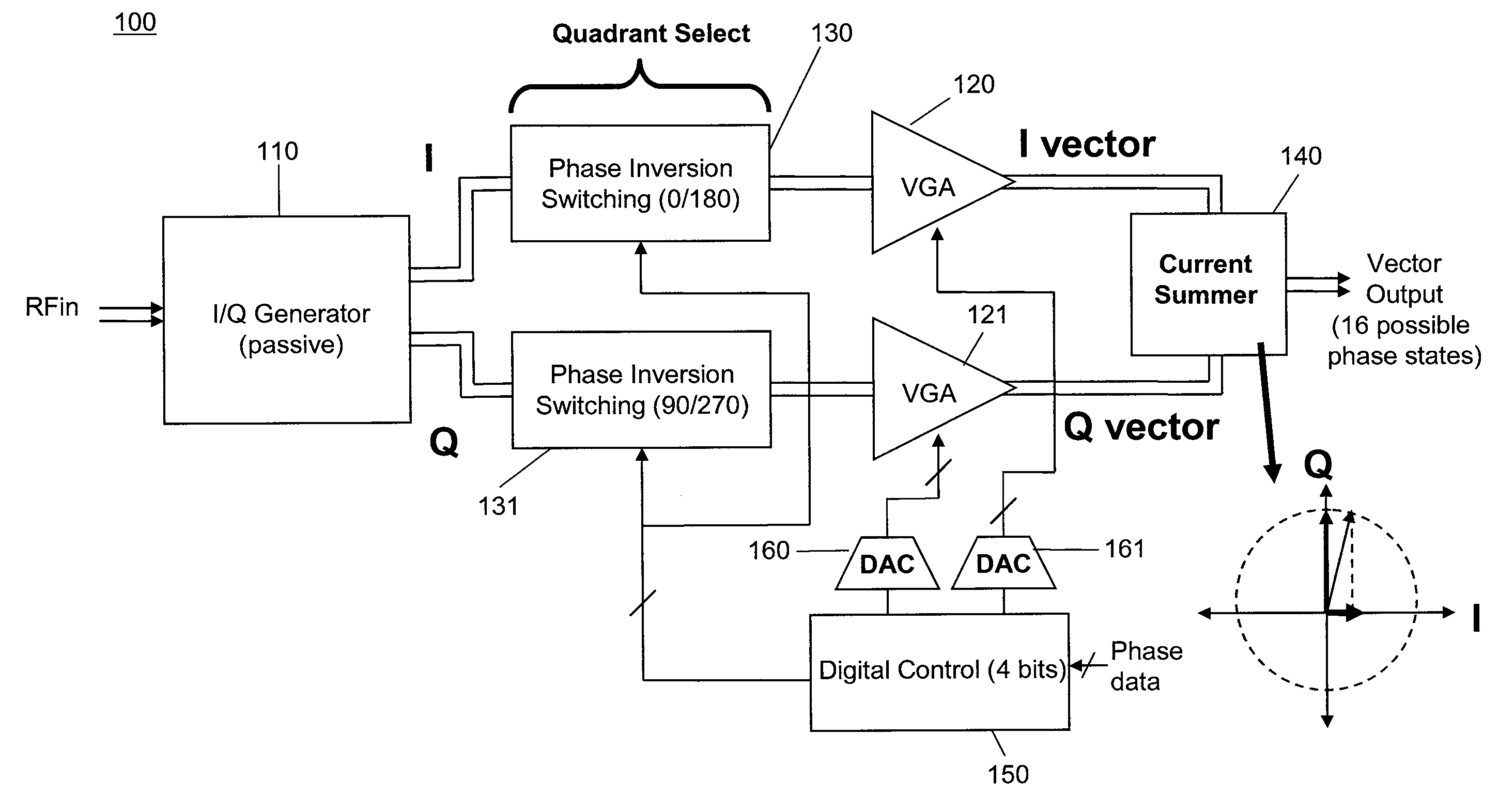

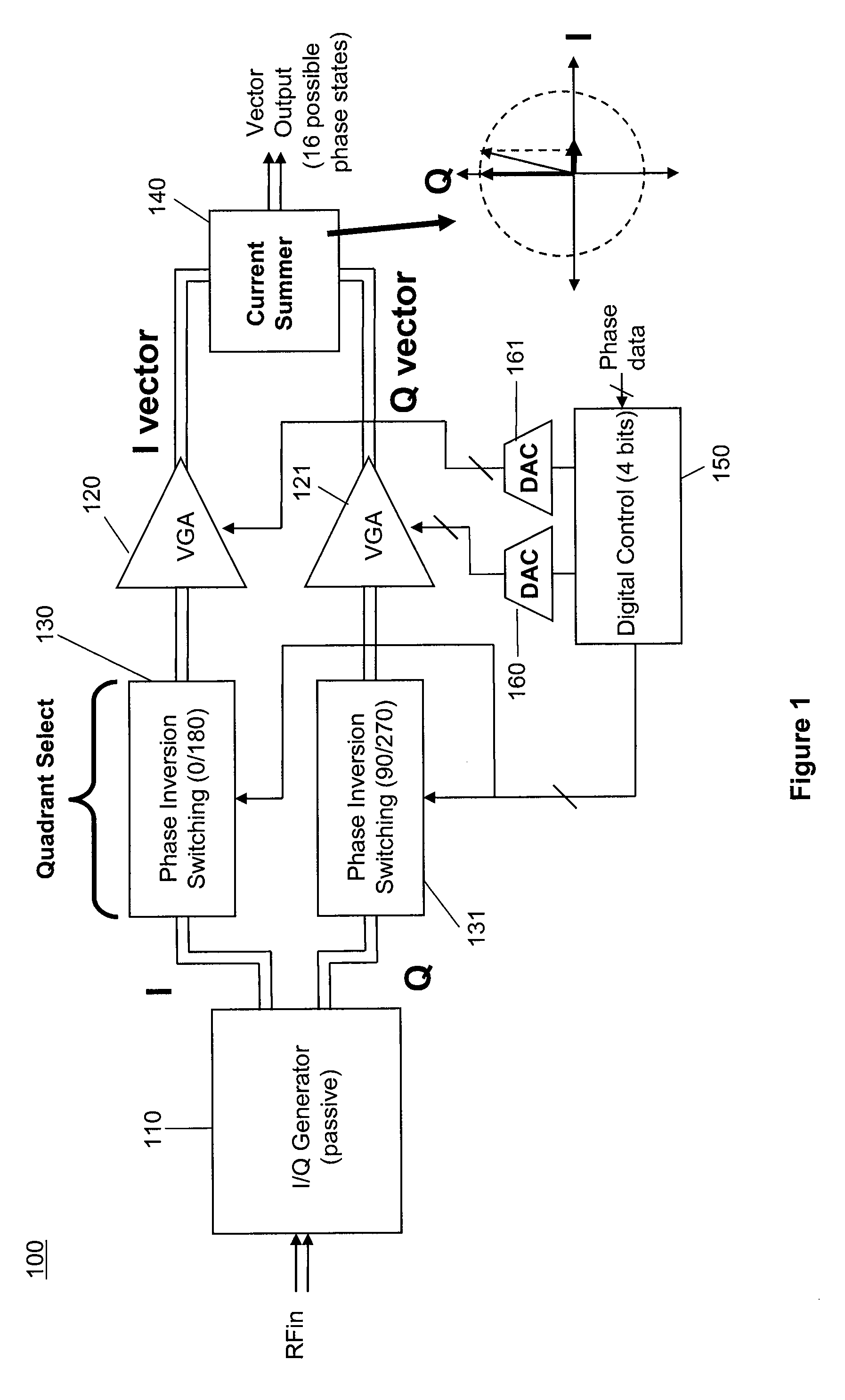

Apparatus, system, and method for integrated phase shifting and amplitude control of phased array signals

ActiveUS20100013527A1Simplifies reduces costSimpler variable phase and amplitude shifterModulation transferencePulse automatic controlPhase shiftedAmplitude control

An apparatus, system, and method are disclosed for phase shifting and amplitude control. A two-phase local oscillator generates an in-phase sinusoidal signal of a fixed frequency and a quadrature sinusoidal signal of the fixed frequency having a ninety degree phase shift from the in-phase sinusoidal signal. A signal generator receives the in-phase sinusoidal signal and the quadrature sinusoidal signal and generates a controllable sinusoidal signal of the fixed frequency. The controllable sinusoidal signal has a variable amplitude and a shiftable phase. A mixer varies the amplitude and shifts the phase of an input signal by mixing the input signal with the controllable sinusoidal signal to generate an output signal. The input signal and the output signal carry phase and amplitude information required for phased array signal processing. Either a receiver or a transmitter may be implemented using the present invention.

Owner:OVZON LLC

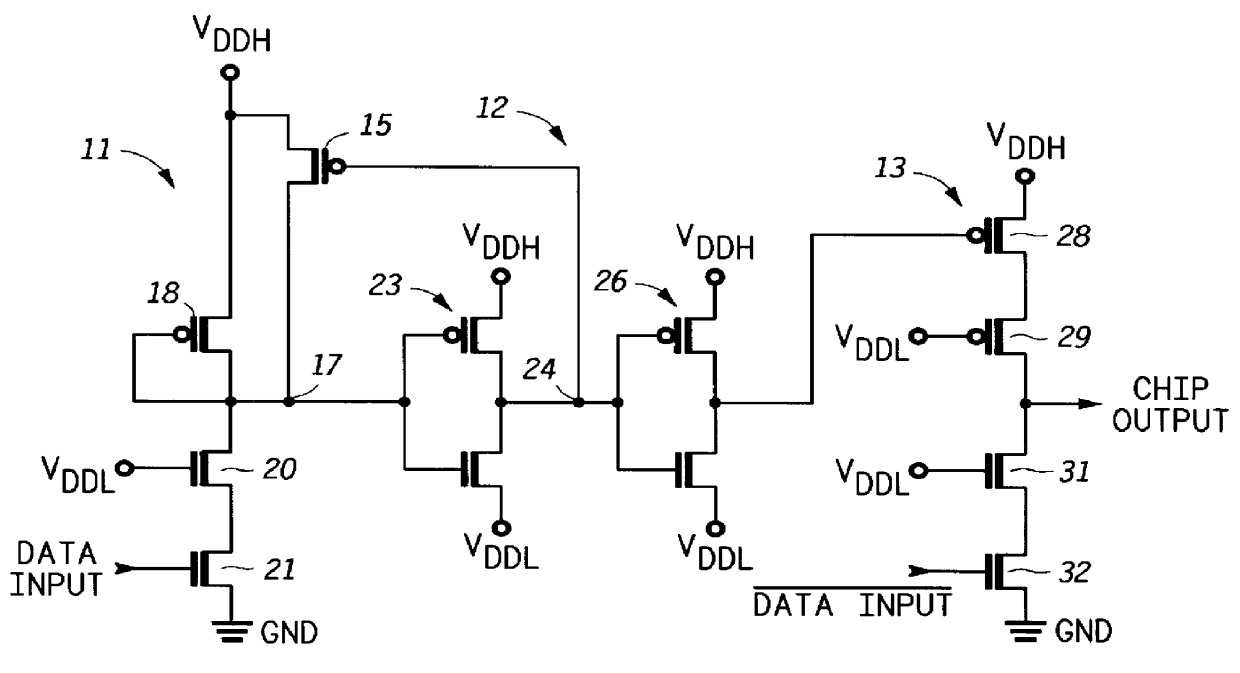

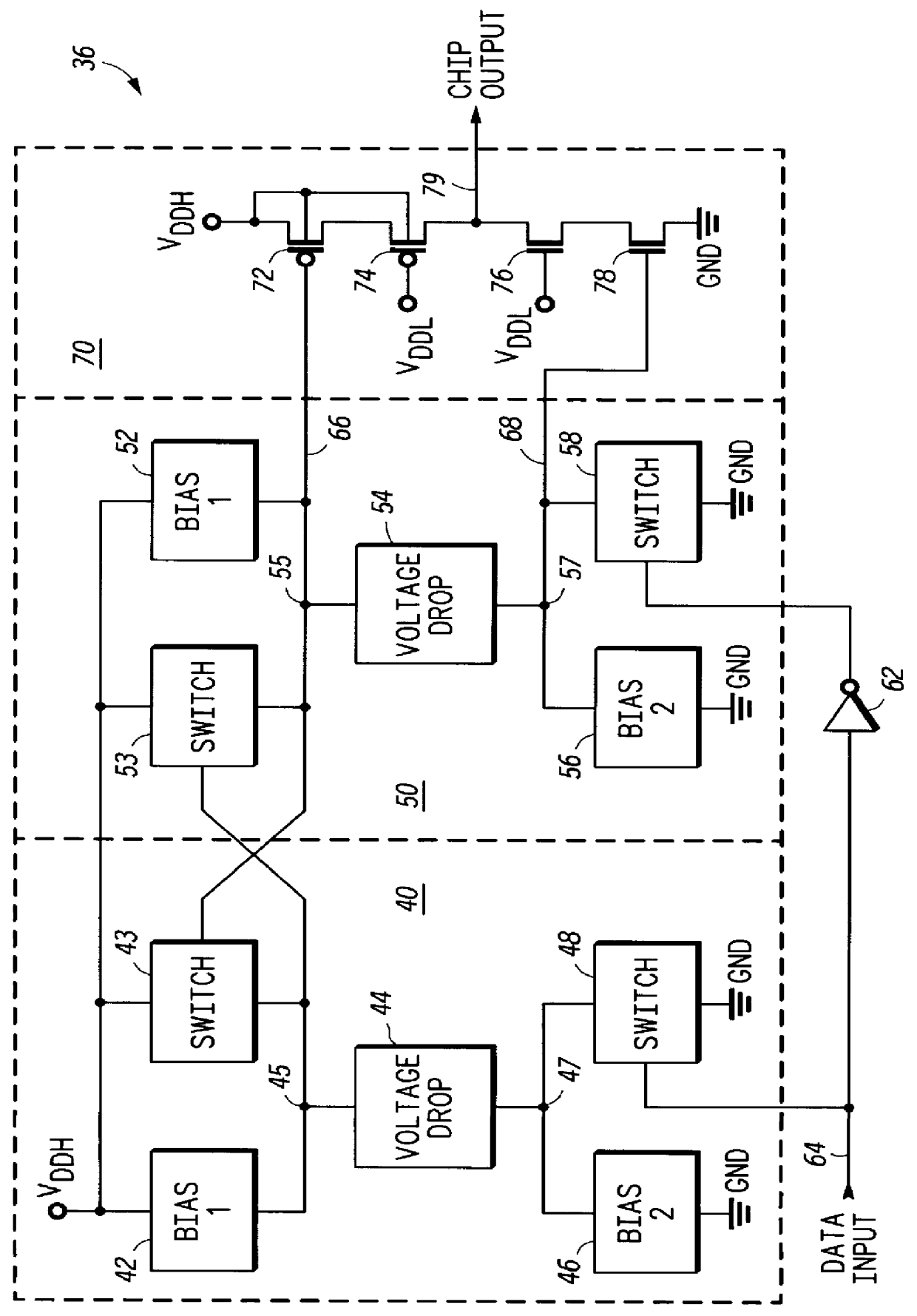

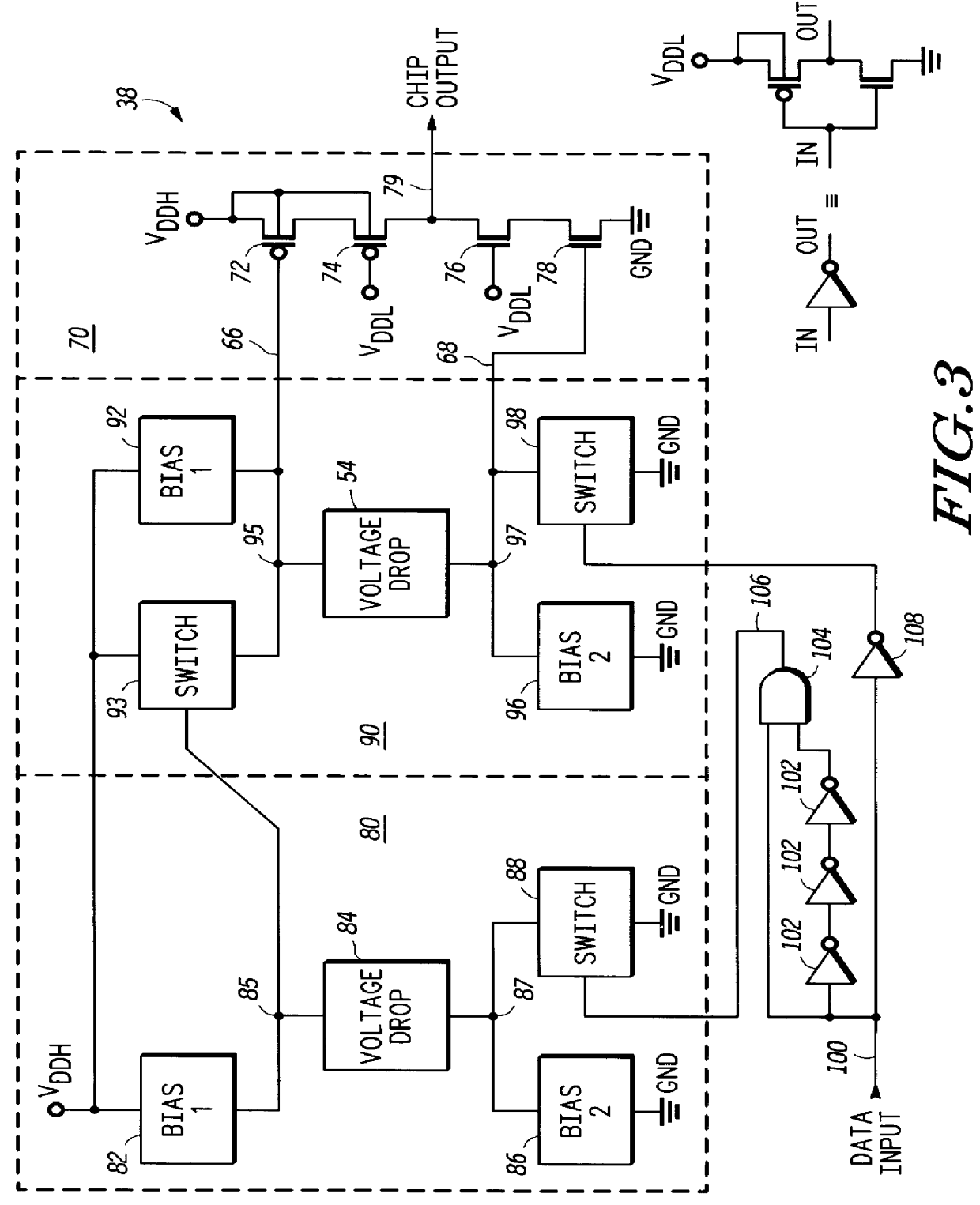

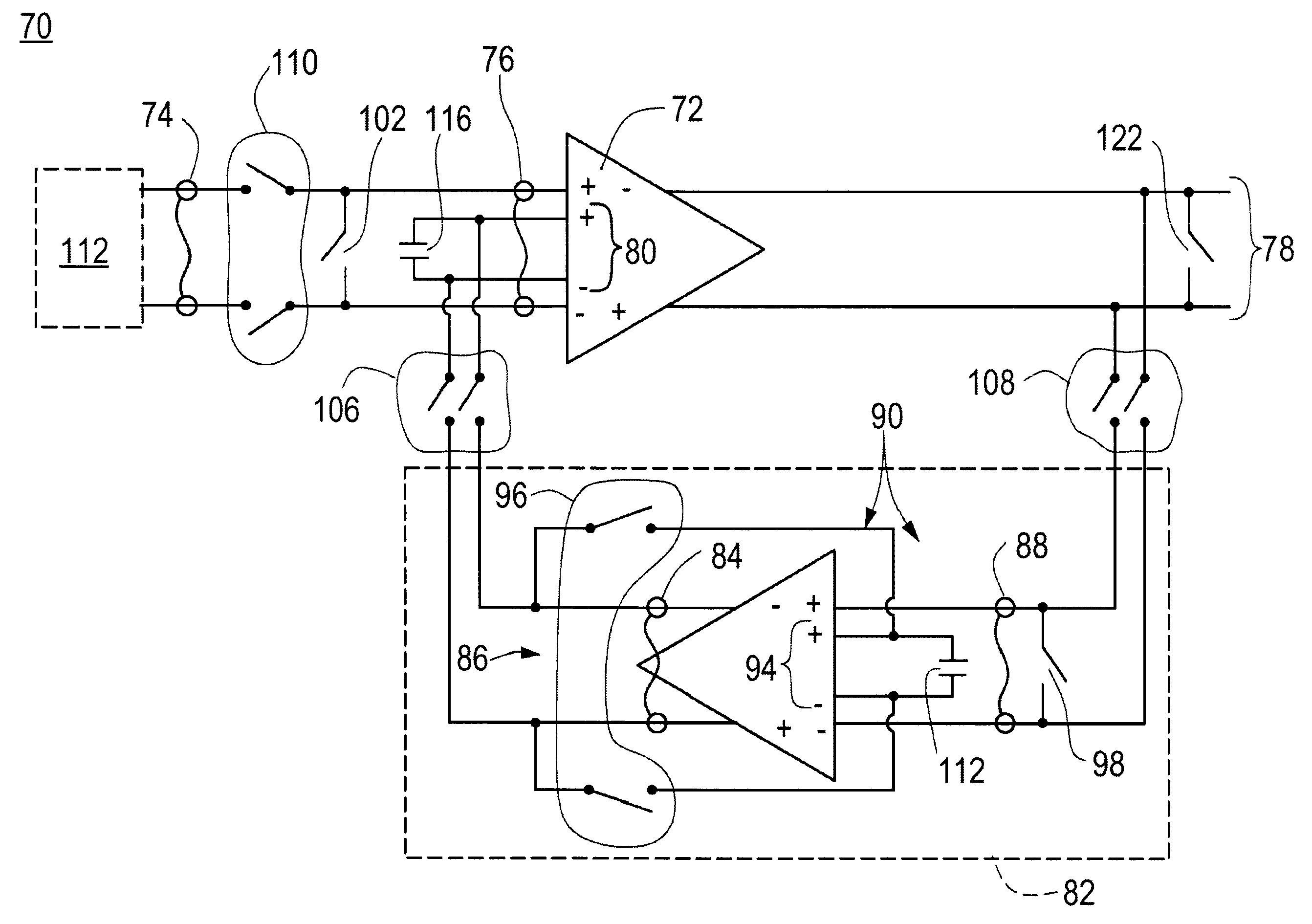

Digital output buffer for multiple voltage system

An output buffer translates digital input signals which toggle between ground and V.sub.DDL to signals which toggle between ground and V.sub.DDH. The technology dielectric breakdown voltage limit is less than the magnitude of V.sub.DDH, such that use of a traditional output stage would subject transistors' dielectrics to voltages which exceed their dielectric breakdown limit, and would thus be damaged. Predrive circuits (40, 50) control output stage (70) transistors' (72, 78) gates, and voltage dropping circuits control output stage (70) transistors (74, 76). These control signals are generated specifically to maximize output stage transistor drive strengths, thereby minimizing output stage size. Output buffer functions when V.sub.DDL =V.sub.DDH, and its performance is V.sub.DDL independent. Temperature compensation is incorporated into the output buffer by deliberately offsetting temperature effects on output stage transistor drive strengths. Desired performance and temperature compensation are accomplished without subjecting any dielectrics to voltages which exceed the technology dielectric breakdown limit.

Owner:NXP USA INC

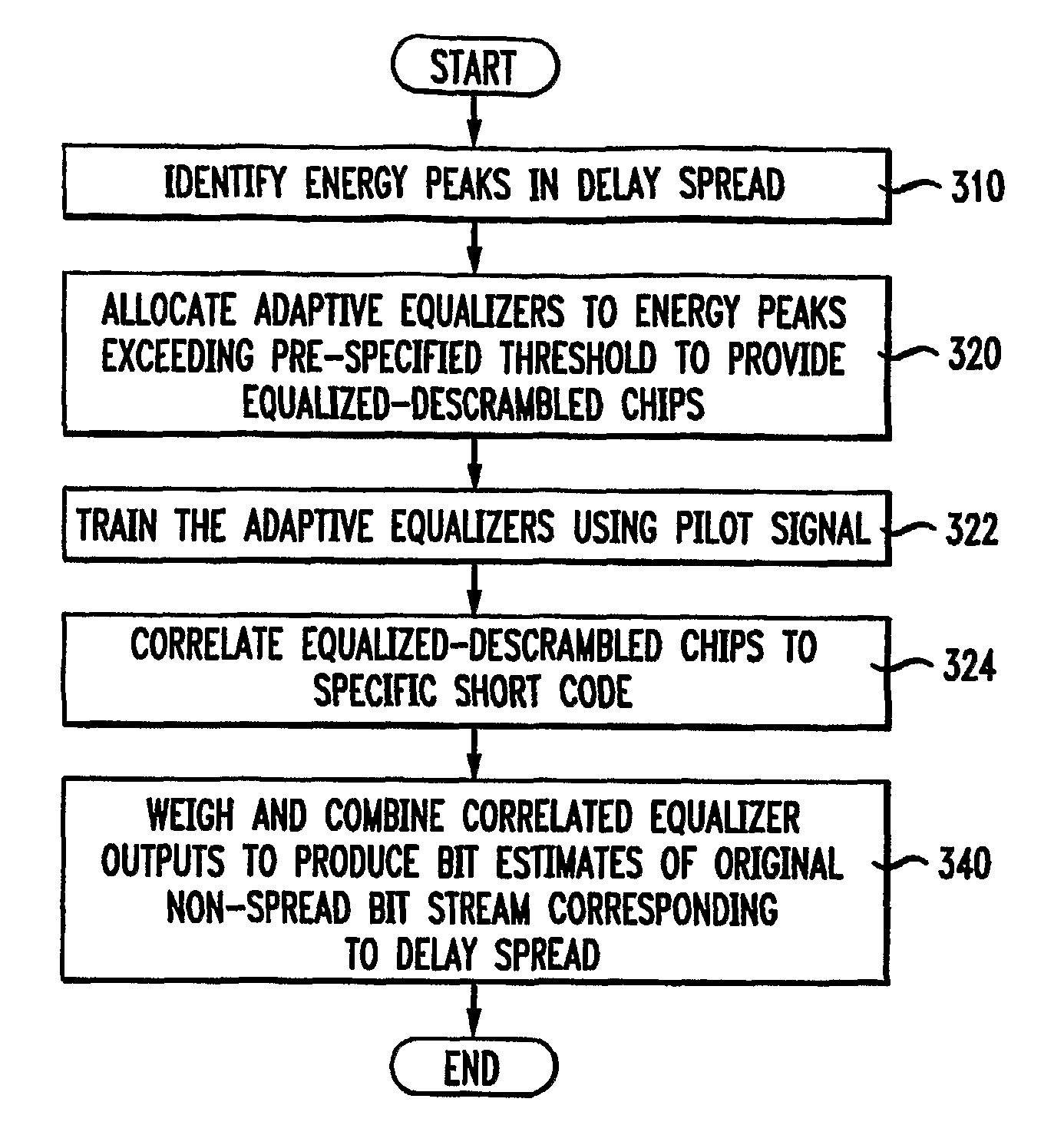

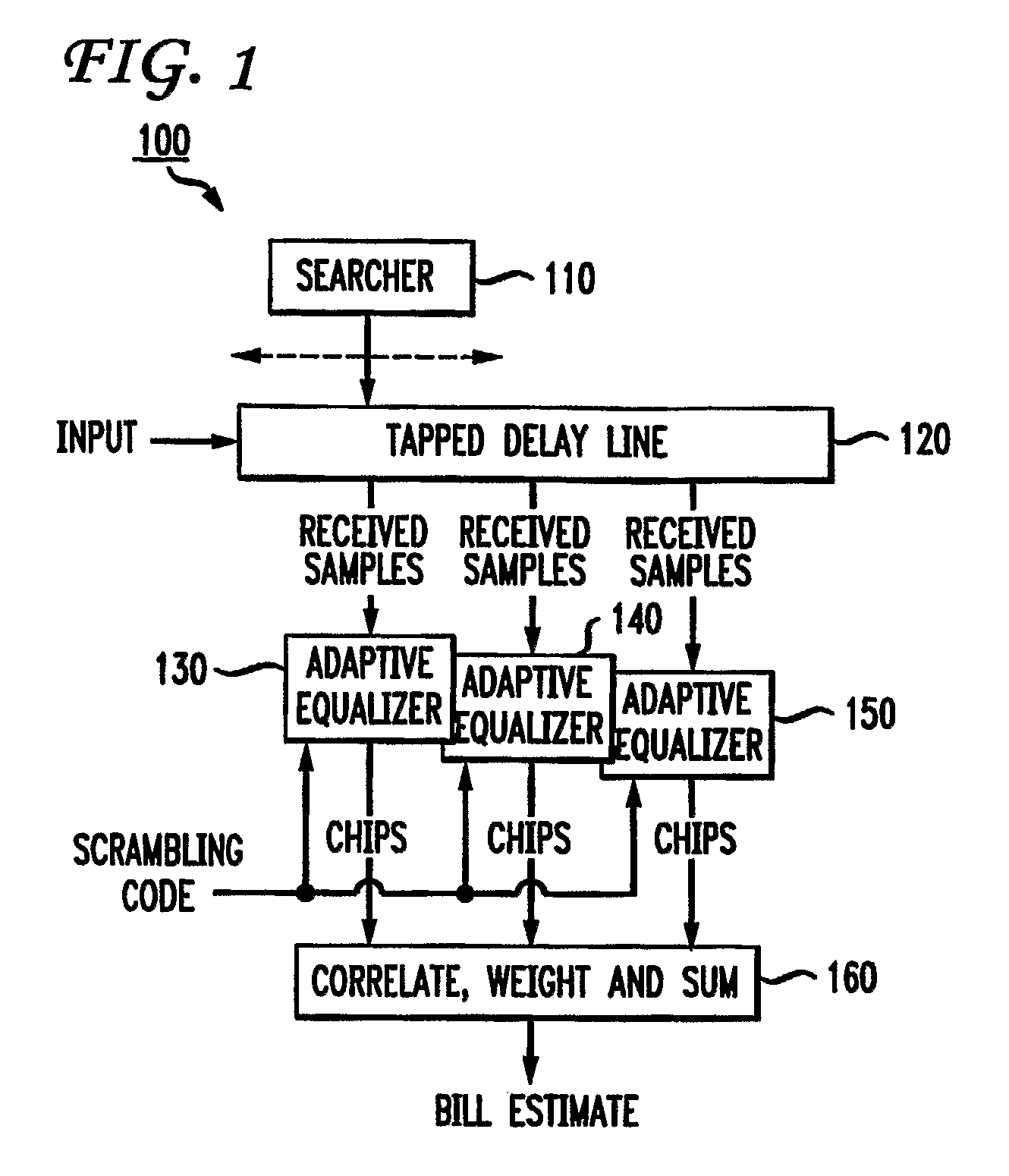

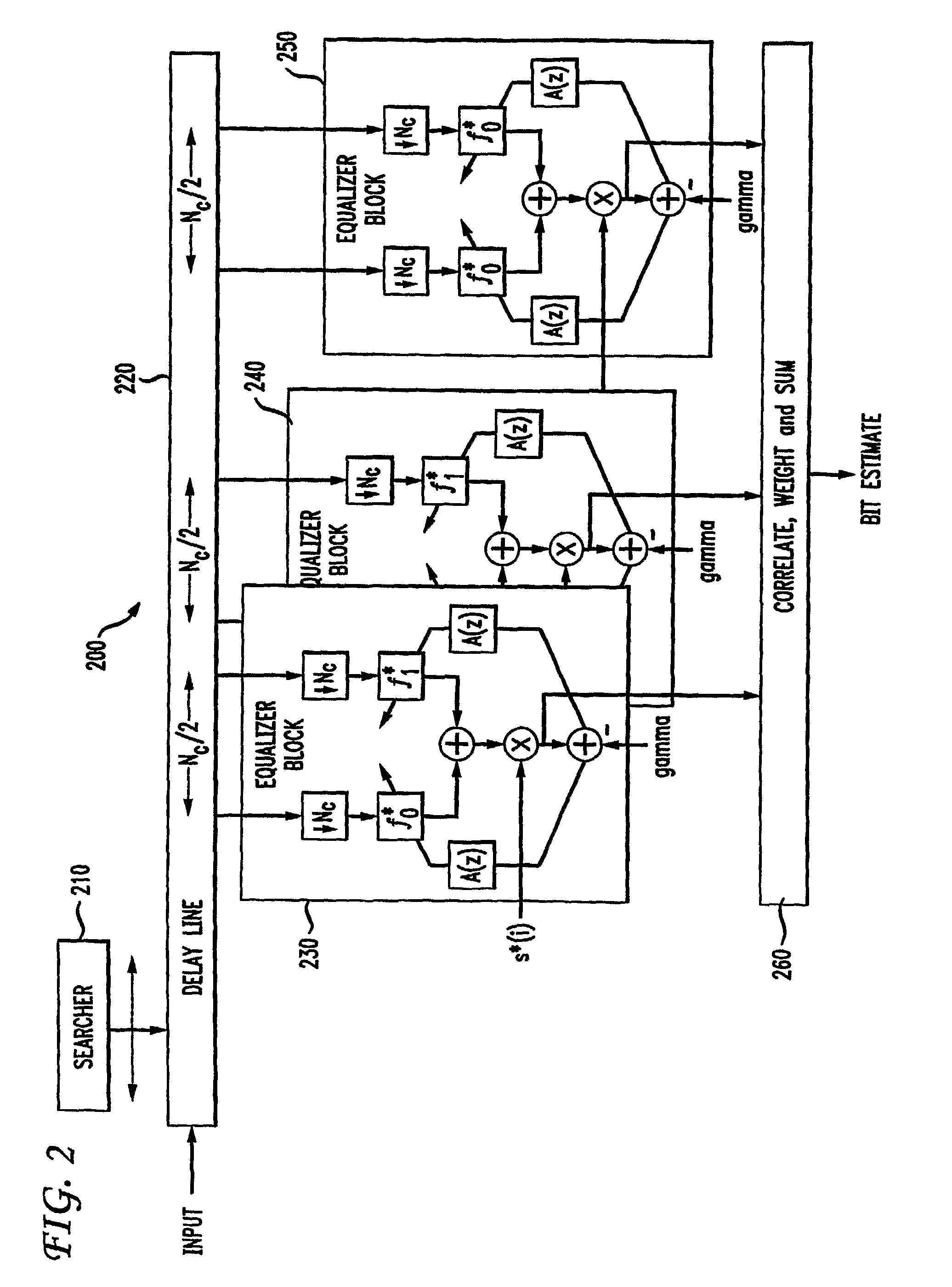

Hybrid rake/equalizer receiver for spread spectrum systems

There is provided a hybrid rake / equalizer receiver for correlating a delay spread in a spread spectrum system. The hybrid rake / equalizer receiver includes a plurality of adaptive equalizers, each for filtering different regions of the delay spread that have an energy level above a pre-specified threshold to respectively provide equalized-descrambled chip sequences for correlation. Equalizer coefficients respectively corresponding to the plurality of adaptive equalizers are updated individually.

Owner:INTERDIGITAL MADISON PATENT HLDG

Phase-combining circuit and timing signal generator circuit for carrying out a high-speed signal transmission

InactiveUS20090179674A1Simple structureError minimizationAnalogue/digital conversionElectric signal transmission systemsControl signalEngineering

A phase-combining circuit for combining cyclic timing waveforms that have been phase-controlled by control signals based on three or more input signals of different phases, has a weight signal generating circuit and a weighting circuit. The weight signal generating circuit generates weights according to the control signals, and the weighting circuit gives the weights to the respective input signals, with a positive or negative polarity for each one signal.

Owner:FUJITSU LTD

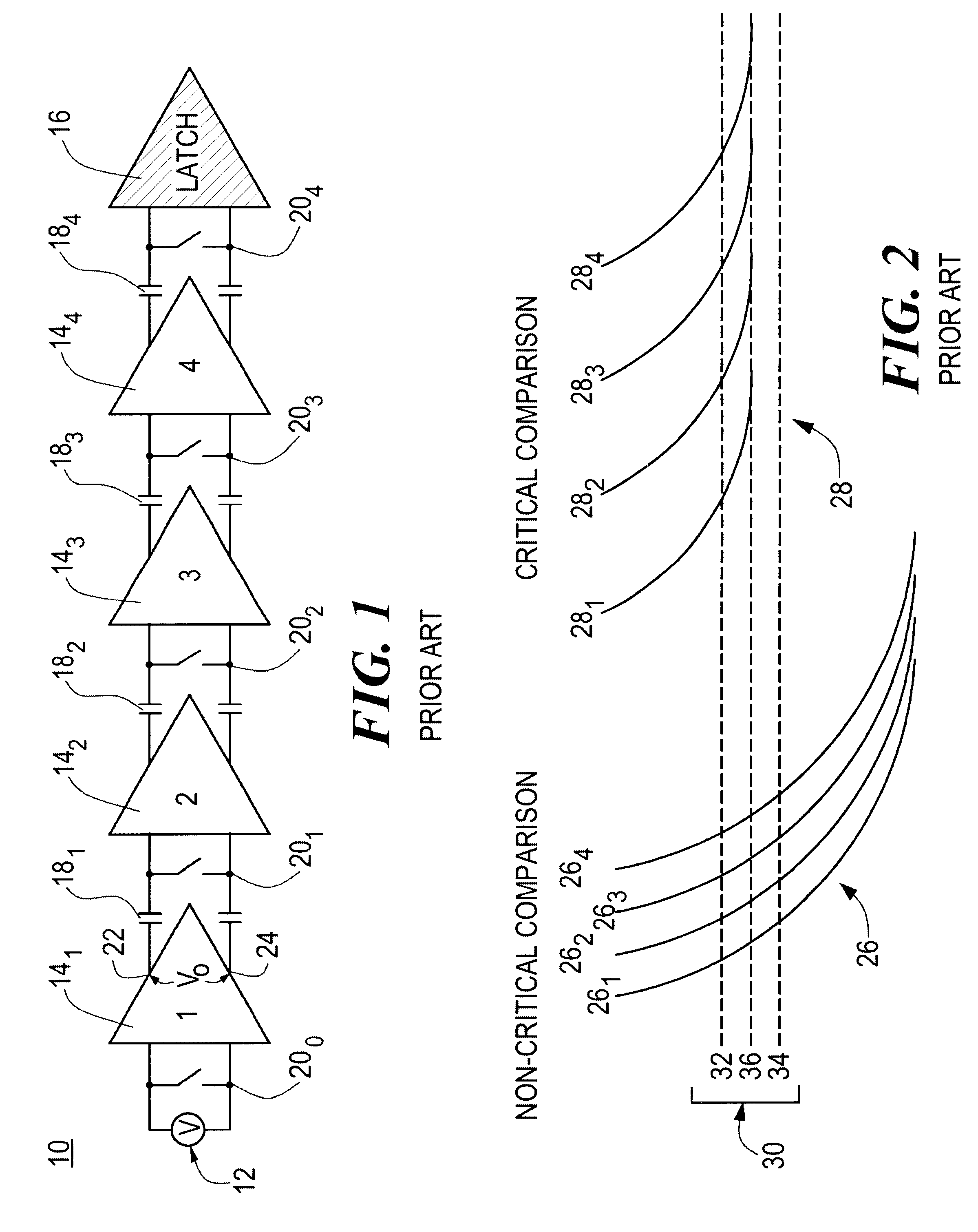

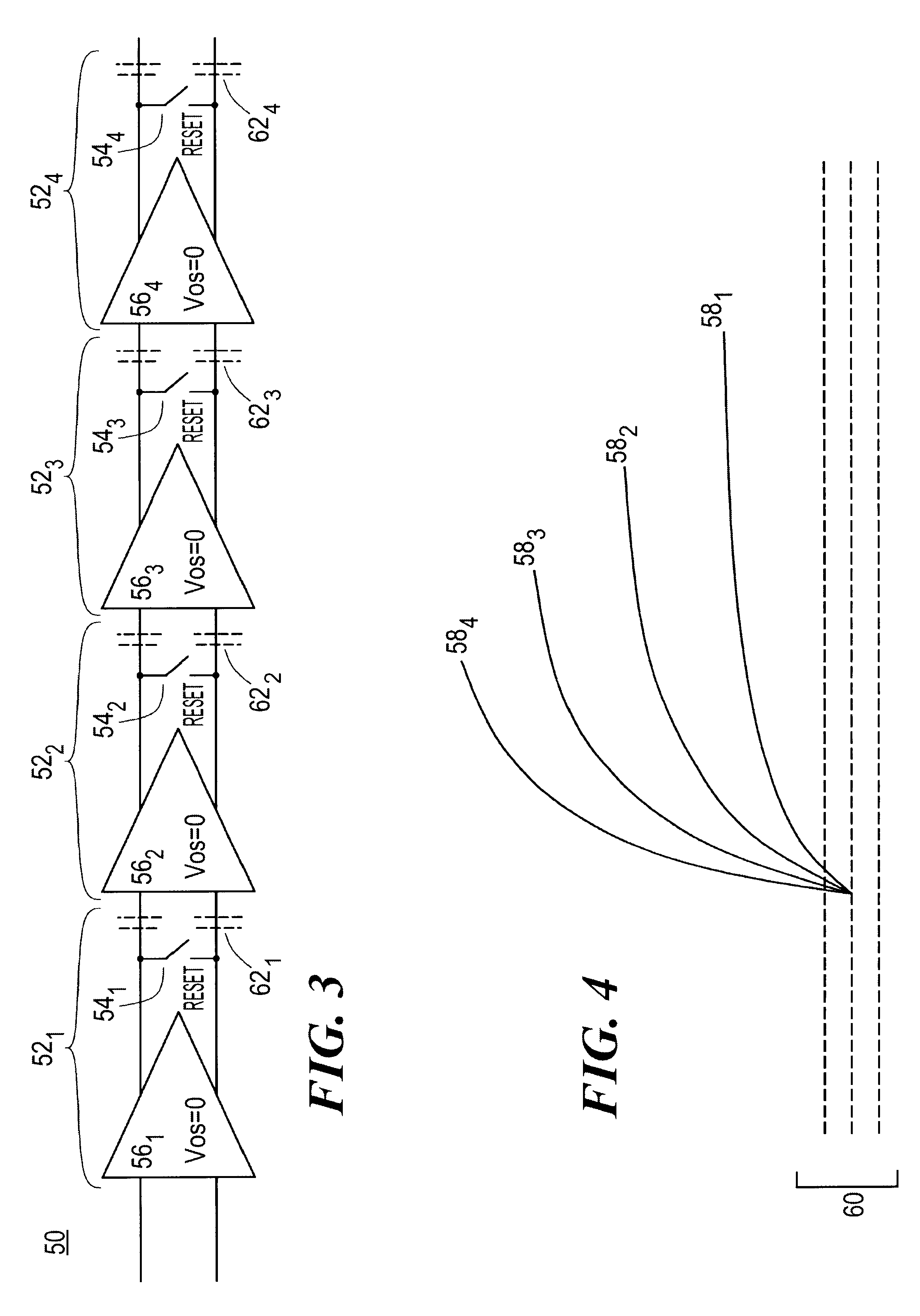

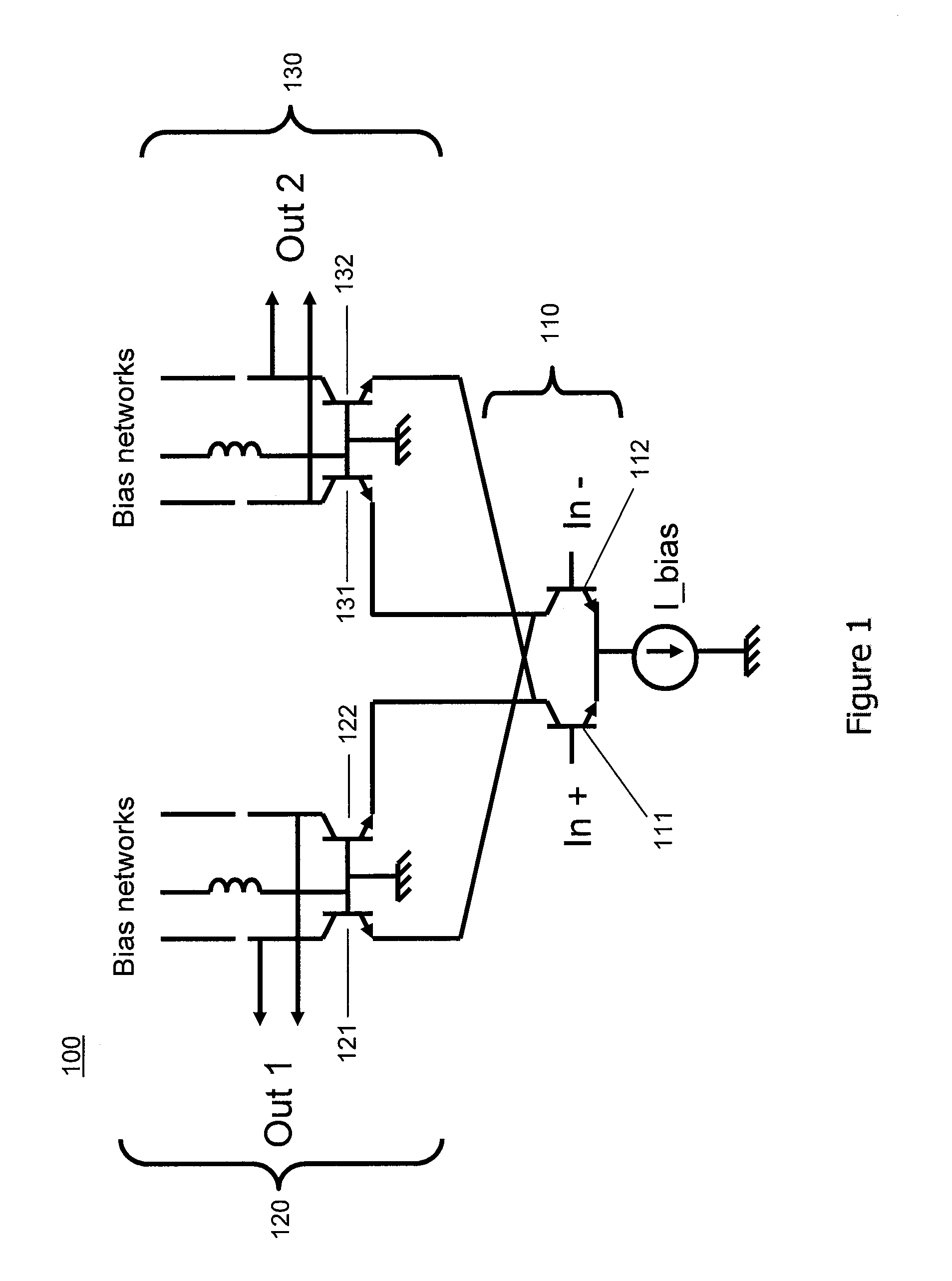

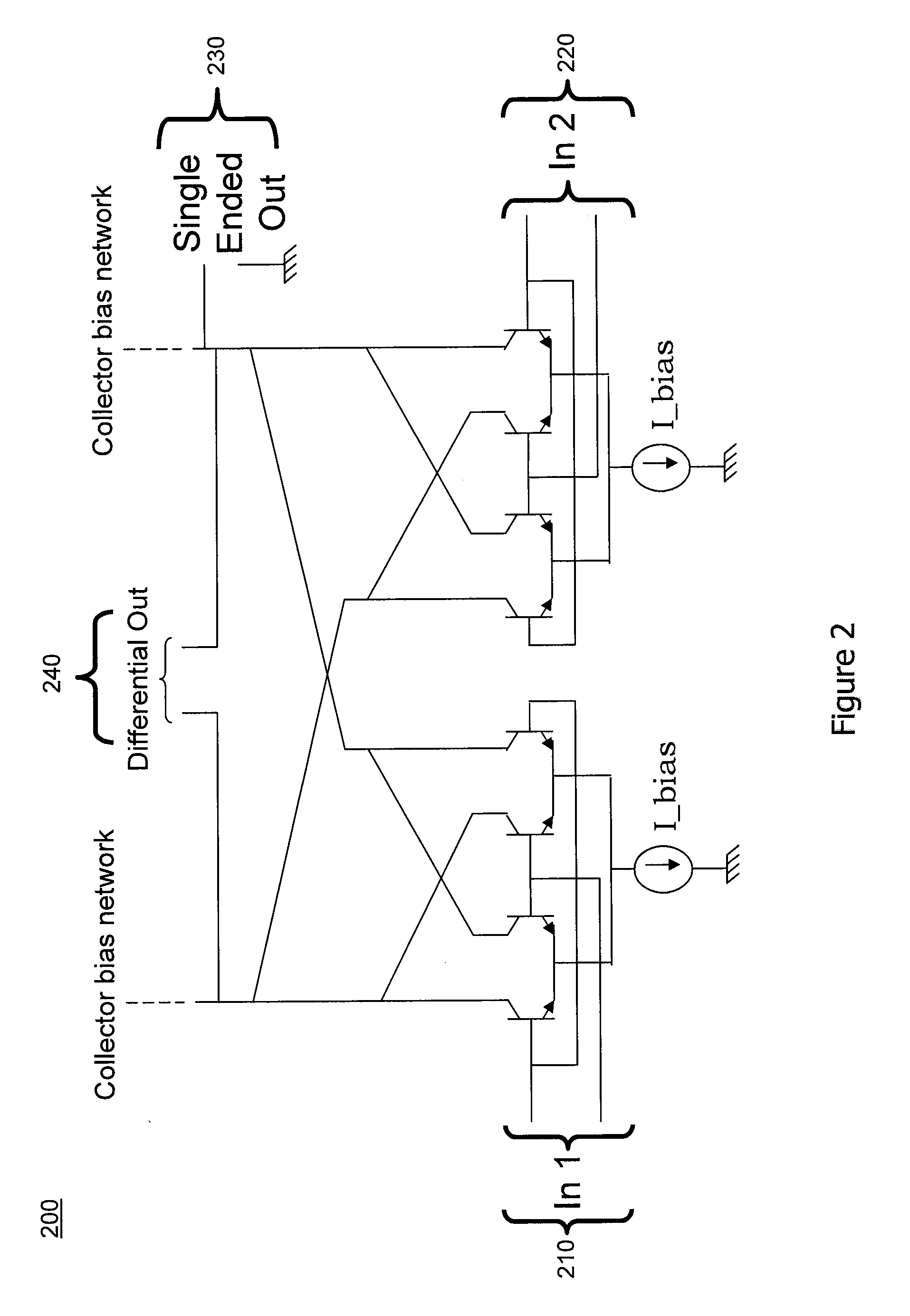

Multi-stage, low-offset, fast-recovery, comparator system and method

InactiveUS6429697B1Delay minimizationImprove processing speedMultiple input and output pulse circuitsNegative-feedback-circuit arrangementsAudio power amplifierEngineering

A multi-stage, low-offset, fast-recovery, comparator system and method for: reducing the input offset voltage of the zeroing amplifier by a factor essentially equal to gain of the zeroing amplifier; reducing the input offset voltage of the combined main and zeroing amplifiers by a factor essentially equal to the product of the gains of the main and zeroing amplifiers; and amplifying the input signal to the amplification stage in accordance with the gain of the main amplifier to generate an amplified high-resolution signal.

Owner:ANALOG DEVICES INC

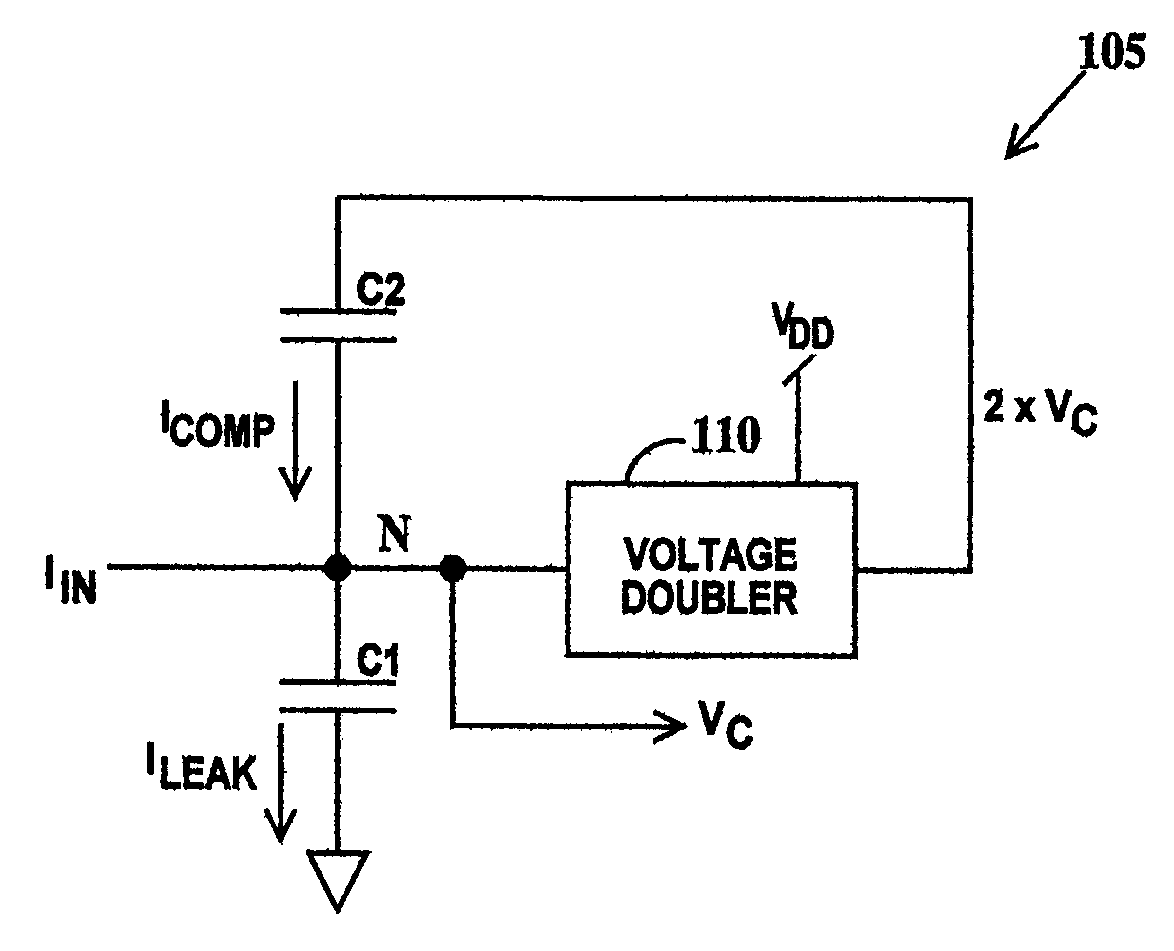

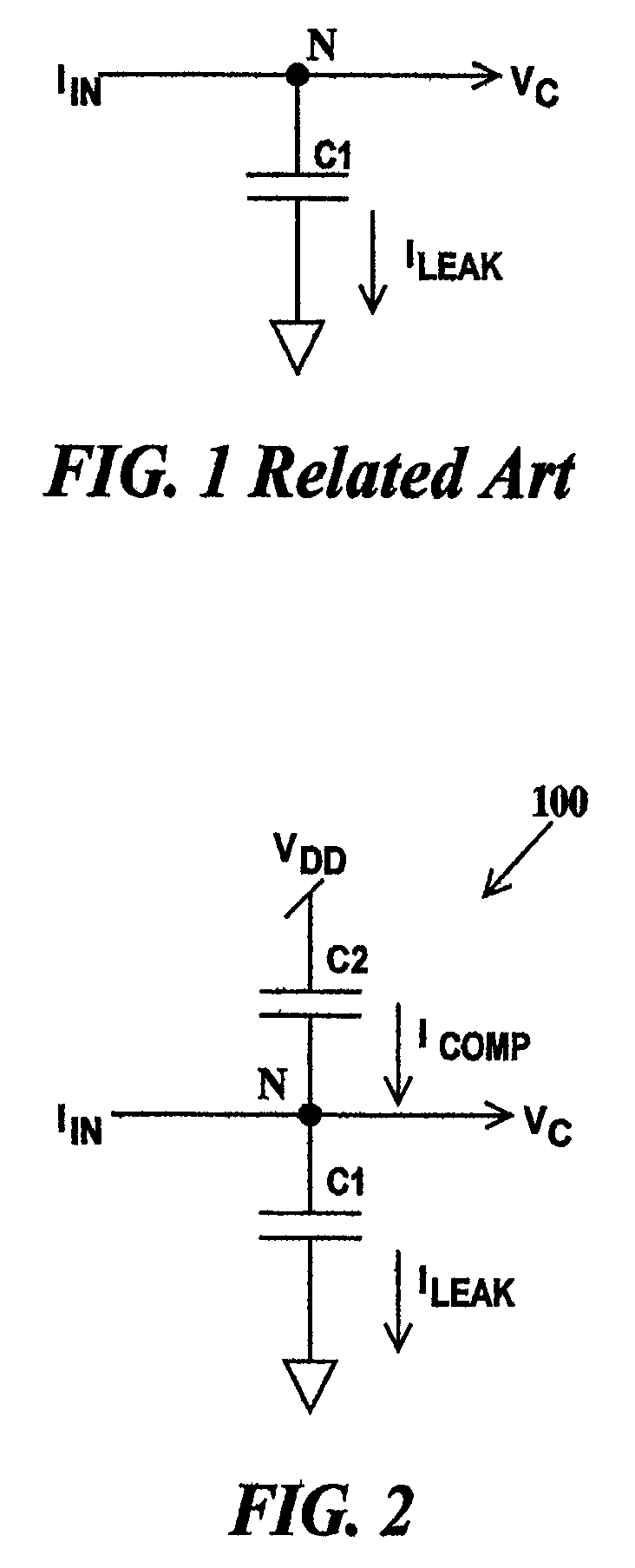

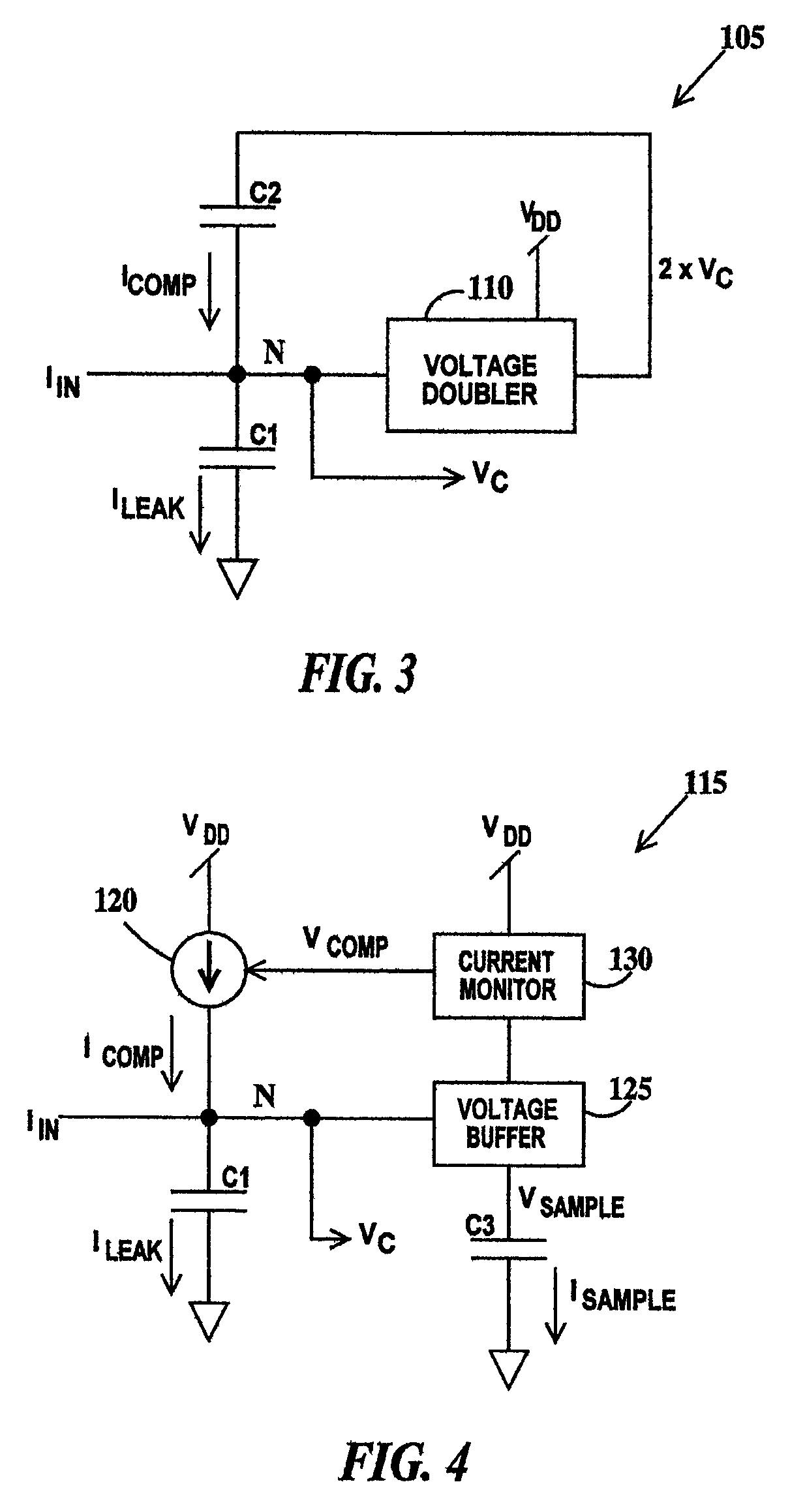

Leakage compensation circuit

A circuit, including: a capacitor coupled between a first circuit node and a second circuit node and that leaks a leakage current from the first circuit node to the second circuit node; and a compensation circuit adapted to supply a compensatory current to compensate for the leakage current to the first circuit node.

Owner:INT BUSINESS MASCH CORP

Radio-Frequency (RF) Amplifier Circuits and Related Techniques

ActiveUS20110187437A1Reduce lossesSmall output powerAmplifier with semiconductor-devices/discharge-tubesComputing operation arrangementsLinear amplificationEngineering

A power combining and outphasing system and related techniques for simultaneously providing both wide-bandwidth linear amplification and high average efficiency is described. Providing linear amplification encompasses the ability to dynamically control an RF output power level over a wide range while still operating over a wide frequency bandwidth. The system and techniques described herein also operate to maintain high efficiency across a wide range of output power levels, such that a high average efficiency can be achieved for highly modulated output waveforms.

Owner:MASSACHUSETTS INST OF TECH

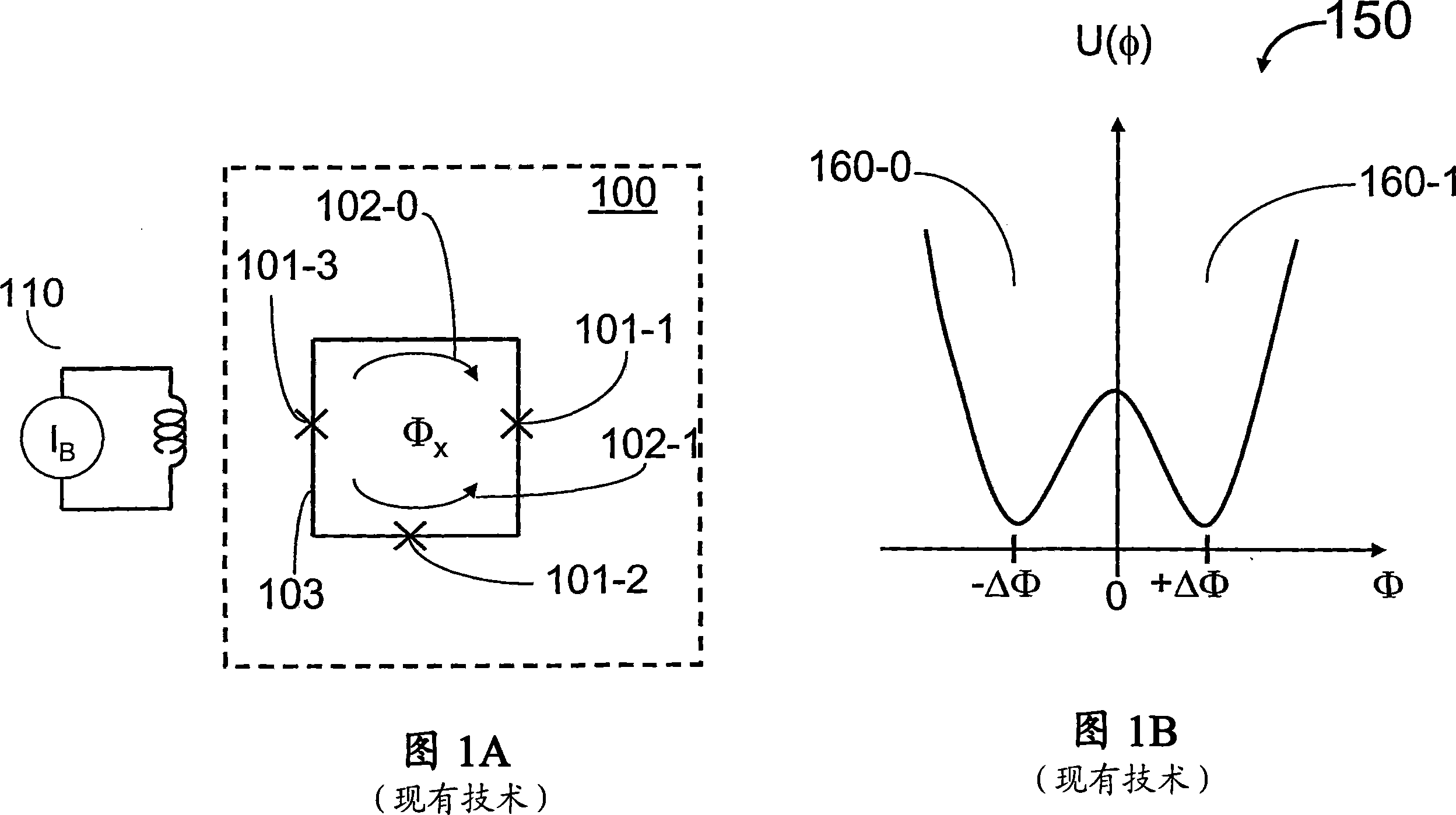

Analog processor comprising quantum devices

ActiveUS20090167342A1Quantum computersLogic circuits characterised by logic functionComputational problemAnalog processor

Analog processors for solving various computational problems are provided. Such analog processors comprise a plurality of quantum devices, arranged in a lattice, together with a plurality of coupling devices. The analog processors further comprise bias control systems each configured to apply a local effective bias on a corresponding quantum device. A set of coupling devices in the plurality of coupling devices is configured to couple nearest-neighbor quantum devices in the lattice. Another set of coupling devices is configured to couple next-nearest neighbor quantum devices. The analog processors further comprise a plurality of coupling control systems each configured to tune the coupling value of a corresponding coupling device in the plurality of coupling devices to a coupling. Such quantum processors further comprise a set of readout devices each configured to measure the information from a corresponding quantum device in the plurality of quantum devices.

Owner:D WAVE SYSTEMS INC

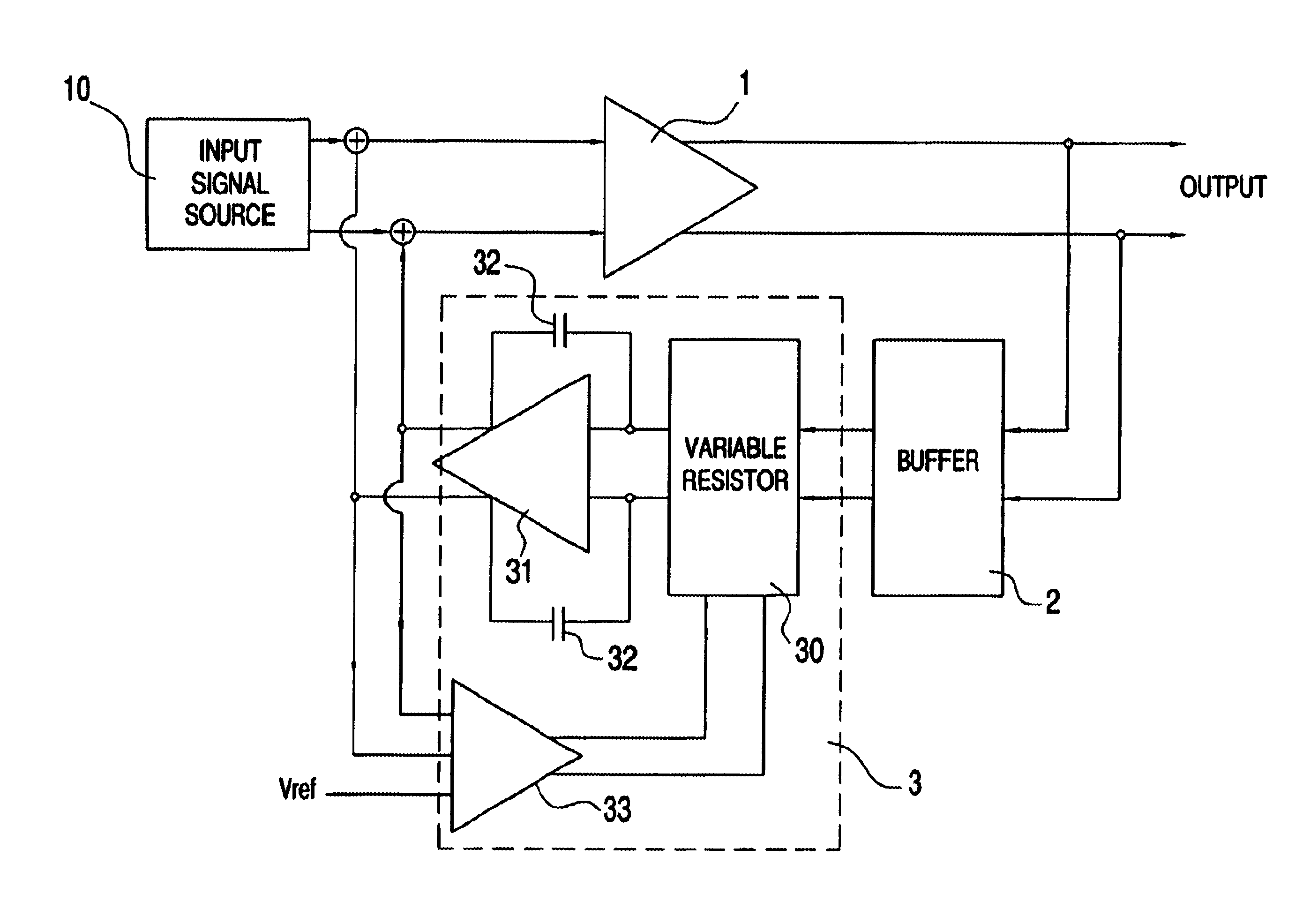

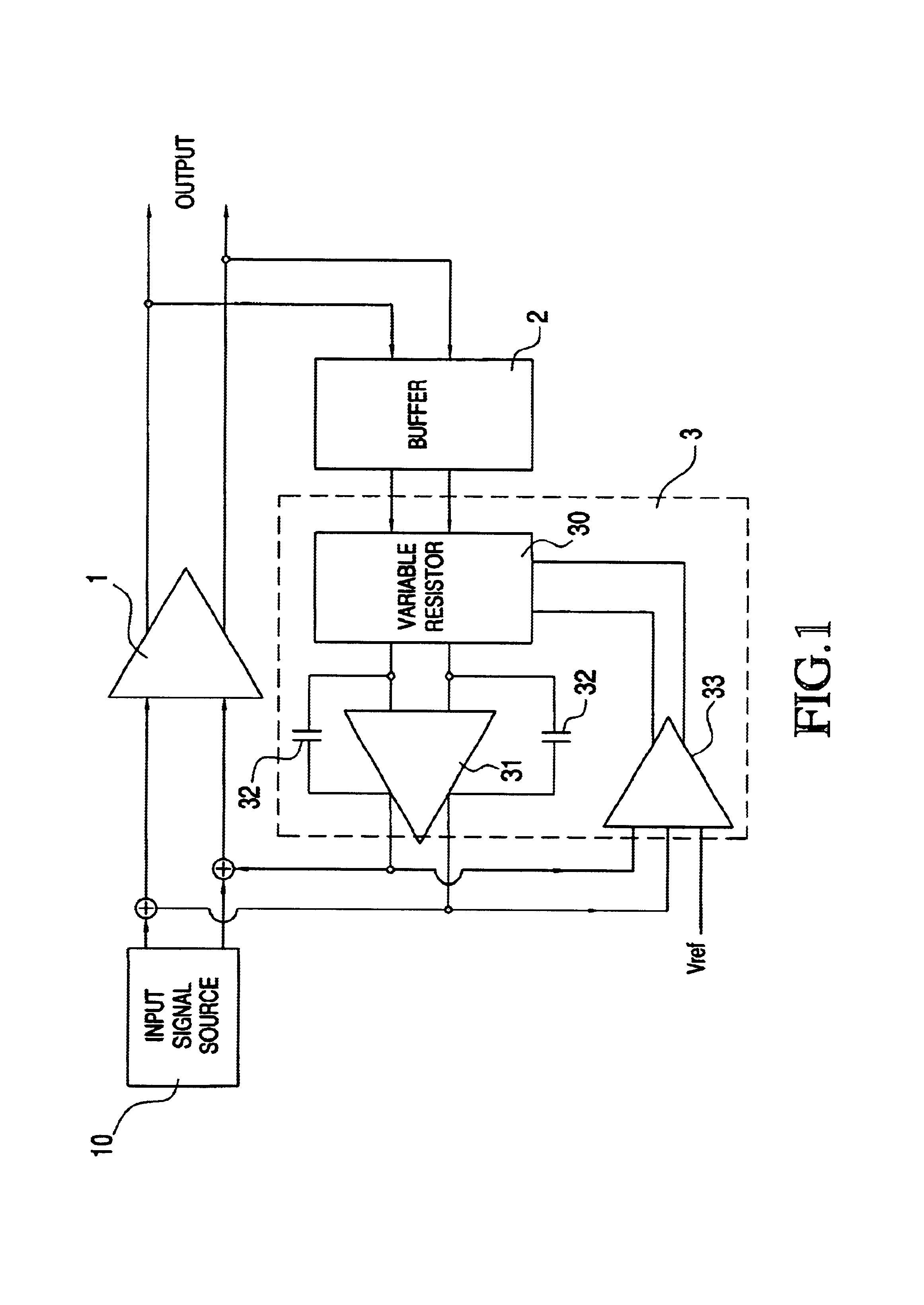

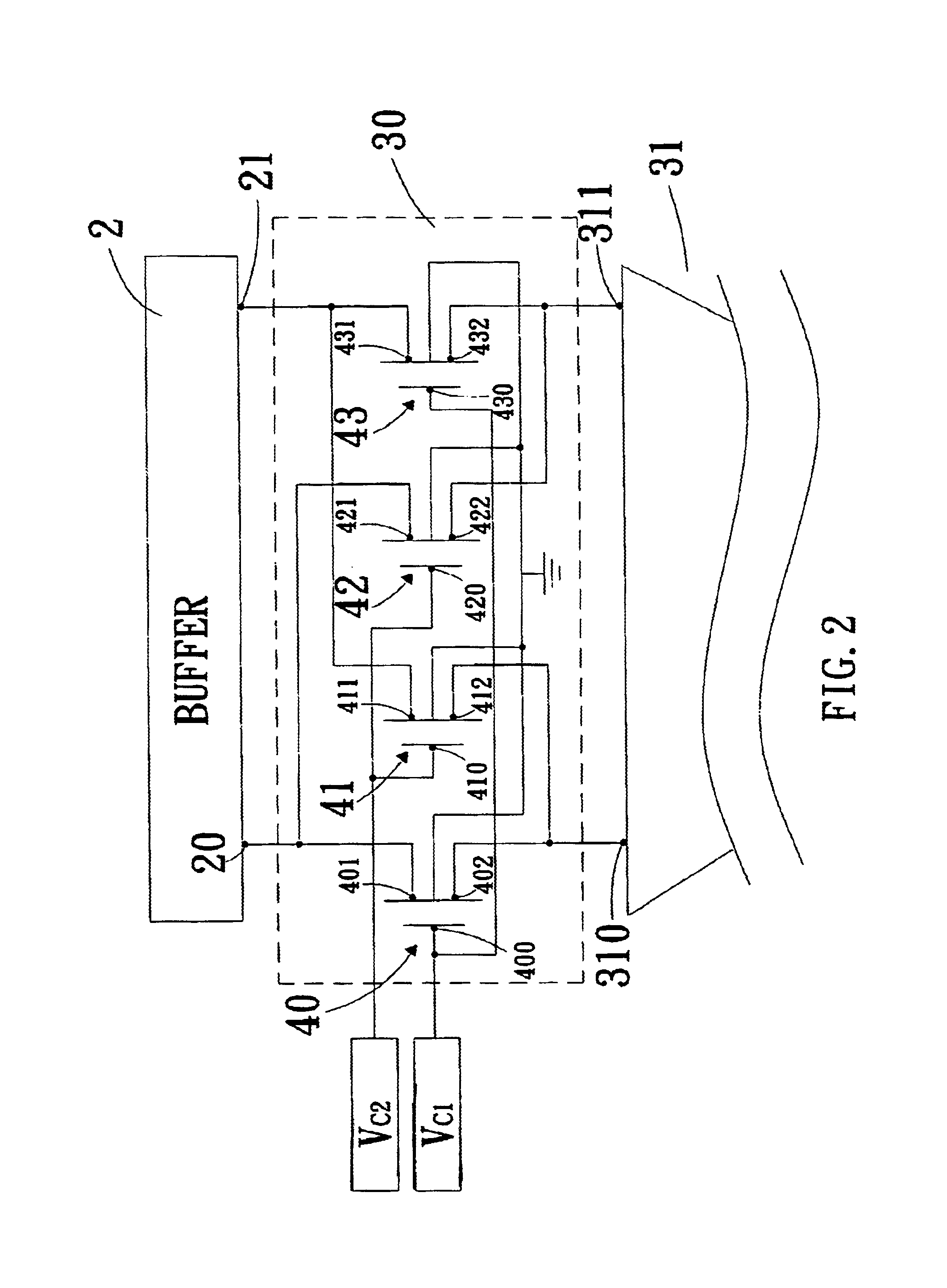

Gain amplifier with DC offset cancellation circuit

ActiveUS6903593B2Shorten convergence timePulse automatic controlComputing operation arrangementsNegative feedbackAudio power amplifier

A DC offset cancellation circuit employs multiple feedback factors for canceling DC offset by increasing convergence time. The DC offset cancellation circuit features an active low-pass analogue filter including a variable resistor, an amplifier, a capacitor pair and a comparator, the amplifier being coupled to an output of the variable resistor. Negative feedback is provided from the output of the variable resistor to the input signal source, the capacitor pair is coupled to the amplifier, one input of the comparator is coupled to an output of the amplifier, and a second input of the comparator is coupled to a reference voltage source such that a comparison signal is output by the comparator to the variable resistor after comparing the negative feedback signal with a reference voltage.

Owner:IND TECH RES INST

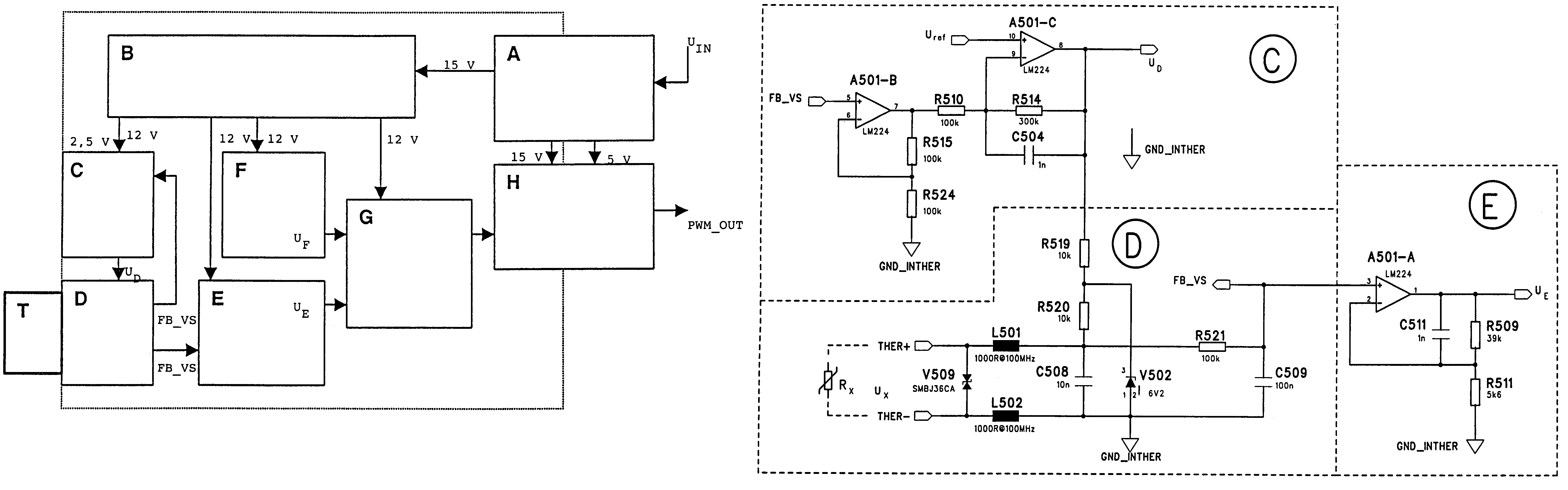

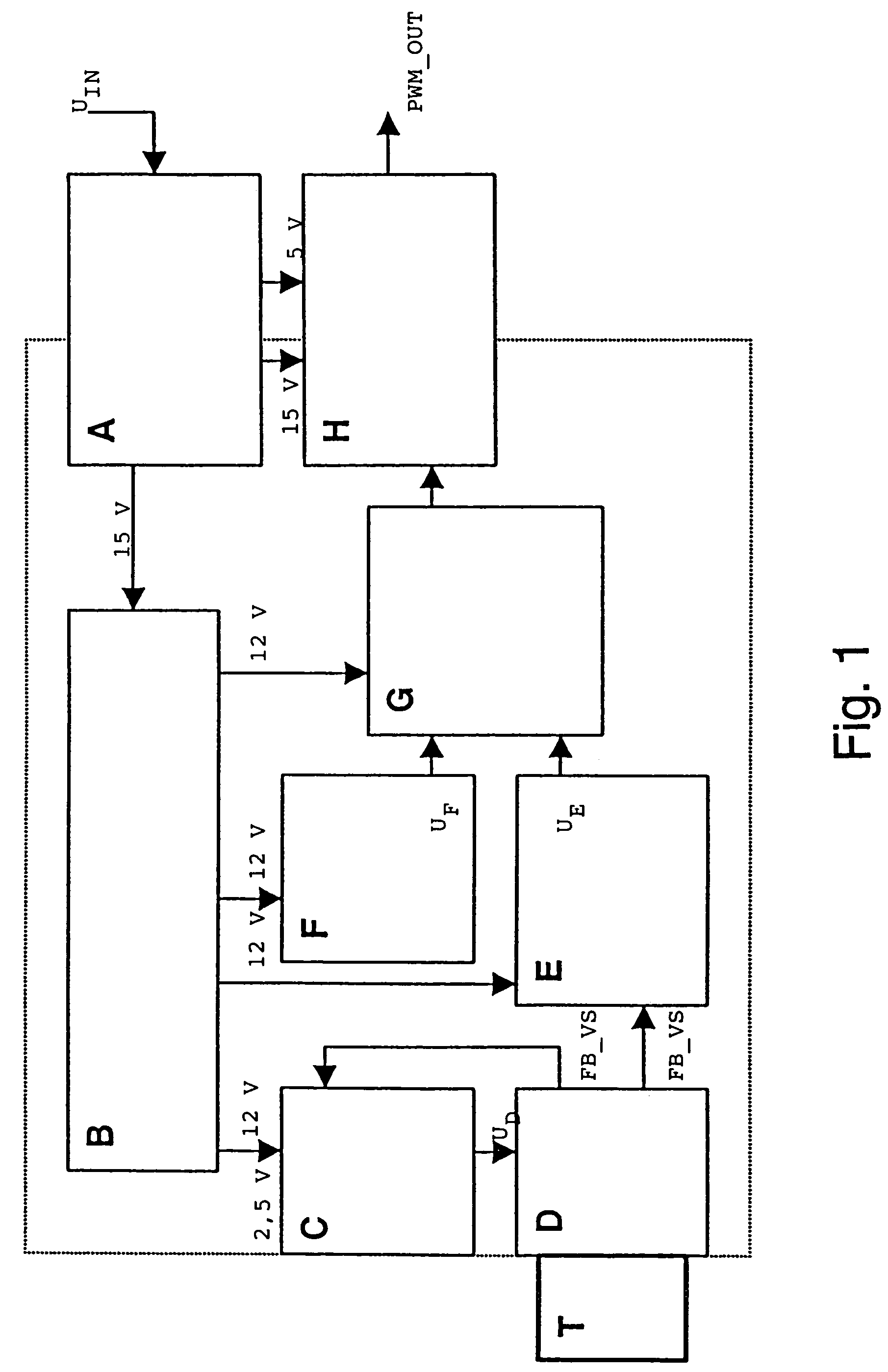

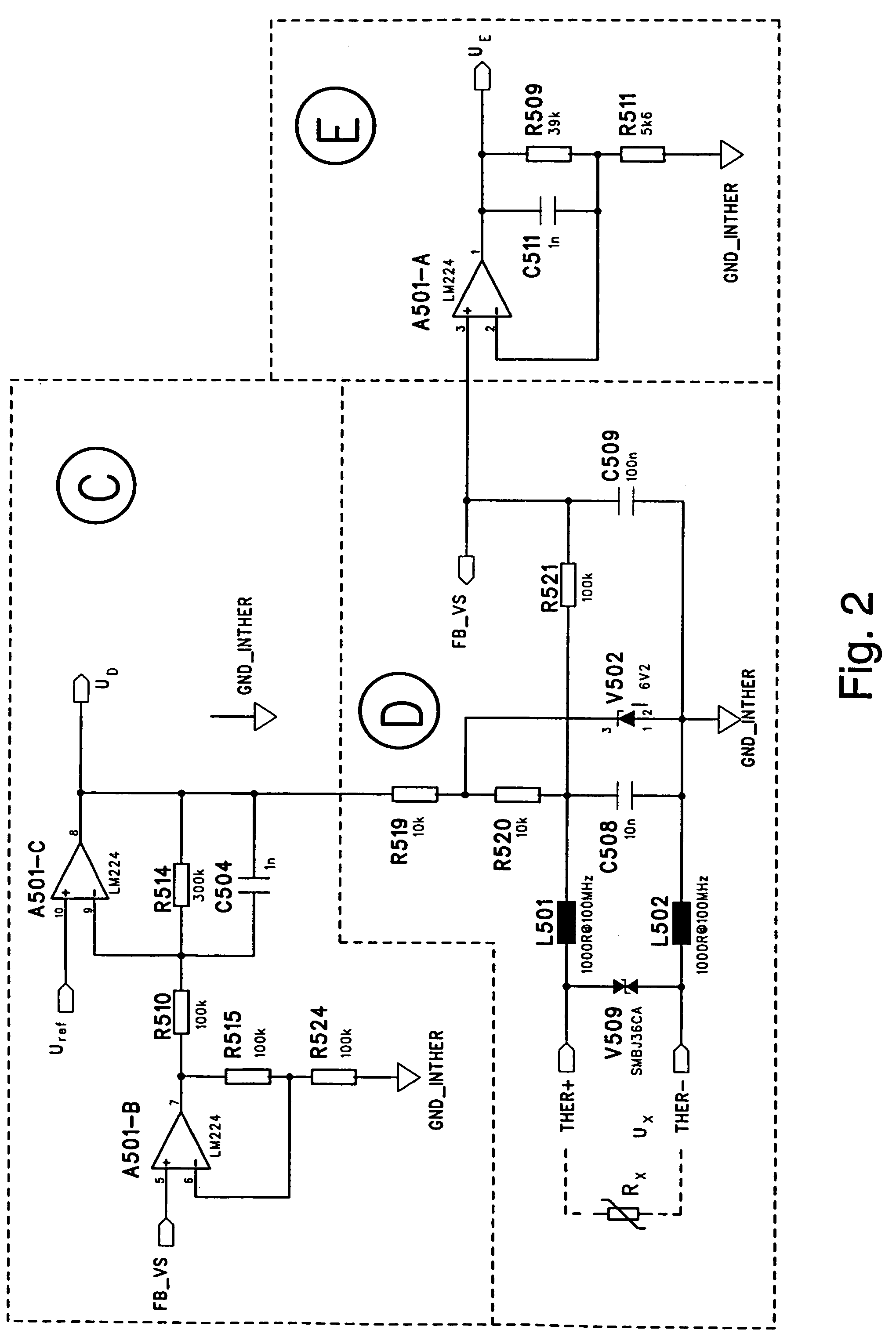

Isolated measurement circuit for sensor resistance

InactiveUS7592820B2Reliable indicationNo longer indicateBurglar alarm by openingResistance/reactance/impedenceResistive sensorsElectrical conductor

A circuit and method is disclosed for measuring the resistance of a resistive sensor, such as a PTC or NTC temperature sensor used for monitoring the temperature of the windings of an electric motor. The measurement circuit is based on an electronic circuit in which conductors from a sensor located in the object to be monitored are connected to an amplifier circuit in a feedback configuration that reduces the DC level supplied to the voltage divider when the sensor resistance increases. The measured signal is amplified and, using a comparator to compare it with the output voltage of a sawtooth generator, a continuous PWM (Pulse Width Modulation) signal is generated and transmitted in digital format to a SELV electronic circuit, for example through an opto-isolator. The essentially logarithmic signal amplification makes it possible to reliably distinguish between a short circuit in the sensor circuit and low values of sensor resistance.

Owner:ABB OY

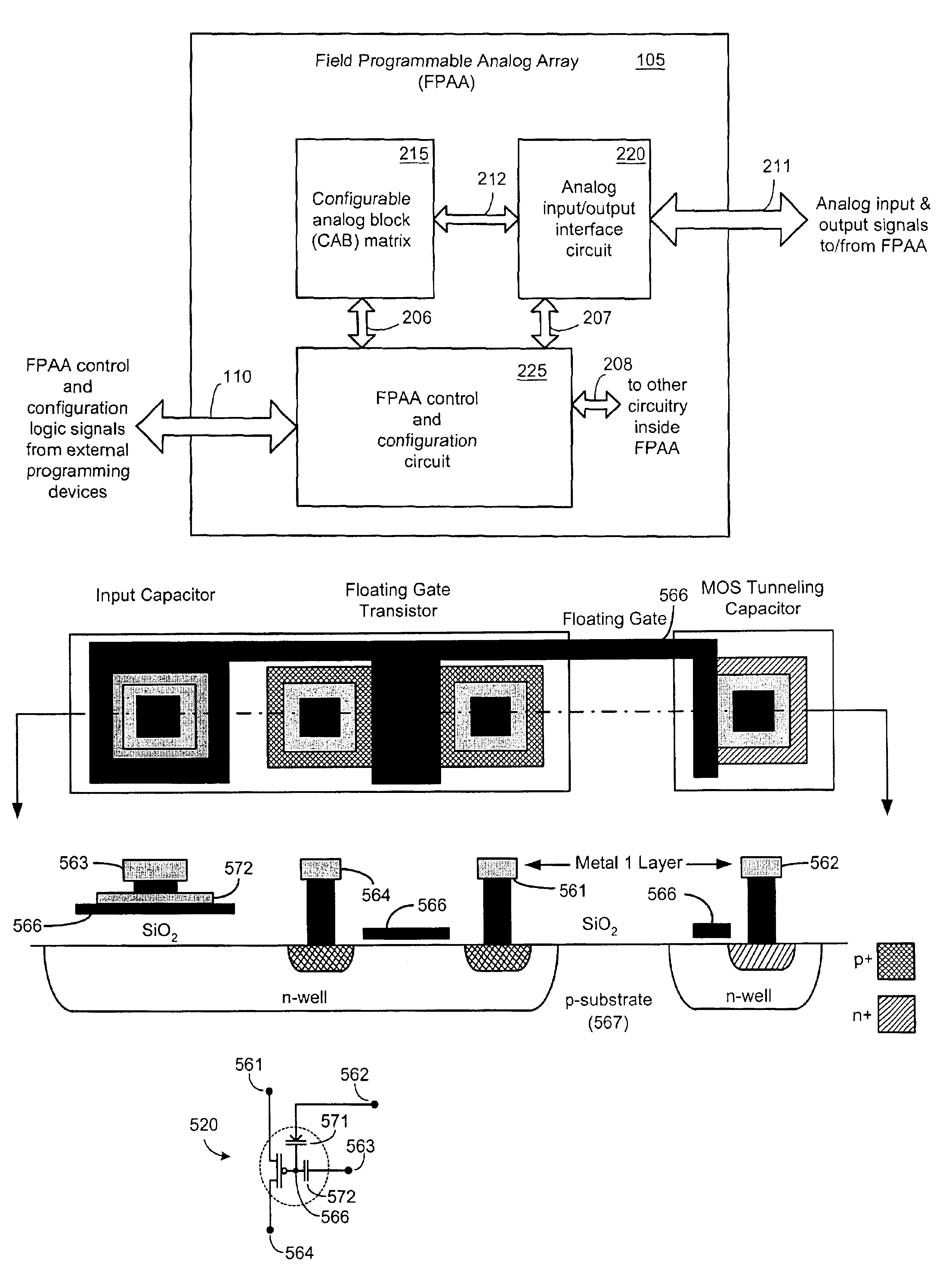

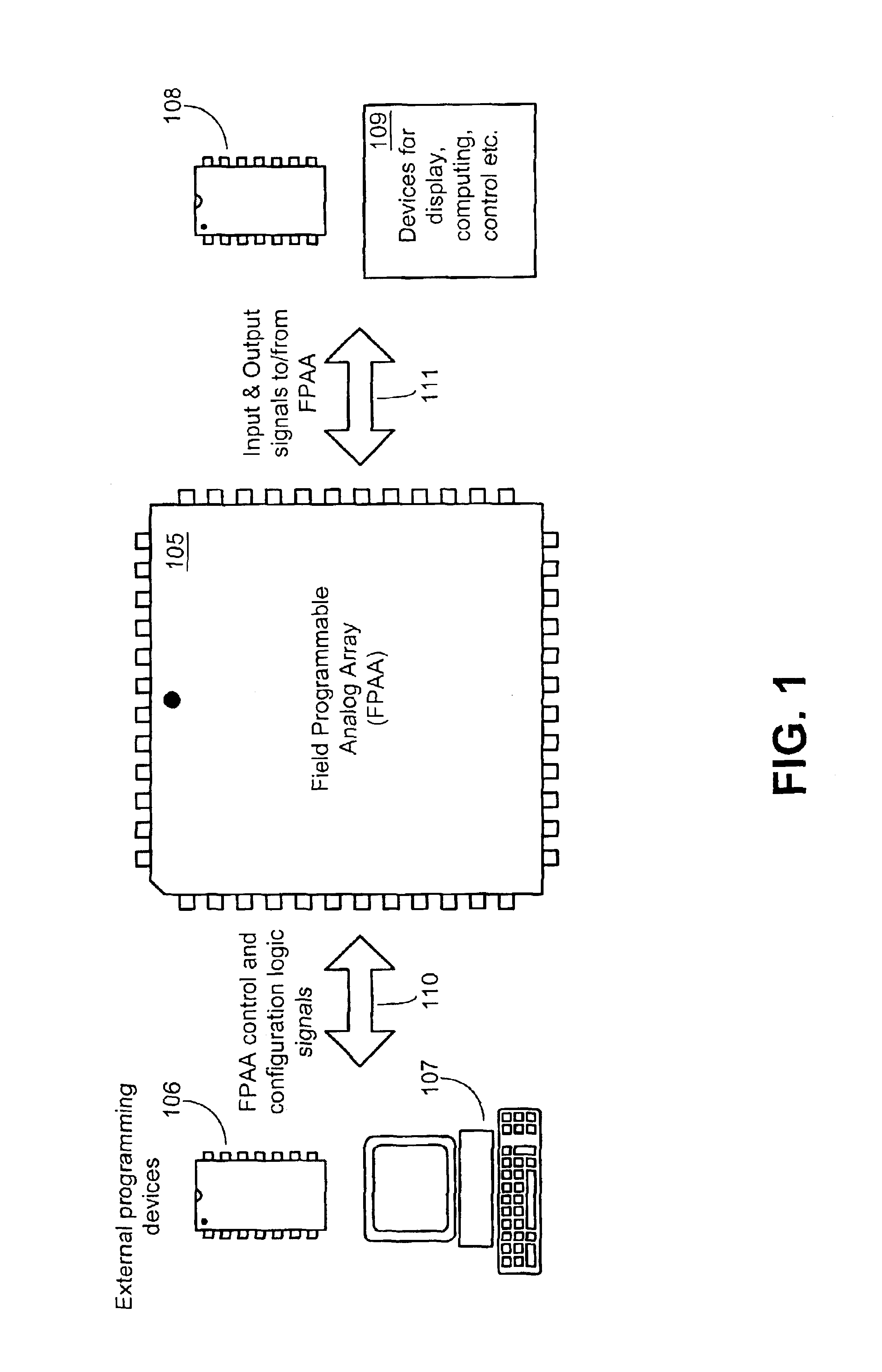

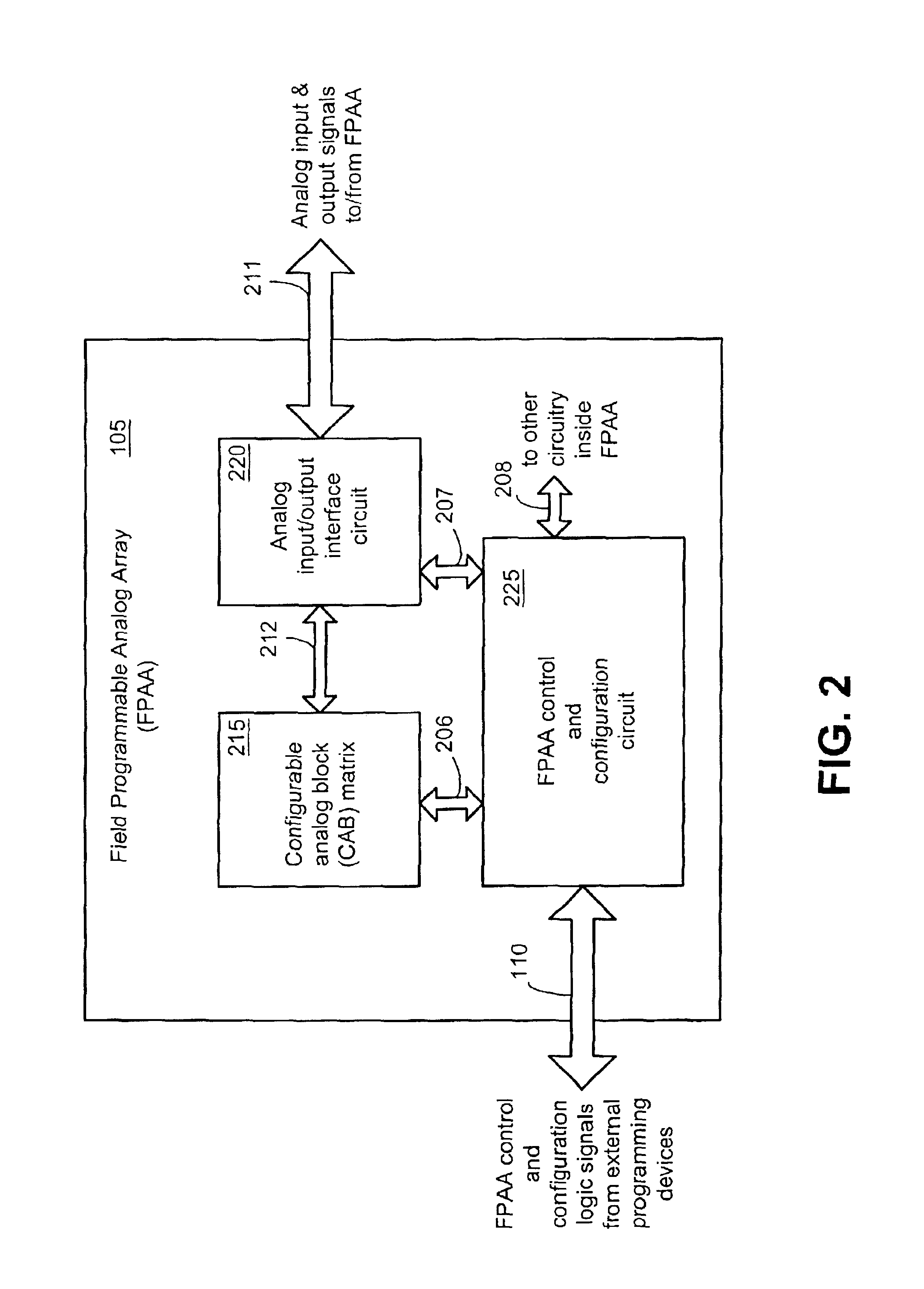

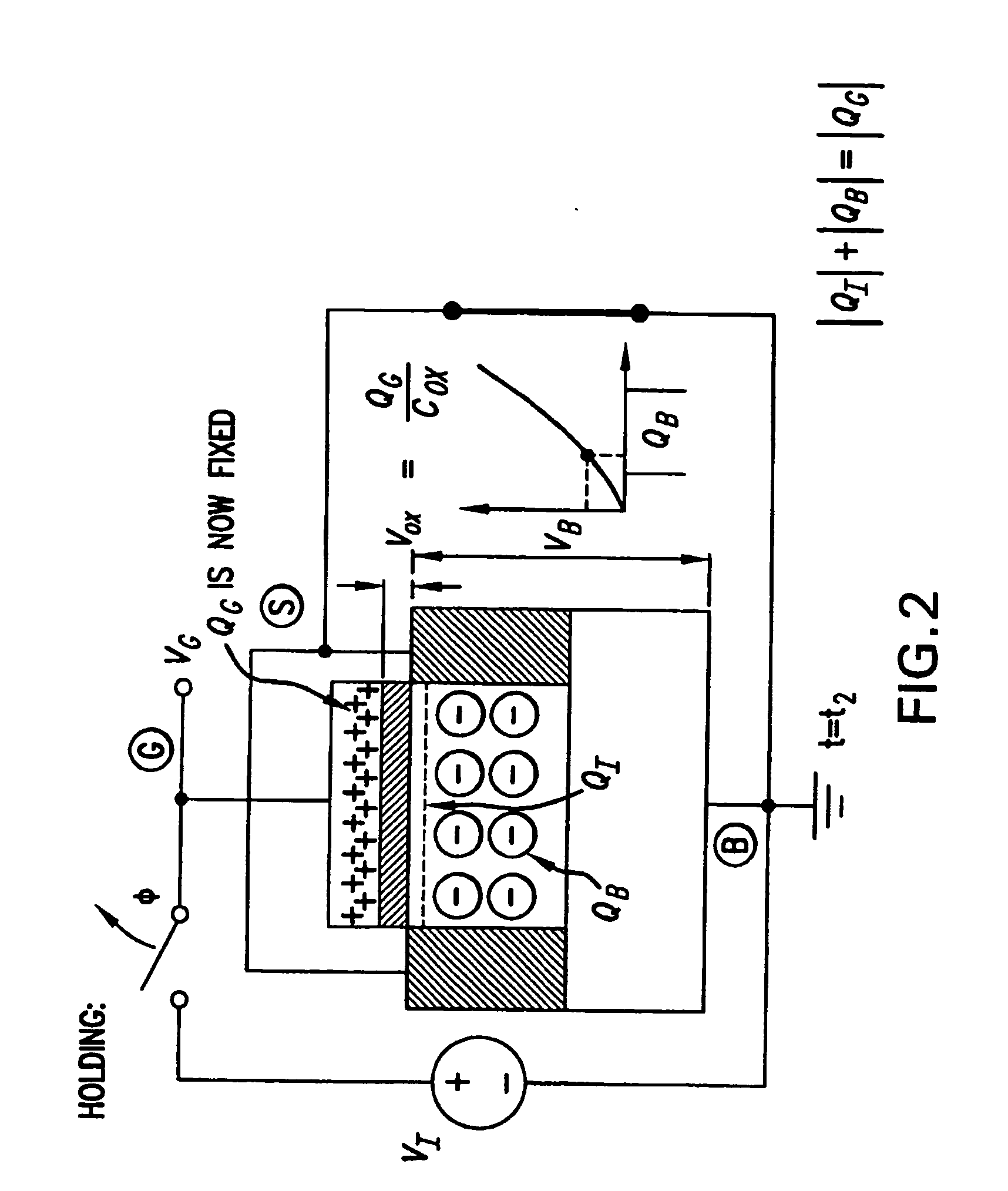

Floating-gate analog circuit

In one exemplary embodiment, a programmable analog array (PAA) contains a configurable analog matrix having two floating-gate field effect transistors (FETs). Also contained in the PAA is an interconnect circuit that is programmable to configure the configurable analog matrix to operate in one or more of several matrix modes. A few examples of such matrix modes include a switching matrix mode, a memory matrix mode, and a computing matrix mode. In an exemplary method of configuring the PAA. PAA, the the method includes programming an interconnection, for example, between a first terminal of the first floating-gate FET and a first terminal of the second floating-gate FET. The method further includes programming an interconnection, for example, between a gate terminal of the first floating-gate FET and a fixed voltage source, for setting a floating gate charge on the first floating-gate FET.

Owner:GEORGIA TECH RES CORP

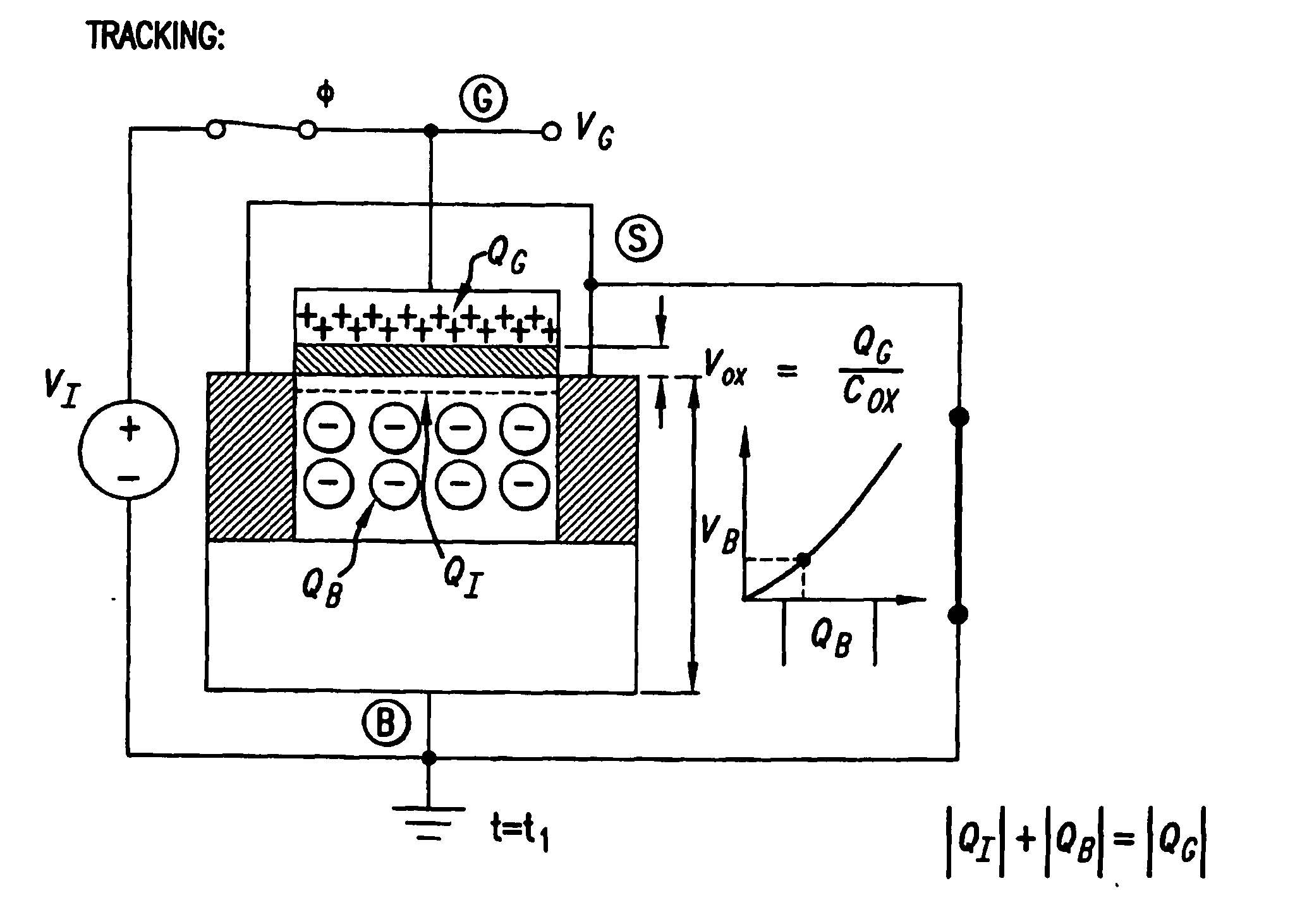

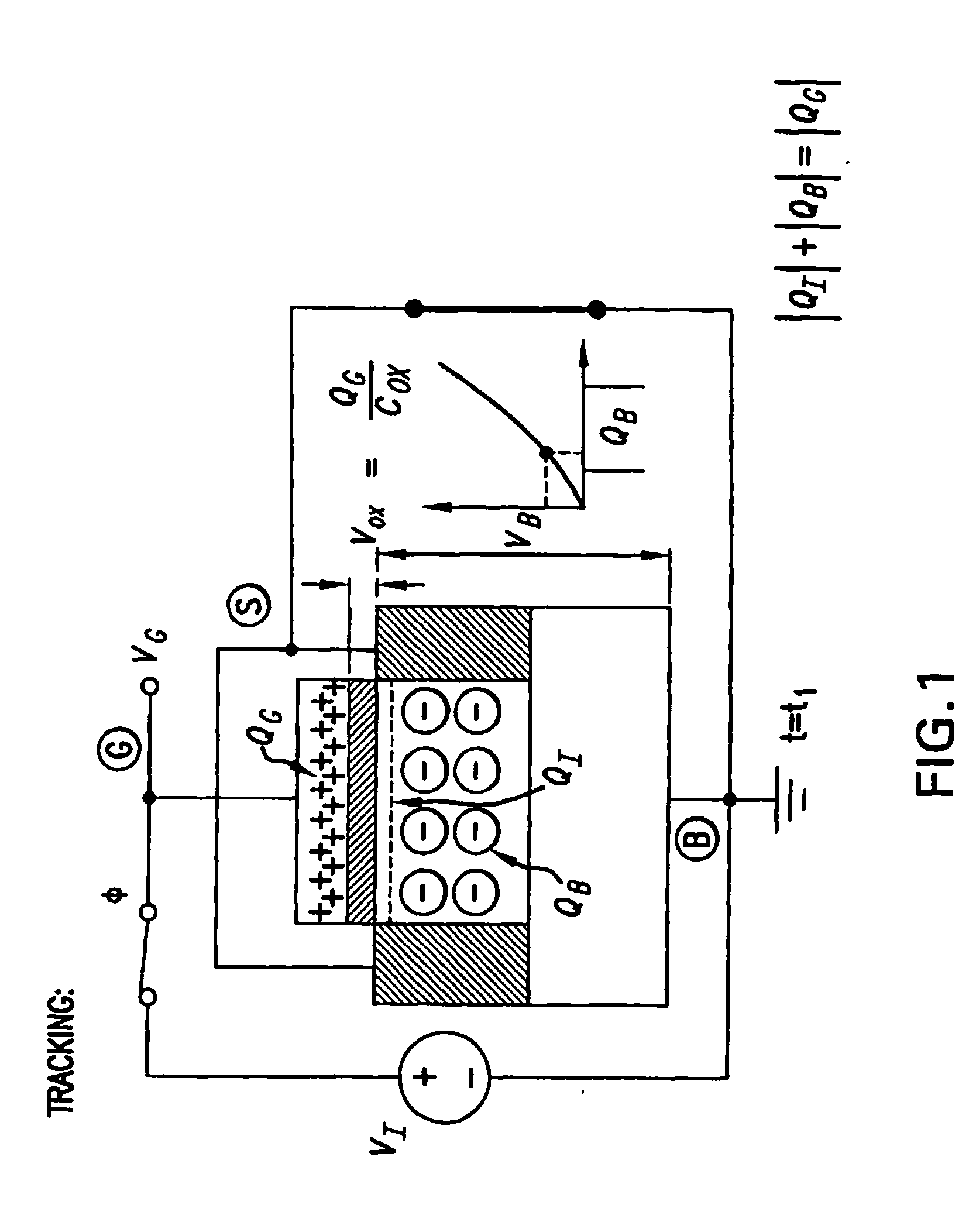

MOSFET parametric amplifier

InactiveUS20050275026A1Low powerOvercomes drawbackModulation transference by semiconductor devices with minimum 2 electrodesSolid-state devicesMOSFETEngineering

A circuit includes an input terminal adapted to receive an input voltage, a MOSFET having its drain terminal and its source terminal connected together, a first switching arrangement configured to be controlled by a first clock signal and adapted to selectively couple the gate terminal to the input terminal, and a further switching arrangement configured to be controlled by a further clock signal in timing relationship with the first clock signal and adapted to selectively couple the source terminal and a first voltage which is capable of pulling carriers out of a channel when the first switching arrangement is not coupling the input terminal to the gate terminal.

Owner:THE TRUSTEES OF COLUMBIA UNIV IN THE CITY OF NEW YORK

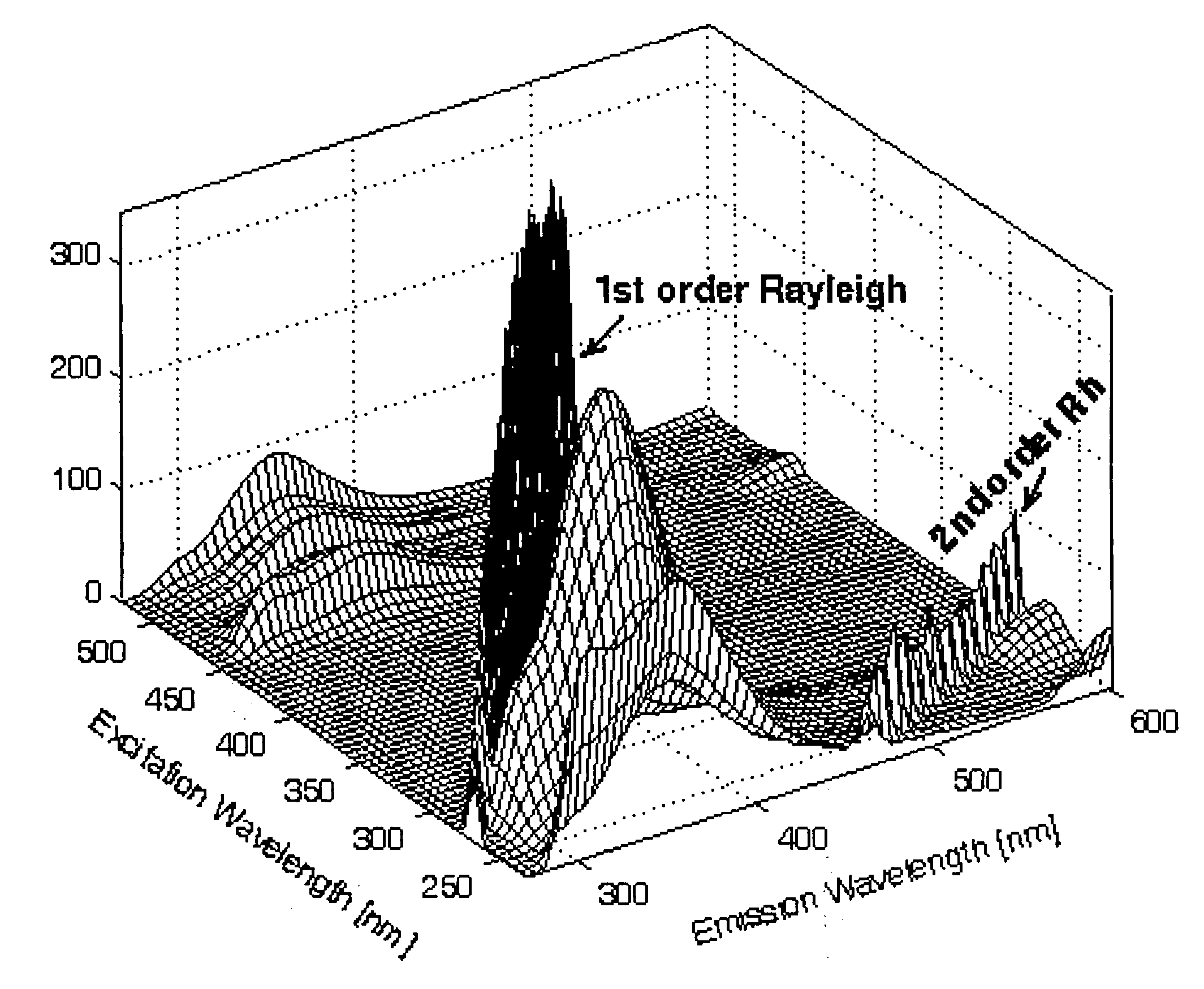

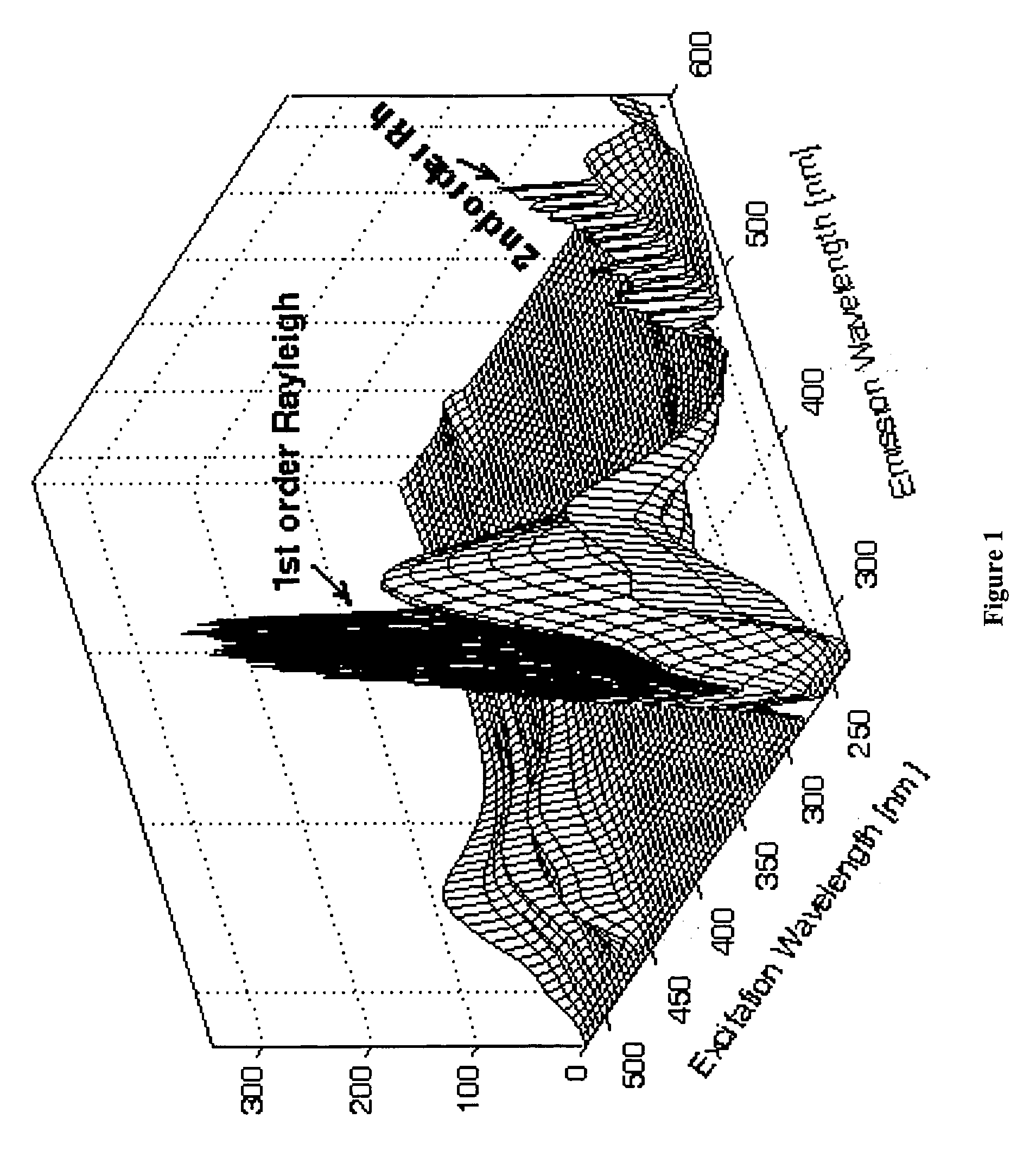

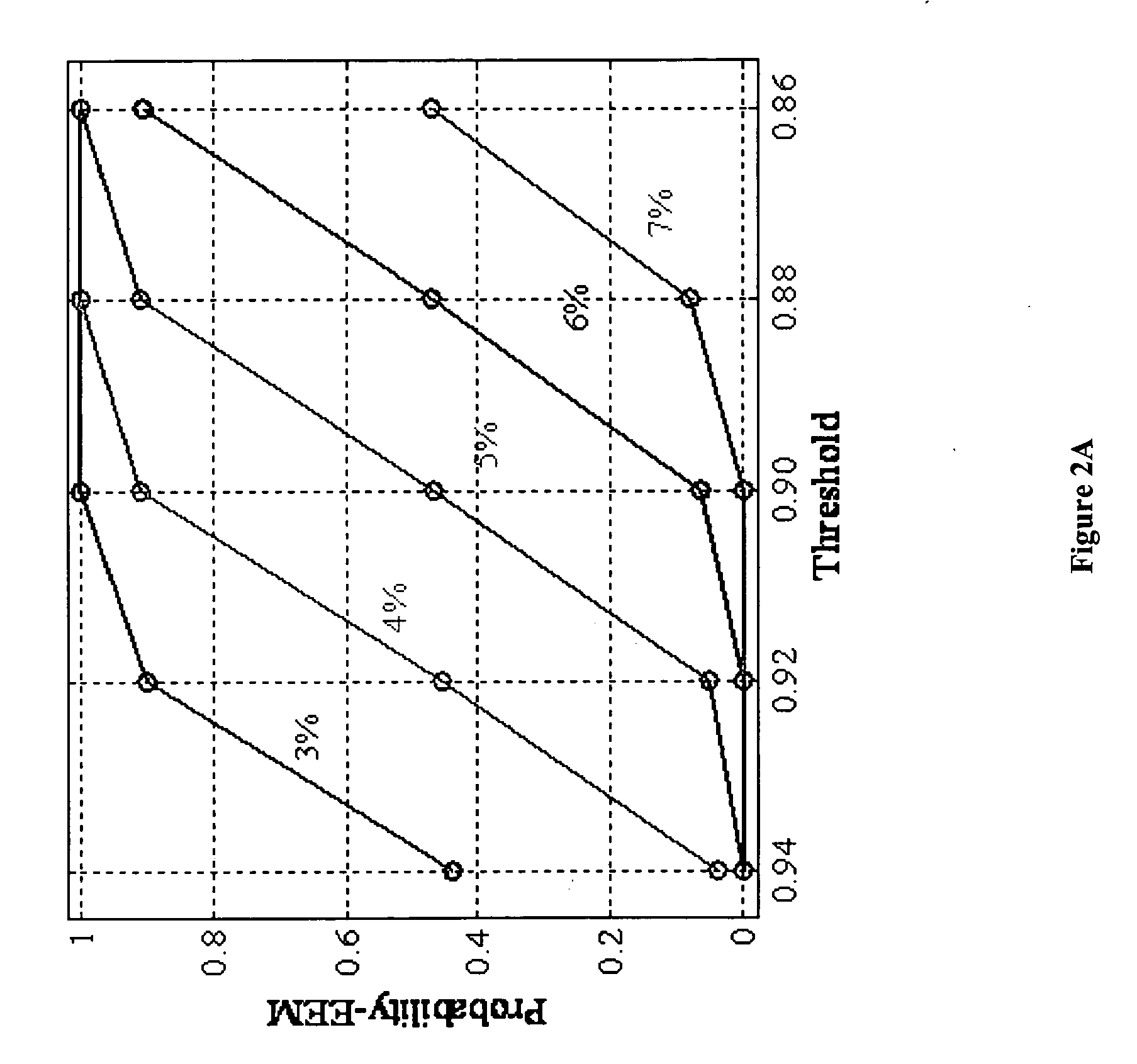

Similarity index: a rapid classification method for multivariate data arrays

InactiveUS20090306932A1Rapid classification and analysisDigital computer detailsRaman scatteringData setSpectroscopy

Similarity Index: a rapid classification method for multivariate data arrays The present invention is directed to a method of determining the similarity between a first multivariate data set and a second multivariate data set. The method is versatile and can be applied to a number of different multivariate data sets, for example, a spectroscopy multivariate data set. In particular, the method may be applied to rapidly assess the similarity between fluorescence spectroscopy multivariate data sets. The method comprises the steps of representing the data of a first and a second multivariate data set in matrix form to yield a multivariate data matrix, wherein each multivariate data matrix has the same dimensions. Subsequently, the magnitude of an additive and subtractive combination of each multivariate data matrix is calculated. The concept of a penalty parameter is introduced to set a detectable limit of variance between said first multivariate data set and said second multivariate data set. The penalty parameter is ascribed a value and is used in combination with the magnitude of an additive and subtractive combination of each multivariate data matrix to determine a similarity value. The determined similarity value indicates the variance between said first multivariate data set and said second multivariate data set.

Owner:THE NAT UNIV OF IRELAND GALWAY

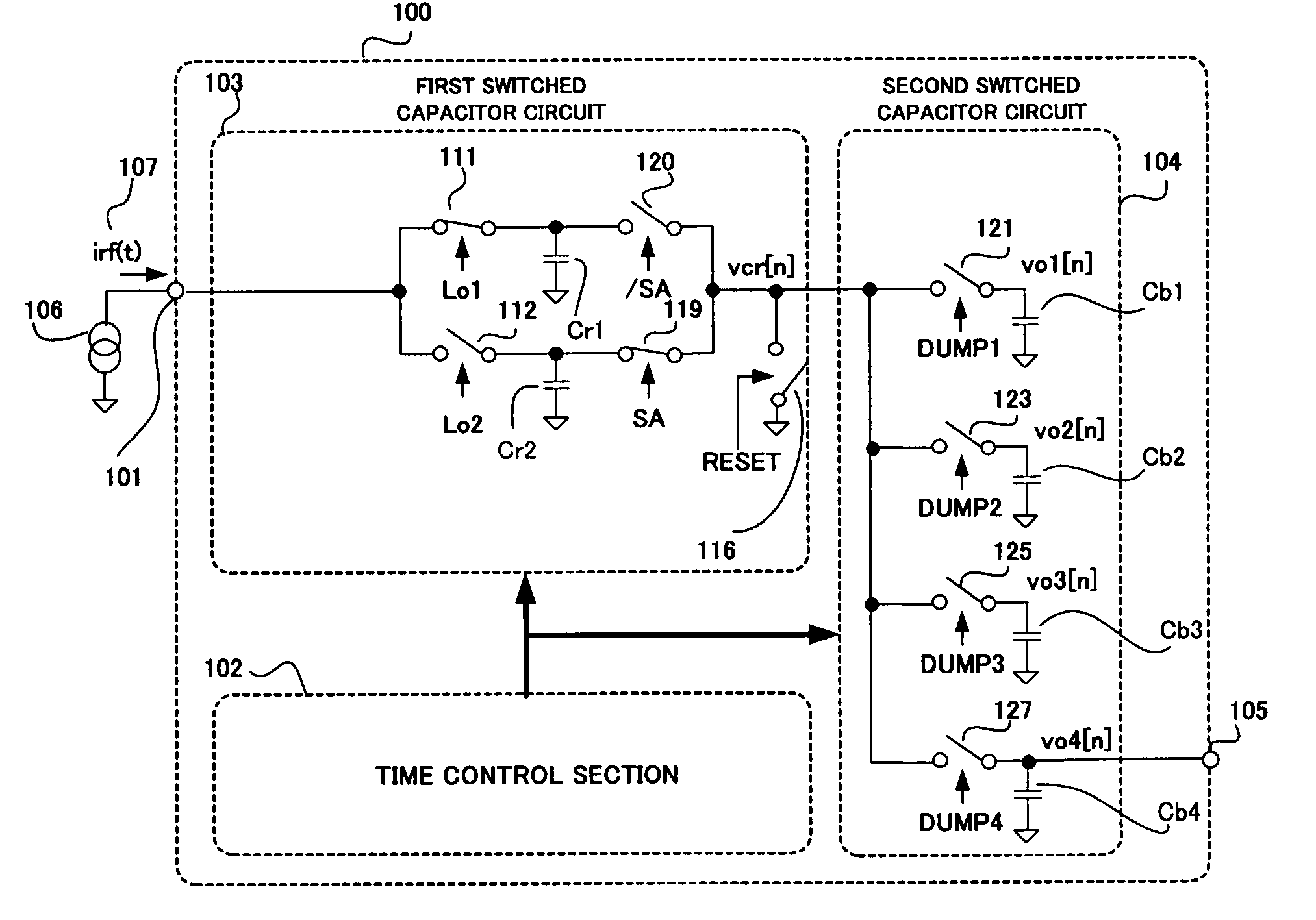

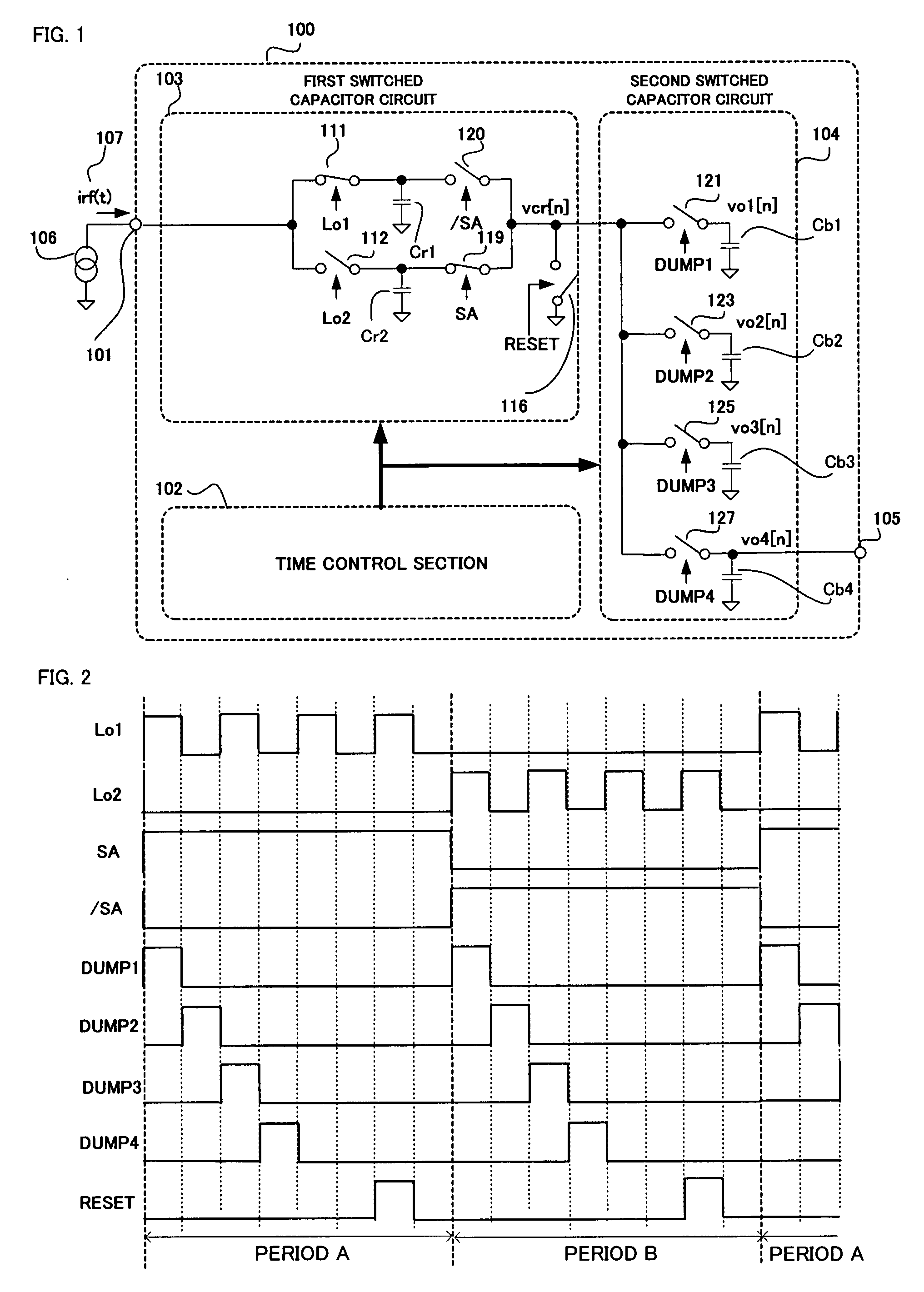

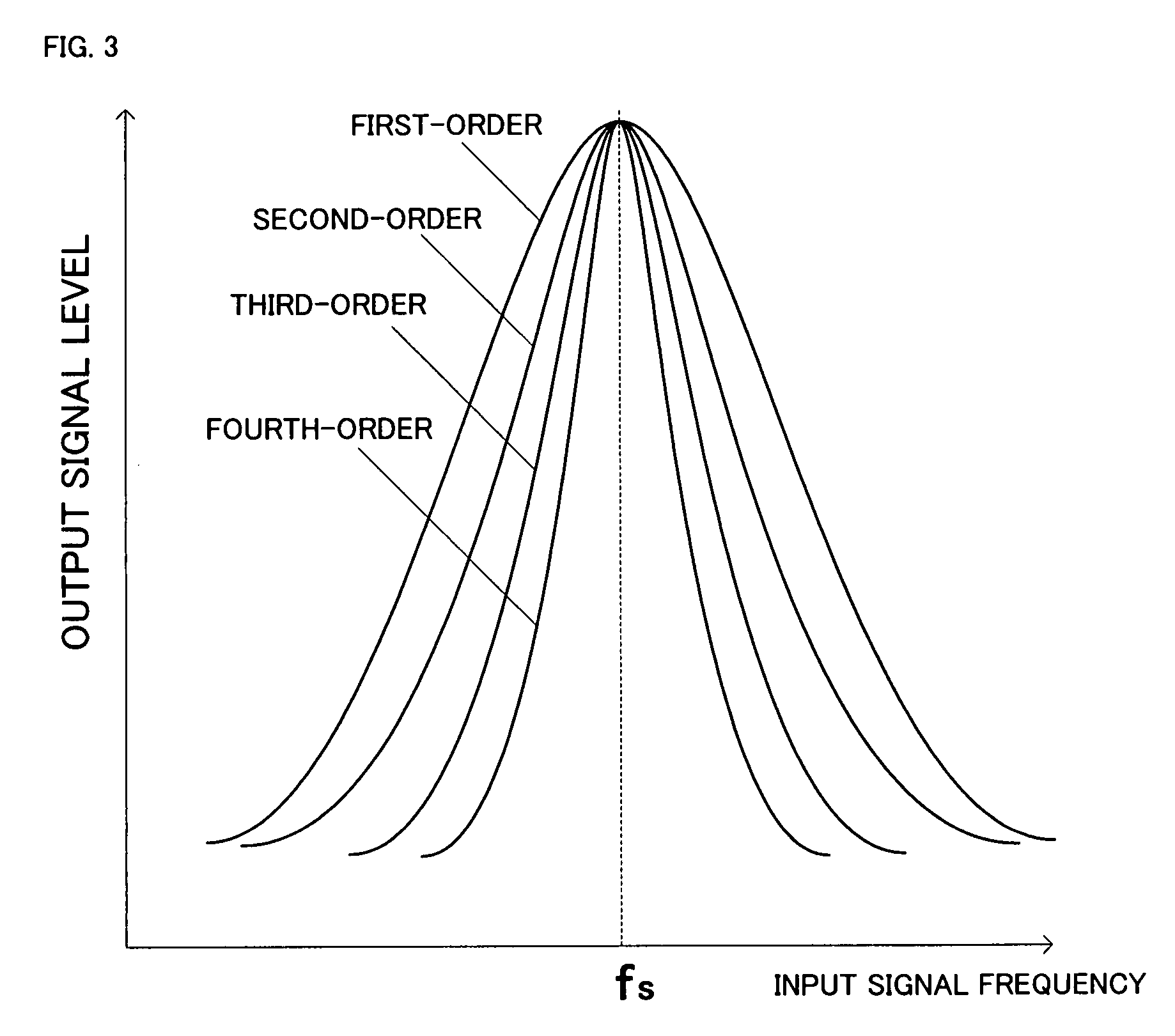

Mixer having frequency selection function

InactiveUS20070275684A1Enhanced frequency selection functionPass loss reducedModulation transference balanced arrangementsElectric analogue storesIir filteringCapacitance

A mixer which has an enhanced frequency selection characteristic and generates no pass loss is realized without using an operation control signal having a frequency higher than a sampling frequency. Provided are a time control section 102 for supplying control signals, a first switched capacitor circuit 100 for outputting a discrete time sample stream of the input signal 107 in accordance with integration operation control signals Lo1 and Lo2, and a second switched capacitor circuit 104 functioning as a high-order IIR filter by sharing a charge, and a frequency of each of the integration operation control signals Lo1 and Lo2 is higher than frequencies of other control signals.

Owner:PANASONIC CORP

Analog processor comprising quantum devices

ActiveCN101088102AComputing modelsDissimilar materials junction devicesAnalog processorComputational problem

Analog processors for solving various computational problems are provided. Such analog processors comprise a plurality of quantum devices, arranged in a lattice, together with a plurality of coupling devices. The analog processors further comprise bias control systems each configured to apply a local effective bias on a corresponding quantum device. A set of coupling devices in the plurality of coupling devices is configured to couple nearest-neighbor quantum devices in the lattice. Another set of coupling devices is configured to couple next-nearest neighbor quantum devices. The analog processors further comprise a plurality of coupling control systems each configured to tune the coupling value of a corresponding coupling device in the plurality of coupling devices to a coupling. Such quantum processors further comprise a set of readout devices each configured to measure the information from a corresponding quantum device in the plurality of quantum devices.

Owner:D WAVE SYSTEMS INC

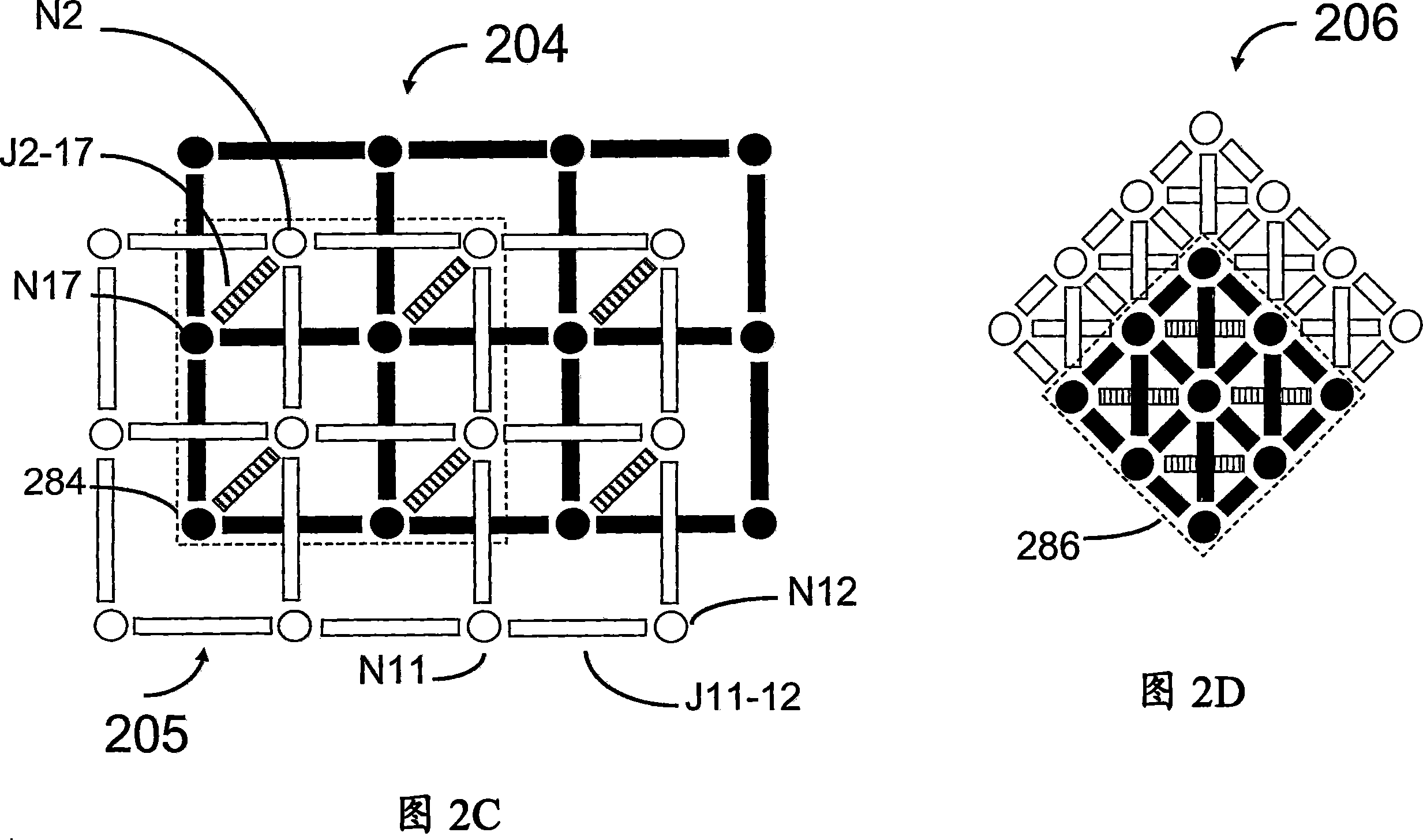

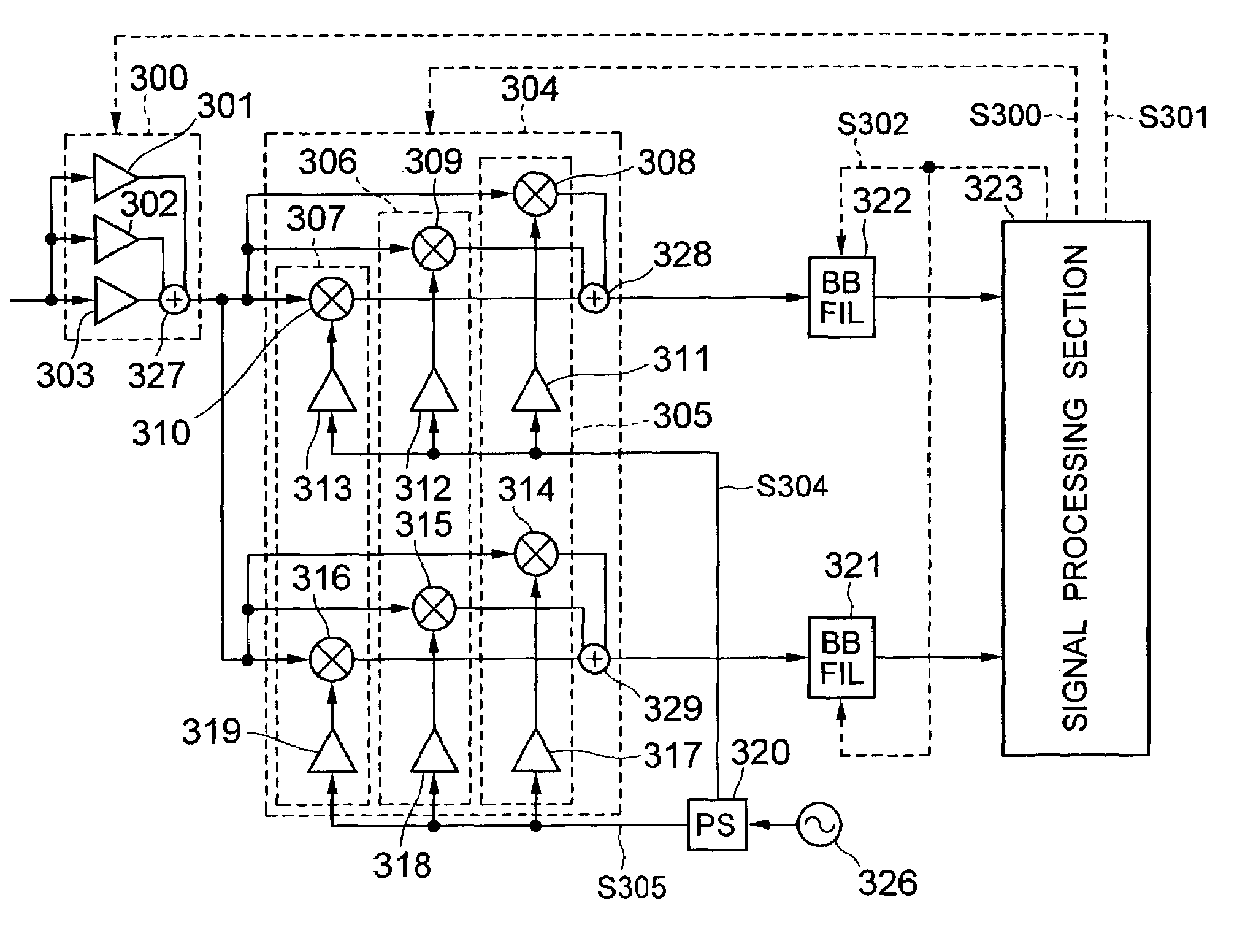

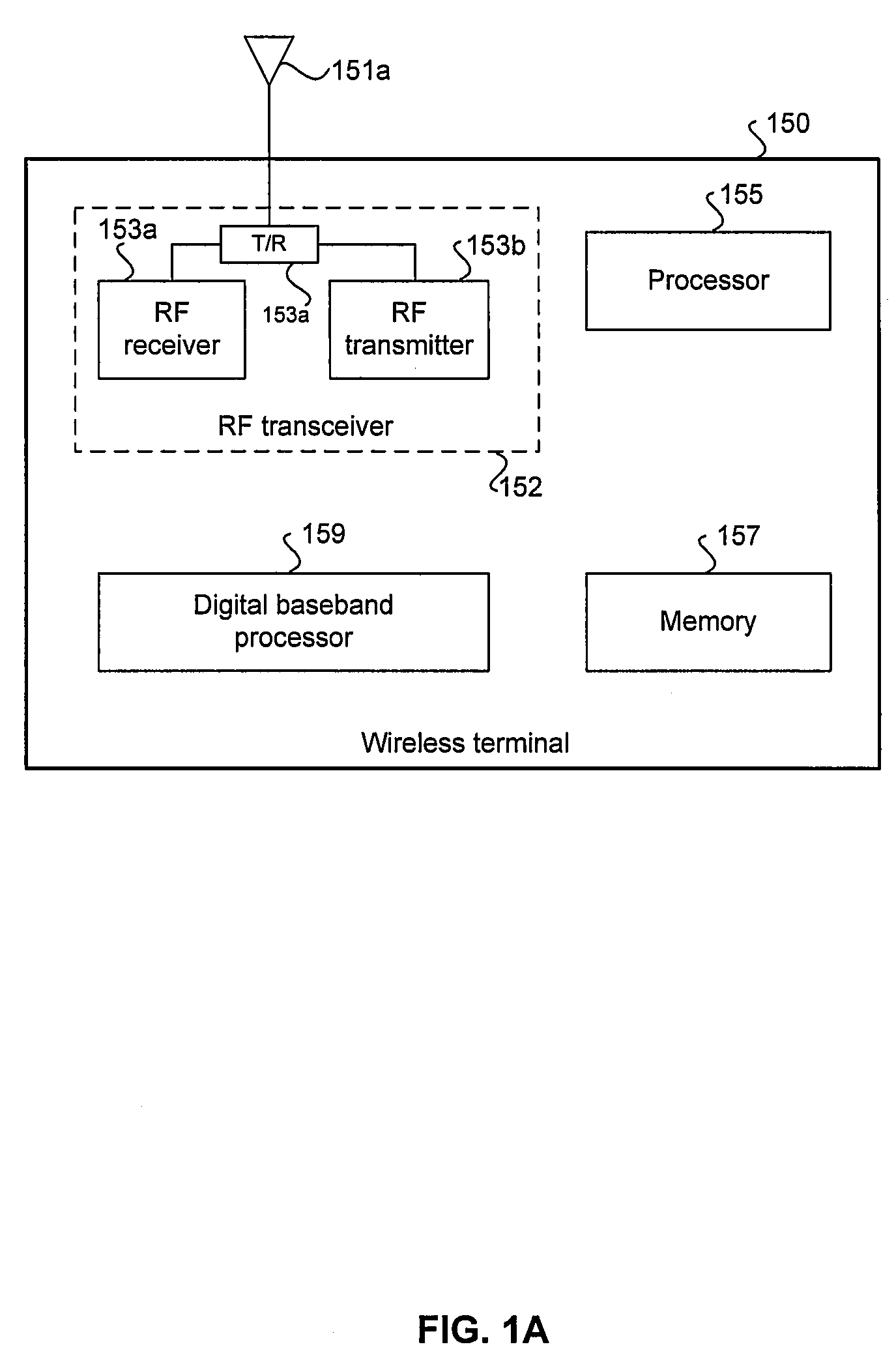

Receiver apparatus controlling the power consumption according to the reception signal level

InactiveUS7076231B2Reduce power consumptionImprove dynamic rangeComputing operation arrangementsOscillations generatorsFrequency changerControl signal

A receiver apparatus is provided with a receiver section including an amplifying stage for amplifying a high frequency signal received by an antenna, a frequency converting stage for converting a frequency of the output signal of the amplifying stage, a local oscillator for supplying a local oscillating signal to the frequency converting stage, and a signal processing section for supplying a control signal to the receiver section depending on signal intensity inputted to the receiver section, or to the signal processing section from the receiver section. The frequency converting section includes a plurality of parallel frequency converters, and an adder for adding output signals of the frequency converters. The signal processing section controls the number of the frequency converters to be operated.

Owner:HITACHI LTD

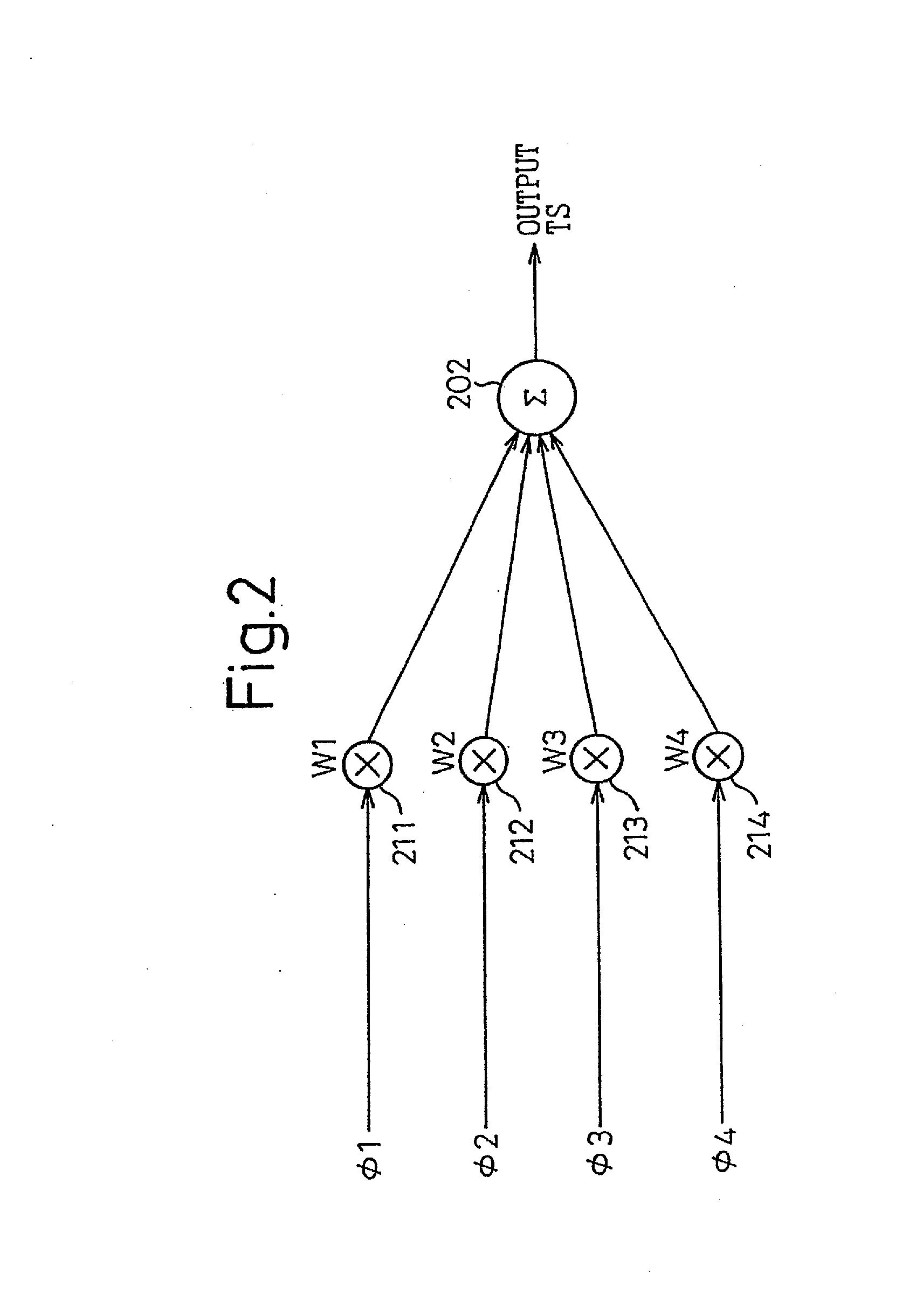

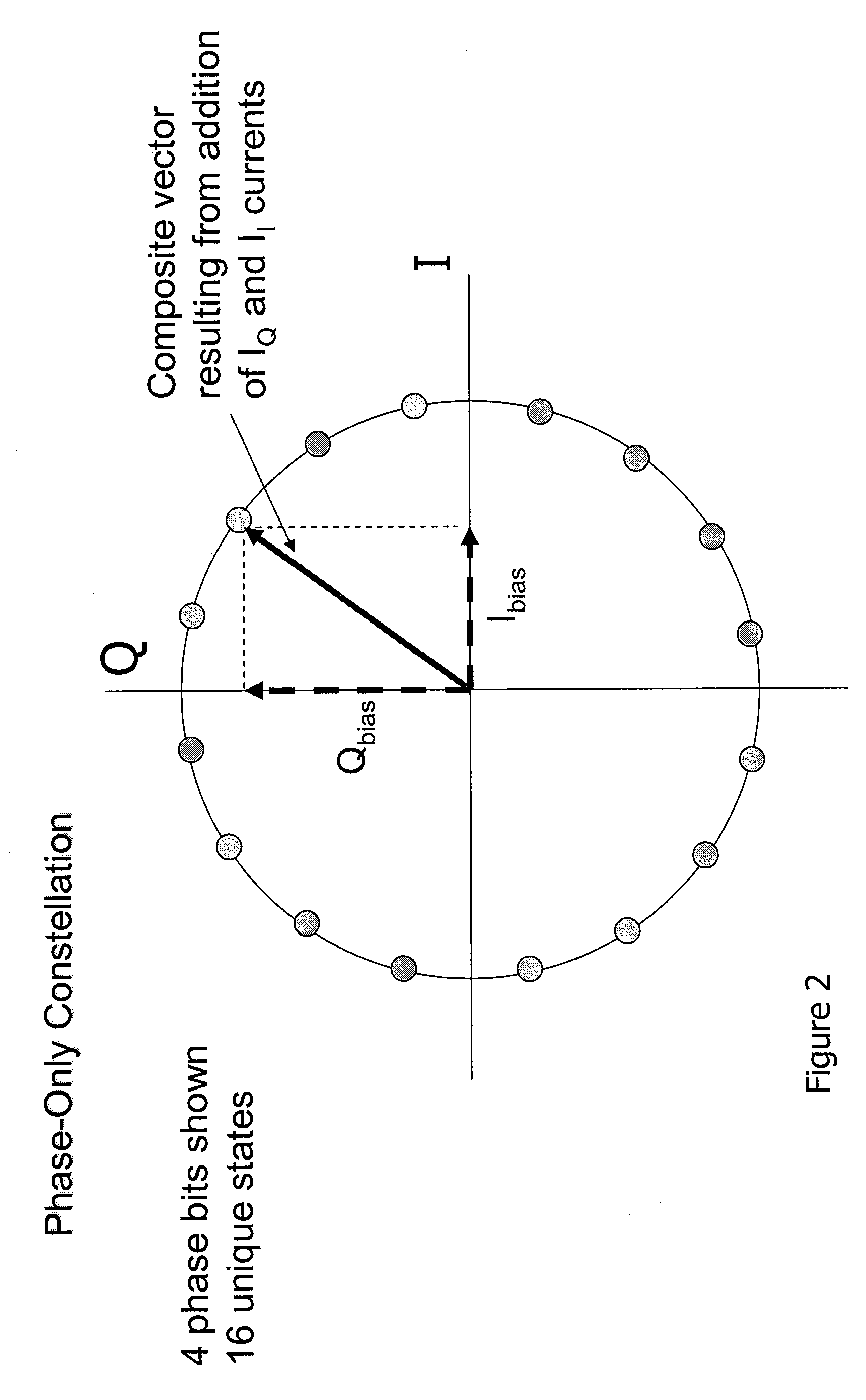

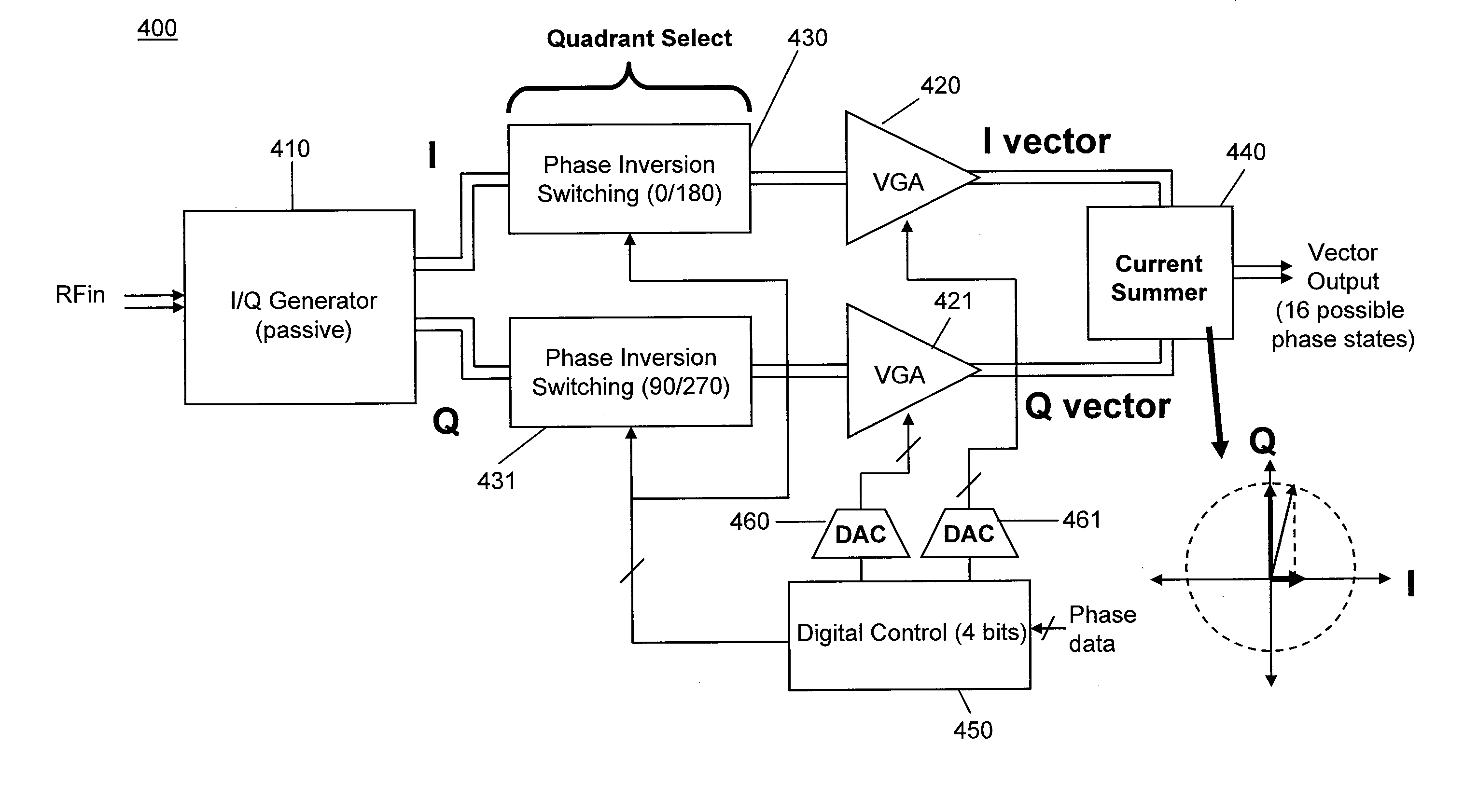

Digital amplitude control of vector generator

ActiveUS20100260285A1Easy CalibrationImprove system flexibilityModulated-carrier systemsActive element networkDigital analog converterAmplitude control

In an exemplary embodiment, an active vector generator is configured to generate a composite vector with controlled phase and amplitude, where the active vector generator generates the composite vector with independent variable phase control and independent variable amplitude control. Furthermore, in another exemplary embodiment, an active vector generator is configured to generate a unique number of phase states and configured to generate a unique number of amplitude states. Specifically, an exemplary active vector generator comprises a digital-to-analog converter (DAC) configured to set the phase of the composite vector, a current multiplying switch network configured to control the amplitude of the composite vector, a variable current multiplier configured to adjust the amplitude of the composite vector, and a differential adder configured to control the quadrant of the composite vector and generate the composite vector.

Owner:VIASAT INC

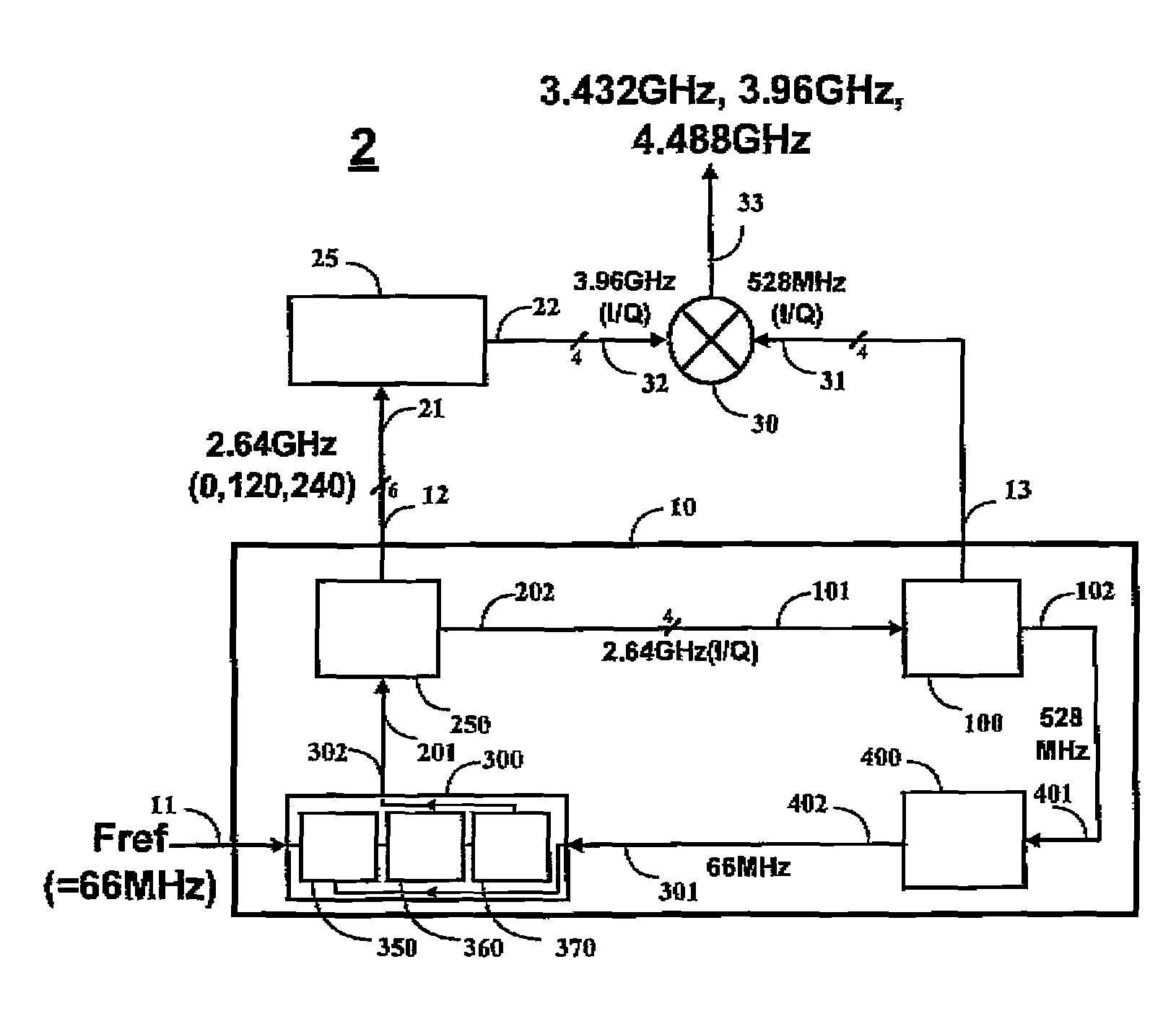

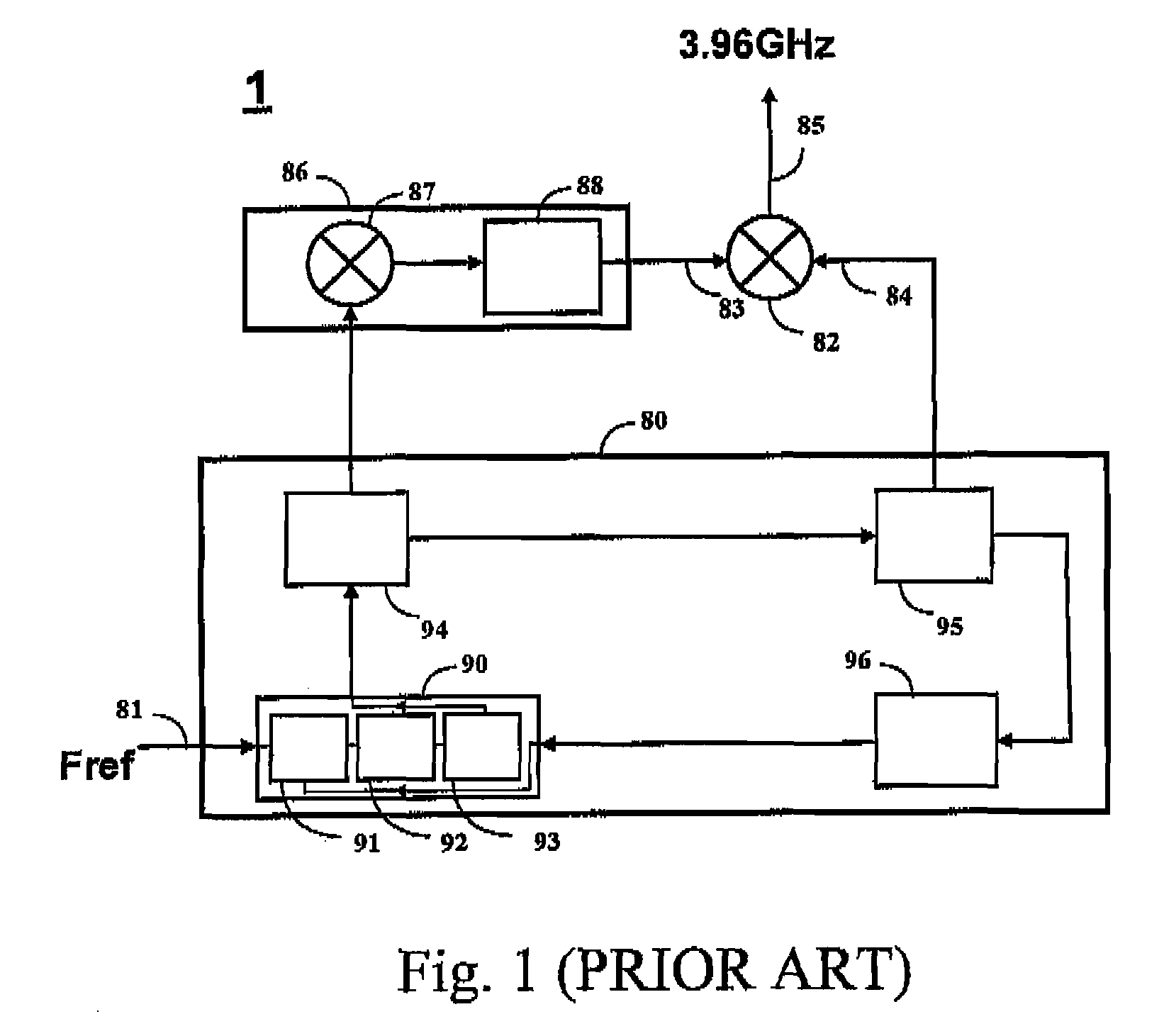

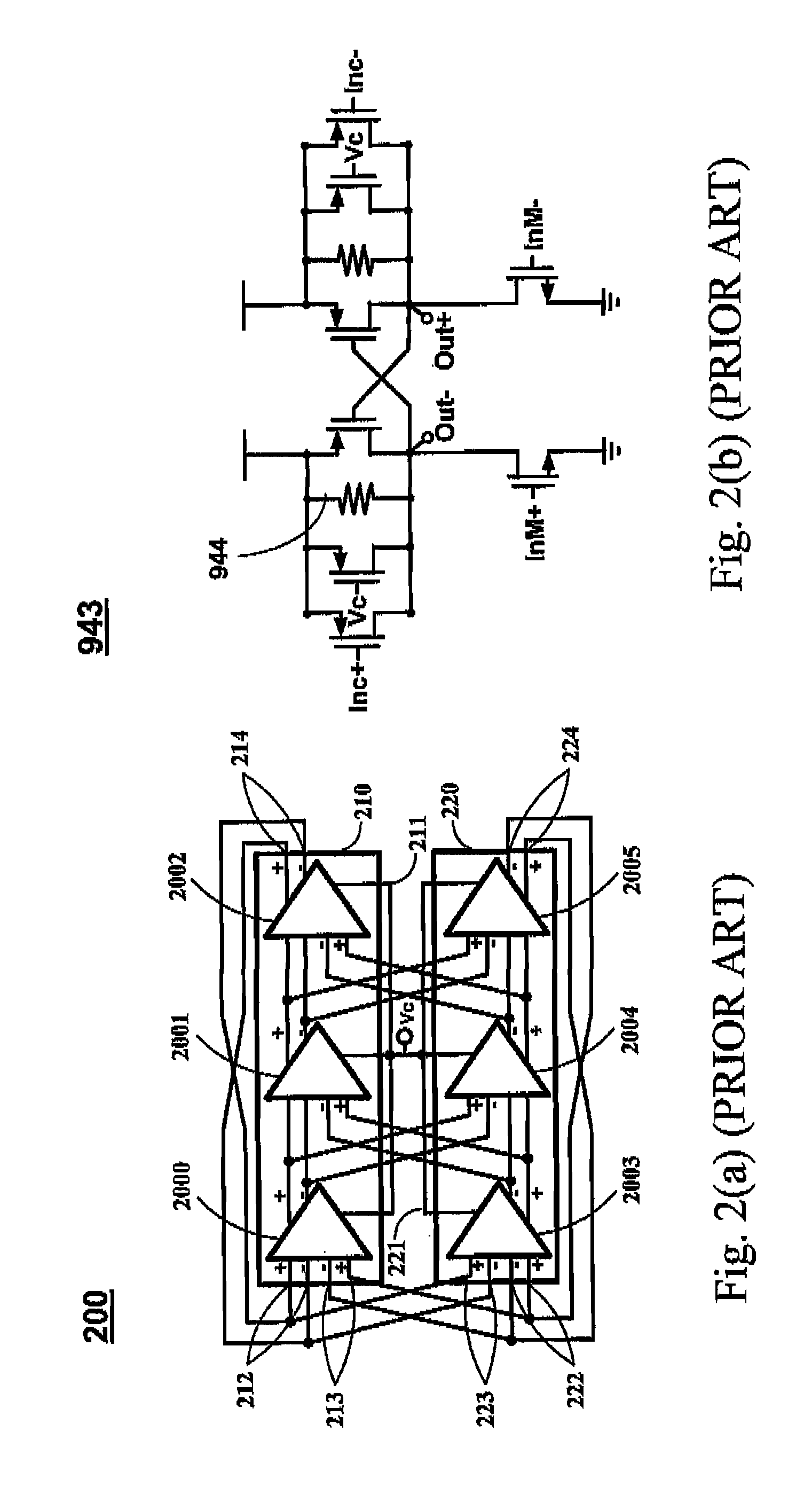

Frequency synthesizer, coupled divide-by-N circuit, current-reuse multiply-by-M circuit

InactiveUS7671635B2Reduce a mismatch generatedPulse automatic controlCounting chain synchronous pulse countersFrequency mixerFrequency synthesizer

A frequency synthesizer is provided in the present invention. The frequency synthesizer includes a single phase-locked loop having a reference frequency signal input, a first output, a second output and a pair of divide-by-N circuits coupled with each other and electrically connected to the second output; a multiply-by-M circuit having a first input electrically connected to the first output and a third output; and a combination of a buffer and a mixer having a second input electrically connected to the second output and a third input electrically connected to the third output generating a frequency signal output.

Owner:NAT TAIWAN UNIV

Active butler and blass matrices

ActiveUS20100259446A1Low costImprove isolationComputing operation arrangementsAntennasPower combinerEngineering

In an exemplary embodiment, a monolithic active solution is configured to generate the fixed spatial beams of a Butler matrix operation or a Blass matrix operation. The exemplary Butler matrix comprises active RF hybrids and vector generators, and is designed for broadband performance in an ultra-compact size, which is size independent of the operating frequency. Furthermore, an exemplary Blass matrix comprises vector generators, active power combiners, and active power splitters. The Blass matrix is designed for broadband performance in an ultra-compact size, which is size independent of the operating frequency. Both the exemplary Butler matrix and exemplary Blass matrix may be configured generate steerable beams. Advantages of both the exemplary Butler matrix and exemplary Blass matrix include that they have neutral or slight positive power gain rather than high losses, and have ultra broadband range which enables operation over multiple frequency bands.

Owner:VIASAT INC

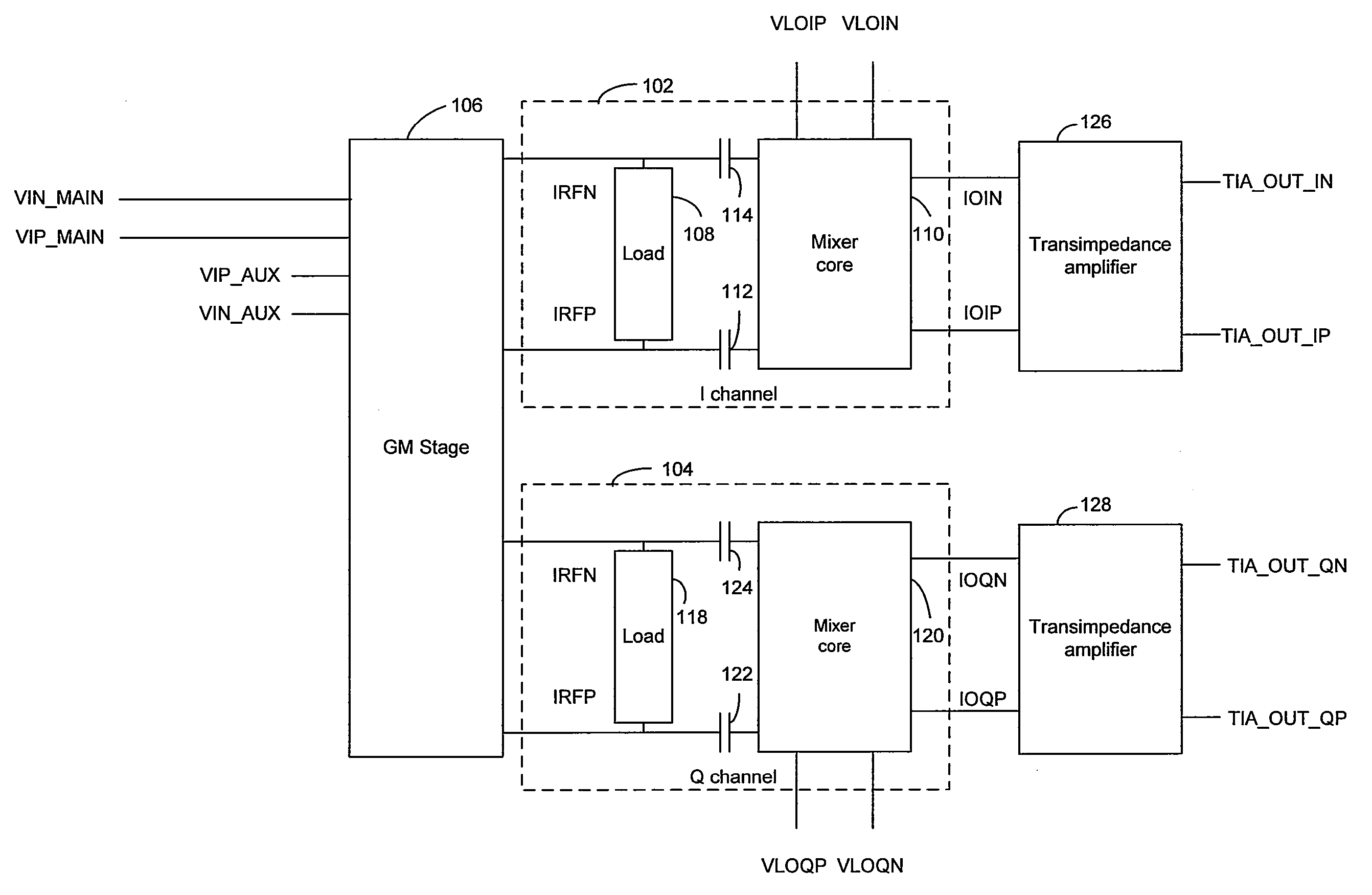

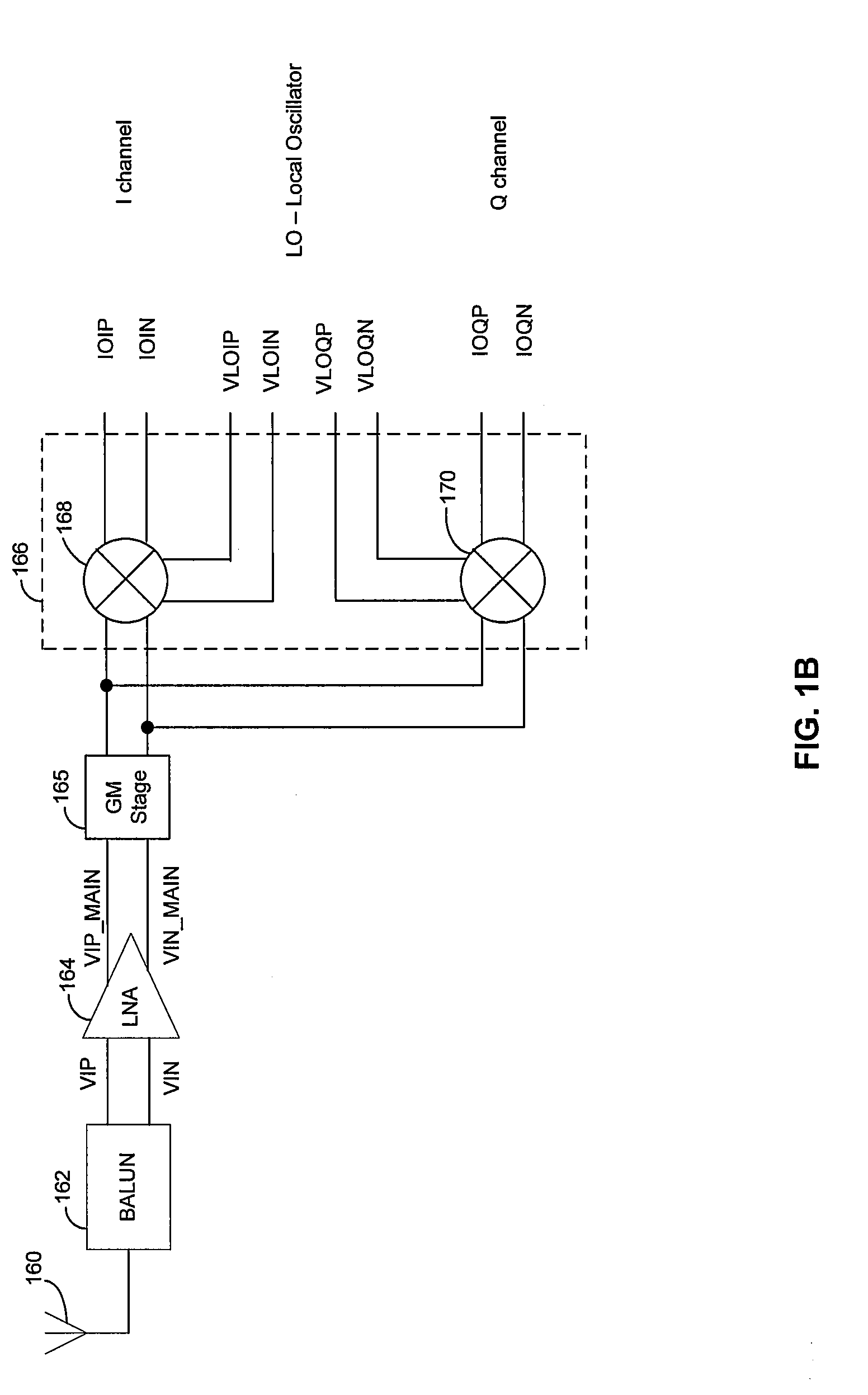

Method and system for a shared gm-stage between in-phase and quadrature channels

InactiveUS20080139162A1Frequency-modulated carrier systemsComputing operation arrangementsUltrasound attenuationFrequency mixer

Aspects of a method and system for a shared GM-stage between in-phase and quadrature channels may include processing an in-phase (I) component signal for the I channel and a quadrature (Q) component signal for the Q channel via one or more shared transconductance stages in a frequency demodulator. The I channel may be isolated from the Q channel and the Q channel may be isolated from the I channel using isolation resistors. The values of the isolation resistors may be selected so as to balance the isolation and signal attenuation. A folding circuit, comprising active devices, may isolate the I channel from the Q channel. A generated voltage may be utilized to bias the folding circuit. An oscillator for the I channel may be isolated from a mixer for the Q channel and an oscillator for the Q channel may be isolated from a mixer for the I channel.

Owner:AVAGO TECH INT SALES PTE LTD