Patents

Literature

92results about How to "Reduce silicon area" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

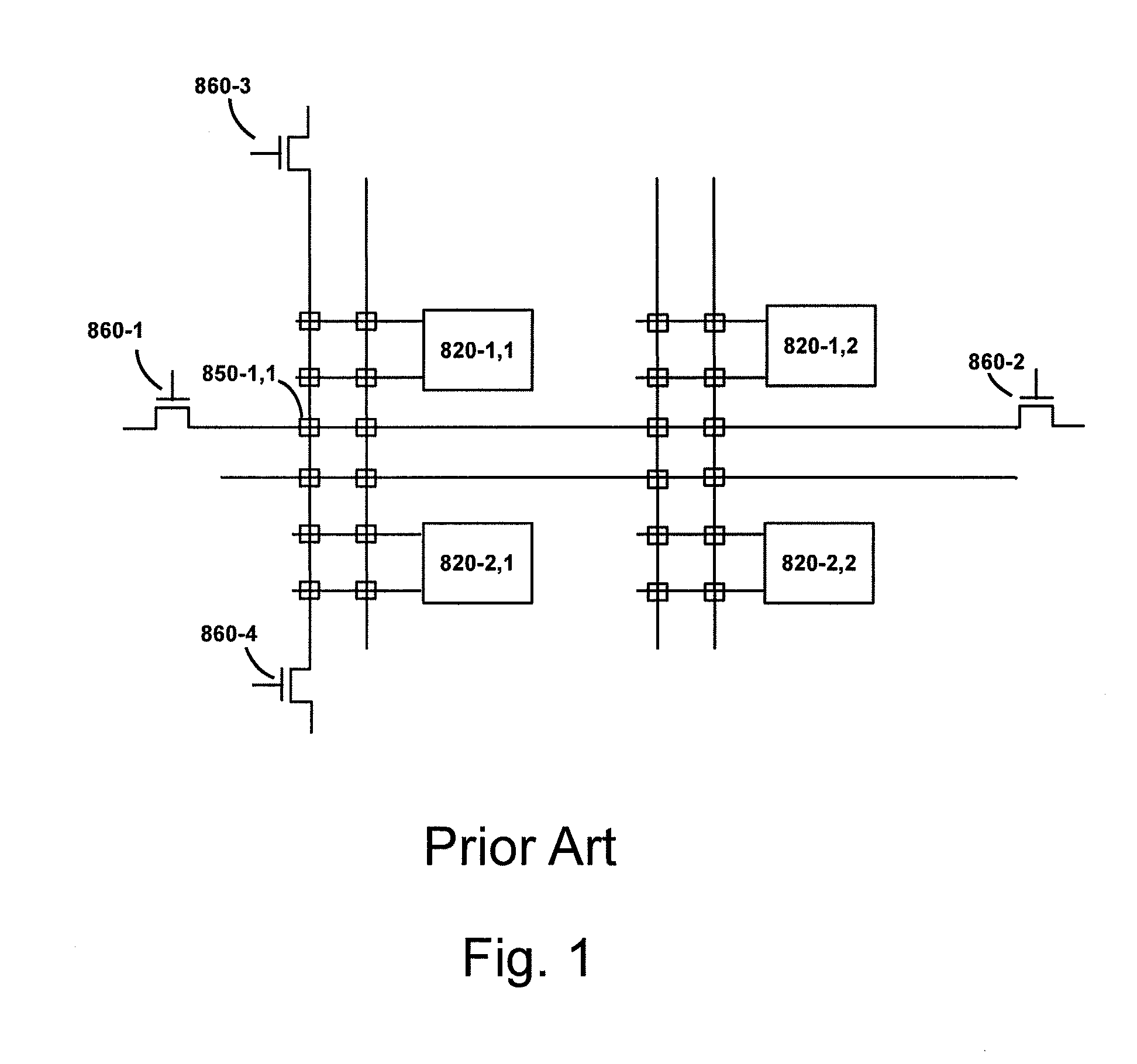

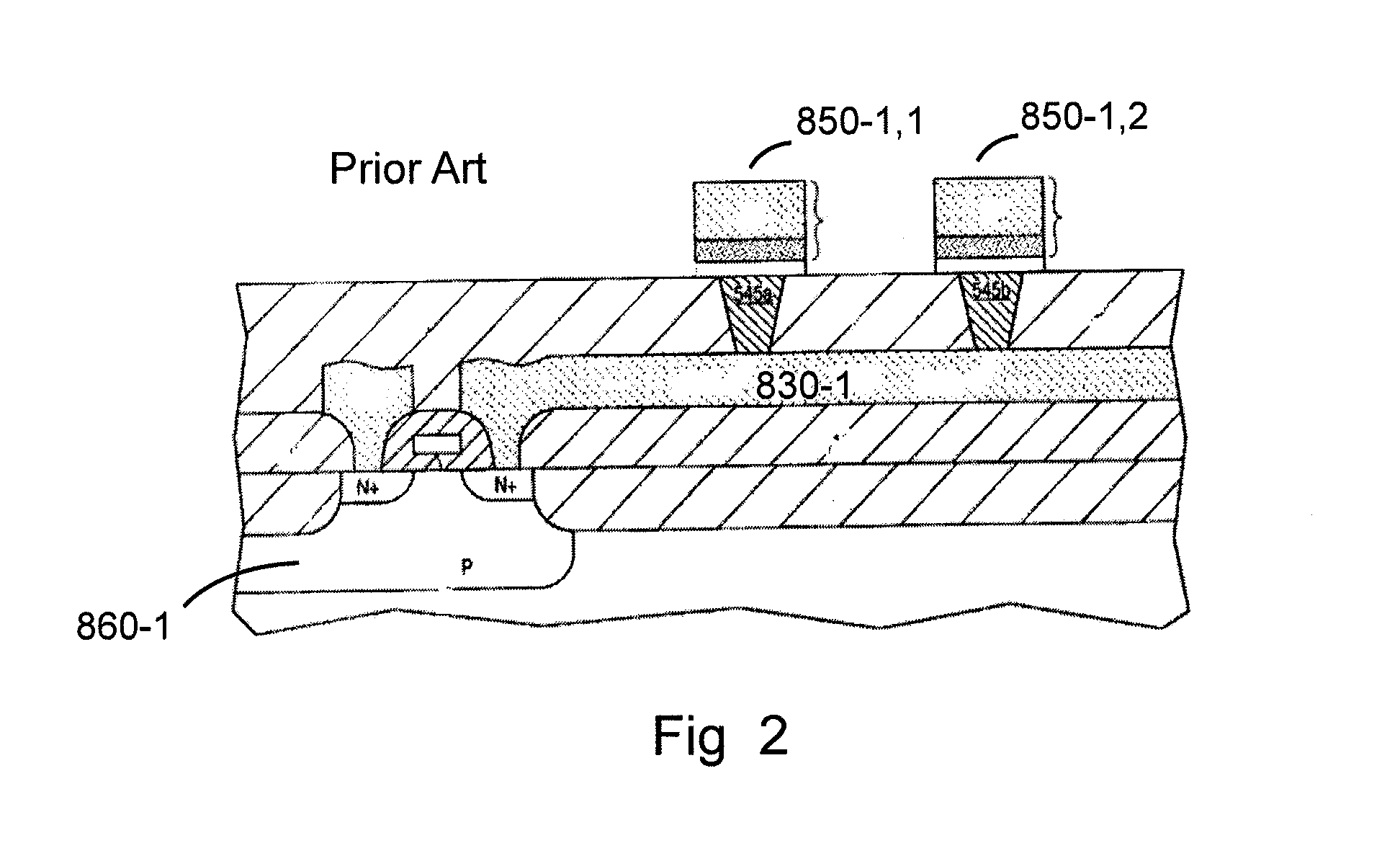

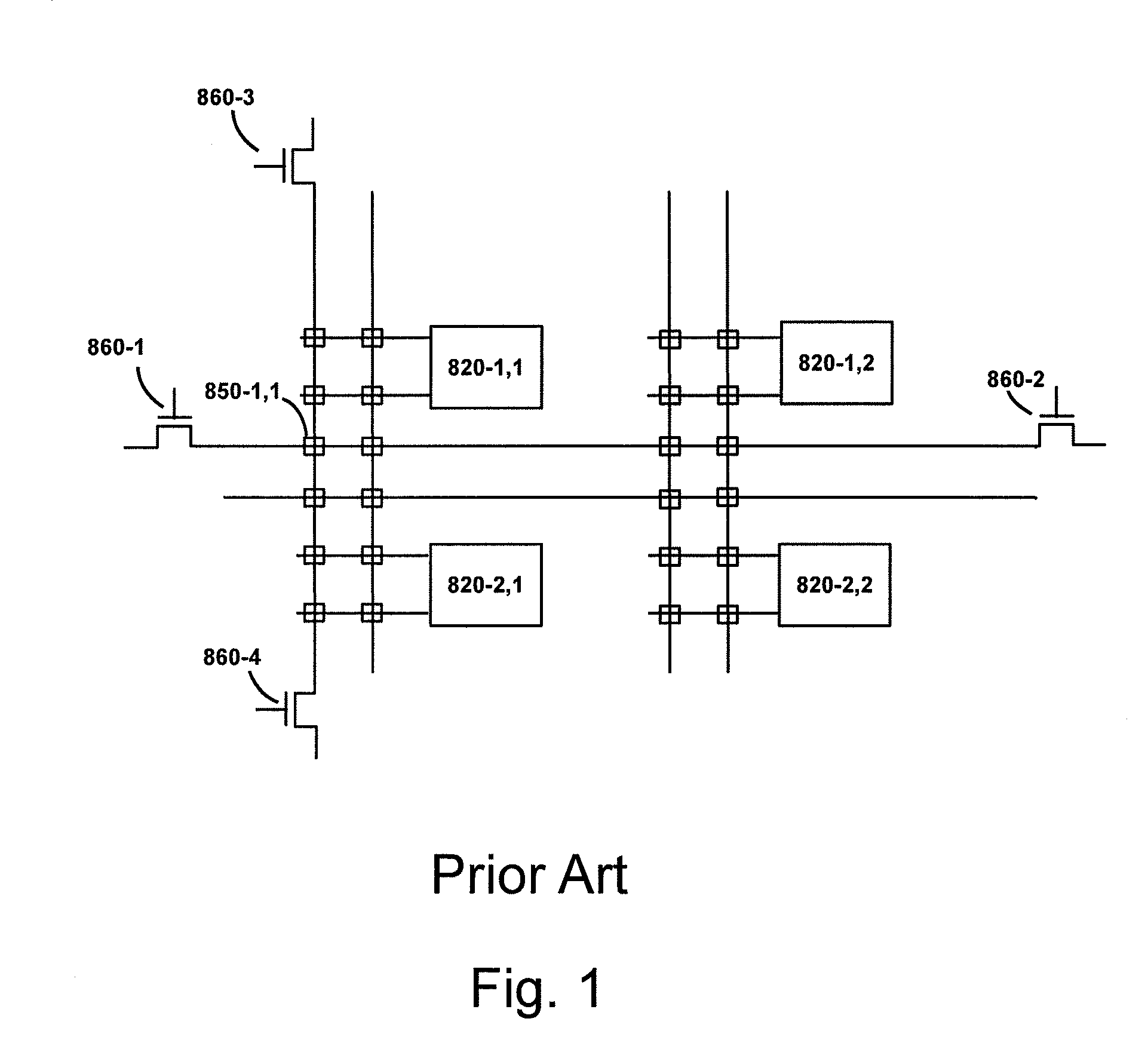

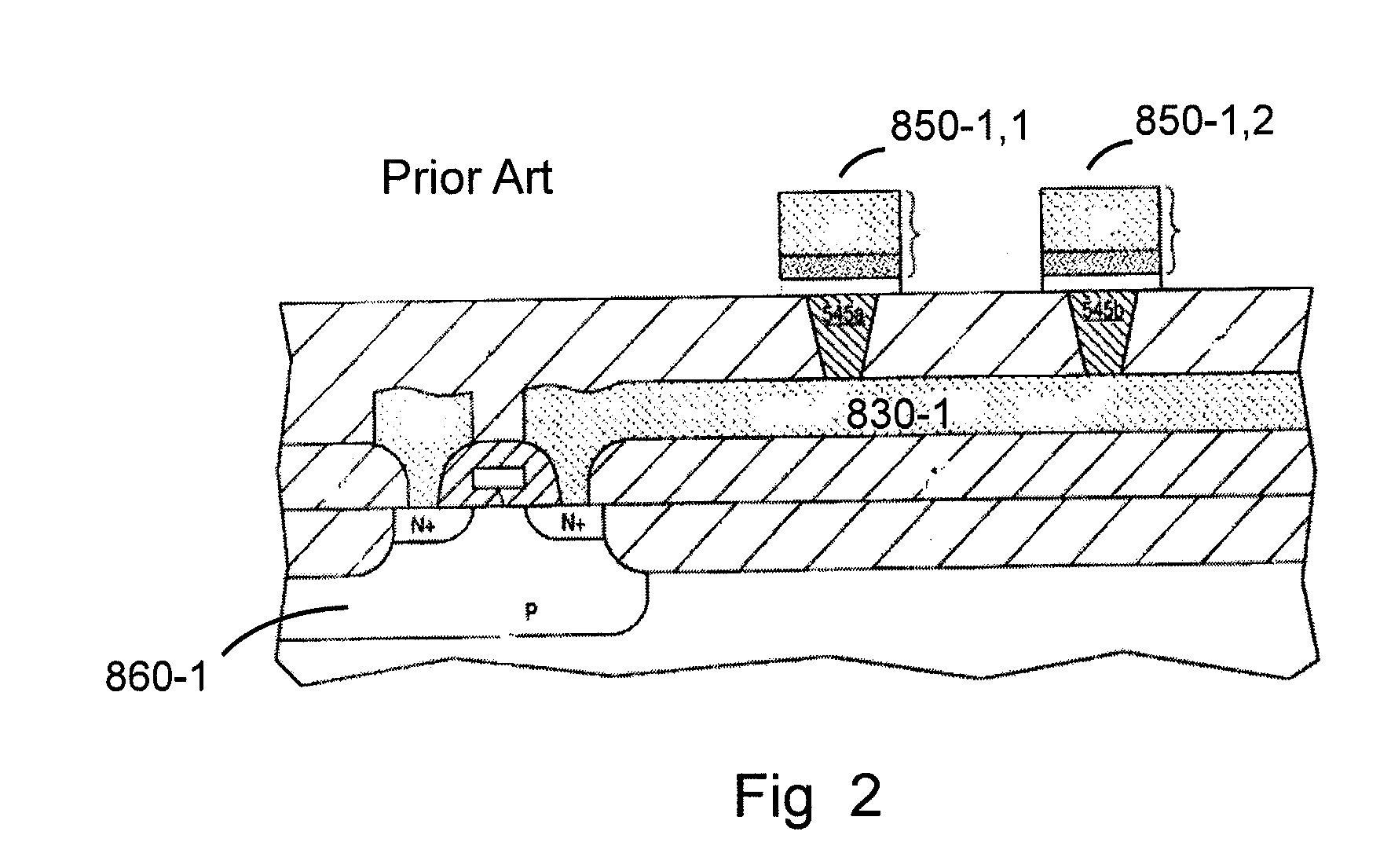

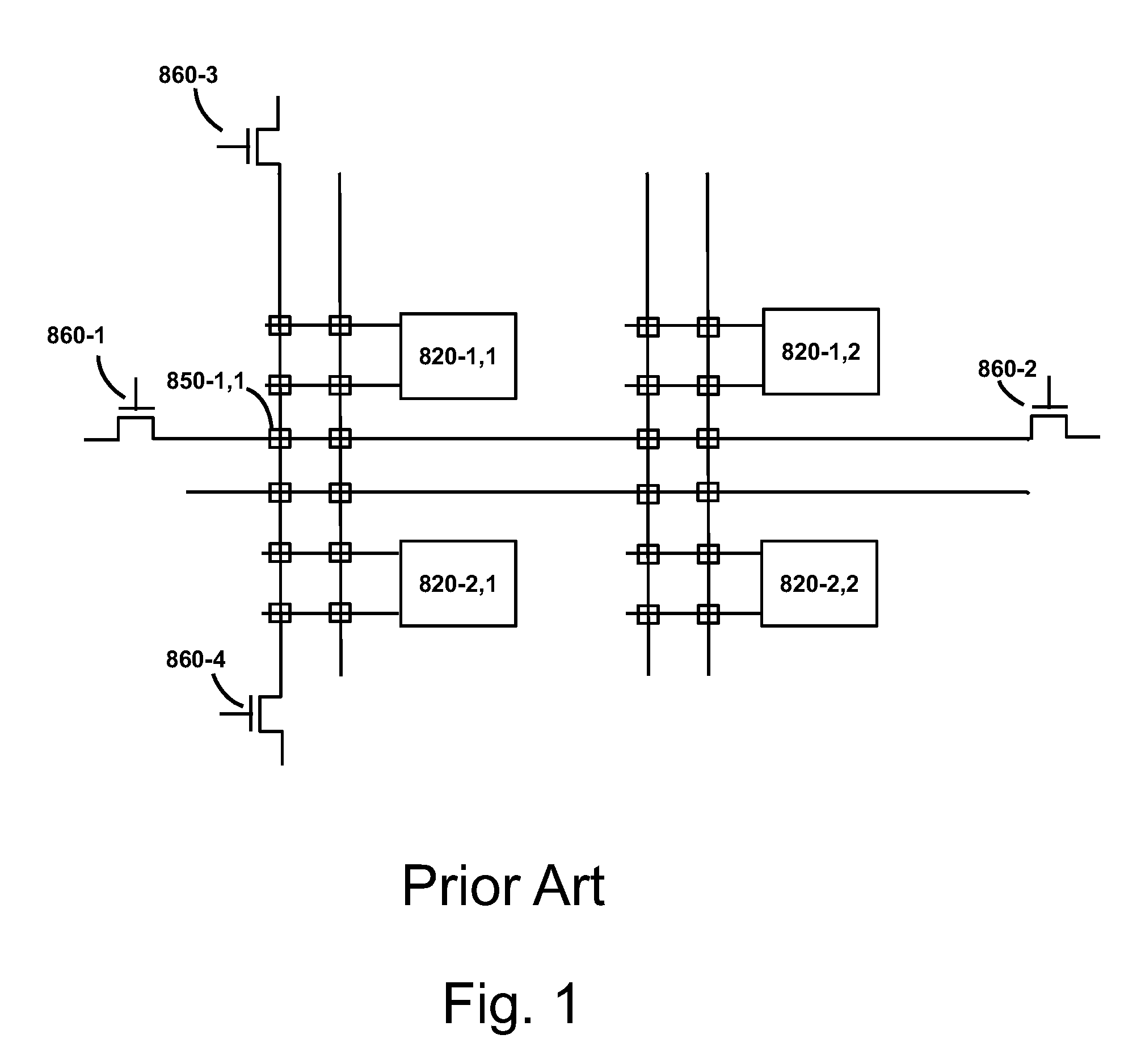

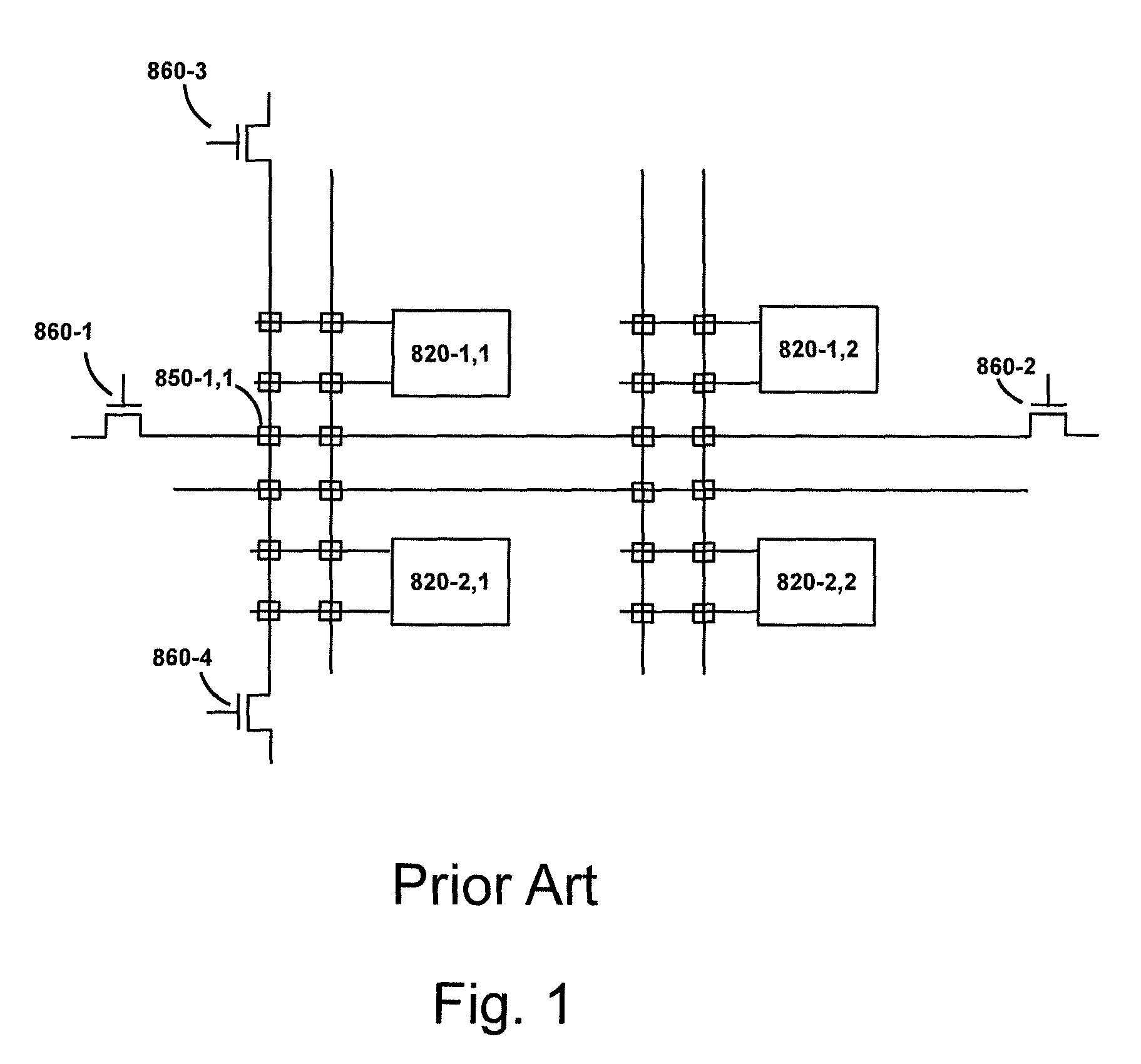

OLED Display Driver Circuits and Techniques

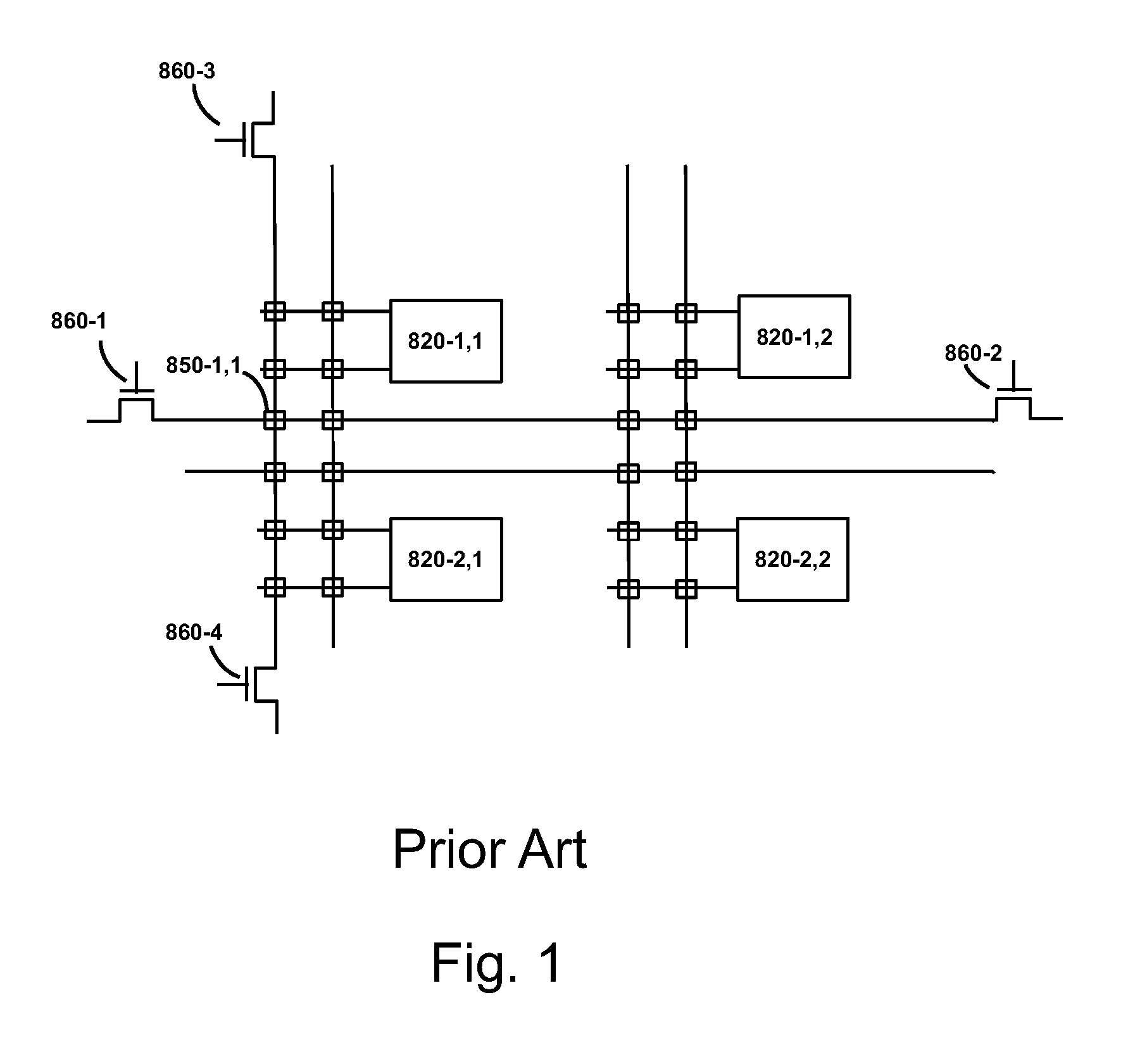

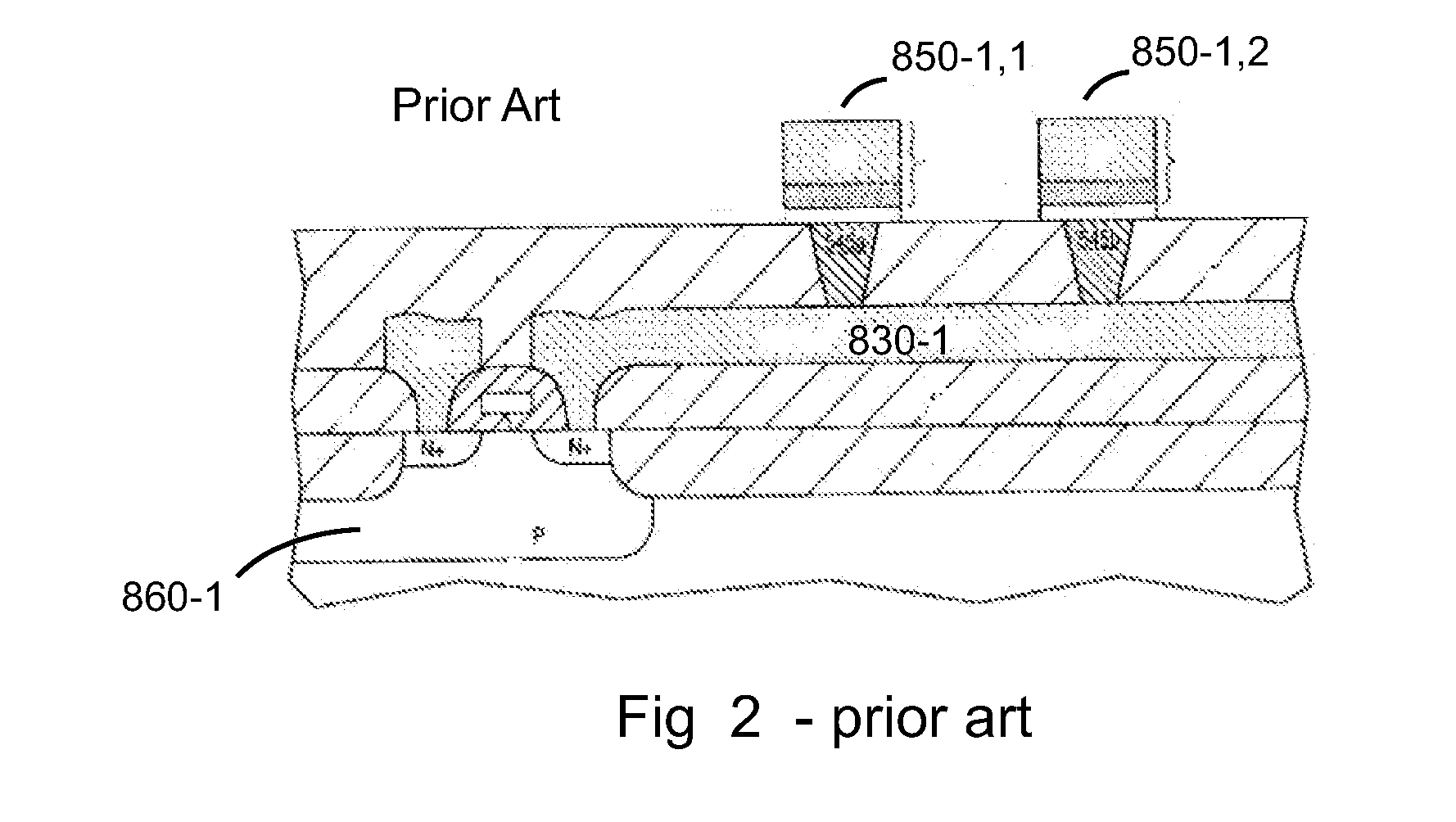

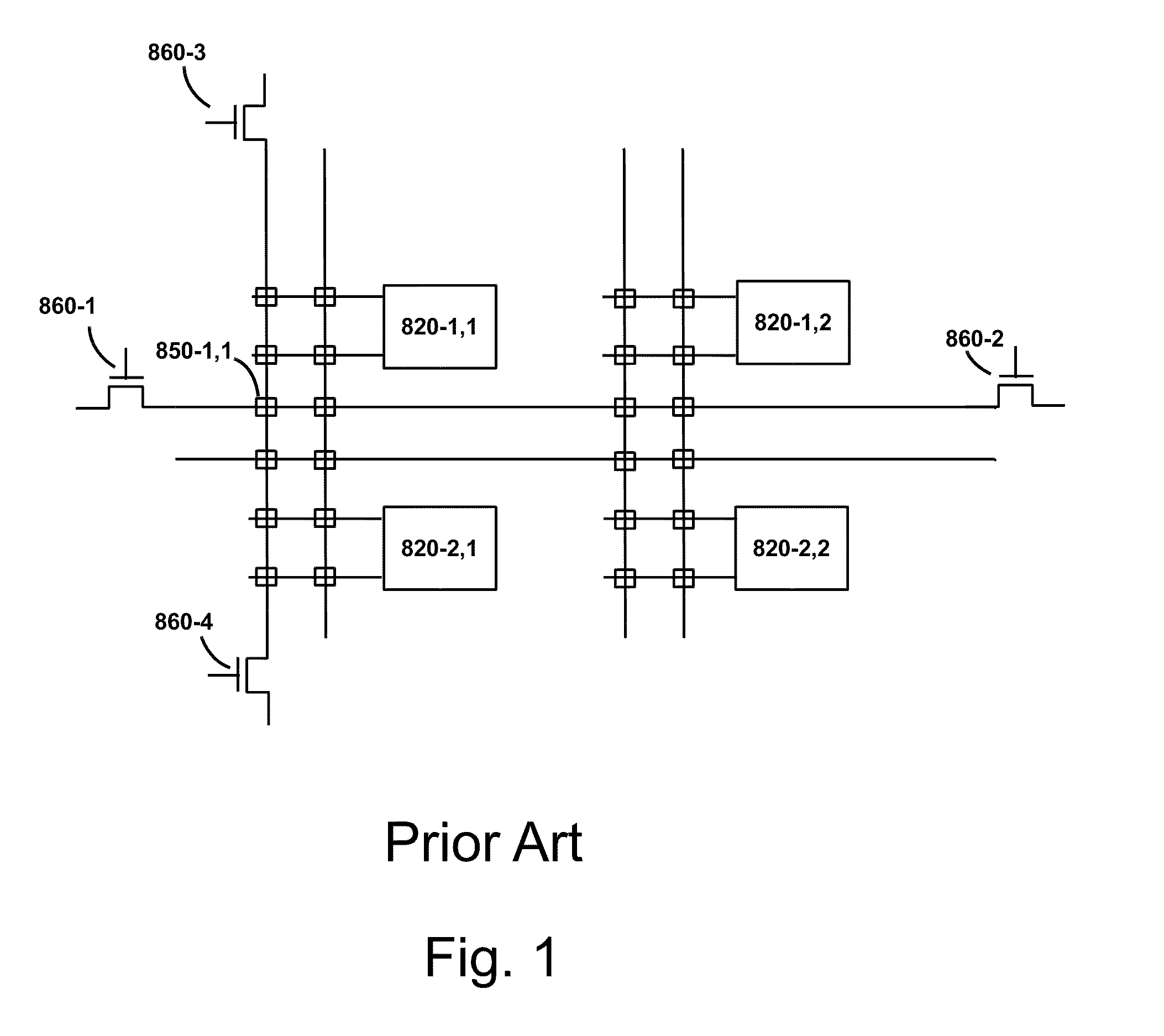

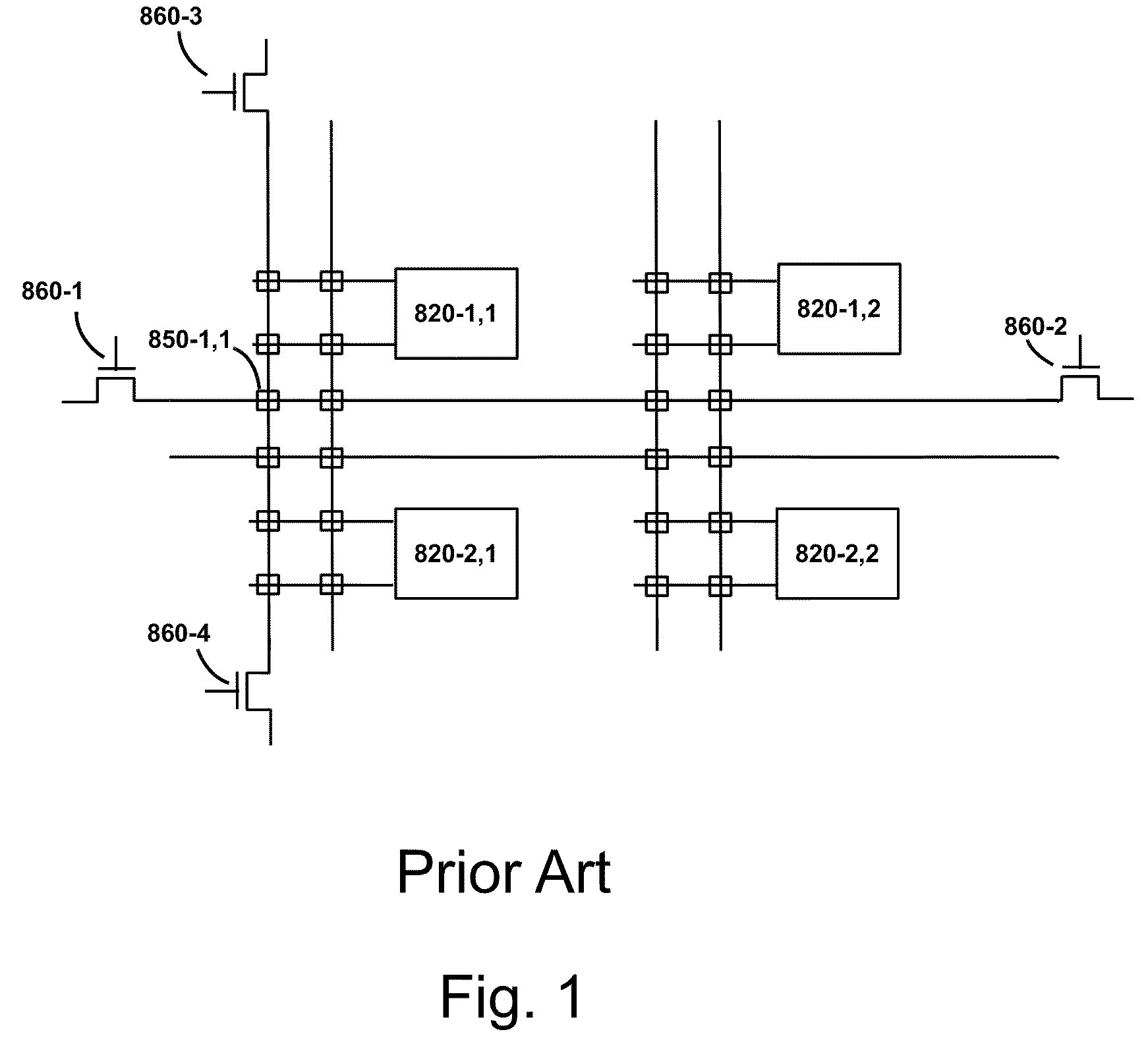

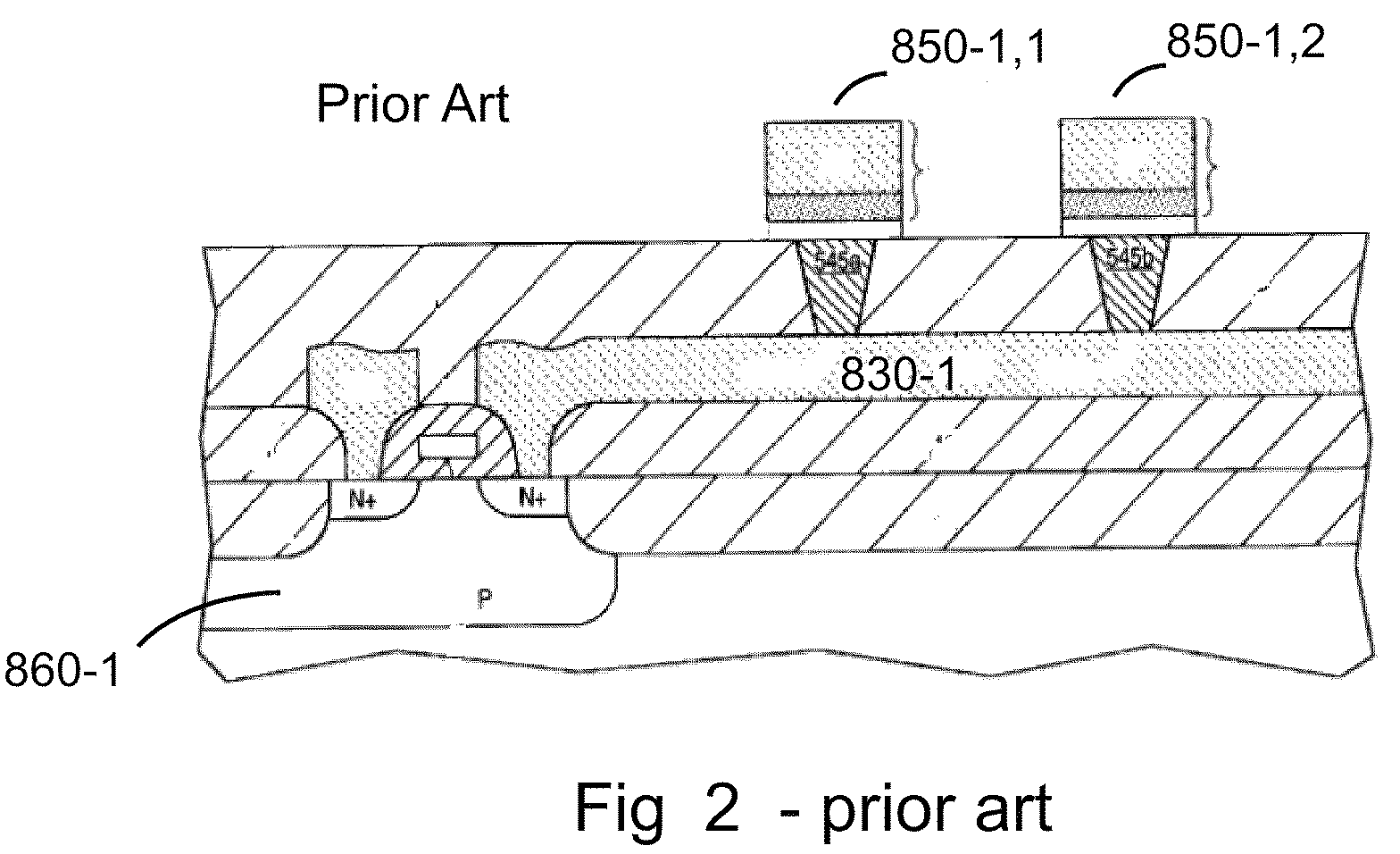

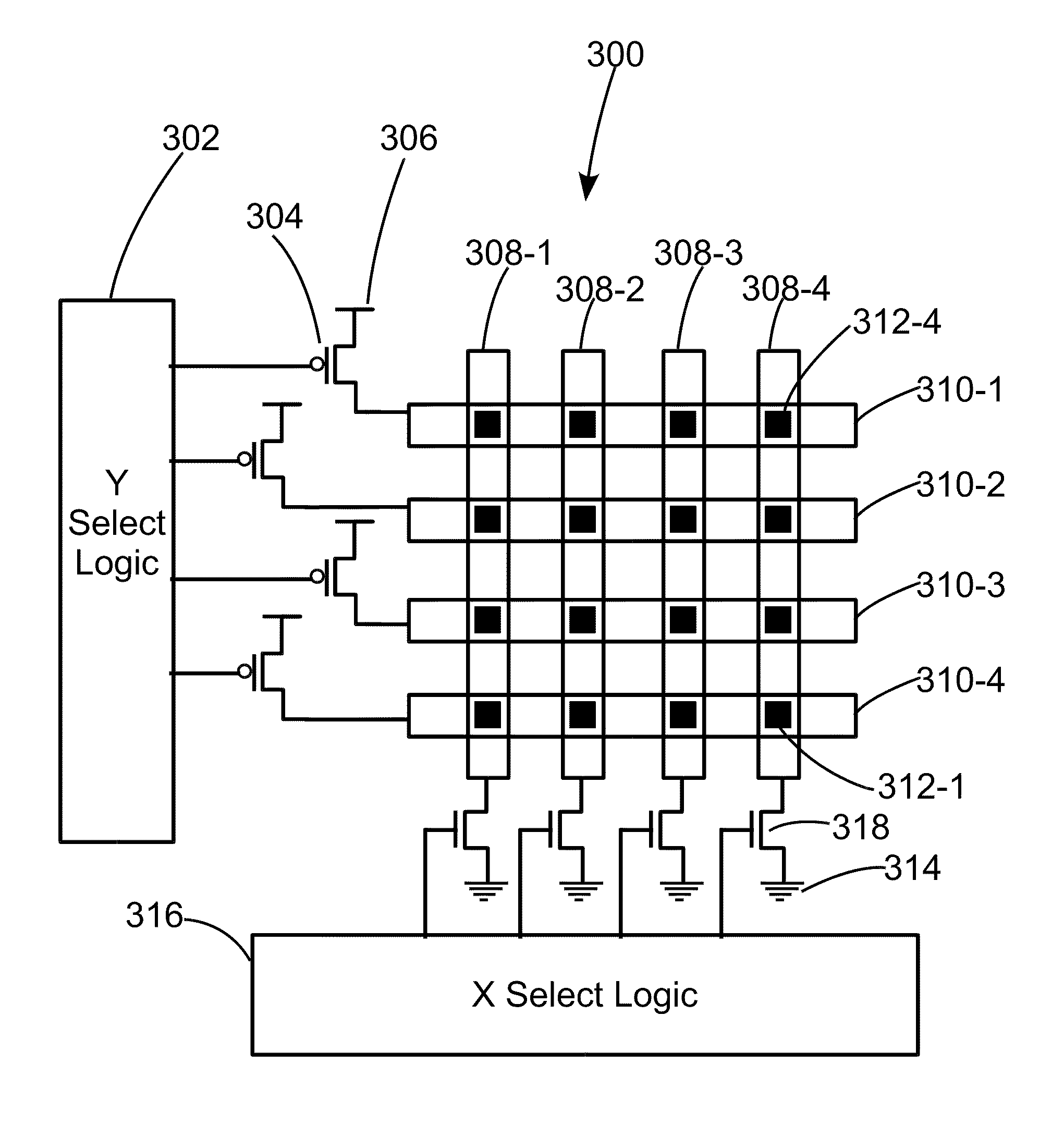

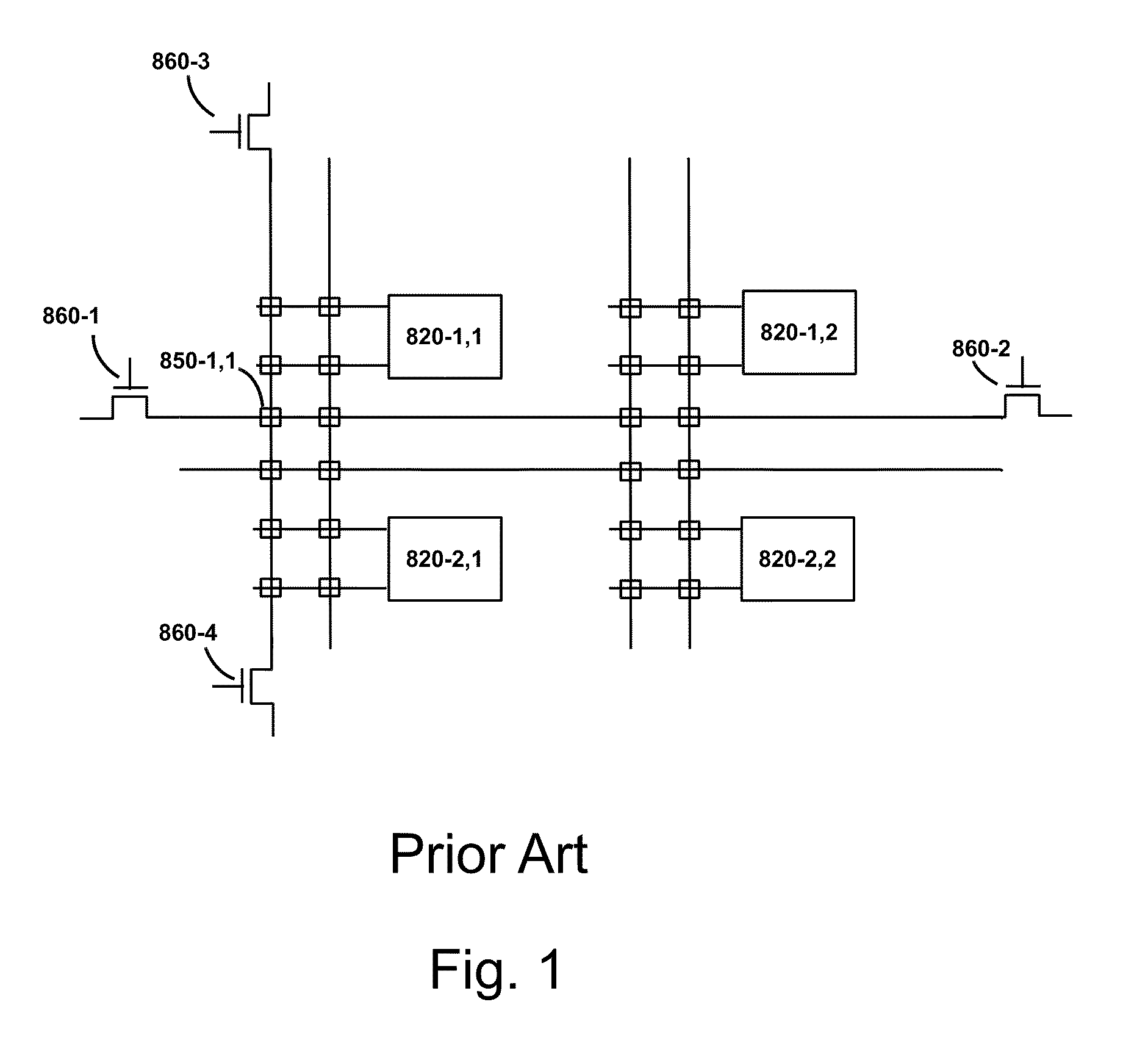

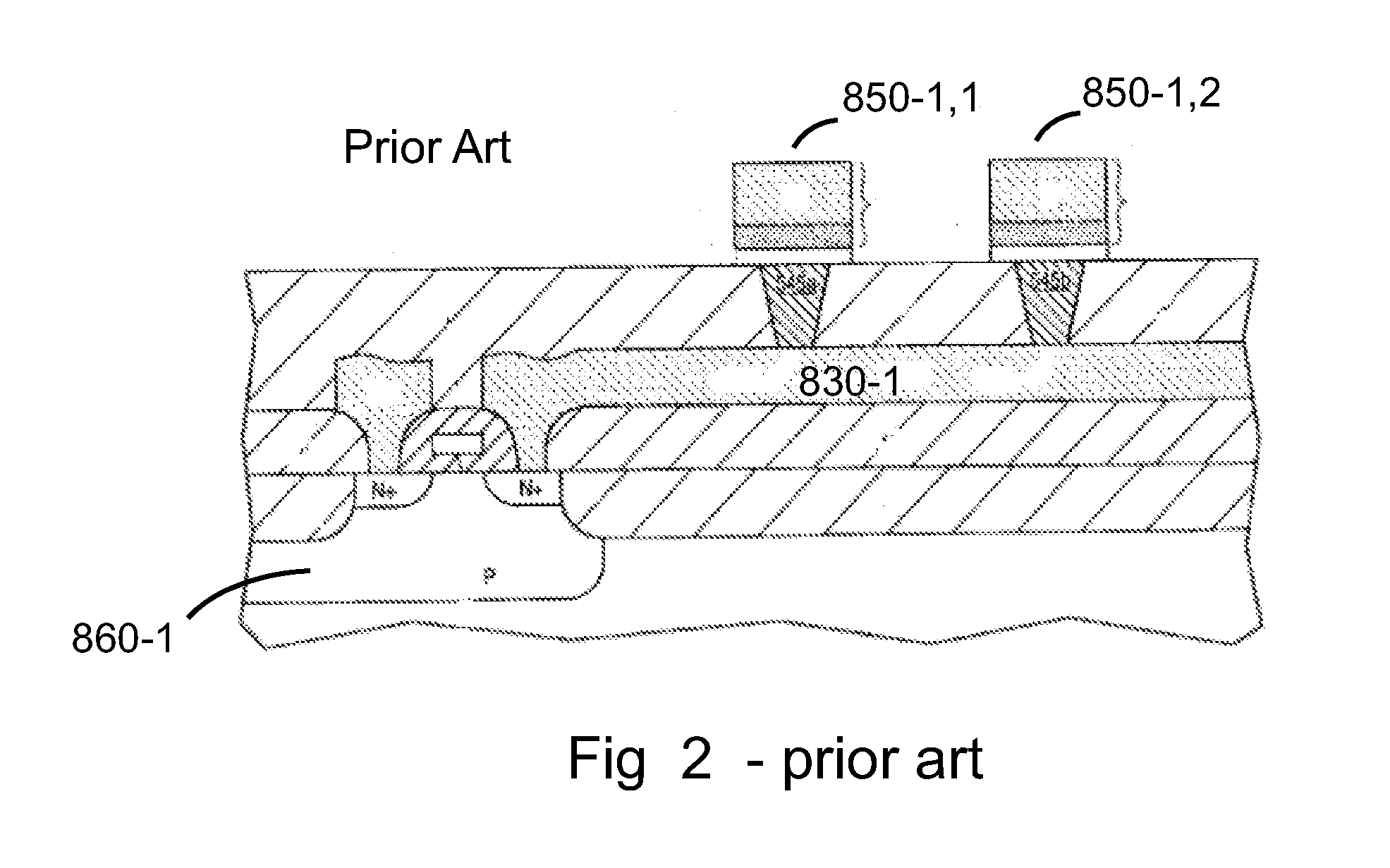

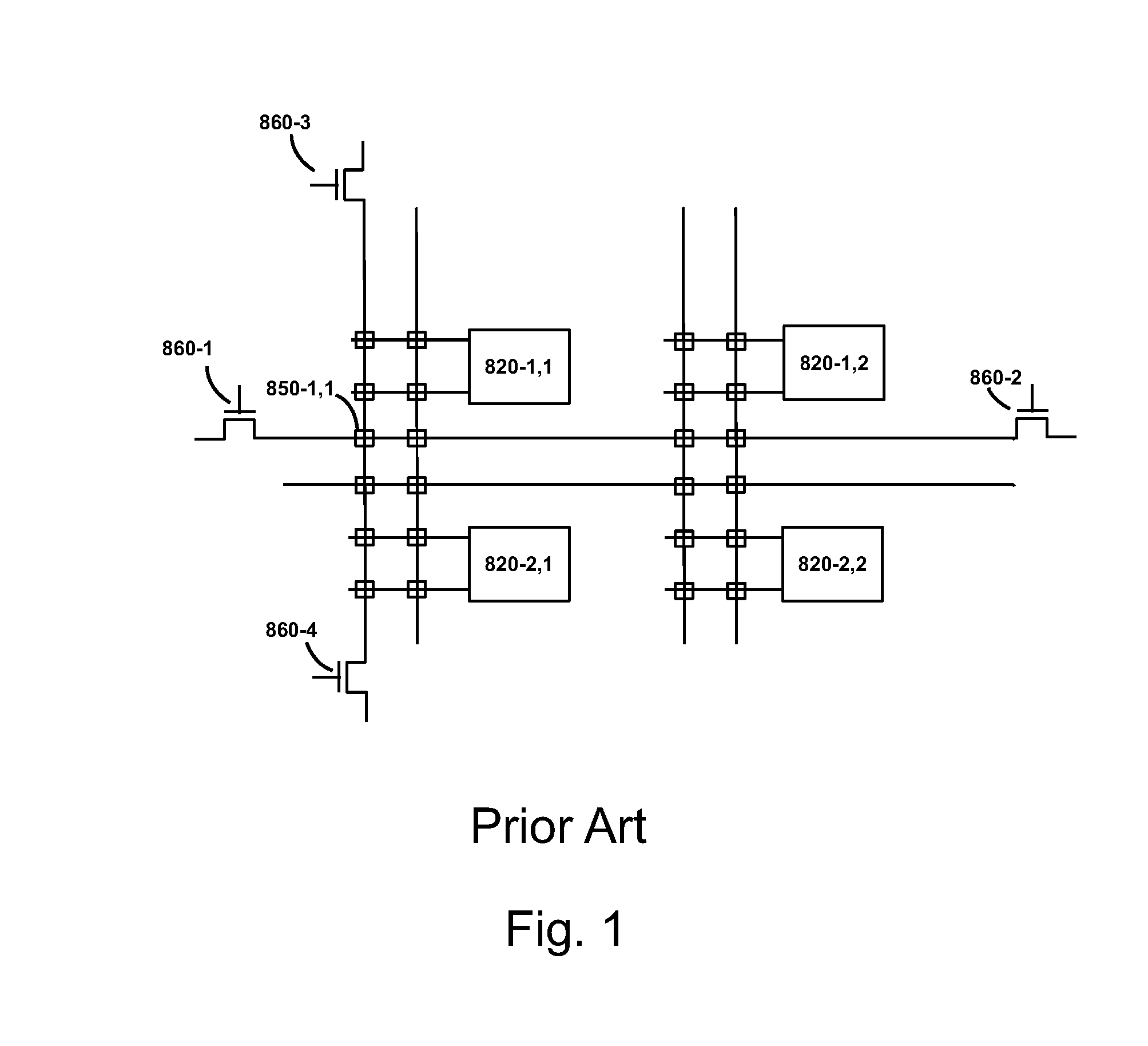

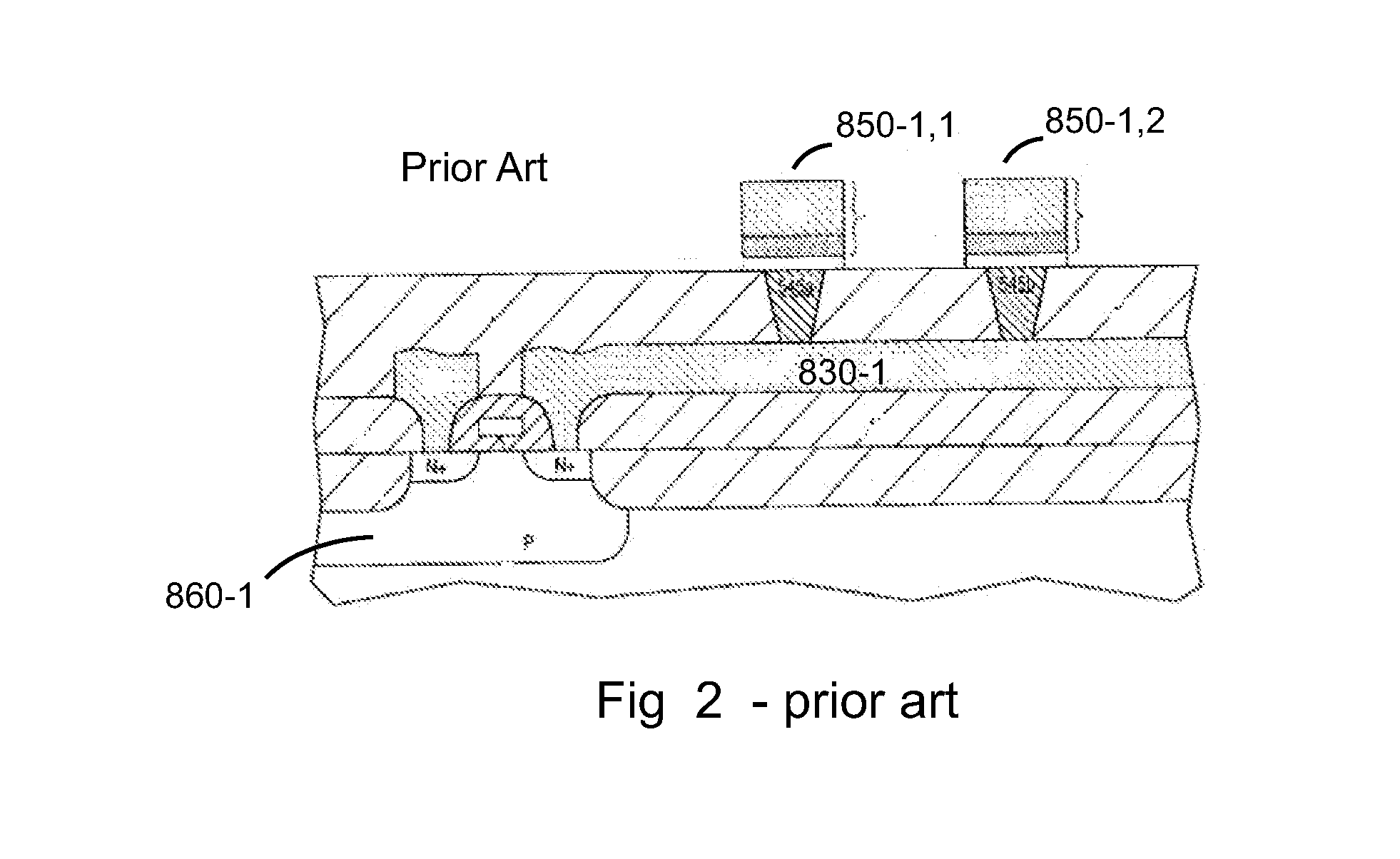

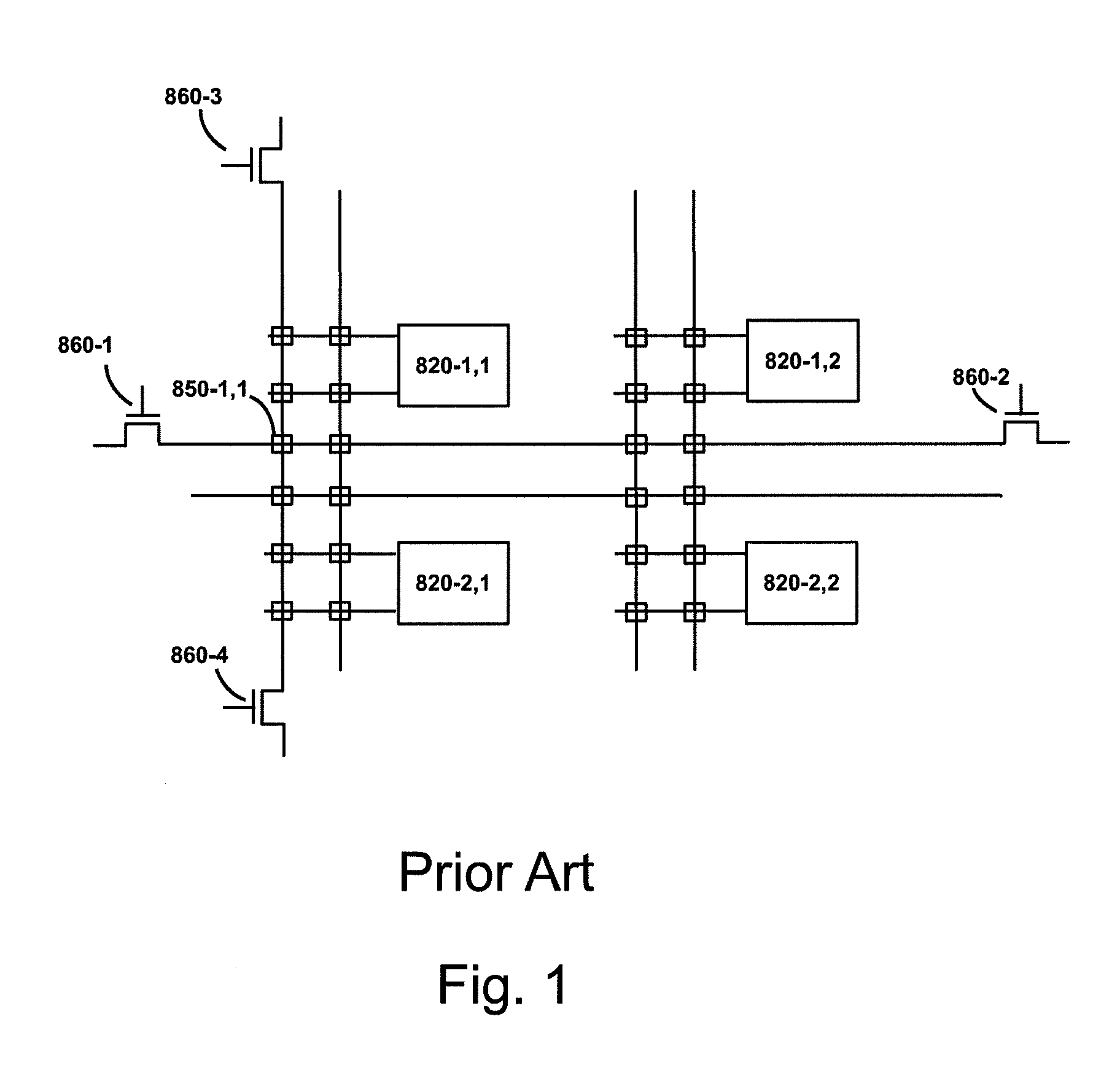

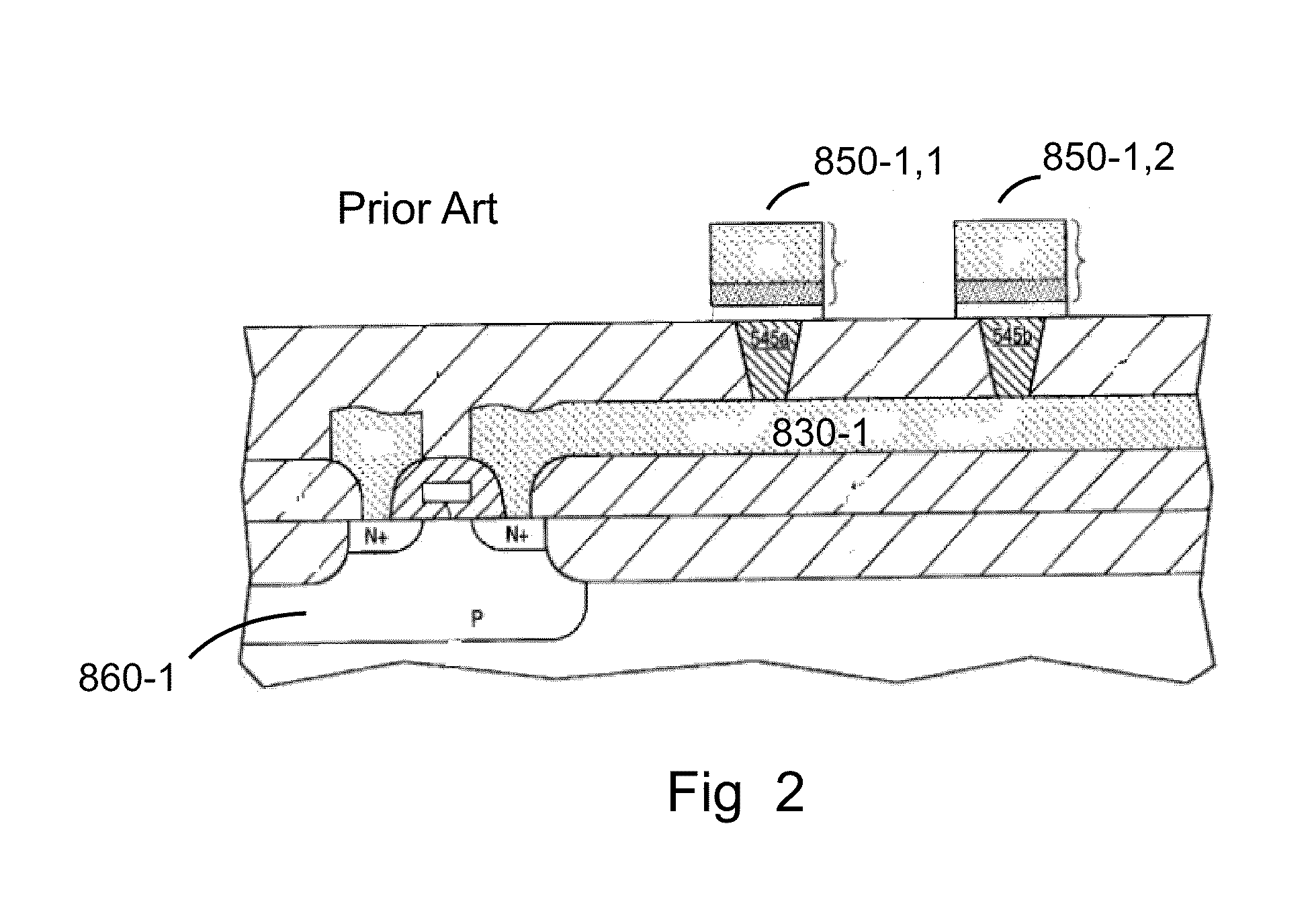

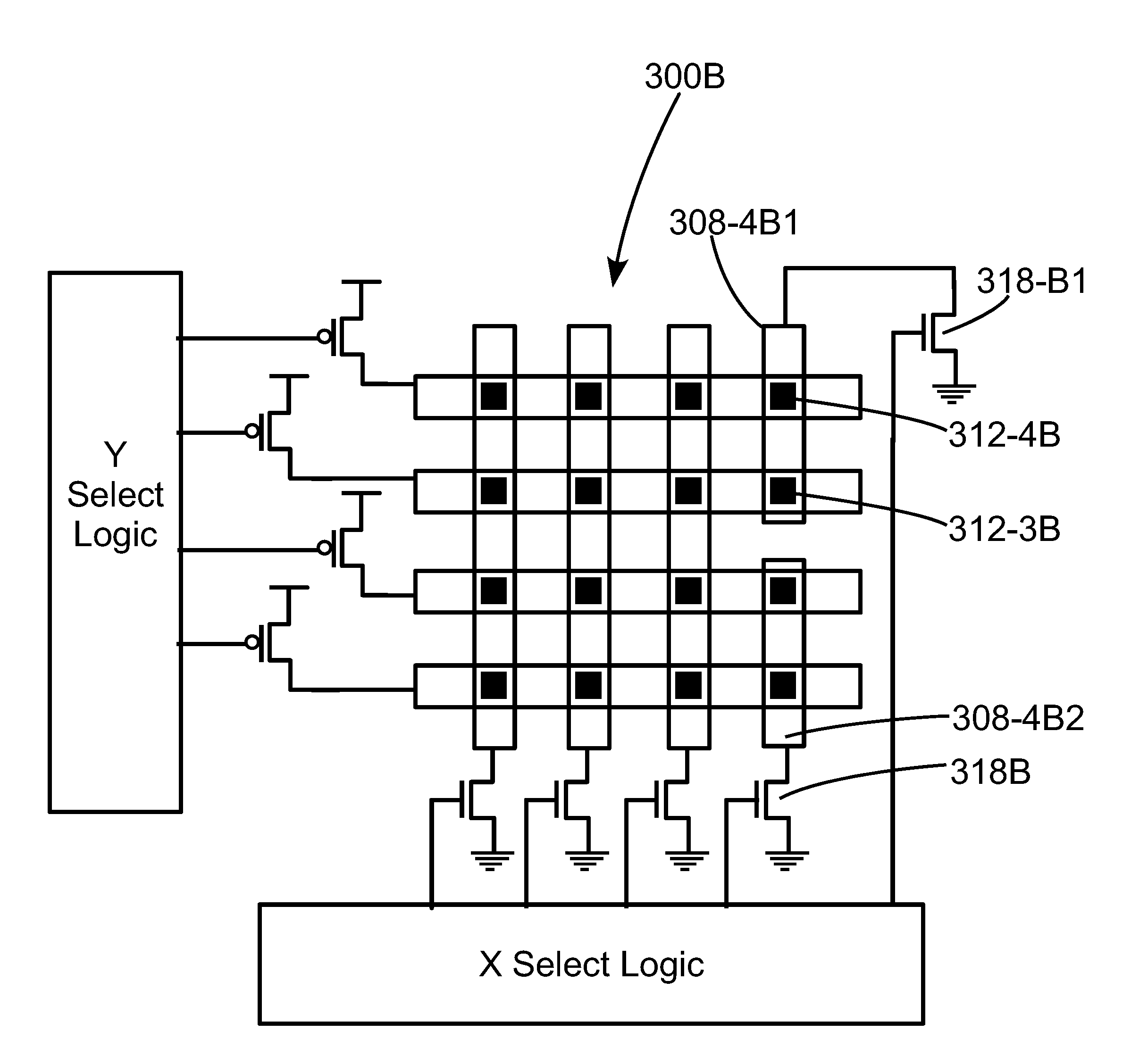

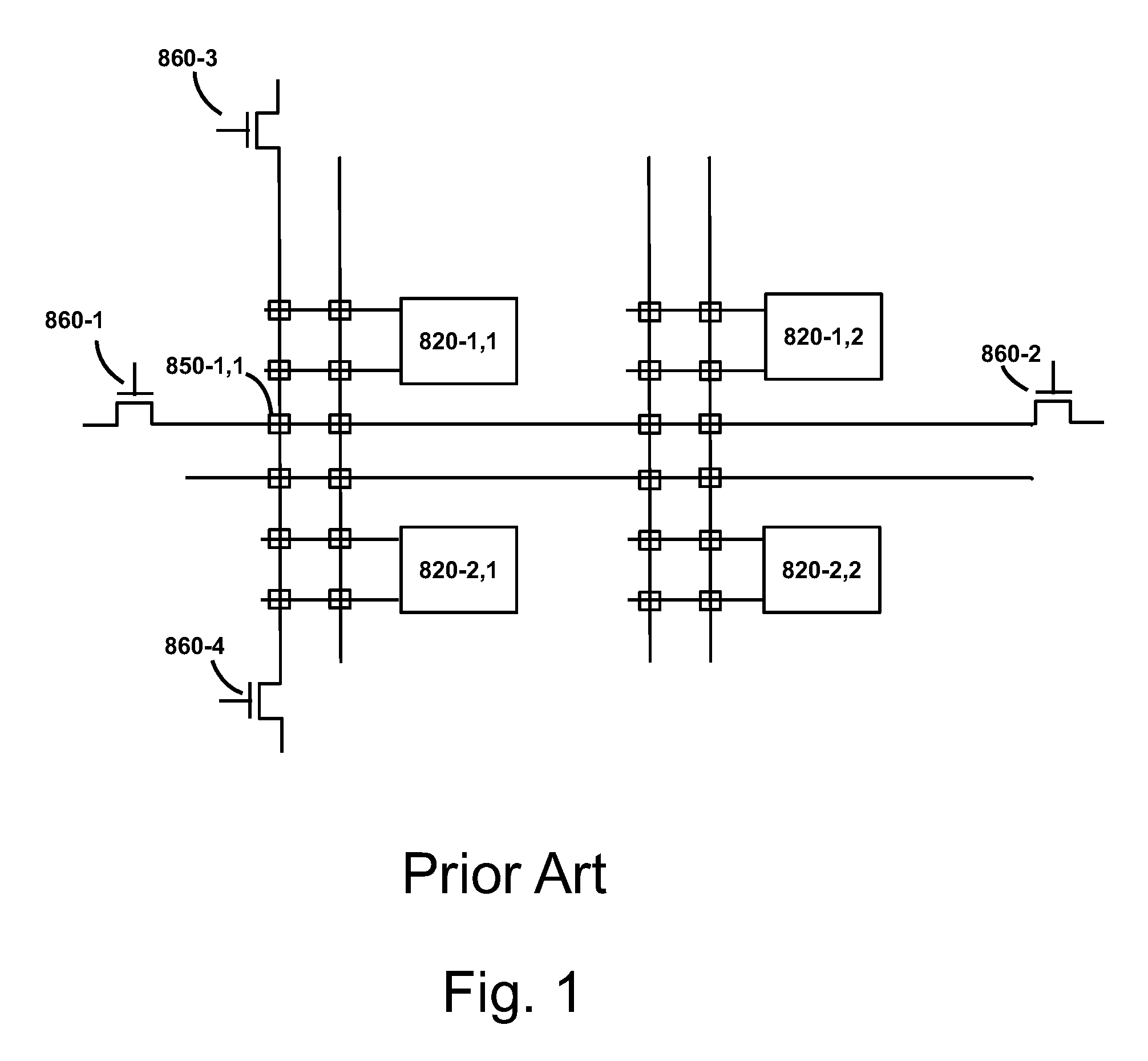

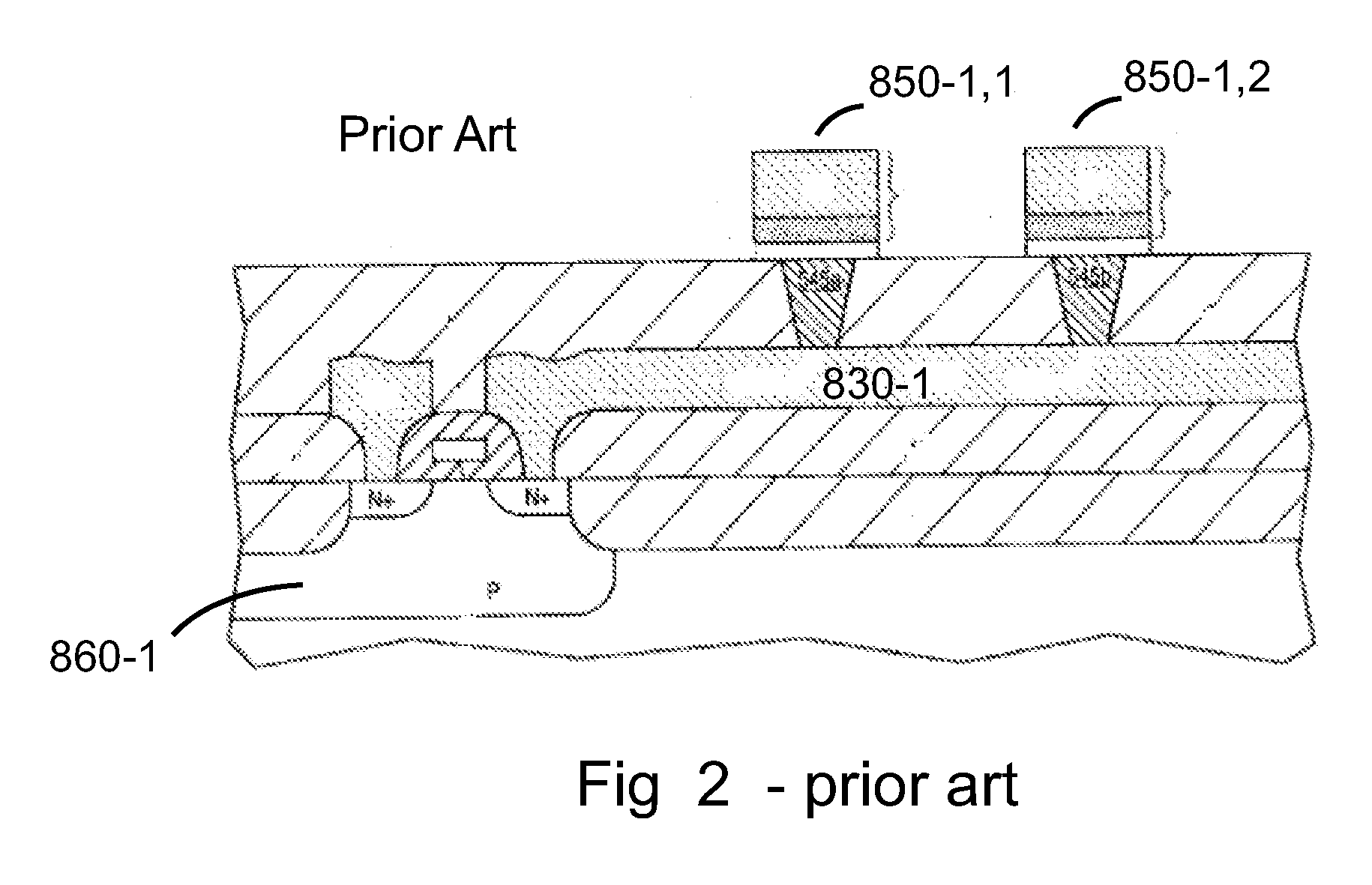

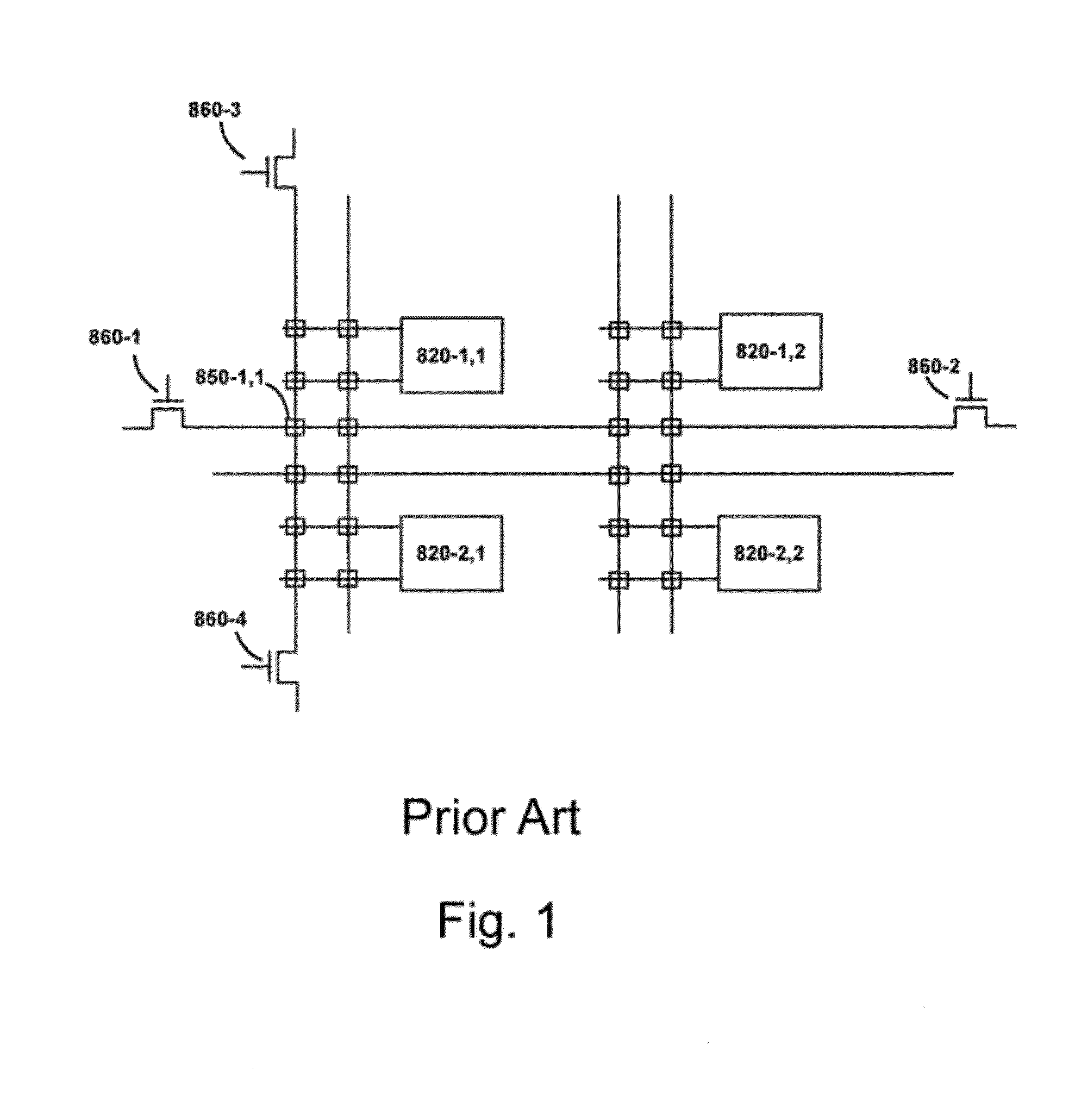

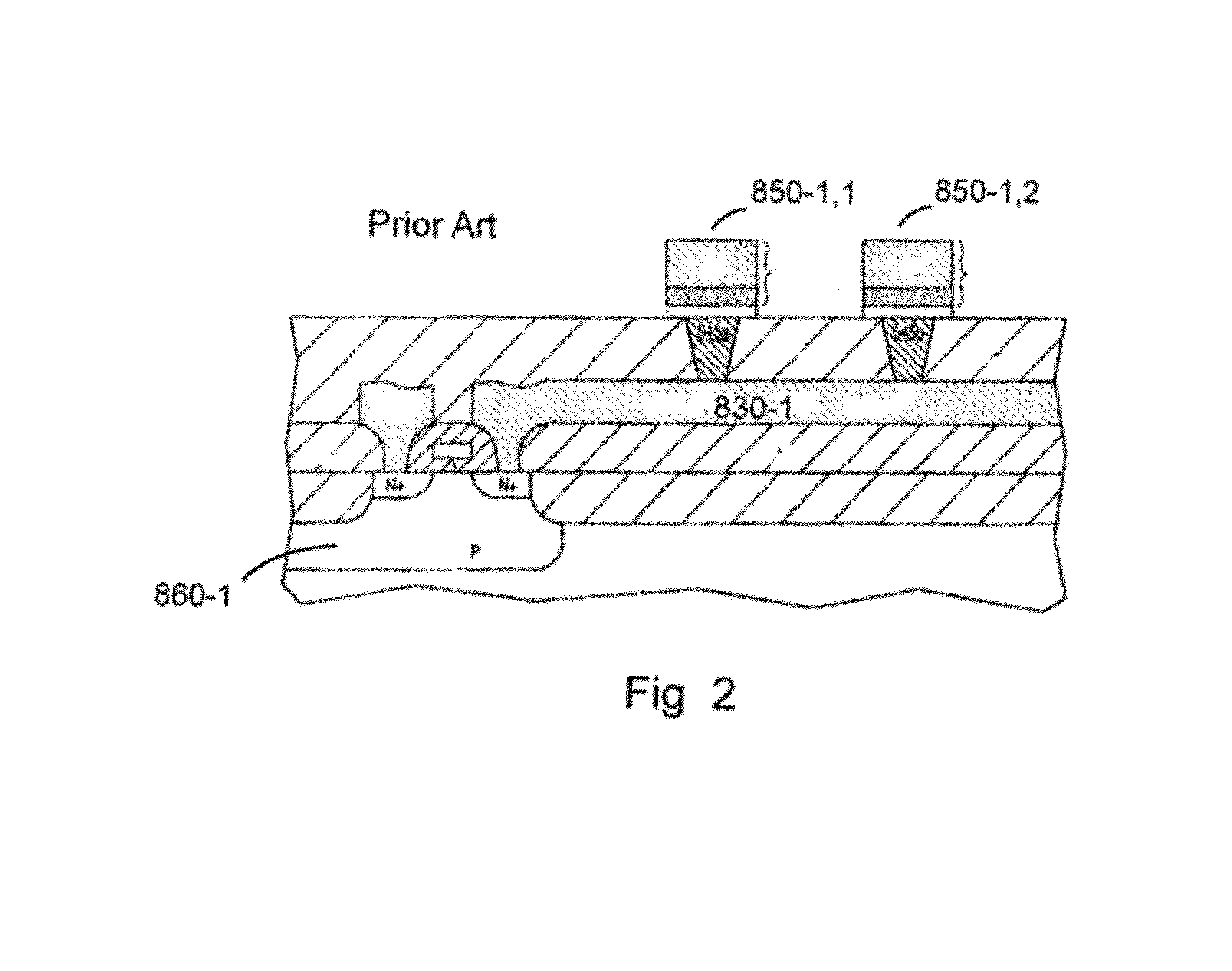

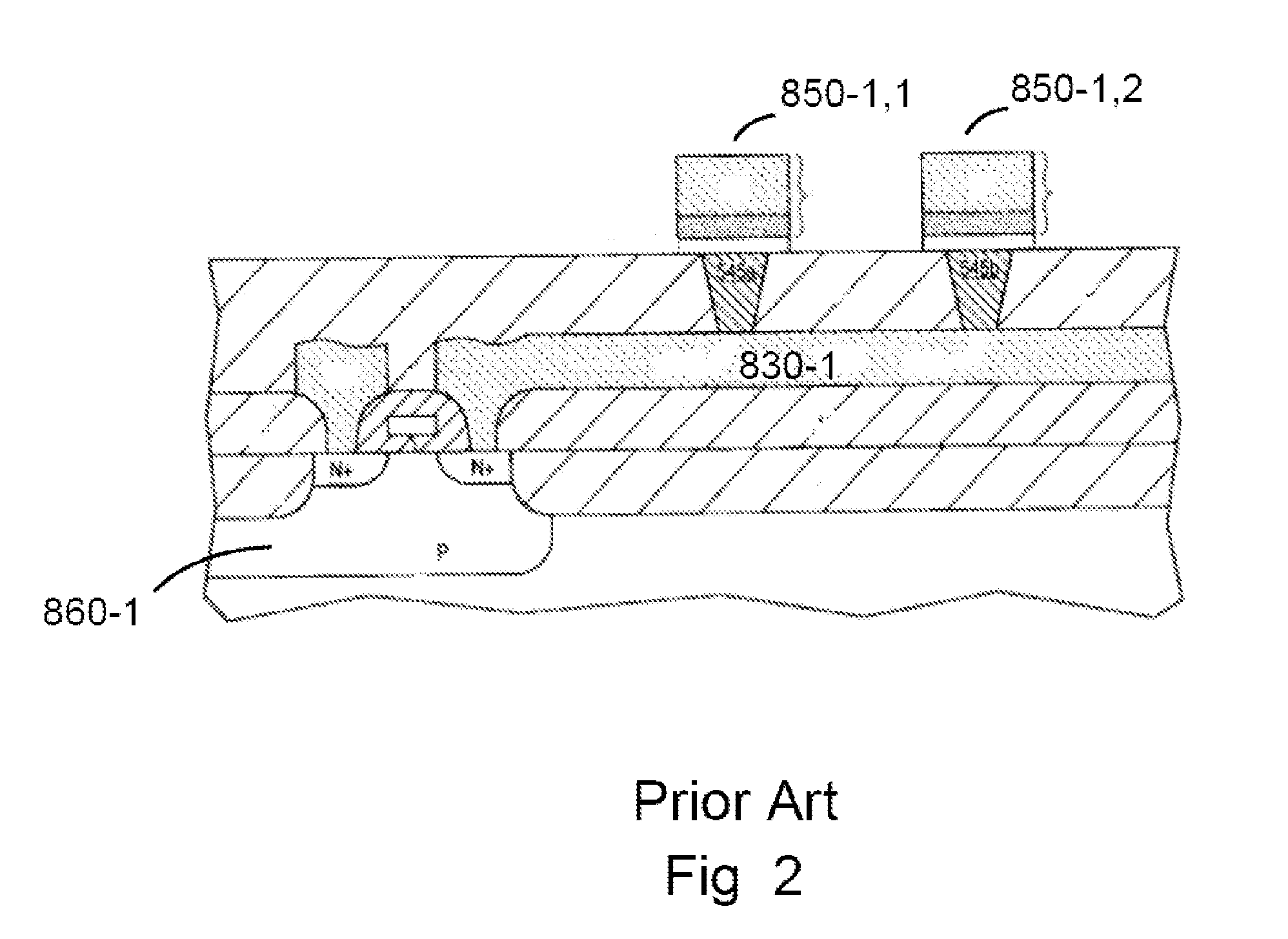

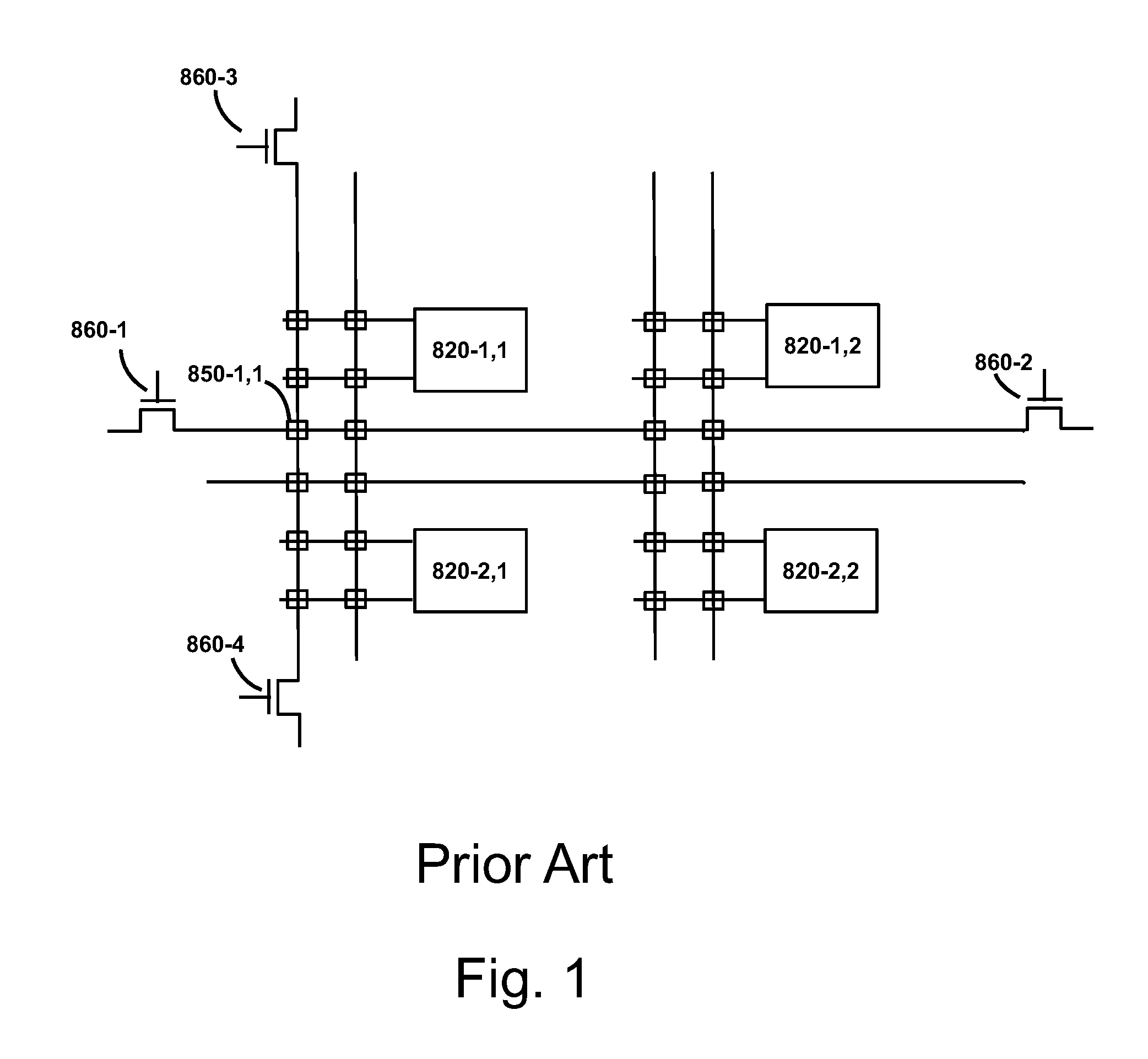

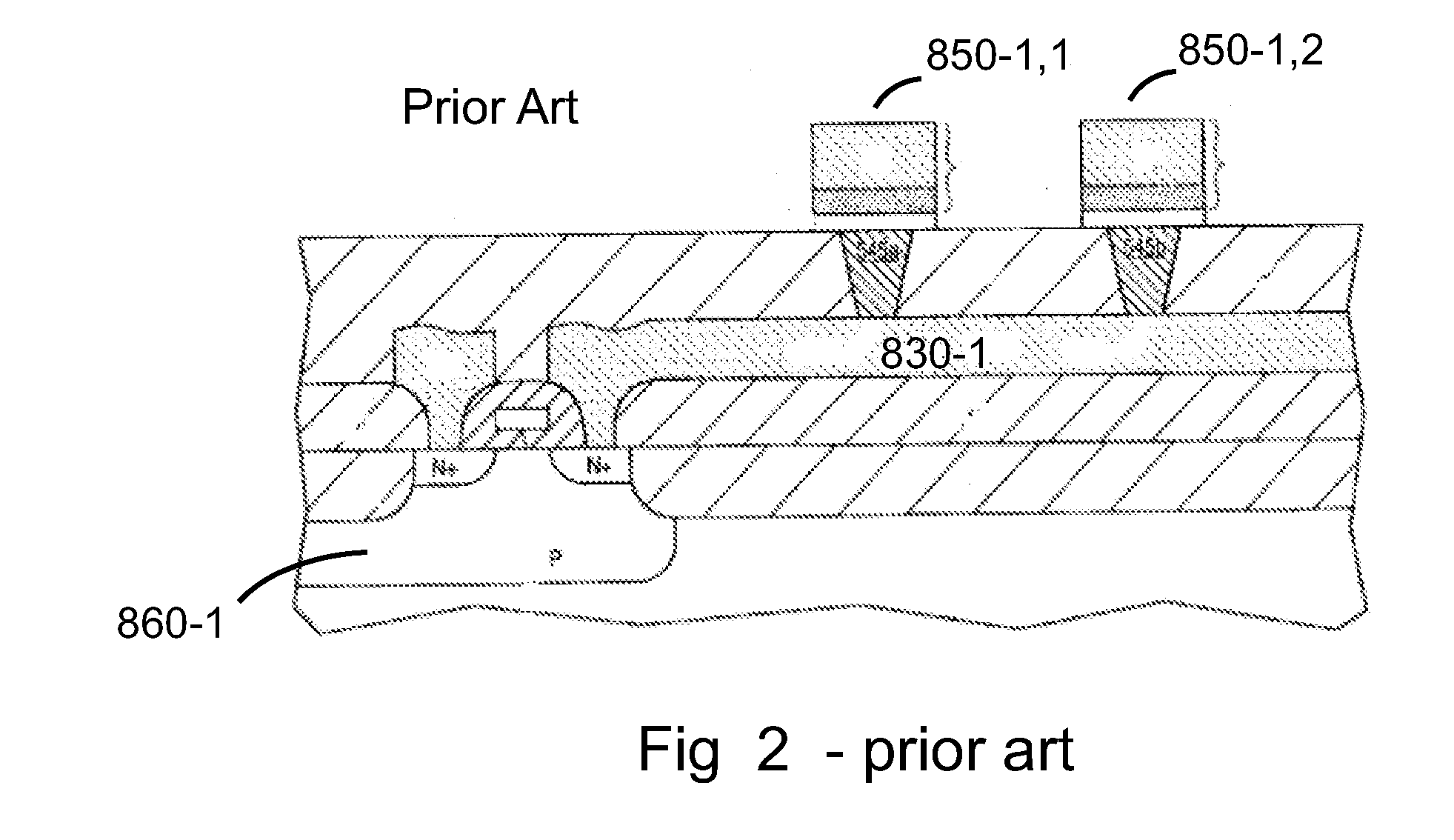

InactiveUS20130088416A1Reduce silicon areaLow costStatic indicating devicesSolid-state devicesDriver circuitEngineering

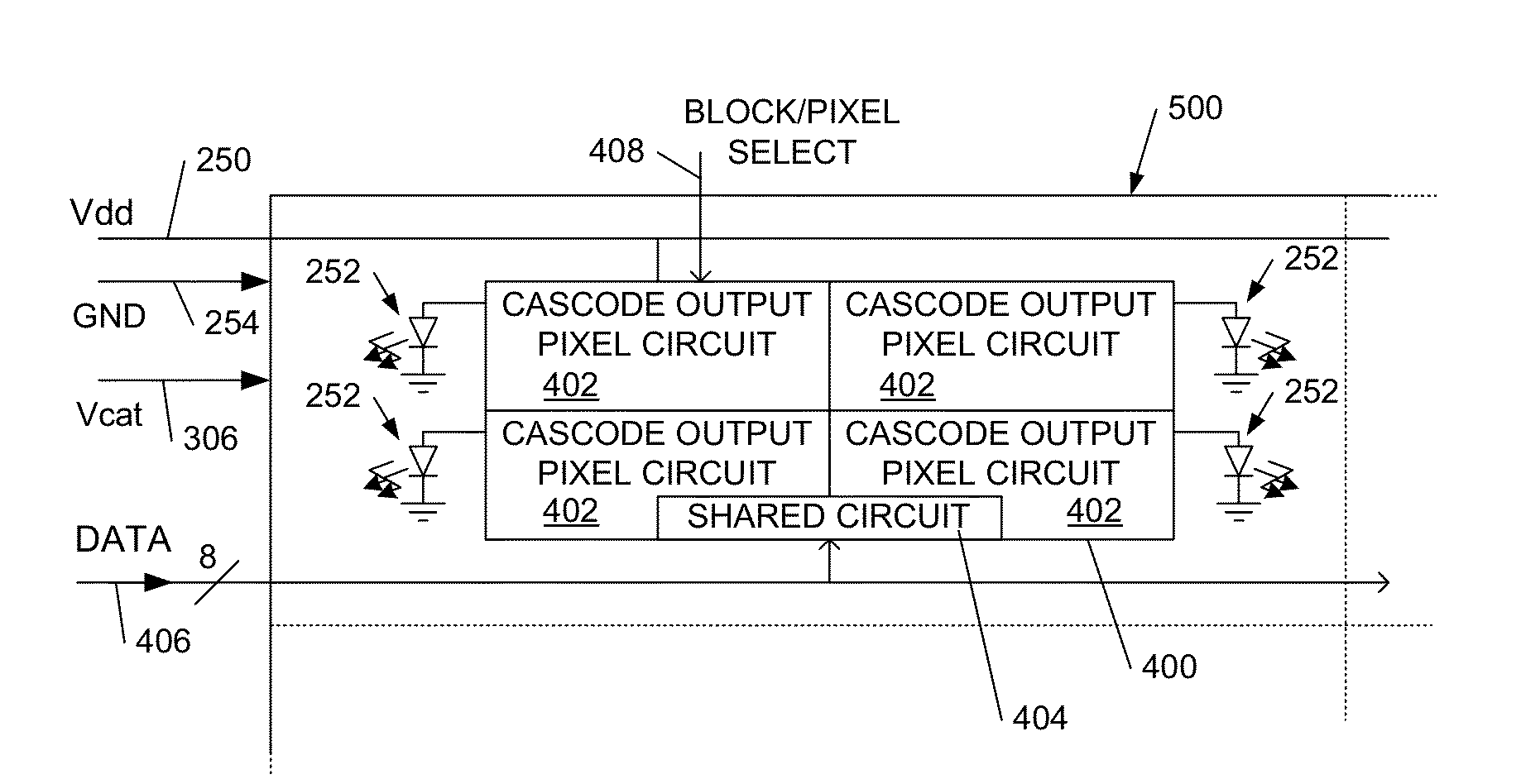

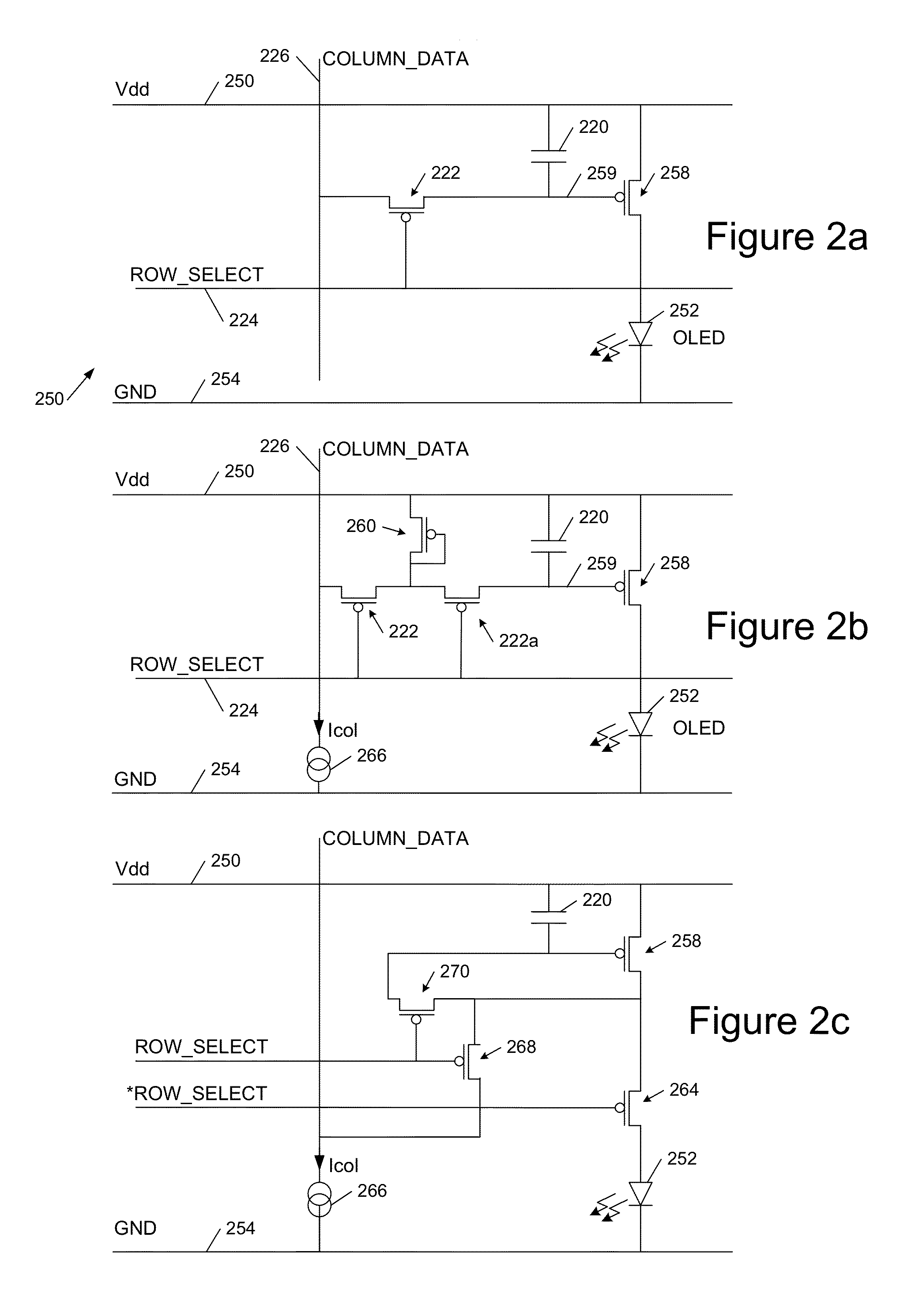

We describe a method of driving an OLED display. The OLED display comprises a plurality of pixel driver circuits on chiplets, each pixel driver circuit comprising an output transistor for driving a first connection of an associated OLED pixel. A cascode transistor on the chiplet is coupled between the output transistor and the first connection of said associated OLED pixel. A power supply is provided to the chiplet, defining a chiplet voltage range. A second connection of the associated OLED pixel is connected to an OLED voltage outside said chiplet voltage range. The OLED pixel is then driven using the pixel driver circuit on the chiplet over an OLED voltage range greater than said chiplet voltage range. In some preferred embodiments a drain connection of the cascode transistor is set at a voltage below a ground or negative (Vss) power supply to a chiplet.

Owner:CAMBRIDGE DISPLAY TECH LTD

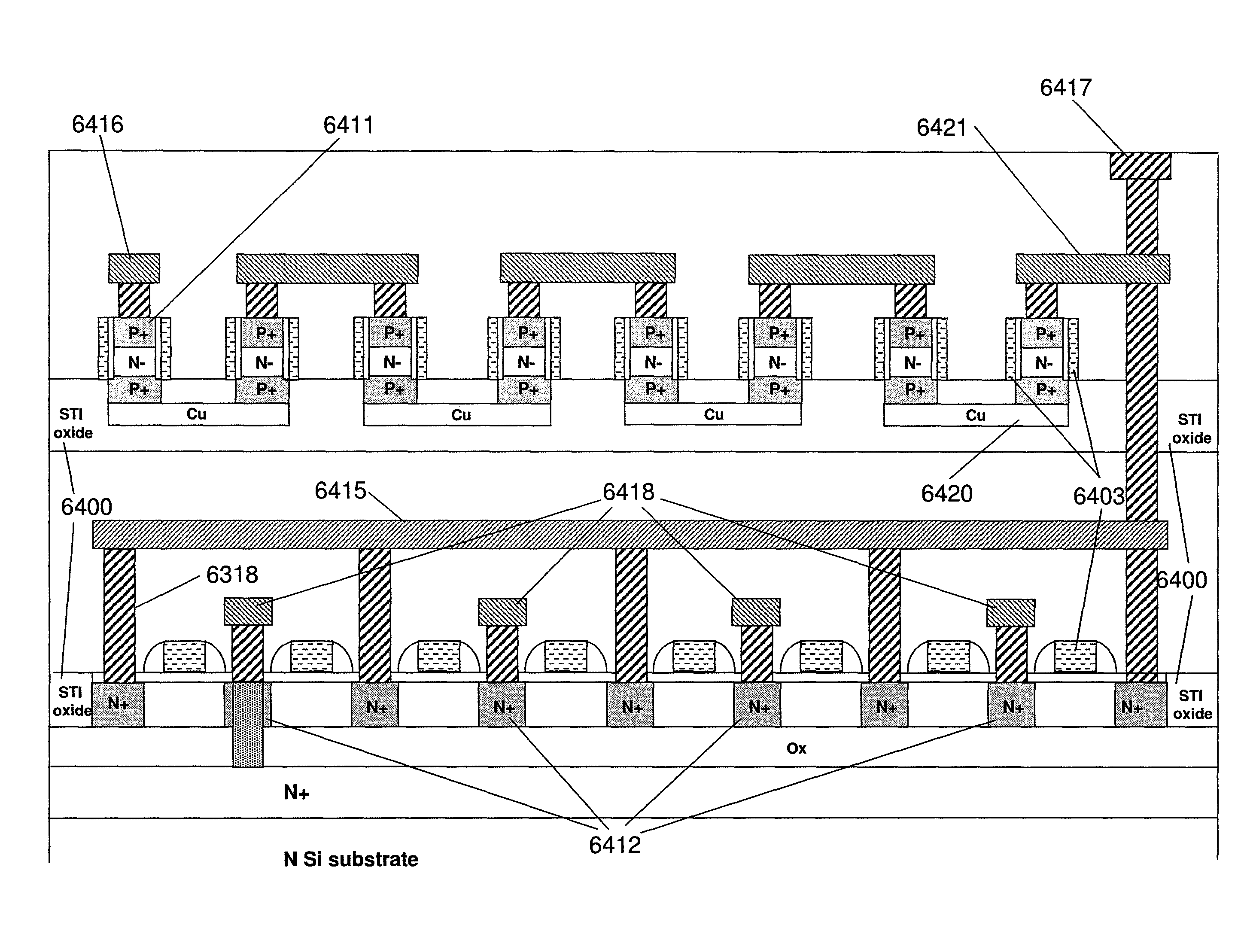

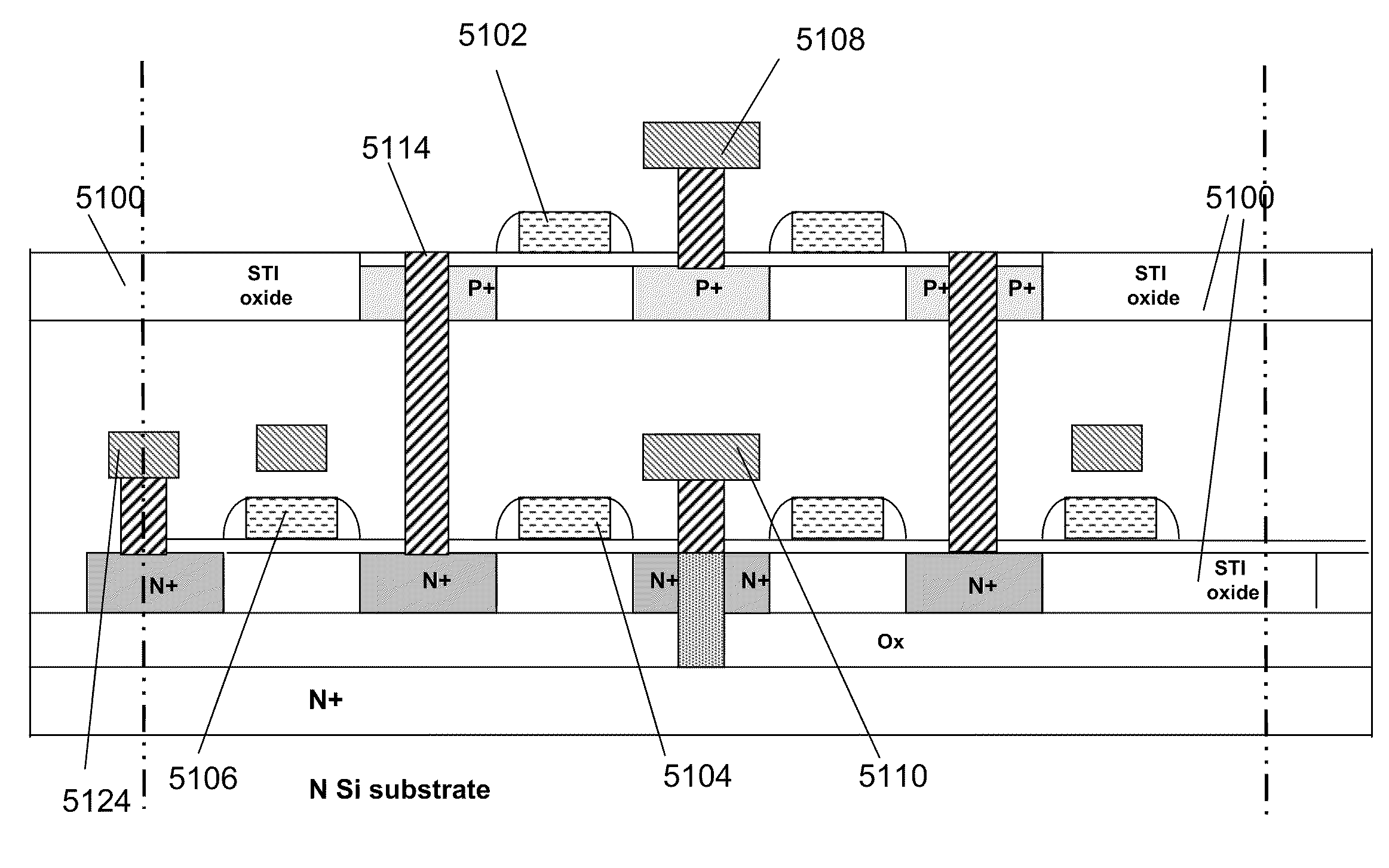

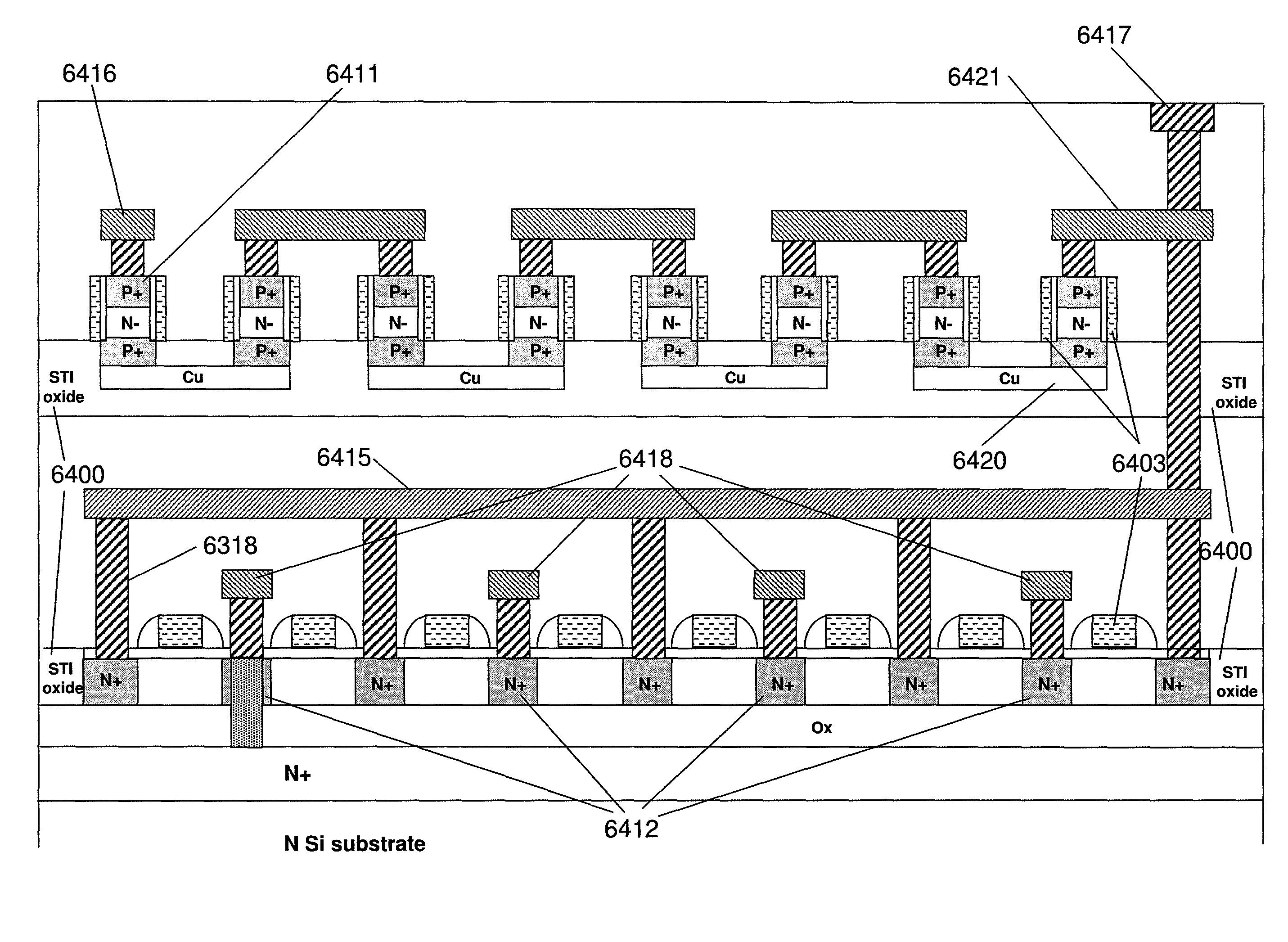

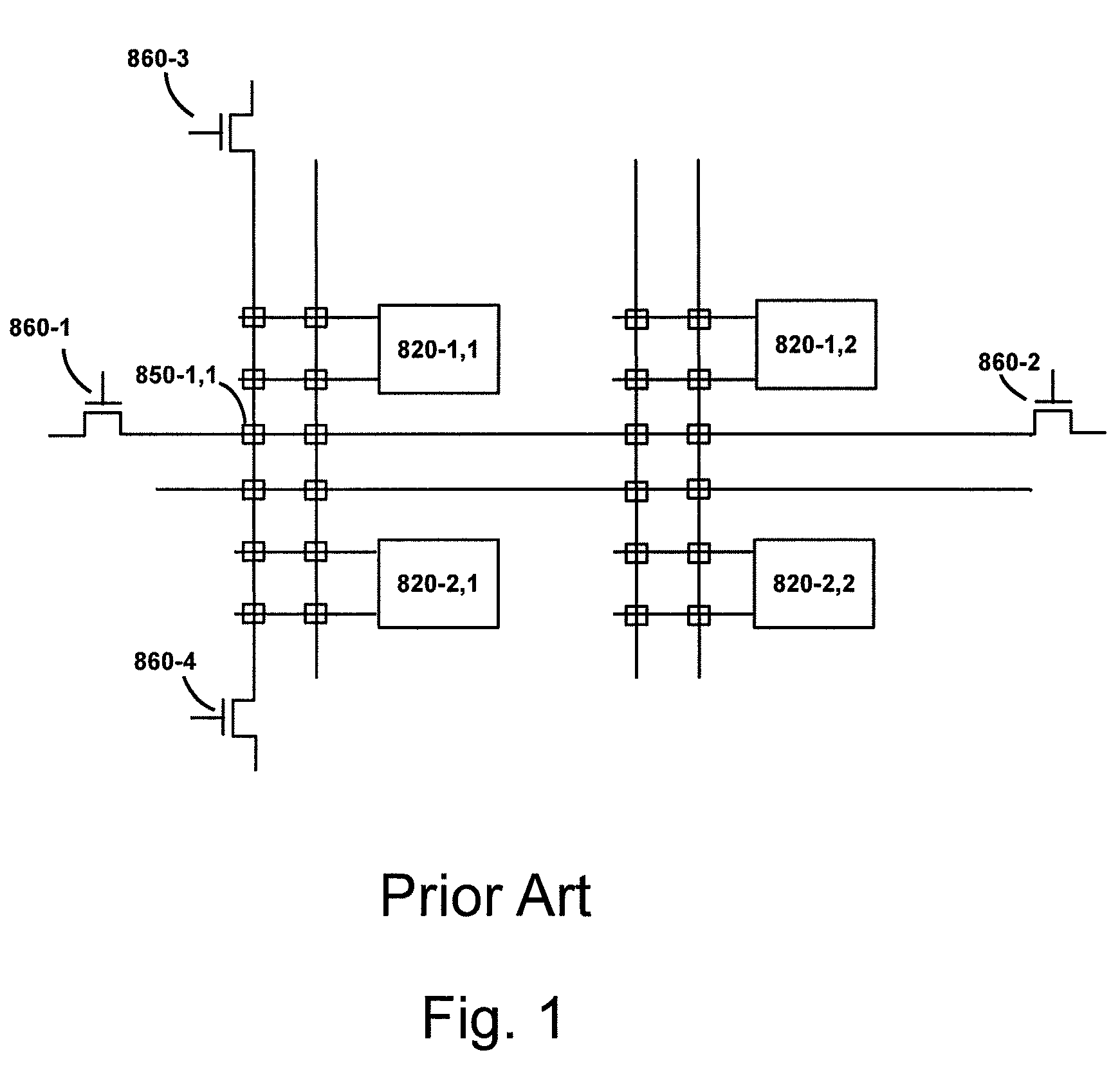

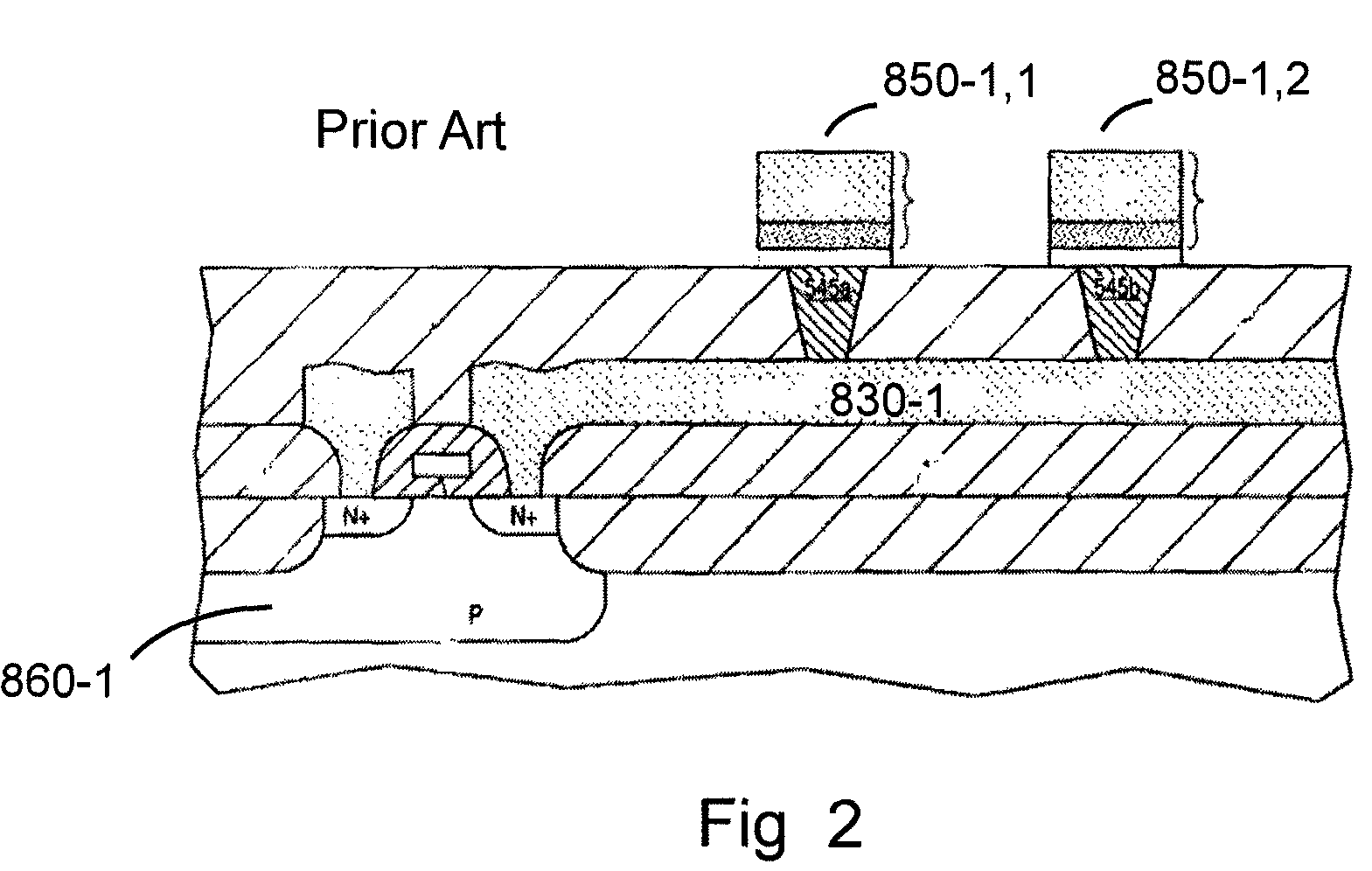

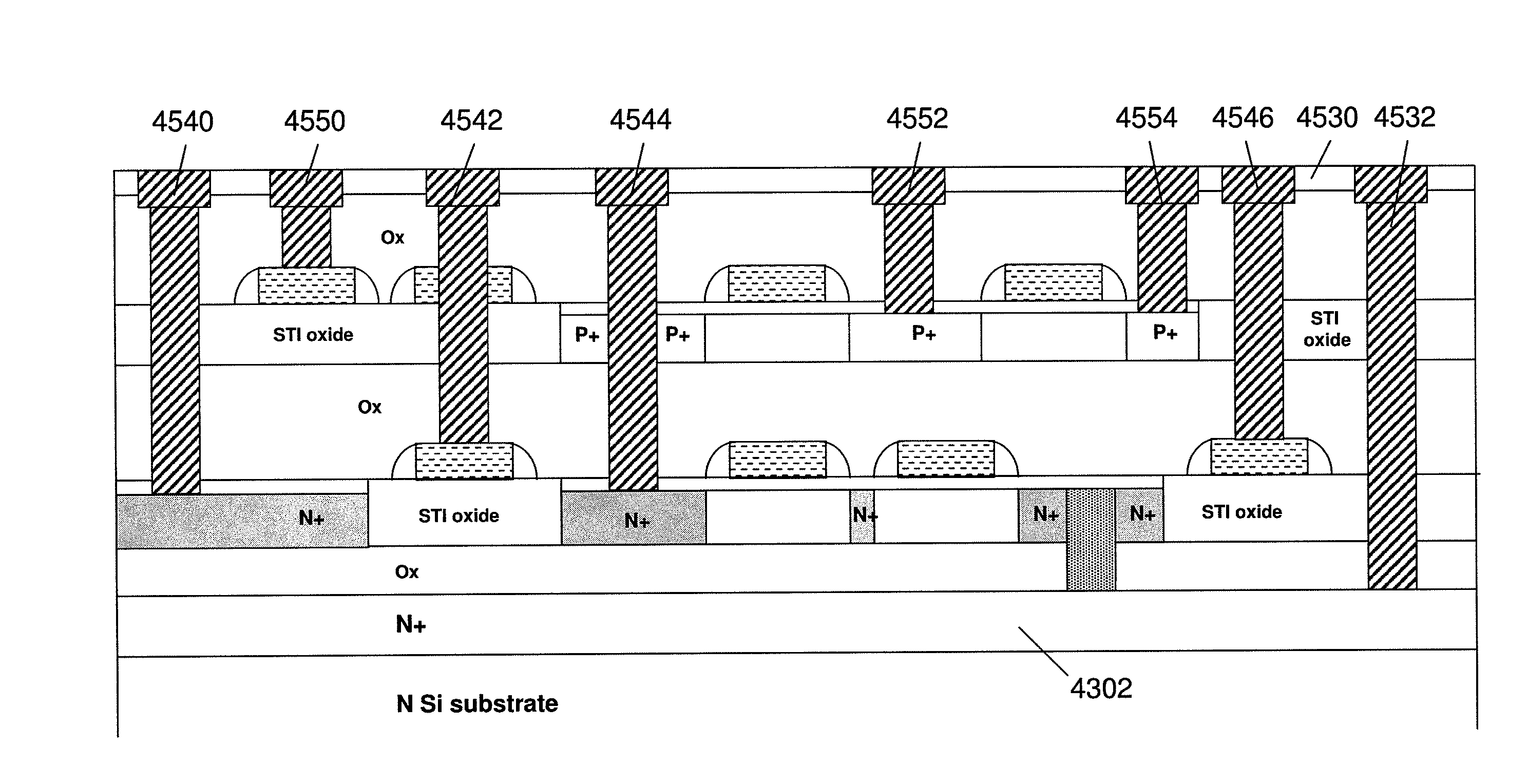

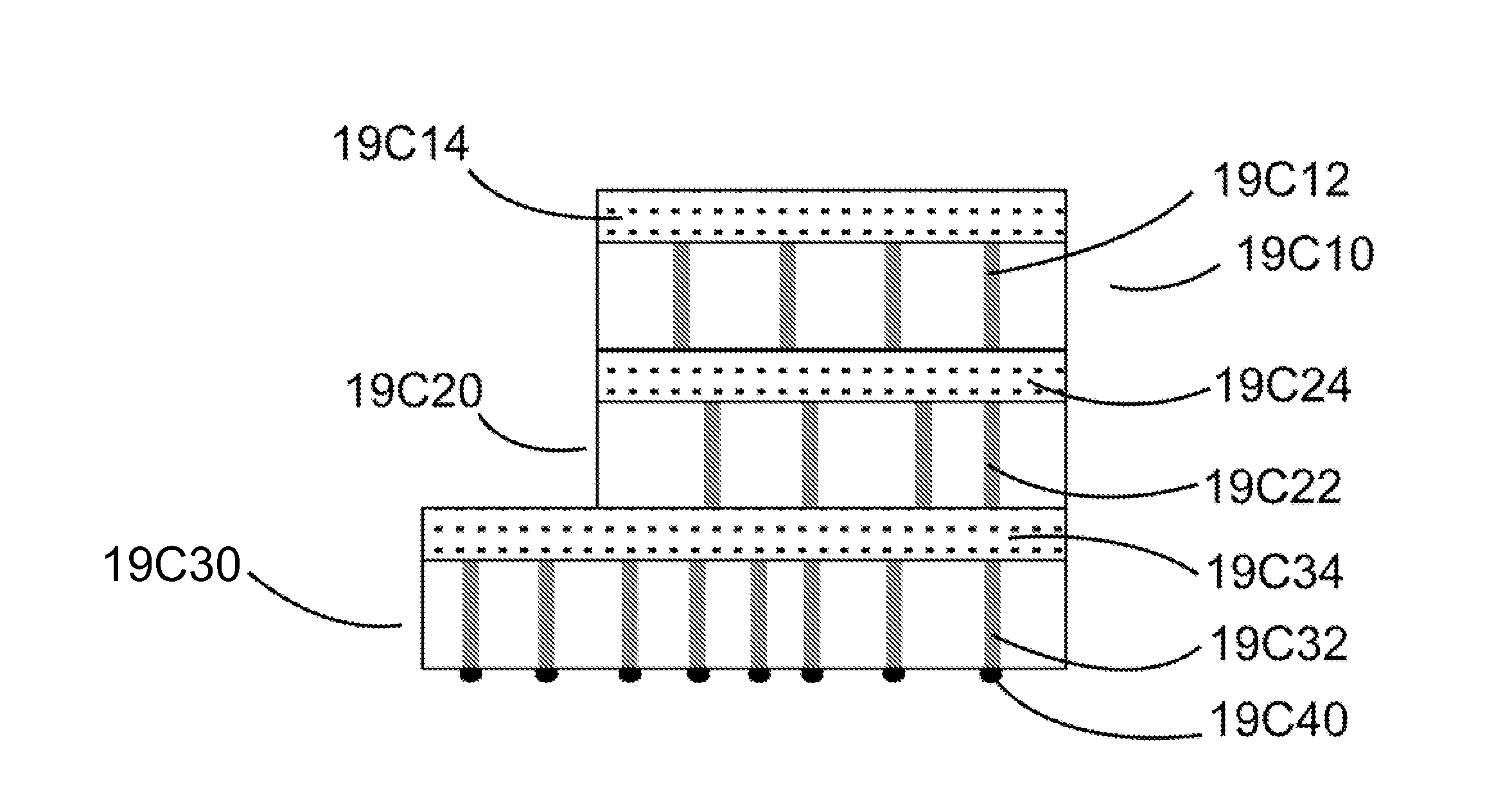

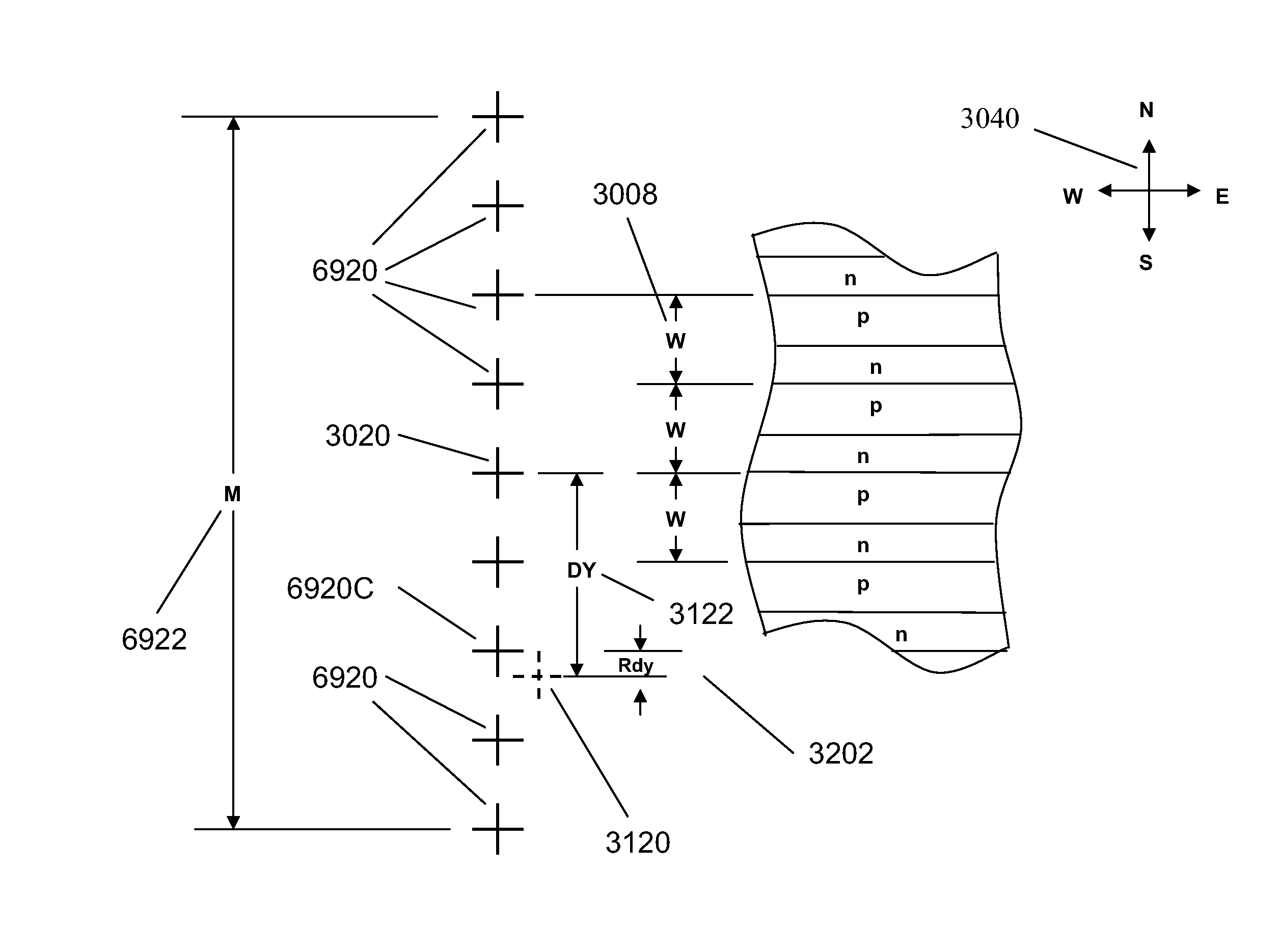

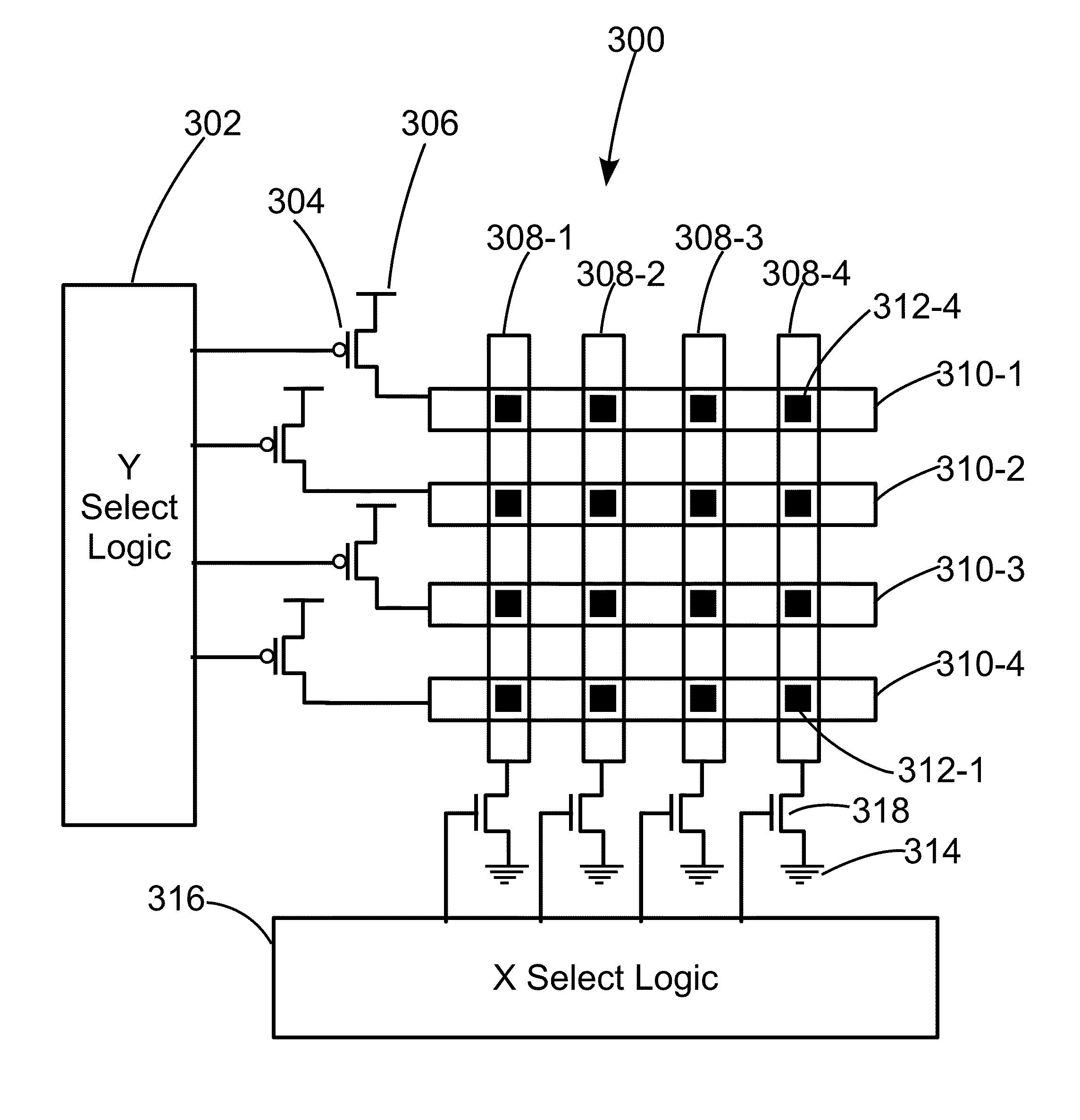

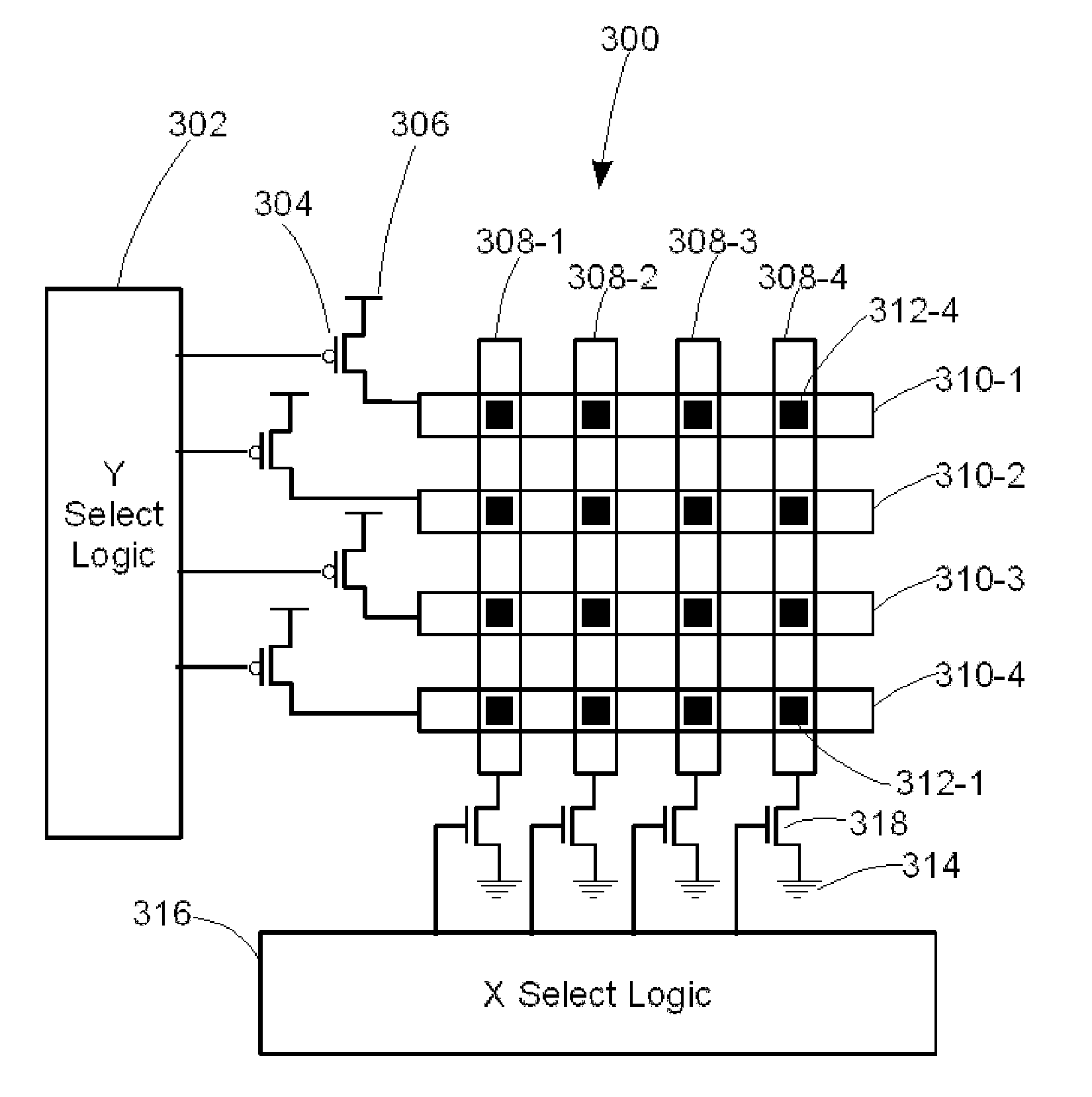

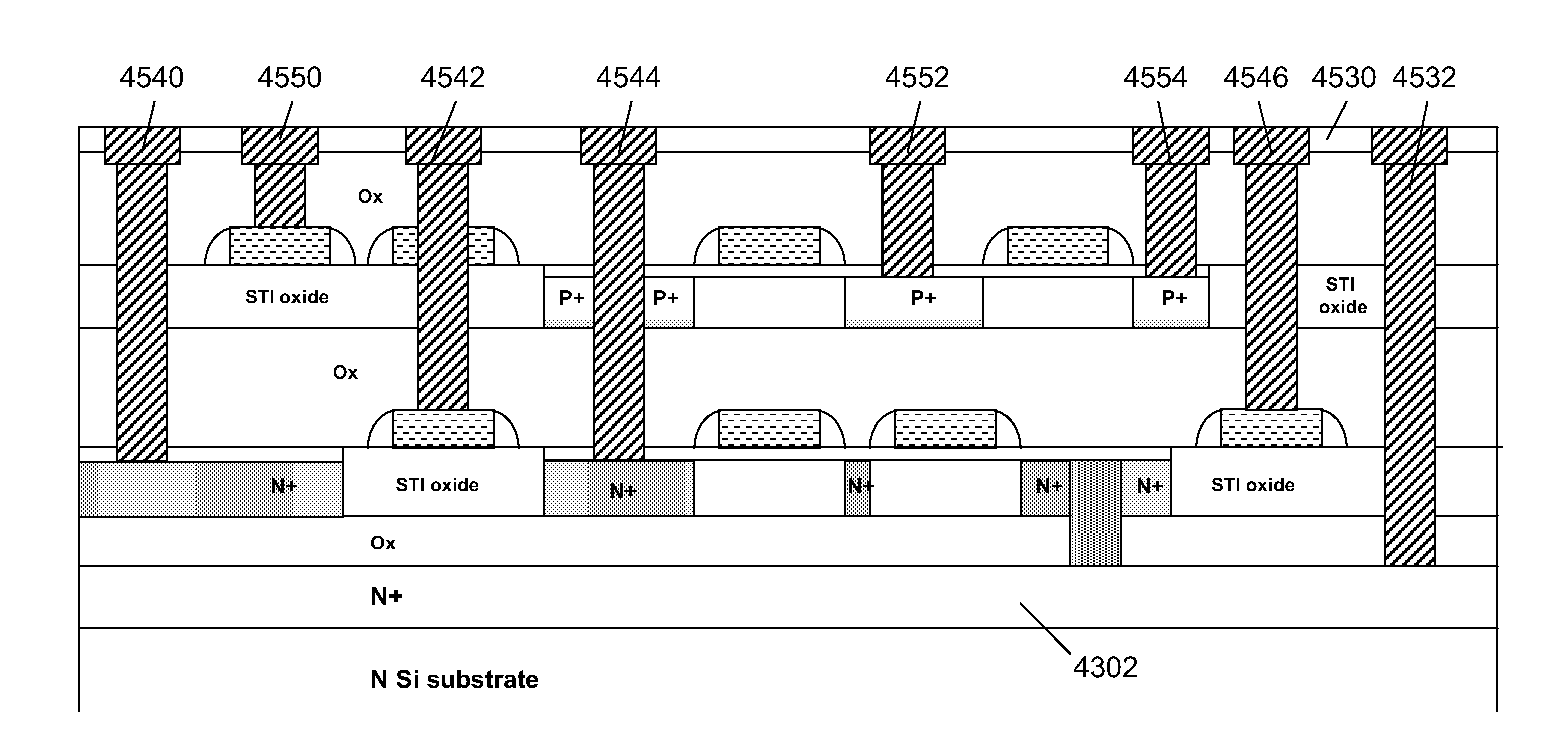

System comprising a semiconductor device and structure

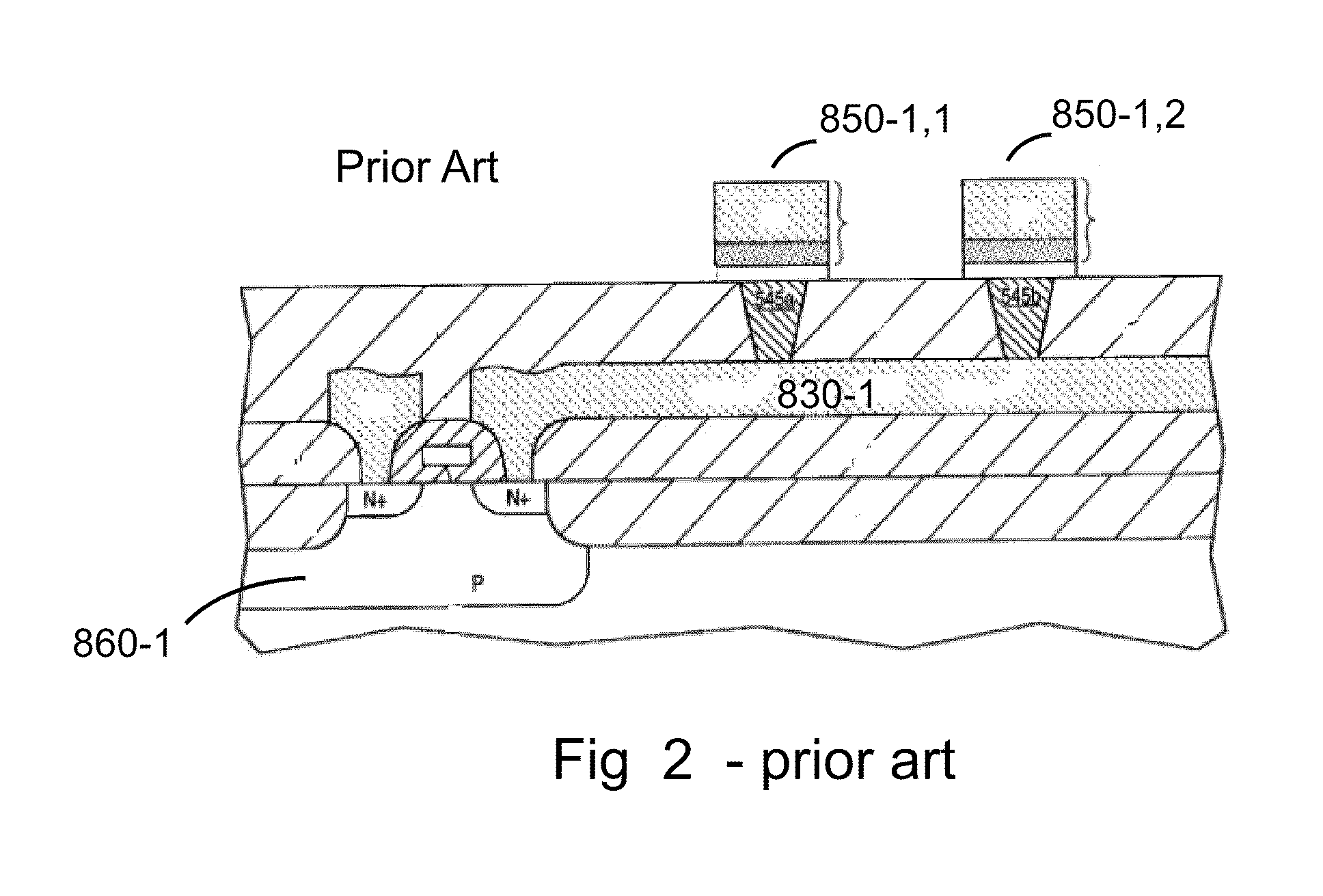

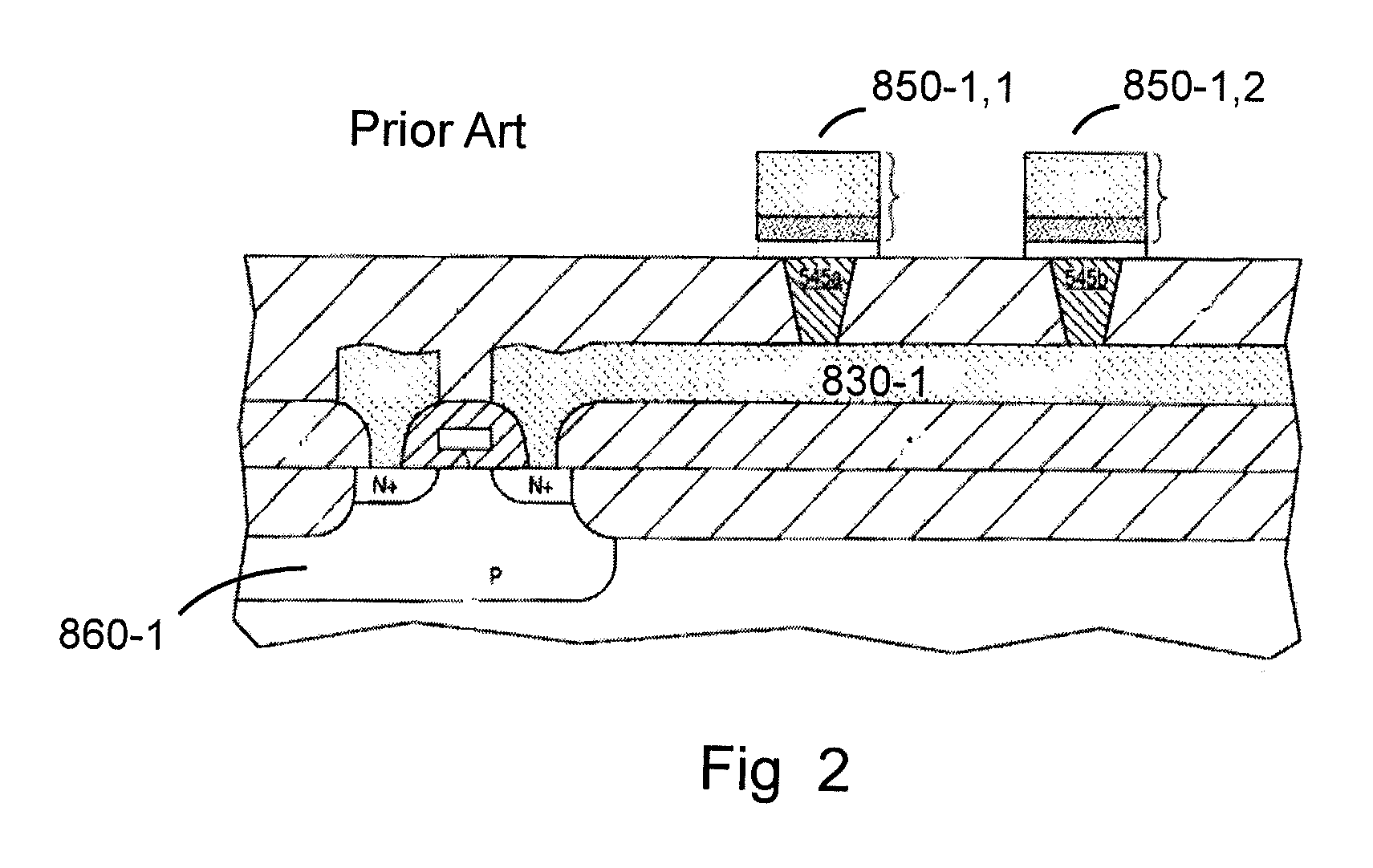

InactiveUS20110084314A1Reduced flexibilityReduce high cost of manufacturingTransistorSemiconductor/solid-state device detailsPower semiconductor deviceSemiconductor

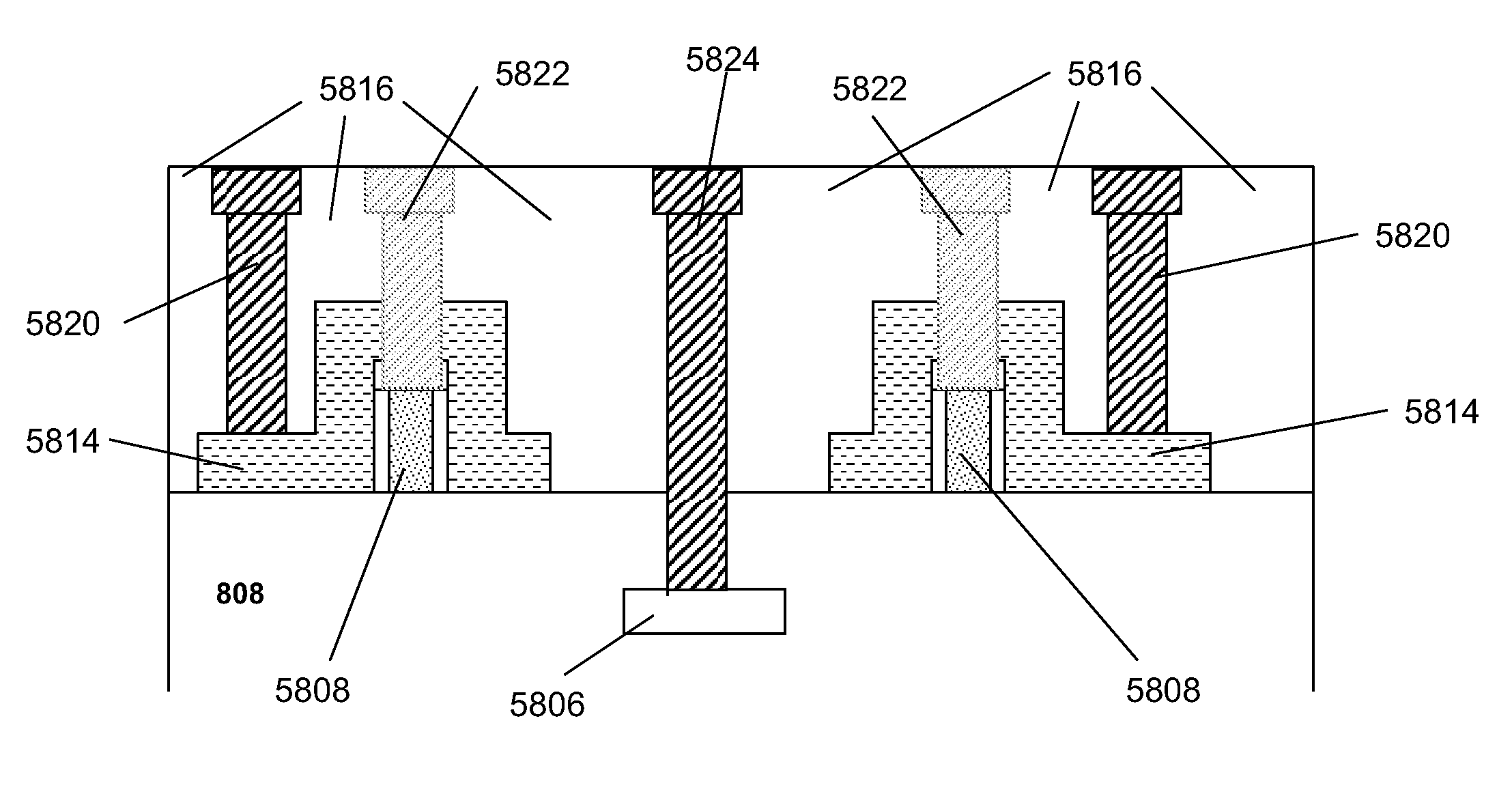

A system includes a semiconductor device. The semiconductor device includes a first single crystal silicon layer comprising first transistors, first alignment marks, and at least one metal layer overlying the first single crystal silicon layer, wherein the at least one metal layer comprises copper or aluminum more than other materials; and a second single crystal silicon layer overlying the at least one metal layer. The second single crystal silicon layer comprises a plurality of second transistors arranged in substantially parallel bands. Each of a plurality of the bands comprises a portion of the second transistors along an axis in a repeating pattern.

Owner:MONOLITHIC 3D

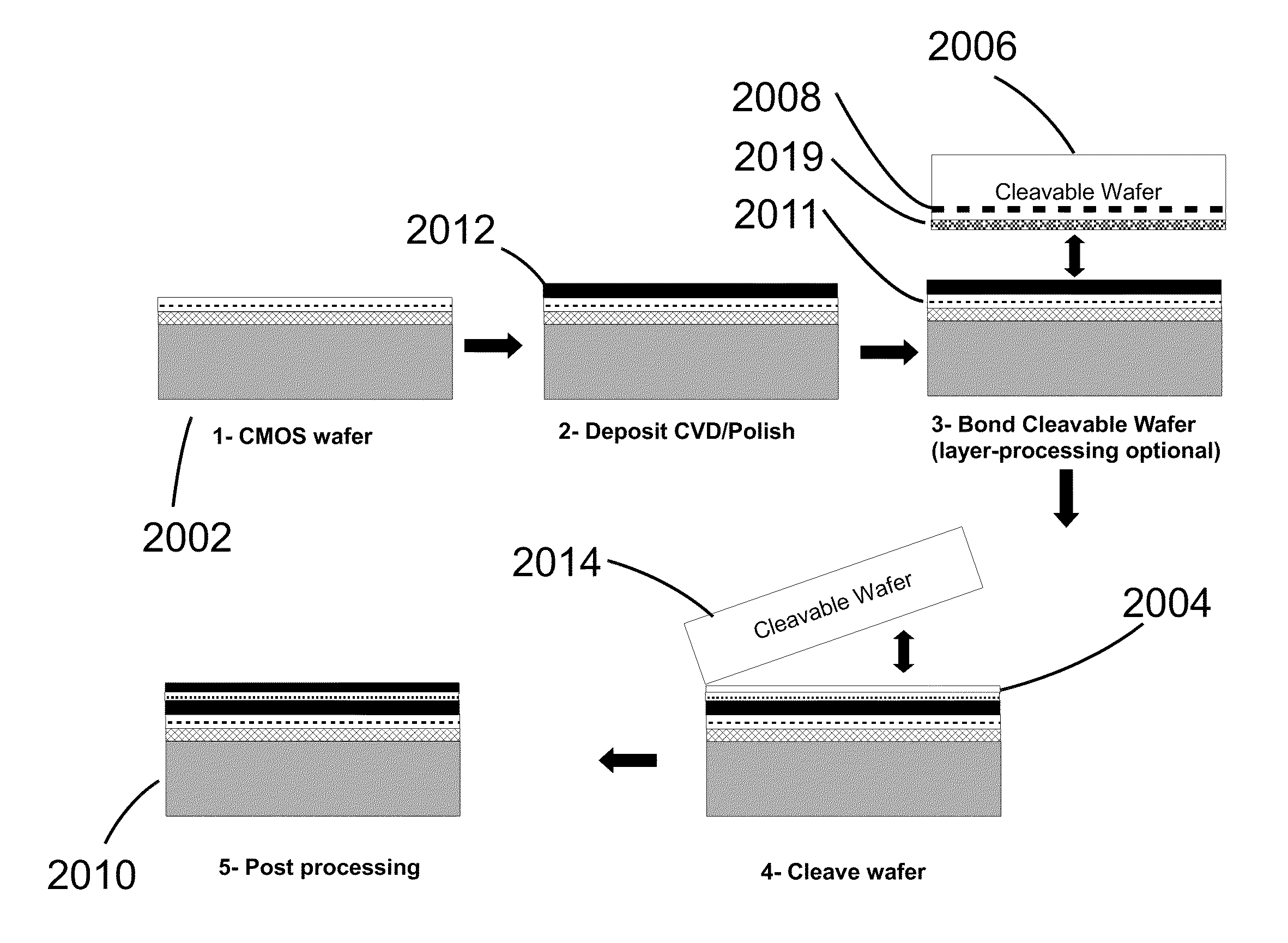

Method for fabrication of a semiconductor device and structure

ActiveUS8058137B1High mask-set costLow flexibilityTransistorSemiconductor/solid-state device detailsSingle crystalSemiconductor

A method of manufacturing a semiconductor wafer, the method including: providing a base wafer including a semiconductor substrate, metal layers and first alignment marks; transferring a monocrystalline layer on top of the metal layers, wherein the monocrystalline layer includes second alignment marks; and performing a lithography using at least one of the first alignment marks in a first direction and at least one of the second alignment marks in a second direction.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for fabrication of a semiconductor device and structure

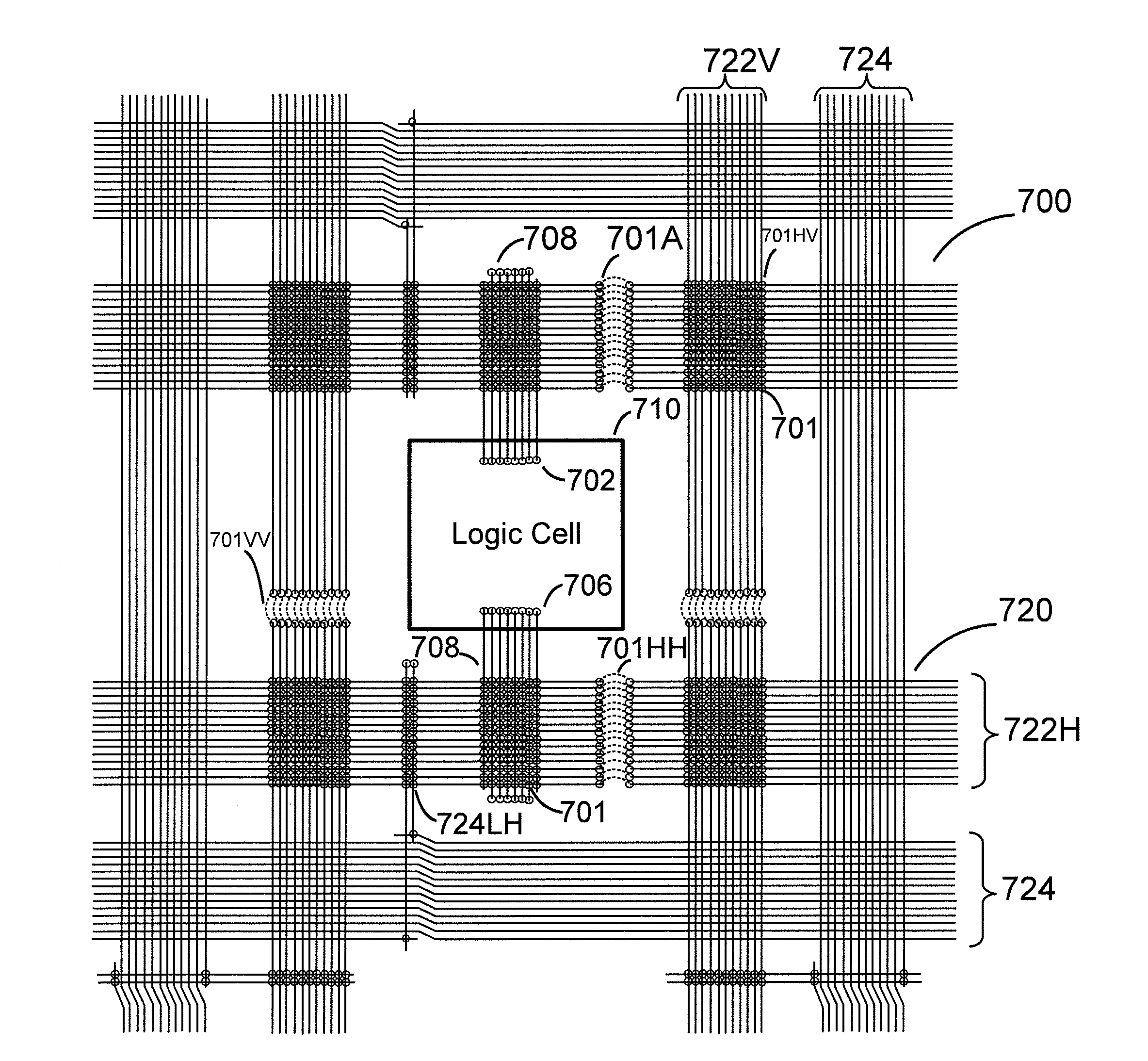

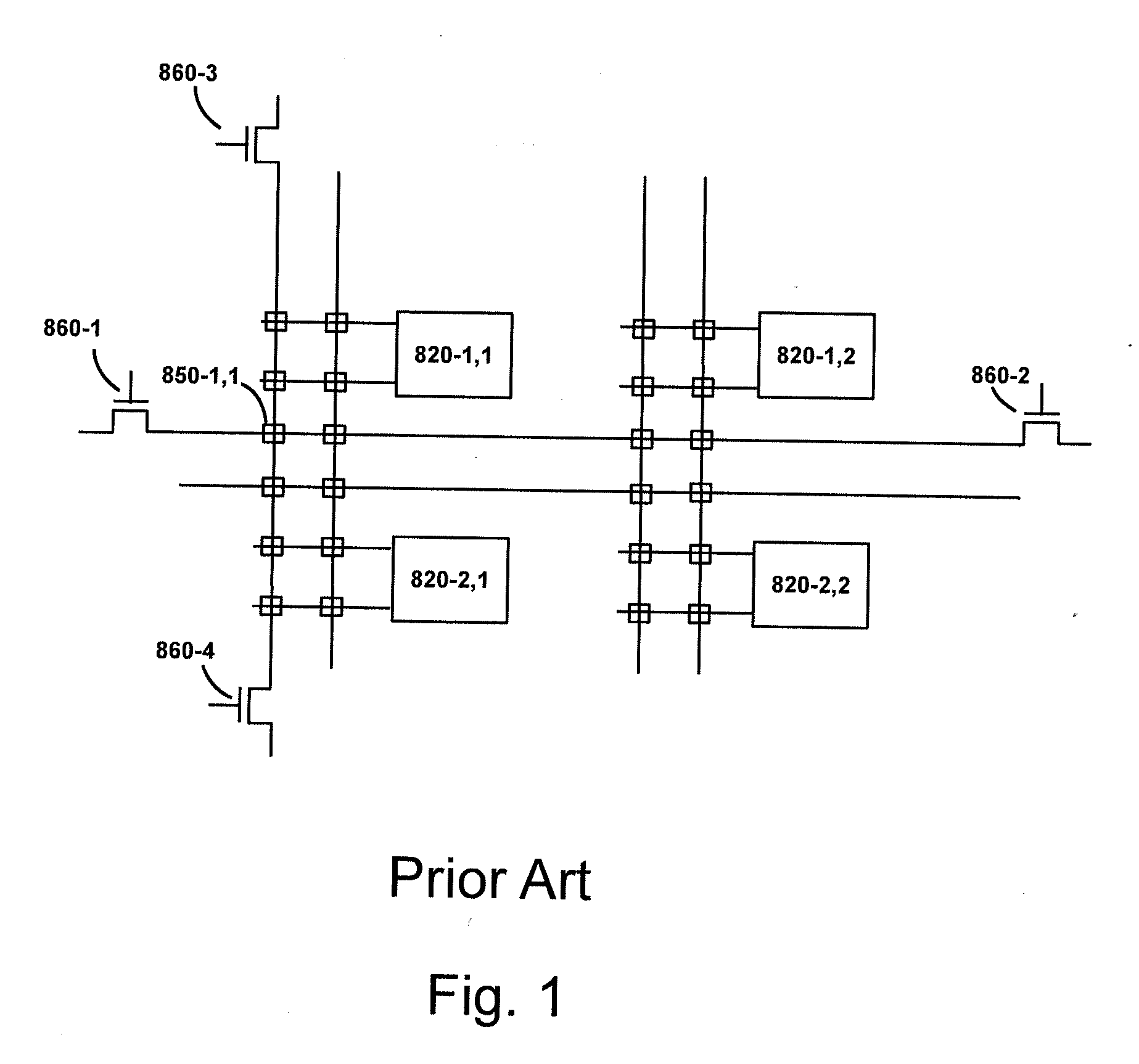

InactiveUS20100259296A1Reduced flexibilityReduce high cost of manufacturingSolid-state devicesLogic circuits using elementary logic circuit componentsEngineeringSemiconductor

A configurable integrated circuit (IC) system comprising: a first die comprising input / output cells; and a configurable logic second die connected by a first plurality of through-silicon-vias (TSVs) to the first die.

Owner:MONOLITHIC 3D

Method for fabrication of a semiconductor device and structure

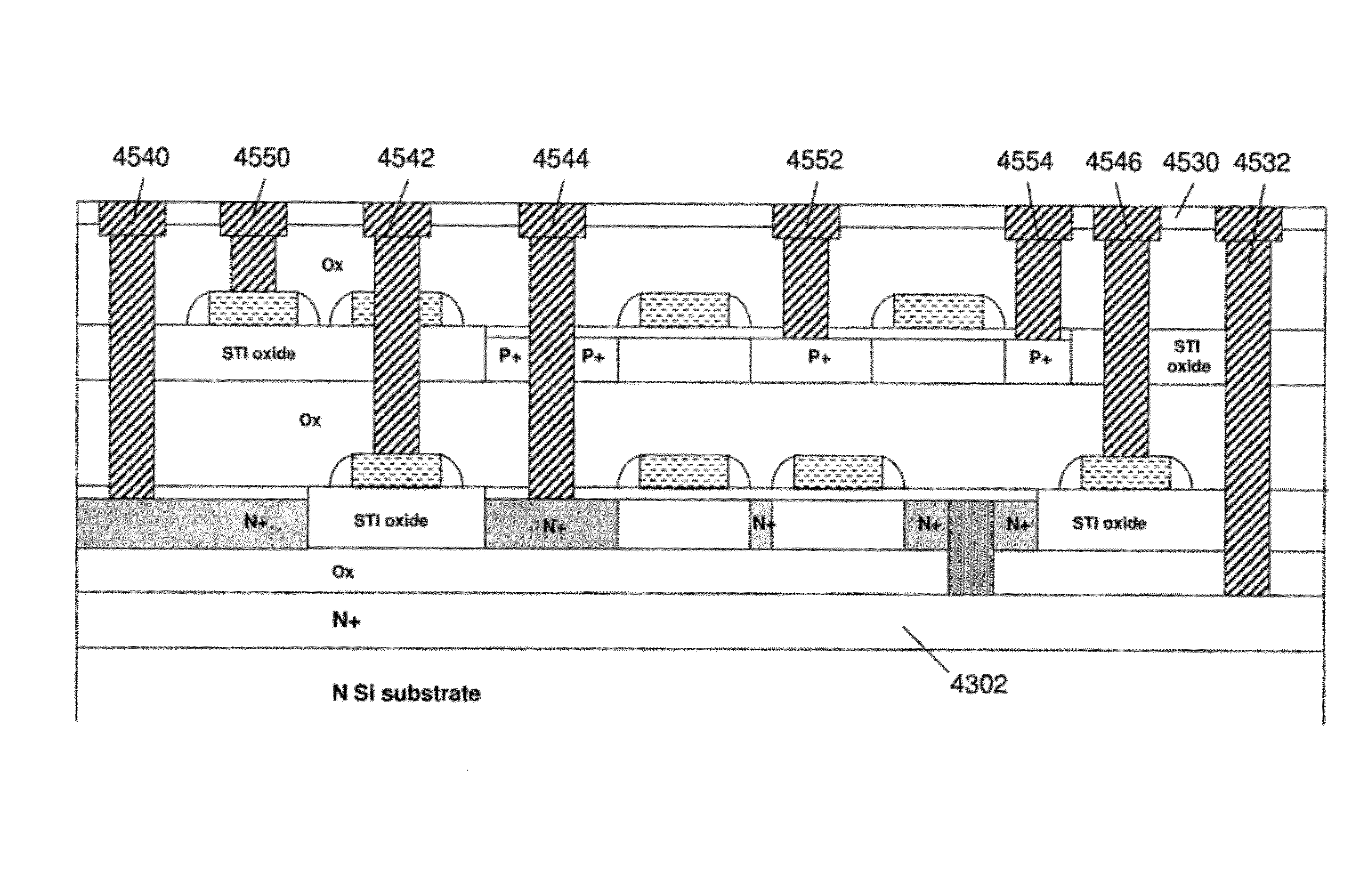

InactiveUS20100295136A1Reduced flexibilityReduce high cost of manufacturingTransistorSemiconductor/solid-state device detailsInsulation layerInterconnection

A method for fabrication of 3D semiconductor devices utilizing a layer transfer and steps for forming transistors on top of a pre-fabricated semiconductor device comprising transistors formed on crystallized semiconductor base layer and metal layer for the transistors interconnections and insulation layer. The advantage of this approach is reduction of the over all metal length used to interconnect the various transistors.

Owner:MONOLITHIC 3D

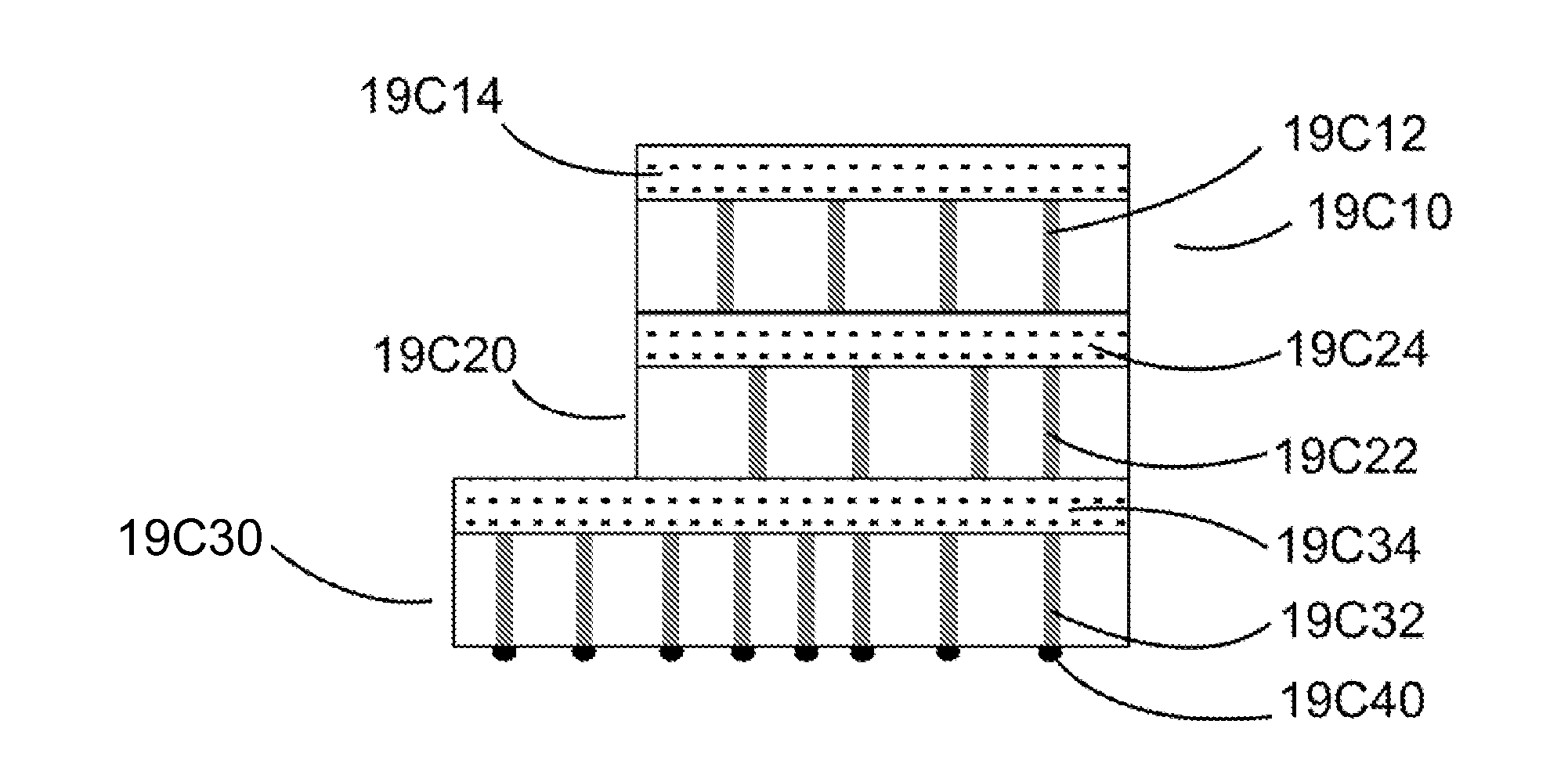

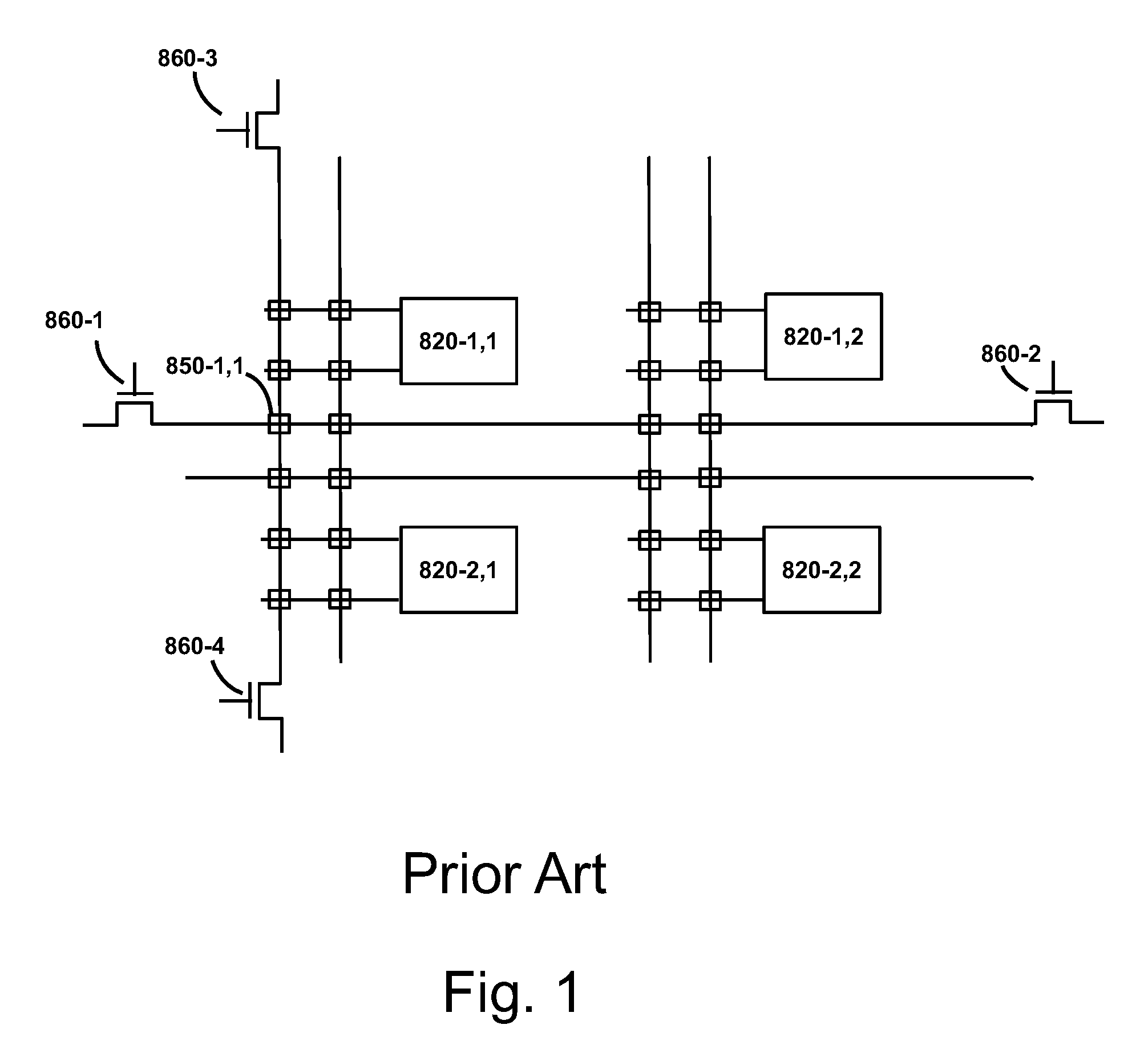

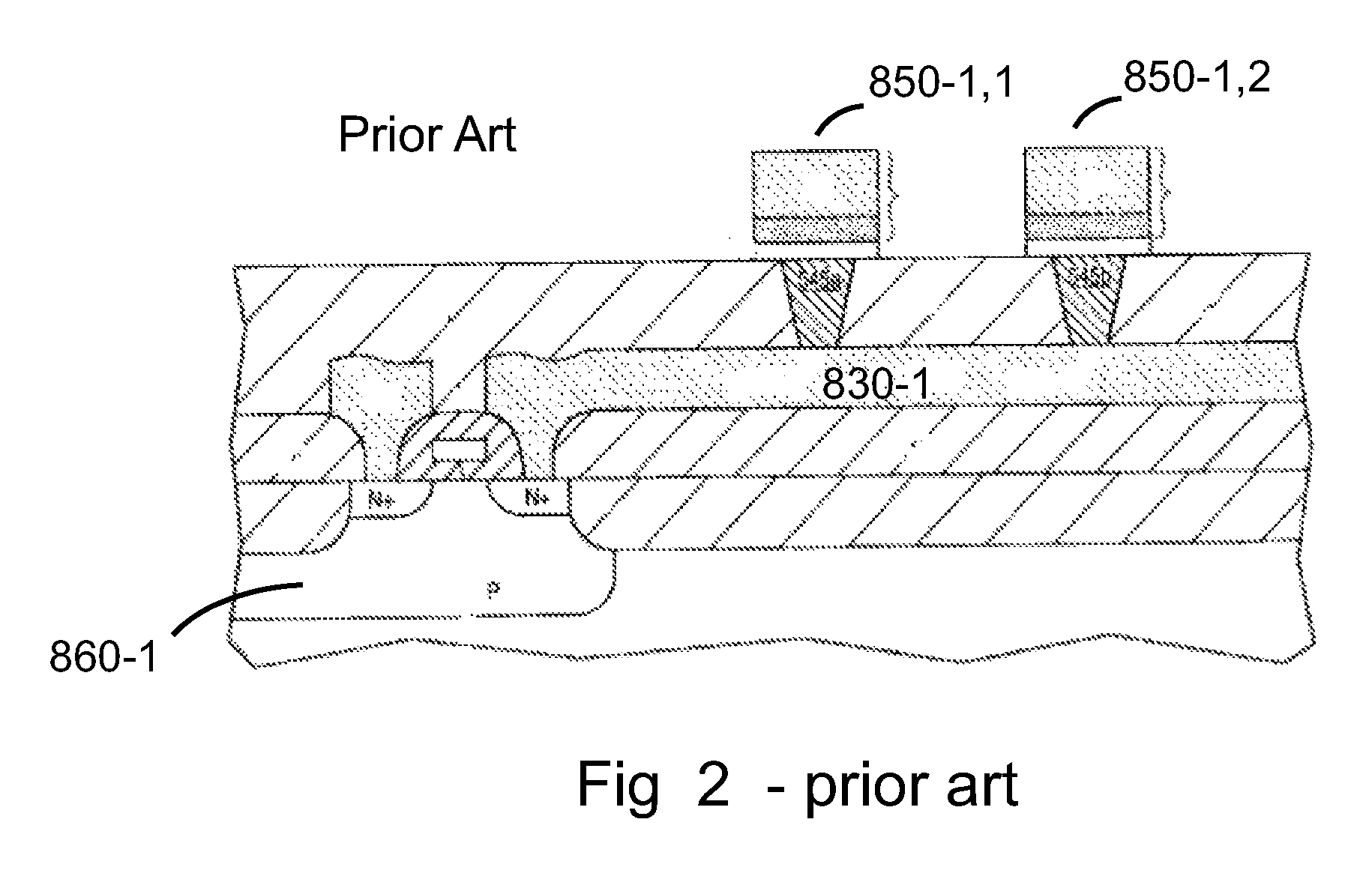

Monolithic three-dimensional semiconductor device and structure

ActiveUS8754533B2Reduce high cost of manufacturingReduced flexibilityTransistorSemiconductor/solid-state device detailsDevice materialLogic cell

A semiconductor device includes a first mono-crystallized layer including first transistors, and a first metal layer forming at least a portion of connections between the first transistors; and a second layer including second transistors, the second transistors including mono-crystalline material, the second layer overlying the first metal layer, wherein the first metal layer includes aluminum or copper, and wherein the second layer is less than one micron in thickness and includes logic cells.

Owner:SAMSUNG ELECTRONICS CO LTD

System comprising a semiconductor device and structure

ActiveUS20110108888A1Reduced flexibilityReduce high cost of manufacturingTransistorSemiconductor/solid-state device detailsCrystalline materialsSecondary layer

A semiconductor device includes a first mono-crystallized layer including first transistors, and a first metal layer forming at least a portion of connections between the first transistors; and a second layer including second transistors, the second transistors including mono-crystalline material, the second layer overlying the first metal layer, wherein the first metal layer includes aluminum or copper, and wherein the second layer is less than one micron in thickness and includes logic cells.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for fabrication of a semiconductor device and structure

InactiveUS20100289064A1Reduced flexibilityReduce high cost of manufacturingSemiconductor/solid-state device detailsSolid-state devicesCopperSemiconductor

A semiconductor device comprising: a first single crystal silicon layer comprising first transistors, first alignment marks, and at least one metal layer overlying the first single crystal silicon layer, wherein the at least one metal layer comprises copper or aluminum more than other materials; and a second single crystal silicon layer overlying the at least one metal layers; wherein the second single crystal silicon layer comprises a plurality of second transistors arranged in substantially parallel bands wherein each of a plurality of the bands comprises a portion of the second transistors along an axis in a repeating pattern.

Owner:MONOLITHIC 3D

Method for fabrication of a semiconductor device and structure

InactiveUS7964916B2Reduce high cost of manufacturingReduced flexibilityTransistorSemiconductor/solid-state device detailsInsulation layerDevice material

A method for fabrication of 3D semiconductor devices utilizing a layer transfer and steps for forming transistors on top of a pre-fabricated semiconductor device comprising transistors formed on crystallized semiconductor base layer and metal layer for the transistors interconnections and insulation layer. The advantage of this approach is reduction of the over all metal length used to interconnect the various transistors.

Owner:MONOLITHIC 3D

Method for fabrication of a semiconductor device and structure

InactiveUS20110233617A1Reduce high cost of manufacturingReduced flexibilityTransistorSemiconductor/solid-state device detailsPower semiconductor deviceInsulation layer

A method for fabrication of 3D semiconductor devices utilizing a layer transfer and steps for forming transistors on top of a pre-fabricated semiconductor device comprising transistors formed on crystallized semiconductor base layer and metal layer for the transistors interconnections and insulation layer. The advantage of this approach is reduction of the over all metal length used to interconnect the various transistors.

Owner:MONOLITHIC 3D

System comprising a semiconductor device and structure

ActiveUS20110049577A1Reduced flexibilityReduce high cost of manufacturingTransistorSemiconductor/solid-state device detailsDevice materialCopper

A system includes a semiconductor device. The semiconductor device includes a first single crystal silicon layer comprising first transistors, first alignment marks, and at least one metal layer overlying the first single crystal silicon layer, wherein the at least one metal layer comprises copper or aluminum more than other materials; and a second single crystal silicon layer overlying the at least one metal layer. The second single crystal silicon layer comprises a plurality of second transistors arranged in substantially parallel bands. Each of a plurality of the bands comprises a portion of the second transistors along an axis in a repeating pattern.

Owner:SAMSUNG ELECTRONICS CO LTD

System comprising a semiconductor device and structure

ActiveUS20120012895A1Reduce high cost of manufacturingReduced flexibilityTransistorSemiconductor/solid-state device detailsDevice materialEngineering

A system includes a semiconductor device. The semiconductor device includes a first semiconductor layer comprising first transistors, wherein the first transistors are interconnected by at least one metal layer comprising aluminum or copper. The second mono-crystallized semiconductor layer includes second transistors and is overlaying the at least one metal layer, wherein the second mono-crystallized semiconductor layer is less than 150 nm in thickness, and at least one of the second transistors is an N-type transistor and at least one of the second transistors is a P-type transistor.

Owner:SAMSUNG ELECTRONICS CO LTD

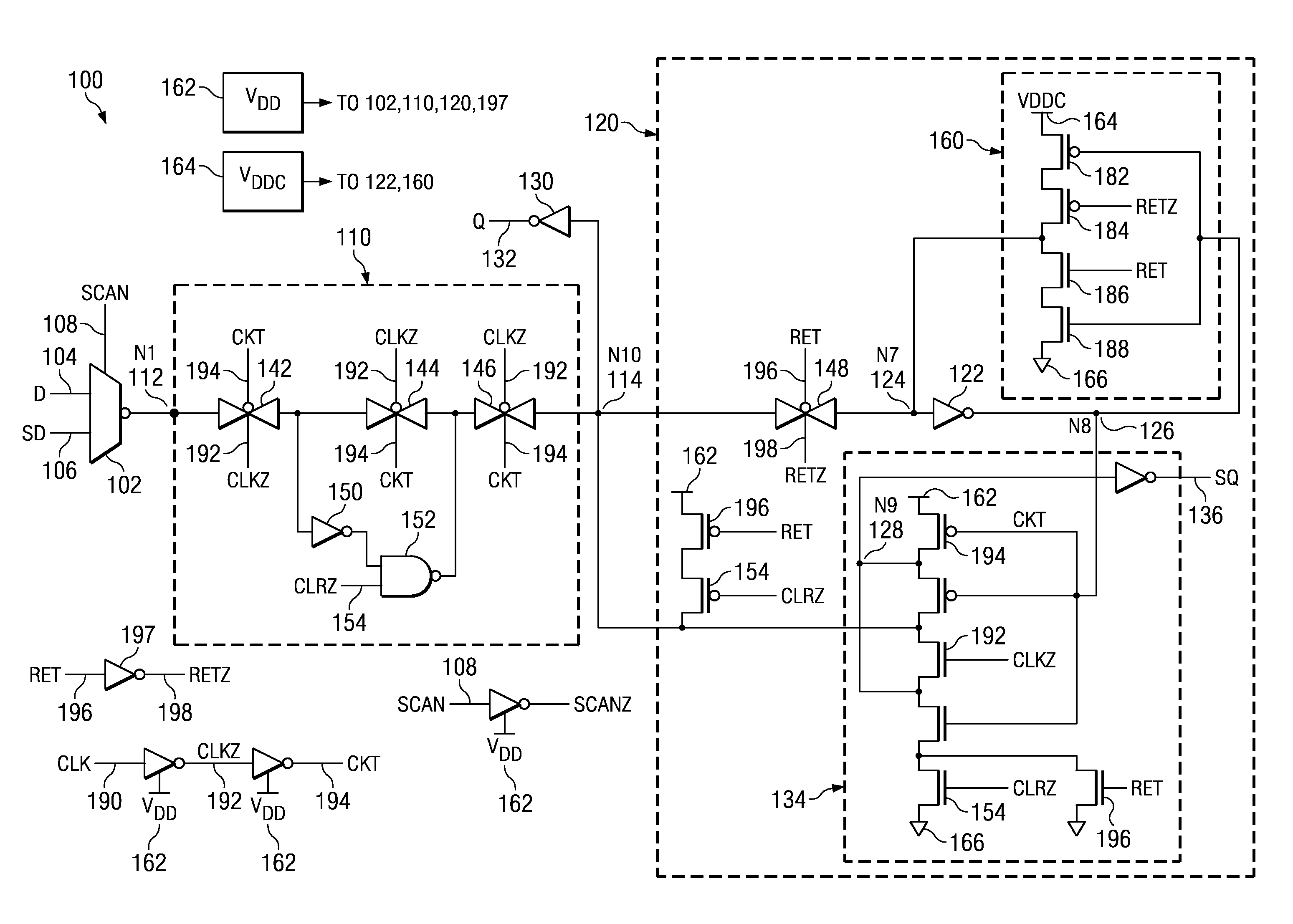

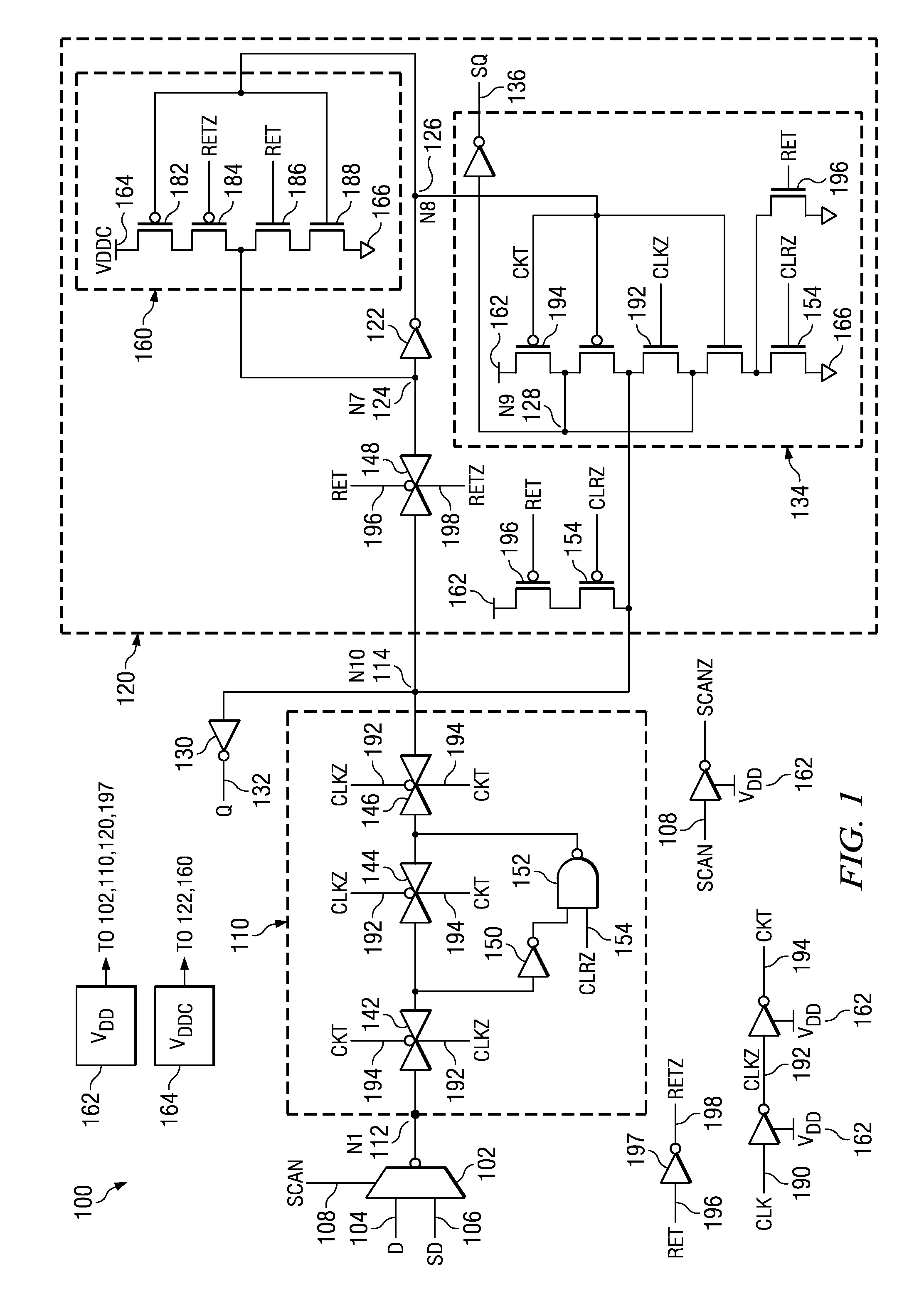

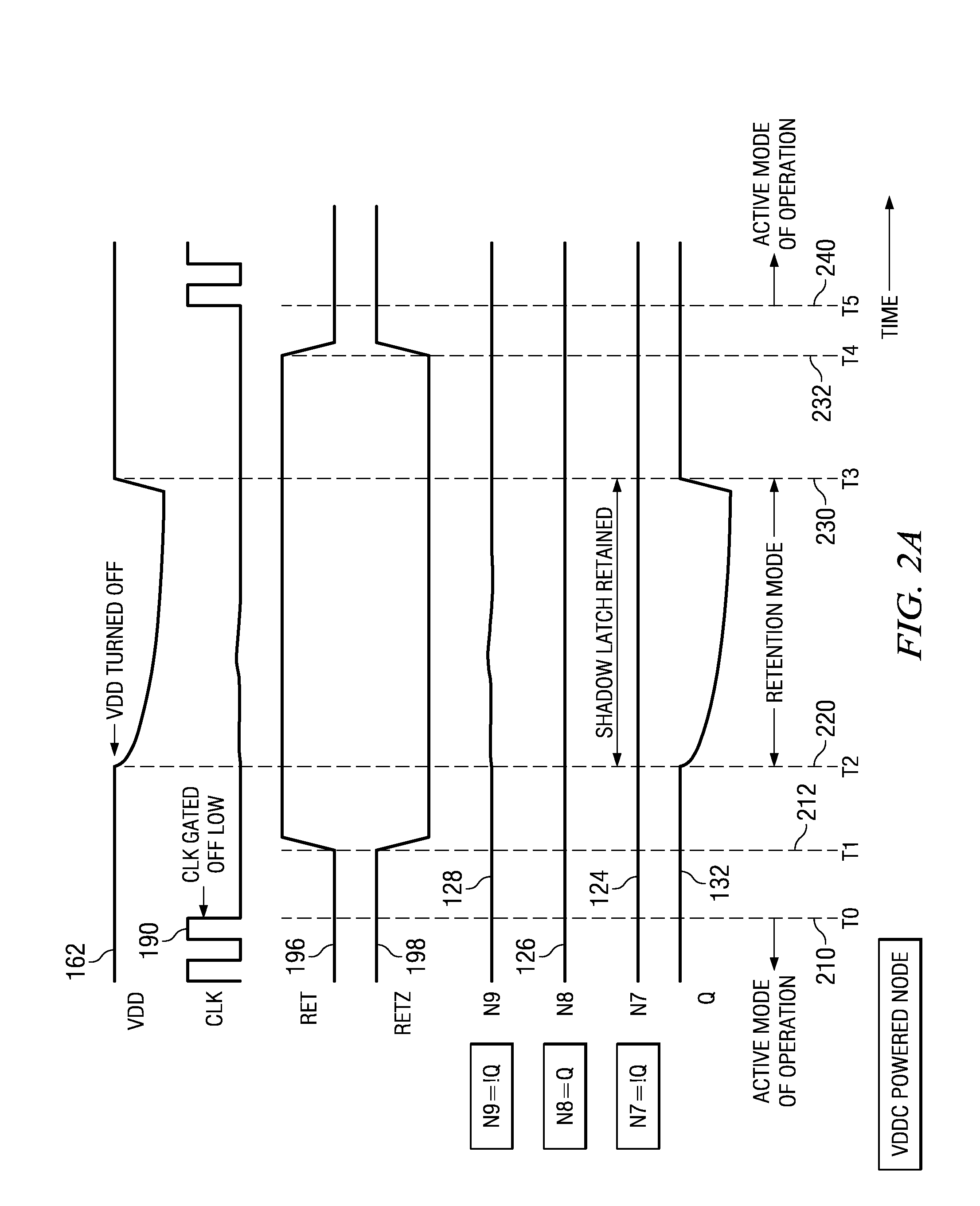

Slave latch controlled retention flop with lower leakage and higher performance

ActiveUS7652513B2Reduce leakage currentDesirable performanceElectric pulse generatorStandby powerLow leakage

In a method and apparatus for data retention, a first latch latches a data input and a second latch that is coupled to the first latch retains the data input while the first latch is inoperative in a standby power mode. The second latch includes a second latch inverter having an inverter input and an inverter output. A switching circuit, which may be implemented as a tristate inverter, is coupled to the inverter output, the inverter input, and a retention signal. The switching circuit is operable in the standby power mode to assert a logic state at the inverter input responsive to the retention signal. The logic state is in accordance with the data input retained in the standby power mode. A standby power source is operable to provide power in the standby power mode to the second latch inverter, the switching circuit and the retention input.

Owner:TEXAS INSTR INC

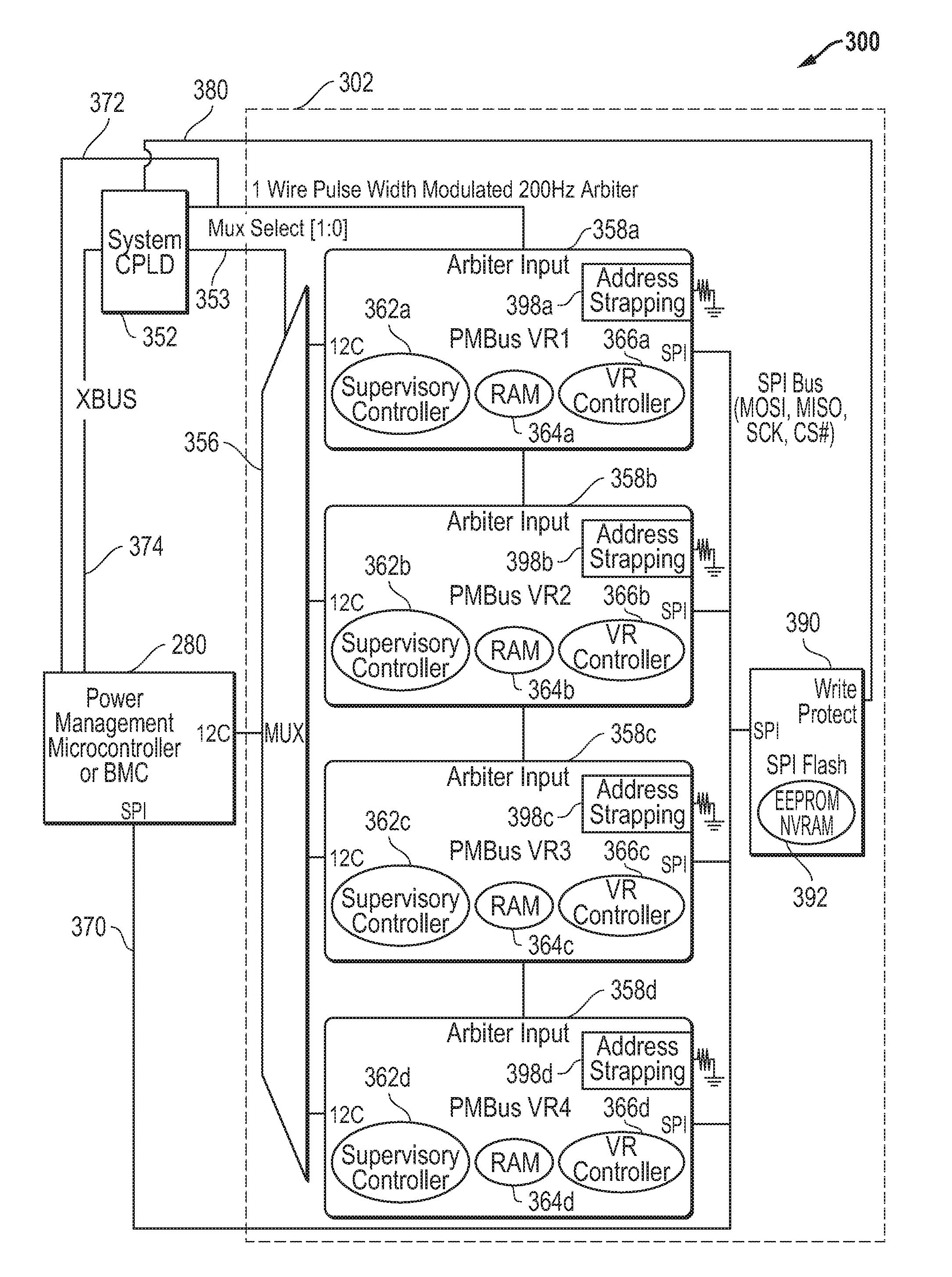

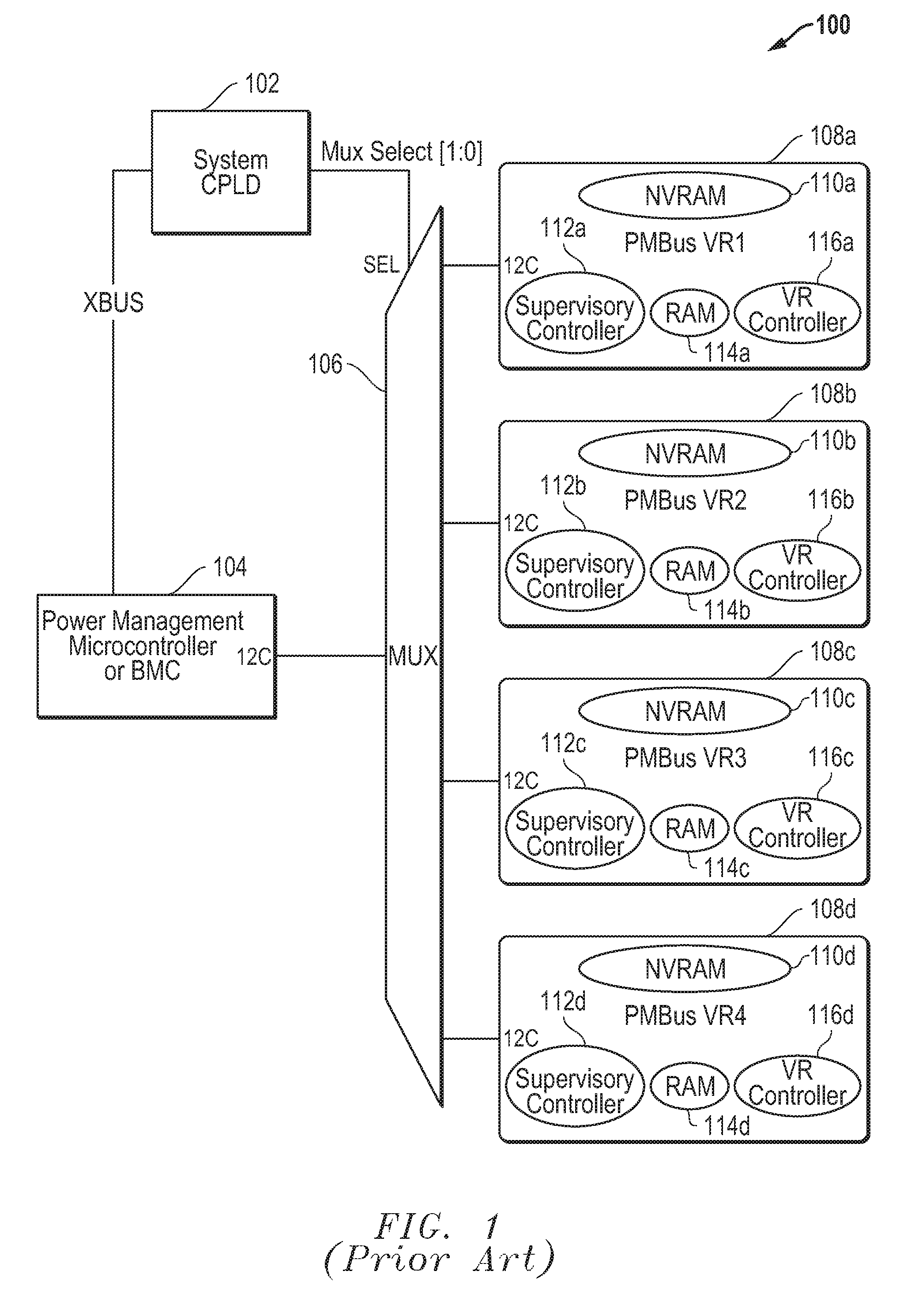

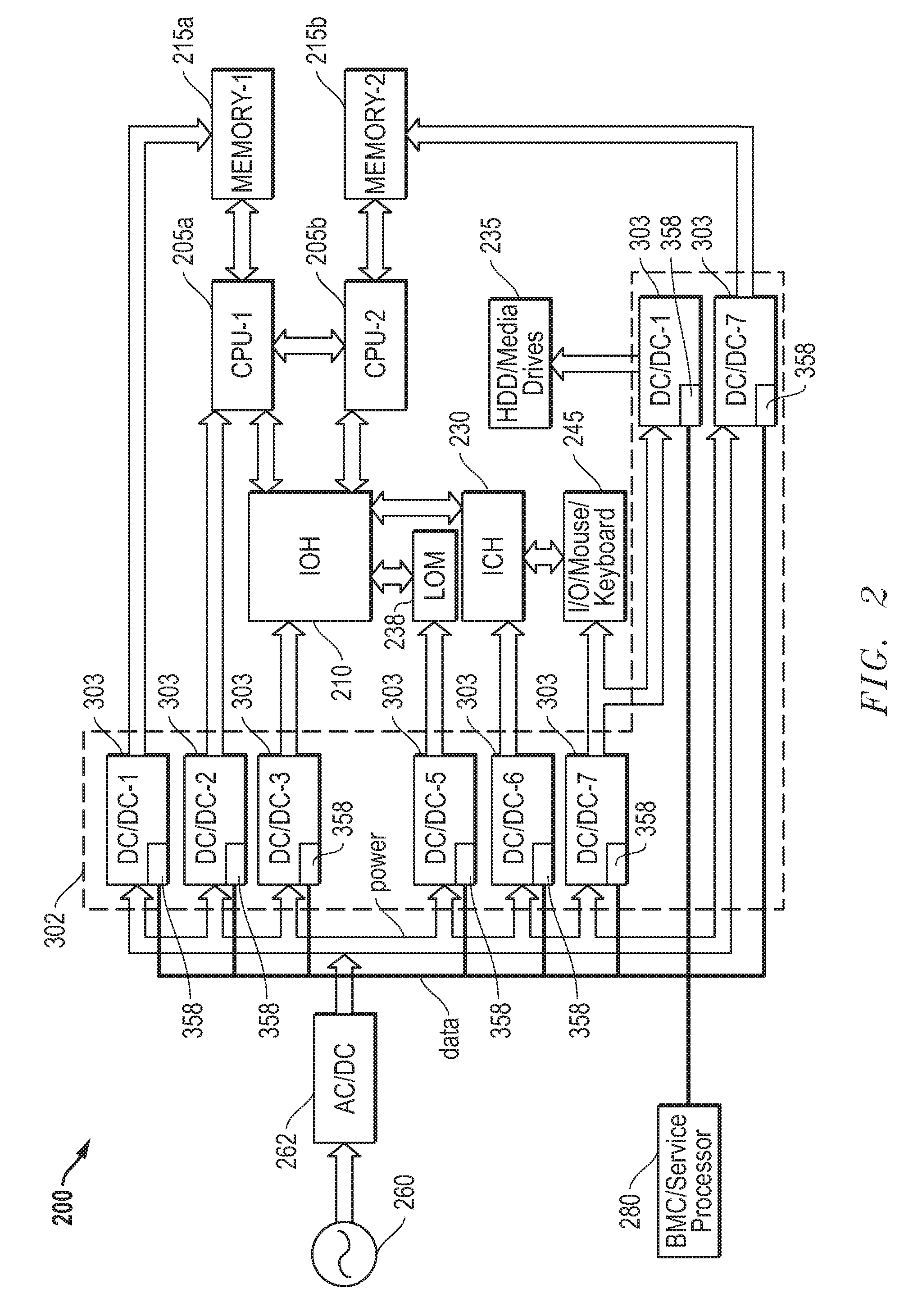

Shared non-volatile storage for digital power control

ActiveUS20120324246A1Save board spaceLow costVolume/mass flow measurementPower supply for data processingPower controllerPower control system

Systems and methods may be implemented in a power device subsystem topology to provide an arbitration and communication scheme between a single consolidated non-volatile random access (NVRAM) memory device and multiple discrete digital power controller devices in a manner that provides data protection and the ability to update the full NVRAM content when needed.

Owner:DELL PROD LP

Method for fabrication of a semiconductor device and structure

InactiveUS8115511B2Reduce high cost of manufacturingReduced flexibilitySolid-state devicesLogic circuits using elementary logic circuit componentsEngineeringSemiconductor

A configurable integrated circuit (IC) system comprising: a first die comprising input / output cells; and a configurable logic second die connected by a first plurality of through-silicon-vias (TSVs) to the first die.

Owner:MONOLITHIC 3D

Method for fabrication of a semiconductor device and structure

InactiveUS7986042B2Reduce high cost of manufacturingReduced flexibilityTransistorSemiconductor/solid-state device detailsCopperSemiconductor

A semiconductor device comprising: a first single crystal silicon layer comprising first transistors, first alignment marks, and at least one metal layer overlying the first single crystal silicon layer, wherein the at least one metal layer comprises copper or aluminum more than other materials; and a second single crystal silicon layer overlying the at least one metal layers; wherein the second single crystal silicon layer comprises a plurality of second transistors arranged in substantially parallel bands wherein each of a plurality of the bands comprises a portion of the second transistors along an axis in a repeating pattern.

Owner:MONOLITHIC 3D

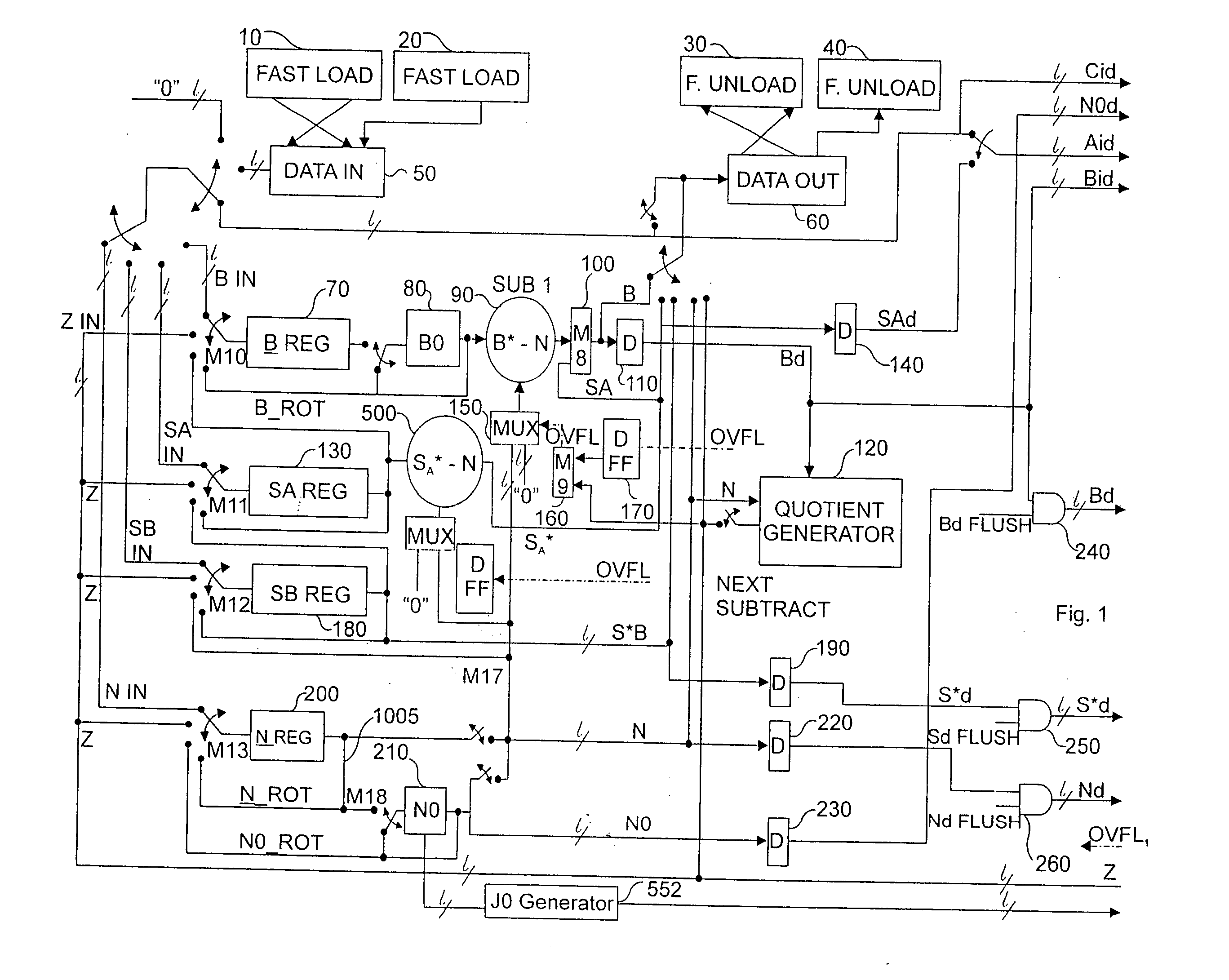

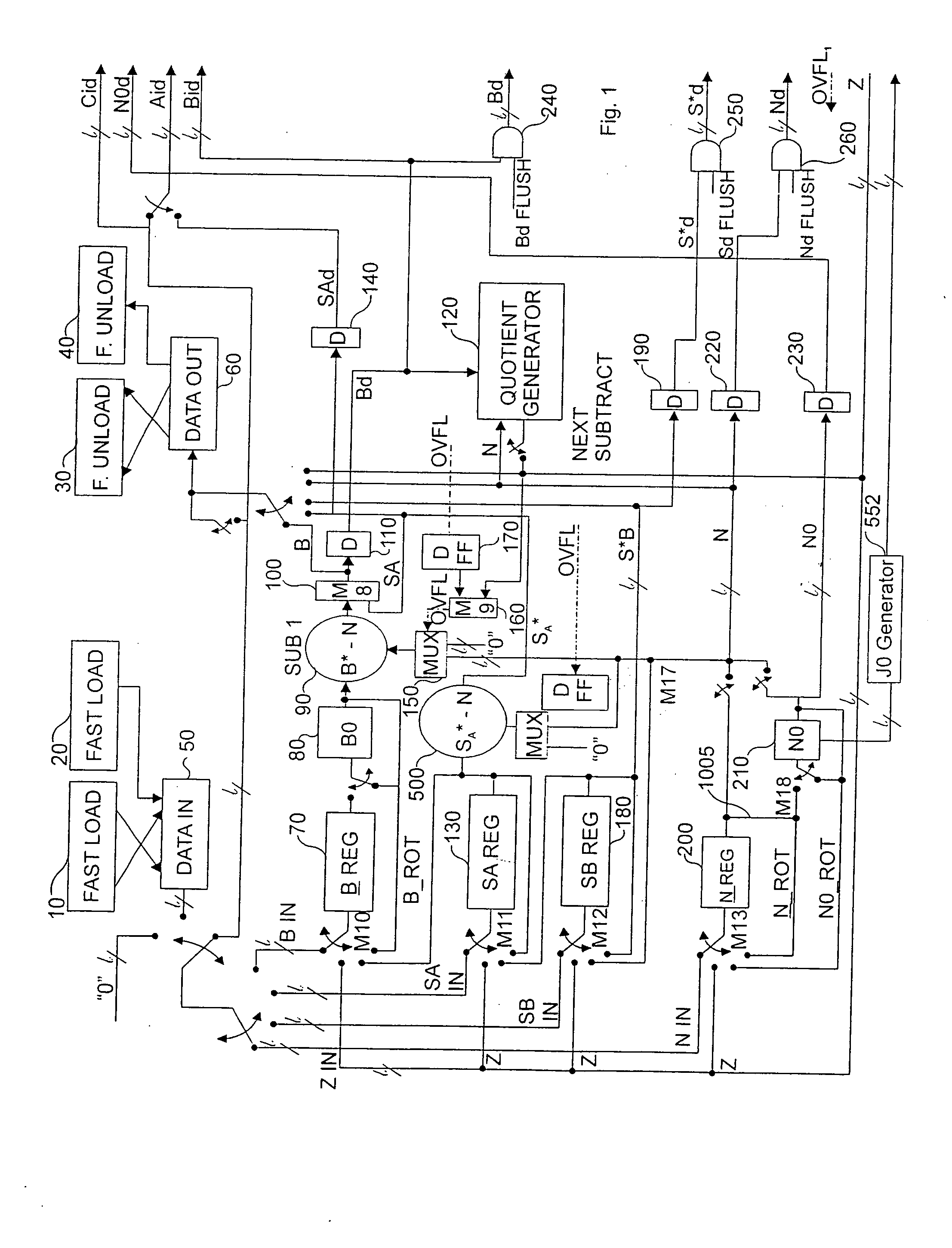

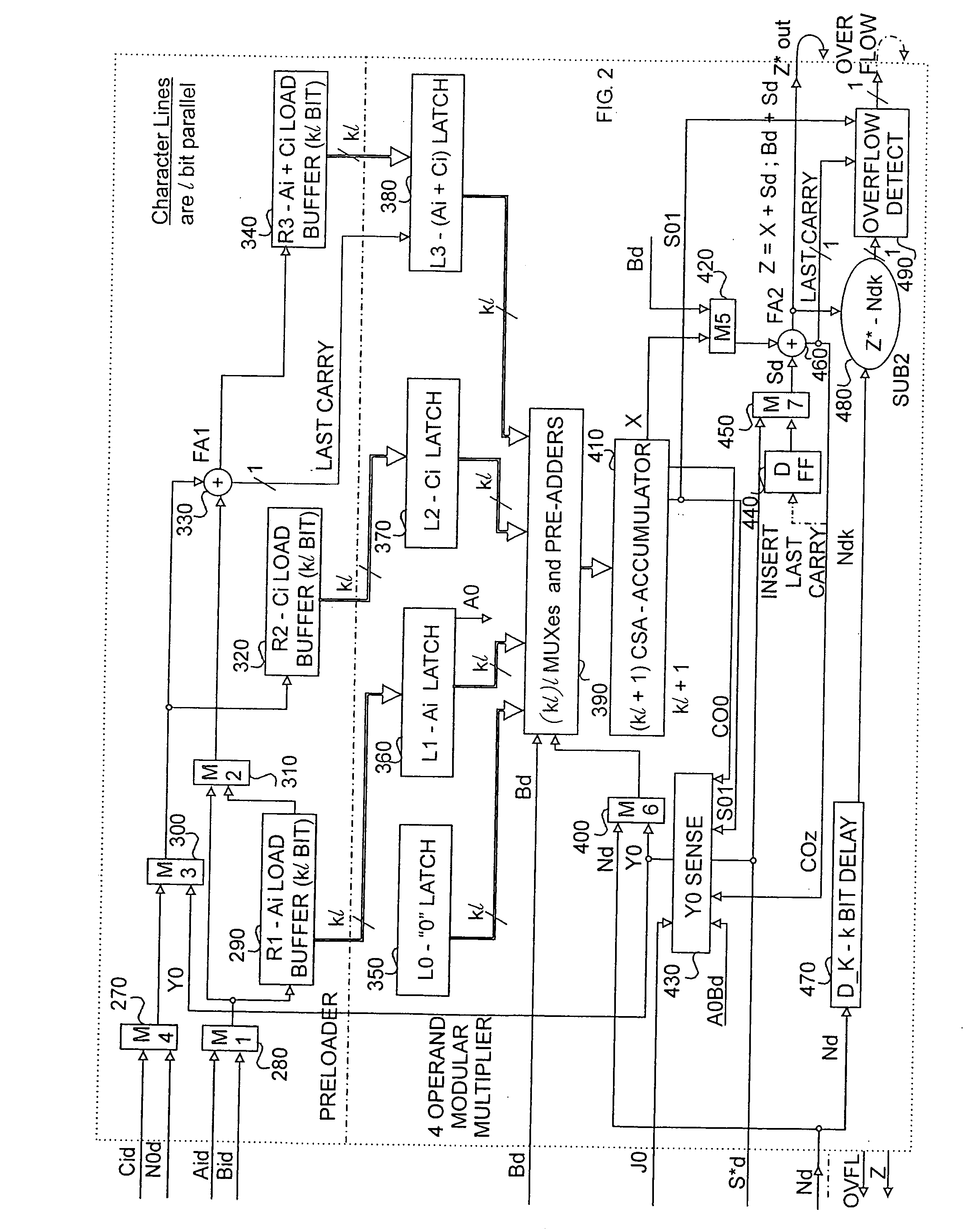

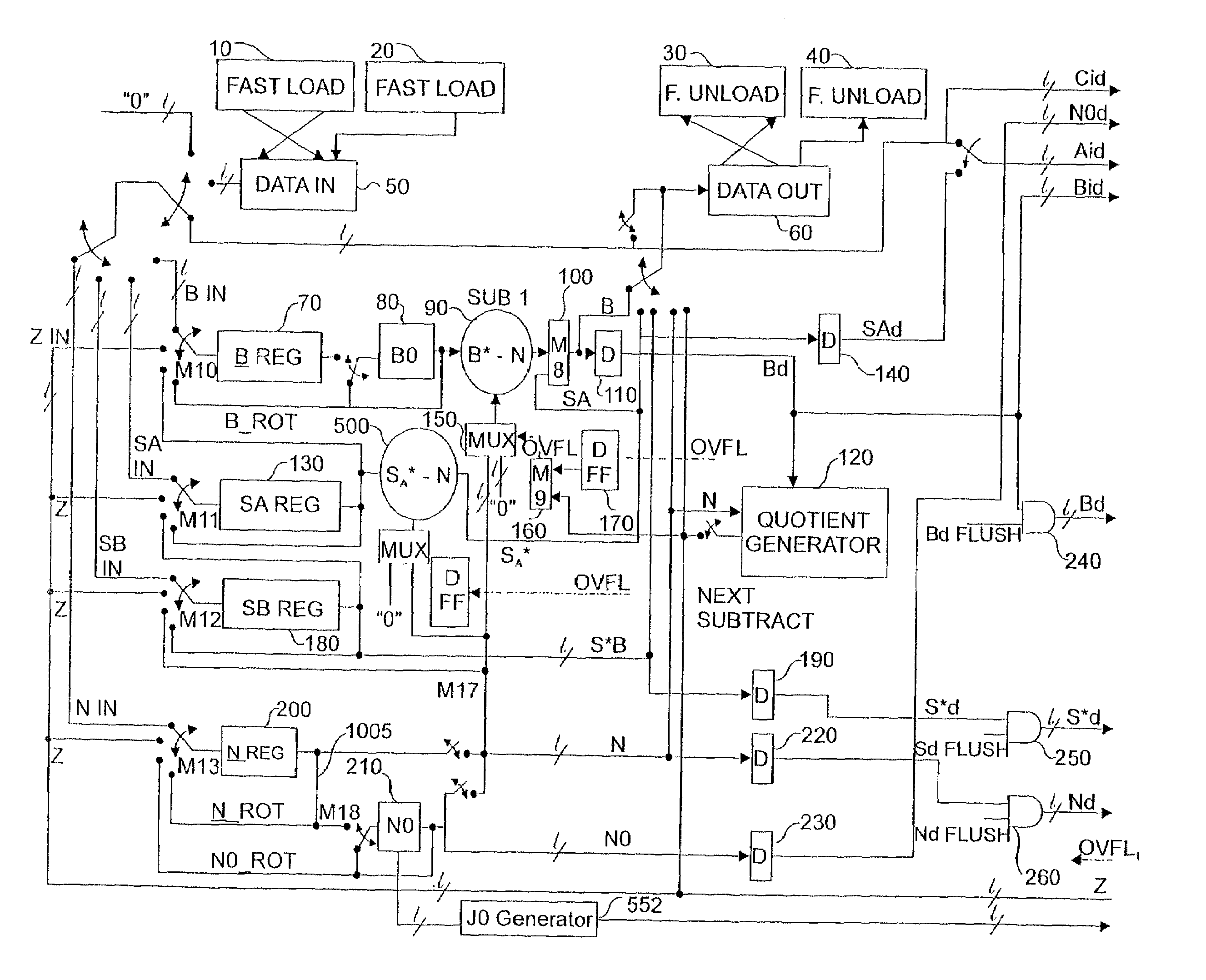

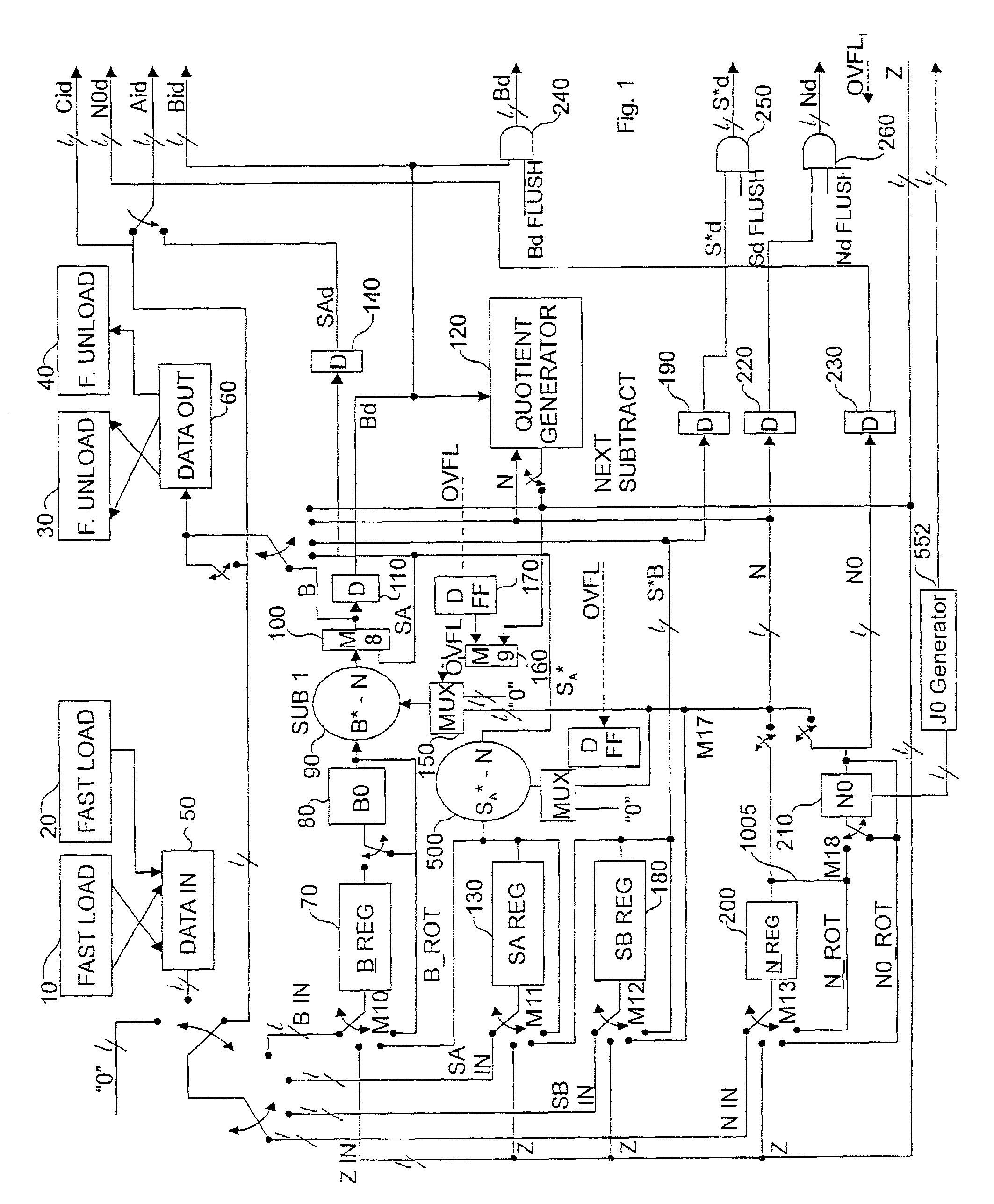

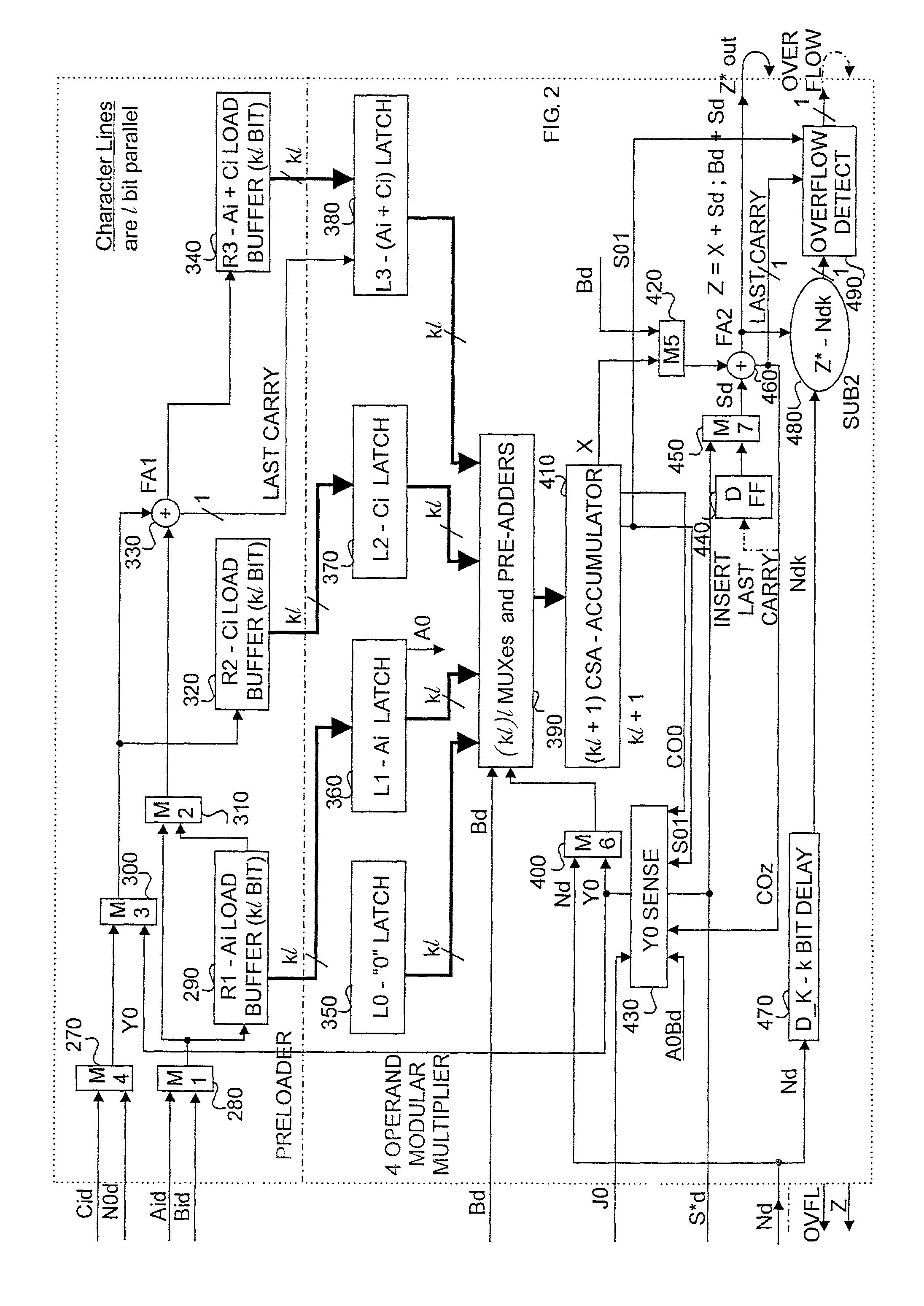

Extending the range of computational fields of intergers

InactiveUS20060269054A1Increase the amount of calculationReduce silicon areaUser identity/authority verificationDigital computer detailsOperandMontgomery reduction

Owner:WESTERN DIGITAL ISRAEL LTD

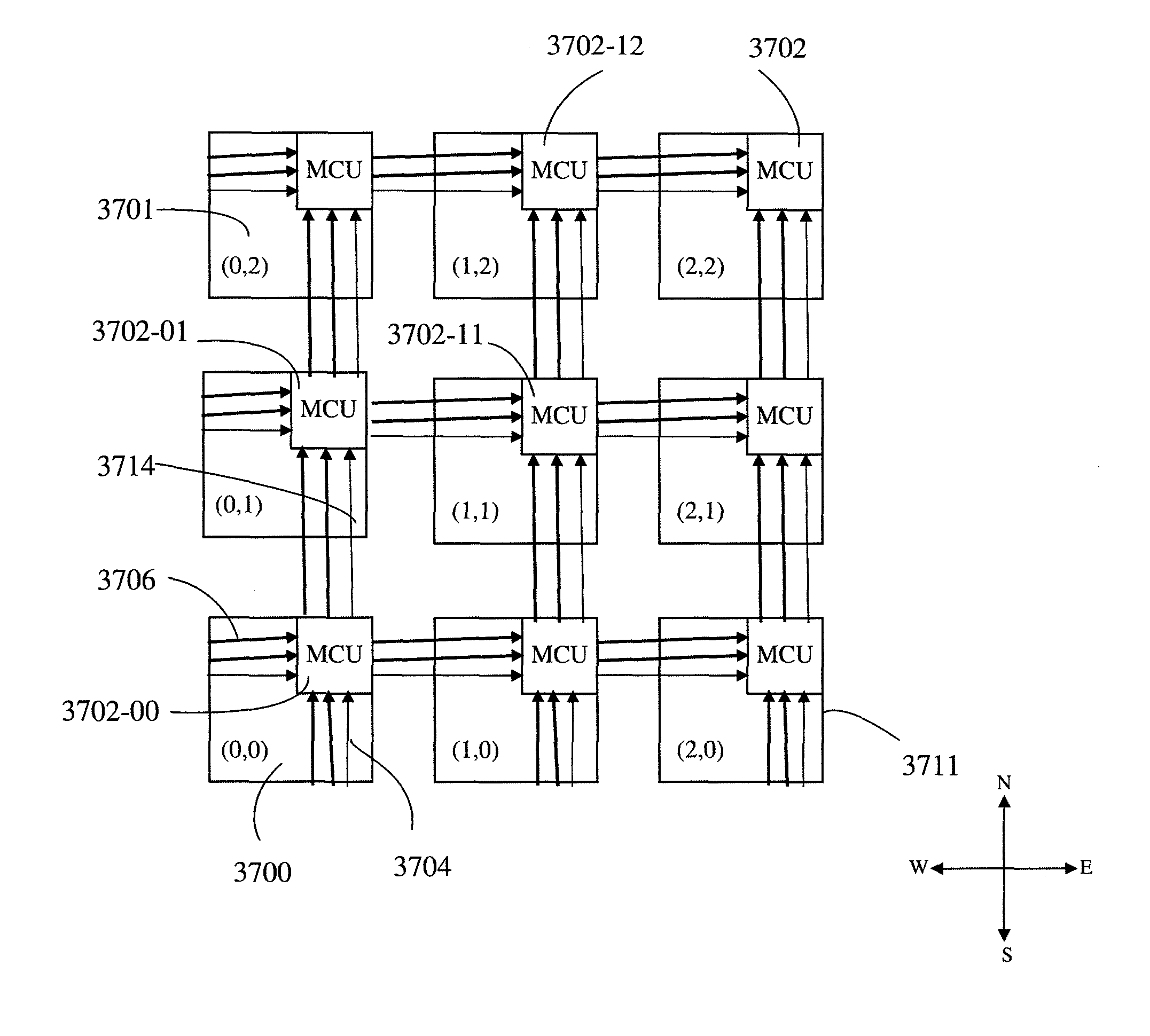

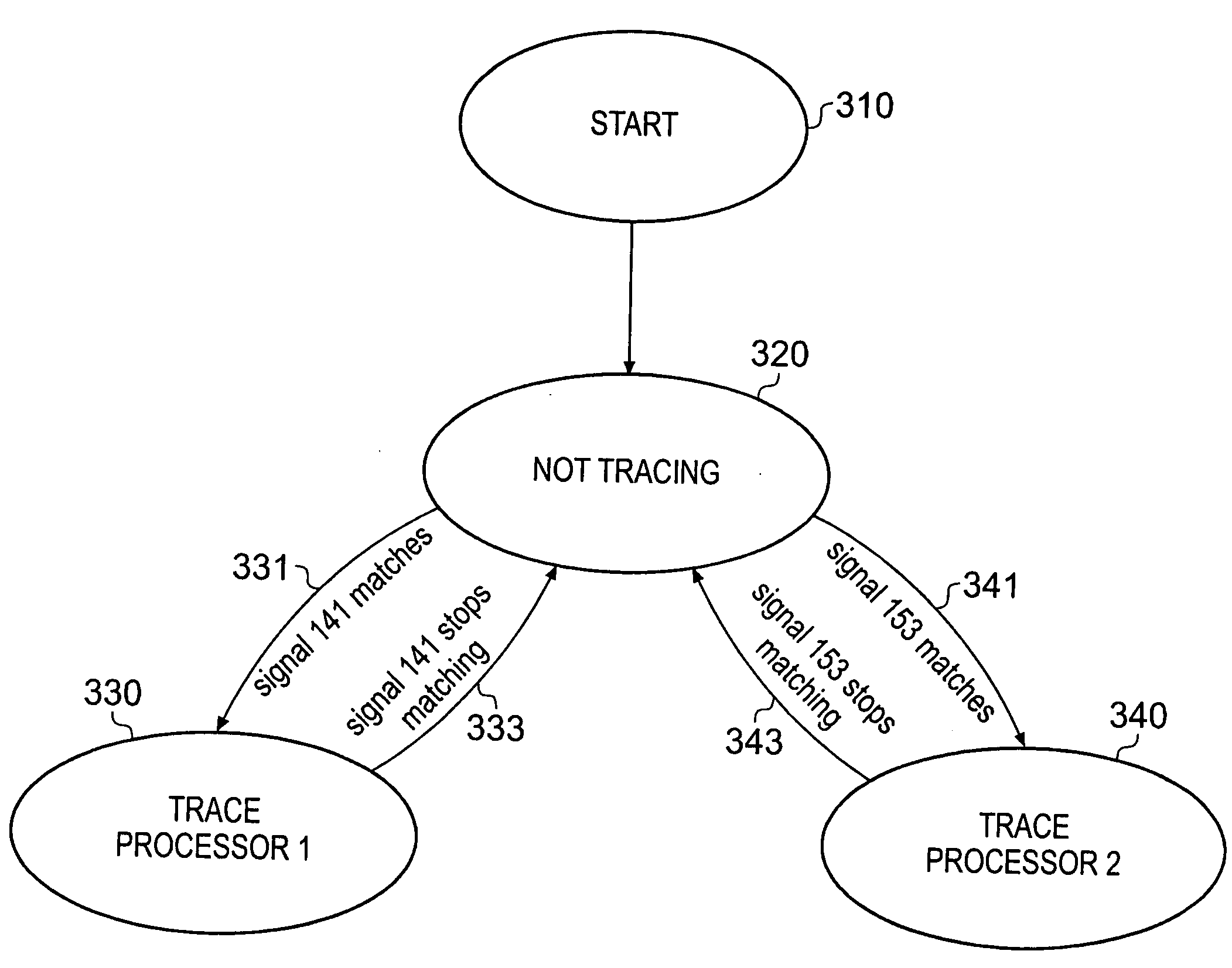

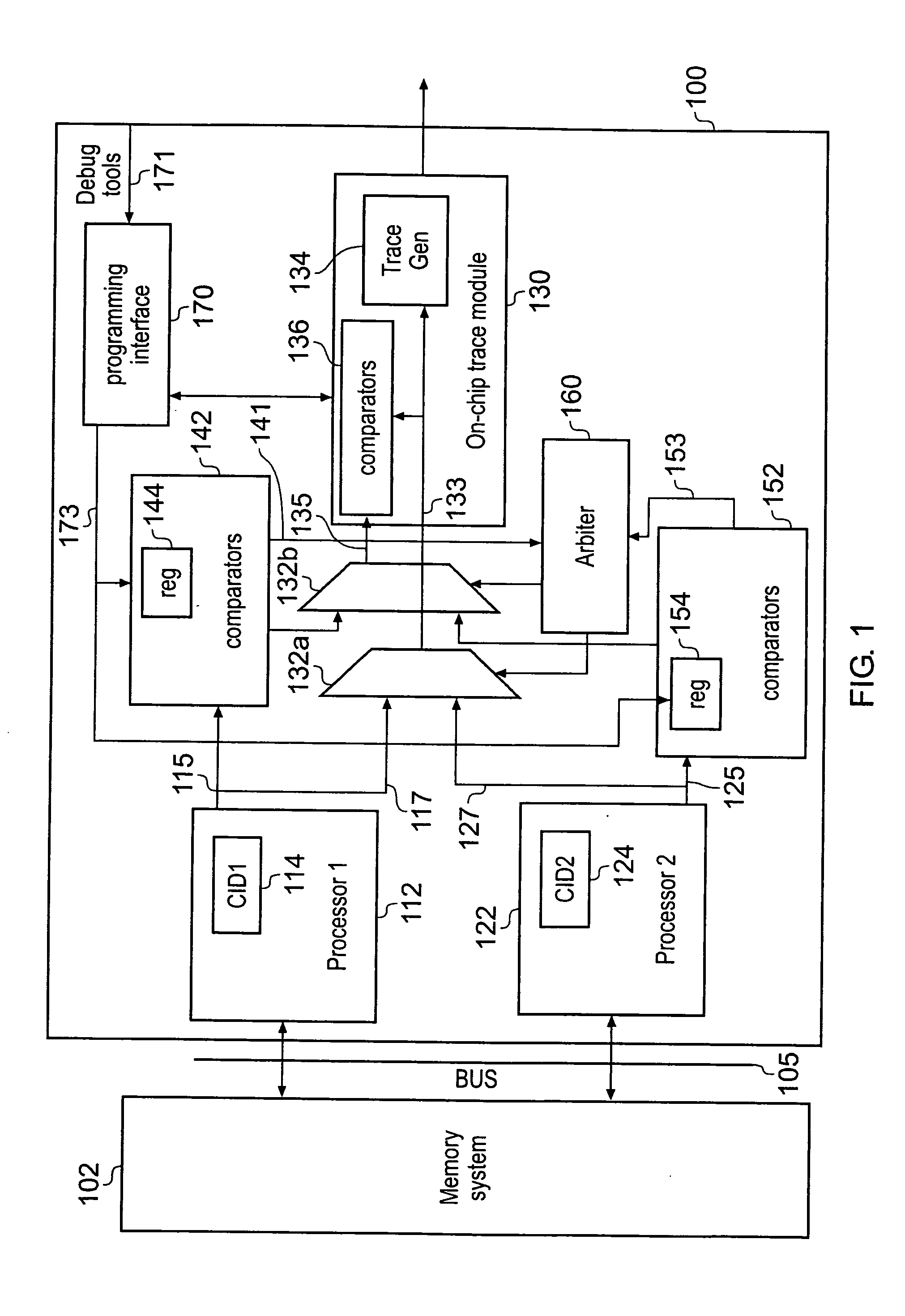

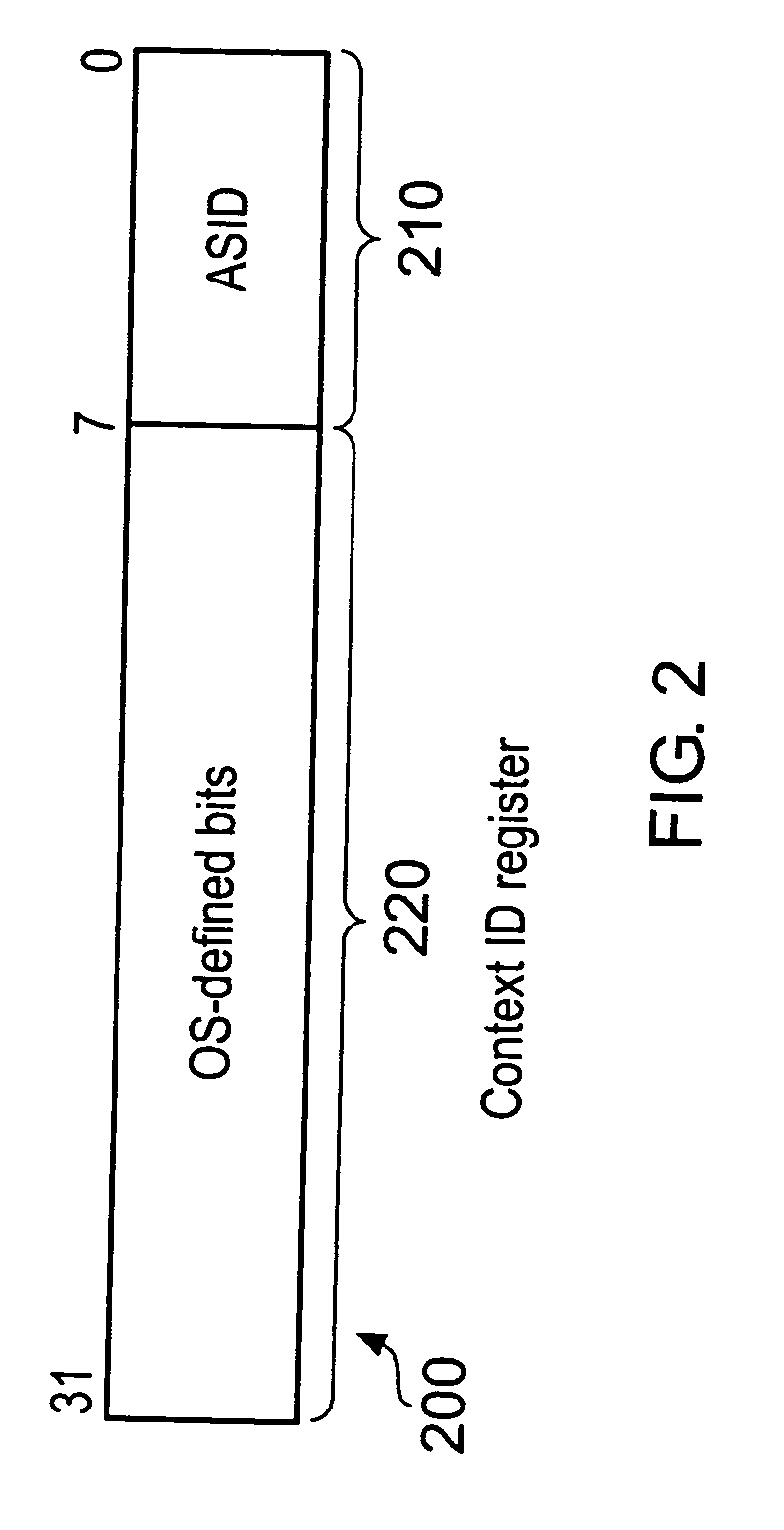

Generation of trace data in a multi-processor system

ActiveUS20090313507A1Conveniently performedEffective trackingHardware monitoringData streamMulti processor

A data processing apparatus is provided having a plurality of processing circuits each having access to a memory. Tracing circuitry is provided for generating a stream of trace data for generating a stream of trace data corresponding to at least one of the plurality of processing circuits. Selection circuitry is provided to enable selective switching of the tracing circuitry from generating a first trace data stream corresponding to a first one of the plurality of processing circuits generating a second different trace data stream corresponding to a different one of the plurality of processing circuits. The selective switching is performed in dependence upon processing state information associating with one or more of the plurality of processing circuits. A corresponding method and computer program product are also provided.

Owner:ARM LTD

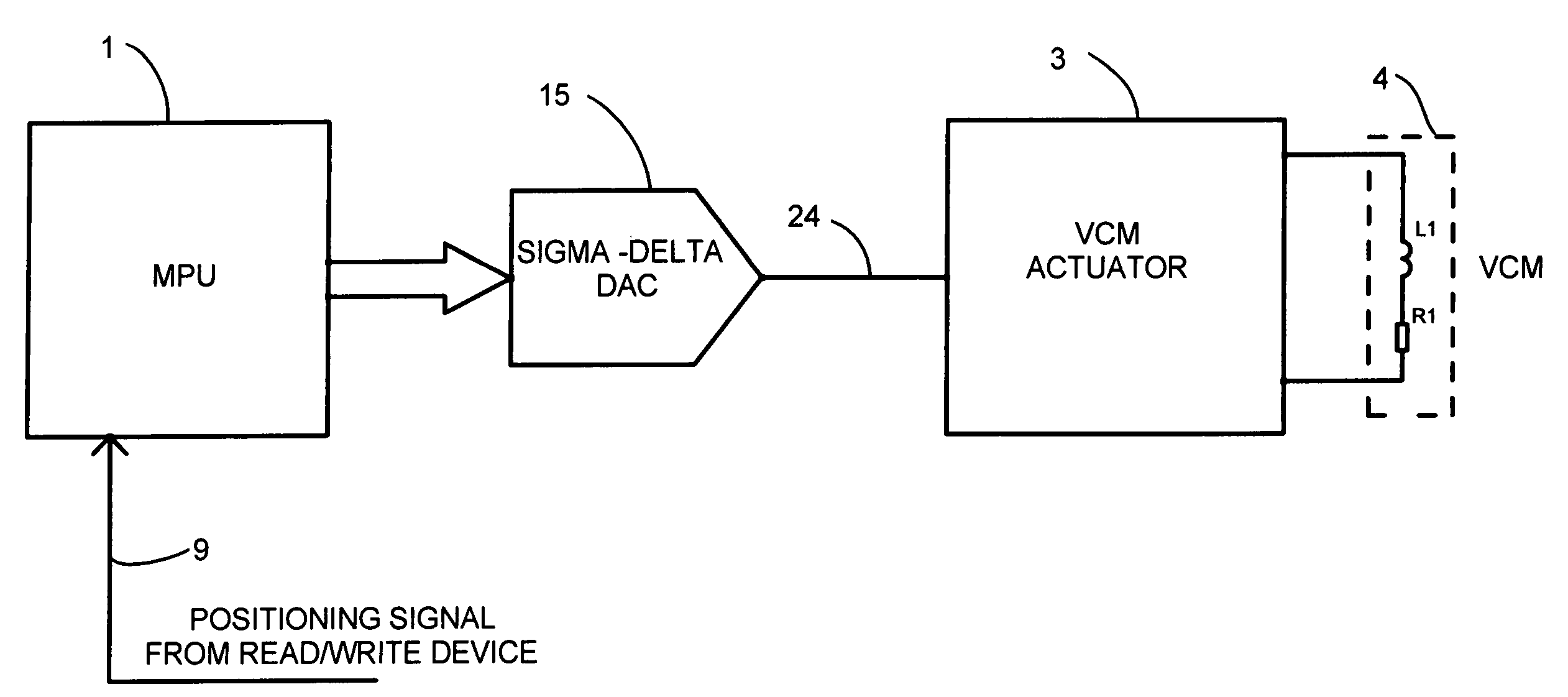

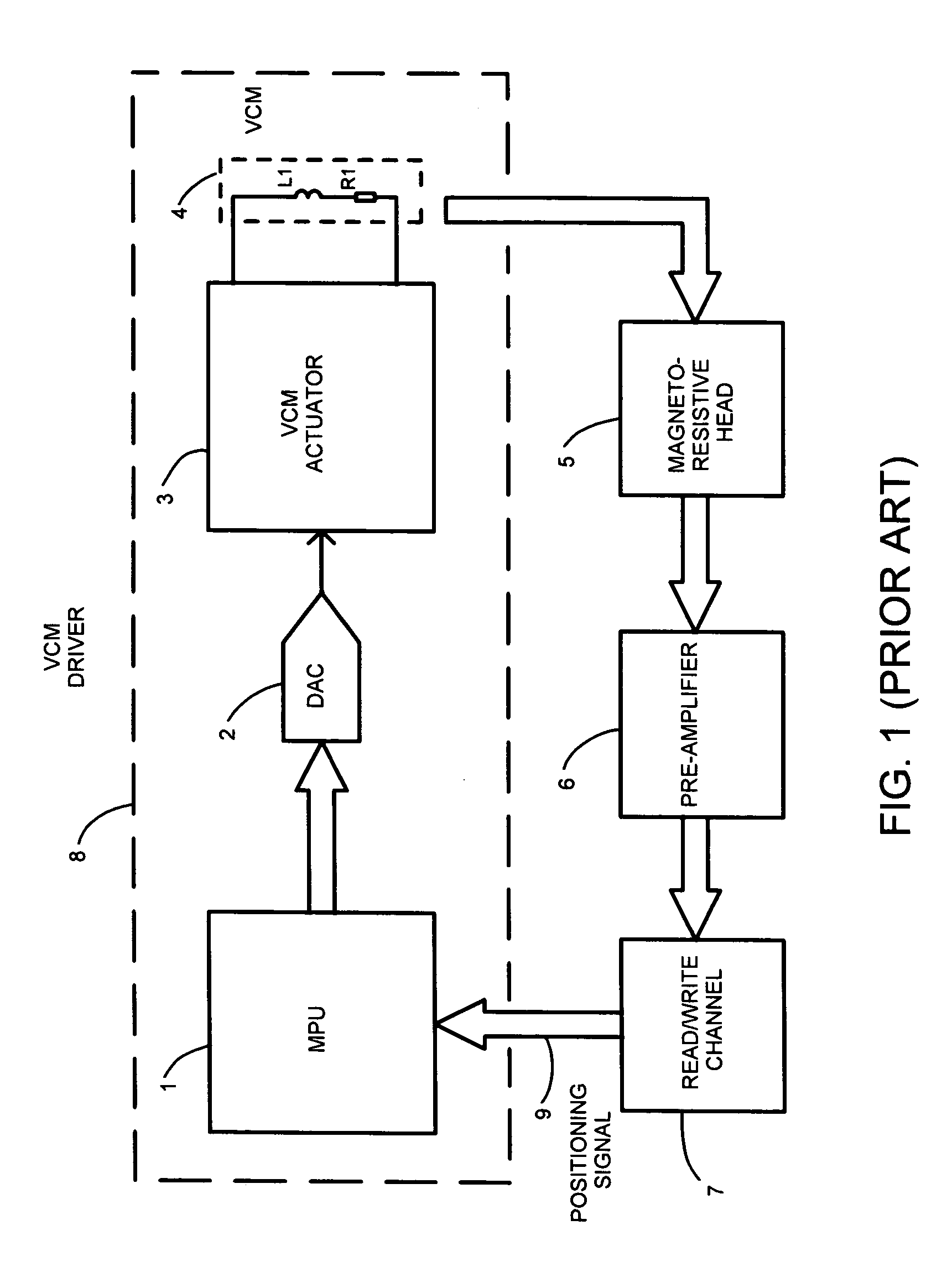

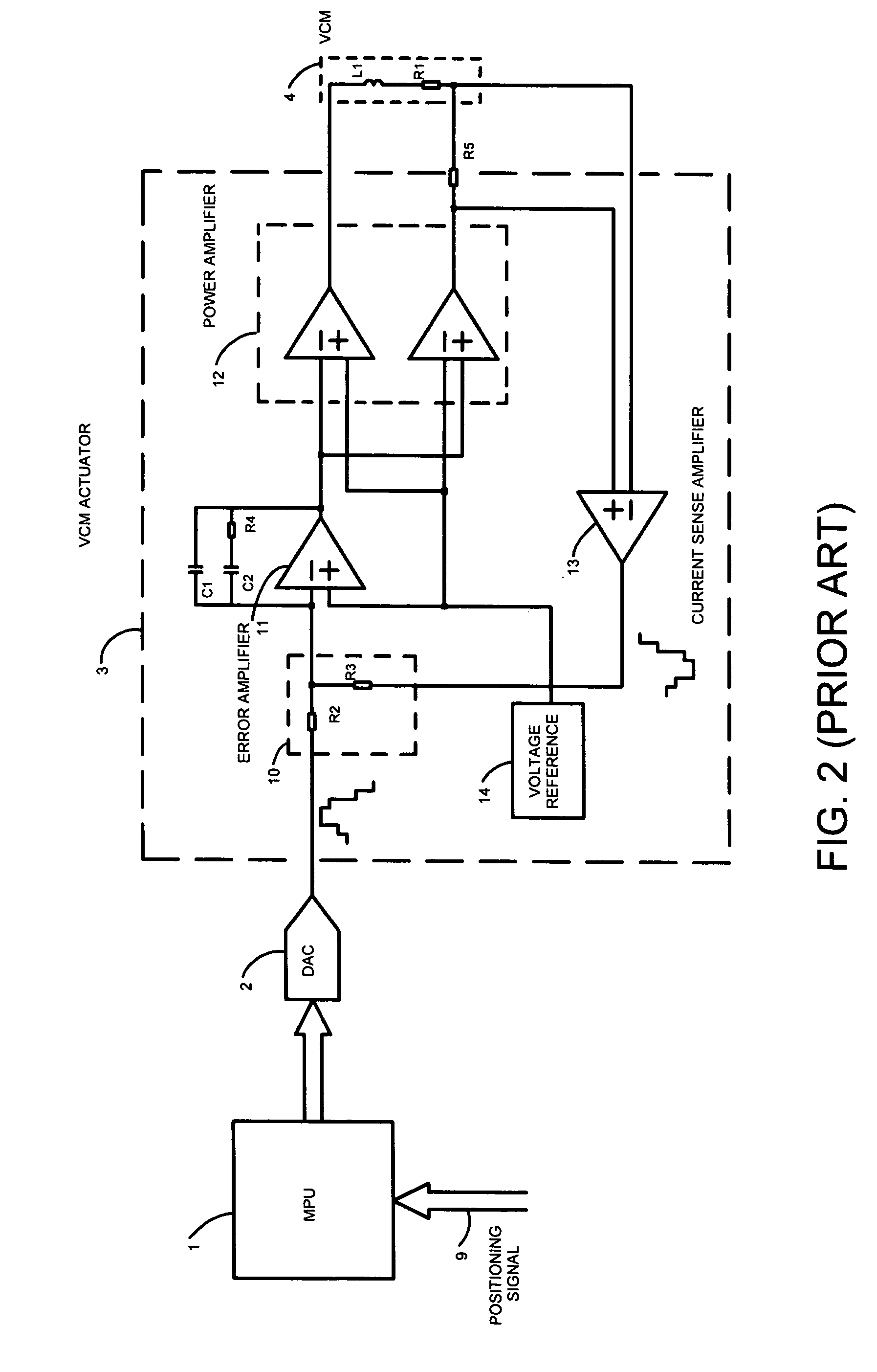

Motor positioning servo loop using oversampling bitstream DAC

InactiveUS7034490B2Improve accuracyImprove resolutionComputer controlSimulator controlLow noiseEngineering

A Hard Disk Drive VCM positioning servo loop comprises an oversampling bitstream Digital to Analog converter. The oversampling DAC is a sigma-delta converter which yields higher resolution and lower noise than Nyquist-rate DACs. This allows driving the VCM with finer level of current control for higher track density. This approach can be implemented in the VCM driver chip (“combo chip”) or in the microprocessor device either in hardware or in software, reducing significantly the development and manufacturing cost. Furthermore this approach can be utilized in combination with a VCM actuation method known as “voltage mode drive” wherein the output of the sigma-delta converter represents the voltage to be applied directly to the VCM actuator. Furthermore this approach can be utilized for optical data storage motor positioning servo loops or any other motor positioning servo loops where high dynamic and resolution is needed.

Owner:DIALOG SEMICONDUCTOR GMBH

Method for fabrication of a semiconductor device and structure

ActiveUS7960242B2Reduce high cost of manufacturingReduced flexibilityTransistorSemiconductor/solid-state device detailsLithographic artistDevice material

Owner:SAMSUNG ELECTRONICS CO LTD

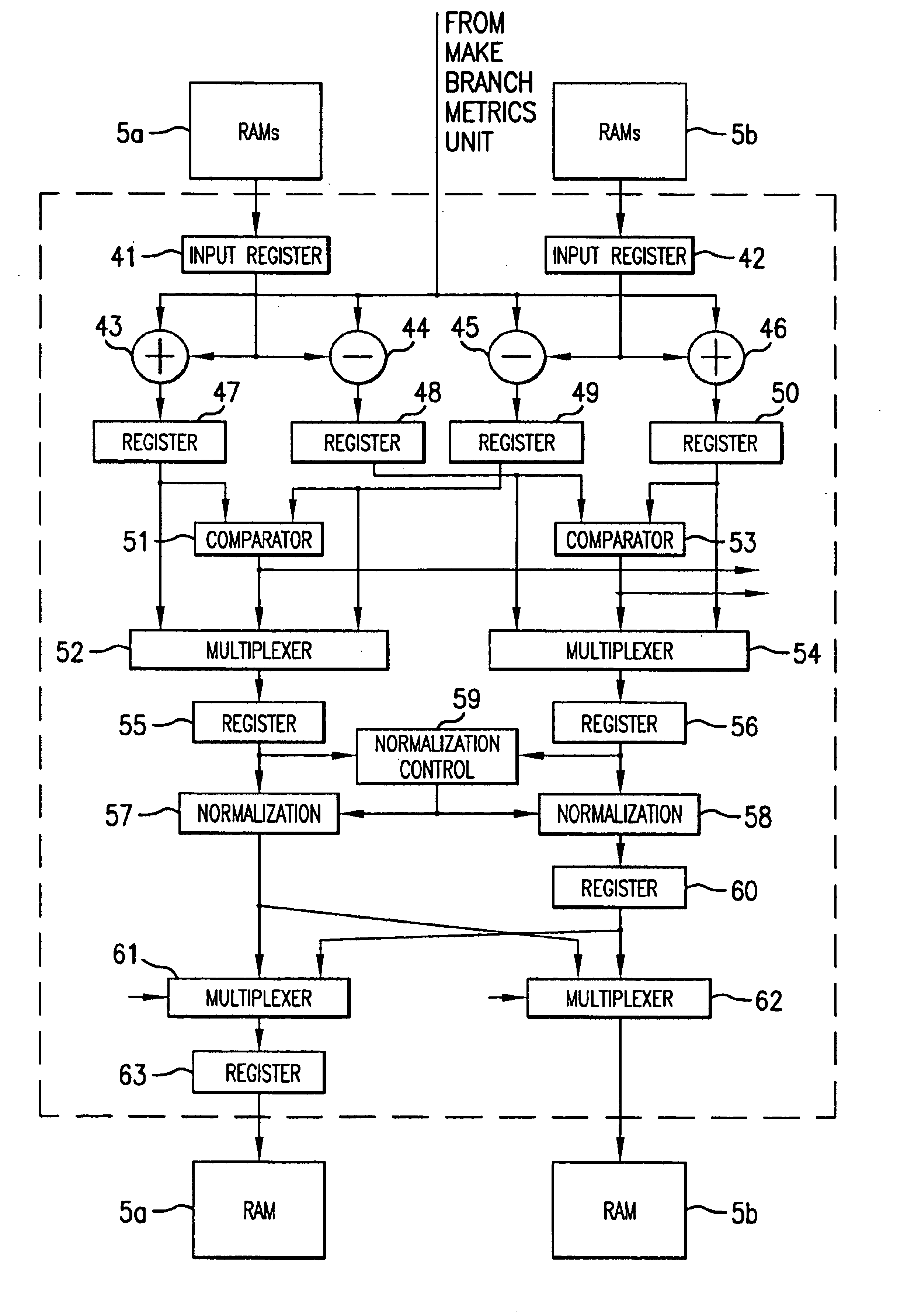

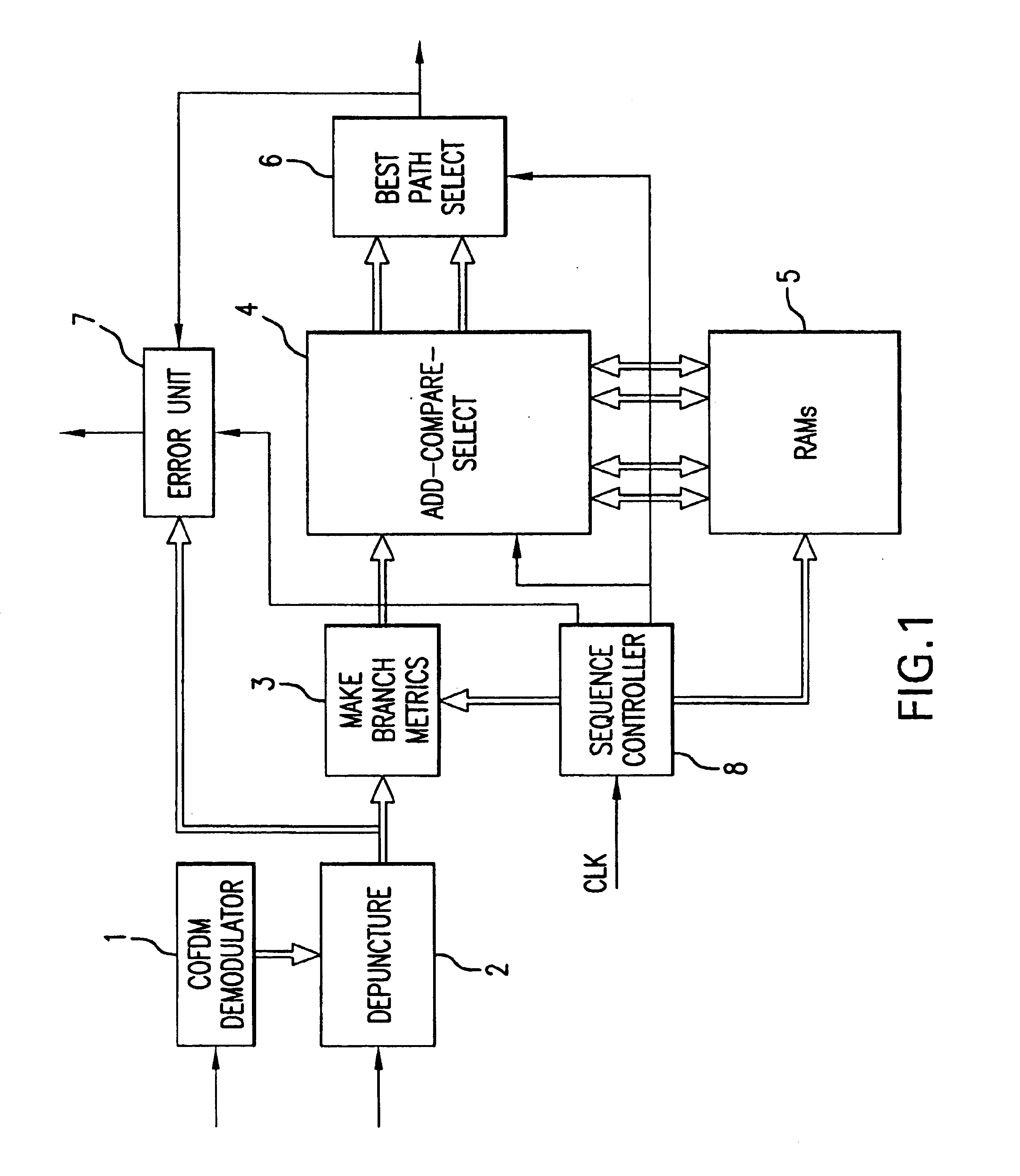

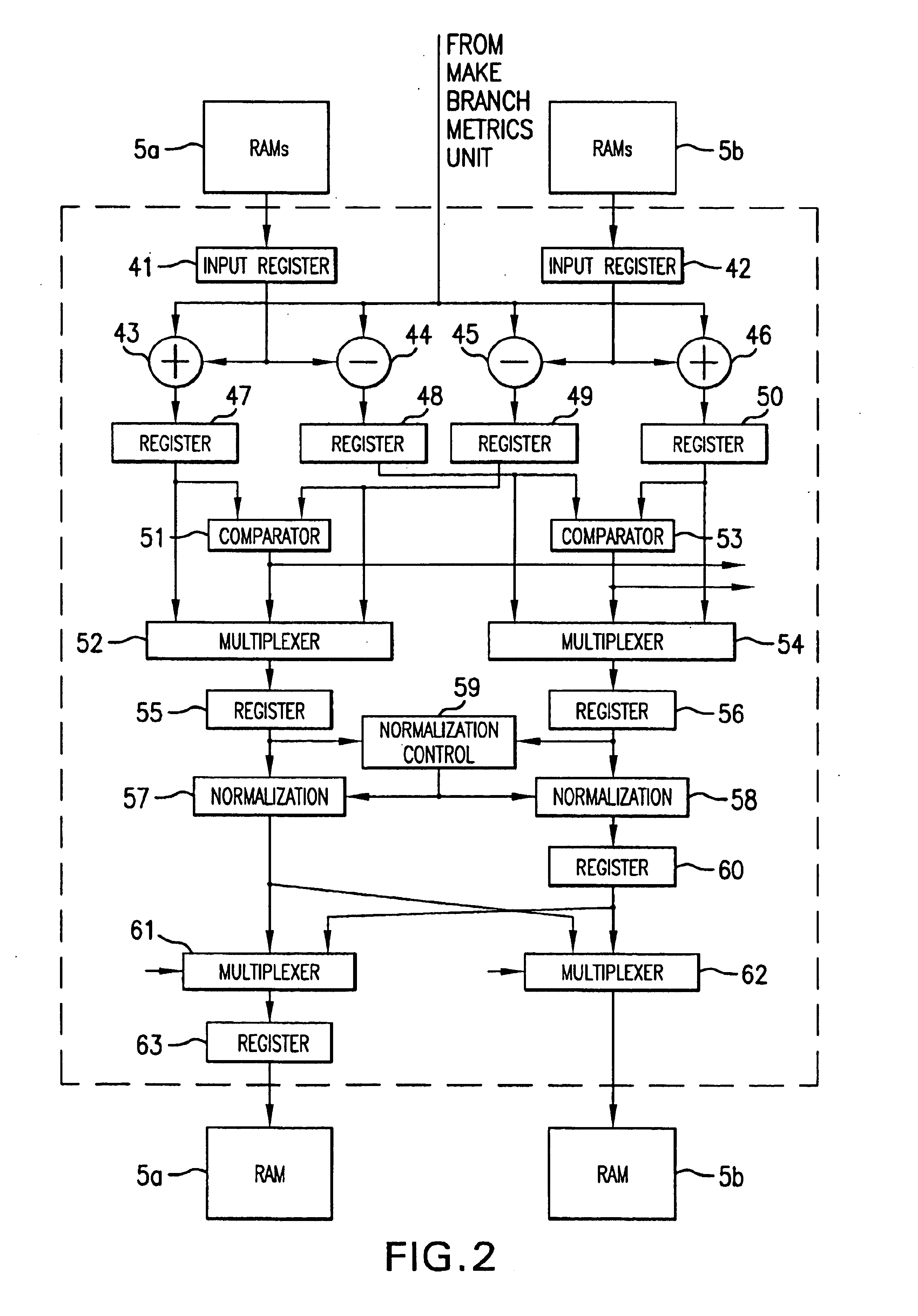

Viterbi decoder with pipelined parallel architecture

InactiveUS6810094B1Improve data throughputEasy to useError correction/detection using convolutional codesOther decoding techniquesParallel processingUnit process

A Viterbi decoder comprises a COFDM modulator, depuncture unit, a branch metrics unit an add-compare-select unit, memory, a best path unit, an error unit and a sequential controller for controlling the operation of the other units. The add-compare-select unit processes path metrics for pairs of states in parallel using a pipeline architecture. The add-compare-select unit also processes path data for pairs of states in parallel using a pipeline architecture. The best path select unit identifies the lowest cost surviving path which is in one frame and outputs a path data bit, produced a predetermined number of frames earlier, as decoded data.

Owner:RENESAS ELECTRONICS CORP

Method for fabrication of a semiconductor device and structure

InactiveUS20110199116A1Low flexibilityReduce high cost of manufacturingSemiconductor/solid-state device detailsSolid-state devicesEngineeringInput/output

A Configurable device comprising, a logic die connected by at least one through silicon-via (TSV), to an input / output (I / O) die.

Owner:MONOLITHIC 3D

Method for fabrication of a semiconductor device and structure

ActiveUS20100291749A1Reduced flexibilityReduce high cost of manufacturingTransistorSemiconductor/solid-state device detailsLithographic artistDevice material

A method of manufacturing a semiconductor wafer, the method comprising: providing a base wafer comprising a semiconductor substrate, metal layers and first alignment marks; transferring a monocrystalline layer on top of said metal layers, wherein said monocrystalline layer comprises second alignment marks; and performing a lithography using an alignment based on a misalignment between said first alignment marks and said second alignment marks.

Owner:SAMSUNG ELECTRONICS CO LTD

Method for fabrication of a semiconductor device and structure

InactiveUS8148728B2Reduce high cost of manufacturingReduced flexibilityTransistorSemiconductor/solid-state device detailsInsulation layerDevice material

A method for fabrication of 3D semiconductor devices utilizing a layer transfer and steps for forming transistors on top of a pre-fabricated semiconductor device comprising transistors formed on crystallized semiconductor base layer and metal layer for the transistors interconnections and insulation layer. The advantage of this approach is reduction of the over all metal length used to interconnect the various transistors.

Owner:MONOLITHIC 3D

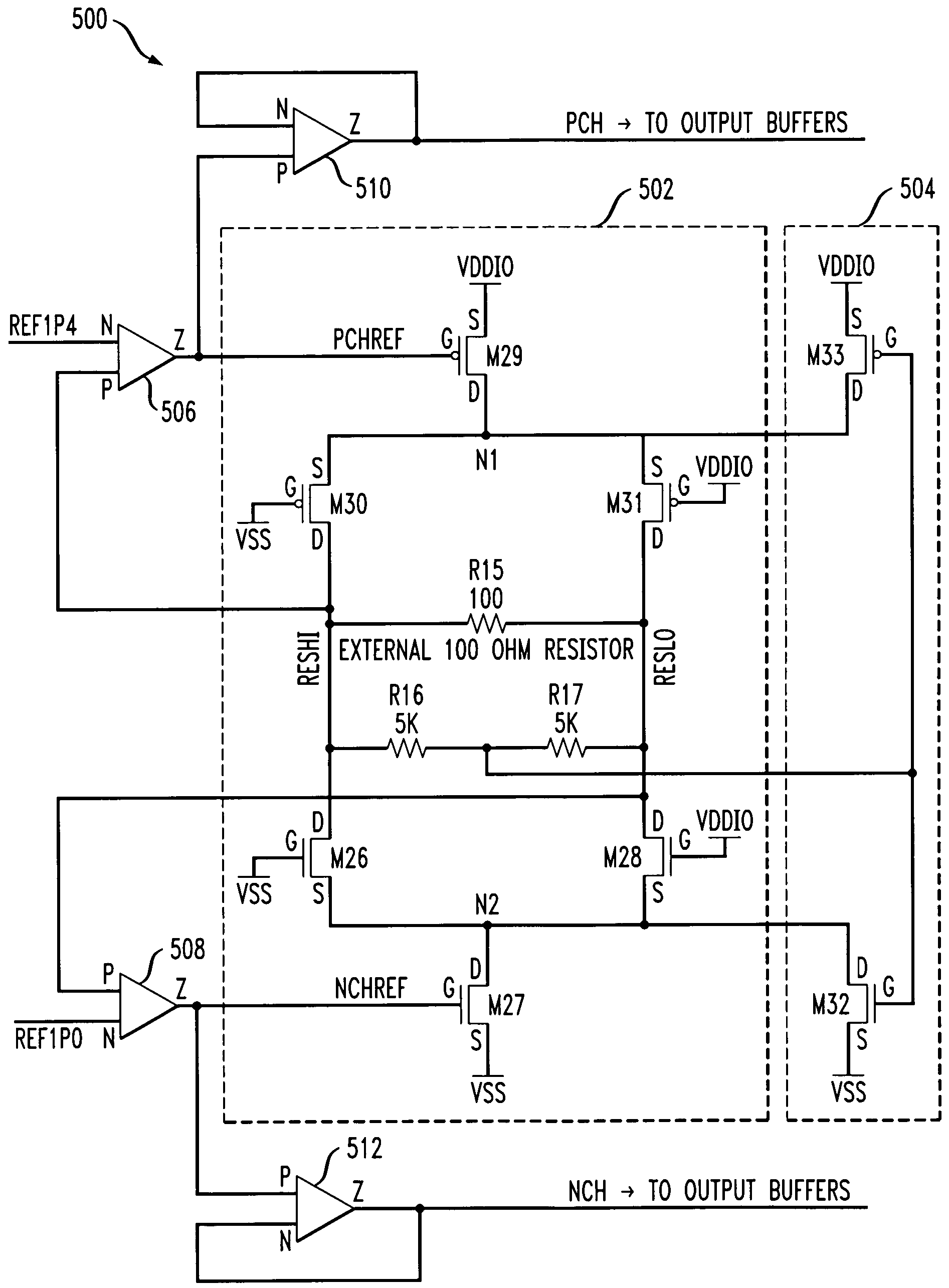

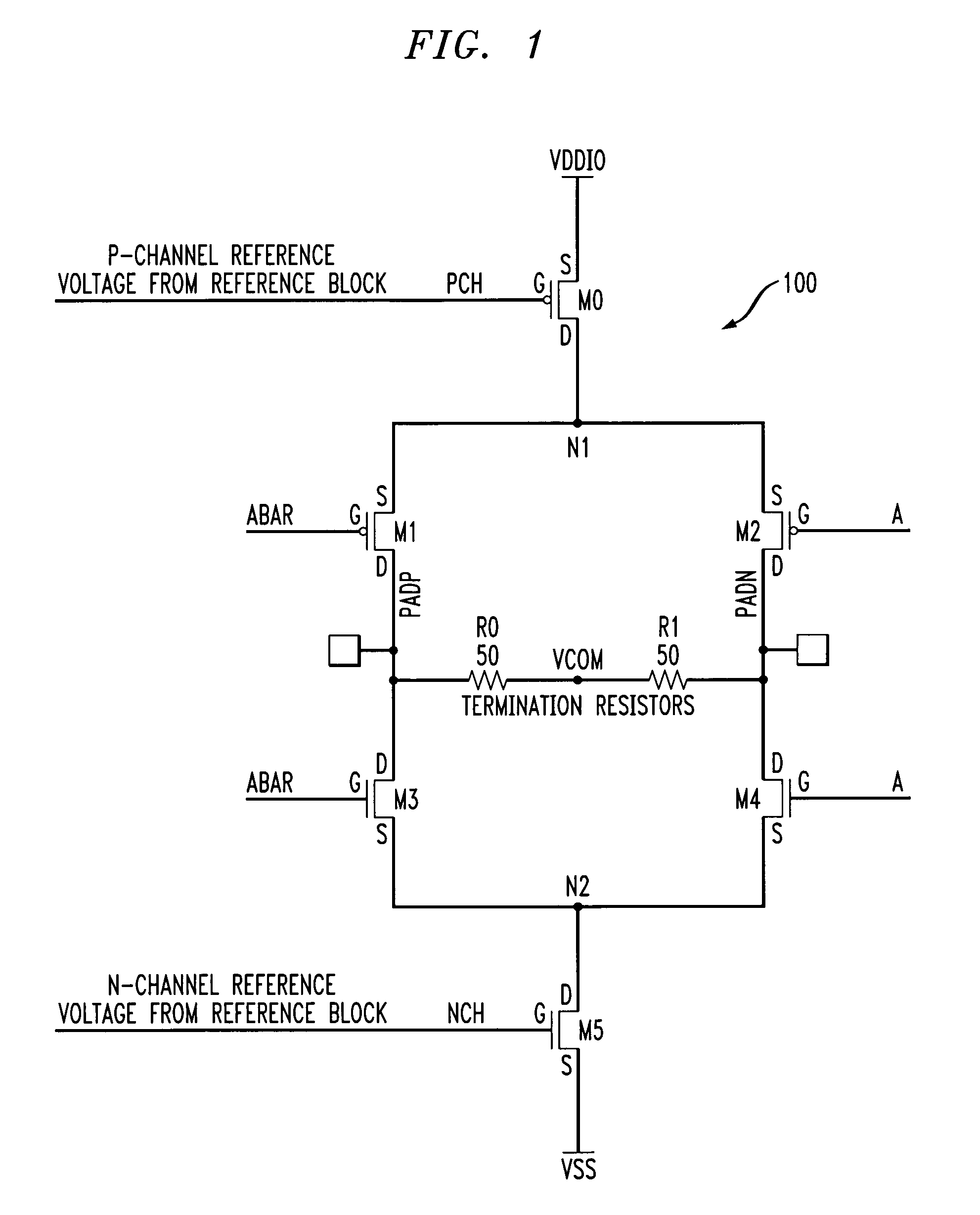

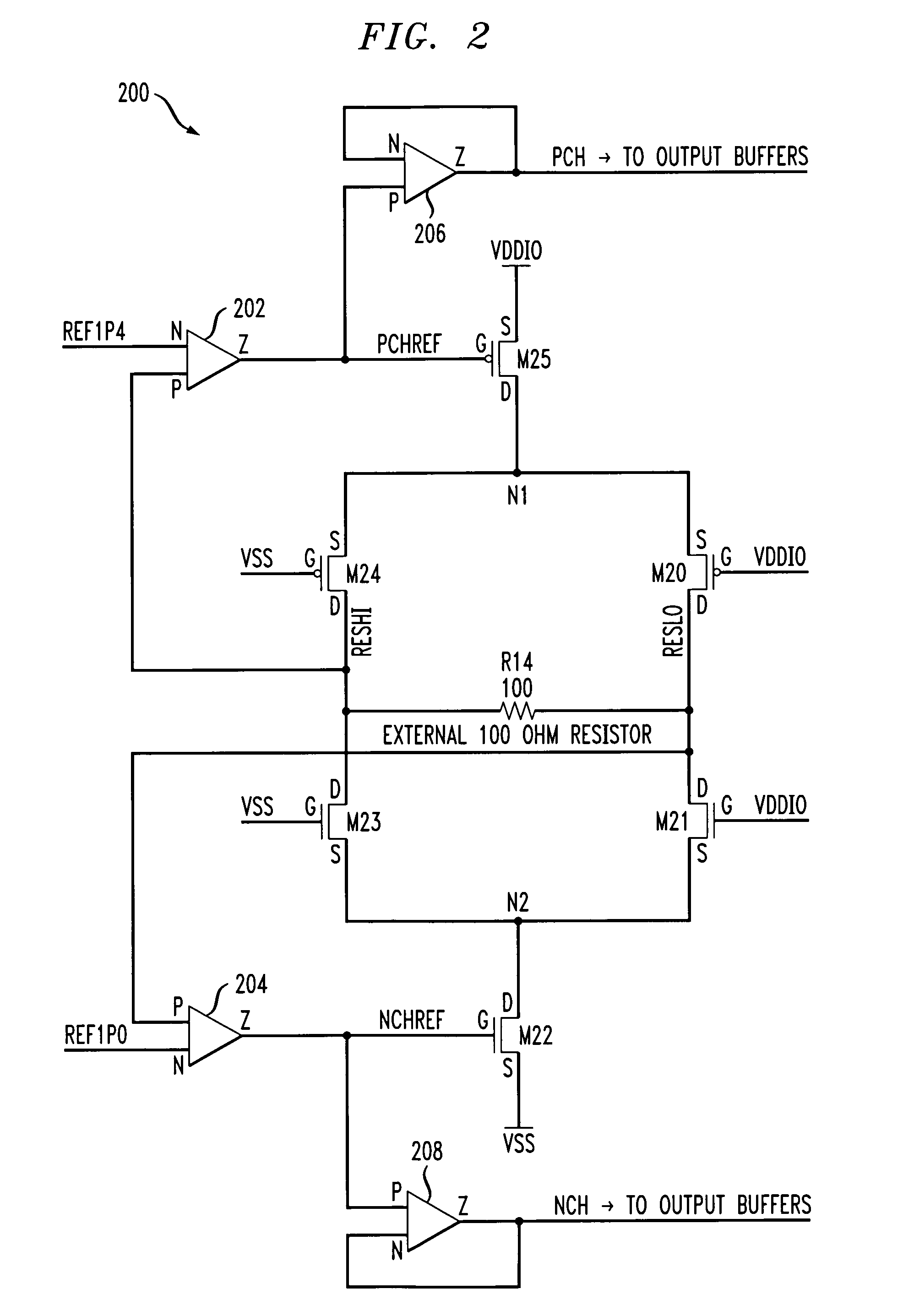

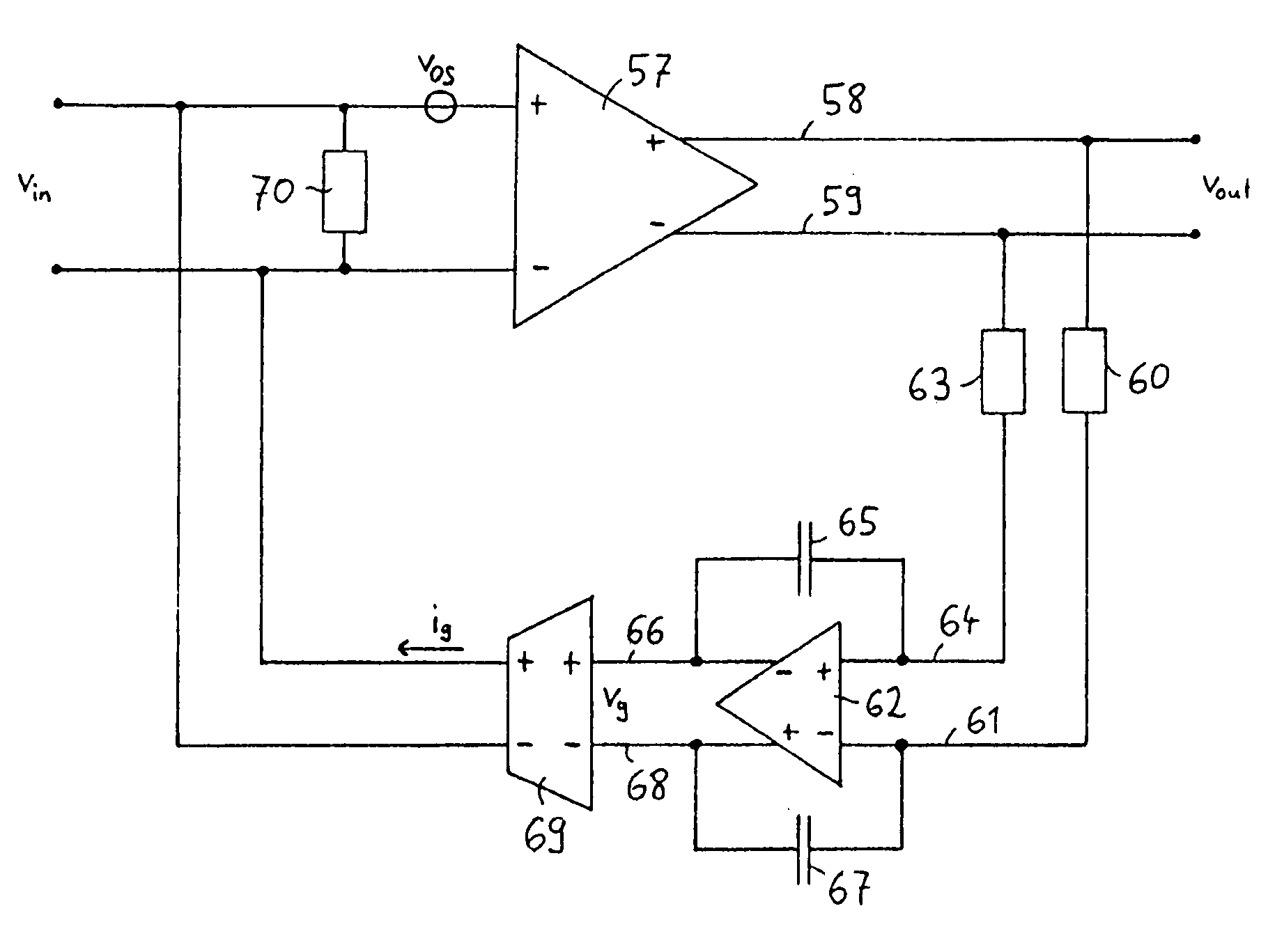

Differential buffer circuit with reduced output common mode variation

InactiveUS7248079B2Reduce common mode voltageReduce silicon areaReliability increasing modificationsElectronic switchingControl signalMode control

A differential buffer circuit includes a current source, a current sink, and a switching circuit connected to the current source at a first node and connected to the current sink at a second node. The switching circuit is operative to selectively control a direction of current flowing through differential outputs of the buffer circuit in response to at least a first control signal. The buffer circuit further includes a common mode detection circuit and a common mode control circuit. The common mode detection circuit is operative to detect an output common mode voltage of the buffer circuit and to generate a second control signal representative of the output common mode voltage. The common mode control circuit includes a first terminal connected to the current source and a second terminal connected to the current sink. The common mode control circuit is operative to selectively control the output common mode voltage of the buffer circuit as a function of the second control signal.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

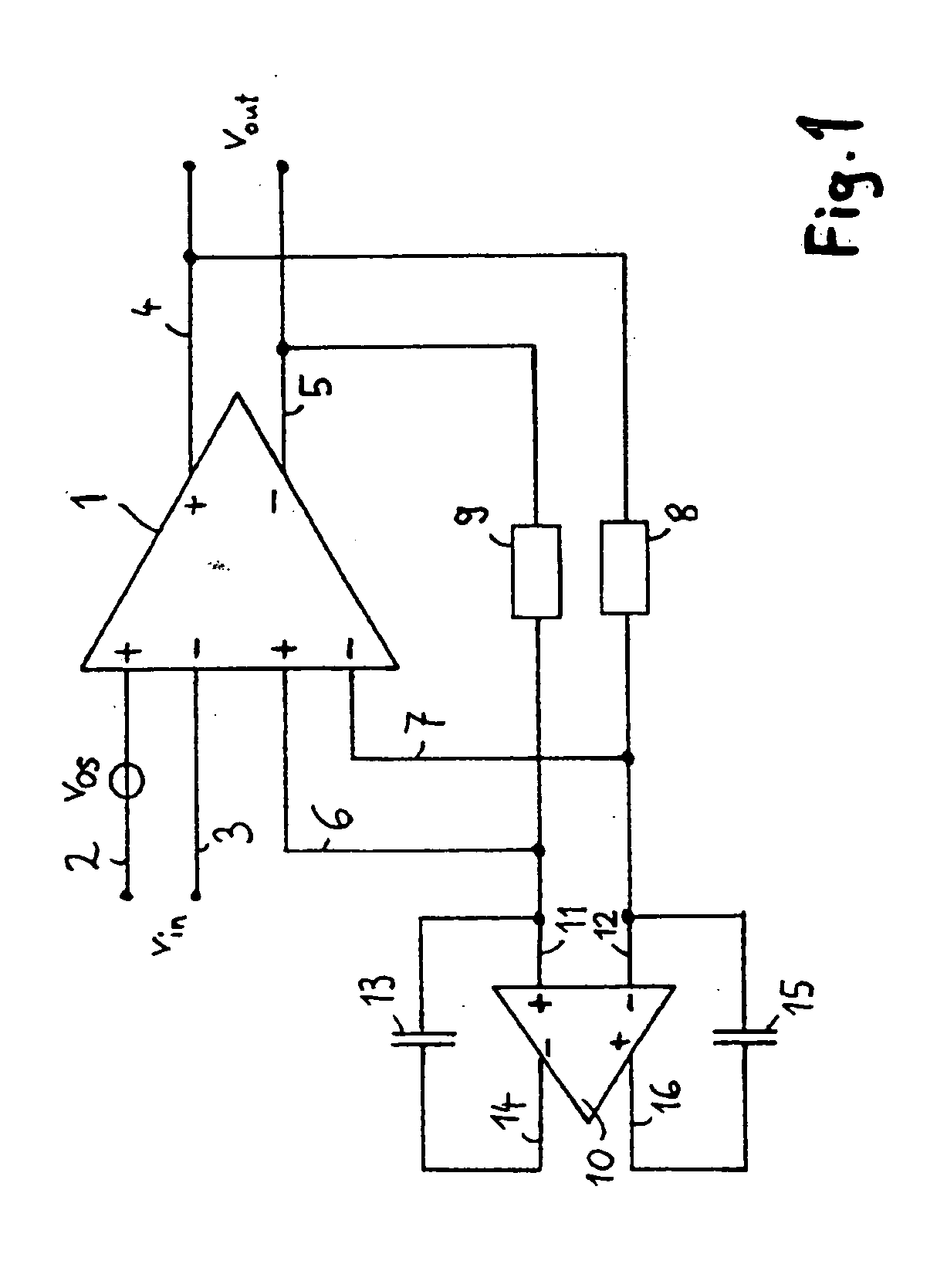

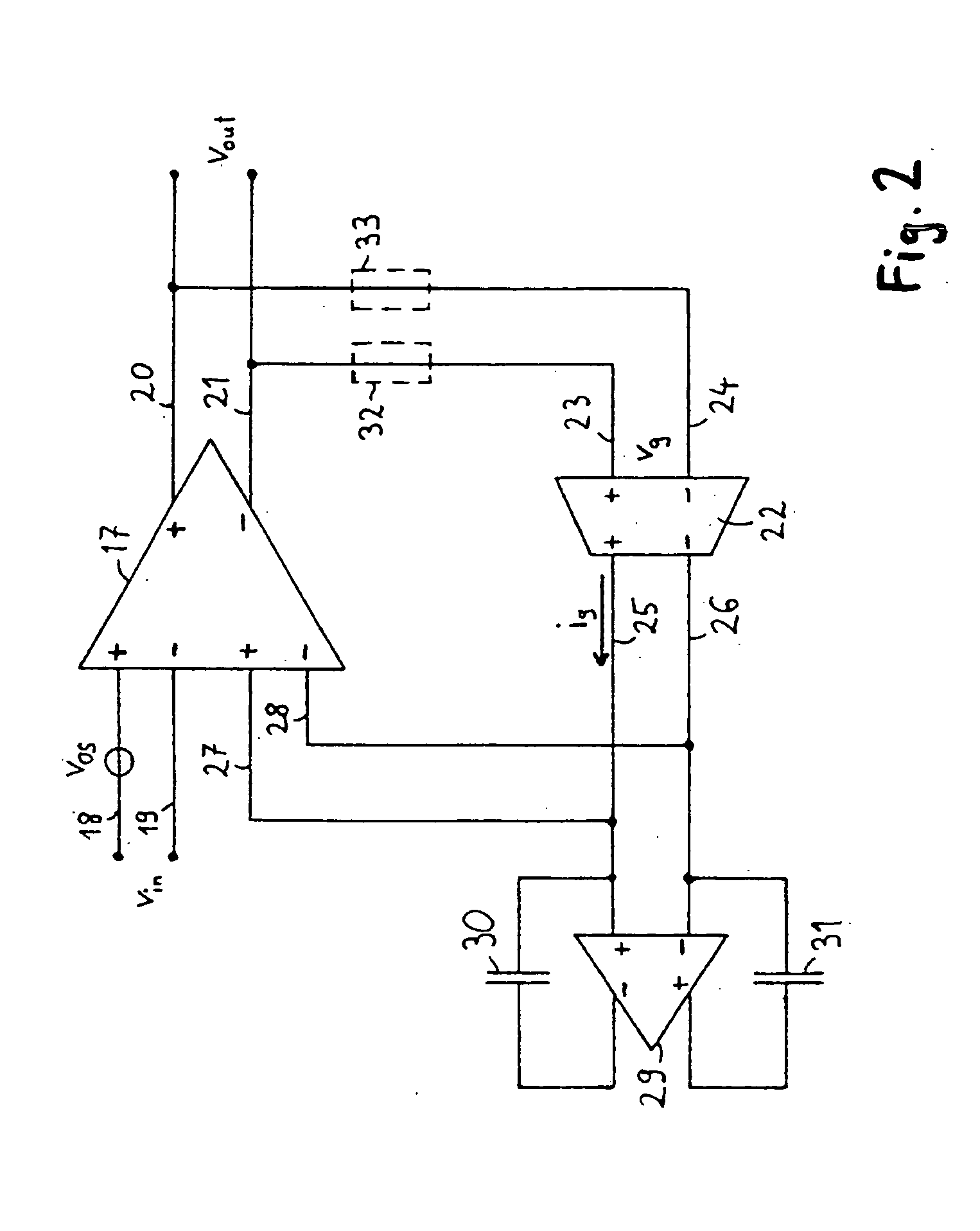

Amplifier with low pass filter feedback

ActiveUS20060097782A1High voltageLarge capacitanceNegative-feedback-circuit arrangementsPulse automatic controlCapacitanceAudio power amplifier

An amplifier is described which amplifies an input signal according to a defined amplification factor, and which generates an output signal. To reduce an offset fraction of the output signal the amplifier comprises a feedback path which has lowpass characteristics and which returns the output signal in a lowpass-filtered state to an input of the amplifier. The feedback path comprises an amplifier stage as well as at least one Miller capacitance connected between an input and an output of the amplifier stage.

Owner:NAT SEMICON GERMANY

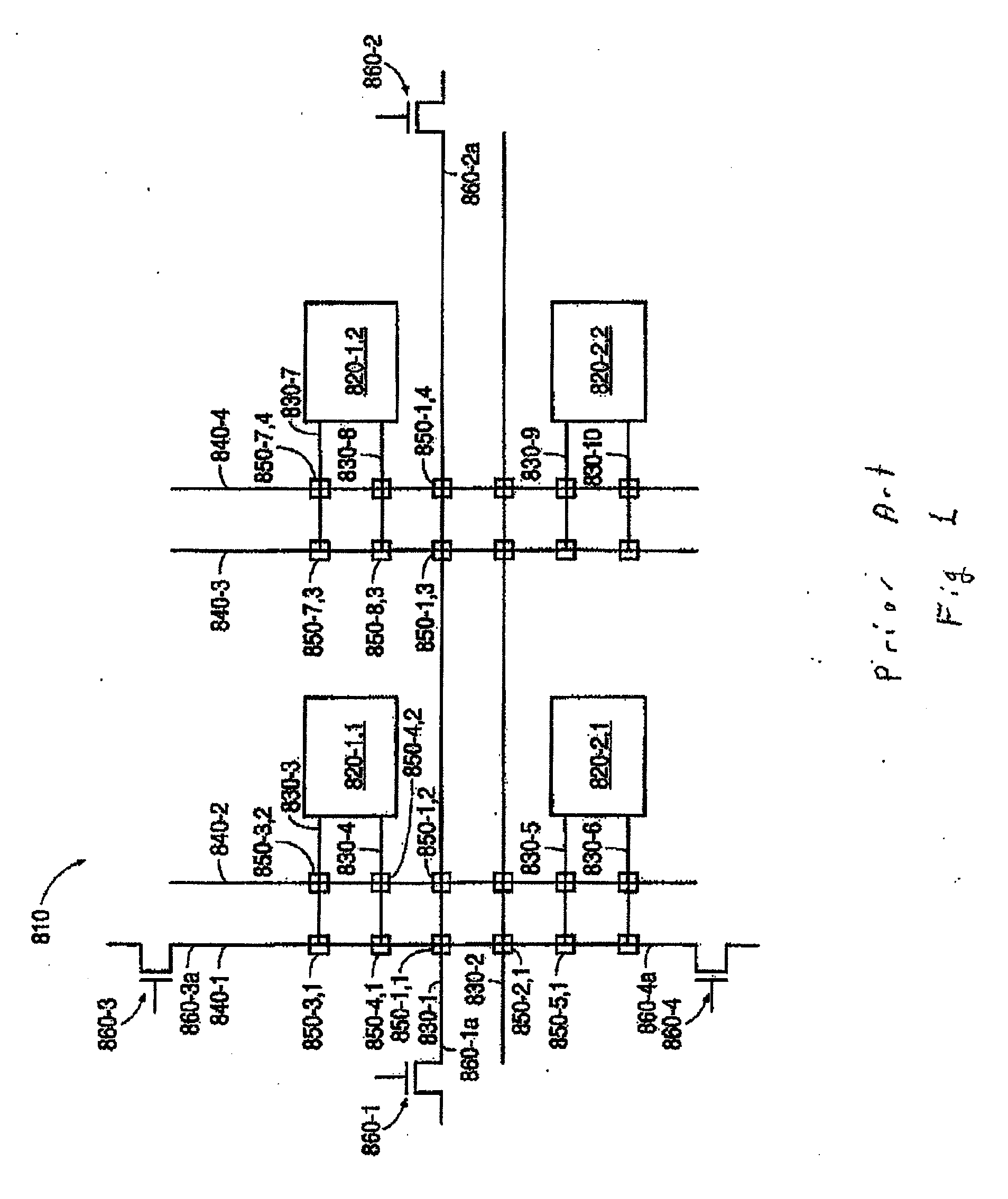

Method for fabrication of a semiconductor device and structure

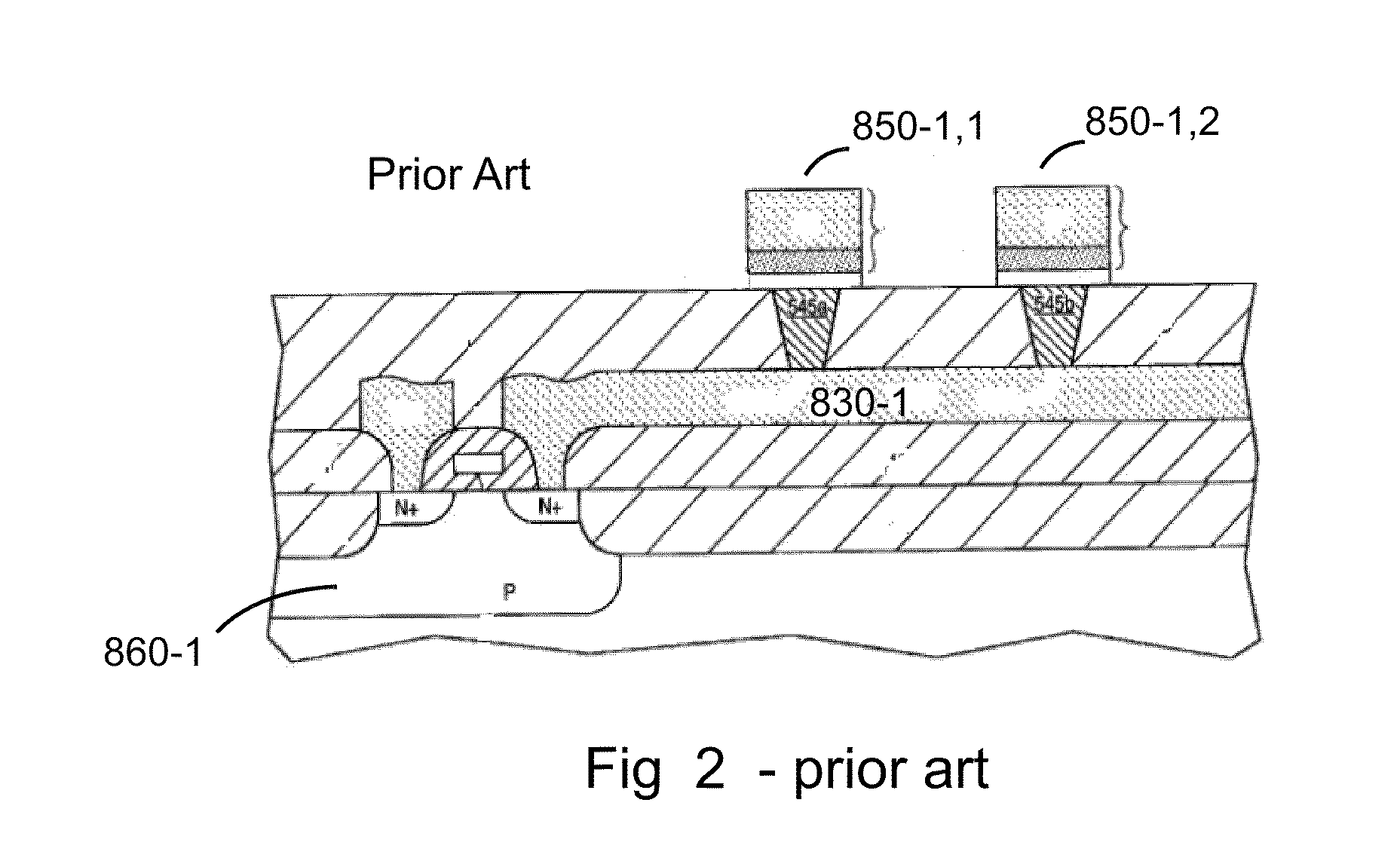

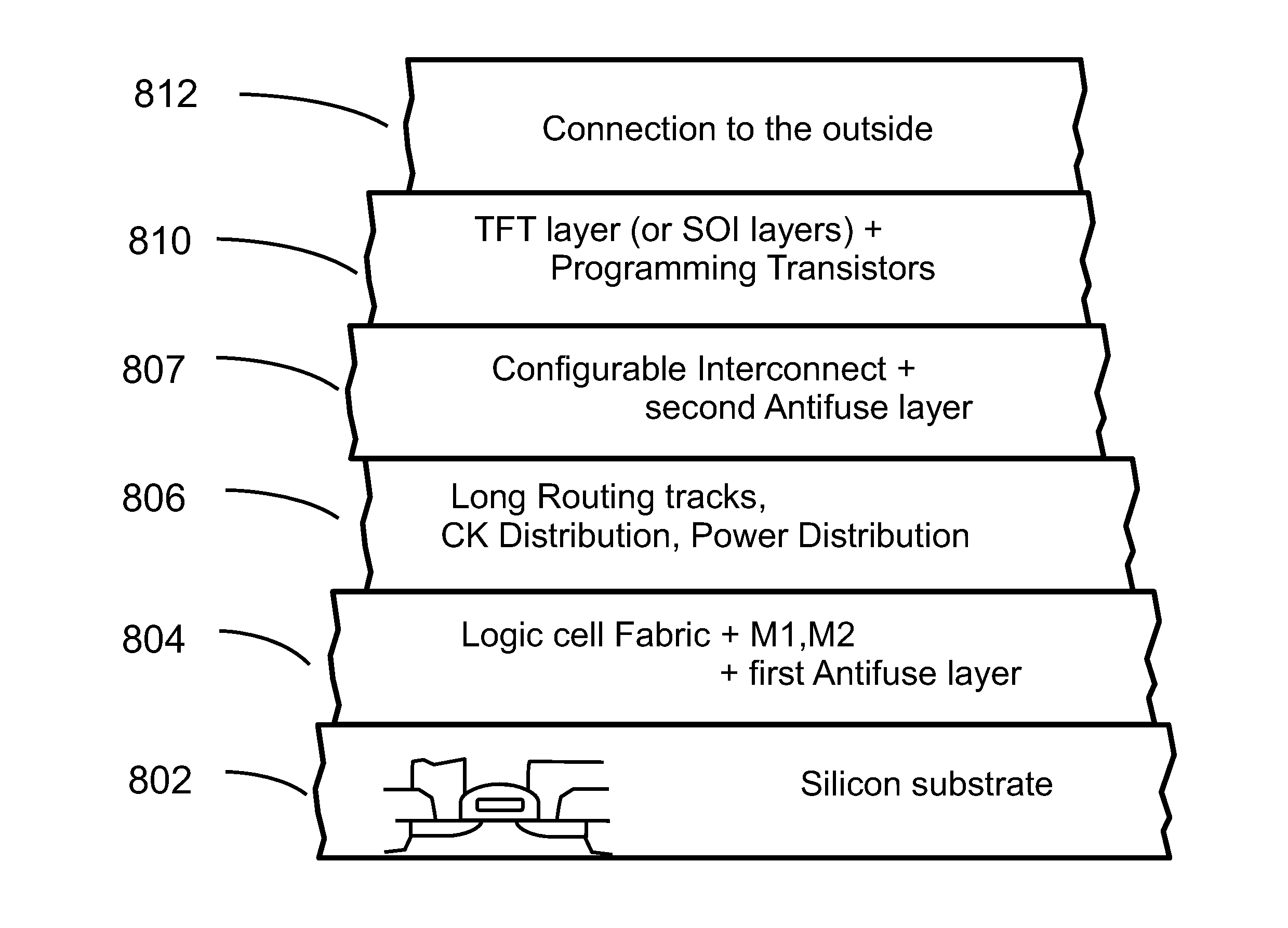

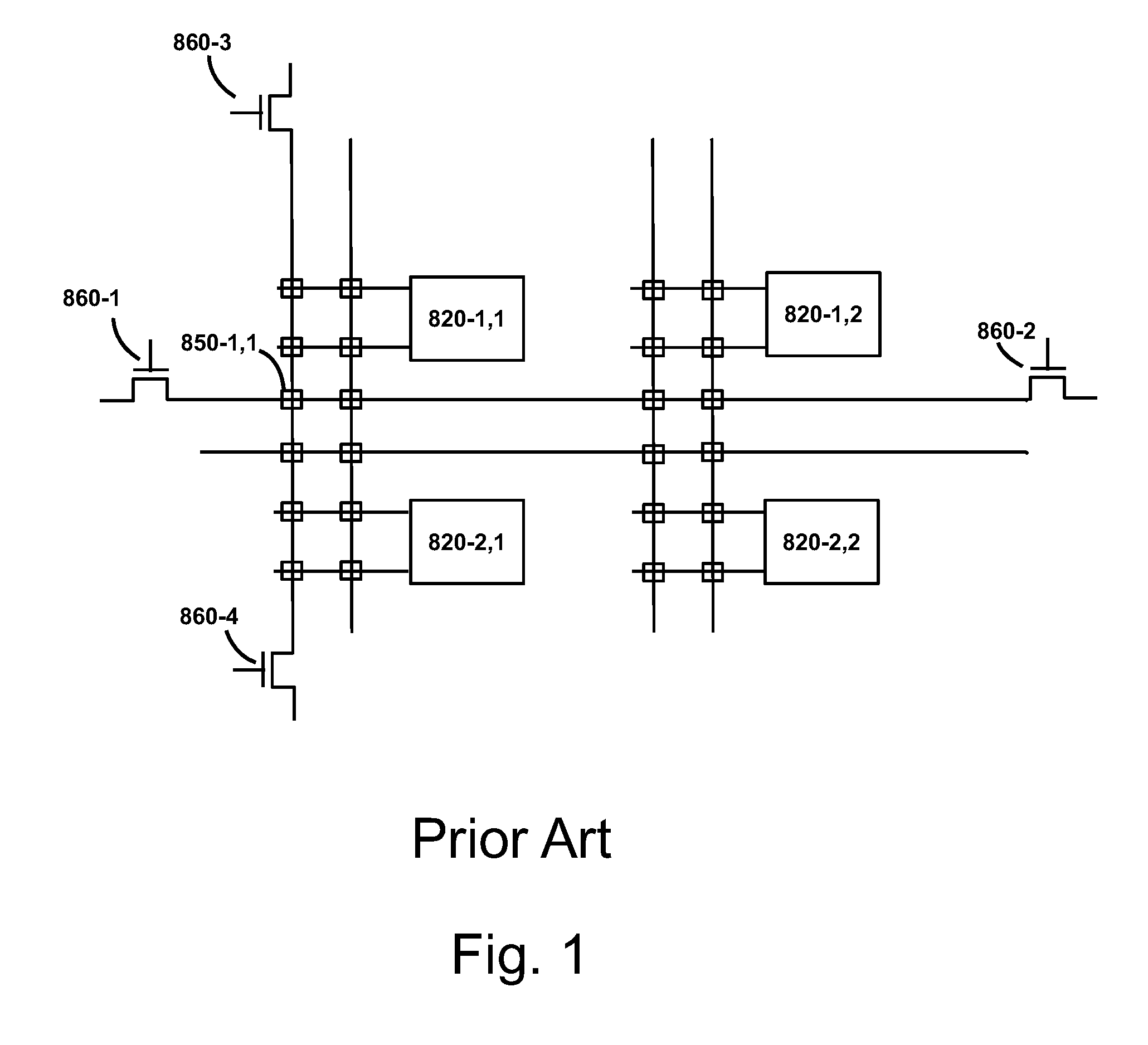

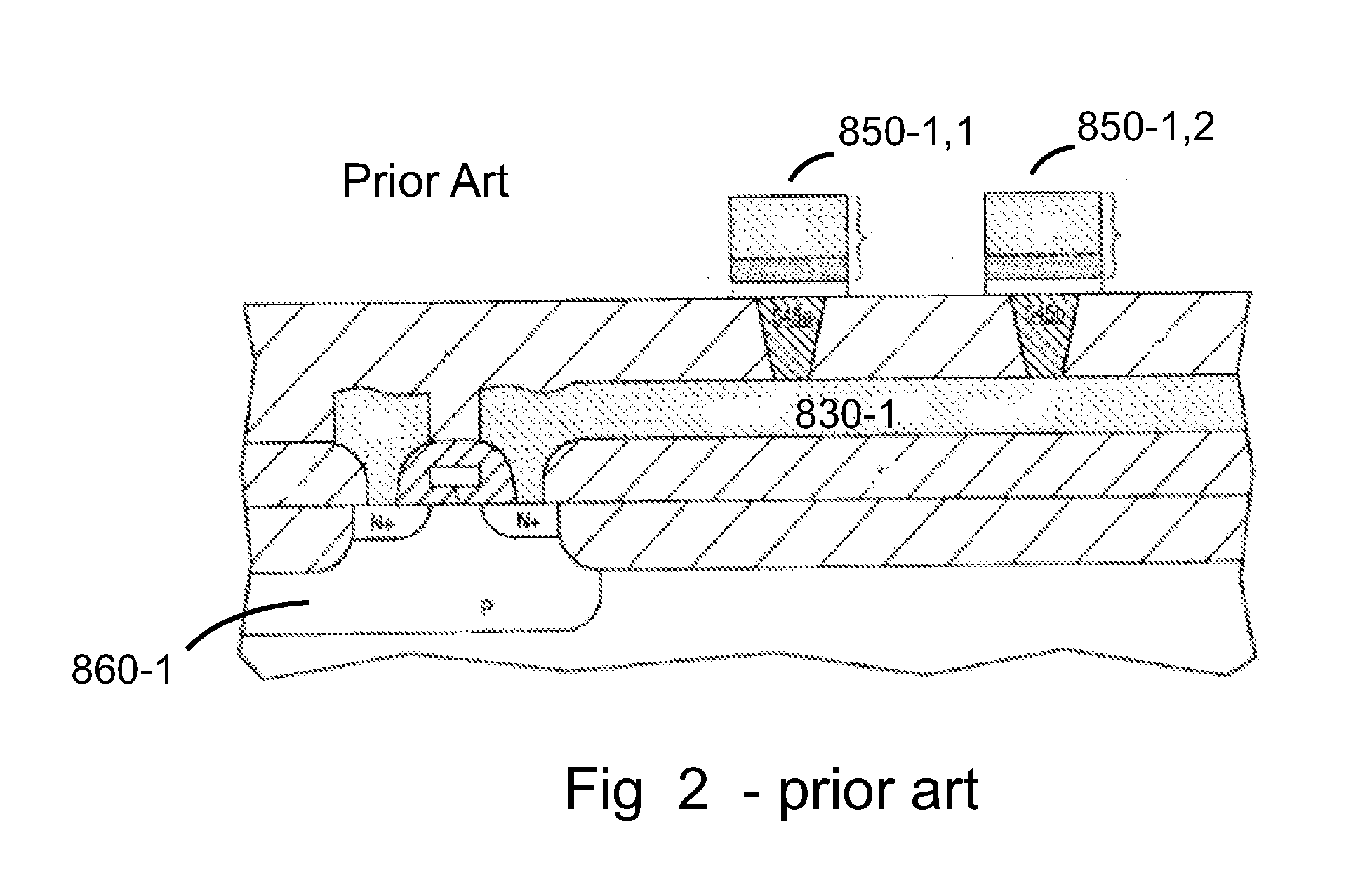

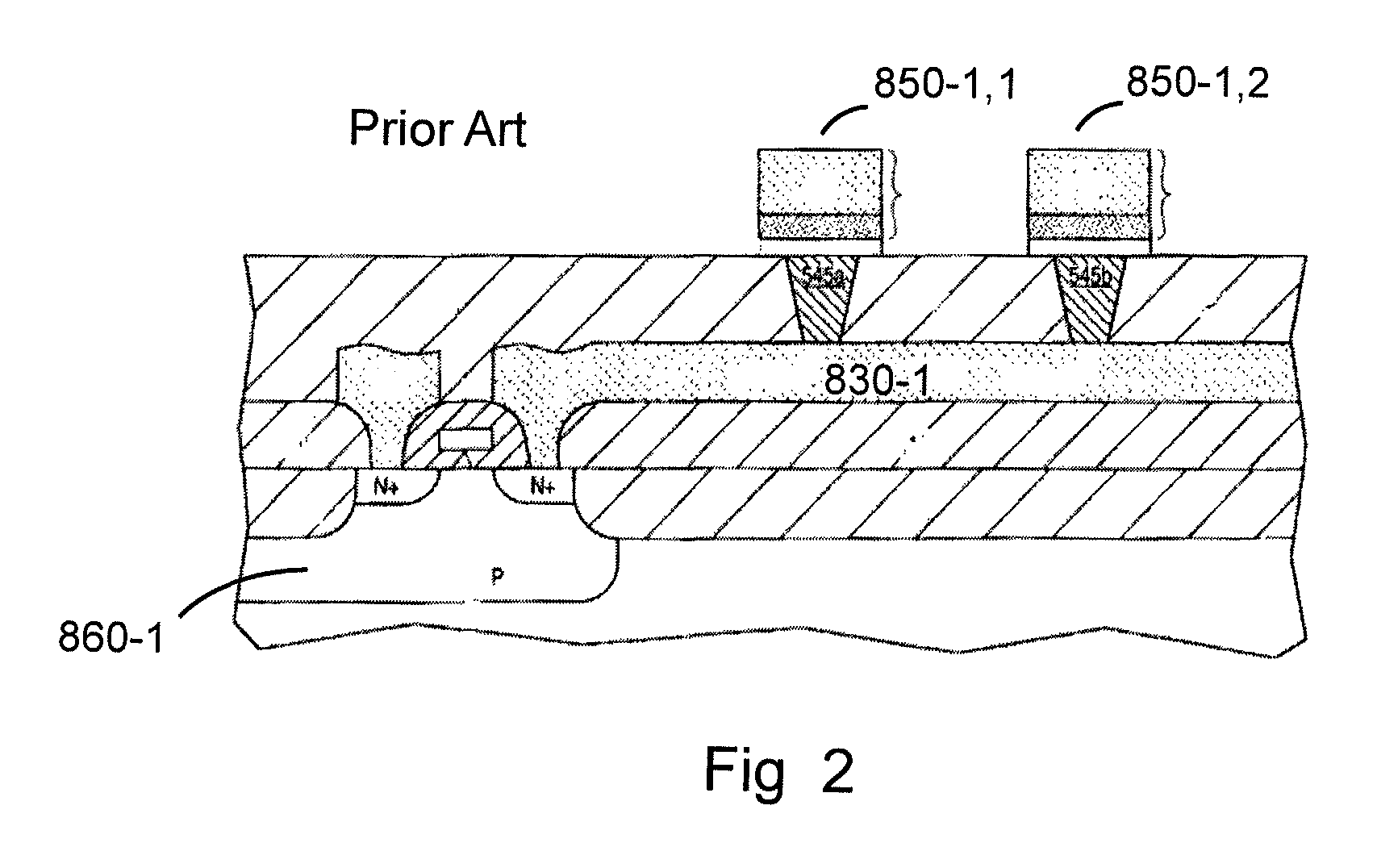

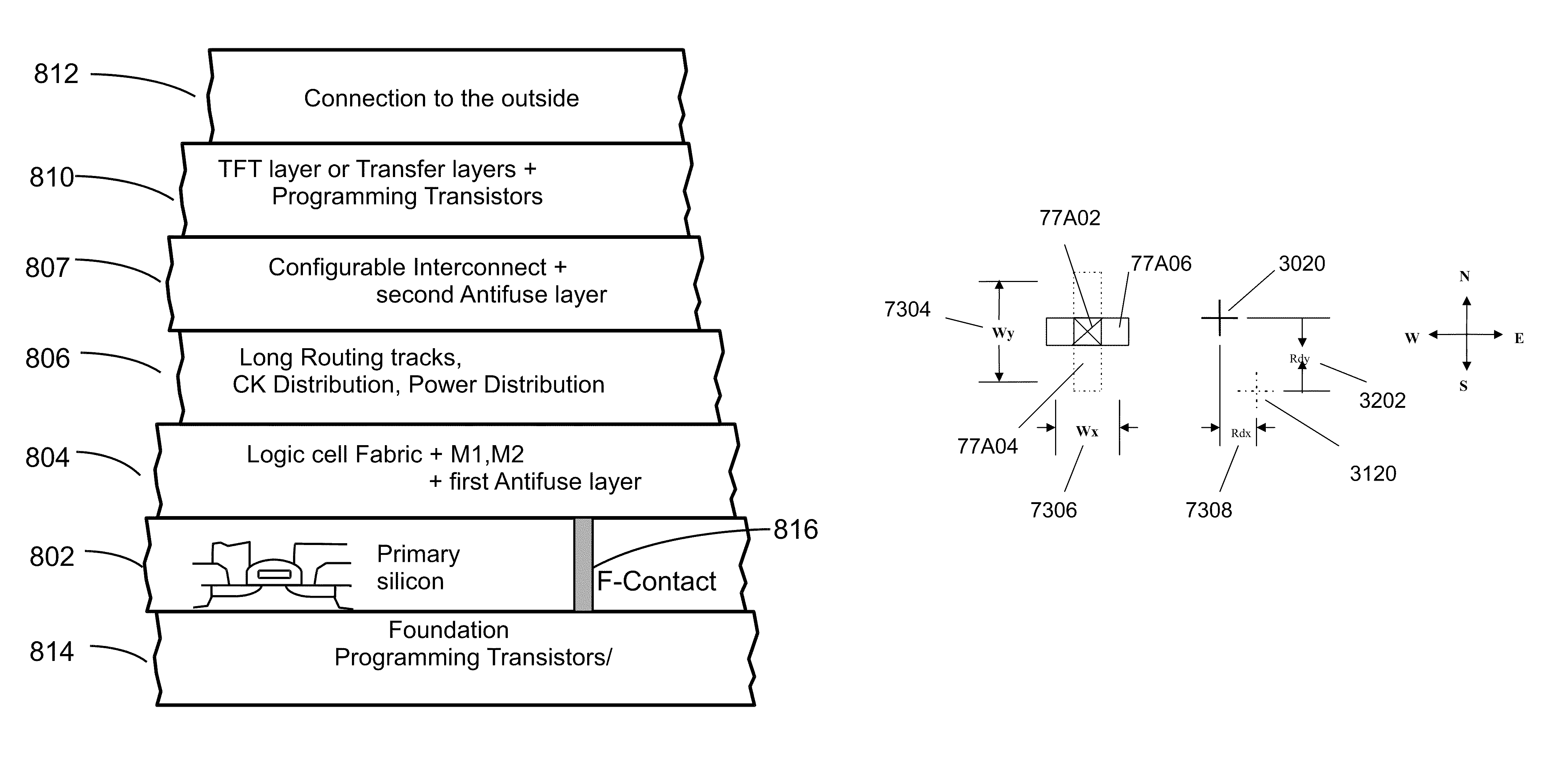

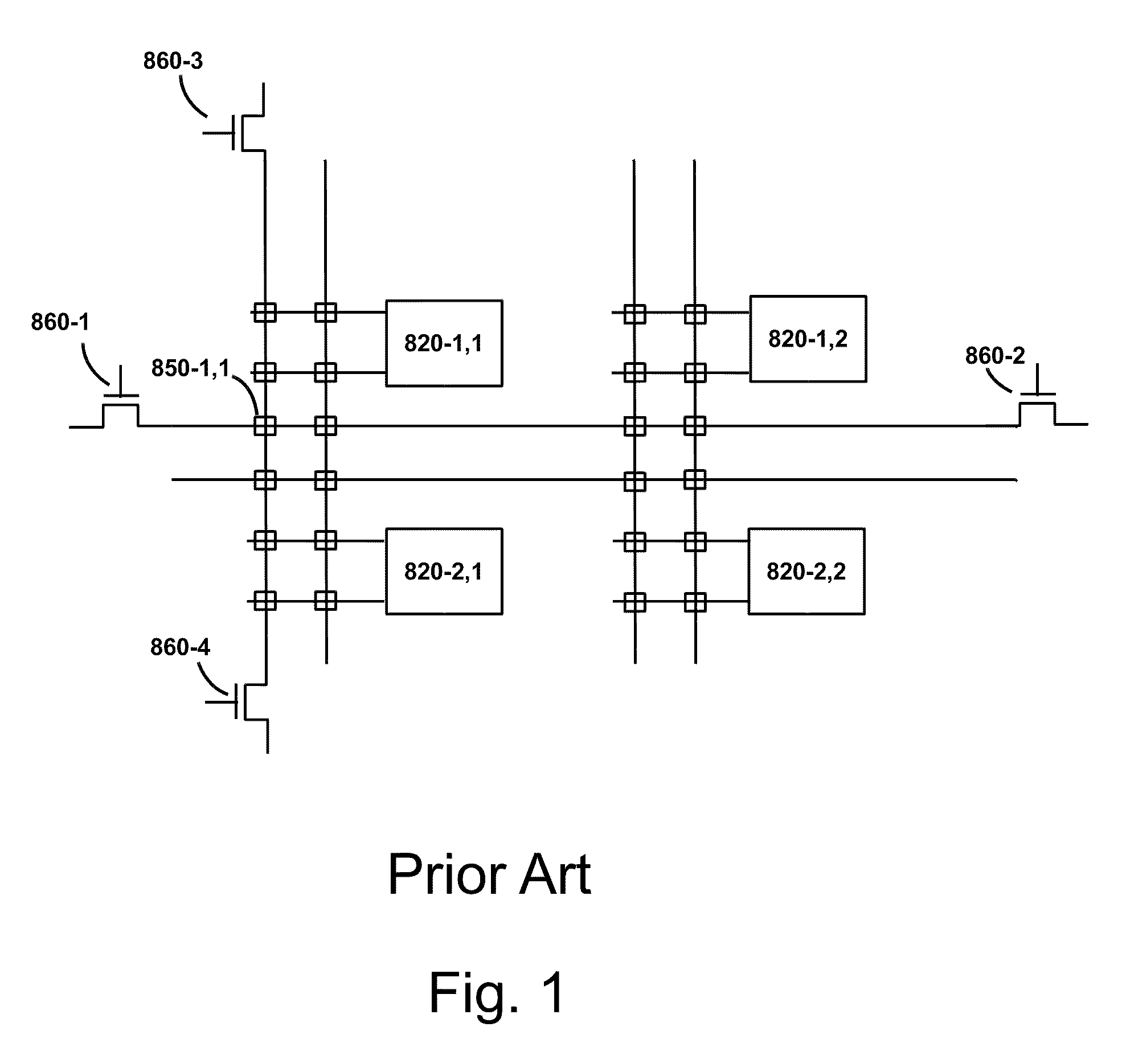

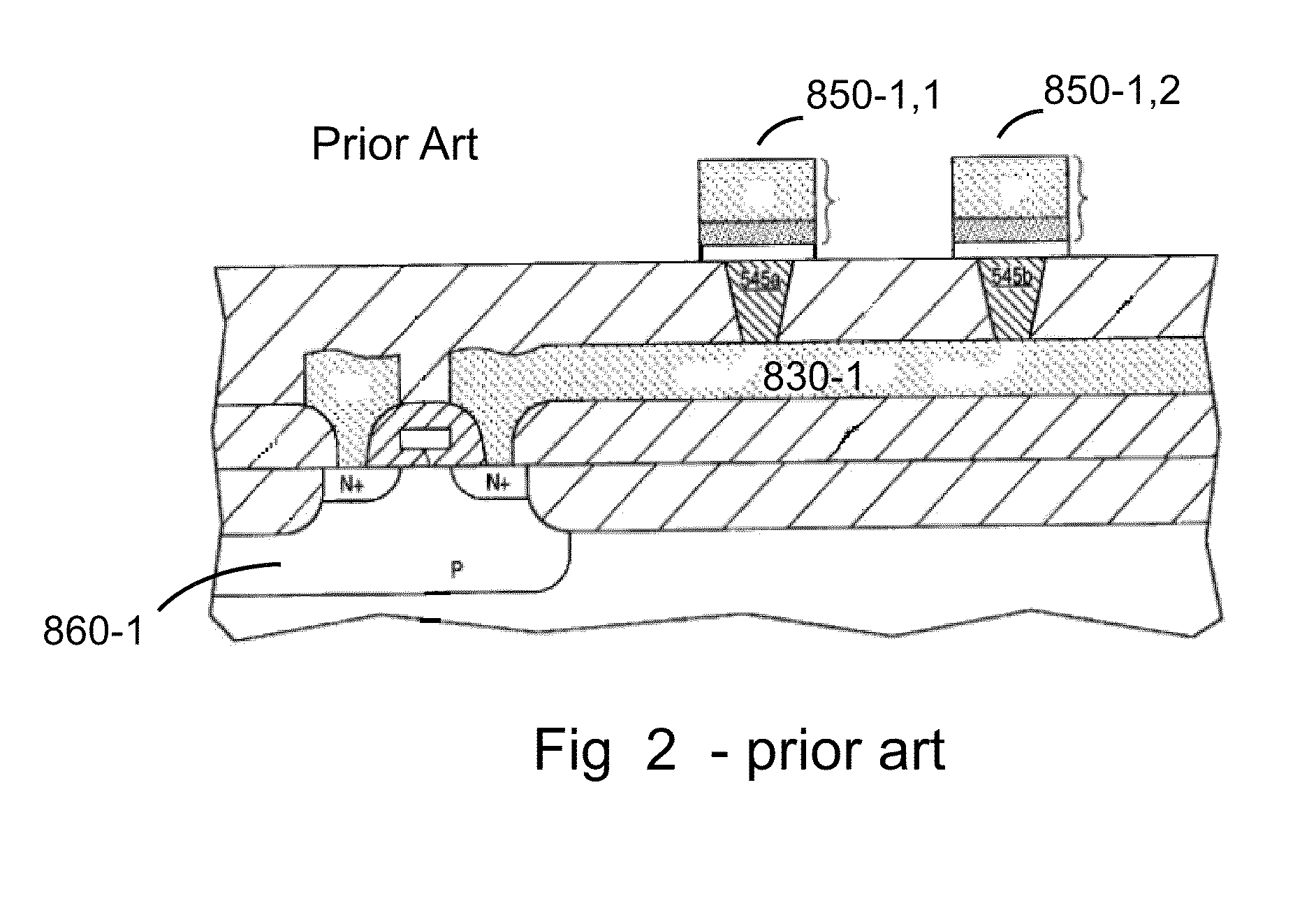

InactiveUS20110031997A1Reduced flexibilityReduce high cost of manufacturingSolid-state devicesLogic circuits using elementary logic circuit componentsDevice materialAntifuse

A method is presented that may be used to provide a Configurable Logic device, which may be Field Programmable with volume flexibility. A method of fabricating an integrated circuit may include the steps of: providing a semiconductor substrate and forming a borderless logic array, and it may also include the step of forming a plurality of antifuse configurable interconnect circuits and / or a plurality of transistors to configure at least one antifuse. The programming transistors may be fabricated over the at least one antifuse.

Owner:MONOLITHIC 3D

Method for fabrication of a semiconductor device and structure

ActiveUS20120028436A1Reduce high cost of manufacturingReduced flexibilityTransistorSemiconductor/solid-state device detailsDevice materialSingle crystal

A method of manufacturing a semiconductor wafer, the method including: providing a base wafer including a semiconductor substrate, metal layers and first alignment marks; transferring a monocrystalline layer on top of the metal layers, wherein the monocrystalline layer includes second alignment marks; and performing a lithography using at least one of the first alignment marks and at least one of the second alignment marks.

Owner:SAMSUNG ELECTRONICS CO LTD

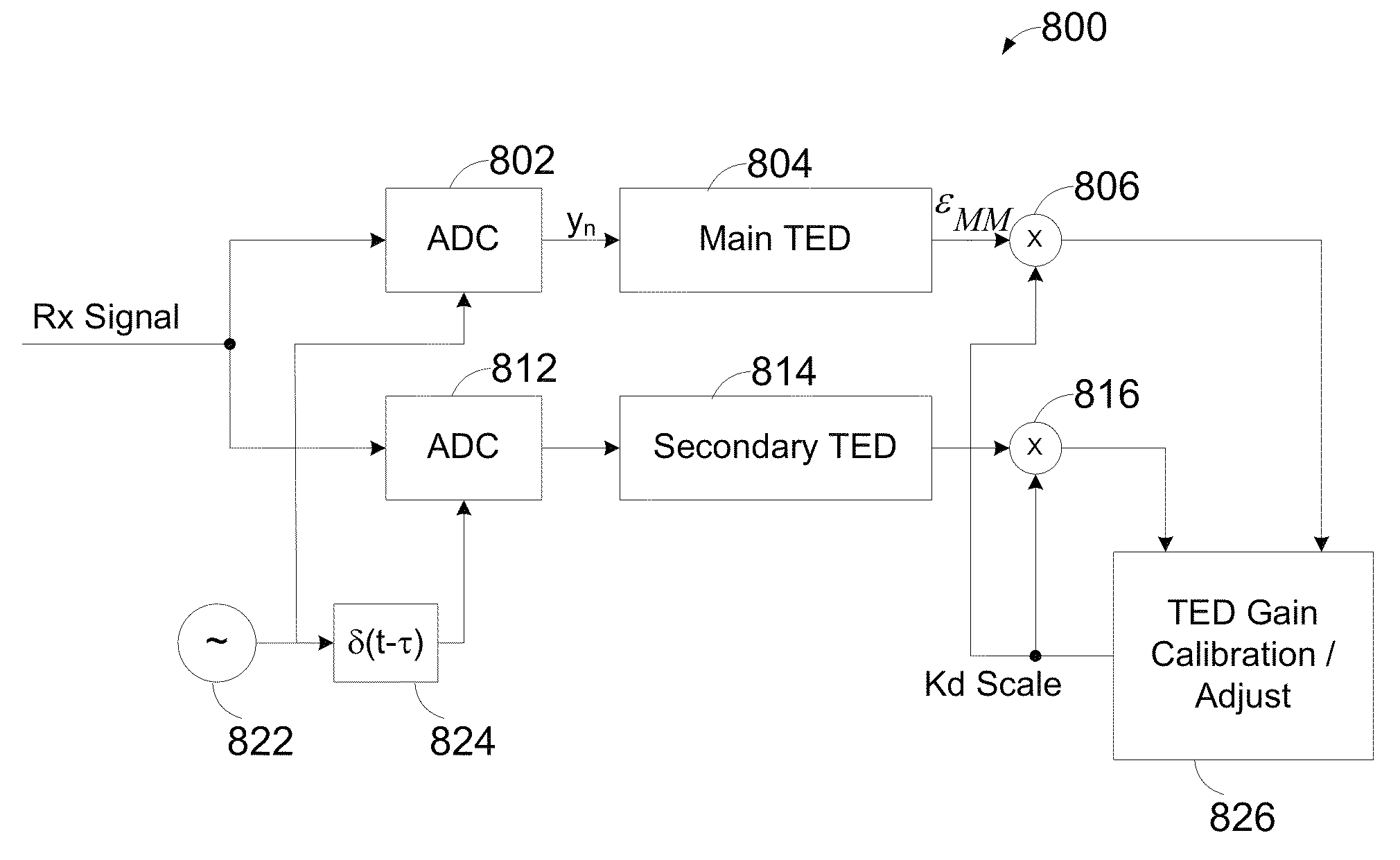

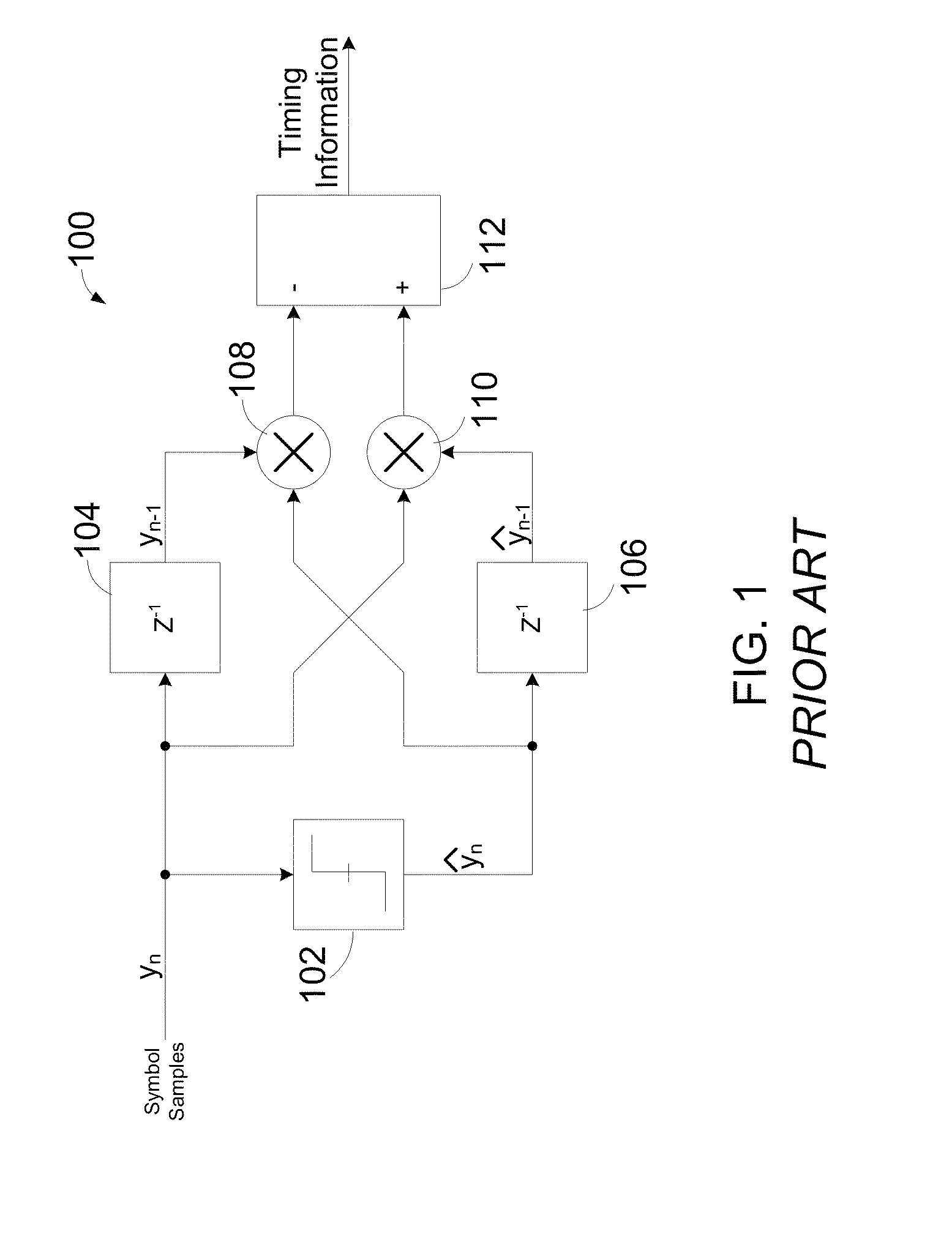

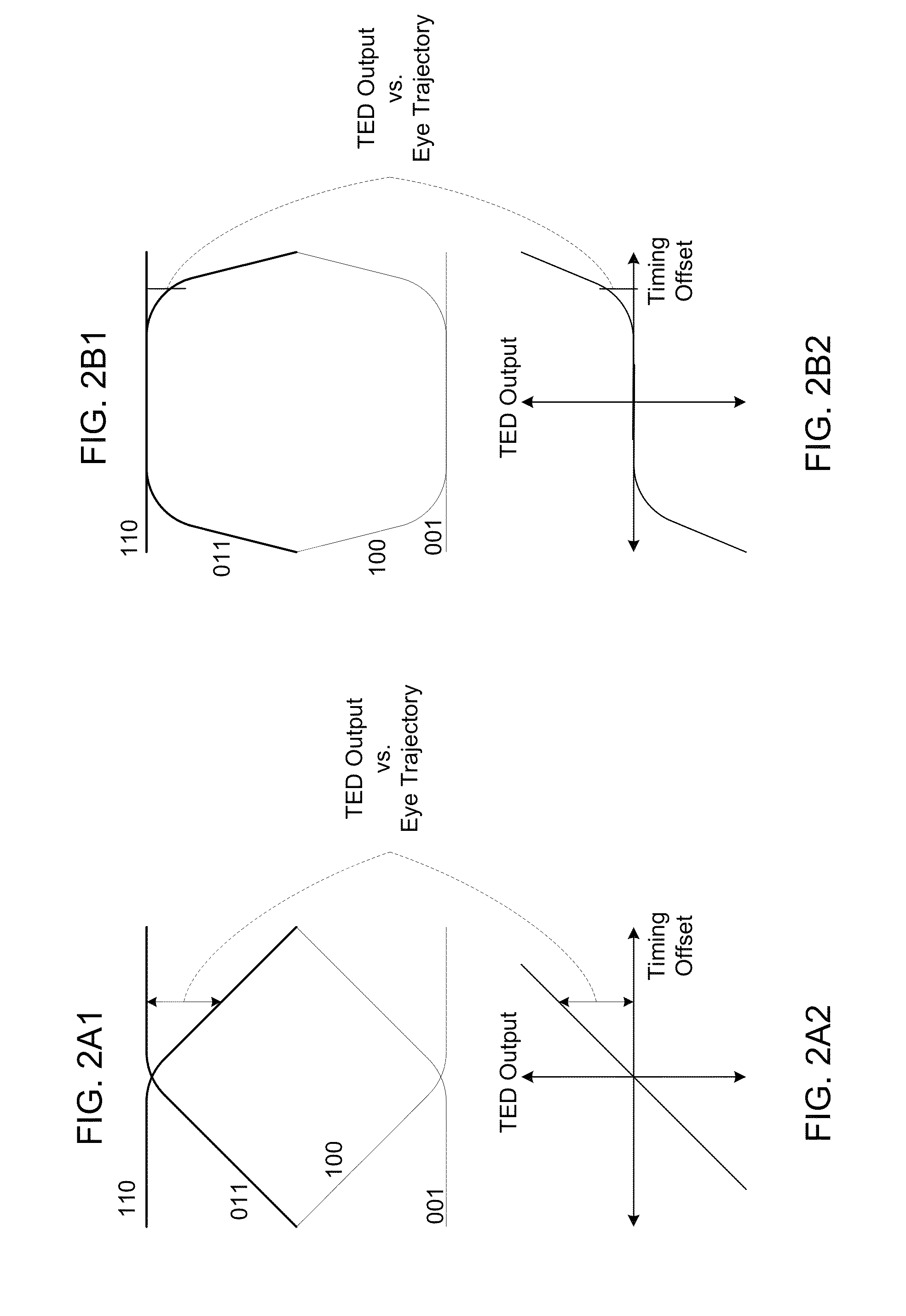

Gain calibration for a Mueller-Muller type timing error detector

ActiveUS8693596B1Less powerReduce unpredictabilityGain controlData switching by path configurationClock recoveryTiming error detector

Apparatus and methods calibrate and control detector gain in a Mueller-Muller timing detector. A main signal path includes a Mueller-Muller based timing error detector (MM TED). The main signal path generates a main error signal for clock recovery. A secondary signal path that includes a secondary MM TED. Each signal path samples soft symbols from a received signal. The sampling of the secondary MM TED is deliberately offset in time. A scale factor applied to the main error signal and to a secondary error signal is adaptively adjusted based on a comparison between the main error signal and the secondary error signal.

Owner:MICROSEMI STORAGE SOLUTIONS