Adaptive router in NoC (network-on-chip) on basis of virtual output queue mechanism

A technology of virtual output queue and network on chip, which is applied in the application field of integrated circuit chip design, and can solve problems such as head blocking

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

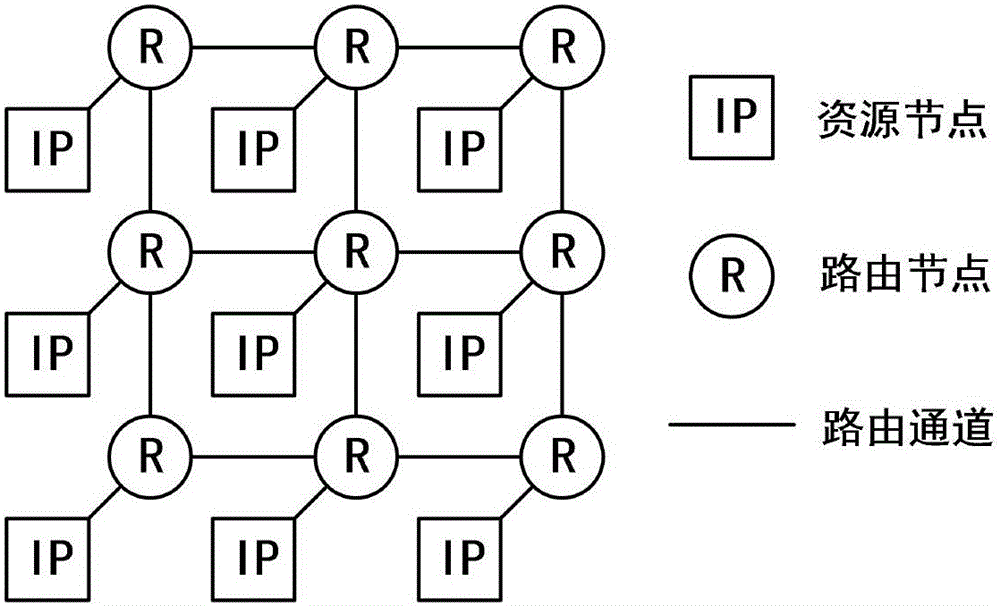

[0059] The network on chip is a two-dimensional grid structure composed of several routing nodes, several resource nodes and several routing channels. figure 1 Shown is a two-dimensional grid structure network on chip with a topology scale of 3*3;

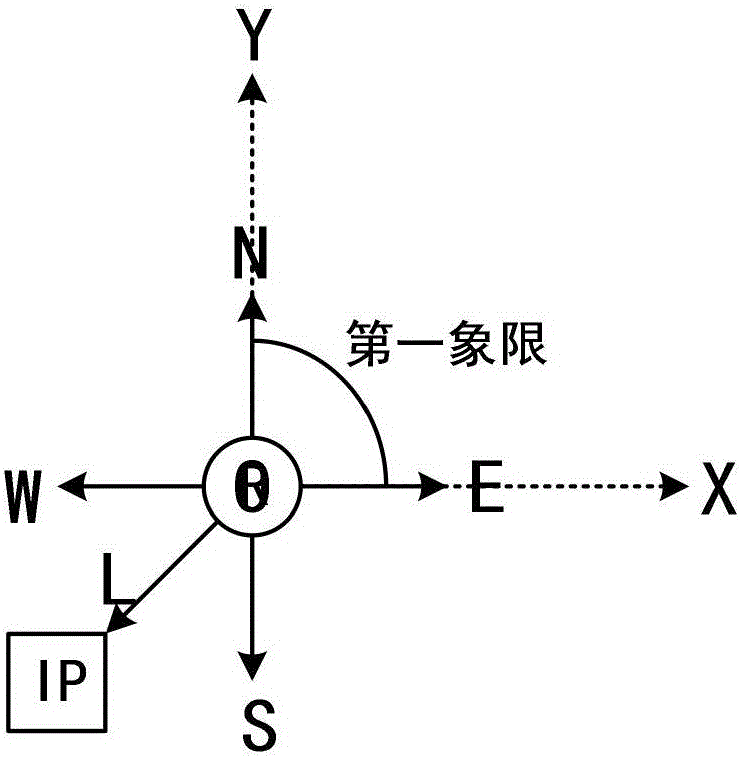

[0060] Take the routing node on any vertex of the on-chip network as the origin O, such as figure 2 As shown, the two routing channels connected to the routing node on the vertex are X-axis and Y-axis respectively, and the coordinate system OXY is established; and the positive direction of the X-axis is the E direction, and the negative direction of the X-axis is the W direction, The positive direction of the Y axis is the N direction, the negative direction of the Y axis is the S direction; the direction connected to the resource node is the L direction; and the area between the N direction and the E direction is defined as the first quadrant; the N The area between the direction and the W direction is defined as the second quad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More