Patents

Literature

128 results about "In-circuit emulator" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

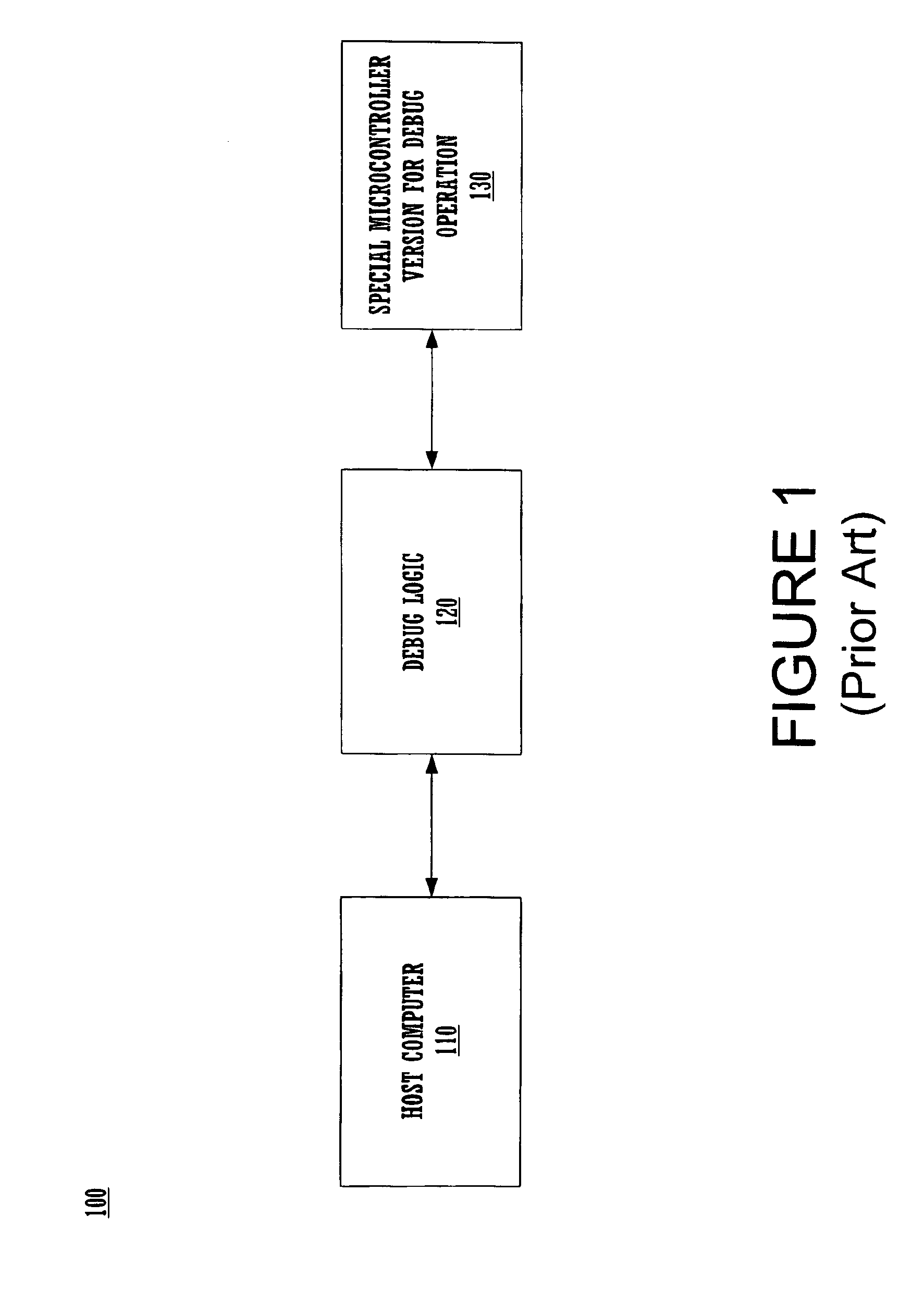

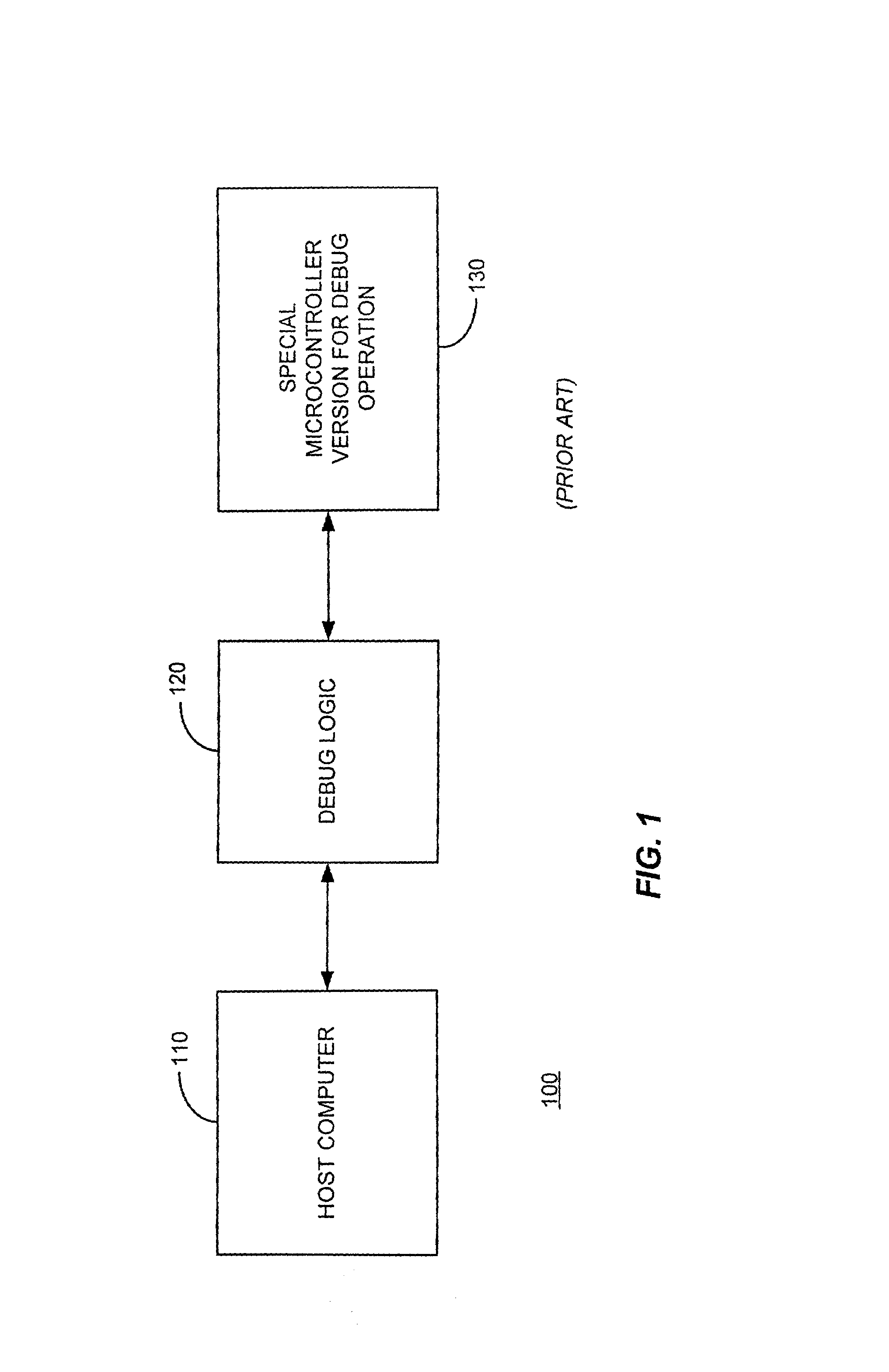

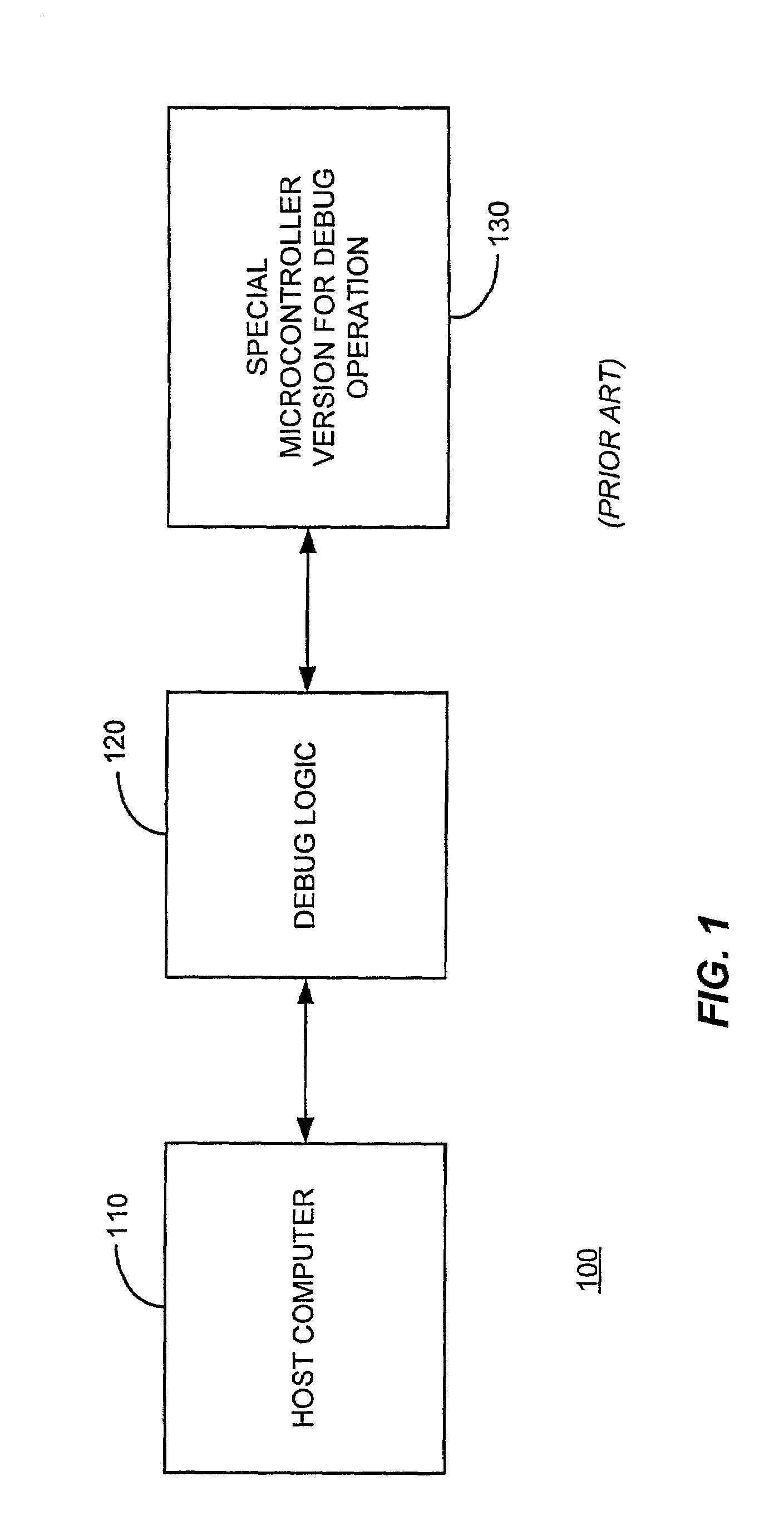

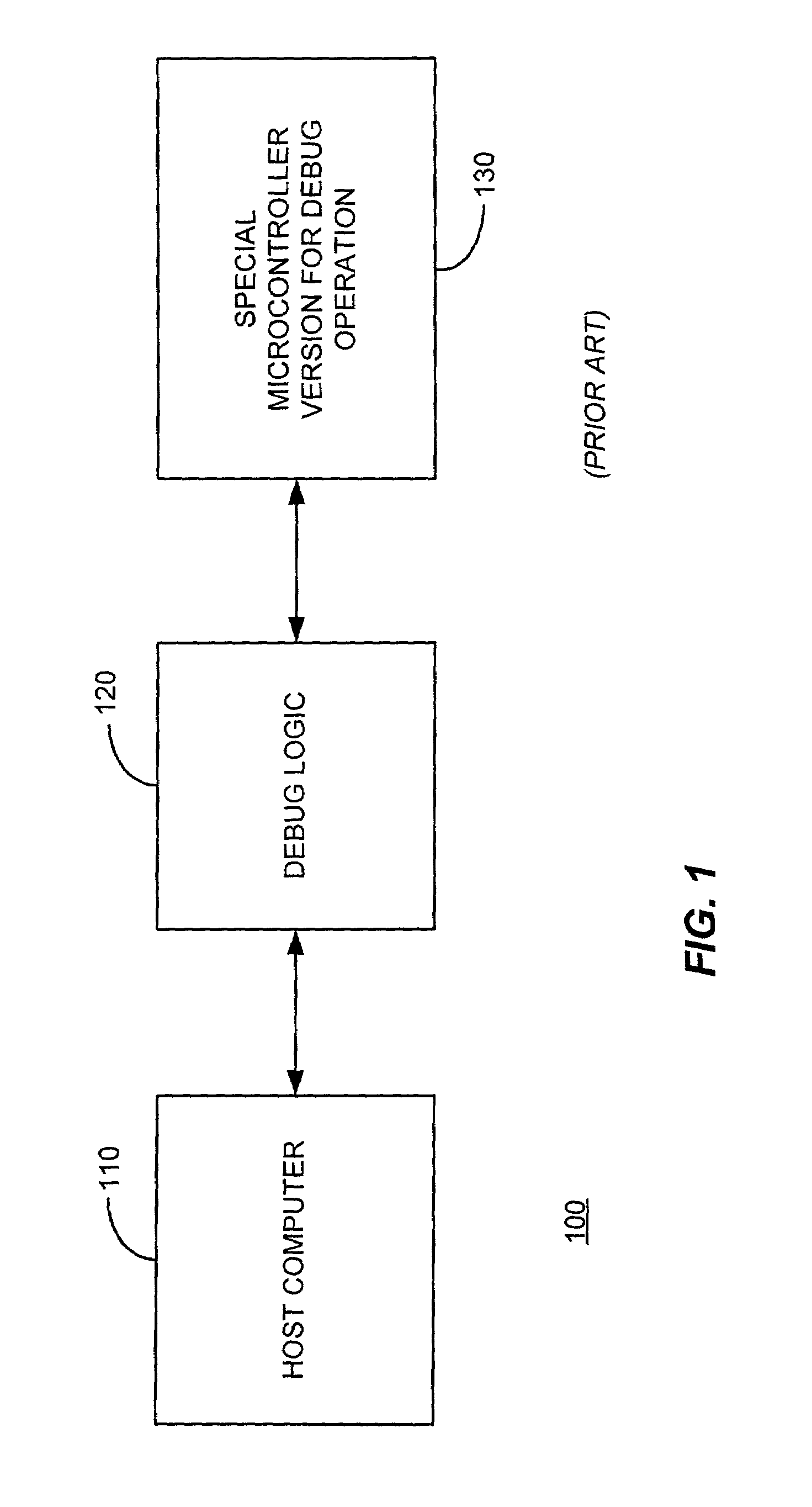

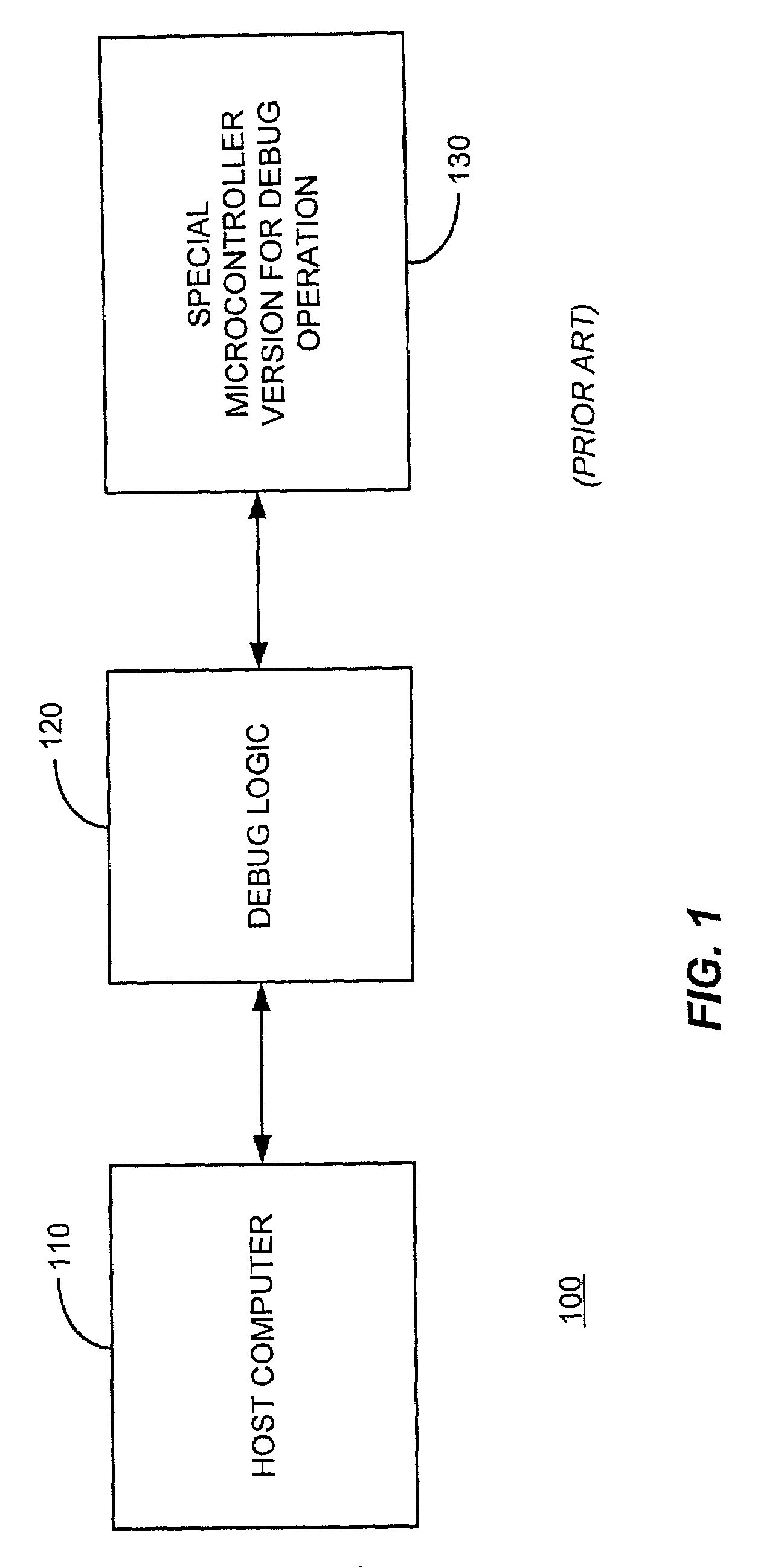

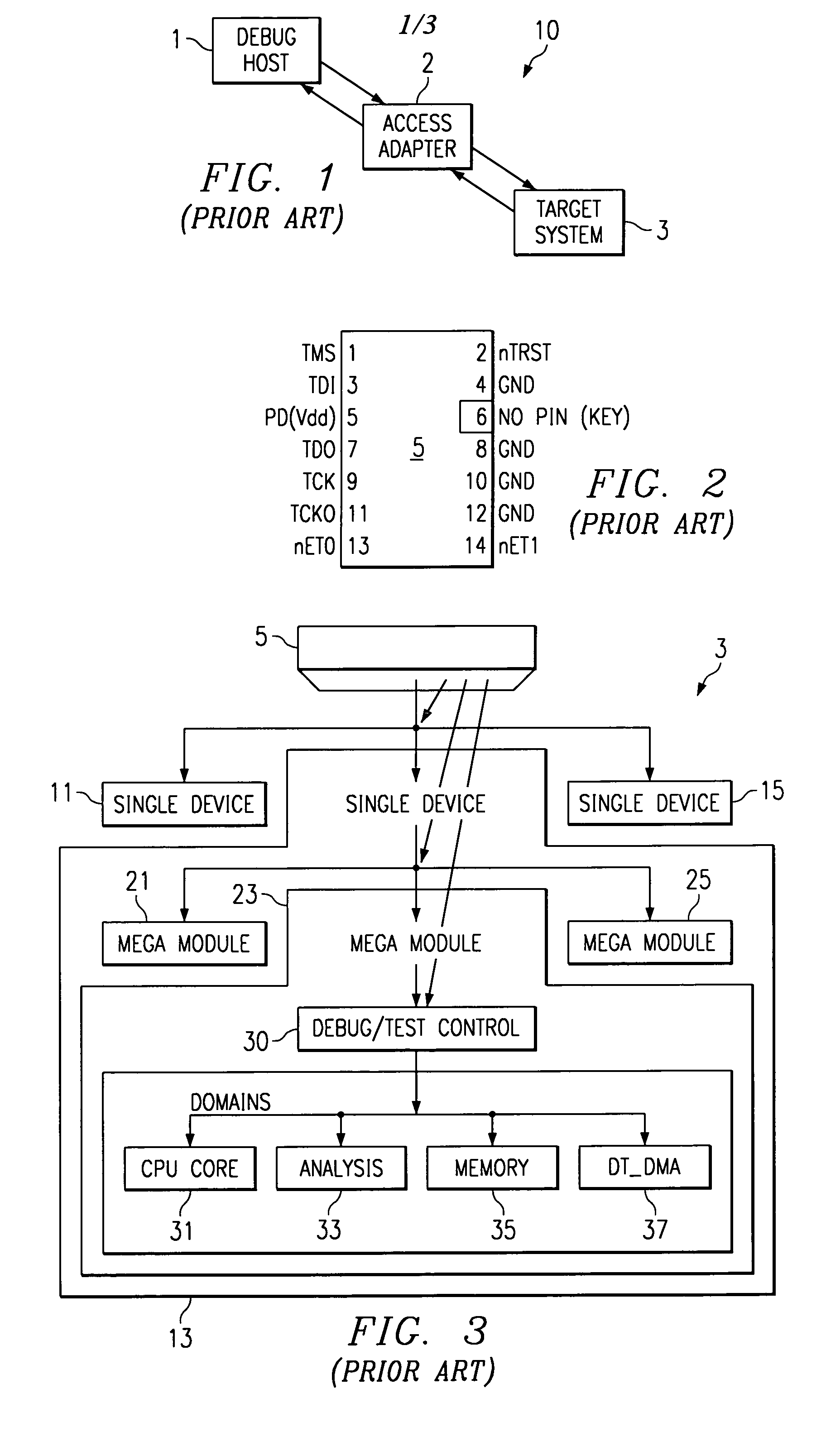

In-circuit emulation (ICE) is the use of a hardware device or in-circuit emulator used to debug the software of an embedded system. It operates by using a processor with the additional ability to support debugging operations, as well as to carry out the main function of the system. Particularly for older systems, with limited processors, this usually involved replacing the processor temporarily with a hardware emulator: a more powerful although more expensive version. It was historically in the form of bond-out processor which has many internal signals brought out for the purpose of debugging. These signals provide information about the state of the processor.

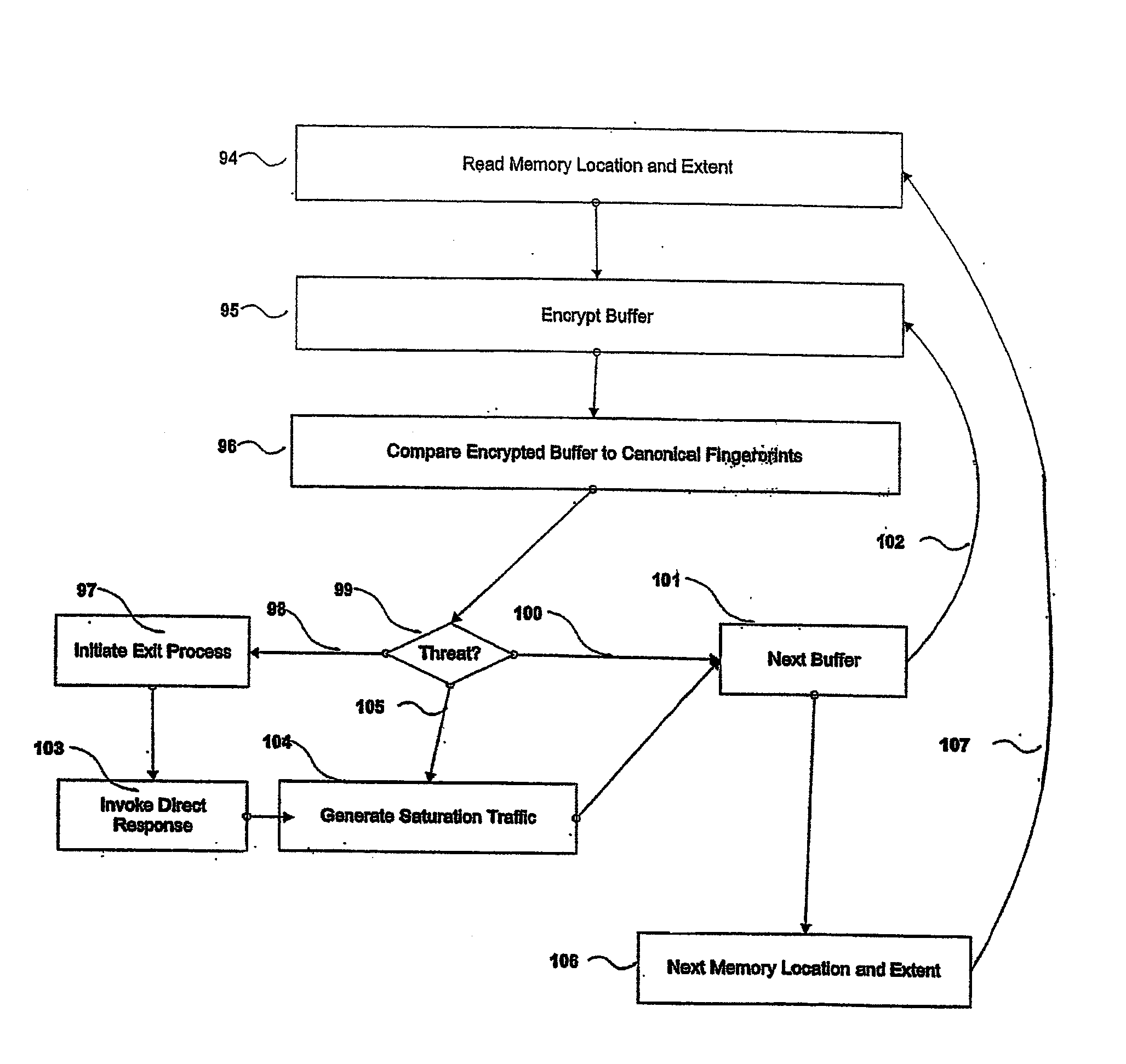

Systems and methods for the prevention of unauthorized use and manipulation of digital content

InactiveUS7328453B2Overwhelm usefulnessHigh normal sclerosisMemory loss protectionDigital data processing detailsTime domainThird party

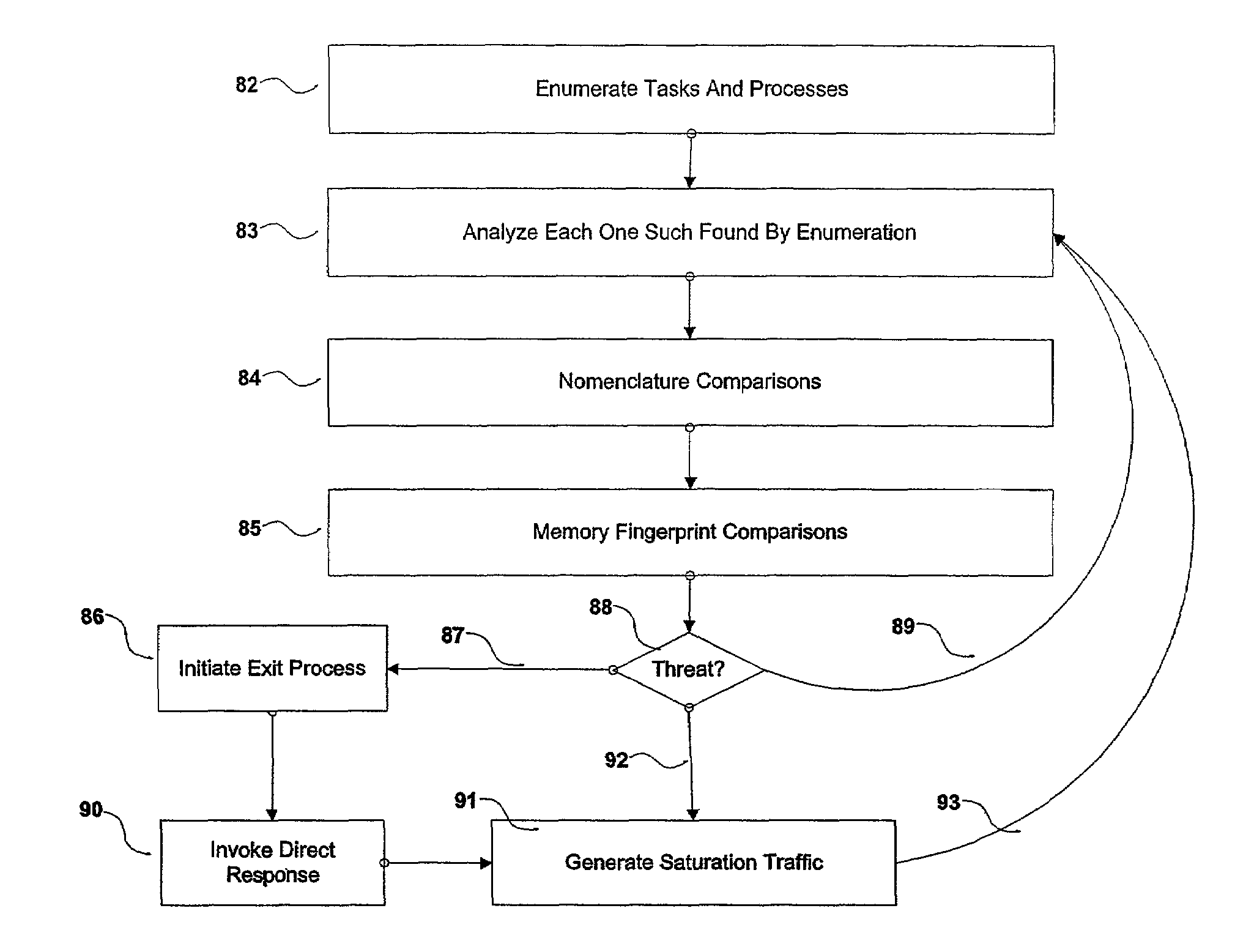

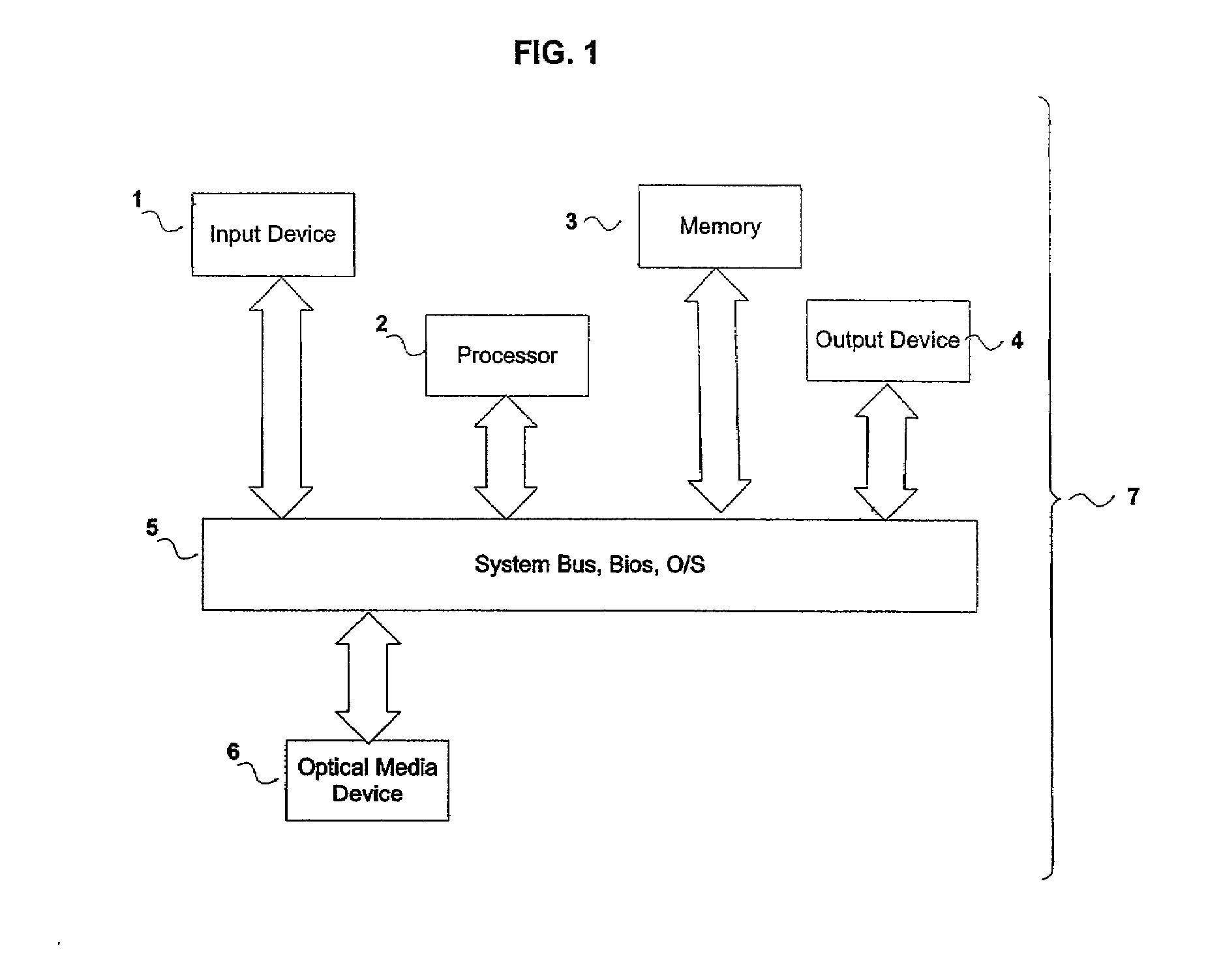

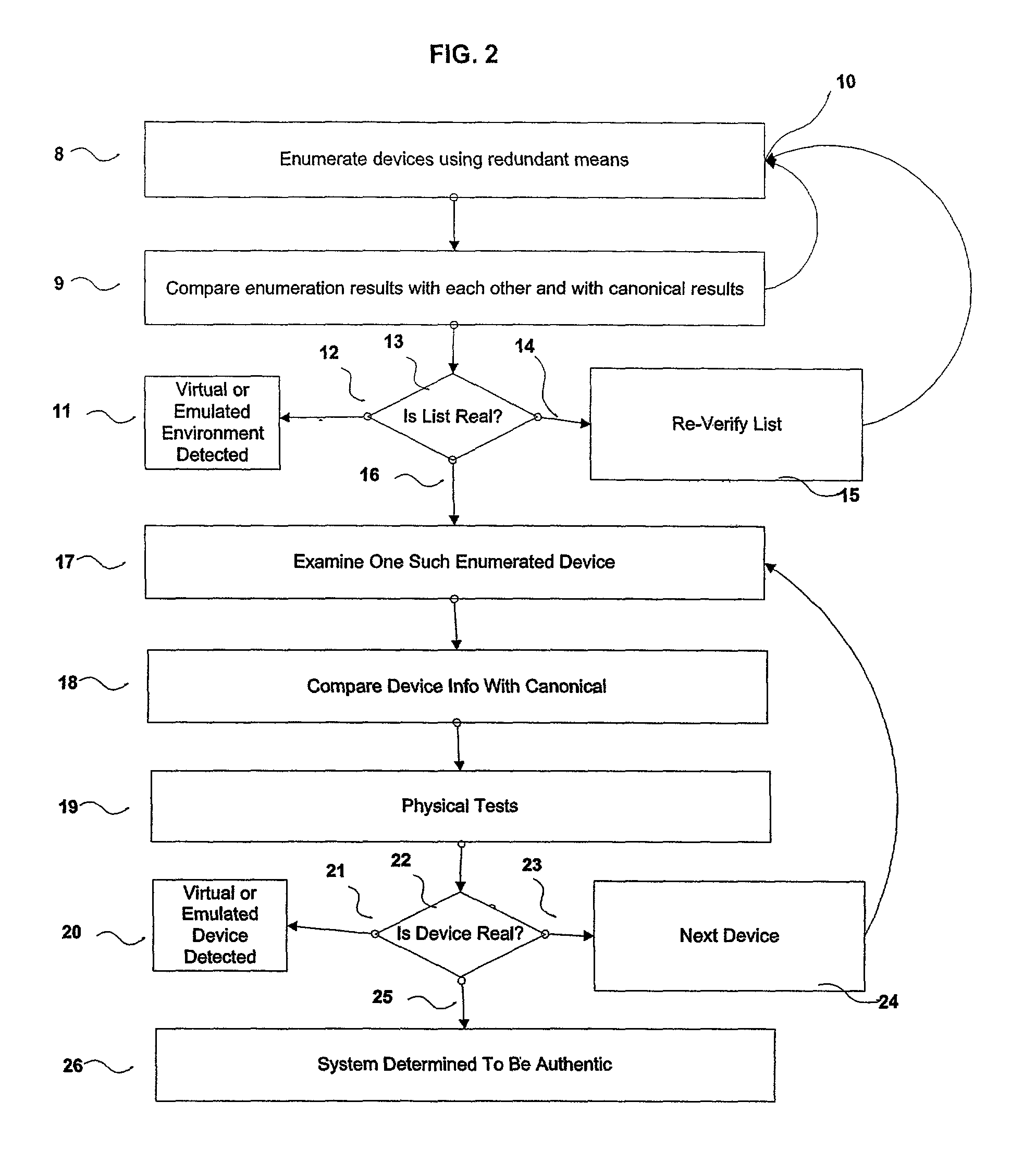

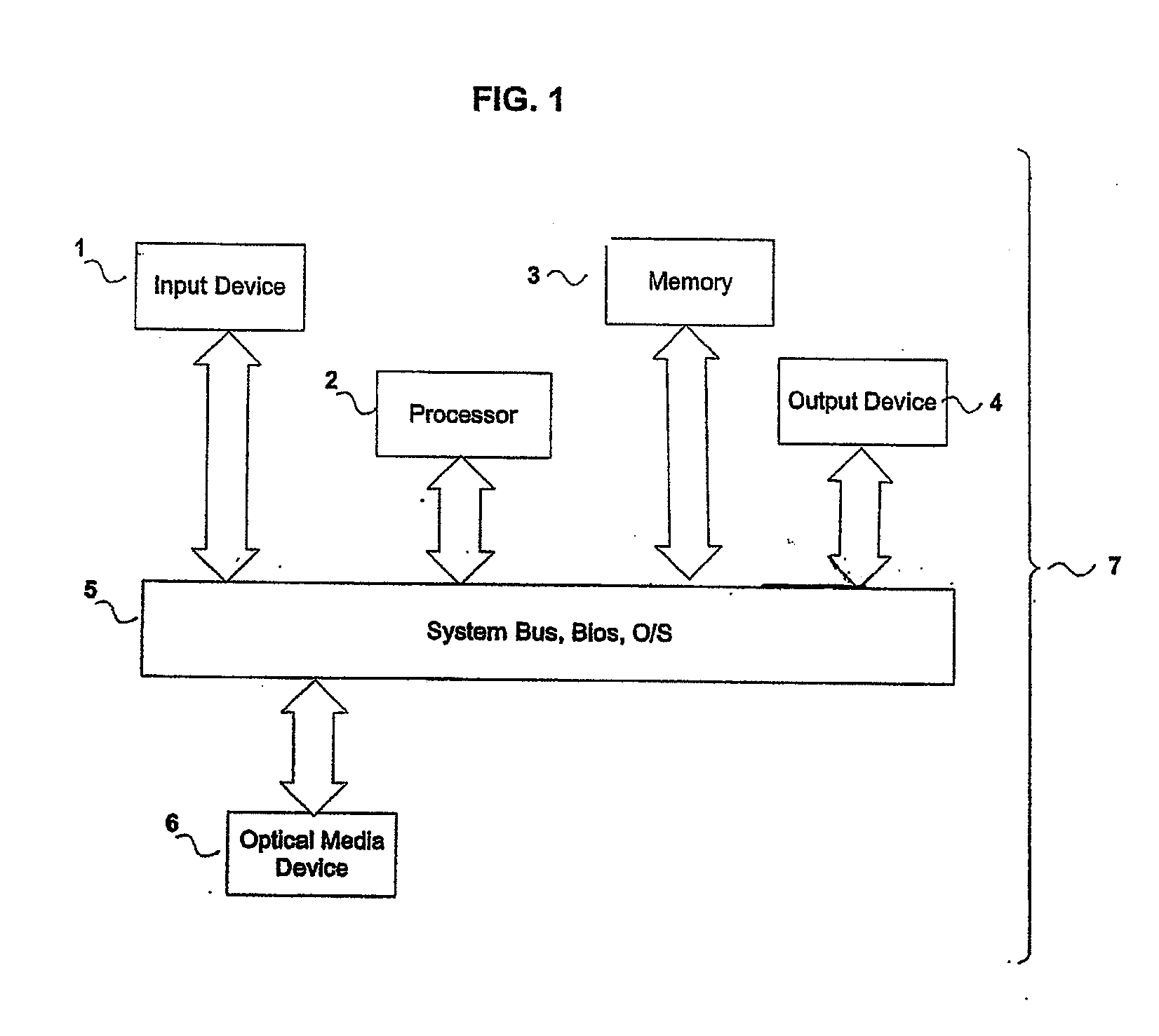

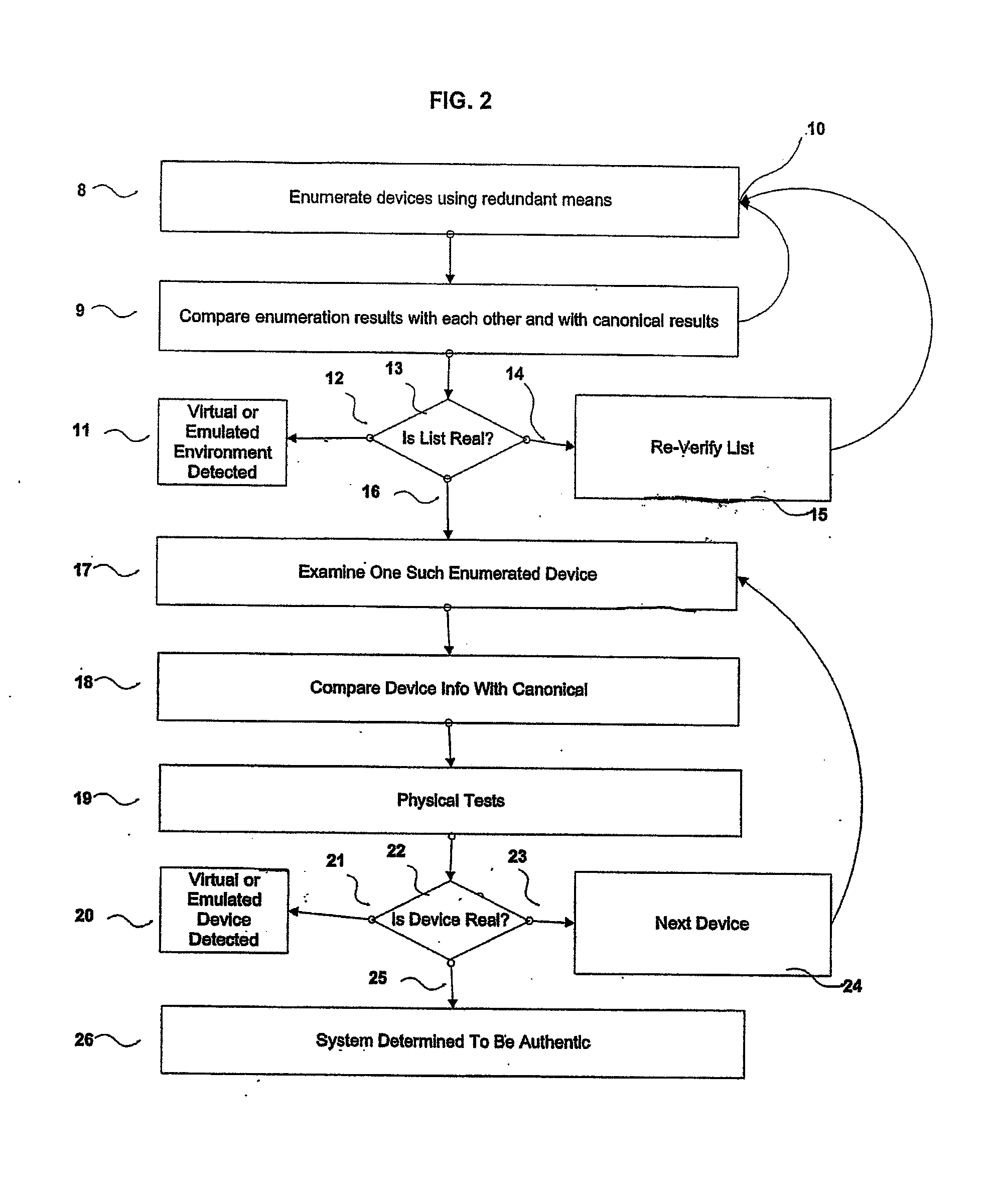

A number of systems and methods, alone, or in combination, achieve various levels of protection against unauthorized modification and distribution of digital content. This encompasses at least unauthorized study, modification, monitoring, reconstruction, and any other means for subversion from the originally intended purpose and license model of the digital content. The invention combines a number of techniques that in whole, or in part, serve to protect such content from unauthorized modification, reconstructive engineering, or monitoring by third parties. This is accomplished by means of methods which protect against subversion by specific tools operating on specific platforms as well as general tools operating on general platforms. Specific time domain attacks are identified, code modification can be identified and reversed, and virtual and emulated systems are identified. In addition, identification of in-circuit emulator tools (both software and hardware), debuggers, and security threats to running programs can be achieved.

Owner:IPLA HLDG

Debug interface including a compact trace record storage

InactiveUS6094729AReliability increasing modificationsHardware monitoringInformation typeParallel computing

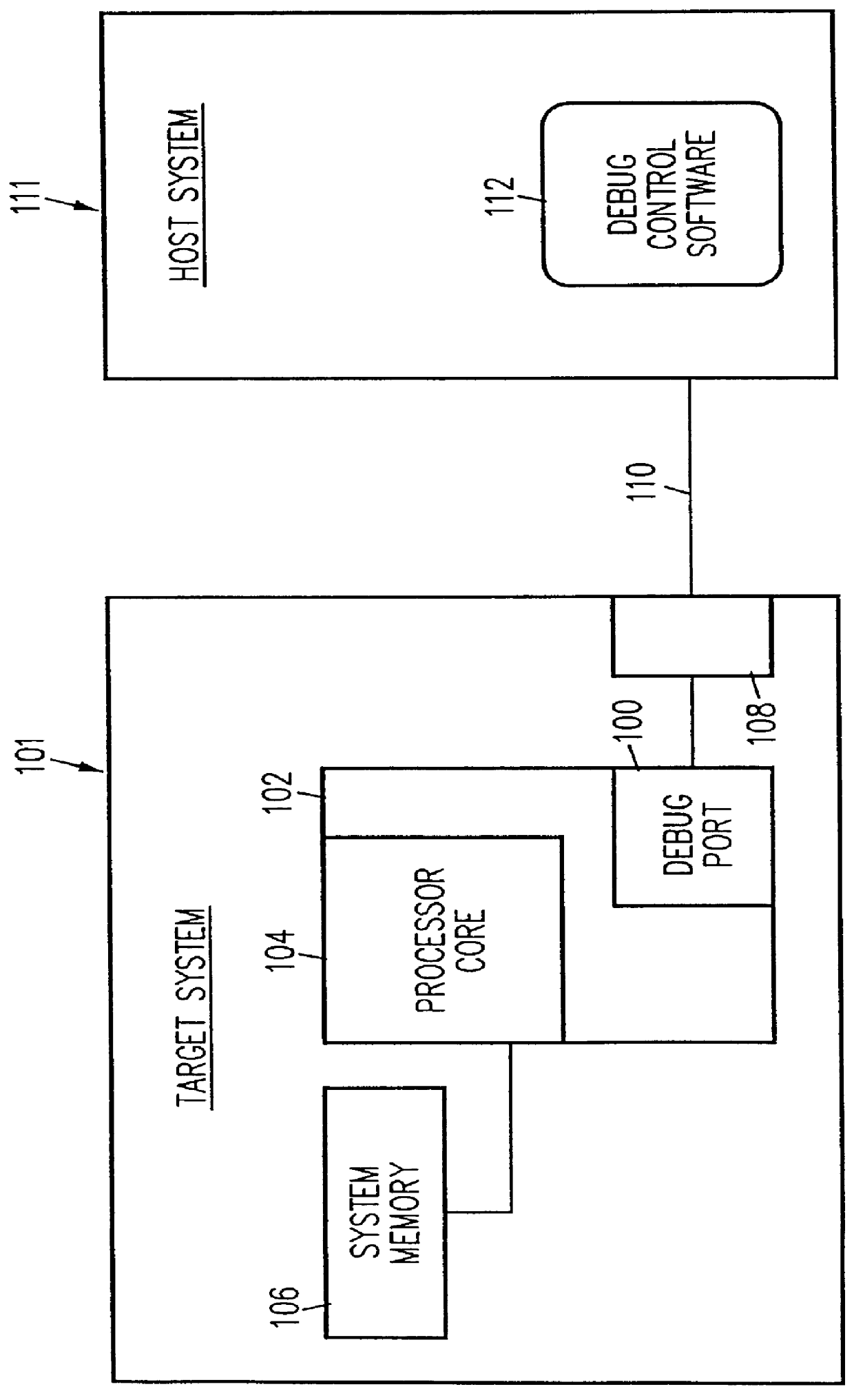

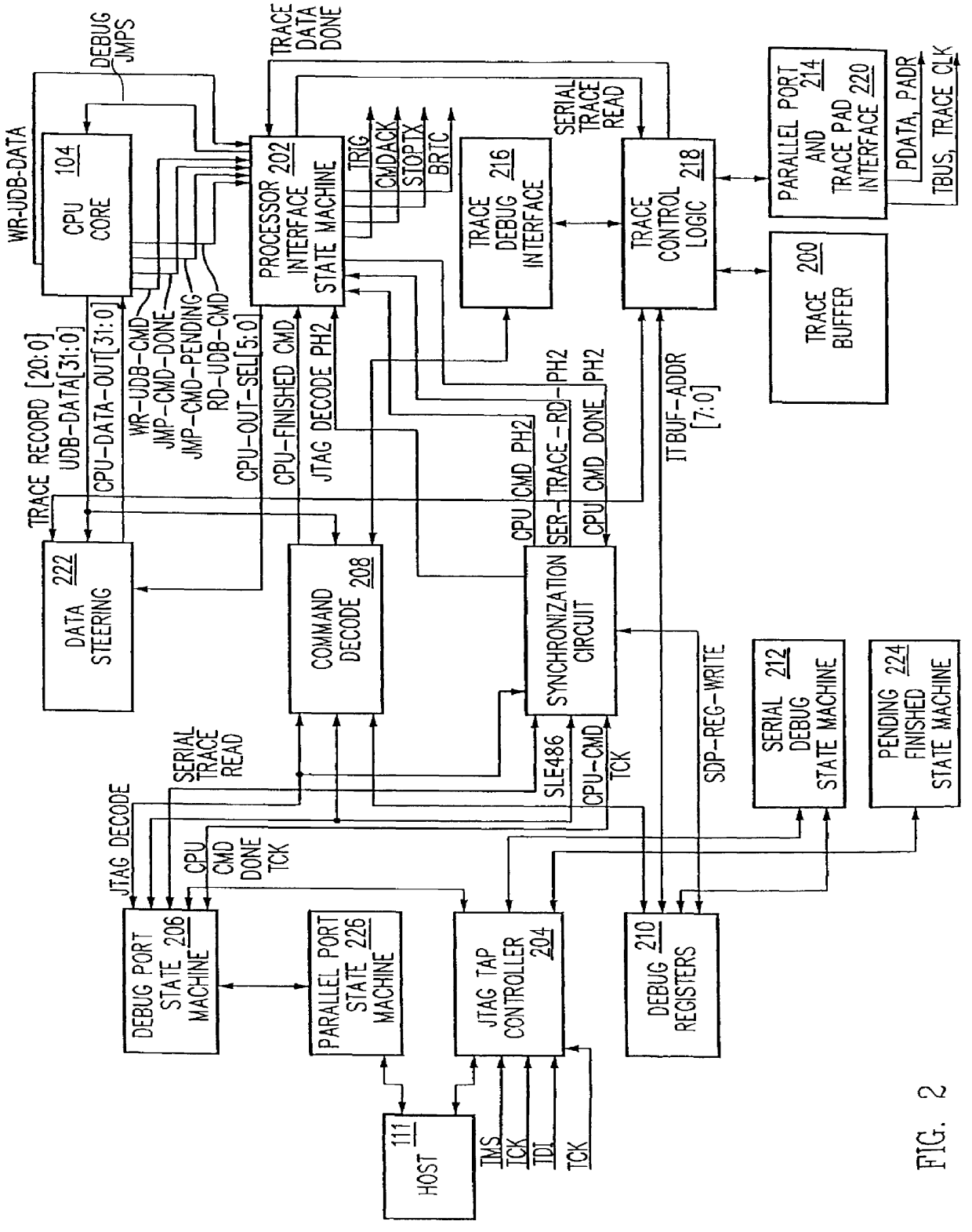

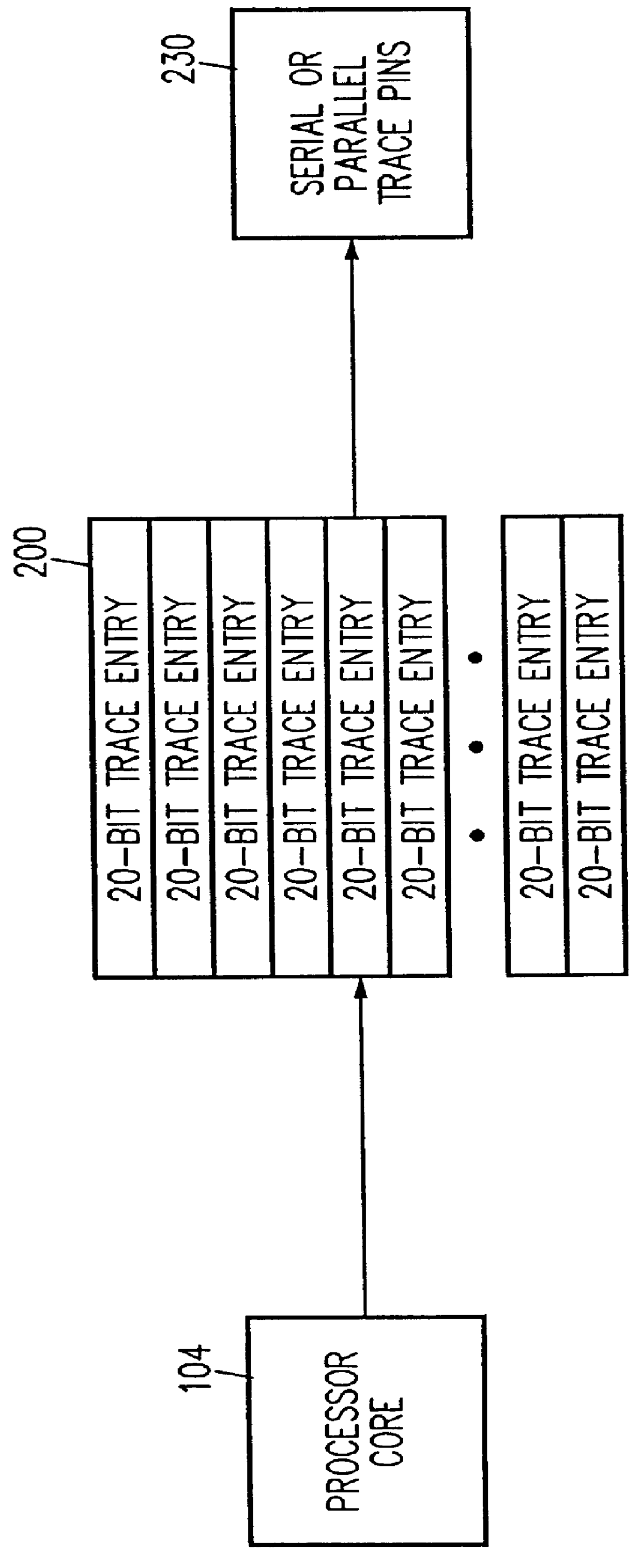

In-circuit emulation (ICE) and software debug facilities are included in a processor via a debug interface that interfaces a target processor to a host system. The debug interface includes a trace controller that monitors signals produced by the target processor to detect specified conditions and produce a trace record of the specified conditions including a notification of the conditions are selected information relating to the conditions. The trace controller formats a trace information record and stores the trace information record in a trace buffer in a plurality of trace data storage elements. The trace data storage elements have a format that includes a trace code (TCODE) field indicative of a type of trace information and a trace data (TDATA) field indicative of a type of trace information data.

Owner:GLOBALFOUNDRIES INC

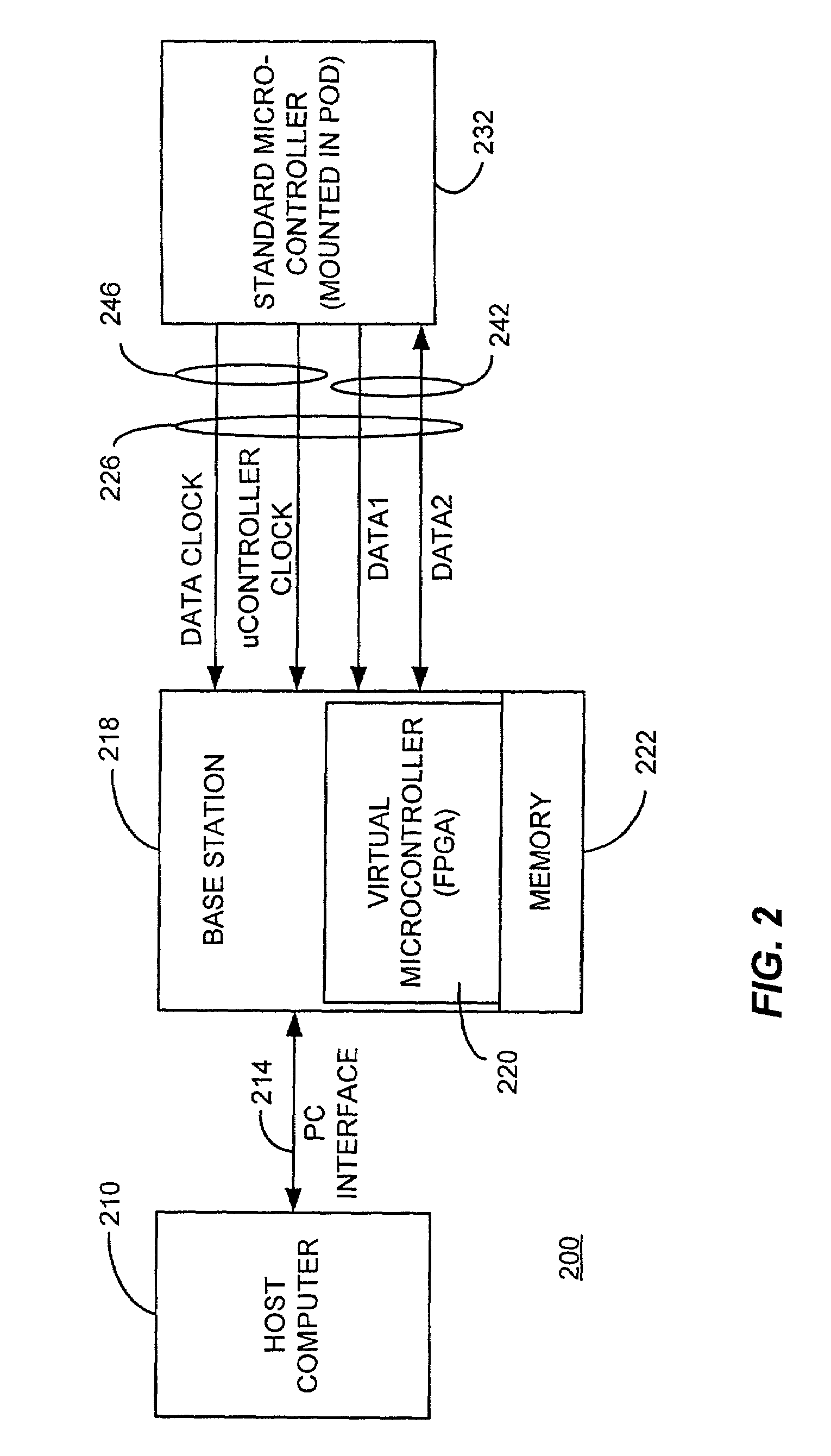

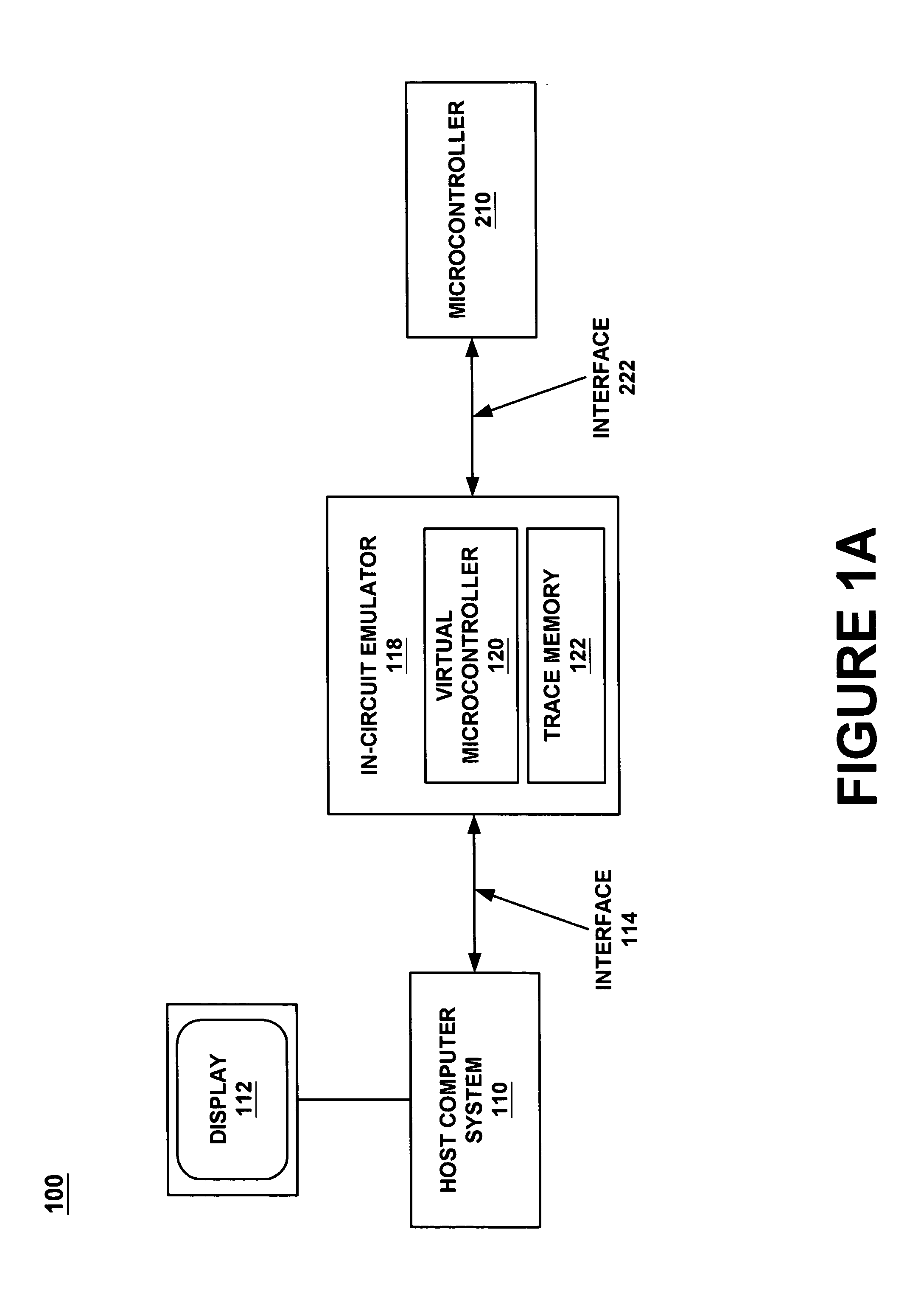

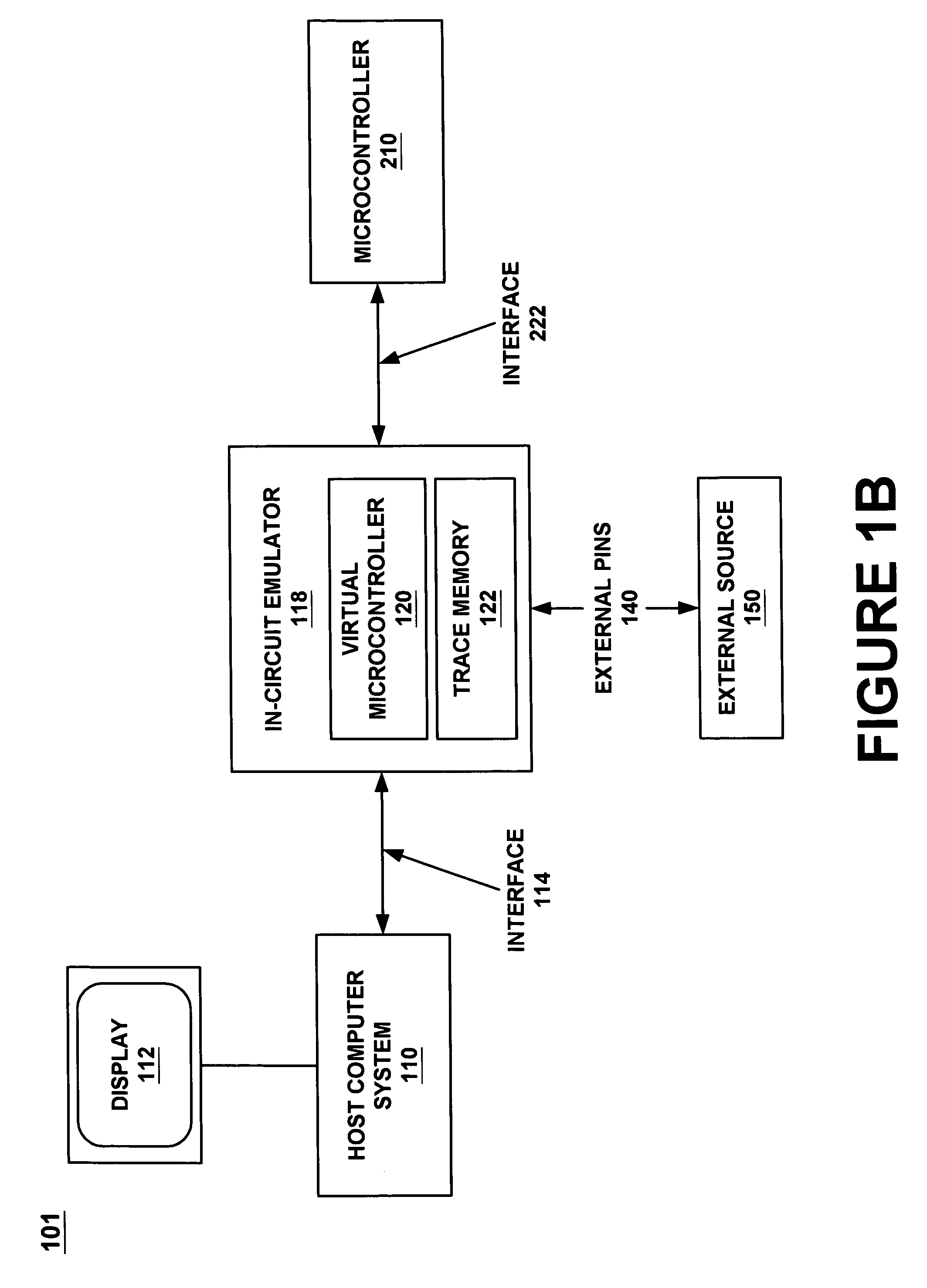

Emulator chip/board architecture and interface

InactiveUS7076420B1Efficient communicationShorten the counting processError detection/correctionSoftware simulation/interpretation/emulationMicrocontrollerCommunication interface

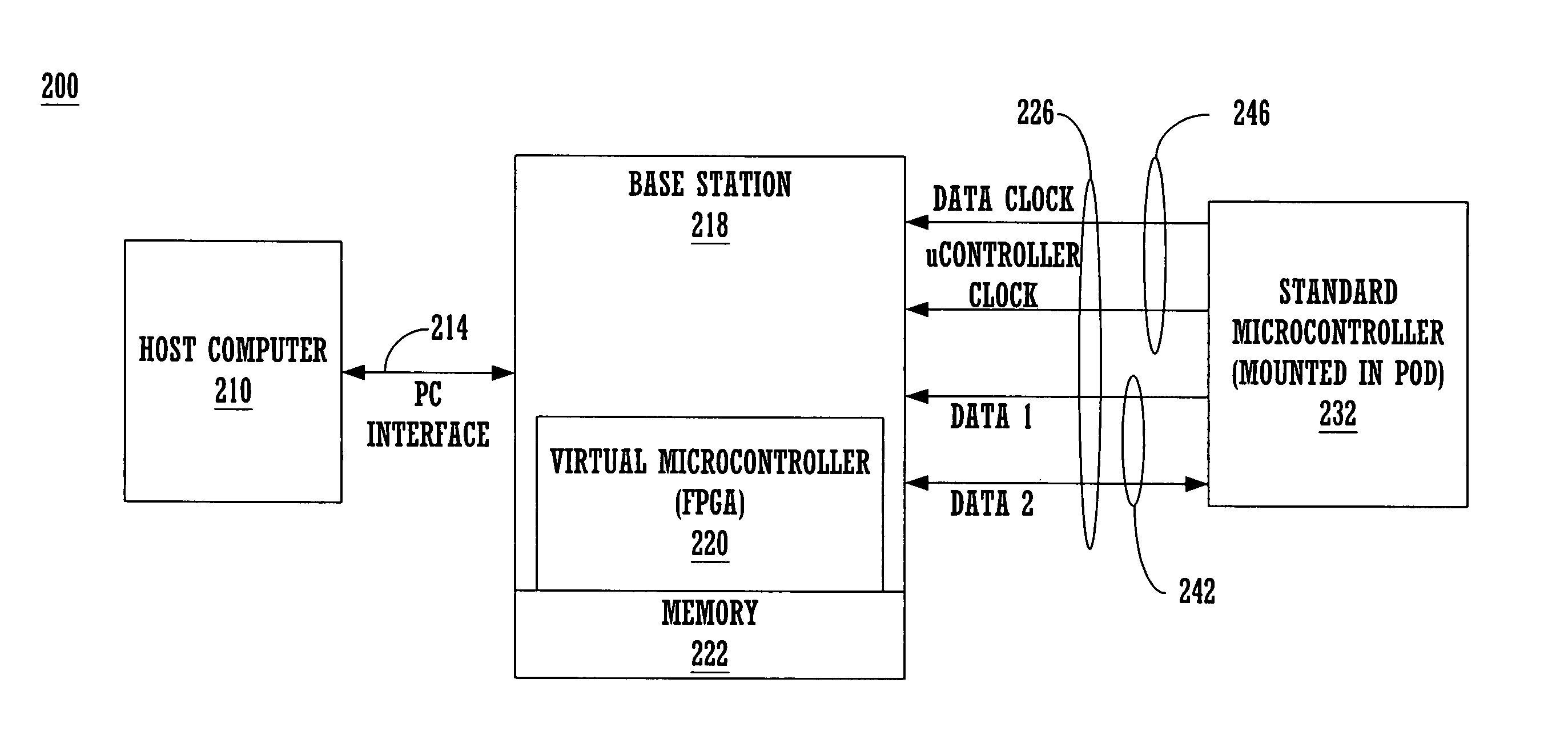

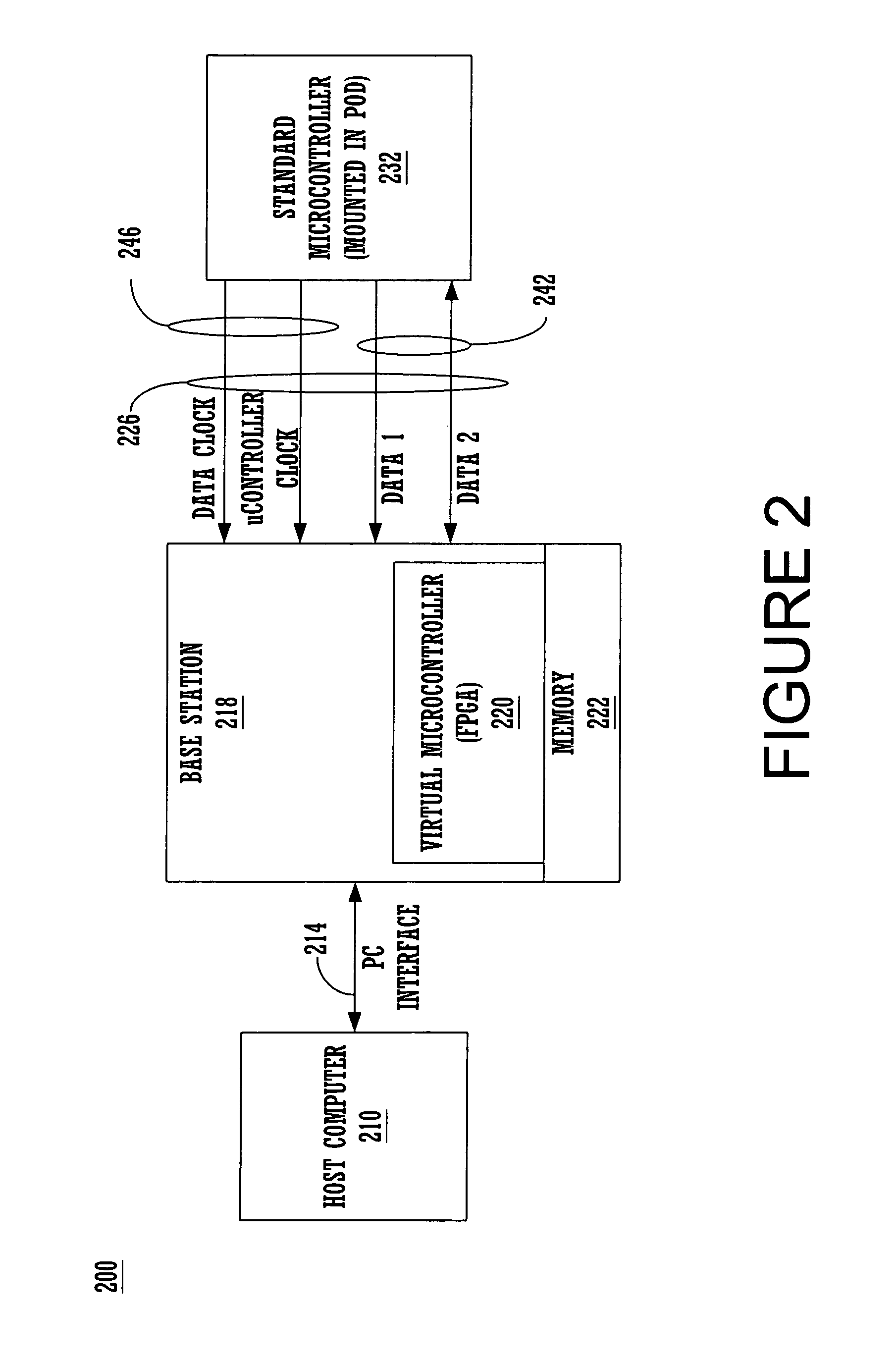

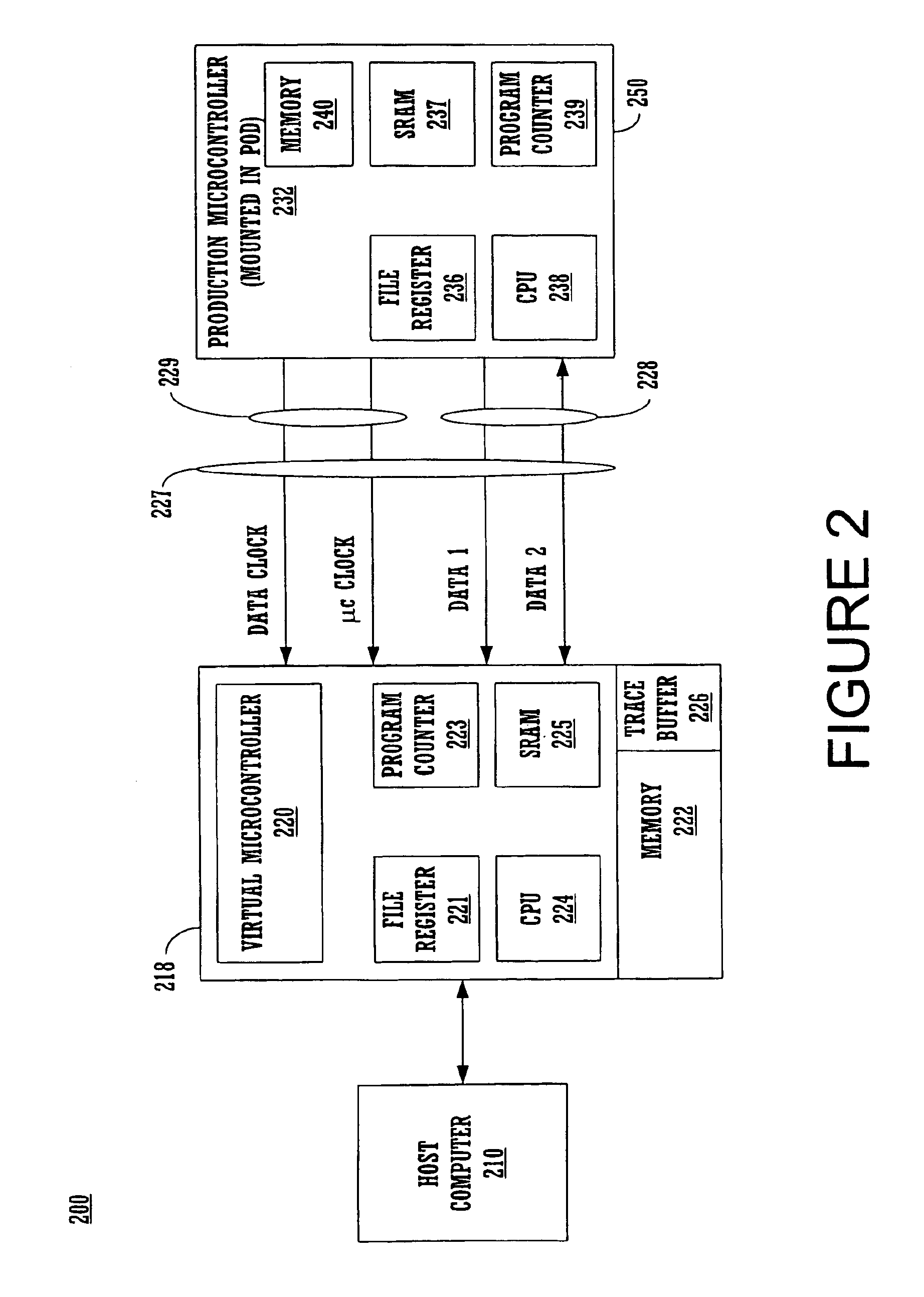

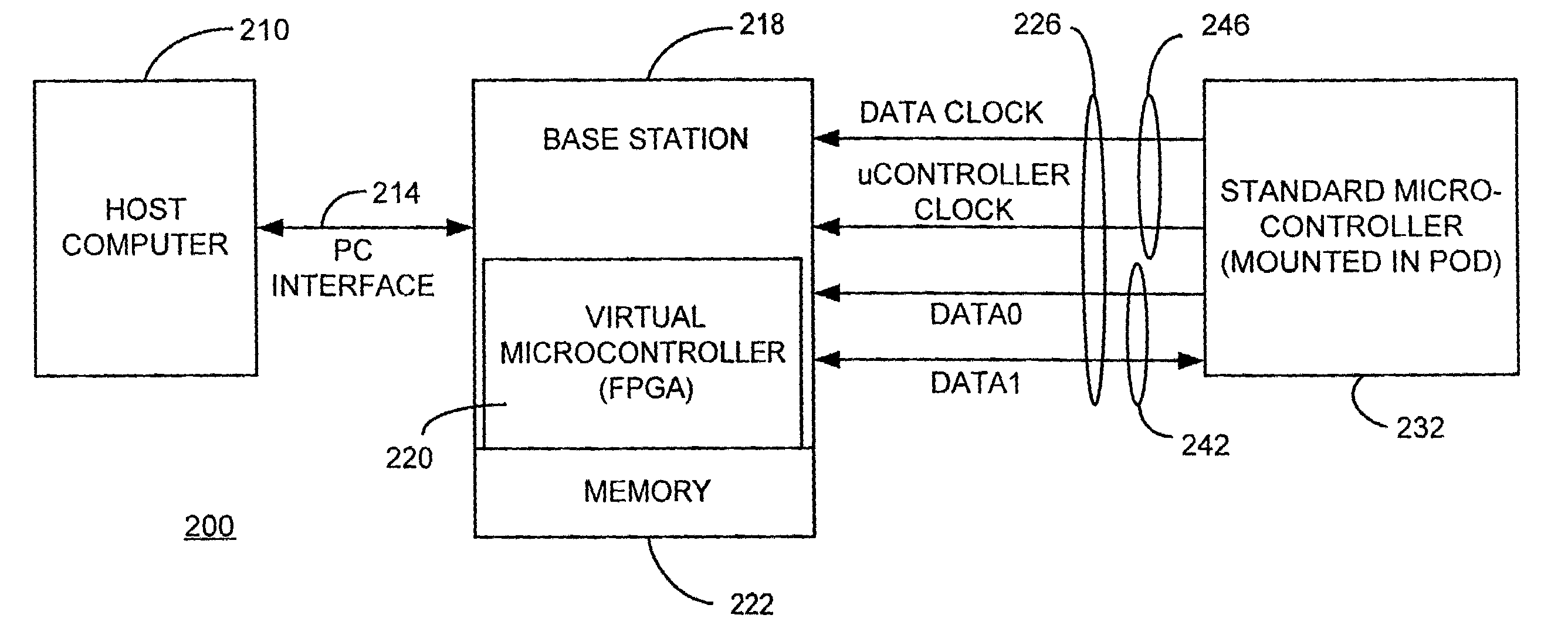

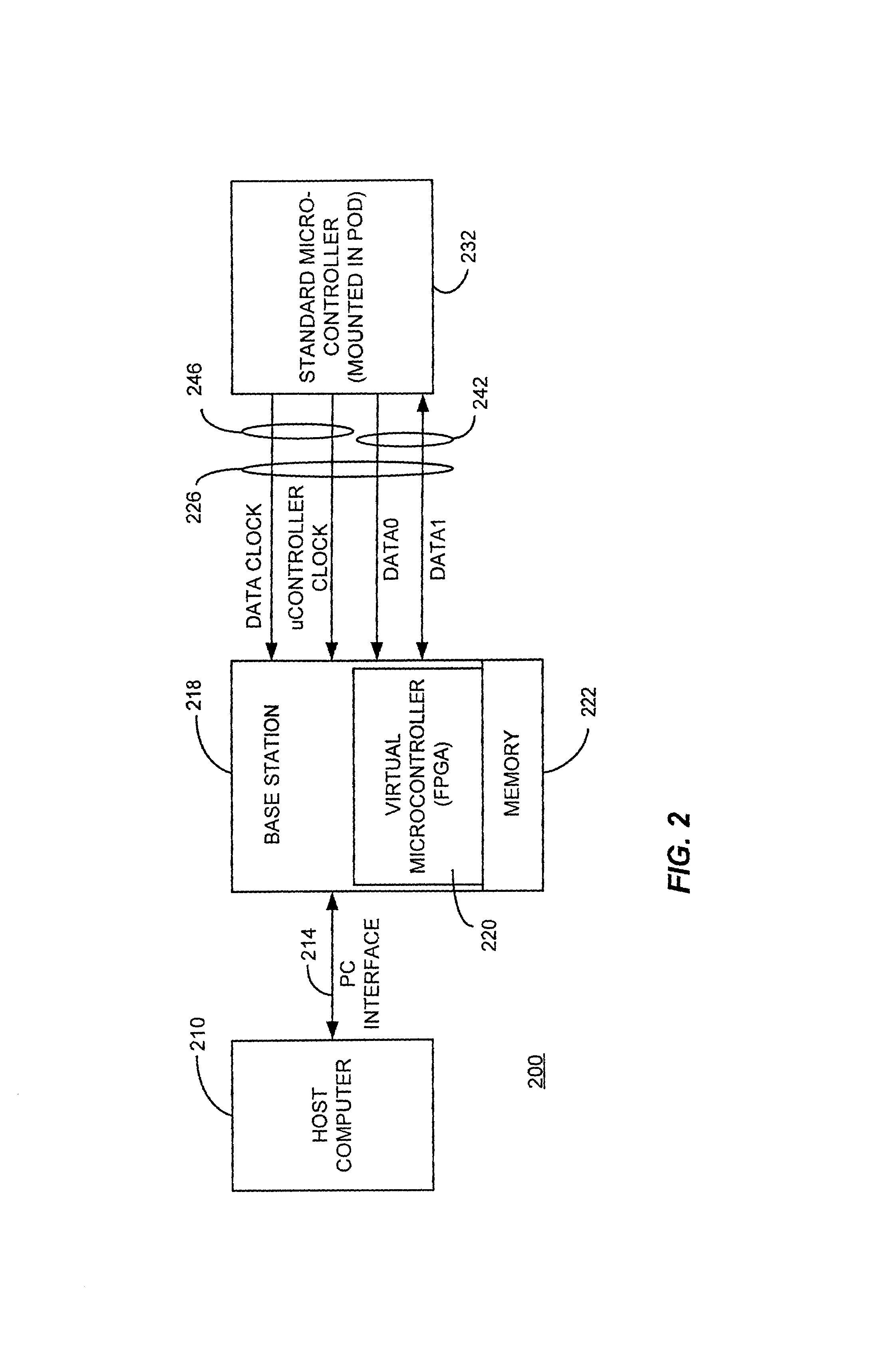

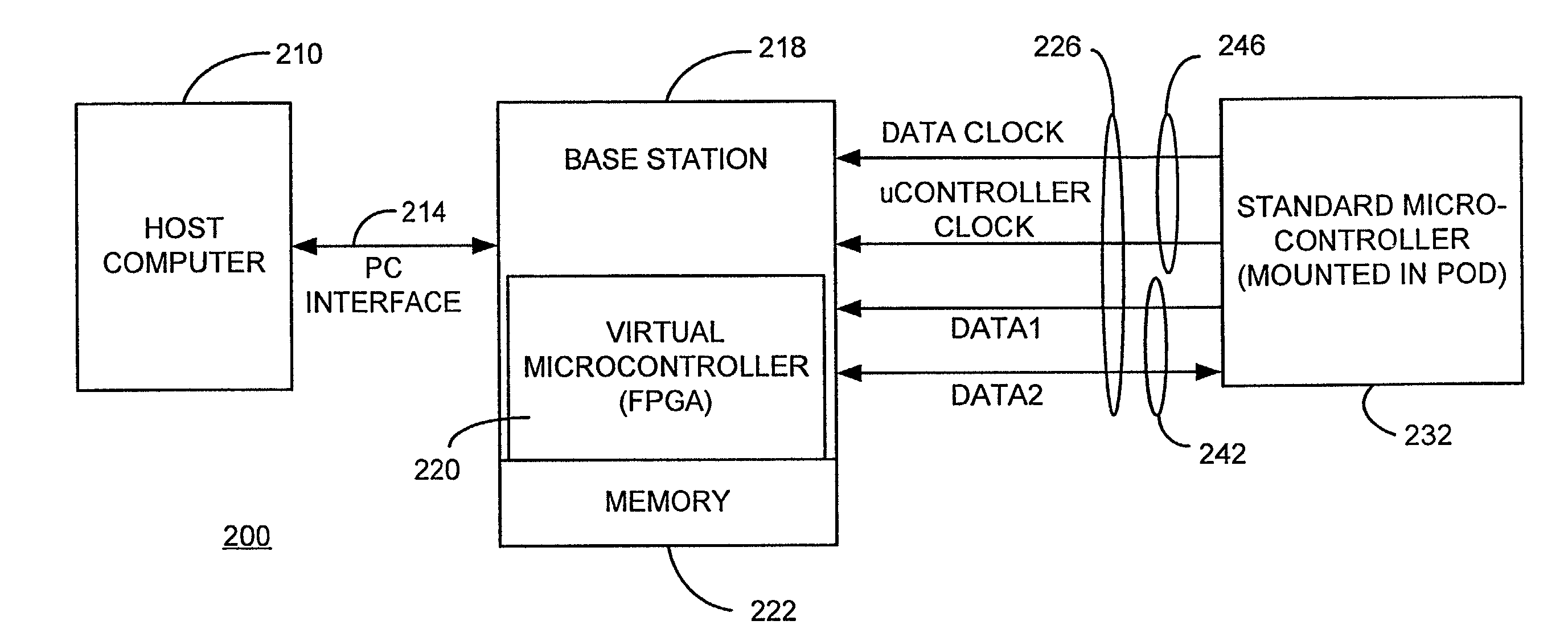

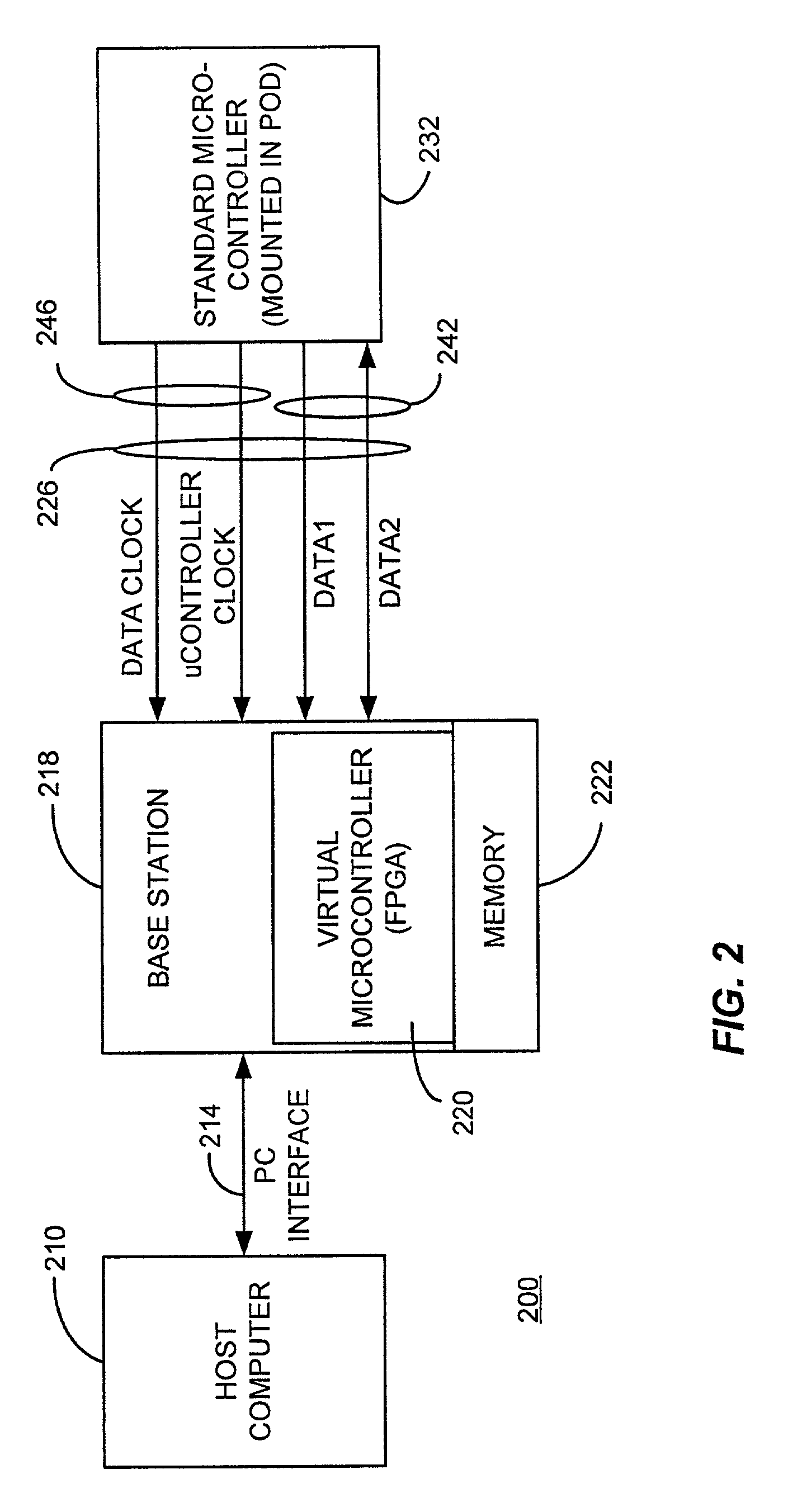

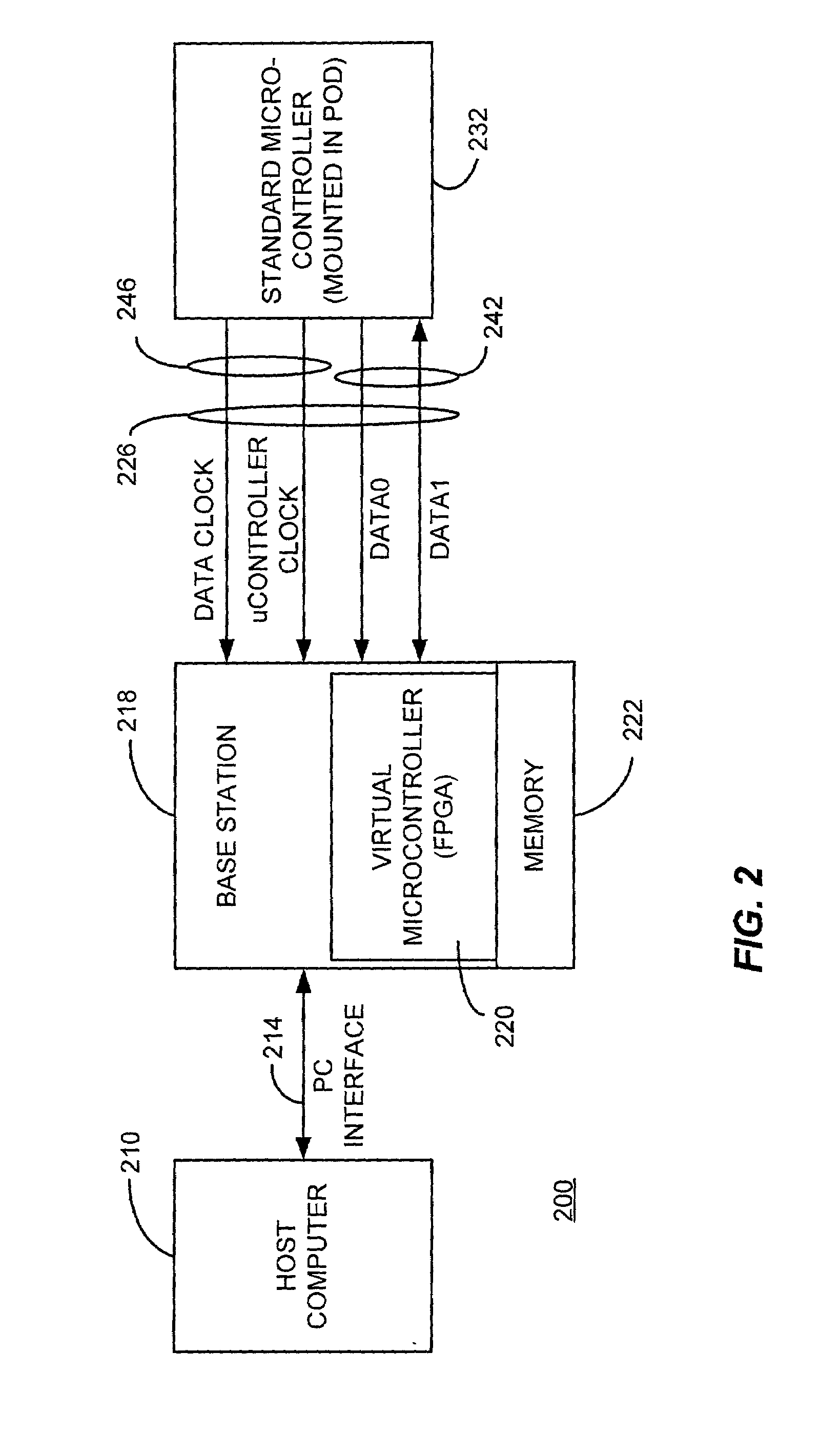

A communication interface for an in-circuit emulation system. The interface uses four pins between a virtual microcontroller (an FPGA emulating a microcontroller) and a real microcontroller under test. The bus is fast enough to allow the two devices to operate in synchronization. I / O reads, interrupt vector information and watchdog information is provided over the bus in a time fast enough to allow execution in lock step. Two data lines are provided, one is bi-directional and one is driven only by the microcontroller. A system clock is provided and the microcontroller supplies its clock signal to the FPGA since the microcontroller can operate at varying clock speeds. The bus is time-dependent so more information can be placed on this reduced-pin count bus. Therefore, instructions and data are distinguished based on the time the information is sent within the sequence. The bus can be used to carry trace information, program the flash memory on the microcontroller, perform test control functions, etc.

Owner:CYPRESS SEMICON CORP

System and a method for checking lock step consistency between an in circuit emulation and a microcontroller while debugging process is in progress

InactiveUS6922821B1Analogue computers for electric apparatusFunctional testingMicrocontrollerParallel computing

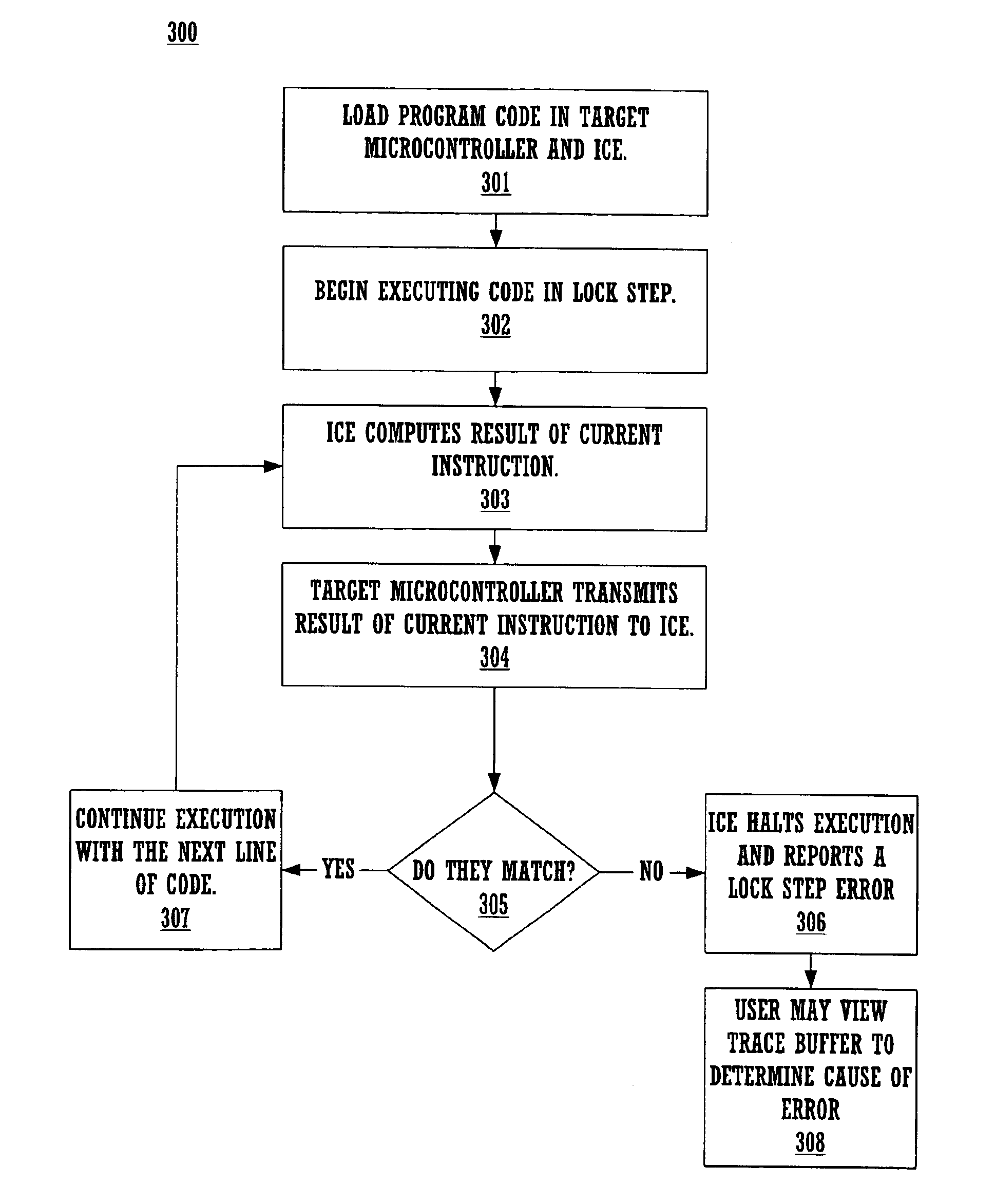

Checking the consistency of a lock step process while debugging a microcontroller code is in progress. A method provides a production microcontroller to execute an instruction code and provides the result of the instruction code to an ICE. The ICE, independent from the production microcontroller and simultaneously, executes the same instruction code and produces a result. The ICE compares the result of its computation and the result received from the production microcontroller. The ICE issues a “lock step error” when the result of the comparison is a mismatch. A trace buffer residing in the host device provides the location of the line of code causing the mismatch. After identifying the line of code causing the mismatch the user debugs the erroneous line of code. The debugging process resumes on the next line of code in the microcontroller code under test.

Owner:MONTEREY RES LLC

In-circuit emulator with gatekeeper for watchdog timer

ActiveUS7162410B1Easy to operate and debugDebug operationError detection/correctionSoftware simulation/interpretation/emulationMicrocontrollerIn-circuit emulator

A watchdog timer control using a gatekeeper in an In-Circuit Emulation system. The In-Circuit Emulation system has a microcontroller operating in lock-step synchronization with a virtual microcontroller. When a watchdog event occurs, the gatekeeper, forming a part of the virtual microcontroller, crowbars the reset line of the virtual microcontroller as well as the real microcontroller. This freezes the state of the virtual microcontroller so that debug operations can be carried out. The gatekeeper operates with its own gatekeeper clock independent of the microcontroller clock. When a watchdog event occurs, the gatekeeper clock is rerouted to the virtual microcontroller to facilitate debug operations of the virtual microcontroller.

Owner:MONTEREY RES LLC

Microprocessor development systems

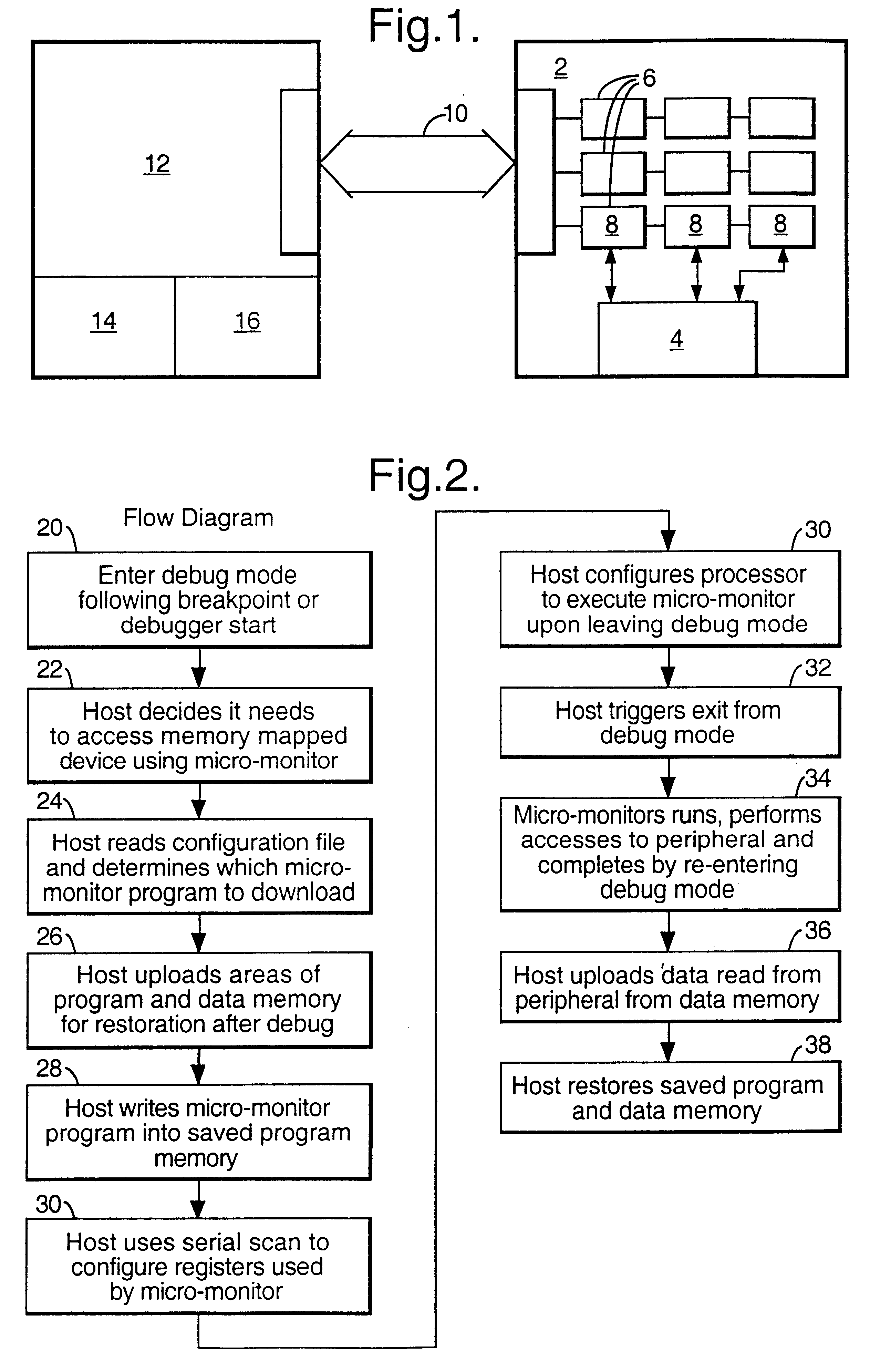

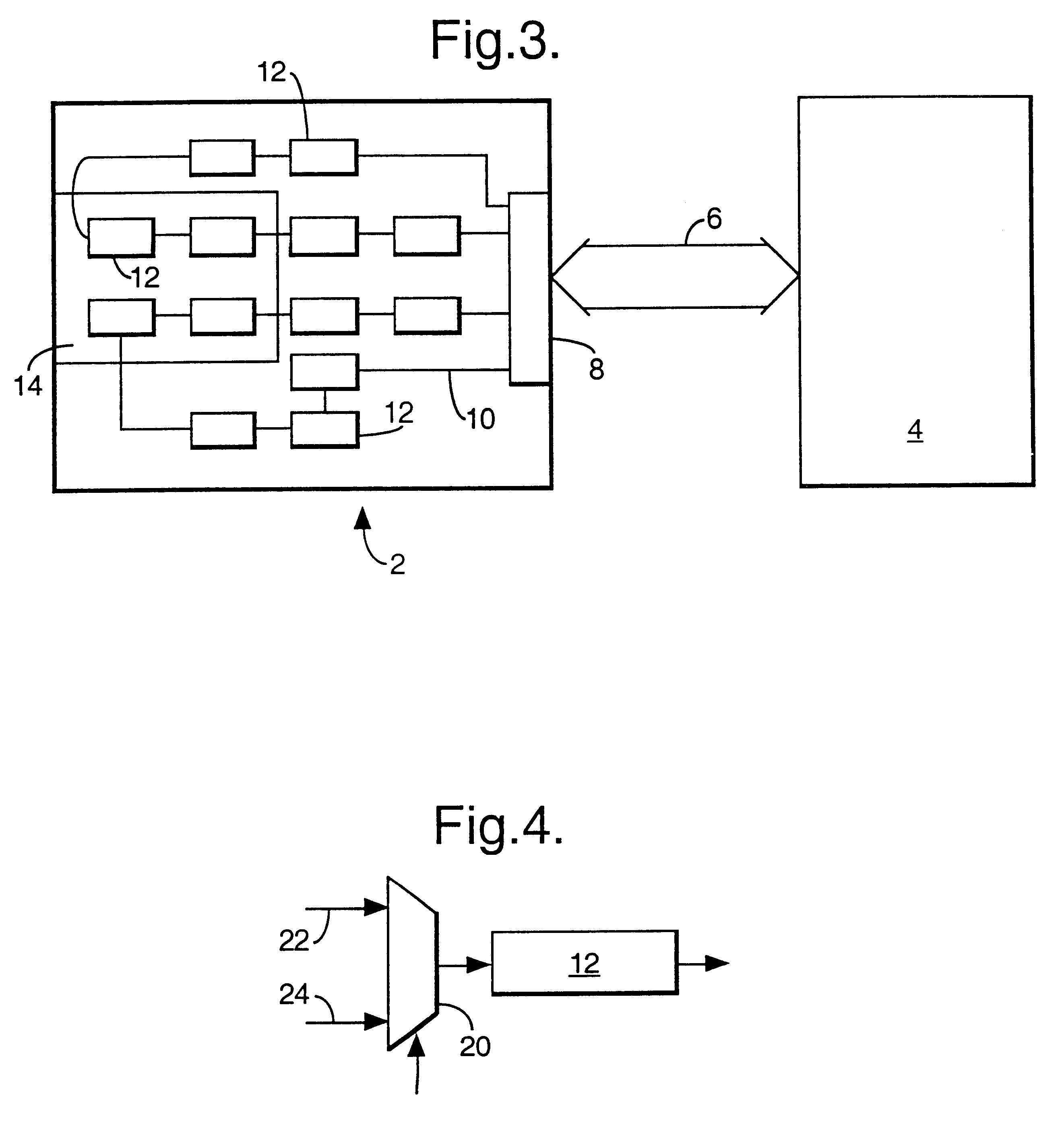

InactiveUS6574590B1Difficult to useSimple memory accessElectronic circuit testingDigital computer detailsEmbedded applicationsTime delays

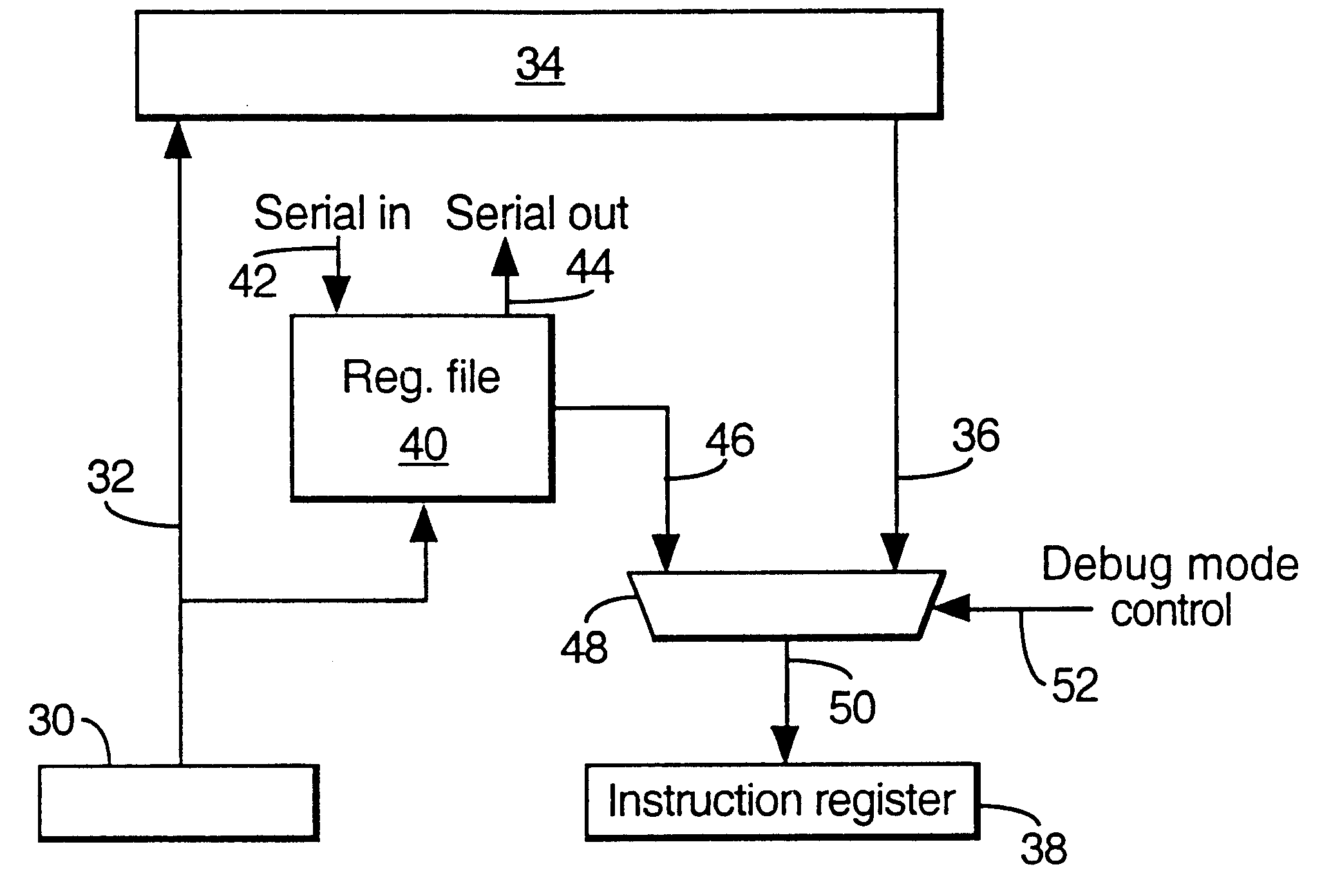

A procedure and processor are disclosed for avoiding lengthy delays in debug procedures during access by a memory mapped peripheral device. The processor includes in-circuit emulation means comprising one or more scan chains or serially connected registers for access by an external host computer system. The procedure comprises:a) the host computer system carrying out a debug procedure via said scan chains, and selectively interrupting such debug procedure for access to a peripheral memory mapped device;b) the host computer system writing into an area or memory of the processor a program for reading and / or writing data at a specified memory location; andc) the host computer system causing said processor to run said program, and then to return to said debug procedure.In another aspect, in order to permit small debugging programs to run, in serial scan in circuit emulation processes, on a processor in a deeply embedded application where no program RAM is provided, the processor includes one or more chains of serially connected registers coupled to interface means for access by an external host to enable a serial scan procedure to be carried out, one such chain including a set of serially coupled registers for storing one or more processor instructions read into a set of registers through the interface means, and the processor including address means, for addressing program memory, coupled to said set of registers for addressing the set of registers, and means for reading the processor instructions in the set of registers to an instruction resister of the processor.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Capturing test/emulation and enabling real-time debugging using an FPGA for in-circuit emulation

ActiveUS7188063B1Improve abilitiesEliminate needError detection/correctionComputer aided designMicrocontrollerFpga implementations

A method for obtaining real-time debug information, e.g., state information and trace information, from an FPGA acting as a virtual microcontroller that is attached to a microcontroller under test. The two devices, the microcontroller and the FPGA execute the same instructions in lock-step with the FPGA acting as an emulator. The FPGA emulates the actual microcontroller and relieves the actual microcontroller from having debug logic installed thereon. FPGA and microcontroller, are coupled using a four pin interface. The FPGA is directly coupled to the PC for both programming and control. The system is implemented such that the microcontroller forwards information regarding I / O reads, interrupt vector information and watchdog information to the FPGA in time before the execution of the next instruction. Thus, the FPGA has an exact copy of the state information of the microcontroller.

Owner:MONTEREY RES LLC

Combined in-circuit emulator and programmer

InactiveUS7089175B1Error detection/correctionSoftware simulation/interpretation/emulationMicrocontrollerProgramming process

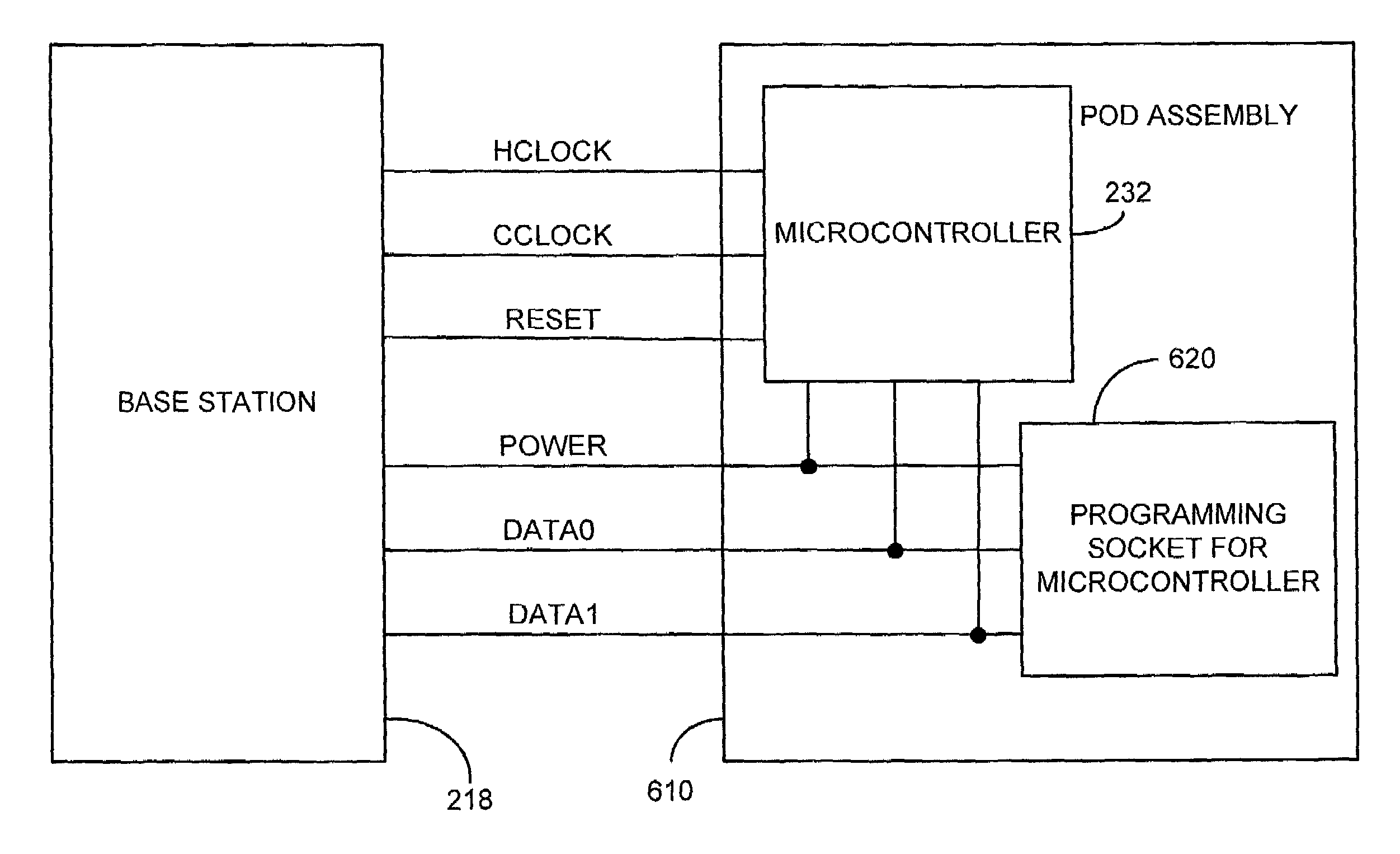

A combined in-circuit emulation system and device programmer. A pod assembly used in an in-circuit emulation system has both a real microcontroller used in the In-Circuit Emulation and debugging process as well as a socket that accommodates a microcontroller to be programmed (a program microcontroller). Programming can be carried out over a single interface that is shared between the microcontroller and the program microcontroller and which is also used to provide communication between the real microcontroller and the In-Circuit Emulation system to carry out emulation functions. In order to assure that the emulation microcontroller does not interfere with the programming process for a microcontroller placed in a programming socket, a special sleep mode is implemented in the emulation microcontroller. This sleep mode is activated by a process that takes place at power on in which the a reset line is released with a specified data line held in a logic high state.

Owner:CYPRESS SEMICON CORP

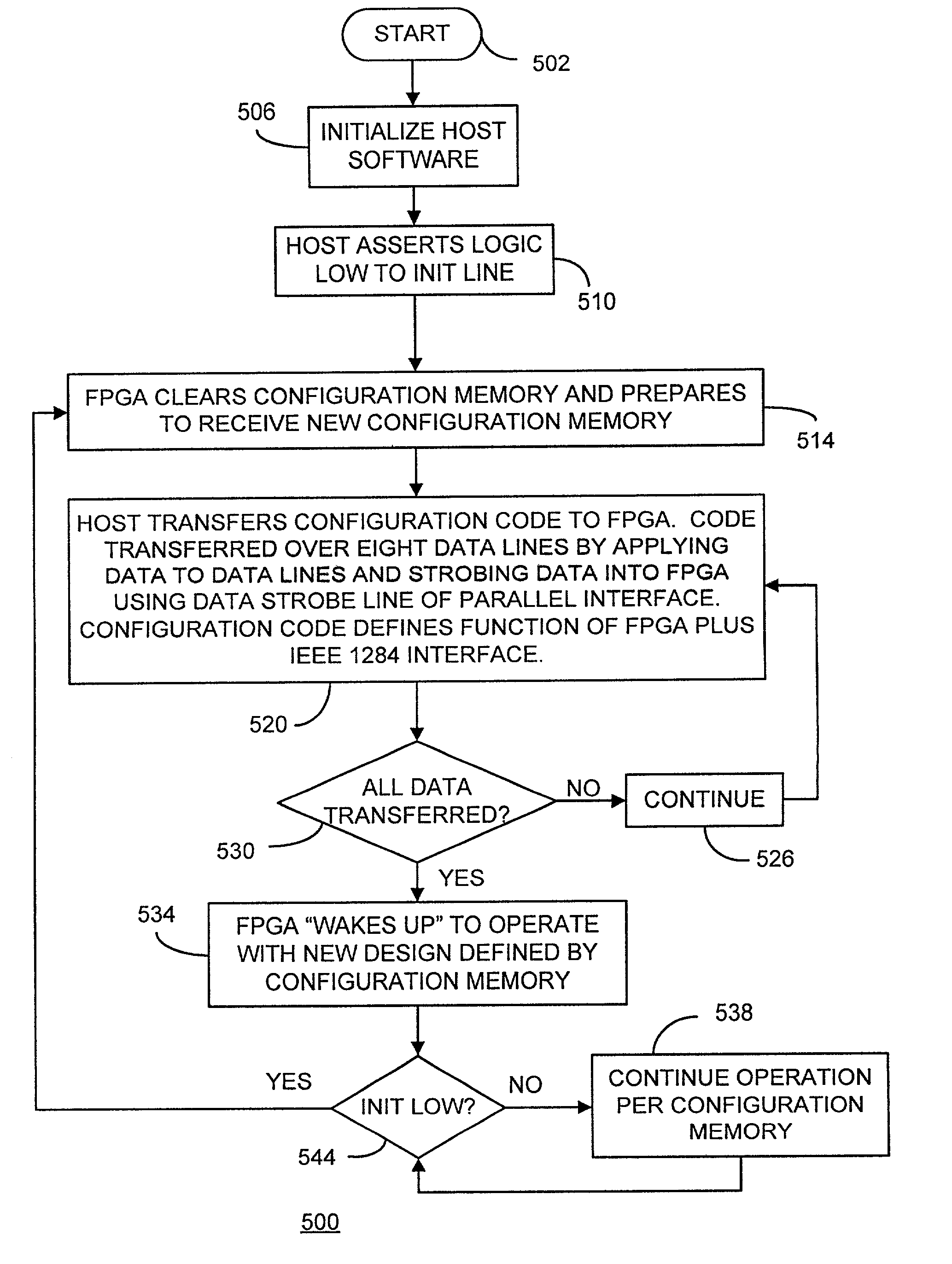

Host to FPGA interface in an in-circuit emulation system

InactiveUS7206733B1Detecting faulty computer hardwareDigital computer detailsMicrocontrollerData shipping

A multi-purpose interface between a host computer and an FPGA. This interface uses an IEEE 1284 compliant EPP mode connection. When the host computer is initialized, a reset of the FPGA is carried out to clear the configuration memory of the FPGA. The data lines of the interface are then used to communicate unidirectional configuration data into the FPGA. The data are clocked by the host computer using the data strobe signal line to clock data into the FPGA. When the FPGA has been fully programmed, including programming an IEEE 1284 compliant EPP mode interface into the FPGA, the data lines are used for bidirectional communication between the host computer and the configured FPGA, in this embodiment operating as a virtual microcontroller.

Owner:CYPRESS SEMICON CORP

Systems and methods for the prevention of unauthorized use and manipulation of digital content

ActiveUS20080178299A1Increases the difficulty of imparting effective modificationDigital data processing detailsMemory adressing/allocation/relocationThird partyTime domain

A number of systems and methods, alone, or in combination, achieve various levels of protection against unauthorized modification and distribution of digital content. This encompasses at least unauthorized study, modification, monitoring, reconstruction, and any other means for subversion from the originally intended purpose and license model of the digital content. The invention combines a number of techniques that in whole, or in part, serve to protect such content from unauthorized modification, reconstructive engineering, or monitoring by third parties. This is accomplished by means of methods which protect against subversion by specific tools operating on specific platforms as well as general tools operating on general platforms. Specific time domain attacks are identified, code modification can be identified and reversed, and virtual and emulated systems are identified. In addition, identification of in-circuit emulator tools (both software and hardware), debuggers, and security threats to running programs can be achieved.

Owner:IPLA HLDG

On-line real-time simulation testing system of wind generating set controller

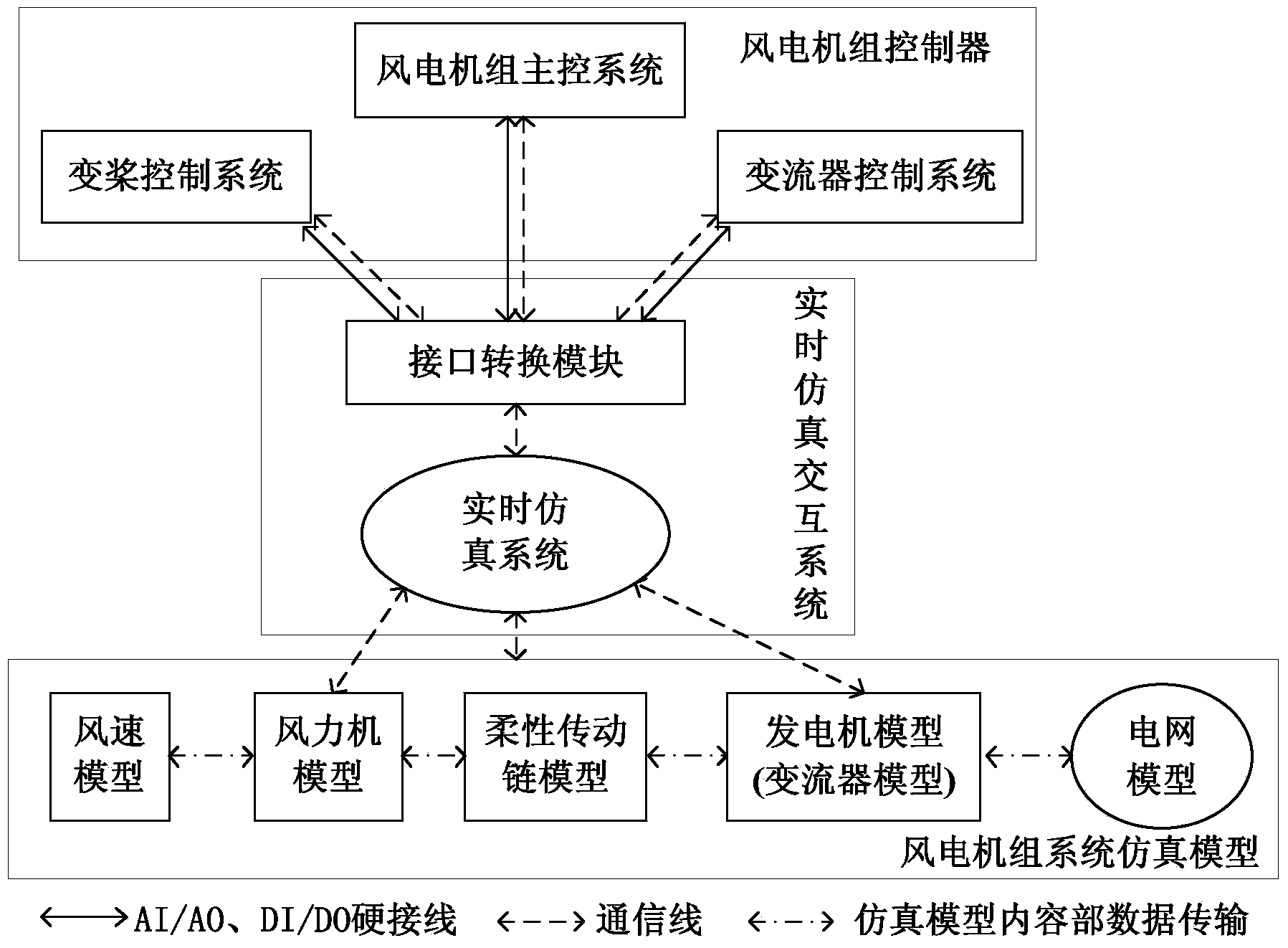

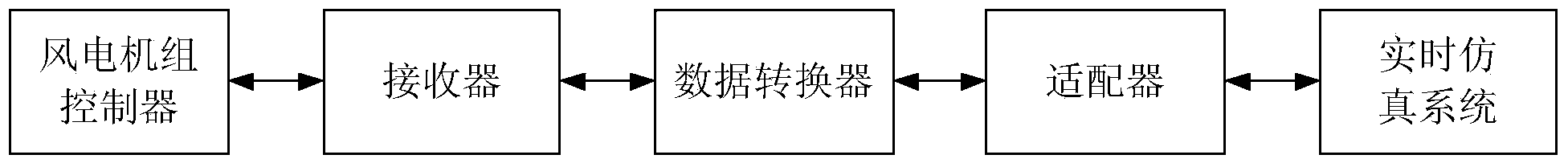

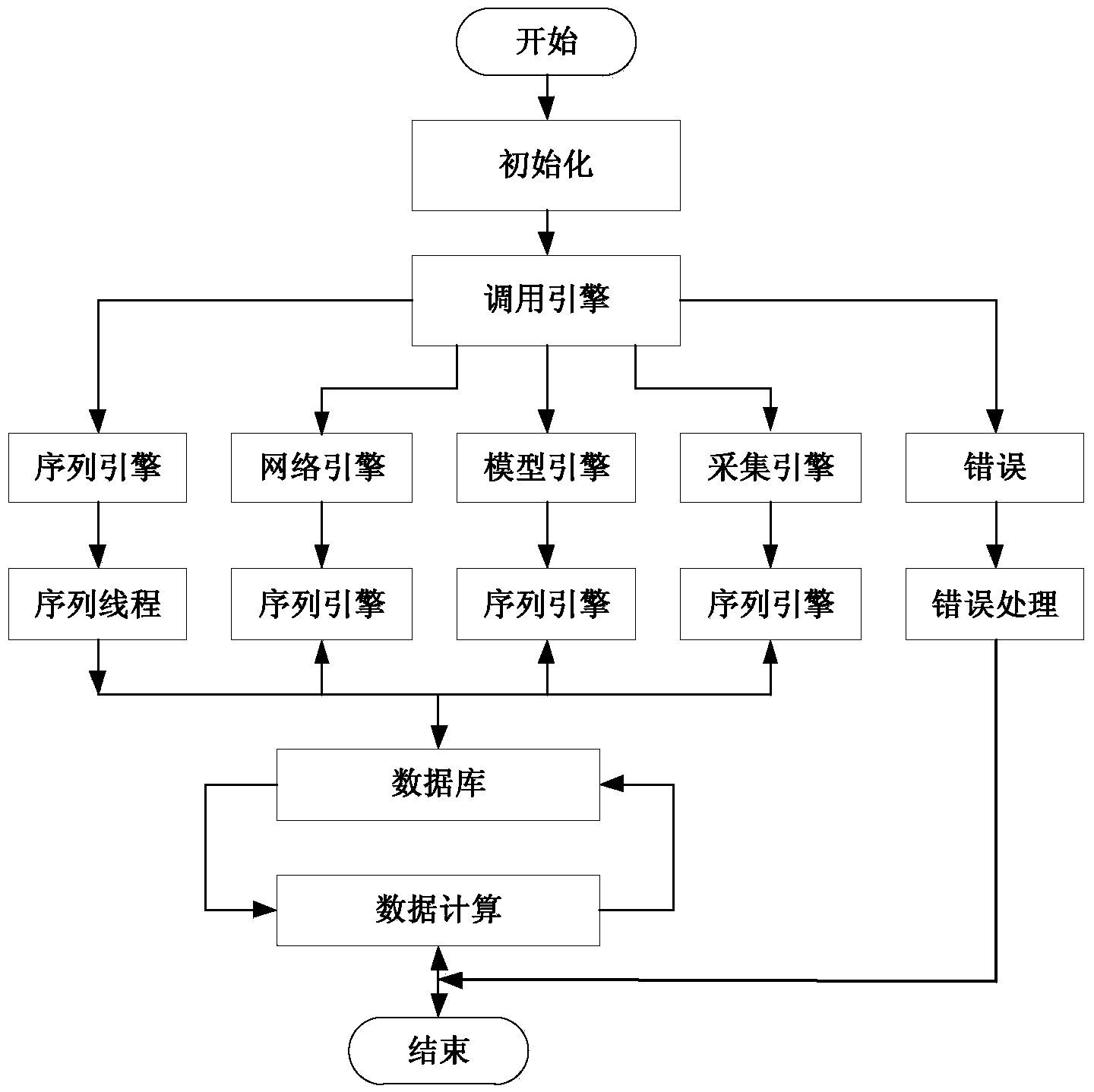

ActiveCN103970128AGuaranteed real-timeGuarantee authenticityElectric testing/monitoringInteraction systemsElectricity

The invention provides an on-line real-time simulation testing system of a wind generating set controller. The on-line real-time testing system comprises the wind generating set controller, a real-time simulation interaction system and a wind generating set system simulation model. The wind generating set controller issues an action instruction to the real-time simulation interaction system. The real-time simulation interaction system converts the received action instruction and transmits the converted action instruction to the wind generation set system simulation model. The wind generating set system simulation model executes the action instruction transmitted by the real-time simulation interaction system, provides a feedback signal needed by the wind generating set controller and feeds the feedback signal back to the wind generating set controller through the real-time simulation interaction system. A communication mode and a hard-wired mode are compatible, and an application platform is provided for kinds of real-time hardware on-line simulation of the wind generating set. The simulation testing system can be used for testing and evaluating operation and protection characteristics of the wind generating set in a laboratory environment, which facilitates rapid experimental verification of a novel control algorithm and a performance improvement scheme.

Owner:STATE GRID CORP OF CHINA +2

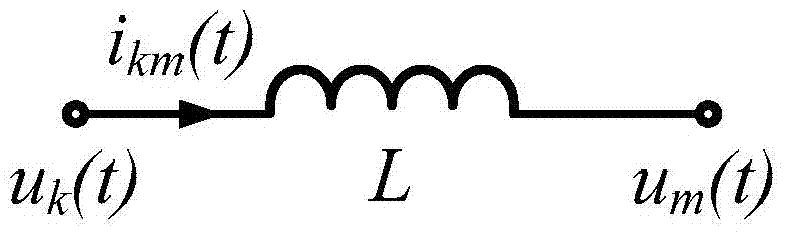

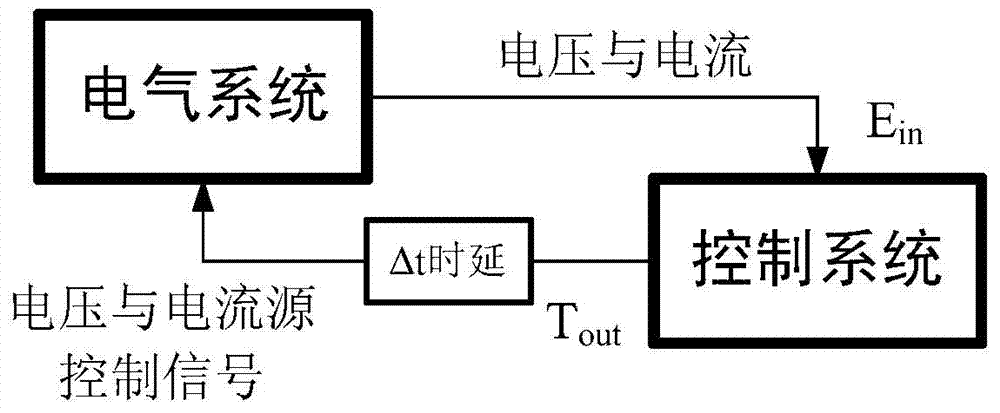

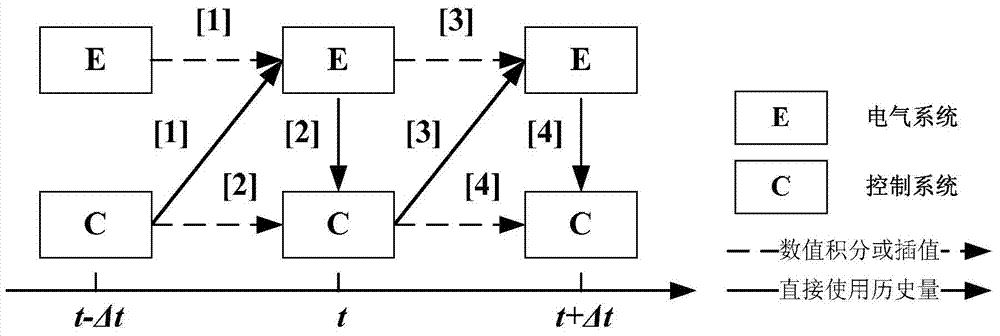

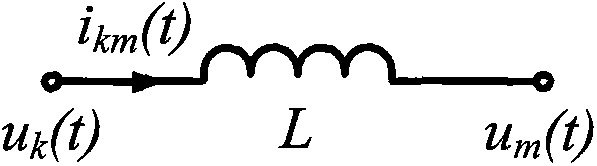

Active power distribution network transient state real-time simulation multi-rate interface method based on FPGA

ActiveCN103942372AReduce the difficulty of implementationGuaranteed real-time simulation accuracySpecial data processing applicationsReal-time simulationIn-circuit emulator

Provided is an active power distribution network transient state real-time simulation multi-rate interface method based on an FPGA. Example basic information is read under an offline environment, and time te needed for calculation of each time step of an electrical system in the FPGA and time tc needed for calculation of each time step of a control system in the FPGA are calculated; a real-time simulation step size delta te of the electrical system is set according to the te; a real-time simulation step size delta tc of the control system is automatically determined according to a formula (please see the formula in the specification); correlation calculation parameters of elements and the example basic information are figured out and uploaded to an online simulation environment, computing resource allocation is carried out, and simulation time t is equal to zero; calculation of one time step and calculation of k time steps are carried out on the electrical system and the control system respectively, wherein t=t+delta tc, and t=t+delta te; the electrical system and the control system carry out multi-rate interface communication; whether the simulation time reaches simulation ending time is judged. The method is easy to achieve, solving time of the electrical system and the control system can be worked out in advance, proper real-time computing time steps are set, multi-rate interface parallel simulation is achieved, on the premise that simulation precision is guaranteed, solving time is greatly shortened, and the implementation difficulty of active power distribution network transient state real-time simulation is reduced.

Owner:TIANJIN UNIV +1

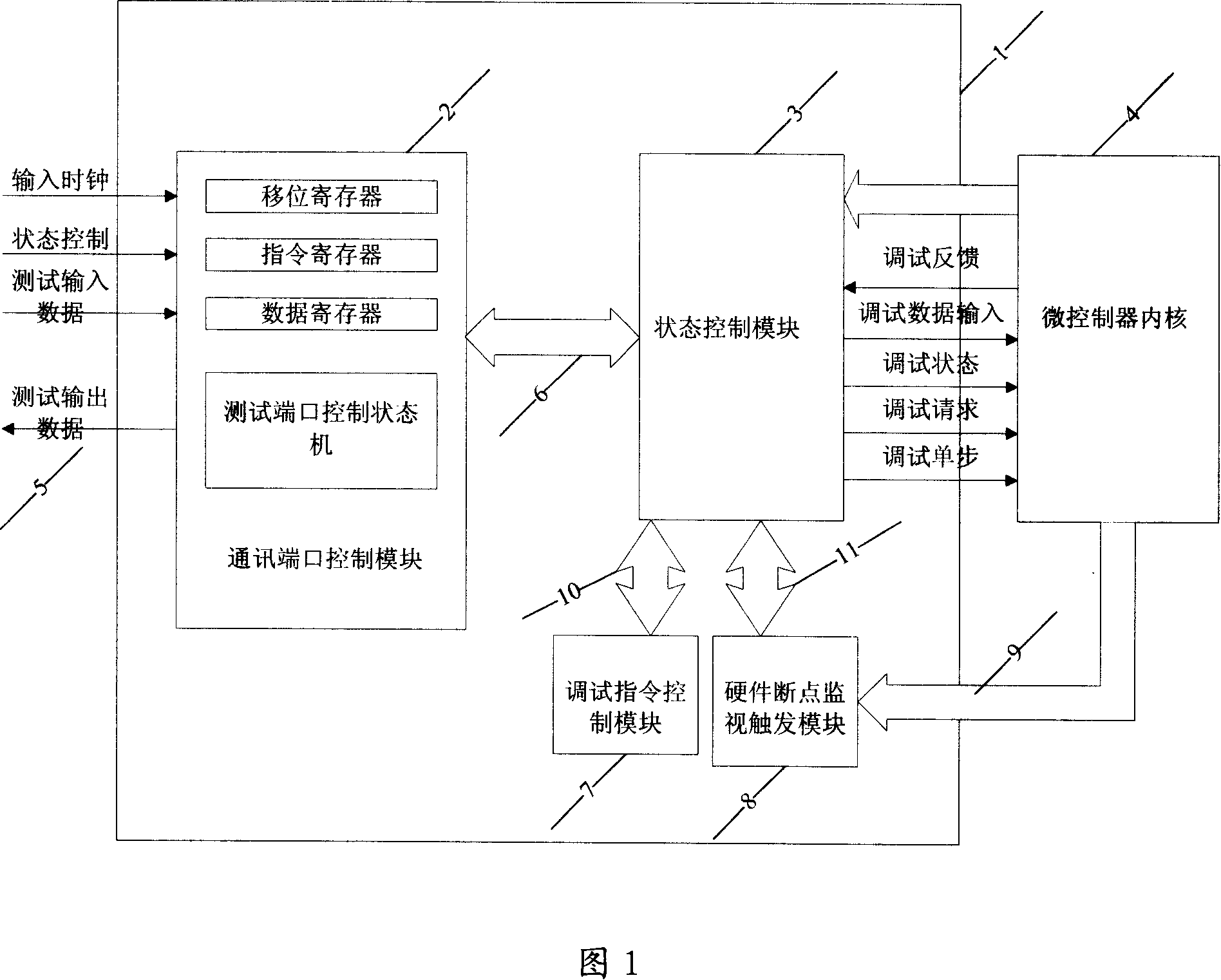

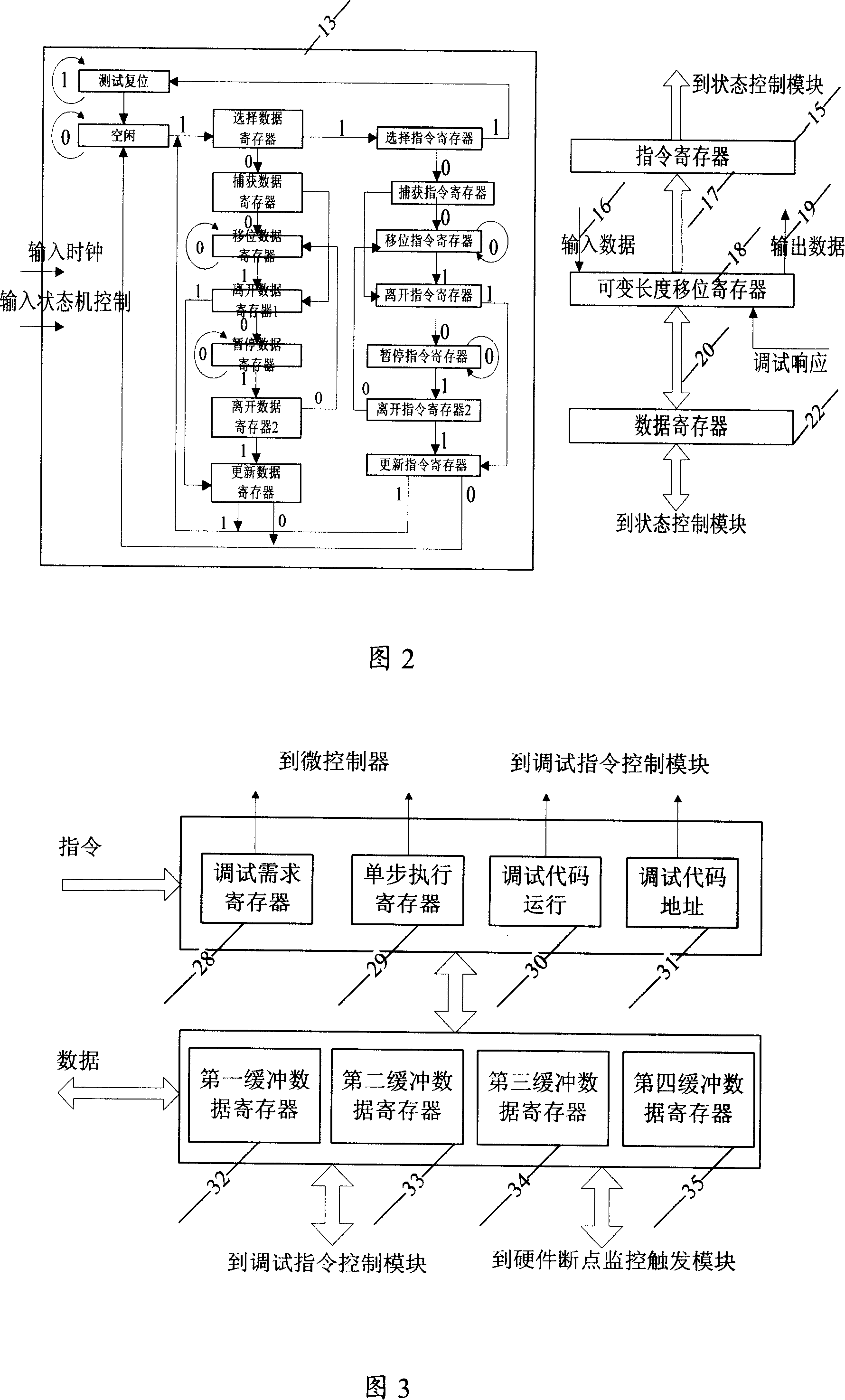

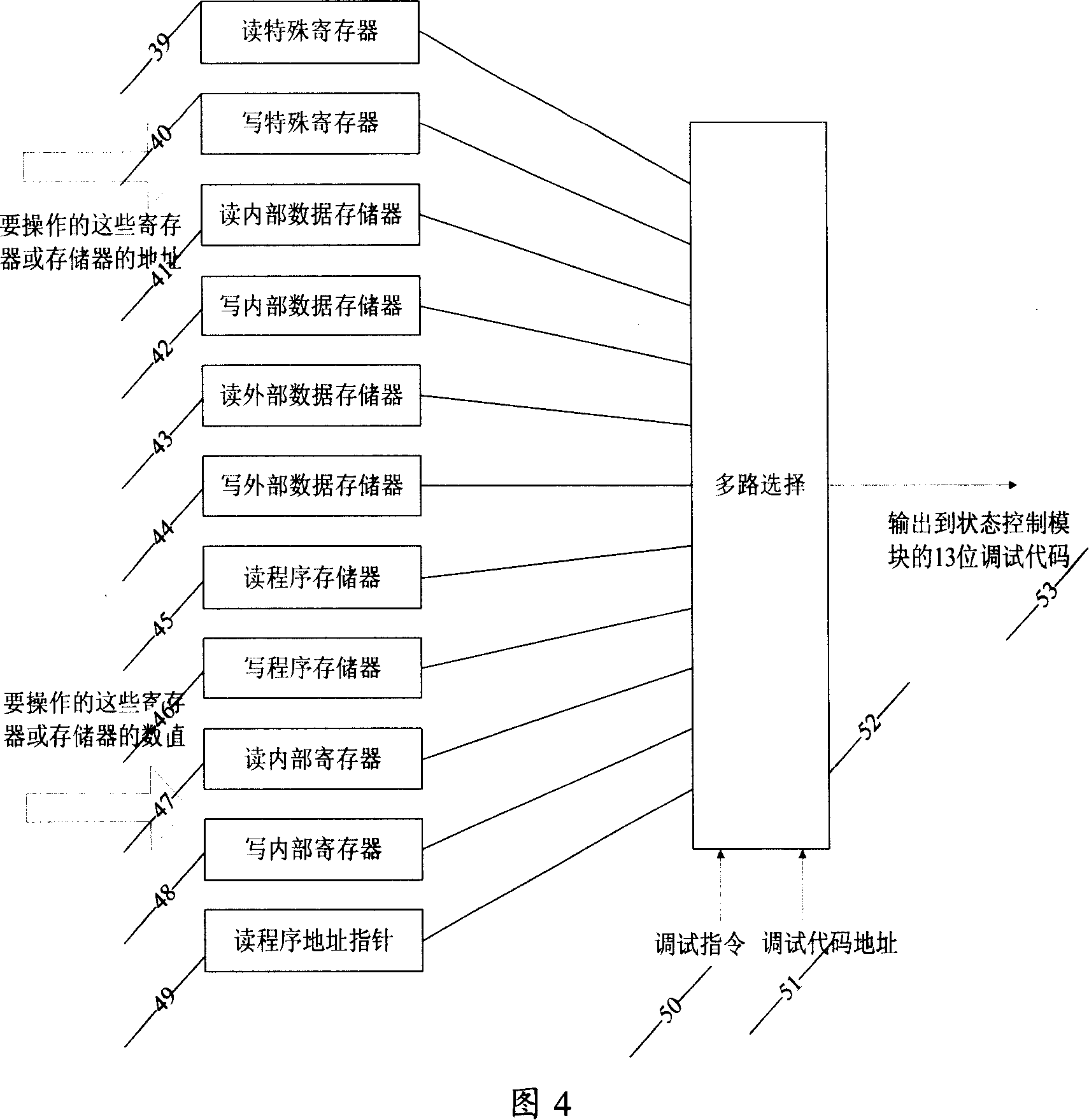

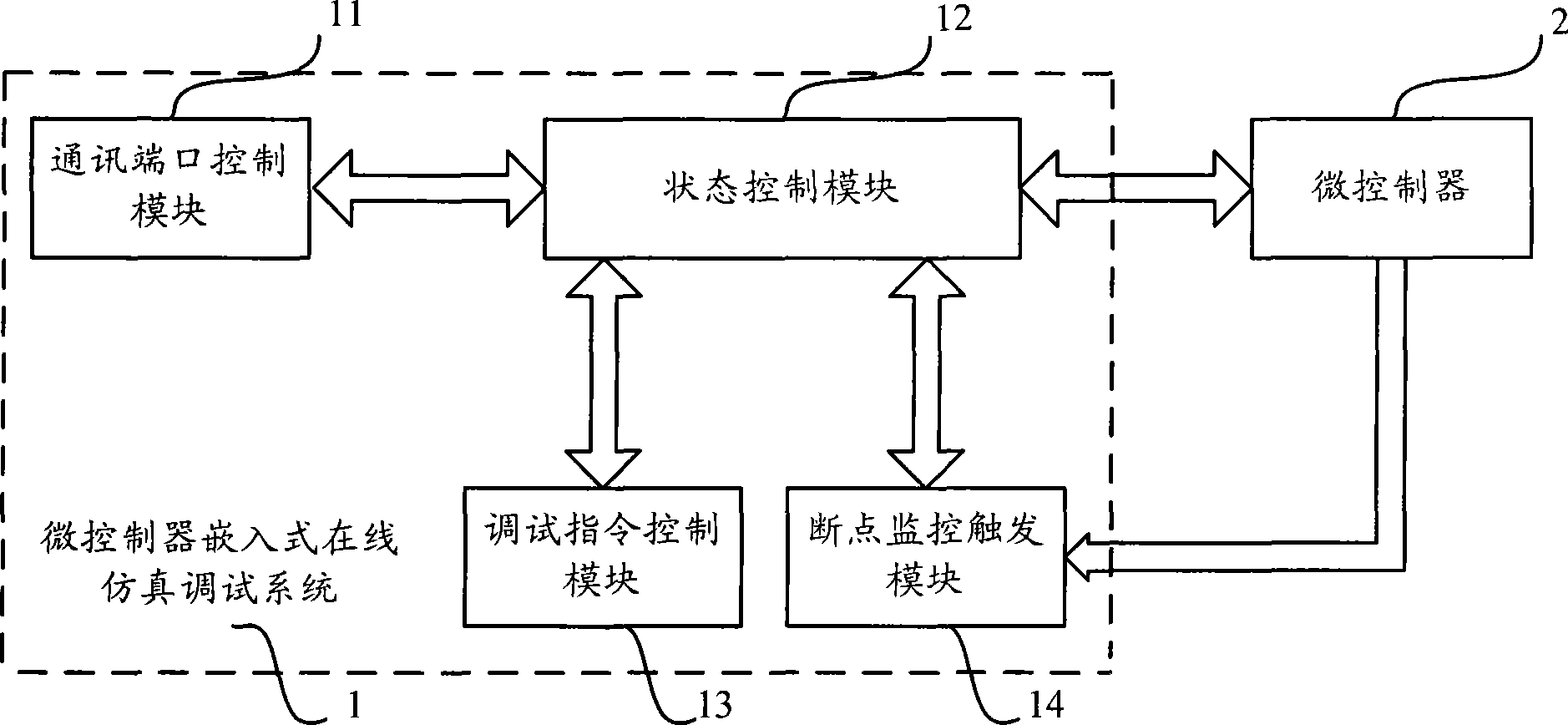

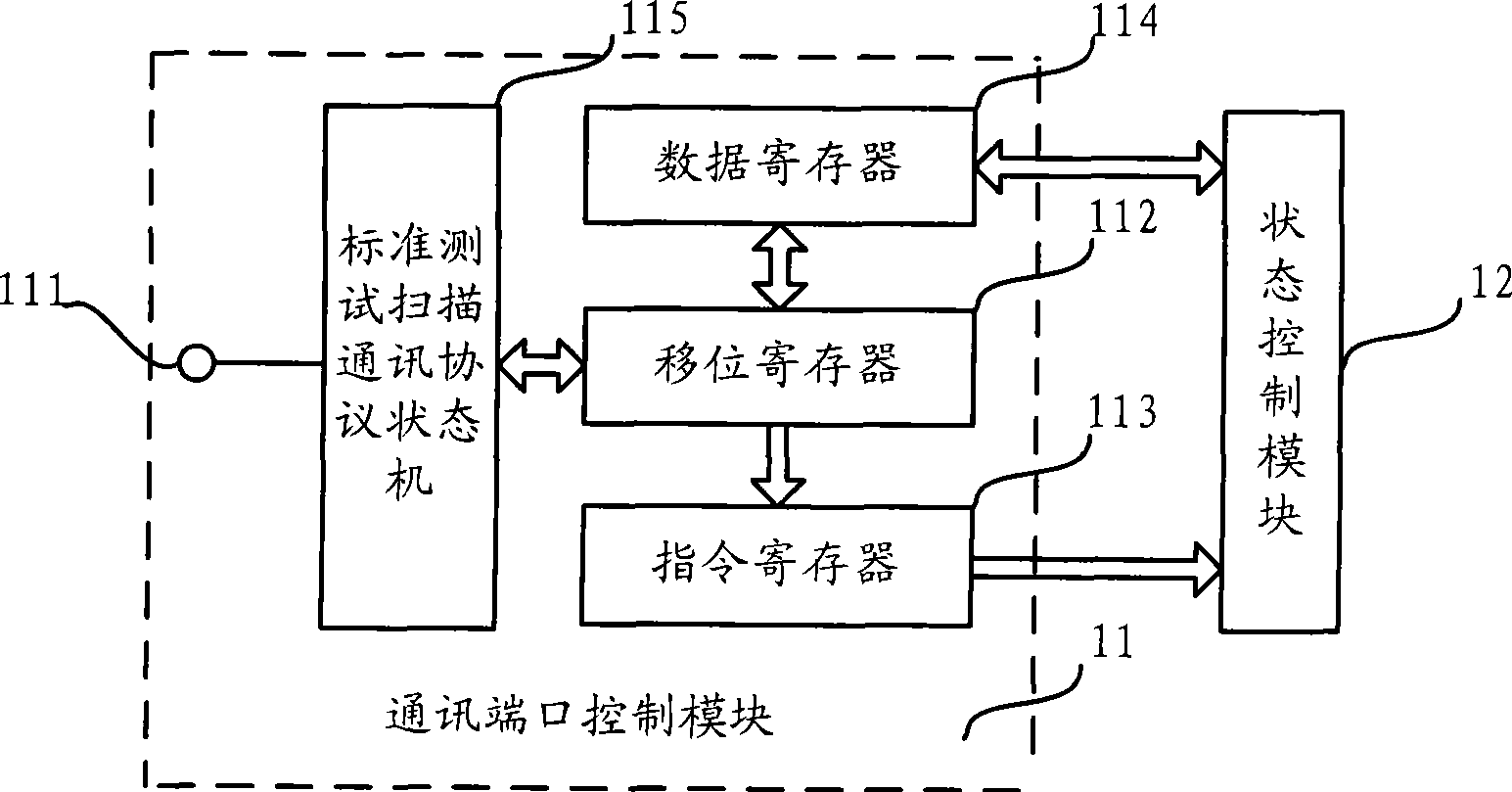

Microcontroller built-in type on-line simulation debugging system

InactiveCN101154183AImproved debugging capabilitiesRealize real-time monitoringSoftware testing/debuggingSpecific functionData memory

The invention provides a microcontroller flush bonding on-line simulation debugging system, comprising a communication port control module, a state control module, a debugging command control module and a hardware breakpoint monitoring trigger module; the modules are collected into a chip through a special debugging command transmitted by a mainboard to control the work of the whole on-line simulation debugging system; complex boundary scan to the inside of the chip through a standard test boundary scan can be finished; the microcontroller chip is controlled according to an outer command to be converted into a debugging mode from a normal mode; a program can be downloaded and numerated from any position in a memorizer of the microcontroller through the debugging communication interface of the mainboard to support the target system single-step debugging and support software breakpoints and hardware breakpoints; the contents of a specific function register, a data memorizer and a program memorizer of the inside of the chip are checked and altered real-time; address bus and data bus are monitored, and the functions of real-time logical tracing, etc. are realized. The invention is of clear and simple structure, high-efficient operating effect and precise real-time monitoring.

Owner:SHANGHAI EASTSOFT MICROELECTRONICS

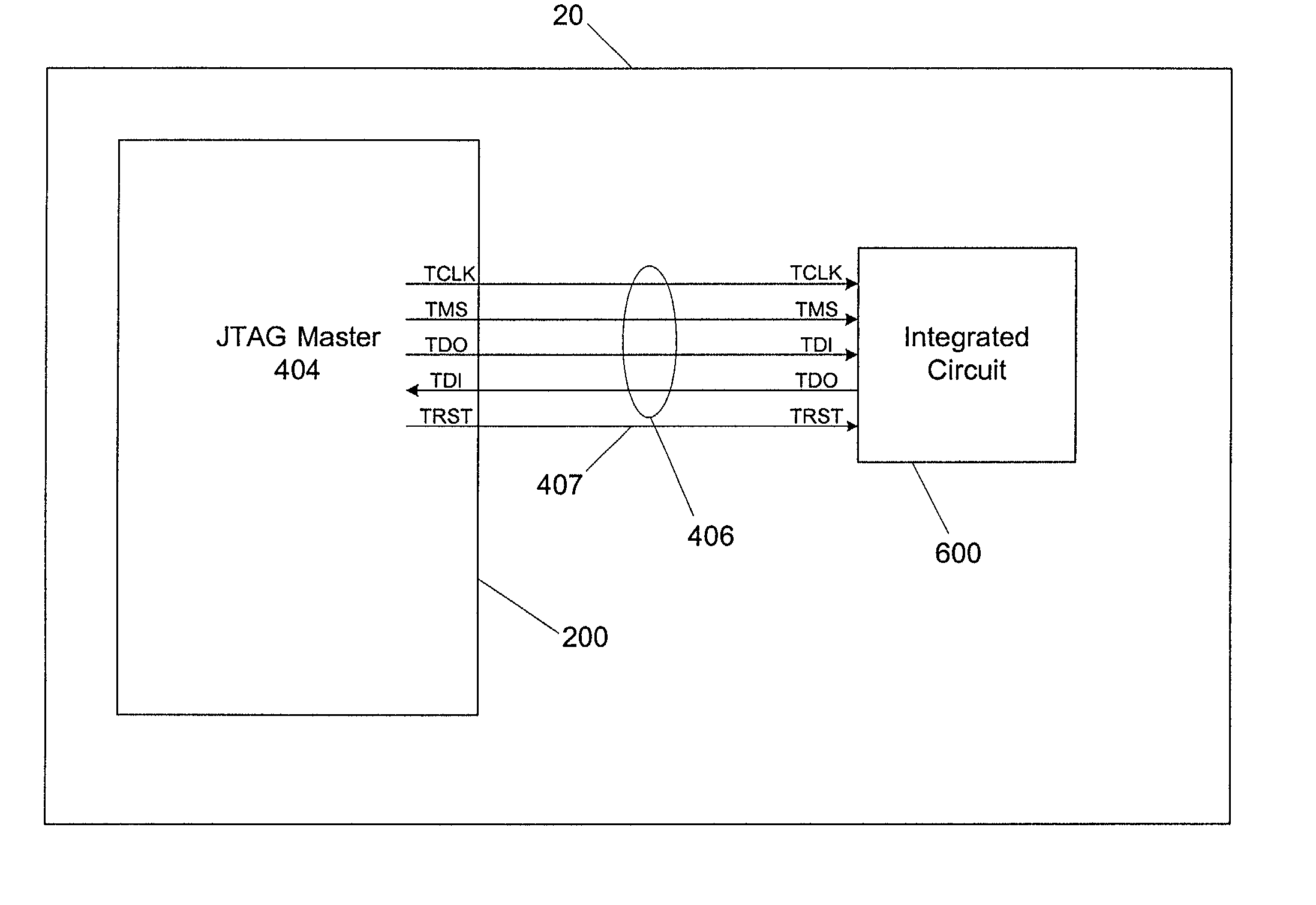

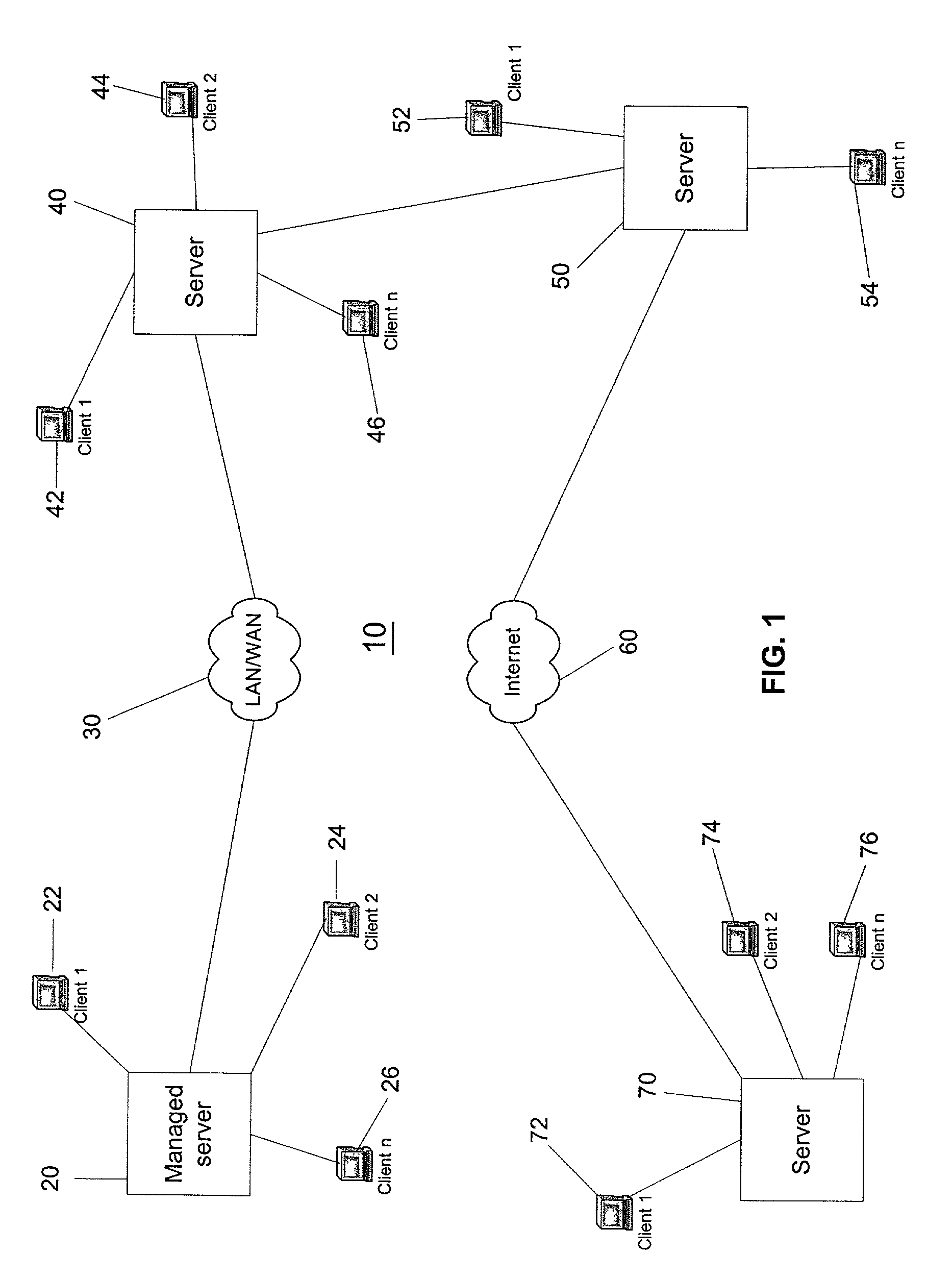

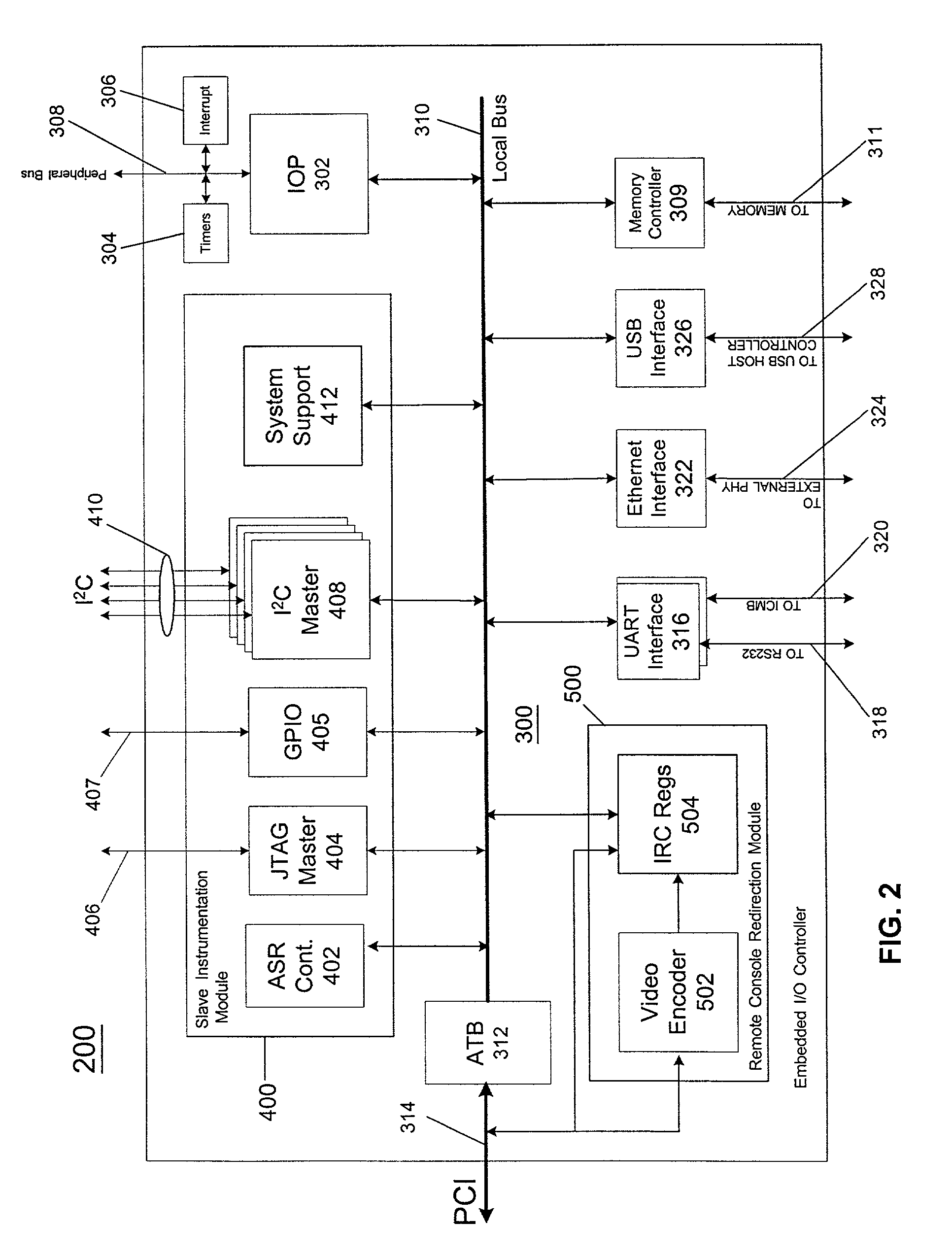

Method and apparatus for providing JTAG functionality in a remote server management controller

InactiveUS7047462B2Electronic circuit testingDetecting faulty hardware by remote testCommand and controlJoint Test Action Group

The disclosed embodiments relate to the field of remote server management. More particularly, the embodiments relate to providing an embedded JTAG master in a remote server management controller. In an exemplary embodiment, the JTAG master is adapted to perform command and control functions on a wide range of integrated circuit components within a managed server. The JTAG master may also be configured to provide communication according to the In-Target Probe (ITP) and In-Circuit Emulation (ICE) test methodologies.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP +1

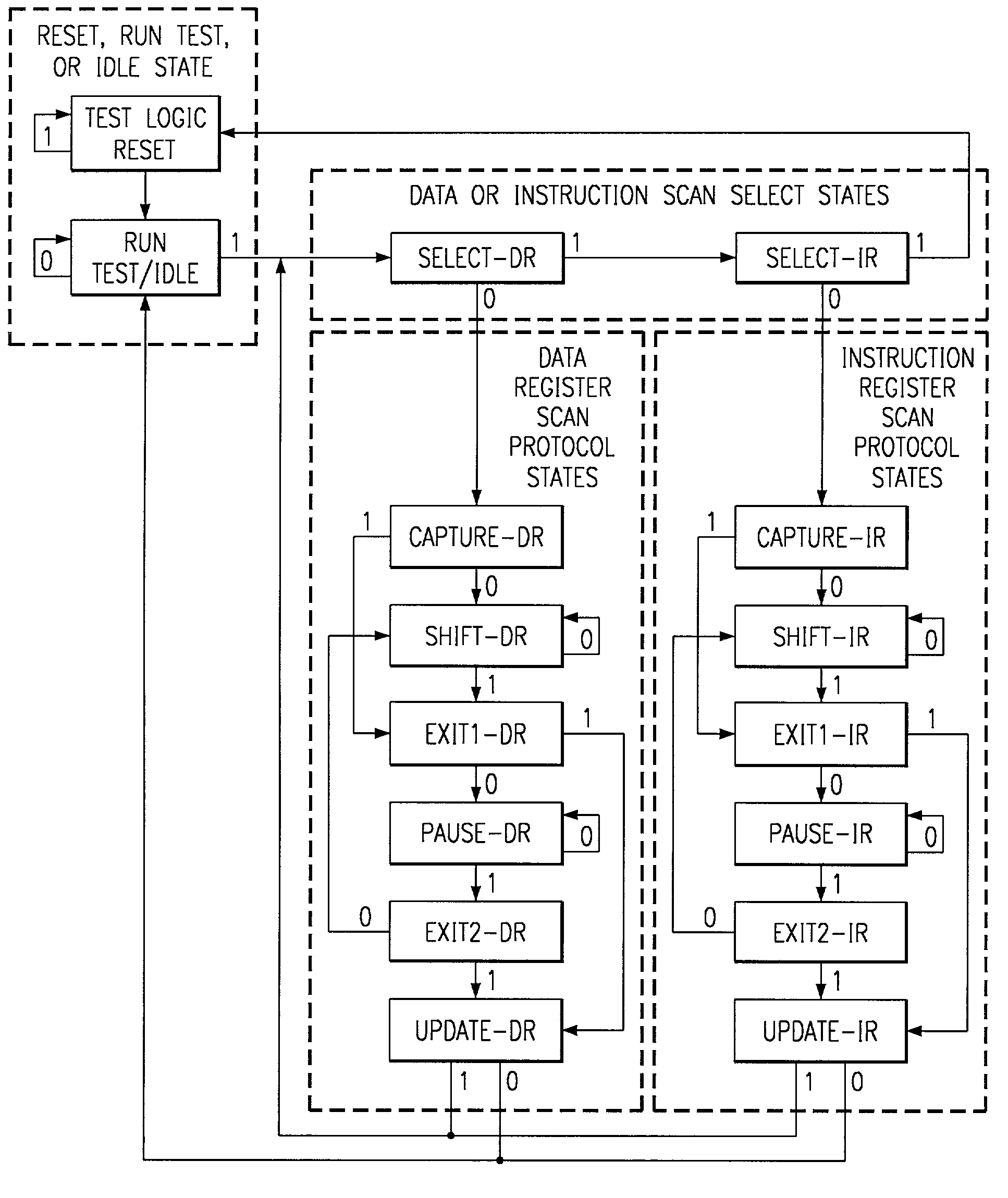

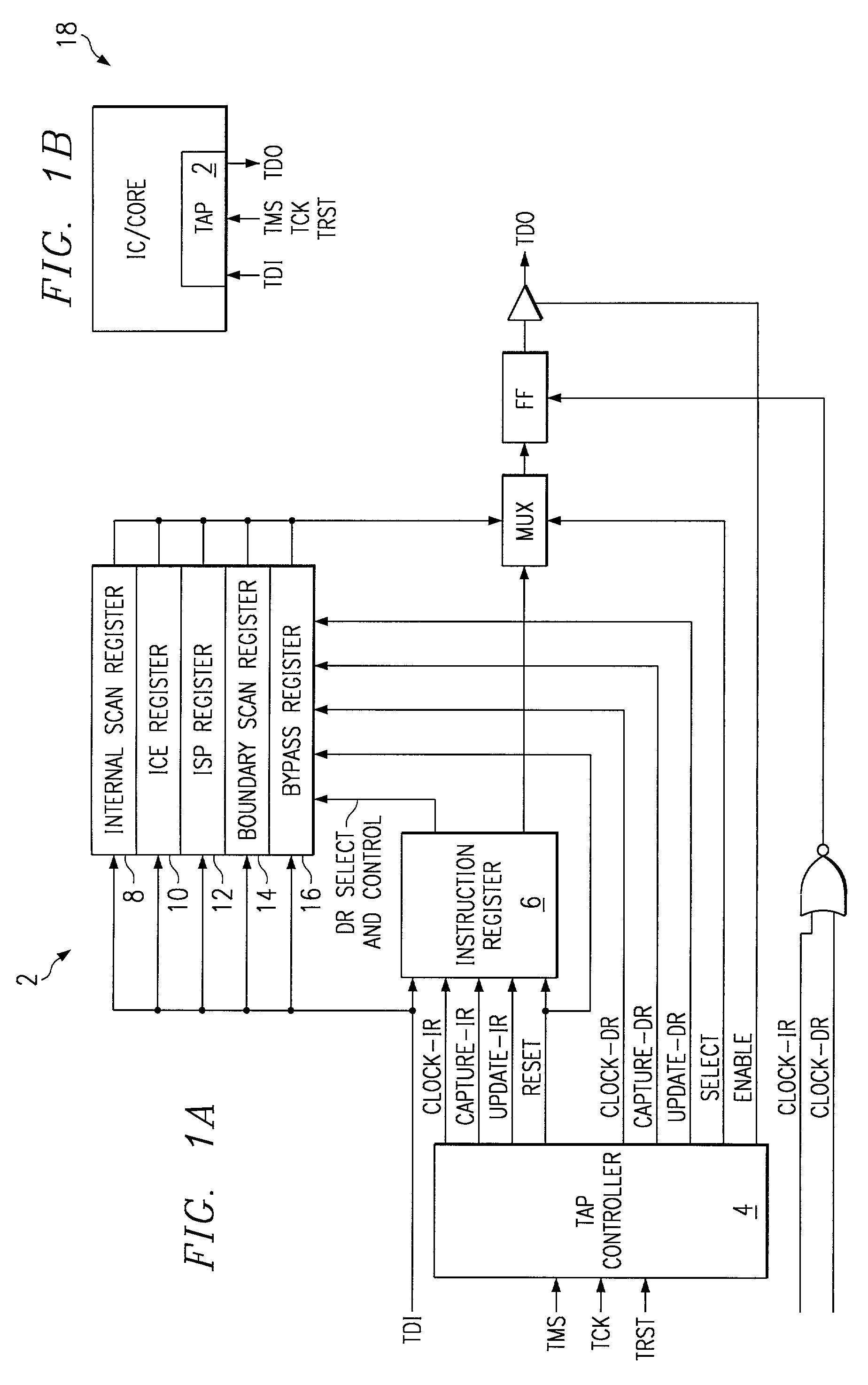

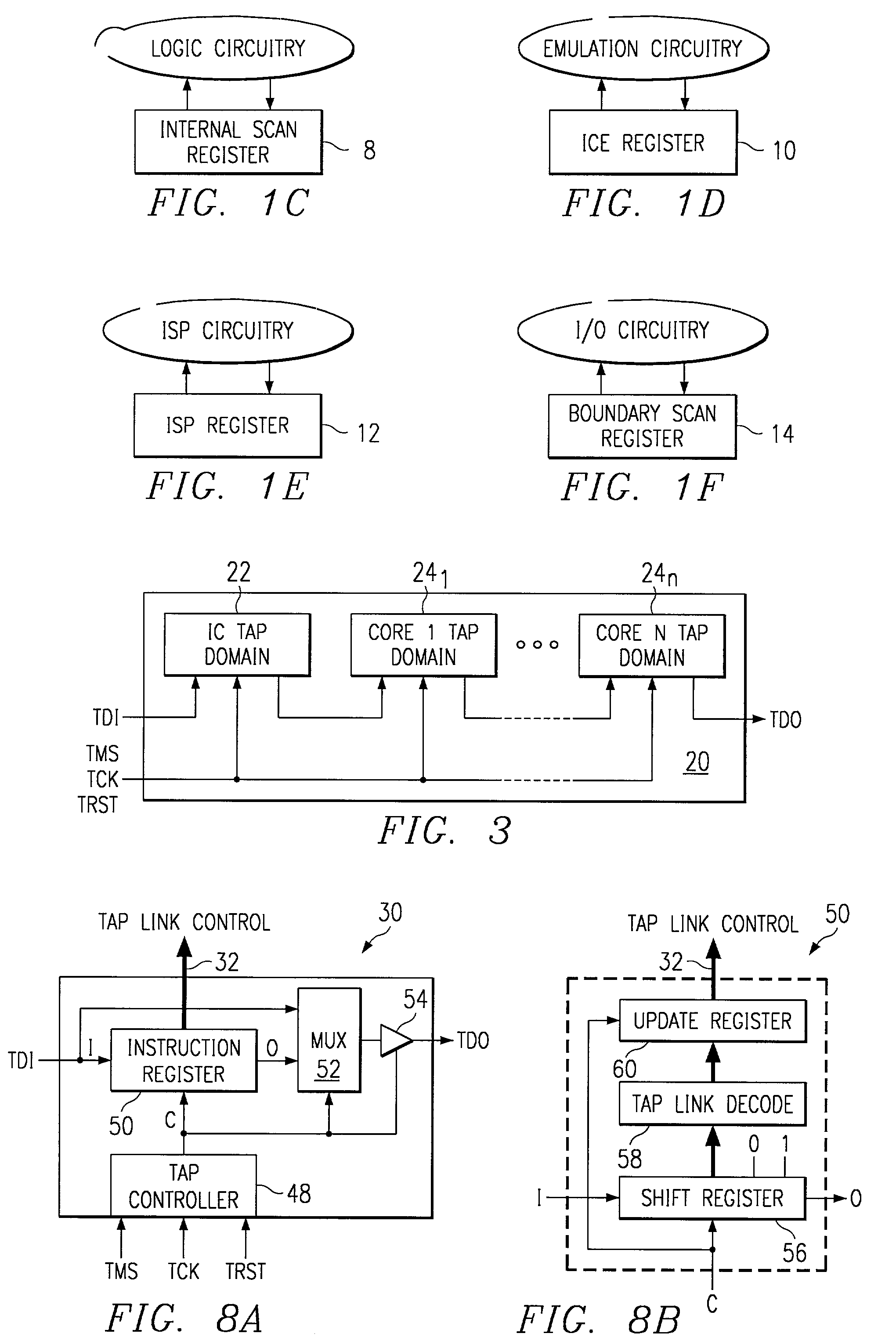

Selecting different 1149.1 TAP domains from update-IR state

InactiveUS7058862B2Electronic circuit testingDetecting faulty computer hardwareIn-circuit emulatorAccess port

IEEE 1149.1 Test Access Ports (TAPs) may be utilized at both IC and intellectual property core design levels. TAPs serve as serial communication ports for accessing a variety of embedded circuitry within ICs and cores including; IEEE 1149.1 boundary scan circuitry, built in test circuitry, internal scan circuitry, IEEE 1149.4 mixed signal test circuitry, IEEE P5001 in-circuit emulation circuitry, and IEEE P1532 in-system programming circuitry. Selectable access to TAPs within ICs is desirable since in many instances being able to access only the desired TAP(s) leads to improvements in the way testing, emulation, and programming may be performed within an IC. A TAP linking module is described that allows TAPs embedded within an IC to be selectively accessed using 1149.1 instruction scan operations.

Owner:TEXAS INSTR INC

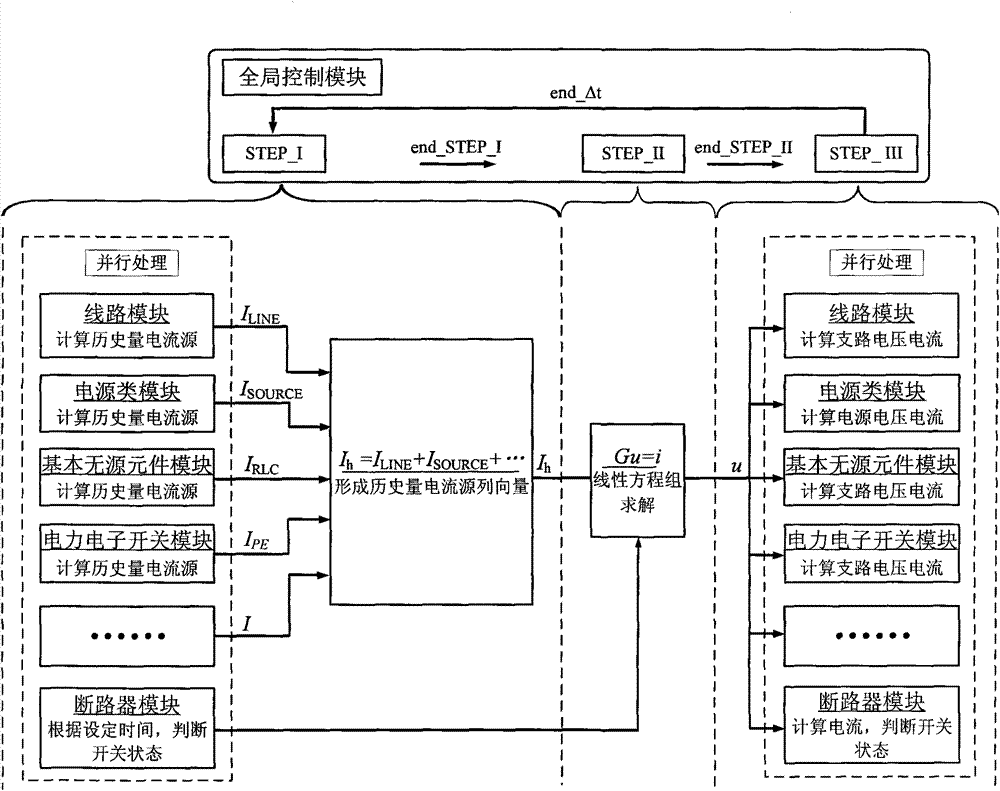

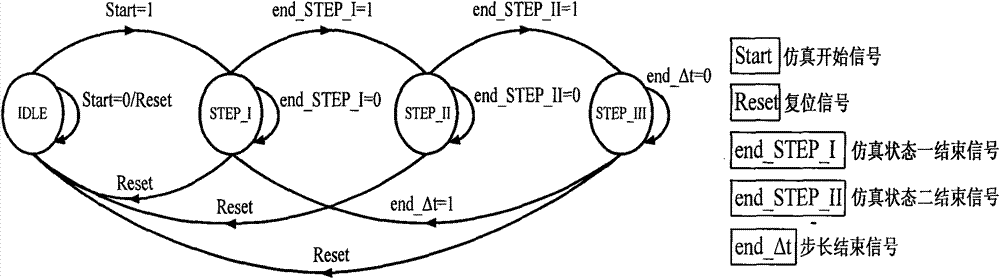

Active power distribution network transient state real-time simulation system designing method based on FPGA

InactiveCN103793562AVerify feasibilityGuaranteed real-timeSpecial data processing applicationsTransient stateSystems design

The invention relates to an active power distribution network transient state real-time simulation system designing method based on an FPGA. The active power distribution network transient state real-time simulation system designing method can be implemented in an off-line simulation environment and an on-line simulation environment in a dividing mode, the off-line simulation environment is responsible for calculating the total clock period number-n<total> and simulation using time-t<total> calculated in each time step, the simulation step size deltat is set according to the real-time simulation using time-t<total>, relevant parameters calculated according to the simulation step size deltat and the read basic parameter information are uploaded to the on-line simulation environment based on the FPGA. Real-time simulation calculation is completed in the on-line simulation environment, the simulation state is controlled through a finite-state machine, each time step includes the steps of historical item current source column vector calculation of all elements, total historical item current source column vector formation of the elements and linear equation system solving and updating of the elements, and the historical item current source column vector calculation step of the elements and the updating step are completely independent and can be processed in a concurrent mode. According to the active power distribution network transient state real-time simulation system designing method based on the FPGA, the real-time performance of the transient state simulation process of the whole system is guaranteed, and the good feasibility and the good applicability are achieved.

Owner:GUANGDONG POWER GRID CO LTD +2

Emulation system with peripherals recording emulation frame when stop generated

InactiveUS7392431B2Software testing/debuggingSpecific program execution arrangementsDigital dataProgram instruction

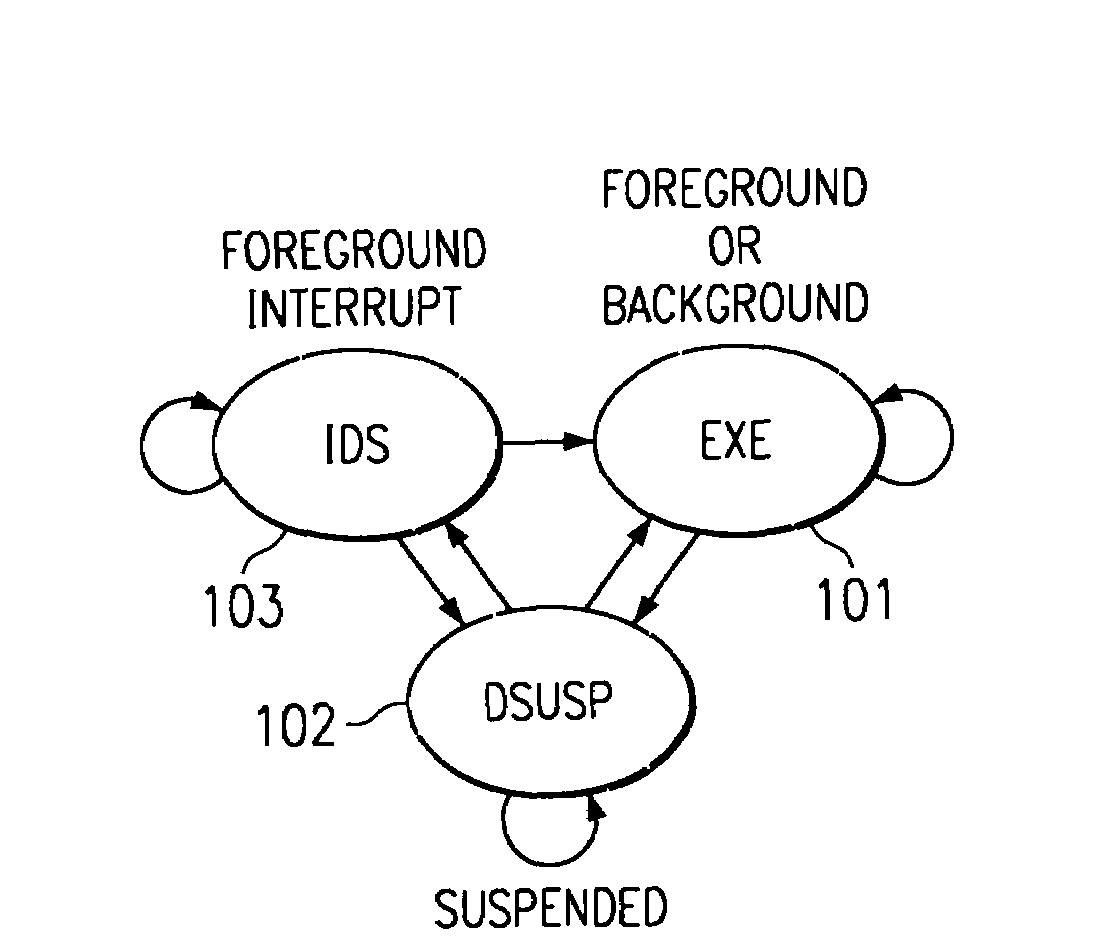

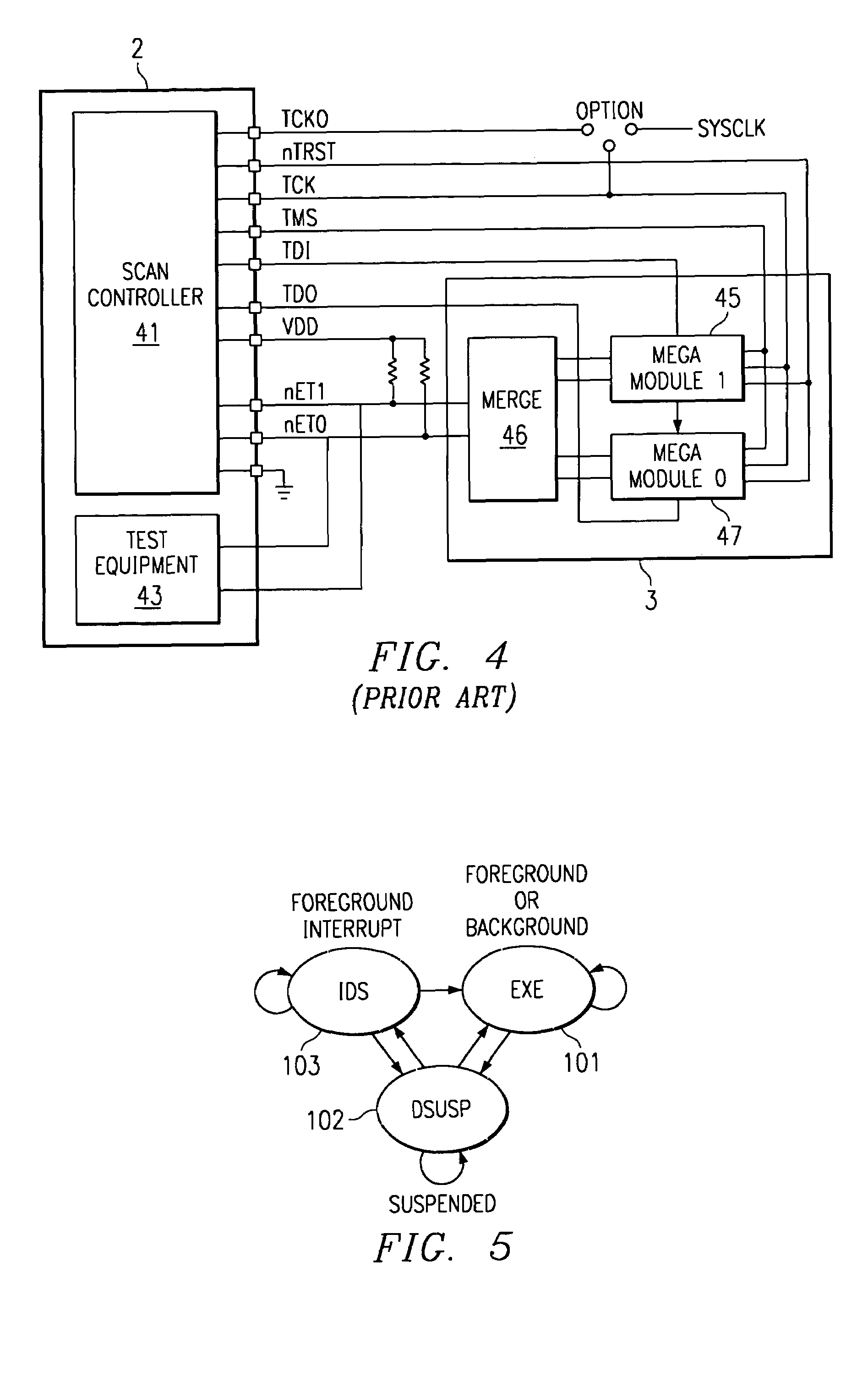

In-circuit-emulation of an integrated circuit includes a digital data processor capable of executing program instructions. A first debug event is detected during normal program execution. The causes the in-circuit-emulation to suspend program execution except for real time interrupts. A debug frame counter increments on each interrupt and decrements on each return from interrupt. If a debug event is detected during an interrupt service routine, that interrupt service routine is suspended and the count of the debug frame counter is stored. Execution of other interrupt service routines in response to corresponding interrupts is still permitted. The integrated circuit includes plural debug event detectors and the debug frame count is stored at the detector detecting a debug event during an interrupt service routine. This permits a determination of the order of interrupts triggering debug events by reading the stored debug frame count from each debug event detector.

Owner:TEXAS INSTR INC

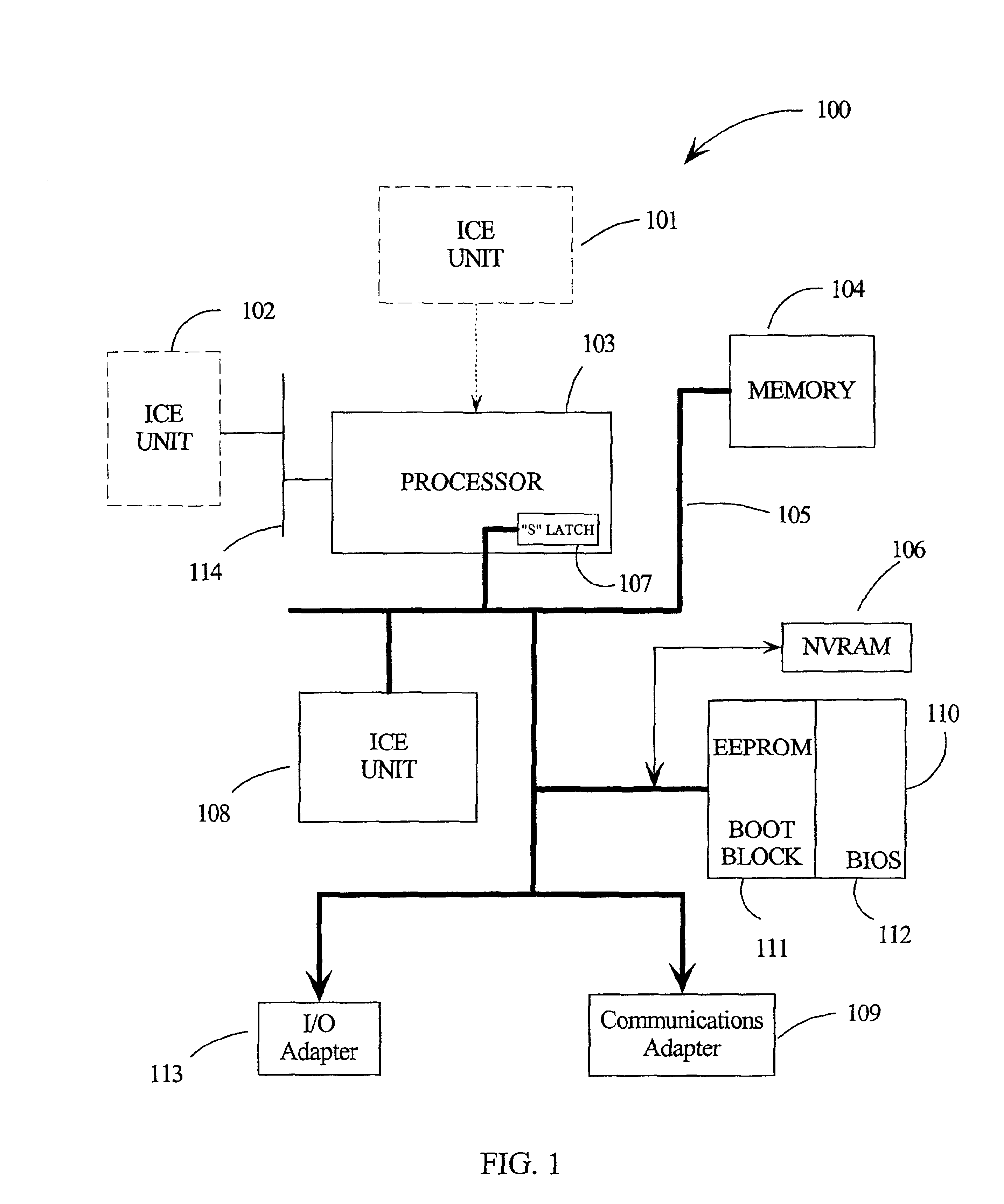

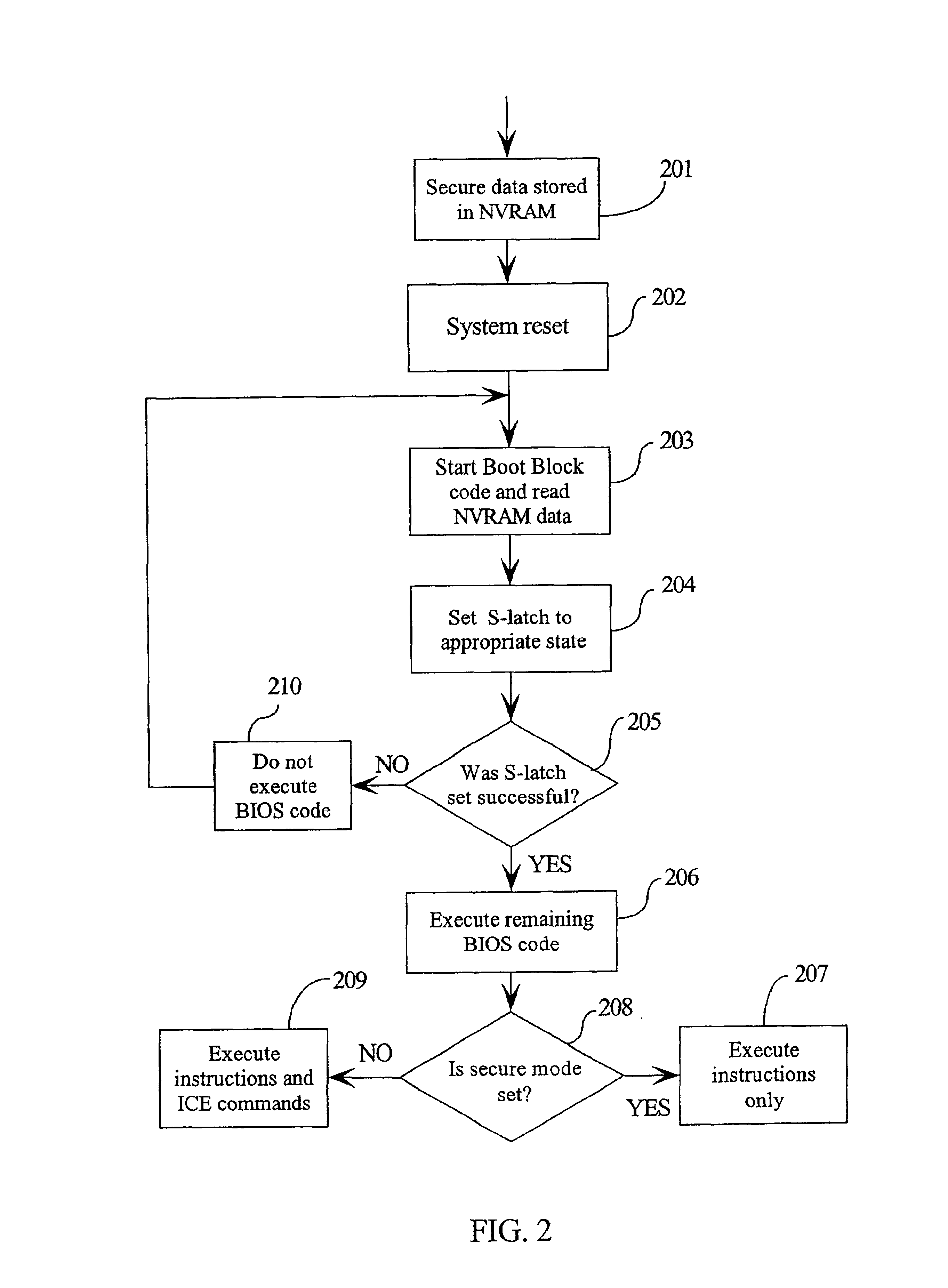

Method and system for setting a secure computer environment

InactiveUS6925570B2None of methods is secureDigital data processing detailsDigital computer detailsBlock codeComputerized system

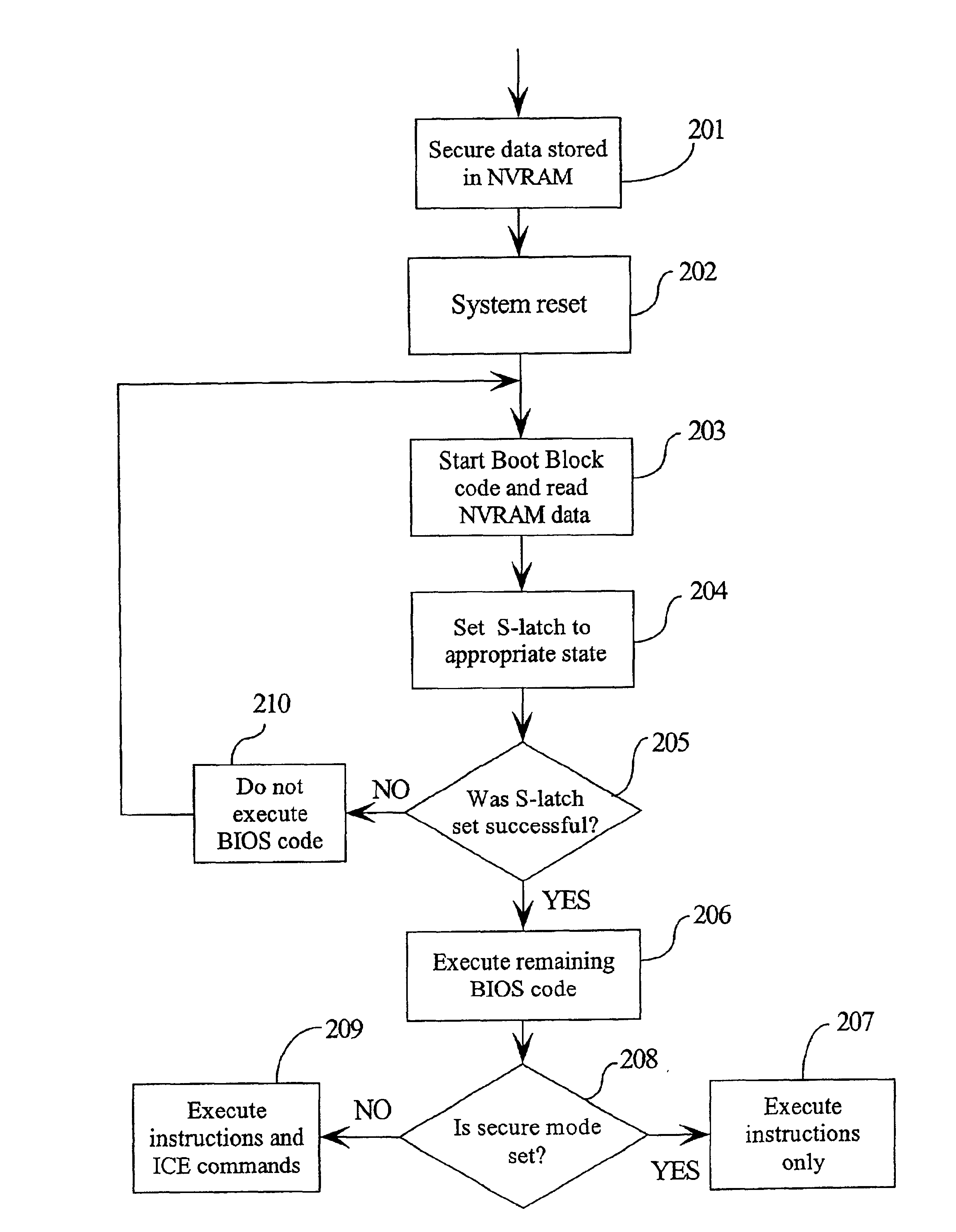

A computer system processor incorporates a special S-latch which may only be set by secure signals. One state of the S-latch sets the processor into a secure mode where it only executes instructions and not commands from an In Circuit Emulator (ICE) unit. A second state of the S-latch sets the processor into a non-secure mode. A non-volatile random access memory (NVRAM) is written with secure data which can only be read by boot block code stored in a BIOS storage device. The boot block code is operable to read the secure data in the NVRAM and set the S-latch to an appropriate security state. If the boot block code cannot set the S-latch, then remaining boot up with BIOS data is stopped. On boot up the boot block code reads the NVRAM and sets the S-latch into the appropriate security state.

Owner:LENOVO (SINGAPORE) PTE LTD

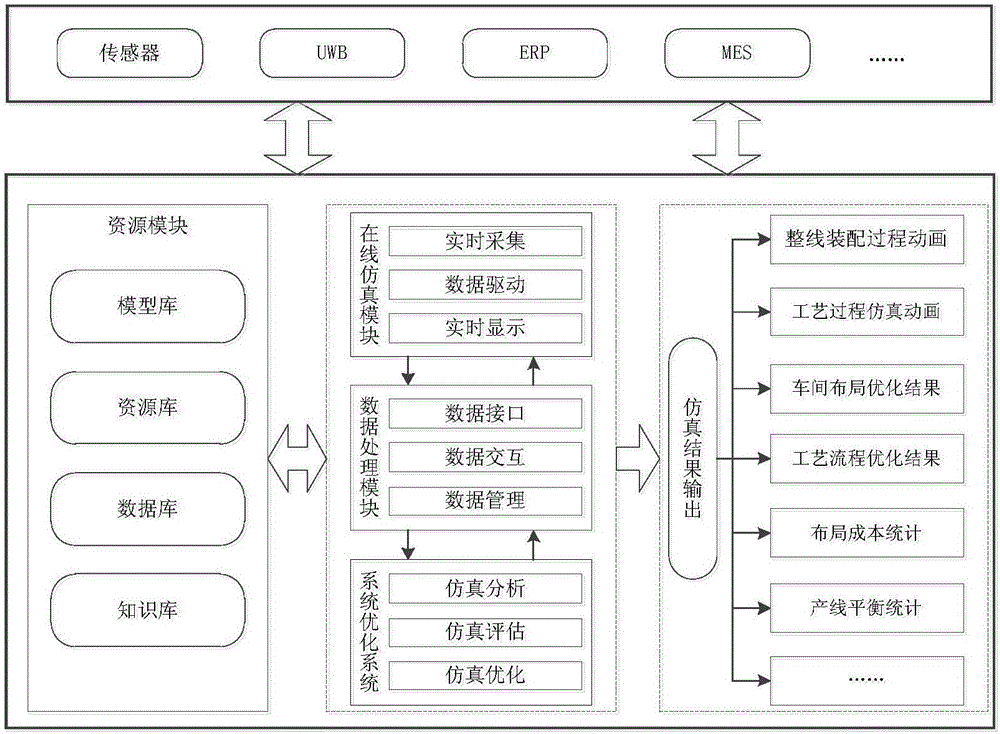

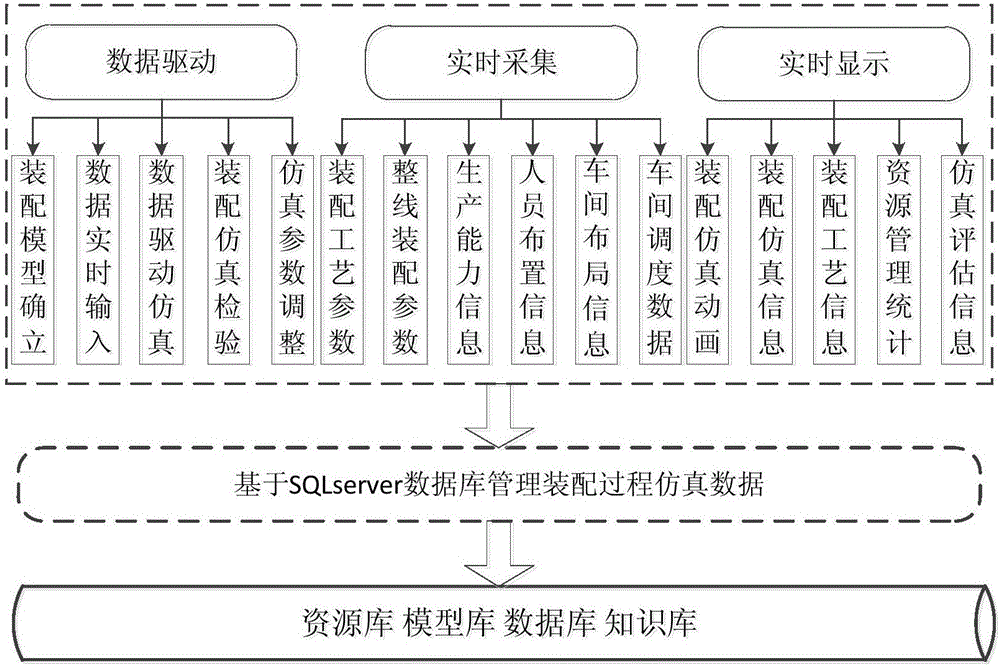

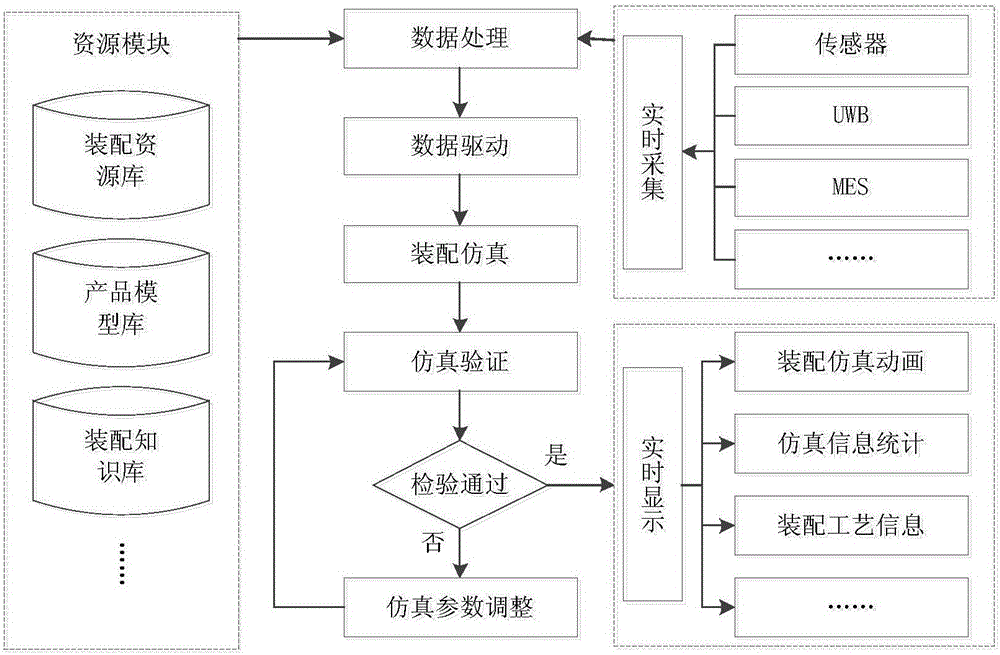

An airplane assembling process online simulating optimization system

InactiveCN106407570AImprove assembly efficiencyGeometric CADDesign optimisation/simulationJet aeroplaneData interface

The invention provides an airplane assembling process online simulating optimization system comprising an online simulating module, a data processing module and a system optimization module. The modules mainly have the following functions: real-time data collection, data drive simulation, simulation real-time display, system data interaction, system data management, data interface standardization, simulation scheme evaluation, simulation scheme analysis and simulation scheme optimization. The system realizes online simulation of an on-site airplane assembling process by means of real-time data drive, and can optimize assembling schemes failing to meet the on-site assembling requirements, so that optimal assembling schemes can be provided for on-site assembly in real time and the airplane assembling efficiency can be increased.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

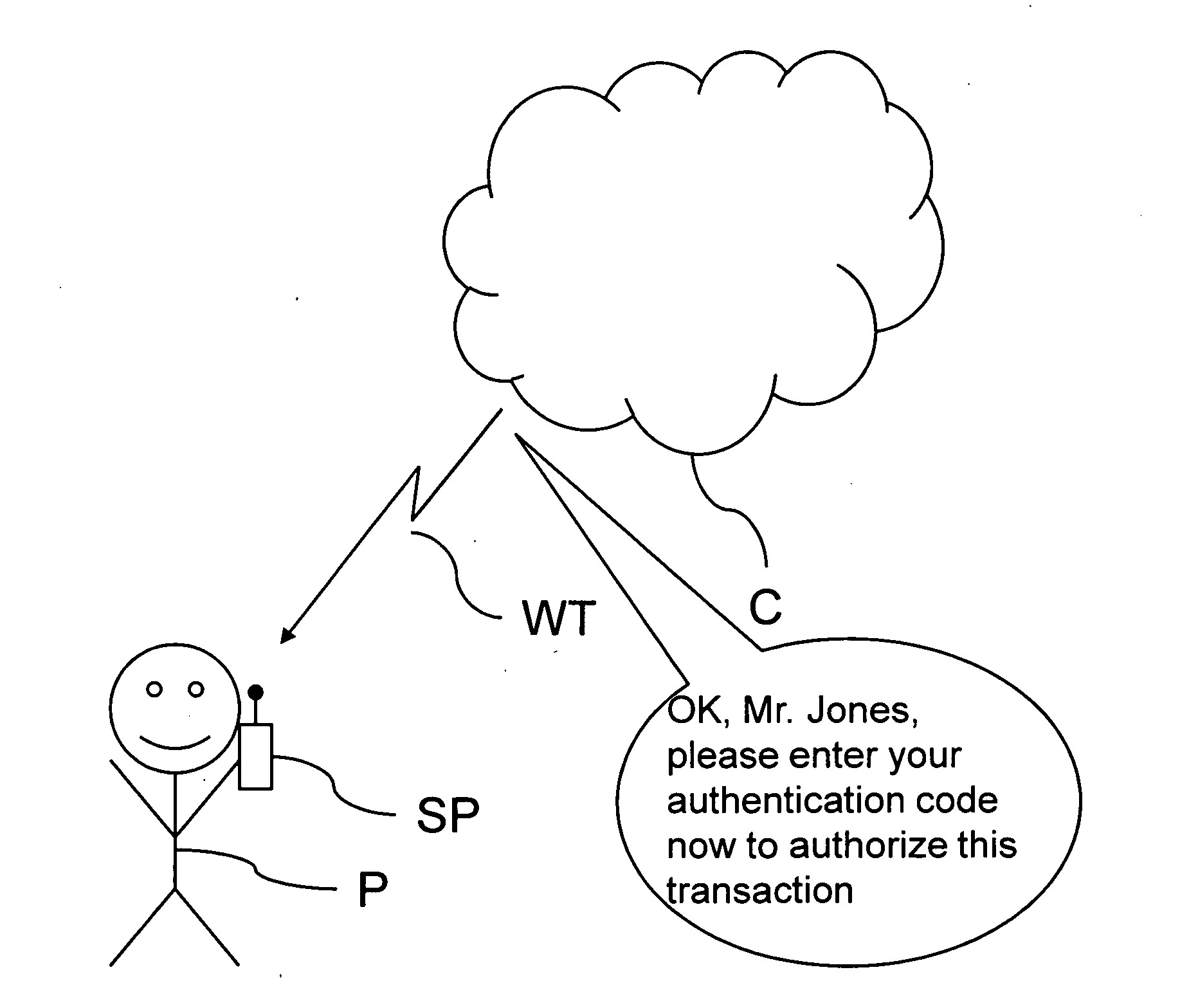

Secure cloud computing system

InactiveUS20120185692A1Comprehensive understandingDigital data processing detailsUser identity/authority verificationElectronic systemsProtection system

The present invention provides a method and apparatus for securing electronic systems, including computers, information appliances and communication devices. The invention in question addresses the problem of preventing compromise by severe attacks directed at the protected systems. A severe attack could mean any of the following: low level debugging, use of in-circuit emulators or logic analyzers, removal of silicon dice and inspection including by lapping and micro-photography, and other well-known methods of attack such as distributed denial of service. In order to protect systems and data from such severe attacks, a mechanism is required whose operation is irreparably altered by the attempt to understand its operation through such attacks. Moreover, the mechanism must cease operation instantly upon detection of any intrusion associated with an attack, whether by software or by hardware based means.

Owner:BLACKRIDGE TECH HLDG

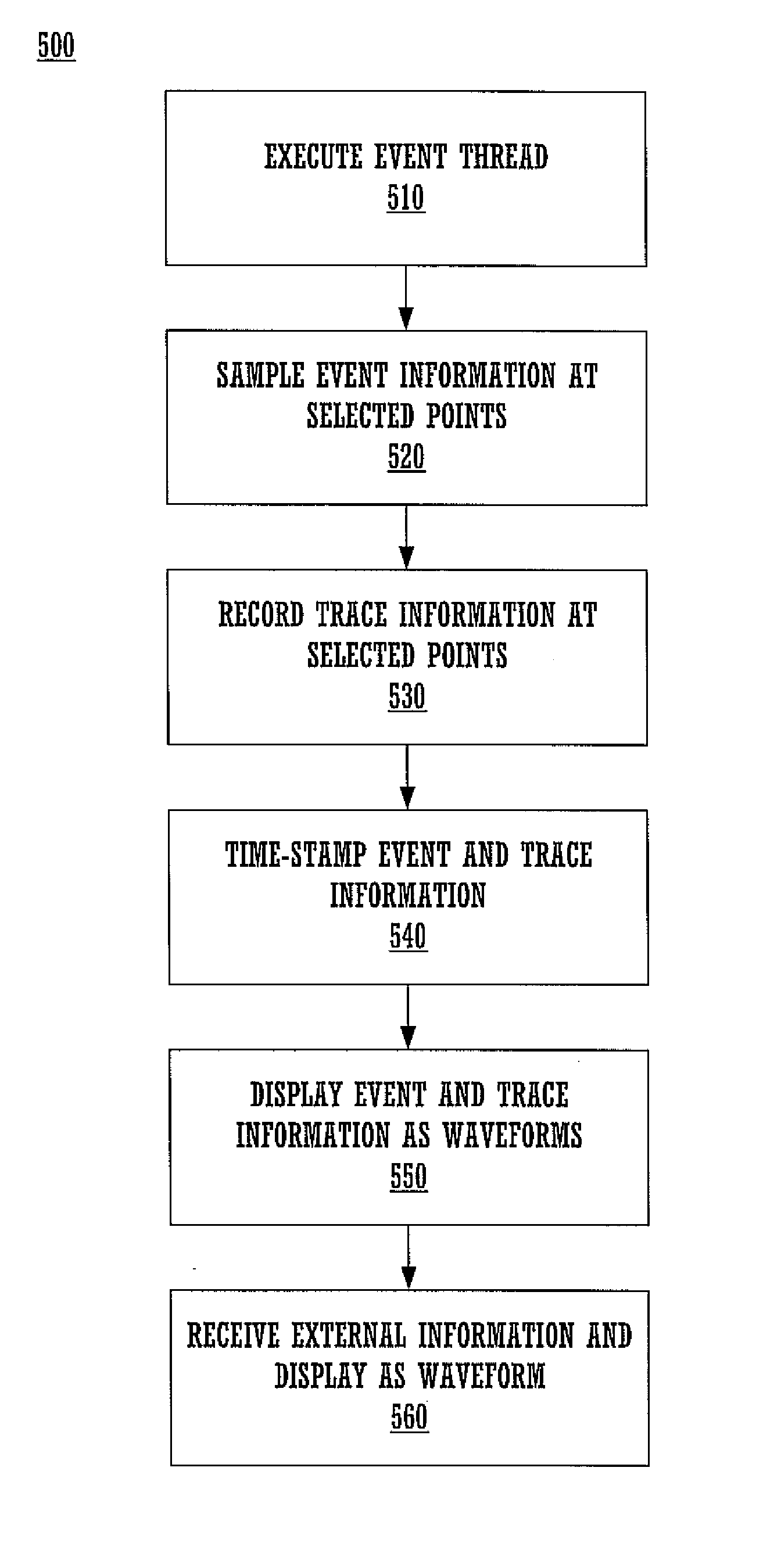

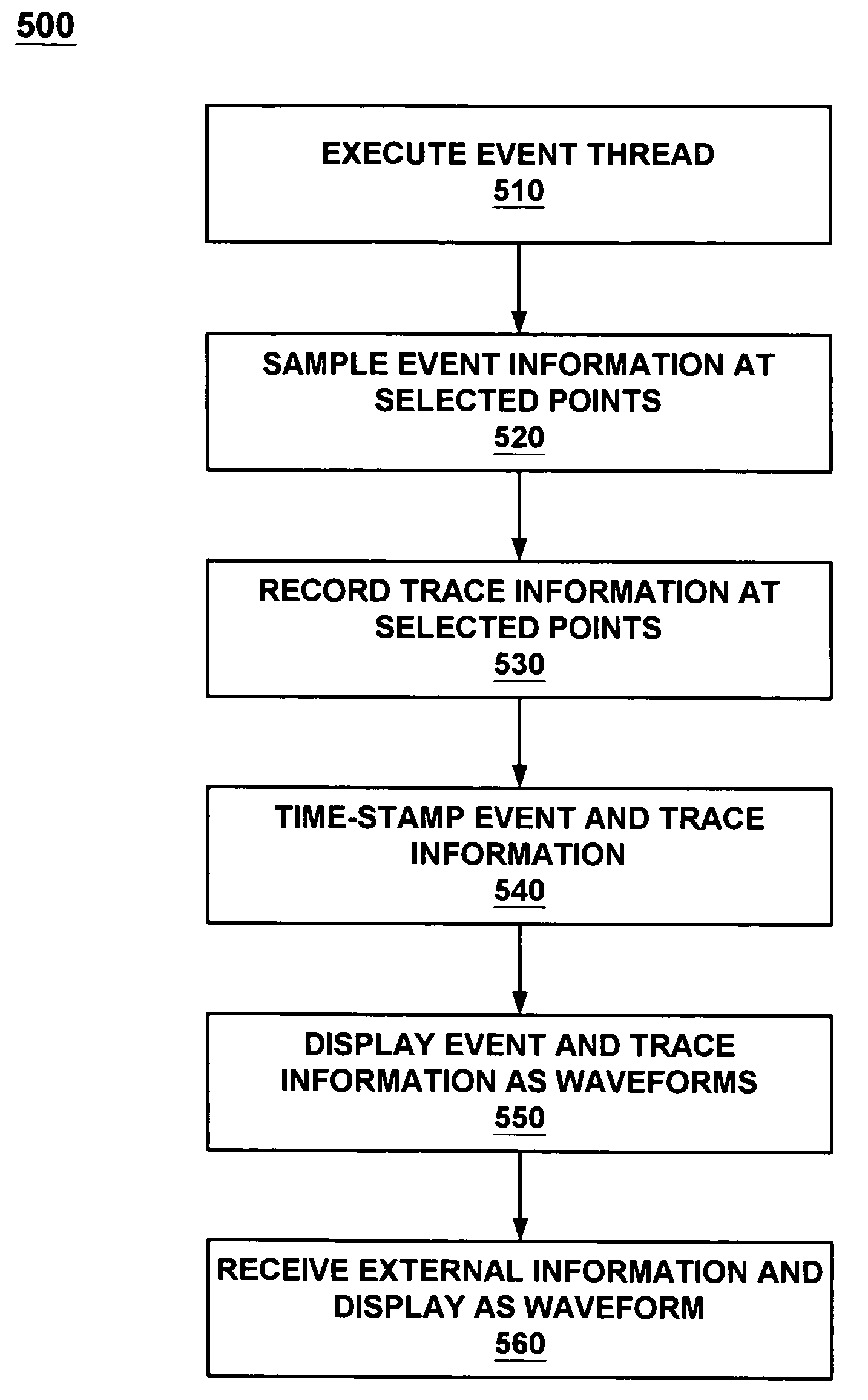

Method for integrating event-related information and trace information

InactiveUS7379860B1More memory resourceFacilitates taskElectronic circuit testingError detection/correctionMicrocontrollerComputer science

A method for emulating and debugging a microcontroller. In one embodiment, an event thread is executed on an emulator that operates in lock-step with the microcontroller. Event information is sampled at selected points. Trace information is also recorded at the selected points. As such, the event information and trace information are effectively pre-filtered. Accordingly, it is not incumbent on a designer to read and understand the event and trace information and sort out the information that is of interest. Instead, this task is essentially done automatically, helping the designer and reducing the probability of error. Furthermore, because only selected event and trace information is recorded, the resources of the in-circuit emulator system are not taxed.

Owner:MONTEREY RES LLC

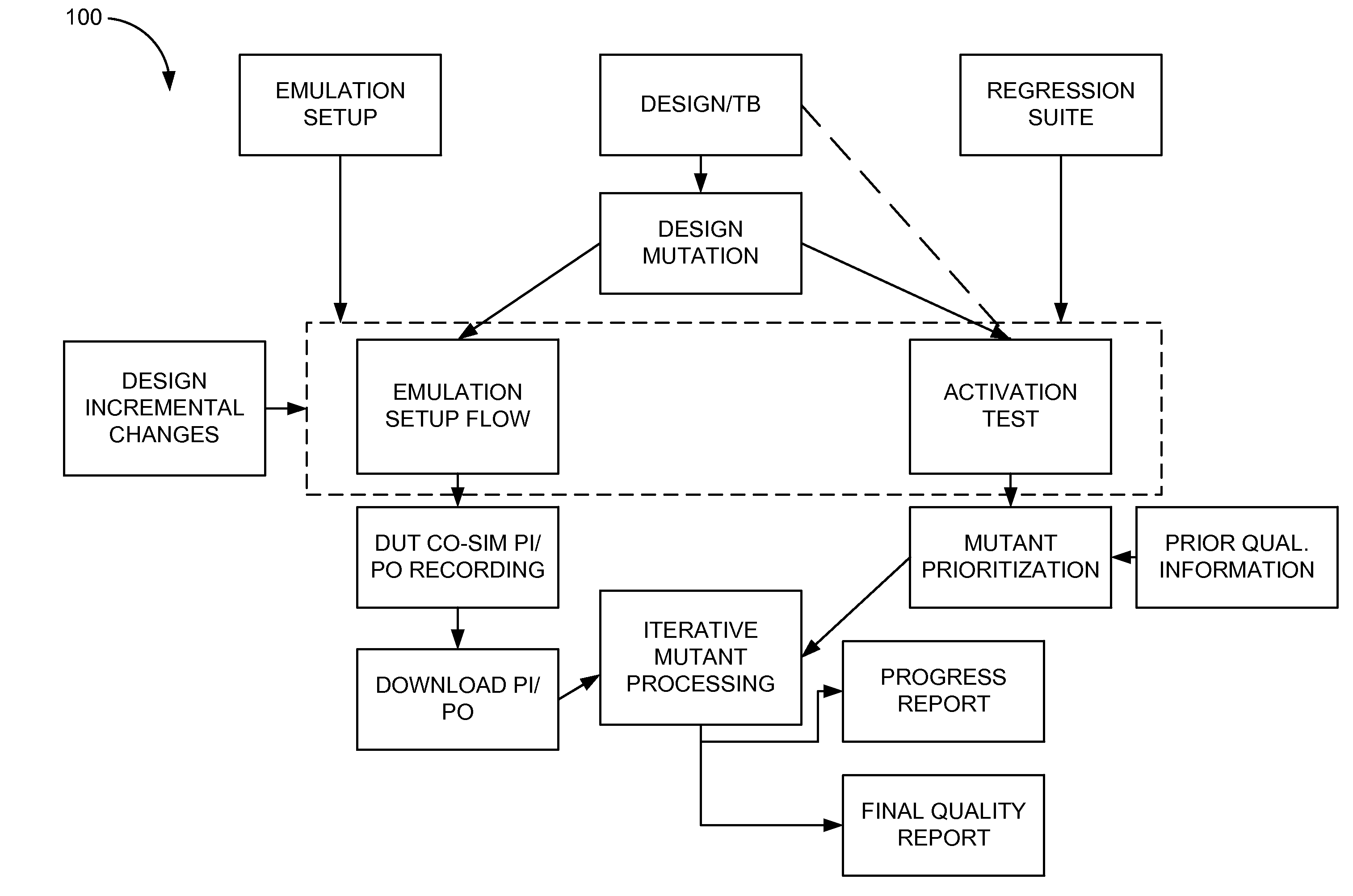

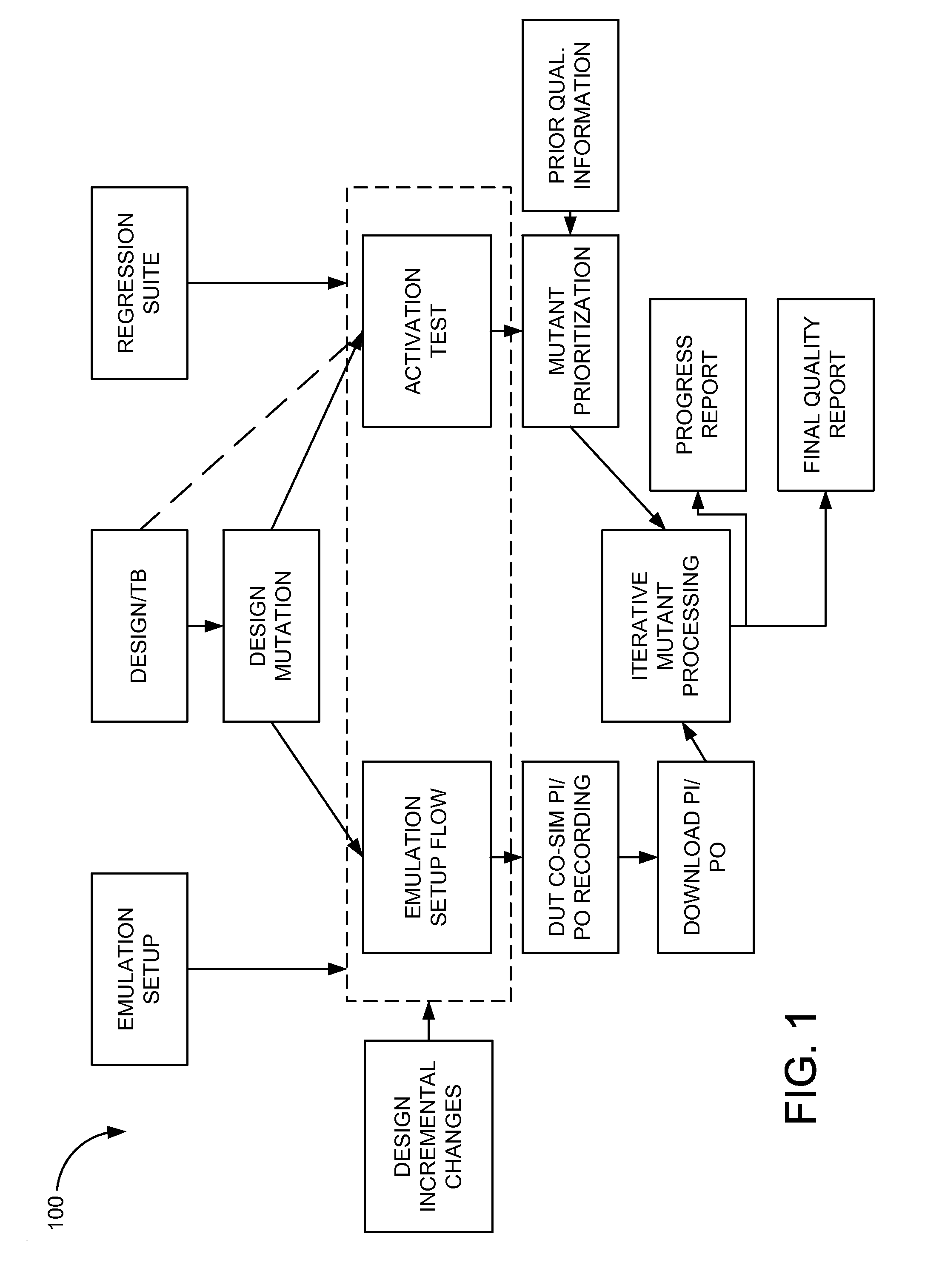

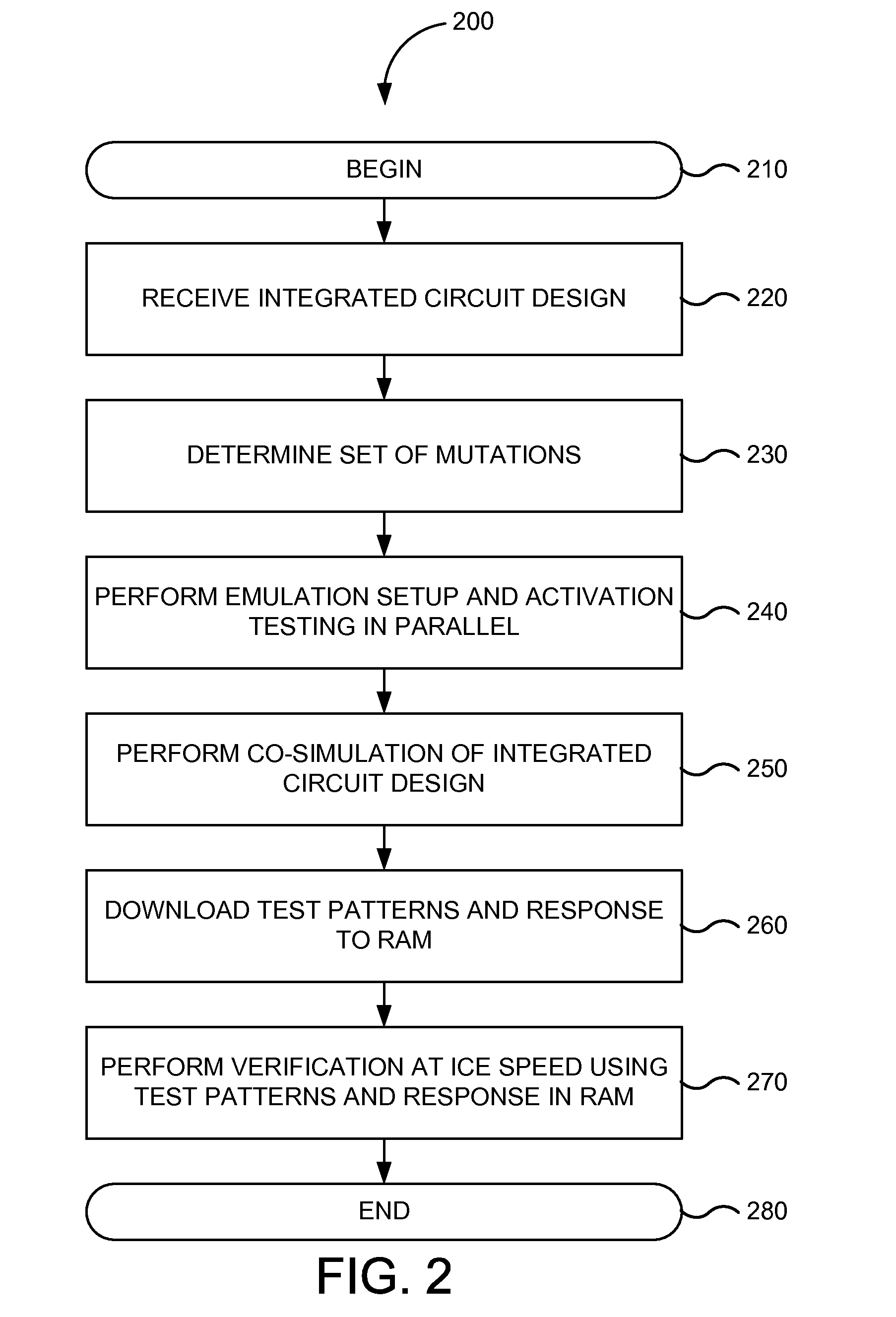

Emulation-based functional qualification

ActiveUS20150040096A1Maximize computing resourceDetecting faulty computer hardwareComputer aided designComputer moduleBiological activation

Techniques for emulation-based functional qualification are disclosed that use an emulation platform to replace simulation in mutation-based analysis. A method for functional qualification of an integrated circuit design includes receiving an integrated circuit design having one or more mutations. Emulation setup and activation simulation are performed in parallel to maximize computing resources. A prototype board can then be programmed according to the integrated circuit design and a verification module. A set of test patterns and response generated by a simulation of the integrated circuit using the set of test patterns are stored in a memory of the prototyping board allowing enumeration of mutants to occur at in-circuit emulation speed.

Owner:SYNOPSYS INC

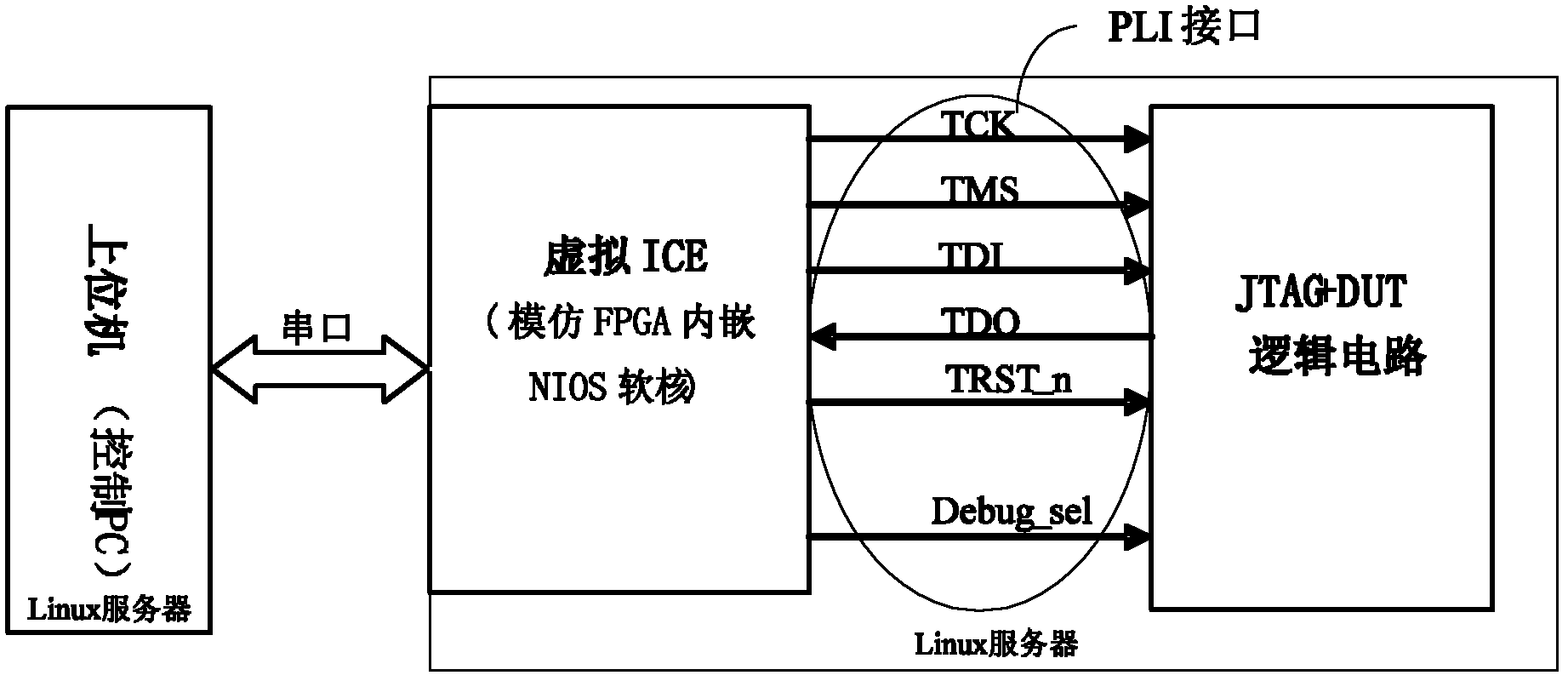

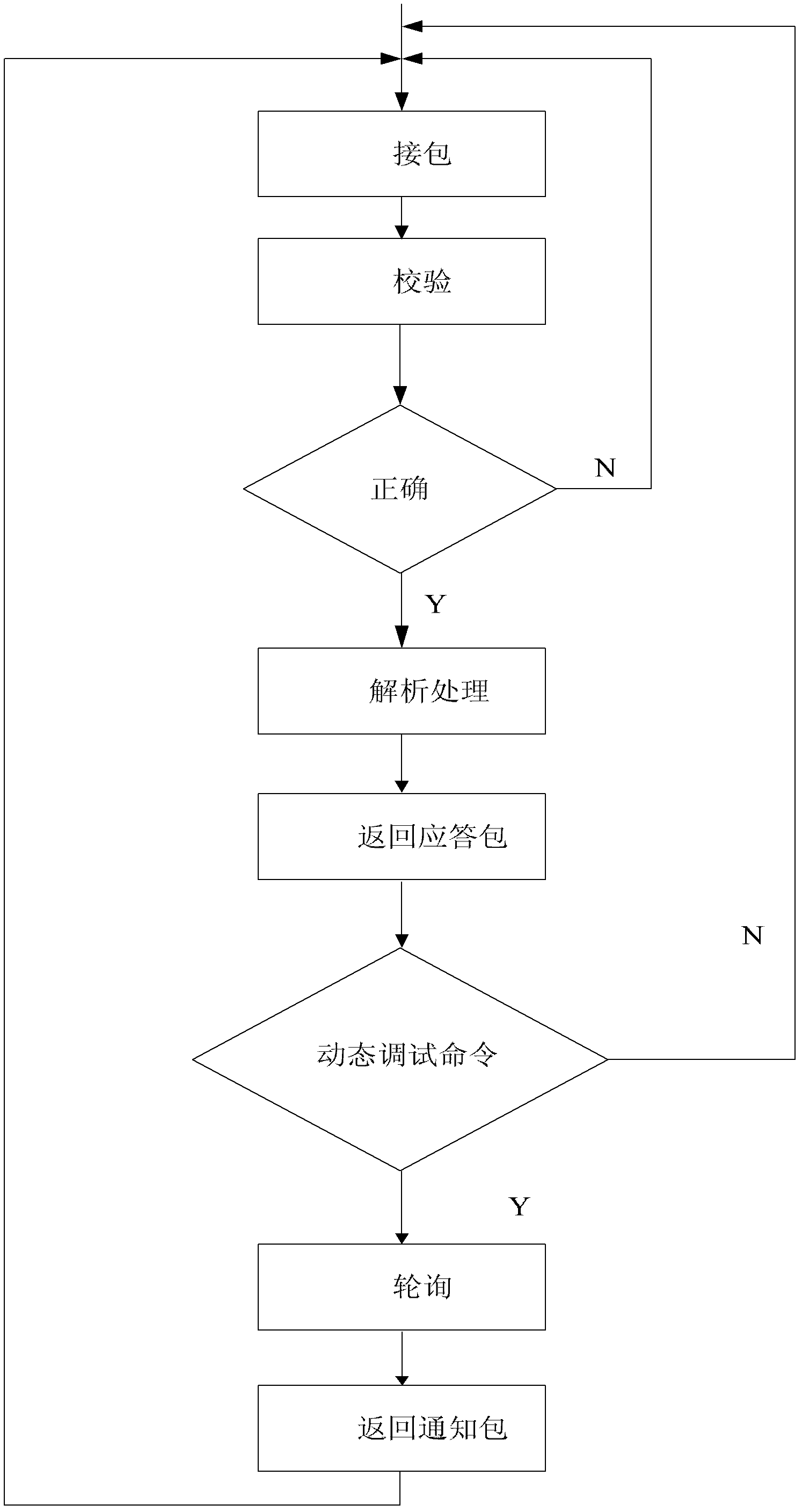

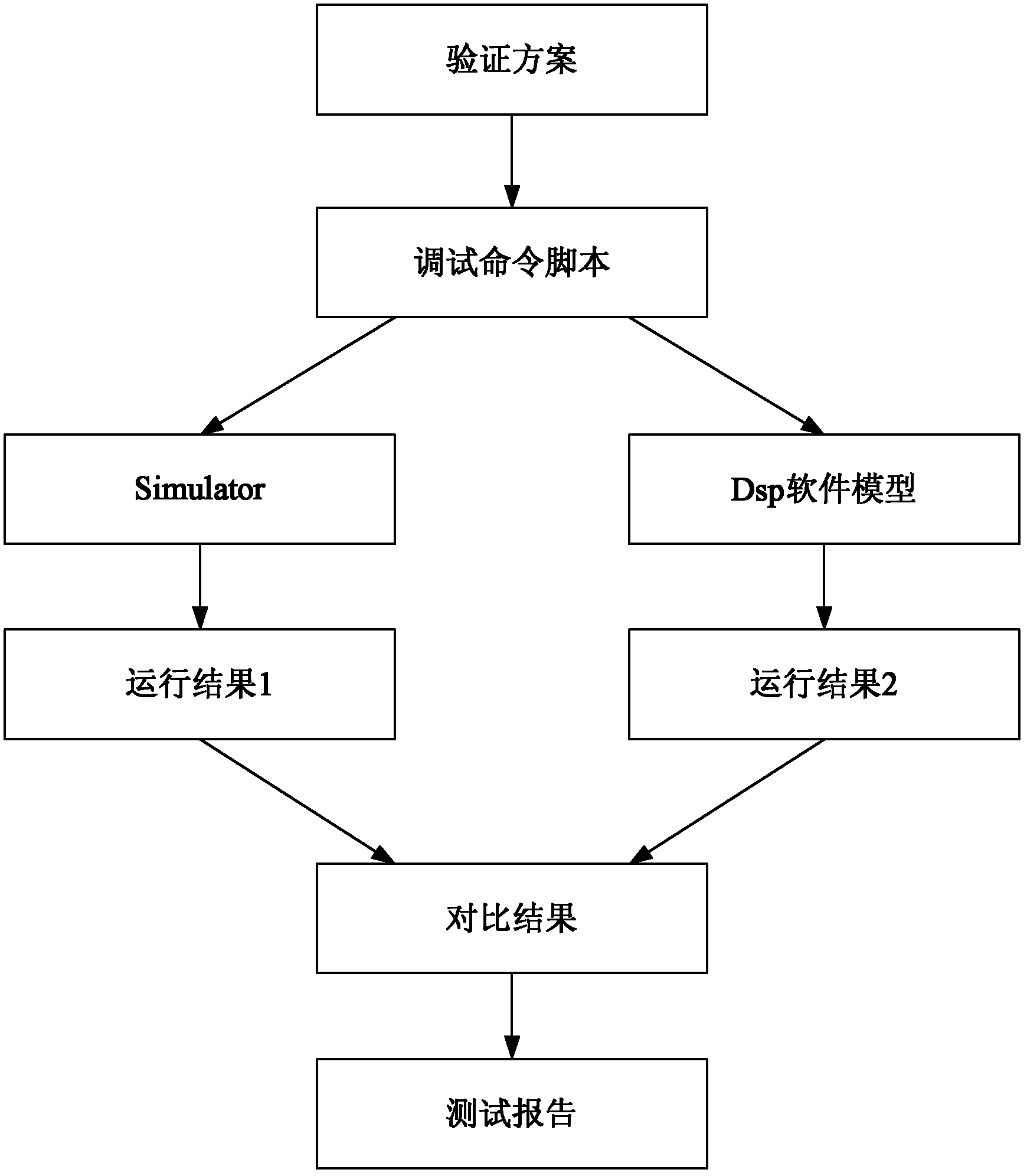

Software-hardware co-verification platform

The invention discloses a software-hardware co-verification platform, which comprises an upper computer, a virtual in-circuit emulator (ICE), a design under verification (DUV) and a communication part, wherein the virtual ICE communicates with the upper computer through a serial port between servers and is connected with the DUV through programming language interfaces (PLIs); the upper computer is realized on a server equipped with a Linux operating system; and the virtual ICE, the PLI and the DUV are realized on another server equipped with a Linux operating system. The verification environment of the verification platform can be realized only by using the servers with relatively large storage space, so that the problem of limited capacity of a software-hardware co-verification product is solved, and system-level verification of a chip at a design front end can be realized; the prices of the servers are low, so that the cost of integrated product development is reduced; and besides, as the software-hardware co-verification platform is completely realized by using software, a lengthy period of hardware debugging is avoided, the development process of the product is accelerated, and precious time is strived for early listing of the product.

Owner:CHINA ELECTRONIC TECH GRP CORP NO 38 RES INST

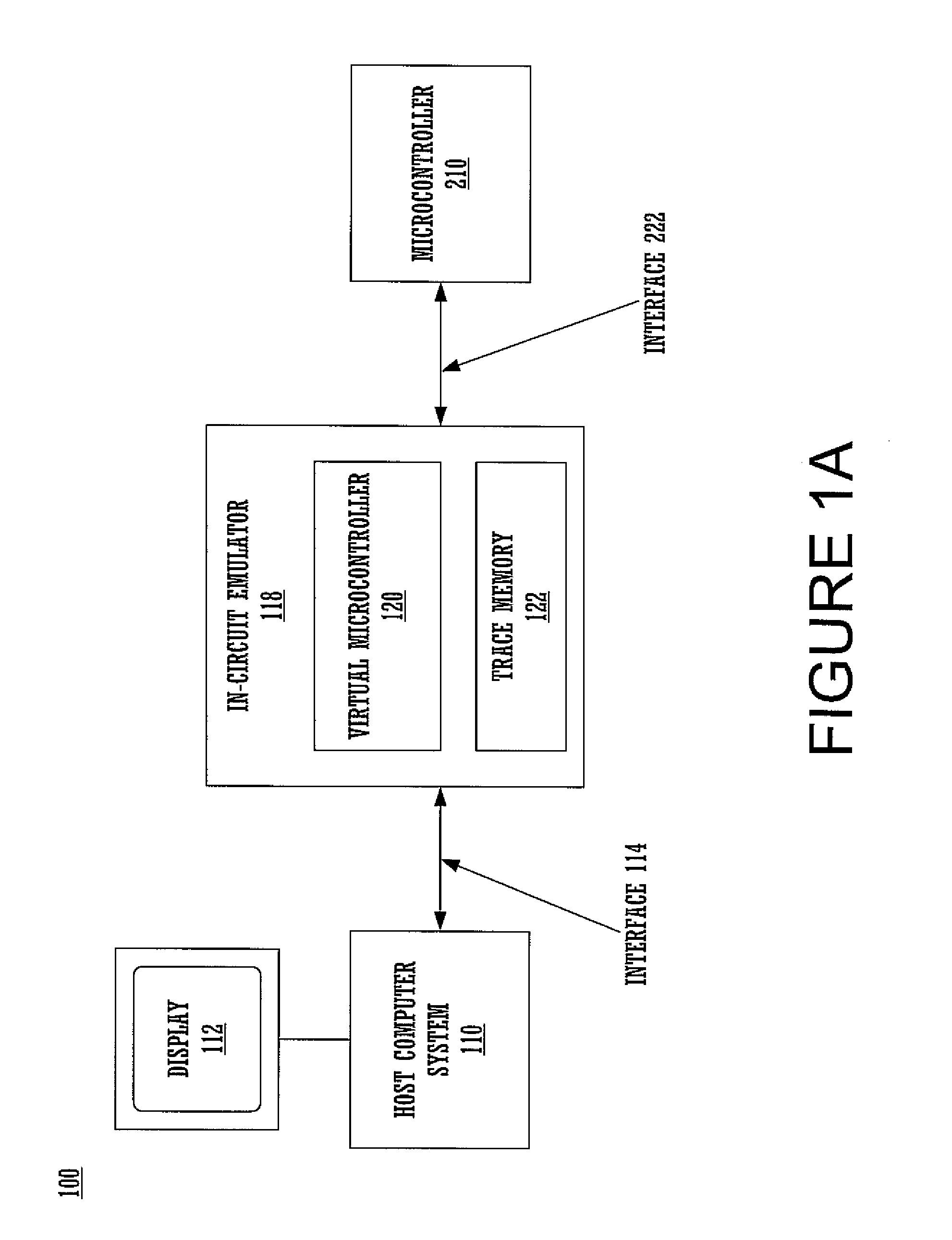

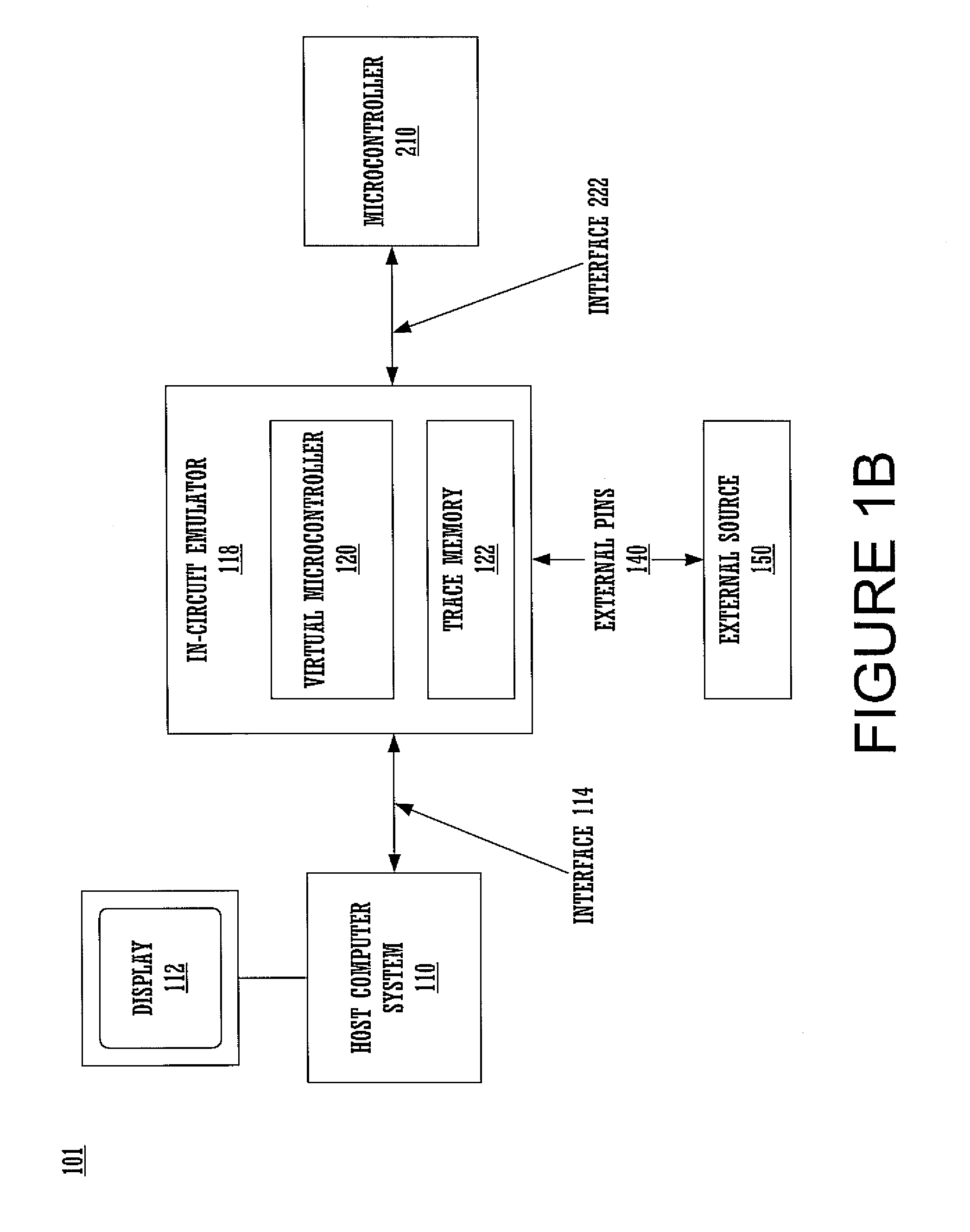

System for integrating event-related information and trace information

InactiveUS7103530B1Error detection/correctionSoftware simulation/interpretation/emulationMicrocontrollerDisplay device

An emulation and debugging system that includes an in-circuit emulator couplable to a microcontroller. The in-circuit emulator is adapted to execute an event thread in lock-step with the microcontroller. Event information generated as a result of executing the event thread is sampled at selected points and the sampled event information is stored in memory. Trace information is also recorded at the selected points. The sampled event information and the recorded trace information are time-stamped. In one embodiment, a display device is coupled to the in-circuit emulator. The display device is used for displaying analog and / or digital waveforms representing the sampled event information and the recorded trace information. Accordingly, an in-circuit emulator system can also function as an oscilloscope and / or as a logic analyzer, allowing a user to view event and trace information, along with other information, that are generated as part of the debugging process.

Owner:MONTEREY RES LLC

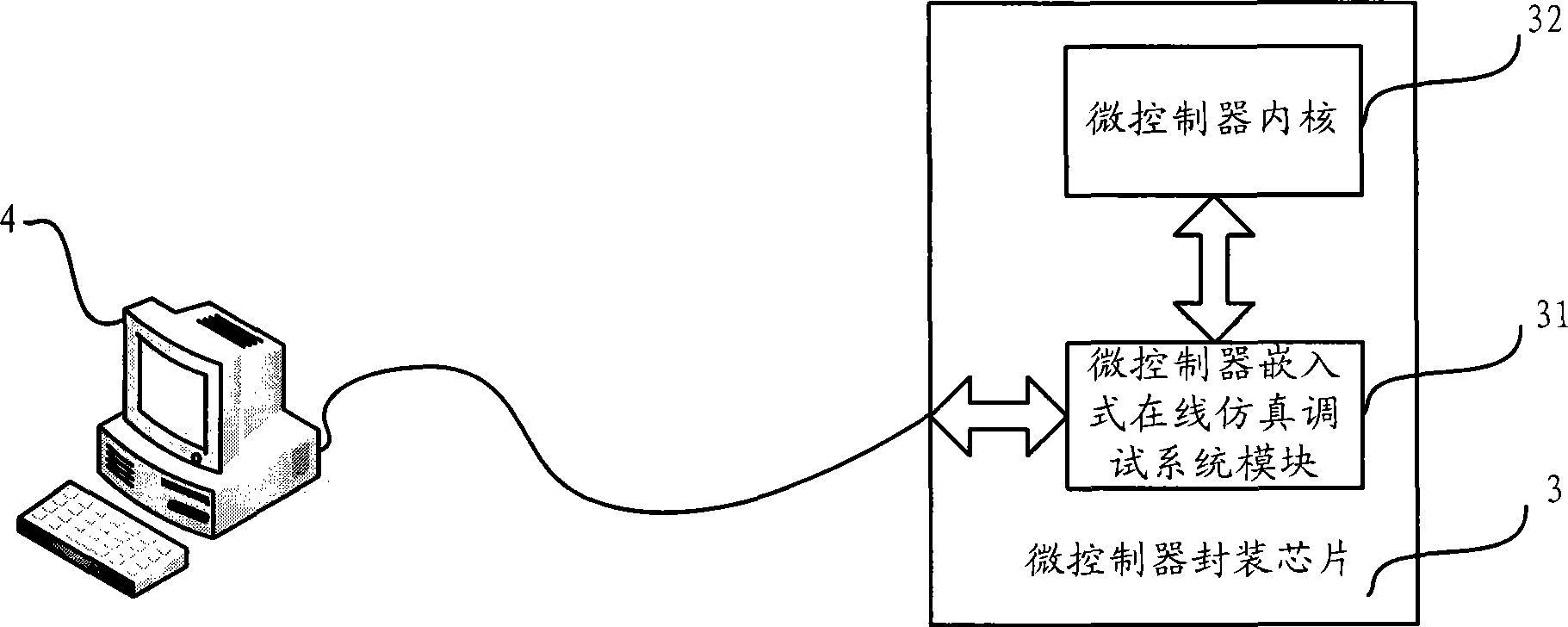

Embedded on-line emulation debugging system for microcontroller

ActiveCN101458652ACost-effectiveImproved debugging capabilitiesSoftware testing/debuggingMicrocontrollerHost machine

The invention relates to an embedded type on-line emulation debug system of microcontroller, comprising a communication port control module for receiving an exterior debugging instruction and controlling the data communication between the system, the exterior host computer and the microcontroller; a status control module for outputting a corresponding debug instruction code generating instruction and a breakpoint control instruction based on the exterior debug instruction and performing the on-line emulation debug for the microcontroller based on the corresponding debug instruction code and the breakpoint; a debug instruction control module for generating the corresponding debug performing code based on the debug control instruction; a breakpoint monitoring and triggering module for triggering the corresponding breakpoint of the microcontroller based on the breakpoint control instruction. The invention has simple structure, high-efficiency operation effect and accurate real time monitoring, the invention can be integrated into different microcontroller chips to implement the real time monitoring, the debugging and the emulation control of the chip on the chip grade, the chip debugging capability based on embedded type microcontroller can be greatly improved.

Owner:SHANGHAI EASTSOFT MICROELECTRONICS

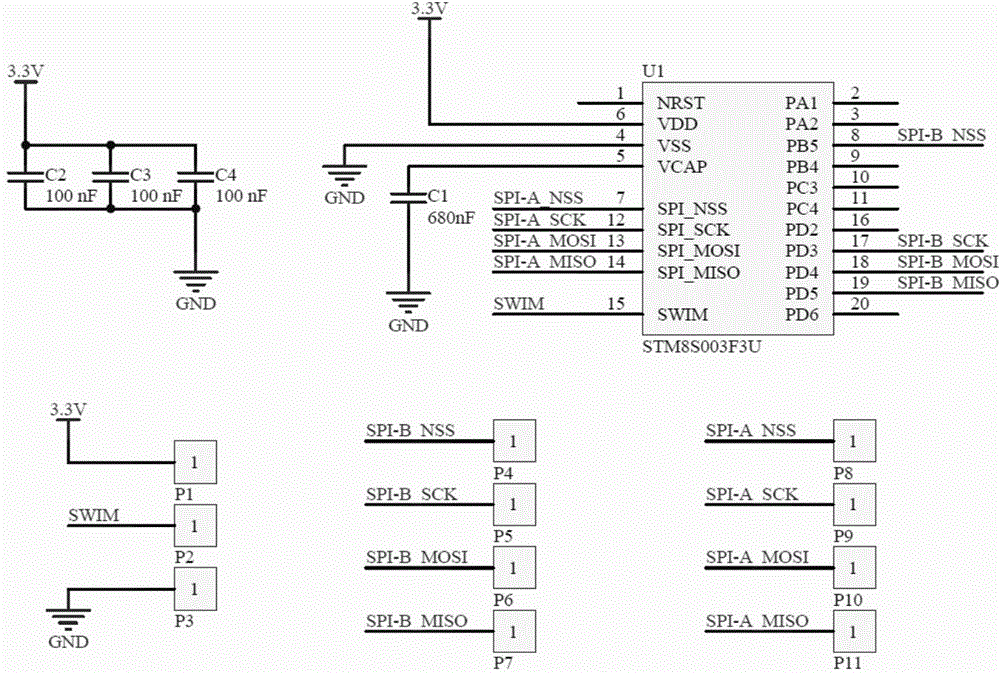

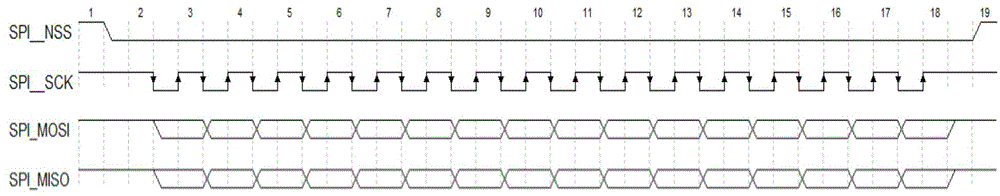

Mini embedded controller device and method for simulating SPI interface through I/O port

InactiveCN104020704ARespond promptly to communication requestsReal-time reliable interactive dataProgramme controlComputer controlComputer moduleEmbedded controller

The invention provides a mini embedded controller device and method for simulating an SPI interface through an I / O port and relates to the embedded type technical field. The mini embedded controller device comprises a control center module, an SPI-A interface module, an SPI-B interface module and an on-line simulation debugging interface module, and the size of the mini embedded controller device is only 12 mm * 10 mm. According to the mini embedded controller device, a chip small in size, high in integration and small in pin number is adopted by the mini embedded controller device. The method comprises the steps of sequentially calling an SPI timing sequence initialization module and an SPI timing sequence analogue module when the device is used as a main device, and an SPI timing sequence initialization module and an SPI timing sequence analog module based on the interrupt processing technology when the device is used as a slave device. According to the device and the method, on the premise of meeting the requirements for the number of interfaces and the overall dimension, simulating of the SPI interface through the I / O port is realized with the low cost; when the mini embedded controller device is used as the main device or the slave device, full-duplex communication timing sequences under an SPI working mode can be realized; the interrupt processing technology is adopted, and therefore the reliability and the real-time property of communication can be improved.

Owner:DALIAN UNIV OF TECH

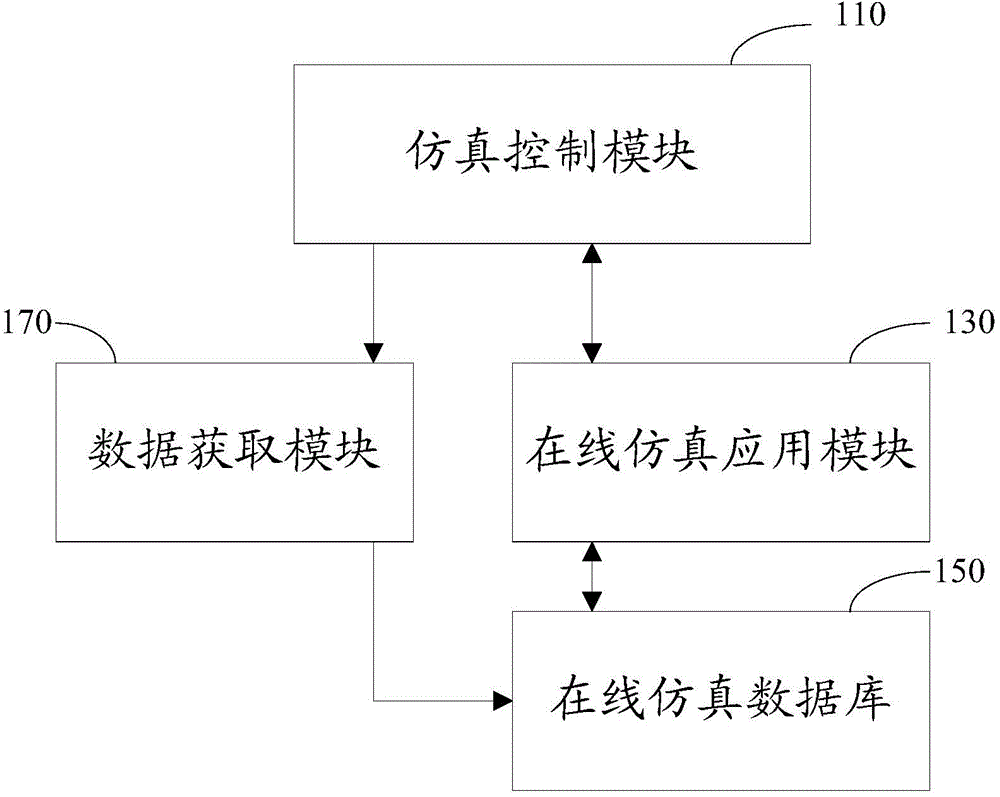

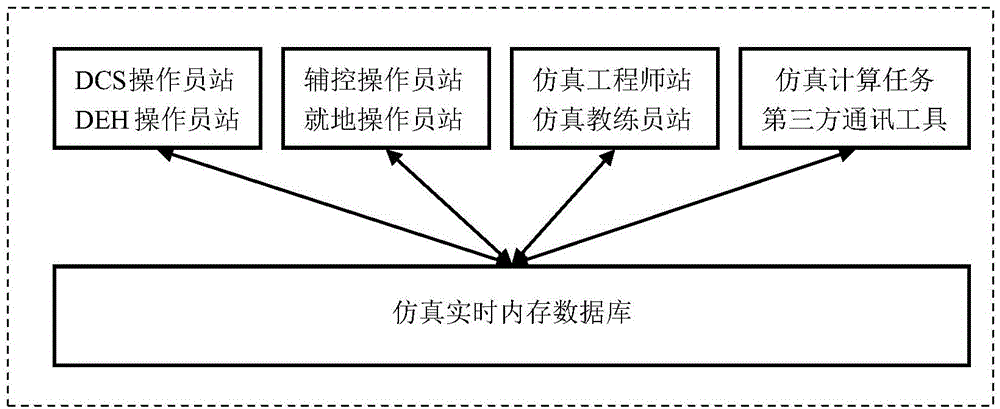

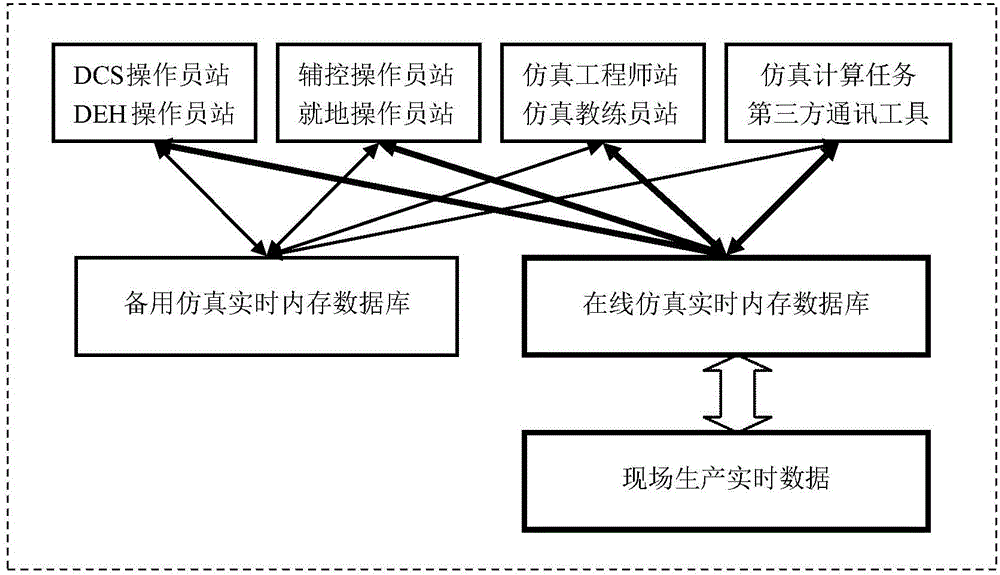

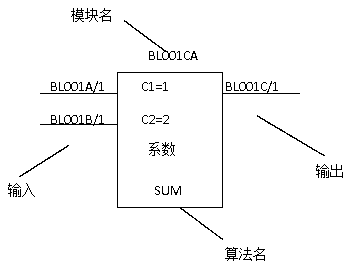

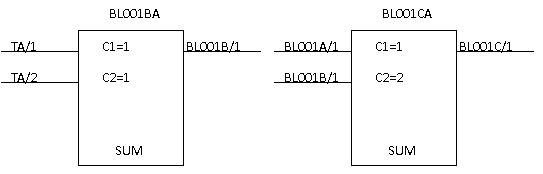

Online simulation system and method for power plant

ActiveCN104462730AIn line with operational conditionsHigh precisionData processing applicationsSpecial data processing applicationsReal-time dataData source

The invention provides an online simulation system and method for a power plant. The system comprises a simulation control module, an online simulation application module, a data obtaining module and an online simulation database. The data obtaining module is used for obtaining production real-time data and production historical data and transmitting the production real-time data and the production historical data to the online simulation database; the online simulation application module is used for calling a simulation module function, the production real-time data and the production historical data from the online simulation database for simulation analysis, and writing a simulation result into the online simulation database. By means of the system, the production real-time data and the production historical data are obtained through the data obtaining module and are transmitted to the online simulation database, so that the relevance degree of data sources of the online simulation database and the onsite real-time production data is large, and simulation analysis precision is high.

Owner:ELECTRIC POWER RES INST OF GUANGDONG POWER GRID

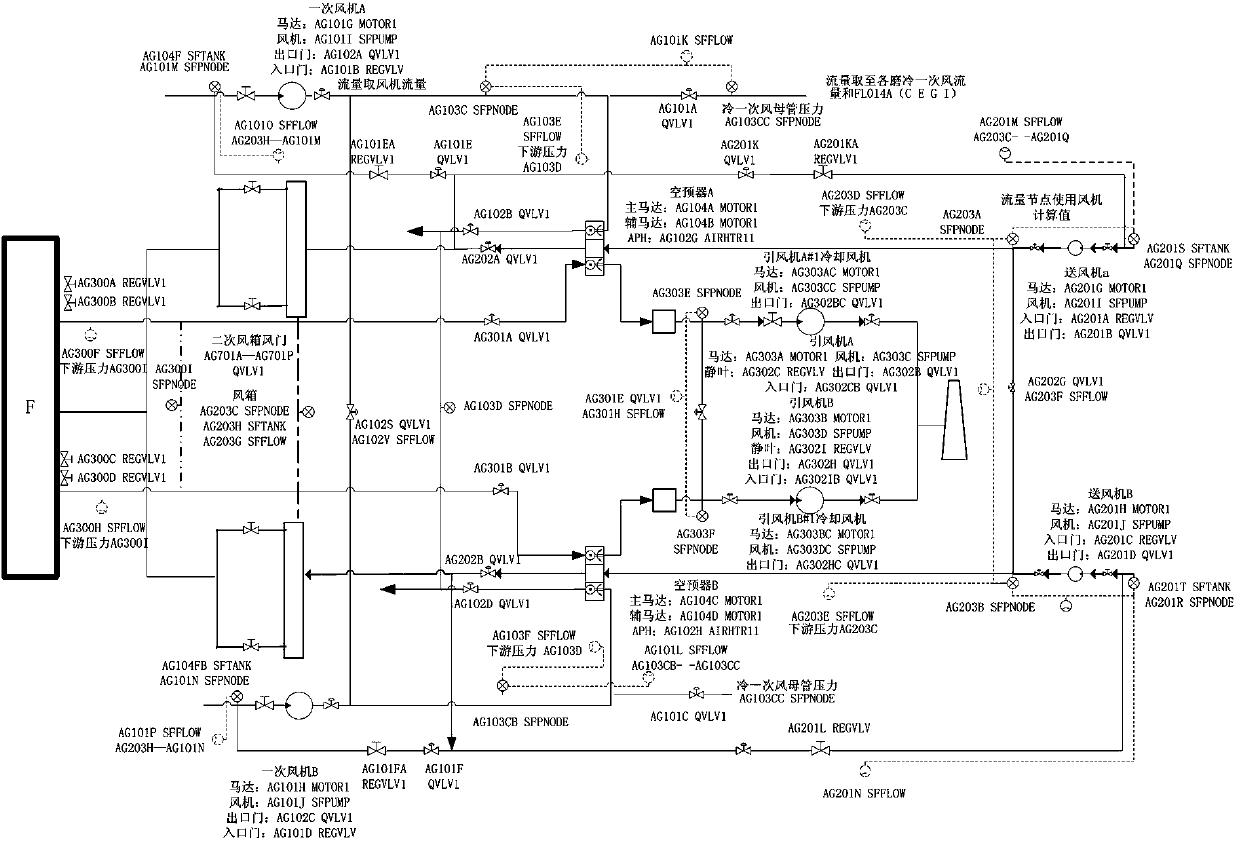

Sub-critical thermal power generating unit enhancing stimulation and simulation modeling method based on LABVIEW

ActiveCN105512388AHigh riskOn-site commissioning cycle is longData processing applicationsComputer aided designTransient stateData modeling

The invention discloses a sub-critical thermal power generating unit enhancing stimulation and simulation modeling method based on LABVIEW and belongs to the field of simulation data modeling. The method comprises the following steps that 1, boundary conditions for enhancing stimulation and simulation modeling are defined; 2, according to the boundary conditions defined in the step 1, all related online unit data in the boundary conditions described in the step 1 are classified; 3, a unit enhancing stimulation and simulation model is set up; 4, the online unit data and the unit enhancing stimulation and simulation model are in butt joint, and unit operation control data and a DCS(distributed control system) correlated to the sub-critical thermal power generating unit simulation model are in butt joint; 5, the deviation between parameters of the unit enhancing stimulation and simulation model and actual unit characteristic parameters is compared, and parameter values in a boiler side and turbine side enhancing stimulation and simulation model are corrected and optimized to obtain a simulation model; 6, stability precision is verified; 7, transient state precision is verified; 8, online simulation modeling is adjusted. According to the method, the simulation model meeting the production test requirement and approximate to the actual unit characteristic can be obtained.

Owner:STATE GRID HEBEI ENERGY TECH SERVICE CO LTD

Apparatus and method for testing and debugging an integrated circuit

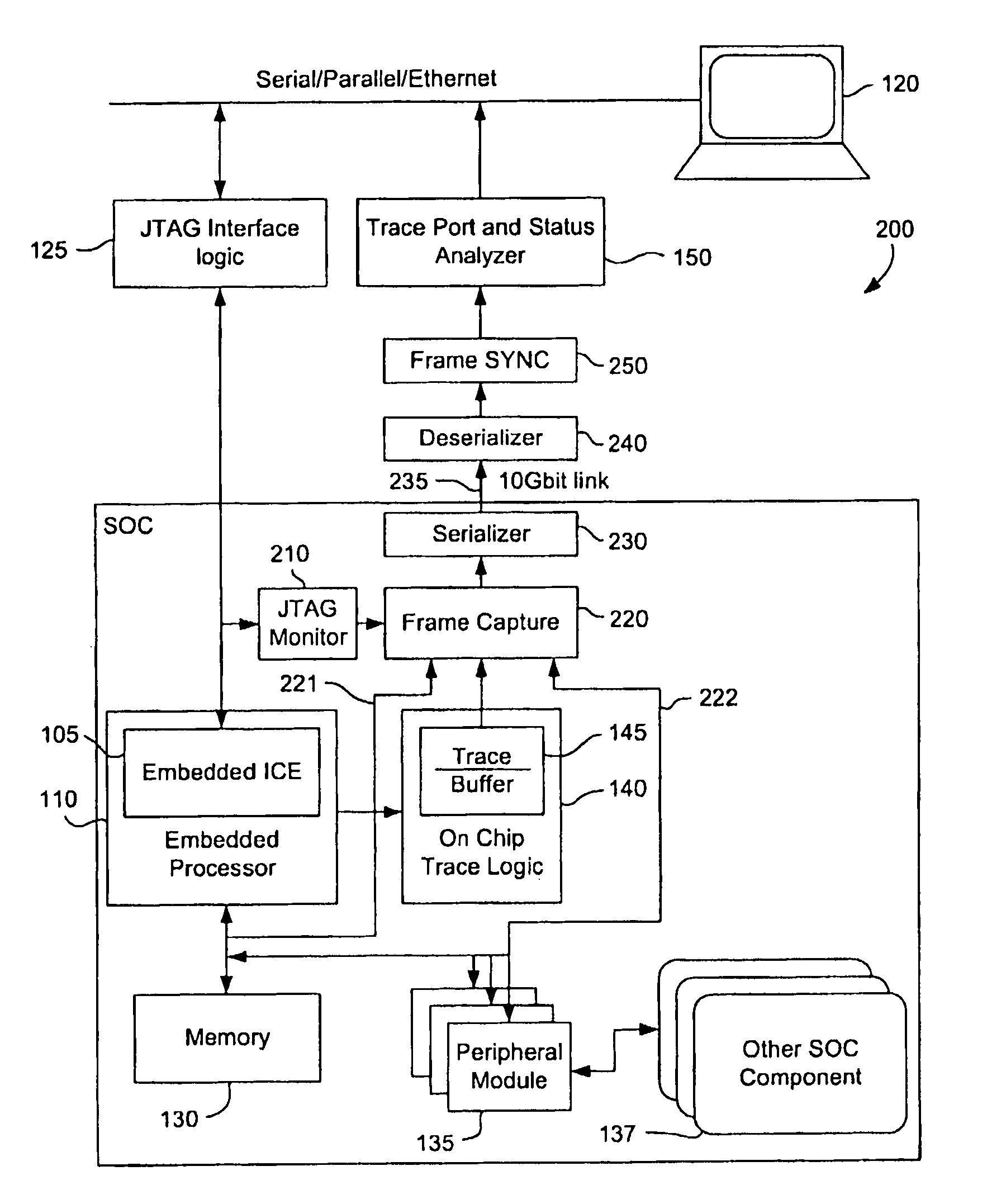

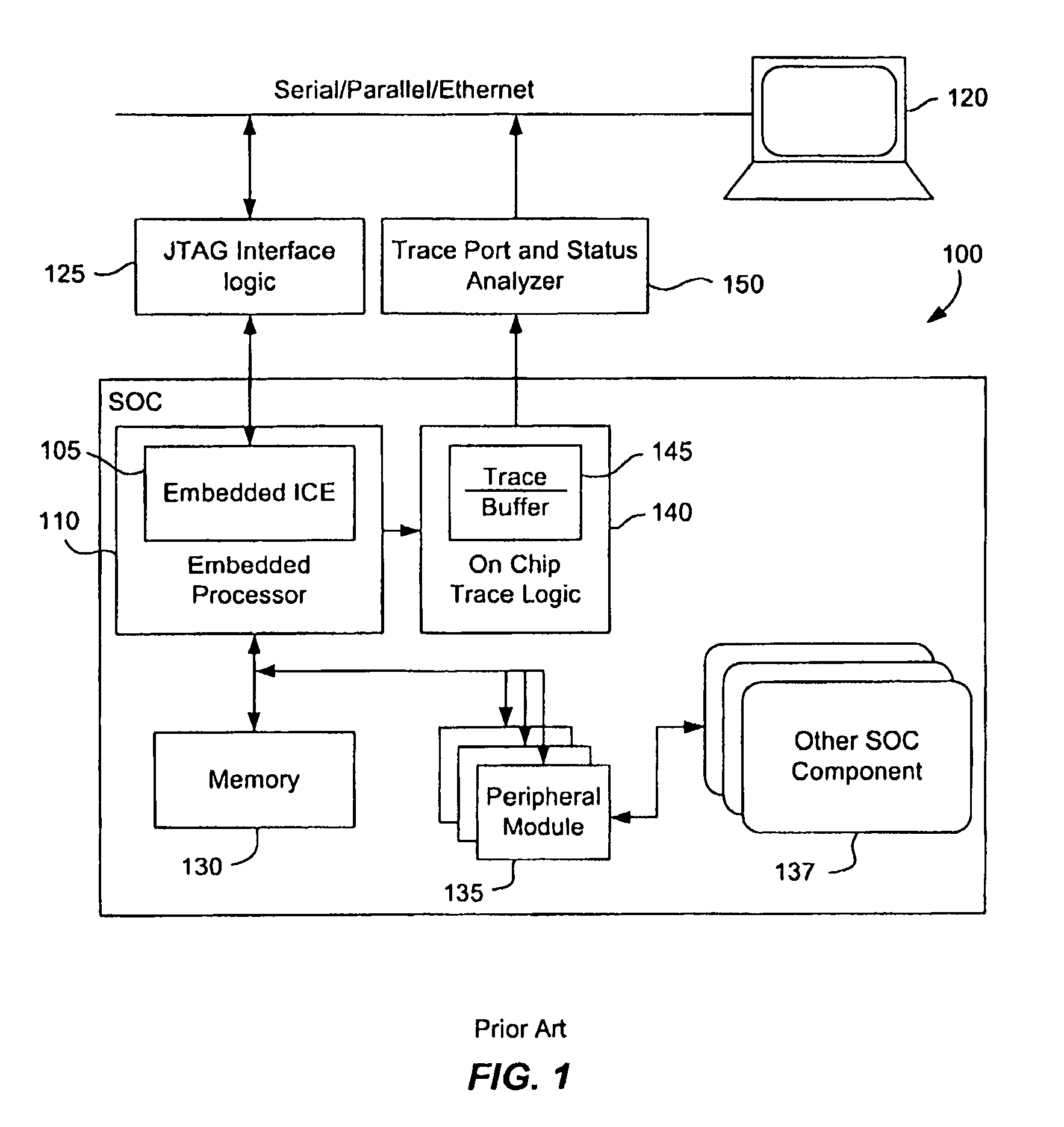

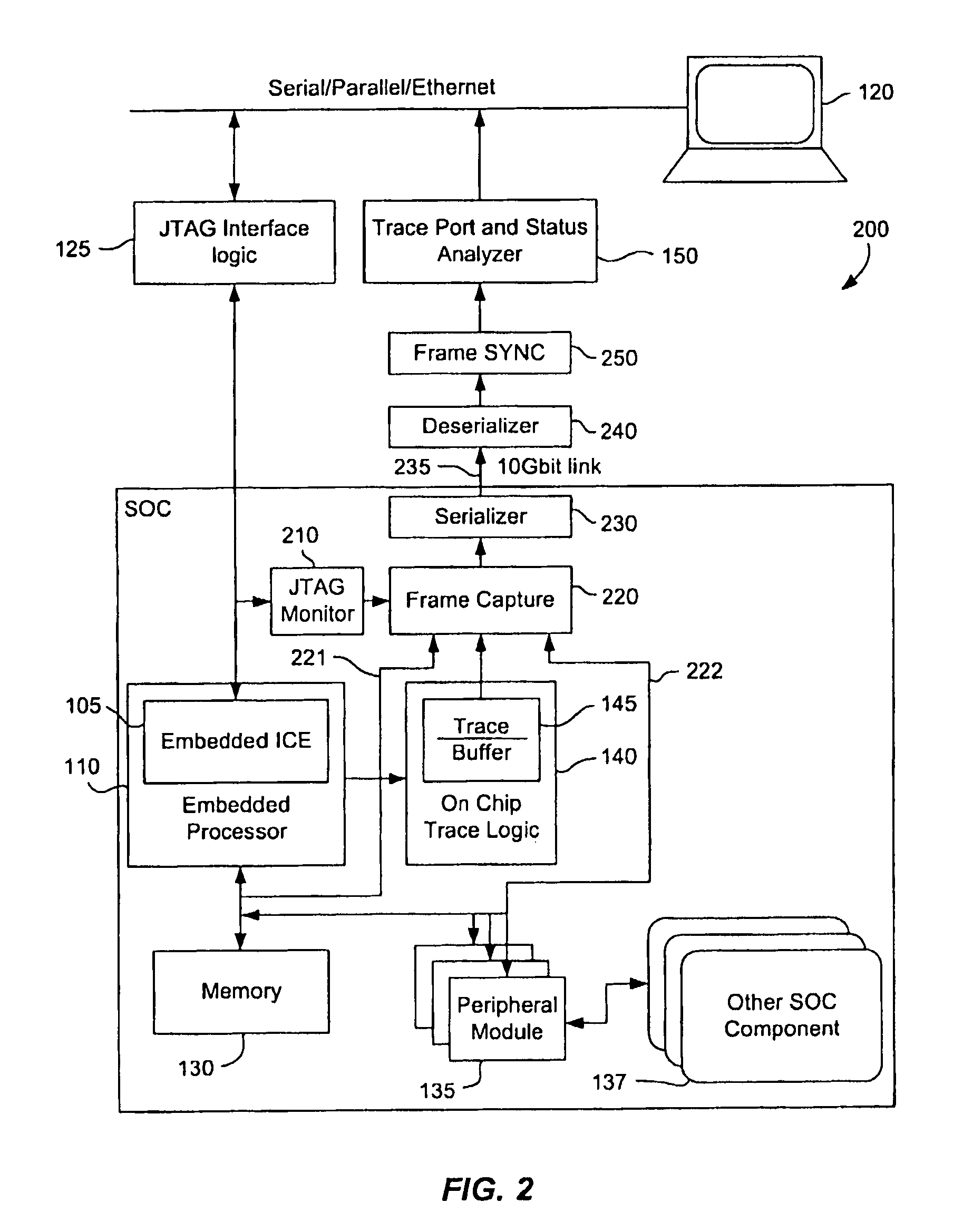

InactiveUS7562276B1Multiplex system selection arrangementsElectronic circuit testingIntegrated circuitSerializer

An integrated circuit (IC) comprises an embedded processor. An embedded in-circuit emulator (ICE) emulates at least one function of the embedded processor, performs at least one of testing and debugging on the IC, and generates testing results based on the at least one of the testing and the debugging. A serializer located on the IC receives the testing results from at least one of the embedded ICE and the embedded processor, serializes the testing results, and serially outputs the testing results from the IC.

Owner:MARVELL ASIA PTE LTD

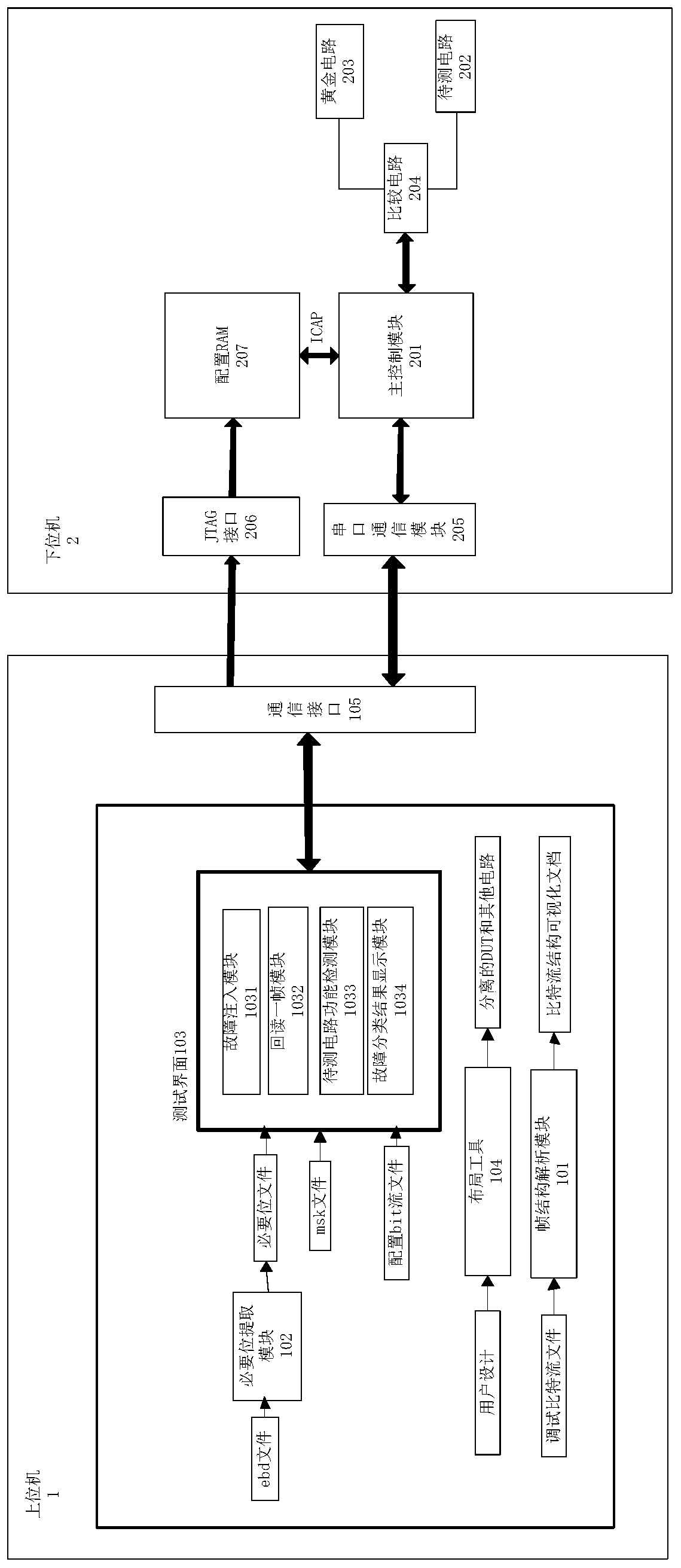

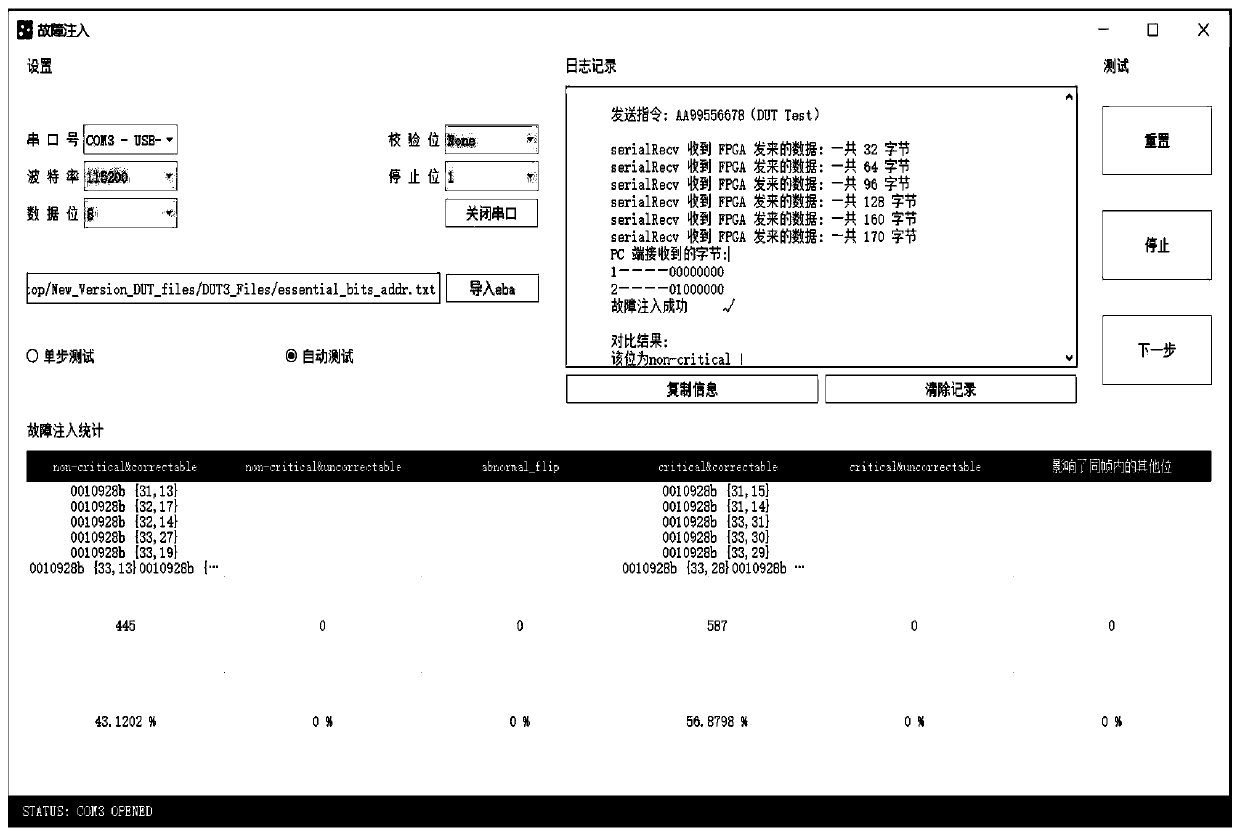

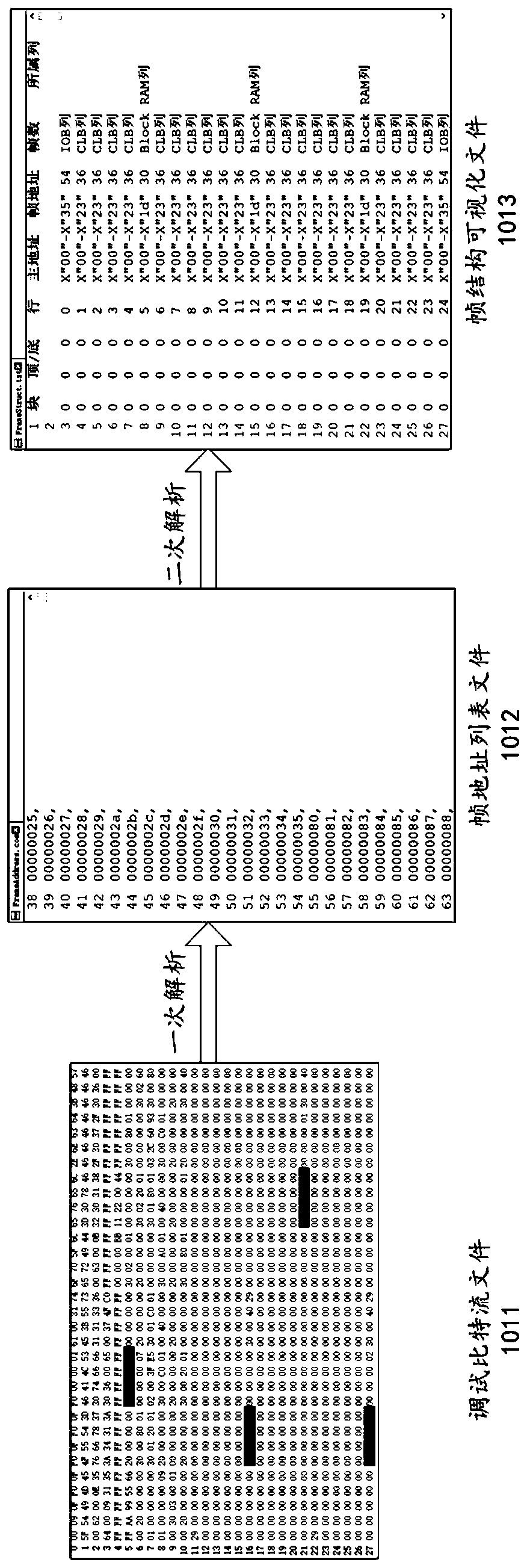

Online simulation system for necessary bit single event upset fault on SRAM type FPGA

ActiveCN109858195AReduce the number of framesGuaranteed priorityDigital storageSpecial data processing applicationsCommunication interfaceSystems design

The invention discloses an online simulation system for a necessary bit single event upset fault on an SRAM type FPGA. The system design method belongs to the technical field of testing. The system isdesigned to be composed of an upper computer (1), namely a PC end, and a lower computer (2), namely an FPGA end. The system design of the upper computer (1) comprises a test interface (101), a necessary bit file extraction module (102), a debugging bit stream file analysis module (103) and a communication interface (104); the system design of the lower computer (2) comprises a main control module(201), a to-be-tested circuit (202), a gold circuit (203), a comparison circuit (204), a serial port communication module (205), a JTAG interface (206) and a configuration RAM (207). A test interface(101) located on an upper computer (1) sends an instruction command to a lower computer (2) to control a simulation process of single event upset fault simulation, and the lower computer (2) executescorresponding operation according to the received command and then returns a result. The method does not need participation of a processor, does not need external hardware expenditure, and can be flexibly transplanted to other ICAP-supporting FPGA chips.

Owner:INST OF OPTICS & ELECTRONICS - CHINESE ACAD OF SCI