Online simulation system for necessary bit single event upset fault on SRAM type FPGA

A technology of single particle flipping and particle flipping, which is applied in static memory, special data processing applications, instruments, etc., and can solve problems such as small instruction space and non-reprogrammable SEM controller

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0060] Embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings. This embodiment is carried out on the premise of the technical solution of the present invention, and the detailed implementation and specific operation process are given, but the protection scope of the present invention is not limited to the following embodiments.

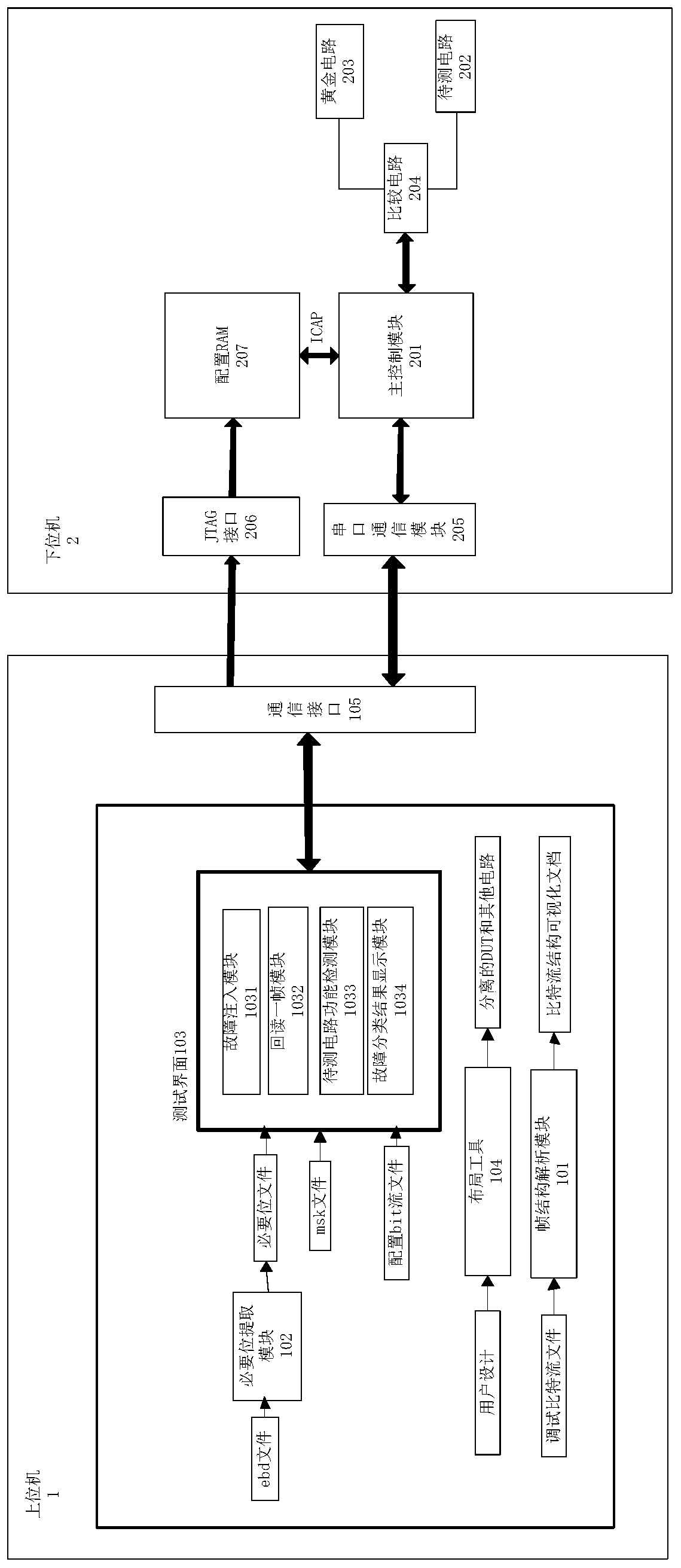

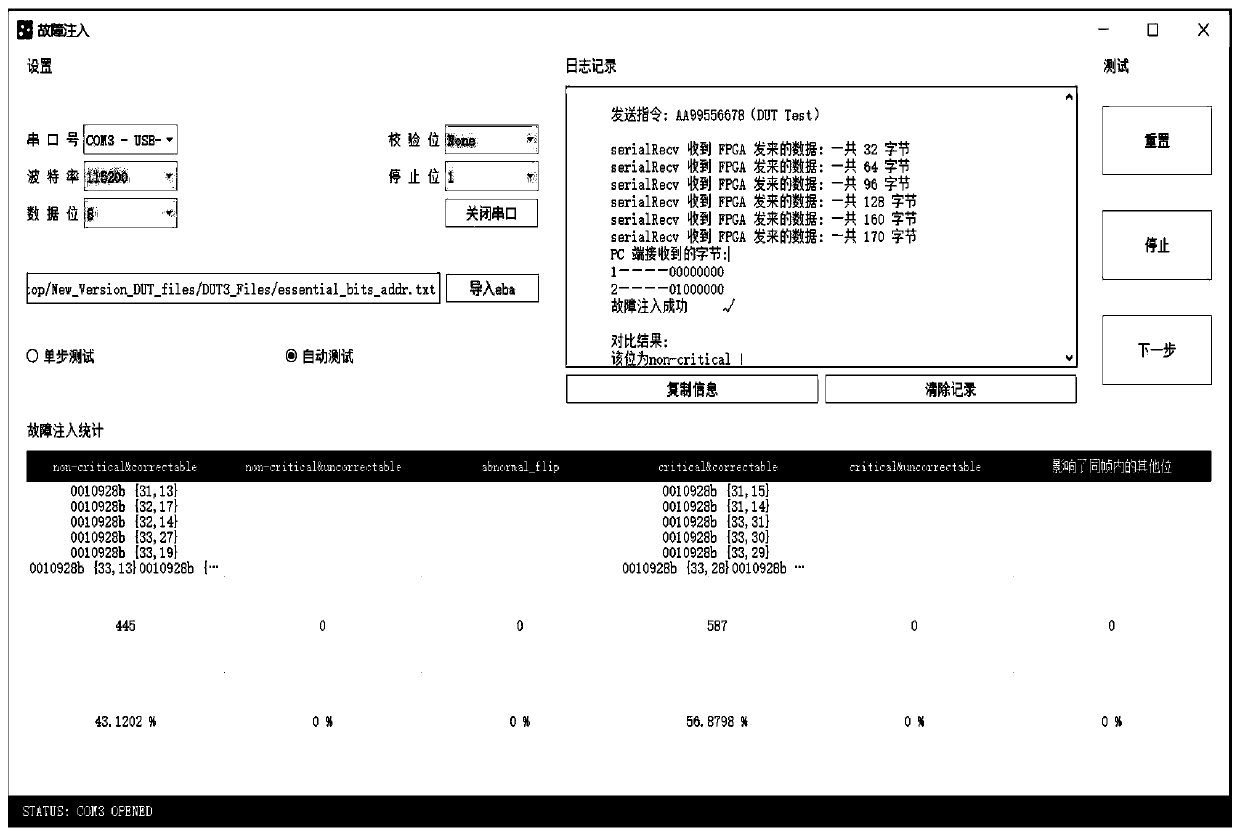

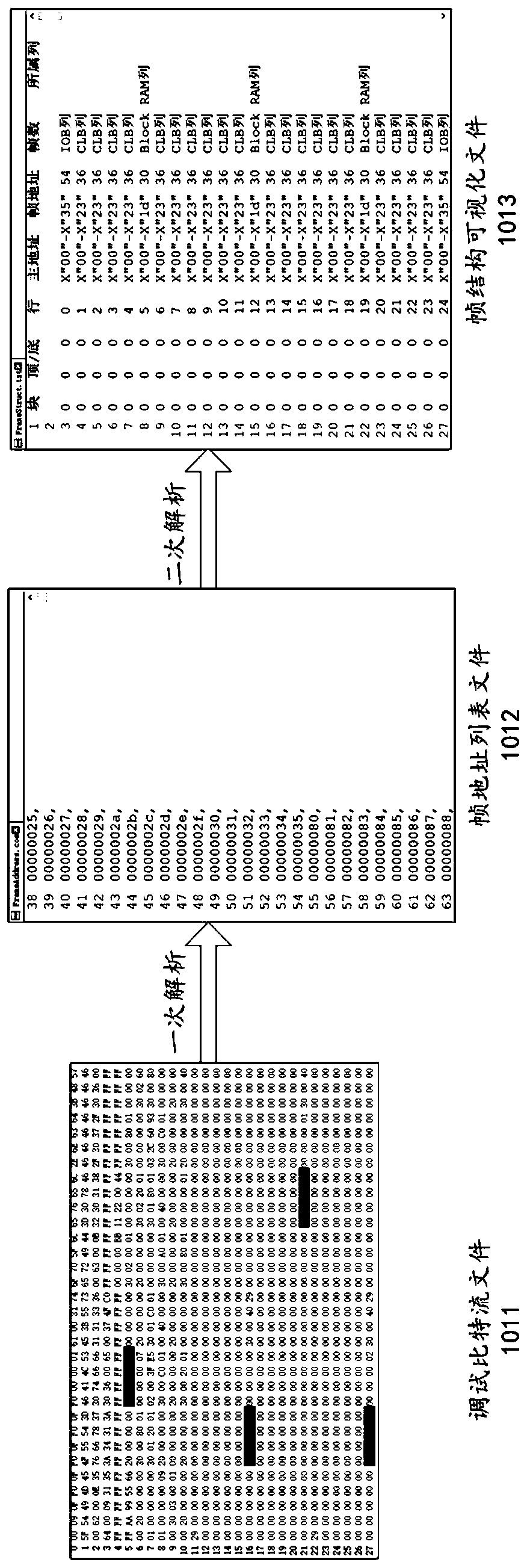

[0061] refer to figure 1 , shows a structural block diagram of an online simulation system for a necessary bit single event upset fault on a SRAM FPGA in an embodiment of the present invention. The system design is composed of an upper computer 1, namely the PC terminal, and a lower computer 2, namely the FPGA terminal. Among them, the upper computer 1 system design includes: test interface 101, necessary bit file extraction module 102, analysis and debugging bit stream file module 103, communication interface 104; lower computer 2 system design includes: main control module 201, circuit t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More