Special graph avoiding method and device for optimizing manufacturability of integrated circuit

An integrated circuit, manufacturable technology, applied in special data processing applications, electrical digital data processing, instruments, etc., to achieve the effect of optimizing and improving manufacturability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

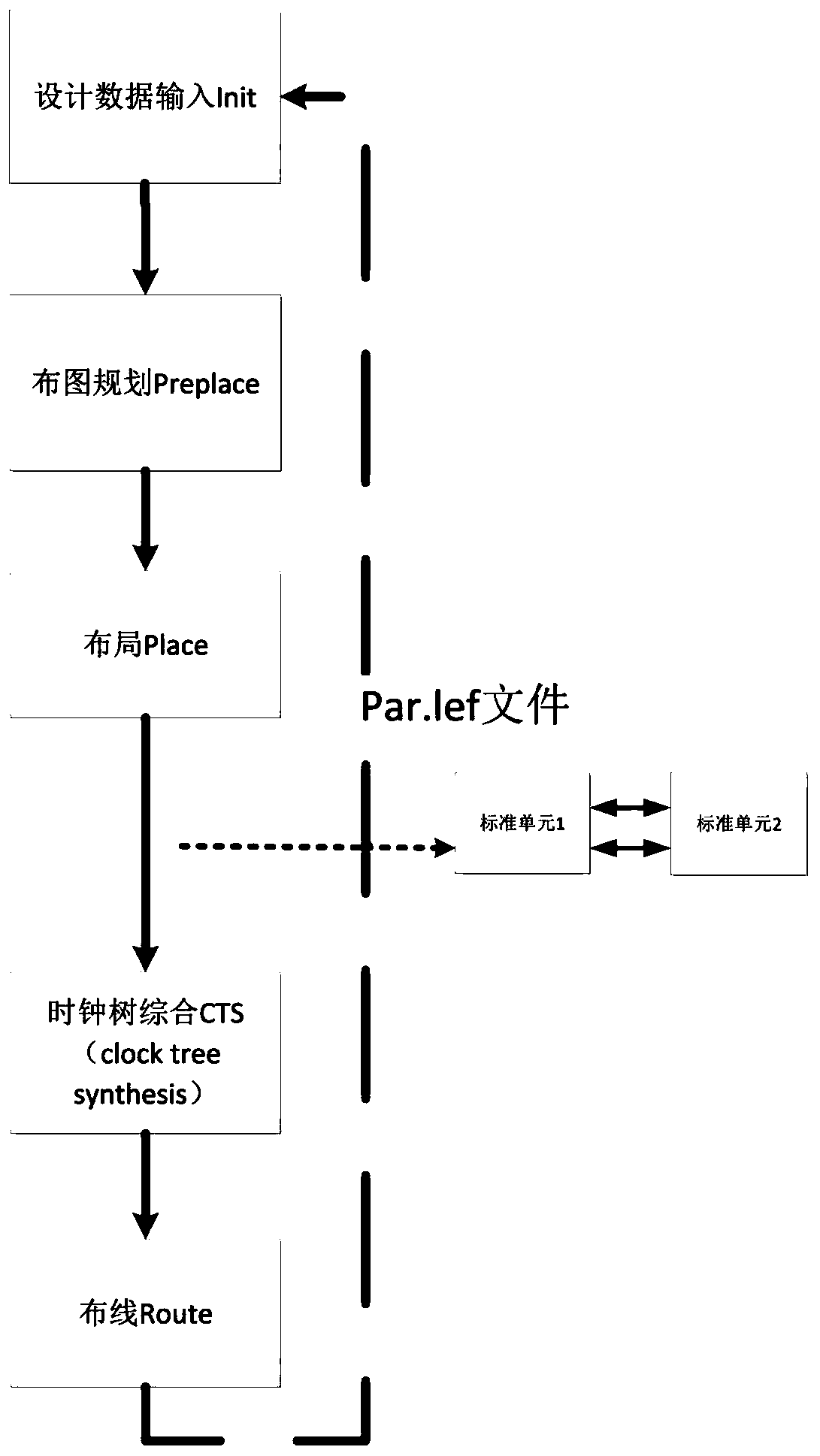

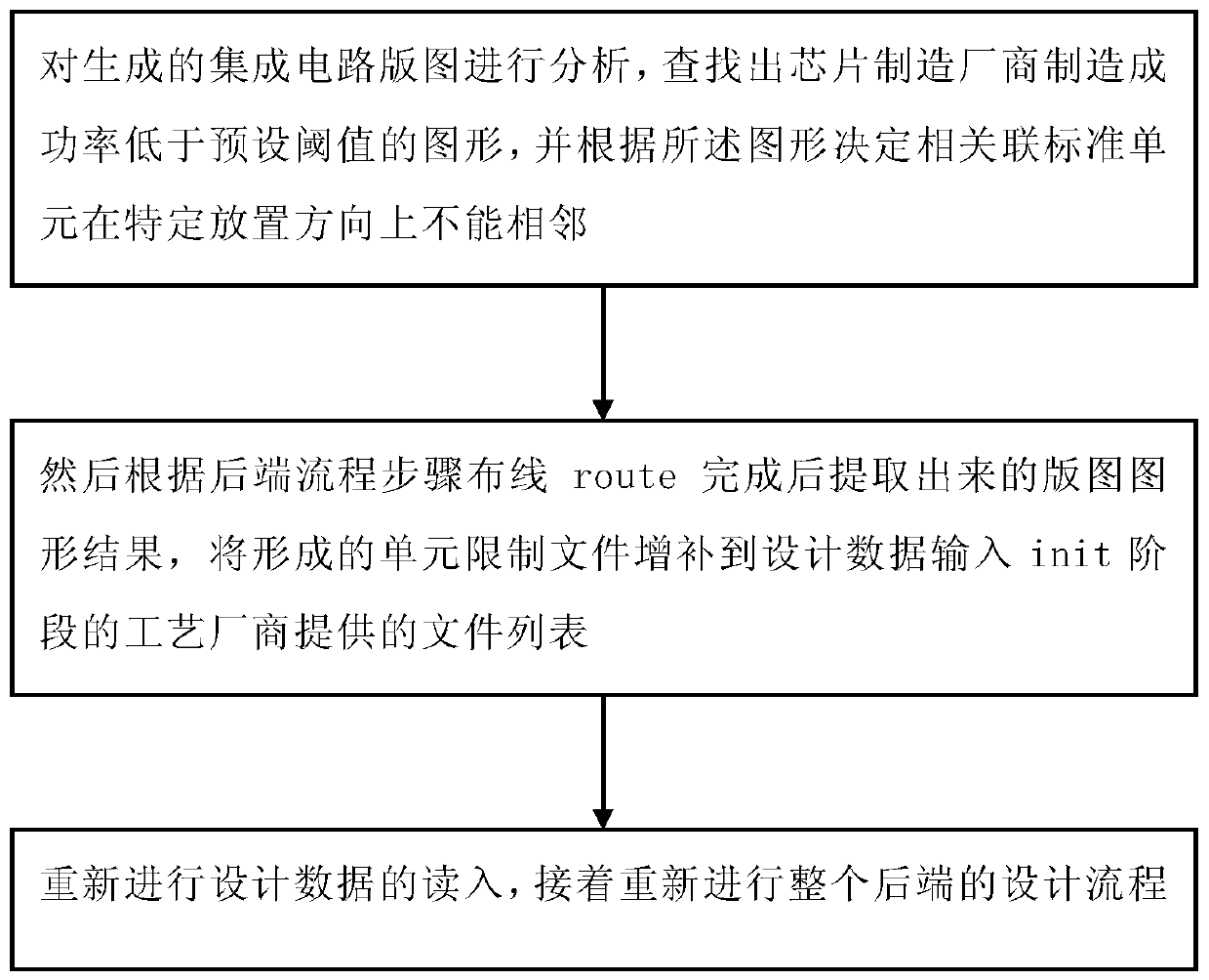

[0026] Such as figure 2 As shown, according to a special graphic circumvention method for optimizing the manufacturability of an integrated circuit according to an embodiment of the present invention, the integrated circuit back-end process includes design data input Init, layout planning Preplace, layout Place, clock tree synthesis CTS (clock tree synthesis) and five basic steps of wiring Route. After the above steps are completed, analyze the generated integrated circuit layout, find out the graphics whose manufacturing success rate is lower than the preset threshold by the chip manufacturer, and decide according to the graphics Associated standard cells cannot be adjacent to each other in a specific placement direction; then, according to the layout graphics results extracted after the routing route is completed in the back-end process steps, a cell restriction file is formed, and the formed cell restriction file is added to the design data input process in the init stage ...

Embodiment 2

[0035] This embodiment describes the present invention from the perspective of hardware, a special graphics avoidance device for optimizing the manufacturability of integrated circuits, a back-end design module, and the back-end process of the integrated circuit is executed through the back-end design module, and the process includes design data Input the five basic steps of Init, layout planning Preplace, layout Place, clock tree synthesis CTS (clock tree synthesis) and routing Route, including the analysis module, which is executed after the above steps are completed, and the generated integrated circuit layout is analyzed. Analyze and find out the graphics whose manufacturing success rate is lower than the preset threshold by the chip manufacturer, and determine that the associated standard units cannot be adjacent in a specific placement direction according to the graphics; the execution module, the execution module is wired according to the back-end process steps After the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More