Patents

Literature

450 results about "Chip fabrication" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

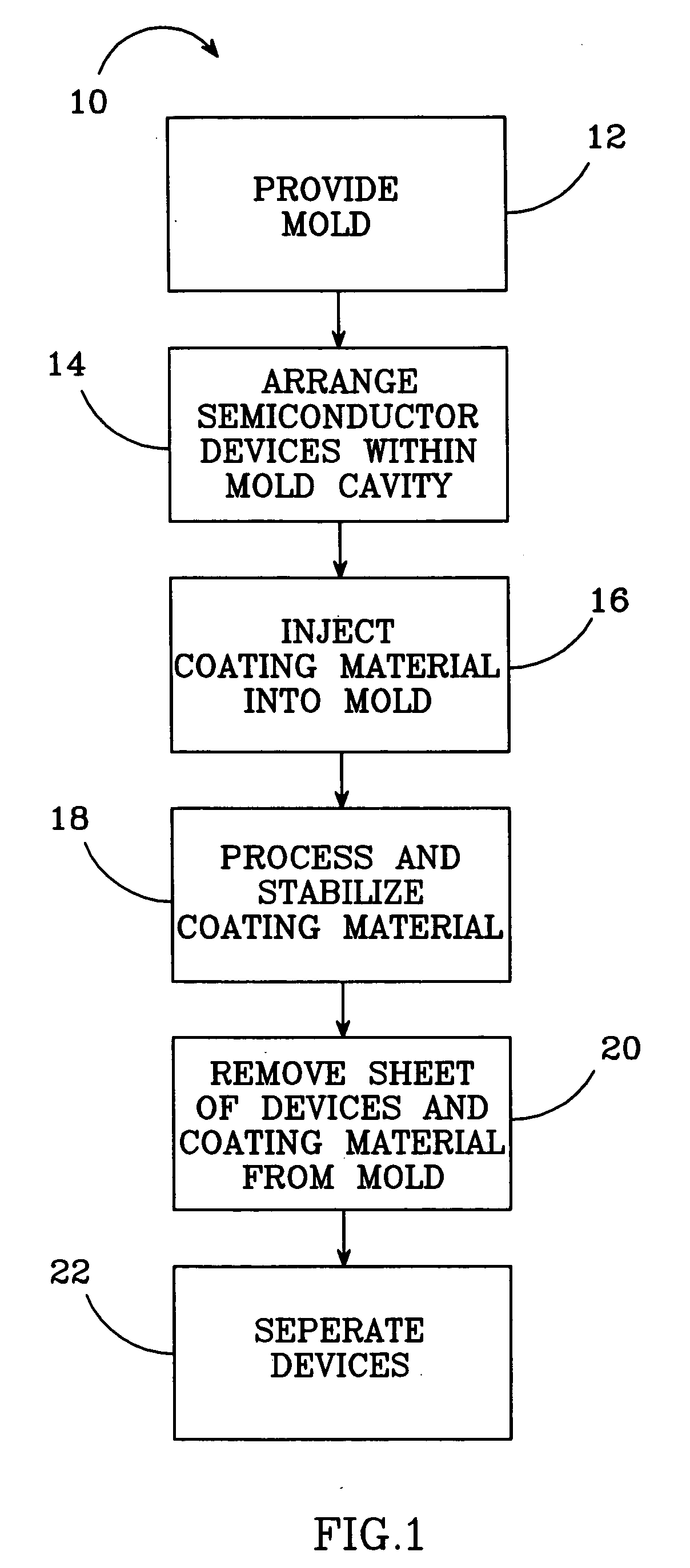

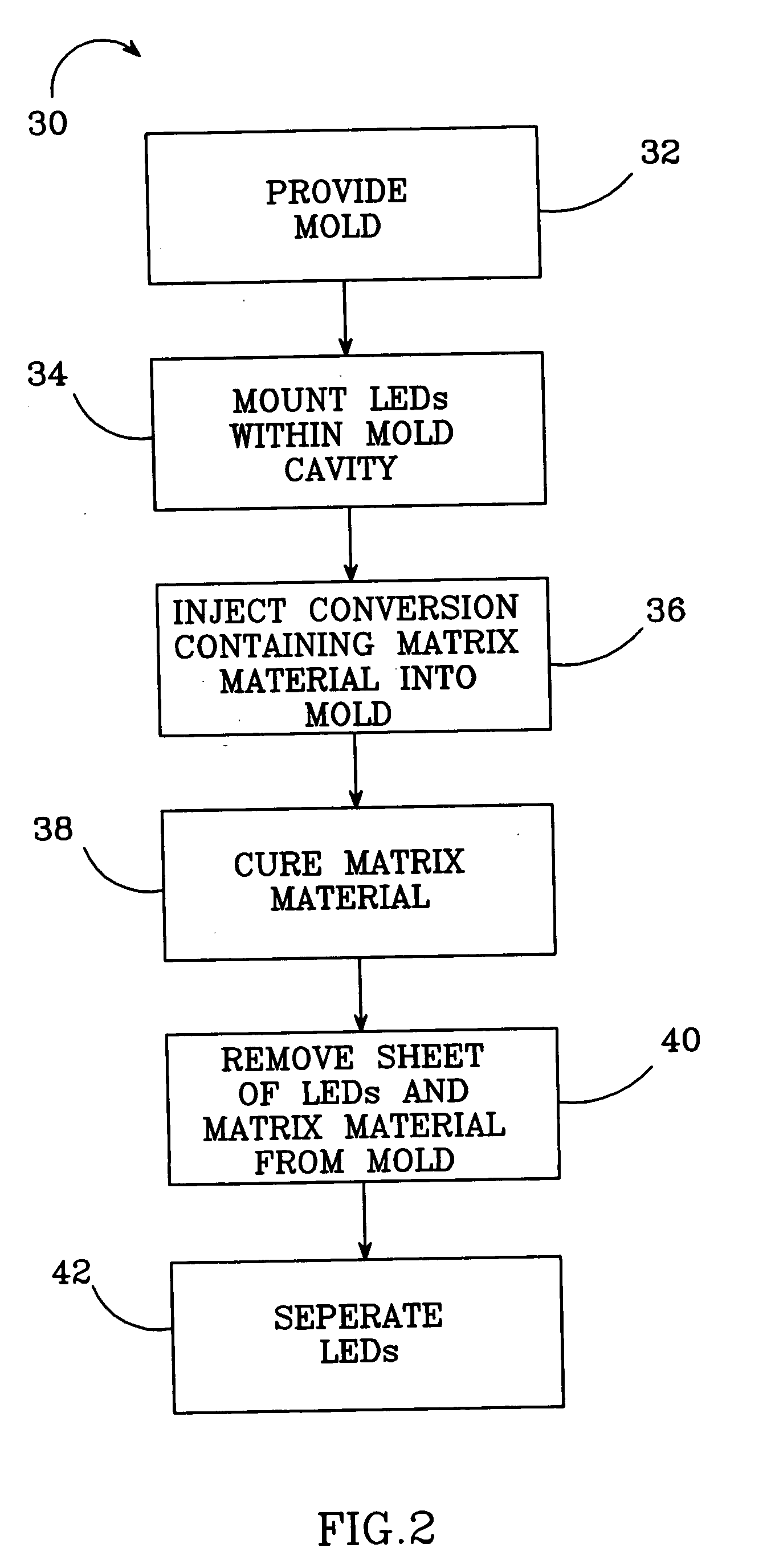

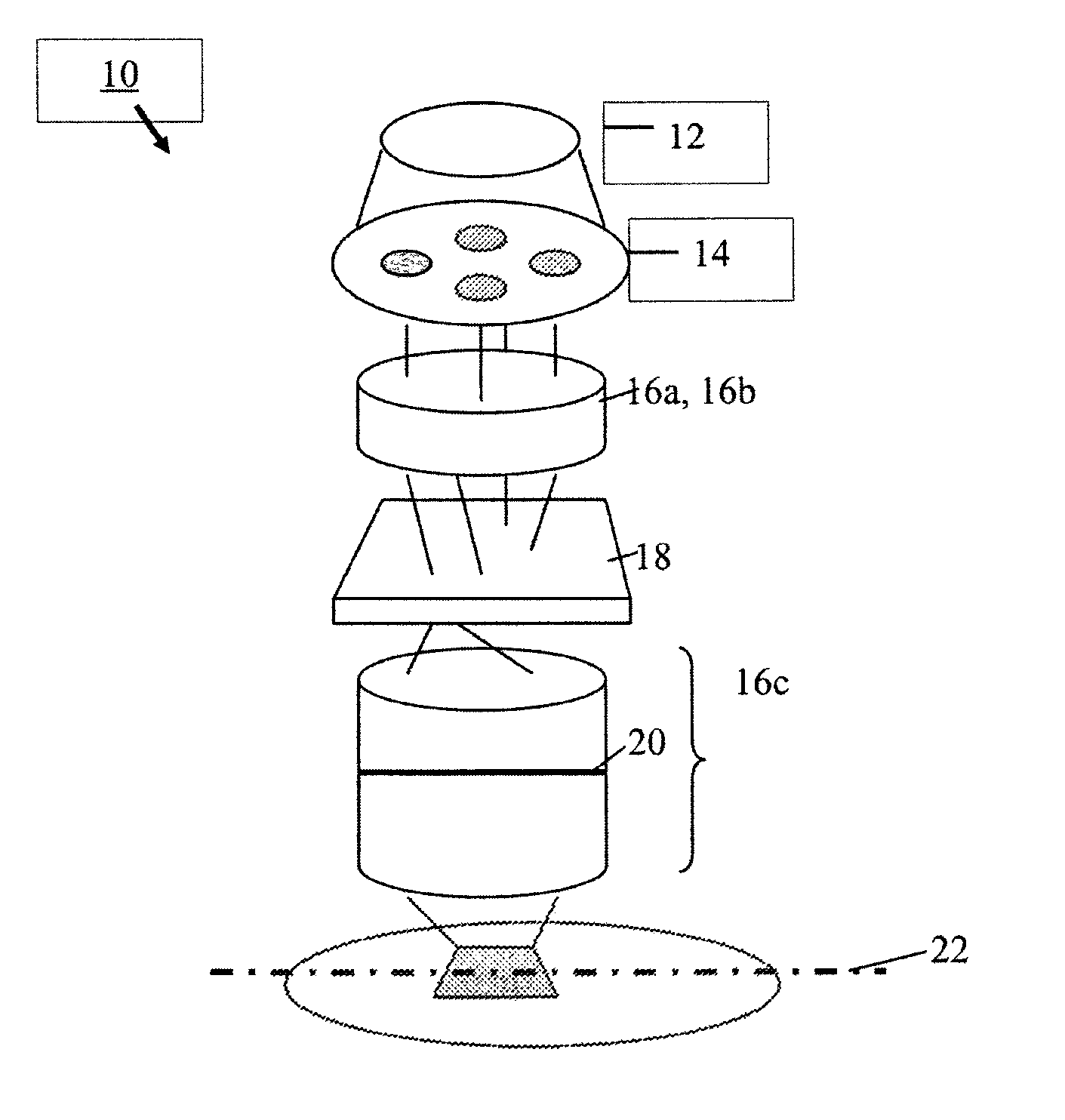

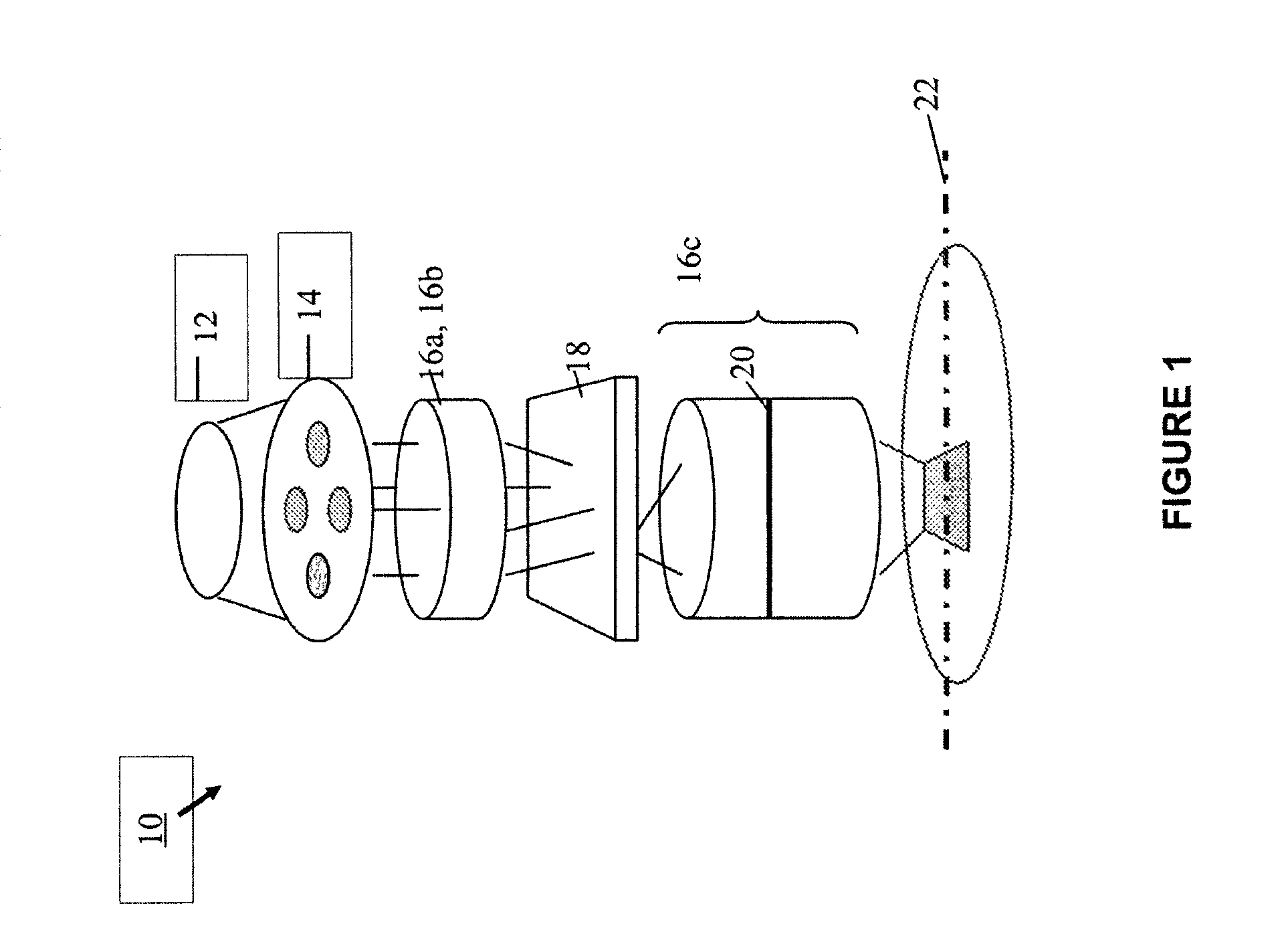

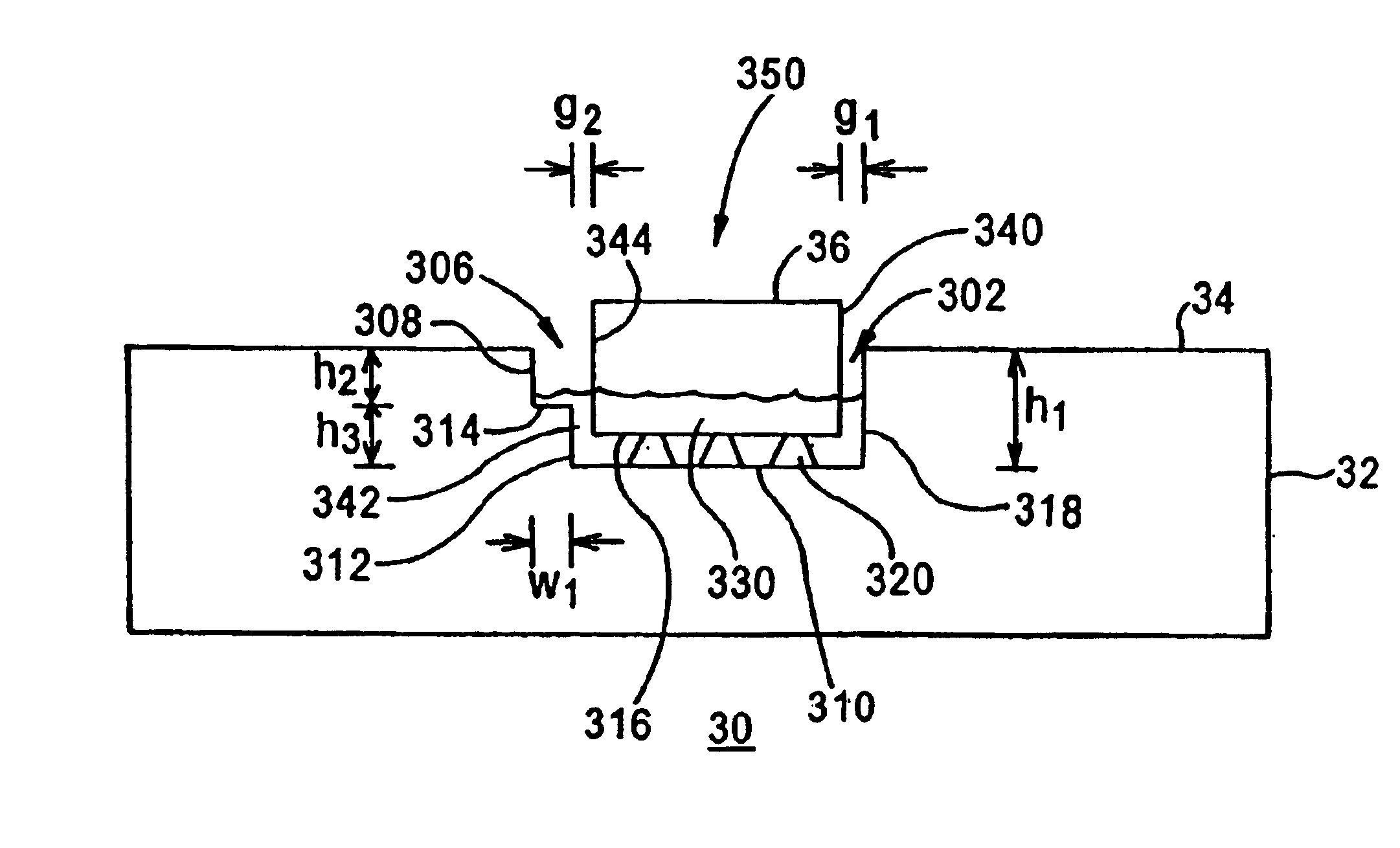

Molded chip fabrication method and apparatus

InactiveUS20050062140A1Efficient use ofUniform color temperatureSemiconductor/solid-state device detailsSolid-state devicesDevice materialSemiconductor

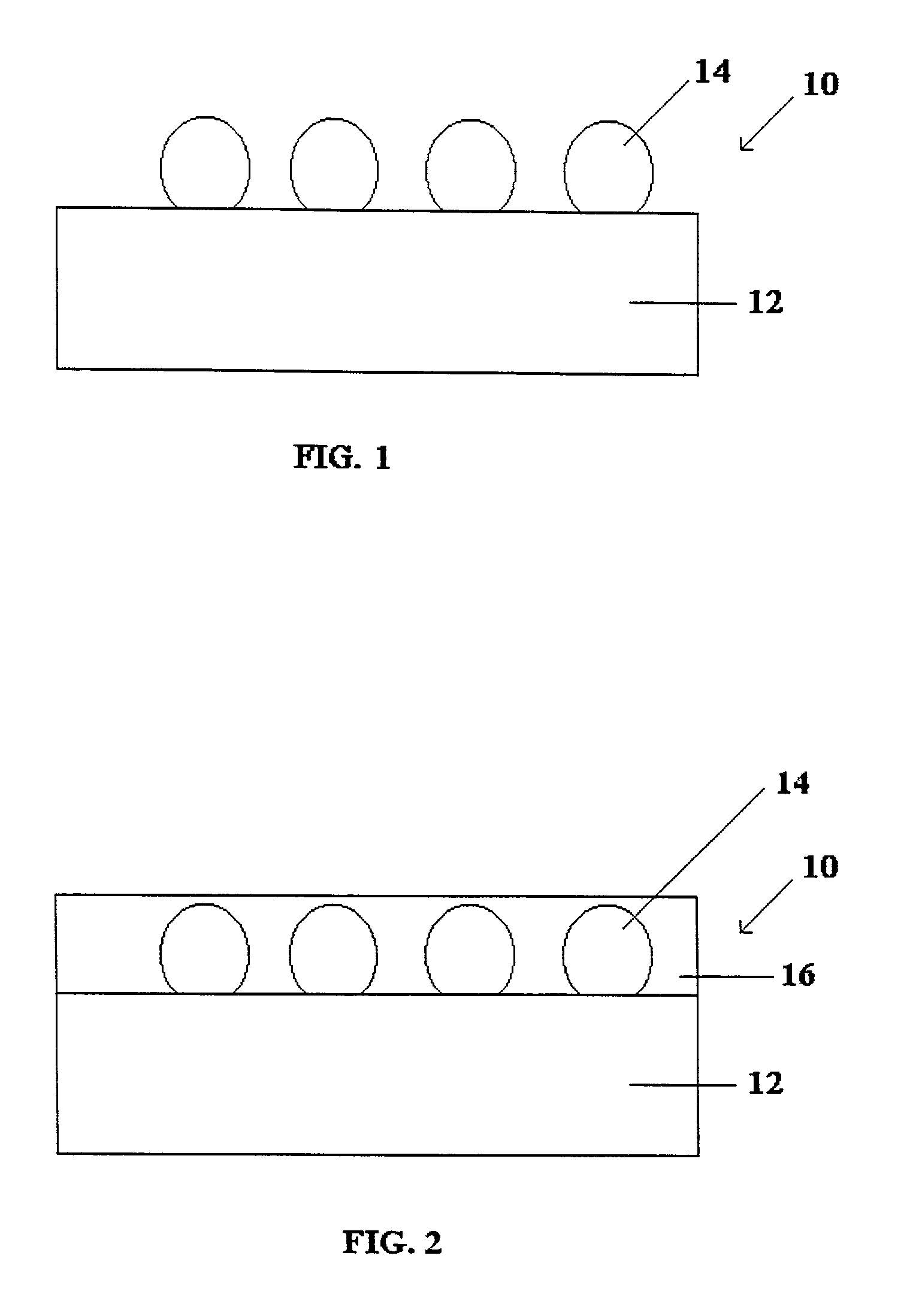

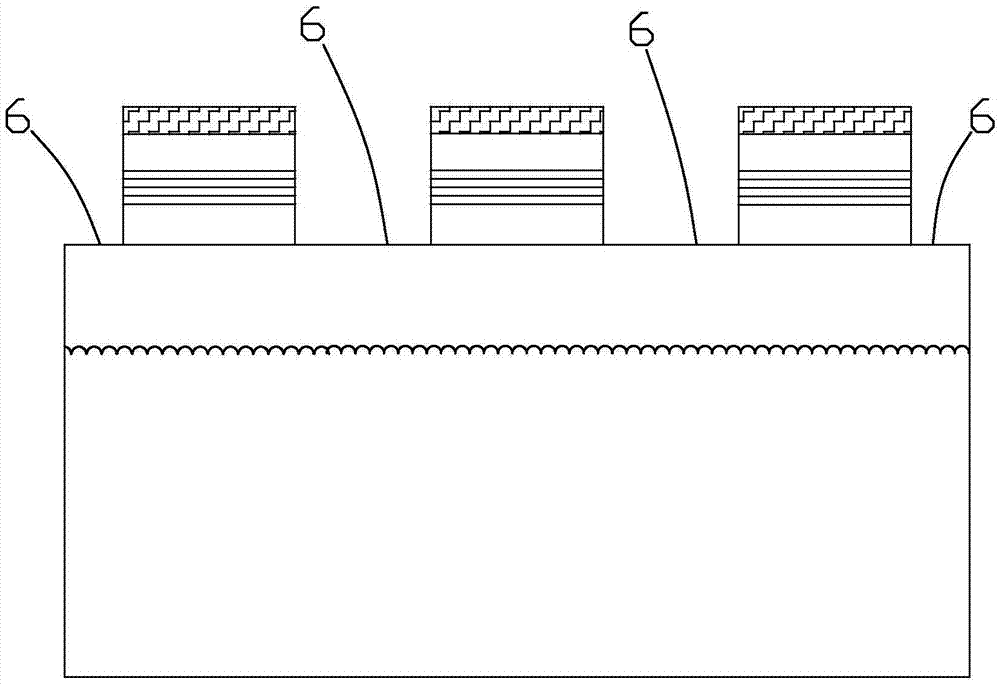

A method and apparatus for coating a plurality of semiconductor devices that is particularly adapted to coating LEDs with a coating material containing conversion particles. One method according to the invention comprises providing a mold with a formation cavity. A plurality of semiconductor devices are mounted within the mold formation cavity and a curable coating material is injected or otherwise introduced into the mold to fill the mold formation cavity and at least partially cover the semiconductor devices. The coating material is cured so that the semiconductor devices are at least partially embedded in the cured coating material. The cured coating material with the embedded semiconductor devices is removed from the formation cavity. The semiconductor devices are separated so that each is at least partially covered by a layer of the cured coating material. One embodiment of an apparatus according to the invention for coating a plurality of semiconductor devices comprises a mold housing having a formation cavity arranged to hold semiconductor devices. The formation cavity is also arranged so that a curable coating material can be injected into and fills the formation cavity to at least partially covering the semiconductor devices.

Owner:CREELED INC

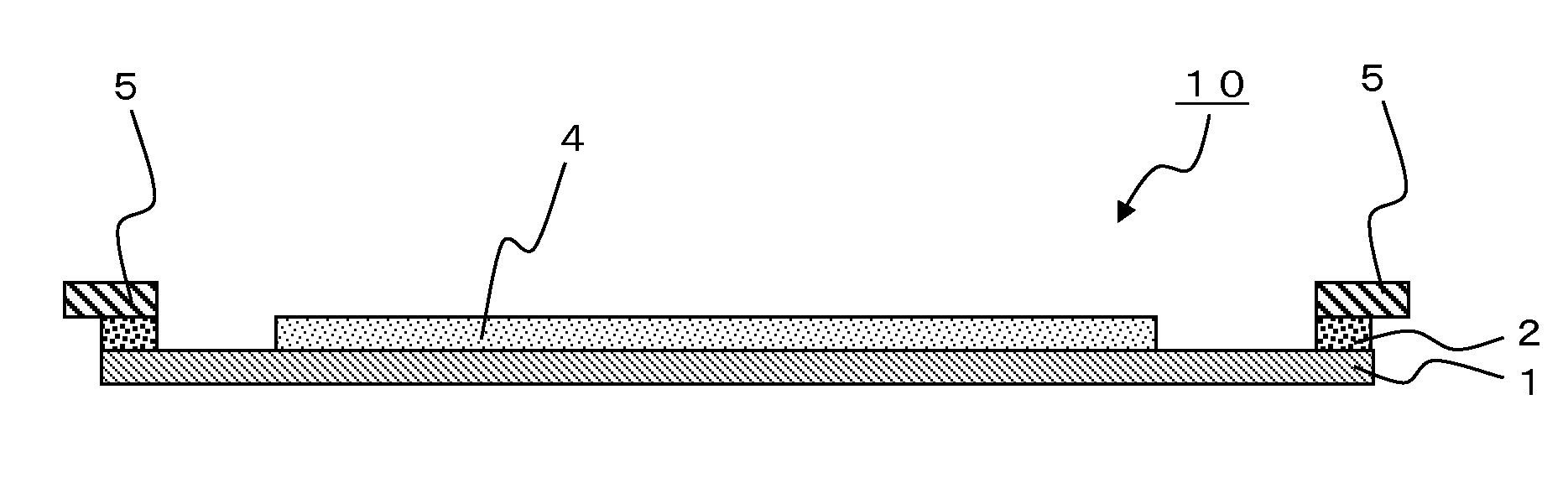

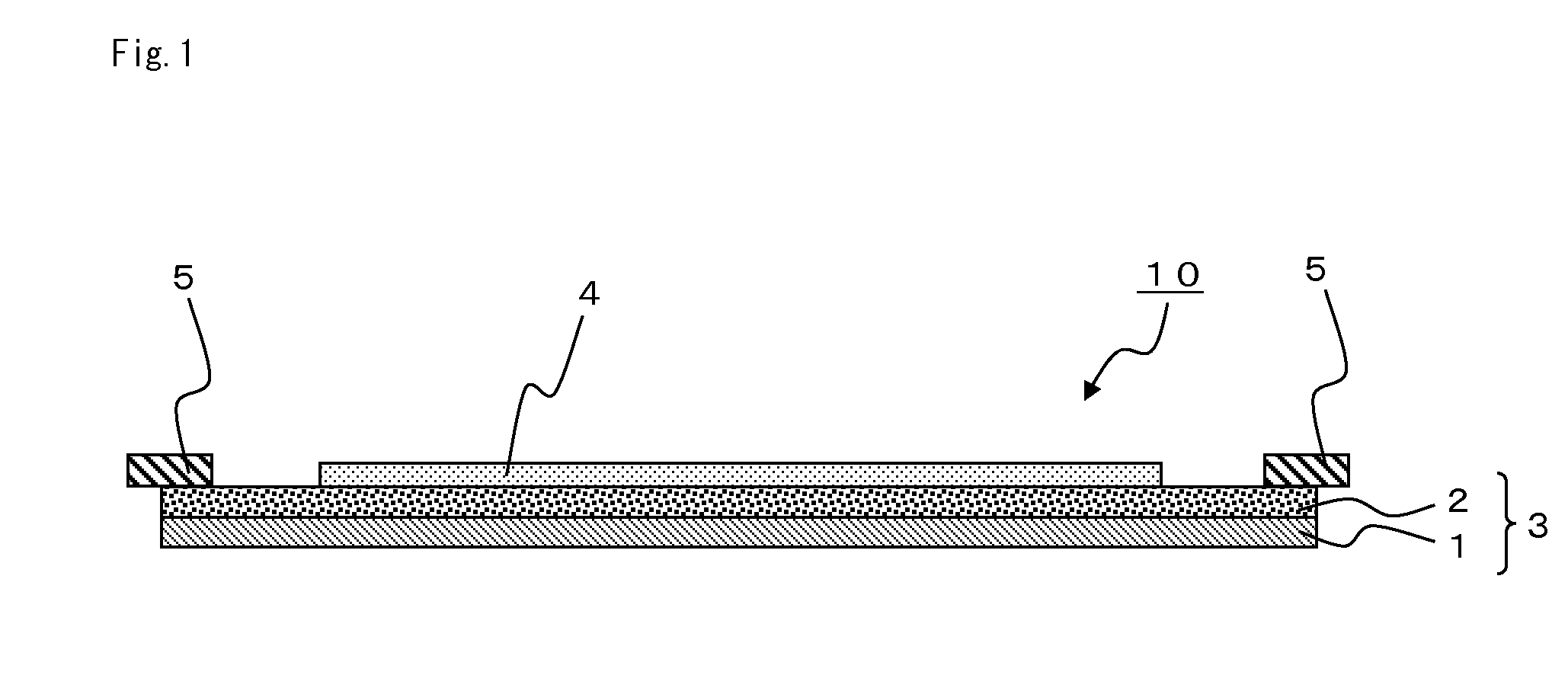

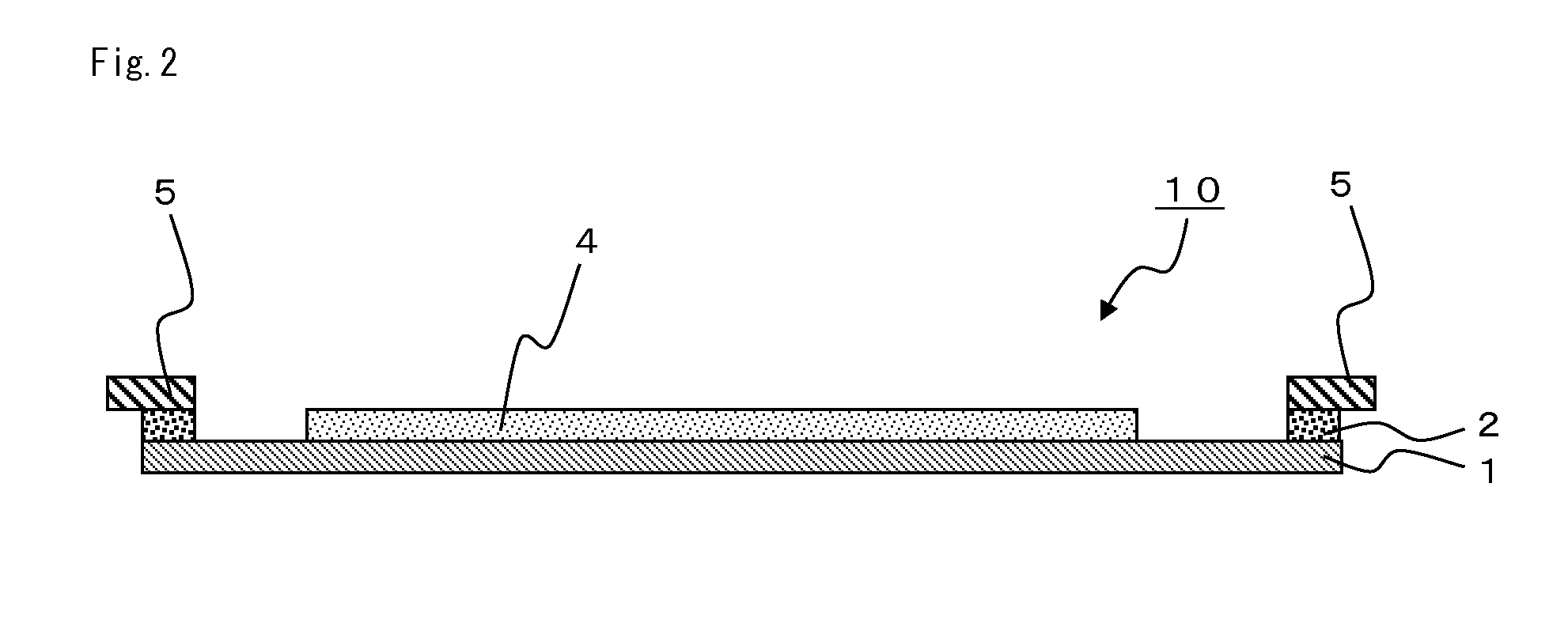

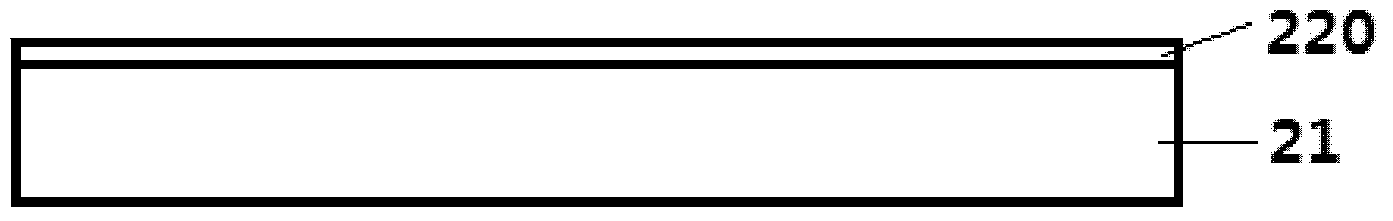

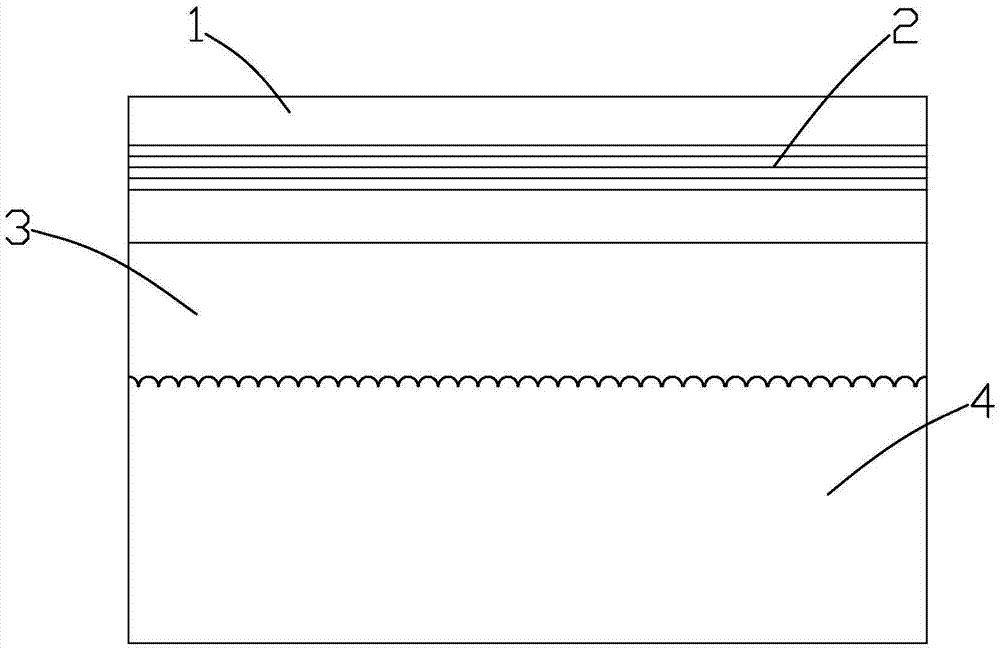

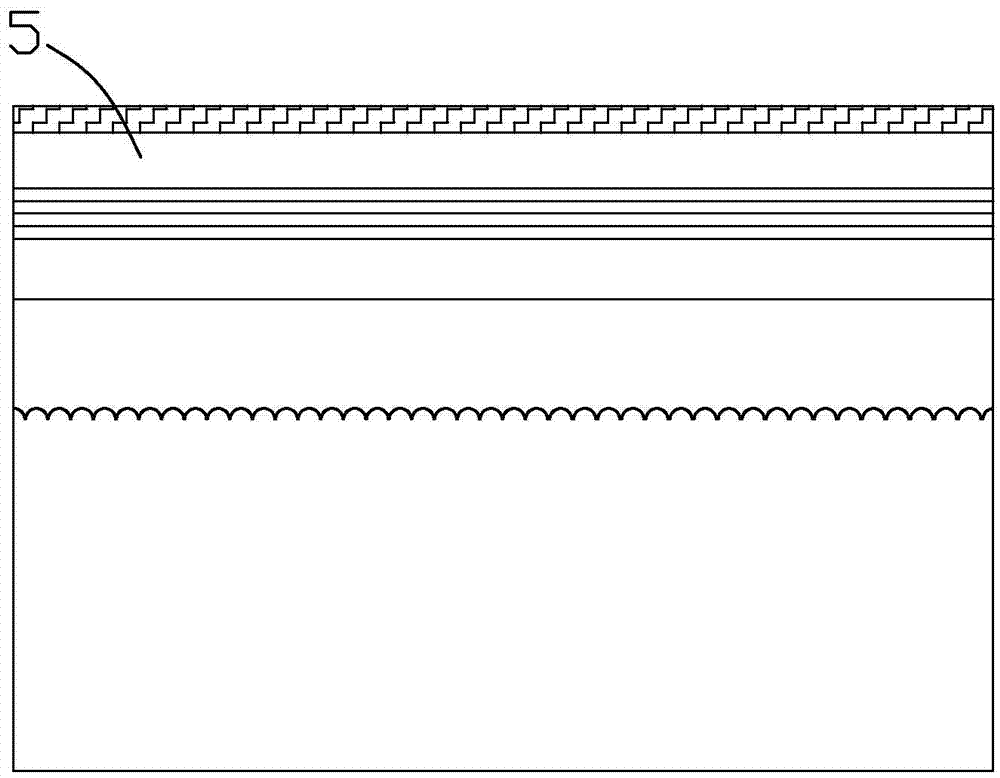

Dicing Sheet with Protective Film Forming Layer and Chip Fabrication Method

ActiveUS20140295646A1Improve printing accuracyWell formedLayered productsSemiconductor/solid-state device detailsTectorial membraneThermal contraction

A dicing sheet with a protective film forming layer has a substrate film, an adhesive layer, and a protective film forming layer, and at a minimum, the adhesive layer is formed in an area surrounding the protective film forming layer in a planar view, and the substrate film has the following characteristics (a)-(c): (a) the melting point either exceeds 130° C. or the film has no melting point; (b) the thermal contraction rate under conditions of heating at 130° C. for two hours is from −5 to +5%, and (c) the degree of elongation-to-break in the MD direction and the CD direction is at least 100%, and the stress at 25% is no more than 100 MPa.

Owner:LINTEC CORP

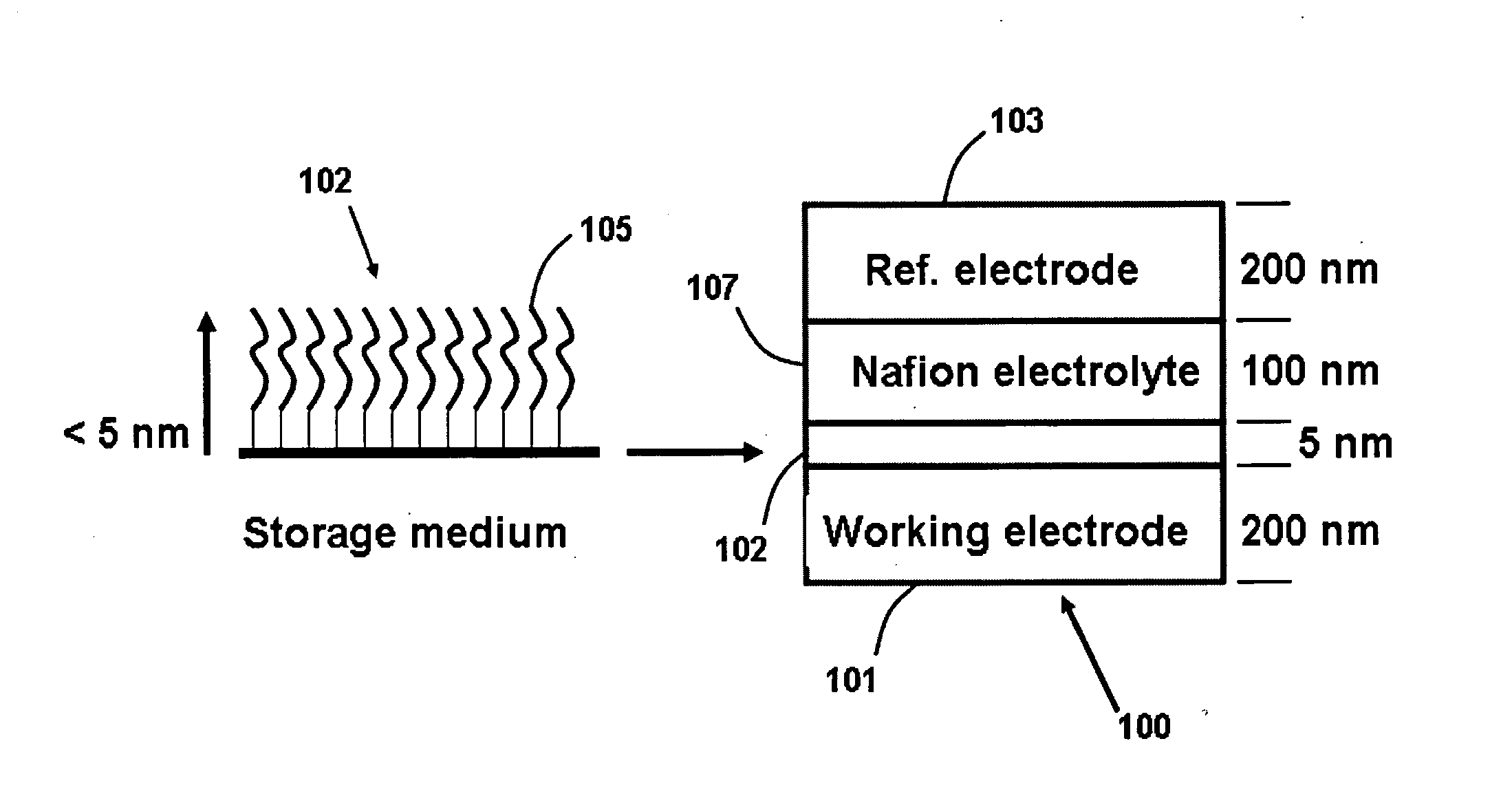

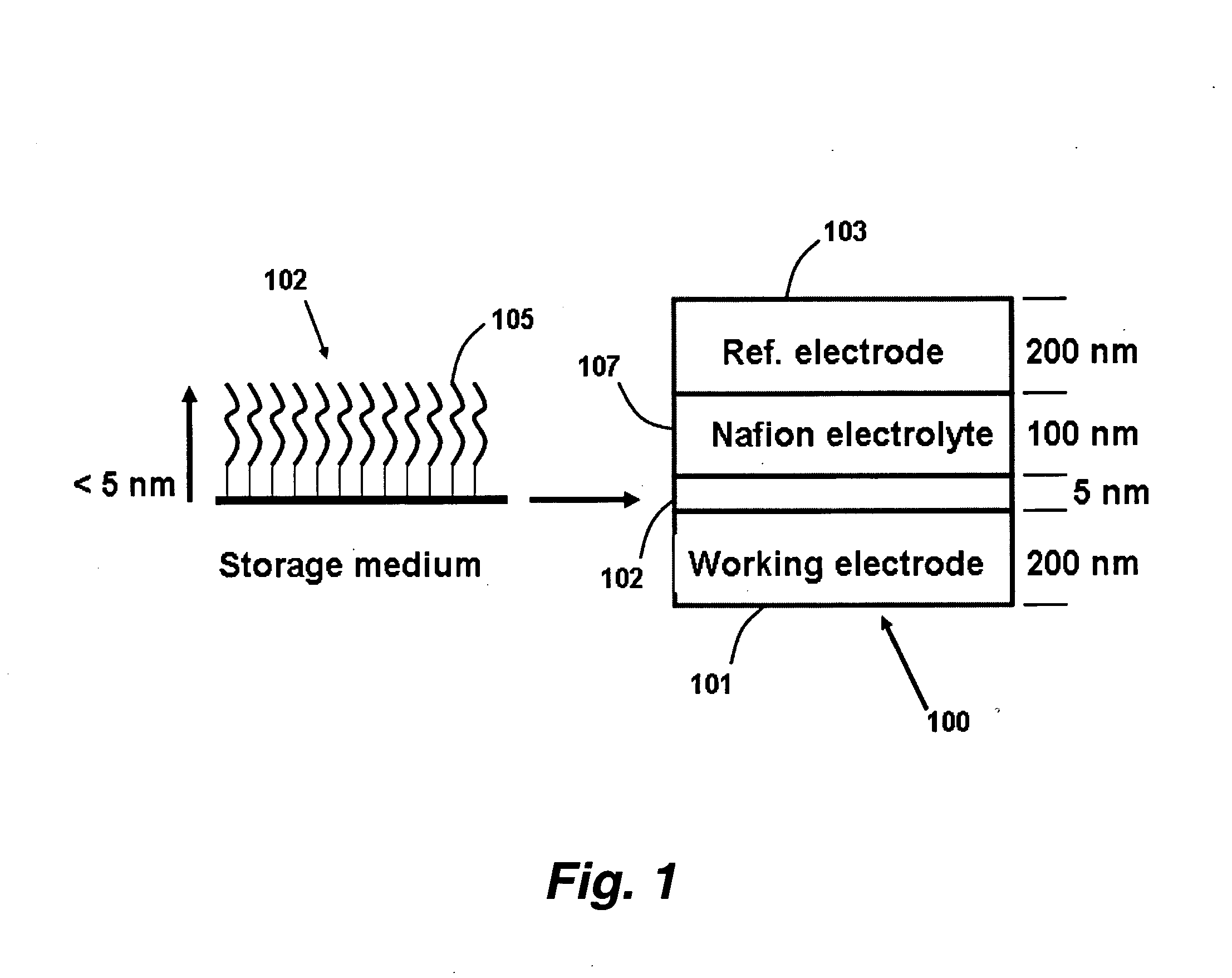

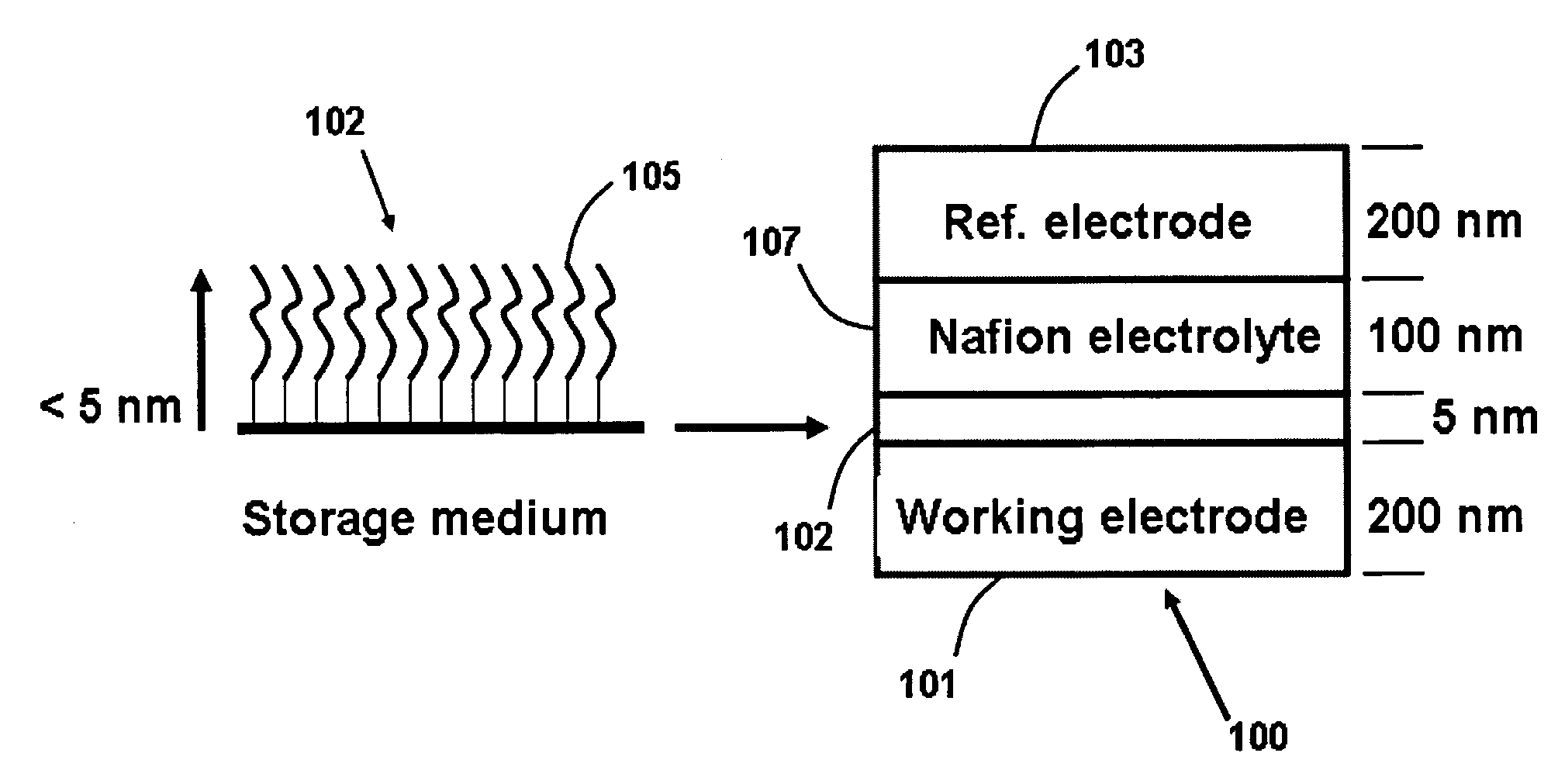

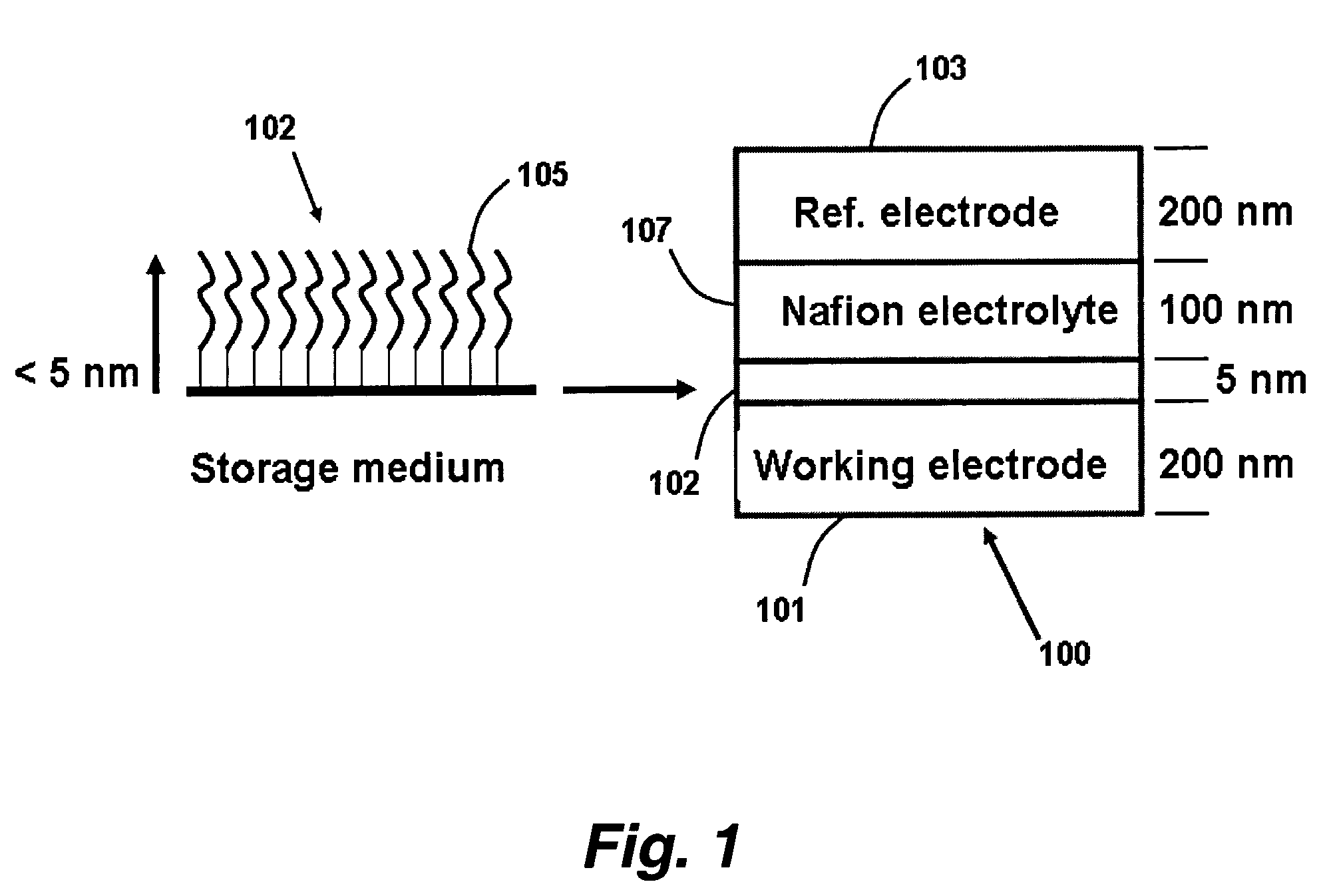

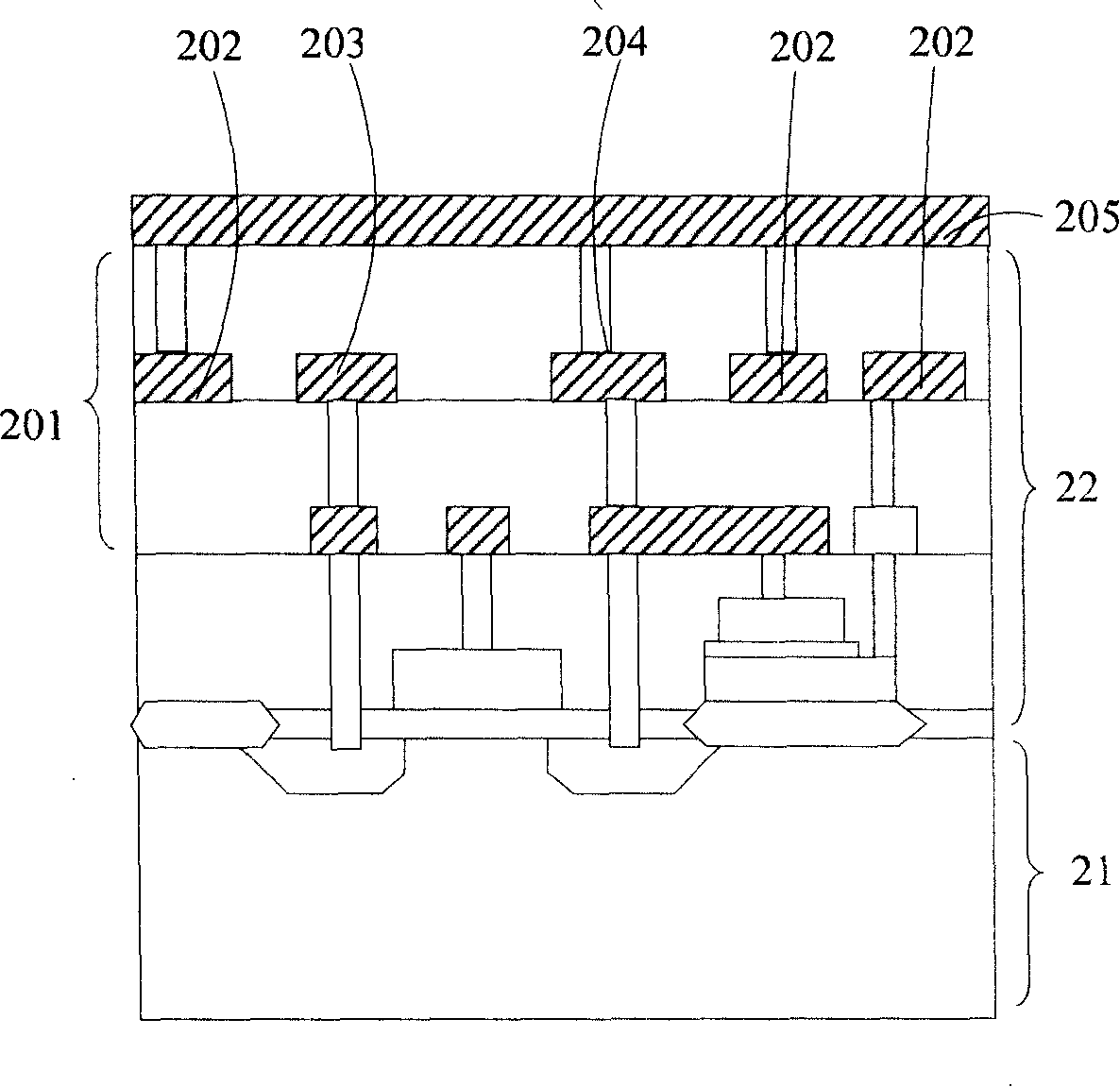

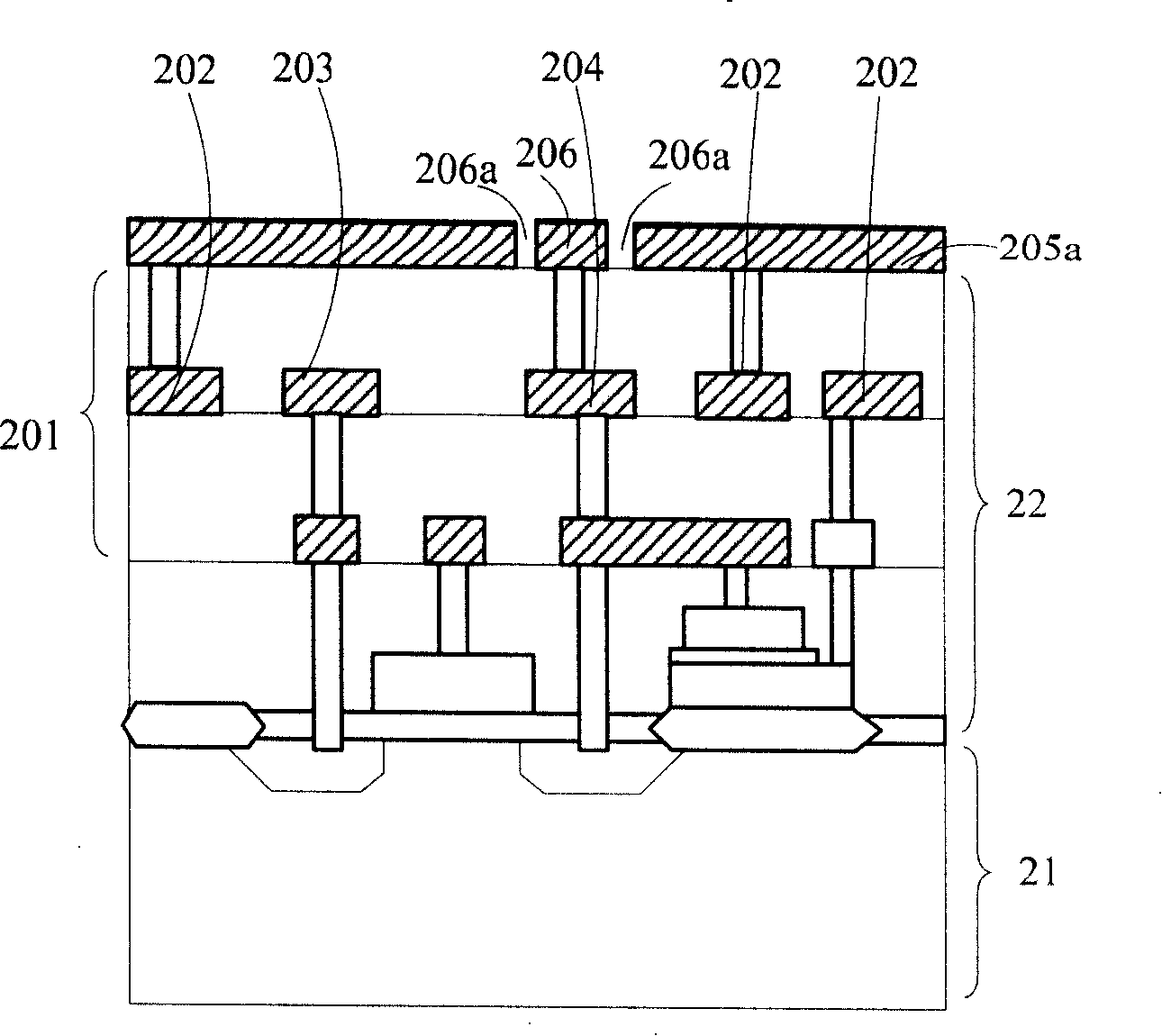

High density non-volatile memory device

InactiveUS20050041494A1Suitable mechanical propertyPrevent charge leakageNanoinformaticsSolid-state devicesChemical synthesisFault tolerance

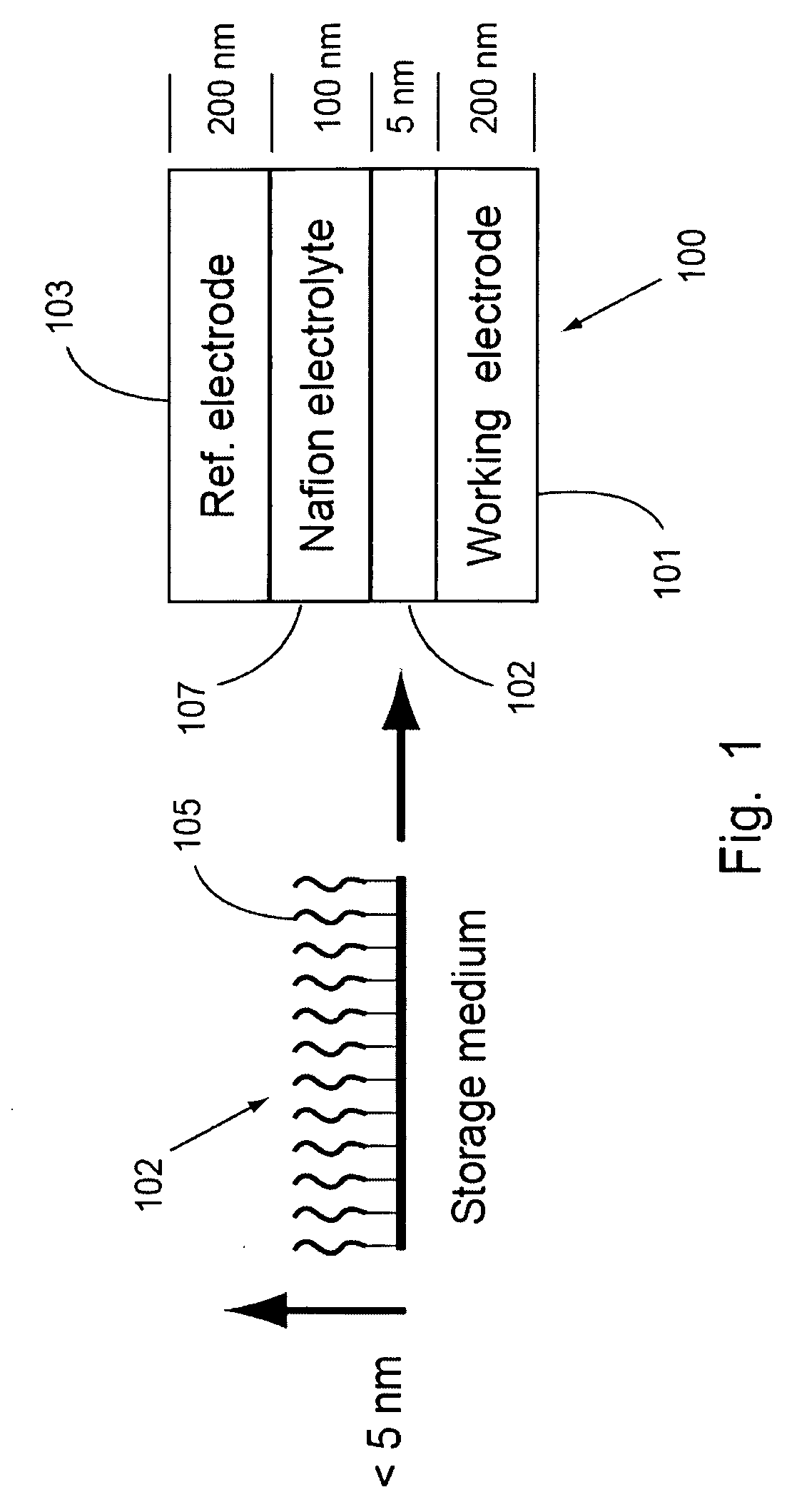

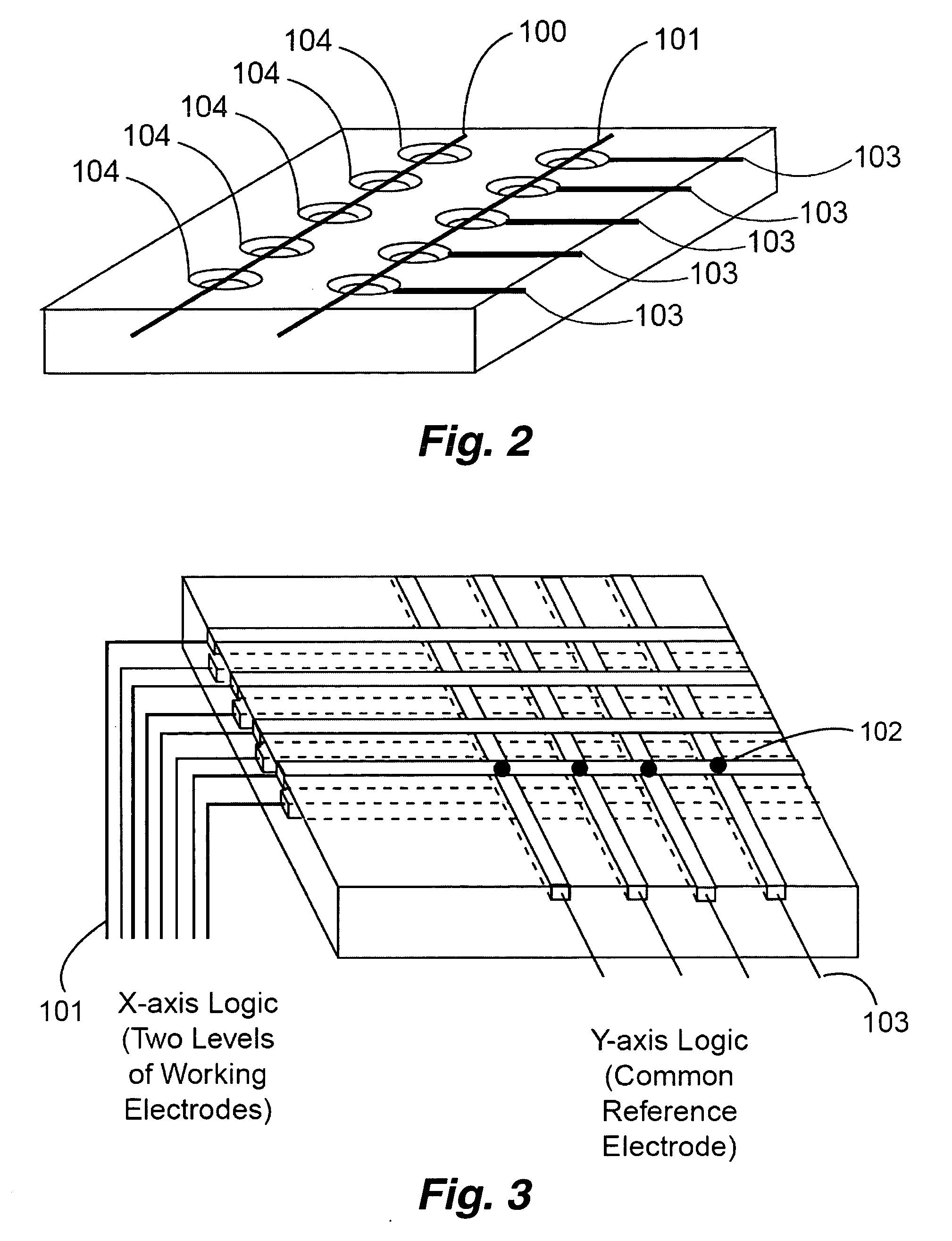

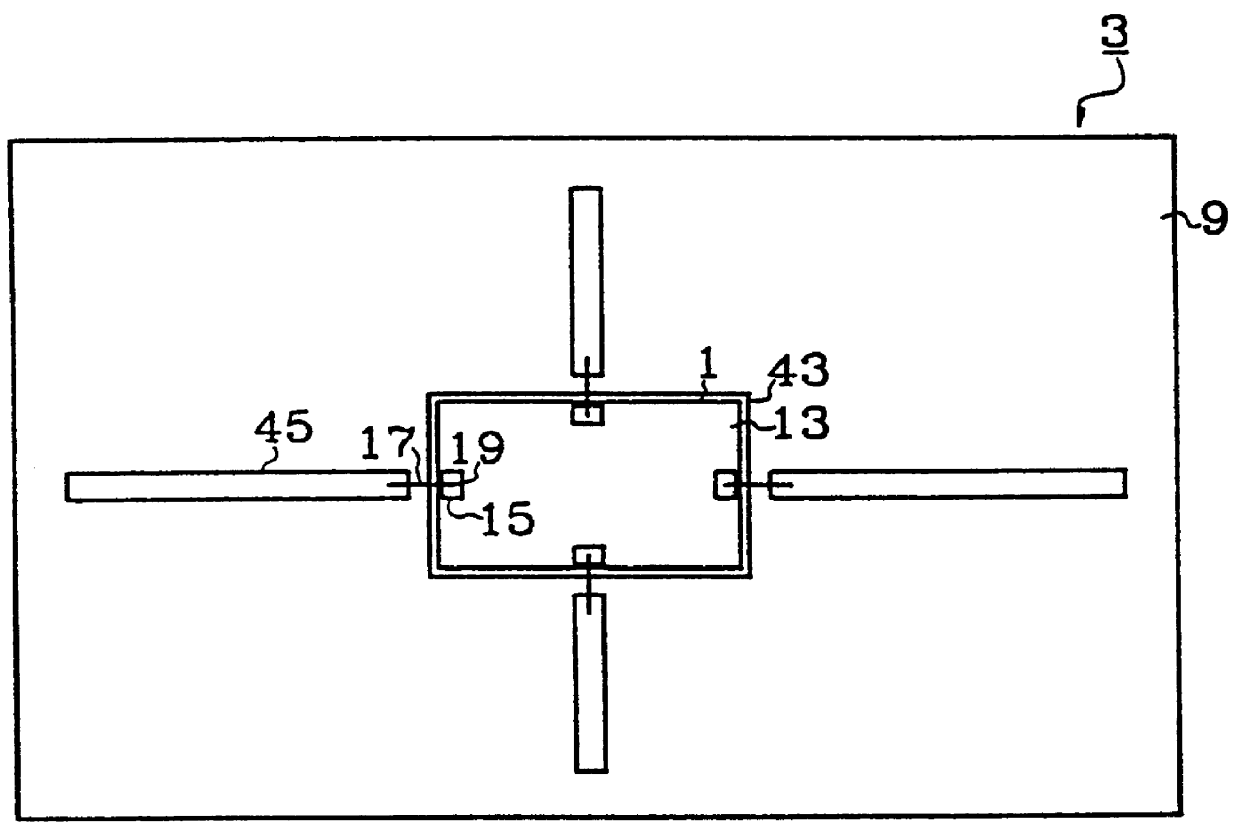

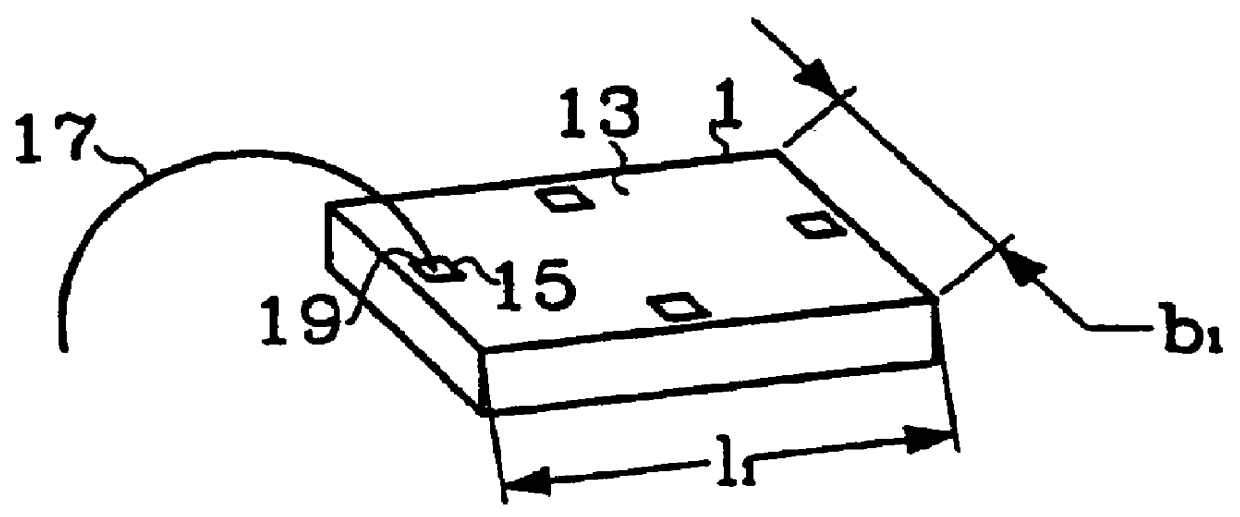

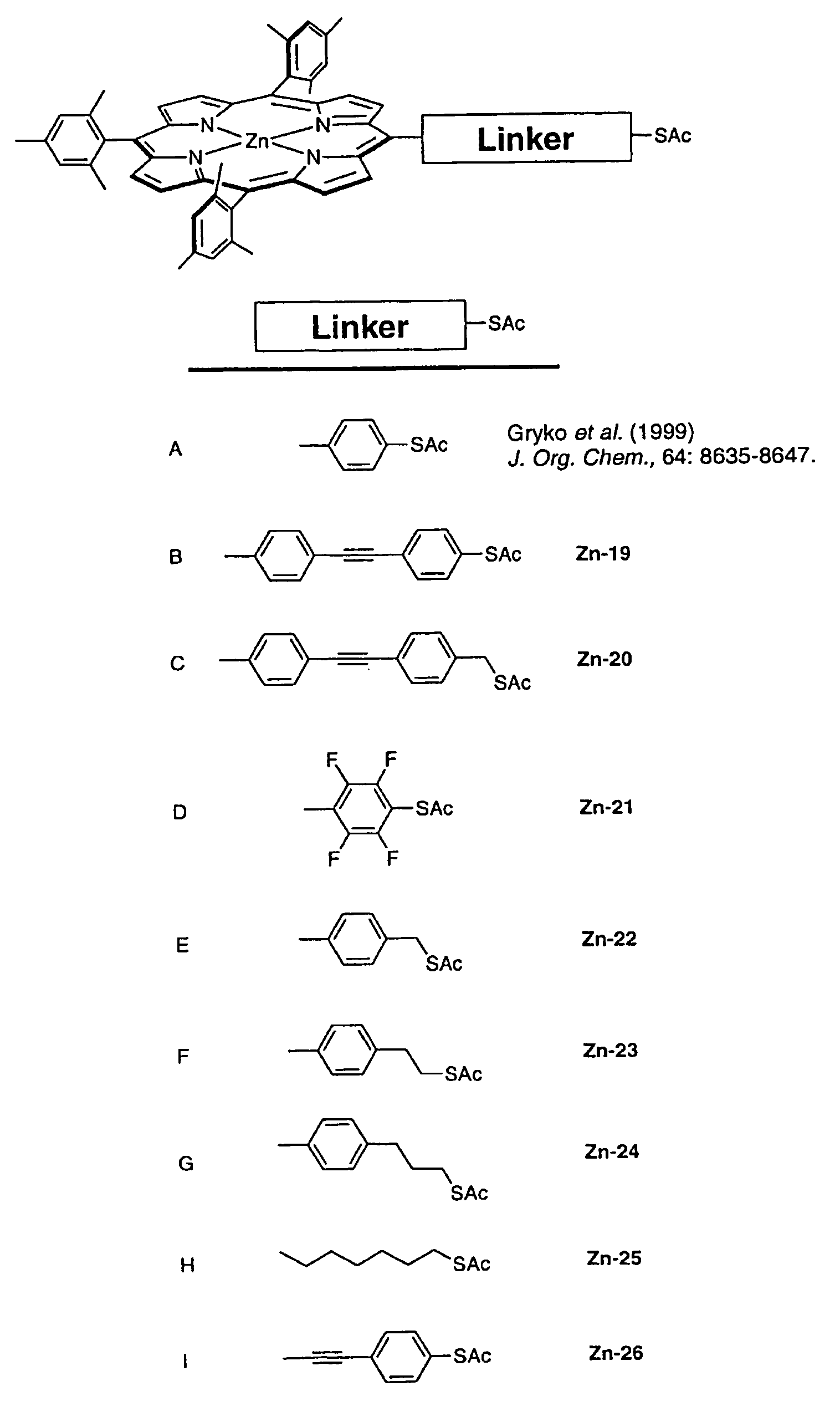

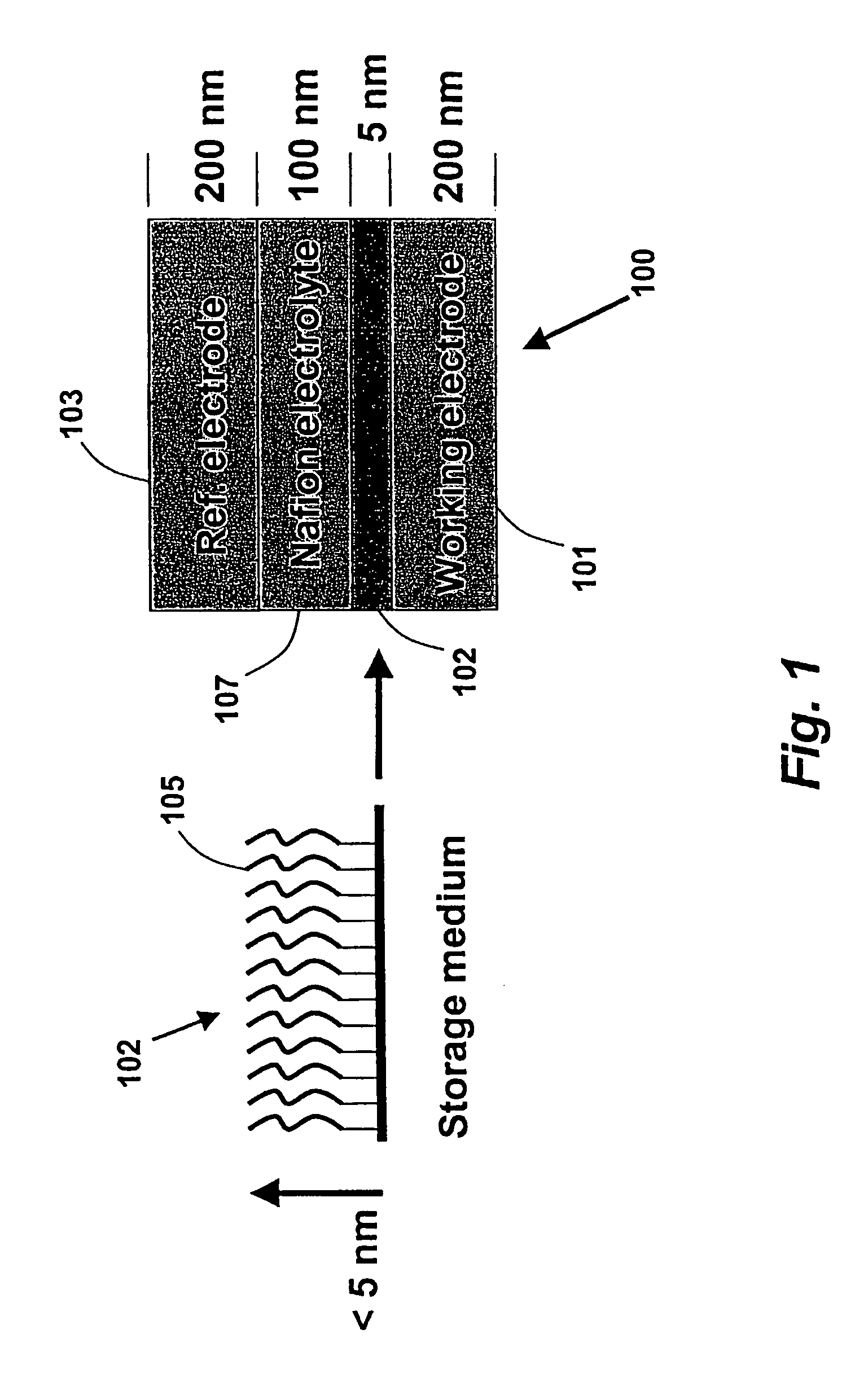

This invention provides novel high density memory devices that are electrically addressable permitting effective reading and writing, that provide a high memory density (e.g., 1015 bits / cm3), that provide a high degree of fault tolerance, and that are amenable to efficient chemical synthesis and chip fabrication. The devices are intrinsically latchable, defect tolerant, and support destructive or non-destructive read cycles. In a preferred embodiment, the device comprises a fixed electrode electrically coupled to a storage medium having a multiplicity of different and distinguishable oxidation states wherein data is stored in said oxidation states by the addition or withdrawal of one or more electrons from said storage medium via the electrically coupled electrode.

Owner:NORTH CAROLINA STATE UNIV +1

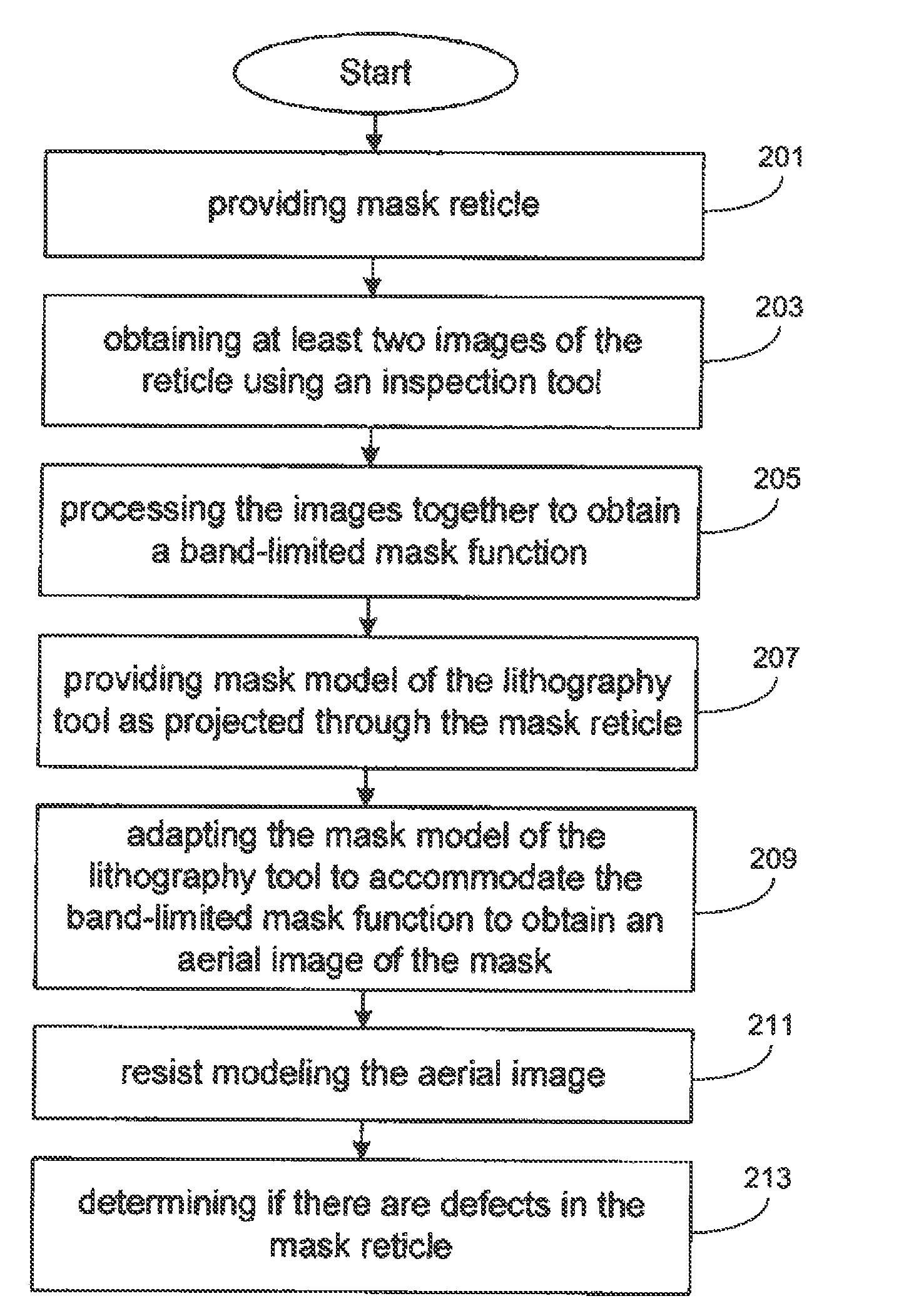

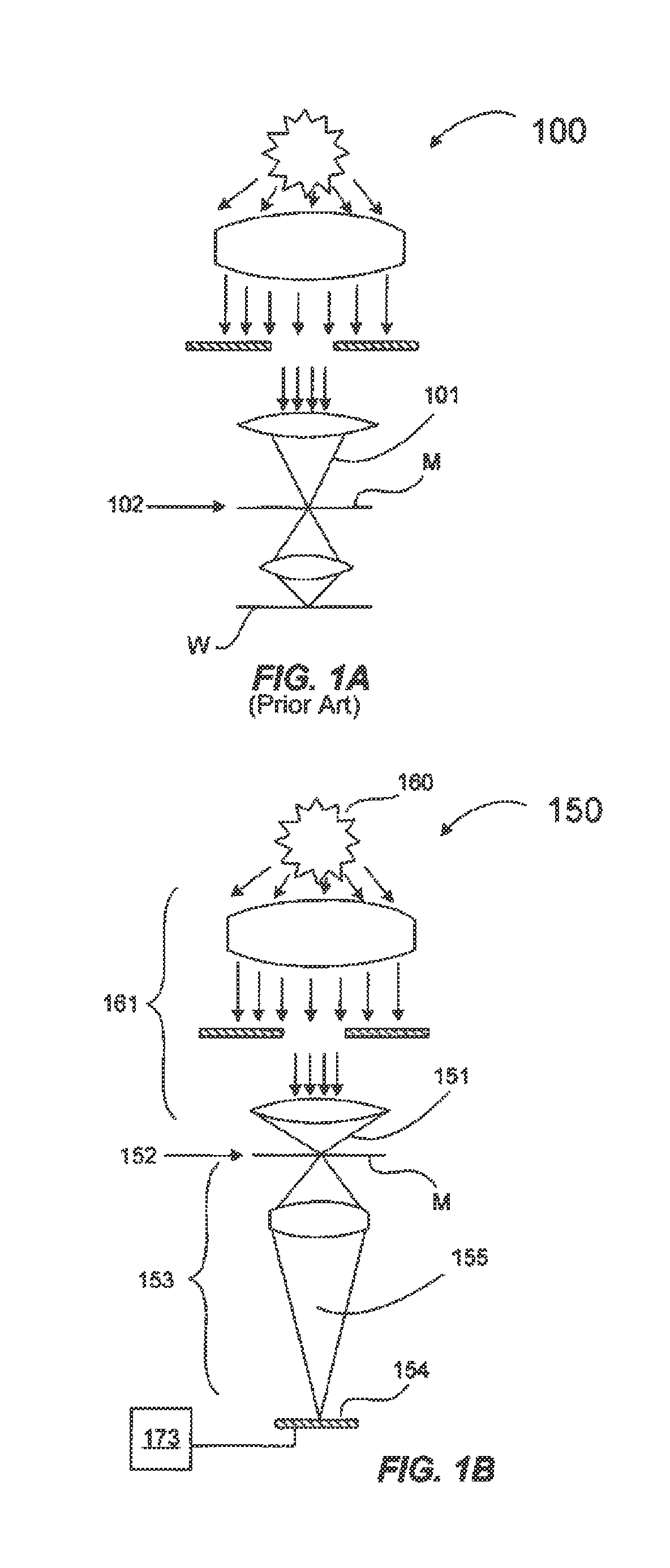

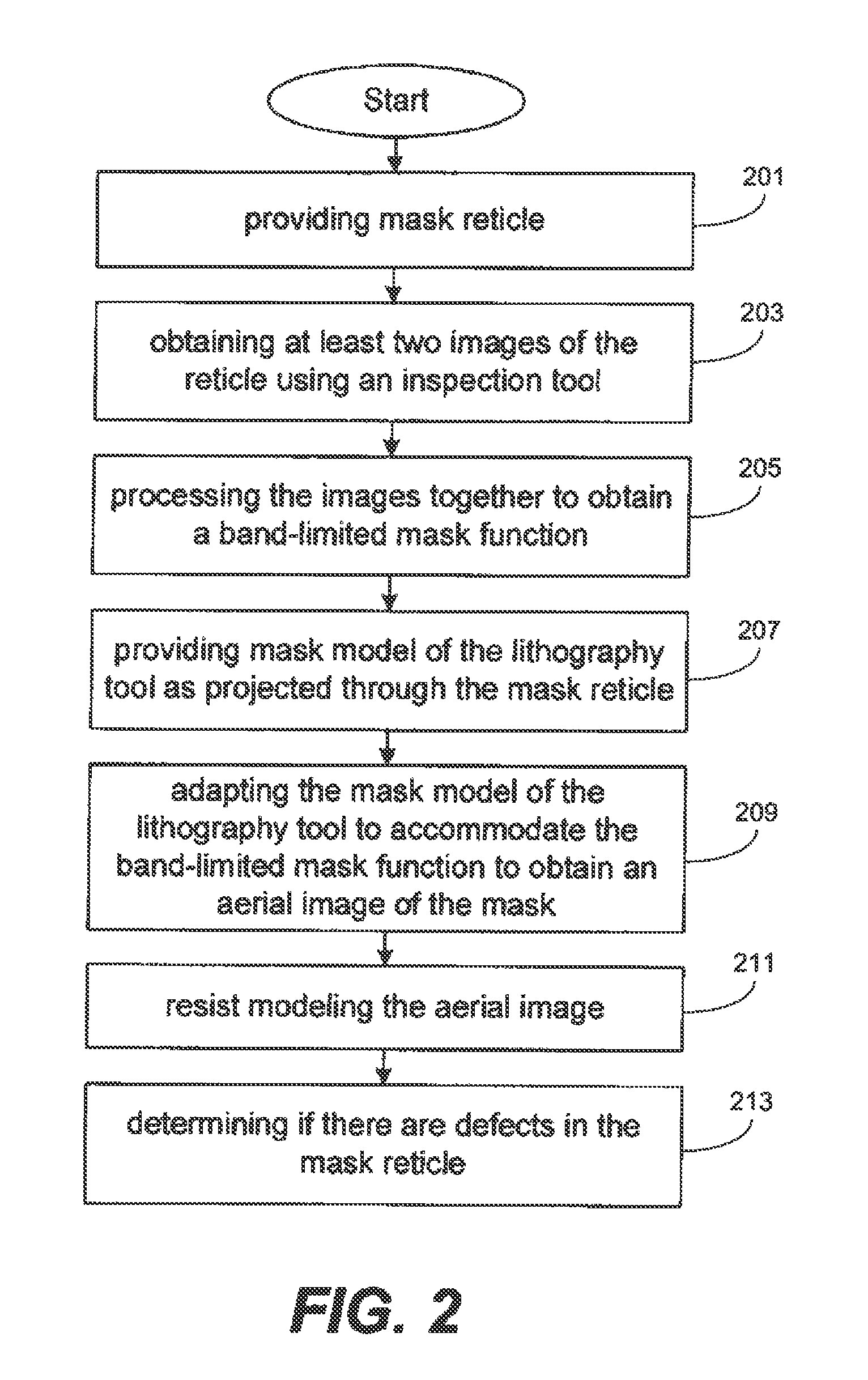

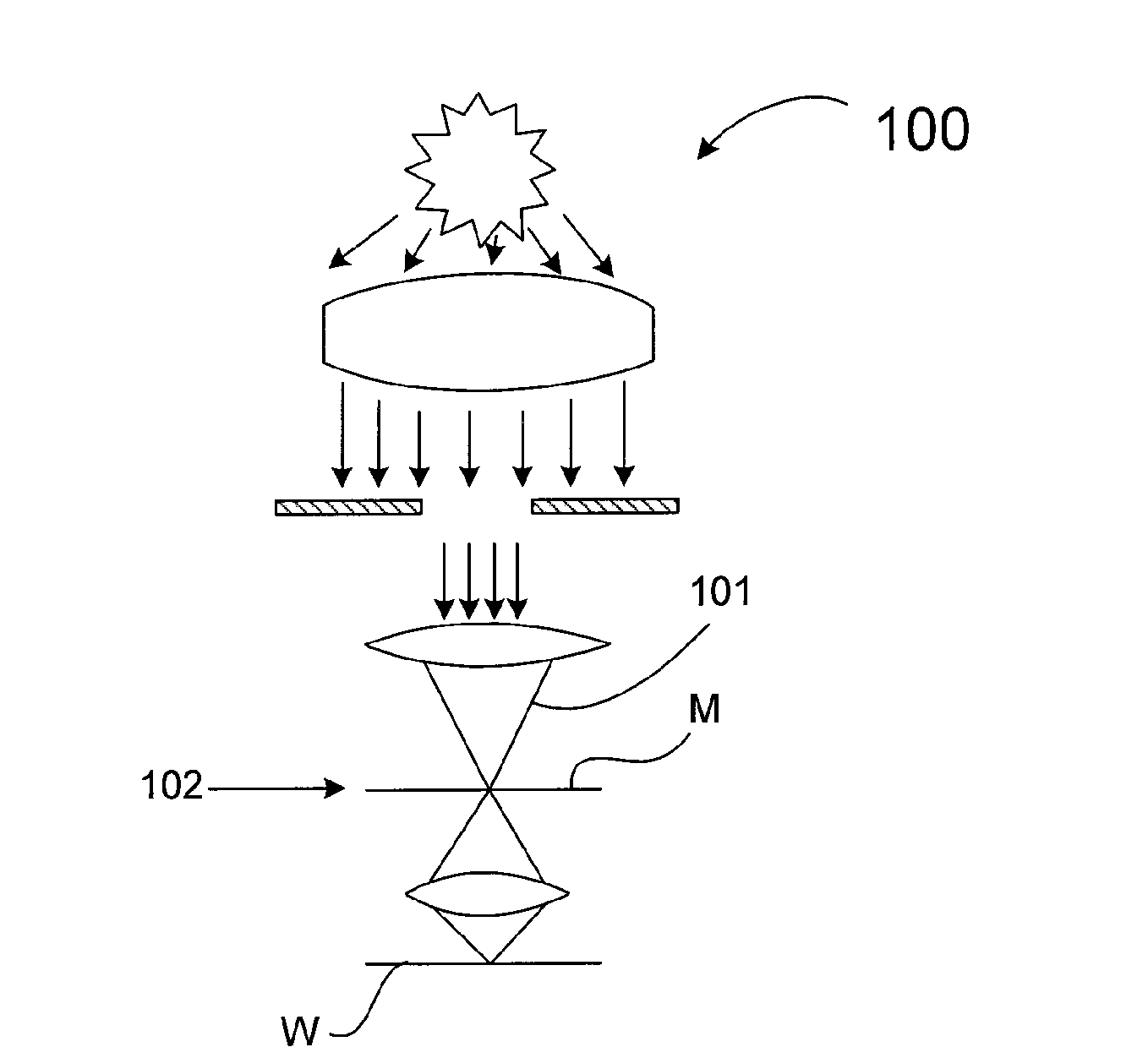

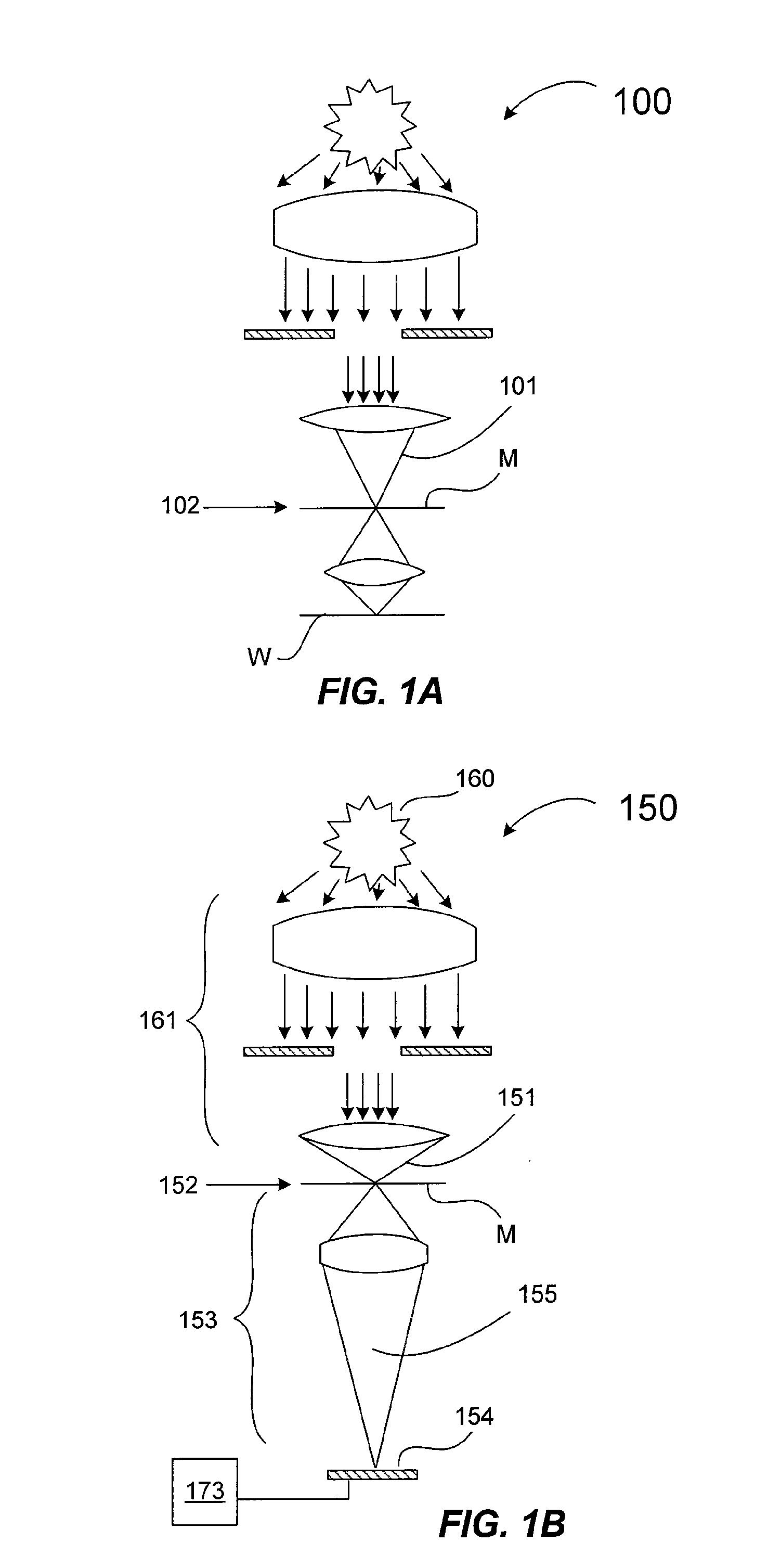

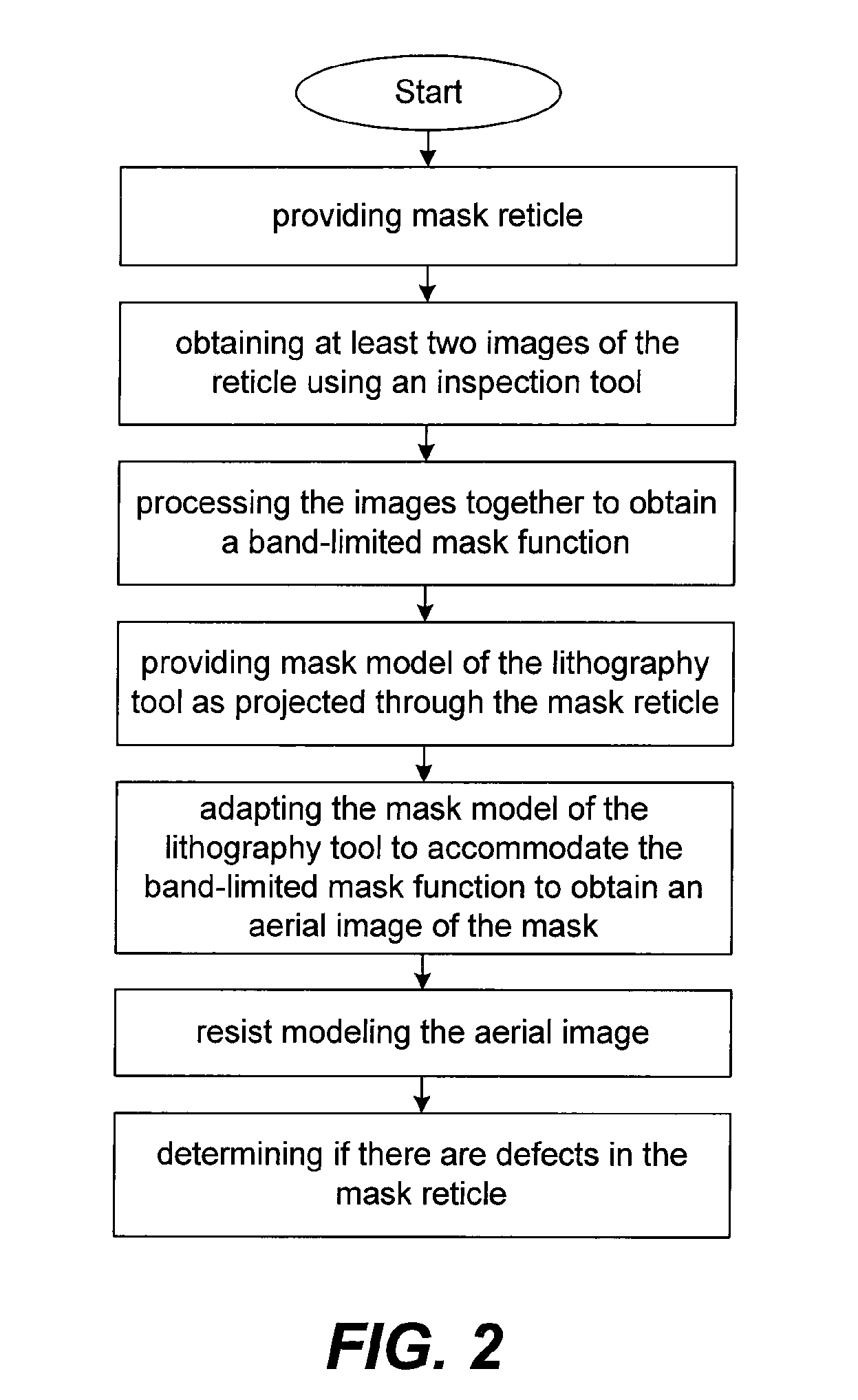

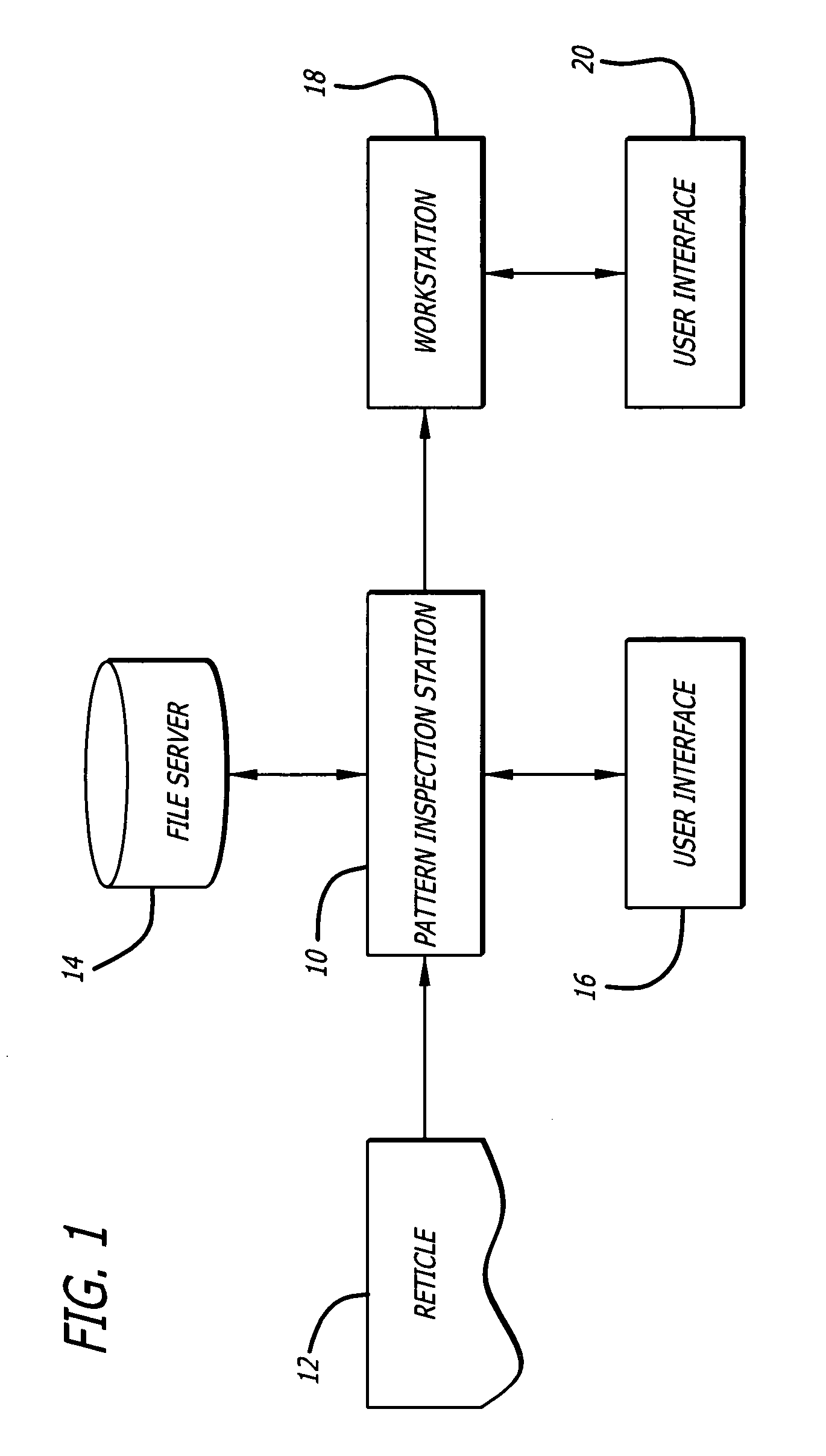

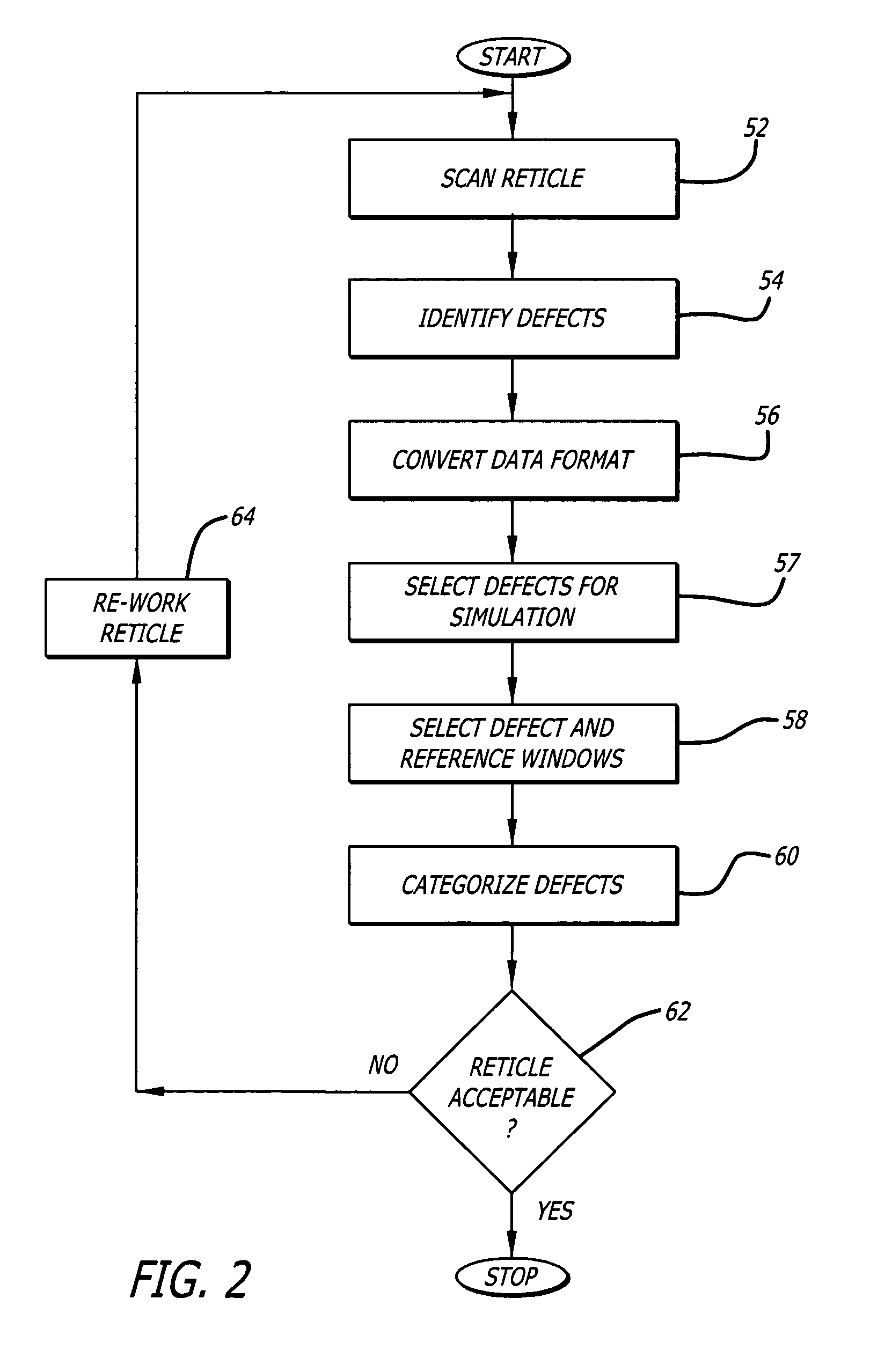

Method for detecting lithographically significant defects on reticles

ActiveUS7873204B2Character and pattern recognitionOriginals for photomechanical treatmentPattern recognitionResist

A method for identifying lithographically significant defects. A photomask is illuminated to produce images that experience different parameters of the reticle as imaged by an inspection tool. Example parameters include a transmission intensity image and a reflection intensity image. The images are processed together to recover a band limited mask pattern associated with the photomask. A model of an exposure lithography system for chip fabrication is adapted to accommodate the band limited mask pattern as an input which is input into the model to obtain an aerial image of the mask pattern that is processed with a photoresist model yielding a resist-modeled image. The resist-modeled image is used to determine if the photomask has lithographically significant defects.

Owner:KLA CORP

Method for detecting lithographically significant defects on reticles

ActiveUS20080170773A1Character and pattern recognitionOriginals for photomechanical treatmentPattern recognitionResist

A method for identifying lithographically significant defects. A photomask is illuminated to produce images that experience different parameters of the reticle as imaged by an inspection tool. Example parameters include a transmission intensity image and a reflection intensity image. The images are processed together to recover a band limited mask pattern associated with the photomask. A model of an exposure lithography system for chip fabrication is adapted to accommodate the band limited mask pattern as an input which is input into the model to obtain an aerial image of the mask pattern that is processed with a photoresist model yielding a resist-modeled image. The resist-modeled image is used to determine if the photomask has lithographically significant defects.

Owner:KLA TENCOR TECH CORP

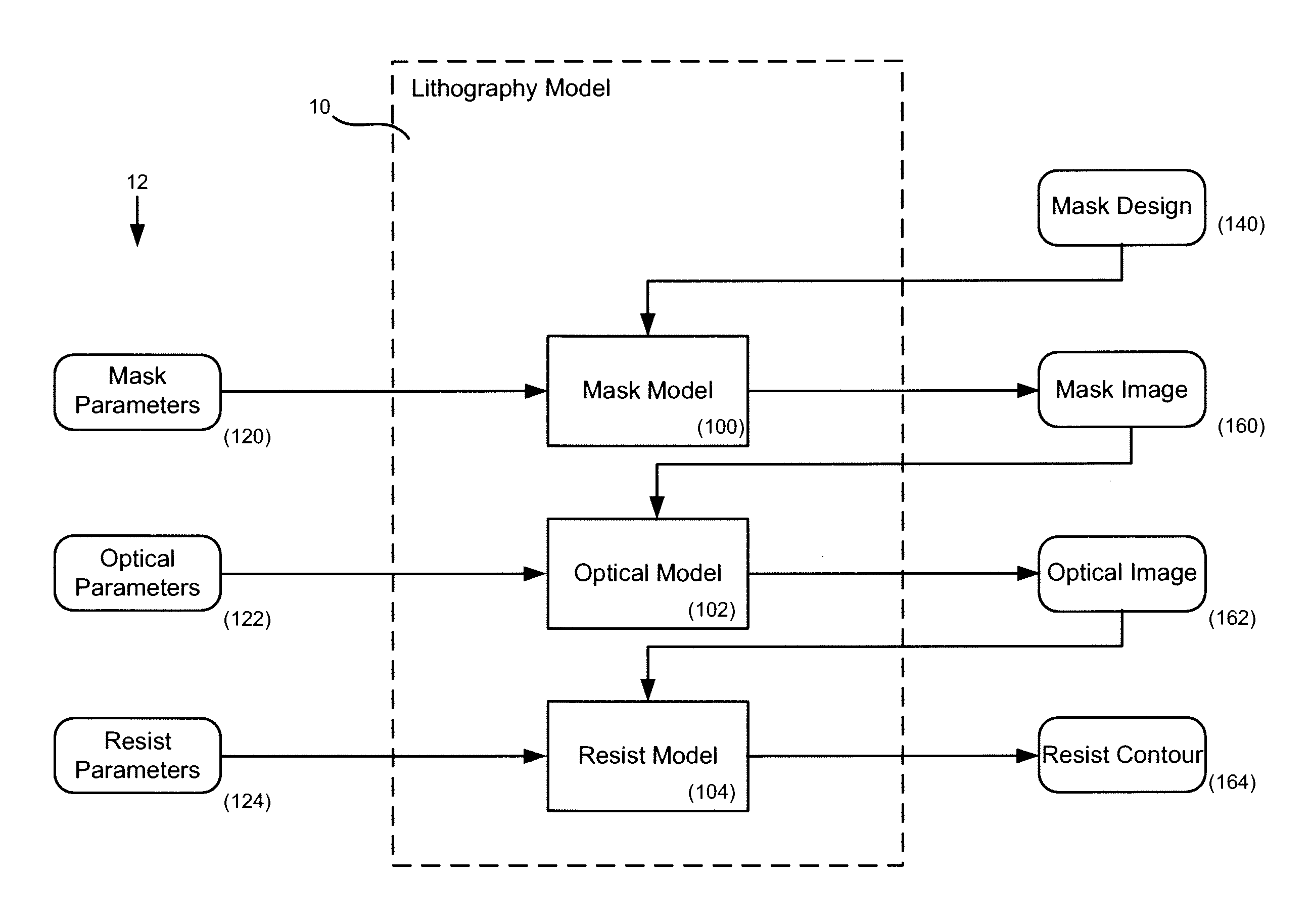

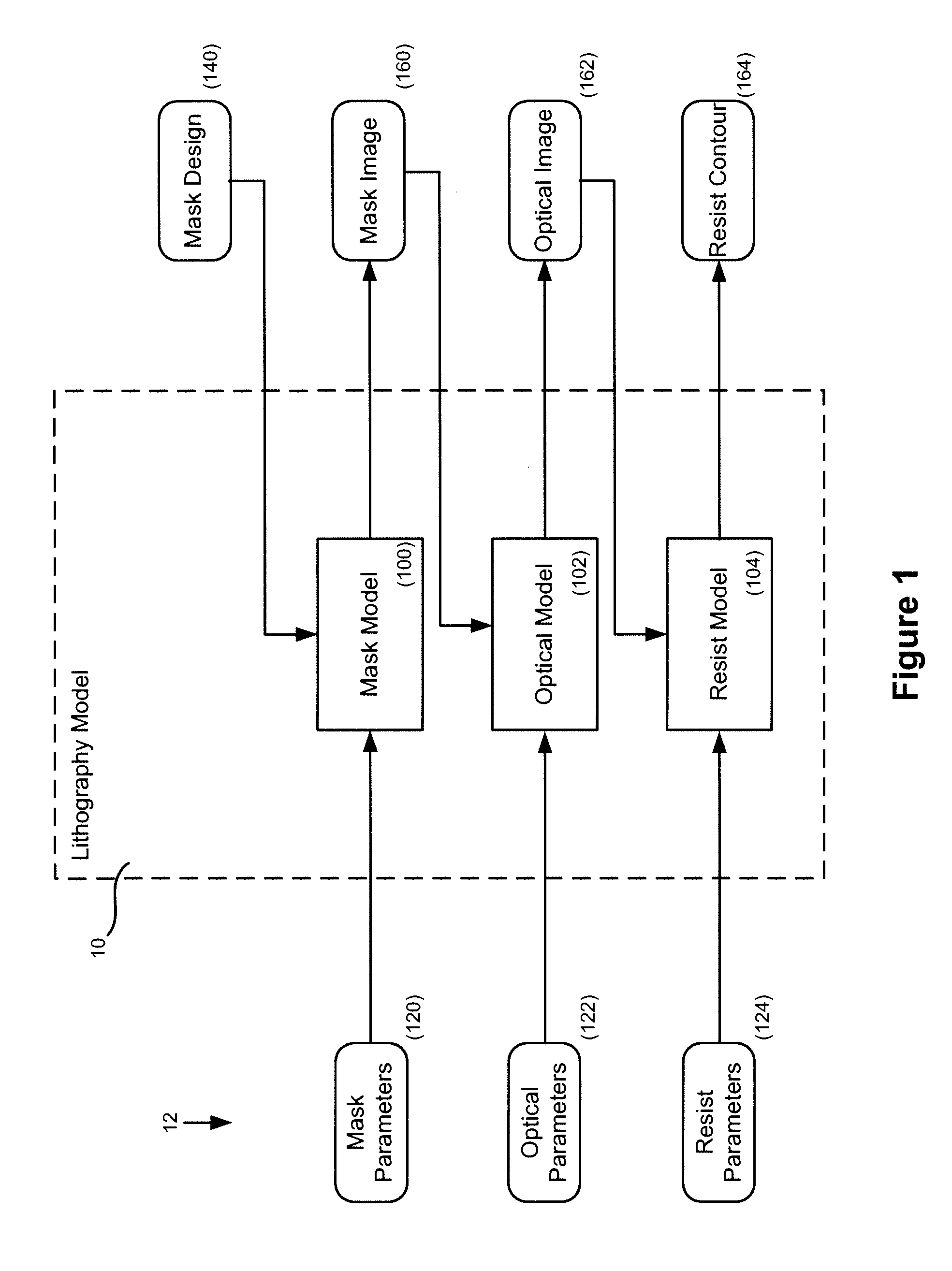

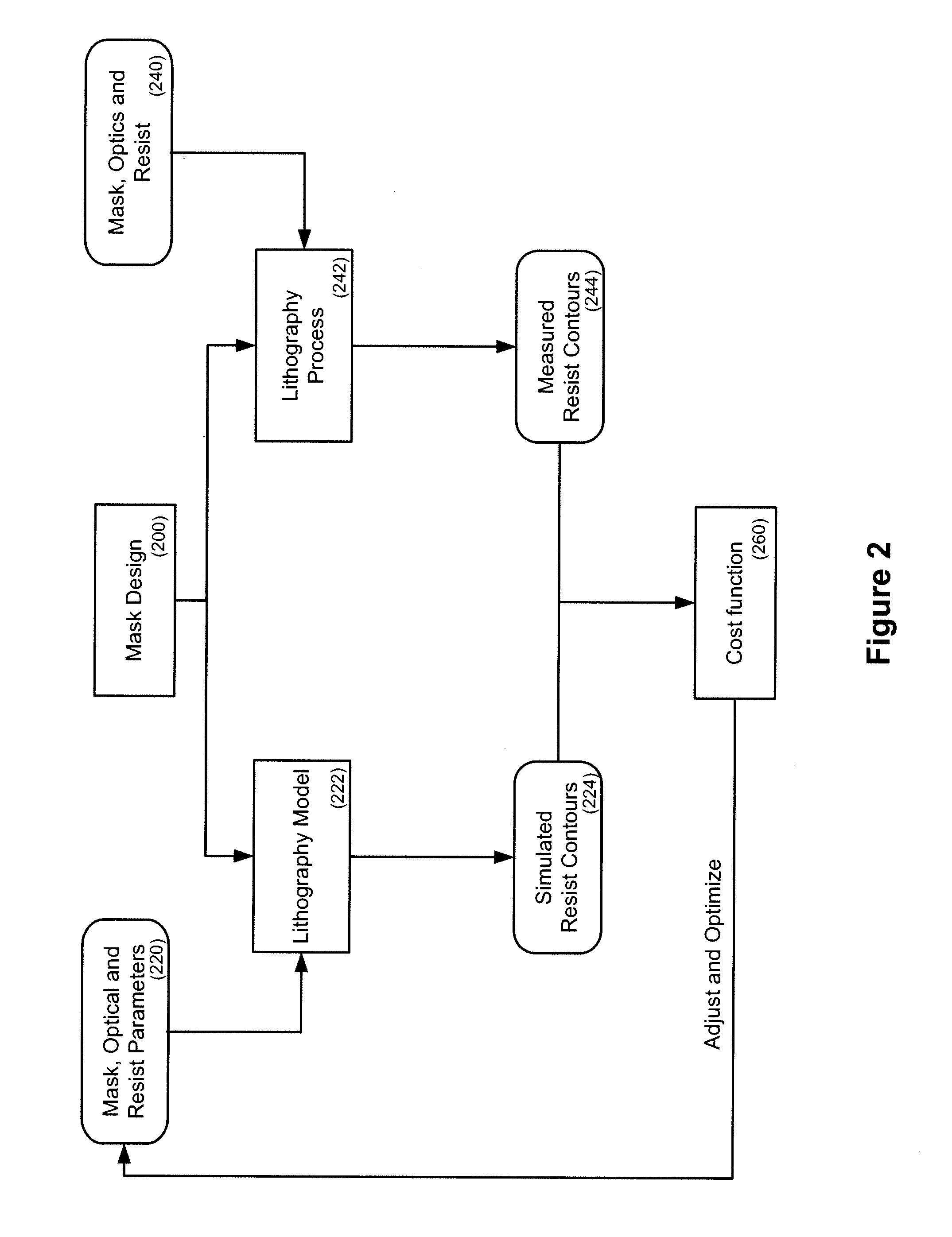

Model-based process simulation systems and methods

ActiveUS20090300573A1Semiconductor/solid-state device manufacturingDesign optimisation/simulationReference modelCritical dimension

Owner:ASML NETHERLANDS BV

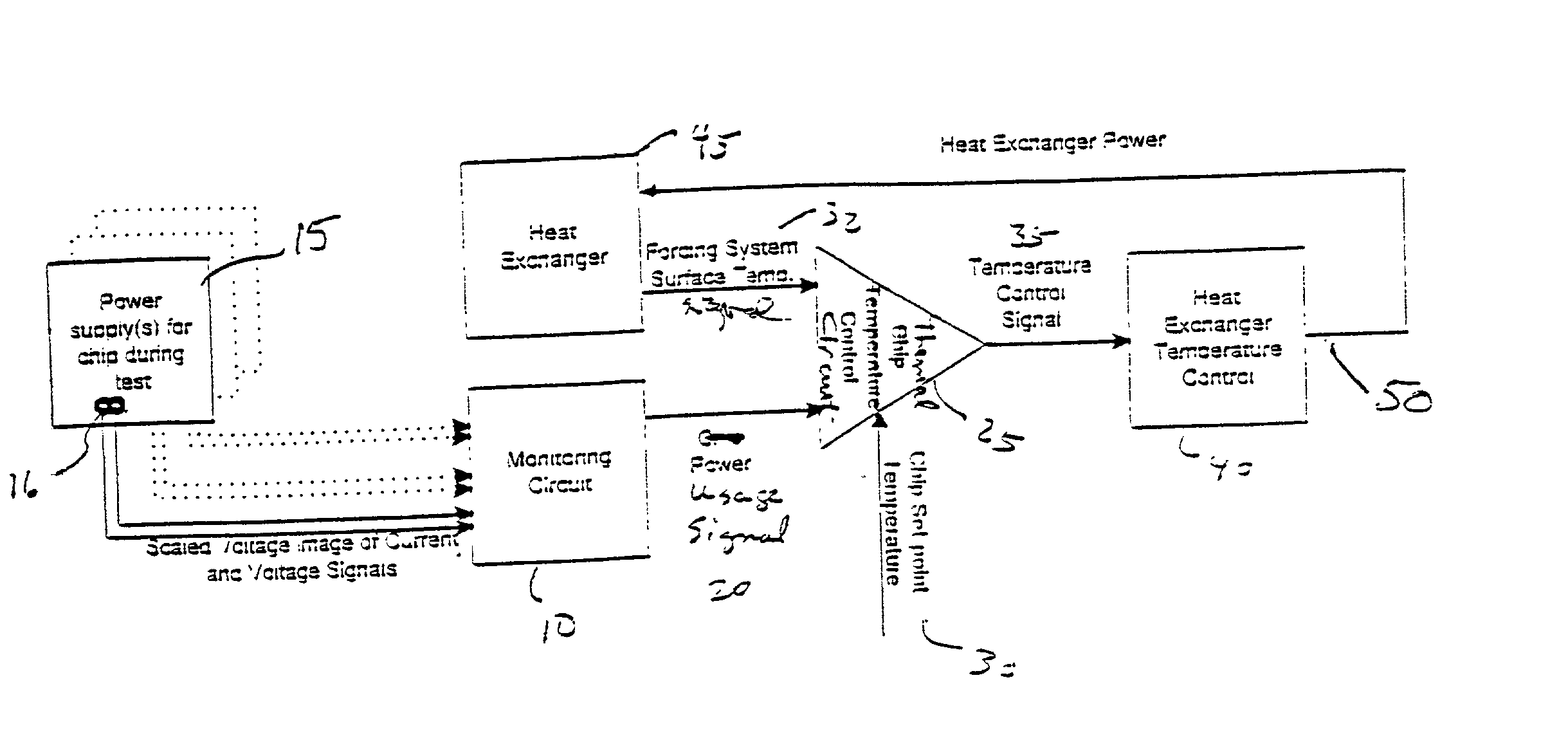

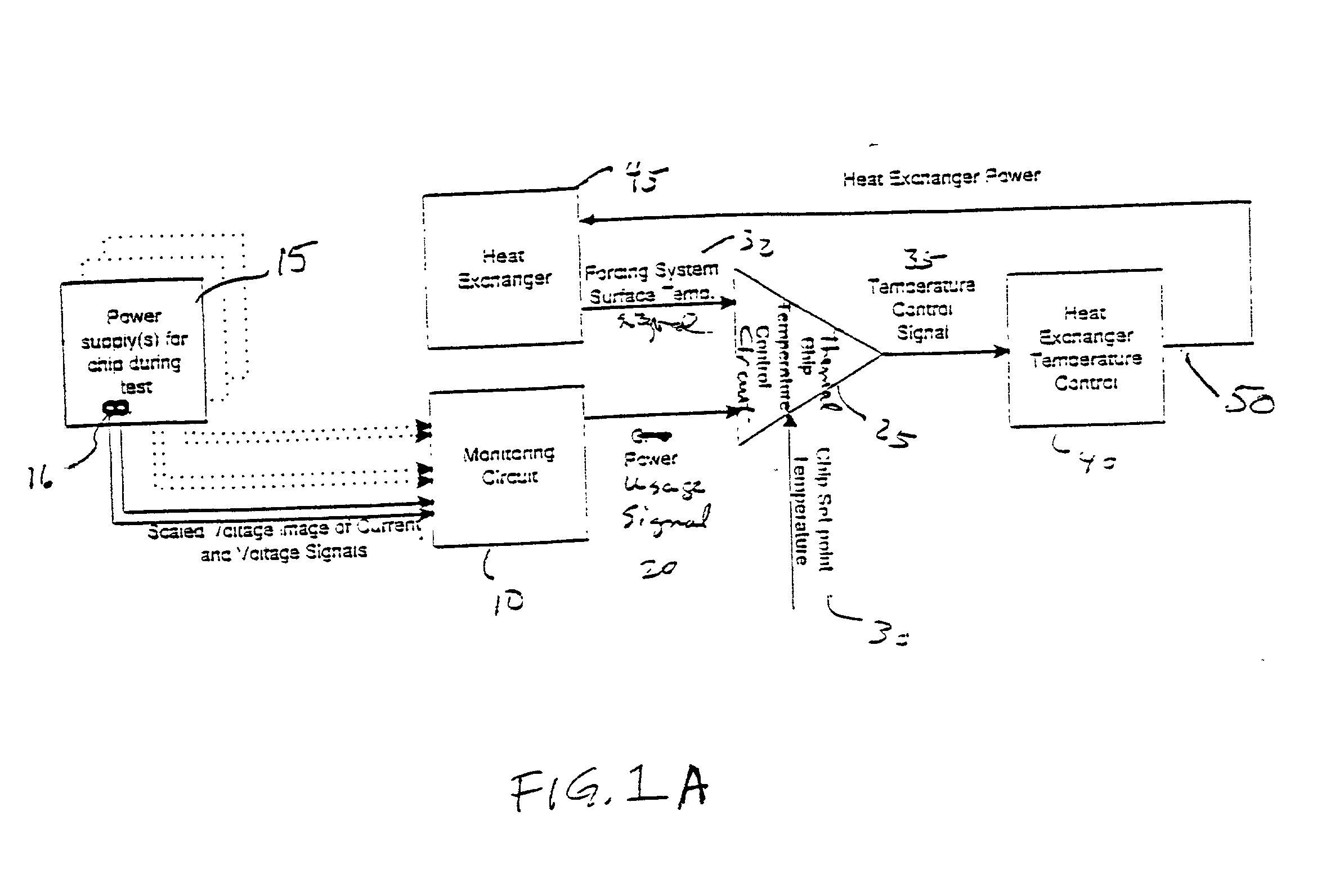

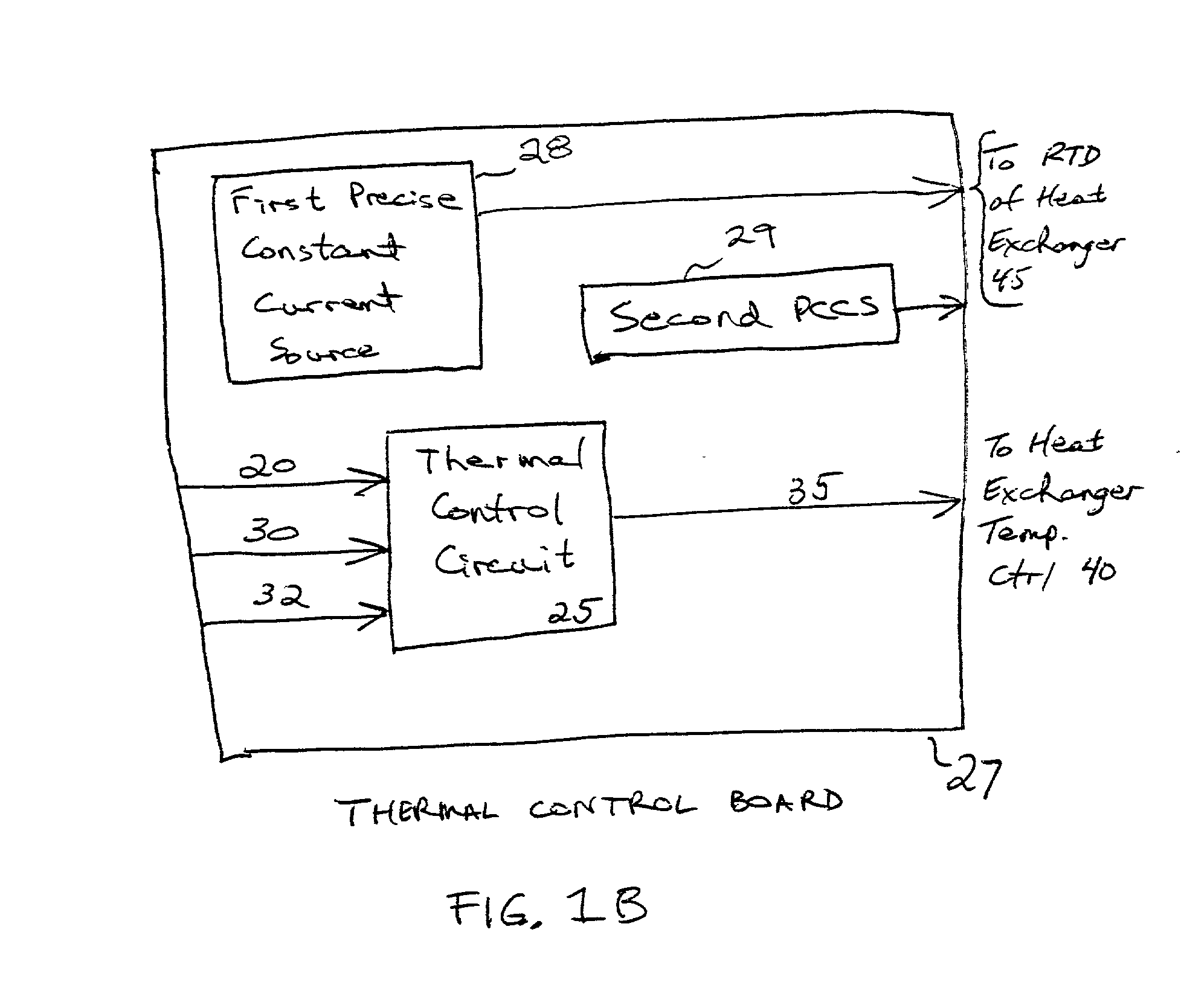

Temperature control of electronic devices using power following feedback

InactiveUS20020050833A1Easy to useEliminate needTemperatue controlSemiconductor/solid-state device detailsTemperature controlEngineering

A method for controlling a device temperature measures a parameter related to device power consumption and utilizes the parameter to control the device temperature. This can be achieved with a system including a heat exchanger, a power monitor, and a circuit which controls the temperature setting of the heat exchanger. The circuit uses as inputs the power level, heat exchanger temperature, and set point. The system thus eliminates the need for temperature sensing devices in or connected to a chip, responds to the temperature of the device and not the package, can be used for high volume chip manufacturing, does not require significant surface area of a device for temperature sensing, and eliminates the need for chip power profiles. Significantly, the system allows a set point to be maintained with minimal overshoot or undershoot.

Owner:SCHLUMBERGER AUTOMATED TEST EQUIP +1

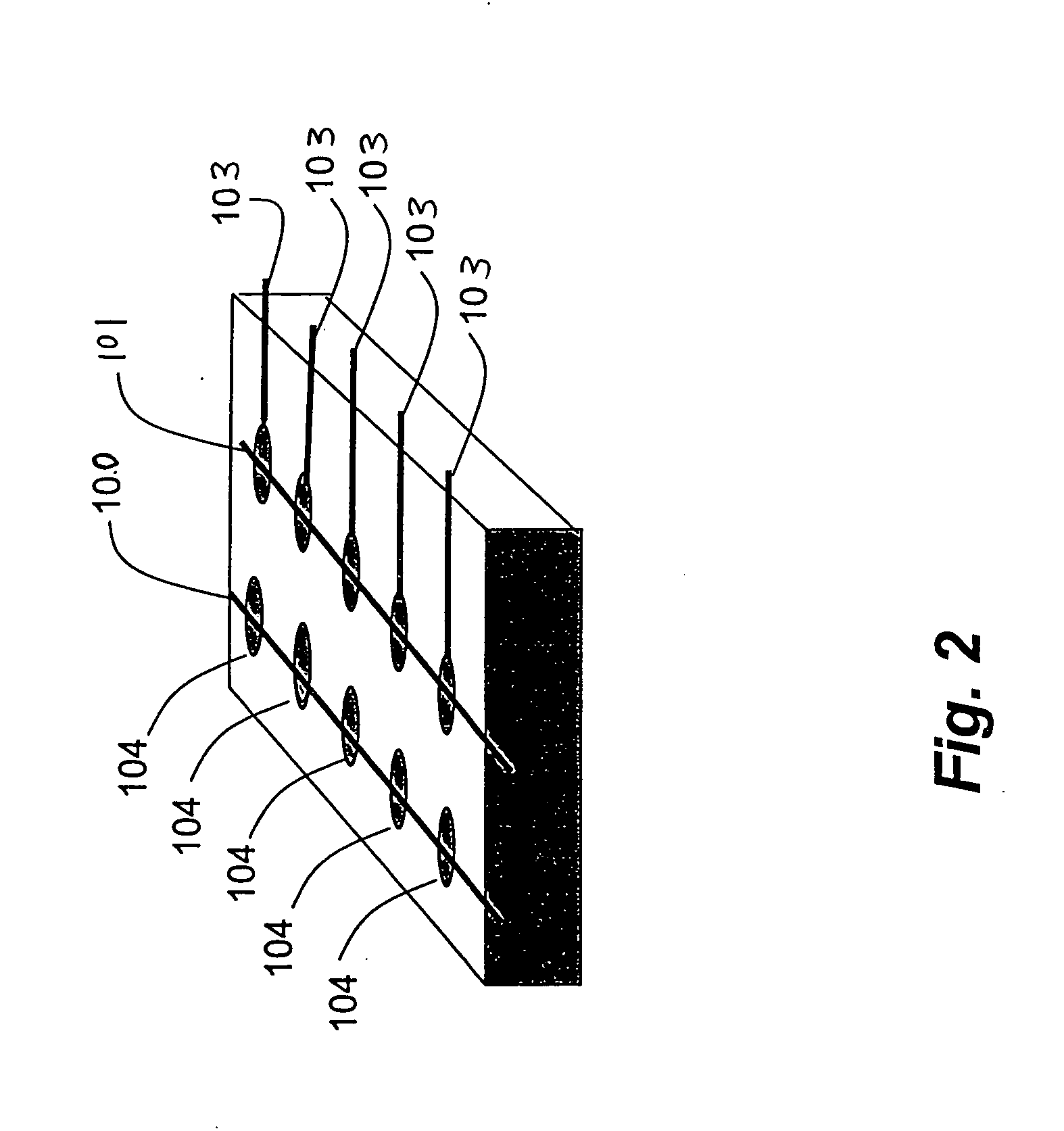

High density memory device

InactiveUS20060209587A1Easy constructionEasy to manufactureMaterial nanotechnologyNanoinformaticsFault toleranceChemical synthesis

Owner:RGT UNIV OF CALIFORNIA +1

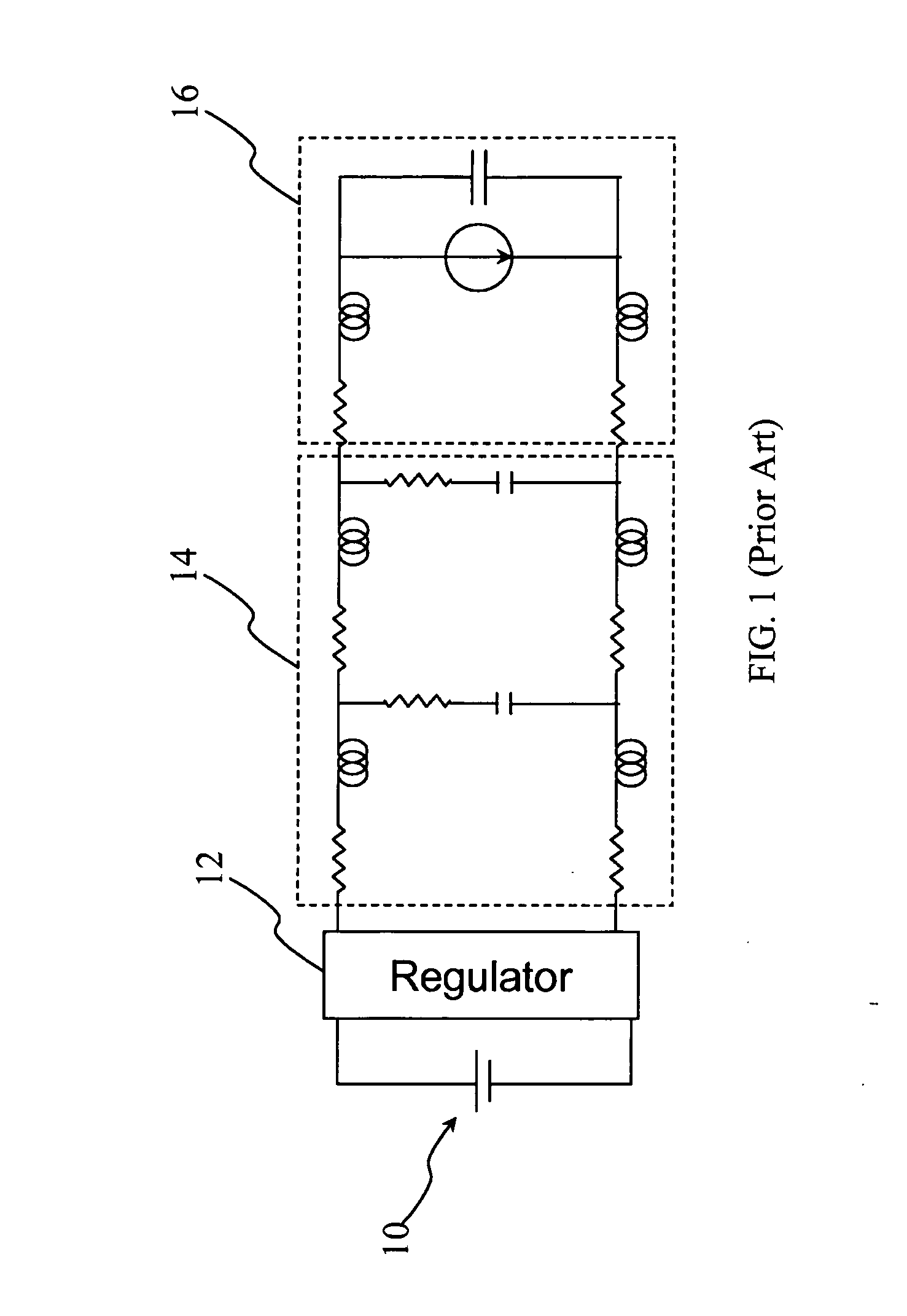

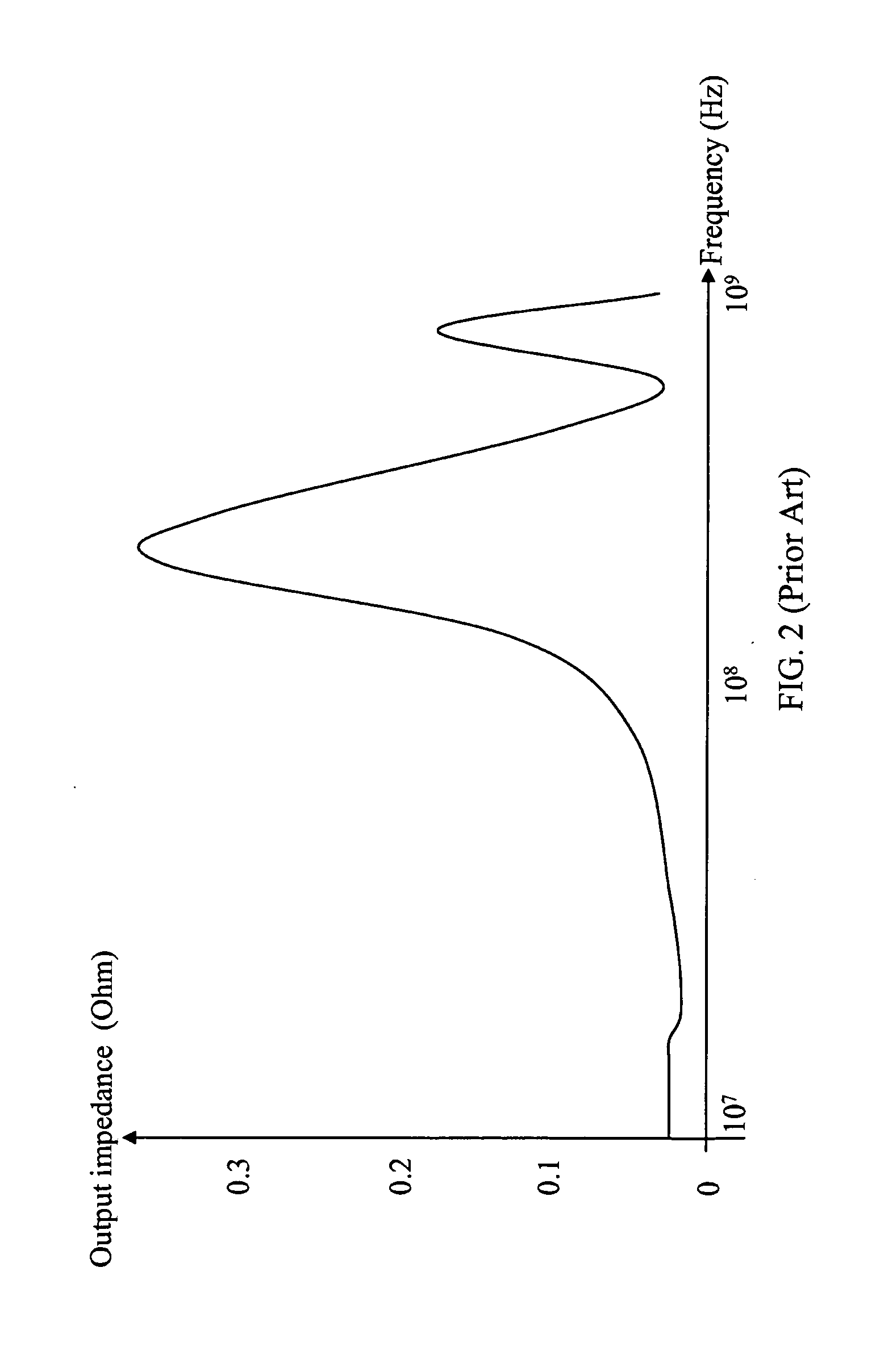

Voltage Regulator Integrated with Semiconductor Chip

ActiveUS20080150623A1Decrease in transient response timeReduce the difficulty of circuit designSemiconductor/solid-state device detailsSolid-state devicesSemiconductor chipElectrical devices

The present invention reveals a semiconductor chip structure and its application circuit network, wherein the switching voltage regulator or converter is integrated with a semiconductor chip by chip fabrication methods, so that the semiconductor chip has the ability to regulate voltage within a specific voltage range. Therefore, when many electrical devices of different working voltages are placed on a Printed Circuit Board (PCB), only a certain number of semiconductor chips need to be constructed. Originally, in order to account for the different demands in voltage, power supply units of different output voltages, or a variety of voltage regulators need to be added. However, using the built-in voltage regulator or converter, the voltage range can be immediately adjusted to that which is needed. This improvement allows for easier control of electrical devices of different working voltages and decreases response time of electrical devices.

Owner:QUALCOMM INC

High density molecular memory device

InactiveUS7061791B2Suitable mechanical propertyPrevent charge leakageNanoinformaticsSolid-state devicesFault toleranceChemical synthesis

This invention provides novel high density memory devices that are electrically addressable permitting effective reading and writing, that provide a high memory density (e.g., 1015 bits / cm3), that provide a high degree of fault tolerance, and that are amenable to efficient chemical synthesis and chip fabrication. The devices are intrinsically latchable, defect tolerant, and support destructive or non-destructive read cycles. In a preferred embodiment, the device comprises a fixed electrode electrically coupled to a storage medium having a multiplicity of different and distinguishable oxidation states wherein data is stored in said oxidation states by the addition or withdrawal of one or more electrons from said storage medium via the electrically coupled electrode.

Owner:NORTH CAROLINA STATE UNIV +1

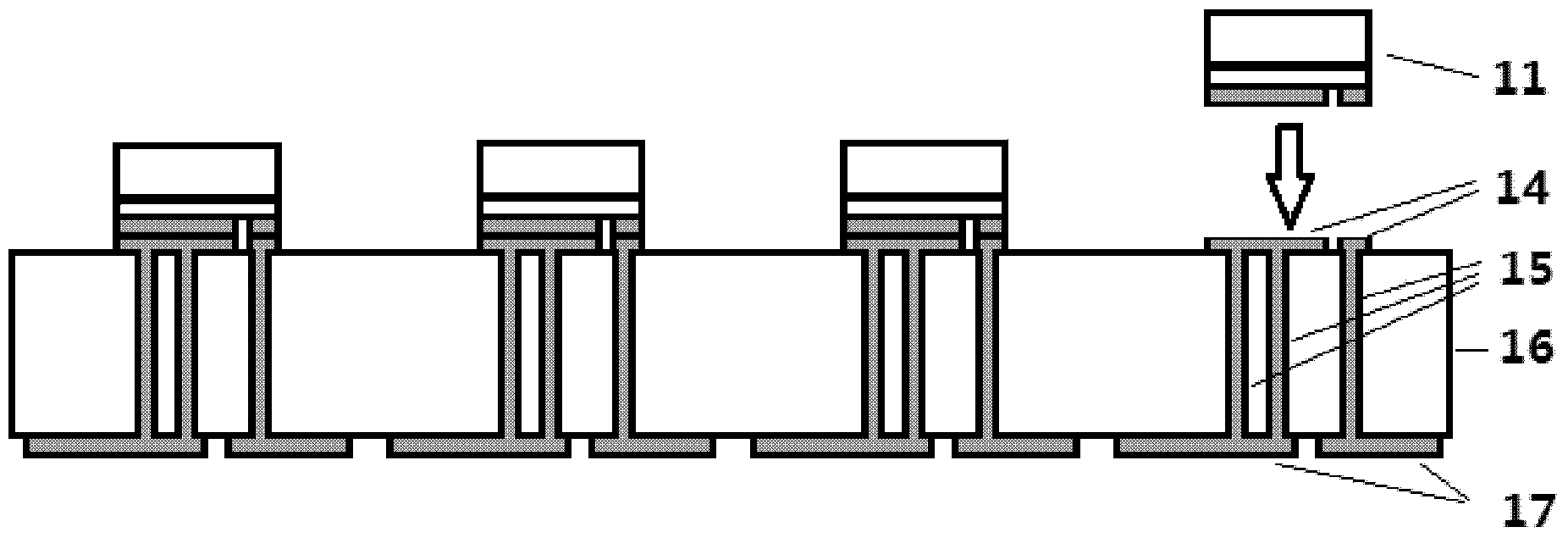

Chip transfer method for LED (light-emitting diode) wafer level package

ActiveCN103647012AImprove automationIncrease productivitySemiconductor/solid-state device manufacturingSemiconductor devicesLed arrayUnit device

A chip transfer method for LED (light-emitting diode) wafer level package includes the steps: manufacturing an LED unit device array on an LED epitaxial wafer, manufacturing metal layers on parts of unit devices of the unit device array to serve as middle metal layers in bonding, and forming a unit device array to be bonded; manufacturing metal patterns corresponding to electrodes of the unit device array to be bonded on the front surface of a base plate, forming heat conduction channels and electric conduction channels below the metal patterns, and connecting electrodes of an LED unit device with a metal bonding pad on the back surface of the base plate through the electric conduction channels; conversely mounting the unit device array to be bonded on the base plate in a bonding mode; finally, sequentially stripping the unit devices to be bonded in a laser stripping mode, separating the epitaxial layers of the unit devices to be bonded from a substrate, and forming a whole film LED array by the separated epitaxial layers and the base plate. The chip transfer method can be used for wafer level package of the LED devices, package efficiency is improved, and cost is reduced.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

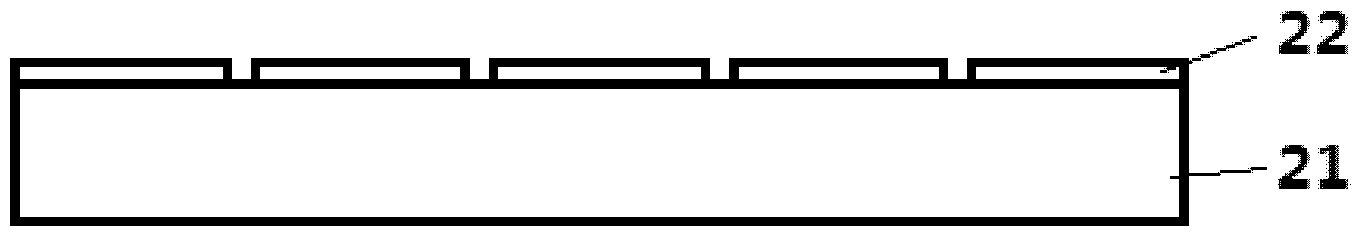

Means and method for mounting electronics

InactiveUS6108205ALow costSimple and low methodSemiconductor/solid-state device detailsPrinted circuit aspectsThin layerEngineering

The present invention relates to a method and device for making a temperature-compensated bedding for chips on printed boards, at which a temperature-compensated device is totally or partly recessed in a carrier in the printed board. The chips is placed over the temperature-compensated device. The temperature-compensated device includes a piece of metal recessed in the carrier under the chip. A layer of copper is fixed against the upper side of the carrier and the upper side of the metal piece. The thickness of the copper layer and the thickness of the metal piece are dimensioned so that the resulting coefficient of linear expansion at the upper side of the copper layer is equally big as or a bit bigger than the coefficient of linear expansion of the chip. The temperature-compensated device can as an alternative to the above include a module recessed in the carrier under the chip. A thin layer of dielectric is fixed against the carrier, so that the coefficient of linear expansion of the dielectric layer don't appreciable affect the resulting coefficient of linear expansion of the temperature-compensated device.

Owner:TELEFON AB LM ERICSSON (PUBL)

High density non-volatile memory device

InactiveUS7042755B1Suitable mechanical propertyPrevent charge leakageMaterial nanotechnologyNanoinformaticsFault toleranceChemical synthesis

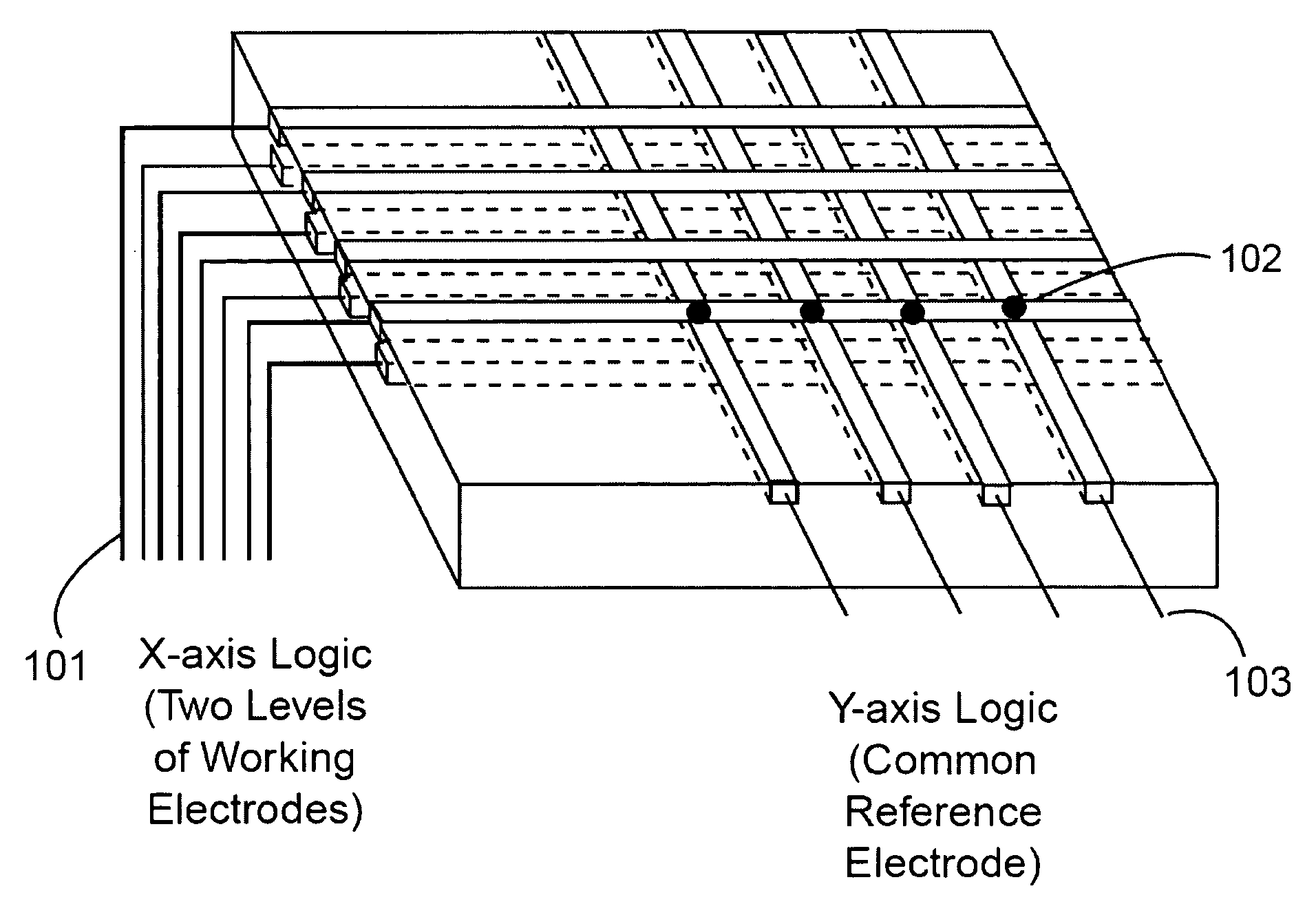

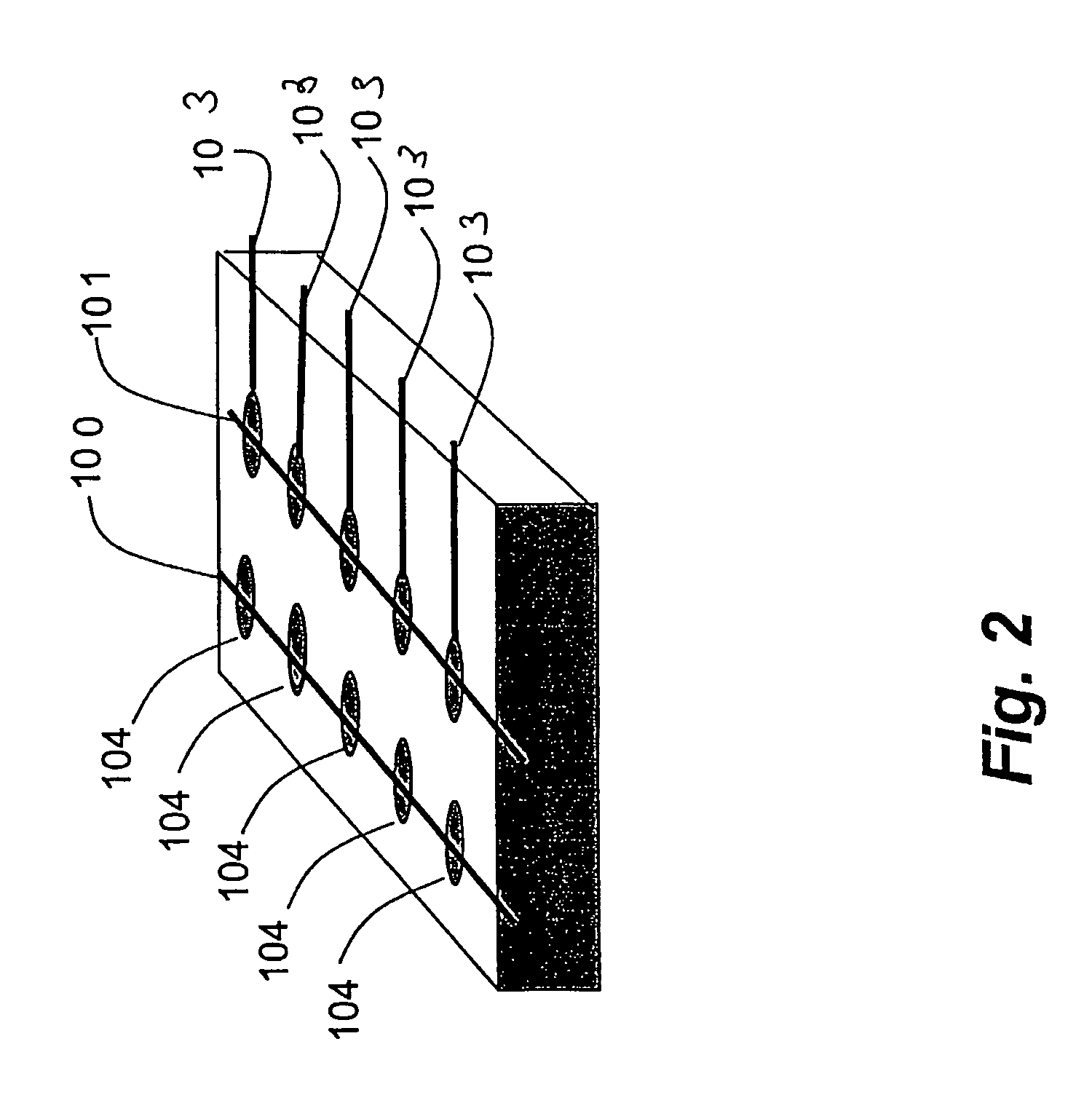

This invention provides novel high density memory devices (FIG. 3) that are electrically addressable permitting effective reading and writing, that provide a high memory density (102), that provide a high degree of fault tolerance, and that are amenable to efficient chemical synthesis and chip fabrication. The devices arc intrinsically latchable, defect tolerant, and support destructive or non-destructive read cycles. In a preferred embodiment, the device comprises a fixed electrode electrically coupled to a storage medium having a multiplicity of different and distinguishable oxidation states wherein data is stored in said oxidation states by the addition or withdrawal of one or more electrons from said storage medium via the electrically coupled electrode.

Owner:NORTH CAROLINA STATE UNIV +1

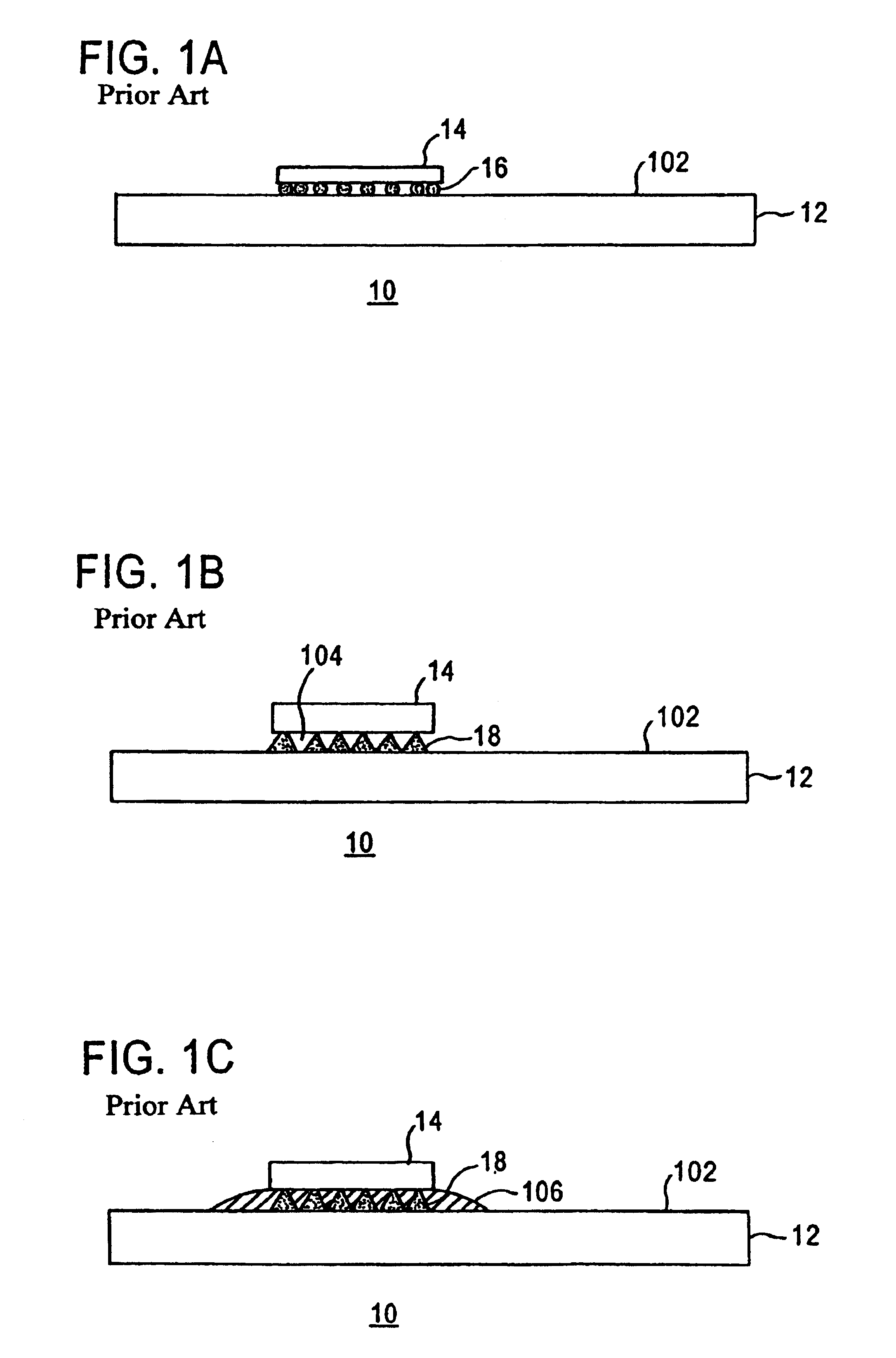

Flip chip with integrated flux and underfill

InactiveUS20010003058A1Printed circuit assemblingSemiconductor/solid-state device detailsEngineering physicsMechanical engineering

A flip chip having solder bumps and an integrated flux and underfill, as well as methods for making such a device, is described. The resulting device is well suited for a simple one-step application to a printed circuit board, thereby simplifying flip chip manufacturing processes which heretofore have required separate fluxing and underfilling steps.

Owner:FRY S METALS INC

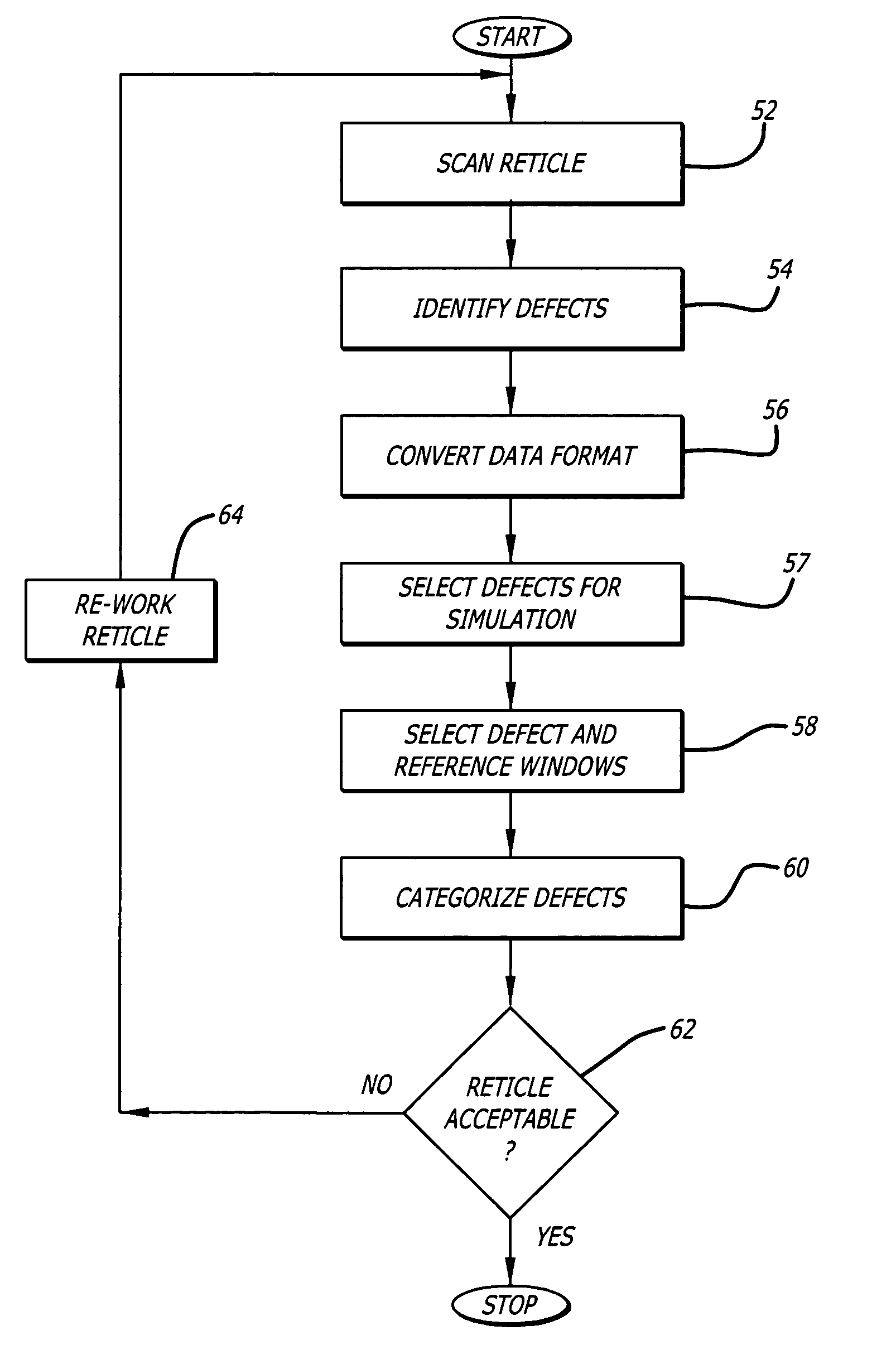

Reticle defect detection using simulation

InactiveUS6999611B1Reduce degradationLow costMaterial analysis by optical meansCharacter and pattern recognitionLaser scanningDigital image data

Defects are detected in a reticle used in integrated circuit chip fabrication by obtaining digital image data corresponding to an image of the reticle. Typically, this is accomplished by scanning the reticle using a laser scanner. The digital image data are then processed according to predetermined criteria to identify defects. Such processing may include, for example, processing the digital image data in comparison to reference digital image data for the same or a similar portion of the reticle. Next, a response that would be produced if the reticle were to be utilized in a photolithographic system is simulated by processing the digital image data corresponding to the reticle.

Owner:KLA TENCOR TECH CORP

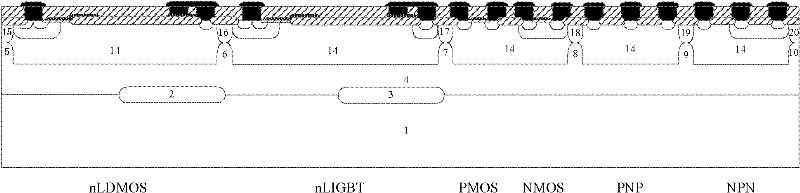

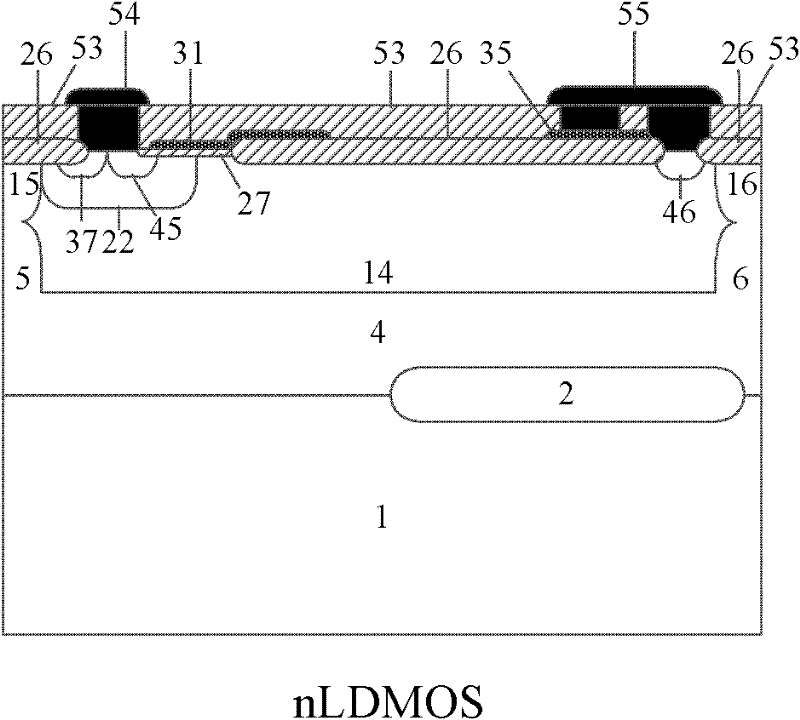

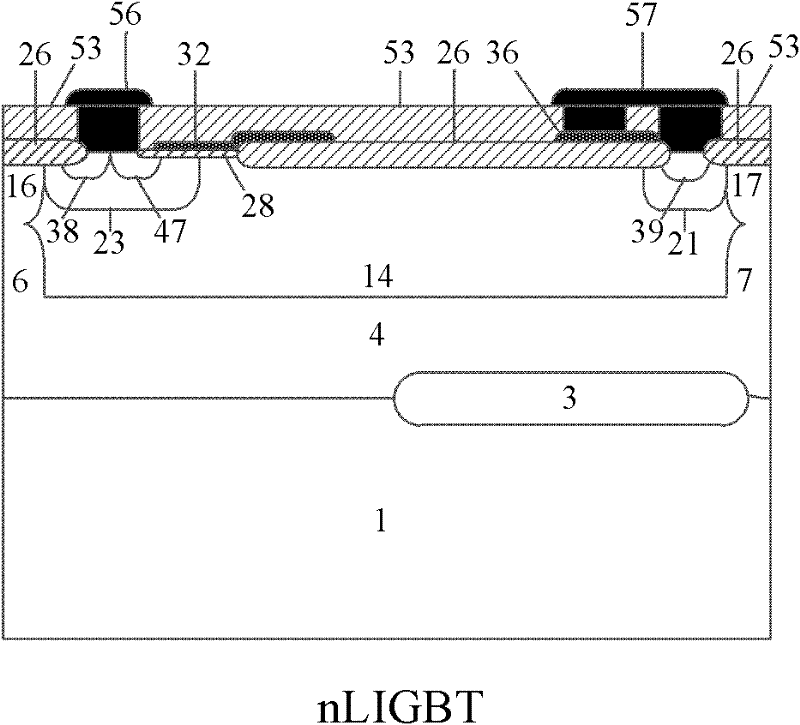

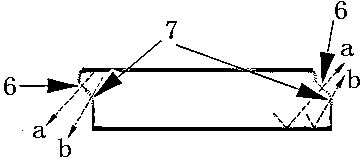

Bipolar CMOS DMOS (BCD) integrated device based on N type extension layer and manufacture method thereof

InactiveCN102201406AIncrease manufacturing costReduce manufacturing costSolid-state devicesSemiconductor/solid-state device manufacturingCMOSLow voltage

A bipolar CMOS DMOS (BCD) integrated device based on a N type extension layer and a manufacture method thereof, which belongs to the semiconductor power device technology field, are disclosed. In the invention, a high voltage nLDMOS device, a high voltage nLIGB device, a low voltage PMOS device, a low voltage NMOS device, a low voltage PNP device and a low voltage NPN device are integrated on a same substrate. All devices are made in an N type extension layer arranged on a surface of a P type extension layer which is on a surface of a P type substrate. And junction isolations of the devices are realized through P<+> isolation regions. N type buried layers are arranged between the P type substrate and the P type extension layer, wherein the P type substrate and the P type extension layer are under the high voltage devices. N type buried layers are / are not arranged between the P type extension layer and the N type extension layer, wherein the P type extension layer and the N type extension layer are under the low voltage devices. The N type buried layers are introduced in the invention to realize that silicon chips with lower resistivity can be used as the substrate at a same breakdown voltage. In the prior art, float-zone technique is adopted to manufacture monocrystalline silicon pieces, which can increase the chip manufacturing costs. In the invention, the float-zone technique is not used so that the chip manufacturing costs can be reduced.

Owner:UNIV OF ELECTRONICS SCI & TECH OF CHINA

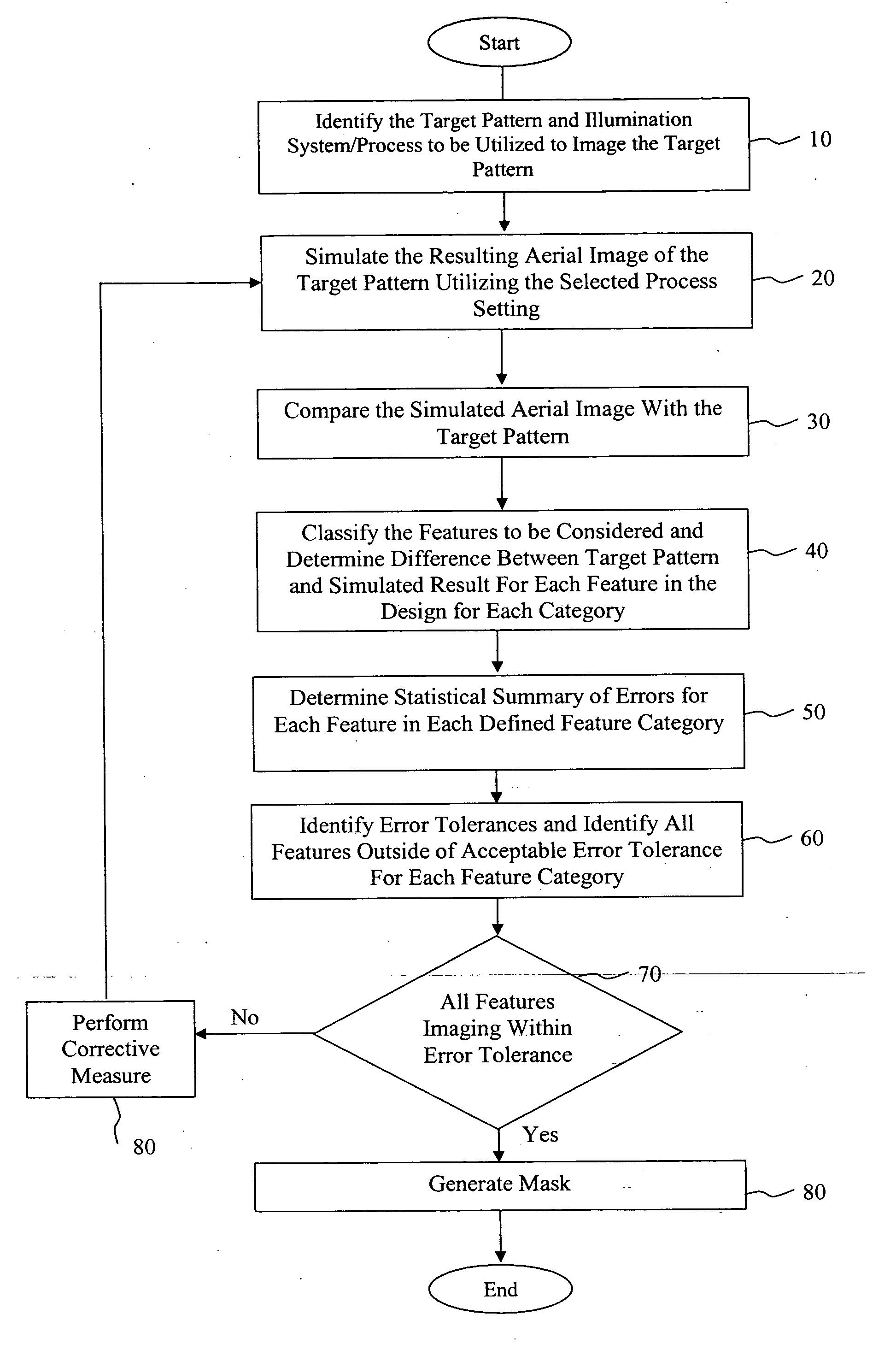

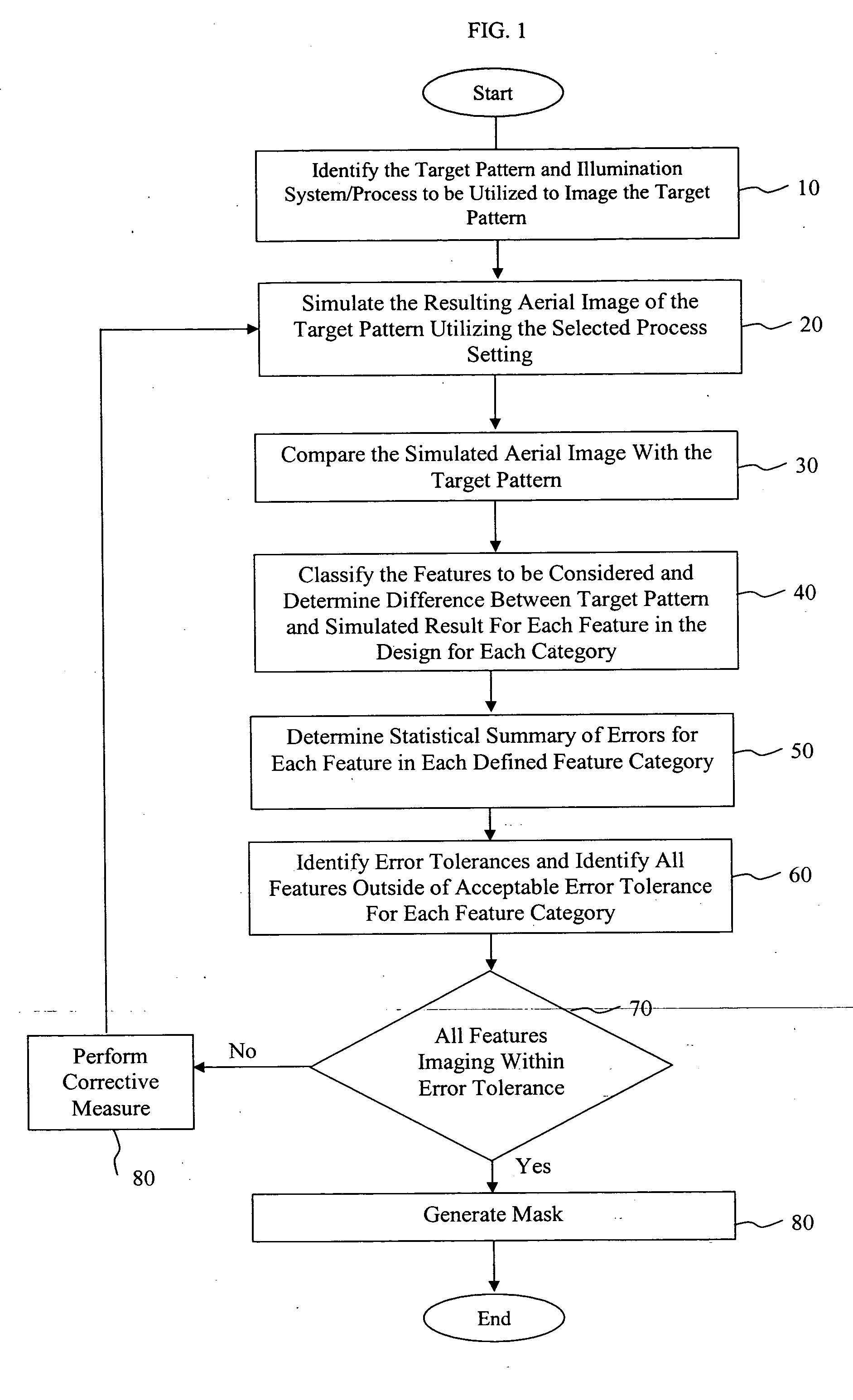

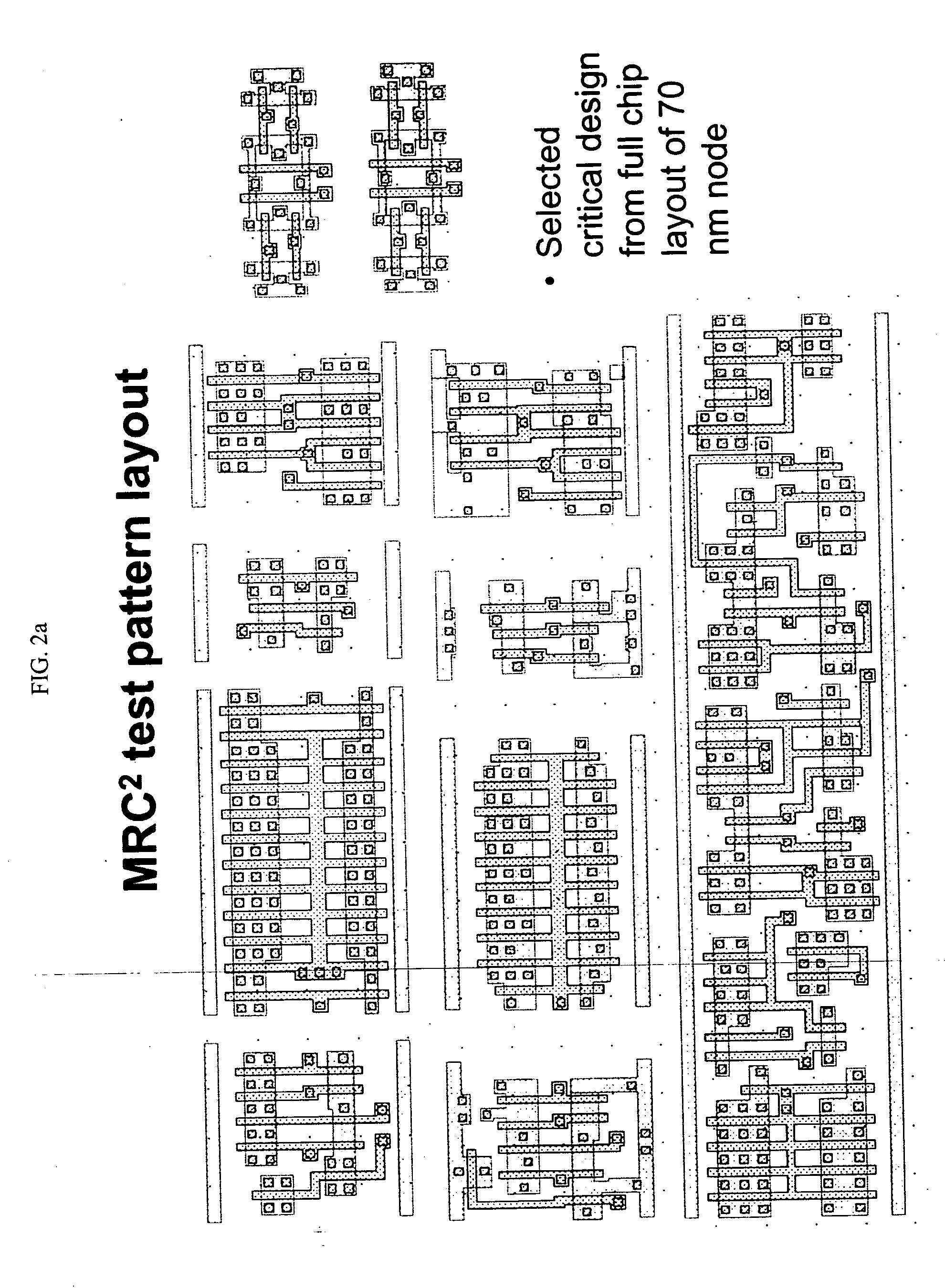

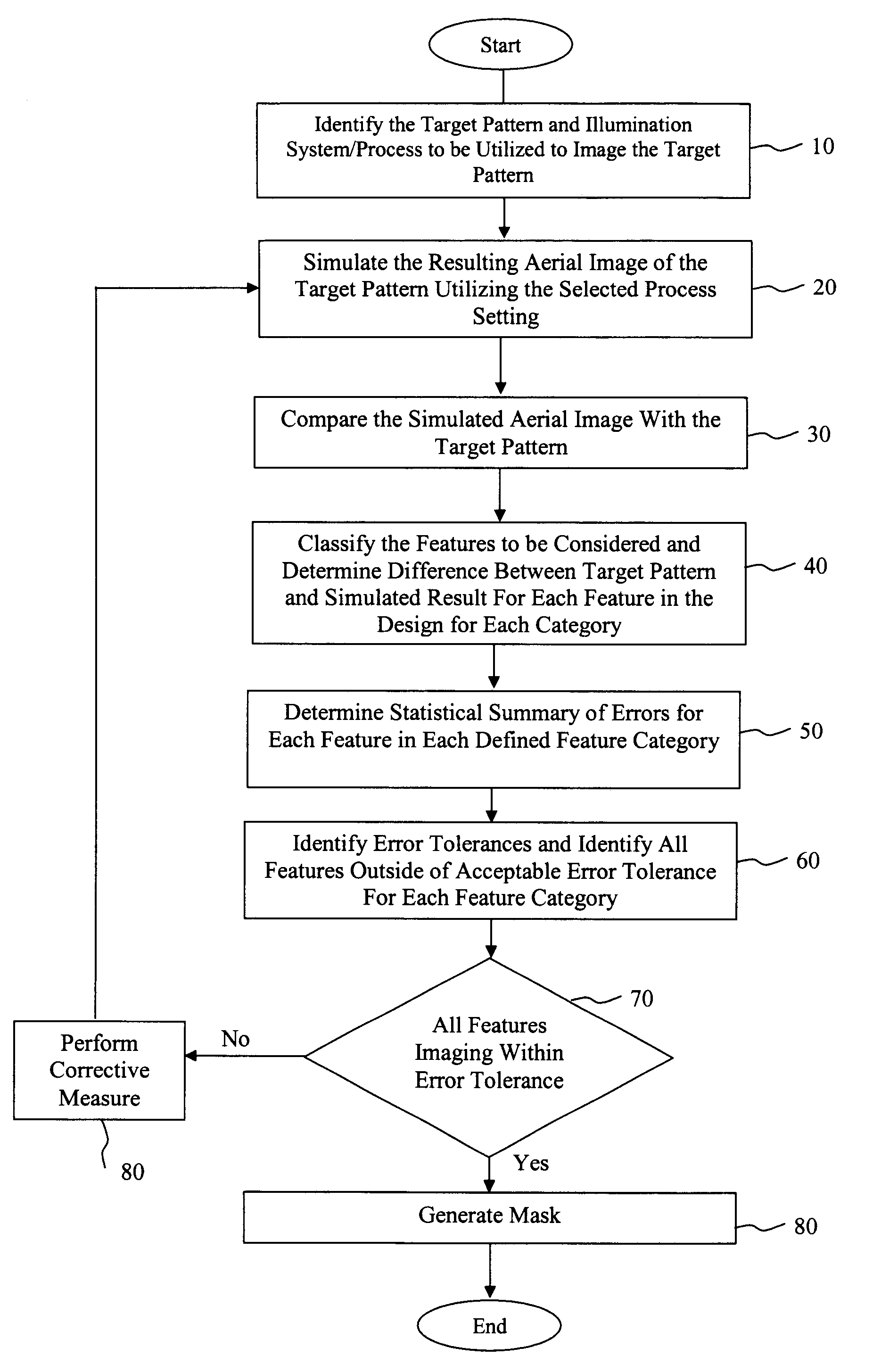

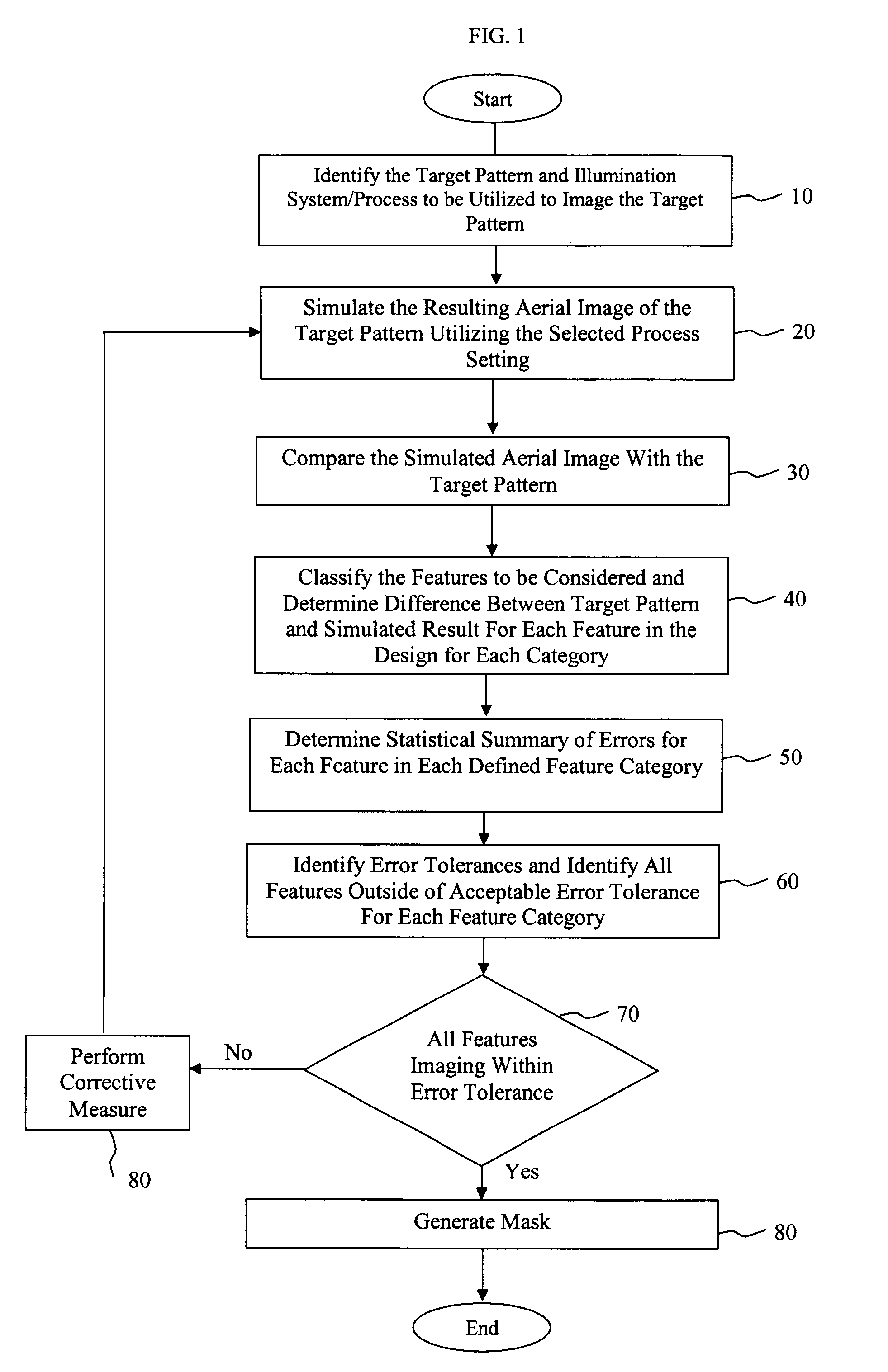

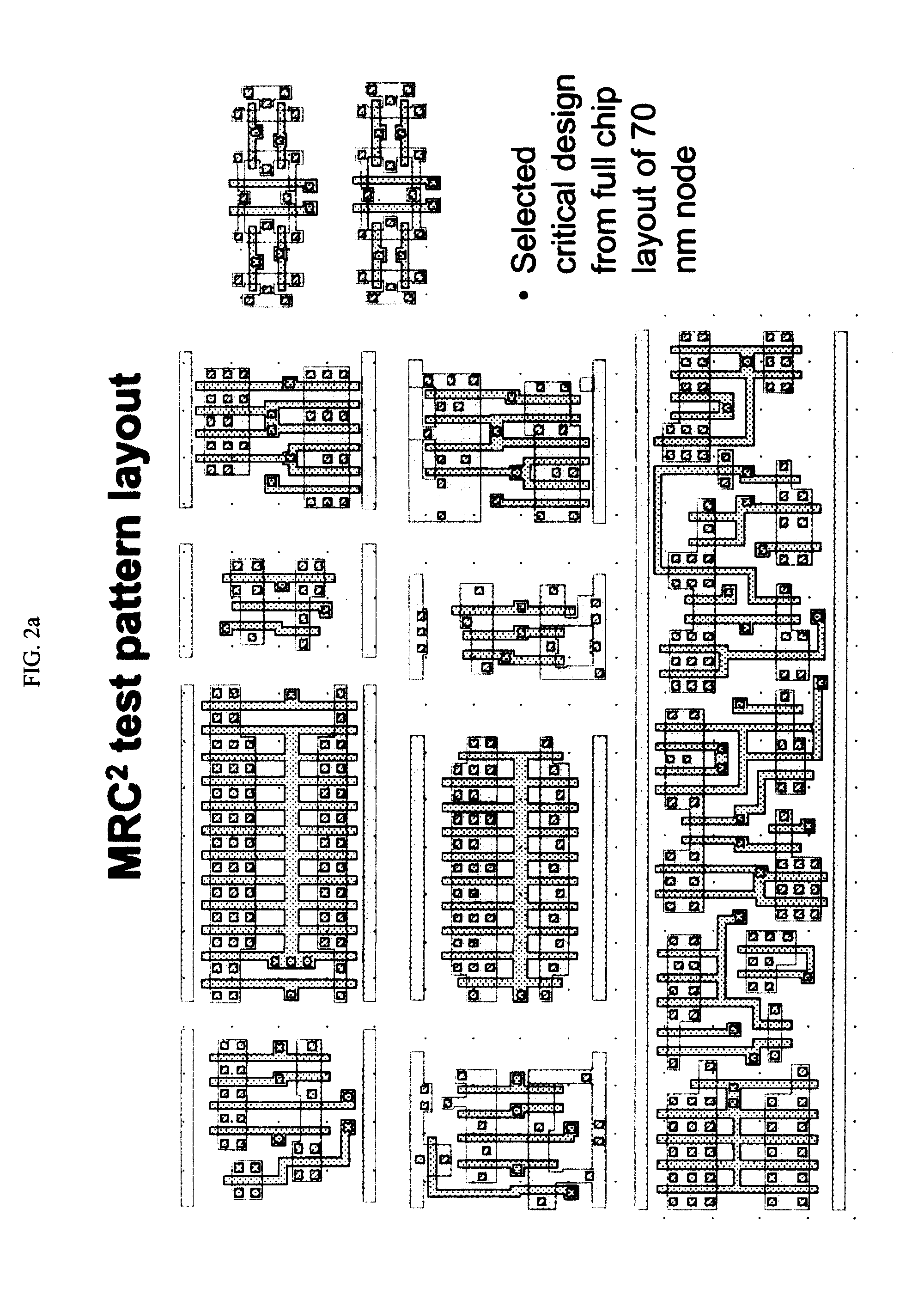

Method for performing full-chip manufacturing reliability checking and correction

ActiveUS20060080633A1Suitable for useMinimize timePhotomechanical apparatusCharacter and pattern recognitionPattern recognitionProcess patterns

A method of generating a mask for use in an imaging process pattern. The method includes the steps of: (a) obtaining a desired target pattern having a plurality of features to be imaged on a substrate; (b) simulating a wafer image utilizing the target pattern and process parameters associated with a defined process; (c) defining at least one feature category; (d) identifying features in the target pattern that correspond to the at least one feature category, and recording an error value for each feature identified as corresponding to the at least one feature category; and (e) generating a statistical summary which indicates the error value for each feature identified as corresponding to the at least one feature category.

Owner:ASML NETHERLANDS BV

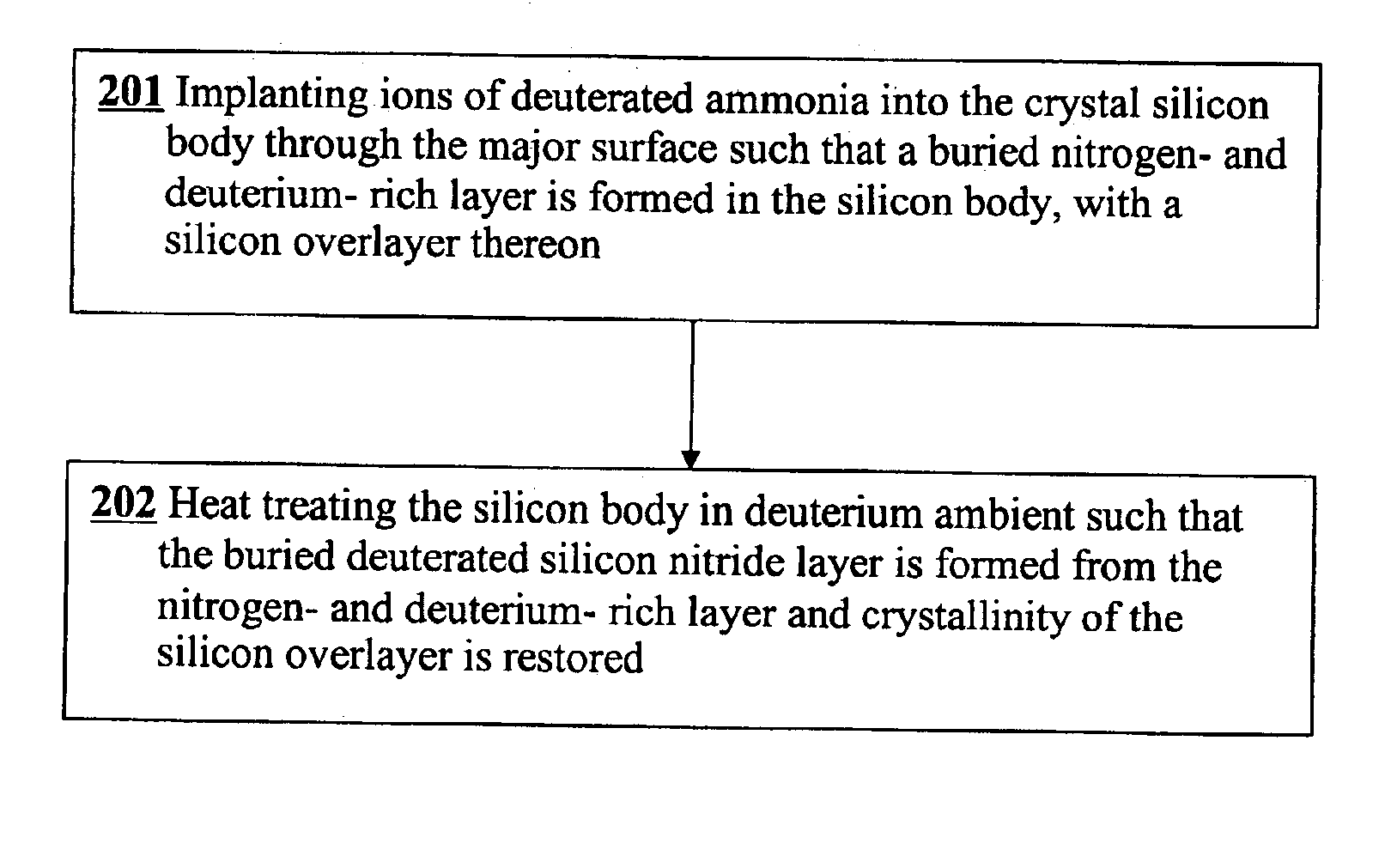

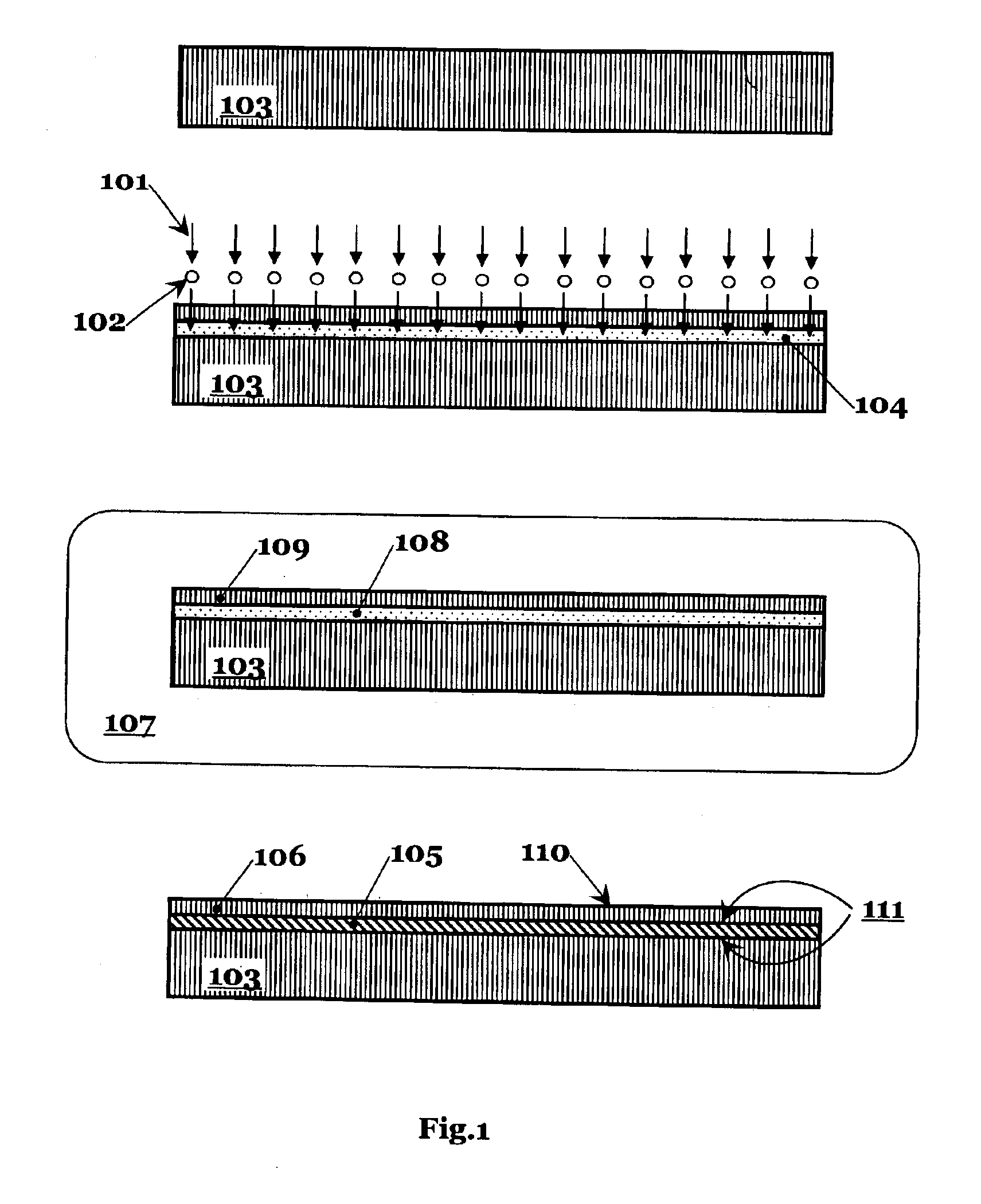

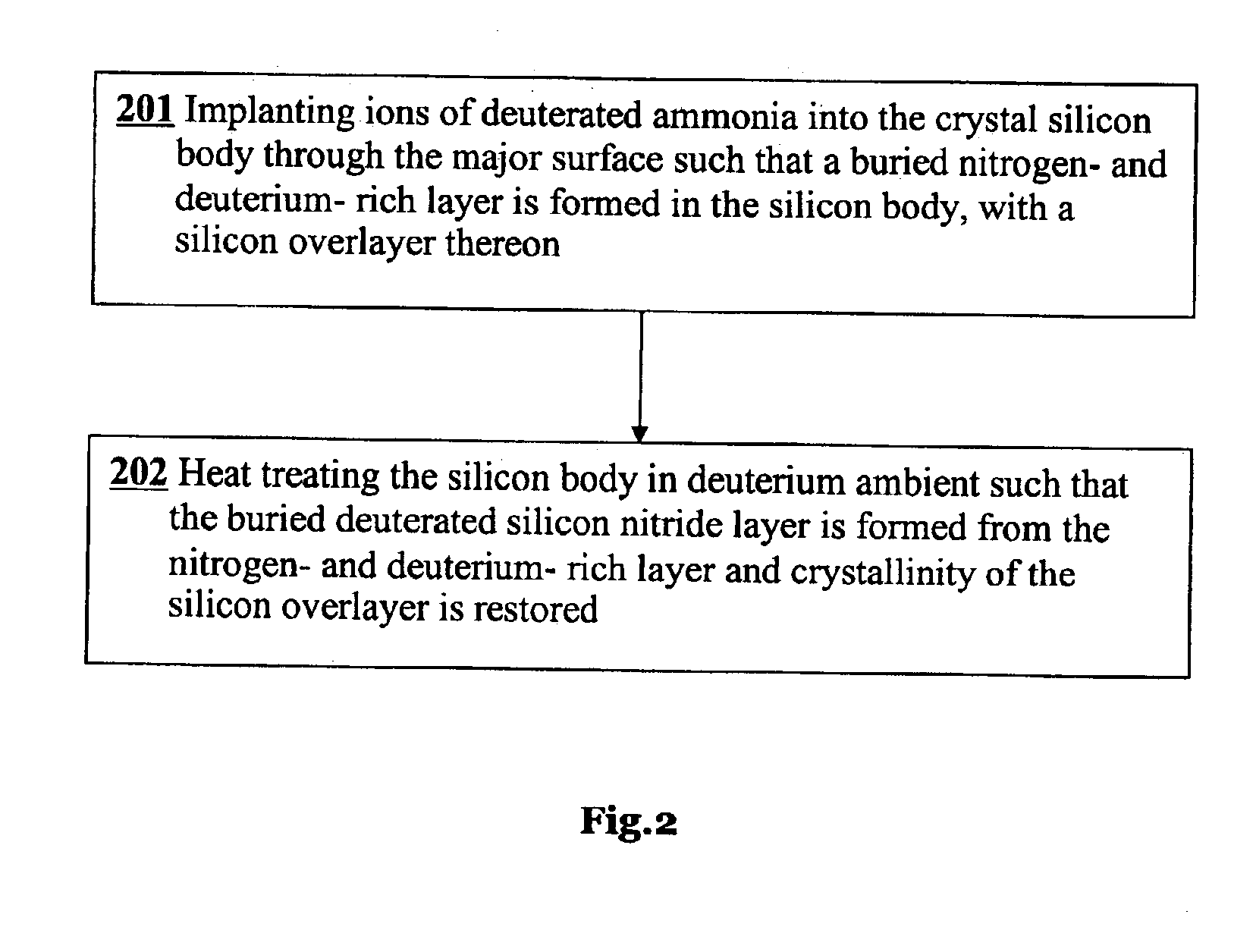

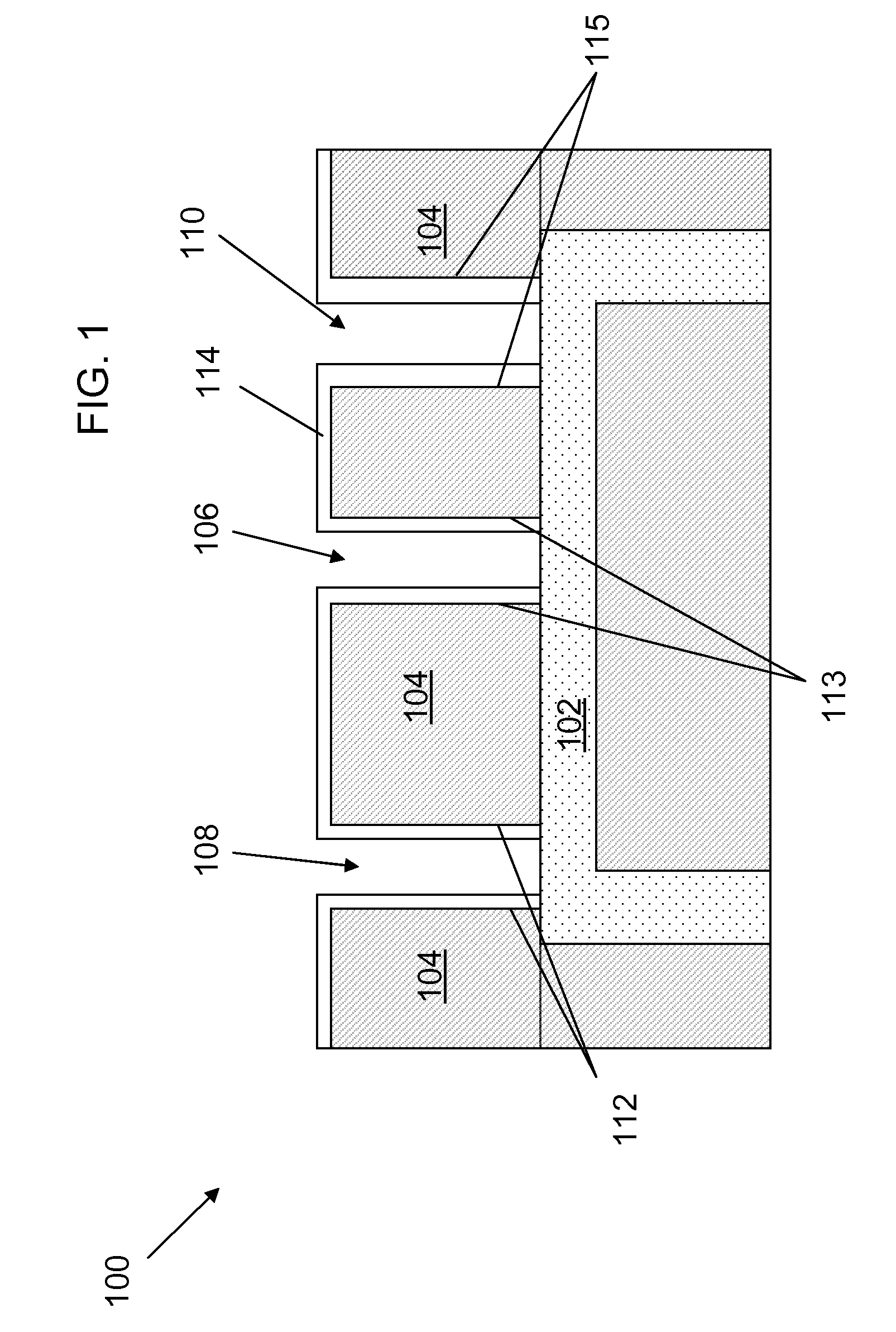

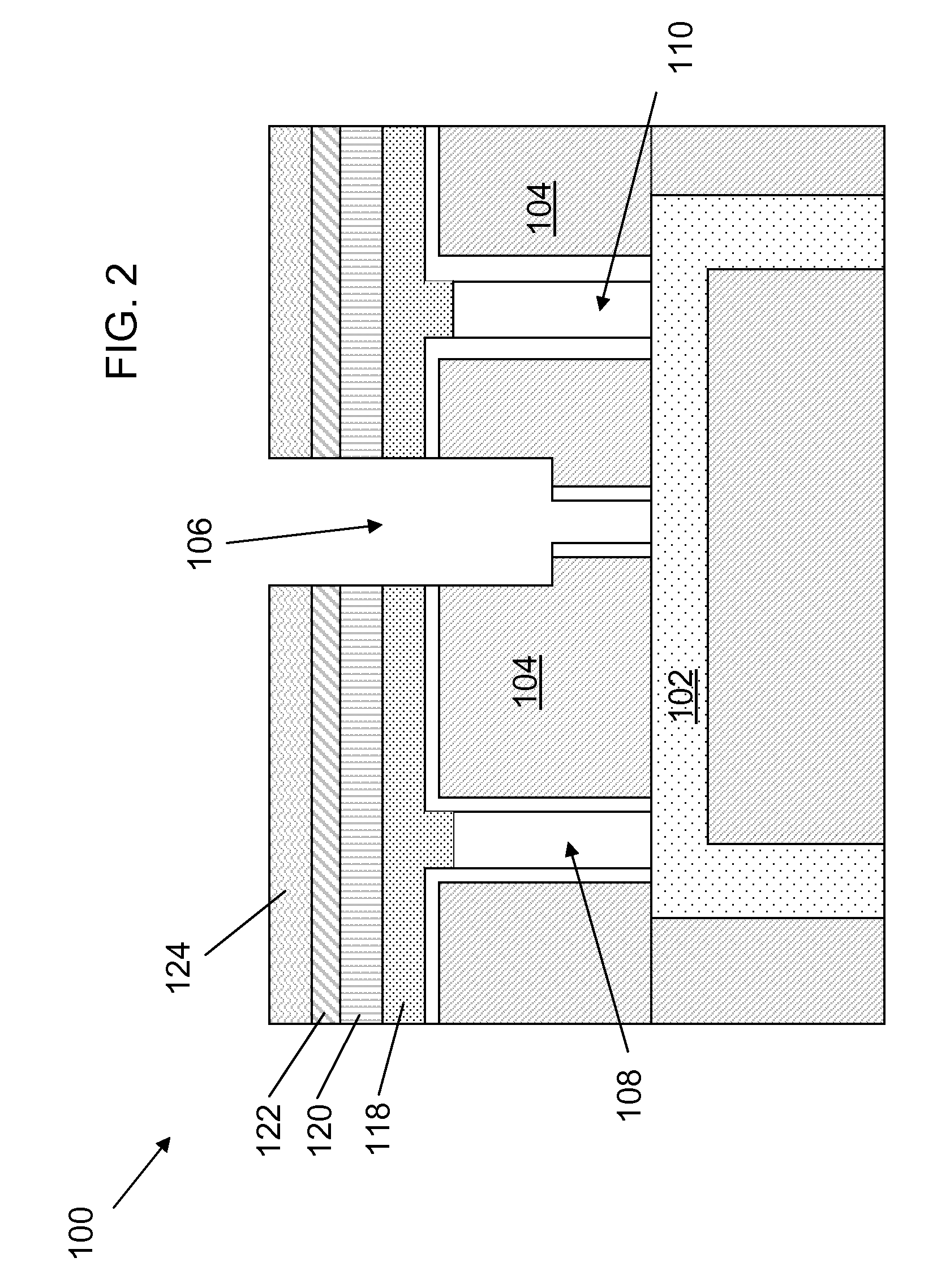

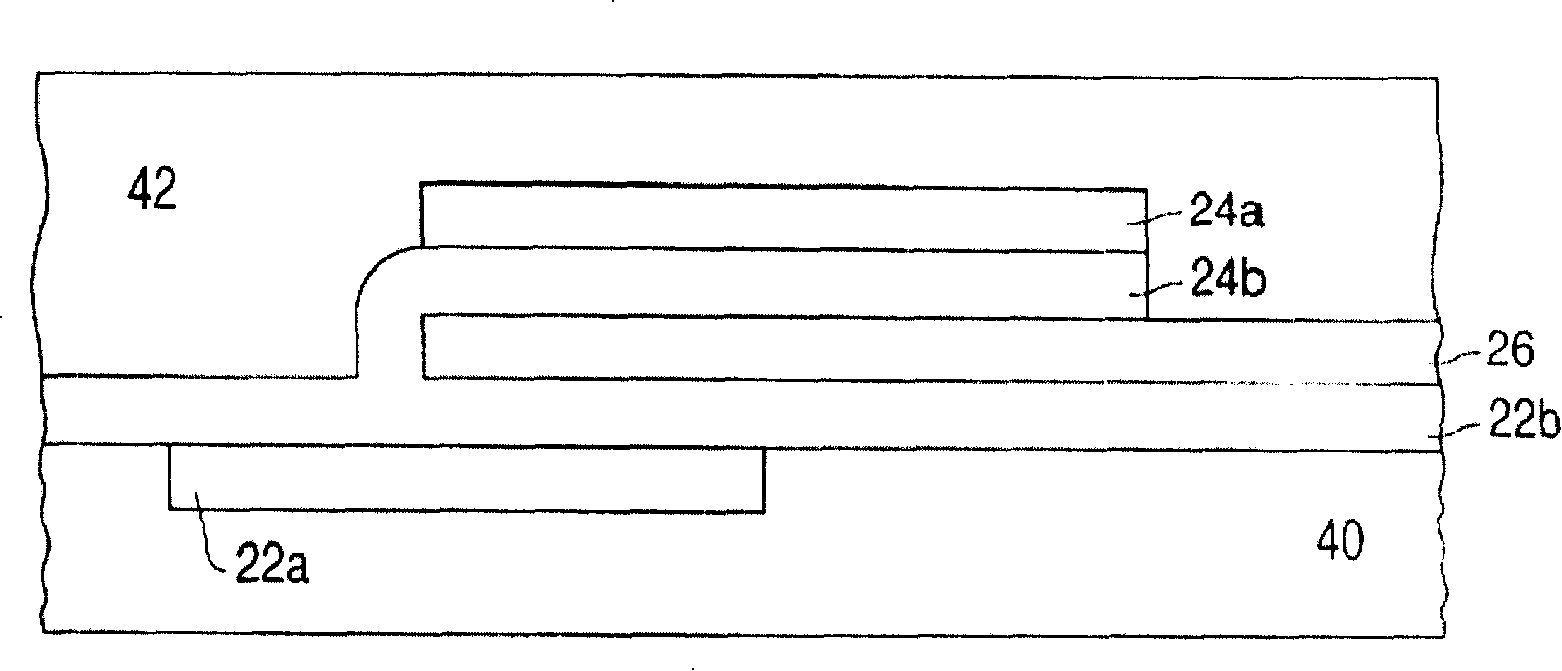

Method of making starting material for chip fabrication comprising a buried silicon nitride layer

InactiveUS6861320B1Simple processReduce the probability of spreadingTransistorSemiconductor/solid-state device manufacturingNitrogenSoi substrate

The invention provides a method of making silicon-on-insulator SOI substrates with nitride buried insulator layer by implantation of molecular deuterated ammonia ions ND3+, instead of implanting nitrogen ions (N+, or N2+) as is done in prior art nitride SOI processes. The resultant structure, after annealing, has a buried insulator with a defect density which is substantially lower than in prior art nitride SOI. The deuterated nitride SOI substrates allow much better heat dissipation than SOI with a silicon dioxide buried insulator. These substrates can be used for manufacturing of high speed and high power dissipation monolithic integrated circuits.

Owner:SILICON WAFER TECH

Computational process control

ActiveUS8856694B2Achieve stabilityIncreased process windowPhotomechanical exposure apparatusMicrolithography exposure apparatusLithography processMetrology

The present invention provides a number of innovations in the area of computational process control (CPC). CPC offers unique diagnostic capability during chip manufacturing cycle by analyzing temporal drift of a lithography apparatus / process, and provides a solution towards achieving performance stability of the lithography apparatus / process. Embodiments of the present invention enable optimized process windows and higher yields by keeping performance of a lithography apparatus and / or parameters of a lithography process substantially close to a pre-defined baseline condition. This is done by comparing the measured temporal drift to a baseline performance using a lithography process simulation model. Once in manufacturing, CPC optimizes a scanner for specific patterns or reticles by leveraging wafer metrology techniques and feedback loop, and monitors and controls, among other things, overlay and / or CD uniformity (CDU) performance over time to continuously maintain the system close to the baseline condition.

Owner:ASML NETHERLANDS BV

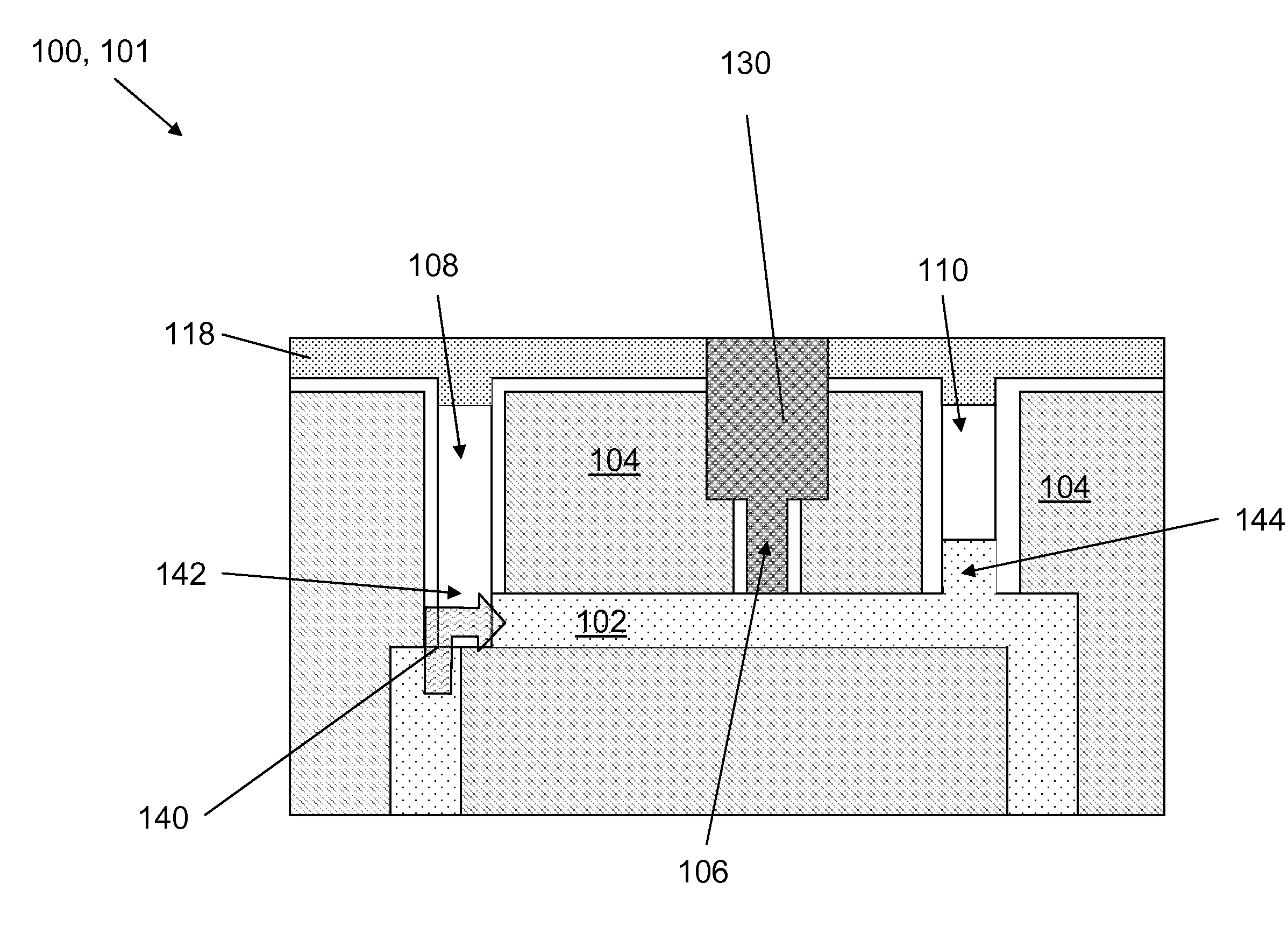

Empty vias for electromigration during electronic-fuse re-programming

ActiveUS7671444B2Fuse disposition/arrangementSemiconductor/solid-state device detailsDielectric layerMetal

The disclosure relates generally to integrated circuit (IC) chip fabrication, and more particularly, to an e-fuse device including an opening, a first via and a second via in an interlayer dielectric, wherein the opening, the first via and the second via are connected to an interconnect below the interlayer dielectric; a dielectric layer that encloses the first via and the second via; and a metal layer over the dielectric layer, wherein the metal layer fills the opening with a metal, and wherein the first via and the second via are substantially empty to allow for electromigration of the interconnect during re-programming of the e-fuse device.

Owner:TWITTER INC

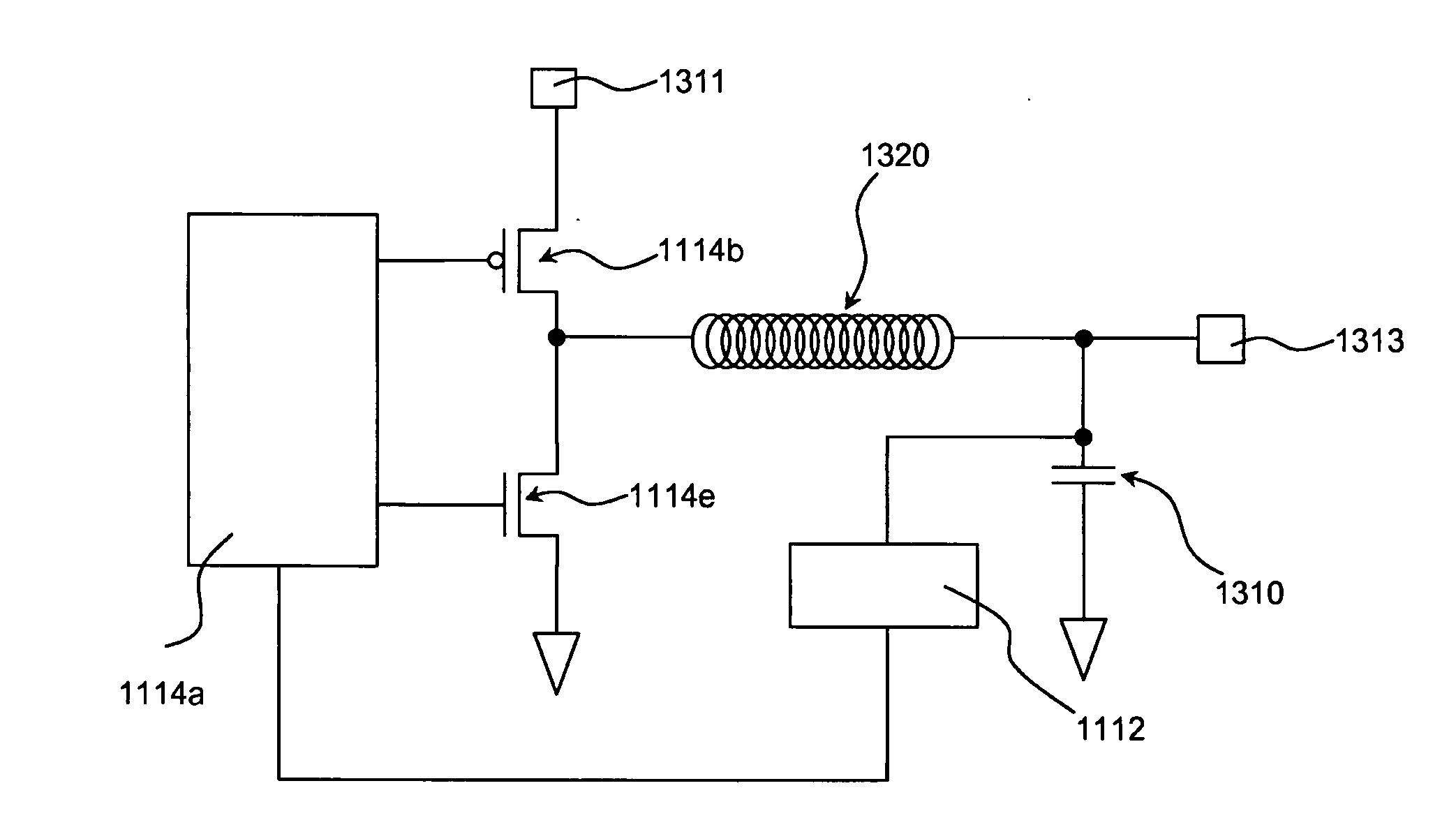

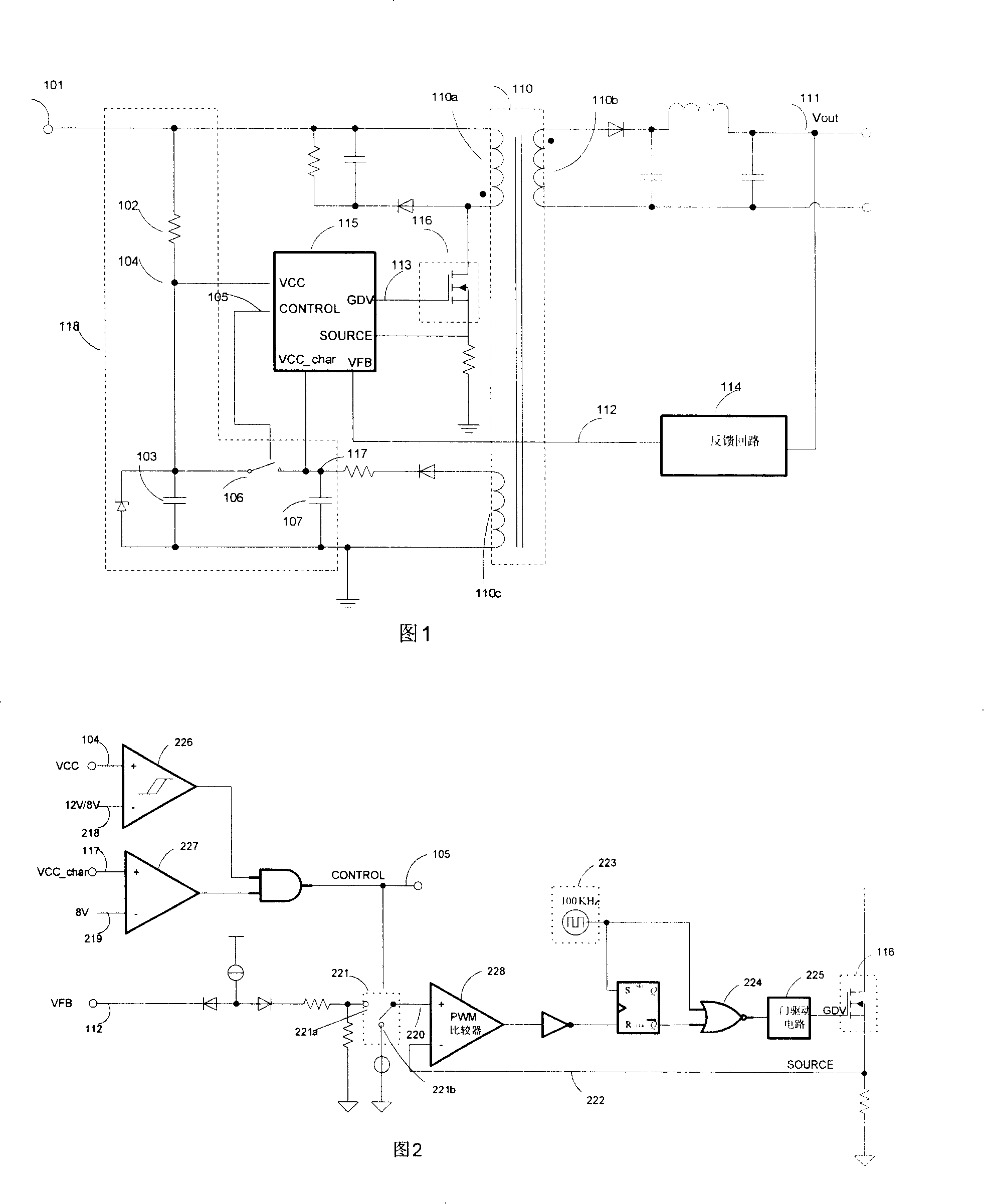

Starting circuit and switch power source thereof

ActiveCN101207332AReduce manufacturing costReduce processing requirementsApparatus with intermediate ac conversionElectric variable regulationStart up timeCapacitance

The invention discloses a switching power source and a starting circuit of the switching power source, wherein, the starting circuit is used for the power supply of a PWM control chip that is used for controlling the switching of the power FET; under the starting mode, the power for the PWM controlling chip is supplied by a starting circuit capacitor with smaller capacity value, thereby guaranteeing that the system has short starting time; after the starting is successful, under the normal working mode, a larger capacitor is connected with the starting circuit capacitor in parallelism through a switch to supply power for the PWM controlling chip, thereby reducing the ripples of the power-supply voltage of the switching power source in normal work and improving the stability of the system. Using the switching power source of the starting circuit prevents a high-voltage element from being introduced into the PWM controlling chip, thereby reducing the production process requirement of the chip, reducing the production cost of the PWM chip and reducing the starting time of the system as far as possible while reducing the power consumption.

Owner:FREMONT MICRO DEVICES SHENZHEN LTD

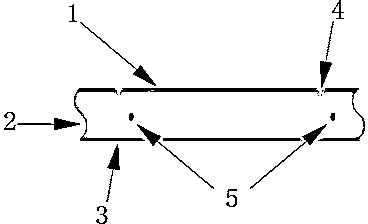

LED chip cutting method and LED chip manufactured by same

InactiveCN103022284AImprove light extraction efficiencyAdd side lightSemiconductor/solid-state device manufacturingSemiconductor devicesLaser scribingCrystallite

The invention discloses an LED chip cutting method on the basis of side-wall corrosion. The LED chip cutting method includes that an LED wafer is subjected to front laser scribing and side-wall corrosion and then is manufactured to form a chip according to a normal LED chip manufacturing process; back laser hidden cutting is carried out after the wafer is subjected to thinning and back plating, and positioning of hidden cutting lines is controlled, so that the hidden cutting lines are staggered from front scribing lines; and an oblique fracture surface is formed on each side wall of a crystal grain under the induction action of stress during fracturing, lateral light emergence is facilitated, the integral luminous flux of the chip is increased, and the appearance and the electric performance of the chip are unaffected. The invention further discloses the LED chip manufactured by the LED chip cutting method. Edges of the LED chip are in the shape of 'Z'-shaped sections with the oblique fracture surfaces. The 'Z'-shaped sections are manufactured by means of laser hidden cutting after the GaN wafer which is a semiconductor substrate is subjected to a chip side-wall corrosion process, accordingly, quantities of emergent light on the side walls are increased, and the brightness of the integral LED chip is improved.

Owner:FOCUS LIGHTINGS SCI & TECH

Method for making high brightness LED chip

InactiveCN101471412AImprove external quantum efficiencySimple processSemiconductor devicesEtchingPhotoresist

The invention discloses a high-brightness LED chip fabrication method, which comprises the following steps: generating an epitaxial wafer on a sapphire substrate; depositing a SiO2 film on the epitaxial wafer; etching an N-region patter on the chip by photolithography using the SiO2 film as the mask; cleaning the SiO2 not protected by the photoresist using a corrosive solution; cleaning with a photoresist removing solution to remove the photoresist; etching N steps and a track with the size of the chip to expose the n-GaN mesa; roughening the N-GAN surface by light-assisting wet etching; depositing an ITO film on the epitaxial wafer surface by evaporating; and evaporating a Cr / Ni / Au P-N electrode. The method can improve the external quantum efficiency of the LED device by increasing the probability of light refraction from the n-GaN to the air. The method can be used for fabricating normal LED chip and vertical LED chip, and has the advantages of simple process and low cost. The method suits industrial production and can greatly improve the external quantum efficiency.

Owner:深圳市方大国科光电技术有限公司

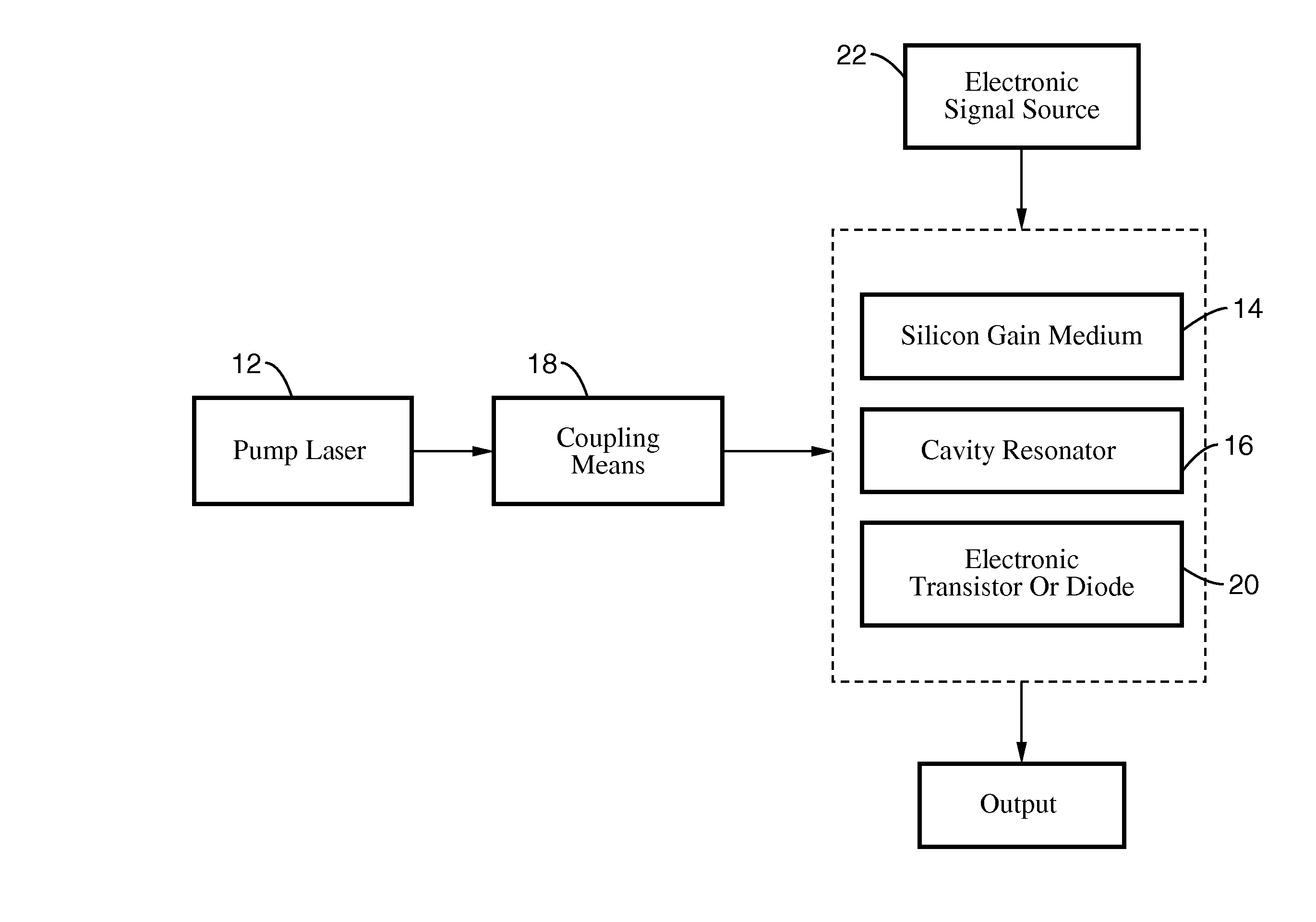

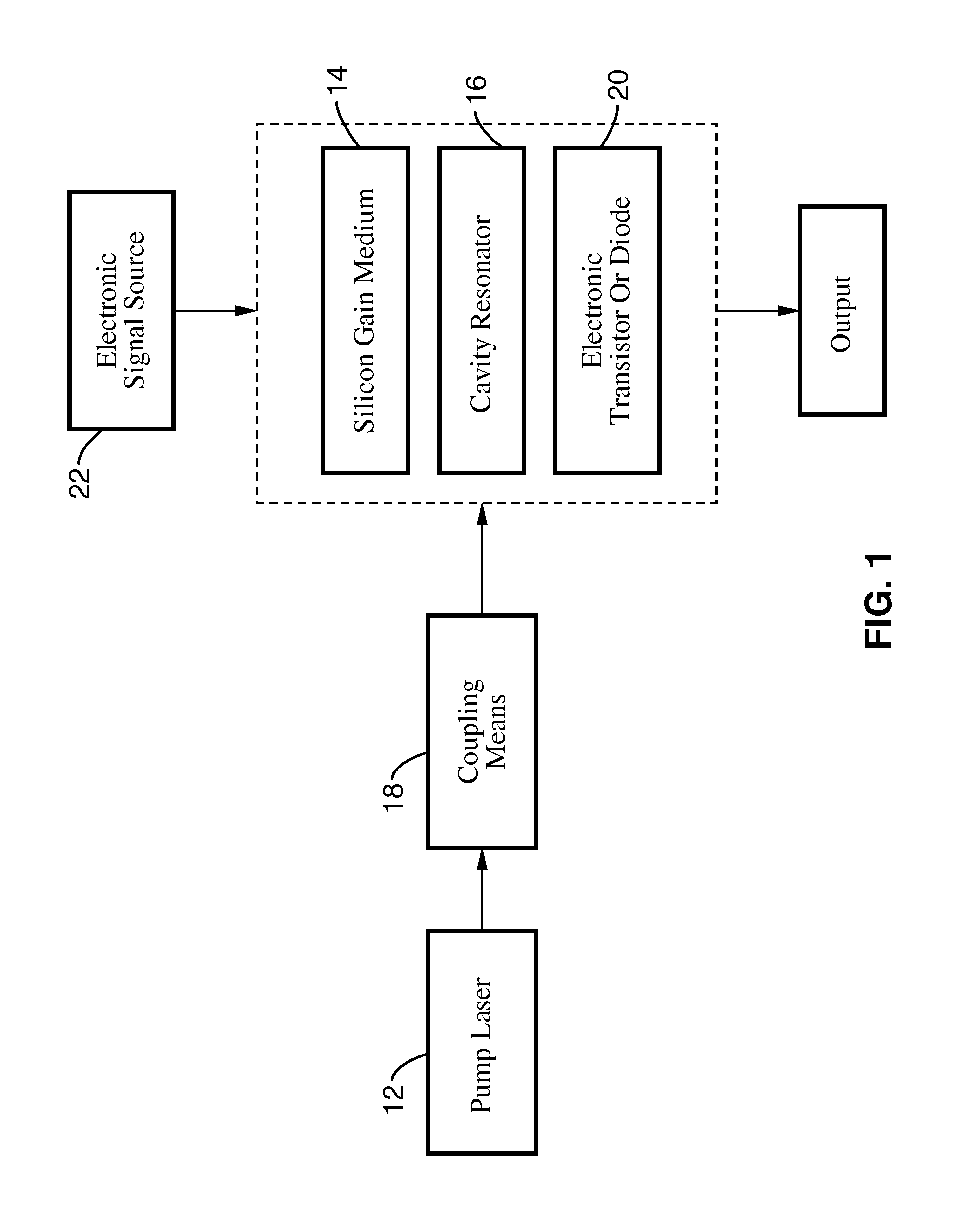

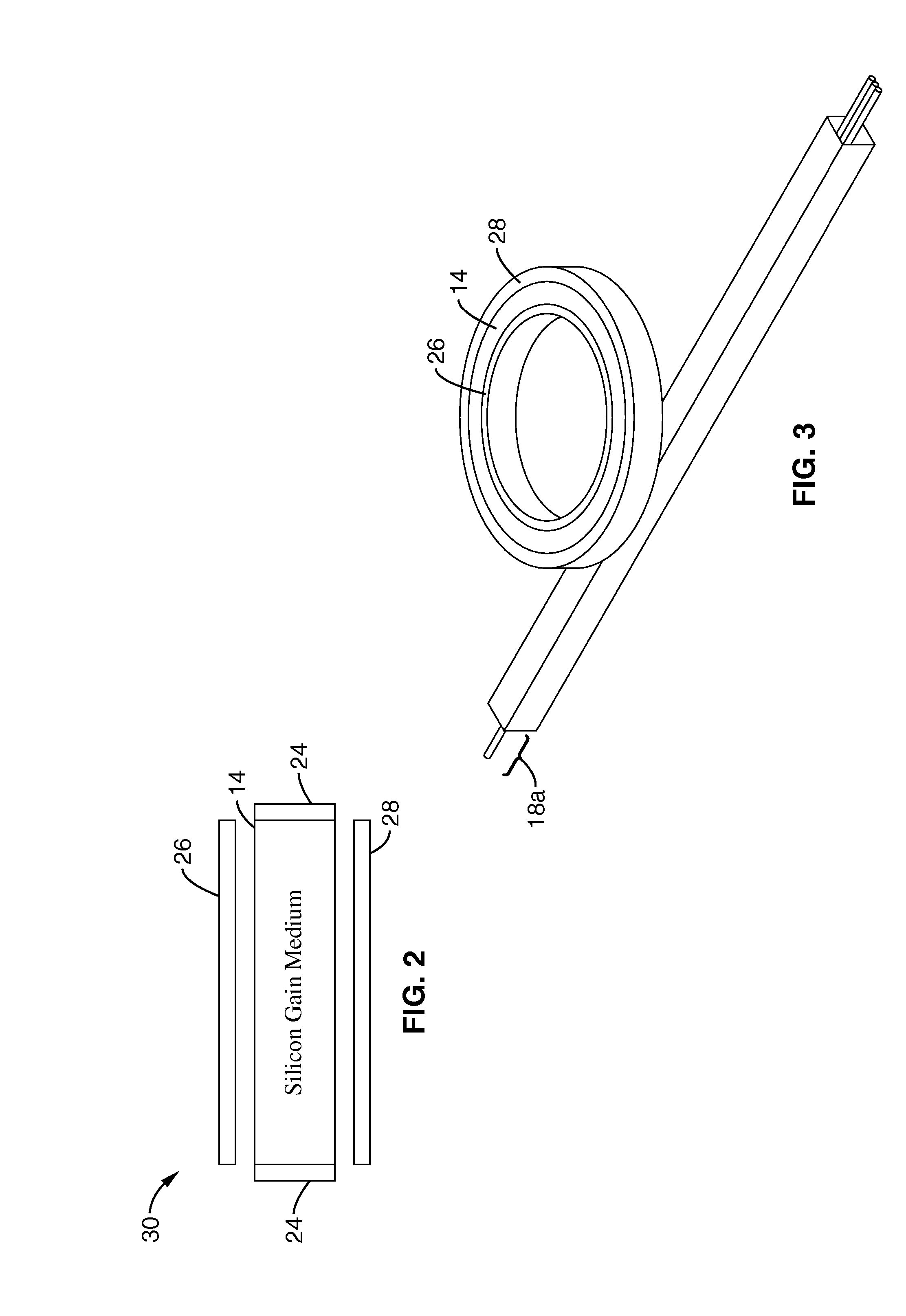

Cascaded cavity silicon raman laser with electrical modulation, switching, and active mode locking capability

A silicon Raman laser that can be electrically switched or modulated and which demonstrates active mode-locking capabilities. The laser can be used with a more traditional glass fiber cavity, or can be fabricated on a single chip with a cavity, or a cascaded cavity, in which the chip fabrication is compatible with widely used silicon chip fabrication methods. The laser can be tuned by adjusting a source pump laser to produce specific output and operates at room temperature. Output is present in the near- and mid-infrared frequency range, and the laser can simultaneously produce output at the Stokes and at the anti-Stokes wavelengths.

Owner:RGT UNIV OF CALIFORNIA

Silicon based LCD unit and method for forming the same

ActiveCN101196656AIncrease capacitanceReduce the refresh rateSolid-state devicesSemiconductor/solid-state device manufacturingCapacitanceLiquid-crystal display

A silicon-based liquid crystal display unit is provided, by grounding a light shielding layer located on a pixel switch circuit layer, a metal-insulating layer-metal (MIM) second capacitor composed by micro reflection micro reflecting mirror layer-insulating later-light shielding layer is formed, the second capacitance is connected with a first capacitance of the pixel switch circuit layer in parallel to be the capacitance of the pixel switch circuit layer together; the invention also provides a forming method of the silicon-based liquid crystal display unit. By fully utilizing the entire pixel area, the invention enlarges the capacitance, lowers the refresh rate of the silicon-based liquid crystal display unit. Simultaneously, the invention enlarges the design area of the switch circuit, designs high performance switch circuit according to different requirements and increases the design flexibility of the switch circuit. The invention also simplifies procedure of capacitance manufacture, so as to lower the total chip manufacture cost.

Owner:SEMICON MFG INT (SHANGHAI) CORP +1

Method for performing full-chip manufacturing reliability checking and correction

ActiveUS7434195B2Suitable for useLow costPhotomechanical apparatusCharacter and pattern recognitionPattern recognitionProcess patterns

Owner:ASML NETHERLANDS BV

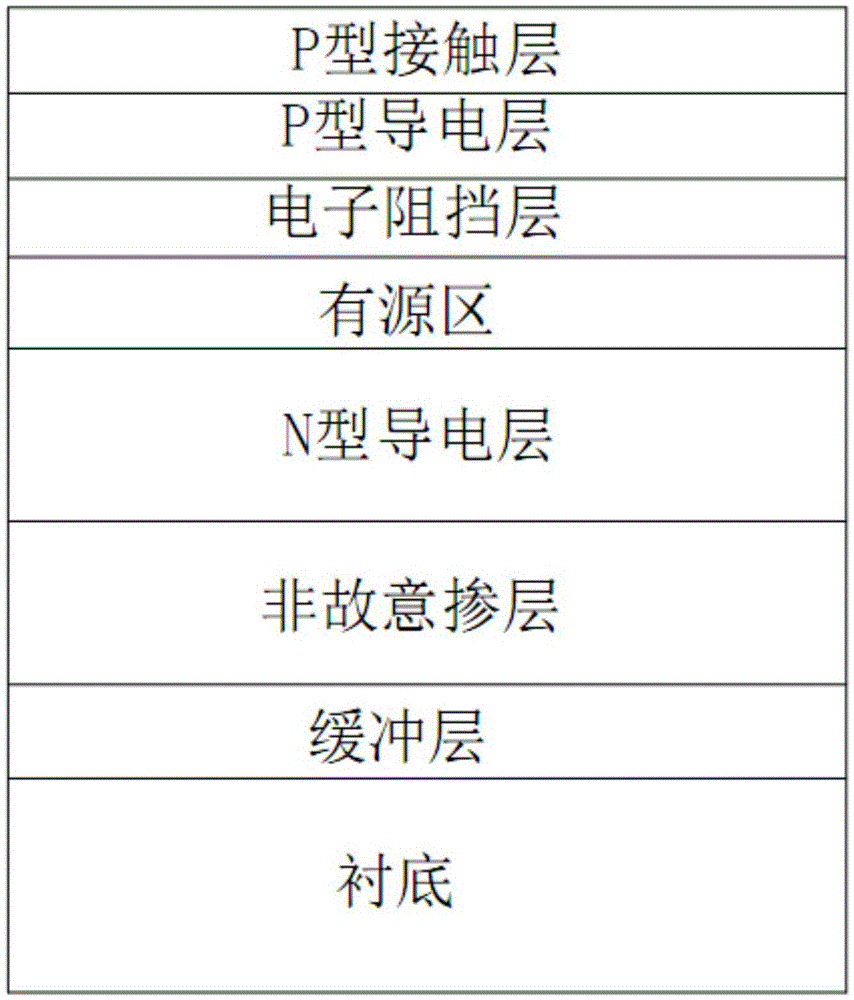

Inversed high-voltage light emitting diode (LED) chip electrode and chip fabrication method

ActiveCN105449084AIncrease reflective surfaceSolve the problems of low packaging yield such as virtual soldering and short circuitSolid-state devicesSemiconductor devicesPower flowQuantum well

The invention discloses an inverted high-voltage light emitting diode (LED) chip electrode and a chip fabrication method. The chip electrode comprises a substrate and an epitaxial layer, wherein the epitaxial layer comprises a P-type GaN layer, a quantum well region and an N-type GaN layer, unit chips which are independent to each other are arranged on the epitaxial layer, each unit chip forms a patterned P-type GaN platform and a patterned N-type GaN platform, more than two groups of unit chips form a high-voltage chip unit, the P-type GaN platform and the N-type GaN platform both adopt a metal electrode to interconnect, the metal electrode comprises a P-type metal reflection electrode, a P-N interconnected electrode, an N-type metal electrode and a bonding pad electrode, and the side wall from the P-type GaN platform and the N-type GaN platform and a deep groove region where the unit chips are interconnected adopt a DBR structure to connect. With the inverted high-voltage LED chip electrode disclosed by the invention, the light emergent efficiency of the chip is improved, the contact area of a bonding pad for chip package is expanded, the stability is improved, the current clustering effect is reduced, moreover, wireless welding is achieved, the cooling effect is good, cost is favorably reduced, and light attenuation is reduced.

Owner:ZHEJIANG NORMAL UNIVERSITY

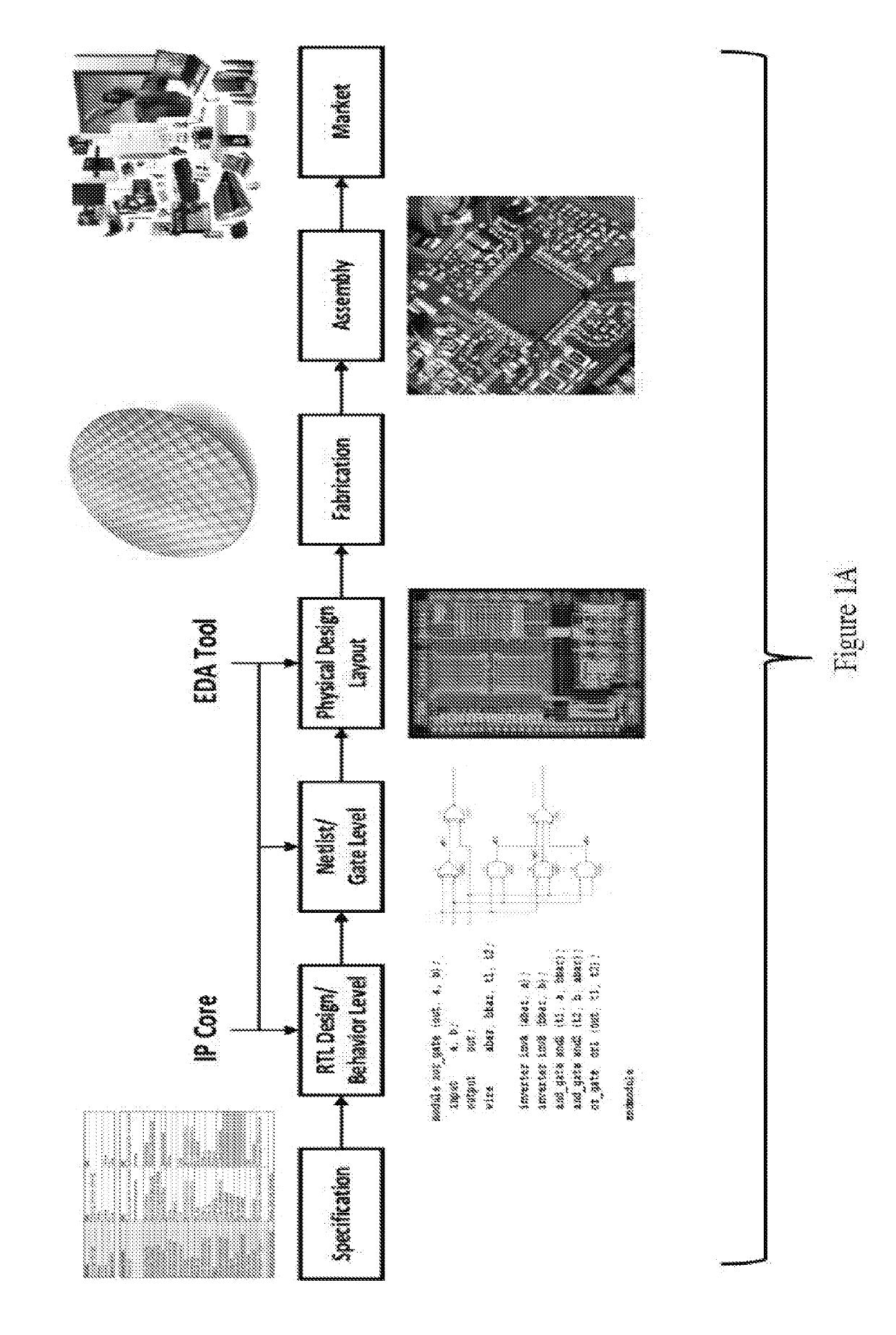

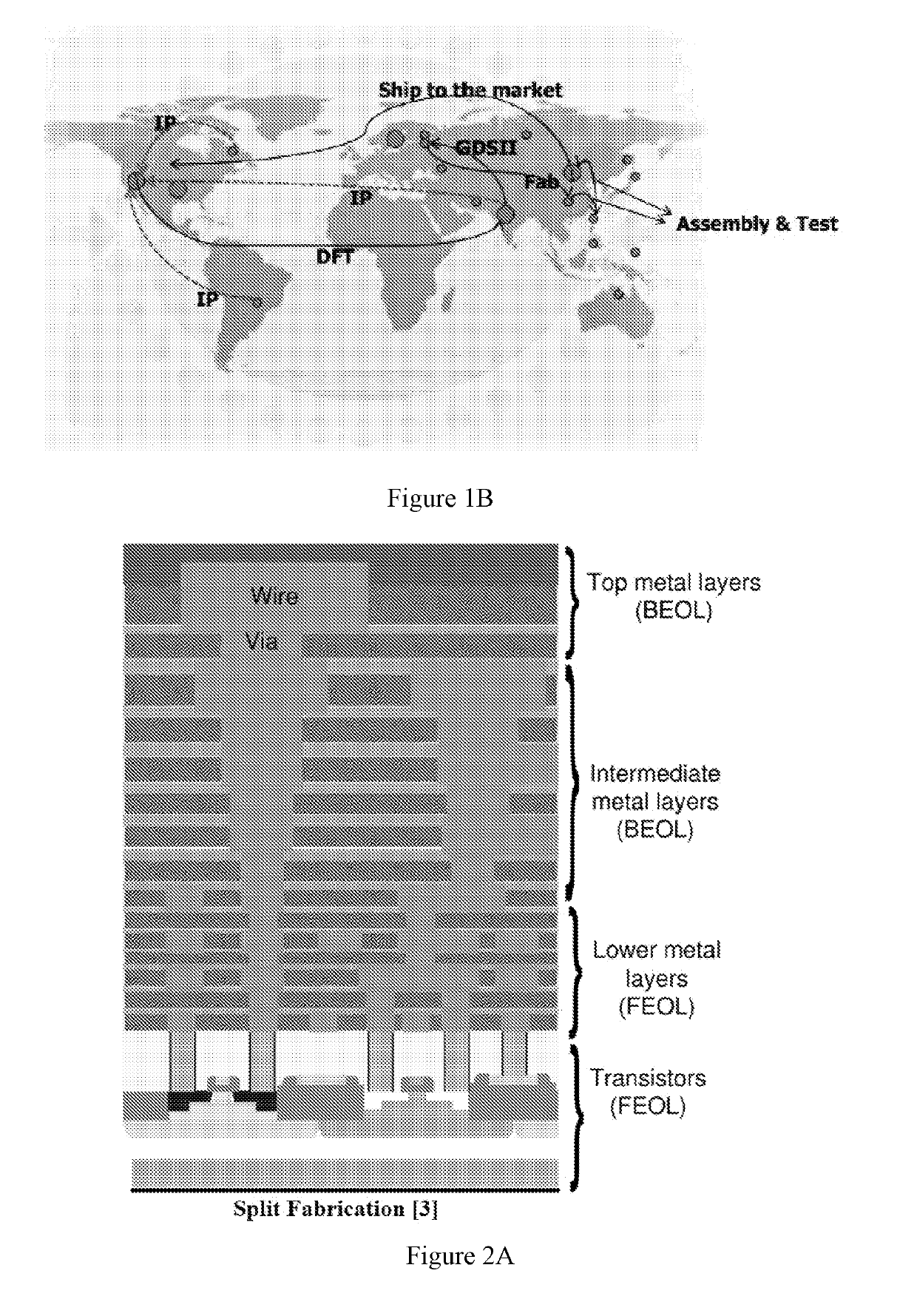

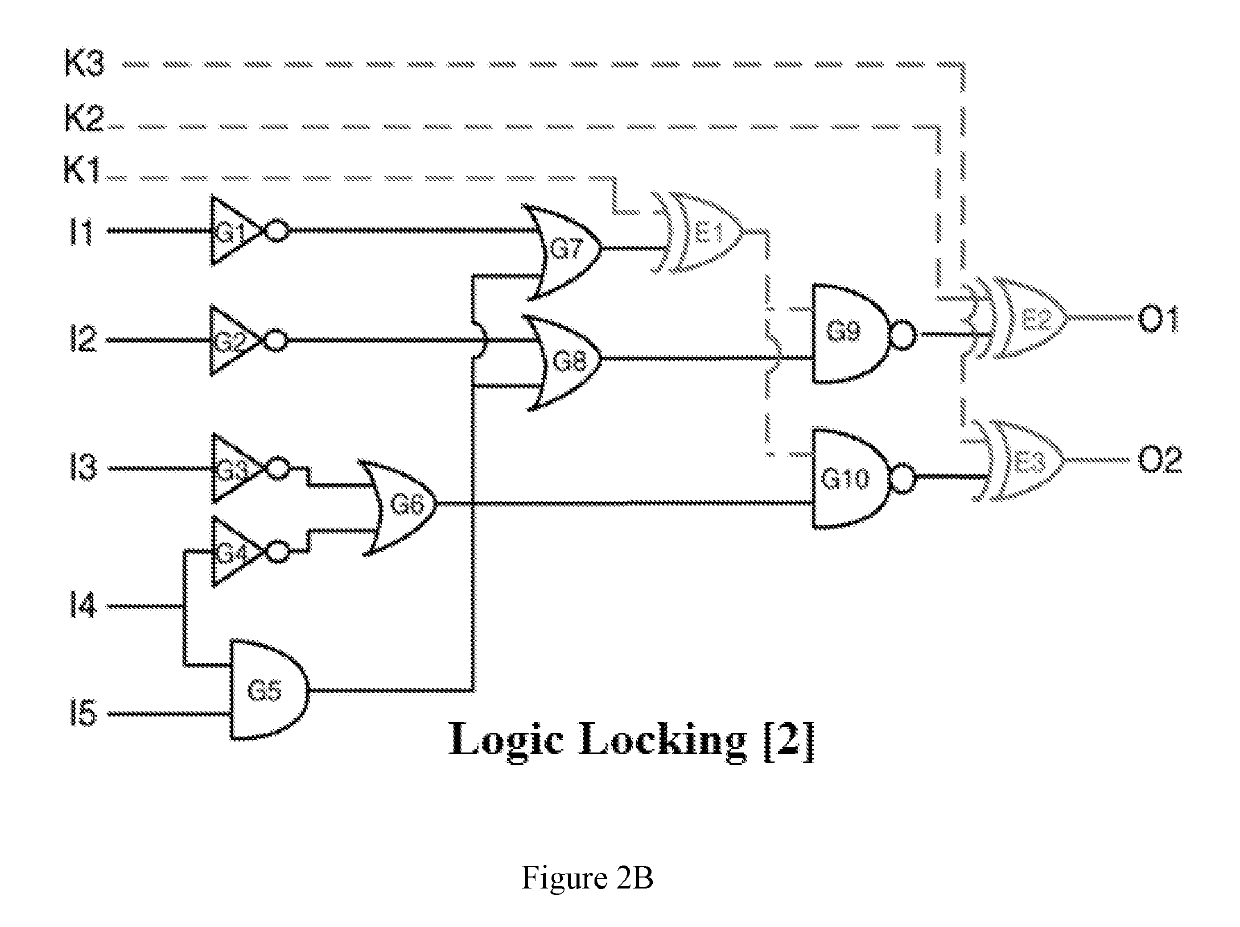

Circuit edit and obfuscation for trusted chip fabrication

ActiveUS20190311156A1Semiconductor/solid-state device detailsSemiconductor/solid-state device manufacturingThird partyObfuscation

Circuits and methods for protecting against intellectual property piracy and integrated circuit piracy from an untrusted third party are provided. A circuit can include an original circuit and an obfuscated circuit incorporated into the original circuit and changing the output of the original circuit, wherein the obfuscated circuit is configured to recover the output of the original circuit by modifying the obfuscated circuit. In addition, a method of manufacturing a semiconductor device can include designing a circuit including an original circuit and an obfuscated circuit, and fabricating the circuit, wherein the obfuscated circuit is configured to change an output of the original circuit and to recover the output of the original circuit by modifying the obfuscated circuit.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

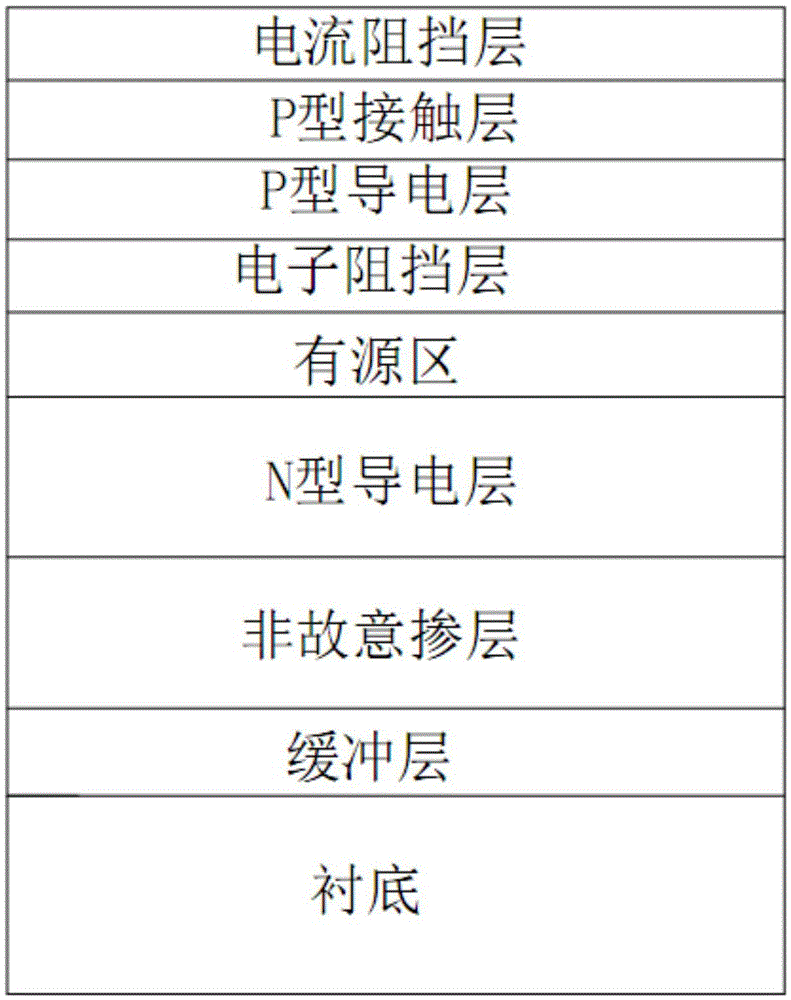

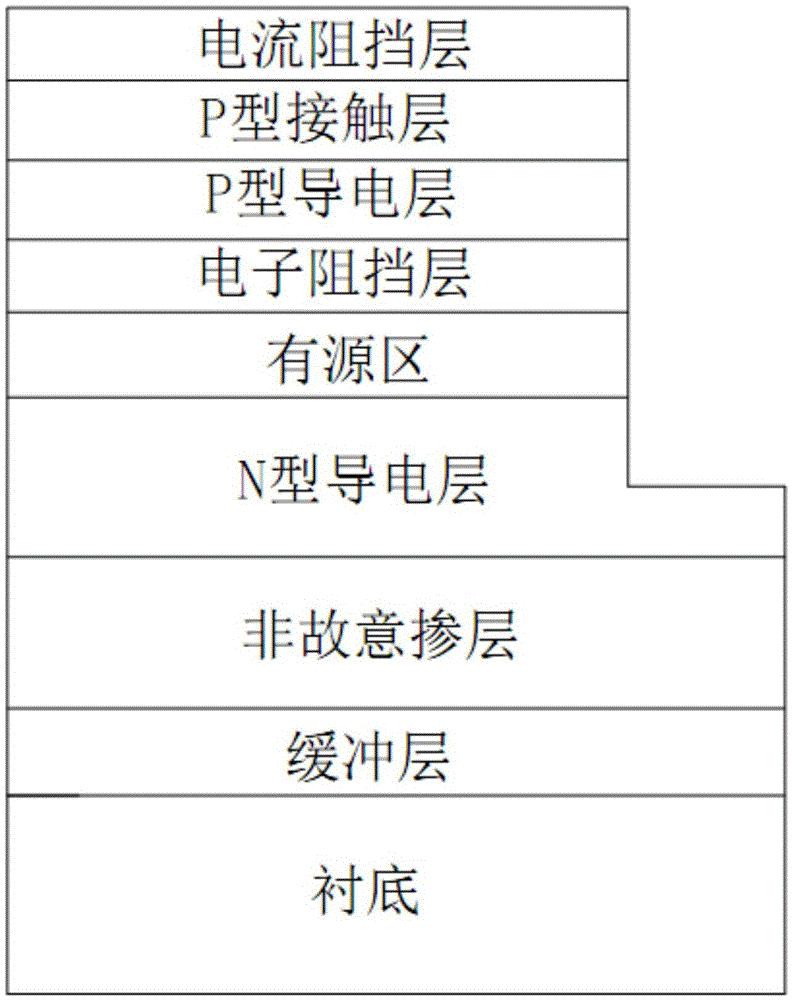

Simple manufacturing method of high-efficient light emitting diode chip

ActiveCN105428474AThe production process is simpleShorten production timeSemiconductor devicesManufacturing technologyEvaporation

The invention discloses a simple manufacturing method of a high-efficient light emitting diode chip. The method comprises the following steps that an epitaxial luminescence structure is formed on a substrate; a non-conducting material is evaporated on an ohmic contact layer so as to be taken as a current barrier layer; silicon dioxide is evaporated on an epitaxial luminescence structure surface and a side surface; all the photoresists on the surface are removed and evaporation is performed on the surface to form an ITO conducting layer; an etchant solution is used to remove the silicon dioxide on the epitaxial luminescence structure side surface and an N-type electrode manufacturing area; silicon nitride is evaporated on a chip surface, a side surface and an electrode isolation groove between an N-type electrode and an epitaxial layer to form a chip protection layer and an electrode isolation layer; a P-type electrode manufacturing area and the N-type electrode manufacturing area are defined on the chip surface; the photoresist is evaporated on and peeled off the P-type electrode manufacturing area and the N-type electrode manufacturing area; the chip is splintered and is separated into independent chip grains. By using method in the invention, a chip manufacturing technology is effectively simplified; chip process time is shortened; chip manufacturing cost is reduced and chip quality is increased.

Owner:XIAMEN CHANGELIGHT CO LTD

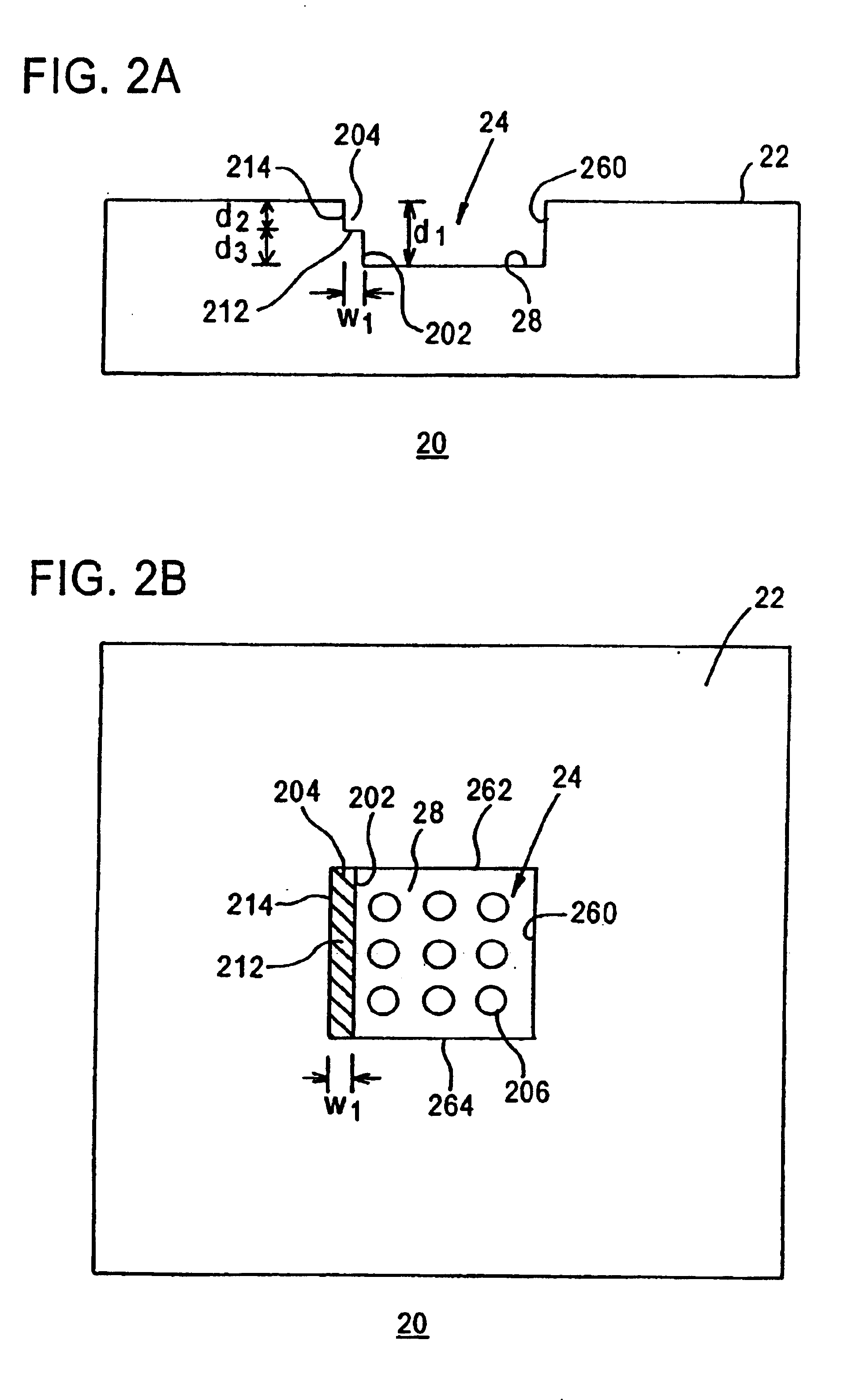

Package and method for making an underfilled integrated circuit

InactiveUS6838758B1Meet actual needsEfficient and complete applicationSemiconductor/solid-state device detailsSolid-state devicesFilling materialsEngineering

An integrated circuit package for use in flip-chip manufacturing has a surface having a depression for receiving a bumped die. The depression has disposed on its floor a plurality of cage pads. The depression has four walls, at least one of which is indented to form a step. In the flip-chip manufacturing process, a bumped die is positioned within the depression so that the solder bumps line up with the cage pads, and is precisely aligned and held in place by the depression. The die-package combination is then heated in a furnace to reflow the solder bumps, thus forming an integrated circuit. Using the indentation in the depression, underfill material is introduced into the depression. The underfill material flows into the depression and under the die, surrounding the reflowed solder bumps.

Owner:ADVANCED MICRO DEVICES INC