Bipolar CMOS DMOS (BCD) integrated device based on N type extension layer and manufacture method thereof

A technology for integrating devices and epitaxial layers, which is applied in semiconductor/solid-state device manufacturing, electrical solid-state devices, semiconductor devices, etc., can solve the problems of increasing the cost of silicon wafers, reduce resistivity, avoid the increase of chip manufacturing costs, and reduce manufacturing costs. cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

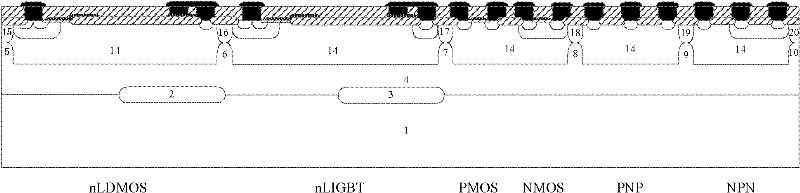

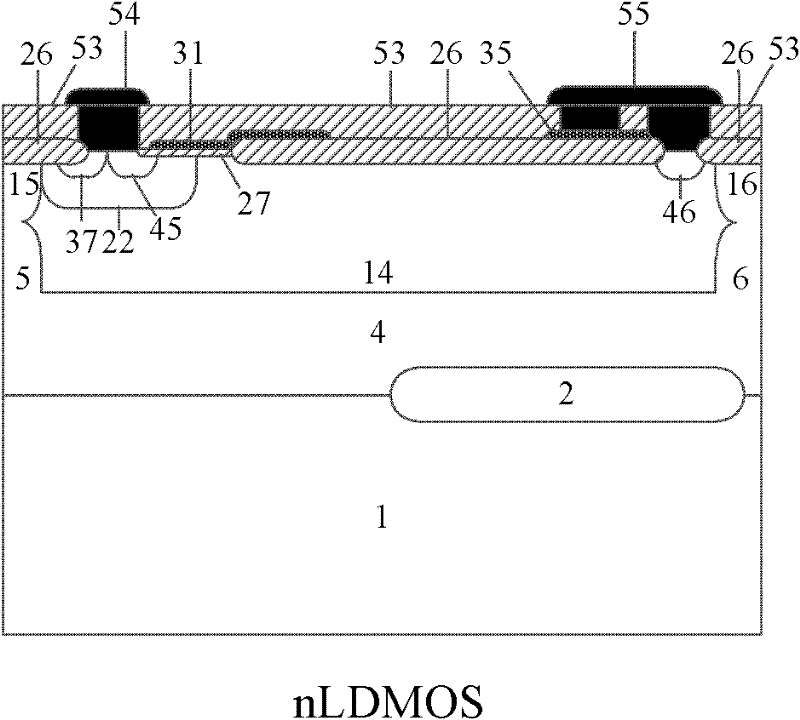

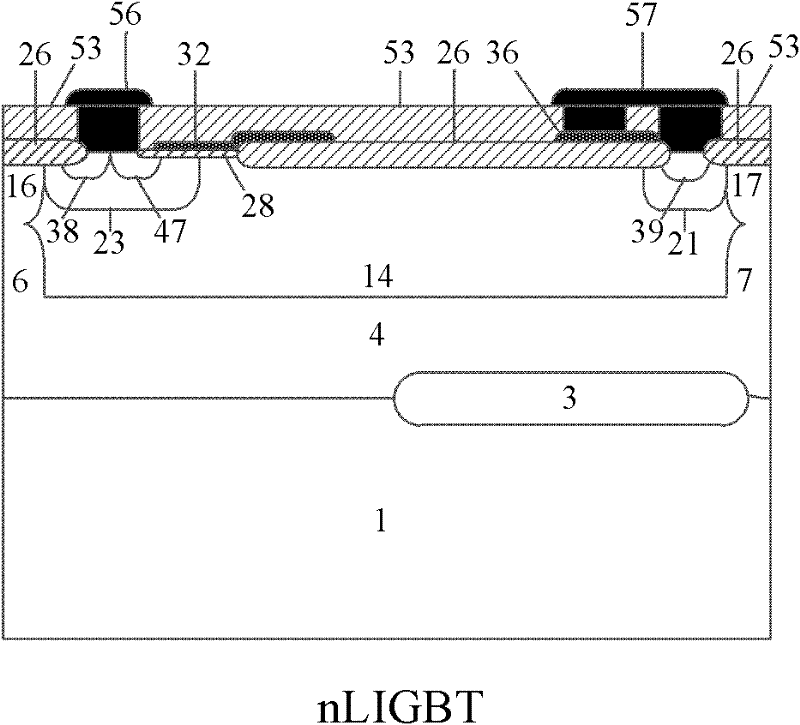

[0027] The present invention provides a BCD integrated device based on an N-type epitaxial layer, such as figure 1 As shown, it includes high-voltage nLDMOS devices, high-voltage nLIGBT devices, low-voltage PMOS devices, low-voltage NMOS devices, low-voltage PNP devices, and low-voltage NPN devices integrated on the same P-type substrate 1. The high-voltage nLDMOS device, high-voltage nLIGBT device, low-voltage PMOS device, low-voltage NMOS device, low-voltage PNP device, and low-voltage NPN device are fabricated in the N-type epitaxial layer 14 on the surface of the P-type epitaxial layer 4 on the surface of the P-type substrate 1, and pass P + To achieve junction isolation in the isolation regions 5-10 and 15-20. There is a first N-type buried layer 2 between the P-type substrate 1 and the P-type epitaxial layer 4 under the high-voltage nLDMOS device, and a second N-type buried layer 2 is provided between the P-type substrate 1 and the P-type epitaxial layer 4 under the high-v...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More