Patents

Literature

35results about How to "Prevent charge leakage" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

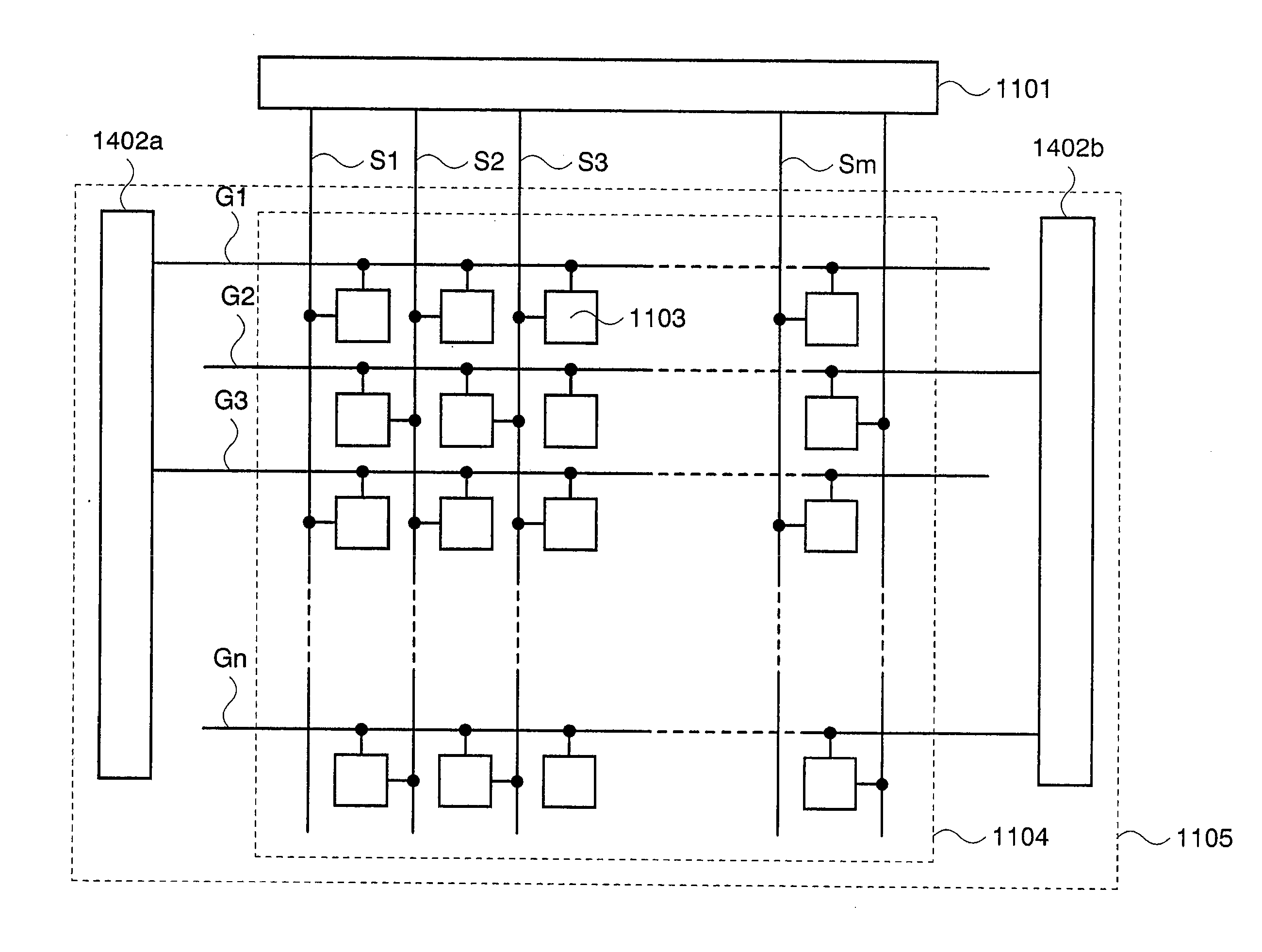

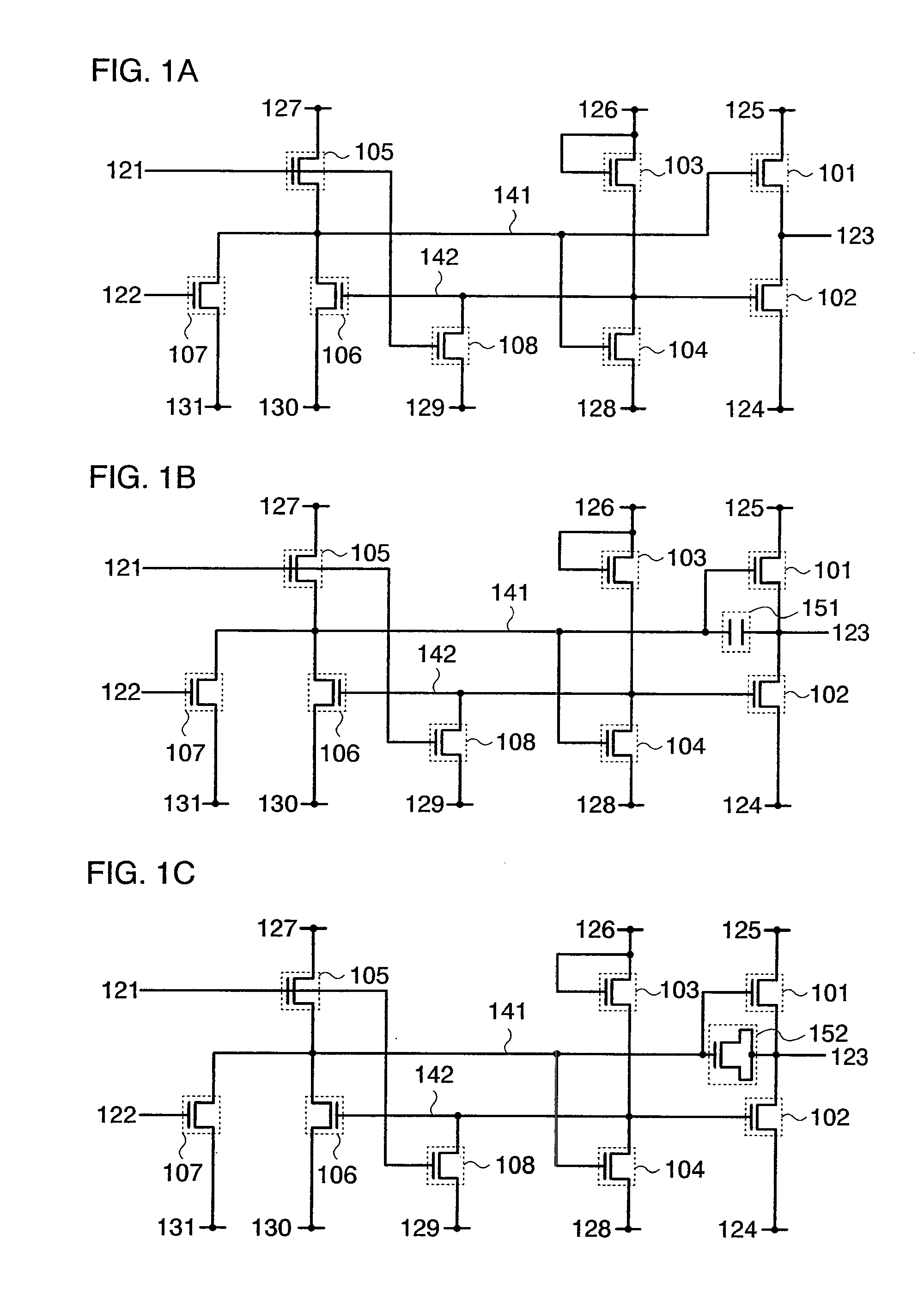

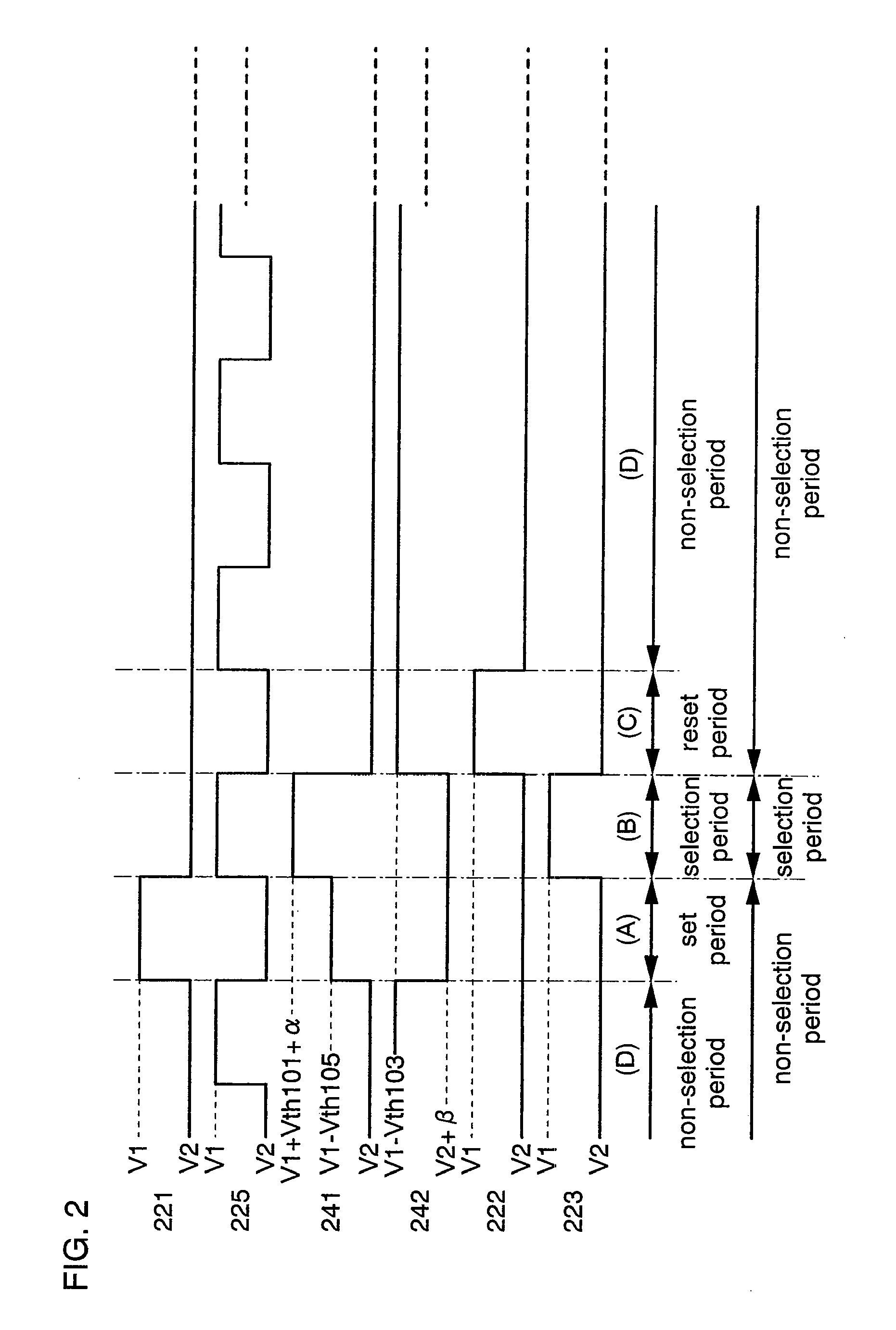

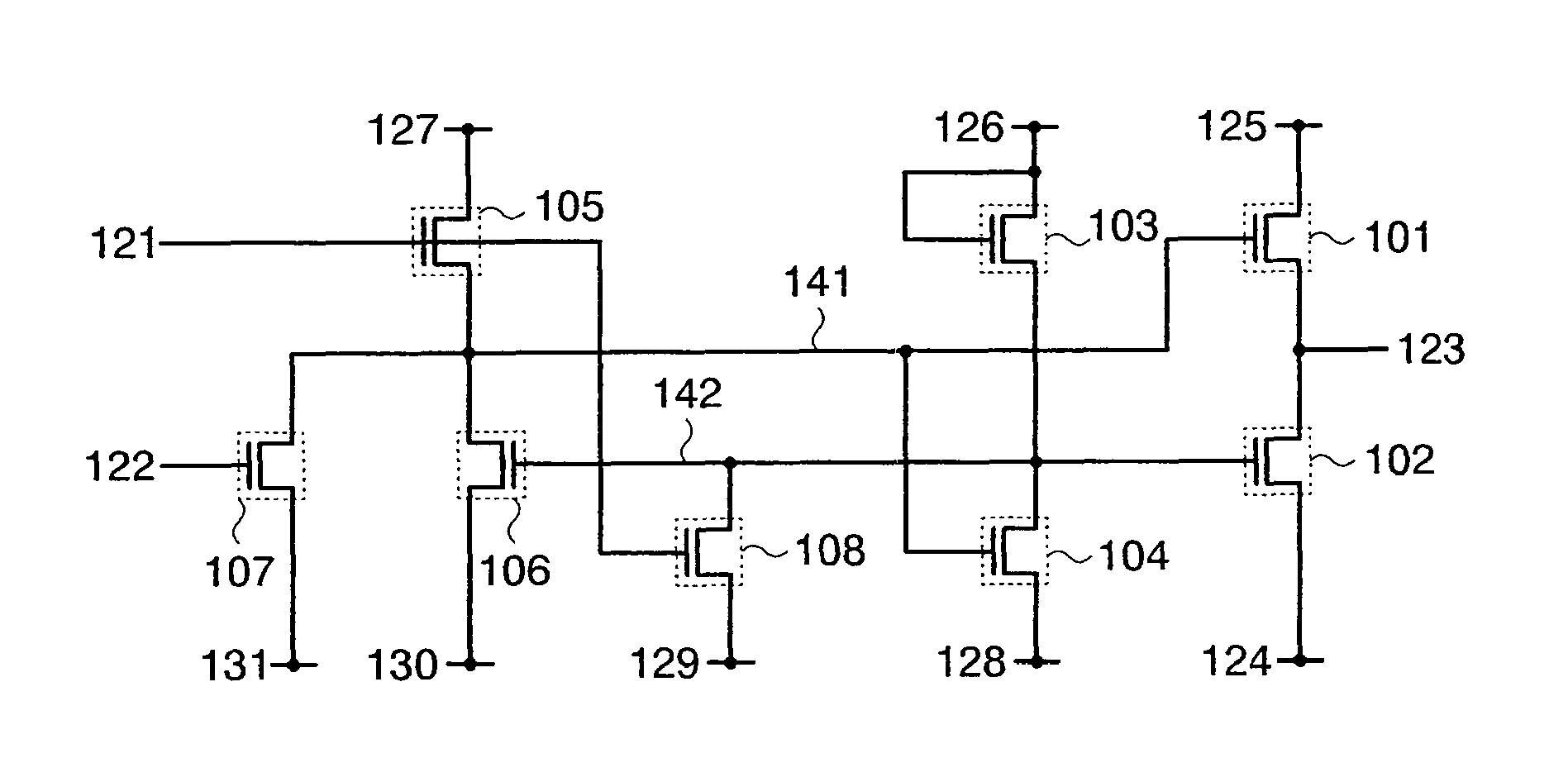

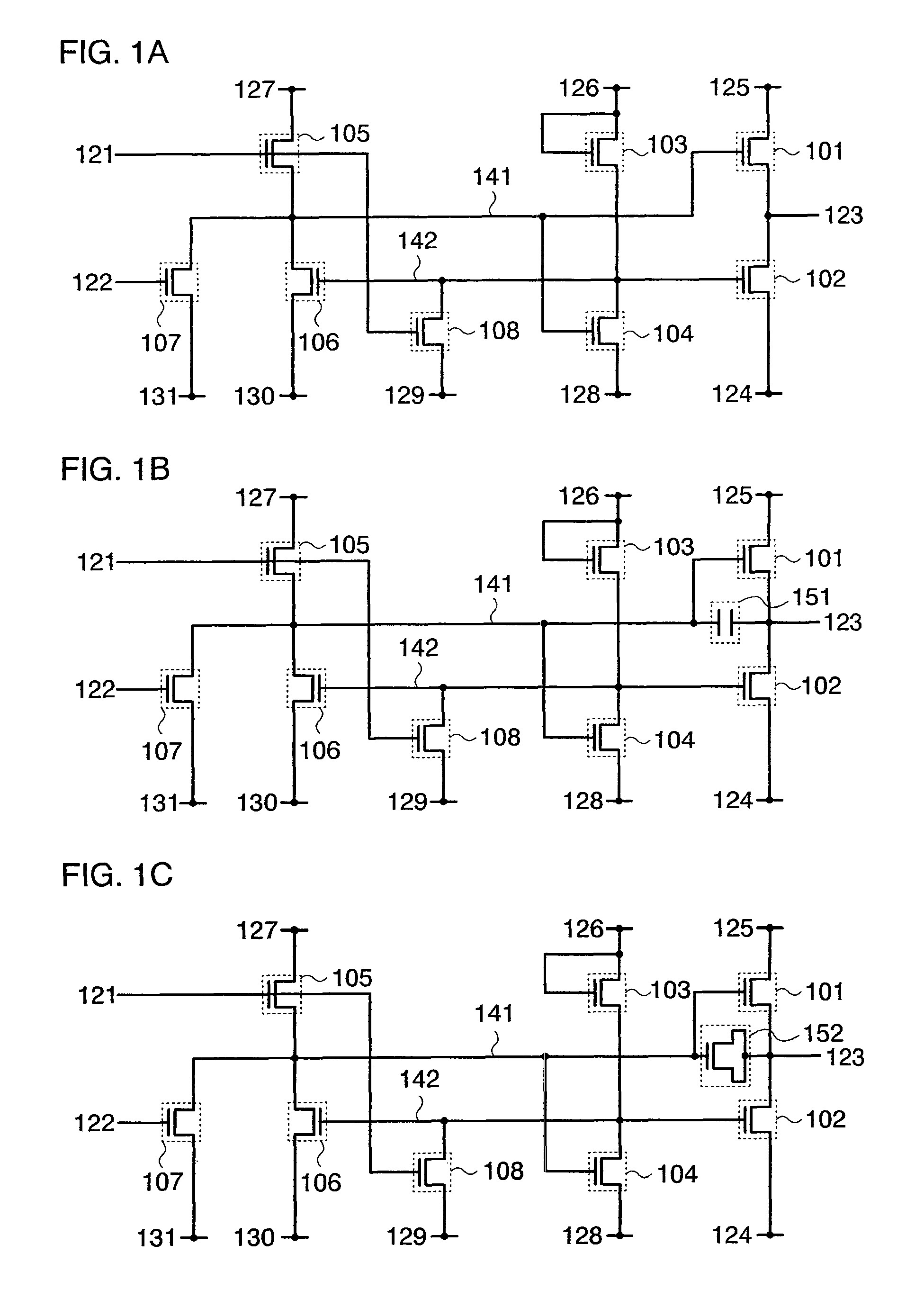

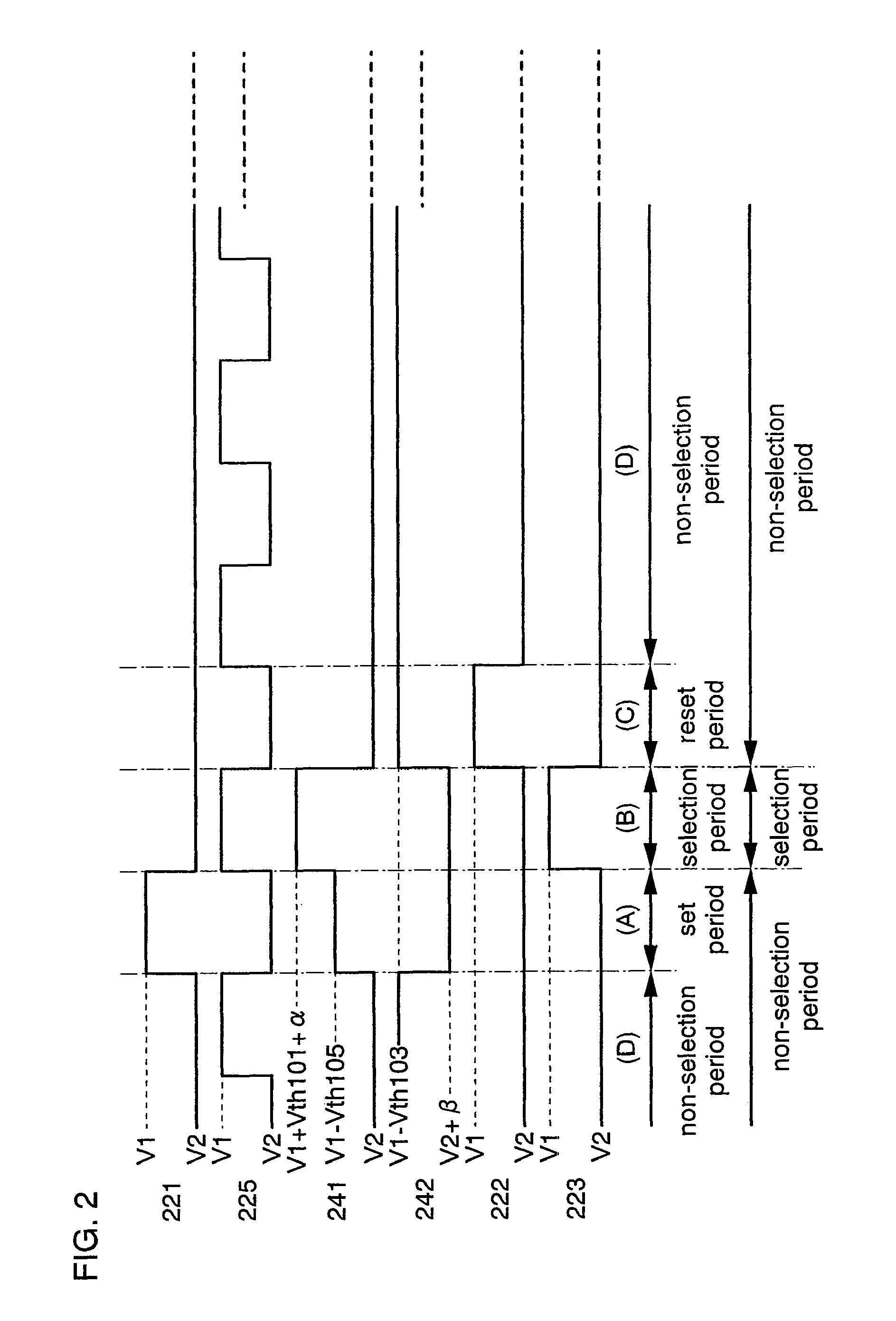

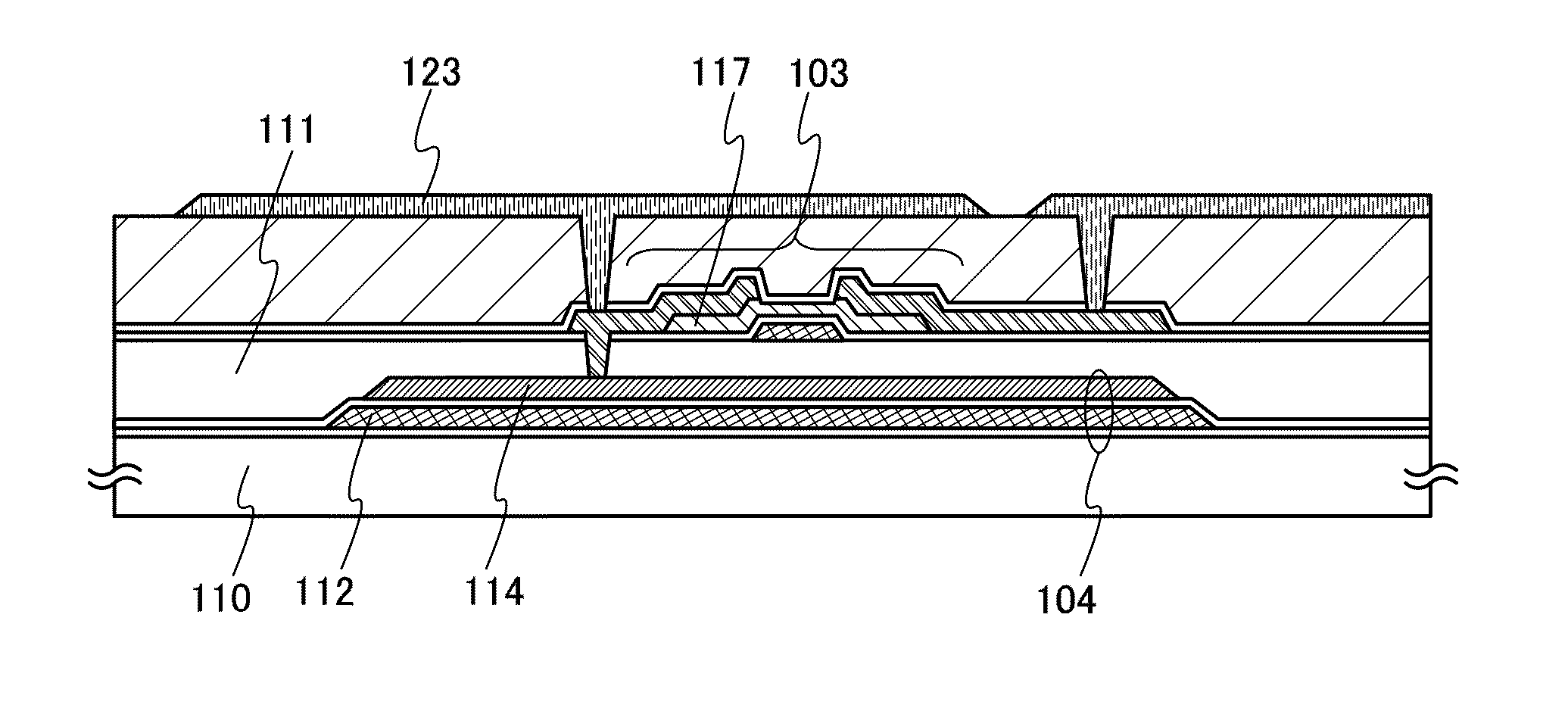

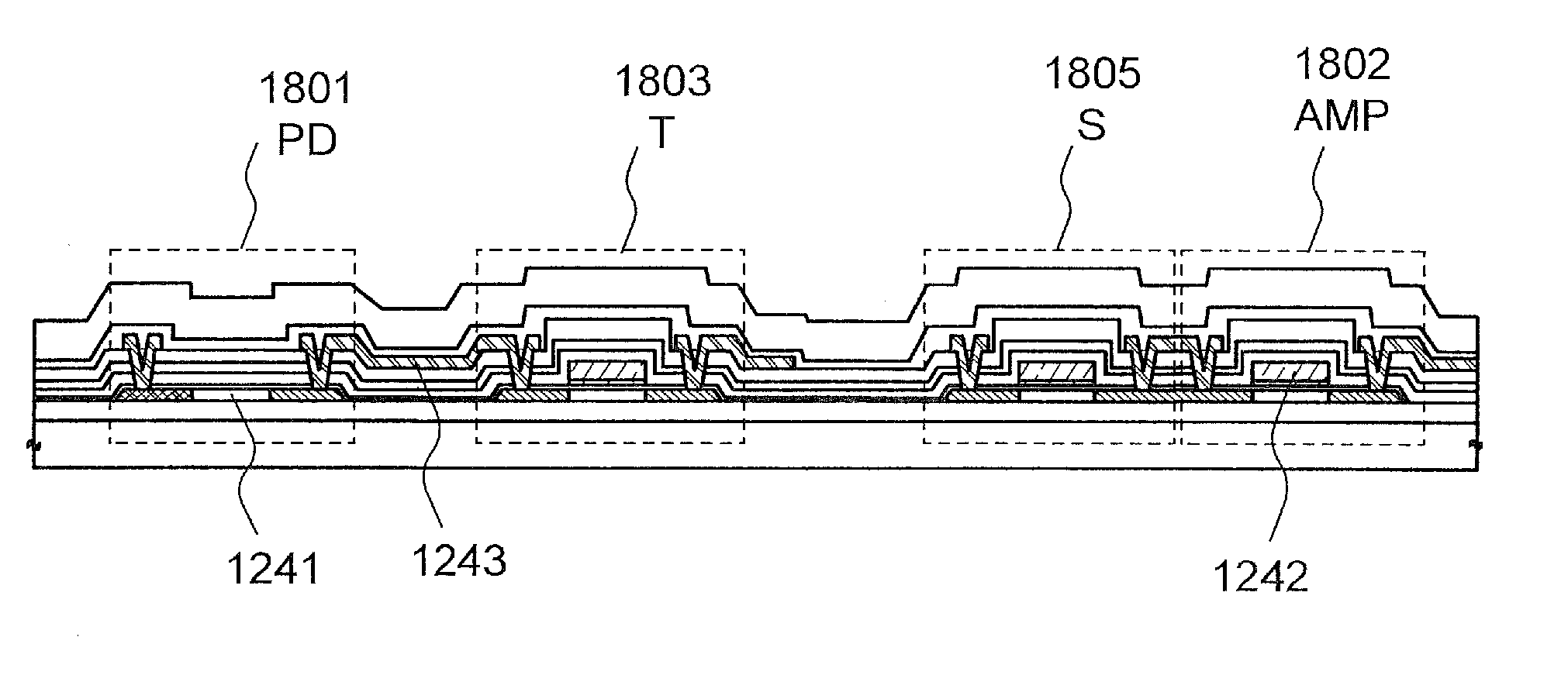

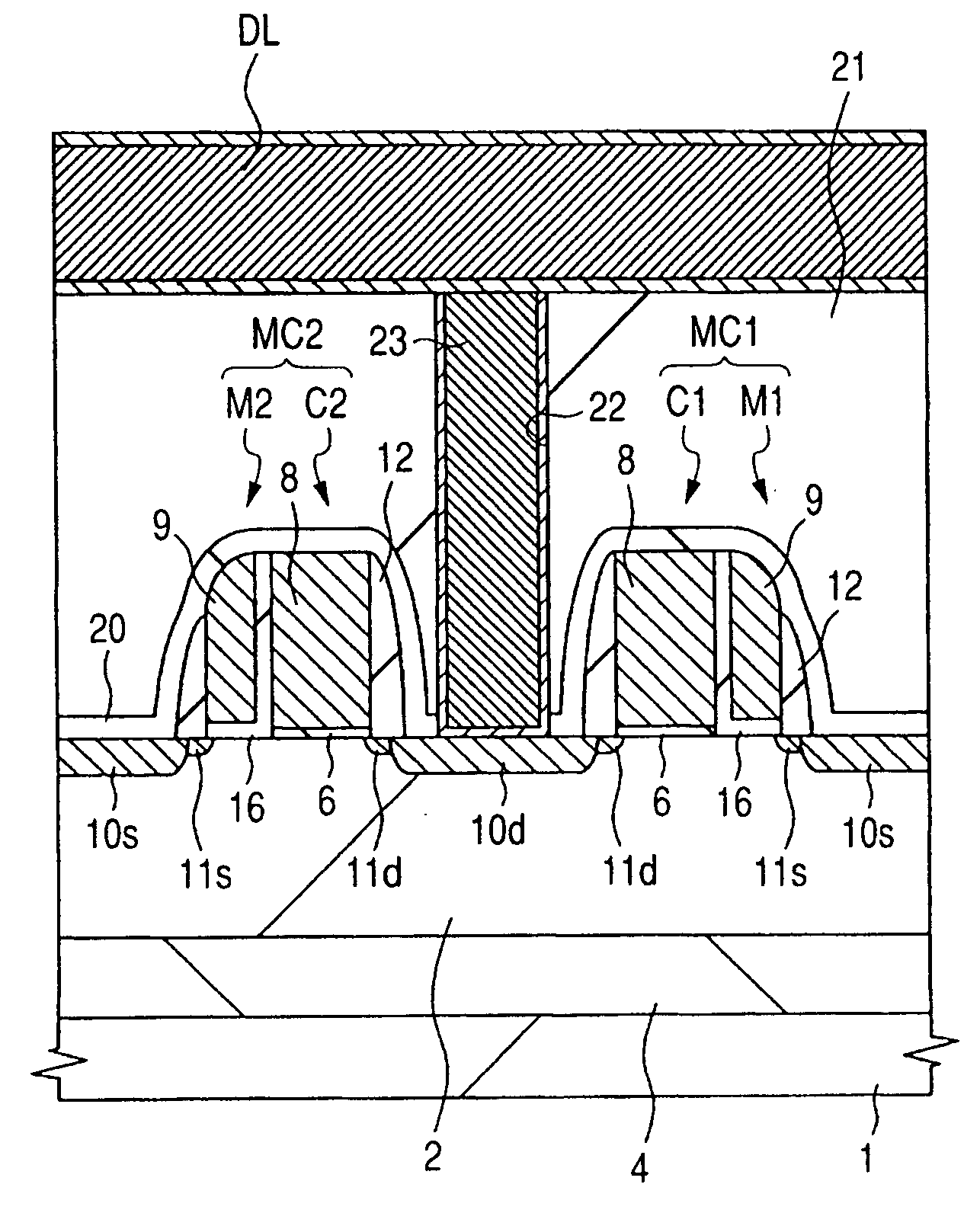

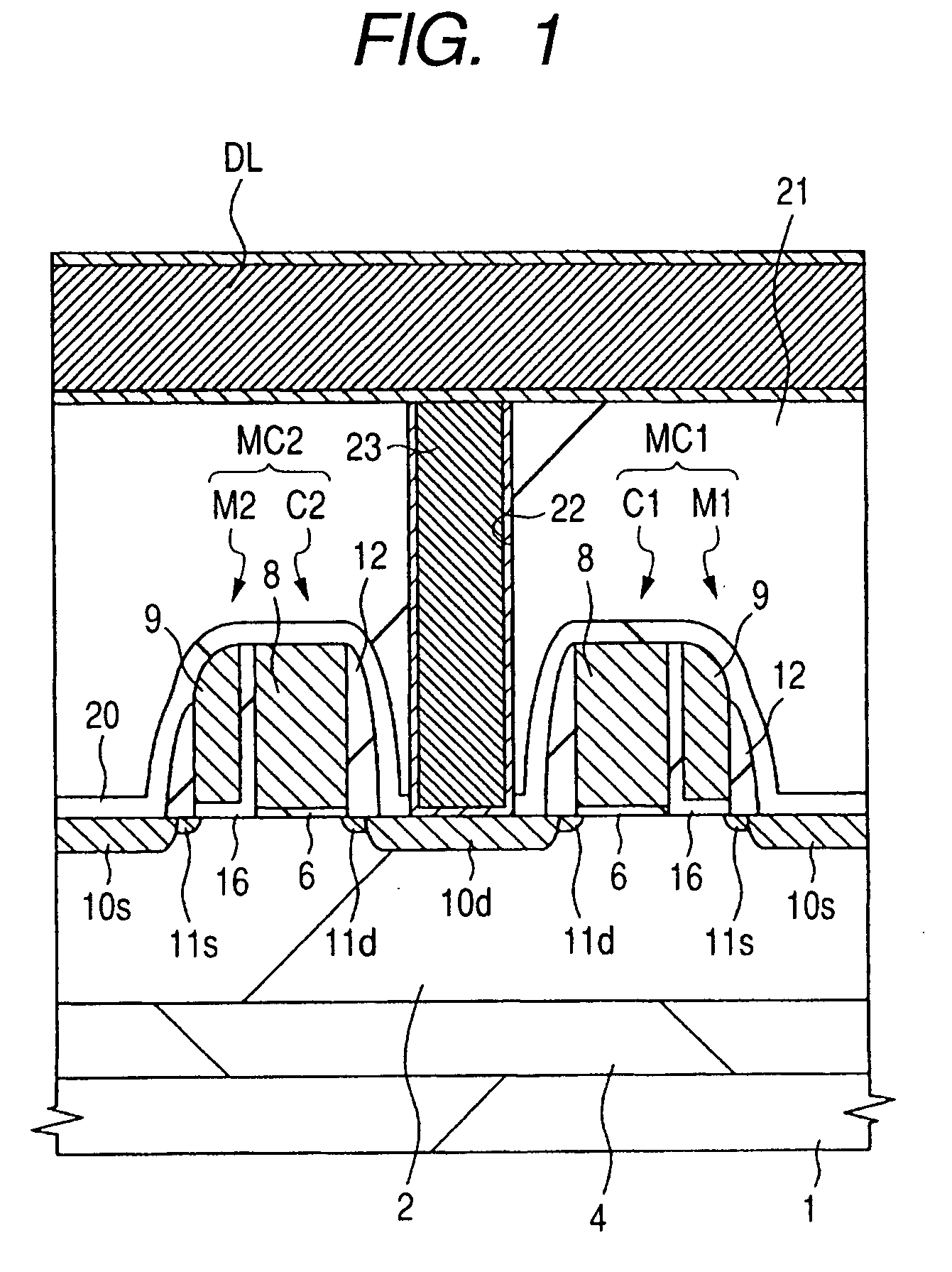

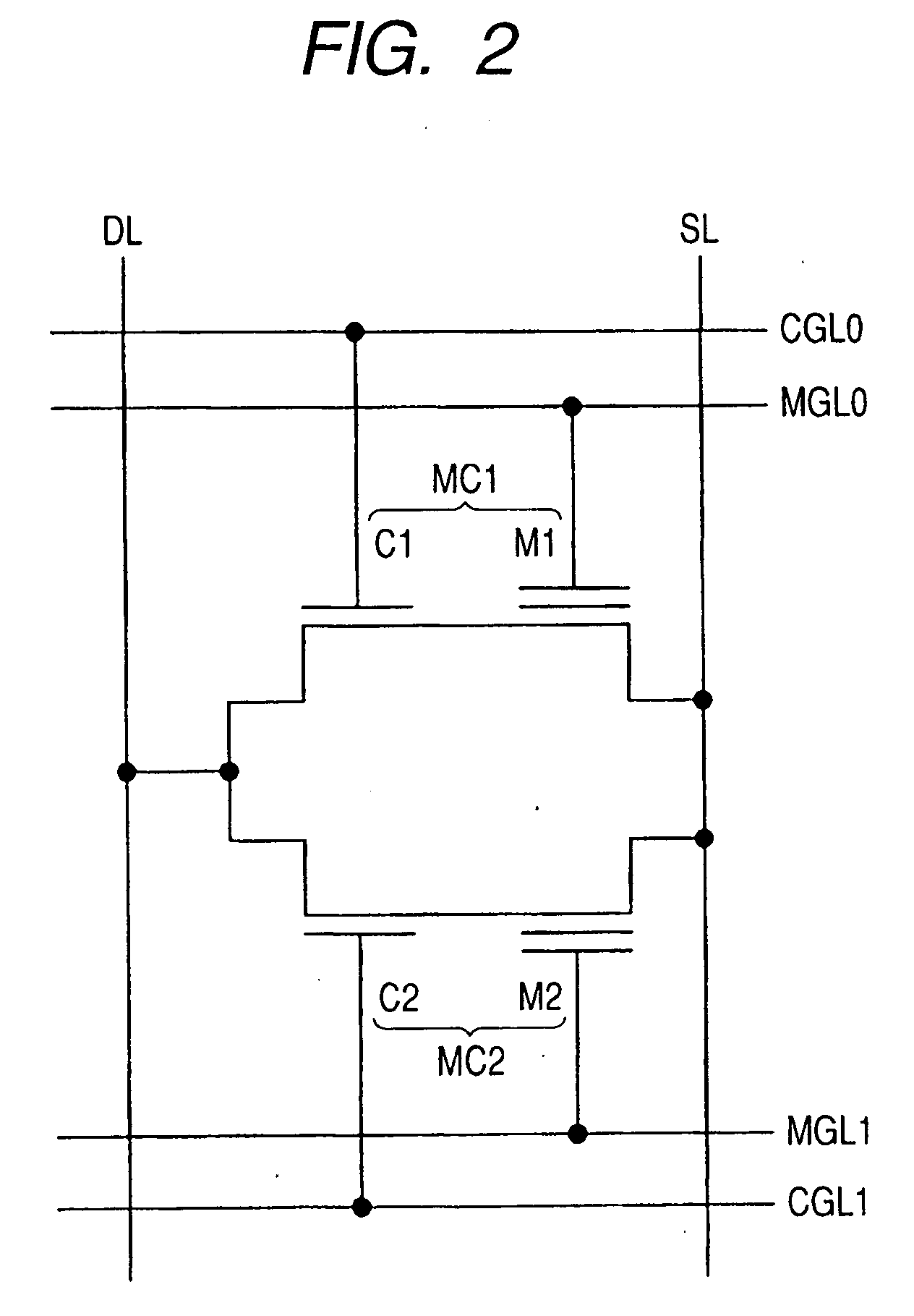

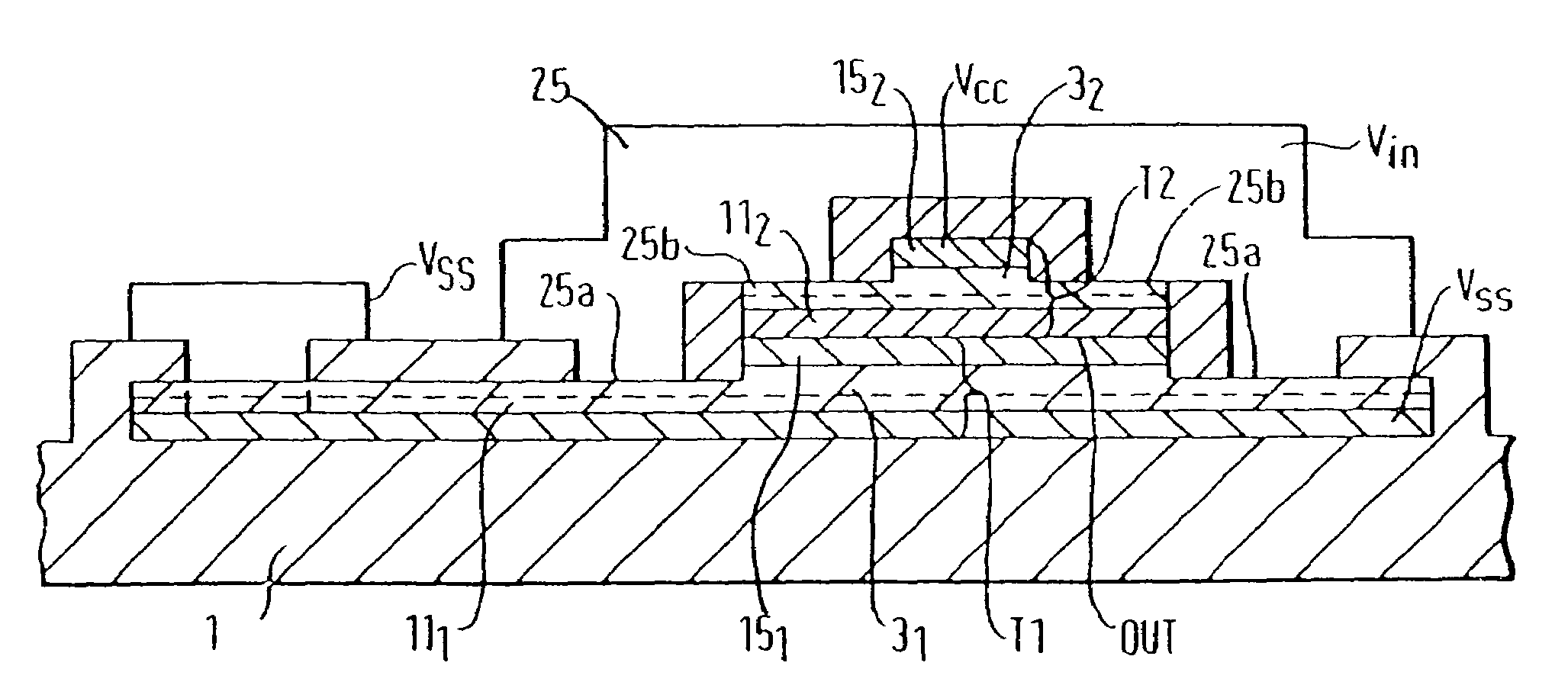

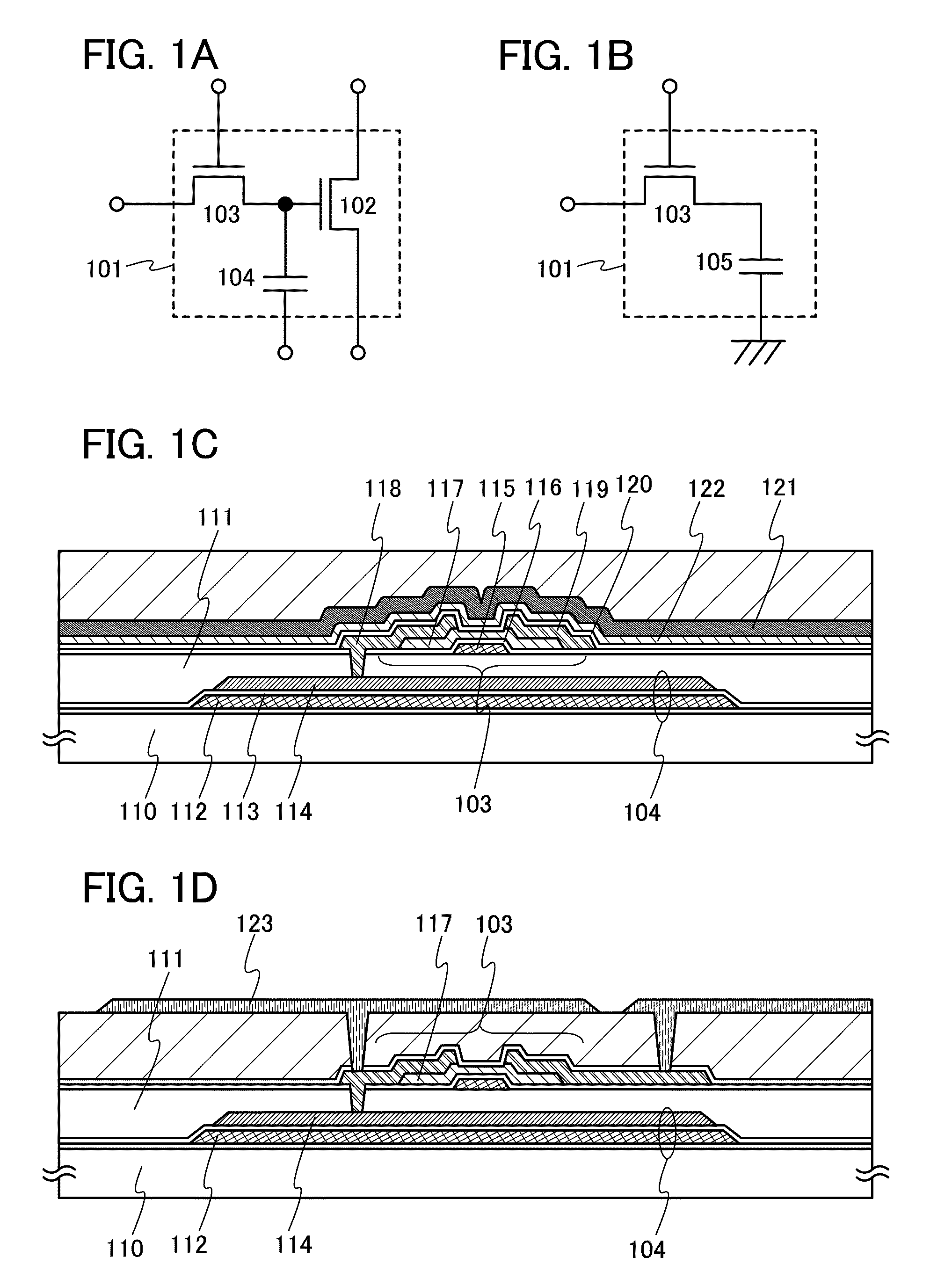

Display device and electronic device

ActiveUS20080079001A1Increase speedRun at high speedStatic indicating devicesSolid-state devicesDisplay deviceHigh definition

An object of the invention is to provide a circuit technique which enables reduction in power consumption and high definition of a display device. A switch controlled by a start signal is provided to a gate electrode of a transistor, which is connected to a gate electrode of a bootstrap transistor. When the start signal is input, a potential is supplied to the gate electrode of the transistor through the switch, and the transistor is turned off. The transistor is turned off, so that leakage of a charge from the gate electrode of the bootstrap transistor can be prevented. Accordingly, time for storing a charge in the gate electrode of the bootstrap transistor can be shortened, and high-speed operation can be performed.

Owner:SEMICON ENERGY LAB CO LTD

Display device and electronic device

InactiveUS7978274B2Prevent charge leakageShorten the timeStatic indicating devicesSolid-state devicesDisplay deviceHigh definition

An object of the invention is to provide a circuit technique which enables reduction in power consumption and high definition of a display device. A switch controlled by a start signal is provided to a gate electrode of a transistor, which is connected to a gate electrode of a bootstrap transistor. When the start signal is input, a potential is supplied to the gate electrode of the transistor through the switch, and the transistor is turned off. The transistor is turned off, so that leakage of a charge from the gate electrode of the bootstrap transistor can be prevented. Accordingly, time for storing a charge in the gate electrode of the bootstrap transistor can be shortened, and high-speed operation can be performed.

Owner:SEMICON ENERGY LAB CO LTD

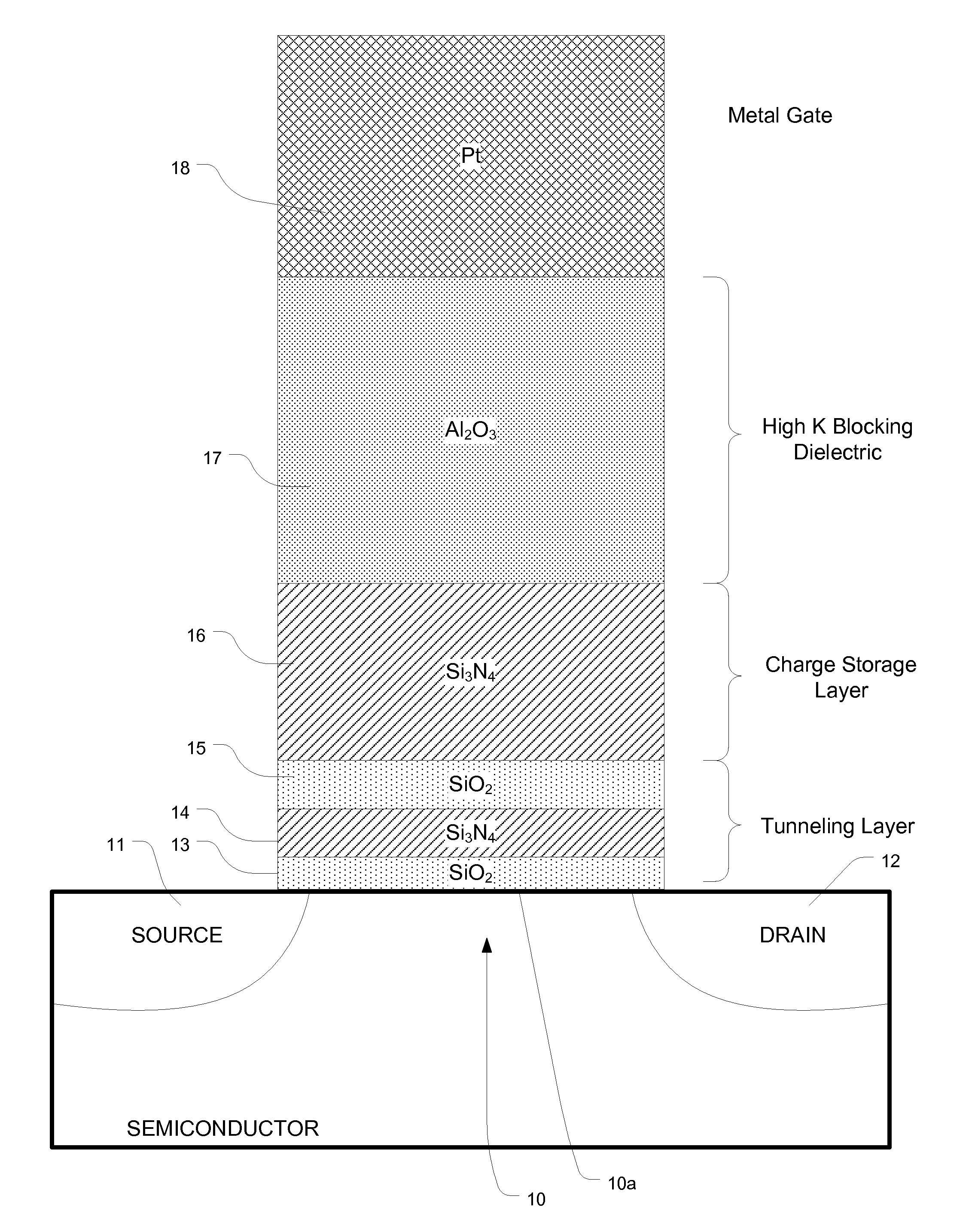

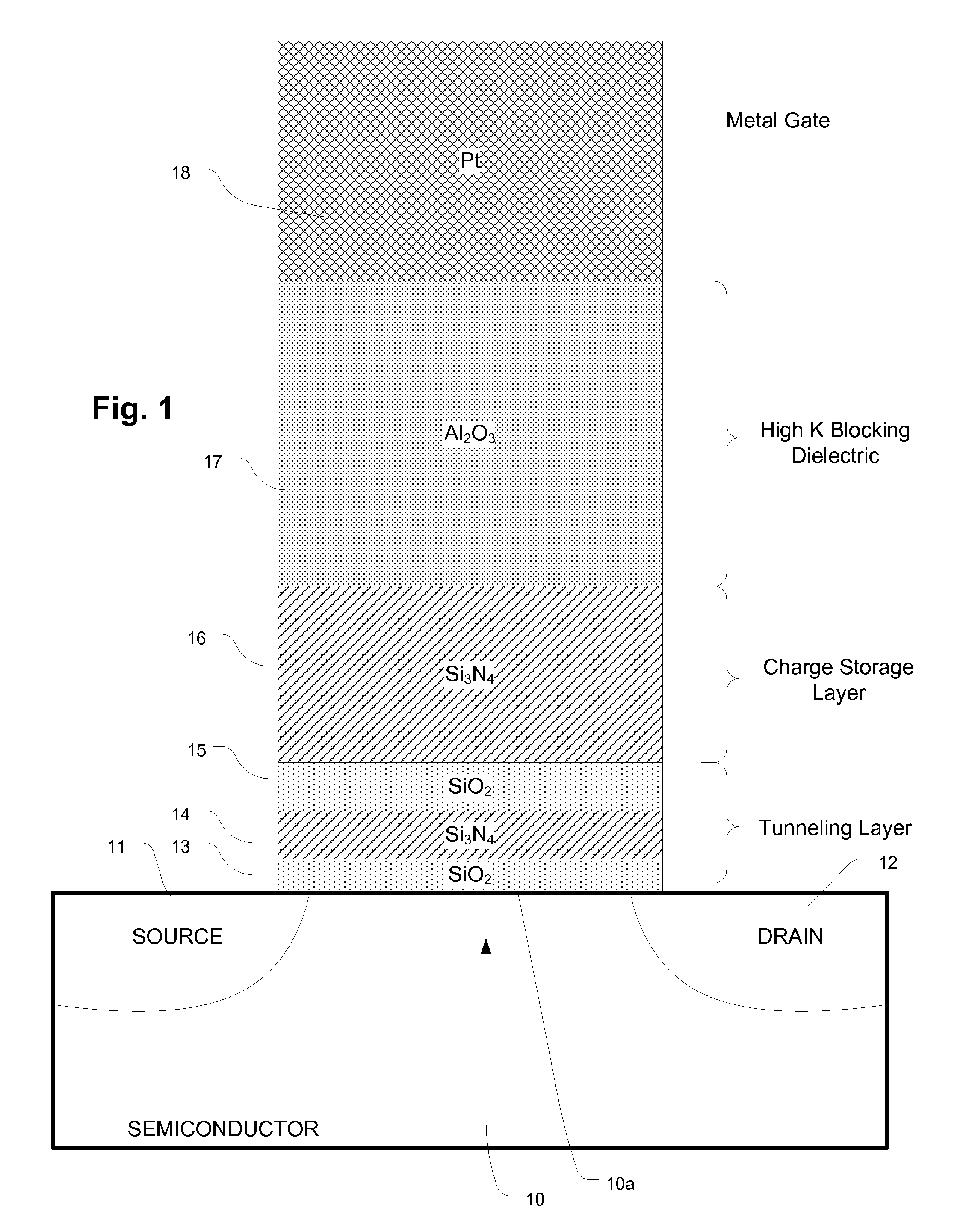

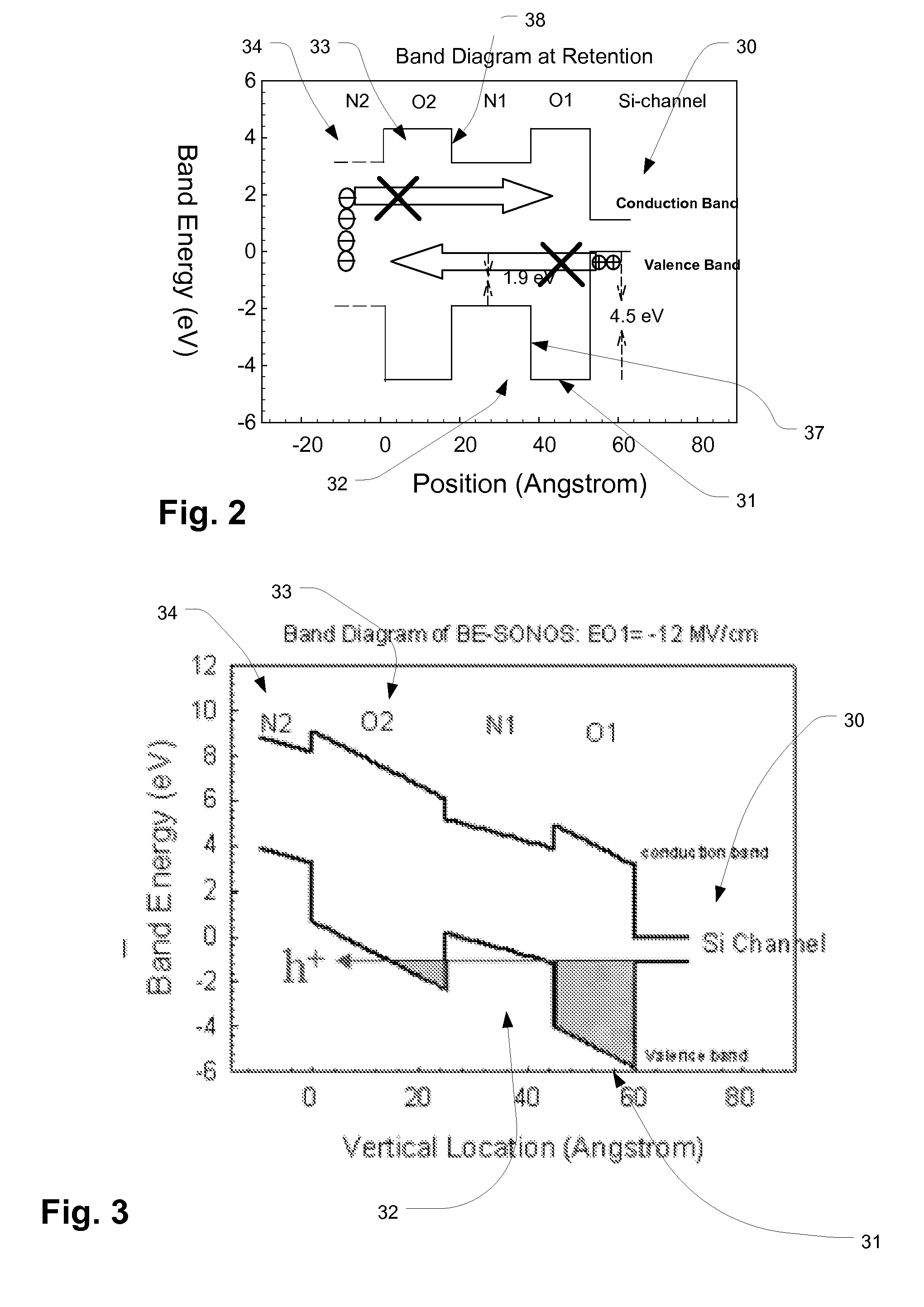

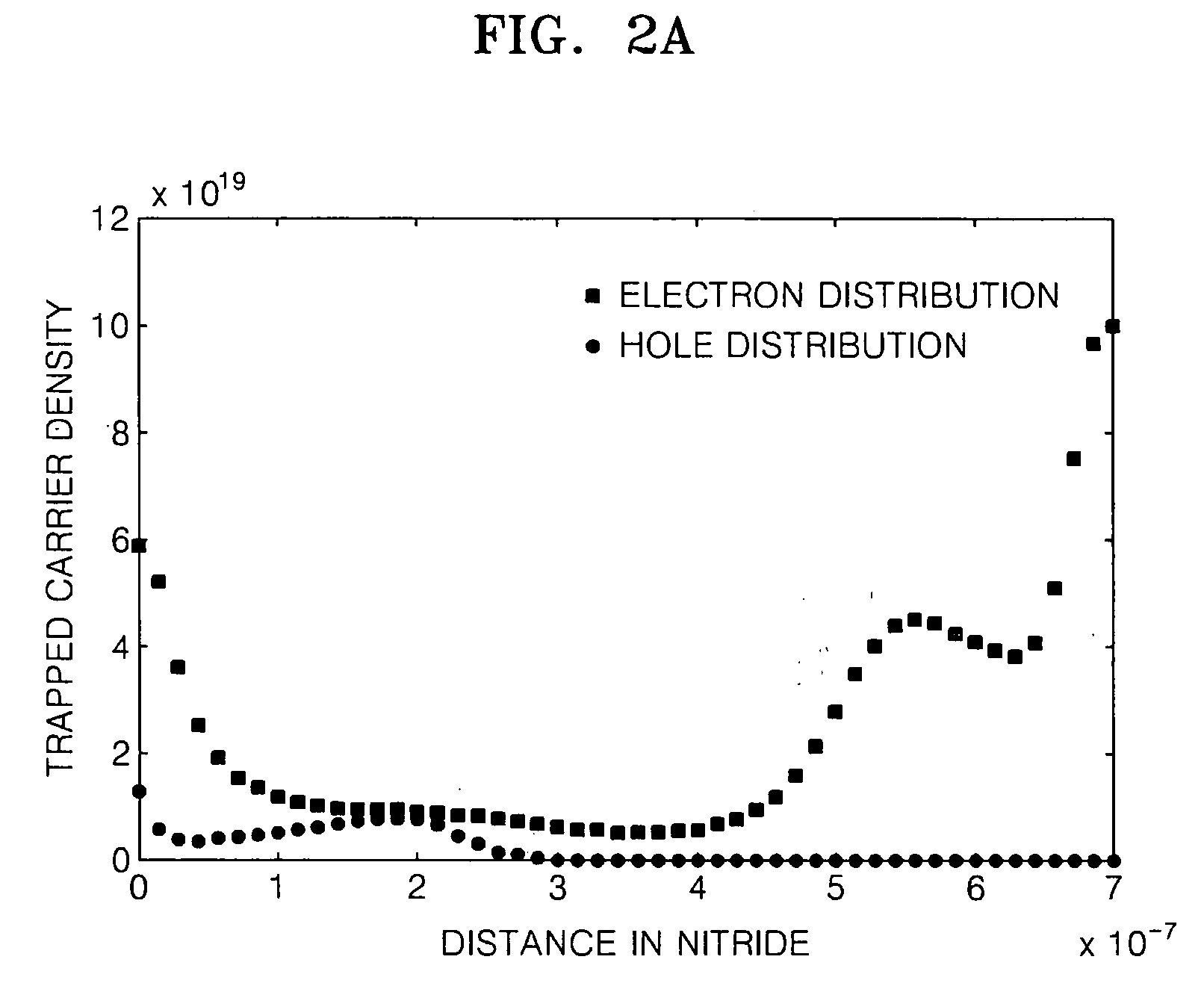

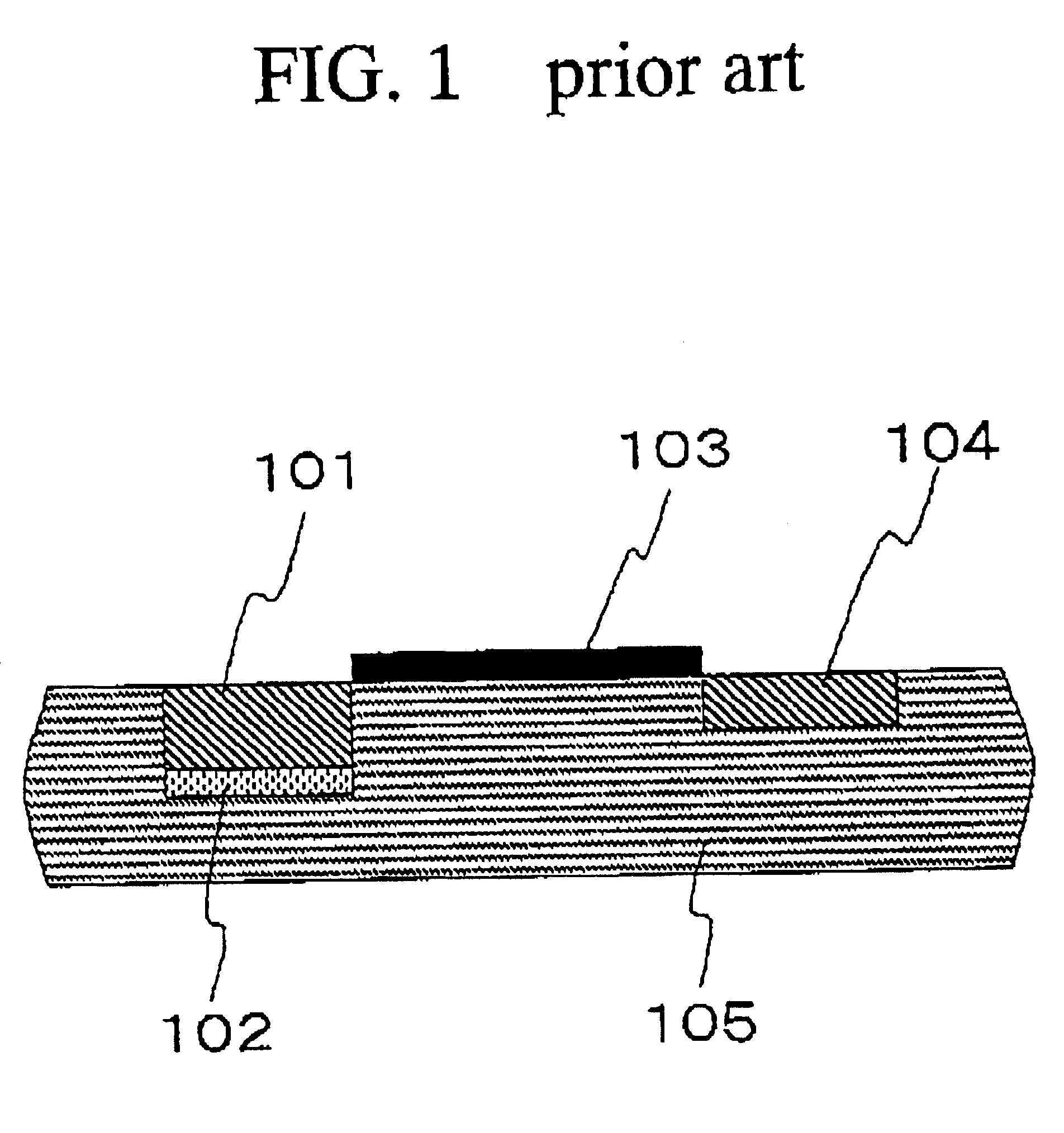

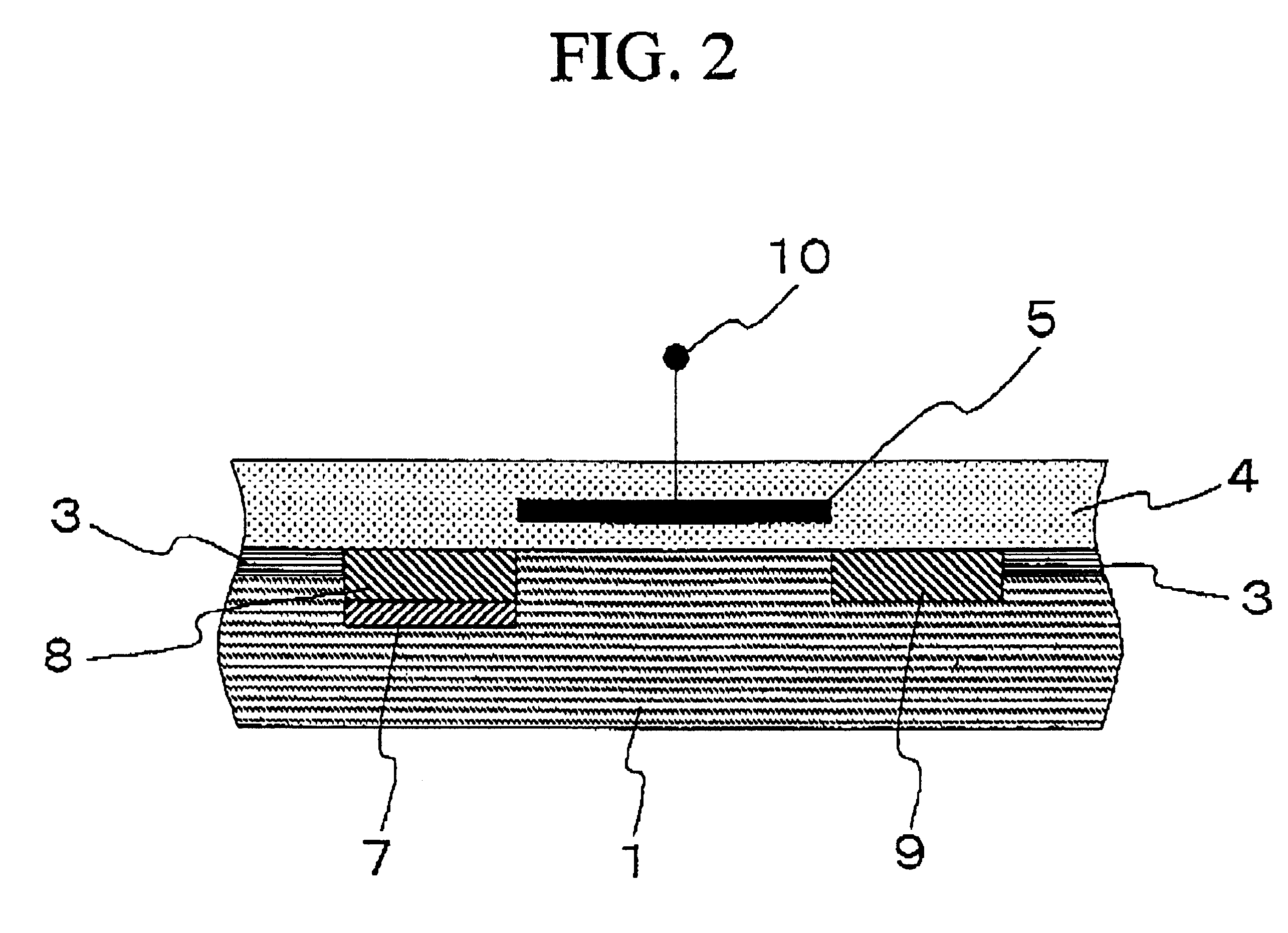

Charge trapping memory cell with high speed erase

InactiveUS20090039414A1Eliminates hole tunneling barrierEffectively preventing charge leakageSolid-state devicesRead-only memoriesDielectricTrapping

A band gap engineered, charge trapping memory cell includes a charge trapping element that is separated from a metal or metal compound gate, such as a platinum gate, by a blocking layer of material having a high dielectric constant, such as aluminum oxide, and separated from the semiconductor body including the channel by an engineered tunneling dielectric. Fast program and erase speeds with memory window as great as 7 V are achieved.

Owner:MACRONIX INT CO LTD

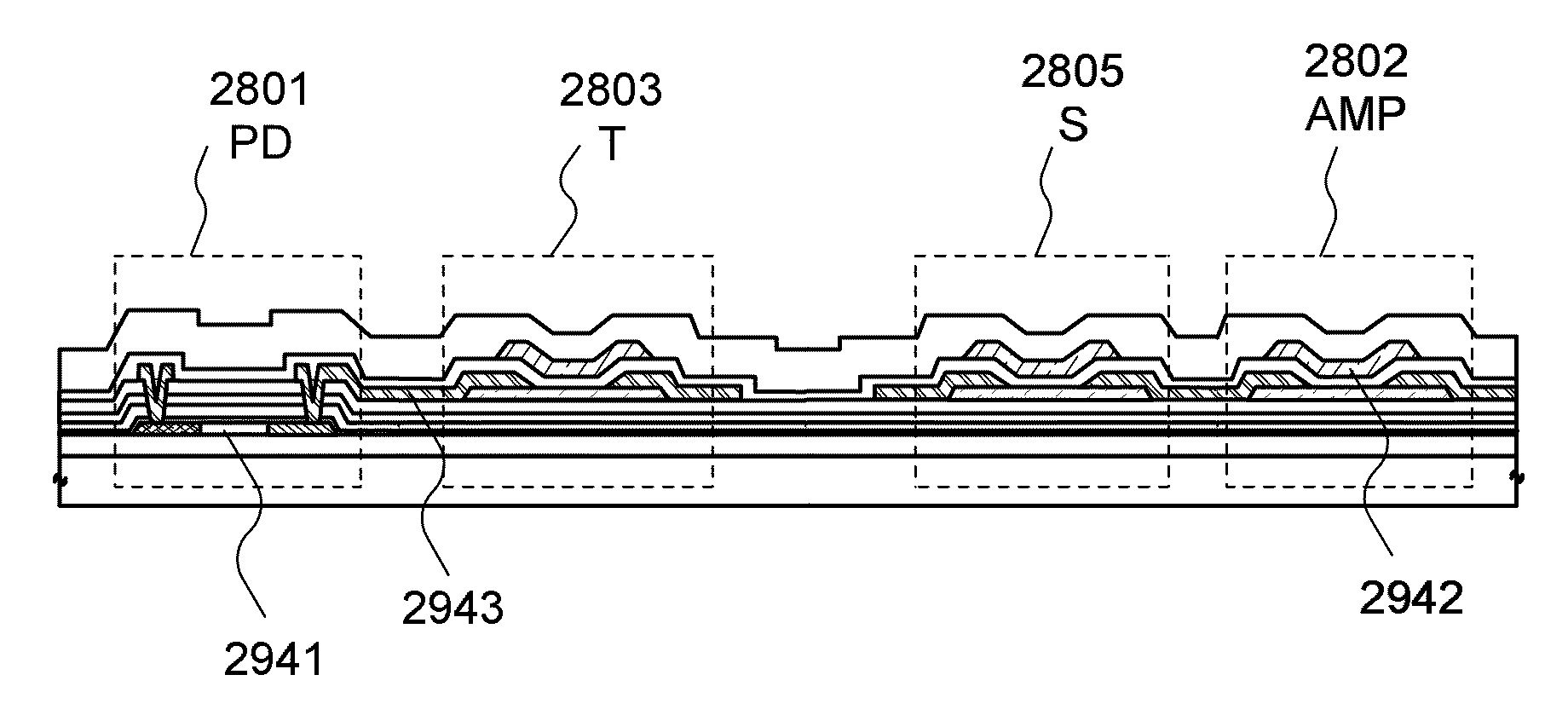

Semiconductor device and manufacturing method thereof

In a CMOS image sensor in which a plurality of pixels is arranged in a matrix, a transistor in which a channel formation region includes an oxide semiconductor is used for each of a charge accumulation control transistor and a reset transistor which are in a pixel portion. After a reset operation of the signal charge accumulation portion is performed in all the pixels arranged in the matrix, a charge accumulation operation by the photodiode is performed in all the pixels, and a read operation of a signal from the pixel is performed per row. Accordingly, an image can be taken without a distortion.

Owner:SEMICON ENERGY LAB CO LTD

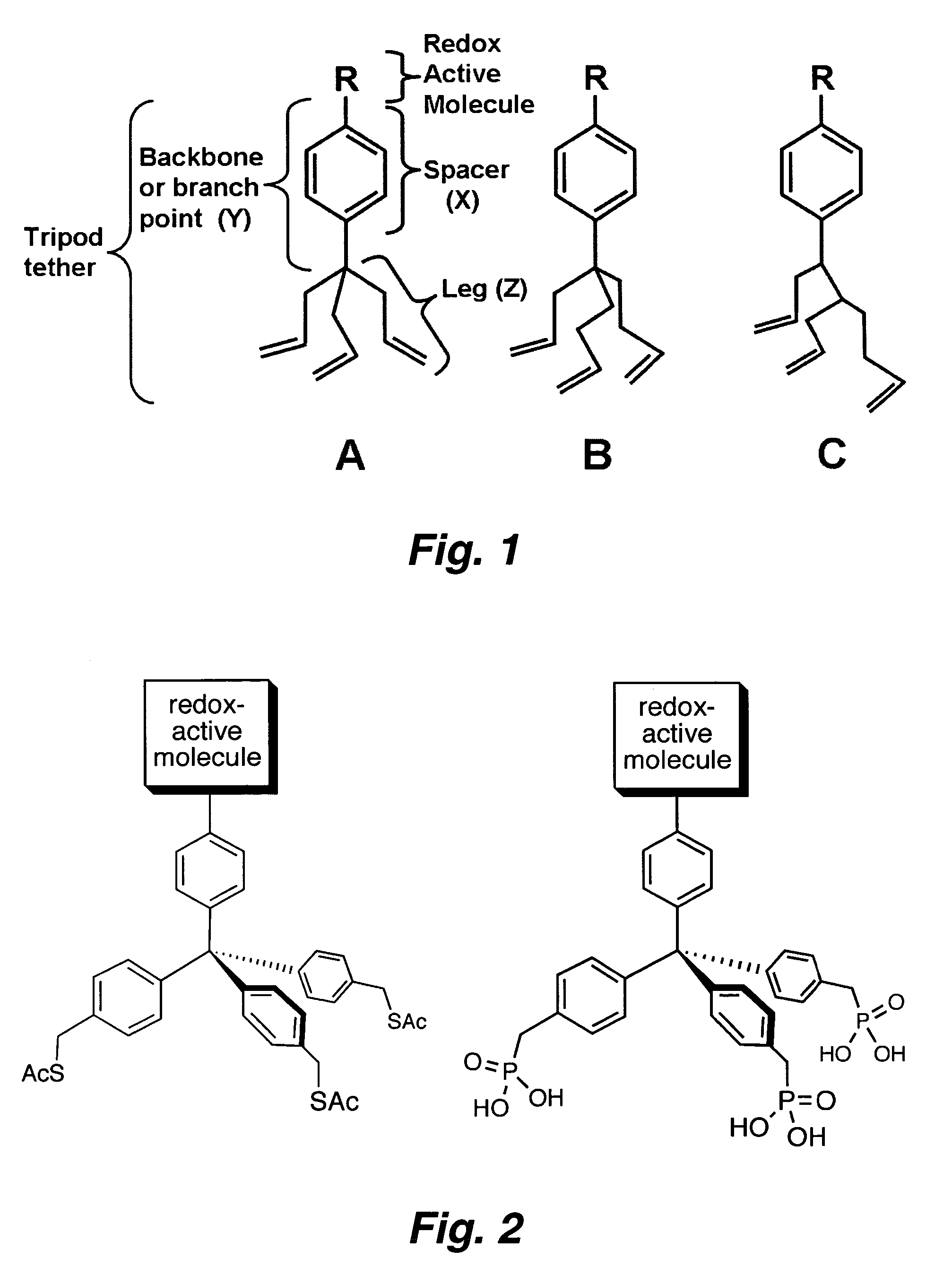

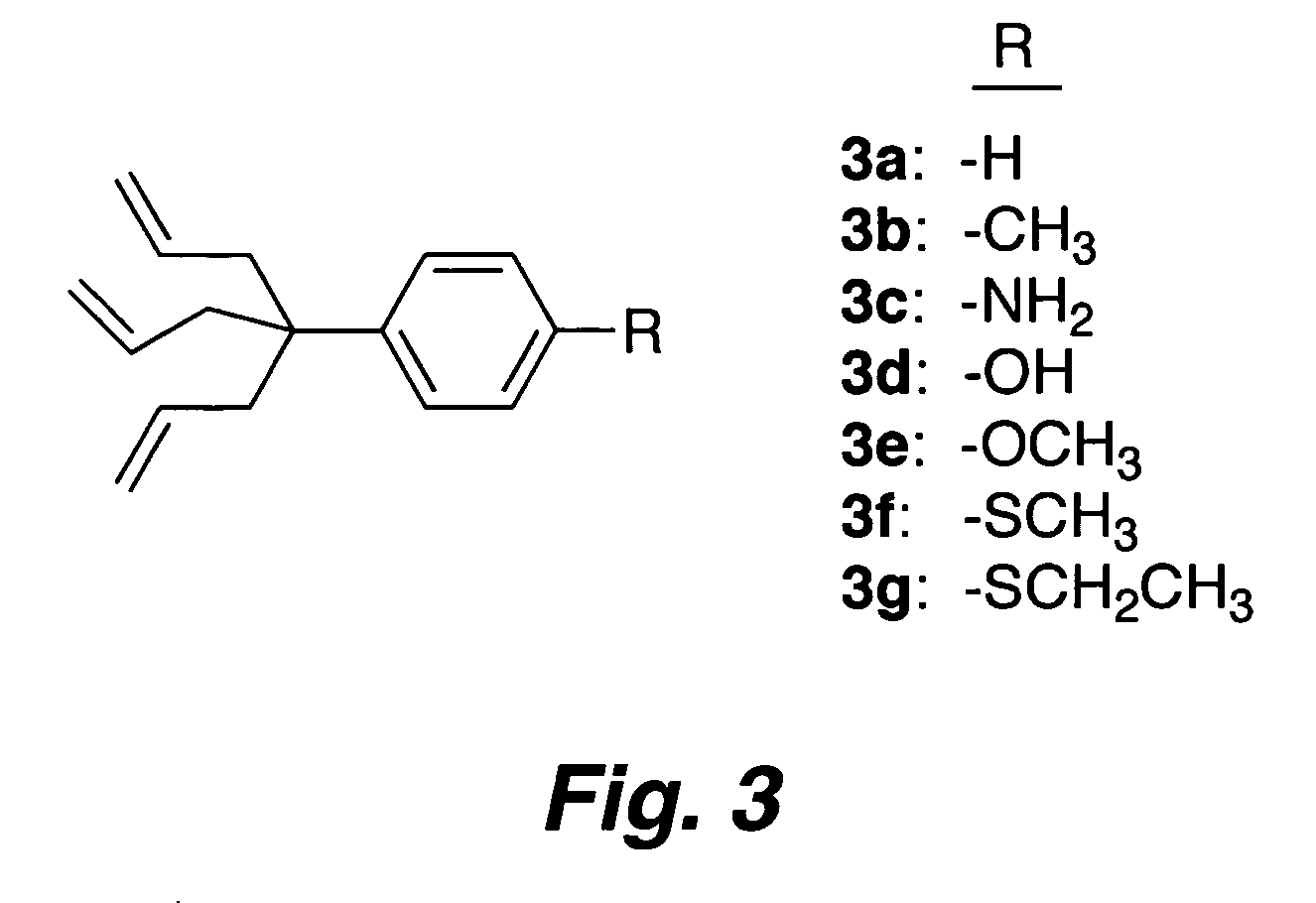

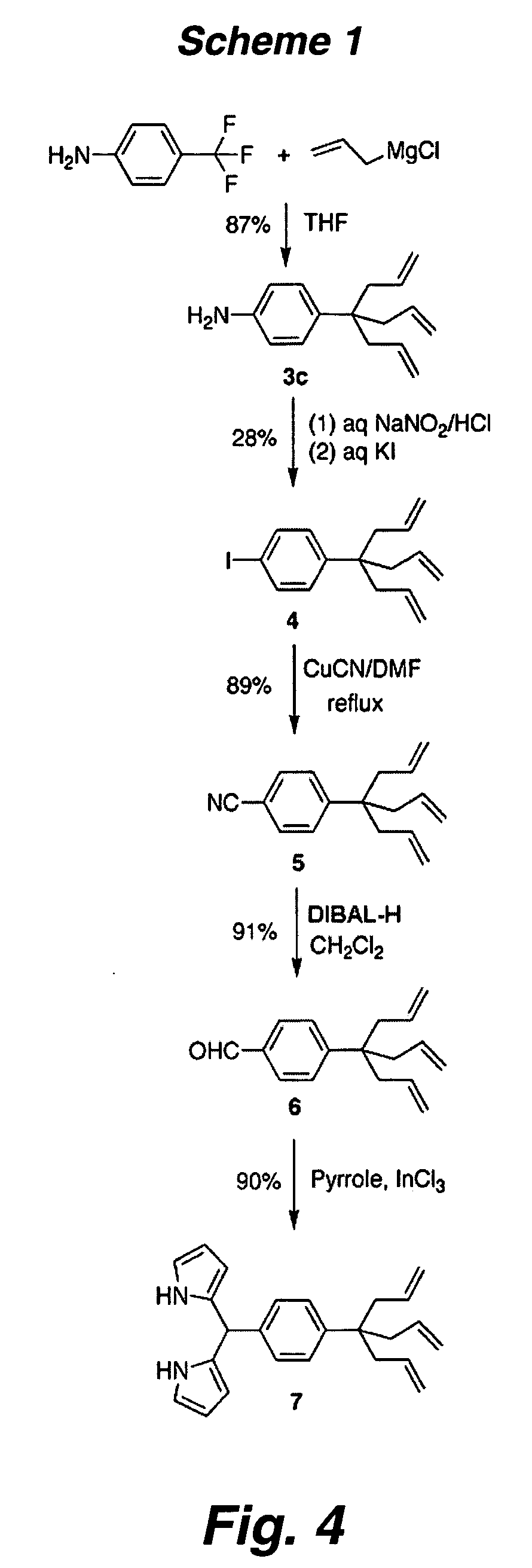

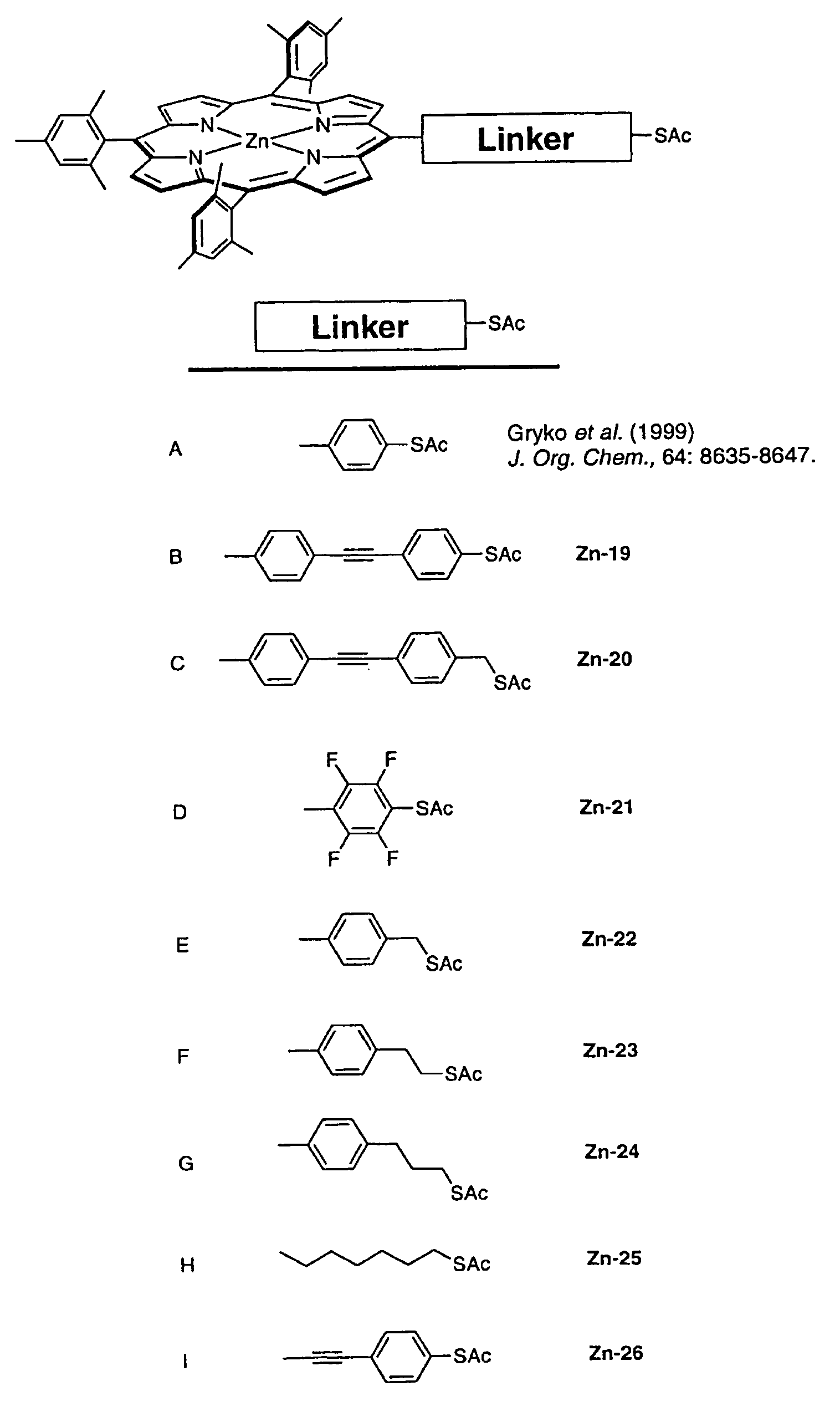

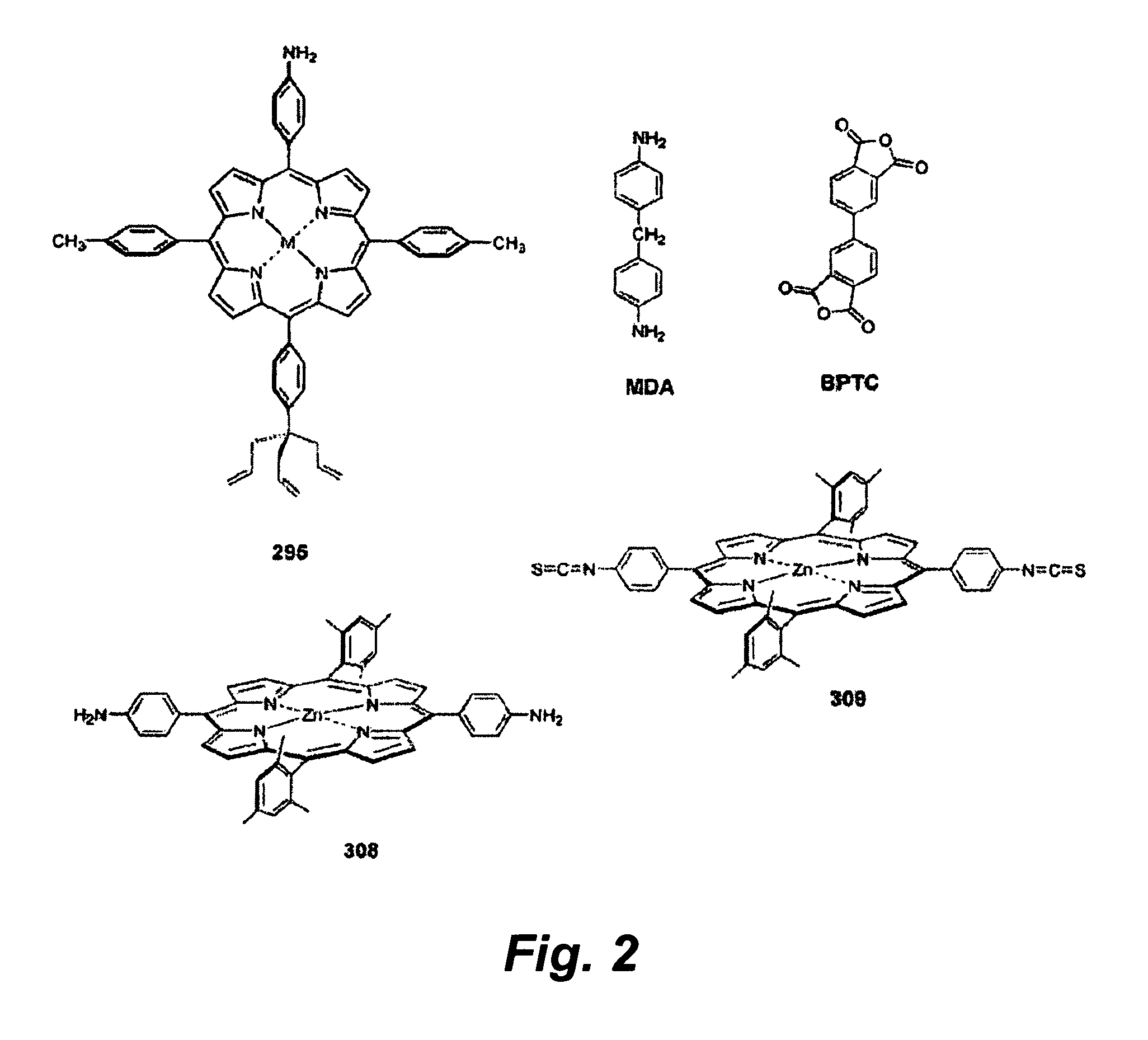

Multypodal tethers for high-density attachment of redox-active moieties to substrates

InactiveUS20070108438A1Increase charge storage densityHigh charge densityMaterial nanotechnologyNanoinformaticsHigh densityCombinatorial chemistry

This invention provides redox-active molecules attached to polypodal (e.g., bipodal, tripodal, quadrapodal, pentapodal, etc.) tethers that can be used for attachment of the redox-active molecules to a substrate (e.g., an electrode). The tethered redox-active molecules are useful for the fabrication of memory devices.

Owner:RGT UNIV OF CALIFORNIA +2

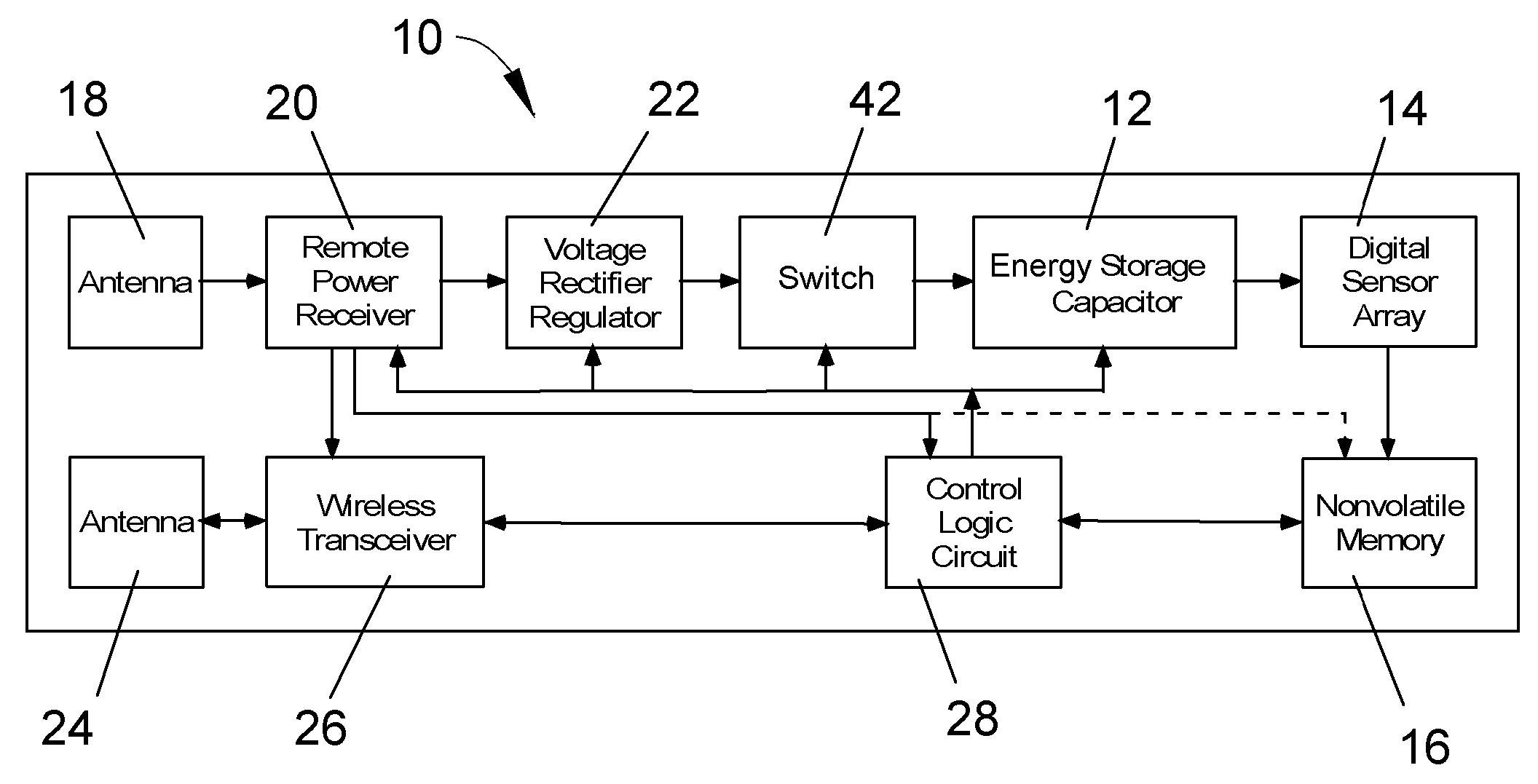

Micro-electro-mechanical module

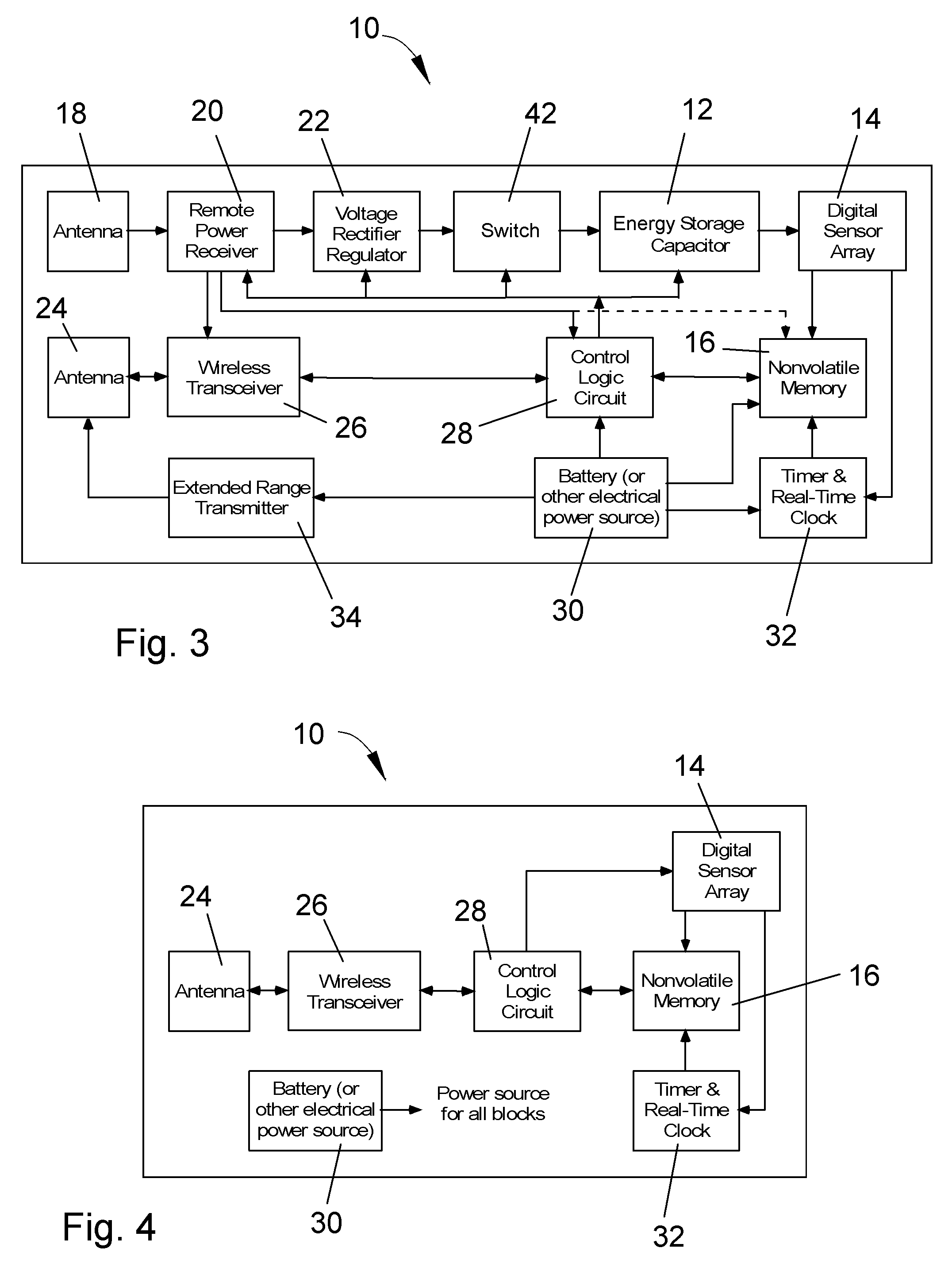

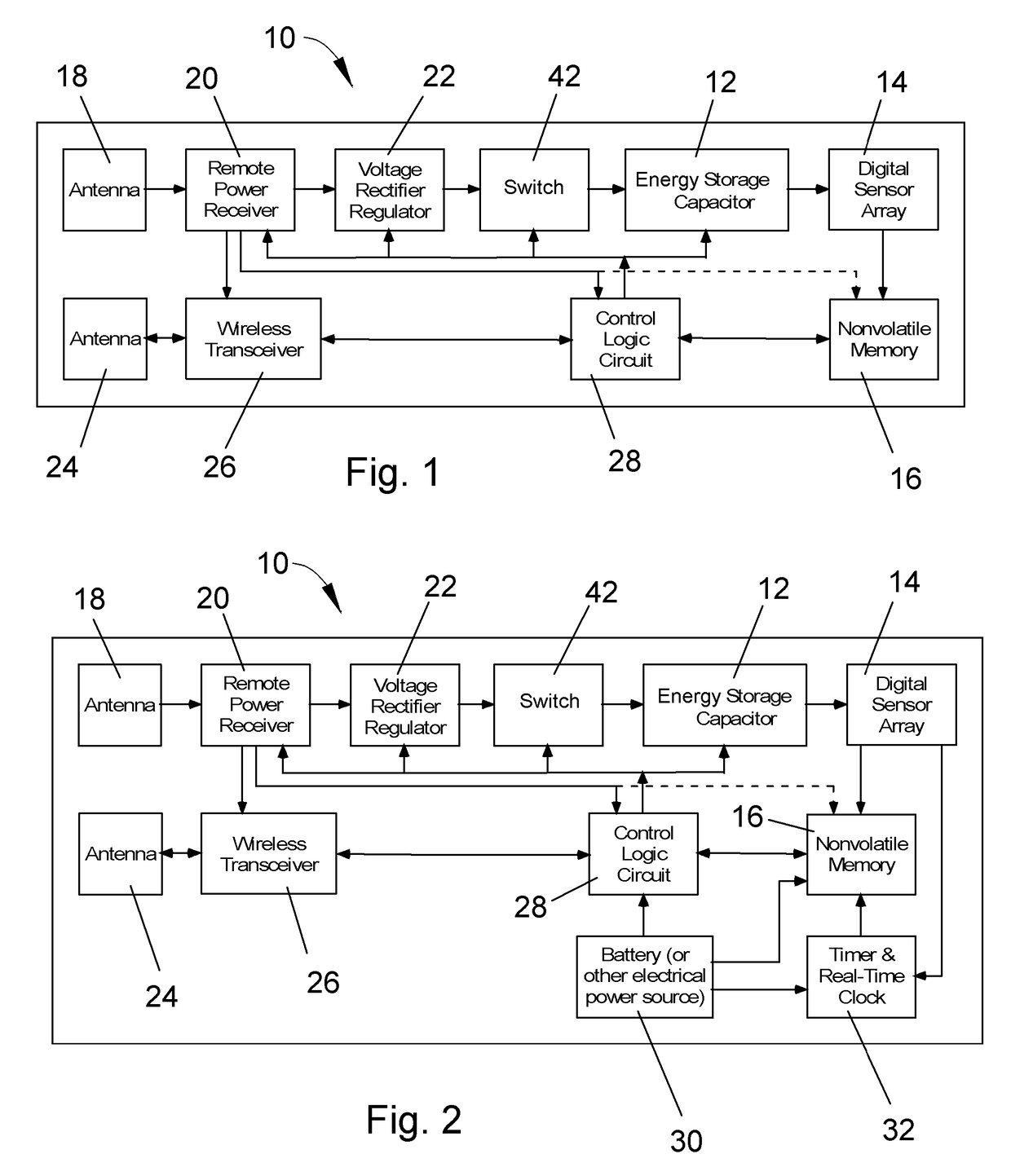

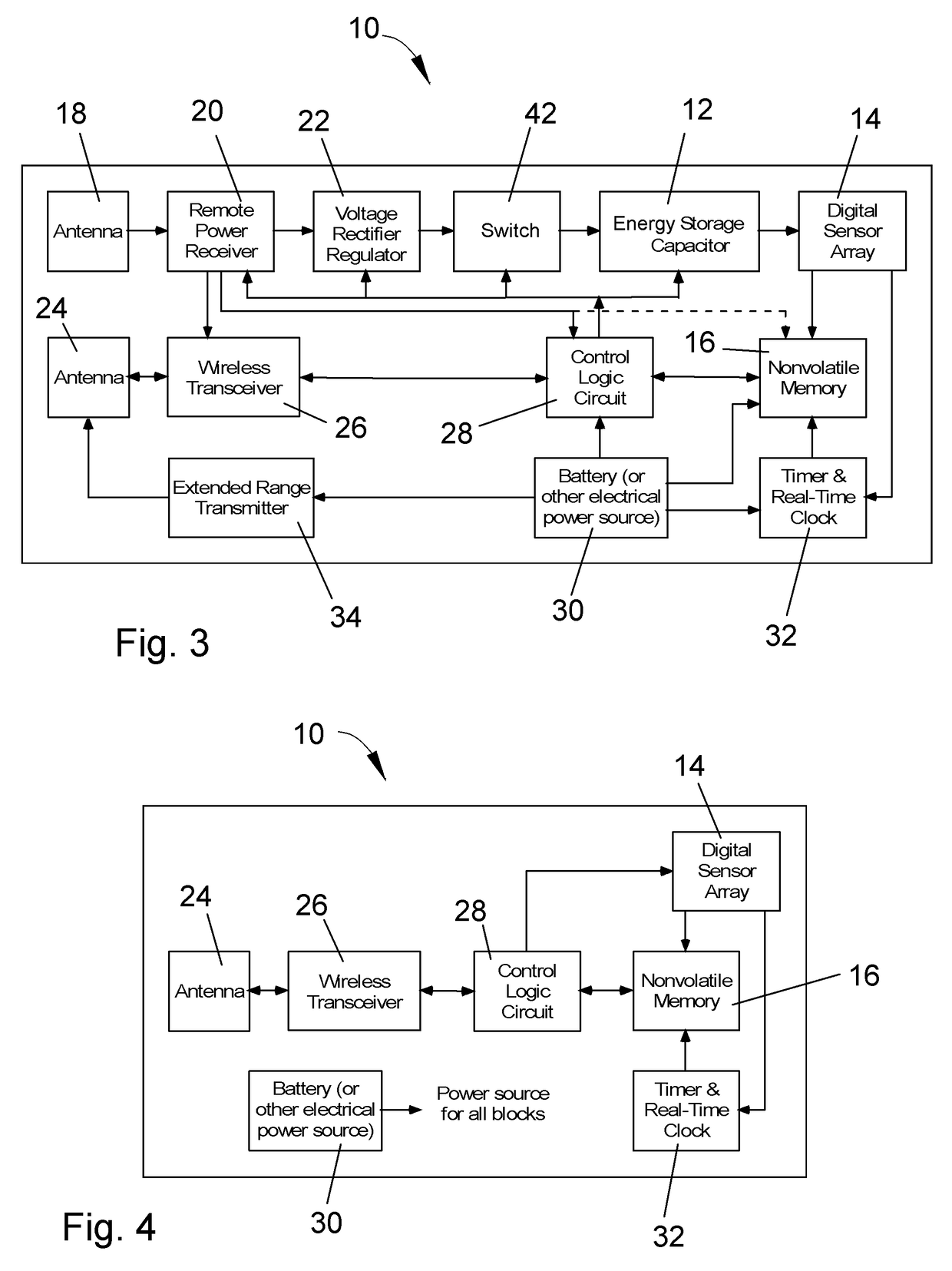

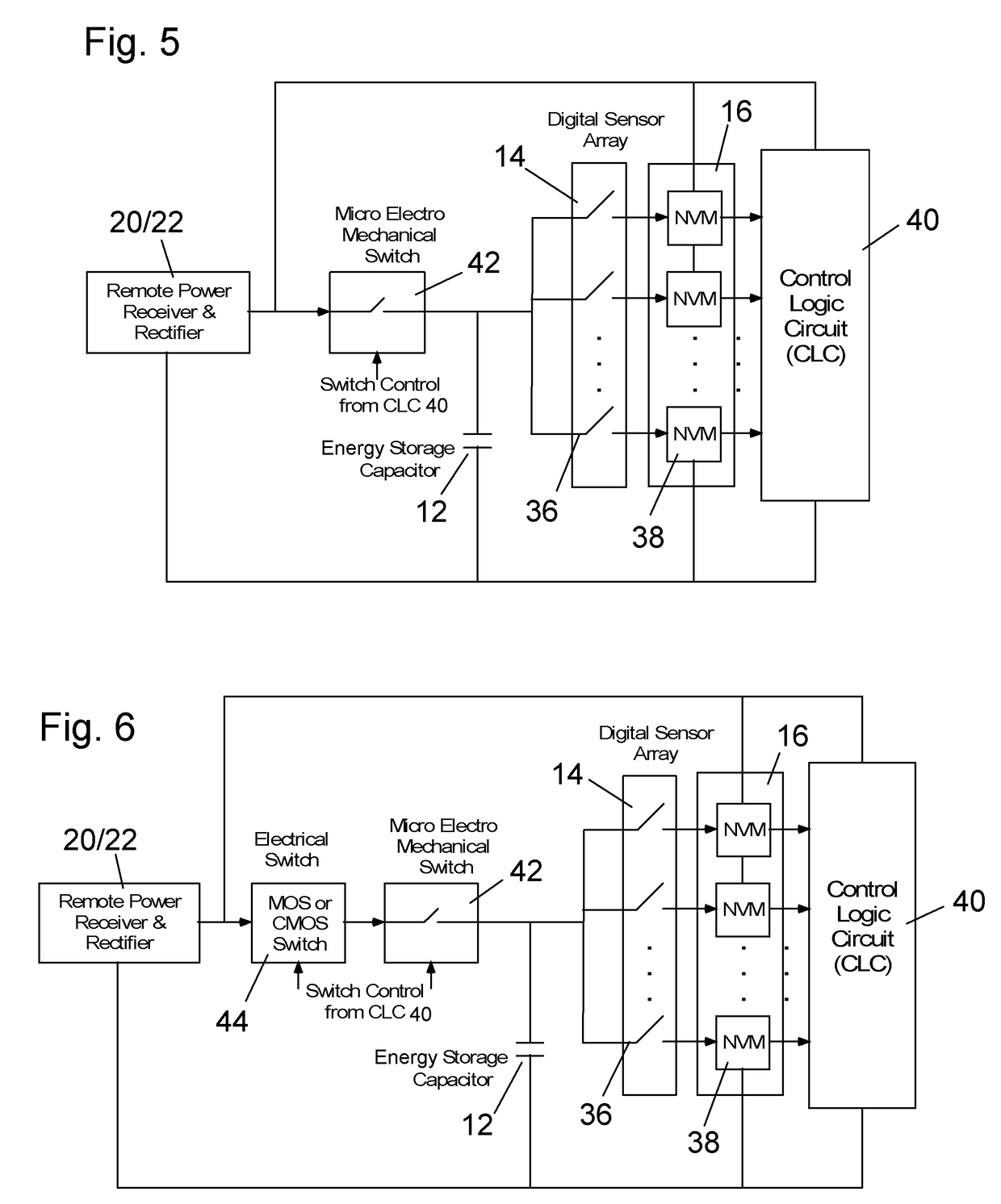

ActiveUS20070273463A1Available powerPrevent charge leakageThermometers using material expansion/contactionThermal micromechanical switchesElectronic circuitDigital memory

A MEMS module that contains at least one integrated energy storage device whose discharge is minimized and controlled, so that power is available for system operation over longer periods of time. The MEMS module includes a device electrically coupled to the energy storage device for controlling charge transfers from the energy storage device while preventing charge leakage from the energy storage device. The controlling device includes a plurality of integrated MEMS switches that define open electrical paths that prevent charge leakage from the energy storage device through the MEMS switches, and are then operable to define closed electrical paths to allow charge transfers from the energy storage device, and preferably also allow charge transfers to the energy storage device, through the MEMS switches. The charge transfer can be utilized to power electronic circuits or store data in non-volatile digital memory.

Owner:BELLUTECH LLC

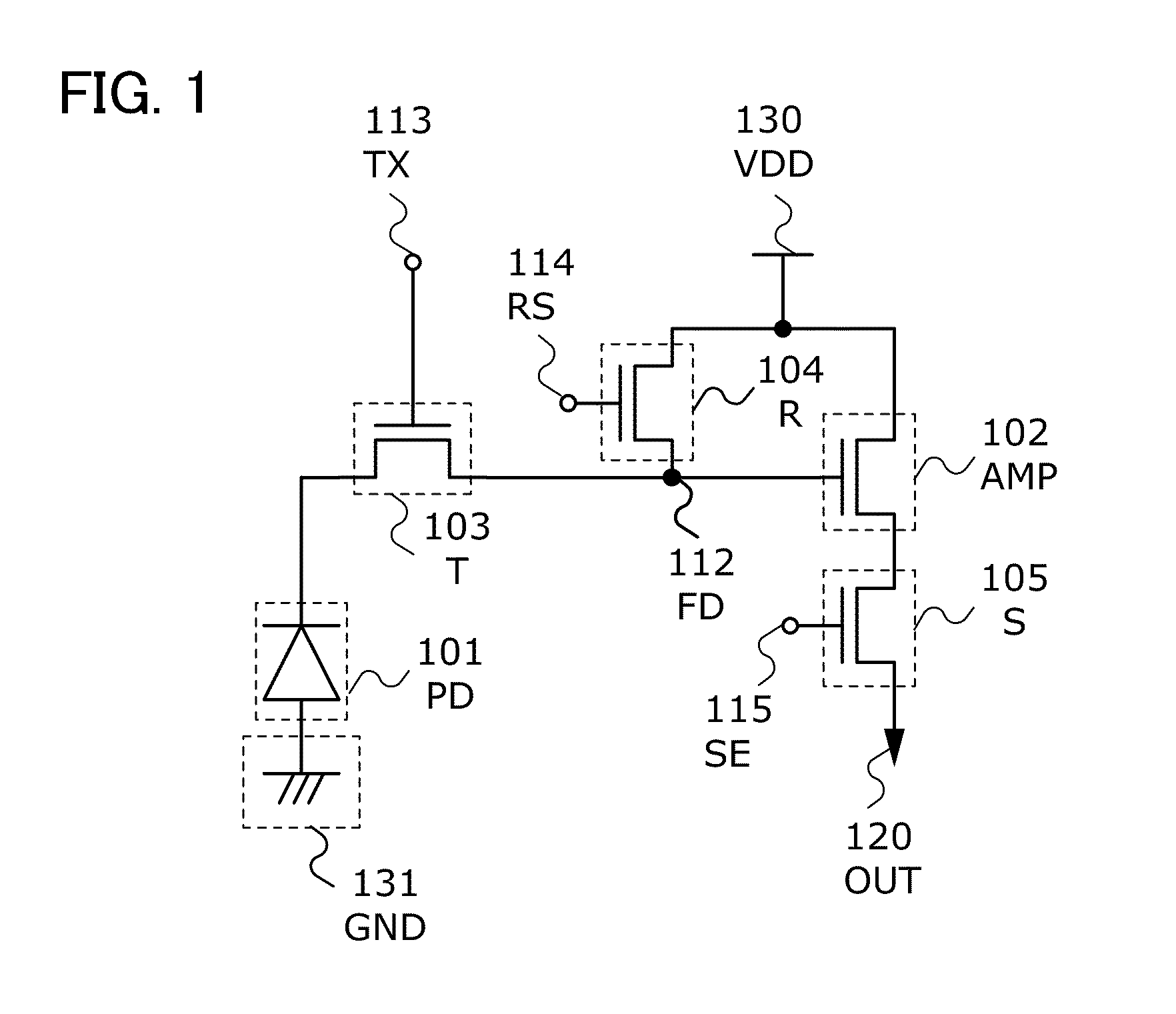

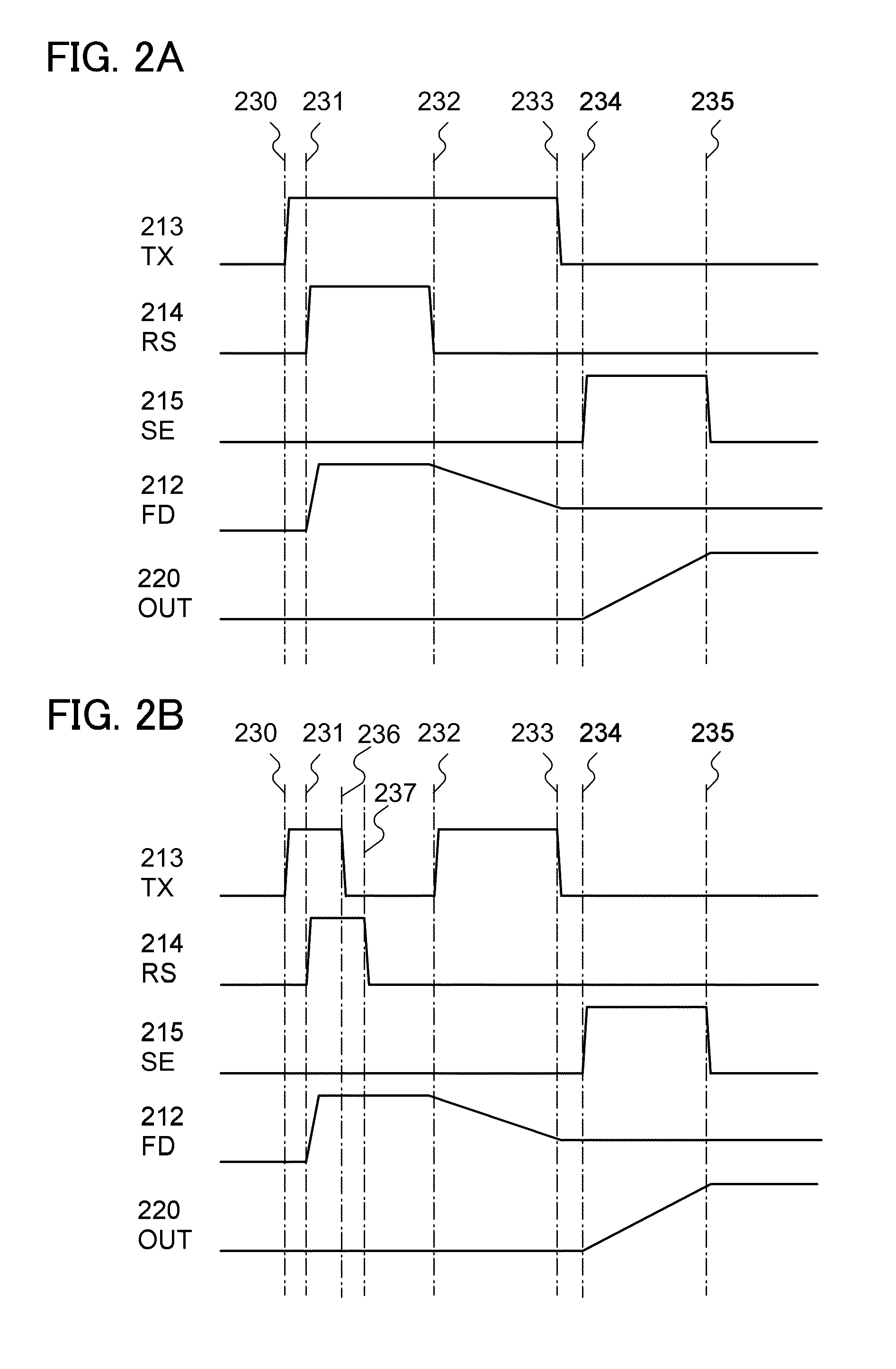

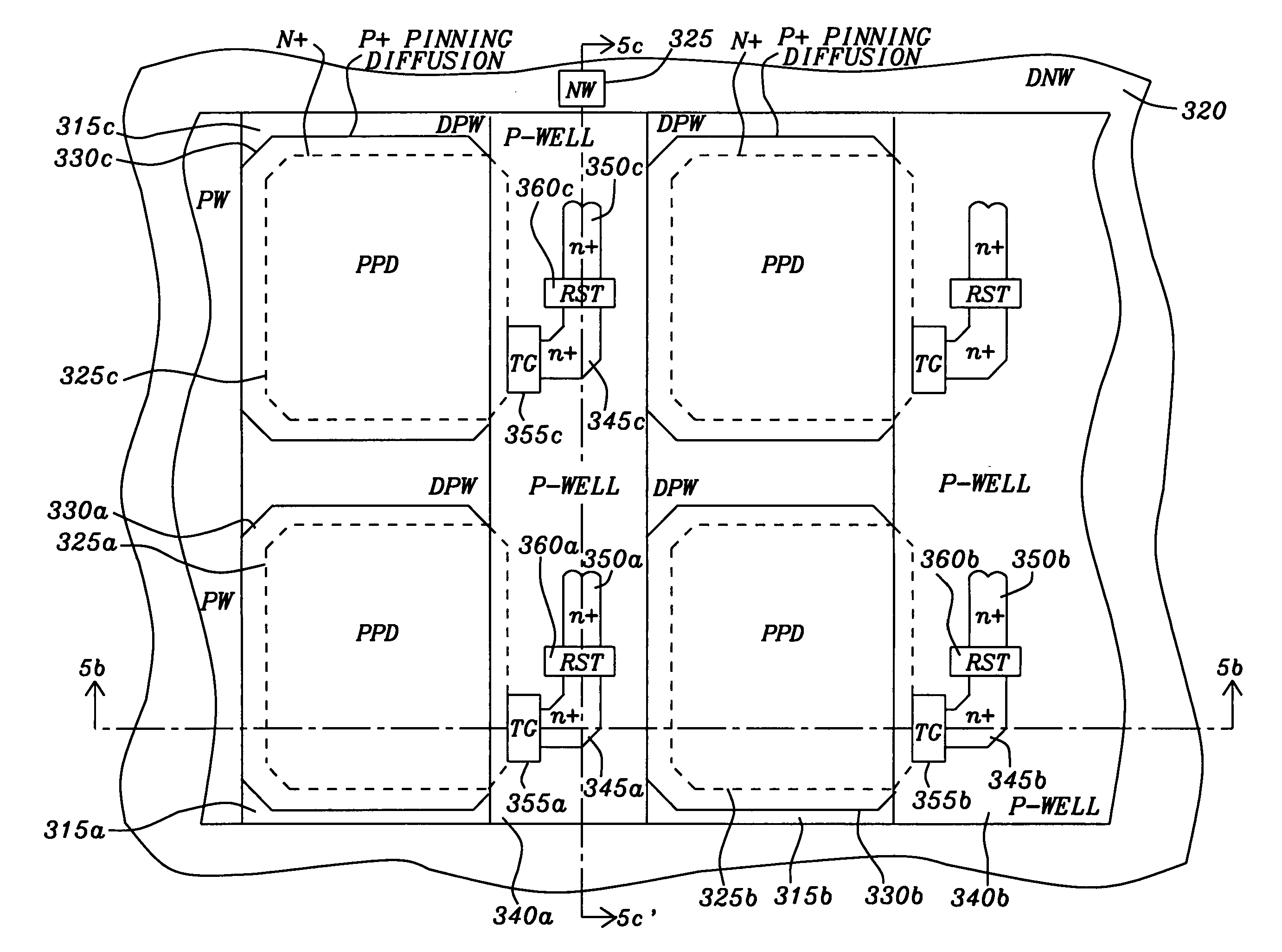

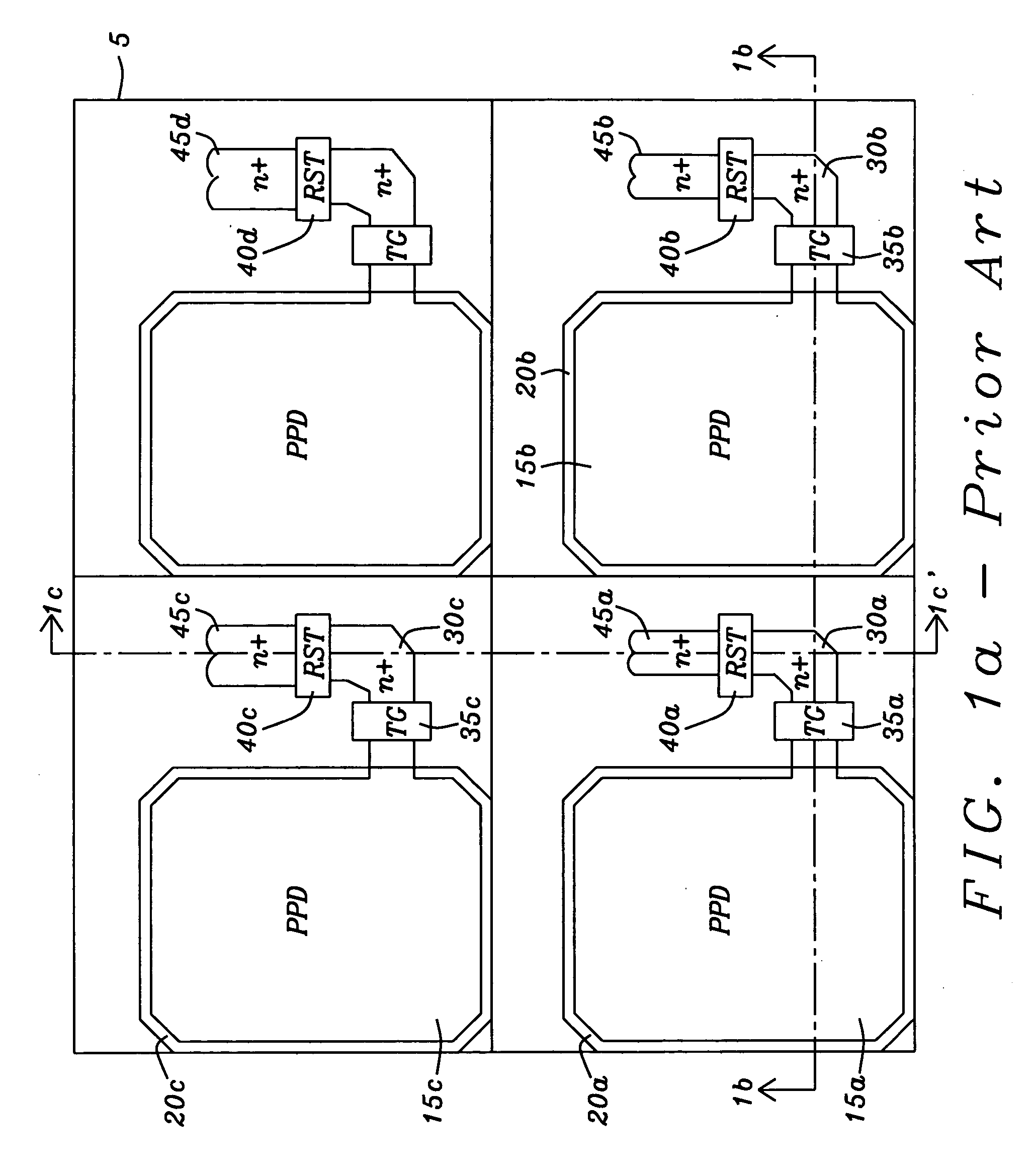

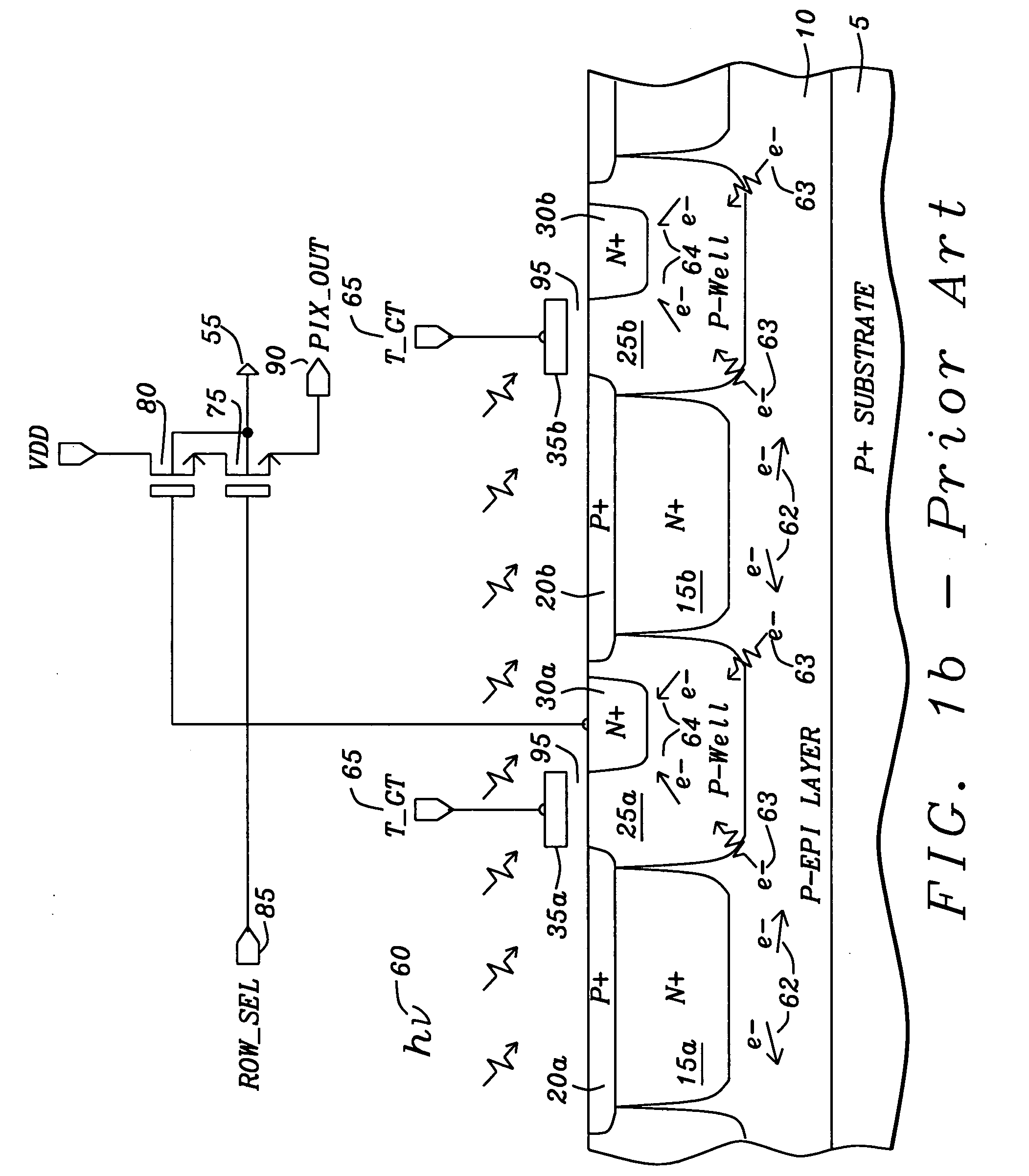

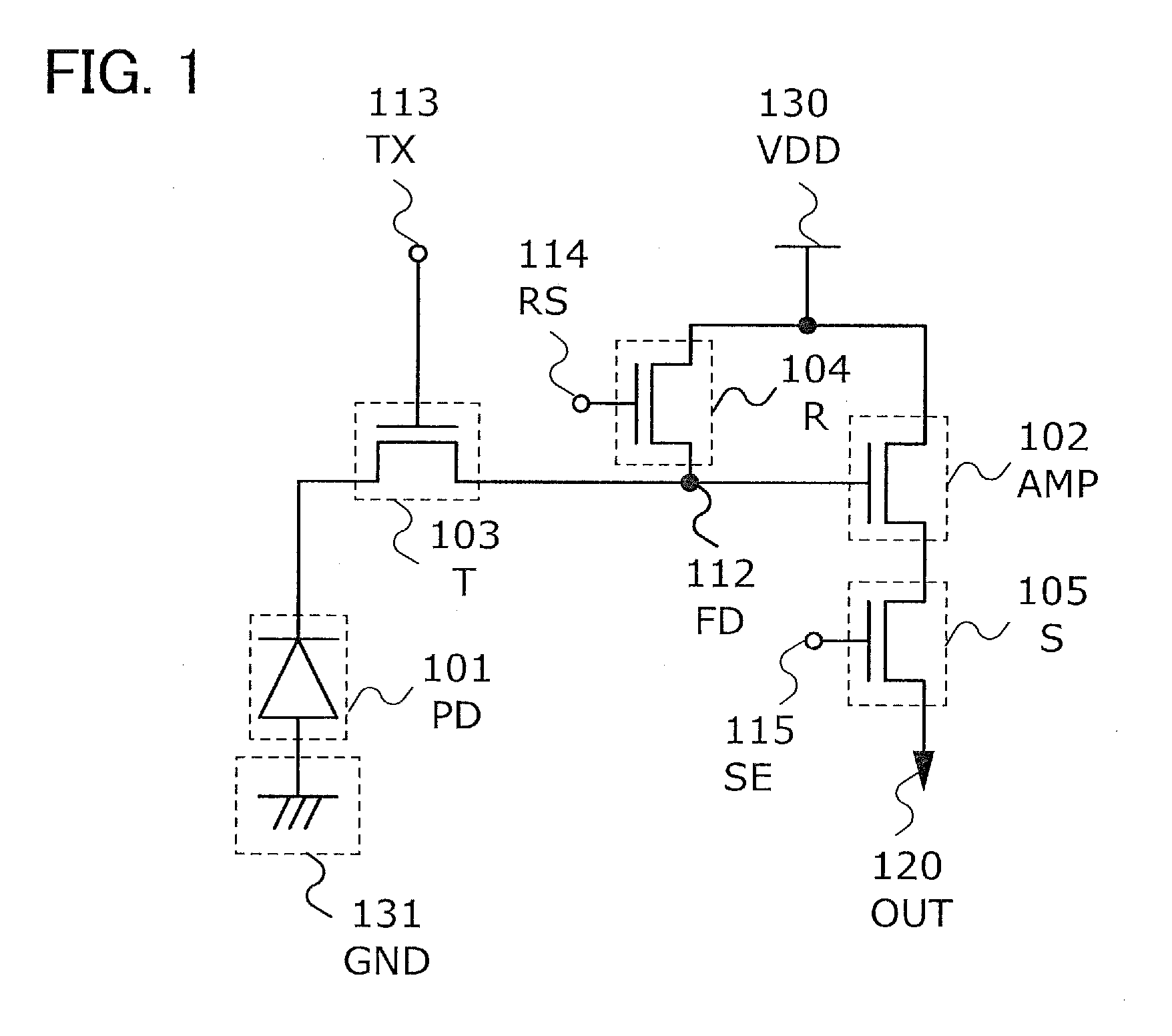

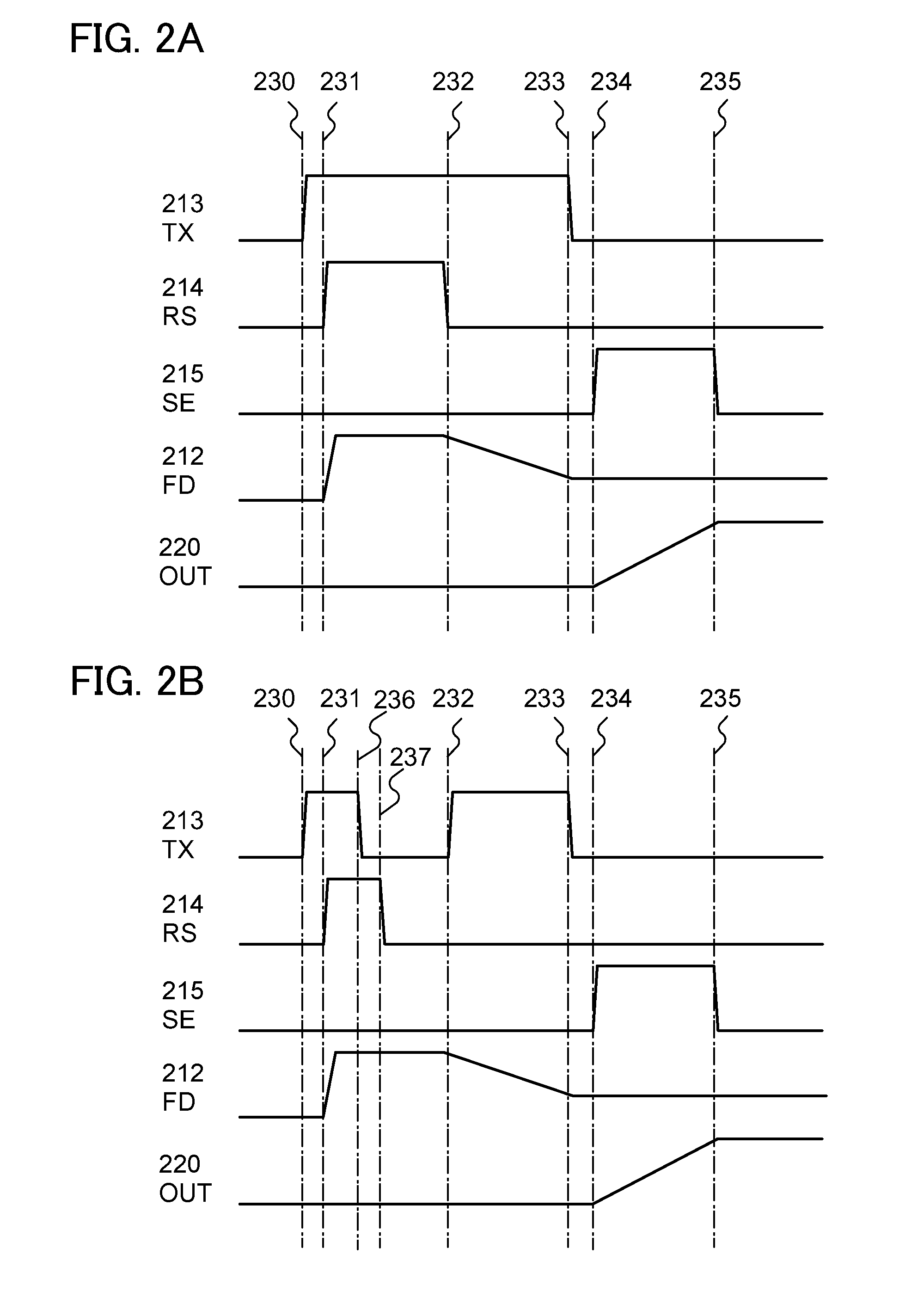

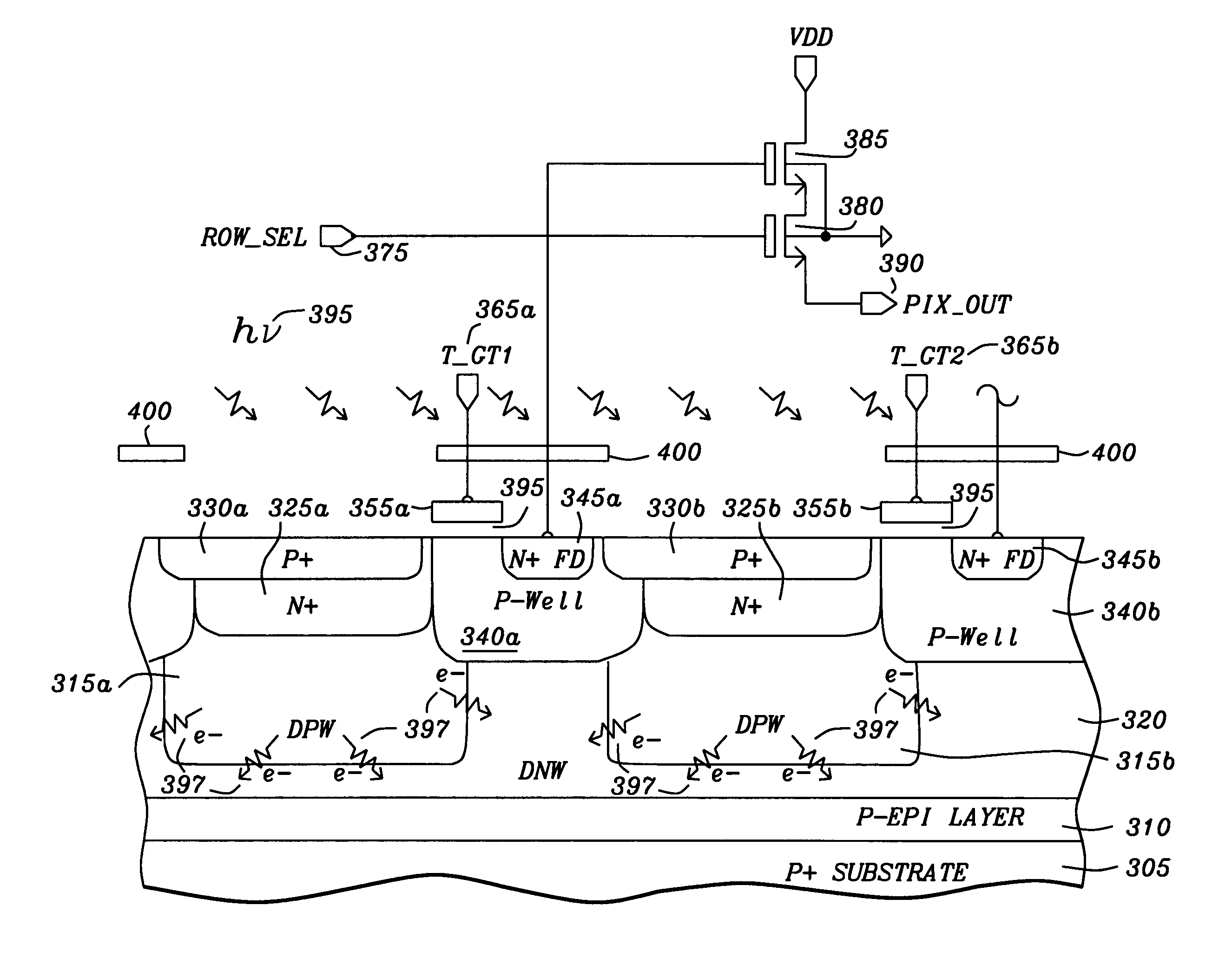

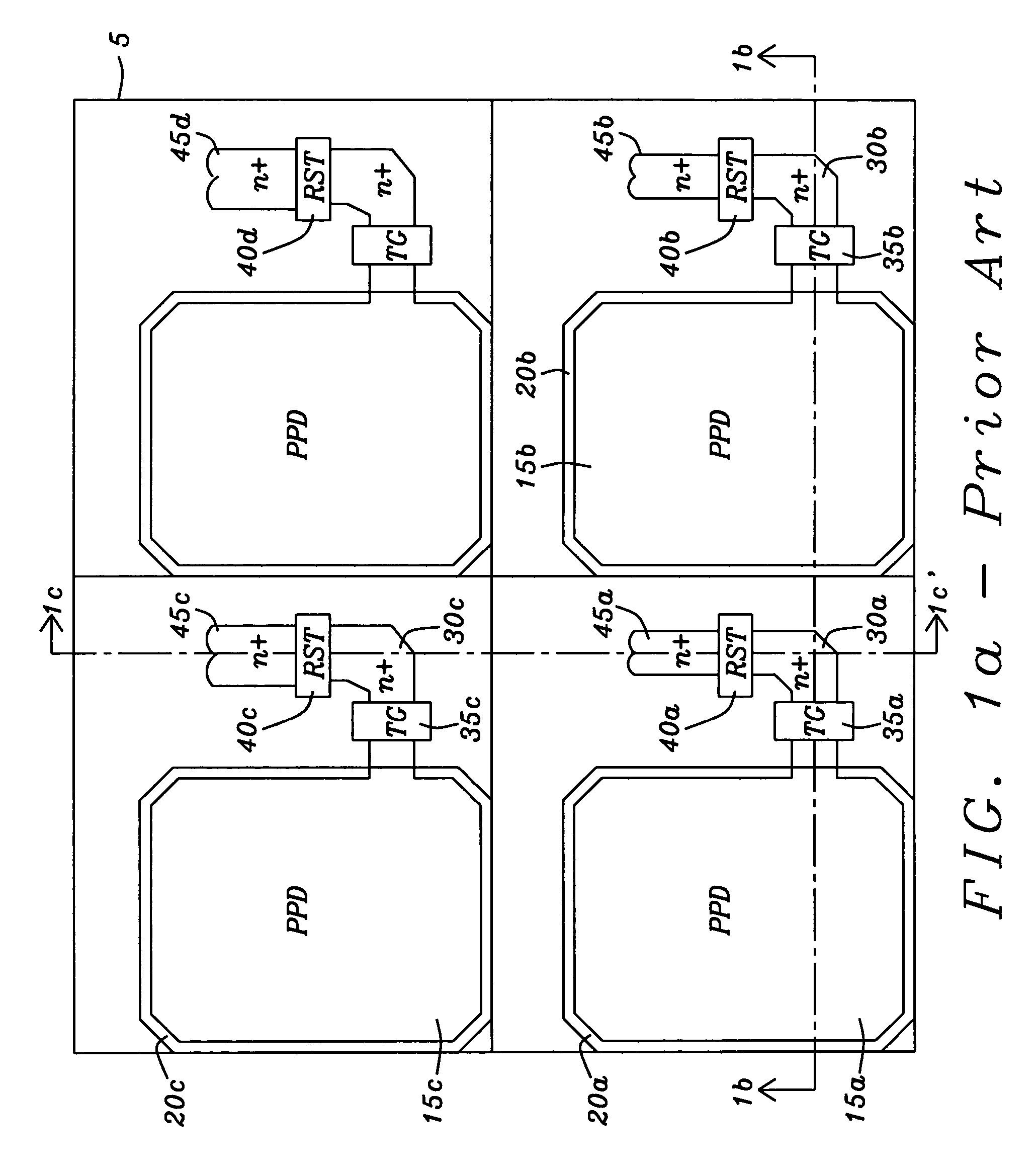

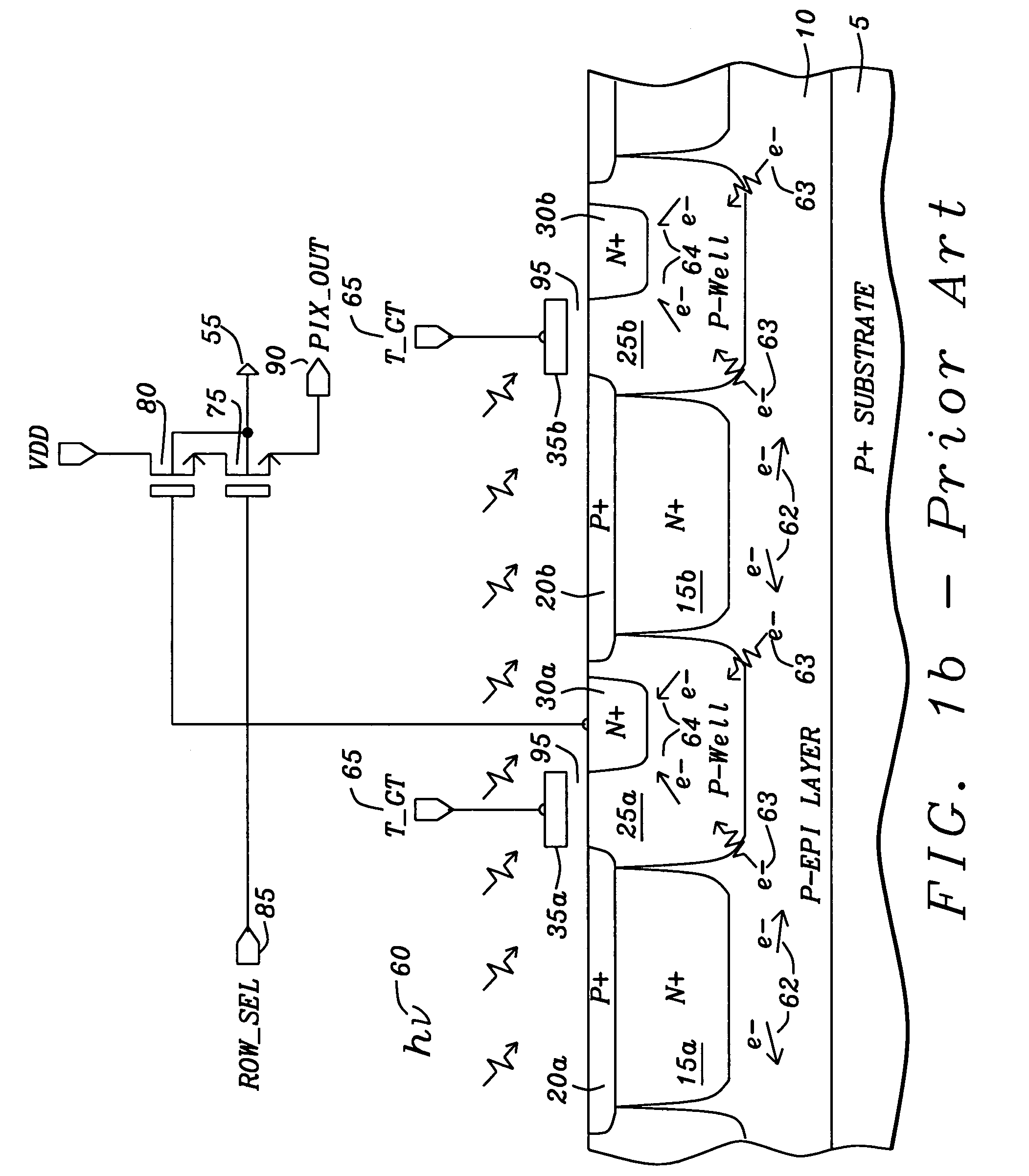

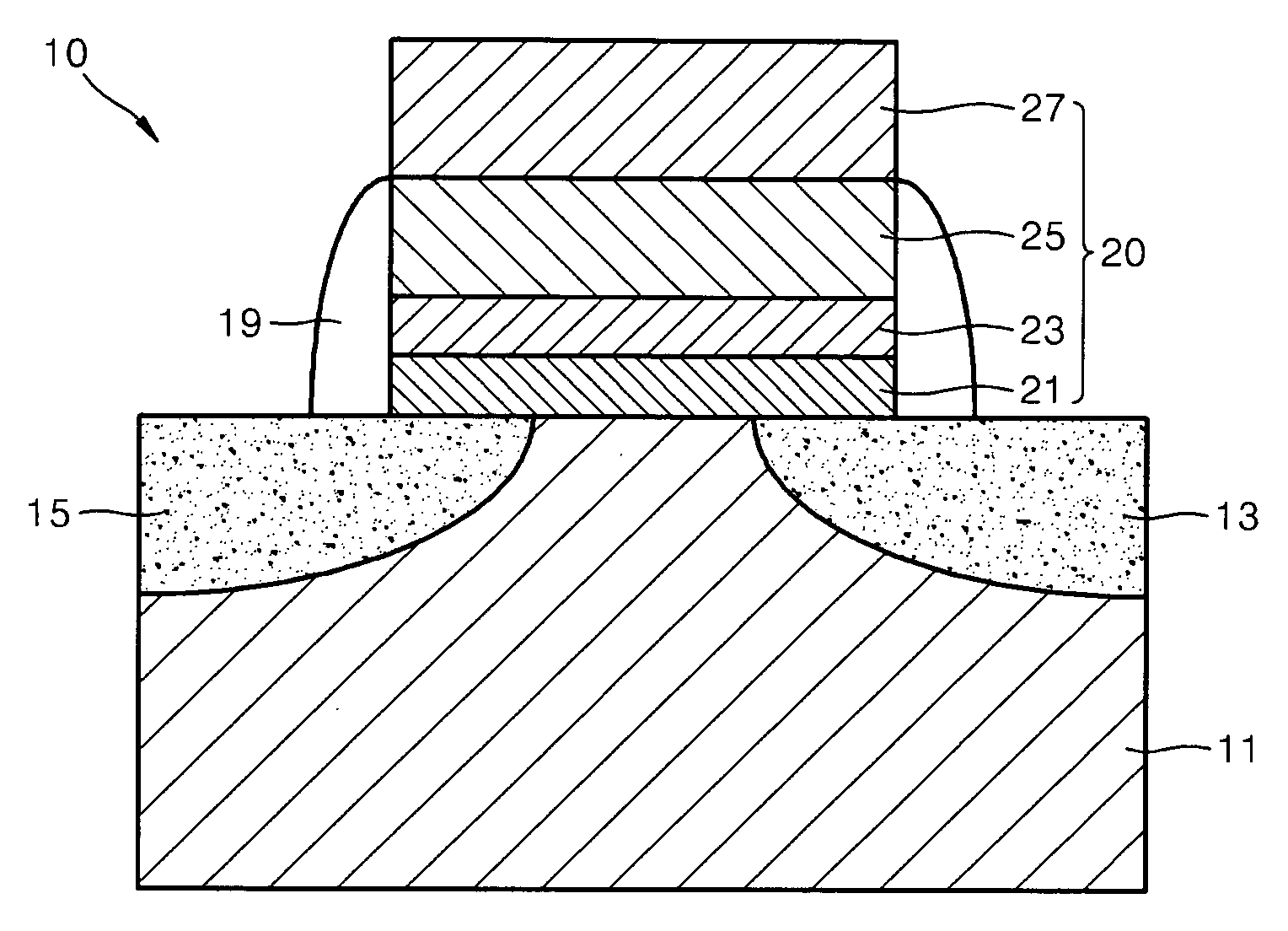

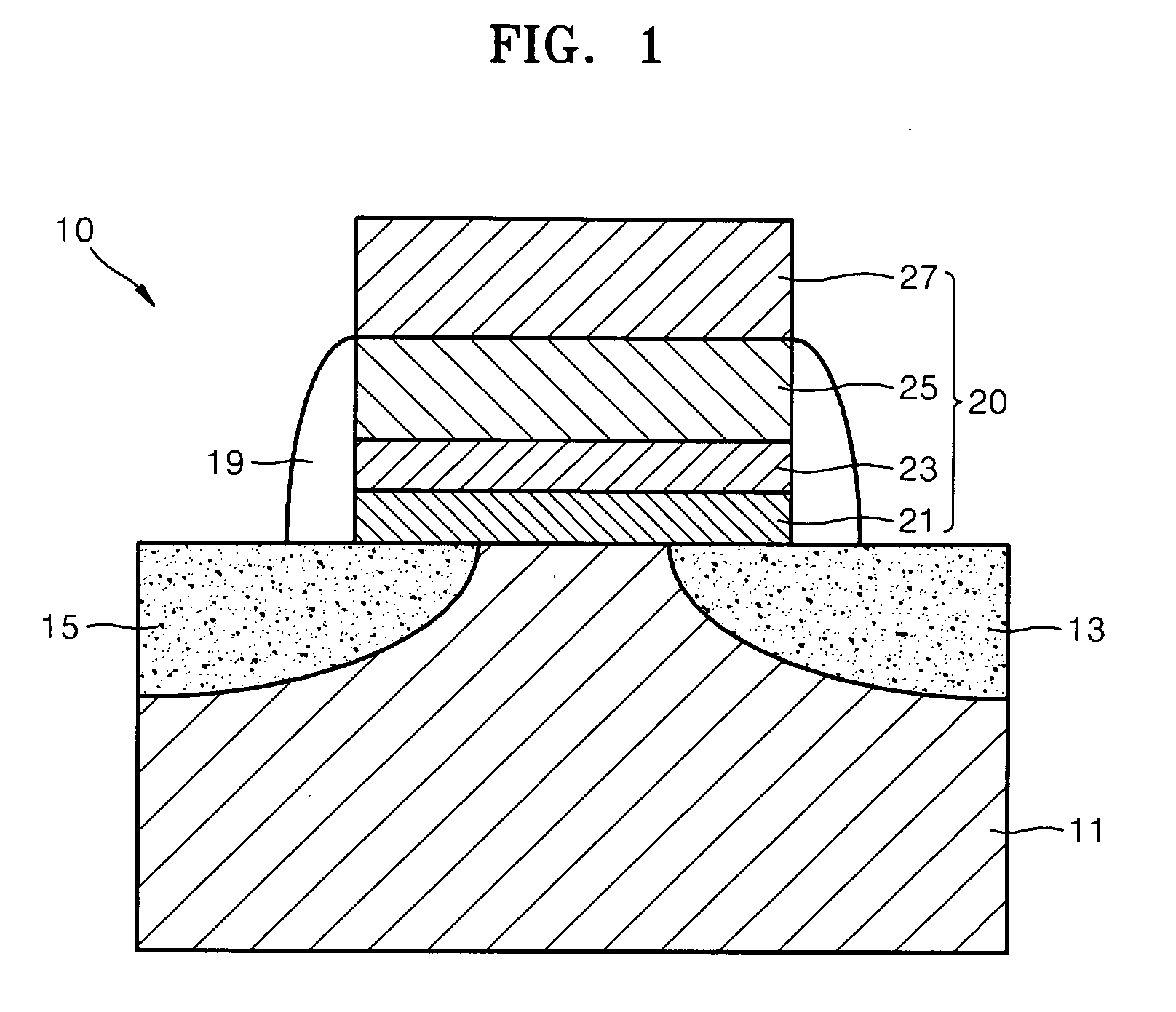

Pinned photodiode (PPD) pixel with high shutter rejection ratio for snapshot operating CMOS sensor

ActiveUS20070114629A1Prevent substrate charge leakageAvoid it happening againSolid-state devicesRadiation controlled devicesCMOS sensorFloating diffusion

A pixel image sensor has a high shutter rejection ratio that prevents substrate charge leakage to a floating diffusion storage node of the pixel image sensor and prevents generation of photoelectrons within the floating diffusion storage node and storage node control transistor switches of the pixel image sensor. The pixel image sensor that prevents substrate charge leakage of photoelectrons from pixel image sensor adjacent to the pixel image sensor. The pixel image sensor is fabricated on a substrate with an isolation barrier and a carrier conduction well. The isolation barrier formed underneath the floating diffusion storage node allows effective isolation by draining away the stray carriers and preventing them from reaching the floating diffusion storage node. The carrier conduction well in combination with the deep N-well isolation barrier separates the pinned photodiode region from the deep N-well isolation barrier that is underneath the floating diffusion storage node.

Owner:GULA CONSULTING LLC

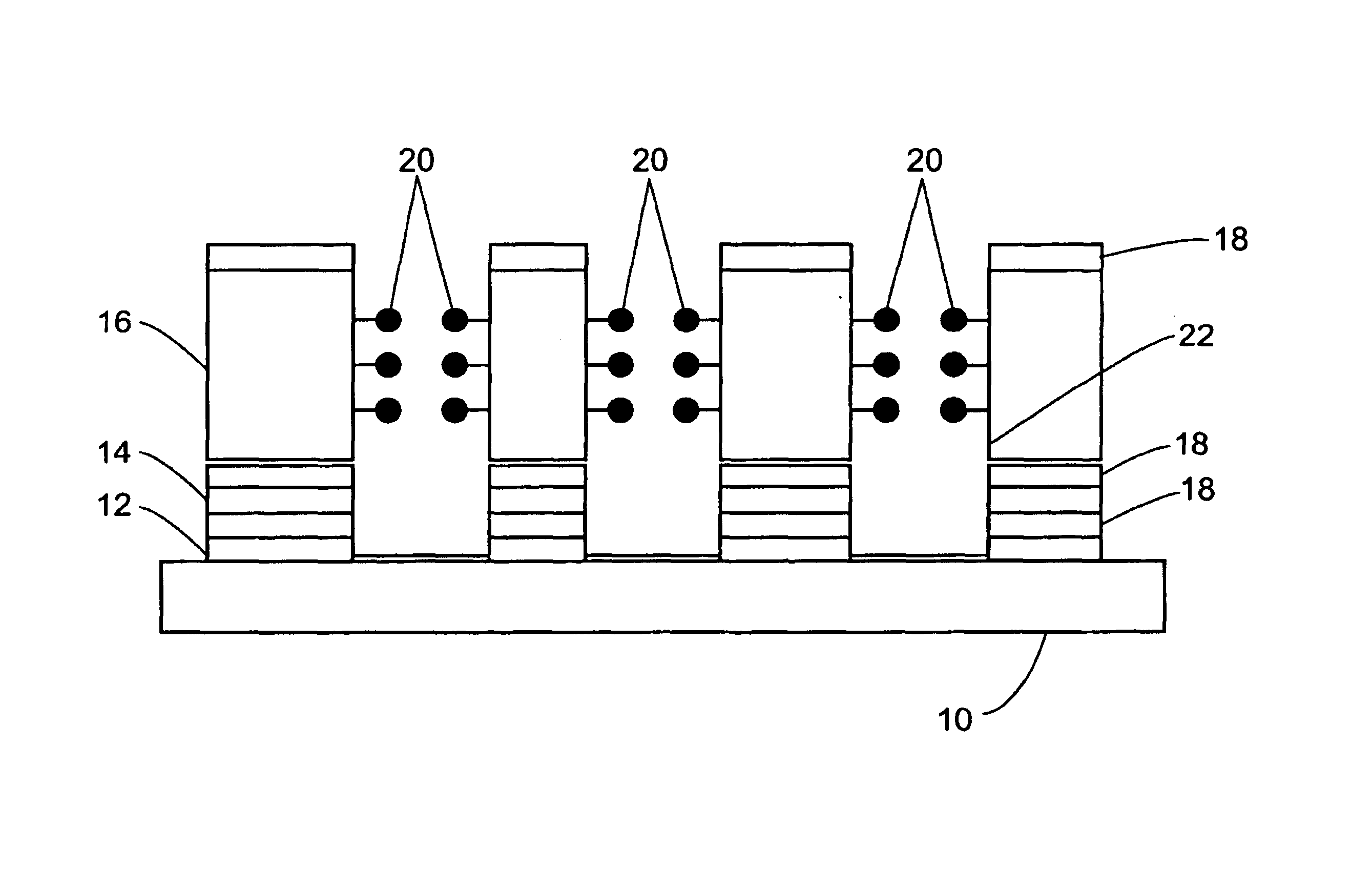

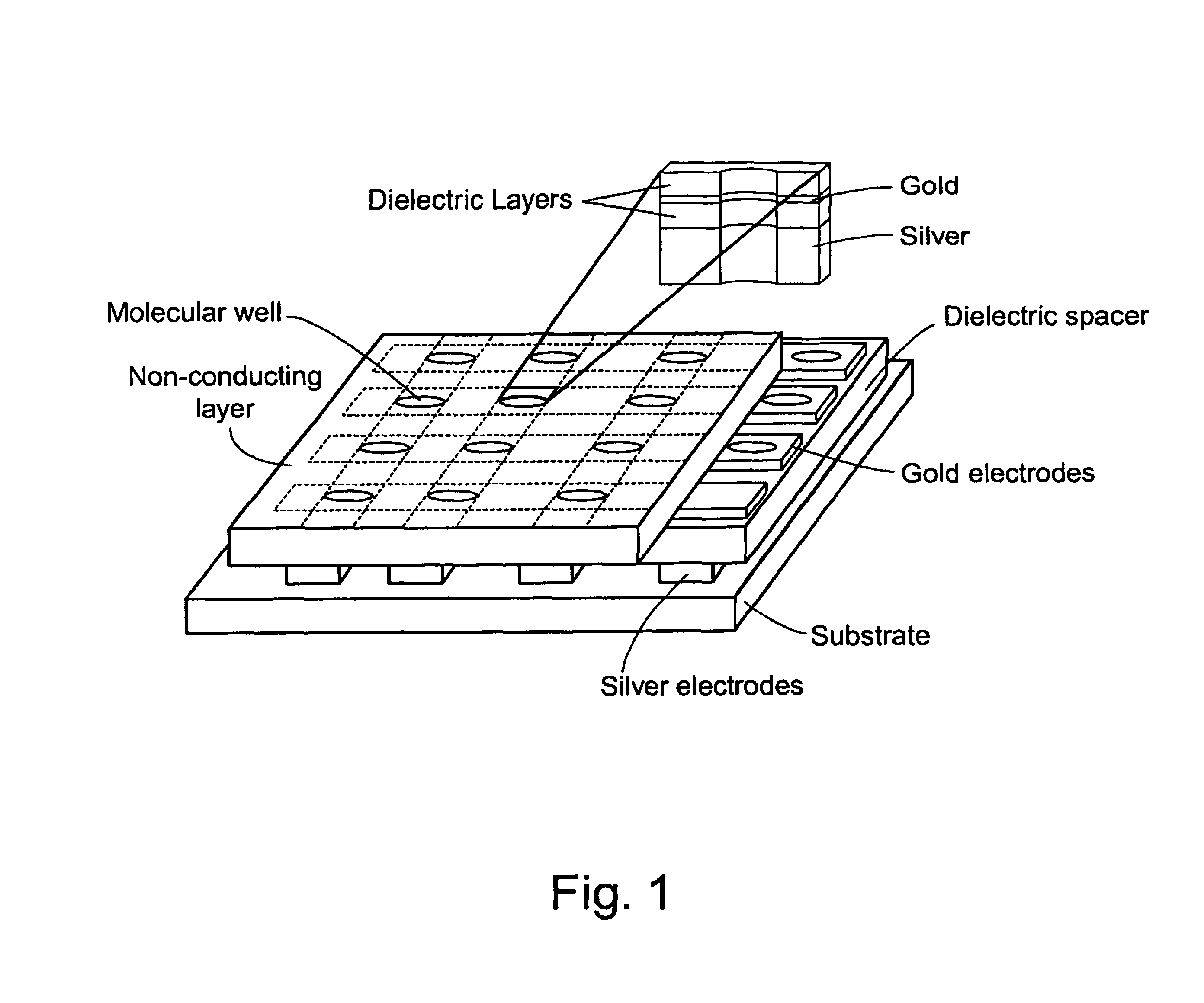

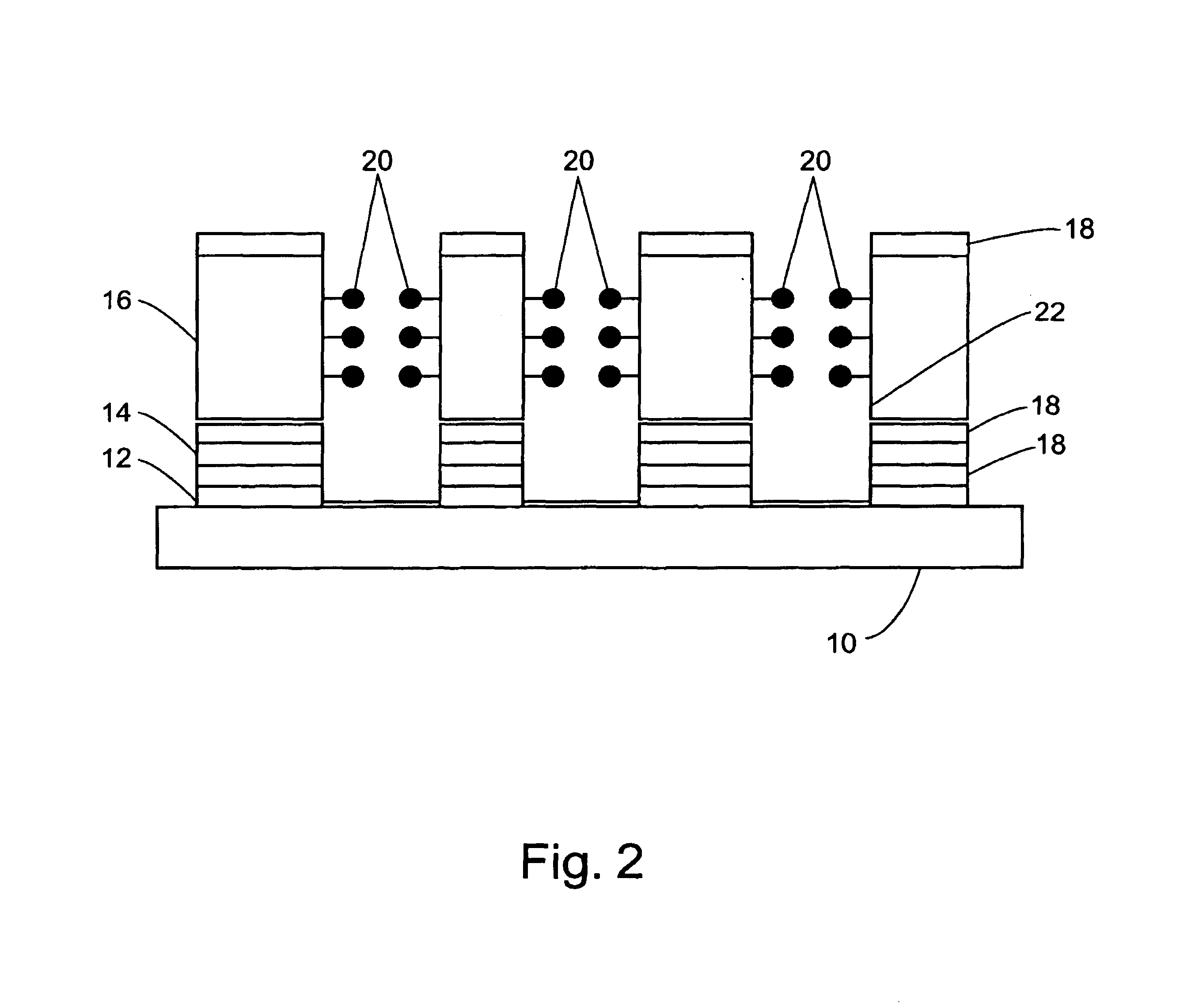

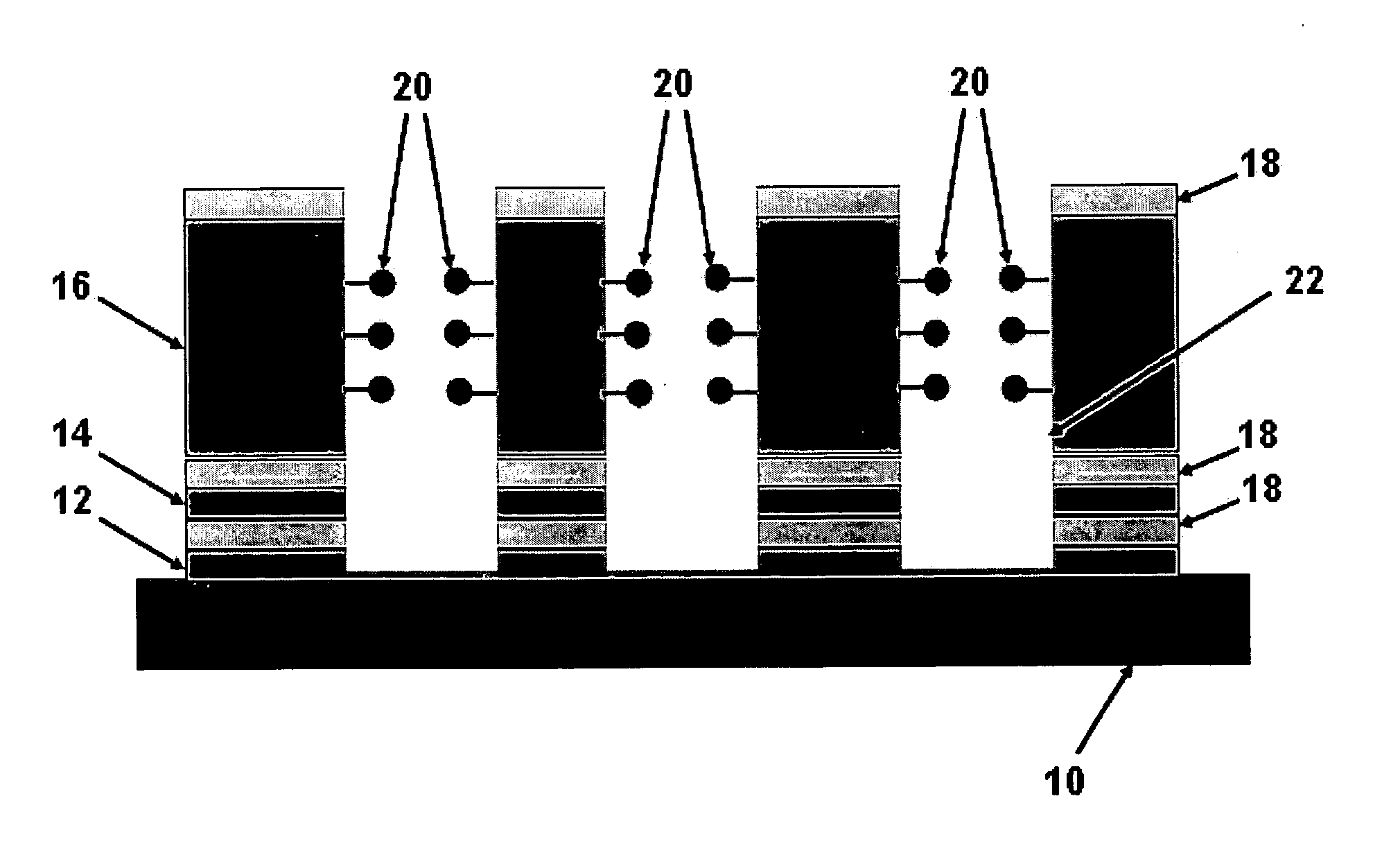

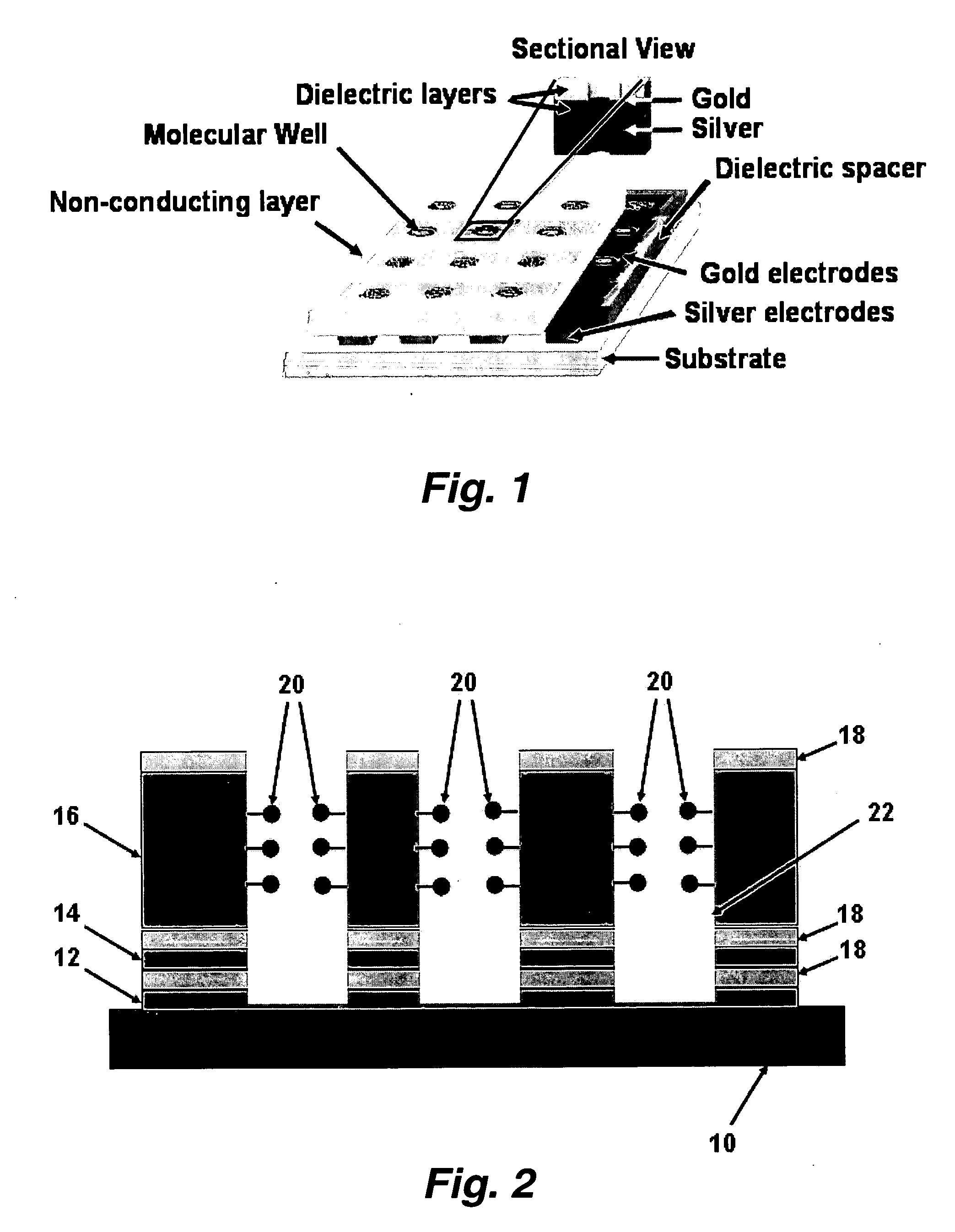

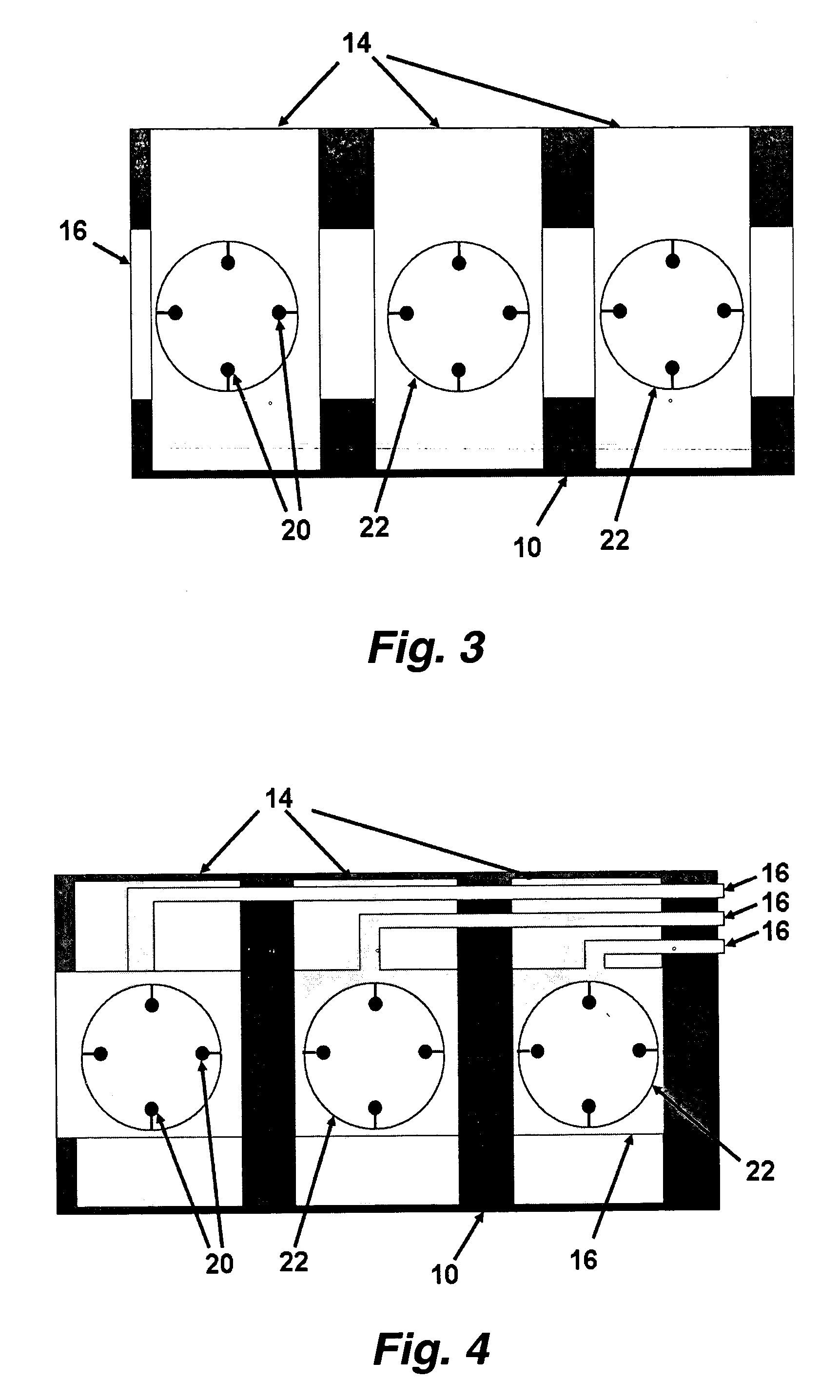

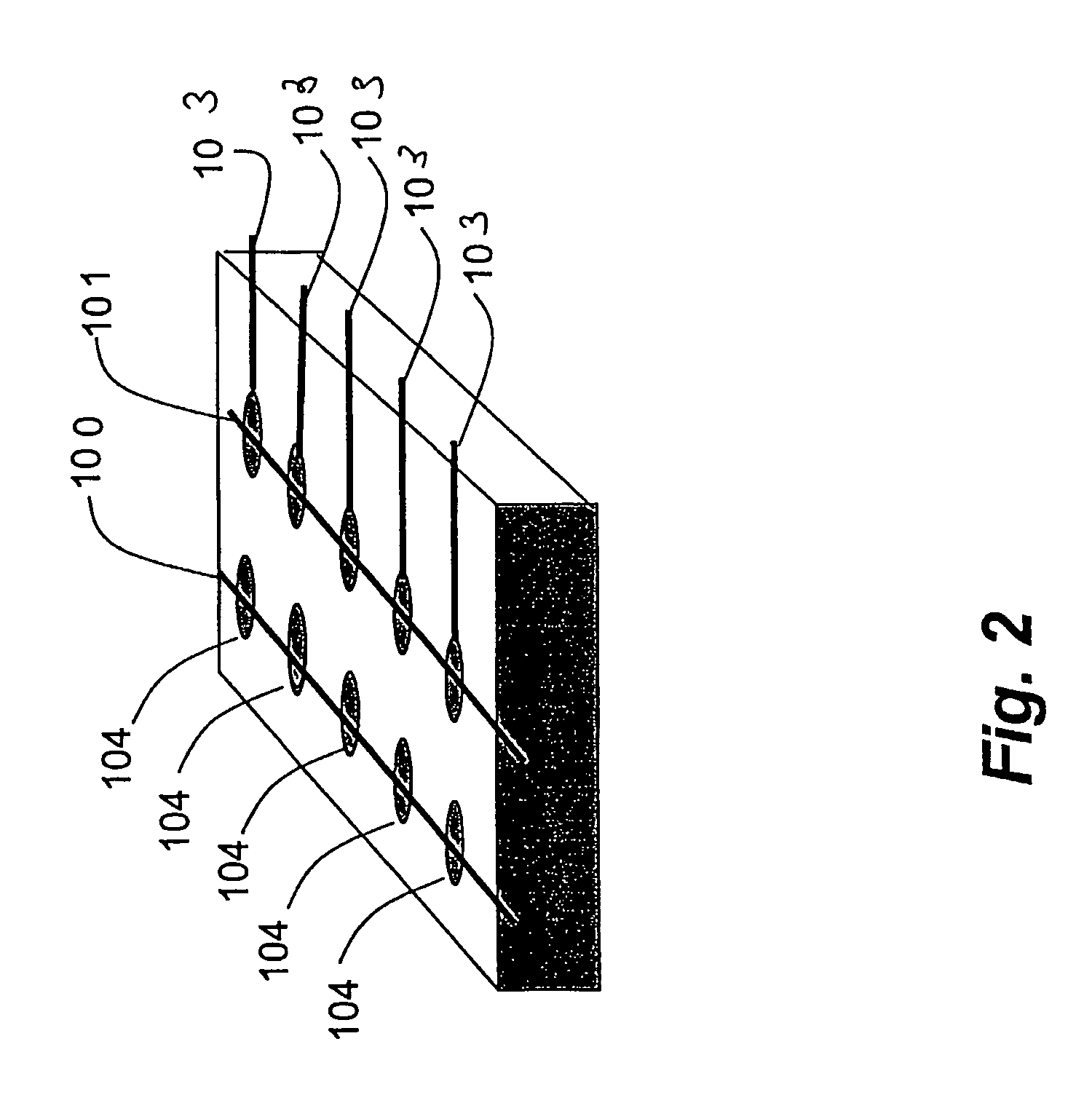

Molehole embedded 3-D crossbar architecture used in electrochemical molecular memory device

InactiveUS7074519B2Suitable mechanical propertyPrevent charge leakagePrimary cell to battery groupingCell electrodesMiniaturizationElectrochemical cell

This invention provides a new design and fabrication for a three-dimensional crossbar architecture embedding a sub-micron or nanometer sized hole (called a molehole) in each cross-region. Each molehole is an electrochemical cell consisting of two or more sectional surfaces separated by a non-conductor (e.g. a dialectric layer and solid electrolyte). When used in electrochemical molecular memory device (EMMD), the architecture provides unique features such as a nano-scale electroactive surface, no interaction between memory elements, and easier miniaturization and integration.

Owner:RGT UNIV OF CALIFORNIA

Molehole embedded 3-D crossbar architecture used in electrochemical molecular memory device

InactiveUS20060081950A1Suitable mechanical propertyPrevent charge leakageCell electrodesFinal product manufactureMiniaturizationElectrochemical cell

This invention provides a new design and fabrication for a three-dimensional crossbar architecture embedding a sub-micron or nanometer sized hole (called a molehole) in each cross-region. Each molehole is an electrochemical cell consisting of two or more sectional surfaces separated by a non-conductor (e.g., a dialectric layer and solid electrolyte). When used in electrochemical molecular memory device (EMMD), the architecture provides unique features such as a nano-scale electroactive surface, no interaction between memory elements, and easier miniaturization and integration.

Owner:RGT UNIV OF CALIFORNIA

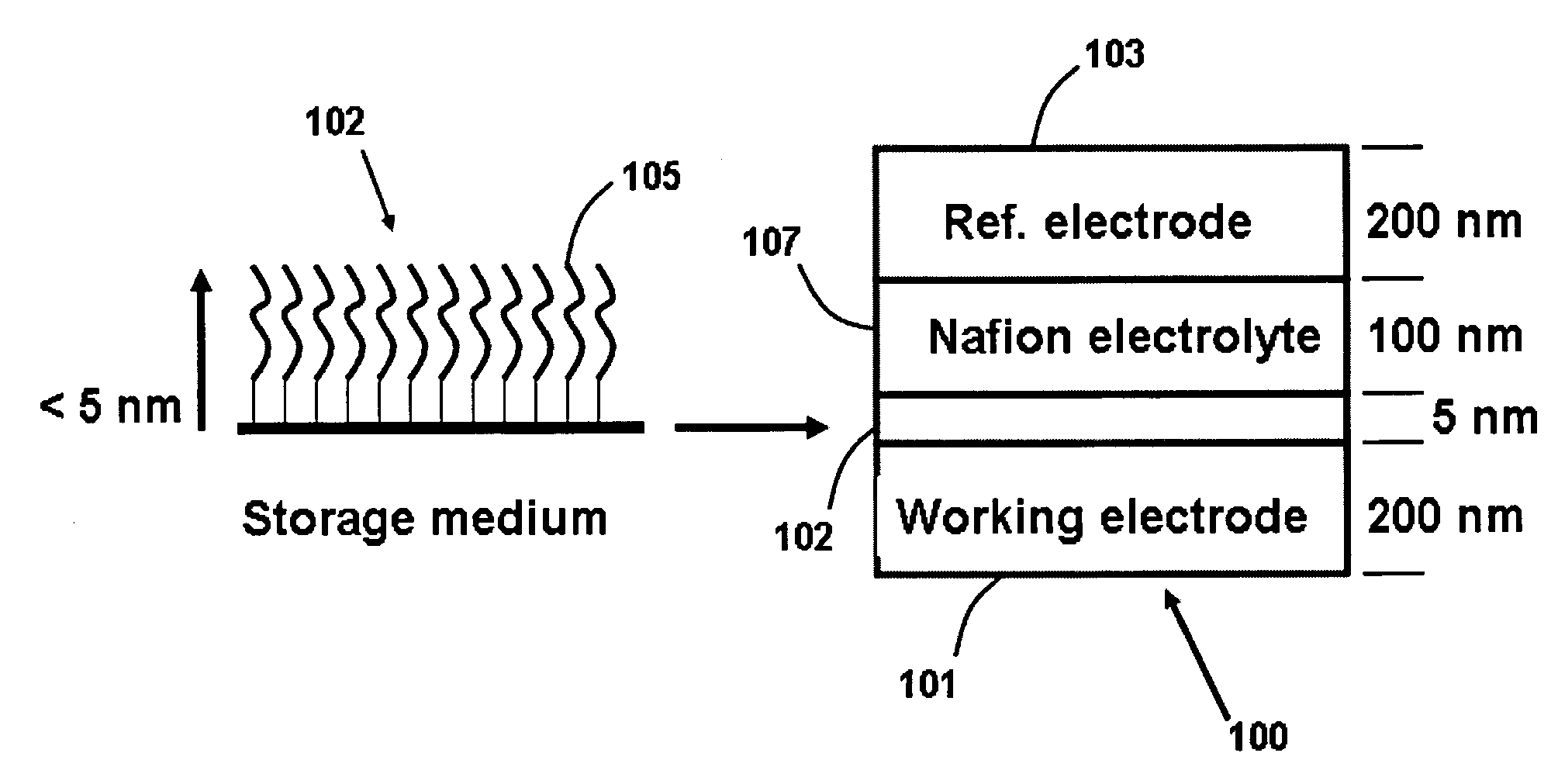

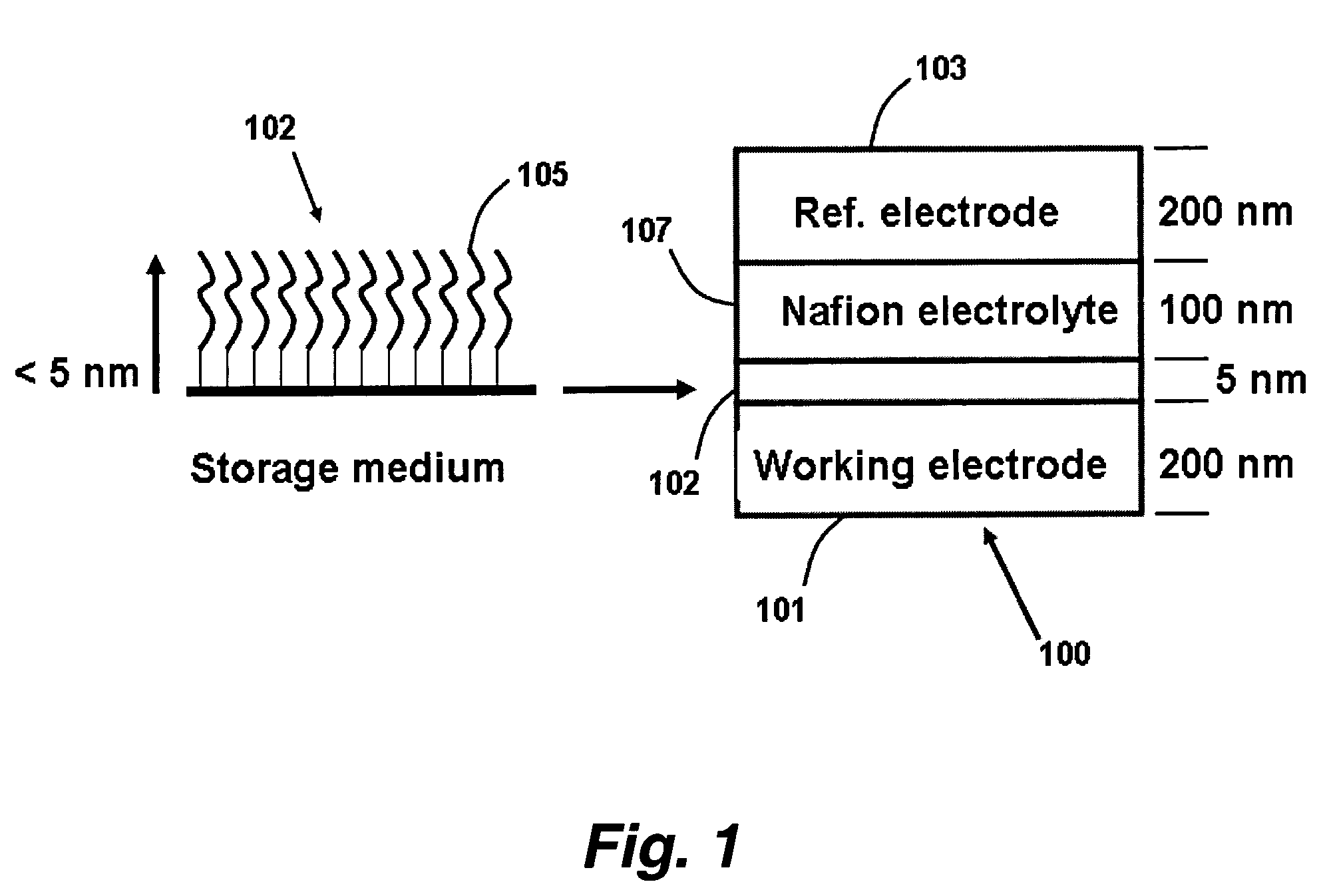

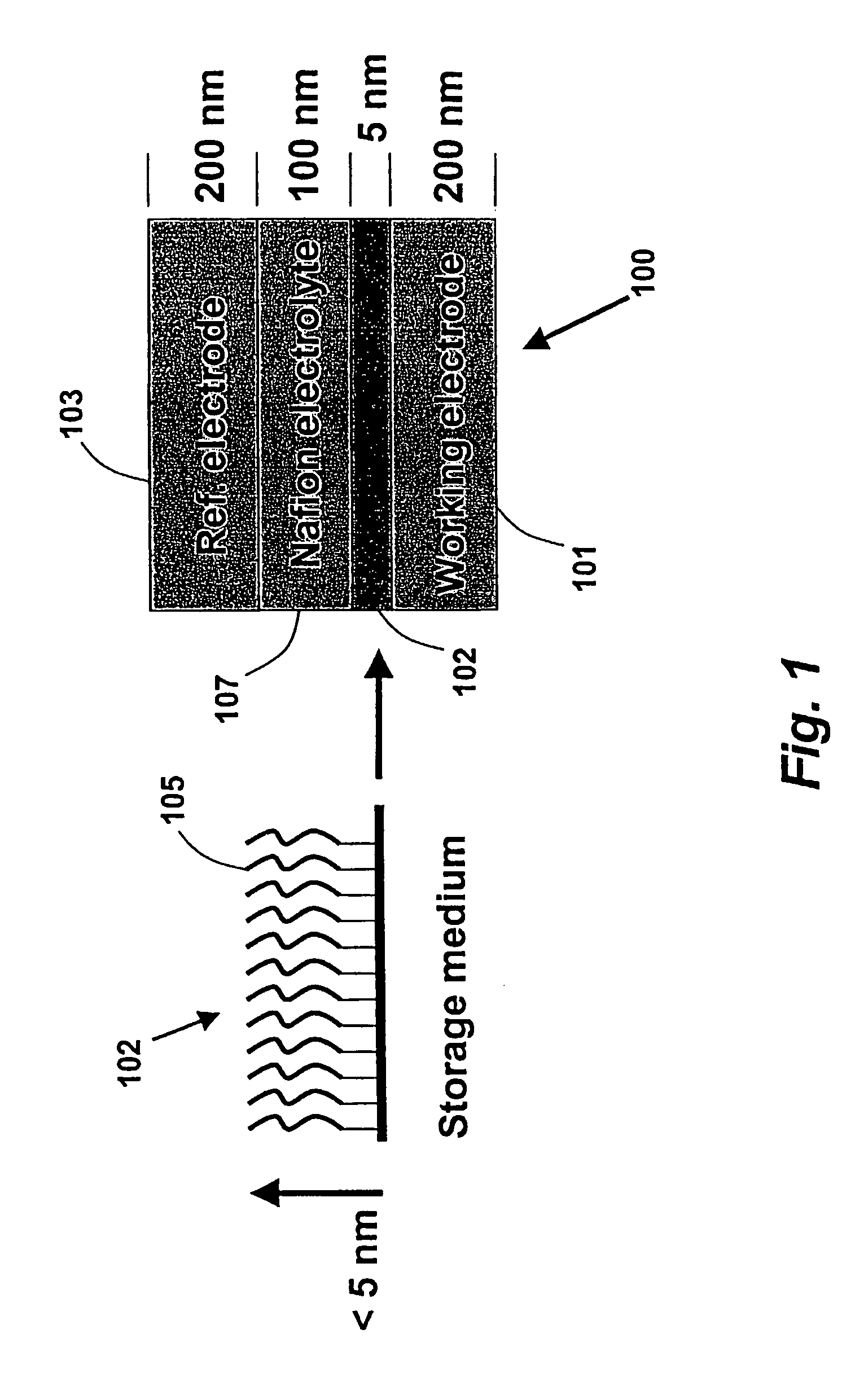

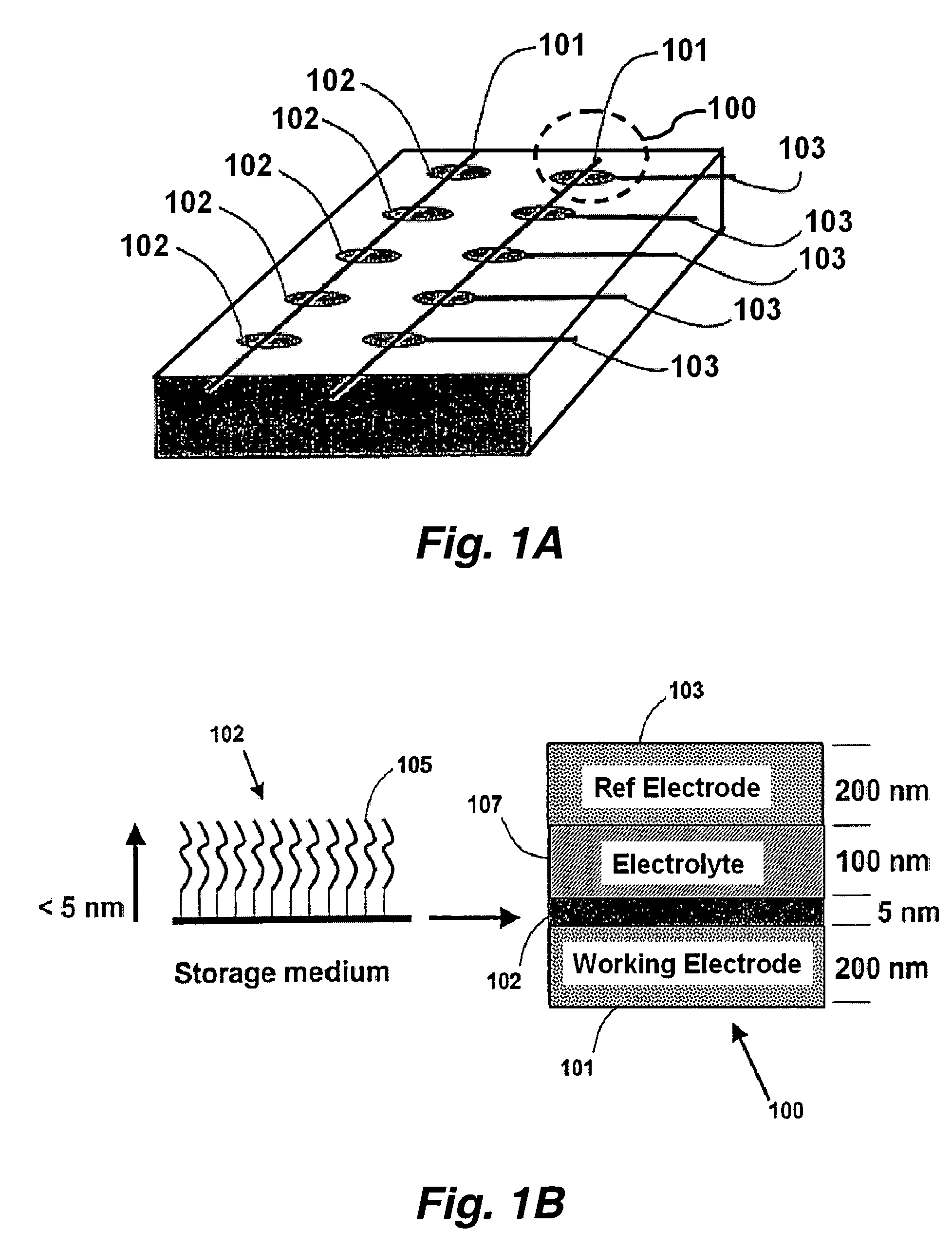

High density molecular memory device

InactiveUS7061791B2Suitable mechanical propertyPrevent charge leakageNanoinformaticsSolid-state devicesFault toleranceChemical synthesis

This invention provides novel high density memory devices that are electrically addressable permitting effective reading and writing, that provide a high memory density (e.g., 1015 bits / cm3), that provide a high degree of fault tolerance, and that are amenable to efficient chemical synthesis and chip fabrication. The devices are intrinsically latchable, defect tolerant, and support destructive or non-destructive read cycles. In a preferred embodiment, the device comprises a fixed electrode electrically coupled to a storage medium having a multiplicity of different and distinguishable oxidation states wherein data is stored in said oxidation states by the addition or withdrawal of one or more electrons from said storage medium via the electrically coupled electrode.

Owner:NORTH CAROLINA STATE UNIV +1

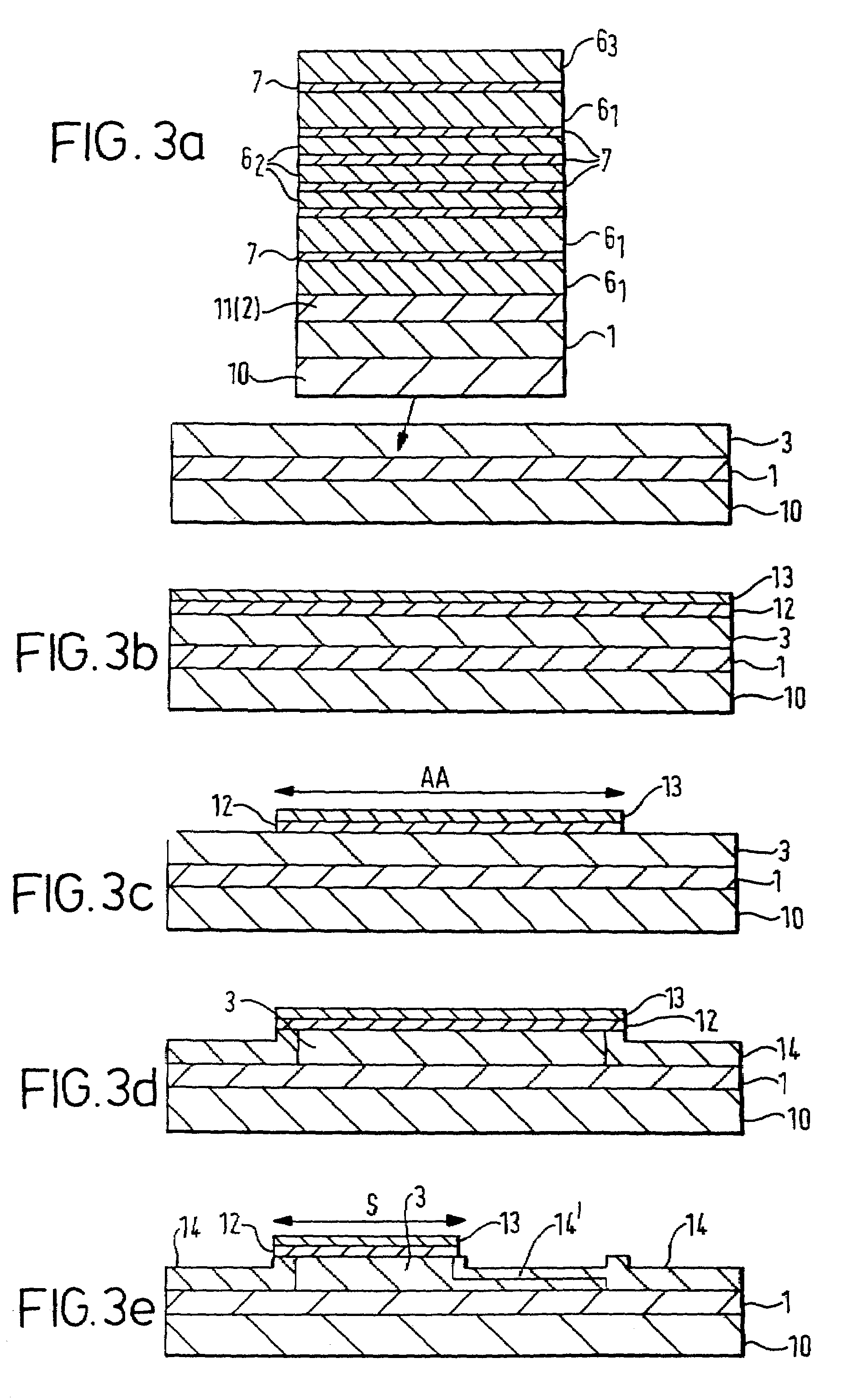

High density non-volatile memory device

InactiveUS7042755B1Suitable mechanical propertyPrevent charge leakageMaterial nanotechnologyNanoinformaticsFault toleranceChemical synthesis

This invention provides novel high density memory devices (FIG. 3) that are electrically addressable permitting effective reading and writing, that provide a high memory density (102), that provide a high degree of fault tolerance, and that are amenable to efficient chemical synthesis and chip fabrication. The devices arc intrinsically latchable, defect tolerant, and support destructive or non-destructive read cycles. In a preferred embodiment, the device comprises a fixed electrode electrically coupled to a storage medium having a multiplicity of different and distinguishable oxidation states wherein data is stored in said oxidation states by the addition or withdrawal of one or more electrons from said storage medium via the electrically coupled electrode.

Owner:NORTH CAROLINA STATE UNIV +1

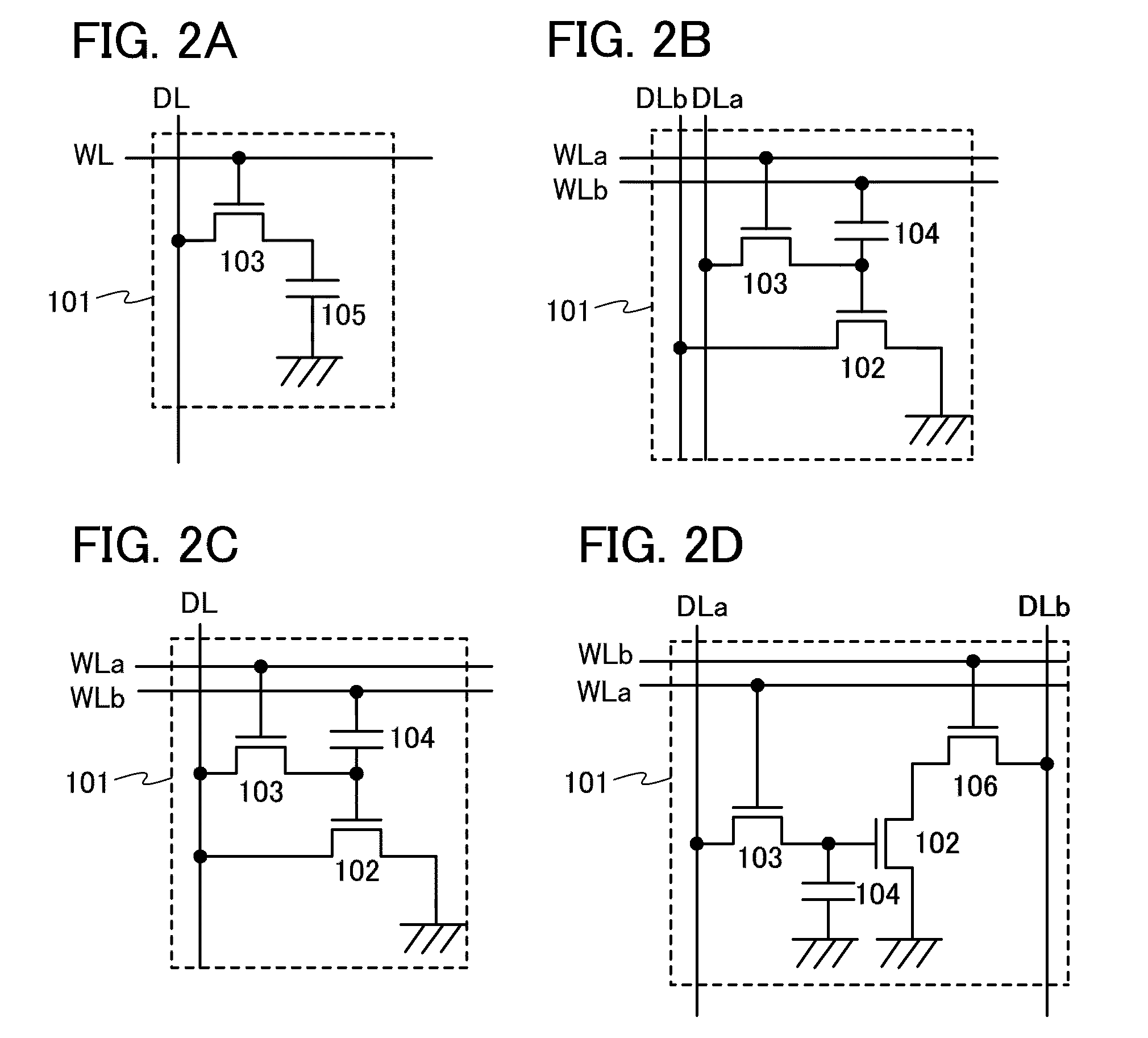

Memory device and semiconductor device

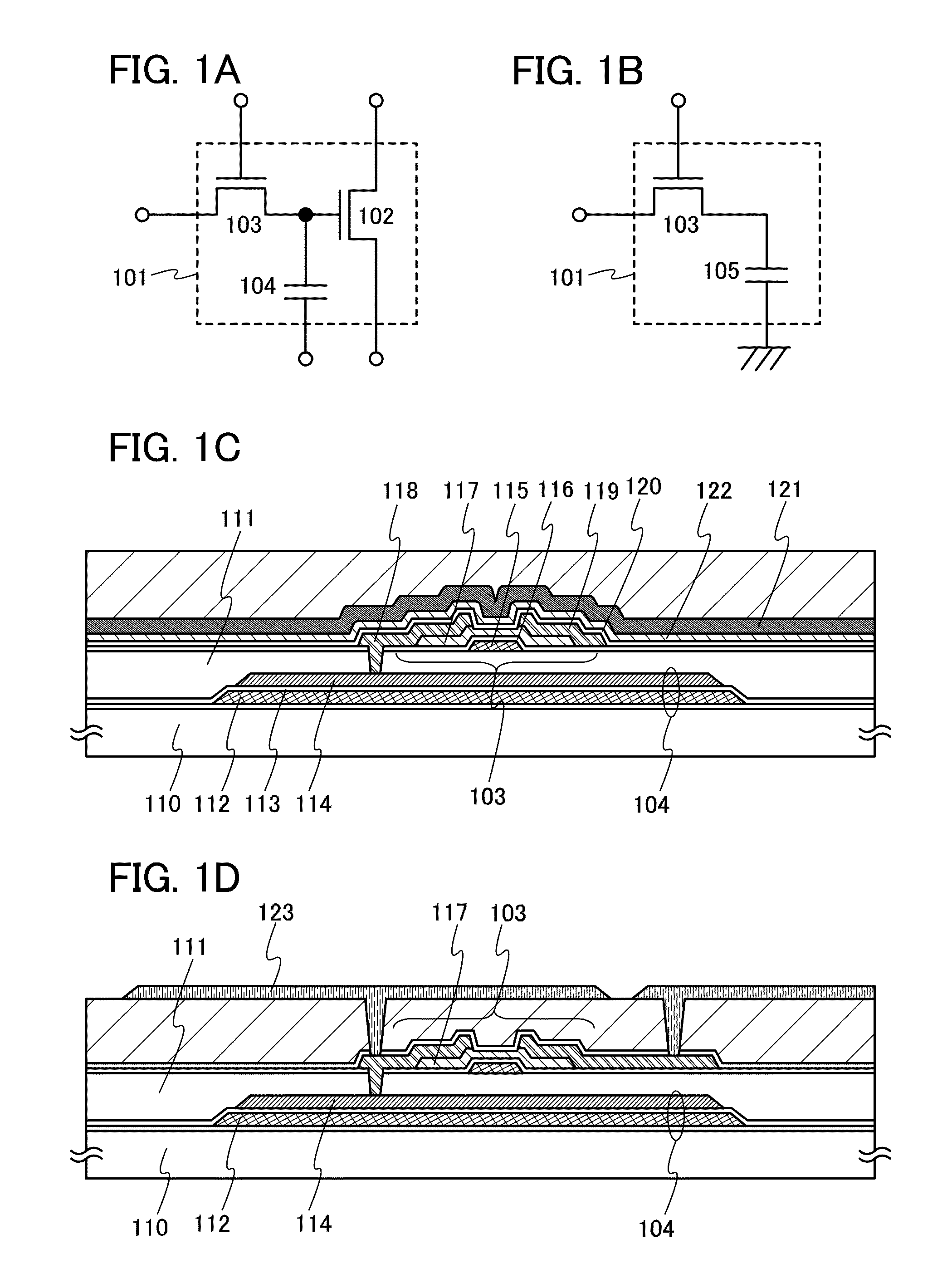

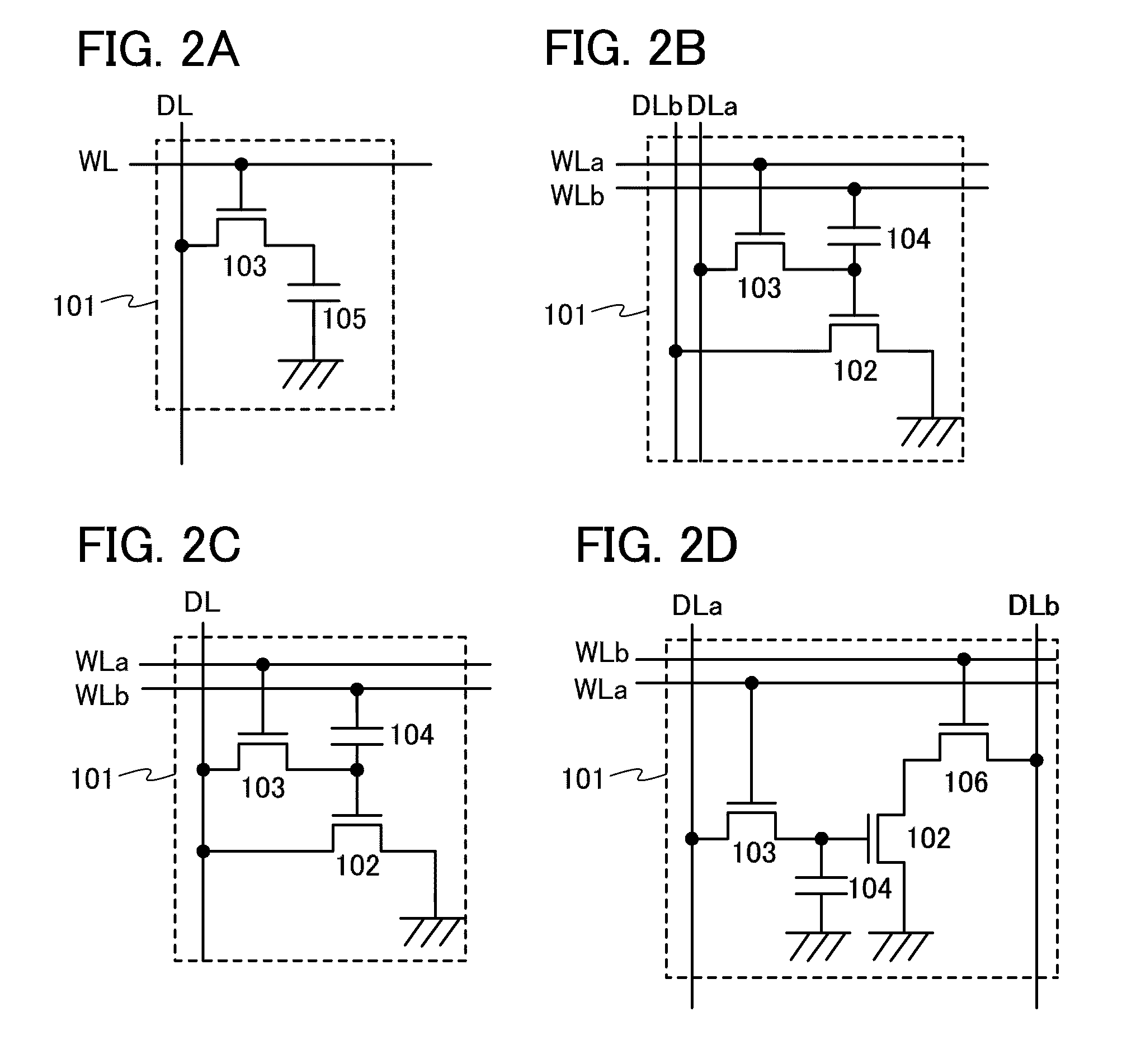

ActiveUS20110284838A1Easy dischargeShorten the overall cycleSolid-state devicesRead-only memoriesActive layerCapacitor

One object is to propose a memory device in which a period in which data is held can be ensured and memory capacity per unit area can be increased. The memory device includes a memory element, a transistor including an oxide semiconductor in an active layer for control of accumulating, holding, and discharging charge in the memory element, and a capacitor connected to the memory element. At least one of a pair of electrodes of the capacitor has a light-blocking property. Further, the memory device includes a light-blocking conductive film or a light-blocking insulating film. The active layer is positioned between the electrode having a light-blocking property and the light-blocking conductive film or the light-blocking insulating film.

Owner:SEMICON ENERGY LAB CO LTD

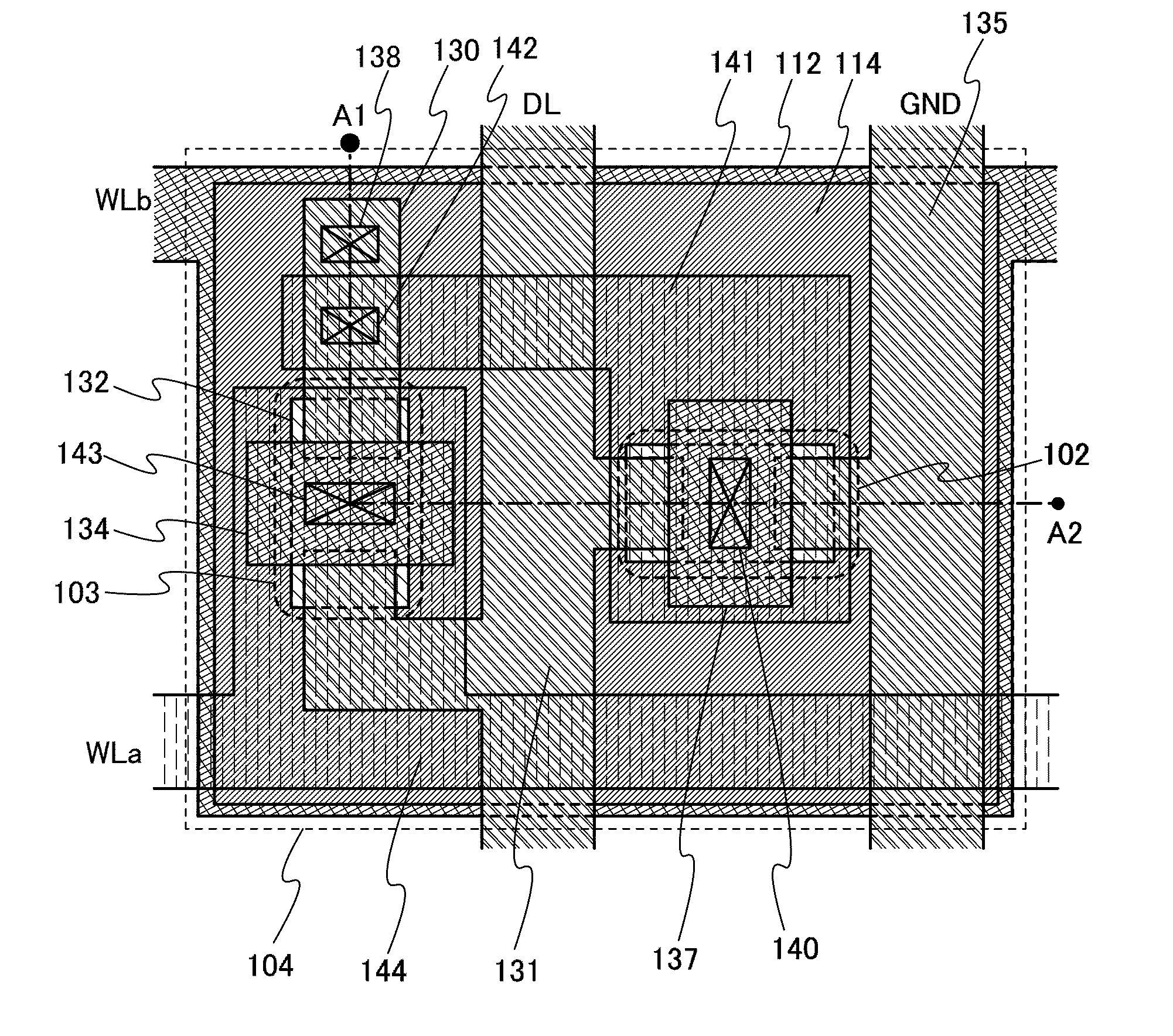

Semiconductor device

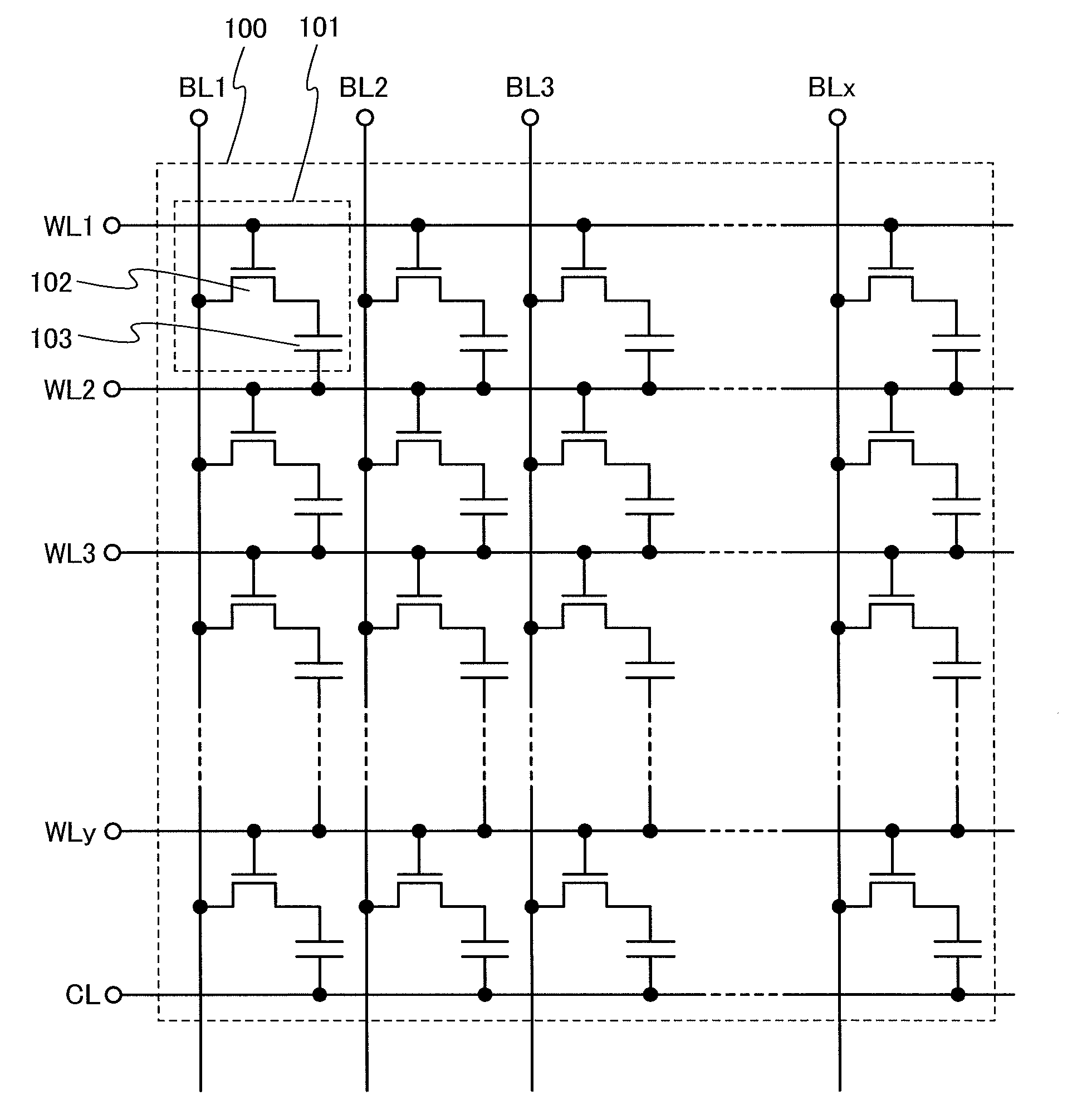

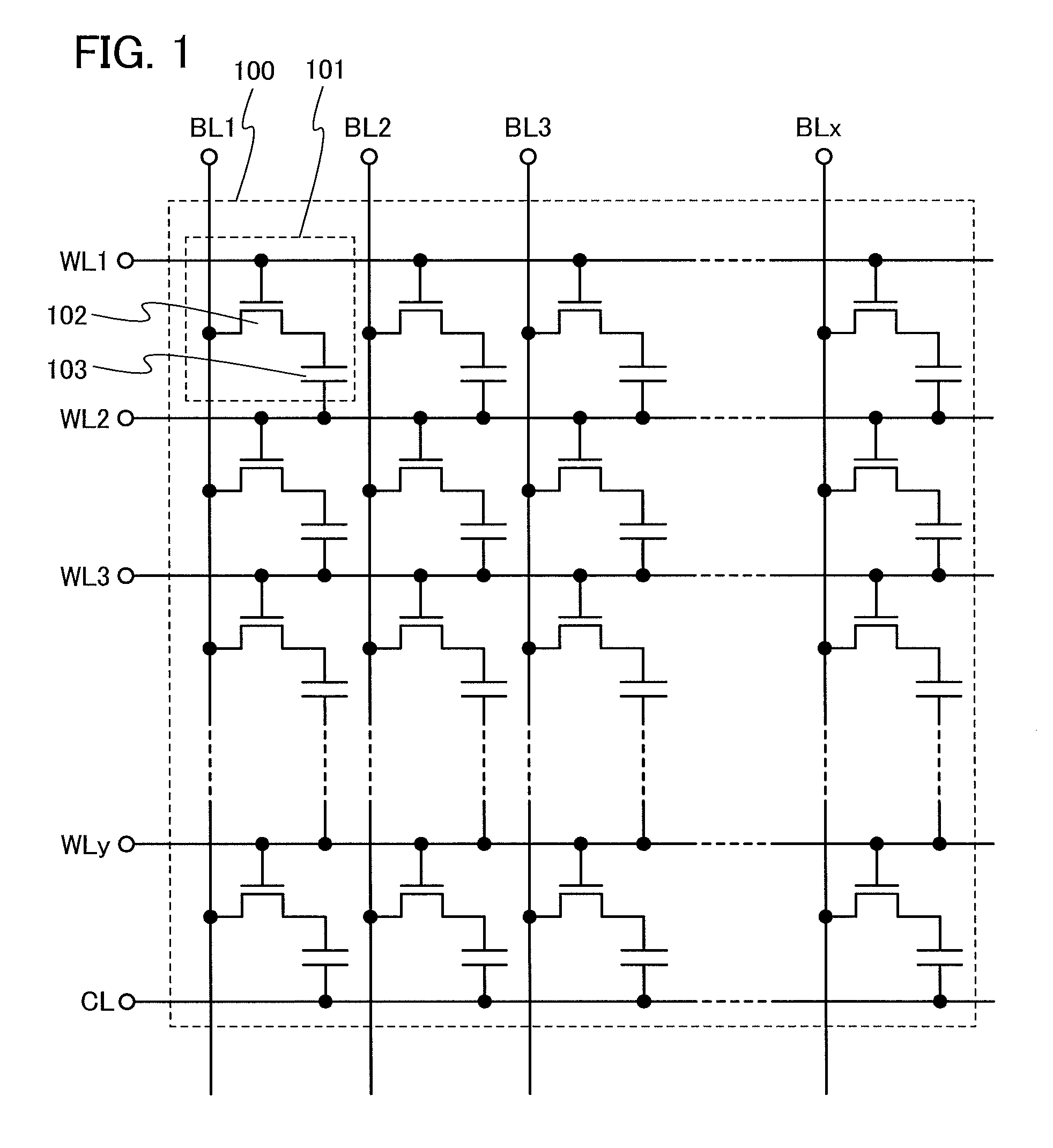

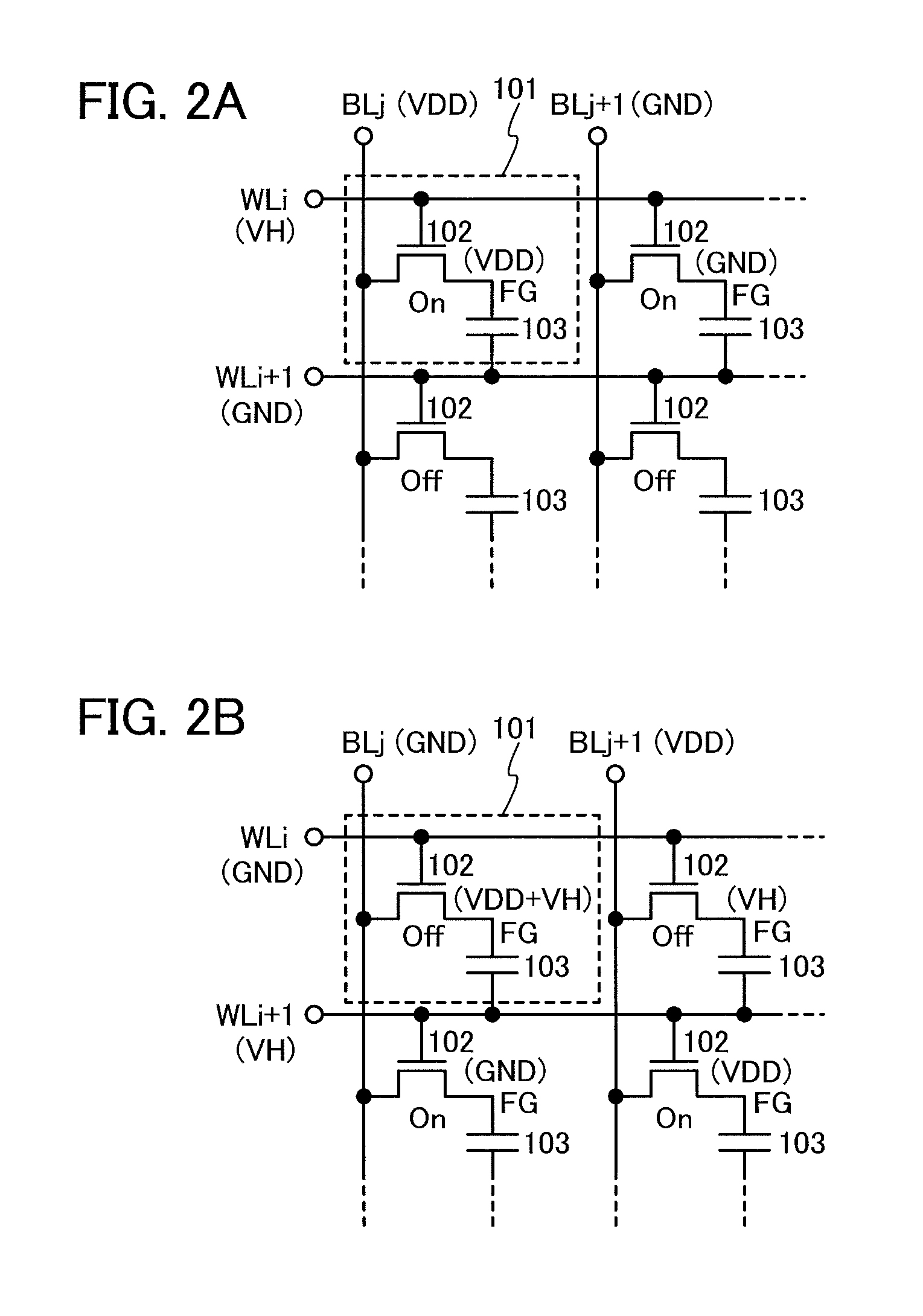

ActiveUS8797785B2Increasing memory capacity per unit areaMiniaturized and highly sophisticatedDigital storageSemiconductor devicesCapacitorSemiconductor

Provided is a memory device in which memory capacity per unit area is increased without making the manufacturing process complicated. The memory device includes a plurality of memory cells, a plurality of word lines, and a plurality of bit lines. Each of the plurality of memory cells includes a switching element and a capacitor including a first electrode and a second electrode. In at least one of the plurality of memory cells, in accordance with a potential applied to one of the plurality of word lines, the switching element controls a connection between one of the plurality of bit lines and the first electrode, and the second electrode is connected to another one of the plurality of word lines.

Owner:SEMICON ENERGY LAB CO LTD

Micro-electro-mechanical module

InactiveUS7907037B2Available powerPrevent charge leakageThermometers using material expansion/contactionThermal micromechanical switchesElectricityElectric power

A MEMS module that contains at least one integrated energy storage device whose discharge is minimized and controlled, so that power is available for system operation over longer periods of time. The MEMS module includes a device electrically coupled to the energy storage device for controlling charge transfers from the energy storage device while preventing charge leakage from the energy storage device. The controlling device includes a plurality of integrated MEMS switches that define open electrical paths that prevent charge leakage from the energy storage device through the MEMS switches, and are then operable to define closed electrical paths to allow charge transfers from the energy storage device, and preferably also allow charge transfers to the energy storage device, through the MEMS switches. The charge transfer can be utilized to power electronic circuits or store data in non-volatile digital memory.

Owner:BELLUTECH LLC

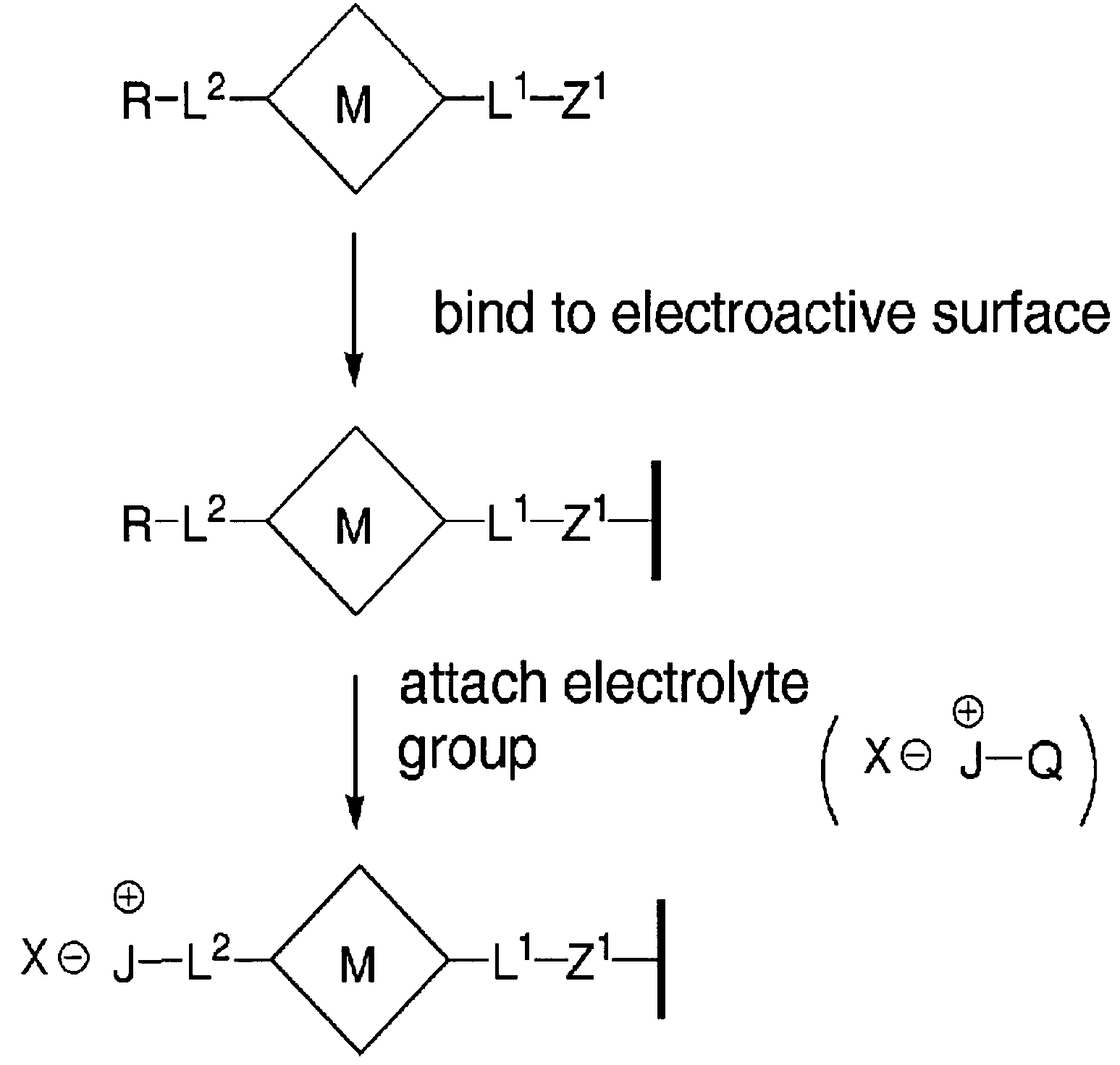

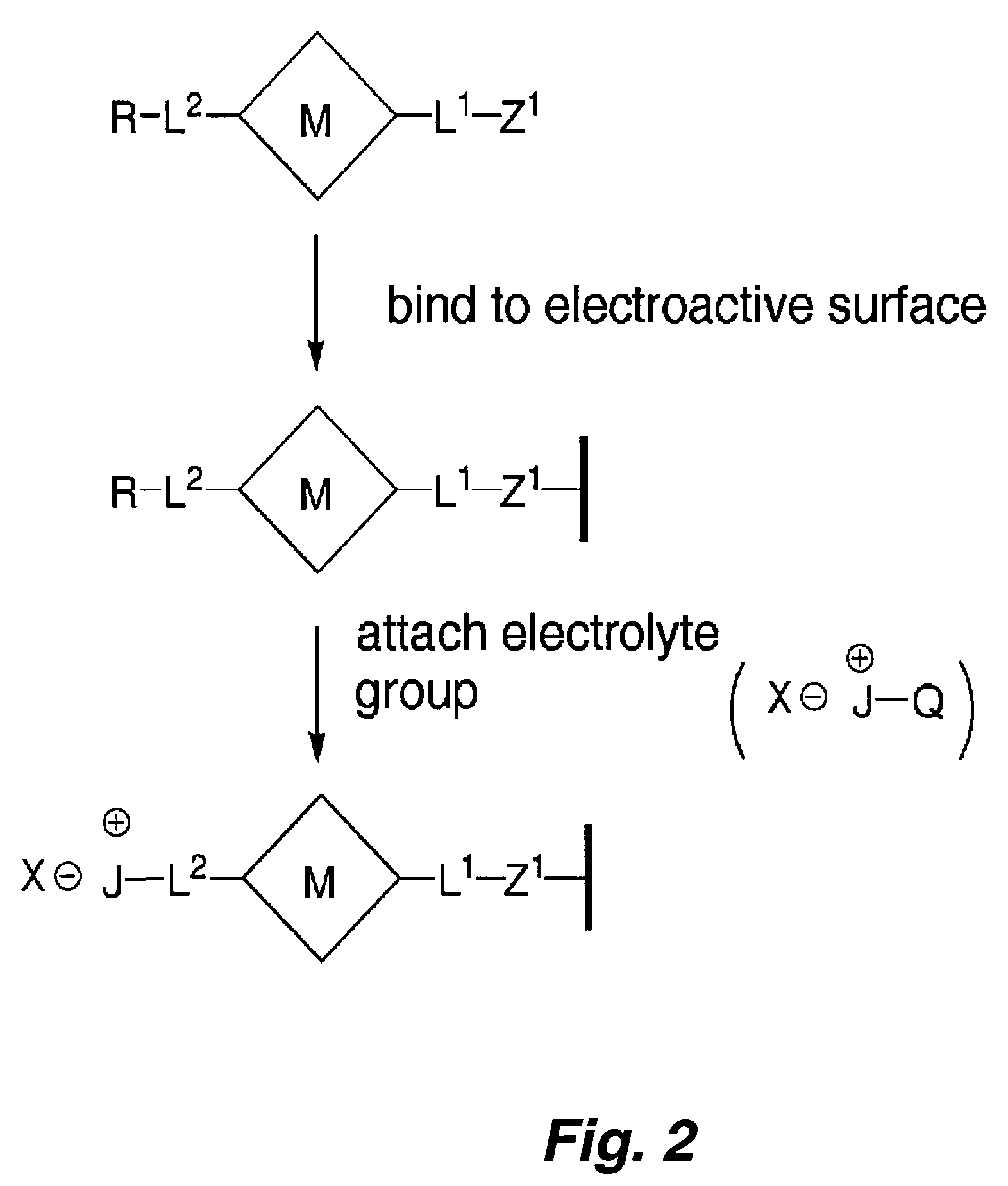

In situ patterning of electrolyte for molecular information storage devices

InactiveUS7312100B2Suitable mechanical propertyPrevent charge leakageNanoinformaticsOrganic electrolyte cellsReactive siteCombinatorial chemistry

This invention pertains to methods assembly of organic molecules and electrolytes in hybrid electronic. In one embodiment, a method is provided that involves contacting a surface / electrode with a compound of formula: R-L2-M-L1-Z1 where Z1 is a surface attachment group; L1 and L2 are independently linker or covalent bonds; M is an information storage molecule; and R is a protected or unprotected reactive site or group; where the contacting results in attachment of the redox-active moiety to the surface via the surface attachment group; and ii) contacting the surface-attached information storage molecule with an electrolyte having the formula: J-Q where J is a charged moiety (e.g., an electrolyte); and Q is a reactive group that is reactive with the reactive group (R) and attaches J to the information storage molecule thereby patterning the electrolyte on the surface.

Owner:NORTH CAROLINA STATE UNIV +1

Semiconductor device and manufacturing method thereof

ActiveUS20130299888A1Low costControl is complicatedTransistorTelevision system detailsEngineeringPhotodiode

In a CMOS image sensor in which a plurality of pixels is arranged in a matrix, a transistor in which a channel formation region includes an oxide semiconductor is used for each of a charge accumulation control transistor and a reset transistor which are in a pixel portion. After a reset operation of the signal charge accumulation portion is performed in all the pixels arranged in the matrix, a charge accumulation operation by the photodiode is performed in all the pixels, and a read operation of a signal from the pixel is performed per row. Accordingly, an image can be taken without a distortion.

Owner:SEMICON ENERGY LAB CO LTD

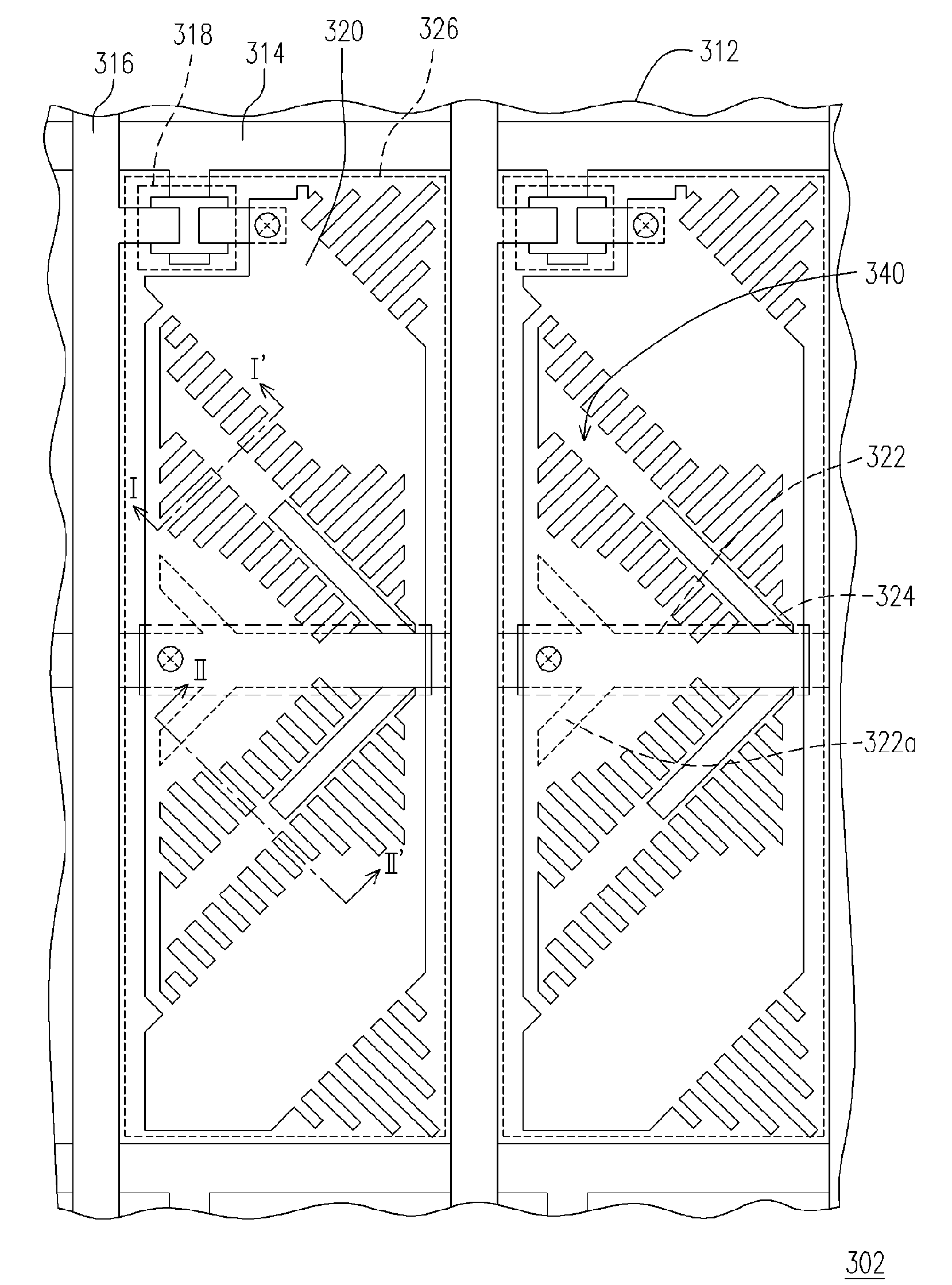

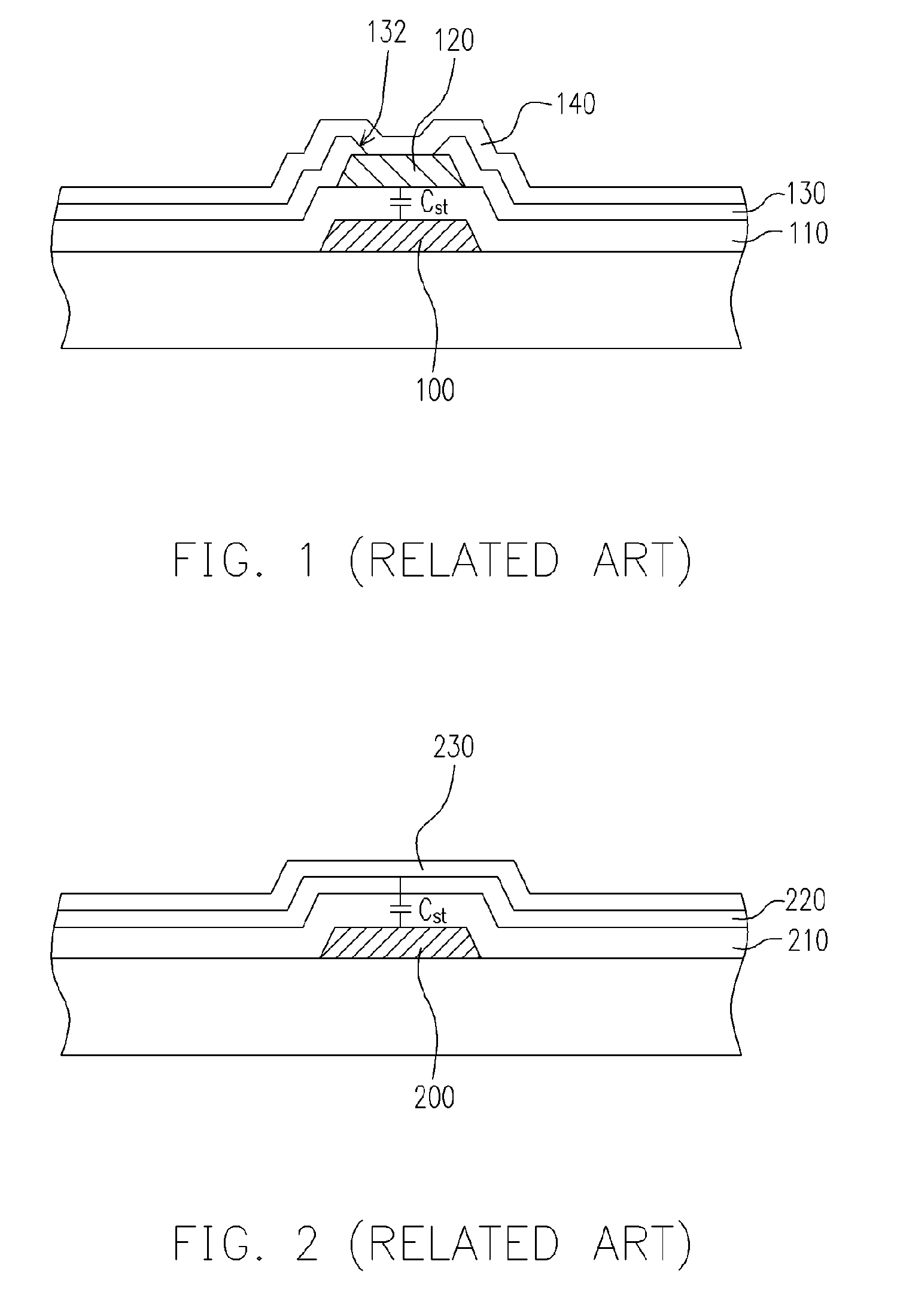

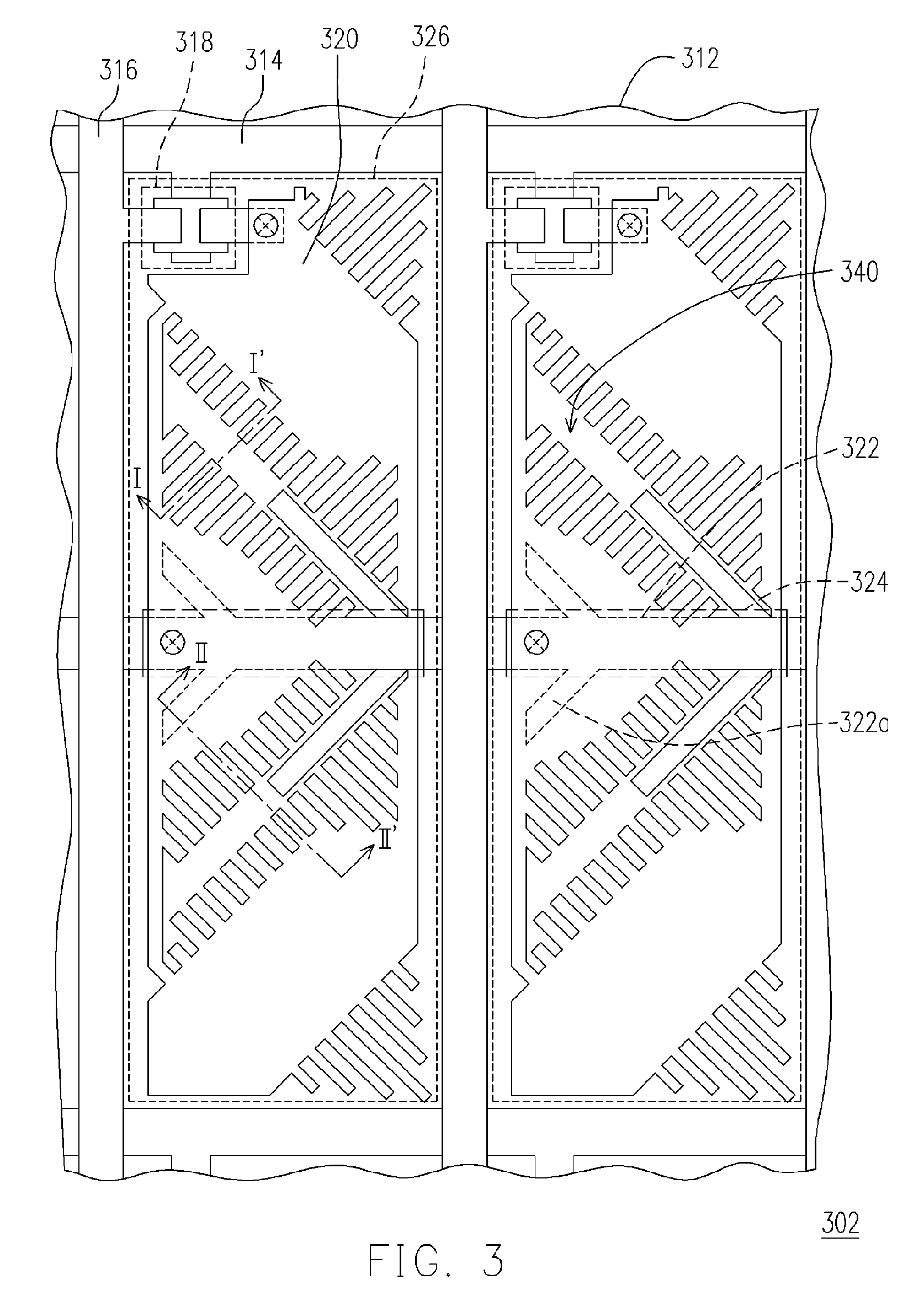

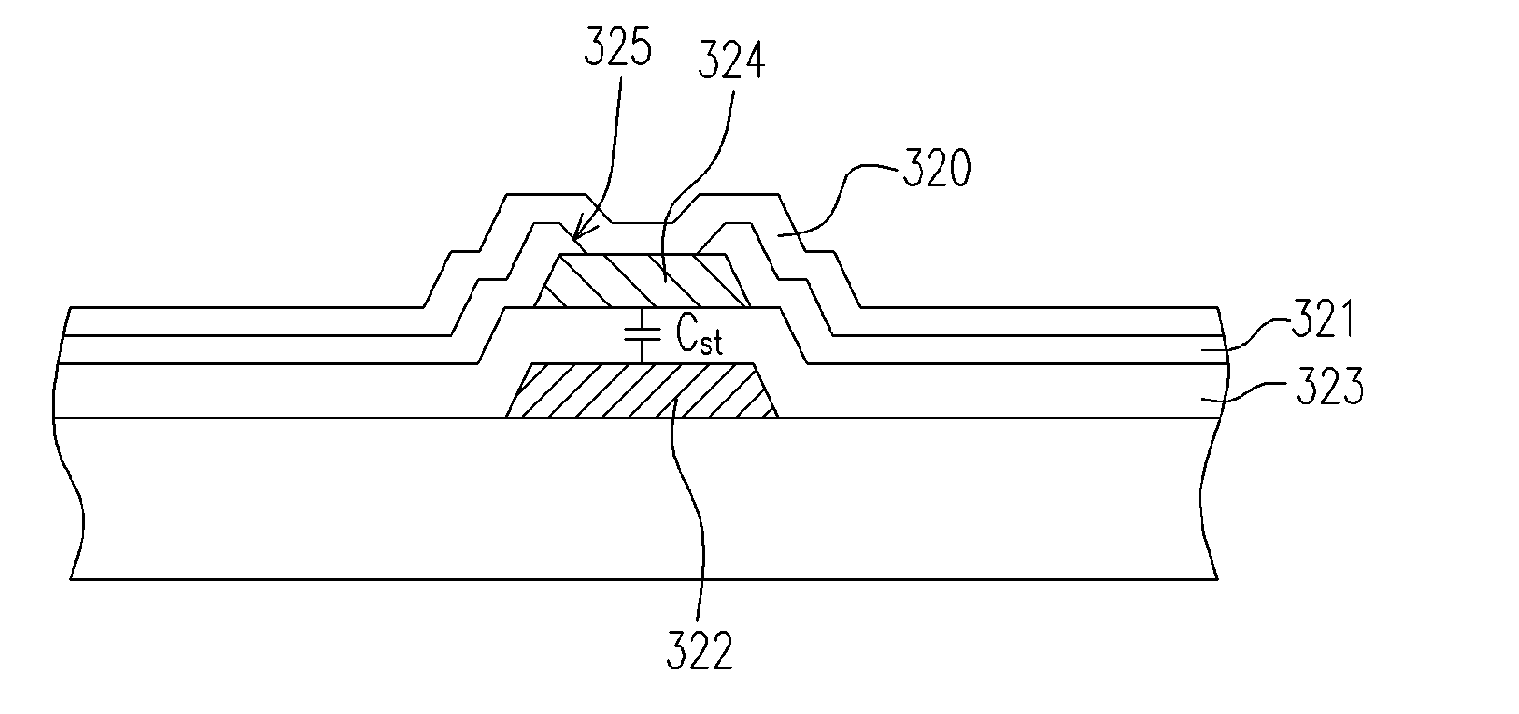

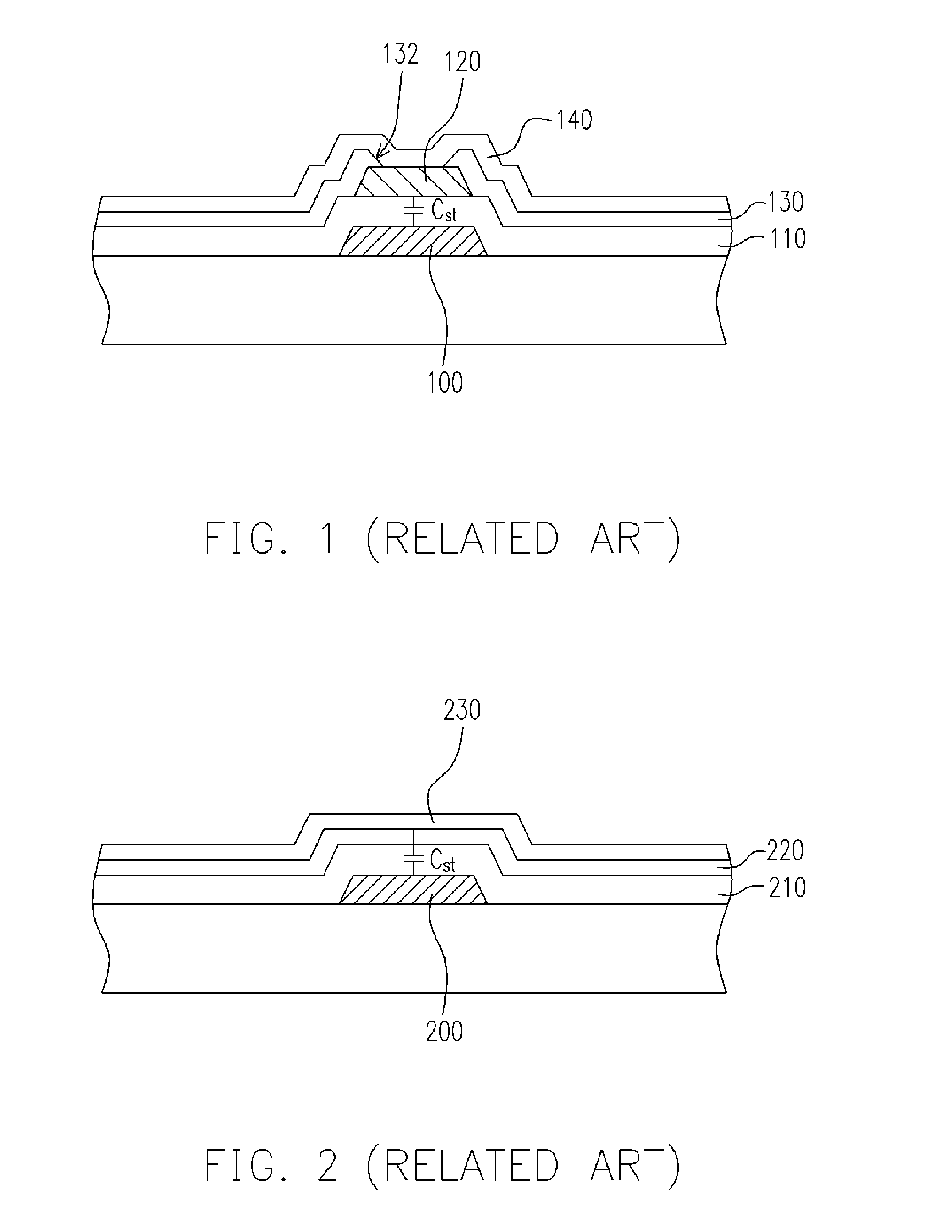

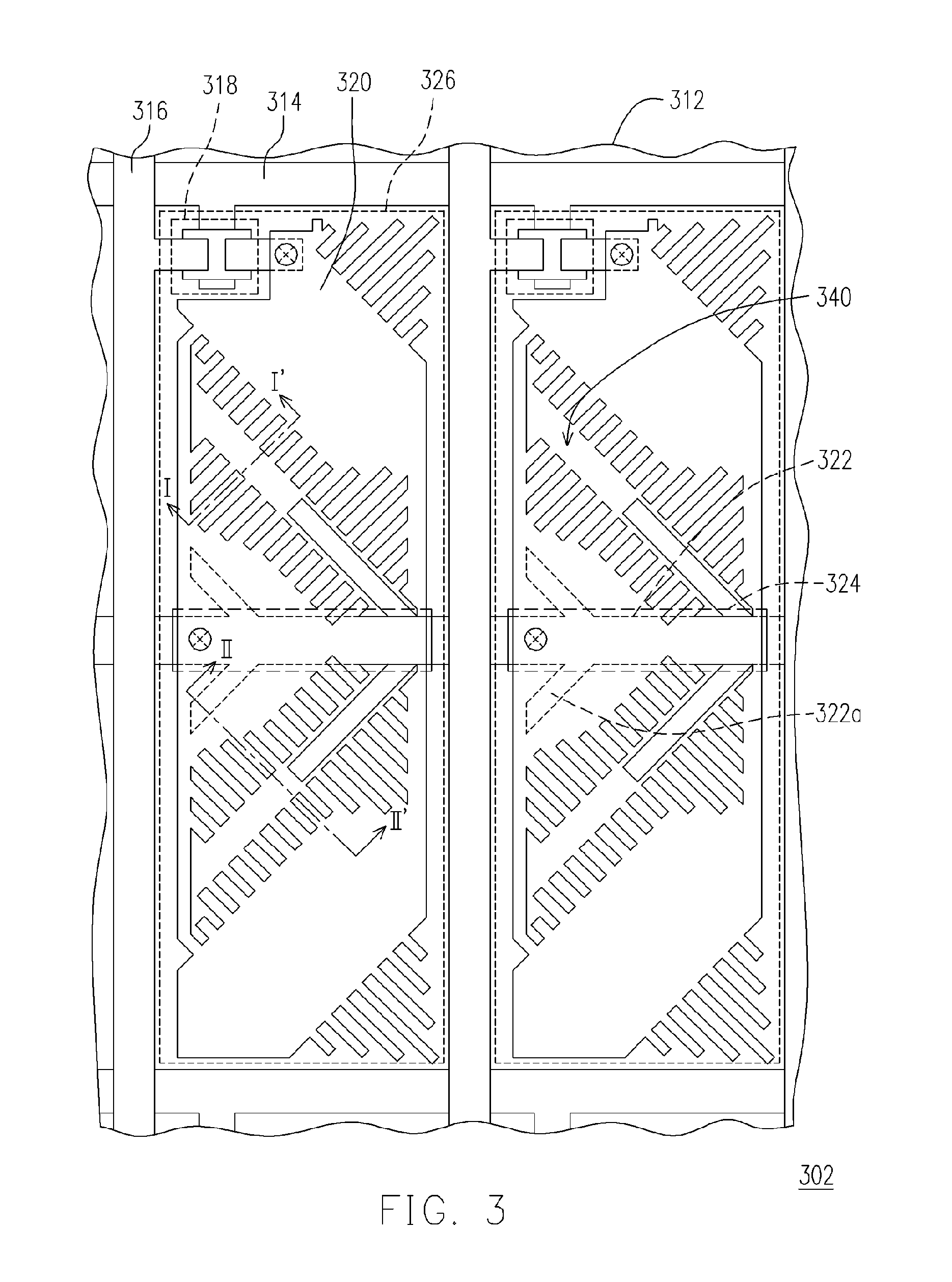

Liquid crystal display panel and thin film transistor array

ActiveUS7362390B2Improve performancePrevent charge leakageNon-linear opticsTransistor arrayCapacitance

Owner:AU OPTRONICS CORP

Method of manufacturing a semiconductor device

InactiveUS20070269972A1Improve uniformityFew defectSolid-state devicesSemiconductor/solid-state device manufacturingHydrogenSilicon oxide

Provided is a method of manufacturing a semiconductor device having an ONO film composed of a bottom silicon oxide film, a silicon nitride film and a top silicon oxide film over a substrate. The top silicon oxide film of the ONO film is formed in the following manner. A silicon oxide film is formed over the silicon nitride film, and then a hydrogen gas and an oxygen gas are reacted over the silicon nitride film by heating the silicon nitride film (substrate) while reducing the pressure from the atmospheric pressure to grow the silicon oxide film into the top silicon oxide film. According to the present invention, a silicon oxide film having good uniformity and fewer defects can be formed over a silicon-containing underlayer.

Owner:RENESAS TECH CORP

Pinned photodiode (PPD) pixel with high shutter rejection ratio for snapshot operating CMOS sensor

ActiveUS7423302B2Prevent leakageAvoid it happening againSolid-state devicesRadiation controlled devicesCMOS sensorFloating diffusion

A pixel image sensor has a high shutter rejection ratio that prevents substrate charge leakage to a floating diffusion storage node of the pixel image sensor and prevents generation of photoelectrons within the floating diffusion storage node and storage node control transistor switches of the pixel image sensor. The pixel image sensor that prevents substrate charge leakage of photoelectrons from pixel image sensor adjacent to the pixel image sensor. The pixel image sensor is fabricated on a substrate with an isolation barrier and a carrier conduction well. The isolation barrier formed underneath the floating diffusion storage node allows effective isolation by draining away the stray carriers and preventing them from reaching the floating diffusion storage node. The carrier conduction well in combination with the deep N-well isolation barrier separates the pinned photodiode region from the deep N-well isolation barrier that is underneath the floating diffusion storage node.

Owner:GULA CONSULTING LLC

Liquid crystal display panel, thin film transistor array and capacitor structure

ActiveUS20060023136A1Increase capacitanceImprove performanceNon-linear opticsCapacitanceTransistor array

A thin film transistor array comprising a plurality of common lines for providing the storage capacitance of pixels is provided. In particular, each of the common lines comprises a plurality of branches. Wherein, the common line and the branches thereof, and the pixel electrode constitute the storage capacitor. The branches are disposed at pixels where the luminance quality is bad. Therefore, the storage capacitance of the pixels can be enhanced without altering the aperture ratio of the pixels. Accordingly, the performance of the liquid crystal display panel can be improved.

Owner:AU OPTRONICS CORP

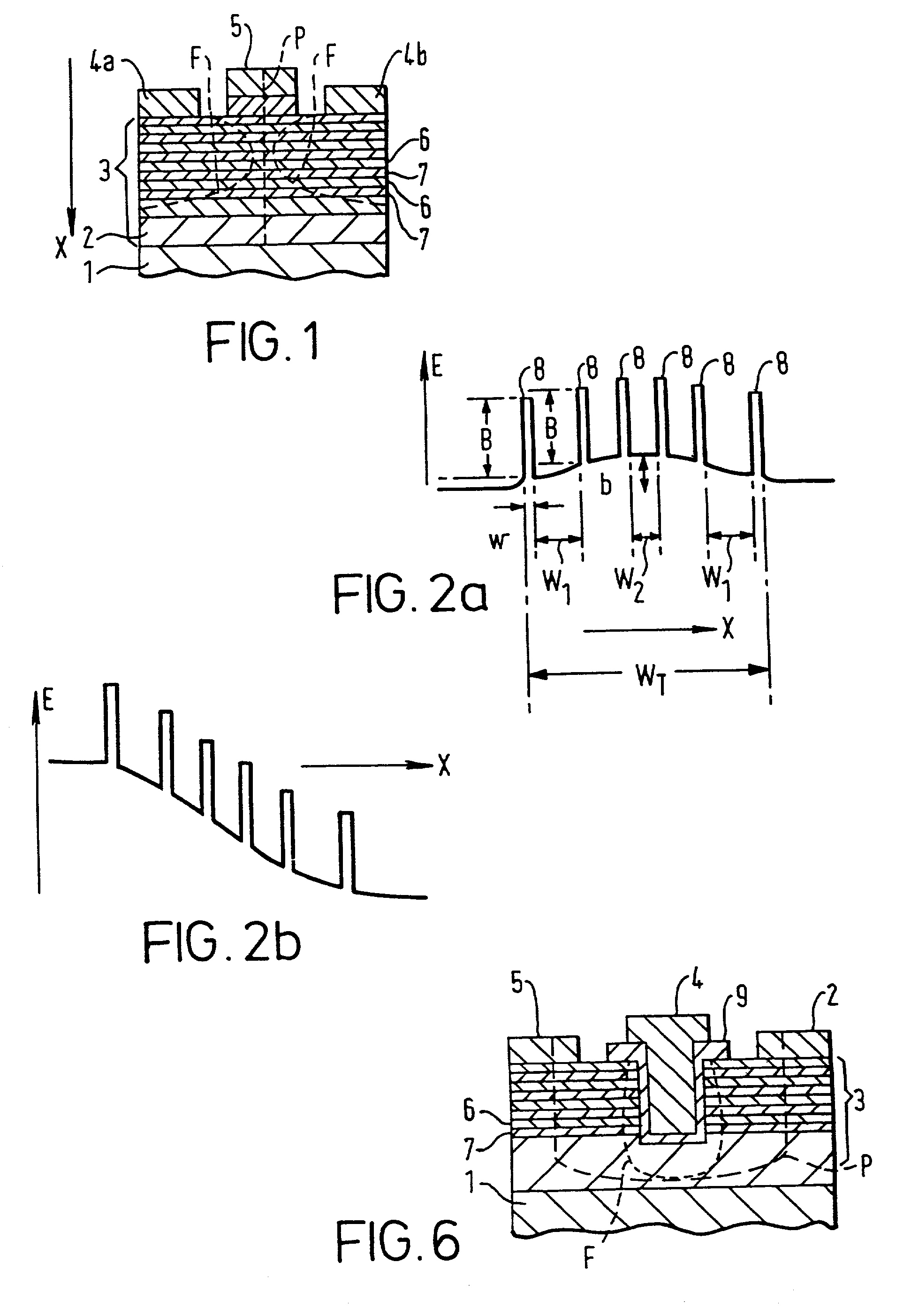

Controllable conduction device with electrostatic barrier

InactiveUS7132713B2Large on/off current ratioPrevent charge leakageTransistorNanoinformaticsCharge carrierRandom access memory

A controllable conduction device in the form of a transistor comprises source and drain regions 5, 2 between which extends a conduction path P for charge carriers, a gate 4 for controlling charge carrier flow along the conduction path and a multiple layer structure 3 providing a multiple tunnel junction configuration in the conduction path, with the result that current leakage is blocked by the multiple tunnel junction configuration when the transistor is in its off state. Vertical and lateral transistor configurations are described, together with use of the transistor in complimentary pairs and for a random access memory cell. Improved gate structures are described which are also applicable to memory devices that incorporate the tunnel barrier configuration to store charge on the memory node.

Owner:HITACHI LTD

Semiconductor device with light-blocking layers

ActiveUS9299723B2Easy dischargeShorten the overall cycleTransistorSolid-state devicesEngineeringActive layer

Owner:SEMICON ENERGY LAB CO LTD

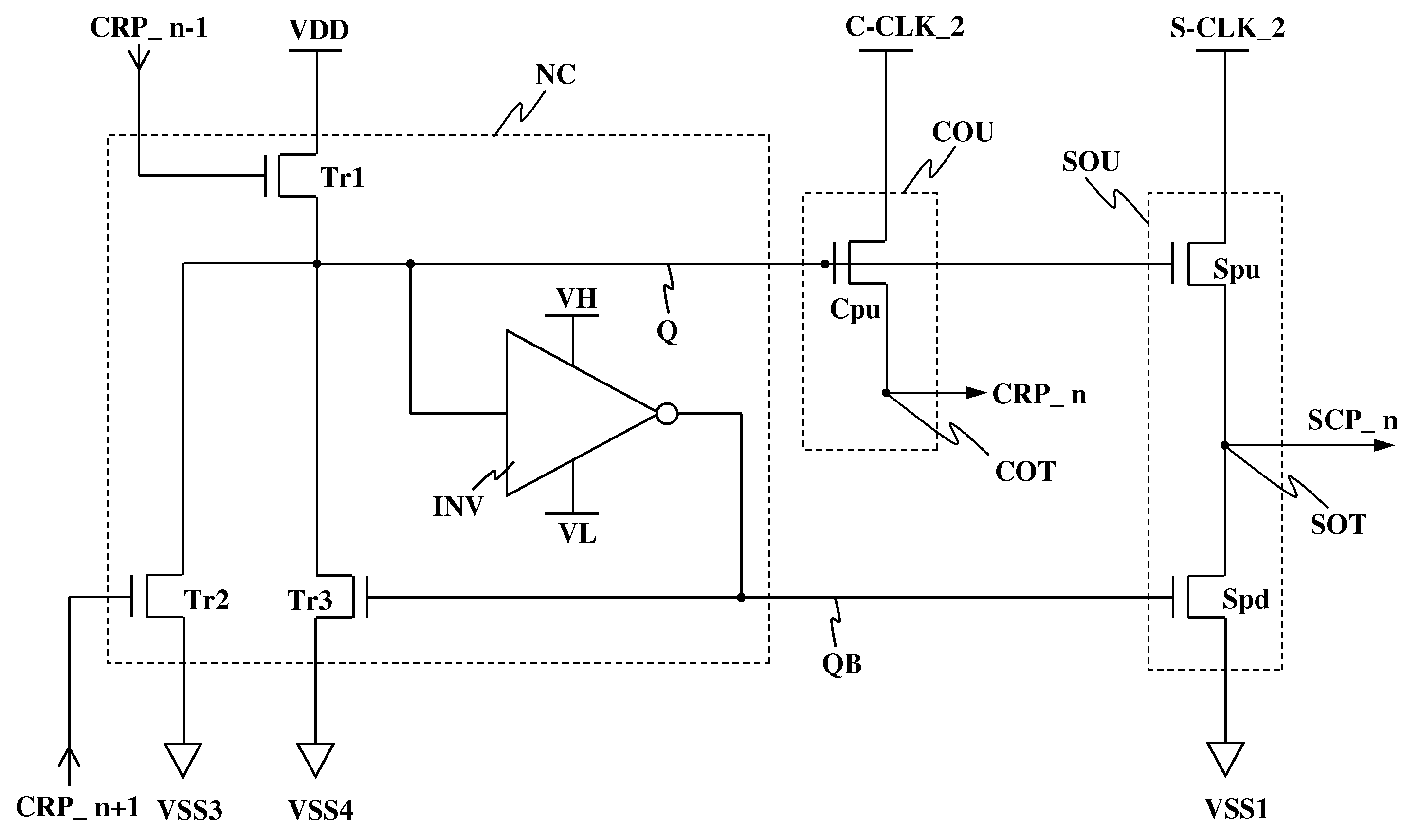

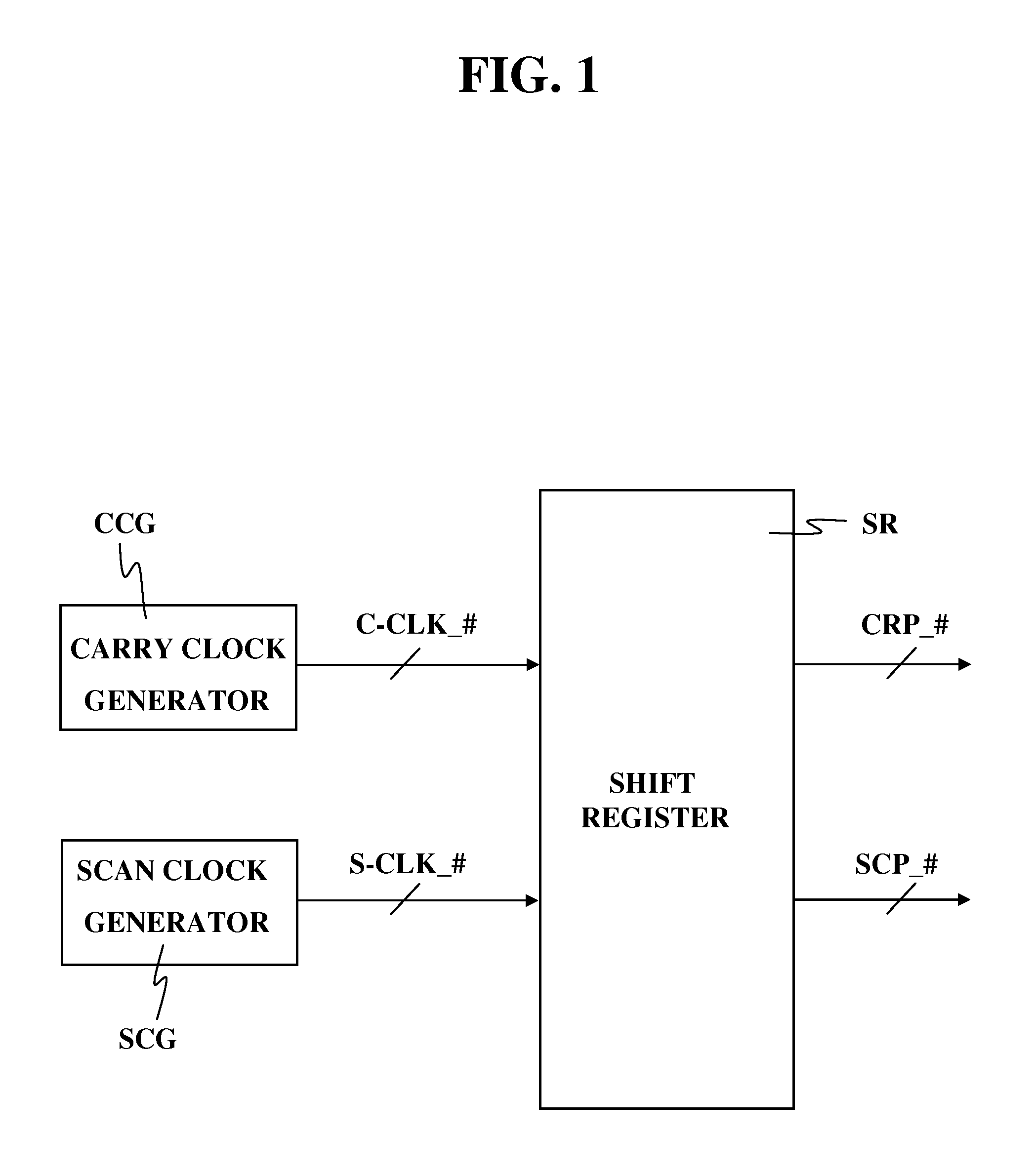

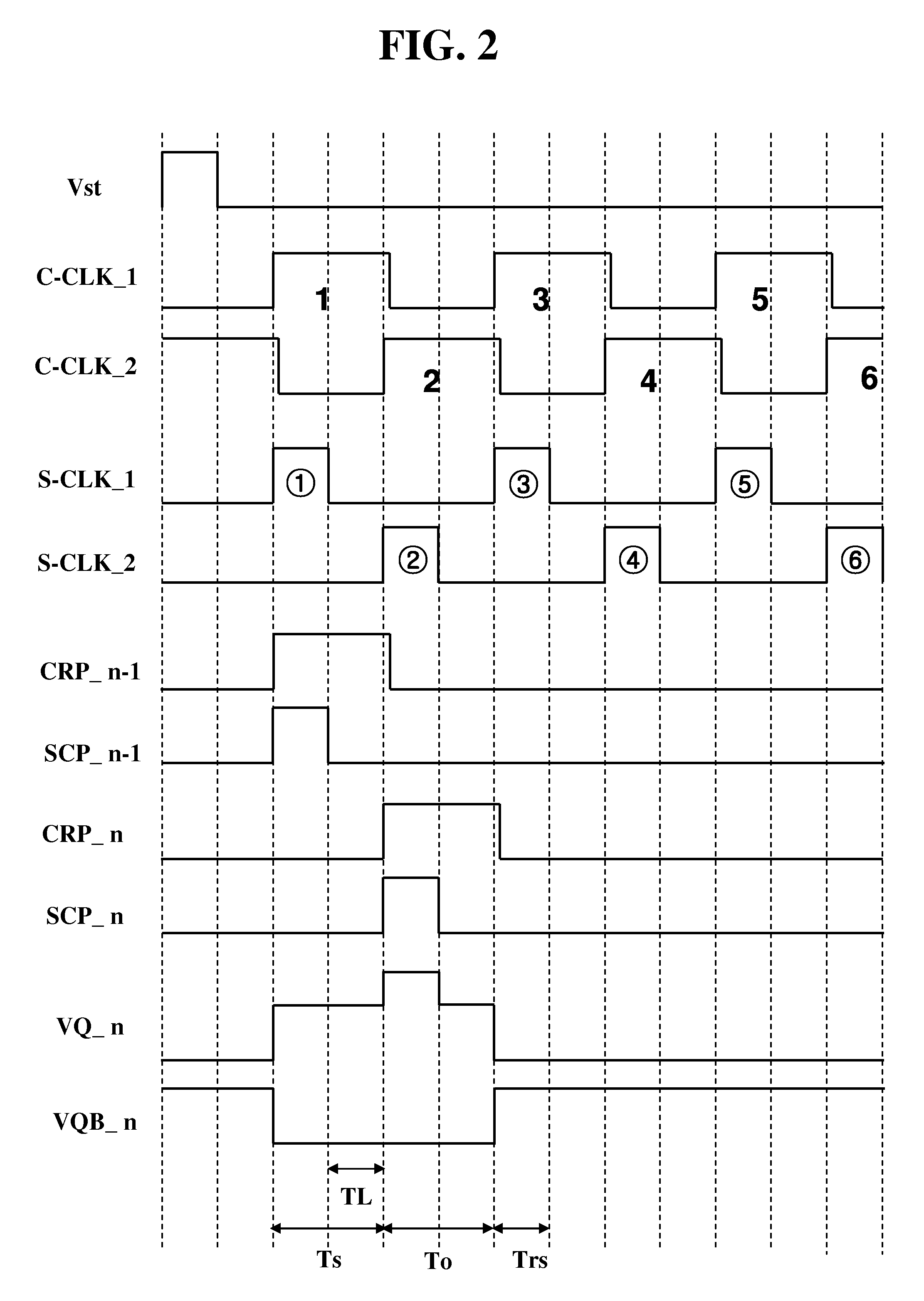

Shift register

ActiveUS8842803B2Prevent charge leakageStatic indicating devicesDigital storageShift registerEngineering

Disclosed herein is a shift register which is capable of preventing leakage of charges at a set node which occurs when the duty ratio of a scan pulse is small, so as to normally output a scan pulse. The shift register includes a plurality of stages for sequentially generating outputs thereof. Each of the stages includes a carry output unit for outputting a carry pulse to drive at least one of a downstream stage and an upstream stage, and a scan output unit for outputting a scan pulse to drive a gate line. Each of the outputs generated from the stages includes the carry pulse and the scan pulse. The carry pulse and the scan pulse are paired to correspond to each other. The paired carry pulse and scan pulse have different durations.

Owner:LG DISPLAY CO LTD

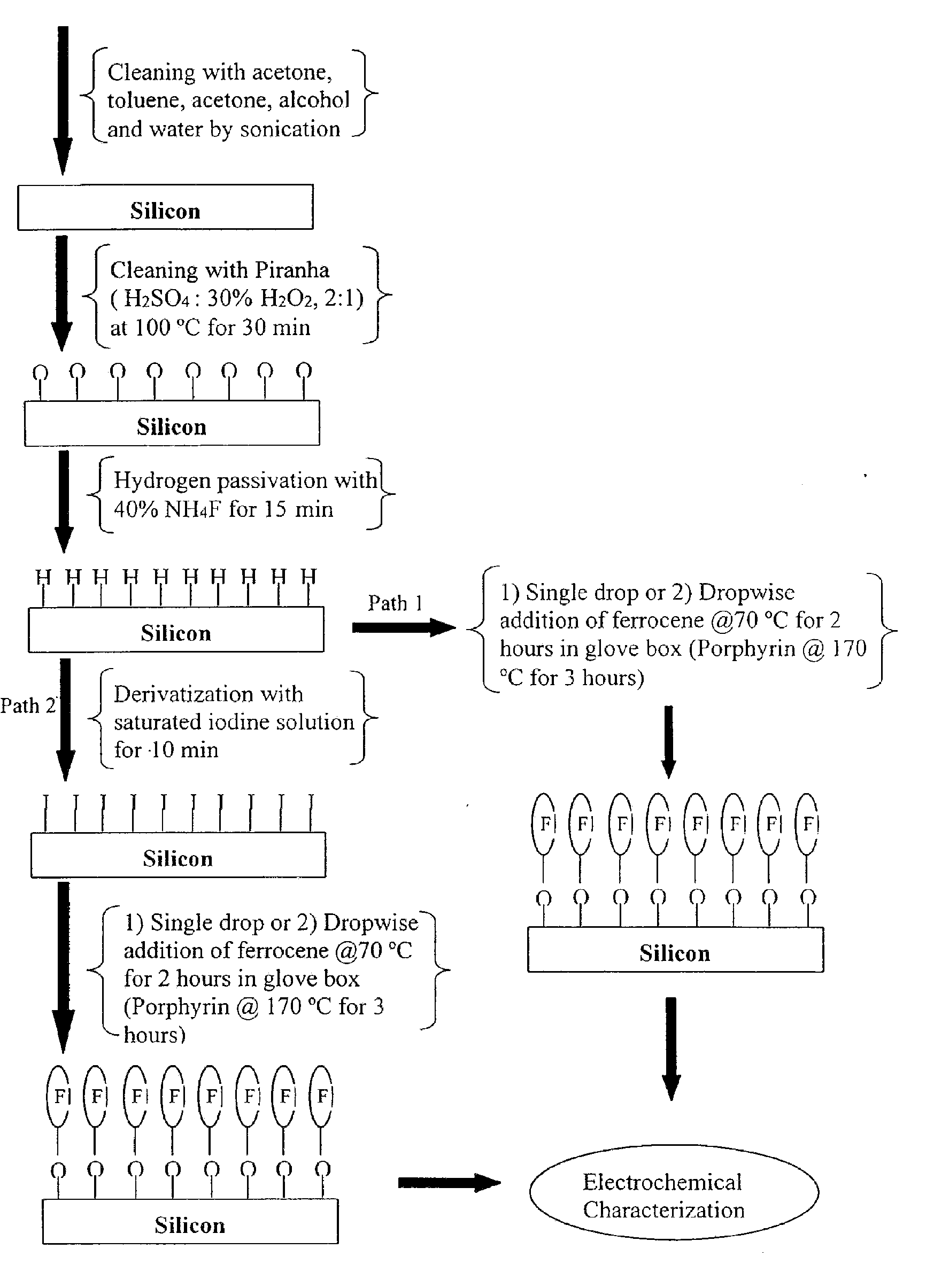

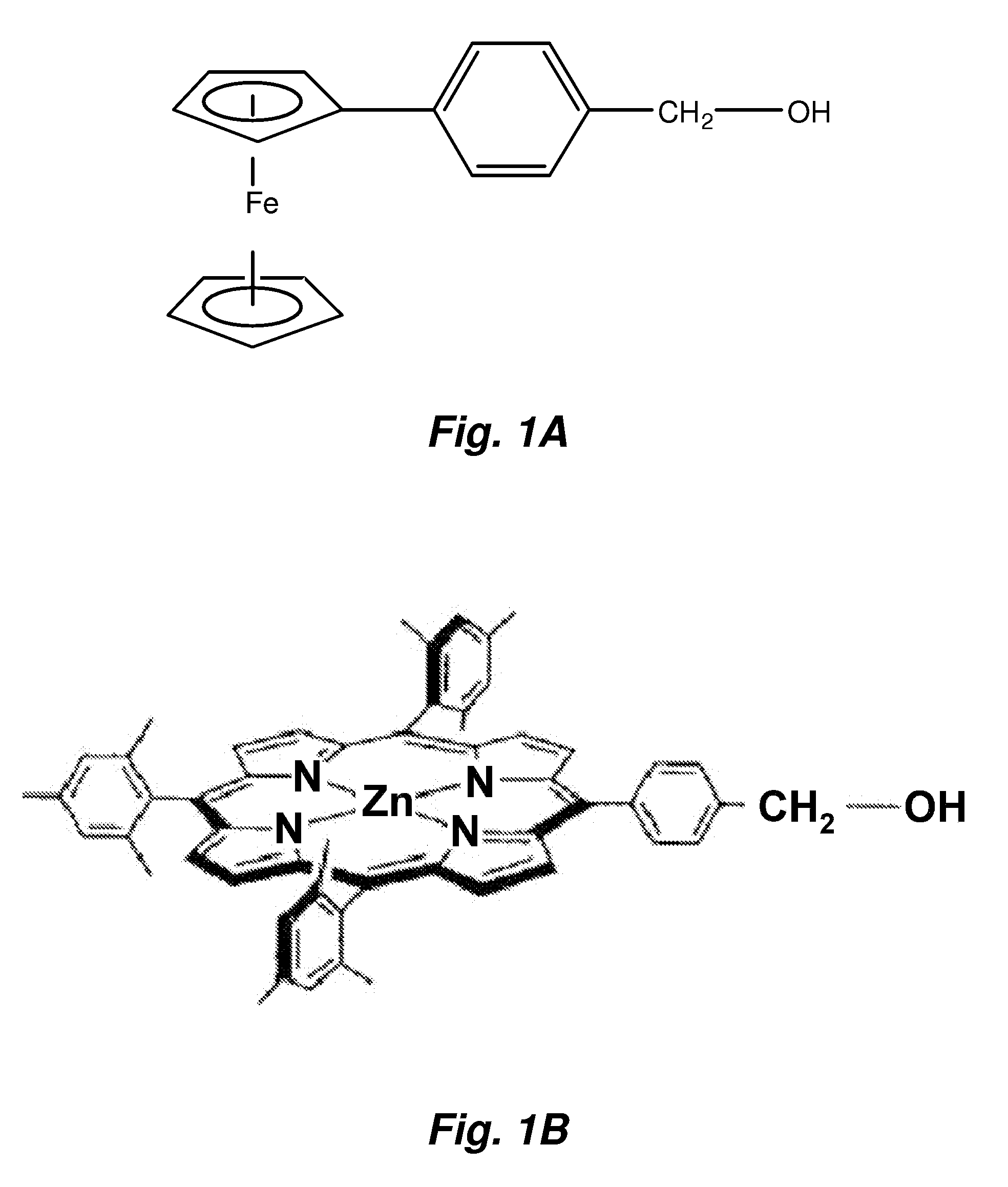

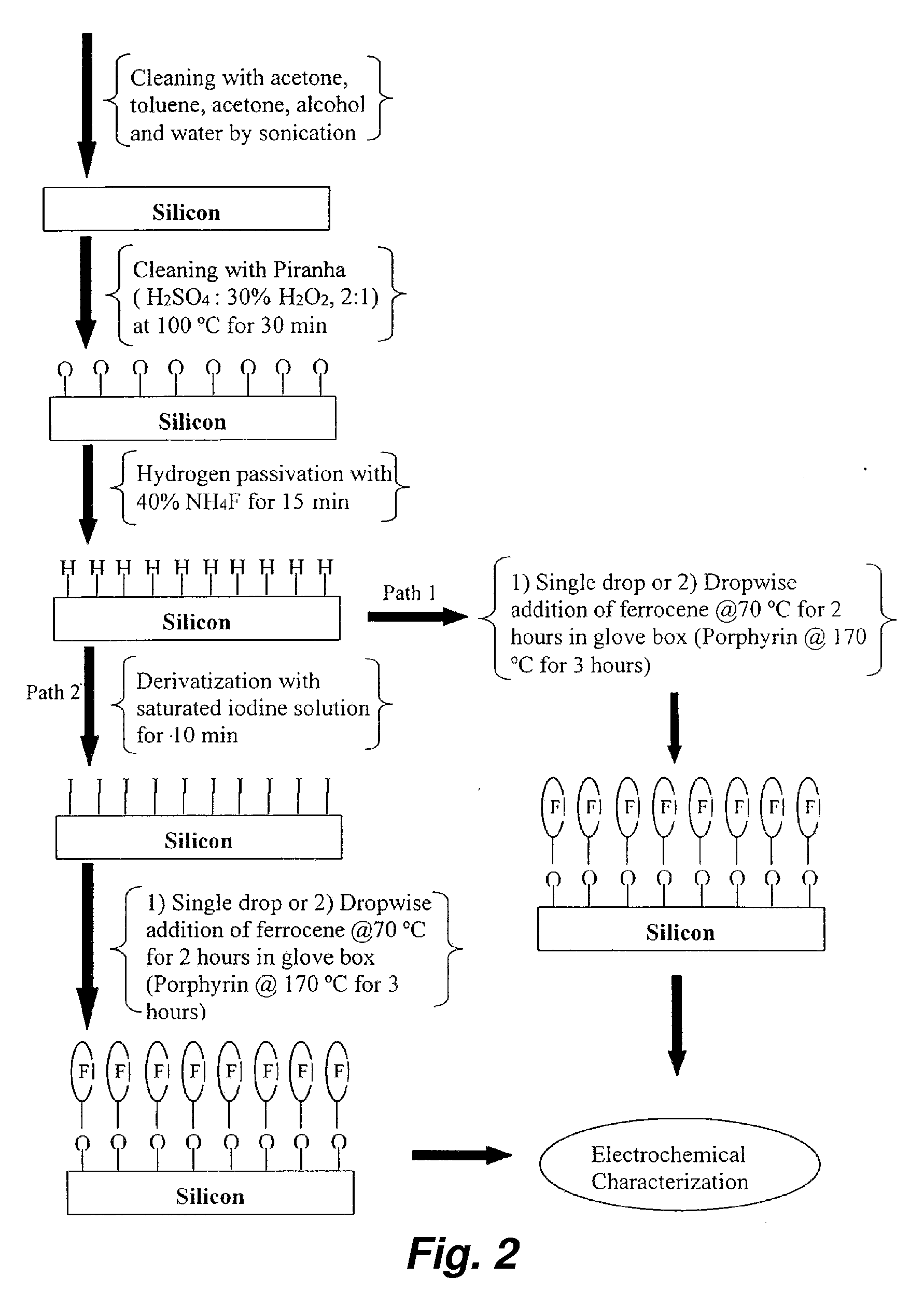

Formation of self-assembled monolayers on silicon substrates

InactiveUS20090121210A1Suitable mechanical propertyPrevent charge leakageMaterial nanotechnologyLiquid surface applicatorsAlcoholThiol

This invention provides a new method of forming a self-assembling monolayer (SAM) of alcohol-terminated or thiol-terminated organic molecules (e.g. ferrocenes, porphyrins, etc.) on a silicon or other group IV element surface. The assembly is based on the formation of an E-O— or an E-S— bond where E is the group IV element (e.g. Si, Ge, etc.). The procedure has been successfully used on both P- and n-type group IV element surfaces. The assemblies are stable under ambient conditions and can be exposed to repeated electrochemical cycling.

Owner:RGT UNIV OF CALIFORNIA

Non-volatile memory device including charge trap layer and method of manufacturing the same

InactiveUS20090050954A1Charge leakageReduce operating speedSemiconductor/solid-state device manufacturingSemiconductor devicesCharge layerCrystalline materials

Provided are a non-volatile memory device and a method of manufacturing the non-volatile memory device. The non-volatile memory device includes a charge trap layer having a crystalline material. In the method, a tunneling insulating layer is formed on a substrate, and a crystalline charge trap layer is formed on the tunneling insulating layer.

Owner:SAMSUNG ELECTRONICS CO LTD

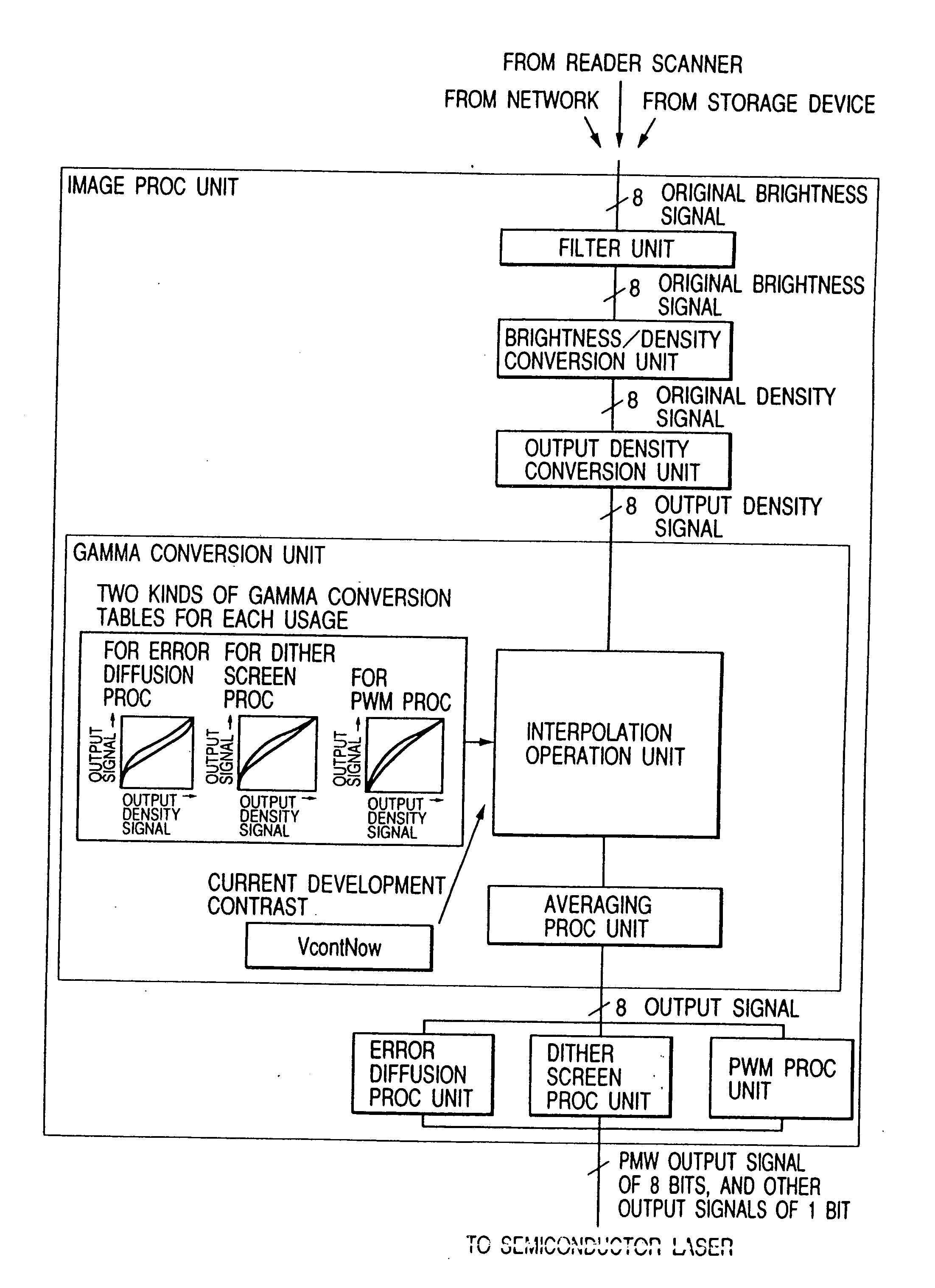

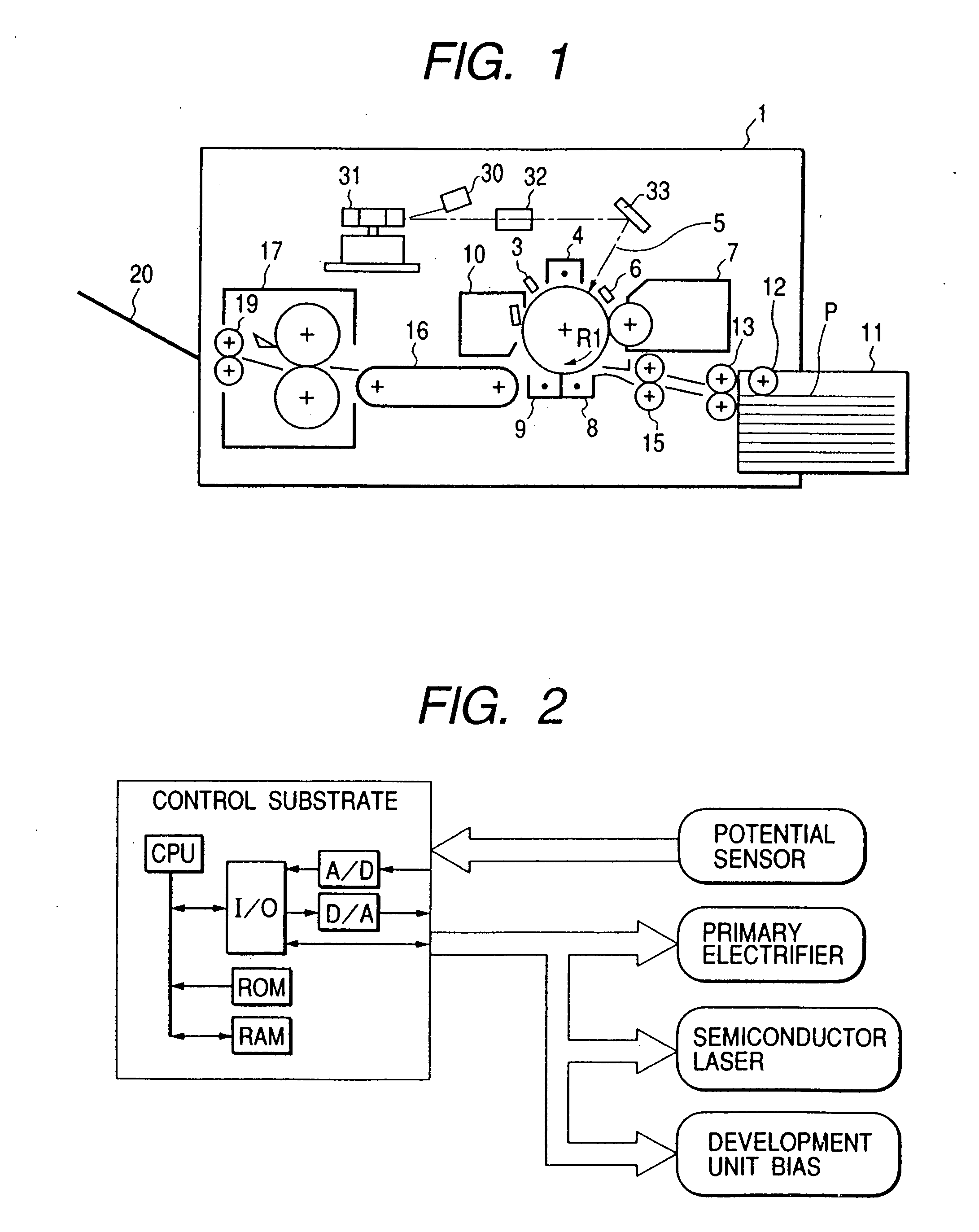

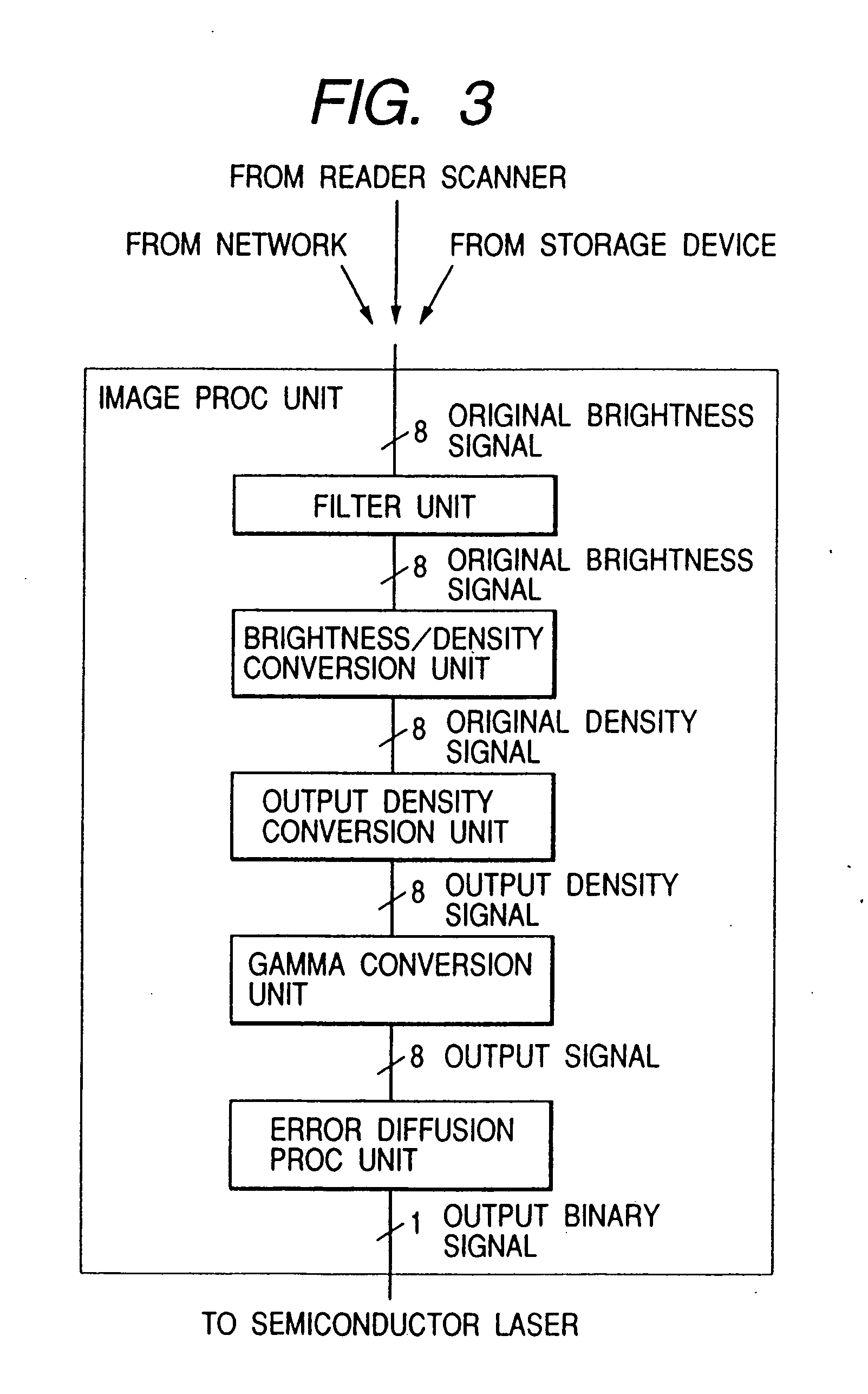

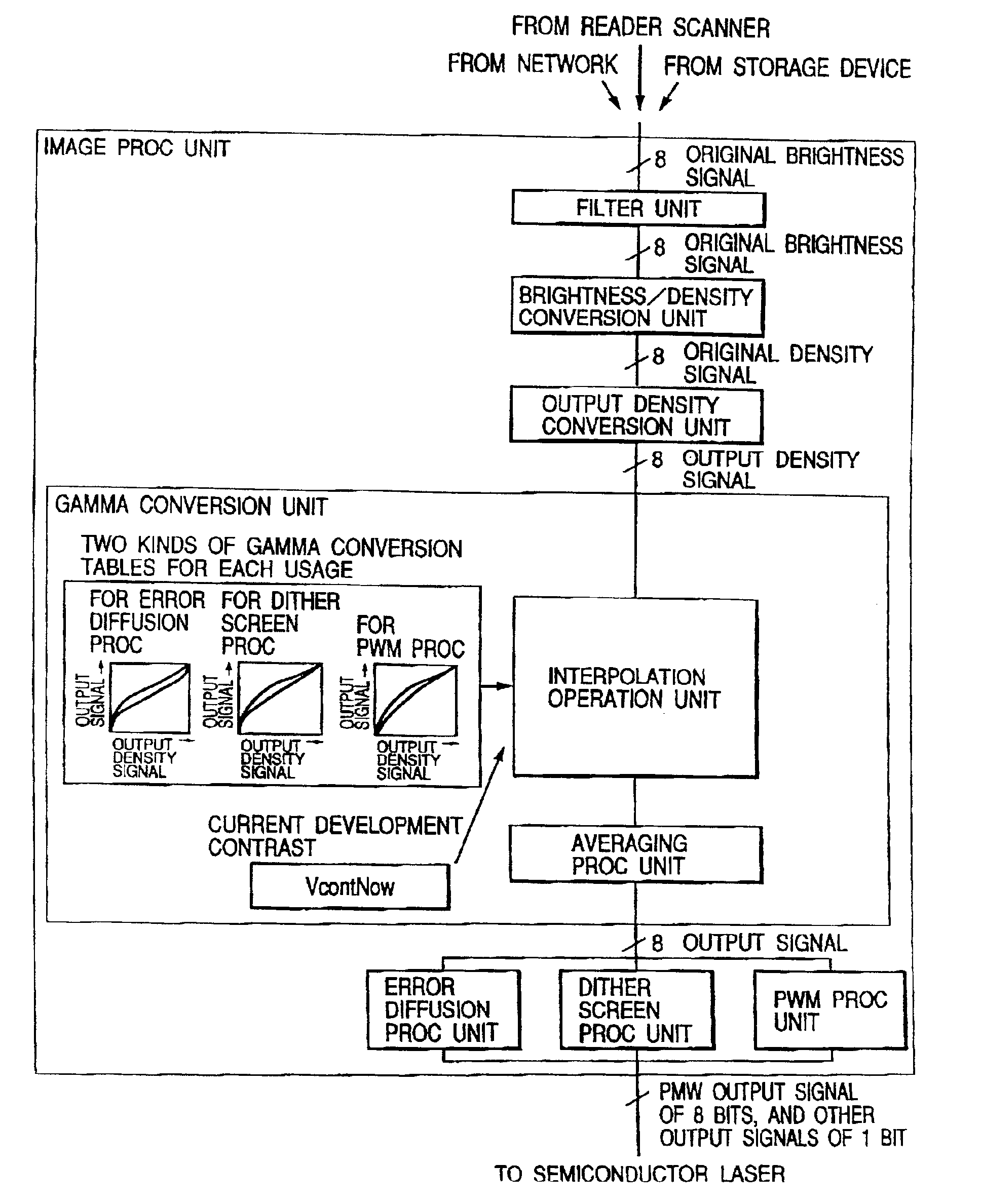

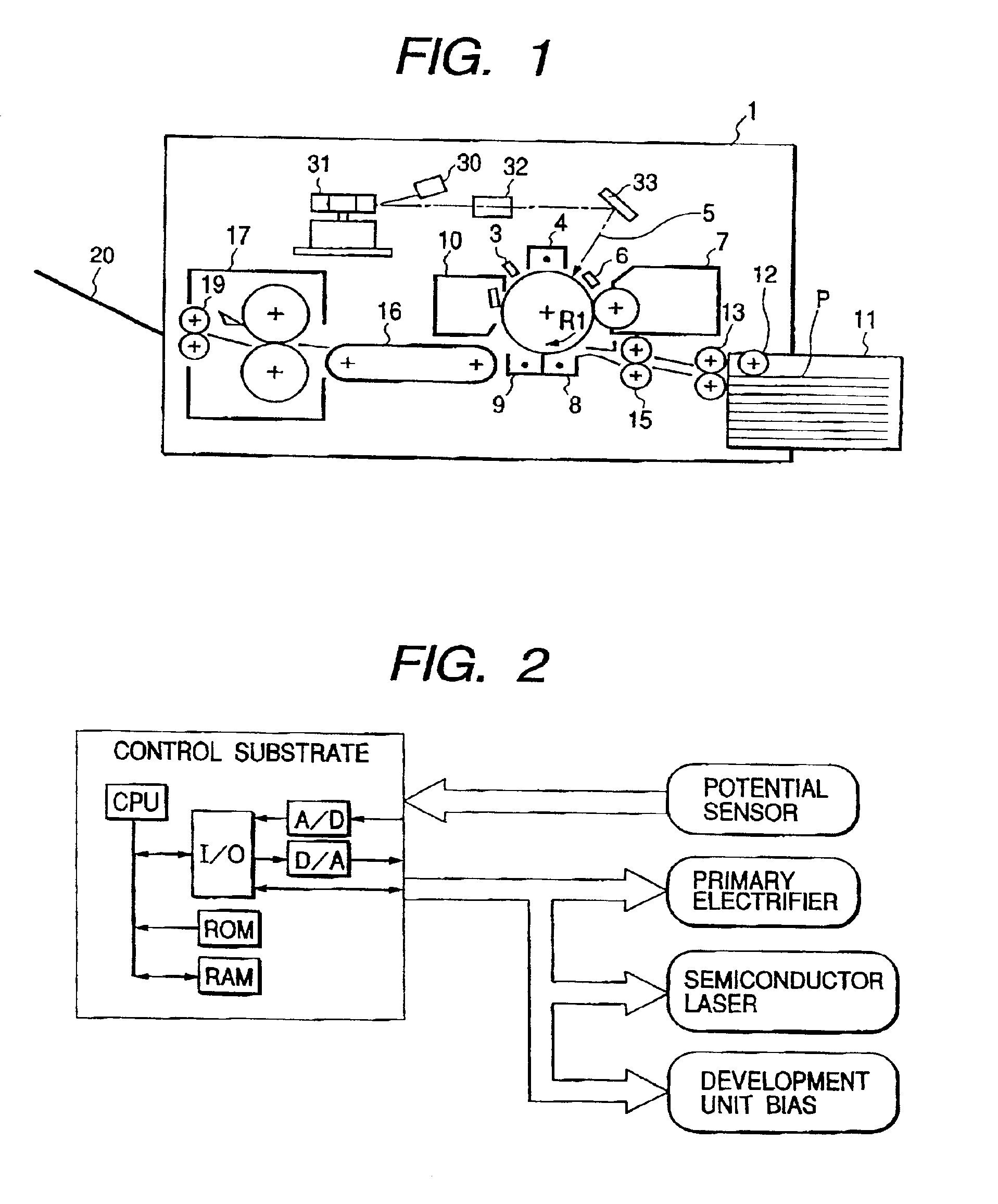

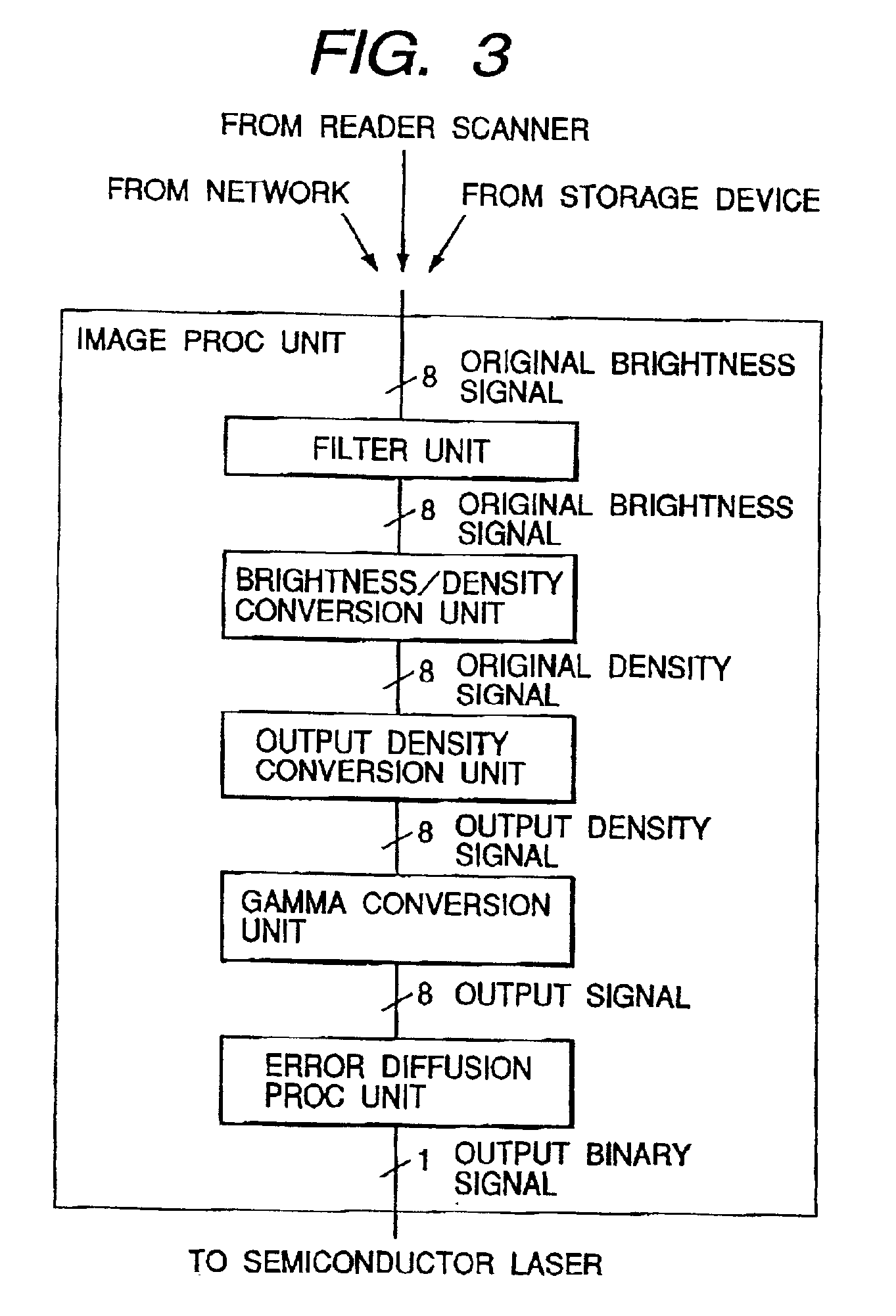

Image forming apparatus with gamma conversion means

InactiveUS20050195444A1Little deteriorationPreventing Image Quality DeteriorationImage enhancementElectrographic process apparatusImage contrastImage formation

The invention provides an image forming apparatus and an image forming method, capable of providing an image with little deterioration, even in case the image contrast has to be adjusted not for the purpose of image adjustment, such as for reducing the toner consumption amount or for preventing the leak in the charging device.

Owner:CANON KK

Image forming apparatus with gamma conversion means

InactiveUS6987576B2Little deteriorationPreventing Image Quality DeteriorationElectrographic process apparatusVisual presentationImage contrastImage formation

Owner:CANON KK

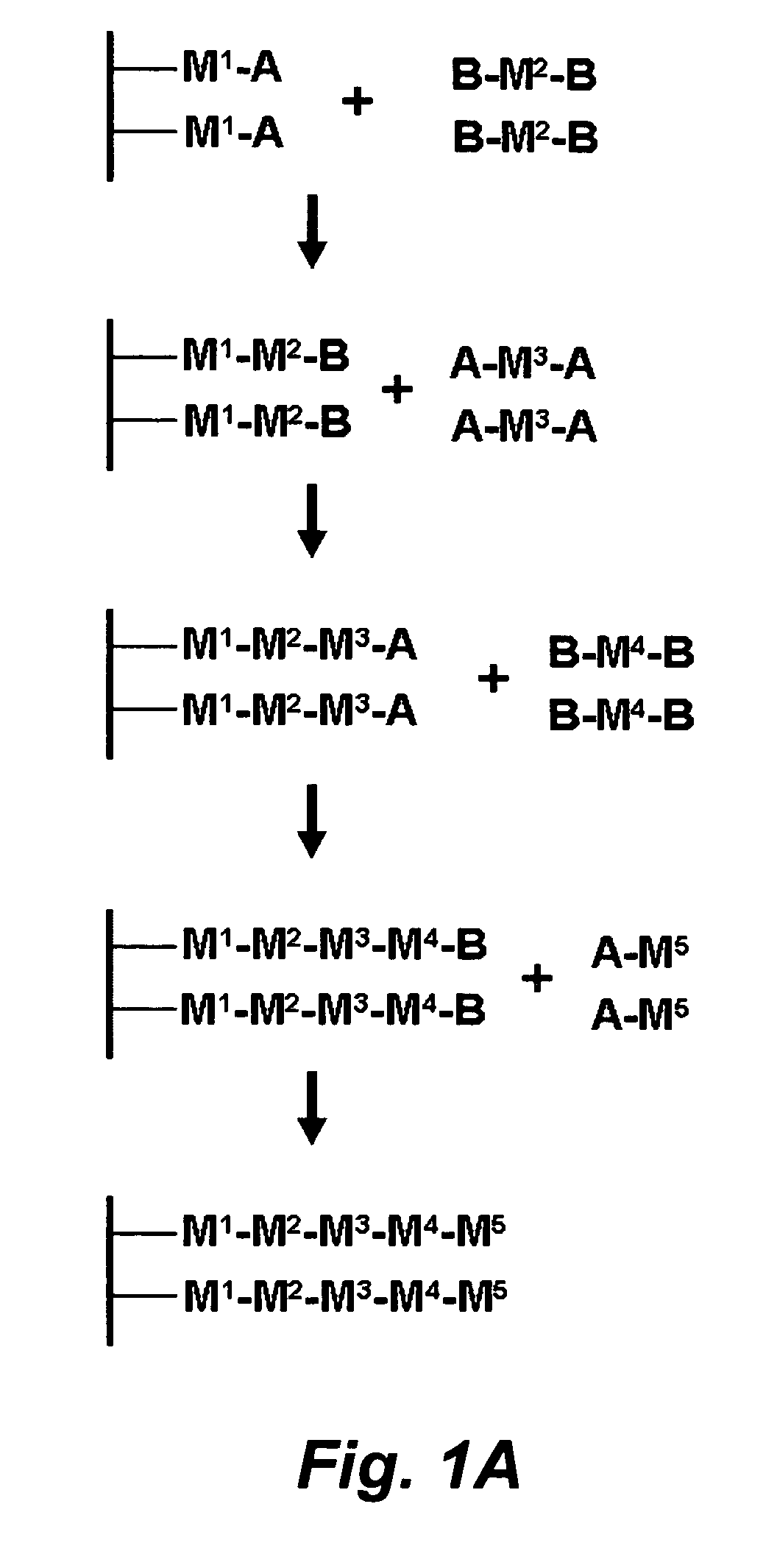

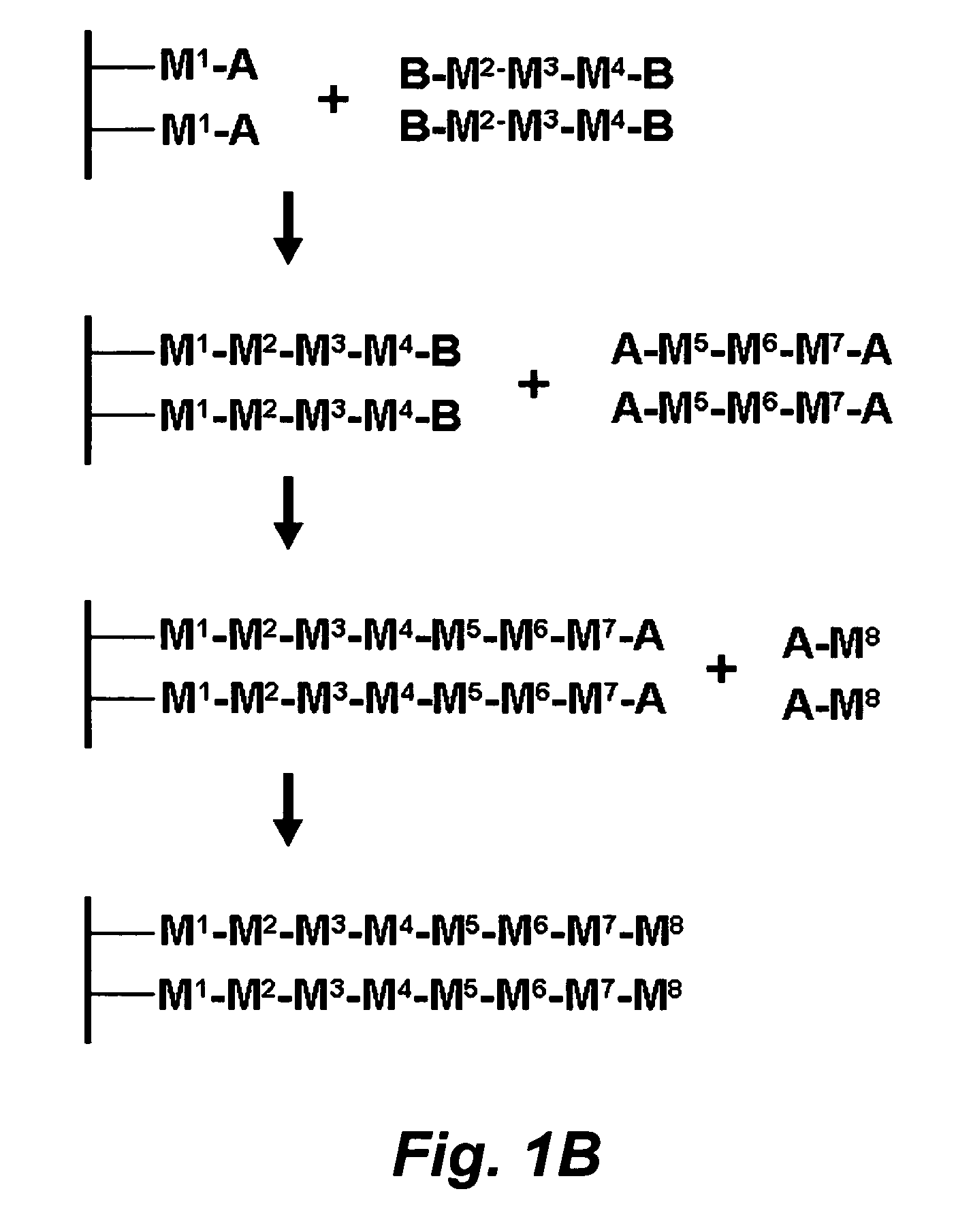

Stepwise growth of oligomeric redox-active molecules on a surface without the use of protecting groups

ActiveUS8062756B2Eliminate usePrevent charge leakageLiquid surface applicatorsNanoinformaticsOligomerPorphyrin

This invention provides a procedure for growing oligomers via a stepwise process. The oligomers can include porphyrins, which have been previously shown to be attractive candidates for molecular-based information storage. The stepwise synthesis procedure requires no protecting groups, thus eliminating protection / deprotection reactions that add complexity to the process.

Owner:RGT UNIV OF CALIFORNIA +1

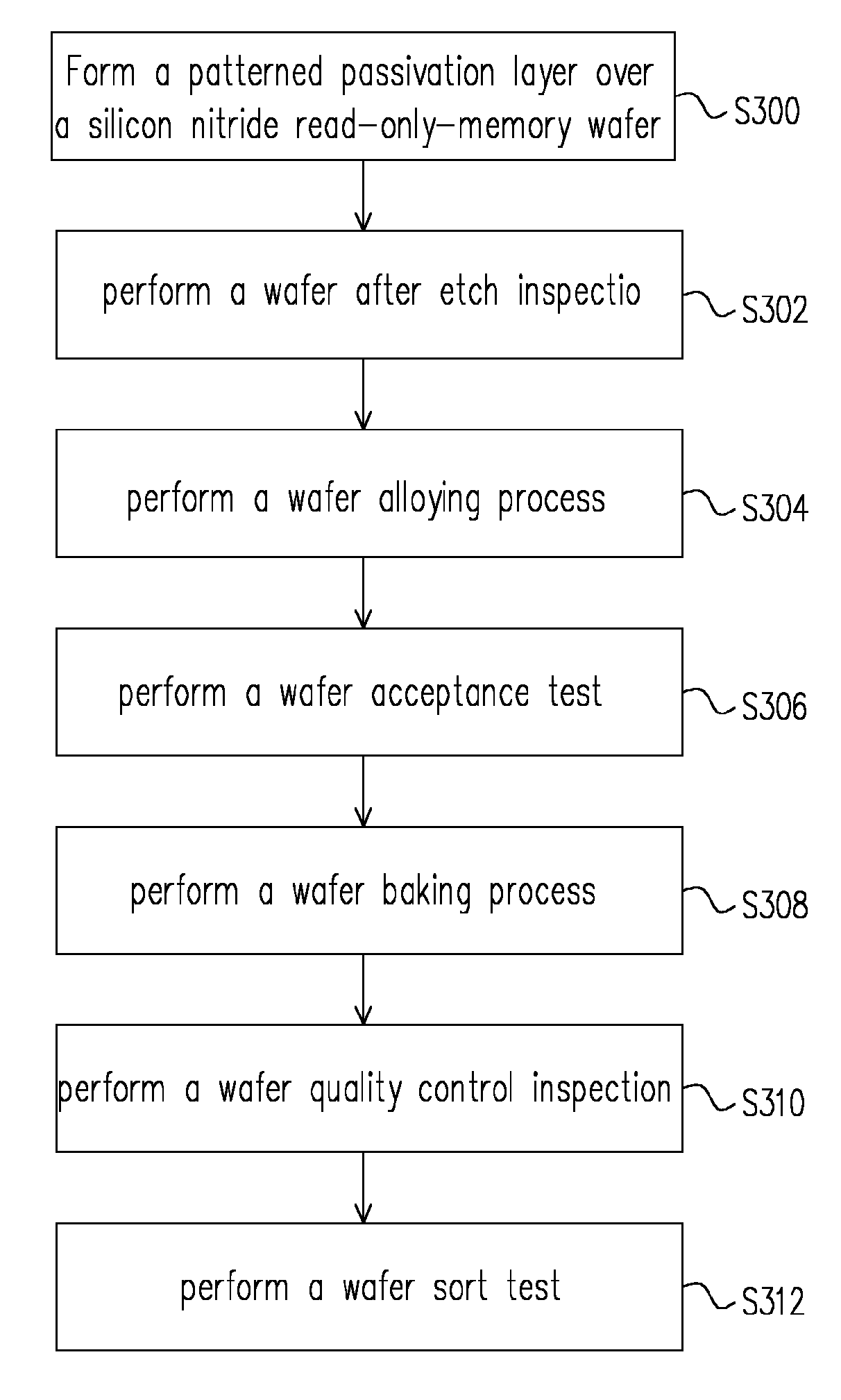

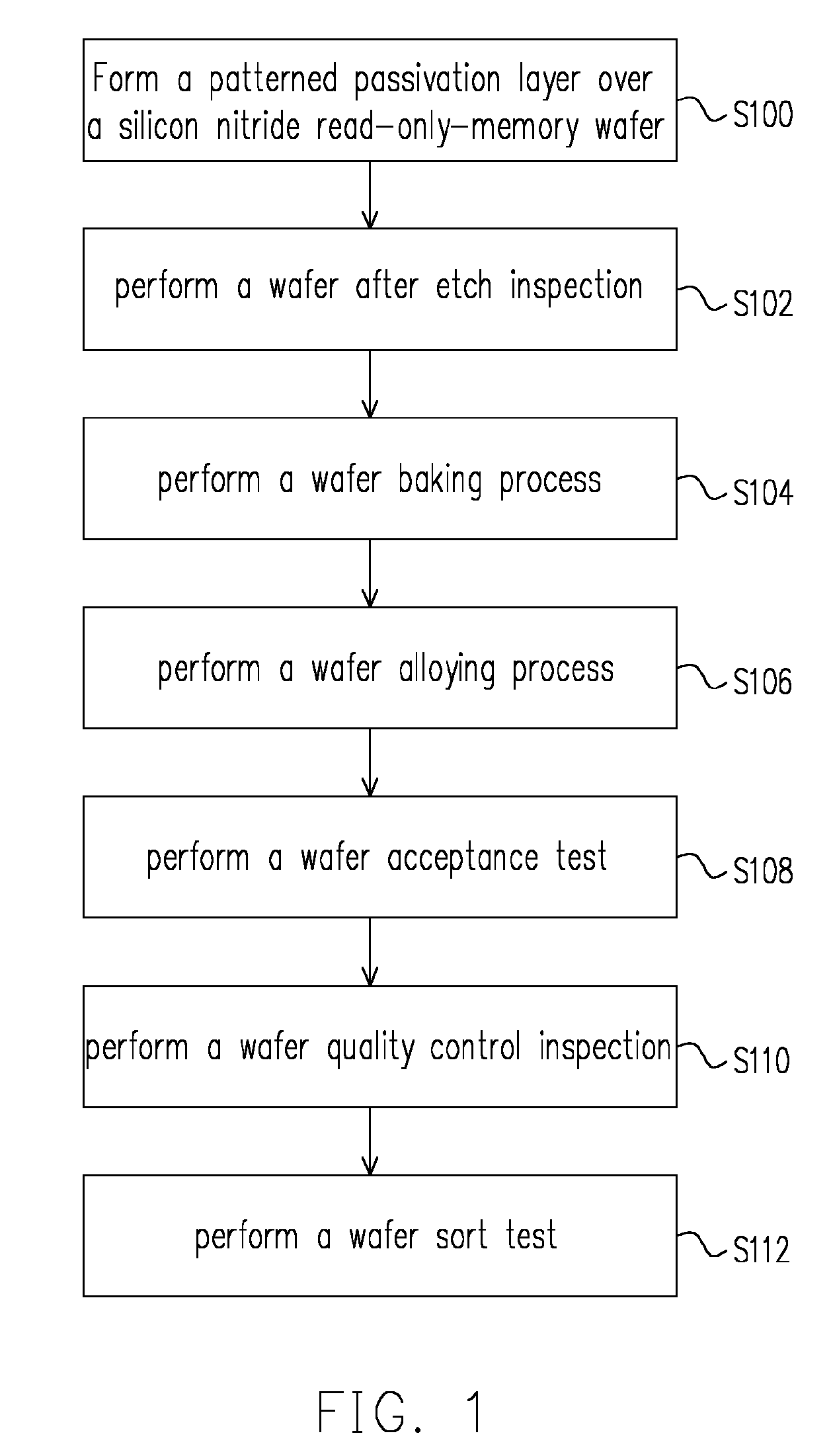

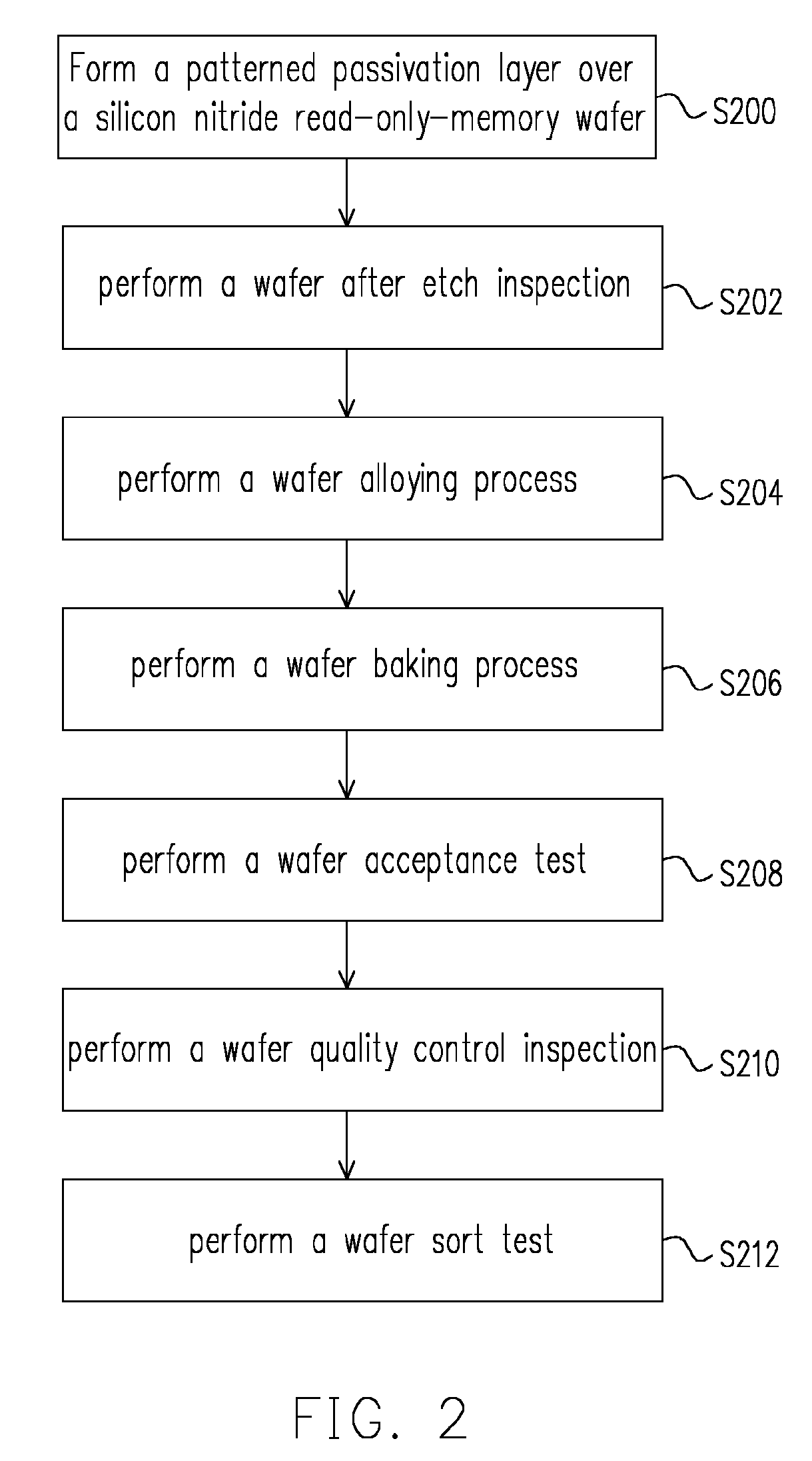

Method of increasing cell retention capacity of silicon nitride read-only-memory cell

ActiveUS7132302B2Improve retentionConstant voltageSemiconductor/solid-state device testing/measurementSemiconductor/solid-state device manufacturingCooking & bakingOptoelectronics

Owner:MACRONIX INT CO LTD

Solid-state image sensor with reduced smear and noise

InactiveUS6590195B2Noise-reduced imagePrevent charge leakageTelevision system detailsSolid-state devicesRegioselectivityEngineering

A solid-state image sensor includes a semiconductor bulk region of a first conductivity type; at least a drain region of a second conductivity type selectively provided in the semiconductor bulk region; at least a photoelectric converter region of the second conductivity type selectively provided in the semiconductor bulk region, and the photoelectric converter region being separated from the drain region; and at least a potential barrier region of the first conductivity type selectively provided in the semiconductor bulk region, the potential barrier region being adjacent to at least a part of bottom and side faces of the photoelectric converter region, and the potential barrier region having a higher impurity concentration than the semiconductor bulk region.

Owner:NEC ELECTRONICS CORP