Patents

Literature

55 results about "Language construct" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

A language construct is a syntactically allowable part of a program that may be formed from one or more lexical tokens in accordance with the rules of a programming language. The term "language construct" is often used as a synonym for control structure.

Verifying intermediate language code

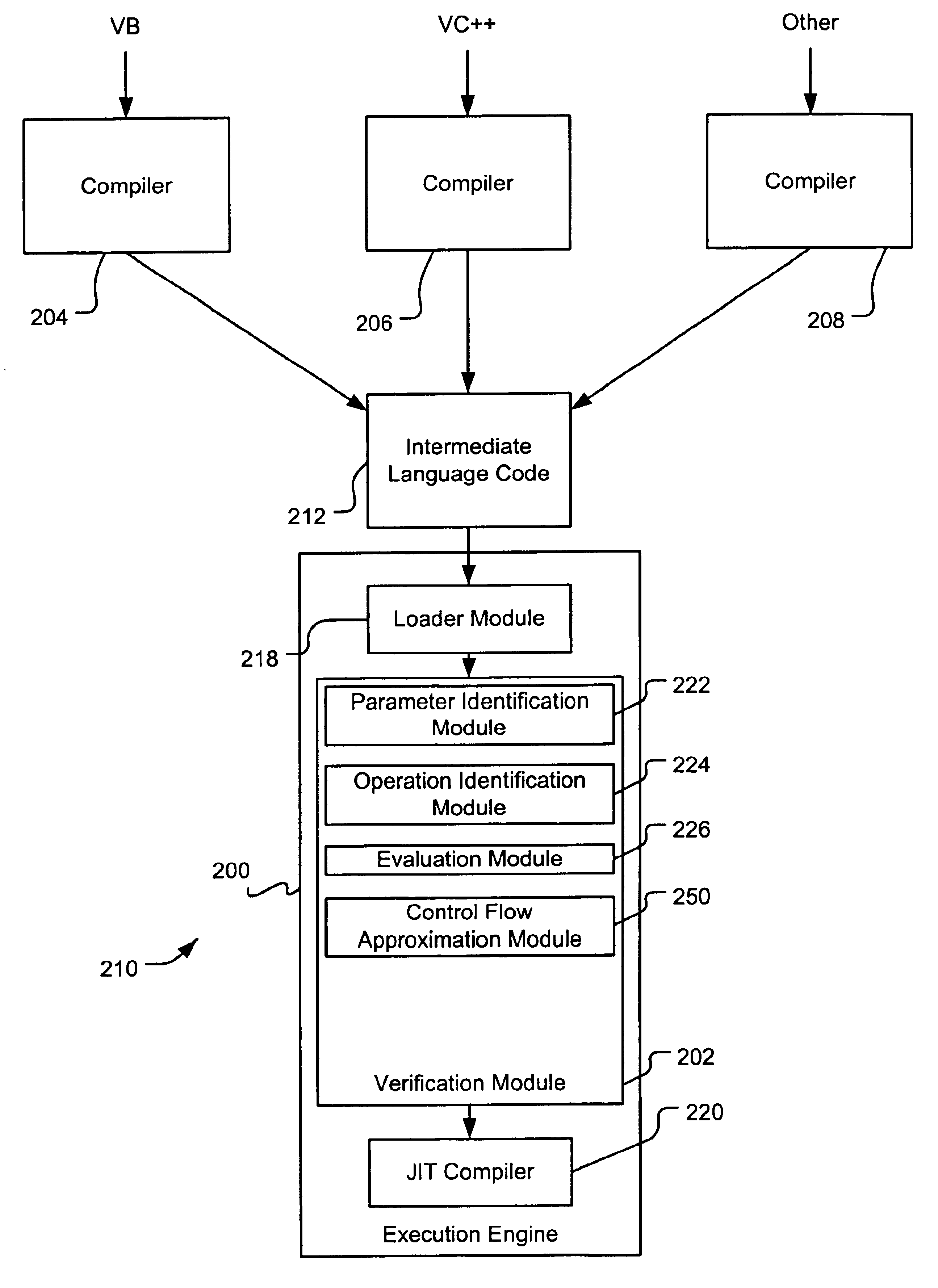

InactiveUS6851108B1Existing techniqueRich varietyProgram loading/initiatingMemory systemsLanguage constructComputerized system

A verification module evaluates intermediate language code to verify that the code is type safe before passing the code for execution. Code that is not deemed type safe can cause execution errors, corrupt the runtime environment in which the code is executing, or cause unauthorized access to protected system resources. As such, the verification module protects a computer system from intentional or inadvertent breaches of the computer system's defenses. The verification module verifies the type safety of intermediate language code that supports significant high-level language constructs prohibited by verification modules in the prior art. One exemplary verification module verifies intermediate language code that includes one or more reference-based parameter, such as a pointer (or reference), a value class containing pointers, a RefAny parameter, or a nested pointer.

Owner:MICROSOFT TECH LICENSING LLC

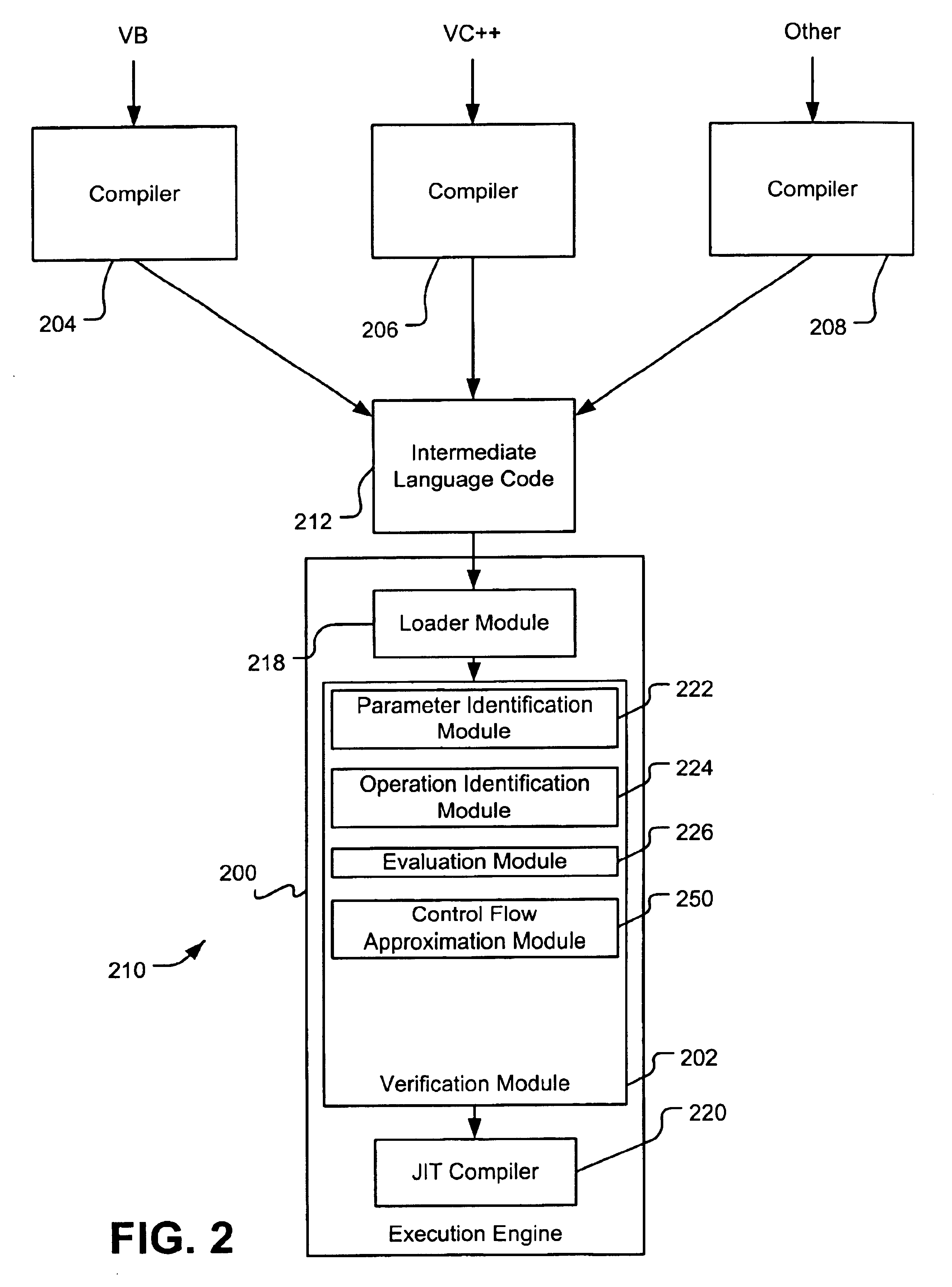

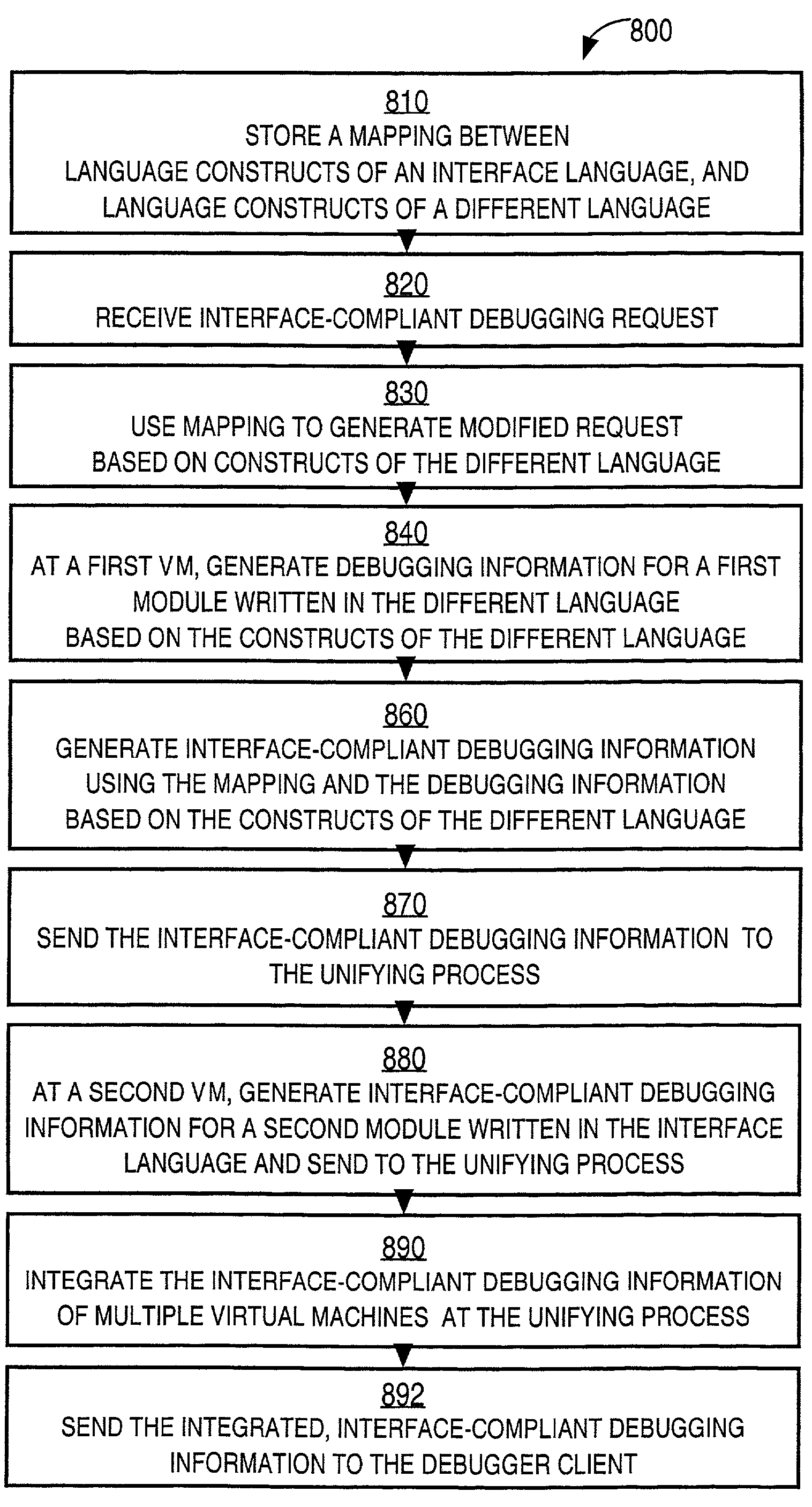

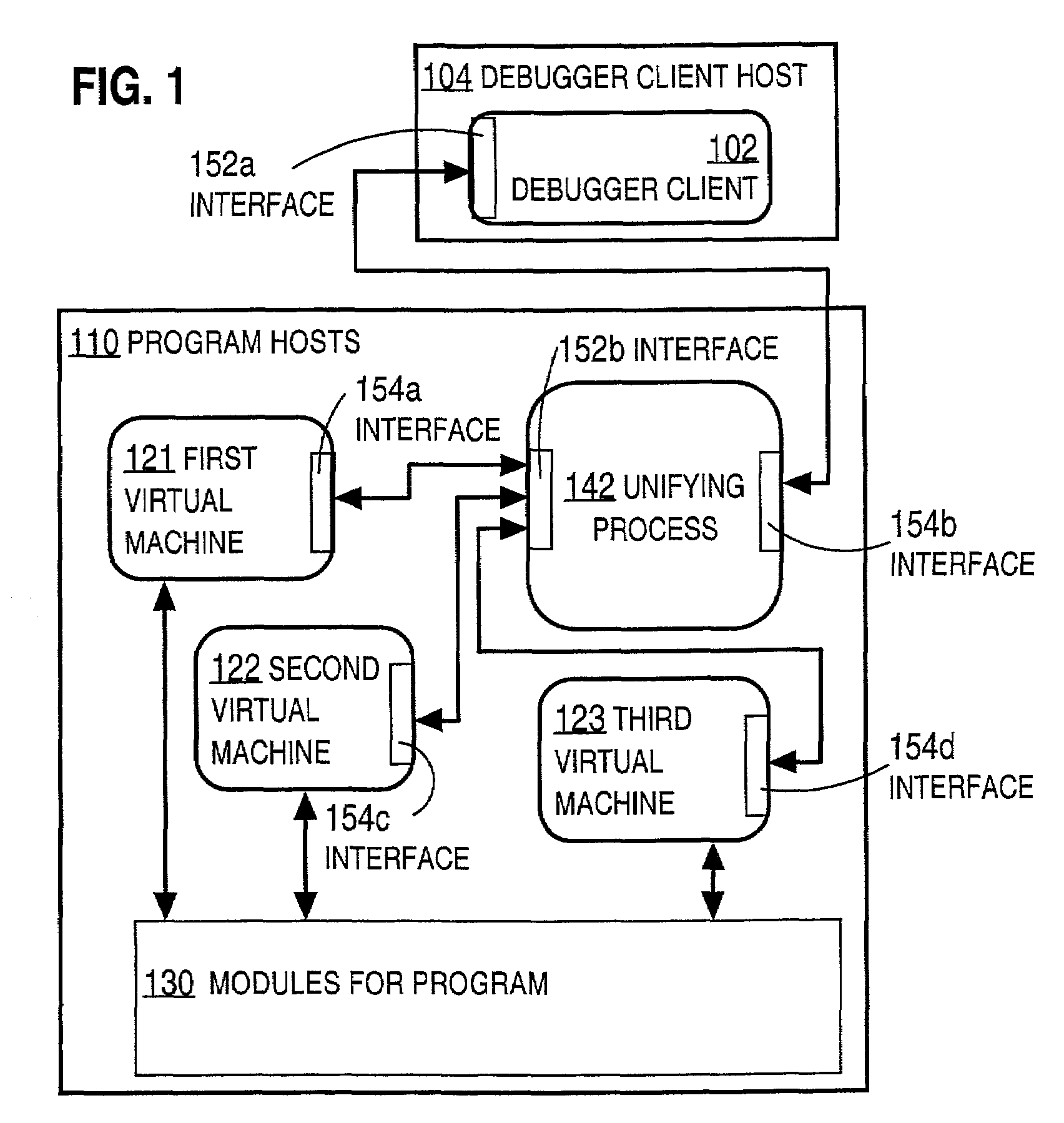

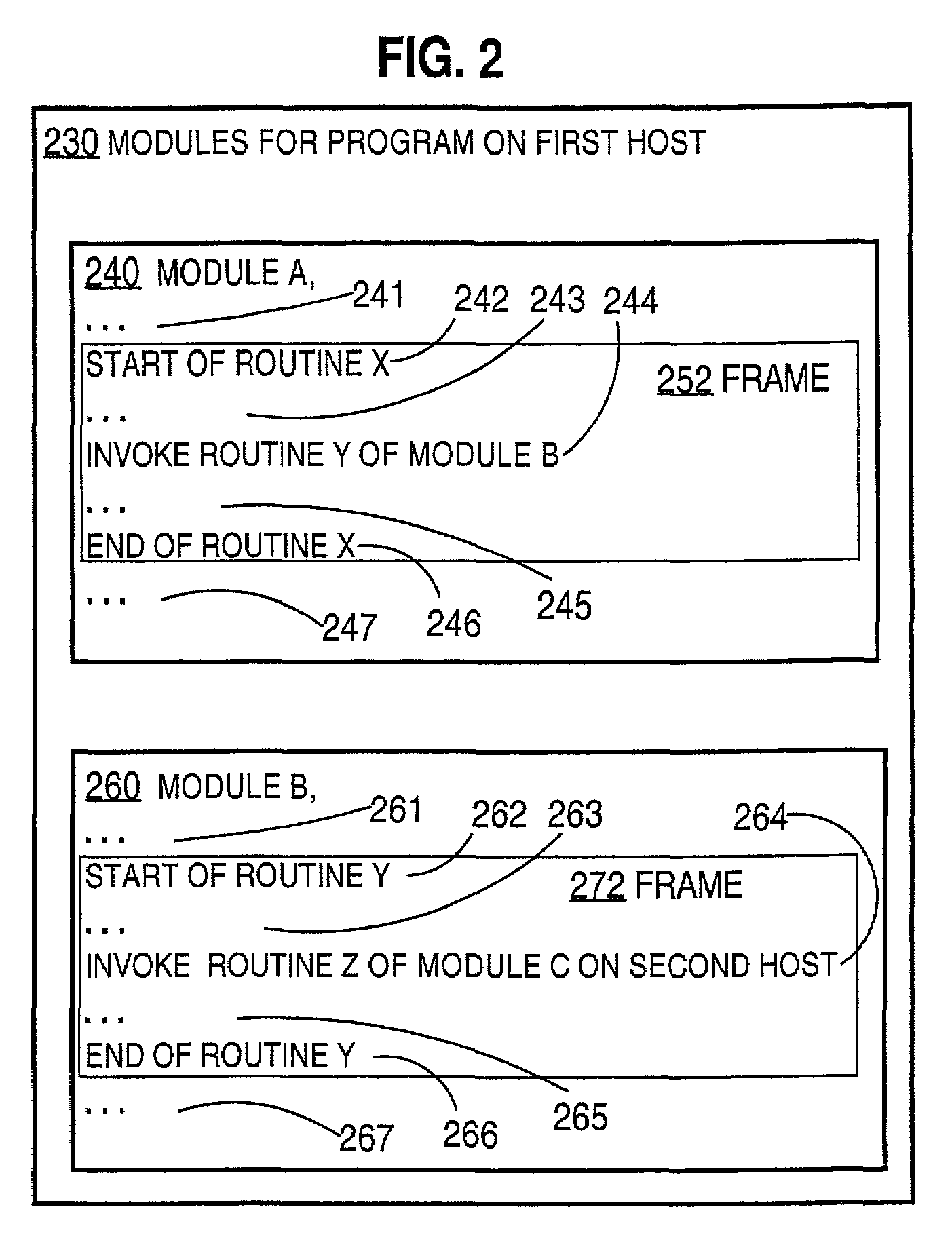

Techniques for debugging computer programs involving multiple programming languages

ActiveUS7107578B1Error detection/correctionSpecific program execution arrangementsLanguage constructProcess design

Techniques for debugging a computer program that includes multiple modules written in multiple languages allow machines for the multiple languages to interface with a single debugger client using a standard interface. The techniques include storing a mapping that maps language constructs of a first language into language constructs of a second language. While a first machine is executing a first module that is written in the first language, the mapping is used to generate debugging information based on language constructs of the second language. The debugging information is sent to a debugger process designed for debugging programs written in the second language.

Owner:ORACLE INT CORP

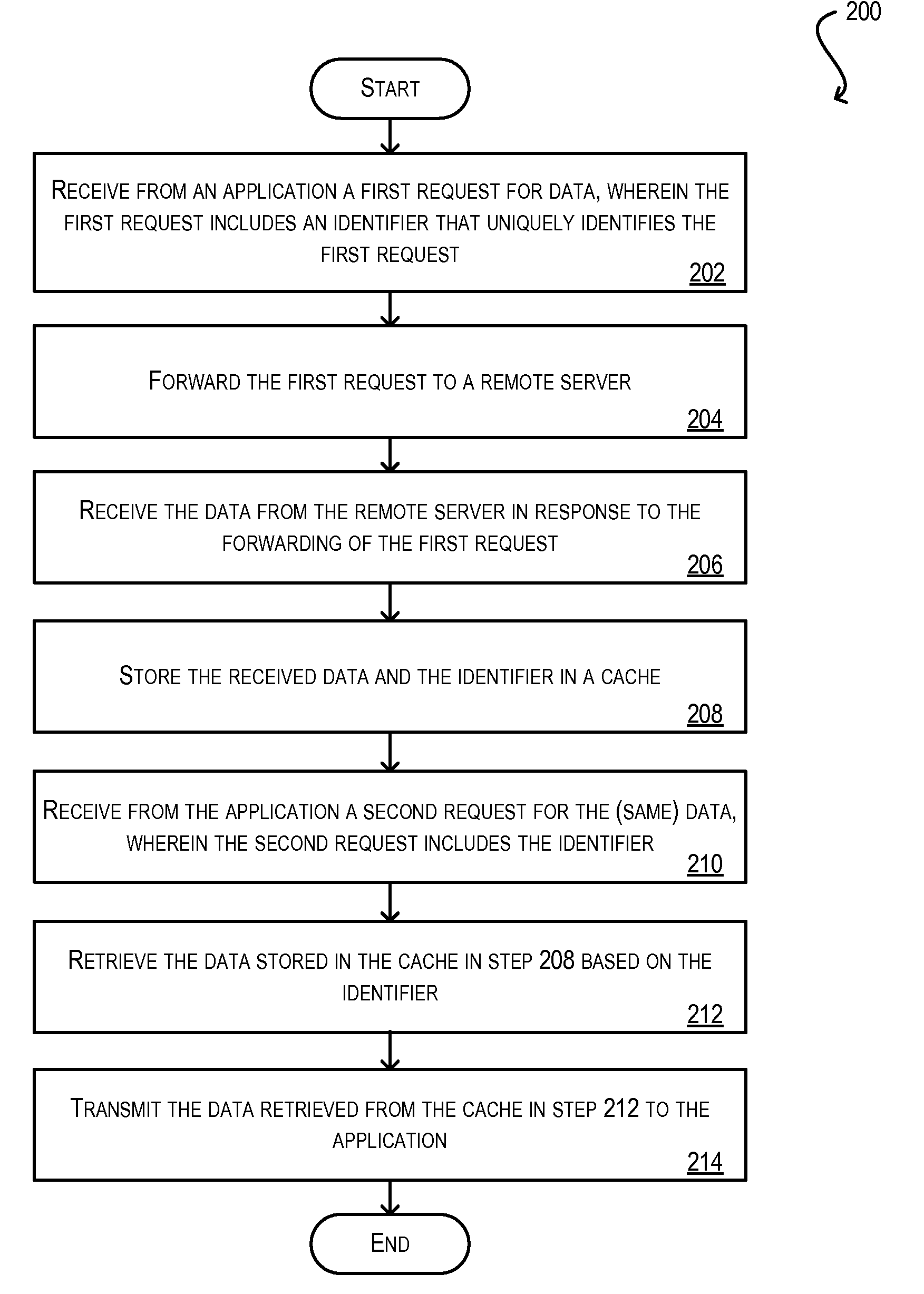

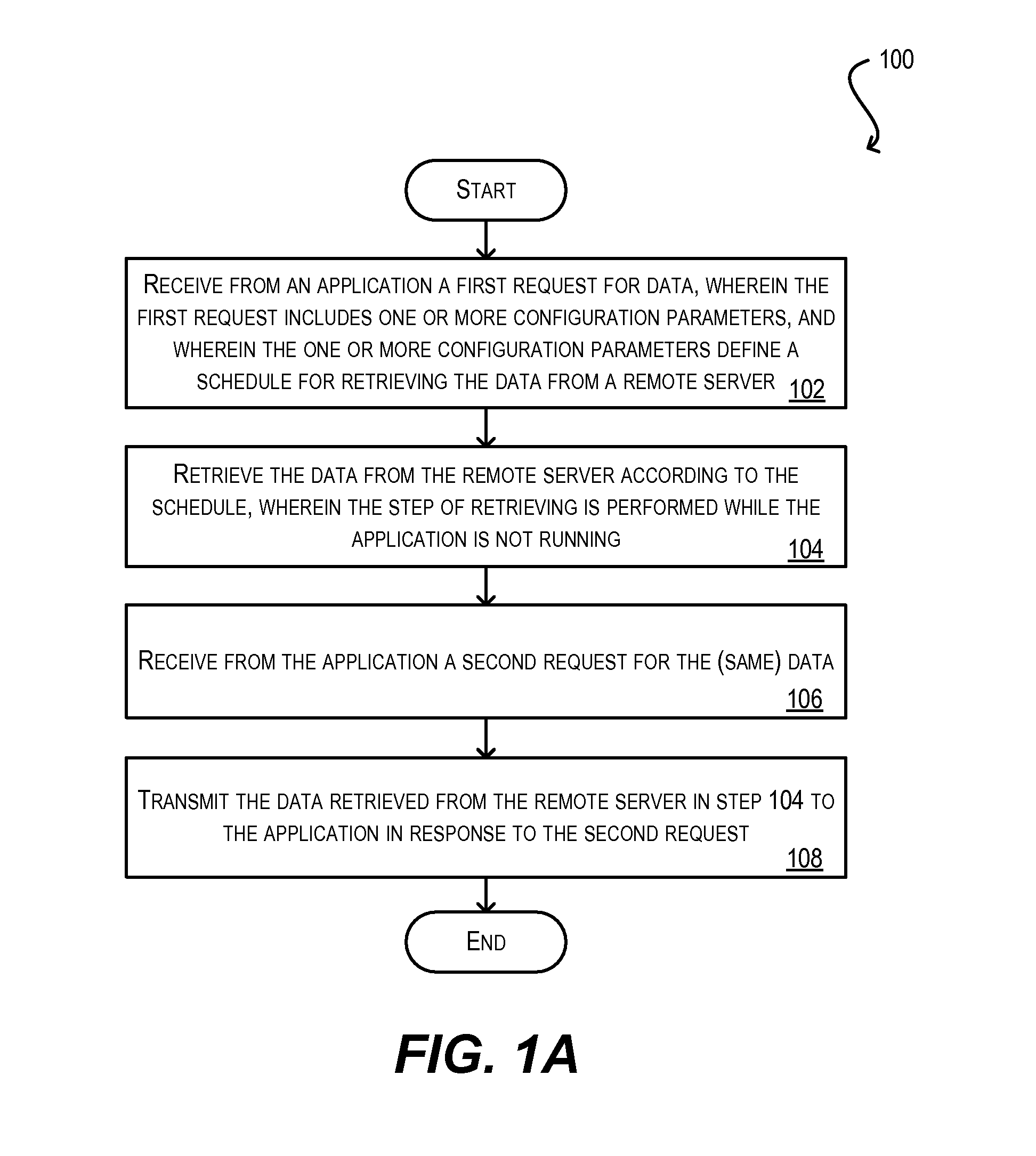

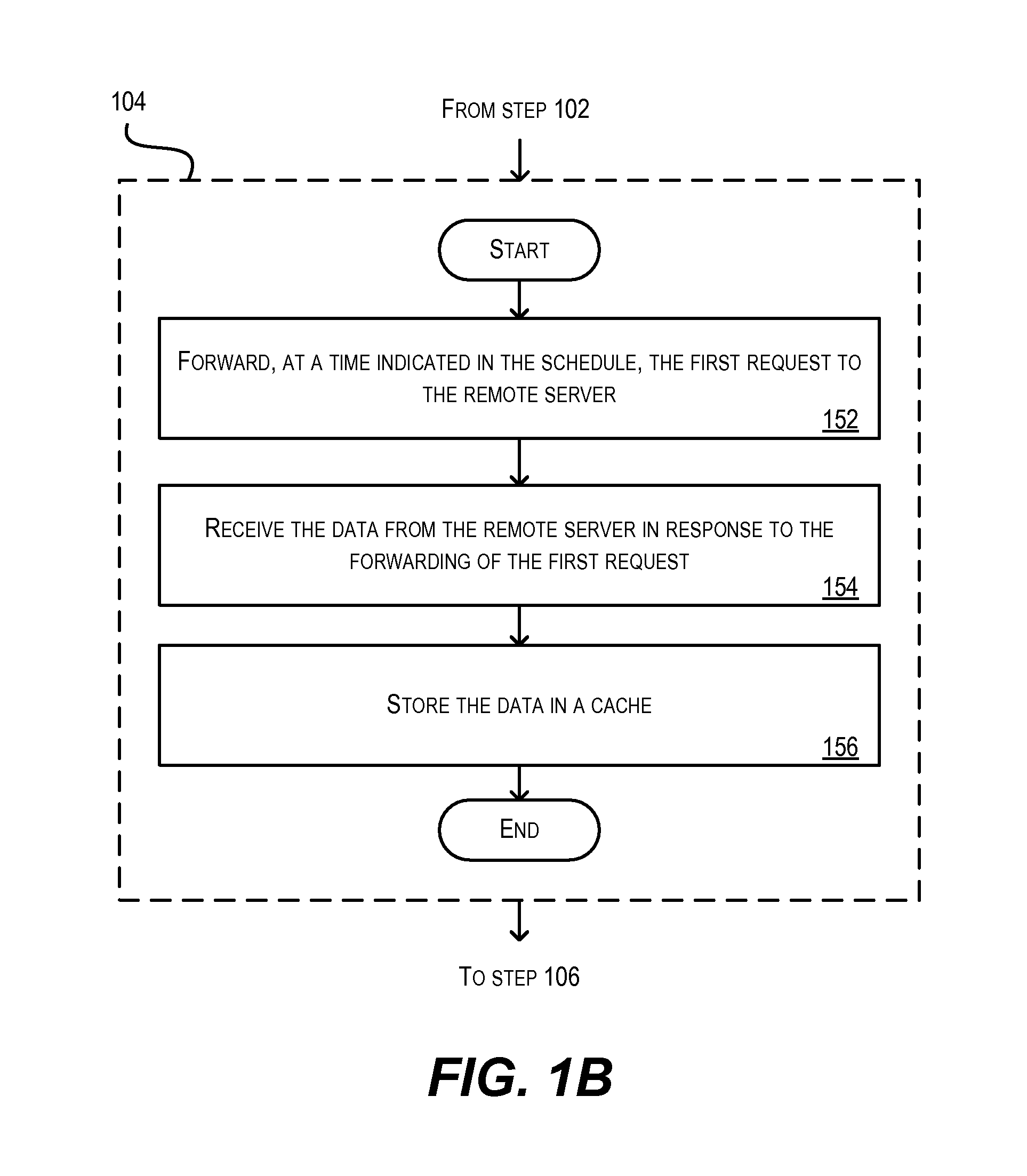

Offline automated proxy cache for web applications

InactiveUS20080098093A1Improve connection qualityEnergy efficient ICTMultiple digital computer combinationsLanguage constructApplication software

Embodiments of the present invention provide techniques for managing content updates for web-based applications. In one set of embodiments, a configurable proxy cache is provided that executes rule-based content updates of web content on the behalf of an application (e.g., web browser) while the application is not running. This allows for better management of intermittent connection quality, memory / power savings for mobile devices, and caching of information that can be shared with the application and other network-aware applications / services. In various embodiments, the proxy cache is controlled by the application via standard web language constructs such as HTTP headers, thereby enabling interoperability with web-based applications that implement common asynchronous data-loading technologies.

Owner:QUALCOMM INC

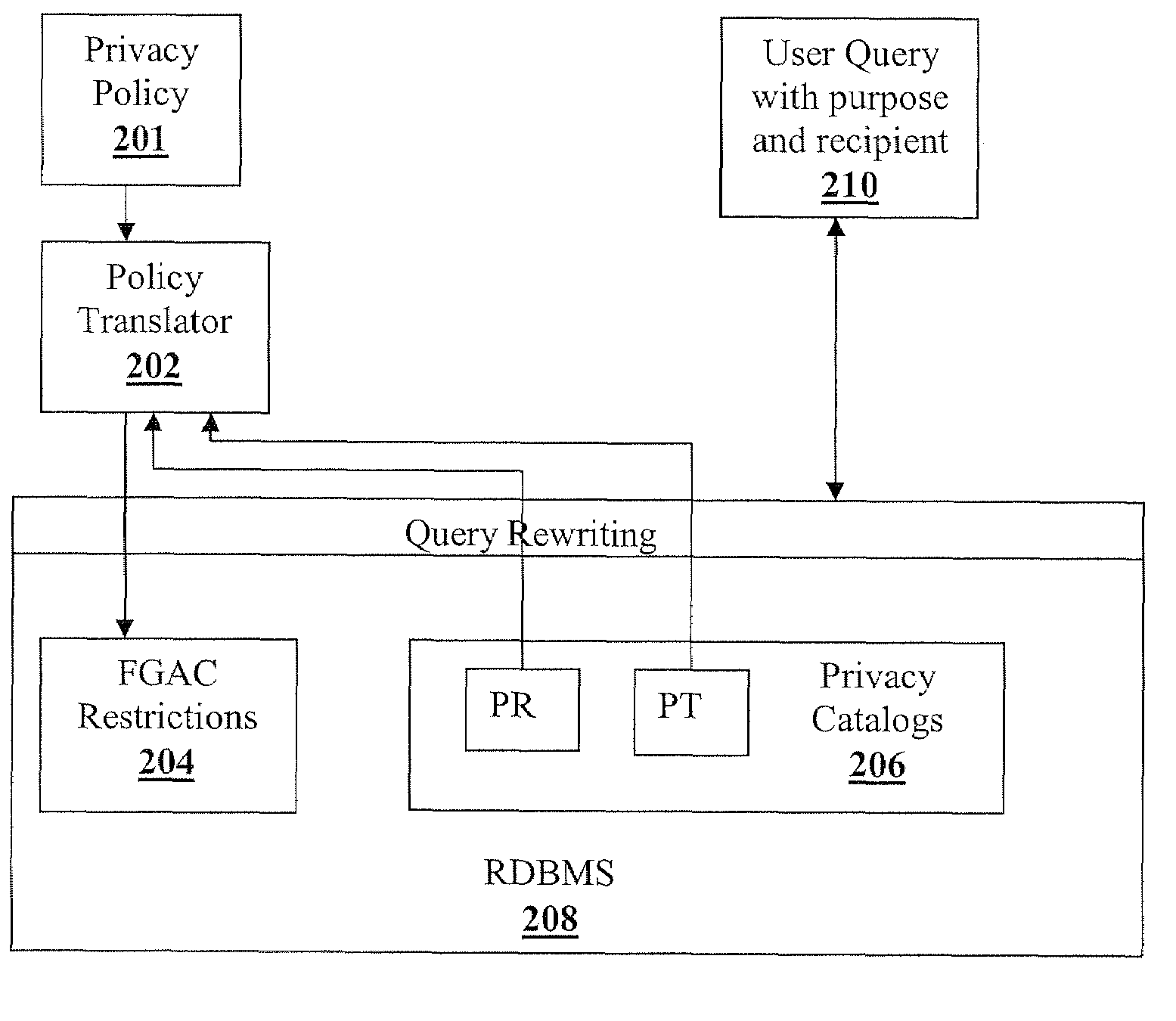

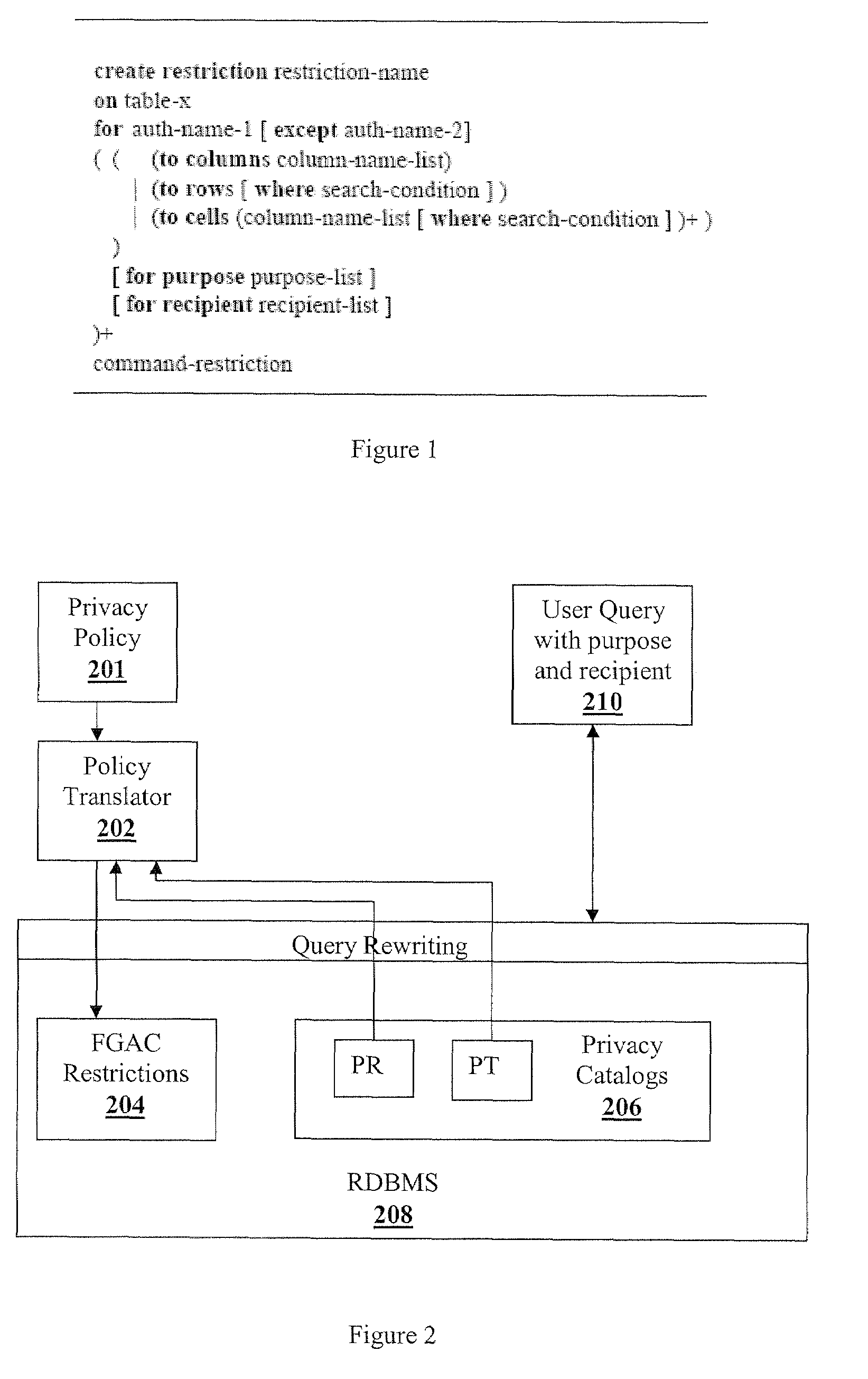

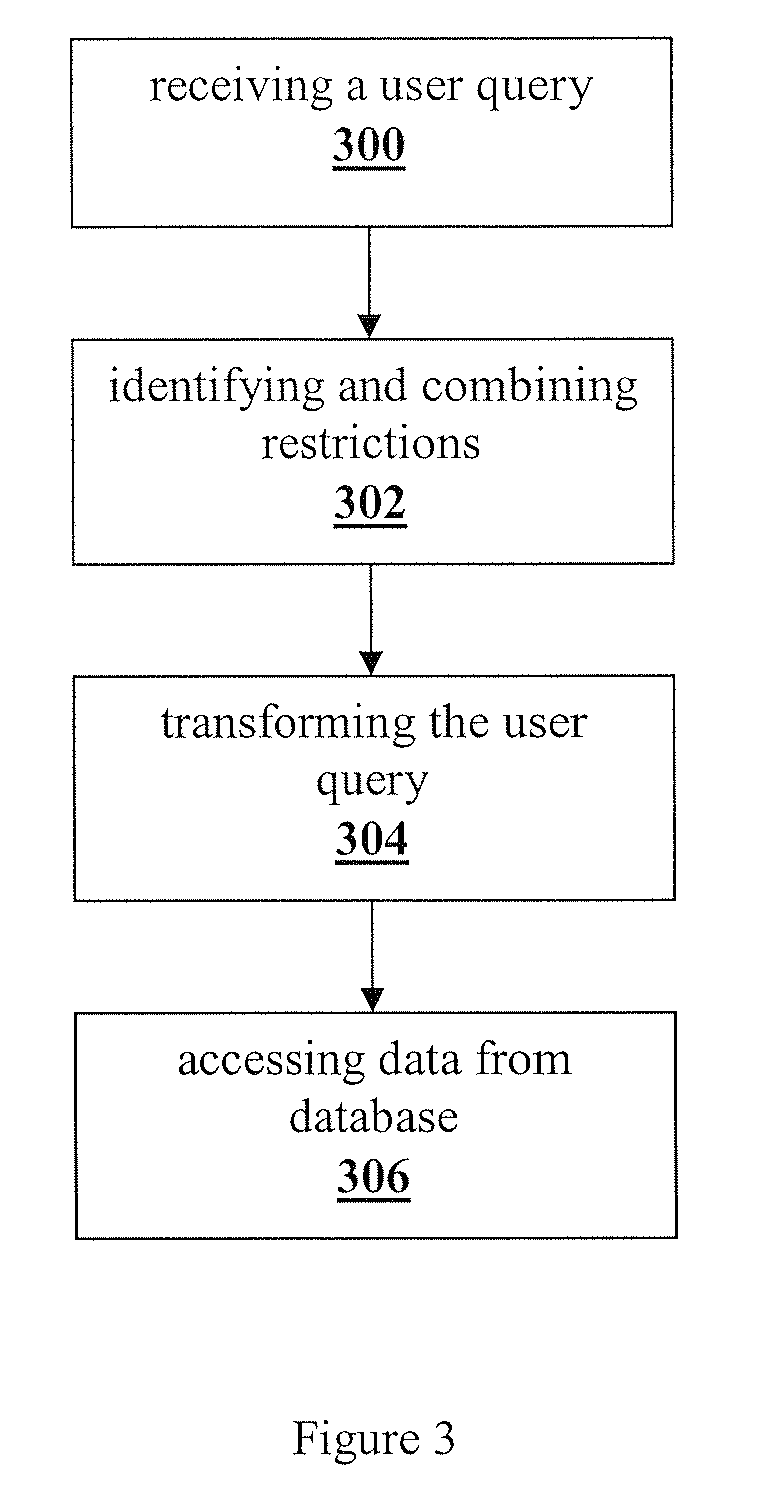

Extending relational database systems to automatically enforce privacy policies

ActiveUS7243097B1Data processing applicationsDigital data information retrievalLanguage constructPrivacy protection

A method of transforming relational database management systems into their privacy-preserving equivalents is provided. Language constructs allow fine grained access control (FGAC) restrictions to be specified on the access to data in a table at the level of a row, a column or a cell. Fine grained restrictions are a combination of access control and privacy policy restrictions, which ensure compliance with current privacy legislation mandates.

Owner:IBM CORP

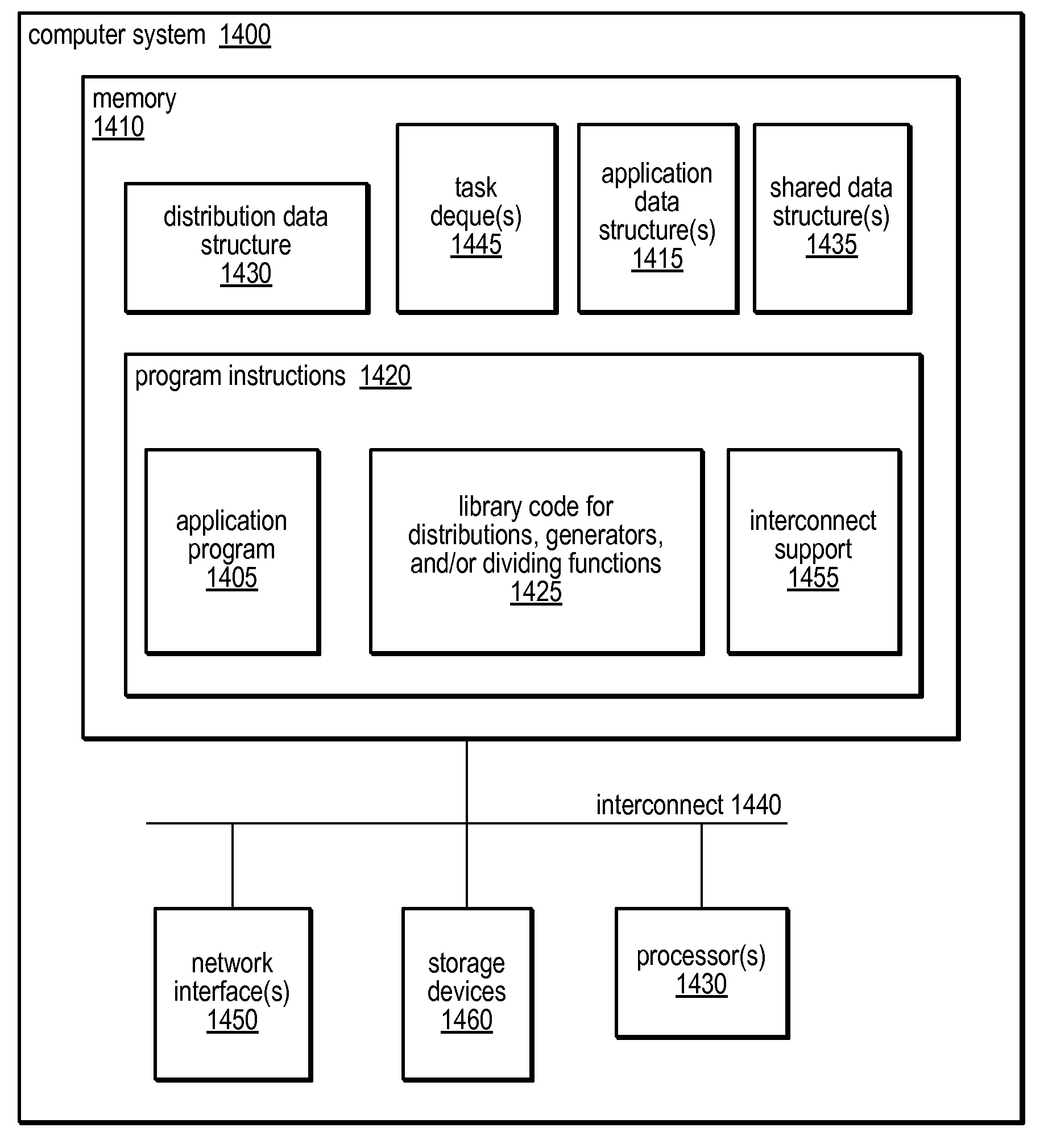

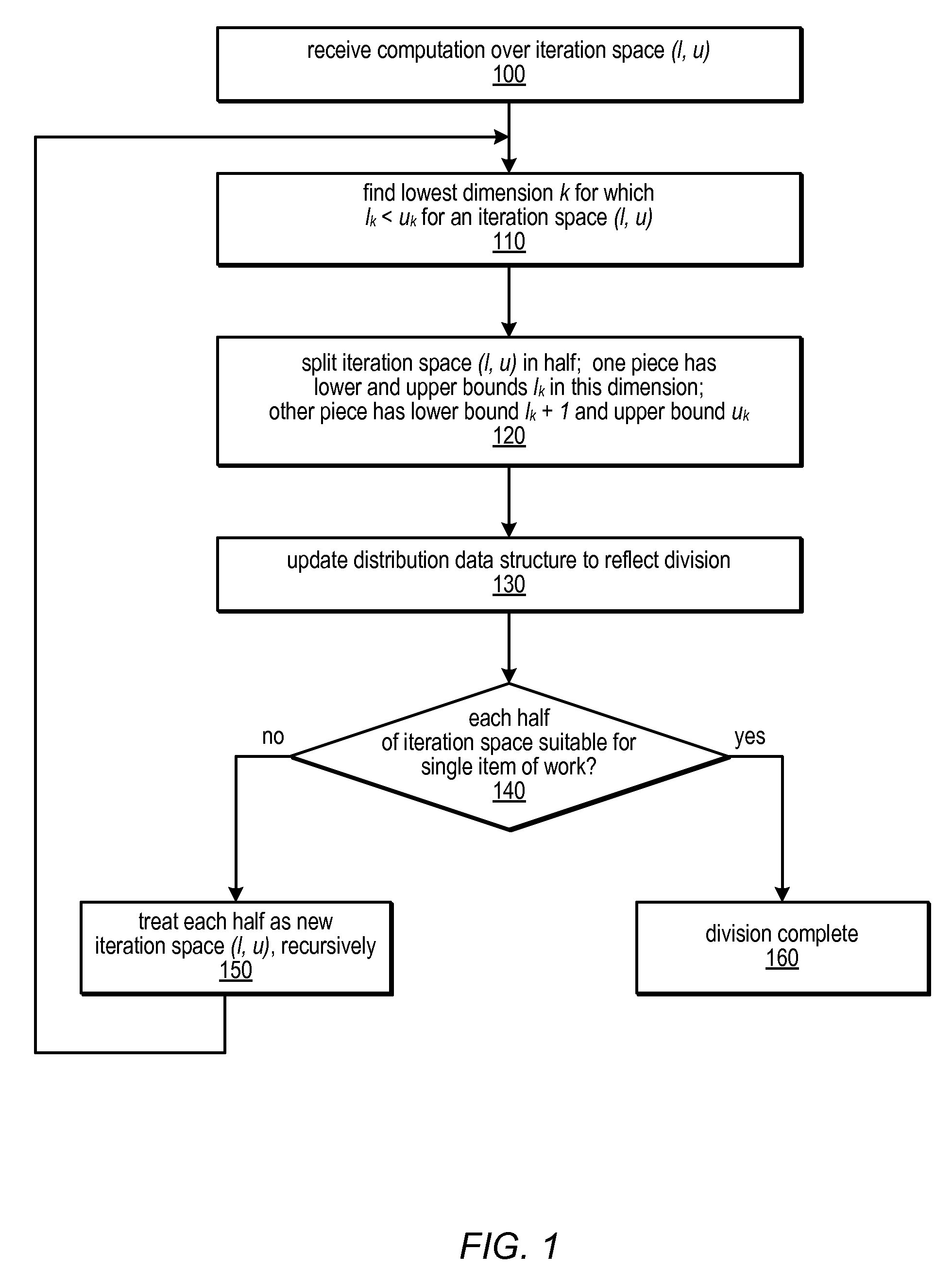

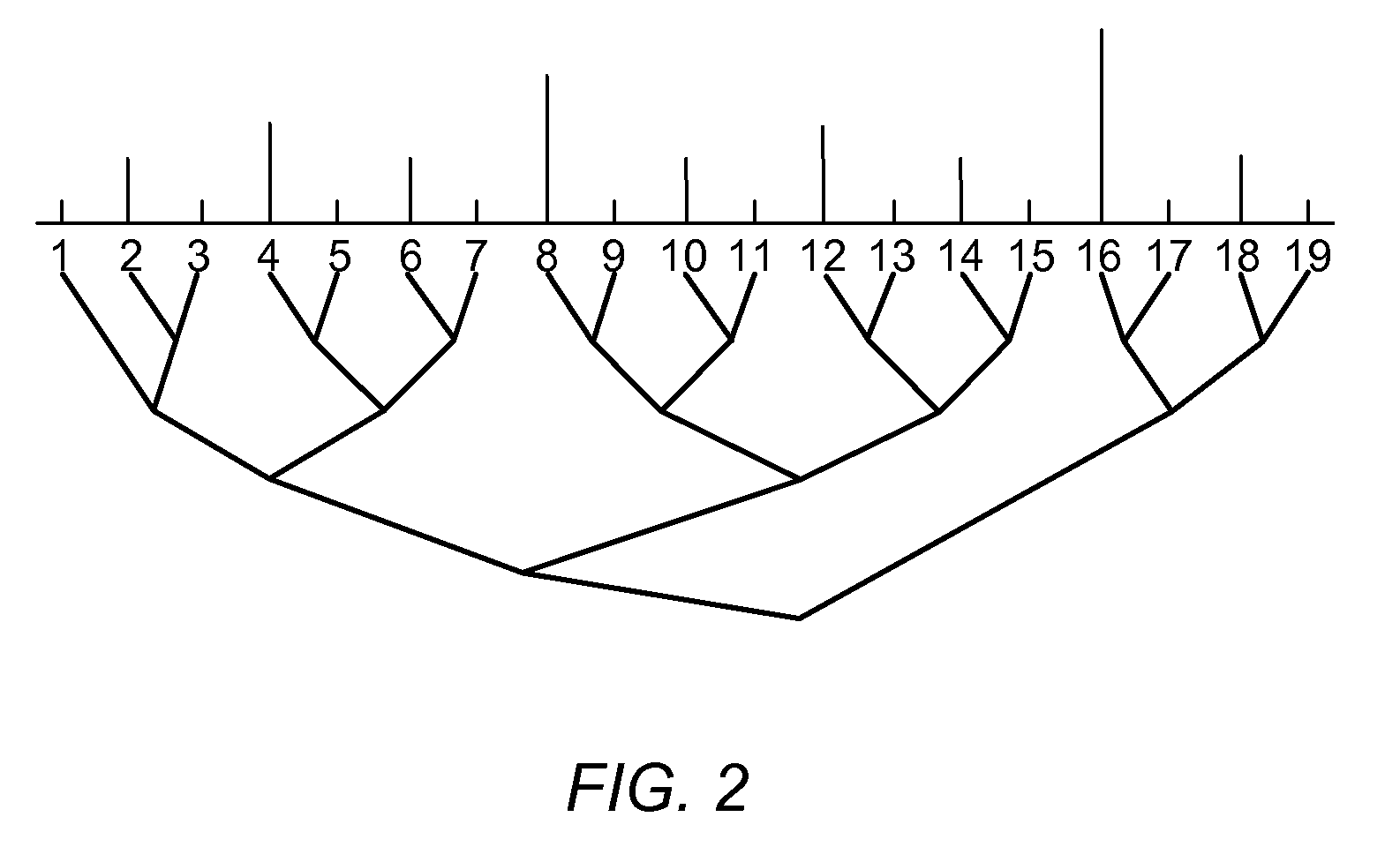

Distribution Data Structures for Locality-Guided Work Stealing

ActiveUS20100031267A1Keep localProvide load balancingResource allocationMemory systemsLocality of referenceLanguage construct

A data structure, the distribution, may be provided to track the desired and / or actual location of computations and data that range over a multidimensional rectangular index space in a parallel computing system. Examples of such iteration spaces include multidimensional arrays and counted loop nests. These distribution data structures may be used in conjunction with locality-guided work stealing and may provide a structured way to track load balancing decisions so they can be reproduced in related computations, thus maintaining locality of reference. They may allow computations to be tied to array layout, and may allow iteration over subspaces of an index space in a manner consistent with the layout of the space itself. Distributions may provide a mechanism to describe computations in a manner that is oblivious to precise machine size or structure. Programming language constructs and / or library functions may support the implementation and use of these distribution data structures.

Owner:SUN MICROSYSTEMS INC

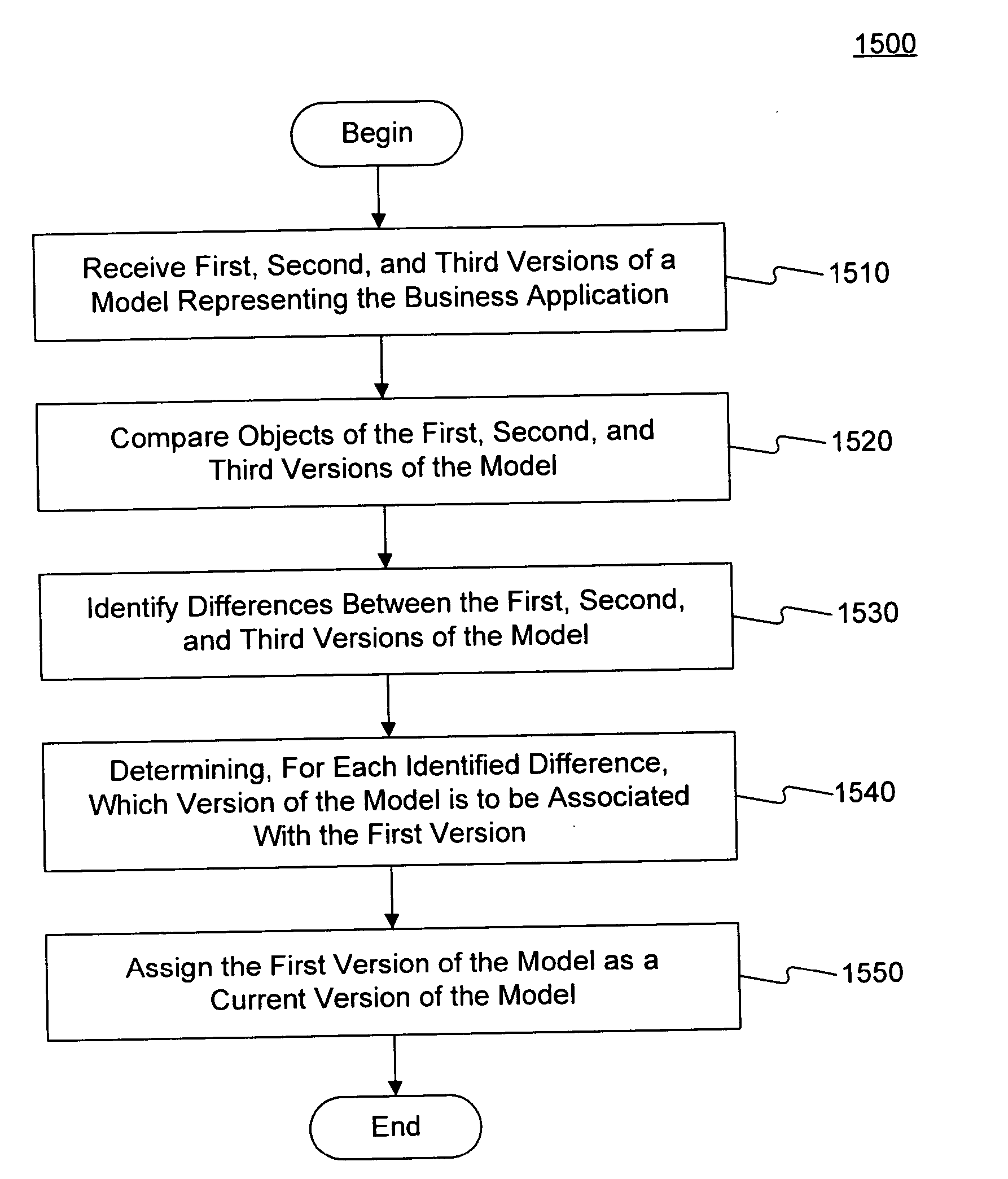

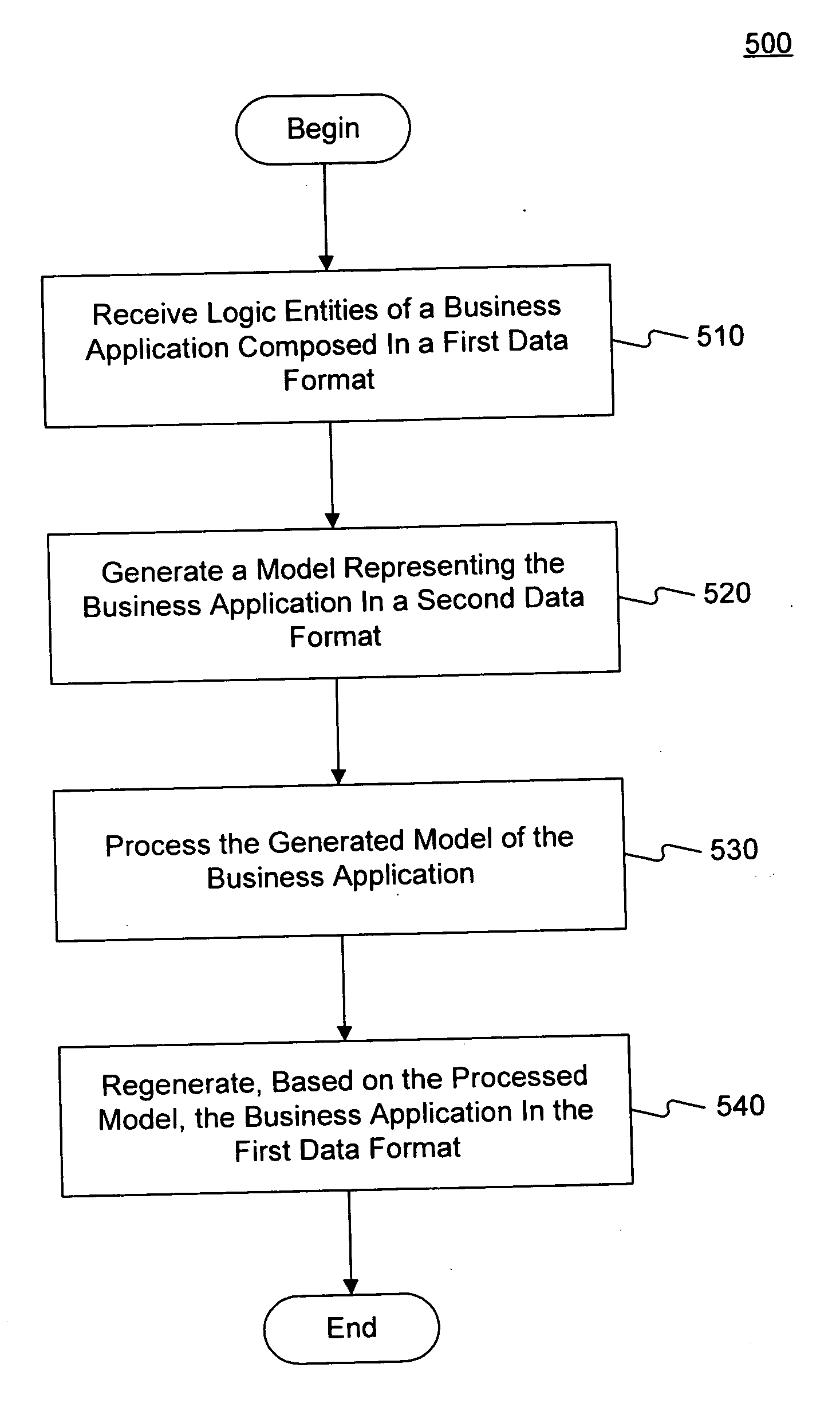

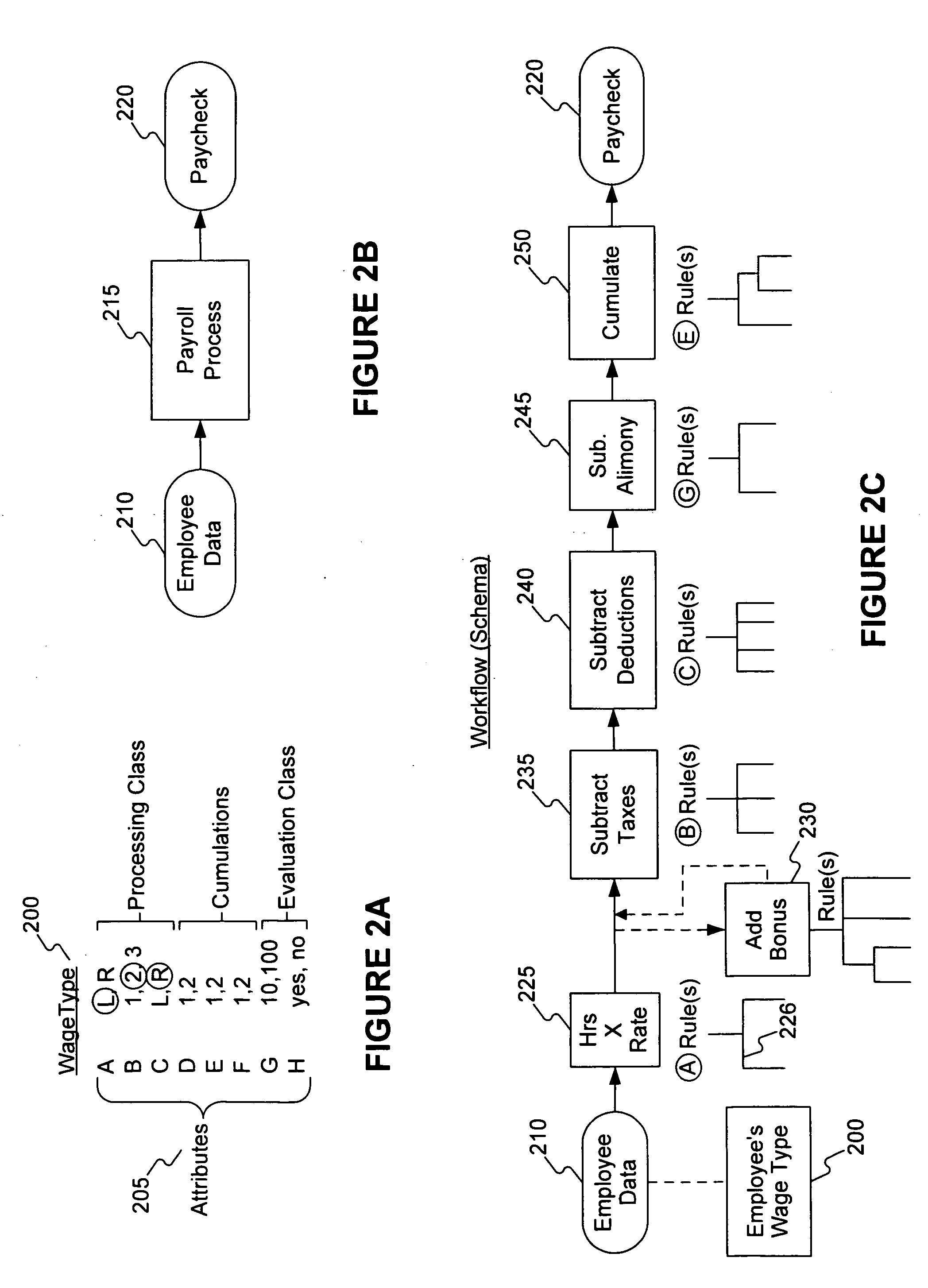

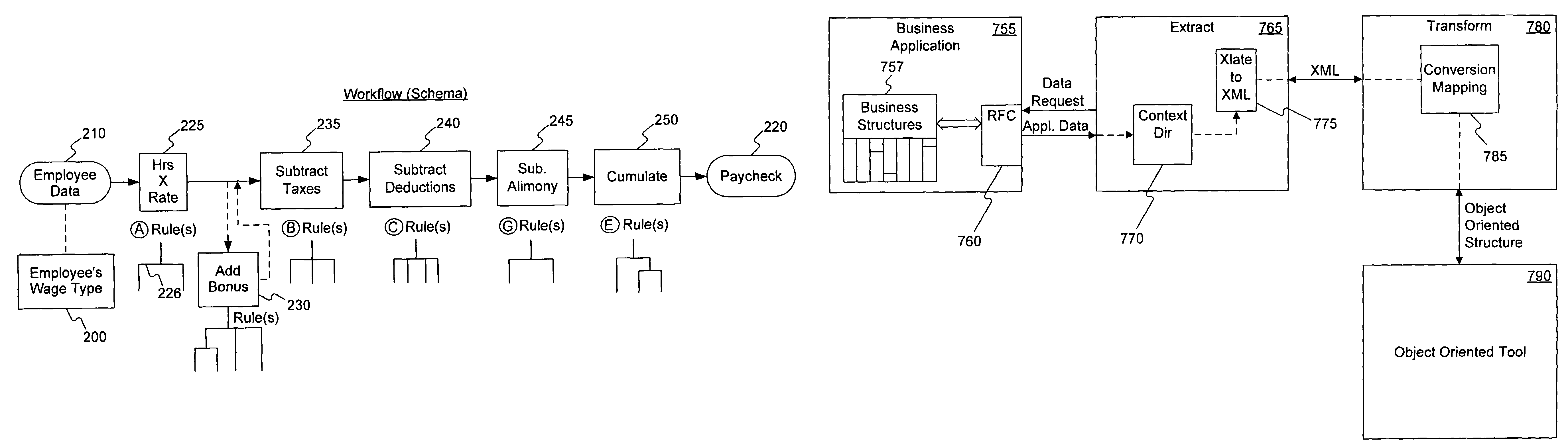

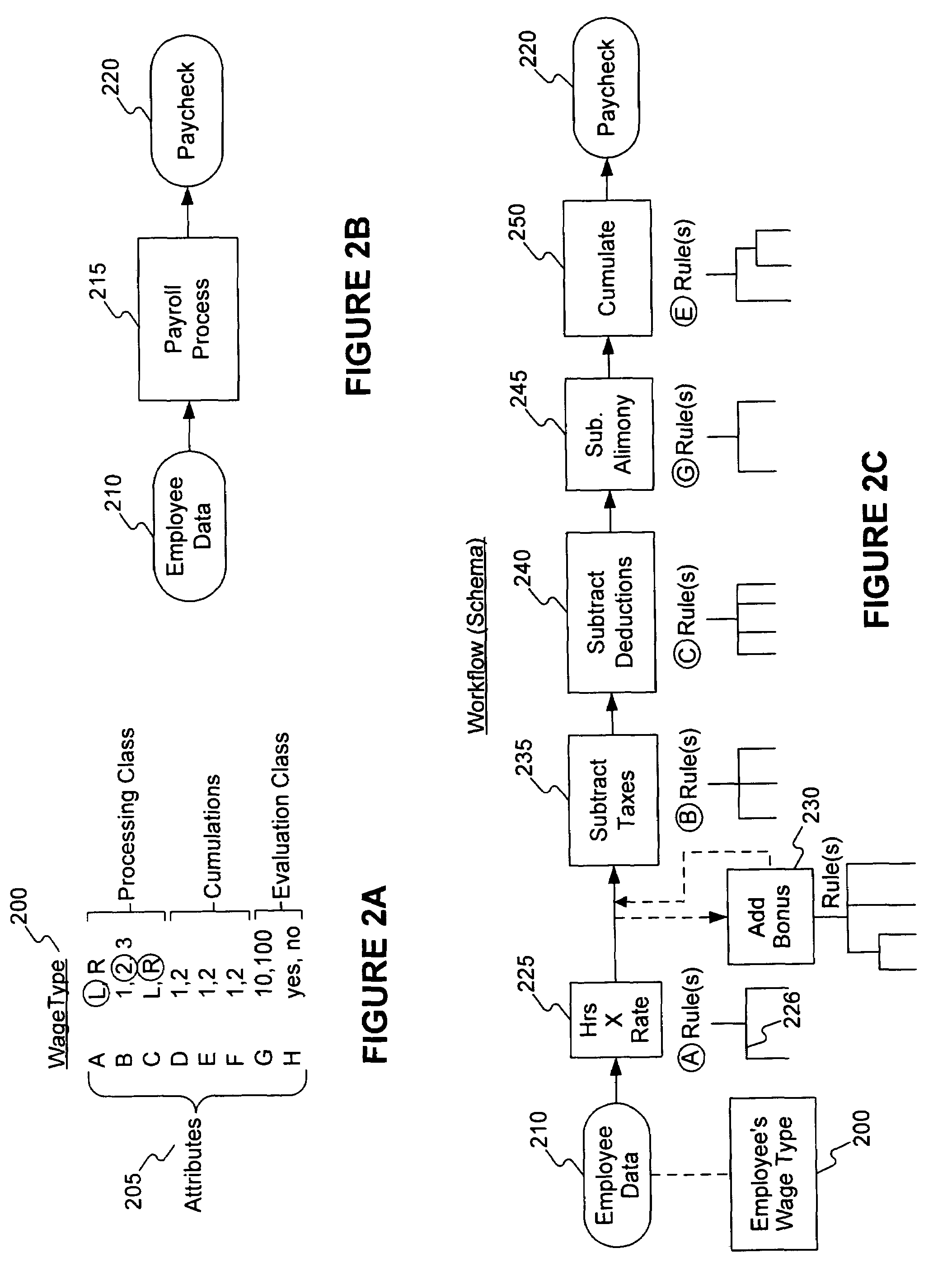

Methods of comparing and merging business process configurations

ActiveUS20060242207A1Data processing applicationsCode refactoringLanguage constructSoftware engineering

Exemplary methods and systems consistent with the present invention allow a user to compare different versions of a business application using an object-oriented model of the business application. By transforming business application structures into object-oriented structures, such as object-oriented language constructs, structures, and other elements, individual differences between versions of the business applications may be identified and displayed to a user, for example, on a user interface. A user may display object-oriented models of the business application representing, for instance, the latest control version, the latest deployed version, and a test version including test modifications. Having all three versions represented in object-oriented models allows a user to perform a three-way comparison between the object-oriented models, increasing productivity and efficiency of maintaining, debugging, modifying, controlling and deploying the business application.

Owner:SAP AG

Dynamic code generation system

ActiveUS7536675B2Data processing applicationsSpecific program execution arrangementsLanguage constructContainer Object

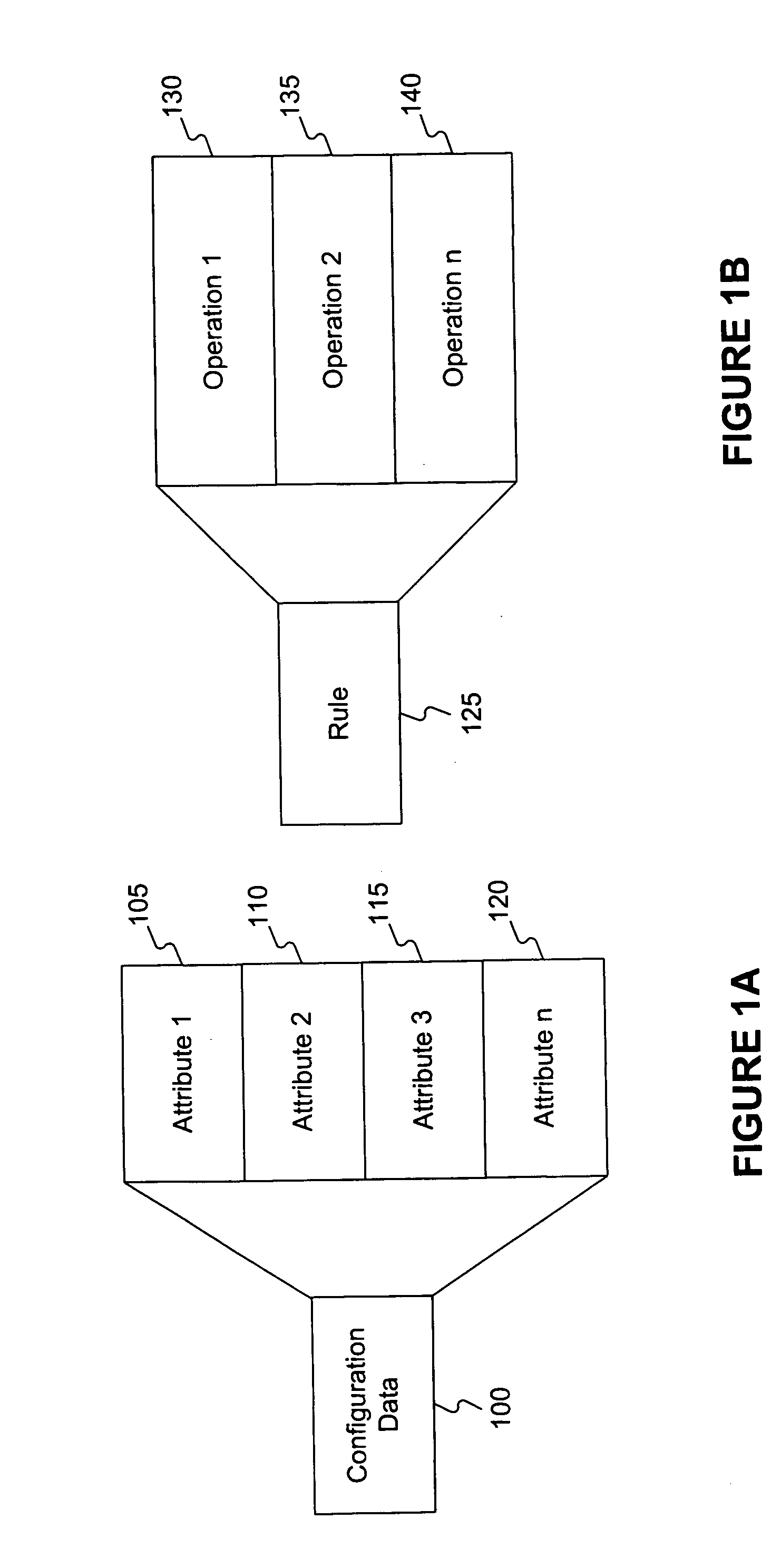

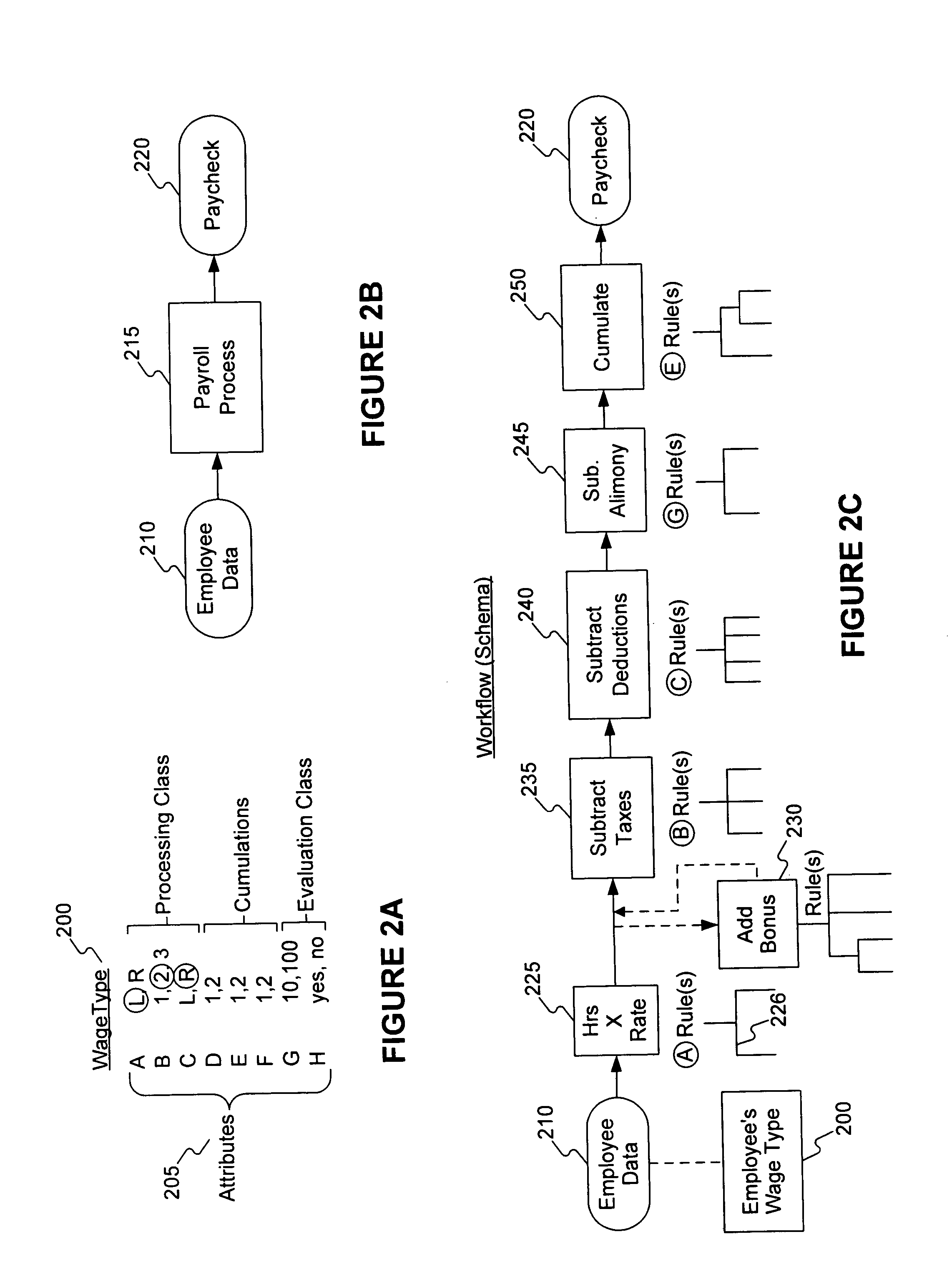

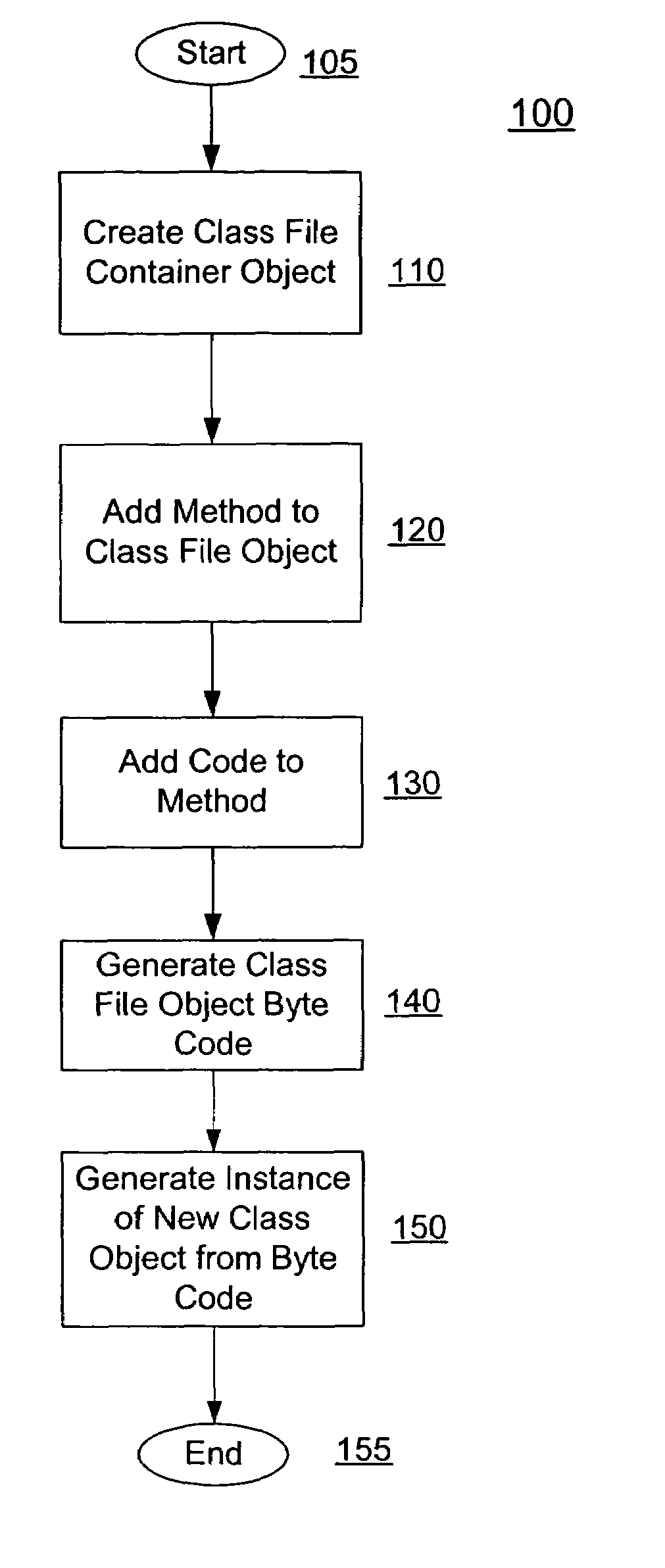

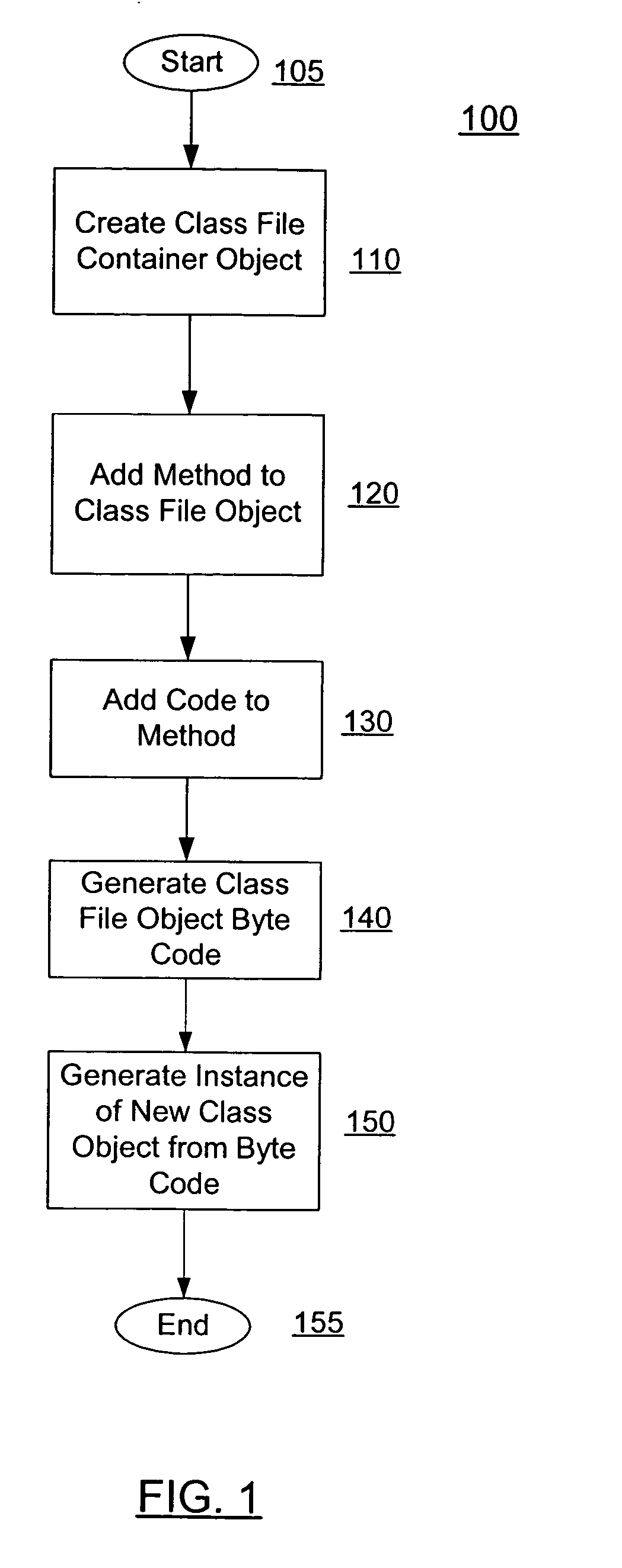

A system for high level dynamic hot code generation. A class file container object is first created. Methods and code are then added to the class file container object. Byte code is then generated from the populated class file container object. From the byte code, instances of the new class object can by generated. The program code generator is configured to generate code at a programming language construct level, thereby working at a level of program language statements, expressions, variables, and other constructs.

Owner:ORACLE INT CORP

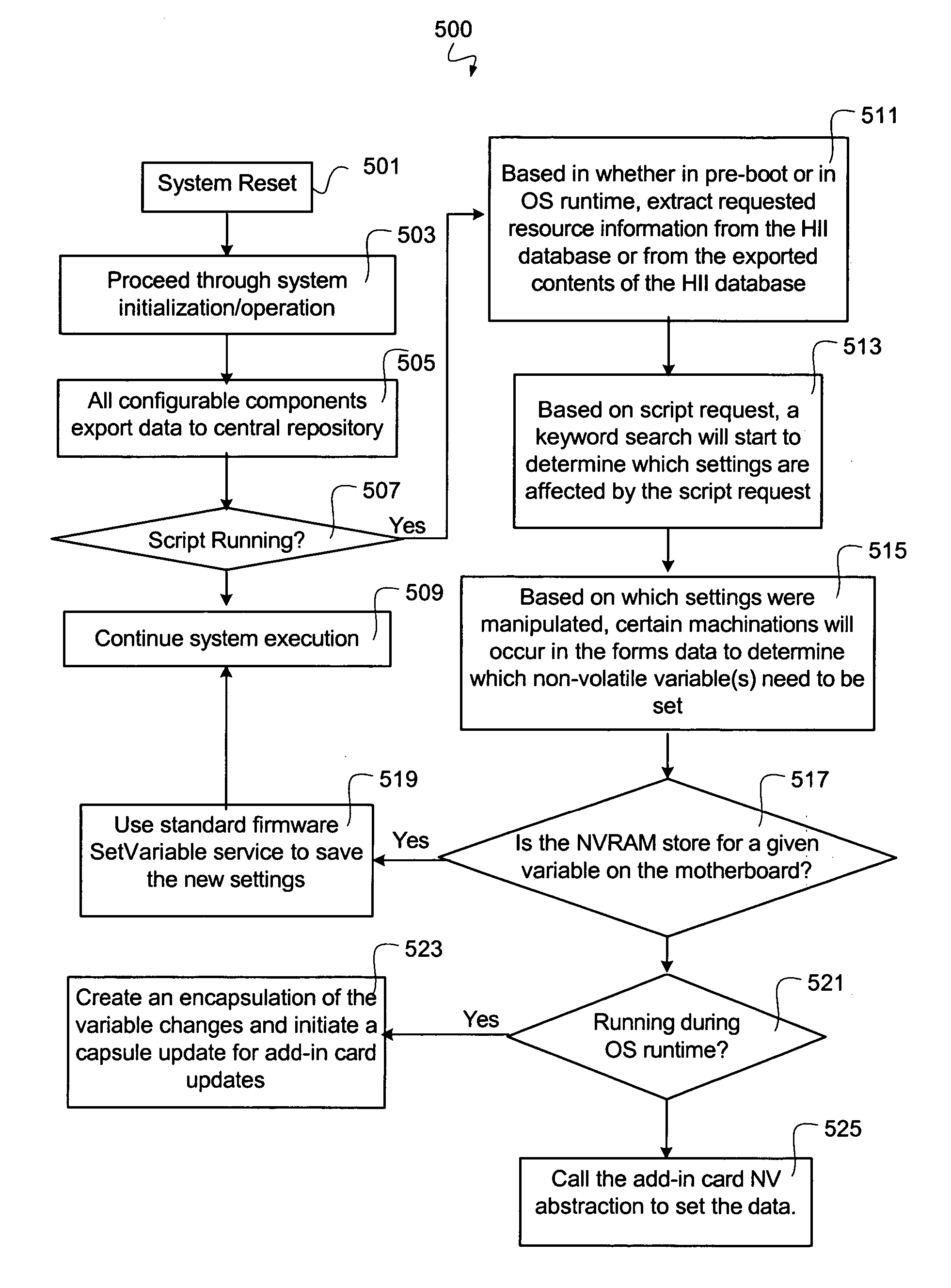

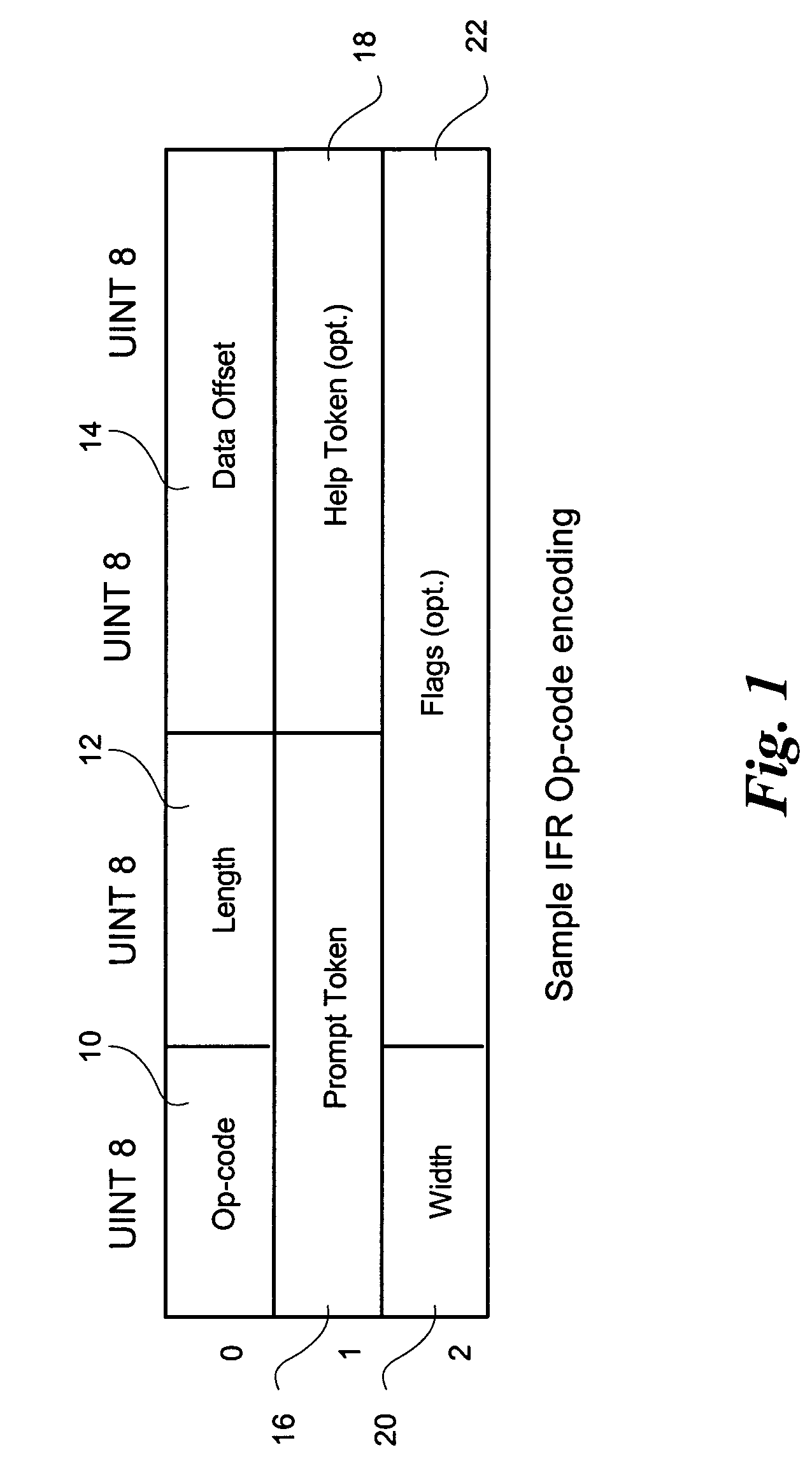

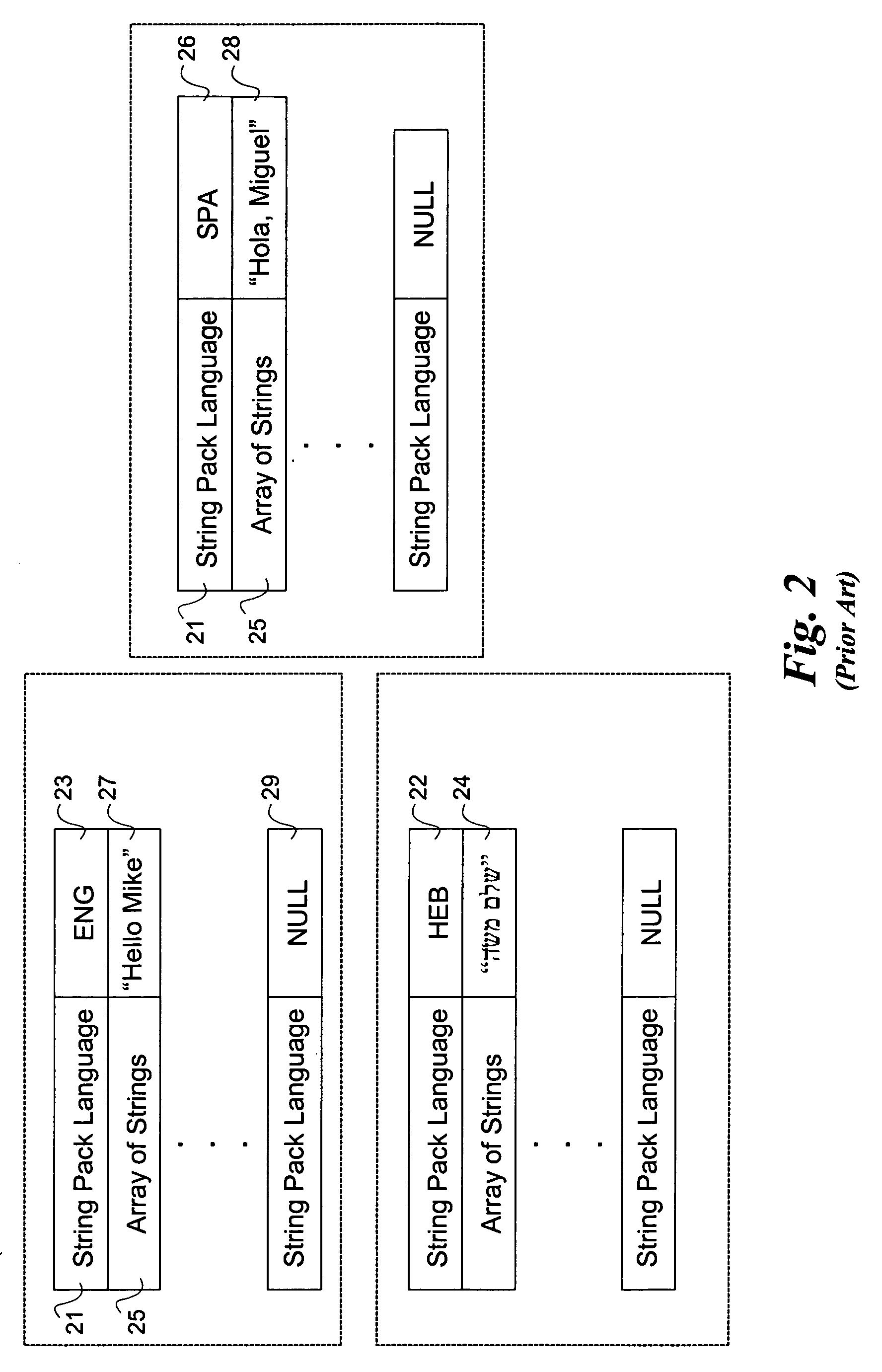

System and method to seamlessly enable enhanced management and scripting of a computer system and its add-in devices

An embodiment of the present invention is a system and method relating to seamlessly enable enhanced management and scripting of a computer system and its add-in devices. In at least one embodiment, the present invention enables a system administrator or integrator to script a common configuration for multiple devices and then automatically configure the devices using the script. The language construct and central data repository for configuration settings are extended to comprehend a scripting language. A script is read by a script engine during either pre-boot or runtime. The script engine searches a keyword database on the central data repository to determine requested configuration settings. A data offset is corresponding to a specific op-code is used to determine where configuration settings are located, for modification.

Owner:INTEL CORP

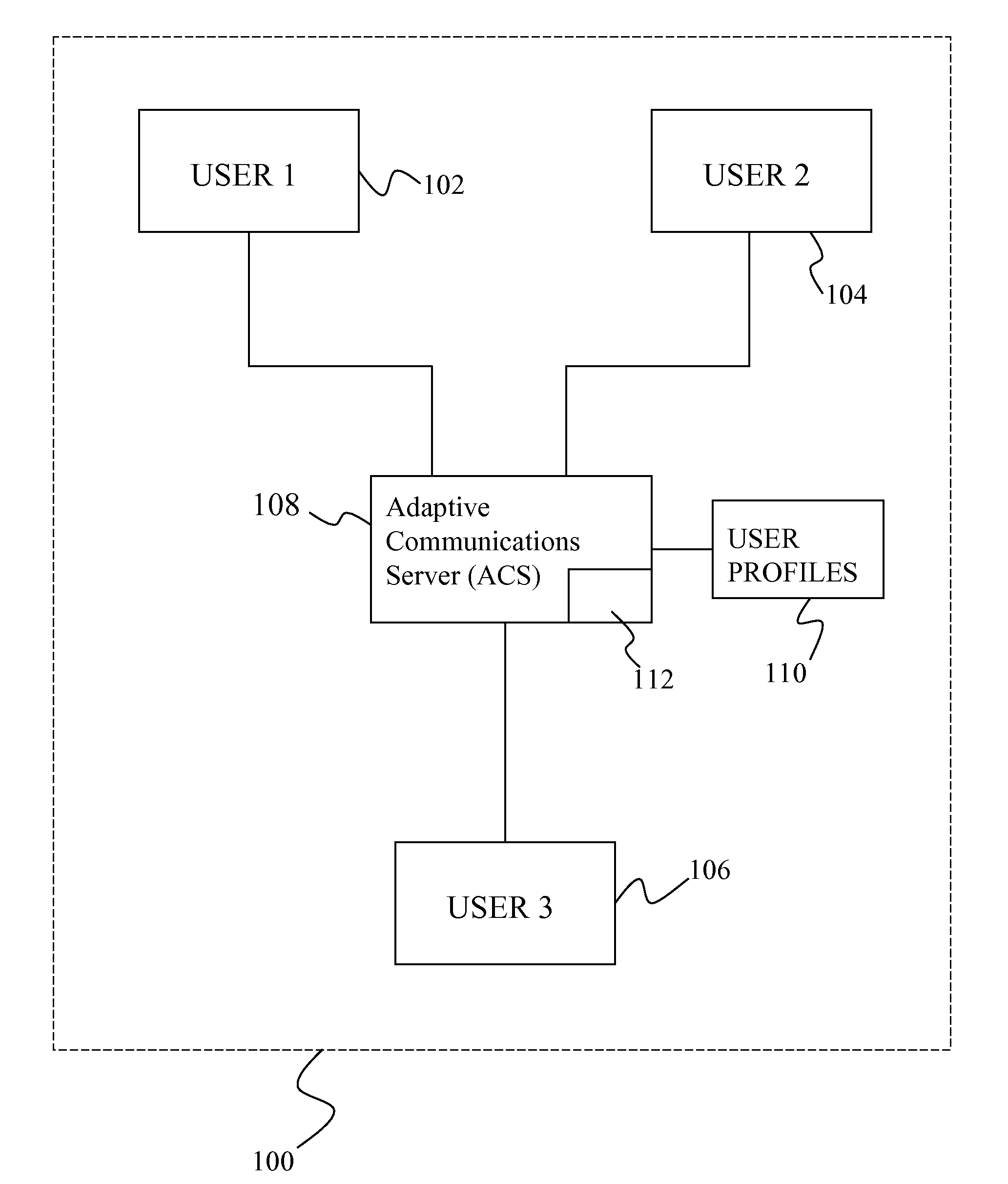

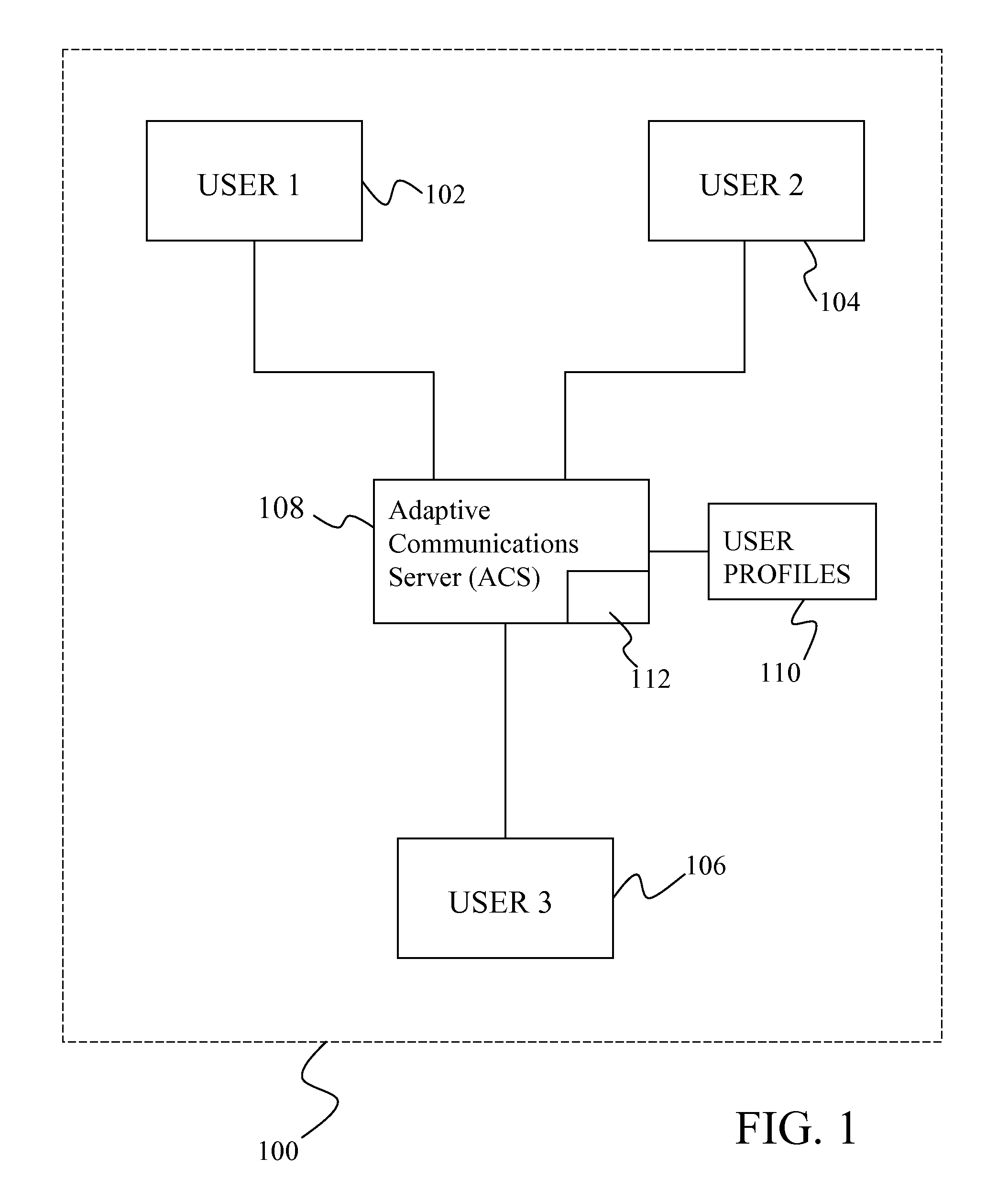

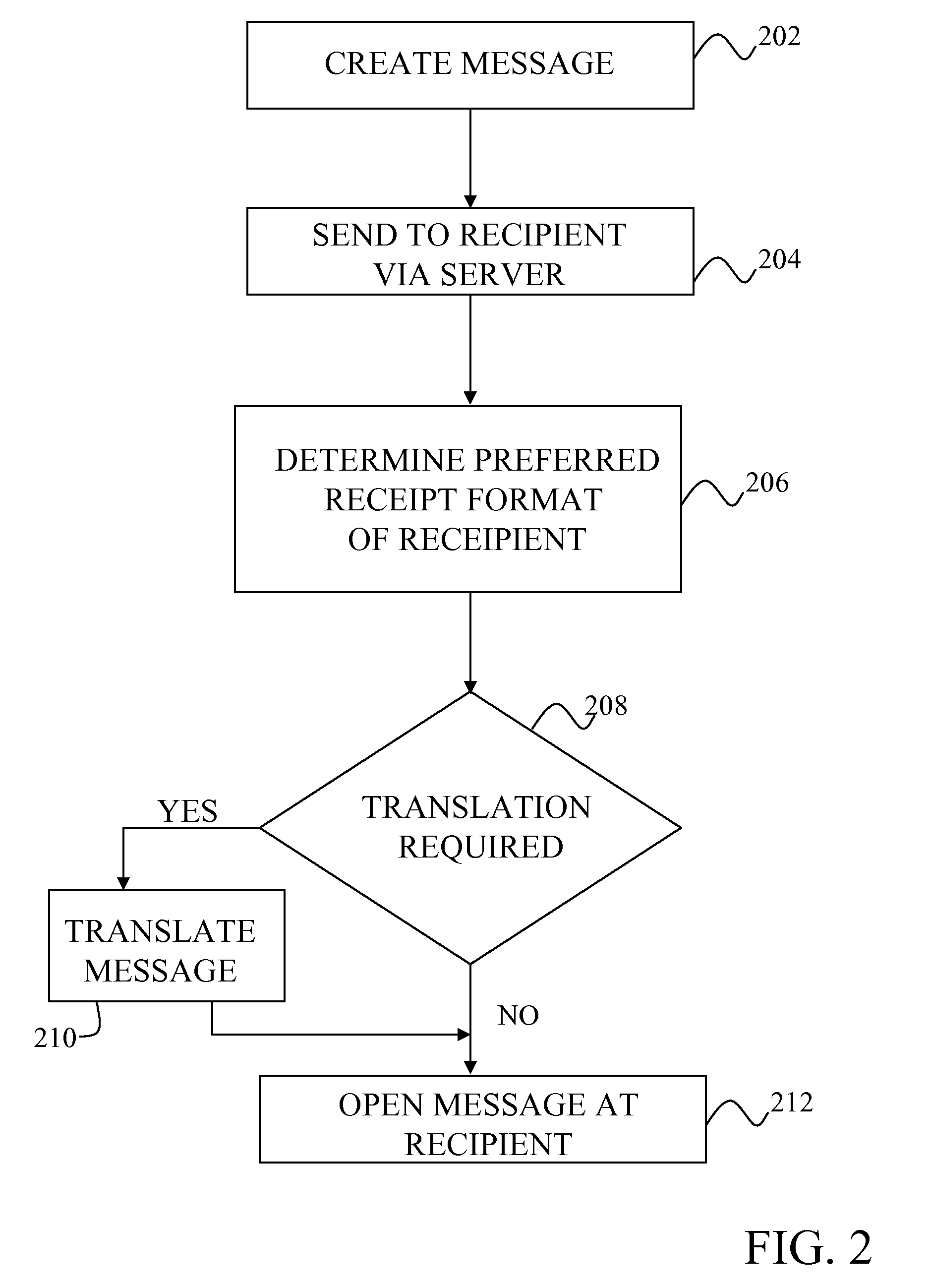

Systems and methods for enabling inter-language communications

InactiveUS20090234633A1Natural language translationSpecial data processing applicationsLanguage constructMessage passing

A method of enabling communication between a first person and a second person is disclosed. The method includes receiving at a server a message from the first person, the message addressed to the second person constructed in a first language; determining a preferred language of receipt of a message by the second person; determining whether the preferred language is different than the first language; translating the message from the first language to the preferred language of receipt of the second person to create a translated message whenever the preferred language is different than the first language; and delivering the translated message to the second person.

Owner:IBM CORP

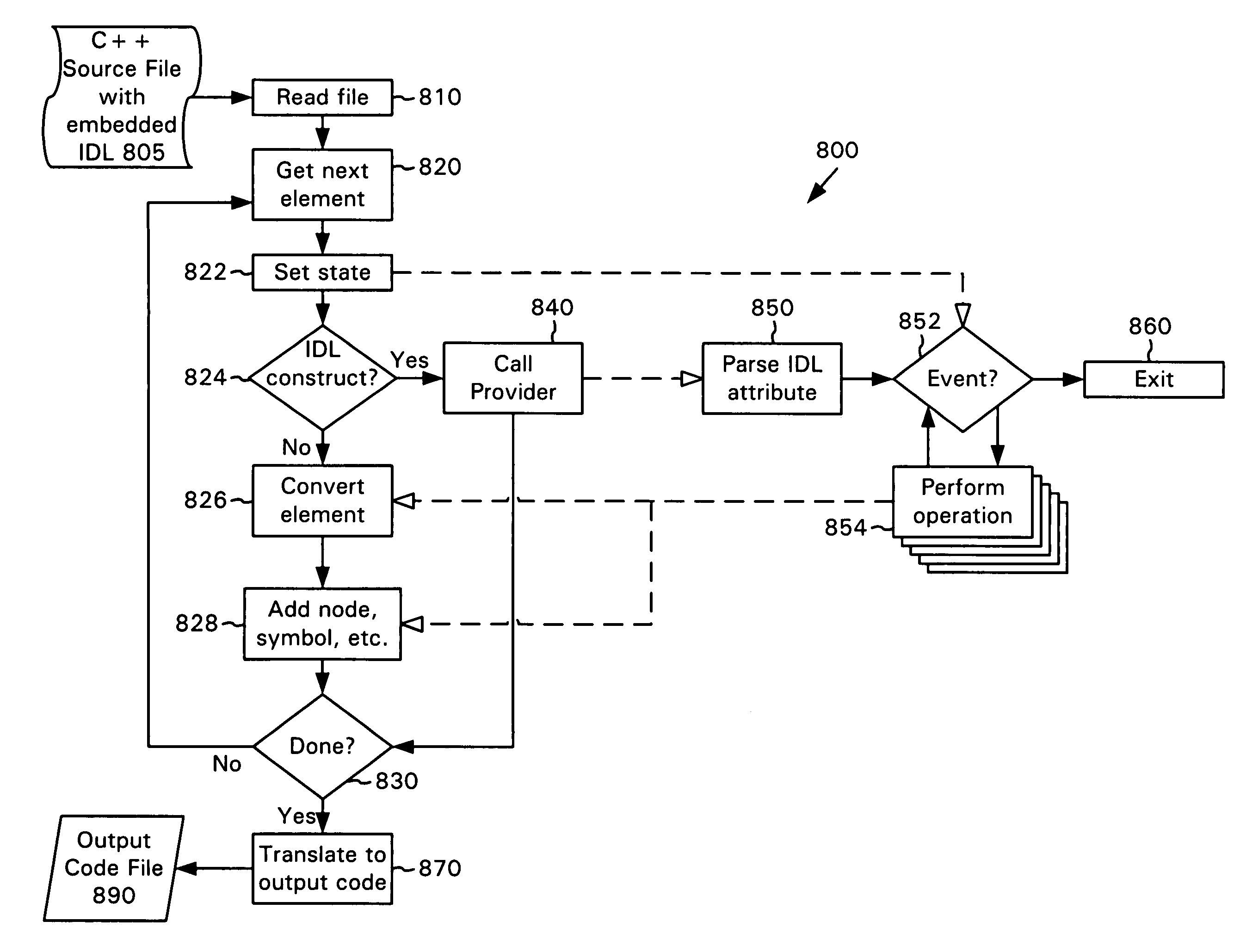

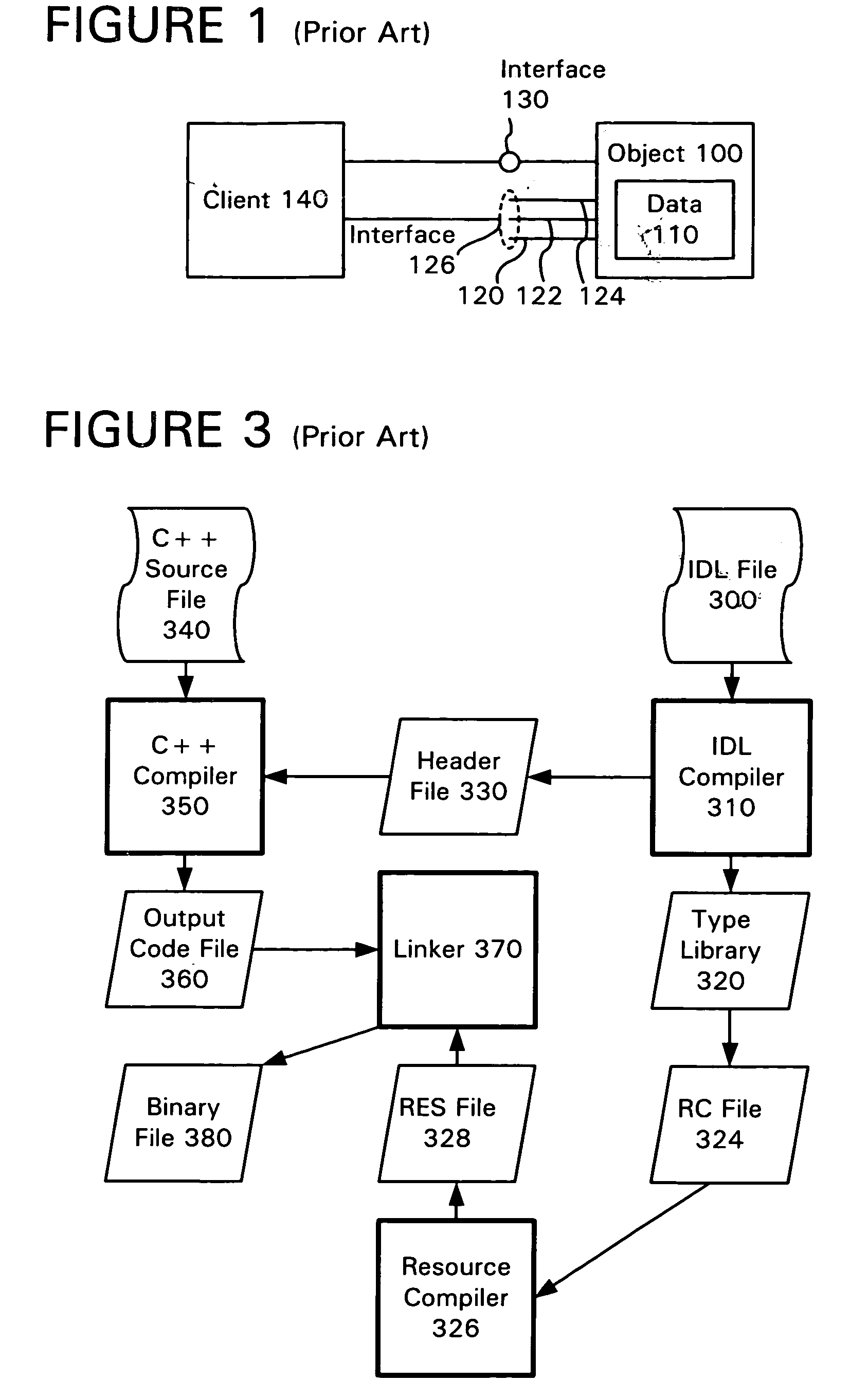

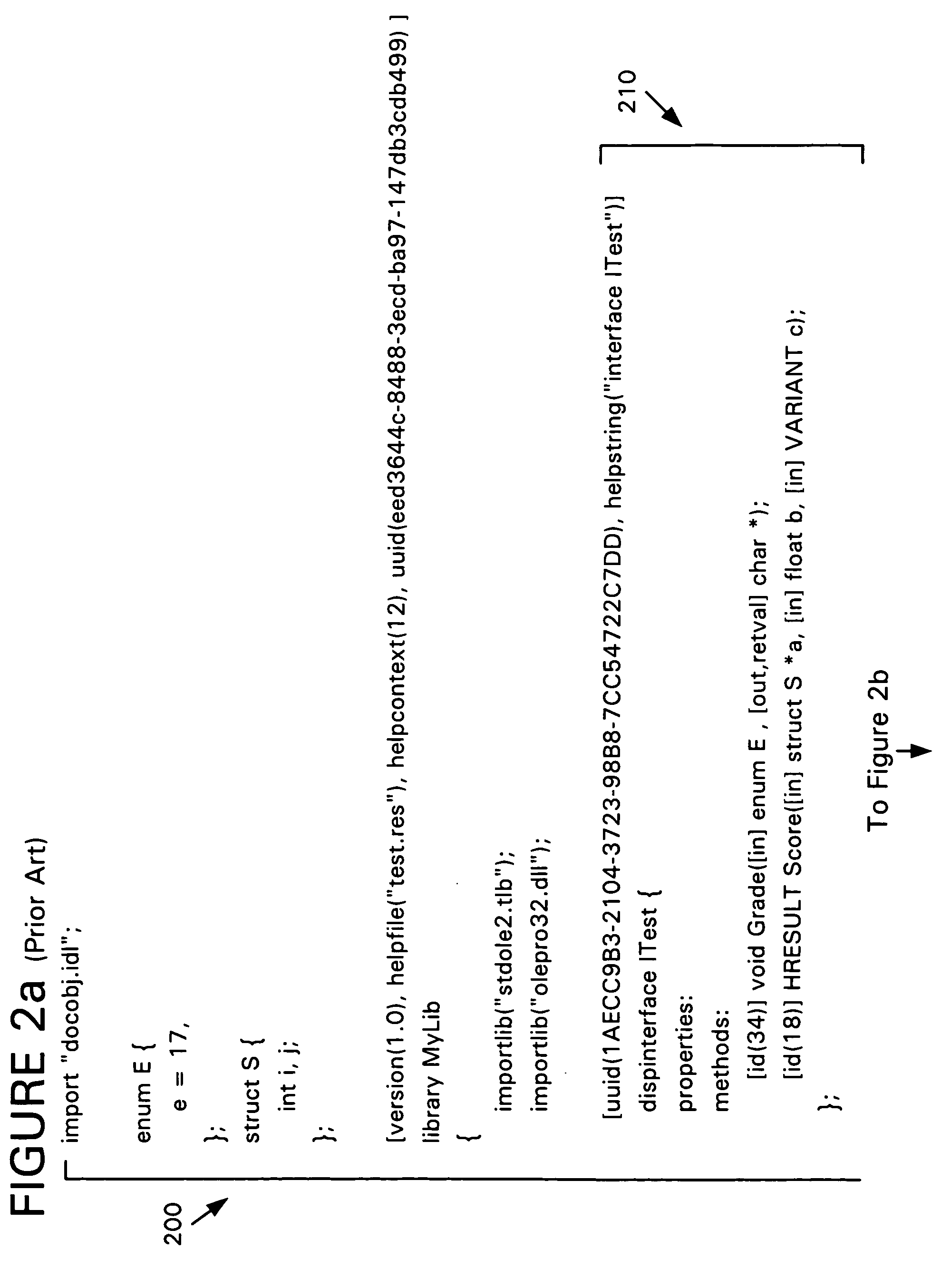

Unification of a programming language and a definition language

InactiveUS7150010B1Powerful toolEasy programmingSoftware engineeringProgram controlLanguage constructR language

Unification of a programming language with a definition language creates a powerful tool for object-oriented programming. A programming language is extended to include definition language constructs. In a compiler environment, a compiler recognizes the definition language constructs in programming language code. The compiler environment unifies representation of the definition language information and programming language code in a unified parse tree, and derives semantic meaning from definition language information. The compiler environment also checks for lexical, syntax, and semantic errors.

Owner:MICROSOFT TECH LICENSING LLC

Methods of exposing application layer integrity as object oriented programming language elements

InactiveUS20060242196A1Code refactoringSpecial data processing applicationsLanguage constructSoftware engineering

Embodiments of the invention may transform business application relationships or links into OOP constructs that represent the relationship, tying together different types of business objects, such as data and operations, in a manner that allows automated OOP tools to check the integrity of the relationships and thus the integrity of relationships in the modeled business application. In one embodiment, an automated system uses an object-oriented language construct, such as an assignment operator (e.g., “=” in Java), to link together OOP objects representing business data and business operations. The object-oriented language construct binds different OOP objects representing business application objects and enforces a relationship between them. Representing the business object relationships as OOP language constructs, such as an assignment operator, allows the use of a OOP language tool, such as a Java debugger, to walk through referential relationships and discover referential problems in the integrity of the business application layer.

Owner:SAP AG

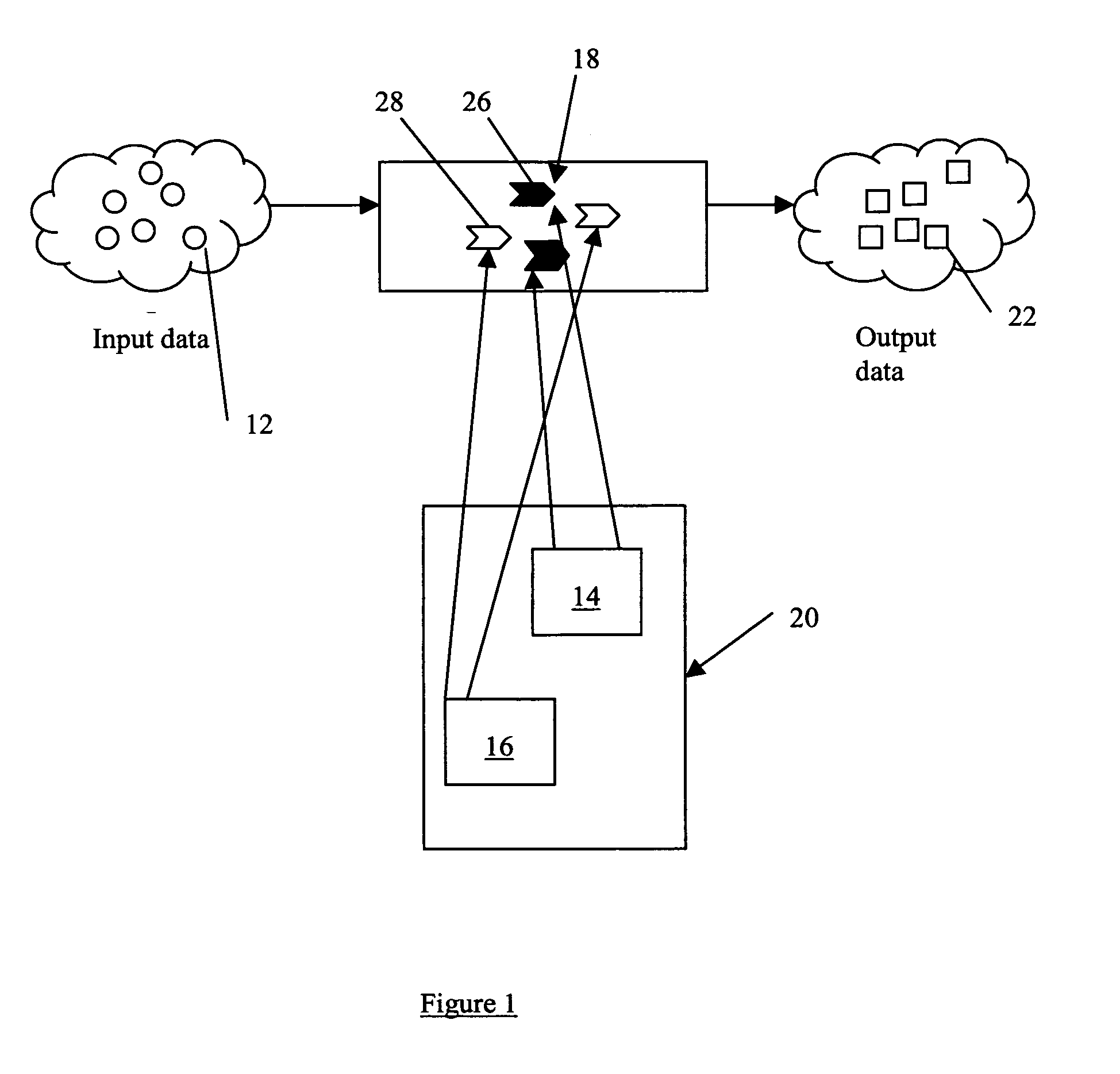

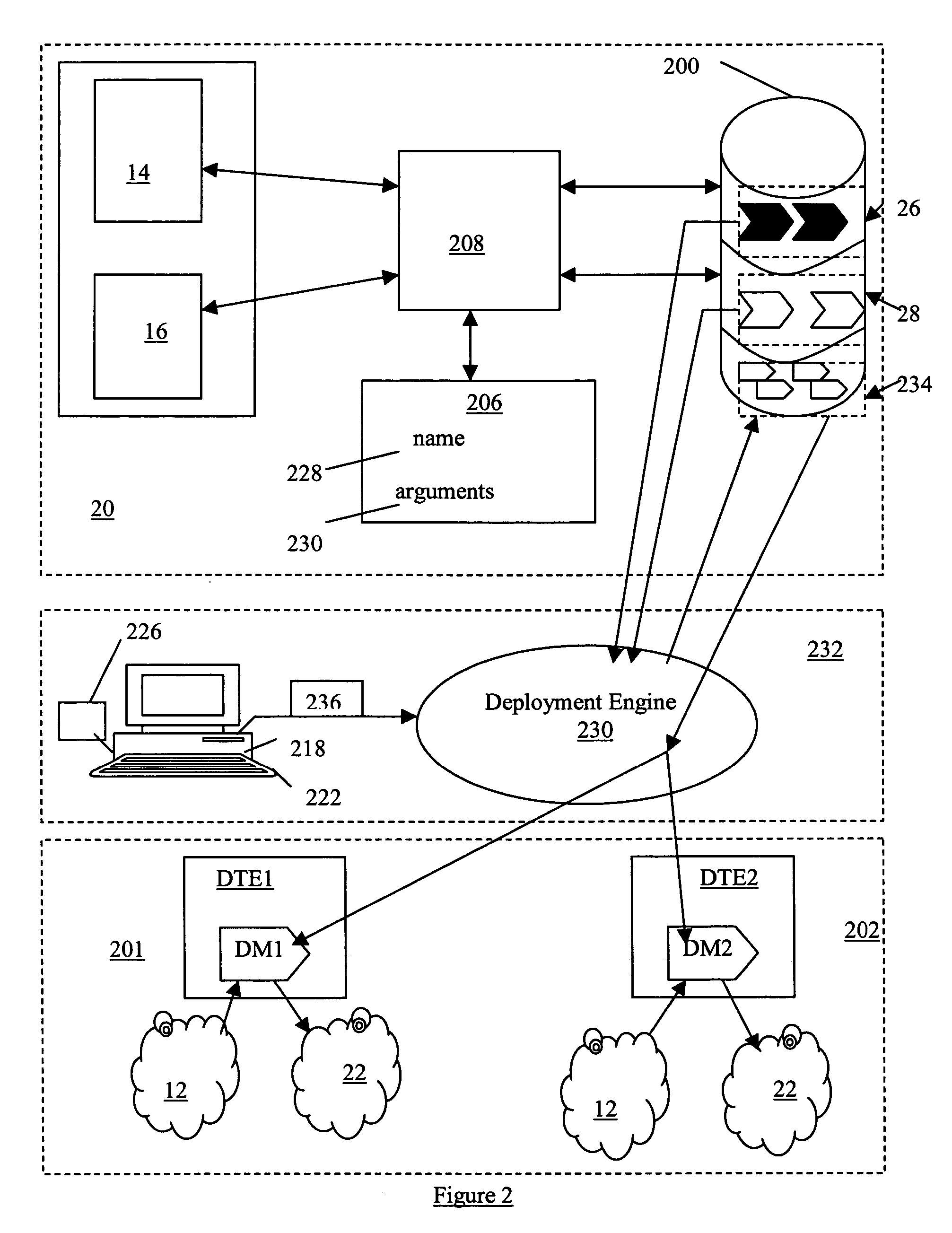

Integrated visual and language- based system and method for reusable data transformations

InactiveUS20050137852A1Digital data information retrievalDigital data processing detailsLanguage constructData conversion

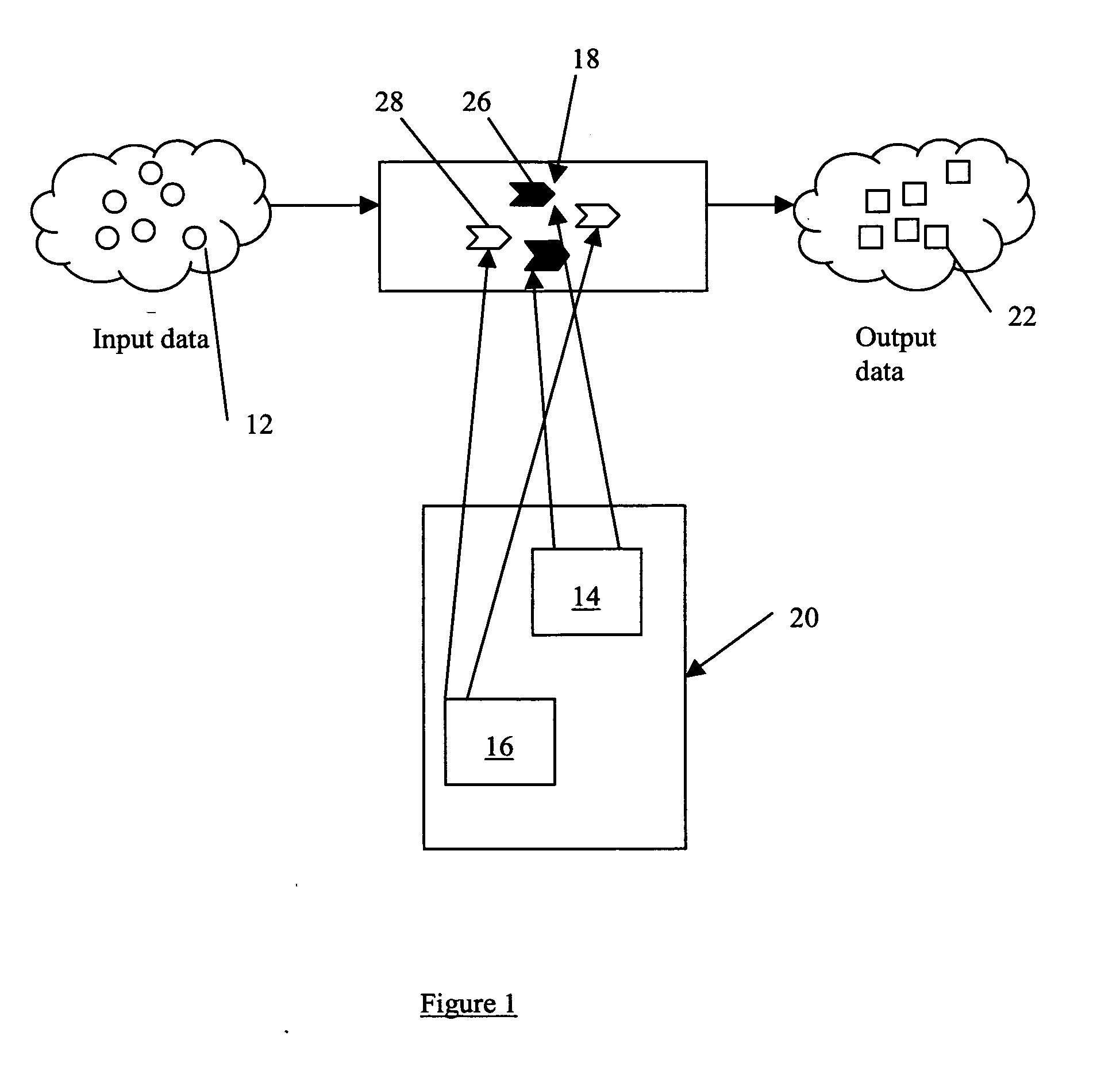

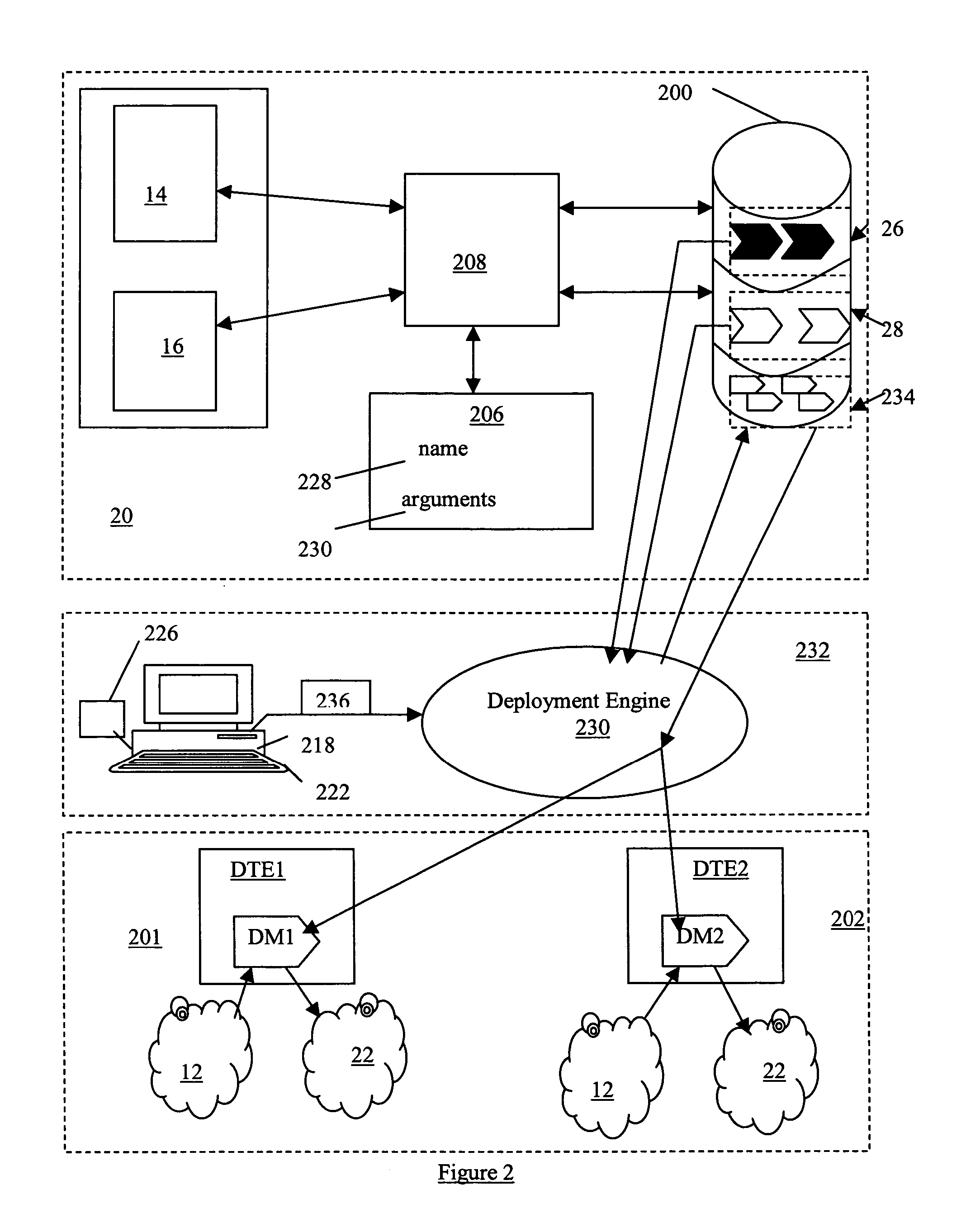

There is provided a system and method for deploying a set of coupled data transformation modules describing a data transformation, the data transformation for transforming a data structure from a first format to a second format, the method including the steps of receiving an instruction for selecting the set of transformation modules from a memory; converting each of the set of transformation modules to a common model format, the set of modules having at least one transformation module being of a module type of a type set including language constructed modules and visually constructed modules; and generating an executable version of the converted transformation modules suitable for execution by a data transformation engine; wherein the executable version when executed transforms the data structure from the first format to the second format.

Owner:IBM CORP

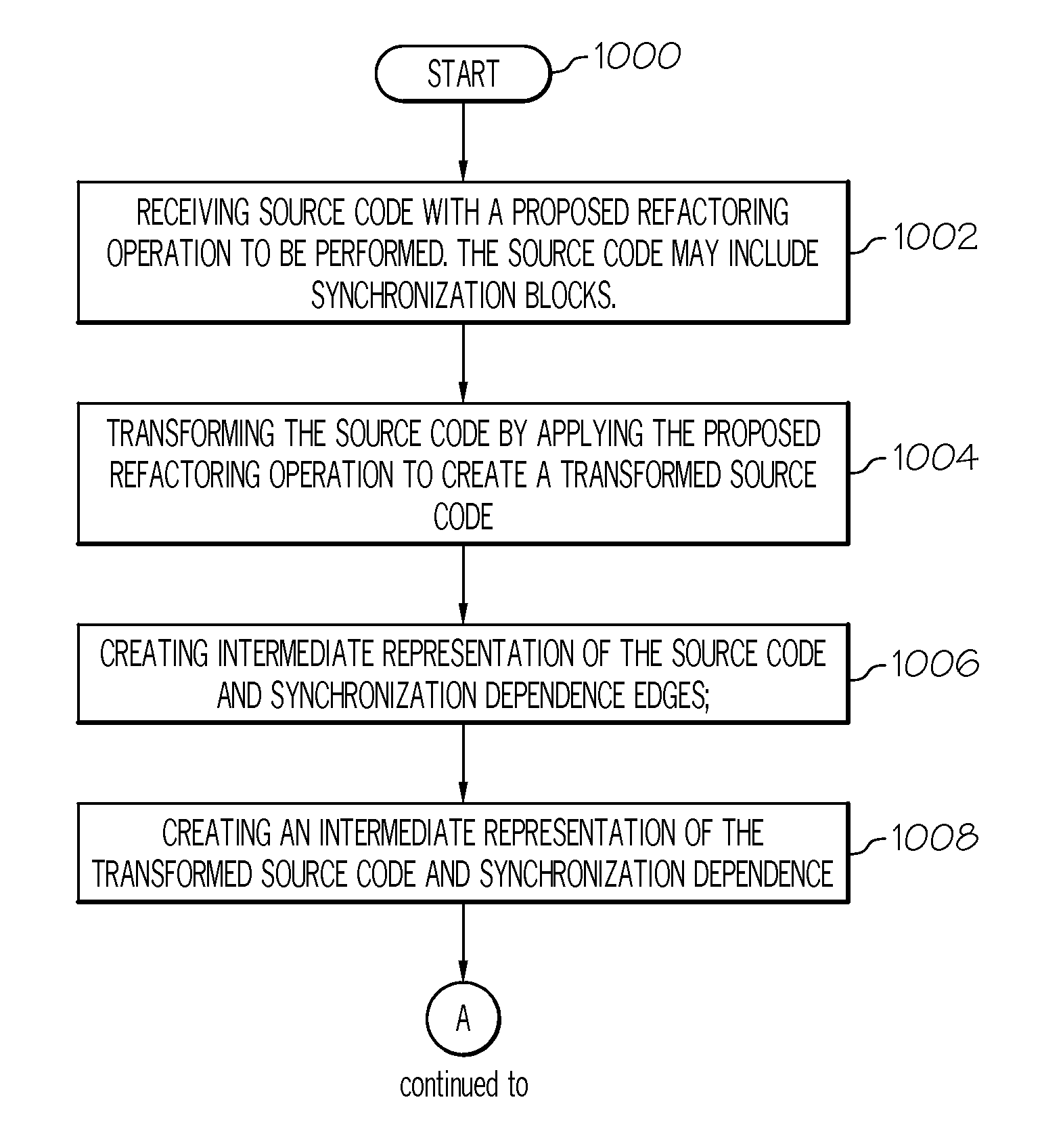

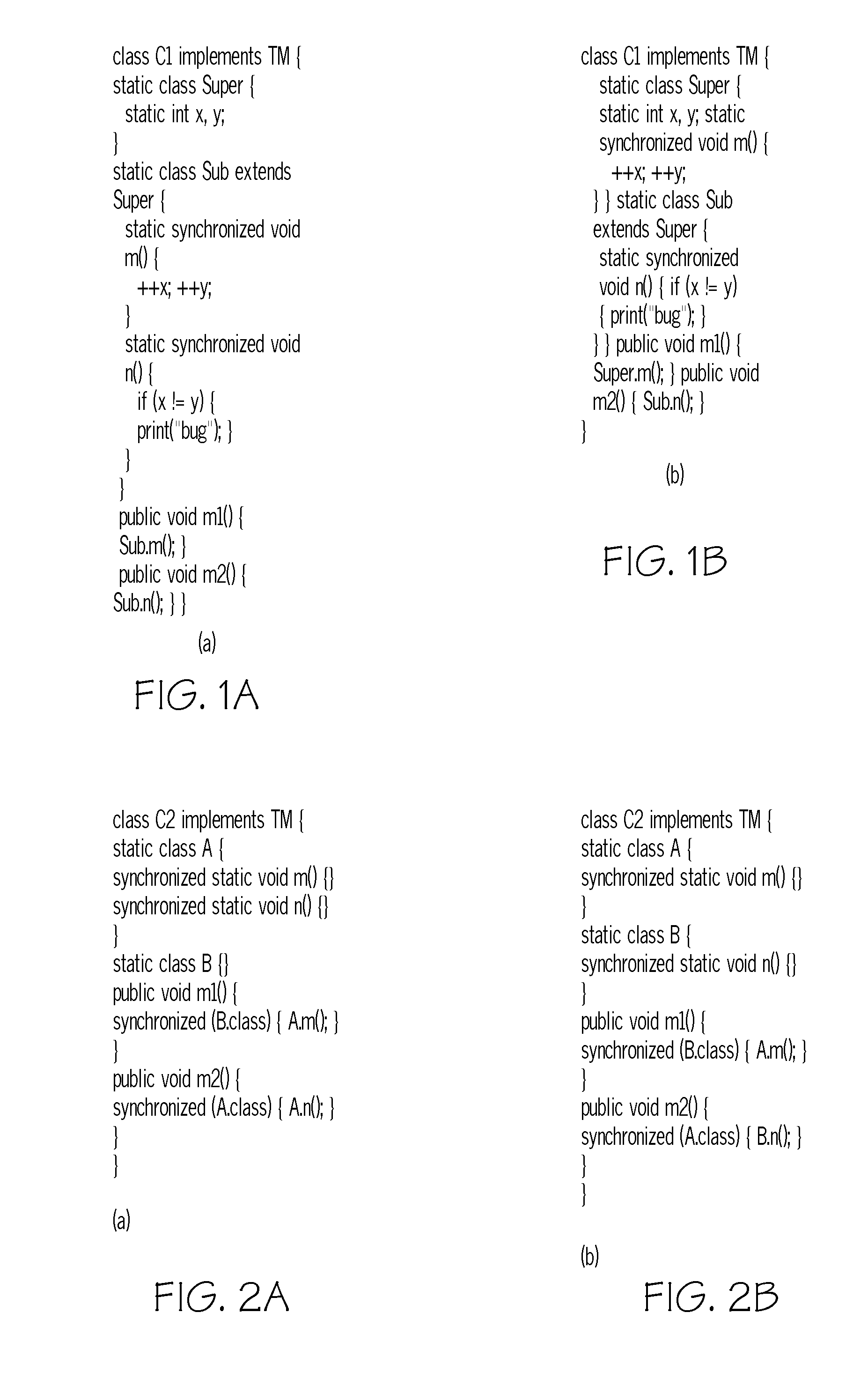

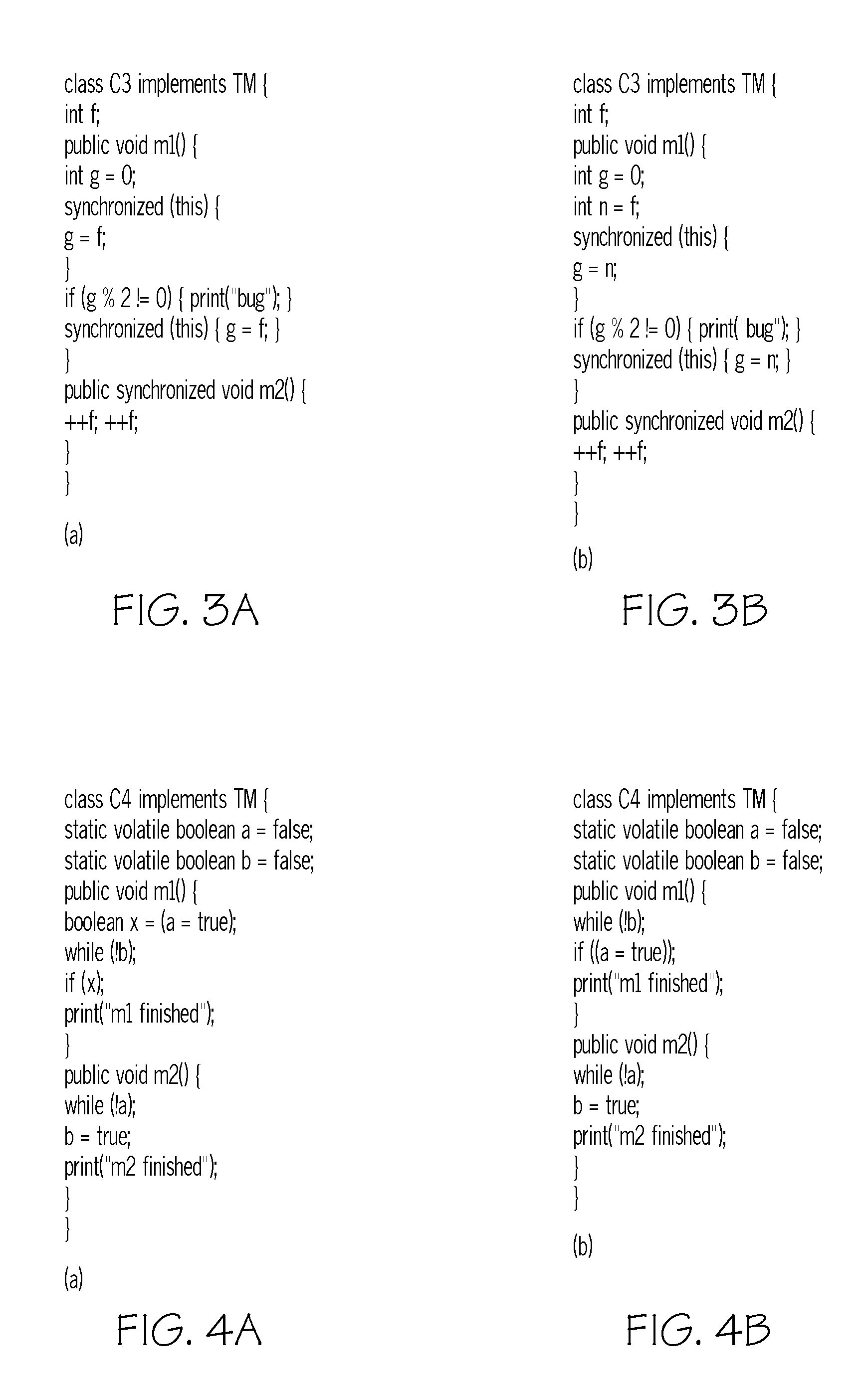

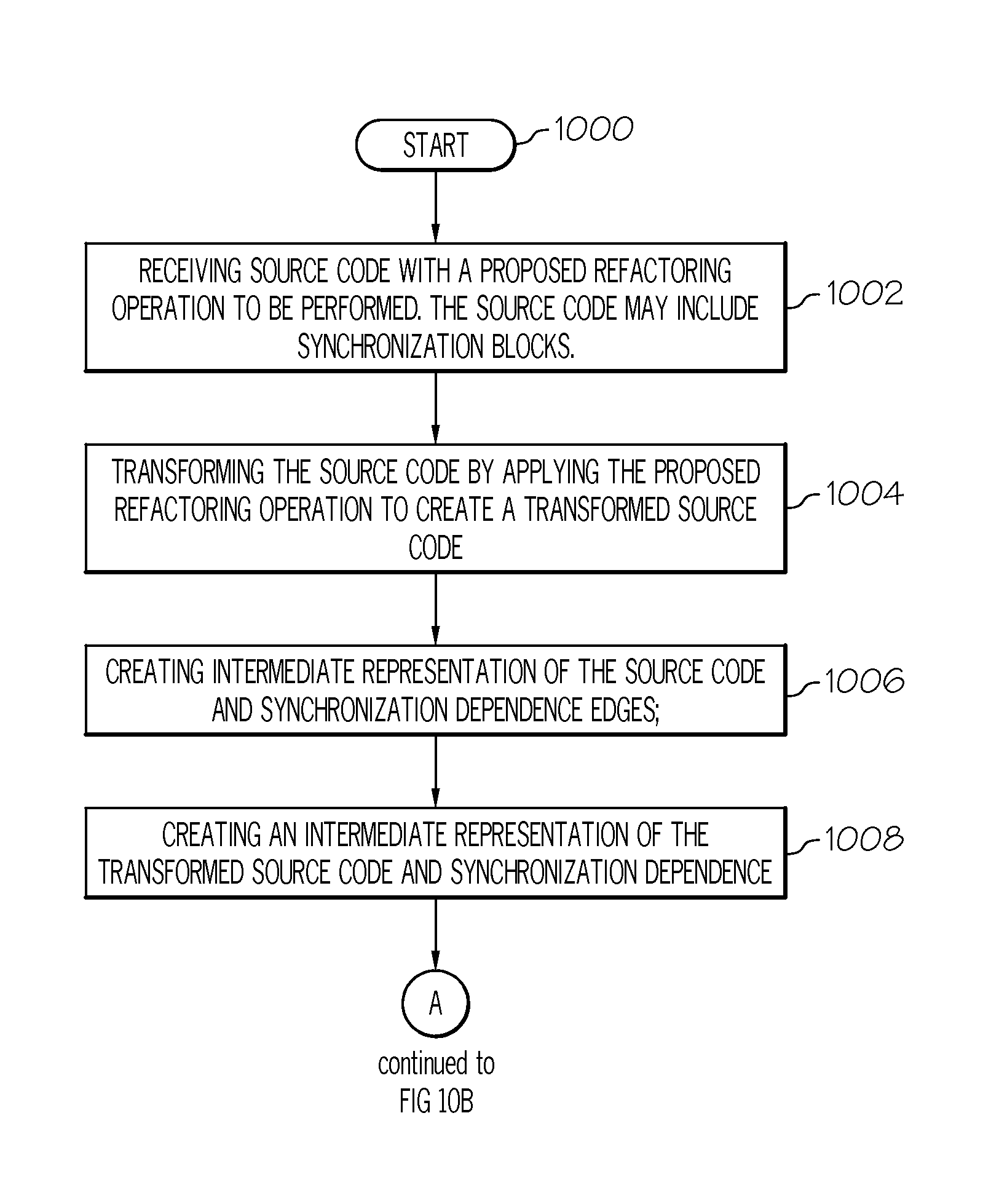

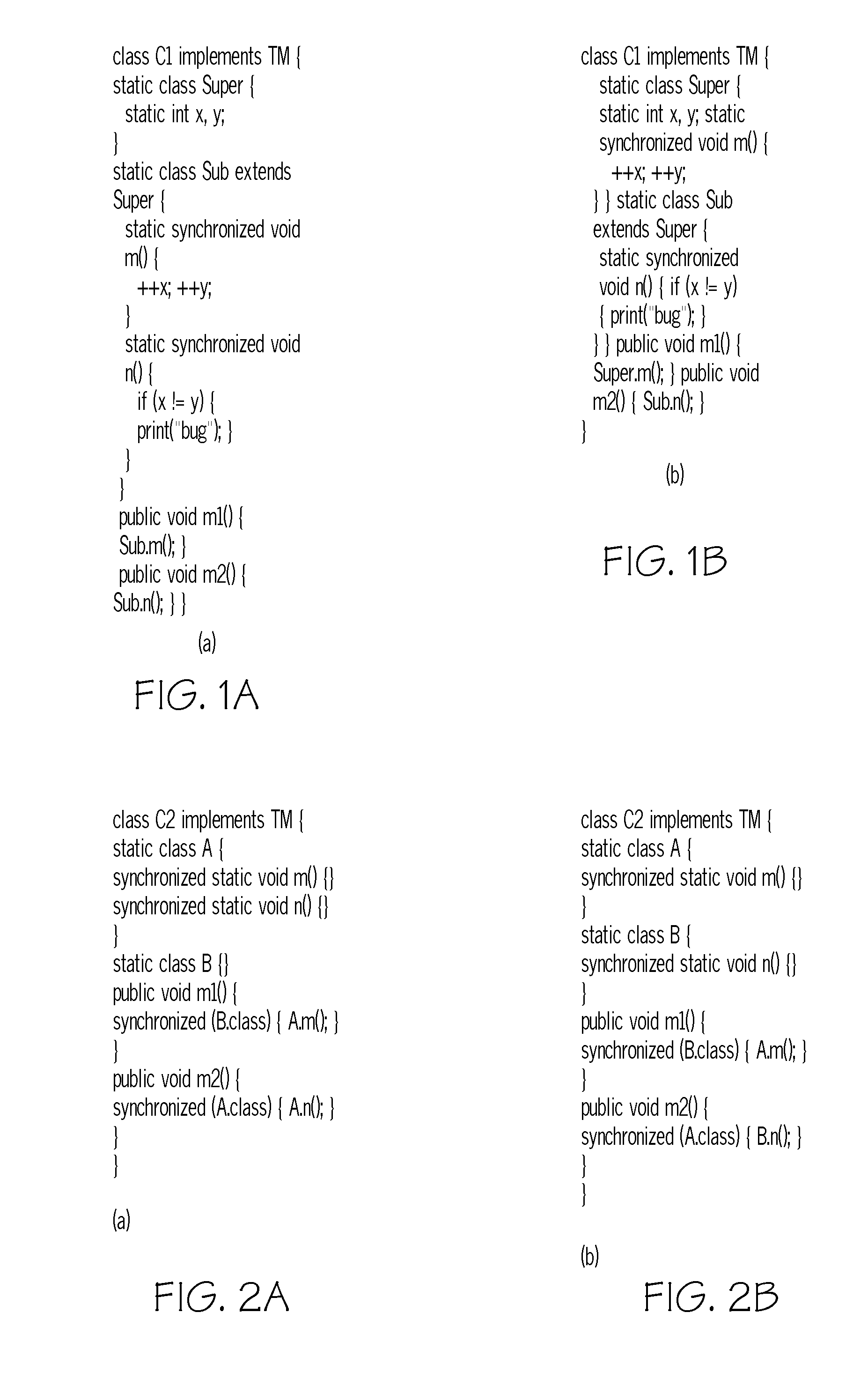

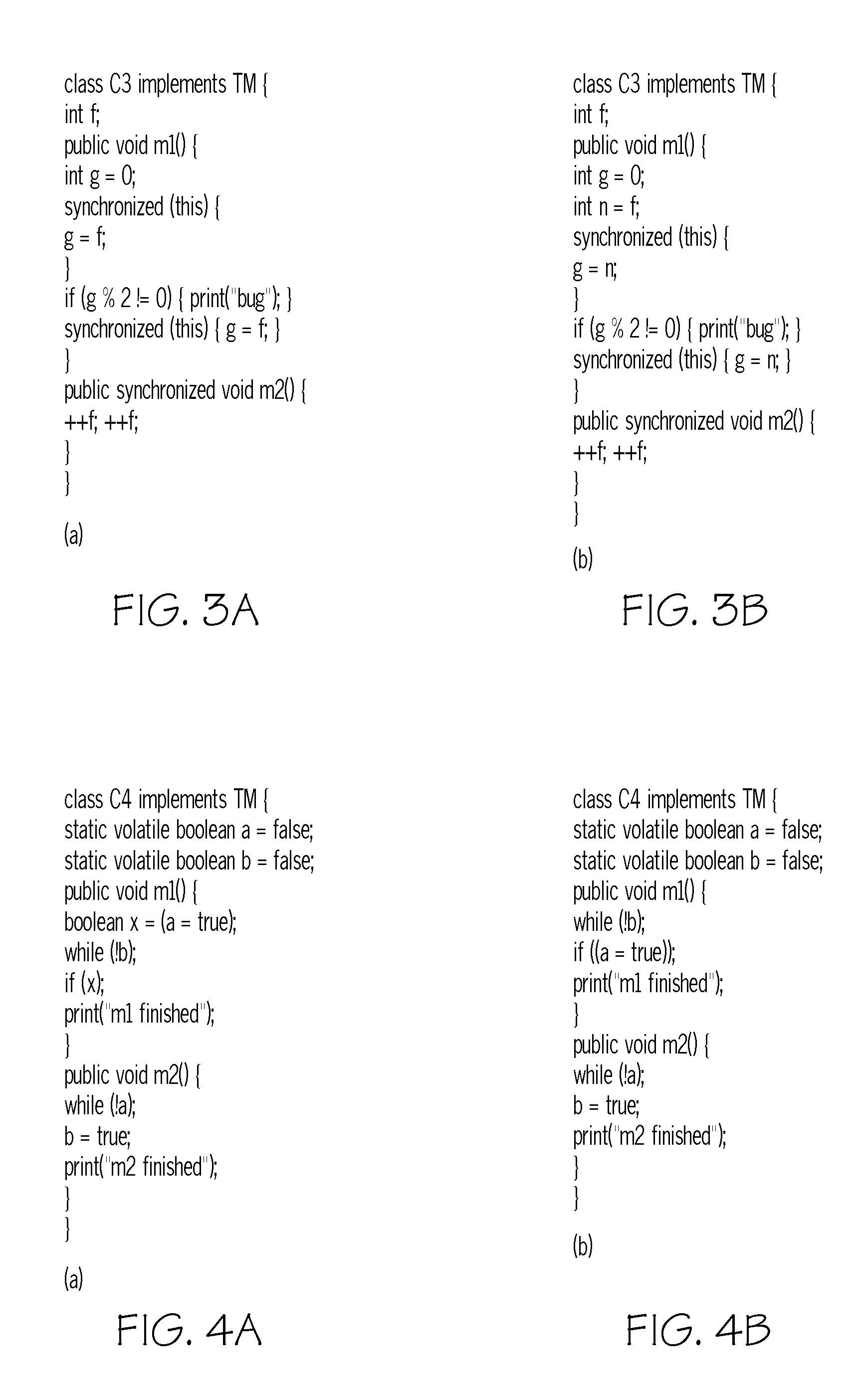

Correct refactoring of concurrent software

InactiveUS20110219361A1Precise correctness resultEasy to implementCode refactoringProgram controlLanguage constructJava Memory Model

Automated refactorings as implemented in modern IDEs for Java usually make no special provisions for concurrent code. Thus, refactored programs may exhibit unexpected new concurrent behaviors. We analyze the types of such behavioral changes caused by current refactoring engines and develop techniques to make them behavior-preserving, ranging from simple techniques to deal with concurrency-related language constructs to a framework that computes and tracks synchronization dependencies. By basing our development directly on the Java Memory Model we can state and prove precise correctness results about refactoring concurrent programs. We show that a broad range of refactorings are not influenced by concurrency at all, whereas other important refactorings can be made behavior-preserving for correctly synchronized programs by using our framework. Experience with a prototype implementation shows that our techniques are easy to implement and require only minimal changes to existing refactoring engines.

Owner:IBM CORP

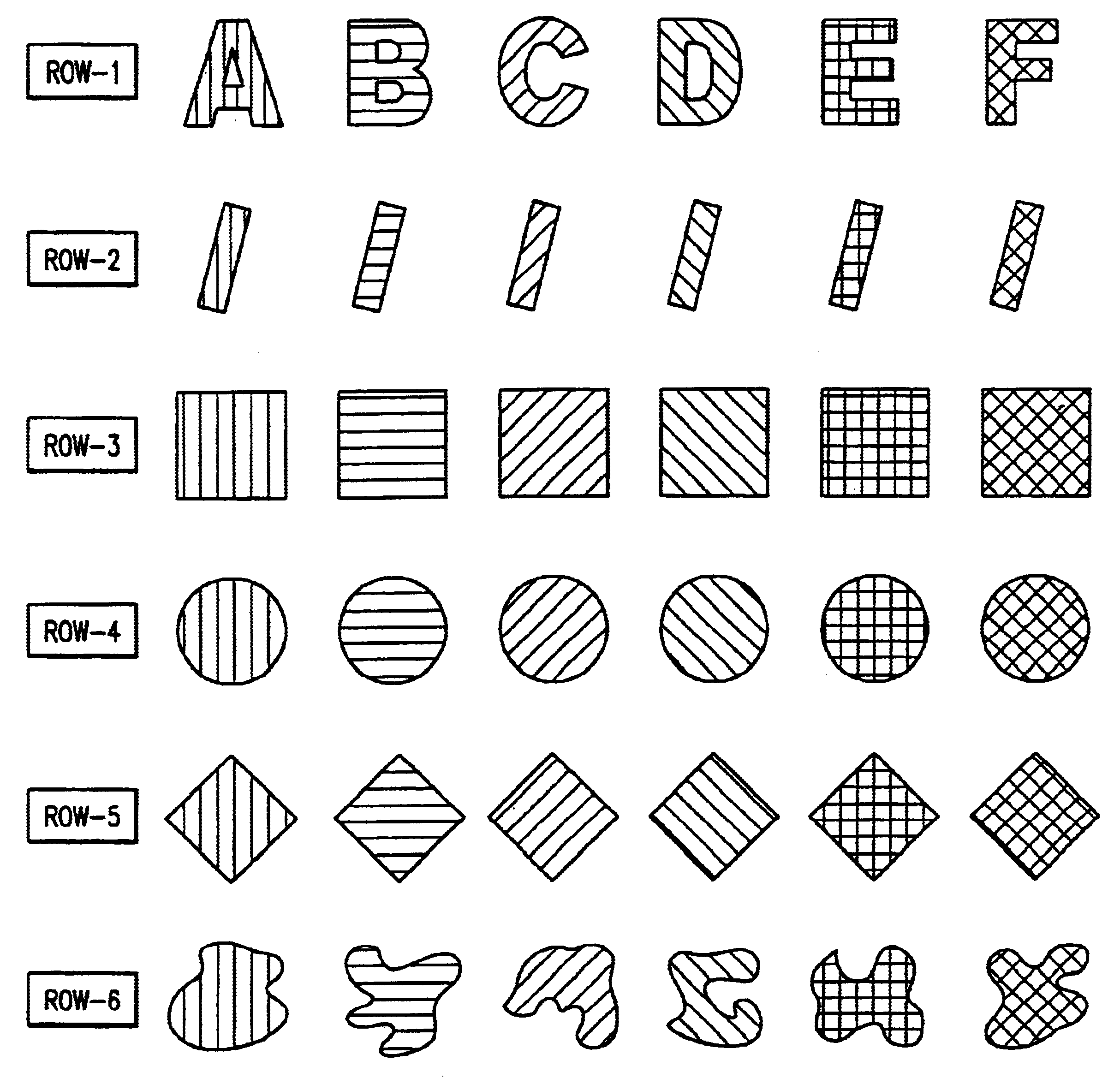

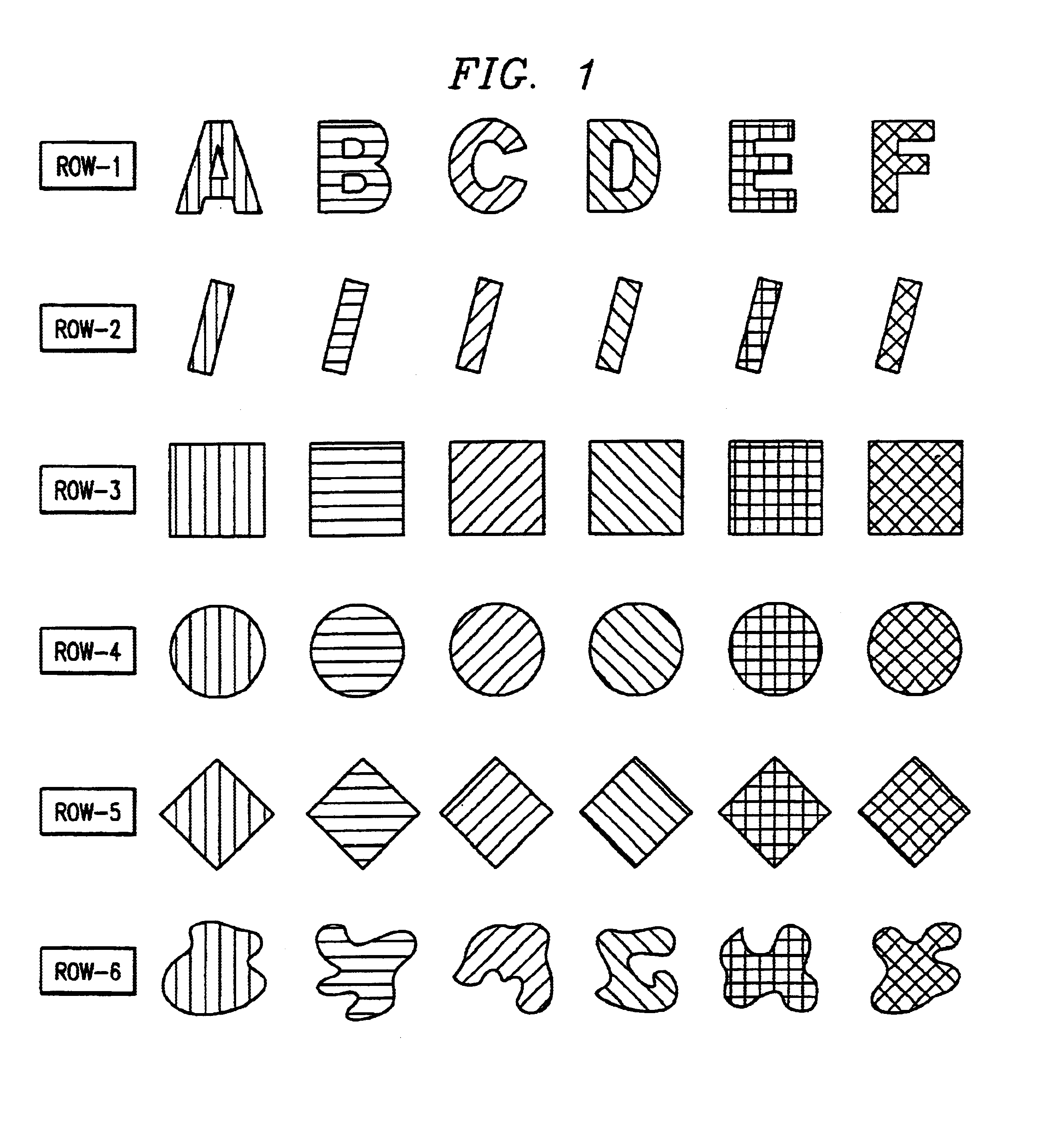

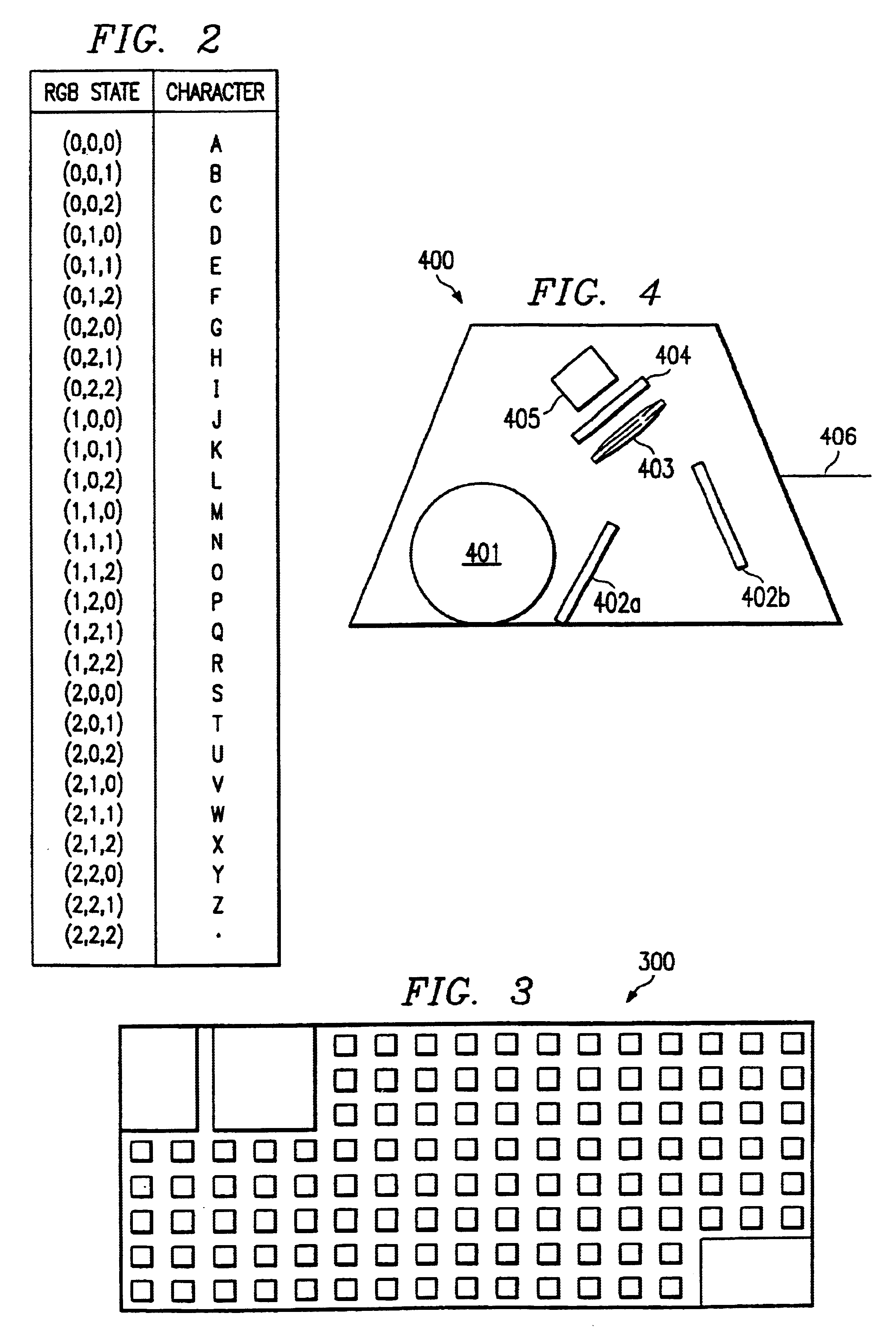

System and method for communication of character sets via supplemental or alternative visual stimuli

InactiveUS6884075B1Easy to learnImprove overall utilizationTeaching apparatusMechanical appliancesRepresentation languageLanguage construct

Owner:TROPOLOC GEORGE A

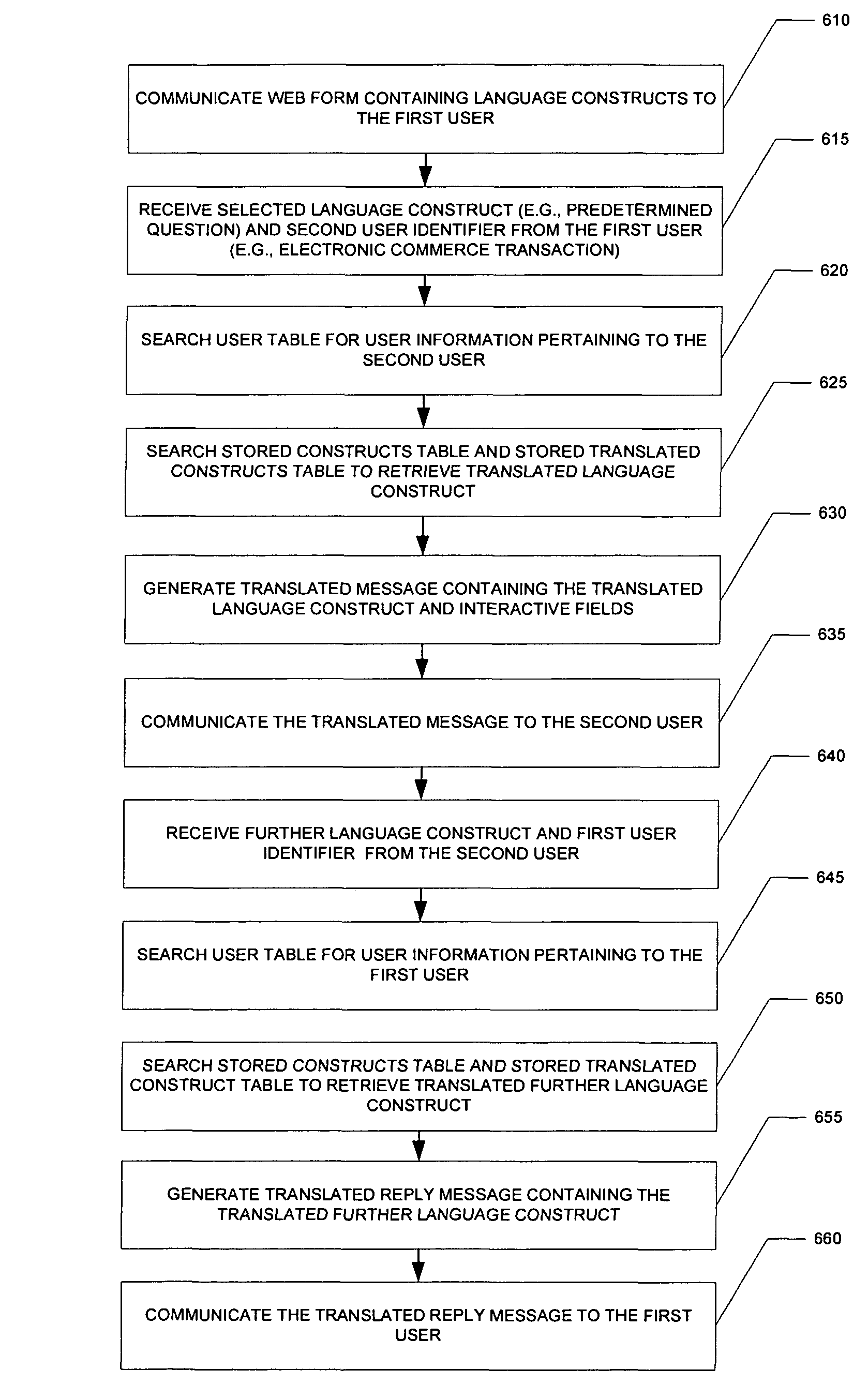

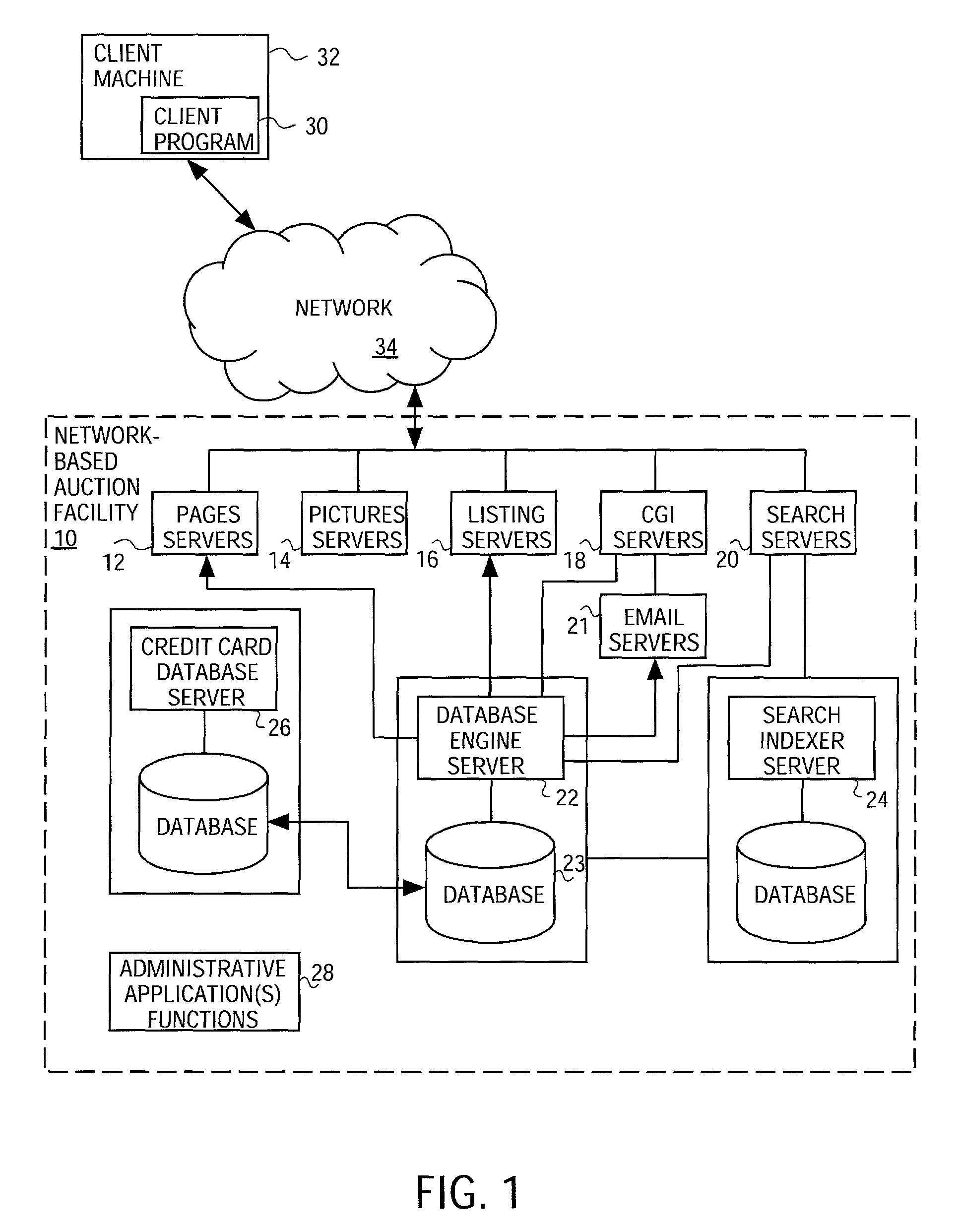

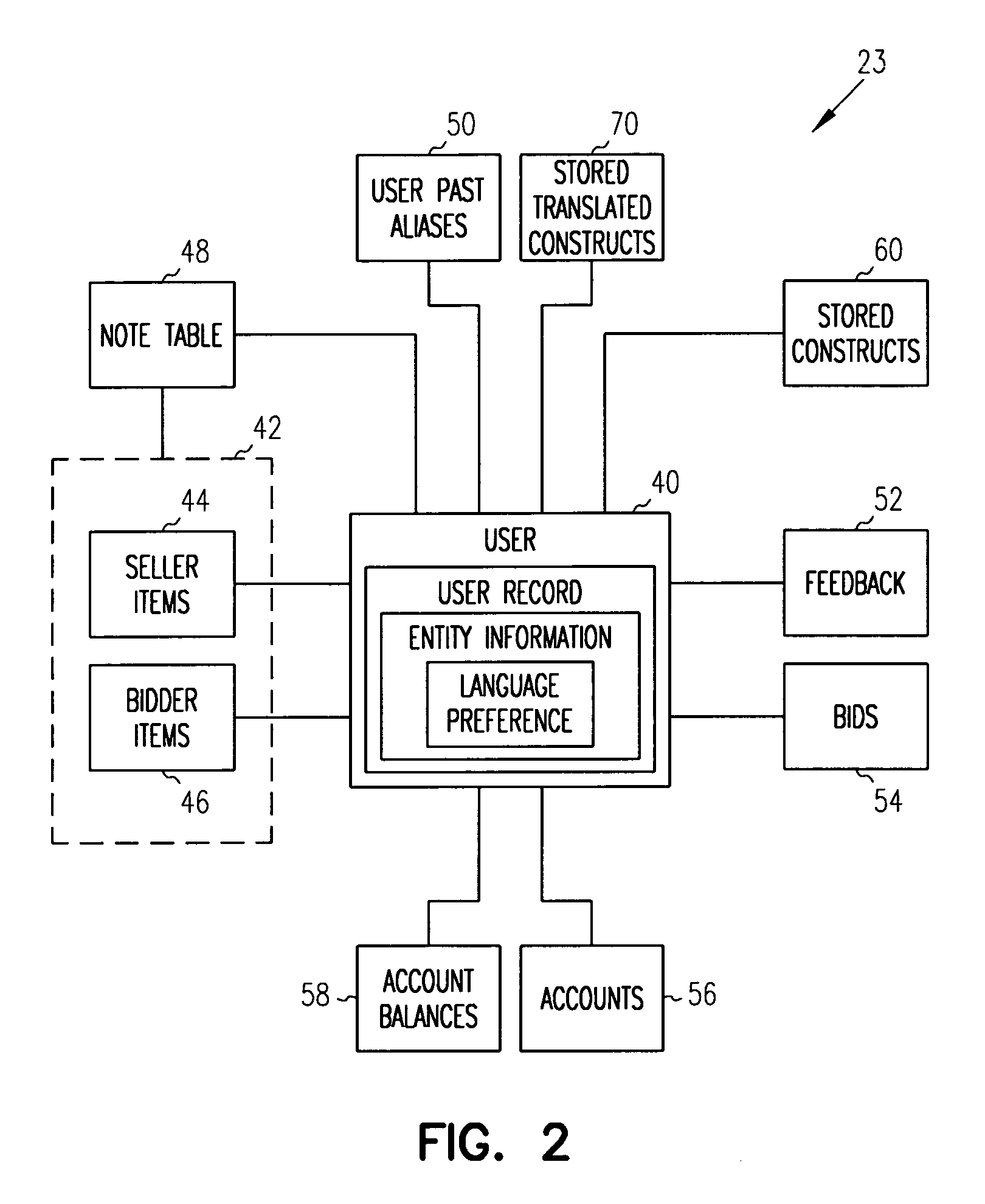

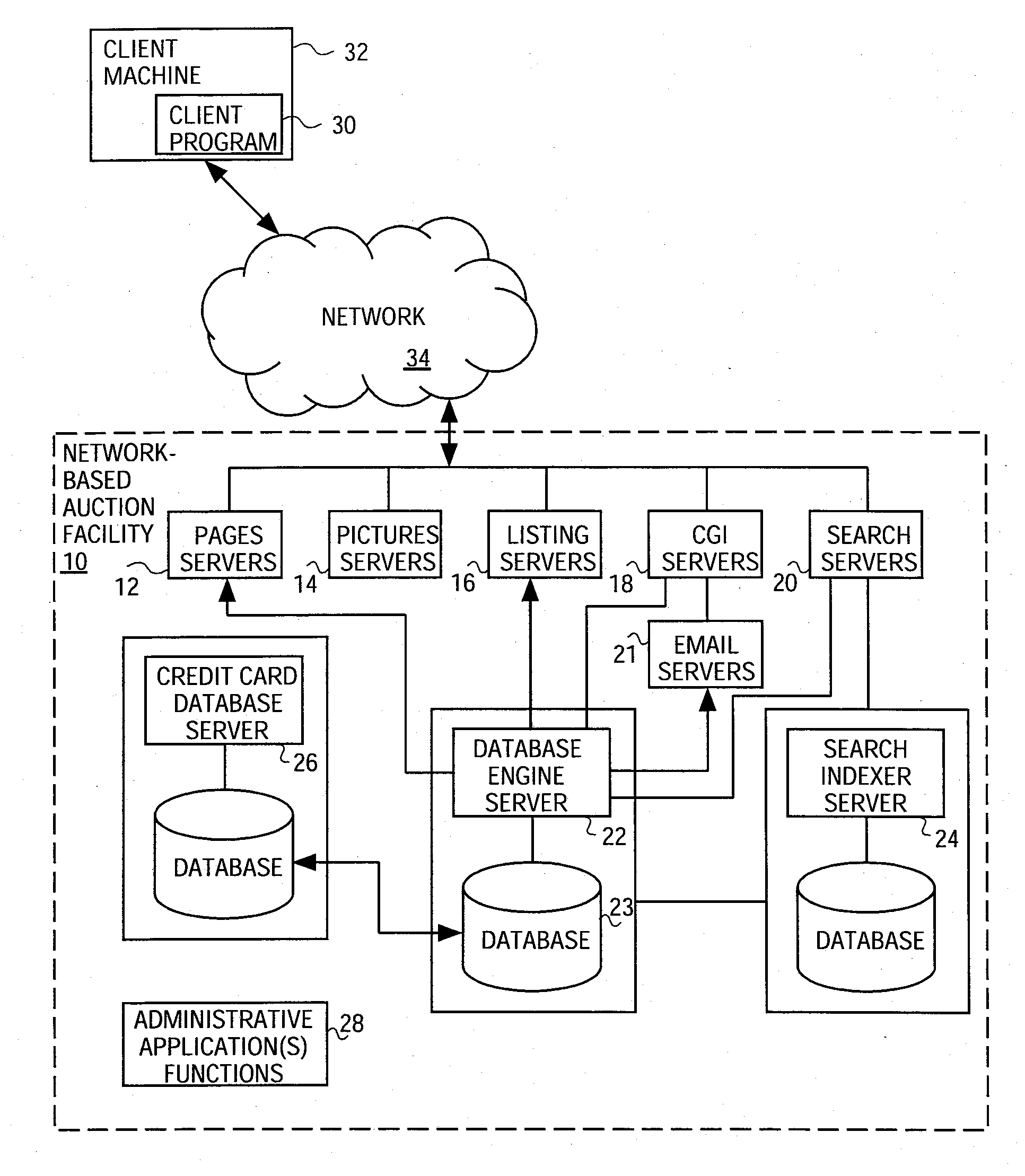

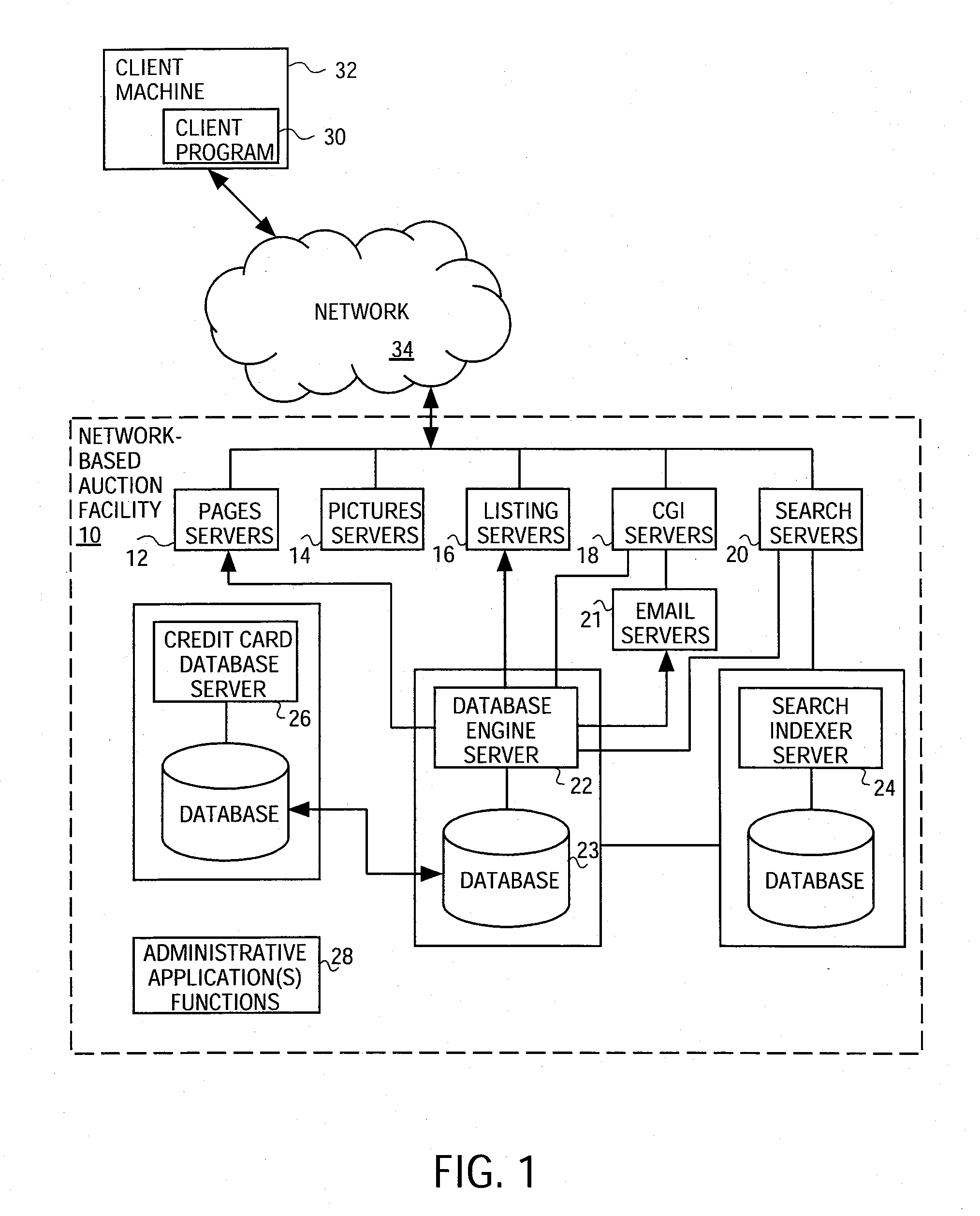

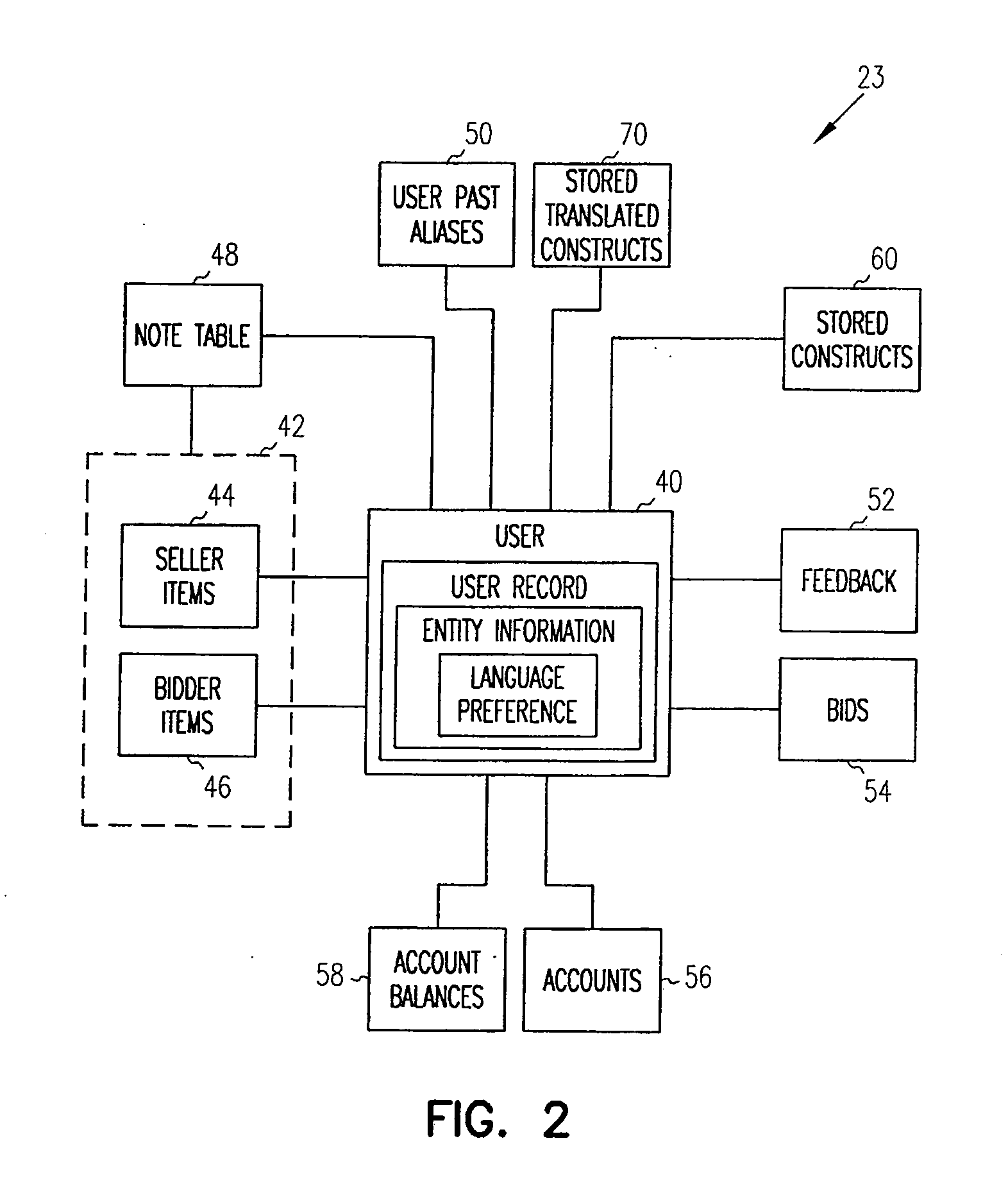

System and method to facilitate translation of communications between entities over a network

InactiveUS7752266B2Improve translationNatural language translationMultiple digital computer combinationsLanguage constructTranslation language

A system and method to facilitate translation of communications between entities over a network are described. Multiple predetermined language constructs are communicated to a first entity as a first transmission over the network. Responsive to selection by the first entity of a language construct from the predetermined language constructs, a translated language construct corresponding to the selected language construct is identified. Finally, the translated language construct is communicated to a second entity as a second transmission over the network.

Owner:EBAY INC

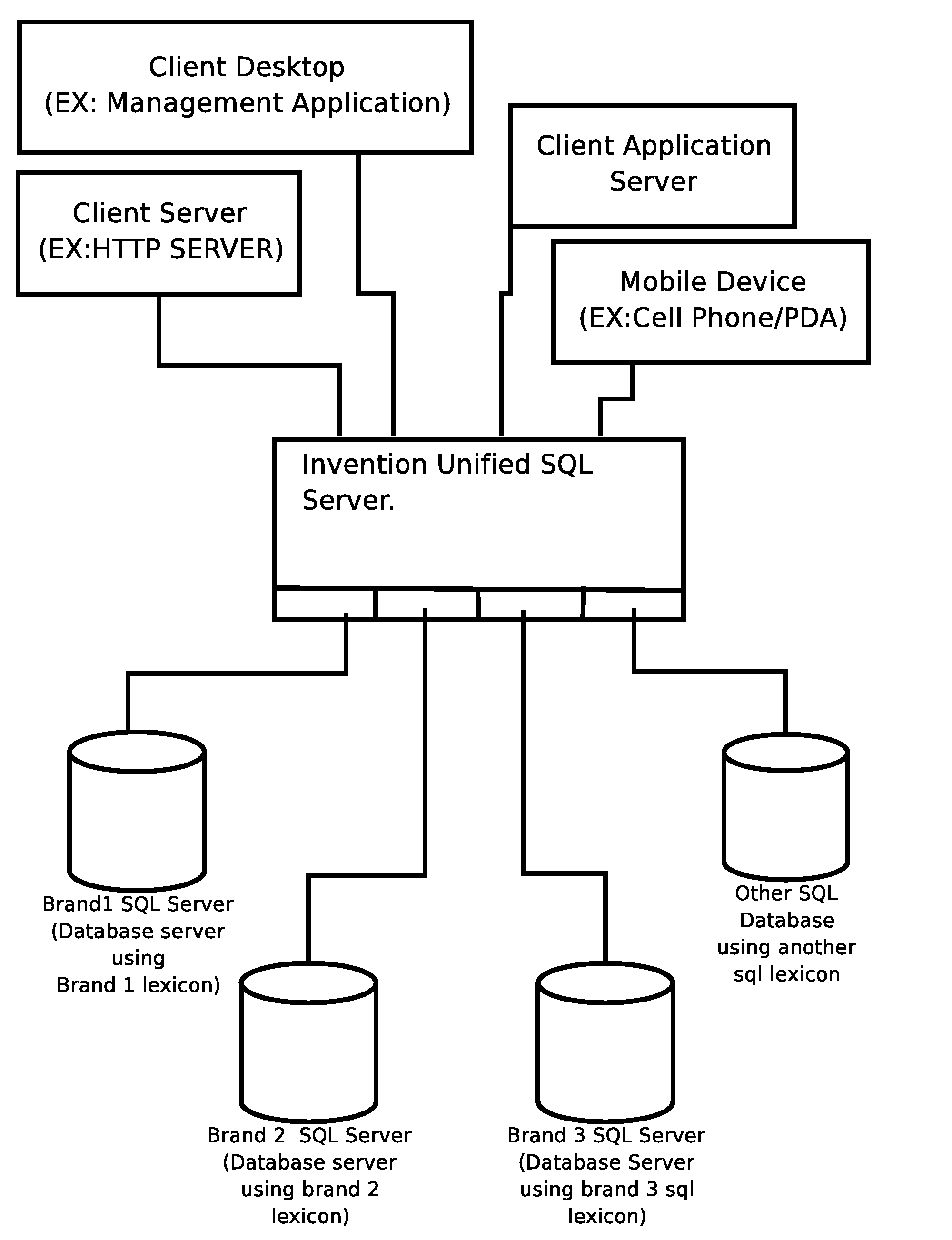

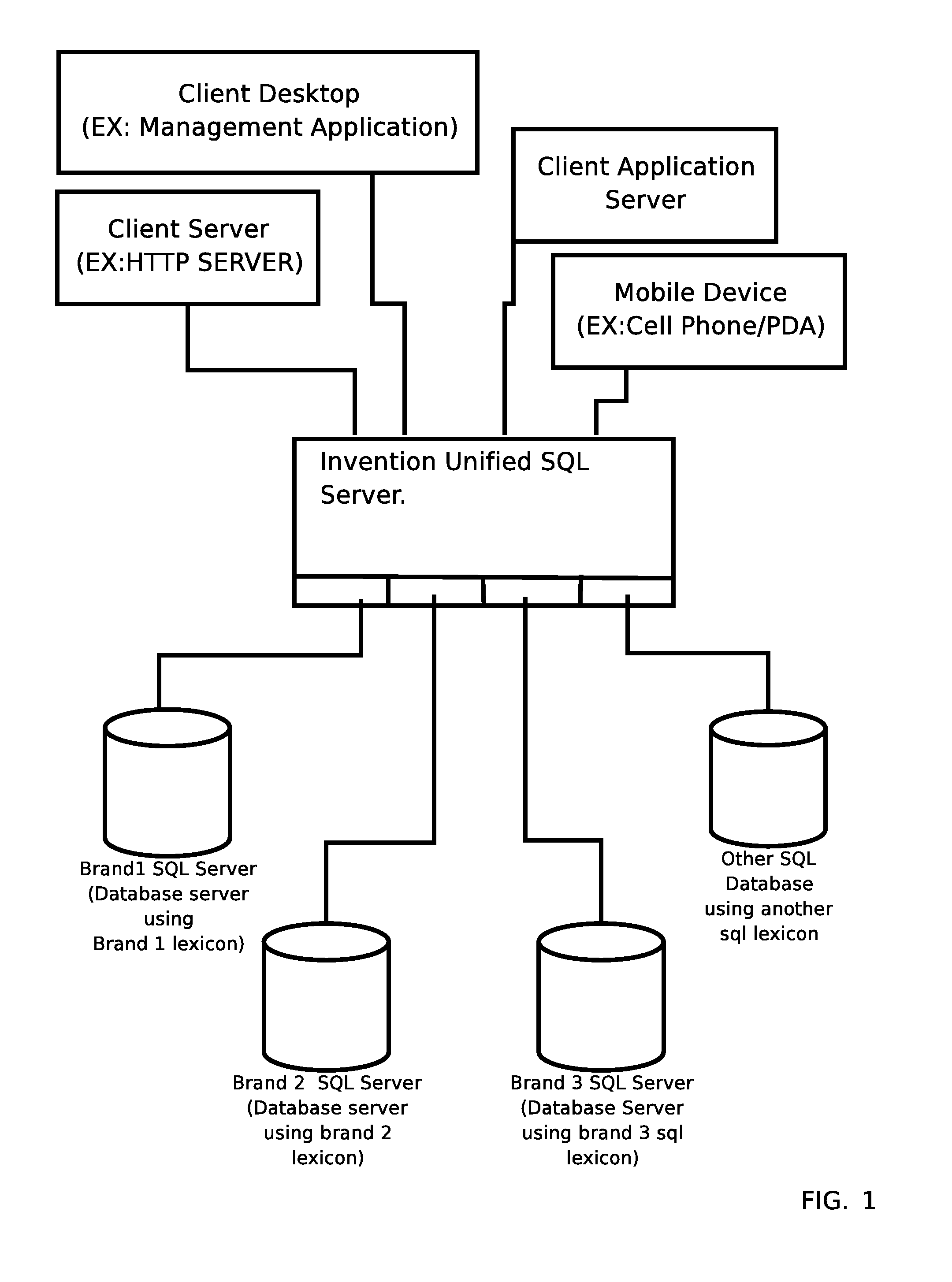

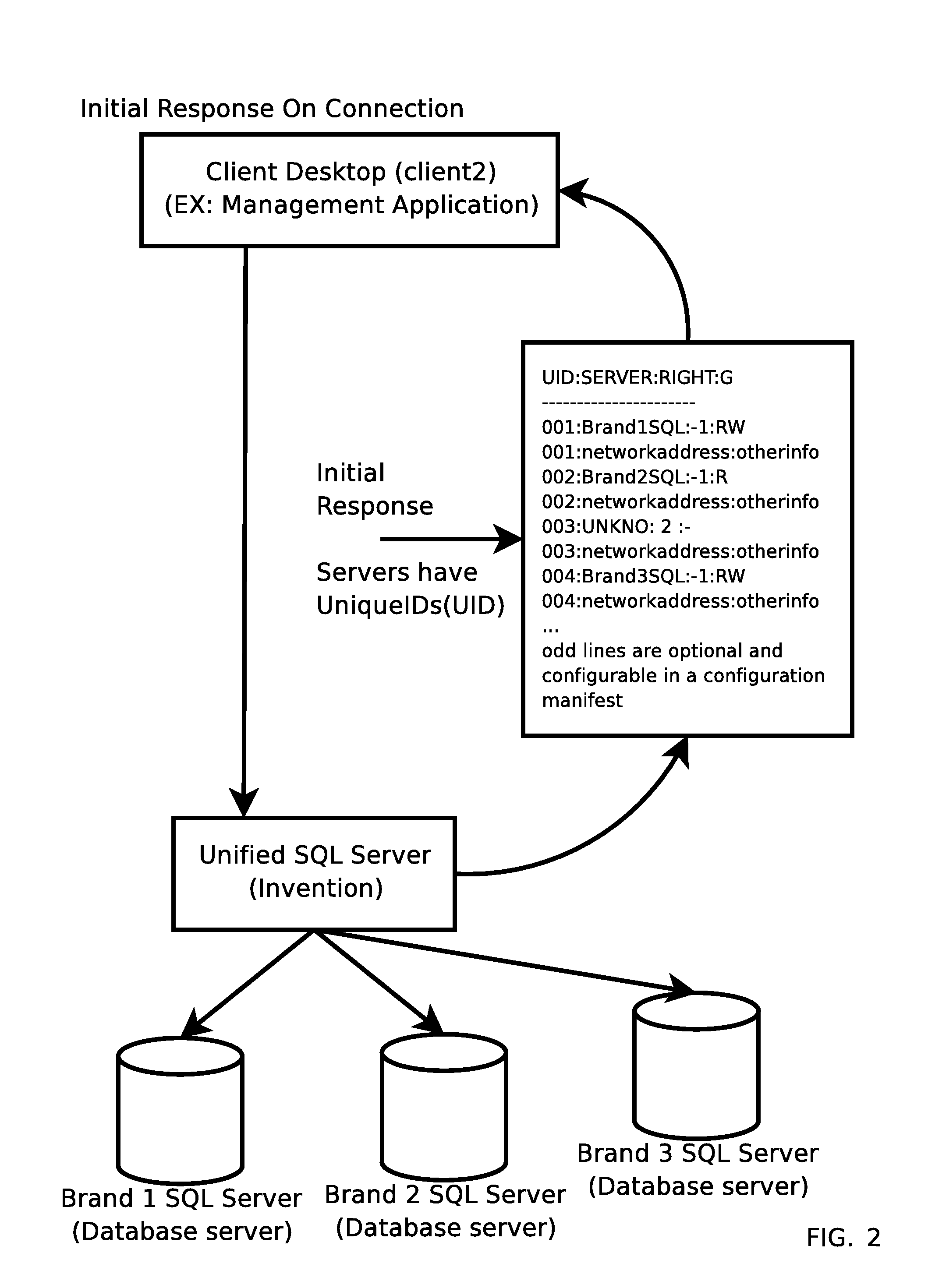

SQL Faceplate

InactiveUS20080177748A1Digital data information retrievalSpecial data processing applicationsLanguage constructData source

Structured query language server data sources often times have different language constructs for interacting with software data consuming clients. A unified structured query language data server is interposed in the network chain between the structured query language server data sources and the networked data consuming software clients to present an interface to retrieve networked data from different SQL database server types in one single structured query language to software consumers in the form of computer programs accessing the data on a network. These data consuming clients can now access any number of SQL database sources with one single set of structured query language commands through the invention which acts as a query language translating device, though not exclusively. The invention also provides a unified authentication method to access data in structured query language server data sources connected to it. Data consuming software clients can also use the invention to collate several requests from same or different types of structured query language data servers into one single structured data response based on a set of requests using one structured query language based on the ISO / ANSI SQL standard.

Owner:RONDOT CHRISTOPHER

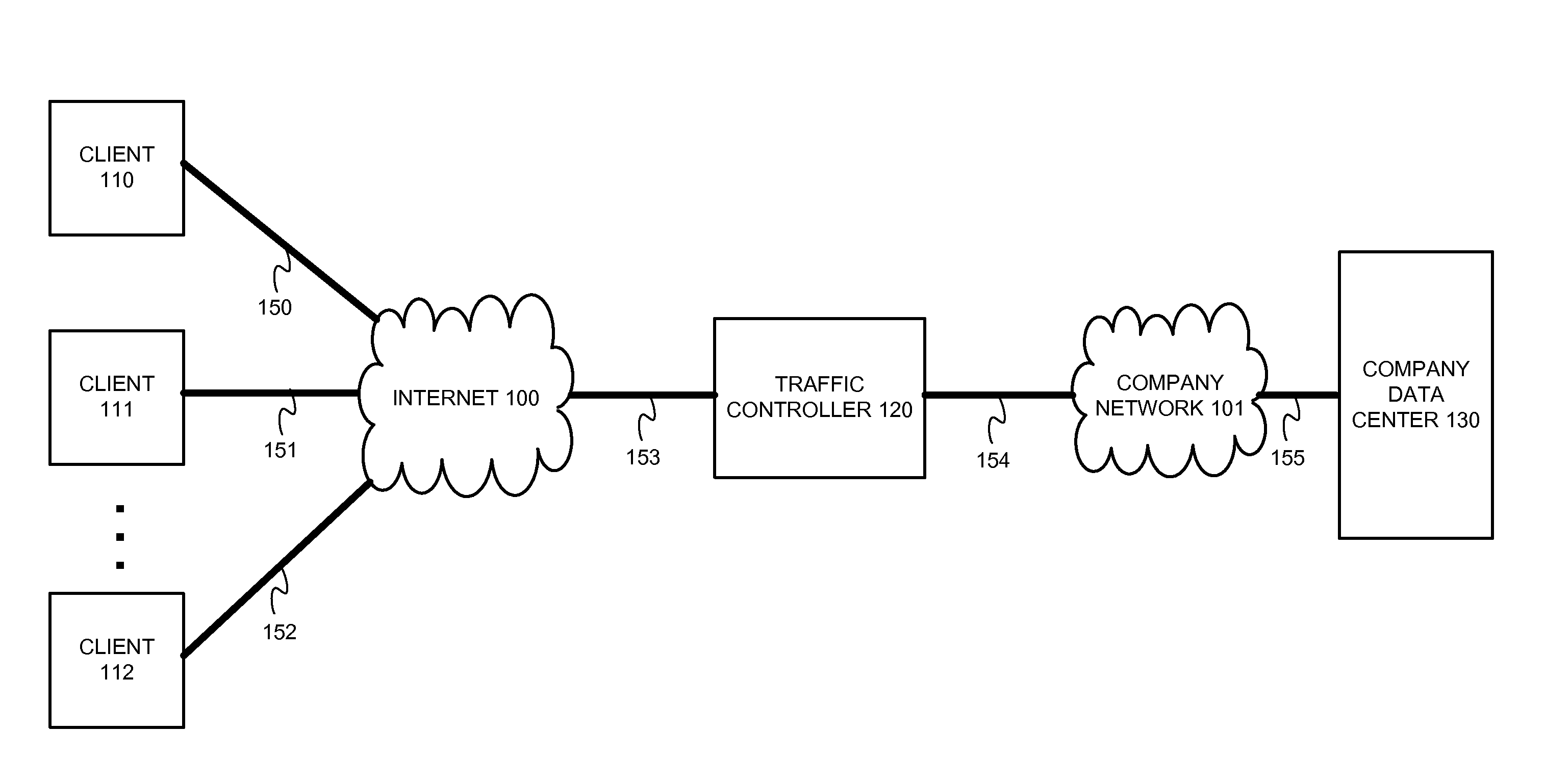

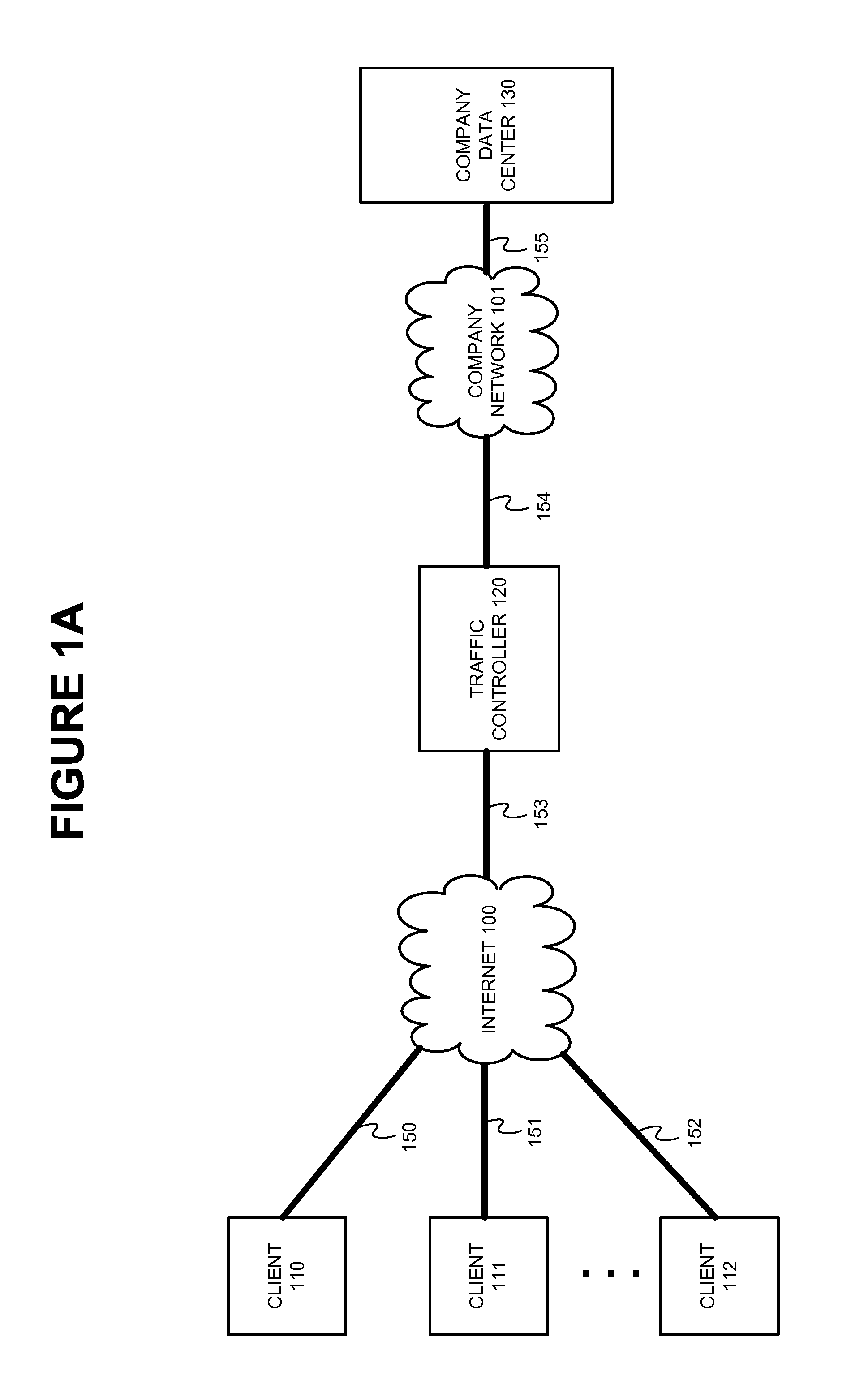

System and Method for Customizing the Identification of Application or Content Type

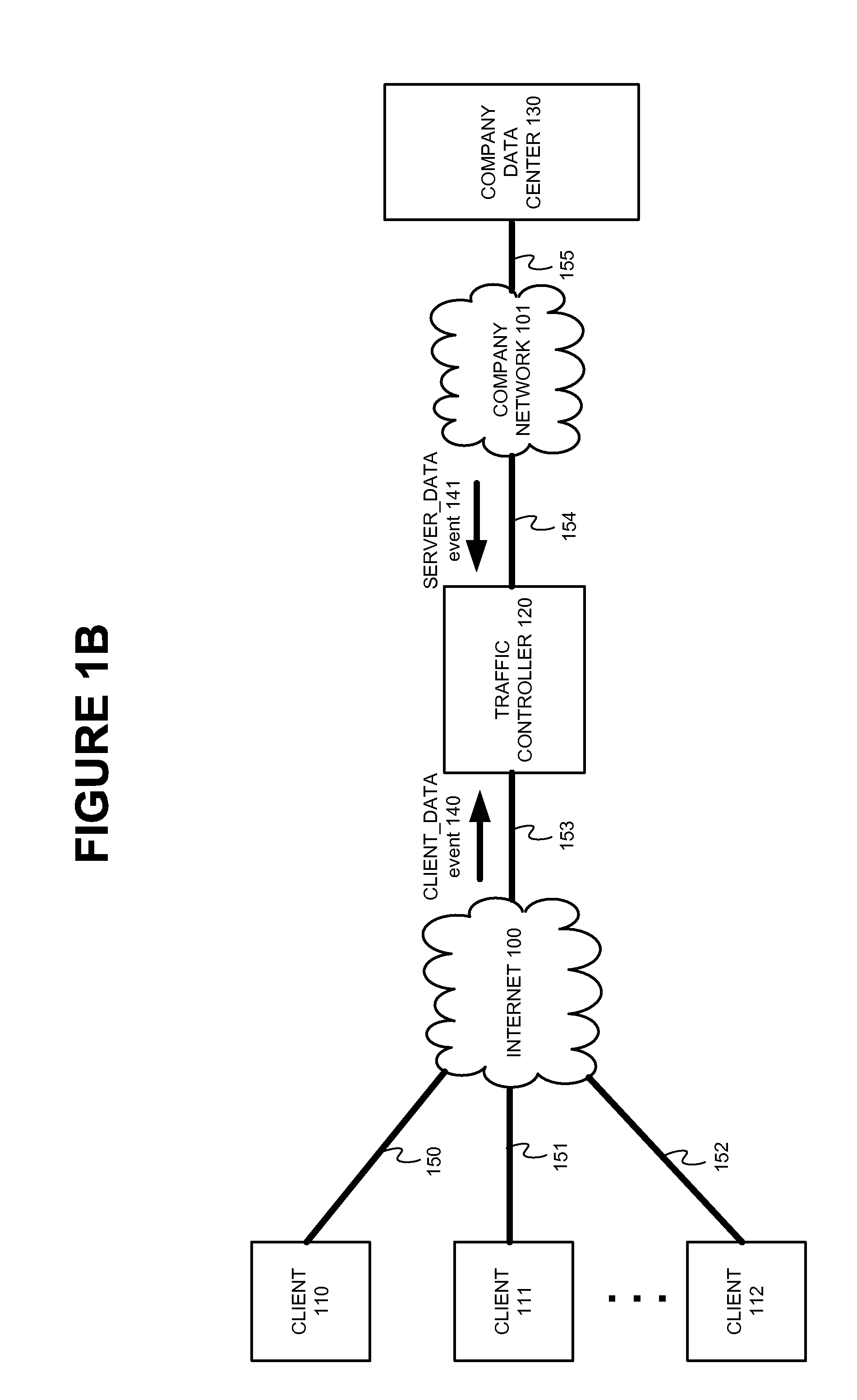

Expertise, for performing classification of a type of network traffic, can be encapsulated in a module. A set of modules, as currently available to a traffic controller, can be referred to as a collection. Programming language constructs are introduced that facilitate the writing of modules customized to identify network traffic that is peculiar to a particular user, or to a relatively small group of users. An example programming language, based on Tcl, is introduced. A key aspect is event-driven programming, and the “when” command construct is introduced. Three important event types, that can trigger a “when” command, are CLIENT_DATA, SERVER_DATA, and RULE_INIT. Another key aspect is an ability to keep state information between events. Constructs for intra-session, intra-module, and global state are introduced. A module can be blocked from executing more than once for a session. Successful execution of a module can be specified by a “match” statement.

Owner:A10 NETWORKS

System and method to facilitate translation of communications between entities over a network

InactiveUS20100228536A1Natural language translationMultiple digital computer combinationsLanguage constructTranslation language

A system and method to facilitate translation of communications between entities over a network are described. Multiple predetermined language constructs are communicated to a first entity as a first transmission over the network. Responsive to selection by the first entity of a language construct from the predetermined language constructs, a translated language construct corresponding to the selected language construct is identified. Finally, the translated language construct is communicated to a second entity as a second transmission over the network.

Owner:EBAY INC

Correct refactoring of concurrent software

InactiveUS8689191B2Easy to implementThe result is accurateCode refactoringProgram controlLanguage constructJava Memory Model

Automated refactorings as implemented in modern IDEs for Java usually make no special provisions for concurrent code. Thus, refactored programs may exhibit unexpected new concurrent behaviors. We analyze the types of such behavioral changes caused by current refactoring engines and develop techniques to make them behavior-preserving, ranging from simple techniques to deal with concurrency-related language constructs to a framework that computes and tracks synchronization dependencies. By basing our development directly on the Java Memory Model we can state and prove precise correctness results about refactoring concurrent programs. We show that a broad range of refactorings are not influenced by concurrency at all, whereas other important refactorings can be made behavior-preserving for correctly synchronized programs by using our framework. Experience with a prototype implementation shows that our techniques are easy to implement and require only minimal changes to existing refactoring engines.

Owner:INT BUSINESS MASCH CORP

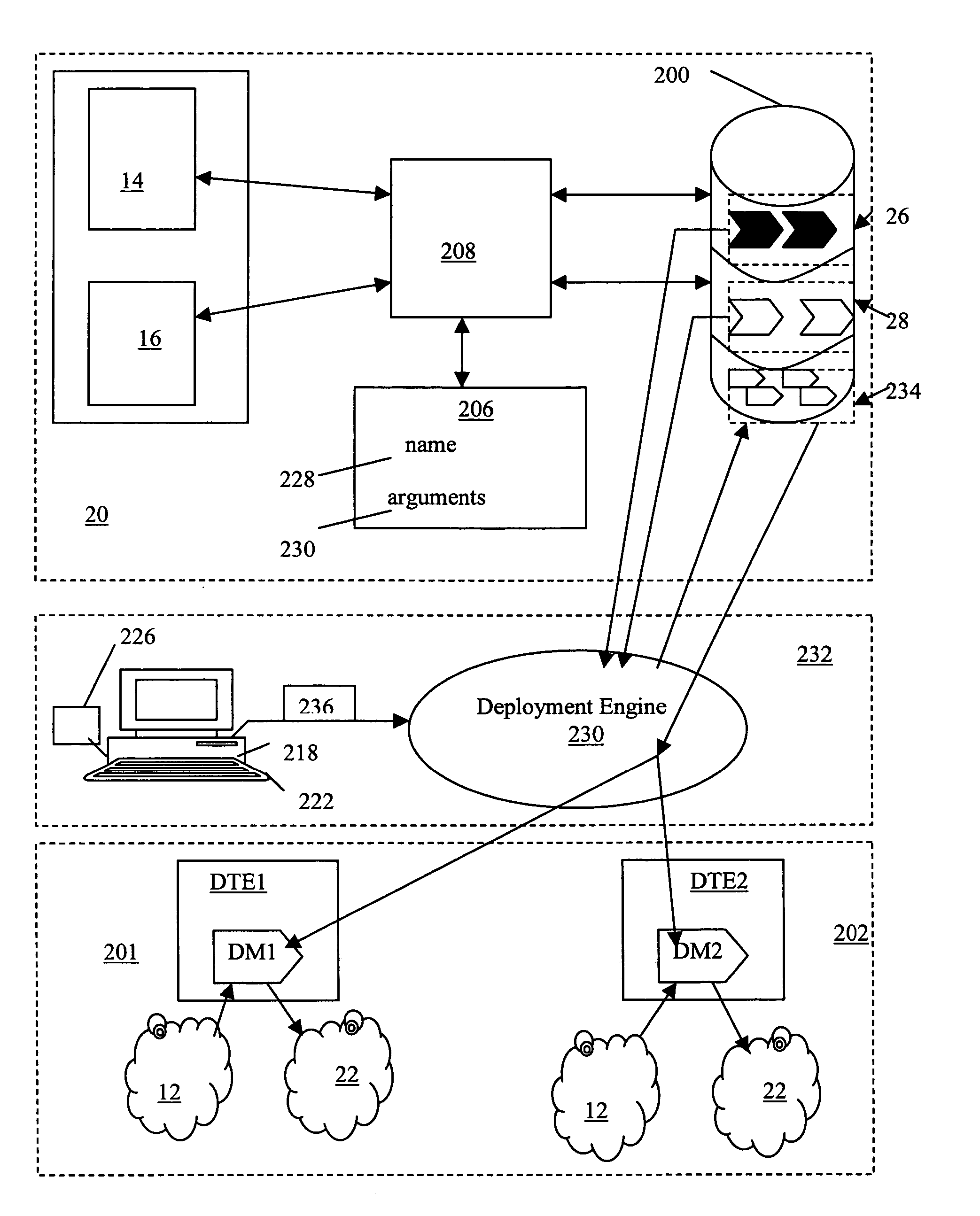

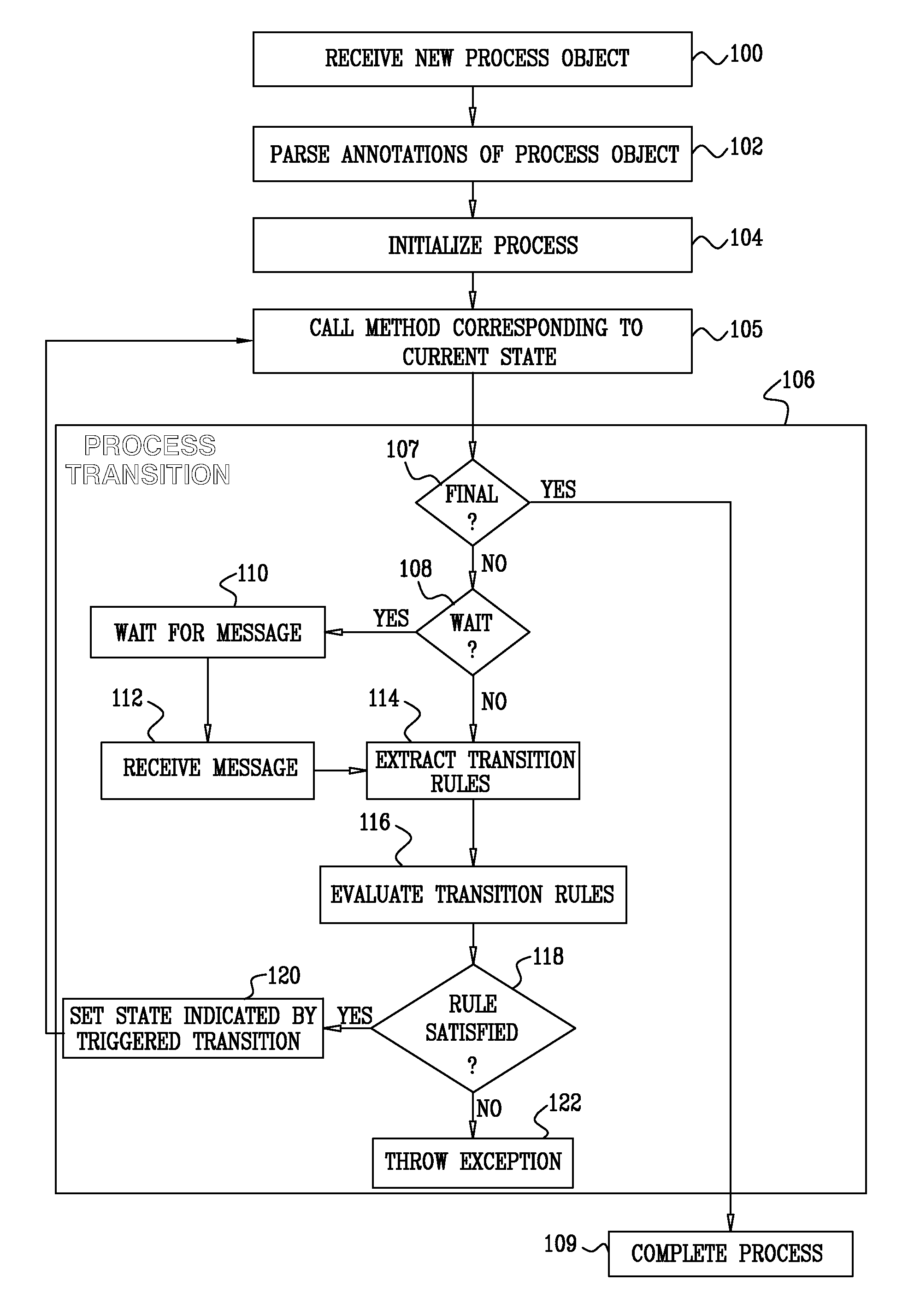

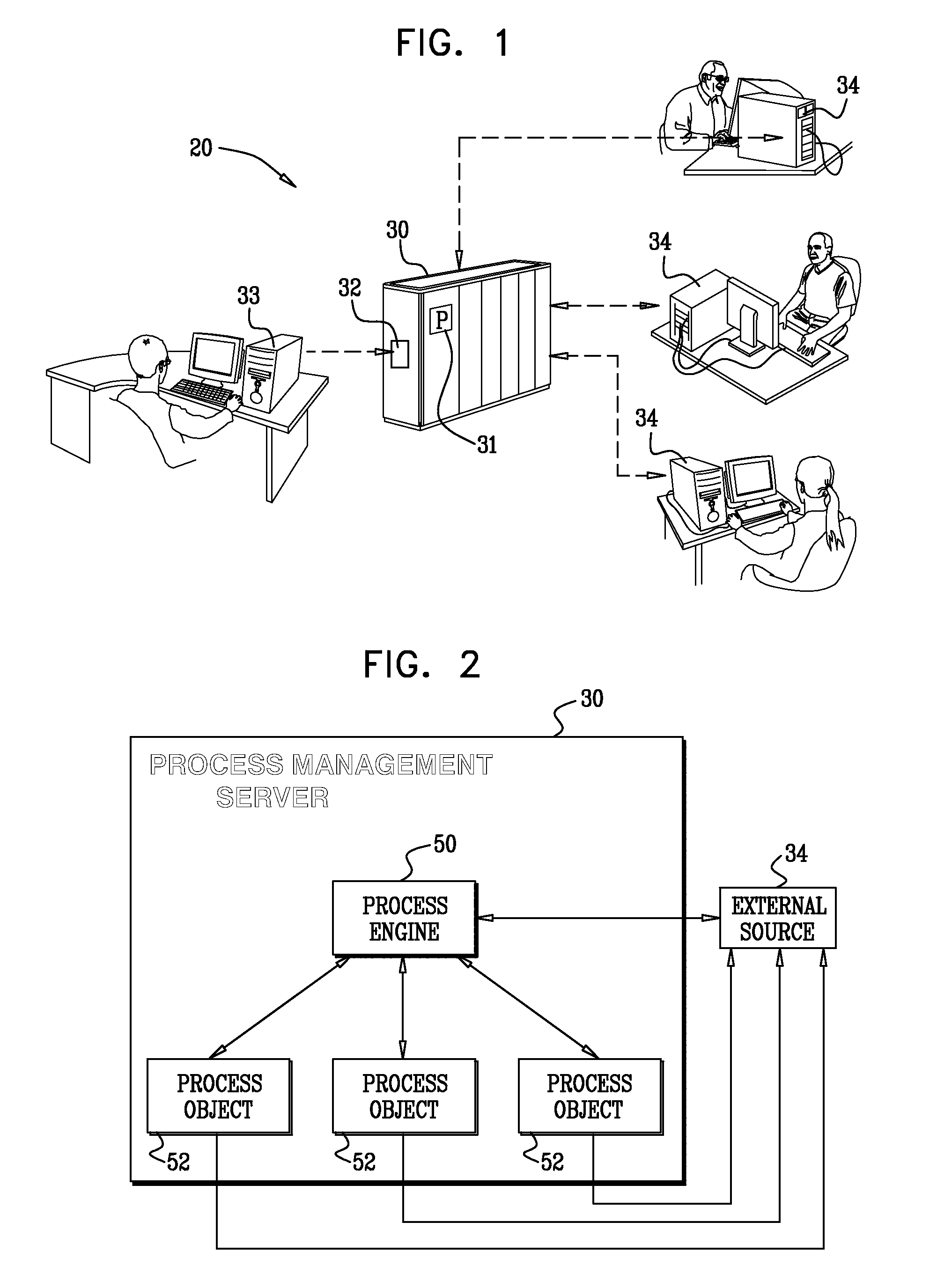

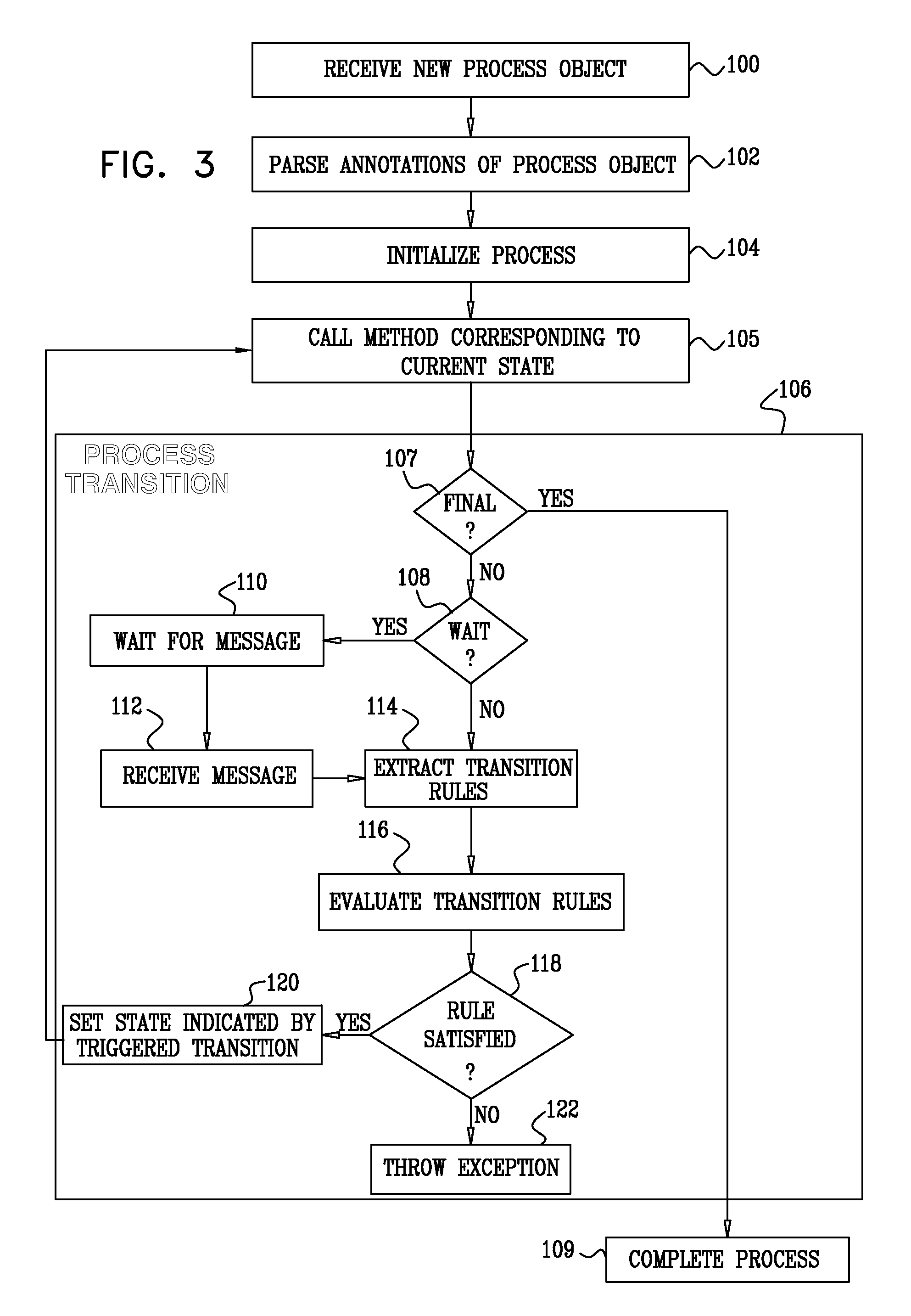

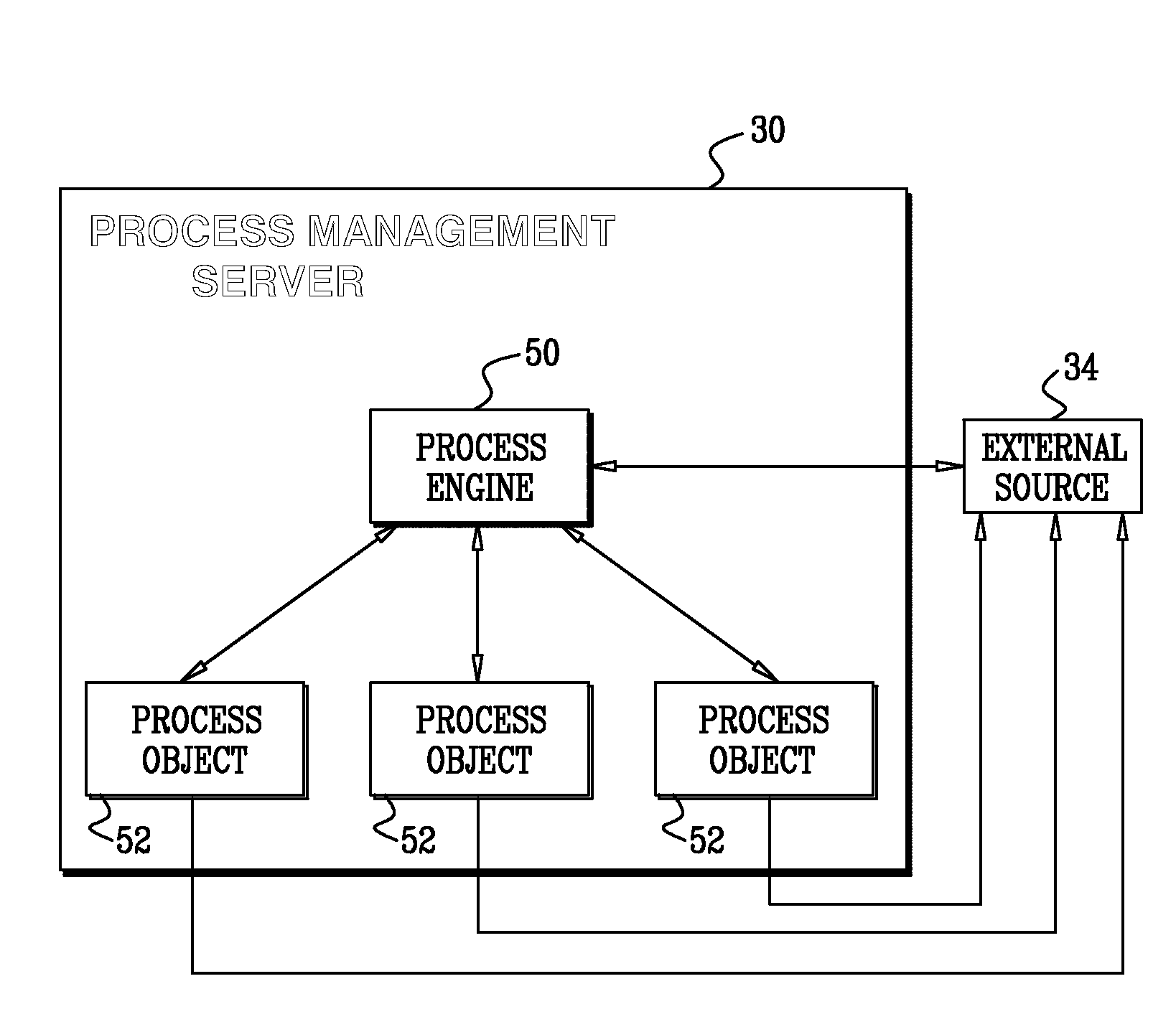

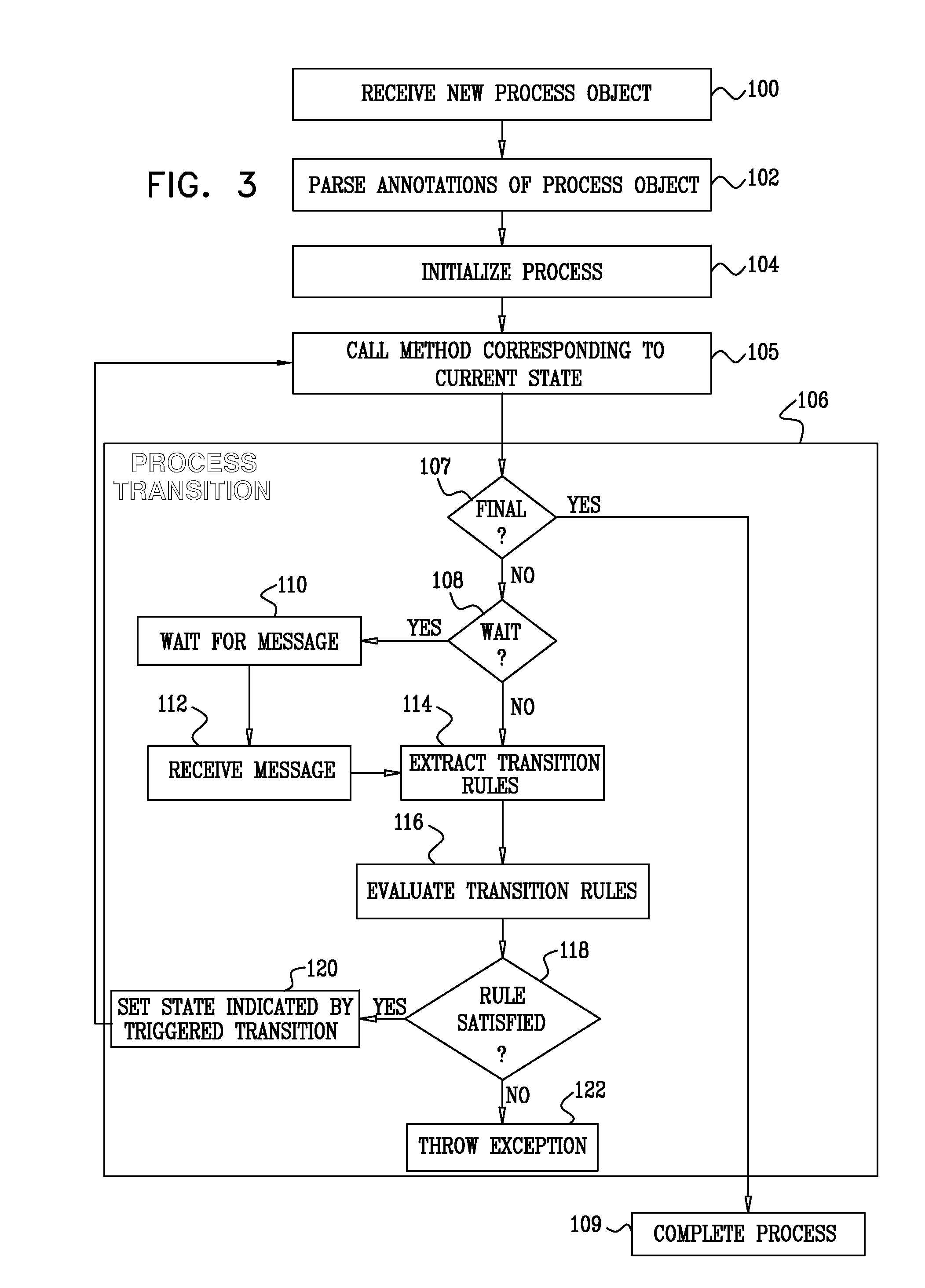

Defining and executing processes using declarative programming language constructs

ActiveUS8108834B2Multiprogramming arrangementsProgramming languages/paradigmsLanguage constructRunning time

A computer-implemented technique for executing a process is provided. The technique includes providing a class having at least one annotation that defines at least a portion of the process. The annotation is a run-time-readable, non-executable declarative programming construct that is associated with a first method of the class, and specifies at least one transition rule and a second method of the class associated with the transition rule. A process engine, which runs on a computer and is not an instance of the class, parses the annotation to extract the transition rule. The process engine receives a message from a source external to the process engine, and evaluates whether the transition rule is satisfied, responsively to the message. Upon finding that the transition rule is satisfied, the process engine invokes the second method, so as to generate an output with respect to the message. Other embodiments are also described.

Owner:SAP AG

Defining and executing processes using declarative programming language constructs

ActiveUS20080235682A1Multiprogramming arrangementsProgramming languages/paradigmsLanguage constructRunning time

A computer-implemented technique for executing a process is provided. The technique includes providing a class having at least one annotation that defines at least a portion of the process. The annotation is a run-time-readable, non-executable declarative programming construct that is associated with a first method of the class, and specifies at least one transition rule and a second method of the class associated with the transition rule. A process engine, which runs on a computer and is not an instance of the class, parses the annotation to extract the transition rule. The process engine receives a message from a source external to the process engine, and evaluates whether the transition rule is satisfied, responsively to the message. Upon finding that the transition rule is satisfied, the process engine invokes the second method, so as to generate an output with respect to the message. Other embodiments are also described.

Owner:SAP AG

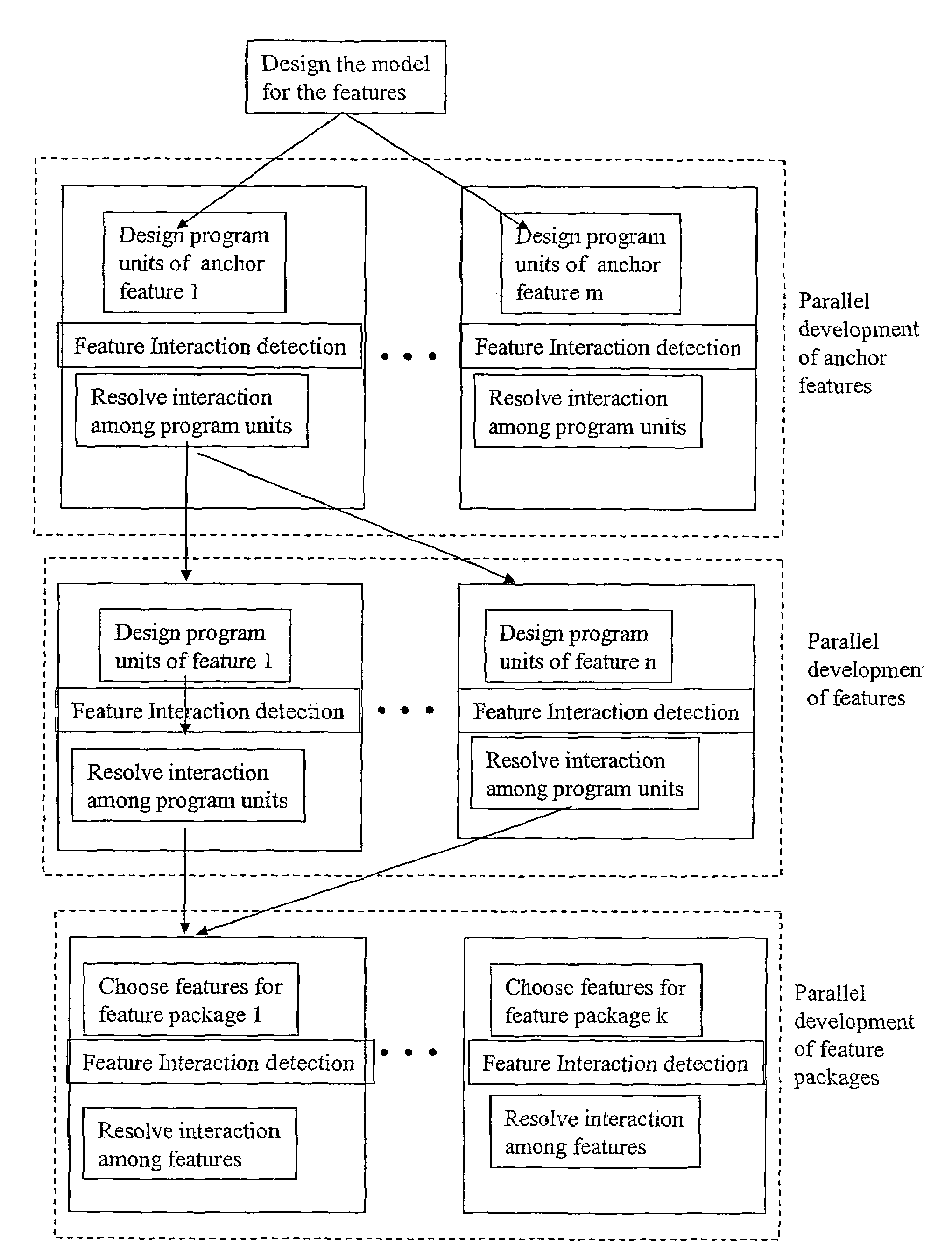

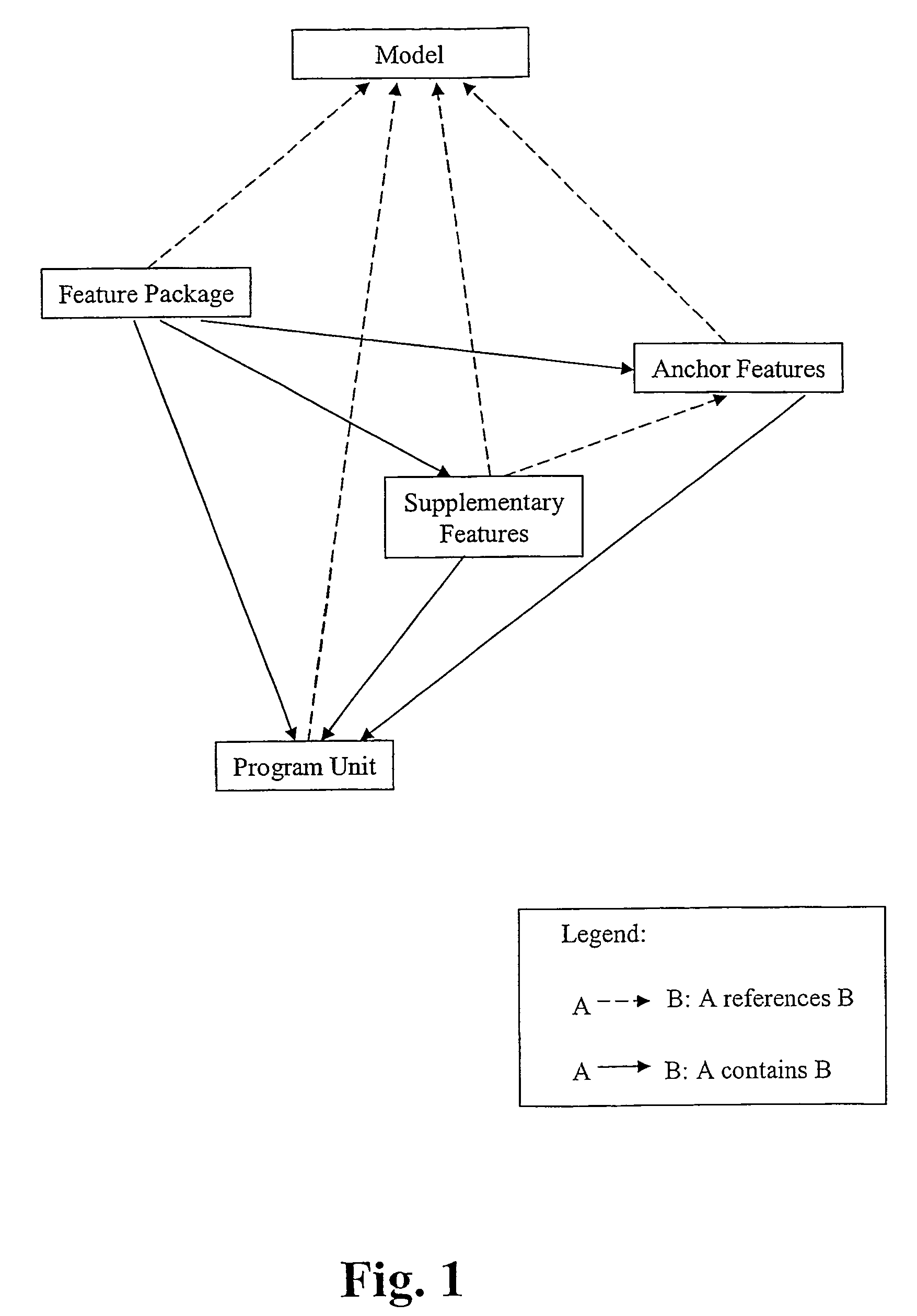

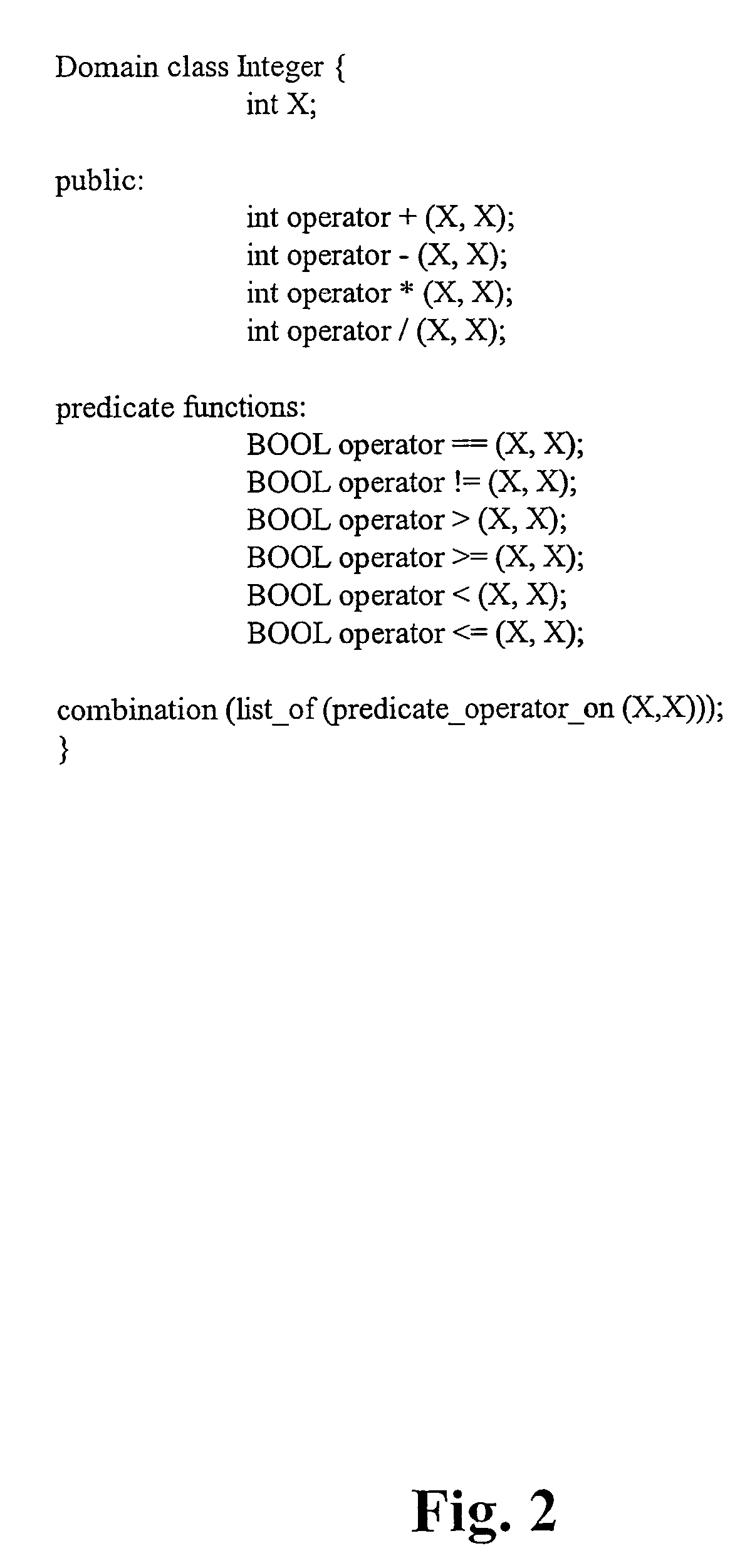

Method to add new software features without modifying existing code

A computer-aided method (FIG. 12) for developing software by which programmers may implement different features of an application as independent reusable components, even though these features affect the control flows of one another. A programmer may add new features to an application without the labor intensive tasks of examining and modifying existing code. The programmer uses a set of programming language constructs to specify nonprocedural program units, organize the program units into reusable features and integrate several features together into a feature package. An interaction detection algorithm analyzes program units and determines whether there is interaction among program units in a feature and among features in a feature package. The programmer must resolve the interaction, if detected, before the programs can be executed. A run time system specification supports the semantics of the programming language constructs and preserves the conditions that enable interaction detection.

Owner:LEUNG WU HON FRANCIS

Methods of comparing and merging business process configurations

Exemplary methods and systems consistent with the present invention allow a user to compare different versions of a business application using an object-oriented model of the business application. By transforming business application structures into object-oriented structures, such as object-oriented language constructs, structures, and other elements, individual differences between versions of the business applications may be identified and displayed to a user, for example, on a user interface. A user may display object-oriented models of the business application representing, for instance, the latest control version, the latest deployed version, and a test version including test modifications. Having all three versions represented in object-oriented models allows a user to perform a three-way comparison between the object-oriented models, increasing productivity and efficiency of maintaining, debugging, modifying, controlling and deploying the business application.

Owner:SAP AG

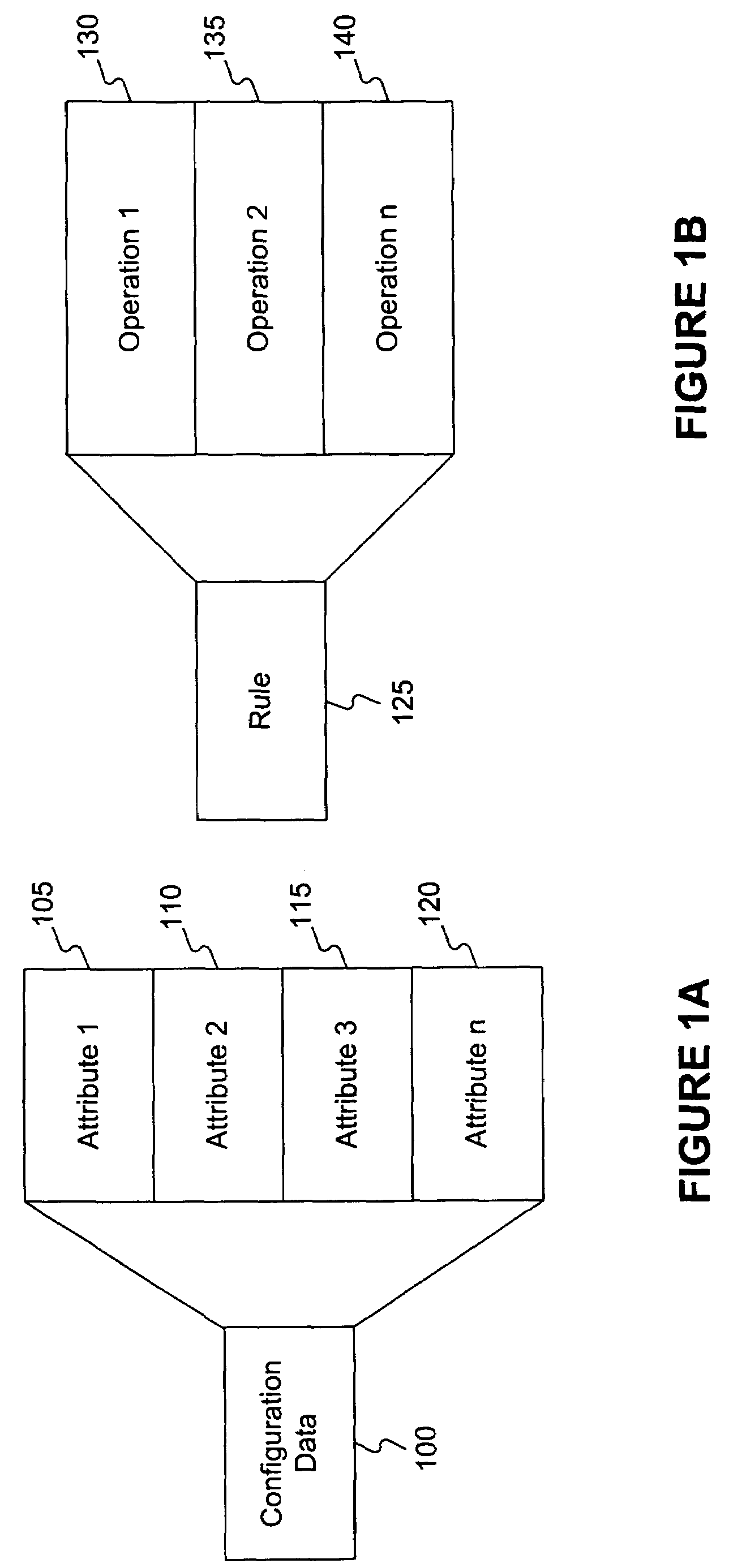

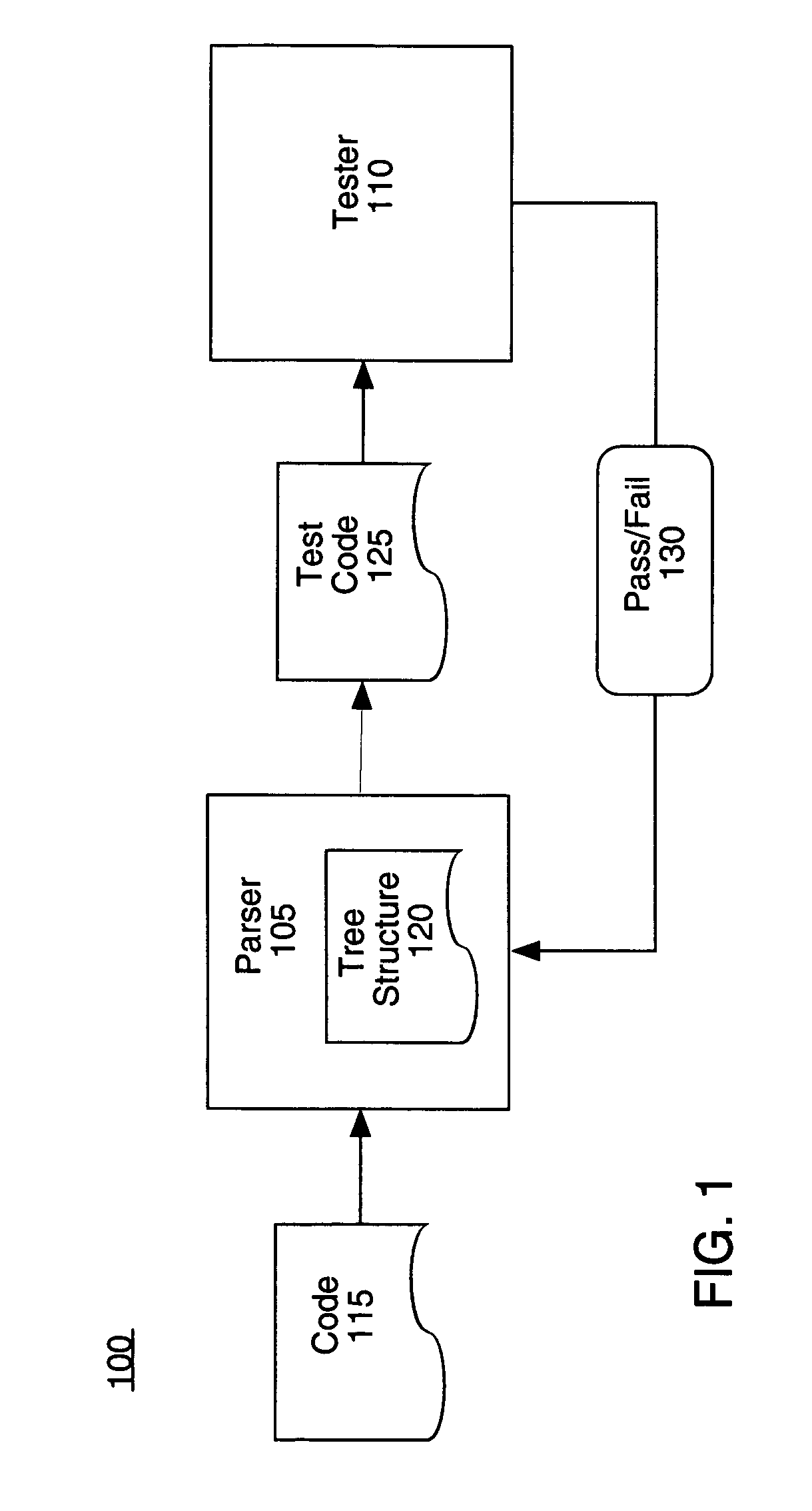

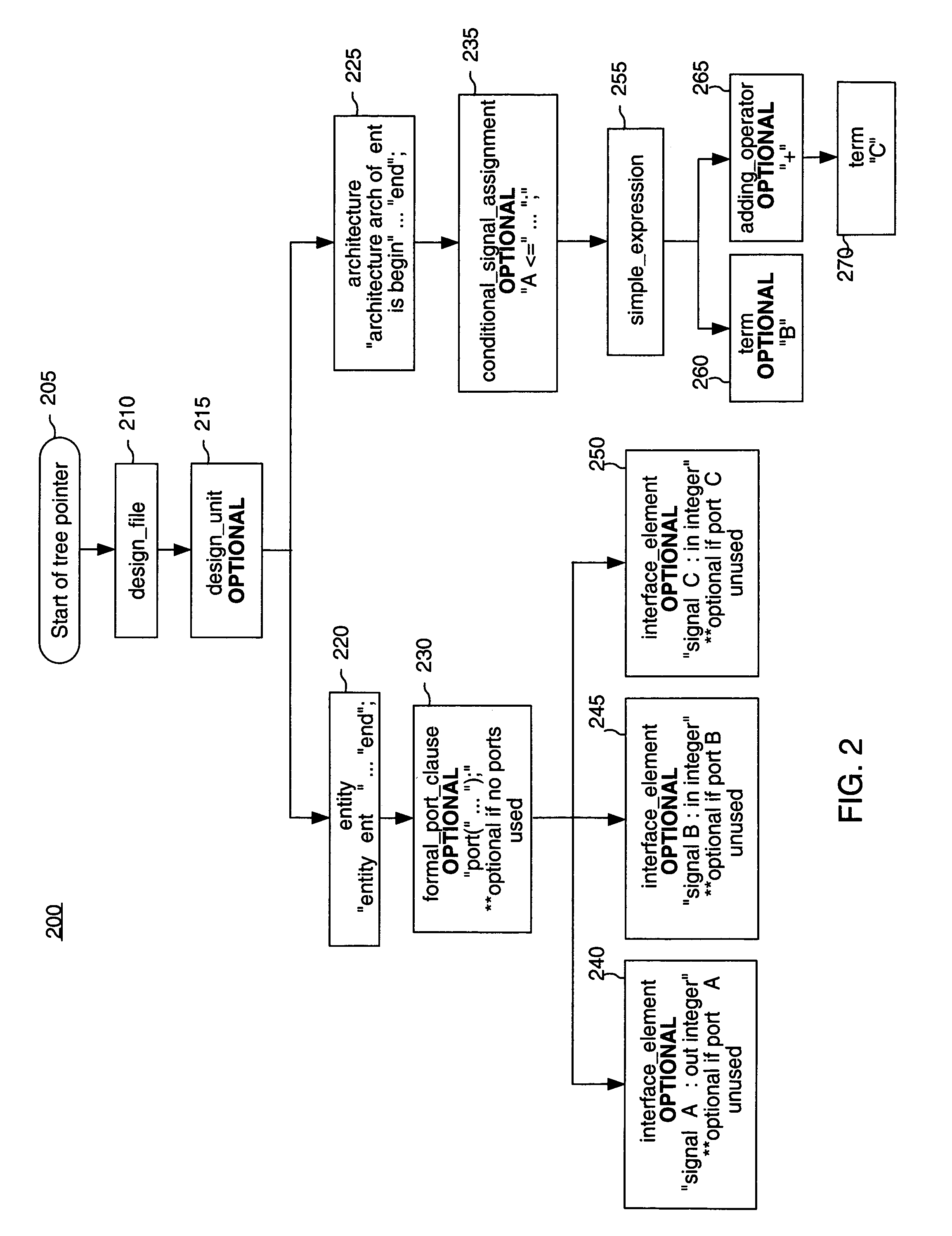

Automatic bug isolation in computer programming languages

InactiveUS7539977B1Reduce the amount of codeError detection/correctionSpecific program execution arrangementsLanguage constructComputer programming

A method, system, and apparatus relating to automatically reducing an amount of code necessary for reproducing errors within programming language code is presented. The method can include identifying optional nodes of a hierarchical tree of programming language code, wherein each node of the tree corresponds to a type of programming language construct. A target node can be selected from the optional nodes. The method further can include excluding the target node and any sub-nodes of the target node from the programming language code, and determining whether the programming language code passes at least one test case.

Owner:XILINX INC

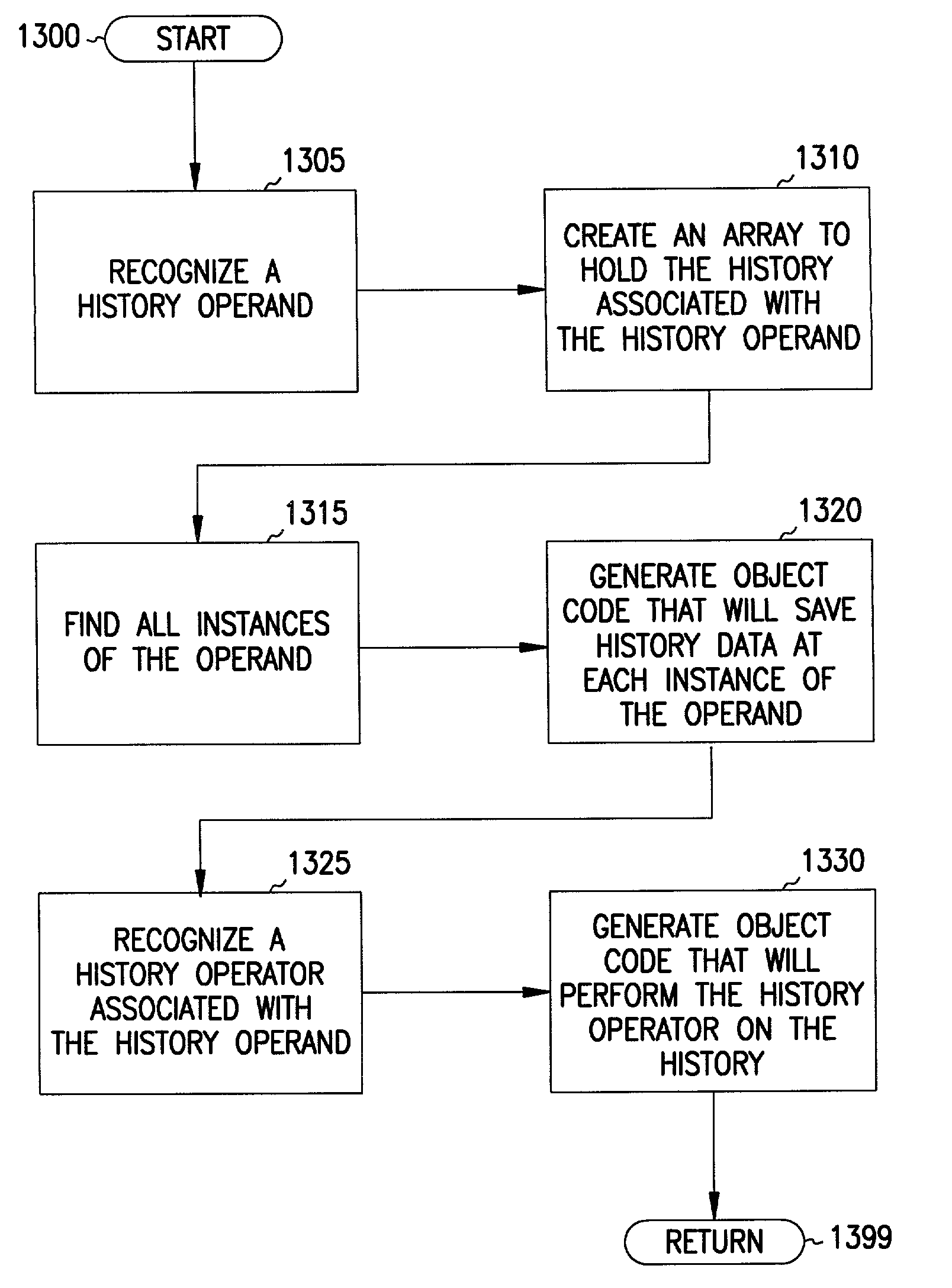

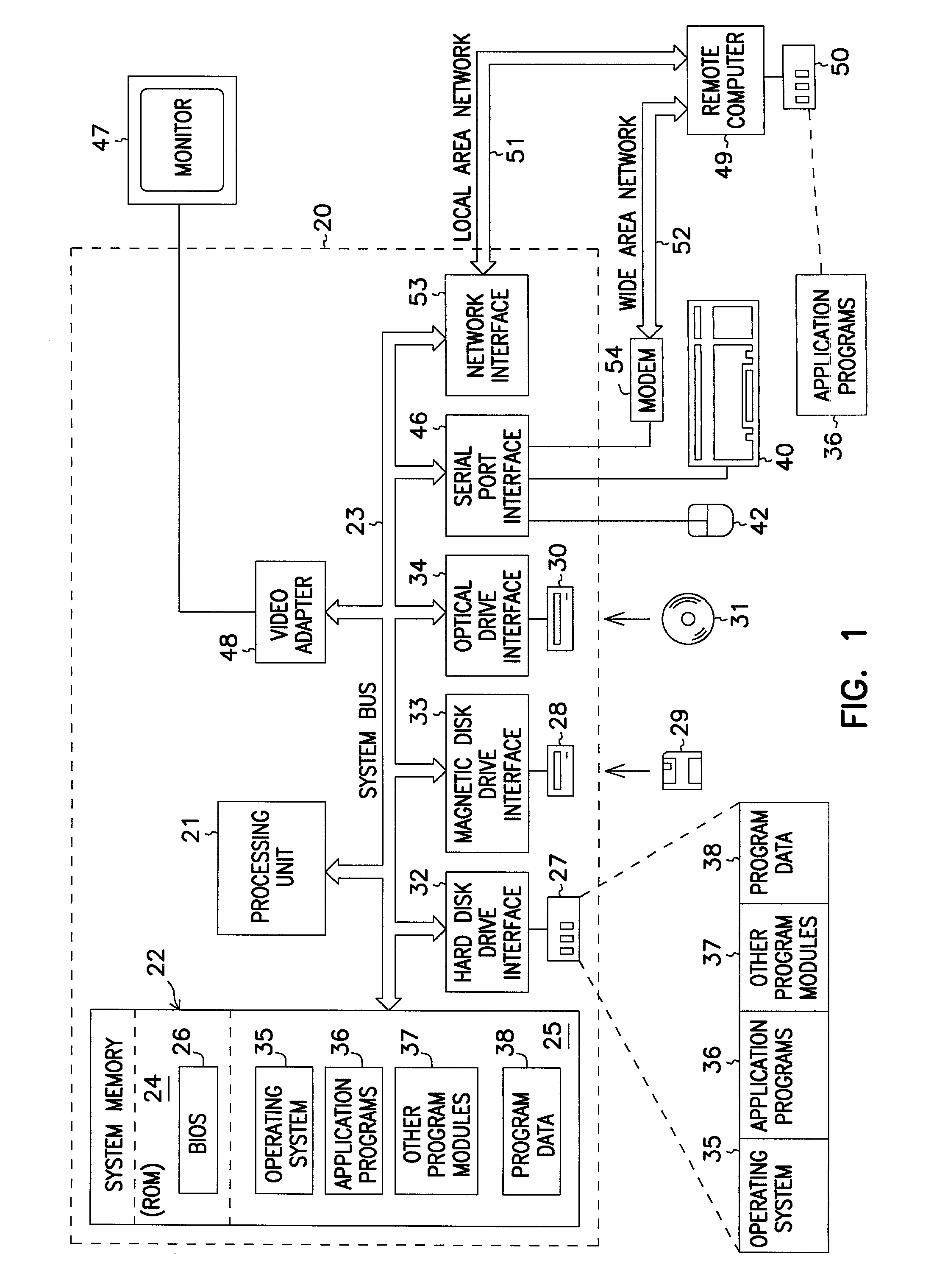

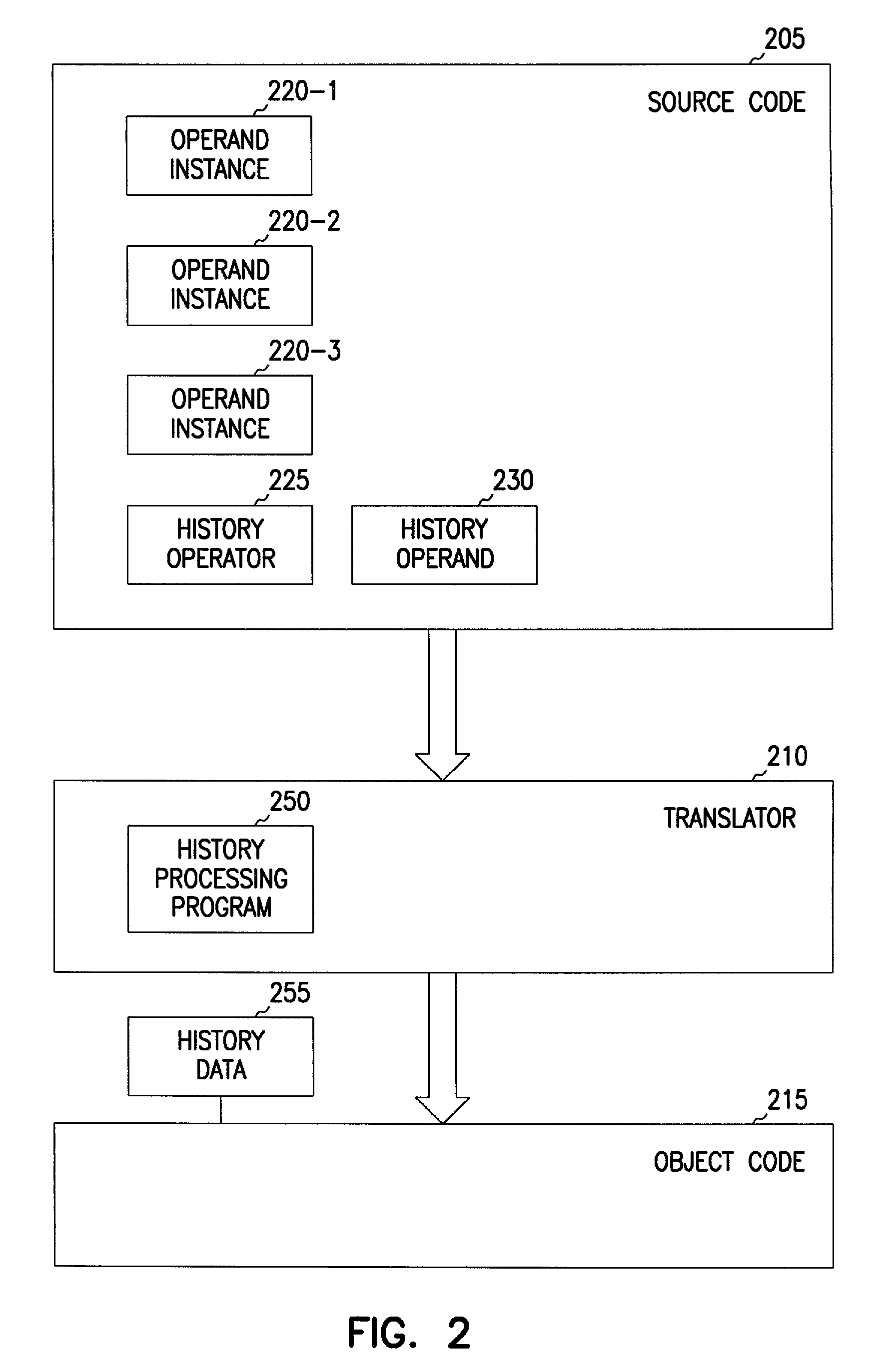

Program history in a computer programming language

InactiveUS7111283B2Programming languages/paradigmsSpecific program execution arrangementsLanguage constructOperand

A programming-language construct called a program history, and a method, system, apparatus, and data structure for translating computer source code that contains the program history construct. A program history captures data regarding the state of the program as it executes and makes this data available to functions called history operators, which operate on the data. The source code contains a history operand, an instance of the history operand, and the history operator. The presence of the history operand directs a translator to cause history data to be saved regarding the sequence of data that is associated with the operand instance as the program executes. The presence of the history operator directs the translator to cause a function to be performed that saves history data. In this way, the programmer is freed from writing tedious and error-prone bookkeeping code that declares variables and saves history data into those declared variables.

Owner:MICROSOFT TECH LICENSING LLC

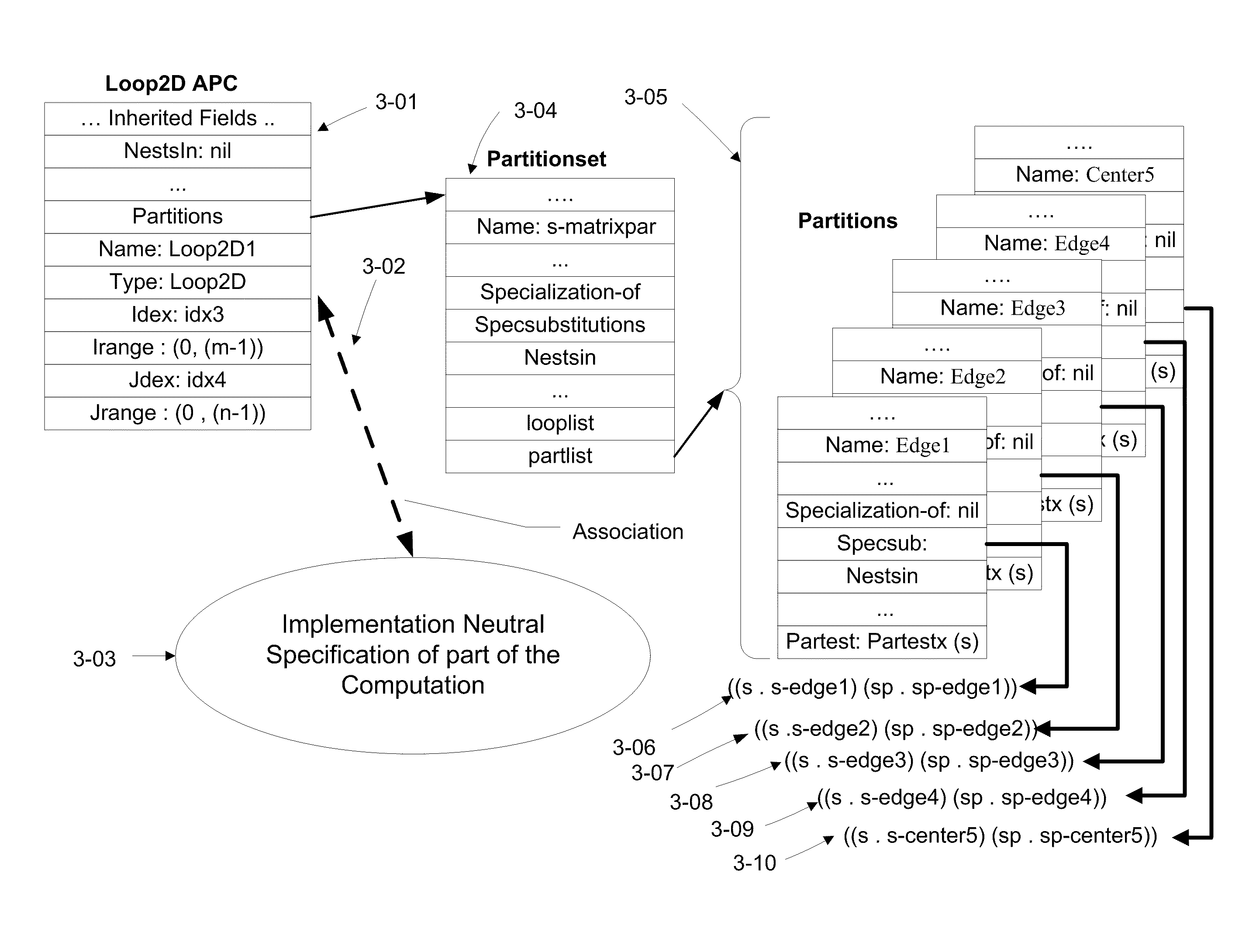

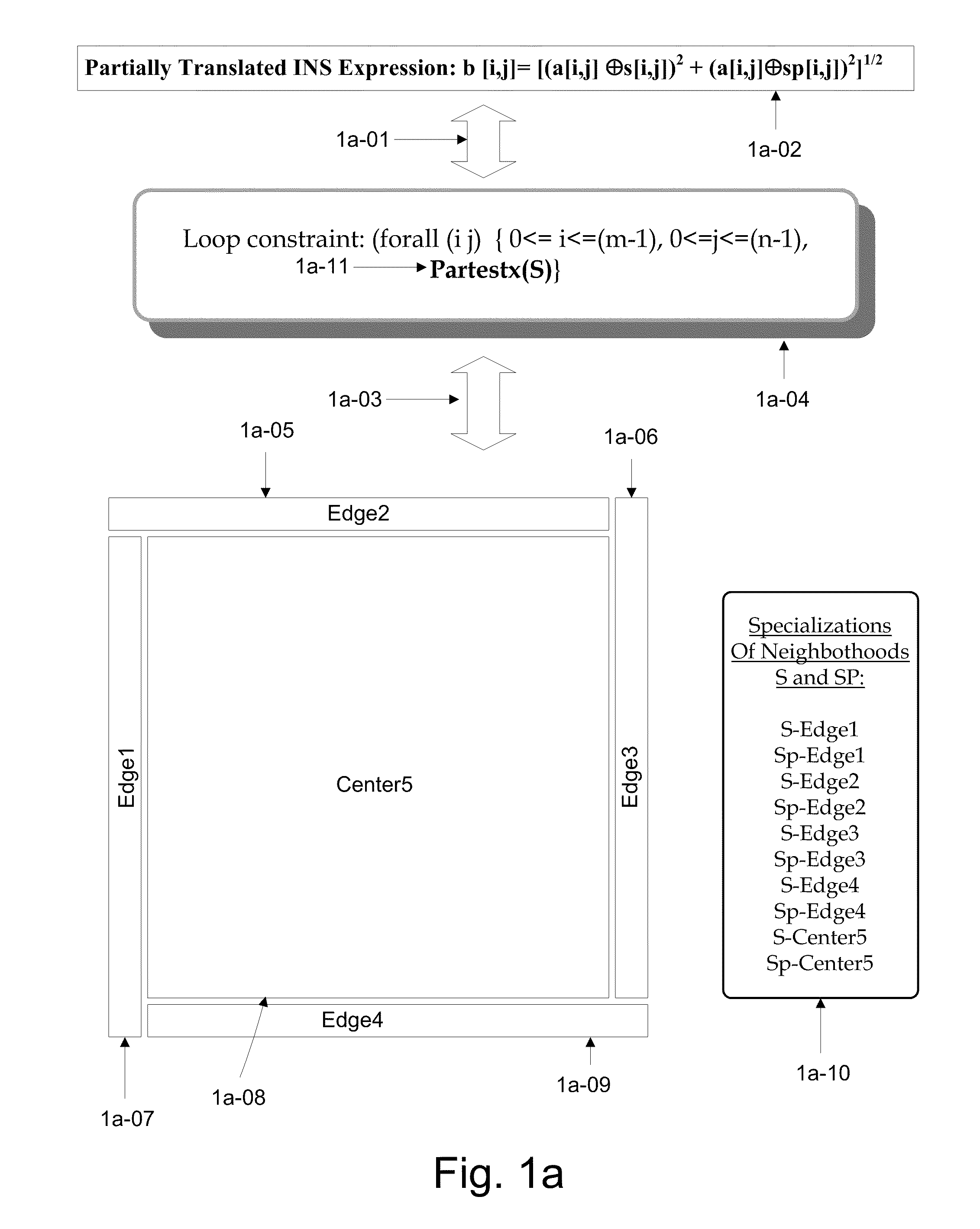

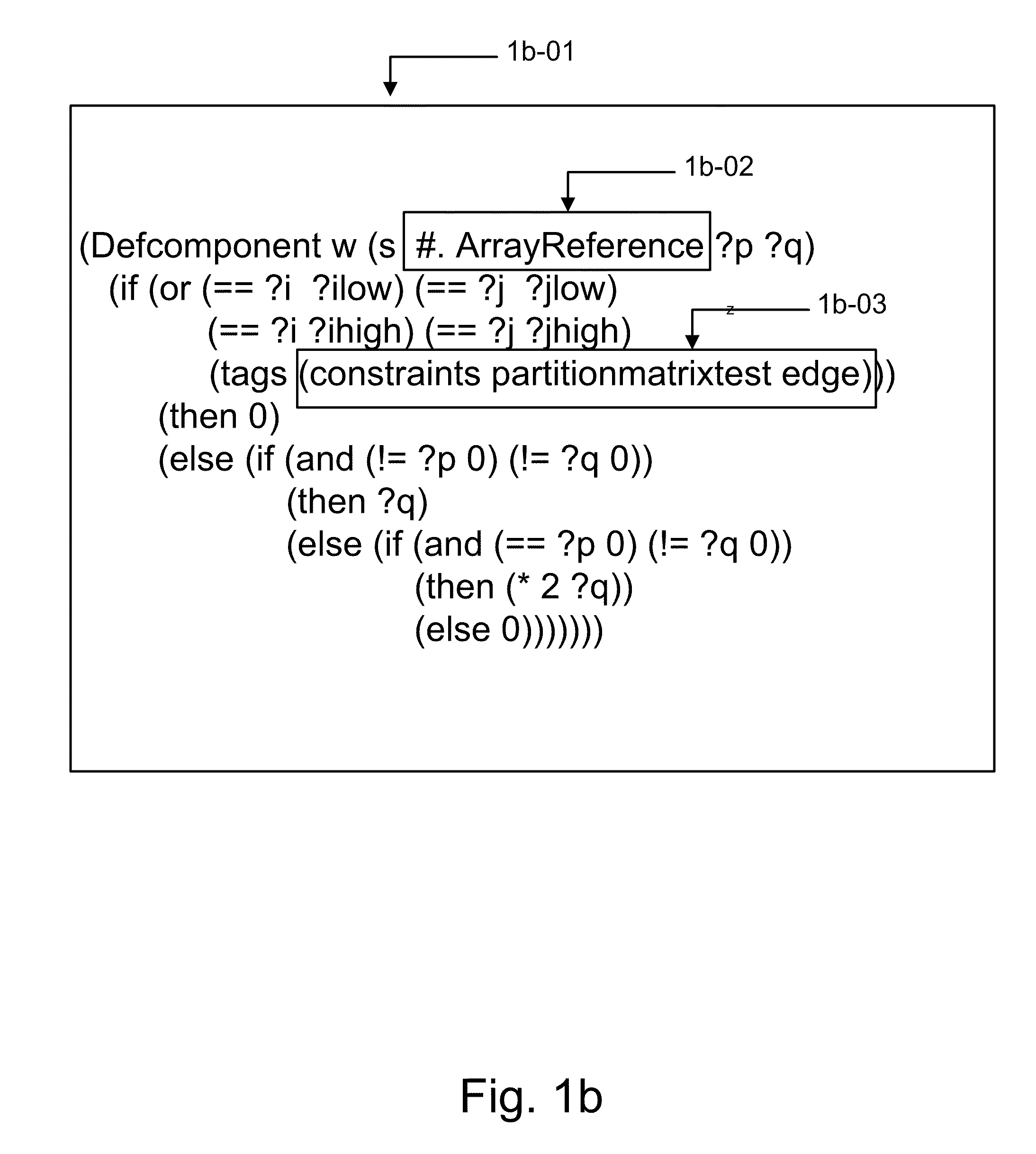

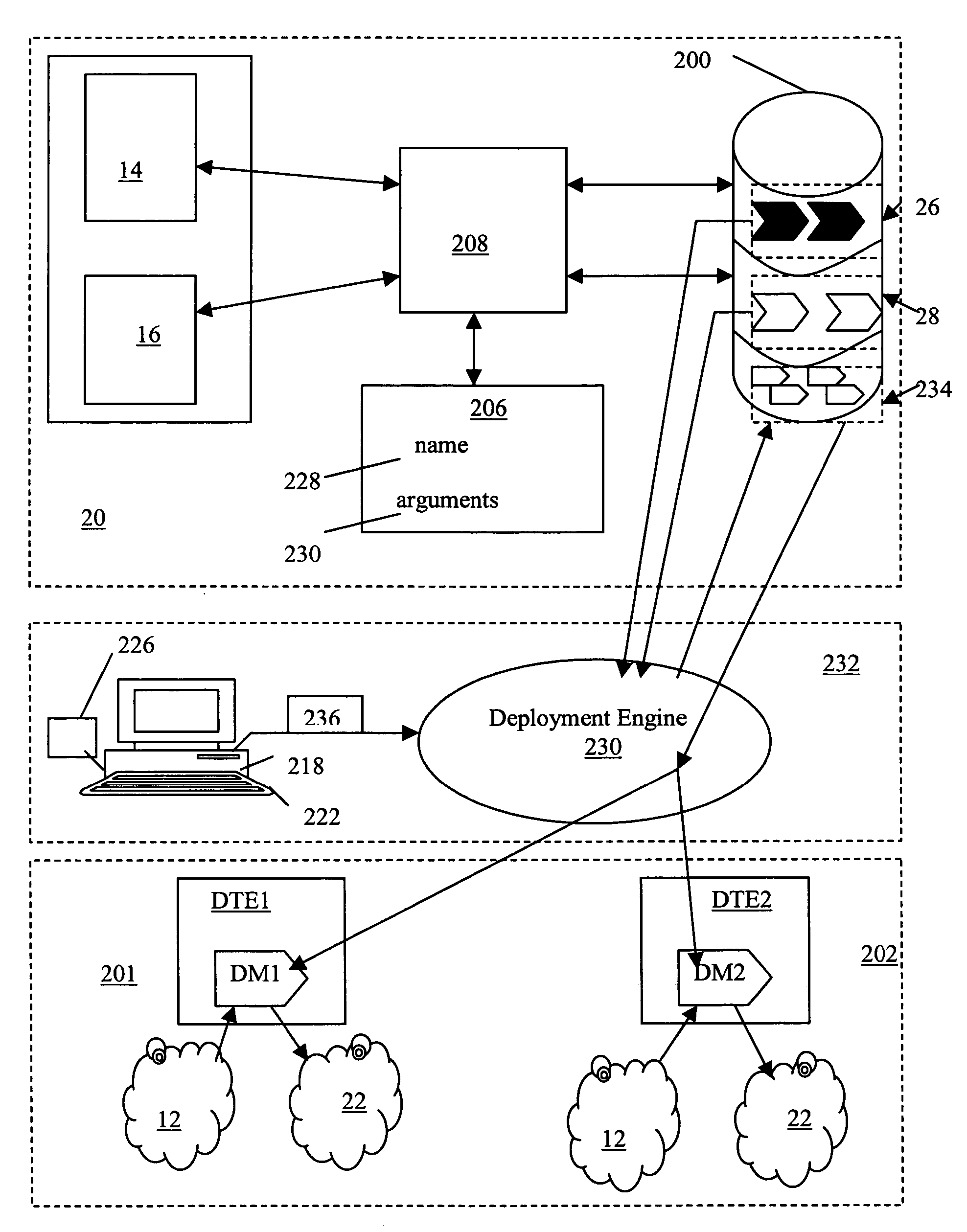

Synthetic Partitioning for Imposing Implementation Design Patterns onto Logical Architectures of Computations

ActiveUS20110314448A1Balance computing loadProgram code adaptionSpecific program execution arrangementsLanguage constructComputer architecture

A method and a system for using synthetic partitioning constraints to impose design patterns containing desired design features (e.g., distributed logic for a threaded, multicore based computation) onto logical architectures (LA) specifying an implementation neutral computation. The LA comprises computational specifications and related logical constraints (i.e., defined by logical assertions) that specify provisional loops and provisional partitionings of those loops. The LA contains virtually no programming language constructs. Synthetic partitioning constraints add implementation specific design patterns. They define how to find frameworks with desired design features, how to reorganize the LA to accommodate the frameworks, and how to map the computational payload from the LA into the frameworks. The advantage of synthetic partitioning constraints is they allow implementation neutral computations to be transformed into custom implementations that exploit the high capability features of arbitrary execution platform architectures such as multicore, vector, GPU, FPGA, virtual, API-based and others.

Owner:BIGGERSTAFF TED J

Integrated visual and language-based method for reusable data transformations

InactiveUS7512937B2Digital data information retrievalDigital data processing detailsLanguage constructHuman language

A method deploys a set of coupled data transformation modules describing a data transformation, the data transformation for transforming a data structure from a first format to a second format. The method includes receiving an instruction for selecting the set of transformation modules from a memory; converting each of the set of transformation modules to a common model format, the set of modules having at least one transformation module being of a module type of a type set including language constructed modules and visually constructed modules; and generating an executable version of the converted transformation modules suitable for execution by a data transformation engine. The executable version, when executed, transforms the data structure from the first format to the second format.

Owner:INT BUSINESS MASCH CORP

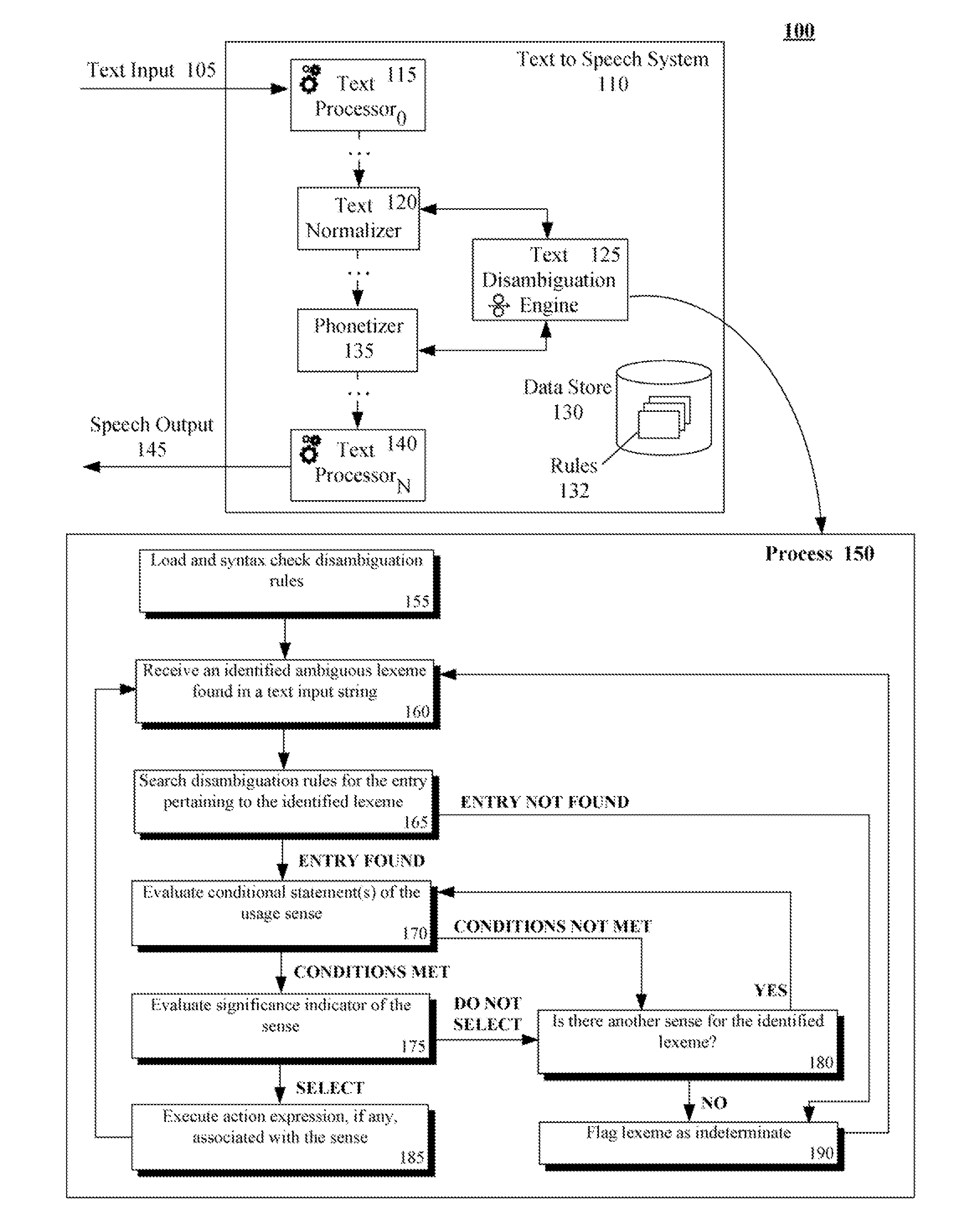

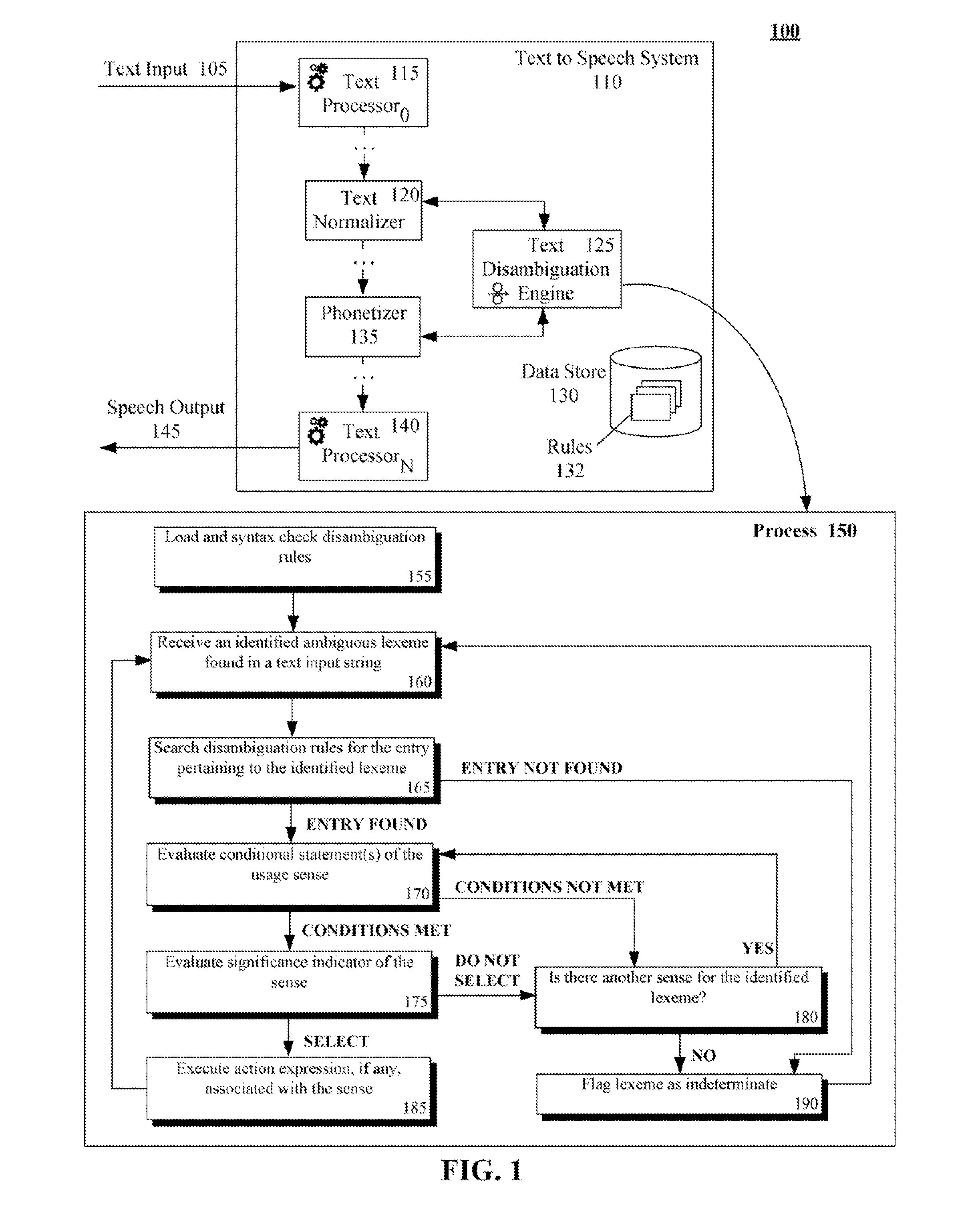

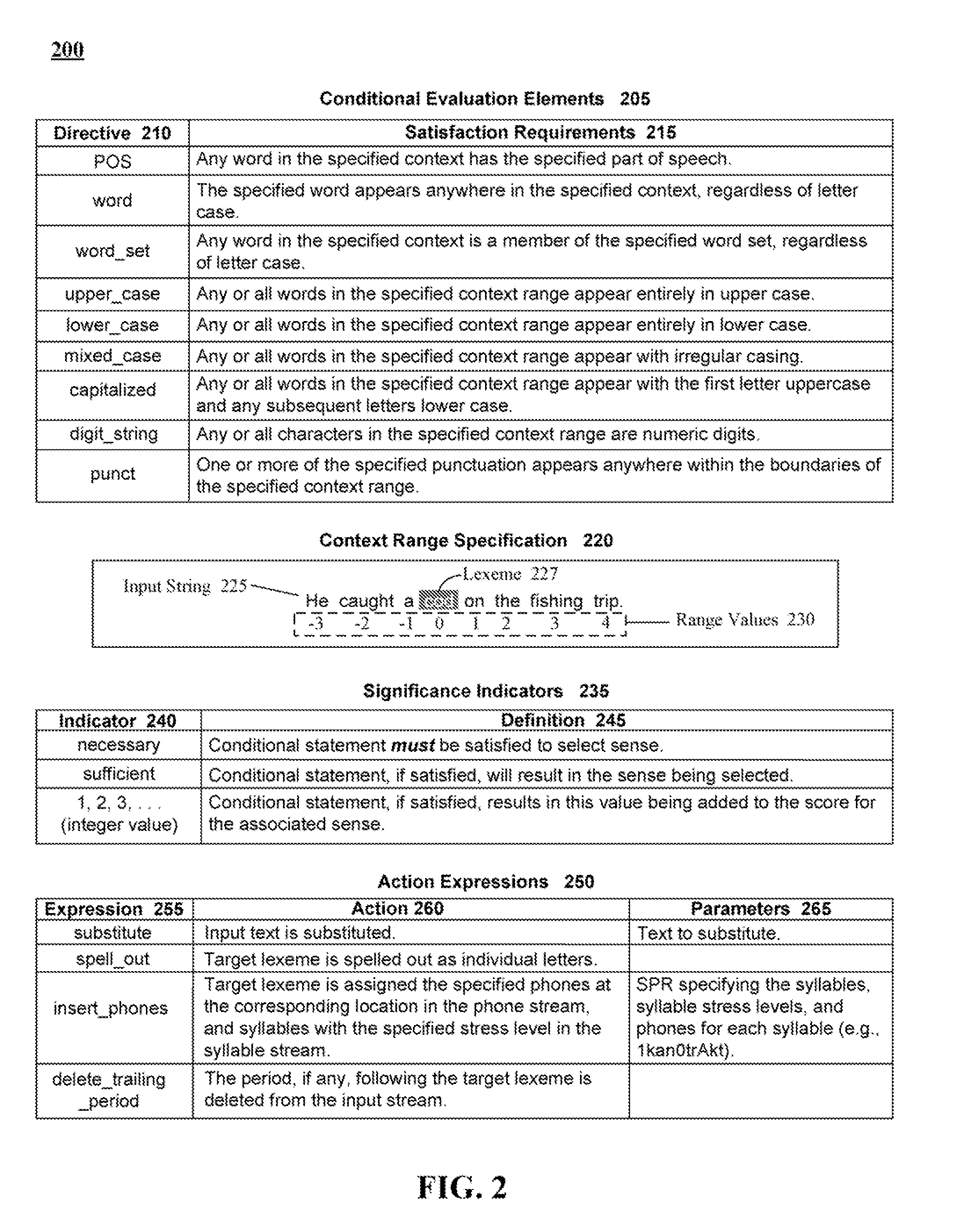

Disambiguating text that is to be converted to speech using configurable lexeme based rules

ActiveUS20080235004A1Special data processing applicationsSpeech synthesisLanguage constructNatural language processing

A software language including language constructs for disambiguating text that is to be converted to speech using configurable lexeme based rules. The language can include at least one conditional statement and a significance indicator. The conditional statement can define a sense of usage for a lexeme. The significance indicator can define a criteria for selecting an associated sense of usage. The language can also include an action expression that is associated with a conditional statement that defines a set of programmatic actions to be executed upon a selection of the associated usage sense. The conditional statement can include a context range specification that defines a scope of an input string for examination when evaluating the conditional statement. Further, the conditional statement can include a directive that represents a defined condition of the lexeme or the text surrounding the lexeme.

Owner:CERENCE OPERATING CO

Integrated visual and language-based system and method for reusable data transformations

InactiveUS20050138222A1Digital data processing detailsVisual/graphical programmingLanguage constructVisual perception

There is provided a method and system for developing a transformation program to transform a data structure from a first format to a second format, the program including a plurality of coupled data transformation modules describing the transformation, the method comprising the steps of: generating a first transformation module of the plurality of transformation modules for assembling the program, the first module being a module type of a set of module types including a language constructed module type and a visually constructed module type; extracting reference information from the first module for accessing the first module when stored in a memory; and updating a module registry to include a first entry corresponding to the reference information of the first module, the module registry configured for having reference information entries extracted from both the language constructed modules and visually constructed modules.

Owner:IBM CORP

System for Interpolating Data into Data Fields in an Image or Text Based Project

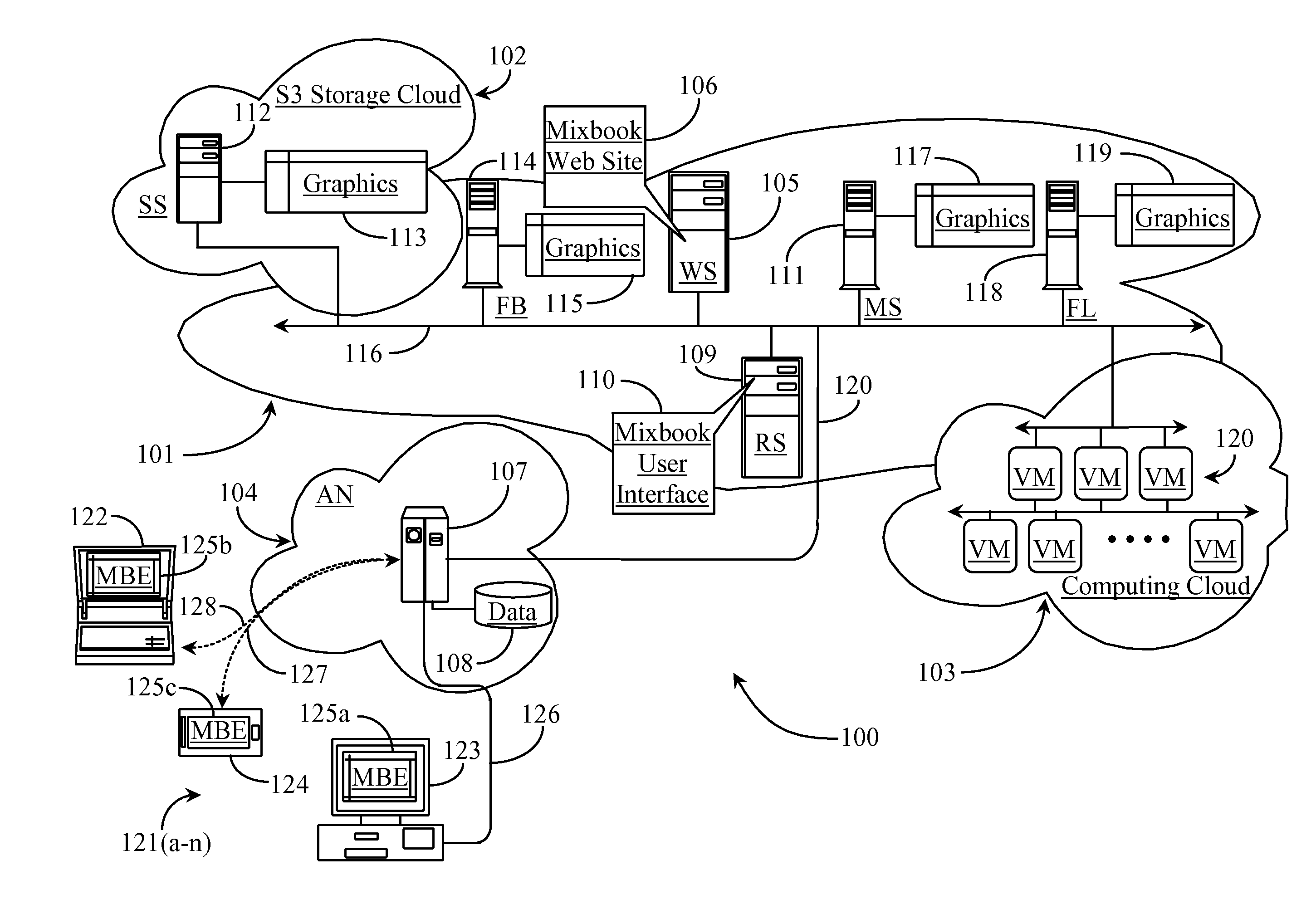

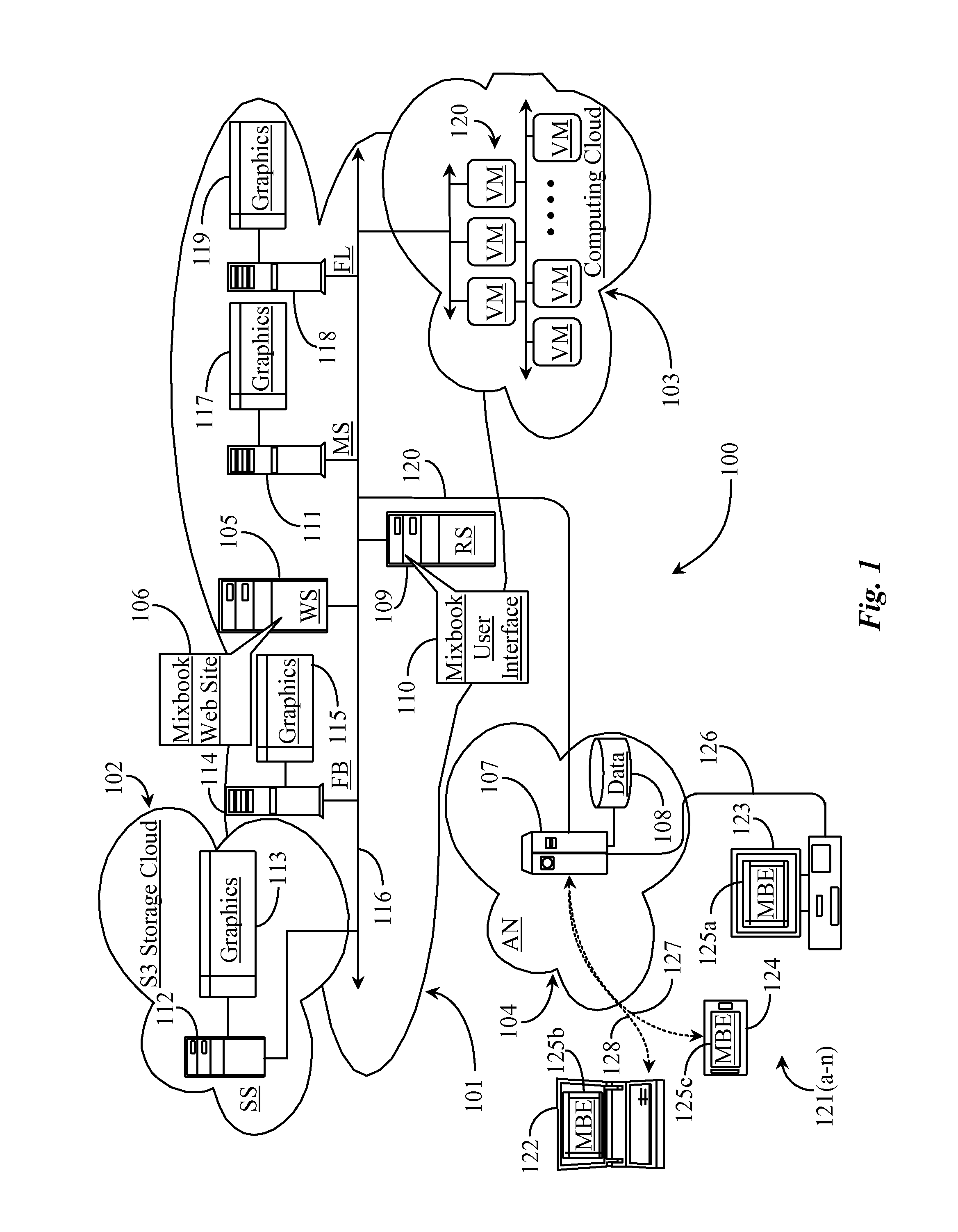

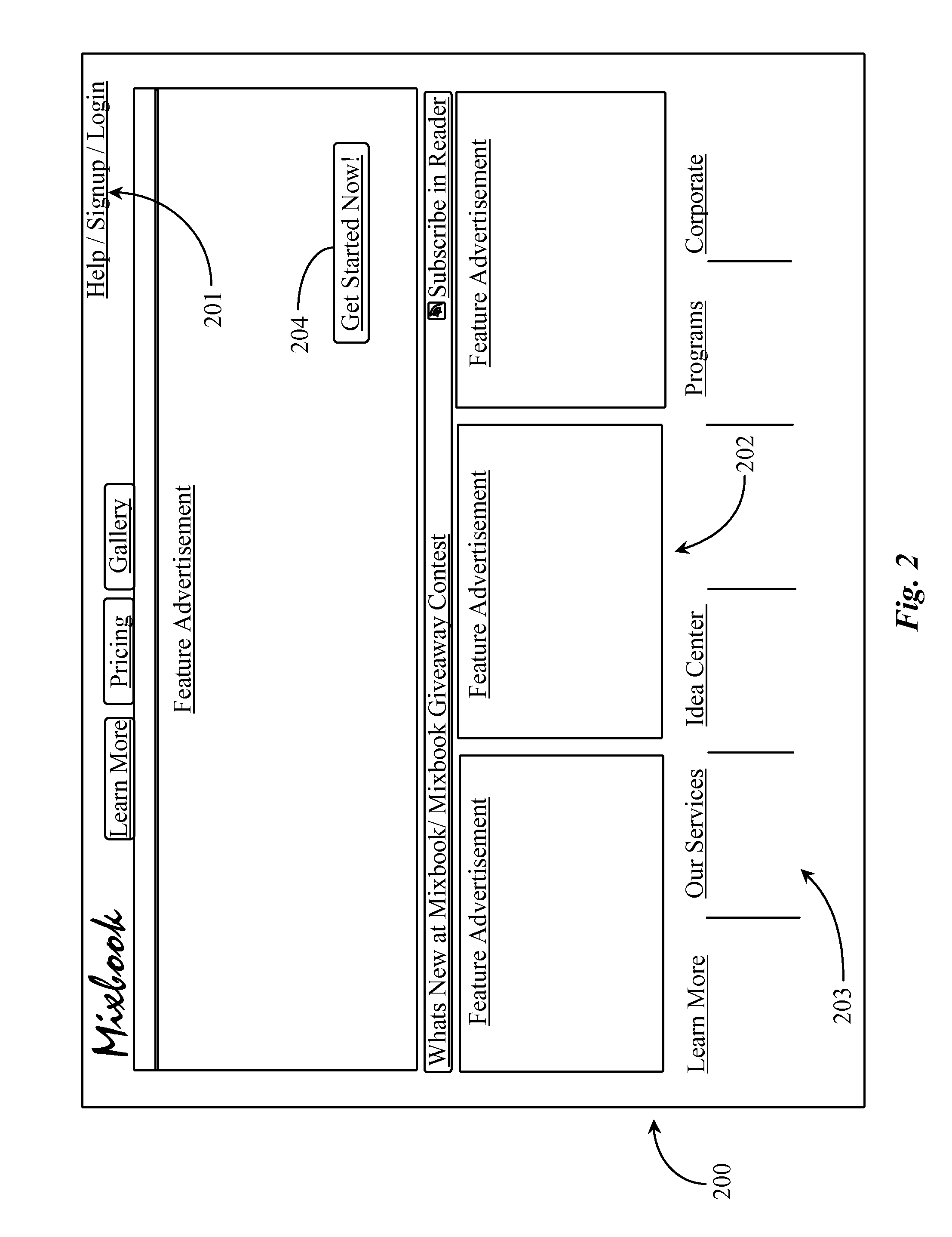

InactiveUS20110016412A1Reduce printing errorsQuickly populateStill image data indexingCharacter and pattern recognitionGraphicsLanguage construct

In a server-based system for creating and editing image and or text-based projects, the system having access to a digital medium containing an executable graphics user interface (GUI) accessible by computer browser, a system for automatically interpolating data into data fields belonging to an image and or text-based project includes a source of markup language constructs and or a tool implemented in software on a digital medium, and an intermediate data population form resident on a digital medium, the data population form receiving marked up data fields.

Owner:INTERACTIVE MEMORIES