Method for designing triple-modular redundancy type fault-tolerant computer IP core with fault spontaneous restoration function

A redundancy fault-tolerant, computer technology, the redundancy applied in the hardware is used for data error detection, response error generation and other directions, which can solve the problems of data loss, time loss, etc., to ensure correctness, reasonable resource occupation, and use. handy effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0012] In order to make the realization and advantages of the present invention clearer, a detailed description will be made below in conjunction with the accompanying drawings. Here, the exemplary embodiments of the present invention and their descriptions are used to explain the principles and methods of the invention, but are not intended to limit the present invention.

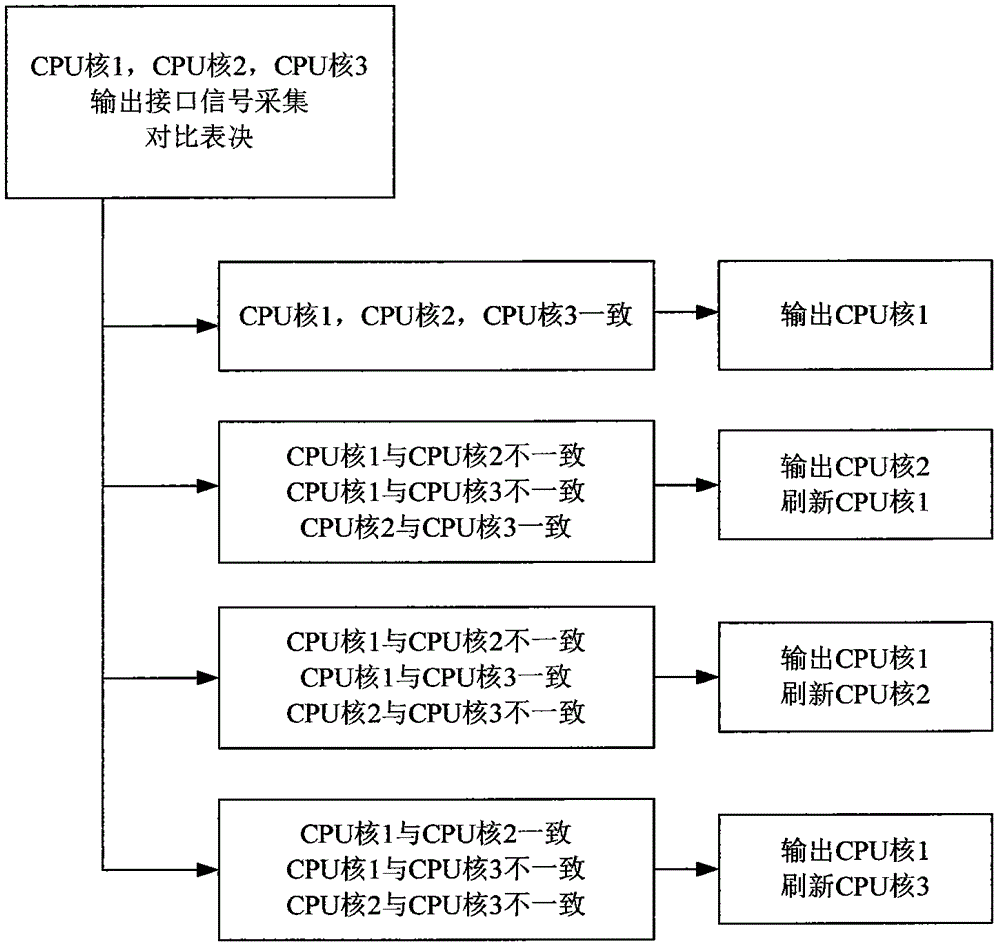

[0013] The implementation case of the present invention provides the working principle of the triple-mode redundant CPU core, based on the hot backup work of the three basic CPUs, the voting principle of two out of three, and the flow and algorithm of refreshing control logic implementation. The implementation process of the present invention is shown in detail below.

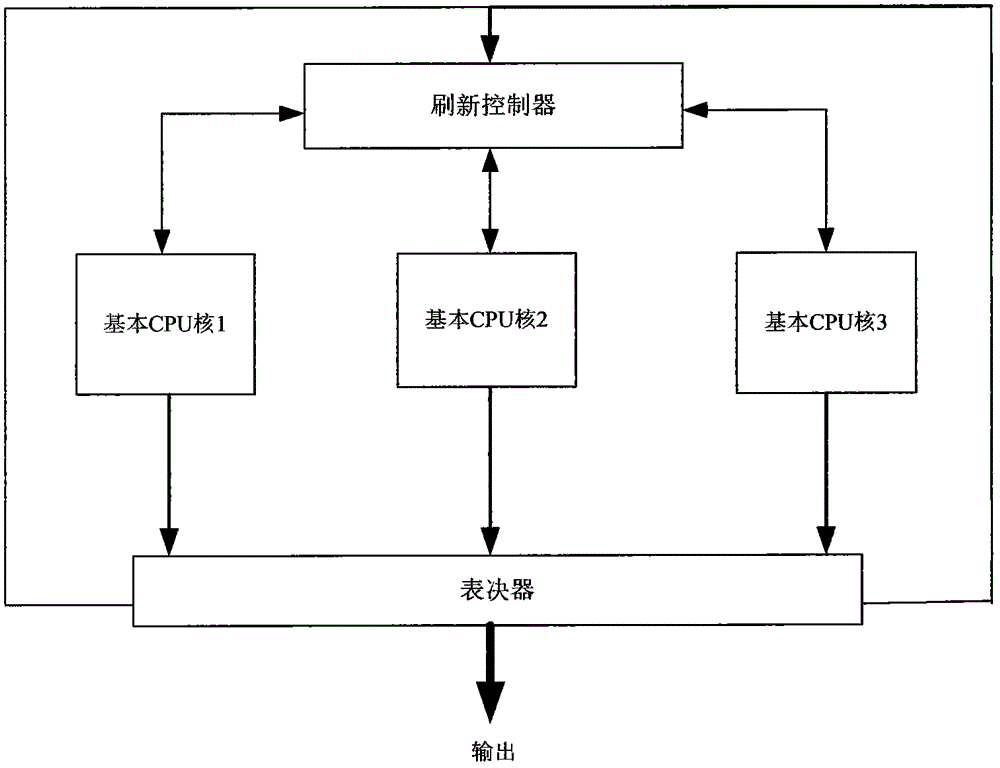

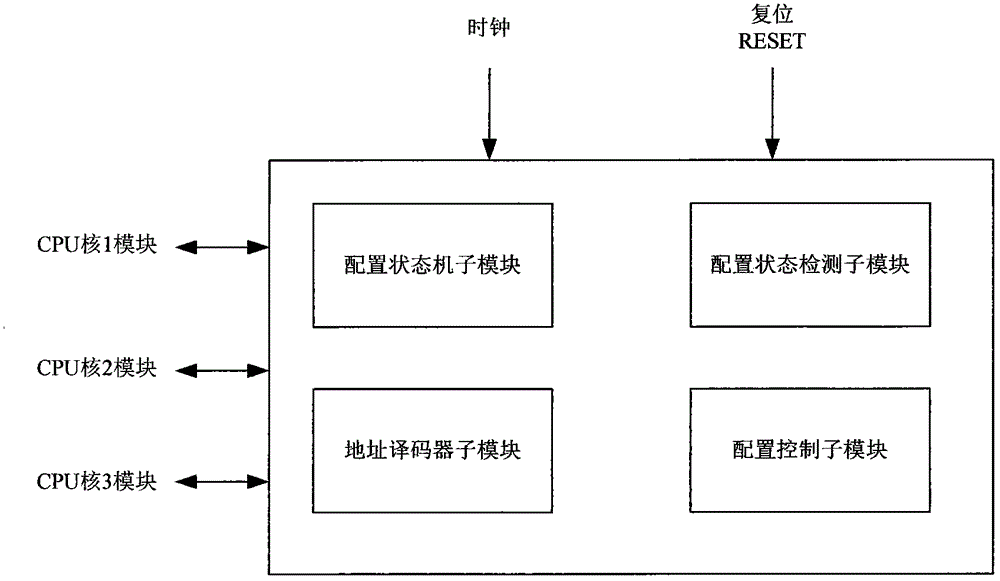

[0014] attached figure 1 Is the general principle diagram of the present invention. The three basic CPU cores work in the hot backup state, and the calculation results are output in the form of two out of three through the voter. The ref...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More