Determining hardware parameters specified when configurable IP is synthesized

a hardware parameter and configurable technology, applied in the field of semiconductor chip design, can solve the problems of confusion for new users, placing customization constraints, and difficulty in mentally keeping track of which particular copy contains hardware features of which particular values of configurable parameters

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

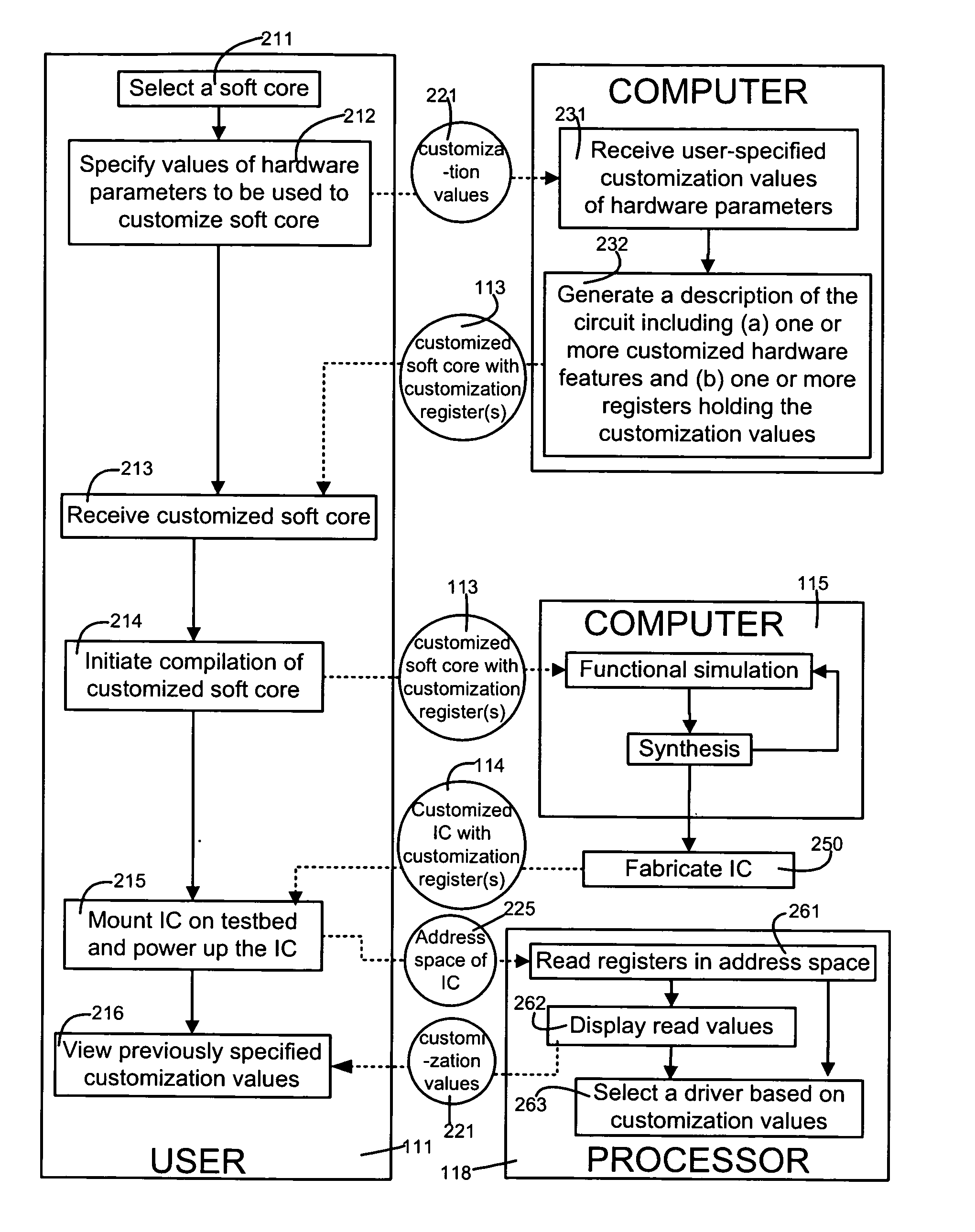

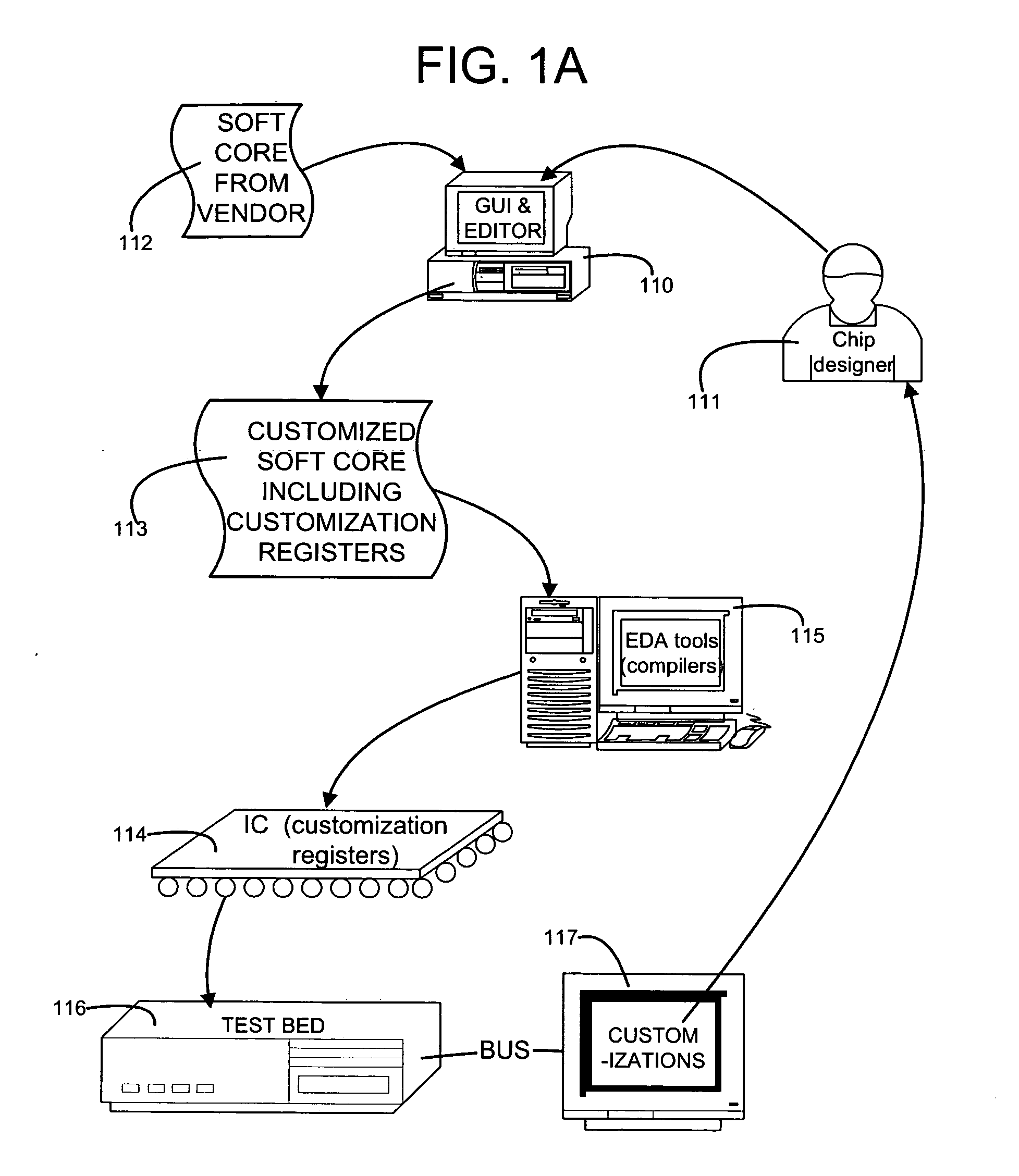

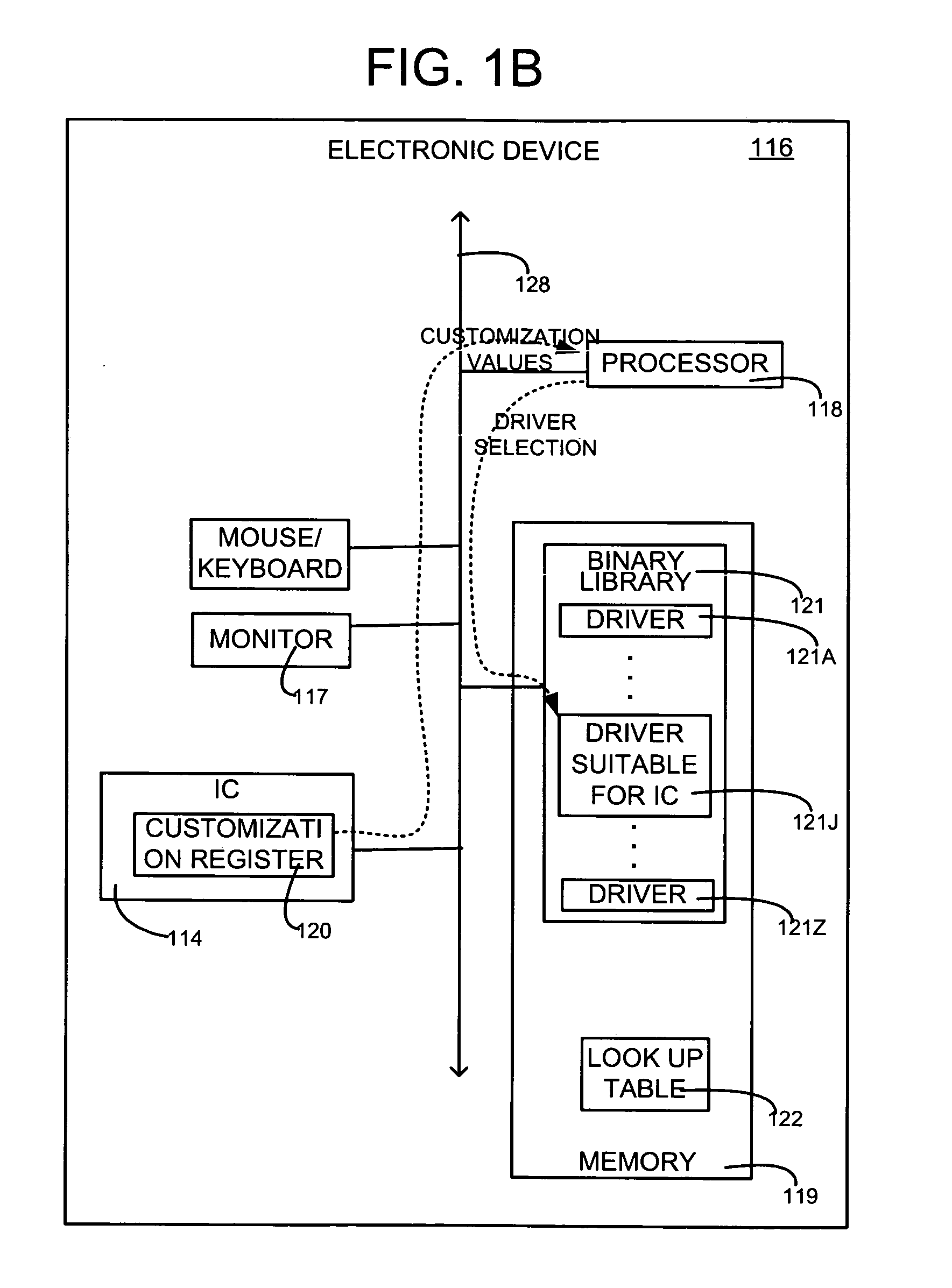

[0022] In several embodiments of the invention, a computer 110 (FIG. 1A) is programmed to receive from a chip designer 111 (also called “user”) one or more values of one or more parameters of one or more hardware features to be customized in a soft core 112 (e.g. in the form of a text file that can be edited by a human) that is prepared by a vendor of intellectual property (IP). Note that although a text file is mentioned as an example of the format of soft core, in other examples soft core may be provided in other formats, such as a binary format or a byte code format as long as such format is sufficiently meaningful to a tool supplied to chip designer 111 for customization of the soft core (and an example of such a tool is a GUI as described next). Computer 110 may receive the values to be used in hardware customization via a graphical user interface (GUI), depending on the embodiment. Thereafter, the user-specified values are used by computer 110 to generate (e.g. through an edit...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More