Patents

Literature

54 results about "Custom hardware" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

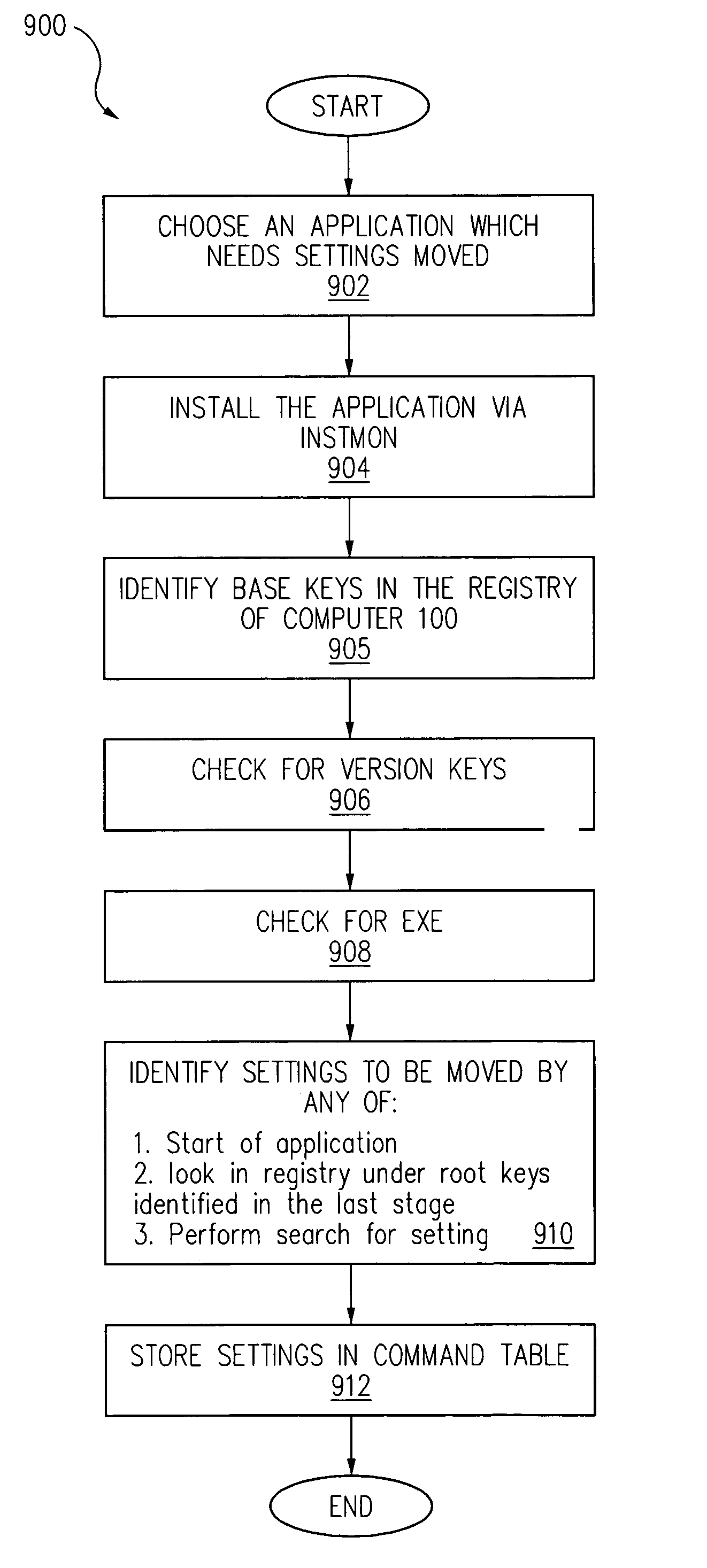

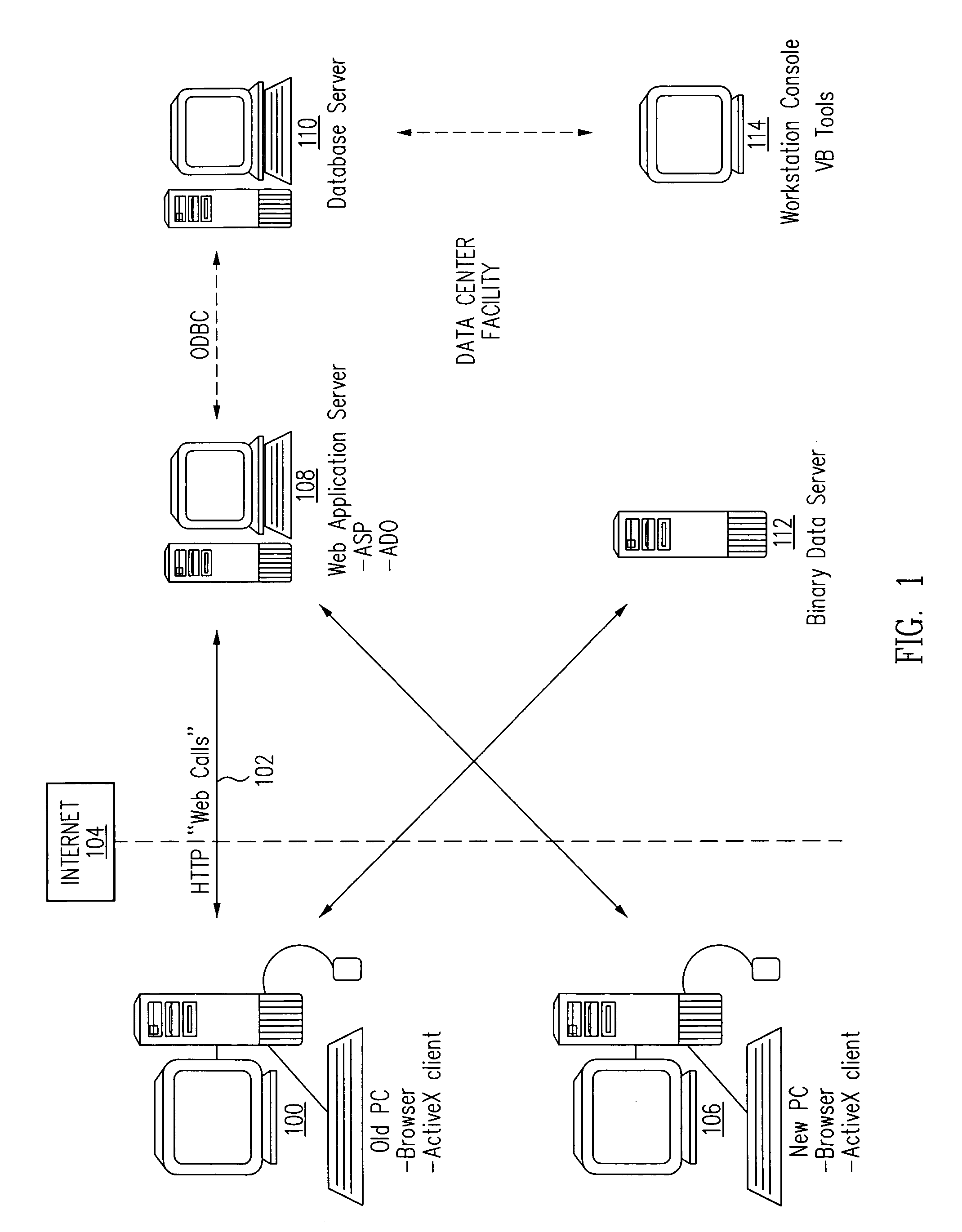

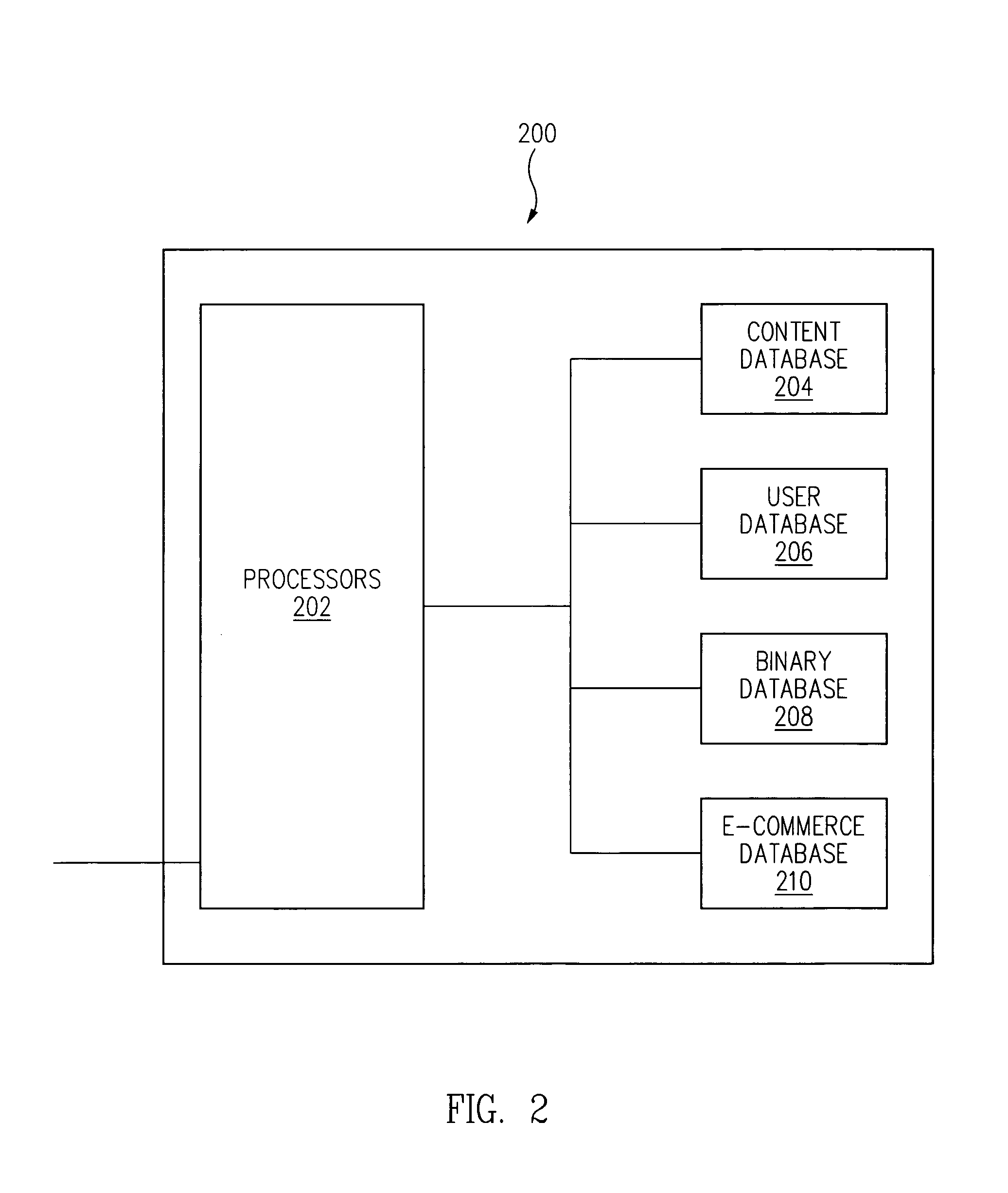

System for transferring customized hardware and software settings from one computer to another computer to provide personalized operating environments

InactiveUS6963908B1Simplify the shipping processOptimization mechanismDigital computer detailsProgram loading/initiatingPersonalizationWeb site

A method and system for transferring information from a first computer-based device to a web site, for temporary storage and later transfer of the stored information from the web site to a second computer-based device. First, a communication link is established between a first computer-based device and the web site. Next, the first computer-based device is scanned, via the web site, to determine the information contained on the first computer-based device. The user then selects which of the scanned information is to be uploaded from the first computer-based device onto the web site for temporary storage. Finally, the selected information is transferred from the first computer-based device onto the web site for temporary storage. Once retrieval of the temporarily stored information is desired, the user establishes a communication link between a second computer-based device and the web site. The second computer-based device is scanned, via the web site, to determine the information contained on the second computer-based device. The temporarily stored information, from the first computer-based device on the web site, is then displayed to the user and the user selects which of this temporary information, from the first computer-based device, is to be downloaded from the web site onto the second computer-based device. The selected information is finally downloaded from the website onto the second computer-based device.

Owner:CLOUDING

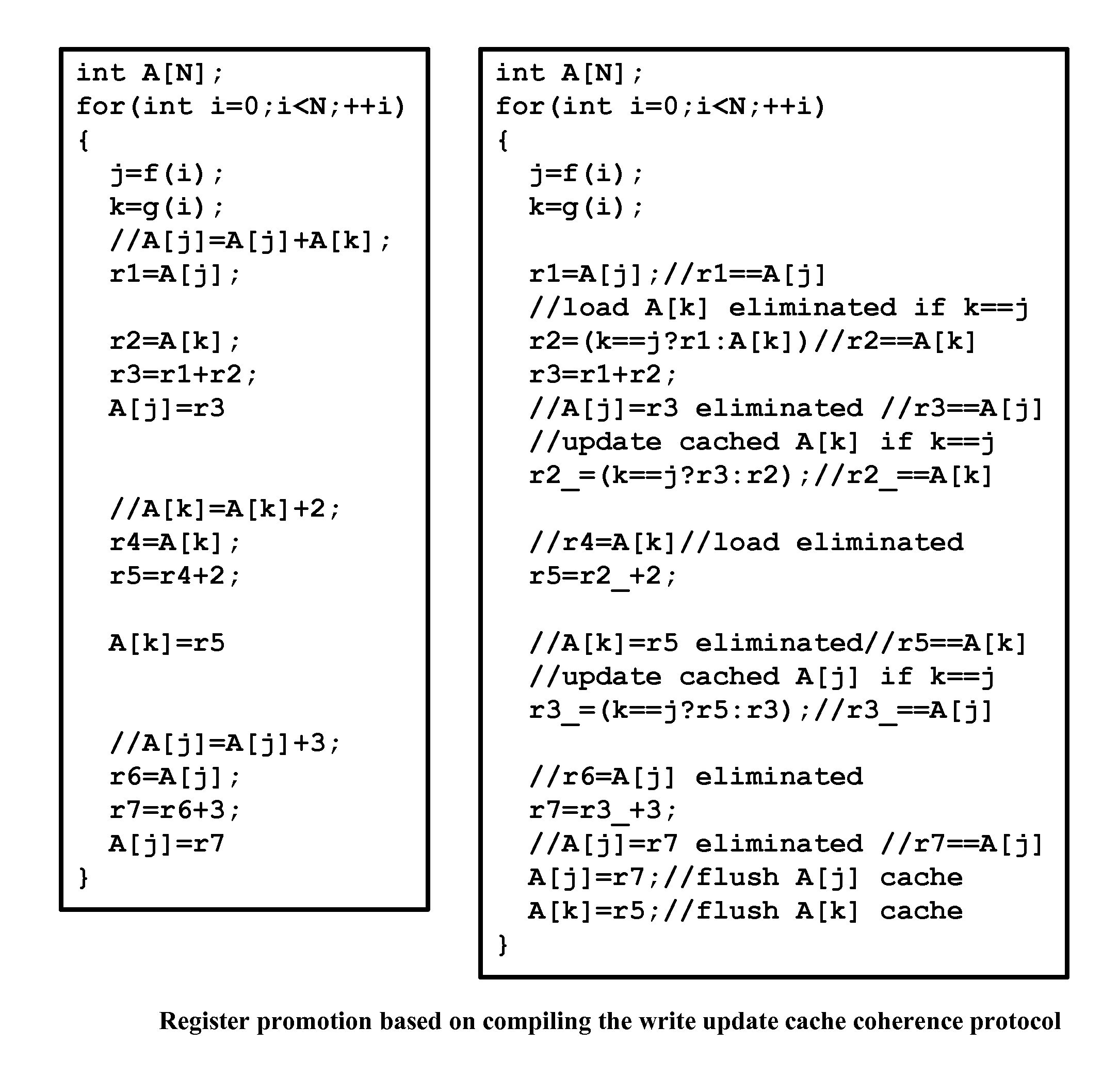

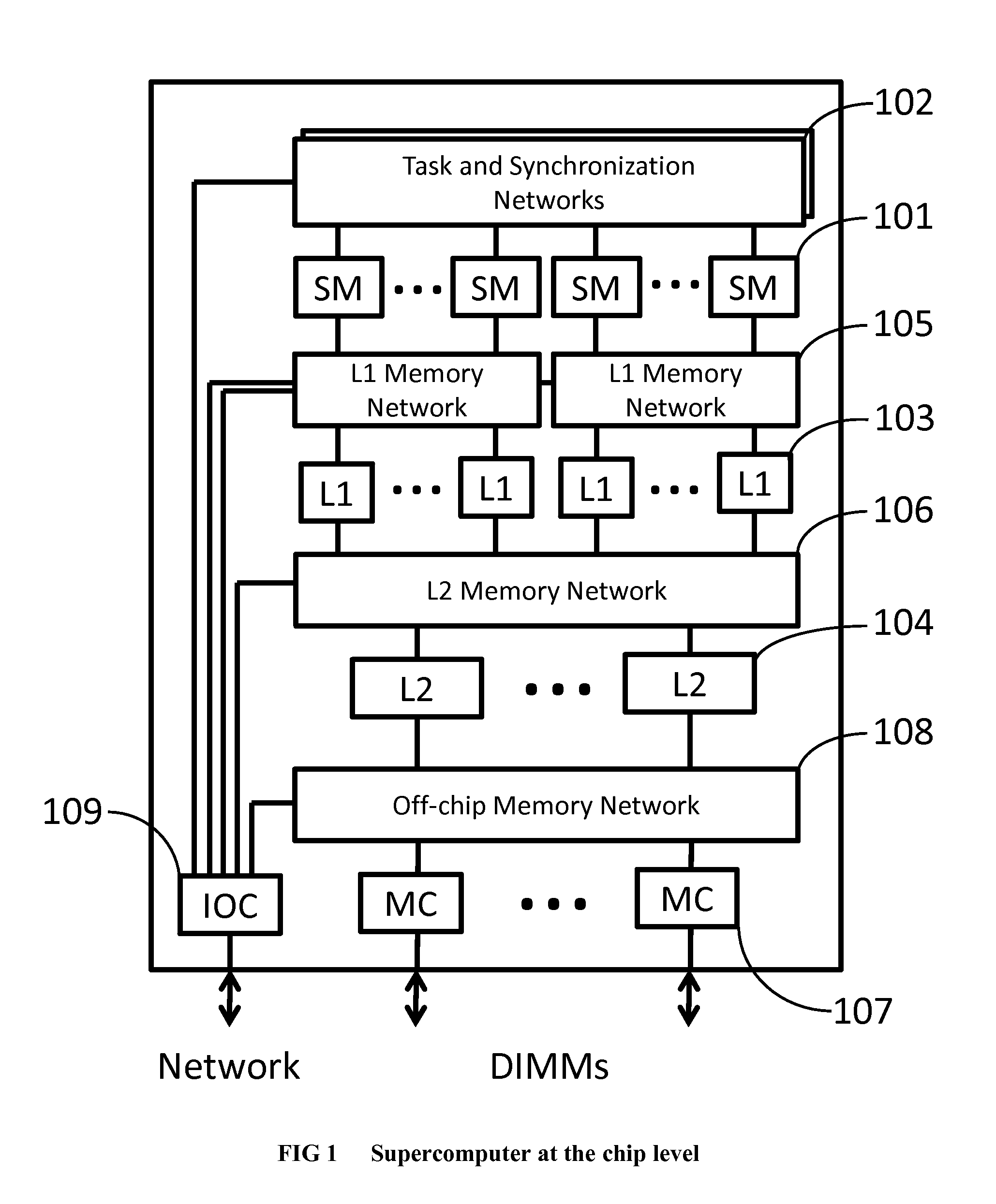

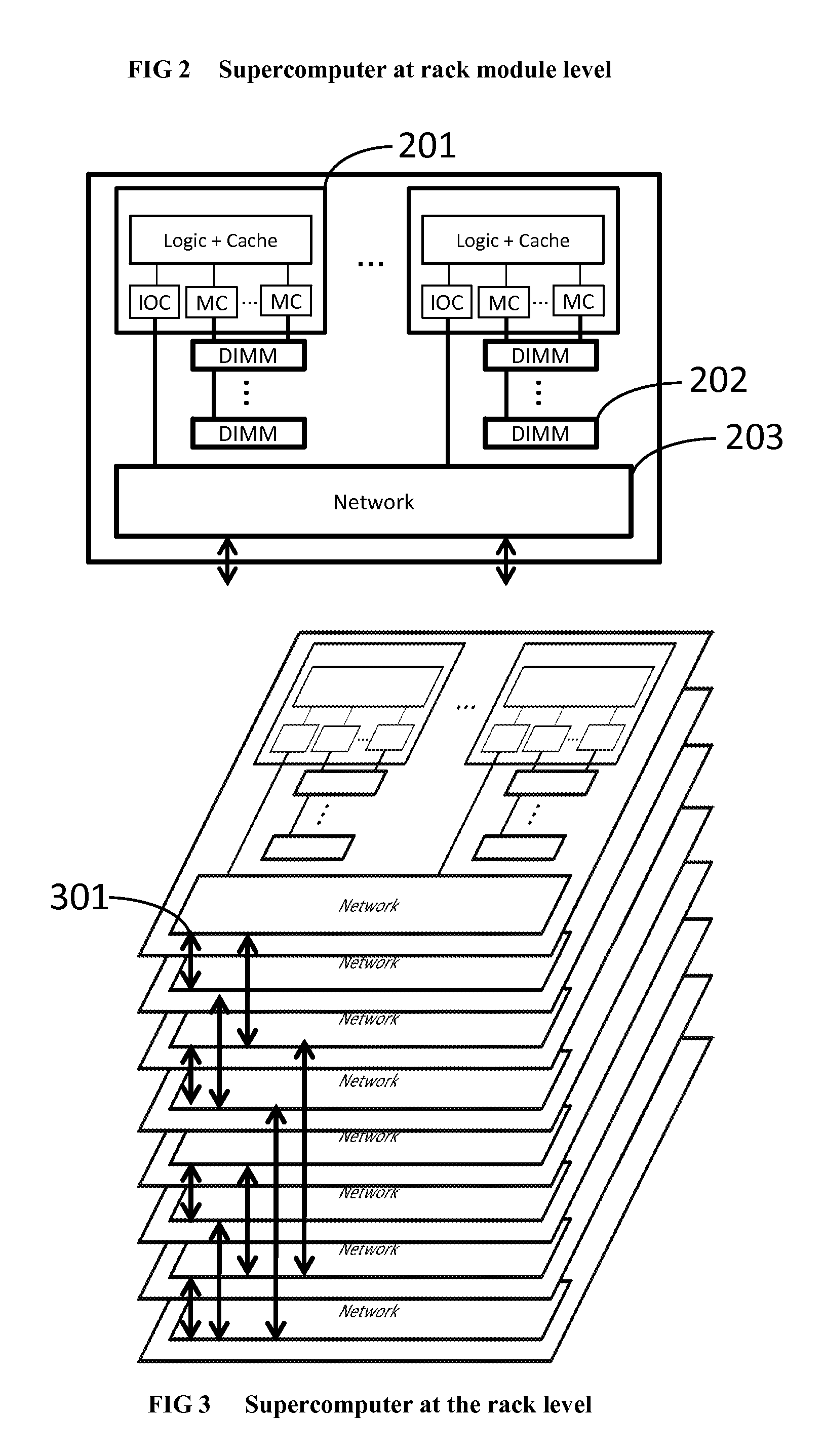

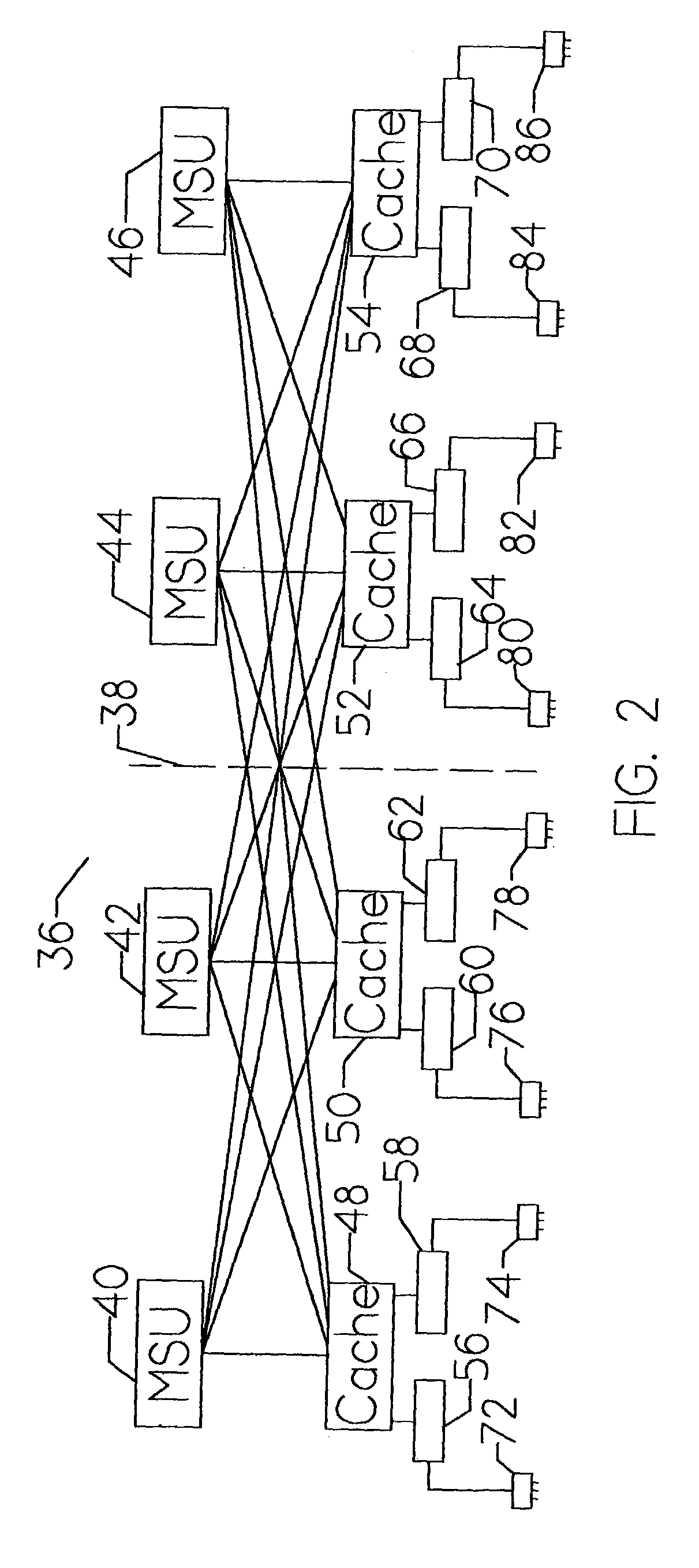

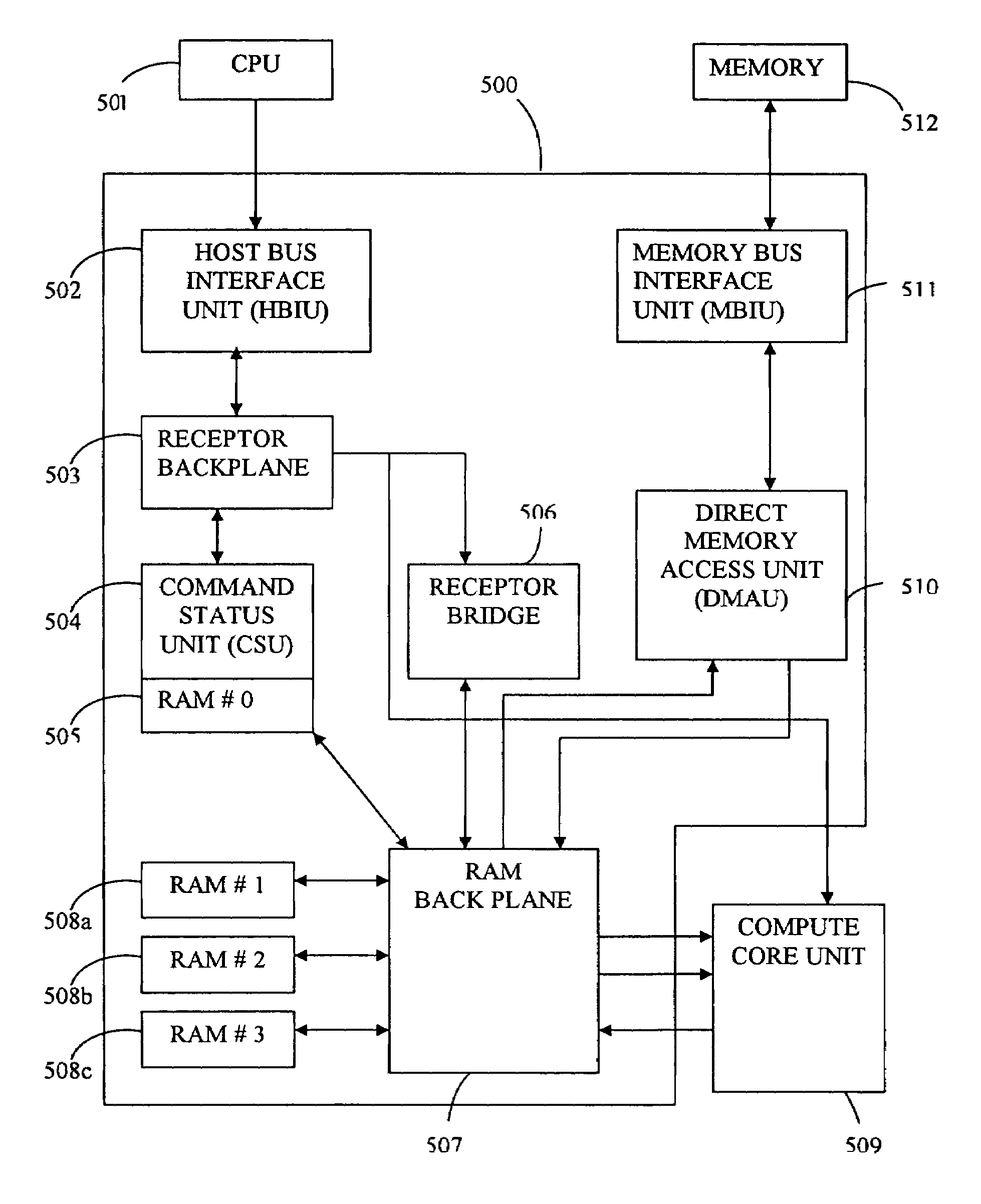

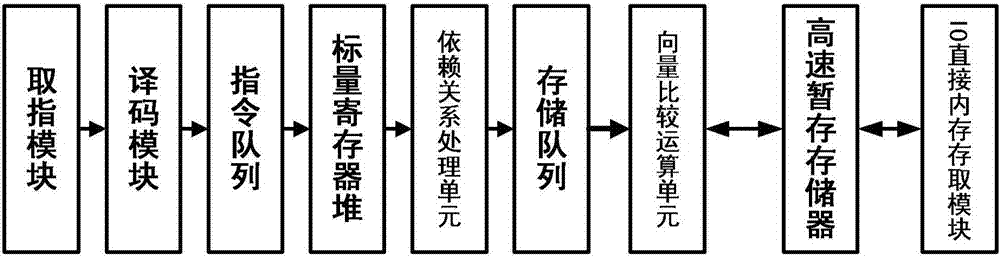

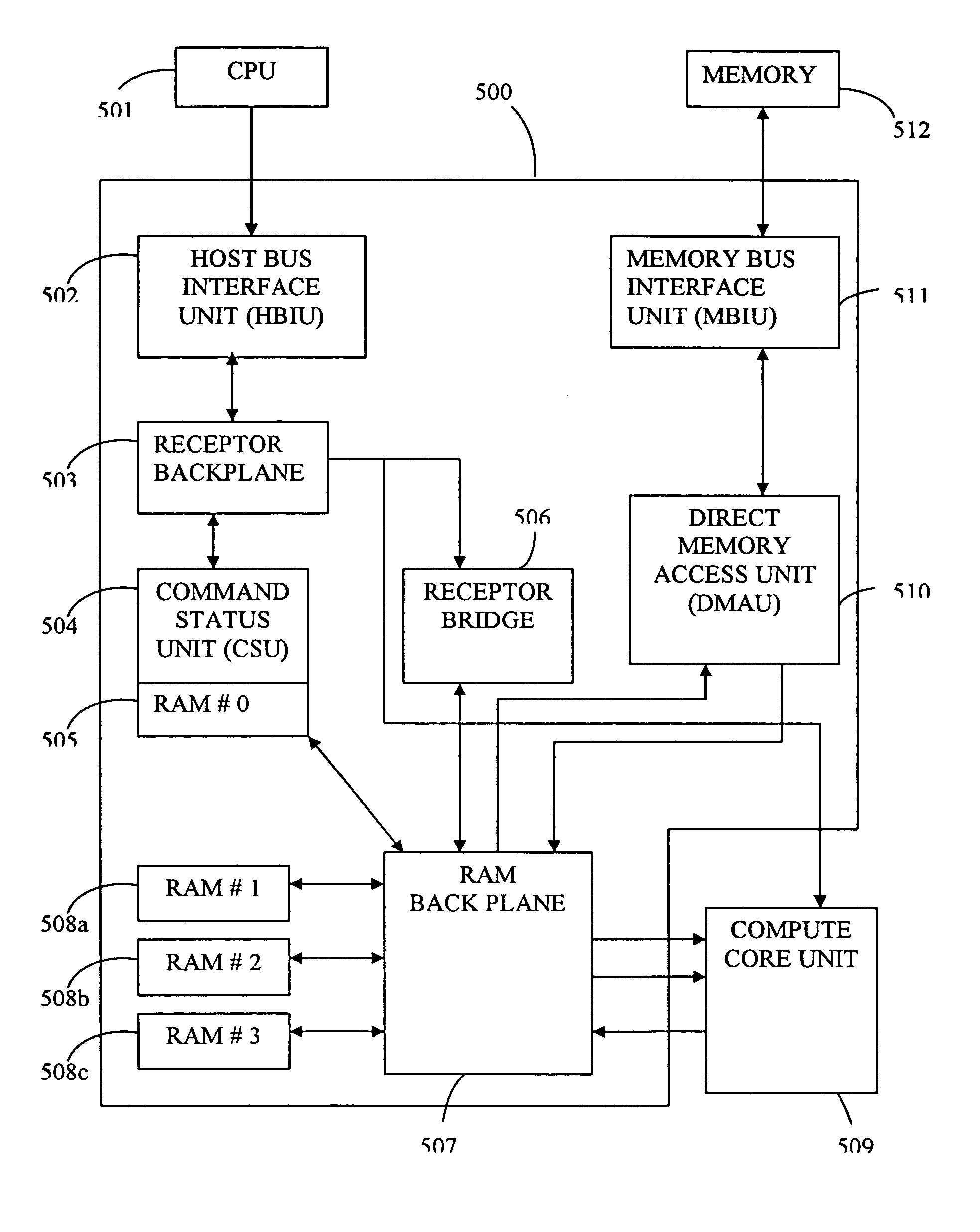

Method and system for converting a single-threaded software program into an application-specific supercomputer

ActiveUS20130125097A1Improve efficiencyLow overhead implementationMemory architecture accessing/allocationTransformation of program codeSupercomputerComputer architecture

The invention comprises (i) a compilation method for automatically converting a single-threaded software program into an application-specific supercomputer, and (ii) the supercomputer system structure generated as a result of applying this method. The compilation method comprises: (a) Converting an arbitrary code fragment from the application into customized hardware whose execution is functionally equivalent to the software execution of the code fragment; and (b) Generating interfaces on the hardware and software parts of the application, which (i) Perform a software-to-hardware program state transfer at the entries of the code fragment; (ii) Perform a hardware-to-software program state transfer at the exits of the code fragment; and (iii) Maintain memory coherence between the software and hardware memories. If the resulting hardware design is large, it is divided into partitions such that each partition can fit into a single chip. Then, a single union chip is created which can realize any of the partitions.

Owner:GLOBAL SUPERCOMPUTING CORP

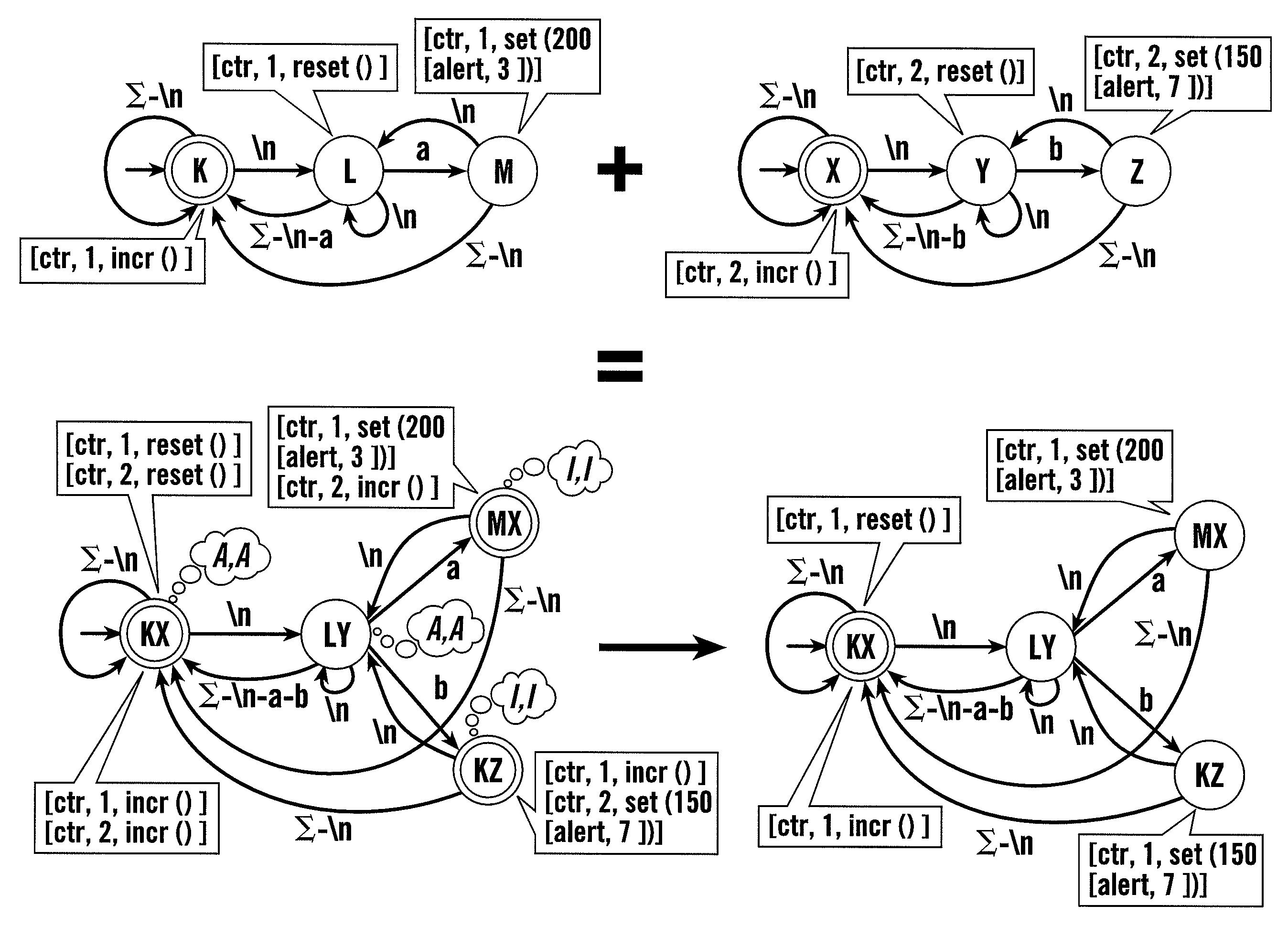

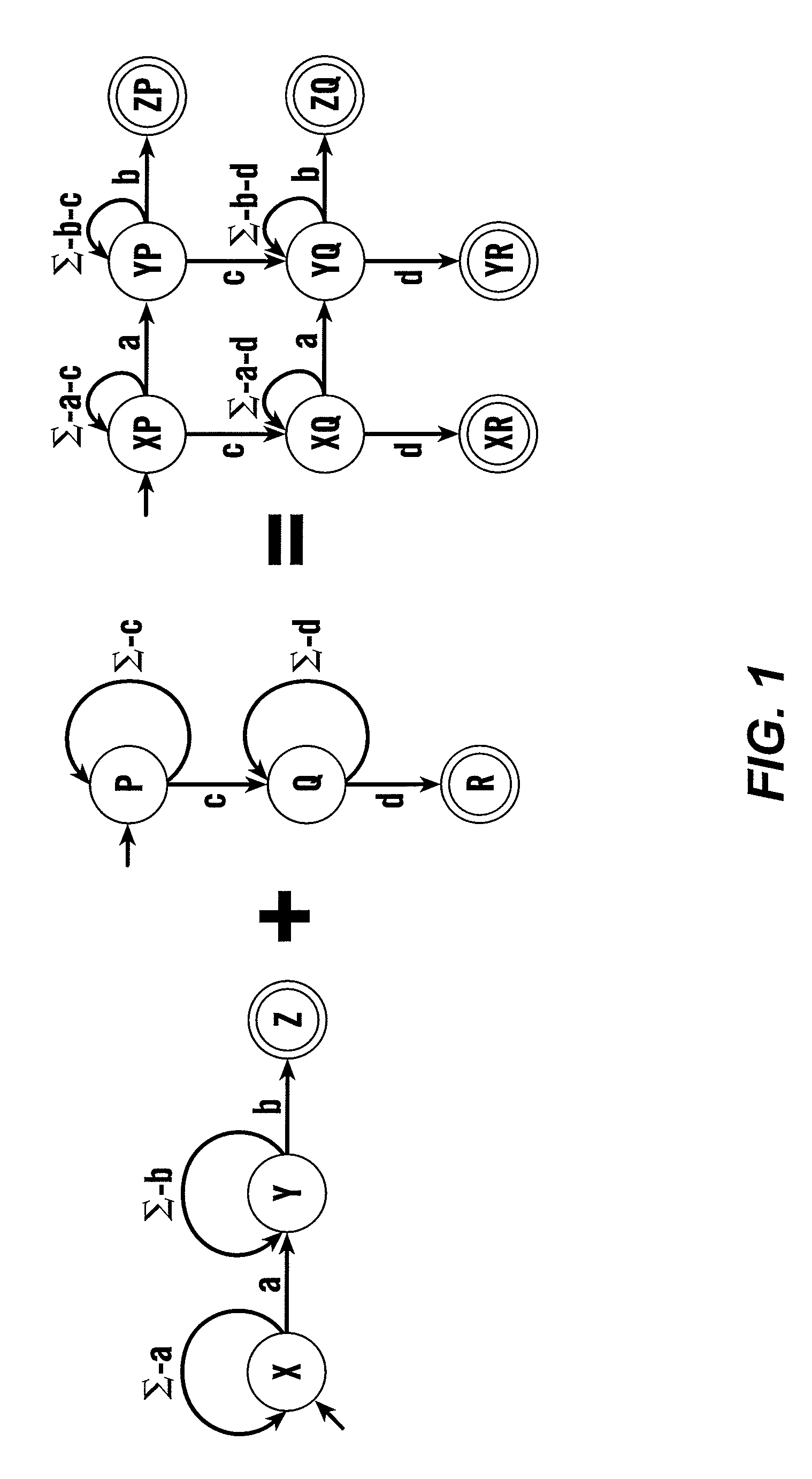

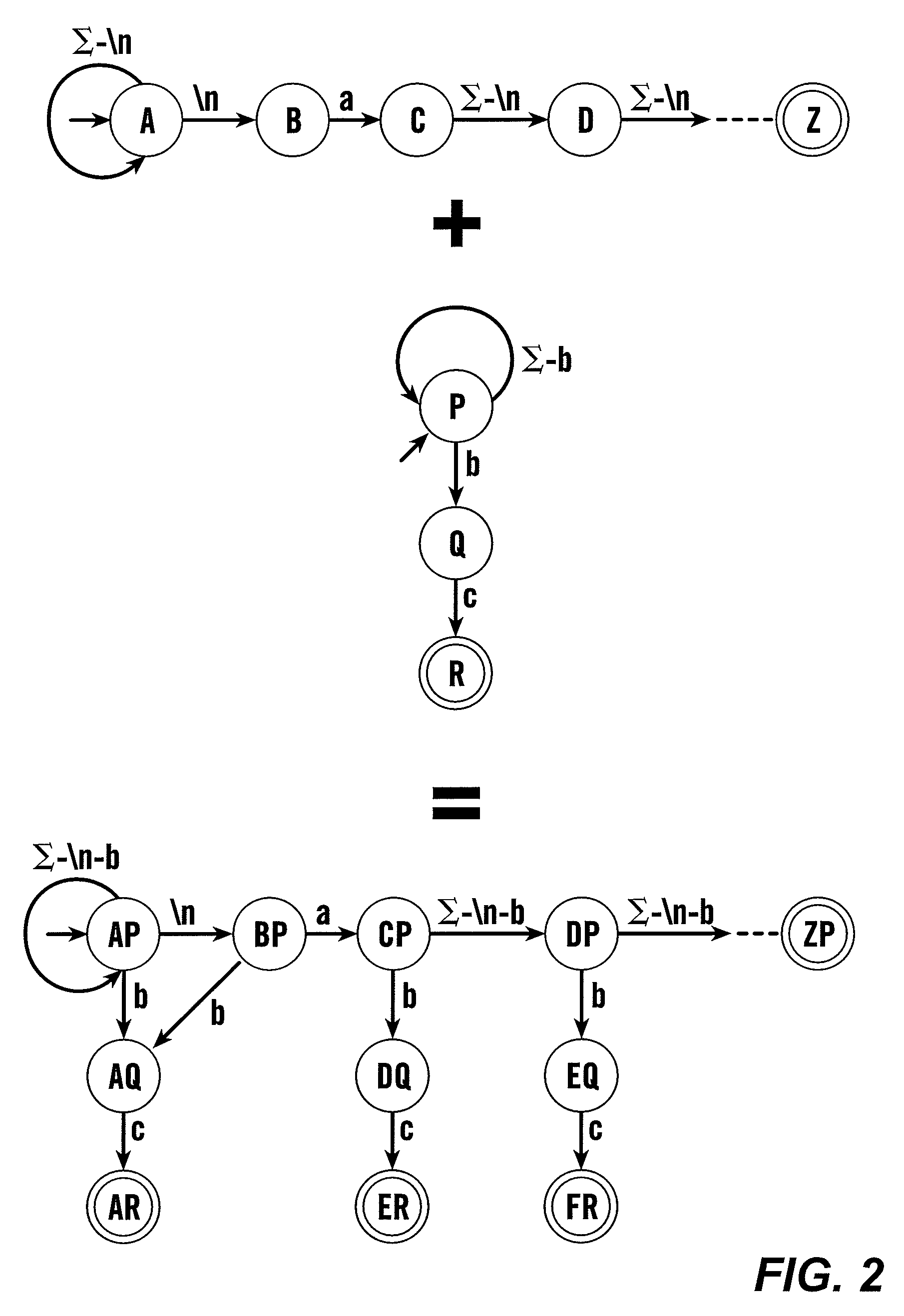

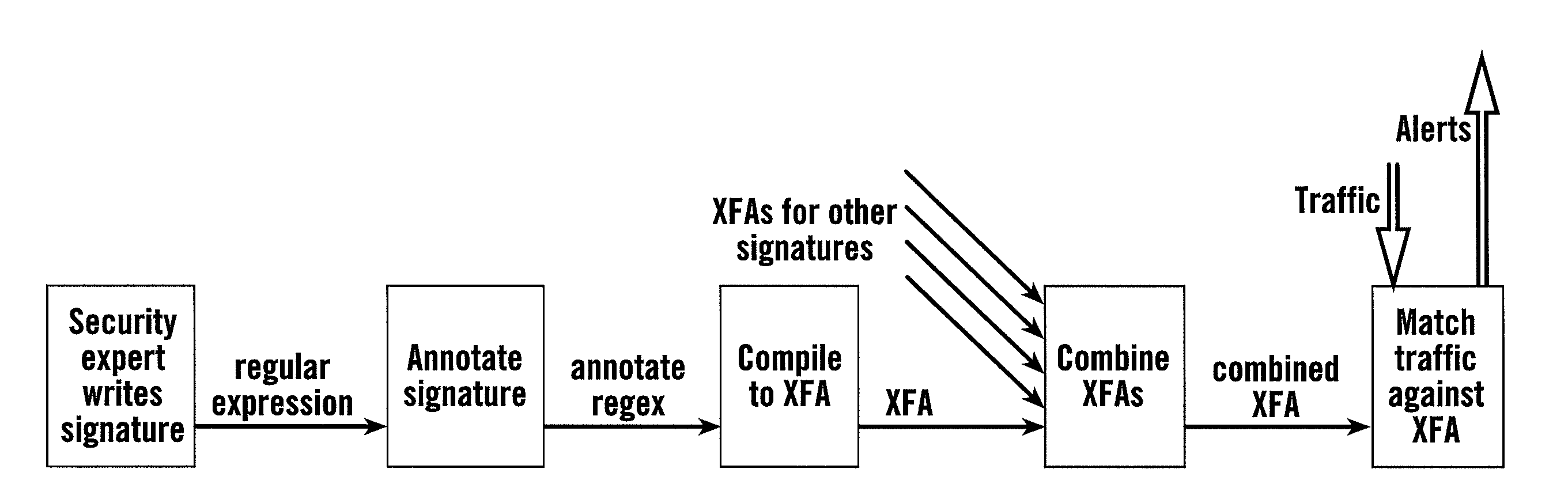

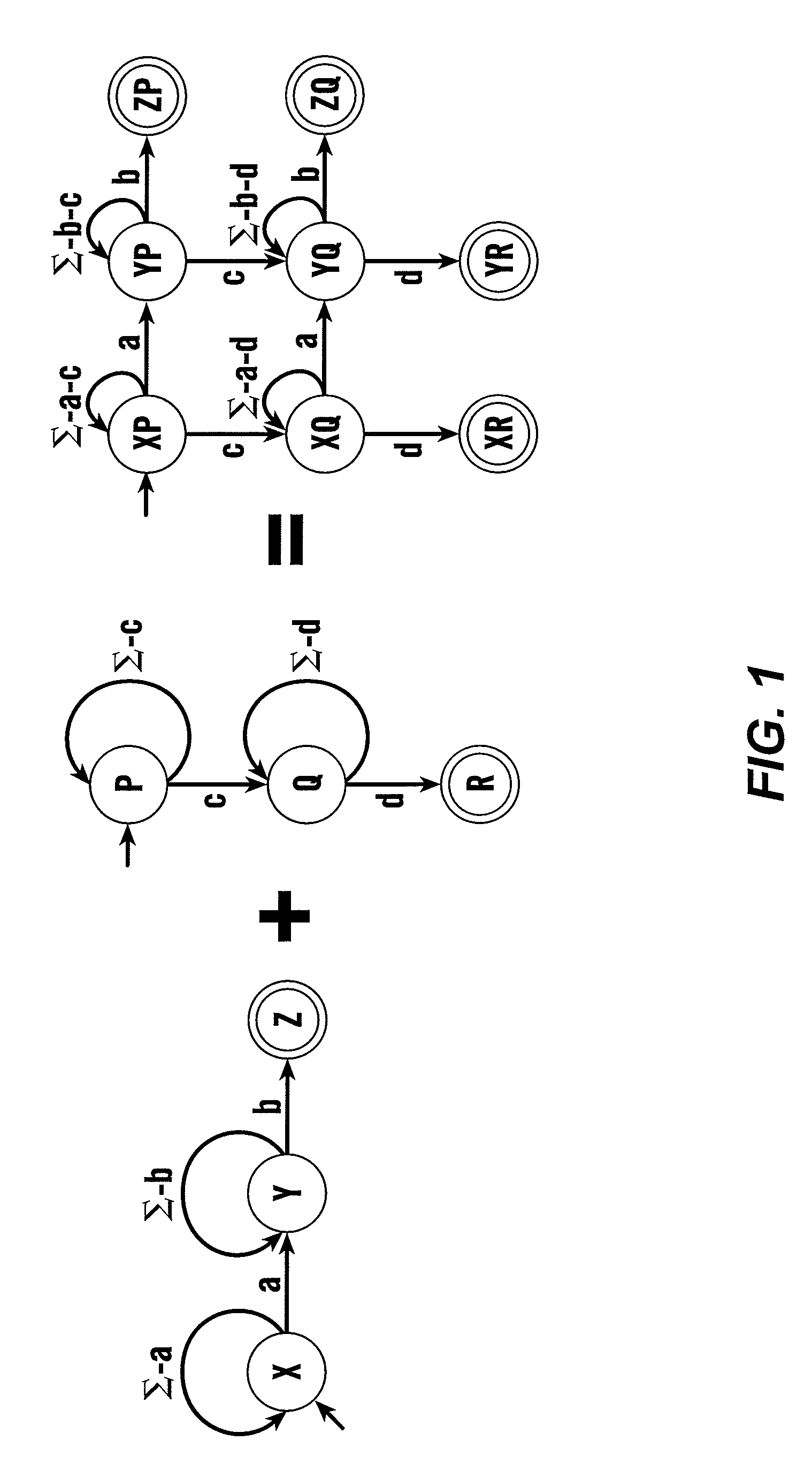

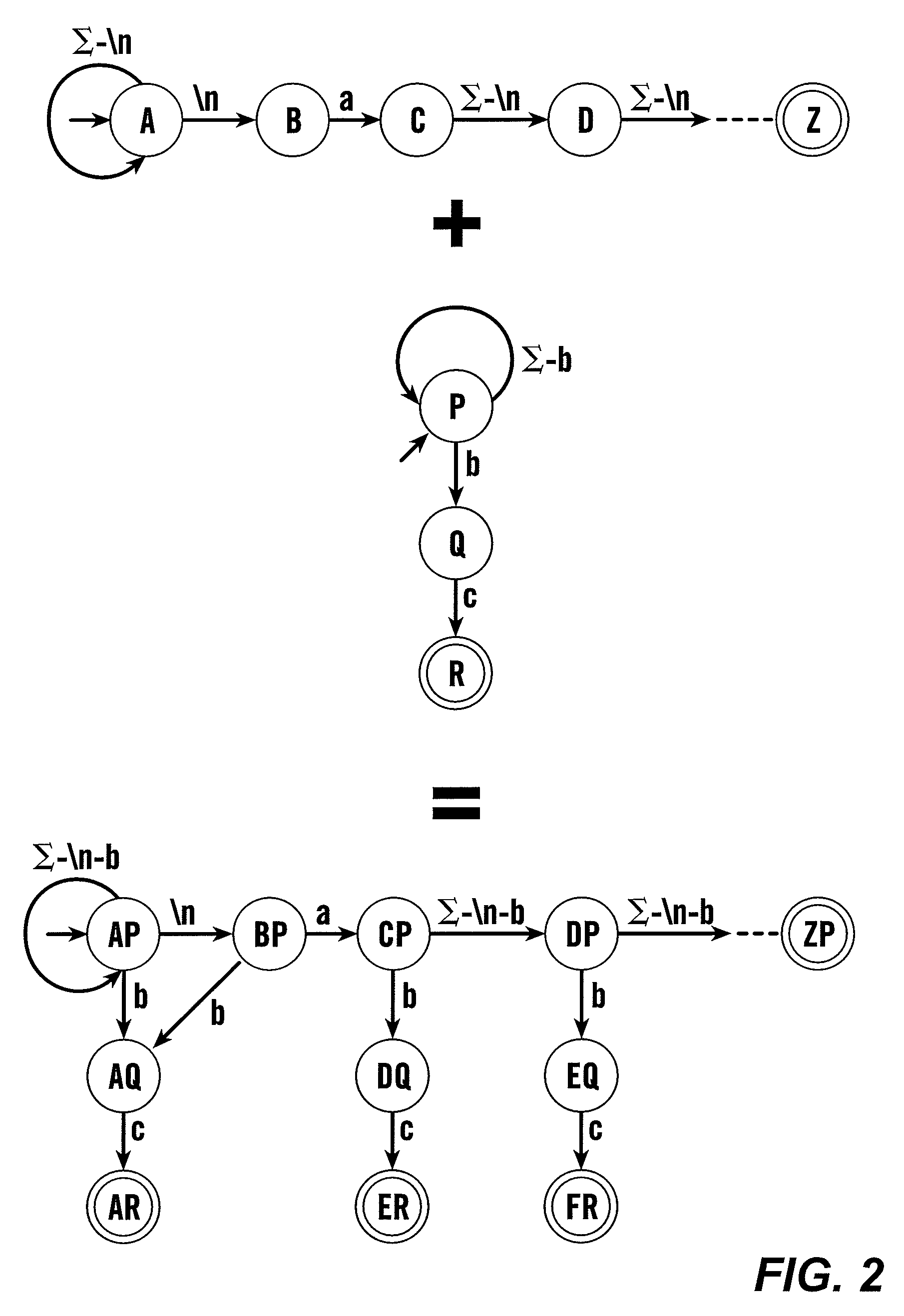

Extended finite state automata and systems and methods for recognizing patterns using extended finite state automata

Deterministic finite automata (DFAs) are popular solutions to deep packet inspection because they are fast and DFAs corresponding to multiple signatures are combinable into a single DFA. Combining such DFAs causes an explosive increase in memory usage. Extended finite automata (XFAs) are an alternative to DFAs that avoids state-space explosion problems. XFAs extend DFAs with a few bytes of “scratch memory” used to store bits and other data structures that record progress. Simple programs associated with automaton states and / or transitions manipulate this scratch memory. XFAs are deterministic in their operation, are equivalent to DFAs in expressiveness, and require no custom hardware support. Fully functional prototype XFA implementations show that, for most signature sets, XFAs are at least 10,000 times smaller than the DFA matching all signatures. XFAs are 10 times smaller and 5 times faster or 5 times smaller and 20 times faster than systems using multiple DFAs.

Owner:WISCONSIN ALUMNI RES FOUND

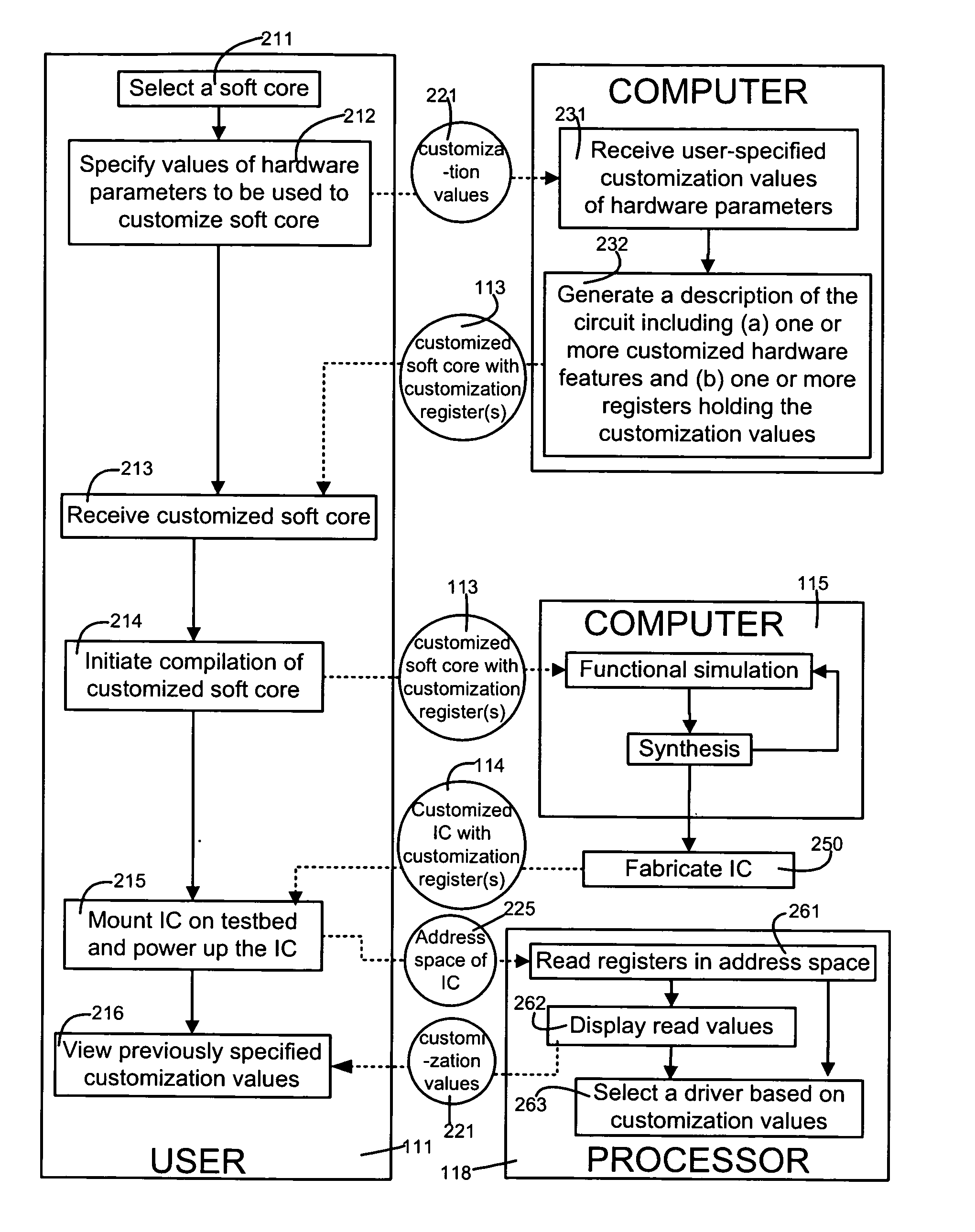

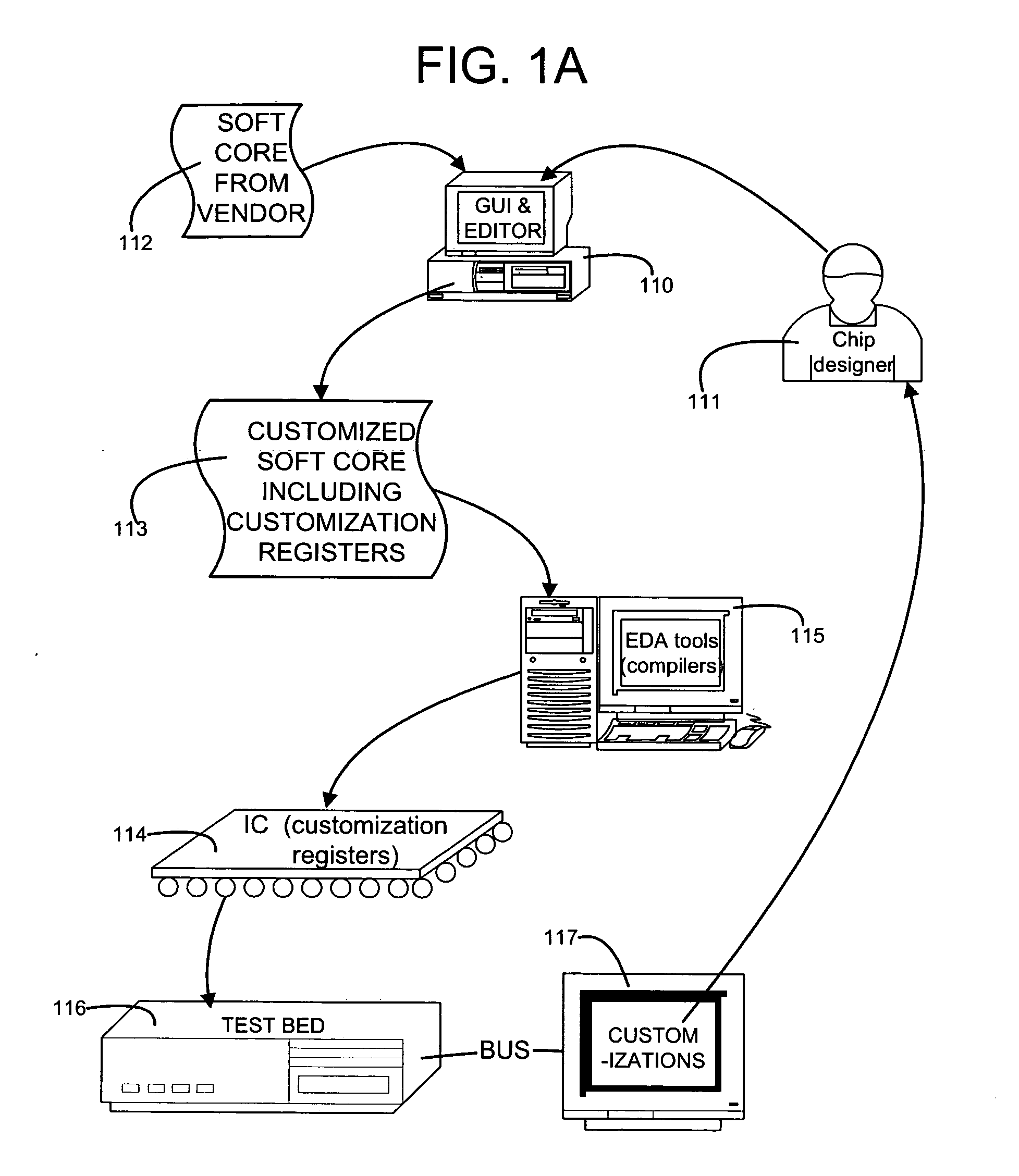

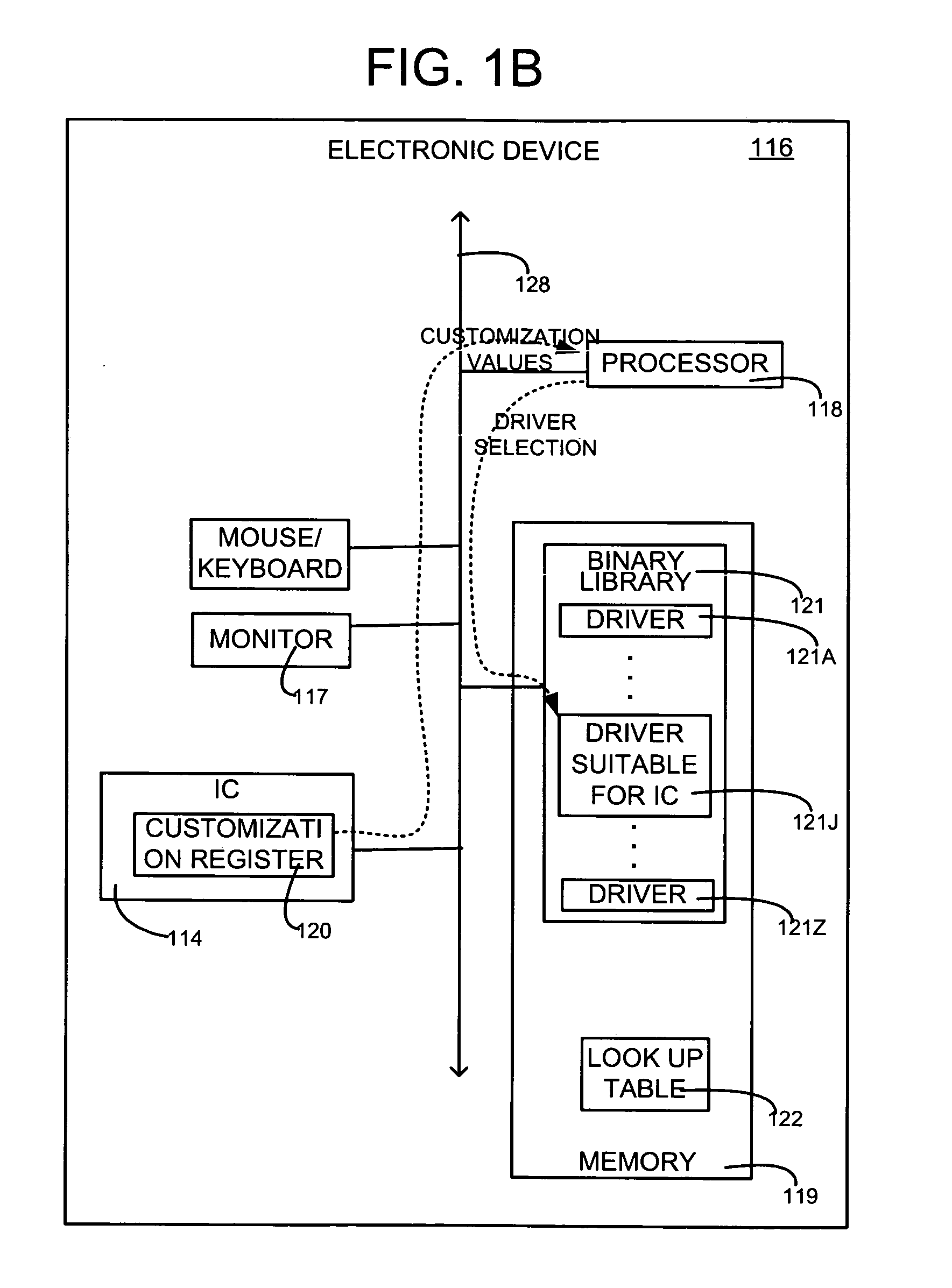

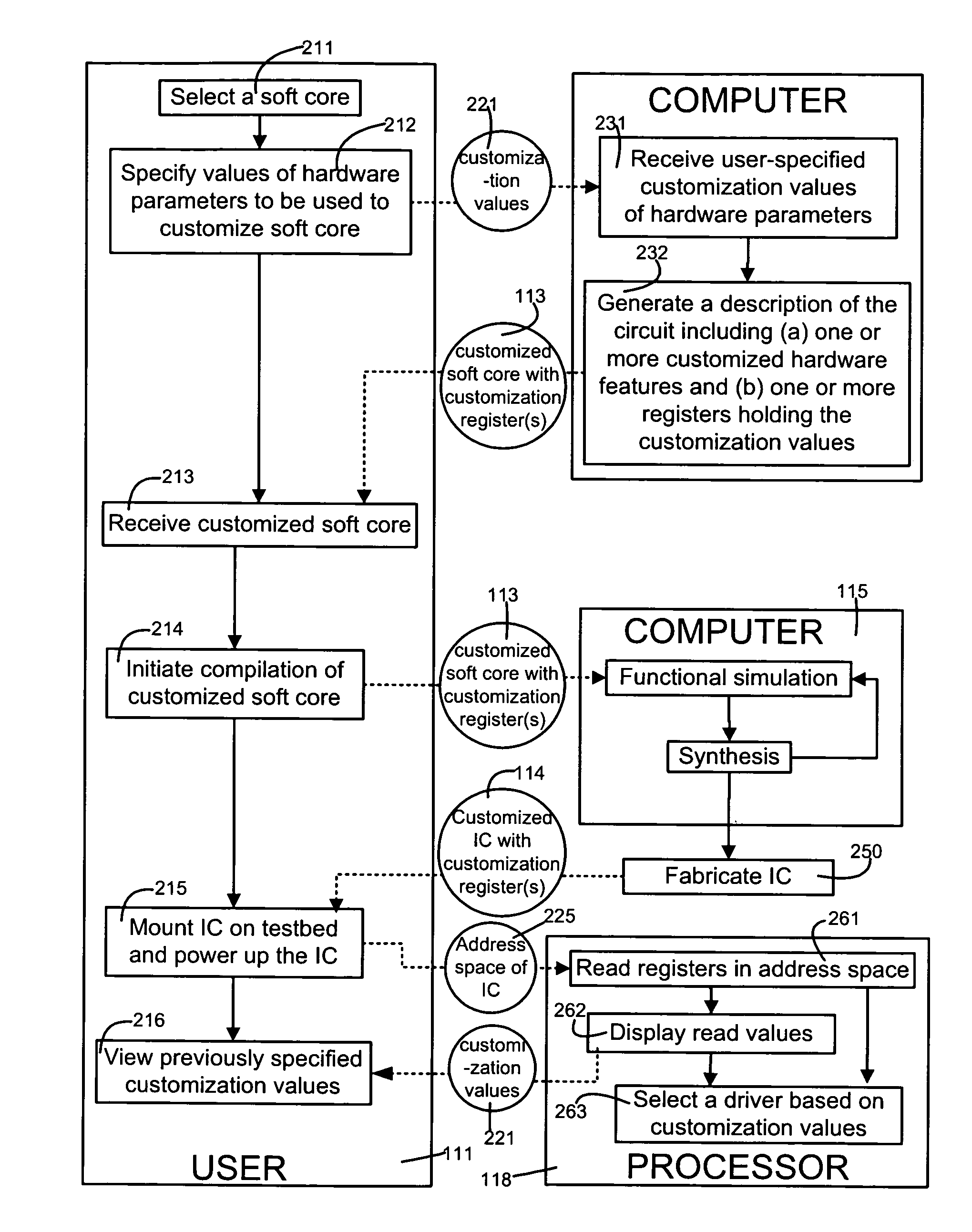

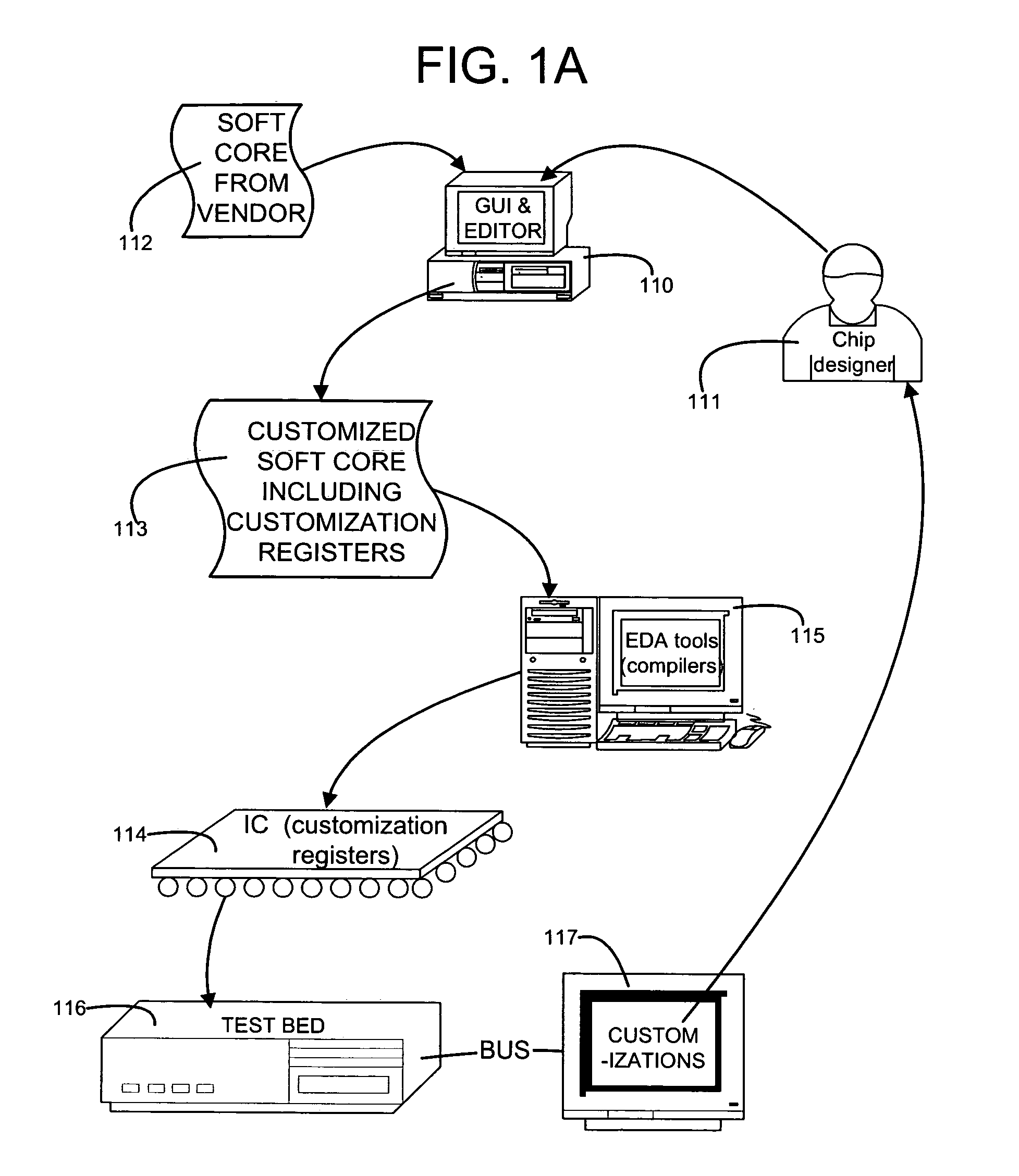

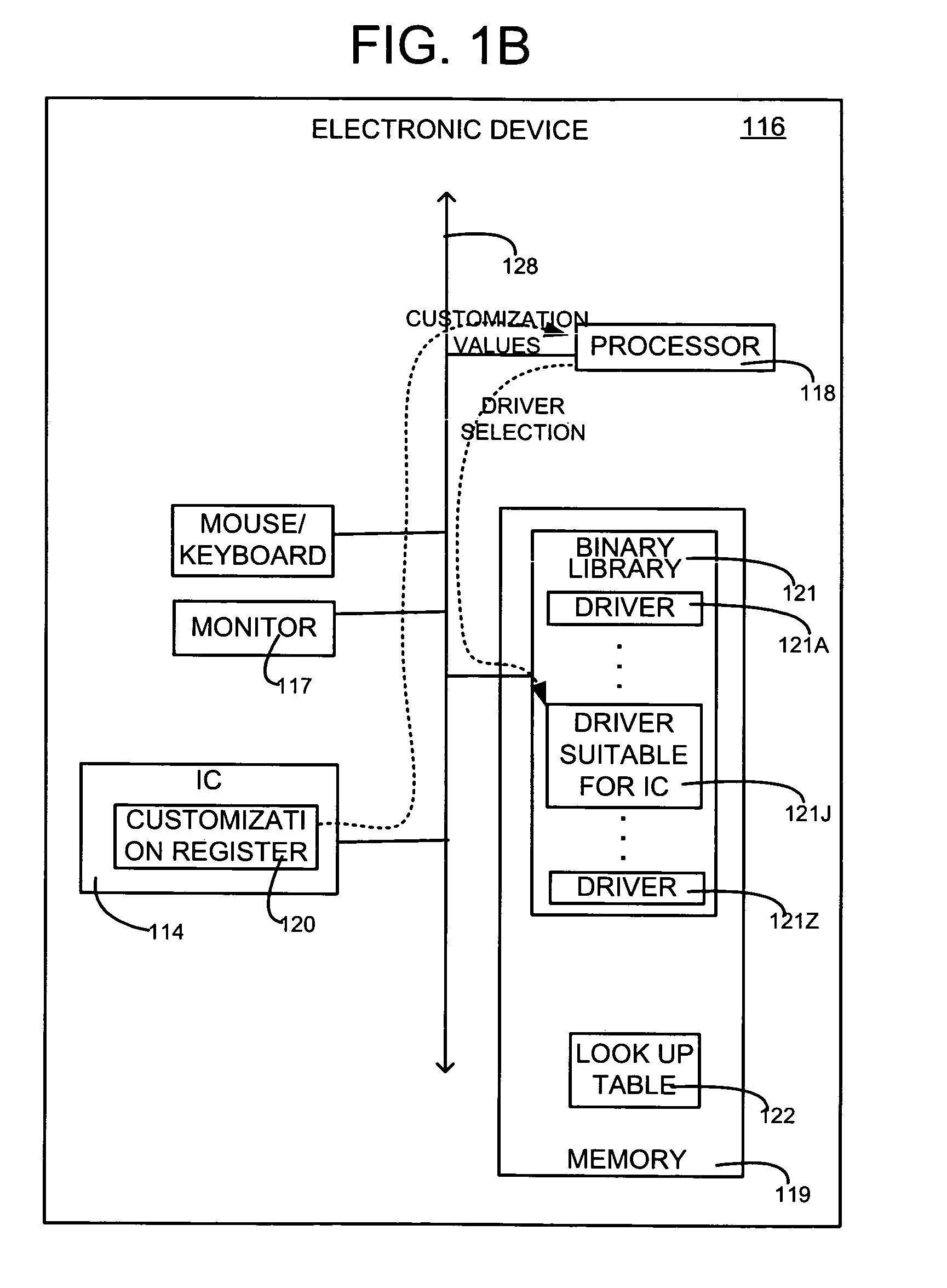

Determining hardware parameters specified when configurable IP is synthesized

ActiveUS20050278682A1Digital computer detailsCAD circuit designComputer hardwareComputer architecture

An attribute of a hardware feature to be customized in a soft core is parameterized so that a value received from a user can be used to generate a description of a circuit containing the customized hardware feature. The generated description also describes, in accordance with the invention, a register that is indicative of the customization. For example, the generated (customized) description may describe the register as containing the value. After the circuit is created, the register may be read (at any time) to identify the customization. Hence, access to such a register eliminates the need for a user to maintain documentation on values specified during customization. Such a register may additionally be used to identify a device driver that is appropriate for use with the customized hardware feature. Additional registers may be included in the generated description, e.g. to identify the function of the circuit, and the version number.

Owner:SYNOPSYS INC

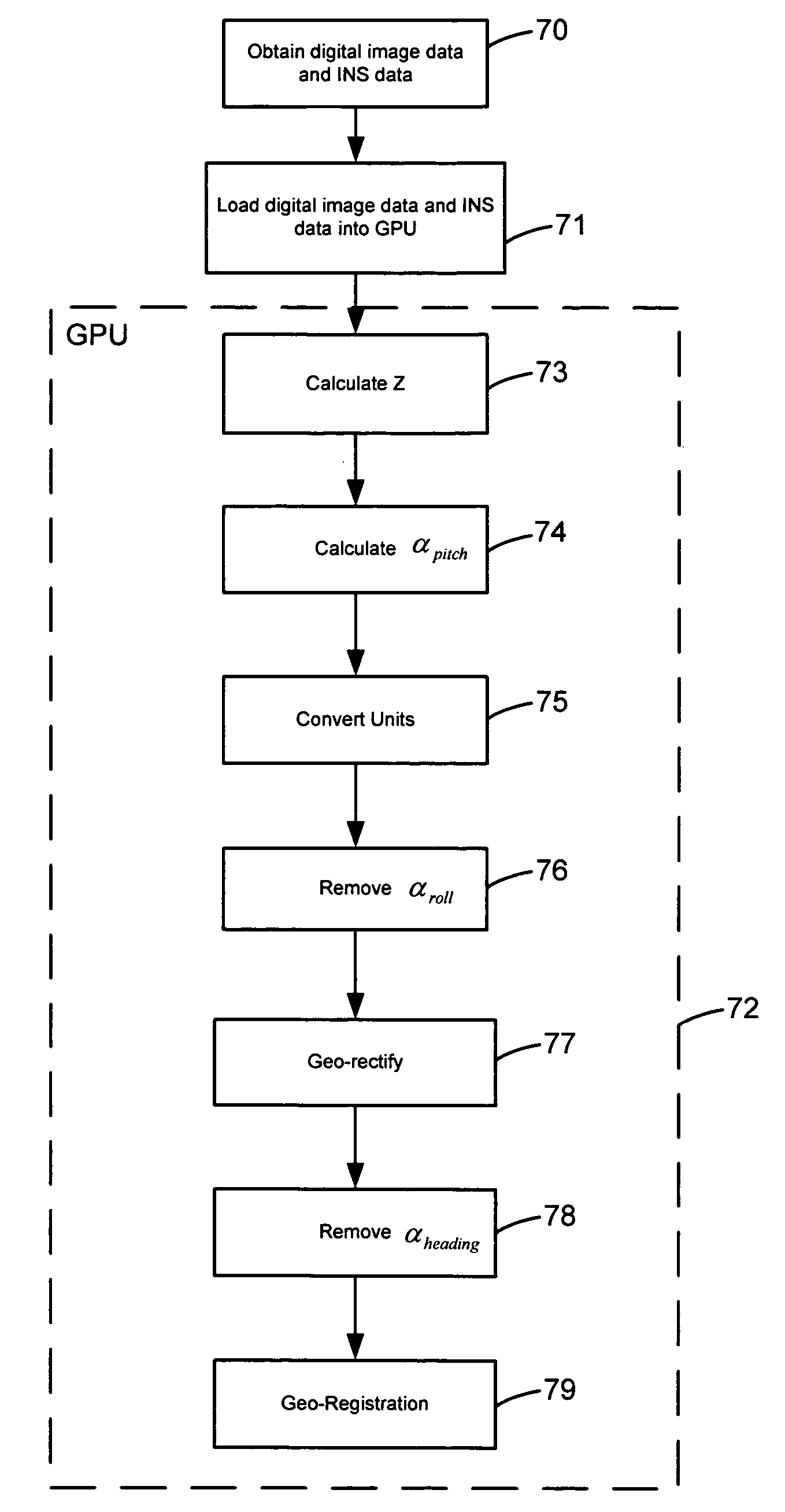

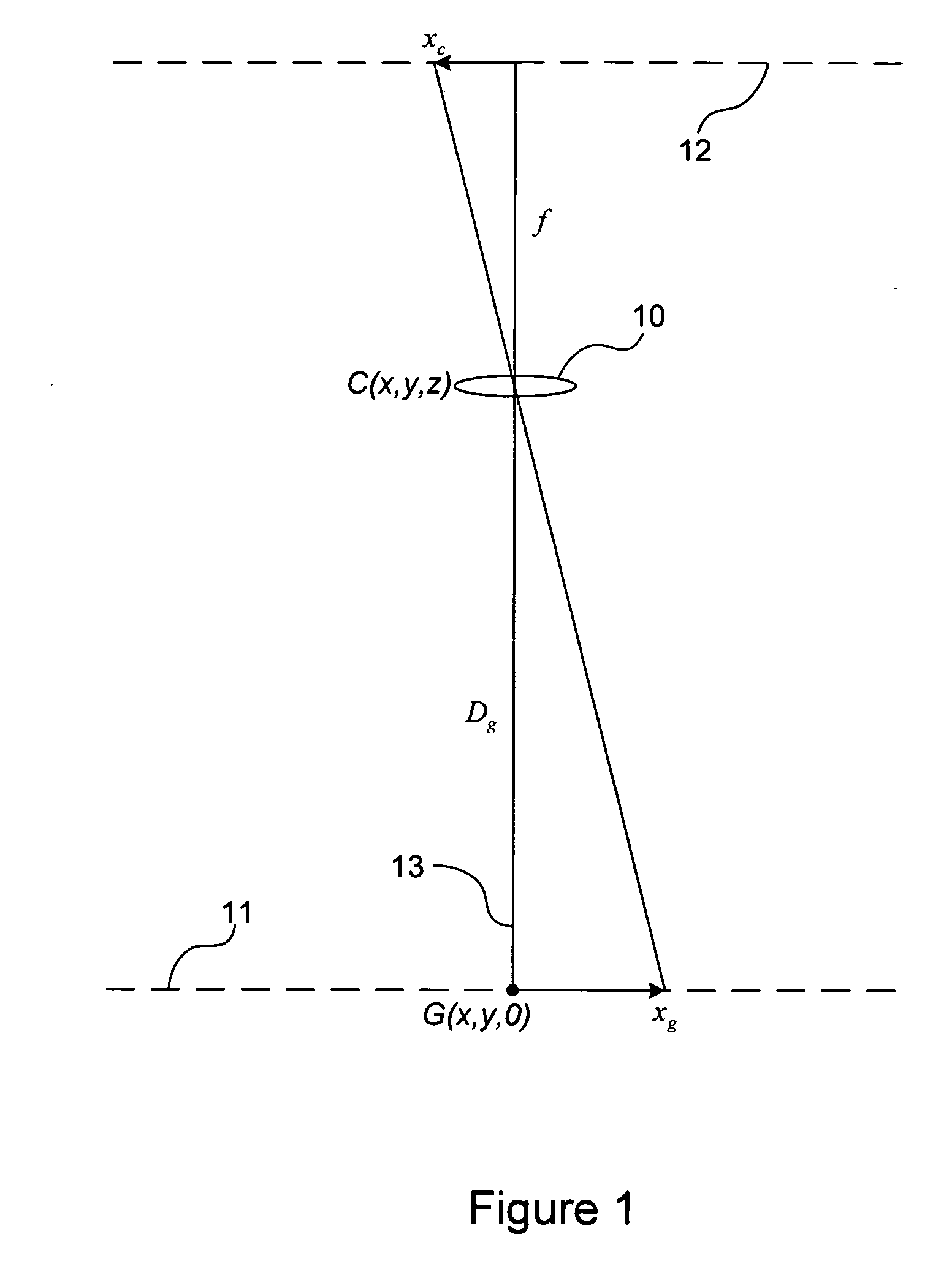

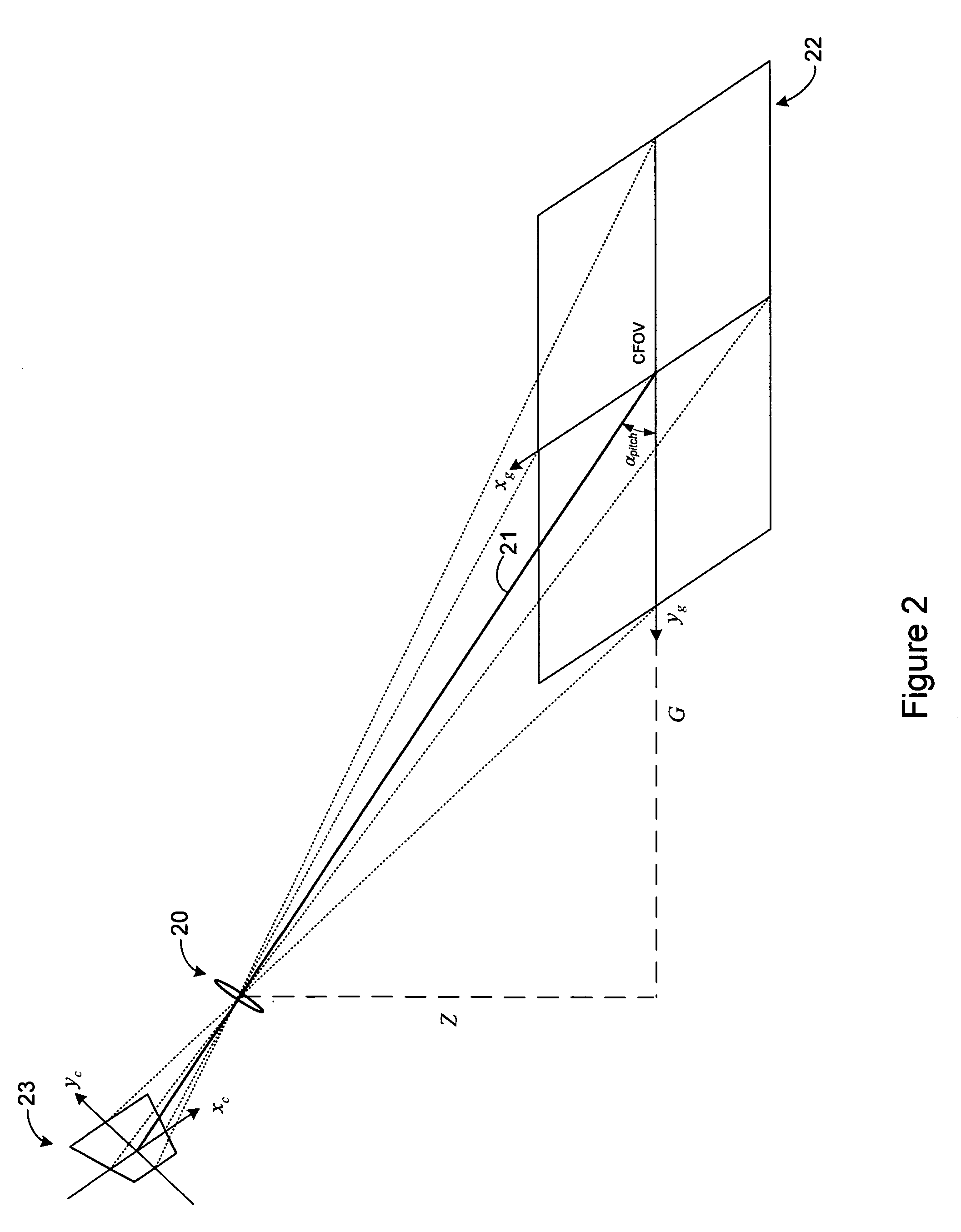

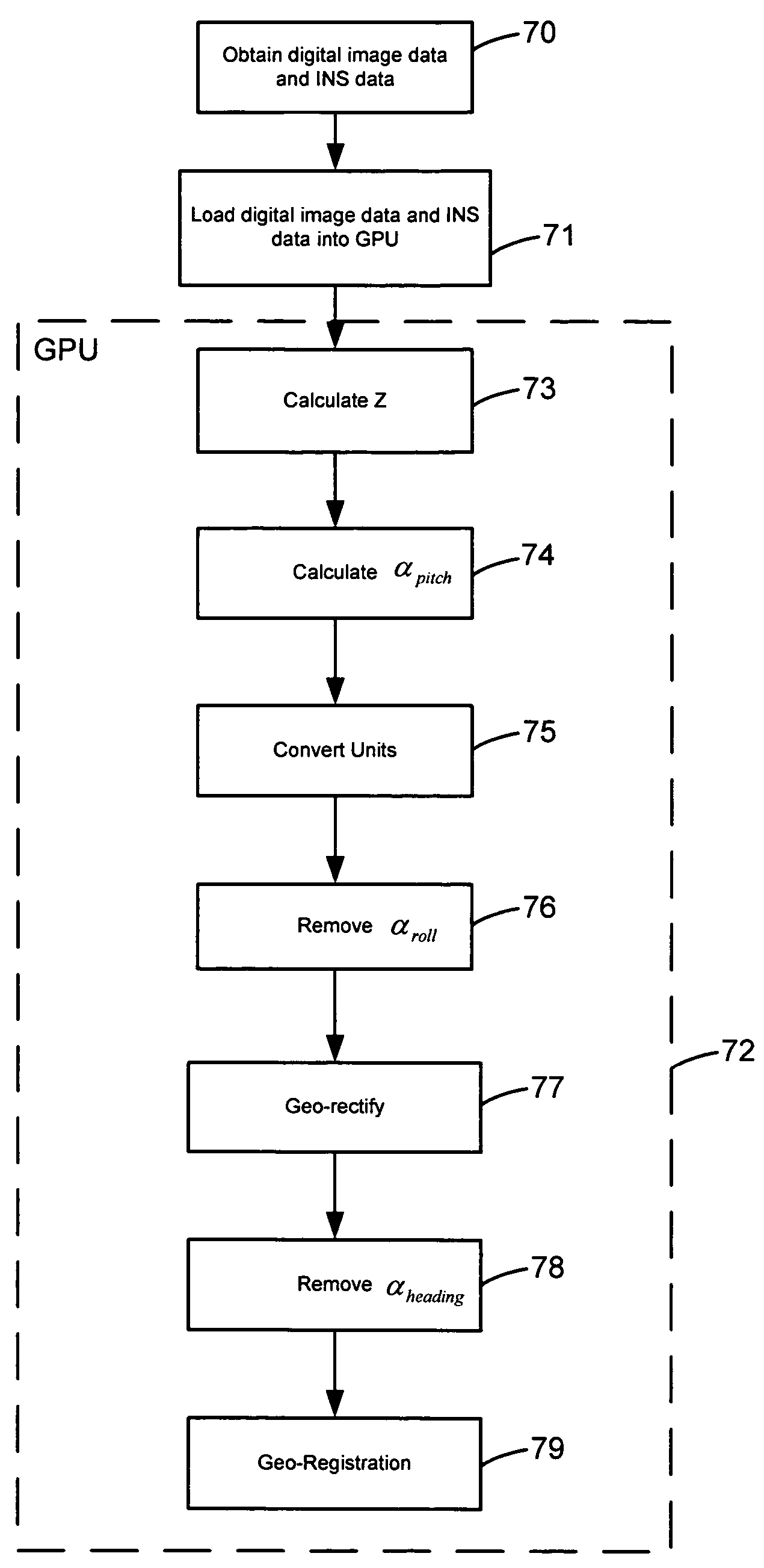

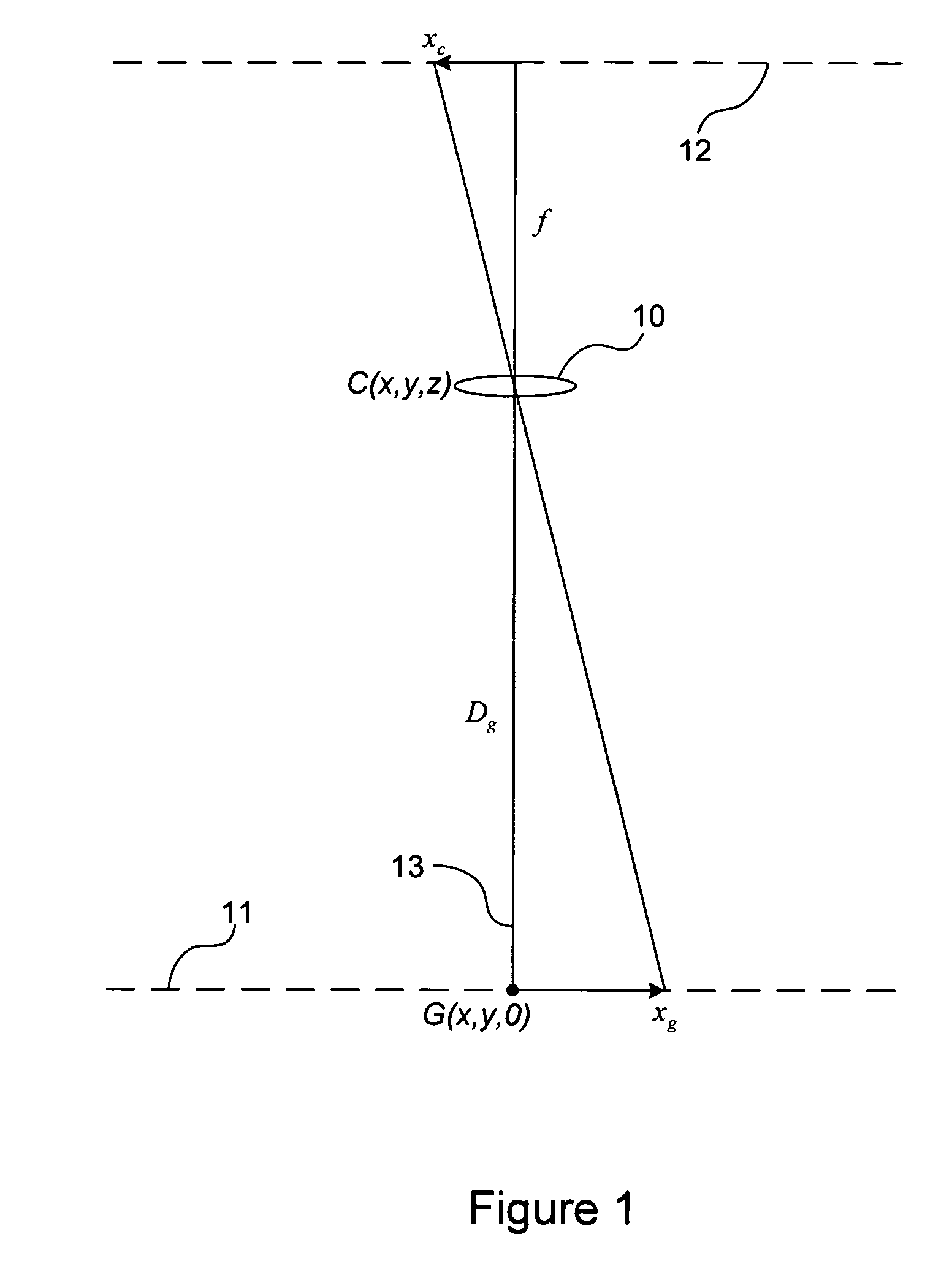

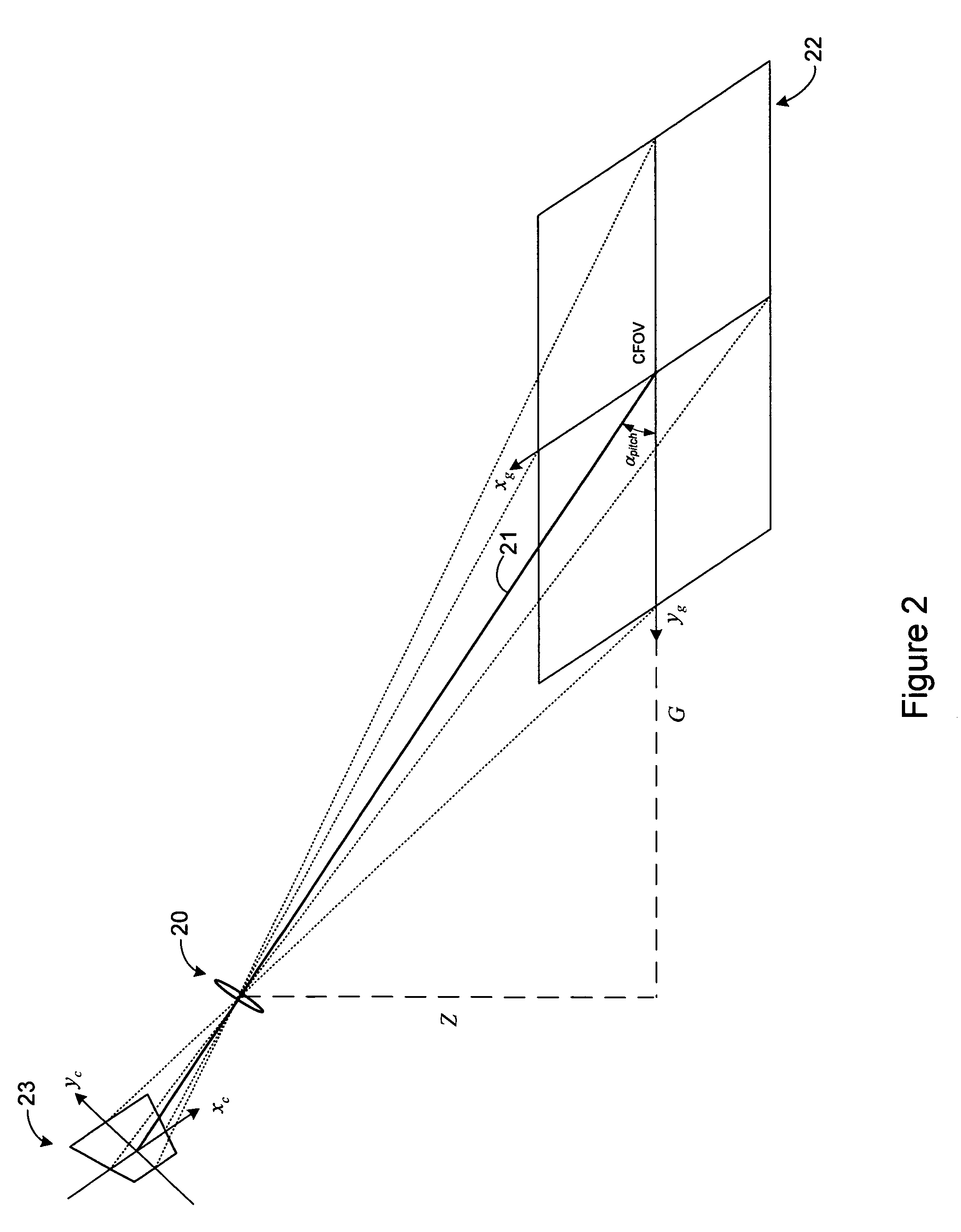

Real-time geo-registration of imagery using cots graphics processors

InactiveUS20060197837A1High resolution imageLess expensiveImage enhancementImage analysisImage conversionGraphics processing unit

A method of performing real-time geo-registration of high-resolution digital imagery using existing graphics processing units (GPUs) already found in current personal computers, rather than the main central processing unit (CPU). Digital image data captured by a camera (along with inertial navigation system (INS) data associated with the image data) is transferred to and processed by the GPU to perform the calculations involved in transforming the captured image into a geo-rectified, nadir-looking image. By using the GPU, the order-of-magnitude increase in throughput over conventional software techniques makes real-time geo-registration possible without the significant cost of custom hardware solutions.

Owner:LAWRENCE LIVERMORE NAT SECURITY LLC

Extended finite state automata and systems and methods for recognizing patterns in a data stream using extended finite state automata

Deterministic finite automata (DFAs) are popular solutions to deep packet inspection because they are fast and DFAs corresponding to multiple signatures are combinable into a single DFA. Combining such DFAs causes an explosive increase in memory usage. Extended finite automata (XFAs) are an alternative to DFAs that avoids state-space explosion problems. XFAs extend DFAs with a few bytes of “scratch memory” used to store bits and other data structures that record progress. Simple programs associated with automaton states and / or transitions manipulate this scratch memory. XFAs are deterministic in their operation, are equivalent to DFAs in expressiveness, and require no custom hardware support. Fully functional prototype XFA implementations show that, for most signature sets, XFAs are at least 10,000 times smaller than the DFA matching all signatures. XFAs are 10 times smaller and 5 times faster or 5 times smaller and 20 times faster than systems using multiple DFAs.

Owner:WISCONSIN ALUMNI RES FOUND

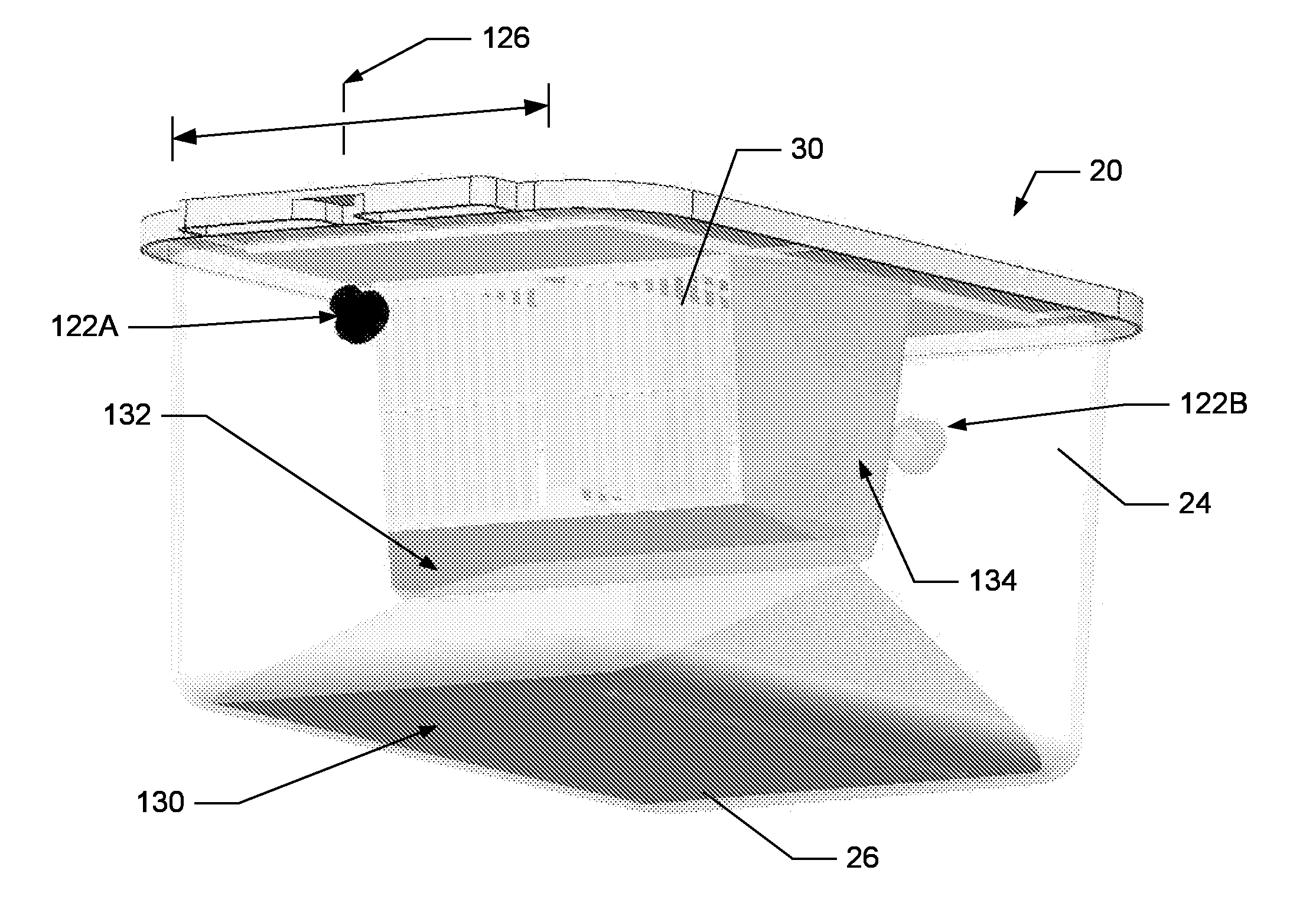

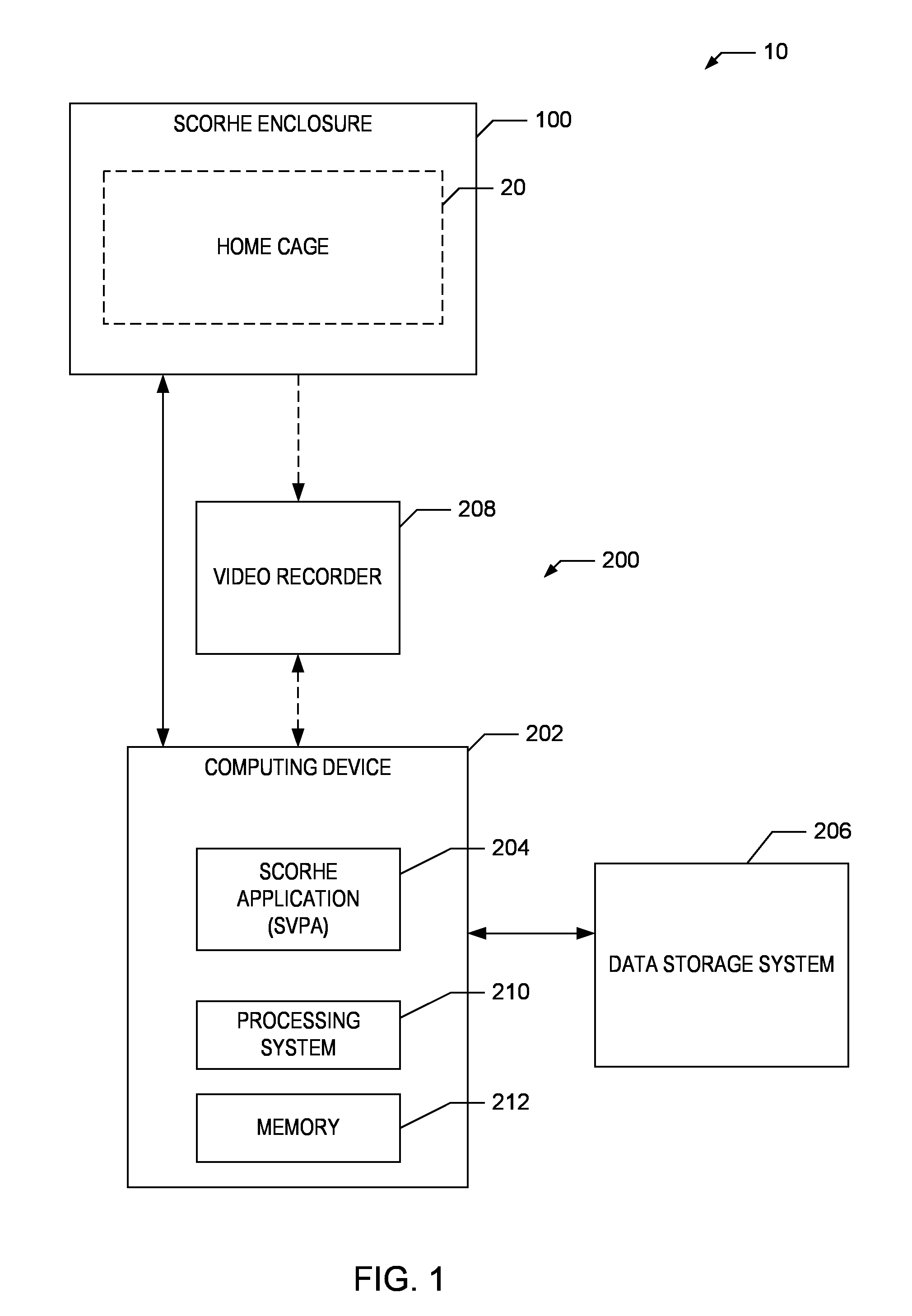

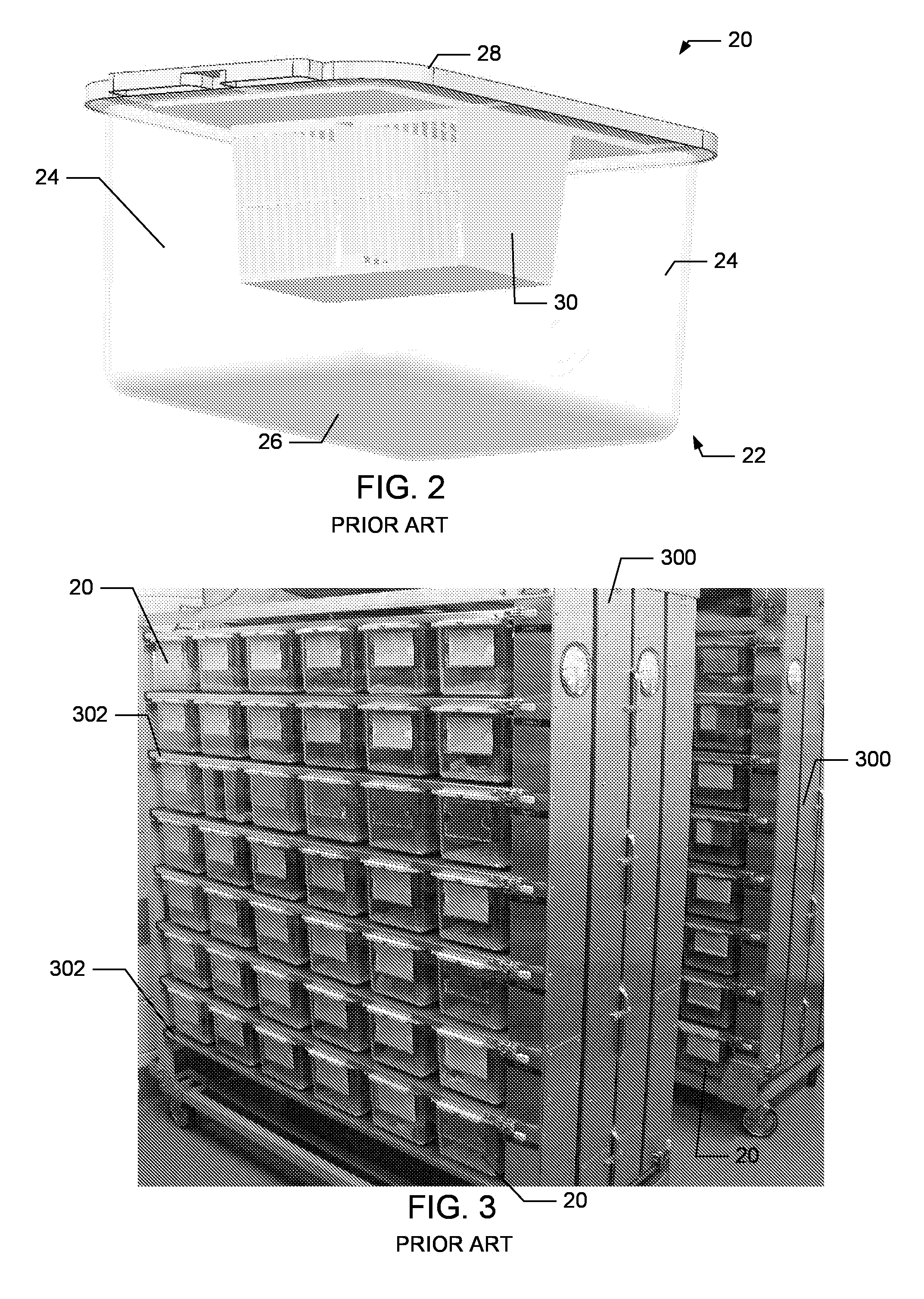

Systems and methods of video monitoring for vivarium cages

The System for Continuous Observation of Rodents in Home-cage Environment (SCORHE) was developed to quantify activity levels and behavior patterns for mice housed within a home cage that, optional, may be disposed in a commercial ventilated cage rack. The SCORHE home-cage in-rack design provides daytime and night-time monitoring with the stability and consistency of the home-cage environment. The dual-video camera custom hardware design makes efficient use of space, does not require home-cage modification, and is animal facility user-friendly. In various embodiments, a software application integrates the two video streams to extract several mouse activity measures.

Owner:US DEPT OF HEALTH & HUMAN SERVICES

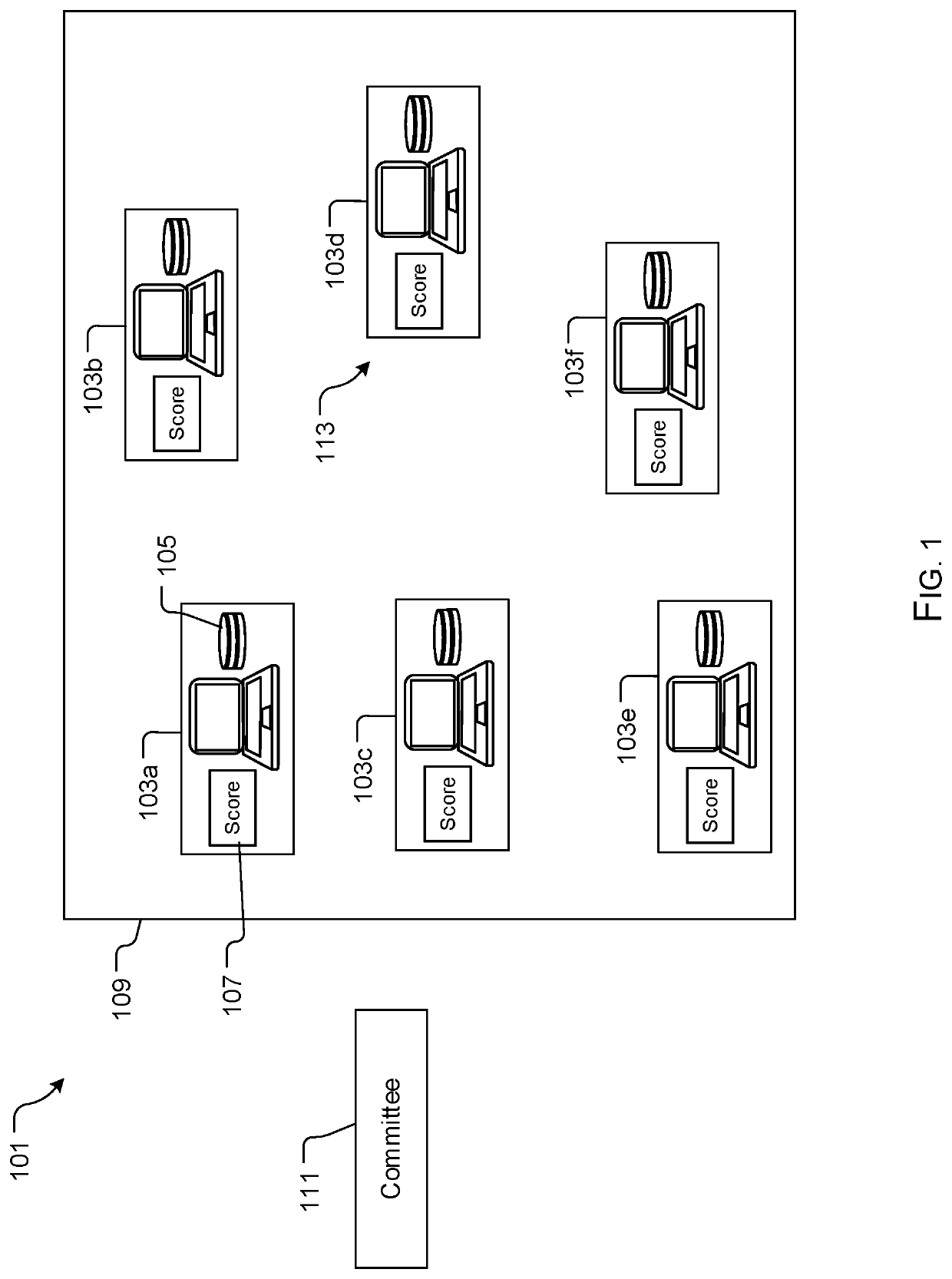

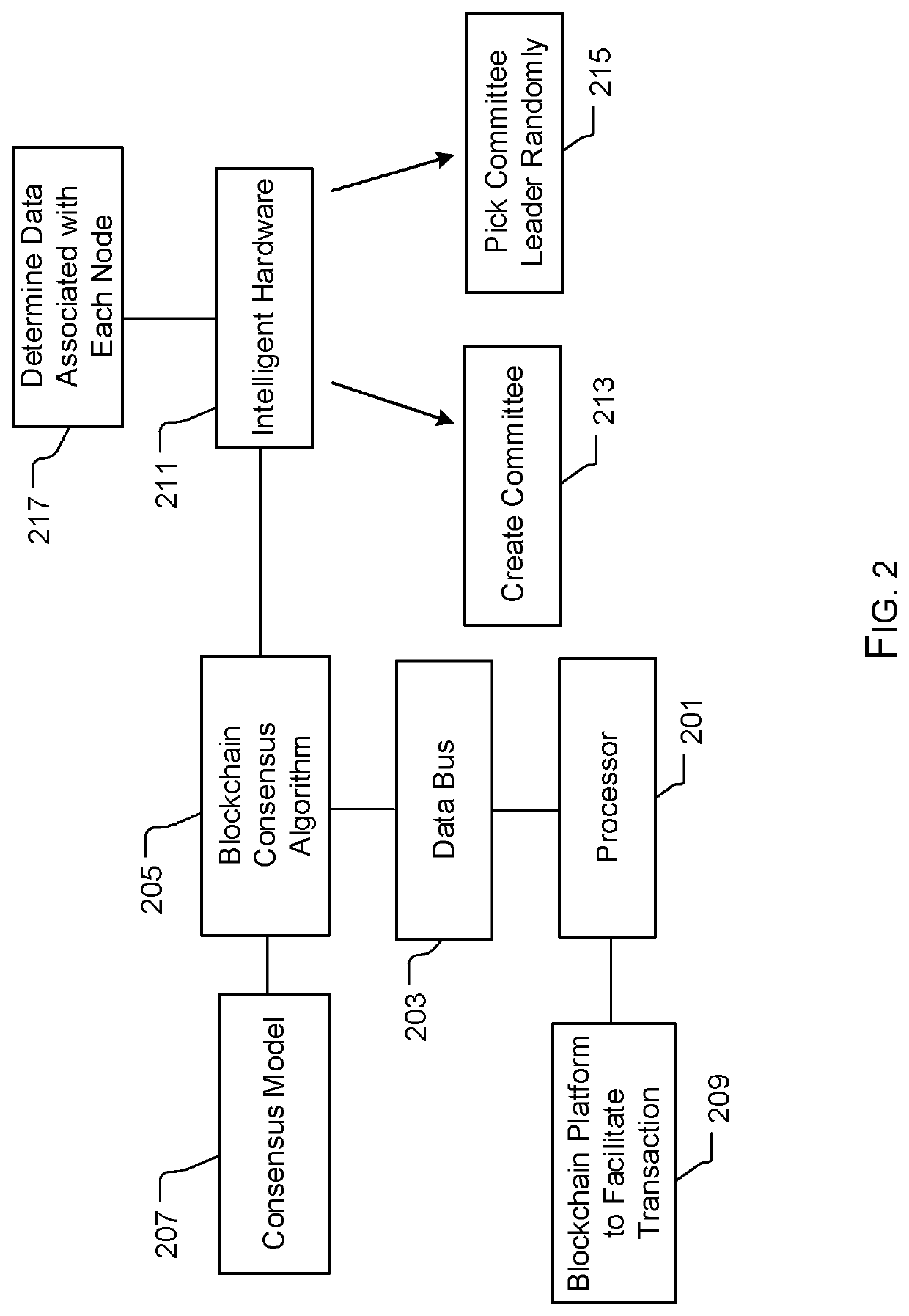

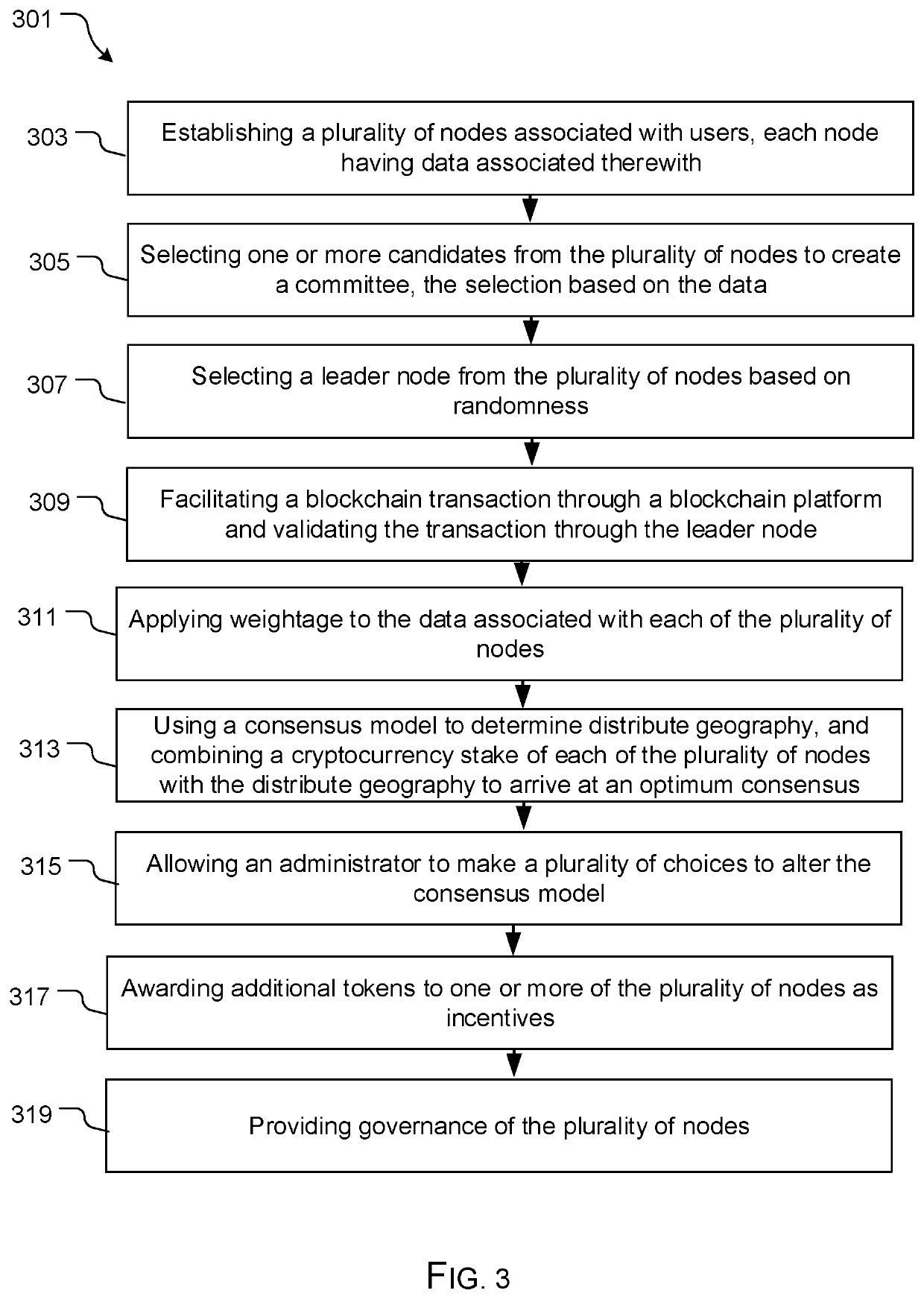

System and method of blockchain consensus mechanism with custom hardware based on geographic distribution, density, node asset and reputation

InactiveUS20200162261A1Increase performance and efficiencyImprove throughputFinanceCryptography processingComputer hardwareConsensus

A system and method for a blockchain consensus mechanism includes a processor couple to a data bus having a blockchain protocol consensus algorithm incorporated; intelligent hardware being auto triggered and having an auto-diagnostics capability, an auto-self healing capability, and to monitor threats in a blockchain infrastructure; establishing nodes representing users and being in communication with the intelligent hardware; determining data associated with the nodes through the intelligent hardware and data bus implementing the protocol consensus algorithm, the data including geographic location, geographic density, the number of cryptographic tokens, crypto assets; and a reputation score; selecting candidate nodes to create a committee, the selection being based on the data associated with each of the nodes; selecting a leader node based on randomness; and ensuring validation of a transaction in a block so as to approve the transaction to be committed to a blockchain platform through the leader node.

Owner:IYER RAMACHANDRAN

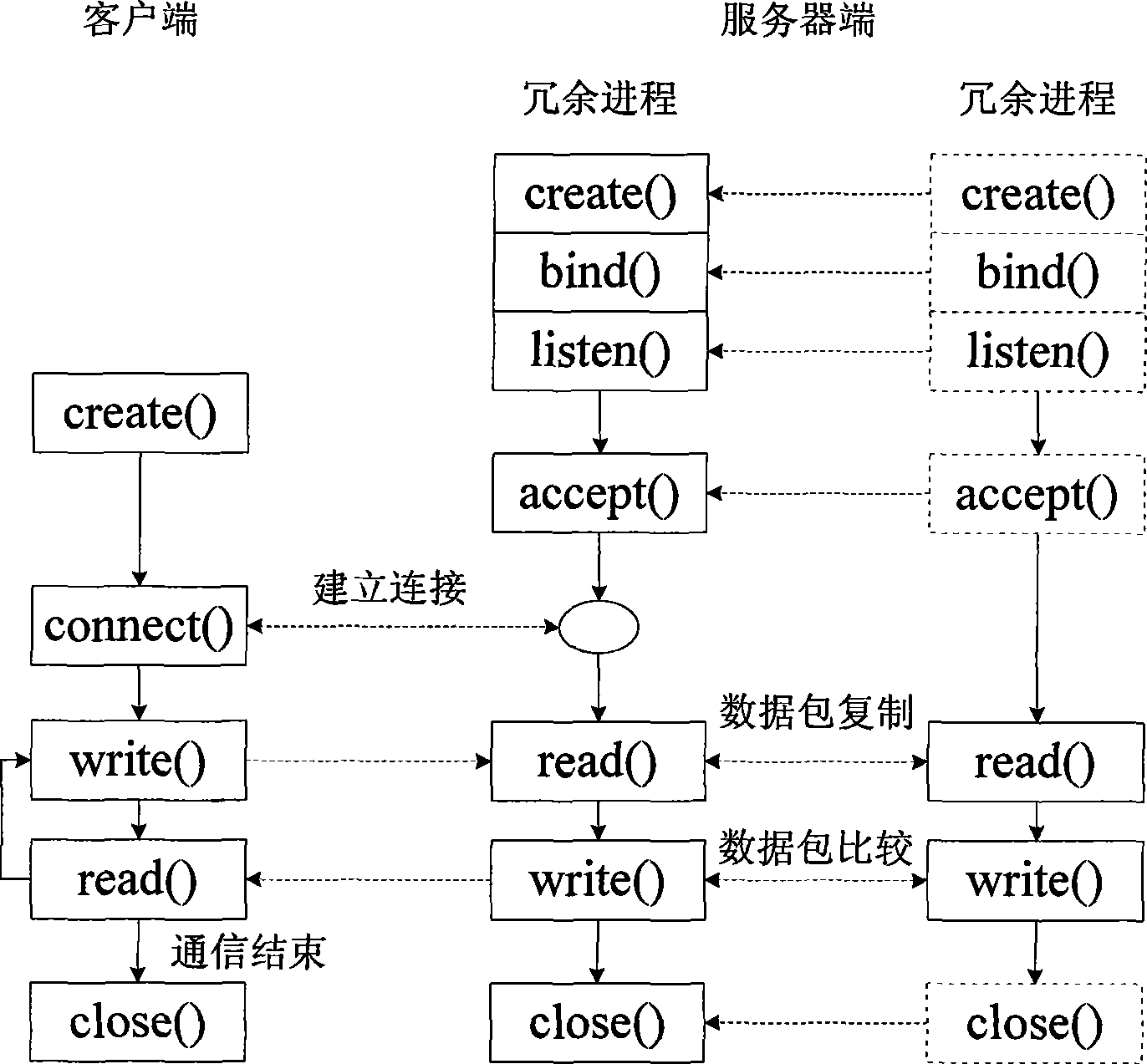

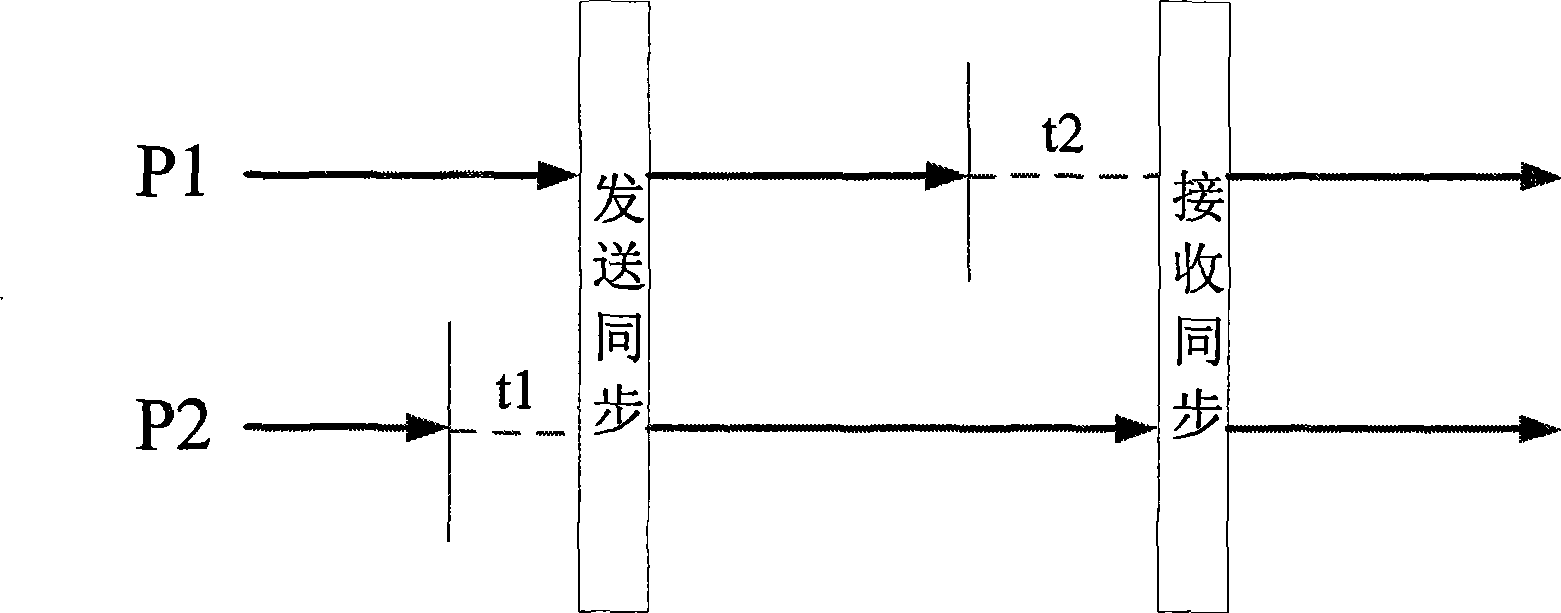

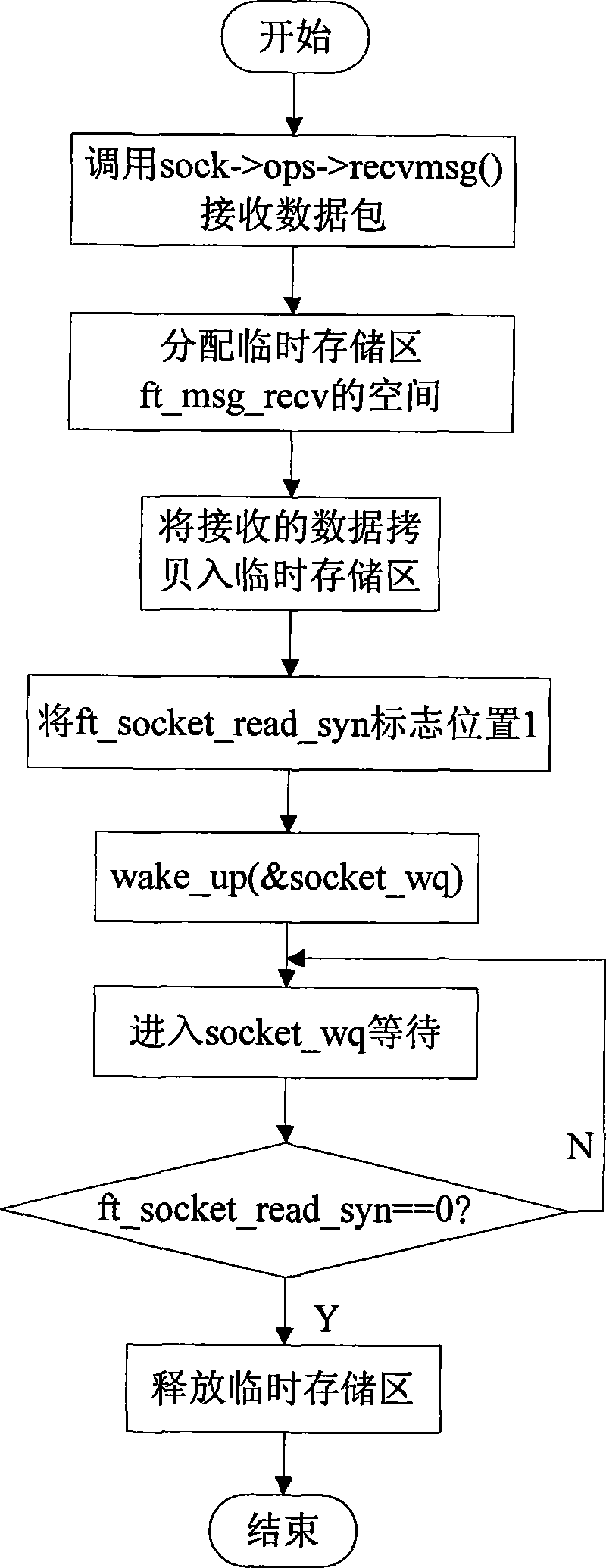

Grid synchronization method for fault tolerant computer system based on socket

InactiveCN101383690ATransparent driveThe upper application is simpleError preventionSynchronising arrangementExtensibilityHardware architecture

The invention discloses a network synchronization method based on a socket fault-tolerant computing system. A monitor is set on a socket interface layer of a Linux network architecture through modifying a Linux operating system so as to monitor the socket communication correlation kernel function. When the duplication redundancy schedule performs the network communication through the socket way, the communication operation is intercepted at the socket interface layer and the synchronization logic is triggered. The synchronization logic is implemented by reconstructing the socket series kernel functions, and the duplication schedule enters the synchronization point and completes the synchronizing process when implementing the reconstructed kernel functions. The implementation of the method is simple without special custom hardware. The reconstructed operating system is suitable for common hardware architectures with strong commonality. The synchronization process is initiatively completed by the operating system, and is fully transparent to the upper application. The invention has better expandability, and can be expanded to a multimode redundancy system.

Owner:XI AN JIAOTONG UNIV

Determining hardware parameters specified when configurable IP is synthesized

ActiveUS7353489B2Digital computer detailsCAD circuit designDocumentation procedureProcessor register

An attribute of a hardware feature to be customized in a soft core is parameterized so that a value received from a user can be used to generate a description of a circuit containing the customized hardware feature. The generated description also describes, in accordance with the invention, a register that is indicative of the customization. For example, the generated (customized) description may describe the register as containing the value. After the circuit is created, the register may be read (at any time) to identify the customization. Hence, access to such a register eliminates the need for a user to maintain documentation on values specified during customization. Such a register may additionally be used to identify a device driver that is appropriate for use with the customized hardware feature. Additional registers may be included in the generated description, e.g. to identify the function of the circuit, and the version number.

Owner:SYNOPSYS INC

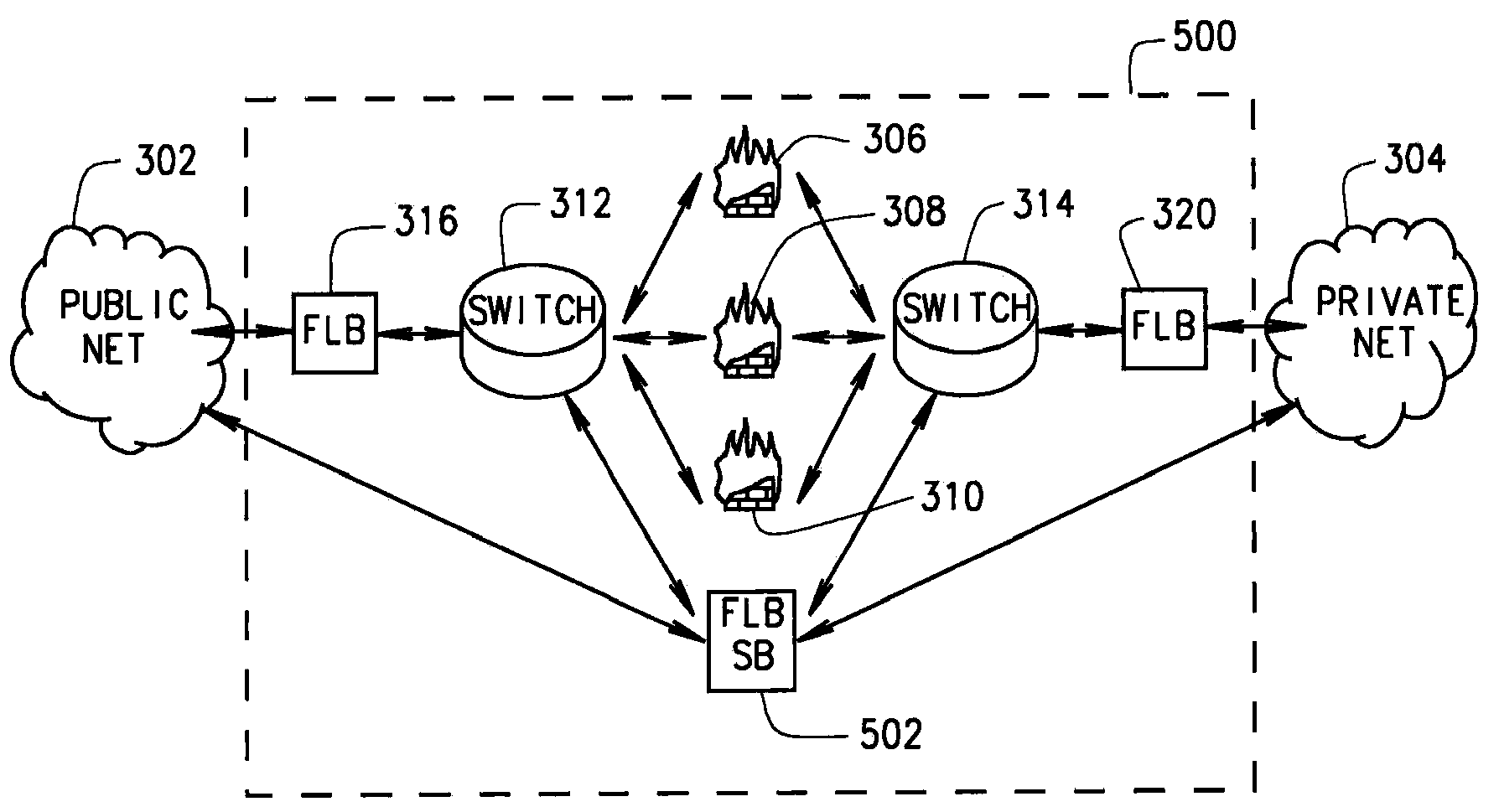

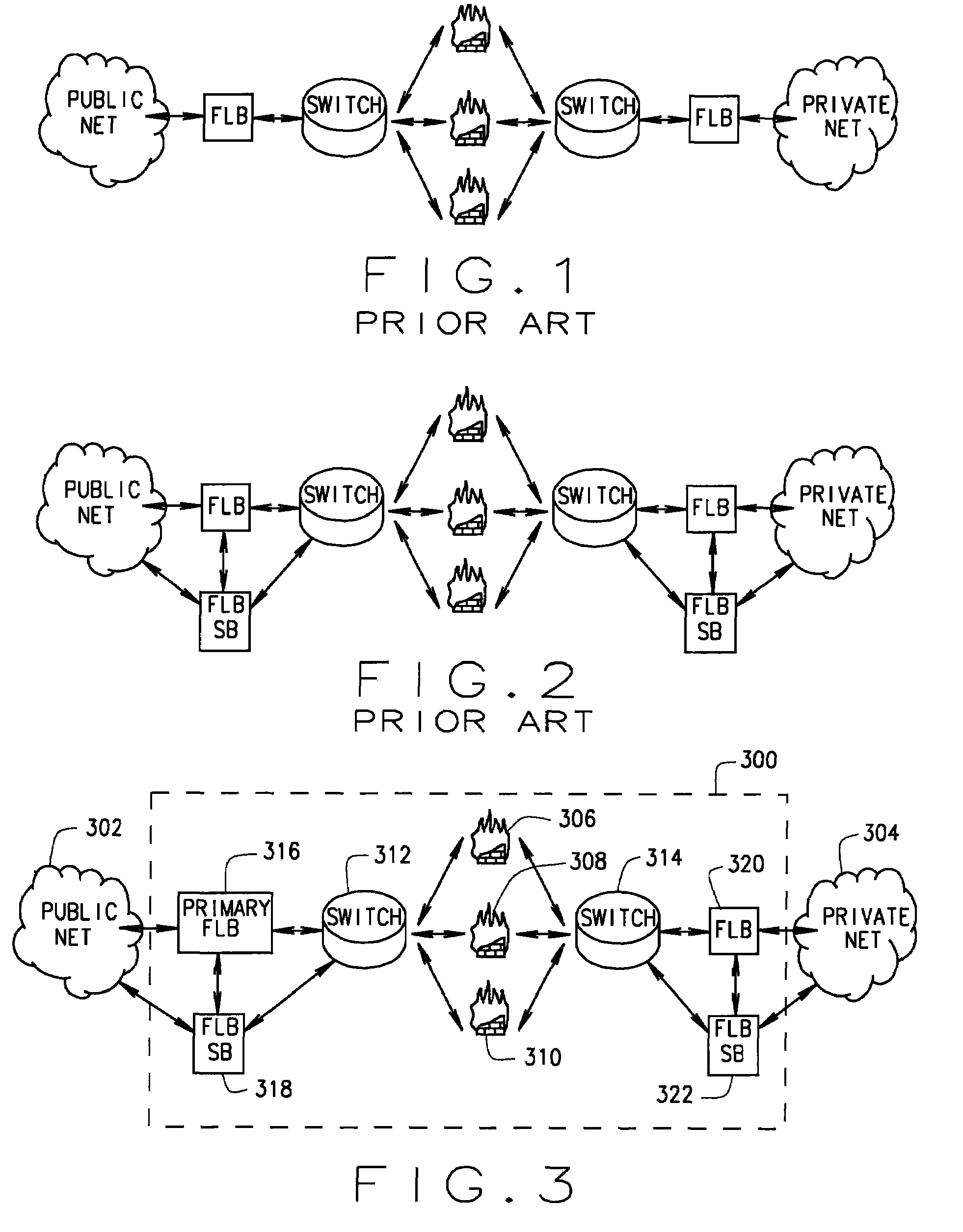

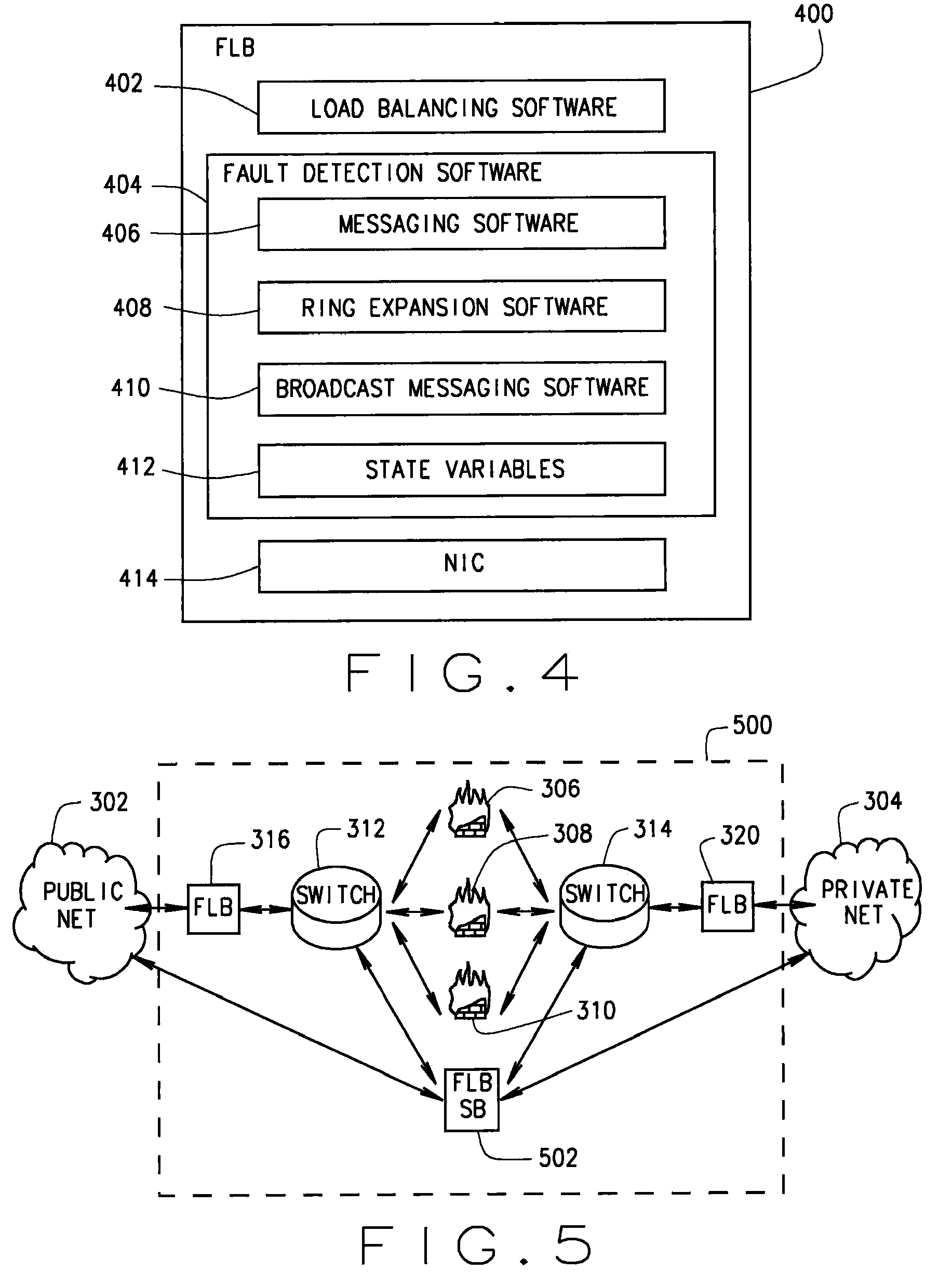

Fault tolerant firewall sandwiches

InactiveUS7254834B2Improve the level ofImprove operational flexibilityHardware monitoringMultiple digital computer combinationsOperational systemEngineering

Firewall sandwich configurations having improved levels of system availability as well as an application-space implementation of a firewall load balancer (FLB) which provides greater operational flexibility while reducing the need for custom hardware and / or operating system software. Also disclosed is a firewall capable of functionally replacing an FLB upon detecting a failure therein.

Owner:BOARD OF RGT UNIV OF NEBRASKA

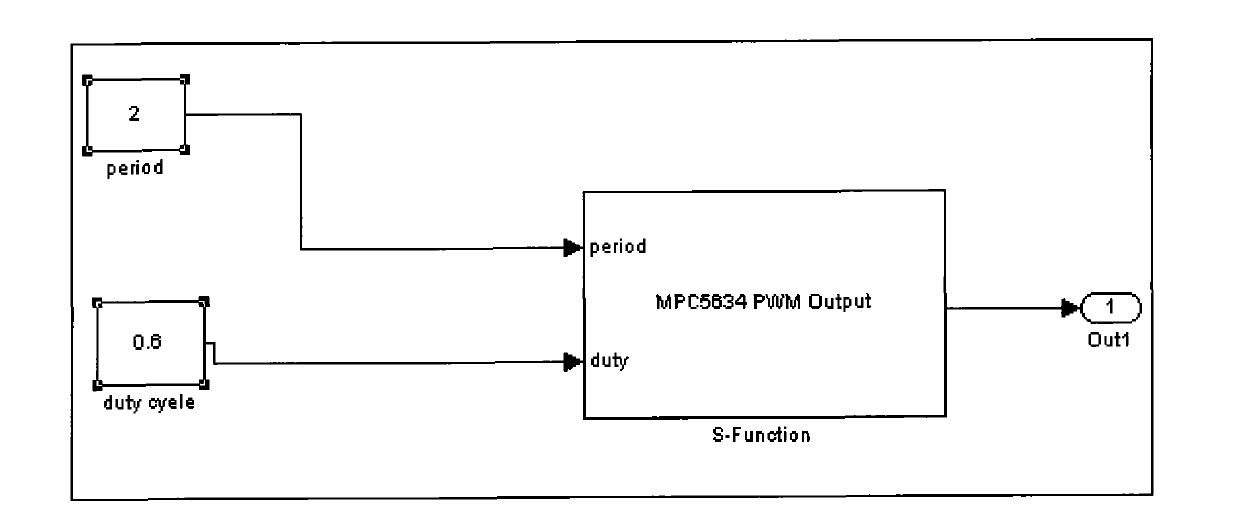

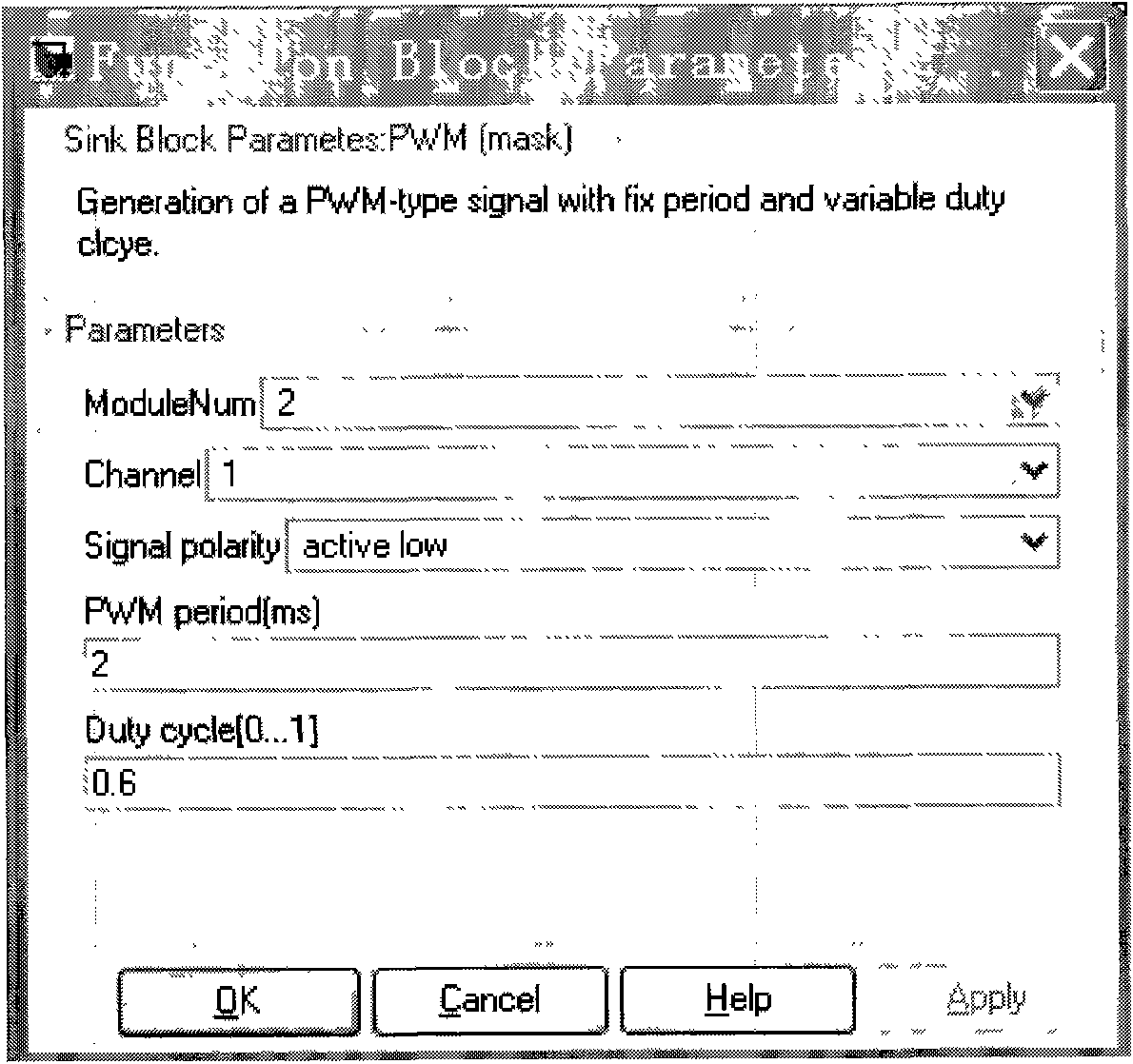

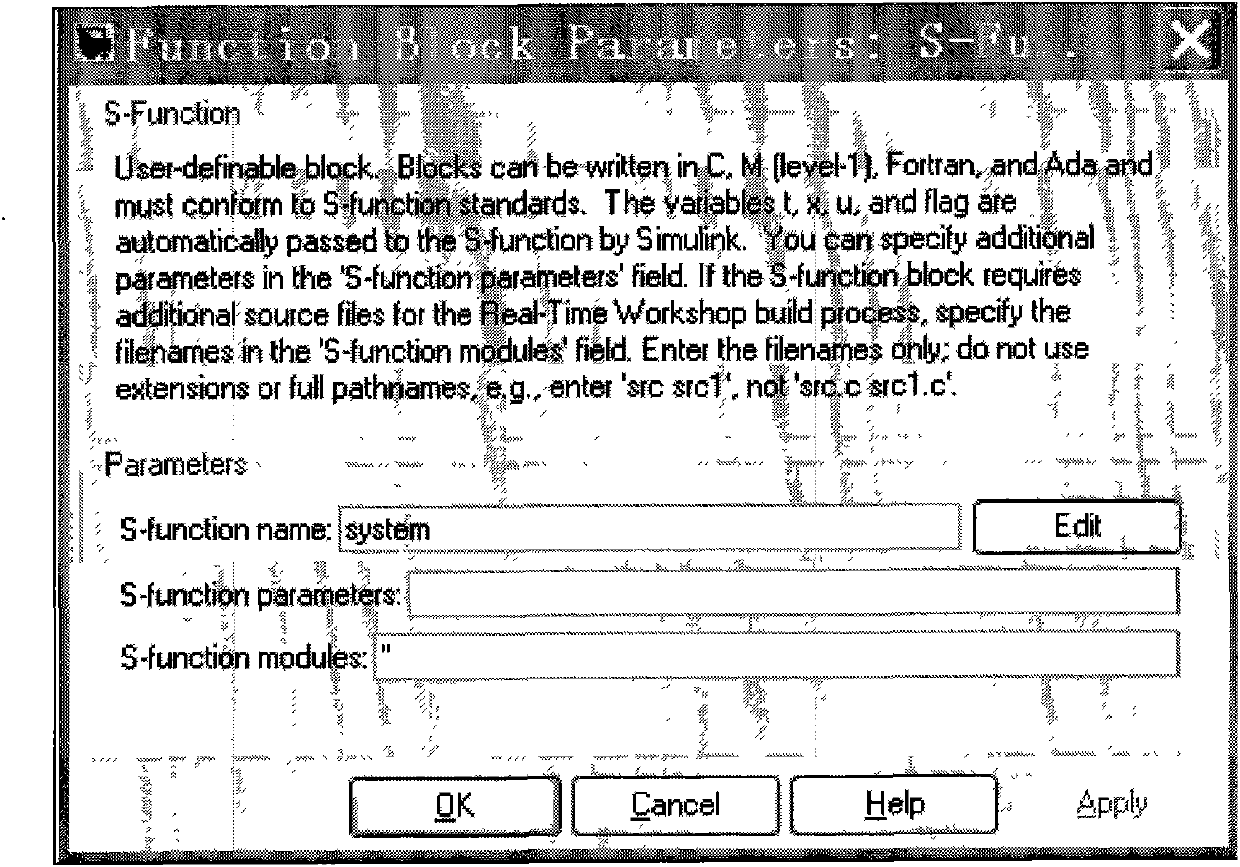

Method for performing model simulation and code generation on custom hardware by using Simulink

InactiveCN102087610AShorten the timeSoftware simulation/interpretation/emulationGraphicsItem generation

The invention discloses a method for performing model simulation on custom hardware by using Simulink. The method comprises the following steps of: compiling a C MEX S file of the custom hardware, and generating a C MEX S file name.mexw32 file in an MATLAB command window according to a mex command; establishing a new model file comprising an S-function module of the custom hardware in the simulink, and packaging the S-function module of the custom hardware to ensure that a connected is established between the C MEX S file and the C MEX S file name.mexw32 file, and a panel and a dialog box of the S-function module of the custom hardware are generated; editing and compiling the model file to obtain MODEL.RTW of the model file; during the simulation of Matlab / simulink, popping up the dialog box of the S-function module of the custom hardware, inputting corresponding parameters from the dialog box and then submitting the parameters; and running a Start Simulation command to output a simulation graph. The invention also discloses a method for performing model code generation on the custom hardware by using the Simulink. The method can be used for performing the model simulation and the code generation on the custom hardware by using the Simulink, so that the time for system development is saved.

Owner:LIANCHUANG AUTOMOBILE ELECTRONICS

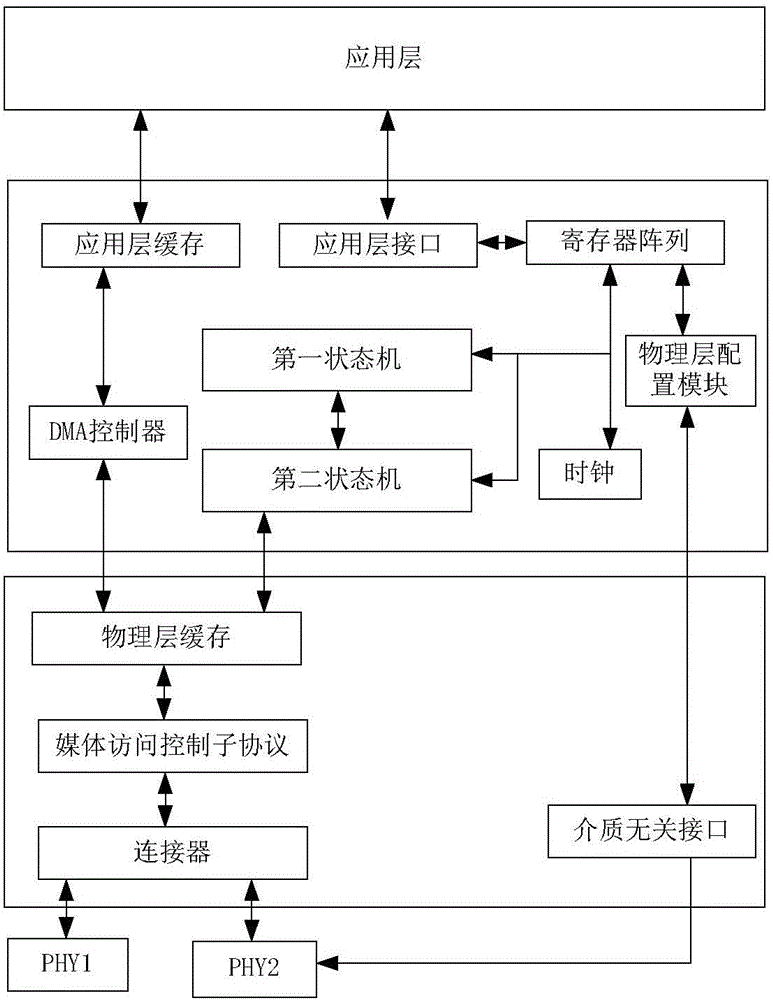

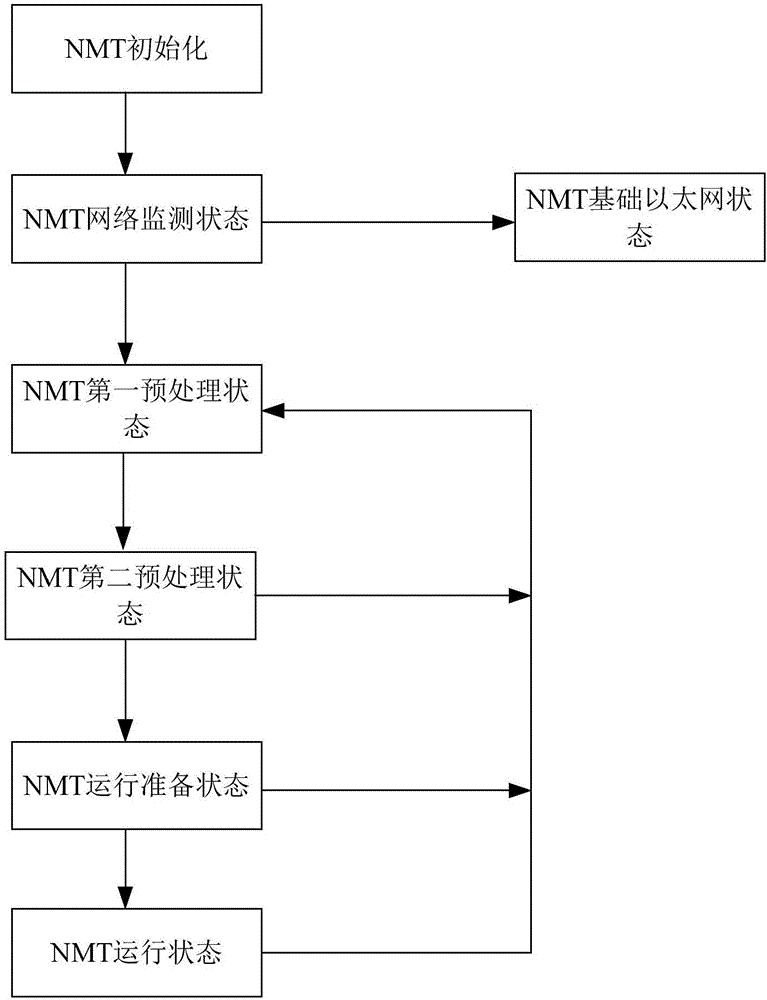

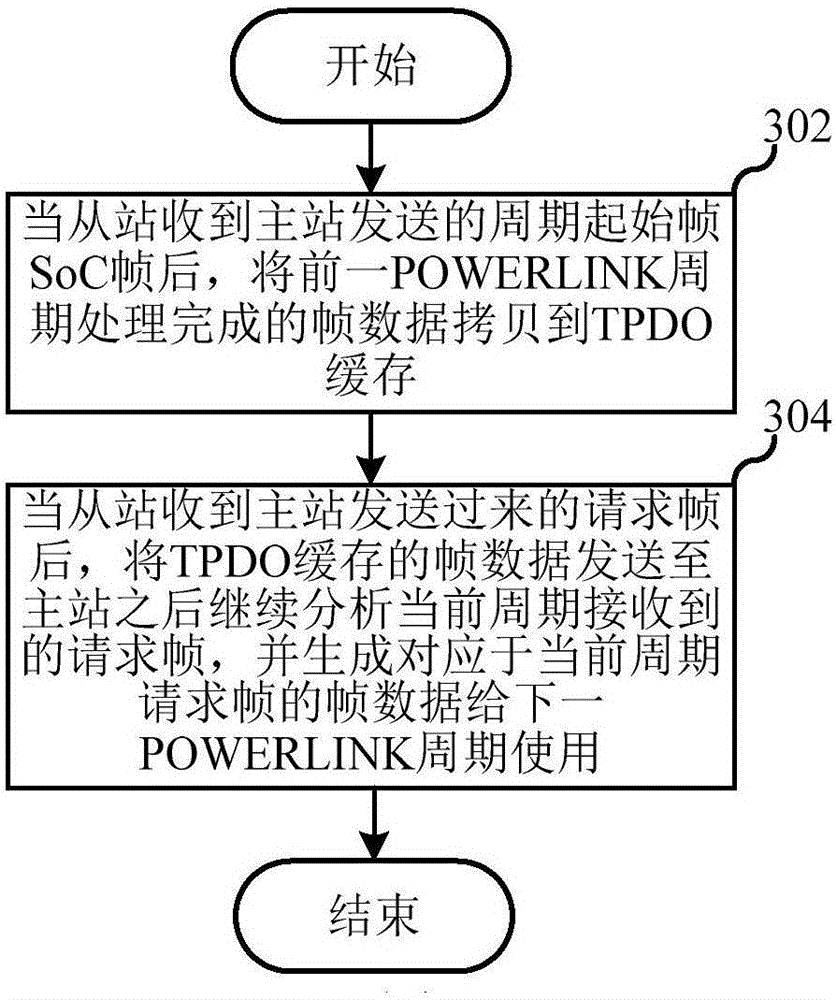

POWERLINK communication protocol hardware realization method

The invention relates to the technical field of industrial Ethernet communication protocols, and discloses a POWERLINK communication protocol hardware realization method. In the embodiment of the invention, the method comprises steps: a data link layer and a physical layer interface of the POWERLINK communication protocol are realized based on any one chip selected from the following: a programmable logic device, a custom hardware chip and a semi-custom hardware chip; and the application layer of the POWERLINK communication protocol is realized based on any one mode selected from the following: a soft core processor, an embedded processor, and a general processor. POWERLINK master station equipment or slave station equipment obtained by adopting the realization method has a high data transmission response capability, high-speed and high-precision industrial field control requirements are met, the expansibility is more flexible, any object dictionary and any number of slave stations can be supported, the cost performance is good, and software and hardware are easy to realize and maintain.

Owner:SHANGHAI STEP ELECTRIC +1

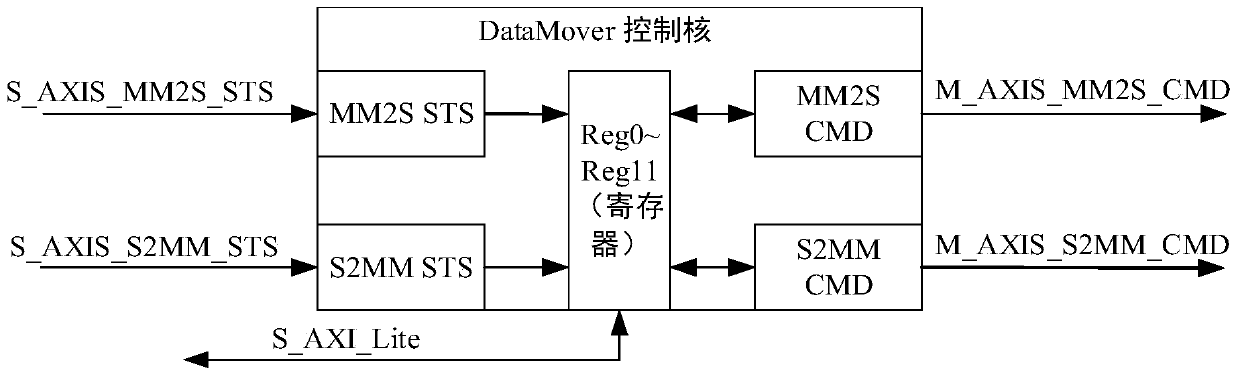

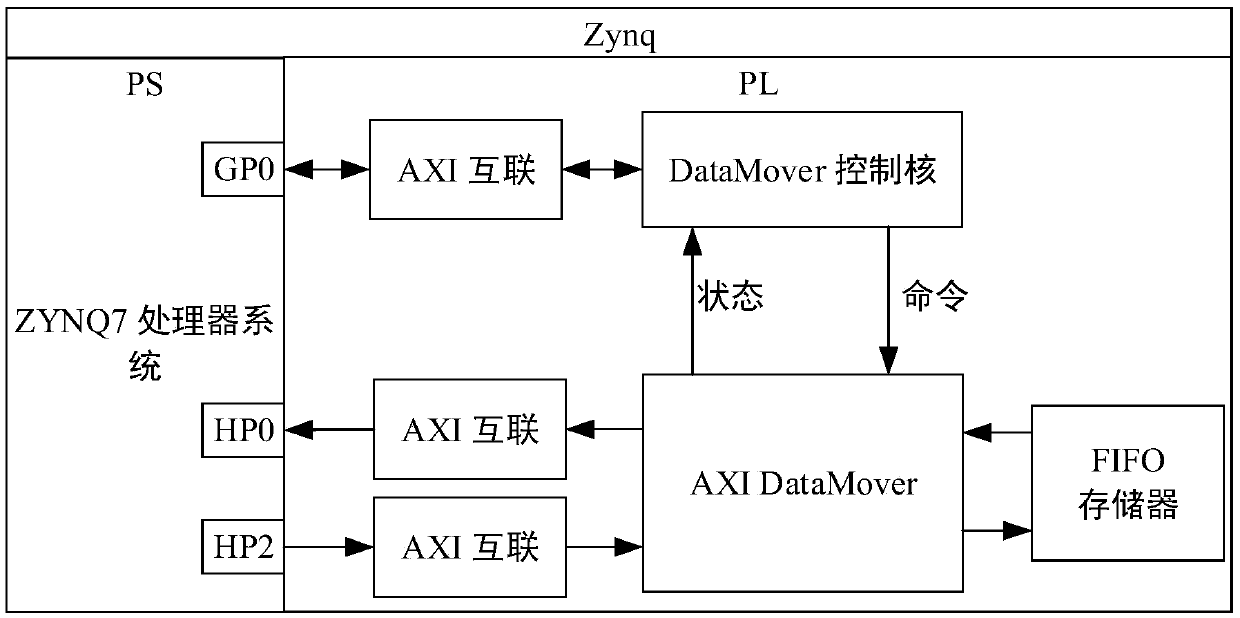

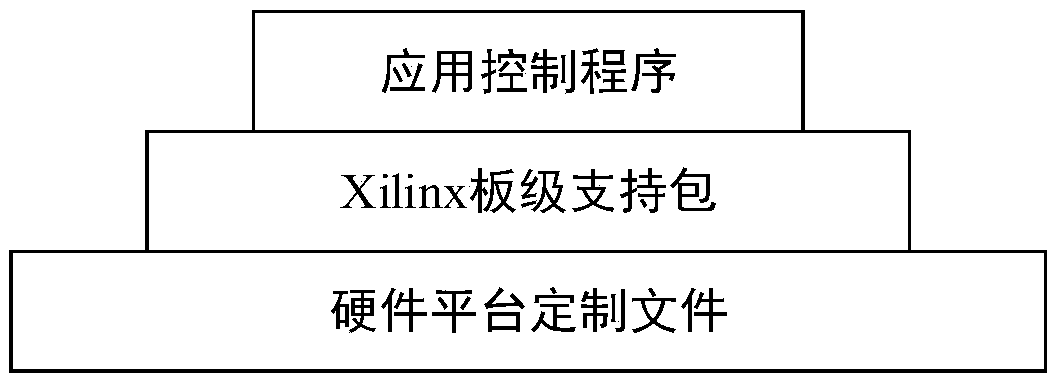

Zynq platform data interaction device

ActiveCN105512084ASimple designEliminate competitionMultiple digital computer combinationsProcessor registerInteraction device

The invention discloses a Zynq platform PS-PL data interaction device. The Zynq platform PS-PL data interaction device comprises a hardware system environment design based on an IP core and a software control program design based on a custom hardware platform. The hardware system is mainly formed by a ZYNQ7processor system, an AXI DataMover, an AXI interconnection interface, an FIFO memory and a self-designed DataMover control core and other IP cores. The software control program completes parameter setting needed by data transmission, starts the DataMover and detects the data transmission state through reading and writing in a register in the DataMover control core.

Owner:THE 28TH RES INST OF CHINA ELECTRONICS TECH GROUP CORP

Real-time geo-registration of imagery using COTS graphics processors

InactiveUS7555143B2High resolution imageLess expensiveImage enhancementImage analysisImage conversionGraphics processing unit

A method of performing real-time geo-registration of high-resolution digital imagery using existing graphics processing units (GPUs) already found in current personal computers, rather than the main central processing unit (CPU). Digital image data captured by a camera (along with inertial navigation system (INS) data associated with the image data) is transferred to and processed by the GPU to perform the calculations involved in transforming the captured image into a geo-rectified, nadir-looking image. By using the GPU, the order-of-magnitude increase in throughput over conventional software techniques makes real-time geo-registration possible without the significant cost of custom hardware solutions.

Owner:LAWRENCE LIVERMORE NAT SECURITY LLC

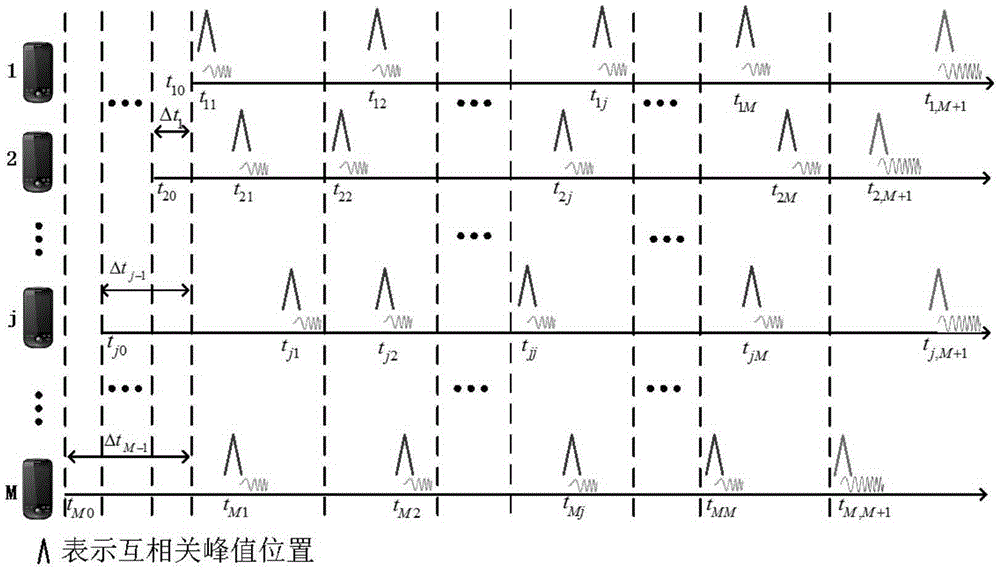

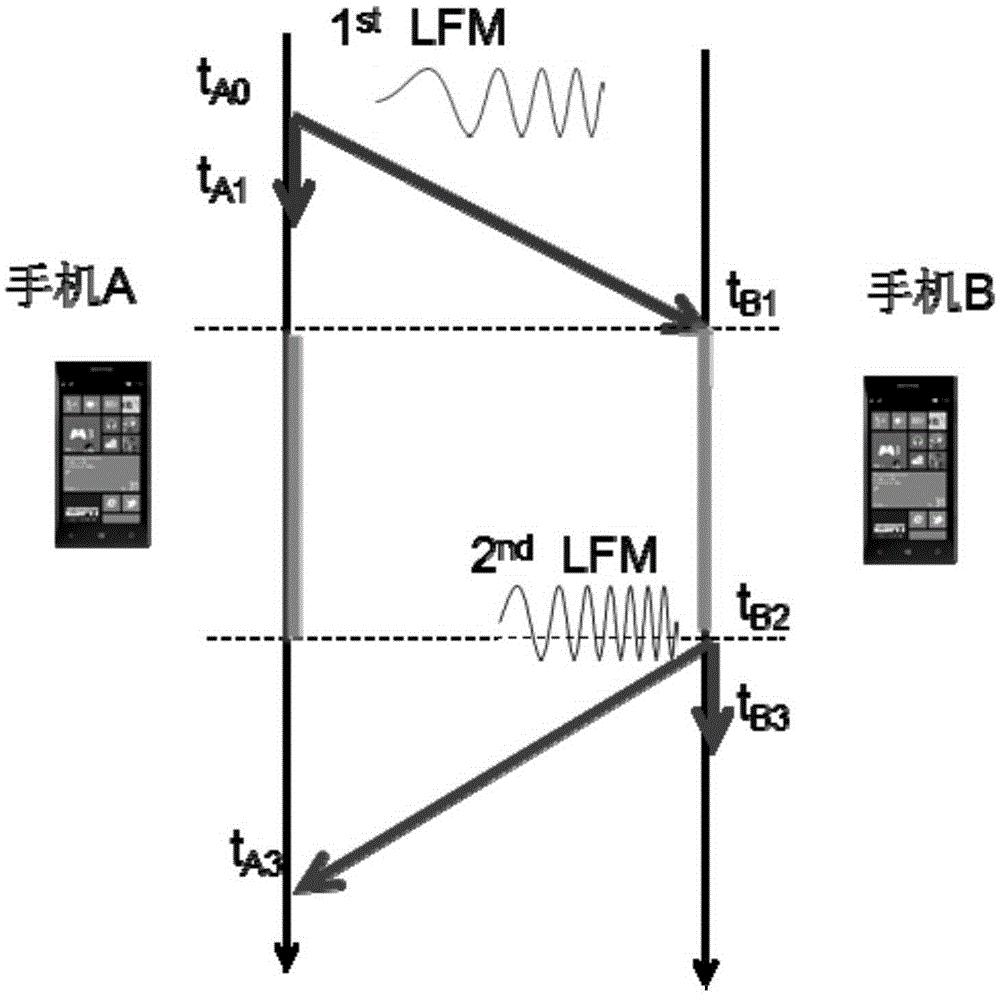

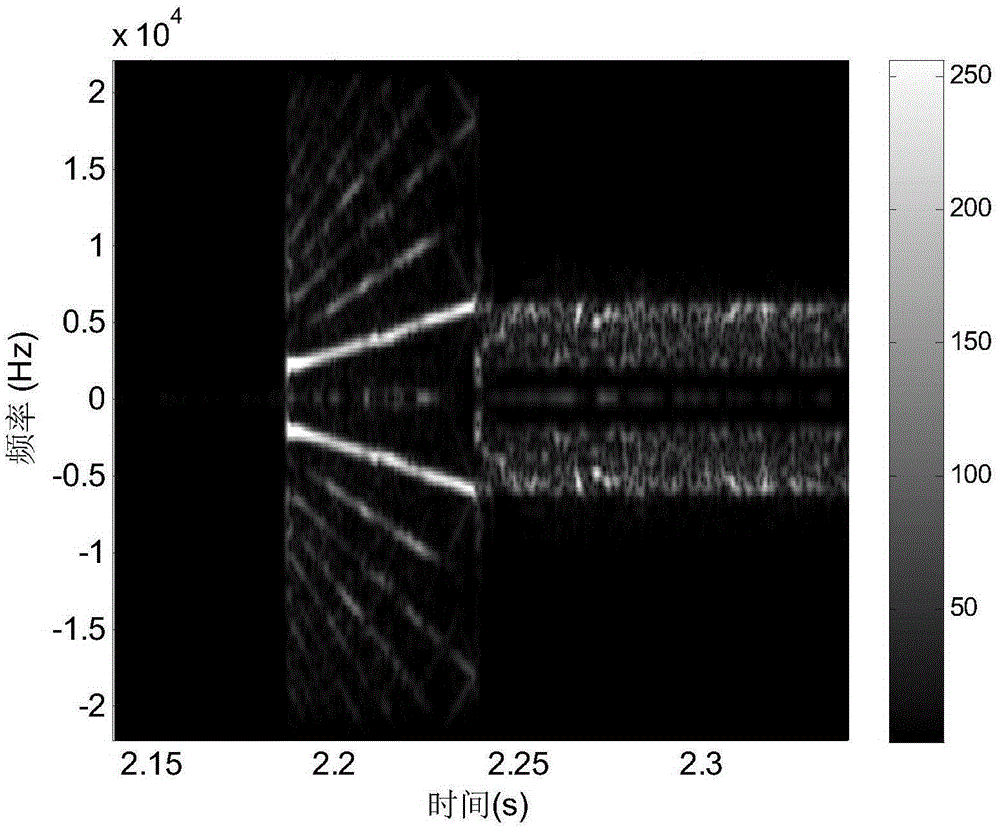

Self-localization method of sensor network node based on smartphone

ActiveCN105323772AHigh positioning accuracyLow costNetwork topologiesNetwork planningTime–frequency analysisFrequency modulation

The invention discloses a self-localization method of a sensor network node based on a smartphone. The method uses a general smartphone to replace a custom hardware module to be used as a network node, a plurality of mobile phone nodes orderly transmit linear frequency modulation (LFM) sound signals of 2k-6kHz by means of a loudspeaker and a microphone, and meanwhile, different mobile phone nodes sample the linear frequency modulation sound signals at a fixed frequency (44.1 kHz). Detection is performed on a sampling waveform by means of a generalized correlation method, and in view of a multipath effect, the self-localization method of the sensor network node based on the smartphone provided by the invention adopts a method of combining a threshold value method and time-frequency analysis to effectively inhibit the multipath effect, so that the arrival time of the linear frequency modulation sound signals can be obtained, then distance information between different nodes can be obtained, and finally, the unknown nodes can be located by adopting a multidimensional scaling (MDS) algorithm. The method of the invention does not need clock synchronization between the mobile phone nodes, and since the frequency is fixed, the arrival time of the sound signals can be accurately estimated through a sampling number; besides, the location accuracy is high, the cost is low, the networking is convenient and the prospect is wide.

Owner:ZHEJIANG UNIV

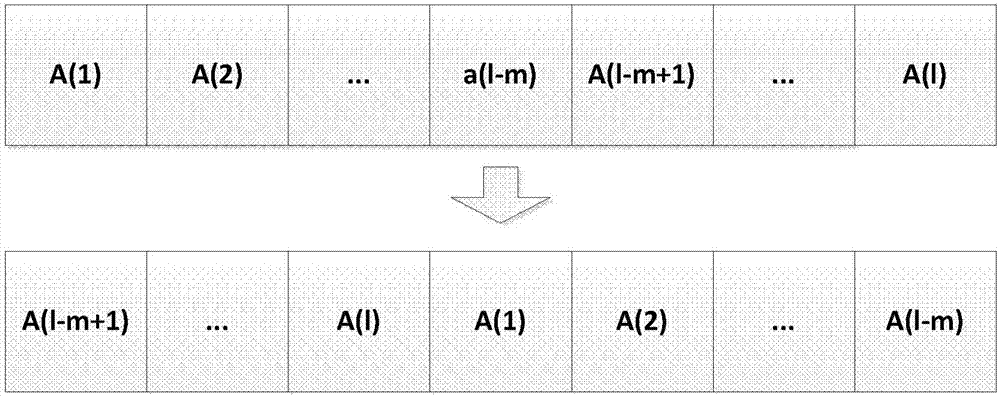

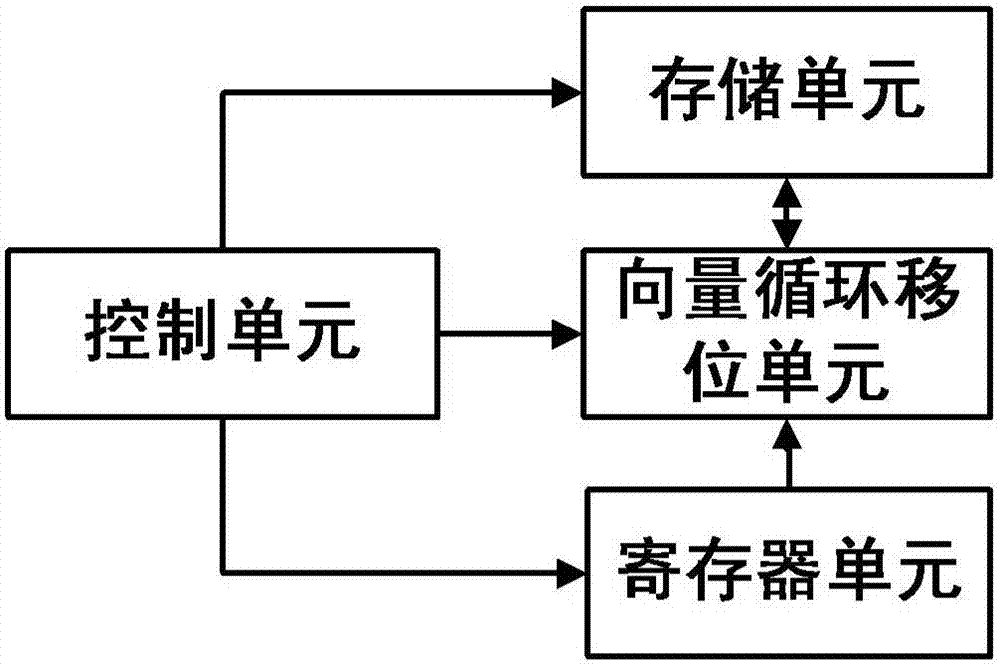

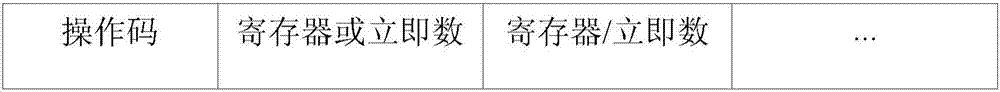

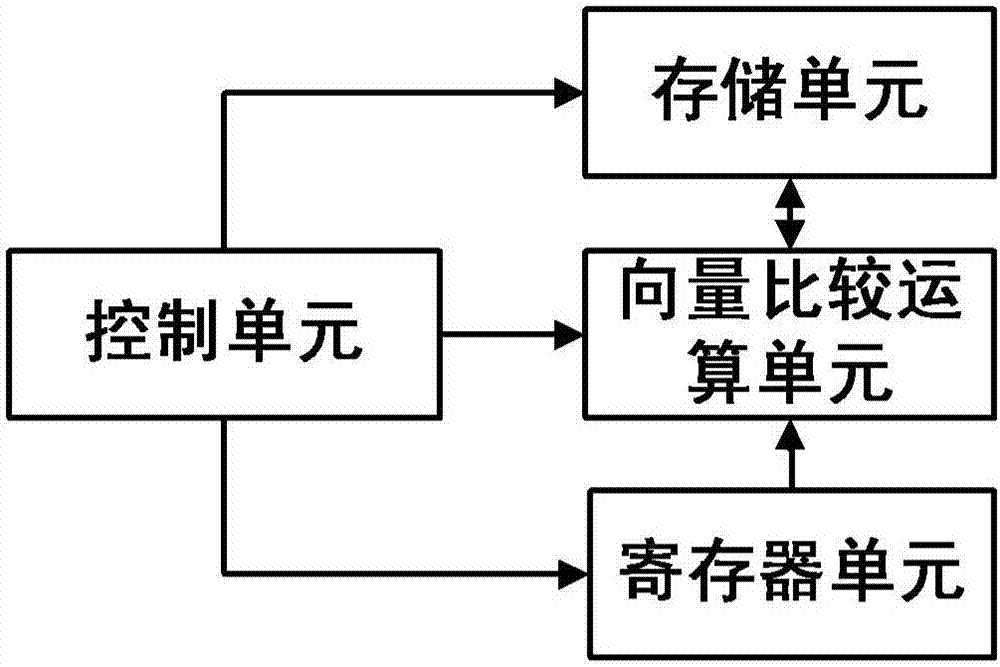

Device and method for executing vector cyclic shift operation

ActiveCN107315566ASimple formatEasy to useMemory architecture accessing/allocationBiological neural network modelsCustom hardwareControl unit

The invention discloses a device and a method for executing vector cyclic shift operation. The device comprises a storage unit, a register unit, a control unit and a cyclic shift unit, wherein the storage unit is used for storing vector data relevant to a vector cyclic shift operation instruction; the register unit is used for storing scalar data relevant to the vector cyclic shift operation instruction; the control unit is used for decoding the vector cyclic shift operation instruction and controlling the operation process of the vector cyclic shift operation instruction; and the cyclic shift unit is used for performing cyclic shift operation on input vector data according to the decoded vector cyclic shift operation instruction, wherein the cyclic shift unit is a custom hardware circuit. According to the device and the method for executing vector cyclic shift operation, the complete process of the simple vector cyclic shift operation instruction is realized through the custom hardware circuit, that is, vector cyclic shift operation can be realized through the simple cyclic shift instruction.

Owner:CAMBRICON TECH CO LTD

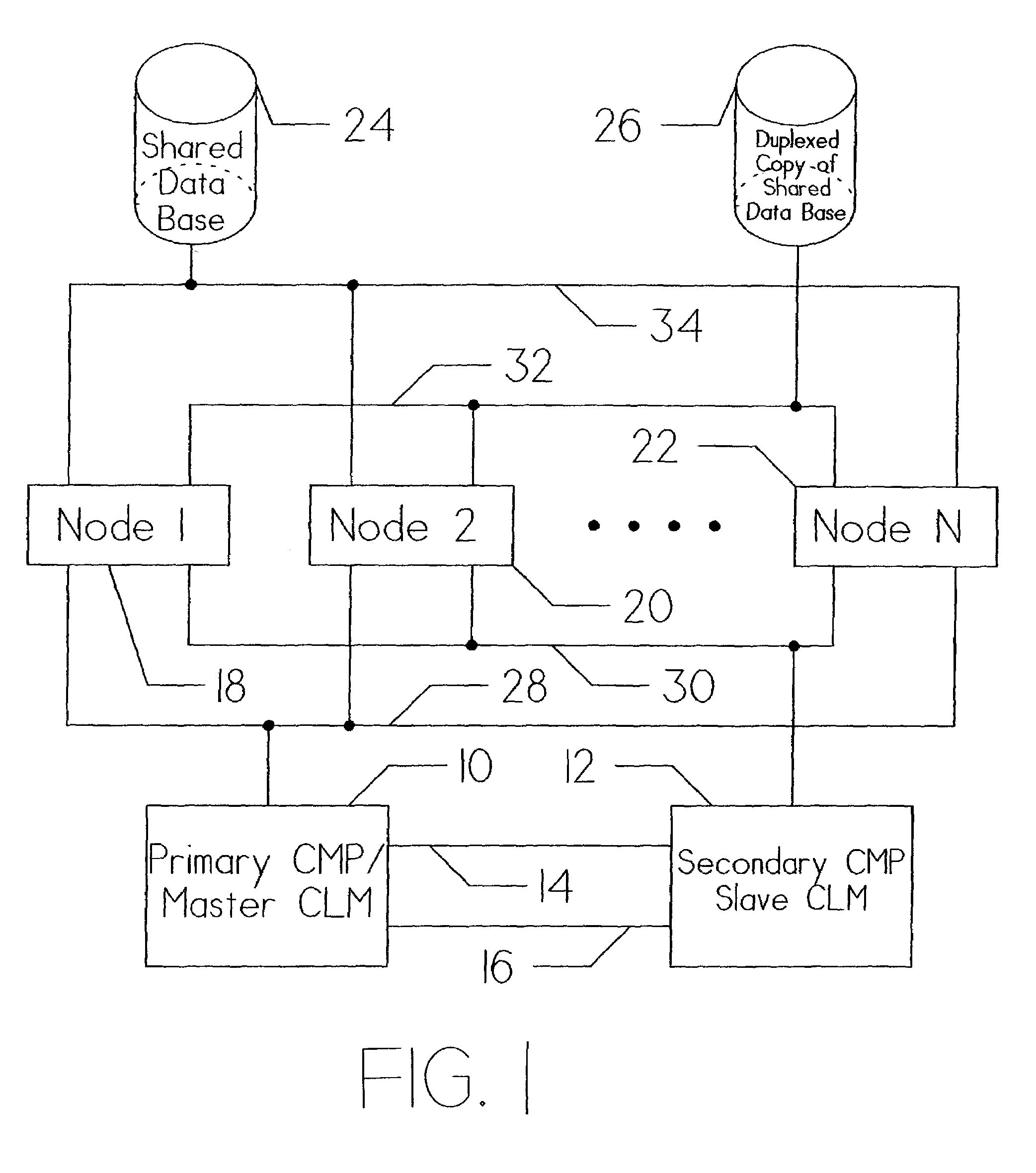

Outboard clustered computer systems manager utilizing commodity components

ActiveUS7366765B1Low costImprove performanceData processing applicationsError detection/correctionOff the shelfSystems management

An apparatus for and method of implementing a cluster lock processing system using highly scalable, off-the-shelf commodity processors. The cluster lock processing system is the central component of a clustered computer system, providing locking and coordination between multiple host systems. The host systems are coupled to the cluster lock processing system using off-the-shelf, low latency interconnects. The cluster lock processing system is composed of multiple commodity platforms that are also coupled to each other using low latency interconnects. Failure of one of the commodity platforms that comprise the cluster lock processing system results in no loss of functionality or interruption of service. This is made possible through the use of specialized software that runs on the commodity platforms. Through the use of custom software and inexpensive hardware the overall system cost is dramatically reduced when compared to typical solutions that use custom built hardware. By allowing the individual commodity platforms to be physically separated, the cluster lock processing system also provides for resiliency against physical damage to an individual platform that may be caused by a catastrophic site failure.

Owner:UNISYS CORP

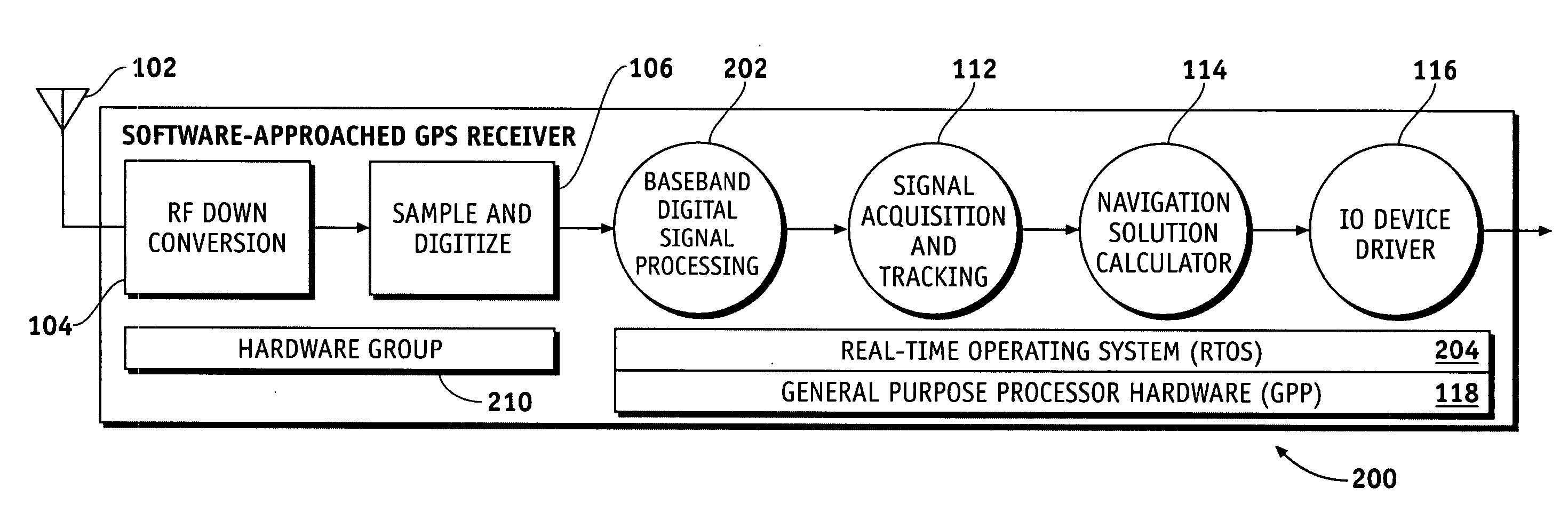

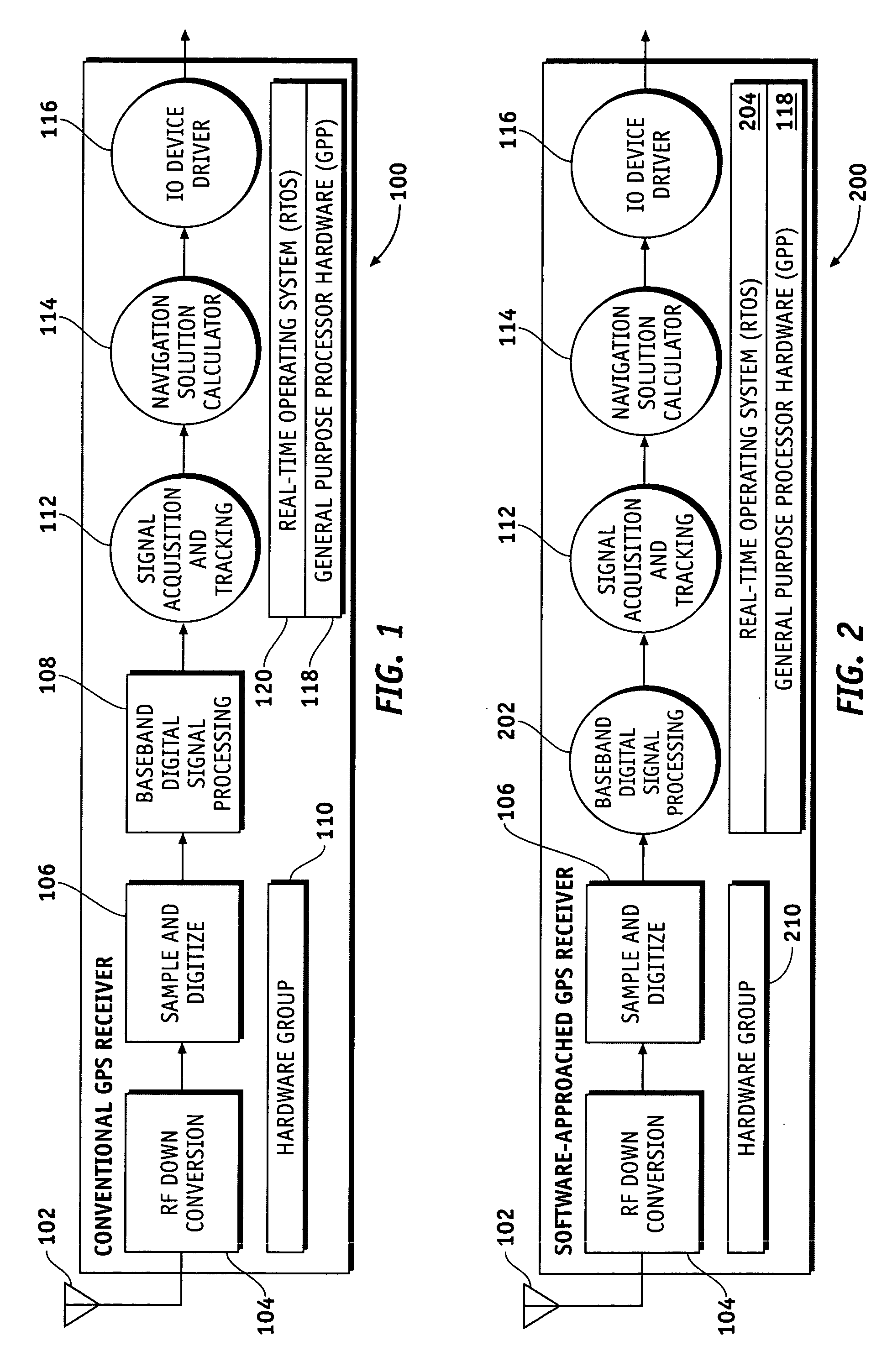

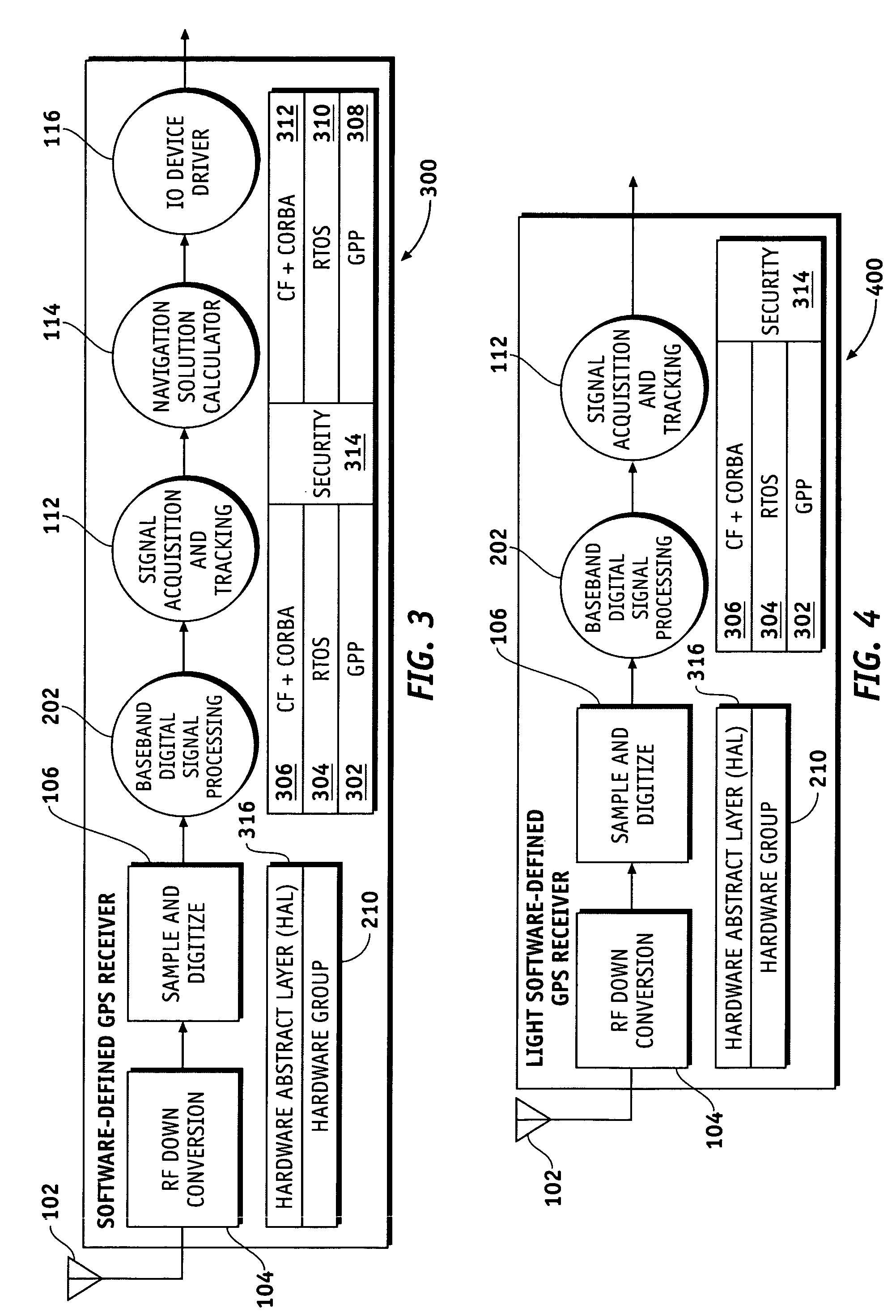

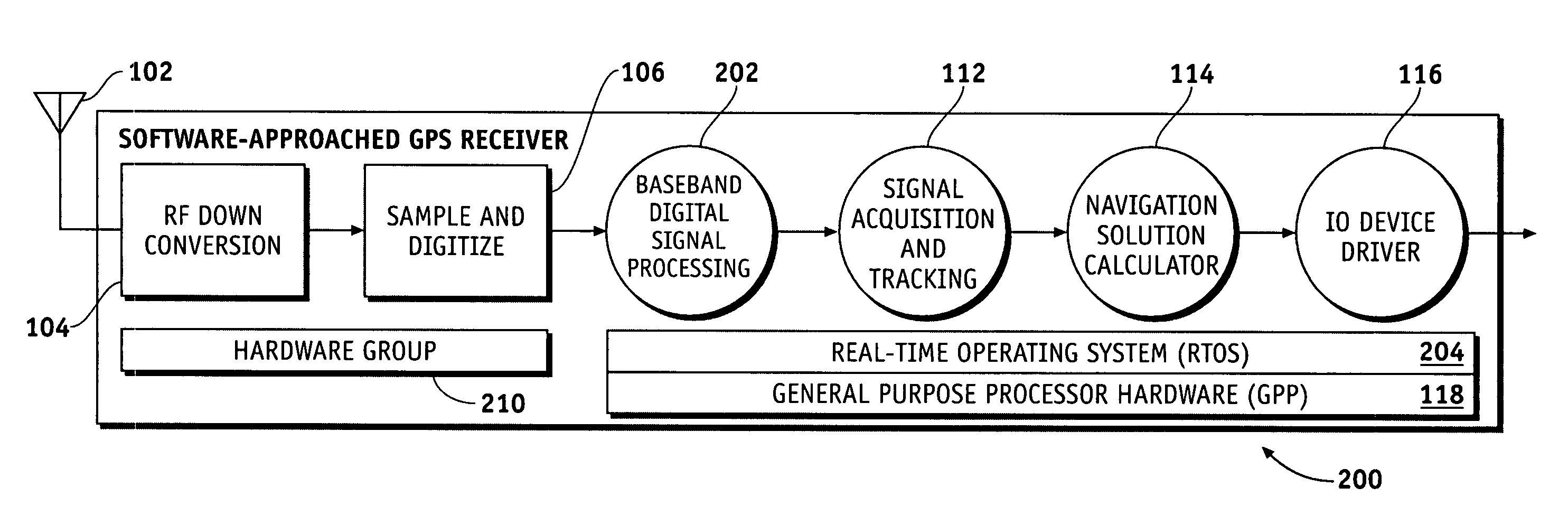

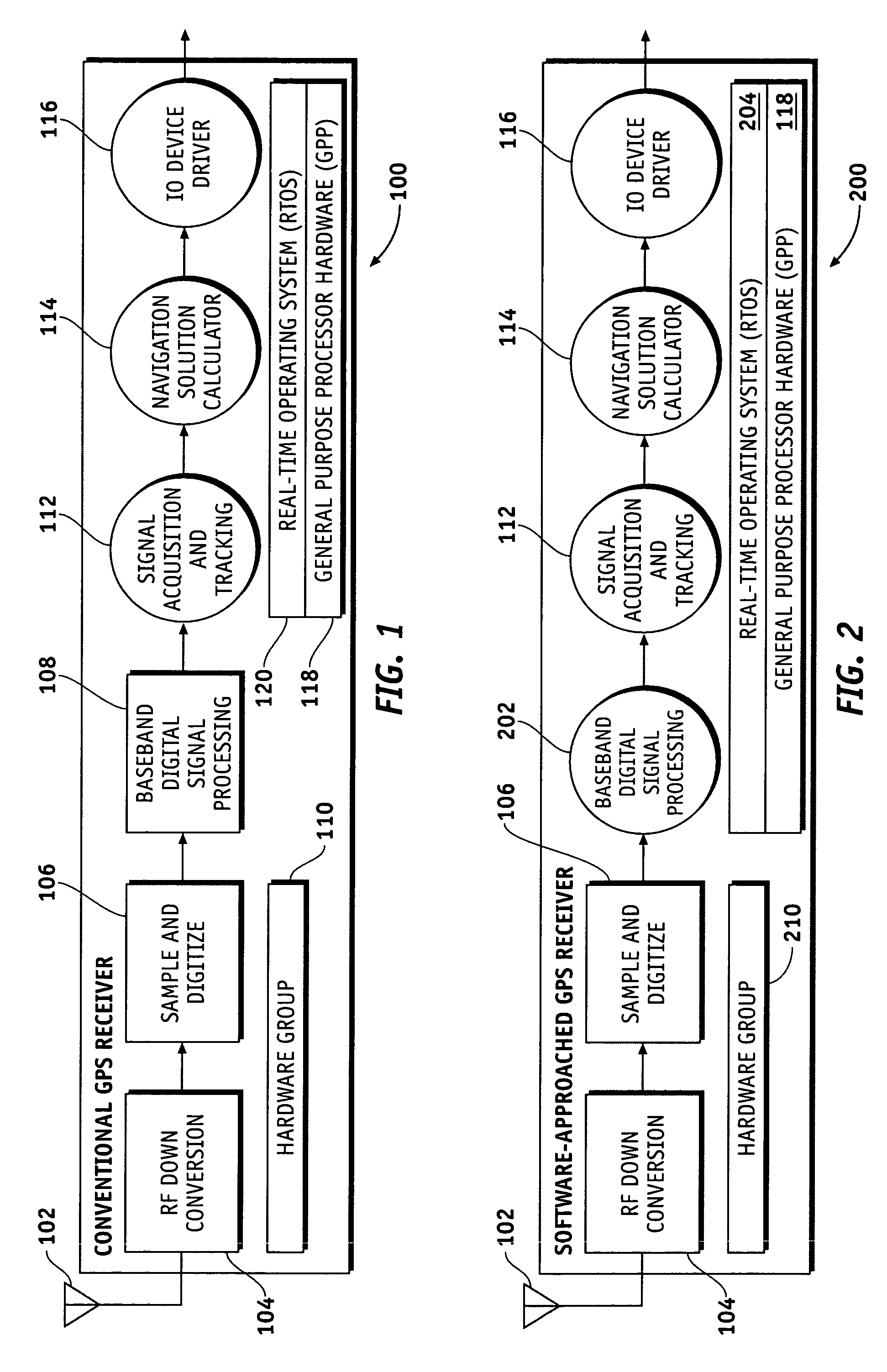

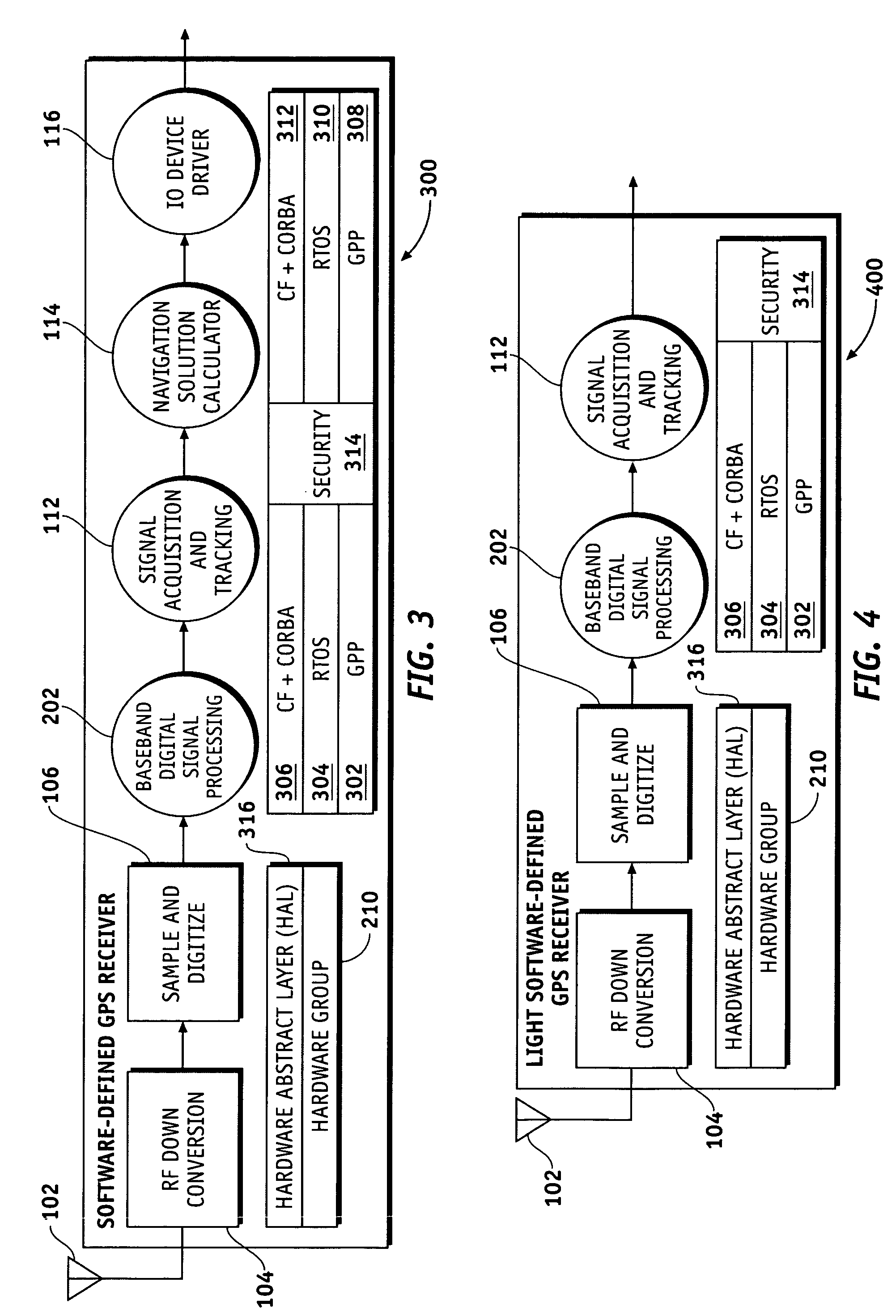

Software-defined GPS receivers and distributed positioning system

ActiveUS20060074554A1Instruments for road network navigationPosition fixationPositioning systemDigitization

A software-defined GPS receiver includes a hardware-oriented front end for down converting and digitizing the signals received from GPS satellites. The GPS signal processing functions, such as acquisition / tracking and navigation computing, can be performed by software running on the receiver central processing unit (CPU), rather than by firmware in a custom hardware device such as an ASIC. The signal processing capabilities of the receiver can therefore be readily reconfigured (e.g., upgraded) to accommodate changes in the satellite signal transmissions. Moreover, by utilizing an operating environment architecture and application programs that are compliant with the Software Communications Architecture (SCA) specification, a distributed positioning system of scalable, portable, and compatible SCA-compliant software-defined GPS receivers can be realized.

Owner:THE BOEING CO

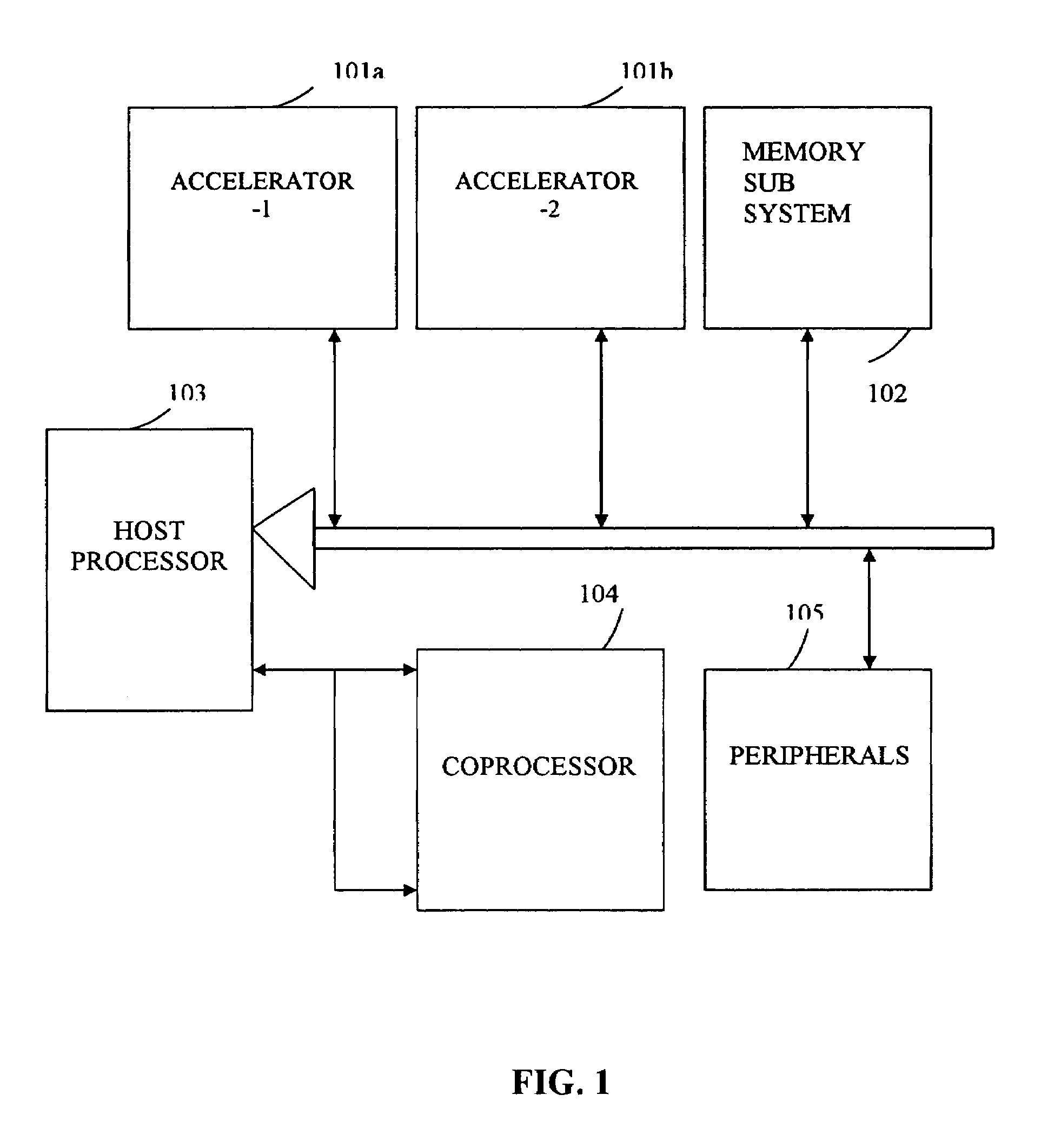

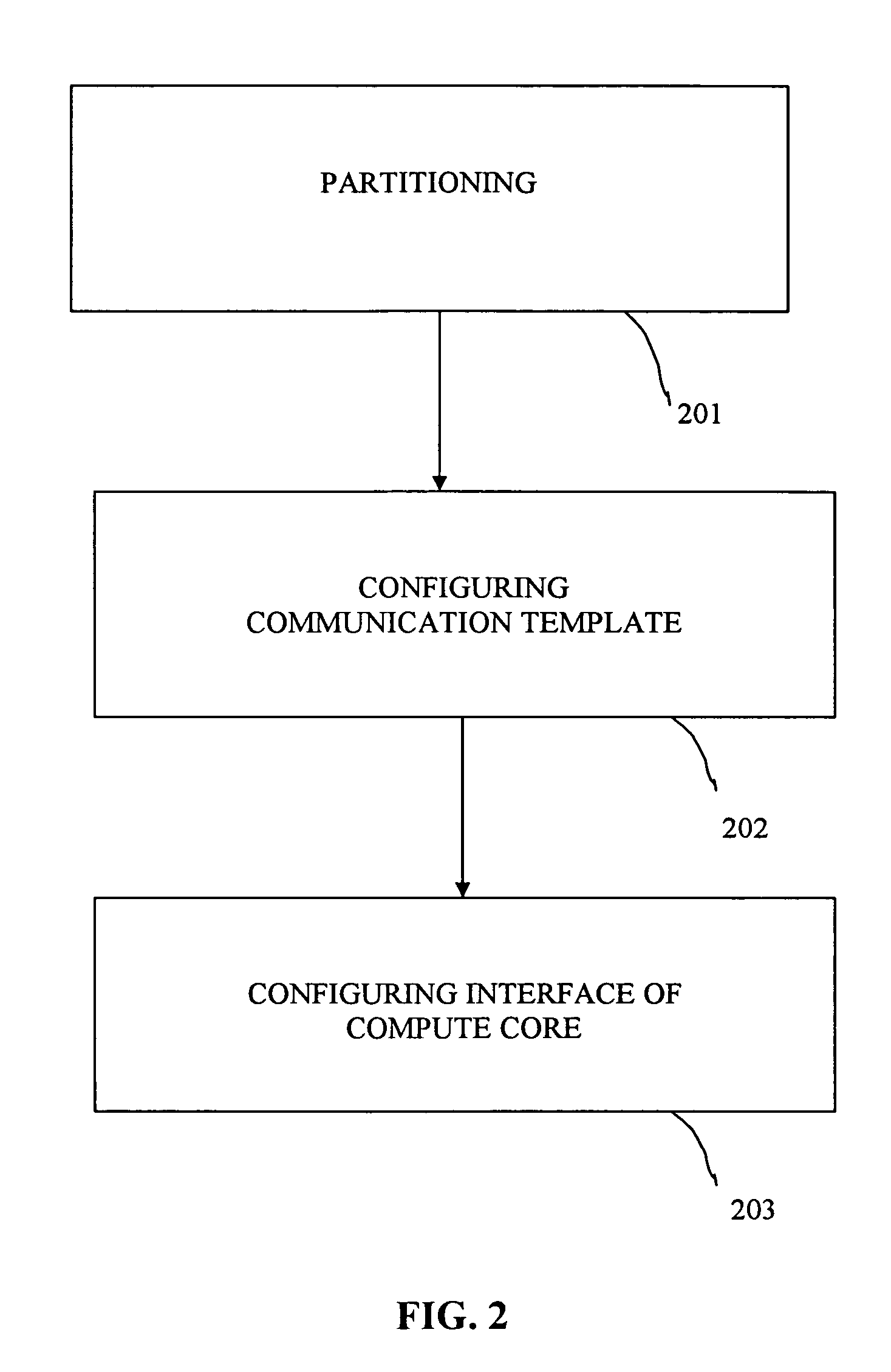

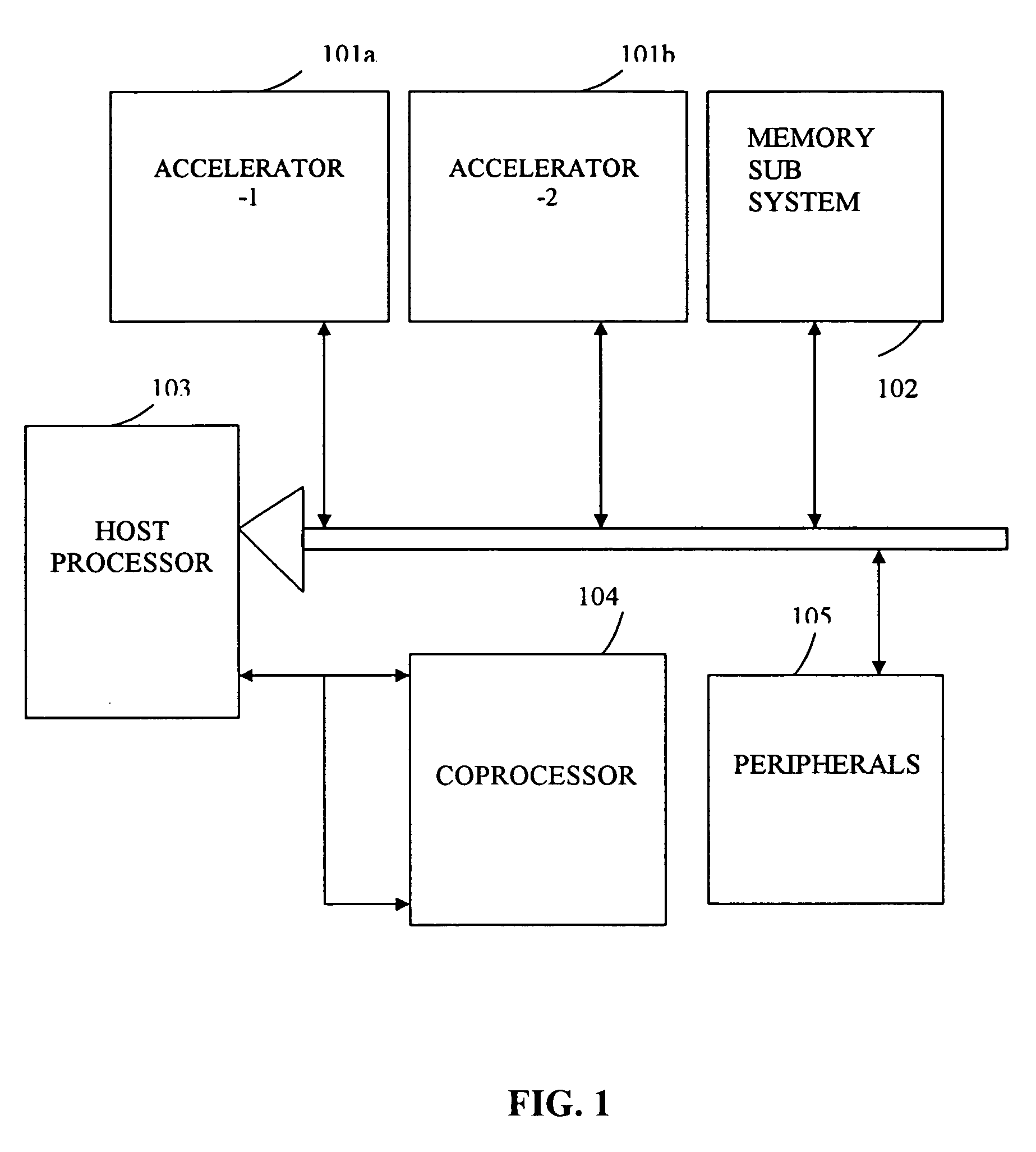

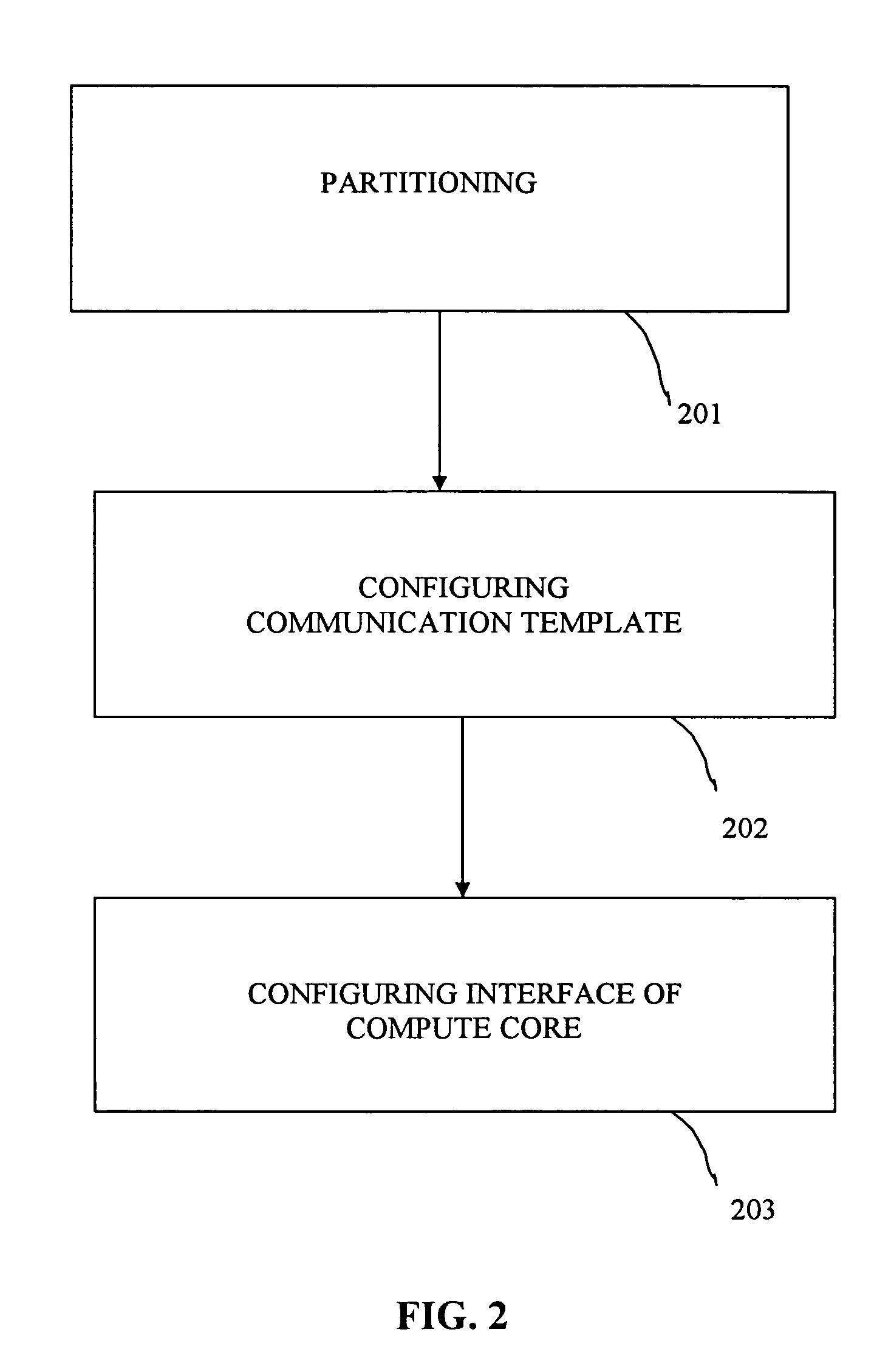

Configurable components for embedded system design

InactiveUS7200703B2Increase speedRaise transfer toCAD circuit designArchitecture with single central processing unitControl flowData control

A system and method of designing an accelerator for a processor-based system. The accelerator design problem is partitioned into a data communicate module design problem and a data compute core module design problem. The hardware design of the data communicate module is achieved through a predetermined communication template which is customized for the particular application. The communication template has individual configurable communication components and a programmable control flow path. The components of the communicate template include a host bus interface, a memory bus interface, a direct memory access, a local memory and a control module. The combination of the communication components in a single configurable communication template and their optimized interconnections increase the speed of data transfer and data control processes in the accelerator. The hardware design of the data compute core module can be achieved through custom hardware design or by automatically generating hardware from software description.

Owner:POSEIDON DESIGN SYST

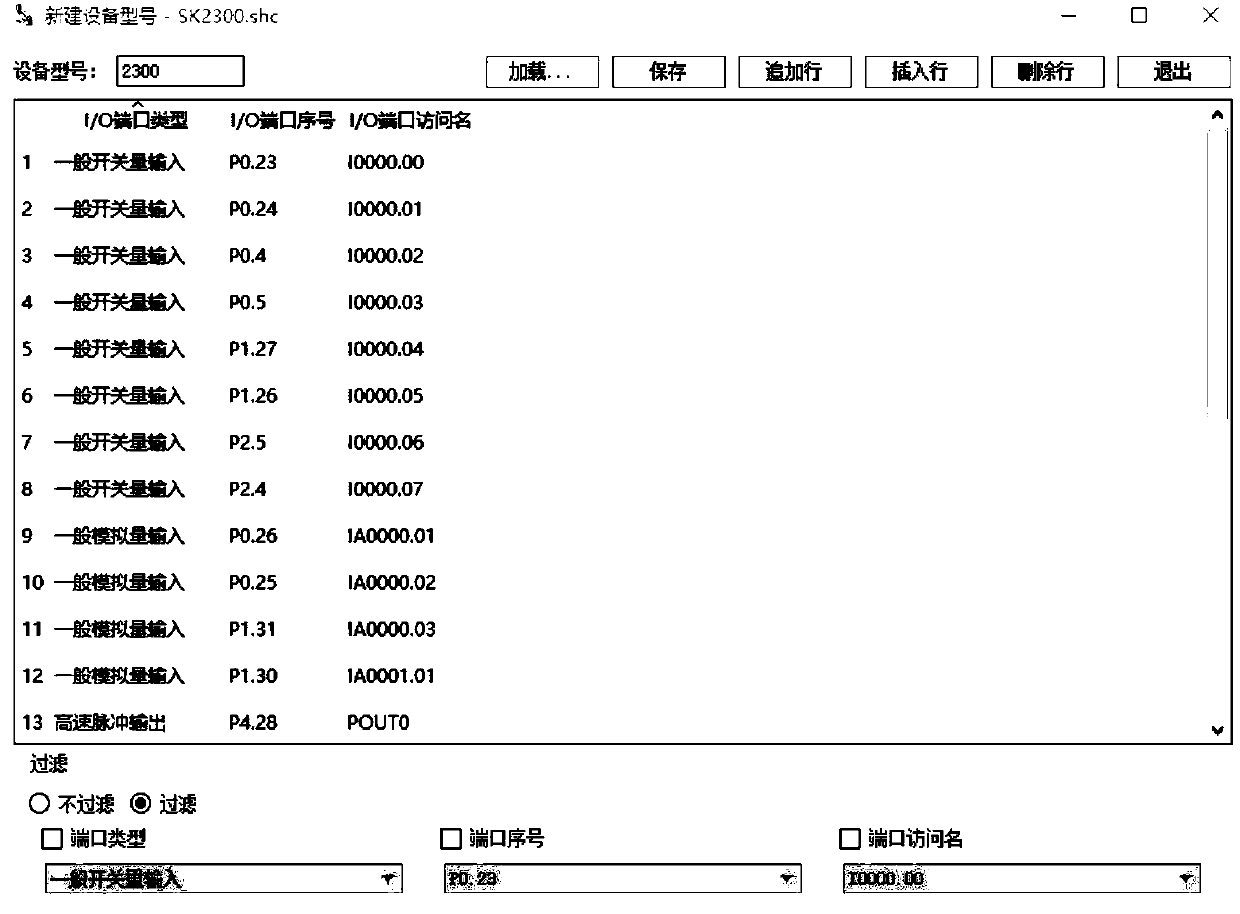

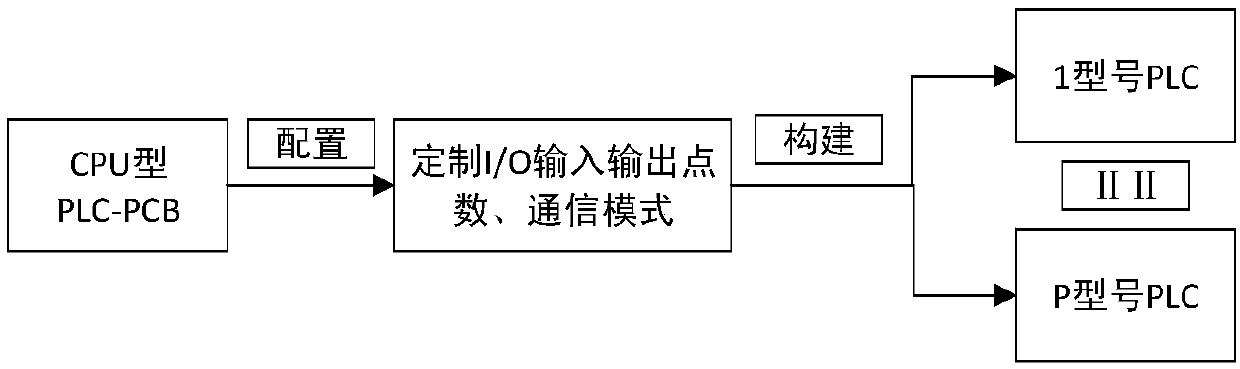

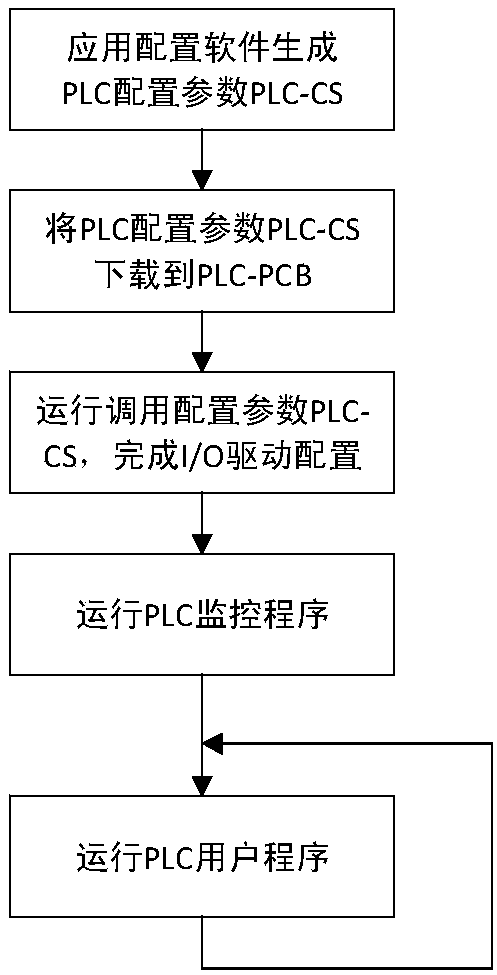

Hardware resource autonomously configurable PLC quick construction method

ActiveCN107861458AProgramme control in sequence/logic controllersOperating systemBuilding construction

The invention provides a hardware resource autonomously configurable PLC quick construction method comprising the steps that (1) a hardware resource configuration parameter list is generated; (2) thehardware resource configuration parameter list PLC-CS is downloaded to a PLC-PCB parameter configuration storage area FLASH, and the PLC monitoring program is downloaded to a PLC-PCB program storage area FLASH so as to complete construction of the PLC; and (3) the constructed PLC operates the implementation procedure; (3.1) the hardware resource configuration parameter list PLC-CS is read to complete I / O driving analysis and complete autonomous configuration of the hardware resources; (3.2) the PLC monitoring program is operated. Autonomous configuration of the hardware is performed on the CPUhardware resources to quickly construct and customize the PLC hardware, and customization of any I / O point number within the range of the CPU hardware resources can be realized through the configuration technology and research and development of series of safety PLC of different I / O point number and different communication modes can be quickly formed.

Owner:SHANDONG COMP SCI CENTNAT SUPERCOMP CENT IN JINAN

Software-defined GPS receivers and distributed positioning system

ActiveUS7542848B2Position fixationMultiple digital computer combinationsApplication softwarePositioning system

A software-defined GPS receiver includes a hardware-oriented front end for down converting and digitizing the signals received from GPS satellites. The GPS signal processing functions, such as acquisition / tracking and navigation computing, can be performed by software running on the receiver central processing unit (CPU), rather than by firmware in a custom hardware device such as an ASIC. The signal processing capabilities of the receiver can therefore be readily reconfigured (e.g., upgraded) to accommodate changes in the satellite signal transmissions. Moreover, by utilizing an operating environment architecture and application programs that are compliant with the Software Communications Architecture (SCA) specification, a distributed positioning system of scalable, portable, and compatible SCA-compliant software-defined GPS receivers can be realized.

Owner:THE BOEING CO

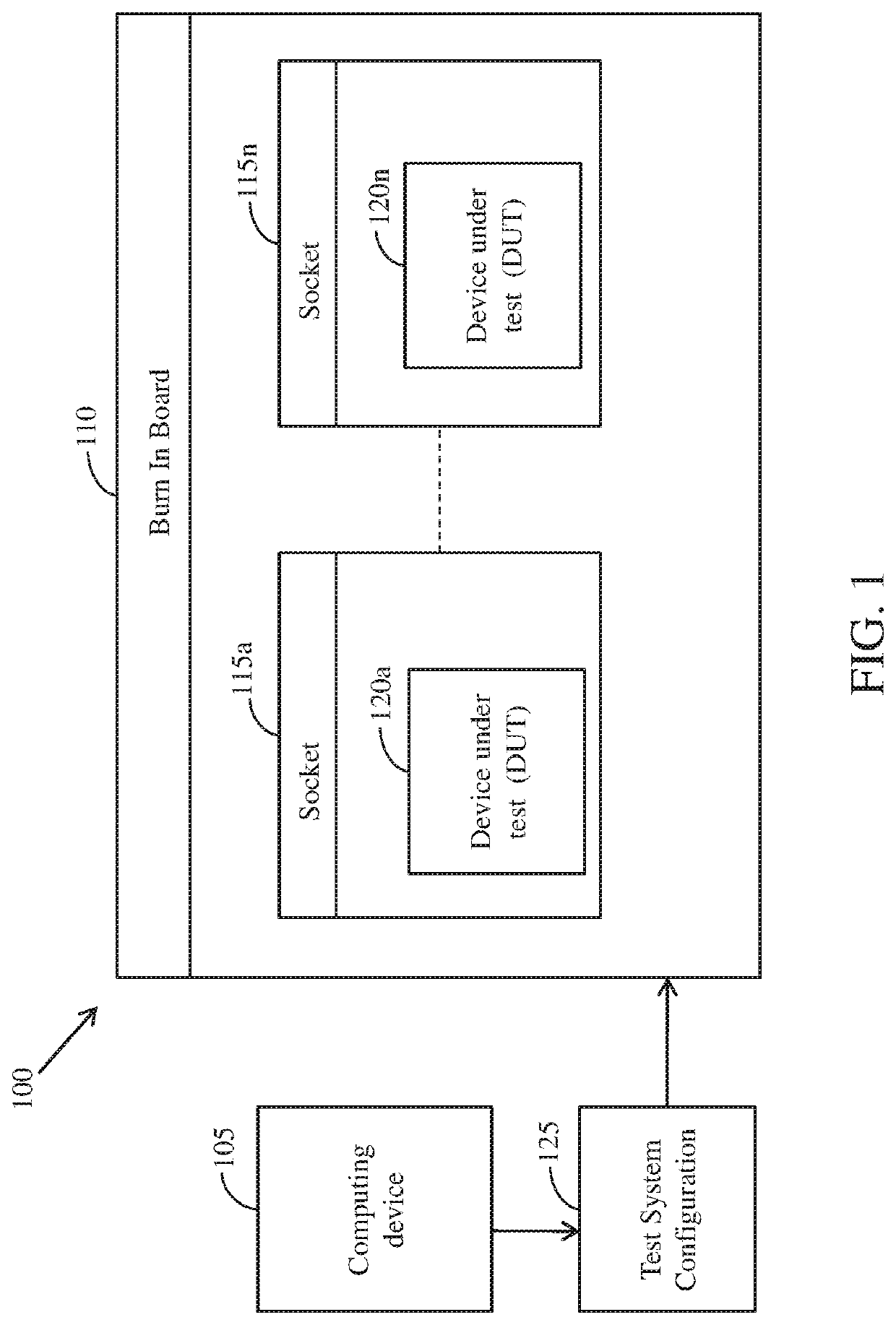

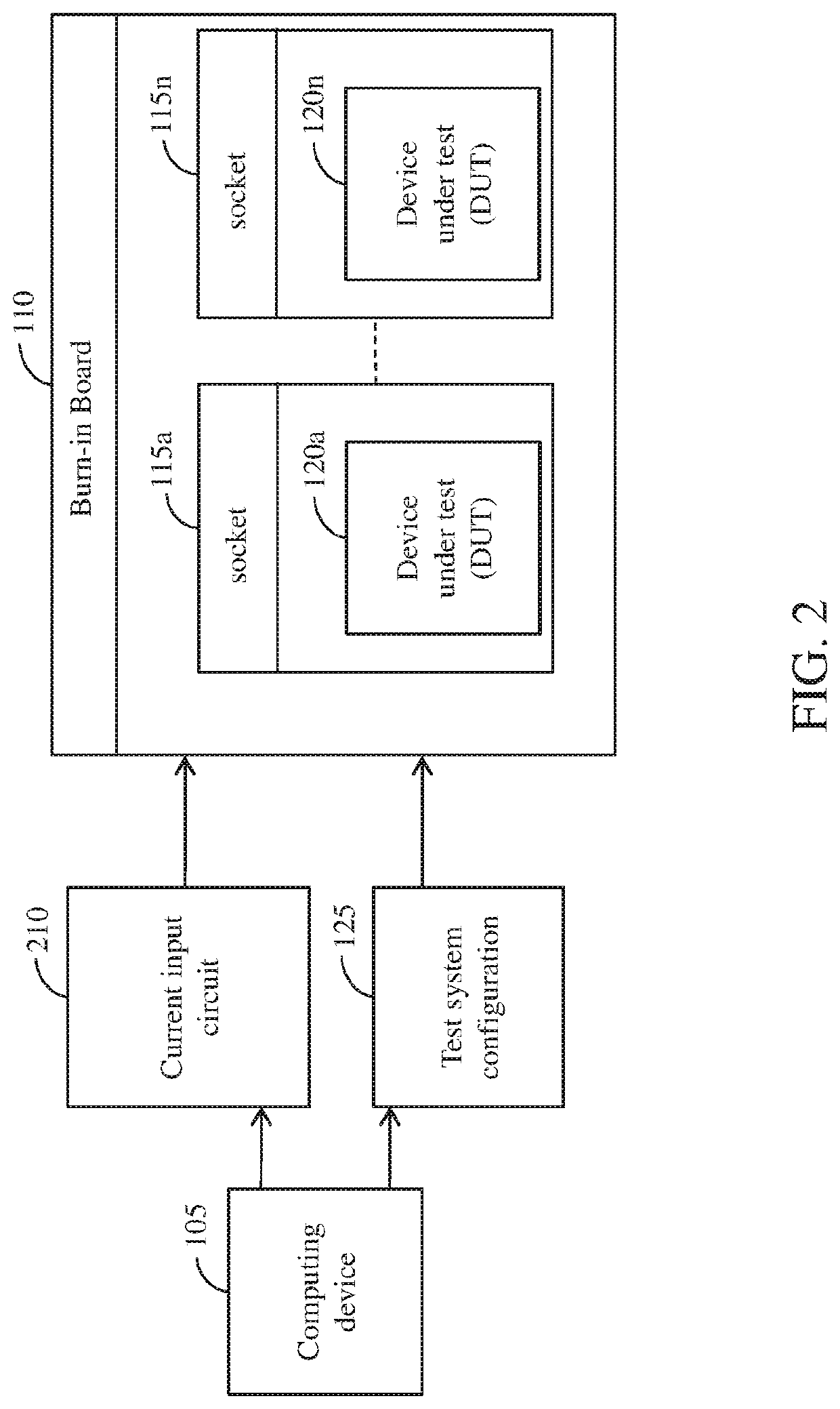

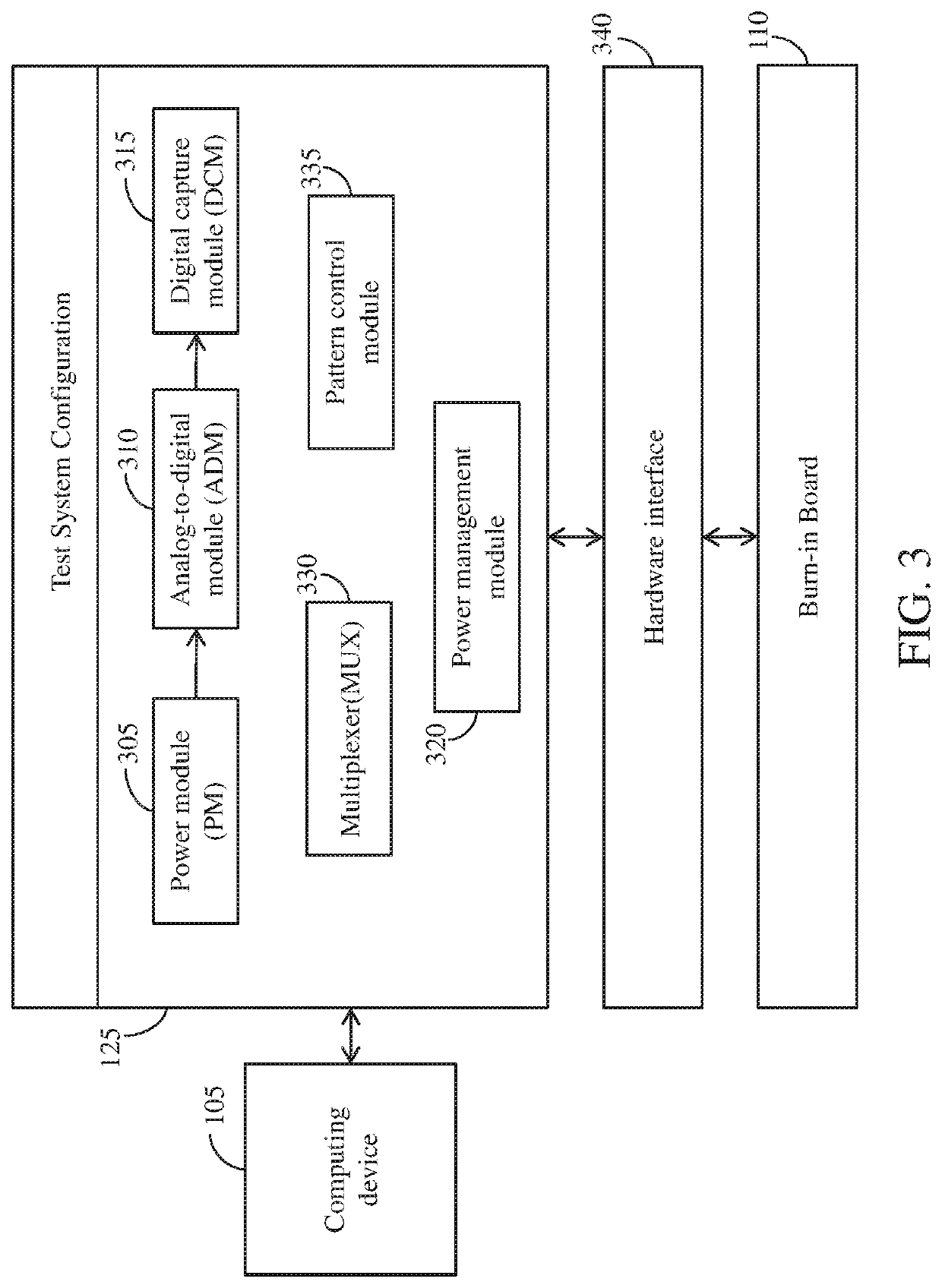

Scalable tester for testing multiple devices under test

ActiveUS11320480B1Electronic circuit testingMeasurement instrument housingEquipment under testTester device

Various embodiments of the invention provide a system and a method for testing one or more devices under test (DUTs) and for checking one or more test setups. Each of the one or more test setups includes a test board having several sockets for receipt of a DUT. A custom hardware interface is used to electrically connect the test board, such as a burn-in board with a test system configuration having multiple modules that can be configured using a computer device and related software to provide customized testing of the DUTs. The system is scalable to accommodate any DUT having any number of channels and to provide customized testing. Results of the testing are sent to the computing device.

Owner:GAOIRAN ALBERT

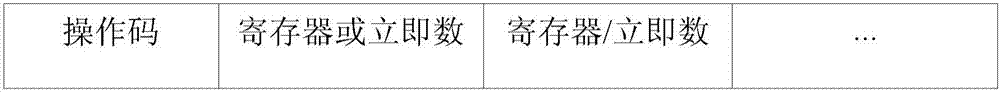

Device and method for executing vector comparison operation

ActiveCN107315563AEasy to useFlexible supportInstruction analysisDigital computer detailsCustom hardwareControl unit

The invention discloses a device and a method for executing vector comparison operation. The device comprises a storage device, a register unit, a control unit and a vector comparison unit, wherein the storage unit is used for storing vector data relevant to a vector comparison operation instruction; the register unit is used for storing scalar data relevant to the vector comparison operation instruction; the control unit is used for decoding the vector comparison operation instruction and controlling the operation process of the vector comparison operation instruction; and the vector comparison unit is used for performing vector comparison operation on two pieces of to-be-compared input vector data according to the decoded vector comparison operation instruction, wherein the vector comparison unit is a custom hardware circuit. Through the device and the method for executing vector comparison operation, a complete process of the simple vector comparison operation instruction is realized through the custom hardware circuit, that is, vector comparison operation can be realized through the simple vector comparison instruction.

Owner:CAMBRICON TECH CO LTD

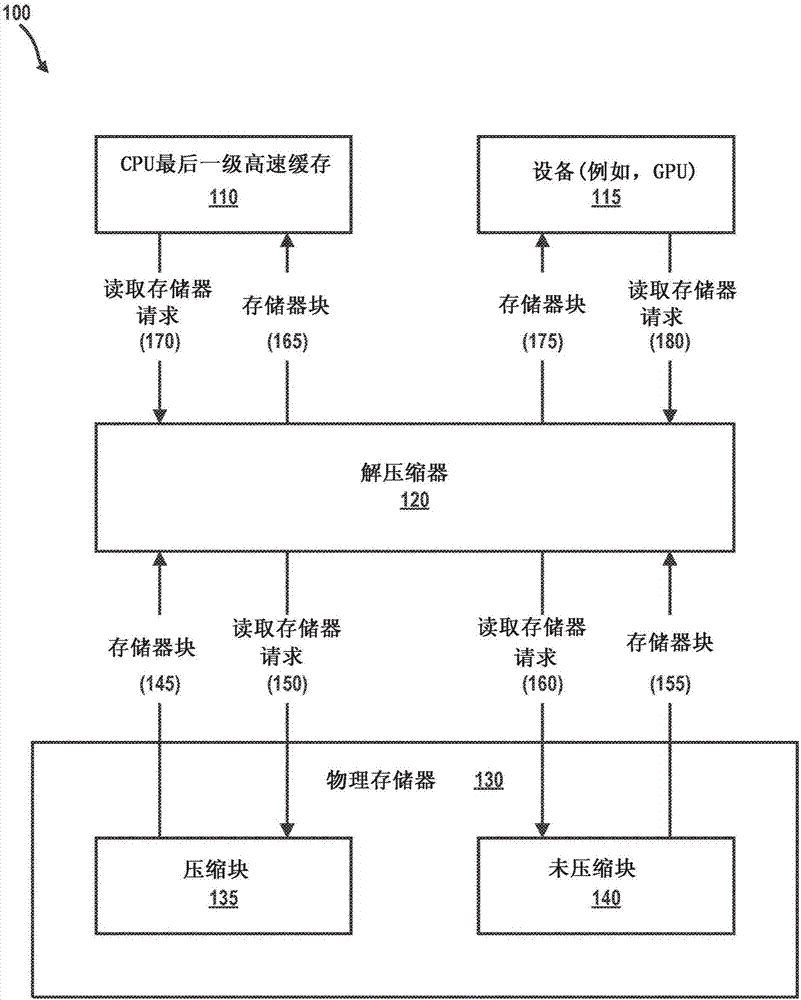

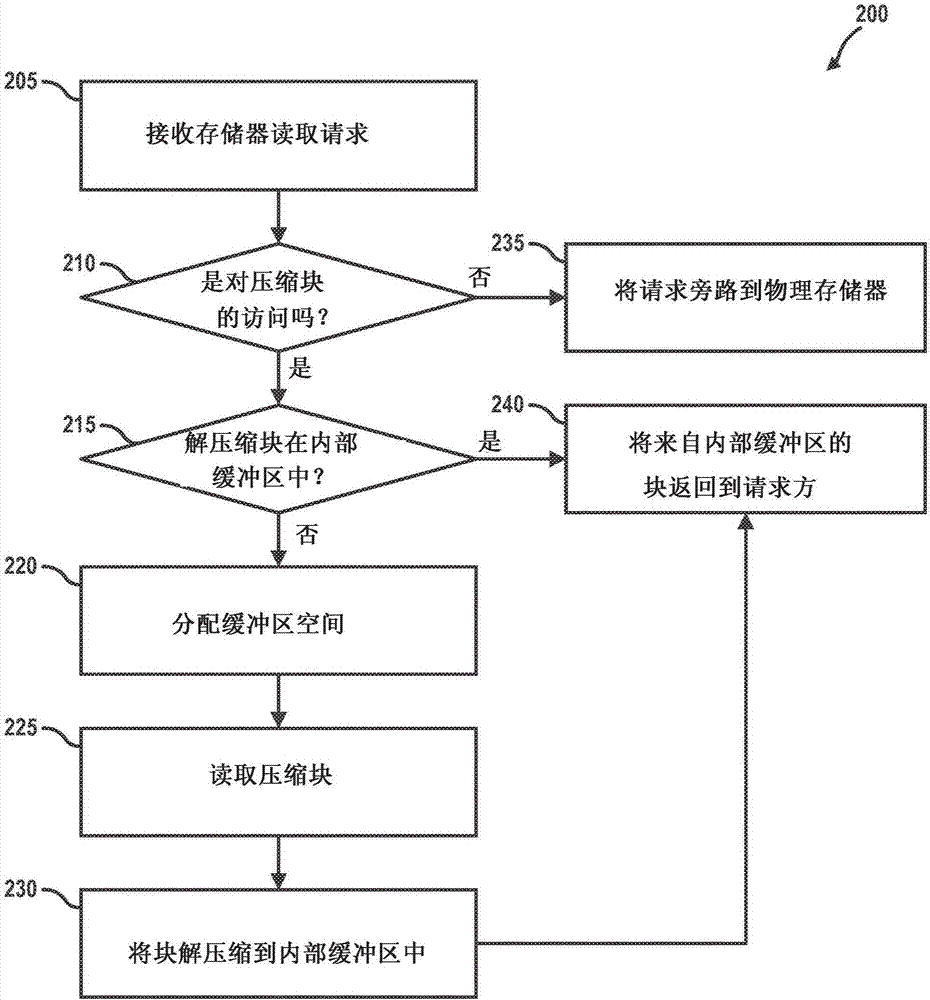

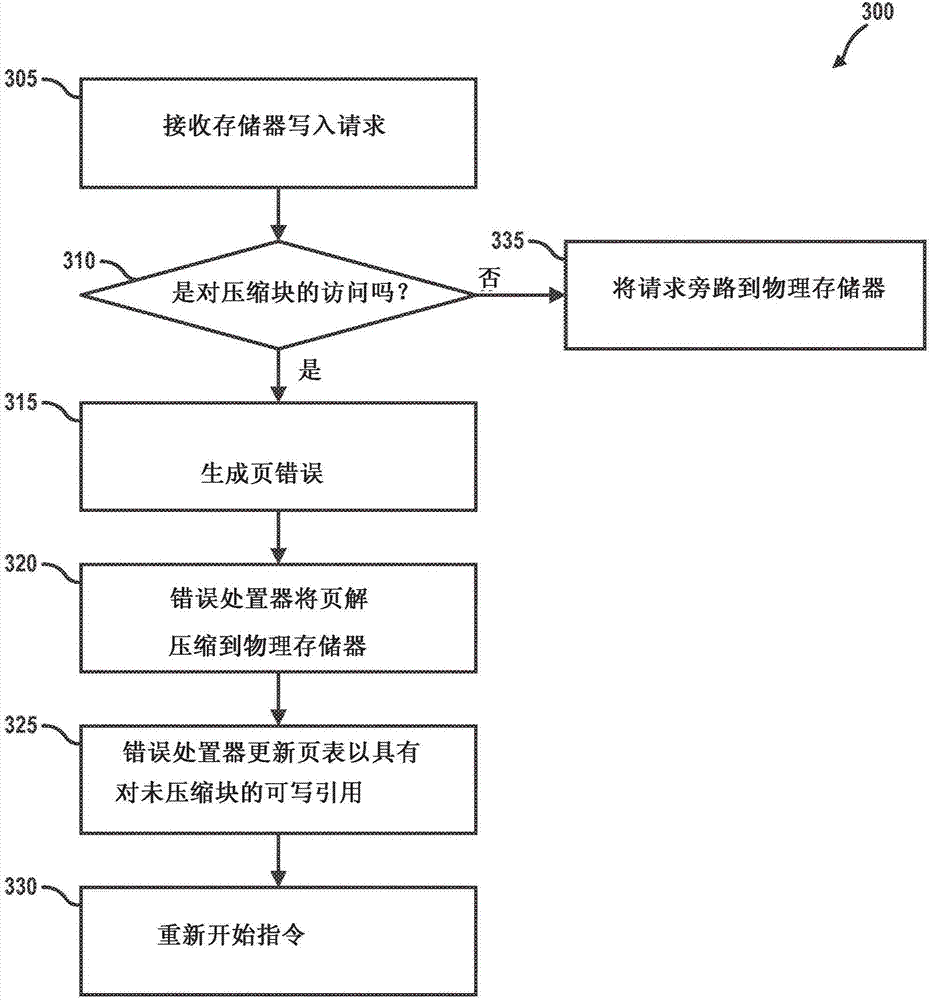

Transparent hardware-assisted memory decompression

ActiveCN107250991AMemory architecture accessing/allocationPower network operation systems integrationPhysical addressAuxiliary memory

Provided are methods and systems for memory decompression using a hardware decompressor that minimizes or eliminates the involvement of software. Custom decompression hardware is added to the memory subsystem, where the decompression hardware handles read accesses caused by, for example, cache misses or requests from devices to compressed memory blocks, by reading a compressed block, decompressing it into an internal buffer, and returning the requested portion of the block. The custom hardware is designed to determine if the block is compressed, and determine the parameters of compression, by checking unused high bits of the physical address of the access. This allows compression to be implemented without additional metadata, because the necessary metadata can be stored in unused bits in the existing page table structures.

Owner:GOOGLE LLC

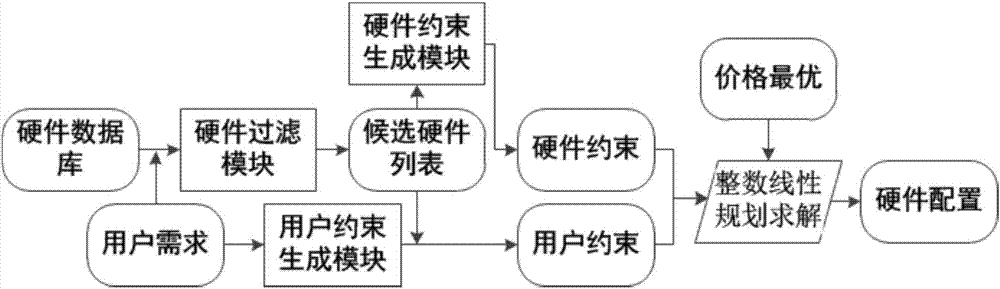

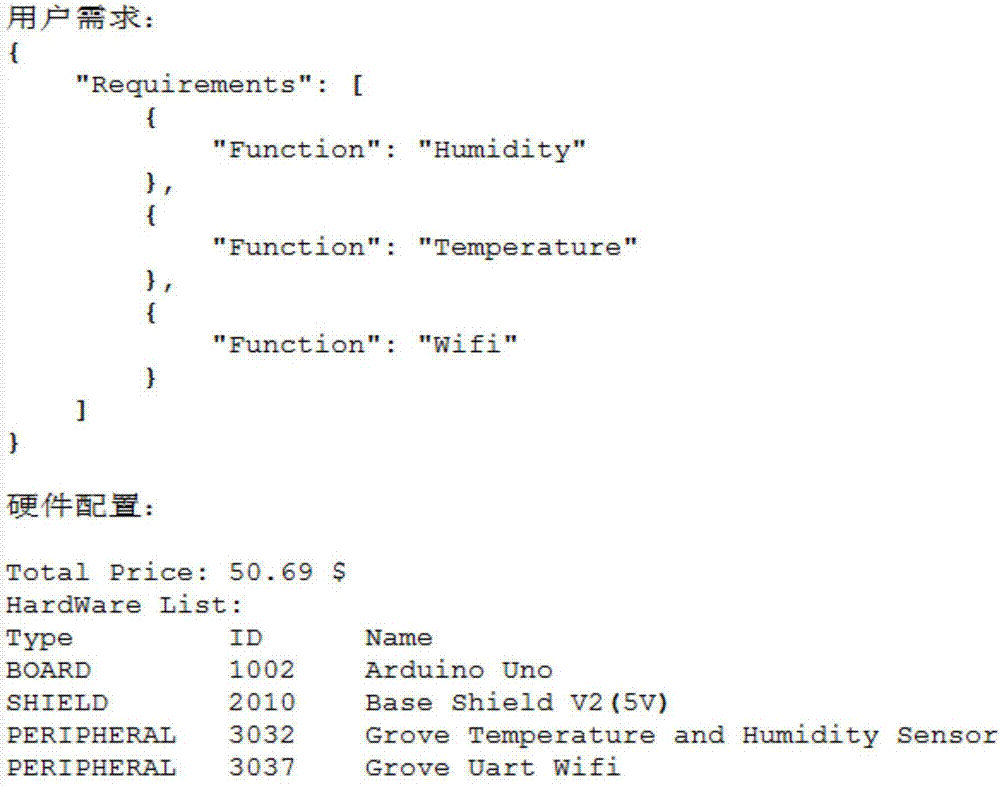

Method for automatically generating Internet-of-Things node hardware configuration

ActiveCN107992339ASpeed up the development processAccurate configurationBootstrappingProgram loading/initiatingComputer hardwareModel selection

The invention discloses a method for automatically generating Internet-of-Things node hardware configuration. The method comprises the steps that according to a user demand on an Internet-of-Things application, functionally irrelevant hardware equipment is filtered from a hardware database, a candidate equipment set is obtained through screening, and a user constraint relation corresponding to thecandidate equipment set is generated according to the user demand; meanwhile, a hardware constraint relation of the candidate equipment set is constructed based on voltage constraint, interface quantity constraint, development board uniqueness constraint and other constraint types; and a corresponding hardware list is generated based on the user constraint relation and the hardware constraint relation with a minimum hardware configuration price generated finally being an optimization goal through an integer linear programming solver. According to the method, based on the Internet-of-Things application demand provided by a user, a corresponding Internet-of-Things node hardware configuration scheme is automatically generated, the Internet-of-Things development process can be accelerated, the difficulty in hardware model selection by the user is lowered, and the effect of flexibly customizing the hardware configuration according to the demand is achieved.

Owner:ZHEJIANG UNIV

Configurable communication template for designing and implementing an accelerator

InactiveUS20050273542A1Improve performanceMinimal timeCAD circuit designArchitecture with single central processing unitControl flowData control

A system and method of designing an accelerator for a processor-based system. The accelerator design problem is partitioned into a data communicate module design problem and a data compute core module design problem. The hardware design of the data communicate module is achieved through a predetermined communication template which is customized for the particular application. The communication template has individual configurable communication components and a programmable control flow path. The components of the communicate template include a host bus interface, a memory bus interface, a direct memory access, a local memory and a control module. The combination of the communication components in a single configurable communication template and their optimized interconnections increase the speed of data transfer and data control processes in the accelerator. The hardware design of the data compute core module can be achieved through custom hardware design or by automatically generating hardware from software description.

Owner:POSEIDON DESIGN SYST

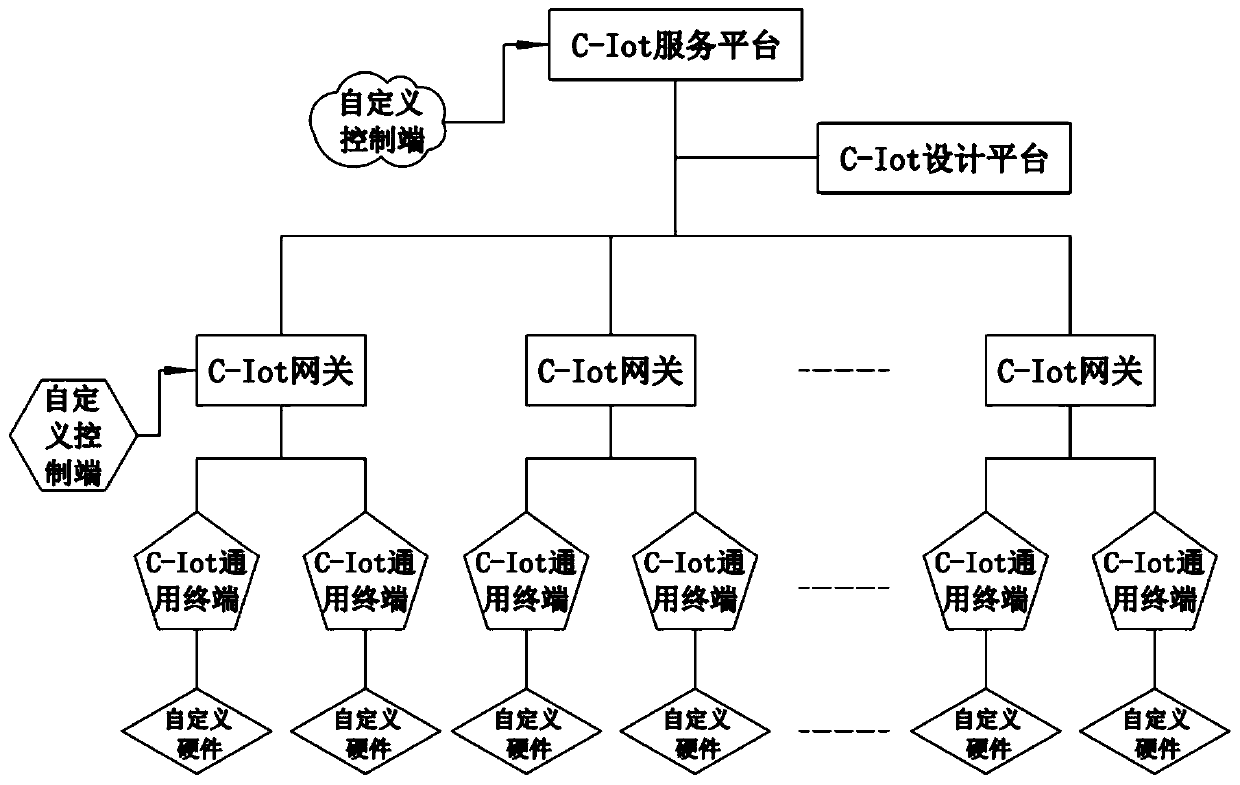

Management and control method and device for open Internet of Things platform

InactiveCN109995578AConvenient remote debuggingGuaranteed uptimeData switching networksSoftware deploymentProcess logicThe Internet

The invention relates to a management and control method for an open Internet of Things platform. The management and control method comprises the following steps: B1, providing at least one gateway toaccess one or more Internet of Things universal terminals in a communication manner; B2, receiving an input signal sent by an input unit of the custom hardware in real time through the Internet of Things universal terminal, and reporting the input signal to the gateway; B3, processing logic operation and data processing by an application program associated with the input unit in a gateway or an Internet of Things universal terminal according to the reported input signal, and sending an execution signal to a target execution unit; and B4, recording an execution result by the gateway and / or theuniversal terminal, and monitoring an application program execution process by the cloud service platform according to needs. The invention also relates to a computer device and a medium for implementing the method. According to the technical scheme, the development process of the Internet of Things application program is simplified, and the development threshold is lowered; the cloud computing service is integrated, and the Internet of Things application program which is open, convenient to publish and stable in operation is provided.

Owner:珠海市横琴新区芯云平台科技有限公司

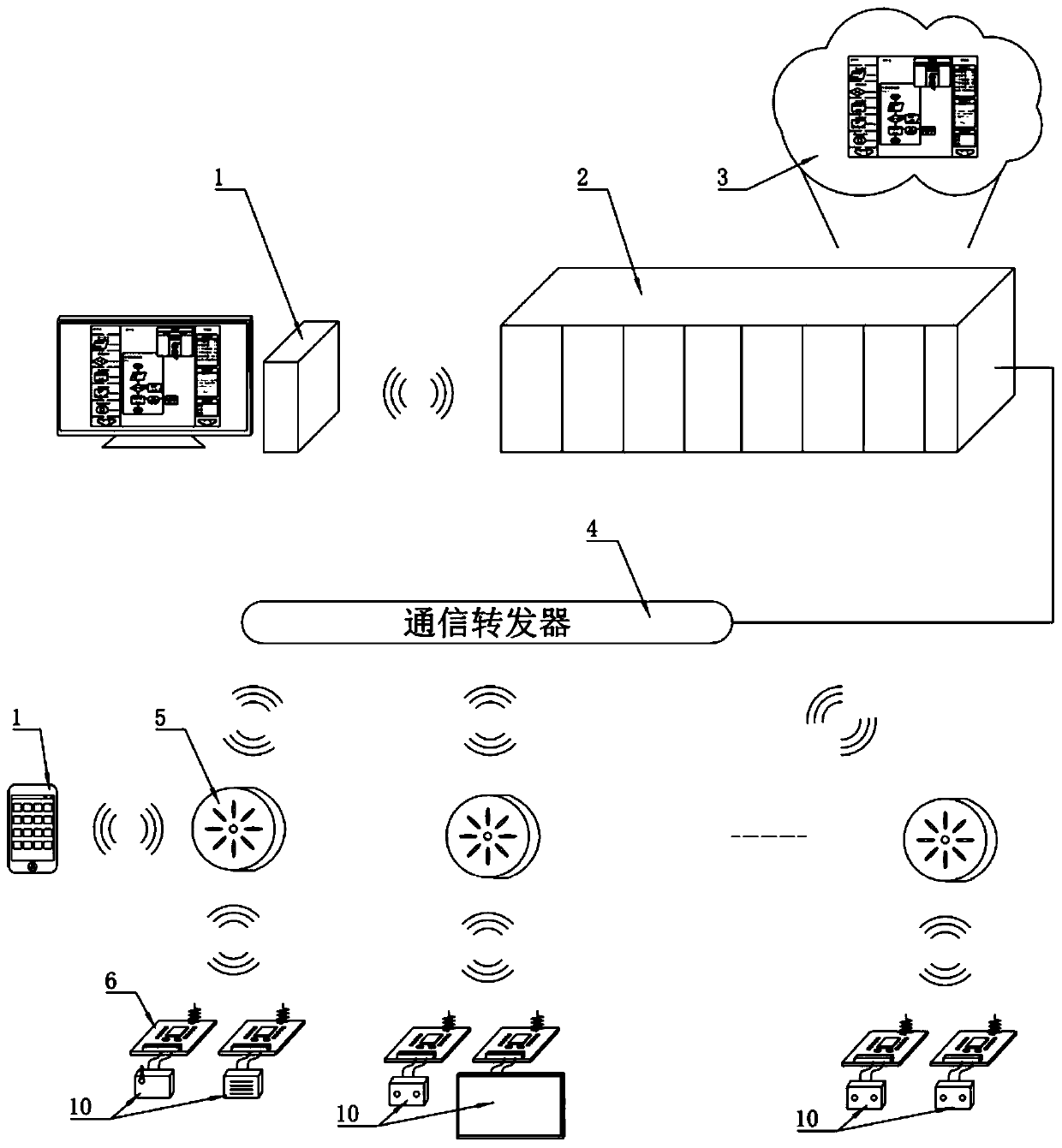

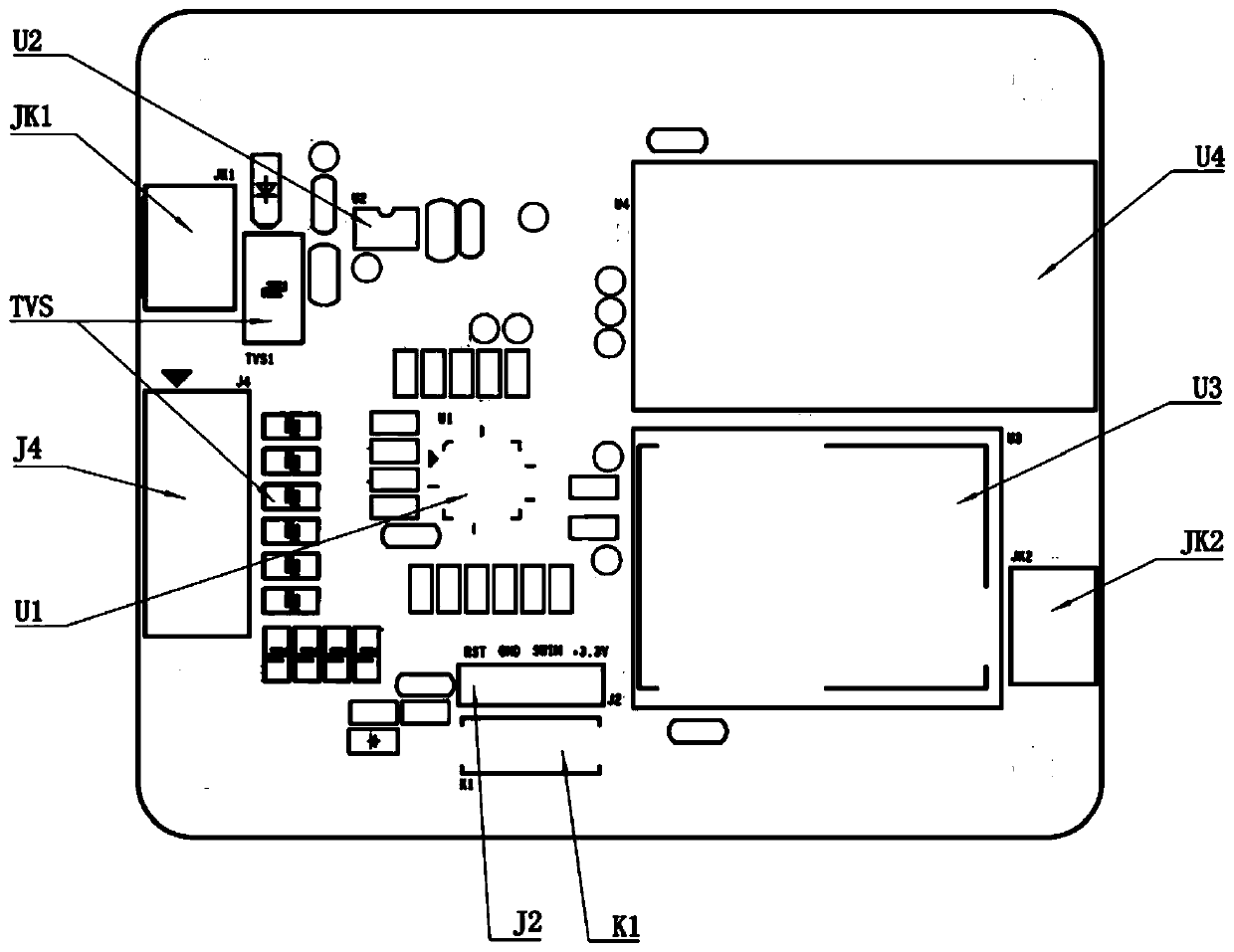

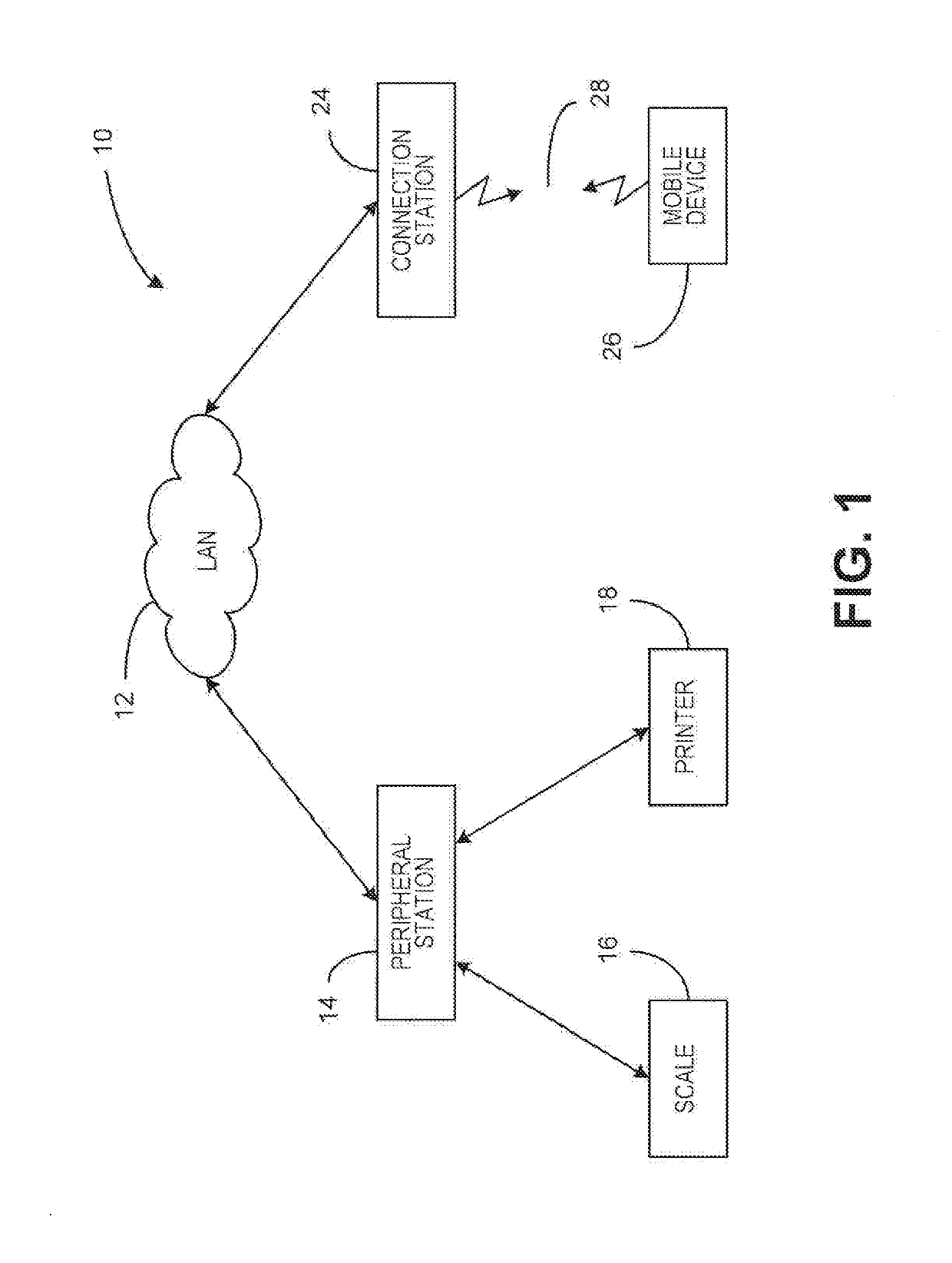

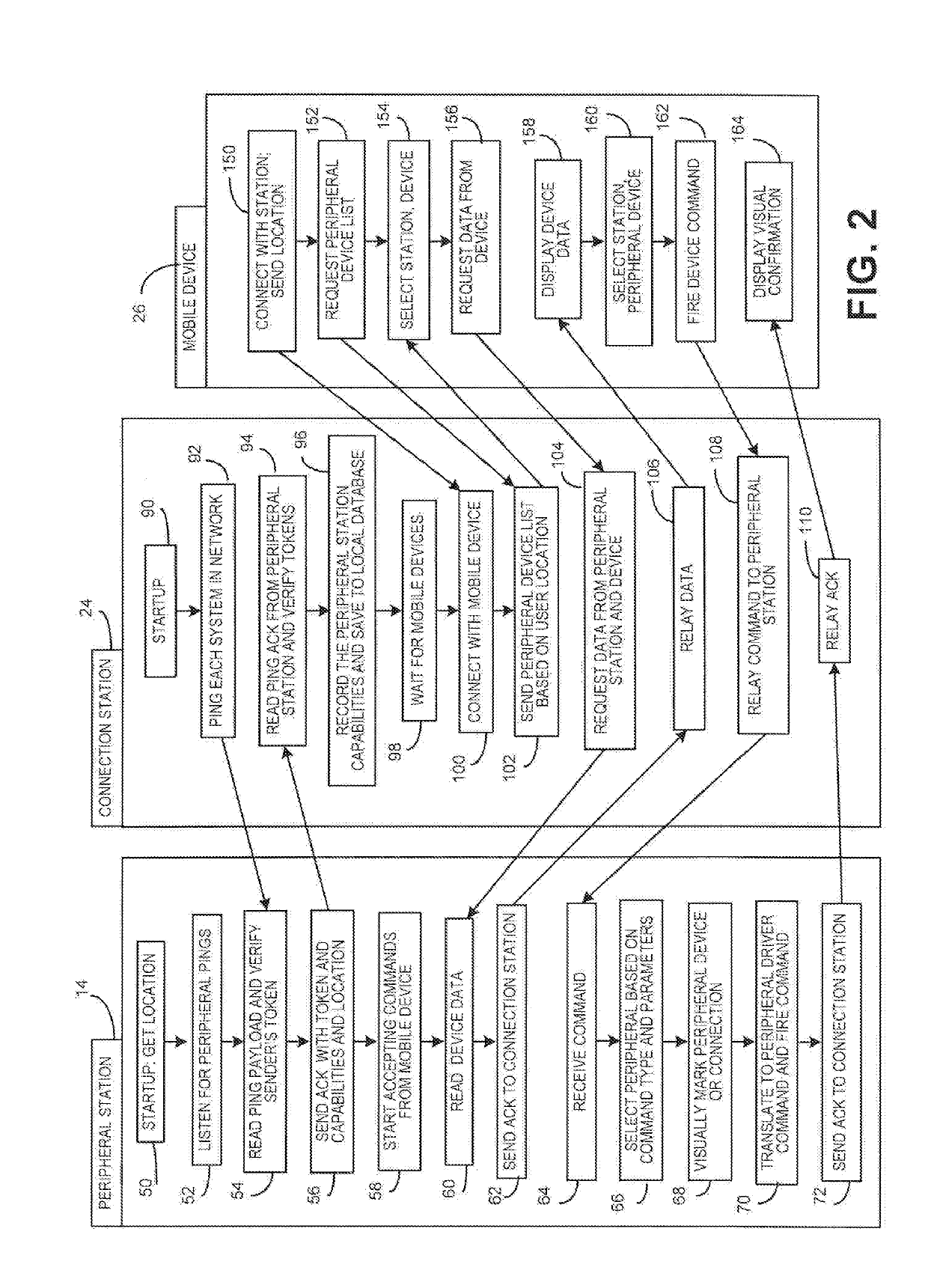

Method and system for mobile devices to communicate with shipping peripheral devices using distributed instances of custom hardware

InactiveUS20190114845A1Overcome problemsVisual presentation using printersFranking apparatusComputer hardwareApplication software

A system and method for mobile devices that do not have hardware interfaces to be able to control shipping peripheral devices that are not connected directly thereto are provided. Intermediary hardware devices are utilized that are connected to a local area network. A first device communicates with the user's mobile device using very-short range communication protocols. A second device has the peripheral devices directly coupled thereto, and includes preinstalled drivers and application software for the peripheral devices. The devices allow the mobile device and peripheral devices to communicate with each other over the local area network. Thus, the mobile device can be used to control the peripheral devices even though the peripheral devices are not directly connected to the mobile device.

Owner:PITNEY BOWES INC

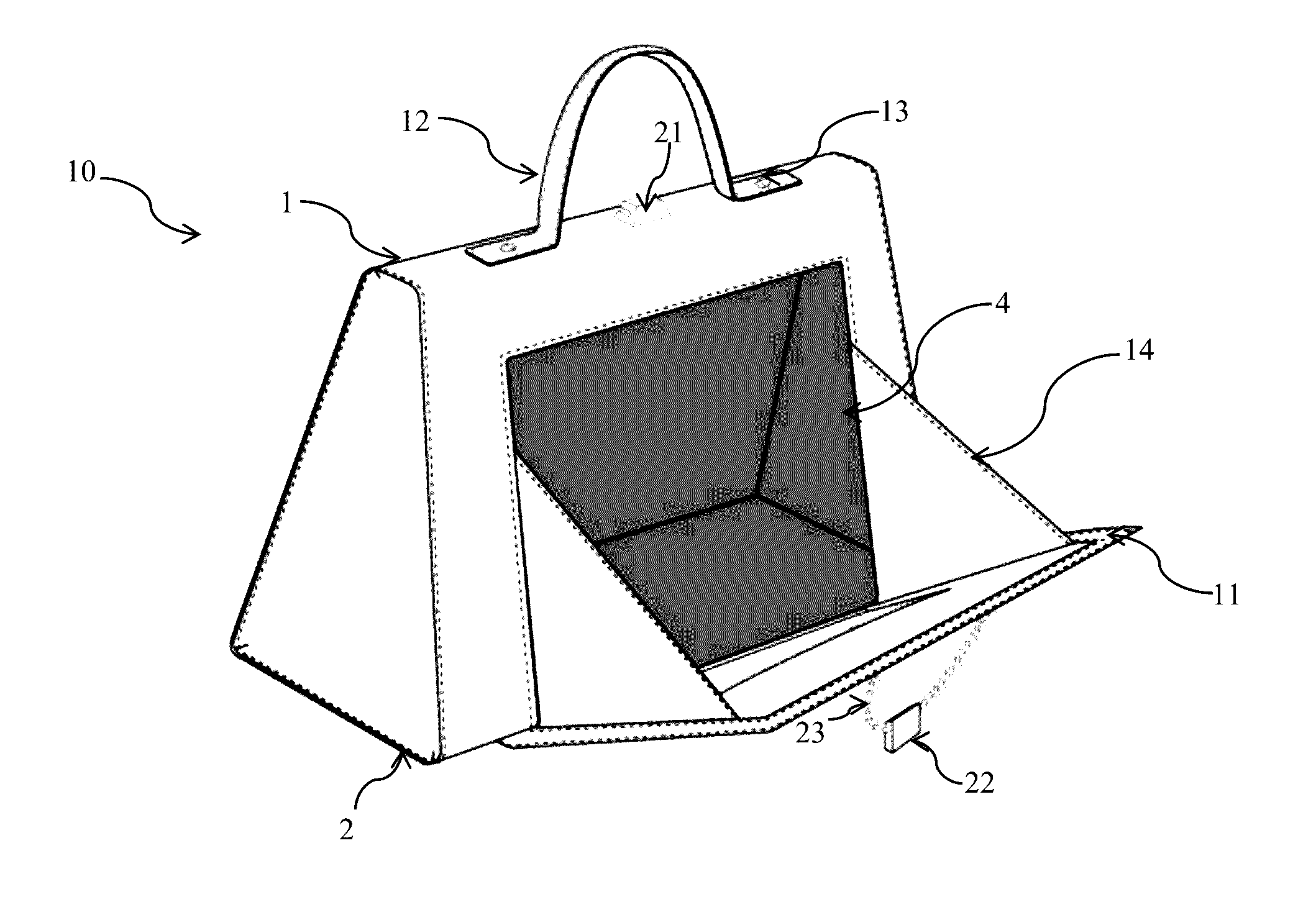

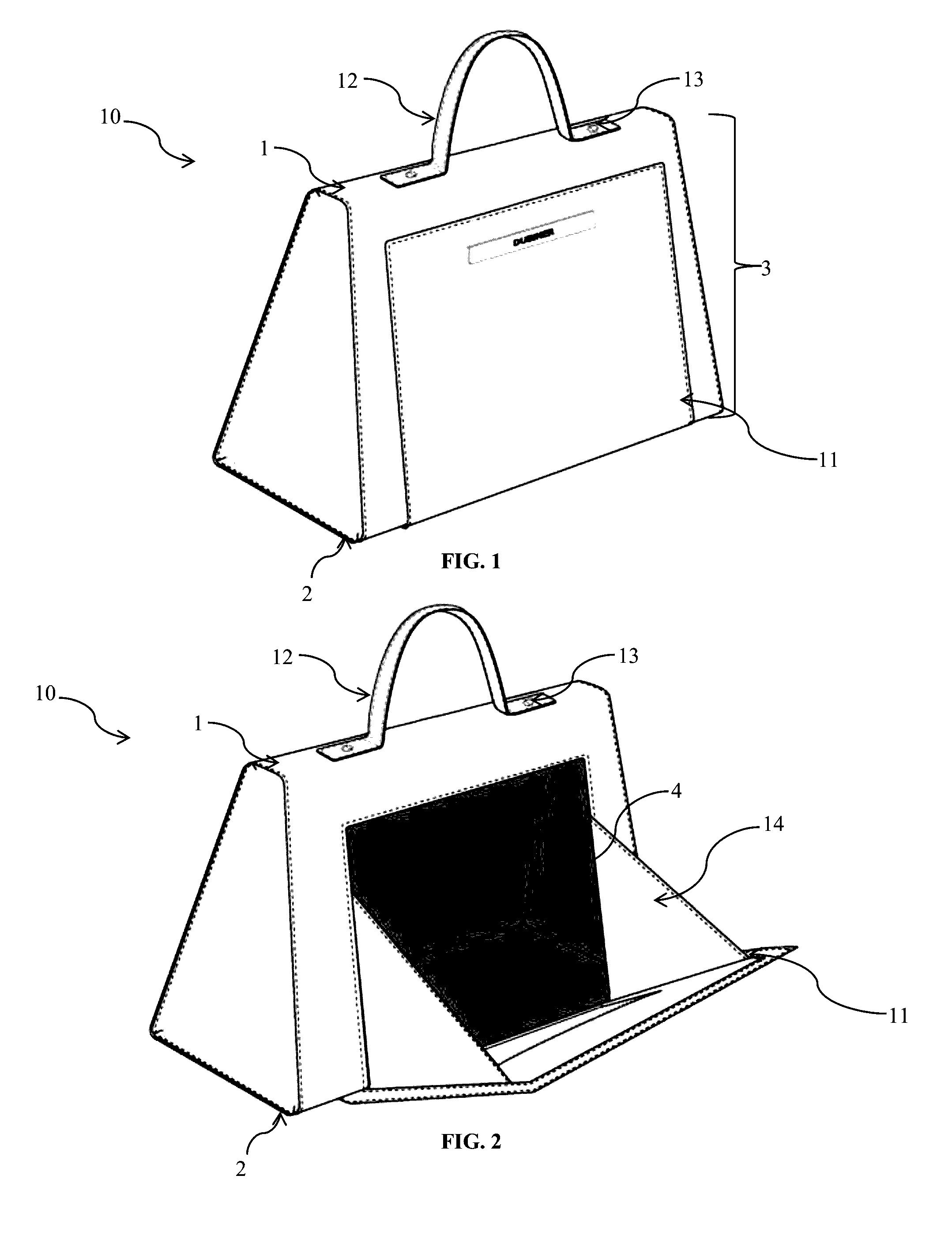

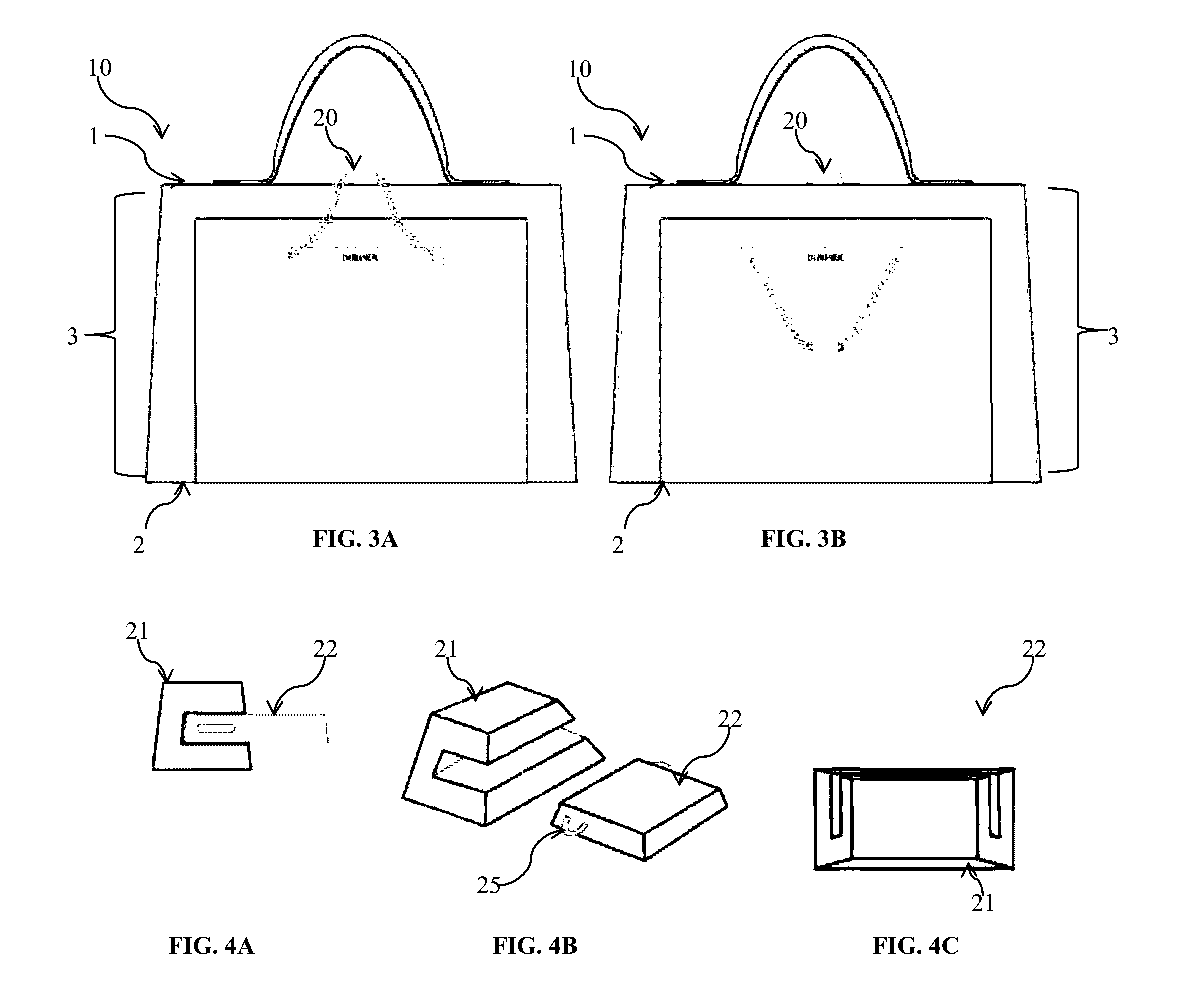

Handbag With Drop Style Opening and Custom Hardware

Owner:DUBINER LLC