Patents

Literature

200 results about "Satisfiability" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

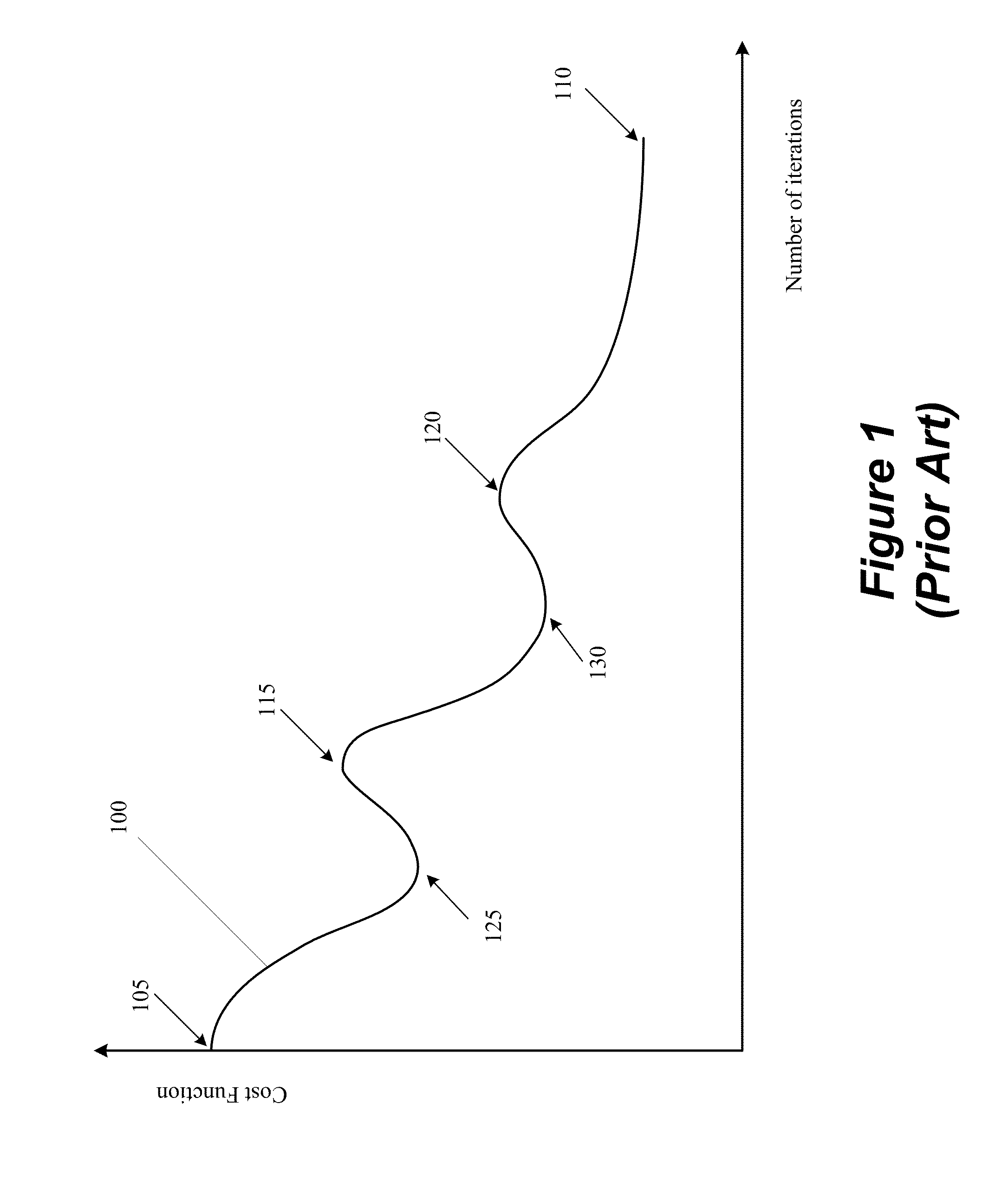

In mathematical logic, satisfiability and validity are elementary concepts of semantics. A formula is satisfiable if it is possible to find an interpretation (model) that makes the formula true. A formula is valid if all interpretations make the formula true. The opposites of these concepts are unsatisfiability and invalidity, that is, a formula is unsatisfiable if none of the interpretations make the formula true, and invalid if some such interpretation makes the formula false. These four concepts are related to each other in a manner exactly analogous to Aristotle's square of opposition.

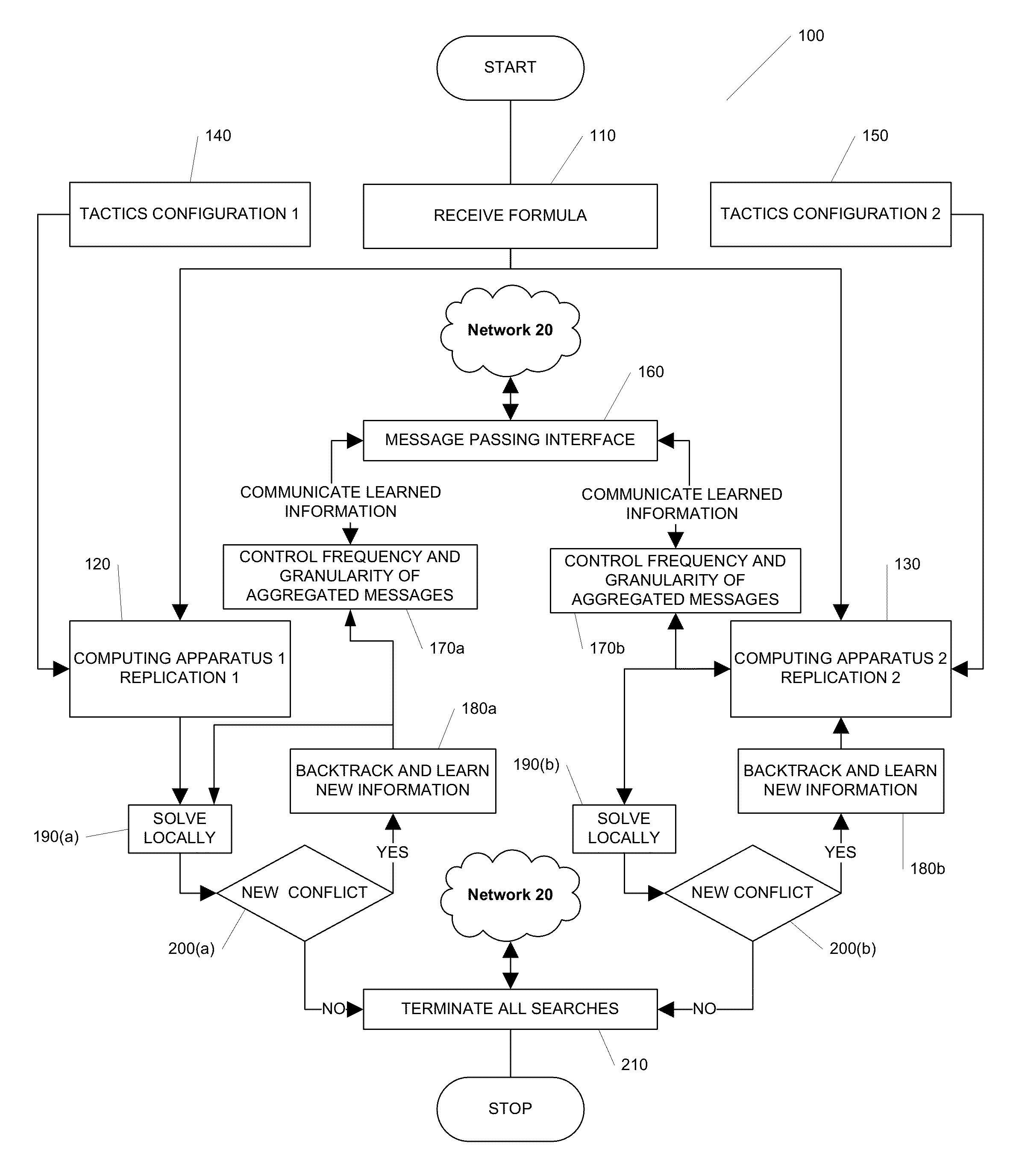

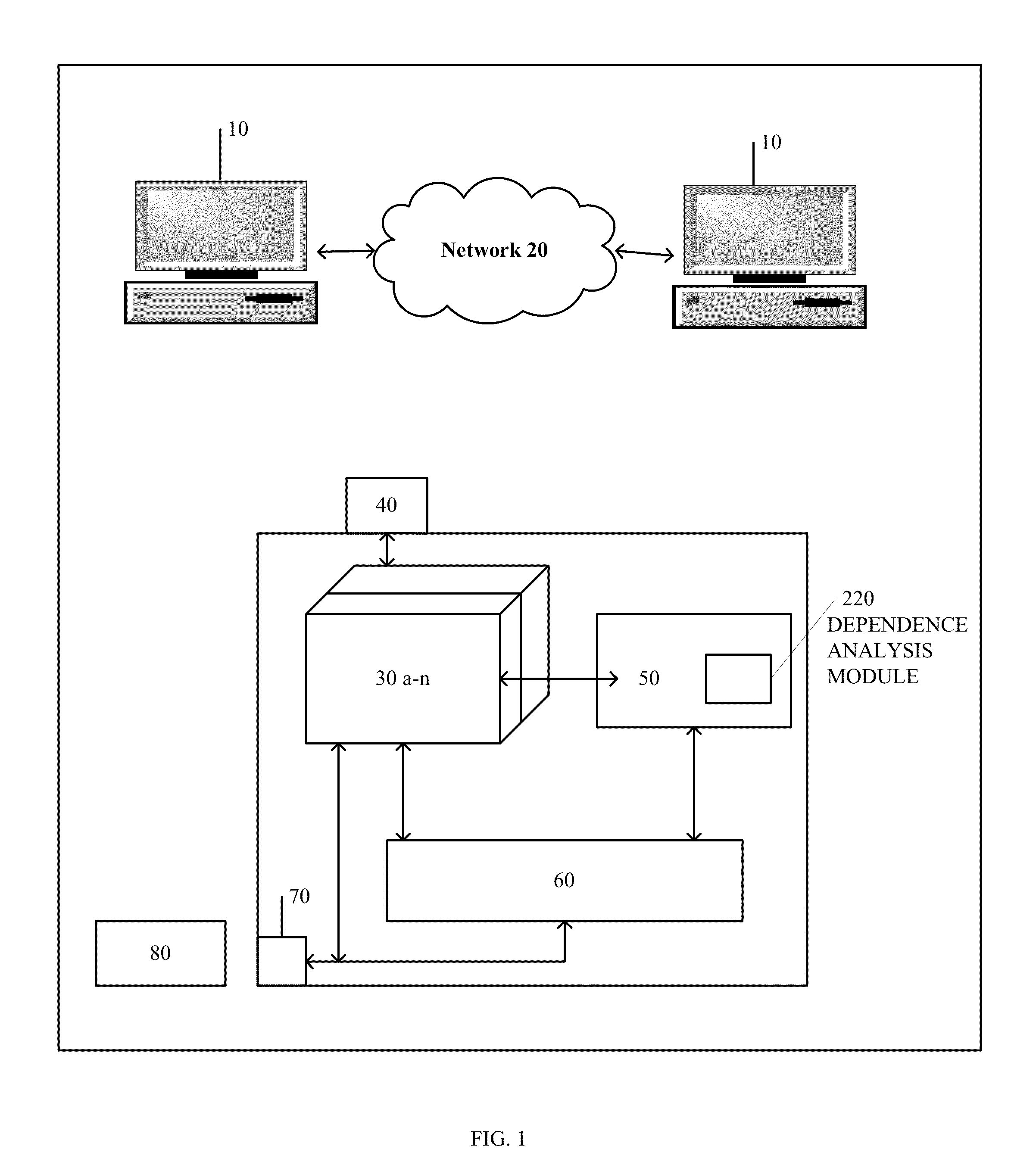

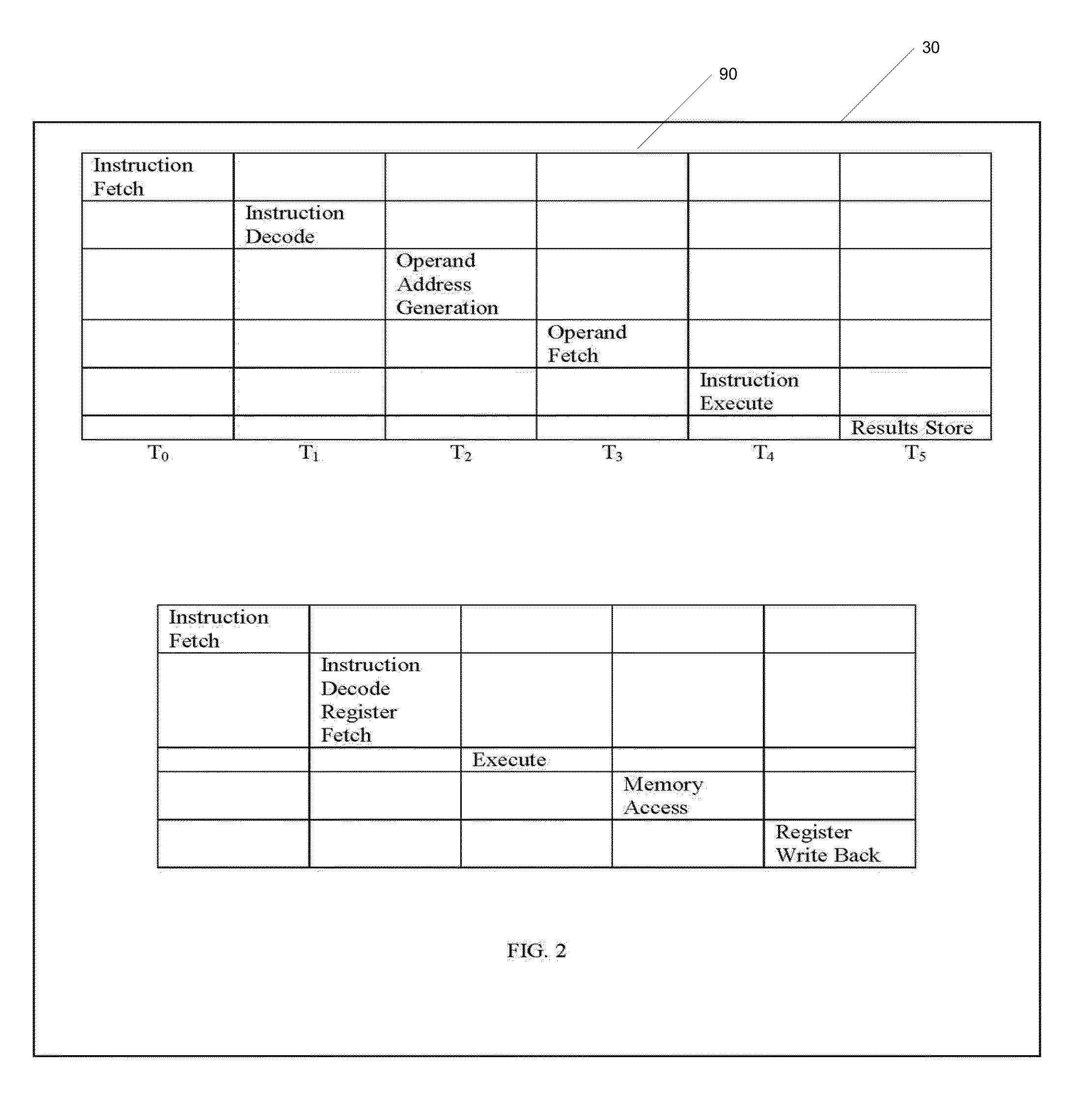

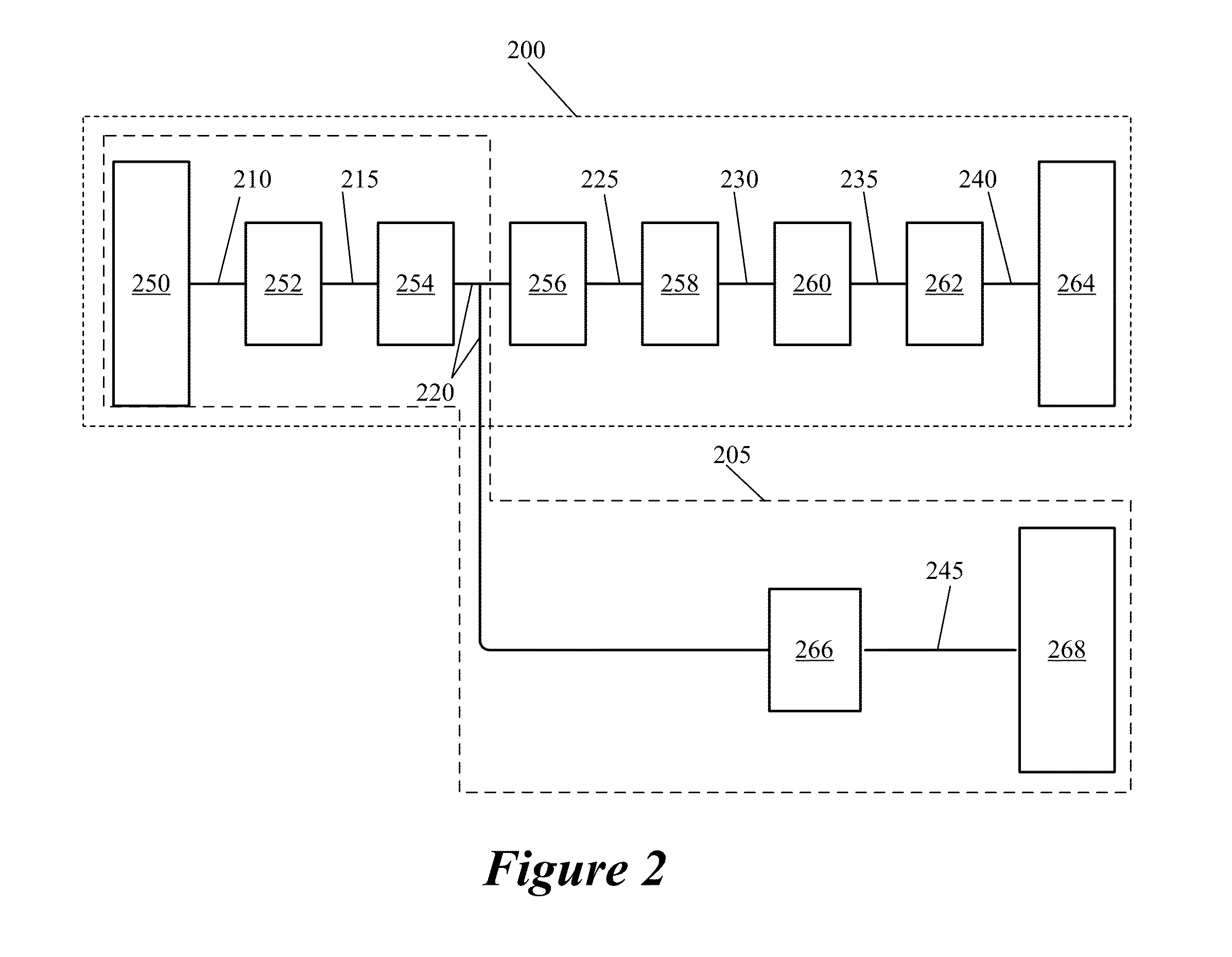

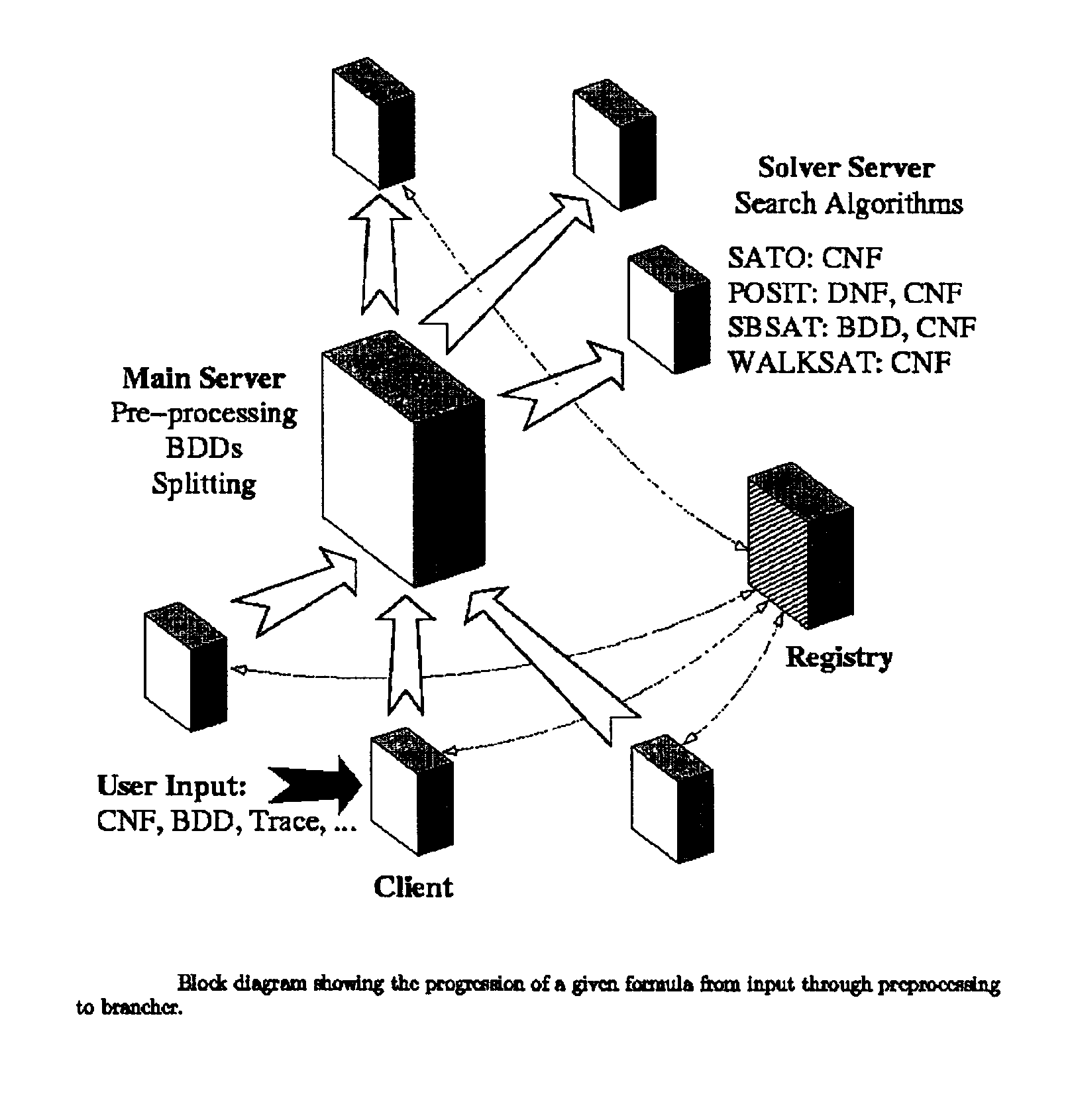

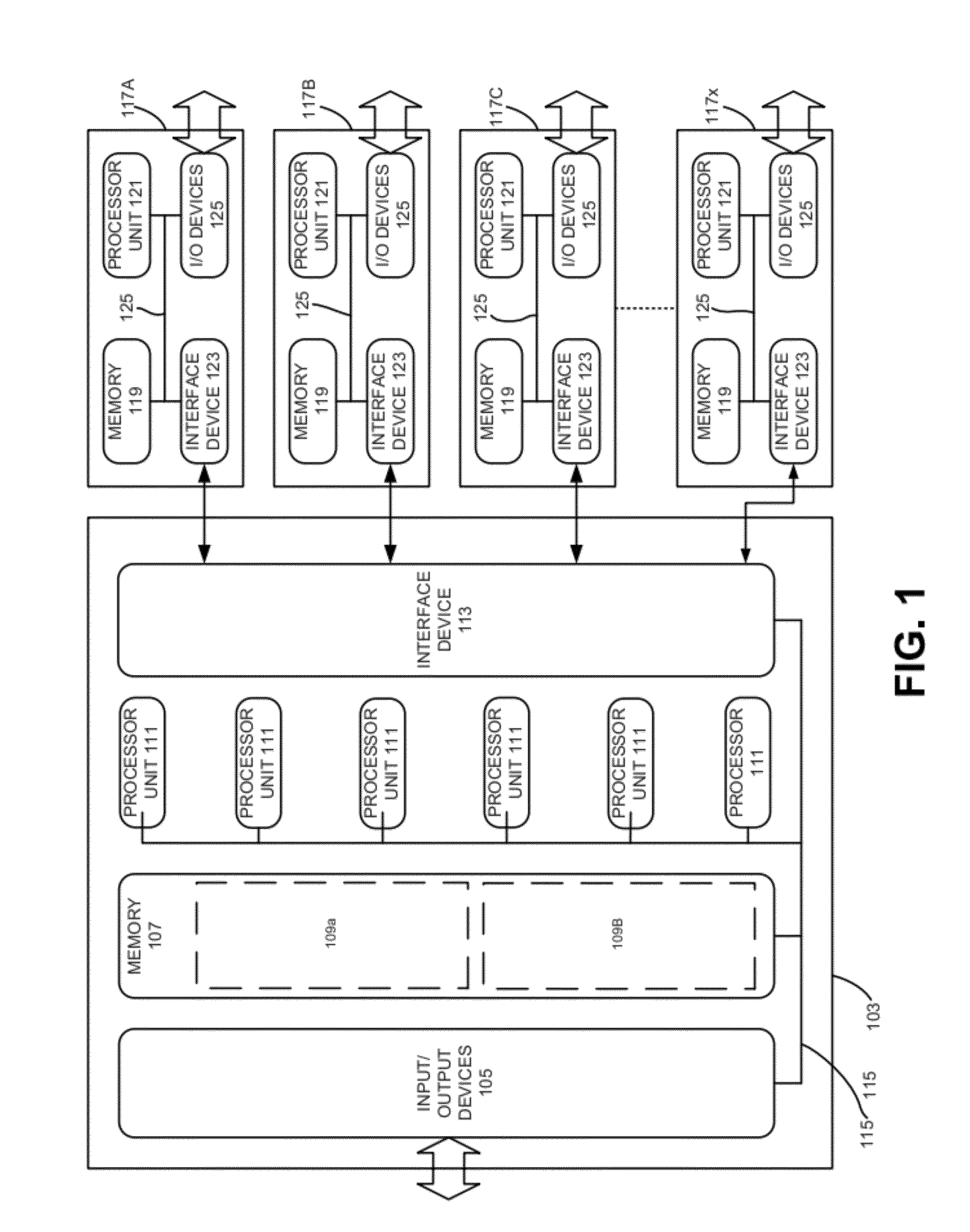

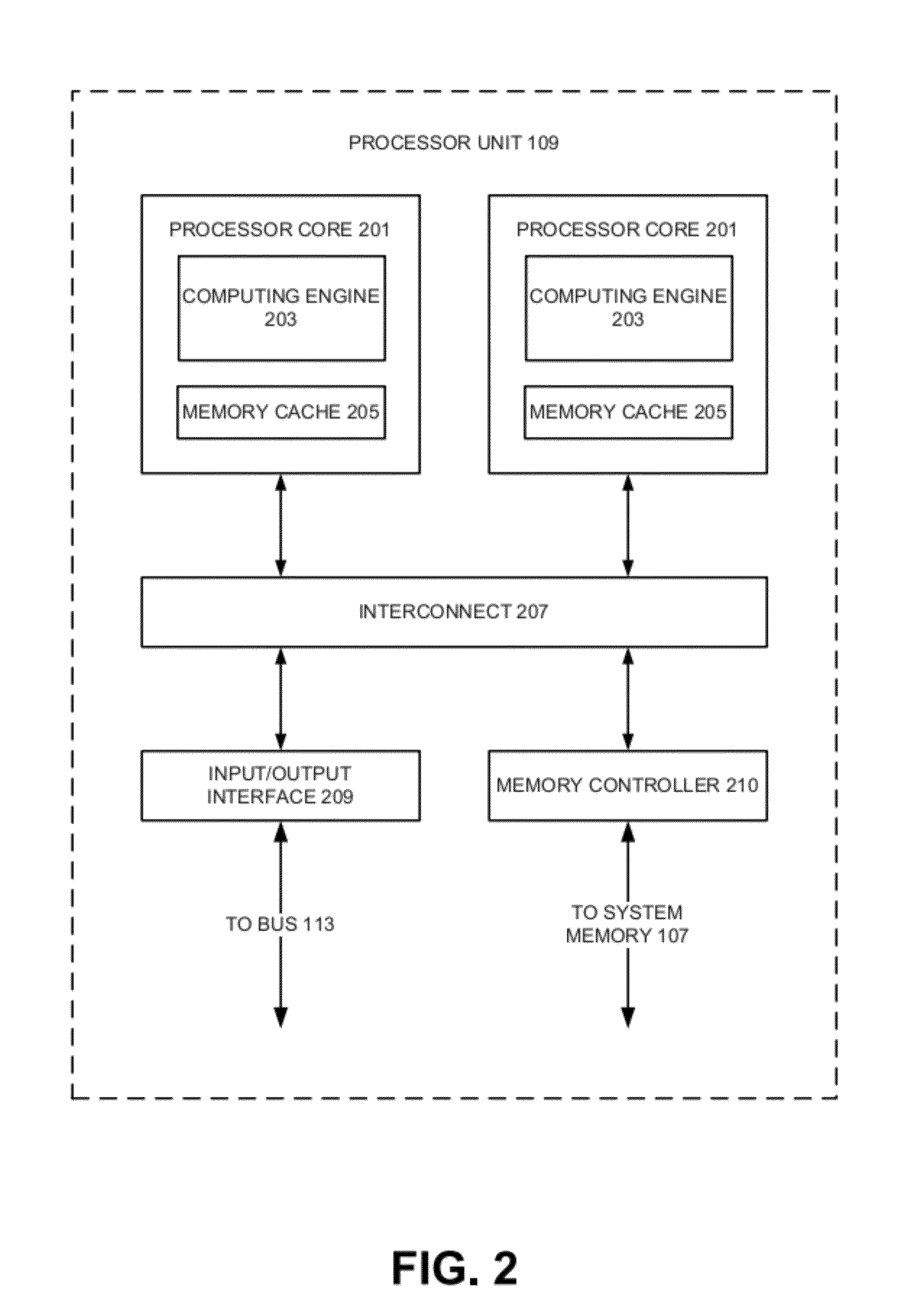

Systems, methods and apparatus for distributed decision processing

Methods, apparatus, and computer software product for making a decision based on the semantics of formal logic are provided. In an exemplary embodiment, two custom computing apparatuses are used to resolve the satisfiability of a logical formula and provide an example. In this embodiment, the two custom computing apparatuses operate in concert to explore the space of possible satisfying examples. This Abstract is provided for the sole purpose of complying with the Abstract requirement rules. This Abstract is submitted with the explicit understanding that it will not be used to interpret or to limit the scope or the meaning of the claims.

Owner:QUALCOMM TECHNOLOGIES INC

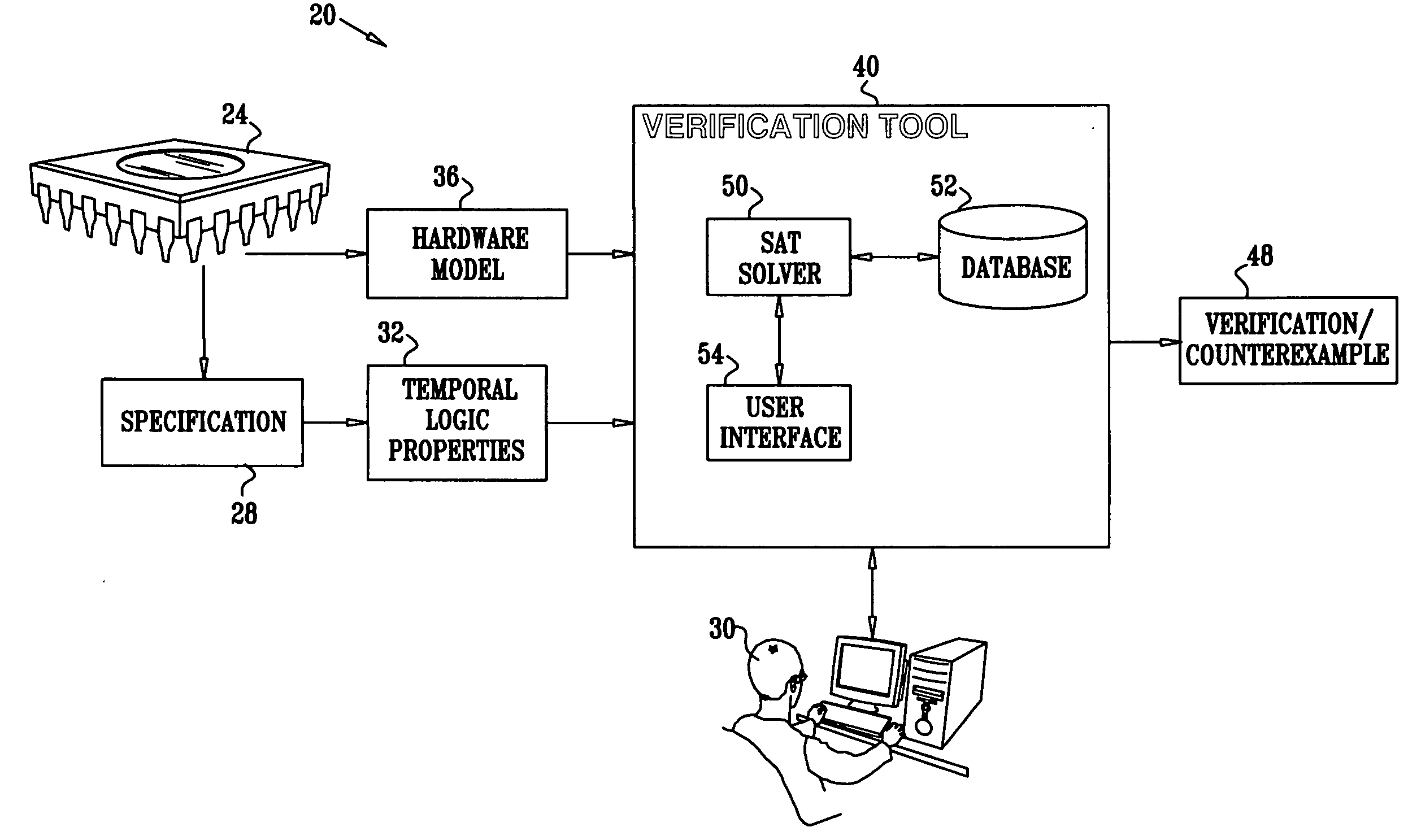

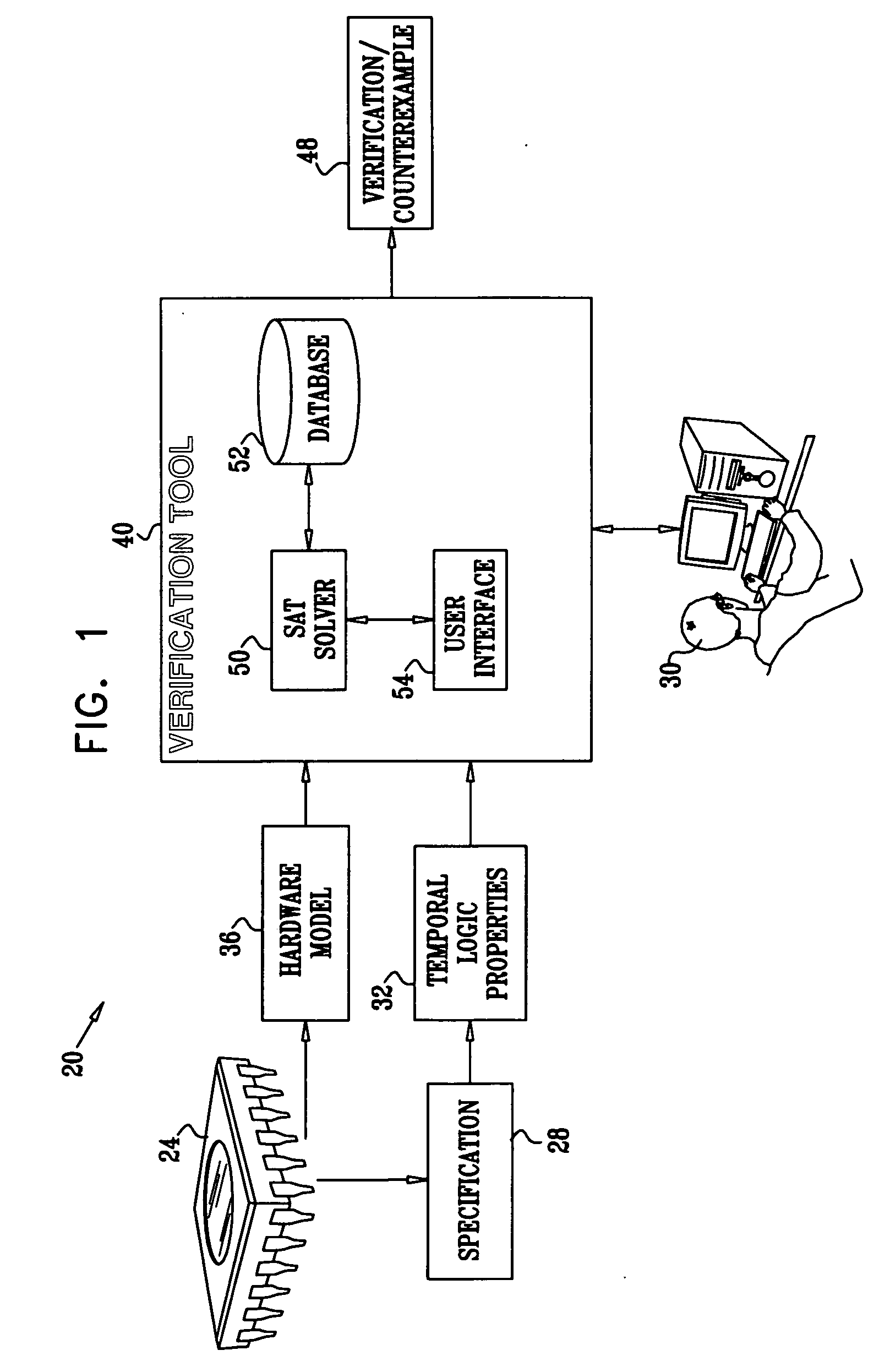

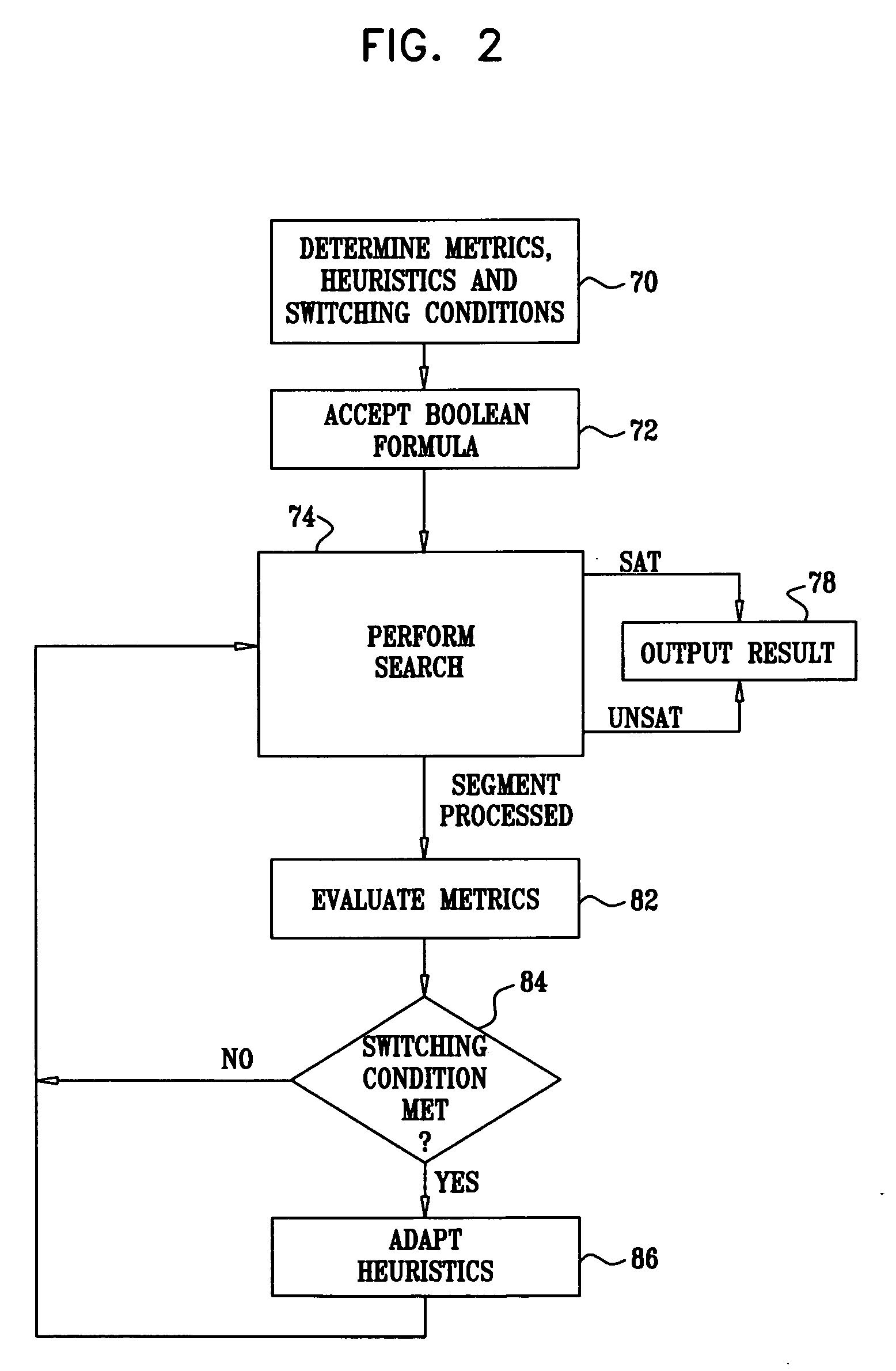

Adaptive application of SAT solving techniques

InactiveUS20070011629A1Computer aided designSoftware simulation/interpretation/emulationValue assignmentGoal system

A computer-implemented method for solving a satisfiability (SAT) problem includes defining a formula, including variables, which refers to properties of a target system. Using a chosen search strategy, a search process is performed over possible value assignments of the variables for a satisfying assignment that satisfies the formula. A performance metric estimating an effectiveness of the search process is periodically evaluated during the search process. The strategy of the search process is modified responsively to the evaluated performance metric. The method determines, using the search process, whether the formula is satisfiable on the target system.

Owner:GOOGLE LLC

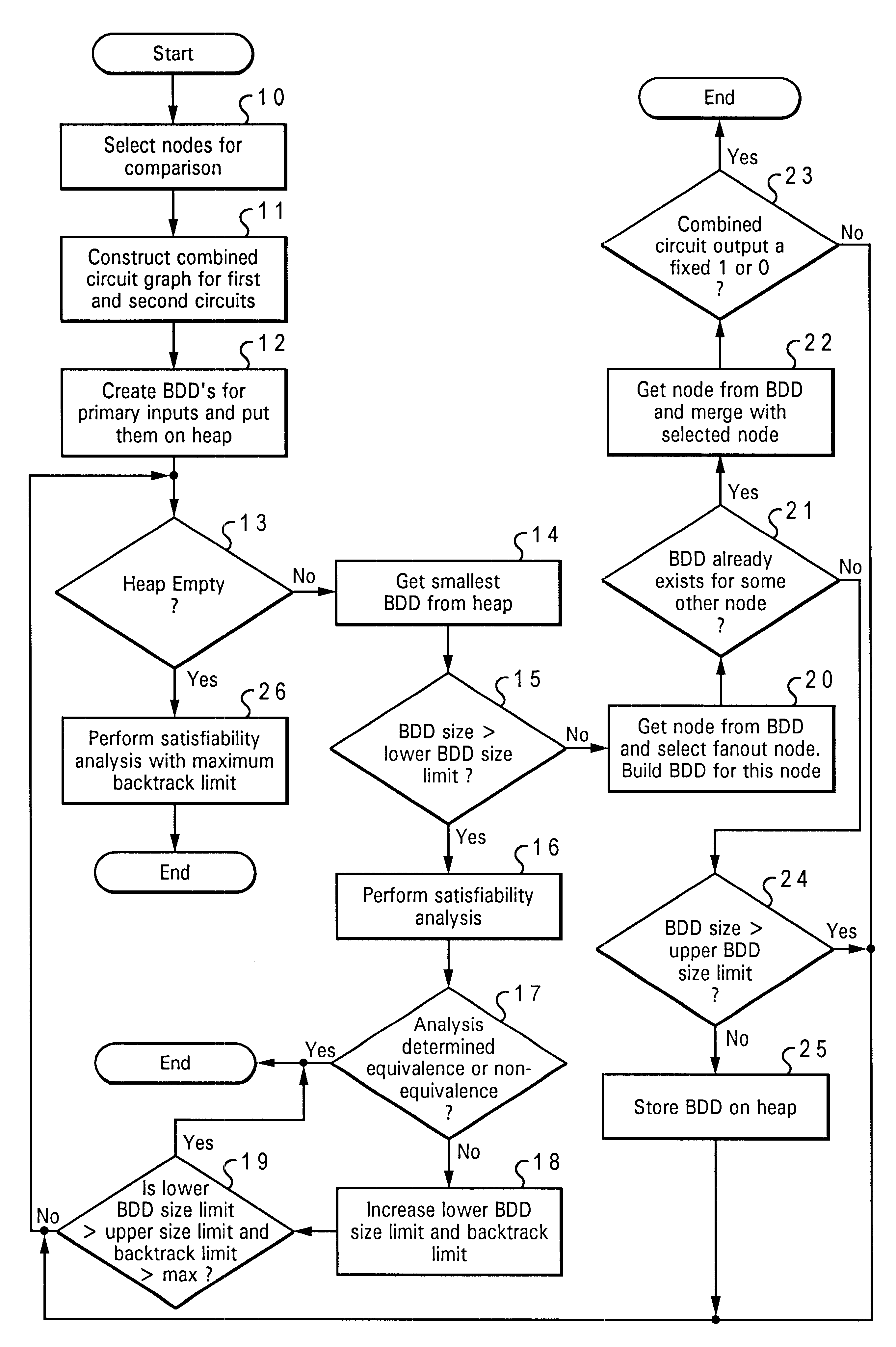

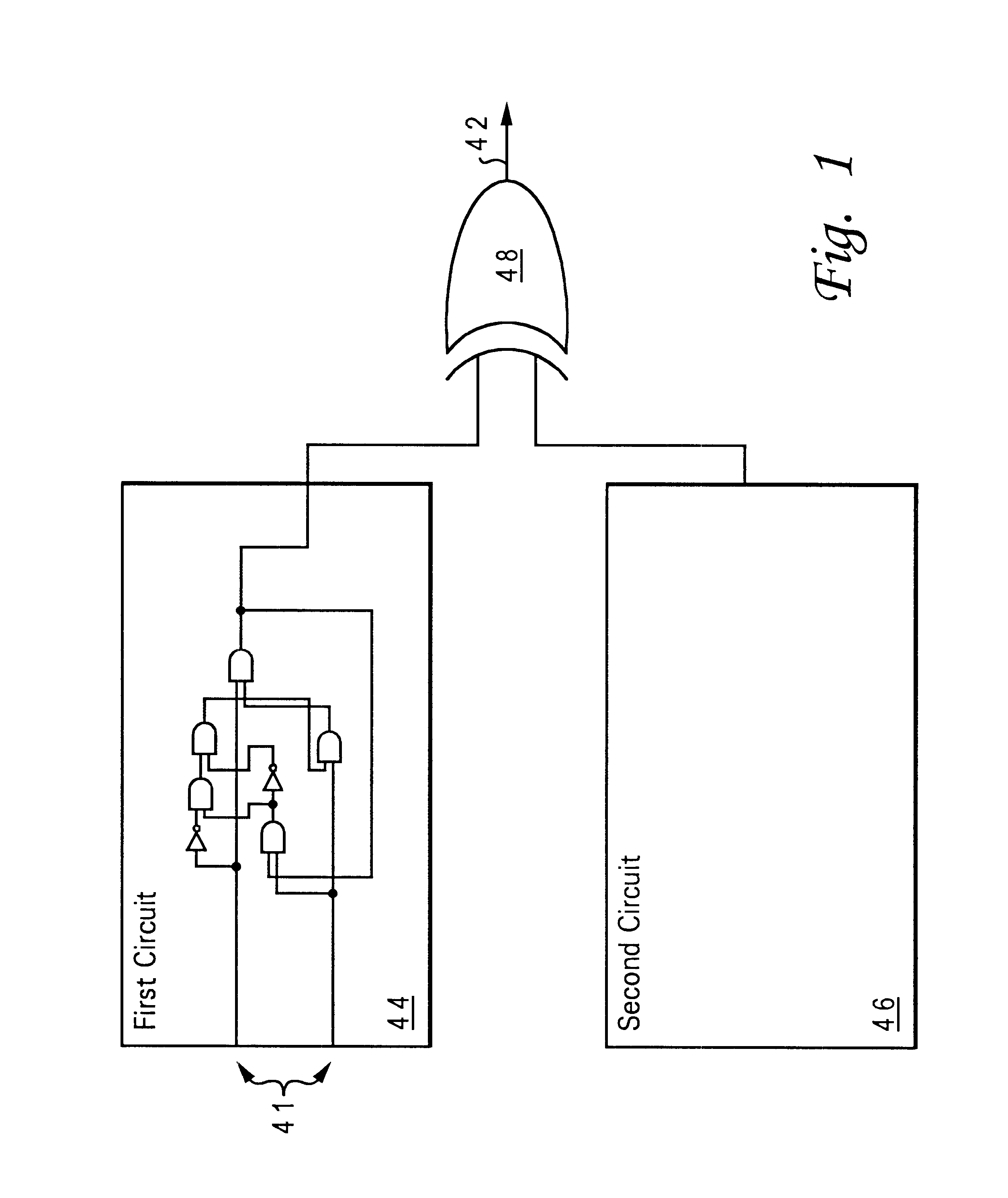

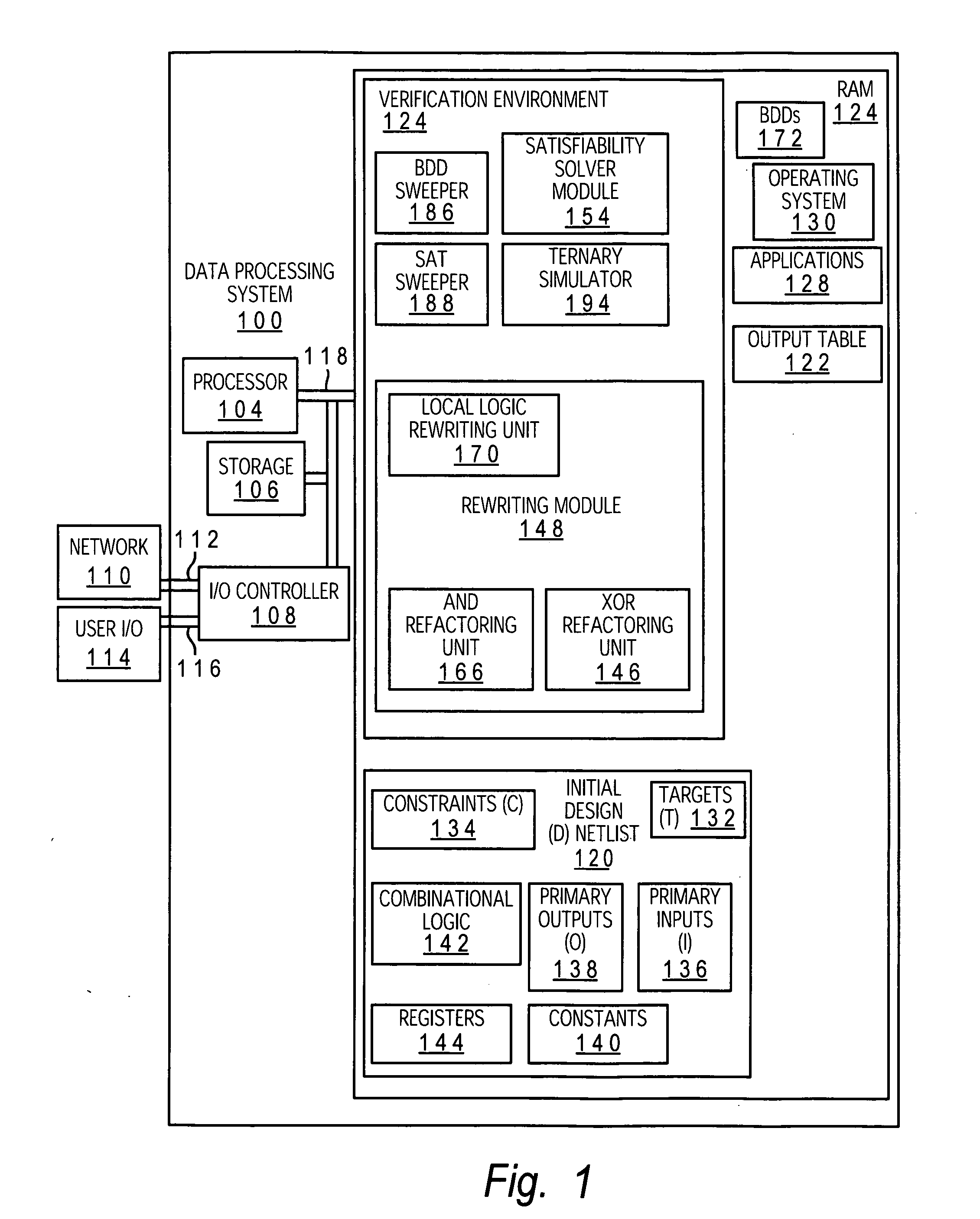

Method and system for equivalence-checking combinatorial circuits using interative binary-decision-diagram sweeping and structural satisfiability analysis

InactiveUS6473884B1Computer aided designSoftware simulation/interpretation/emulationBinary decision diagramLogical network

A method and system for equivalence checking of logical circuits using iterative circuit reduction and satisfiability techniques provide improved performance in computer-based verification and design tools. By intertwining a structural satisfiability solver and binary decision diagram functional circuit reduction method, computer-based tools can make more efficient use of memory and decrease computation time required to equivalence check large logical networks. Using the circuit reduction technique back-to-back with the simulation technique, optimum local and global circuit reduction are simultaneously achieved. By iterating between the structural and functional techniques, and adjusting the size of sub-networks being analyzed within a larger network, sub-networks can be reduced or eliminated, decreasing the amount of memory required to represent the next larger inclusive network.

Owner:IBM CORP

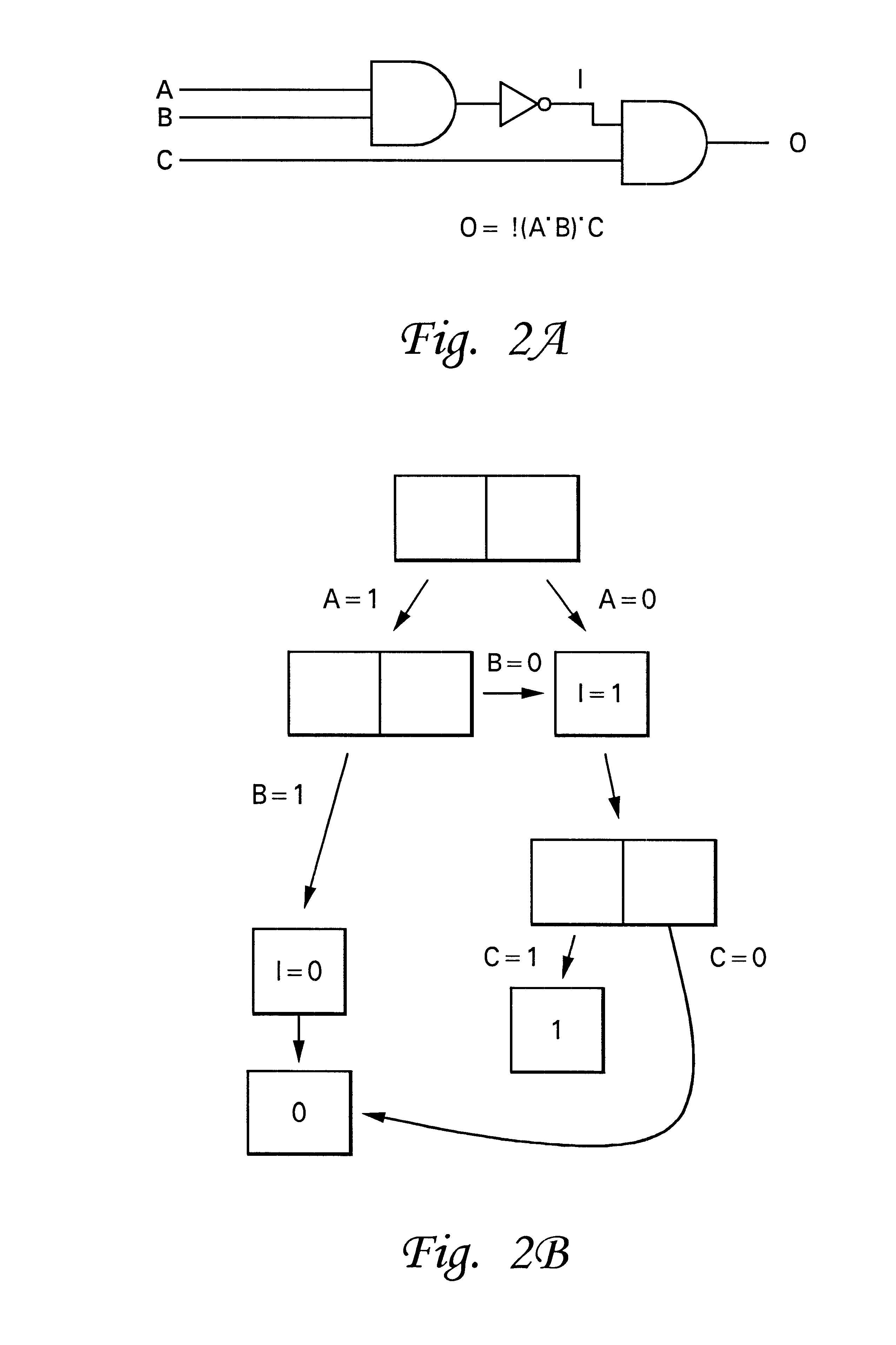

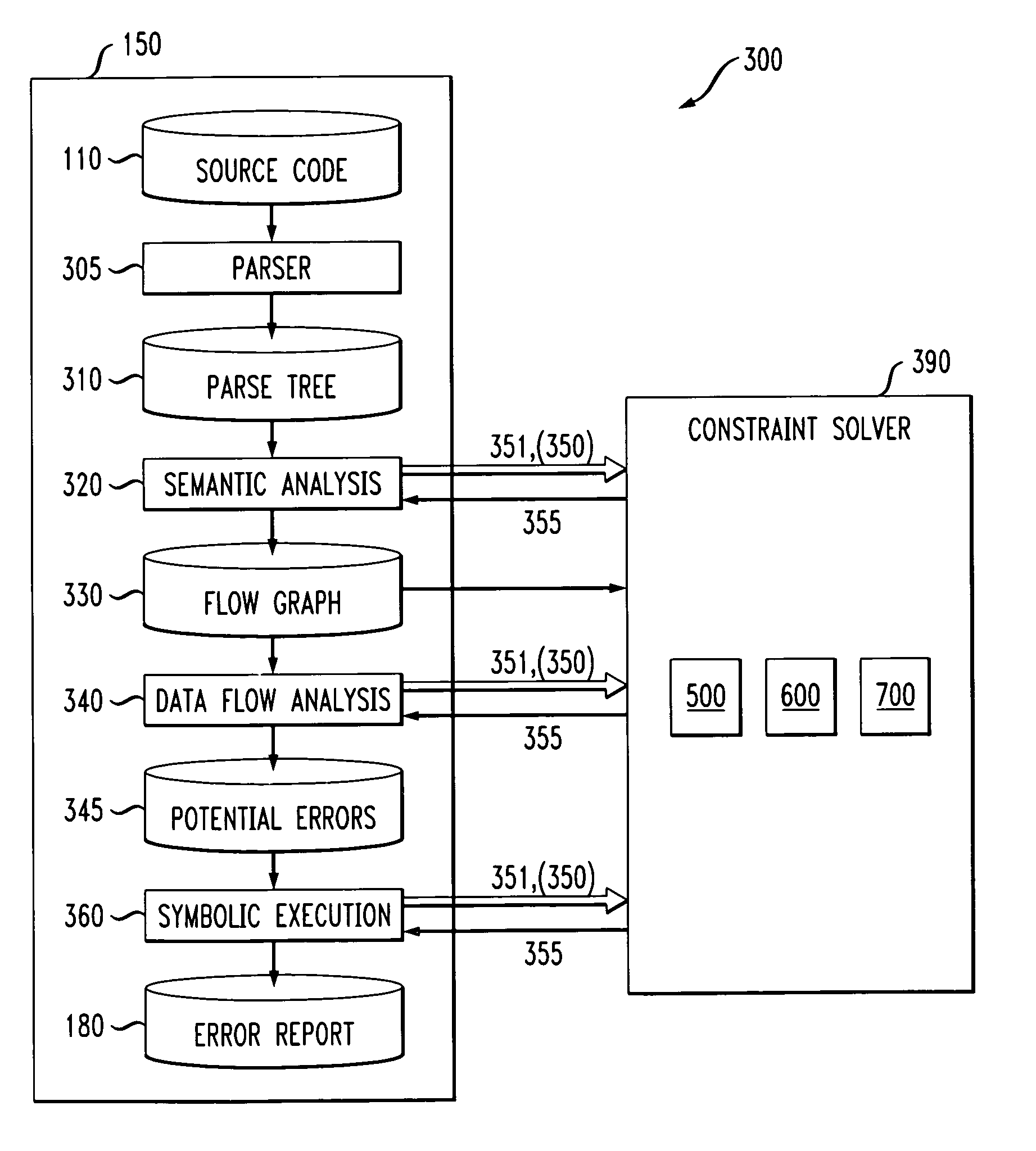

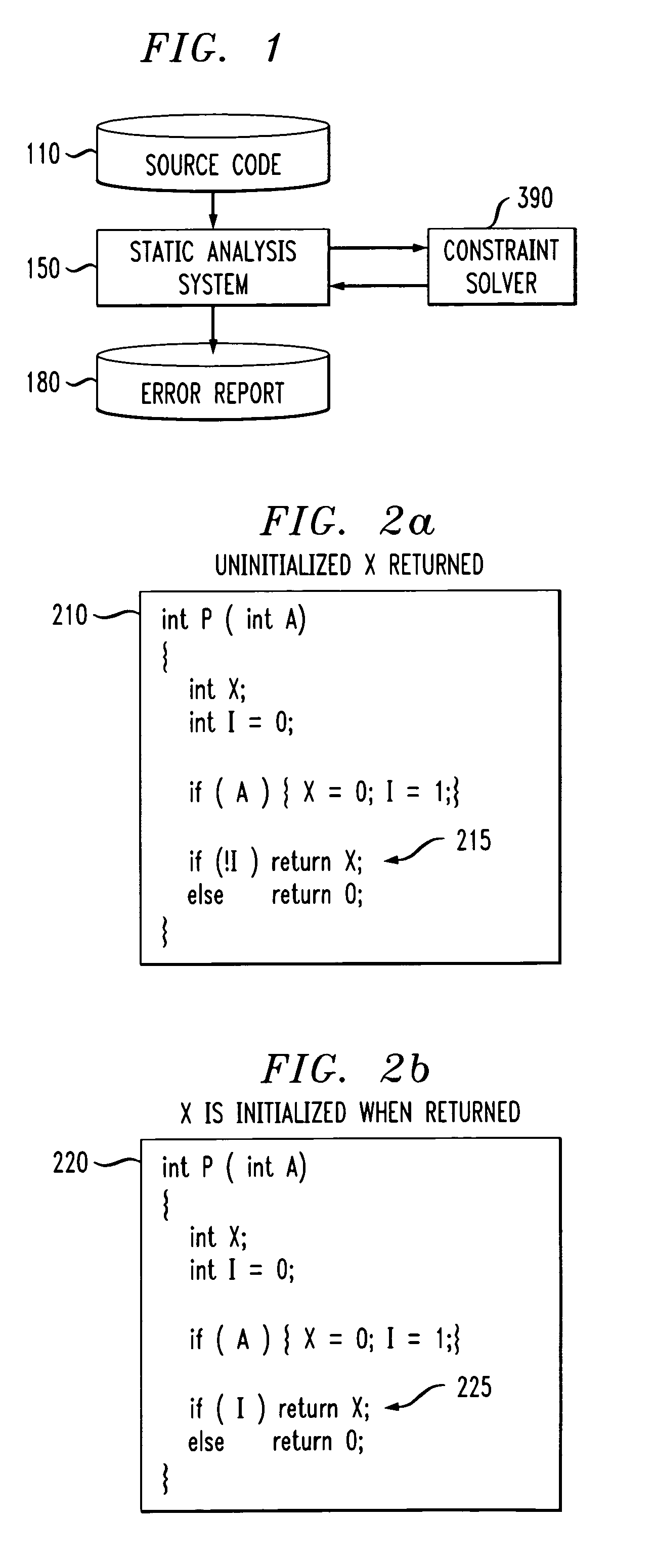

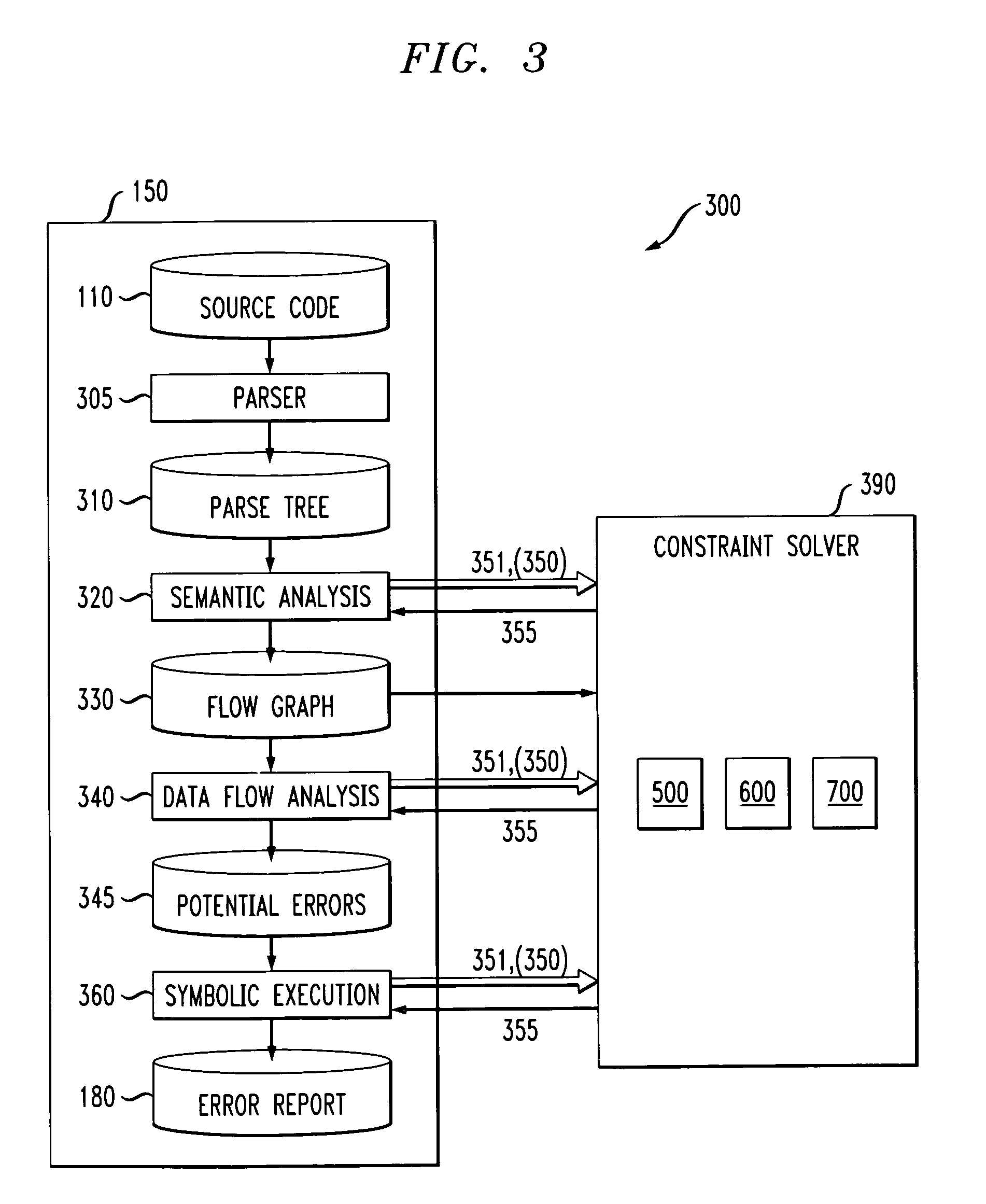

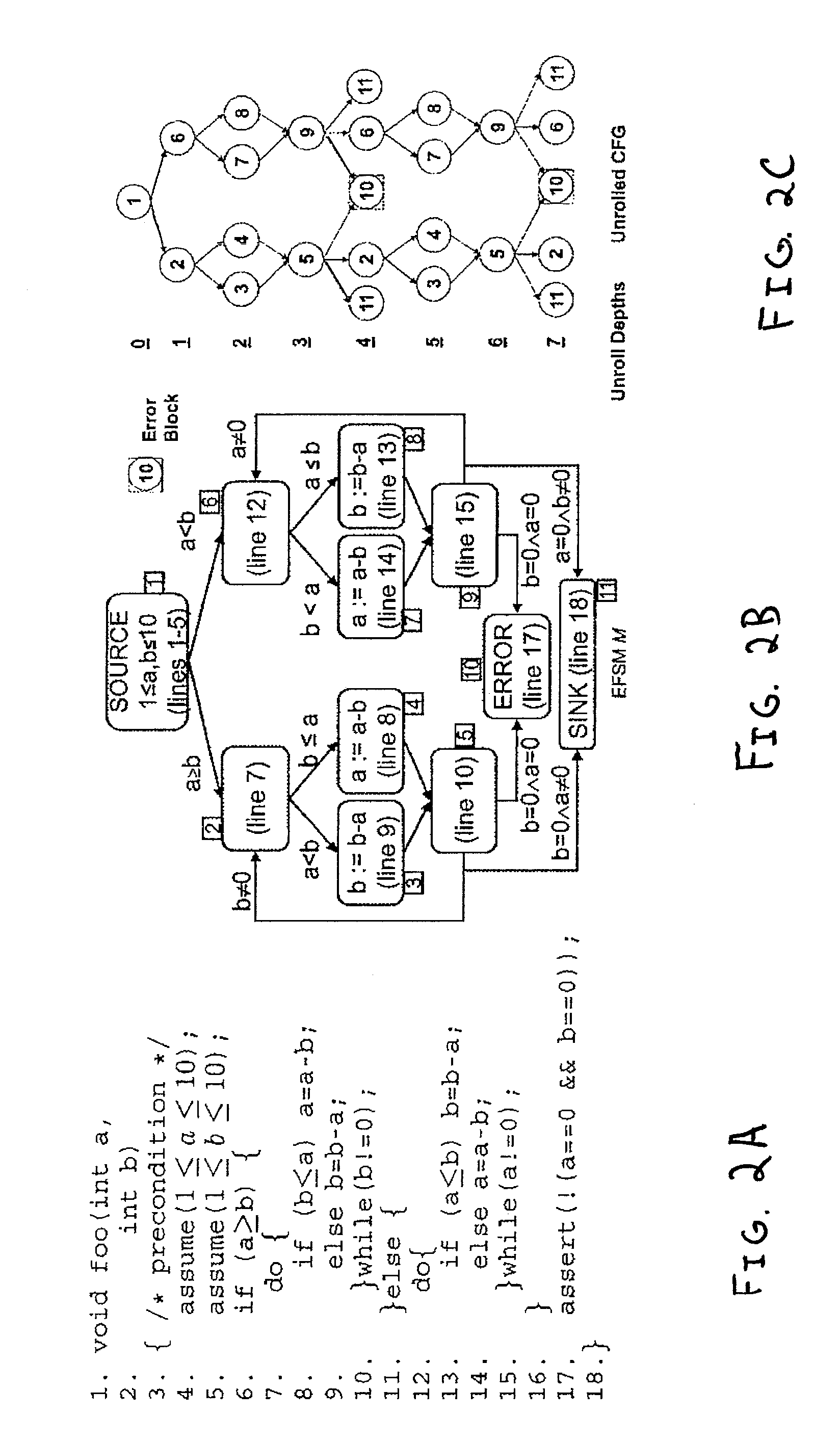

Method and apparatus for finding errors in software programs using satisfiability of constraints

InactiveUS7089542B2Efficient and accurateHandled satisfactorilyError preventionError detection/correctionRewrite ruleSemantics

A method and apparatus are provided for analyzing software programs. The invention combines data flow analysis and symbolic execution with a new constraint solver to create a more efficient and accurate static software analysis tool. The disclosed constraint solver combines rewrite rules with arithmetic constraint solving to provide a constraint solver that is efficient, flexible and capable of satisfactorily expressing semantics and handling arithmetic constraints. The disclosed constraint solver comprises a number of data structures to remember existing range, equivalence and inequality constraints and incrementally add new constraints. The constraint solver returns an inconsistent indication only if the range constraints, equivalence constraints, and inequality constraints are mutually inconsistent.

Owner:IBM CORP

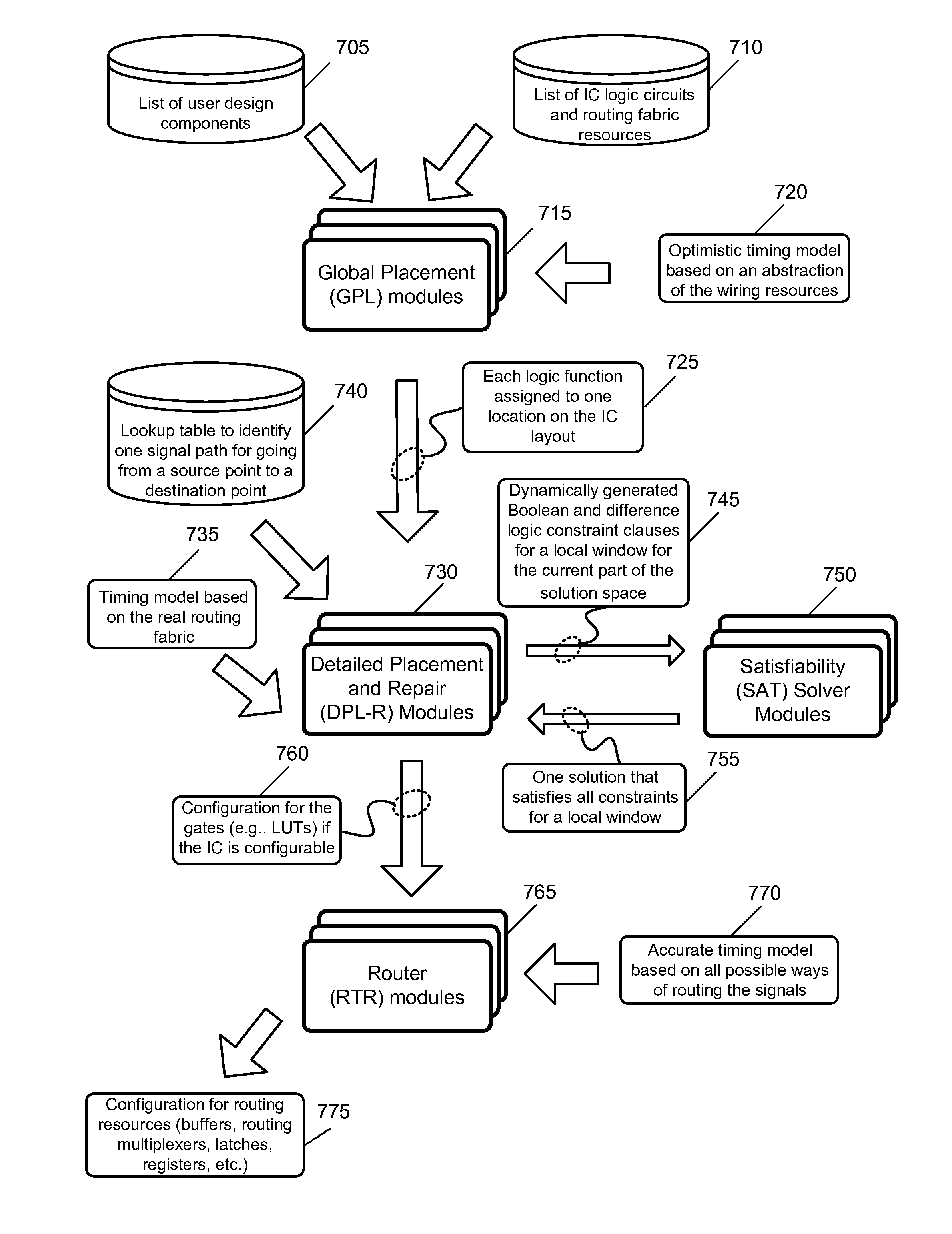

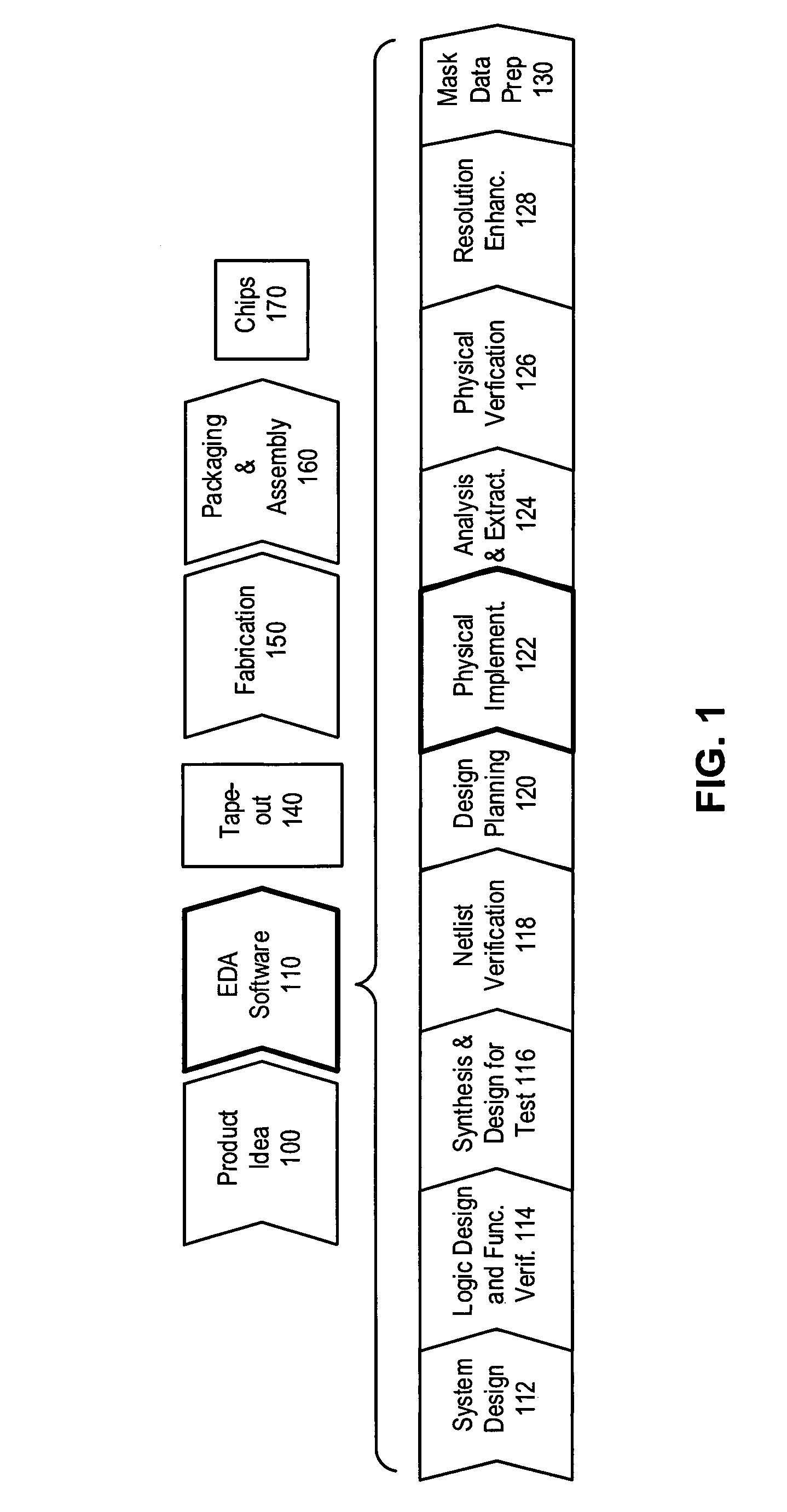

Detailed placement with search and repair

ActiveUS8984464B1Avoid checkingReduce in quantityDetecting faulty computer hardwareDesign optimisation/simulationSatisfiabilitySolver

A method of detailed placement for ICs is provided. The method receives an initial placement and iteratively builds sets of constraints for placement of different groups of cells in the IC design and uses a satisfiability solver to resolve placement violations. In some embodiments, the constraints include mathematical expressions that express timing requirements. The method in some embodiments converts the mathematical expressions into Boolean clauses and sends the clauses to a satisfiability solver that is only capable of solving Boolean clauses. In some embodiments, the method groups several cells in the user design and several sites on the IC fabric and uses the satisfiability solver to resolve all placement issues in the group. The satisfiability solver informs placer after each cell is moved to a different site. The method then dynamically builds more constraints based on the new cell placement and sends the constraints to the satisfiability solver.

Owner:ALTERA CORP

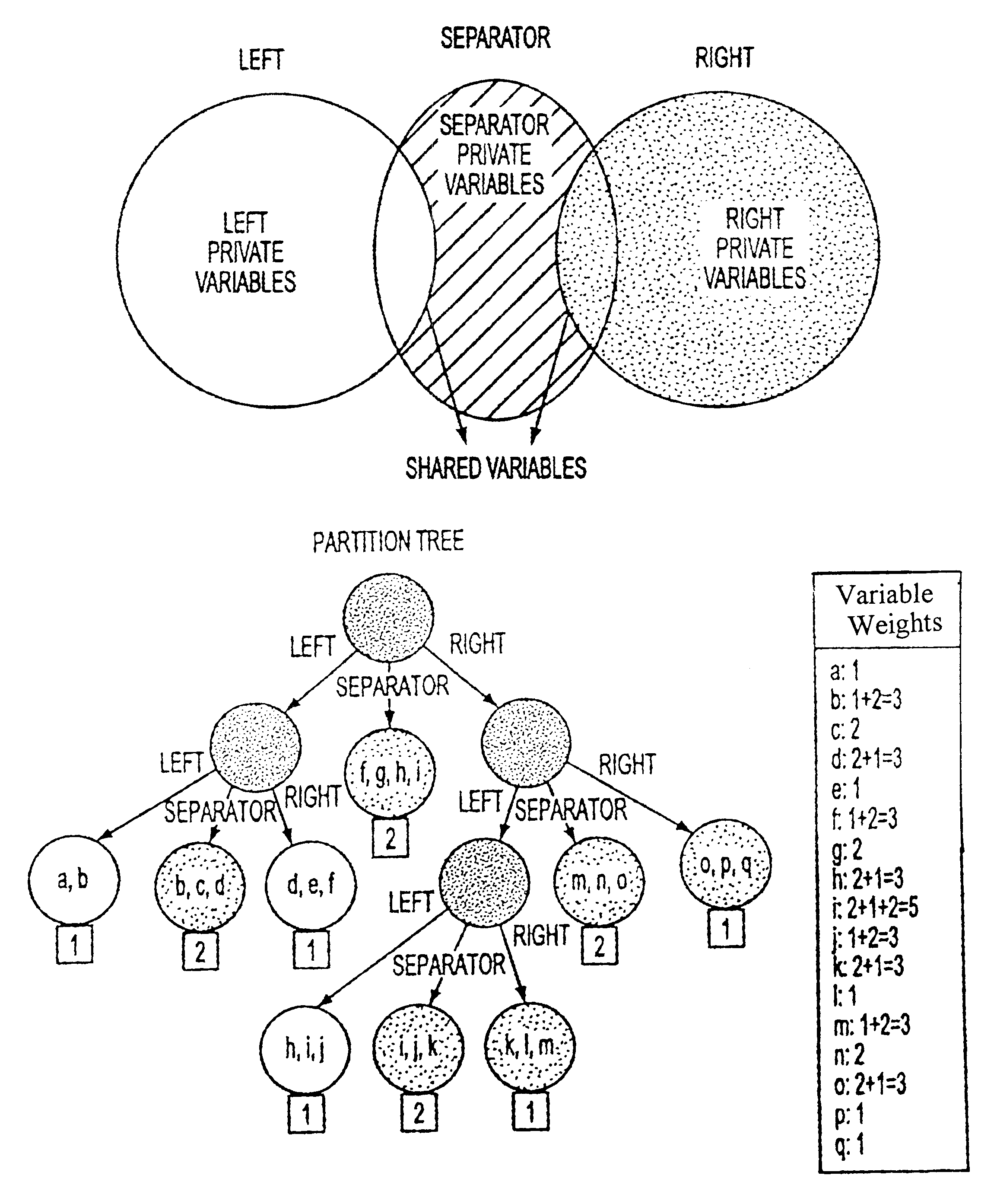

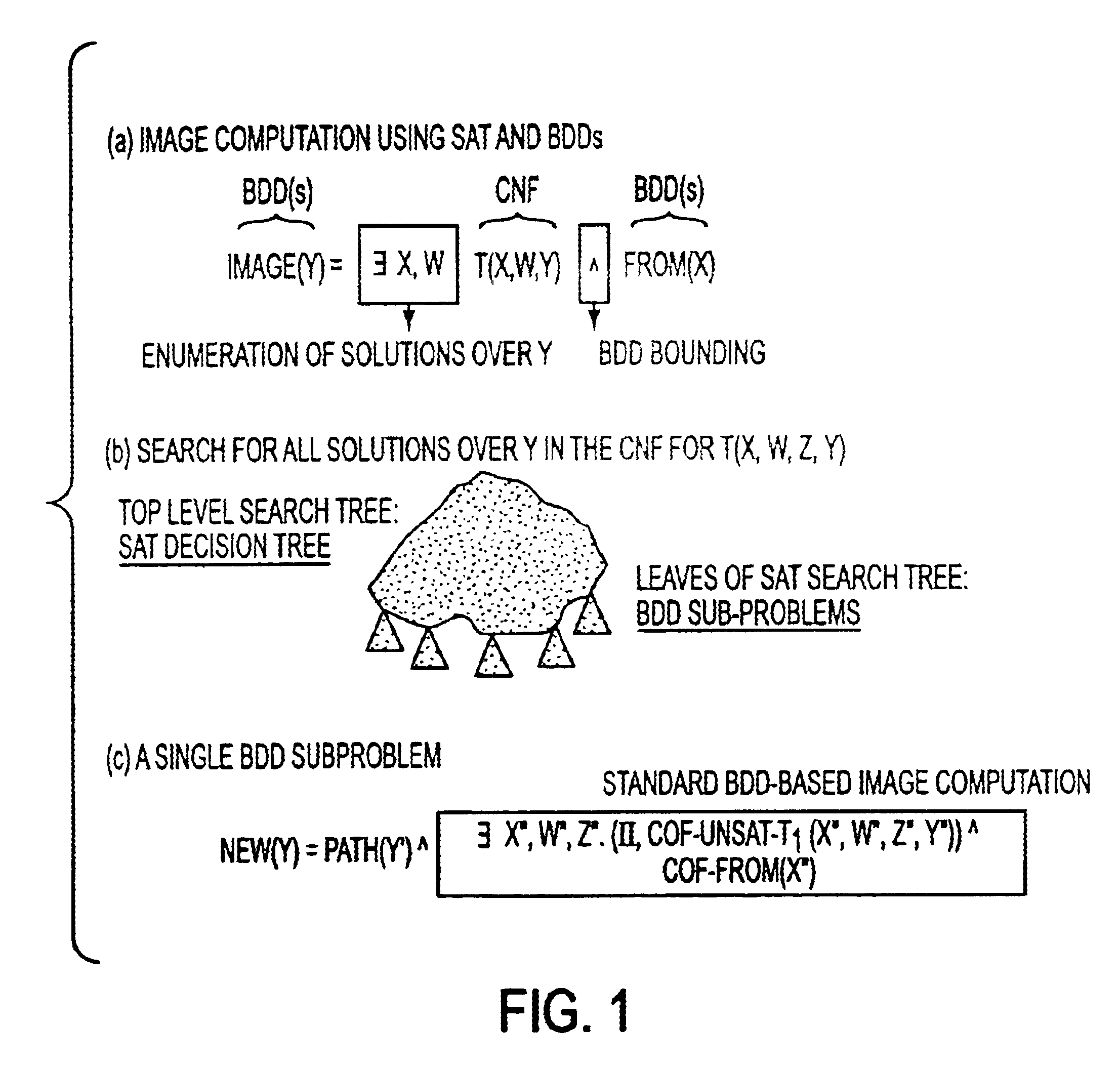

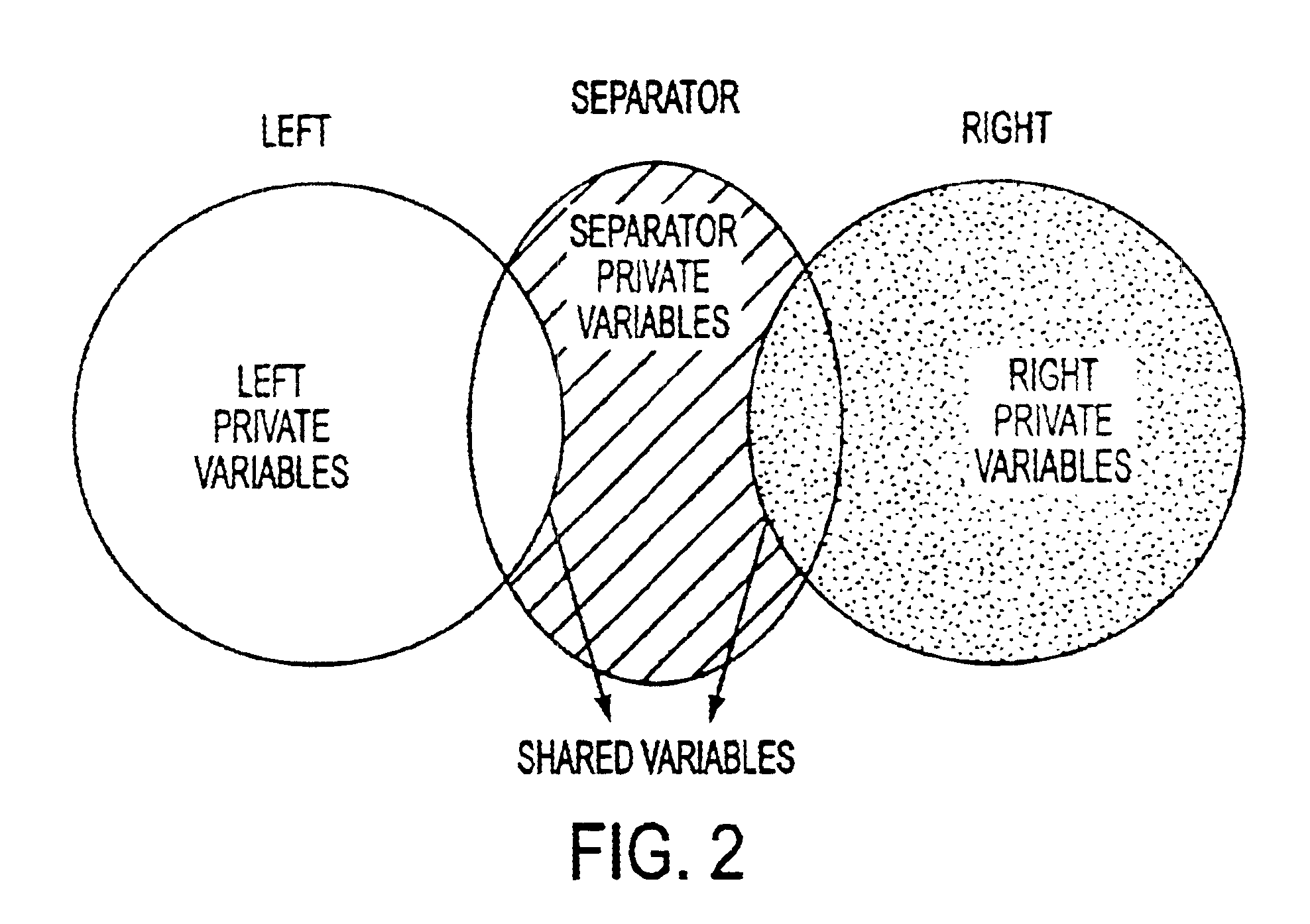

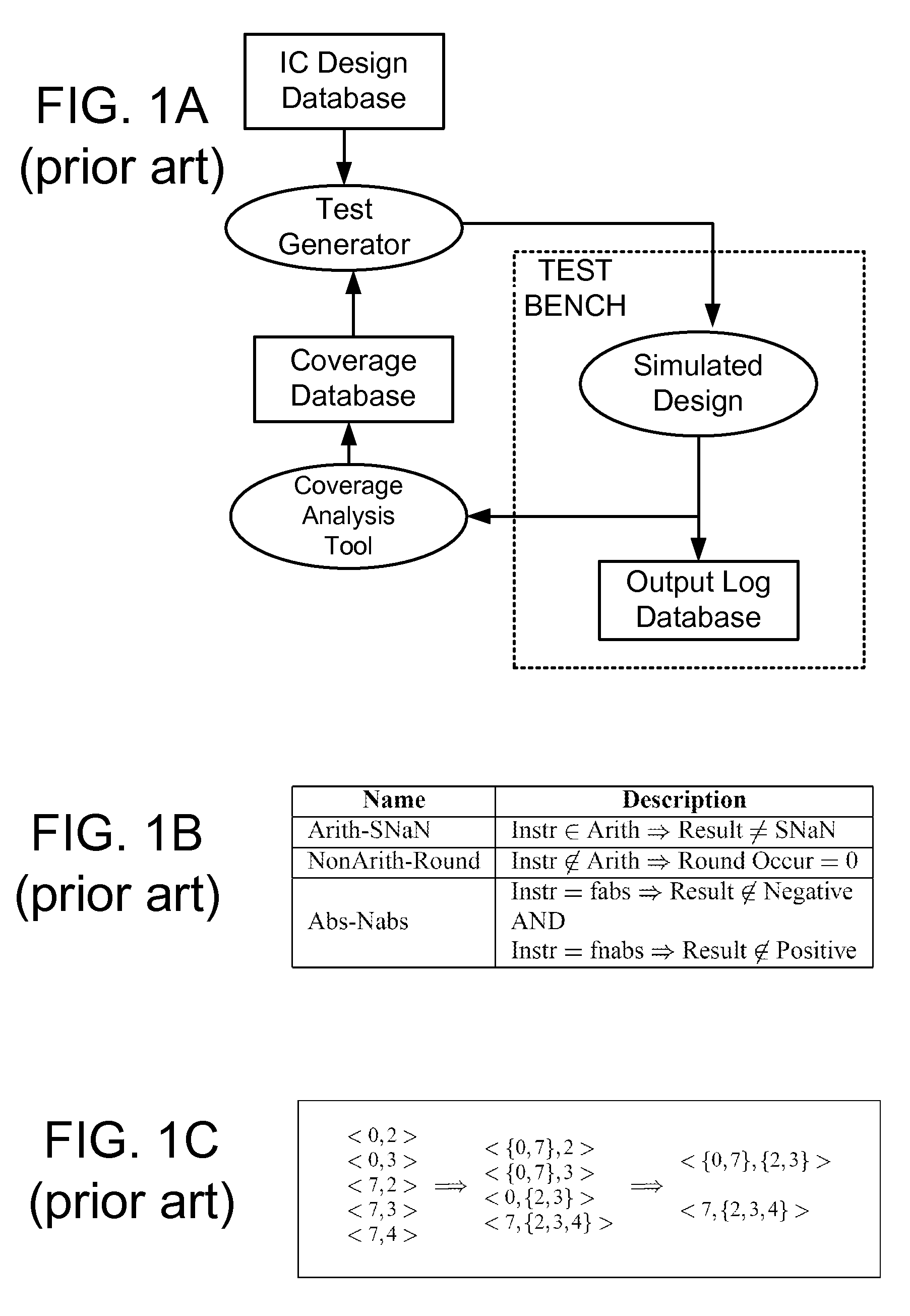

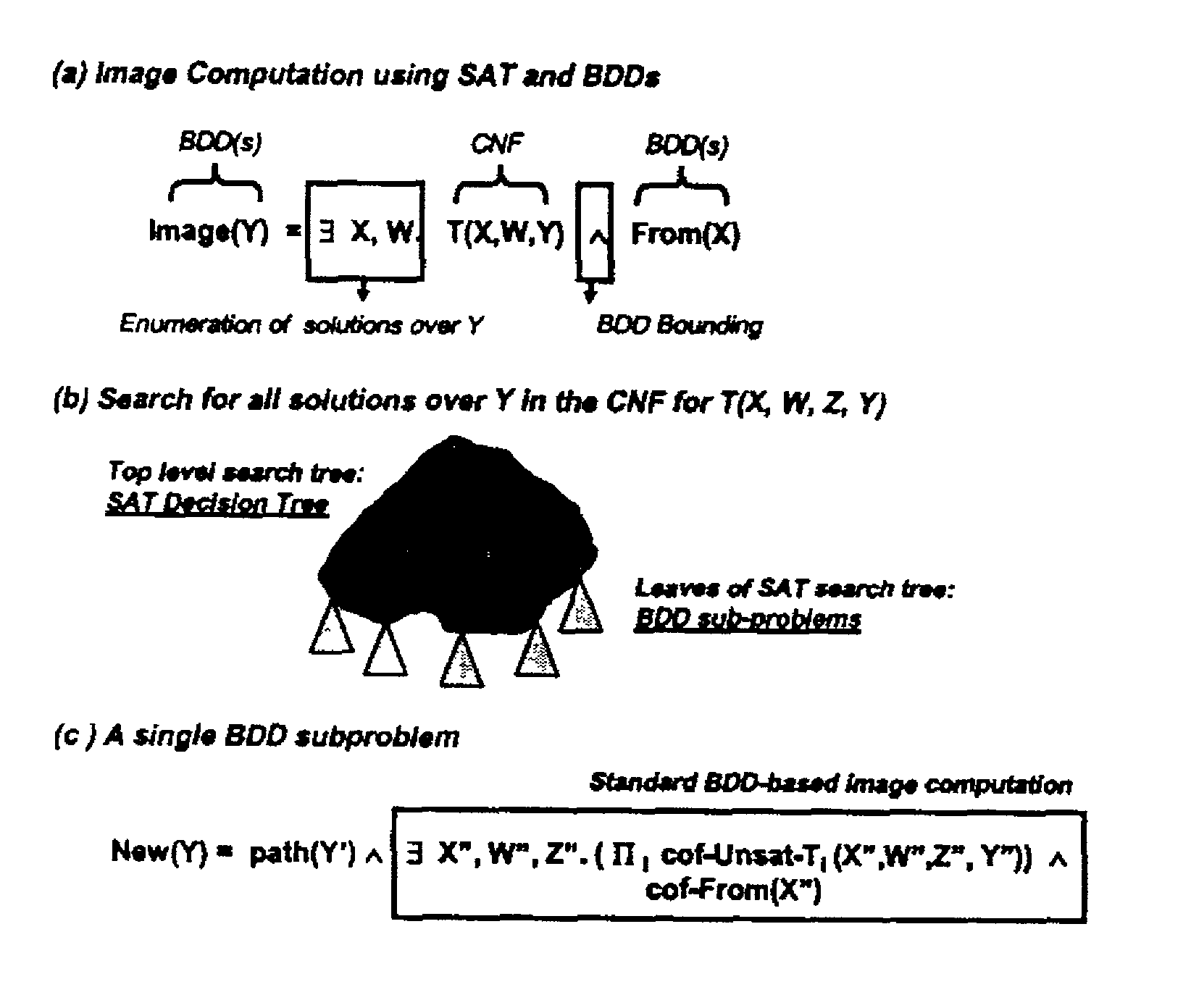

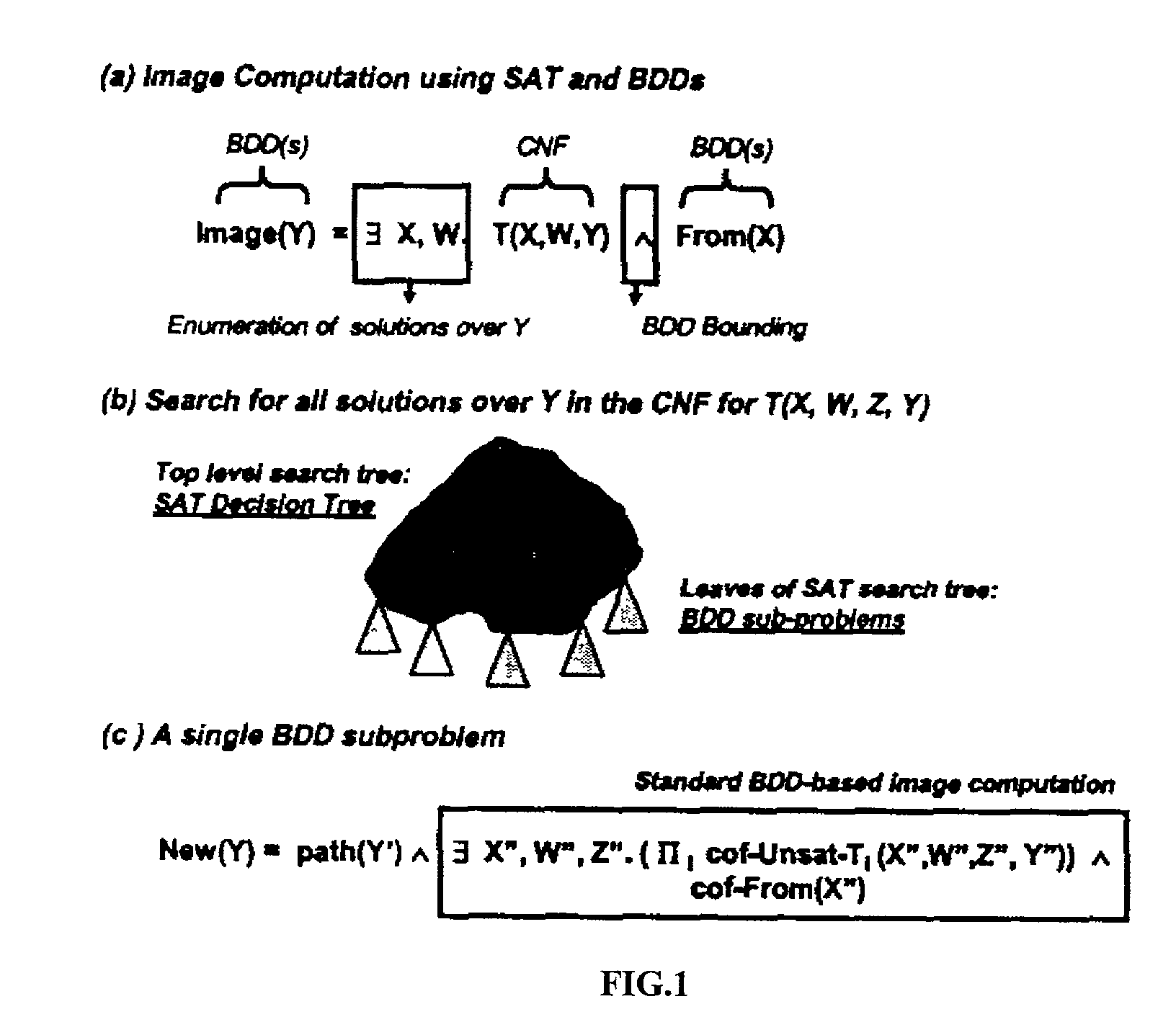

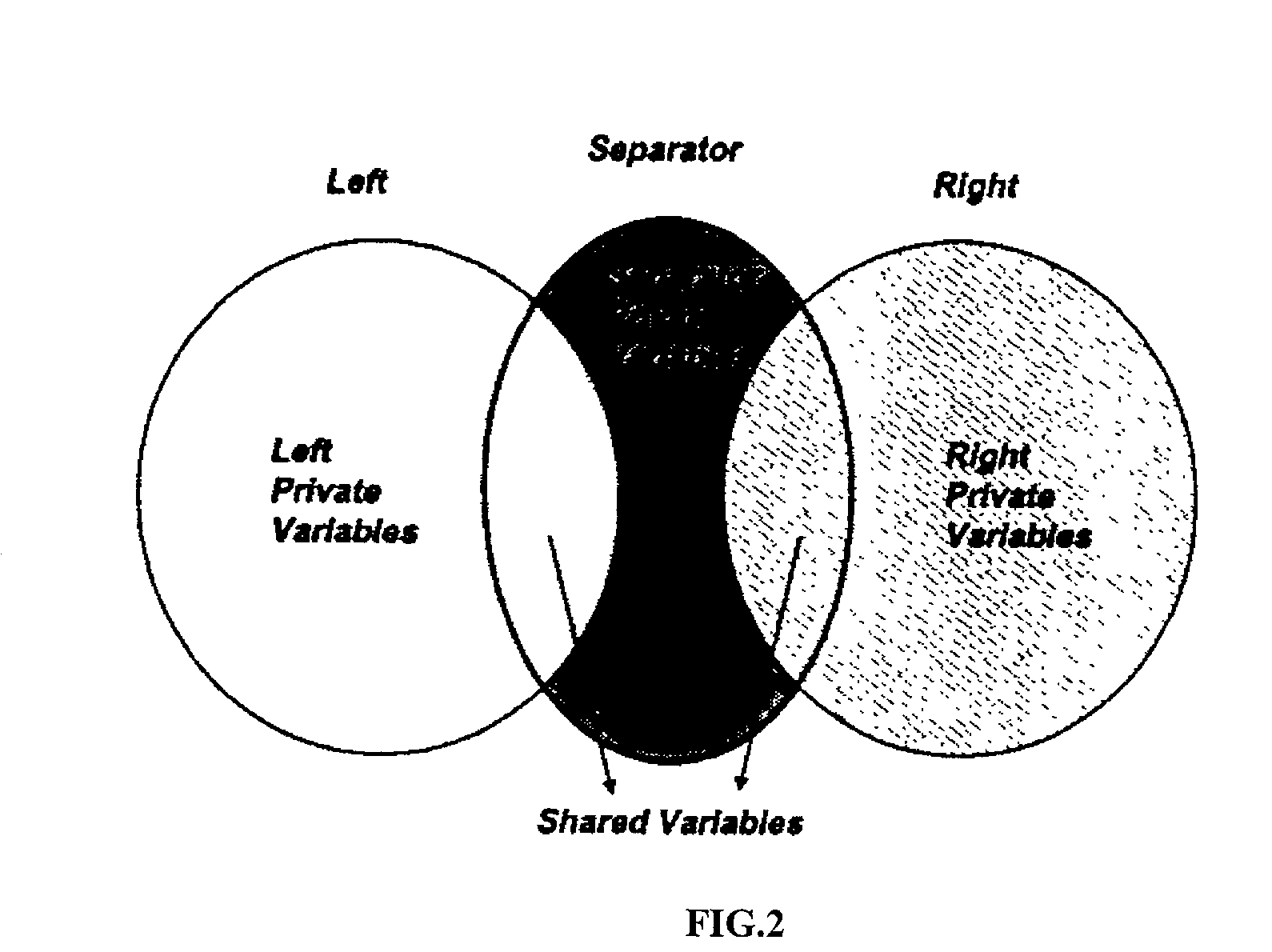

Partition-based decision heuristics for SAT and image computation using SAT and BDDs

InactiveUS6651234B2Reduce partAdd depthComputer aided designSoftware simulation/interpretation/emulationRecognition heuristicConjunctive normal form

A method for Boolean Satisfiability (SAT). The method comprises using a variable decision heuristic in a SAT algorithm and pruning the search space of SAT using said decision heuristic. The decision heuristic is based on partitioning a conjunctive normal form (CNF) of a Boolean formula corresponding to the SAT and the partitioning is induced by a separator set. An image computaion method that uses the disclosed method for solving the SAT.

Owner:NEC CORP

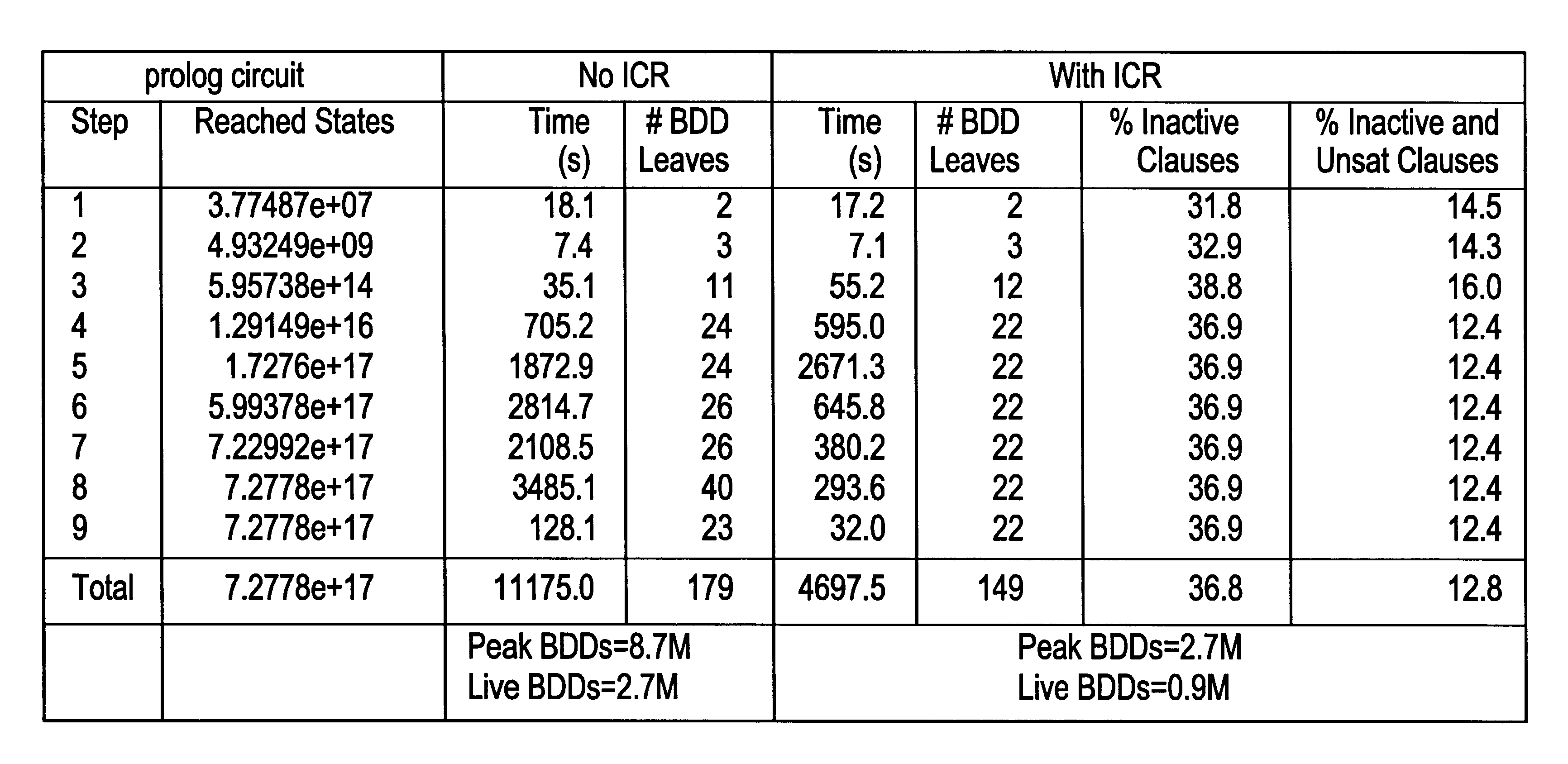

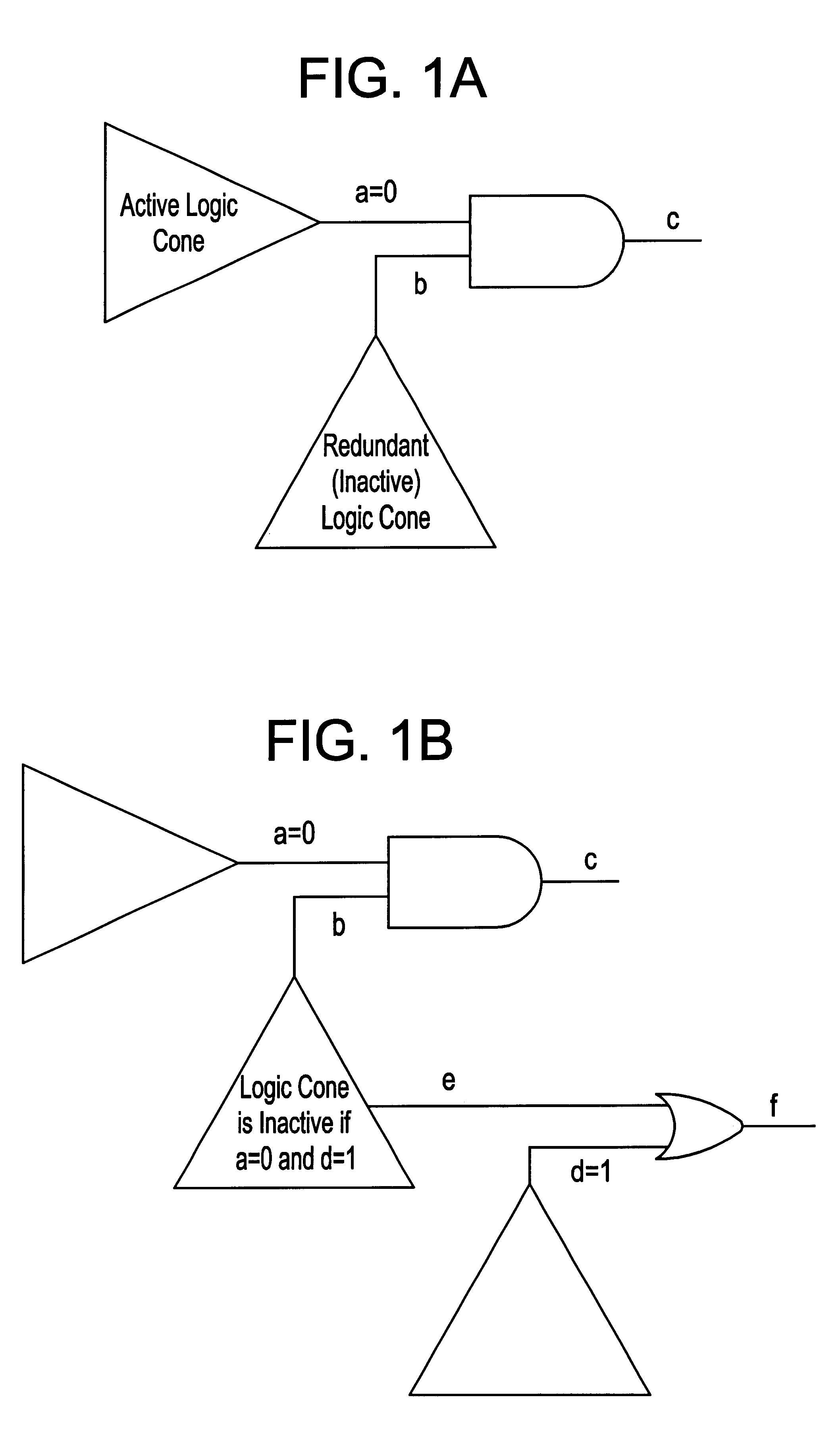

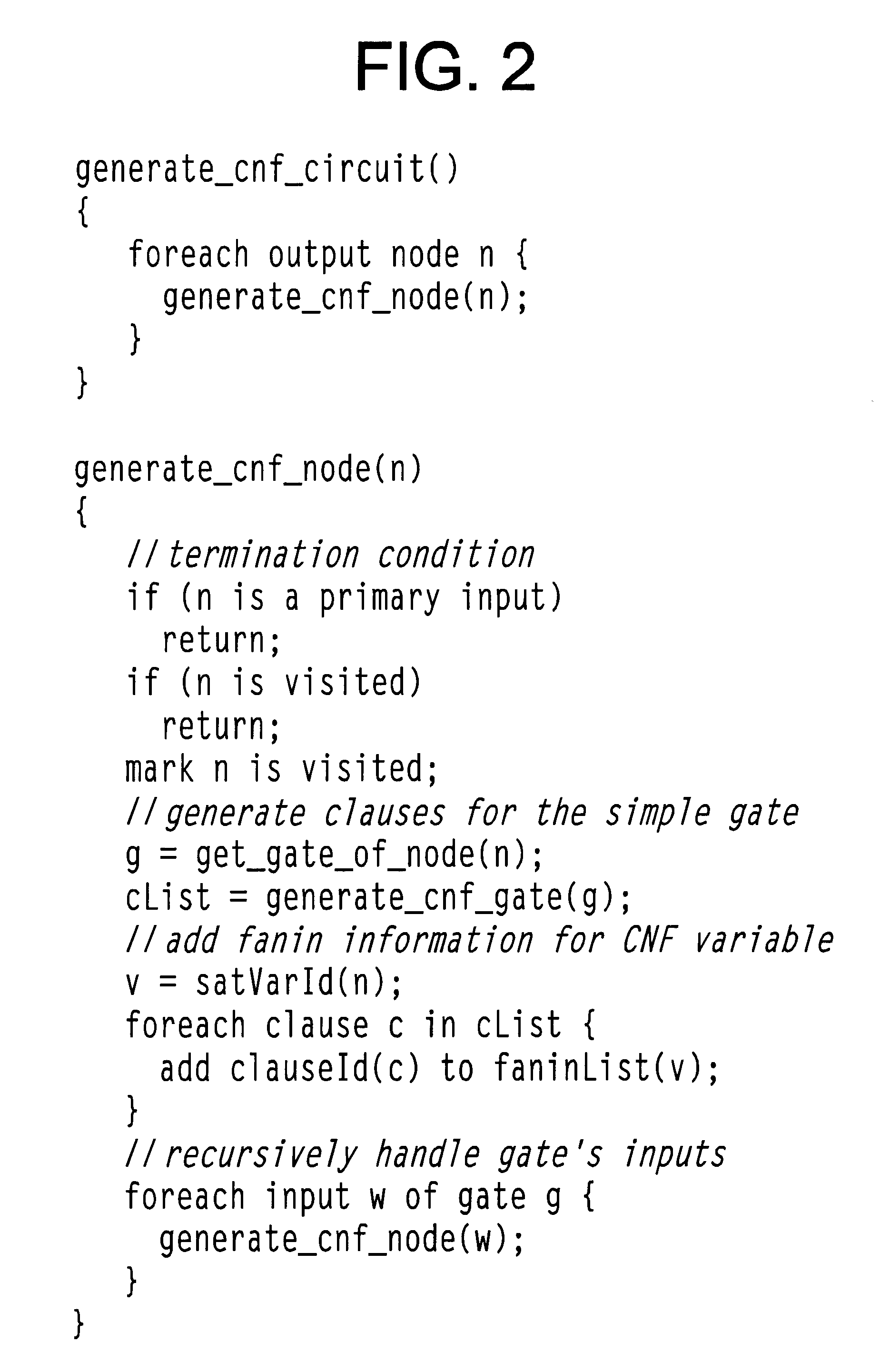

Dynamic detection and removal of inactive clauses in SAT with application in image computation

InactiveUS6496961B2Electronic circuit testingComputation using non-denominational number representationConjunctive normal formSatisfiability

This disclosure teaches a method of Boolean satisfiability checking (SAT) for a circuit. The method comprises identifying inactive clauses in the conjunctive normal form (CNF) of the circuit and removing the inactive clauses from the CNF.

Owner:NEC CORP

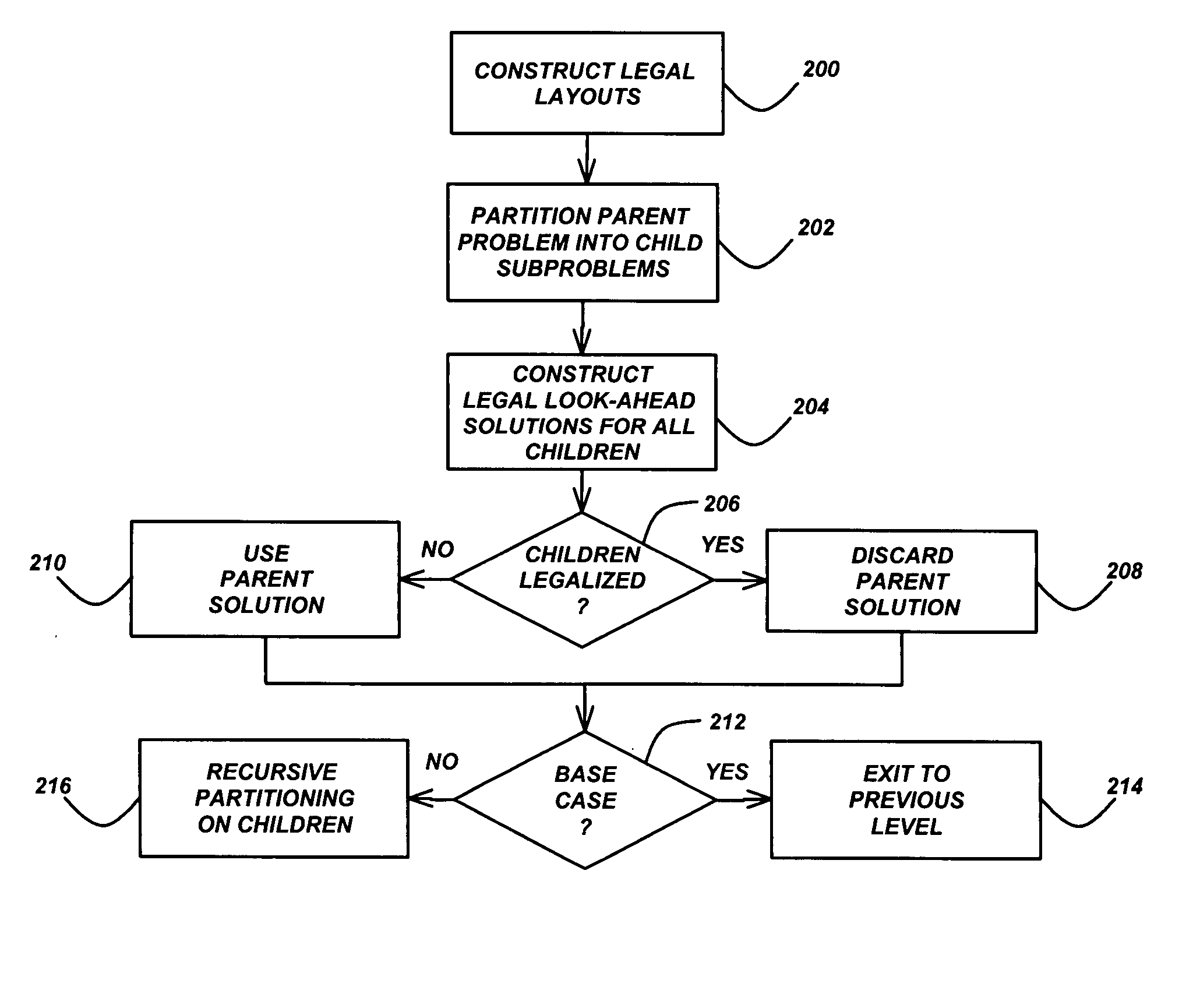

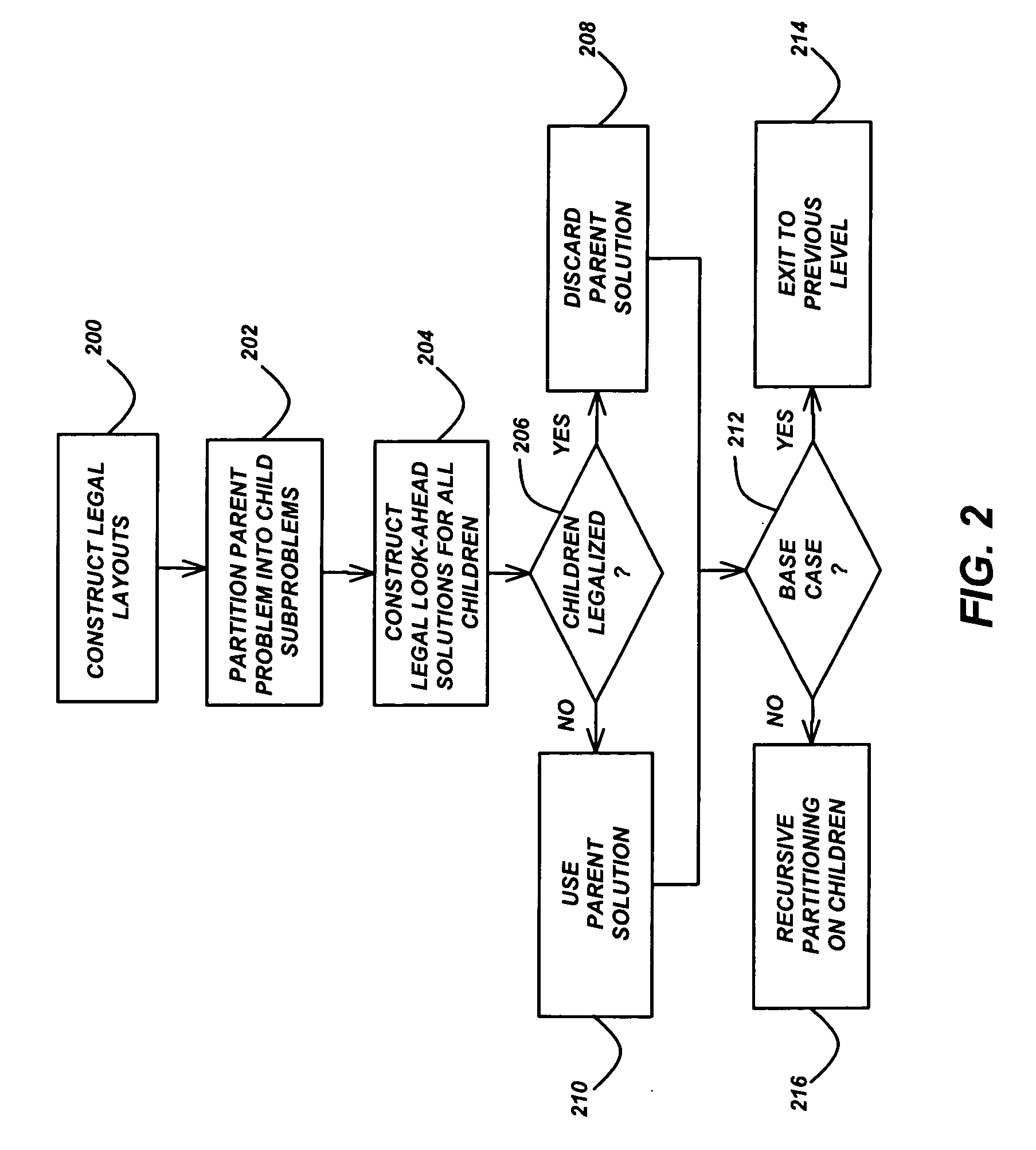

Circuit floorplanning and placement by look-ahead enabled recursive partitioning

InactiveUS20060190889A1Less run timeWirelength resultComputer aided designSoftware simulation/interpretation/emulationBacktrackingSatisfiability

Placement or floorplanning of an integrated circuit is performed by constructing legal layouts at every level of a hierarchy of subsets of modules representing the integrated circuit, by scalably incorporating legalization into each level of the hierarchy, so that satisfiability of constraints is explicitly enforced at every level, in order to eliminate backtracking and post-hoc legalization.

Owner:RGT UNIV OF CALIFORNIA

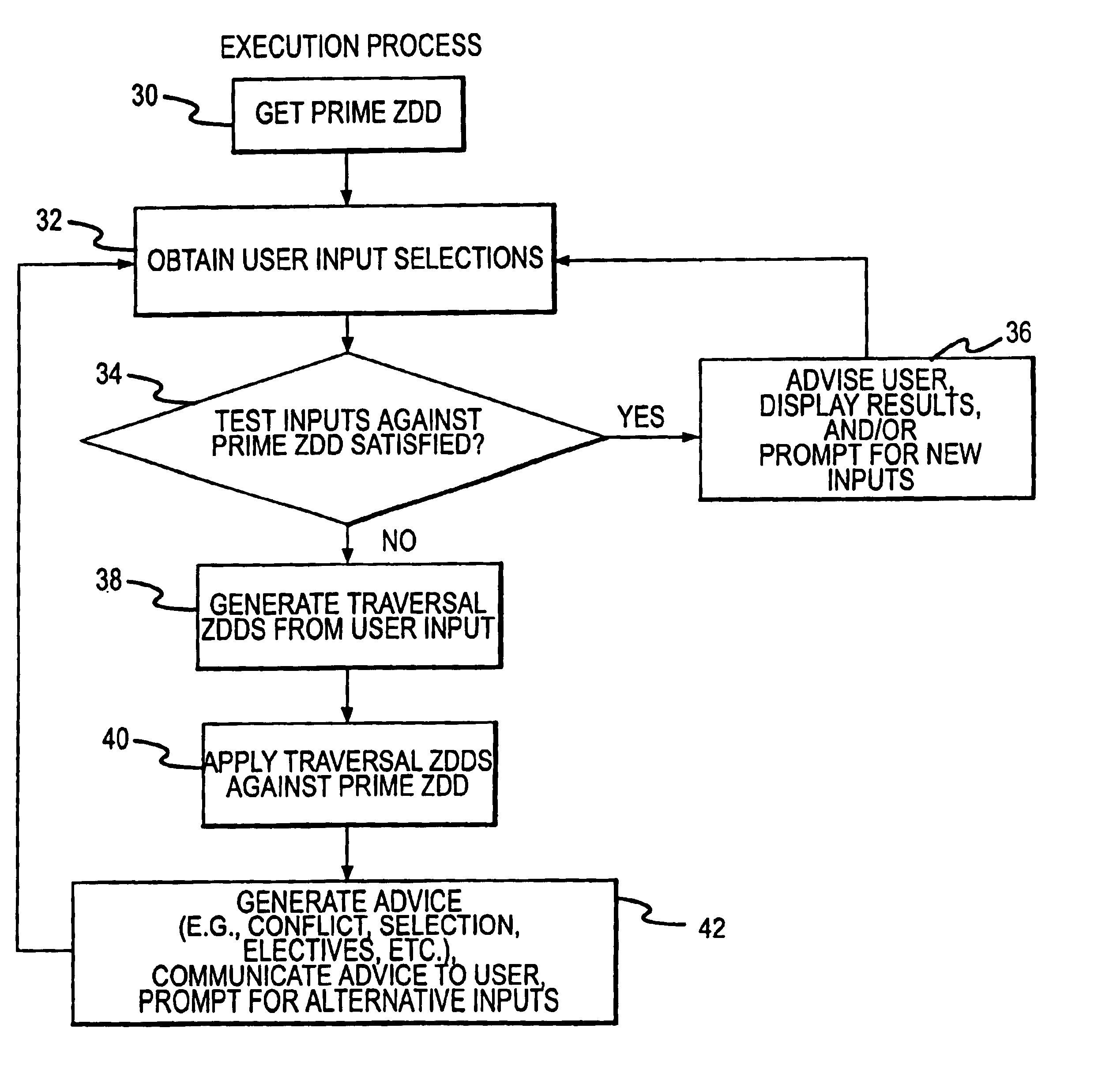

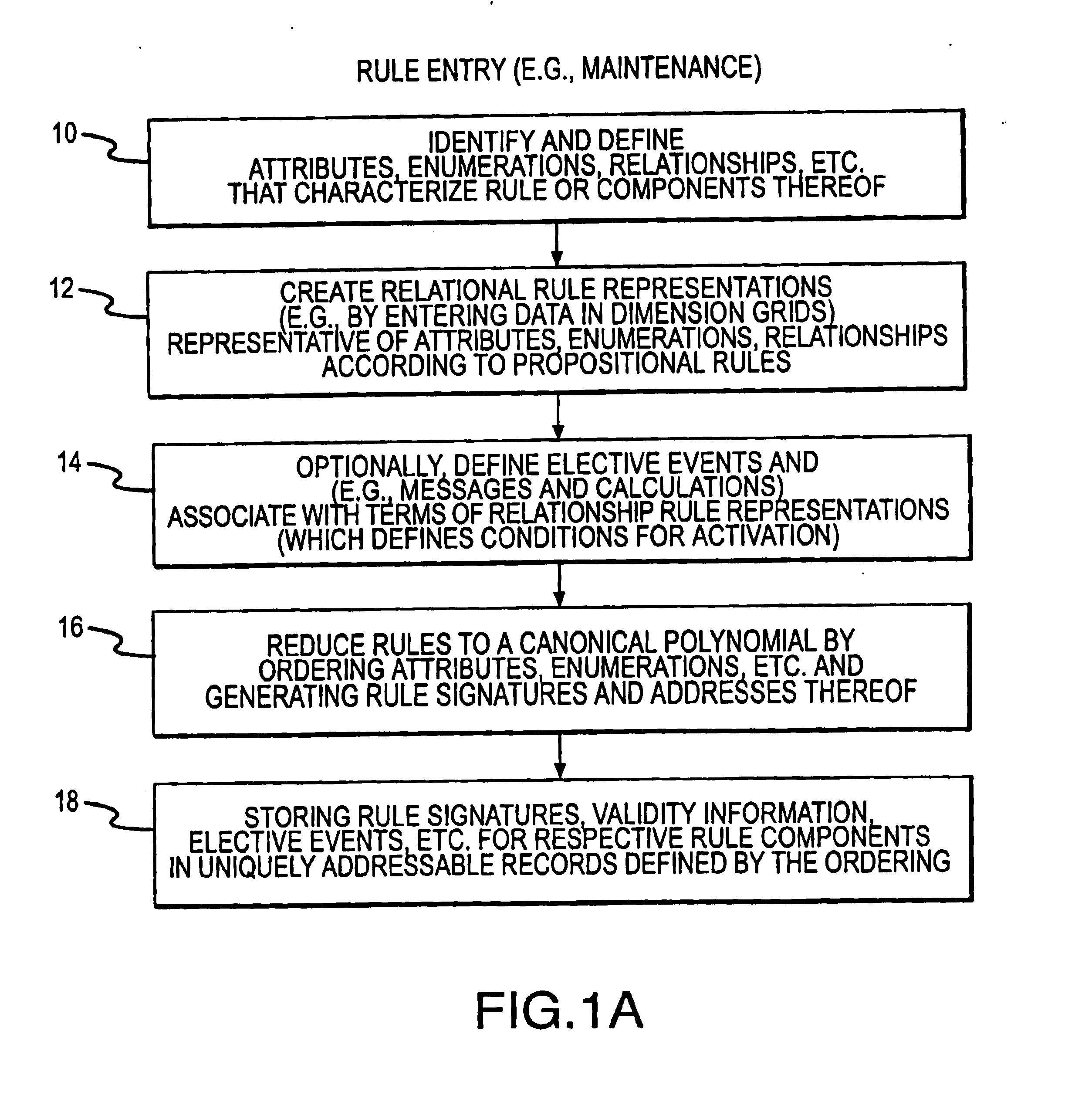

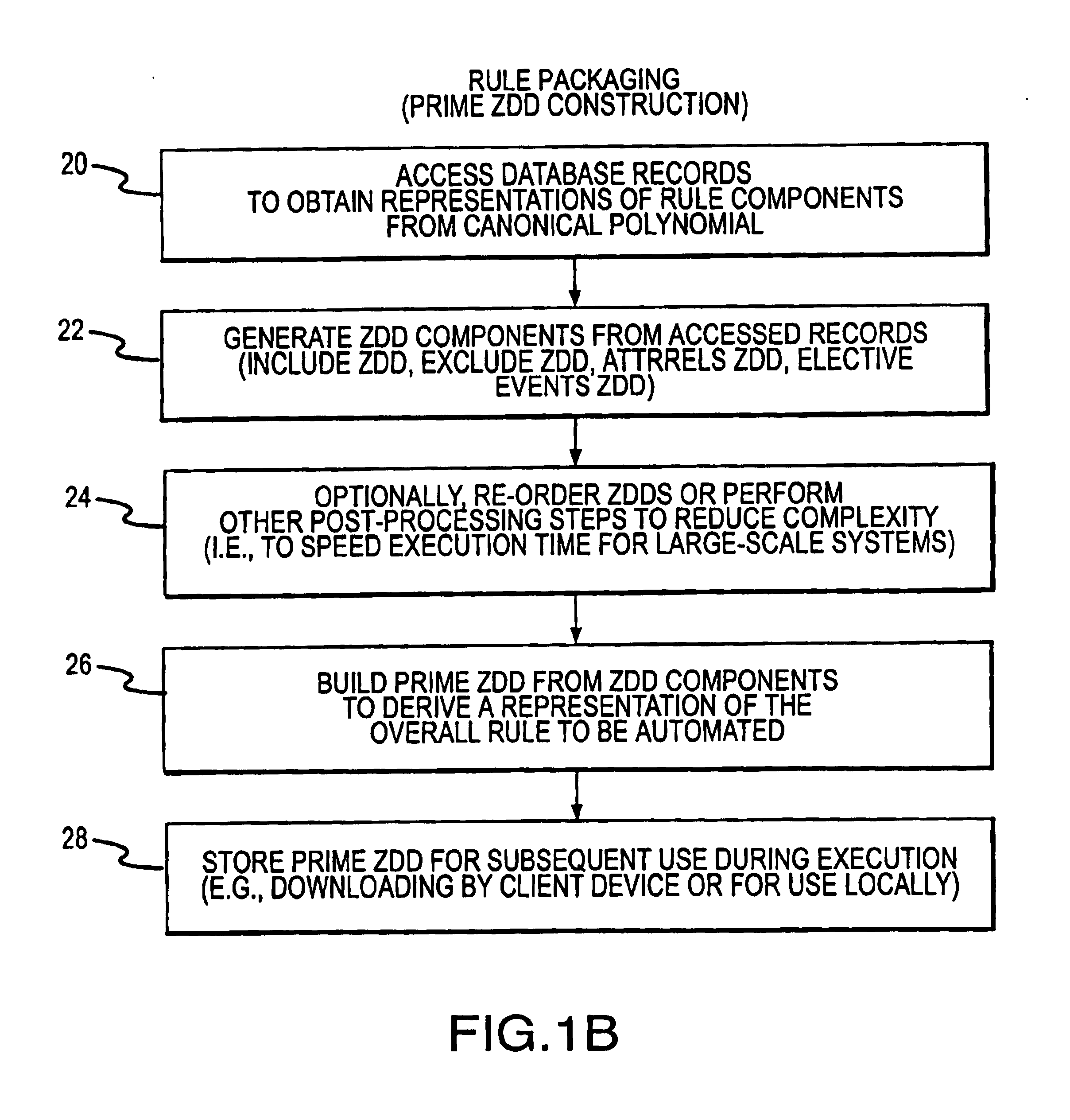

Rule processing methods for automating a decision and assessing satisfiability of rule-based decision diagrams

InactiveUS6965887B2Exceeding computational capacity of present day computing systemsData processing applicationsDigital computer detailsDecision graphBinary decision diagram

A method of rule processing includes defining / entering attributes, enumerations, and / or relationships; packaging the definitions in a reduced canonical form suitable for propositional logic manipulation using zero-suppressed binary decision diagrams (Zdd) to produce a prime Zdd; and / or (iii) executing the rule by applying a series of user inputs to the prime Zdd to determine a result that preferably includes conflict and selection advice to guide the user to satisfaction. Elective events, such as but not limited to the display of messages or the performance of calculations, may optionally be packaged along with the prime rule or components thereof, and presented during execution to help guide the end user to satisfaction or compliancy when choosing among possible selections. The invention automates determination of a complex rule having a combinatorial exploded number of rule components, or a combinatorial number of possible outcomes, exceeding computational capacity of present day computing systems.

Owner:MINERAL LASSEN

Method and system for non-linear state based satisfiability

InactiveUS6912700B1Reduce settingsGenetic modelsDigital computer detailsSatisfiabilityBoolean function

A computerized method and system for solving non-linear Boolean equations is disclosed comprising at least partially solving a Boolean function; developing at least one inference regarding said Boolean function and saving said inference to a state machine; and accessing said inference from said state machine to develop at least one heuristic for determining whether said Boolean function is satisfiable.

Owner:CINCINNATI UNIV OF +1

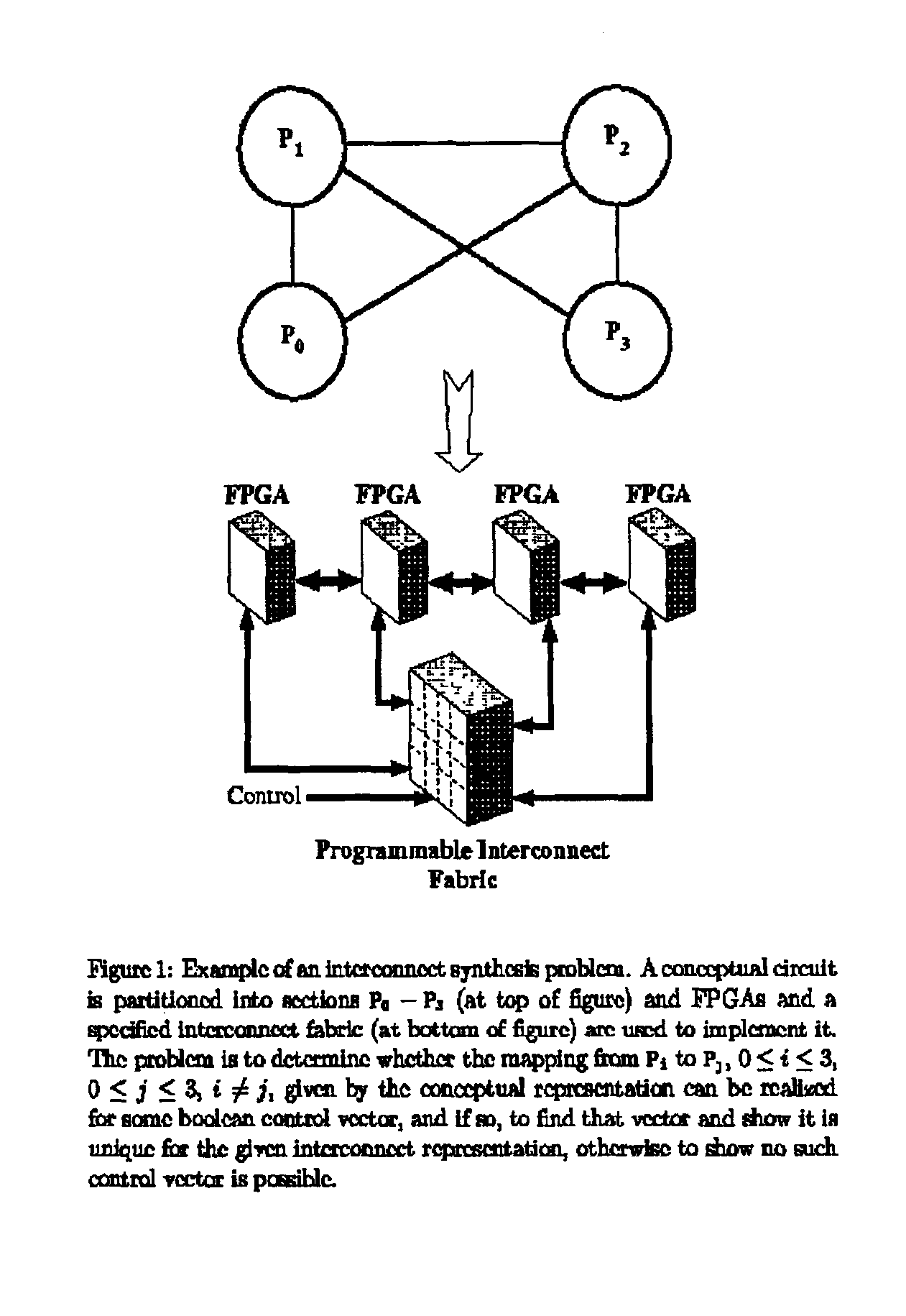

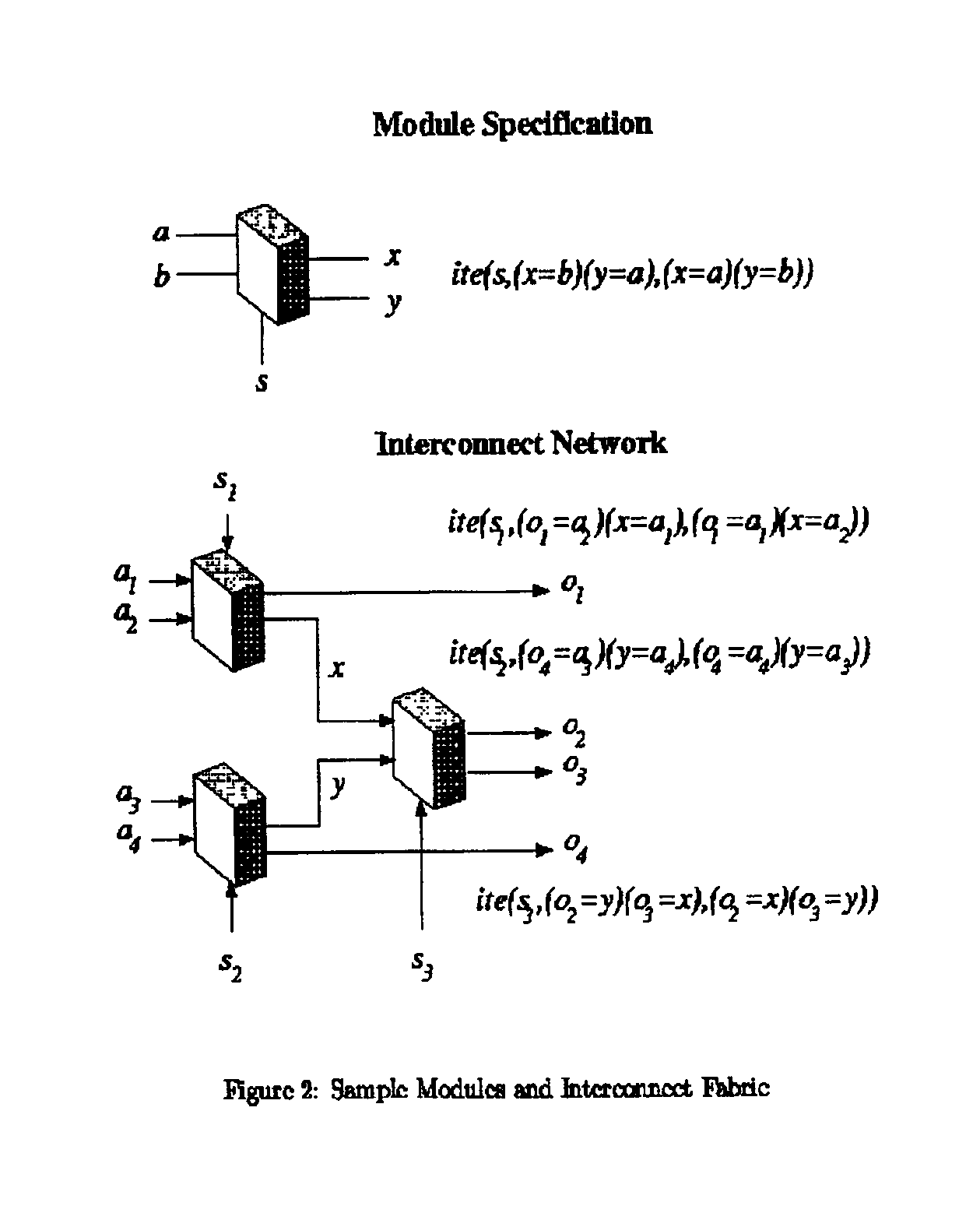

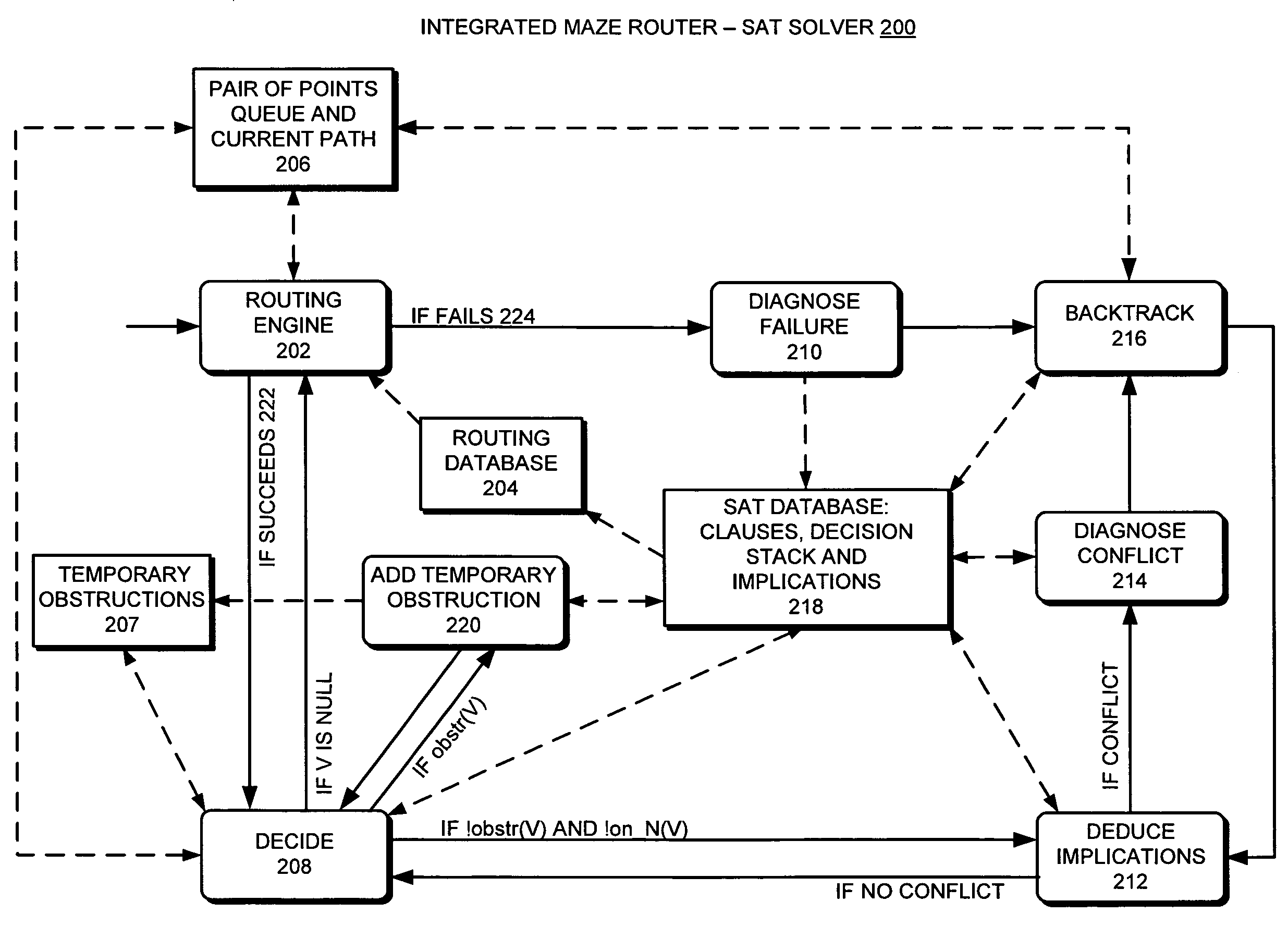

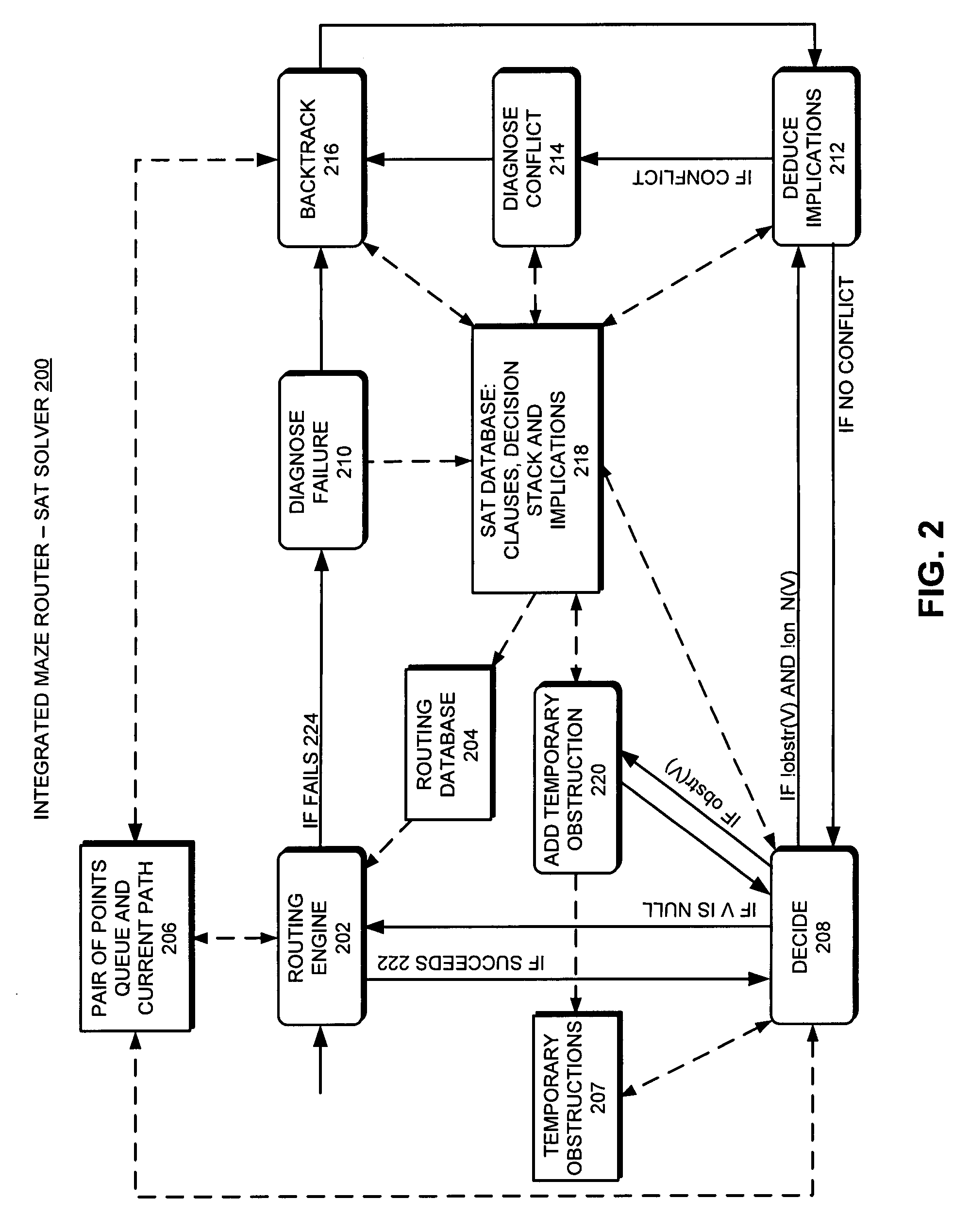

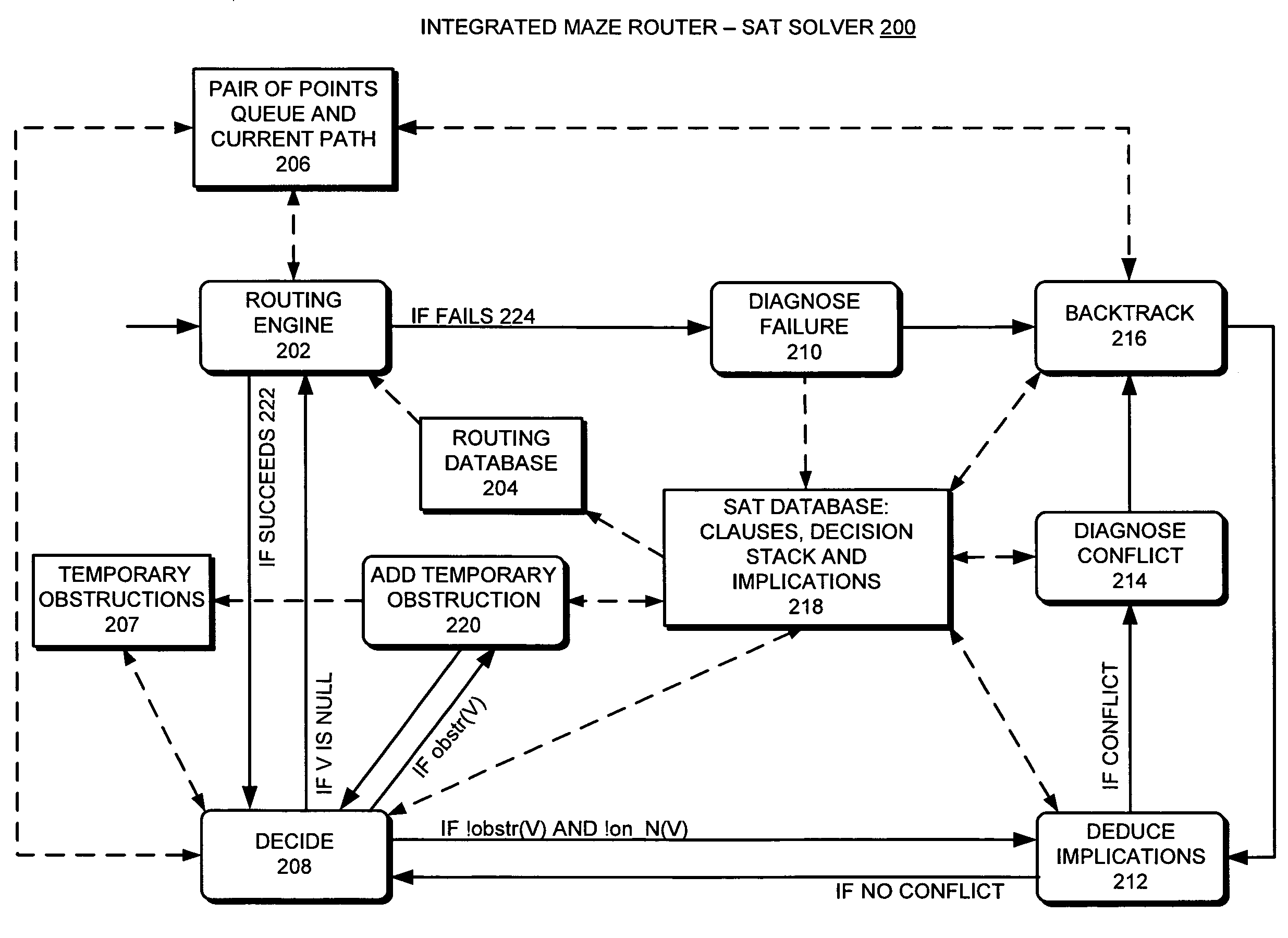

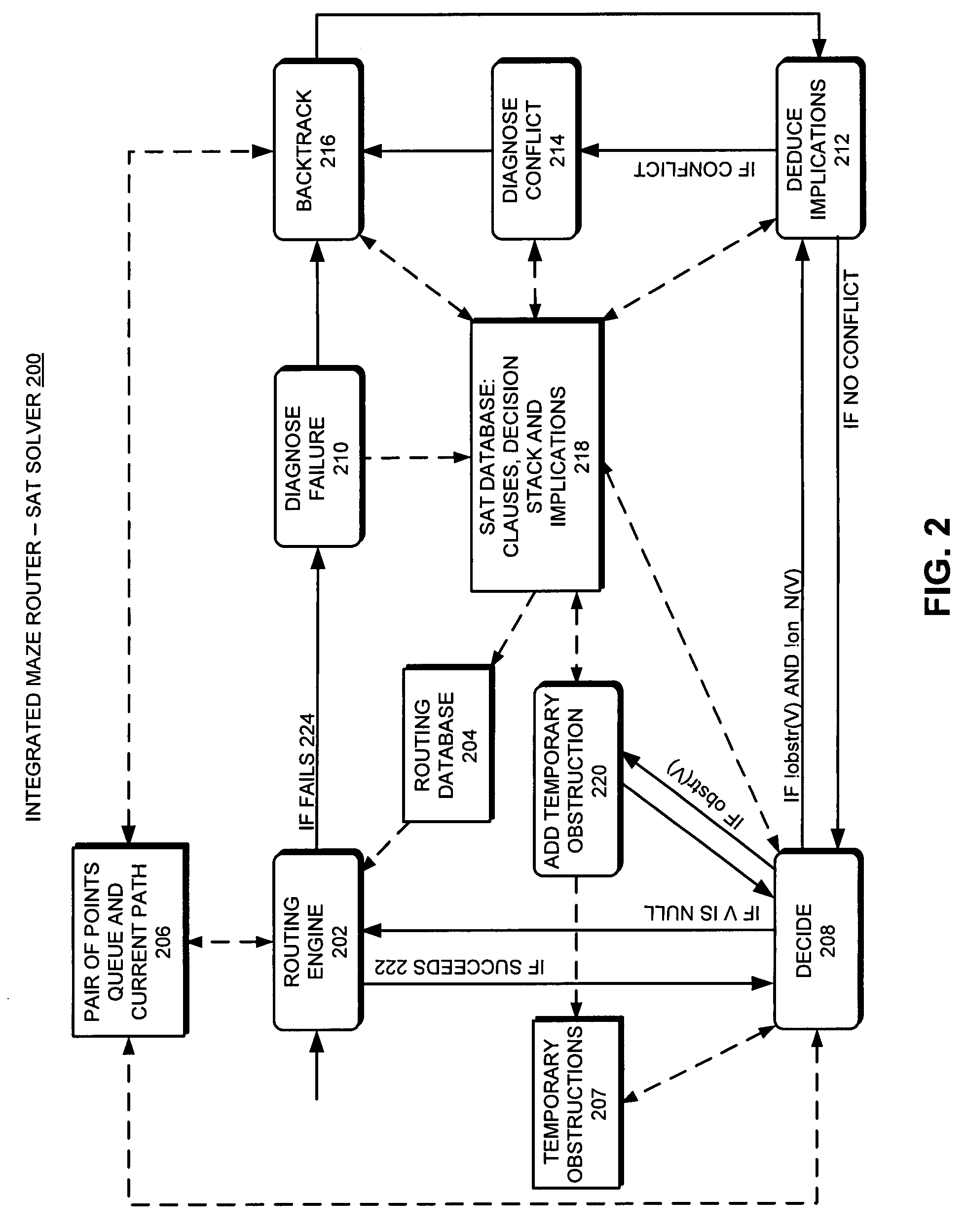

Integrating a boolean SAT solver into a router

ActiveUS7904867B2Computer aided designSpecial data processing applicationsPartial solutionSatisfiability

One embodiment of the present invention provides a system that routes a set of pairs of points during the design of an integrated circuit (IC) chip. The system comprises a routing engine which is configured to search for a path to connect a current pair of points in the set of pairs of points, wherein the path comprises a set of rectangles and vertices. The routing engine uses a routing database, which keeps track of previously routed nets that can obstruct the routing of the current pair of points. The system further comprises a satisfiability (SAT) solver which is capable of solving a set of constraints, wherein the set of constraints are associated with the routability of the set of pairs of points. The SAT solver additionally comprises a SAT database which maintains the set of constraints and a current partial solution to the set of constraints. The SAT database is used to update the routing database if the current partial solution changes.

Owner:SYNOPSYS INC

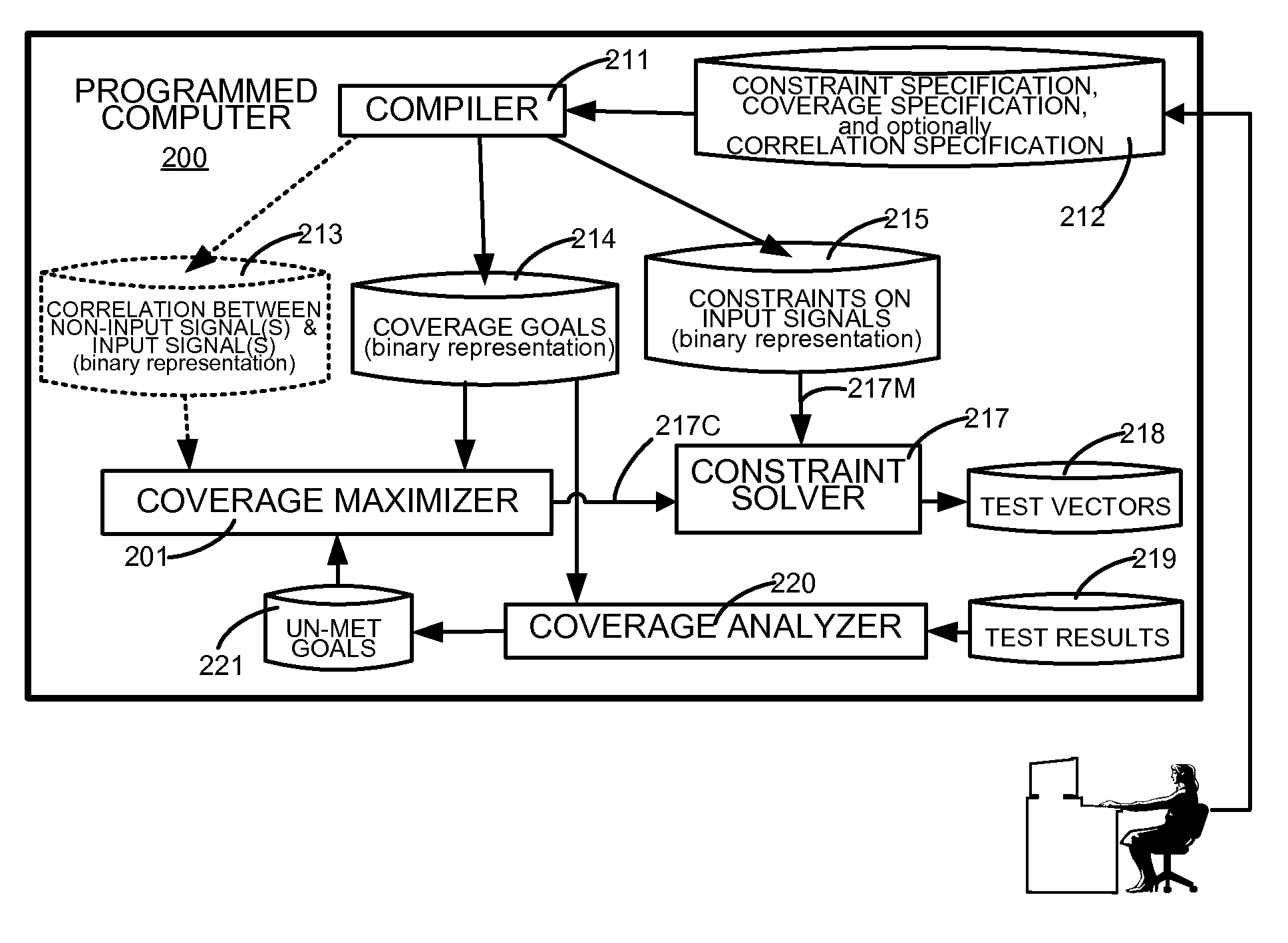

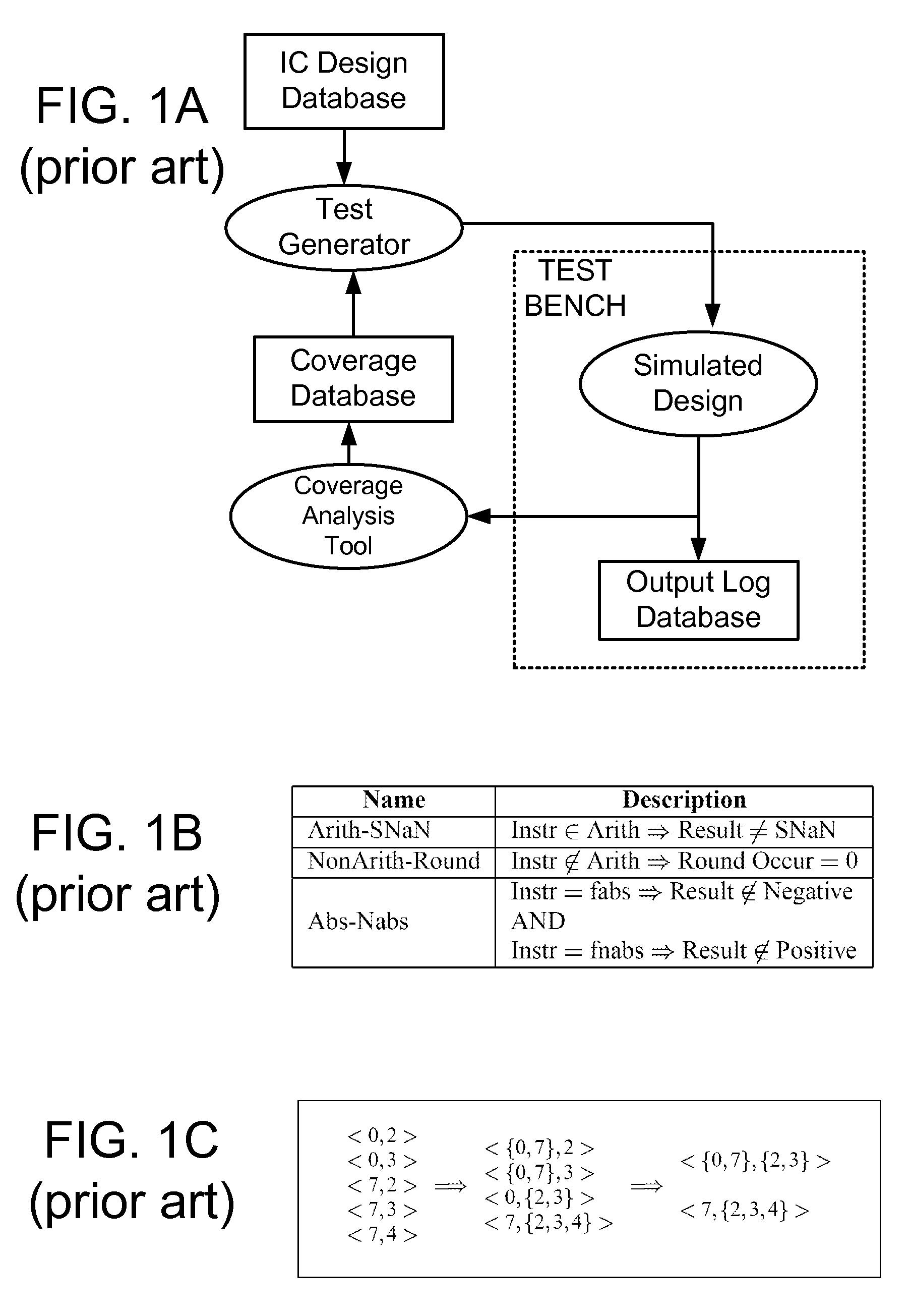

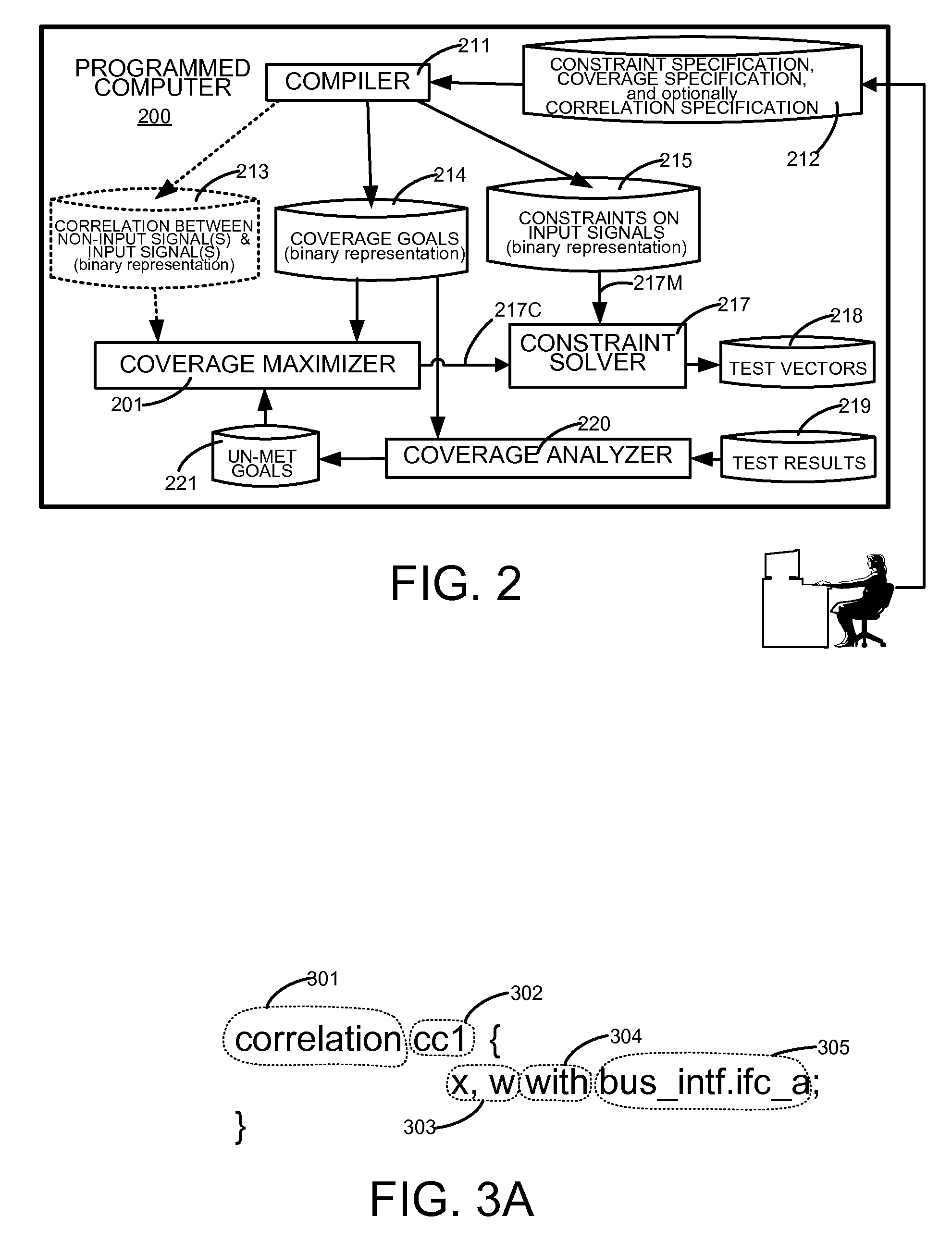

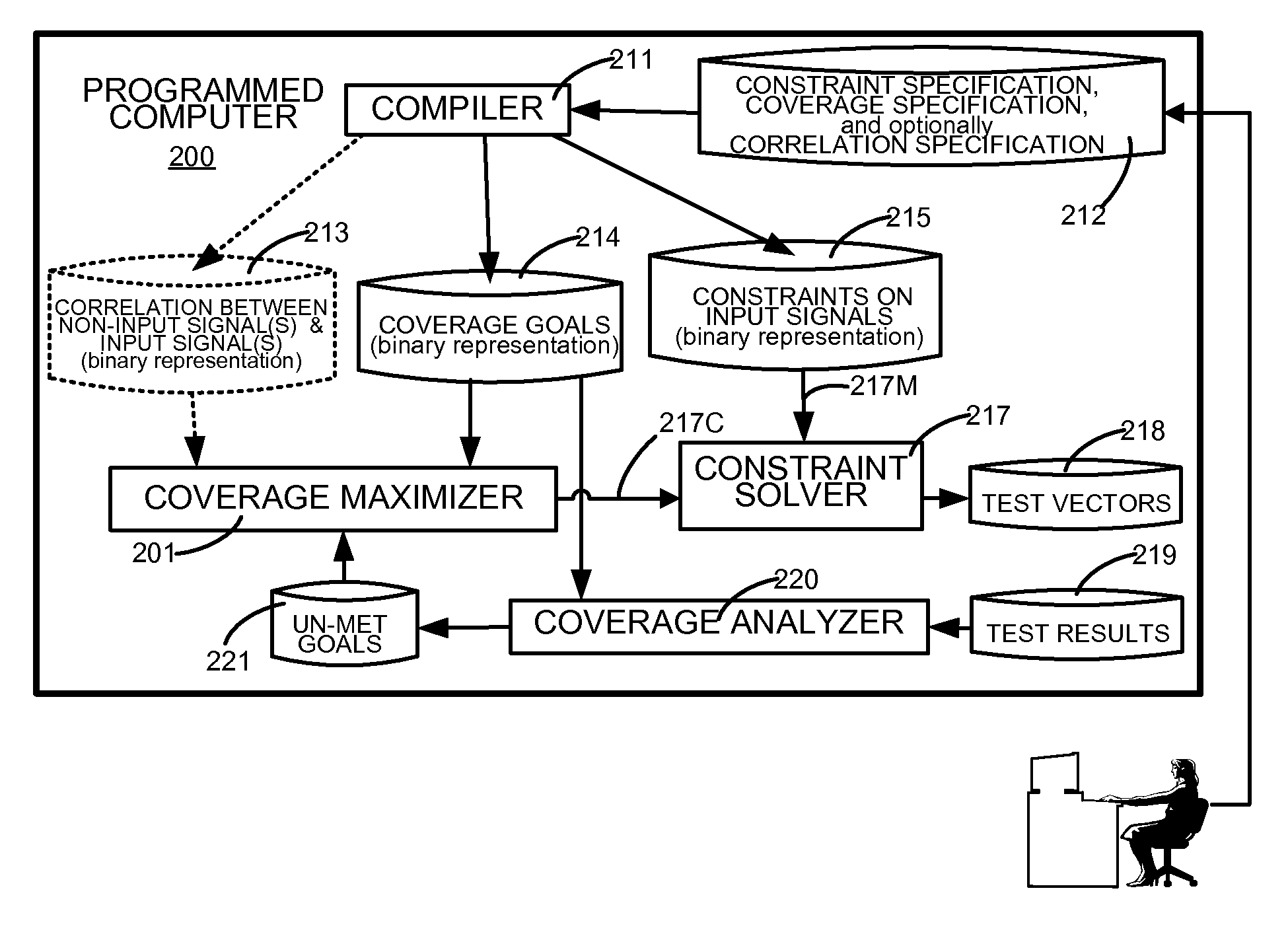

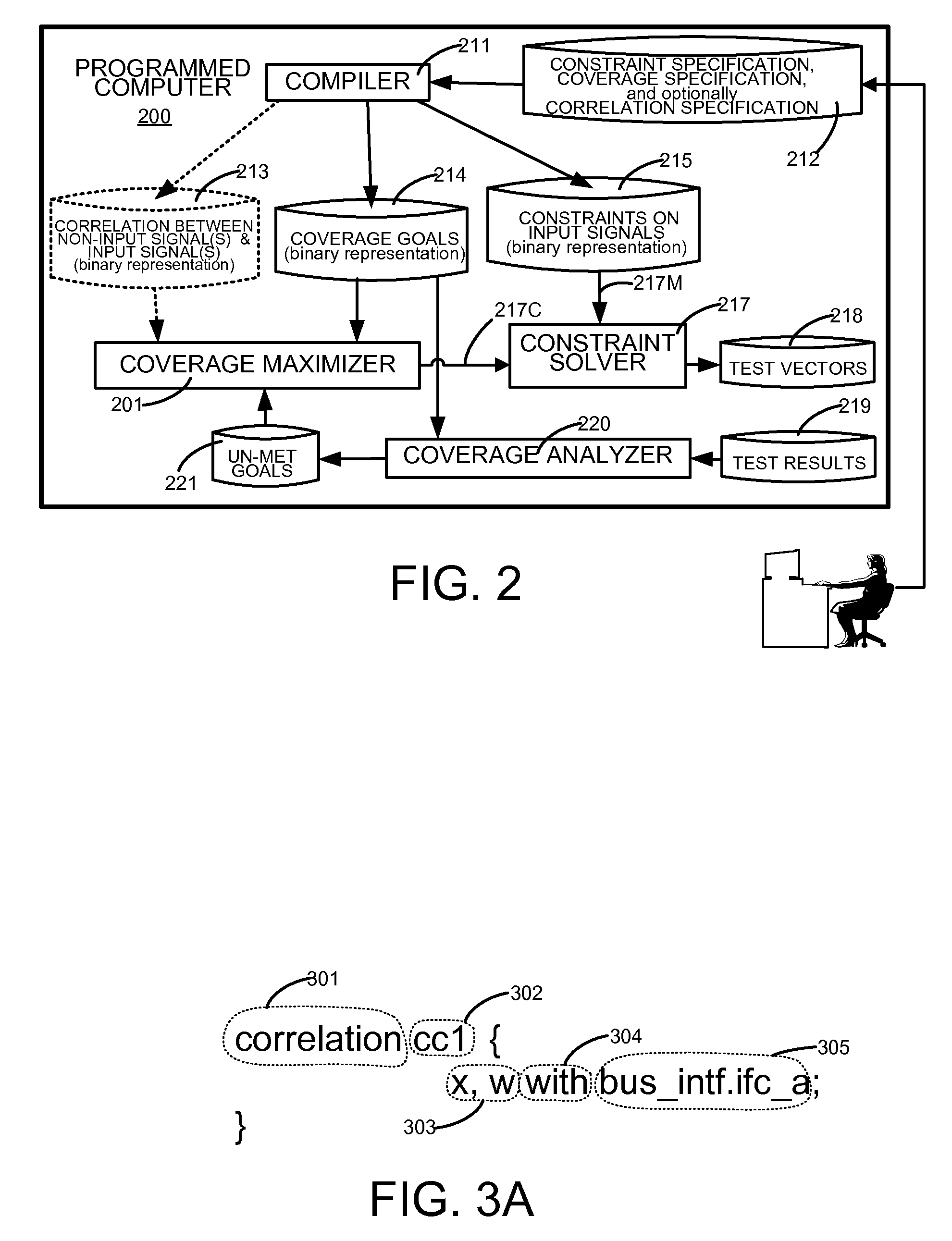

Method For Automatic Maximization of Coverage in Constrained Stimulus Driven Simulation

ActiveUS20090037858A1Improve functional coverageExpand coverageElectronic circuit testingError detection/correctionSignal correlationTest vector

A computer increases coverage in simulation of a design of a circuit by processing goals for coverage differently depending on whether or not the goals are on input signals of the circuit. Specifically, goals on input signals are used to automatically formulate constraints (“directly-derived constraints”) on values of input signals in test vectors. Goals on non-input signals (e.g. internal / output signals) are used with correlations to automatically formulate more additional constraints (“correlation-derived constraints”), by use of goals on non-input signals. The correlations indicate which non-input signals are associated with which input signals. The correlations are received from, for example, a human designer of the circuit. Depending on the embodiment, one or more of the automatically derived constraints are used with human-supplied constraints, to generate test vectors e.g. using a constraints solver, such as a satisfiability (SAT) engine. The test vectors are supplied to a simulator for functional verification.

Owner:SYNOPSYS INC

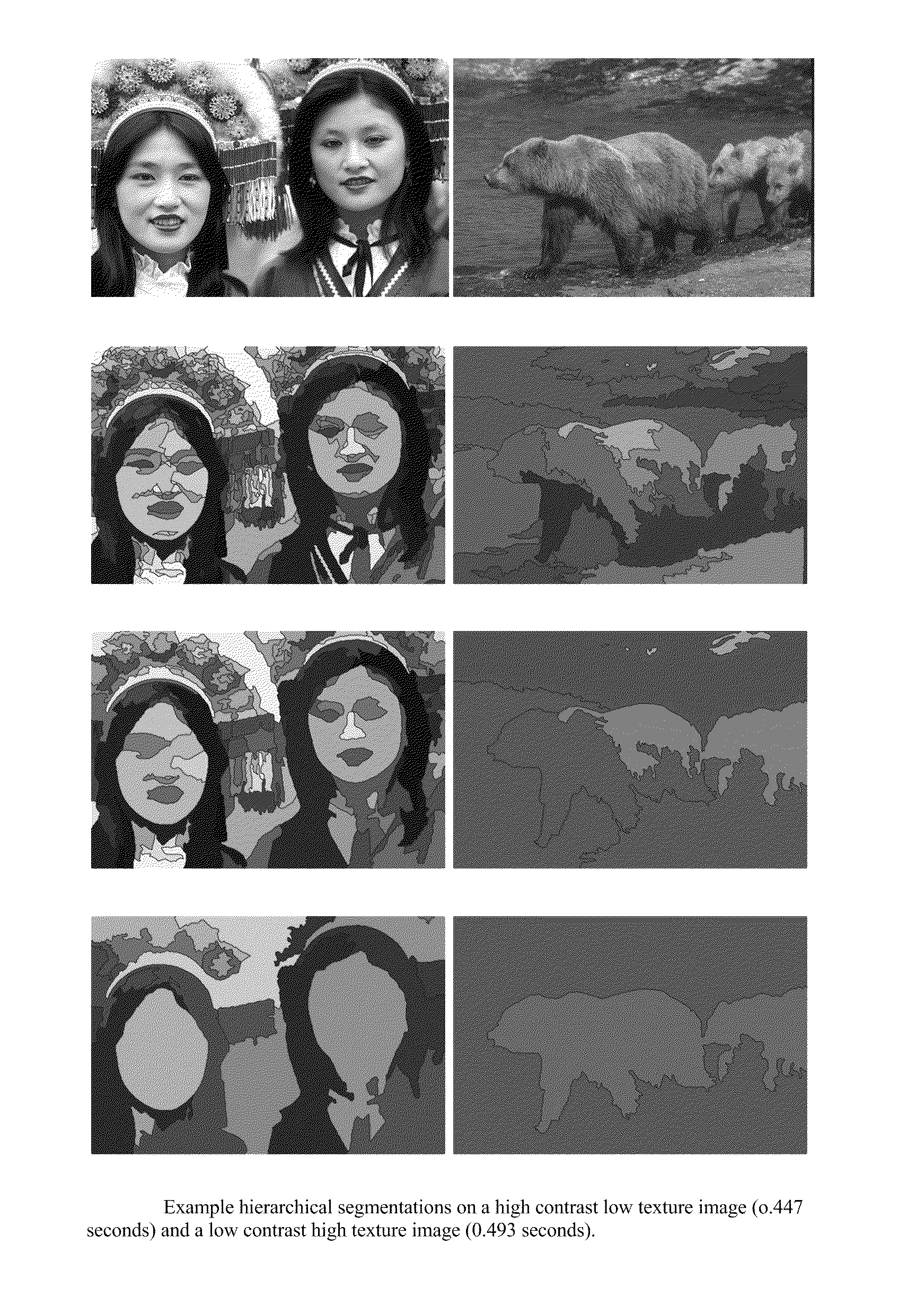

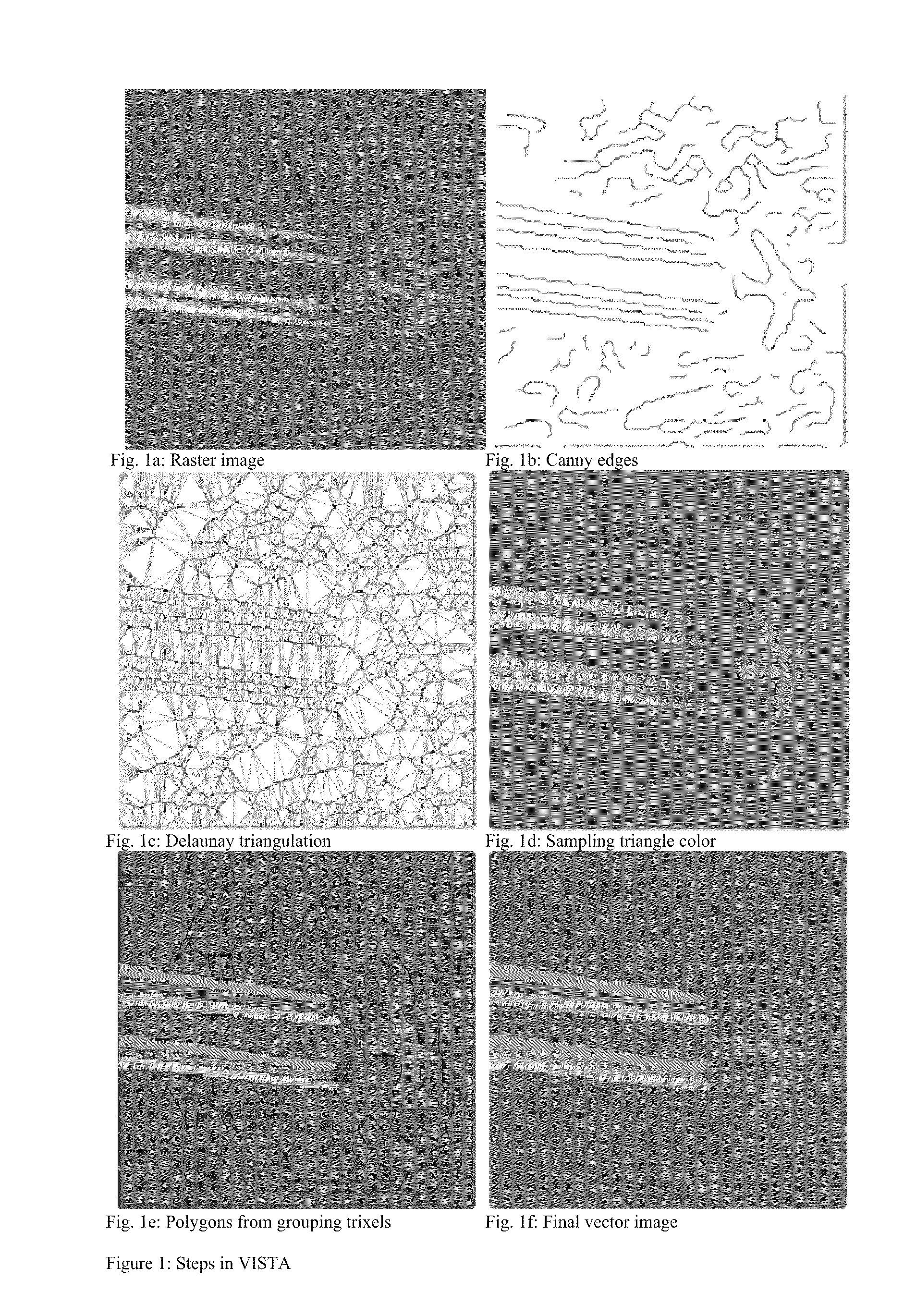

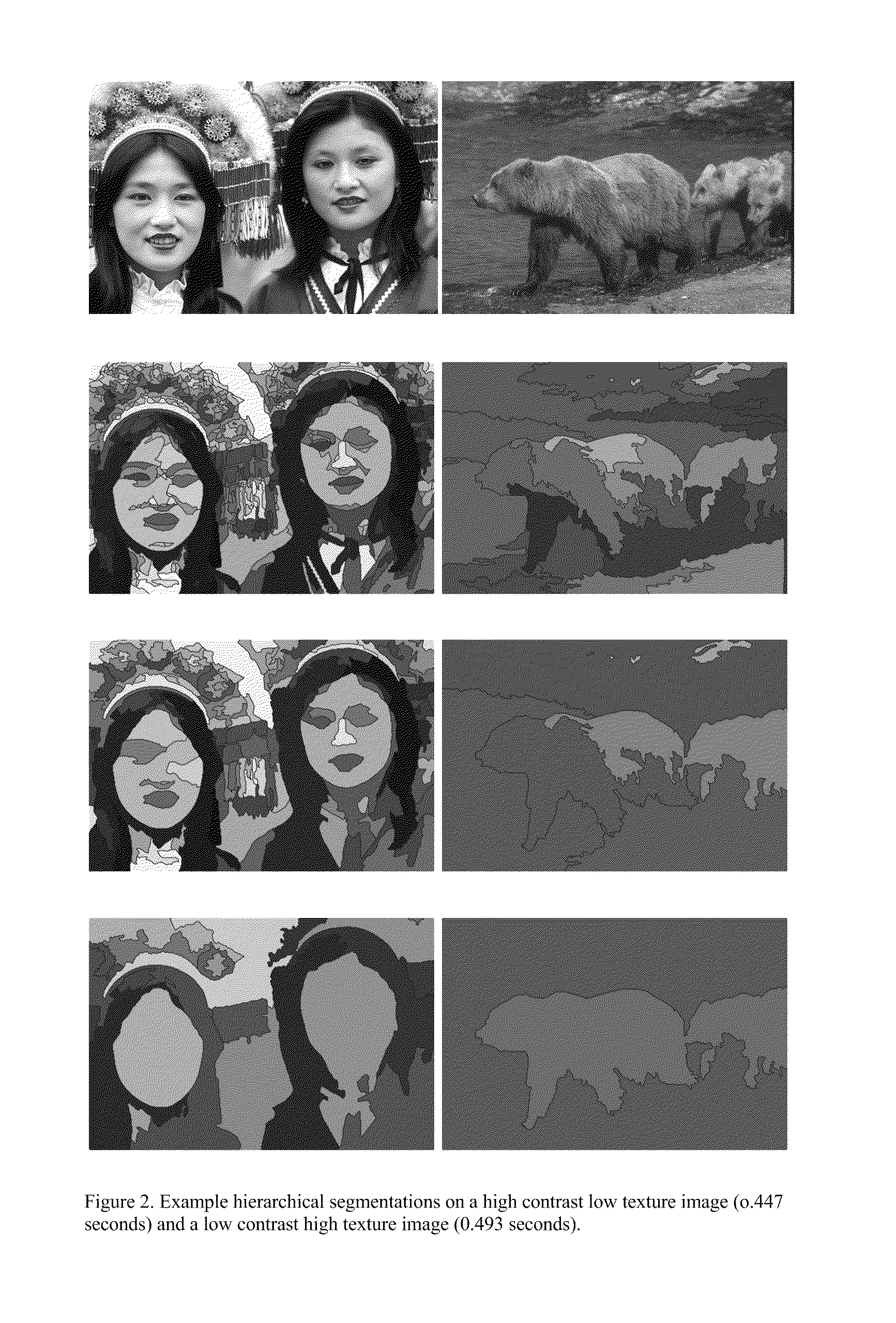

Image segmentation by hierarchial agglomeration of polygons using ecological statistics

A method for rapid hierarchical image segmentation based on perceptually driven contour completion and scene statistics is disclosed. The method begins with an initial fine-scale segmentation of an image, such as obtained by perceptual completion of partial contours into polygonal regions using region-contour correspondences established by Delaunay triangulation of edge pixels as implemented in VISTA. The resulting polygons are analyzed with respect to their size and color / intensity distributions and the structural properties of their boundaries. Statistical estimates of granularity of size, similarity of color, texture, and saliency of intervening boundaries are computed and formulated into logical (Boolean) predicates. The combined satisfiability of these Boolean predicates by a pair of adjacent polygons at a given segmentation level qualifies them for merging into a larger polygon representing a coarser, larger-scale feature of the pixel image and collectively obtains the next level of polygonal segments in a hierarchy of fine-to-coarse segmentations. The iterative application of this process precipitates textured regions as polygons with highly convolved boundaries and helps distinguish them from objects which typically have more regular boundaries. The method yields a multiscale decomposition of an image into constituent features that enjoy a hierarchical relationship with features at finer and coarser scales. This provides a traversable graph structure from which feature content and context in terms of other features can be derived, aiding in automated image understanding tasks. The method disclosed is highly efficient and can be used to decompose and analyze large images.

Owner:TRIAD NAT SECURITY LLC

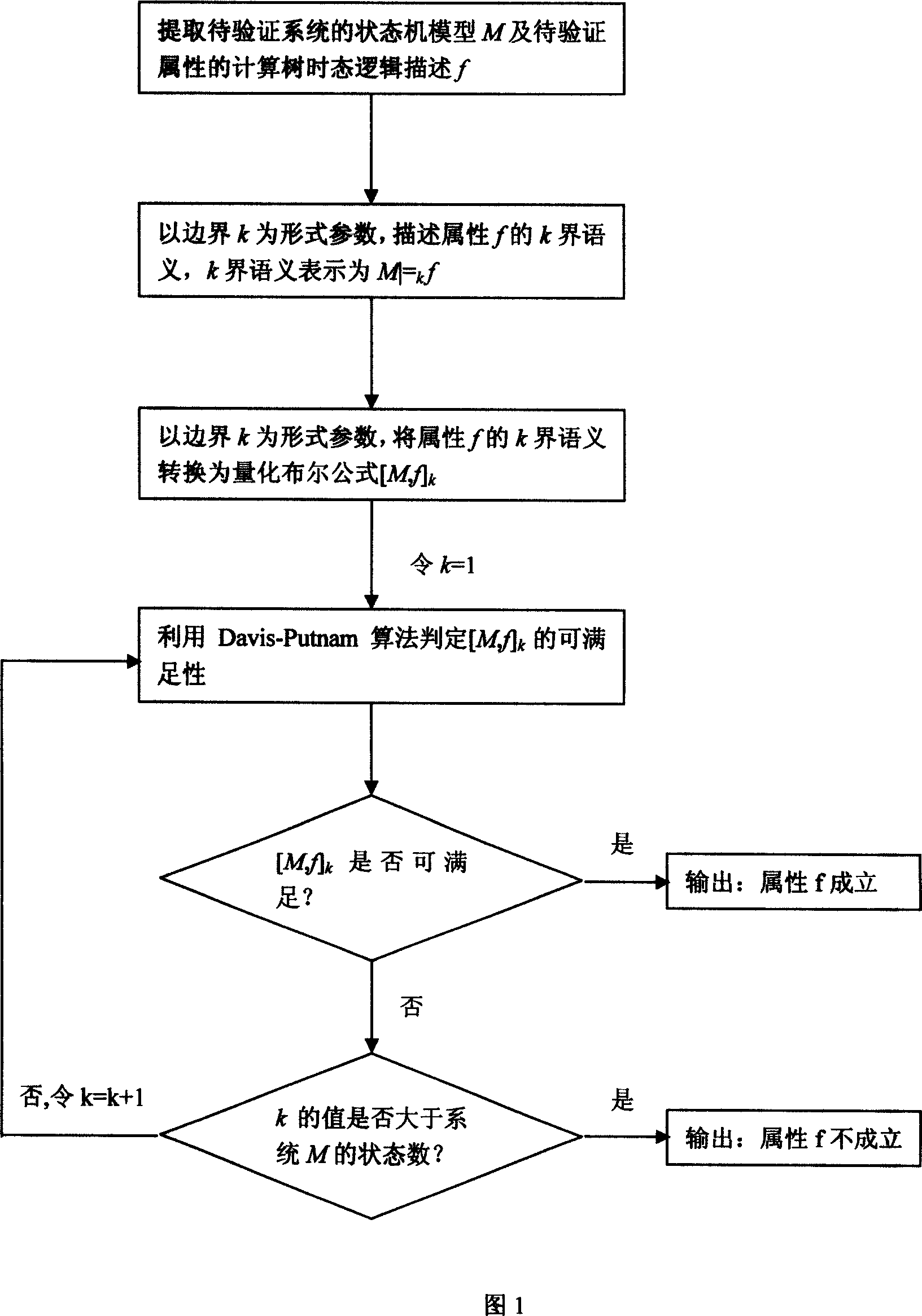

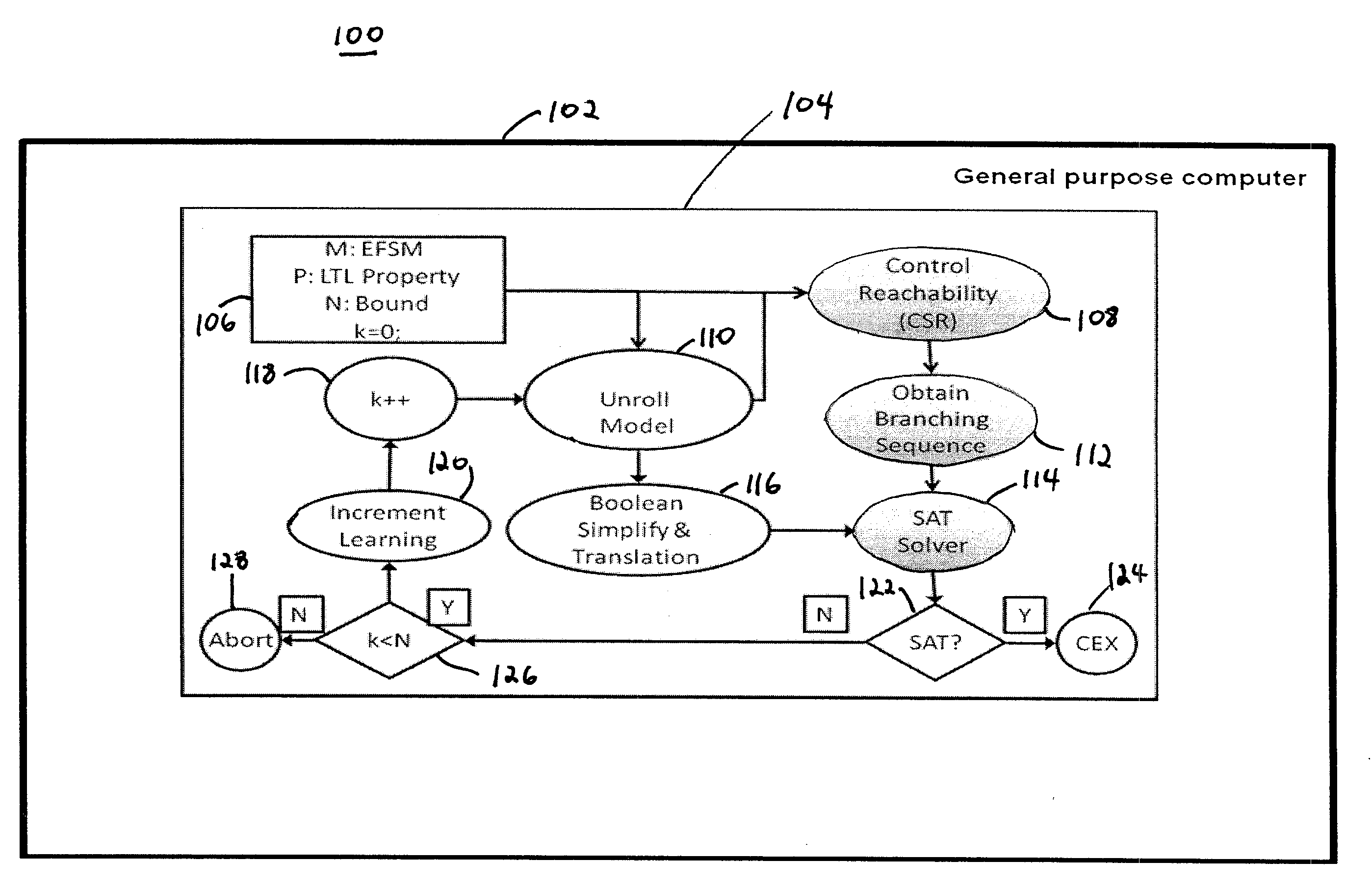

Symbolized model detection method

InactiveCN101013452AOvercoming the state space explosion problemImprove reliabilitySpecial data processing applicationsTemporal logicModel testing

This symbol model detection method is a method to make the model testing practical; the main principle is to use Boolean formula quantitative determination to instead of the CTL model testing. Their method: 1.) extract state machine M of the tested system and the attributes of the tested tree temporal logic description; 2.) taking border k as the form parameters, describe k sector semantics of the attributes f; 3.) taking border k as the form parameters, convert the k sector semantic of attribute f to quantify Boolean formula [M, f] k: 4.) progressive determine whether the system M meets the reliable attribute f: the approach integrates the advantages of symbol model testing based on binary decision diagram and bounded model checking based proposition equitation meeting judgment, also overcomes their shortcomings, which are not dependent on the sort of Boolean variables, or dependent on the property to verify the full name attribute.

Owner:JIANGSU UNIV

Ultra-micro powder plant slice and preparation method thereof

The invention relates to an ultra-micro powder plant slice and a preparation method thereof. The preparation method comprises the steps that ultra-micro plant powder, outer margin fibers, an adhesiveand other additives are homogenized to form adhesive colloidal fluid, the adhesive colloidal fluid is extruded to form a slice shape, and drying formation is conducted. The plant slice is suitable fora heat-not-burn flavor-producing section, the plant slice is large in smoke formation amount, rich in fragrance and high in physiological satisfiability, the smoke flavor is close to natural plant fragrance, the product density and the filling value are close to those of natural plant leaves, the machining performance is high, and the amount of water required during production is small; no wastewater is generated, the raw material utilization rate is high, the plant slice meets the requirements for energy conservation and environment protection, the production technology is simple, and the preparation method is suitable for industrial production.

Owner:YUNNAN TOBACCO BIOLOGICAL TECH CO LTD +1

Method for automatic maximization of coverage in constrained stimulus driven simulation

ActiveUS7617468B2Expand coverageElectronic circuit testingError detection/correctionSignal correlationTest vector

A computer increases coverage in simulation of a design of a circuit by processing goals for coverage differently depending on whether or not the goals are on input signals of the circuit. Specifically, goals on input signals are used to automatically formulate constraints (“directly-derived constraints”) on values of input signals in test vectors. Goals on non-input signals (e.g. internal / output signals) are used with correlations to automatically formulate more additional constraints (“correlation-derived constraints”), by use of goals on non-input signals. The correlations indicate which non-input signals are associated with which input signals. The correlations are received from, for example, a human designer of the circuit. Depending on the embodiment, one or more of the automatically derived constraints are used with human-supplied constraints, to generate test vectors e.g. using a constraints solver, such as a satisfiability (SAT) engine. The test vectors are supplied to a simulator for functional verification.

Owner:SYNOPSYS INC

Partition-based decision heuristics for SAT and image computation using SAT and BDDs

InactiveUS20020178424A1Reduce partAdd depthComputer aided designSoftware simulation/interpretation/emulationRecognition heuristicConjunctive normal form

A method for Boolean Satisfiability (SAT). The method comprises using a variable decision heuristic in a SAT algorithm and pruning the search space of SAT using said decision heuristic. The decision heuristic is based on partitioning a conjunctive normal form (CNF) of a Boolean formula corresponding to the SAT and the partitioning is induced by a separator set. An image computaion method that uses the disclosed method for solving the SAT.

Owner:NEC CORP

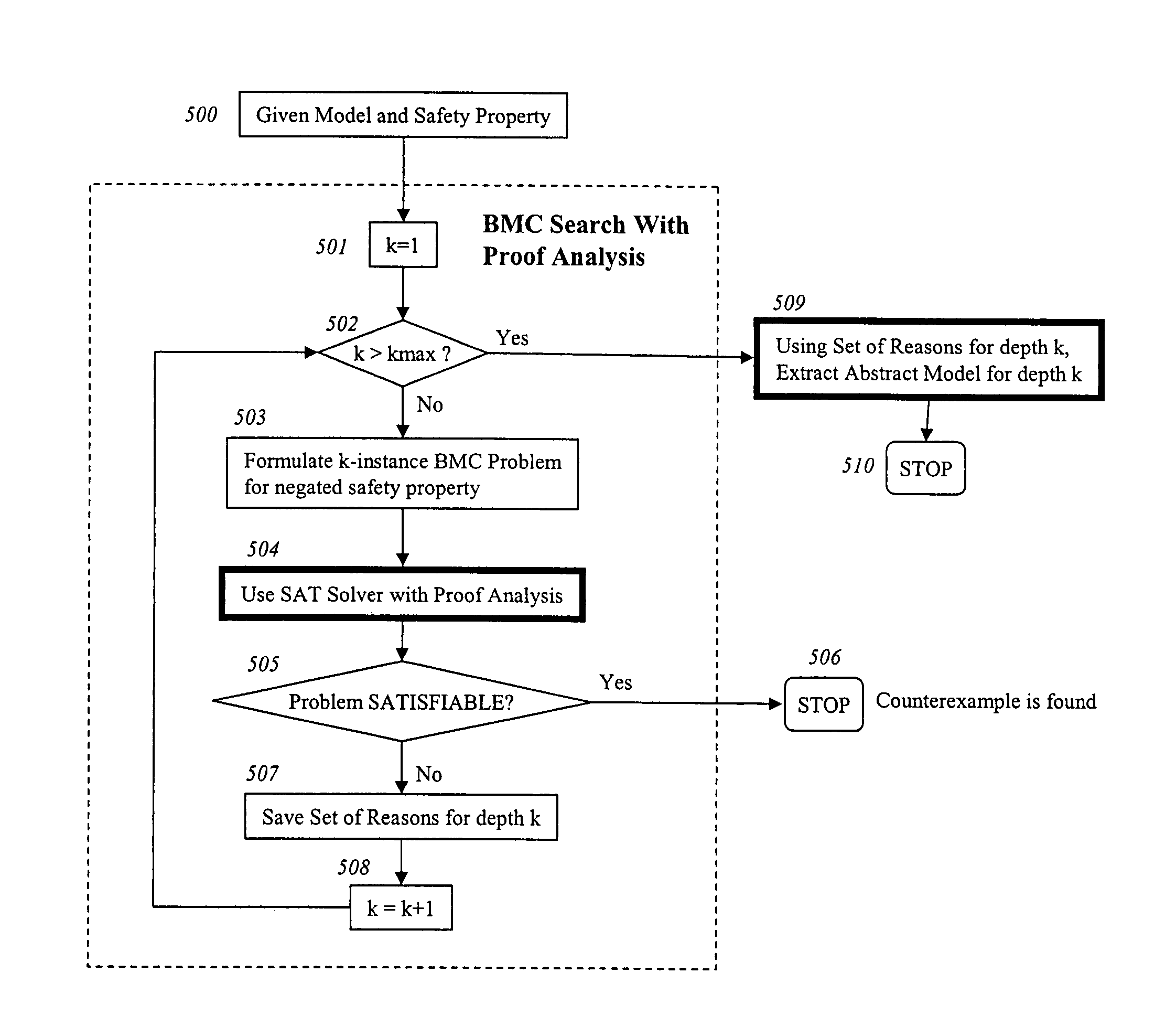

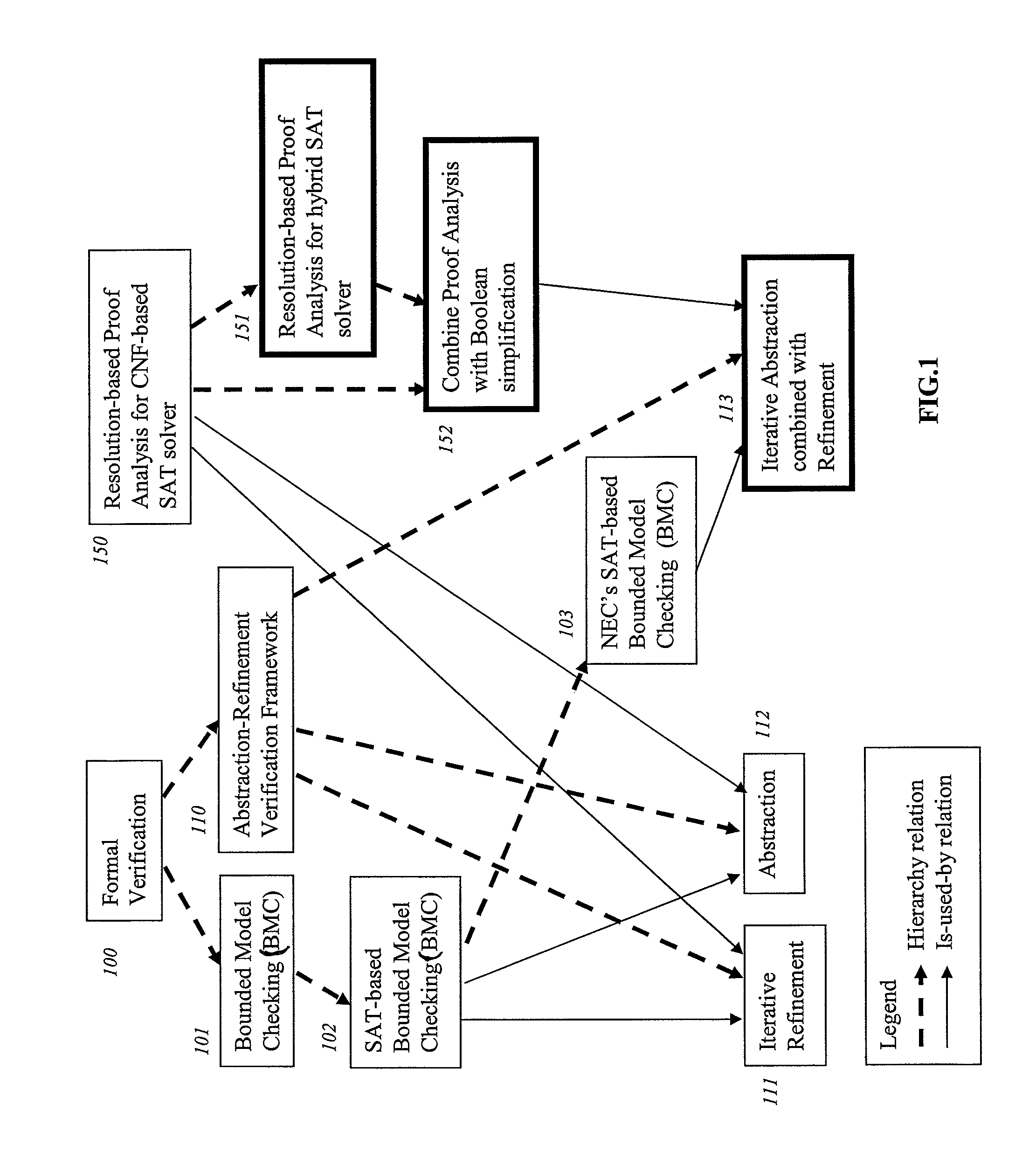

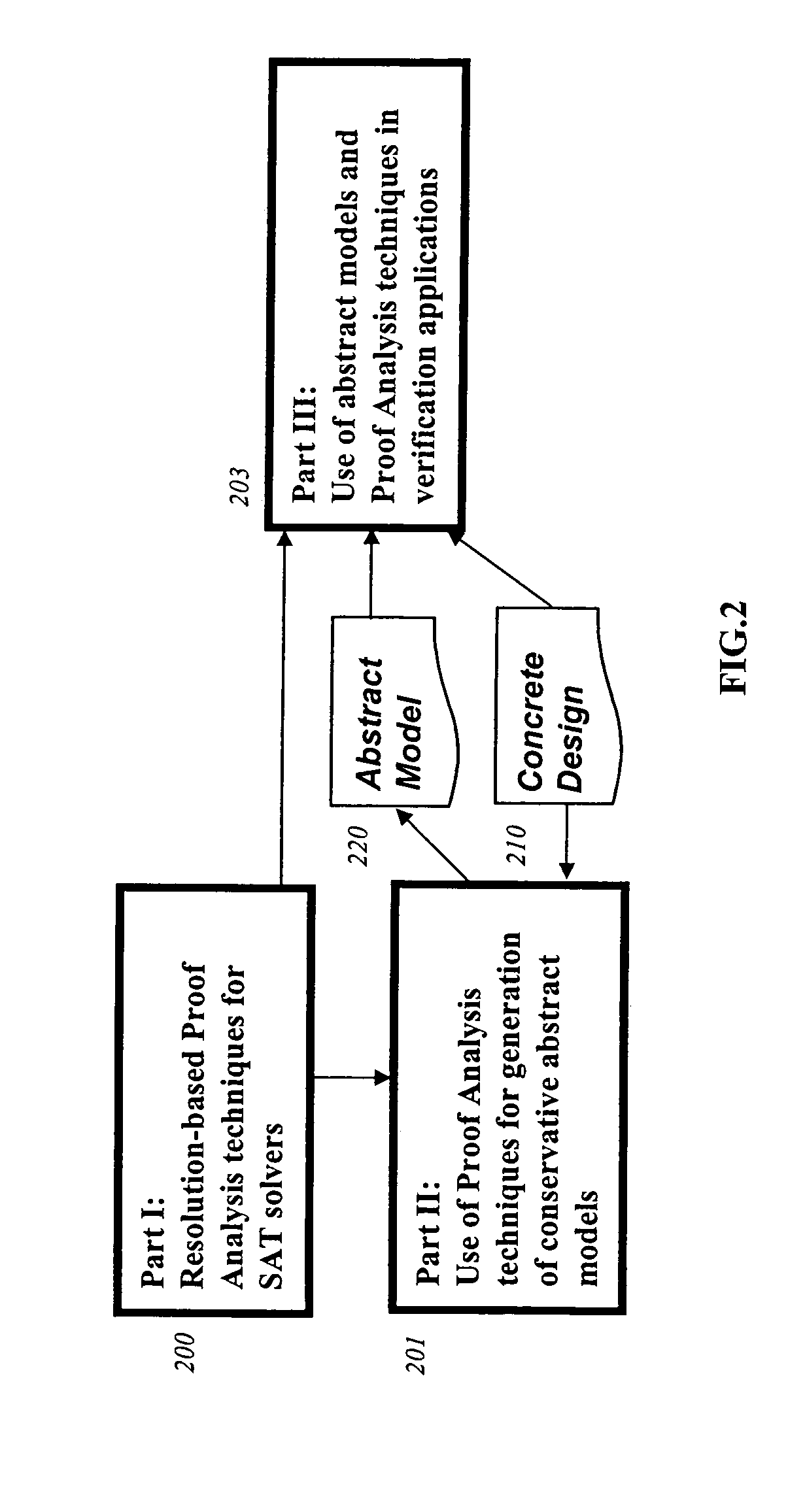

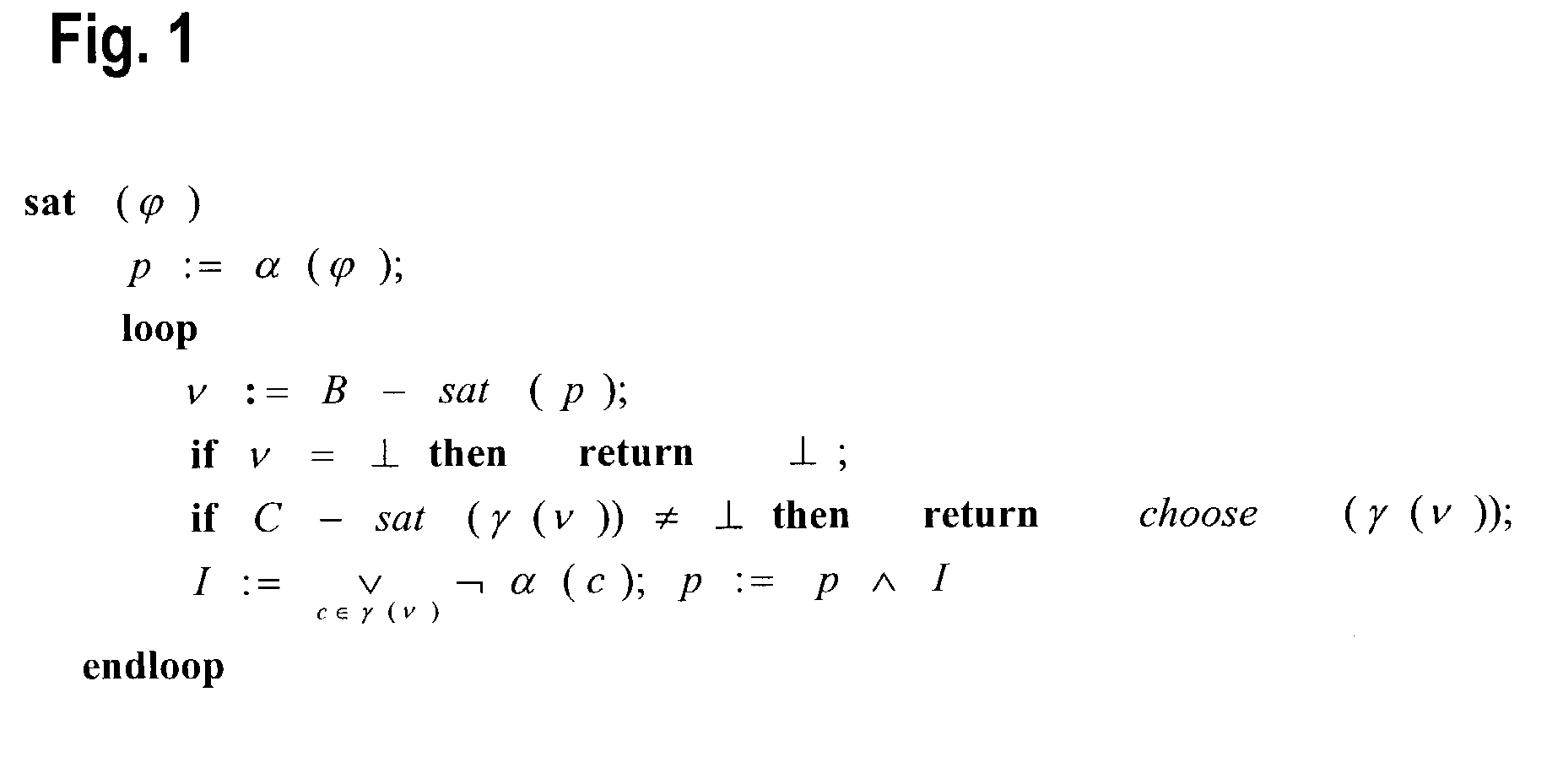

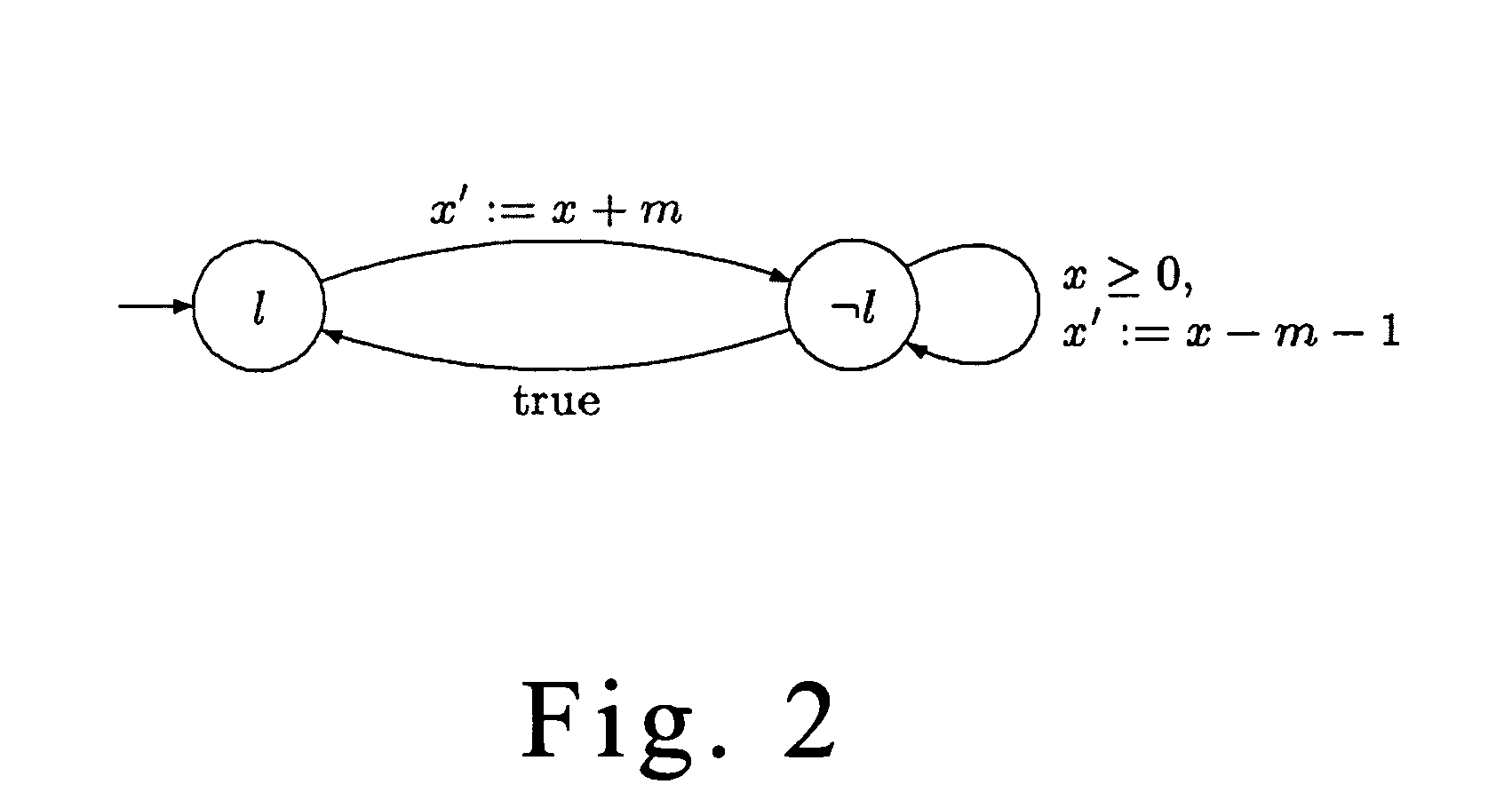

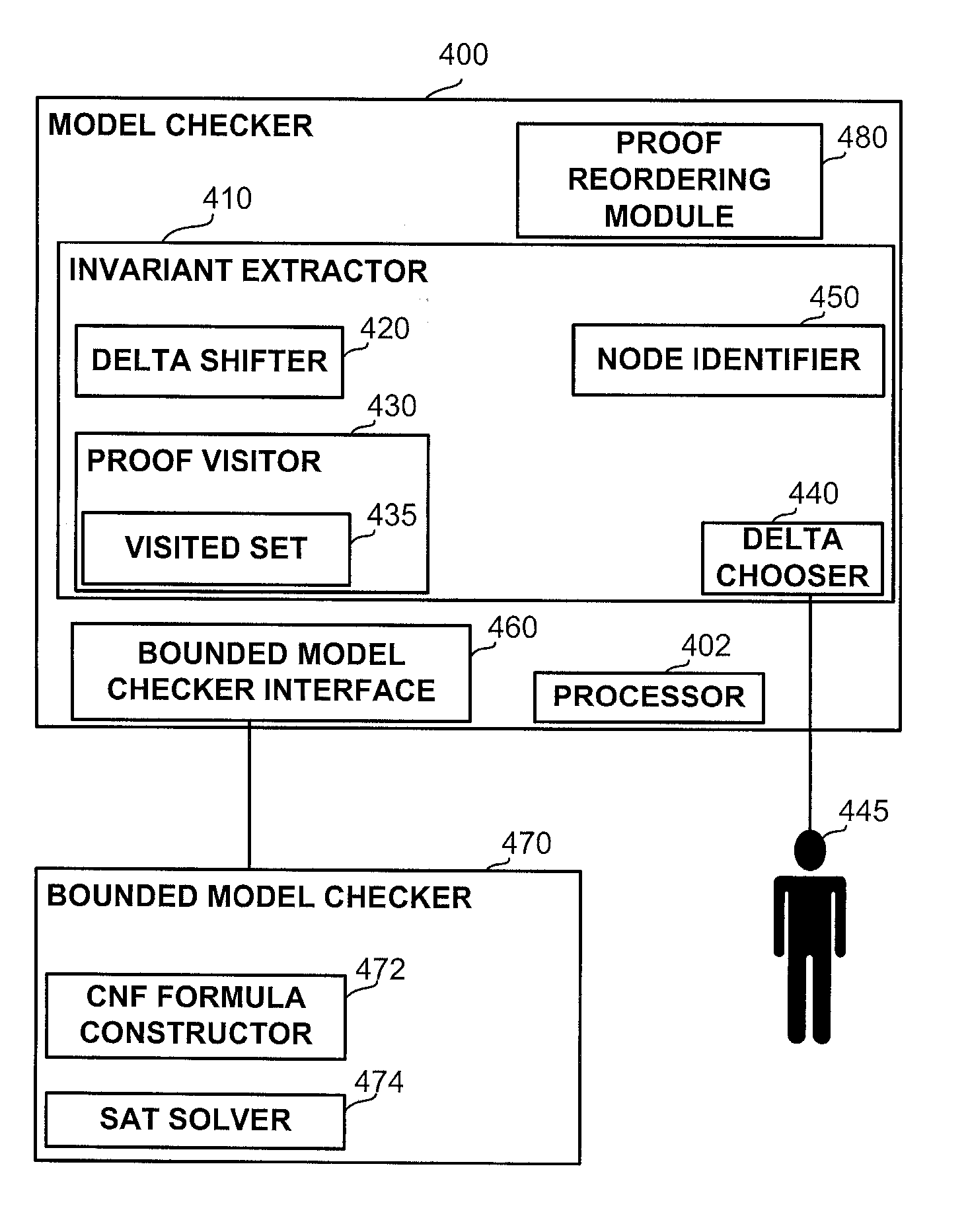

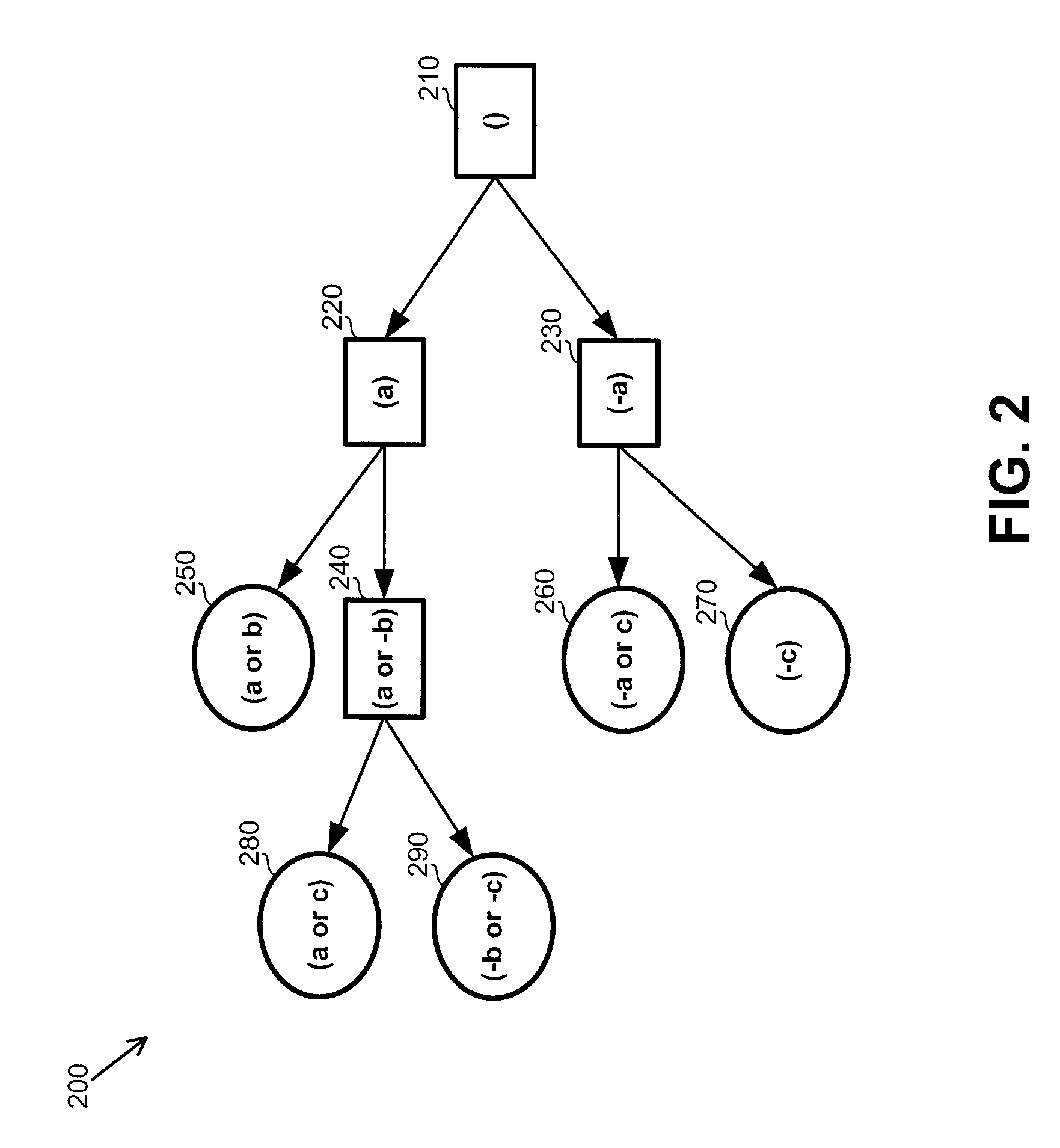

Iterative abstraction using SAT-based BMC with proof analysis

InactiveUS7742907B2Computation using non-denominational number representationComputer aided designBoolean constraintImage resolution

A method of obtaining a resolution-based proof of unsatisfiability using a SAT procedure for a hybrid Boolean constraint problem comprising representing constraints as a combination of clauses and interconnected gates. The proof is obtained as a combination of clauses, circuit gates and gate connectivity constraints sufficient for unsatisfiability.

Owner:NEC CORP

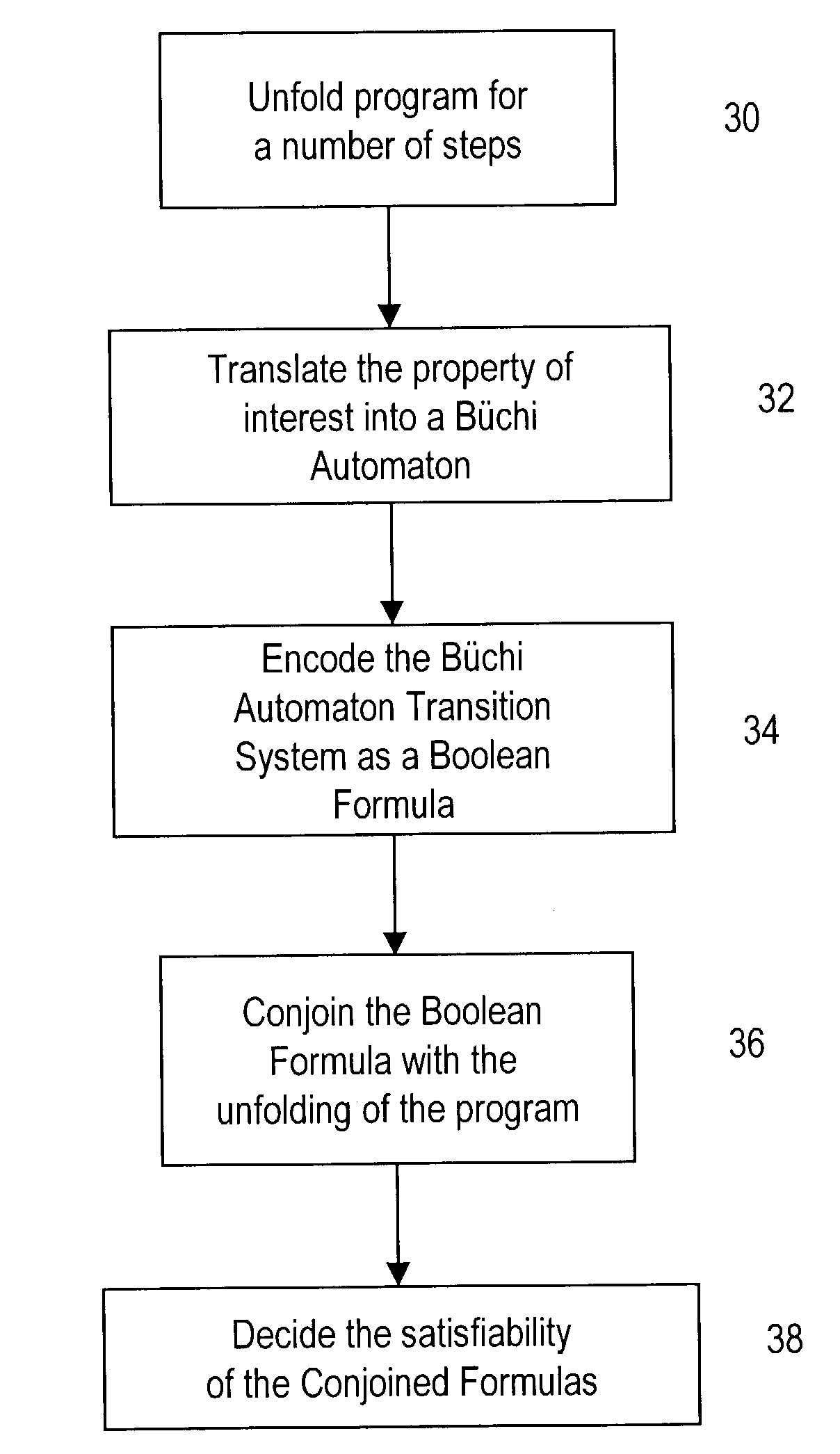

Method for combining decision procedures with satisfiability solvers

The invention provides bounded model checking of a program with respect to a property of interest comprising unfolding the program for a number of steps to create a program formula; translating the property of interest into an automaton; encoding the transition system of the automaton into a Boolean formula creating a transition formula; conjoining the program formula with the transition formula to create a conjoined formula; and deciding the satisfiability of the conjoined formula.

Owner:SRI INTERNATIONAL

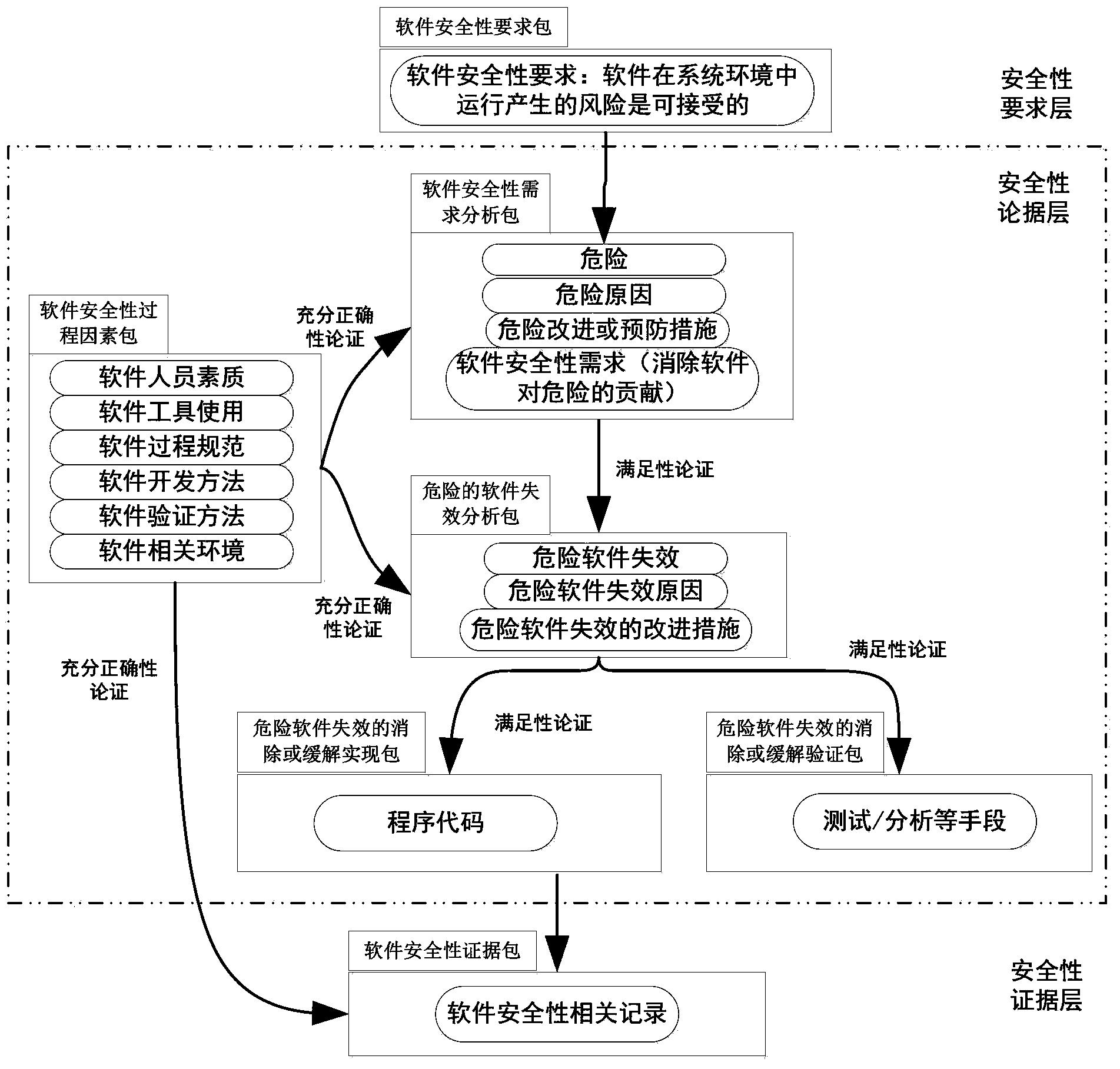

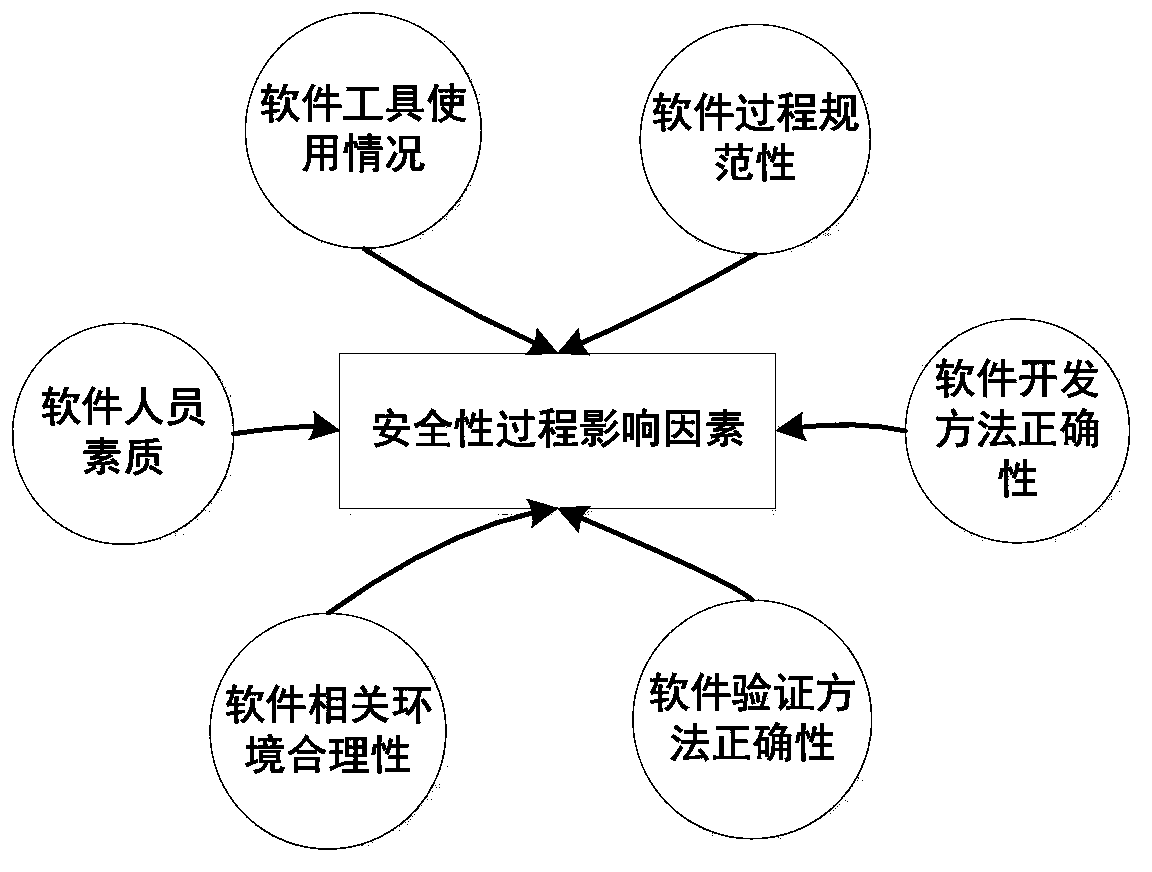

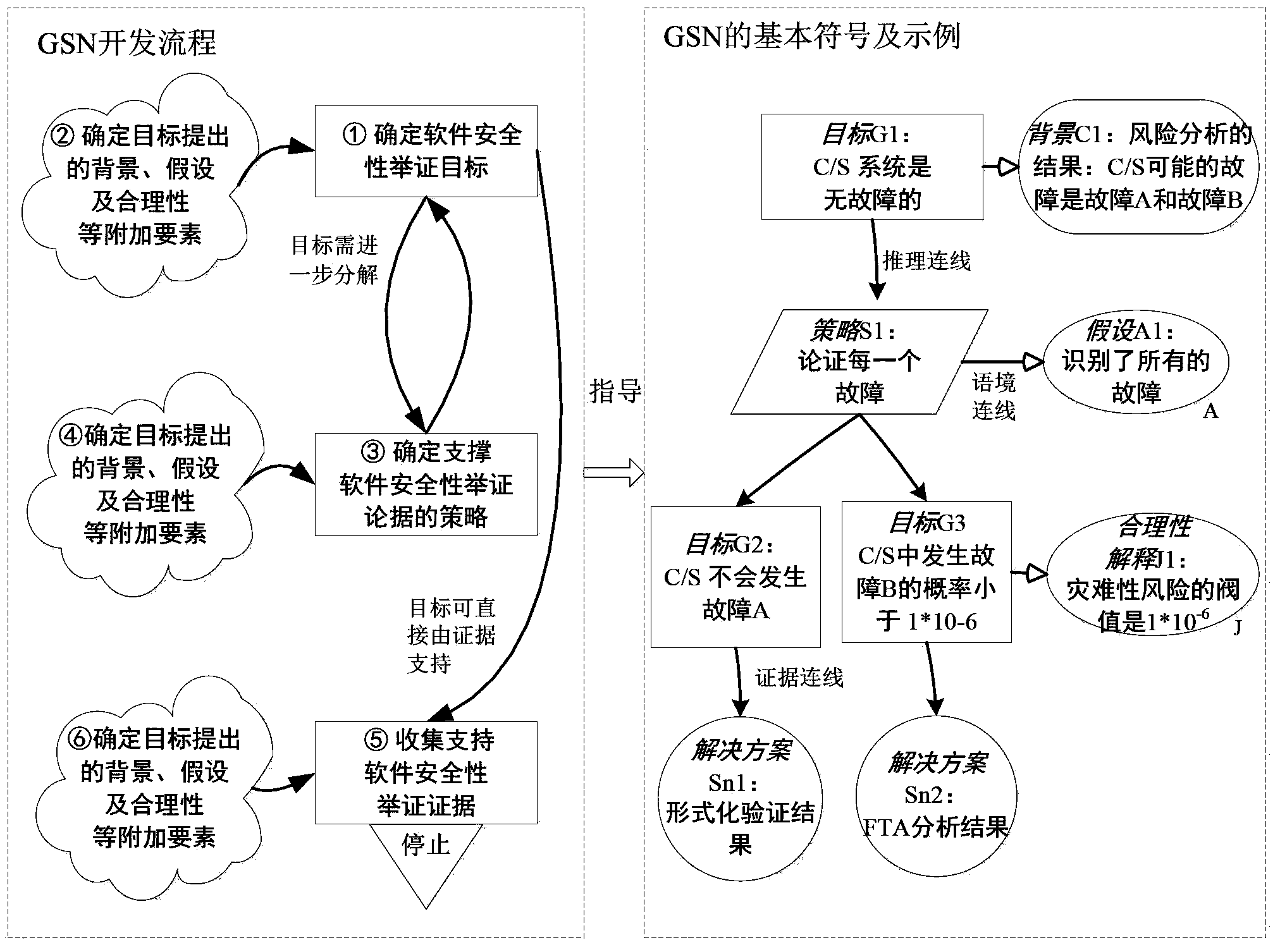

Software safety proof development method combining product and process

ActiveCN103383722AConfidenceOvercoming the Shortcomings of Software Security EvidenceSoftware testing/debuggingProgram/content distribution protectionSoftware engineeringSatisfiability

The invention discloses a software safety proof development method combining a product and a process. The method takes danger or danger control as the core, realizes risk management of system safety from the aspect of software, and launches proofing of two aspects including satisfiability and full correctness surrounding the top target. The purpose of satisfiability proofing is to prove that proofed objects are realized and satisfied, so as to perform proofing from the aspects of danger, danger control, and danger control realization, all based on the product method which serves as a main line. The purpose of full correctness is to prove that the objects are complete and correct, so as to enhance the realization confidence based on process method and through the factors such as 'process standardization, personnel quality and development method'. The software safety proof development method overcomes the deficiency of software safety proofing only through product or only through process, can effectively guide the development of software safety proofing, and provide a more effective method for a software-related party to check the safety and other related situation.

Owner:天航长鹰(江苏)科技有限公司

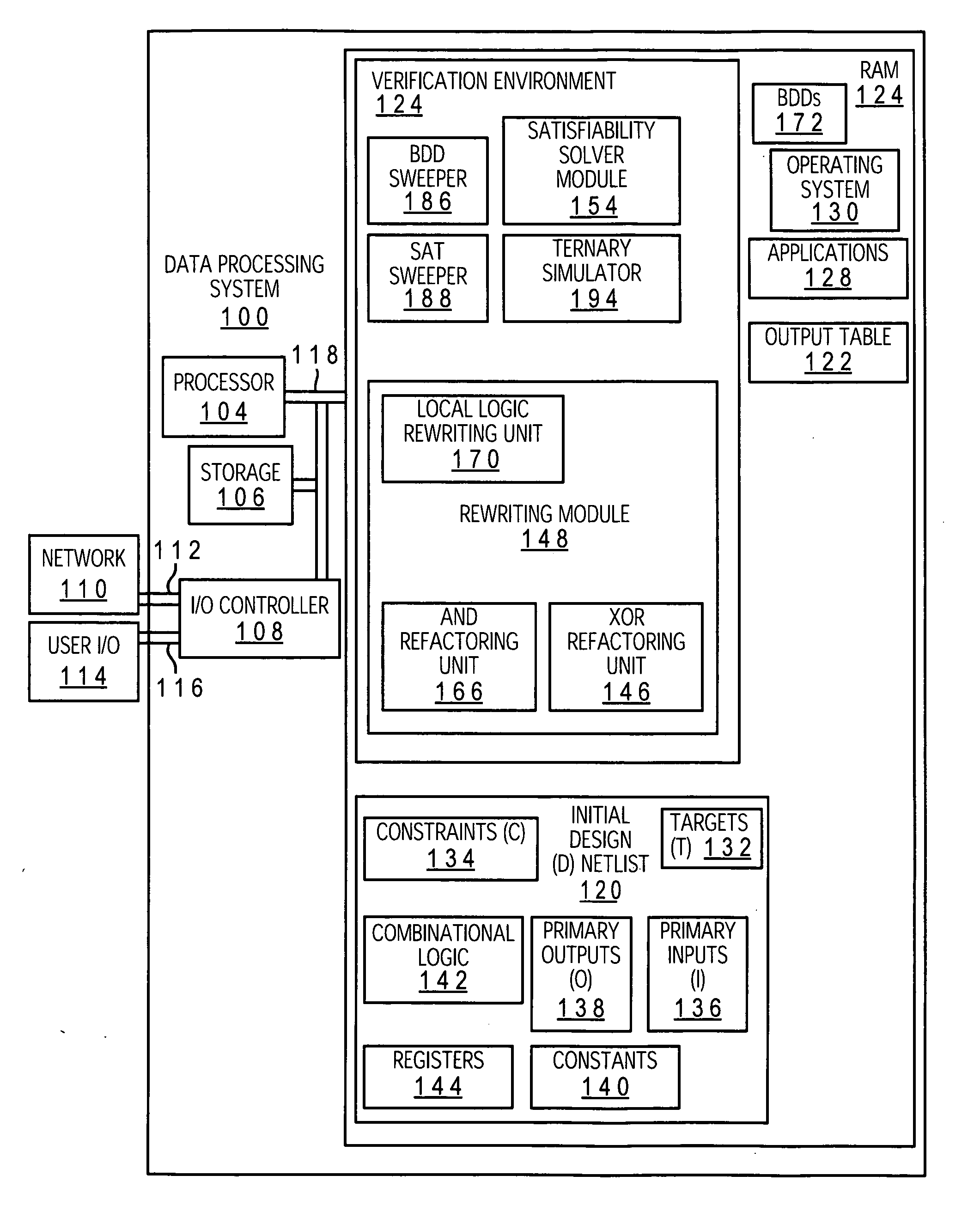

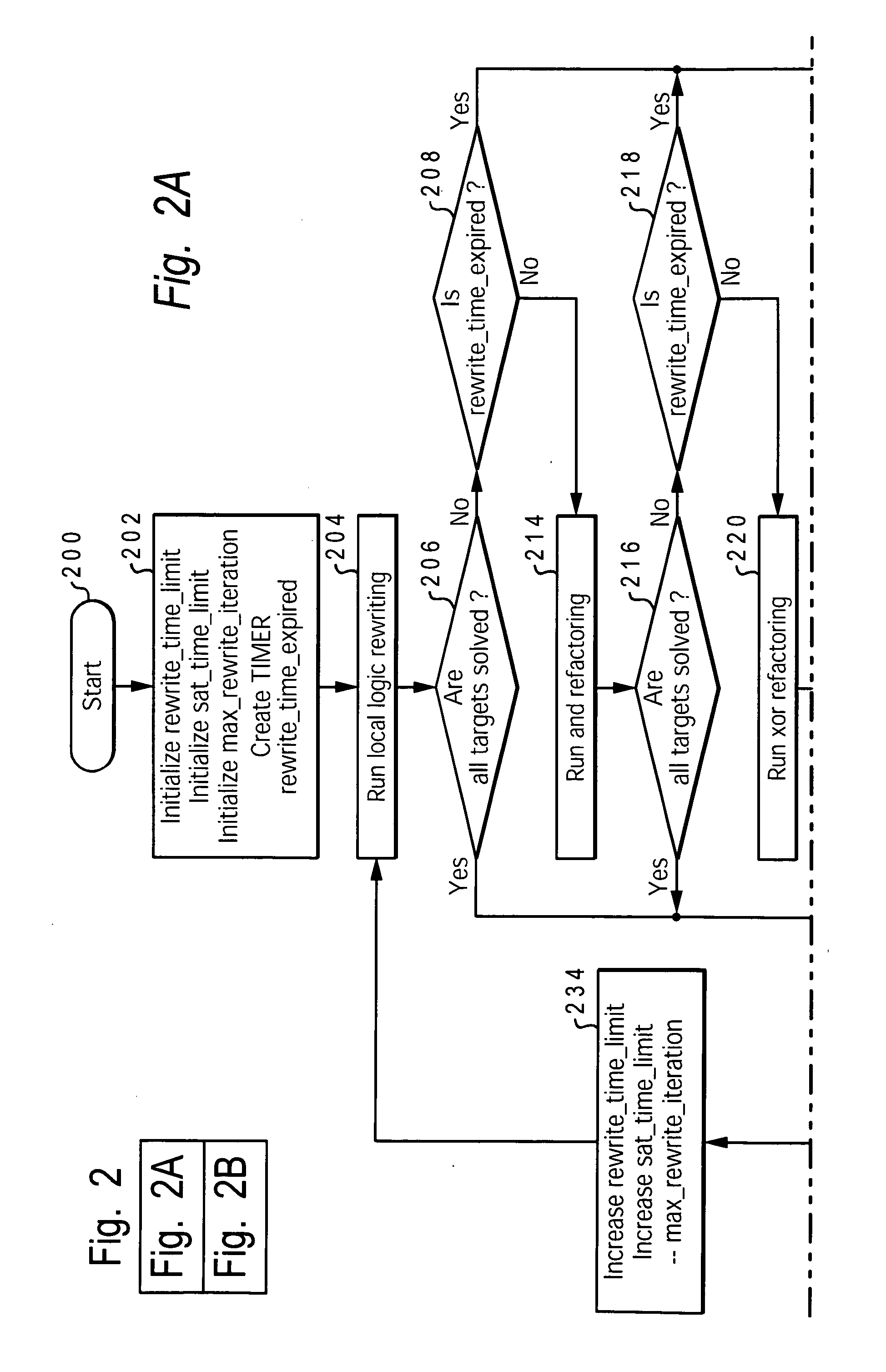

Method and system for enhanced verification by closely coupling a structural satisfiability solver and rewriting algorithms

A method, system and computer program product are disclosed. The method includes initializing a first variable to limit a rewrite time for rewrite operations with respect to an initial design by a rewriting module, a second variable to limit a time for satsifability solver operations with respect to said initial design by a staisfiability solver module and a third variable to limit a maximum number of rewrite iterations with respect to said initial design. A timer is called to track said rewrite time and a local logic rewriting operation is run on said initial design with said rewrite module. In response to determining that all of all targets for said initial design netlist are not solved, whether a rewrite time is expired is determined. In response to determining that said rewrite time is not expired, AND refactoring is run. In response to determining that said rewrite time is not expired, XOR refactoring is run.

Owner:INT BUSINESS MASCH CORP

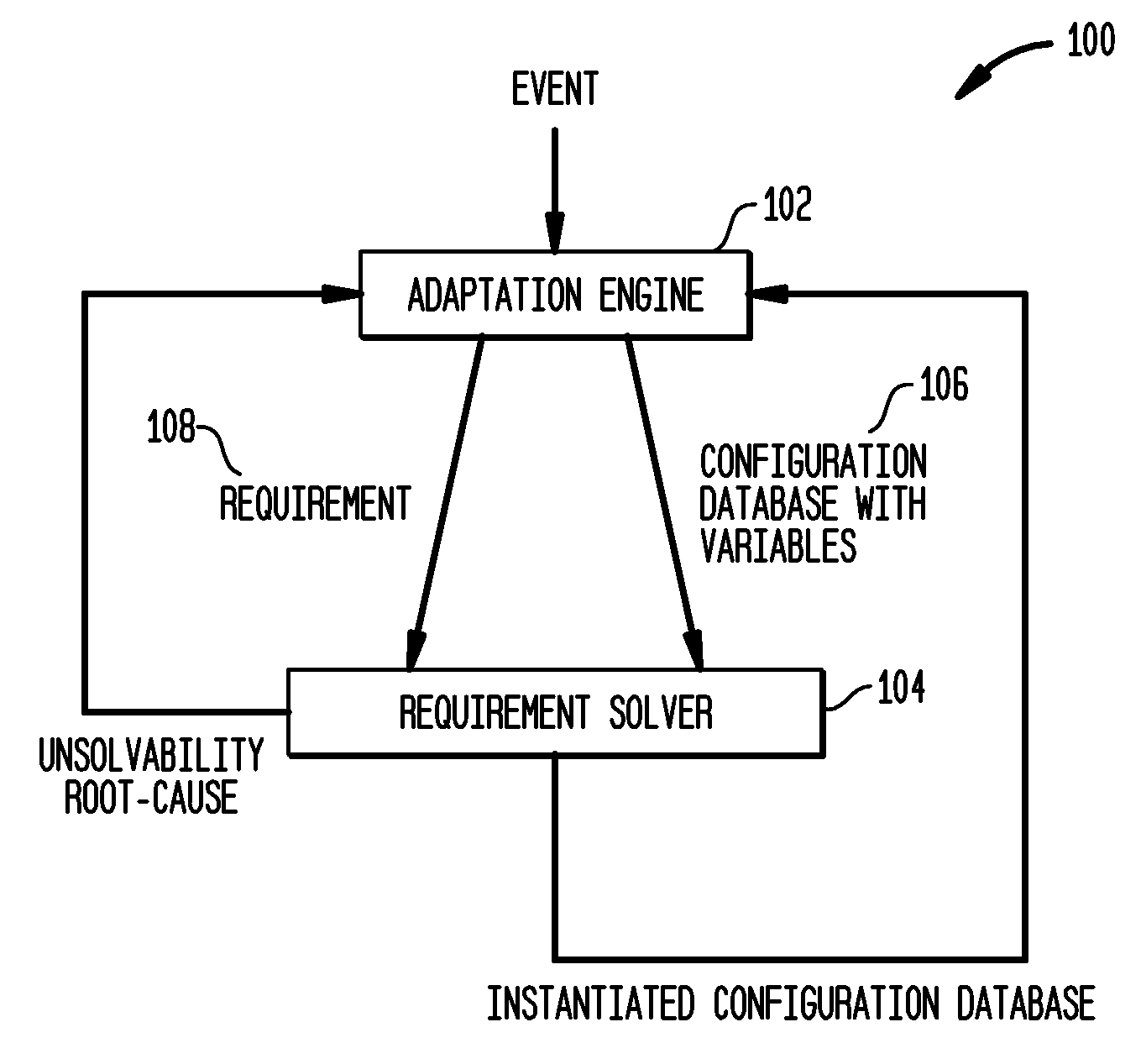

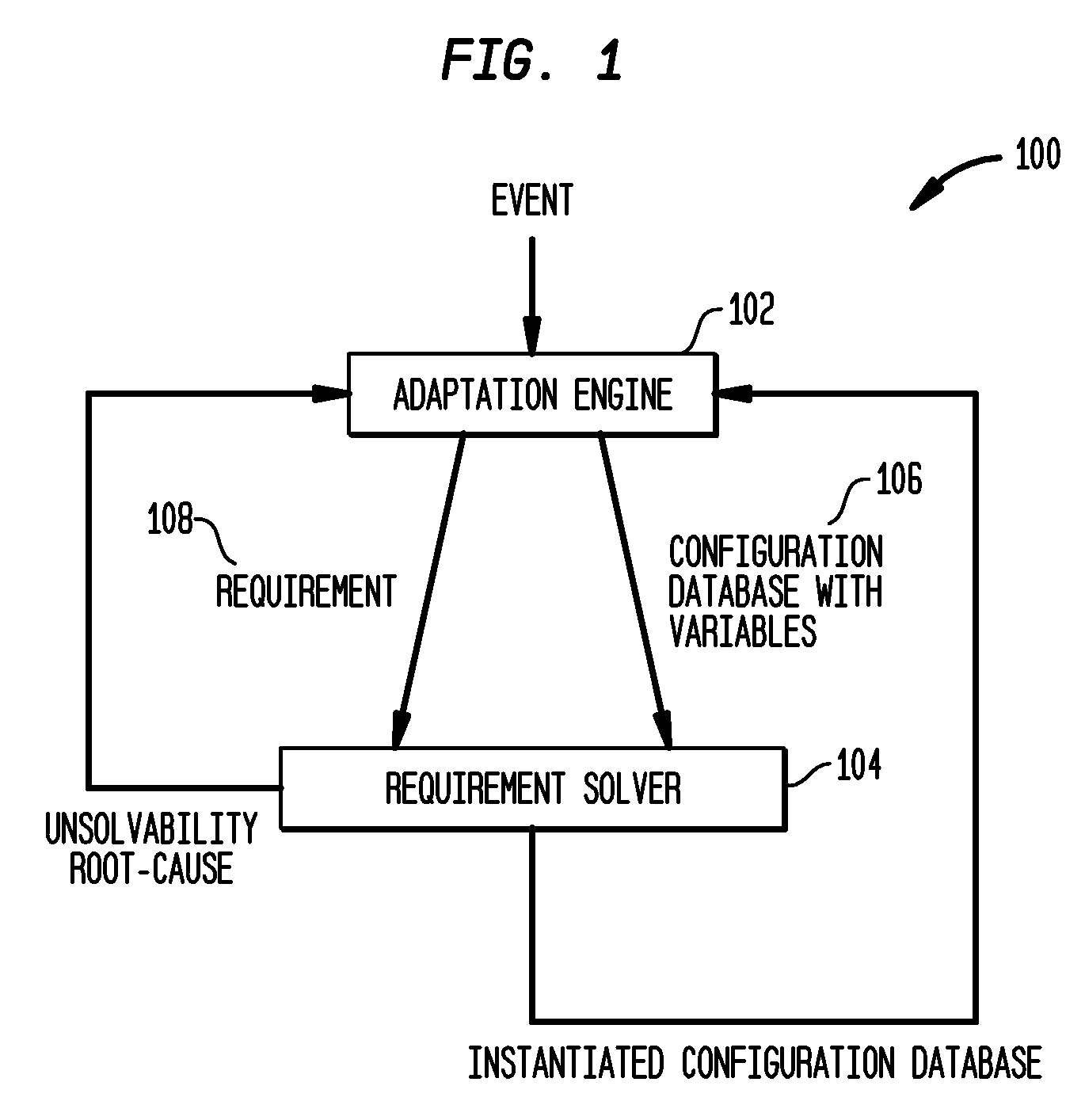

Scalable and Interactive Method of Generating and Modifying Network Configurations to Enforce Compliance with High-Level Requirements

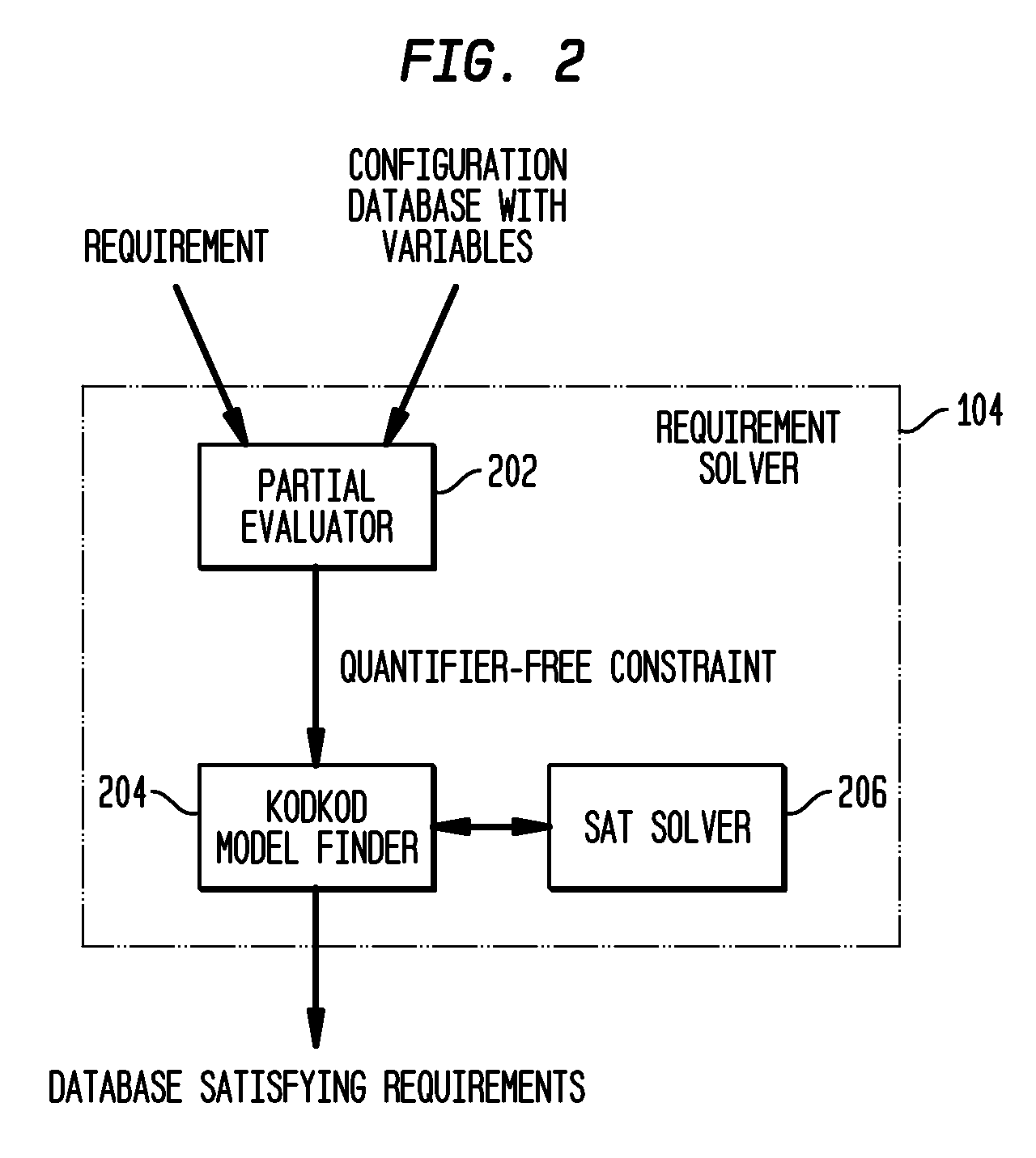

ActiveUS20090265296A1Efficient solutionSuppress generationDigital computer detailsDigital dataModel findingImage resolution

A system and method provides a solution to the problem of applying end-to-end requirements of connectivity, security, reliability and performance to configure a network and ultimately assign network components to the network. All requirements are modeled as constraints and a constraint solver does the resolution Not every constraint to be solved is solved by the model-finder. Instead, we “factor away” subsets of a constraint that can be efficiently solved via a special-purpose constraint solver, such as an SQL / Prolog engine, linear programming system, or even an algorithm, leaving behind a constraint that truly requires the power of model-finding, and that is often efficiently solvable by existing model-finders. Such constraints are compiled into quantifier-free constraints that are Boolean combinations of constraints of two forms x=y and x=c where x, y are variables and c is a constant. Such constraints can be efficiently solved by modern SAT-based model-finders. The system intelligently removes the quantifiers instead of having the model-finder remove the quantifiers. An “unsatisfiability-core” analysis efficiently guides the search for configurations to change to restore consistency.

Owner:PERSPECTA LABS INC

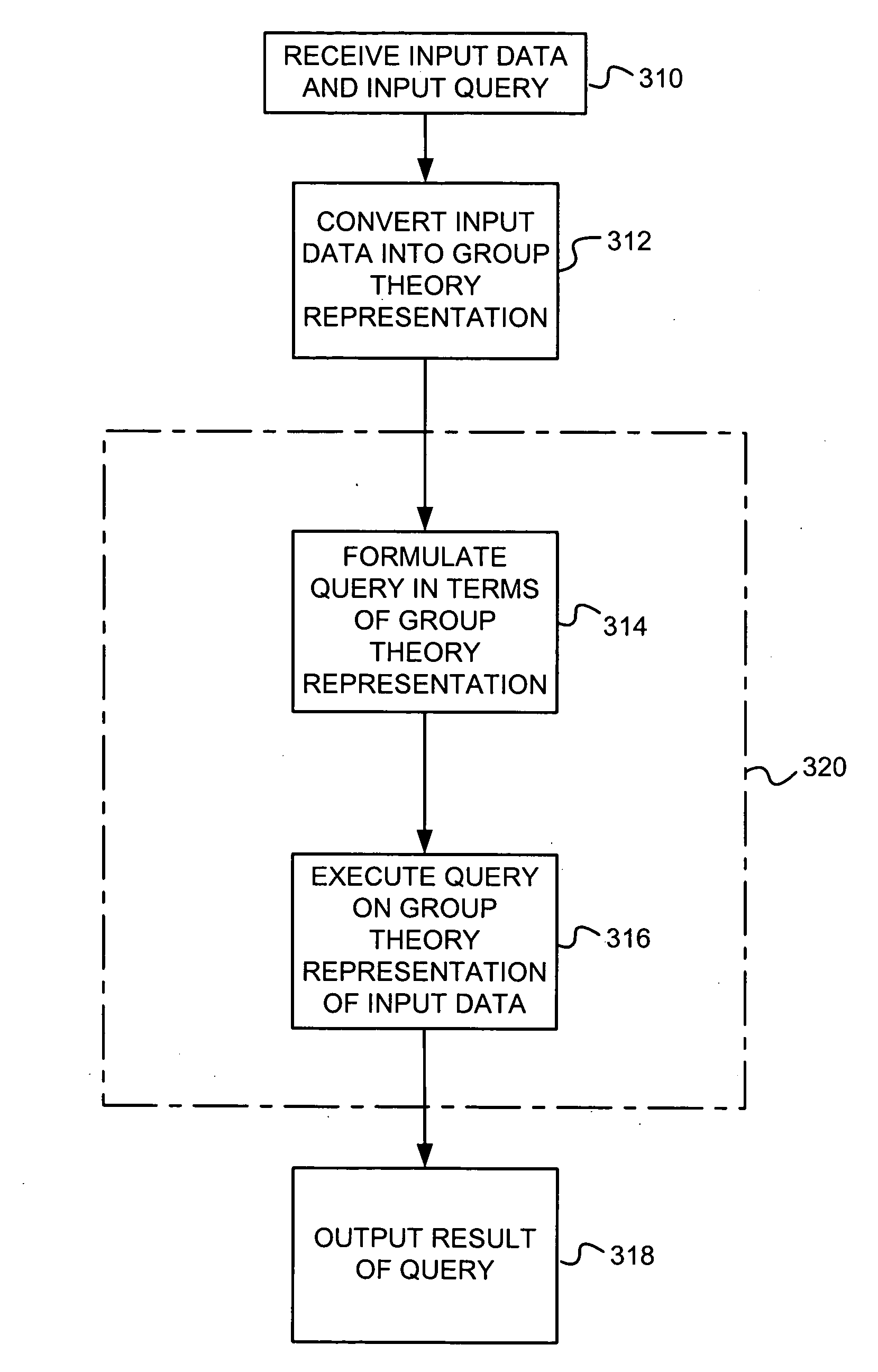

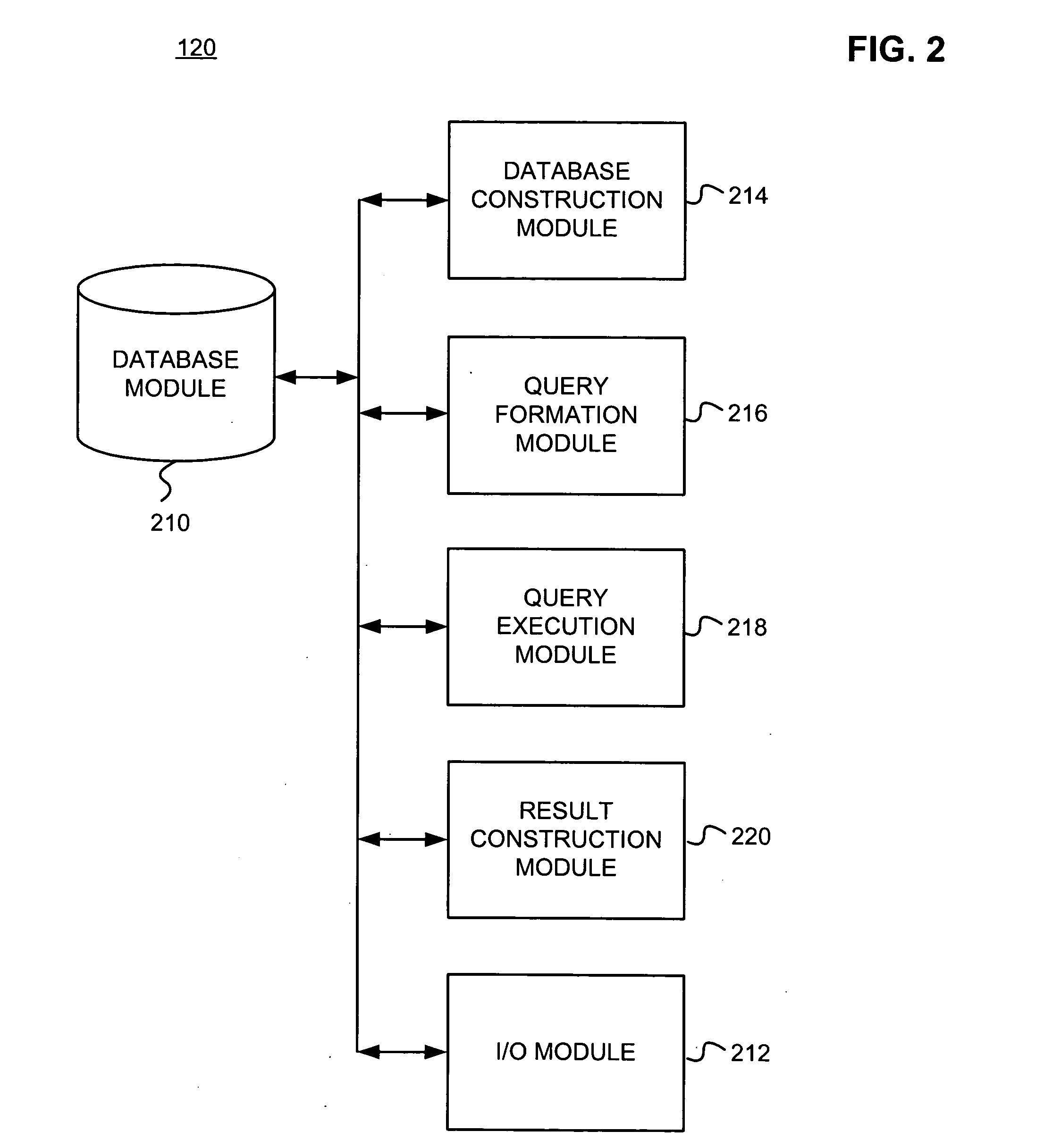

Database manipulations using group theory

InactiveUS20050187905A1Efficiently usDigital data information retrievalDigital data processing detailsData descriptionGroup element

Owner:STATE OF OREGON ACTING BY & THROUGH STATE BOARD OF HIGHER EDUCATION ON BEHALF OF THE UNIV OF OREGON THE

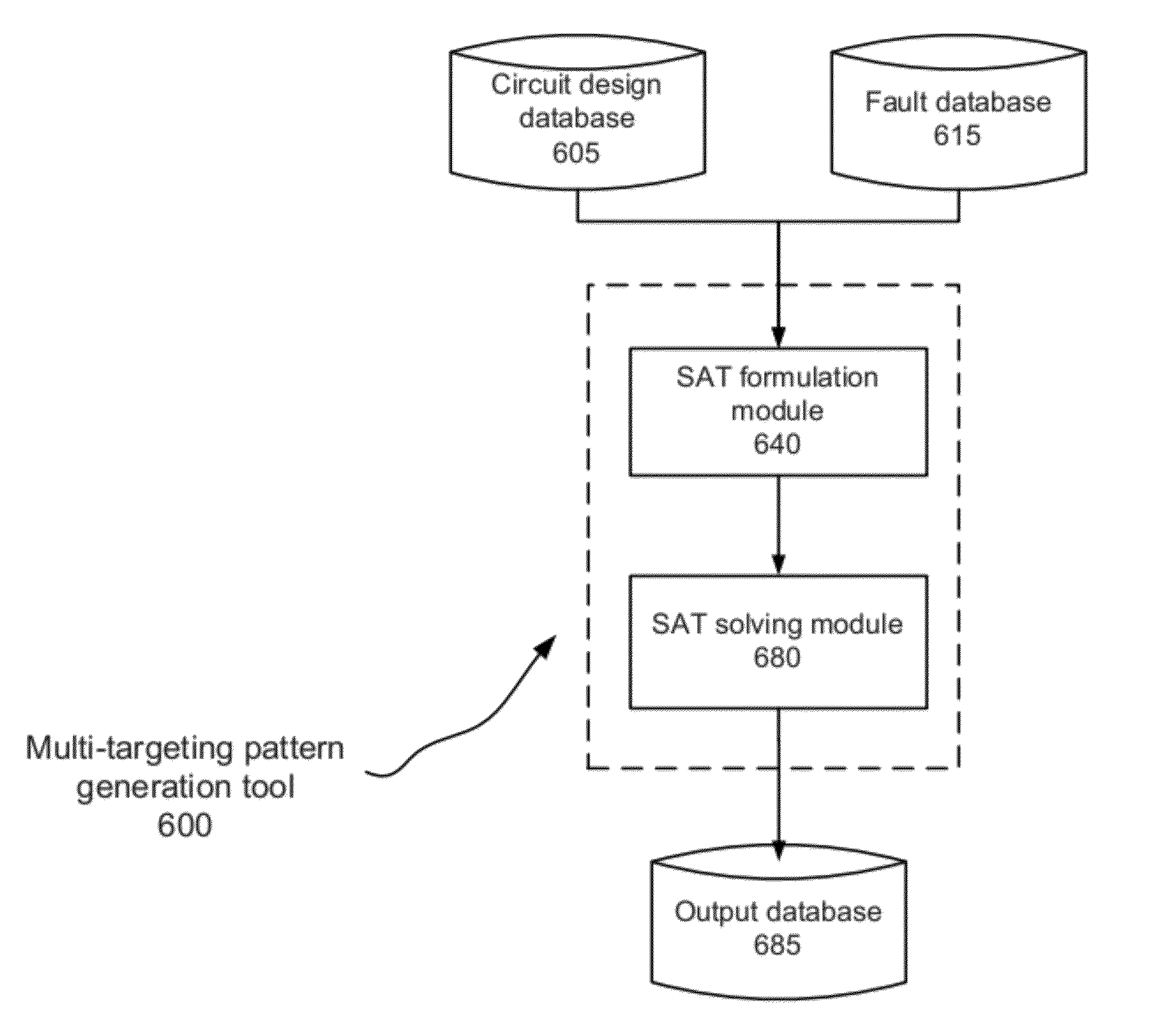

Multi-targeting boolean satisfiability-based test pattern generation

ActiveUS20120317454A1Electronic circuit testingError detection/correctionPattern generationAutomatic test pattern generation

Disclosed are representative examples of methods, apparatus, and systems for generating test patterns targeting multiple faults using Boolean Satisfiability (SAT)-based test pattern generation methods. A SAT instance is constructed based on the circuit design information and a set of faults being targeted. A SAT solving engine is applied to the SAT instance to search for a test pattern for detecting the set of faults. The SAT instance or the SAT solving engine may be modified so that the SAT solving engine will search for a test pattern for detecting a maximum number of faults in the set of faults.

Owner:SIEMENS PROD LIFECYCLE MANAGEMENT SOFTWARE INC

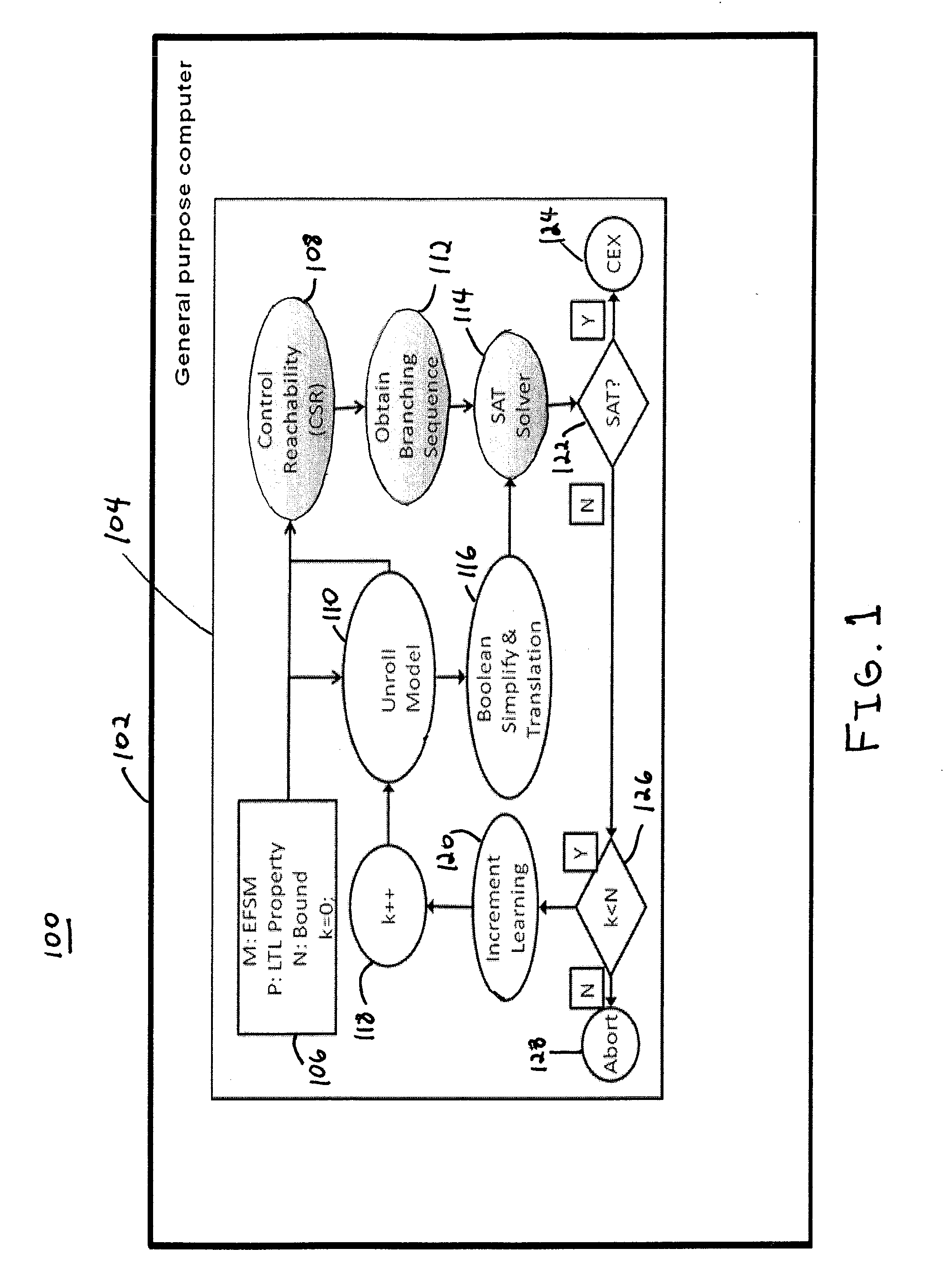

Dpll-based sat solver using with application-aware branching

ActiveUS20110184705A1Improve performanceRaise priorityError detection/correctionComputation using non-denominational number representationState variableTarget control

Owner:NEC CORP

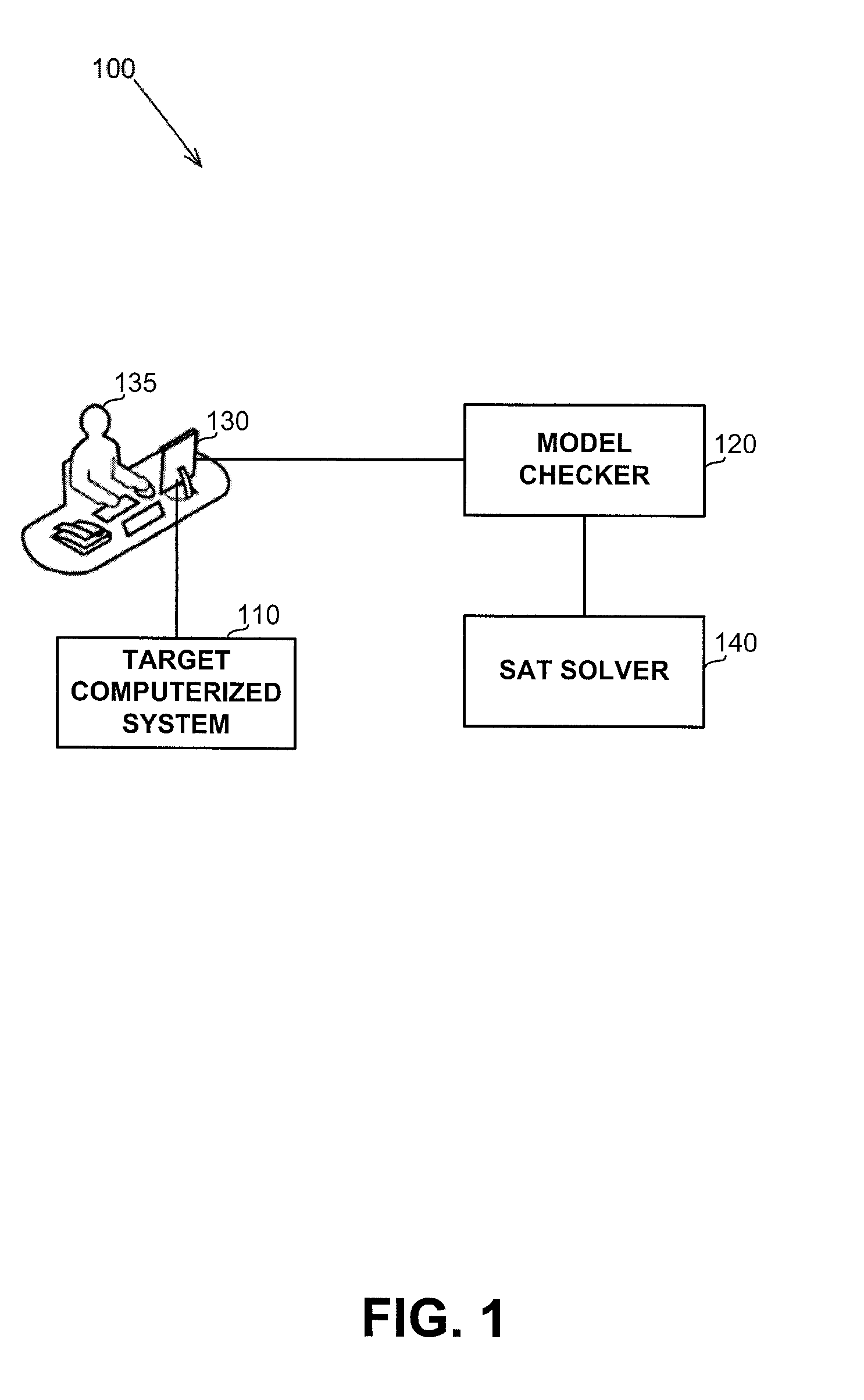

Utilizing an unsat proof for model checking

InactiveUS20110010139A1Computation using non-denominational number representationComputer aided designTemporal successionSatisfiability

Owner:GLOBALFOUNDRIES INC

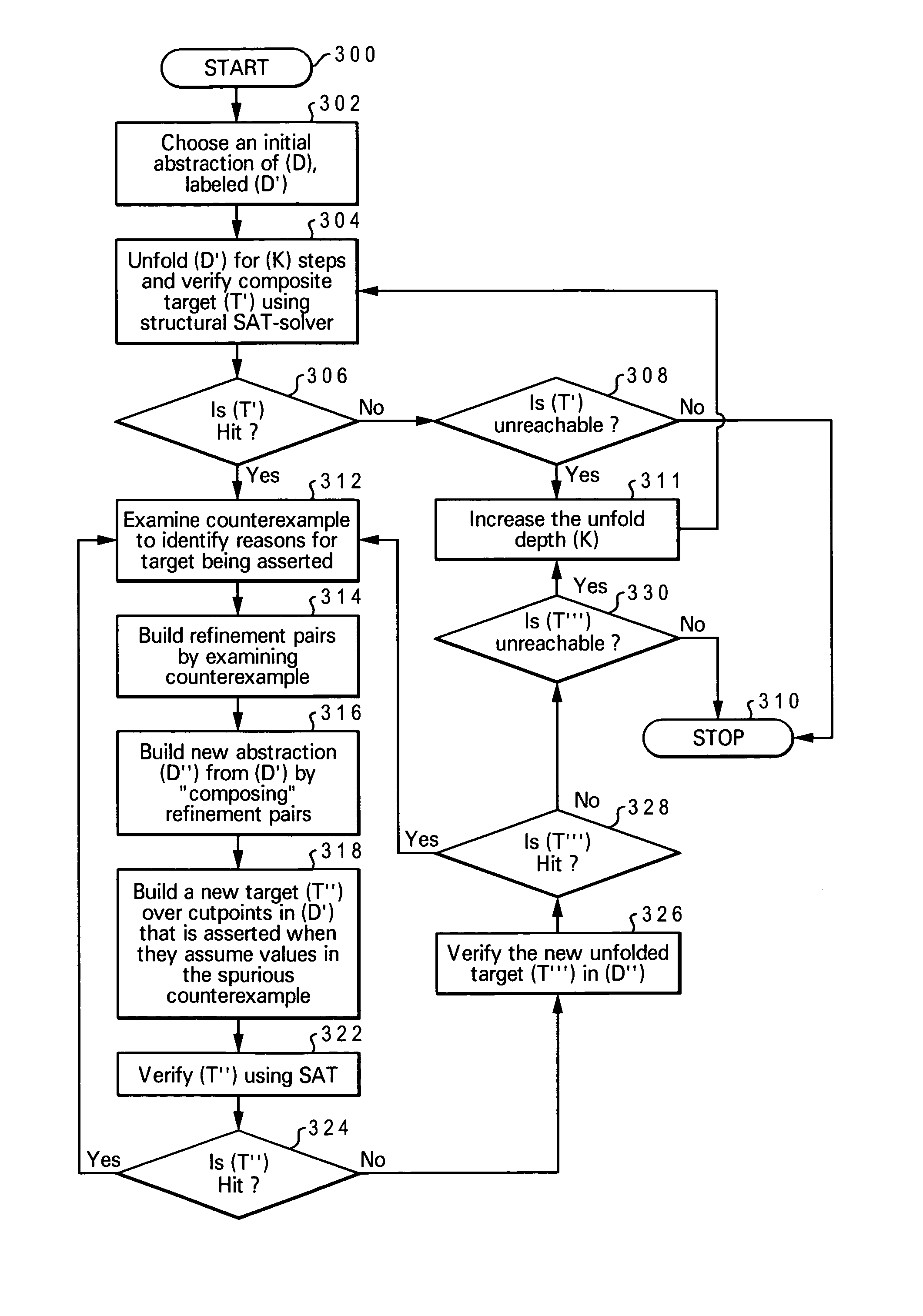

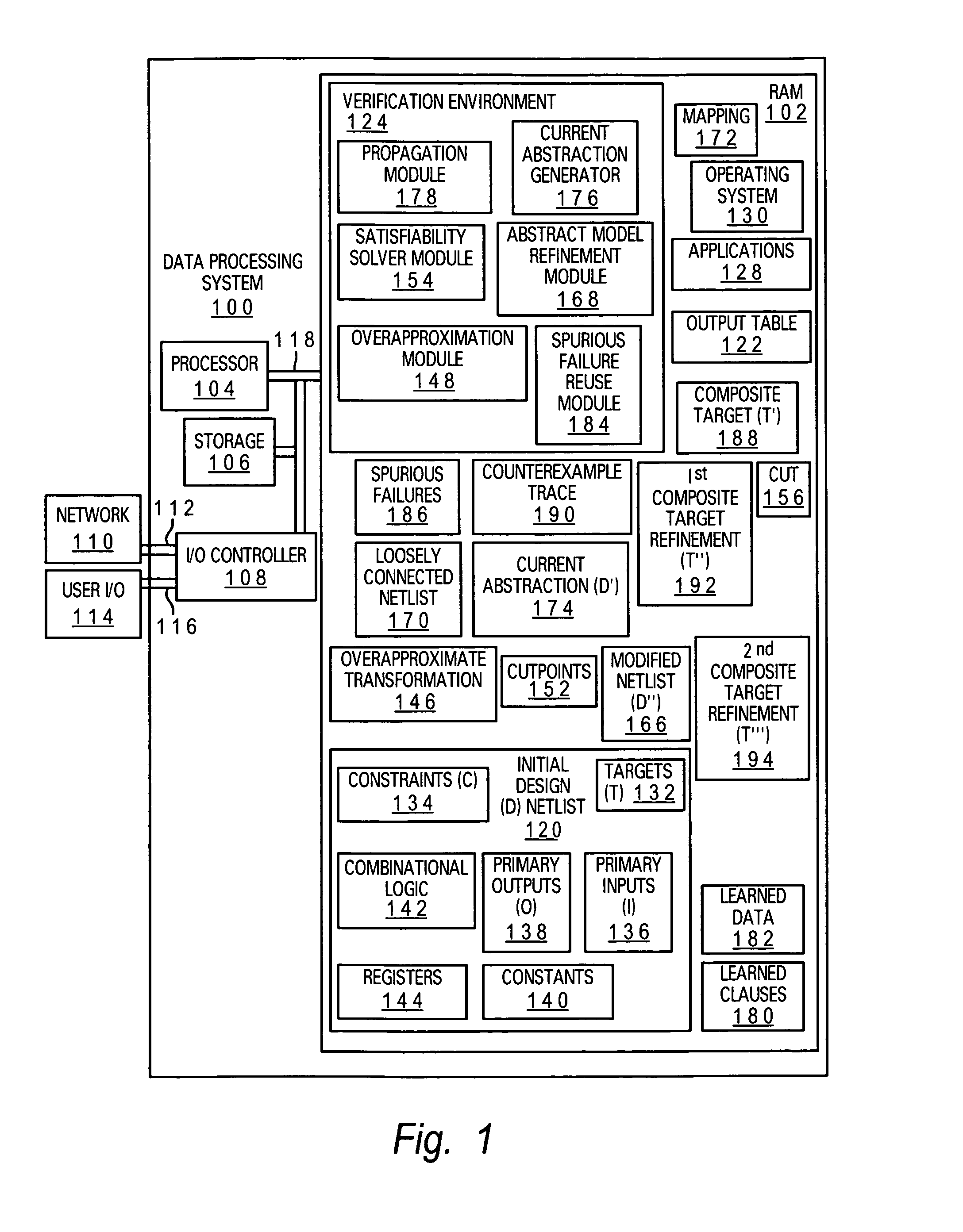

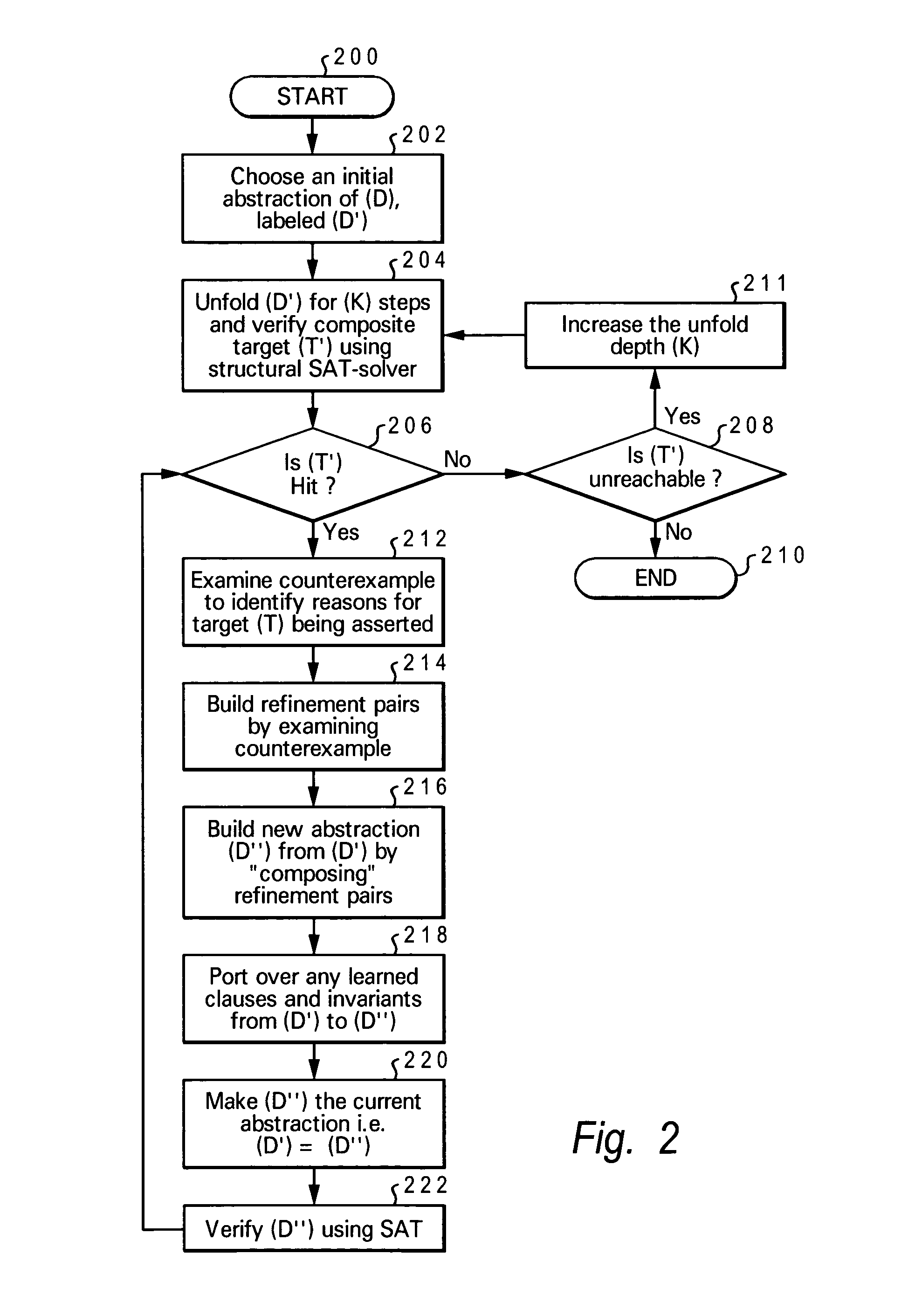

Method and system for enhanced verification by closely coupling a structural overapproximation algorithm and a structural satisfiability solver

ActiveUS7356792B2Computer aided designSoftware simulation/interpretation/emulationNetlistSatisfiability

A method, system and computer program product for performing verification are disclosed. A first abstraction of an initial design netlist containing a first target is created and designated as a current abstraction, and the current abstraction is unfolded by a selectable depth. A composite target is verified using a satisfiability solver, and in response to determining that the verifying step has hit the composite target, a counterexample to is examined to identify one or more reasons for the first target to be asserted. One or more refinement pairs are built by examining the counterexample, and a second abstraction is built by composing the refinement pairs. One or more learned clauses and one or more invariants to the second abstraction and the second abstraction is chosen as the current abstraction. The current abstraction is verified with the satisfiability solver.

Owner:GLOBALFOUNDRIES U S INC

Integrating a boolean SAT solver into a router

ActiveUS20080250376A1Computer aided designSpecial data processing applicationsPartial solutionPoint pair

One embodiment of the present invention provides a system that routes a set of pairs of points during the design of an integrated circuit (IC) chip. The system comprises a routing engine which is configured to search for a path to connect a current pair of points in the set of pairs of points, wherein the path comprises a set of rectangles and vertices. The routing engine uses a routing database, which keeps track of previously routed nets that can obstruct the routing of the current pair of points. The system further comprises a satisfiability (SAT) solver which is capable of solving a set of constraints, wherein the set of constraints are associated with the routability of the set of pairs of points. The SAT solver additionally comprises a SAT database which maintains the set of constraints and a current partial solution to the set of constraints. The SAT database is used to update the routing database if the current partial solution changes.

Owner:SYNOPSYS INC

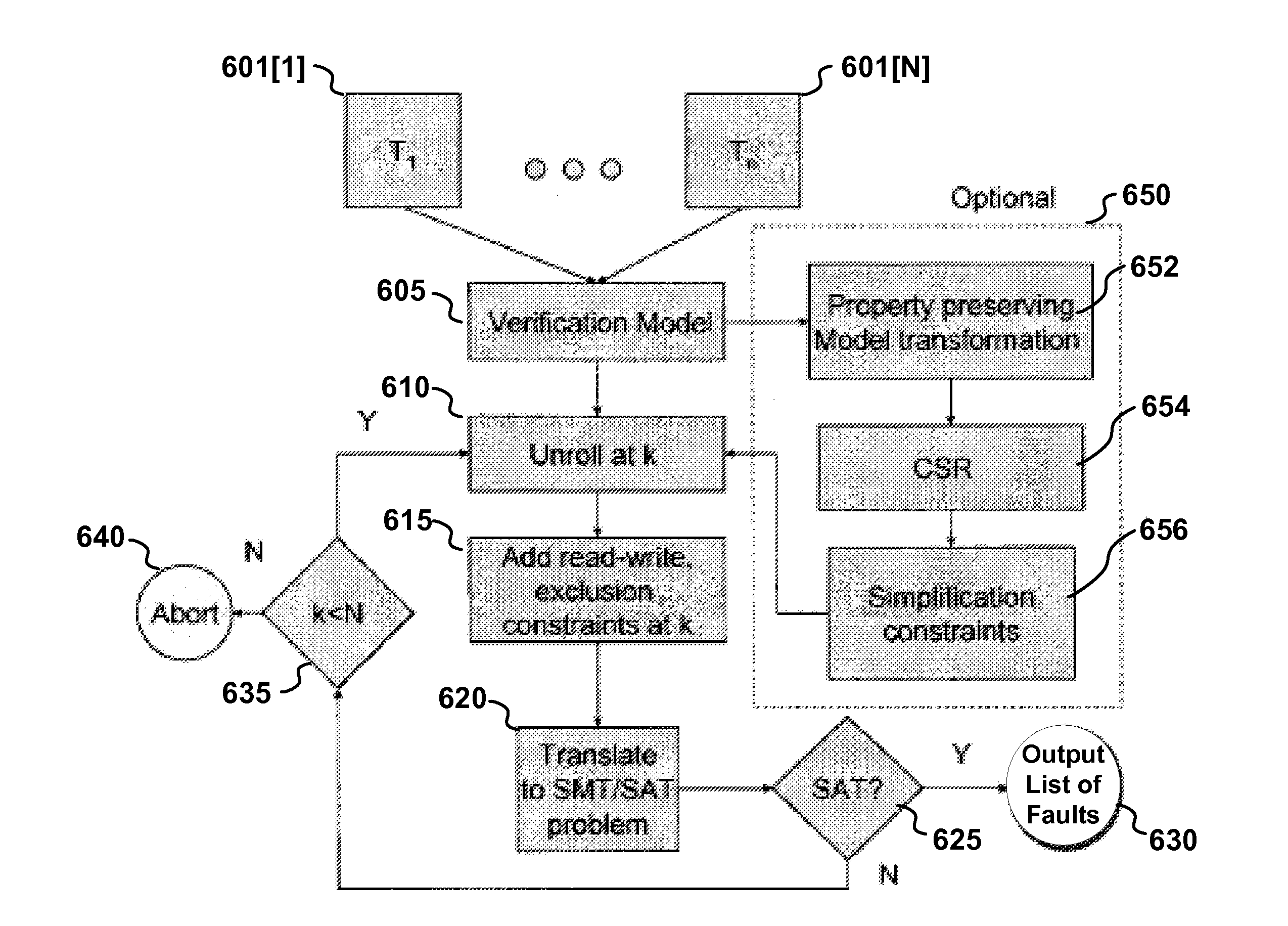

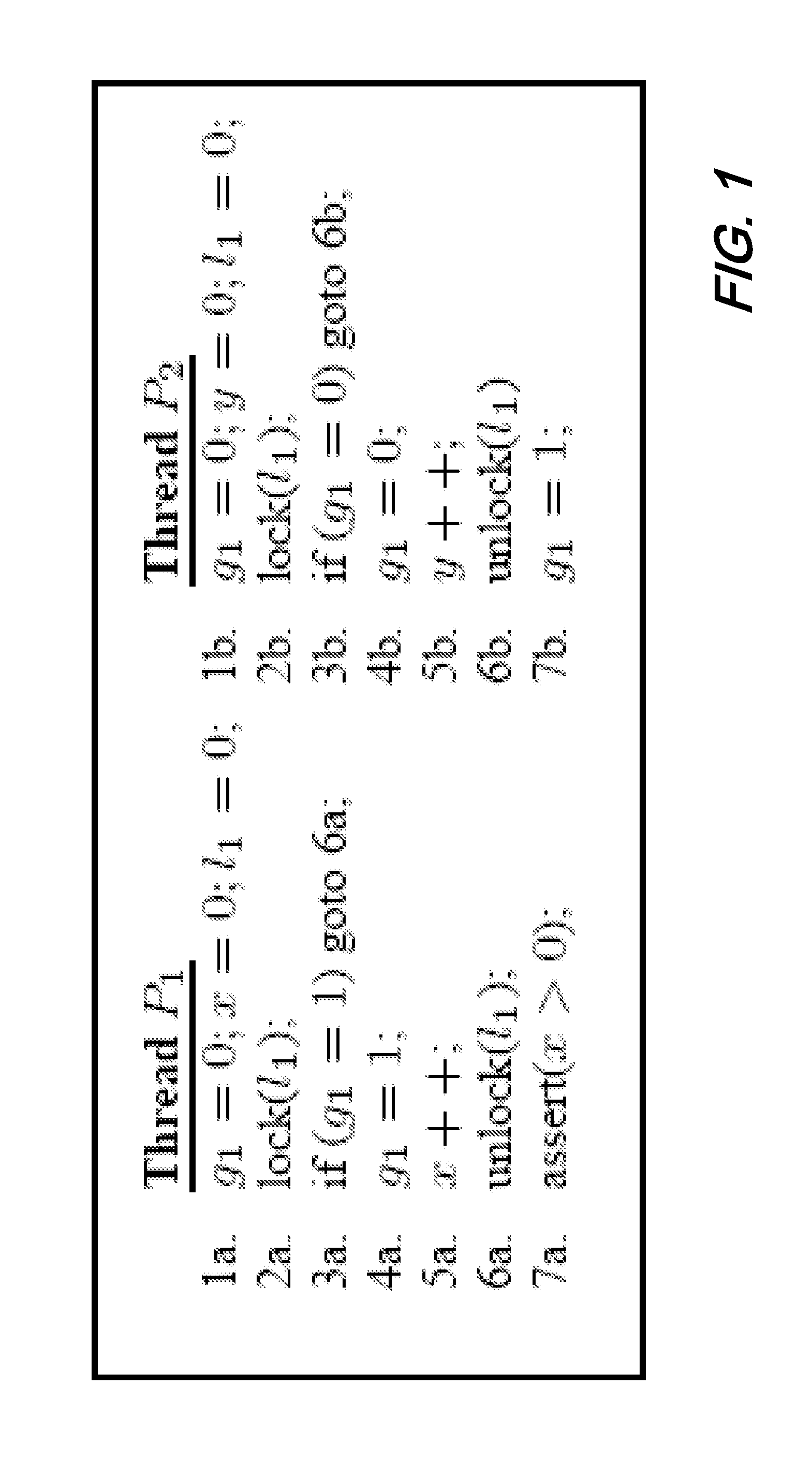

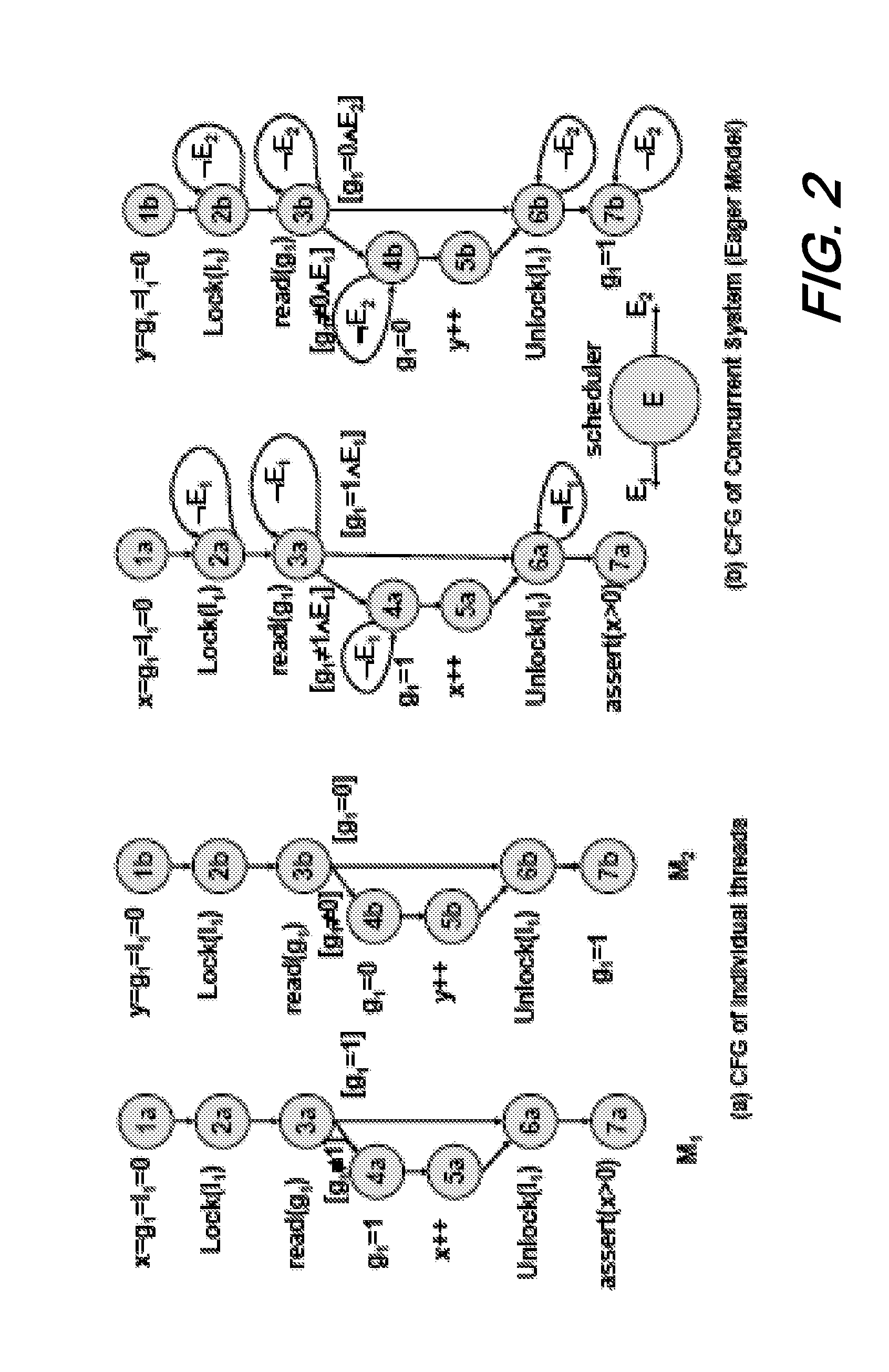

Modeling and verification of concurrent systems using smt-based bmc

ActiveUS20080281563A1Small sizeImprove performanceError detection/correctionAnalogue computers for electric apparatusSemanticsSecurity properties

A computer implemented method for modeling and verifying concurrent systems which uses Satisfiability-Modulo Theory (SMT)-based Bounded Model Checking (BMC) to detect violations of safety properties such as data races. A particularly distinguishing aspect of our inventive method is that we do not introduce wait-cycles in our symbolic models for the individual threads, which are typically required for considering an interleaved execution of the threads. These wait-cycles are detrimental to the performance of BMC. Instead, we first create independent models for the different threads, and add inter-model constraints lazily, incrementally, and on-the-fly during BMC unrolling to capture the sequential consistency and synchronization semantics. We show that our constraints provide a sound and complete modeling with respect to the considered semantics. One benefit of our lazy modeling method is the reduction in the size of the BMC problem instances, thereby, improving the verification performance in both runtime and memory.

Owner:NEC CORP

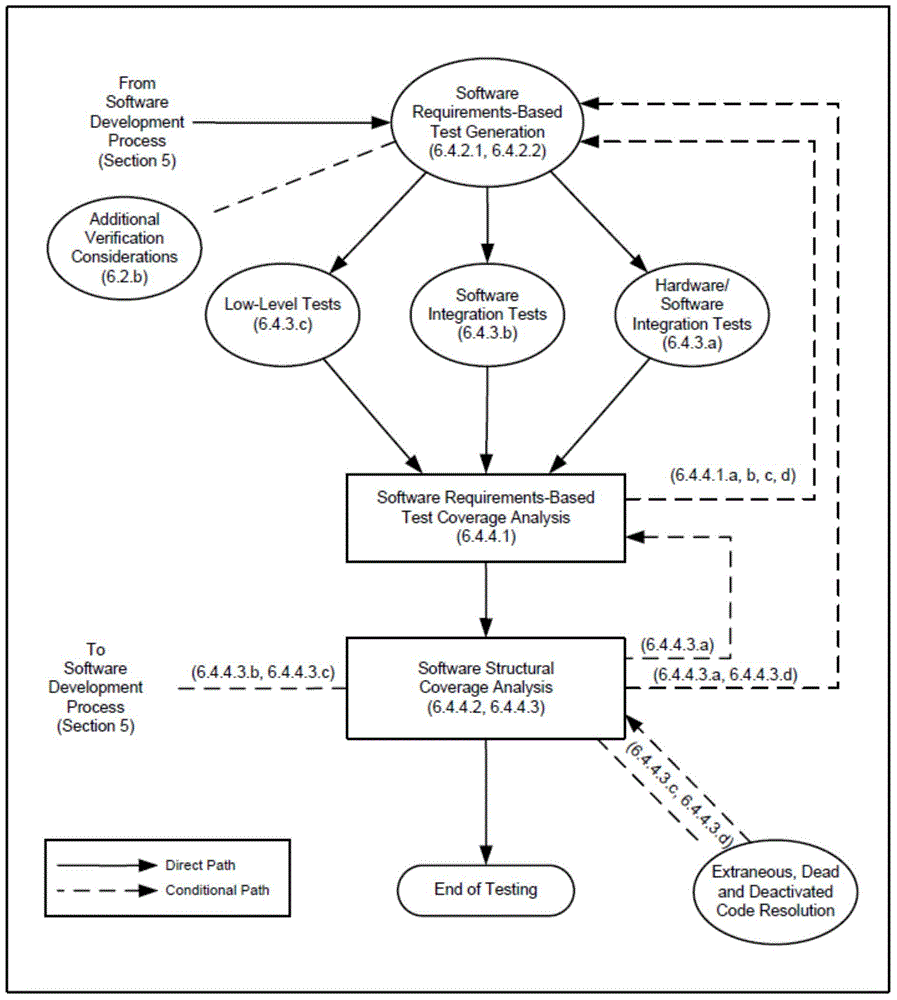

DO-178C software test process orientated object verification and evidence model extracting method

The invention relates to a DO-178C software test process orientated object verification and evidence model extracting method. A demonstration structure of objects associated with a software test process is established; corresponding evidence requirements are analyzed out and an evidence model is established according to the evidence requirements; and according to the evidence model, object demonstration automation is realized when project data is corresponding to the evidence model; and an auto-reasoning solution is disclosed for realizing objects in the DO-178 software test process. According to the DO-178C software test process orientated object verification and evidence model extracting method, the software test process conforms to airworthiness certification specifications better, and effective help is provided for determining the objects of the software test process which passes the airworthiness certification; the step of collecting evidence is completed in a more efficient mode, so that the cost is reduced; automatic reasoning of the object satisfiability is realized, so that the cost is reduced; and especially when a great deal of data needs to demonstrate, the efficiency is remarkably improved.

Owner:BEIHANG UNIV