Patents

Literature

39 results about "Conjunctive normal form" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

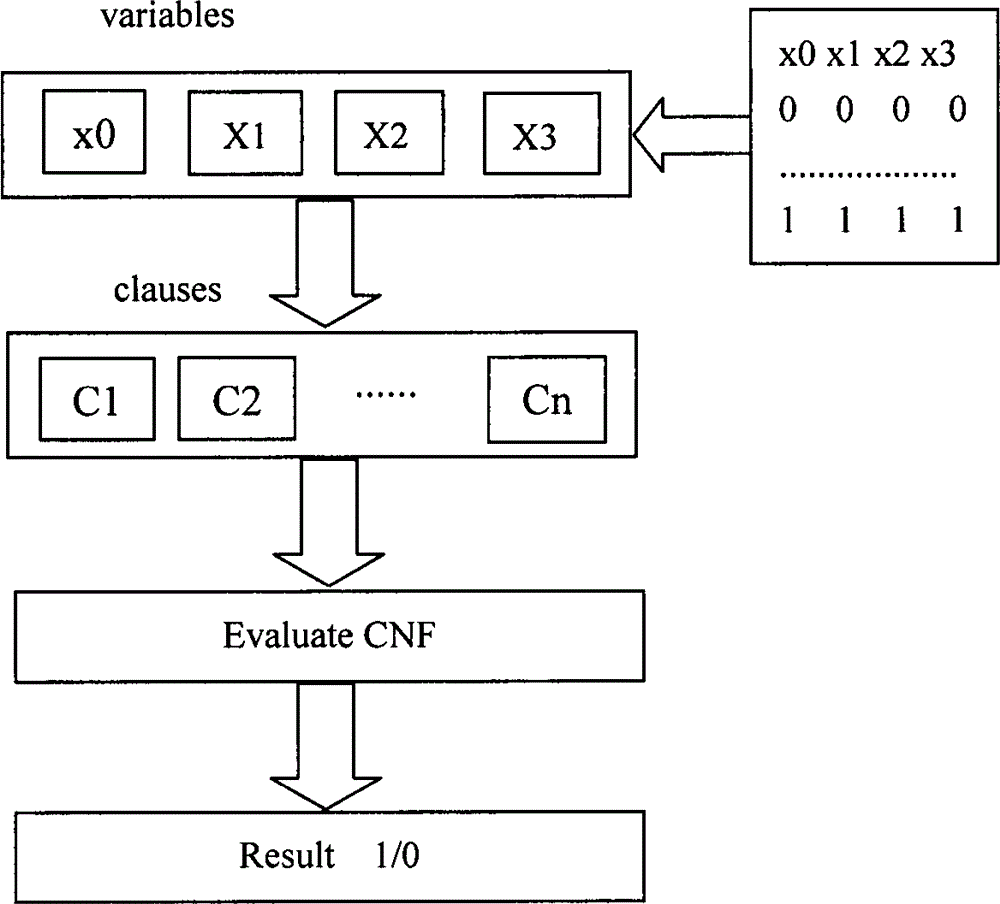

In Boolean logic, a formula is in conjunctive normal form (CNF) or clausal normal form if it is a conjunction of one or more clauses, where a clause is a disjunction of literals; otherwise put, it is an AND of ORs. As a canonical normal form, it is useful in automated theorem proving and circuit theory.

Prime implicates and query optimization in relational databases

InactiveUS20020143754A1Digital data information retrievalData processing applicationsRelational databaseQuery optimization

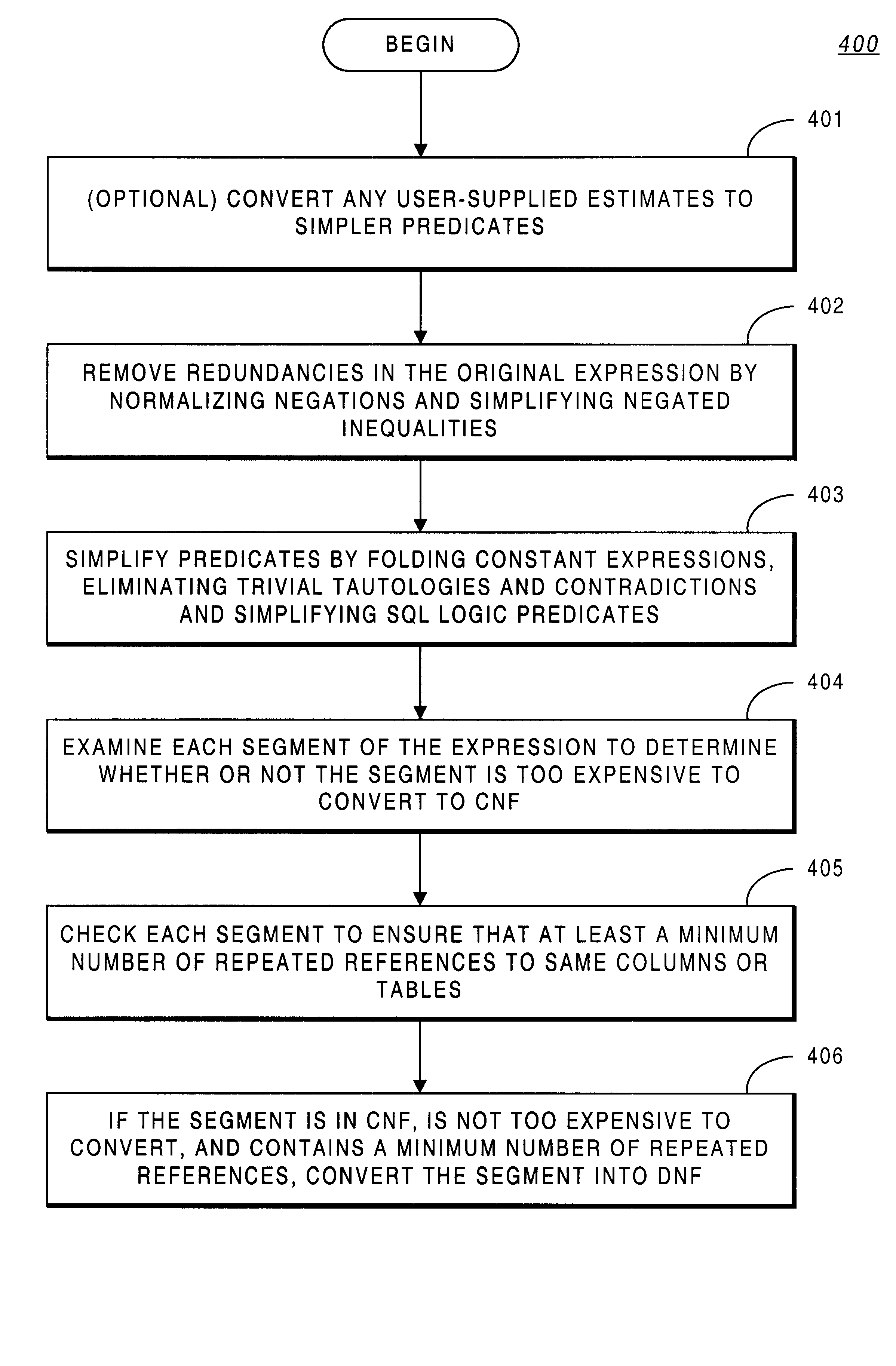

An improved normalization methodology enabling better optimization of SQL queries is described. The normalization methodology effectively handles three-valued SQL search conditions and operates in reduced memory environments. A query is examined and selectively normalized by examining each segment of the query to determine whether it is advantageous to fully convert that segment to conjunctive normal form (CNF). If full conversion of the segment to CNF is not advantageous, then only the useful conjunctive conditions (prime implicates) that can be derived from the original input are saved. These useful conjuncts (prime implicates) are unioned with the original statement, resulting in a search condition that is semantically equivalent to the original expression, but that can be better exploited by a query optimizer. This enables better optimization of the original query without the system overhead that would result from full normalization of the query.

Owner:IANYWHERE SOLUTIONS

Prime implicates and query optimization in relational databases

InactiveUS6665664B2Data processing applicationsDigital data information retrievalRelational databaseQuery optimization

An improved normalization methodology enabling better optimization of SQL queries is described. The normalization methodology effectively handles three-valued SQL search conditions and operates in reduced memory environments. A query is examined and selectively normalized by examining each segment of the query to determine whether it is advantageous to fully convert that segment to conjunctive normal form (CNF). If full conversion of the segment to CNF is not advantageous, then only the useful conjunctive conditions (prime implicates) that can be derived from the original input are saved. These useful conjuncts (prime implicates) are unioned with the original statement, resulting in a search condition that is semantically equivalent to the original expression, but that can be better exploited by a query optimizer. This enables better optimization of the original query without the system overhead that would result from full normalization of the query.

Owner:IANYWHERE SOLUTIONS

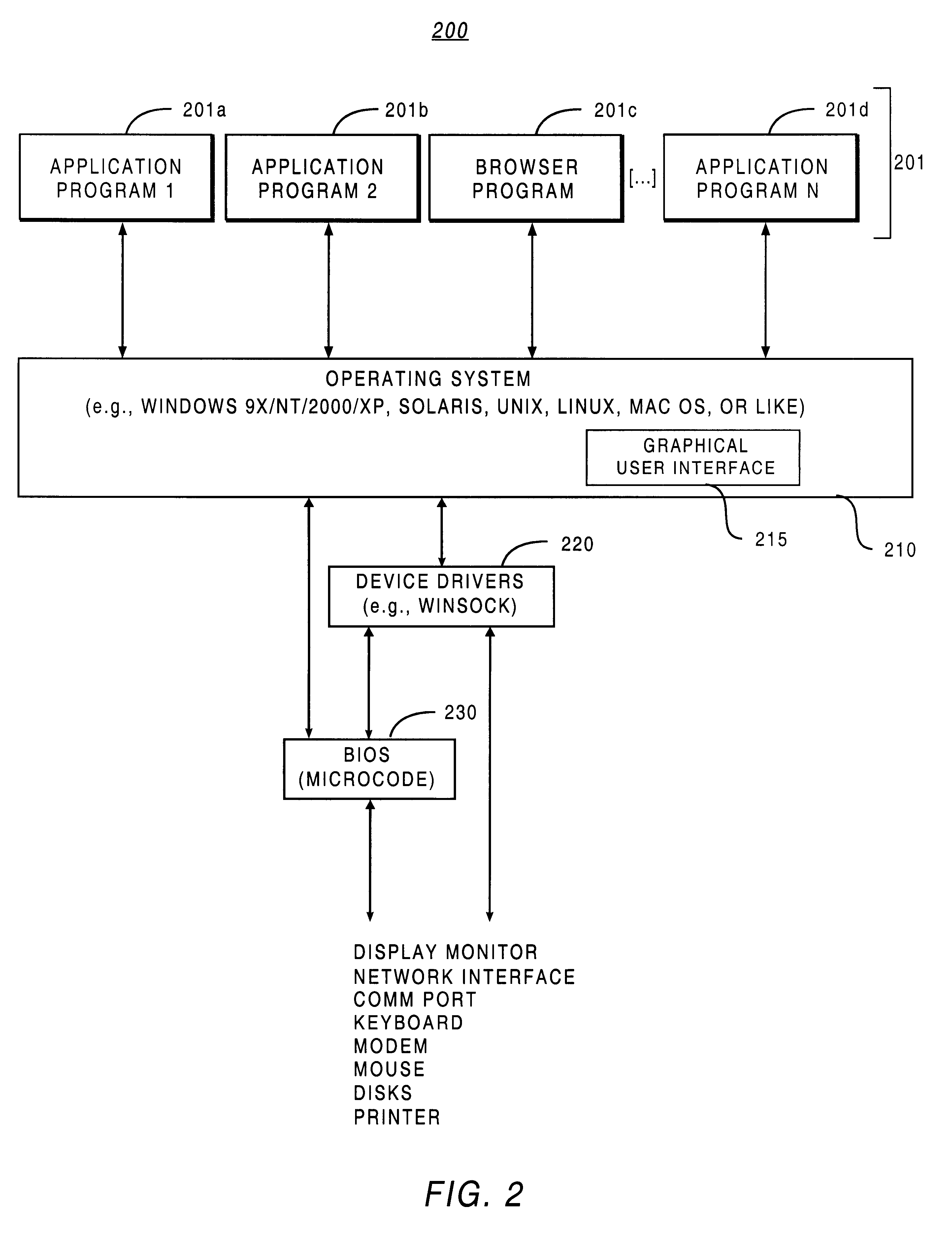

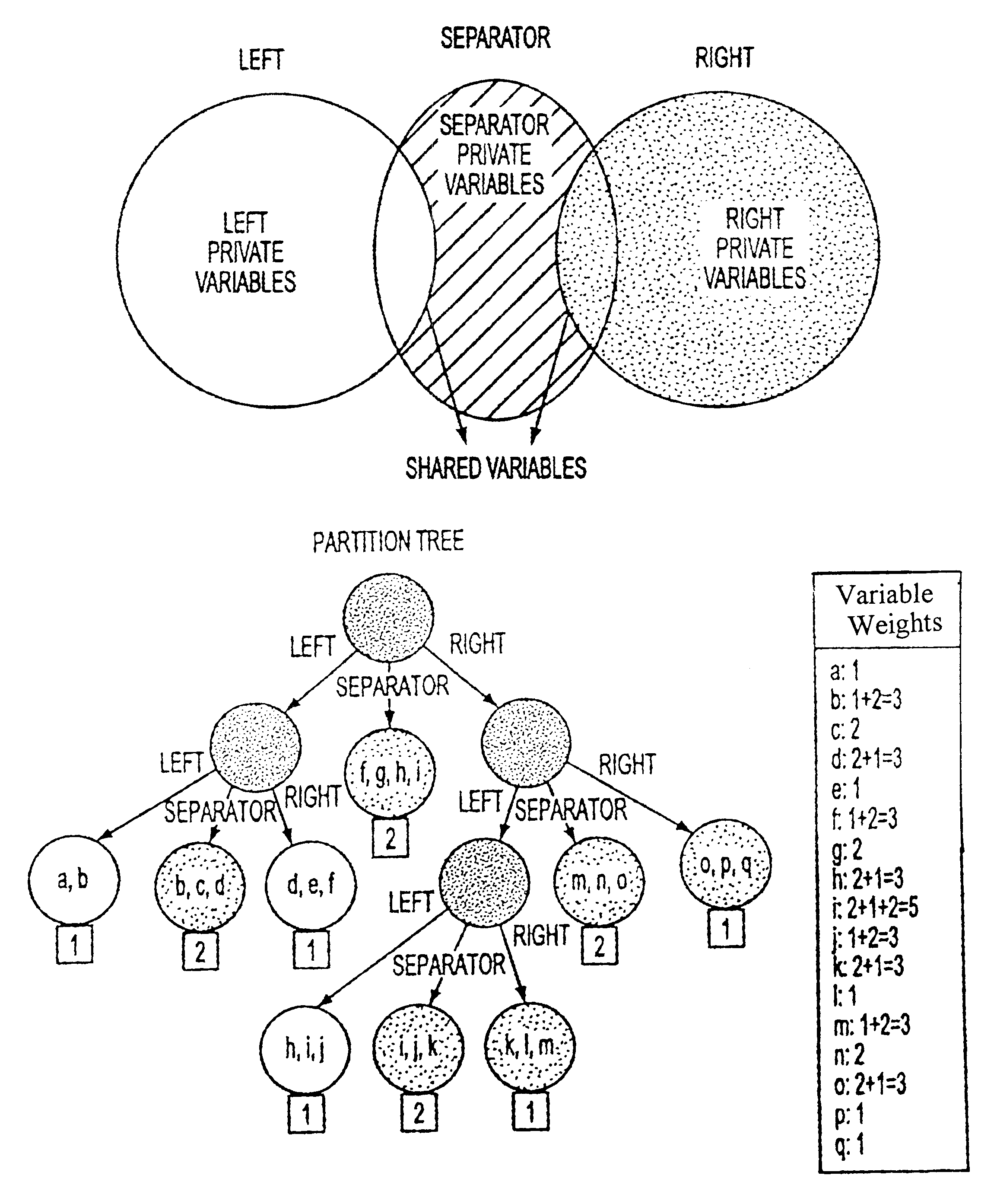

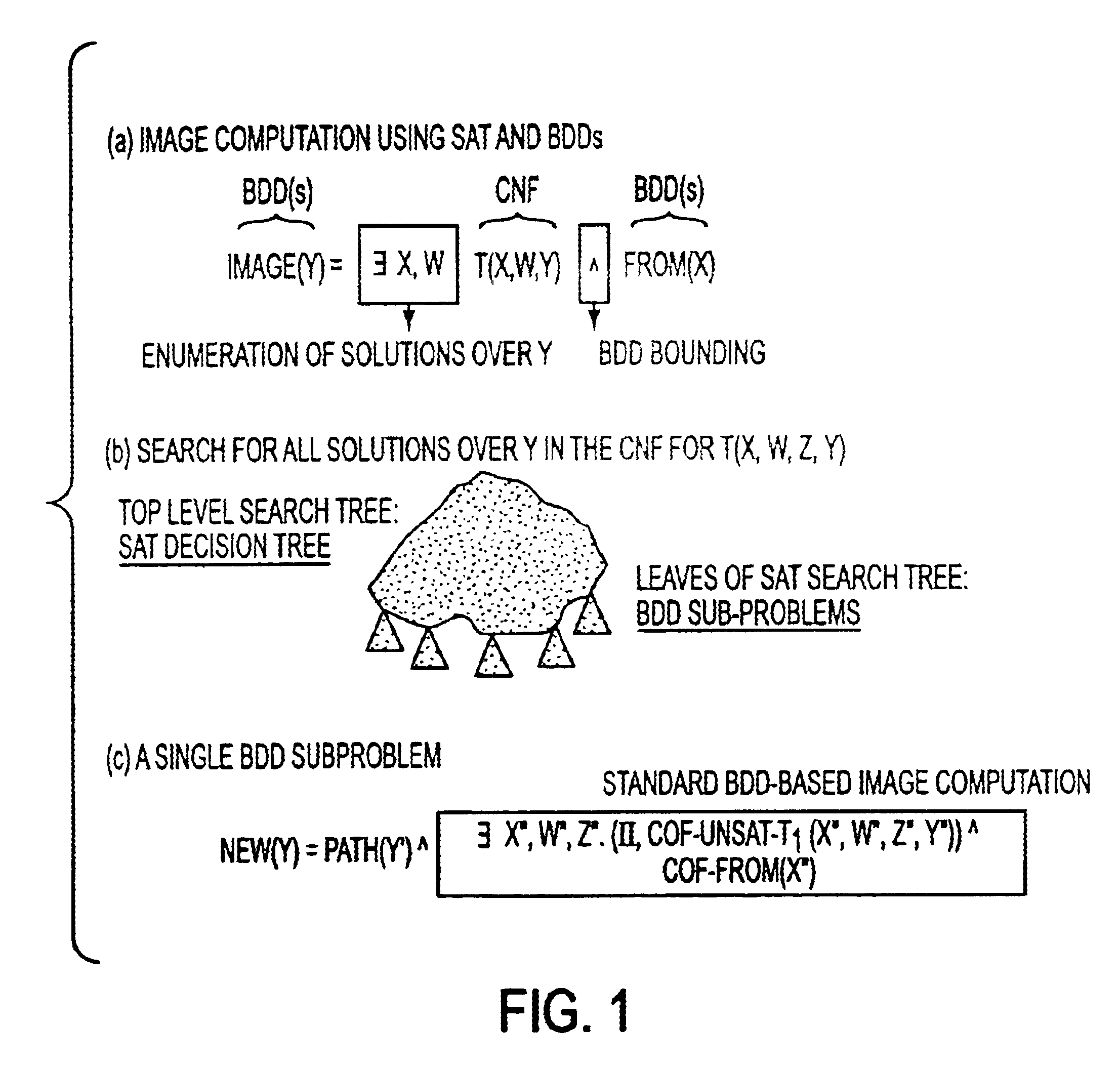

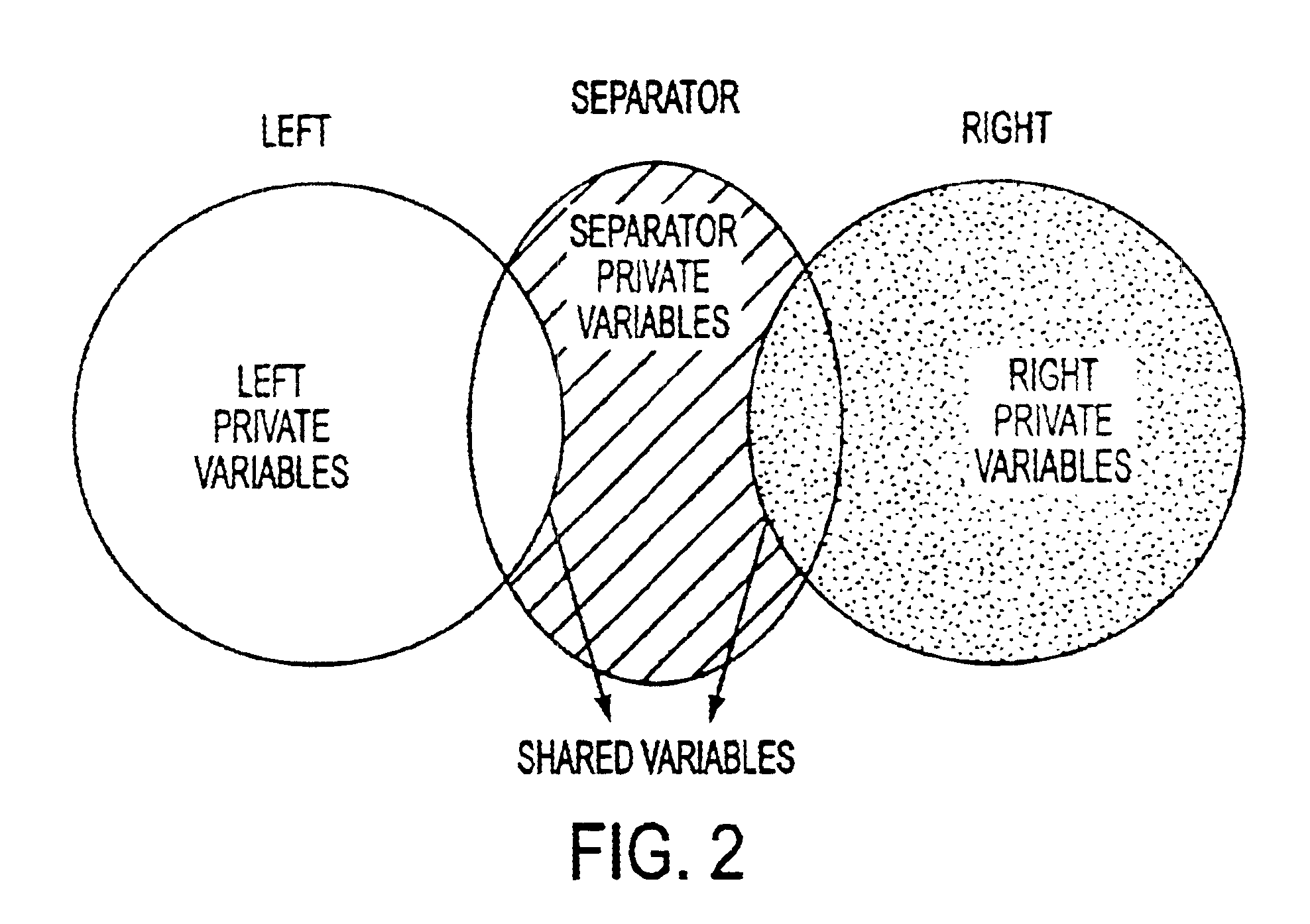

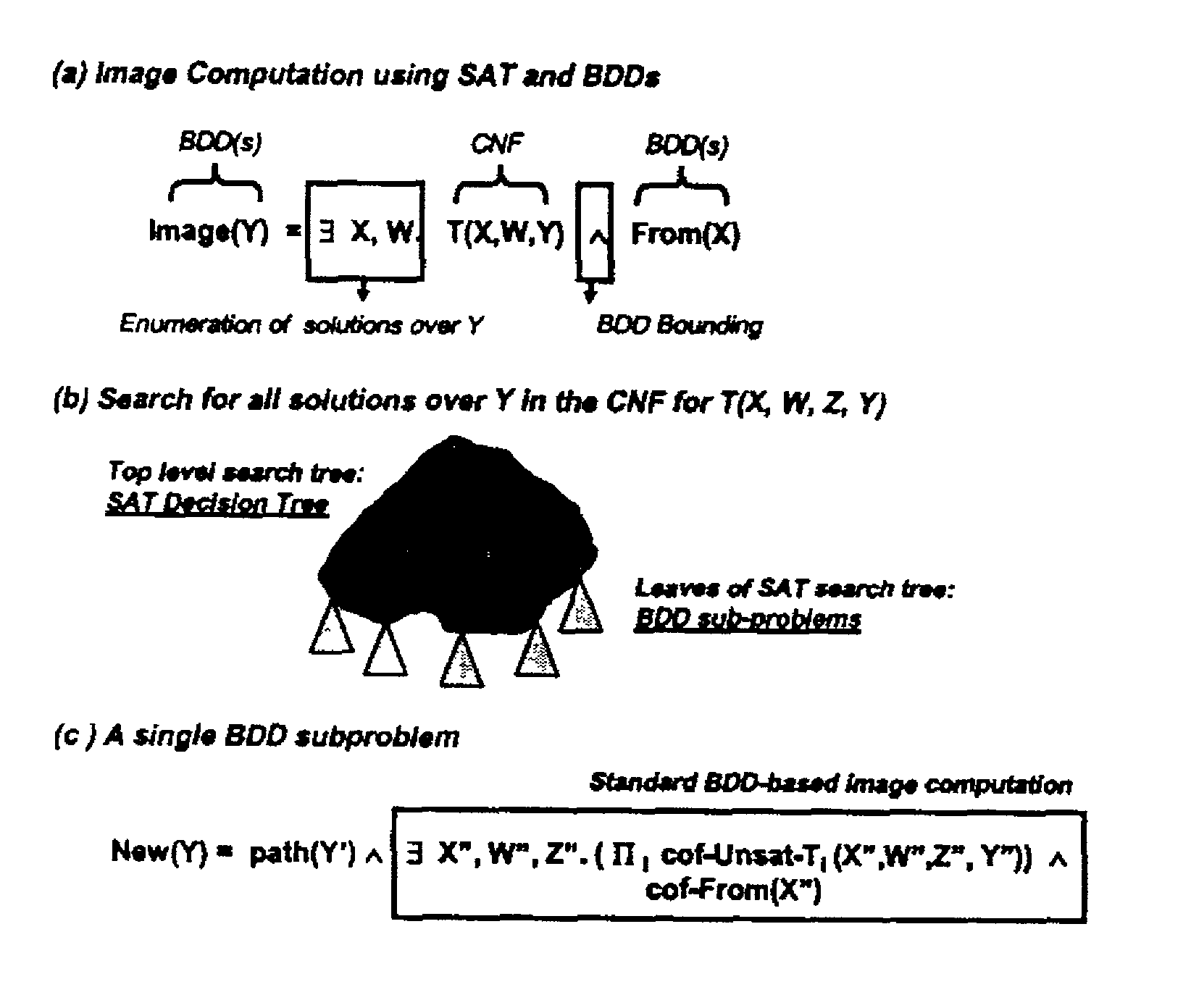

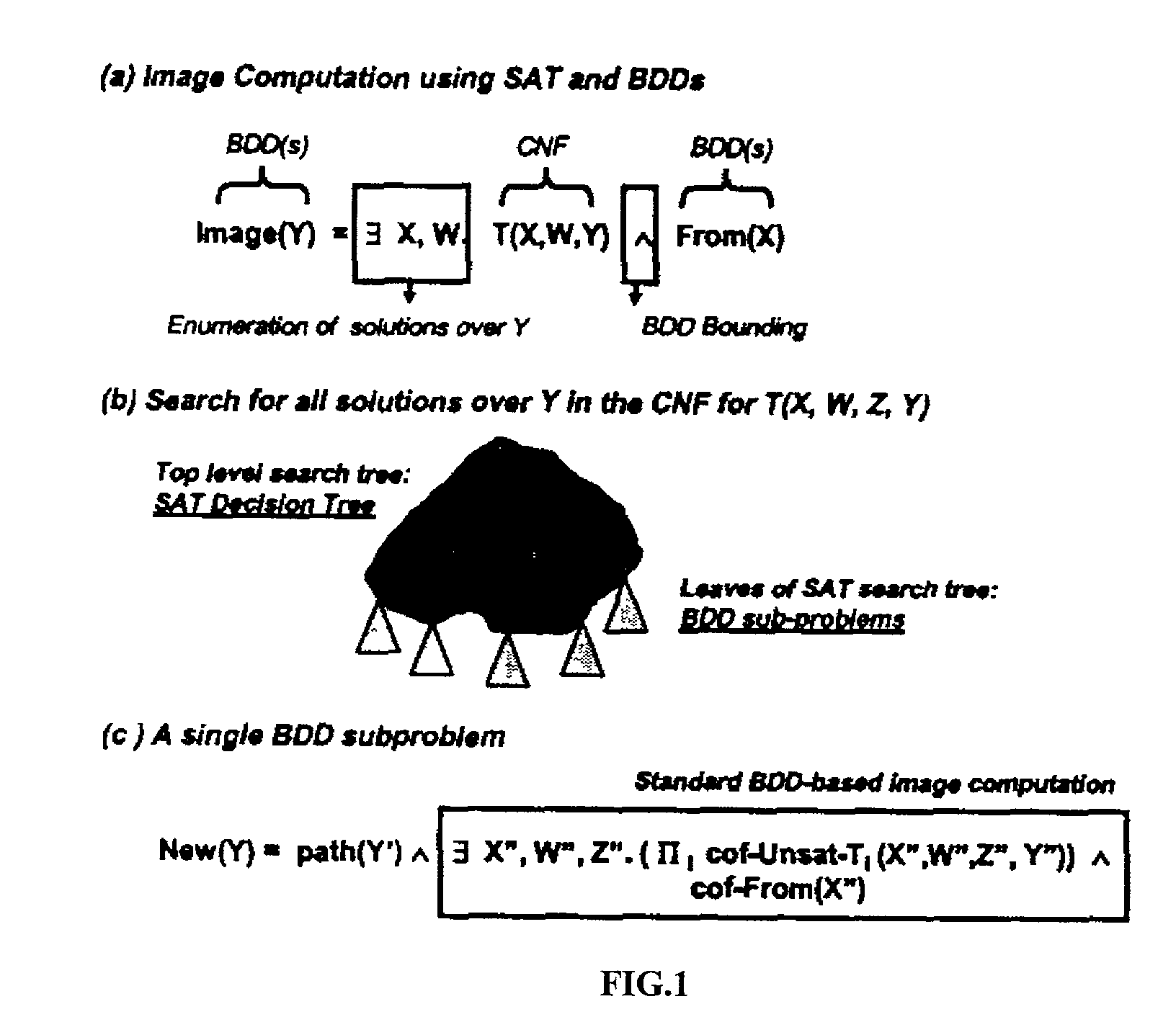

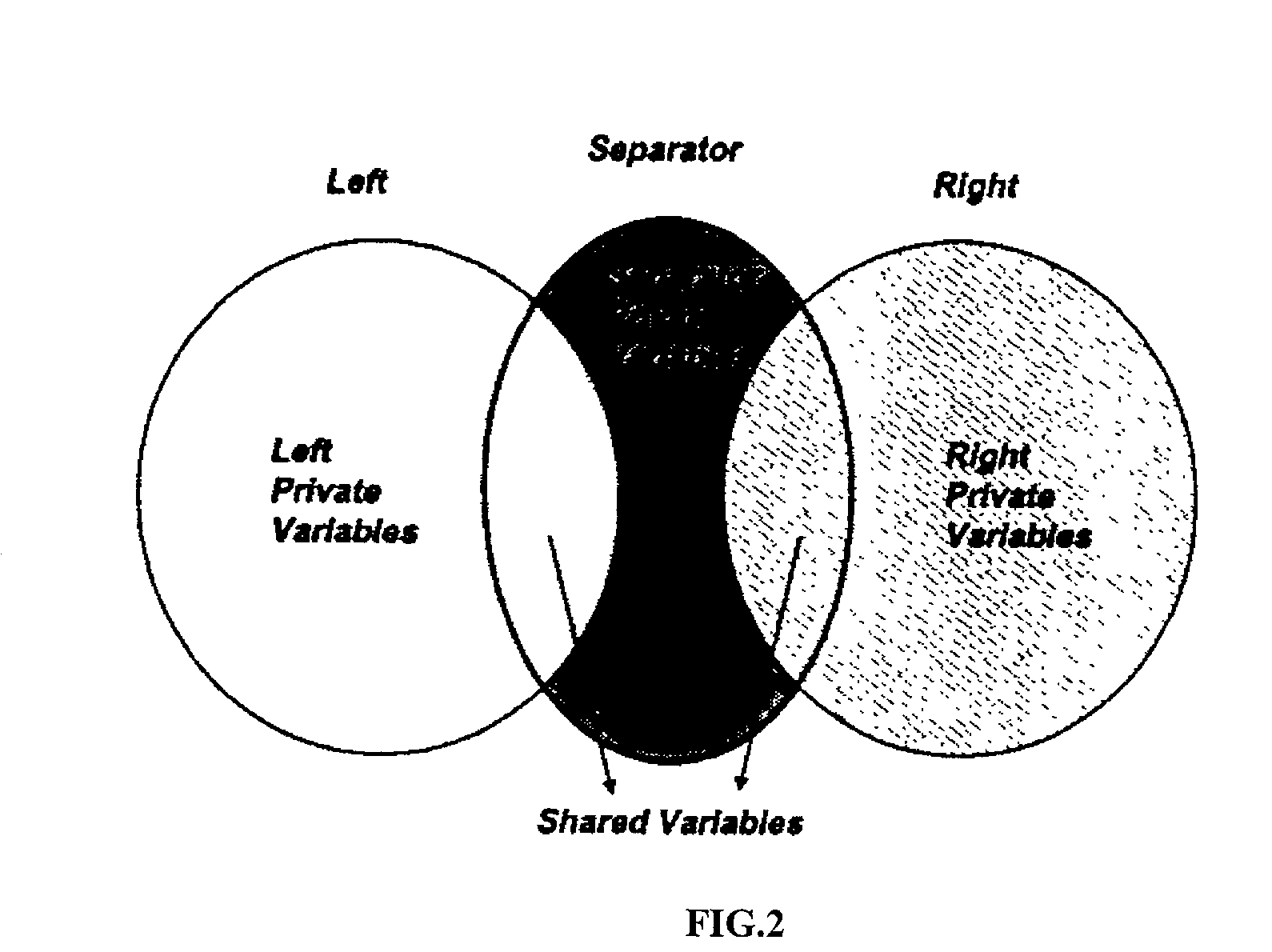

Partition-based decision heuristics for SAT and image computation using SAT and BDDs

InactiveUS6651234B2Reduce partAdd depthComputer aided designSoftware simulation/interpretation/emulationRecognition heuristicConjunctive normal form

A method for Boolean Satisfiability (SAT). The method comprises using a variable decision heuristic in a SAT algorithm and pruning the search space of SAT using said decision heuristic. The decision heuristic is based on partitioning a conjunctive normal form (CNF) of a Boolean formula corresponding to the SAT and the partitioning is induced by a separator set. An image computaion method that uses the disclosed method for solving the SAT.

Owner:NEC CORP

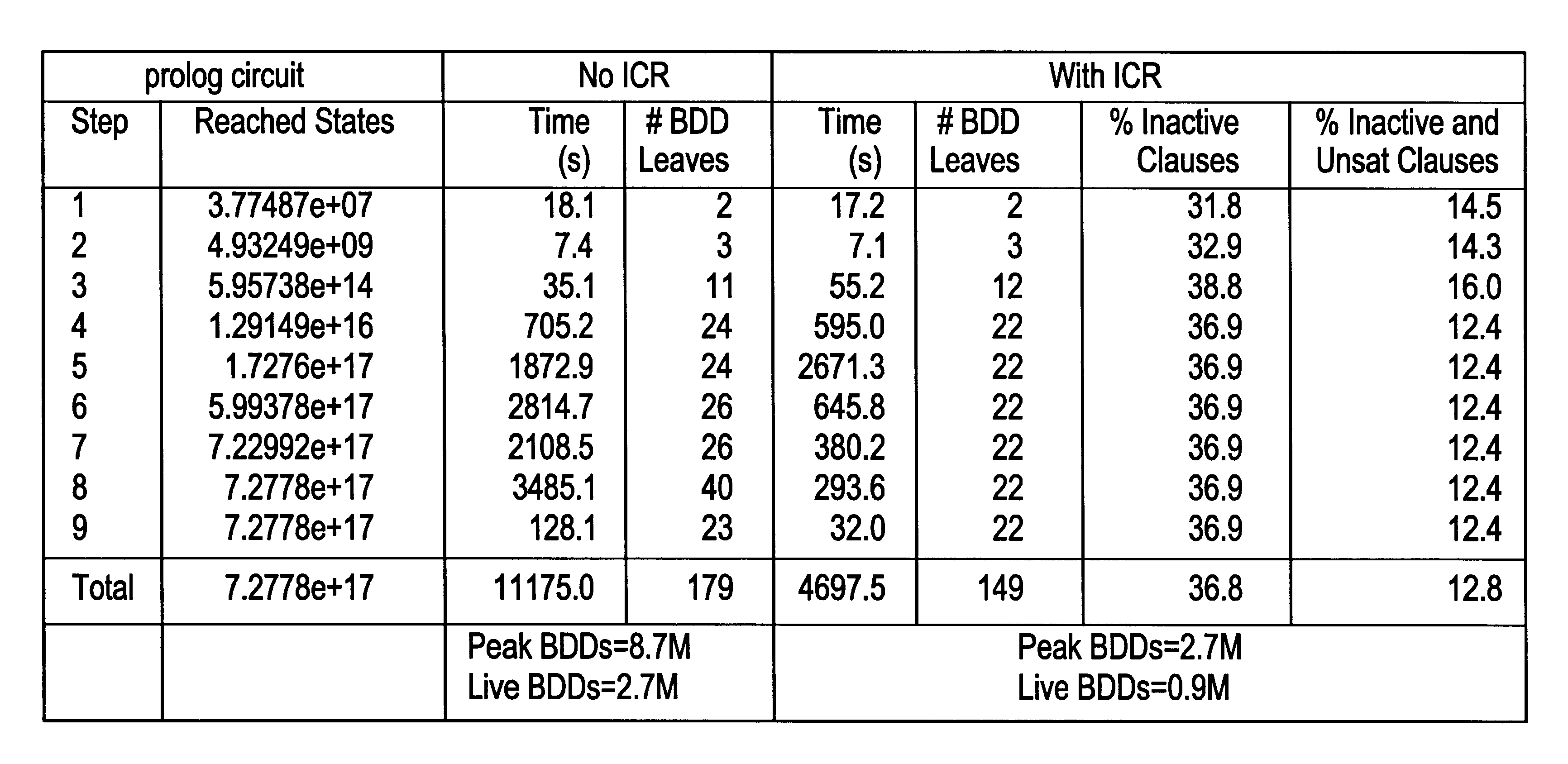

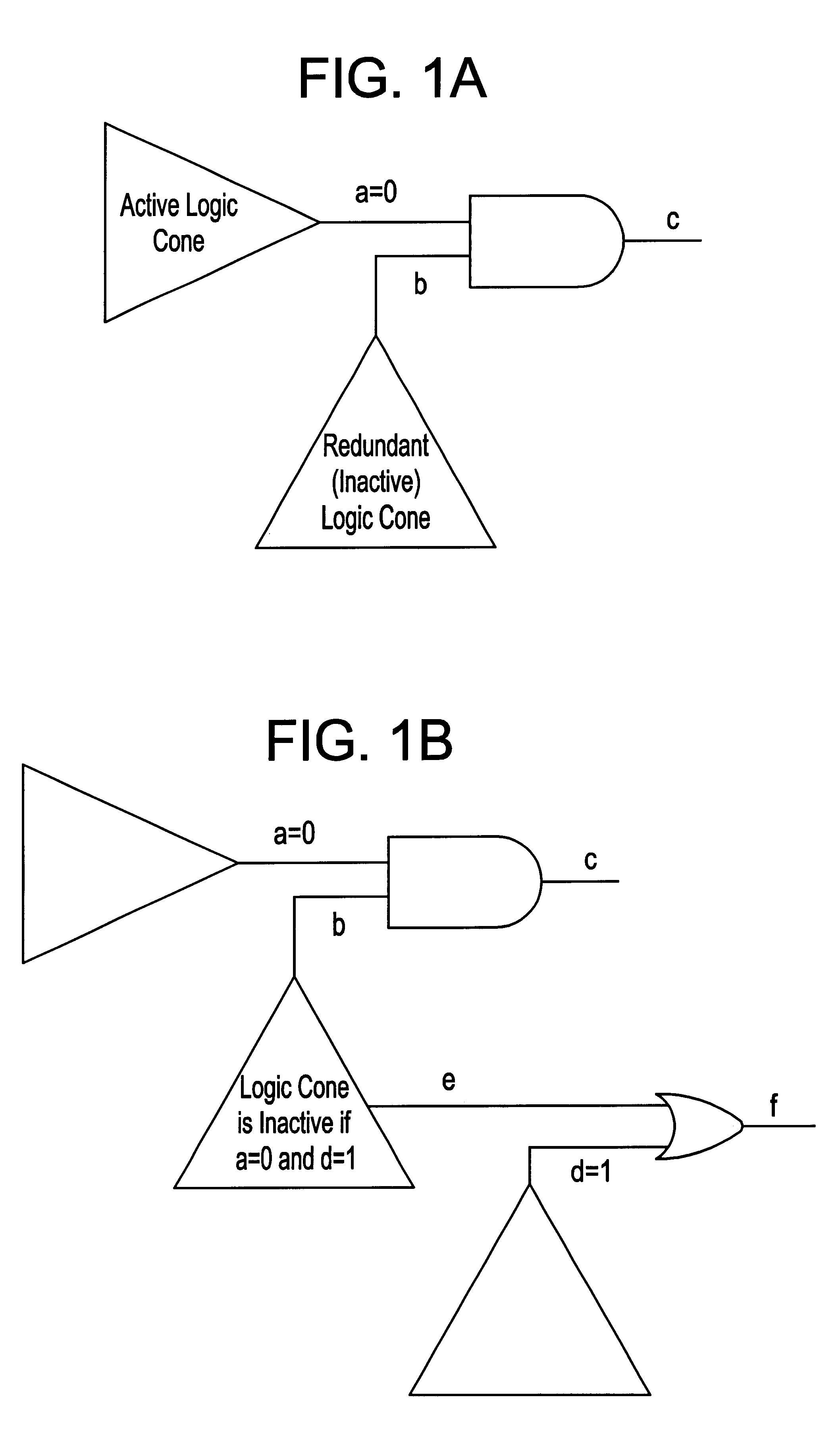

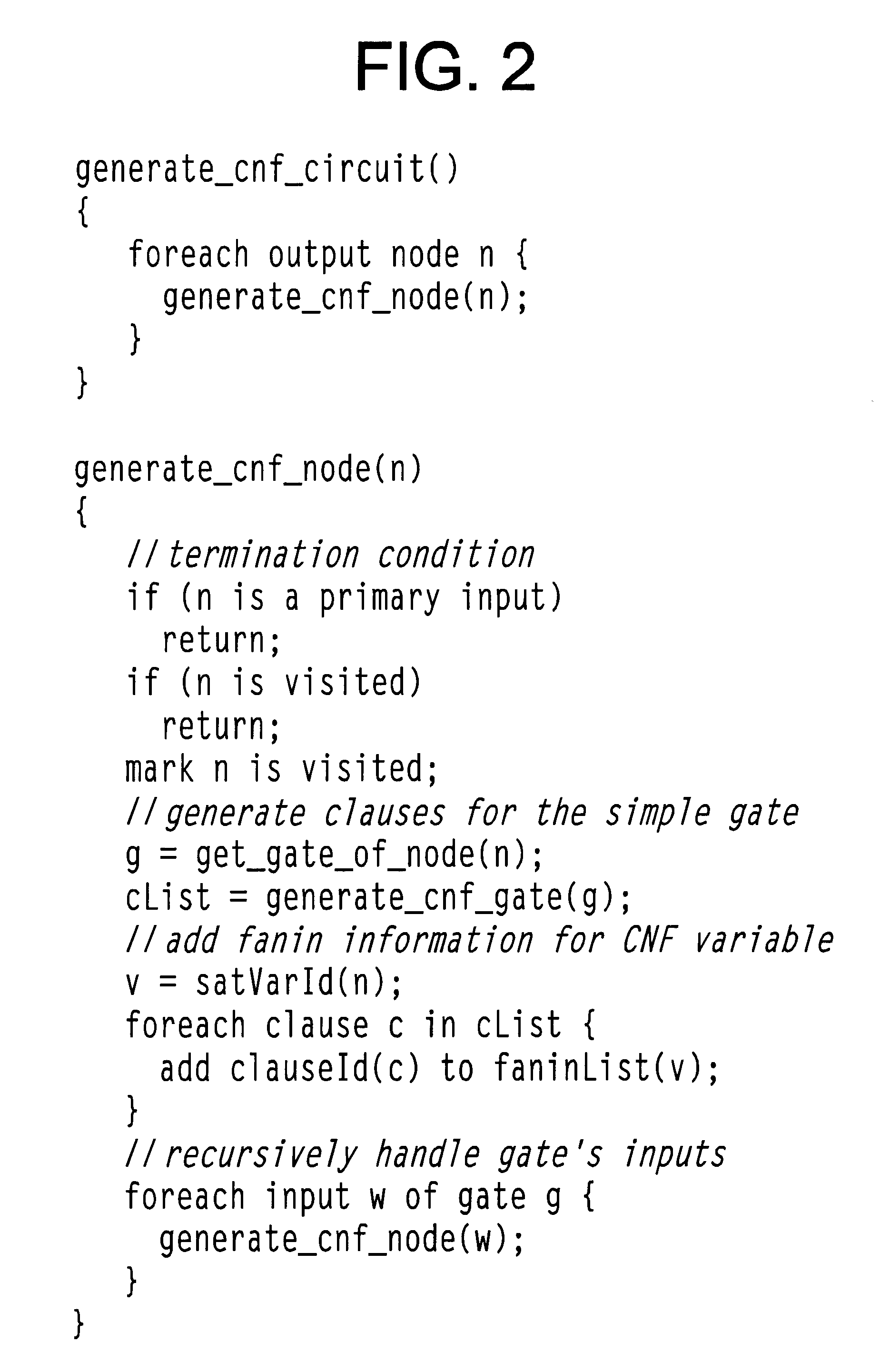

Dynamic detection and removal of inactive clauses in SAT with application in image computation

InactiveUS6496961B2Electronic circuit testingComputation using non-denominational number representationConjunctive normal formSatisfiability

This disclosure teaches a method of Boolean satisfiability checking (SAT) for a circuit. The method comprises identifying inactive clauses in the conjunctive normal form (CNF) of the circuit and removing the inactive clauses from the CNF.

Owner:NEC CORP

Partition-based decision heuristics for SAT and image computation using SAT and BDDs

InactiveUS20020178424A1Reduce partAdd depthComputer aided designSoftware simulation/interpretation/emulationRecognition heuristicConjunctive normal form

A method for Boolean Satisfiability (SAT). The method comprises using a variable decision heuristic in a SAT algorithm and pruning the search space of SAT using said decision heuristic. The decision heuristic is based on partitioning a conjunctive normal form (CNF) of a Boolean formula corresponding to the SAT and the partitioning is induced by a separator set. An image computaion method that uses the disclosed method for solving the SAT.

Owner:NEC CORP

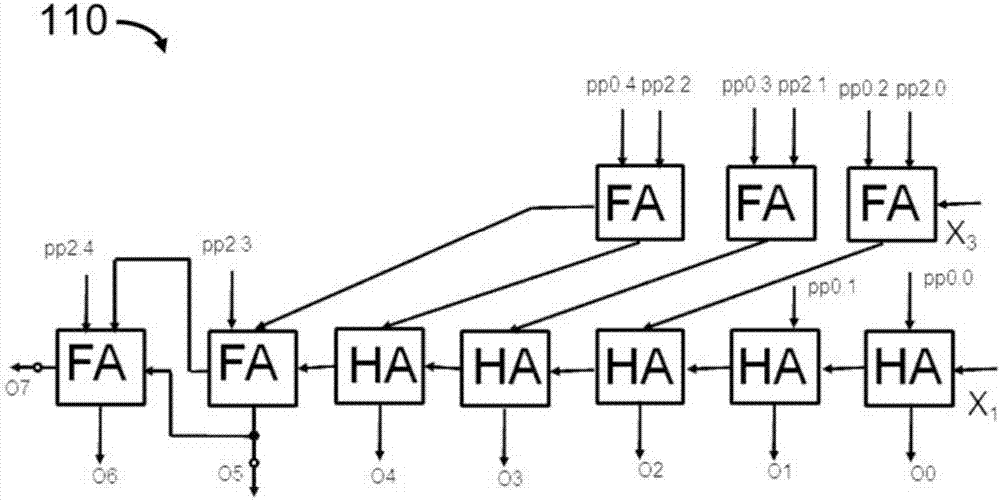

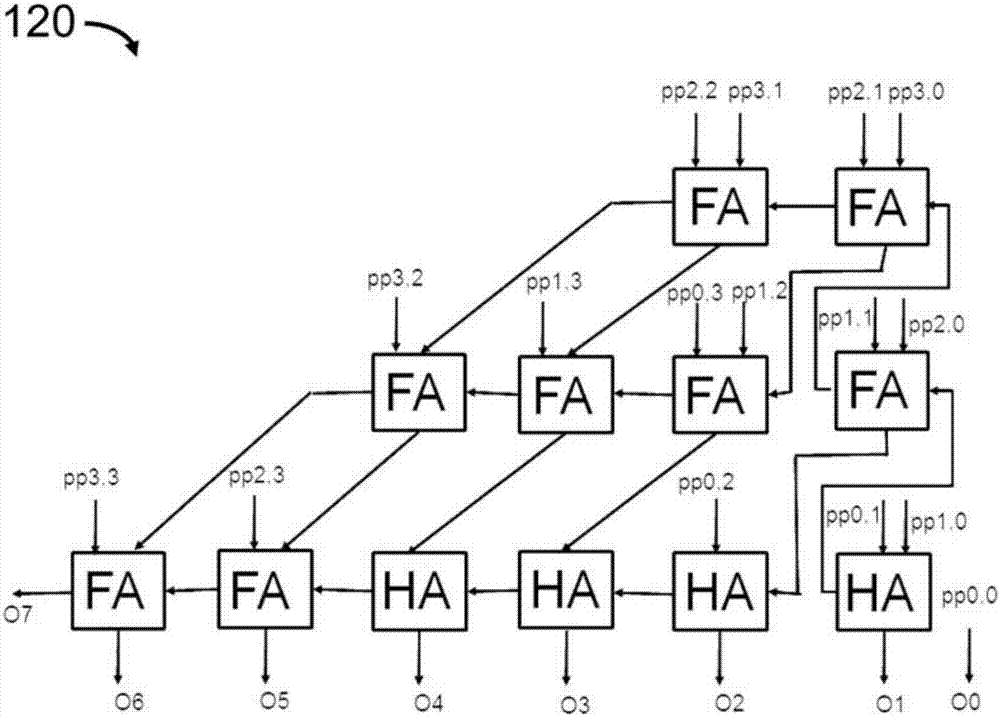

Circuit verification

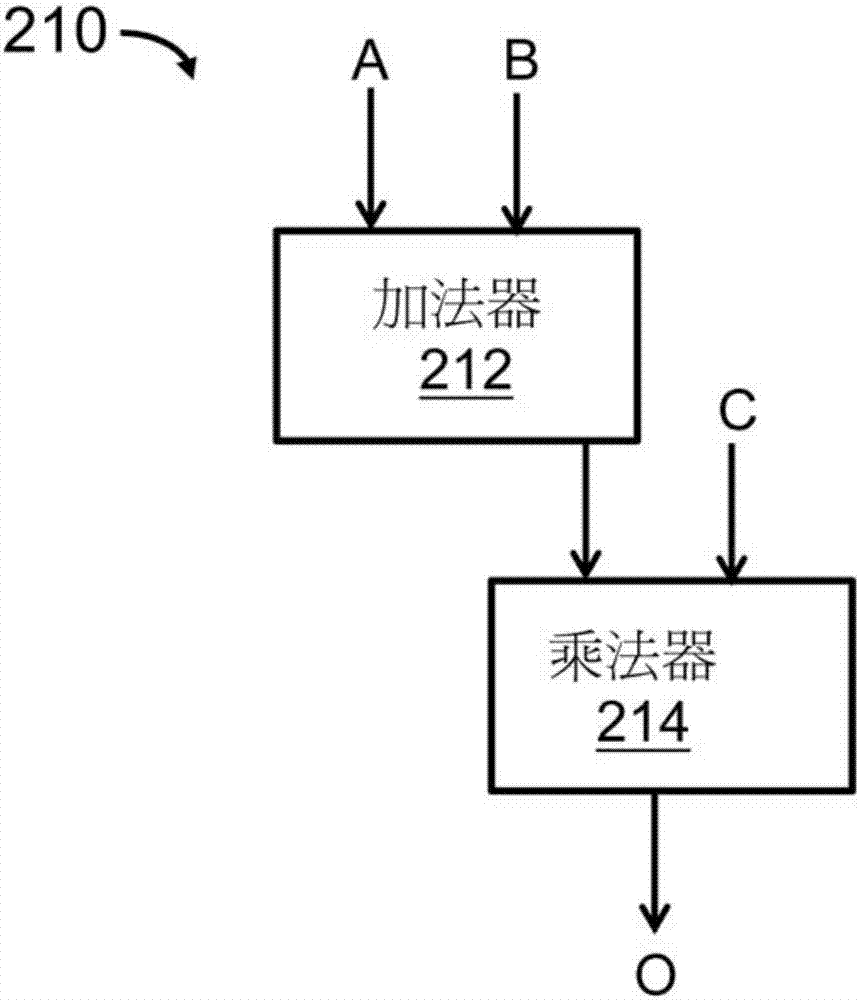

InactiveCN106997408ACAD circuit designSpecial data processing applicationsStructure propertyFormal methods

Provided is a totally new formal verification algorithm aiming at an arithmetic circuit. One example embodiment provides a new formal method which couples (combines) a satisfiability (SAT) solver and a unique Reverse Engineering (RE) method which makes use the arithmetic logical circuit structure properties (e.g. 1-bit adder structure, Carry tree structure) to achieve the algorithm for arithmetic circuits regardless of its size. The example embodiment provides basic through of how to optimize the operational complexity of a conventional arithmetic circuit verification method. The basic through is shown as followed: assuming that there are two arithmetic circuits f and g; conducting equivalence checking of the two arithmetic circuits by firstly generating a conjunctive normal form (CNF) encoding; and determining whether the encoding of the two arithmetic circuits is equal through a satisfiability (SAT) tool. If the structural difference between f and g is minimized as far as possible before generating a conjunctive normal form (CNF) encoding, the arithmetic circuit verification is completed in polynomial time rather than in exponential time.

Owner:EASY LOGIC TECH LTD

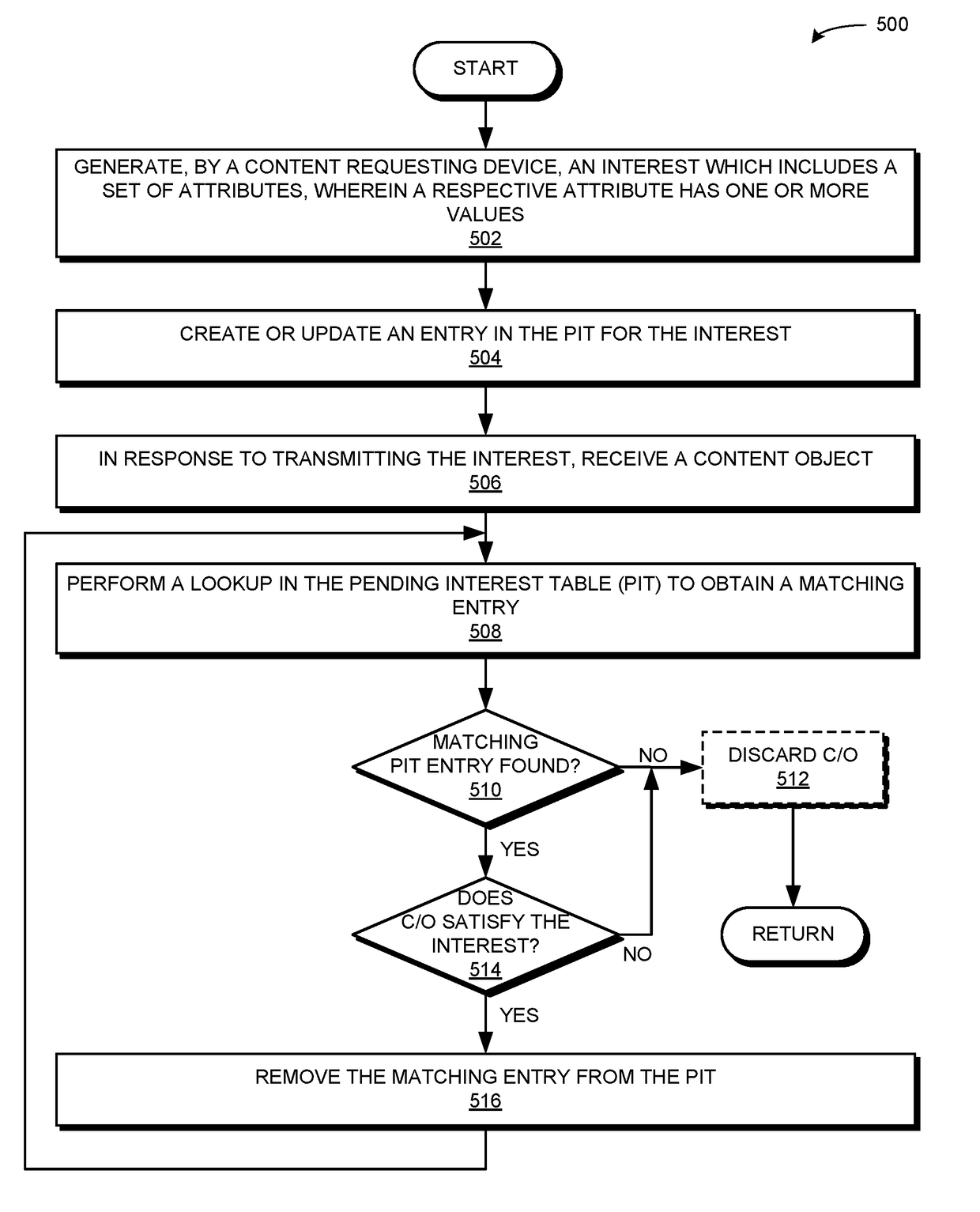

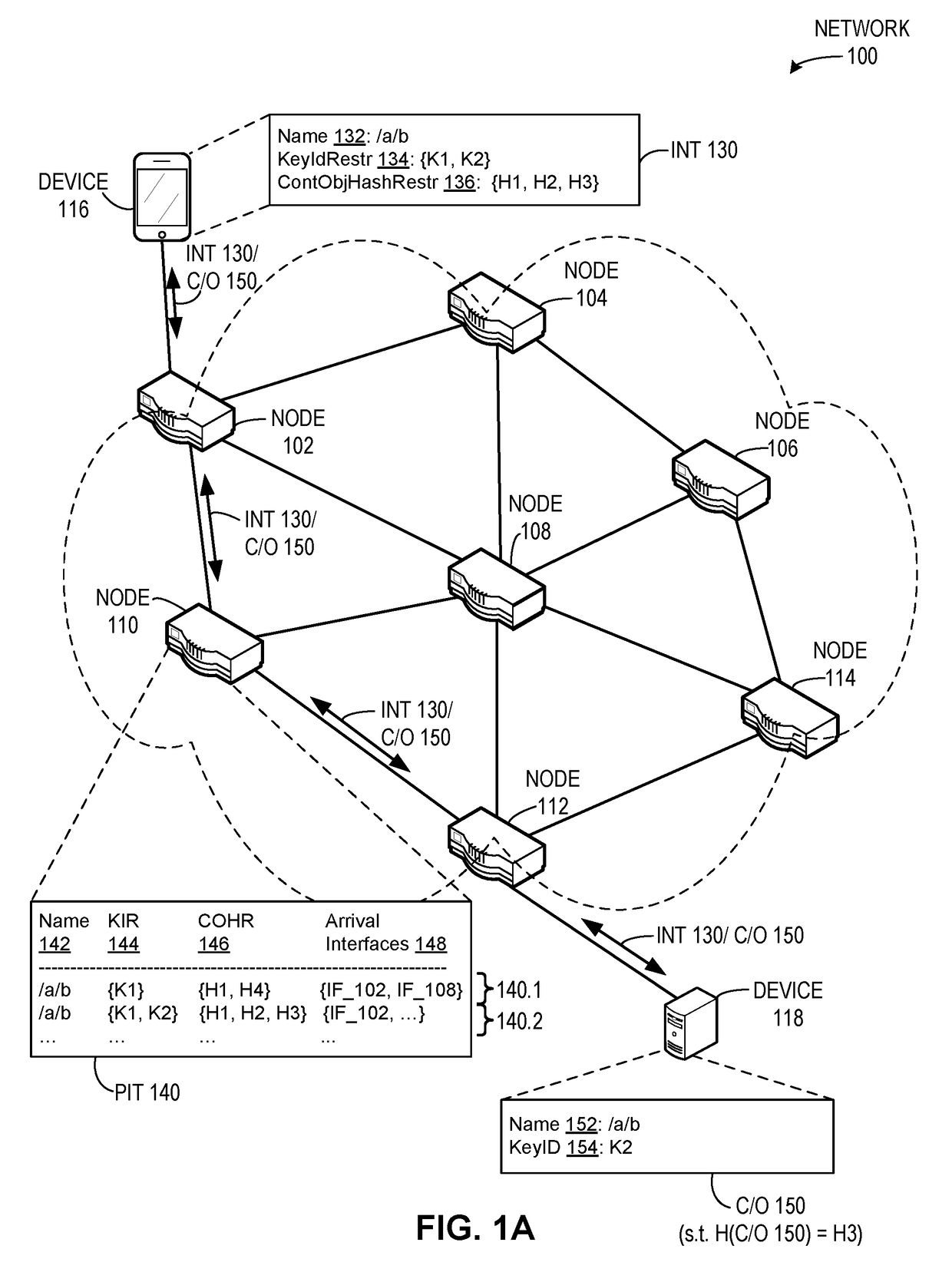

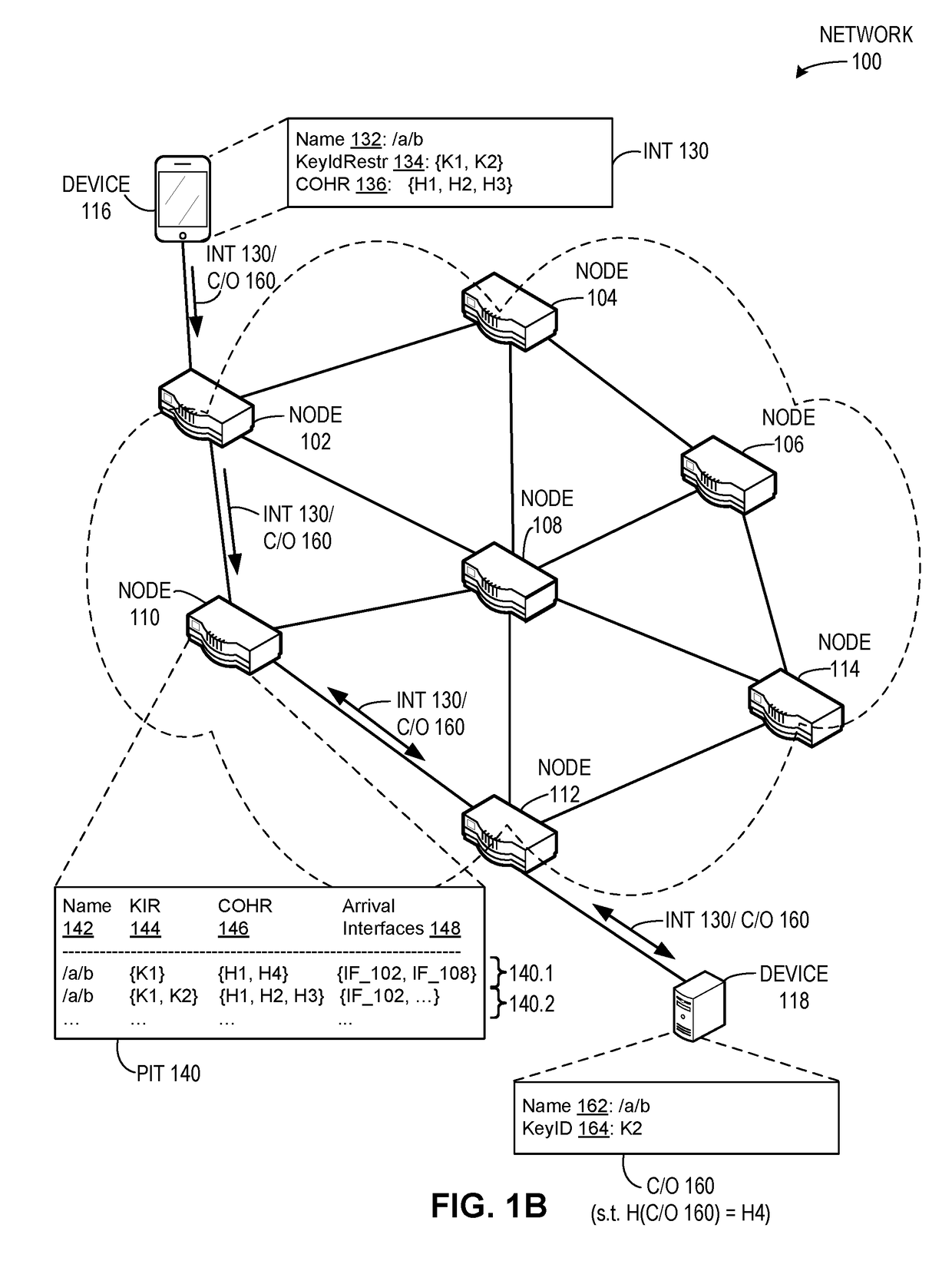

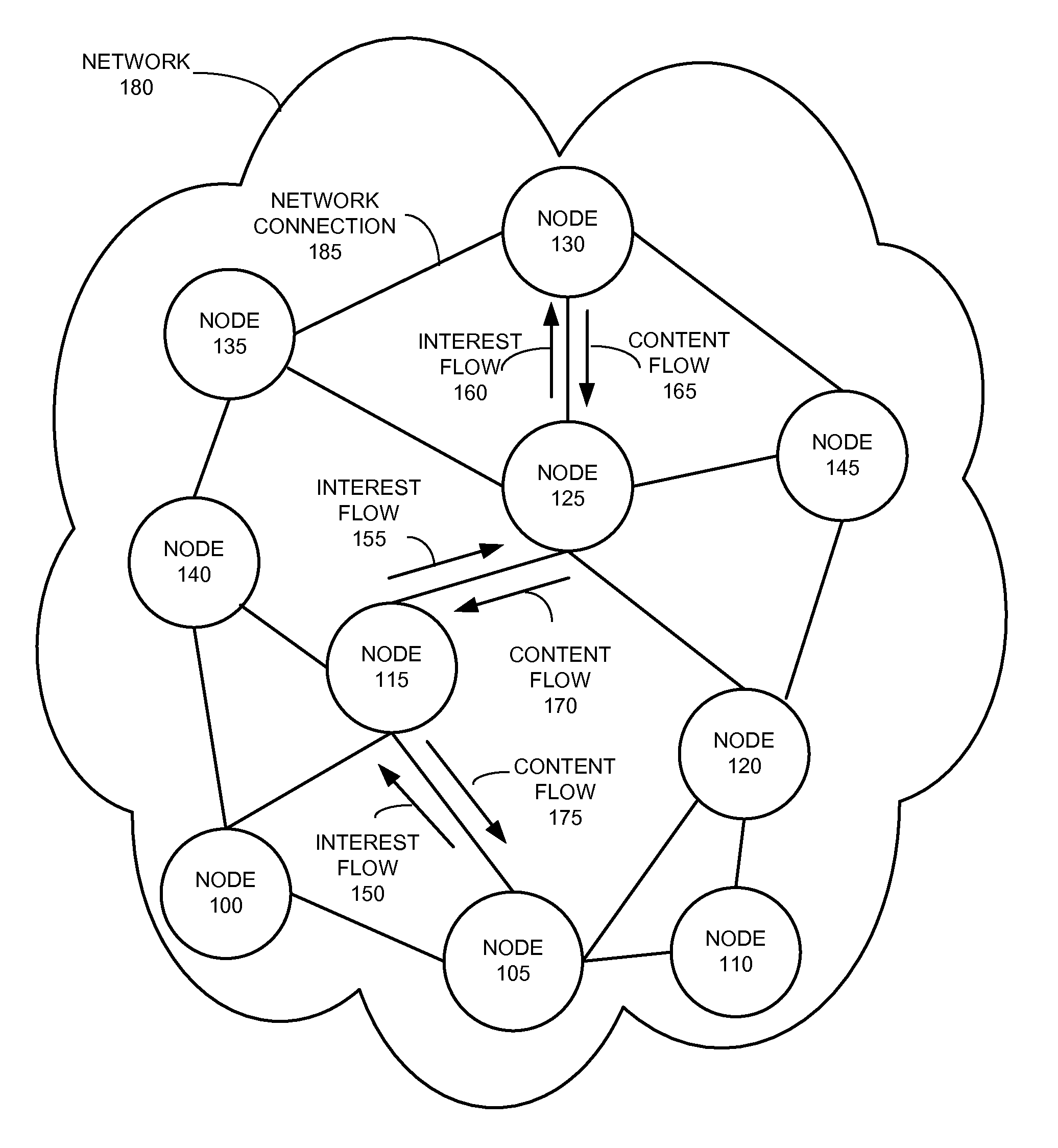

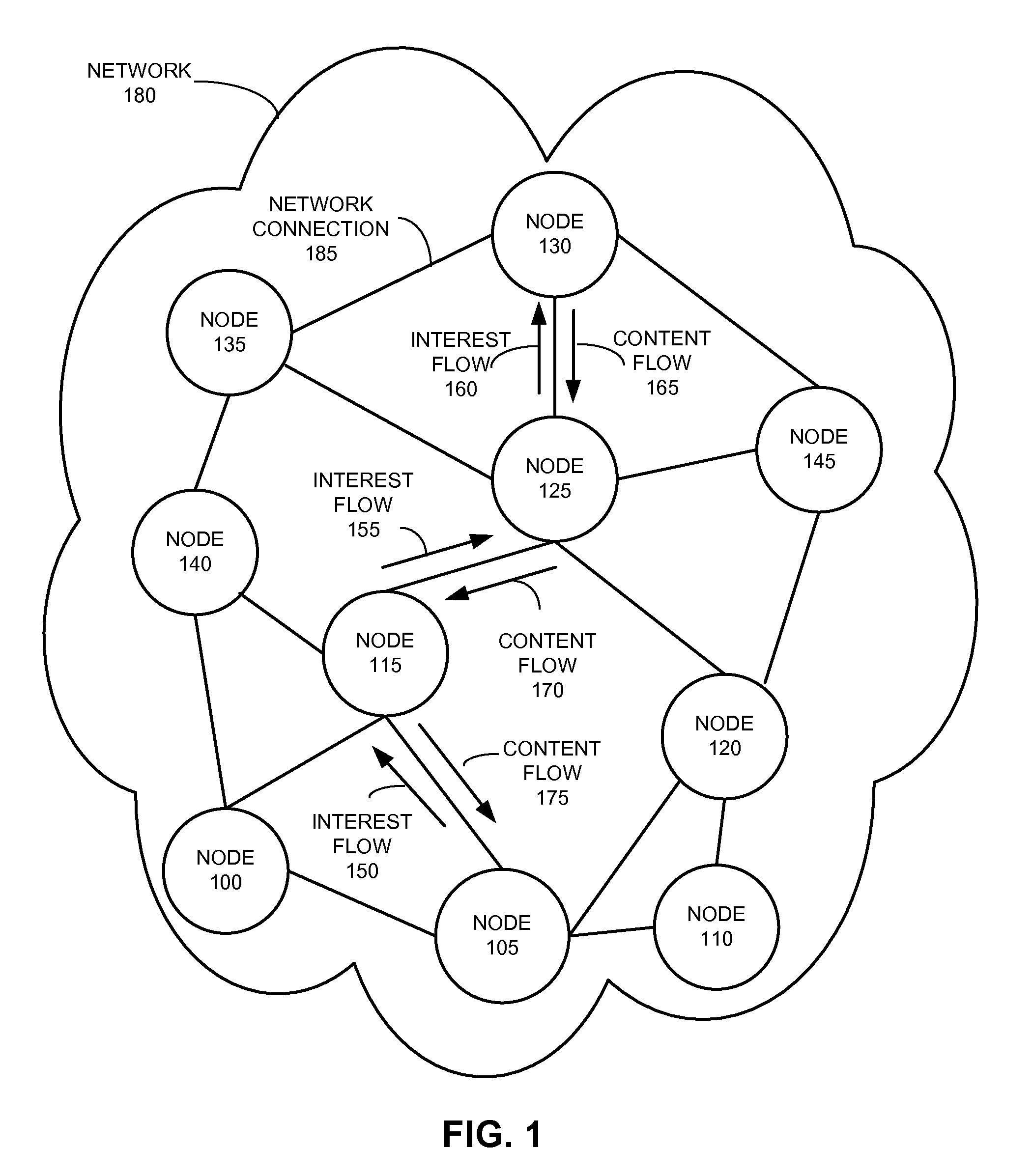

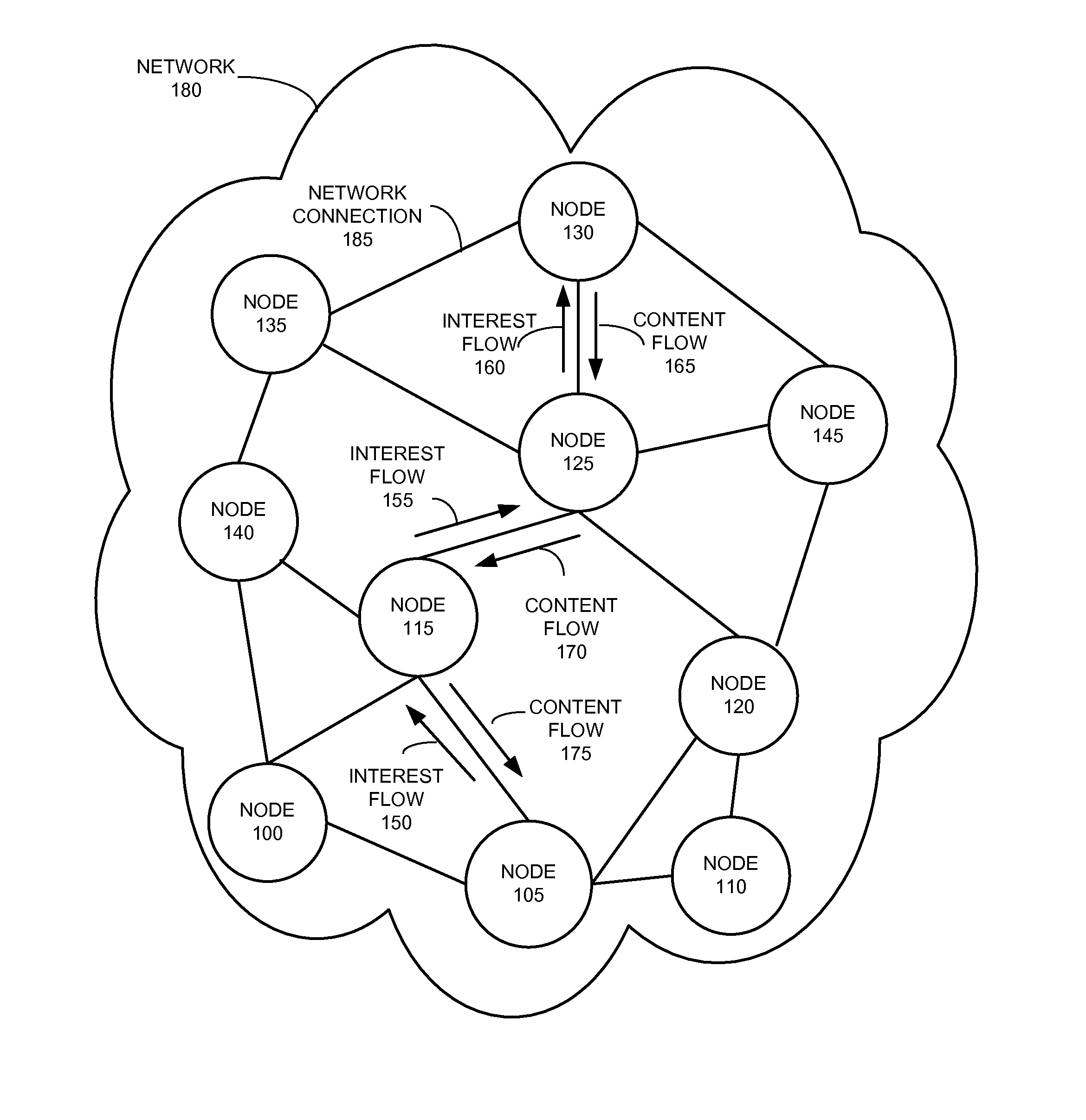

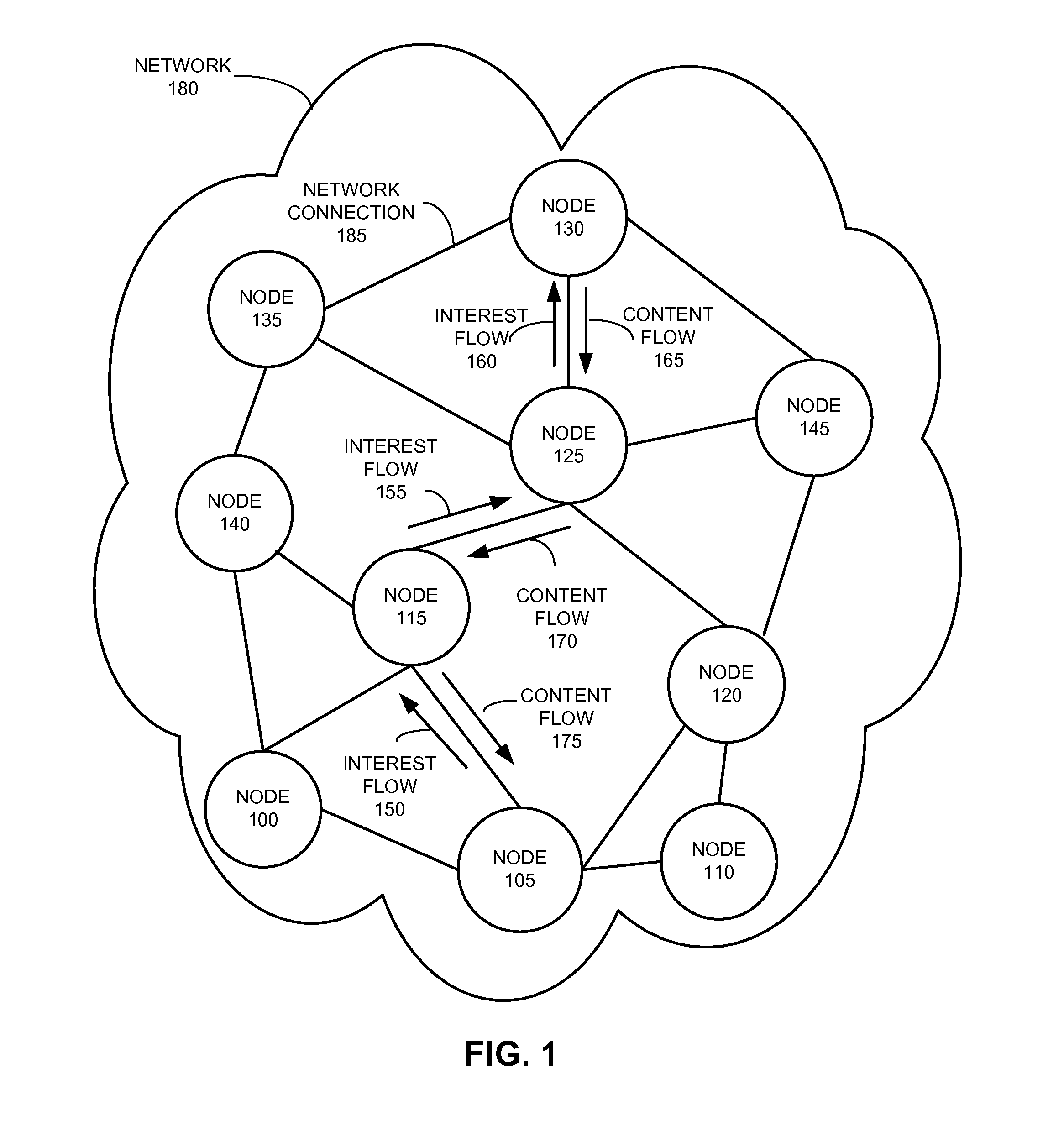

Method and system for conjunctive normal form attribute matching in a content centric network

ActiveUS20180046667A1Flexible and convenientOther databases indexingData switching networksContent centricConjunctive normal form

One embodiment provides a system that facilitates a flexible strategy for matching content objects and interests. During operation, the system receives, by a computing device, an interest which includes a set of attributes, wherein a respective attribute has one or more values. In response to not obtaining a matching entry for the interest in a pending interest table, the system adds to the pending interest table a first entry which indicates the interest based on the attributes and their values. The system determines whether a received content object satisfies the interest indicated in the first entry based on the attributes of the first entry and attributes of the content object. In response to determining that the content object satisfies the interest, the system forwards the content object, thereby facilitating a flexible strategy for matching content objects to interests.

Owner:CISCO TECH INC

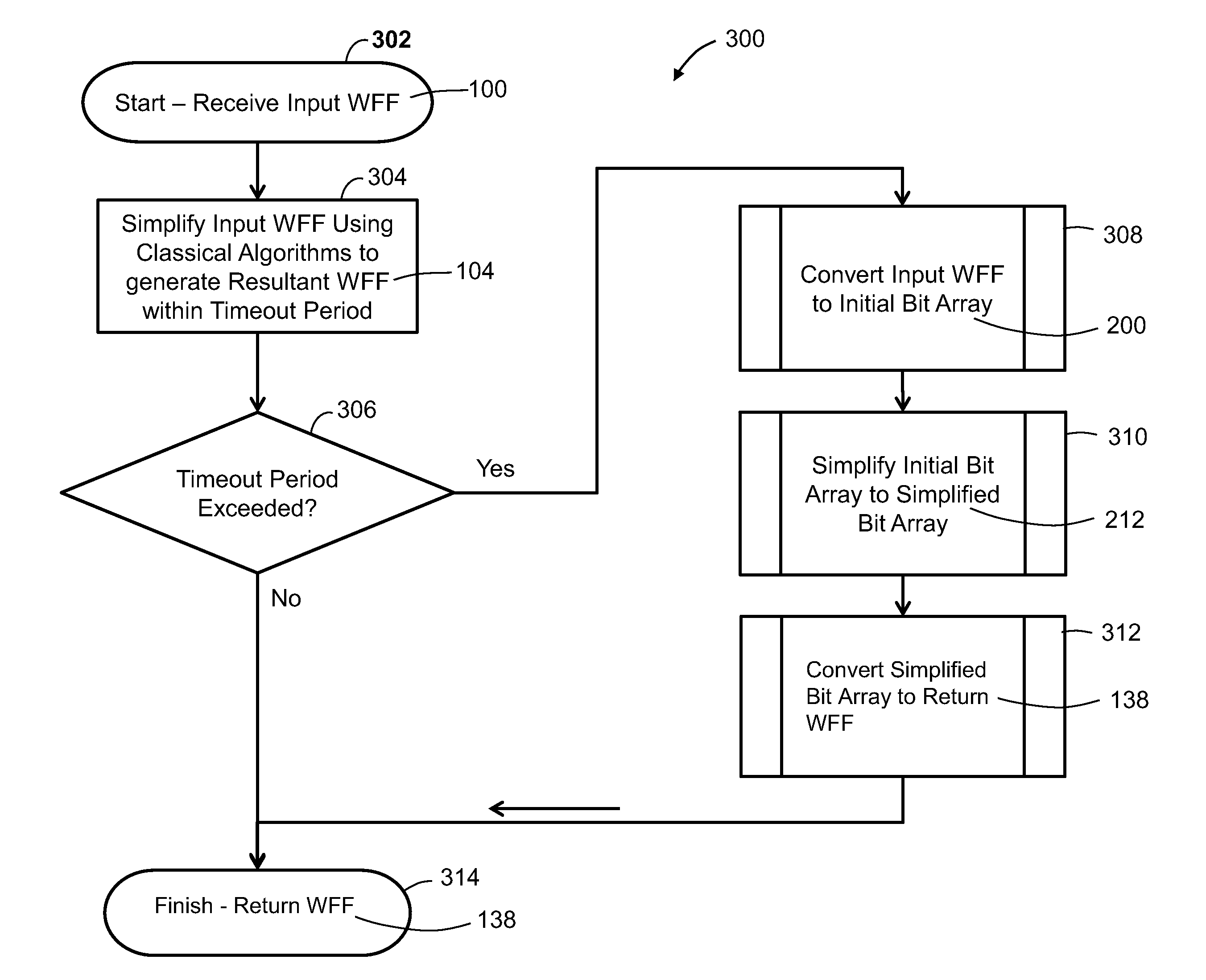

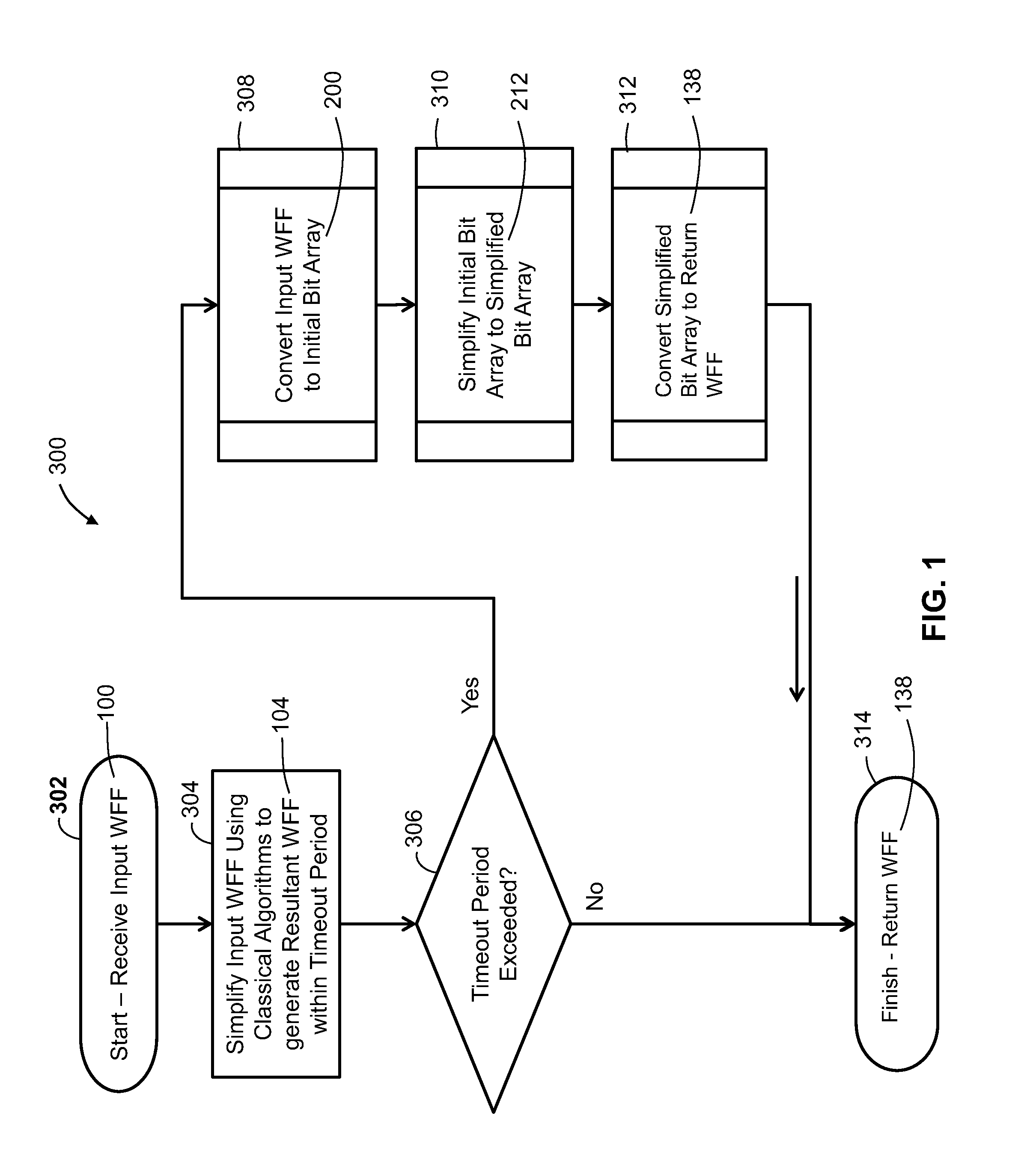

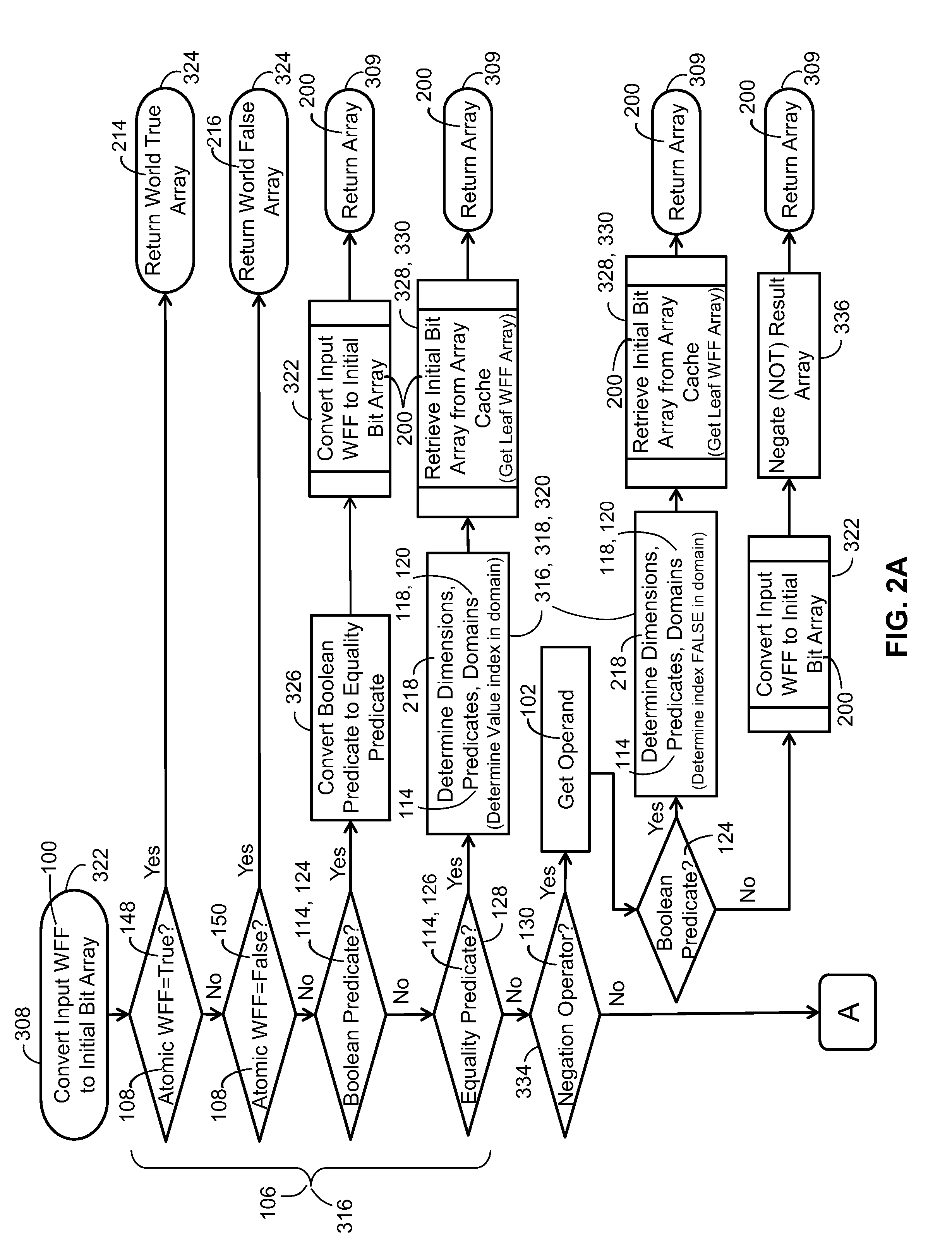

System and method for rapid management of logic formulas

ActiveUS20130246016A1Rapid designSimplify the initial bit arrayComputation using non-denominational number representationKnowledge representationWell-formed formulaBit array

A method for simplifying a complex well-formed formula (WFF) may include receiving, in a formula processor, an input WFF and converting the input WFF into an initial bit array. The method may further include simplifying the initial bit array into a simplified bit array by removing predicates from the initial bit array not necessary to represent the input WFF. The method may include converting the simplified bit array into a return WFF in either a conjunctive normal form or a disjunctive normal form.

Owner:THE BOEING CO

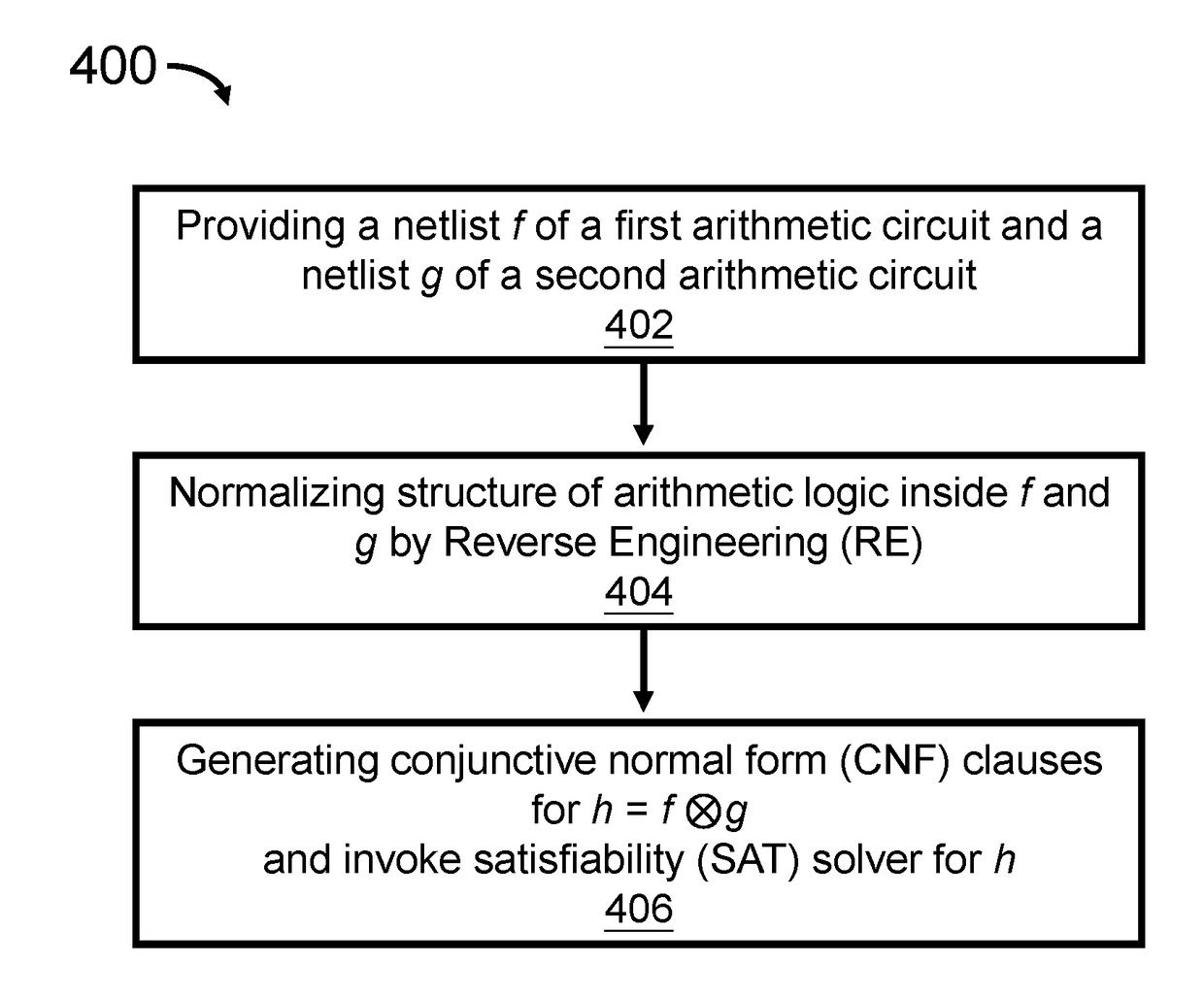

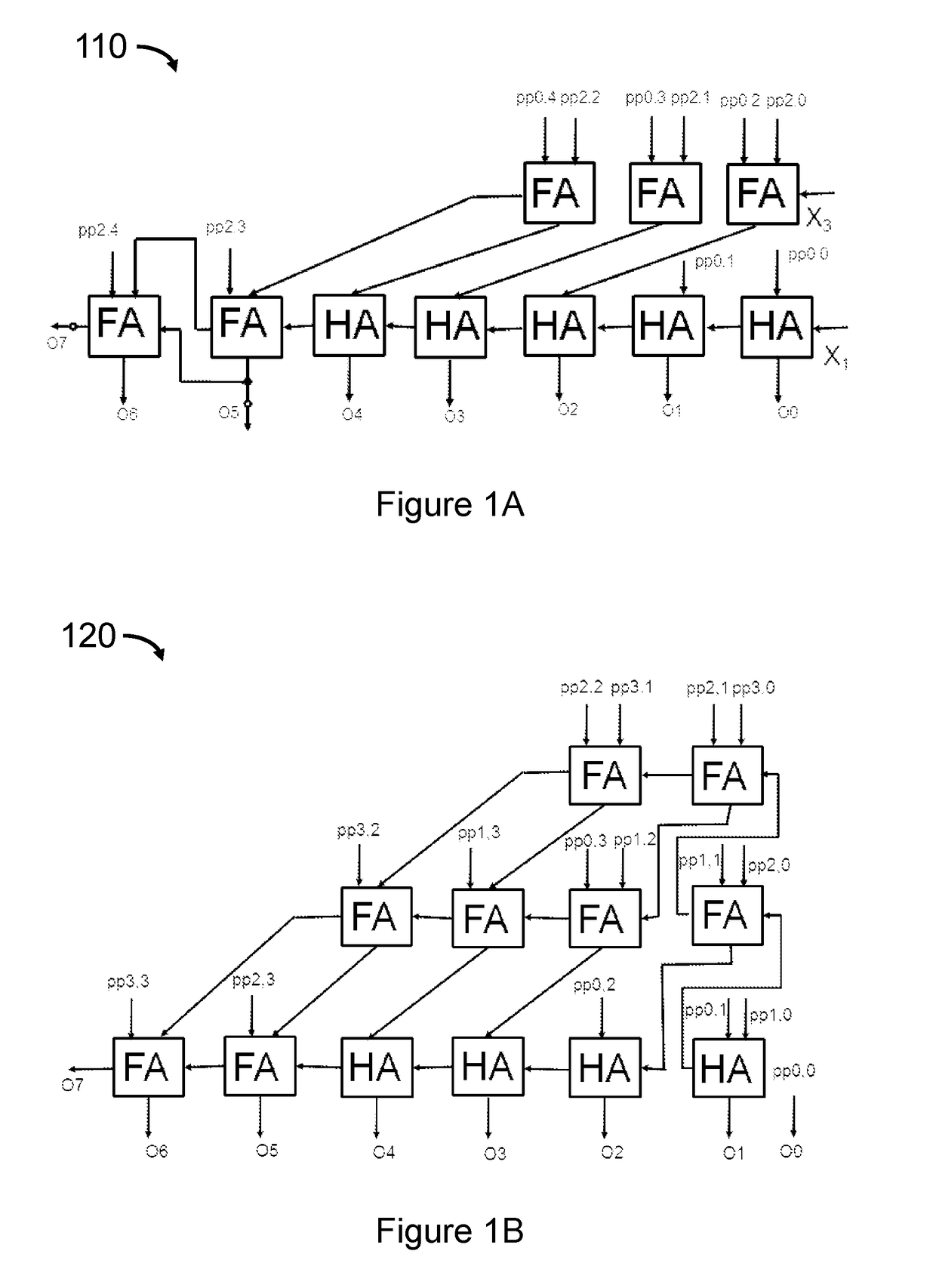

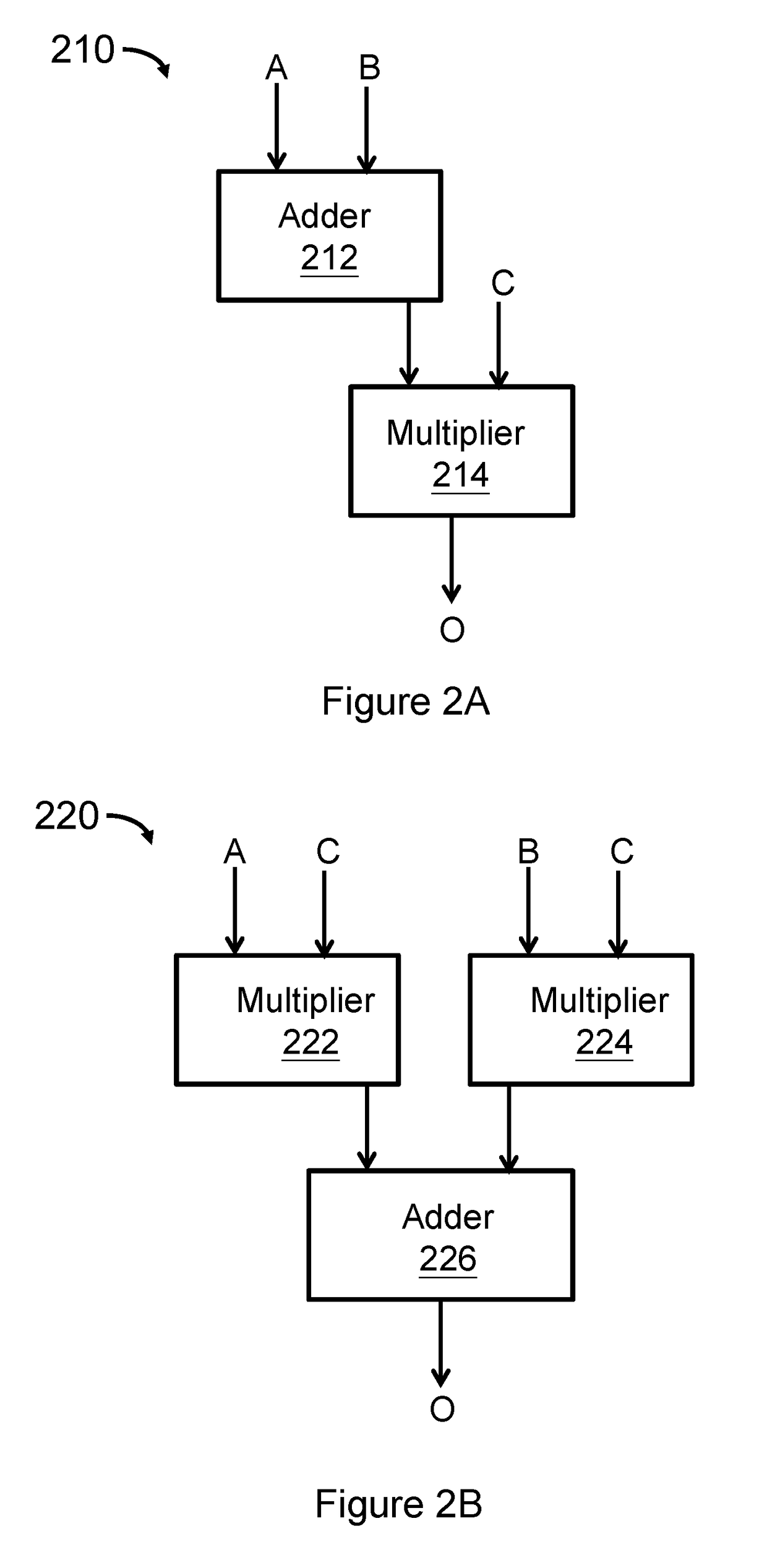

Circuit Verification

InactiveUS20170212968A1Improved runtime complexityImproves runtime complexityDigital data processing detailsCAD circuit designConjunctive normal formNetlist

A method enables arithmetic circuit verification with improved runtime complexity by coupling reverse engineering and a SAT solver together. The method provides a netlist f of a first arithmetic circuit and a netlist g of a second arithmetic circuit; and improves the runtime complexity by conducting equivalence checking between the netlist f and the netlist g such that structural difference between the netlist f and the netlist g is minimized by reverse engineering before generating a conjunctive normal form (CNF) encoding that is solved by a satisfiability (SAT) solver such that the arithmetic circuit verification is completed in polynomial time rather than in exponential time.

Owner:EASY LOGIC TECH LTD

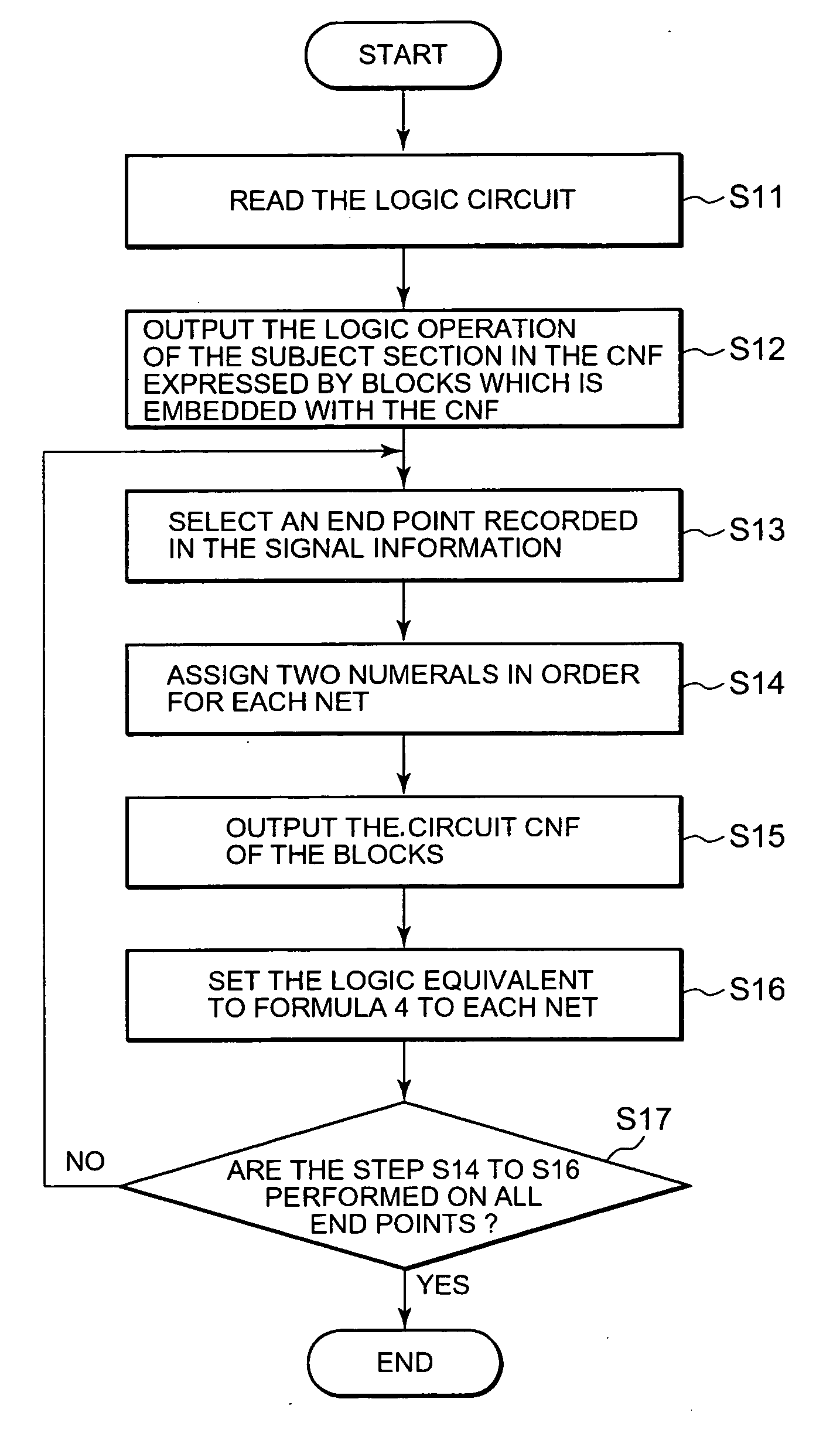

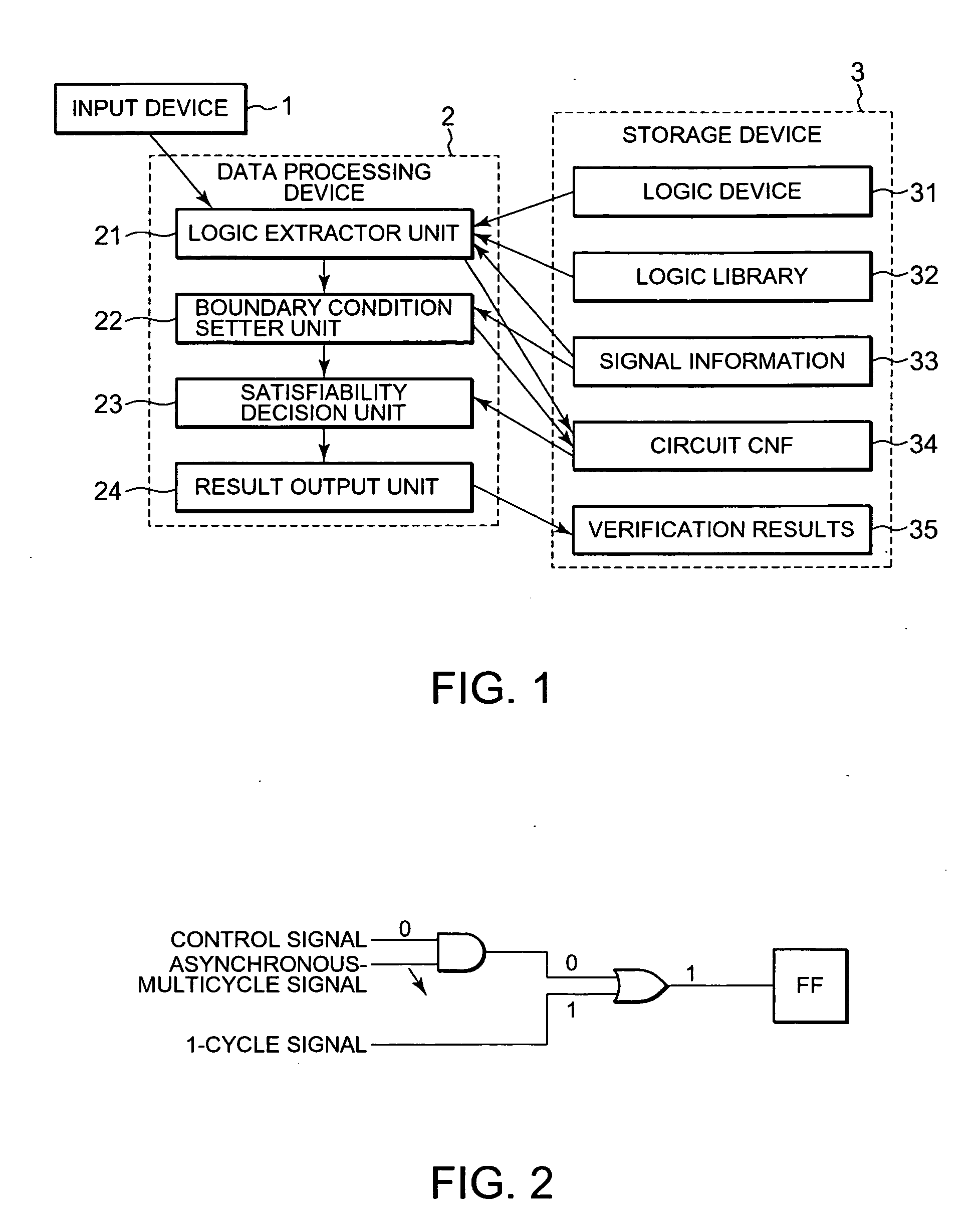

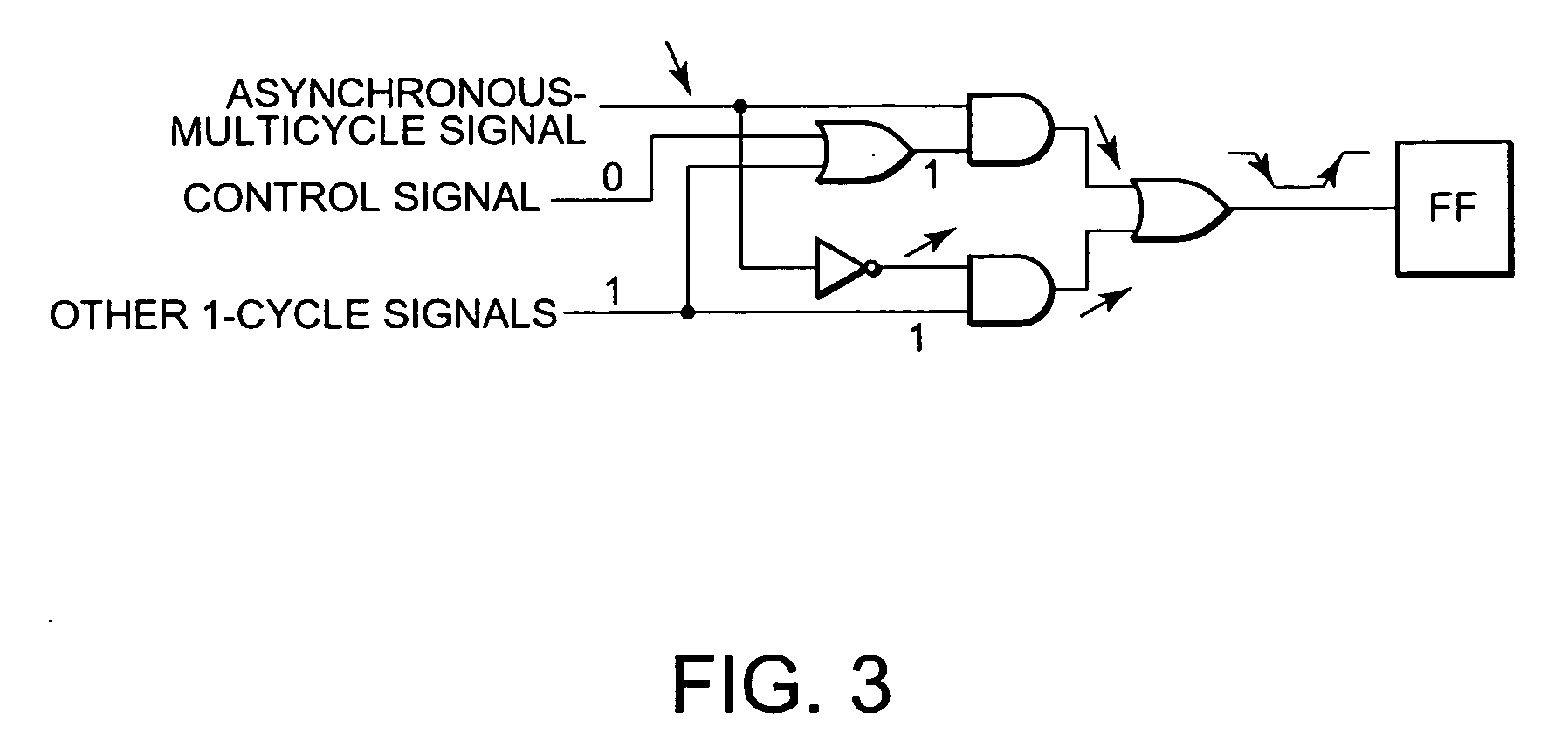

Circuit conjunctive normal form generating method, circuit conjunctive normal form generating device, hazard check method and hazard check device

ActiveUS20070266348A1Computer aided designSoftware simulation/interpretation/emulationPre embeddingConjunctive normal form

A hazard check method and device for making hazard checks of logic circuits containing asynchronous paths and multi-cycle paths. The hazard check device includes a means for equivalent conversion to only pre-embedded conjunctive normal form blocks if not all of the blocks in the logic circuit were embedded conjunctive normal form blocks; a means for tracing each termination point recorded in the signal information from the logic circuit, inputting the signal information to the circuit up to the flip-flop, and assigning numerals to each net; and a means for tracing each termination point recorded in the signal information from the logic circuit, referring to the logic library for each block, and searching for the same logic conjunctive normal form (CNF) as in the logic library, and substituting the conjunctive normal form into the numerals assigned to the connected network, and outputting it as the circuit conjunctive normal form; and a means for adding a circuit conjunctive normal form whose logic is equivalent to that numeral, to each net for each termination point recorded in the signal information.

Owner:NEC CORP

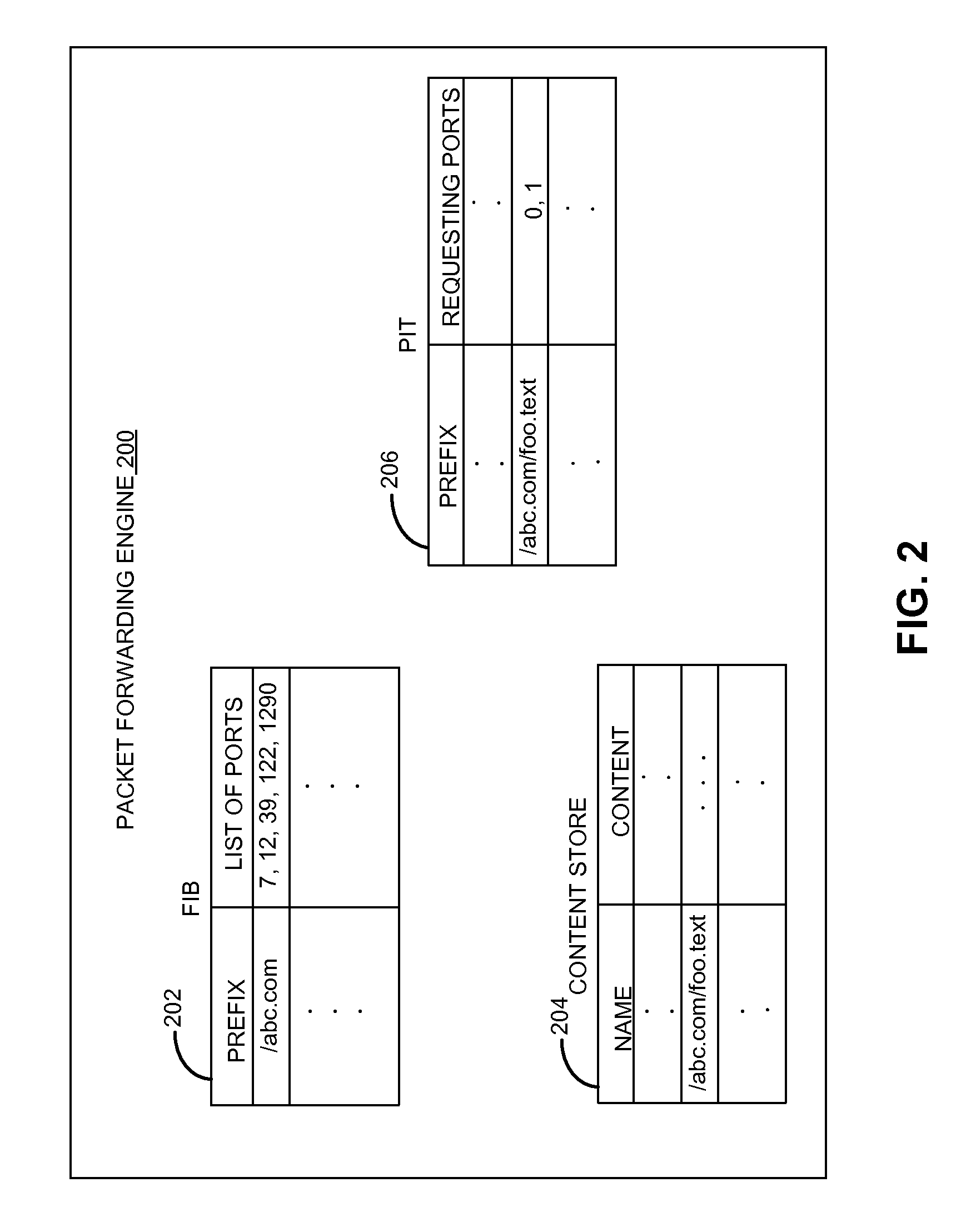

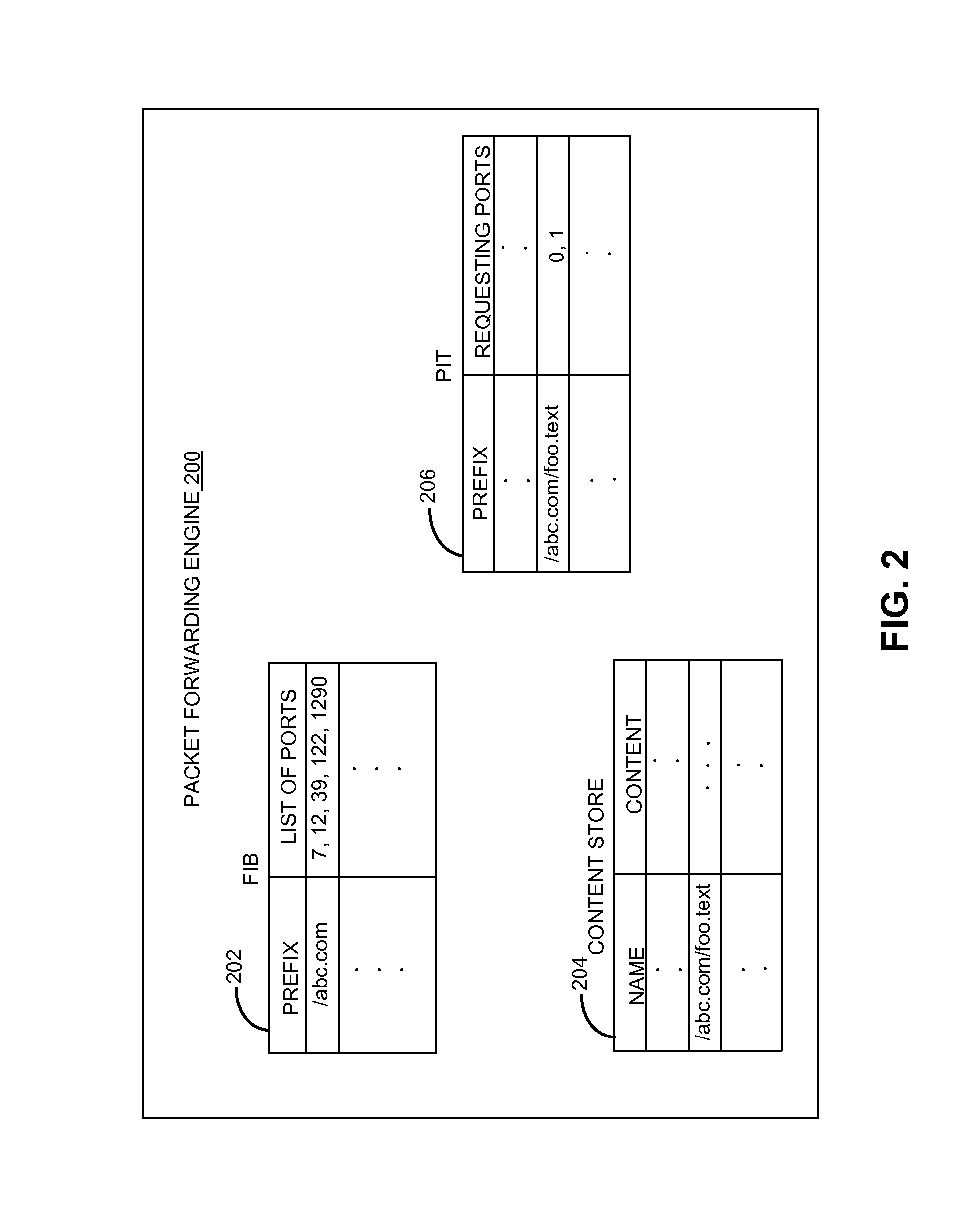

System and method for packet forwarding using a conjunctive normal form strategy in a content-centric network

One embodiment of the present invention provides a system for forwarding packets with hierarchically structured variable-length identifiers (HSVLIs) in a content-centric network (CCN). During operation, the system receives a packet with an HSVLI and determines, based on the HSVLI, a plurality of ports to which the packet should be forwarded. The plurality of ports include a set of individual port groups, and a respective port group includes one or more individual physical ports. The system derives a forwarding strategy based on the set of individual port groups and the one or more individual physical ports. The forwarding strategy is expressed as a formula in conjunctive normal form that indicates a logical conjunction among the set of port groups and a logical disjunction among the one or more individual physical ports. The system then forwards the packet using the derived forwarding strategy.

Owner:CISCO TECH INC

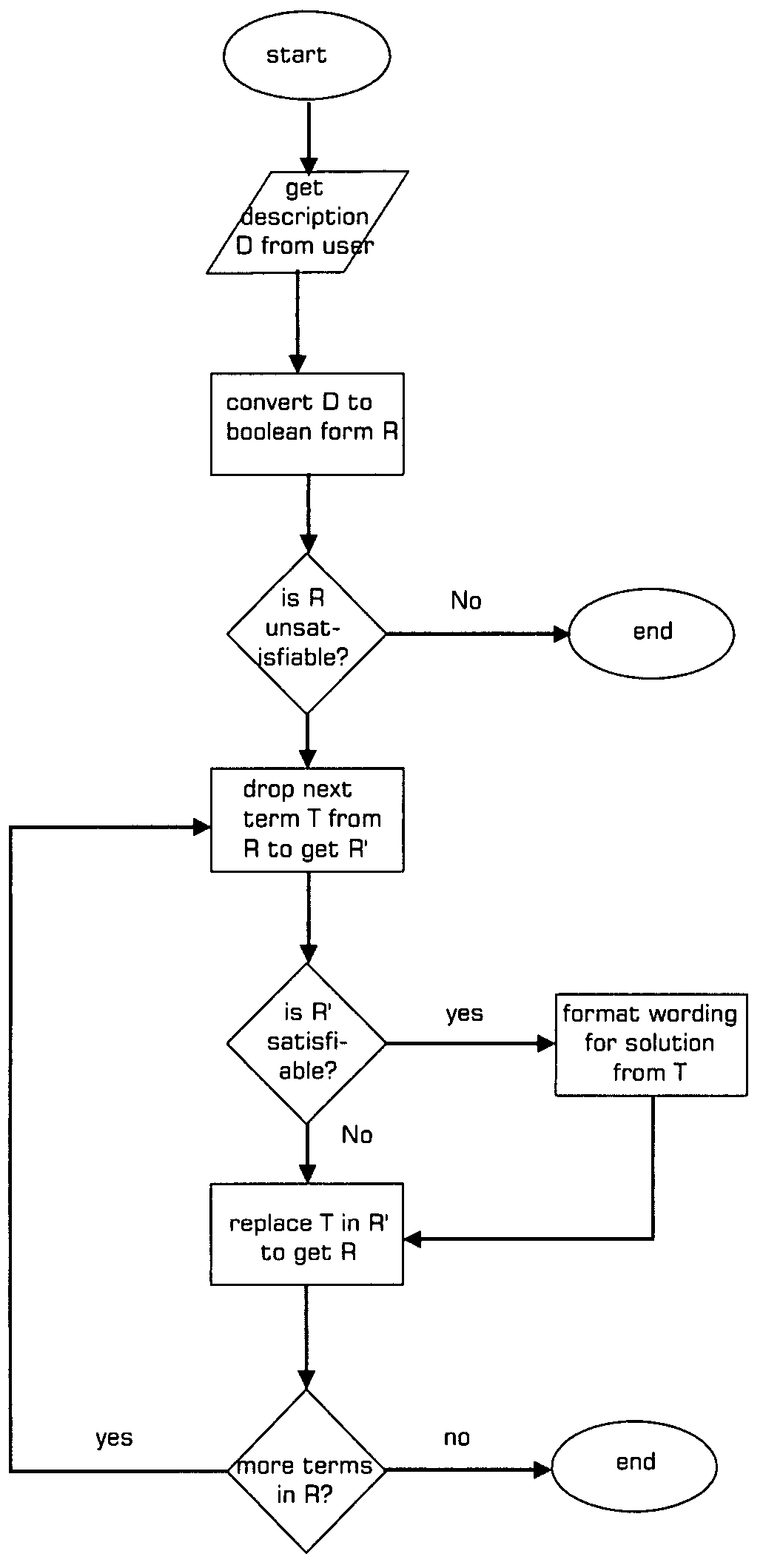

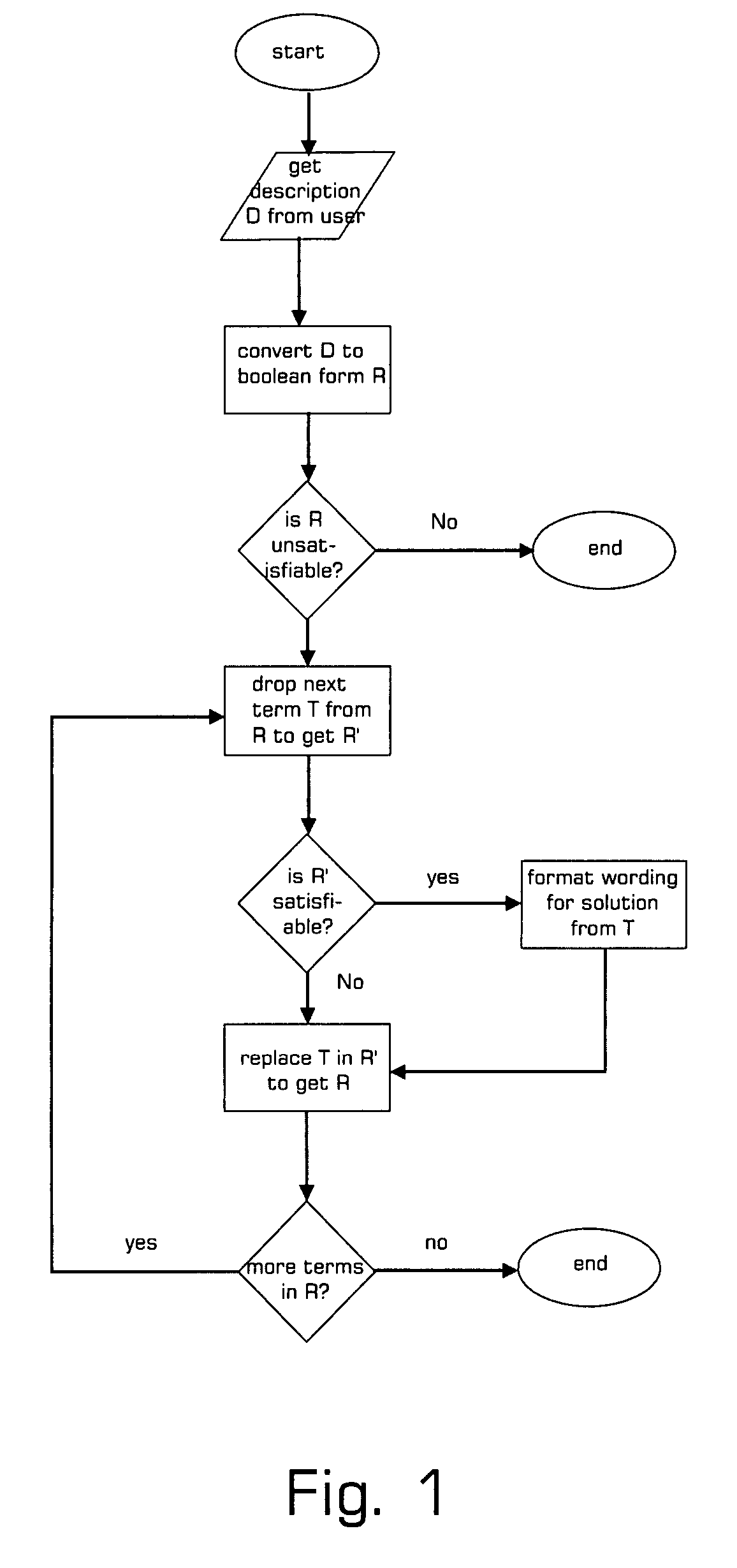

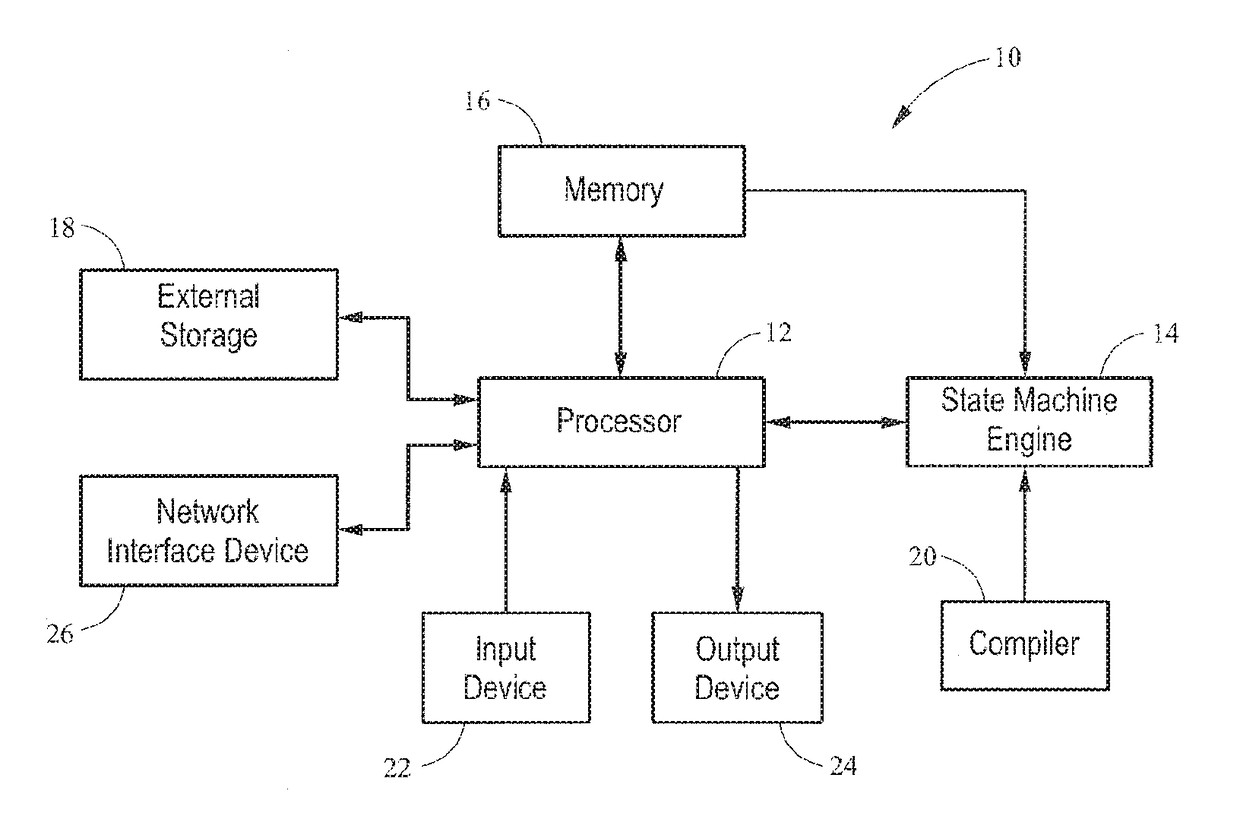

Apparatus and process for conjunctive normal form processing

A method for analyzing system-problems, comprising the steps of: accepting from a user an input describing a system having a problem; parsing the user input to create a boolean representation of the system, the boolean representation comprising a series of equations; determining that the boolean representation comprises an unsatisfiable series of equations; for each equation in the series of equations, performing the steps of: creating a modified series of equations by removing the equation from the series of equations; and determining if the modified series of equations is satisfiable, and, if the modified series of equations is satisfiable, deriving a solution wording from the removed equation.

Owner:HAIMOV EUGENE

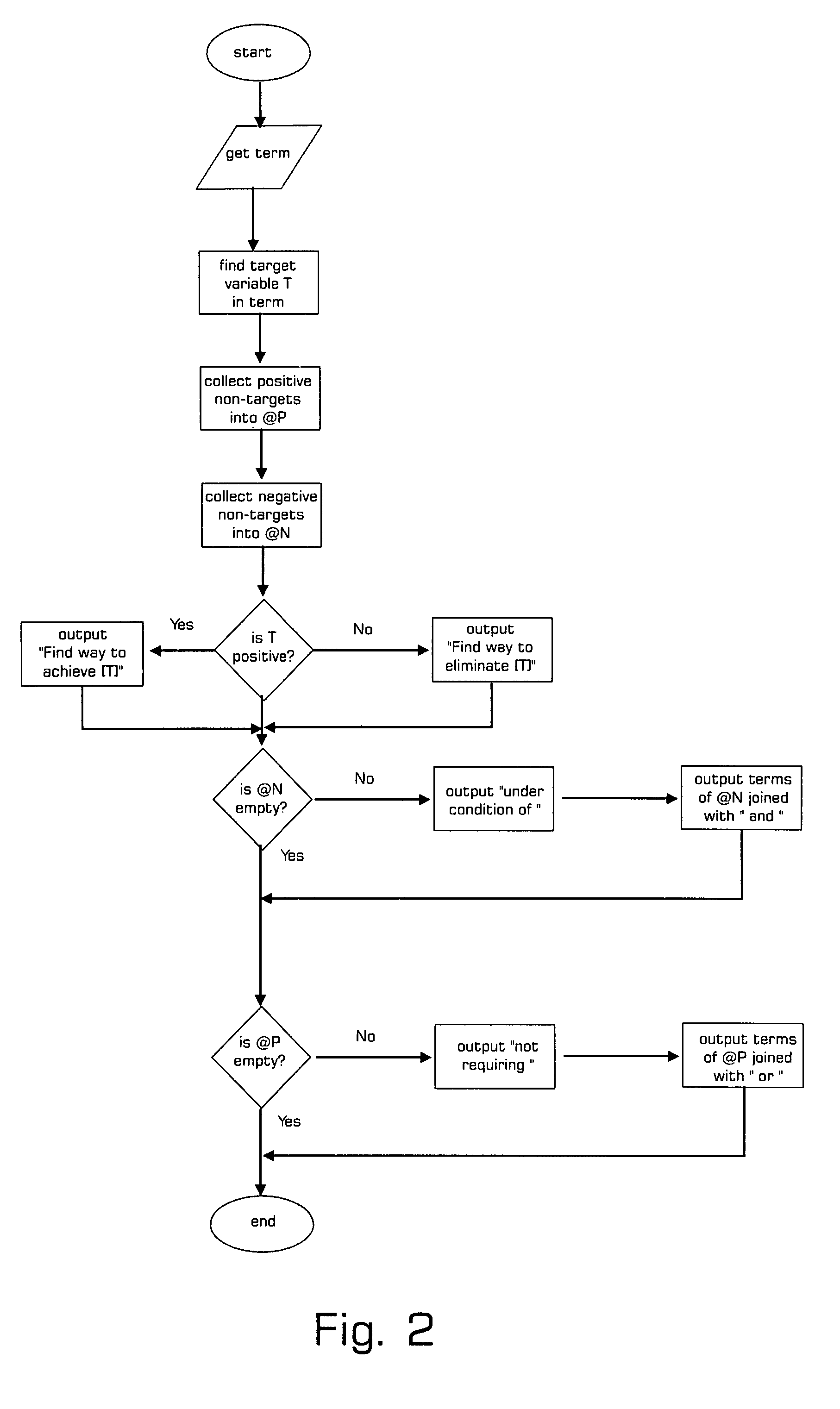

Boolean satisfiability

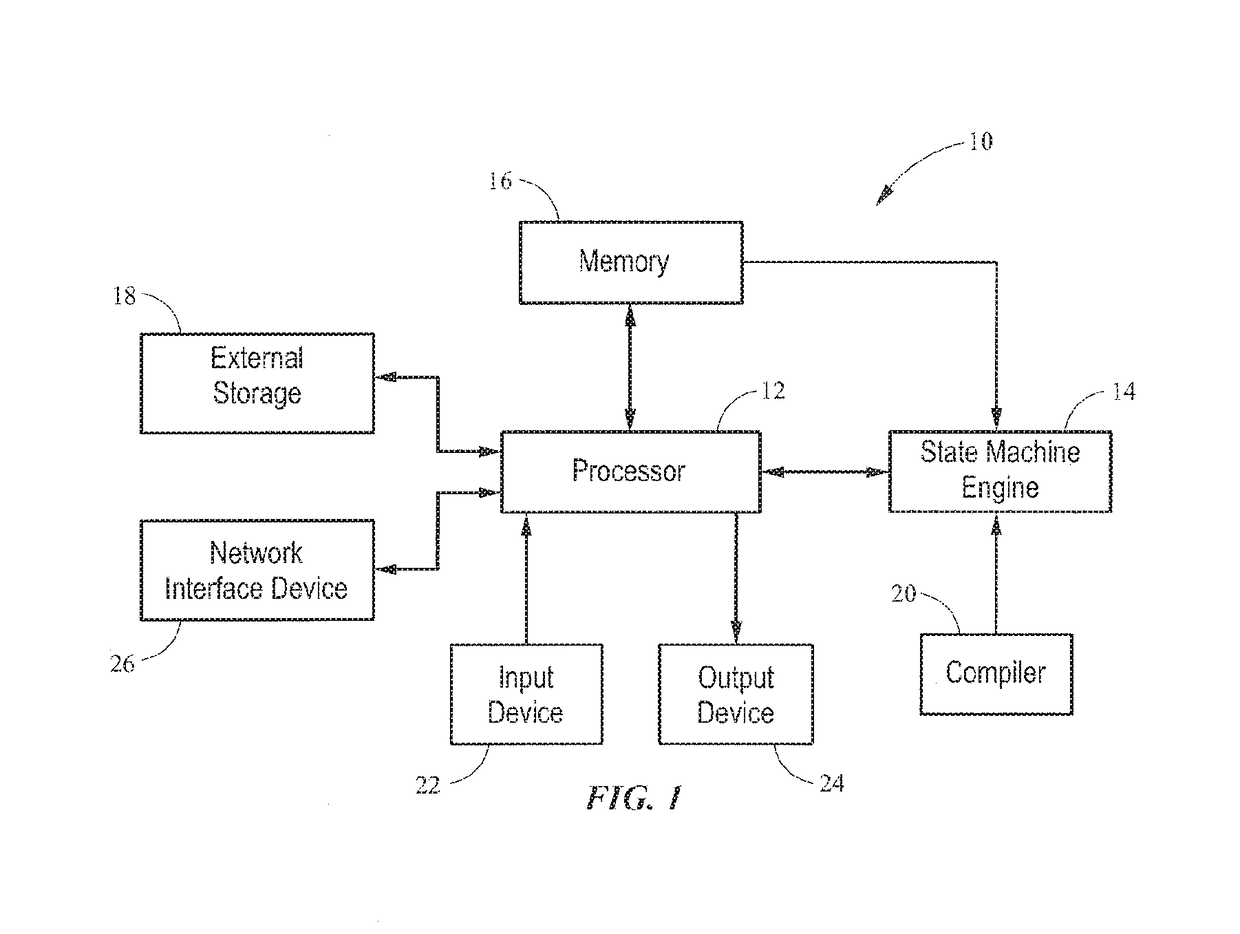

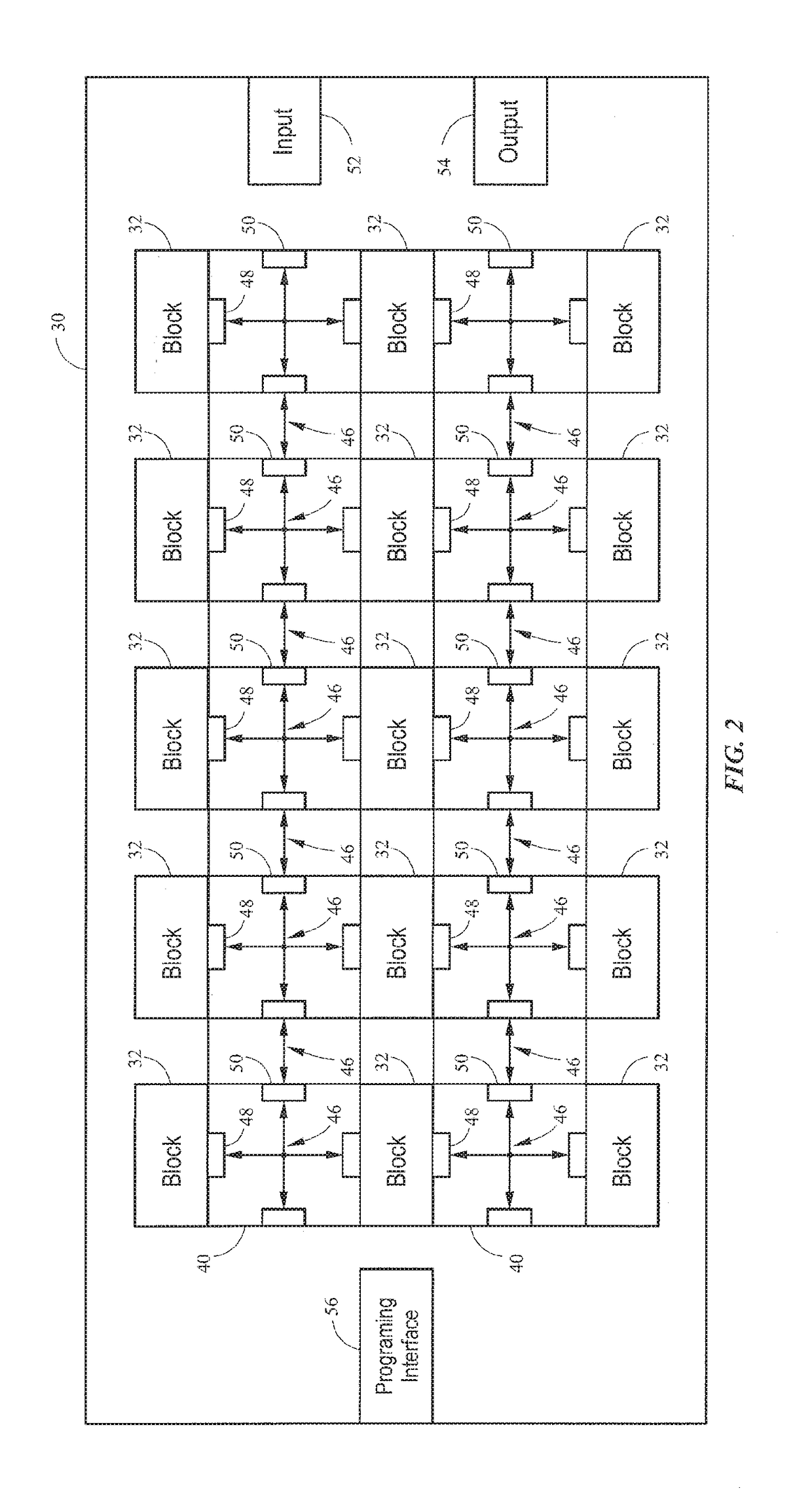

An apparatus includes a state machine engine. The state machine engine may also include an automaton, whereby the automaton is configured to analyze data from a beginning of an input data stream until a point when an end of data signal is seen. The automaton may further be configured to report an event representative of a satisfaction of a Boolean clause of a conjunctive normal form (CNF) Boolean expression representative of a Boolean Satisfiability problem (SAT) by a portion of the input data stream.

Owner:MICRON TECH INC

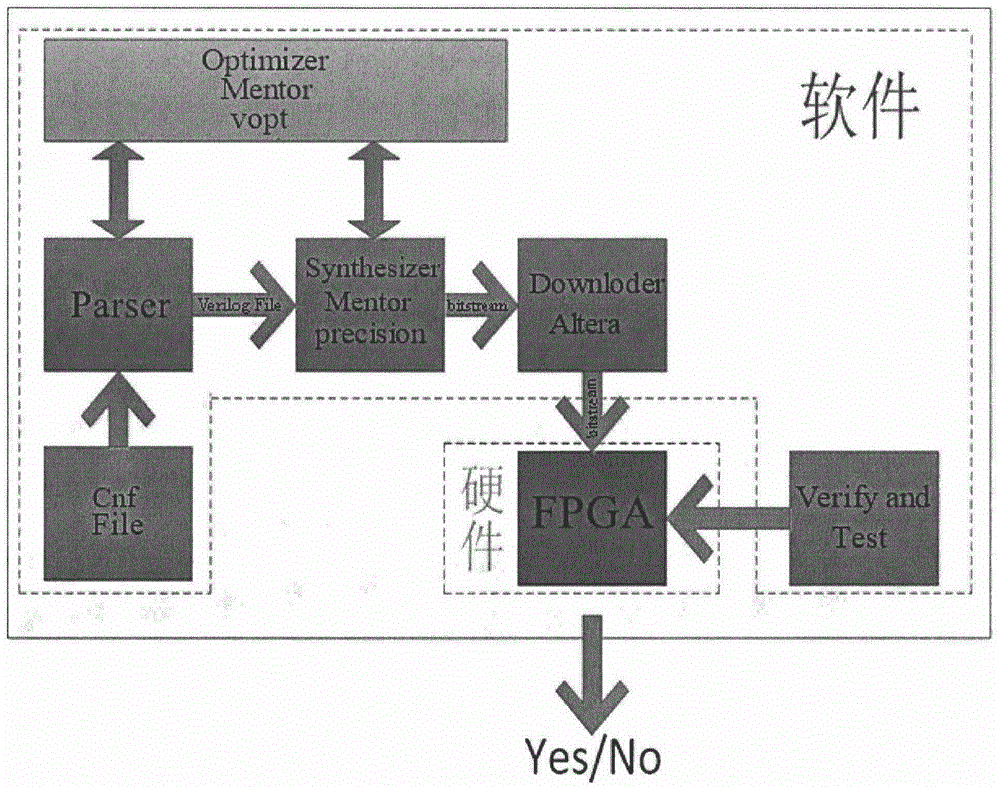

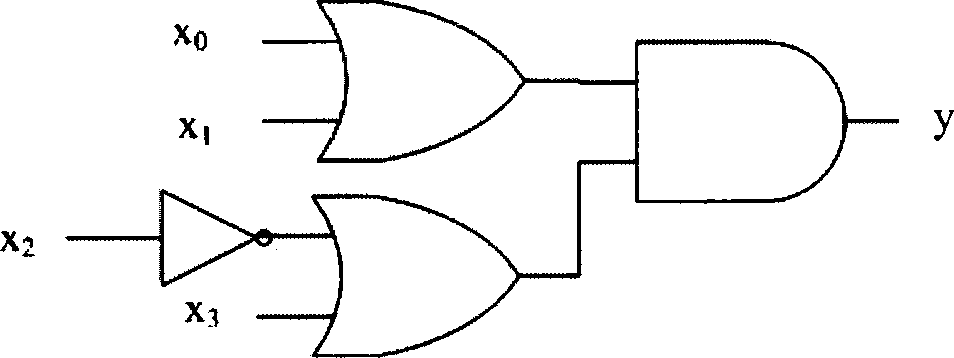

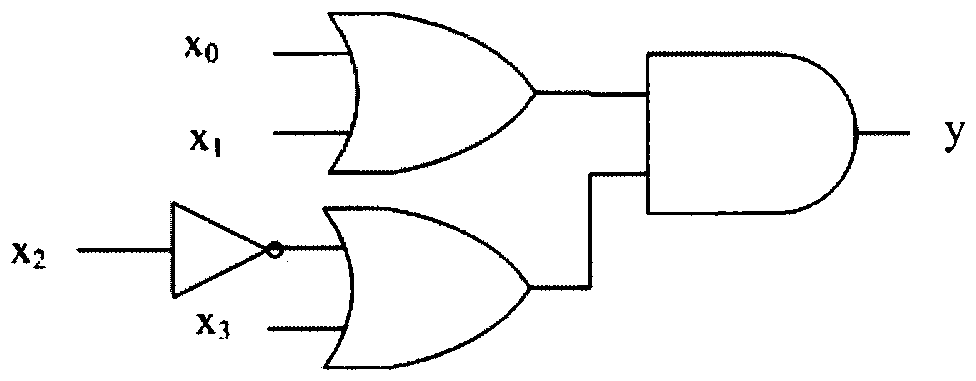

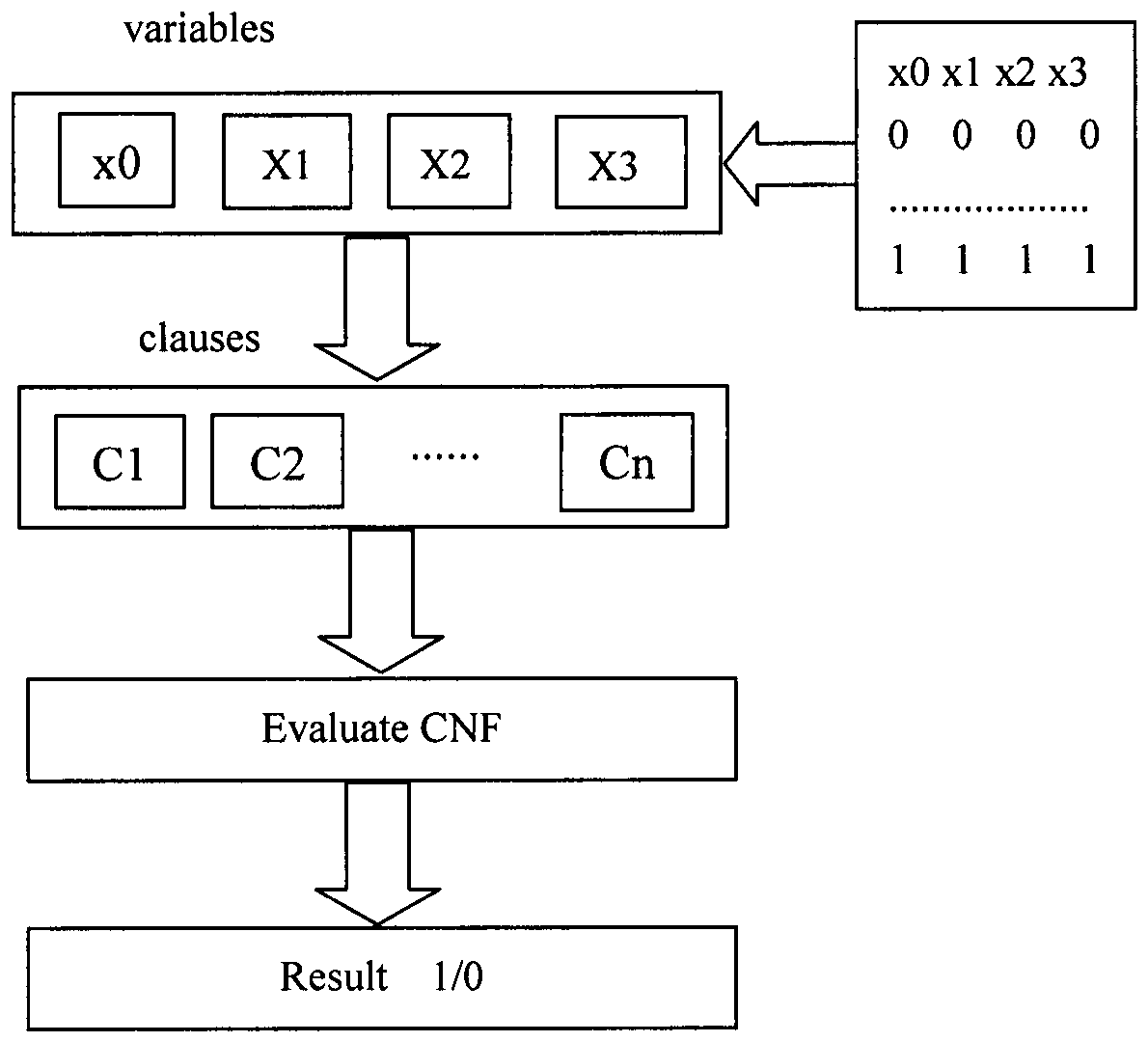

SAT automatic integrated solver based on FPGA

ActiveCN105740206AAccurate time calculationConvenient verificationProgram controlMemory systemsScripting languageFpga chip

The invention provides an SAT automatic integrated solver based on FPGA, which effectively judges that whether CNF can be met. Firstly, the CNF is automatically translated to the verilog language by a C++ translator, i.e. the conjunctive normal form is converted to the gate level circuit form; the gate level circuit is simulated via Questasim software, whether the simulation is the same with a theoretical logic is checked, then the circuit is optimized and synthesized via Precision software, at last QuartusII software integrated into the Precision software is called to perform pin configuration, thus the integrated file is finally downloaded onto the FPGA circuit board to be cured into the hardware logic for verification; and the cured FPGA chip is embedded into the embedded chip, the automation of the whole process for generating a file calling command is achieved through combined programming of the Tcl scripting language and high-level language C++, and thereby whether the CNF can be met is rapidly judged. The hardware compiling configuration time is added, and thereby the time of the whole process can be more accurately computed compared with other hardware SAT solvers.

Owner:何安平

Selecting a normalized form for conversion of a query expression

ActiveUS20210191942A1Digital data information retrievalSpecial data processing applicationsData transformationEngineering

A method for execution by a query processing module includes determining a query expression indicating a query for execution. An operator tree is generated based on a nested ordering of a plurality of operators indicated by the query expression. Conjunctive normal form (CNF) conversion cost data is generated based on the operator tree, and disjunctive normal form (DNF) conversion cost data is also generated based on the operator tree. Conversion selection data is generated based on the CNF conversion cost data and the DNF conversion cost data. The conversion selection data indicates a selection to perform either a CNF conversion or a DNF conversion. A normalized query expression is generated by performing either the CNF conversion or the DNF conversion upon the query expression based on the conversion selection data. Execution of the query is facilitated in accordance with the normalized query expression.

Owner:OCIENT HLDG LLC

System and method for packet forwarding using a conjunctive normal form strategy in a content-centric network

One embodiment of the present invention provides a system for forwarding packets with hierarchically structured variable-length identifiers (HSVLIs) in a content-centric network (CCN). During operation, the system receives a packet with an HSVLI and determines, based on the HSVLI, a plurality of ports to which the packet should be forwarded. The plurality of ports include a set of individual port groups, and a respective port group includes one or more individual physical ports. The system derives a forwarding strategy based on the set of individual port groups and the one or more individual physical ports. The forwarding strategy is expressed as a formula in conjunctive normal form that indicates a logical conjunction among the set of port groups and a logical disjunction among the one or more individual physical ports. The system then forwards the packet using the derived forwarding strategy.

Owner:CISCO TECH INC

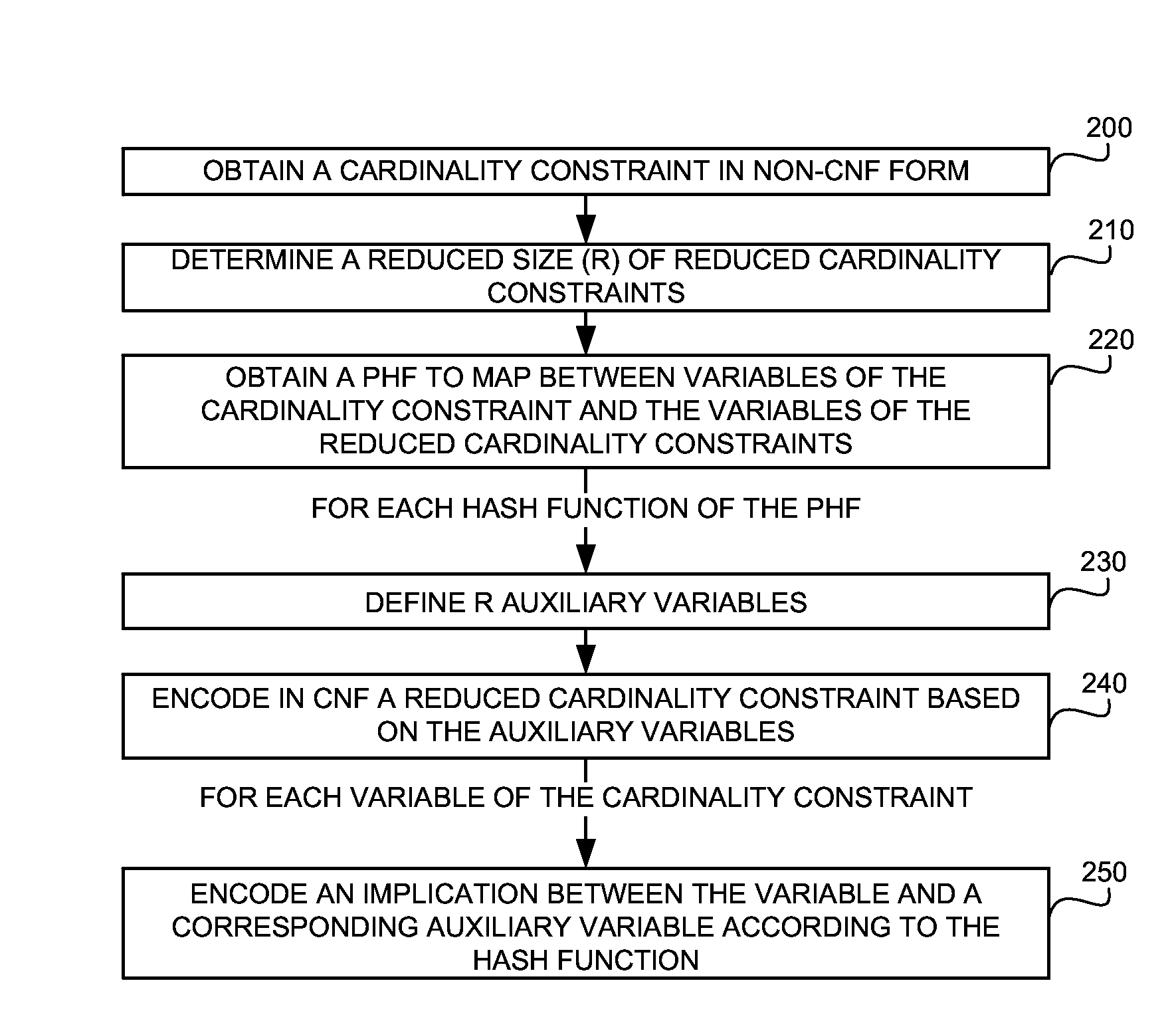

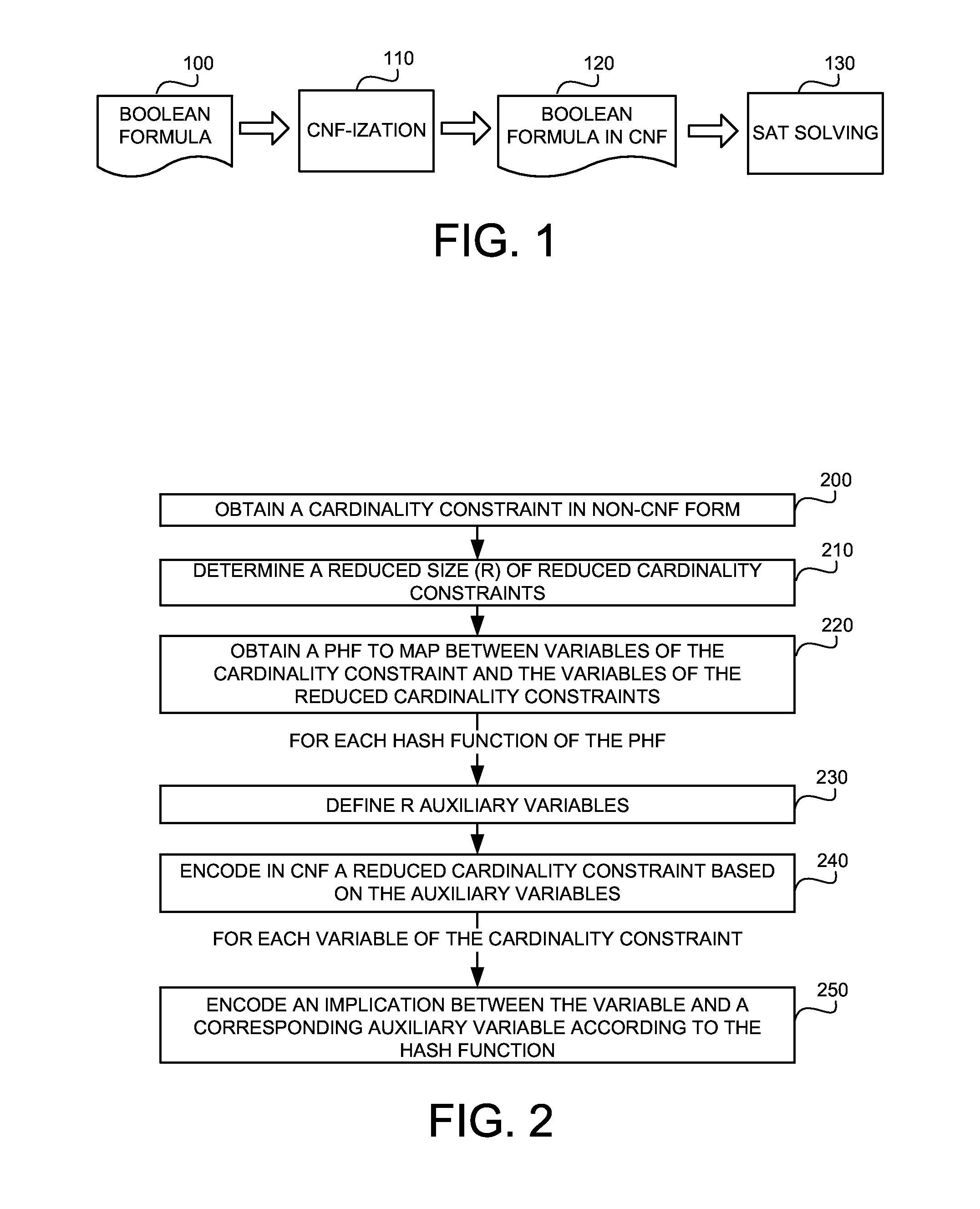

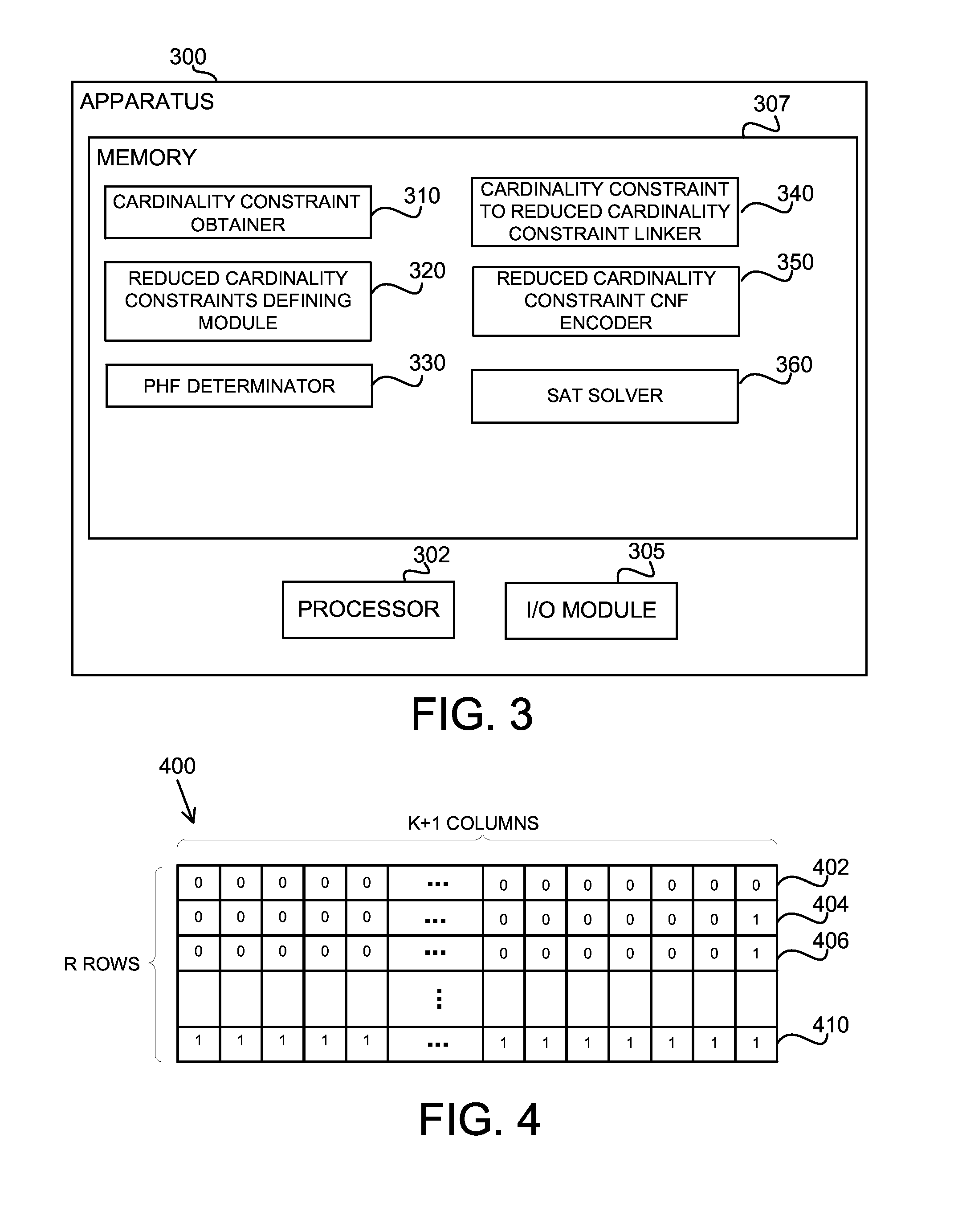

Conjunctive normal form encoding of cardinality constraints

InactiveUS20130325778A1Knowledge representationSpecial data processing applicationsConjunctive normal formBase Number

A method, apparatus and product for encoding a cardinality constraint in Conjunctive Normal Form (CNF). The method comprising: having a Boolean formula comprising a cardinality constraint, wherein the cardinality constraint relating to a set of Boolean variables, the set of variables consisting of N variables, the cardinality constraint given in a non-Conjunctive Normal Form; and encoding the cardinality constraint in Conjunctive Normal Form based on a mapping by a Perfect Hash Family, whereby said memory is modified to retain the CNF encoded cardinality constraint.

Owner:IBM CORP

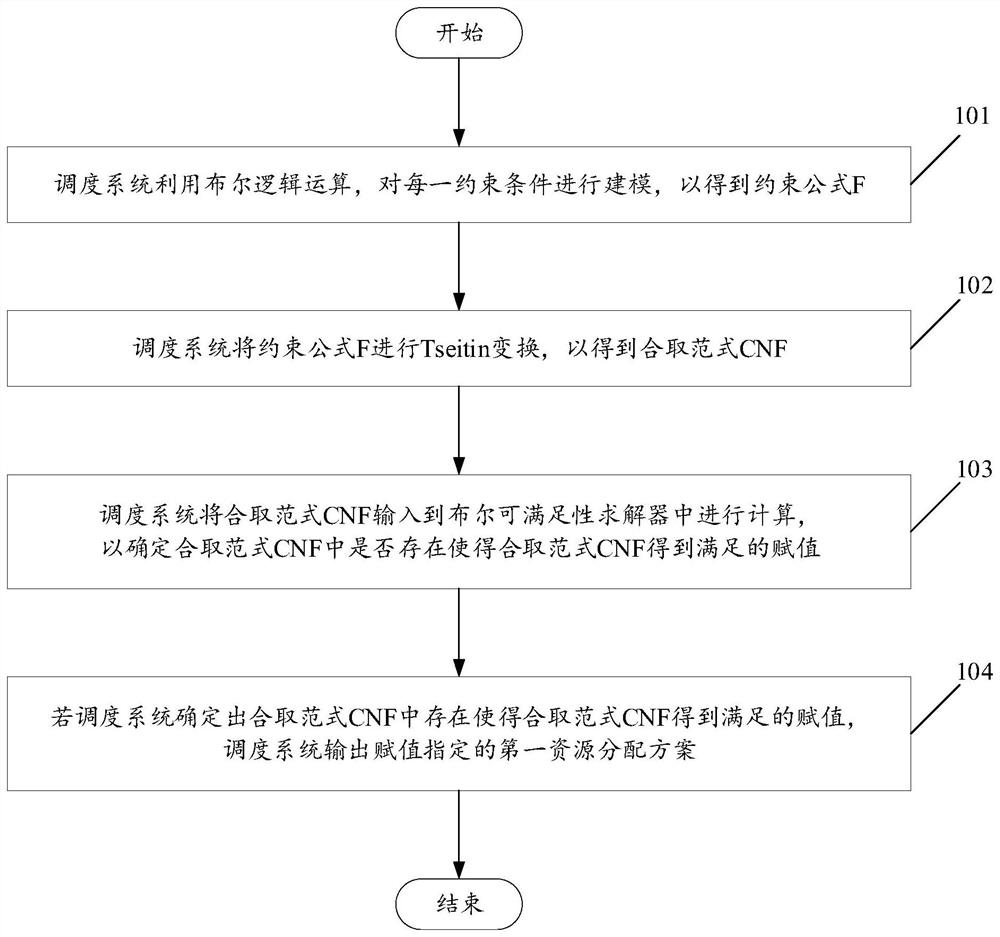

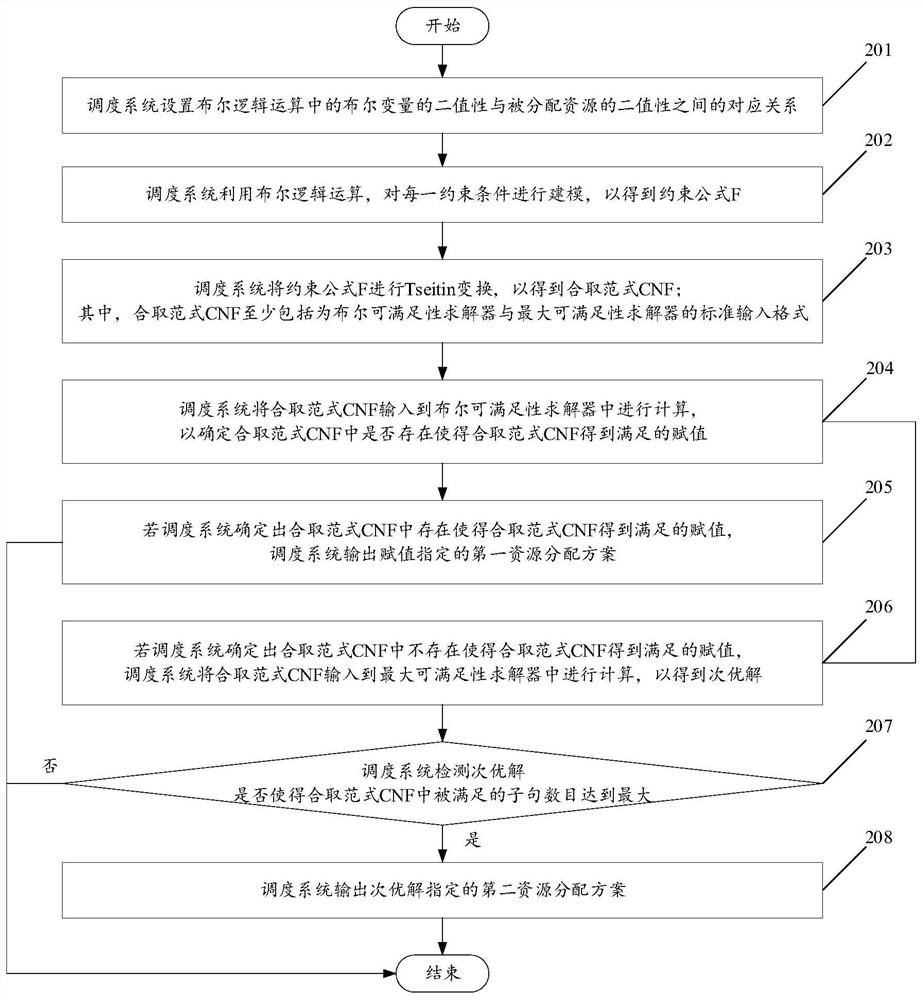

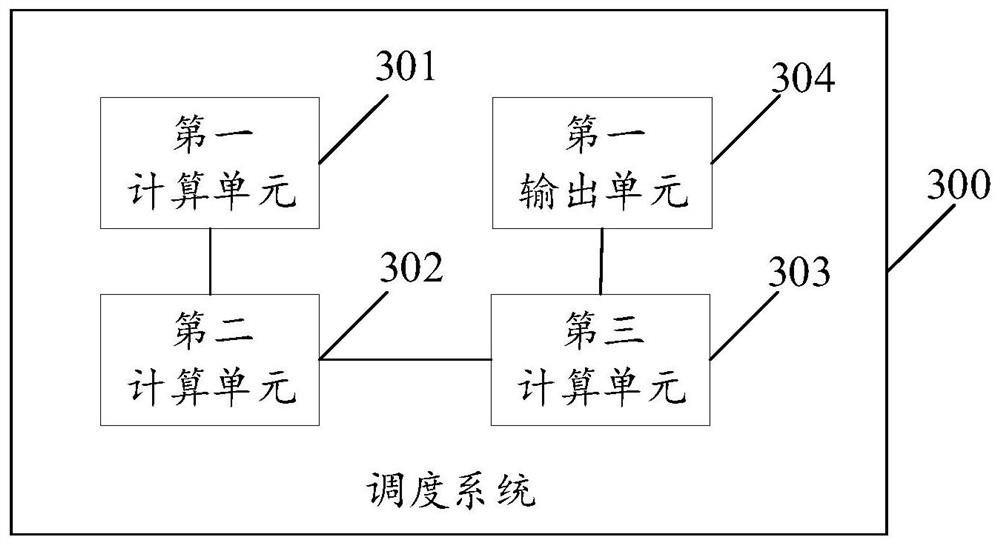

Intelligent scheduling method and scheduling system

PendingCN112951399AImprove quick responseIncrease resourcesDesign optimisation/simulationConstraint-based CADResource assignmentLogical operations

The embodiment of the invention relates to the technical field of artificial intelligence, and discloses an intelligent scheduling method and system. The method comprises the steps: carrying out the modeling of each constraint condition through Boolean logic operation, so as to obtain a constraint formula F; carrying out Tseitin transformation on the constraint formula F to obtain a conjunctive normal form CNF; inputting the conjunctive normal form CNF into a Boolean satisfiability solver for calculation, and determining whether an assignment which enables the conjunctive normal form CNF to be satisfied exists in the conjunctive normal form CNF or not; and if yes, outputting a first resource allocation scheme specified by the assignment. By implementing the method of the invention, the constraint conditions of the existing resources can be quickly modeled, and the resource allocation scheme meeting the constraint conditions is generated in real time, so that the quick response and first-aid resource scheduling capabilities of medical personnel in the emergency department are greatly improved, and more precious time is won for saving lives of patients.

Owner:广东医通软件有限公司

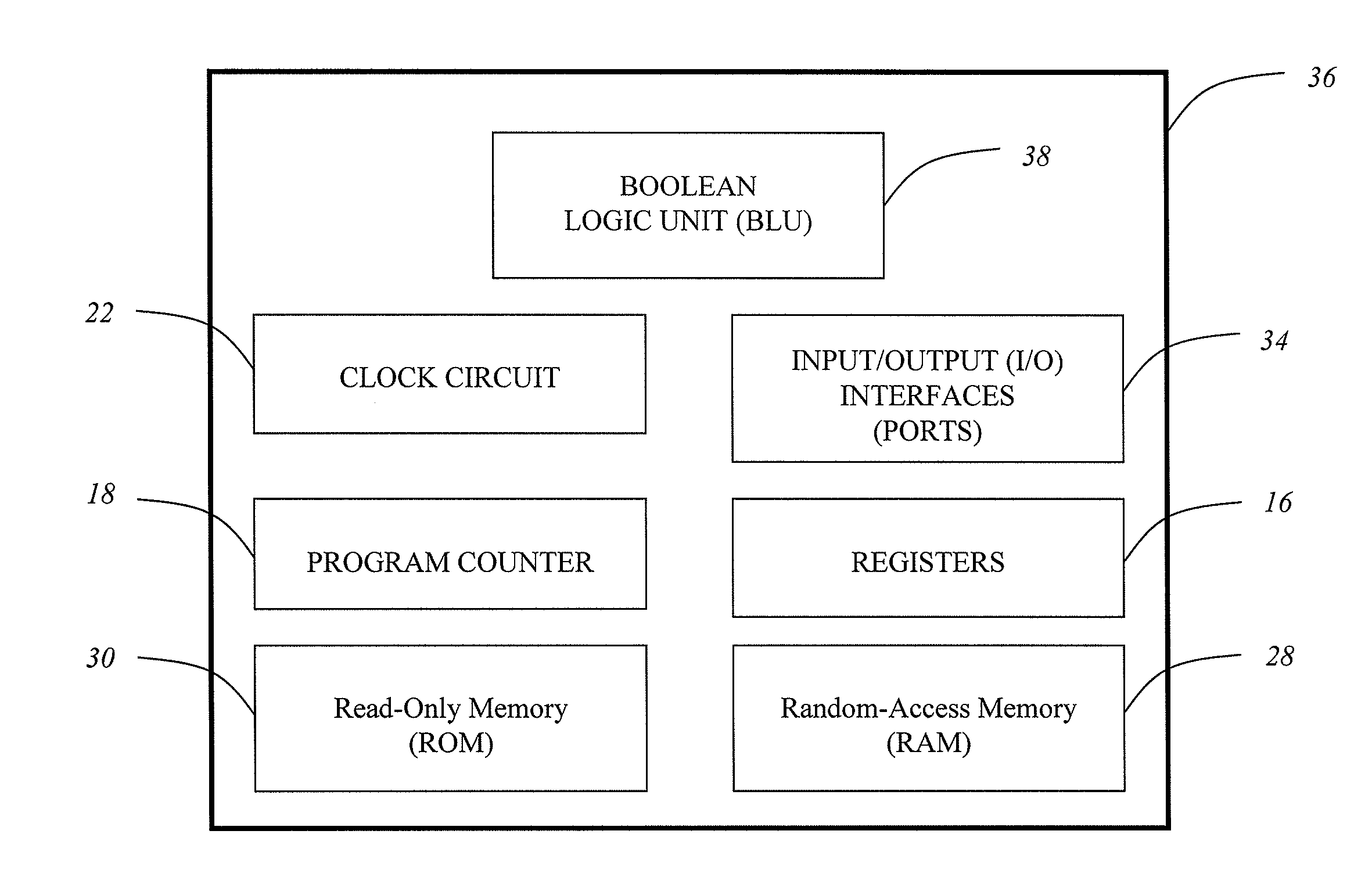

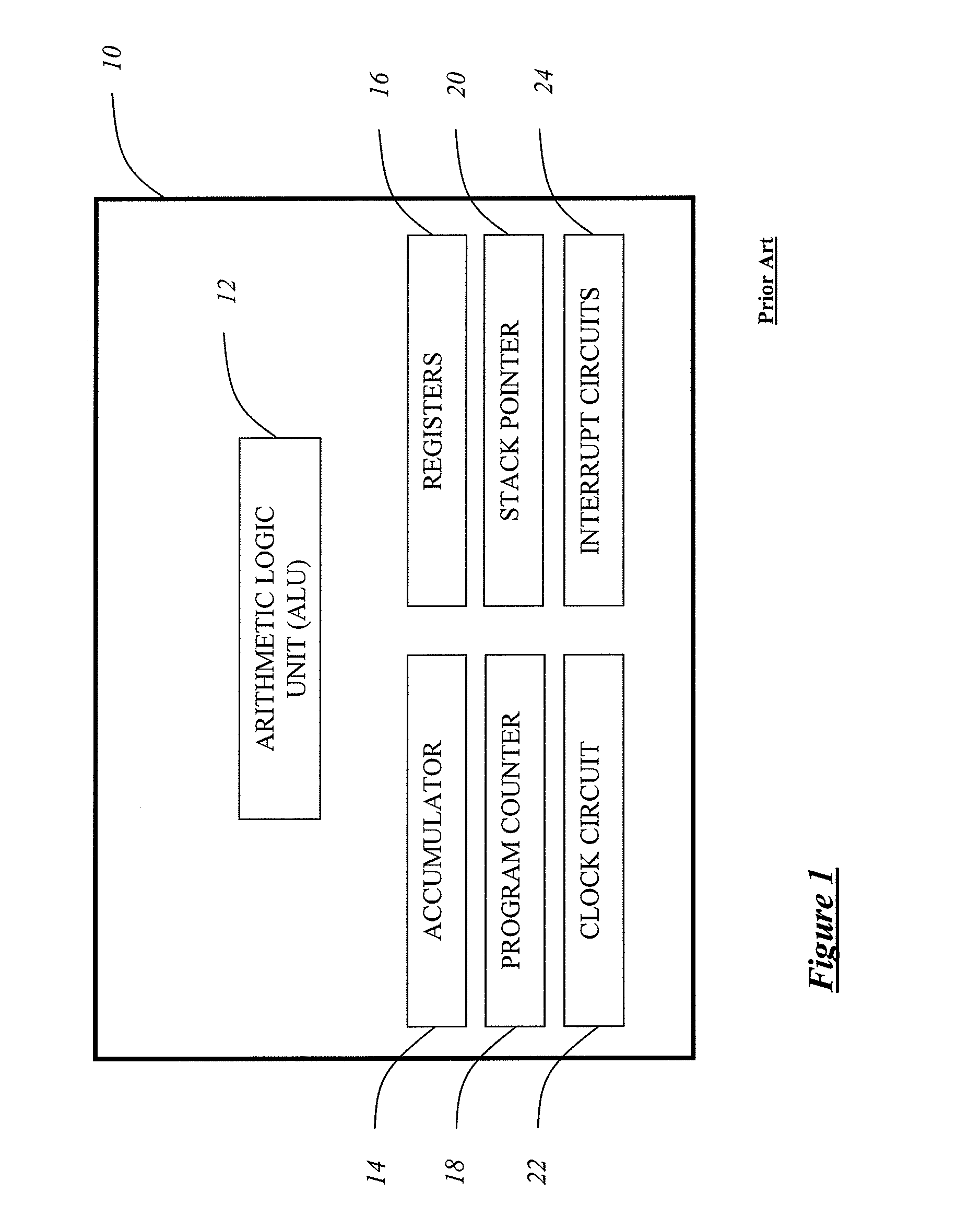

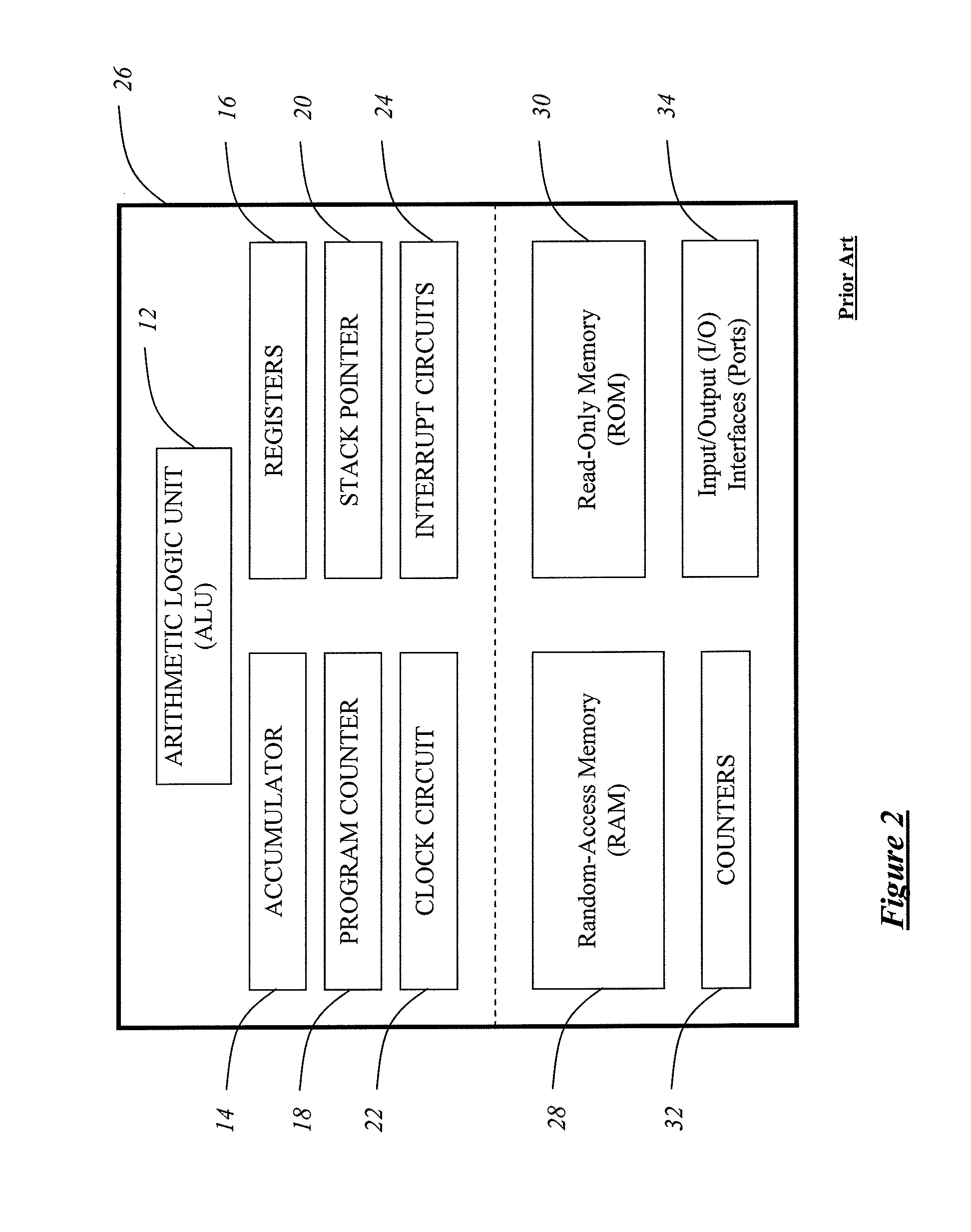

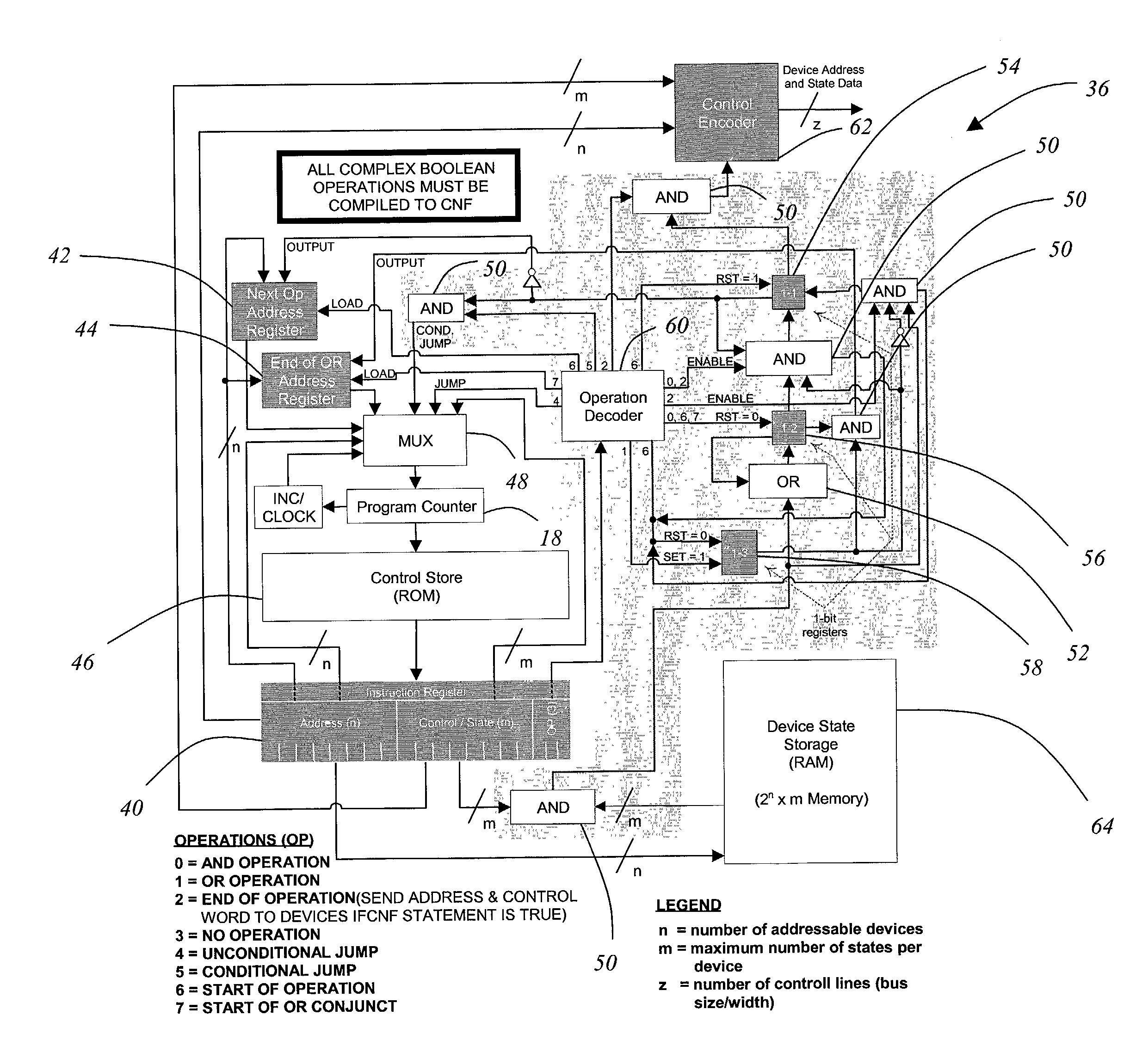

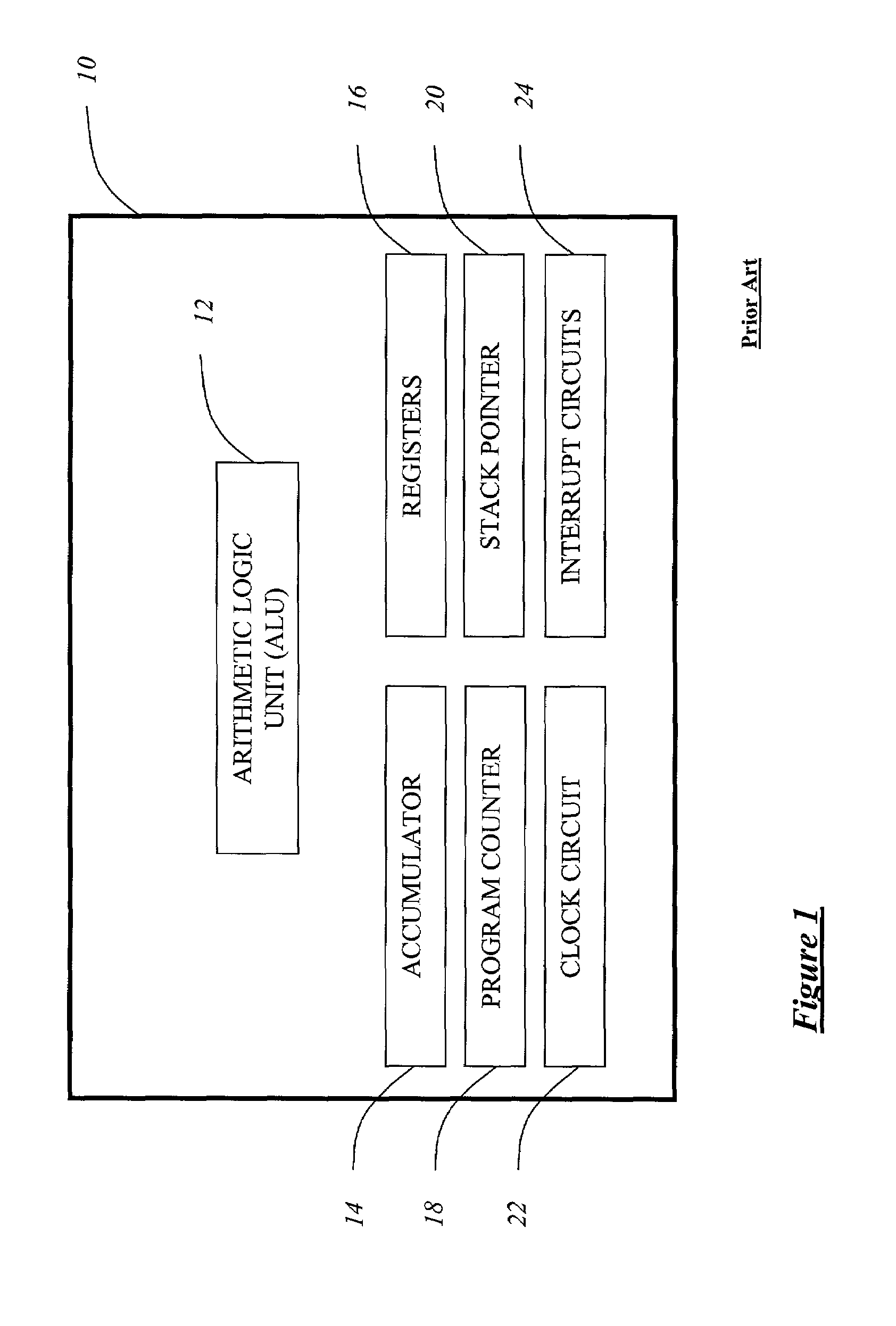

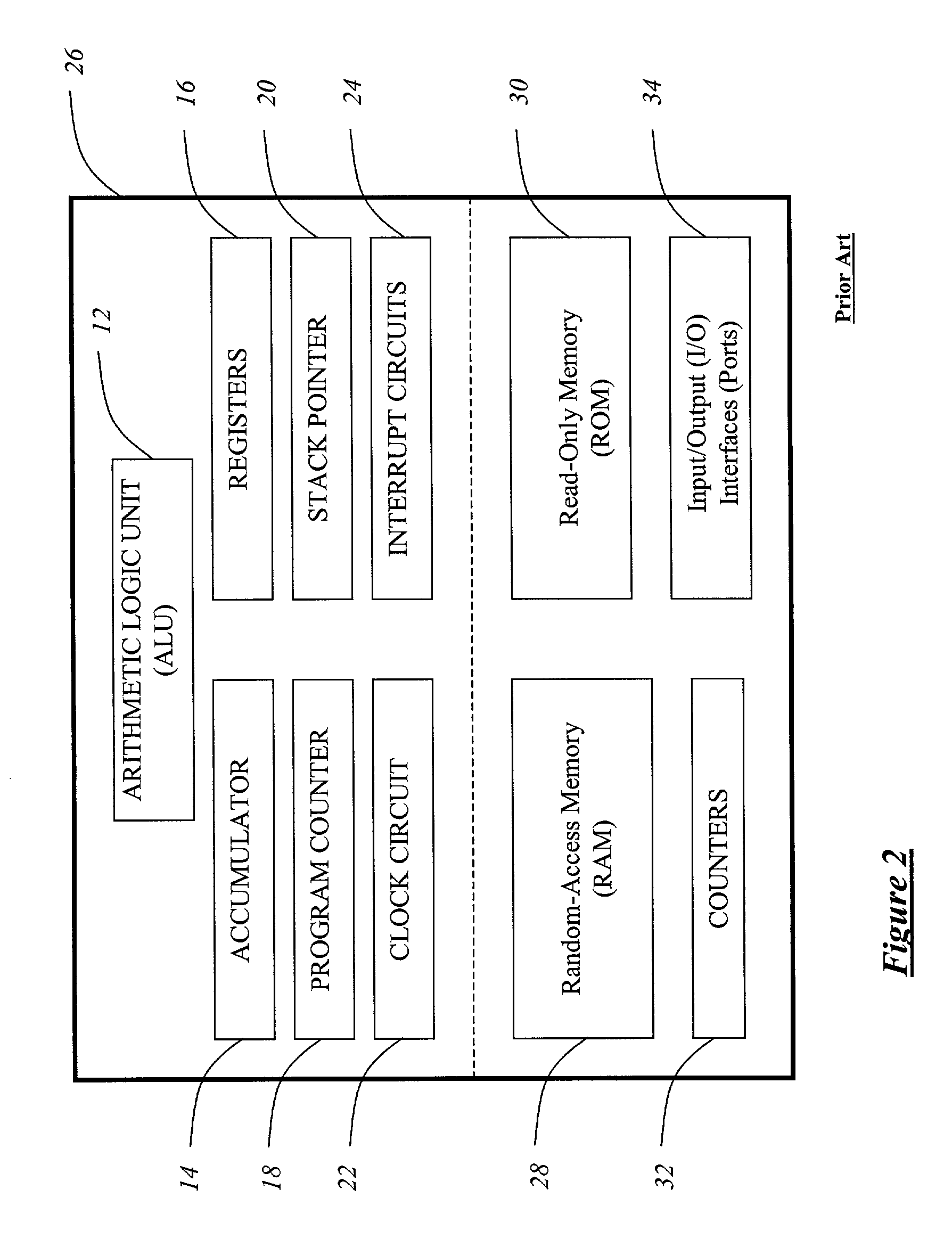

Boolean Processor

InactiveUS20080141007A1Improve performanceImprove computing powerDigital computer detailsSpecific program execution arrangementsLogic cellProcessor register

A processor including a Boolean logic unit, wherein the Boolean logic unit is operable for performing the short-circuit evaluation of Conjunctive Normal Form Boolean expressions / operations, a plurality of input / output interfaces, wherein the plurality of input / output interfaces are operable for receiving a plurality of compiled Boolean expressions / operations and transmitting a plurality of compiled results, and a plurality of registers. An associated processing method including starting an operation related to a Conjunctive Normal Form Boolean expression, wherein the Boolean expression comprises a conjunct, evaluating the conjunct, and selectively short-circuiting a portion of the Boolean expression.

Owner:JUNIVERSITI OF NORT KAROLINA EHT SHARLOTT

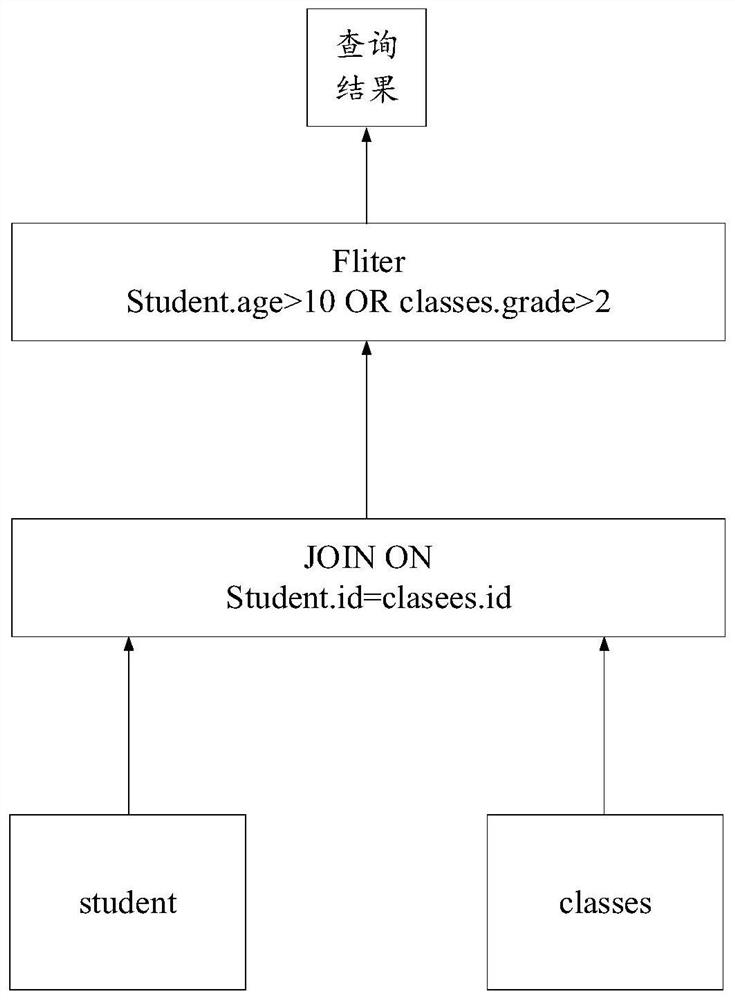

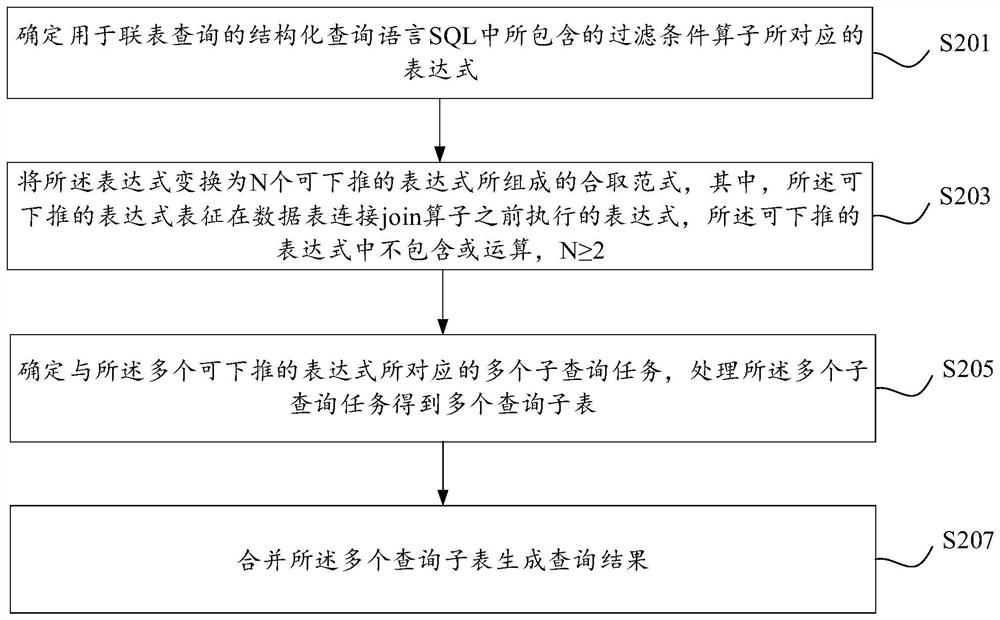

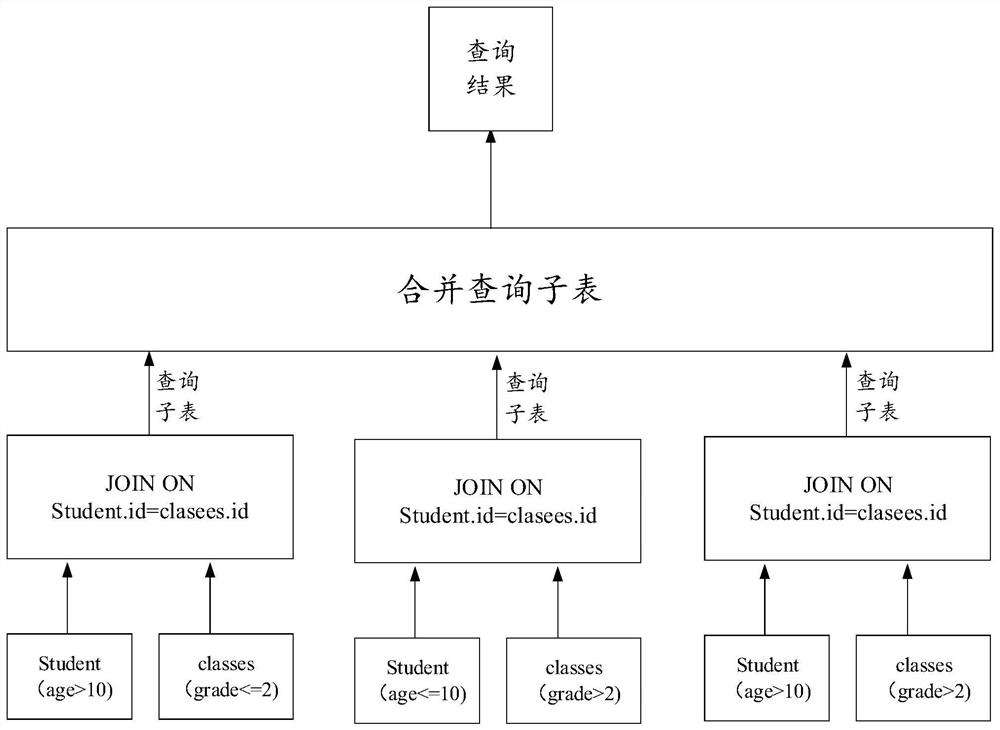

Data processing method and device, electronic equipment and computer storage medium

PendingCN113420023AAvoid full table scanReduce overheadSpecial data processing applicationsDatabase indexingComputer hardwareDatasheet

The embodiment of the invention provides a data processing method and device, electronic equipment and a computer storage medium. According to the scheme provided by the embodiment of the invention, during linked table query, a filtering condition operator of linked table query is converted into a conjunctive normal form composed of N expressions capable of being pushed down, and the expressions capable of being pushed down represent expressions executed before a data table is connected with a join operator. According to the N sub-query tasks corresponding to the N expressions capable of being pushed down, the N sub-query tasks are processed to obtain N query sub-tables; and the N query sub-tables are combined to generate a query result. Through equivalent conversion of the expression of the filtering condition operator, filtering is executed before data table connection, full table scanning is avoided, data scanning overhead is greatly reduced, and query time is shortened.

Owner:ALIBABA GRP HLDG LTD

Boolean processor

InactiveUS7360066B2Improve performanceImprove computing powerDigital computer detailsProgram loading/initiatingProcessor registerLogic cell

A processor including a Boolean logic unit, wherein the Boolean logic unit is operable for performing the short-circuit evaluation of Conjunctive Normal Form Boolean expressions / operations, a plurality of input / output interfaces, wherein the plurality of input / output interfaces are operable for receiving a plurality of compiled Boolean expressions / operations and transmitting a plurality of compiled results, and a plurality of registers. An associated processing method including starting an operation related to a Conjunctive Normal Form Boolean expression, wherein the Boolean expression comprises a conjunct, evaluating the conjunct, and selectively short-circuiting a portion of the Boolean expression.

Owner:JUNIVERSITI OF NORT KAROLINA EHT SHARLOTT

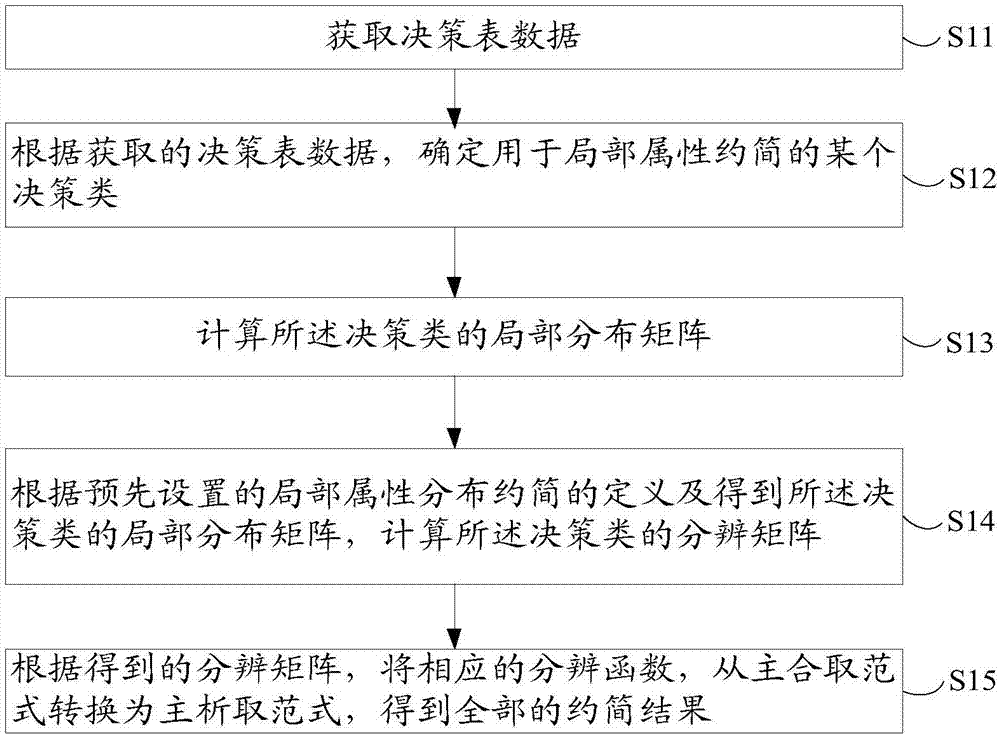

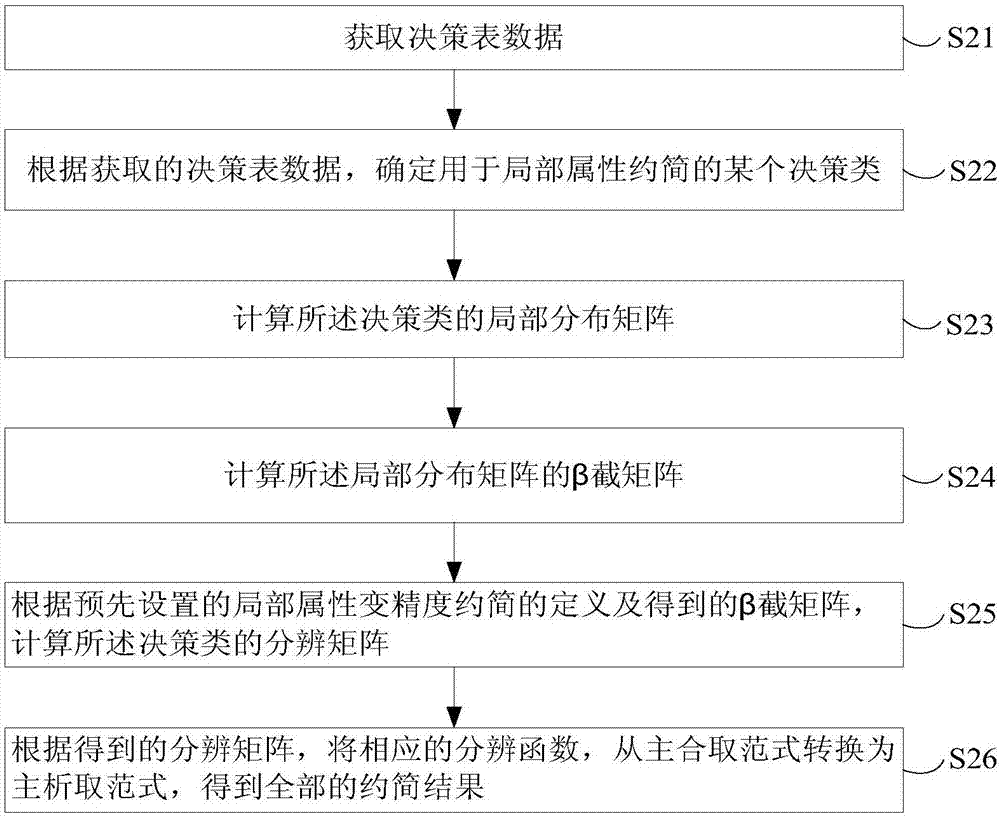

Distribution and variable precision local reduction method of decision table

InactiveCN107544945ALocal attribute reductionReduce computational complexityComplex mathematical operationsDistribution matrixComputation complexity

The invention provides a distribution and variable precision local reduction method of a decision table. The method can conduct attribute reduction on a certain decision class of the decision table and lower the calculation complexity at the same time. The variable precision local reduction method comprises the steps that a certain decision class used for local attribute reduction is determined through acquired decision table data; a local distribution matrix of the decision class is calculated; a beta cutest matrix of the local distribution matrix is calculated; according to preset definitionof local attribute variable precision reduction and the obtained beta cutest matrix, a discernable matrix of the decision class is calculated; according to the obtained discernable matrix, a corresponding discernable function is converted into a principal disjunctive normal form from a principal conjunctive normal form, and all reduction results are obtained. The distribution and variable precision local reduction method of the decision table is suitable for attribute reduction of rough sets.

Owner:BEIJING LANGUAGE AND CULTURE UNIVERSITY

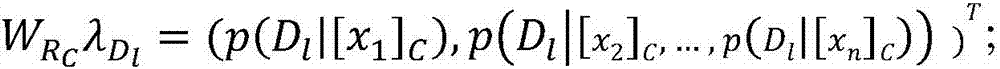

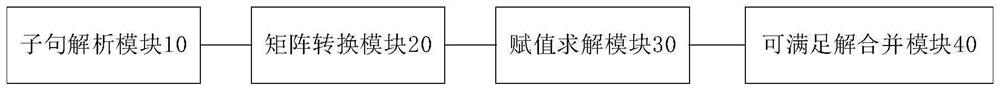

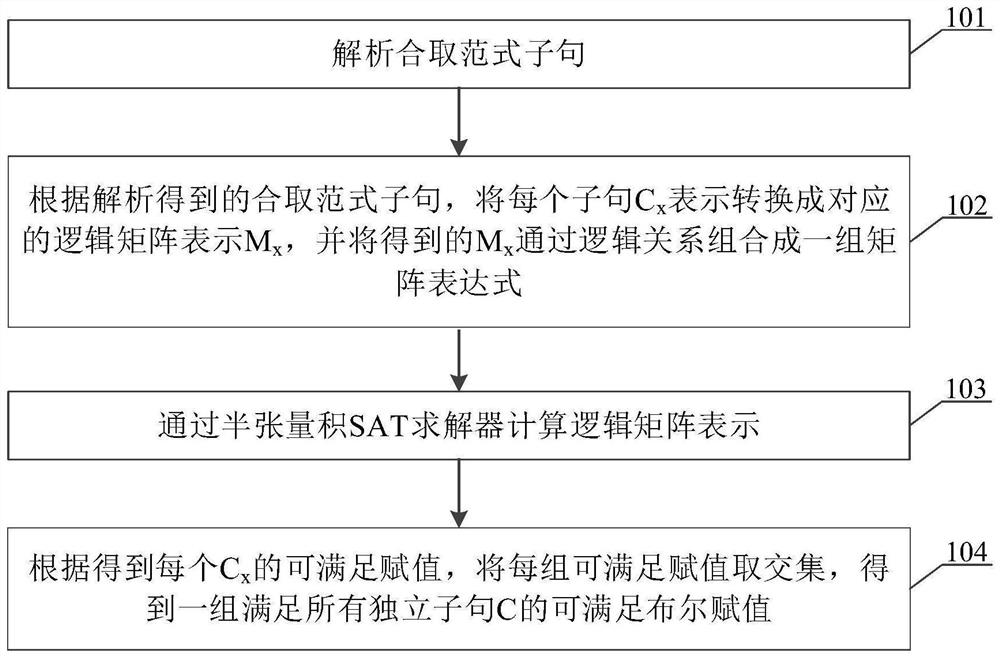

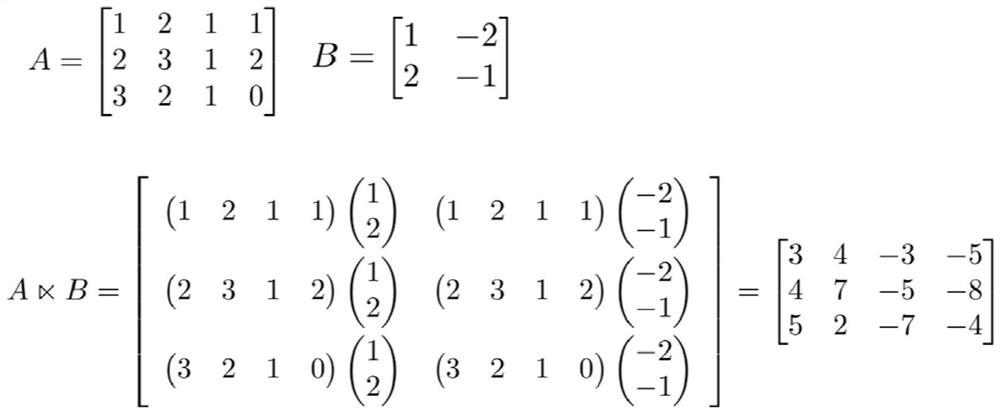

Half tensor product SAT solving method and device based on conjunctive normal form

PendingCN114722748AOptimizing Time AccuracyImprove calculation accuracyComputer aided designComplex mathematical operationsComputational logicMatrix expression

A semi-tensor product SAT solving method based on a conjunctive normal form comprises the steps that a conjunctive normal form clause is analyzed; according to the combined normal form clauses obtained through analysis, converting each clause Cx representation into a corresponding logic matrix representation Mx, and combining the obtained Mx into a group of matrix expressions through a logic relationship; solving and calculating a logic matrix representation according to a semi-tensor product SAT; and according to the satisfactory assignment of each Cx, obtaining an intersection of each group of satisfactory assignments to obtain a group of satisfactory Boolean assignments satisfying all the independent clauses C. According to the semi-tensor product SAT solving method and device based on the conjunctive normal form, the calculation time can be shortened, the calculation efficiency can be improved, and the compactness of the satisfactory solution can be improved.

Owner:上海华大九天信息科技有限公司

SAT solver based on interpretation and truth table analysis

ActiveUS11232174B1Reduce overheadPerformanceComputation using non-contact making devicesCAD circuit designConjunctive normal formTruth table

Techniques and systems for solving Boolean satisfiability (SAT) problems are described. Some embodiments solve SAT problems using efficient construction of truth tables. Some embodiments can improve performance of SAT solvers by using truth tables instead of incurring the overhead of Conjunctive Normal Form (CNF) conversion.

Owner:SYNOPSYS INC

Branch heuristic calculation optimization method, SAT solver and storage medium

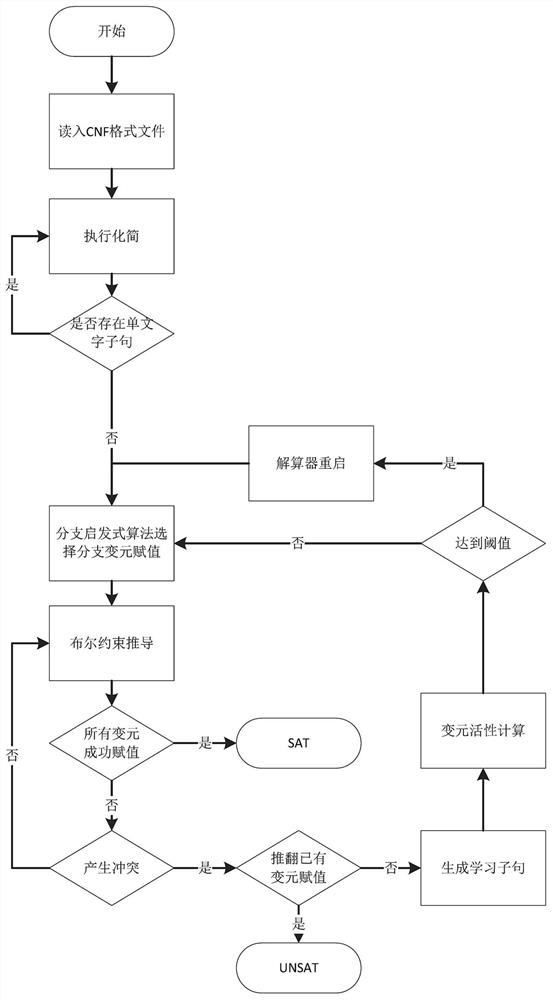

PendingCN113919316ASmall scaleAvoid Larger ProblemsNatural language data processingConjunctive normal formComputer engineering

The invention discloses a branch heuristic calculation optimization method, an SAT solver and a storage medium. The branch heuristic calculation optimization method comprises the following steps: when a conjunctive normal form instance is preprocessed, performing cyclic simplification on the conjunctive normal form instance until a single-character clause does not exist in the conjunctive normal form instance; and in the process of calculating the pre-processed conjunctive normal form instance by adopting a branch heuristic algorithm, when the variable activity is calculated after each conflict occurs, adding the length of the clause with the current conflict into the calculation of the variable activity so as to realize the preferential solution of the long clause. According to the method, branch heuristic calculation is optimized in multiple aspects, and the resolving speed of the SAT resolver is increased.

Owner:深圳国微福芯技术有限公司

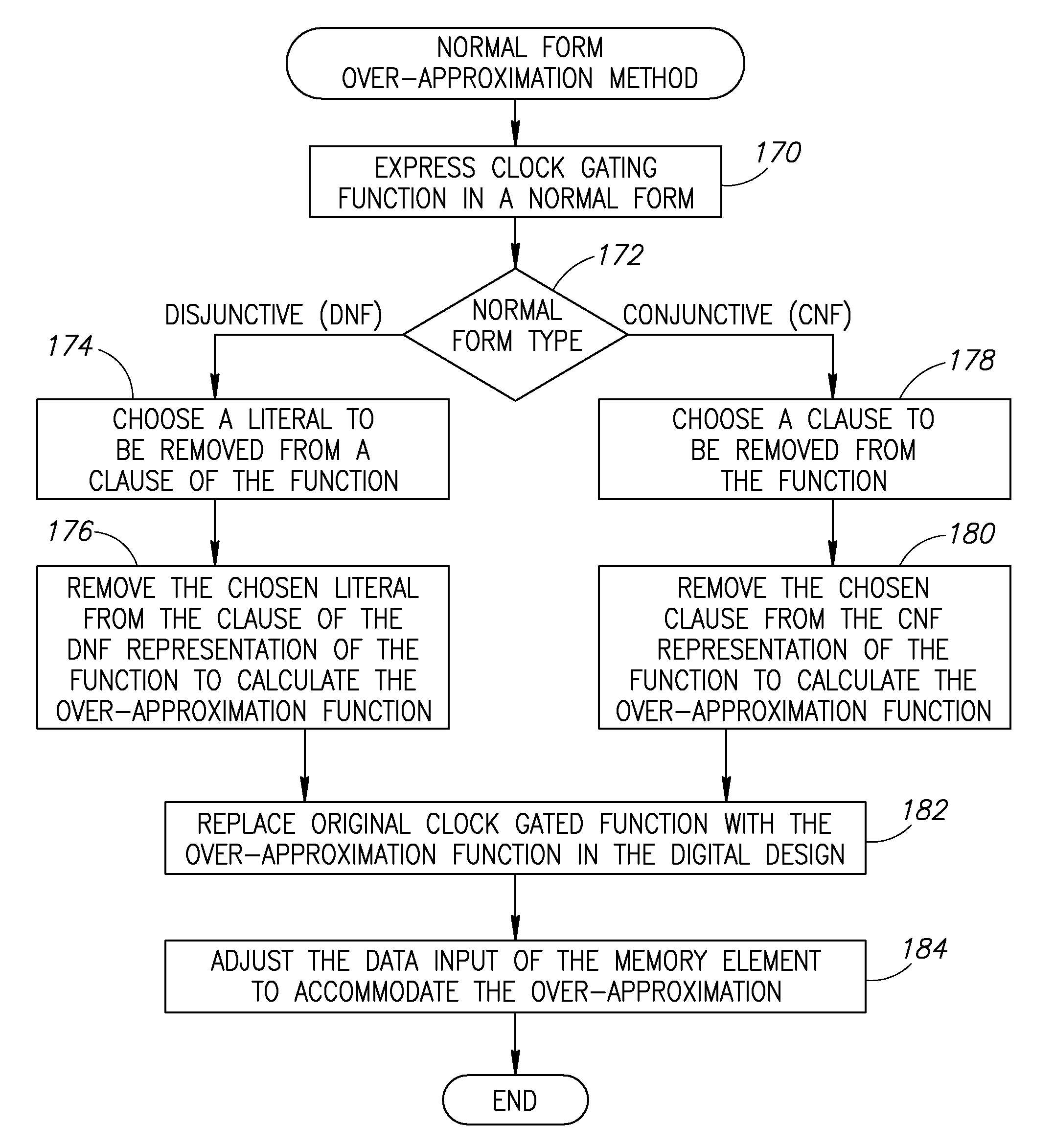

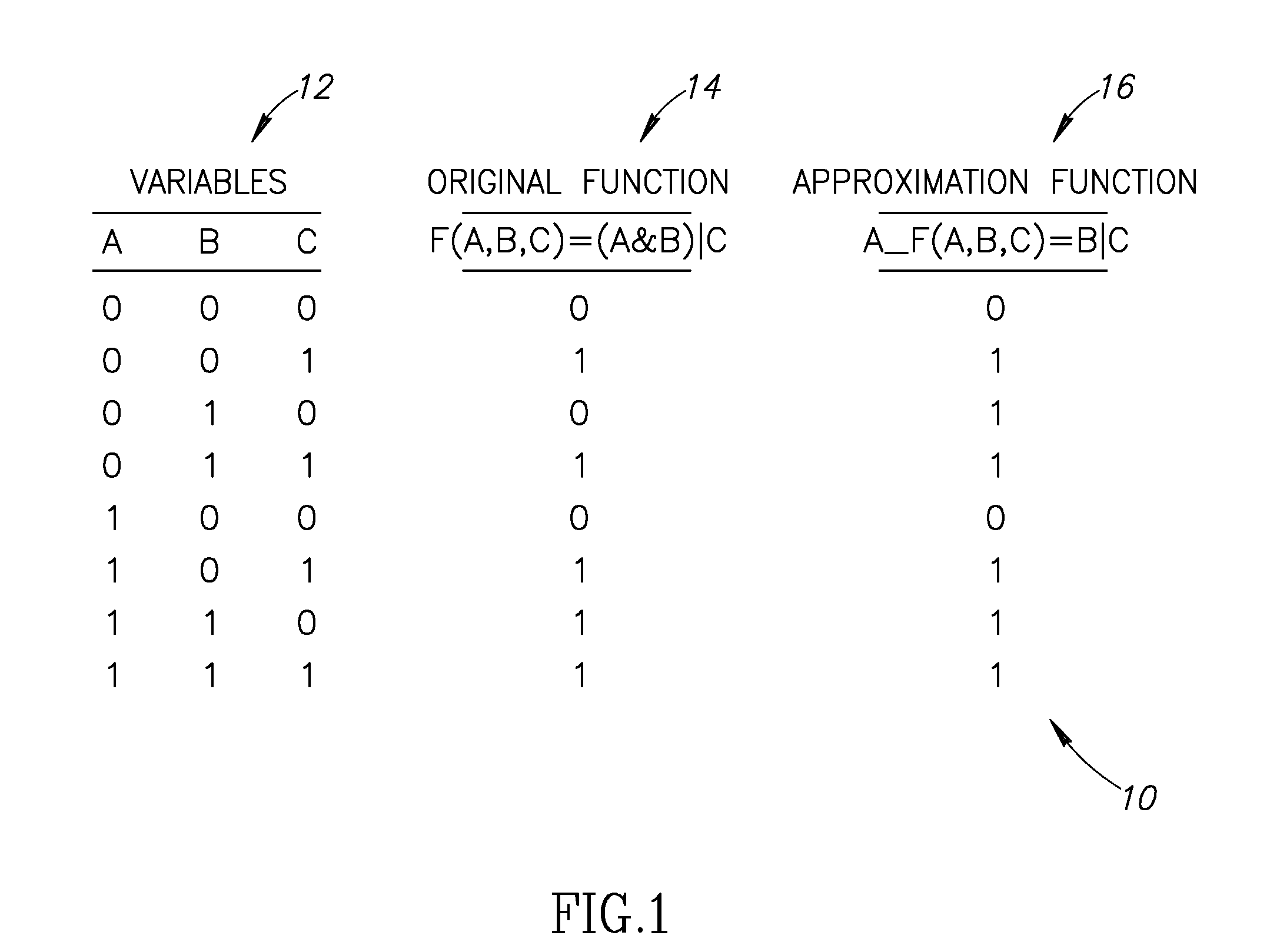

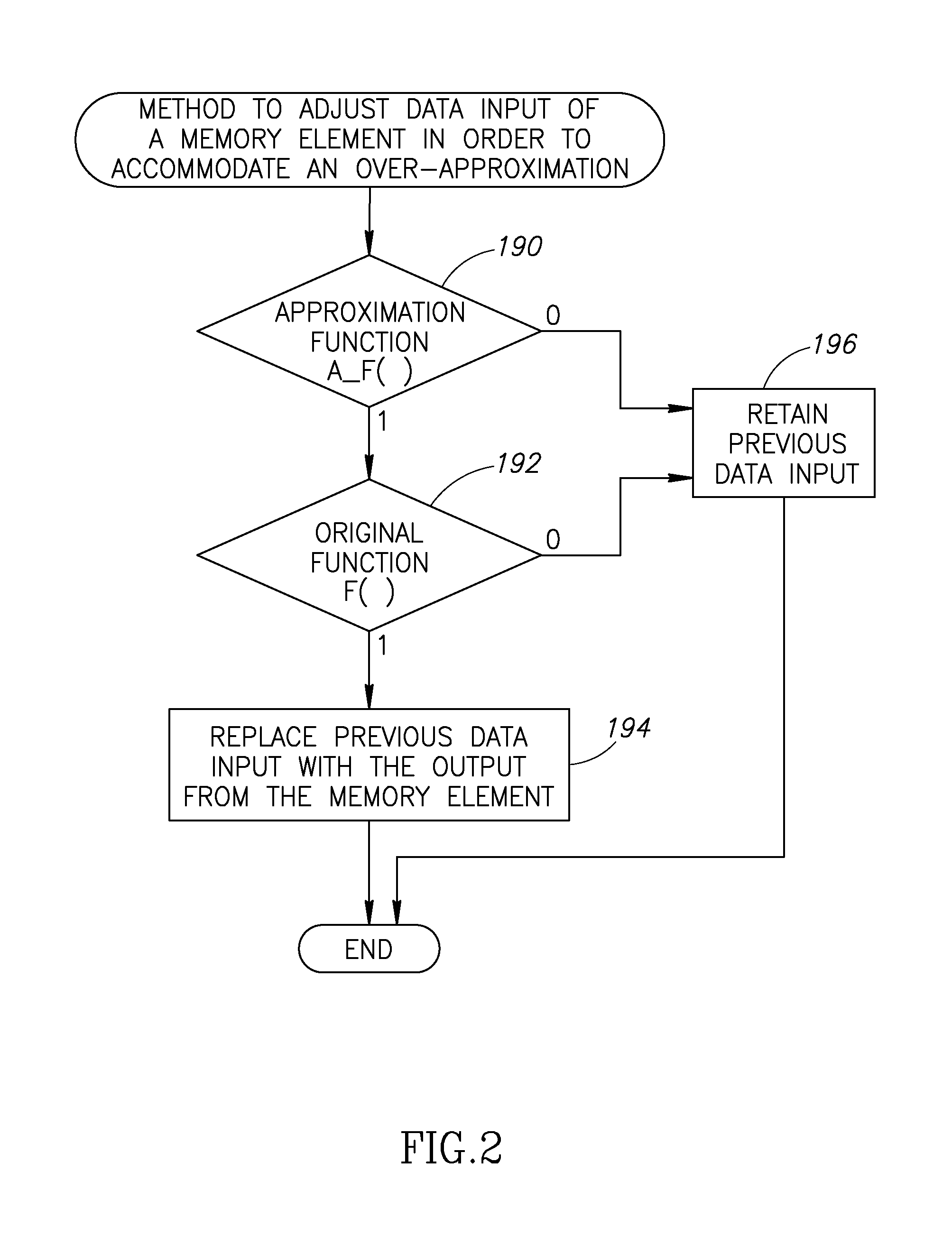

Over approximation of integrated circuit based clock gating logic

InactiveUS20090044154A1Small sizeSolve the real problemCAD circuit designSpecial data processing applicationsApproximation functionIntegrated circuit layout

A novel method for optimizing the implementation of clock gating logic in digital circuits utilizing clock gating. The method over-approximates the clock gating function by removing the variable with the least influence on the resulting approximation function. Approximations of clock gating functions expressed in normal form are performed by removing an appropriate component from the function. Approximations of clock gating functions expressed in conjunctive normal form are performed by removing a clause from the function. Approximations of clock gating functions expressed in disjunctive normal form are performed by removing a literal from a clause in the function.

Owner:LINKEDIN

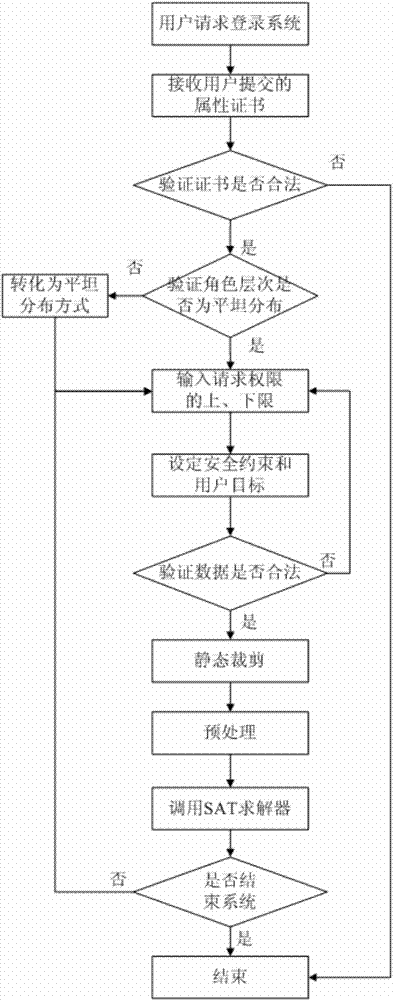

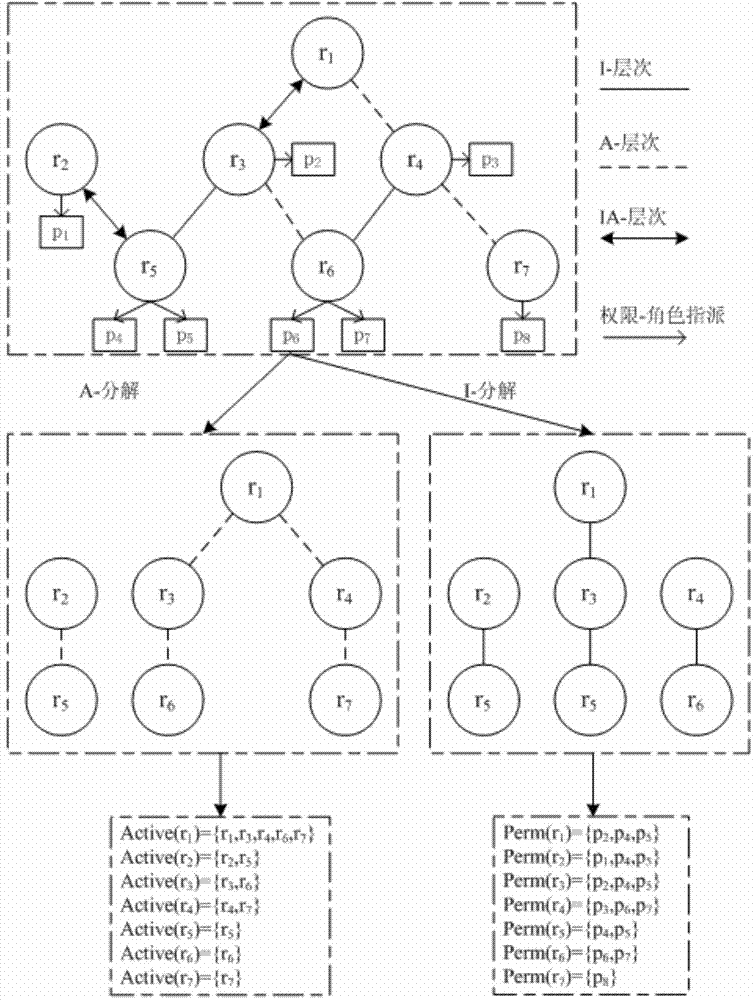

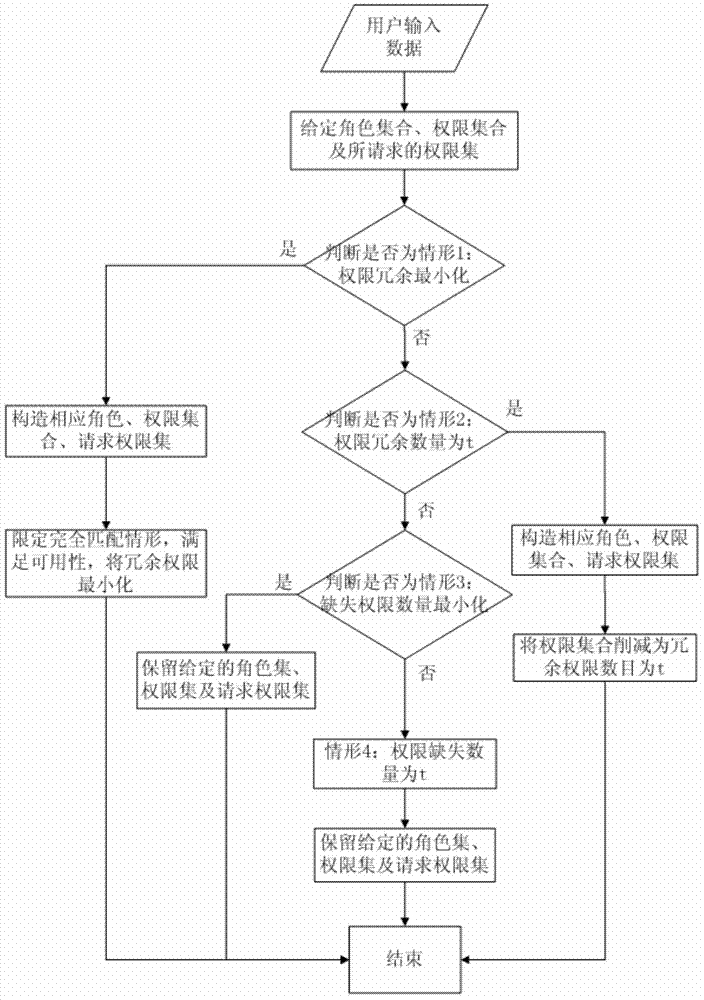

Fast solution method for user authority inquiry request problems of access control system

InactiveCN104504317AIncrease flexibilityEnsure safetyDigital data authenticationControl systemMedia access control

The invention provides a fast solution method for user authority query request problems of an access control system, which is applied to the field of access control. The fast solution method comprises the following steps of introducing zchaff into a RBAC (role-based access control) system; firstly, reducing the scale of the to-be-considered request authority through static clipping; then, reducing the number of roles not containing the request authority through preprocessing; finally, converting the problem, the RBA (role-based access) system state and the safety constraints into a conjunctive normal form, and calling a SAT (satisfiability) solver zchaff, so as to obtain the high-efficiency computation efficiency. The quick solving method has the advantages that under the condition of existing RBAC system state, the high solving efficiency is provided for the user authority query request problem, the security is guaranteed, and the extendibility is better.

Owner:ZHEJIANG NORMAL UNIVERSITY

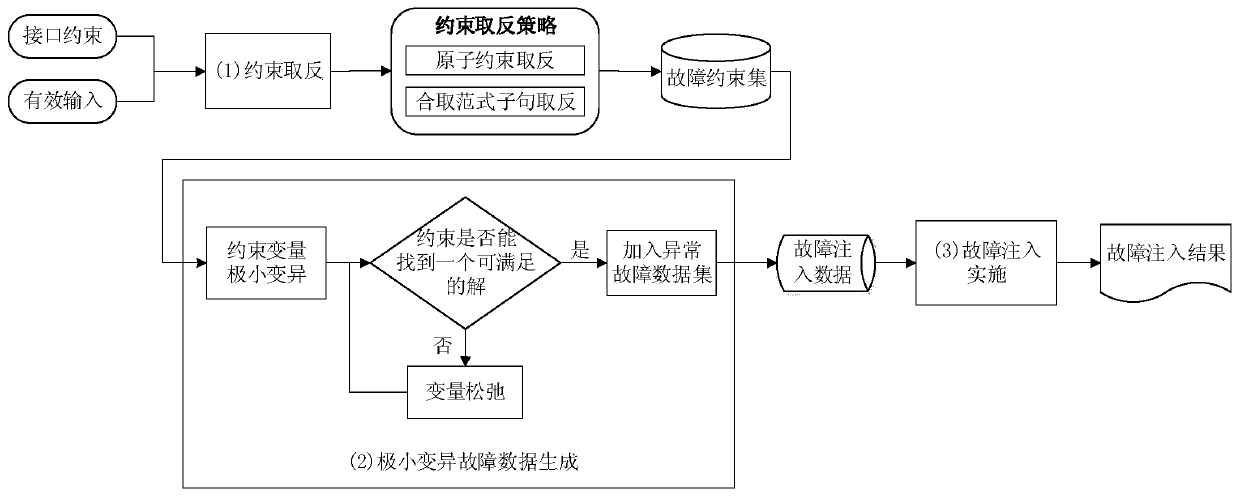

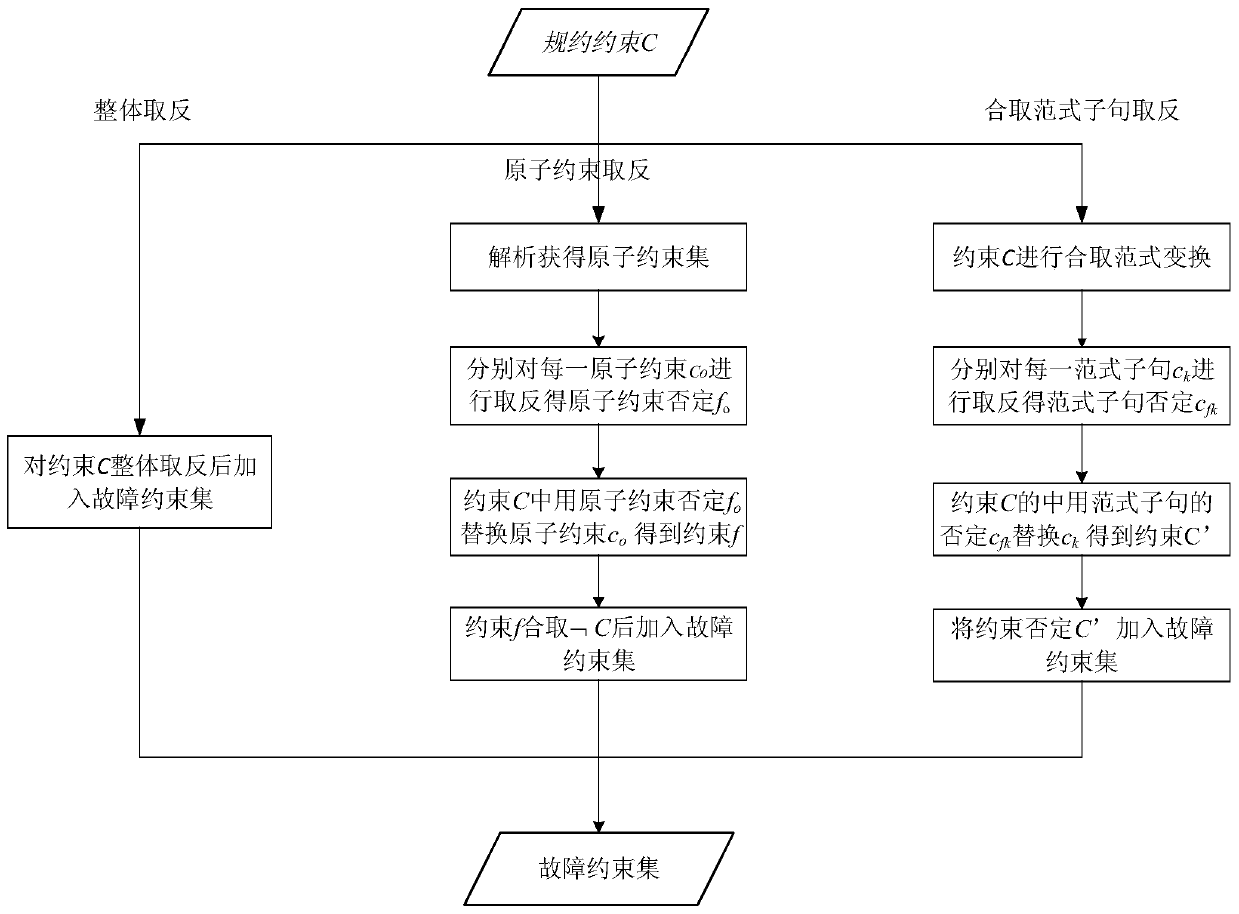

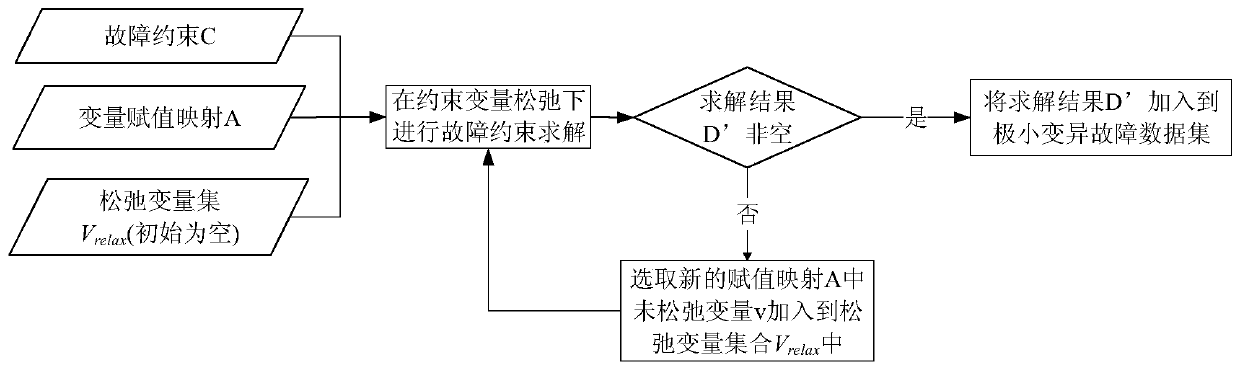

A Constraint-Based System Fault Injection Method

ActiveCN108733528BHigh fault injection test coverageDetection fault toleranceFunctional testingTest inputSlack variable

The invention discloses a constraint-based system fault injecting method. The method comprises the steps of: classifying constraints into atomic condition and conjunction normal form clause levels according to atomic condition inversion and the conjunction normal form clause inversion strategies and solving a group of negative forms of the specification constraints at the levels to serve as basesof generating fault data; replacing constraint variables in the inverted constraints with normal input combinations, gradually carrying out slack replacement on the constraint variables and finding minimum-variation fault data which have the least number of slack variables and are closest to a real situation through a constraint solving operation; carrying out faulty injection on a to-be-tested system by taking the minimum-variation fault data as test inputs to obtain fault injecting results. The method disclosed by the invention has the beneficial effects that by adopting a new fault injecting technology, the more real and more sufficient fault data are generated; the error detecting capability of the fault injection is strengthened; and faults close to the normal state are also beneficial for a tester to repair and eliminate the defects at the same time.

Owner:NANJING UNIV OF AERONAUTICS & ASTRONAUTICS

FPGA-based sat automatic integrated solver

ActiveCN105740206BConvenient verificationComplex mathematical operationsCode compilationScripting languageSoftware engineering

The invention provides an SAT automatic integrated solver based on FPGA, which effectively judges that whether CNF can be met. Firstly, the CNF is automatically translated to the verilog language by a C++ translator, i.e. the conjunctive normal form is converted to the gate level circuit form; the gate level circuit is simulated via Questasim software, whether the simulation is the same with a theoretical logic is checked, then the circuit is optimized and synthesized via Precision software, at last QuartusII software integrated into the Precision software is called to perform pin configuration, thus the integrated file is finally downloaded onto the FPGA circuit board to be cured into the hardware logic for verification; and the cured FPGA chip is embedded into the embedded chip, the automation of the whole process for generating a file calling command is achieved through combined programming of the Tcl scripting language and high-level language C++, and thereby whether the CNF can be met is rapidly judged. The hardware compiling configuration time is added, and thereby the time of the whole process can be more accurately computed compared with other hardware SAT solvers.

Owner:何安平

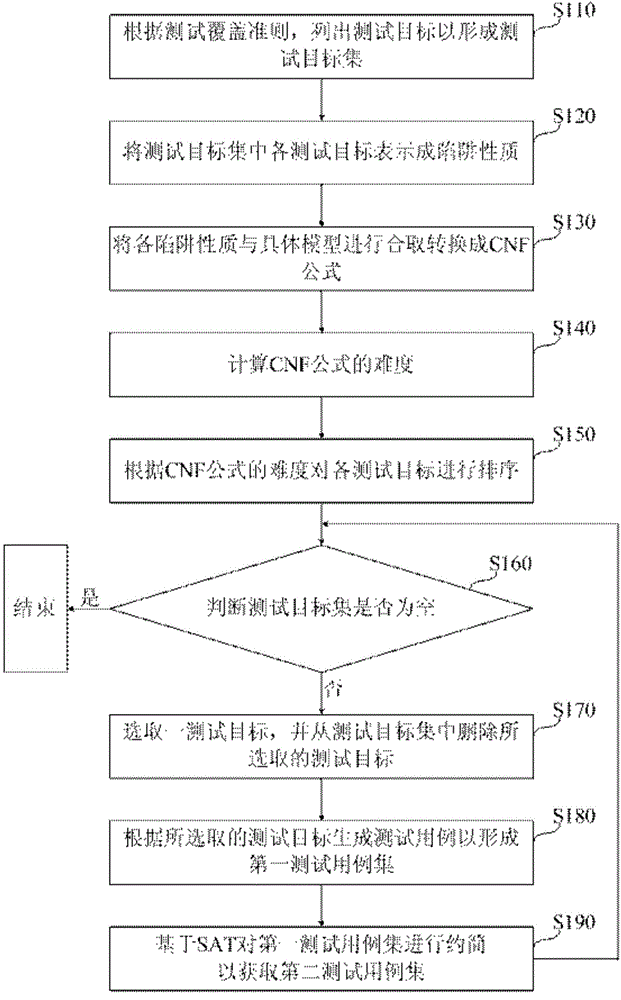

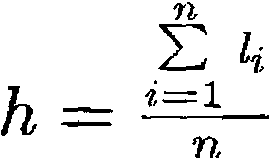

Test case generating method

ActiveCN104090837AReduce detection timesReduce the number of test casesSoftware testing/debuggingProgramming languageGood reduction

The invention provides a test case generating method. The method comprises the steps as follows: a, listing test objectives according to a test coverage norm to form a test objective set; b, expressing all the test objectives in the test objective set as trap properties; c, converting all the trap properties and specific models into a CNF (conjunctive normal form) through conjunction, d, calculating the difficulty of the CNF; e, sequencing all the test objectives according to the difficulty of the CNF; f, judging whether the test objective set is empty or not; g, when the test objective set is not empty, selecting one test objective and deleting the selected test objective from the test objective set; h, generating test cases according to the selected test objective to form a first test case set; i, reducing the first test case set on the basis of SAT to obtain a second test case set. The test case generating method at least has the advantages of good reduction effect and high efficiency.

Owner:SUZHOU VOCATIONAL UNIV