SAT automatic integrated solver based on FPGA

A solver and automatic technology, applied in the direction of instruments, memory systems, complex mathematical operations, etc., can solve problems such as poor versatility and no practical value, and achieve the effects of saving time, improving test efficiency, and powerful functions

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

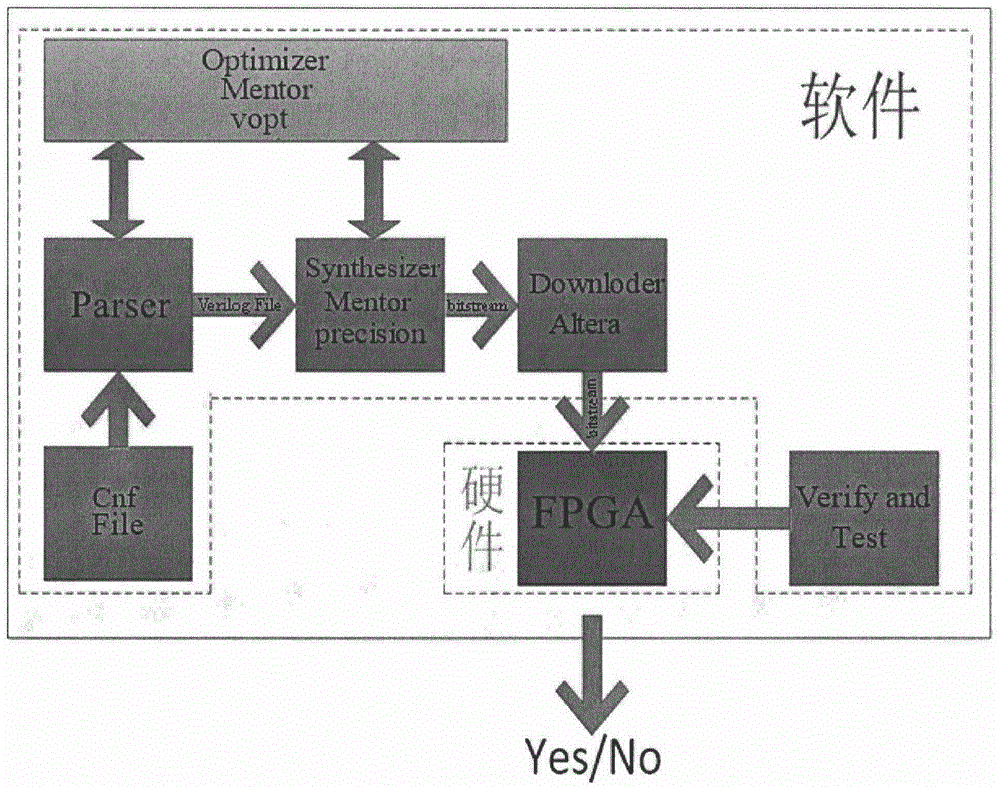

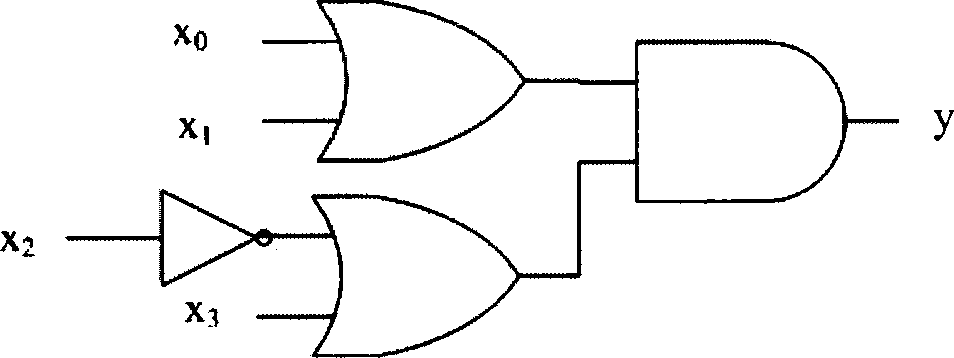

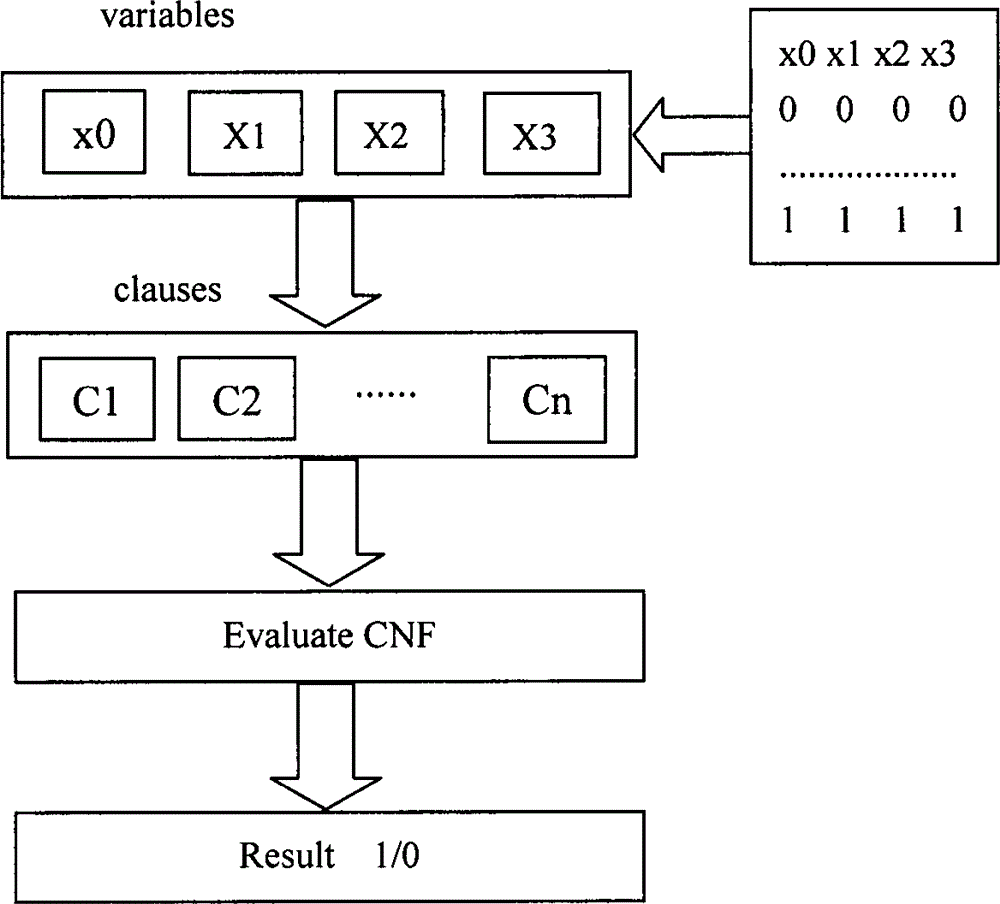

[0044] First, the translator written in C++ automatically translates the CNF formula into verilog language, that is, compiles the CNF into a gate-level circuit form, and then simulates the gate-level circuit through Questasim software to check whether the simulation is the same as the theoretical logic, and then passes Precision to the The circuit is optimized and synthesized, and finally the QuartusII software integrated in Precision is called to configure the pins. Finally, the integrated file is downloaded to the FPGA circuit board and solidified as hardware logic to form a Clause logic calculation module of CNF, which is searched for values by exhaustive method. , to verify the satisfiability of the example, connect the output to the pin of the buzzer or LED light, if the output is high, the buzzer sounds or the LED light is on, it is intuitively proved that this CNF can be satisfied, Otherwise the proof is unsatisfactory. Optimize and synthesize the circuit through Prec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More