Patents

Literature

51 results about "Local logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

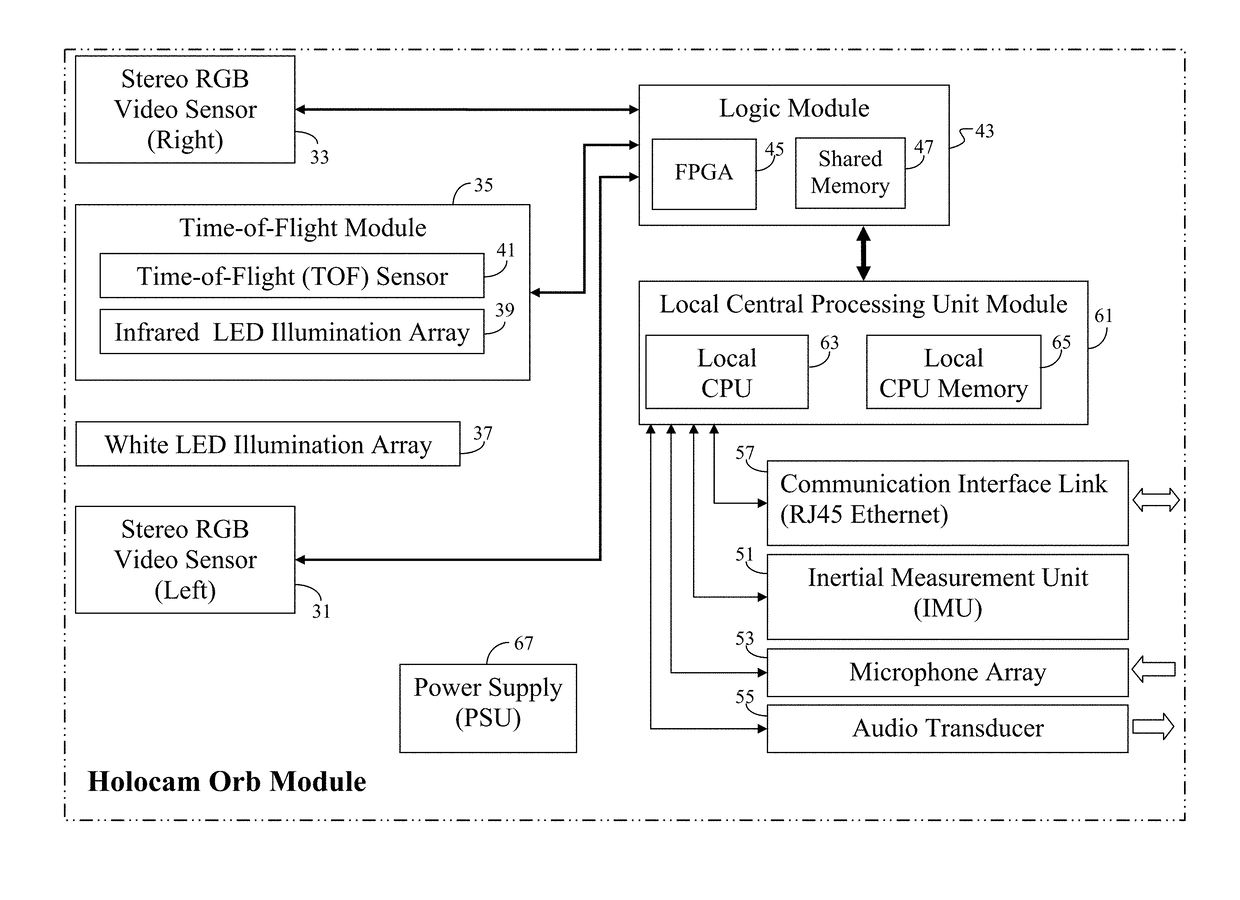

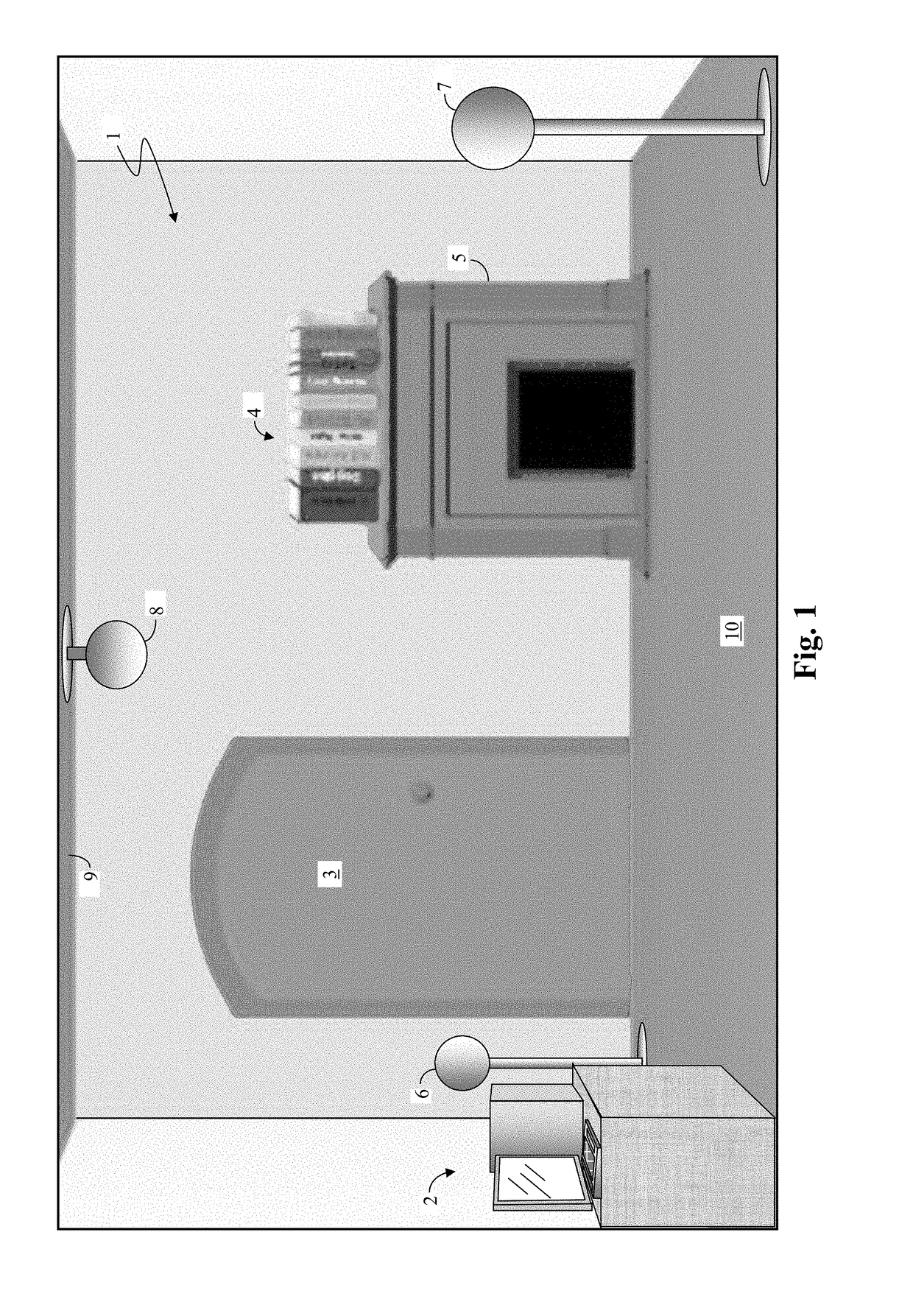

Real Time Sensor and Method for Synchronizing Real Time Sensor Data Streams

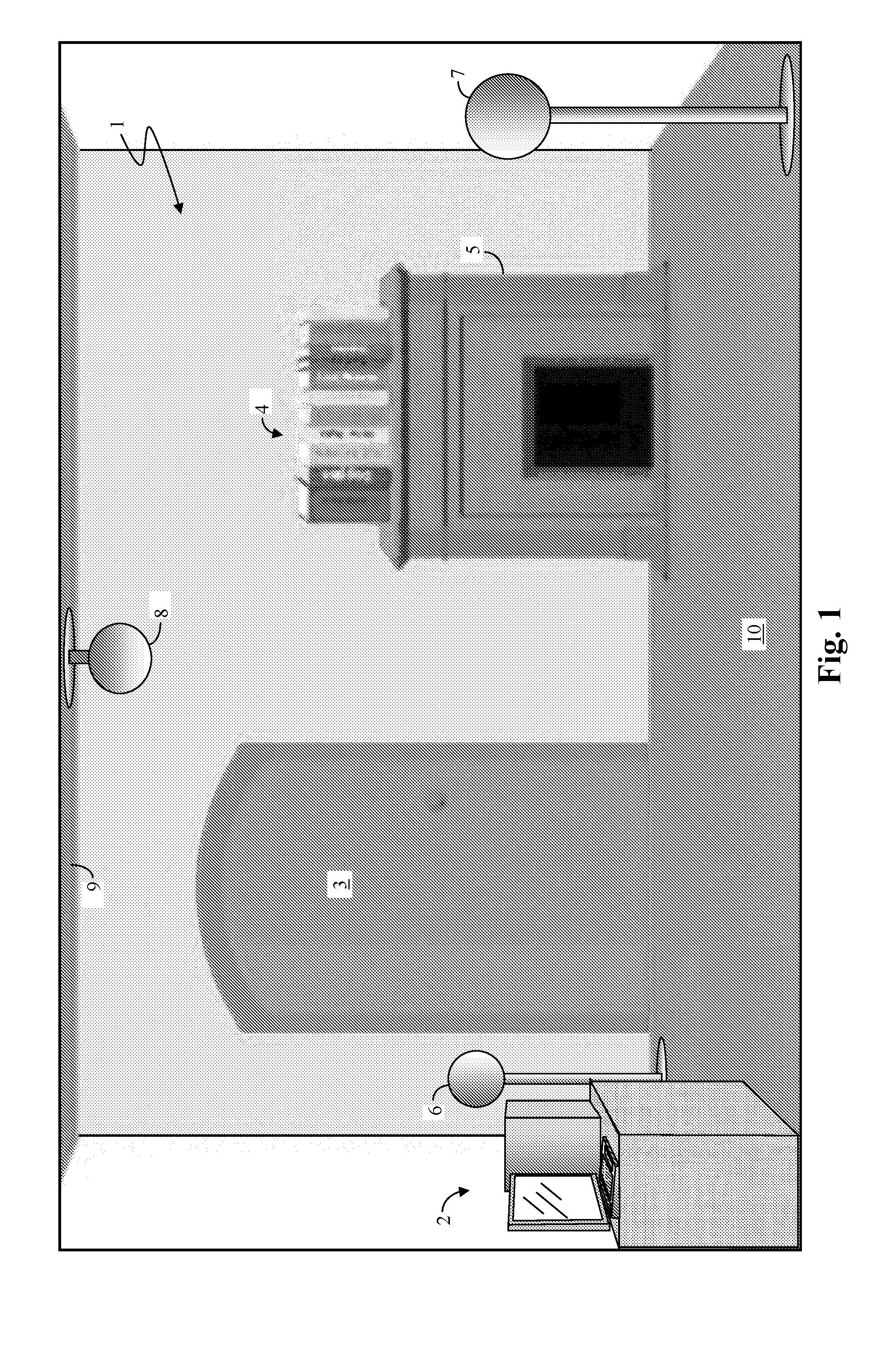

A Holocam Orb system uses multiple Holocam Orbs (Orbs) within a real-life environment to generate an artificial reality representation of the real-life environment in real time. Each Orb is an electronic and software unit that includes a local logic module, a local CPU and multiple synchronous and asynchronous sensors, include stereo cameras, time-of-flight sensors, inertial measurement units and a microphone array. Each Orb synchronizes itself to a common master clock, and packages its asynchrony data into data bundles whose timings are matched to frame timing of synchronous sensors, and all gathered data bundles and data frames are given a time stamp using a reference clock common to all Orbs. The overlapping sensor data from all the Orbs is combined to create the artificial reality representation.

Owner:SEIKO EPSON CORP

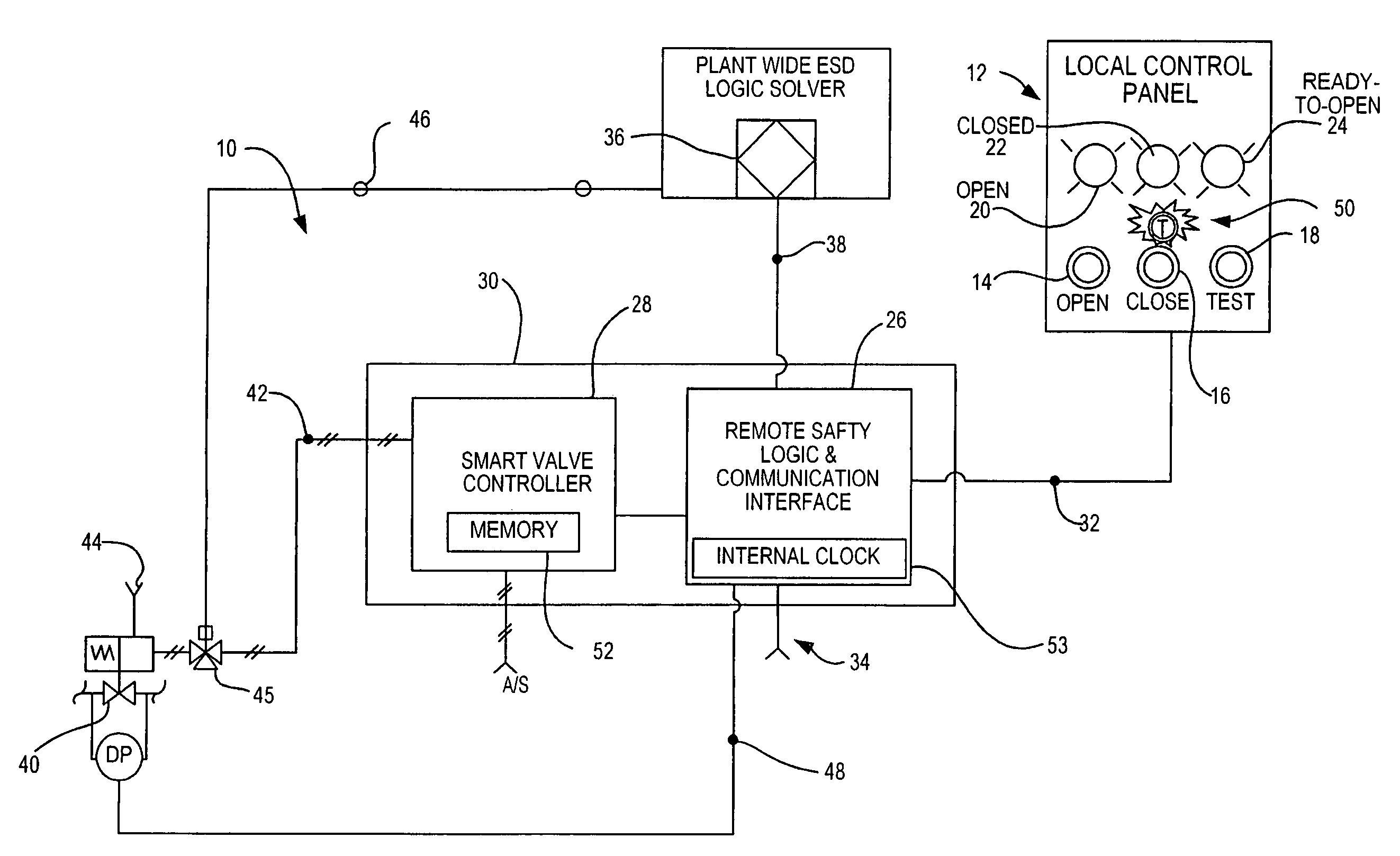

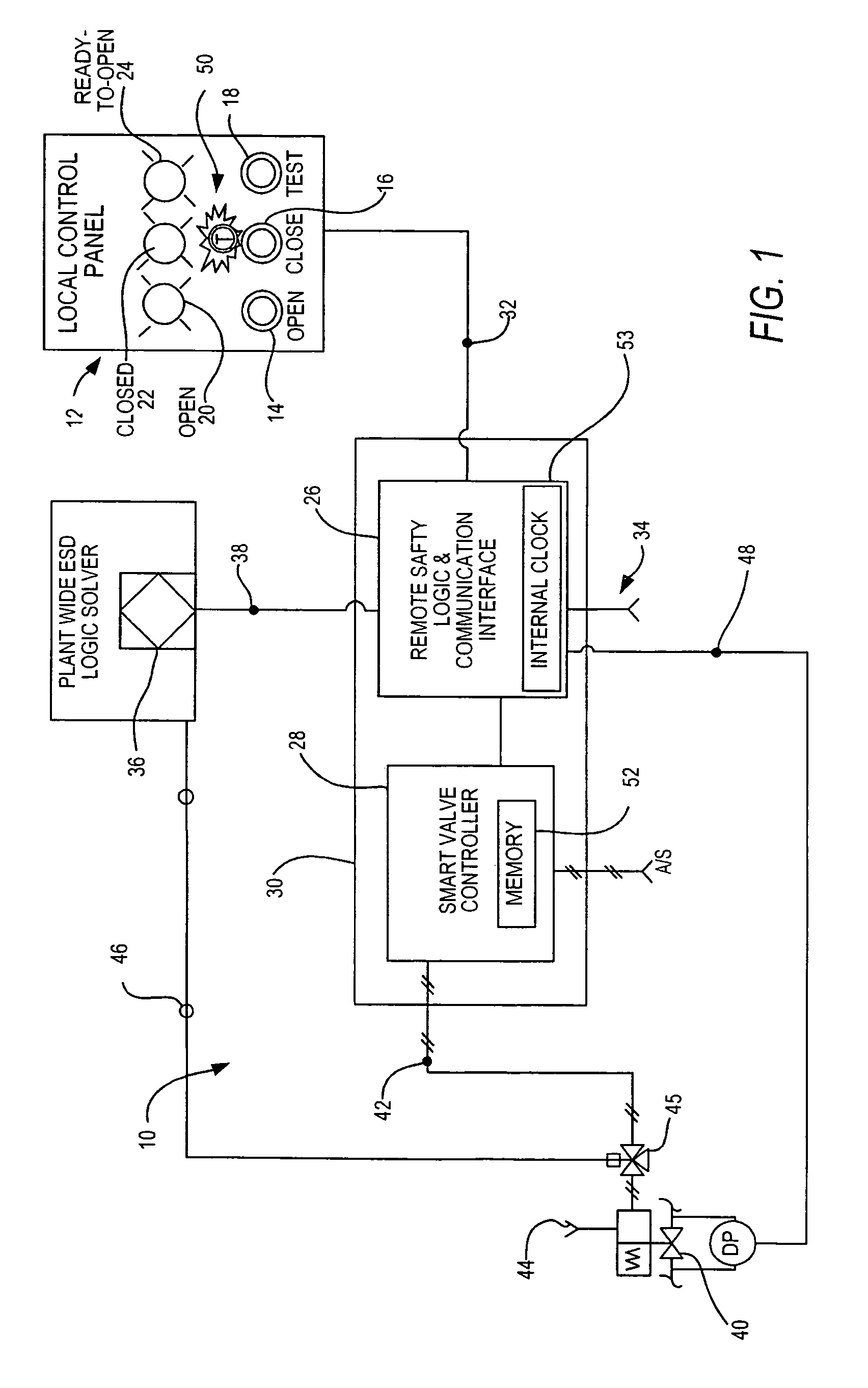

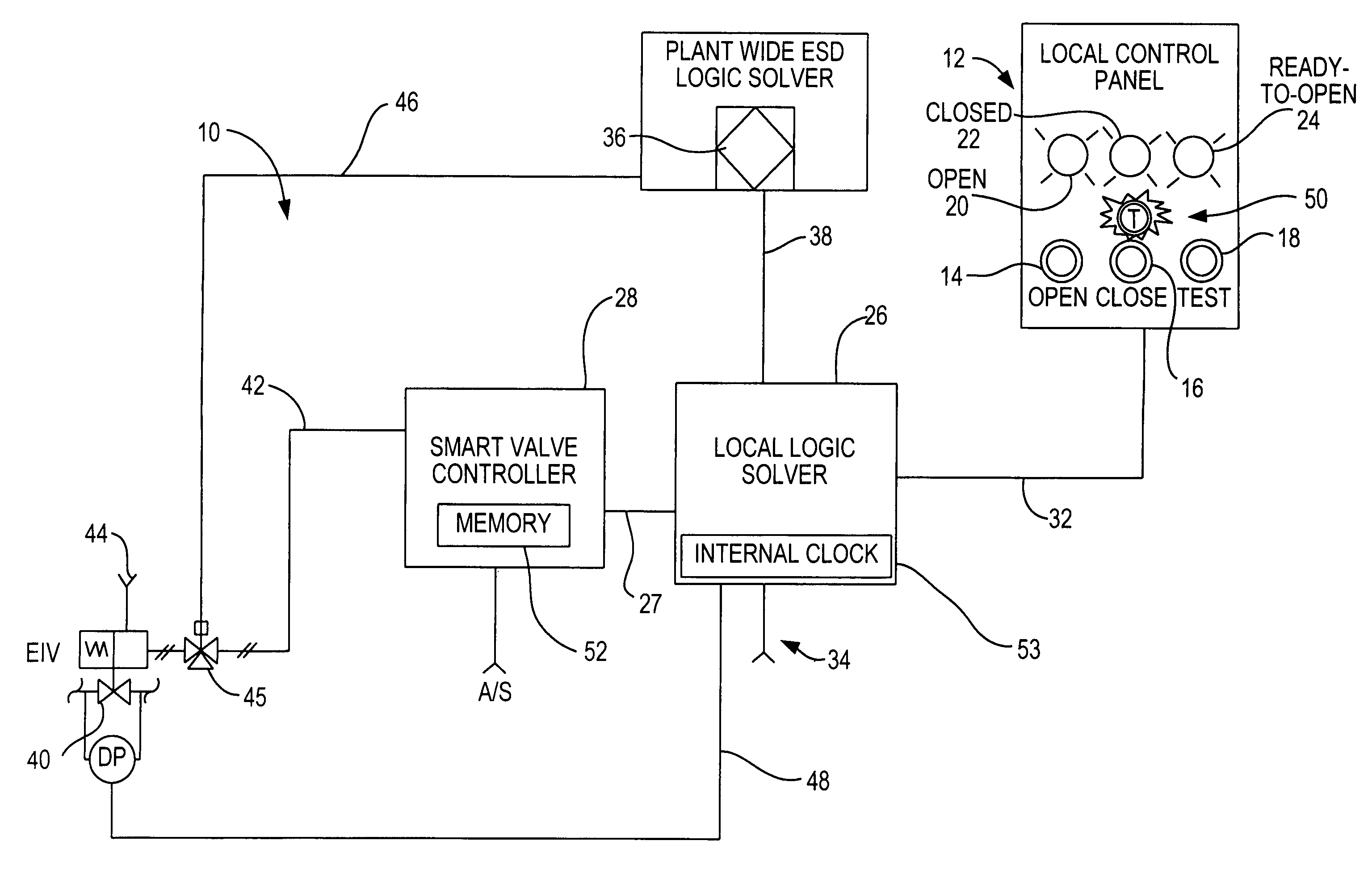

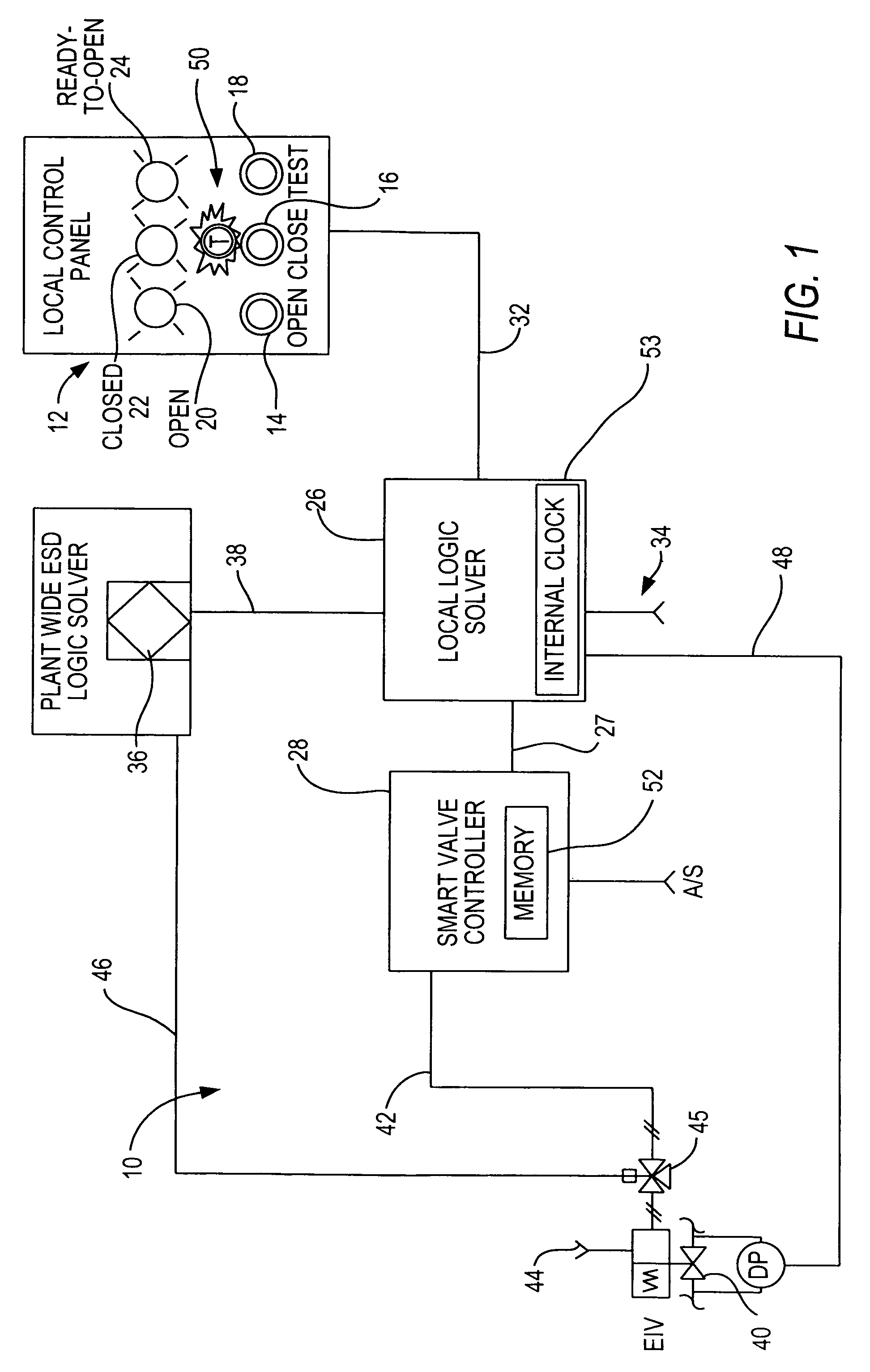

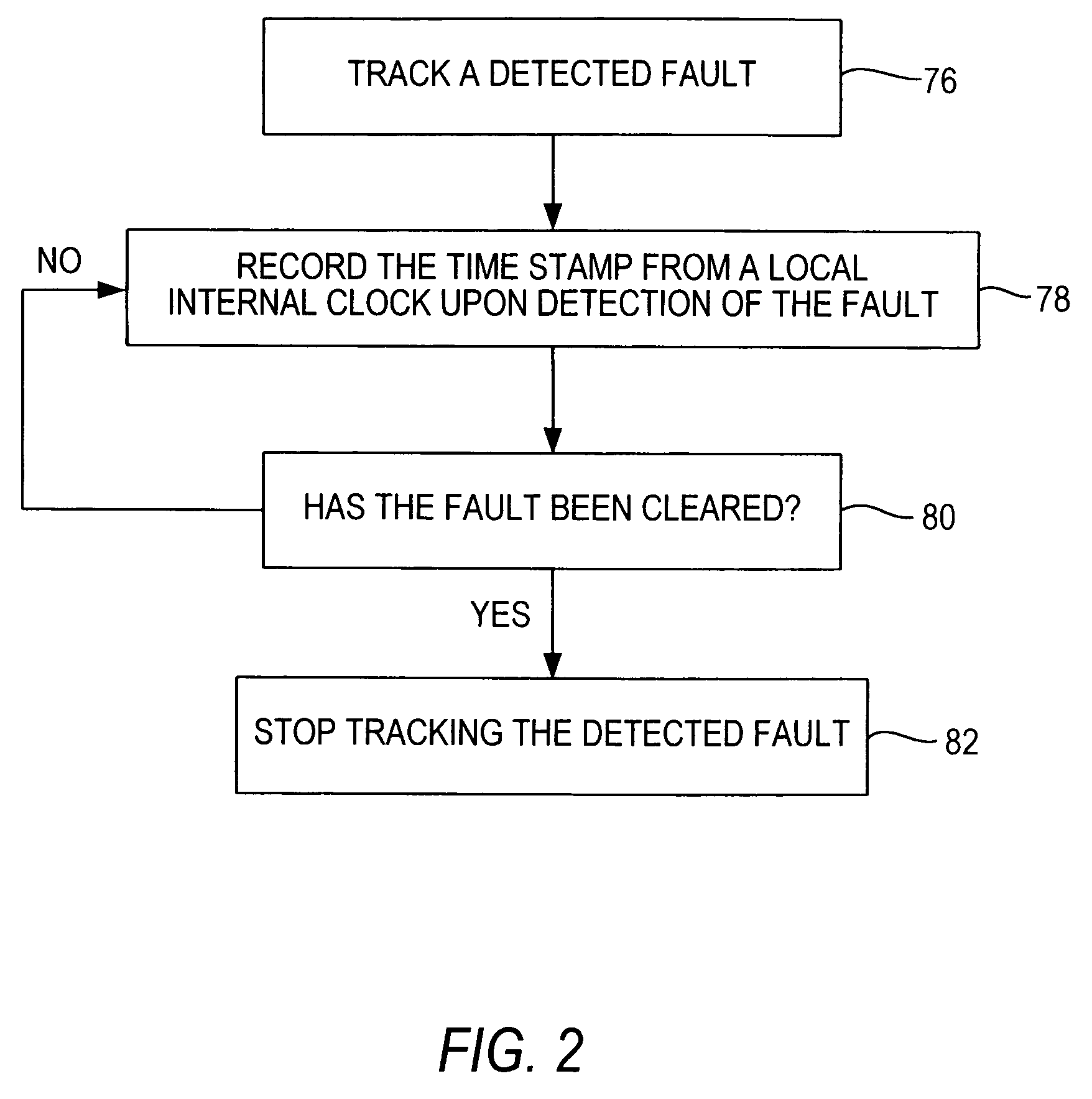

Emergency isolation valve controller with integral fault indicator

ActiveUS20060220844A1Improve performanceReduce complexityOperating means/releasing devices for valvesTesting/monitoring control systemsFault indicatorIsolation valve

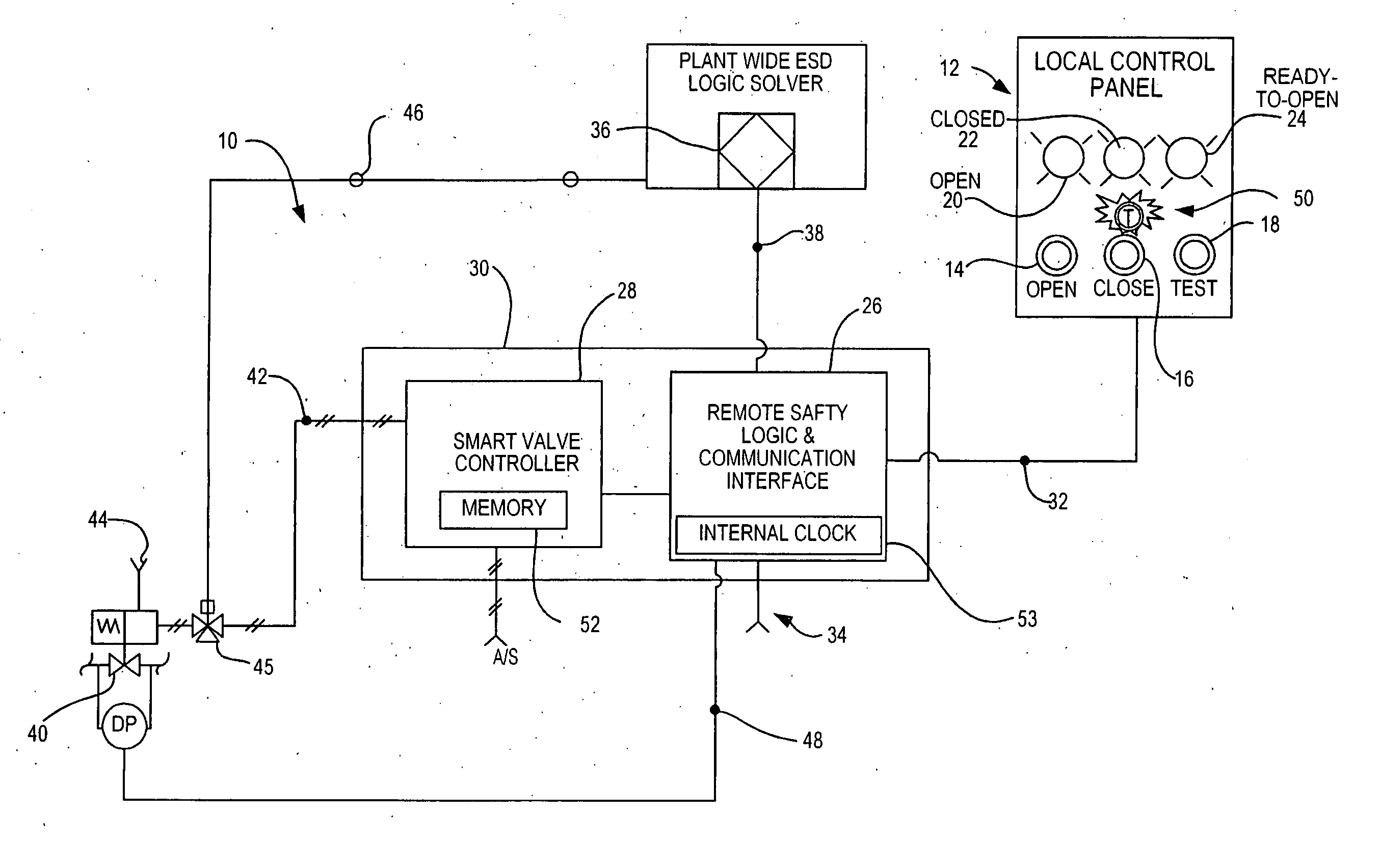

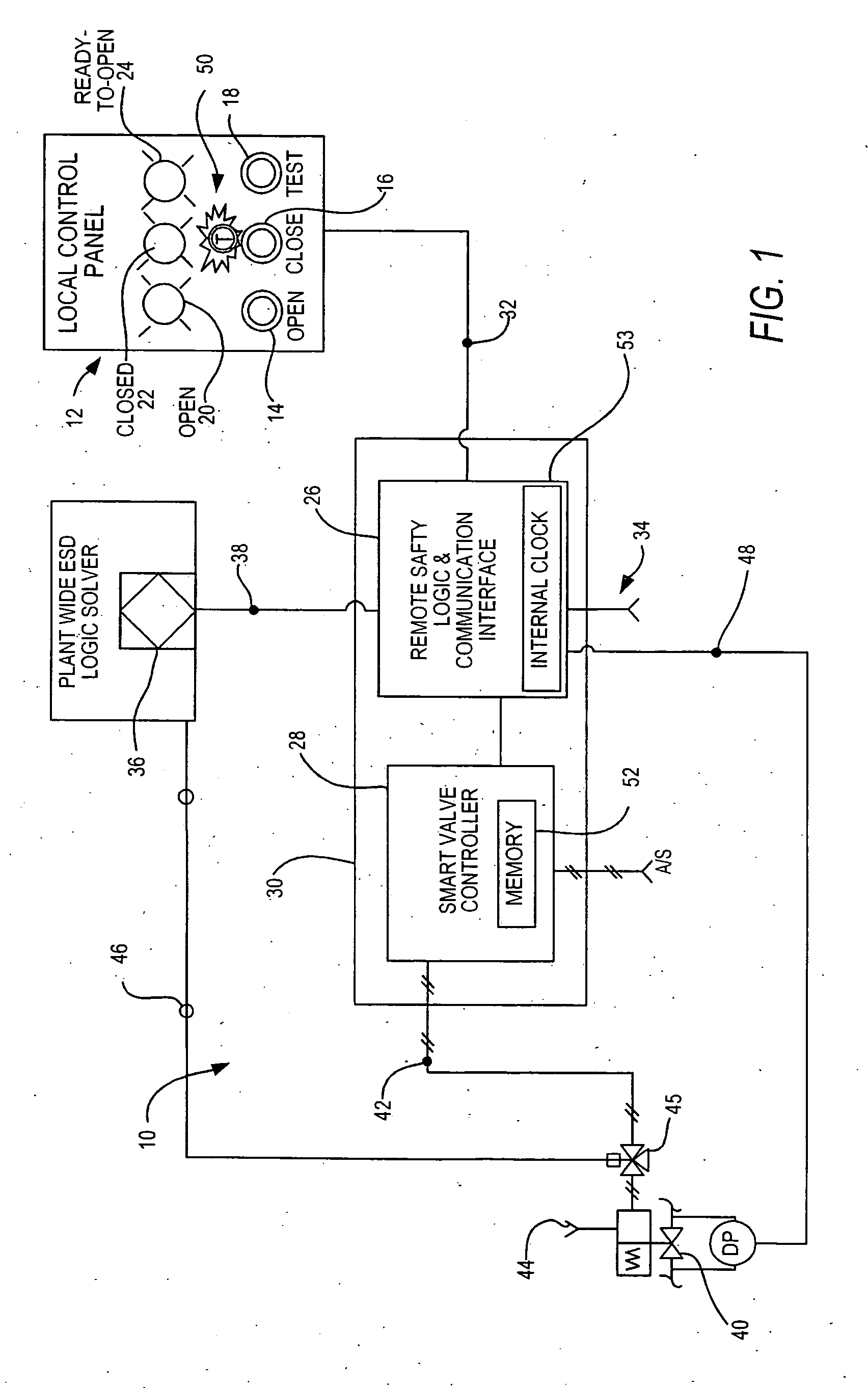

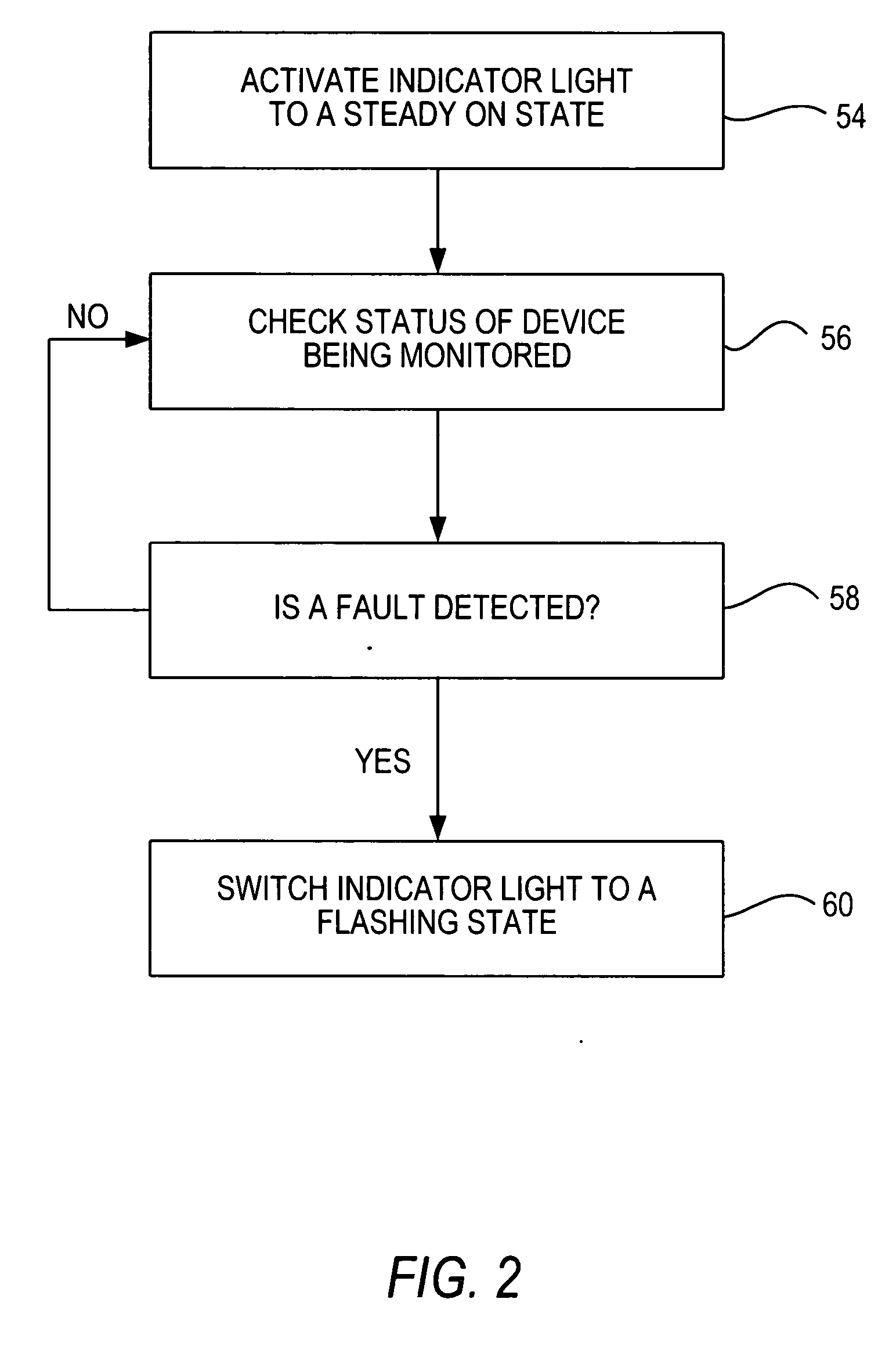

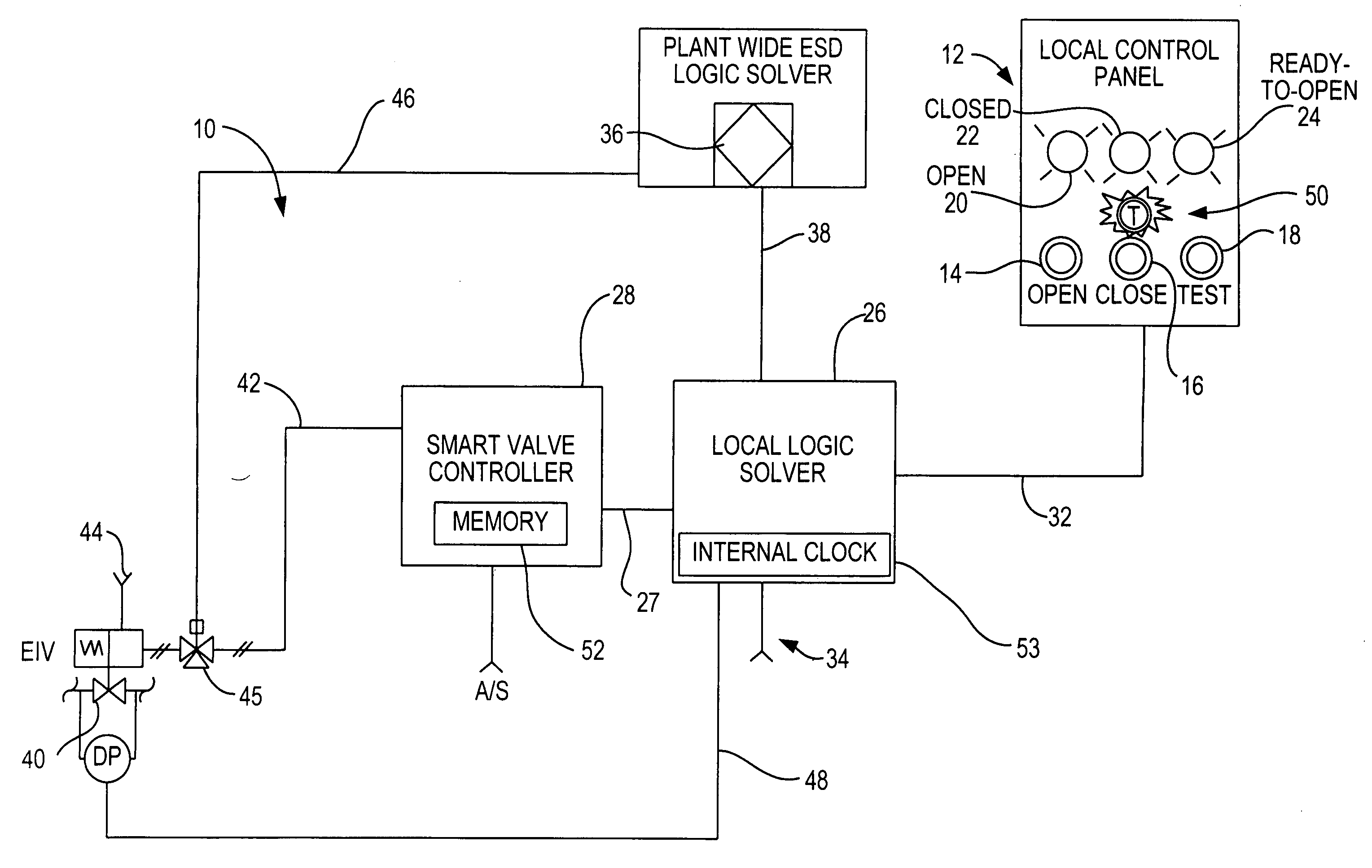

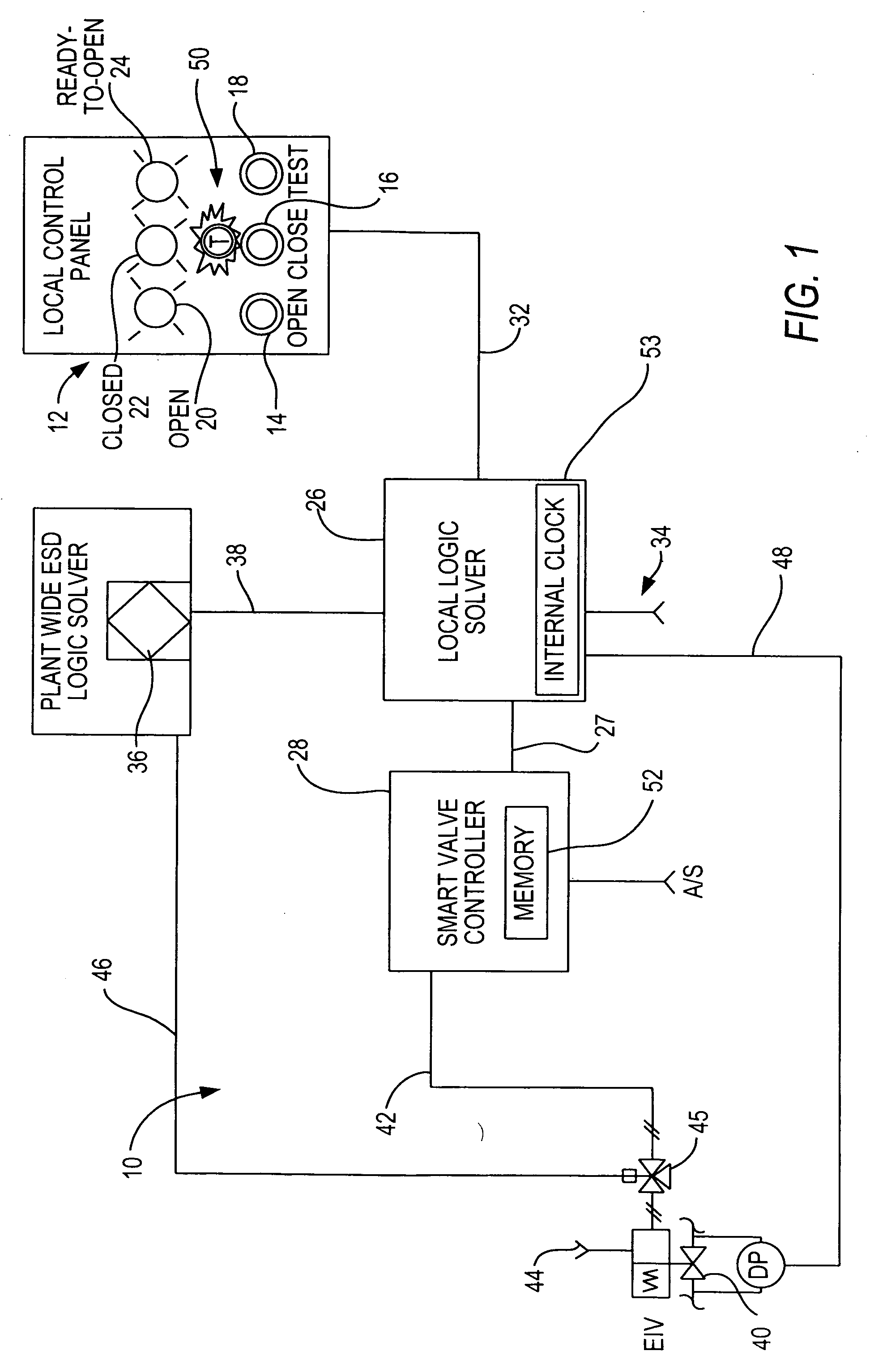

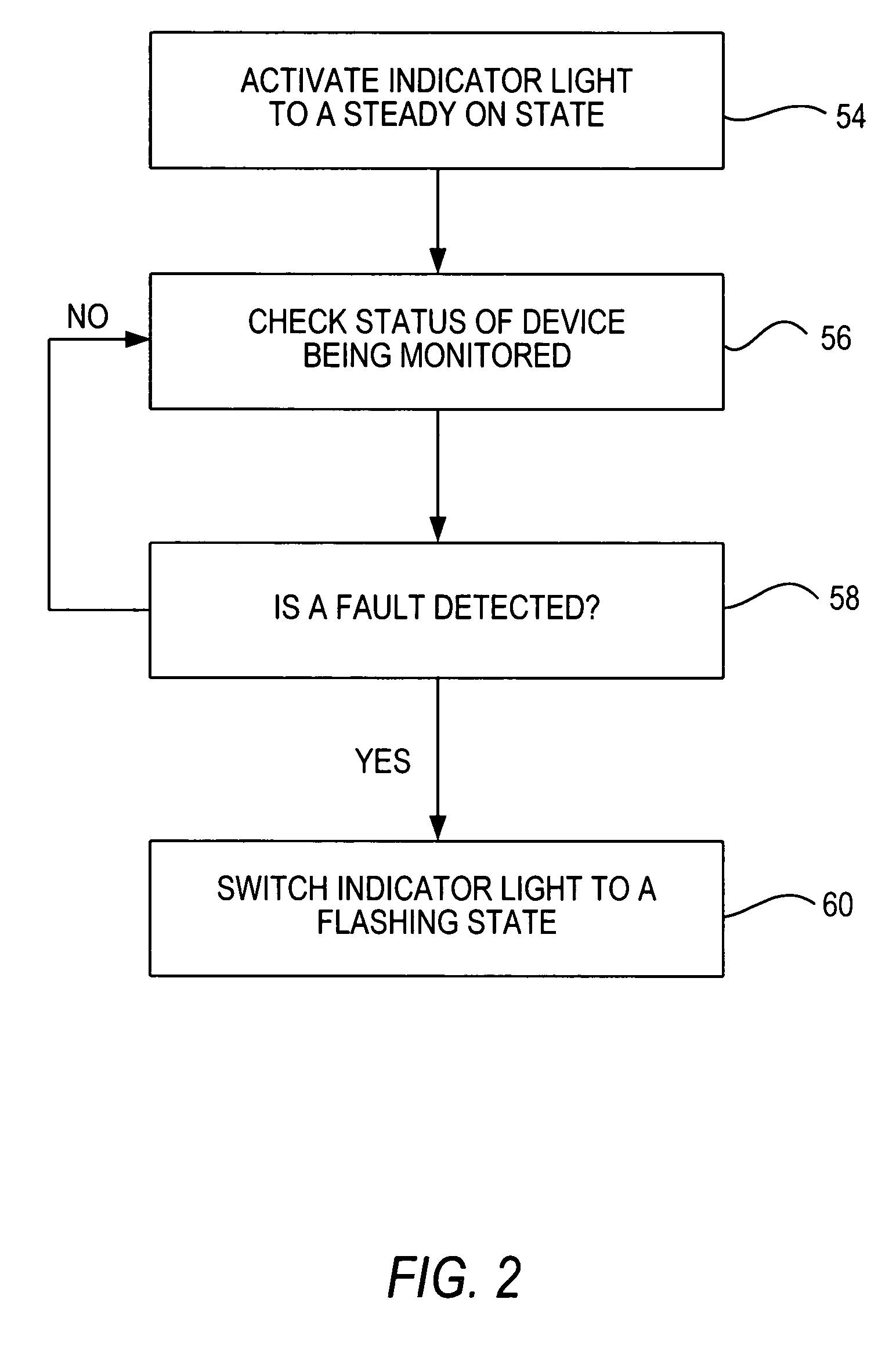

A local logic solver operates with a local smart valve controller to control and test a local field-mounted emergency isolation valve device to which provide a local indication of trouble on the device, which is mounted in the field away from the facility's central control panel for the process. Accordingly, the operation of the overall system is simplified by eliminating the need for an external computer to diagnose any problems. A local control panel includes an indicator light substantially adjacent to or in close proximity to the device being monitored to alert personnel of detected faults. Detected faults are time-stamped locally to provide documentation and tracking of elapsed time, starting when the degraded state of the device was detected and first signaled as a problem.

Owner:SAUDI ARABIAN OIL CO

Local emergency isolation valve controller with diagnostic testing and trouble indicator

InactiveUS20090121868A1Impact system performanceEasy to operateOperating means/releasing devices for valvesWork measurementFault indicatorIsolation valve

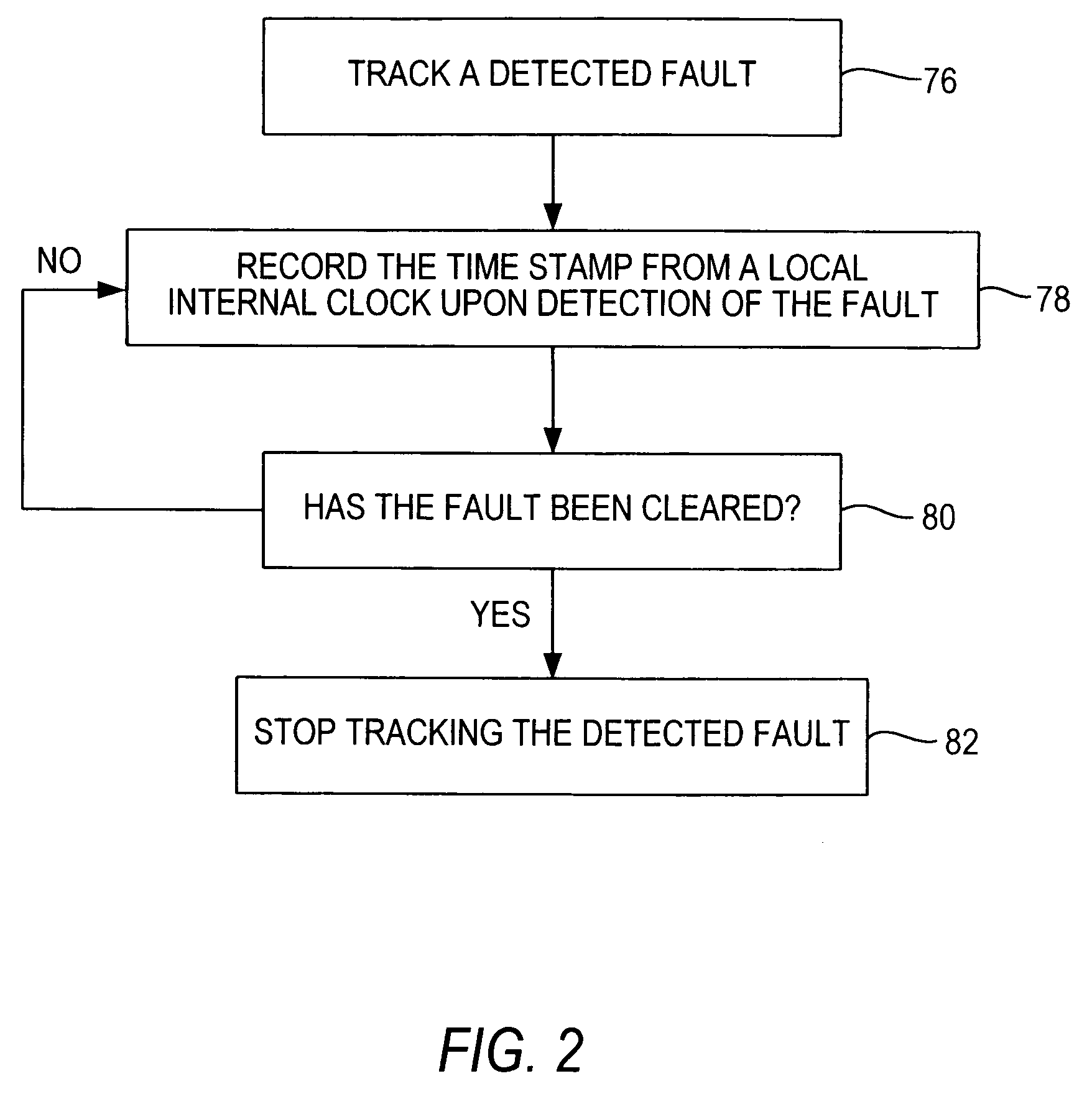

A local logic solver that operates with a local smart valve controller to control, test and monitor performance characteristics of a local field-mounted emergency isolation valve device, outputting a local indication of trouble on the device, which is mounted in the field away from the facility's central control panel for the process. The local logic solver includes a recording function and memory for retrieval of detected faults that are time-stamped and recorded locally to generate documentation and to track the elapsed time, starting when the degraded state of the device was detected and first signaled as a problem; other performance data is also recorded. Accordingly, the operation of the overall system is simplified by eliminating the need for an external computer to diagnose any problems. A local control panel preferably includes pushbuttons and lights used during routine operations of the valve and a fault indicator light substantially adjacent to or in close proximity to the device being monitored to alert personnel of detected faults.

Owner:SAUDI ARABIAN OIL CO

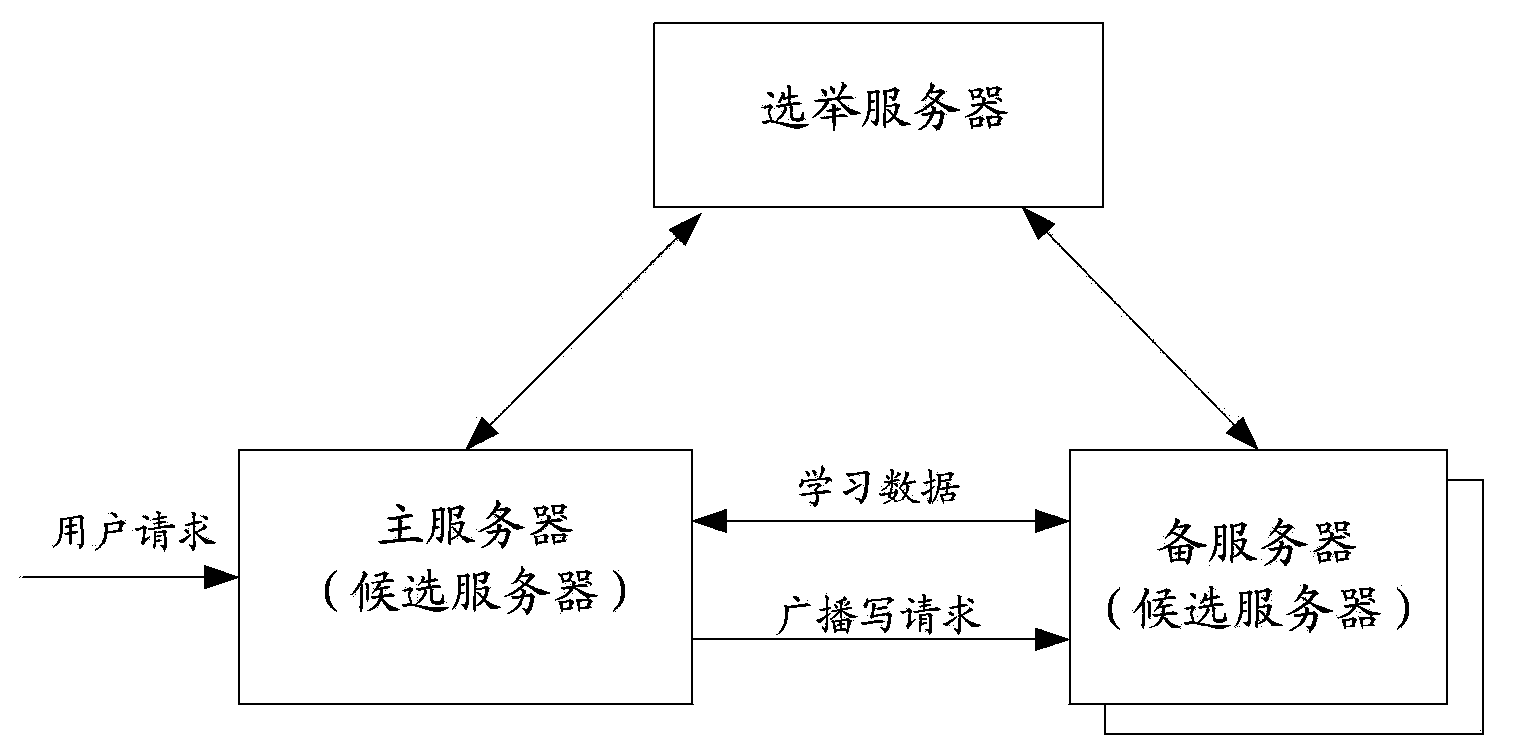

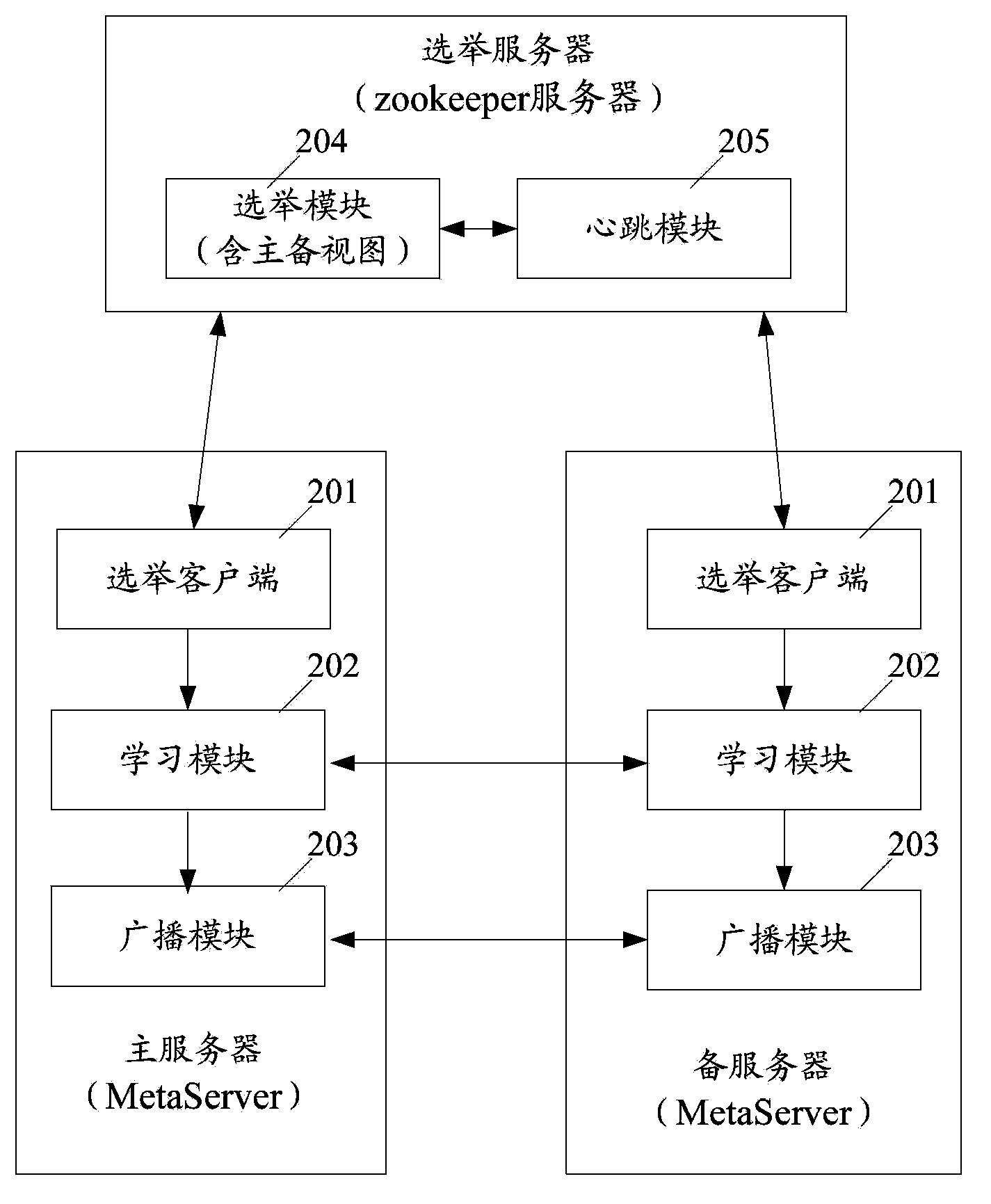

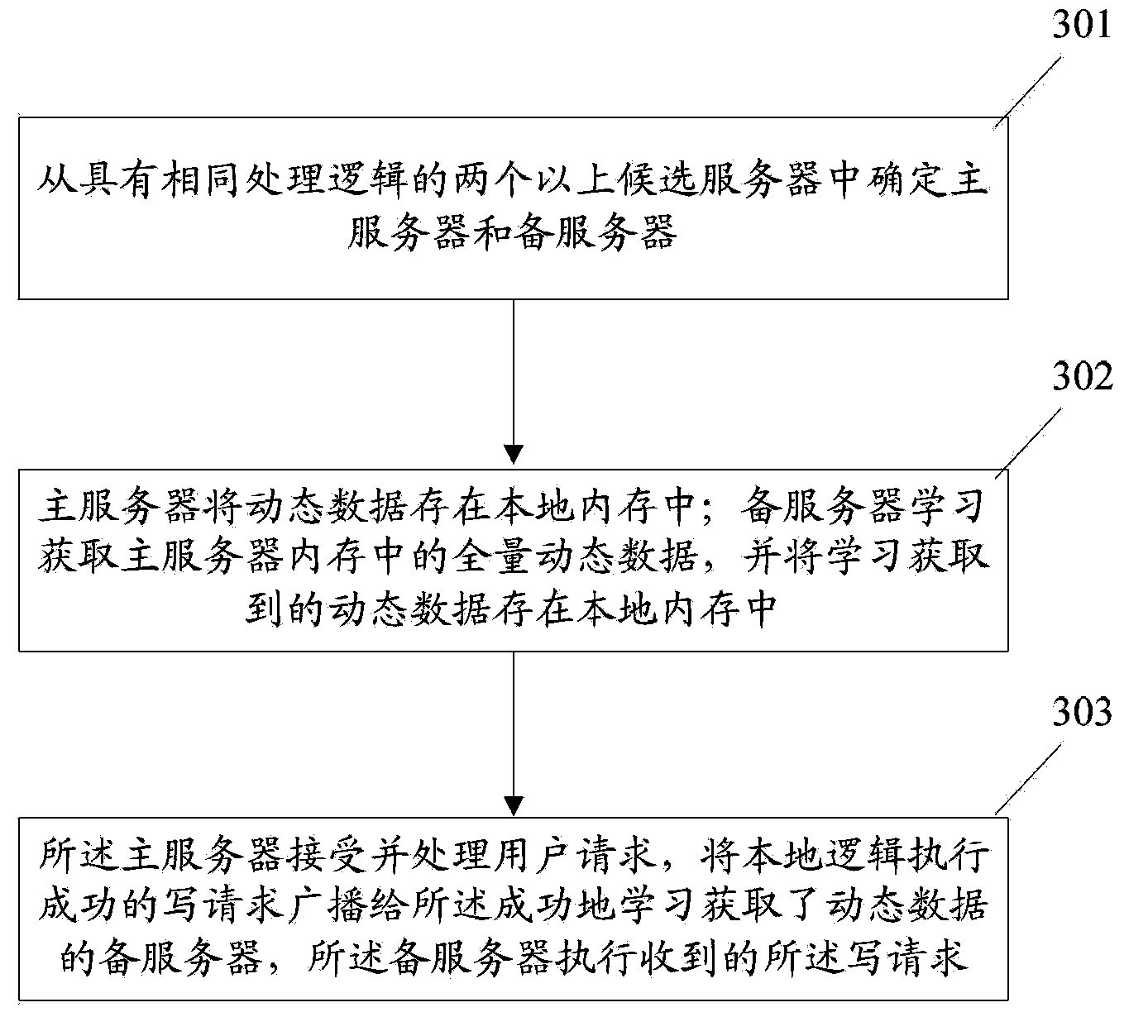

Server hot backup system and method

ActiveCN103530200ASimplify processing logicReduce performance pressureRedundant operation error correctionBroadcastingDynamic data

The invention discloses a server hot backup system and method. The server hot backup system comprises a selecting server and more than two candidate servers with the same processing logic. The selecting server determines a main server and backup servers from the candidate servers; under the condition that the candidate servers are determined to be the backup servers, the candidate servers are used for acquiring all dynamic data in the memory of the main server by studying, the dynamic data acquired by studying are stored in a local memory, and a received writing request of the broadcasting of the main server is executed; under the condition that the candidate servers are determined as the main server, the dynamic data are stored in the local memory, a user request is received and processed, and the writing request which is successfully executed by local logic is broadcasted to the backup servers which successfully acquiring the dynamic data by studying. The server hot backup system and method are used, the processing logic of hot backup can be simplified, and the pressure to the performance of the servers can be lowered.

Owner:TENCENT TECH (SHENZHEN) CO LTD +1

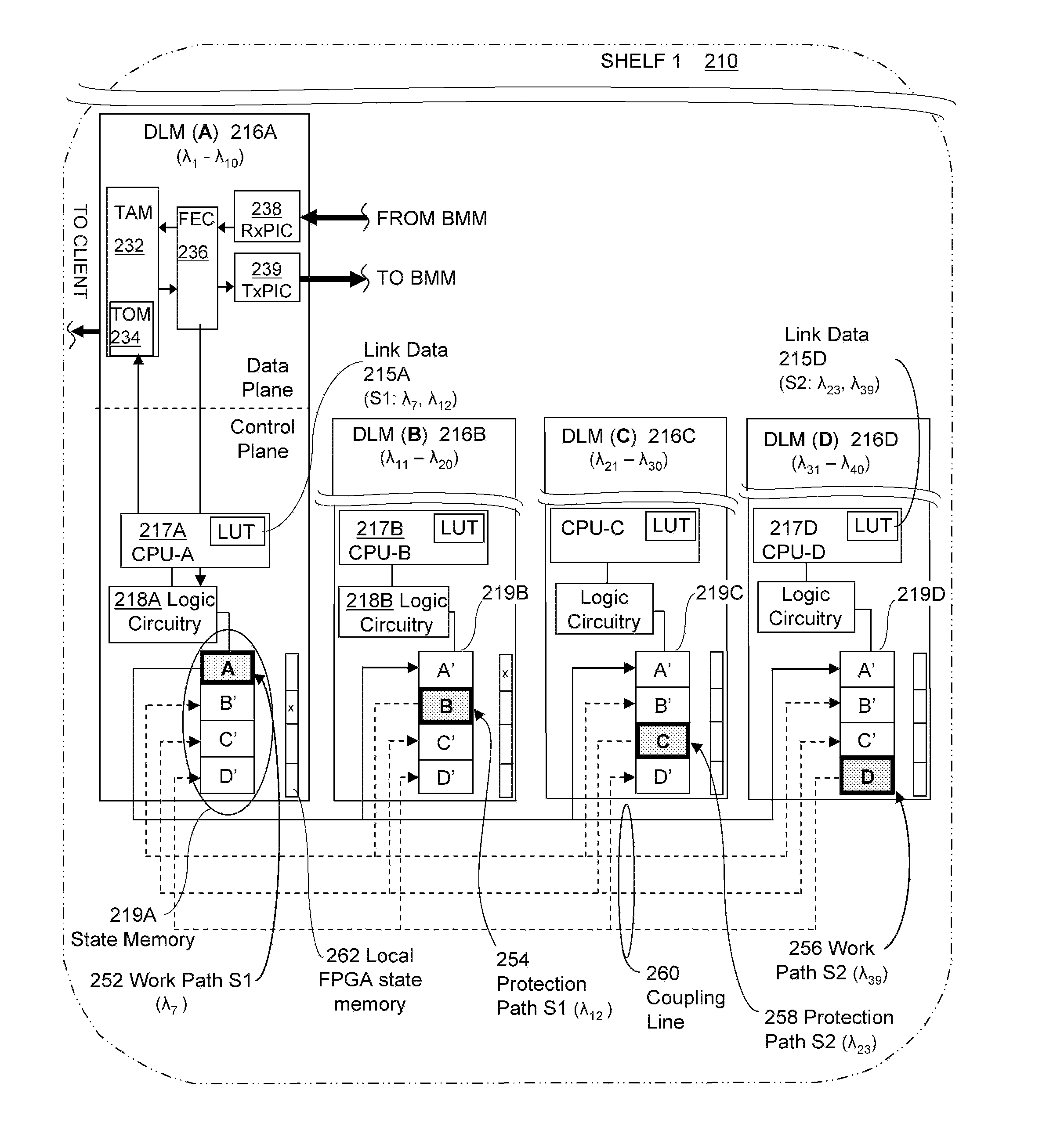

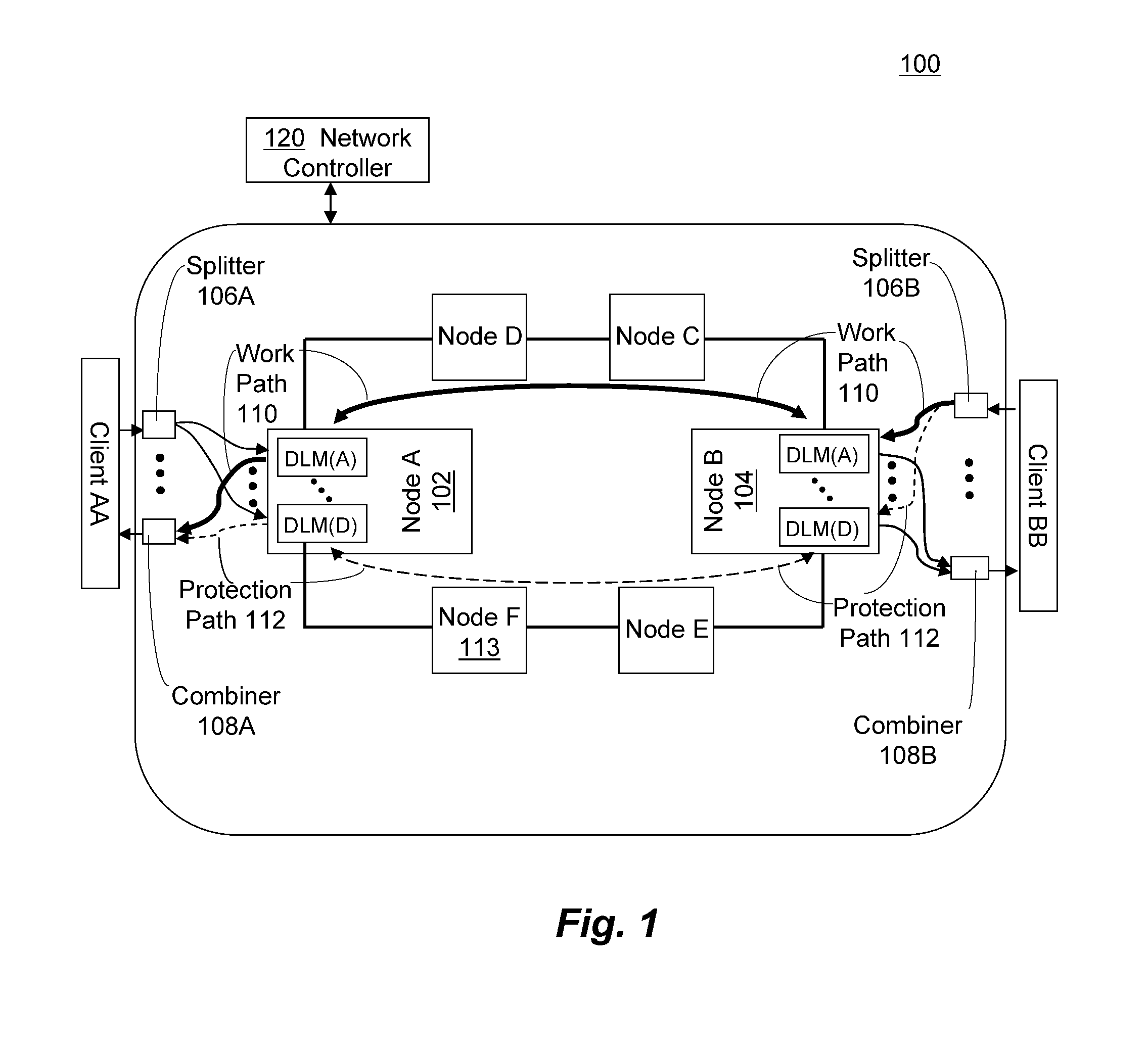

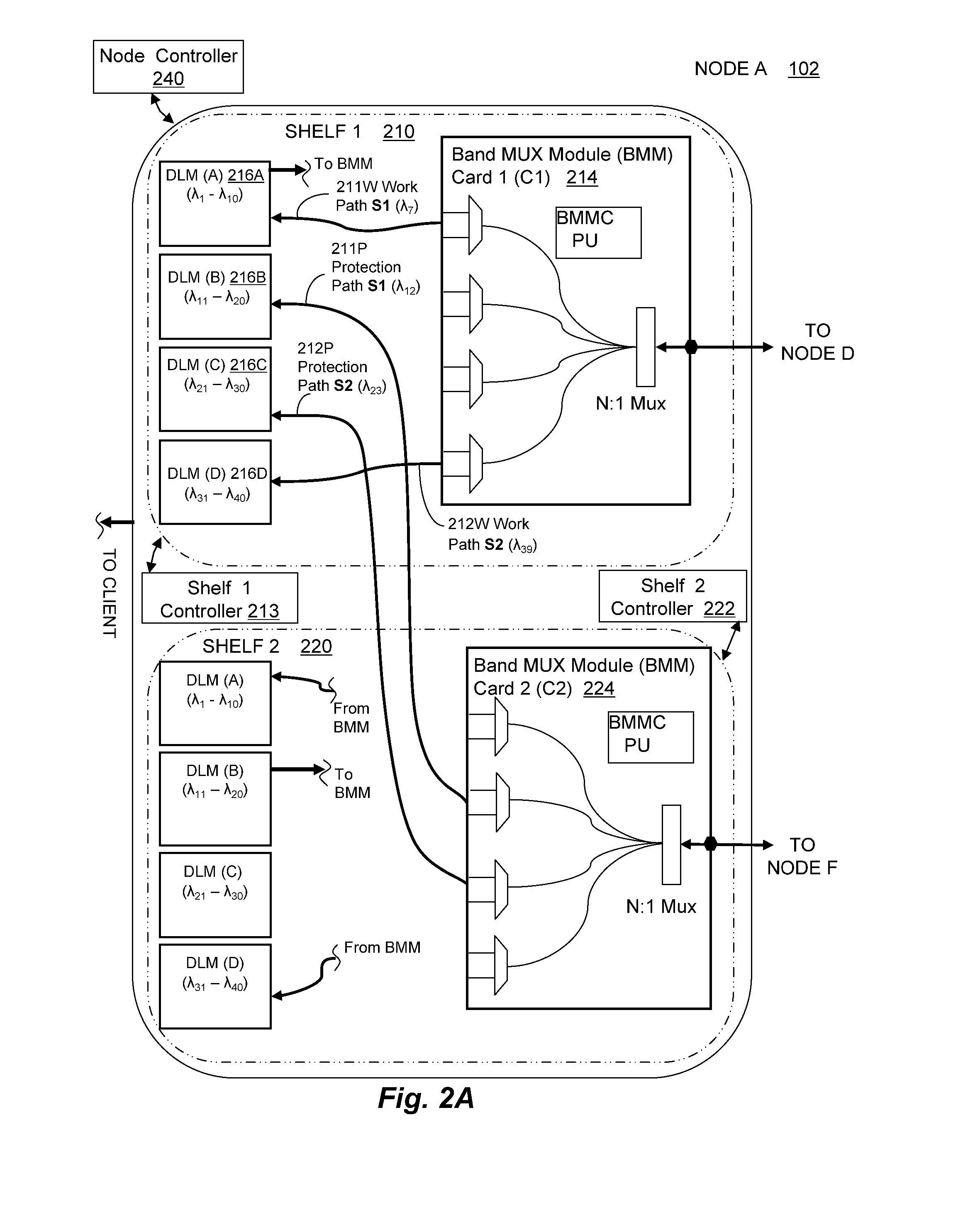

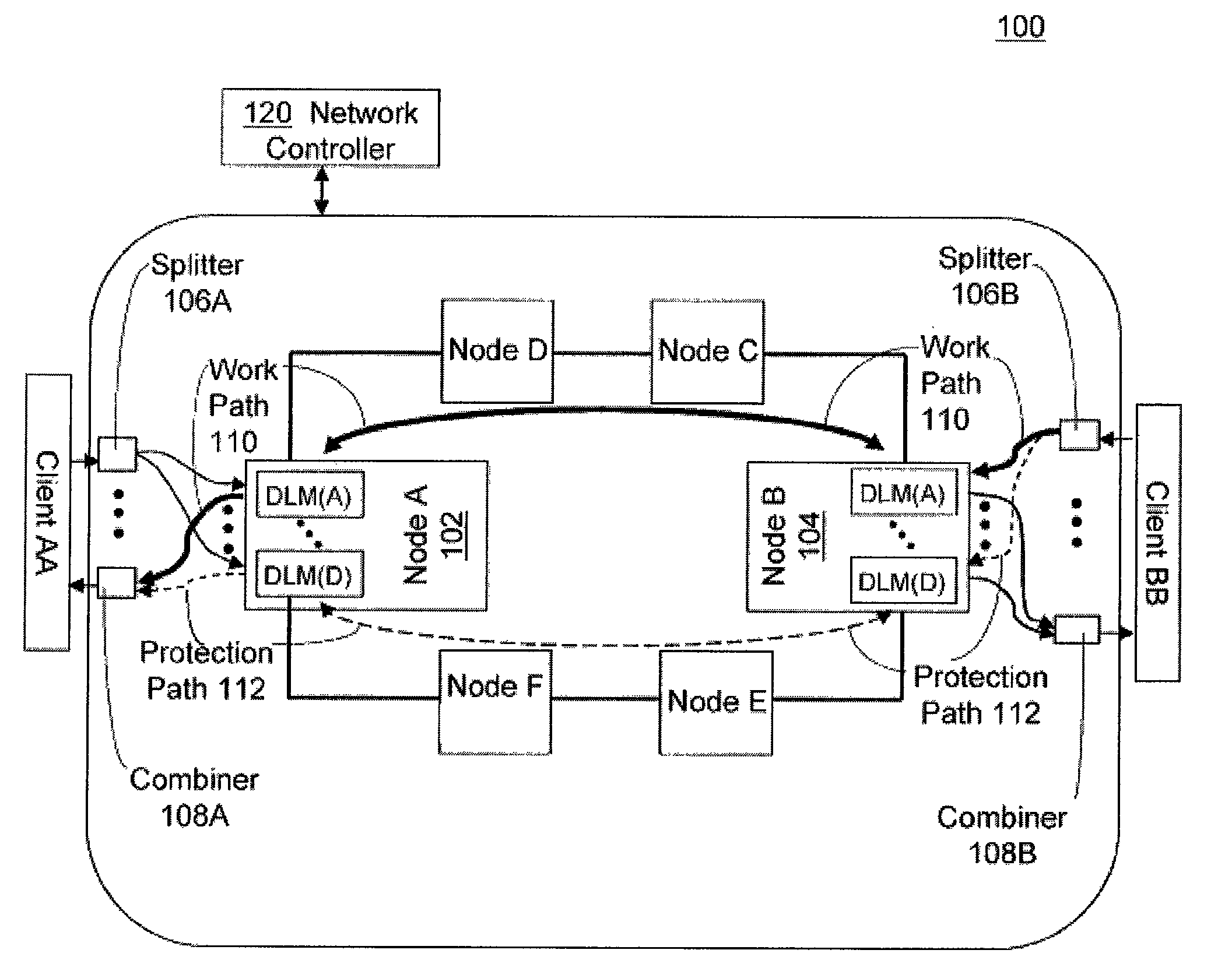

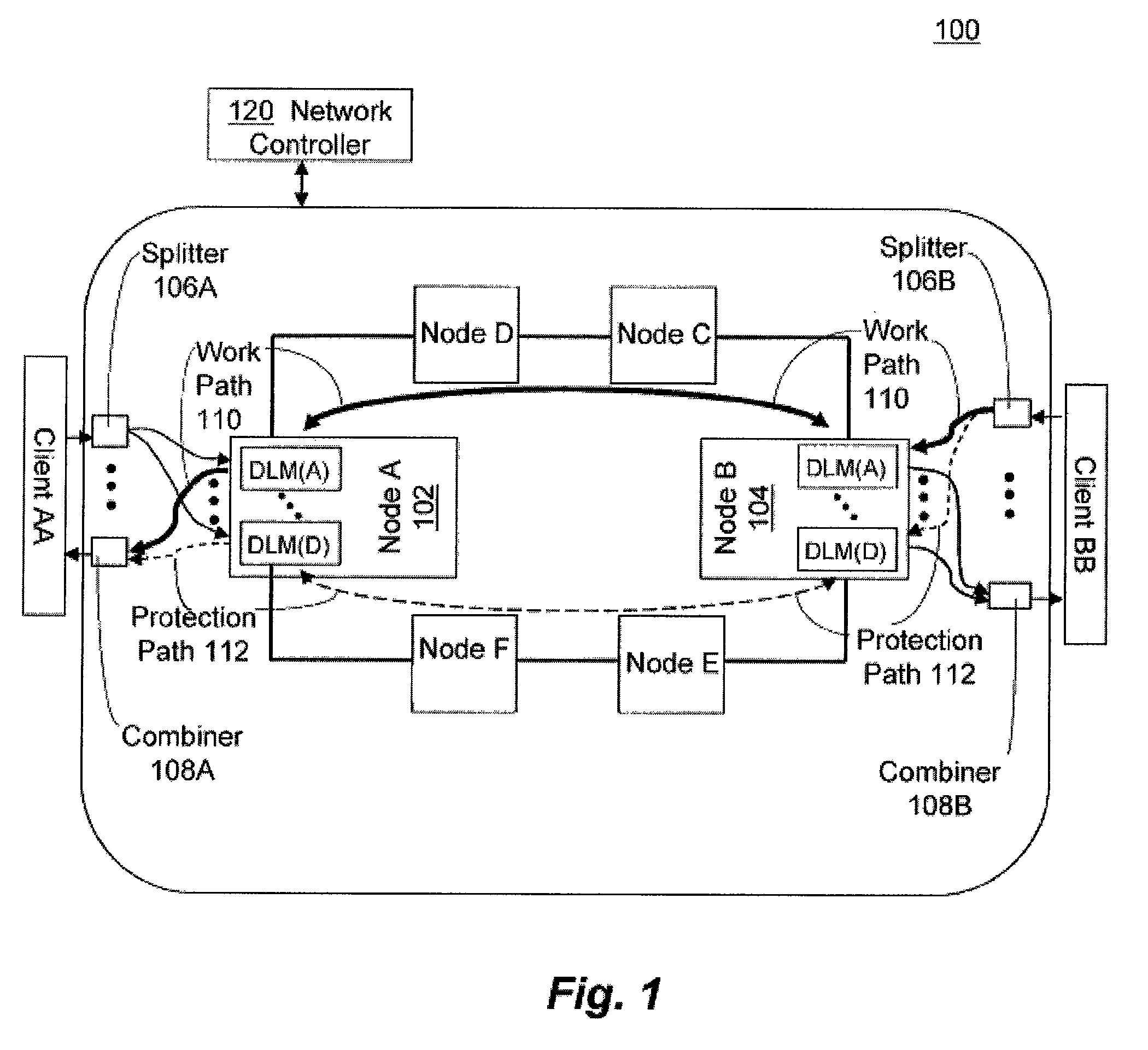

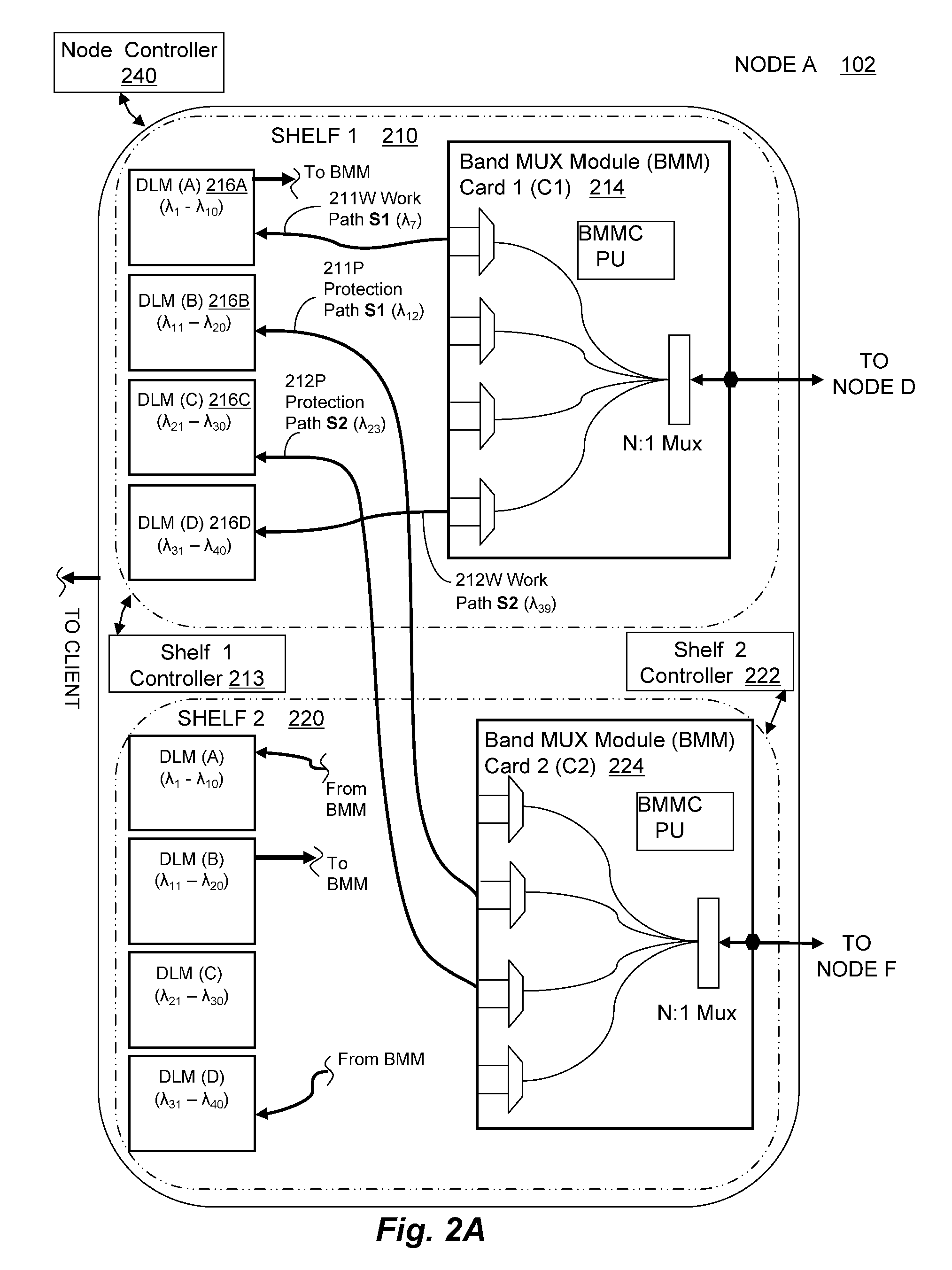

Application of hardware-based mailboxes in network transceivers and distributed approach for predictable software-based protection switching

ActiveUS20070211742A1Quickly and reliably performedConserving host processor resourceMultiplex system selection arrangementsData switching by path configurationError checkingTransceiver

A line card in a network node having a local memory coupled to a local controller and local logic circuit. The local memory in the line card stores state information for signals processed by the line card itself, as well as state information for signals processed by other line cards. The logic circuit and controller implement a same fault detection and signal processing algorithms as all other line cards in the group, to essentially effectuate a distributed and local hardware based control of automatic protection switching (APS) without interrupting a central processor. The line card also performs error checking and supervisory functions to ensure consistency of state among the line cards.

Owner:INFINERA CORP

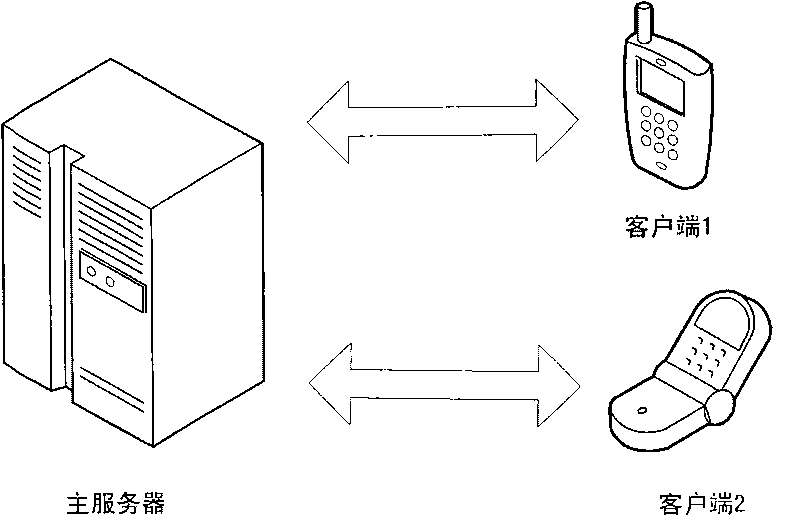

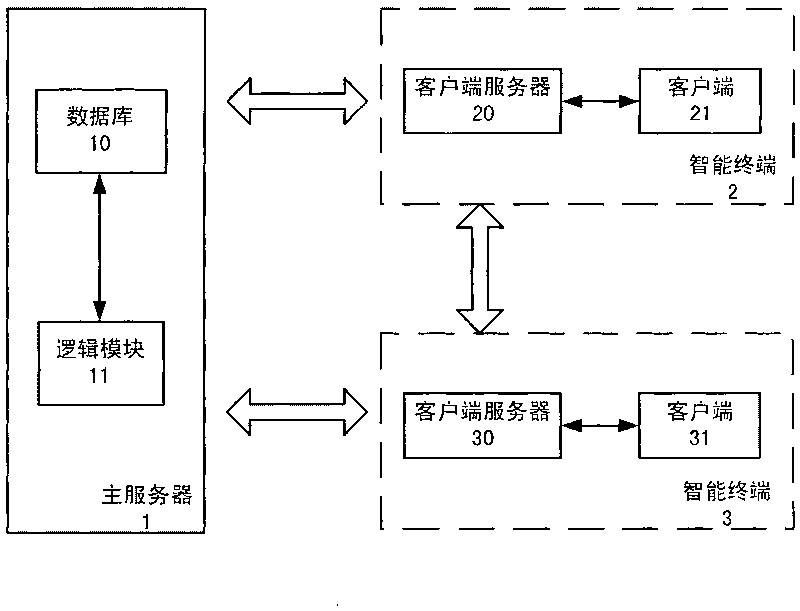

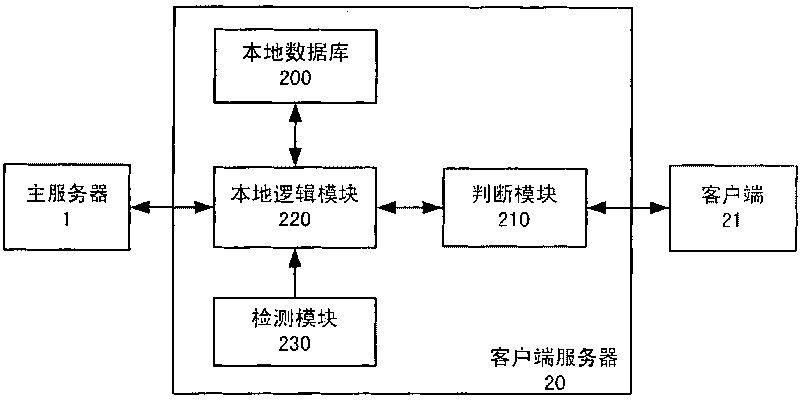

Client server, intelligent terminal, online game system and method

InactiveCN101741653AReduce loadMaintain fairnessData switching by path configurationSpecial data processing applicationsClient-sideComputer science

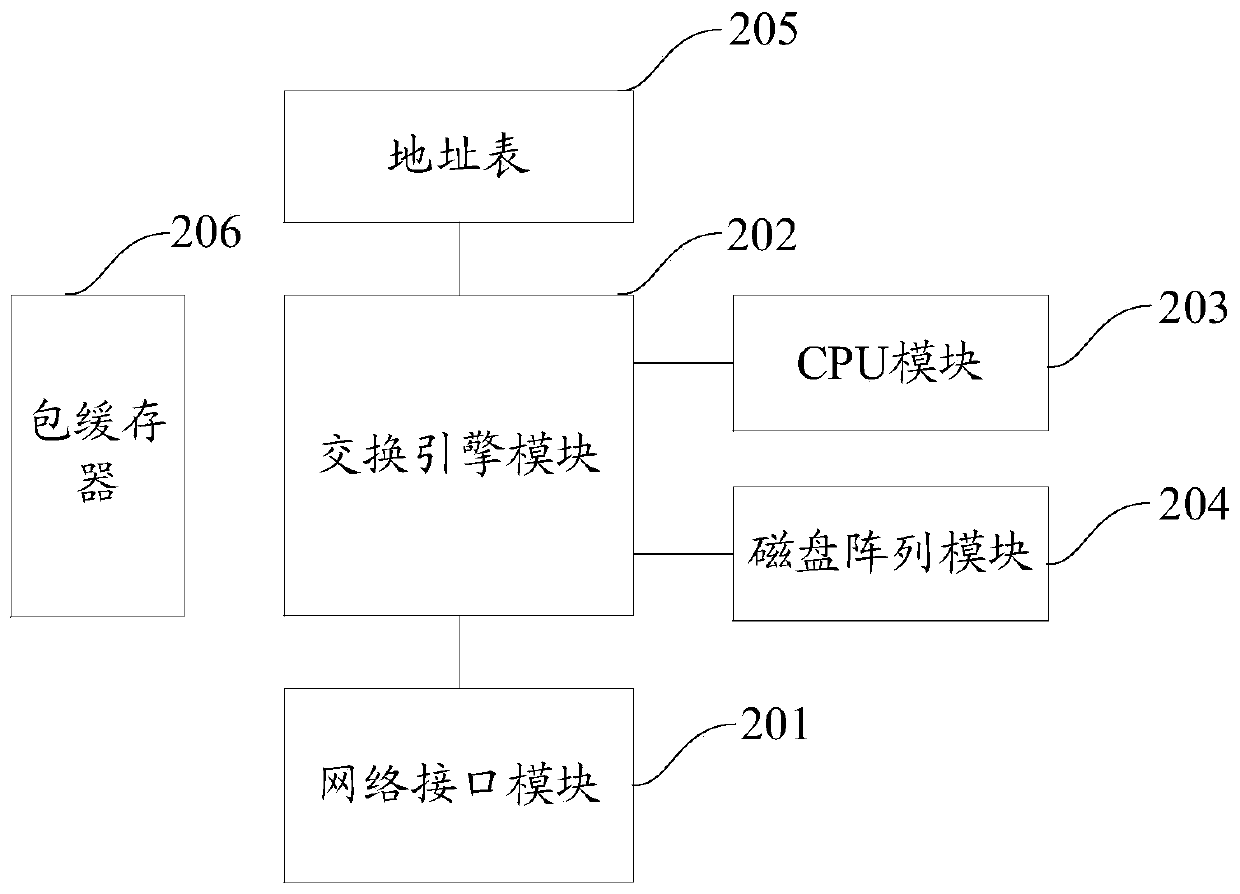

The invention relates to a client server, an intelligent terminal, an online game system and a method, wherein the client server communicates with a client and a main server and comprises a local database, an adjustment module and a local logic module; the local database is used for storing information from the client; the adjustment module is used for judging whether a request from the client can be processed locally at the client serve; and the local logic module is used for processing the request from the client when the judgment module judges that the request from the client can be processed locally at the client serve, and is also used for synchronizing the information stored in the local database to the main server. The invention can be used to relieve the load of the main server of an online game and prevent plug-in and other cheating means.

Owner:爱思开电讯投资(中国)有限公司

Emergency isolation valve controller with integral fault indicator

ActiveUS7504961B2Improve performanceReduce complexityOperating means/releasing devices for valvesTesting/monitoring control systemsFault indicatorIsolation valve

A local logic solver operates with a local smart valve controller to control and test a local field-mounted emergency isolation valve device, outputting a local indication of trouble on the device, which is mounted in the field away from the facility's central control panel for the process. Accordingly, the operation of the overall system is simplified by eliminating the need for an external computer to diagnose any problems. A local control panel includes an indicator light substantially adjacent to or in close proximity to the device being monitored to alert personnel of detected faults. Detected faults are time-stamped locally to generate documentation and to track the elapsed time, starting when the degraded state of the device was detected and first signaled as a problem.

Owner:SAUDI ARABIAN OIL CO

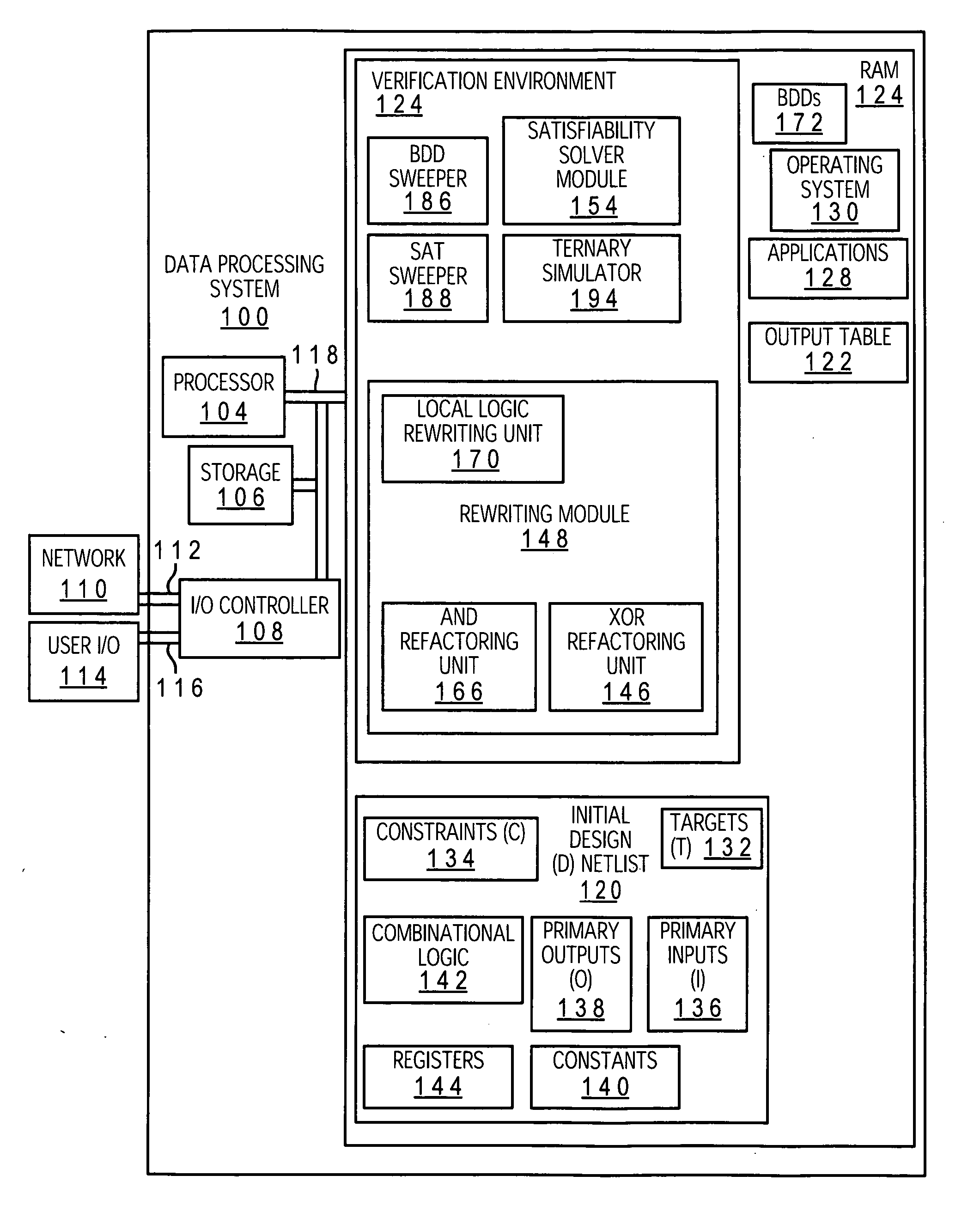

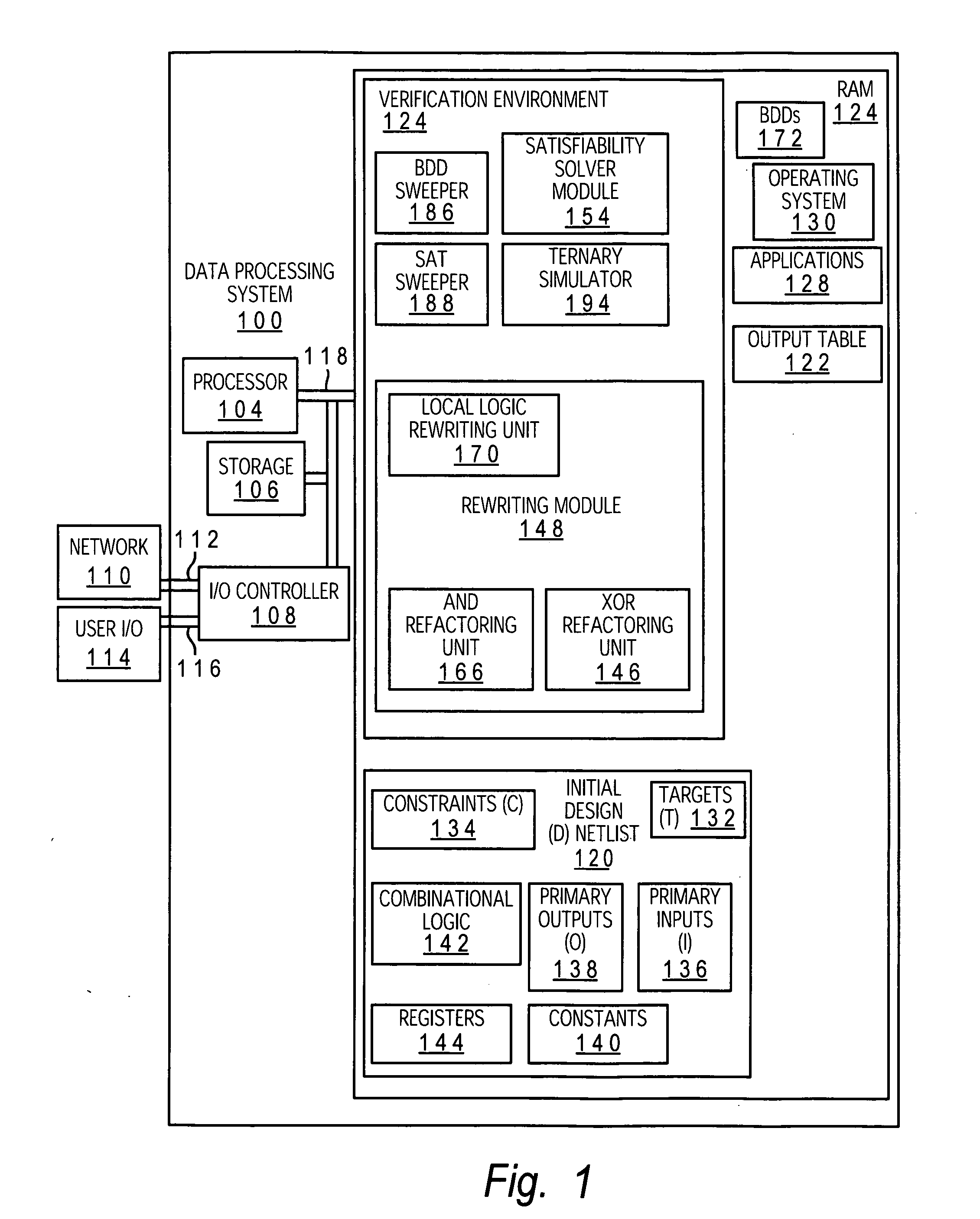

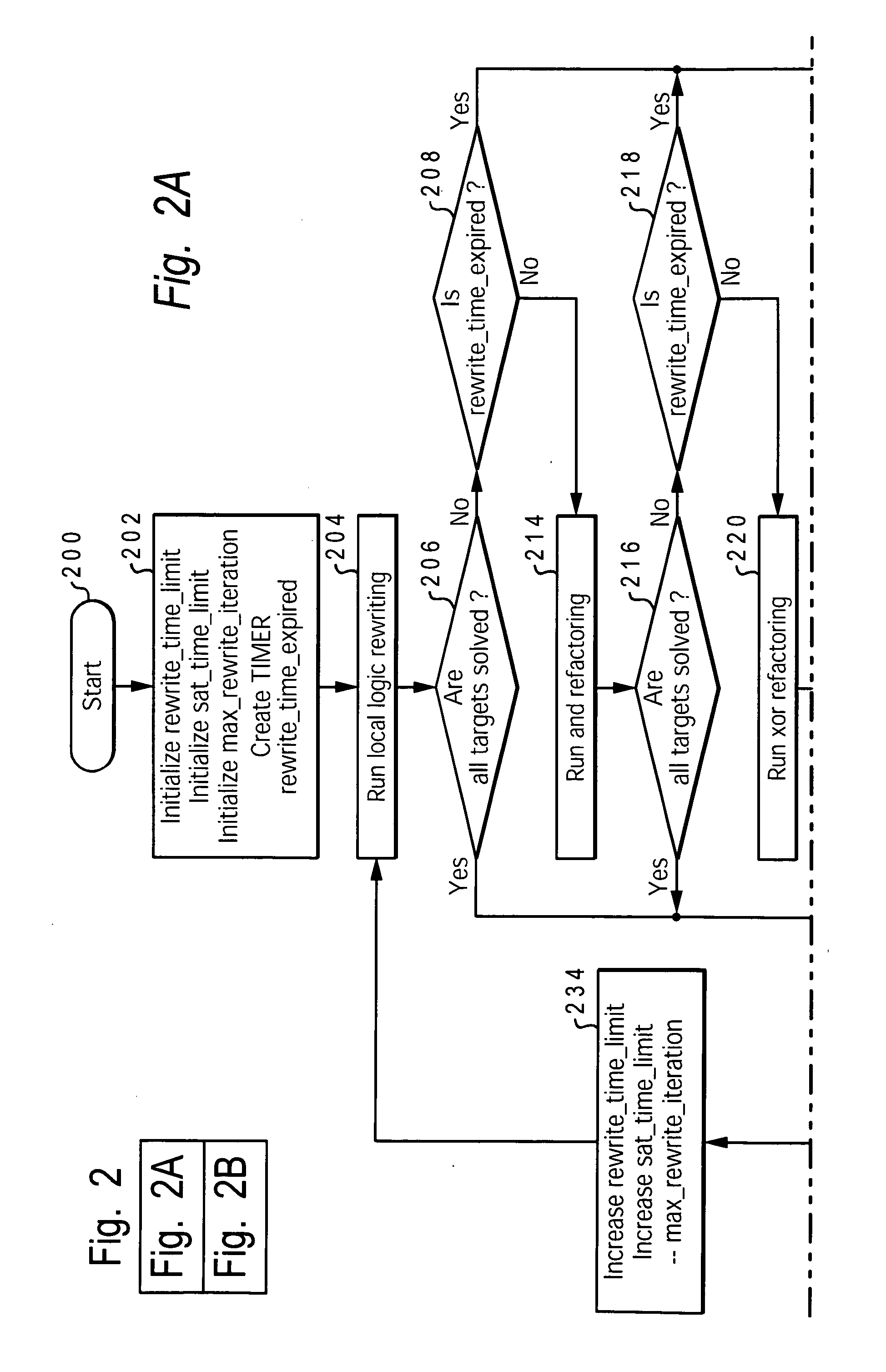

Method and system for enhanced verification by closely coupling a structural satisfiability solver and rewriting algorithms

A method, system and computer program product are disclosed. The method includes initializing a first variable to limit a rewrite time for rewrite operations with respect to an initial design by a rewriting module, a second variable to limit a time for satsifability solver operations with respect to said initial design by a staisfiability solver module and a third variable to limit a maximum number of rewrite iterations with respect to said initial design. A timer is called to track said rewrite time and a local logic rewriting operation is run on said initial design with said rewrite module. In response to determining that all of all targets for said initial design netlist are not solved, whether a rewrite time is expired is determined. In response to determining that said rewrite time is not expired, AND refactoring is run. In response to determining that said rewrite time is not expired, XOR refactoring is run.

Owner:INT BUSINESS MASCH CORP

Local emergency isolation valve controller with diagnostic testing and trouble indicator

InactiveUS8072343B2Easy to operateImpact system performanceOperating means/releasing devices for valvesWork measurementFault indicatorDocumentation procedure

A local logic solver that operates with a local smart valve controller to control, test and monitor performance characteristics of a local field-mounted emergency isolation valve device, outputting a local indication of trouble on the device, which is mounted in the field away from the facility's central control panel for the process. The local logic solver includes a recording function and memory for retrieval of detected faults that are time-stamped and recorded locally to generate documentation and to track the elapsed time, starting when the degraded state of the device was detected and first signaled as a problem; other performance data is also recorded. Accordingly, the operation of the overall system is simplified by eliminating the need for an external computer to diagnose any problems. A local control panel preferably includes pushbuttons and lights used during routine operations of the valve and a fault indicator light substantially adjacent to or in close proximity to the device being monitored to alert personnel of detected faults.

Owner:SAUDI ARABIAN OIL CO

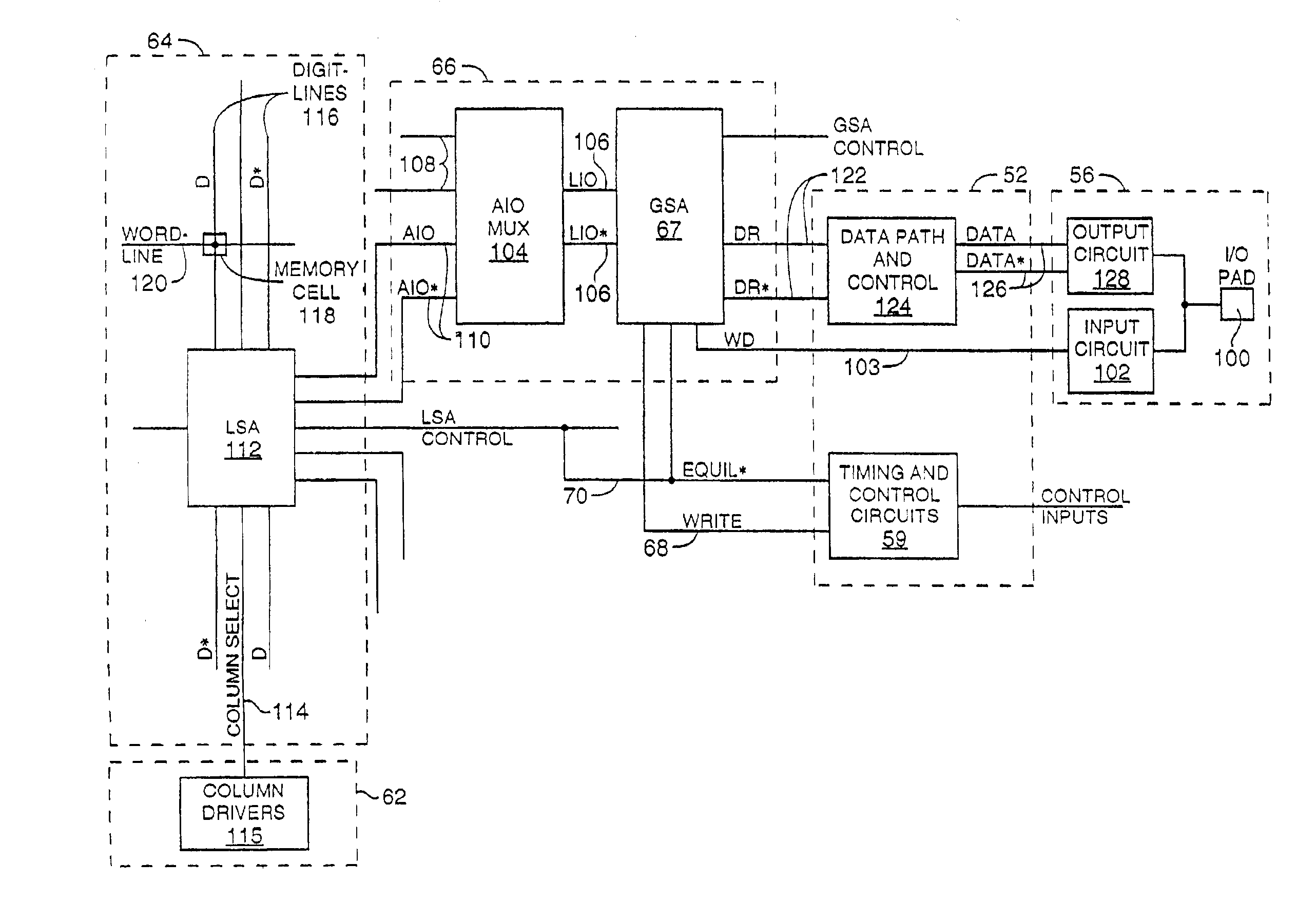

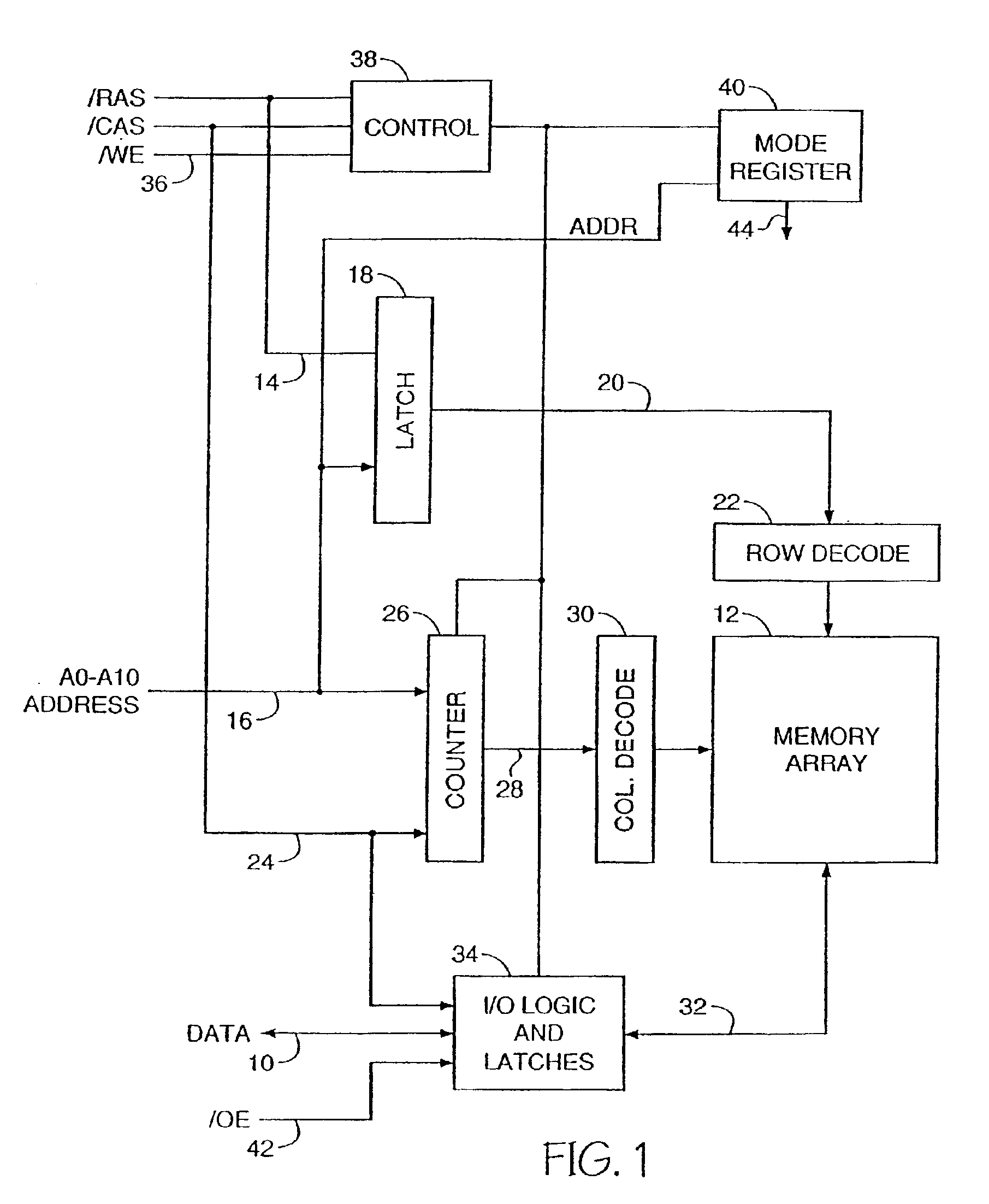

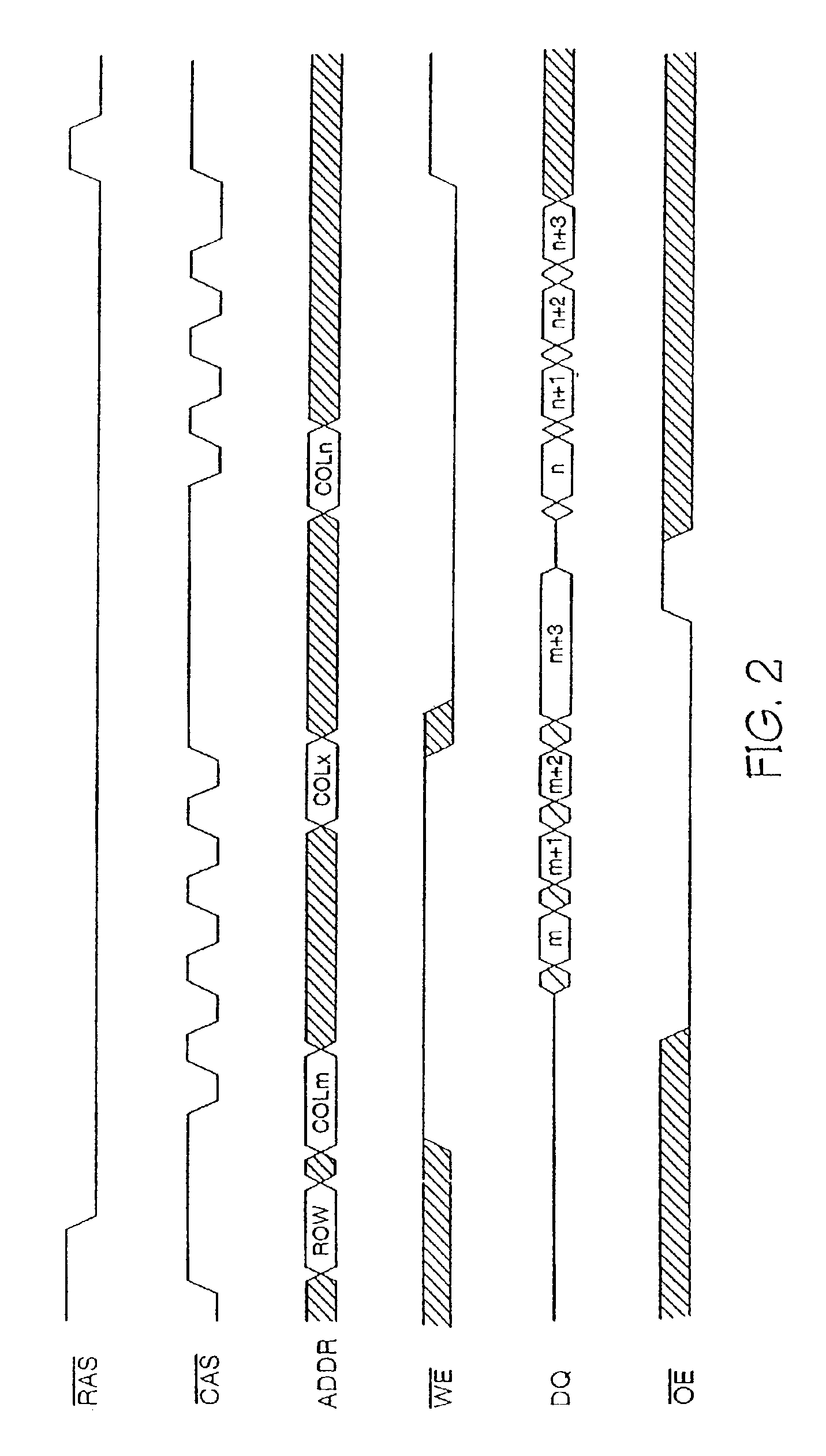

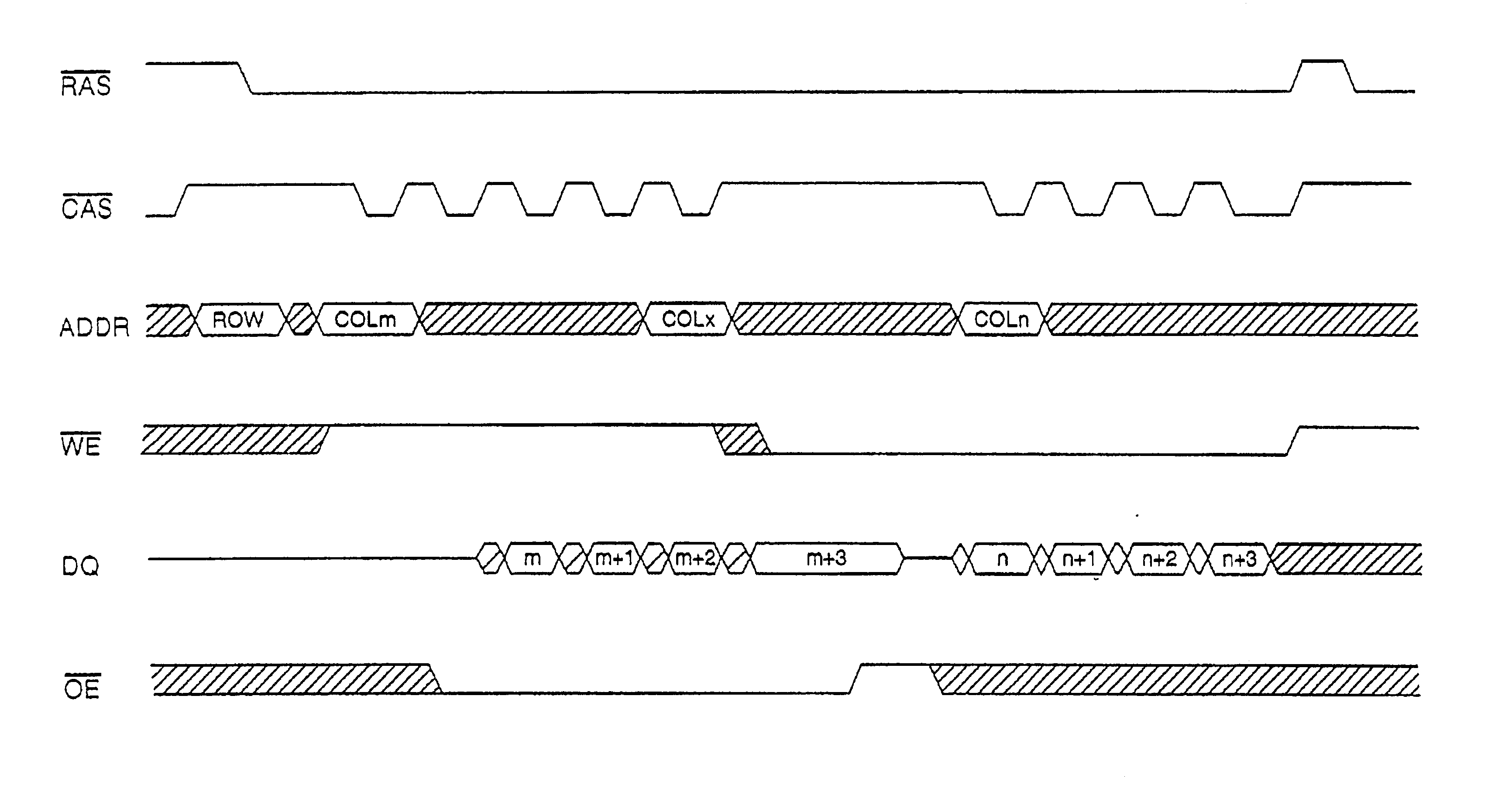

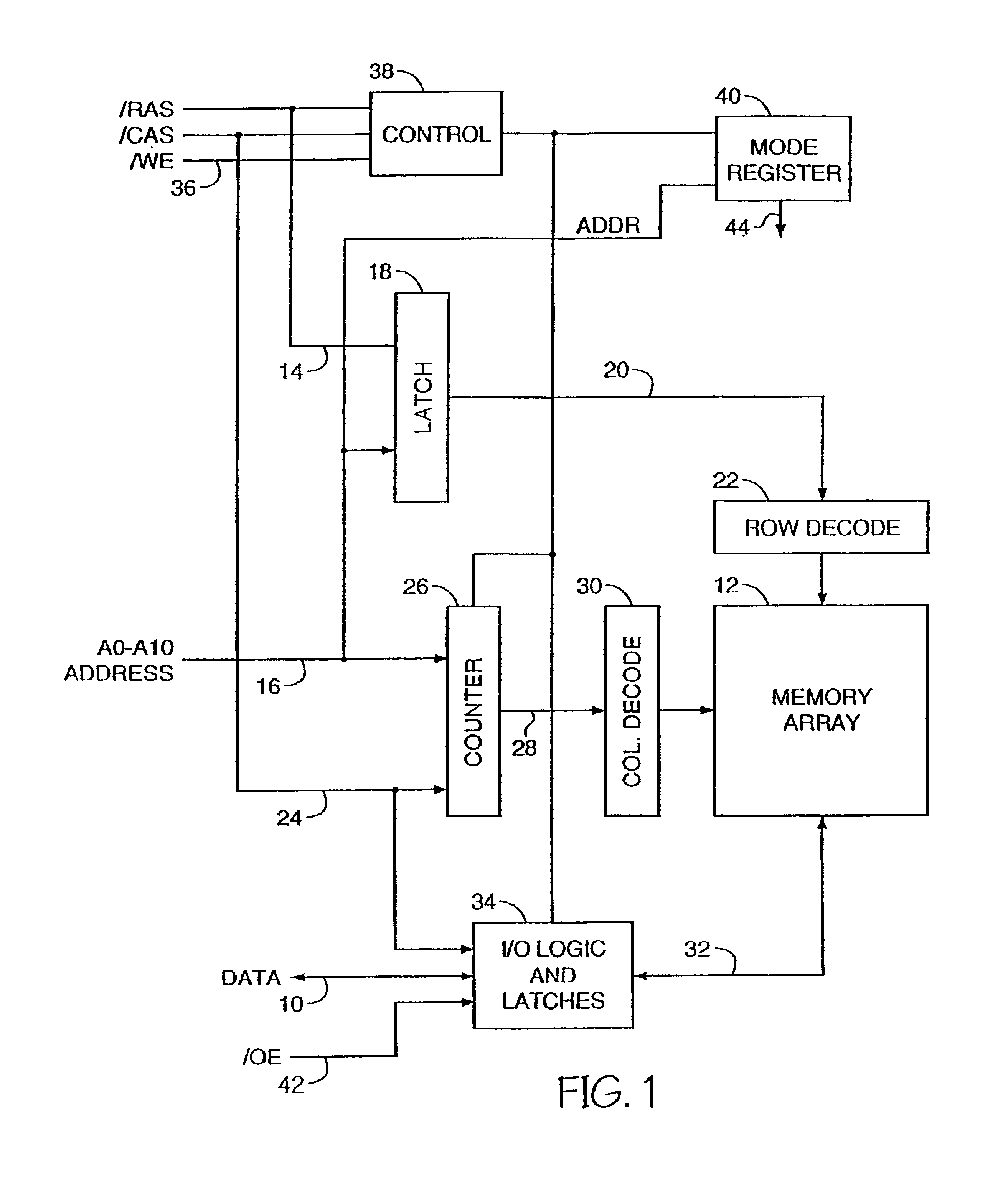

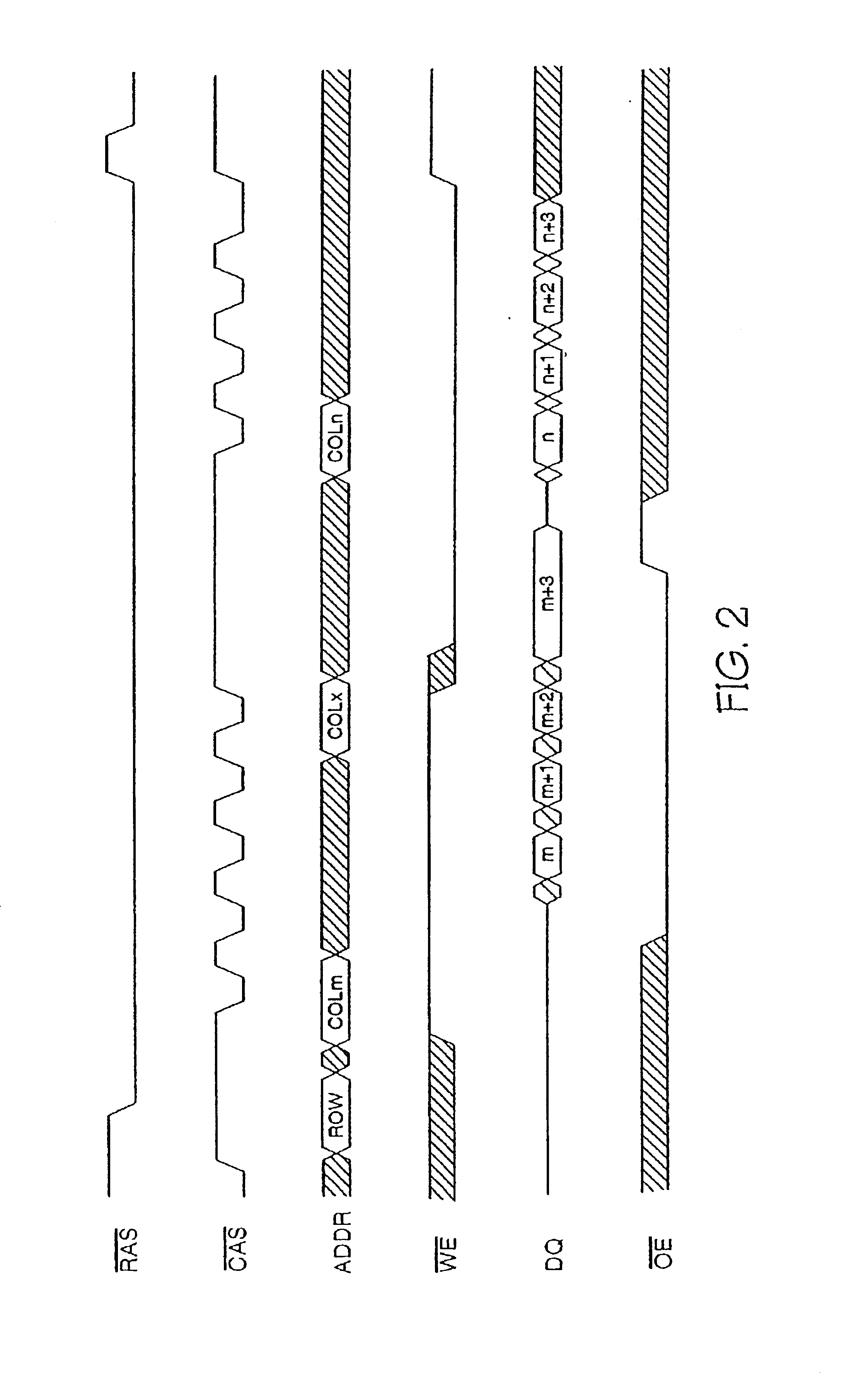

Distributed write data drivers for burst access memories

InactiveUS6914830B2High speed data accessIncrease speedMemory architecture accessing/allocationMemory adressing/allocation/relocationMemory addressCycle control

An integrated circuit memory device is designed to perform high speed data write cycles. An address strobe signal is used to latch a first address. During a burst access cycle the address is incremented internal to the device with additional address strobe transitions. A new memory address is only required at the beginning of each burst access. Read / Write commands are issued once per burst access eliminating the need to toggle the Read / Write control line at the device cycle frequency. A transition of the Read / Write control line during a burst access is used to terminate the burst access and initialize the device for another burst access. Write cycle times are maximized to allow for increases in burst mode operating frequencies. Local logic gates near a nay sense amplifiers are used to control write is data drivers to provide for maximum write times without crossing current during input / output line equilibration periods. By gating global write enable signals with global equilibrate signals locally at data sense amp locations, local write cycle control signals are provided which are valid for essentially the entire cycle time minus an I / O line equilibration period in burst access memory devices. For nonburst mode memory devices such as EDO and Fast Page Mode, the write function may begin immediately following the end of the equilibration cycle to provide a maximum write time without interfering with the address setup time of the next access cycle.

Owner:ROUND ROCK RES LLC

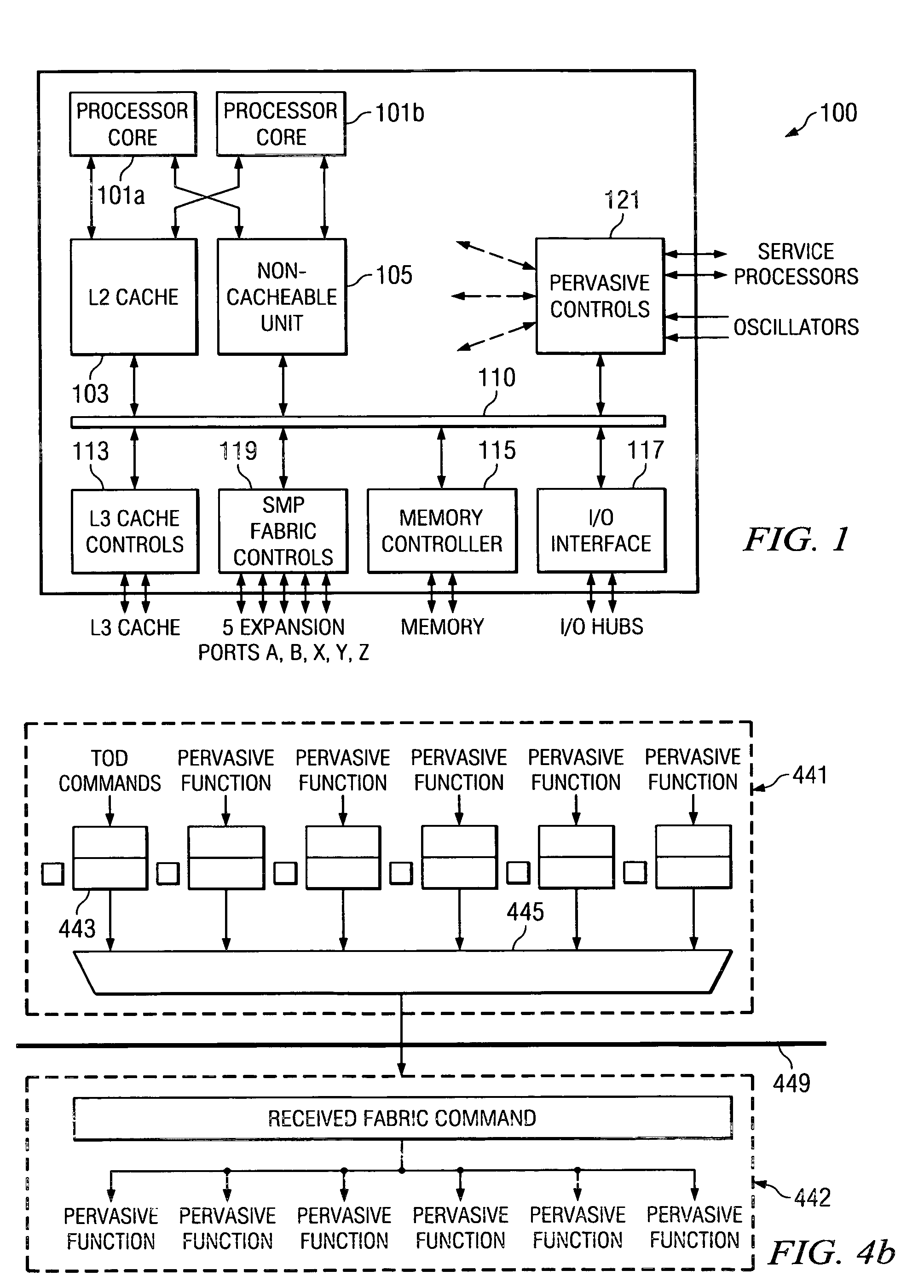

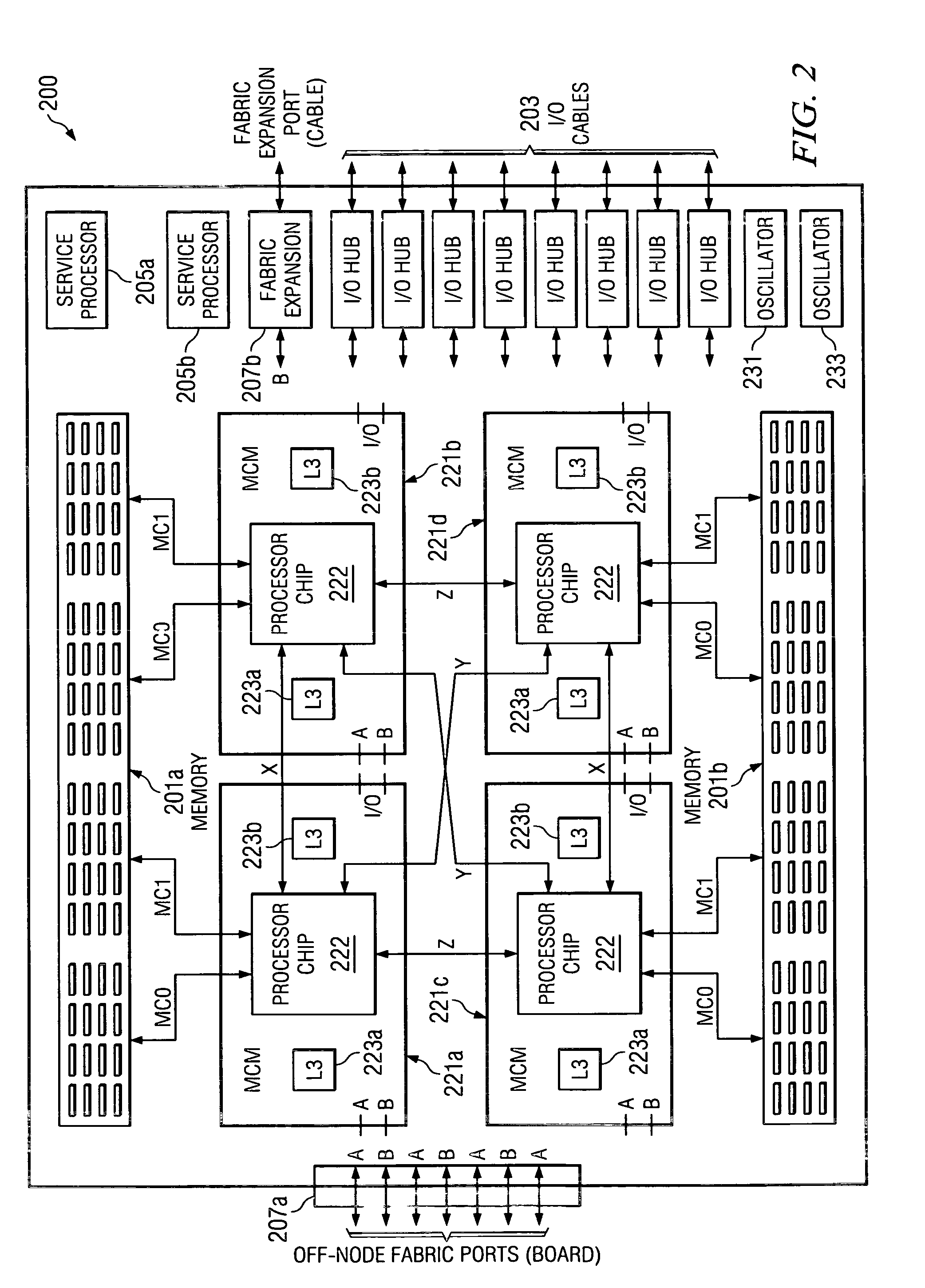

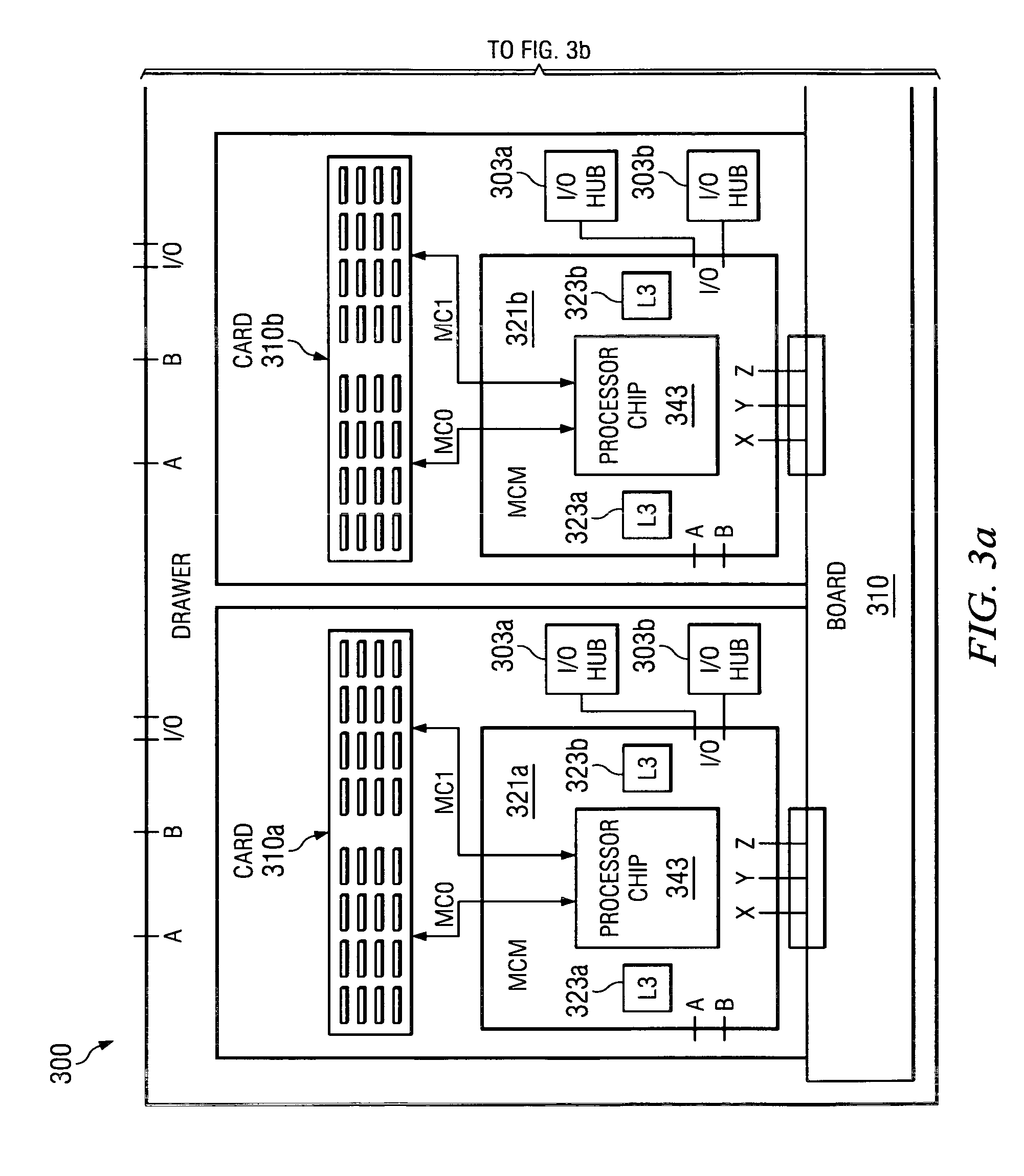

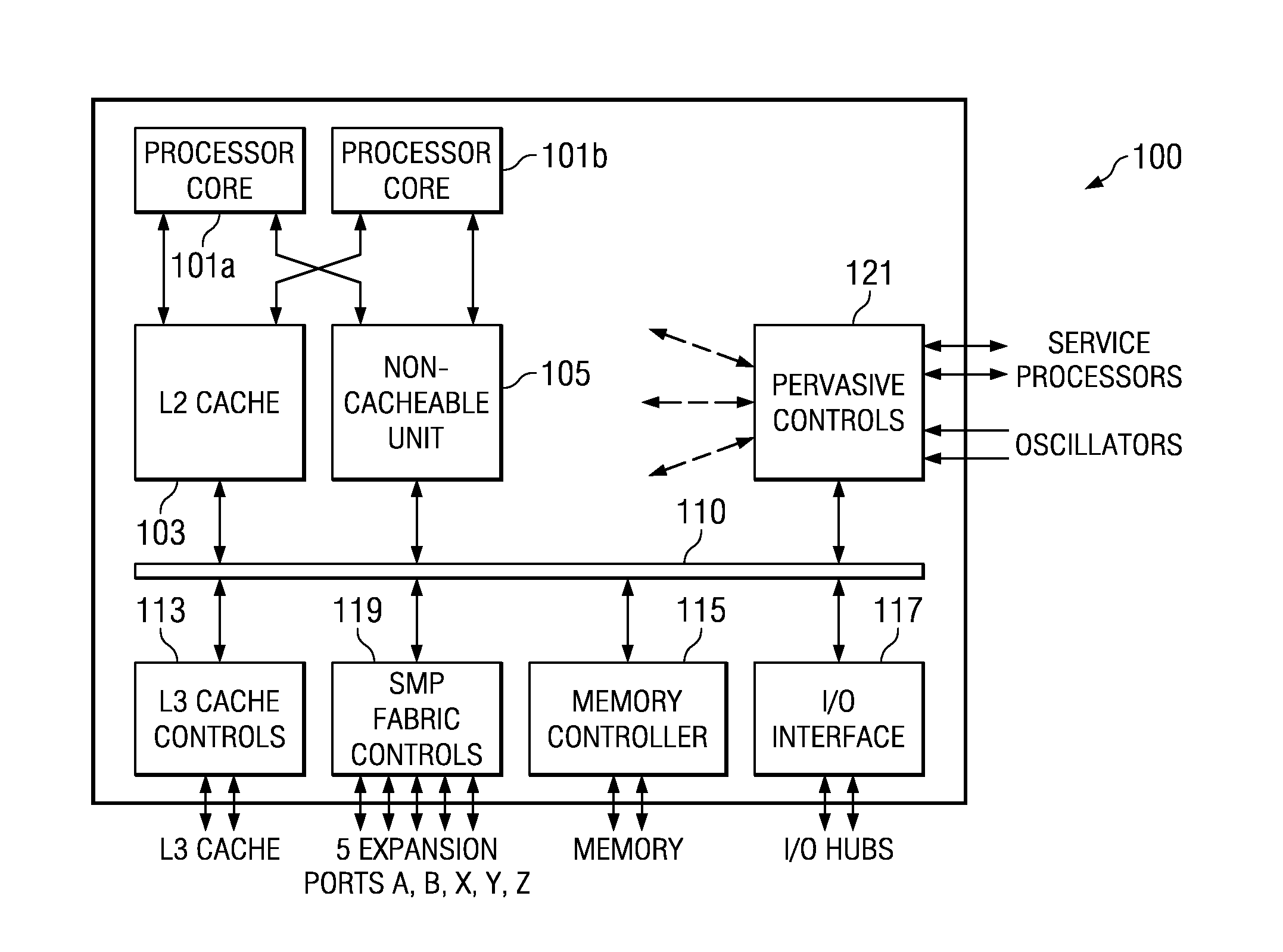

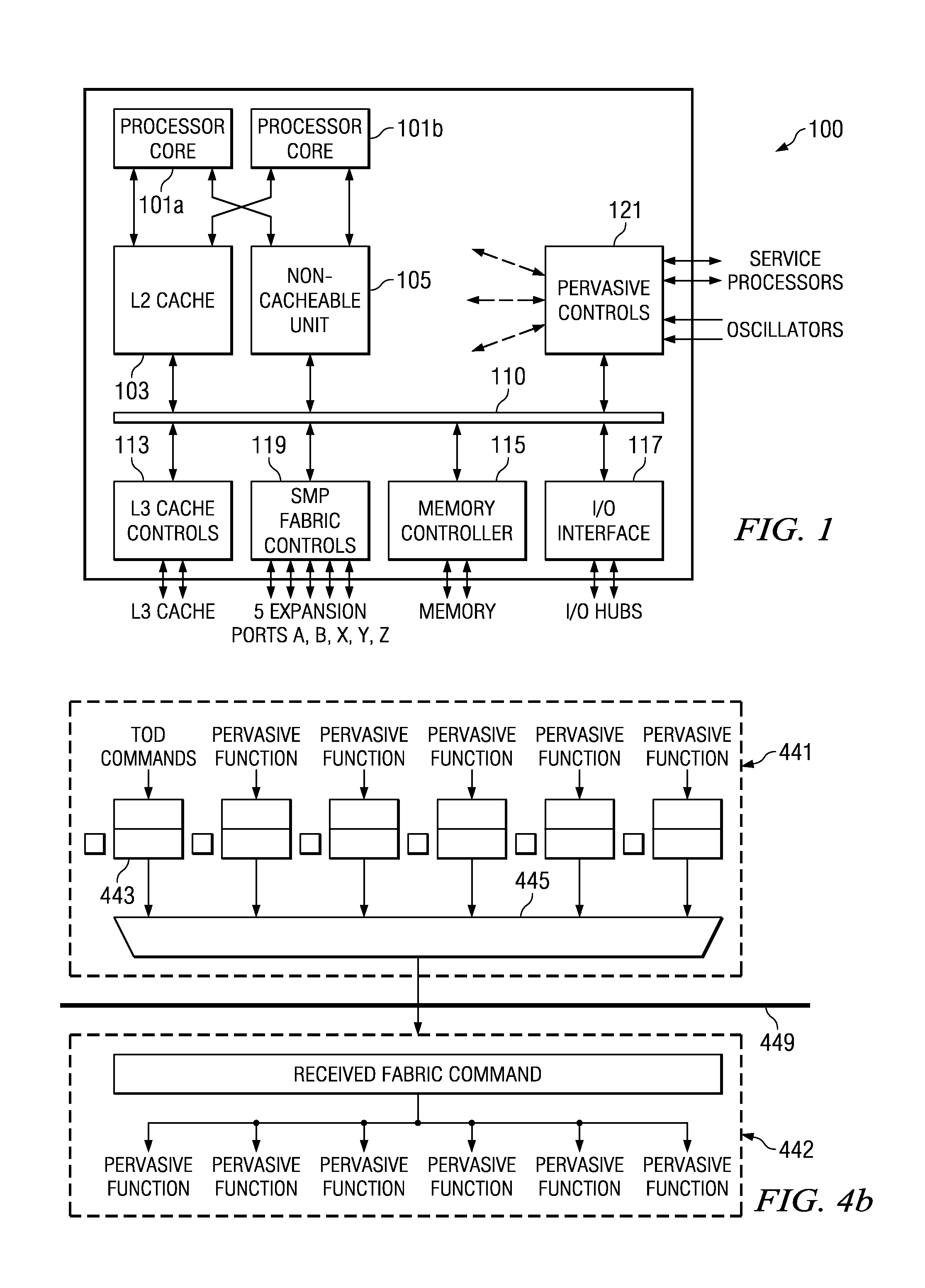

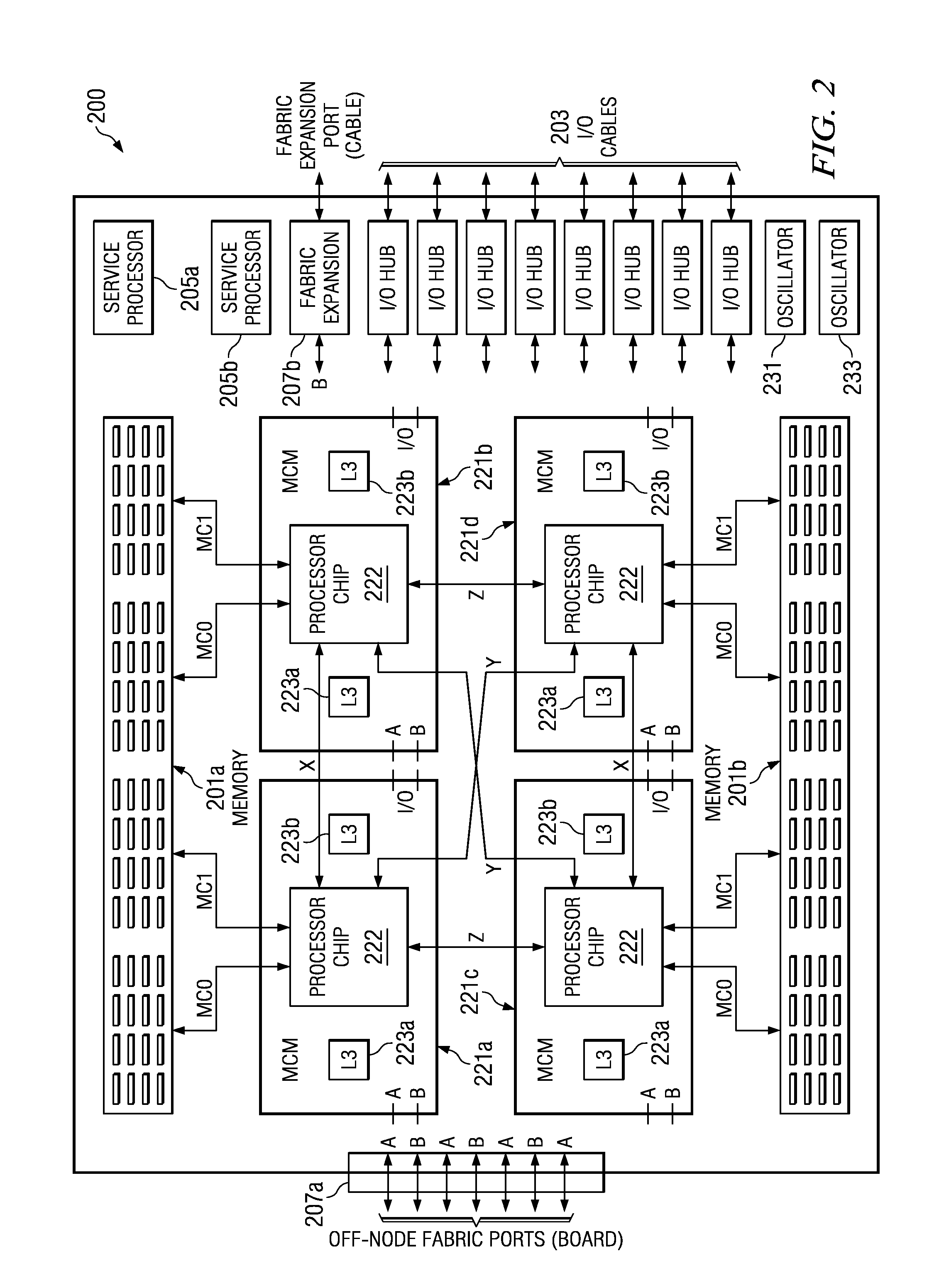

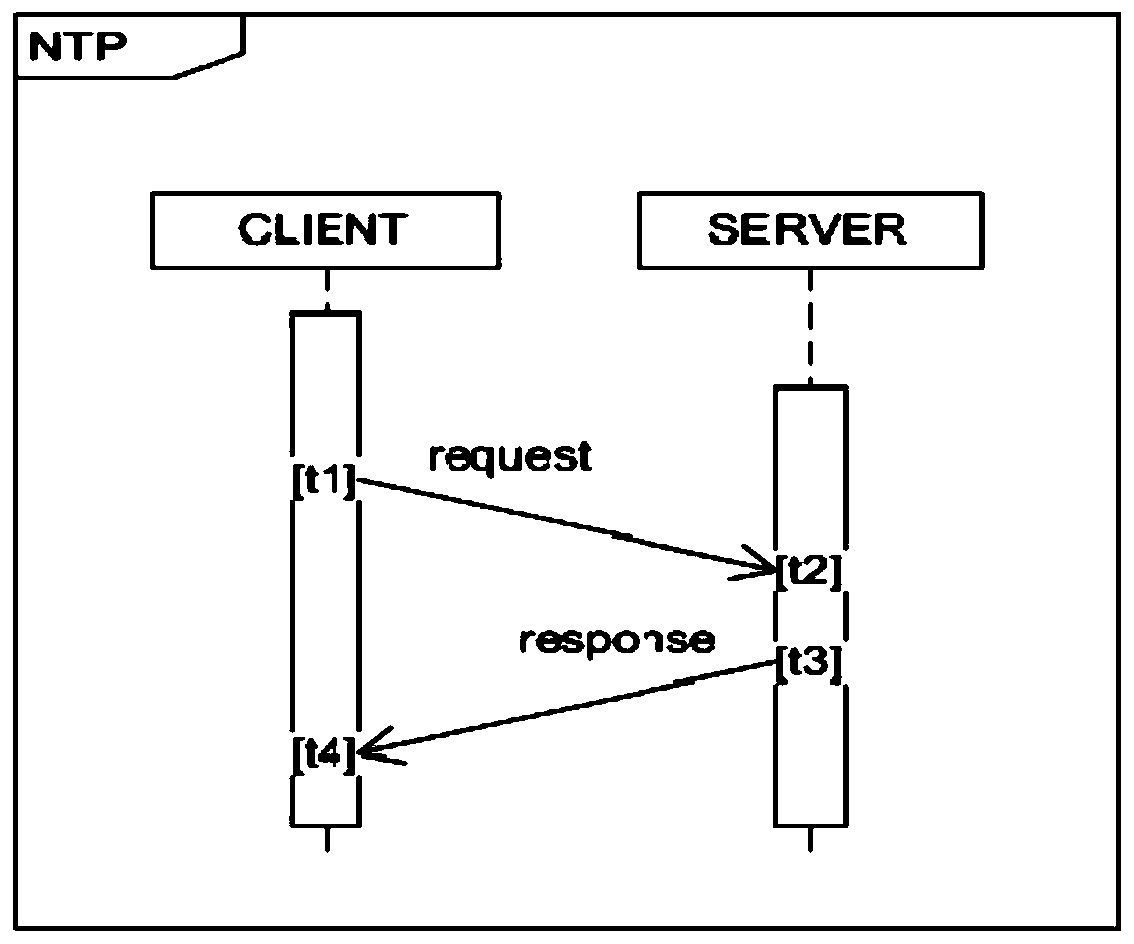

Method and apparatus for fault tolerant time synchronization mechanism in a scaleable multi-processor computer

ActiveUS20060179364A1Avoid lostMultiple digital computer combinationsGenerating/distributing signalsMulti processorControl register

Redundant time-of-day (TOD) oscillators are aligned, within a master oscillator path, to local logic oscillator and used to create independent step-sync signals. A step checker validates and provides selection signals to identify which of the TOD oscillators operates according to a criterion. Independent step-sync signals are transmitted to several sibling chips. Local step and sync signals are delayed to arrive at TOD register nearly synchronous with TOD registers in sibling chips. A slave oscillator path may be used to select time signals generated in a sibling chip, whereby the master oscillator path is deselected. A primary control register set may be used to configure which among several chips is a master chip using the master oscillator path. All remaining chips are slave chips. All segments of the topology are redundant. One of multiple possible alternate topologies is defined in a secondary control register set. Commands and TOD values are passed on the fabric at predefined time increment boundaries to establish, restore, or maintain synchronization across all chips.

Owner:IBM CORP

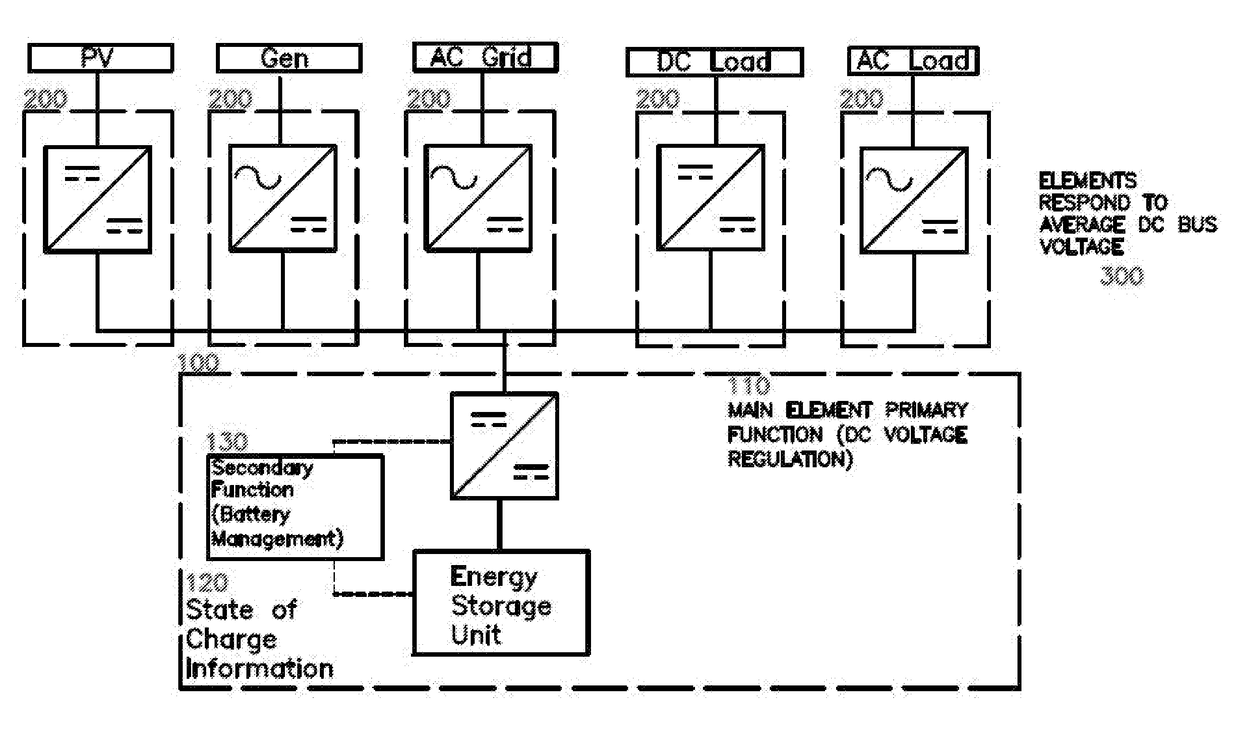

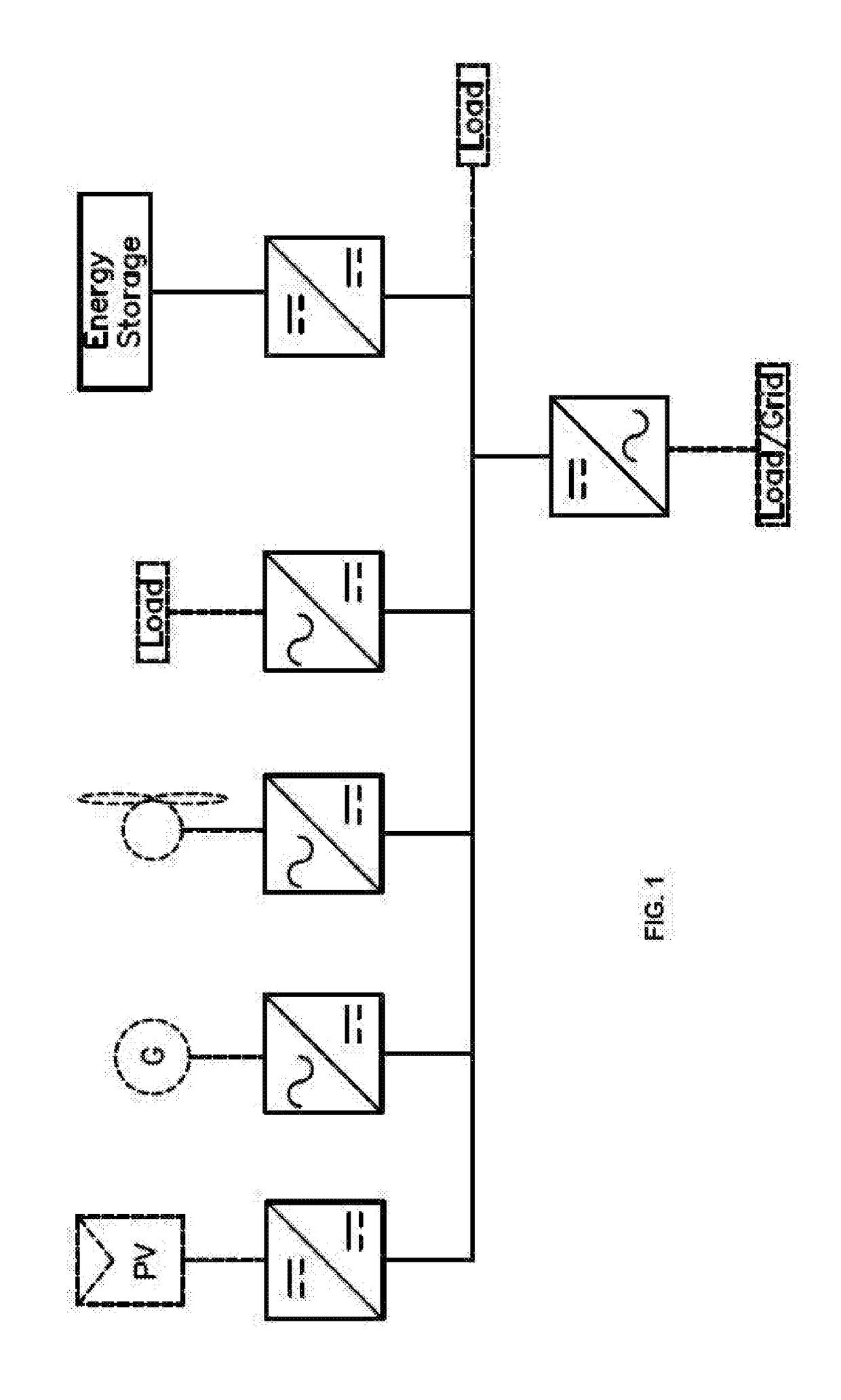

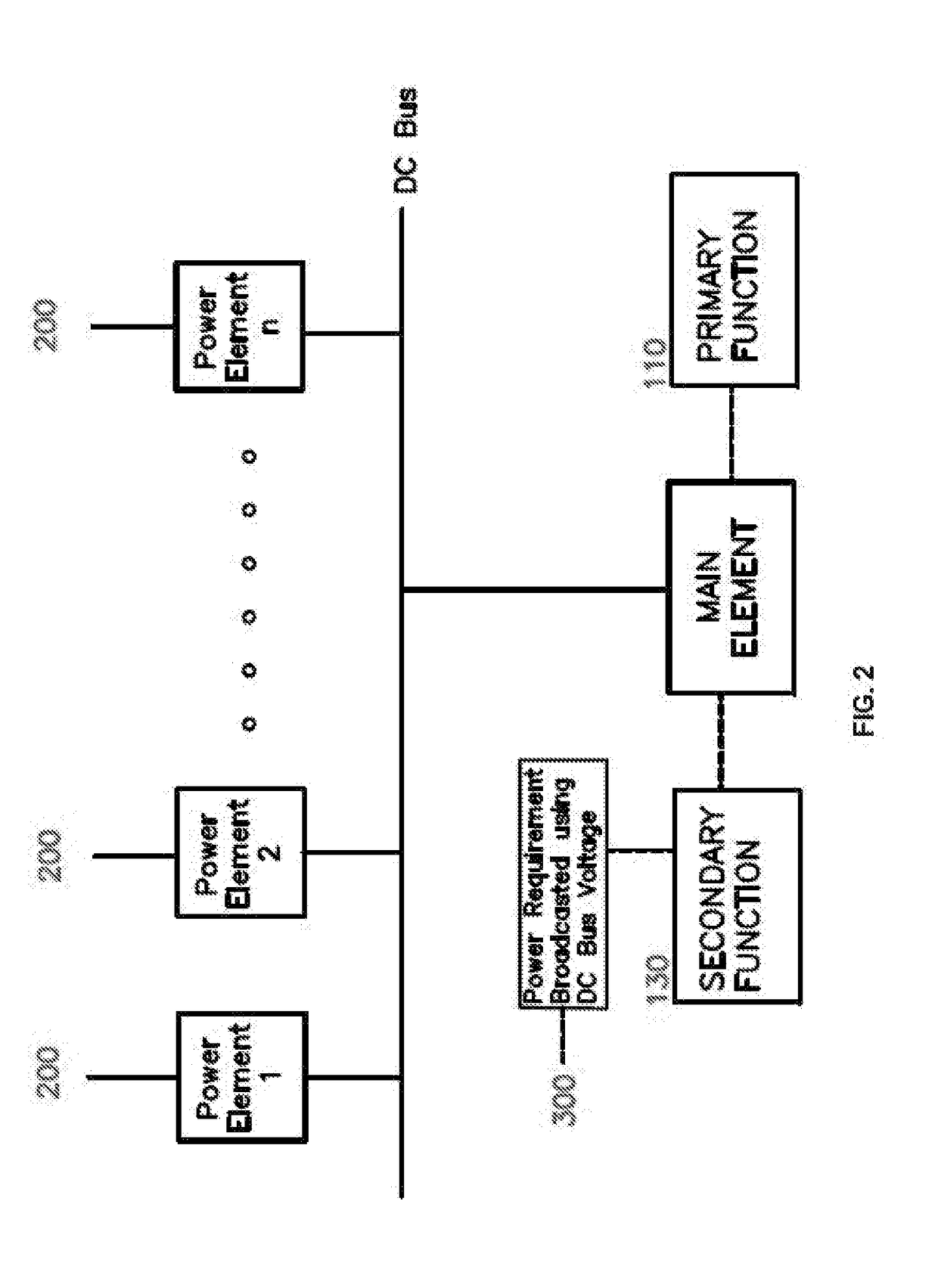

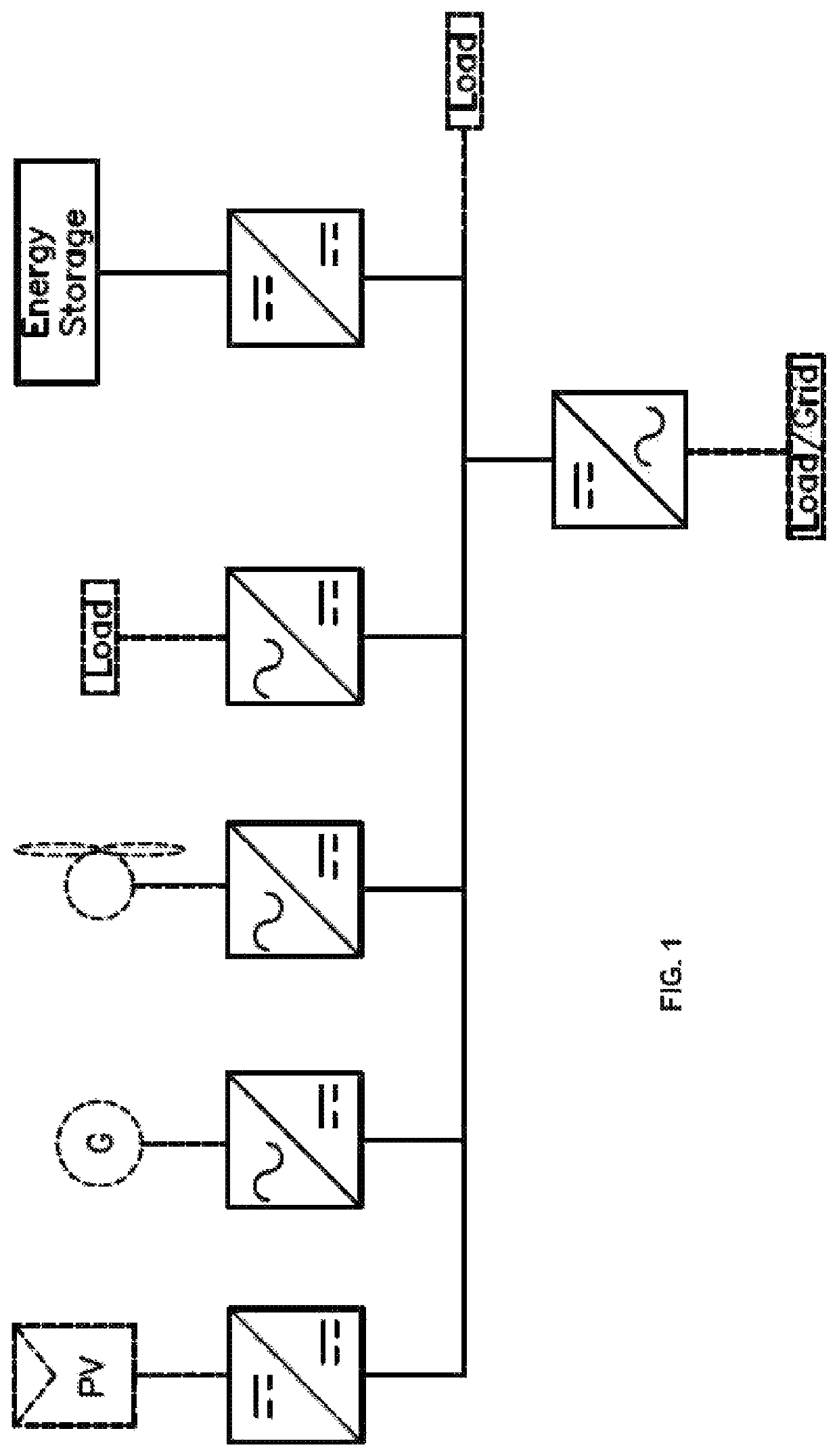

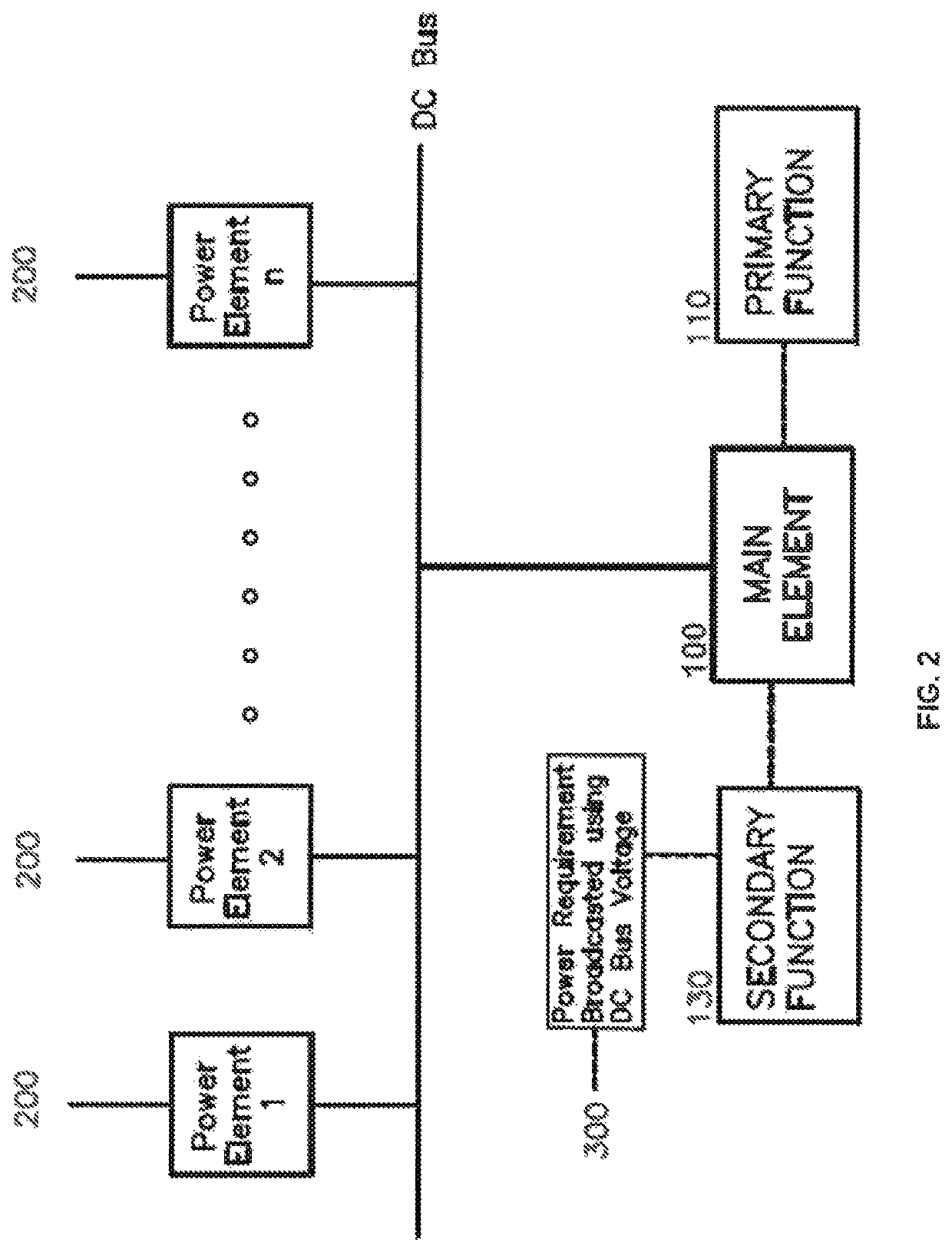

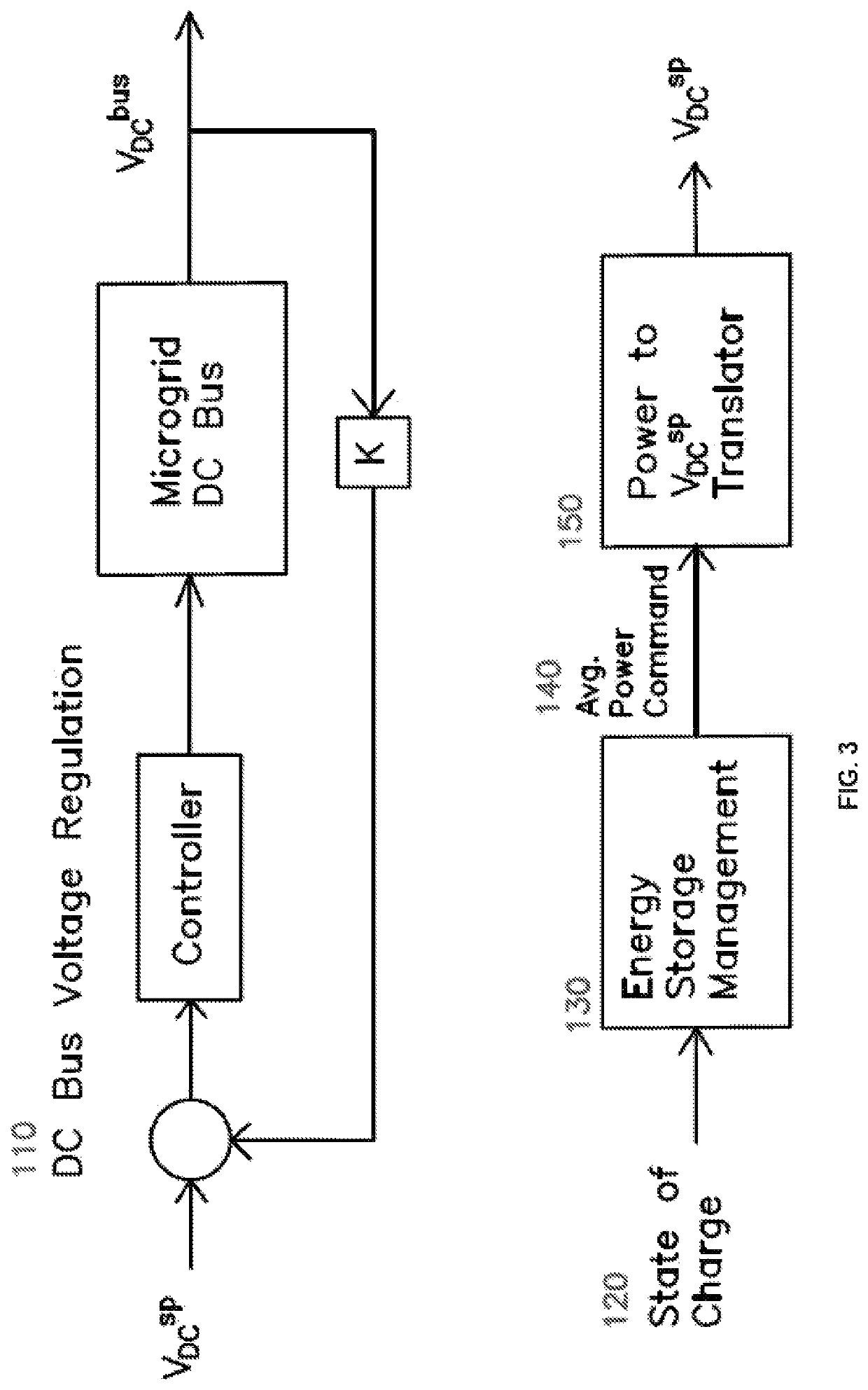

Power management concept in DC distributed systems

ActiveUS20180198276A1Improve system stabilityAchieving self-calibrationLoad balancing in dc networkSingle network parallel feeding arrangementsPower componentDC-BUS

A method includes the steps of providing a common DC bus to interconnect power elements to a DC distribution system using power converters. A first group of one or more of the elements (main element) is used to execute the primary function by automatically maintaining the DC bus voltage following a set point. The DC bus voltage set point is intentionally changed with slow dynamics according to a secondary function executed by the main element such that the average DC bus voltage regulated by the main element changes. A local logic is used on each of the power elements connected to the DC bus but different from the main element to modify their power generation or consumption as a result of changes in the measured average DC bus voltage such that they contribute to the fulfillment of the secondary level of control.

Owner:ARDA POWER

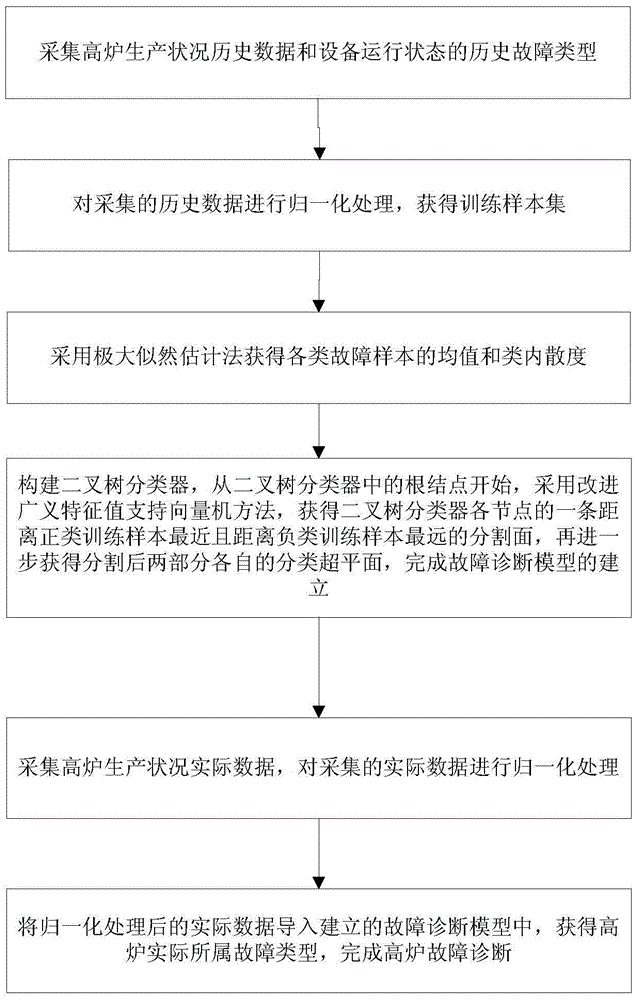

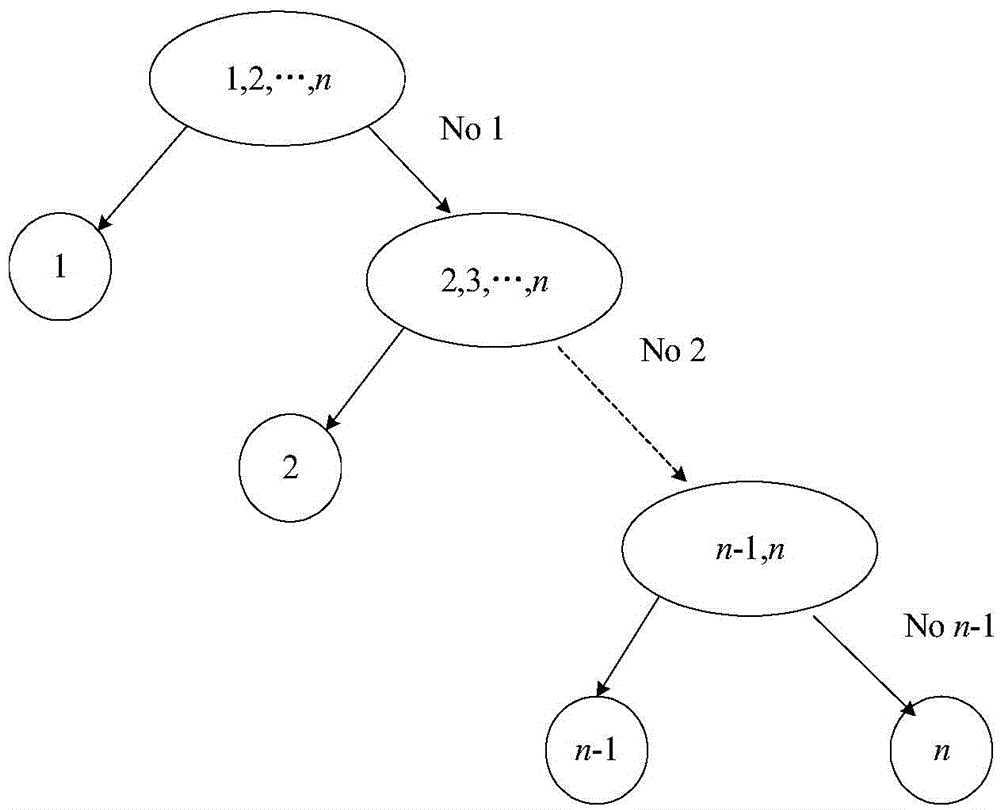

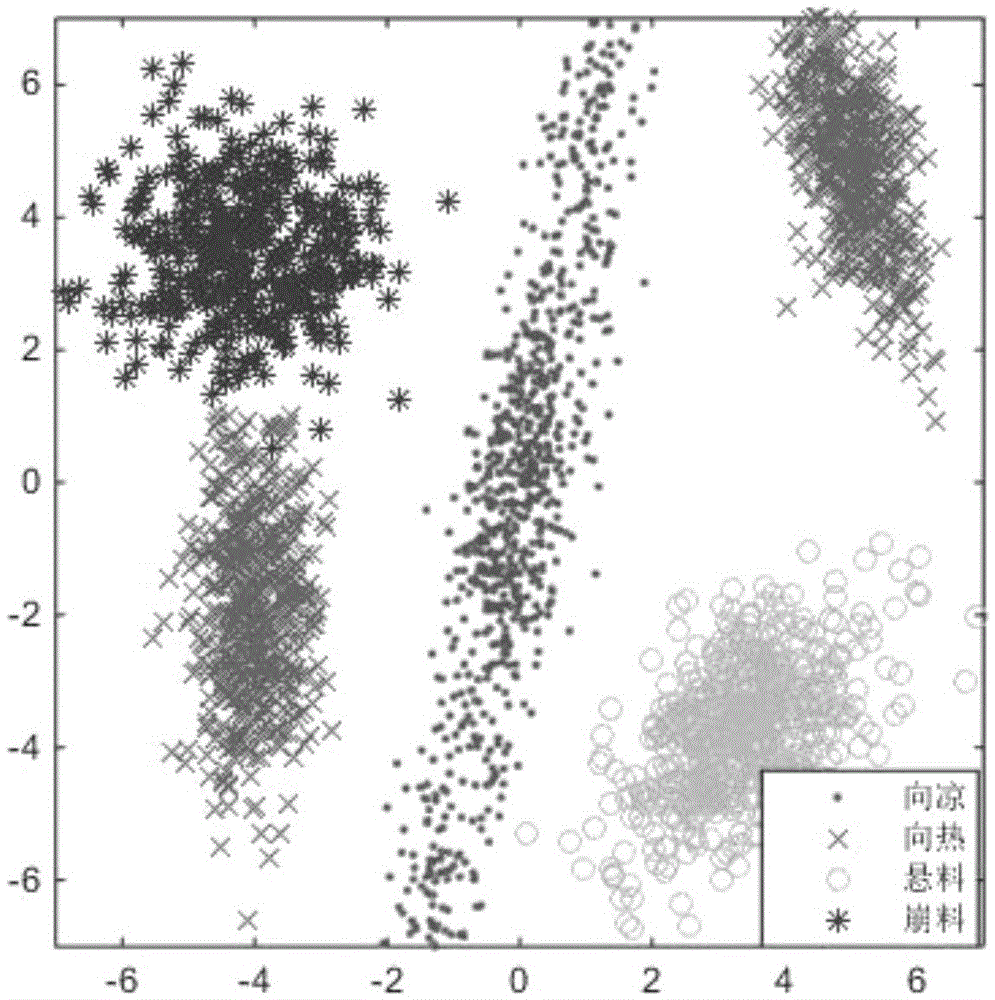

Multi-scale binary tree blast furnace fault diagnosis method based on sample segmentation

InactiveCN105550426ASimple structureReduce complexityGeometric CADSpecial data processing applicationsSupport vector machineDiagnosis methods

The invention discloses a multi-scale binary tree blast furnace fault diagnosis method based on sample segmentation, belonging to the technical field of blast furnace fault diagnosis. The method comprises the following steps of: firstly, acquiring blast furnace production condition and equipment operation state data, detecting the data and performing normalization for the extracted data through a mean-variance normalization method; converting a blast furnace fault diagnosis problem into a dichotomy problem to perform multi-classifier design; finding a segmentation plane through an improved generalized eigenvalue support vector machine, converting into two dichotomy problems, respectively finding a distance measuring matrix having local properties and being adaptive for each type of fault data itself, and designing two classification hyperplanes based on different scales through the support vector machine. The method provided by the invention is suitable for identification of high-dimensional nonlinear fault data; and by means of segmenting sample data and measuring similarity among the samples with a multi-scale standard, the method gives consideration to global and local logic structures of the identified data, reduces complexity of the identified fault problem and improves precision of fault diagnosis.

Owner:NORTHEASTERN UNIV

Method for Fault Tolerant Time Synchronization Mechanism in a Large Scaleable Multi-Processor Computer

InactiveUS20080215906A1Avoid lostMultiple digital computer combinationsGenerating/distributing signalsMulti processorProcessor register

Redundant time-of-day (TOD) oscillators are aligned, within a master oscillator path, to local logic oscillator and used to create independent step-sync signals. A step checker validates and provides selection signals to identify which of the TOD oscillators operates according to a criterion. Independent step-sync signals are transmitted to several sibling chips. Local step and sync signals are delayed to arrive at TOD register nearly synchronous with TOD registers in sibling chips. A slave oscillator path may be used to select time signals generated in a sibling chip, whereby the master oscillator path is deselected. A primary control register set may be used to configure which among several chips is a master chip using the master oscillator path. All remaining chips are slave chips. All segments of the topology are redundant. One of multiple possible alternate topologies is defined in a secondary control register set. Commands and TOD values are passed on the fabric at predefined time increment boundaries to establish, restore, or maintain synchronization across all chips.

Owner:INT BUSINESS MASCH CORP

Distributed write data drivers for burst access memories

InactiveUS7075857B2High speed data accessIncrease speedMemory architecture accessing/allocationMemory adressing/allocation/relocationMemory addressCycle control

An integrated circuit memory device is designed to perform high speed data write cycles. An address strobe signal is used to latch a first address. During a burst access cycle the address is incremented internal to the device with additional address strobe transitions. A new memory address is only required at the beginning of each burst access. Read / Write commands are issued once per burst access eliminating the need to toggle the Read / Write control line at the device cycle frequency. A transition of the Read / Write control line during a burst access is used to terminate the burst access and initialize the device for another burst access. Write cycle times are maximized to allow for increases in burst mode operating frequencies. Local logic gates near array sense amplifiers are used to control write data drivers to provide for maximum write times without crossing current during input / output line equilibration periods. By gating global write enable signals with global equilibrate signals locally at data sense amp locations, local write cycle control signals are provided which are valid for essentially the entire cycle time minus an I / O line equilibration period in burst access memory devices. For nonburst mode memory devices such as EDO and Fast Page Mode, the write function may begin immediately following the end of the equilibration cycle to provide a maximum write time without interfering with the address setup time of the next access cycle.

Owner:ROUND ROCK RES LLC

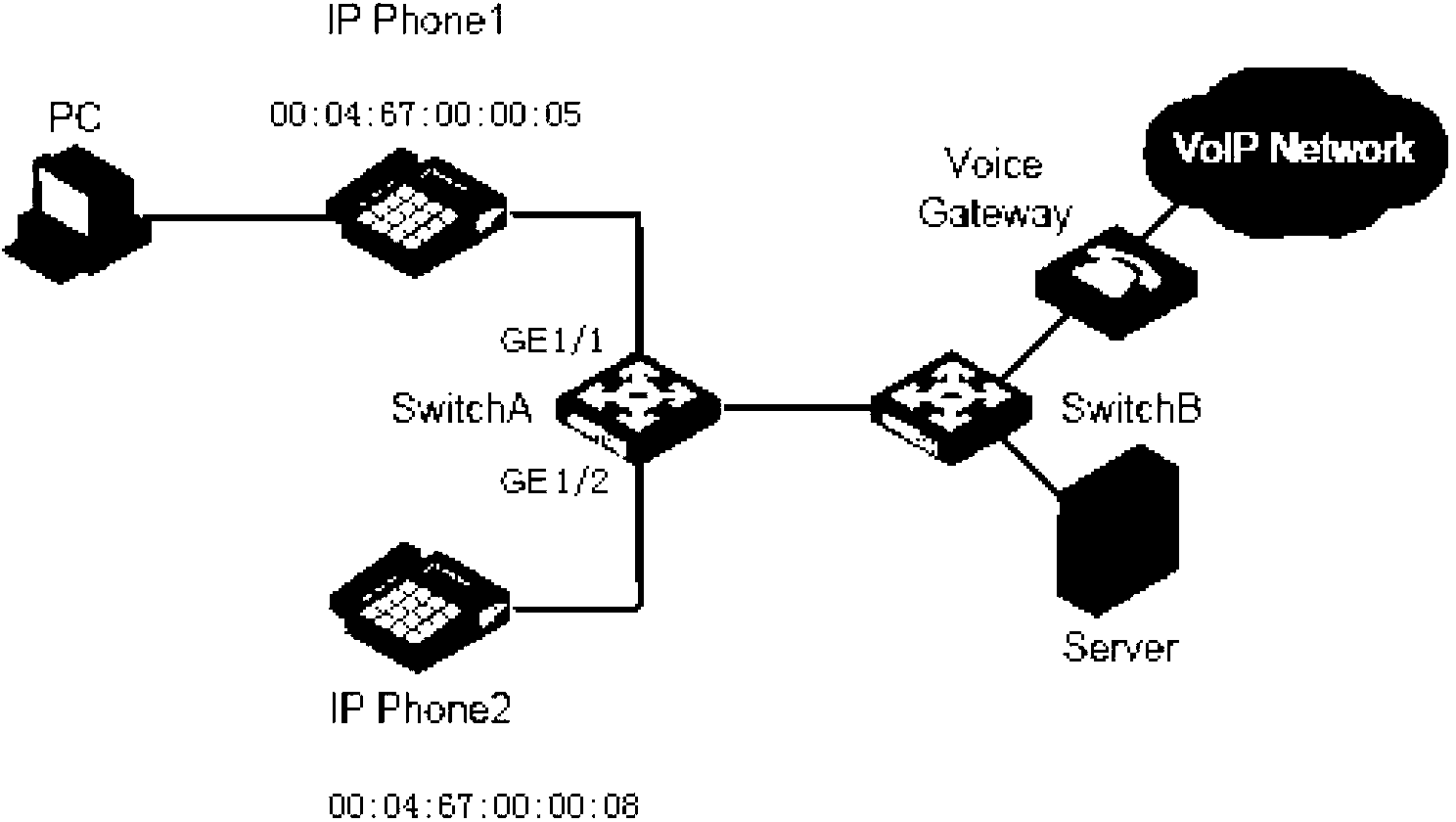

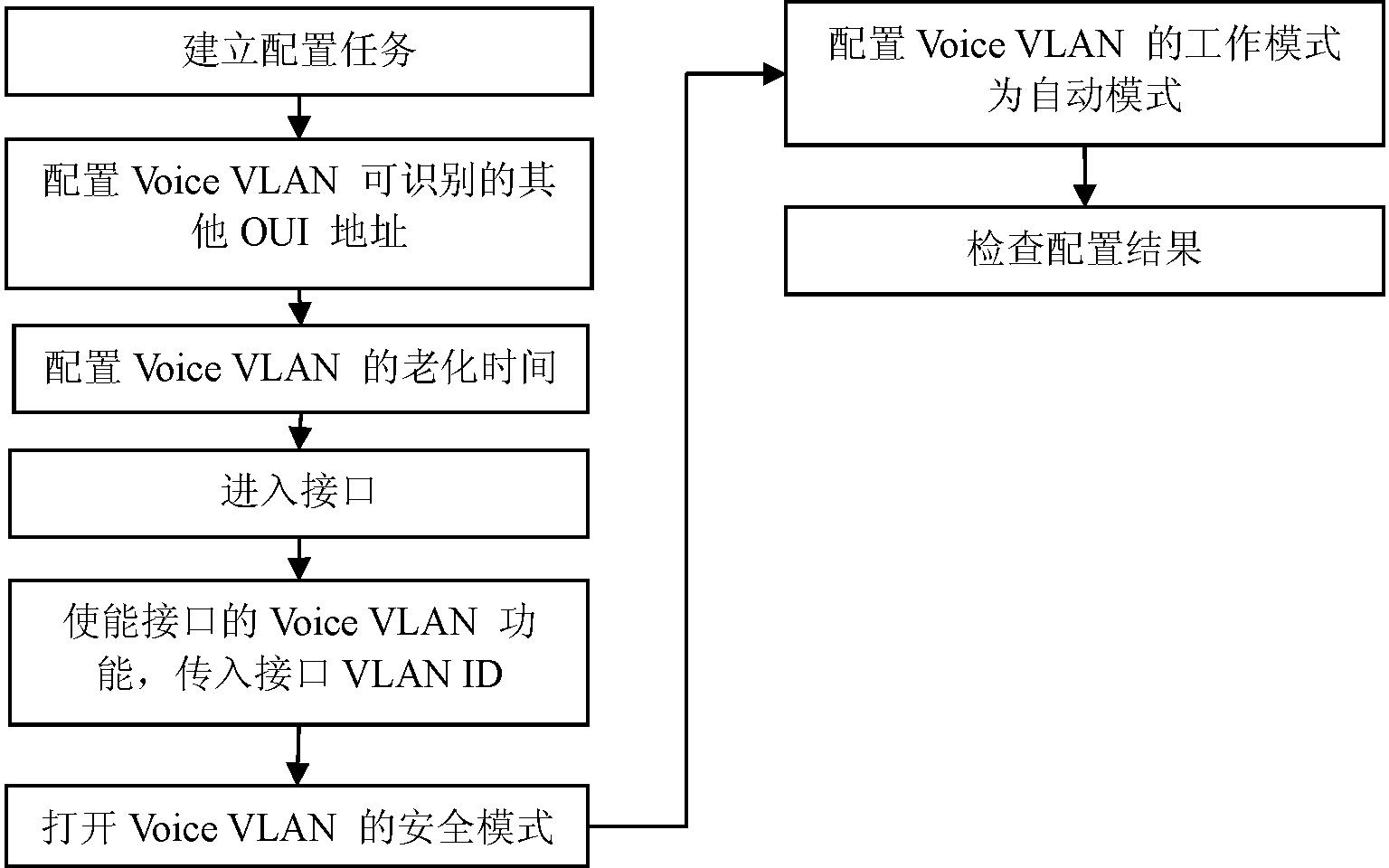

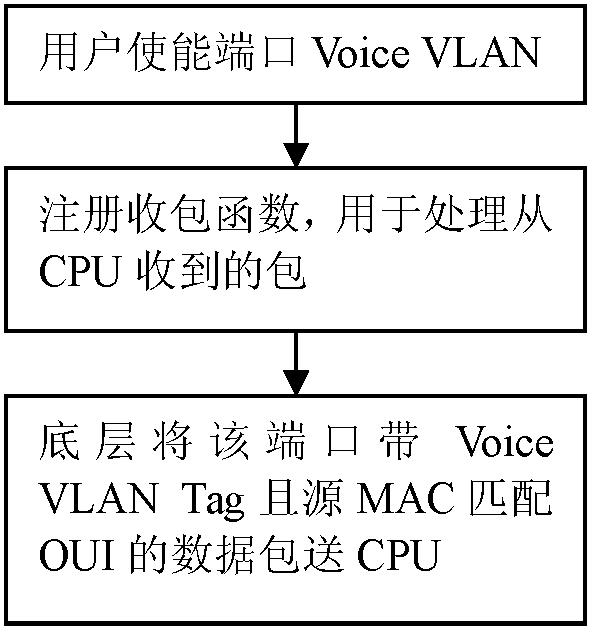

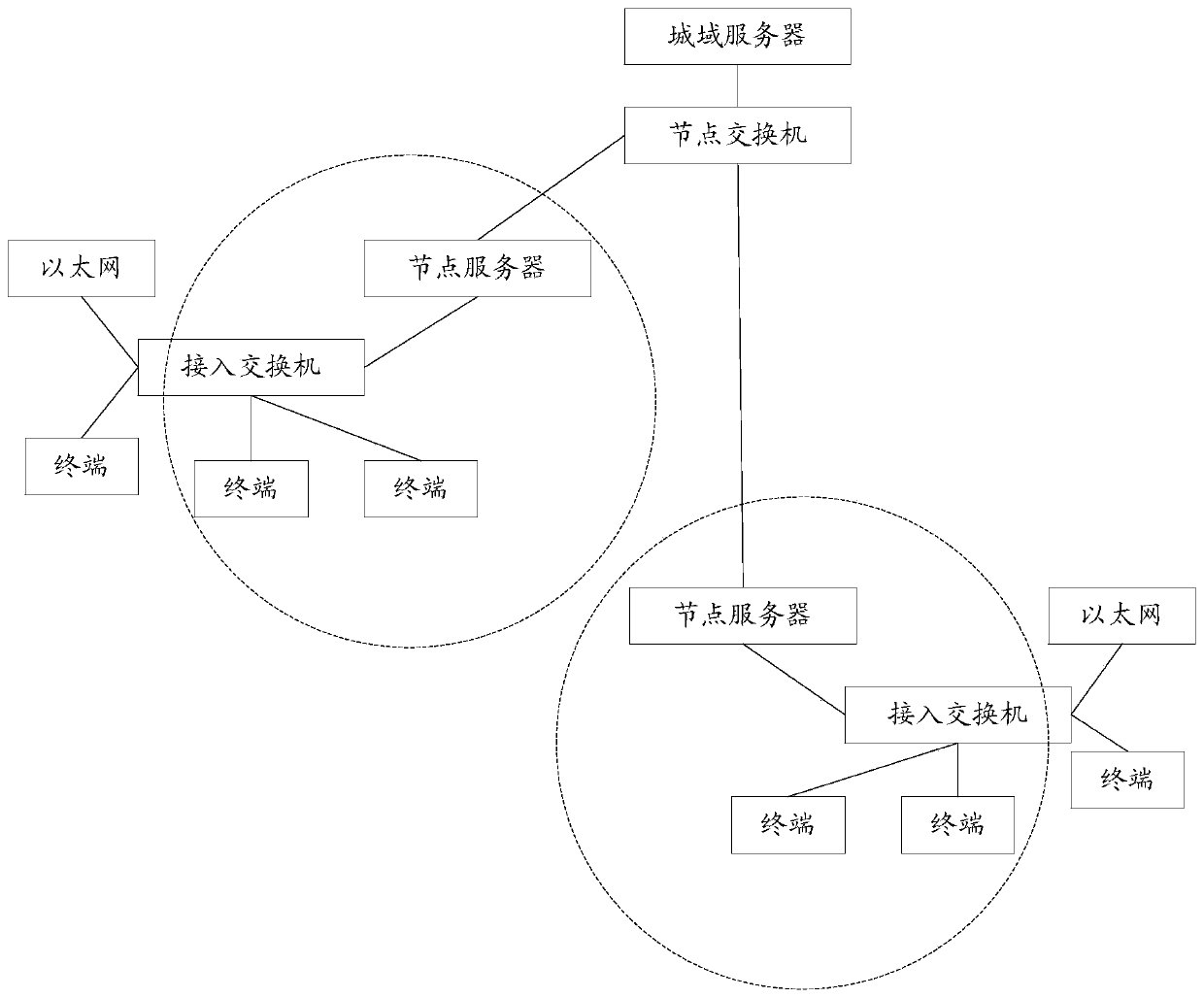

Data transmission method used for Voice VLAN (virtual local logic network)

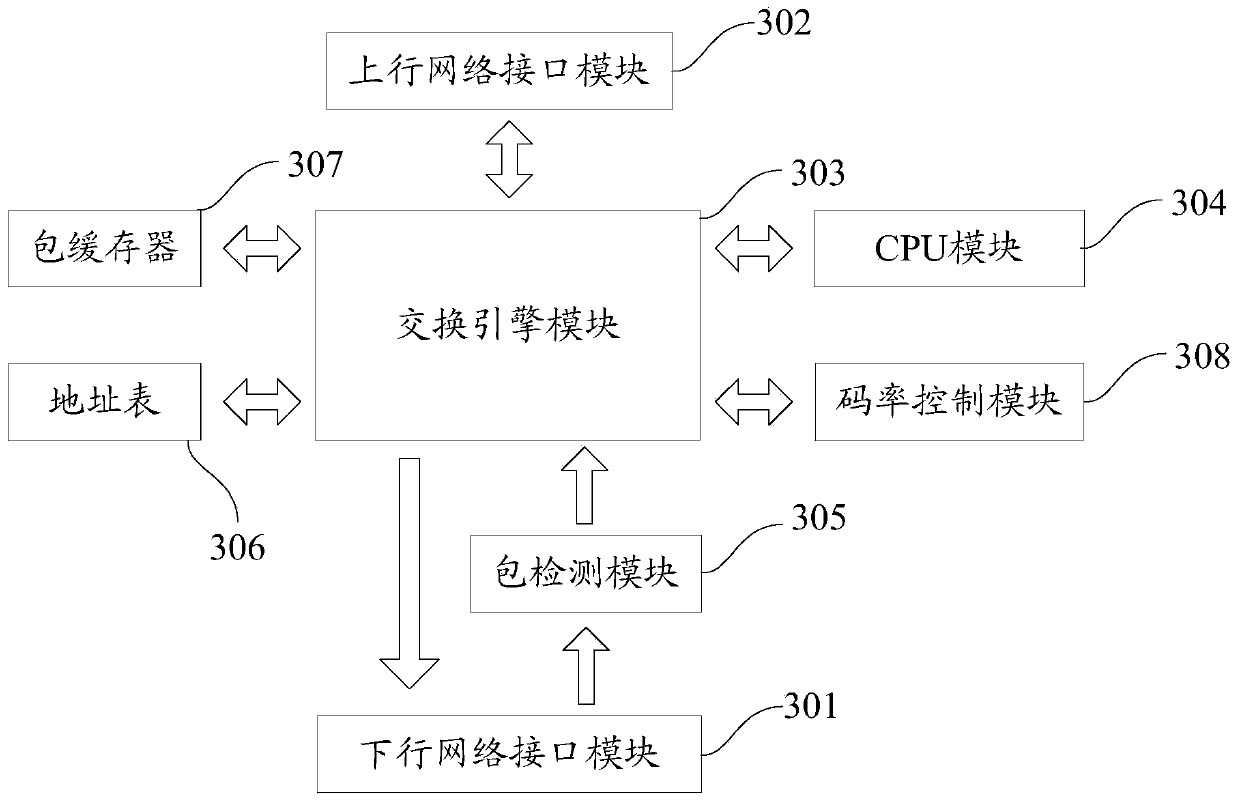

ActiveCN103312908AReduce loadEasy to findInterconnection arrangementsNetworks interconnectionVirtual LANNetwork packet

The invention discloses a data transmission method used for a Voice VLAN (virtual local logic network). The method comprises the steps that A, a port enables the Voice VLAN and sends a data package to a central processing unit (CPU) and registers a package receiving manipulation function to the CPU; B, a received data package is judged according to the packet receiving manipulation function, if the data package meets the preset conditions, the port corresponding to the data package is added into the Voice VLAN and such data packages are transmitted in the Voice VLAN in the mode of high priority, wherein the preset conditions are that the data package has a Voice VLAN Tag and a source MAC is matched with an OUI; and C, the ports enabling and listed into the Voice VLAN are traversed at fixed time in a task mode and aged ports are logged out from the Voice VLAN. By adopting the data transmission method used for the Voice VLAN, the MAC does not need to be enabled for learning, the Voice VLAN port does not need to be added by reading a forwarding table, and the method adopts a package CPU mode, and has the advantages of convenient search and good system real time property.

Owner:FENGHUO COMM SCI & TECH CO LTD

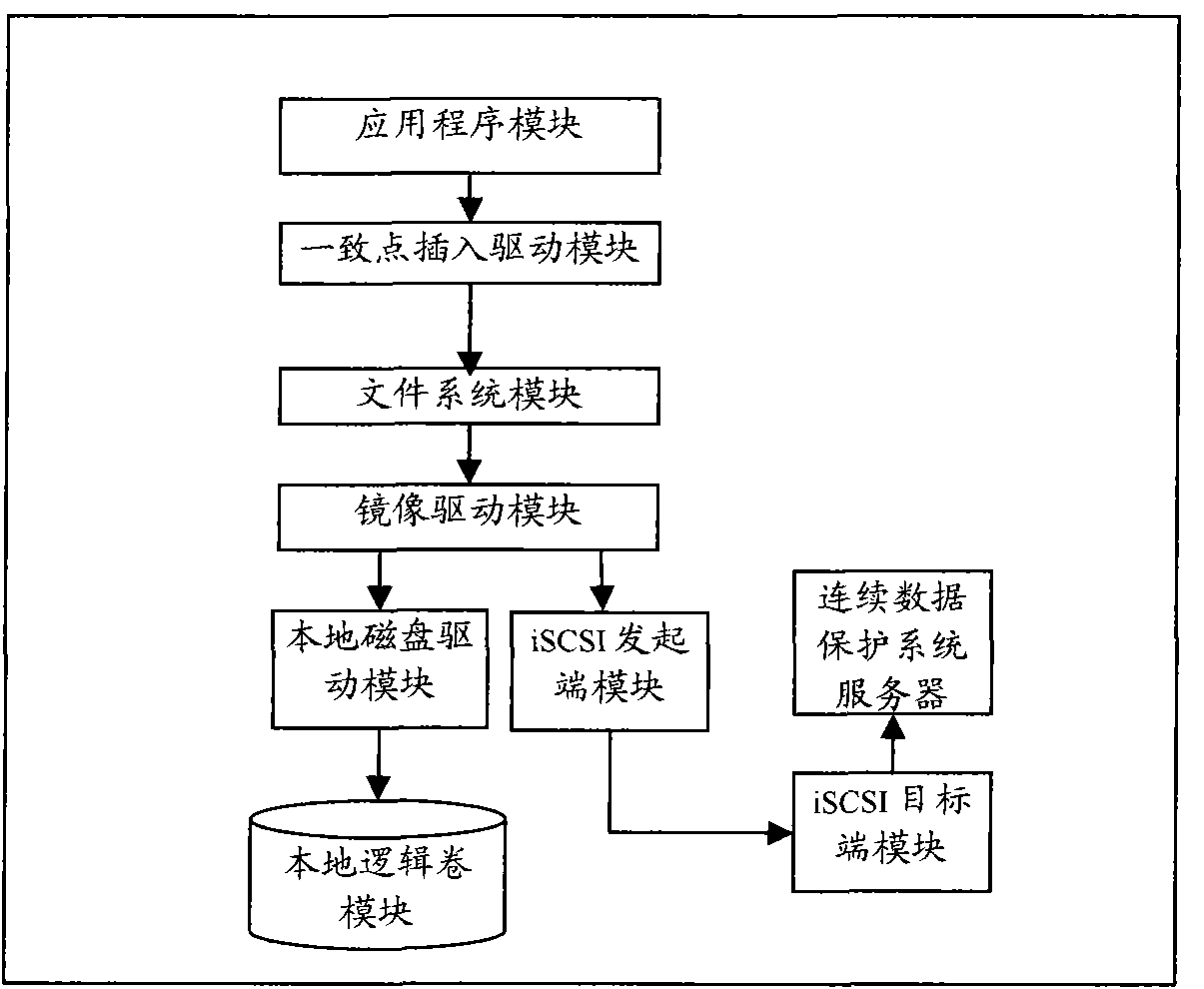

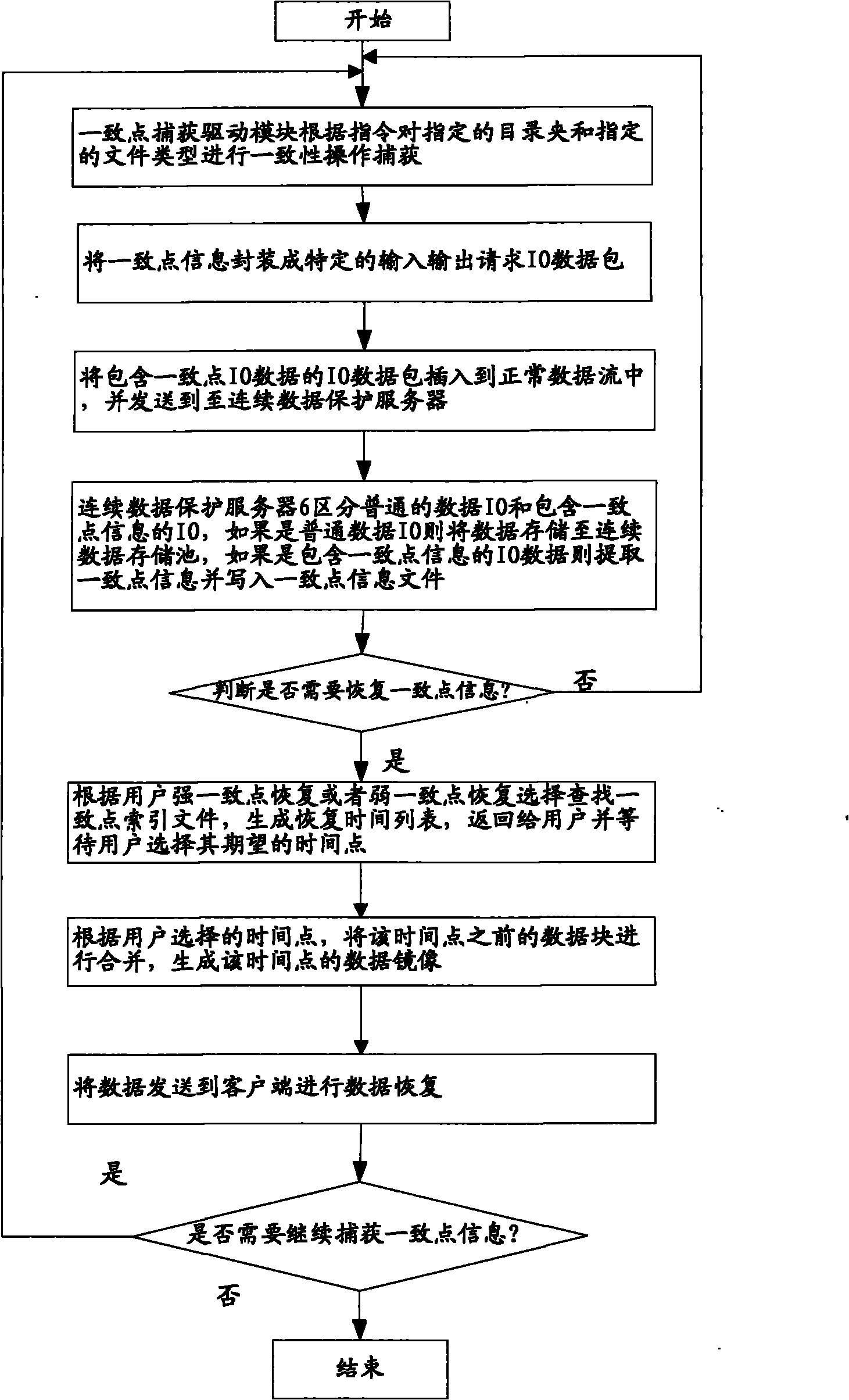

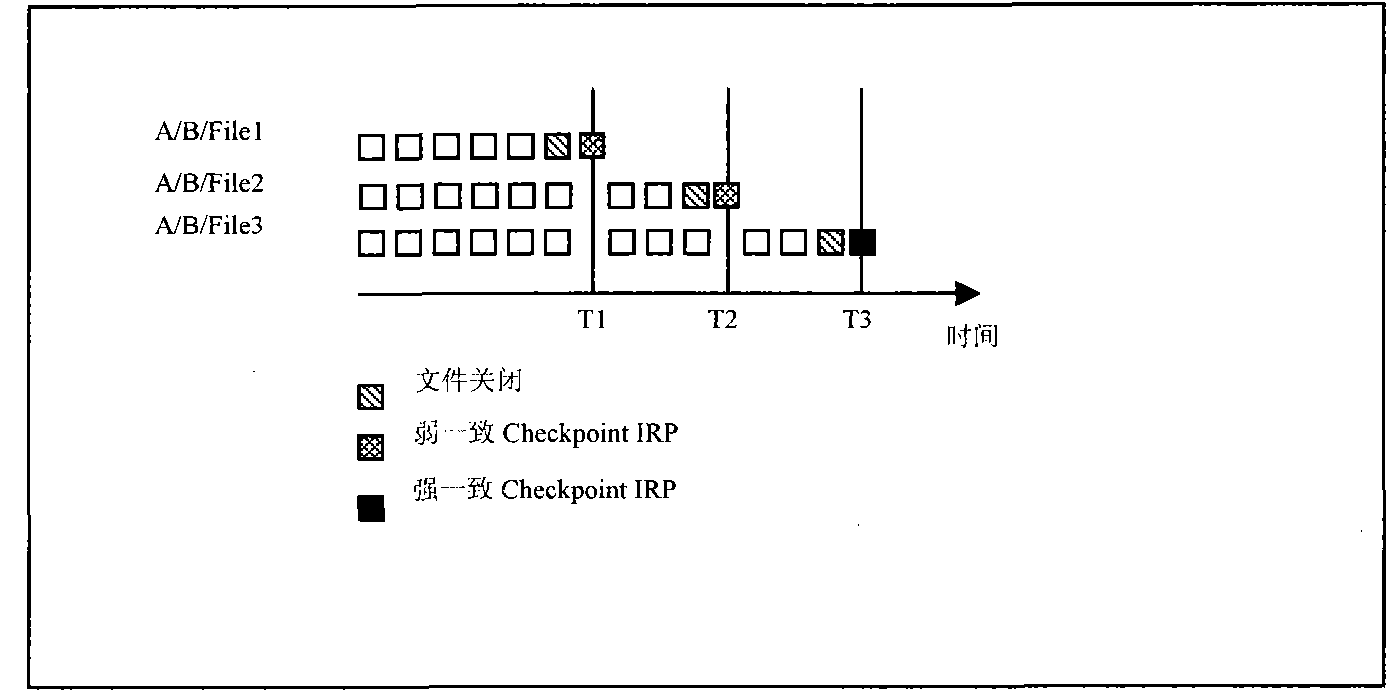

Volume stage continuous data protection system supported by consistent point insertion and recovery and method

InactiveCN101964030AMeet different granularity consistency requirementsImprove general performanceComputer security arrangementsSpecial data processing applicationsData streamNetwork packet

The invention relates to a volume stage continuous data protection system supported by consistent point insertion and recovery, which comprises an application program module, a consistent point insertion drive module, a file system module, a mirror image drive module, a local logic volume module and a continuous data protection system server. The method of the invention comprises the steps of catching and packaging file stage consistent point operation information to an IO data packet and inserting the information into a normal data flow; differentiating the IO data by utilizing the continuous data protection server; storing the common IO data into a continuous data storage pool; extracting and writing the consistent point information to a consistent point information file from the IO data containing the consistent point information; searching a consistent point index file and generating a recovery time list if requiring recovery; and combining data blocks before the time point expected by users to generate data mirror images, and transmitting the data mirror images to a client. The invention has the advantage of strong generality, and can recover and support the continuous data protection consistency of different granularities.

Owner:北京兴宇中科科技开发股份有限公司

Real time sensor and method for synchronizing real time sensor data streams

A Holocam Orb system uses multiple Holocam Orbs (Orbs) within a real-life environment to generate an artificial reality representation of the real-life environment in real time. Each Orb is an electronic and software unit that includes a local logic module, a local CPU and multiple synchronous and asynchronous sensors, include stereo cameras, time-of-flight sensors, inertial measurement units and a microphone array. Each Orb synchronizes itself to a common master clock, and packages its asynchrony data into data bundles whose timings are matched to frame timing of synchronous sensors, and all gathered data bundles and data frames are given a time stamp using a reference clock common to all Orbs. The overlapping sensor data from all the Orbs is combined to create the artificial reality representation.

Owner:SEIKO EPSON CORP

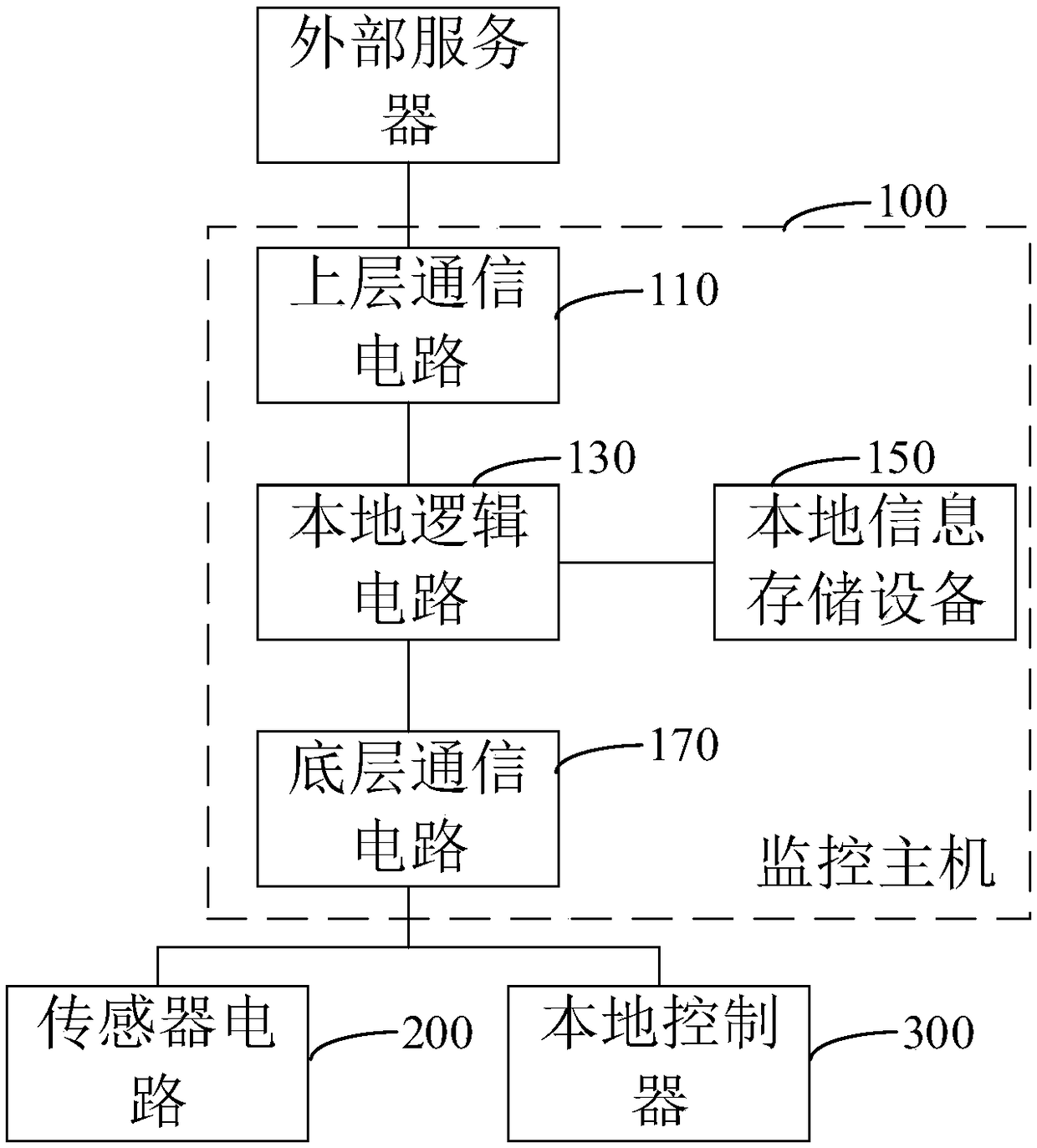

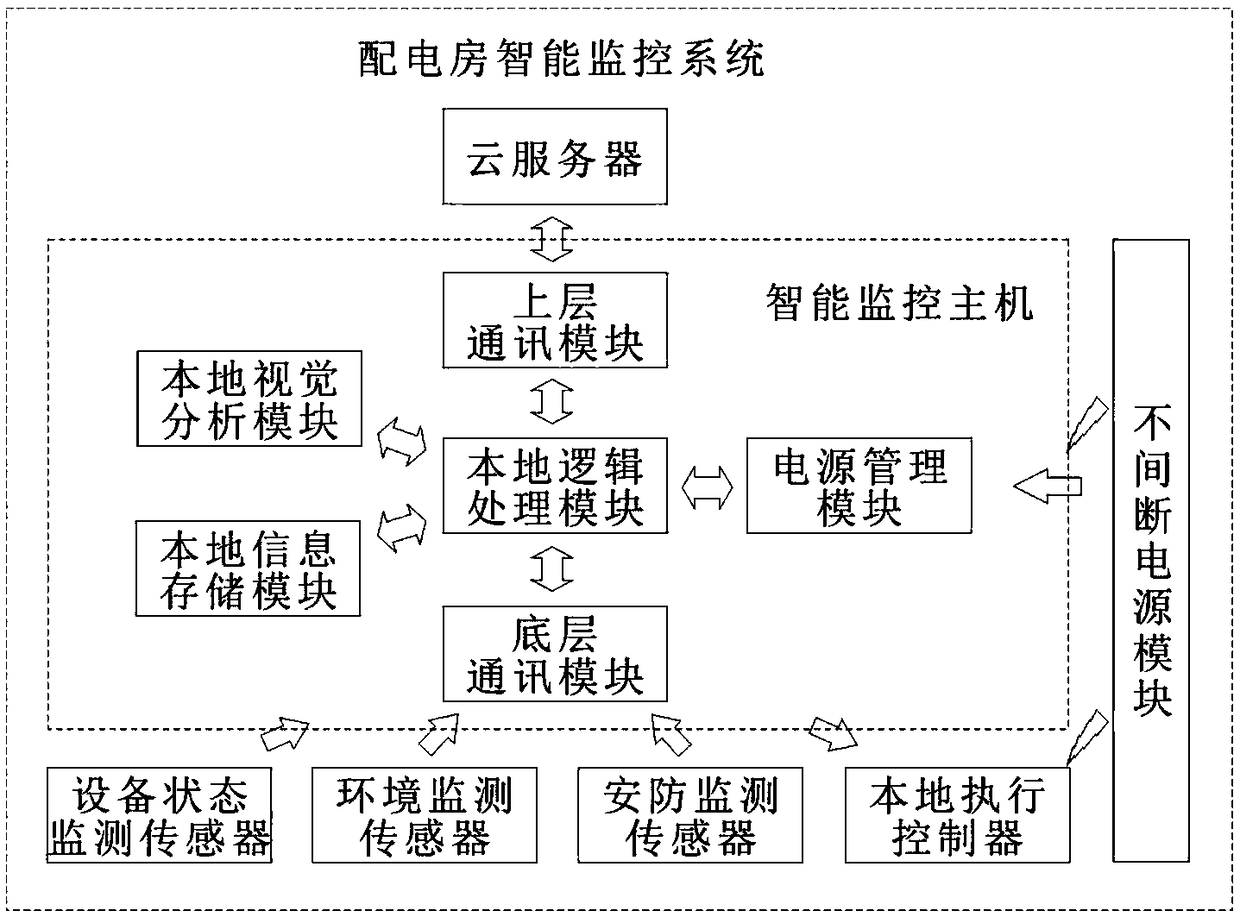

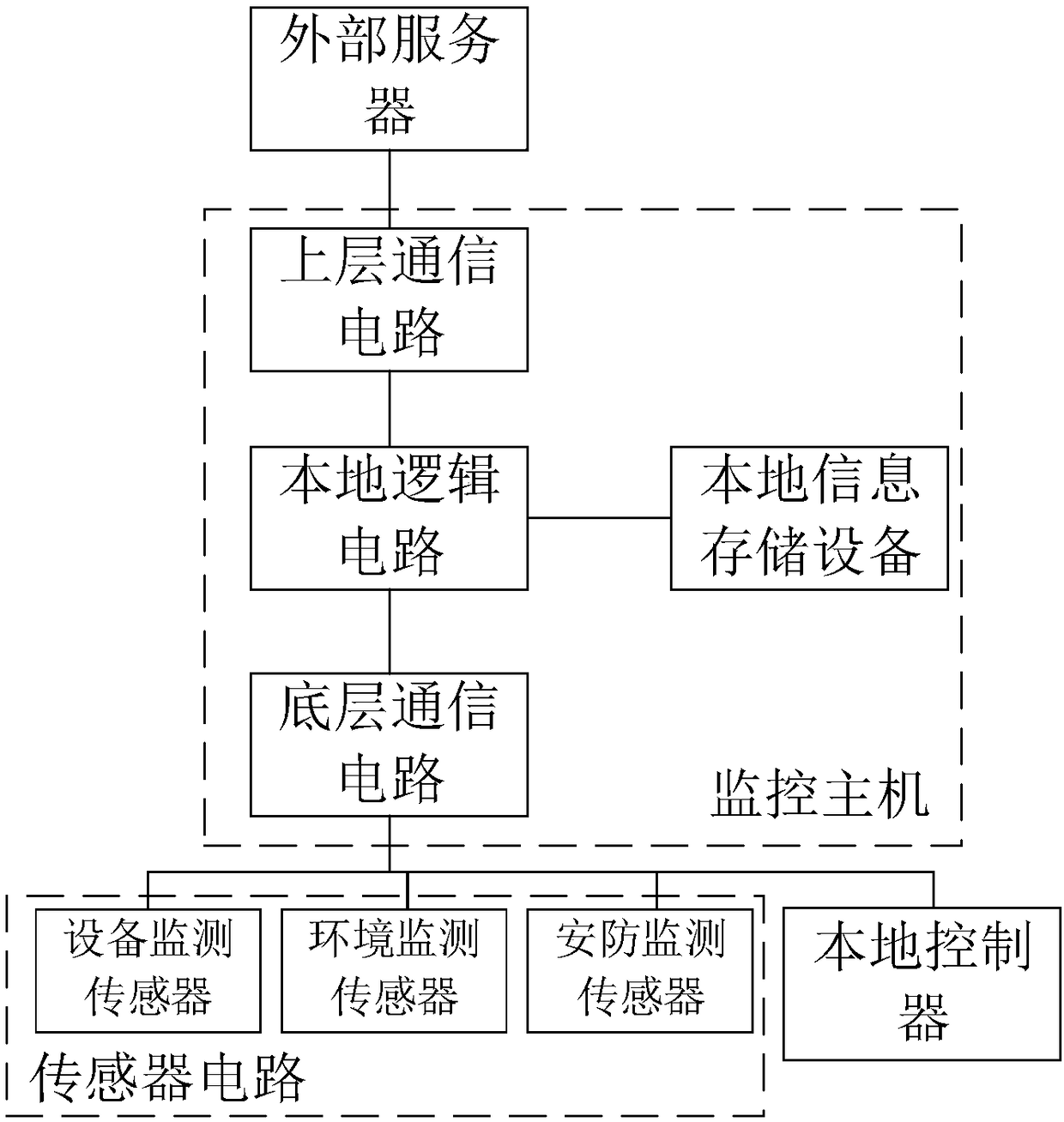

Power distribution room monitoring system

InactiveCN108490859ARealize monitoringGuaranteed uptimeProgramme controlMeasurement devicesIntegrated monitoringClosed loop analysis

The invention relates to a power distribution room monitoring system. The system comprises a monitoring host, a sensor circuit and a local controller. The monitoring host comprises an upper communication circuit connected to an external server, a local logic circuit connected to the upper communication circuit, and a local information storage circuit and an underlying communication circuit connected to the local logic circuit. The underlying communication circuit is connected to the sensor circuit and the local controller respectively. The monitoring host is connected to the structures of thesensor circuit and the local controller, can realize local closed-loop analysis logic and execution instruction issuing functions, can also realize local closed-loop control and regulation functions and possesses real-time performance and reliability. A power distribution room monitoring system is used to realize the integration monitoring of a whole power distribution room. When the power distribution room is abnormal, fault elimination can be performed timely so as to ensure the normal operation of each power supply device in the power distribution room, or operation personnel is notified tomaintain or replace the power supply device in the power distribution room.

Owner:GUANGZHOU POWER SUPPLY CO LTD

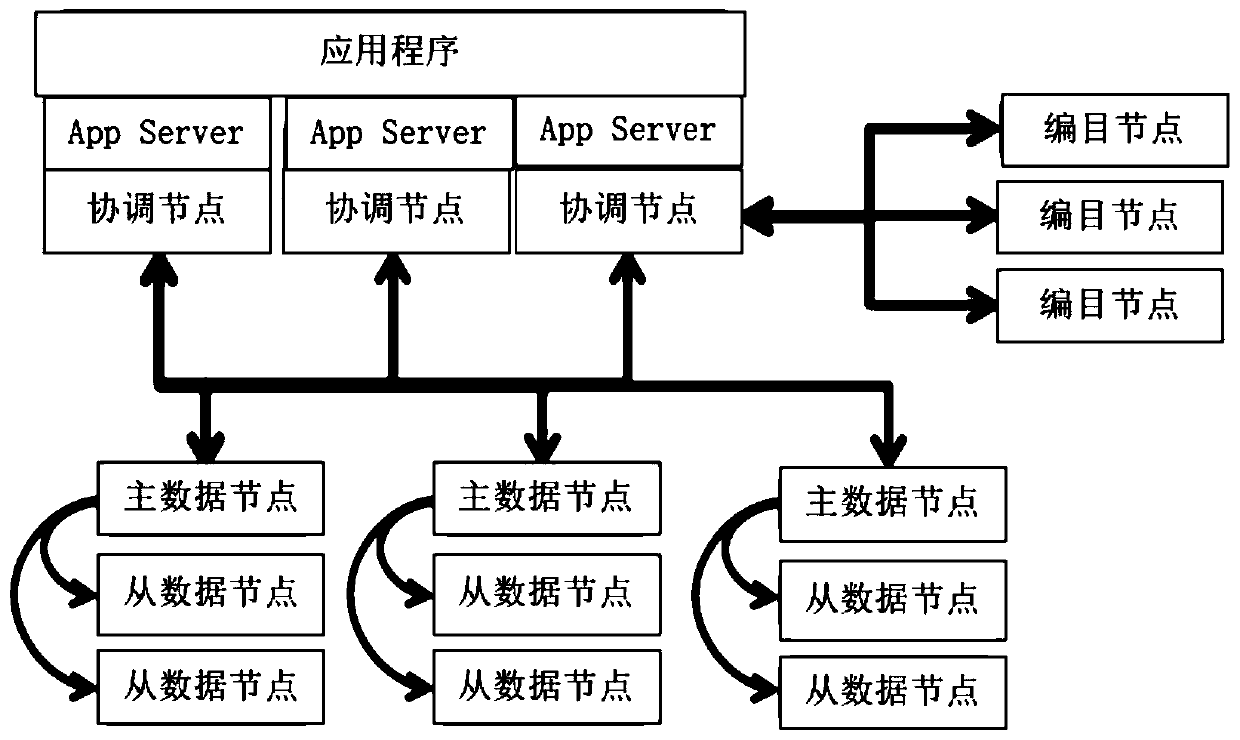

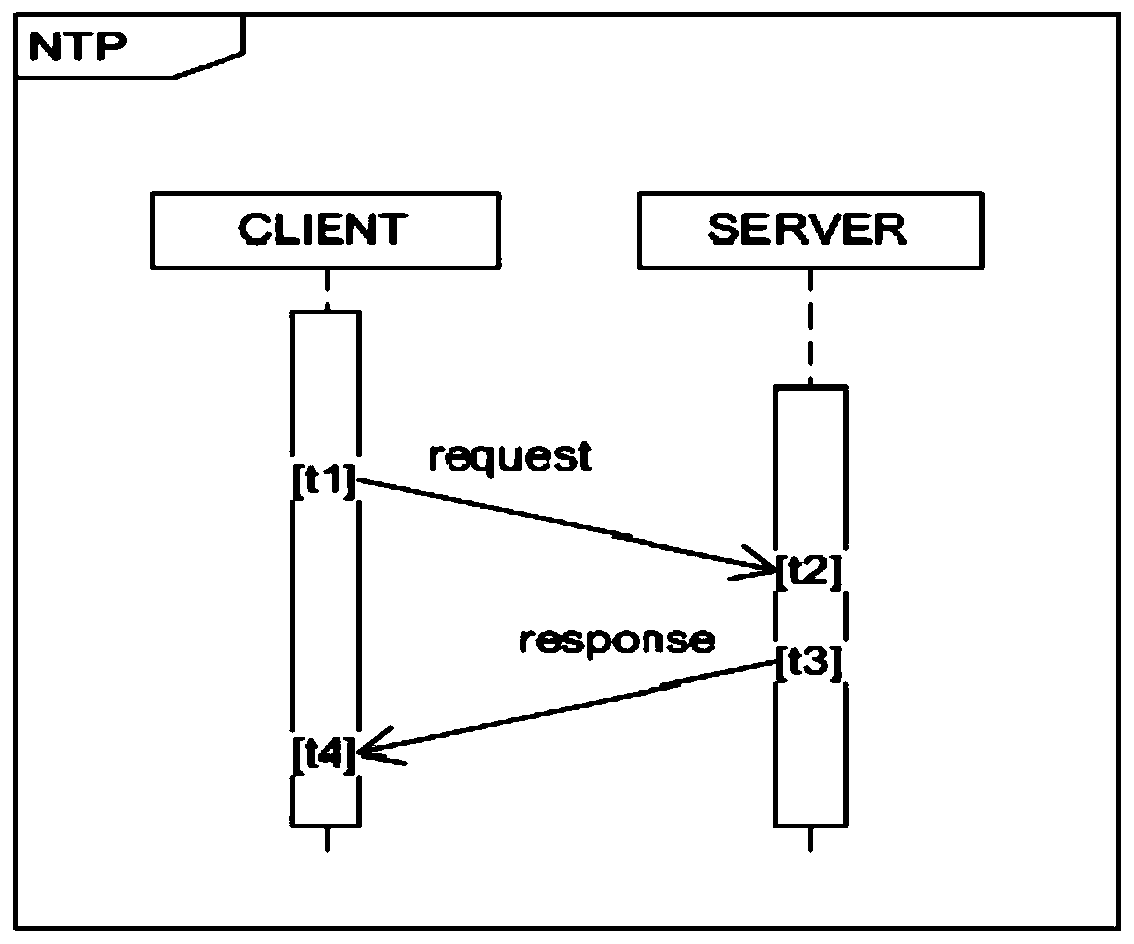

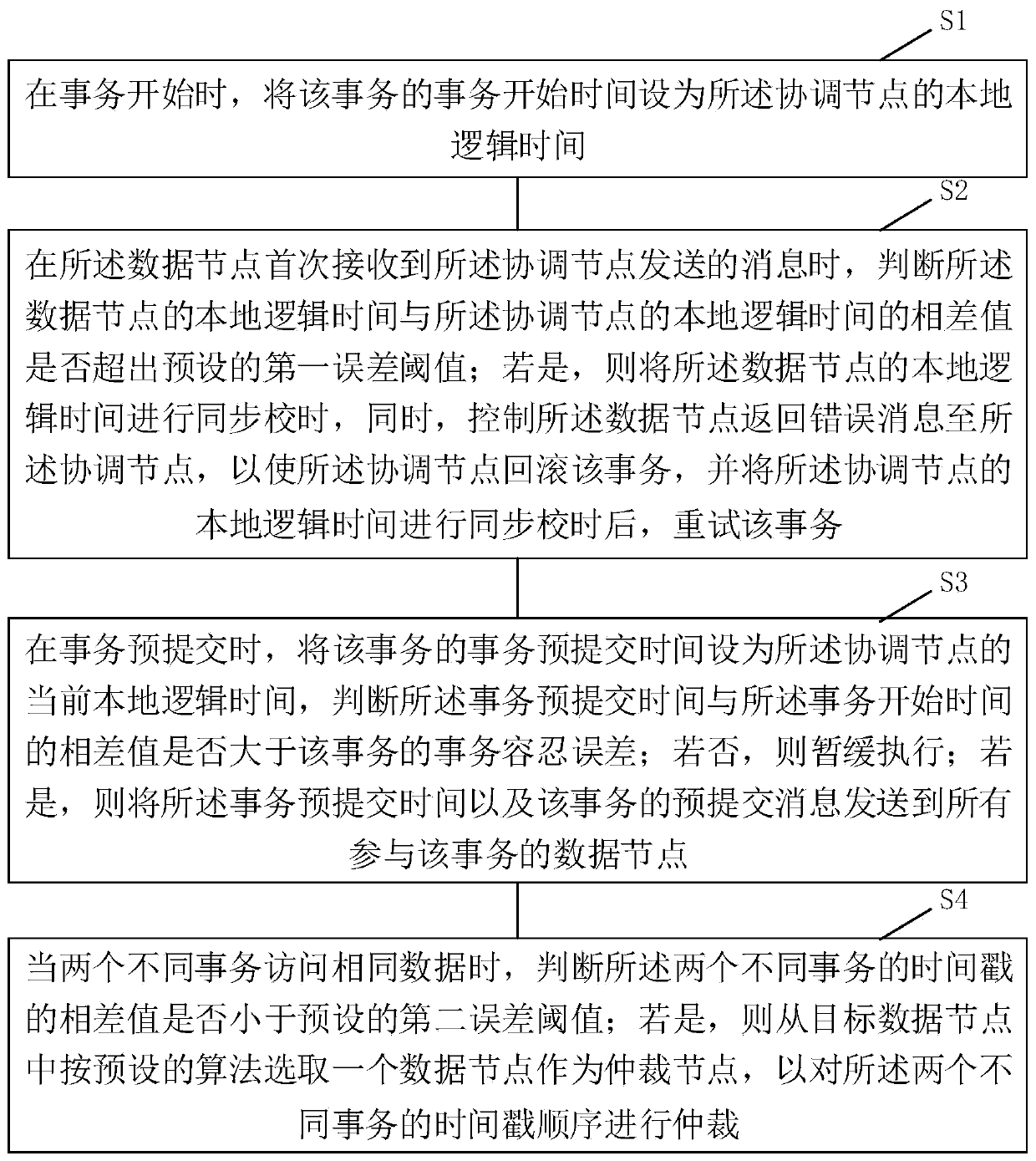

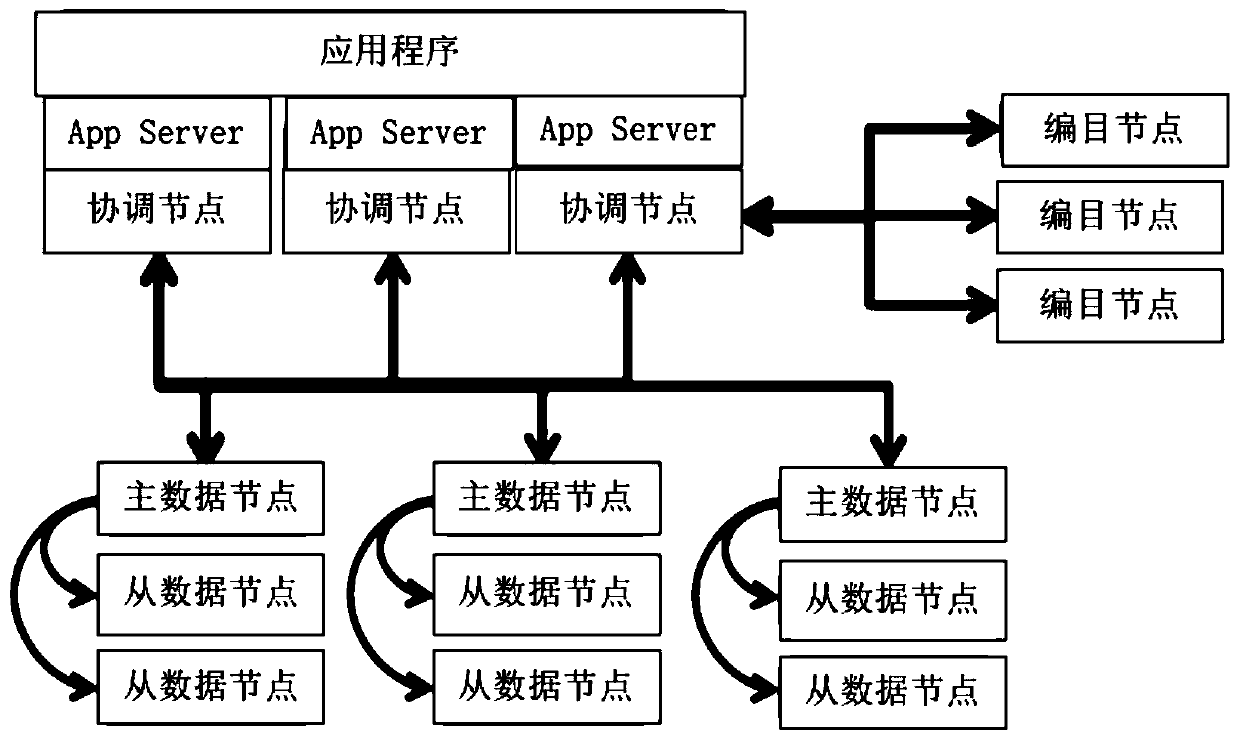

Distributed database management method and device based on distributed logic timestamps

InactiveCN110795506AReduce overheadImprove performanceDatabase distribution/replicationSpecial data processing applicationsStart timeData node

The invention discloses a distributed database management method and device based on a distributed logic timestamp. The method comprises the steps of setting transaction starting time of a transaction; if the difference value between the local logic time of the data node and the local logic time of the coordination node exceeds a preset threshold value, timing the local logic time of the data node, enabling the coordination node to roll back the transaction, and retrying the transaction after timing the time of the coordination node; if the difference between the transaction pre-submission time and the transaction start time is greater than the transaction tolerance error of the transaction, sending the transaction pre-submission time and the pre-submission message of the transaction to all data nodes participating in the transaction; and selecting one data node as an arbitration node to arbitrate the timestamps of the two different transactions according to the difference value condition of the timestamps of the two different transactions. According to the invention, the overhead of the network can be reduced while the requirements of distributed storage and processing are met, sothat the overall performance of the system is effectively improved.

Owner:SEQUOIADB CORP

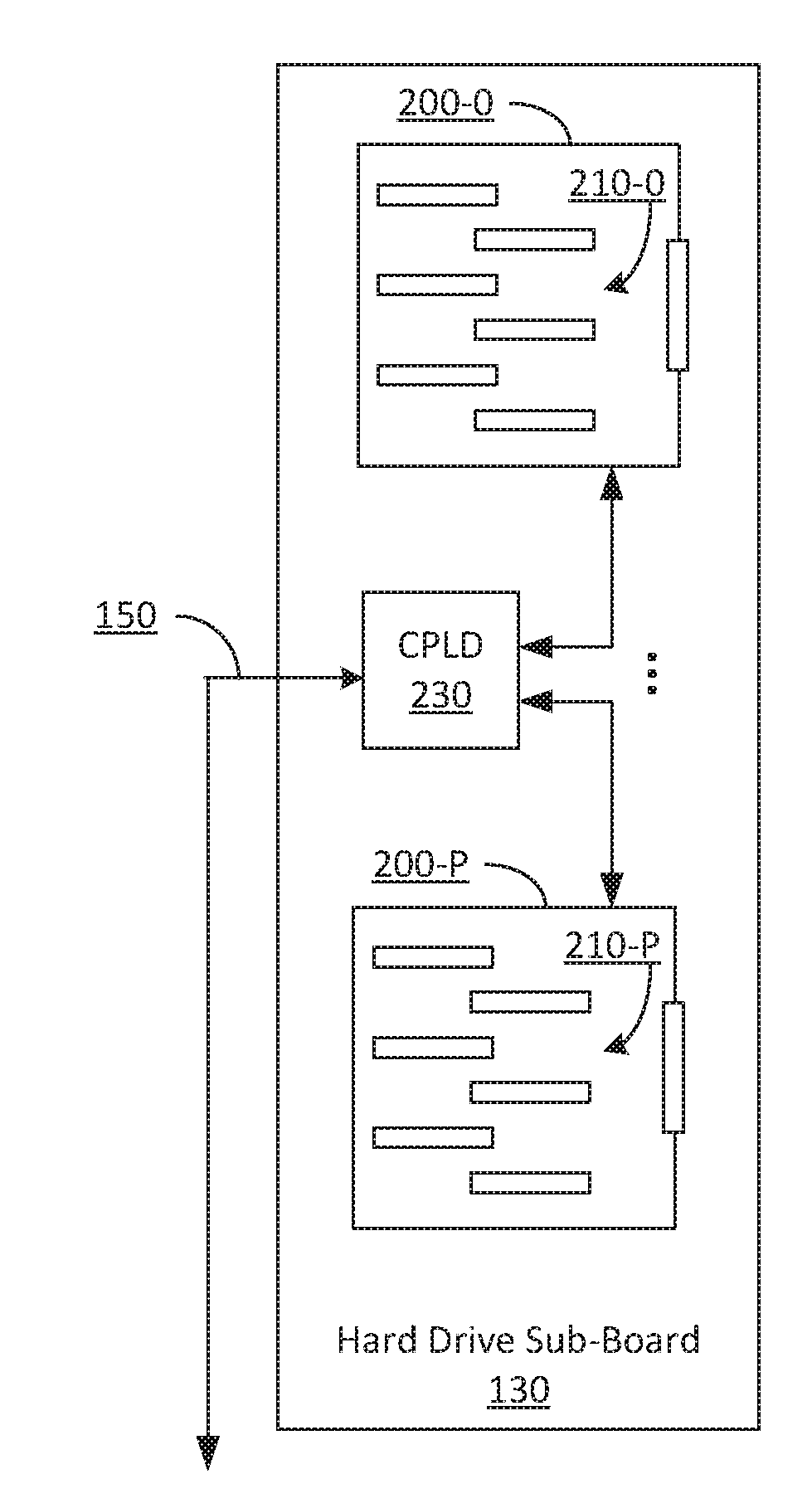

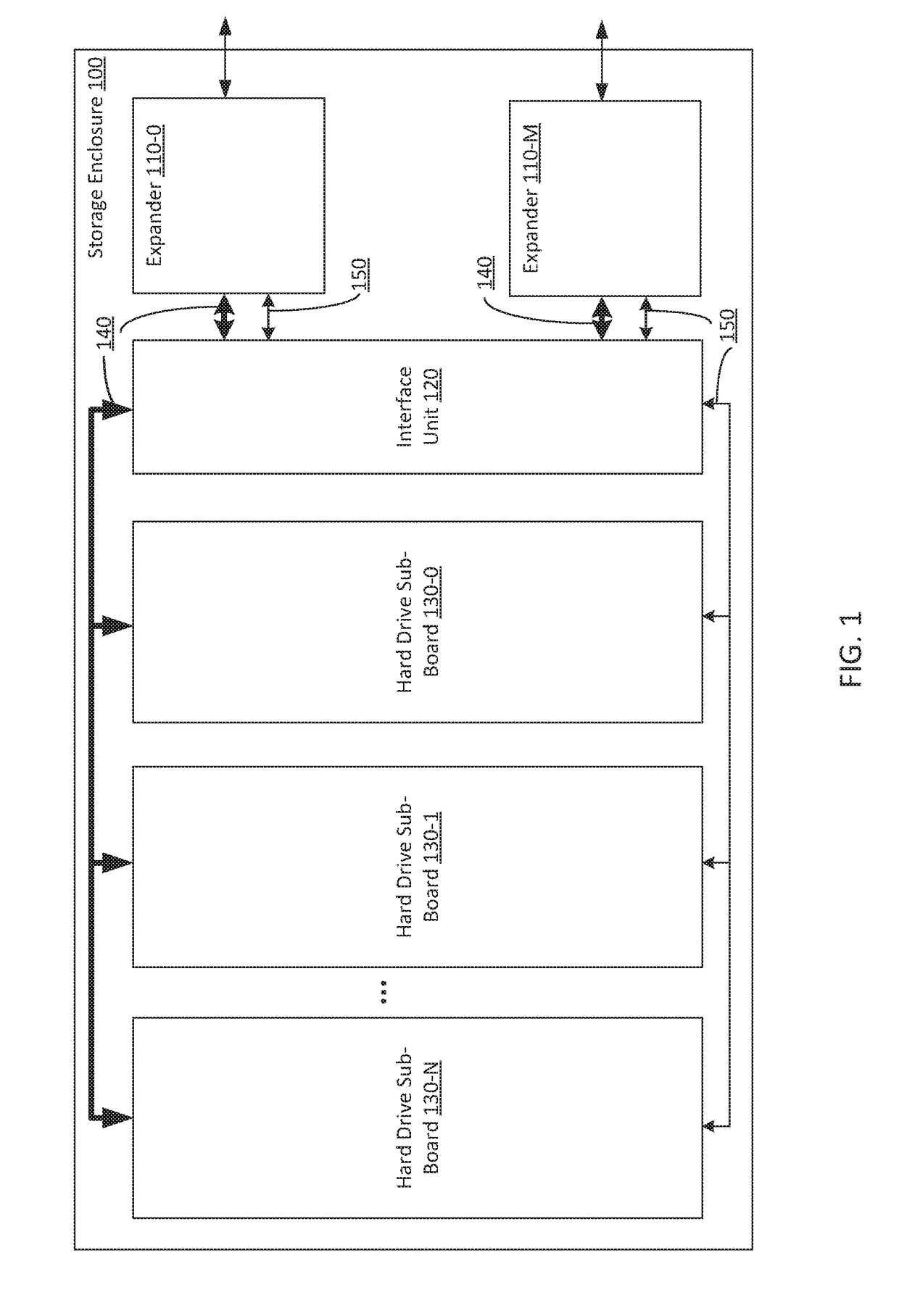

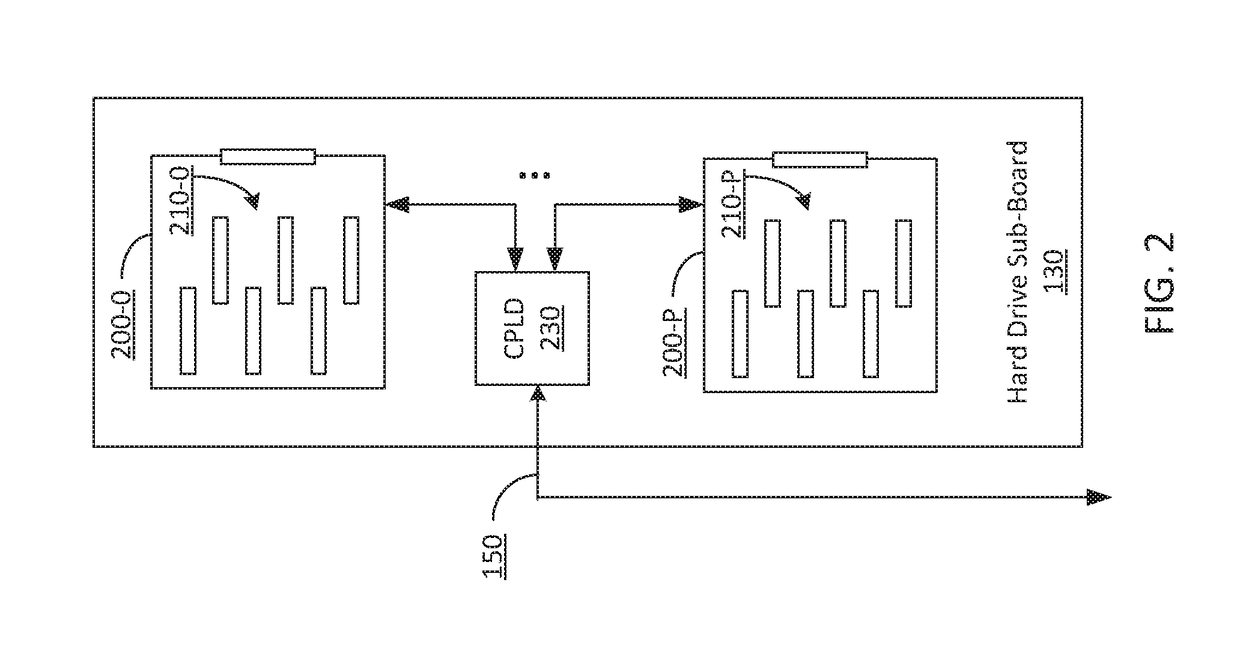

Storage enclosure with daisy-chained sideband signal routing and distributed logic devices

ActiveUS20170300264A1Input/output to record carriersCarrier constructional parts dispositionSignal routingHard disc drive

A storage enclosure includes a plurality of hard drive sub-boards, each configured to include a plurality of hard drives. A local logic device manages each hard drive sub-board. A master logic device manages the local logic devices. The master logic device receives management commands from a host computer system coupled to the storage enclosure, and routes those commands to specific local logic devices. The local logic devices then relay the commands to specifically targeted hard drives. Thus, each hard drive within the storage enclosure can be independently controlled, allowing a single hard drive to be powered down without powering down other hard drives in the enclosure.

Owner:SUPER MICRO COMP

Distributed transaction management method and system based on distributed logic timestamp

ActiveCN111061810AReduce overheadImprove performanceDatabase distribution/replicationSpecial data processing applicationsStart timeEngineering

The invention discloses a distributed transaction management method and system based on a distributed logic timestamp. The method comprises the steps of setting transaction starting time of a transaction; if the difference value between the local logic time of the data node and the local logic time of the coordination node exceeds a preset threshold value, timing the local logic time of the data node, enabling the coordination node to roll back the transaction, and retrying the transaction after the time of the coordination node is timed; if the difference between the transaction pre-submission time and the transaction start time is greater than the transaction tolerance error of the transaction, sending the transaction pre-submission time and the pre-submission message of the transactionto all data nodes participating in the transaction; and selecting one data node as an arbitration node to arbitrate the timestamps of the two different transactions according to the difference value condition of the timestamps of the two different transactions. According to the invention, the overhead of the network can be reduced while the requirements of distributed storage and processing are met, so that the overall performance of the system is effectively improved.

Owner:SEQUOIADB CORP

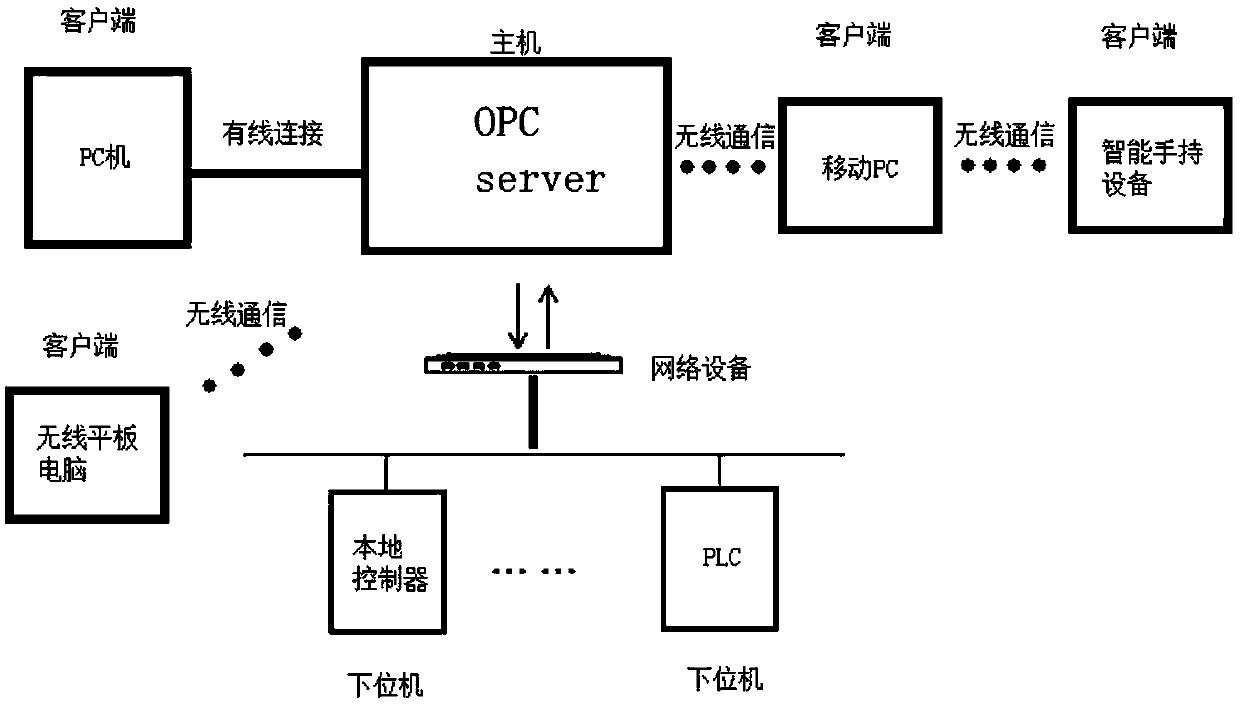

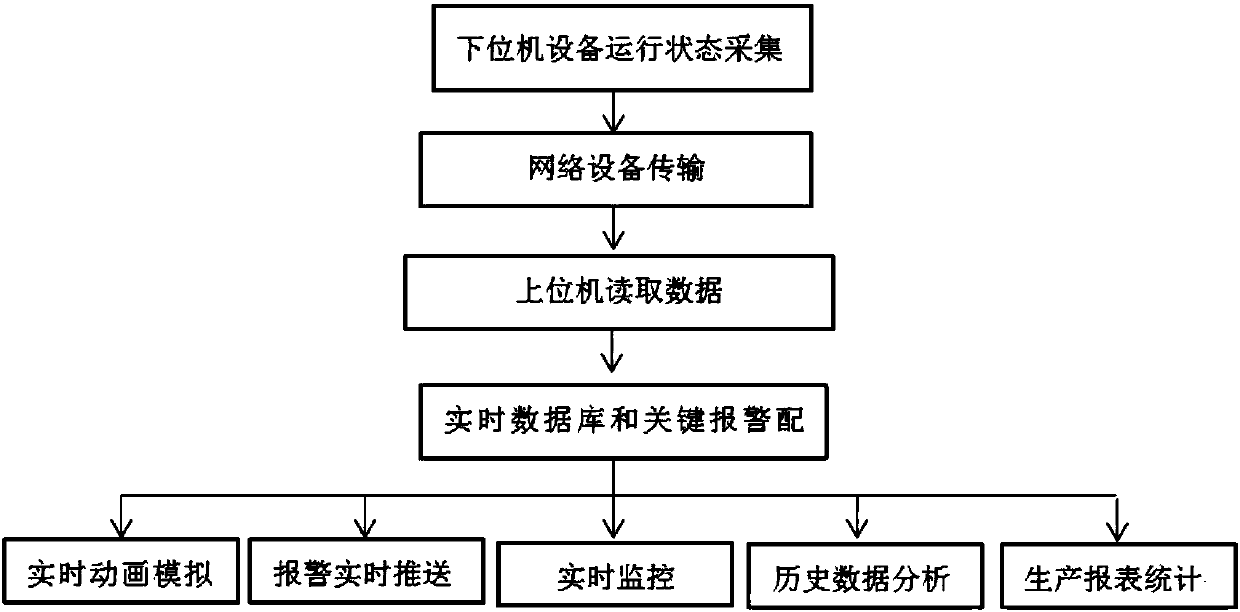

On-line production line management system

PendingCN110580013AImprove maintenance efficiencyImprove labor productivityTotal factory controlProgramme total factory controlProduction lineAnimation

The invention discloses an on-line production line management system. A lower computer is used for realizing local logic control of production line equipment and is responsible for acquiring, converting, transmitting and processing the operation state of each part of the production line equipment so as to complete the process realization function of the production line equipment. Network equipmentis connected with an upper computer and the lower computer and is responsible for real-time signal transmission between the upper computer and the lower computer. The upper computer comprises a hostand a client; the host stores an equipment operation state real-time database and key alarm configuration and is provided with a real-time animation simulation module, an equipment alarm real-time pushing module, an equipment operation state real-time monitoring module, a historical equipment data analysis module and an equipment production report statistics module. The client directly reads the data of the host equipment operation state real-time monitoring module and displays the operation state of line monitoring equipment in real time. Therefore, the operation states of all parts of production line equipment can be monitored in real time; equipment fault points can be found rapidly; the equipment maintenance efficiency is improved; and the product quality and the stability of the technological process are improved indirectly.

Owner:UNITED AUTOMOTIVE ELECTRONICS SYST

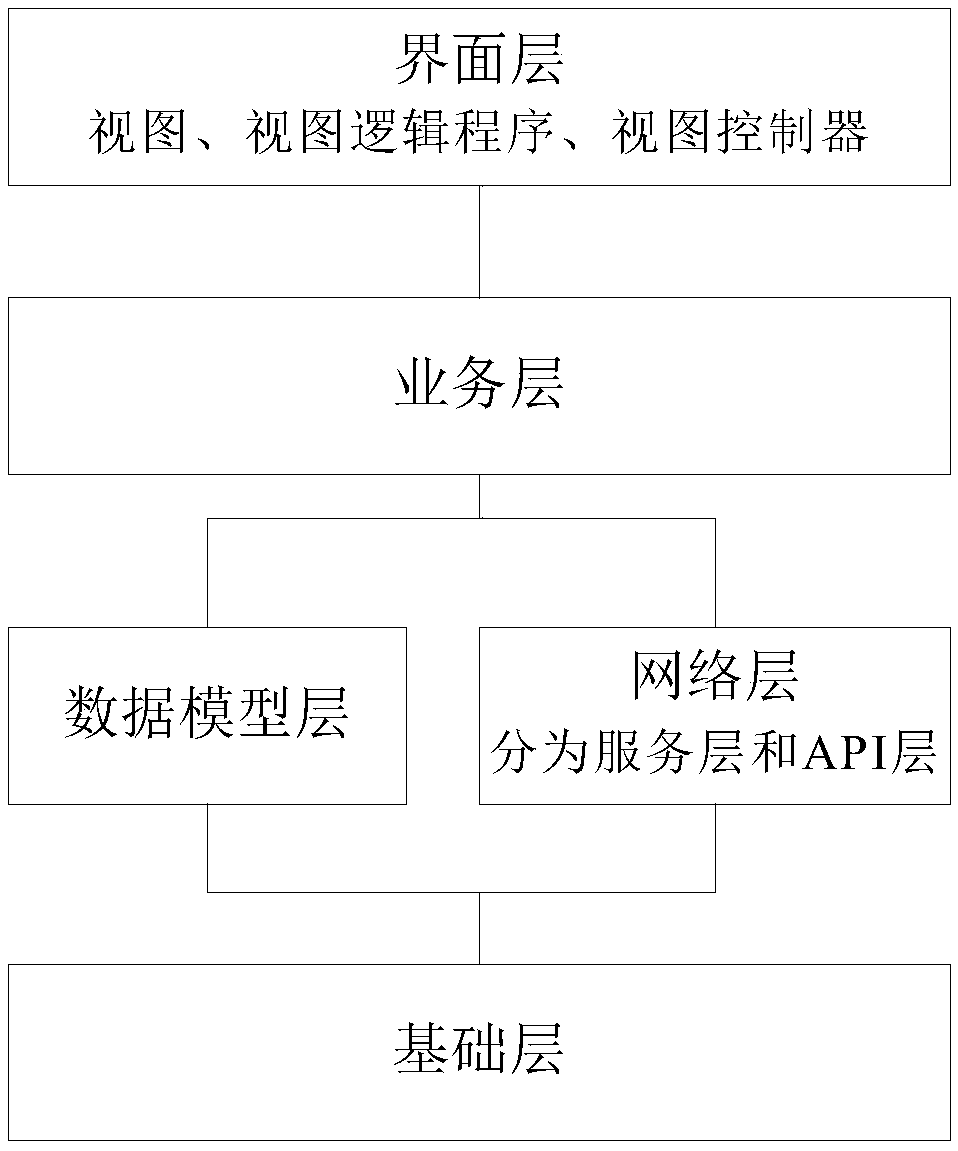

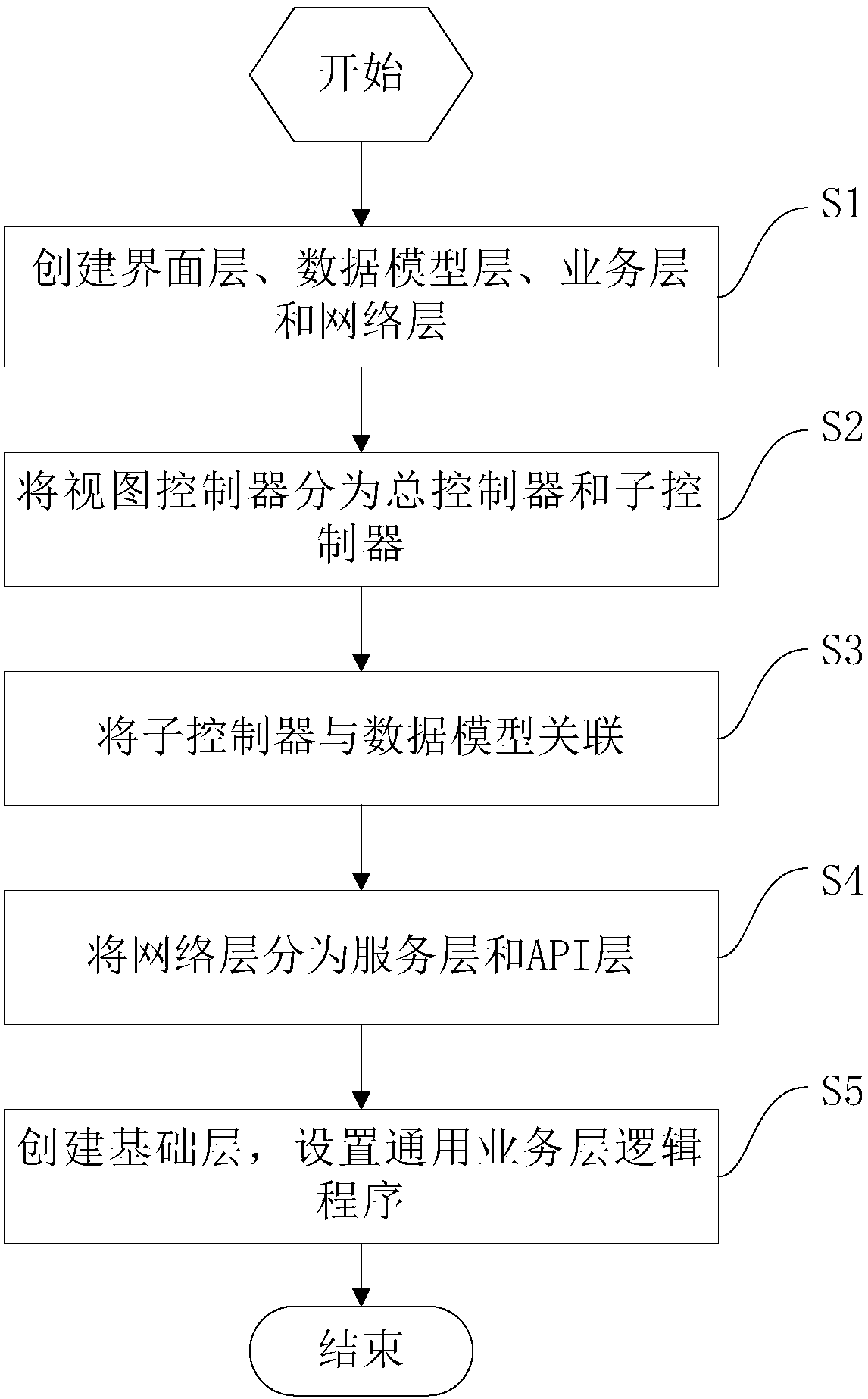

Computer software development system

InactiveCN107817968AImprove robustnessPersonal skill improvementSoftware designRequirement analysisSoftware developmentLogic program

The invention discloses a computer software development system. The computer software development system includes a working layer establishment module for establish a working layer associated with software, wherein the working layer includes an interface layer, a data model layer, a service layer, and a network layer; the interface layer is used for displaying a view interface; the interface layerincludes a view, a view logic program, an a view controller; the view controller is used for setting a view according to a data model in a data model layer; the data model layer is used for storing the data models, and the data models includes a local logic data model and a network data mapping model; the service layer is used for providing a service port for the view logic program and the view controller of the interface layer; and the network layer is used for returning Json data to a network request, and mapping the Json data into a network data mapping model. The beneficial effects of theinvention are that the computer software development system has a universal code organization standard and a decoupling scheme, and can improve the coupling degree; and team developers are independent of each other, and the team efficiency is greatly improved.

Owner:重庆首亨软件股份有限公司

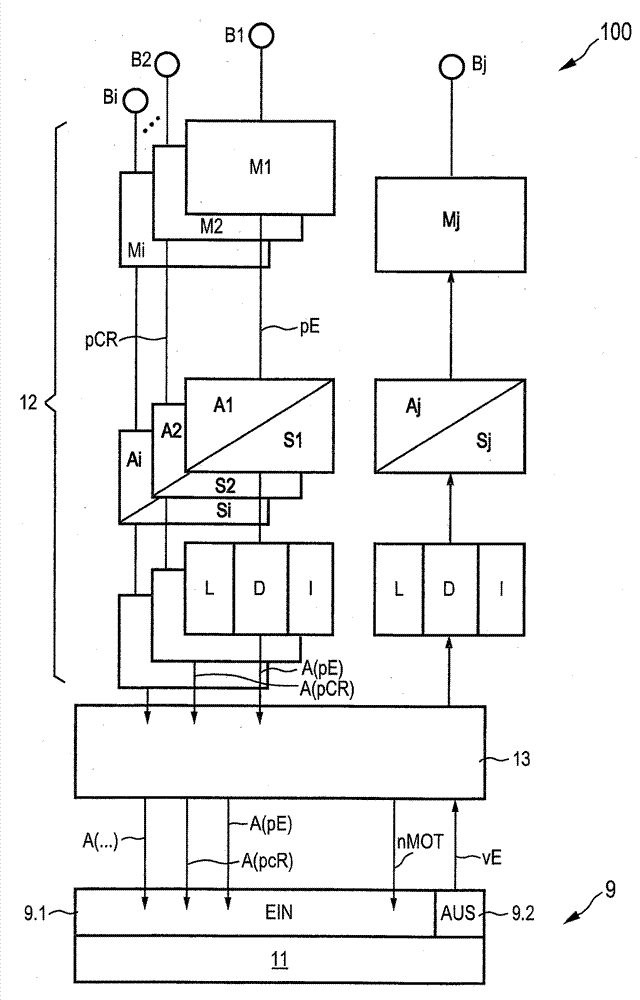

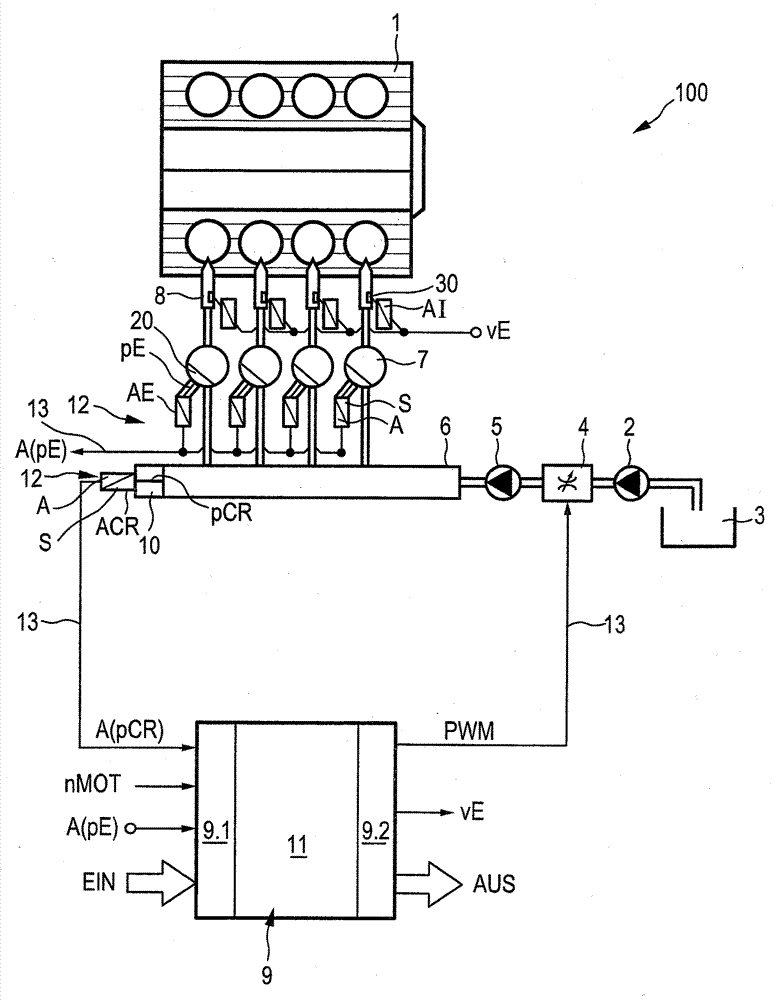

Common rail system, internal combustion engine, and device and method for controlling and/or regulating an internal combustion engine

ActiveCN103946524AReliable assessmentReliable associationElectrical controlFuel injection apparatusElectronic systemsCommon rail

The invention relates to a common rail system (100) for an internal combustion engine (1), comprising: a rail (6) for fuel and an injector (8) that is fluidically connected via a high-pressure guide and used to inject the fuel into a working chamber of the internal combustion engine (1), the high-pressure guide comprising a high-pressure component with a single accumulator (7), and the high-pressure guide and / or the rail (6) comprising a pressure-measuring device (10, 20, 30). According to the invention, the pressure-measuring device is coupled to a local logic and storage unit (AE, ACR, AI) of a decentrally distributed local electronics system (12), which is designed to locally evaluate and store measurement data from the pressure-measurement device, more particularly injector data and / or rail data, and the pressure-measurement device is connected to the central electronics system (9) via the local logic and storage unit (AE, ACR, AI) by means of a bus, and the local logic and storage unit (AE, ACR, AI) is designed, in conjunction with the central electronics system (9), for controlling and / or regulating the common rail system (100) for the internal combustion engine (1).

Owner:ROLLS ROYCE SOLUTIONS GMBH

Application of hardware-based mailboxes in network transceivers and distributed approach for predictable software-based protection switching

ActiveUS8477596B2Save processor resourcesLower latencyMultiplex system selection arrangementsError preventionError checkingTransceiver

A line card in a network node having a local memory coupled to a local controller and local logic circuit. The local memory in the line card stores state information for signals processed by the line card itself, as well as state information for signals processed by other line cards. The logic circuit and controller implement a same fault detection and signal processing algorithms as all other line cards in the group, to essentially effectuate a distributed and local hardware based control of automatic protection switching (APS) without interrupting a central processor. The line card also performs error checking and supervisory functions to ensure consistency of state among the line cards.

Owner:INFINERA CORP

Power management concept in DC distributed systems

ActiveUS10666047B2Improve system stabilityAchieving self-calibrationElectric signal transmission systemsLoad balancing in dc networkConvertersDistribution power system

A method includes the steps of providing a common DC bus to interconnect power elements to a DC distribution system using power converters. A first group of one or more of the elements (main element) is used to execute the primary function by automatically maintaining the DC bus voltage following a set point. The DC bus voltage set point is intentionally changed with slow dynamics according to a secondary function executed by the main element such that the average DC bus voltage regulated by the main element changes. A local logic is used on each of the power elements connected to the DC bus but different from the main element to modify their power generation or consumption as a result of changes in the measured average DC bus voltage such that they contribute to the fulfillment of the secondary level of control.

Owner:ARDA POWER

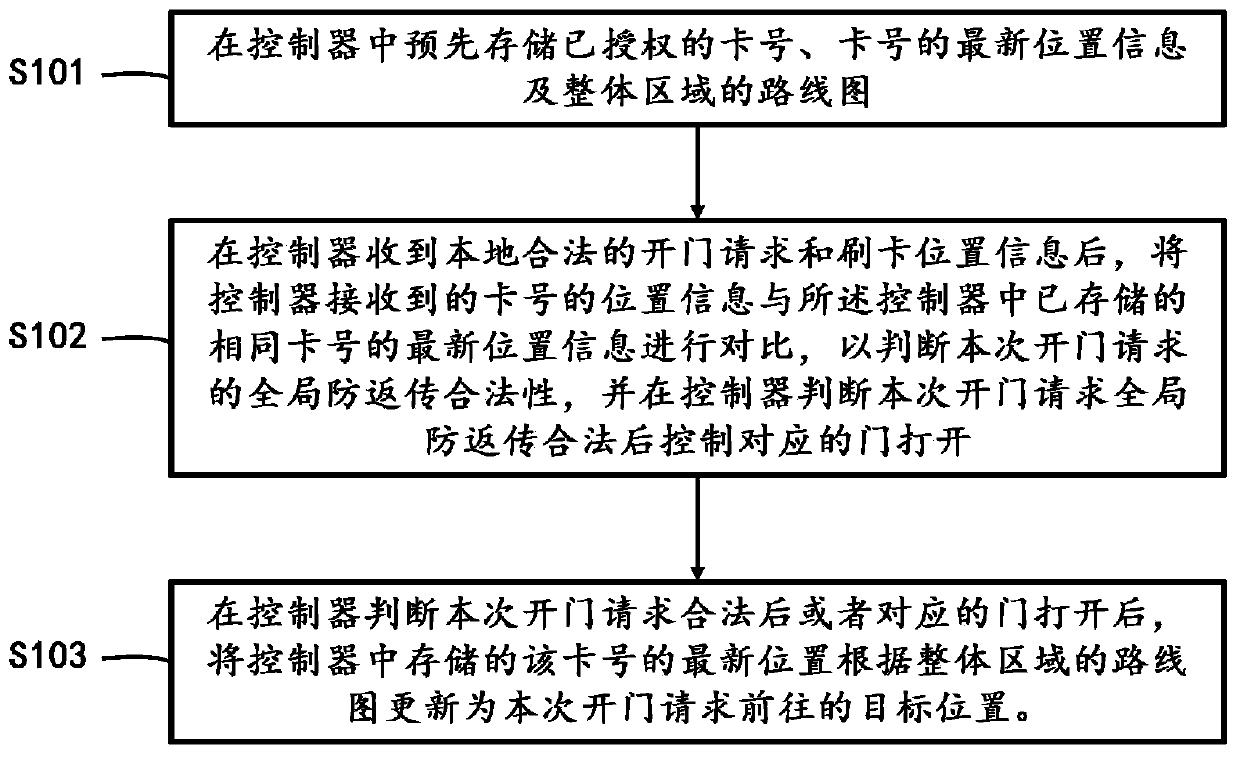

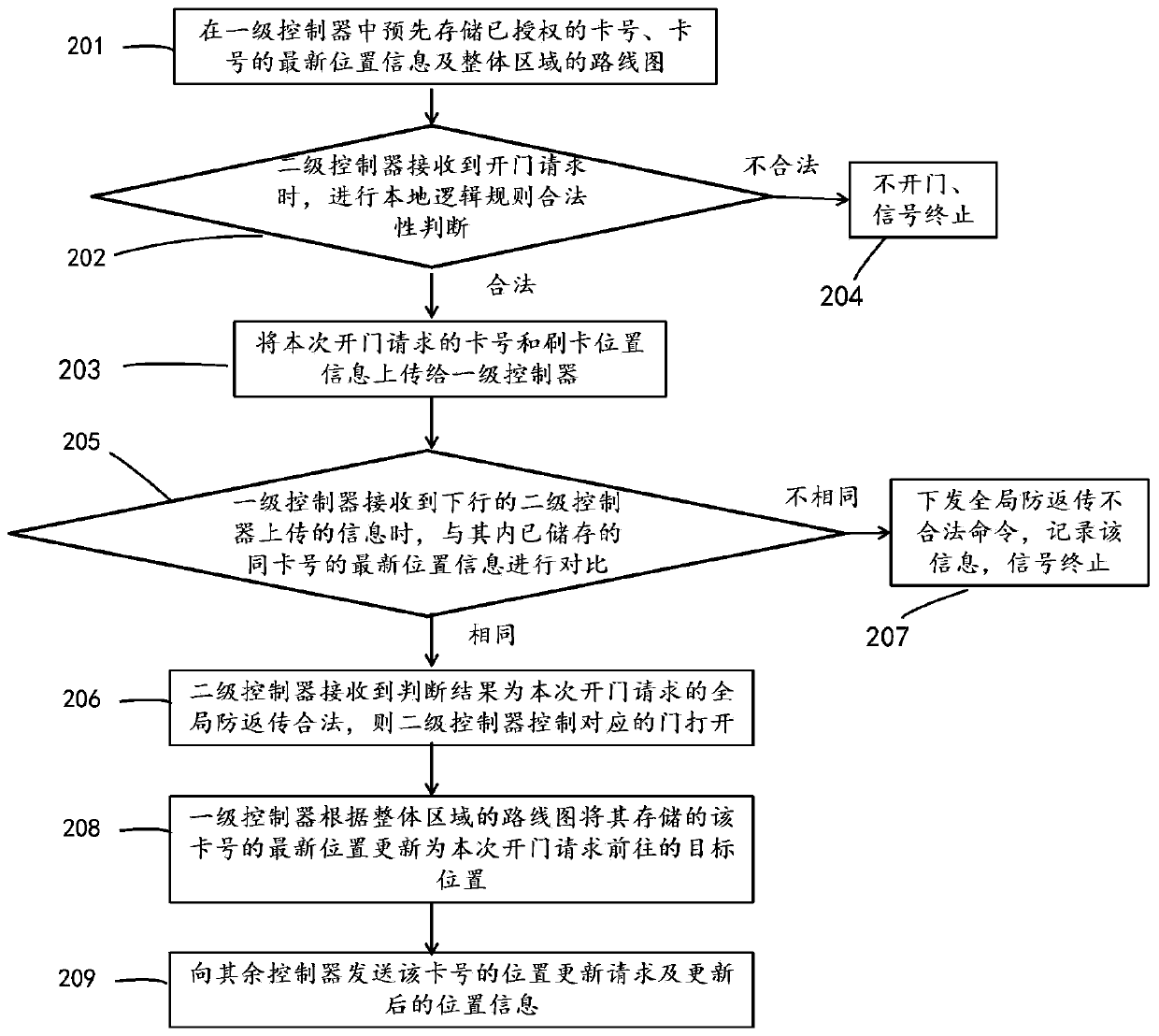

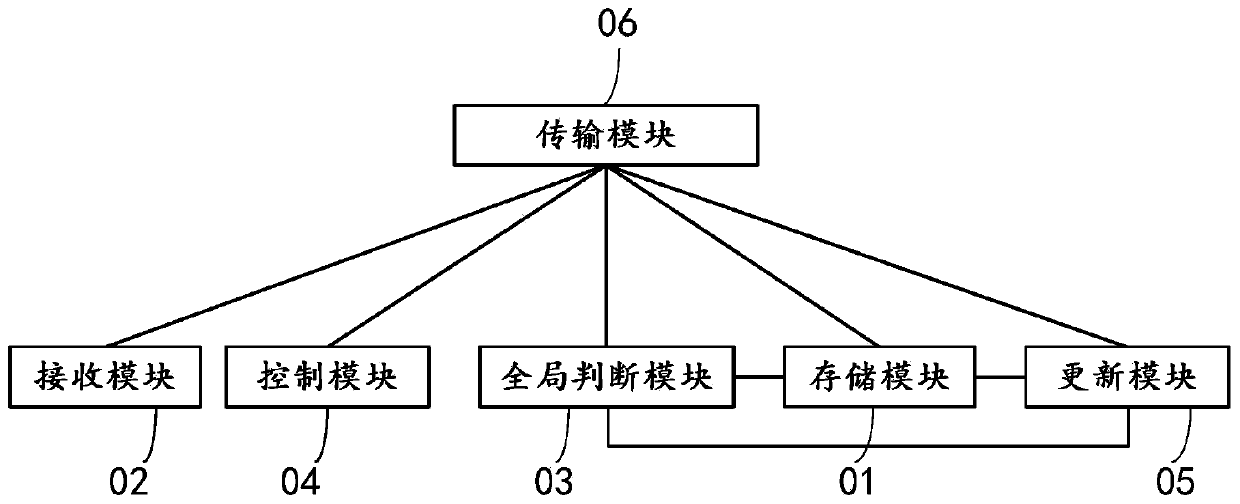

Access control method and system with global anti-back-transmission function

InactiveCN110084941AAvoid unsafe factorsMeet high protection requirementsIndividual entry/exit registersComputer hardwareControl system

The invention provides an access control method and system with a global anti-back-transmission function, comprising the following steps of: pre-storing an authorized card number, latest position information of the card number and a route map of the whole area in a controller; after receiving a legal door opening request and card swiping position information of a local logic rule, comparing the received position information of the card number with the stored latest position information of the card number to judge the overall anti-return transmission legality of the door opening request, and controlling a corresponding door to be opened after judging legality; and updating the latest position of the card number stored in the controller to be the target position to which the door opening request goes according to the route map of the whole area. By adopting the method and the system, whether the card swiping personnel violate the anti-back-transmission behavior rules can be directly judged by using hardware, the adverse effect of the software of the upper computer is eliminated, the unsafe factors such as the card swiping of the passers across defense areas, the card swiping and thecard access of multiple persons by using the same card and the like are effectively solved, and the facility safety is improved.

Owner:CHINA NUCLEAR POWER ENG CO LTD

Equipment access address determination method and device

The embodiment of the invention provides an equipment address access method and device, and the method is applied to an autonomous network based on the articulated naturality web, and comprises the steps: determining the level of a target autonomous cloud of to-be-accessed equipment in the autonomous network; determining the position of the device accessing the target autonomous cloud; determininga logic address corresponding to the device according to the hierarchy and the position, the logic address comprising a local logic address, a logic address prefix and a global logic address; determining a logic port address corresponding to the device; and generating an access address of the equipment according to the logic address and the logic port address. Through the equipment address accessscheme provided by the embodiment of the invention, the unique equipment access address can be automatically and efficiently generated for the equipment accessed into the articulated naturality web.

Owner:VISIONVERA INFORMATION TECH CO LTD

Improved asynchronous programming execution

ActiveCN102681843AReduce switchingProgramming languages/paradigmsSpecific program execution arrangementsProgramming languageExecution plan

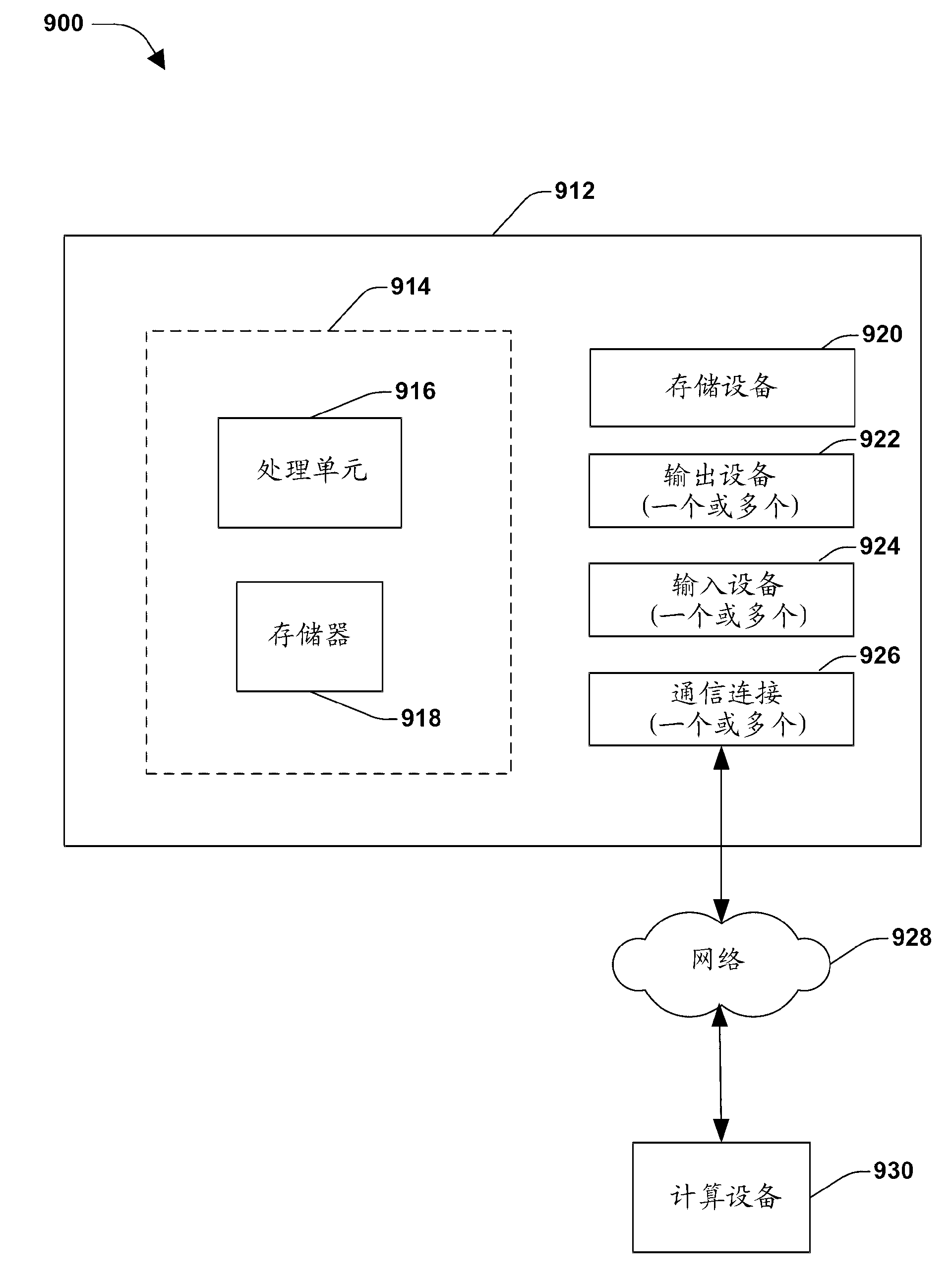

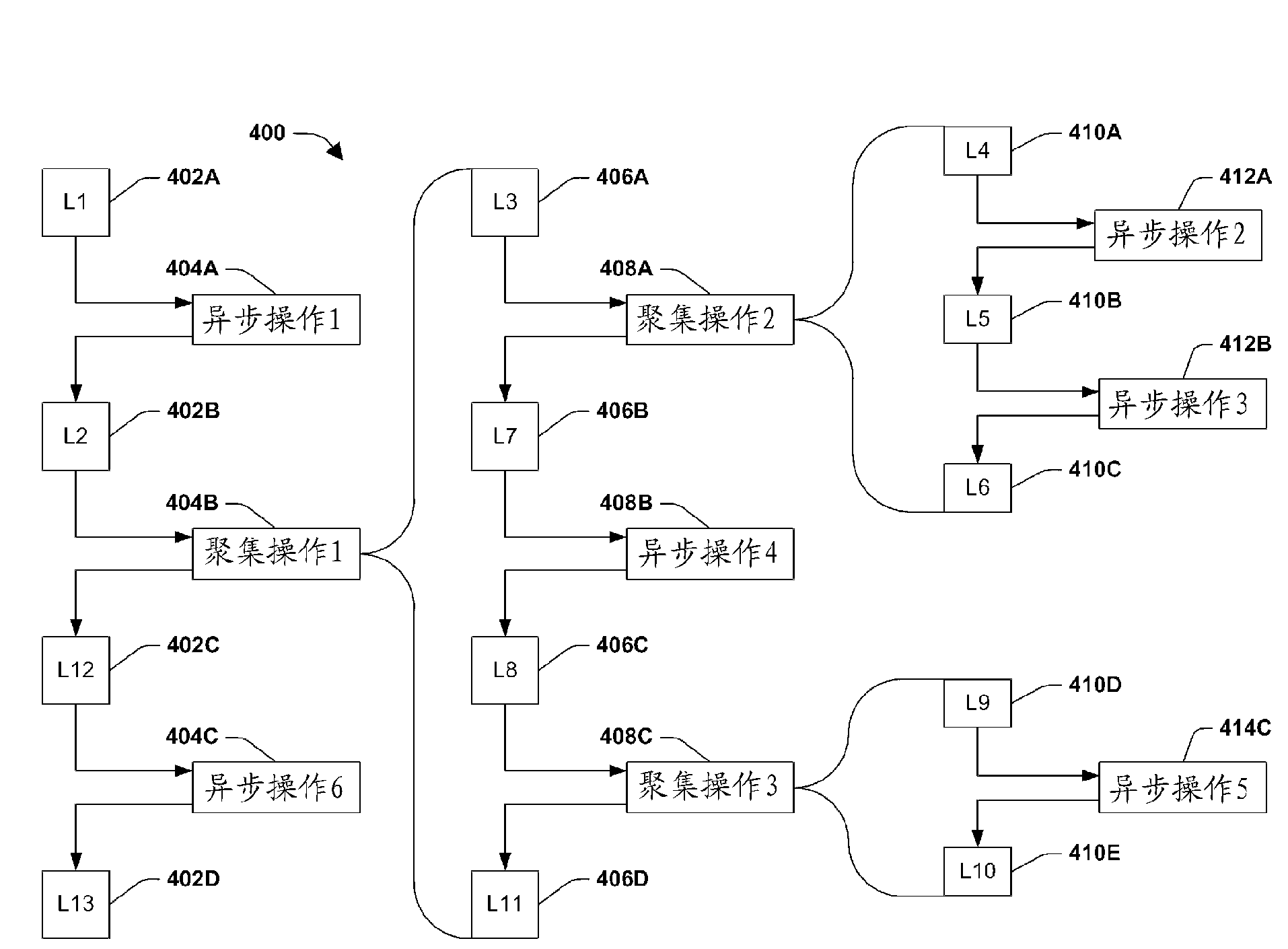

One or more techniques and / or systems are disclosed for improving asynchronous programming execution at runtime. Asynchronous programming code can comprise more than one level of hierarchy, such as in an execution plan. Respective aggregation operations in a portion of the asynchronous programming code are unrolled, to create a single level iterative execution, by combining elements of the multi-level iterative execution of the asynchronous programming code. In this way, the aggregation operations are concatenated to local logic code for the aggregation operations. Thread context switching in the unrolled portion of asynchronous programming code is performed merely at an asynchronous operation, thereby mitigating unnecessary switches. Exceptions thrown during programming code can be propagated up to a top of a virtual callstack for the execution.

Owner:MICROSOFT TECH LICENSING LLC