Patents

Literature

410results about How to "Convenience to merge" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

SiCOH dielectric

InactiveUS20070173071A1Improve cohesive strengthReduce brittlenessSemiconductor/solid-state device detailsSolid-state devicesDielectricDevice material

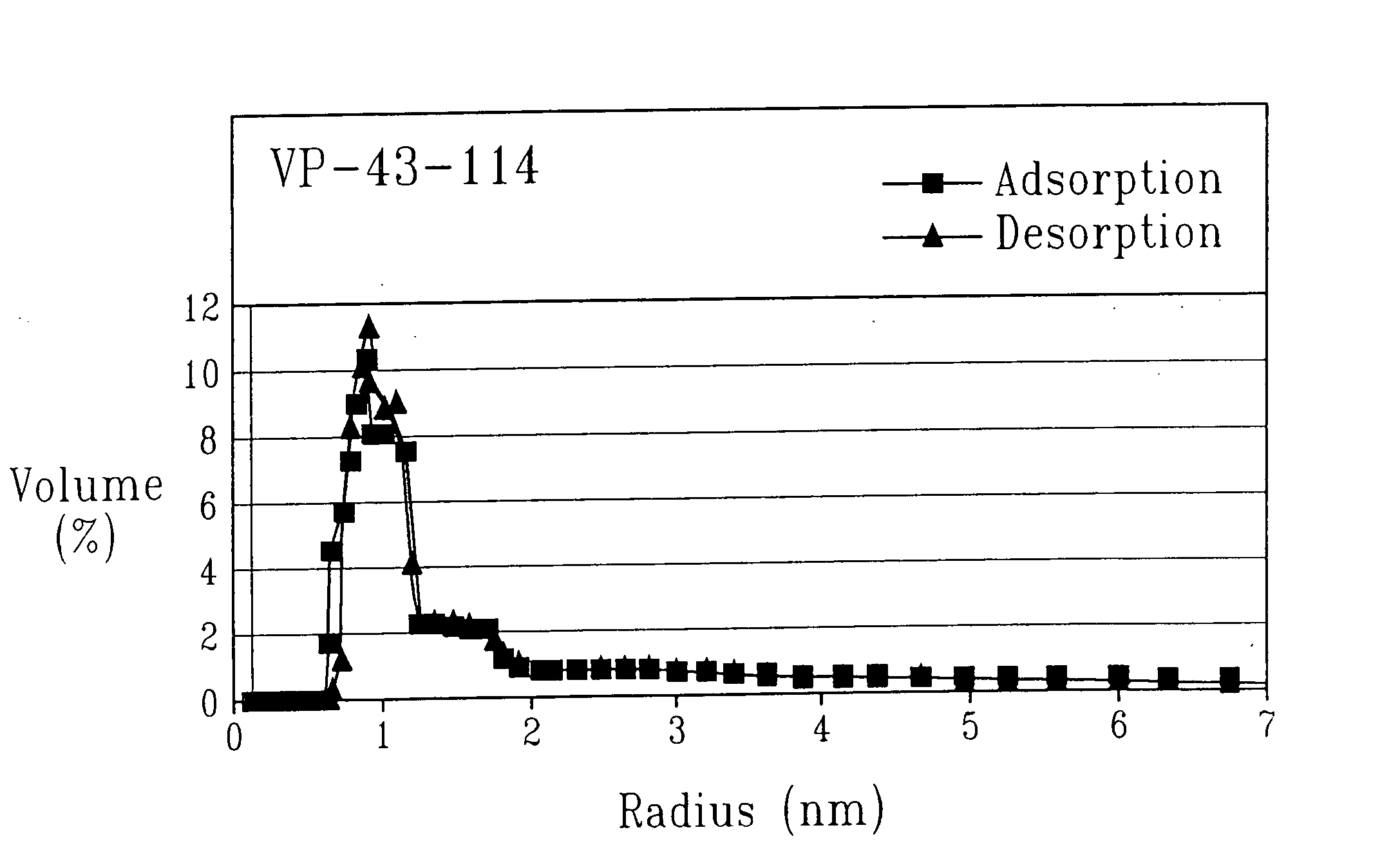

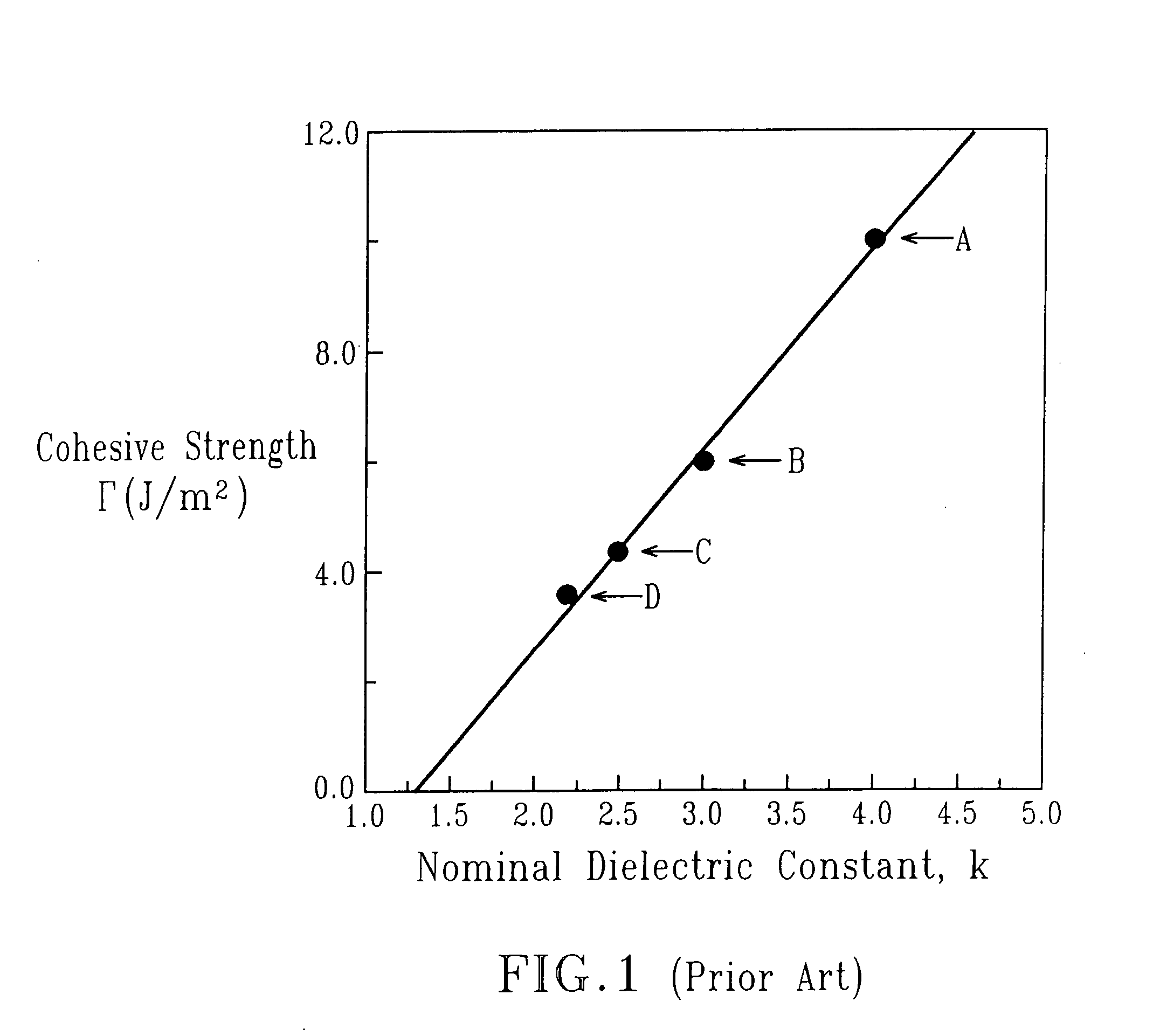

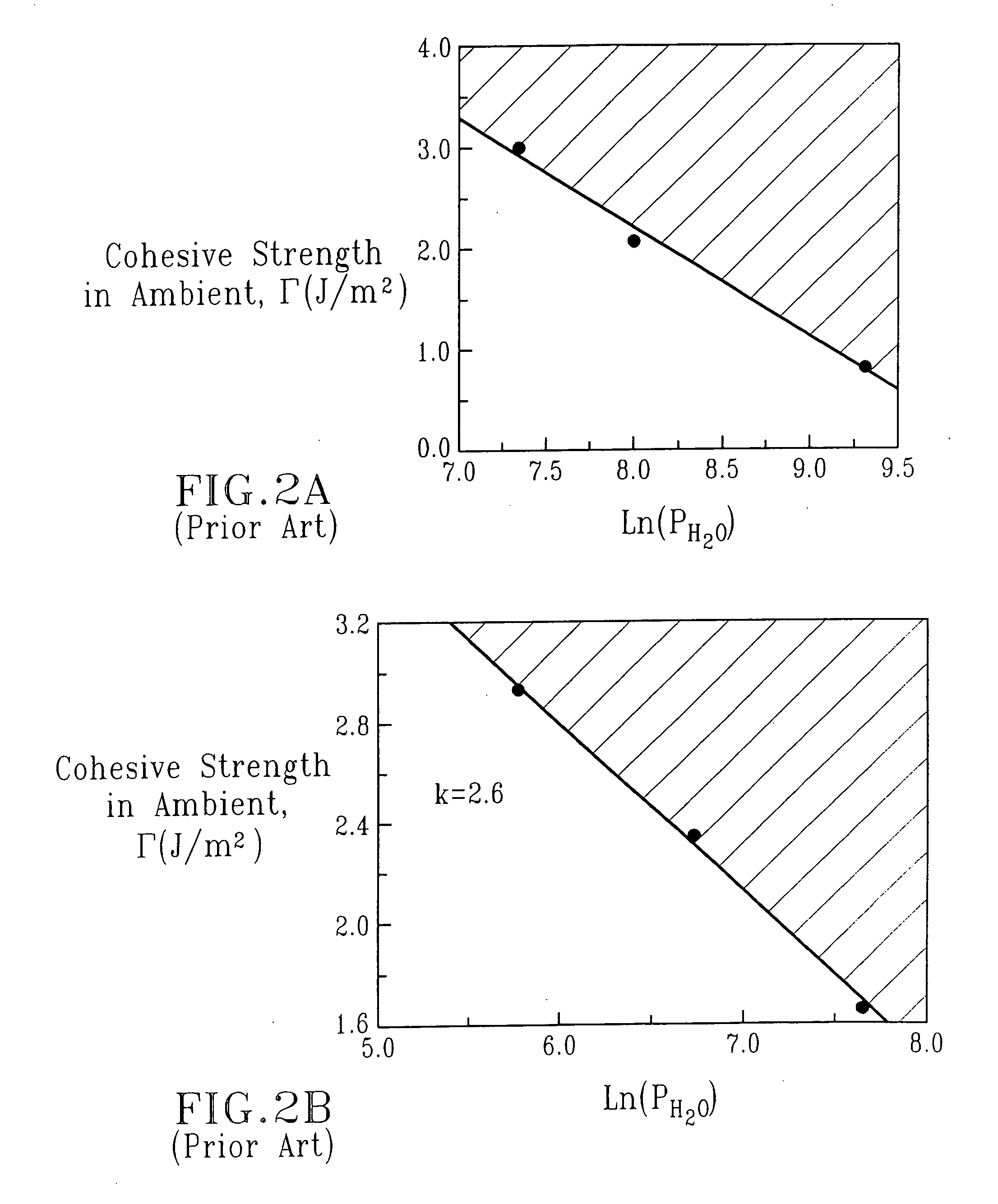

A porous composite material useful in semiconductor device manufacturing, in which the diameter (or characteristic dimension) of the pores and the pore size distribution (PSD) is controlled in a nanoscale manner and which exhibits improved cohesive strength (or equivalently, improved fracture toughness or reduced brittleness), and increased resistance to water degradation of properties such as stress-corrosion cracking, Cu ingress, and other critical properties is provided. The porous composite material is fabricating utilizing at least one bifunctional organic porogen as a precursor compound

Owner:INTEL CORP

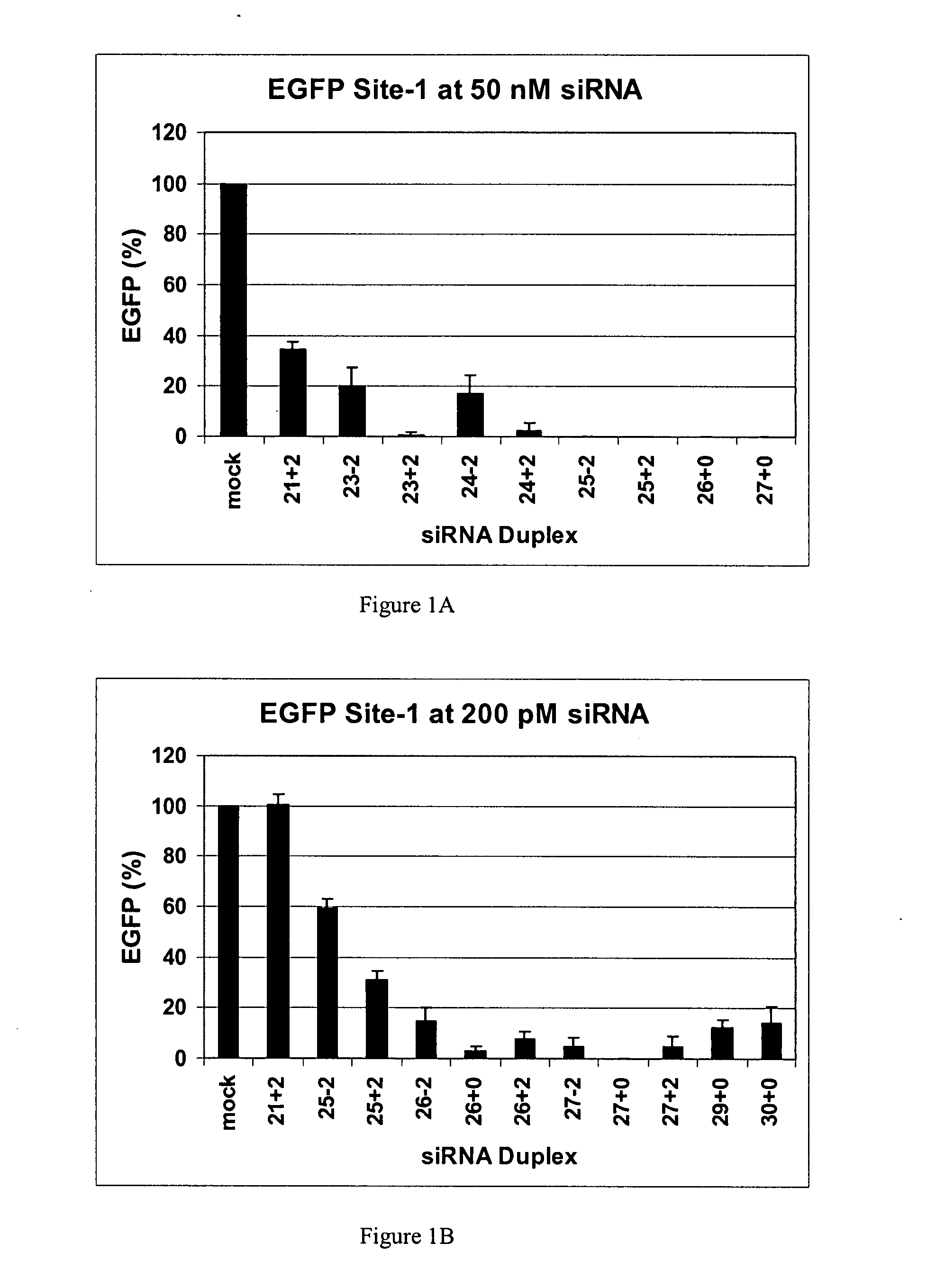

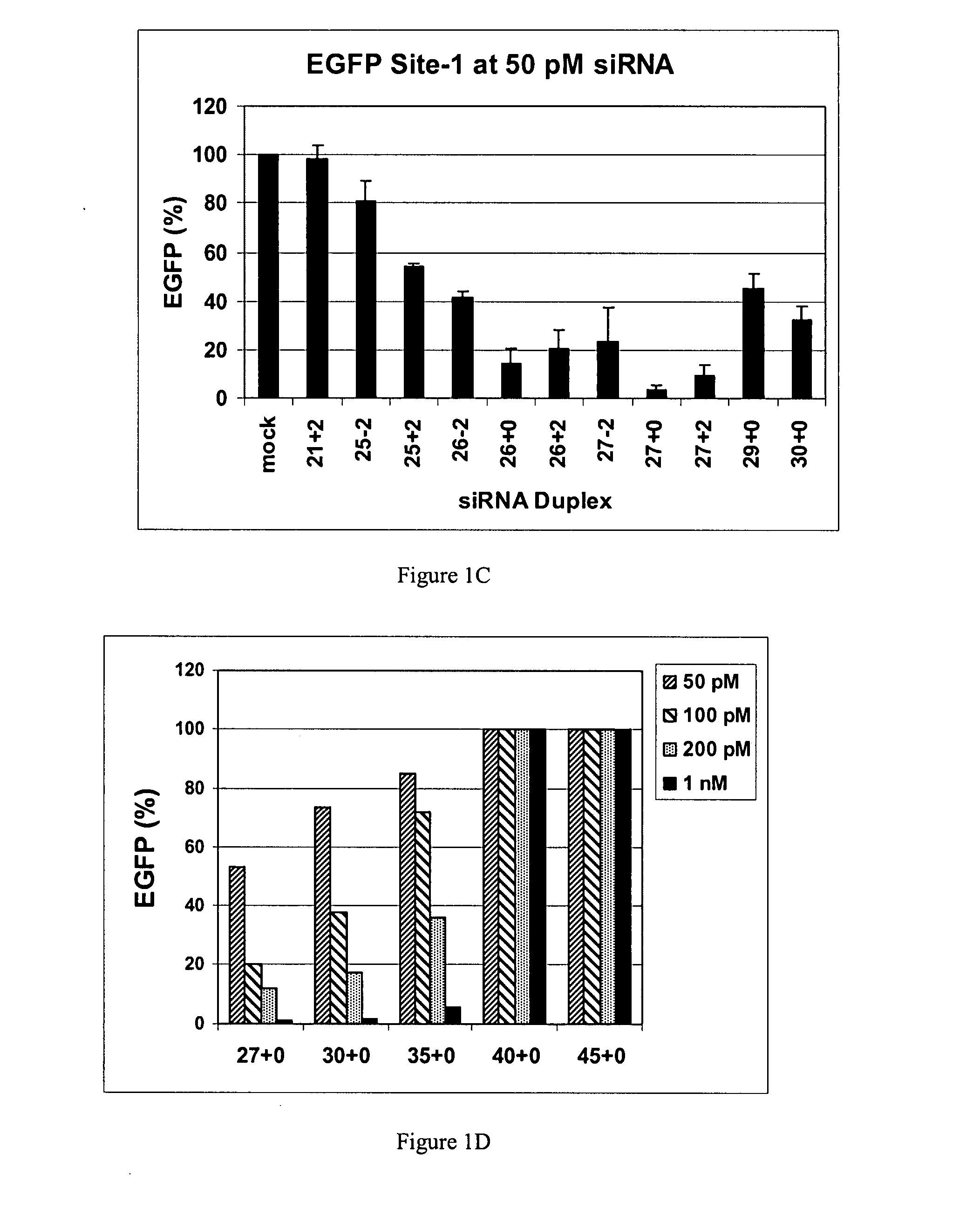

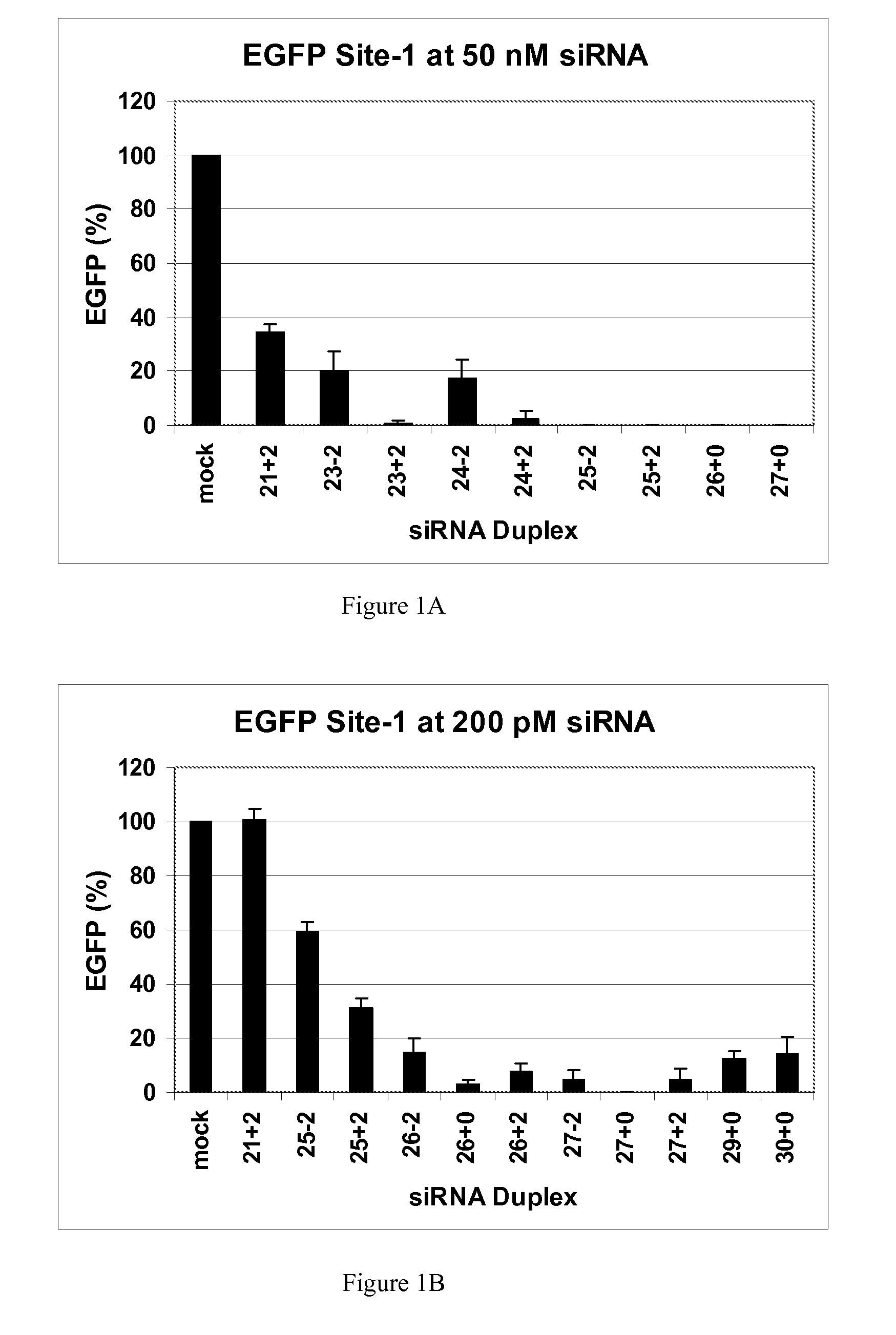

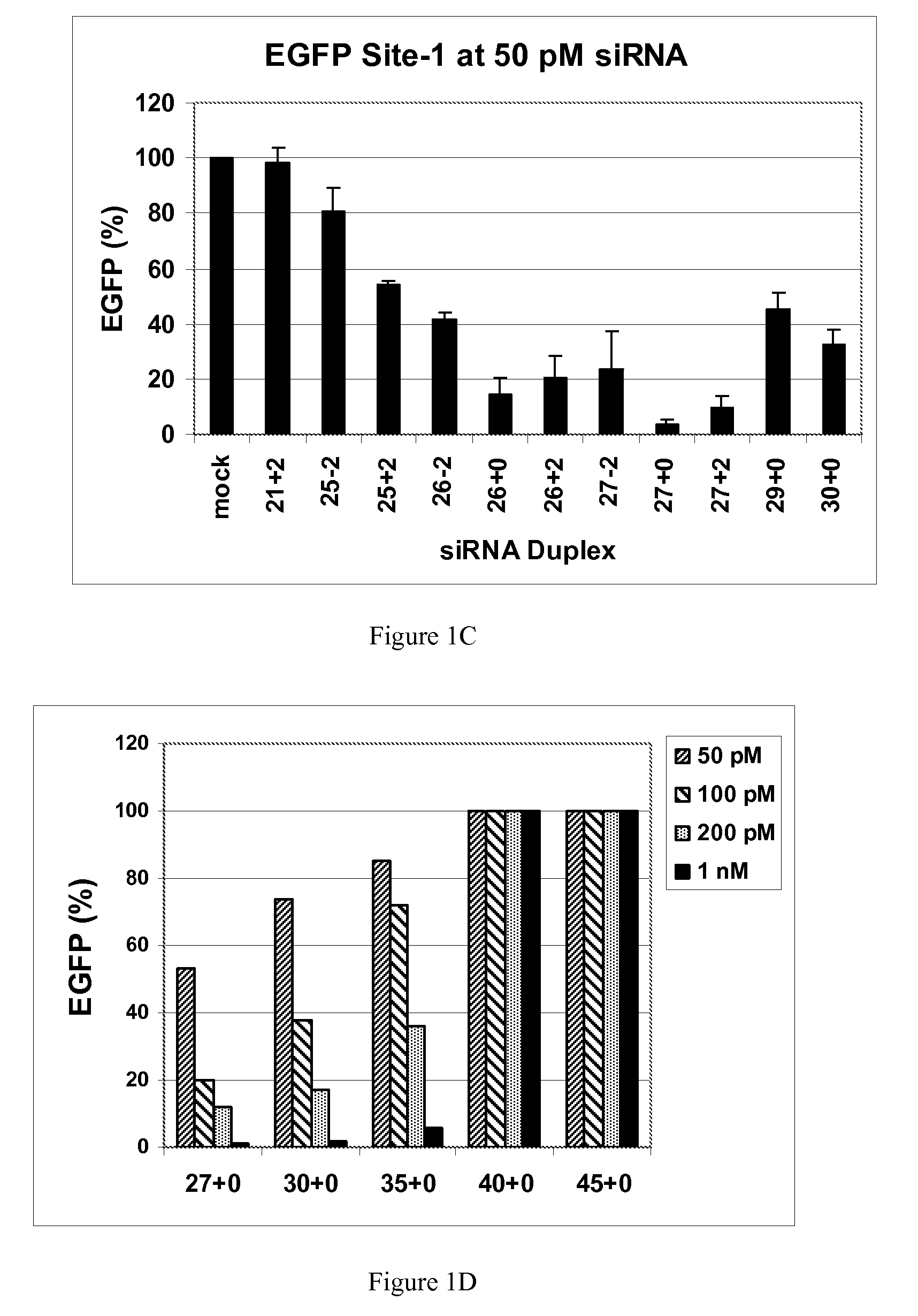

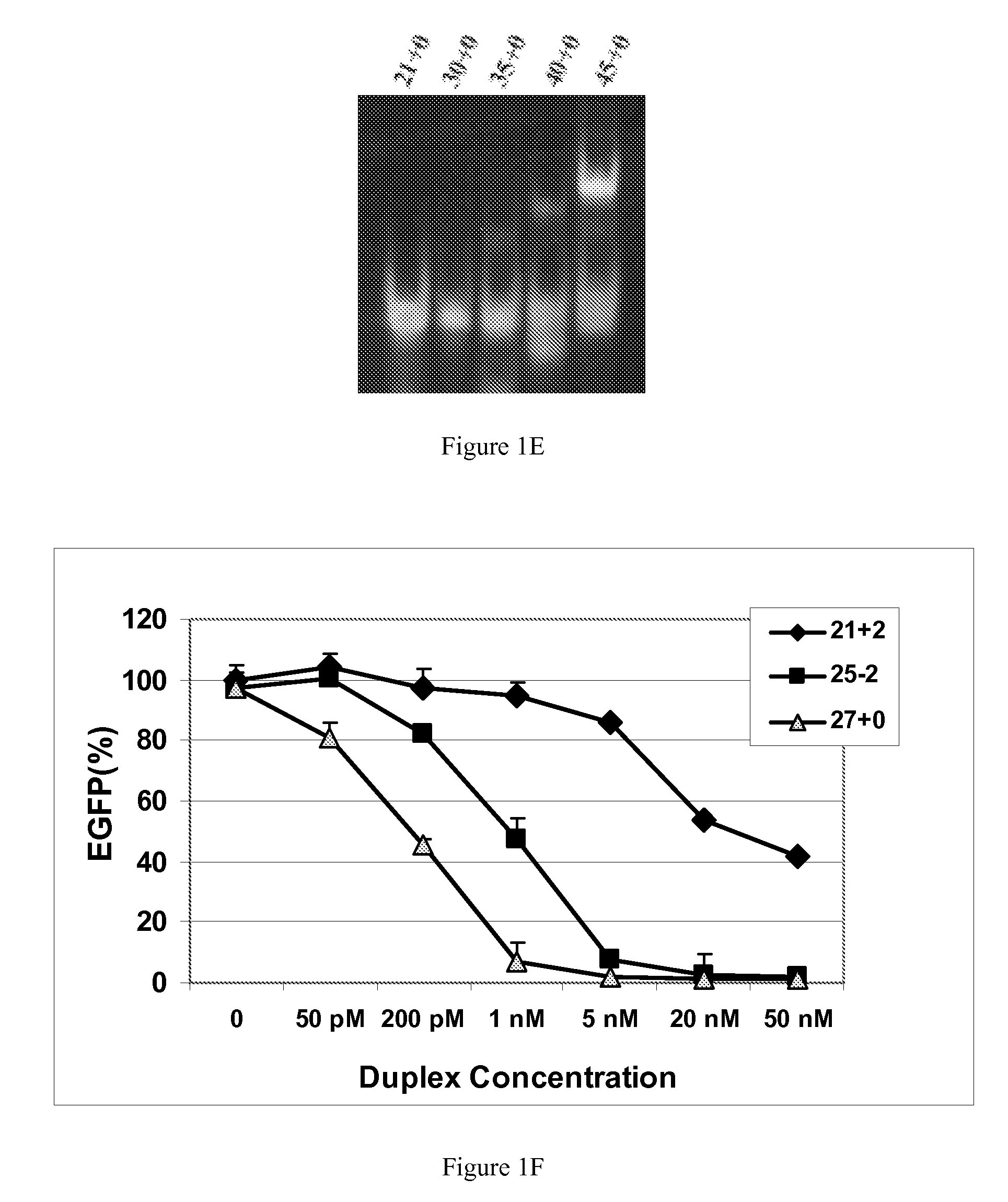

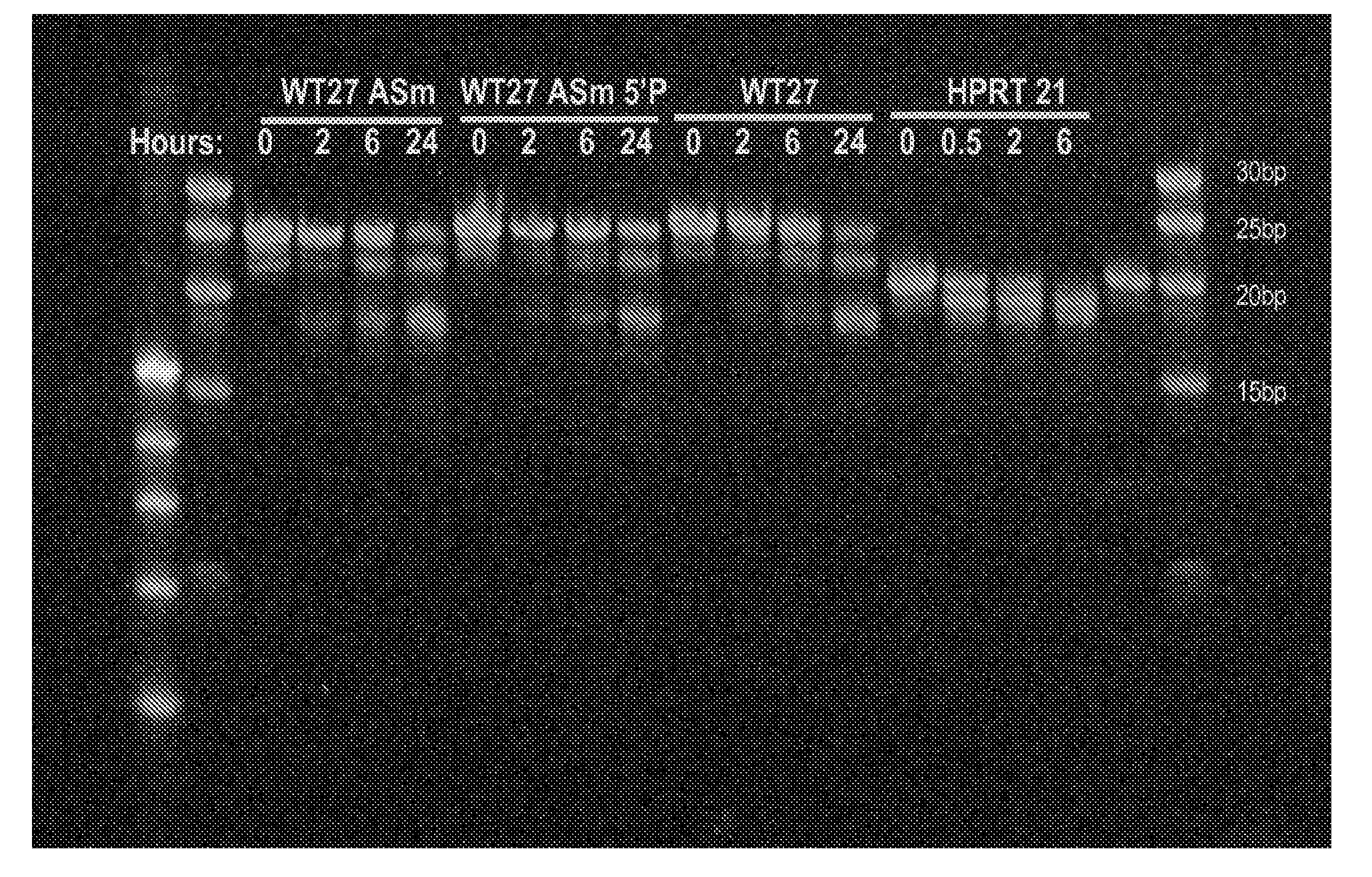

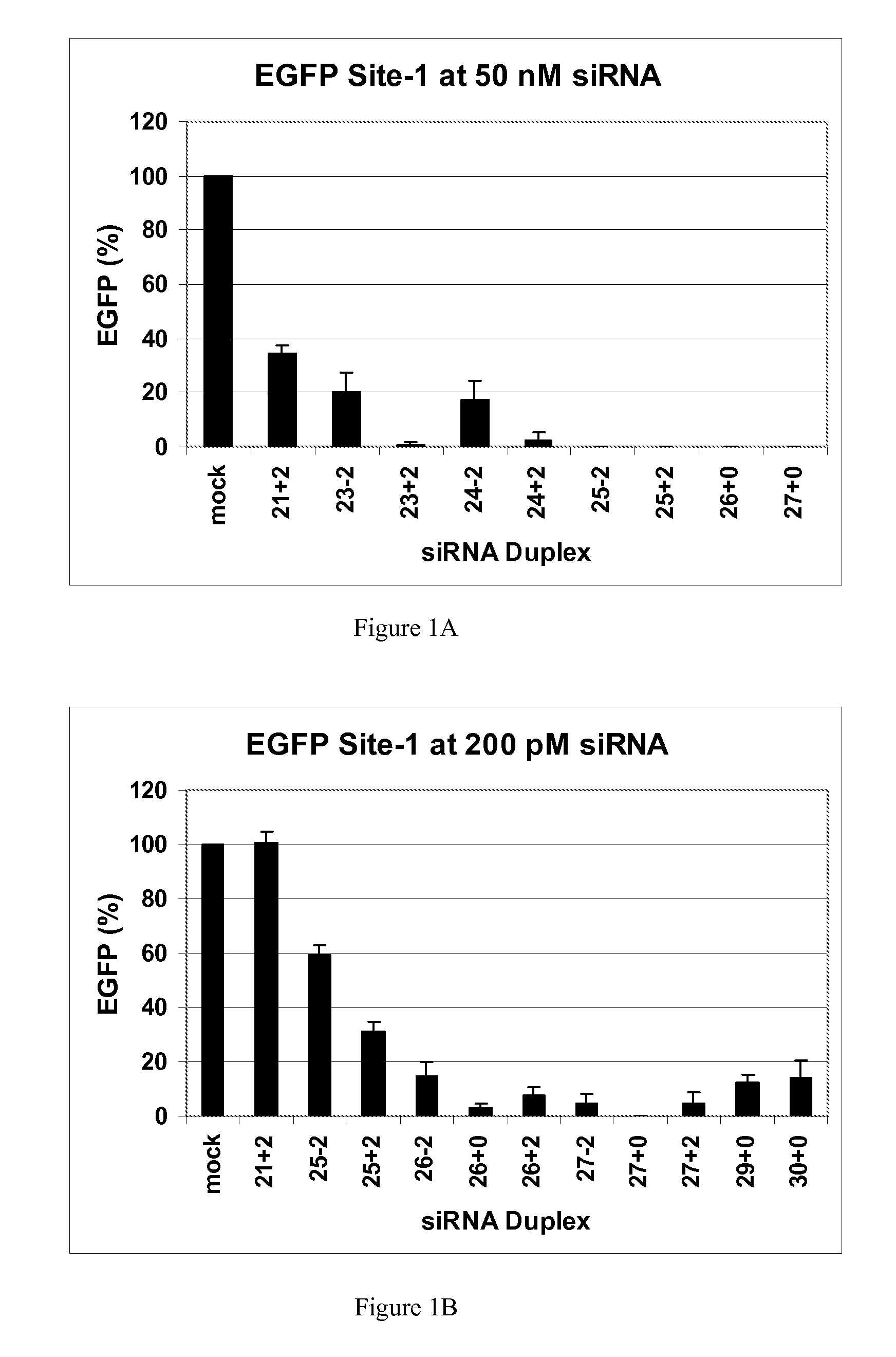

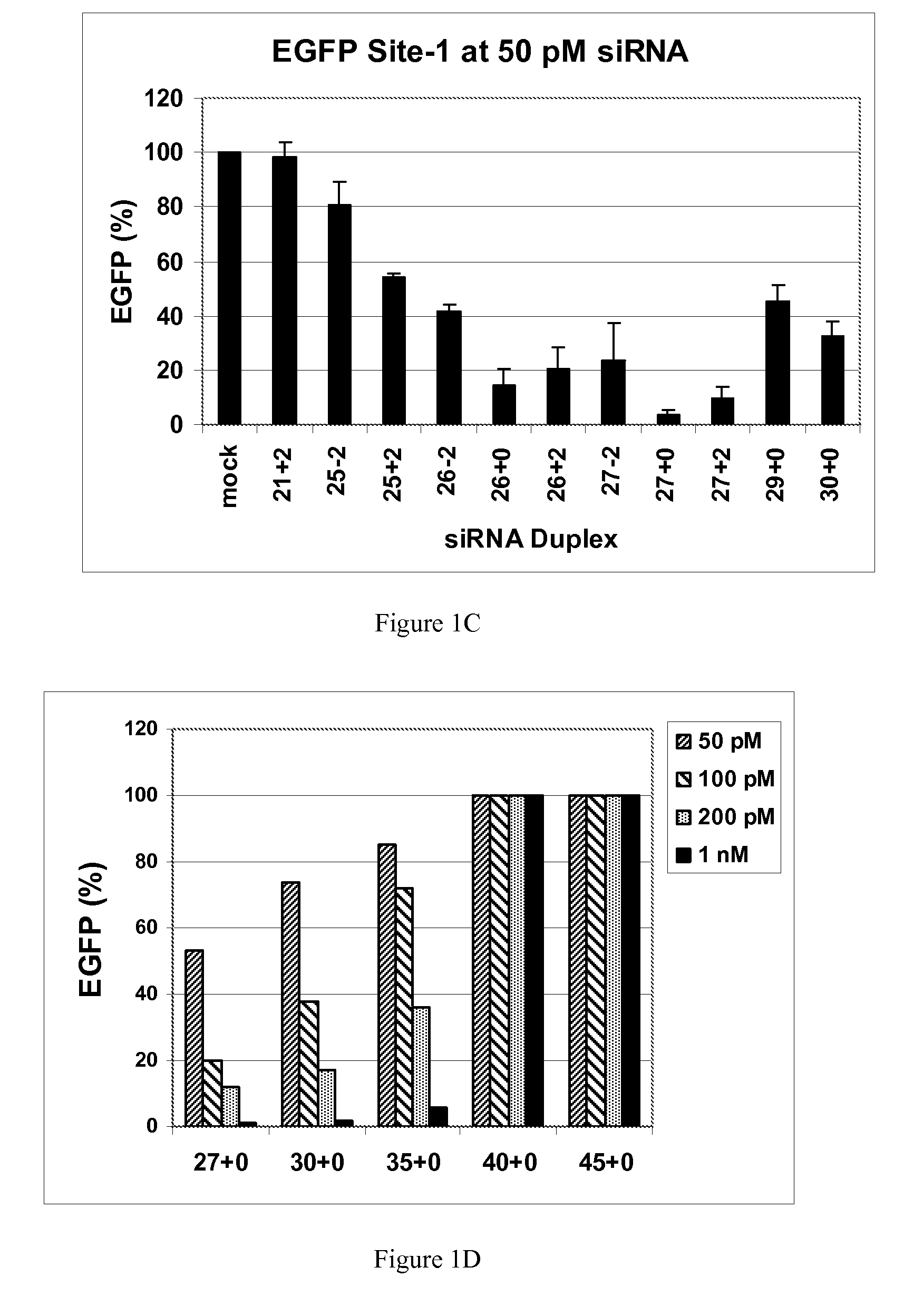

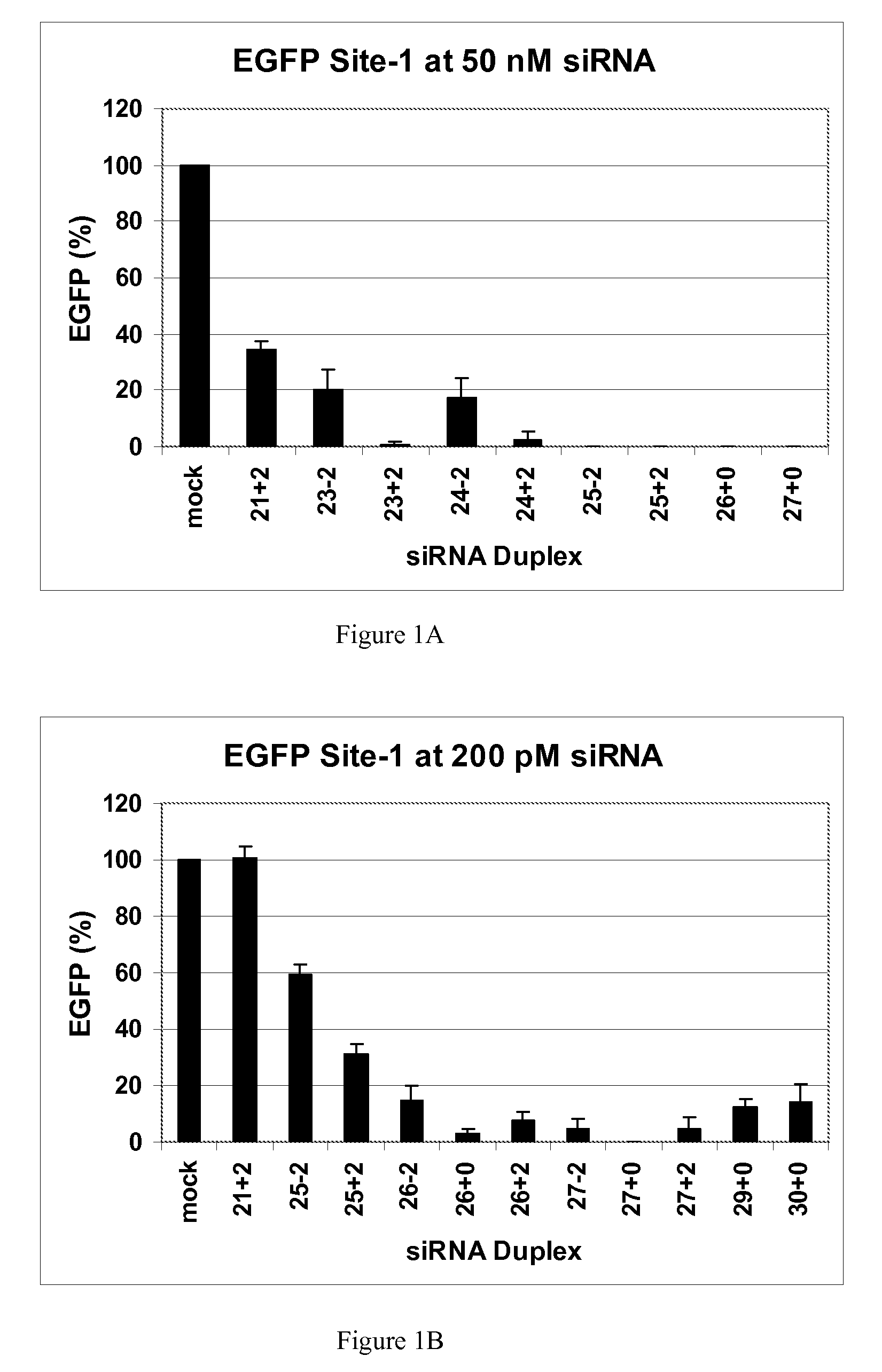

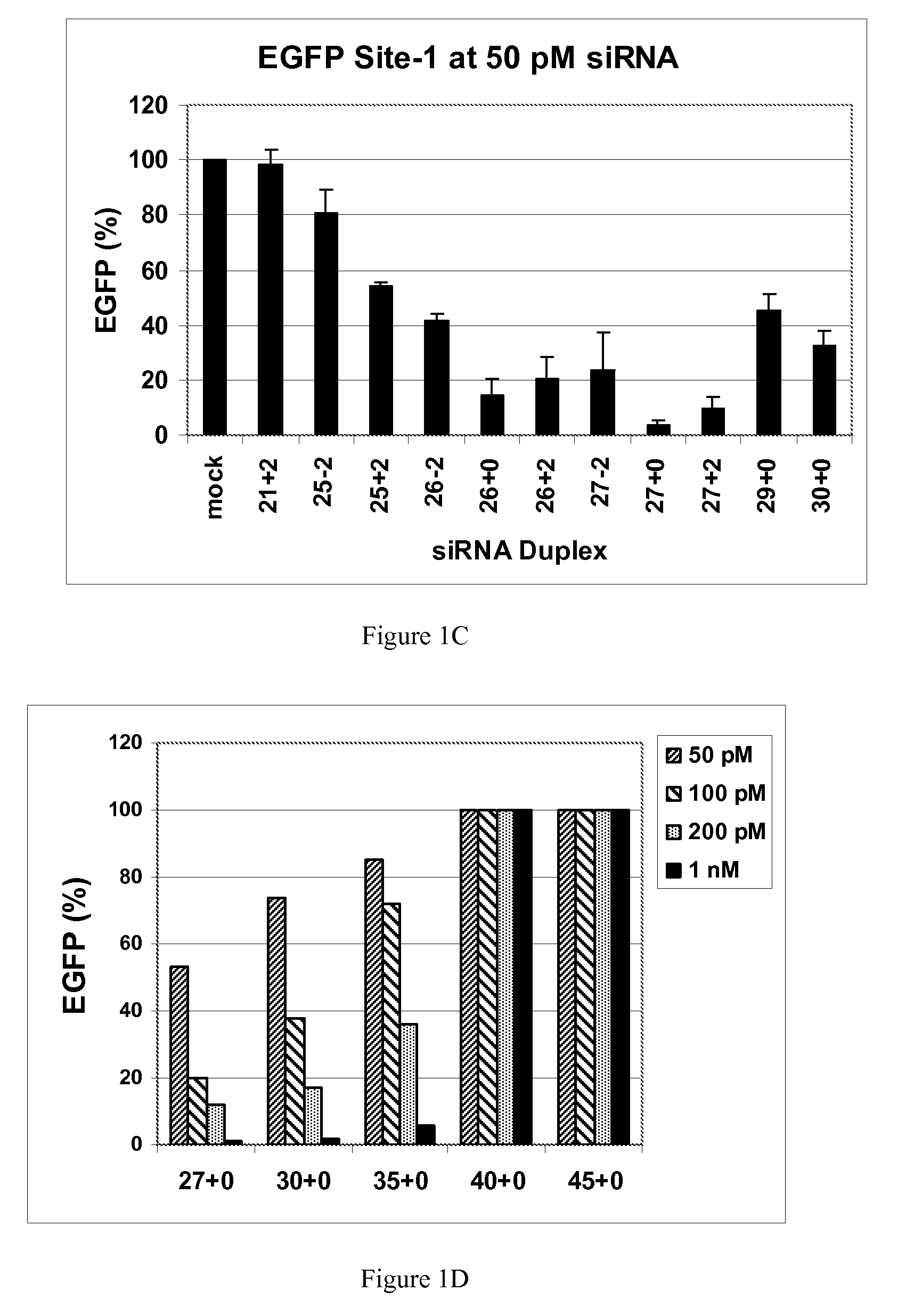

Methods and compositions for the specific inhibition of gene expression by double-stranded RNA

InactiveUS20070265220A1Improve stabilityConvenience to mergeSenses disorderAntipyreticDouble strandOligonucleotide

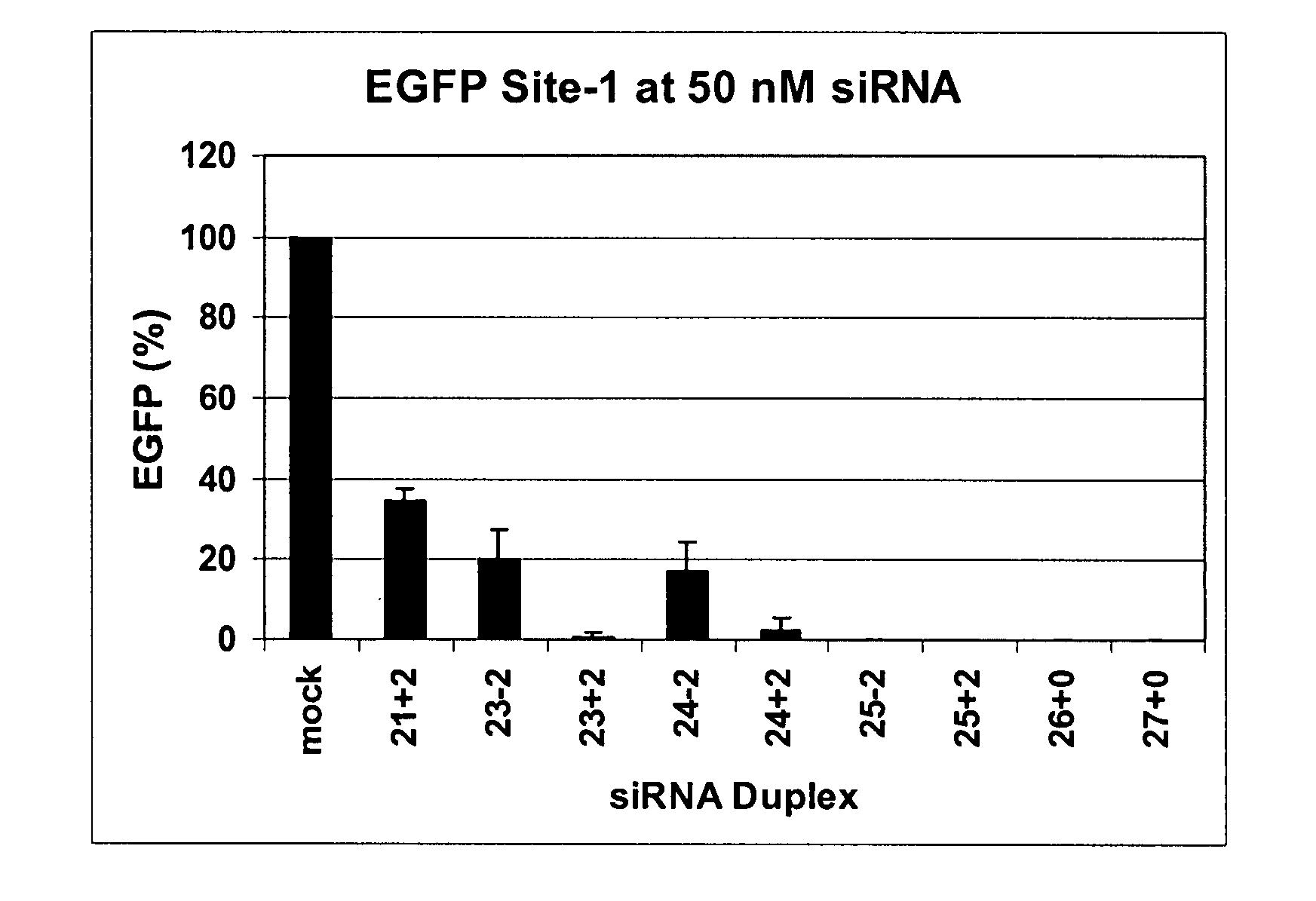

The invention is directed to compositions and methods for selectively reducing the expression of a gene product from a desired target gene in a cell, as well as for treating diseases caused by the expression of the gene. More particularly, the invention is directed to compositions that contain double stranded RNA (“dsRNA”), and methods for preparing them, that are capable of reducing the expression of target genes in eukaryotic cells. The dsRNA has a first oligonucleotide sequence that is between 25 and about 30 nucleotides in length and a second oligonucleotide sequence that anneals to the first sequence under biological conditions. In addition, a region of one of the sequences of the dsRNA having a sequence length of at least 19 nucleotides is sufficiently complementary to a nucleotide sequence of the RNA produced from the target gene to trigger the destruction of the target RNA by the RNAi machinery.

Owner:CITY OF HOPE +1

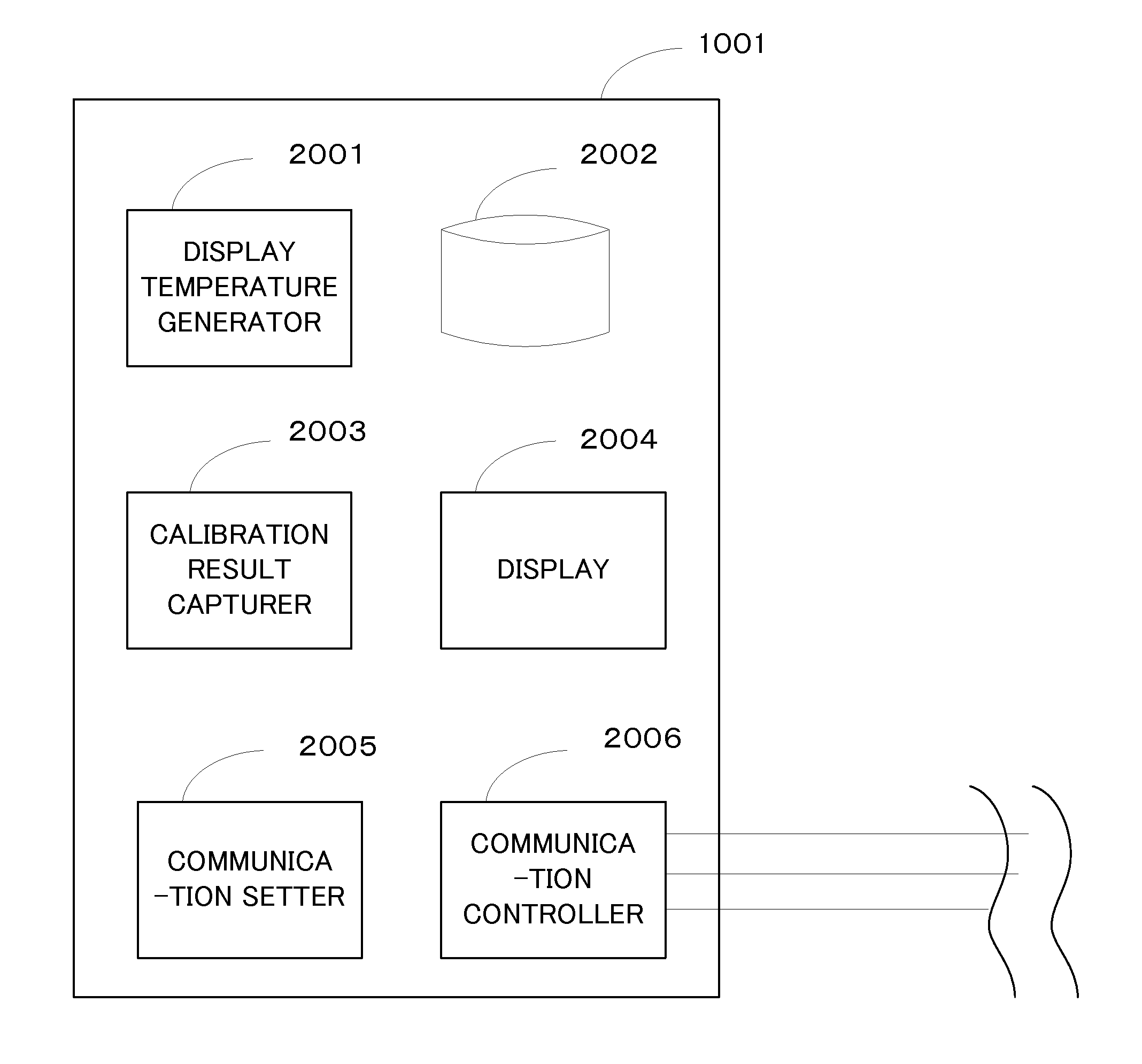

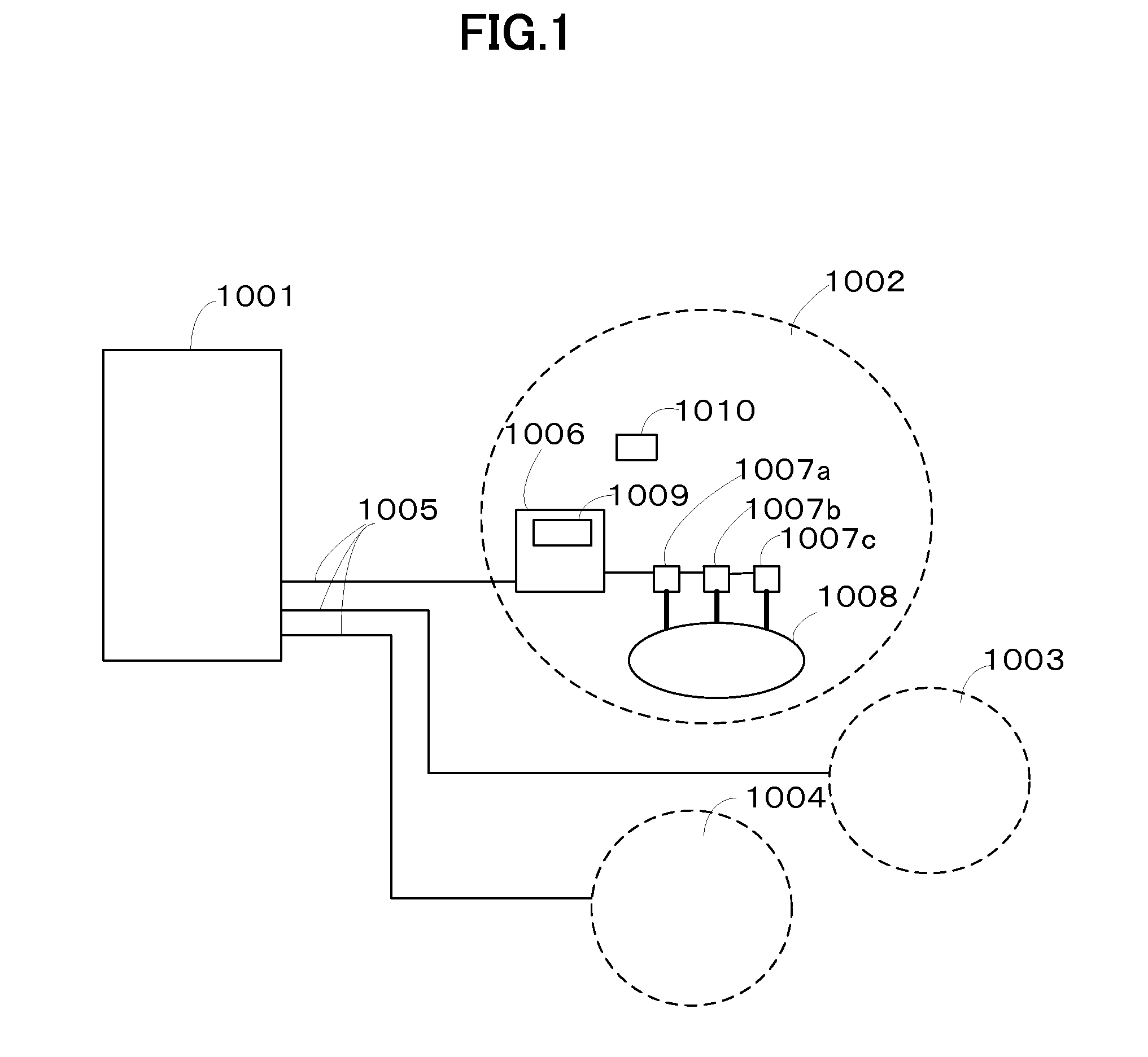

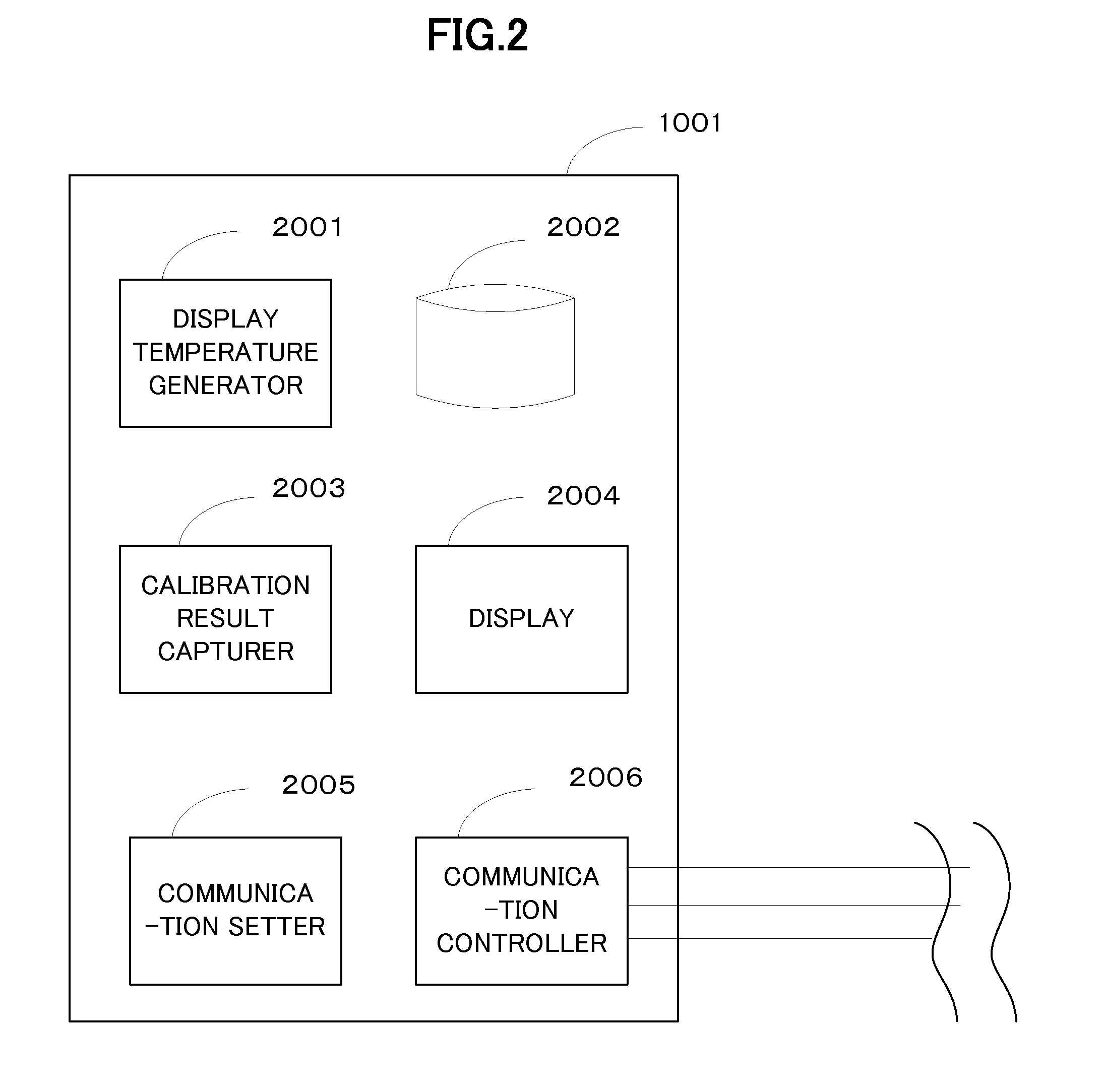

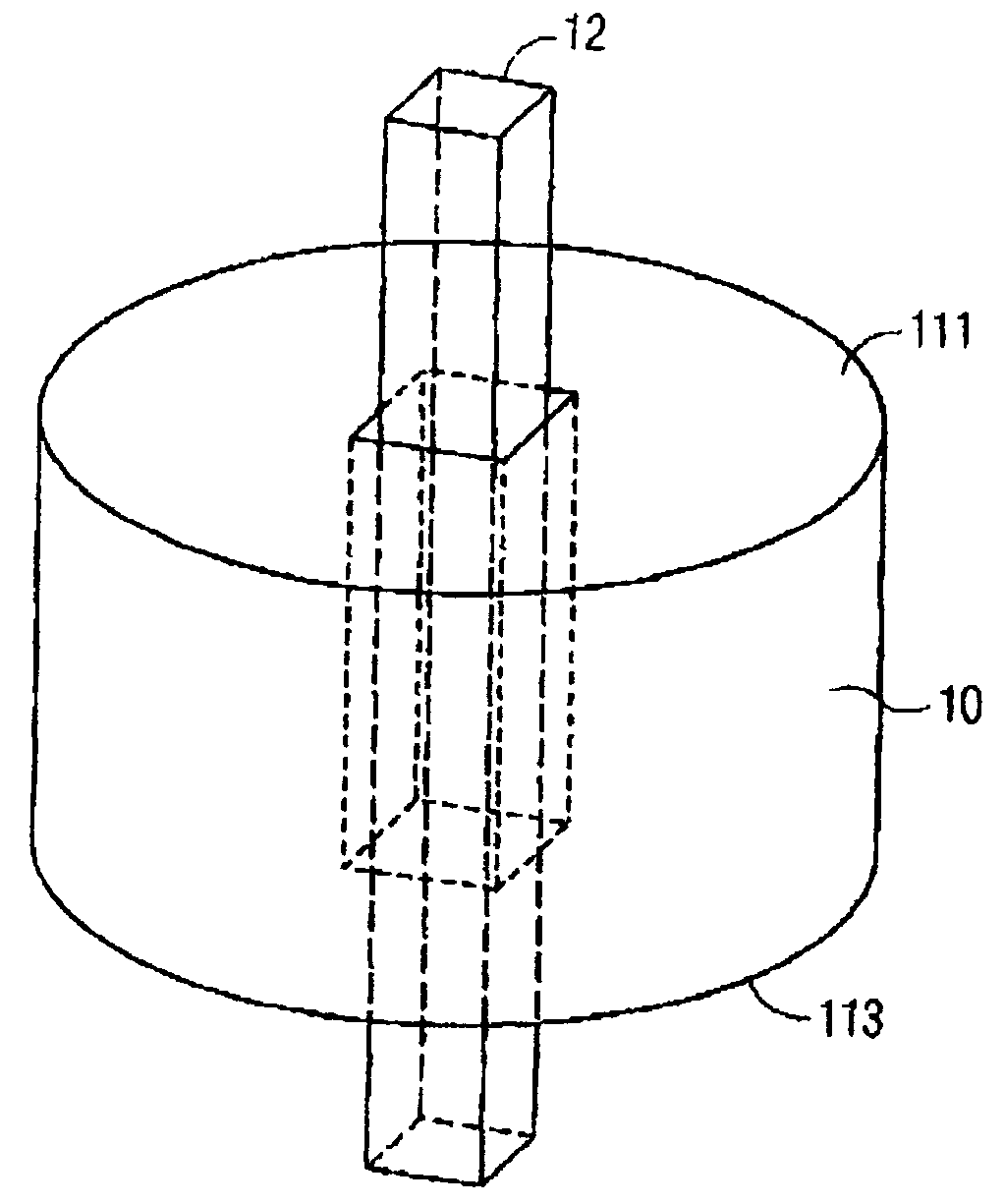

Thermometer Management System

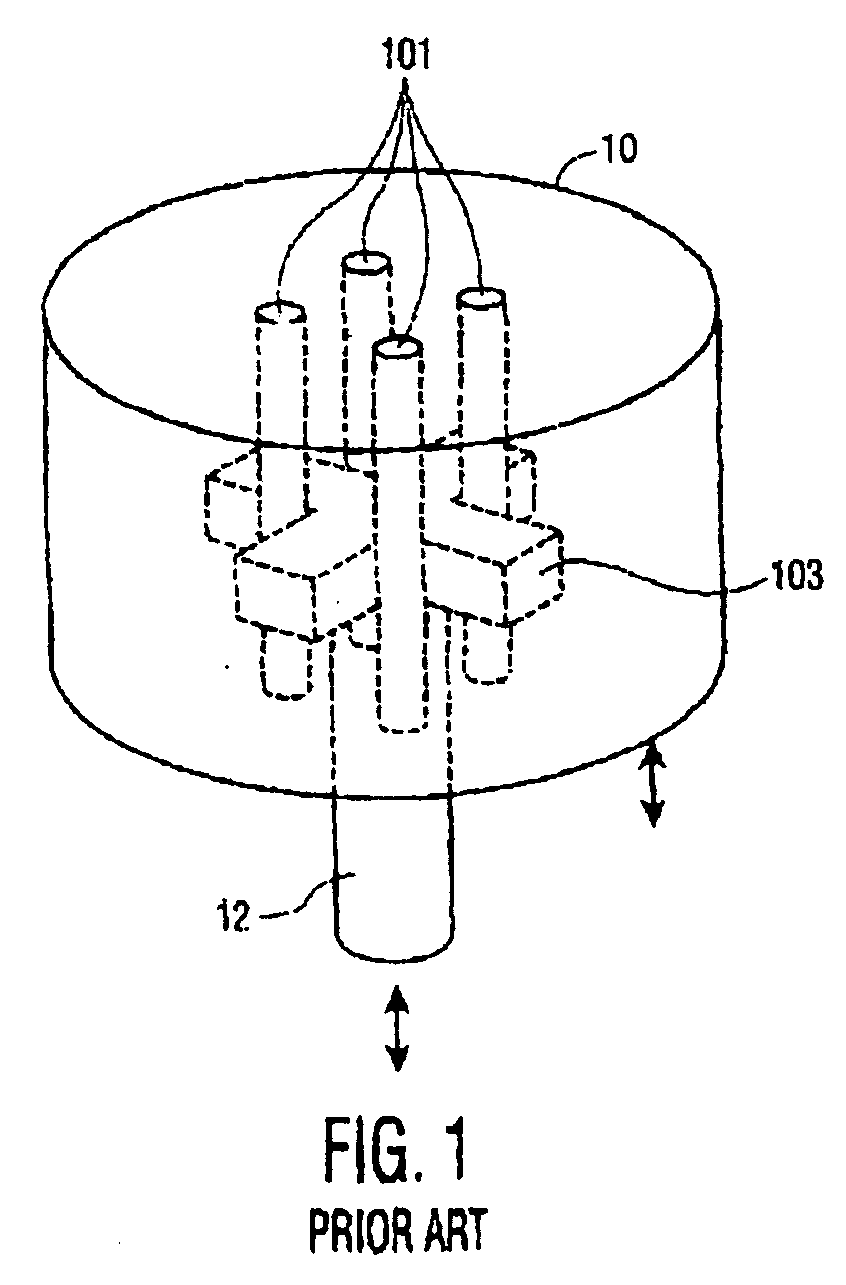

ActiveUS20150110147A1Convenience to mergeEasy to implementThermometer detailsTemperature measurement in household appliancesRadio frequencyManagement system

A body of a thermometer (1001), a first location to be measured (1002), a second location to be measured (1003) and a third installation location (1004) is established by the thermometer management system. Further, communication lines (1005) are connected to network units at each location to be measured. Network units relay the sensor output from a sensor part to the communication lines. A sensor part is fixed to an object to be measured and sends a sensor output in response to the temperature of the object to be measured. A network unit has a radio frequency identifier (RFID) reader and transmits to the thermometer body commands and the like stored in the memory of an RFID card in response to approach of the RFID card arranged corresponding to a location to be measured. The thermometer body receives the commands and the like and performs predetermined operations.

Owner:MIZUNO YOSHIRO

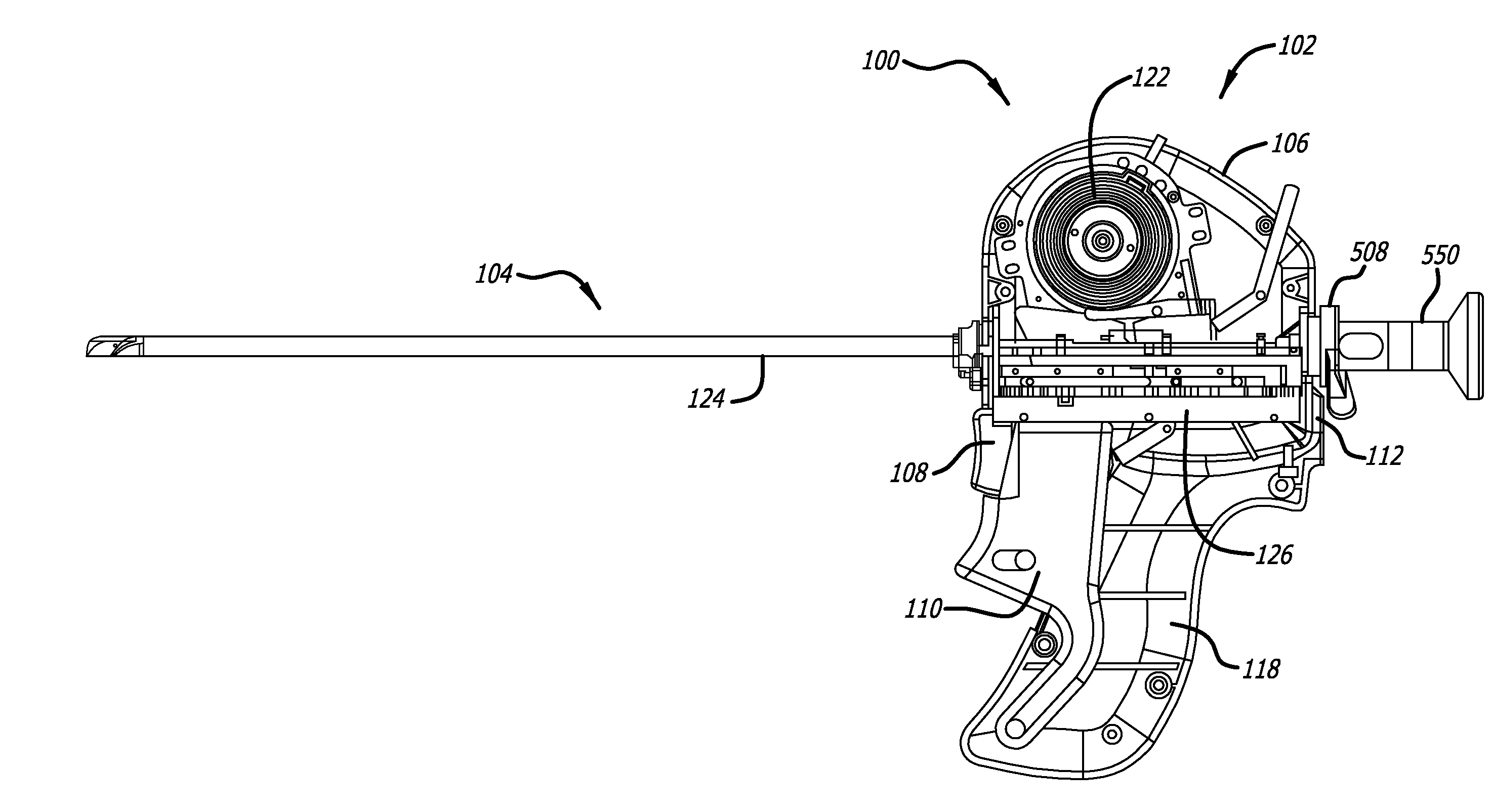

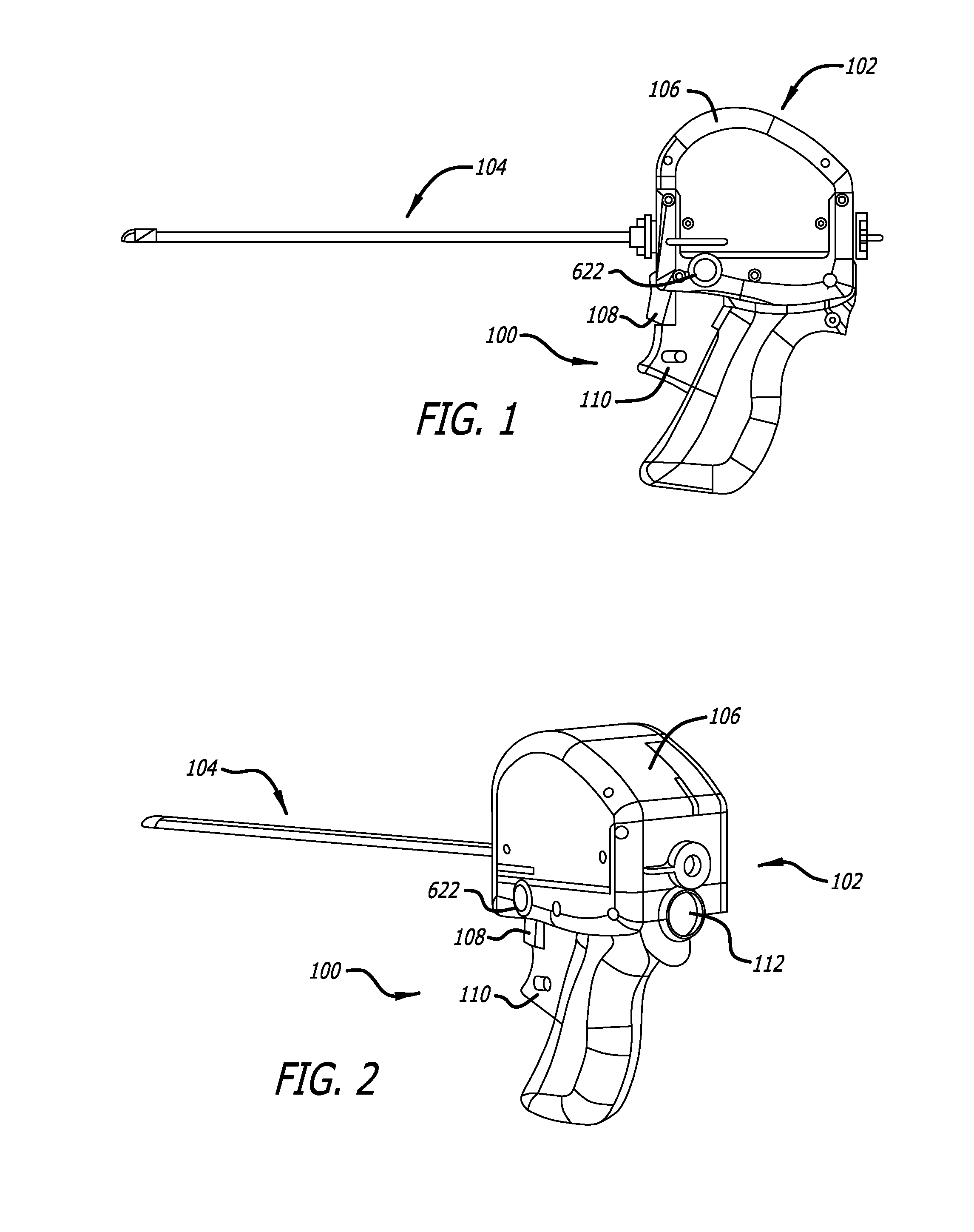

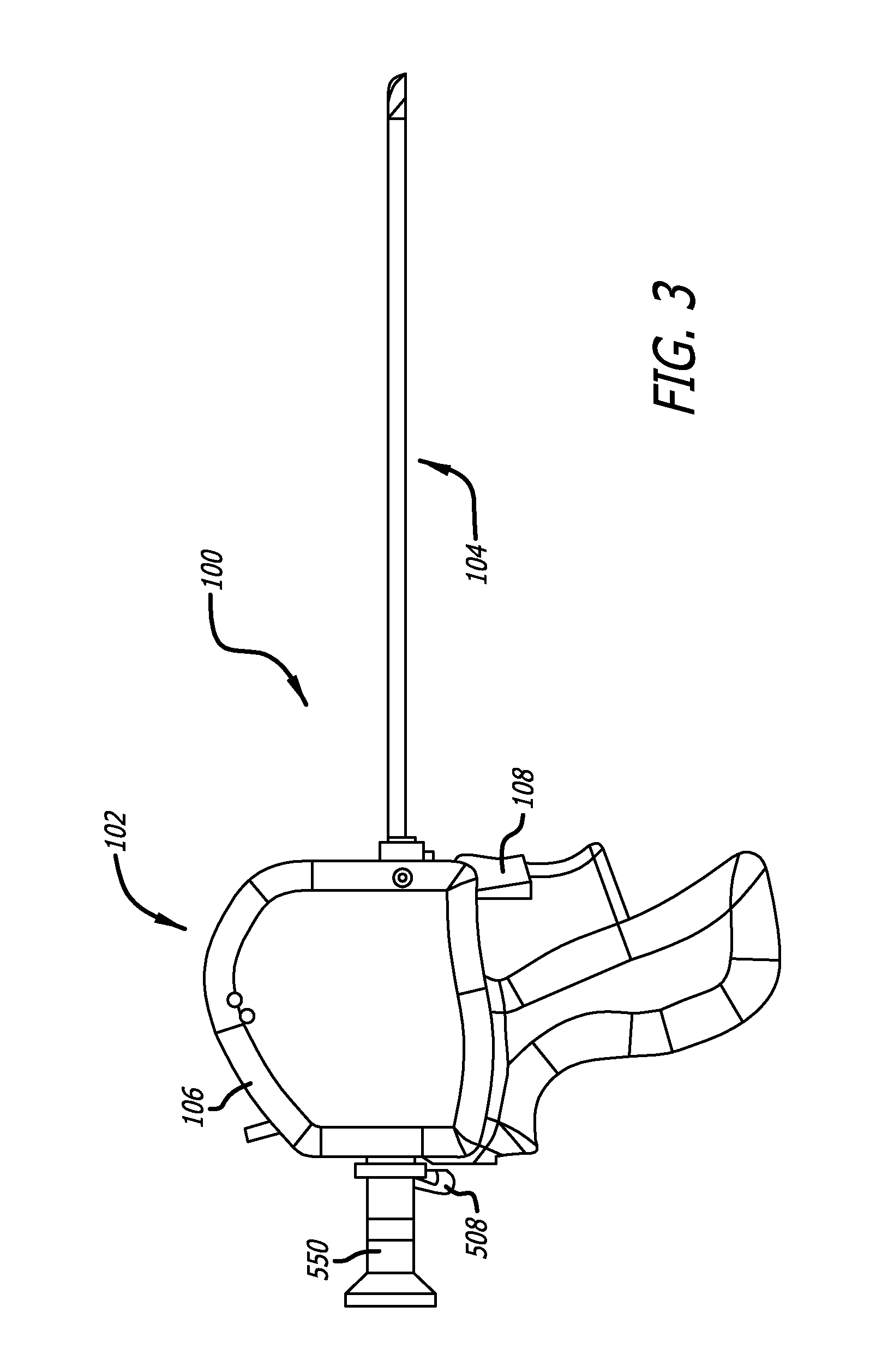

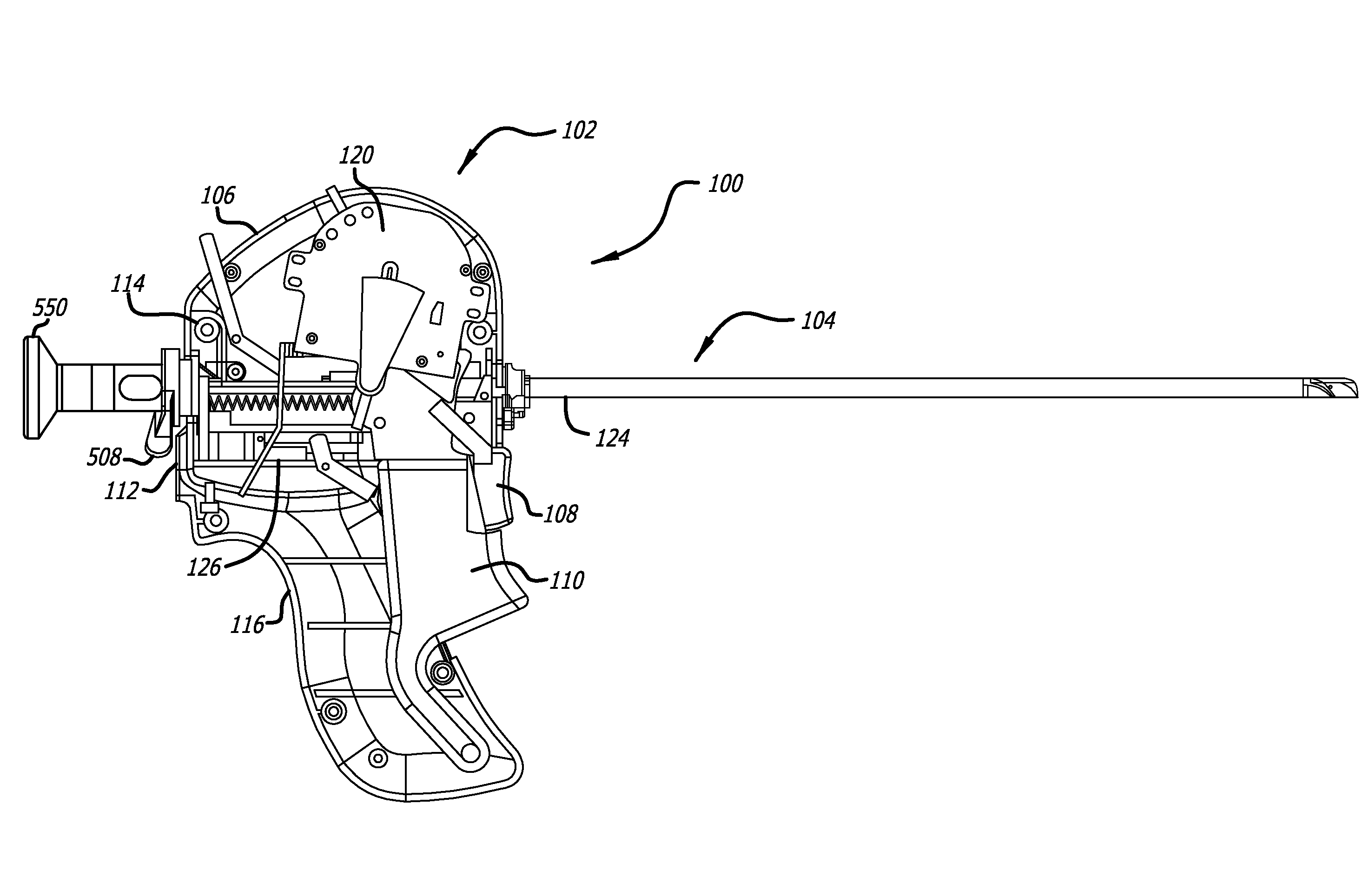

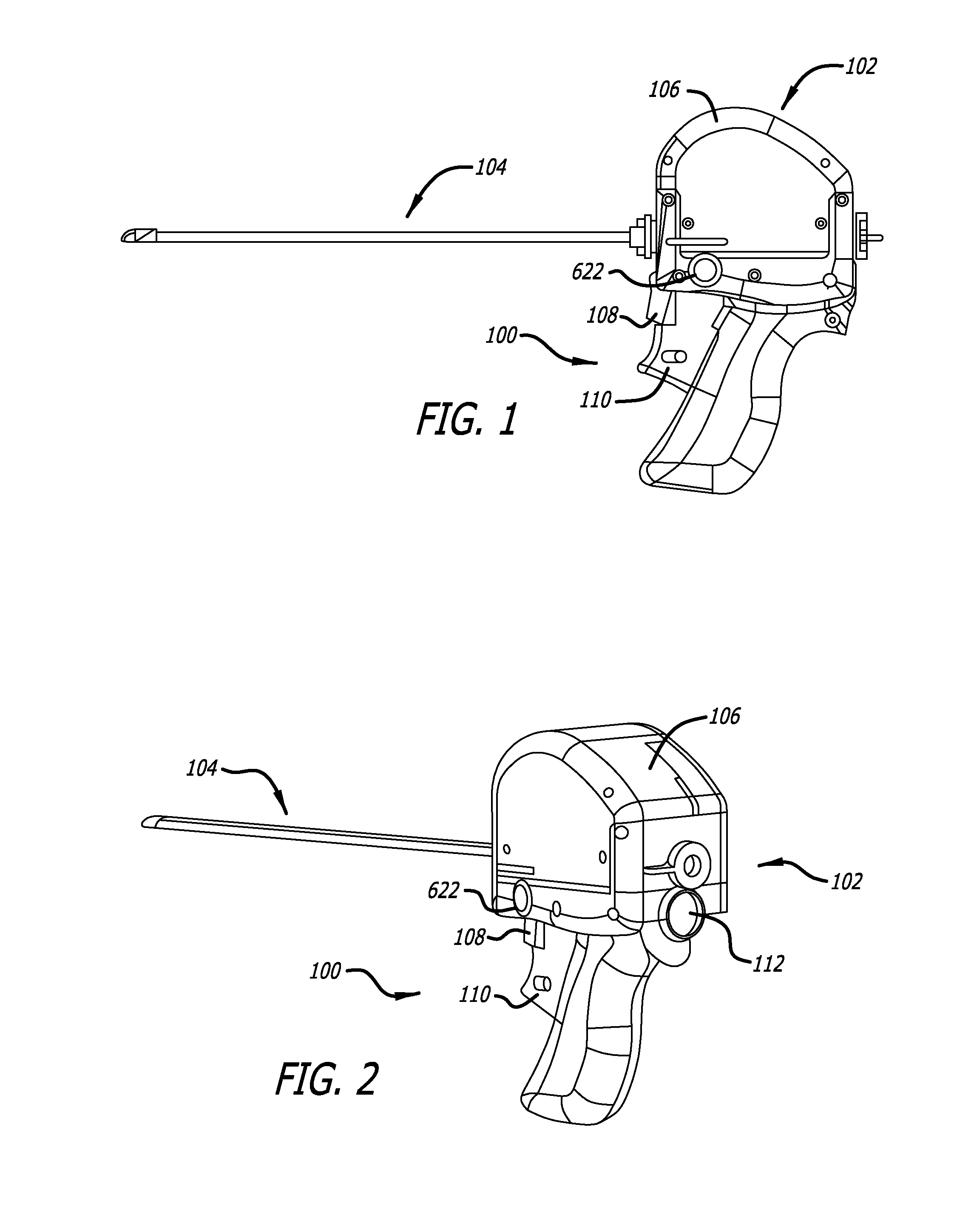

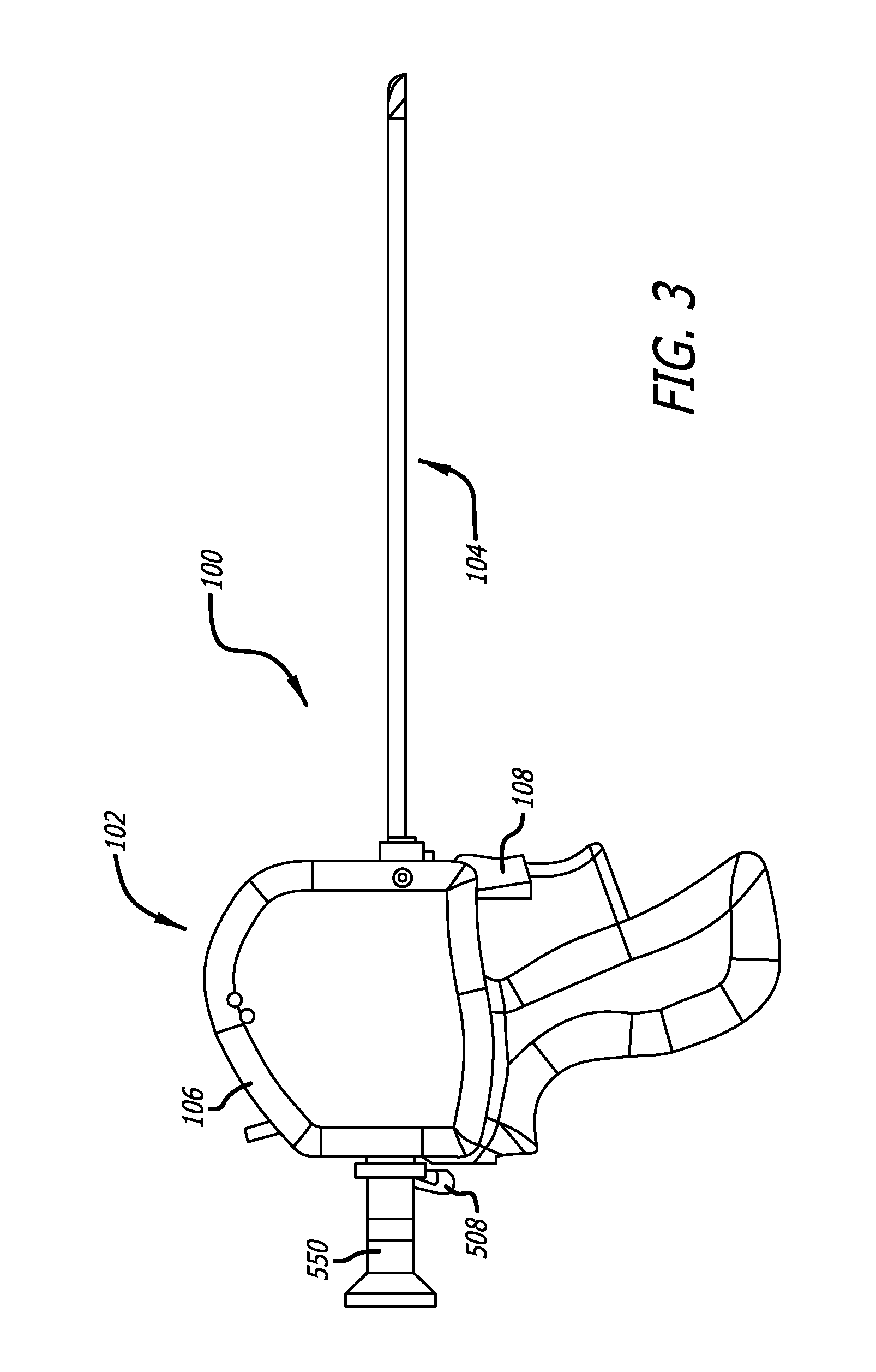

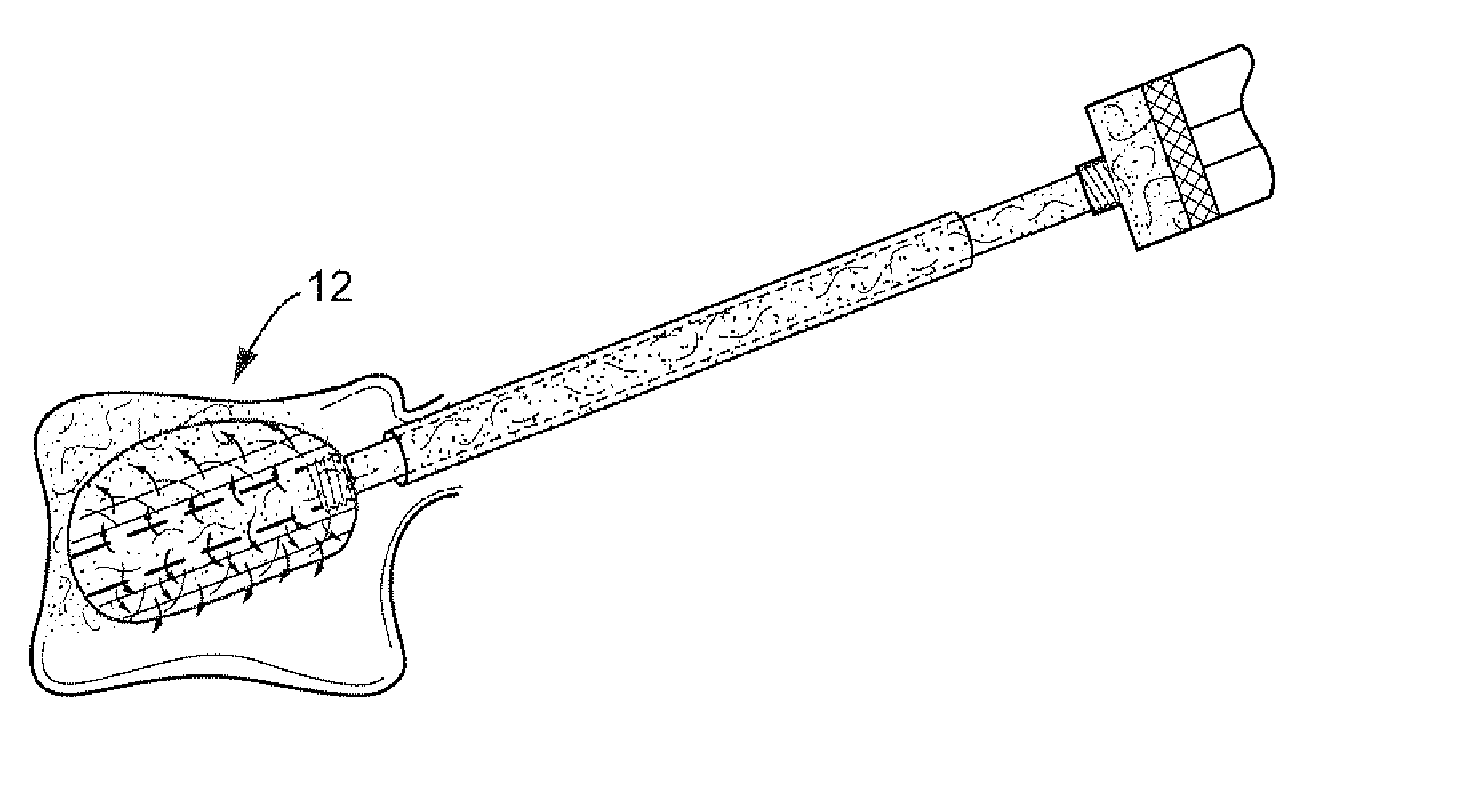

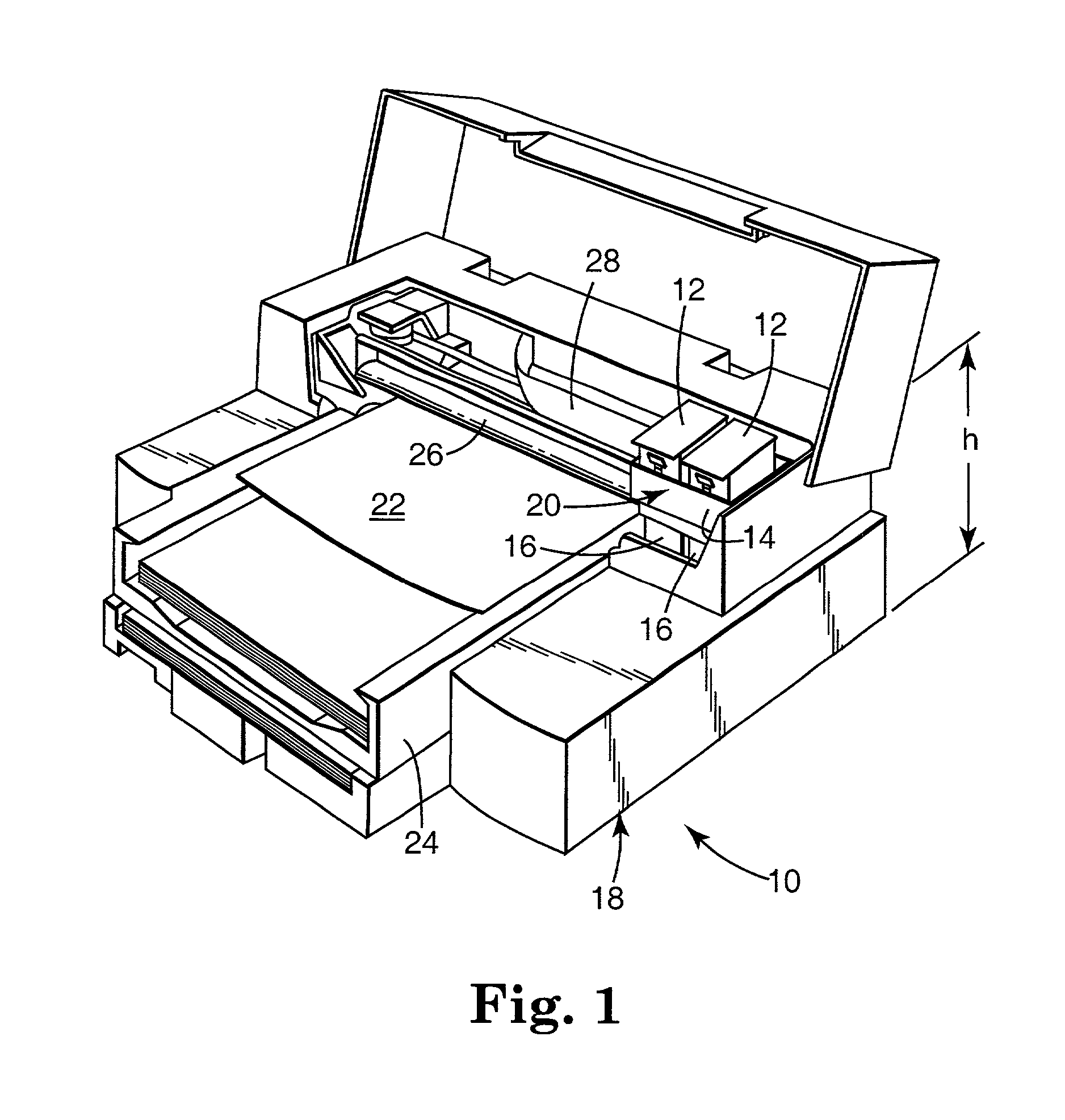

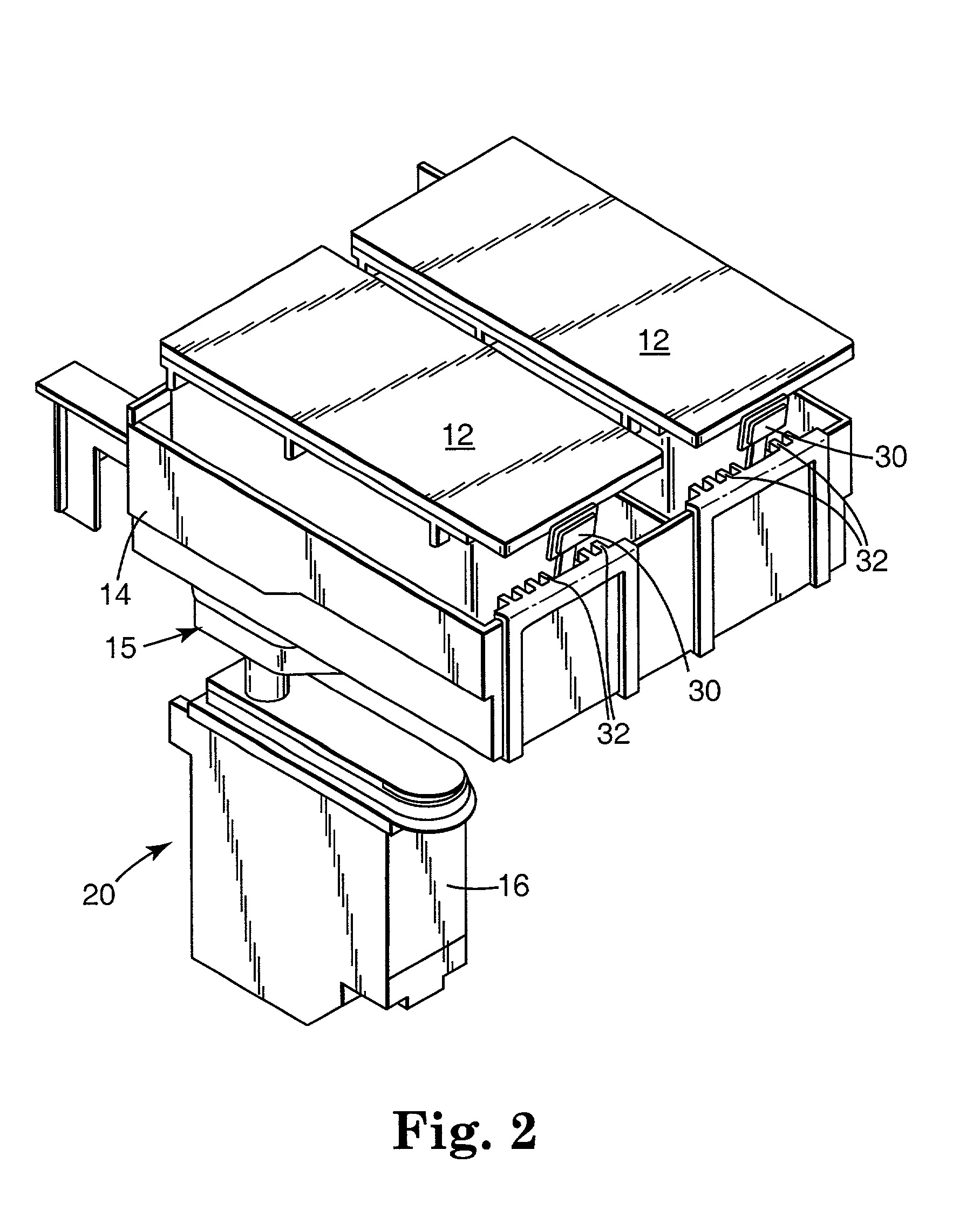

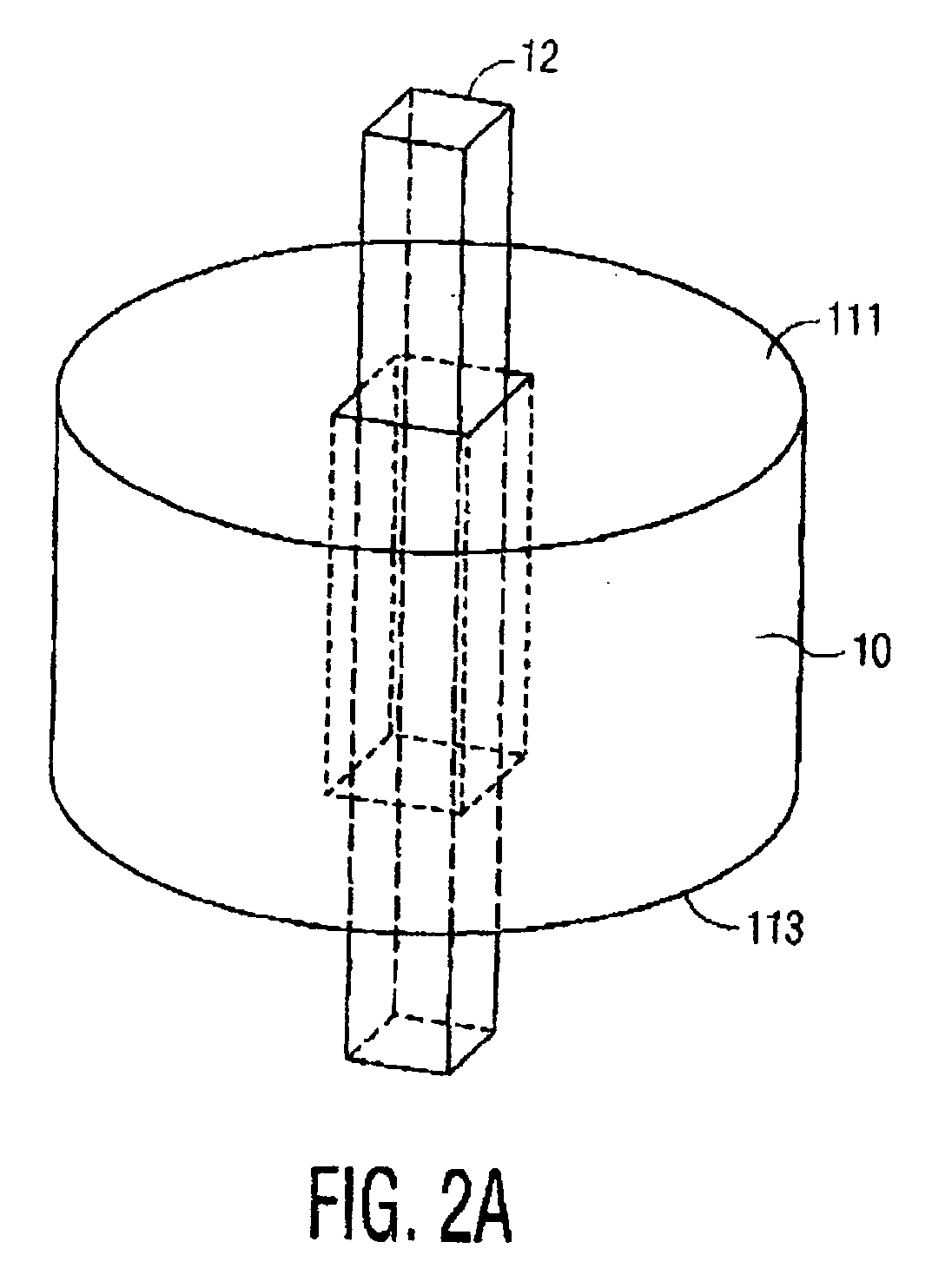

Anchor delivery system with replaceable cartridge

ActiveUS20100030262A1Convenience to mergeSufficient visibilitySuture equipmentsSurgical needlesDiseaseDelivery system

A system and associated method for manipulating tissues and anatomical or other structures in medical applications for the purpose of treating diseases or disorders or other purposes. In one aspect, the system includes a delivery device configured to deploy and implant anchor devices for such purposes.

Owner:TELEFLEX LIFE SCI LTD

Anchor delivery system with replaceable cartridge

ActiveUS8216254B2Convenience to mergeSufficient visibilitySuture equipmentsSurgical needlesDiseaseDelivery system

A system and associated method for manipulating tissues and anatomical or other structures in medical applications for the purpose of treating diseases or disorders or other purposes. In one aspect, the system includes a delivery device configured to deploy and implant anchor devices for such purposes.

Owner:TELEFLEX LIFE SCI LTD

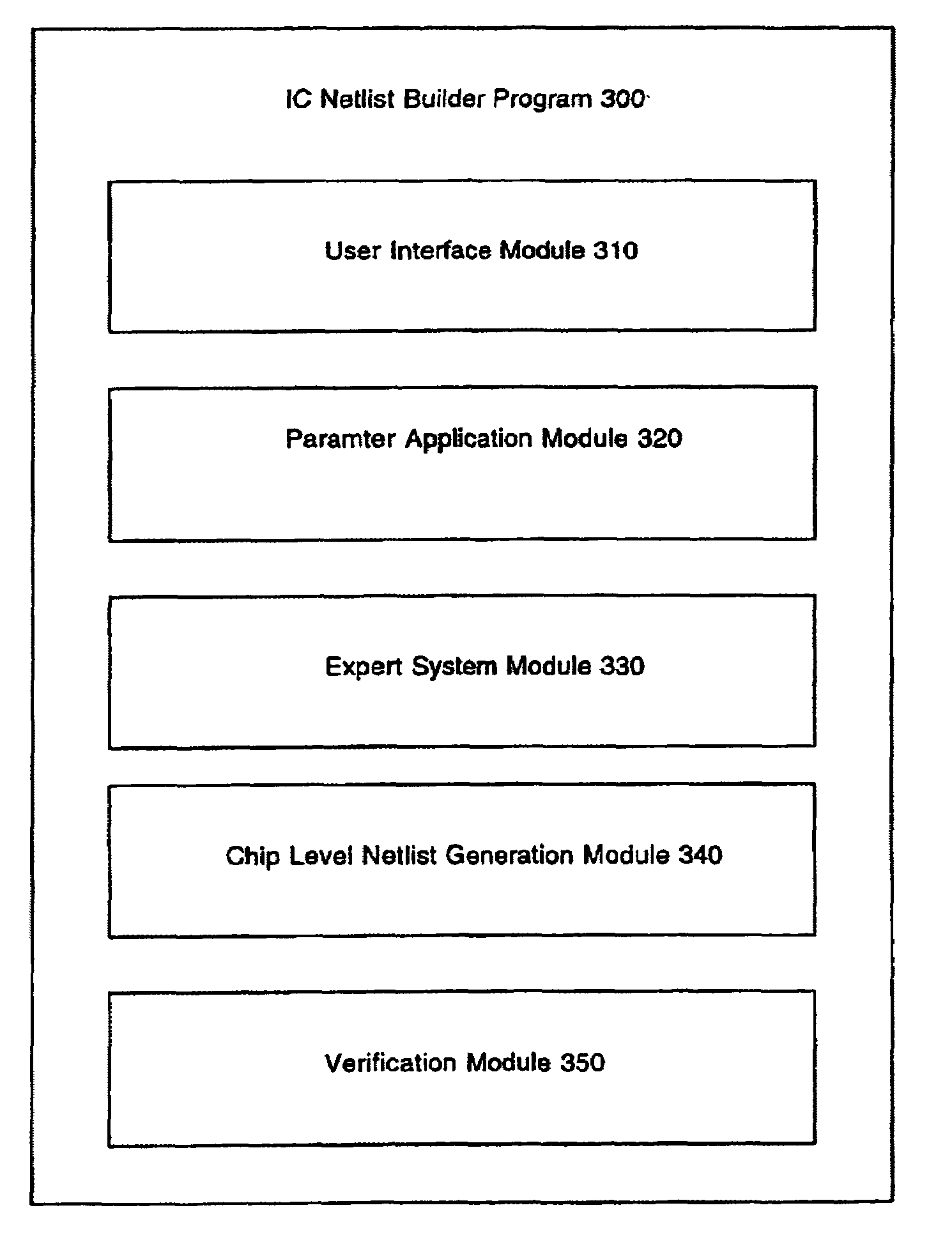

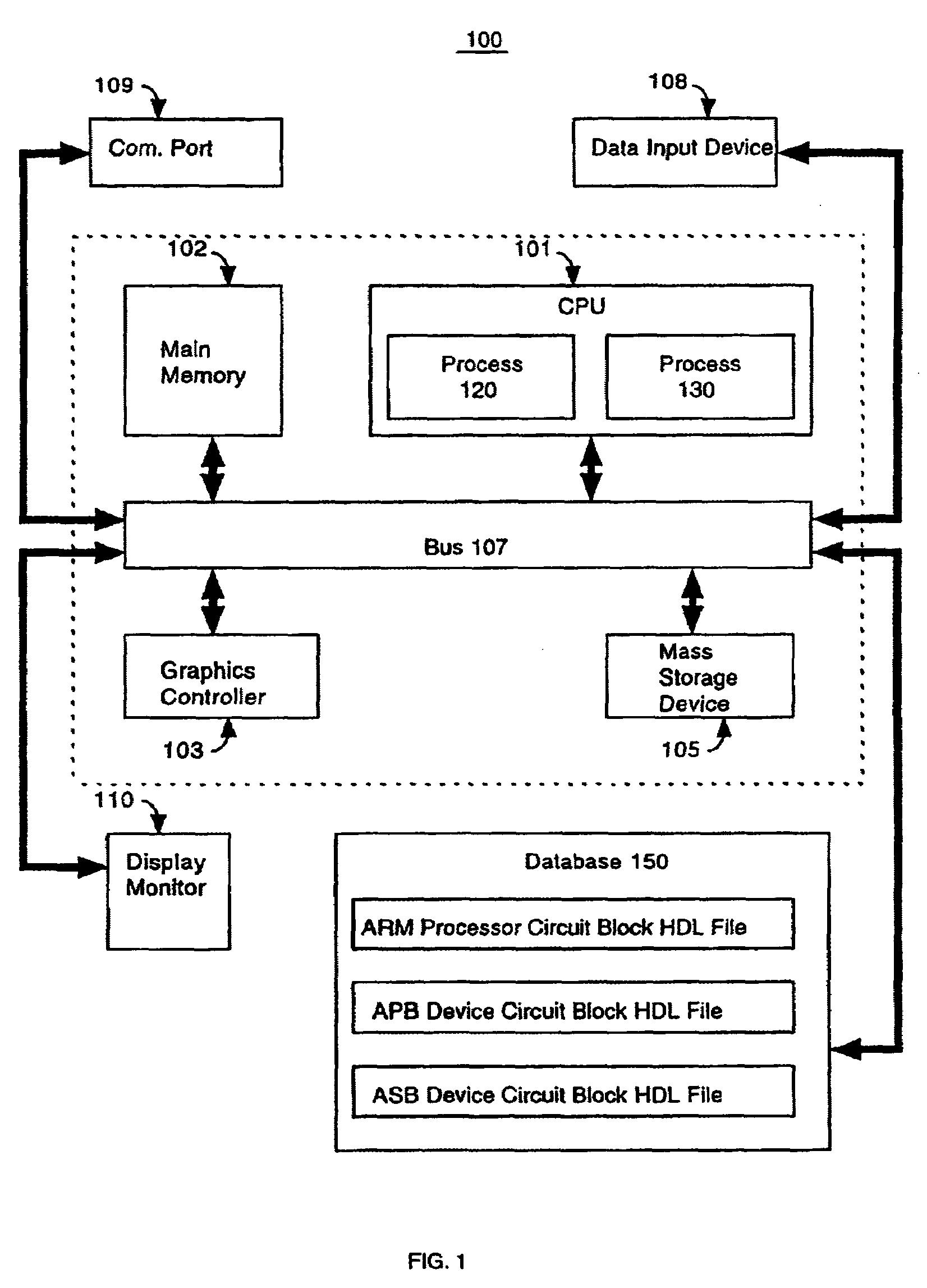

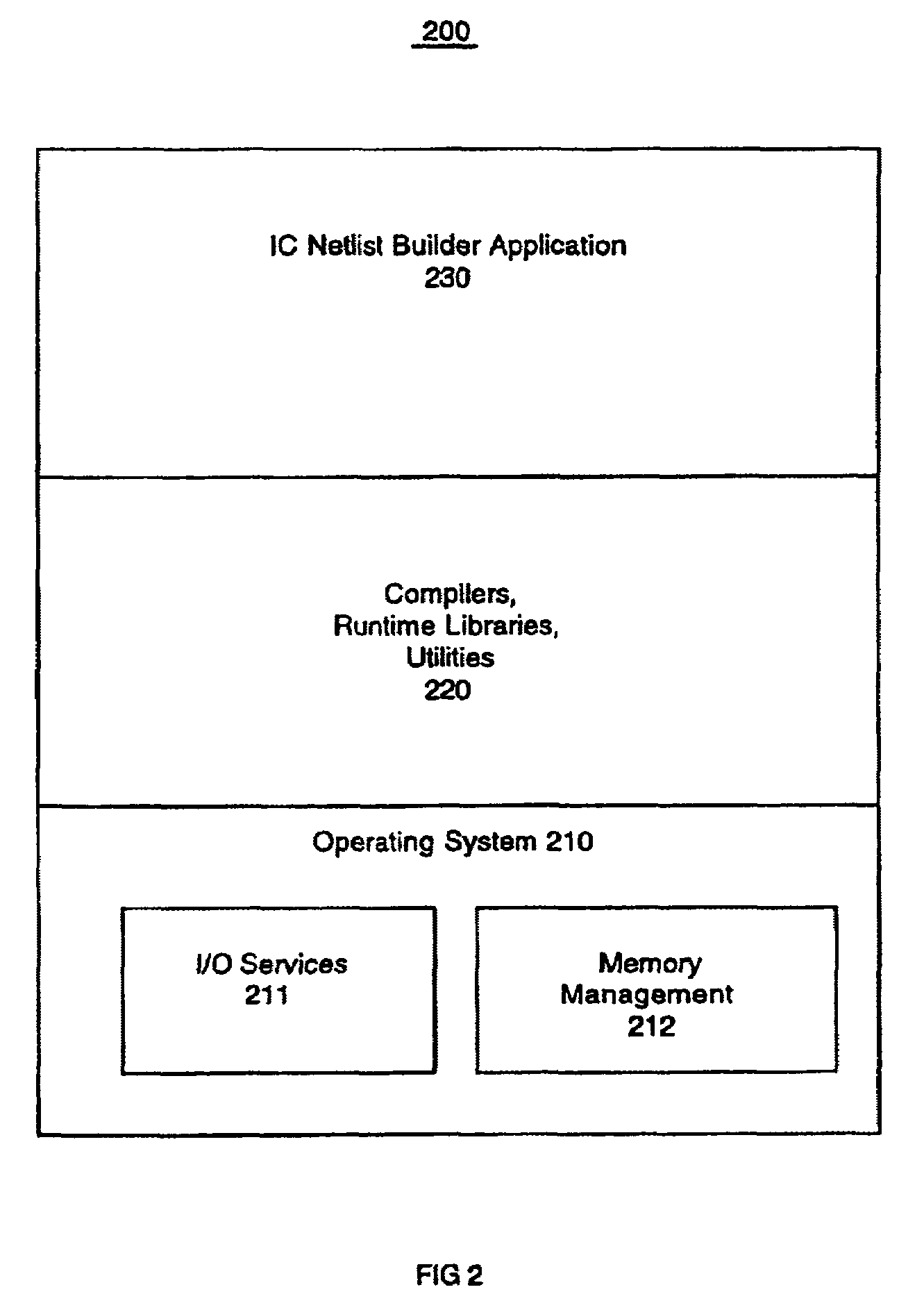

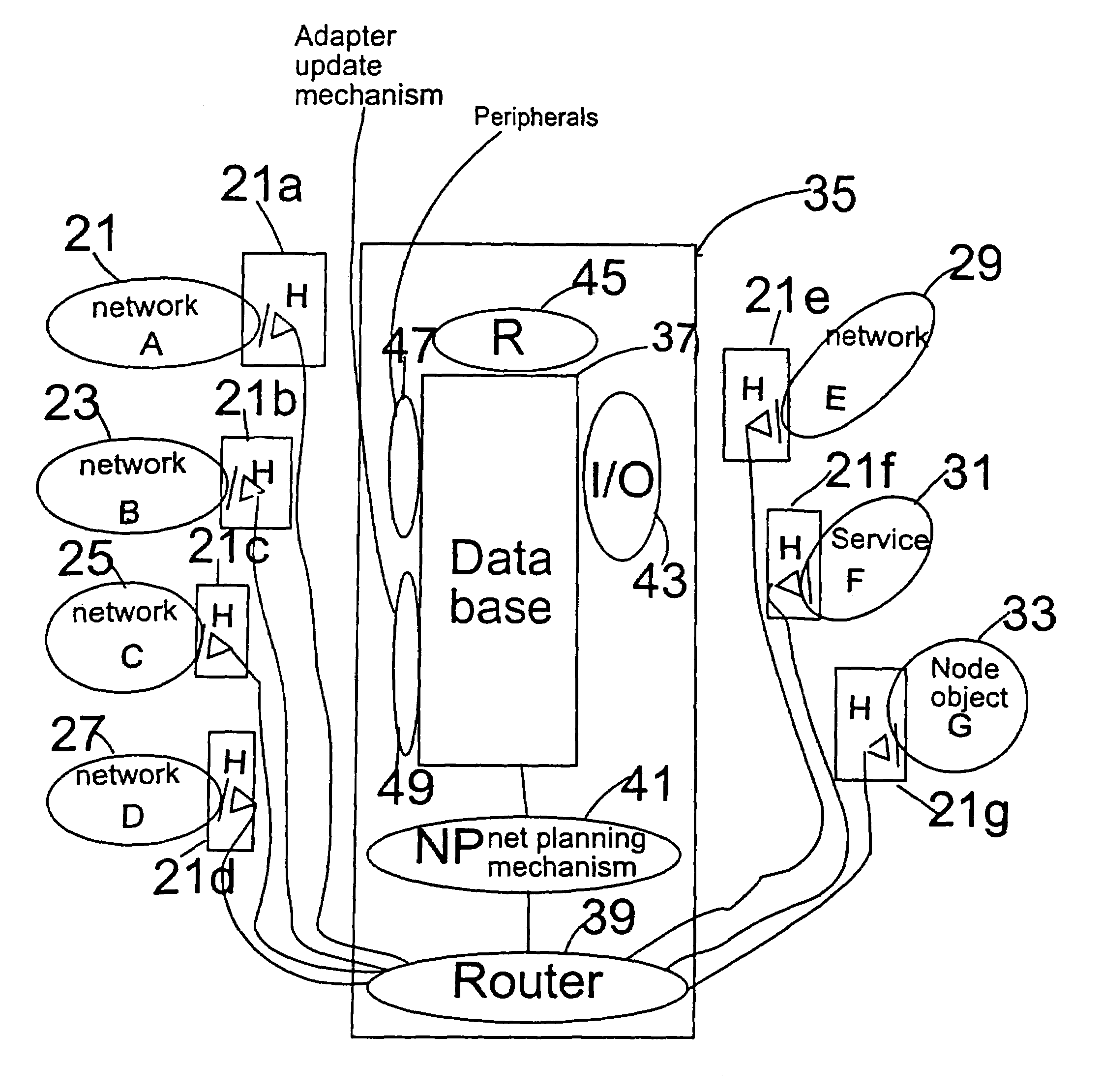

Computer system and method to dynamically generate system on a chip description files and verification information

InactiveUS7100133B1Facilitates efficient and effective creation and modification and verificationConvenience to mergeCAD circuit designSoftware simulation/interpretation/emulationComputer architectureTest platform

The present invention facilitates automation of system on a chip (SoC) design, manufacture and verification in a convenient and efficient manner. In one embodiment, a SoC netlist builder and verification computer system of the present invention includes a user interface module, a parameter application module, an expert system module and a chip level netlist generation module. The user interface module provides user friendly and convenient interfaces that facilitate easy entry and modification of user selections and parameters. The parameter application module interprets information supplied by the user module and the expert system module and creates directions (e.g., command lines) passed to other modules for execution. The expert system module analyzes information and automatically provides SoC building and verification data including automated addition of default architectural features, automated insertion of default parameters, and automated input of information to the verification module. The chip level netlist generation module automatically generates a chip level netlist, including the instantiation of internal IC devices and connections between the circuit blocks for internal signals. The verification module automatically generates a test bench and a logical verification environment including simulation models (e.g., a chip model and a system level model).

Owner:NXP BV

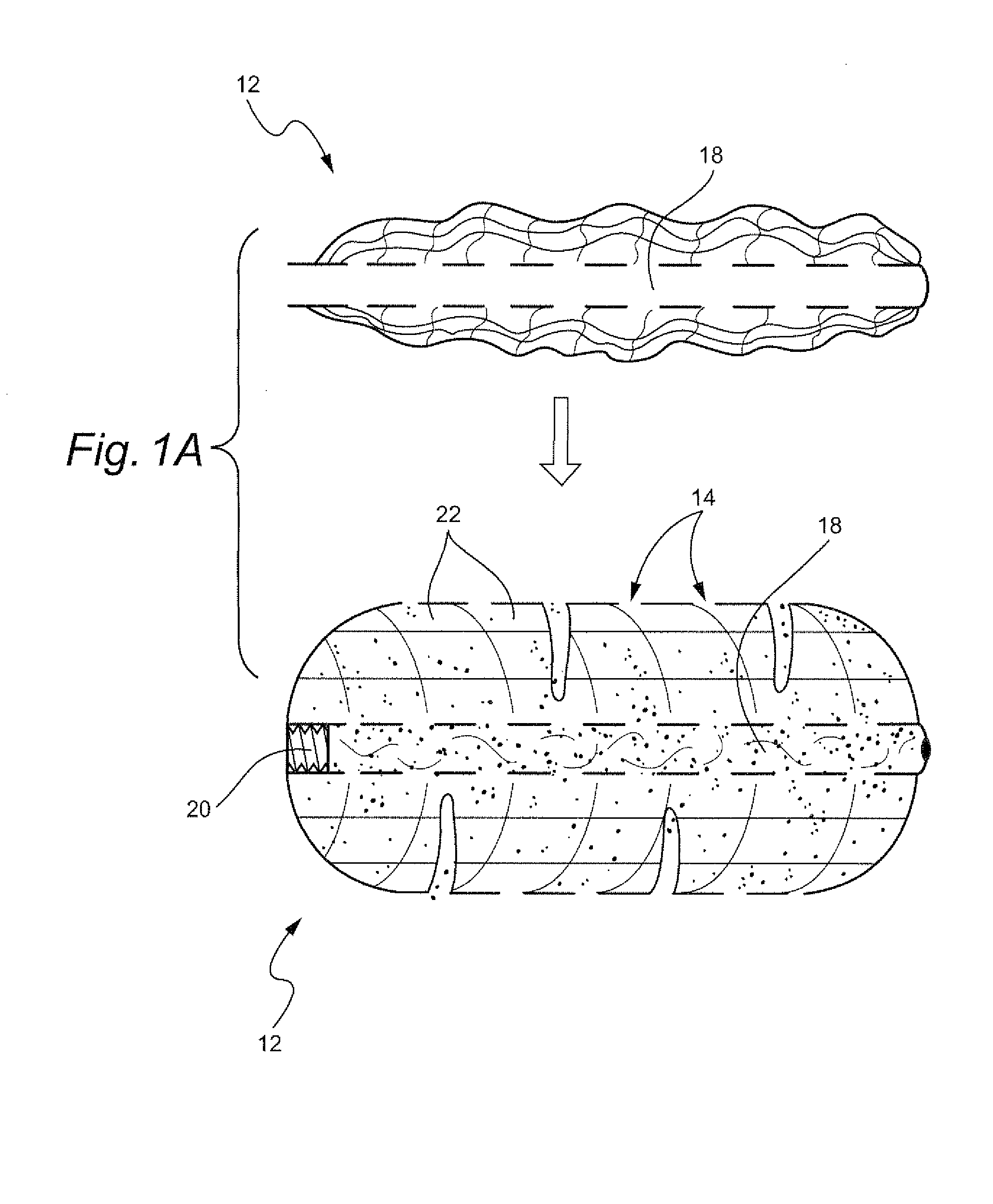

Biologic Vertebral Reconstruction

ActiveUS20090187249A1Minimize extrusionConvenience to mergeInternal osteosythesisBone implantBiomechanicsHost bone

A device and method for biologic vertebral reconstruction utilizes a biologically active jacket inserted into a cavity formed in a vertebra to be reconstructed. An artificial bone material is inserted into the biologically active jacket and allowed to set. The structure and method described herein provide for effective biologic vertebral reconstruction. The use of a biological material and artificial bone enables the host bone to replace the artificial bone over a period of time. Additionally, the structure of the biologically active jacket minimizes any impact into the spinal canal and the paravertebral spaces. Moreover, because of its biomechanical characteristics, which approximate the host bone, there is relative protection of the neighboring vertebral against fracture. Still further, the materials of the biologically active jacket may be impregnated with various substances to achieve various advantageous tasks.

Owner:SPINAL ELEMENTS INC

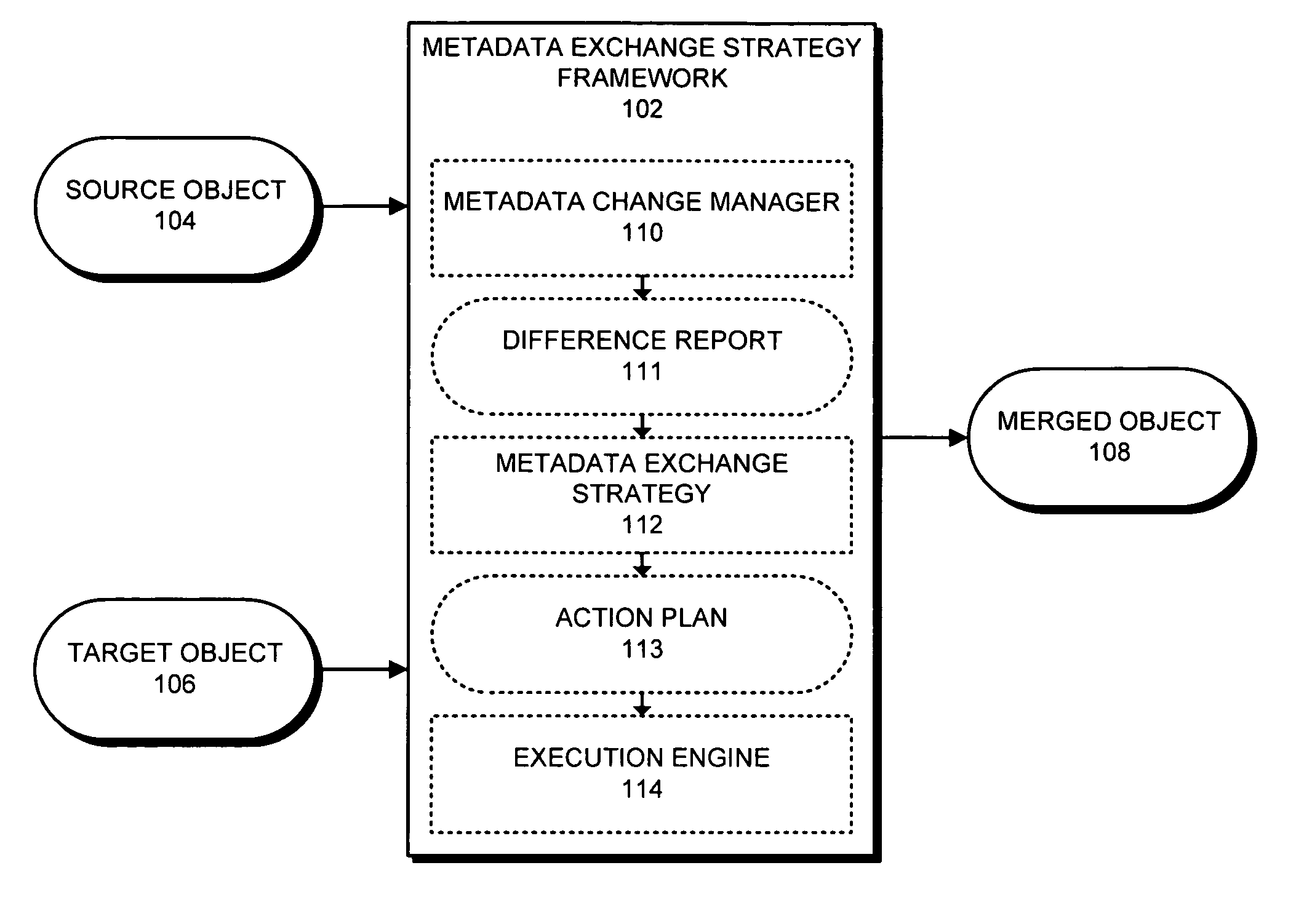

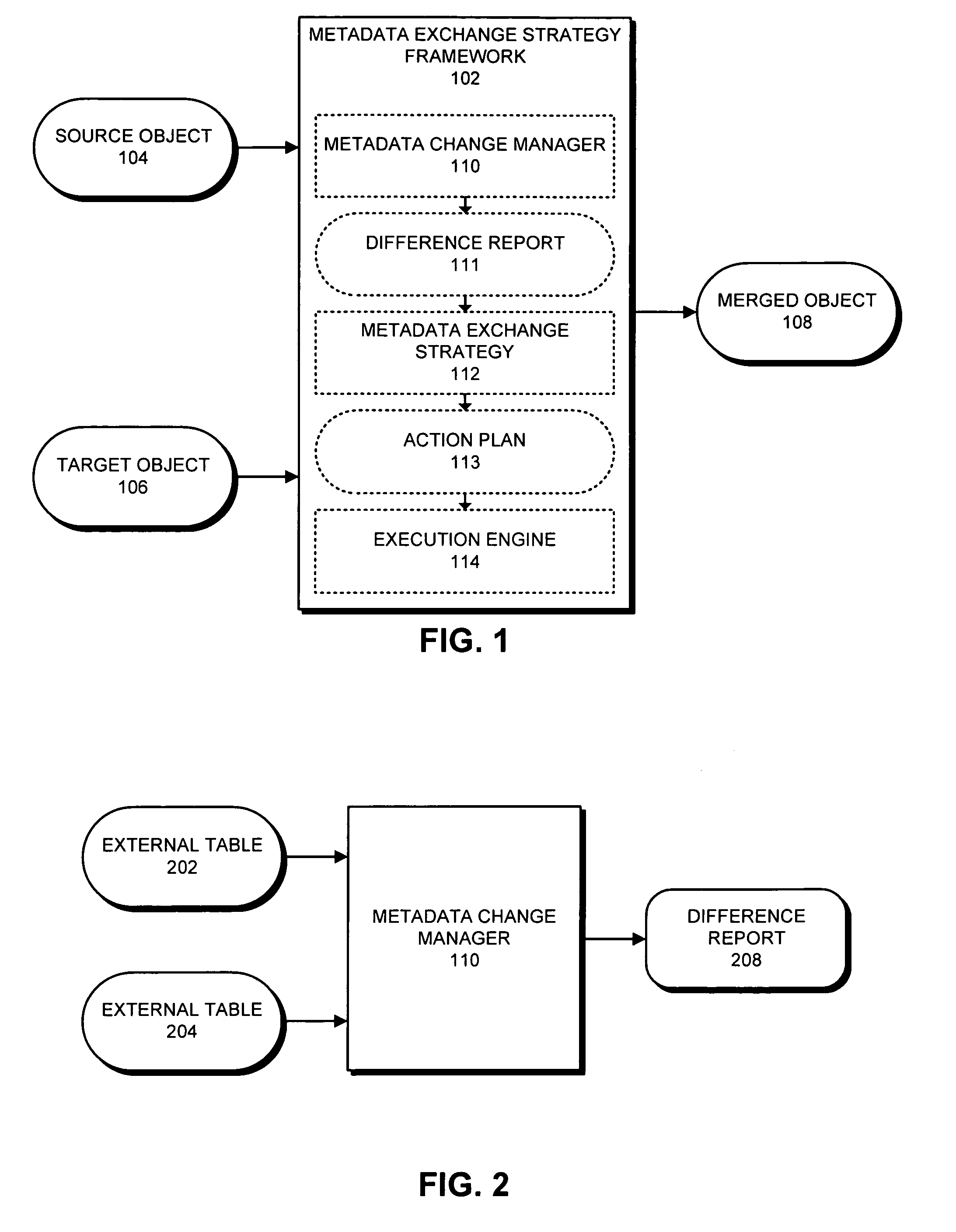

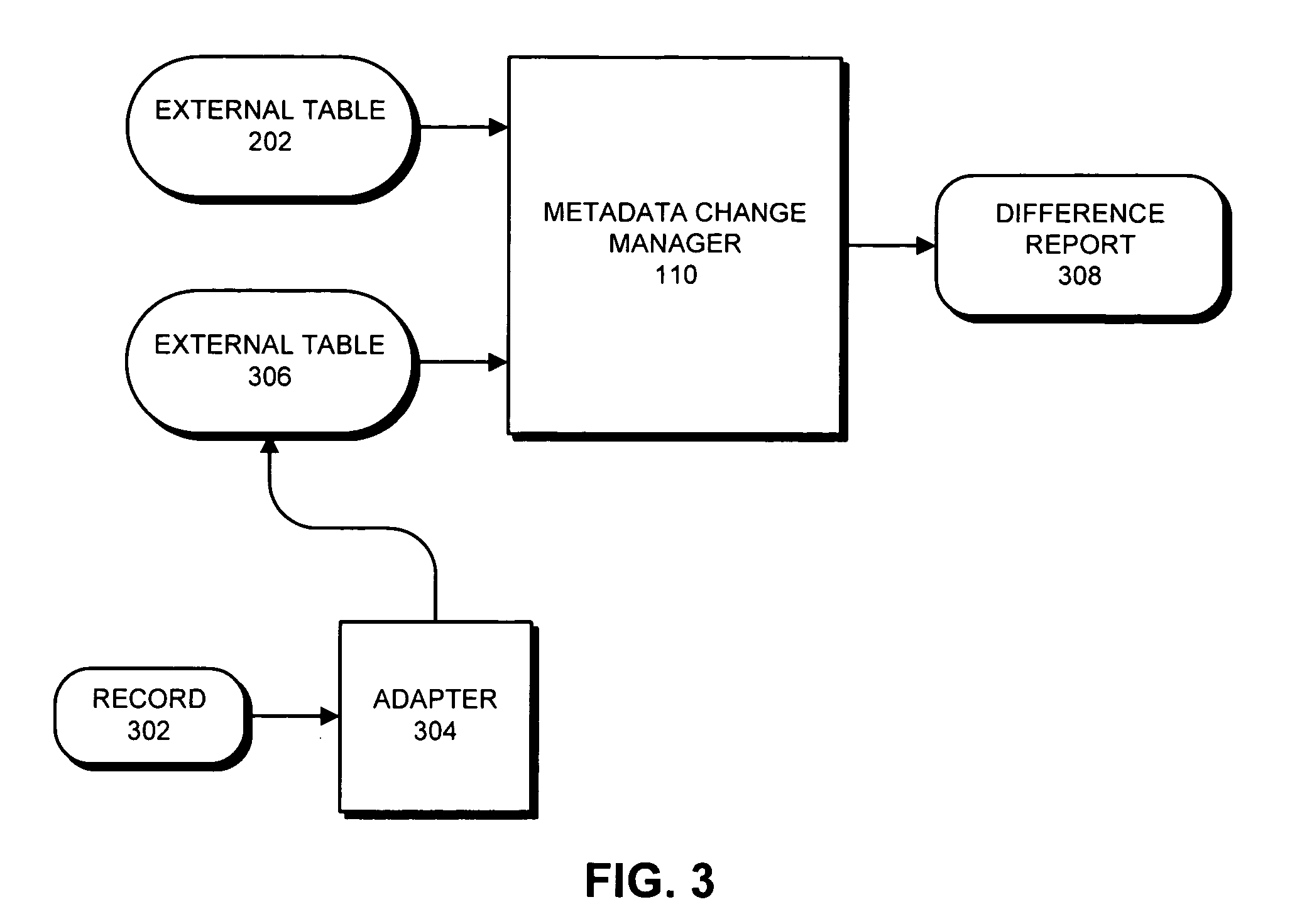

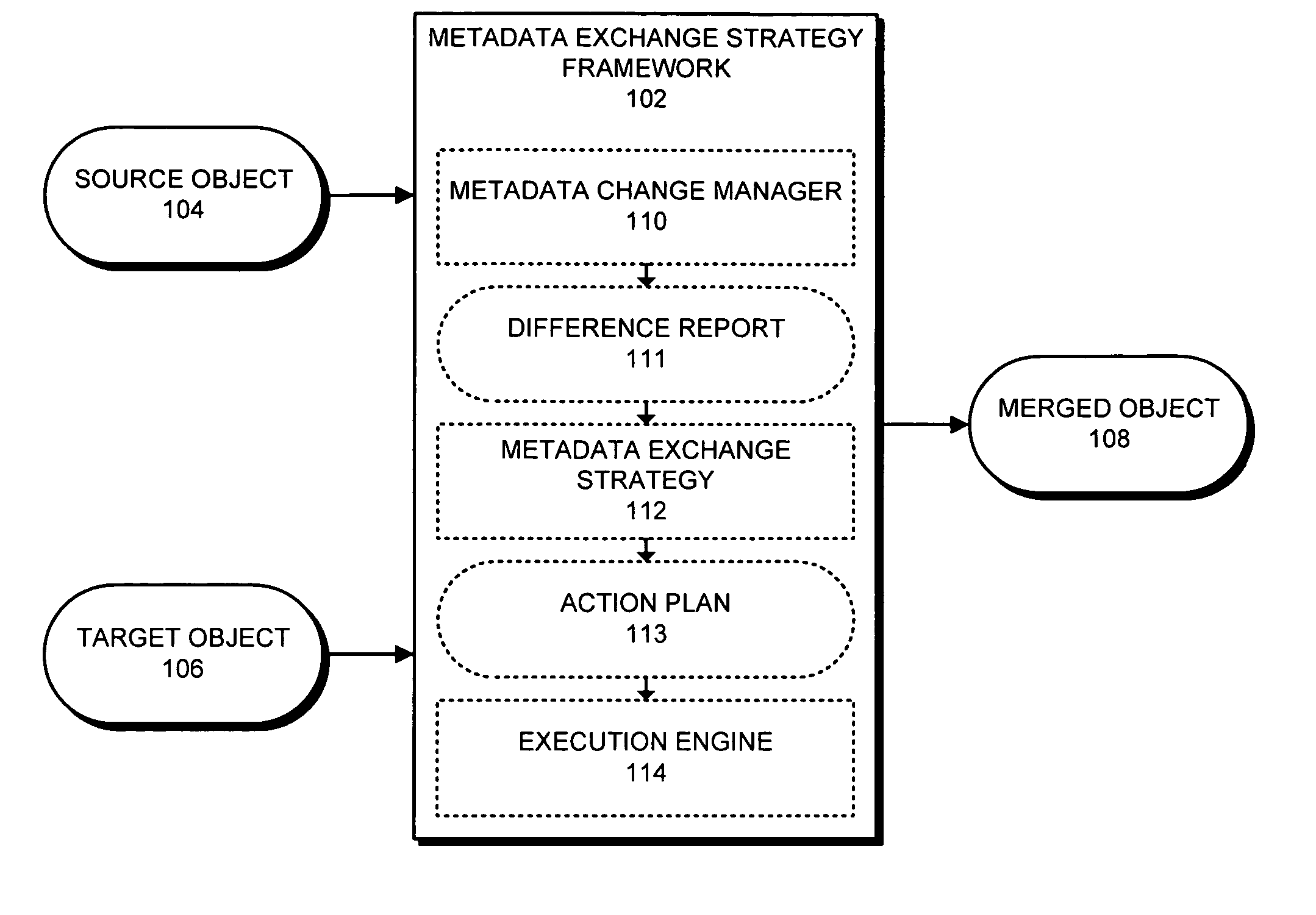

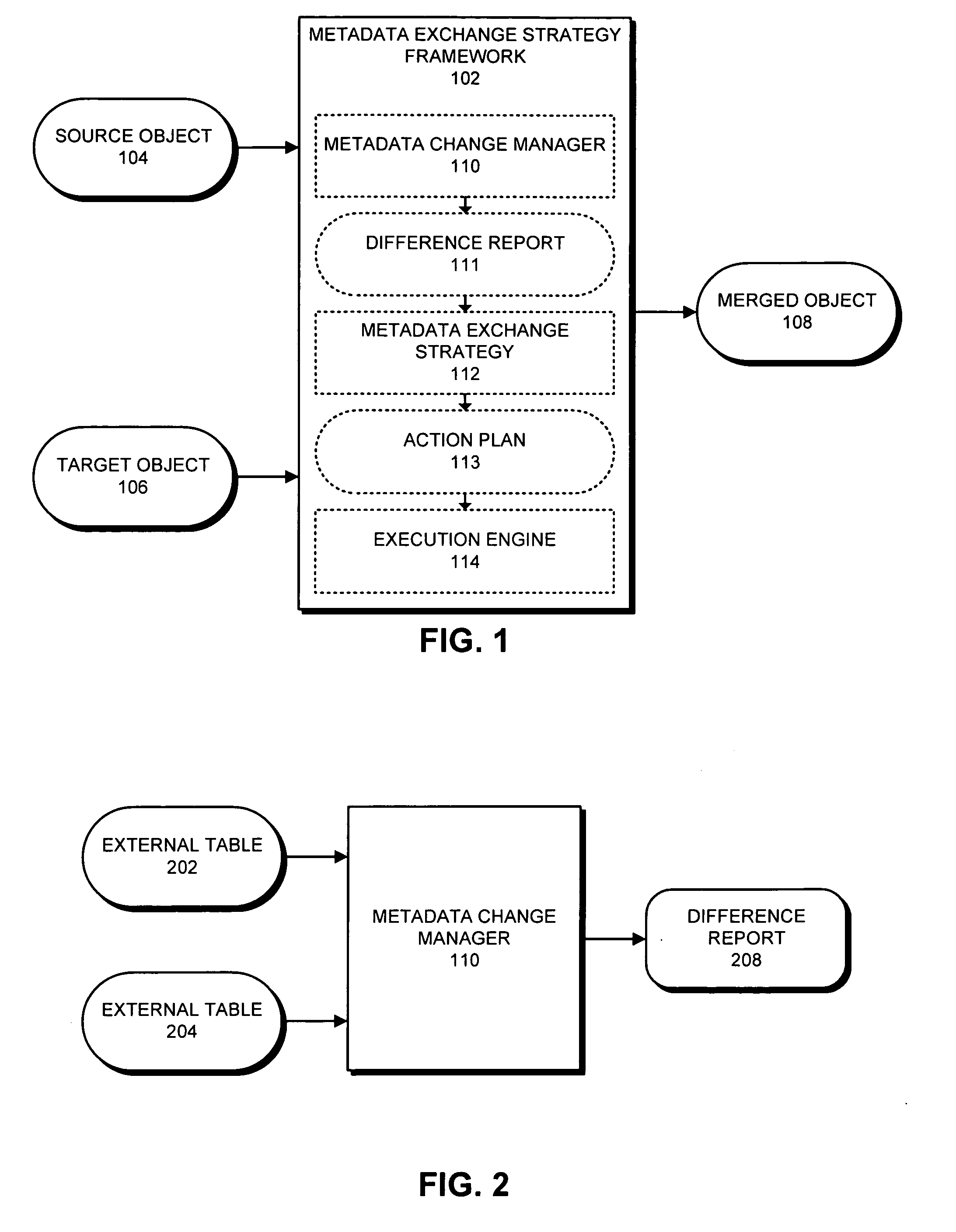

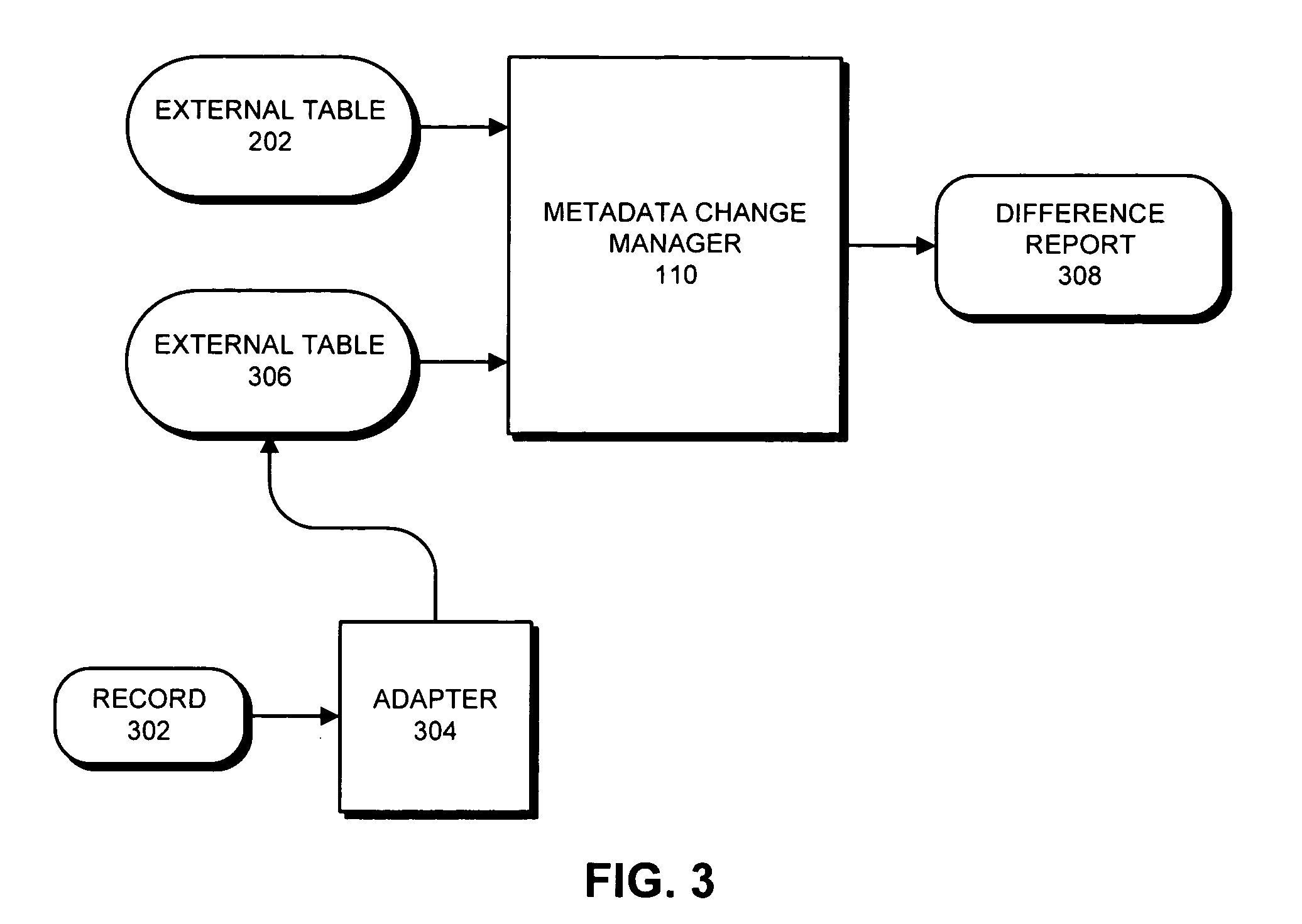

Customizable metadata merging framework

ActiveUS7469262B2Convenience to mergeData processing applicationsDigital data information retrievalAction planSystem usage

One embodiment of the present invention provides a system that facilitates merging different versions of a database object. During operation, the system receives metadata associated with a first version of a database object and a second version of the database object. The system then compares metadata associated with the first version with metadata associated with the second version to create a difference report. Next, the system uses the different report to create an action plan that specifies how to merge the metadata associated with the first and second versions of the metadata object.

Owner:ORACLE INT CORP

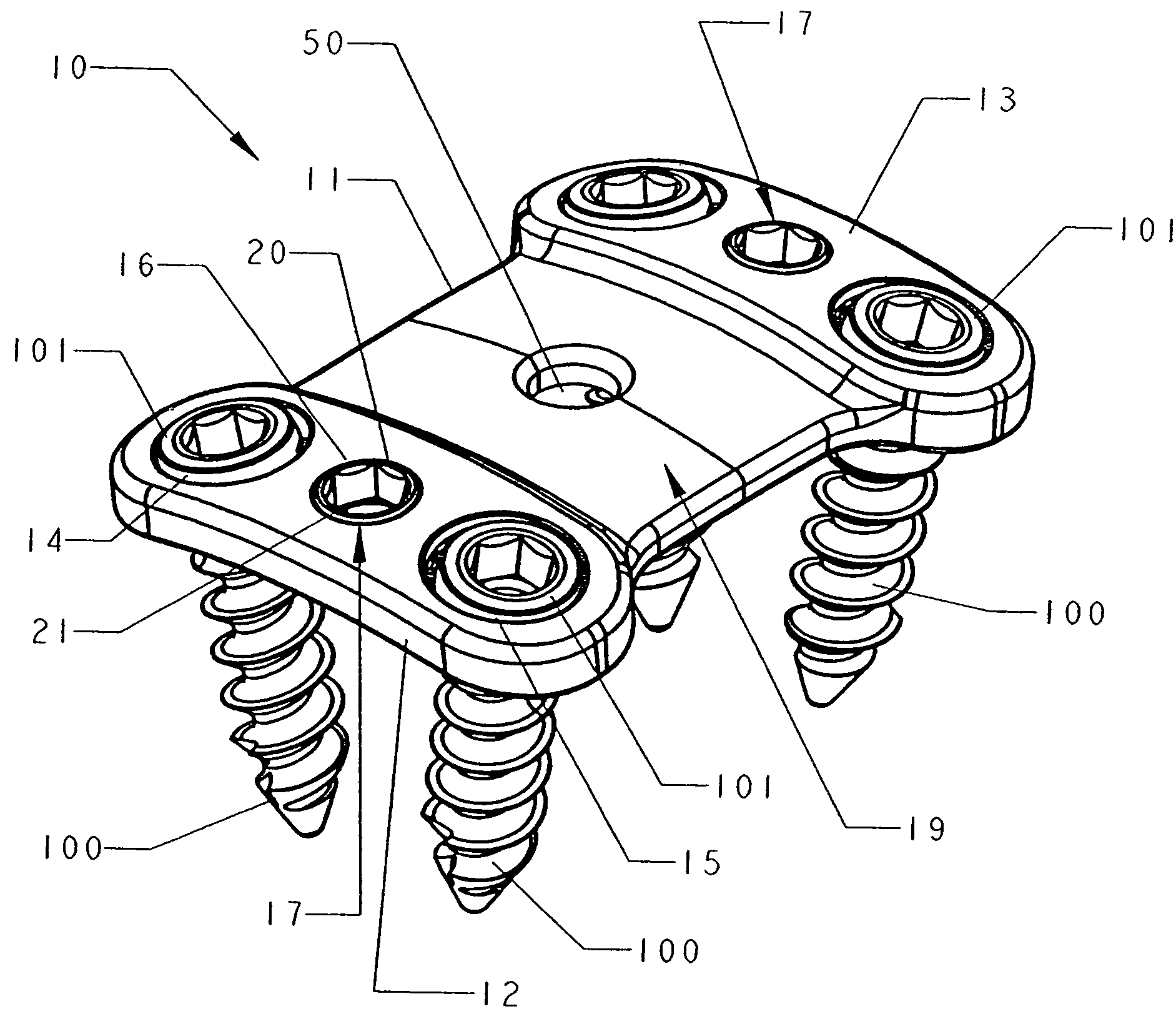

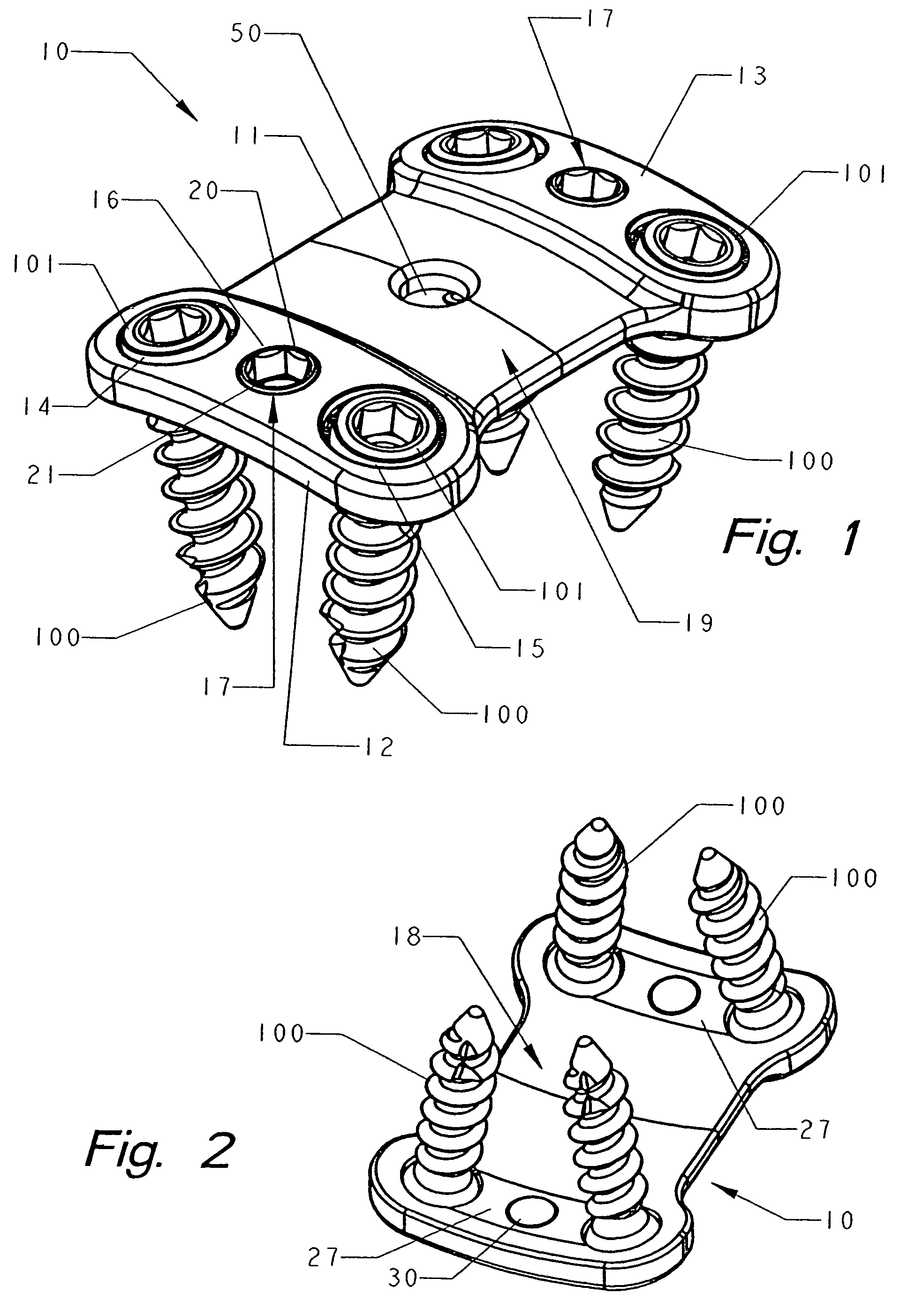

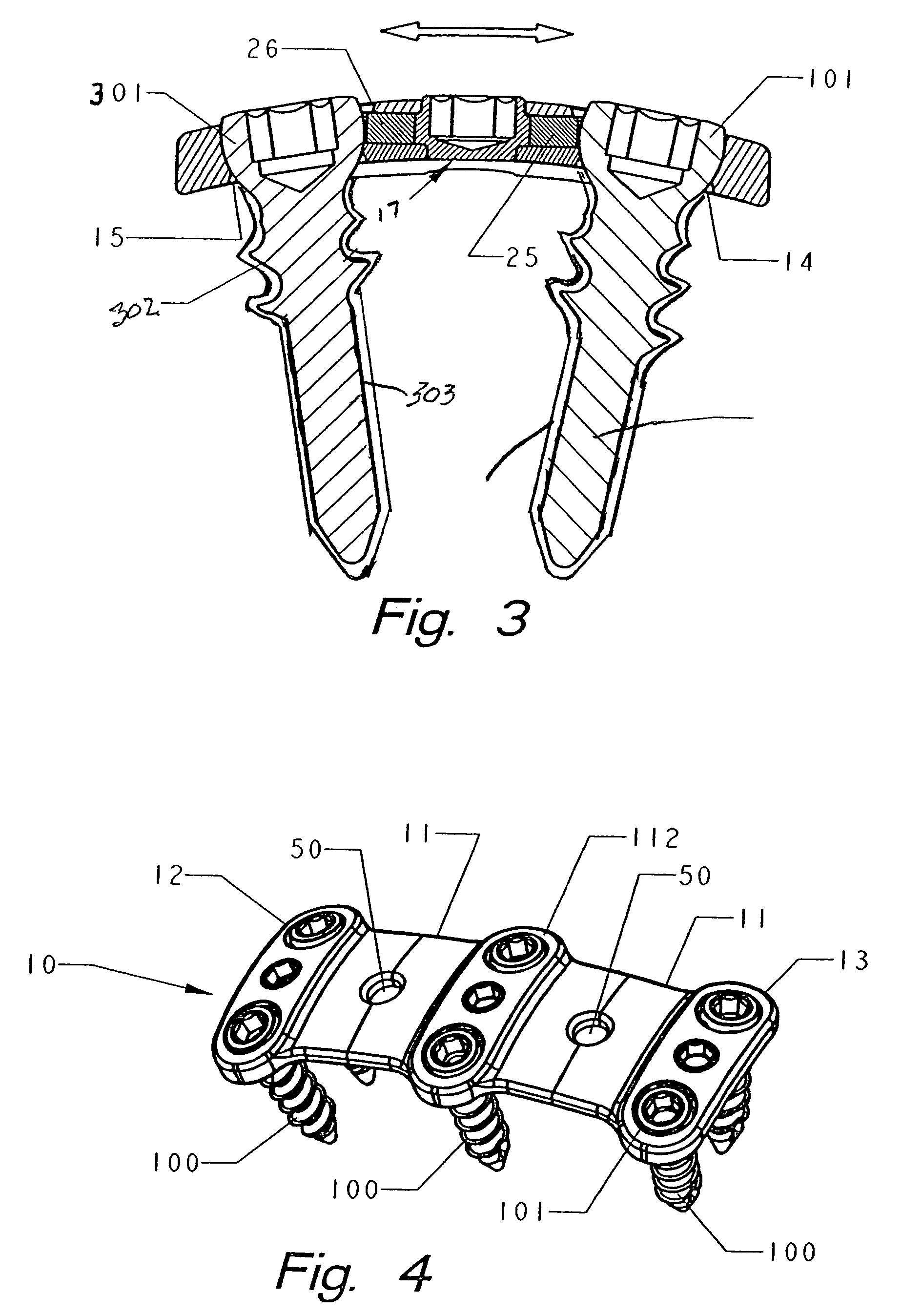

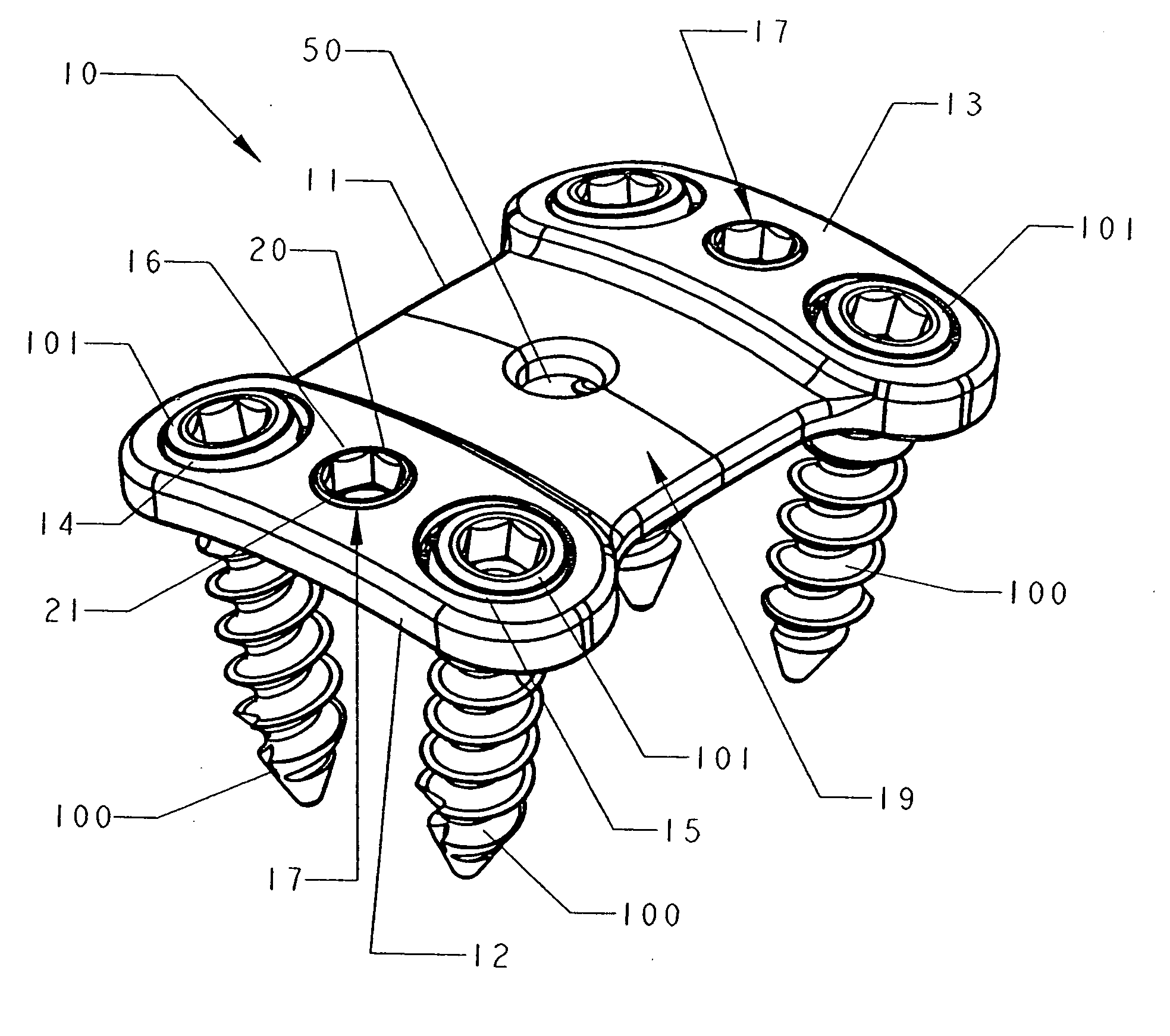

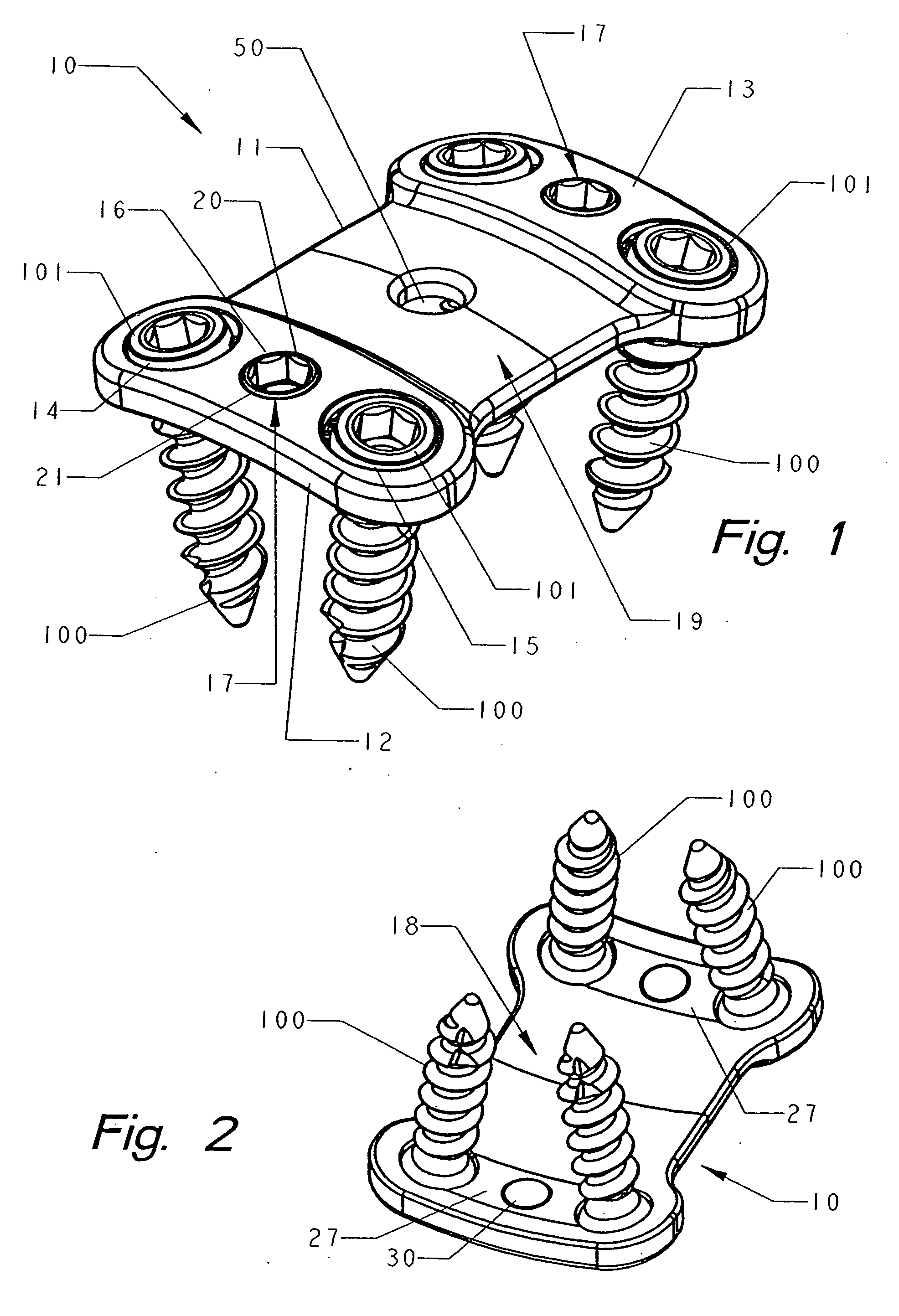

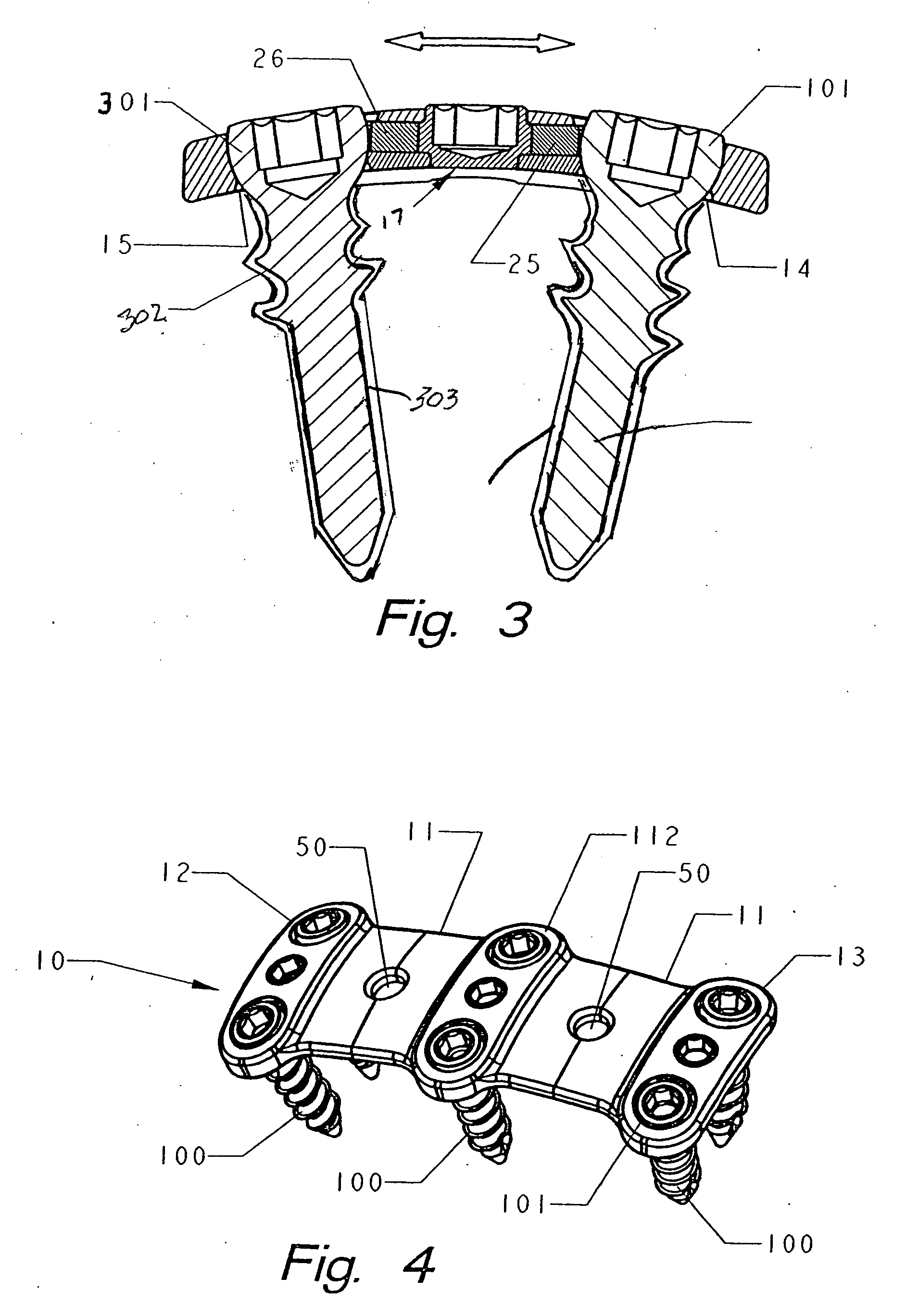

Spinal implant kit

A bone plate kit for stabilizing adjacent vertebrae or ends of a bone includes several bone plates of different sizes and several bone fasteners of the same or different sizes. The fasteners may have the same configuration or several different configurations. The fasteners may be coated with bone growth material. The plates have a span for extending across a discontinuity. The span has brackets for attaching to the bone. The brackets have countersunk apertures terminating through which bone screws are placed in the bone. An eccentric cam bore is located between the countersunk apertures and, upon rotation of an eccentric cam, wedge grip shoes are slid into the countersunk apertures and frictionally engage the spherical heads of the bone screws. To prevent back-out of the bone screws, the eccentric cam is locked into the wedge grip shoes.

Owner:SPINAL

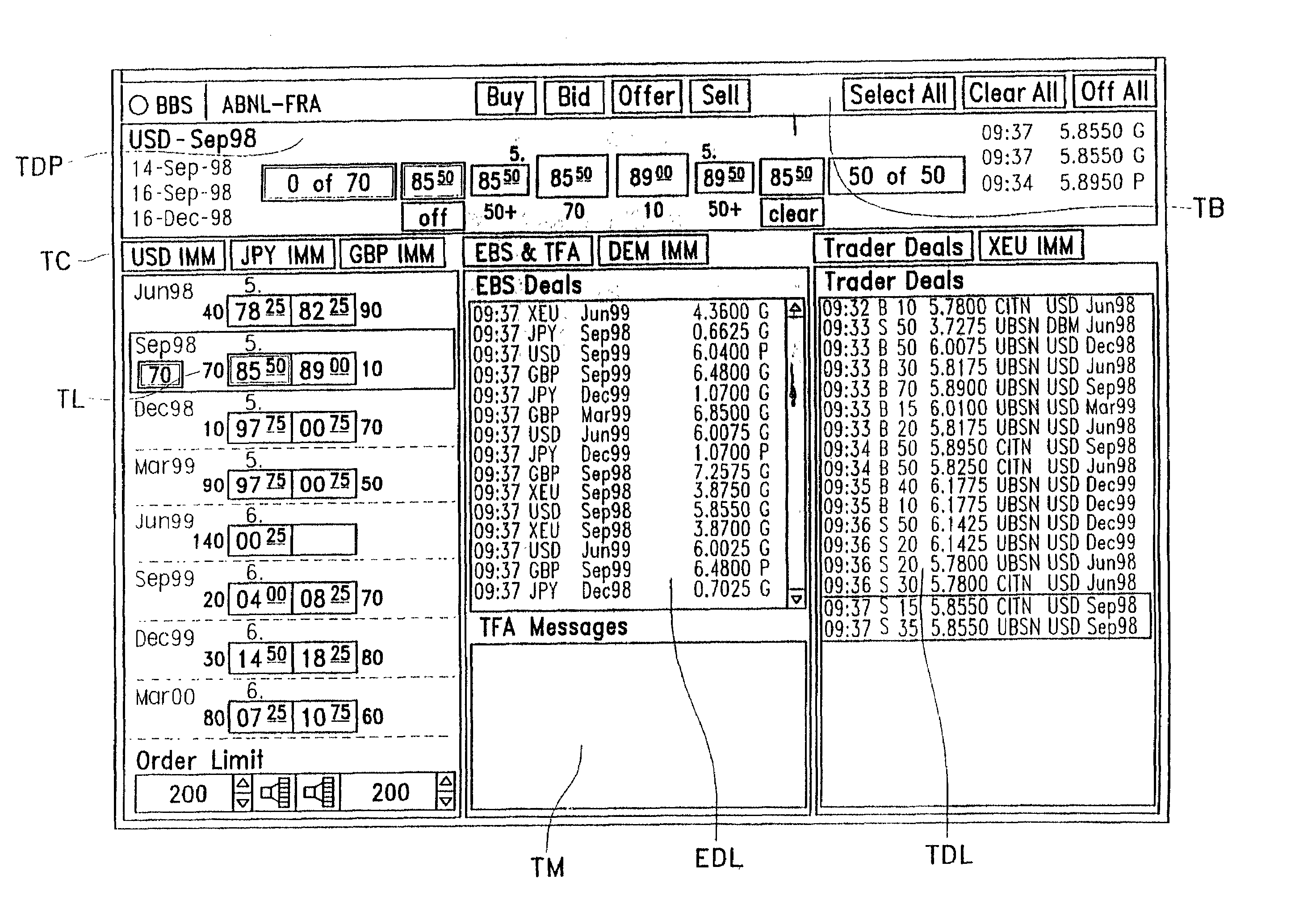

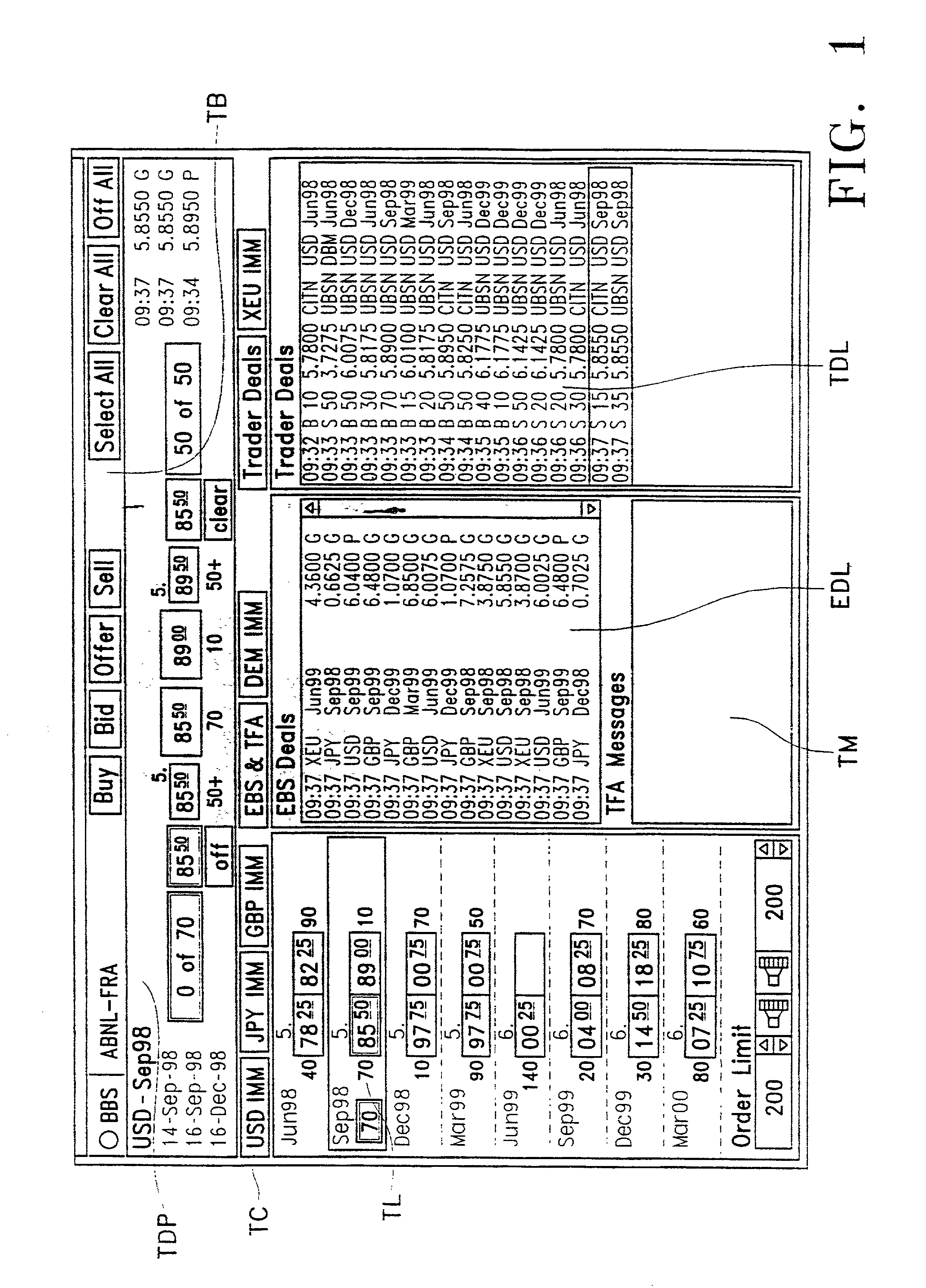

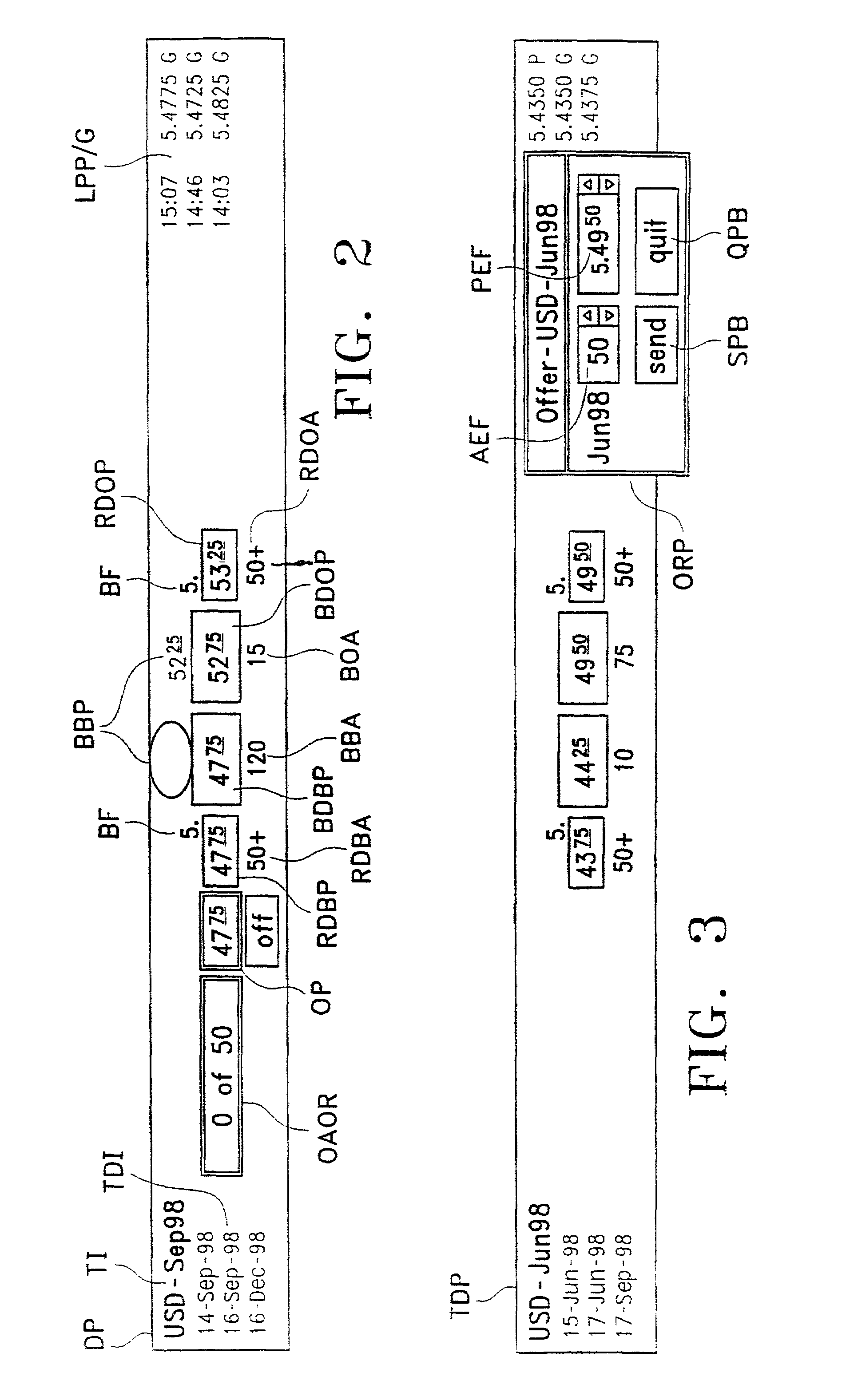

Communication of credit filtered prices in an electronic brokerage system

InactiveUS7636683B1Convenience to mergeFinanceProtocol authorisationTelecommunicationsComputer terminal

Computerized trading system for trading financial instruments having a communication network connecting traders dealing in financial instruments and a plurality of trader terminals connected to the communication network. The communication network comprises a credit store for storing an indication of credit available from each credit granting entity, a price distributor for distributing the price quotation messages to trader terminal for display, a credit filter to filter the price quotation messages to each trader terminal associated with at least one credit granting entity.

Owner:EBS GROUP

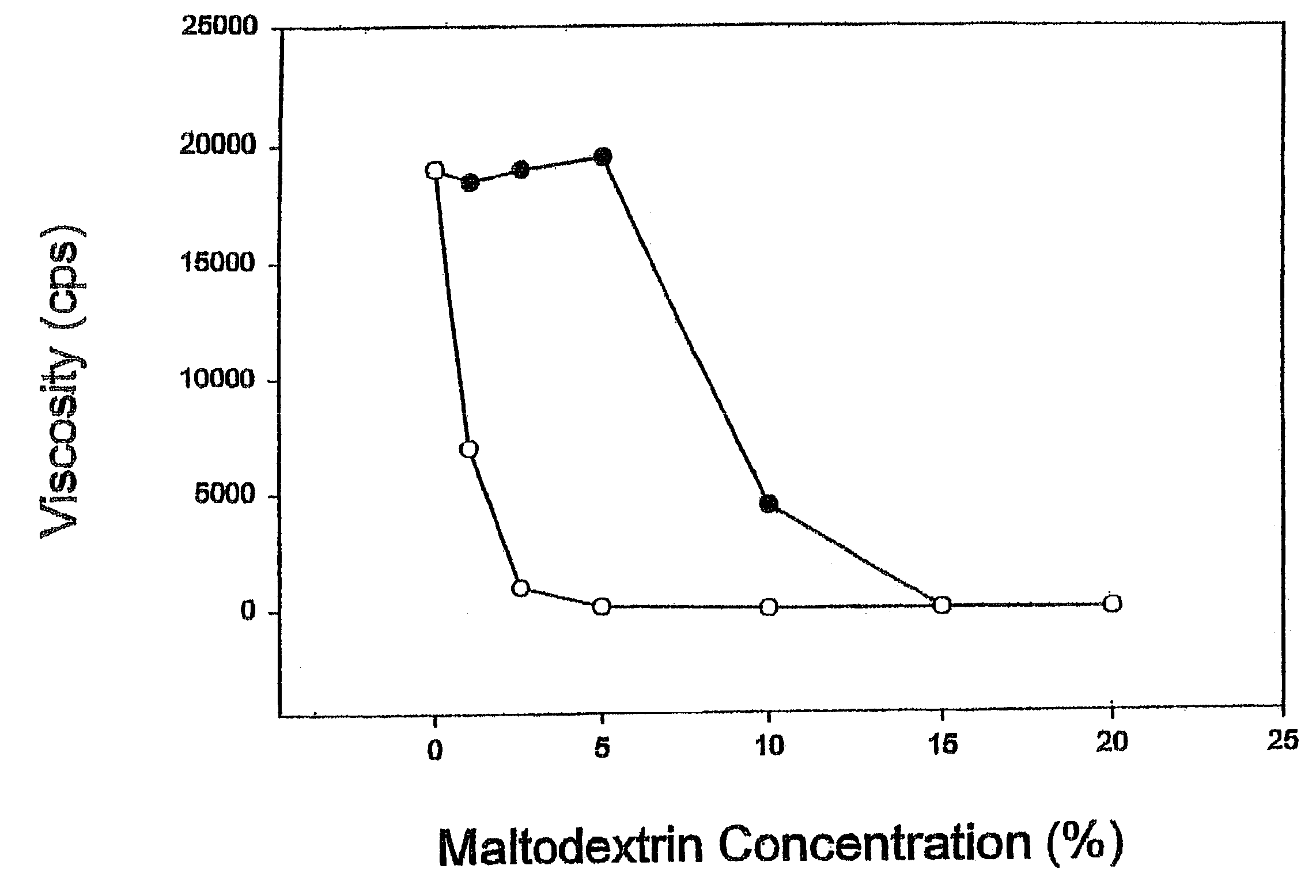

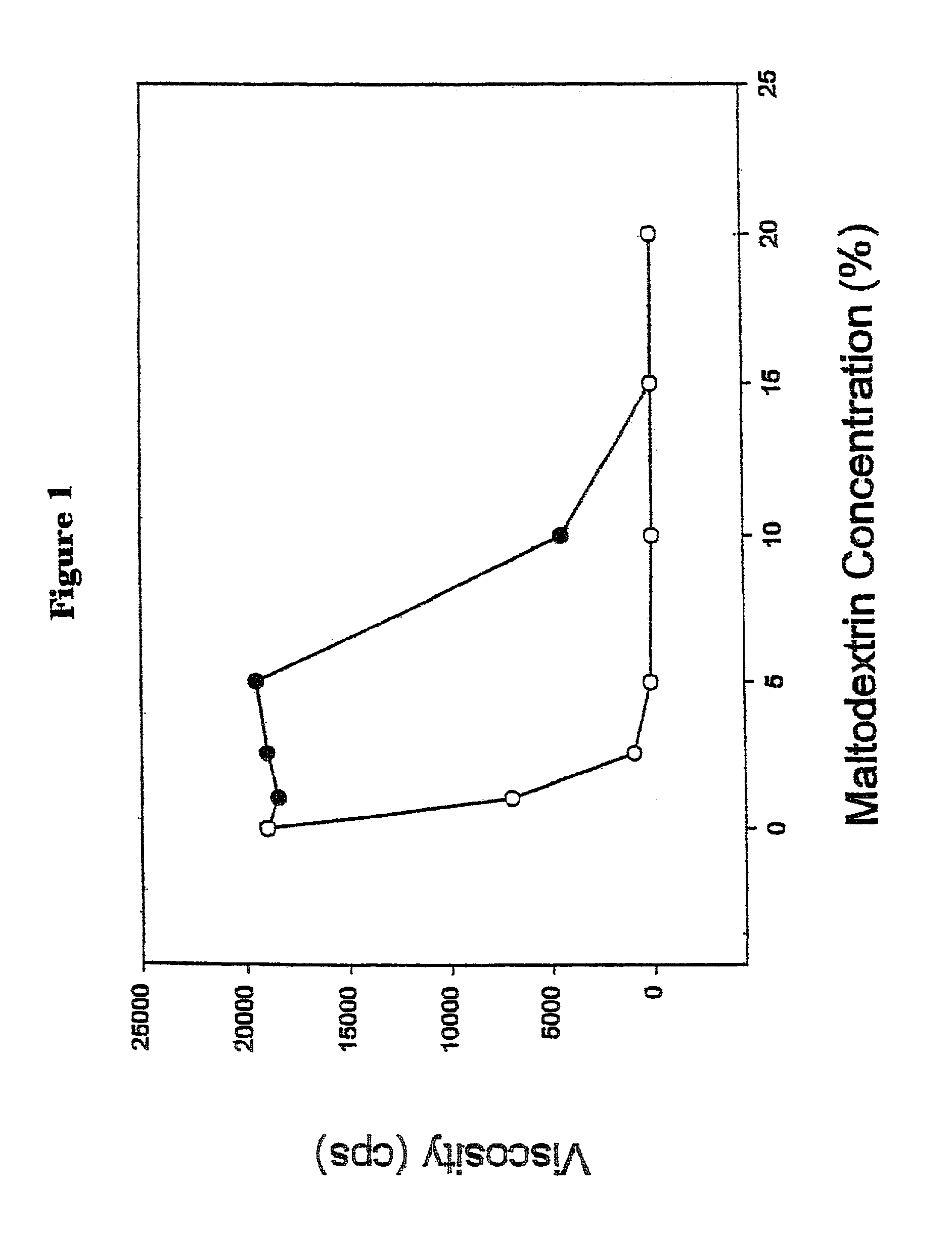

Polymer controlled induced viscosity fiber system and uses thereof

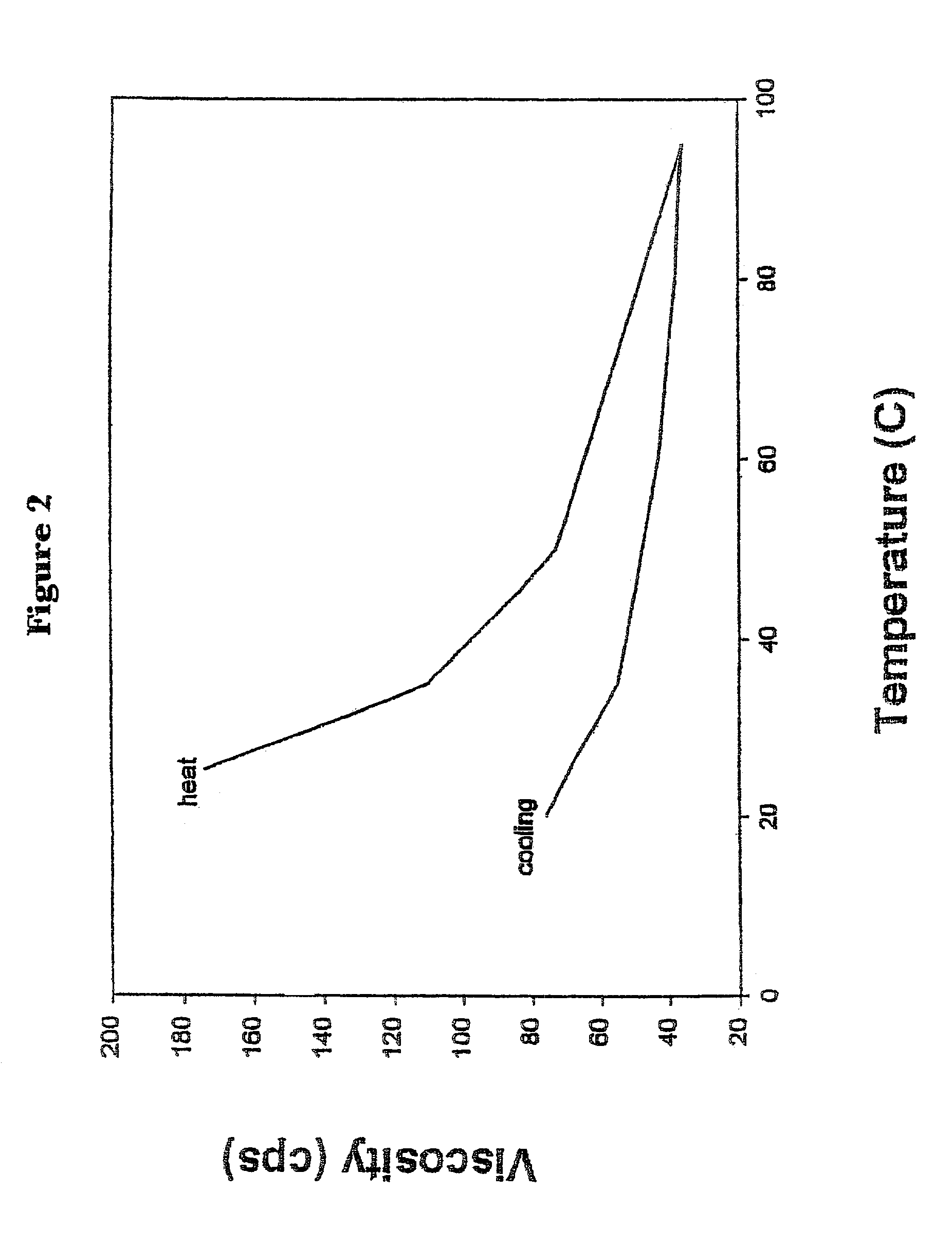

InactiveUS7067498B2Blunt glycemic responsePrevent dissolutionBiocideSugar food ingredientsPhysical stabilityChemistry

The present invention relates generally to a method of blunting the postprandial glycemic response in a human by feeding an induced viscosity fiber system. The invention also relates to an induced viscosity fiber system and the liquid products that incorporate the induced viscosity fiber system. Further, the invention relates to a method of incorporating soluble fiber into a liquid product without the typical negative organoleptic or physical stability issues. The invention also relates to a method of inducing the feeling of fullness and satiety by feeding the induced viscosity fiber system.

Owner:ABBOTT LAB INC

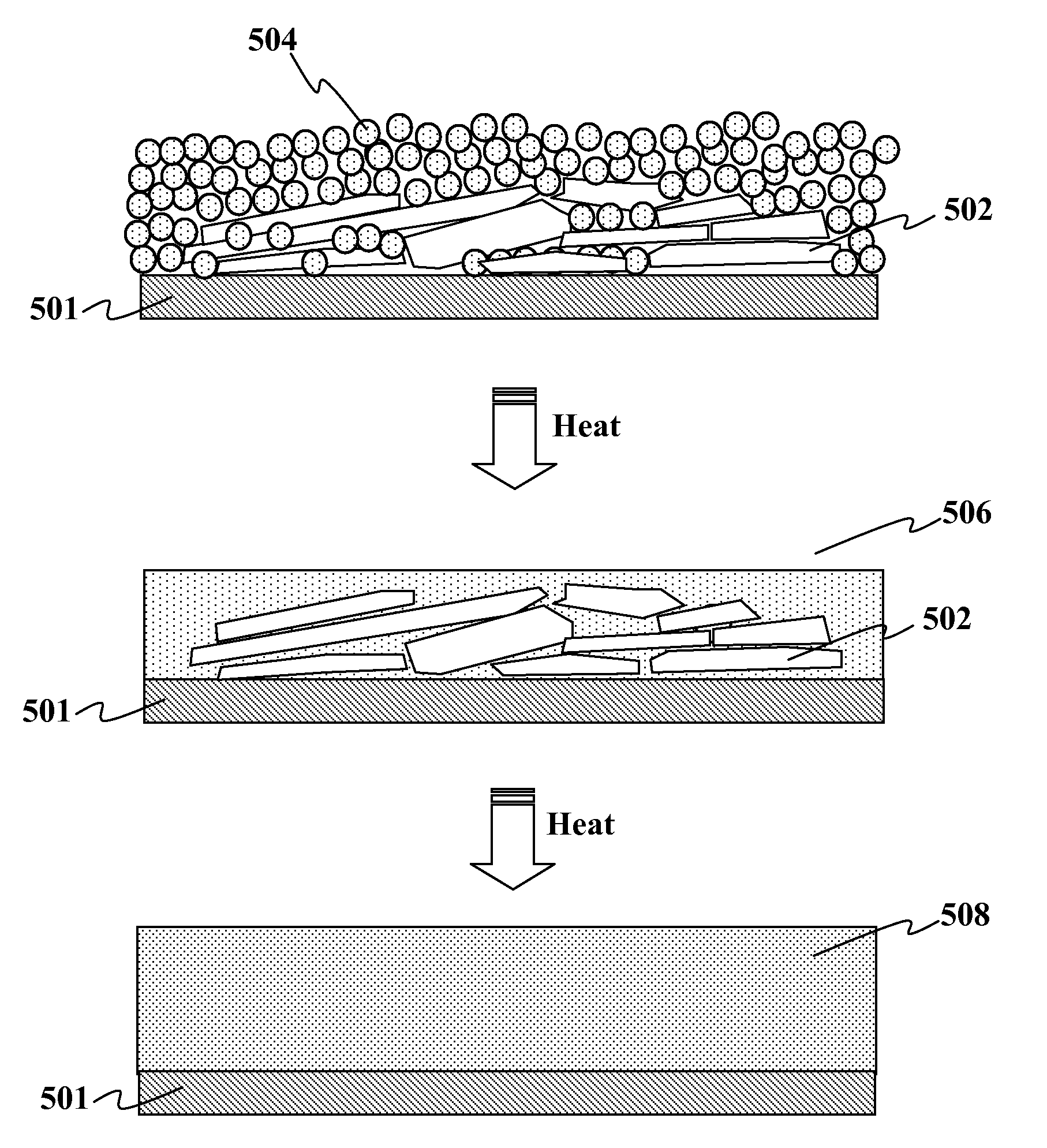

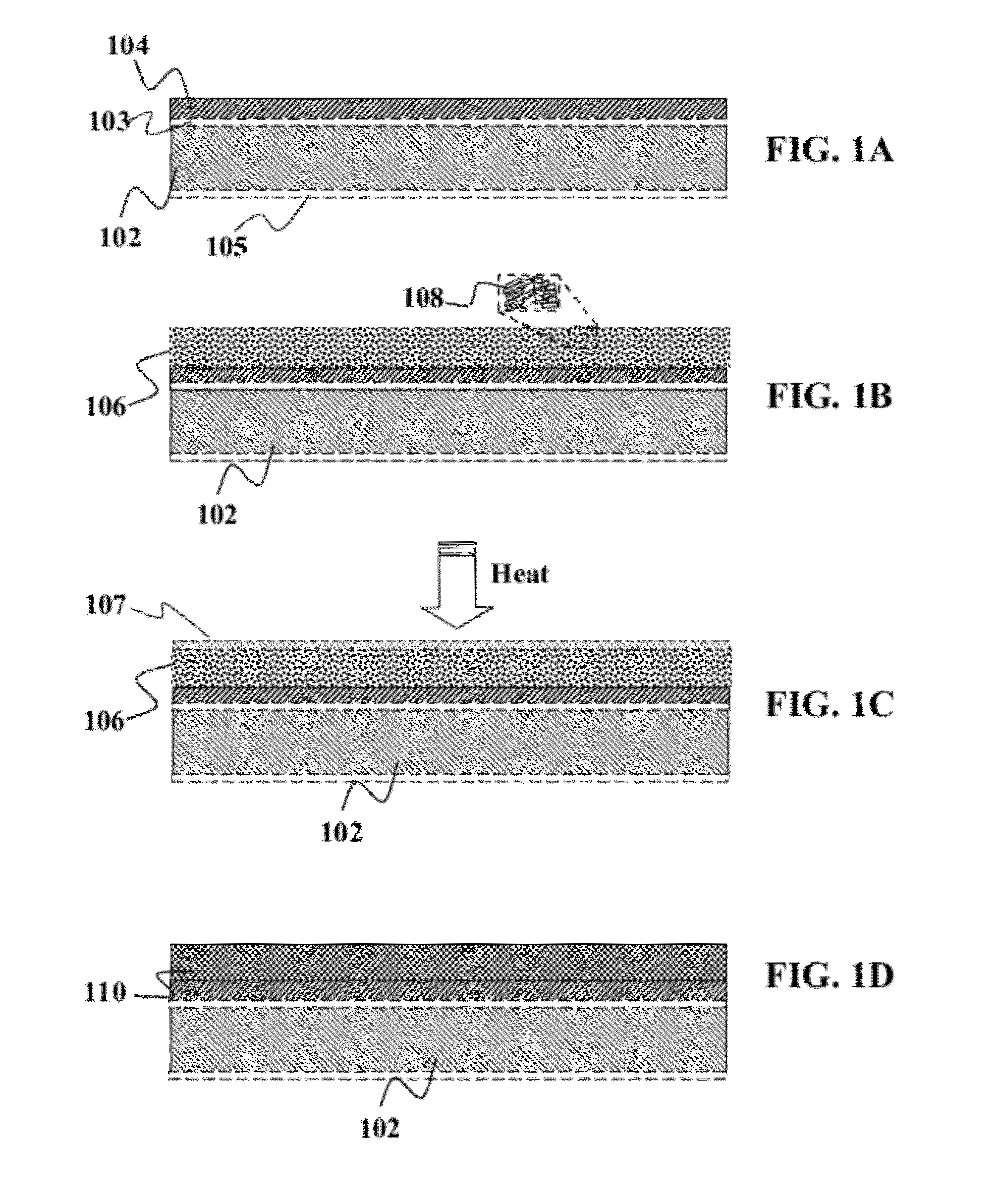

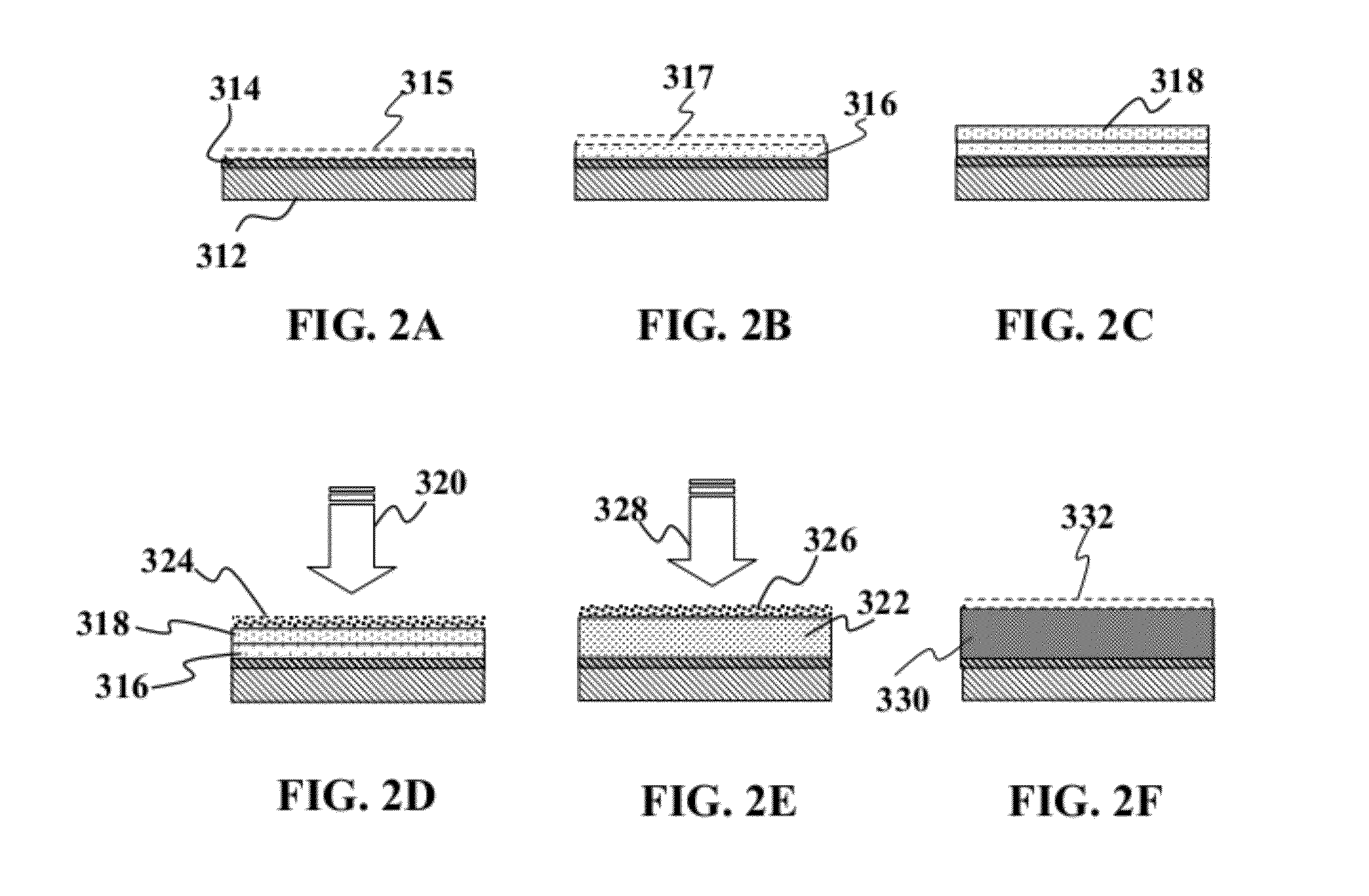

Multi-nary group ib and via based semiconductor

InactiveUS20120313200A1Increase the open circuit voltageLow costSolid-state devicesSemiconductor/solid-state device manufacturingSemiconductor alloysSulfur

Methods and devices are provided for forming multi-nary semiconductor. In one embodiment, a method is provided comprising of depositing a precursor material onto a substrate, wherein the precursor material may include or may be used with an additive to minimize concentration of group IIIA material such as Ga in the back portion of the final semiconductor layer. The additive may be a non-copper Group IB additive in elemental or alloy form. Some embodiments may use both selenium and sulfur, forming a senary or higher semiconductor alloy. It is emphasized that this abstract is provided to comply with the rules requiring an abstract that will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or meaning of the claims.

Owner:AERIS CAPITAL SUSTAINABLE IP

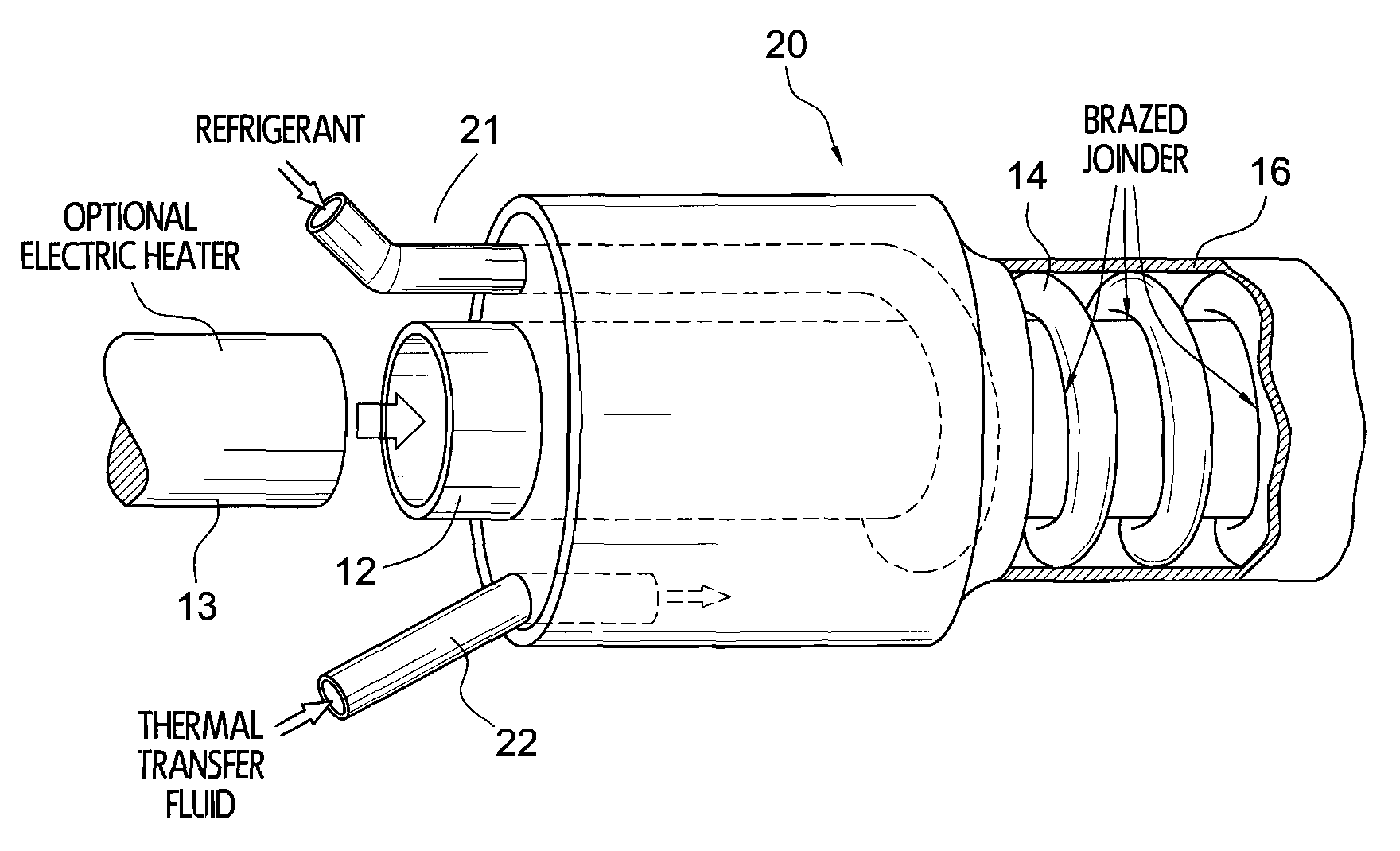

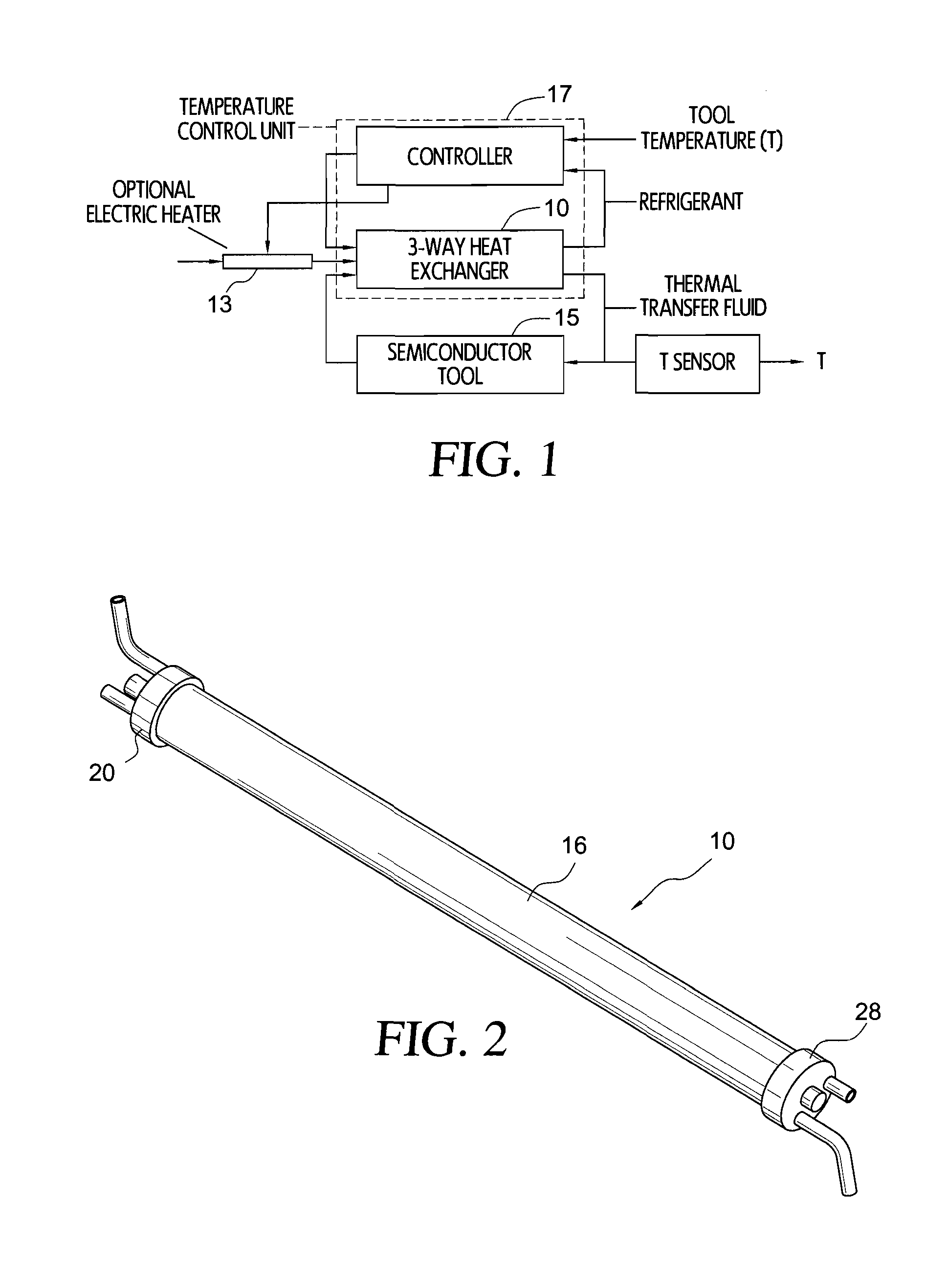

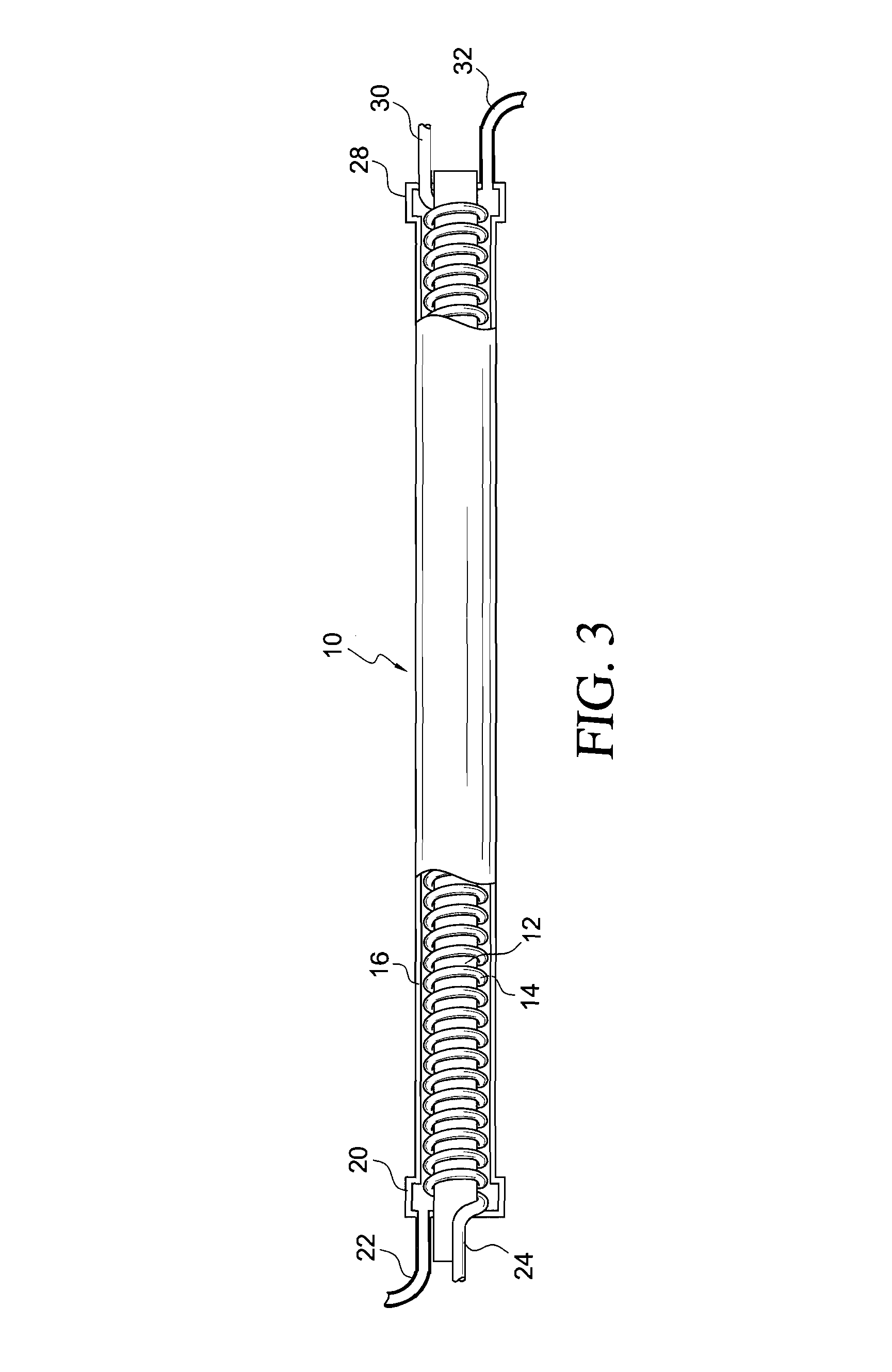

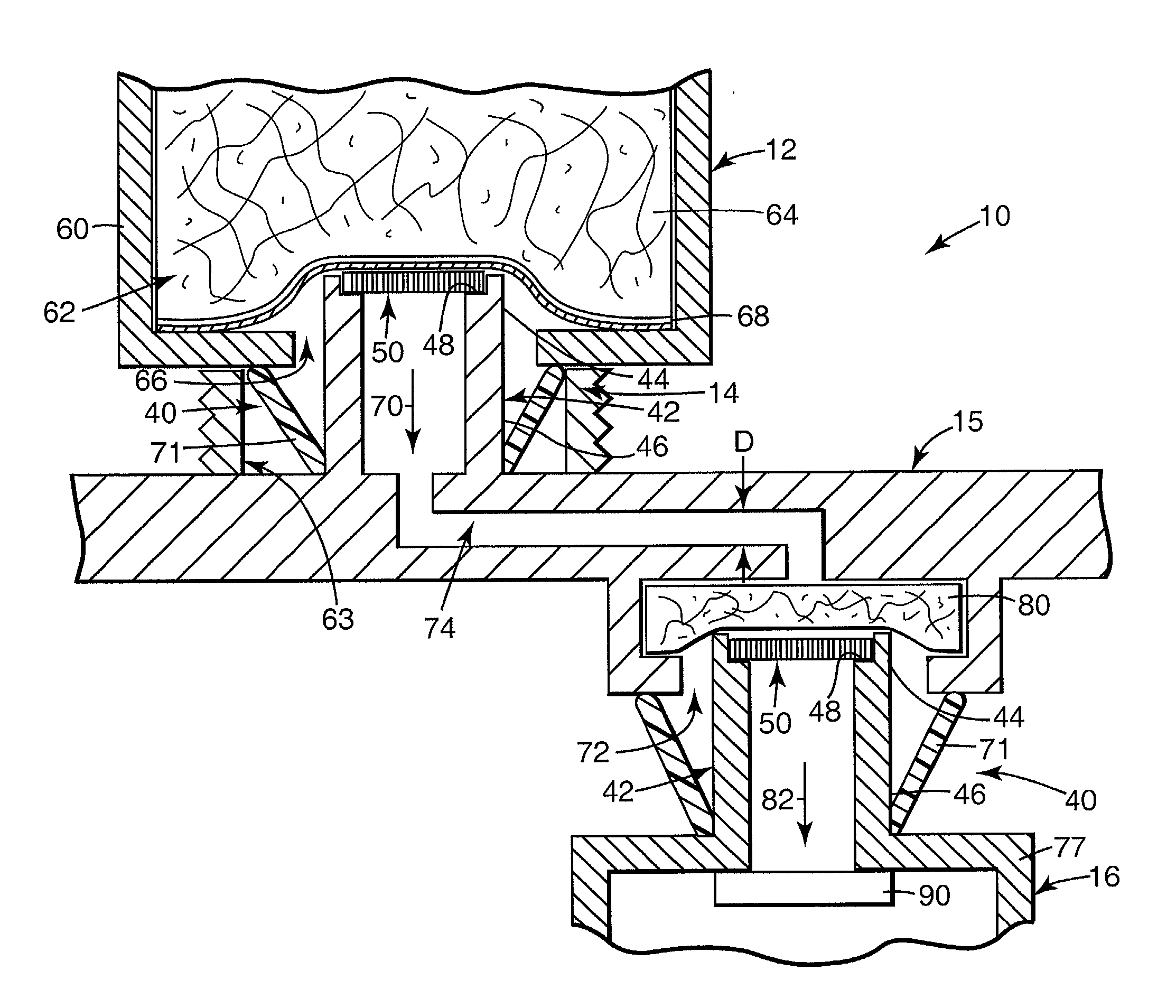

Heat exchangers for fluid media

ActiveUS7661460B1Increase temperatureReduce system costSemiconductor/solid-state device manufacturingCompression machines with several evaporatorsThermal energyCold formed

A compact heat exchanger for interchanging thermal energy between at least two fluids, one of which fluids may be a refrigerant in hot or cold form or in a liquid / vapor phase, and another of which fluids is a thermal transfer fluid. The heat exchanger may incorporate an internal heating element. The thermal transfer fluid is transported between two concentric metal tubes, while the refrigerant moves along a tubing helically wrapped about or between the tubes and is in thermal contact therewith.

Owner:BE AEROSPACE INCORPORATED

Inkjet printing system using filter fluid interconnects for pigmented inks

InactiveUS20020126188A1Prevent cloggingPrevent droolFiltration separationPrintingBiomedical engineeringInkjet printing

Disclosed is a pigmented fluid delivery system for an inkjet printing system. The pigmented fluid delivery system comprises a first printer component and at least a second printer component. The first printer component has a fluid outlet in fluid communication with a supply of pigmented fluid defined by particles suspended in a carrier fluid. The second printer component has a fluid inlet releasably connectable to the fluid outlet of the first printer component. The fluid inlet includes a filter compatible with the supply of pigmented fluid. The filter is an open weave screen defining a plurality of pores. The pores are sized to allow passage of the pigmented fluid while preventing clogging from flocculation of the particles and evaporation of the carrier fluid.

Owner:HEWLETT PACKARD DEV CO LP

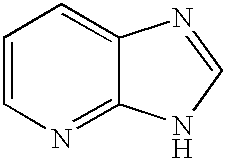

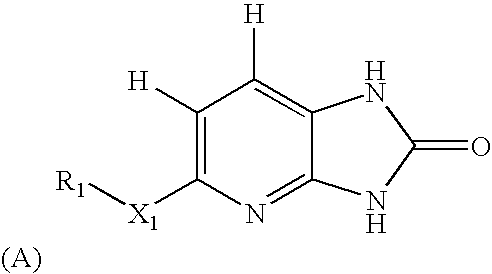

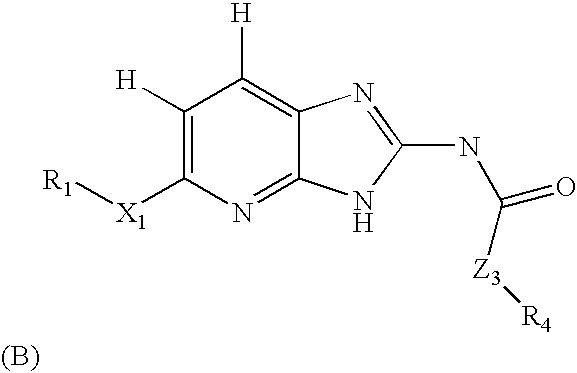

Methods of modulating serine/threonine protein kinase function with azabenzimidazole-based compounds

InactiveUS6855723B2Reduce probabilityAlleviating and abrogating abnormal conditionBiocideOrganic chemistryBiological bodyThreonine

The present invention is directed in part towards methods of modulating the function of serine / threonine protein kinases with azabenzimidazole-based compounds. The methods incorporate cells that express a serine / threonine protein kinase, such as RAF. In addition, the invention describes methods of preventing and treating serine / threonine protein kinase-related abnormal conditions in organisms with a compound identified by the invention. Furthermore, the invention pertains to azabenzimidazole compounds and pharmaceutical compositions comprising these compounds.

Owner:ZENTARIS GMBH

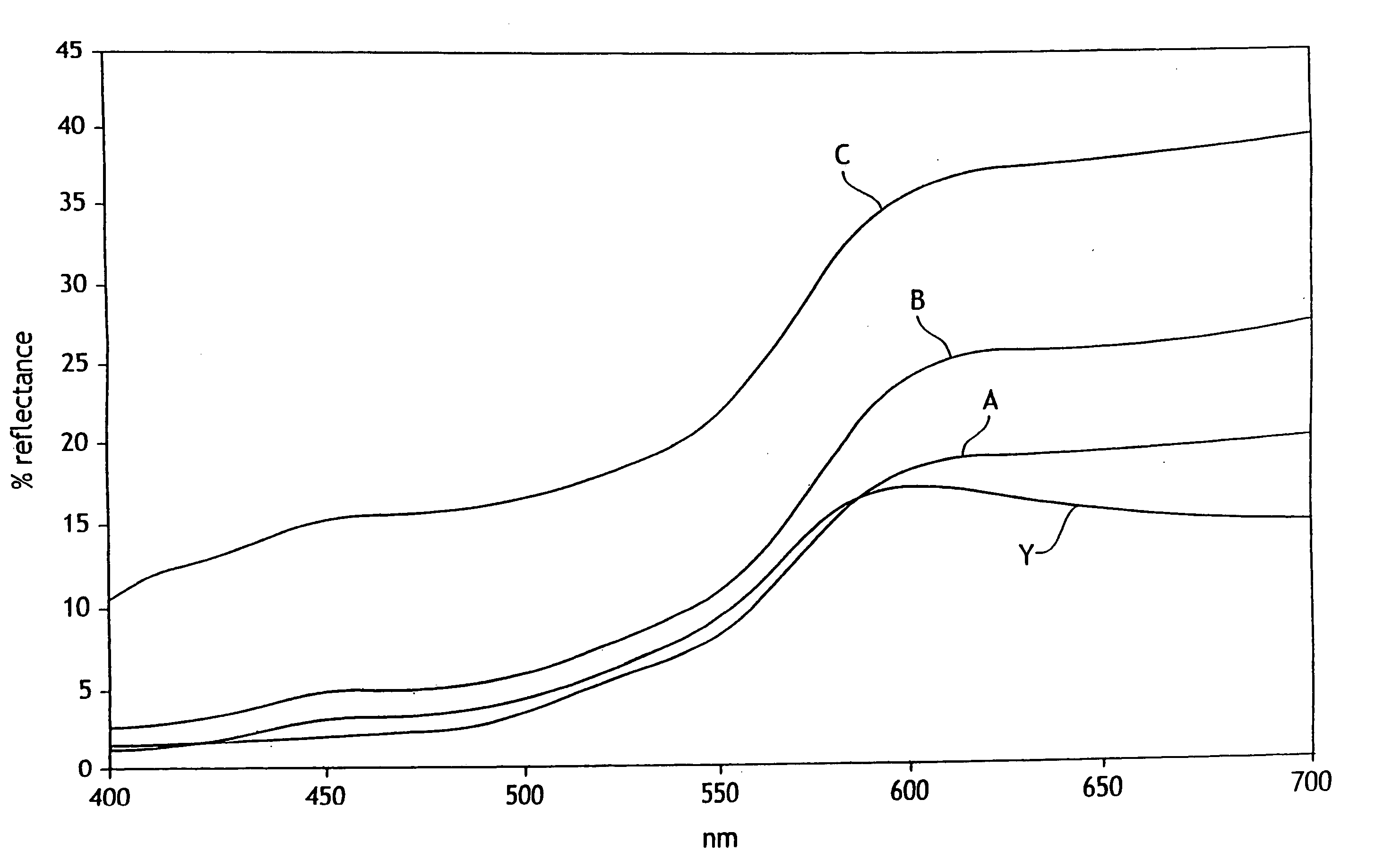

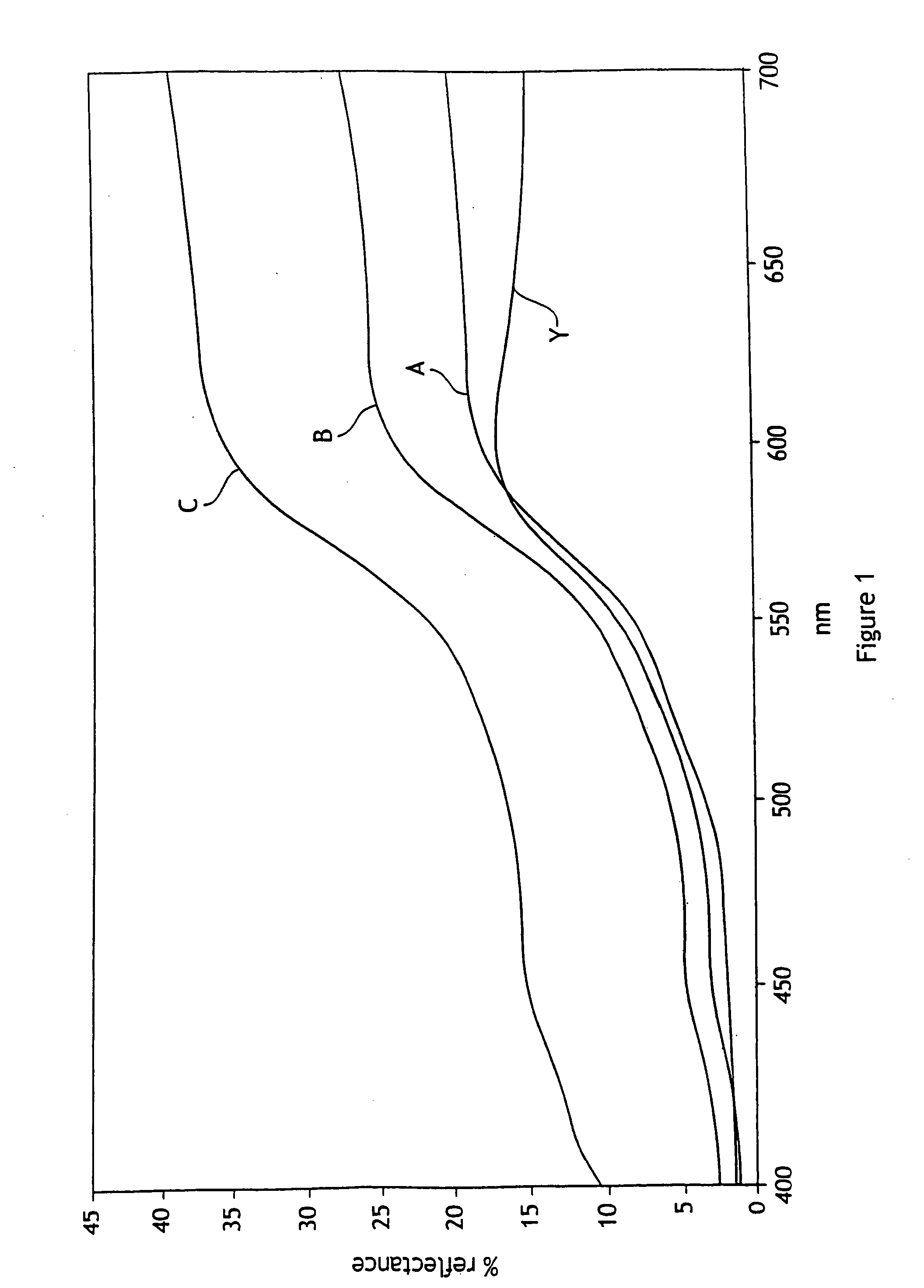

Cosmetic composition of foundation type for making up dark skins

InactiveUS20050019285A1Improve stabilityConvenience to mergeCosmetic preparationsMake-upHueTraditional medicine

The present invention relates to a composition of foundation type, especially for making up the skin, in particular dark skins, comprising, in a physiologically acceptable medium, at least one colouring agent and reflective particles, the said composition having a hue in the colour range extending from pink-beige to orange-brown.

Owner:LOREAL SA

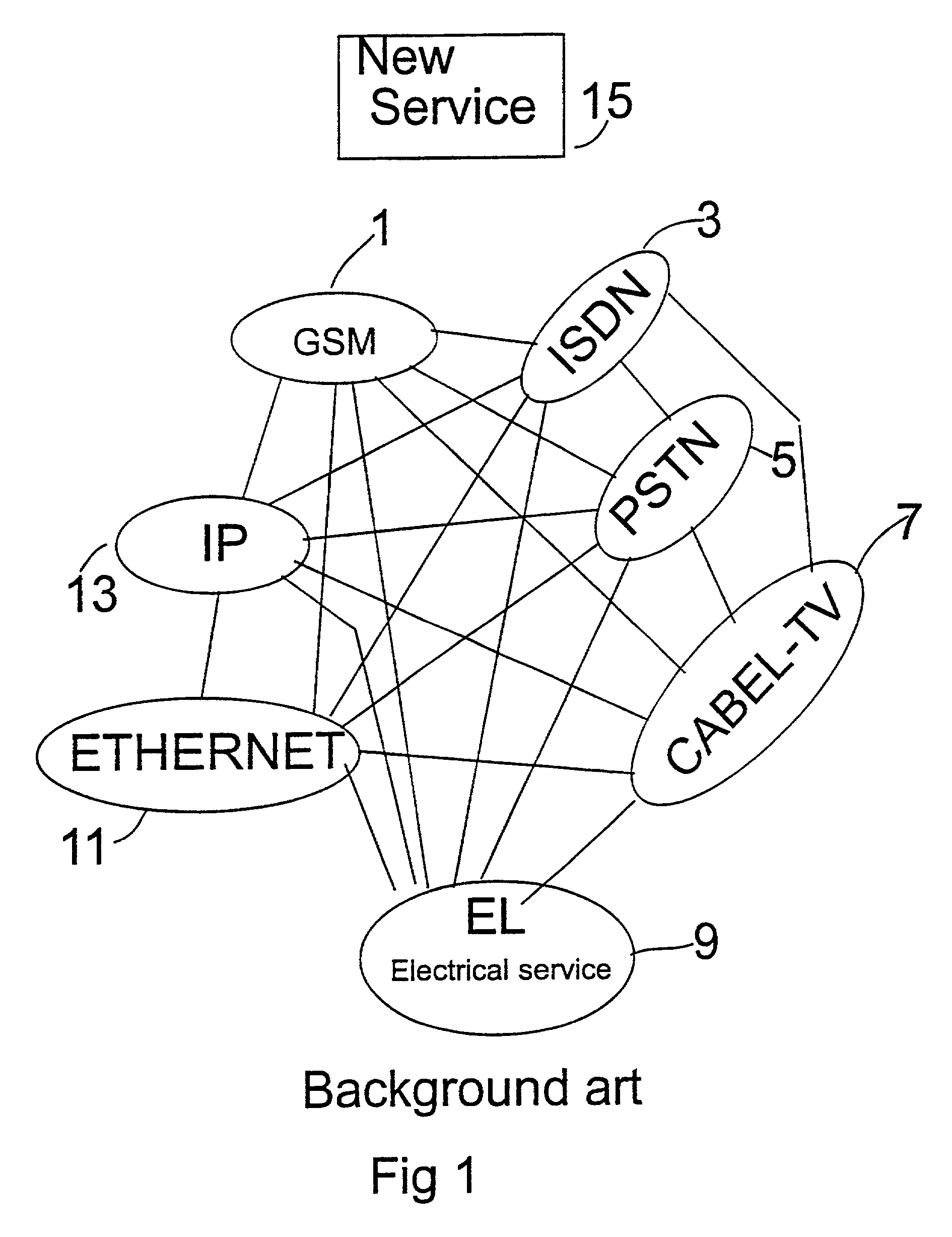

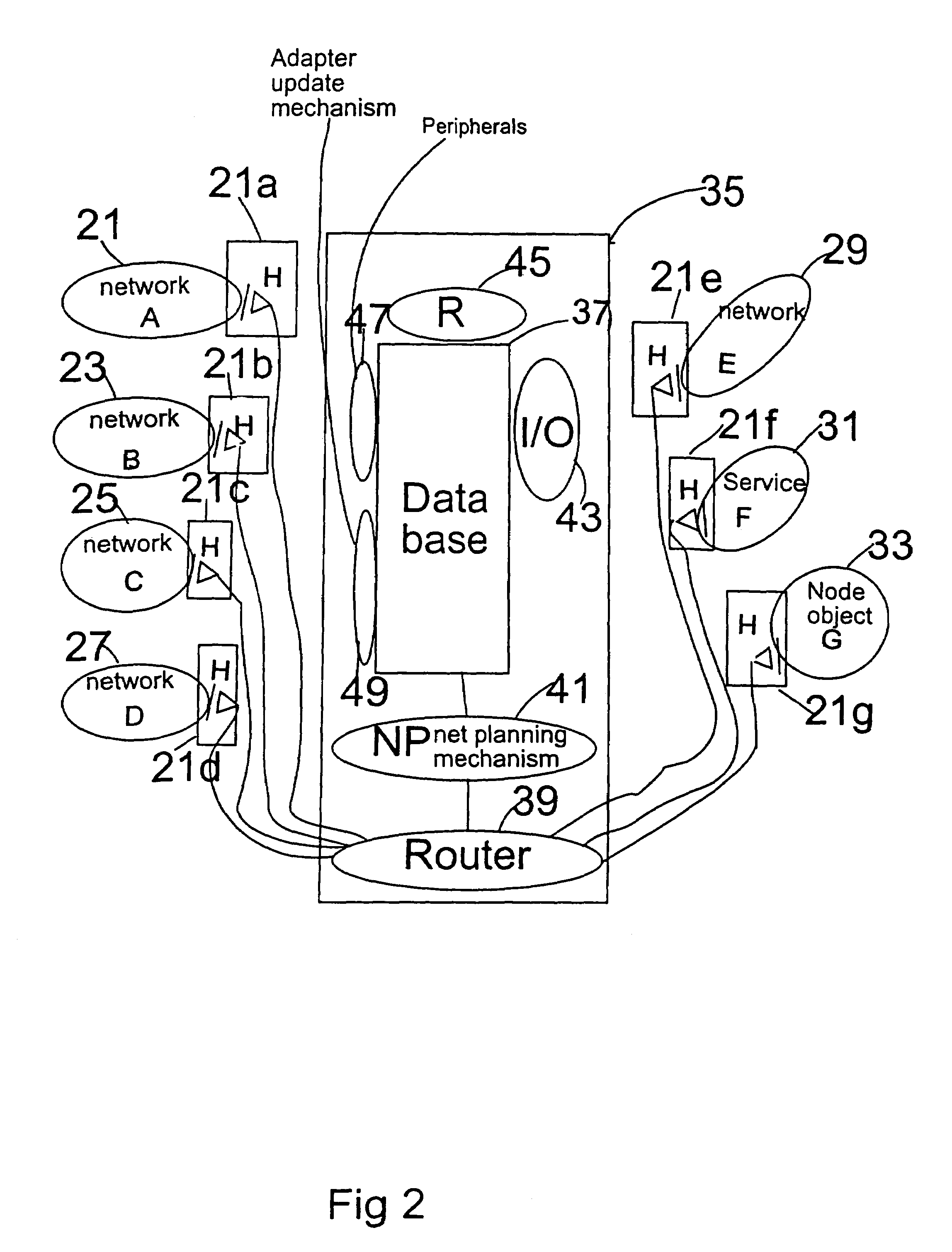

Method, system and device for establishing communication between different communication networks

InactiveUS7212543B1Easy to processFacilitate initial communication and even subsequent communicationInterconnection arrangementsTime-division multiplexCommunications systemCentral unit

A method, system and device for communication establishes communications sessions between otherwise incompatible communication networks. A central unit is used to facilitate communication systems between objects, by referring to a database of communication attributes associated with different communication networks used by a calling part and a called party. Rather than have direct connections from one communication network to a next communication network, and having unique translators to support such direct connections, each of the communications is directed to a central facility, that identifies common protocols that are supported by the different communication networks to be employed when establishing a communication session between a first communication network and a second communication network. Included at the central facility is a database having subscriber information, and a network number associated with a subscriber, where the network number has associated therewith different communication numbers assigned to that subscriber in the different communication networks at which the subscriber may be located.

Owner:TELIASONERA

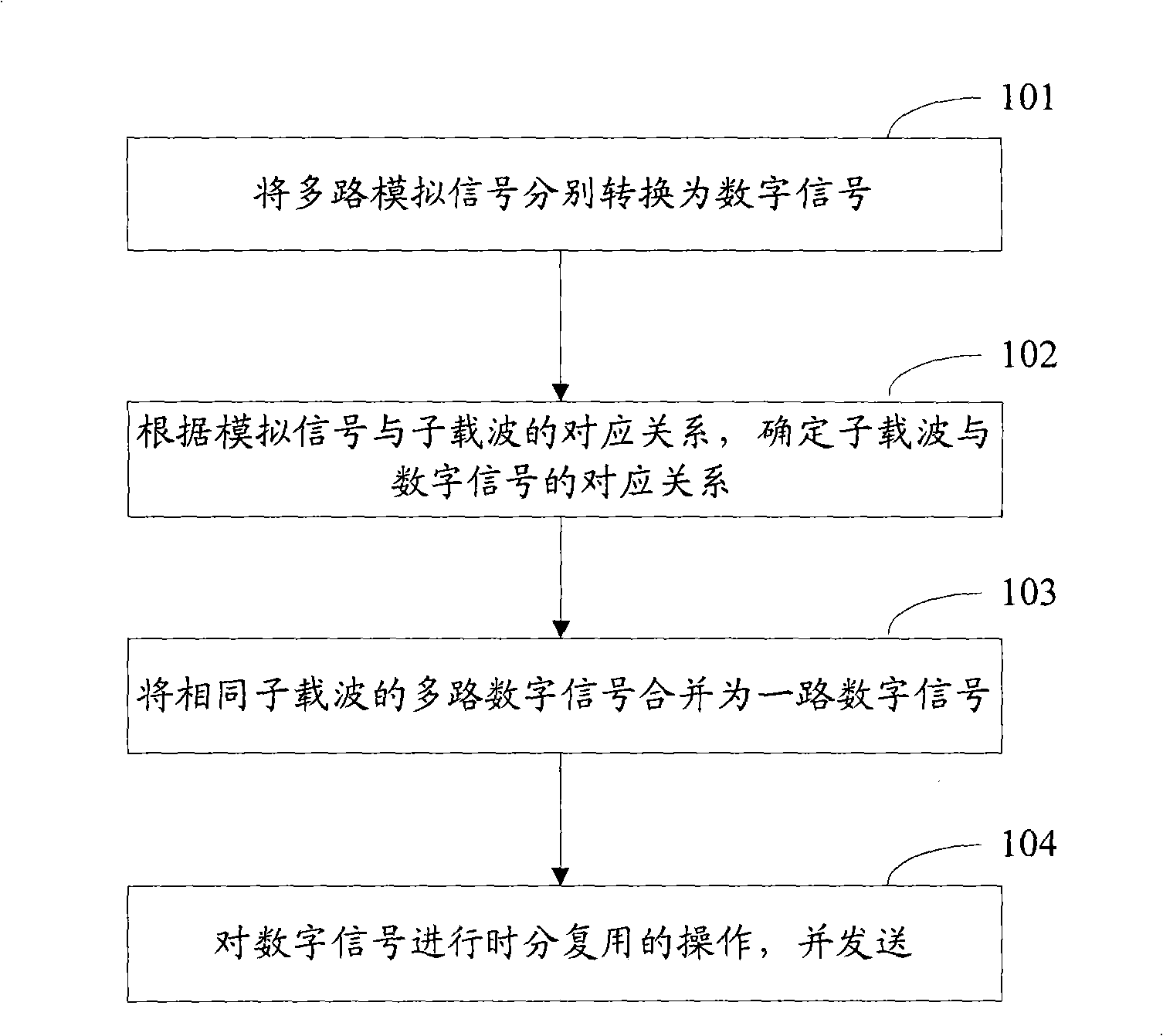

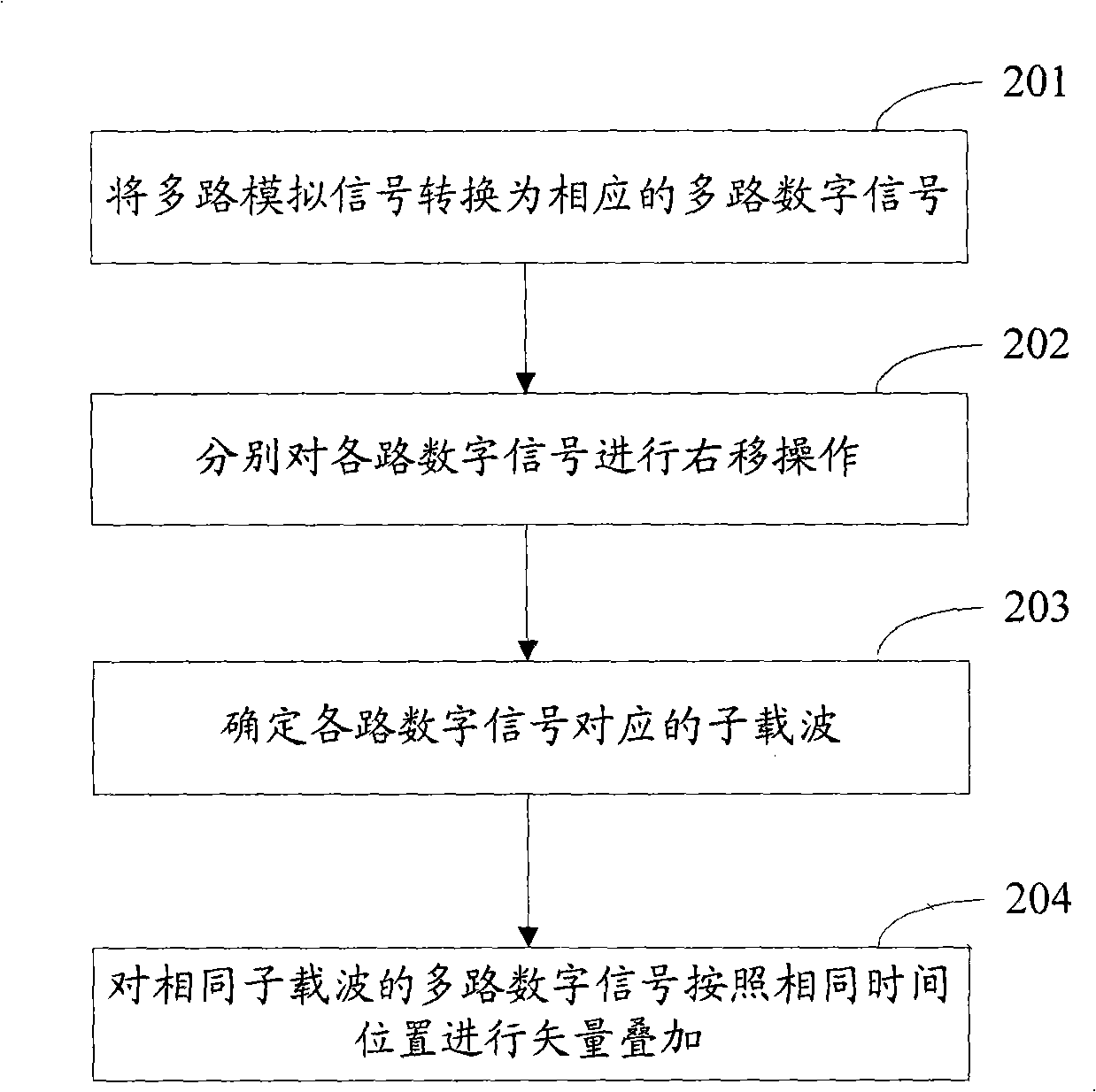

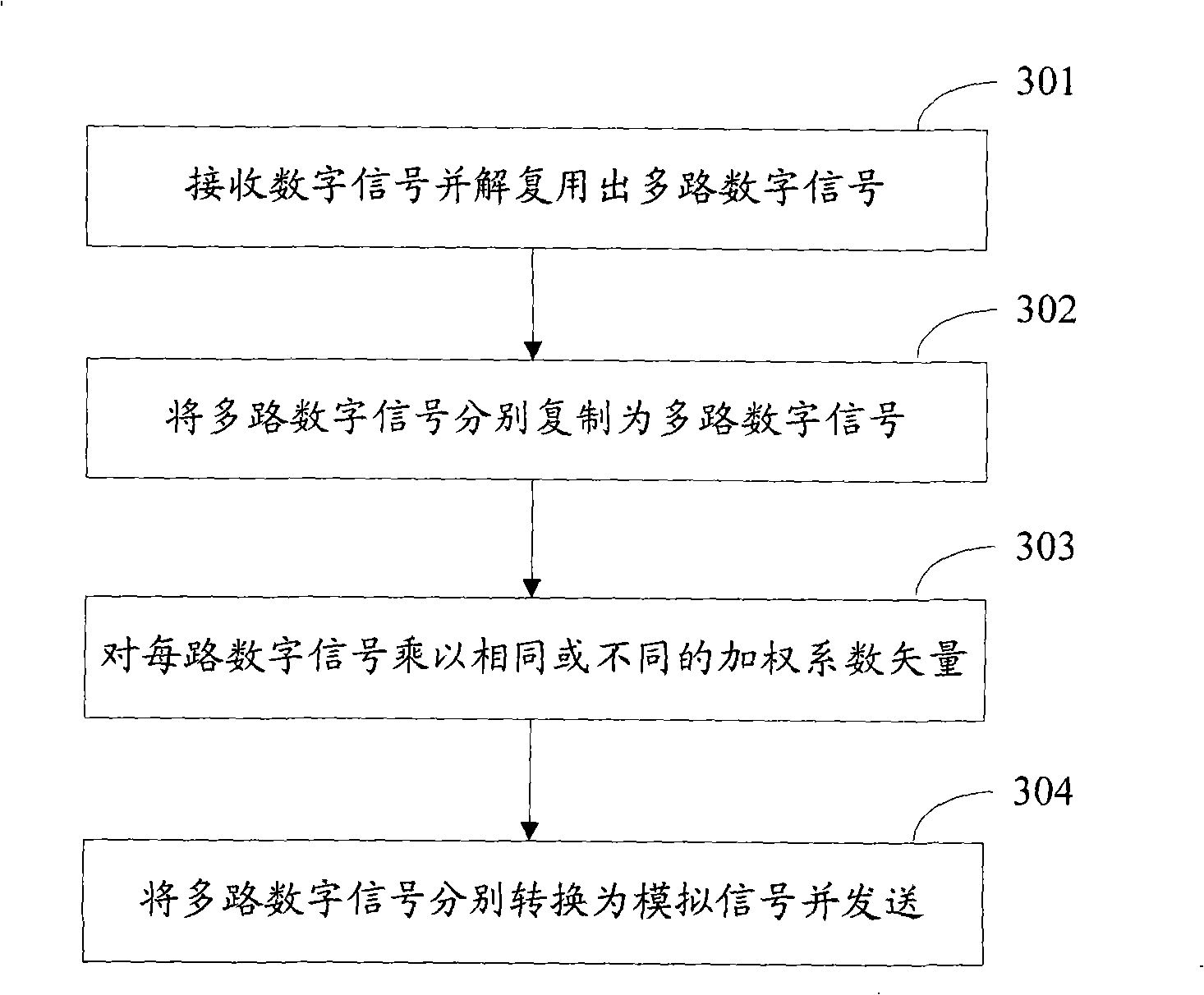

Method and system for processing multi-antenna signal

ActiveCN101350647AConvenience to mergeFlexible networkingSpatial transmit diversityRadio transmission for post communicationAnalog signalEngineering

The present invention discloses a method of processing multi-antenna signals. When the method is used, a single baseband unit BBU in the distributed base station system can support a plurality of antennas which surpass the self designed capacity of the base station system, so as to satisfy the needs of development of communication. Moreover, the network building costs are reduced. In the method, a radio frequency remote unit RRU can respectively transform the multi-channel analog signals received by a plurality of antennas into the corresponding digital signals; the RRU complete the vector superposition of the multi-channel digital signals which are acquired from the multi-channel analog signals of the same subcarrier, according to the same time position; then the multi-channel digital signals are combined to form the digital signals of one path. The present invention also discloses a BBU, a base-band interface unit, a RRU and a system.

Owner:DATANG MOBILE COMM EQUIP CO LTD

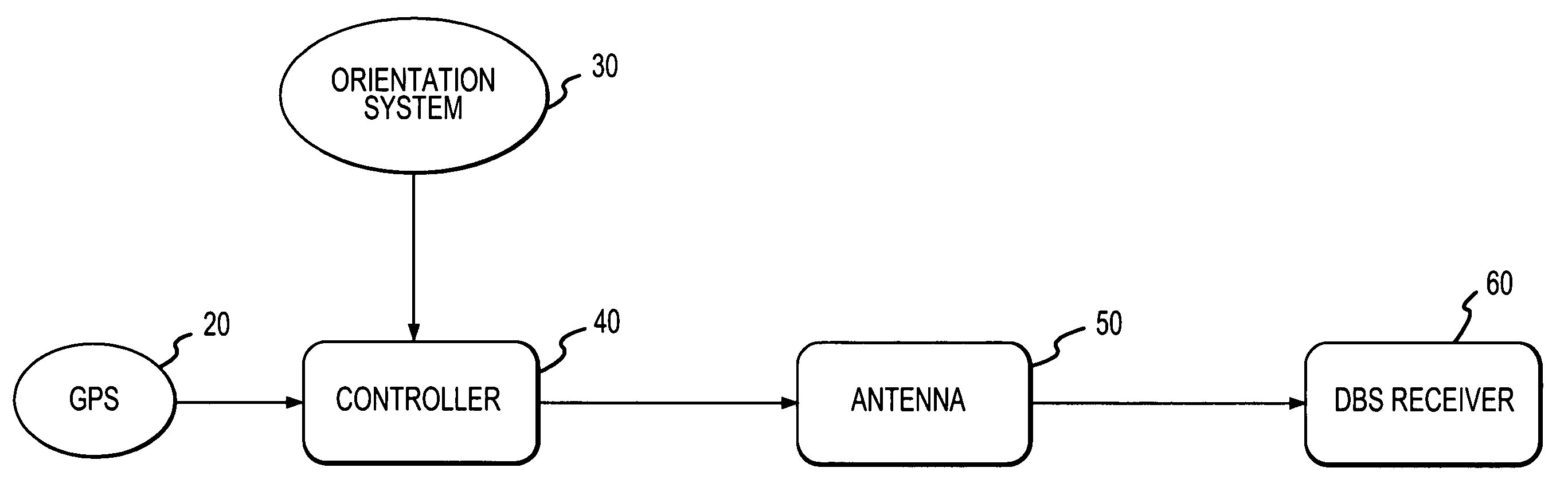

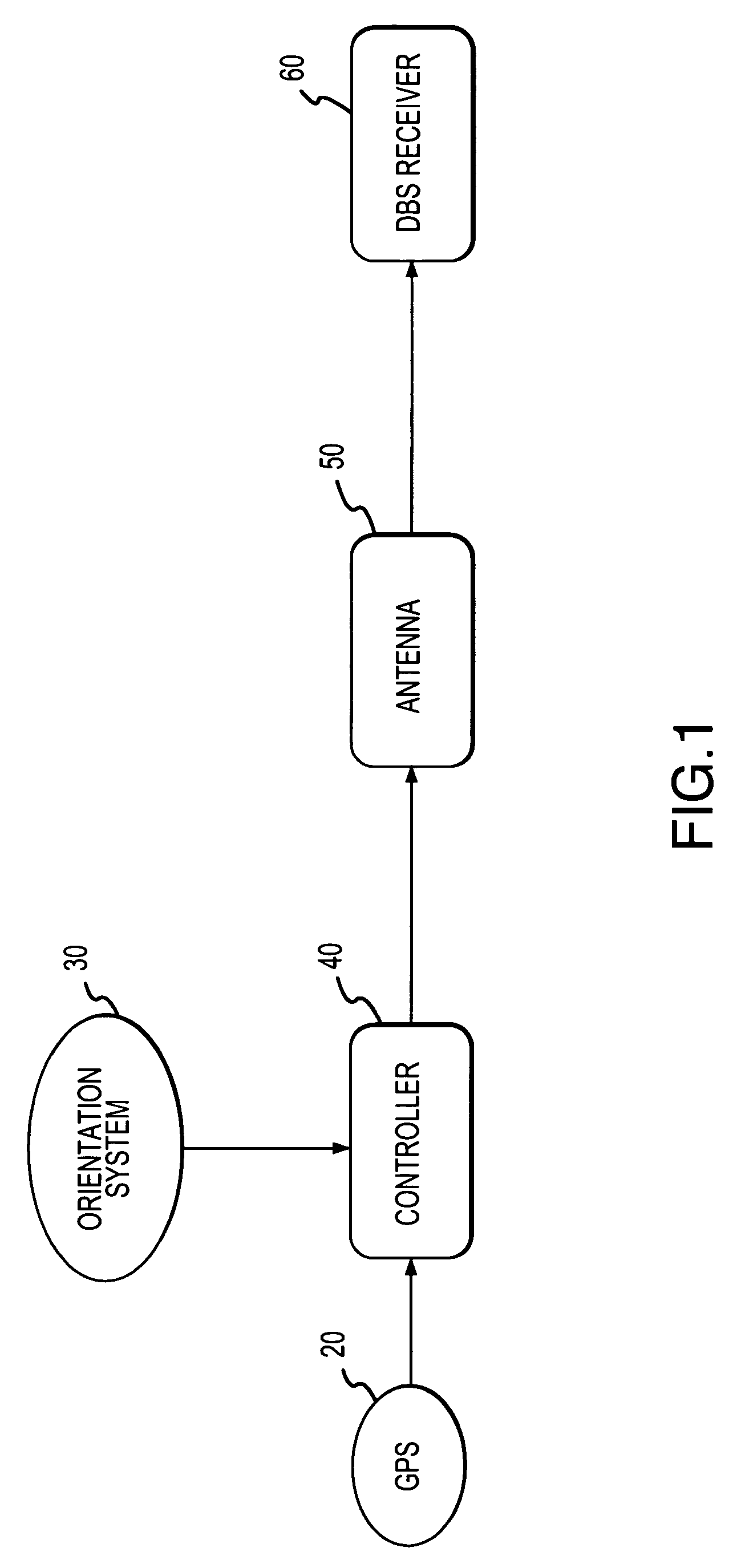

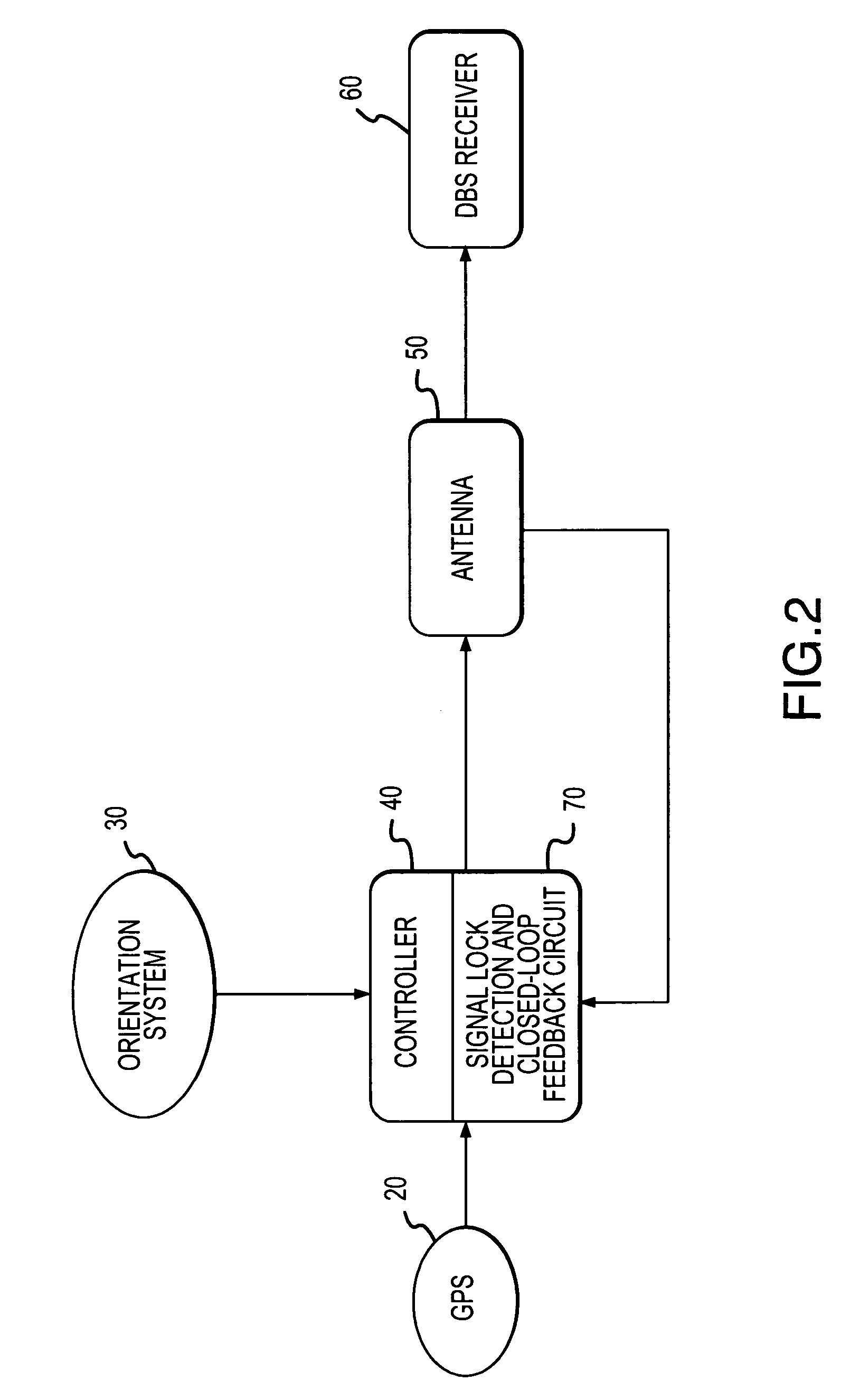

System for access to direct broadcast satellite services

InactiveUS7472409B1Low costConvenience to mergeAntenna adaptation in movable bodiesClosed circuit television systemsTelecommunicationsRadio frequency signal

A system for receiving direct broadcast satellite signals in a mobile craft is disclosed. Generally, the system includes an orientation system for determining the first orientation of the mobile craft, a controller or processor for determining first position control data, and an electronically-pointable antenna adapted to receive first position control data from the controller, such that the antenna is pointable in accordance therewith, such that a first direct broadcast satellite signal is receivable from a first direct broadcast satellite, and a direct broadcast satellite receiver for processing a first radio frequency signal corresponding to the first direct broadcast satellite signal received by the electronically-pointable antenna.

Owner:LOCKHEED MARTIN CORP

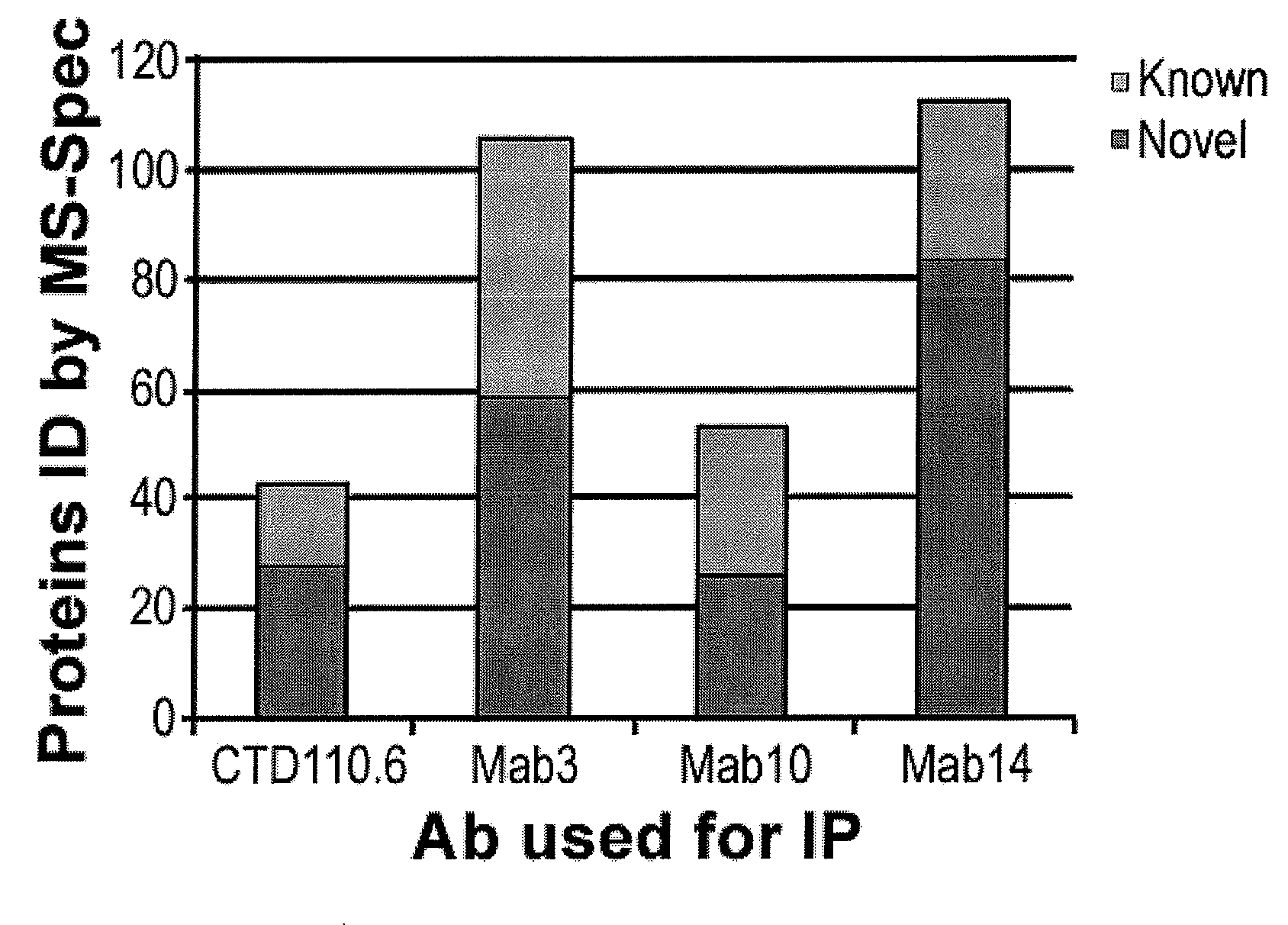

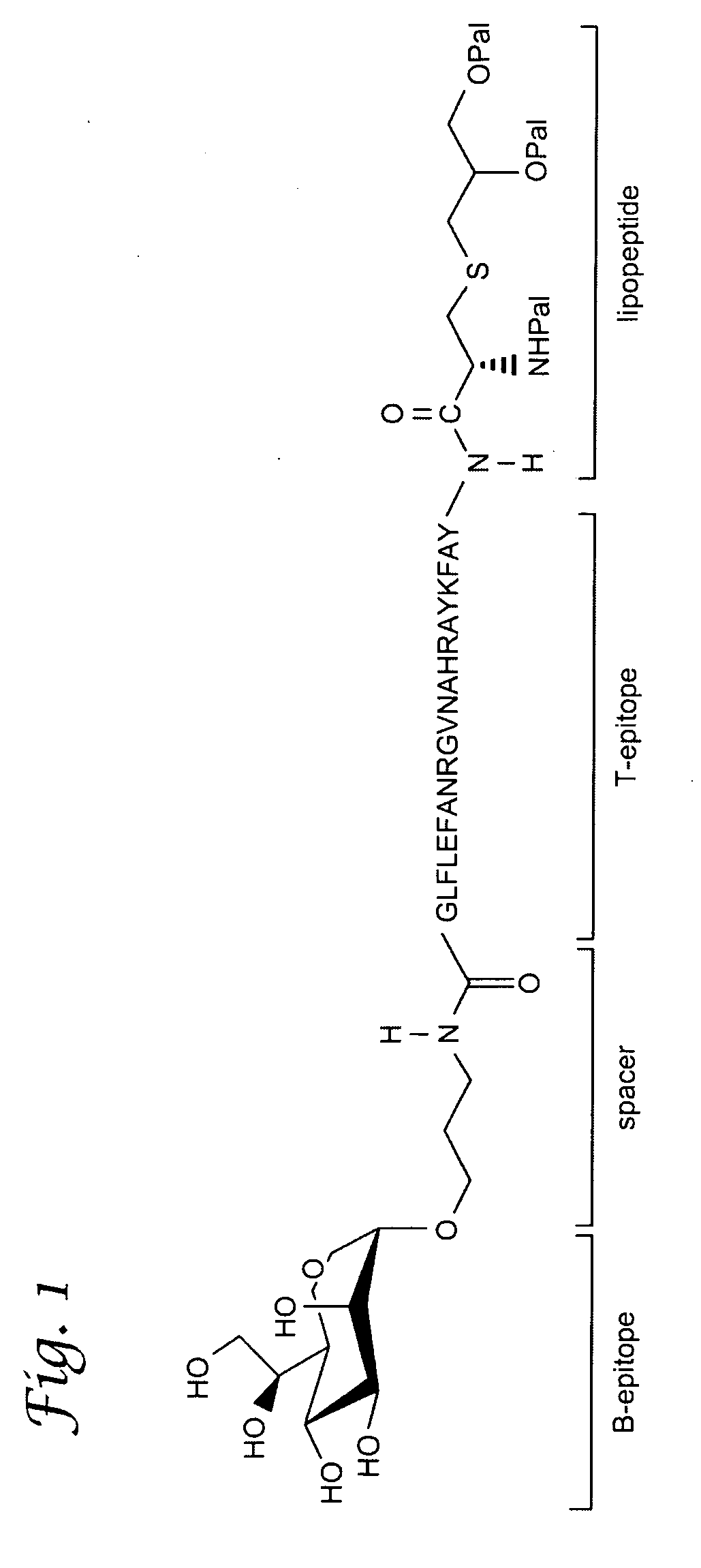

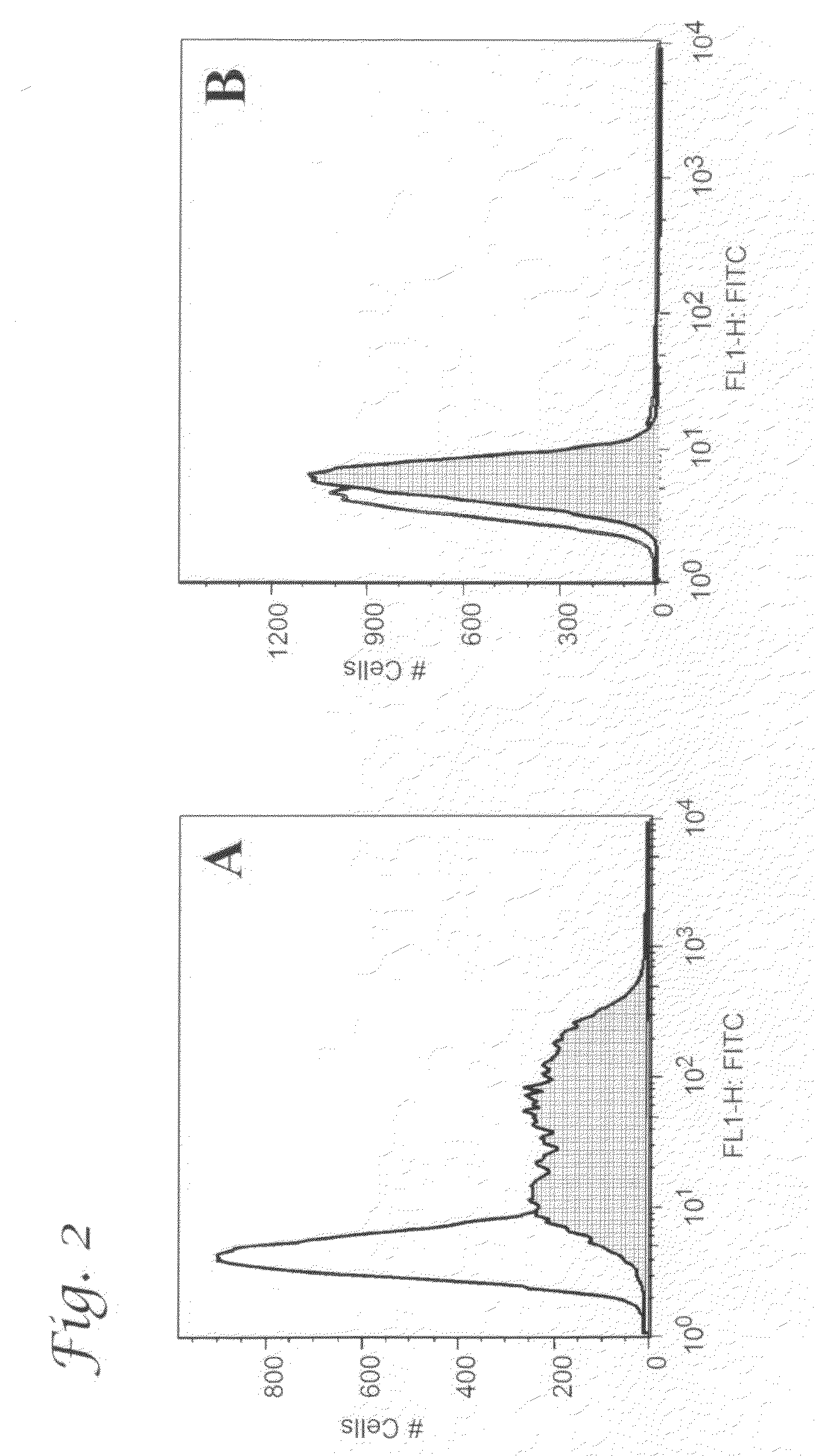

Glycolipopeptide and uses thereof

ActiveUS20090041836A1Reduce deliveryConvenience to mergeAntibacterial agentsVirusesPolyclonal antibodiesGlycolipid

A glycolipopeptide comprising a carbohydrate component, a peptide component and a lipid component, for use as a therapeutic or prophylactic vaccine. Also provided are monoclonal and polyclonal antibodies that recognize the glycolipopeptide of the invention, as well as uses thereof.

Owner:GEORGIA RESERACH FOUND INC UNIV OF

Antirotational structures for wave energy converters

ActiveUS20050237775A1Useful for promotionGood and efficient electromagnetic couplingAC motor controlEngine fuctionsCouplingEngineering

Owner:OCEAN POWER TECHNOLOGIES

Oxygen scavenging monolayer bottles

InactiveUS20020183448A1Lower cost of capitalReduce manufacturing costLiquid degasificationBottlesPolyesterOxygen

Monolayer packages comprised of an oxygen scavenging composition suitable for direct contact with package contents and recycle with other polyester bottles are disclosed. The oxygen scavenging composition is comprised of a modified copolymer which is comprised of predominantly polyester segments and an oxygen scavenging amount of oxygen scavenging segments. The polyester segments comprise segments derived from typical bottling and packaging polyesters such as PET and PEN. Use of these oxygen scavenging copolymers in bottles provides a clear and rigid monolayer bottle similar in appearance to unmodified polyester bottles. In a series of preferred embodiments, bottles fabricated with the oxygen scavenging copolymers of this invention are over 99 wt % PET and contain less than 50 ppb of extractable components.

Owner:COLORMATRIX HLDG

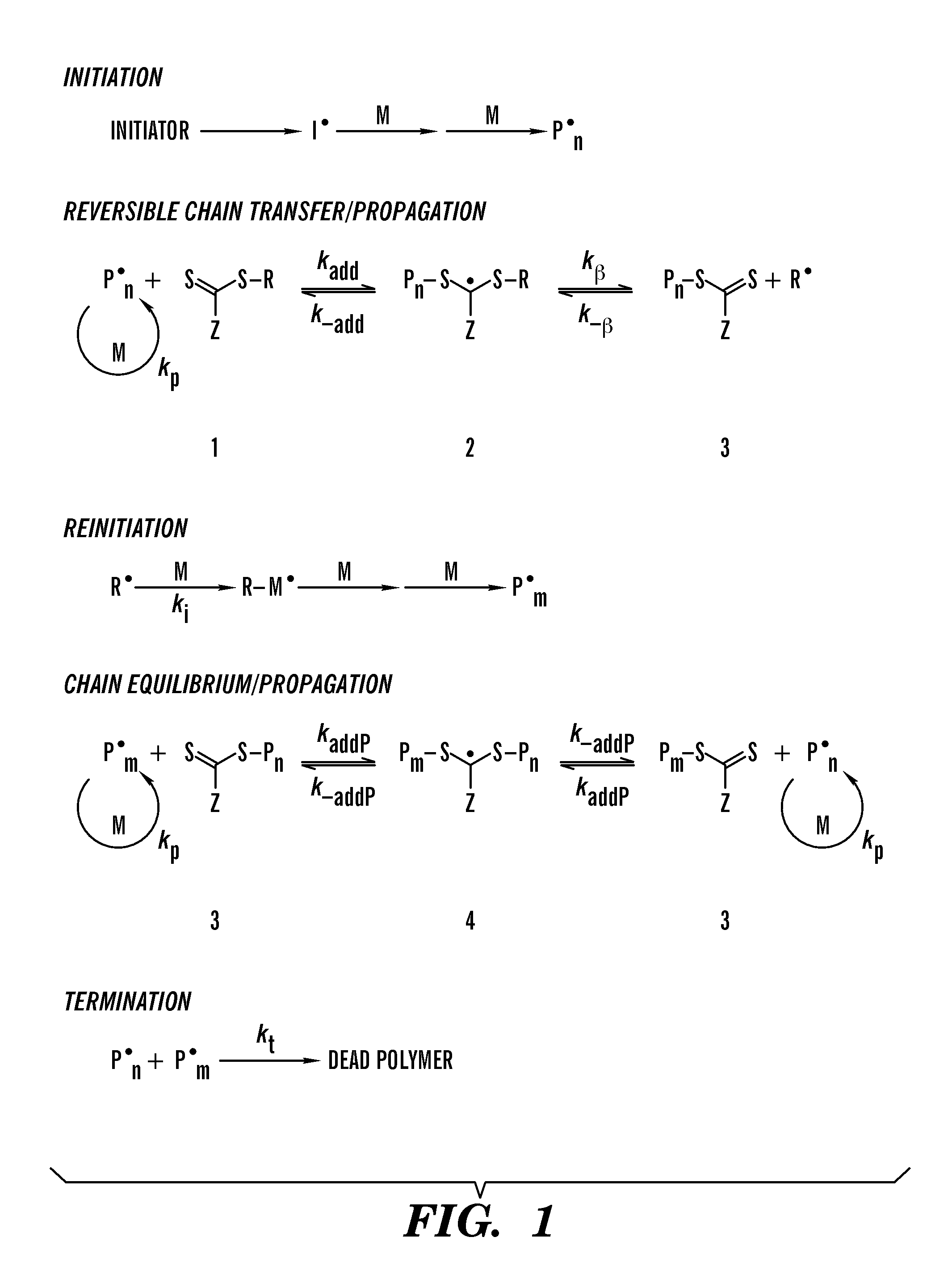

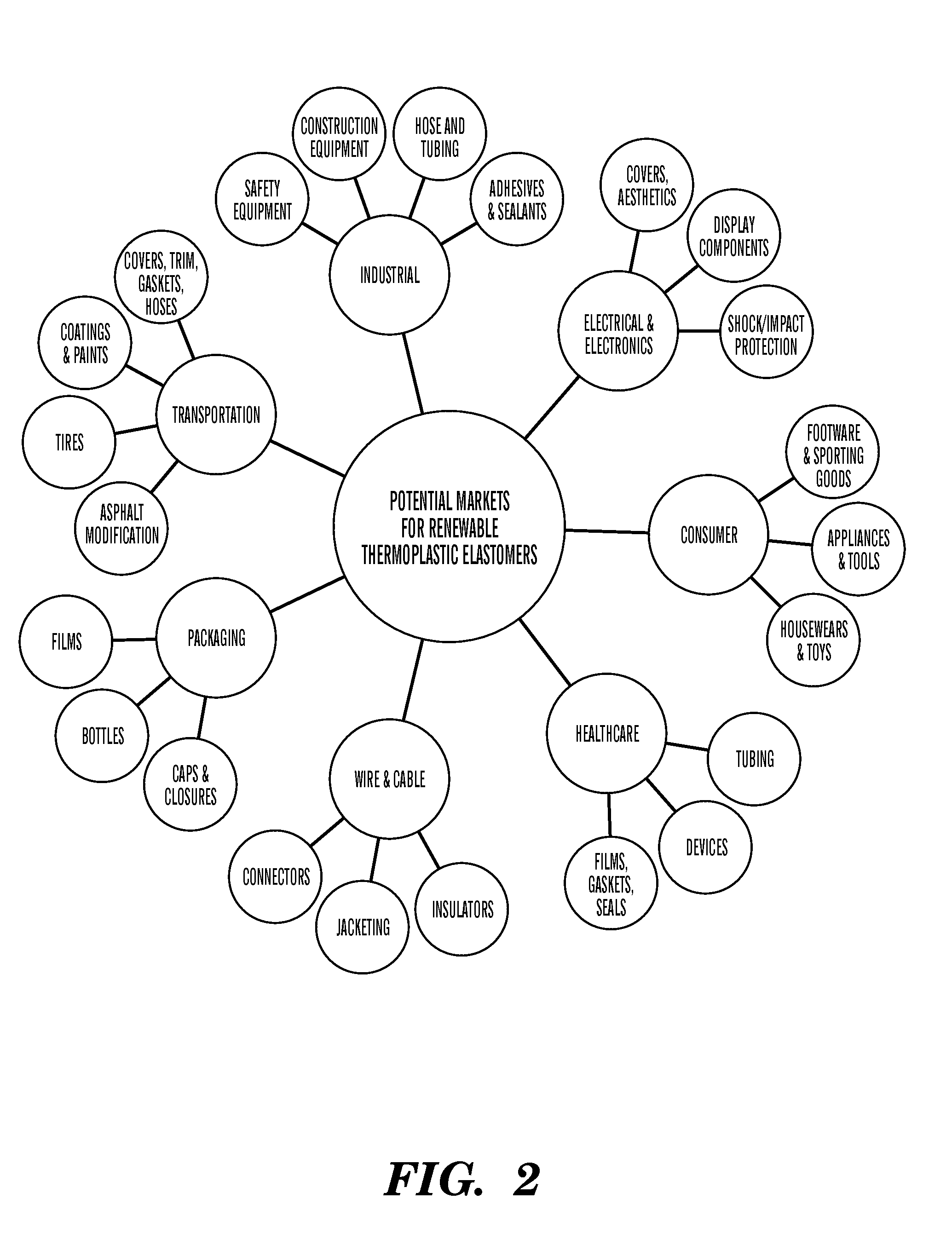

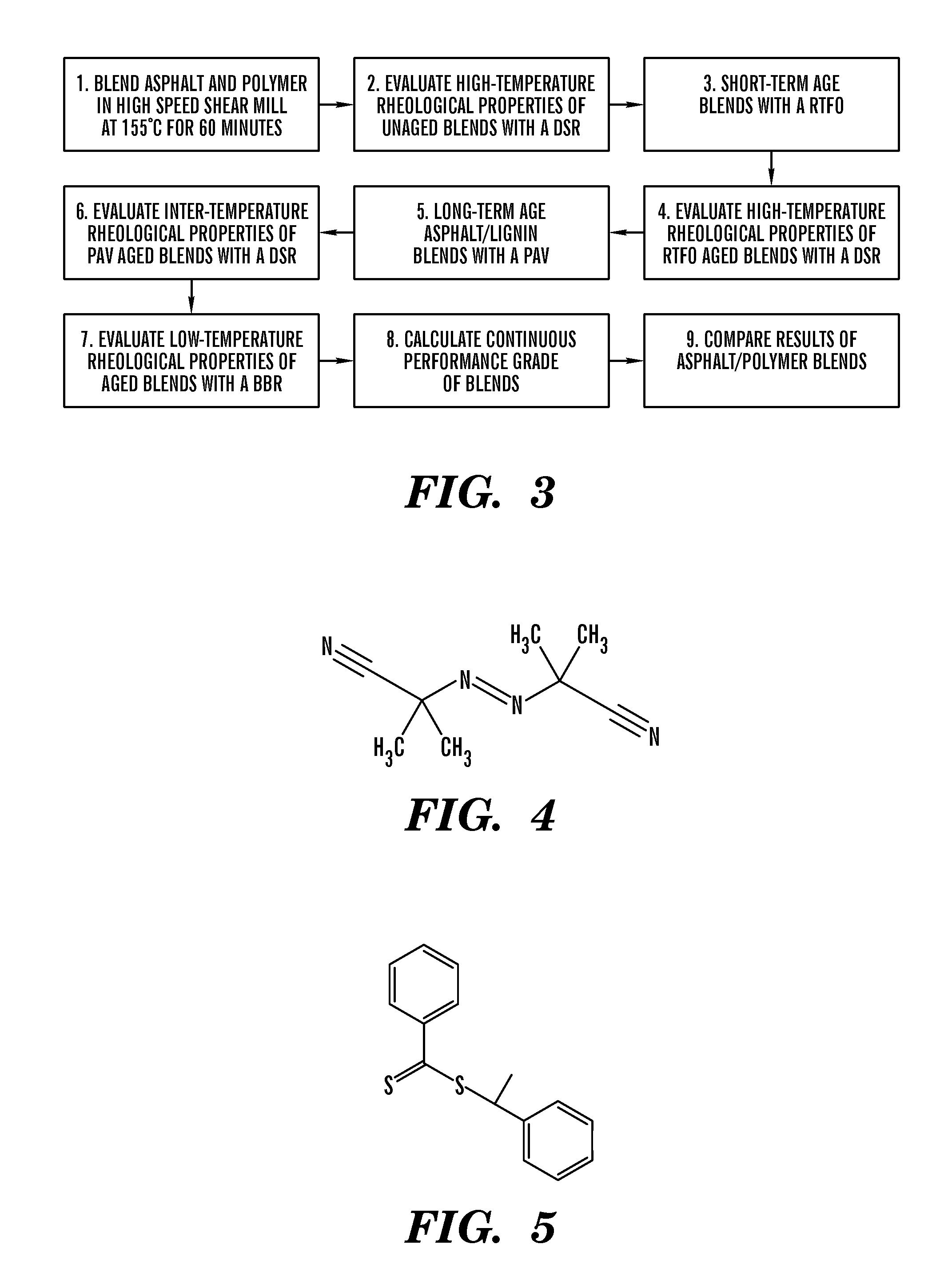

Thermoplastic elastomers via reversible addition-fragmentation chain transfer polymerization of triglycerides

ActiveUS20140343192A1Convenience to mergeCompetitive costVinyl aromatic copolymer adhesivesBituminous coatingsPolymer scienceThermoplastic elastomer

The present invention relates to a thermoplastic block copolymer comprising at least one PA block and at least one PB block. The PA block represents a polymer block comprising one or more units of monomer A, and the PB block represents a polymer block comprising one or more units of monomer B. Monomer A is a vinyl, acrylic, diolefin, nitrile, dinitrile, acrylonitrile monomer, a monomer with reactive functionality, or a crosslinking monomer. Monomer B is a radically polymerizable triglyceride or mixtures thereof, typically in the form of a plant or animal oil. The present invention also relates to a method of preparing a thermoplastic block copolymer or novel thermoplastic statistical copolymers by polymerizing a radically polymerizable monomer with a radically polymerizable triglyceride or mixtures thereof via reversible addition-fragmentation chain-transfer polymerization (RAFT), in the presence of an free radical initiator and a chain transfer agent.

Owner:IOWA STATE UNIV RES FOUND

Methods and compositions for the specific inhibition of gene expression by double-stranded RNA

InactiveUS20090035854A1Convenience to mergeUnanticipated level of potency of the RNAi effectSenses disorderActivity regulationBiological conditionNucleotide

The invention is directed to compositions and methods for selectively reducing the expression of a gene product from a desired target gene in a cell, as well as for treating diseases caused by the expression of the gene. More particularly, the invention is directed to compositions that contain double stranded RNA (“dsRNA”), and methods for preparing them, that are capable of reducing the expression of target genes in eukaryotic cells. The dsRNA has a first oligonucleotide sequence that is between 25 and about 30 nucleotides in length and a second oligonucleotide sequence that anneals to the first sequence under biological conditions. In addition, a region of one of the sequences of the dsRNA having a sequence length of at least 19 nucleotides is sufficiently complementary to a nucleotide sequence of the RNA produced from the target gene to trigger the destruction of the target RNA by the RNAi machinery.

Owner:CITY OF HOPE +1

Methods and compositions for the specific inhibition of gene expression by double-stranded RNA

InactiveUS20090029936A1Convenience to mergeUnanticipated level of potency of the RNAi effectOrganic active ingredientsSenses disorderDiseaseBiological condition

The invention is directed to compositions and methods for selectively reducing the expression of a gene product from a desired target gene in a cell, as well as for treating diseases caused by the expression of the gene. More particularly, the invention is directed to compositions that contain double stranded RNA (“dsRNA”), and methods for preparing them, that are capable of reducing the expression of target genes in eukaryotic cells. The dsRNA has a first oligonucleotide sequence that is between 25 and about 30 nucleotides in length and a second oligonucleotide sequence that anneals to the first sequence under biological conditions. In addition, a region of one of the sequences of the dsRNA having a sequence length of at least 19 nucleotides is sufficiently complementary to a nucleotide sequence of the RNA produced from the target gene to trigger the destruction of the target RNA by the RNAi machinery.

Owner:CITY OF HOPE +1

Methods and compositions for the specific inhibition of gene expression by double-stranded RNA

InactiveUS20090029466A1Convenience to mergeUnanticipated level of potency of the RNAi effectSenses disorderAntipyreticDiseaseBiological condition

The invention is directed to compositions and methods for selectively reducing the expression of a gene product from a desired target gene in a cell, as well as for treating diseases caused by the expression of the gene. More particularly, the invention is directed to compositions that contain double stranded RNA (“dsRNA”), and methods for preparing them, that are capable of reducing the expression of target genes in eukaryotic cells. The dsRNA has a first oligonucleotide sequence that is between 25 and about 30 nucleotides in length and a second oligonucleotide sequence that anneals to the first sequence under biological conditions. In addition, a region of one of the sequences of the dsRNA having a sequence length of at least 19 nucleotides is sufficiently complementary to a nucleotide sequence of the RNA produced from the target gene to trigger the destruction of the target RNA by the RNAi machinery.

Owner:CITY OF HOPE +1

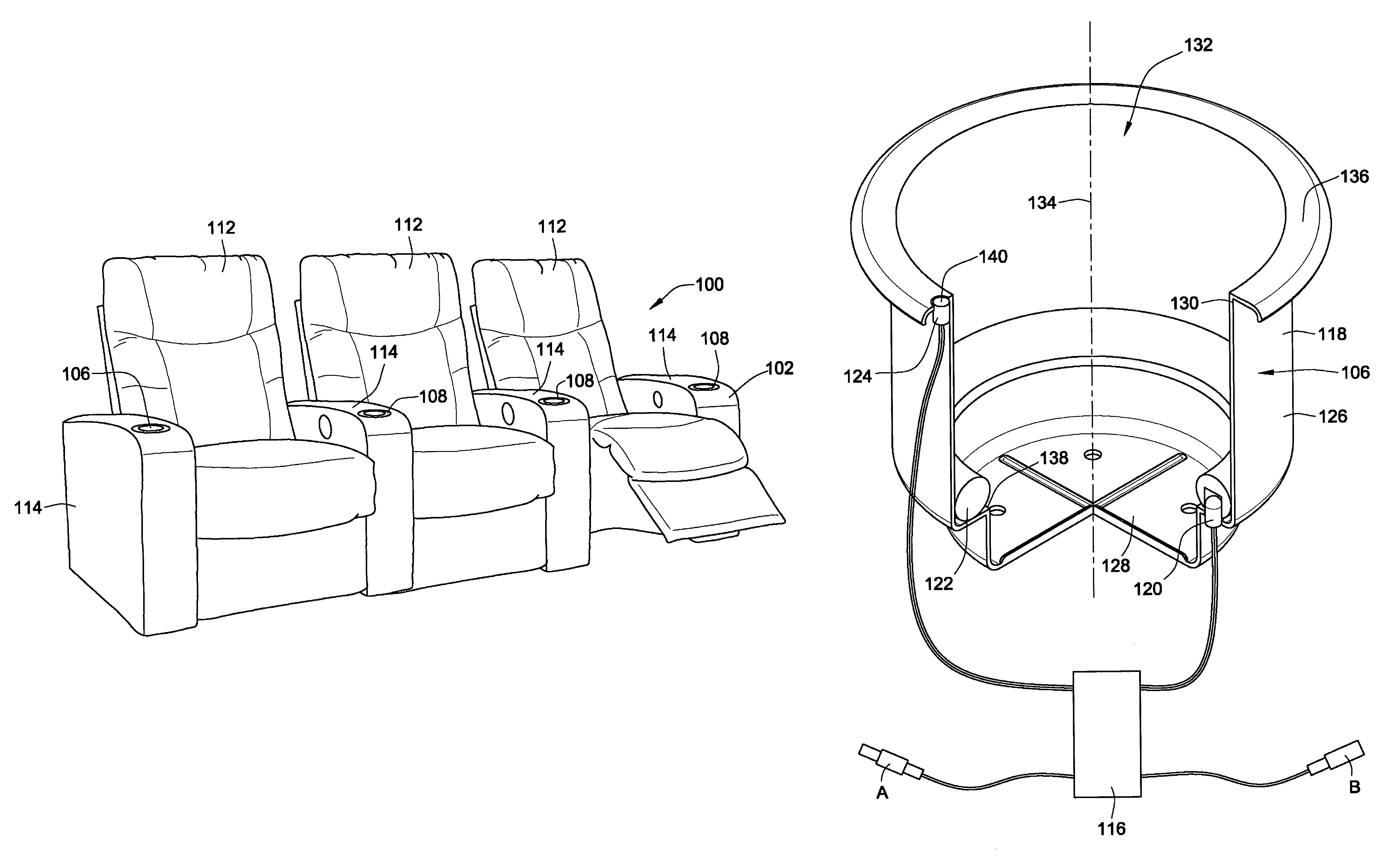

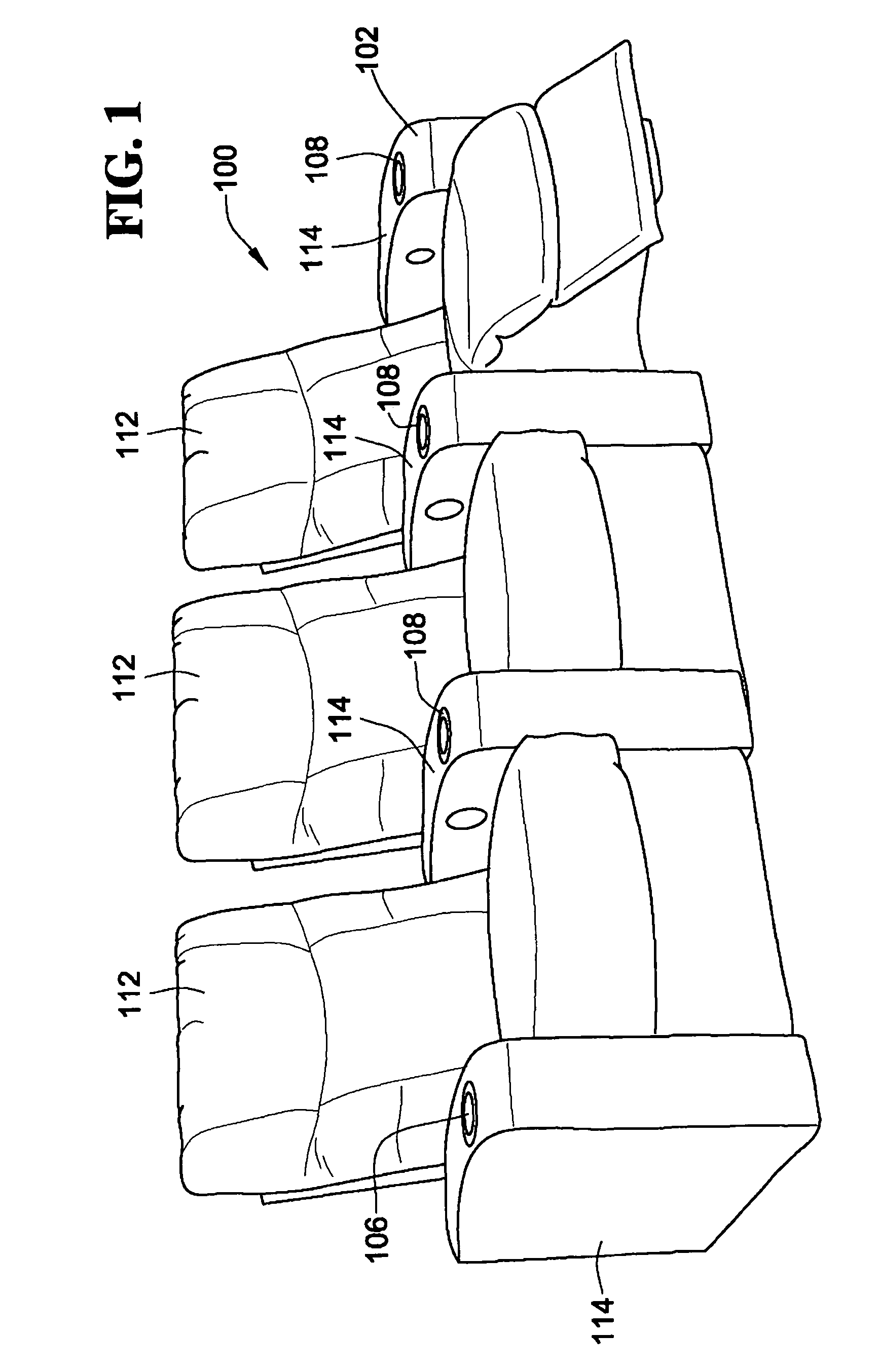

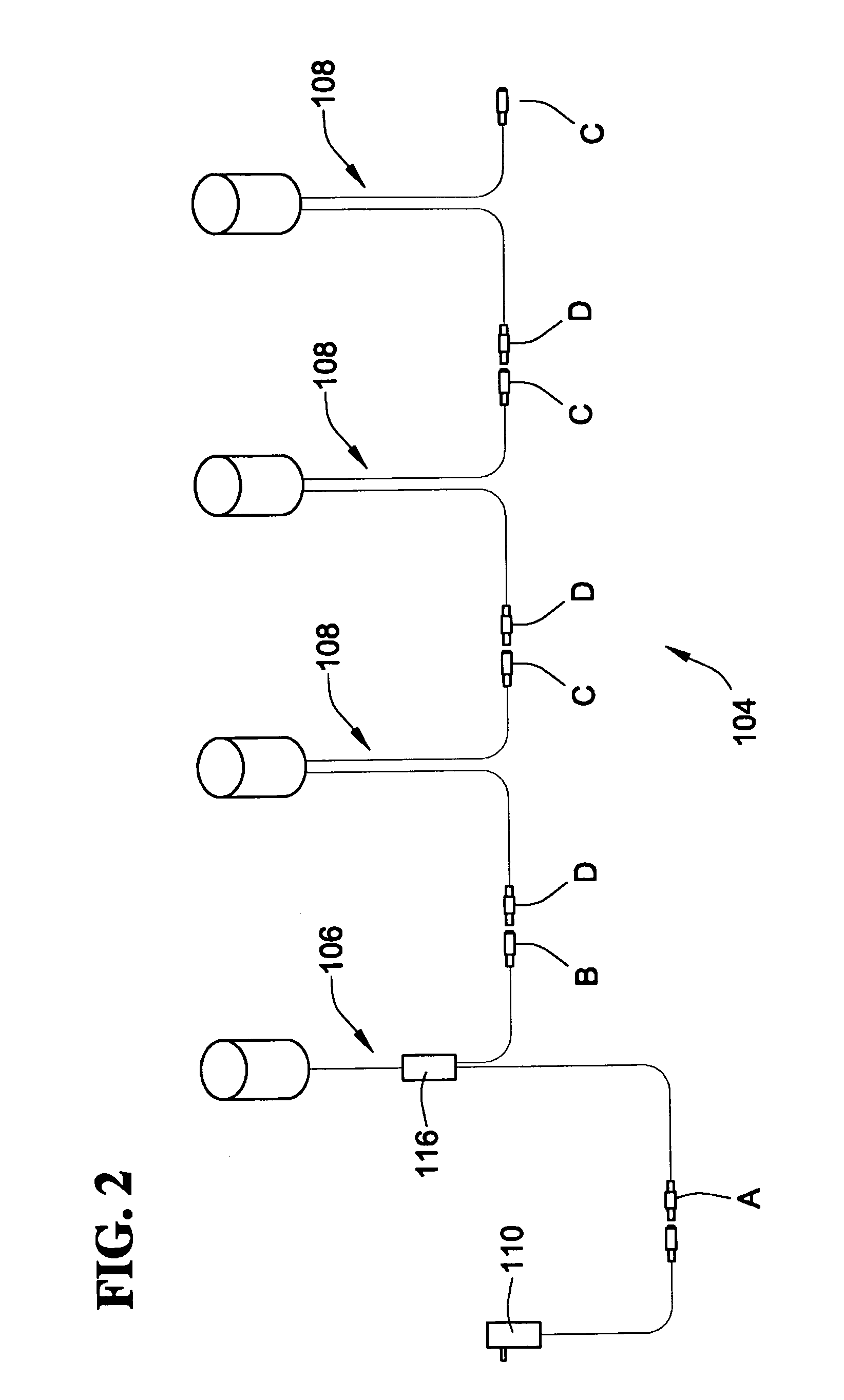

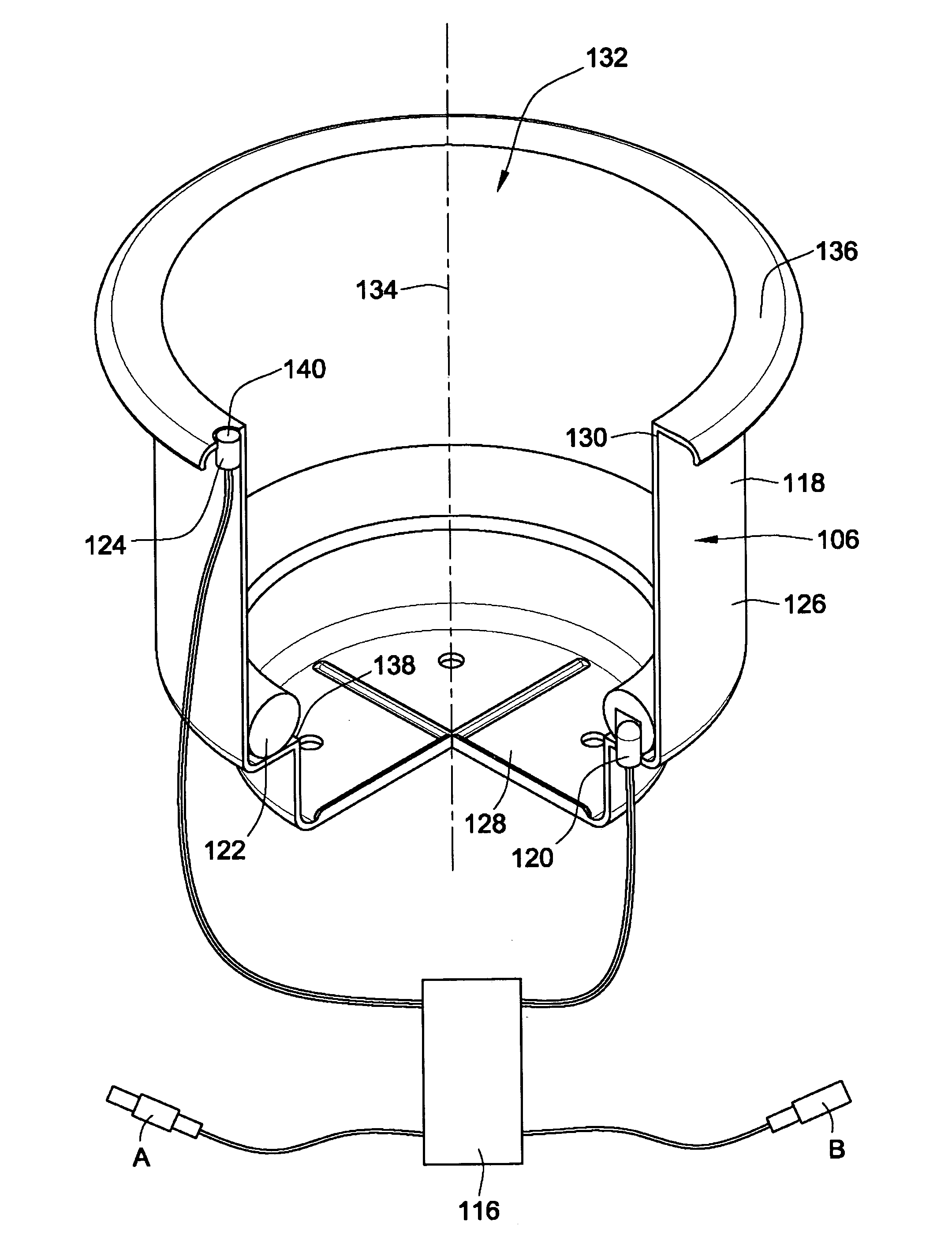

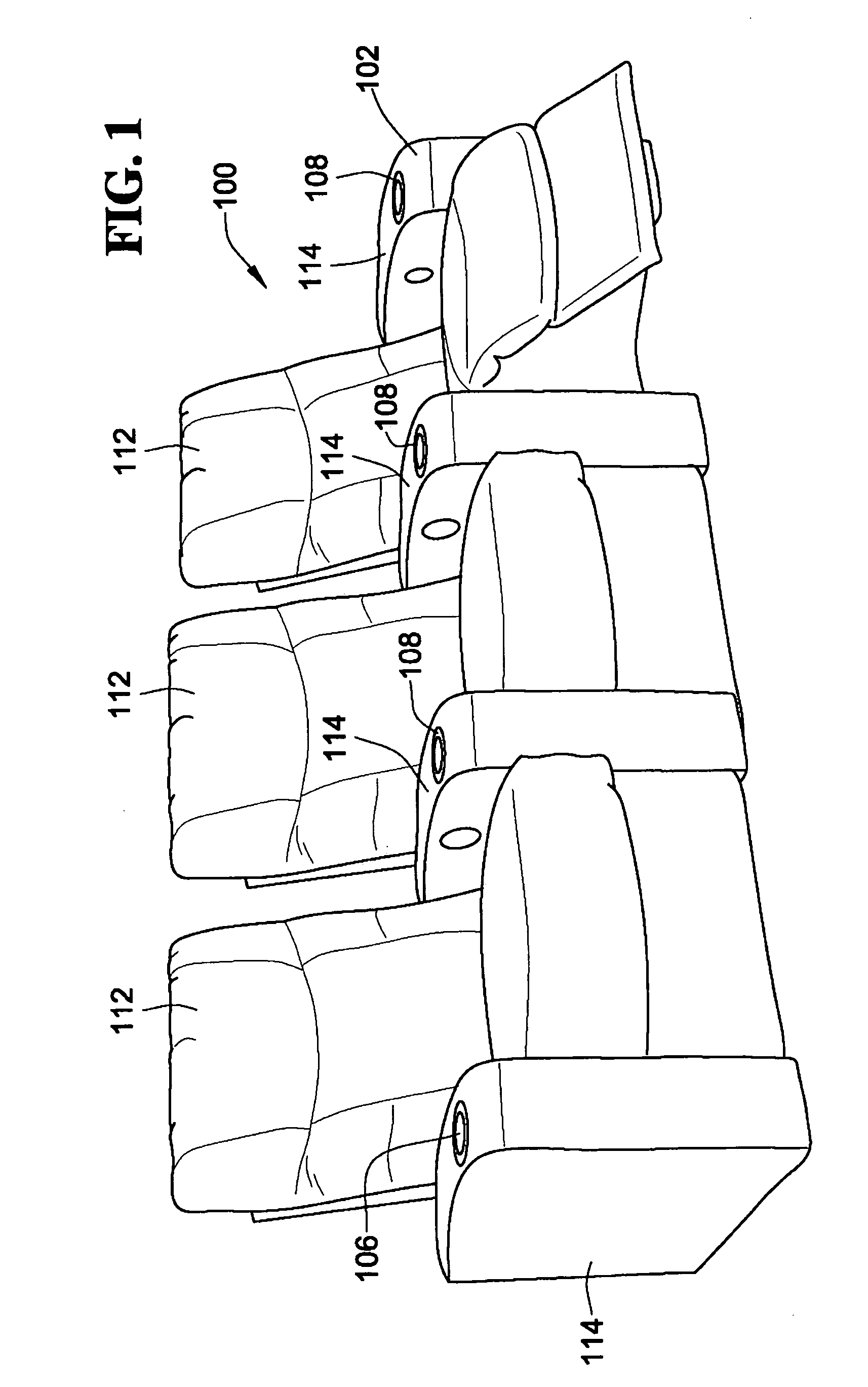

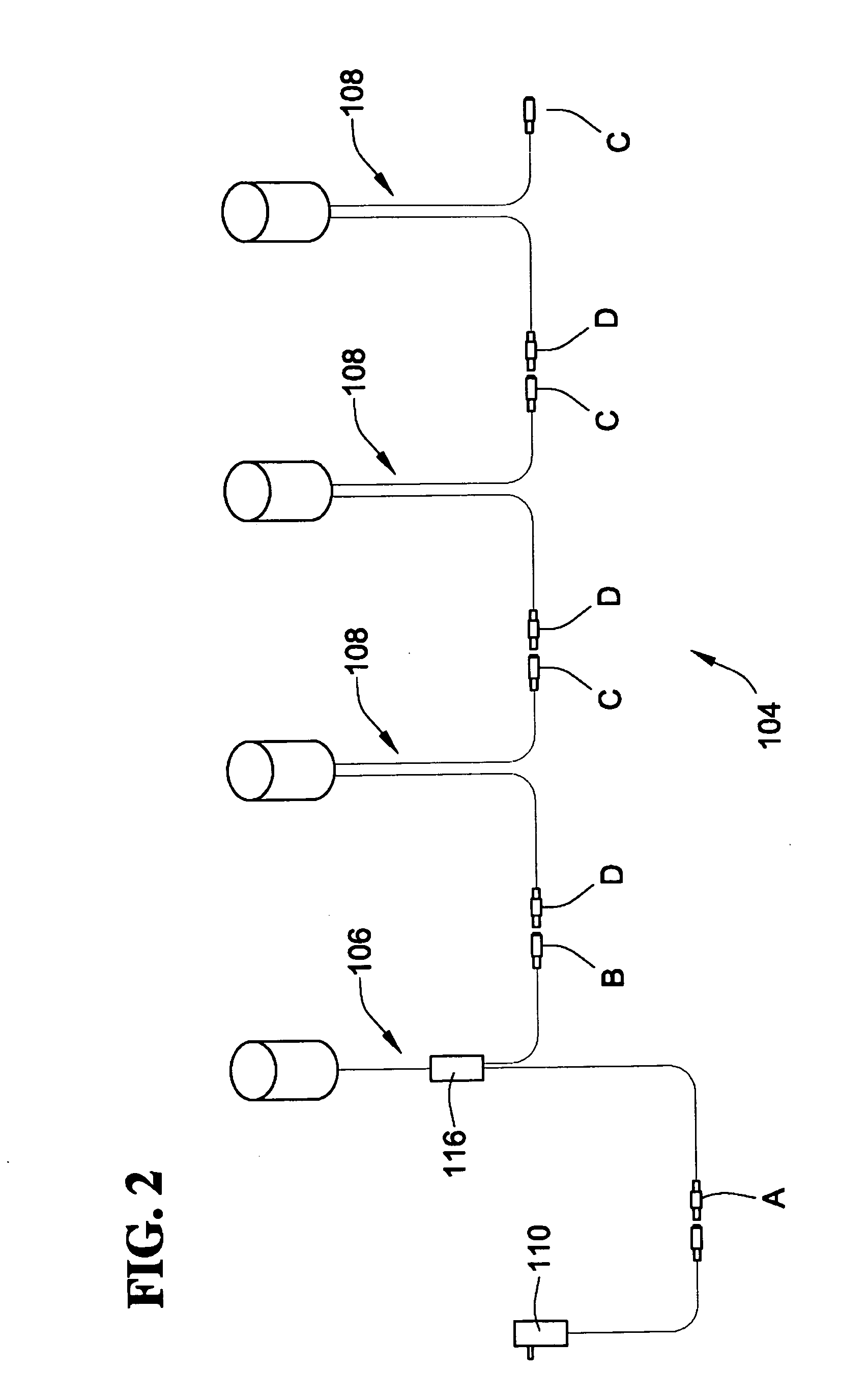

Lighted cup holder for seating arrangements

ActiveUS7766293B2Facilitates location and proper useConvenience to mergeVehicle seatsPoint-like light sourceEngineeringLight source

A method and apparatus include attaching a lighted cup holder to a seating arrangement. The lighted cup holder includes a cup holder body and a light-producing light source, with the cup holder body being attached to the seating arrangement and having a cup receptacle therein, the light-producing source being disposed within the cup receptacle for illuminating the receptacle. A light-sensitive element operatively connected to the light source selectively controls production of light by the light source in such a manner that illumination of the cup holder is provided only under conditions where visibility is reduced to the point that it becomes difficult to locate the cup holder. The light-sensitive element is mounted on a master lighted cup holder and controls illumination of the master lighted cup holder and one or more slave lighted cup holders operatively connected to the master lighted cup holder.

Owner:RAFFEL SYST

Spinal implant kit

A bone plate kit for stabilizing adjacent vertebrae or ends of a bone includes several bone plates of different sizes and several bone fasteners of the same or different sizes. The fasteners may have the same configuration or several different configurations. The fasteners may be coated with bone growth material. The plates have a span for extending across a discontinuity. The span has brackets for attaching to the bone. The brackets have countersunk apertures terminating through which bone screws are placed in the bone. An eccentric cam bore is located between the countersunk apertures and, upon rotation of an eccentric cam, wedge grip shoes are slid into the countersunk apertures and frictionally engage the spherical heads of the bone screws. To prevent back-out of the bone screws, the eccentric cam is locked into the wedge grip shoes.

Owner:SPINAL

Lighted cup holder for seating arrangements

ActiveUS20070247836A1Precise positioningFacilitates proper useVehicle seatsPoint-like light sourceVisibilityEngineering

A method and apparatus include attaching a lighted cup holder to a seating arrangement. The lighted cup holder includes a cup holder body and a light-producing light source, with the cup holder body being attached to the seating arrangement and having a cup receptacle therein, the light-producing source being disposed within the cup receptacle for illuminating the receptacle. A light-sensitive element operatively connected to the light source selectively controls production of light by the light source in such a manner that illumination of the cup holder is provided only under conditions where visibility is reduced to the point that it becomes difficult to locate the cup holder. The light-sensitive element is mounted on a master lighted cup holder and controls illumination of the master lighted cup holder and one or more slave lighted cup holders operatively connected to the master lighted cup holder.

Owner:RAFFEL SYST

Customizable metadata merging framework

ActiveUS20050149583A1Convenience to mergeData processing applicationsDigital data information retrievalDatabase objectAction plan

One embodiment of the present invention provides a system that facilitates merging different versions of a database object. During operation, the system receives metadata associated with a first version of a database object and a second version of the database object. The system then compares metadata associated with the first version with metadata associated with the second version to create a difference report. Next, the system uses the different report to create an action plan that specifies how to merge the metadata associated with the first and second versions of the metadata object.

Owner:ORACLE INT CORP

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com