Patents

Literature

65results about How to "Minimizing amount of data" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

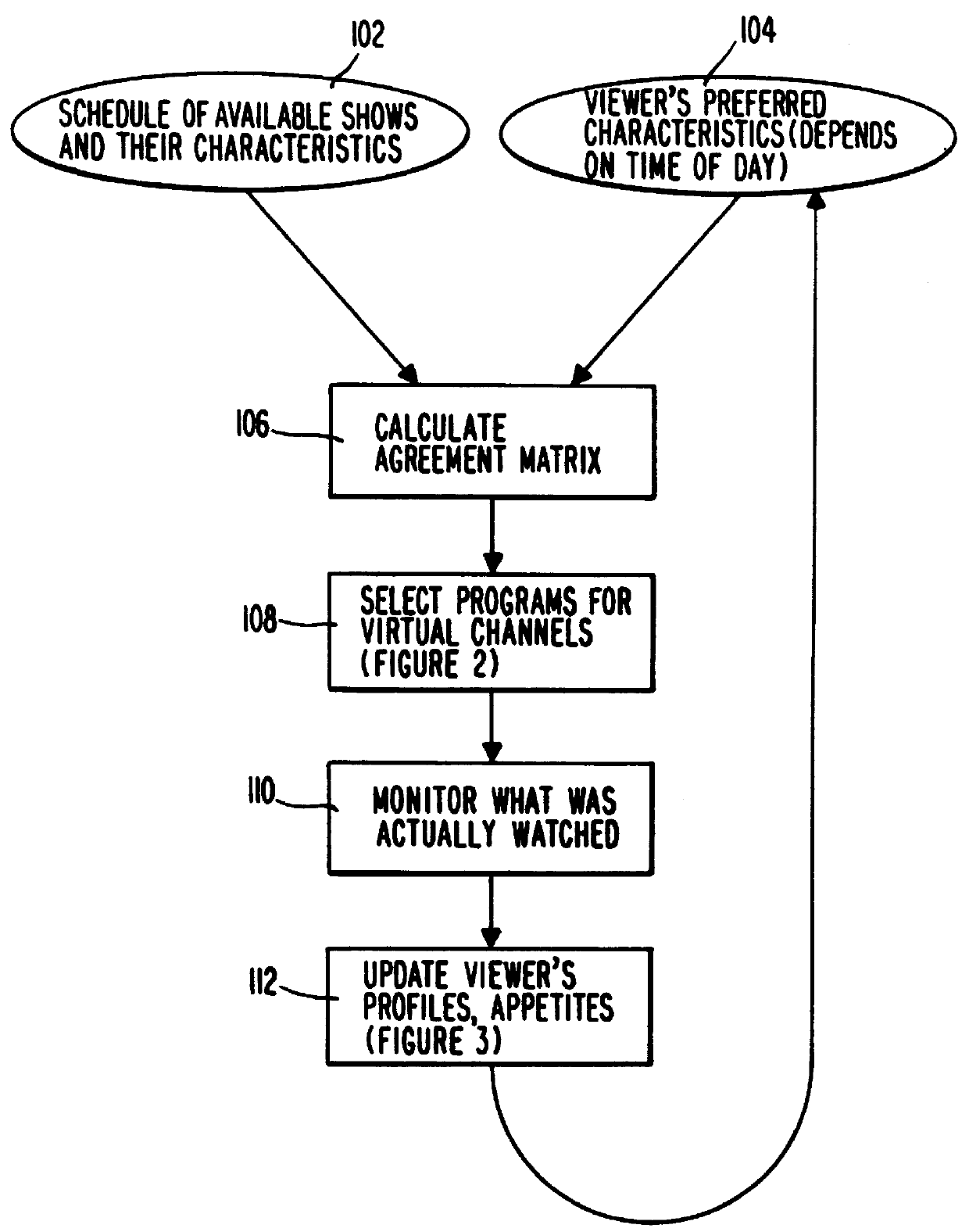

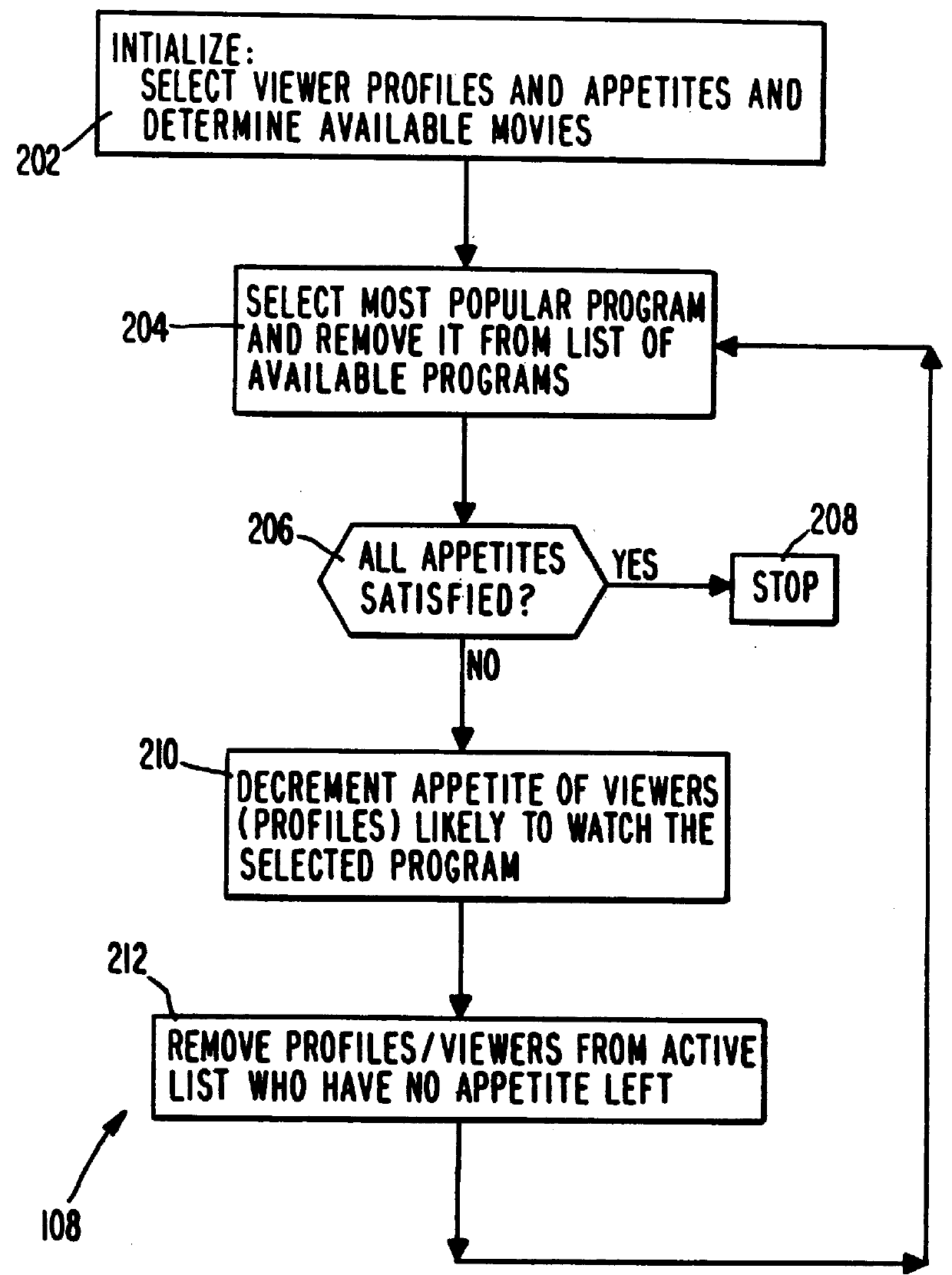

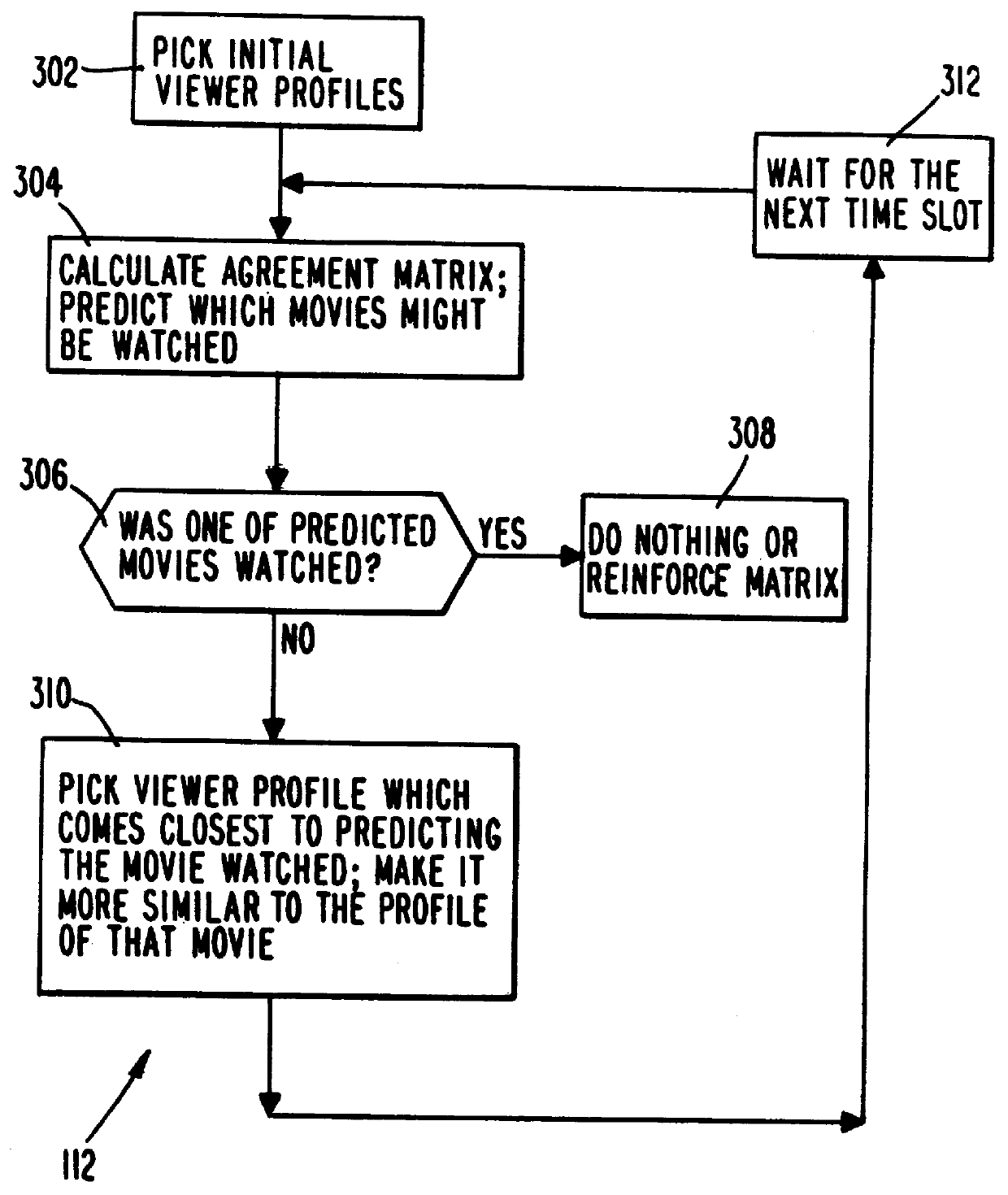

System and method for scheduling broadcast of and access to video programs and other data using customer profiles

InactiveUS6088722AMinimize memory requirementFacilitate text retrievalTelevision system detailsAnalogue secracy/subscription systemsTelevision systemData source

PCT No. PCT / US95 / 15429 Sec. 371 Date Dec. 24, 1997 Sec. 102(e) Date Dec. 24, 1997 PCT Filed Nov. 29, 1995 PCT Pub. No. WO96 / 17467 PCT Pub. Date Jun. 6, 1996A system and method for scheduling the receipt of desired movies and other forms of data from a network, which simultaneously distributes many sources of such data to many customers, as in a cable television system. Customer profiles are developed for the recipient describing how important certain characteristics of the broadcast video program, movie, or other data are to each customer. From these profiles, an "agreement matrix" is calculated by comparing the recipient's profiles to the actual profiles of the characteristics of the available video programs, movies, or other data. The agreement matrix thus characterizes the attractiveness of each video program, movie, or other data to each prospective customer. "Virtual" channels are generated from the agreement matrix to produce a series of video or data programming which will provide the greatest satisfaction to each customer. Feedback paths are also provided so that the customer's profiles and / or the profiles of the video programs or other data may be modified to reflect actual usage, and so that the data downloaded to the customer's set top terminal may be minimized. Kiosks are also developed which assist customers in the selection of videos, music, books, and the like in accordance with the customer's objective profiles.

Owner:FRED HERZ PATENTS

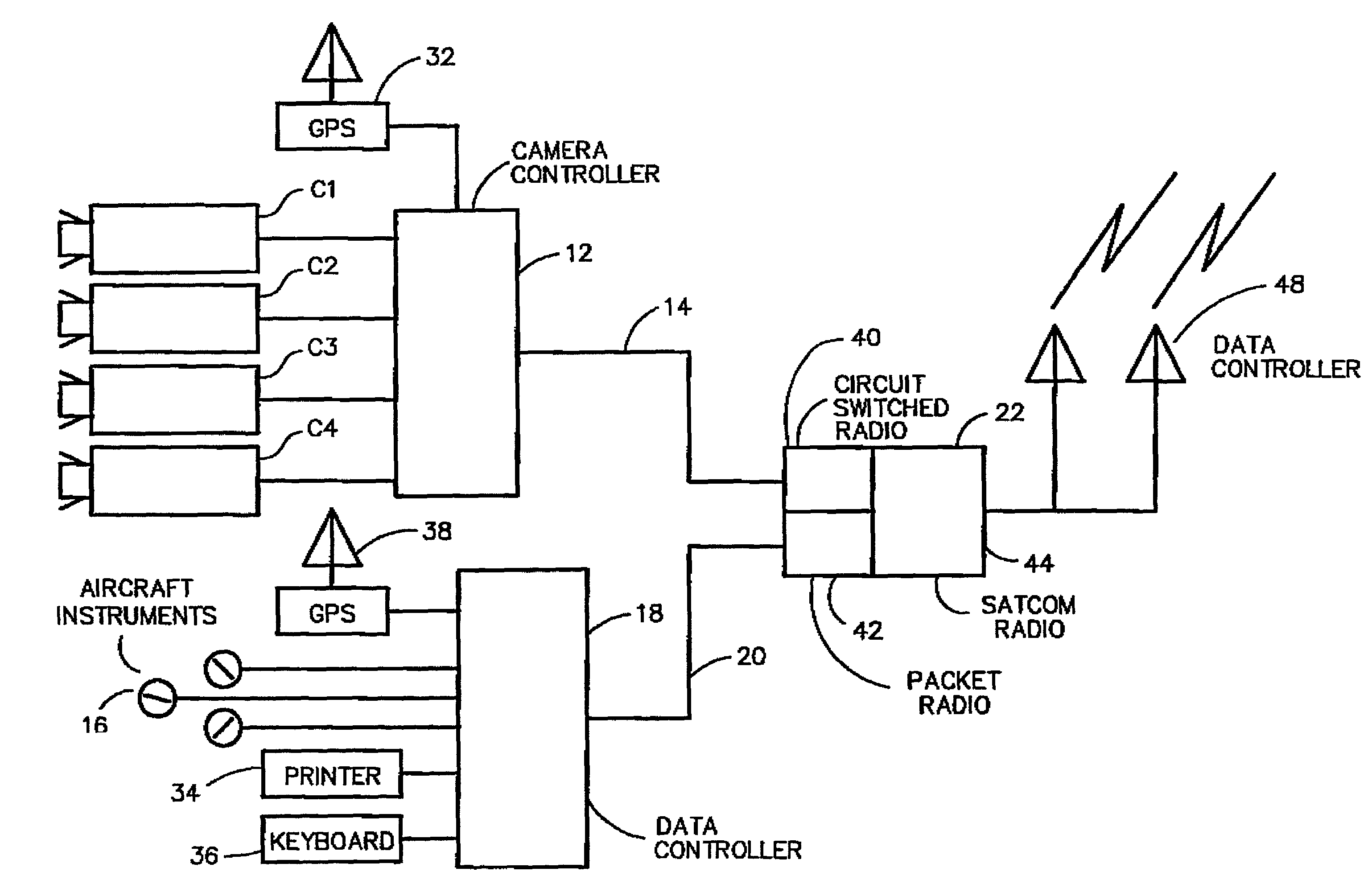

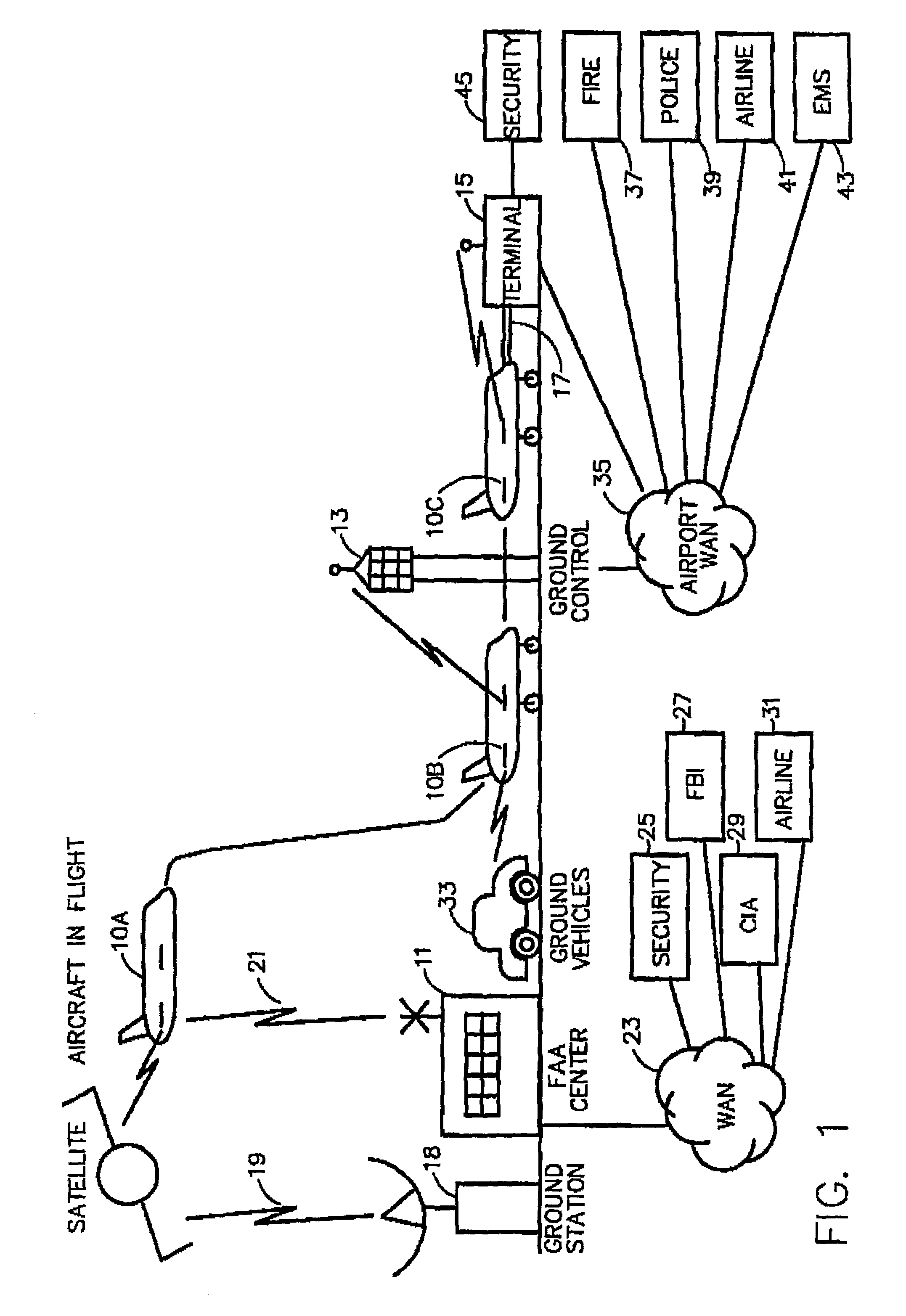

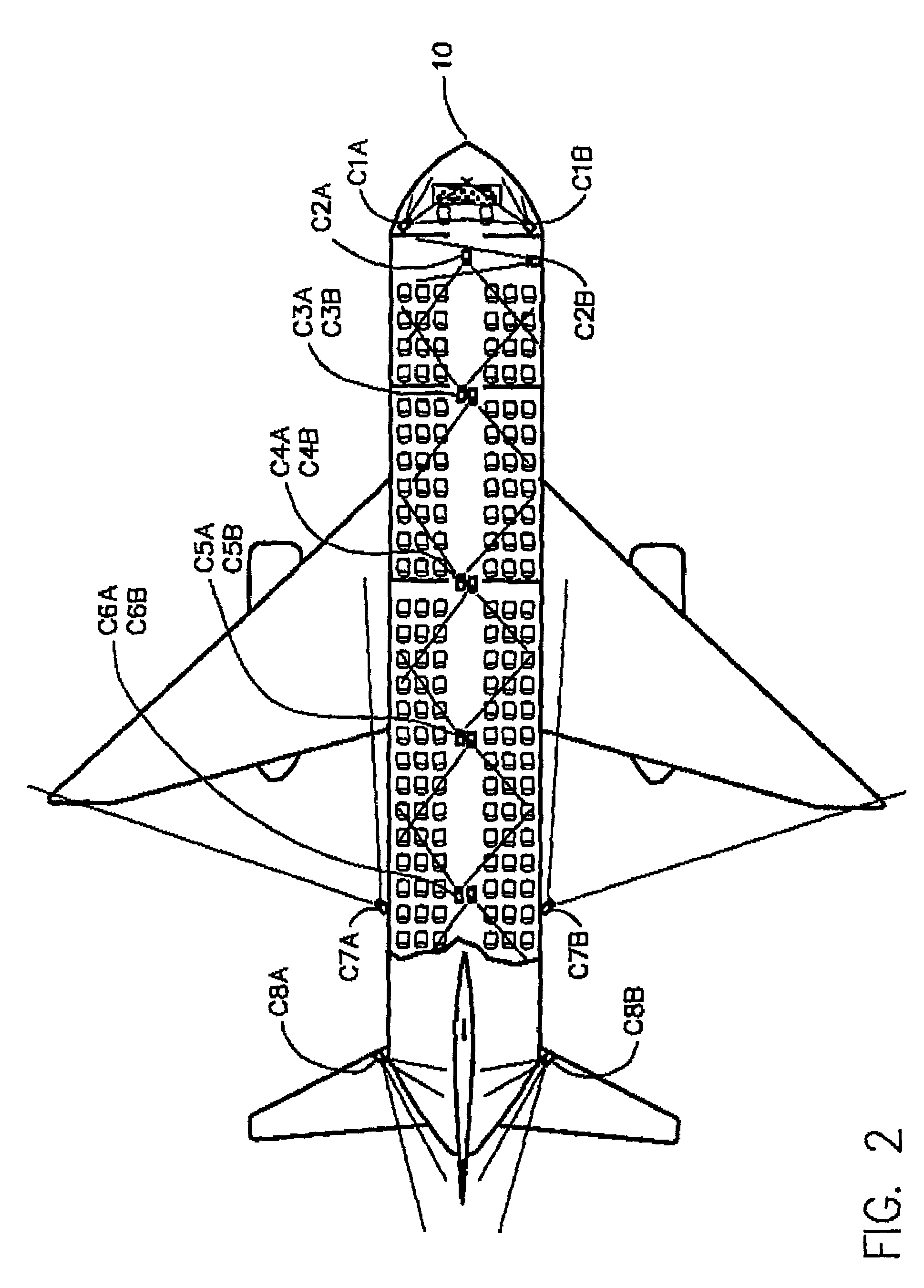

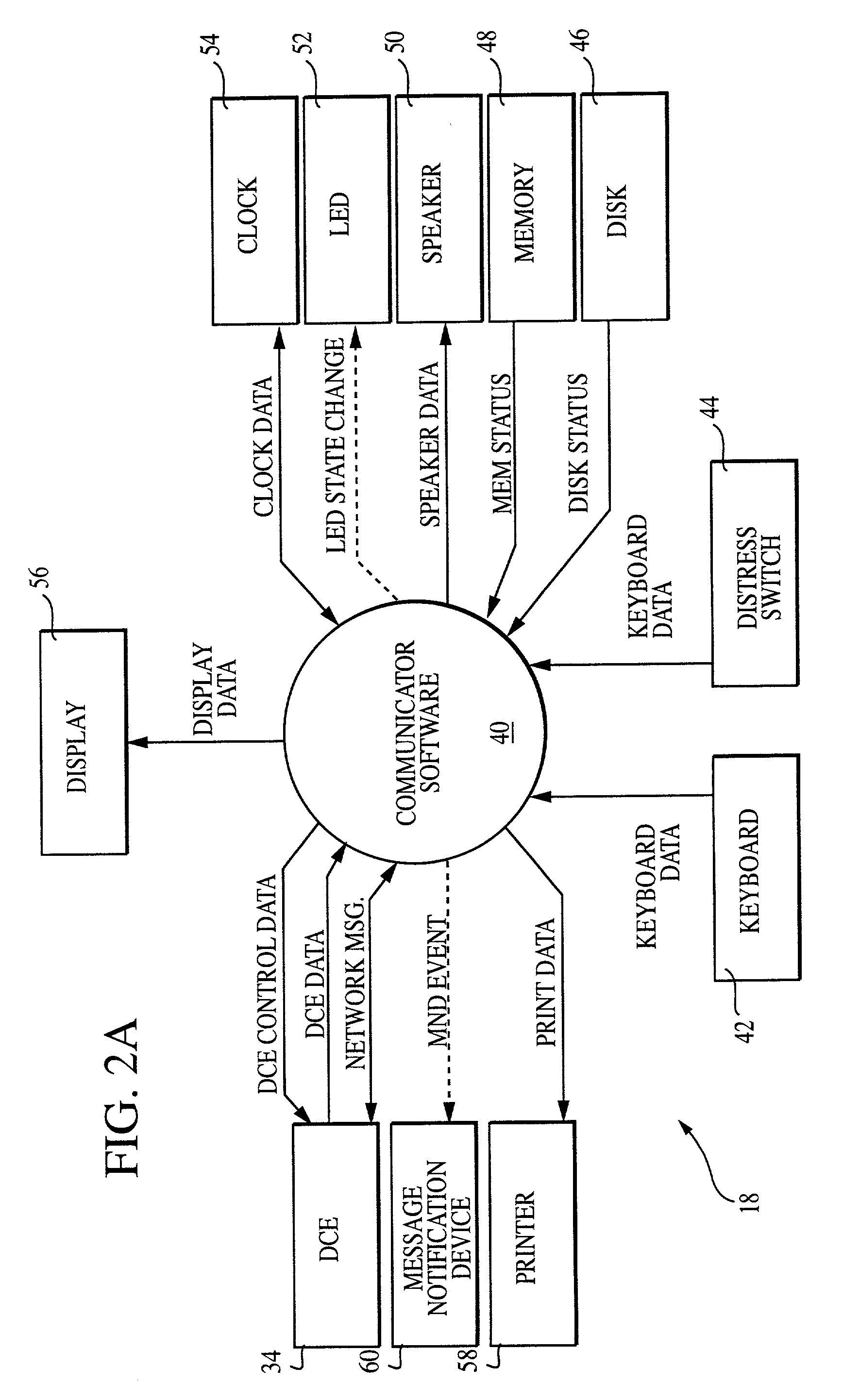

Comprehensive multi-media surveillance and response system for aircraft, operations centers, airports and other commercial transports, centers and terminals

InactiveUS7131136B2Minimizing amount of dataReduce data volumeAnalogue computers for trafficColor television detailsSurveillance cameraGround station

A data collection and distribution system for monitoring aircraft in flight, on the ground and at the gate or terminal for monitoring critical and catastrophic events, managing the emergency during such an event, and for investigating the event. The system generates, transmits and collects critical data generated by monitoring equipment onboard an aircraft or other commercial transport and selectively displays the data on a cockpit display console as well as for downloading, transmitting and displaying data at external monitoring and response stations, including fixed ground stations, roving ground stations and chase aircraft or vehicles. Digital surveillance information is collected, processed, dispatched, and log via remote control and access. The system includes a variety of system appliances such as surveillance cameras, sensors, detectors, and panic buttons and accommodates legacy equipment. Within the commercial transport, the system maybe hardwired or may use wireless transmission and receiving systems.

Owner:PR NEWSWIRE

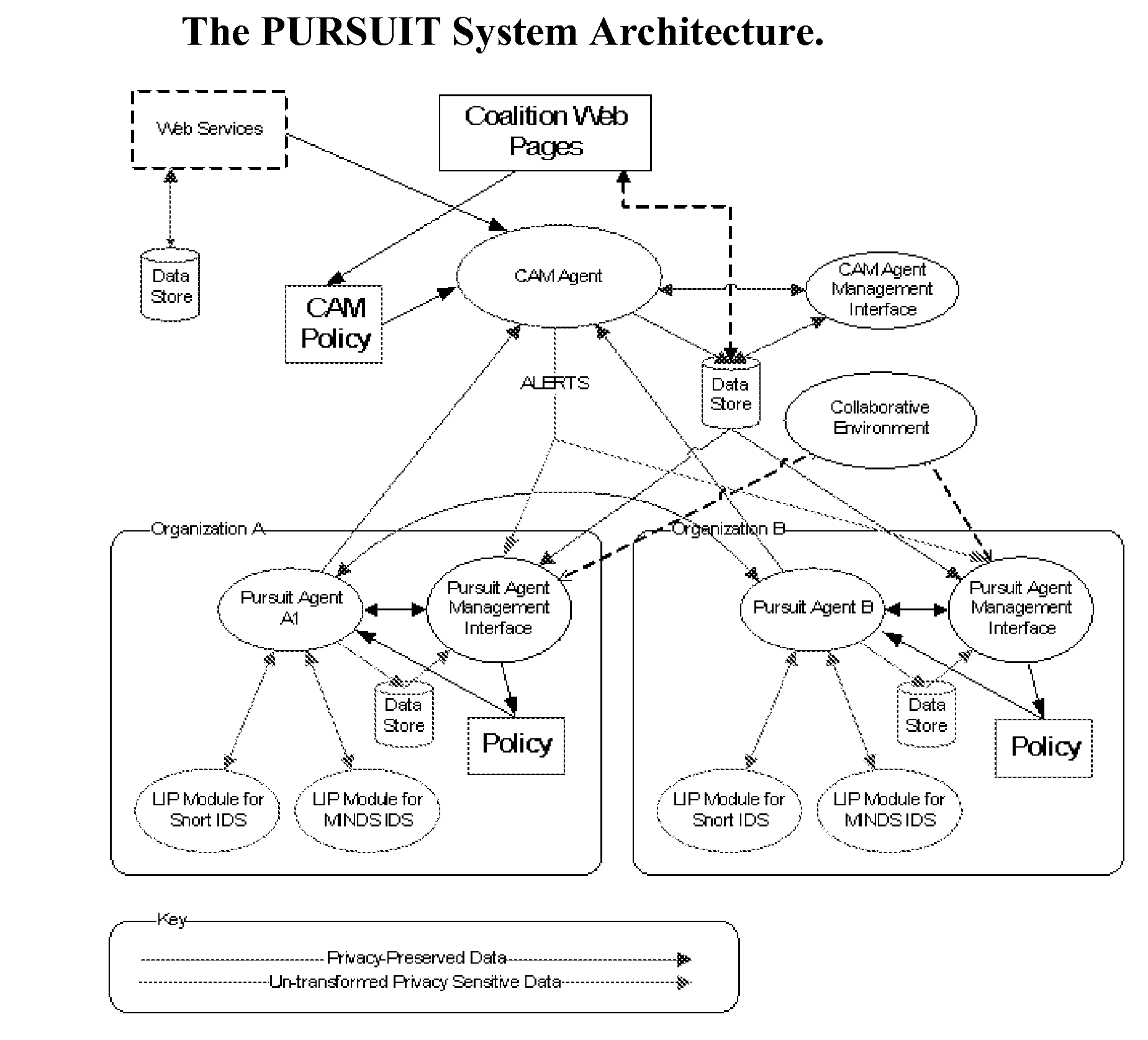

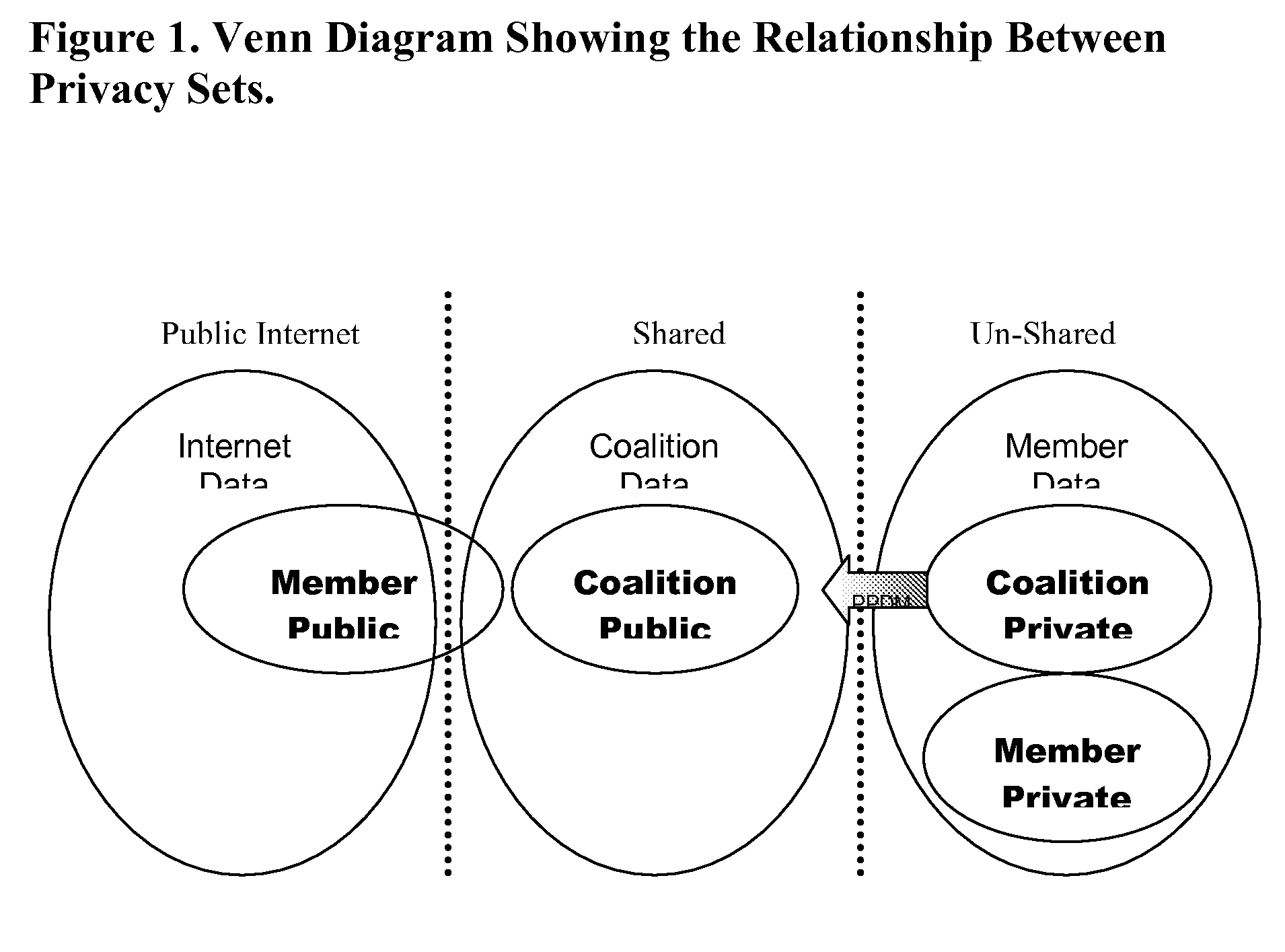

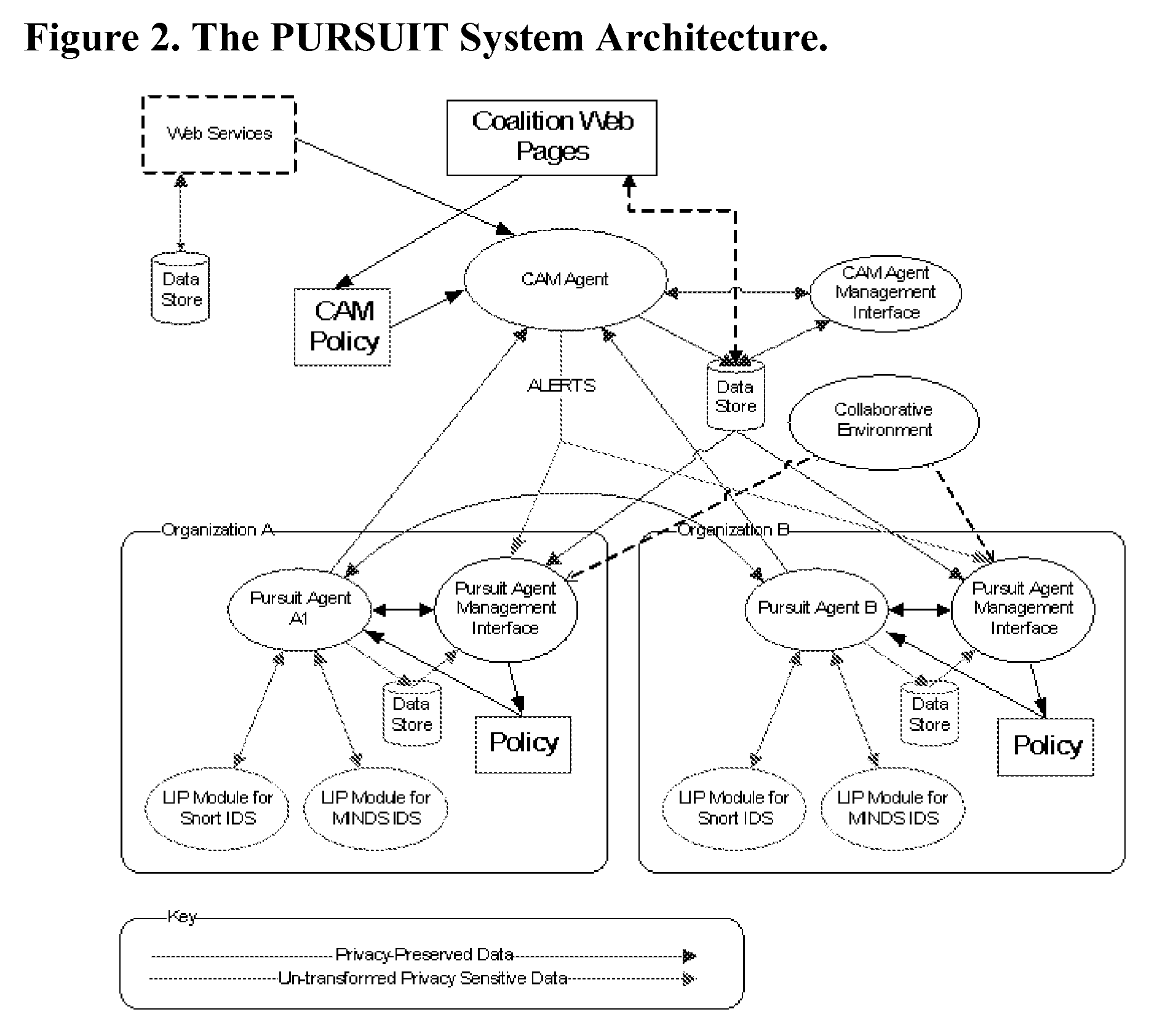

Multi-agent, distributed, privacy-preserving data management and data mining techniques to detect cross-domain network attacks

InactiveUS20100017870A1Fast in response timeMinimize amount of dataMemory loss protectionError detection/correctionGlobal networkMonitoring data

The present invention is a method and a system that uses privacy-preserving distributed data stream mining algorithms for mining continuously generated data from different network sensors used to monitor data communication in a computer network. The system is designed to compute global network-threat statistics by combining the output of the network sensors using privacy-preserving distributed data stream mining algorithms.

Owner:AGNIK

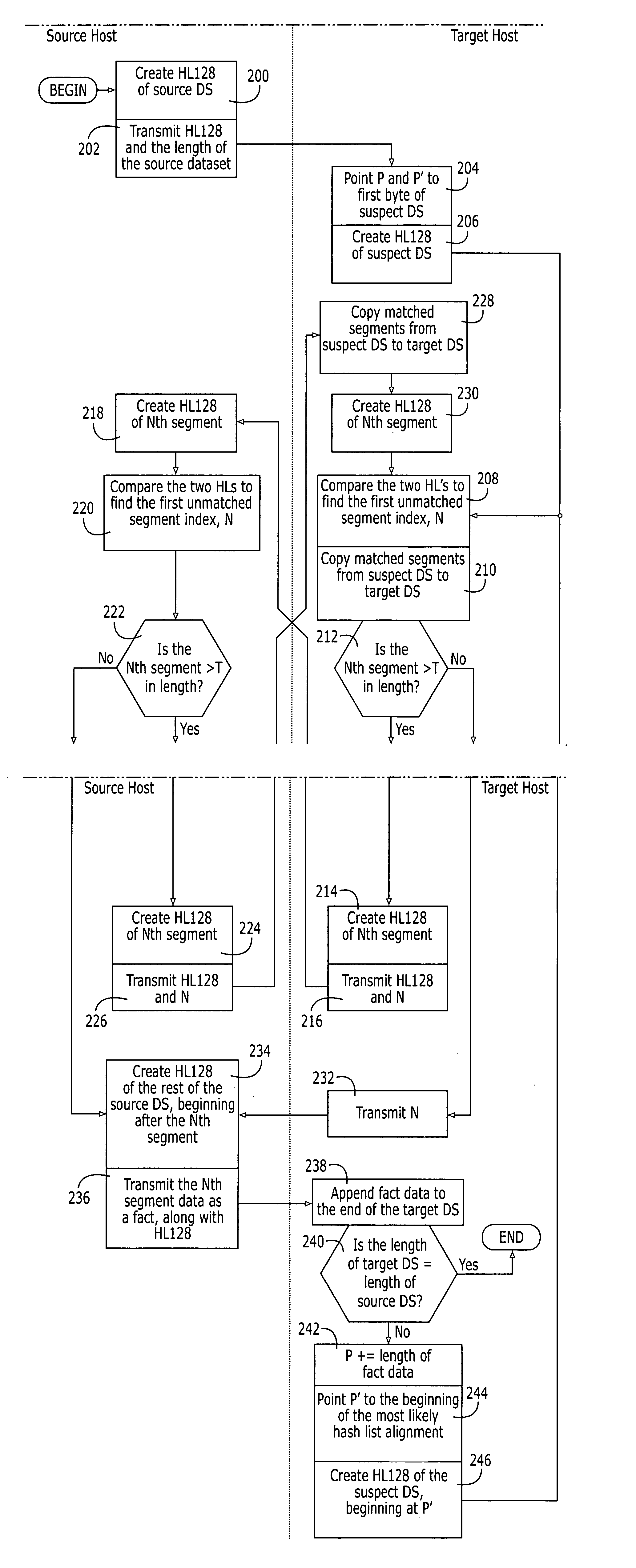

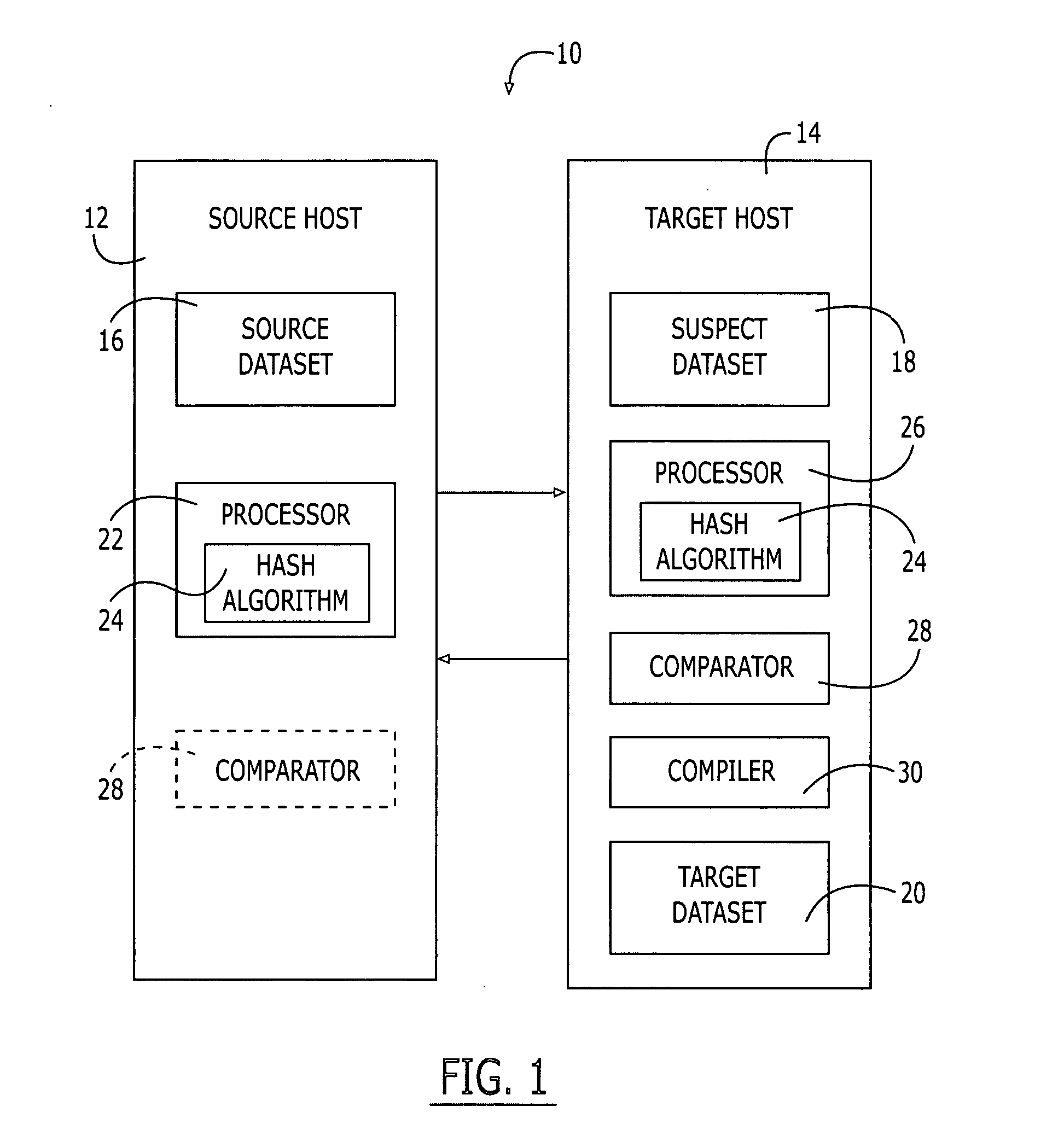

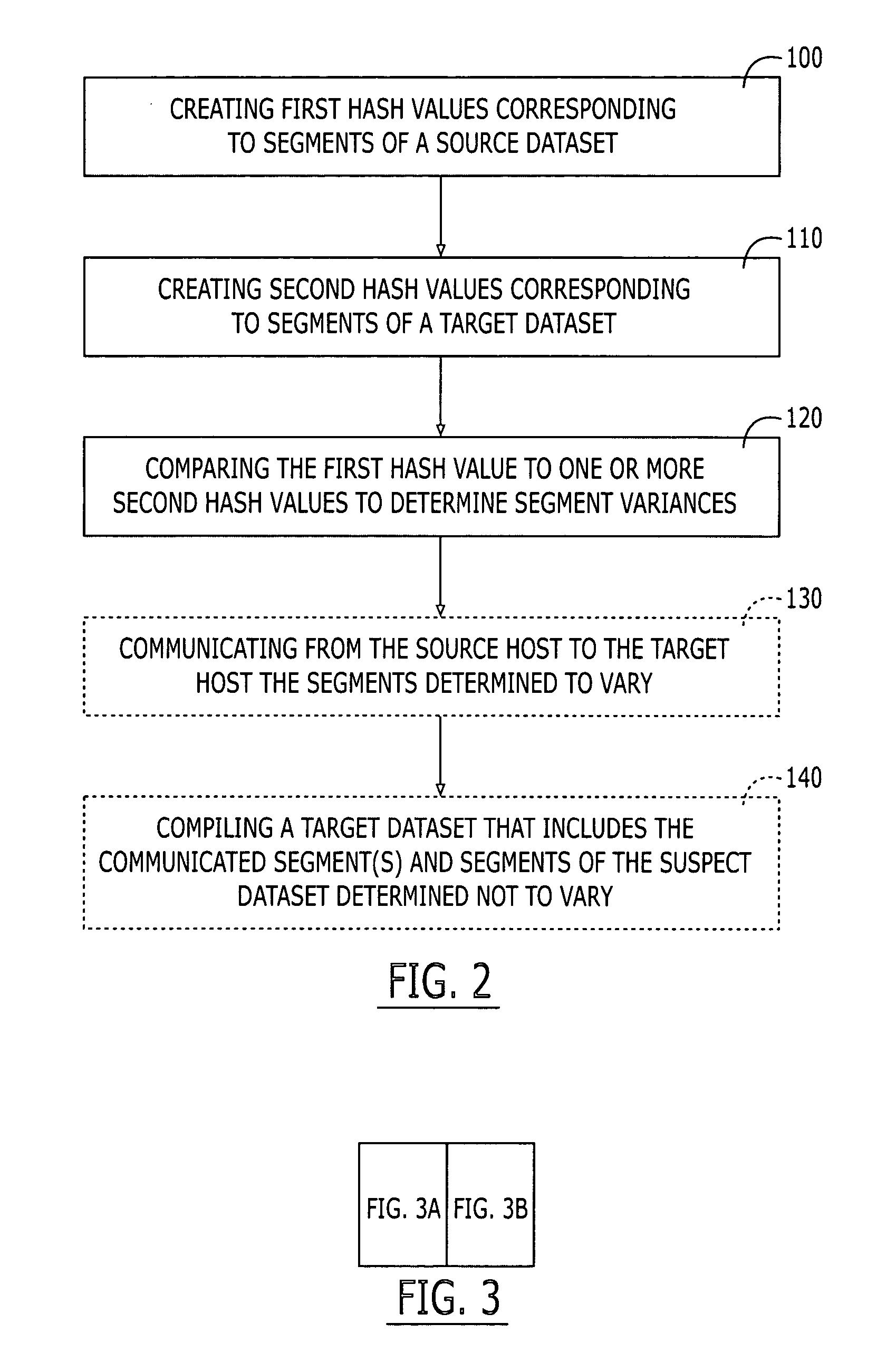

Systems and methods for expedited data transfer in a communication system using hash segmentation

InactiveUS20050004954A1Reduce timeEffective dataStructured data retrievalSpecial data processing applicationsData transmissionData file

The present invention provides for an improved method and system for determining differences in data sets or data files, expedited data transfer and data reconciliation in a communication network using hash segmentation processing. The system and method provides for an efficient means of communicating updated files, new revisions or verifying files between a source host and a target host. By implementing hash segmentation processing, and in many embodiments iterative hash segmentation processing, the updates within the files can be isolated for the purpose of minimizing the amount of data communicated from the source host to the target host. The system and methods provide for the transfer of data between two hosts in instances in which neither host is aware of the revision that exists on the other host. The hash segmentation process may implement a logarithmic hash approach or a sliding linear hash approach.

Owner:HAND HELD PRODS

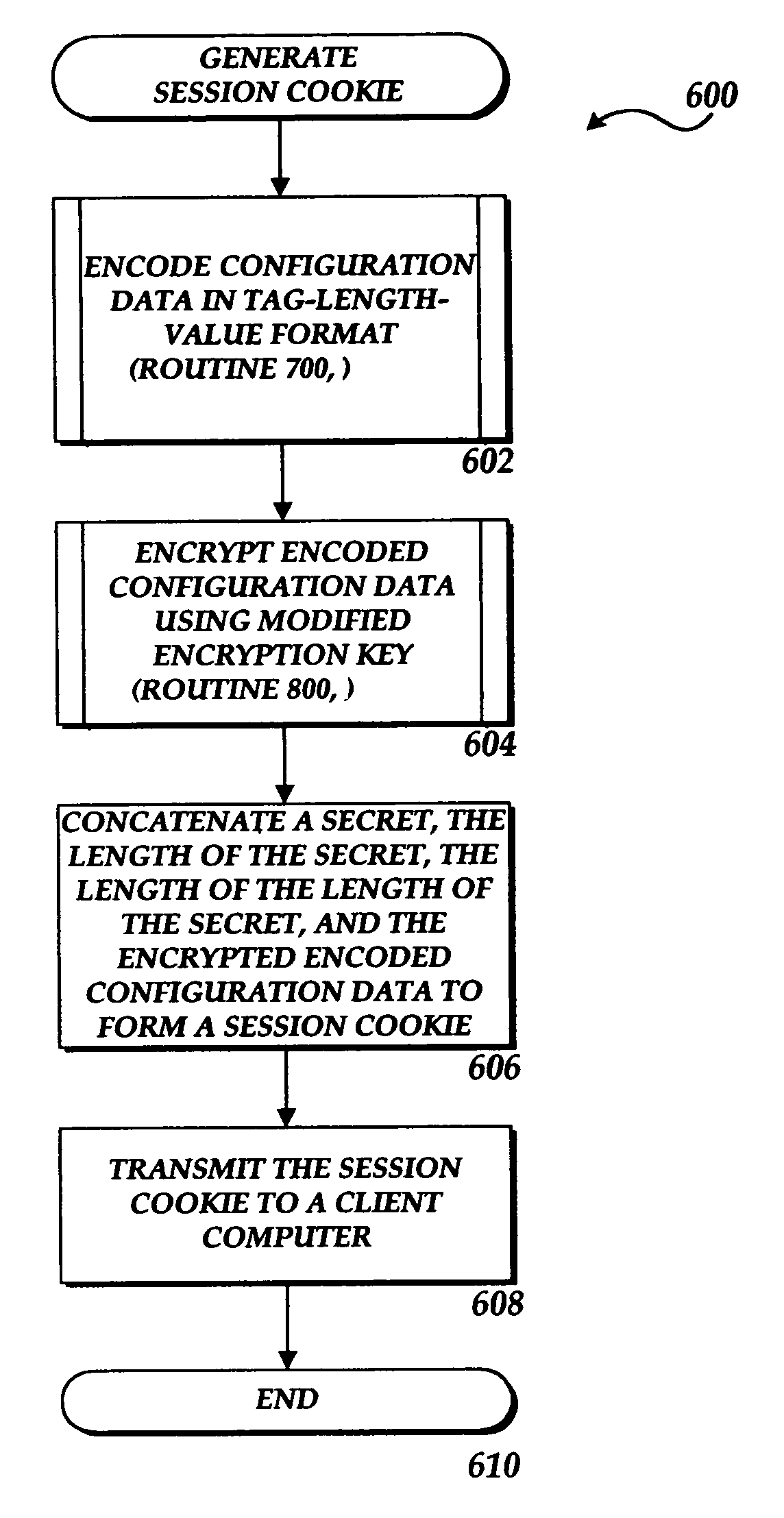

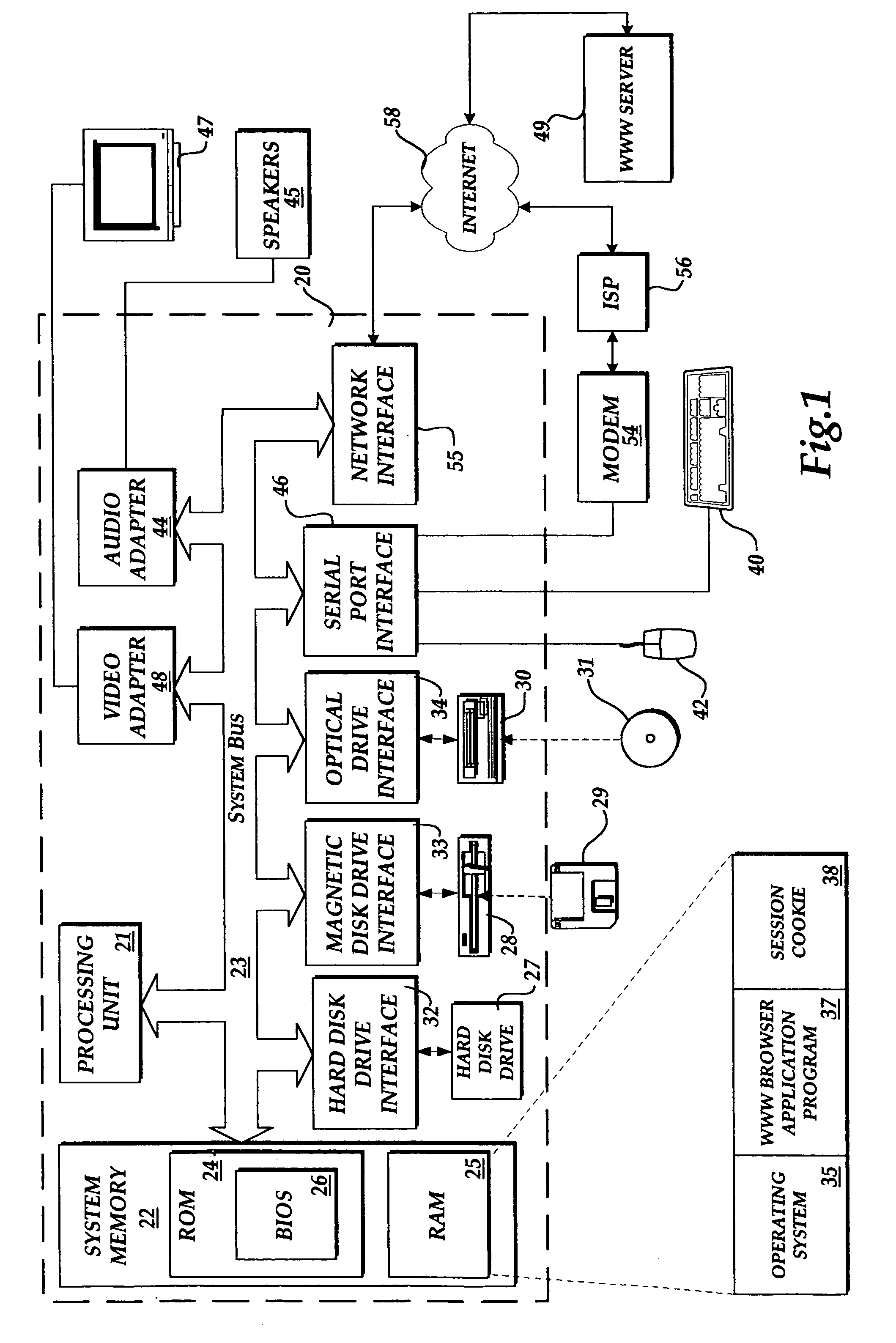

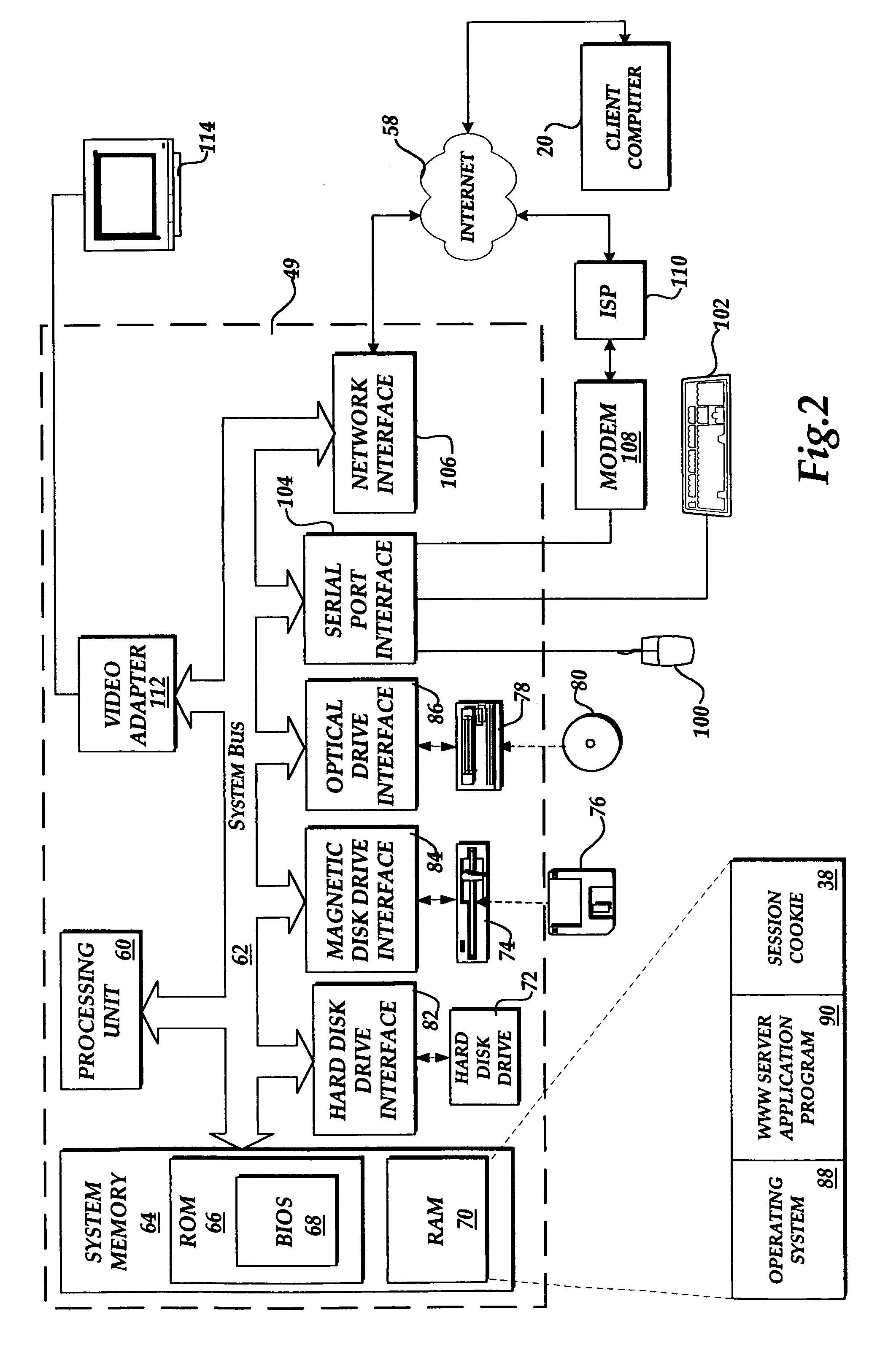

Method and apparatus for encoding and storing session data

InactiveUS7010605B1Minimizing amount of dataQuantity maximizationMultiple digital computer combinationsElectric digital data processingClient-sideEncryption

Session data is encoded in a tag-length-value format and encrypted using a modified encryption key. A session cookie is then formed by concatenating the length of the length of the secret, the length of the secret, the secret itself, and the encoded and encrypted configuration data. The session cookie is transmitted from a server computer to a client computer, where it is stored.

Owner:MICROSOFT TECH LICENSING LLC

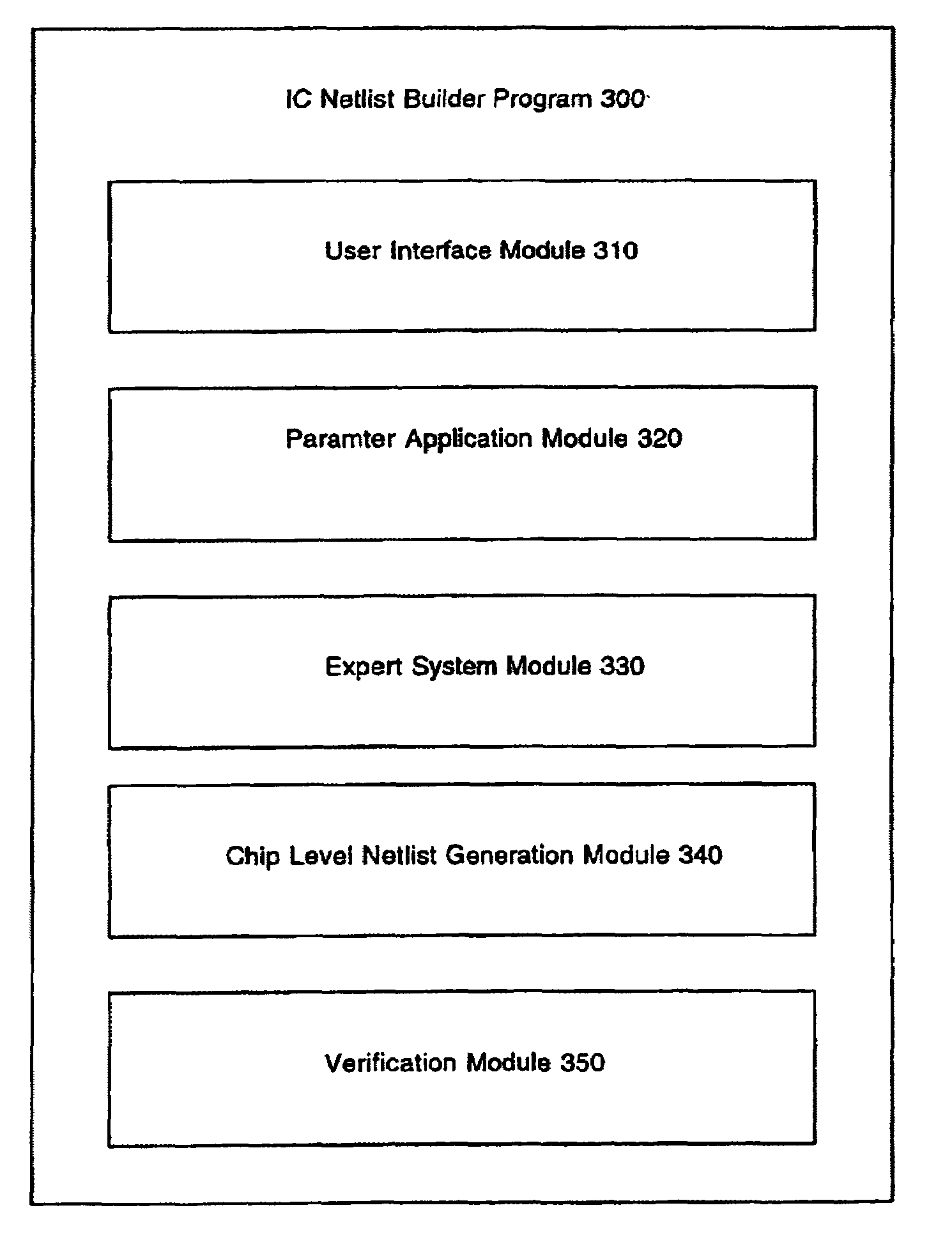

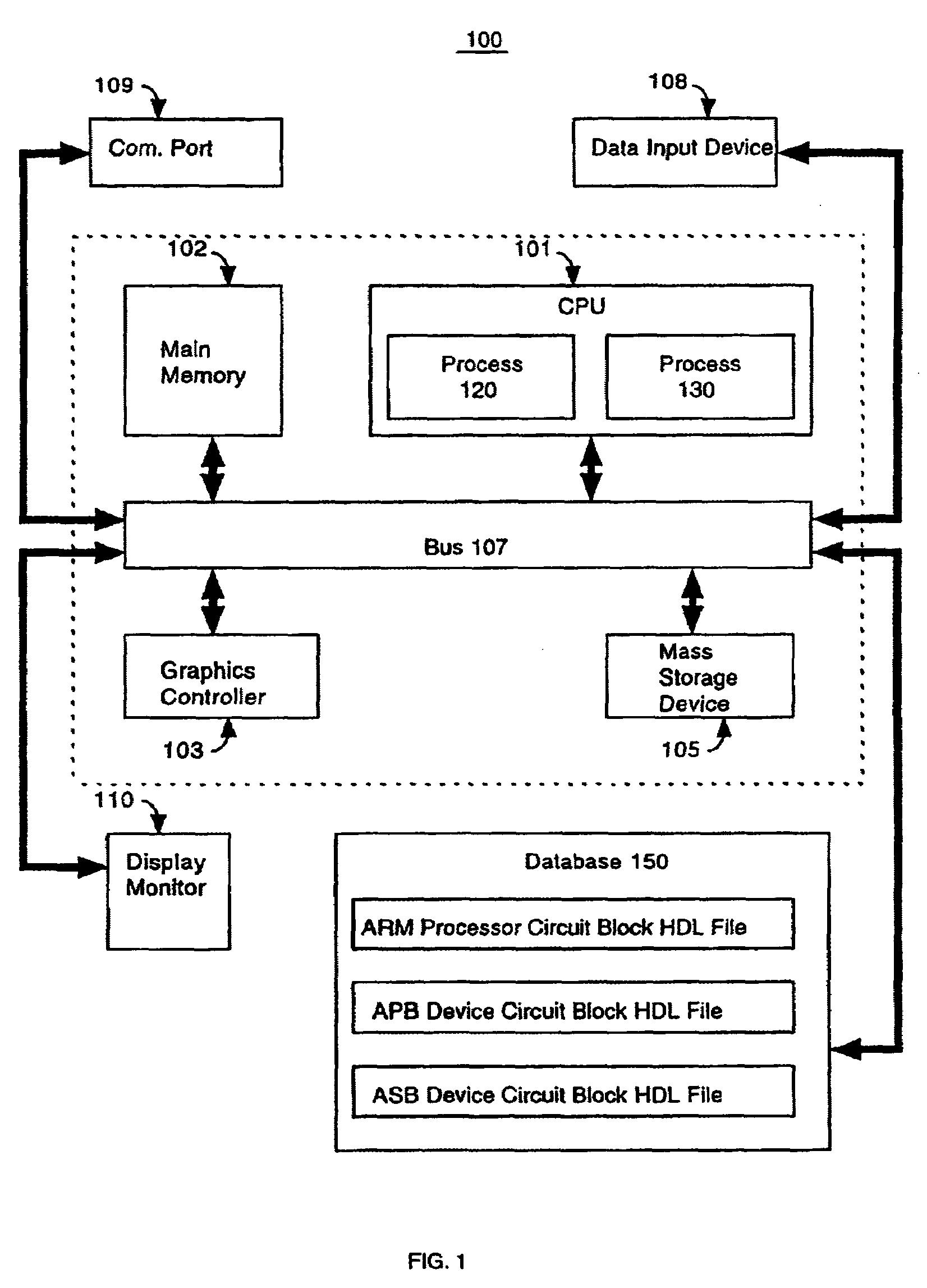

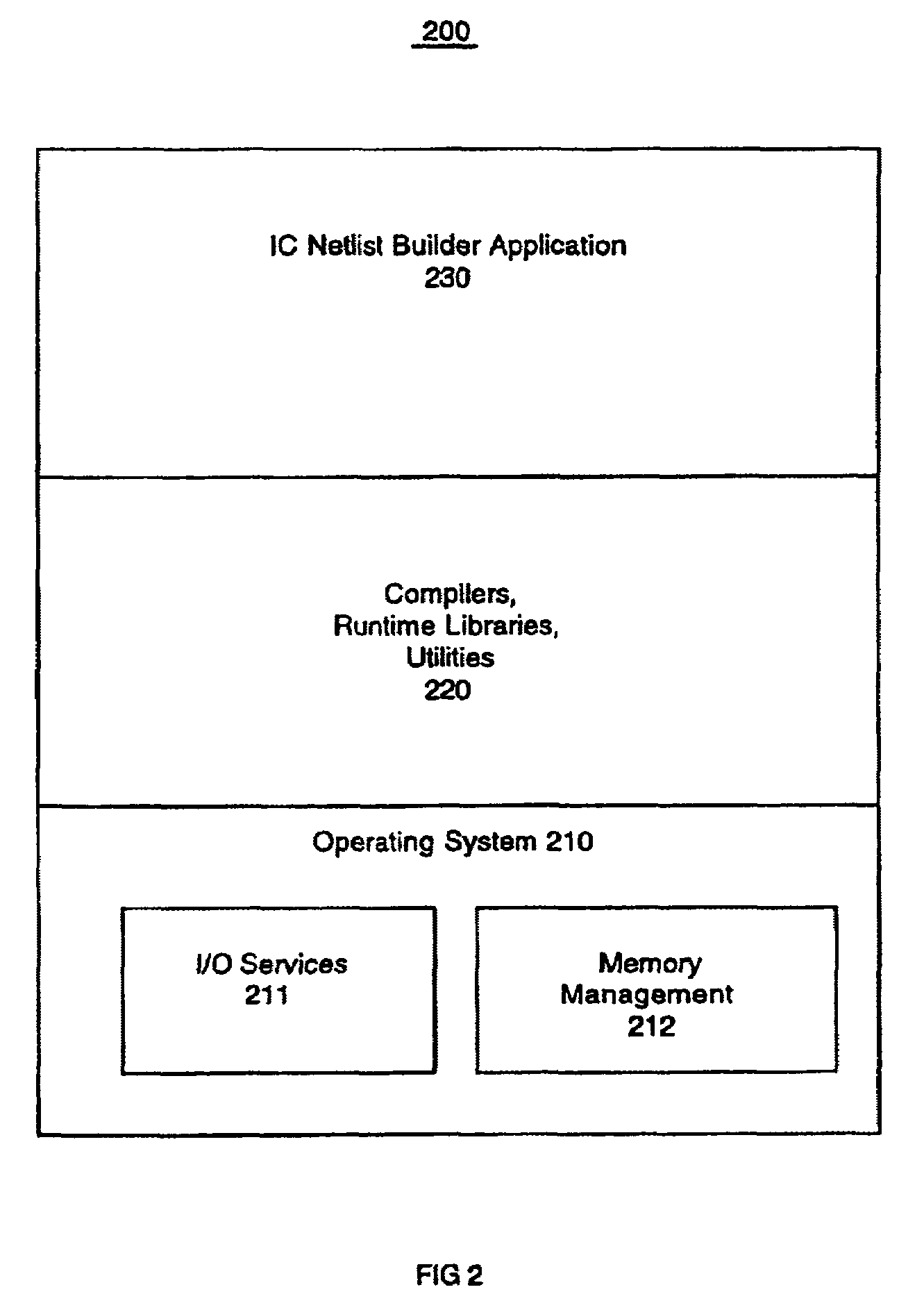

Computer system and method to dynamically generate system on a chip description files and verification information

InactiveUS7100133B1Facilitates efficient and effective creation and modification and verificationConvenience to mergeCAD circuit designSoftware simulation/interpretation/emulationComputer architectureTest platform

The present invention facilitates automation of system on a chip (SoC) design, manufacture and verification in a convenient and efficient manner. In one embodiment, a SoC netlist builder and verification computer system of the present invention includes a user interface module, a parameter application module, an expert system module and a chip level netlist generation module. The user interface module provides user friendly and convenient interfaces that facilitate easy entry and modification of user selections and parameters. The parameter application module interprets information supplied by the user module and the expert system module and creates directions (e.g., command lines) passed to other modules for execution. The expert system module analyzes information and automatically provides SoC building and verification data including automated addition of default architectural features, automated insertion of default parameters, and automated input of information to the verification module. The chip level netlist generation module automatically generates a chip level netlist, including the instantiation of internal IC devices and connections between the circuit blocks for internal signals. The verification module automatically generates a test bench and a logical verification environment including simulation models (e.g., a chip model and a system level model).

Owner:NXP BV

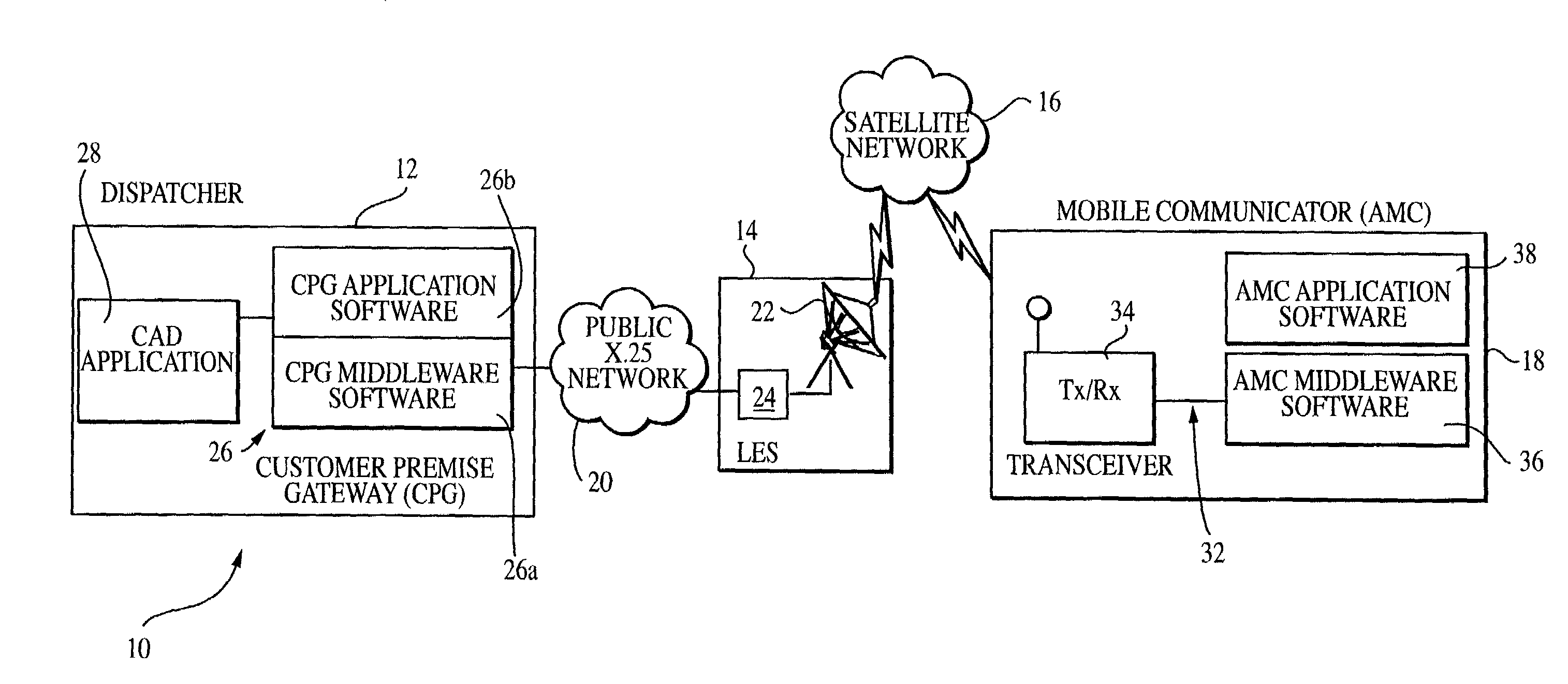

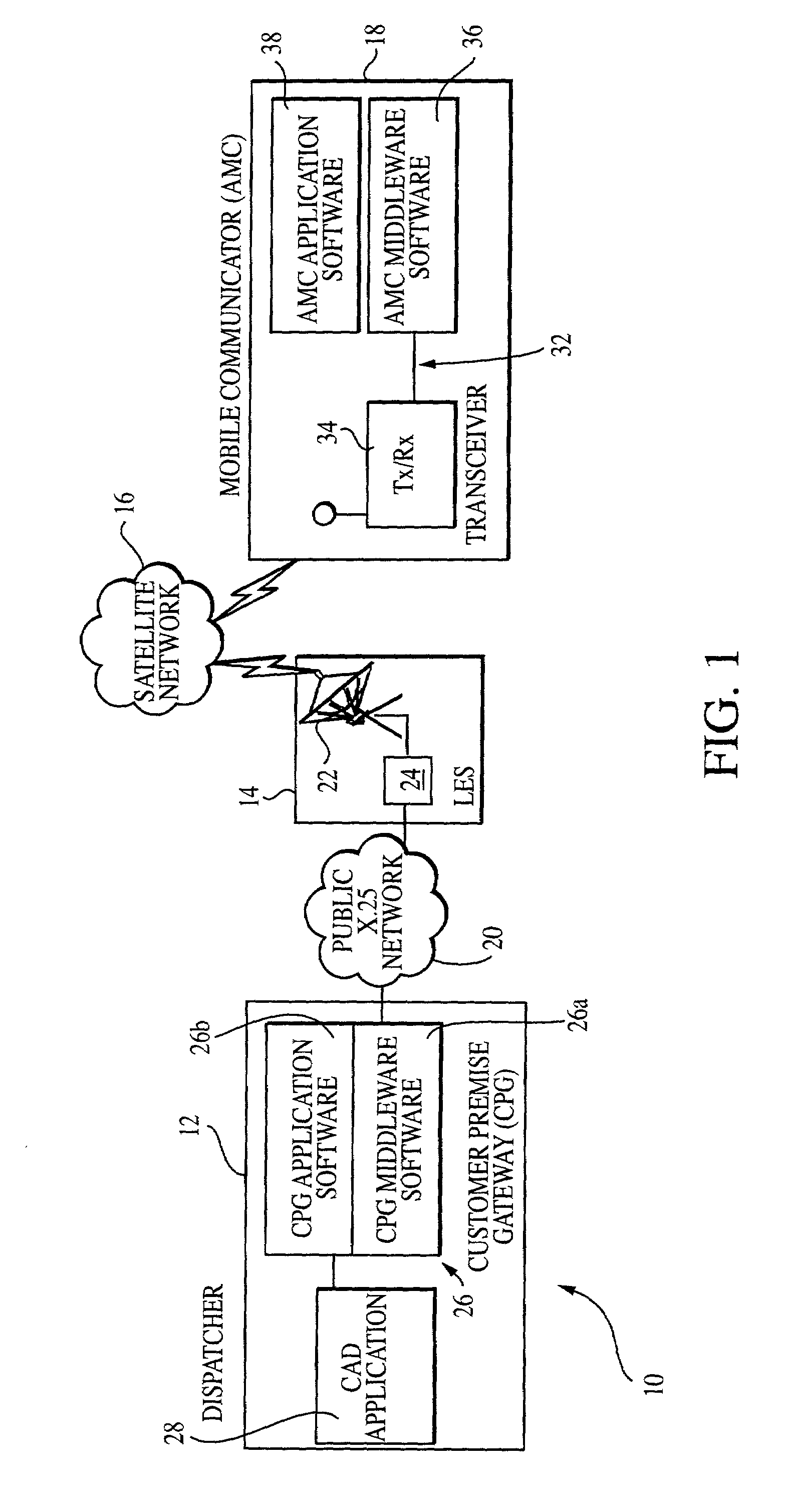

Mobile communications terminal for satellite communications system

InactiveUS6992991B2Minimizing amount of dataMultiplex system selection arrangementsBroadcast transmission systemsTransceiverSoftware system

A mobile communications system transporting messages between mobile terminals and a central control center using a satellite communications system. The central control center and the mobile terminals each store a plurality of message display forms each having a form identifier and a predetermimed display format. The message display forms are selected as templates for generating user messages including message data supplied at the originating station. The satellite messages transmit the user message by transmitting the message data and the form identifier of the corresponding selected message display form. The receiving station, upon receiving the satellite message, accesses the message display form from memory in response to the supplied form identifier, and combines the accessed message display form with the message data to recreate the user message. The mobile terminals are designed as low-cost data terminals requiring a minimum amount of memory. The mobile terminals include a satellite transceiver, a graphic user interface providing a display and accepting key inputs from the user, and a software system including an application layer providing all messaging functions for the user and a middleware layer controlling transport of messages between the application layer and the satellite transceiver. The application layer operates as an event-based state machine, and includes an event handler that controls the application layer operations in accordance with the processing capacity of the middleware layer.

Owner:ATC TECH LLC

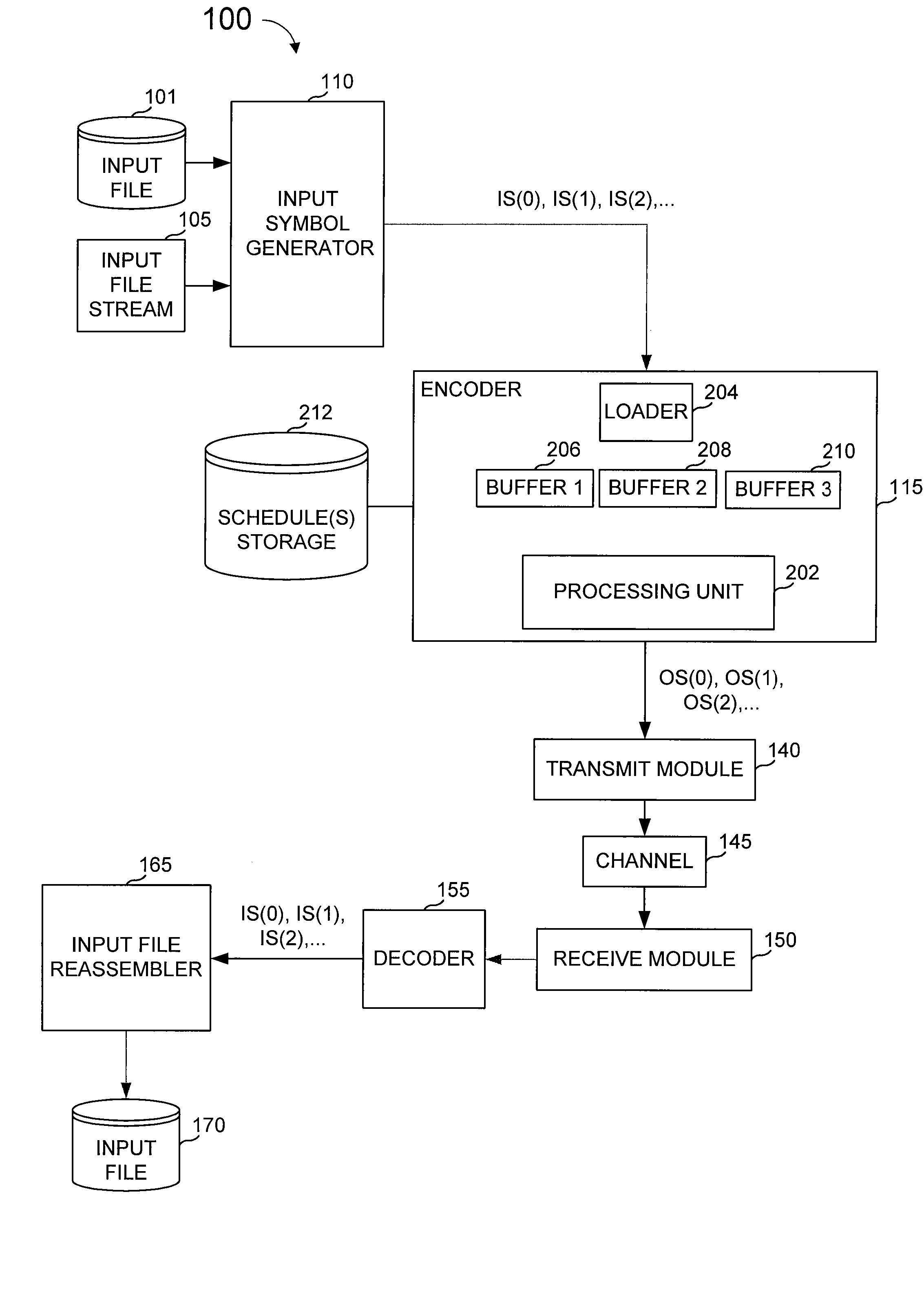

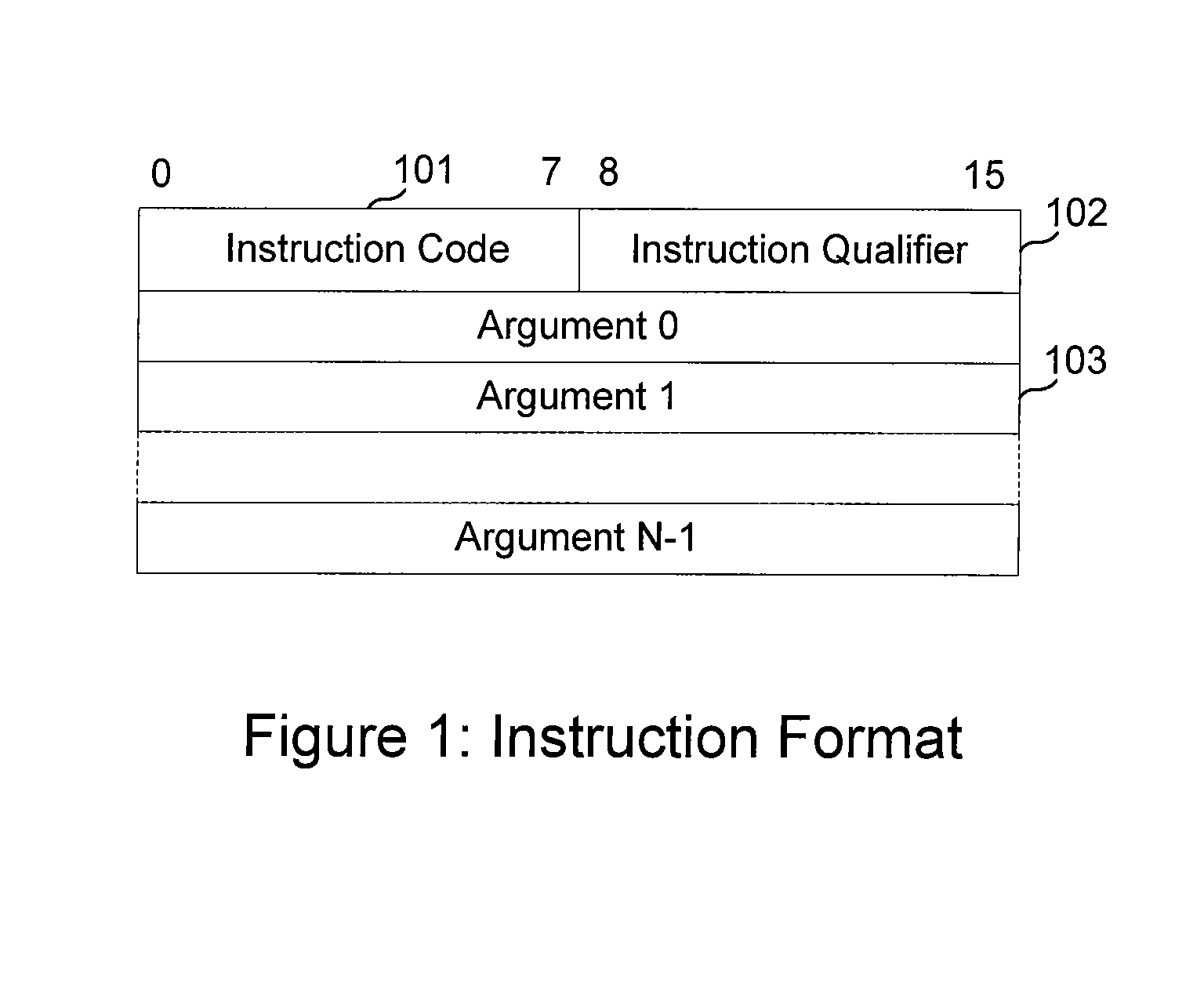

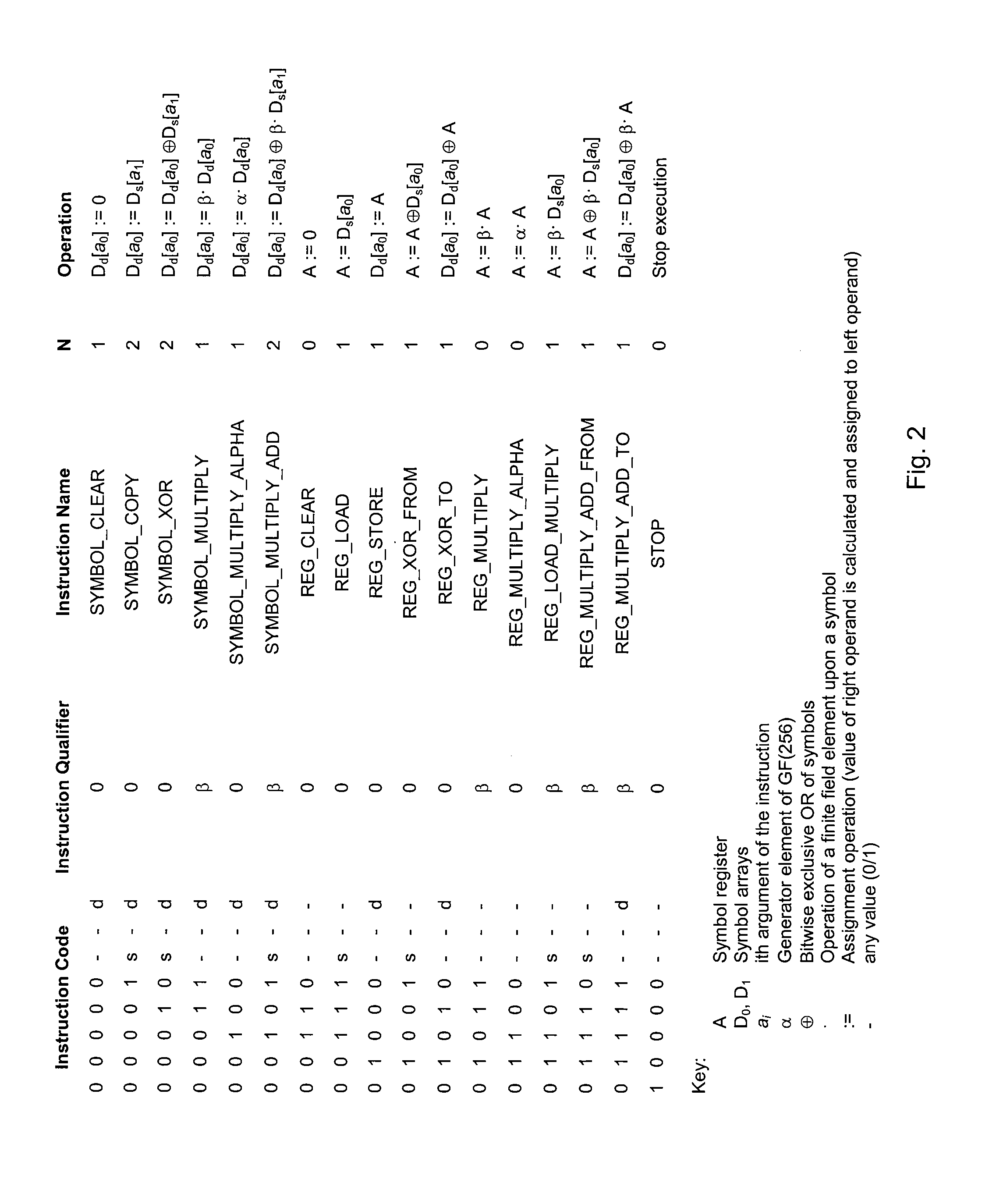

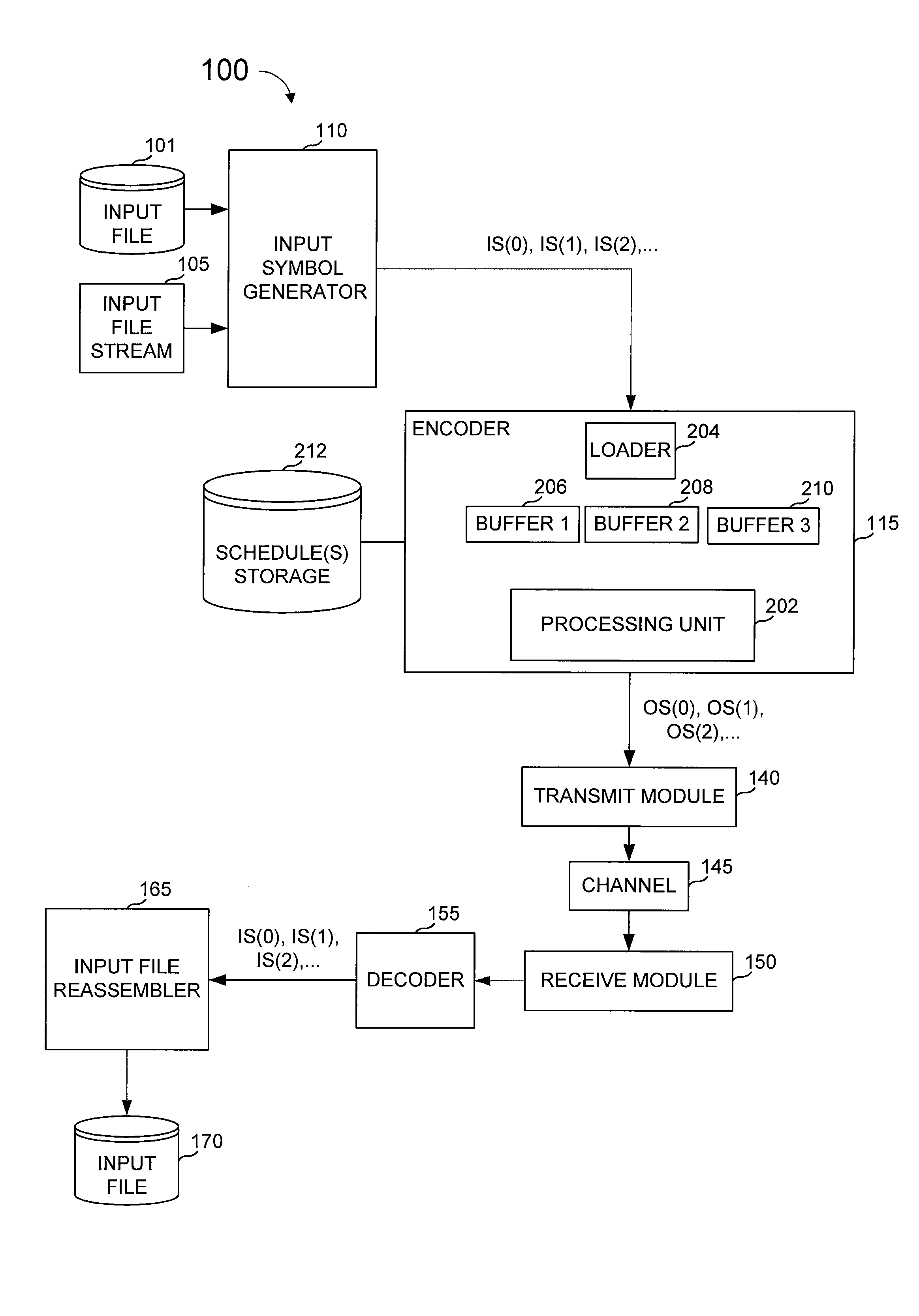

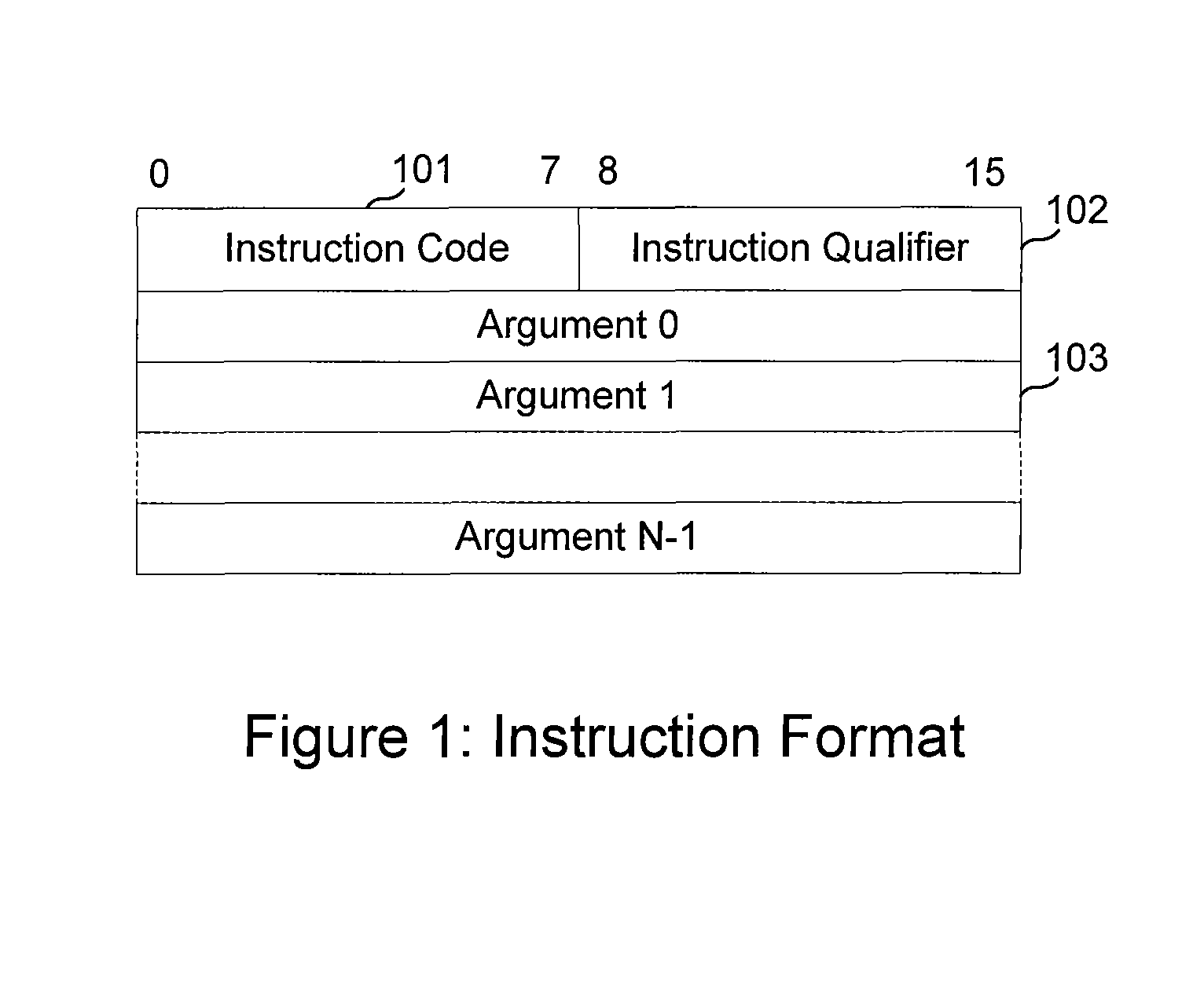

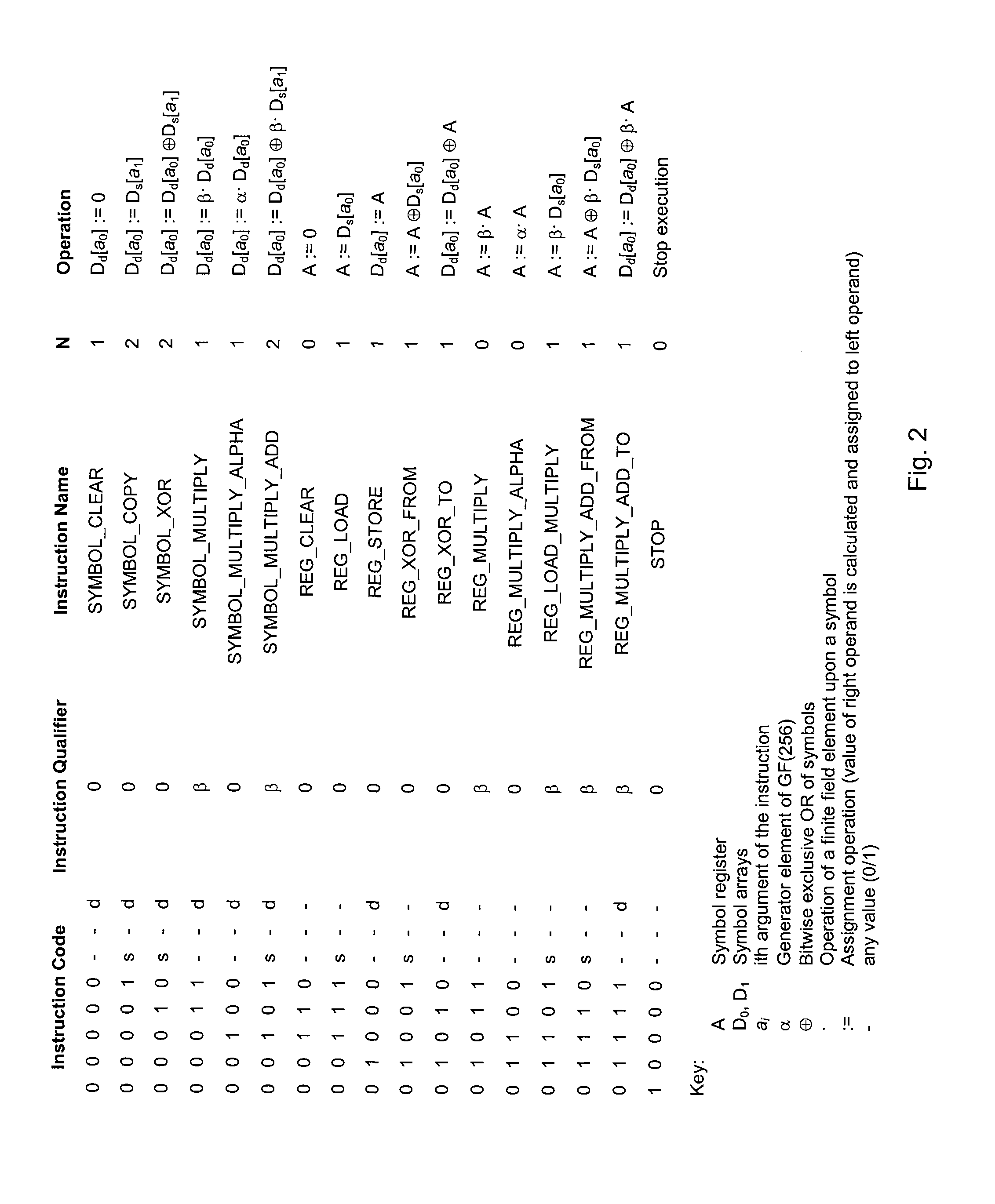

Efficient Encoding and Decoding Methods for Representing Schedules and Processing Forward Error Correction Codes

InactiveUS20080028275A1Reduce computational complexityImprove encodingCode conversionCoding detailsTime scheduleComputer hardware

A sequence of symbol operations (a “schedule representation”) within a data storage device, wherein the operations are those used to process encoding or decoding operations of a forward error correction code (an “FEC code”) upon an arbitrary block of data of a given size (where size can be measured in numbers of symbols). The method is such that the schedule representation can be used to direct the processing of these operations upon a block of data in a way that is computationally efficient. Preferably, the same method can be applied to represent schedules derived from multiple different algorithms for the encoding or decoding of a code or for multiple different codes.

Owner:QUALCOMM INC

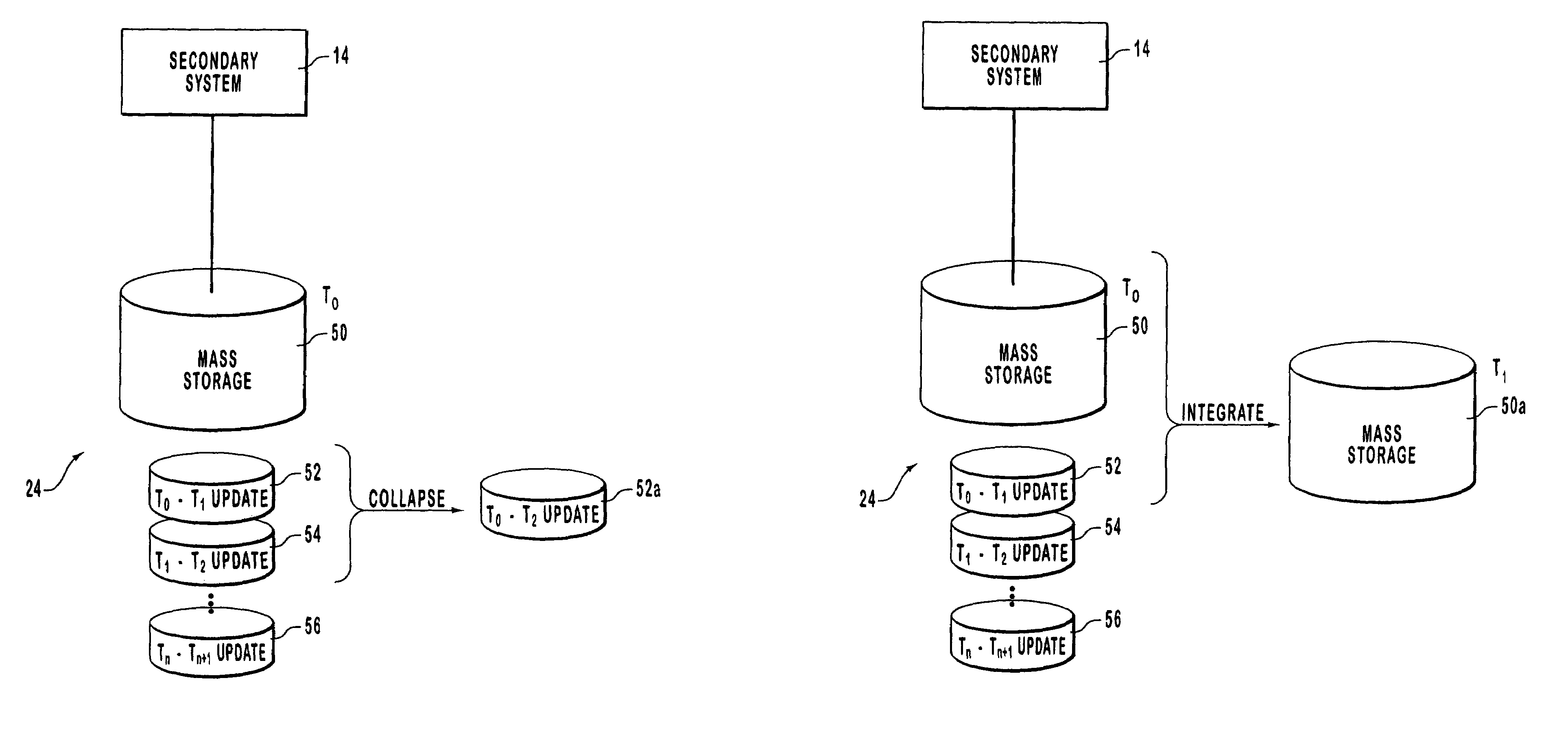

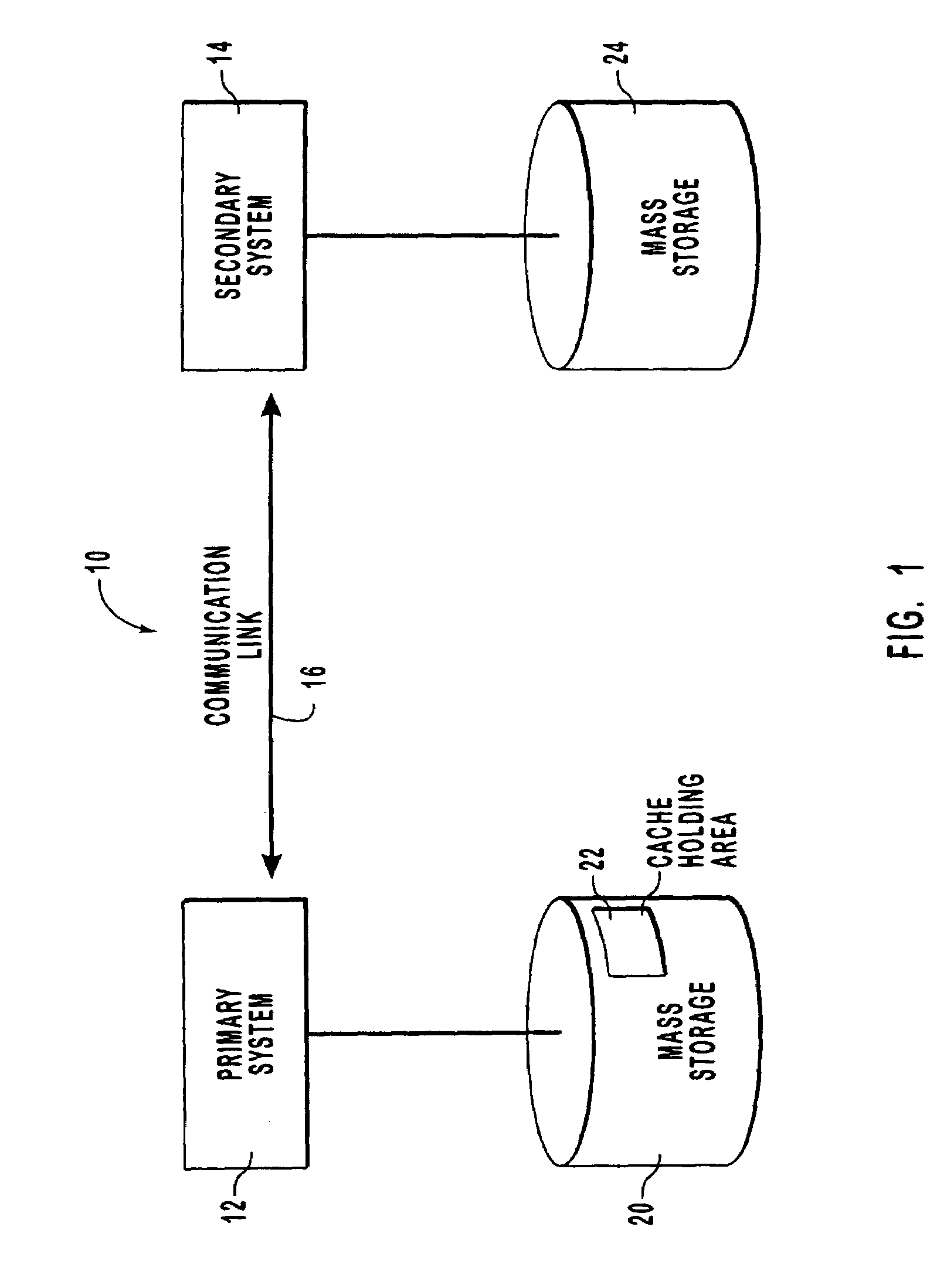

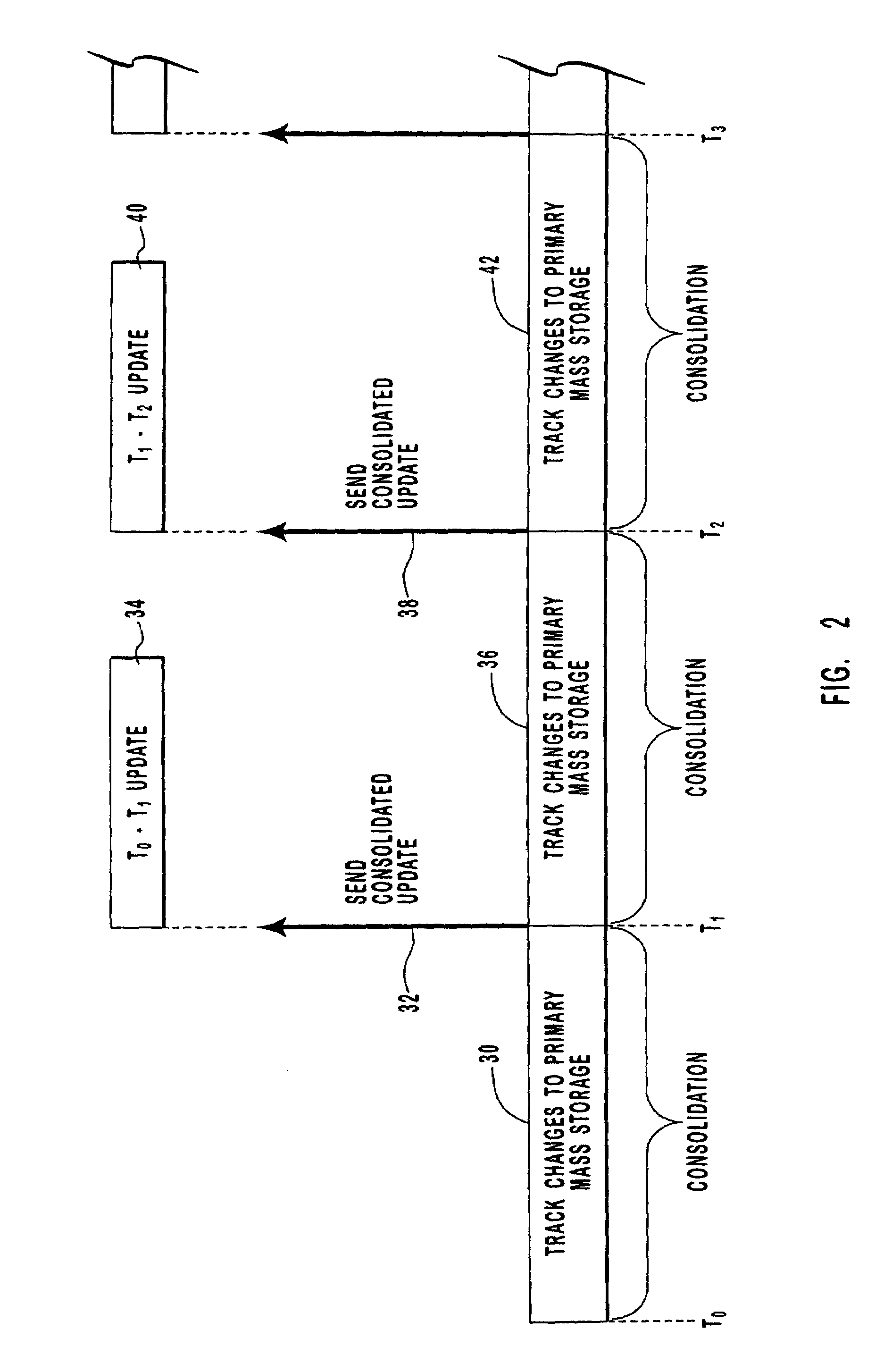

Method and system for mirroring and archiving mass storage

InactiveUS7107418B2Reduce data volumeMinimizing amount of dataData processing applicationsRedundant operation error correctionMass storageFile transmission

A method and system for mirroring and archiving mass storage. A primary mass storage and a secondary mass storage are synchronized to contain the same data. Thereafter, a primary system tracks changes made to the primary mass storage. These changes are consolidated periodically into update files, the consolidations representing changes made to the primary mass storage during a time interval that ends when the primary mass storage is in a logically consistent state. These update files contain only those changes necessary to represent the modified state of the primary mass storage at the time of the update. The primary system then transfers the update files to a secondary system to bring the secondary mass storage current with the primary mass storage. The consolidation minimizes the amount of information that must be transferred and therefore allows for a relatively low band width communication channel. In addition, update files may be cached by the primary system so that requests for mirrored or archived data may be fulfilled by the primary system cache rather than requiring access to the secondary system.

Owner:EMC IP HLDG CO LLC

Method of providing positioning data to mobile device

InactiveUS20160227367A1Attenuation bandwidthReduce consumptionLocation information based serviceUser deviceComputer module

The invention provides a method of providing positioning data to a mobile user device comprising a positioning module for estimating a location of the mobile user device, the method comprising: providing a database comprising positioning data for use by the positioning module of the mobile user device to estimate the location of the mobile user device; providing customised user data specific to a user of the mobile user device; selecting one or more subsets of positioning data from the positioning data provided in the said database responsive to a determination that the said subsets of positioning data meet one or more relevance criteria relating to the said customised user data; and providing the selected subsets of positioning data to the mobile user device.

Owner:HUAWEI TECH CO LTD

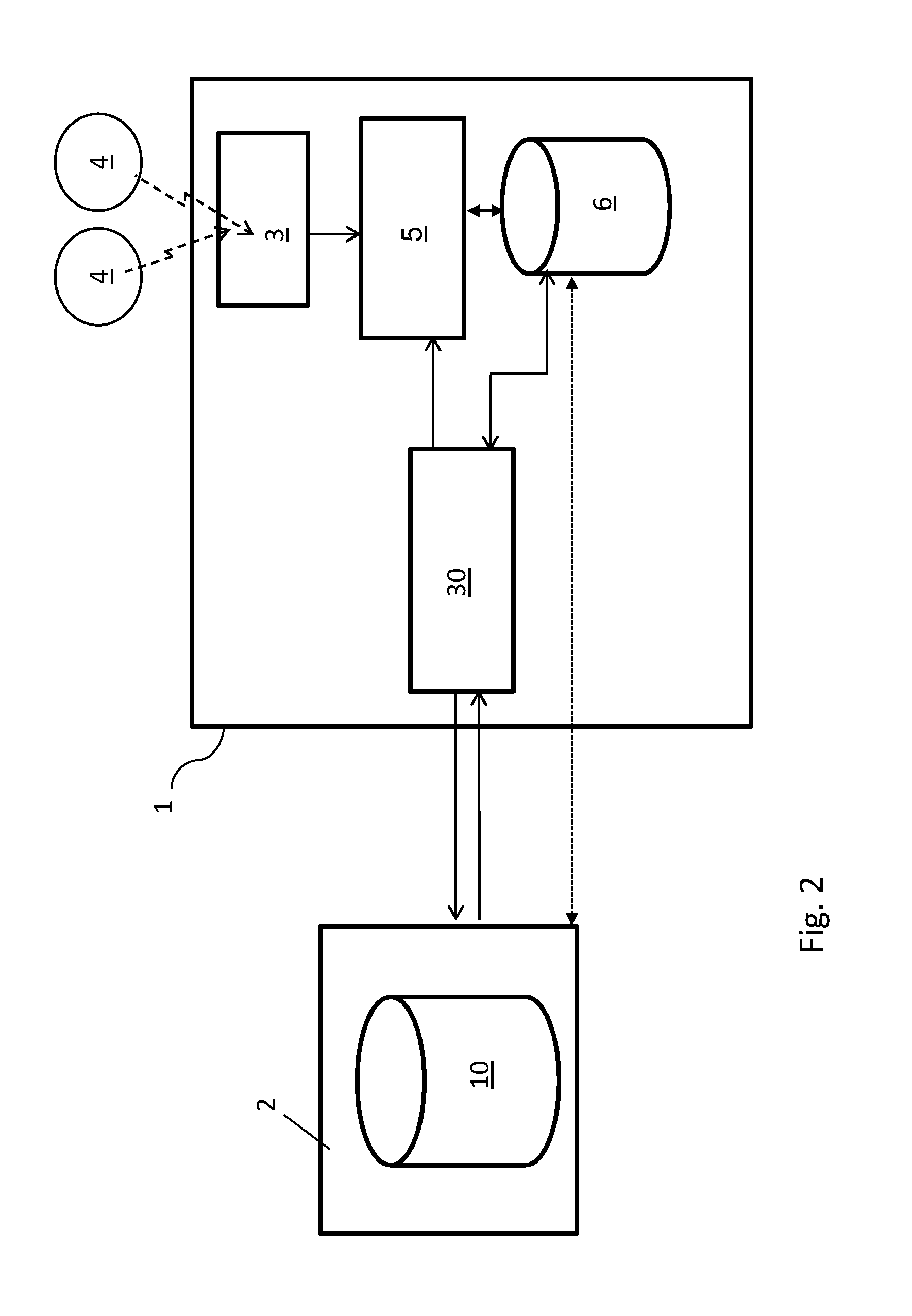

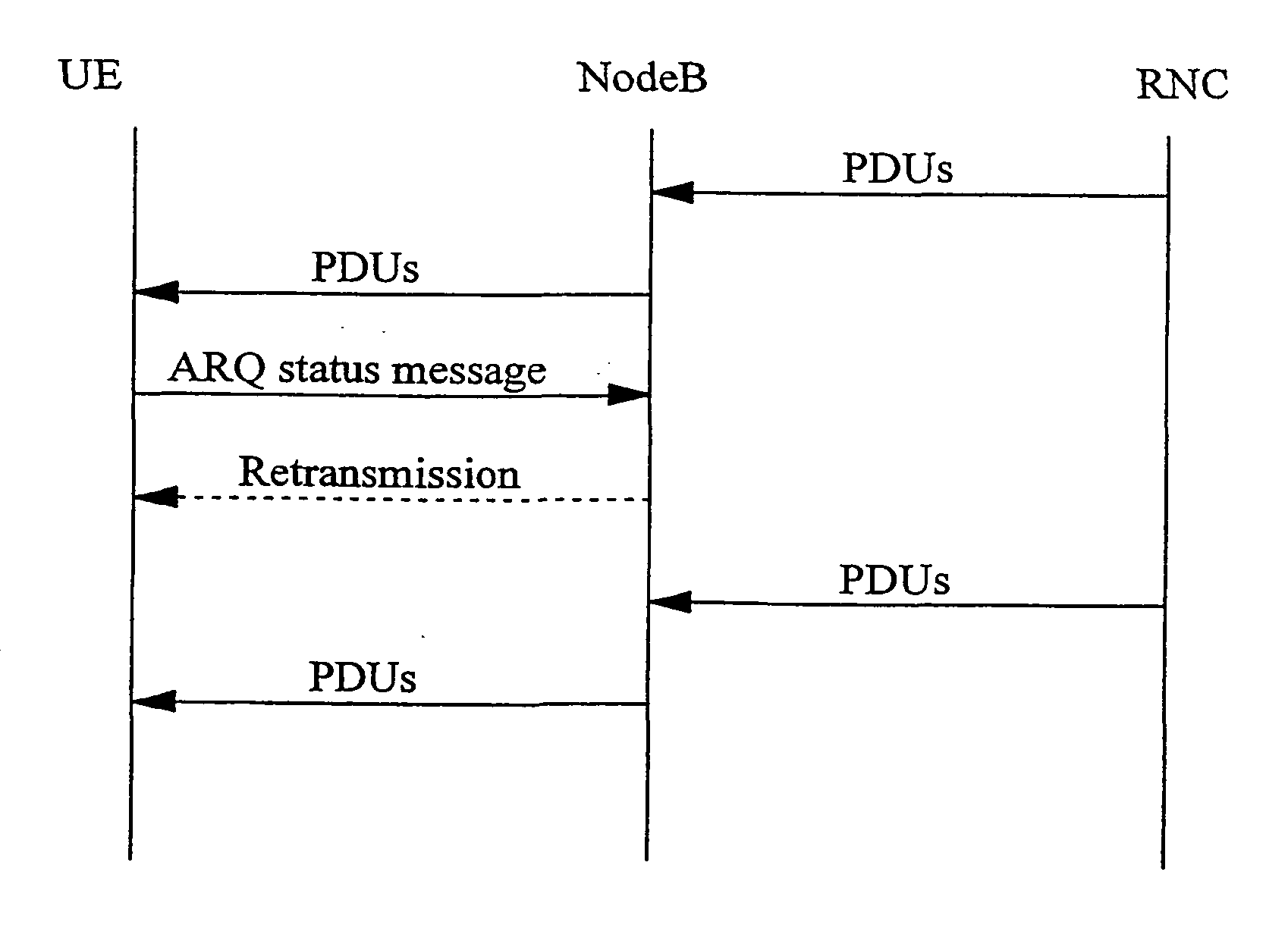

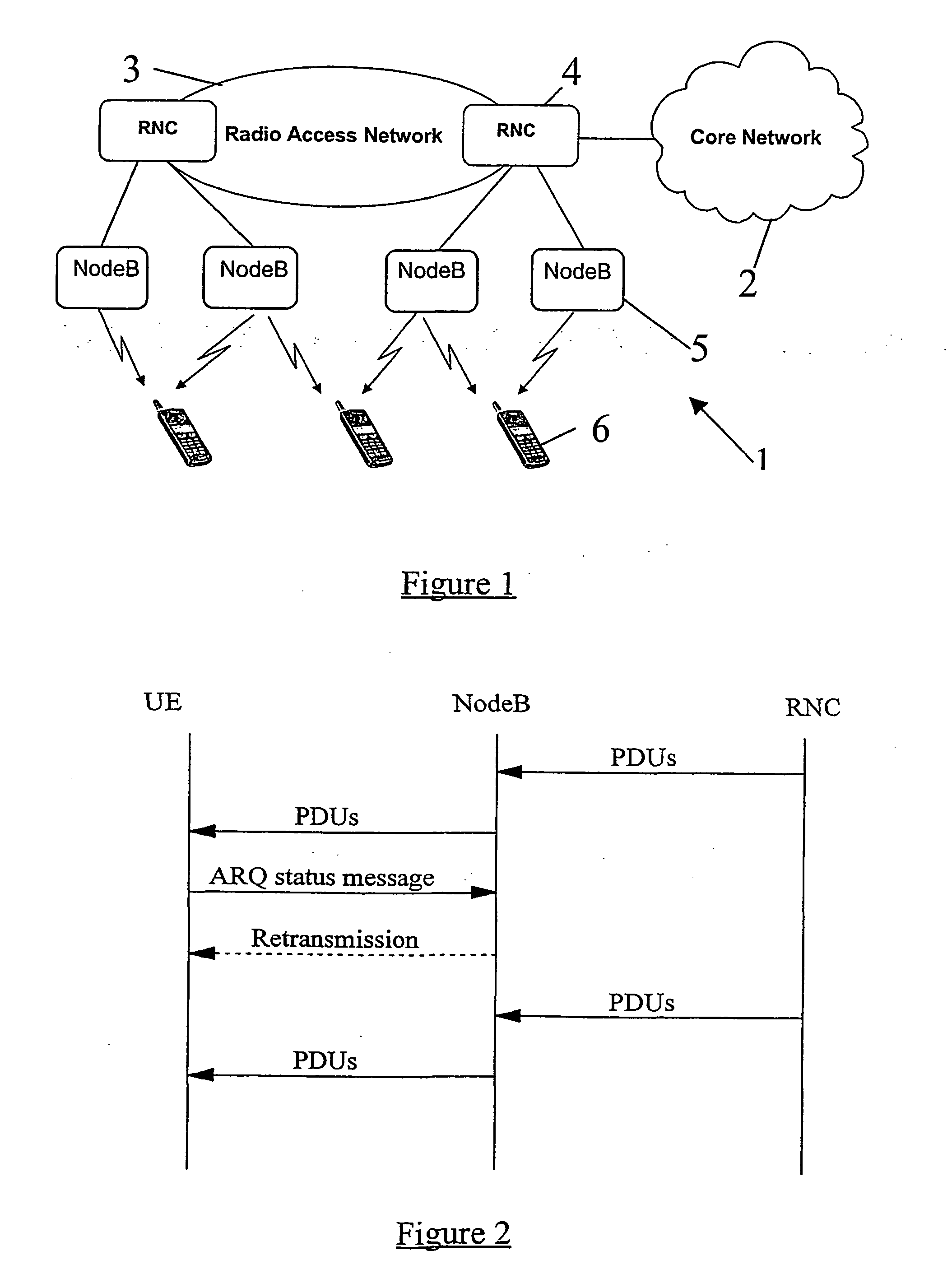

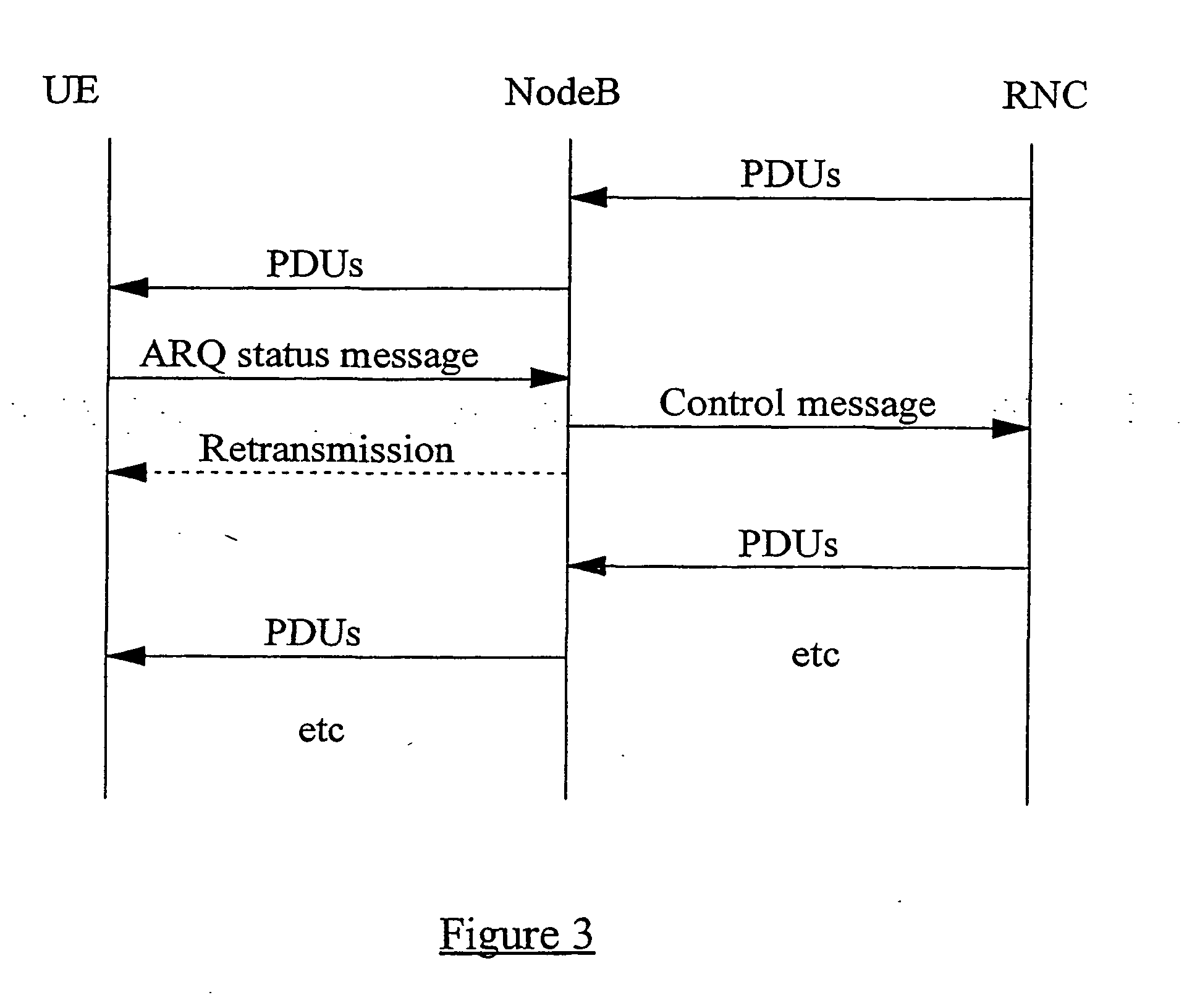

Flow control in a radio access network

InactiveUS20040071108A1Minimize size of bufferReduced effectivenessError prevention/detection by using return channelFrequency-division multiplex detailsTraffic capacityAccess network

A method of controlling the flow of data, in respect of a given mobile terminal, between a Radio Network Controller (RNC) and a NodeB of a UMTS Terrestrial Radio Access Network (UTRAN) where an Automatic-Repeat-Request (ARQ) mechanism is implemented between the NodeB and said mobile terminal to provide for the retransmission of unsuccessfully transmitted data. The method comprises generating control messages at the NodeB and sending these control messages to the RNC, each control message enabling the RNC to identify which data should next be sent to the NodeB.

Owner:TELEFON AB LM ERICSSON (PUBL)

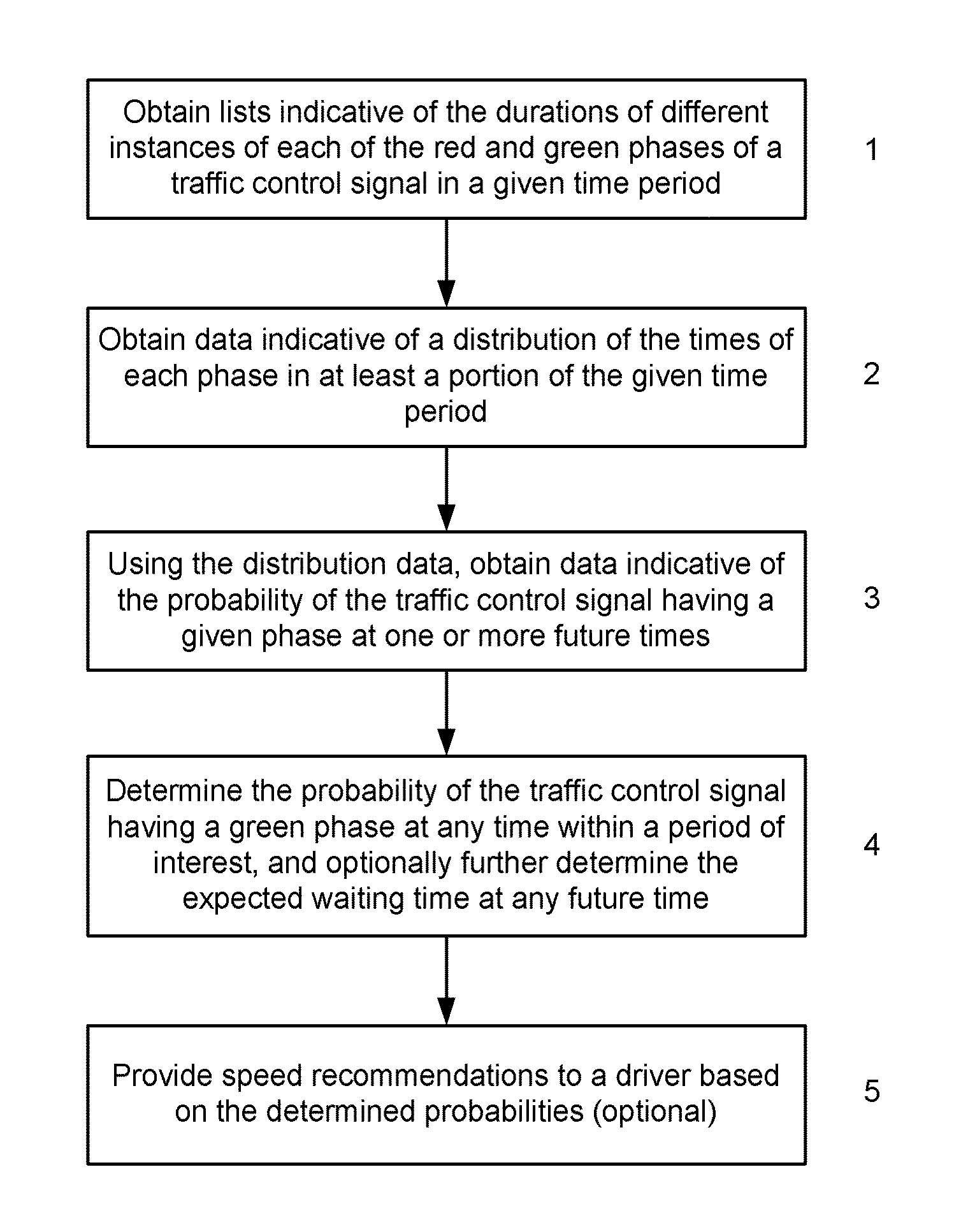

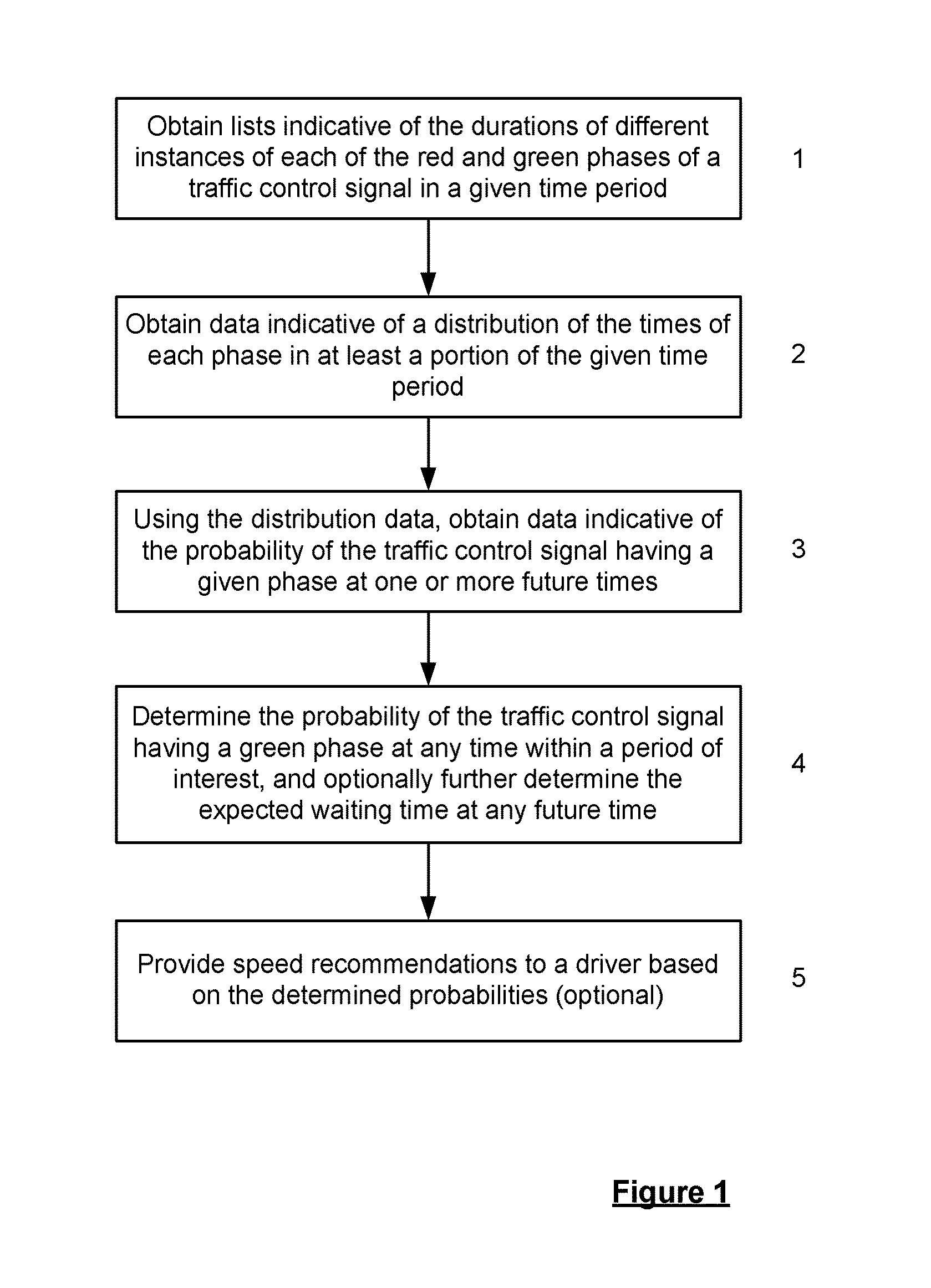

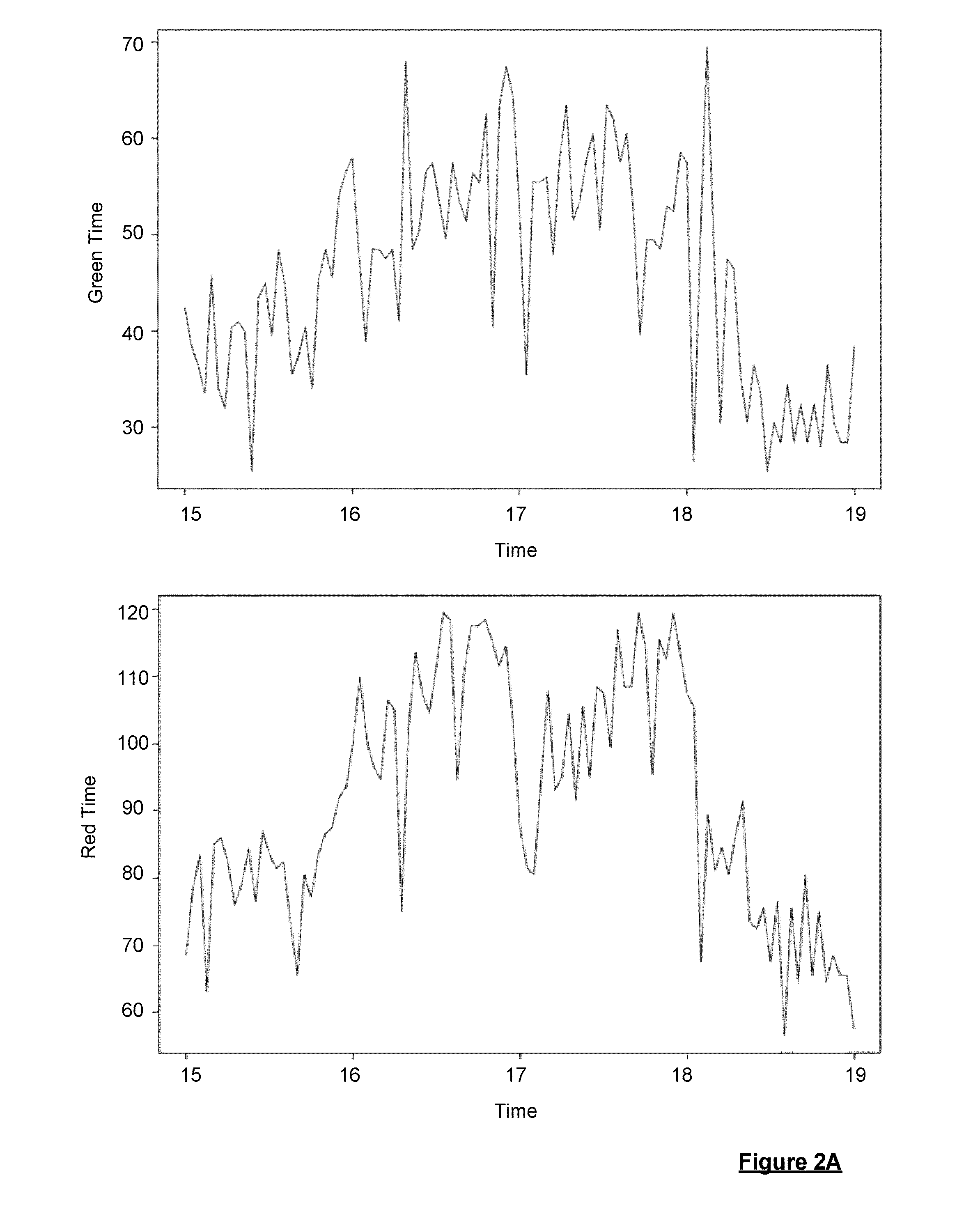

Methods and systems for determining information relating to the operation of traffic control signals

ActiveUS20150015421A1Minimise expected waiting timeMinimises expected waiting timeRoad vehicles traffic controlNavigation instrumentsControl signalWaiting time

Data indicative of the durations of multiple instances of different phases of a traffic control signal in a given time period is determined. The data is used to obtain data indicative of a distribution of the durations of each phase. The distribution data is used to obtain data indicative of a probability of the traffic control signal having a given phase at one or more future time. The probability data may be used to provide an expected waiting time when arriving at the signal at a future time and / or a speed recommendation for a vehicle approaching the signal.

Owner:TOMTOM TRAFFIC

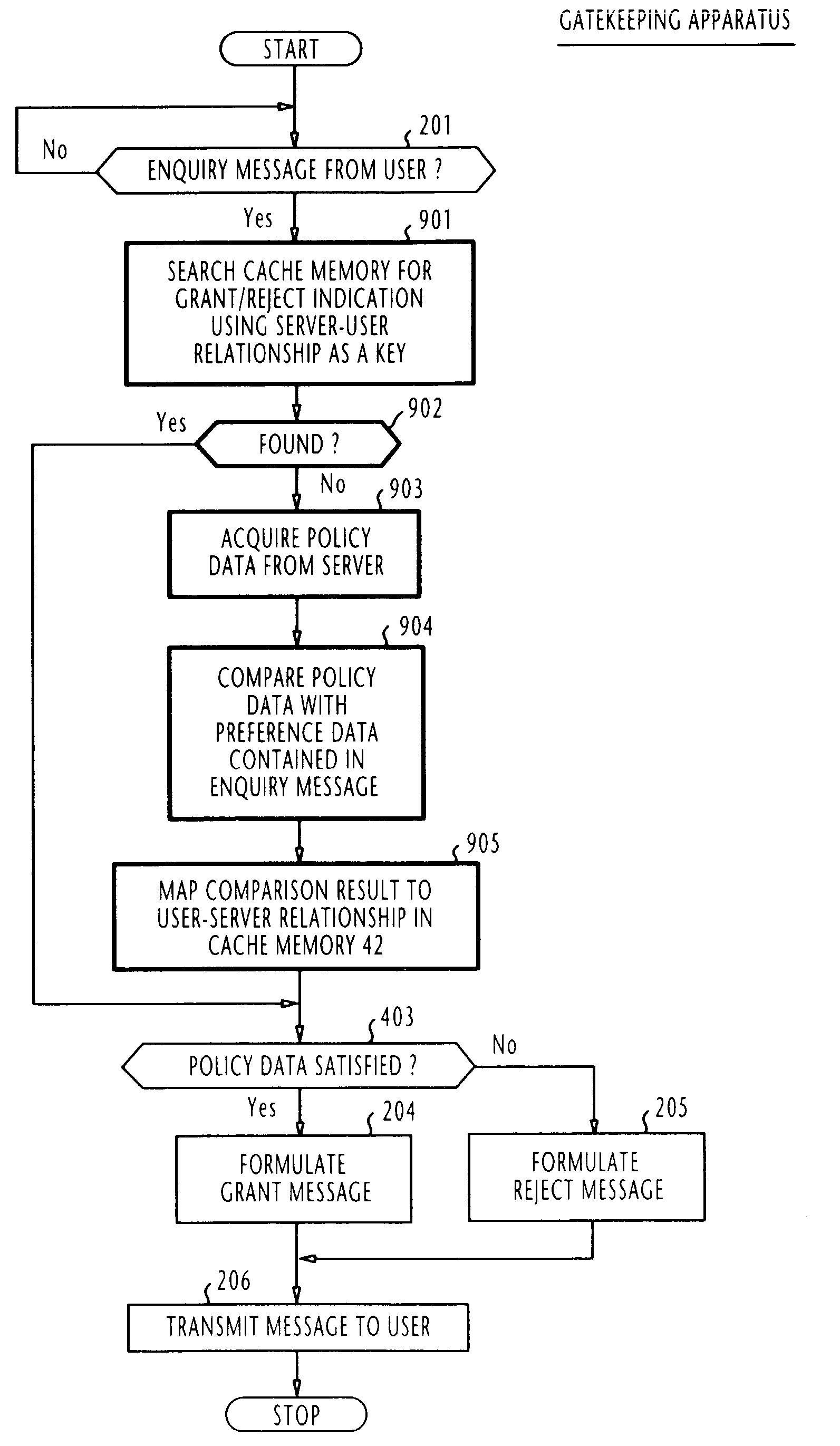

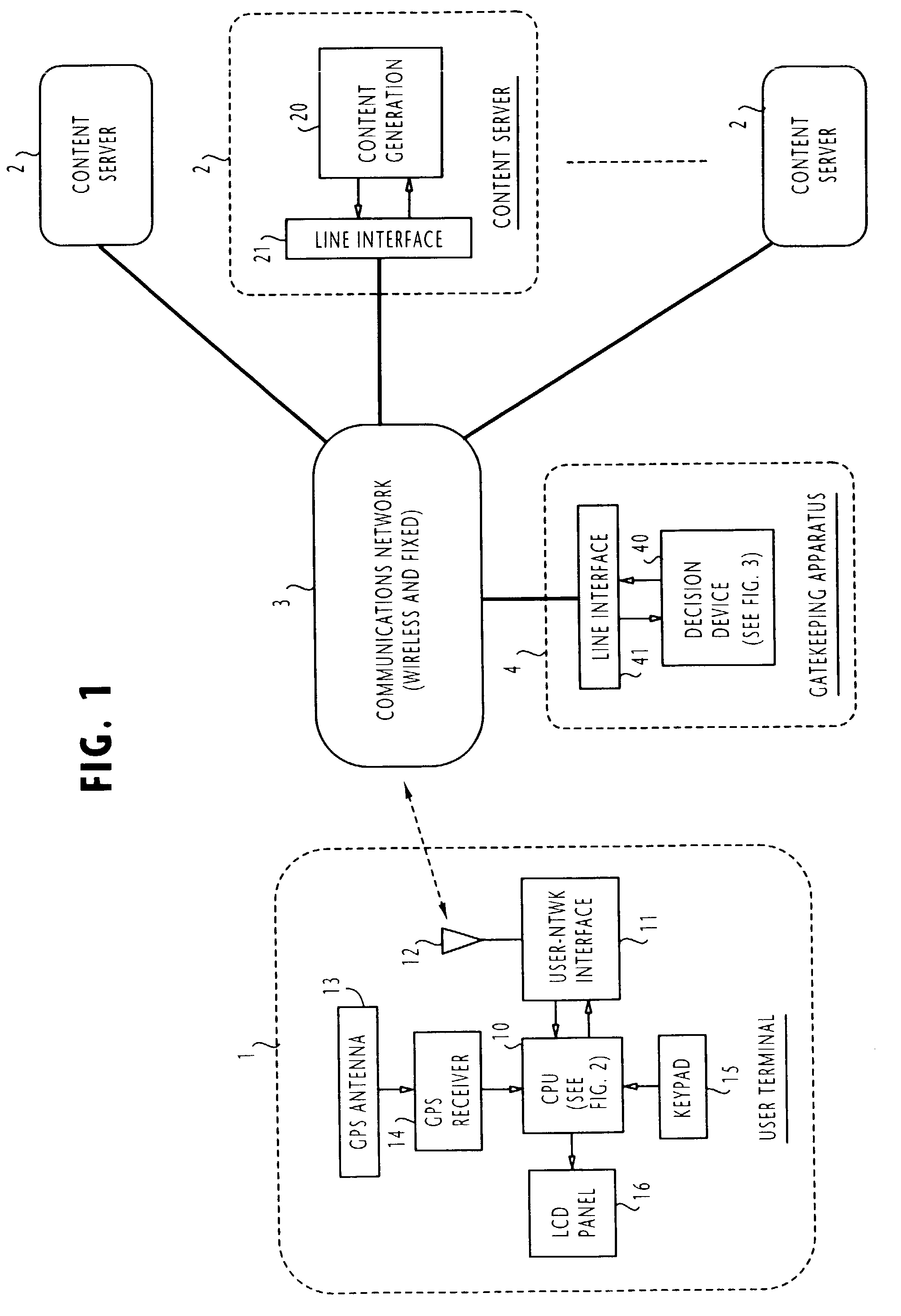

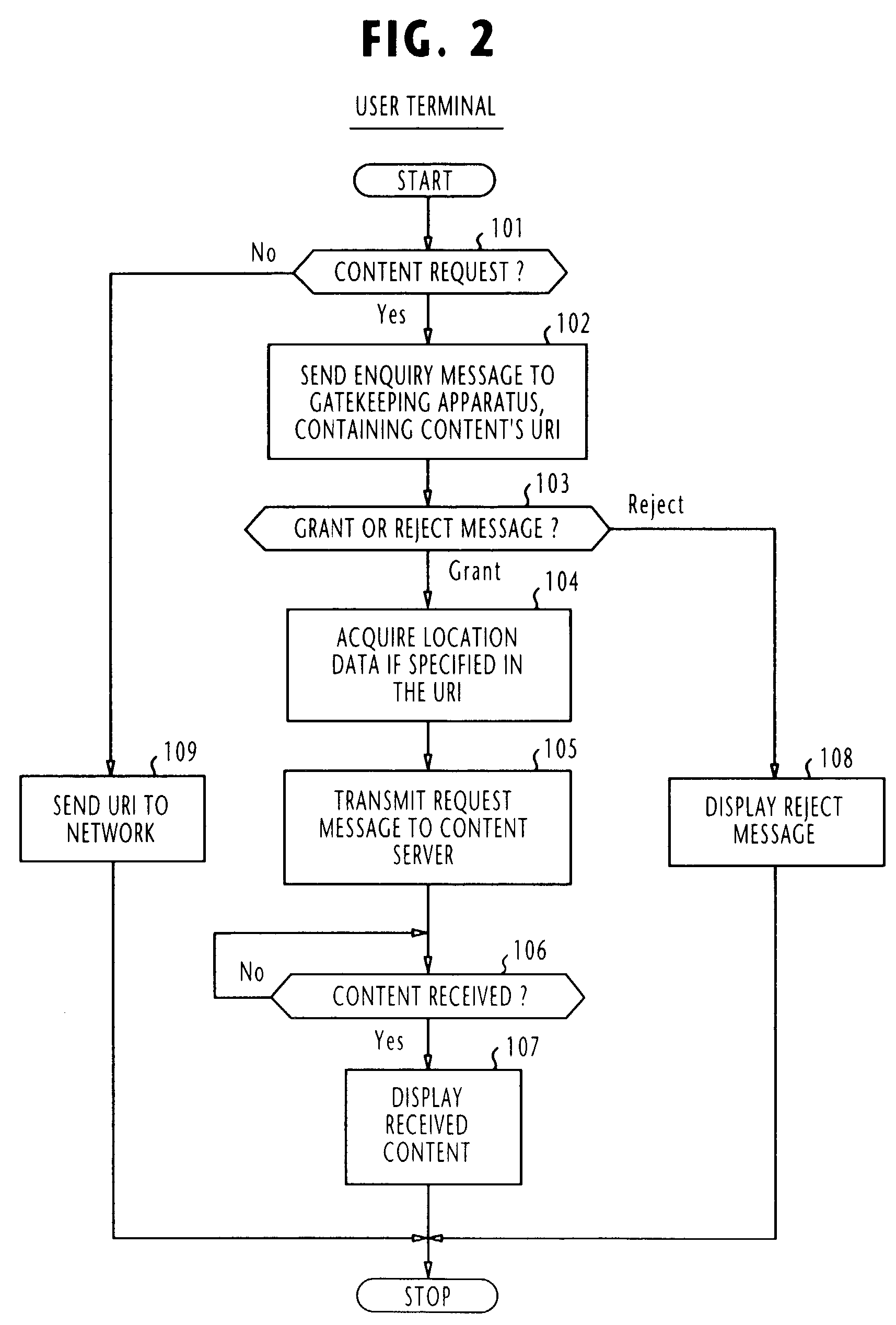

Content delivery system

InactiveUS7567800B2Unnecessary user trafficMinimizing amount of dataInput/output for user-computer interactionData taking preventionContent serverPreference data

In a content delivery system, a gatekeeping apparatus is connected to a network. Prior to the transmission of a request message to a content server, a user terminal transmits an enquiry message to the gatekeeping apparatus. In response, the gatekeeping apparatus makes a decision as to whether or not a content can be retrieved from the content server and performs control on the transmission of the request message according to the decision. If the decision indicates that a content can be retrieved, the user terminal transmits the request message to the content server. In a preferred embodiment, the gatekeeping apparatus makes comparison between user's preference data and server's policy data and determines whether the requested content can be retrieved from the server. A cache memory may be provided in the user terminal or gatekeeping apparatus to store past decisions regarding requested contents.

Owner:NEC CORP

Multimode Heterogeneous IOT Networks

InactiveUS20200145493A1Minimize network induced noiseMaximize signal to noiseKey distribution for secure communicationEncryption apparatus with shift registers/memoriesComputer networkStructure and function

Owner:INNOVATION SCI LLC

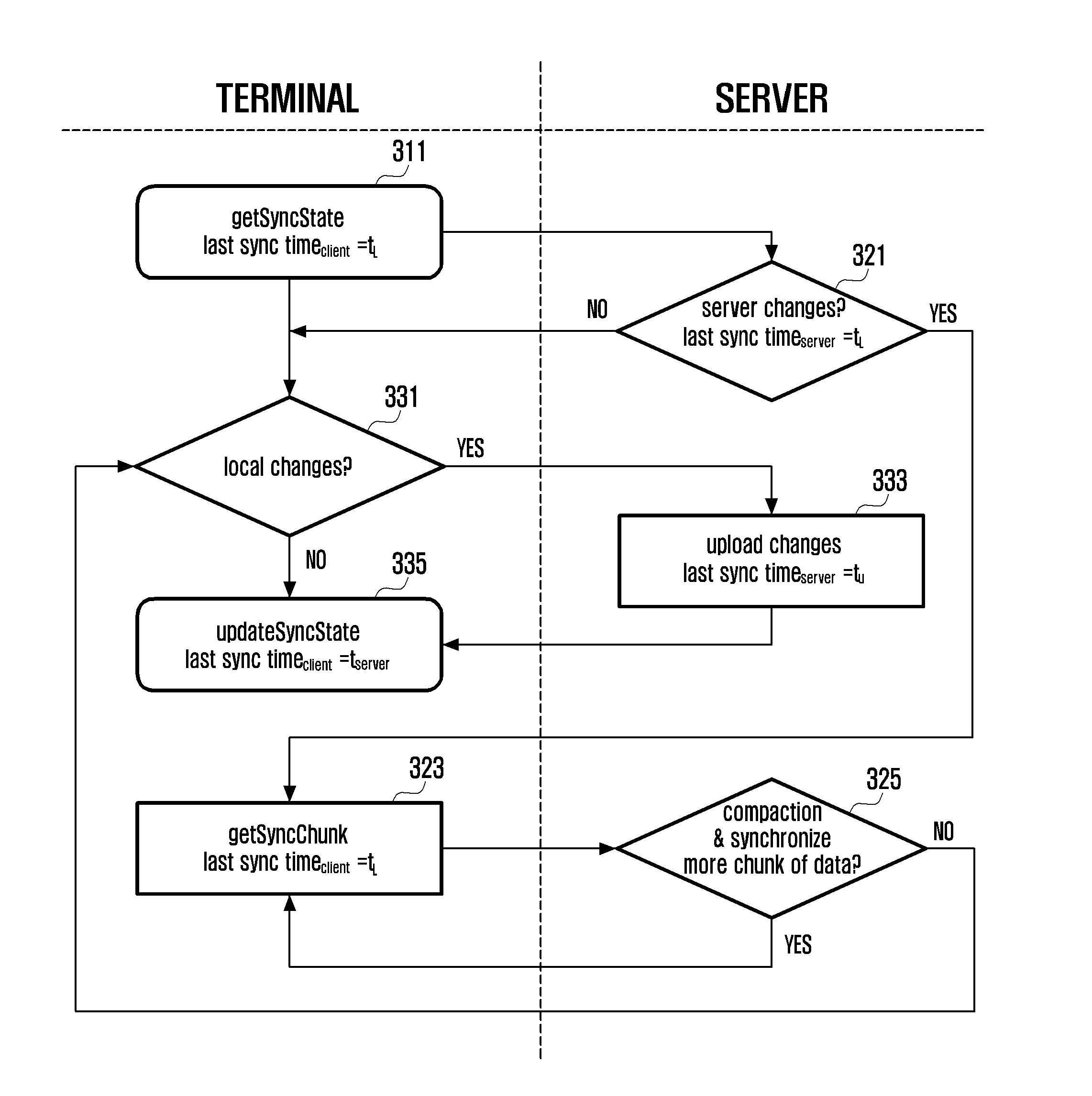

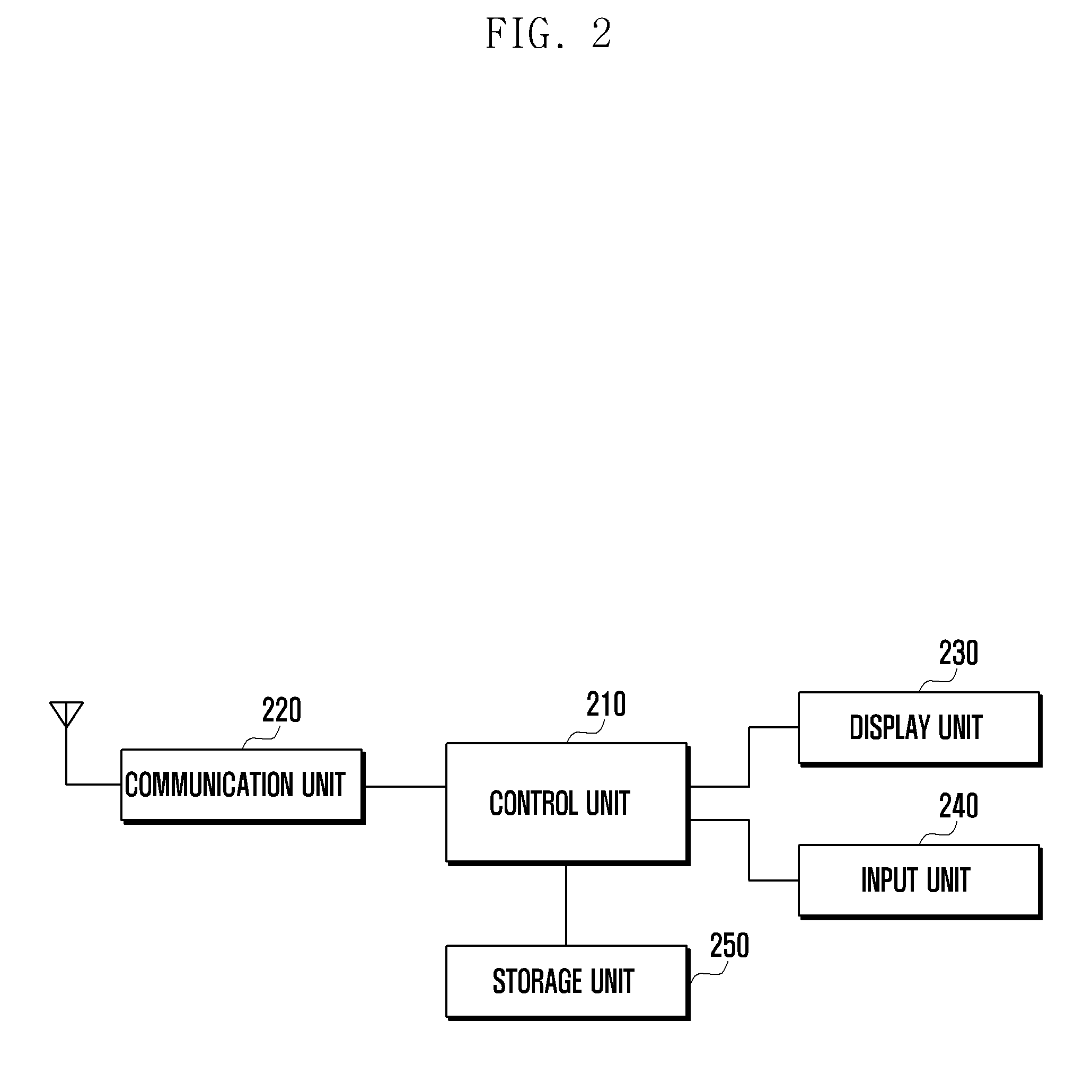

Content synchronization apparatus and method for cloud service system

InactiveUS20140068018A1Reduce stepsMinimizing amount of dataData processing applicationsMultiple digital computer combinationsTime changesMobile context

A method and apparatus for synchronization of contents in a cloud service system for a mobile environment is provided. The synchronization method of a cloud service system includes uploading, at a device when data is changed, the changed data to a server, processing, at the server, the uploaded data, storing, at the server, the processed data along with a time change, transmitting, at the device, a synchronization request signal including a most recent server connection time at a predetermined time, downloading, at the device, a data log on data changed between the most recent server connection time and the current time, synchronizing, at the device, the data based on the data log, and updating the most recent server connection time.

Owner:SAMSUNG ELECTRONICS CO LTD

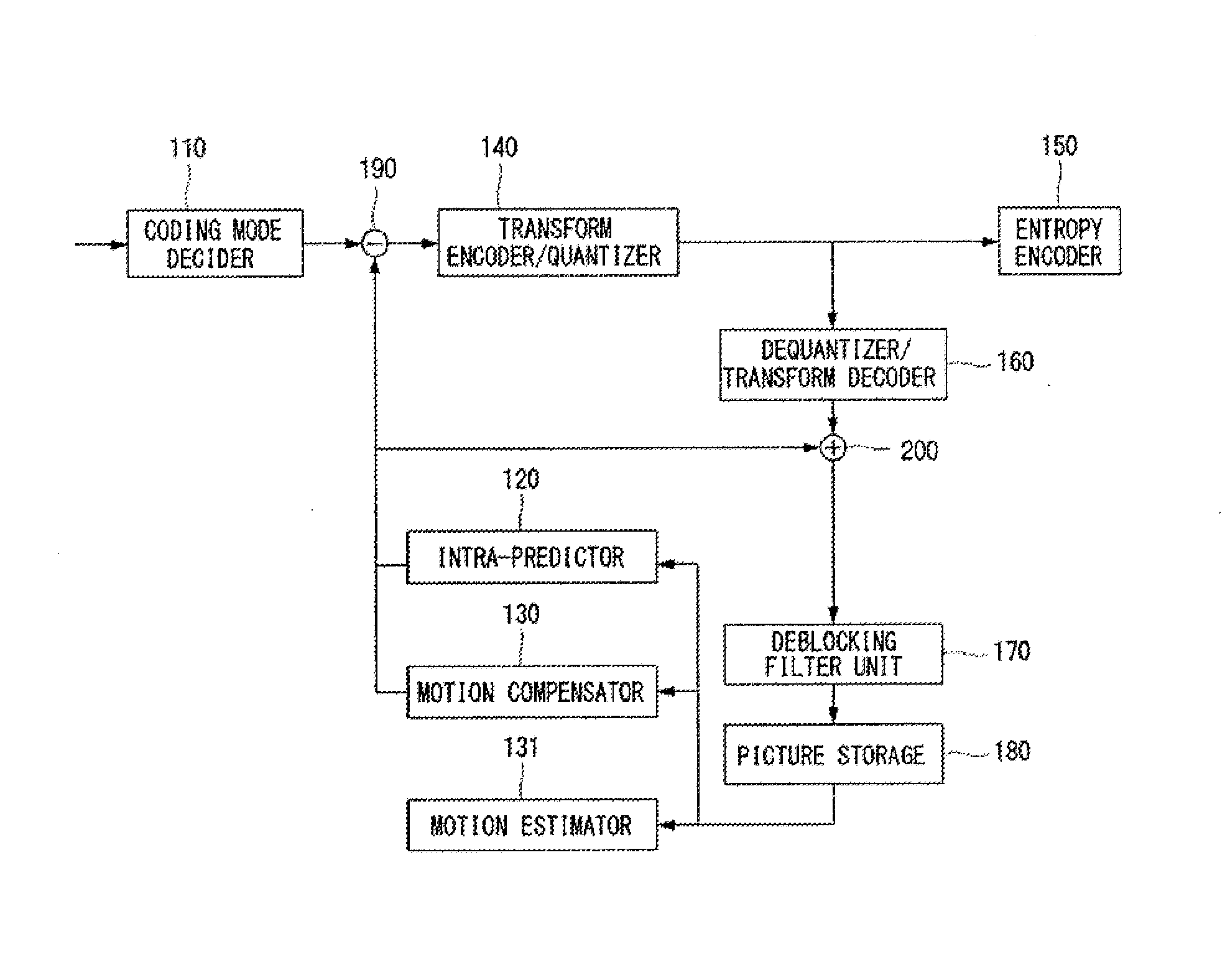

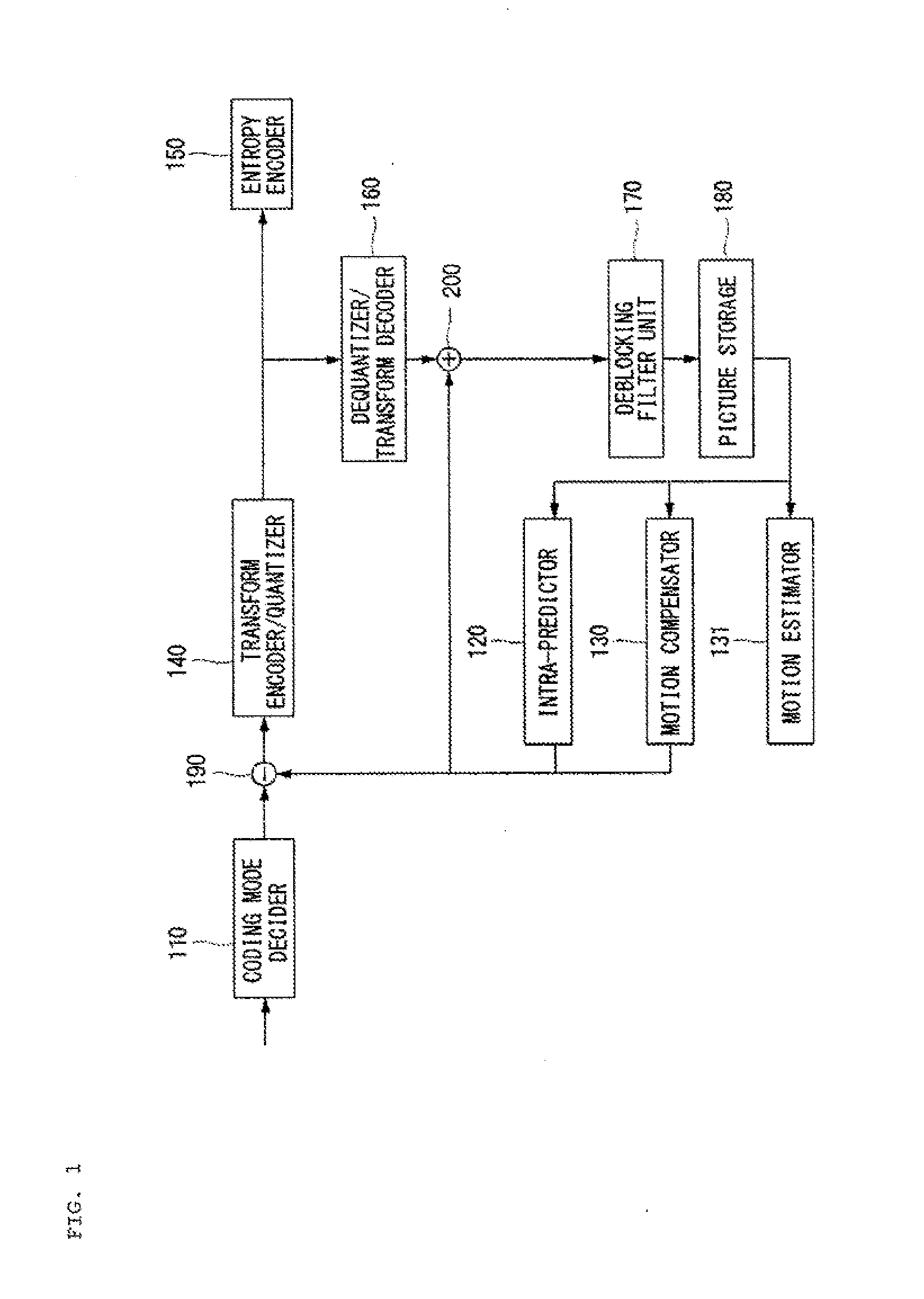

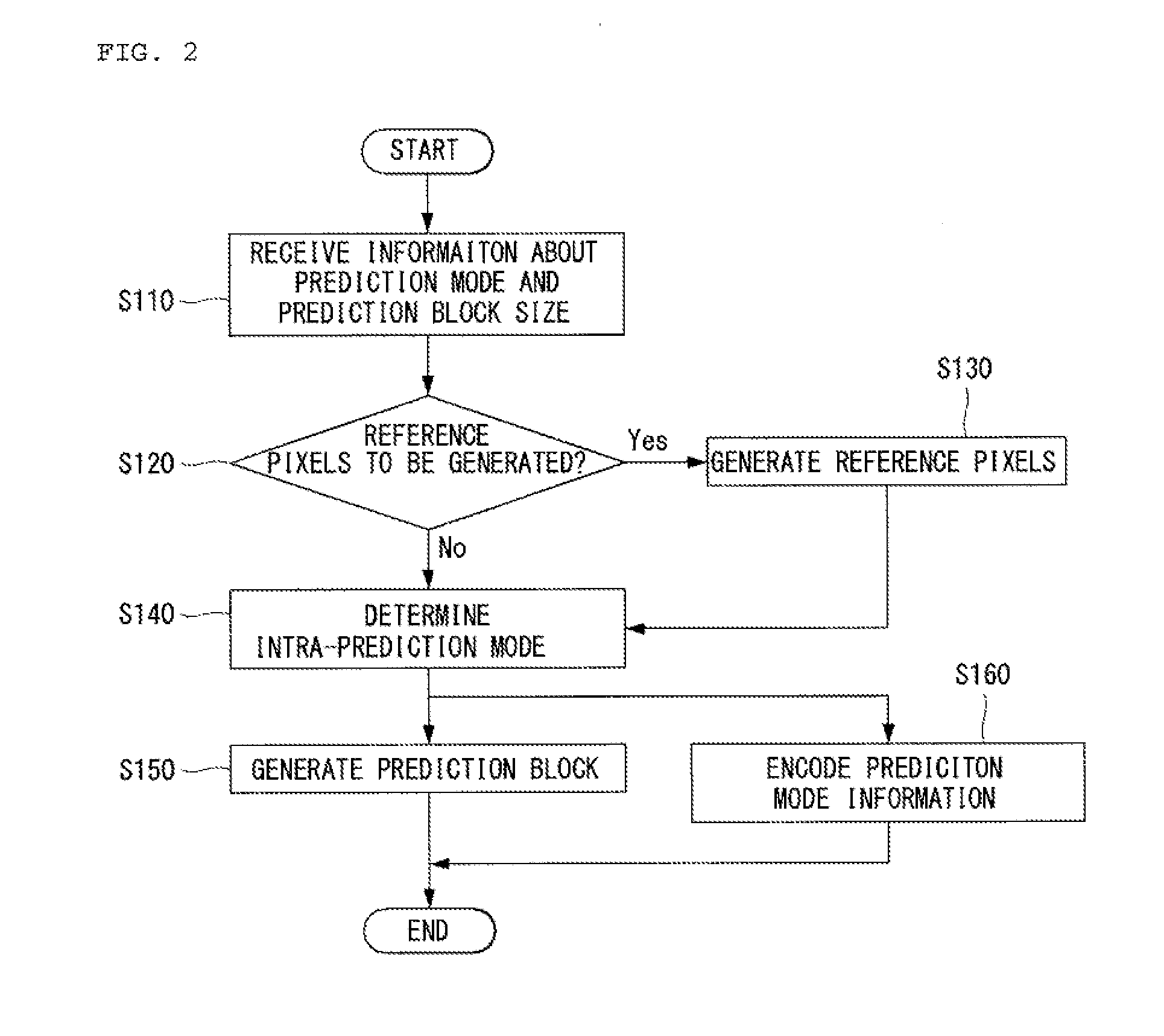

Method of decoding moving pictures in intra prediction

ActiveUS20150117531A1Reduce data volumeImprove video qualityColor television with pulse code modulationColor television with bandwidth reductionPattern generationComputer vision

Owner:IBEX PT HLDG

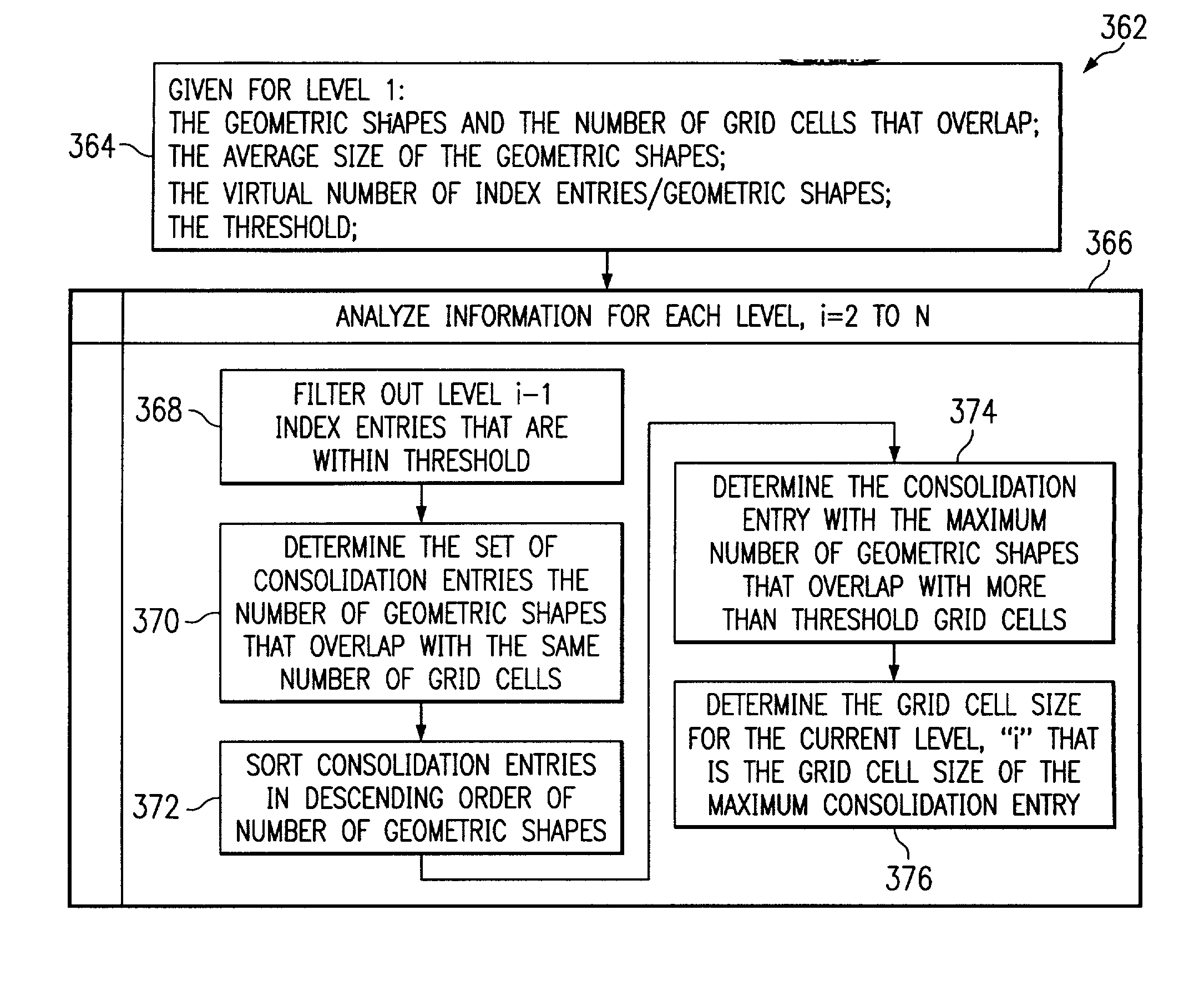

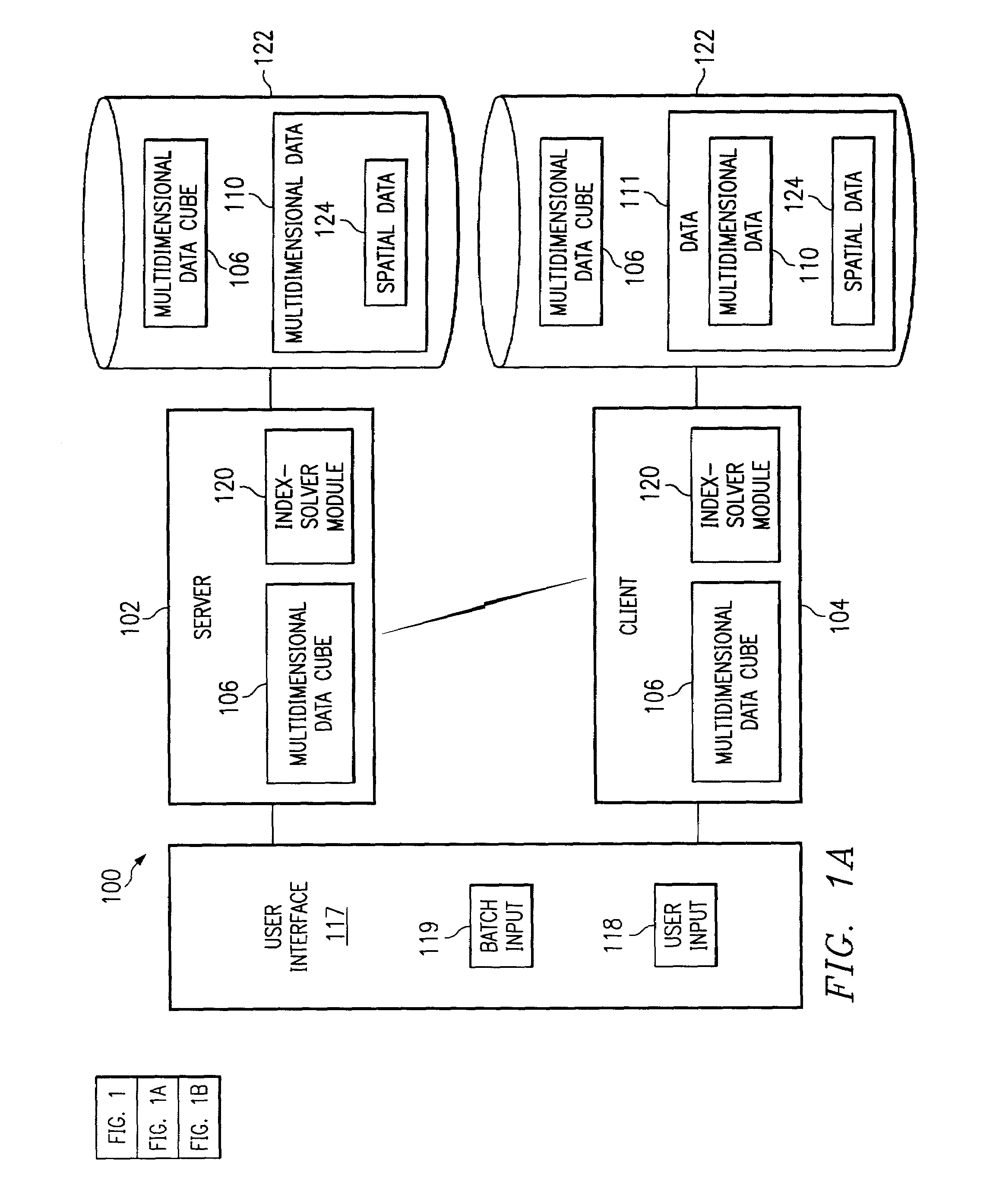

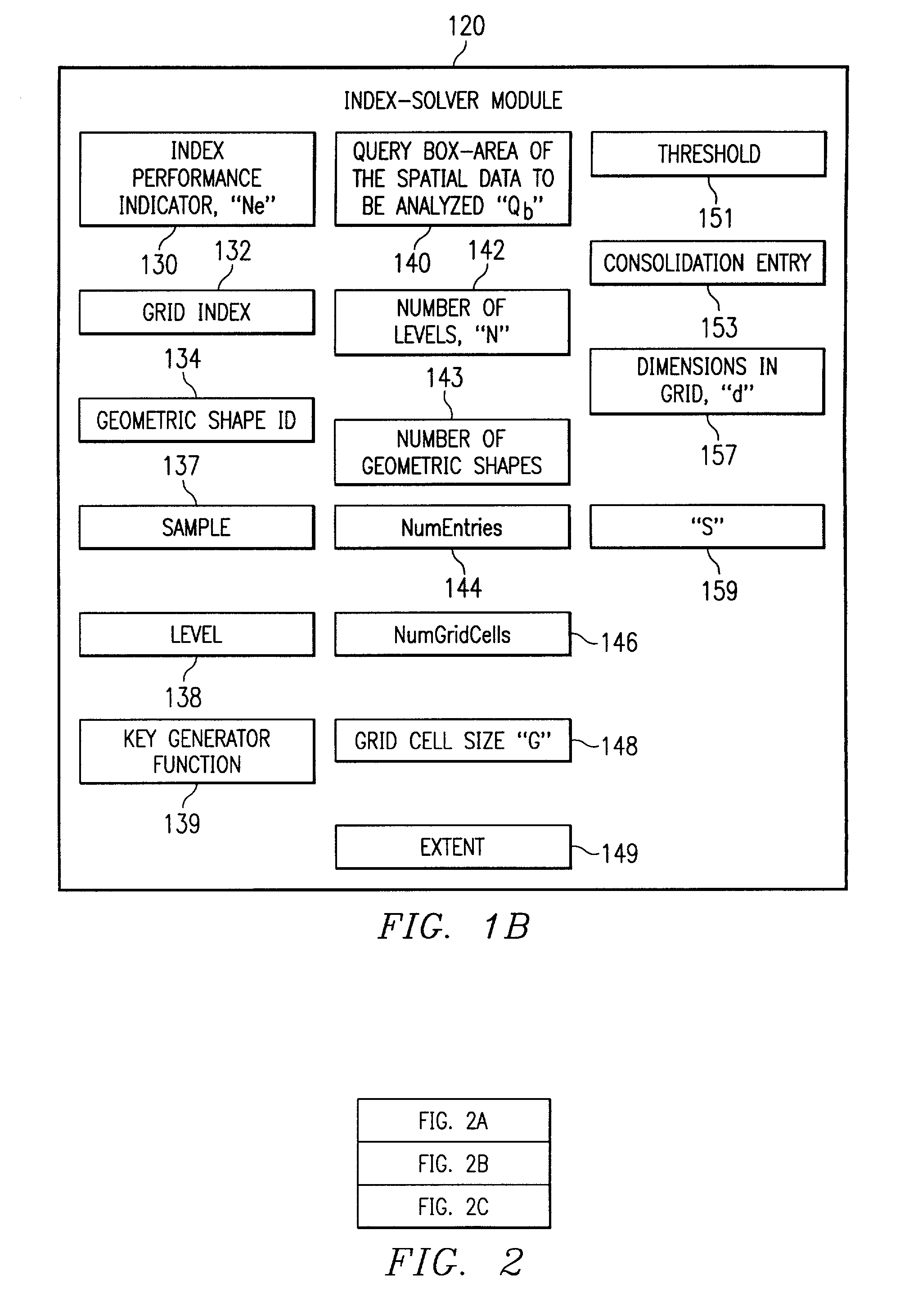

Systems, methods, and computer program products to reduce computer processing in grid cell size determination for indexing of multidimensional databases

InactiveUS7143098B2Minimizing amount of dataPrecise positioningData processing applicationsDigital data information retrievalData setMinimum bounding rectangle

Systems, methods, and computer products that improve the techniques used to search multidimensional databases over techniques of the past. The preferred embodiment of the present invention advantageously improves the technique of determining a grid index that is used to locate a geometric shape in a spatial database. More particularly, the preferred embodiment of the present invention improves the technique of sampling data for defining the grid cell size in a grid for a given data set, thereby improving the grid indexing process that locates a particular minimum-bounding rectangle and the associated geometric shape.

Owner:IBM CORP

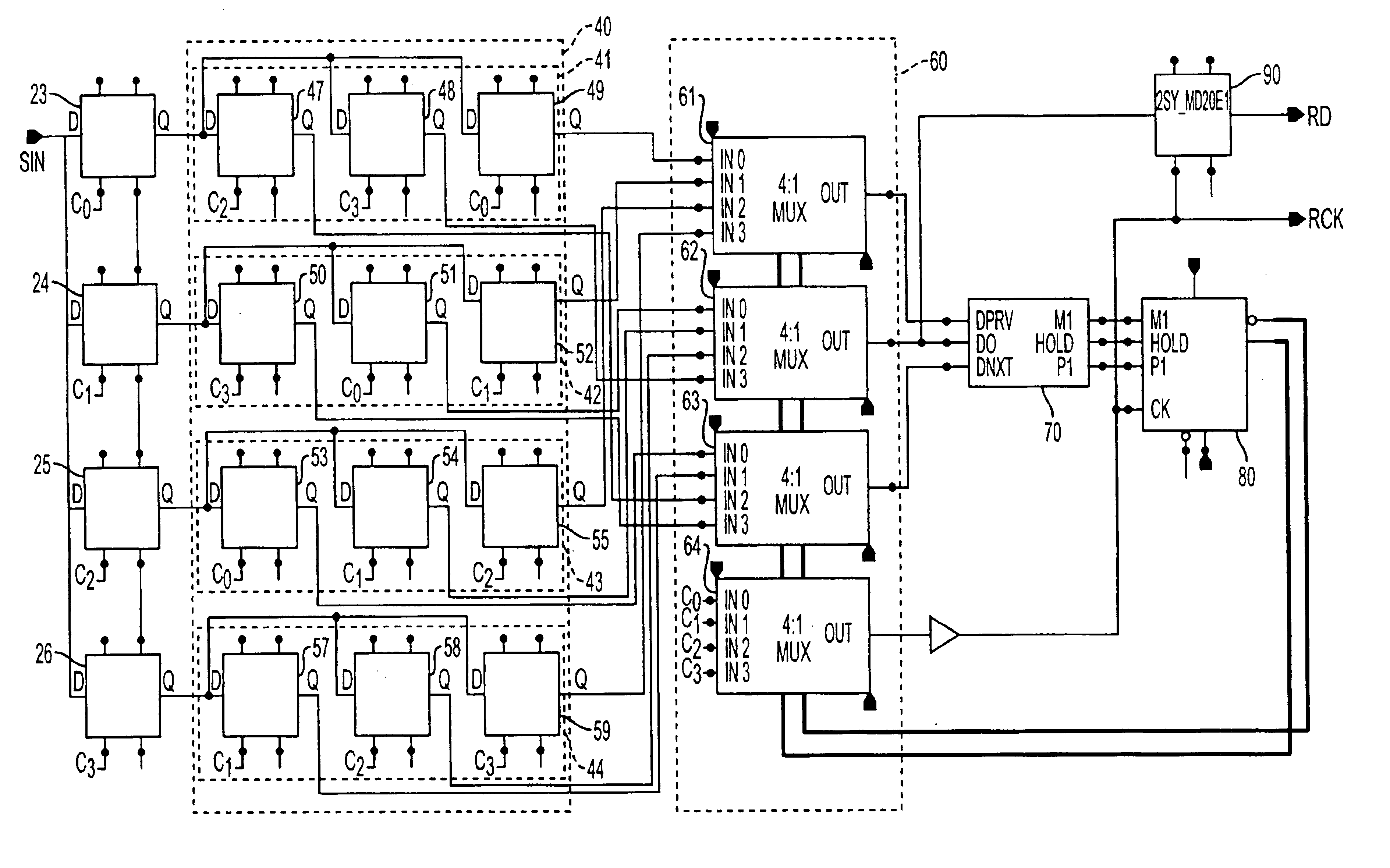

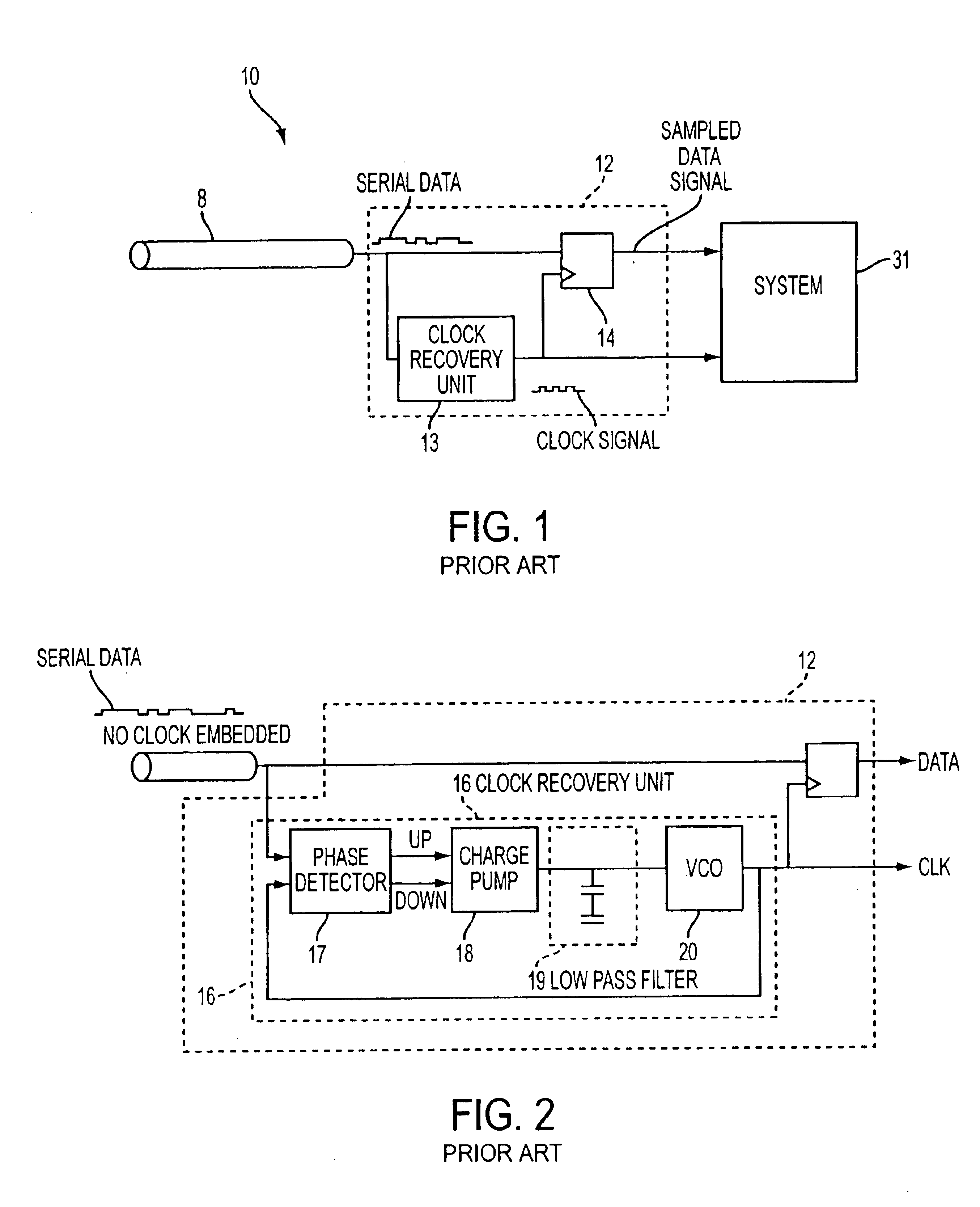

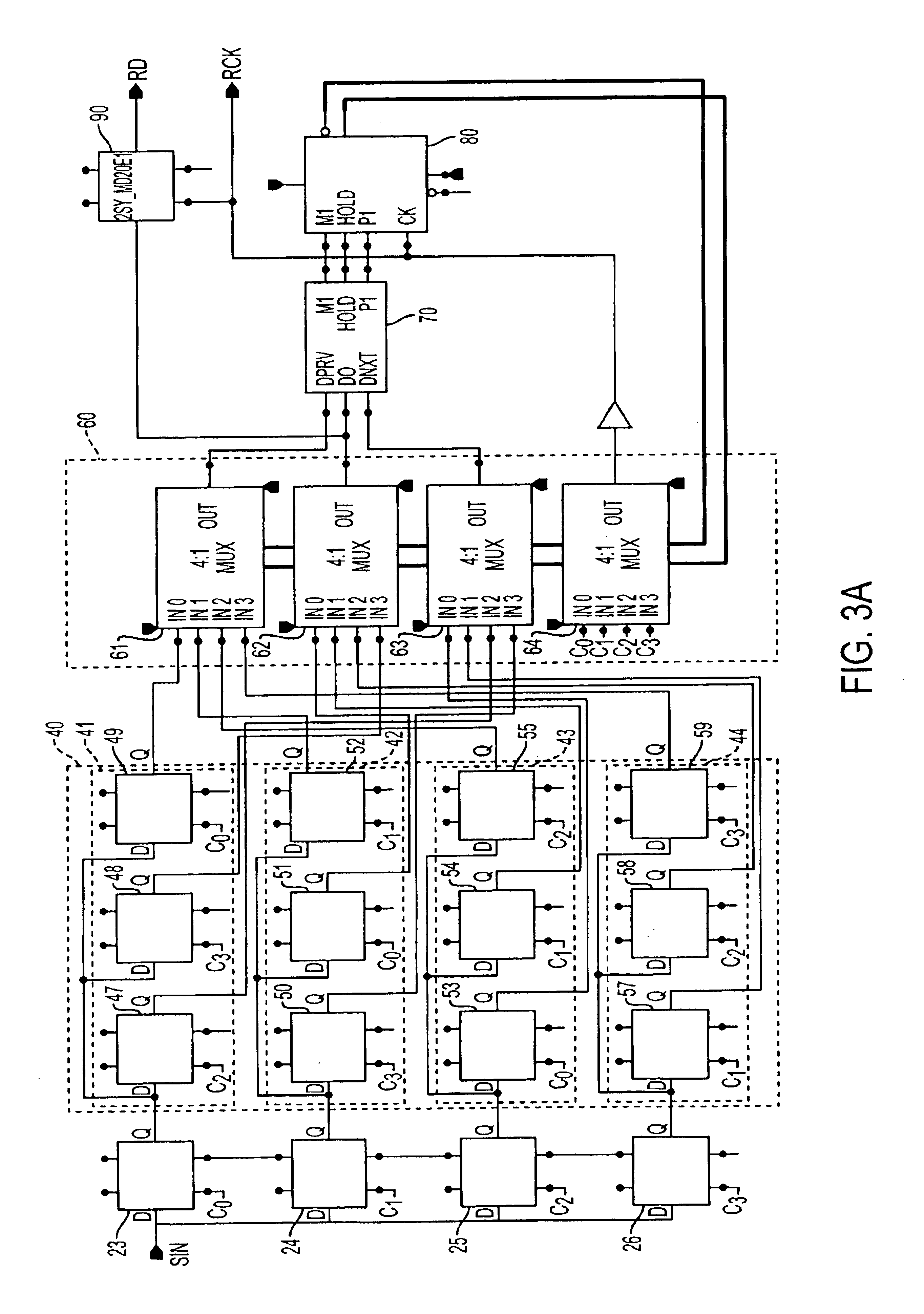

Method and apparatus for recovering a clock signal from an asynchronous data signal

InactiveUS6868134B2Simple and cost-effectiveSimple and cost-effective designPulse automatic controlSynchronising arrangementMultiplexerClock recovery

A clock recovery unit for generating a clock signal corresponding to an asynchronous data signal. The clock recovery unit includes an input port for receiving an incoming data signal; a local oscillator circuit for generating a plurality of clock signals having the same frequency, where the plurality of clock signals are each shifted in phase relative to one another; a sampling unit having a plurality of latches, each of which is clocked by one of the plurality of clock signals generated by the local oscillator circuit, the sampling unit outputting a plurality data samples of the incoming data signal; a data phase alignment unit coupled to the sampling unit, the data phase alignment unit receiving the plurality of data samples as input signals and operative for shifting the phase of the plurality of data samples; a multiplexer circuit coupled to the data phase alignment unit, the multiplexer circuit having a first multiplexer operative for selecting a portion of the plurality of data samples, each of the data samples having a corresponding clock signal, which is one of the plurality of clock signals generated by the local oscillator circuit, the multiplexer circuit having a second multiplexer operative for selecting one of the plurality of clock signals generated by the local oscillator circuit; a phase decoder coupled to the multiplexer circuit, the phase decoder operative for receiving the portion of the plurality of data samples selected by the multiplexer and for generating an output signal indicative of the logic values of the portion of the plurality of the data samples selected by the first multiplexer; and a barrel shifter circuit coupled to the phase decoder, the barrel shifter operative for adjusting the data samples selected by the first multiplexer in accordance with the output signal of the phase decoder.

Owner:PANASONIC CORP

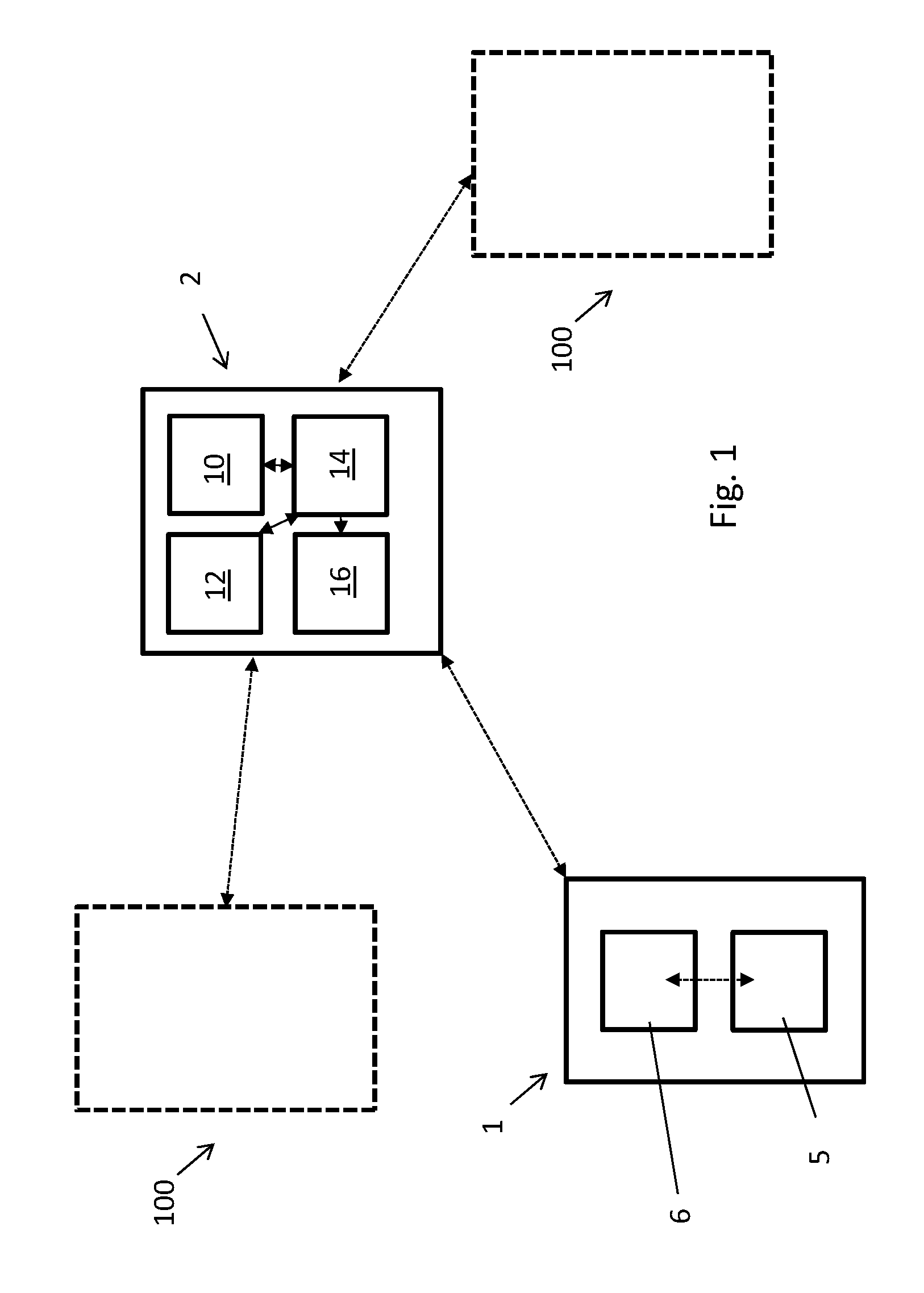

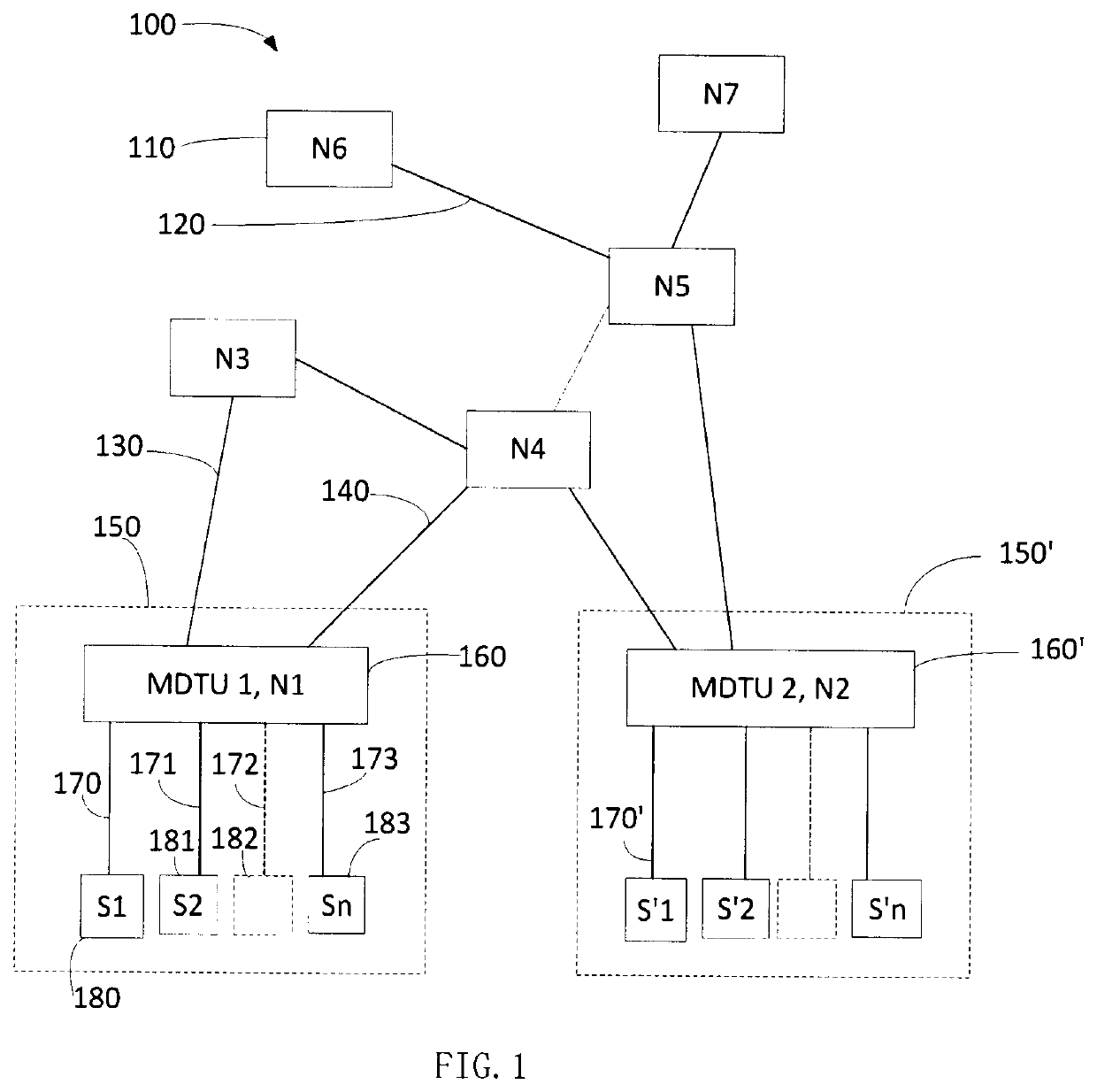

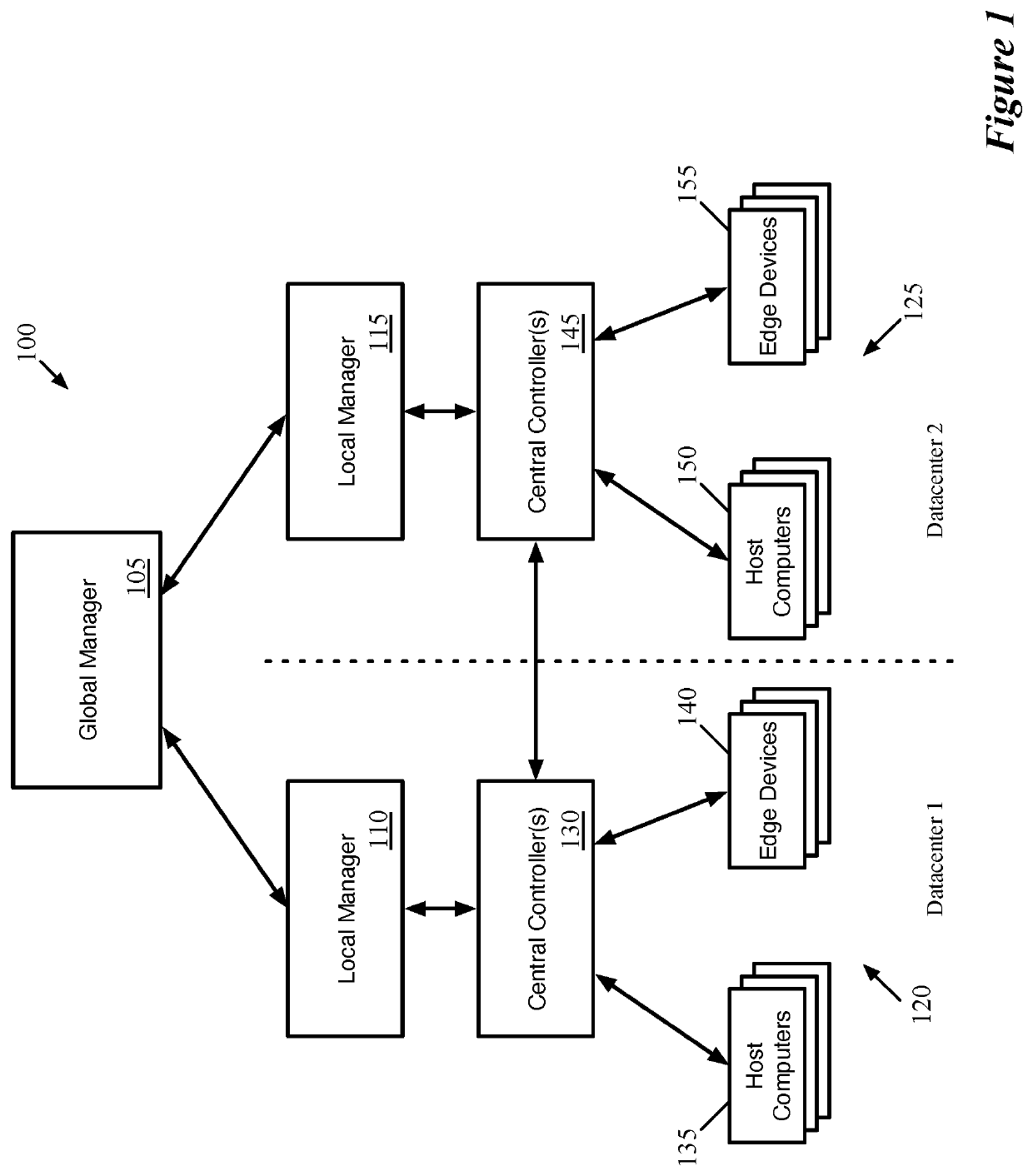

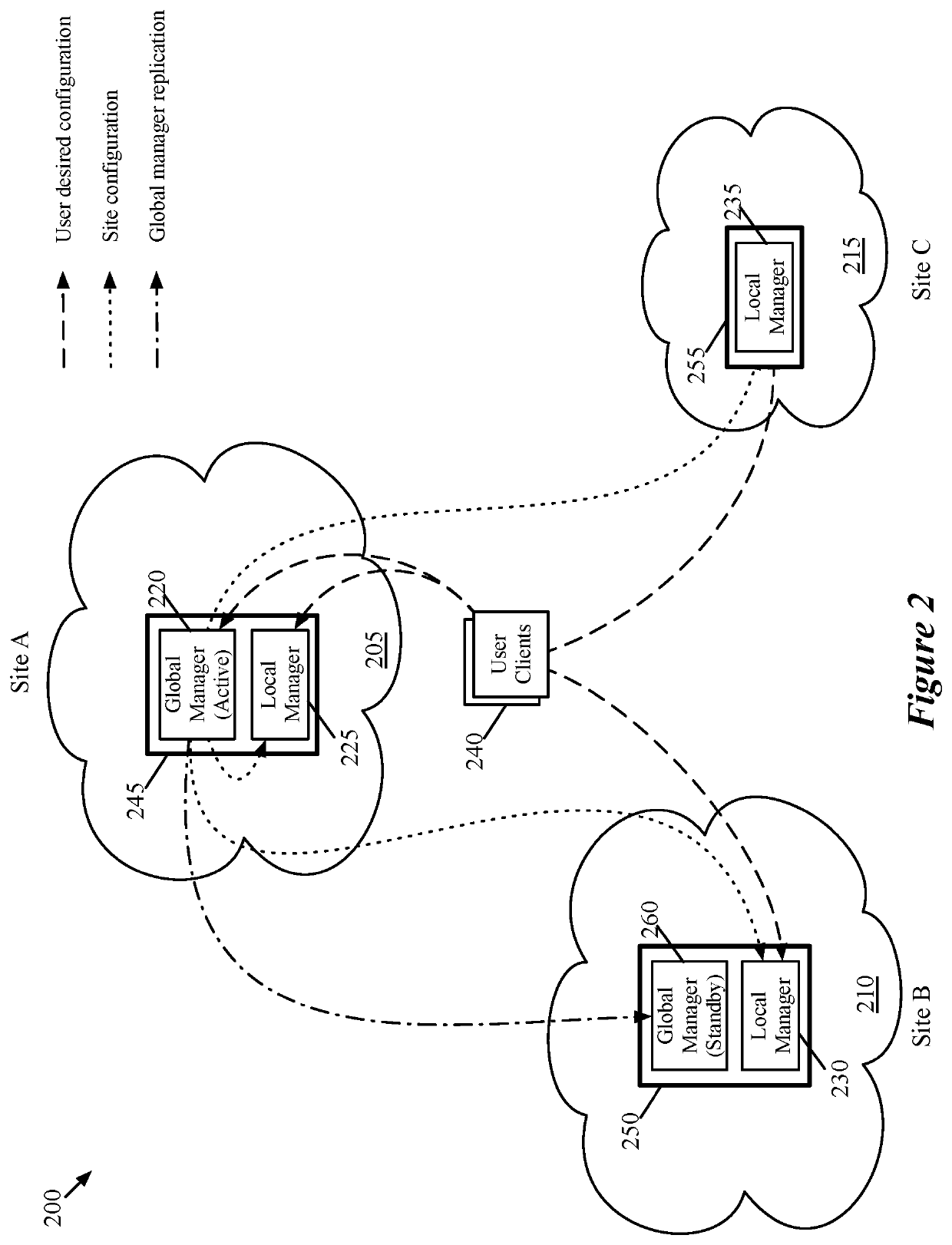

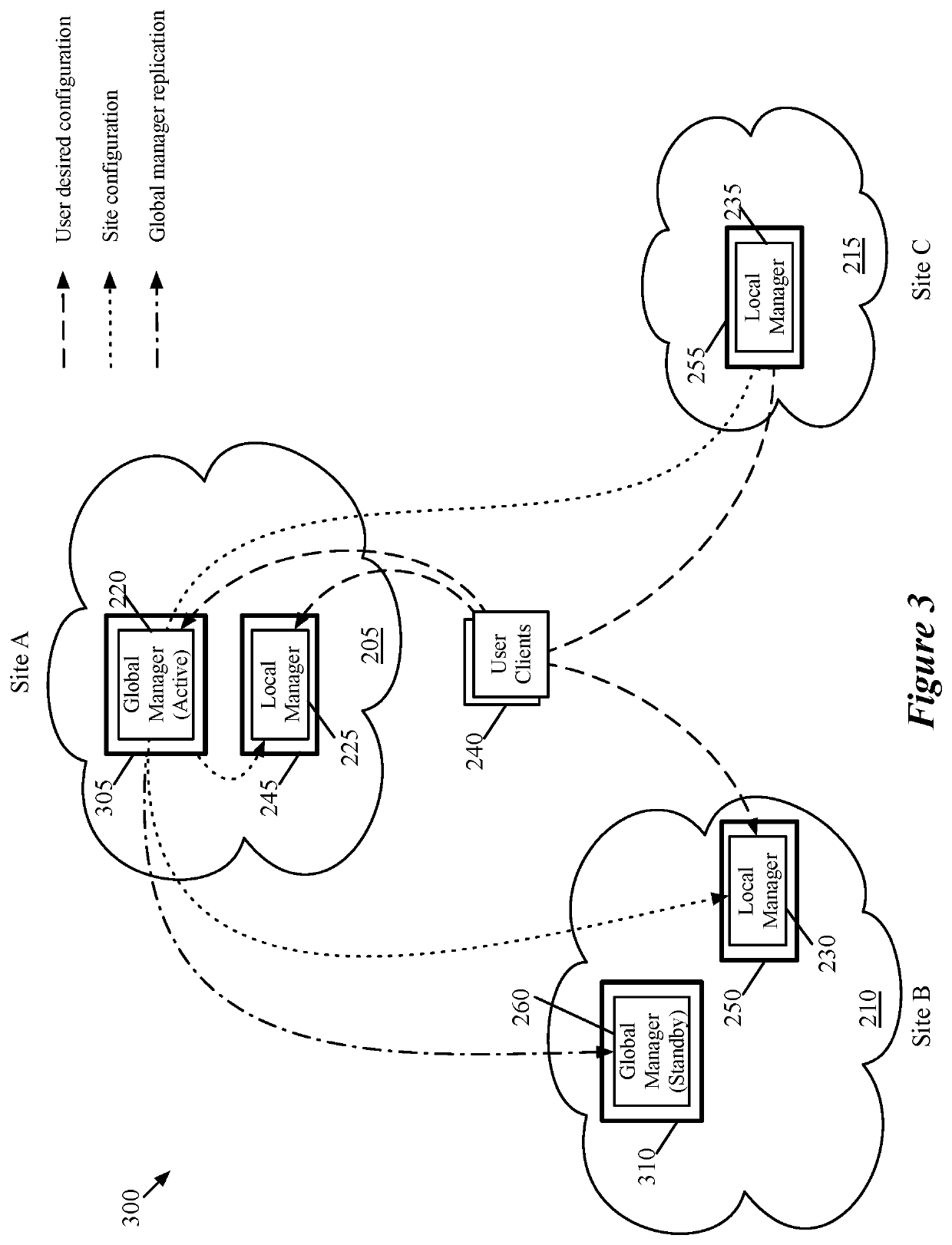

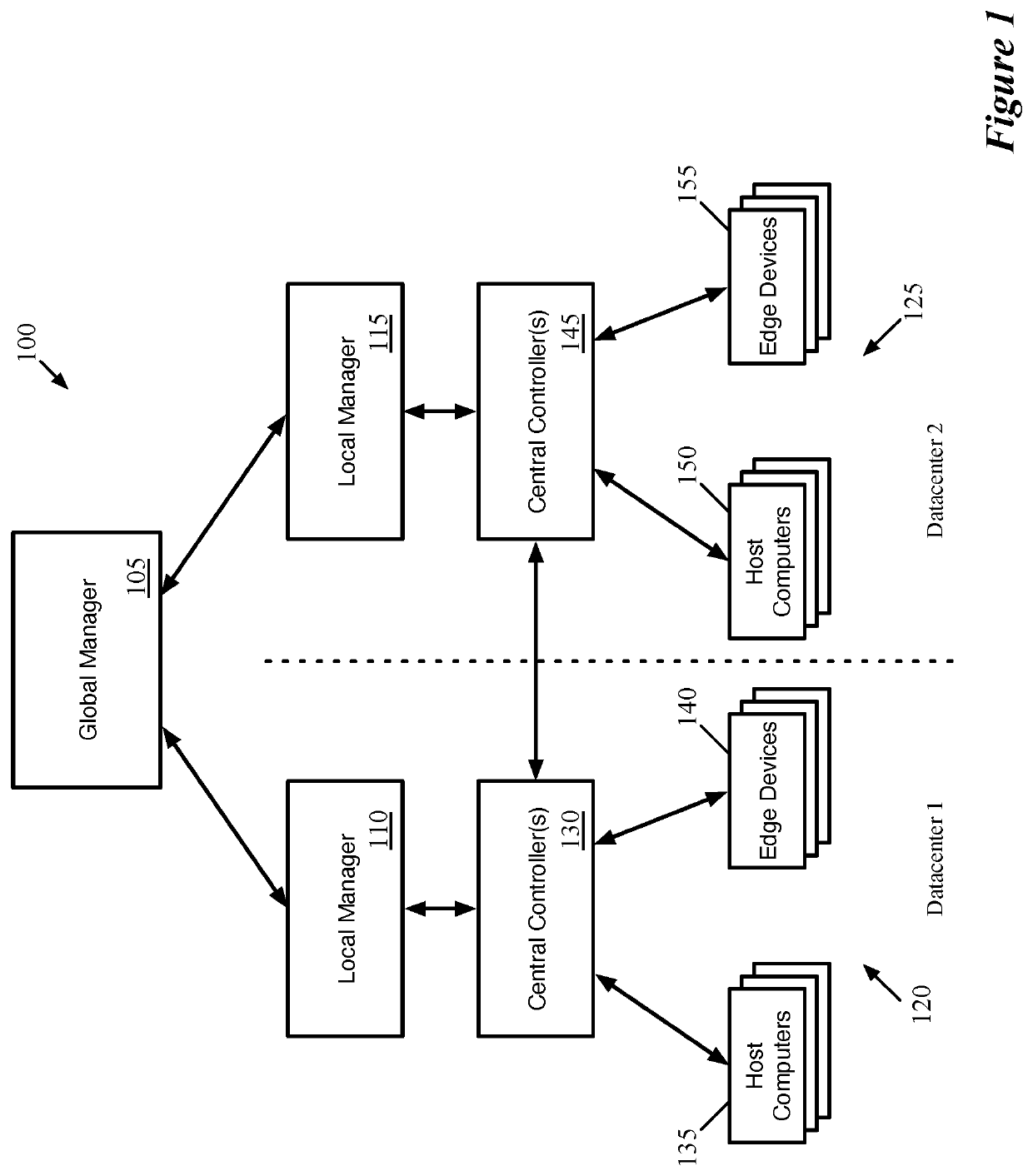

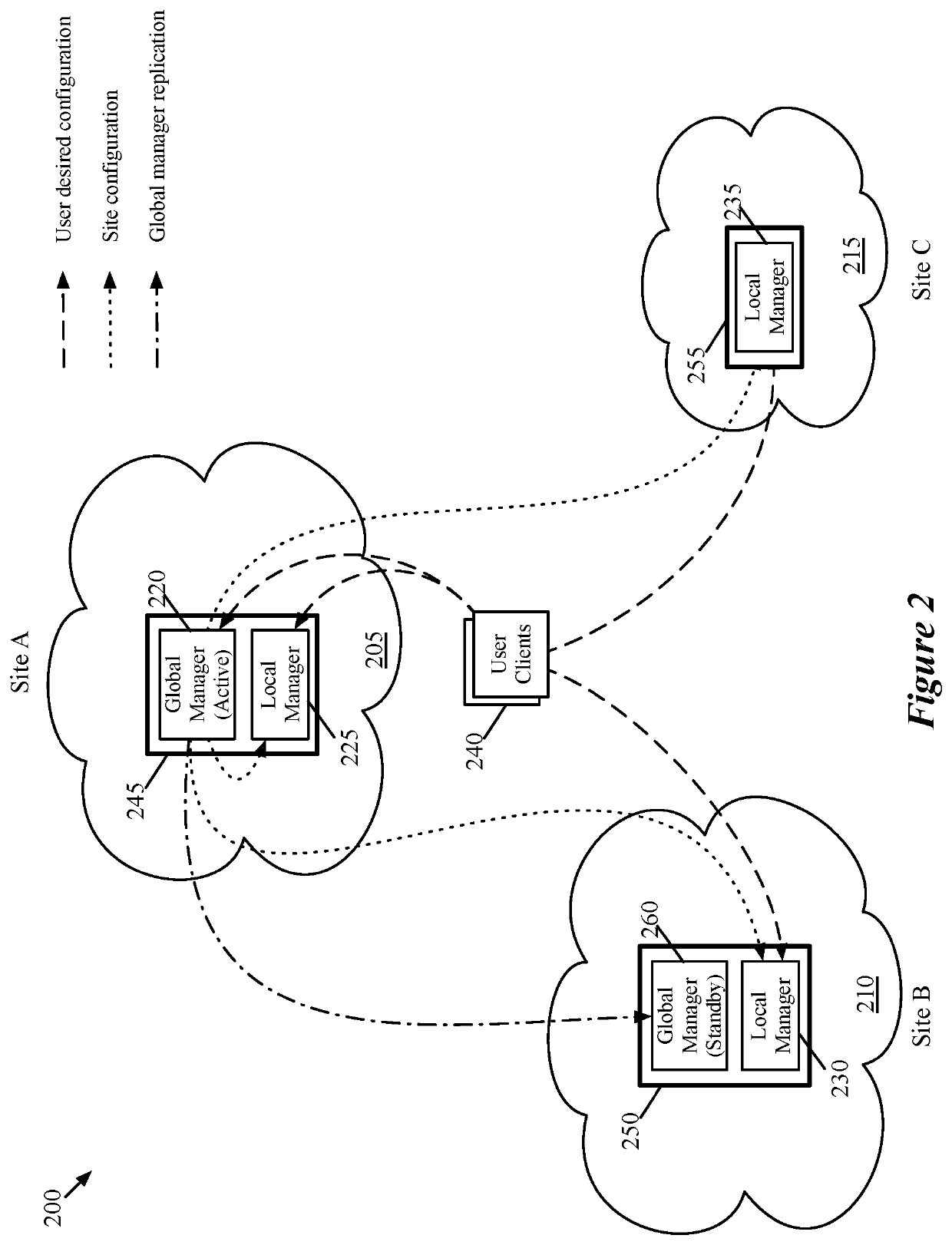

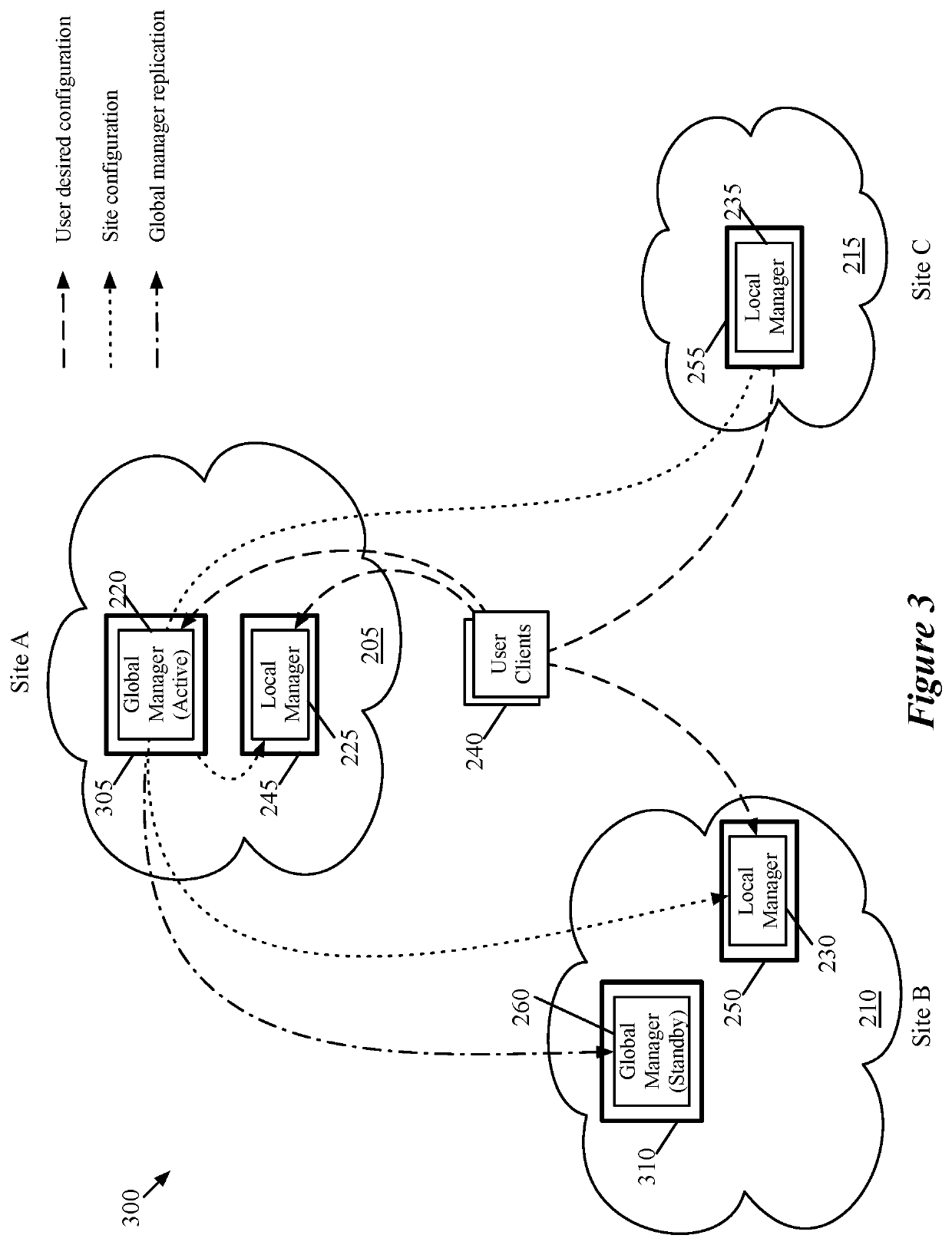

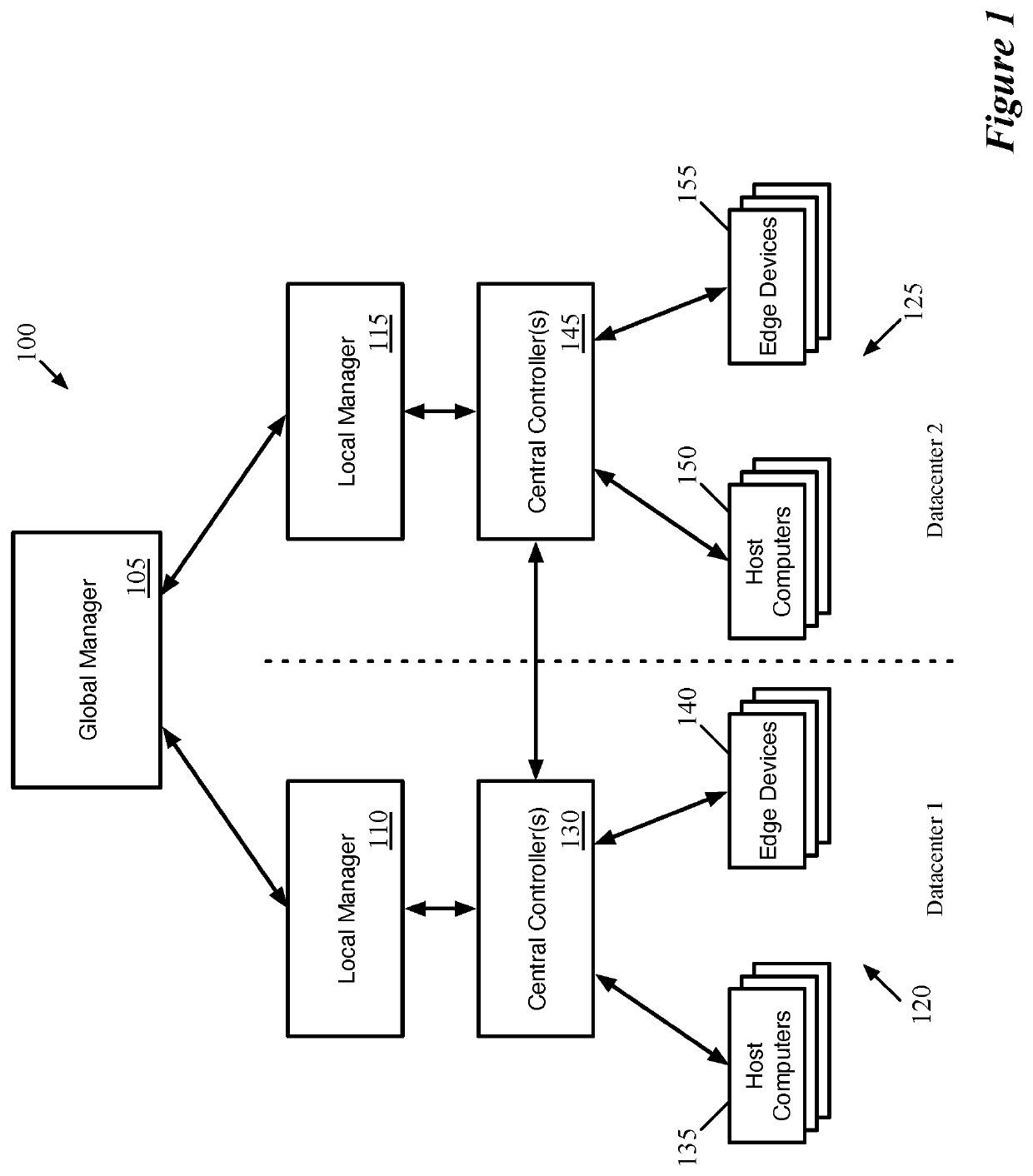

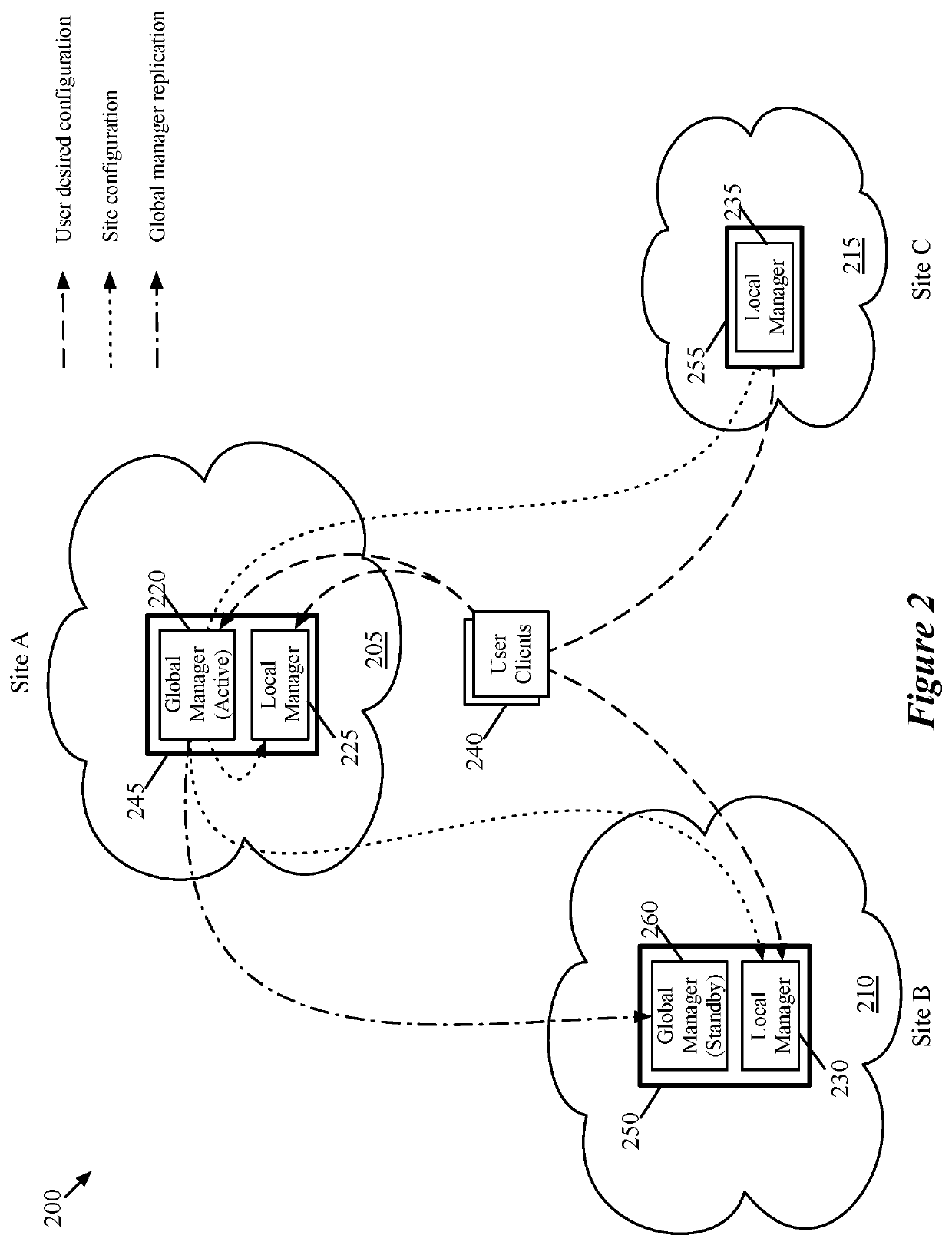

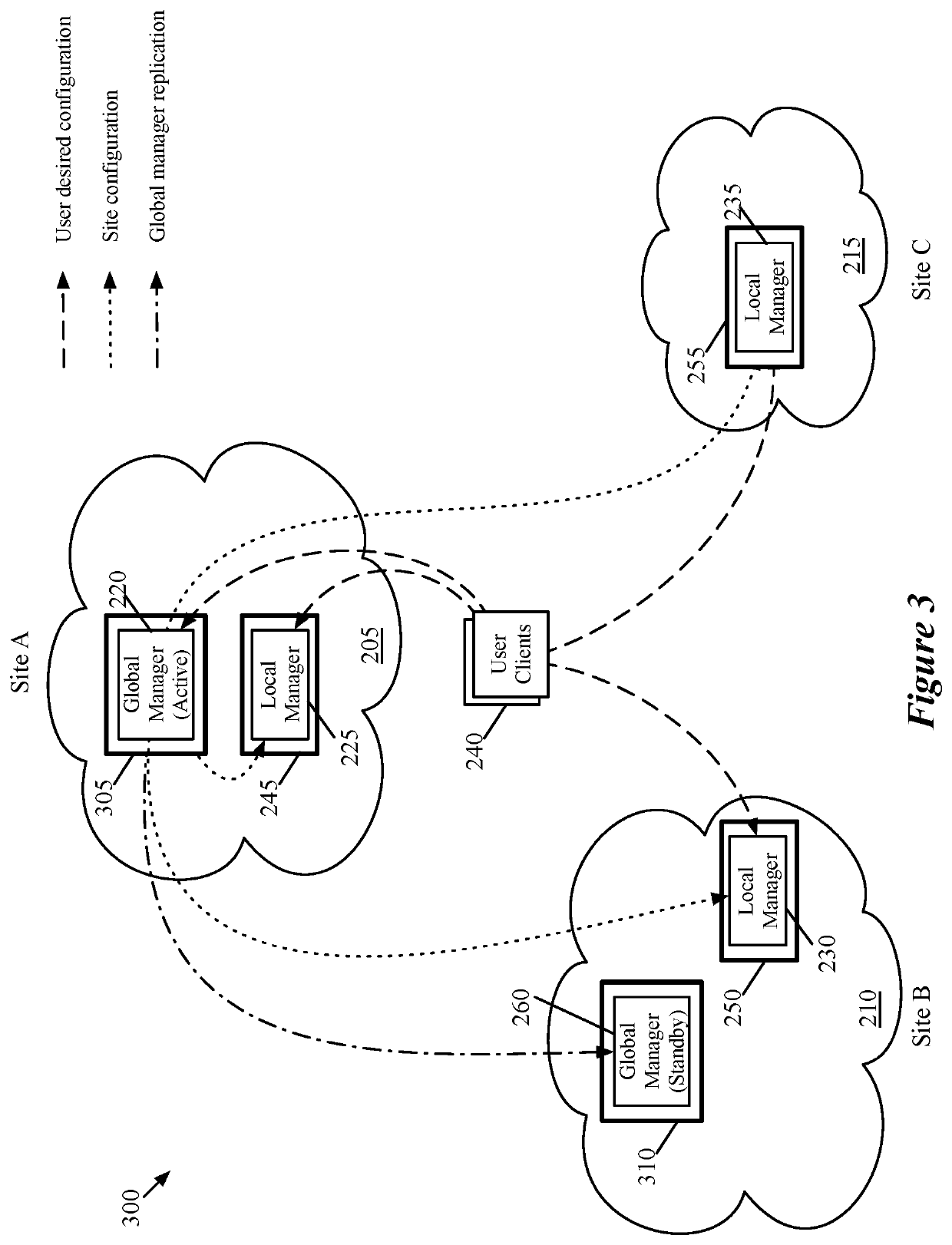

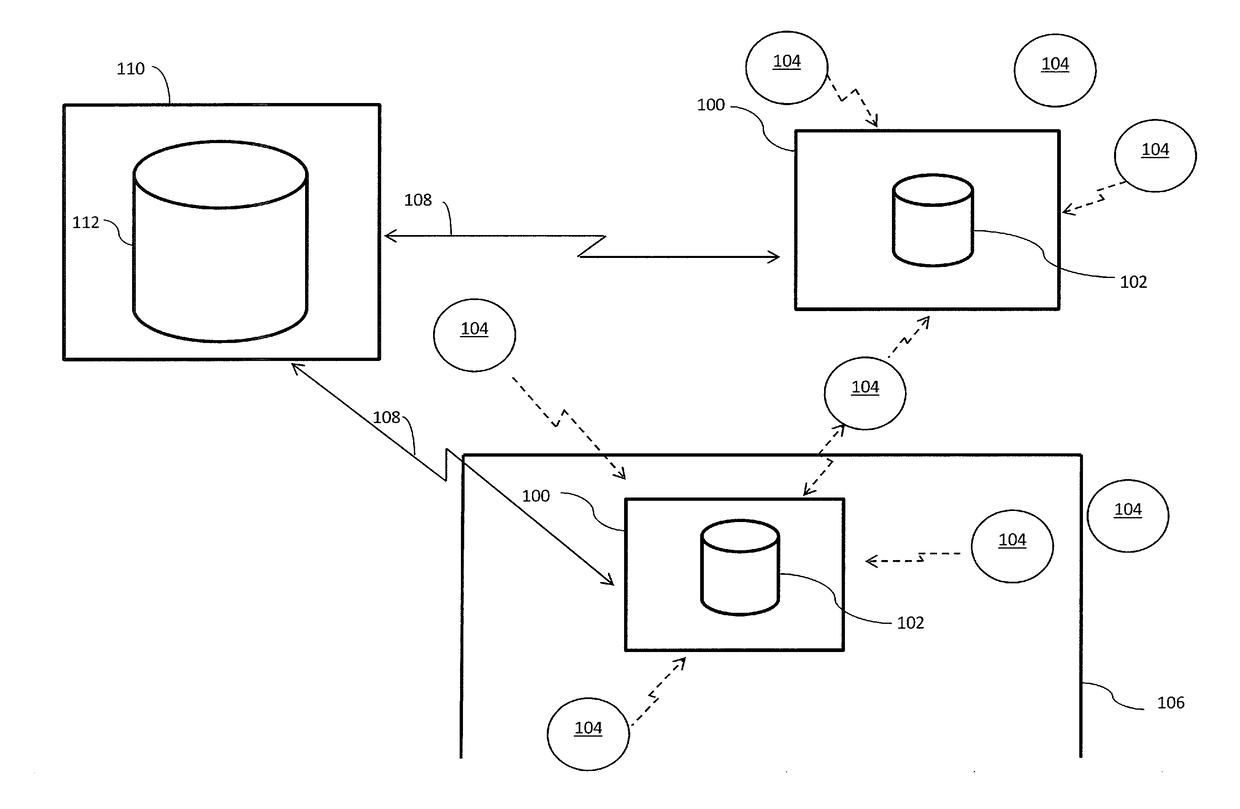

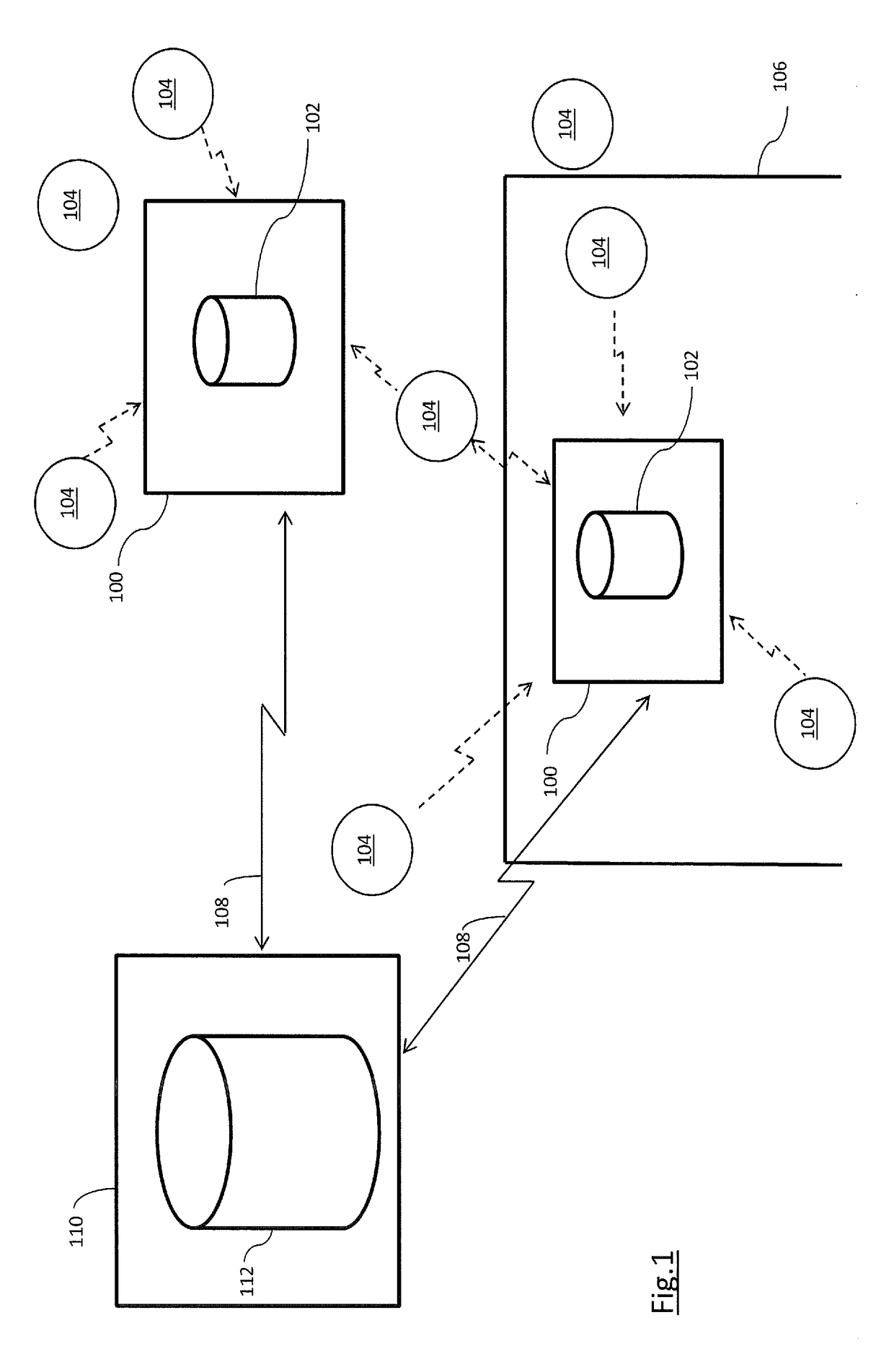

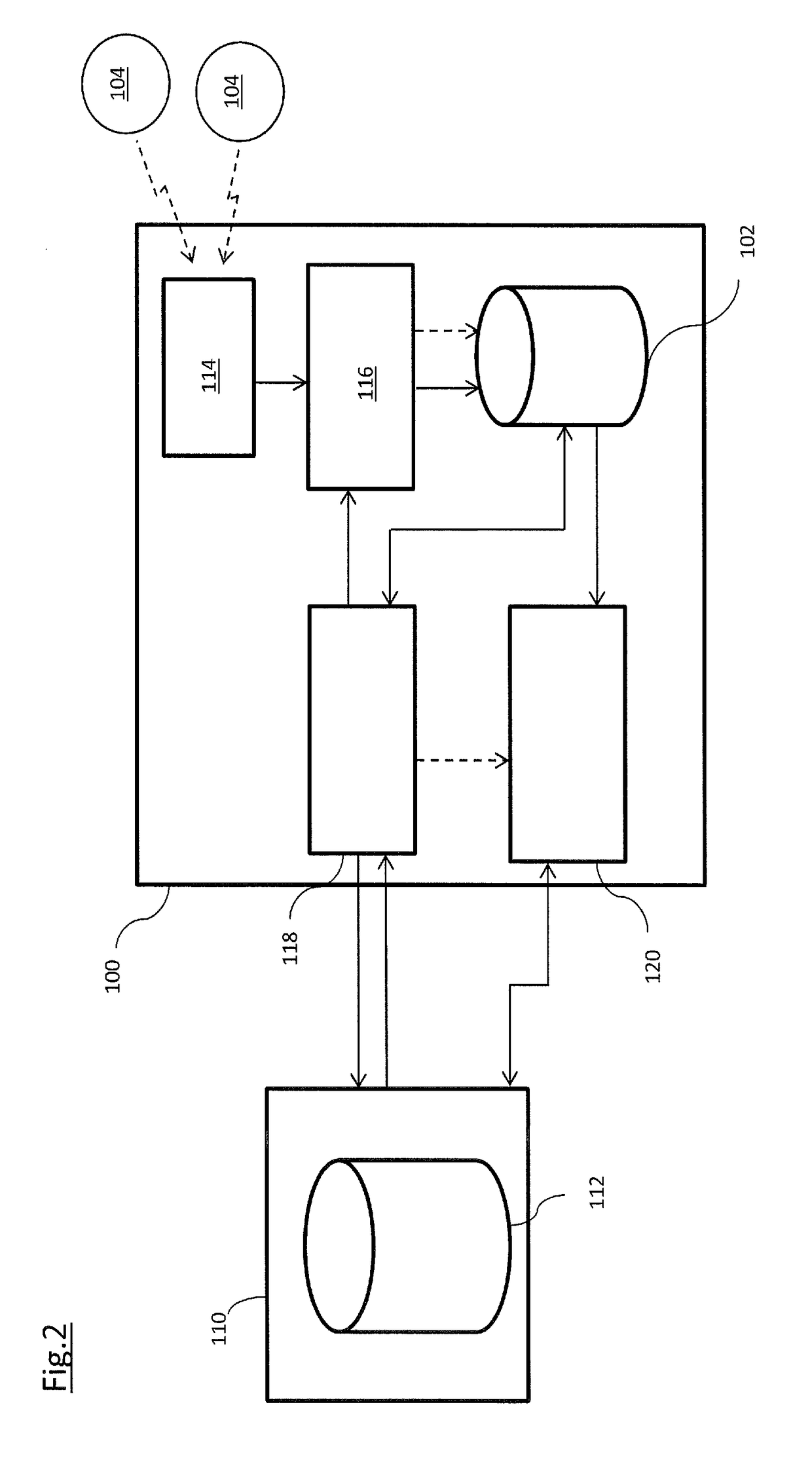

Network management system for federated multi-site logical network

PendingUS20210314212A1Minimizing amount of dataData switching networksInput/output processes for data processingNetwork managementLogical network

Owner:VMWARE INC

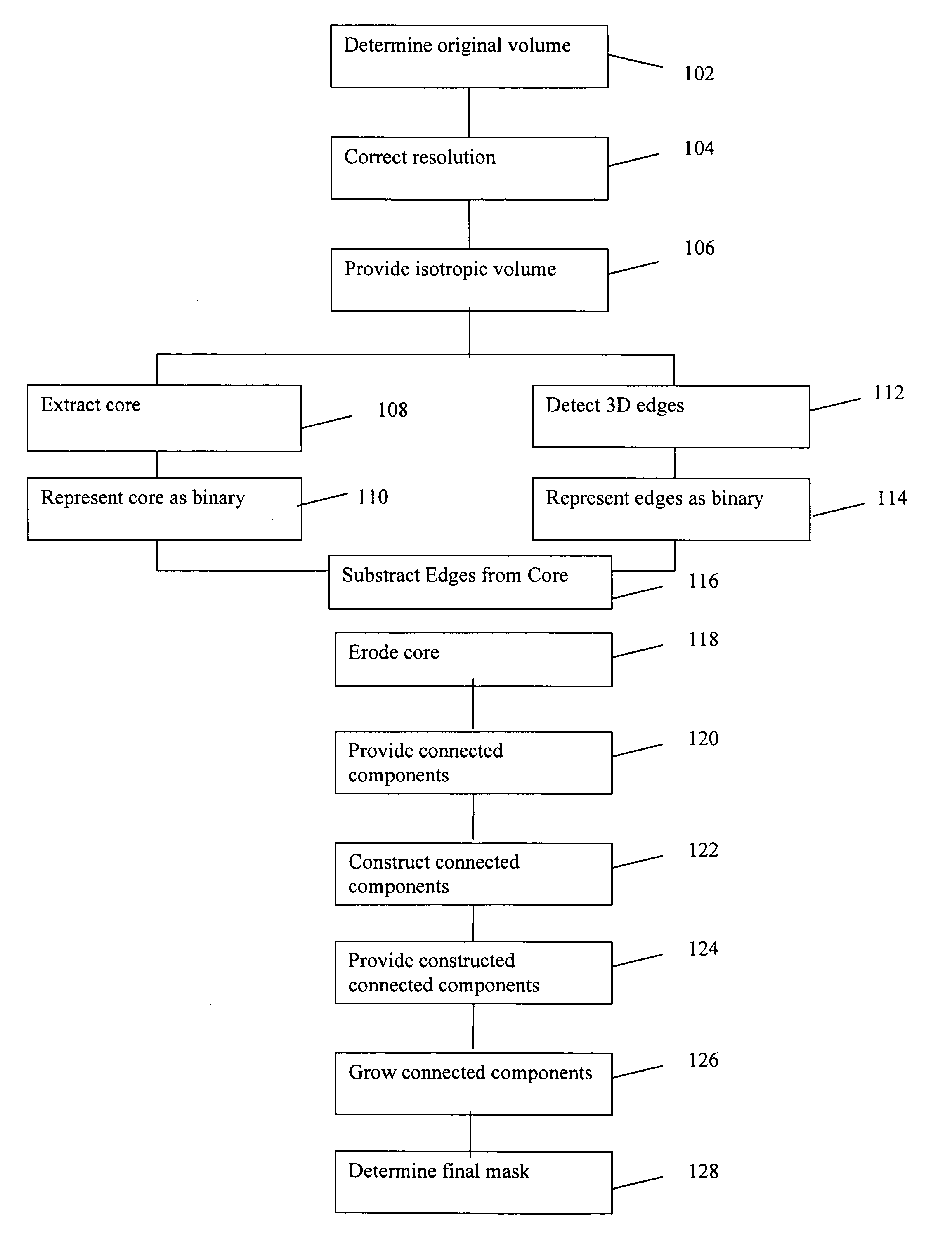

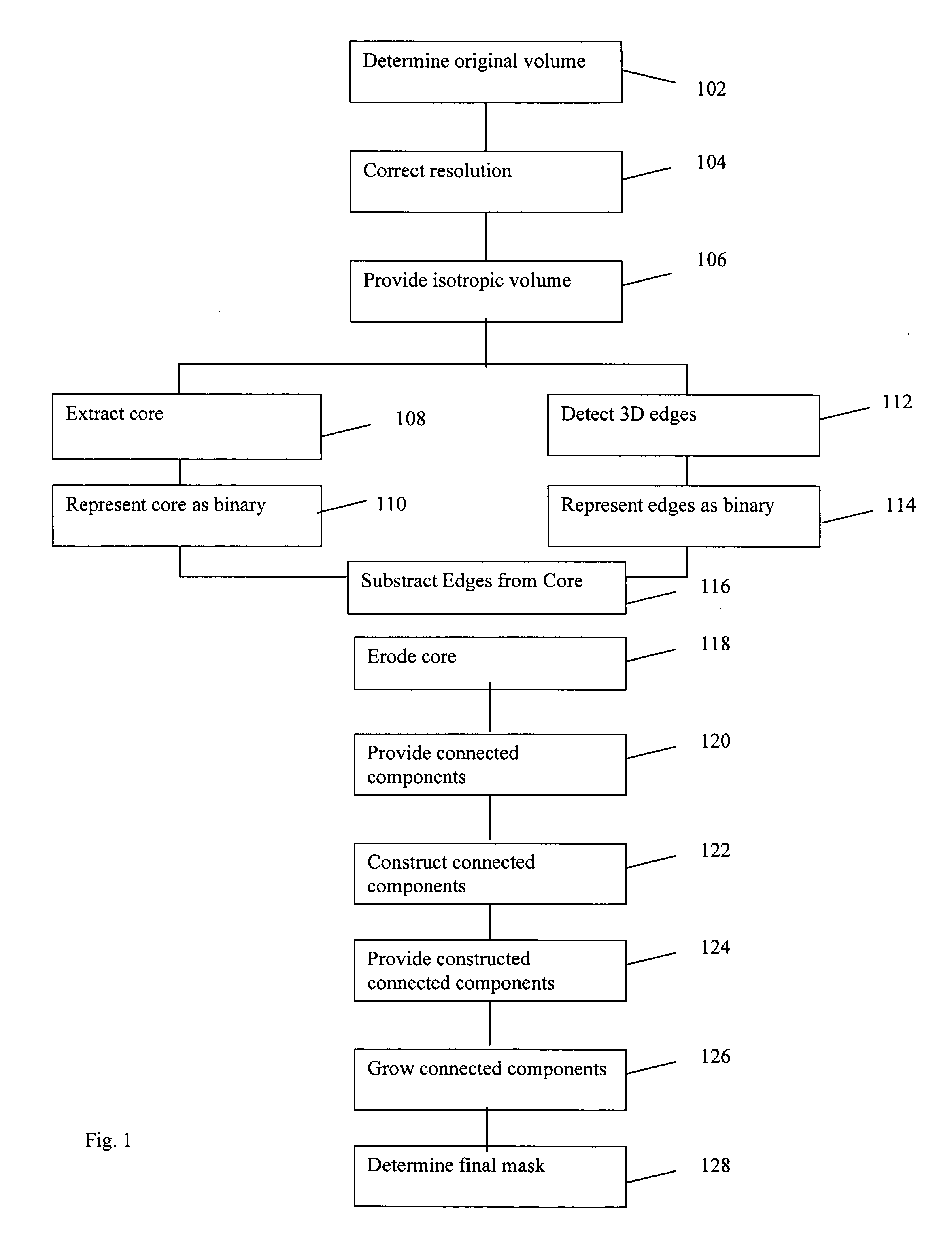

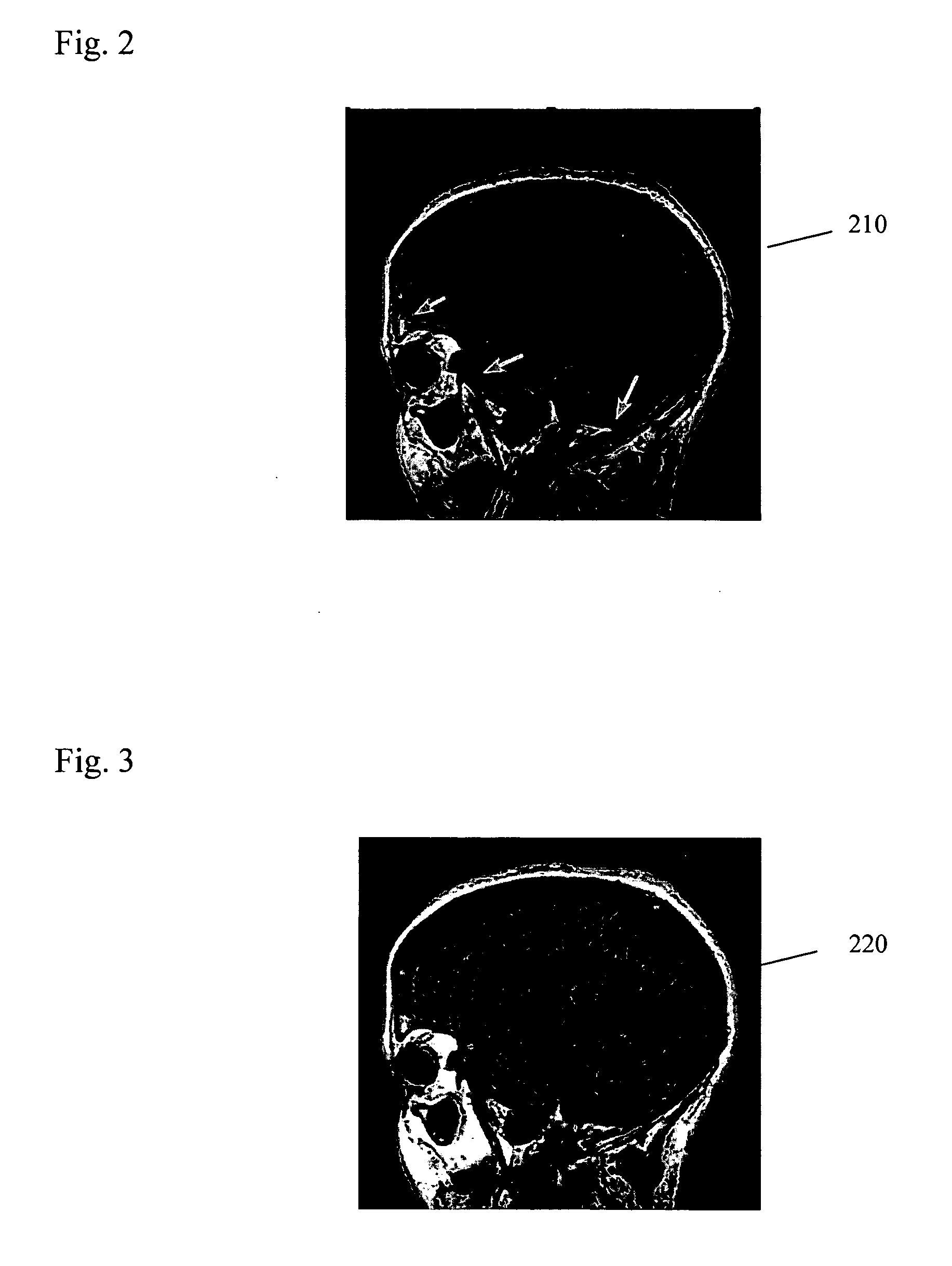

System, software arrangement and method for segmenting an image

ActiveUS20060094961A1Minimizing amount of dataEasy accessUltrasonic/sonic/infrasonic diagnosticsImage enhancementAnatomical structuresVoxel

A logic arrangement, system and method for segmentation using magnetic resonance imaging (“MRI”) are provided. For example, as an end product, an image associated with at least one portion of an anatomical structure is generated. In particular, first data associated with the at least one portion of the anatomical structure is received. Second data can be associated with at least one edge of at least one of the at least one portion is obtained based on the first data. The image can be generated based on the first data and the second data. In addition or as an alternative, it is also possible to generate the image using connected voxel components. Such components are created by processing information associated with an erosion of surface voxels of an image.

Owner:NEW YORK UNIV

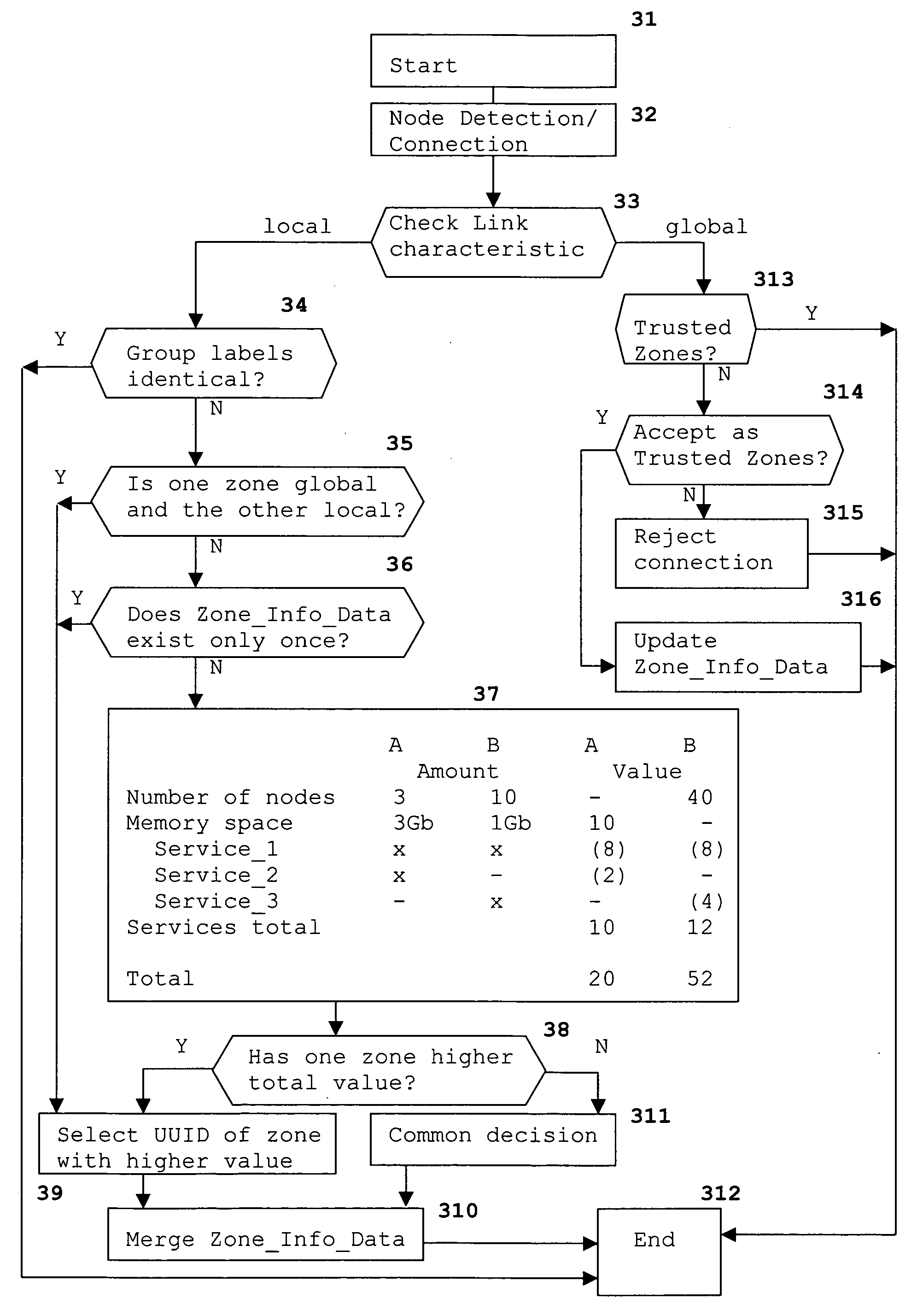

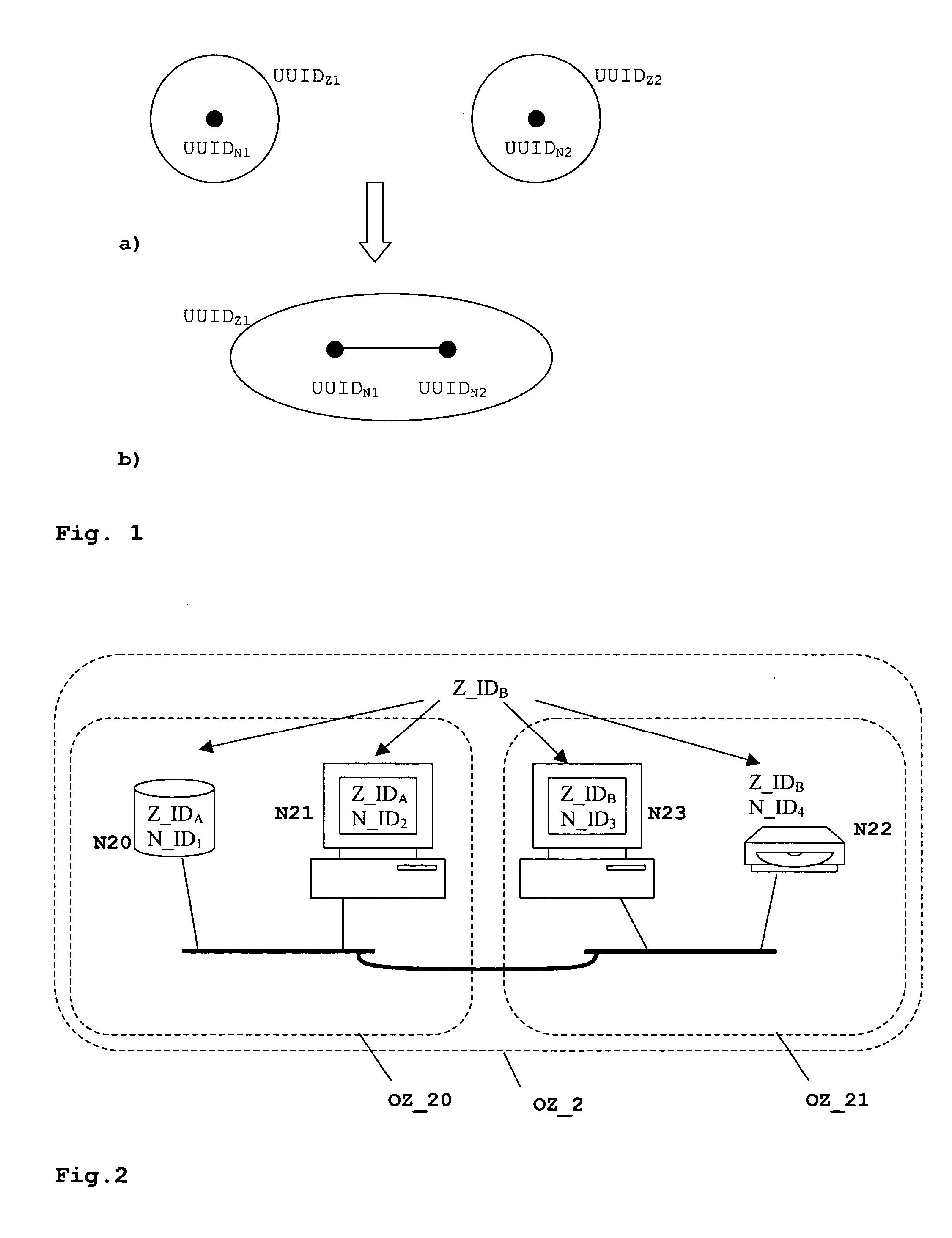

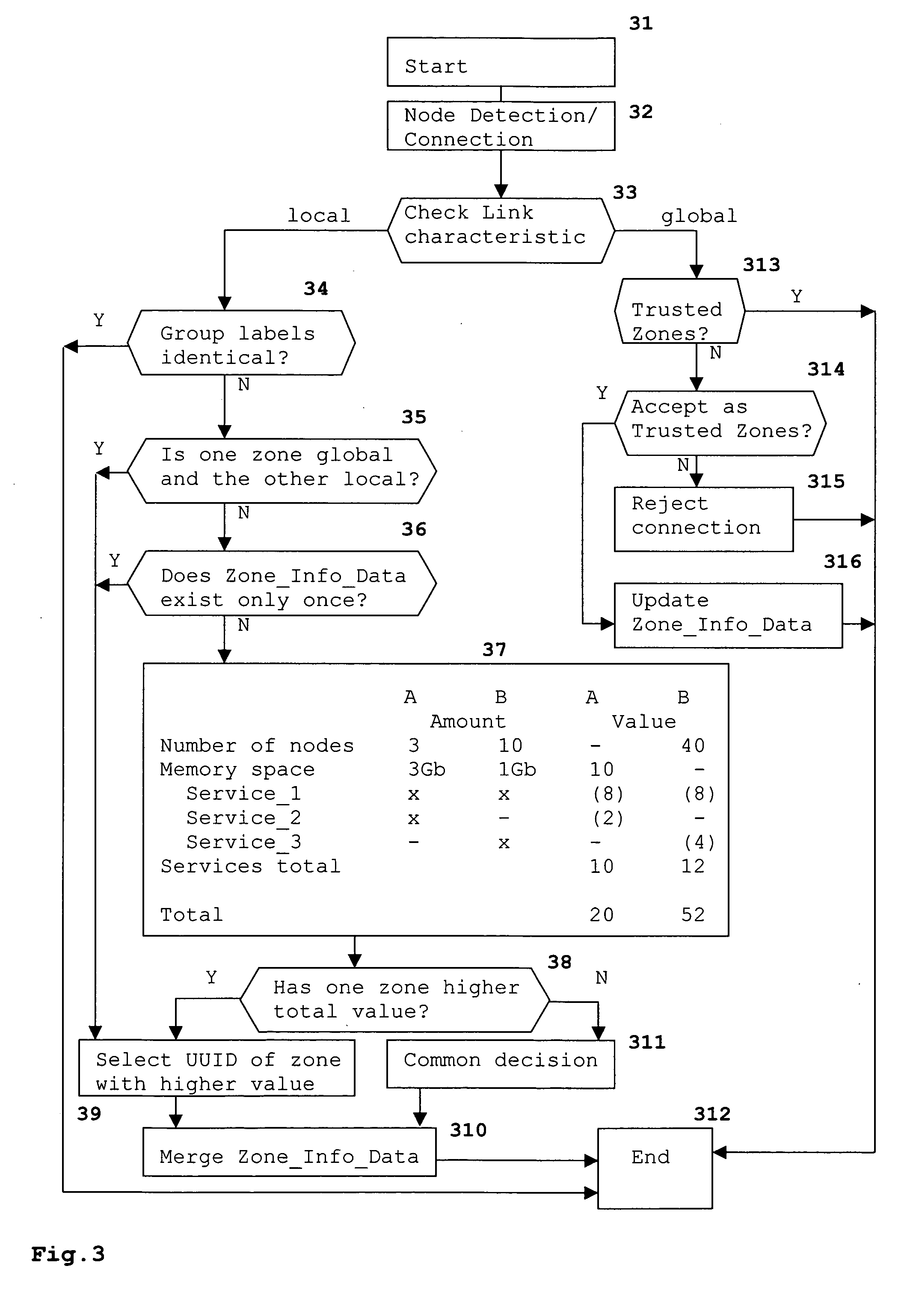

Method for assigning an identifier to a peer-group in a peer-to-peer network

ActiveUS20050021793A1Increased durabilityReduce network trafficDigital data processing detailsData switching by path configurationDistributed computingPeer-to-peer

Networks, particularly home networks, may be implemented using peer-to-peer technology. To relieve the user from administrative tasks, some configuration routines for such networks may be automated. Therefore a peer-group selects one of its peers as negotiation peer, having the task to communicate with single other peers or negotiation peers from other peer-groups. When adding or removing single peers, or merging or splitting peer-groups, the group label is usually modified. But it may be advantageous to keep the group label, especially if that label is known to other peer-groups. If a new peer-group in a peer-to-peer network is created by merging or splitting other peer-groups, a method for selecting a group label for the new peer-group comprises determining a negotiation peer, exchanging information between the negotiation peers in the case of merging, comparing features of the two peer-groups and based on the comparison assigning the label of one of the peer-groups to the new peer-group.

Owner:INTERDIGITAL CE PATENT HLDG

Network controller for multi-site logical network

ActiveUS20210314225A1Minimizing amount of dataData switching networksInput/output processes for data processingNetwork controlEngineering

Some embodiments provide a method for a first network controller executing at a first site of multiple sites spanned by a logical network. Network controllers execute at each site. The method generates logical network state data for the first site based on (i) data received from computing devices that implement the logical network at the first site and (ii) logical network configuration data from a network manager at the first site. The method provides the logical network state data for the first site to a second network controller executing at a second site. The method provides logical network state data received from the second site to the computing devices that implement the logical network at the first site.

Owner:VMWARE INC

User interface for accessing multi-site logical network

ActiveUS20210314235A1Minimizing amount of dataData switching networksInput/output processes for data processingComputer networkStation

Owner:VMWARE INC

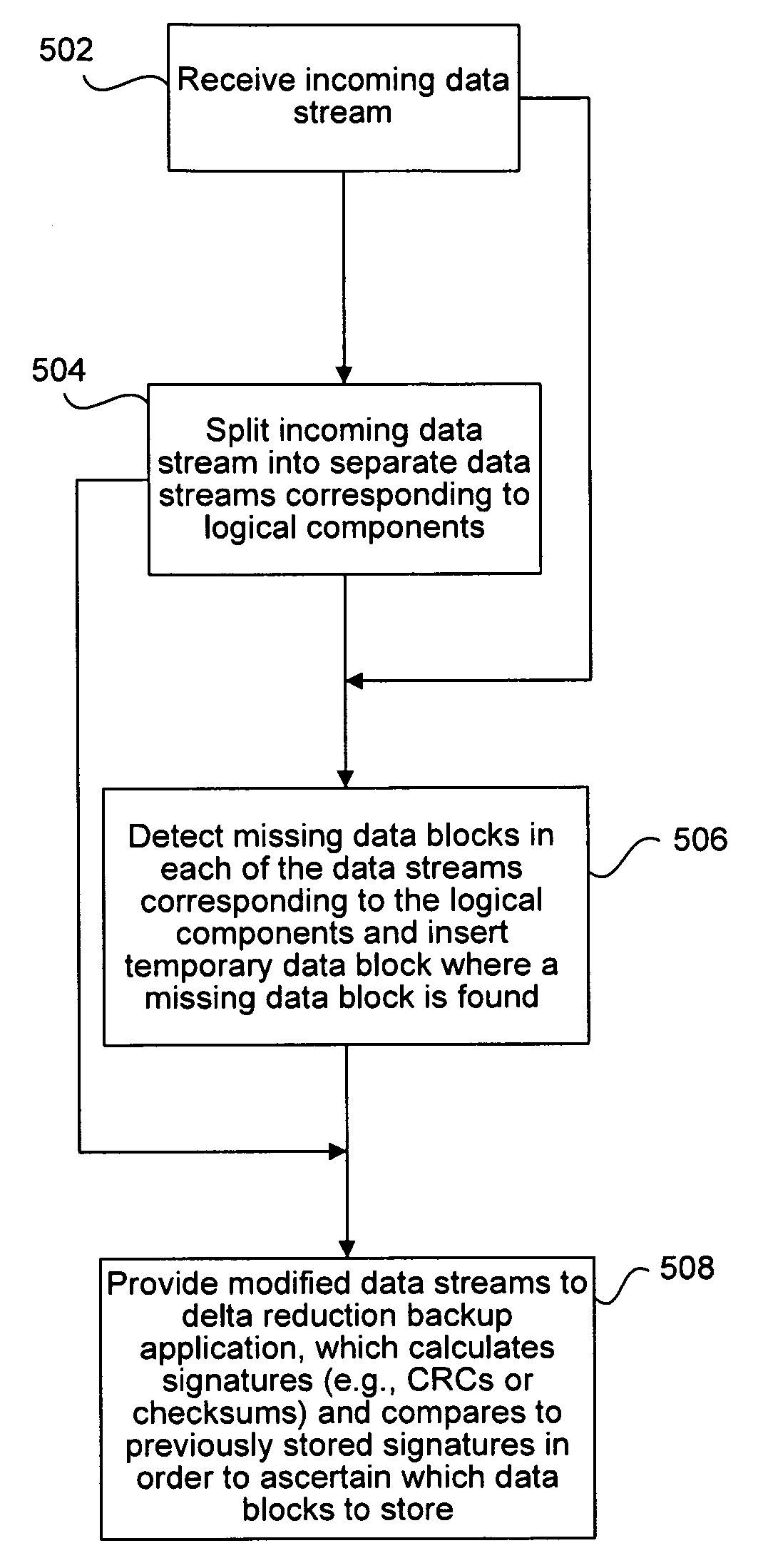

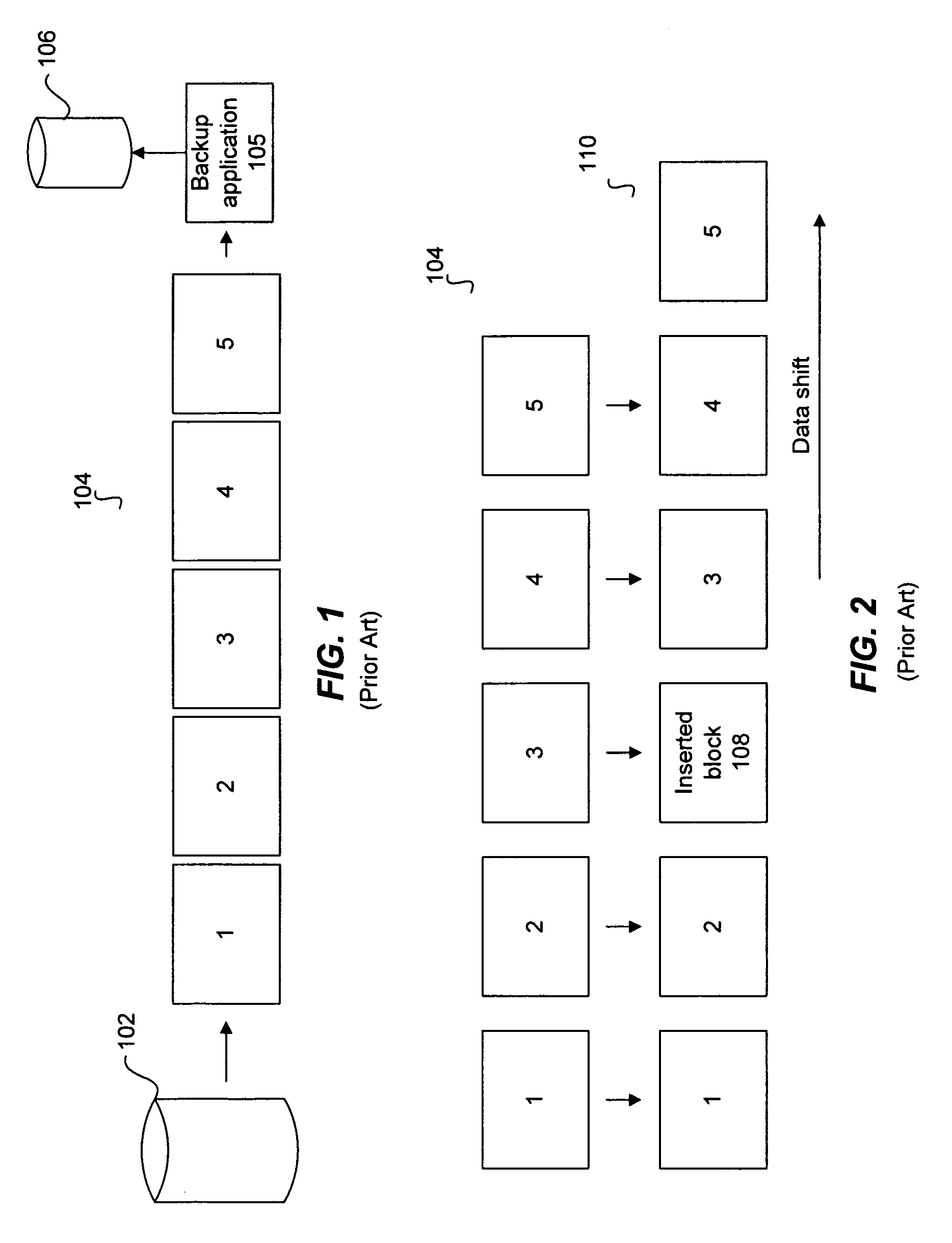

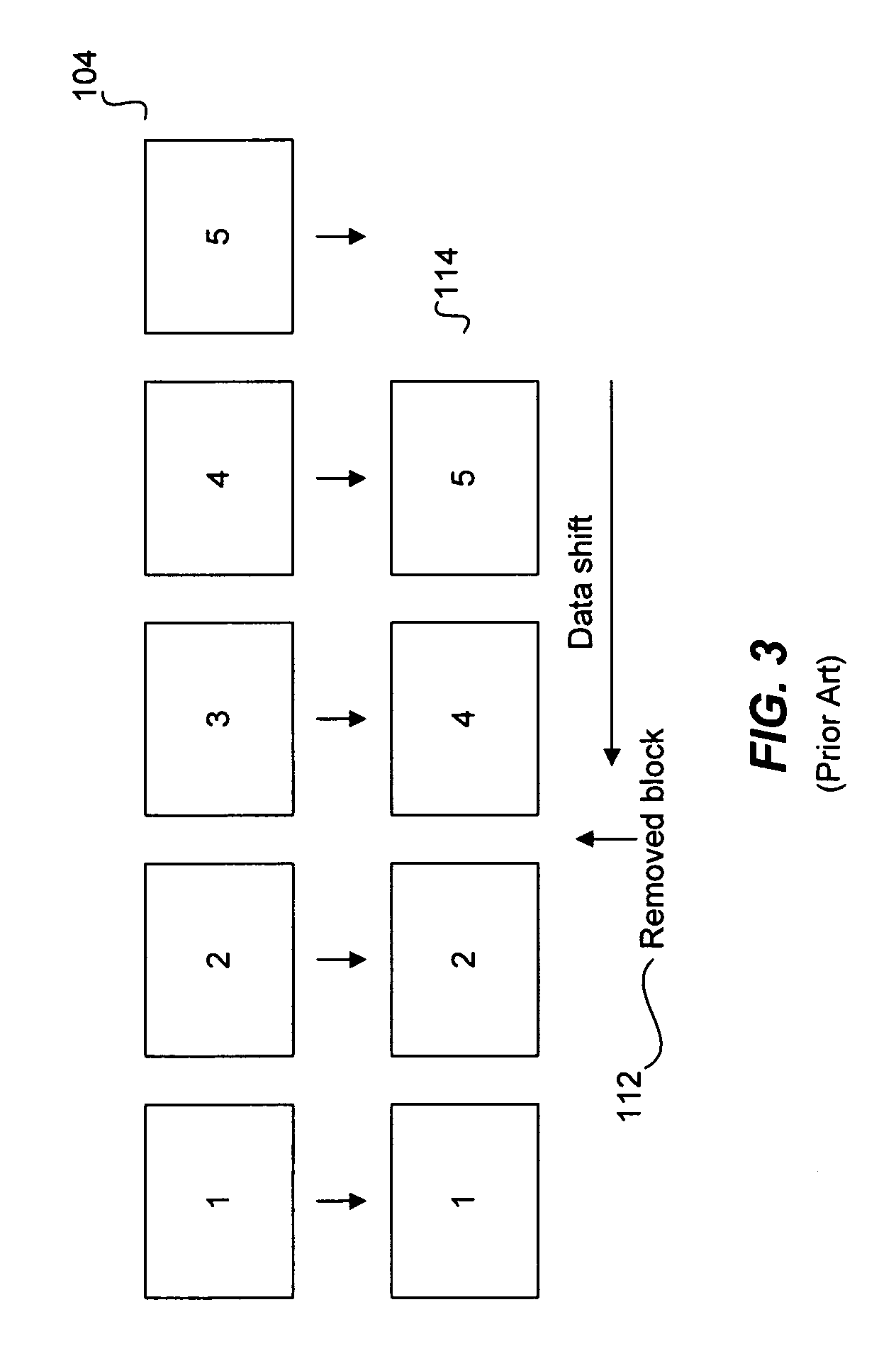

Methods and apparatus for modifying a backup data stream including logical partitions of data blocks to be provided to a fixed position delta reduction backup application

ActiveUS7761766B2Minimizing amount of dataQuantity minimizationInstruments for road network navigationError preventionData streamMissing data

When a data stream is received, the data stream may be parsed into a plurality of logical components, where each of the logical components includes one or more data blocks. Missing data blocks may also be detected in the data stream, and therefore may be detected in each of the plurality of logical components. For instance, each of the logical components may be separated into a separate data stream for which missing data blocks may be detected. A temporary data block is then inserted where each missing data block is detected (e.g., in each of the plurality of logical components). In this manner, inefficiencies introduced into a fixed position delta reduction backup process as a result of new or deleted data in a system implementing a plurality of data blocks which may be stored in the form of logical components are eliminated.

Owner:CARBONITE GMBH

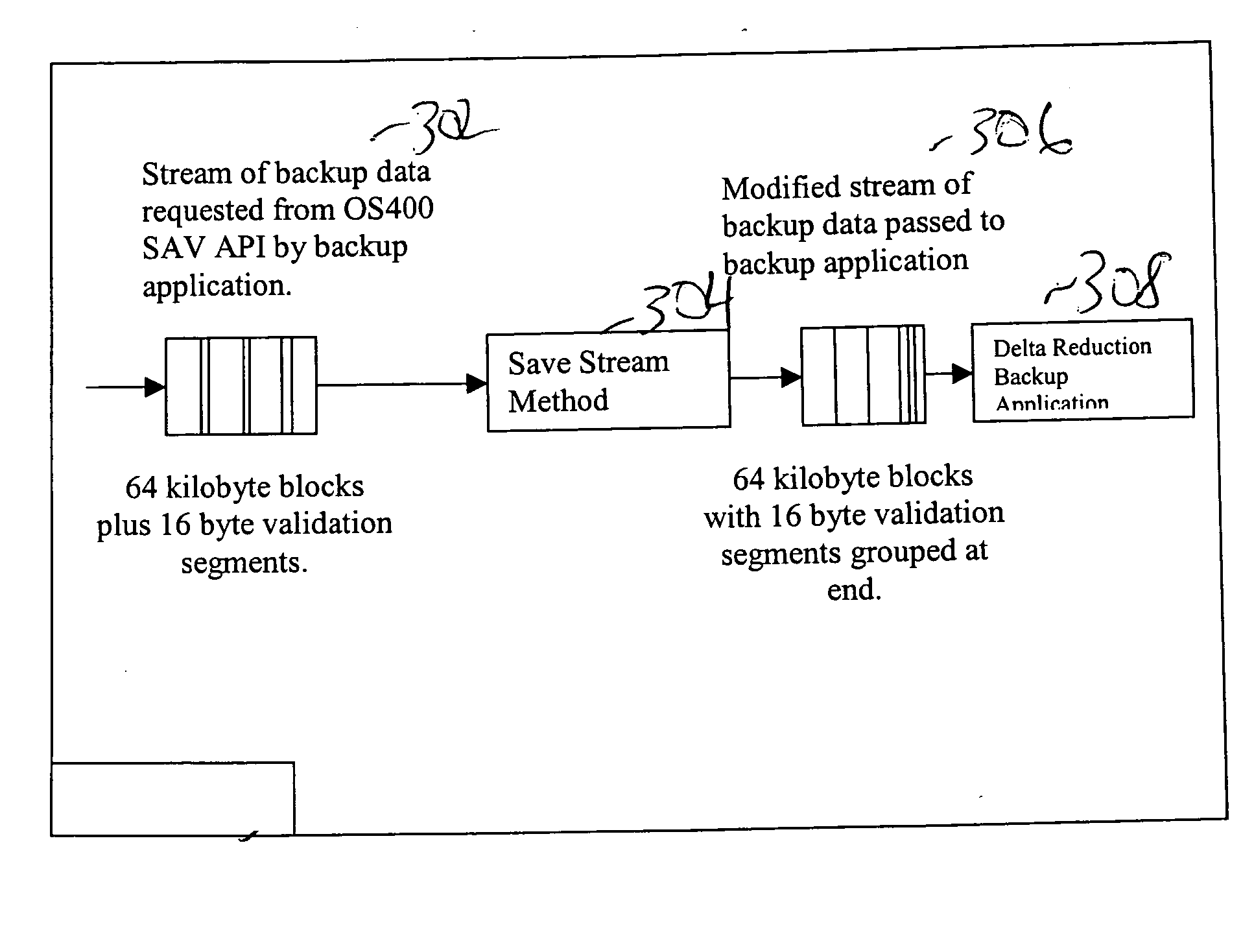

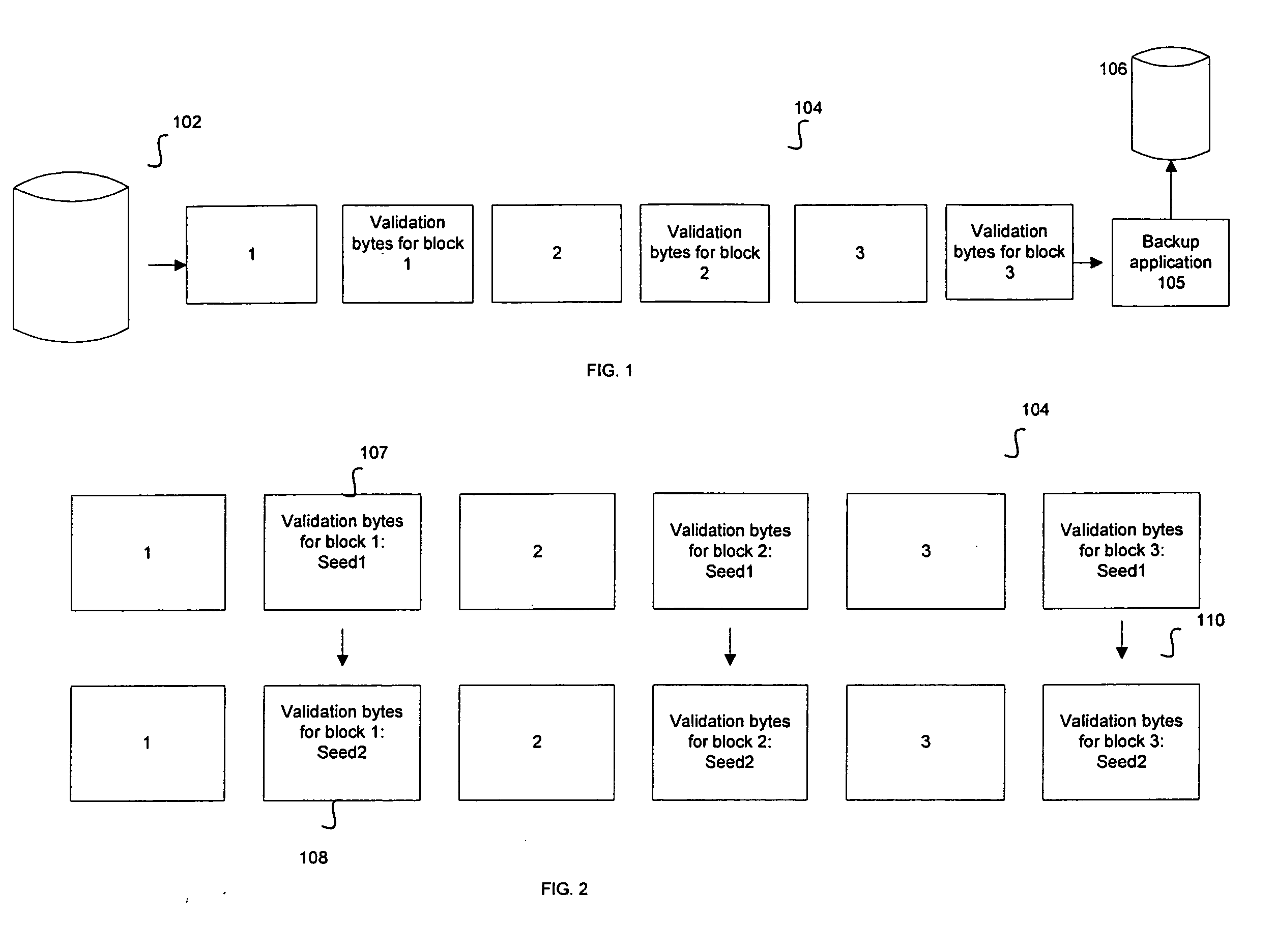

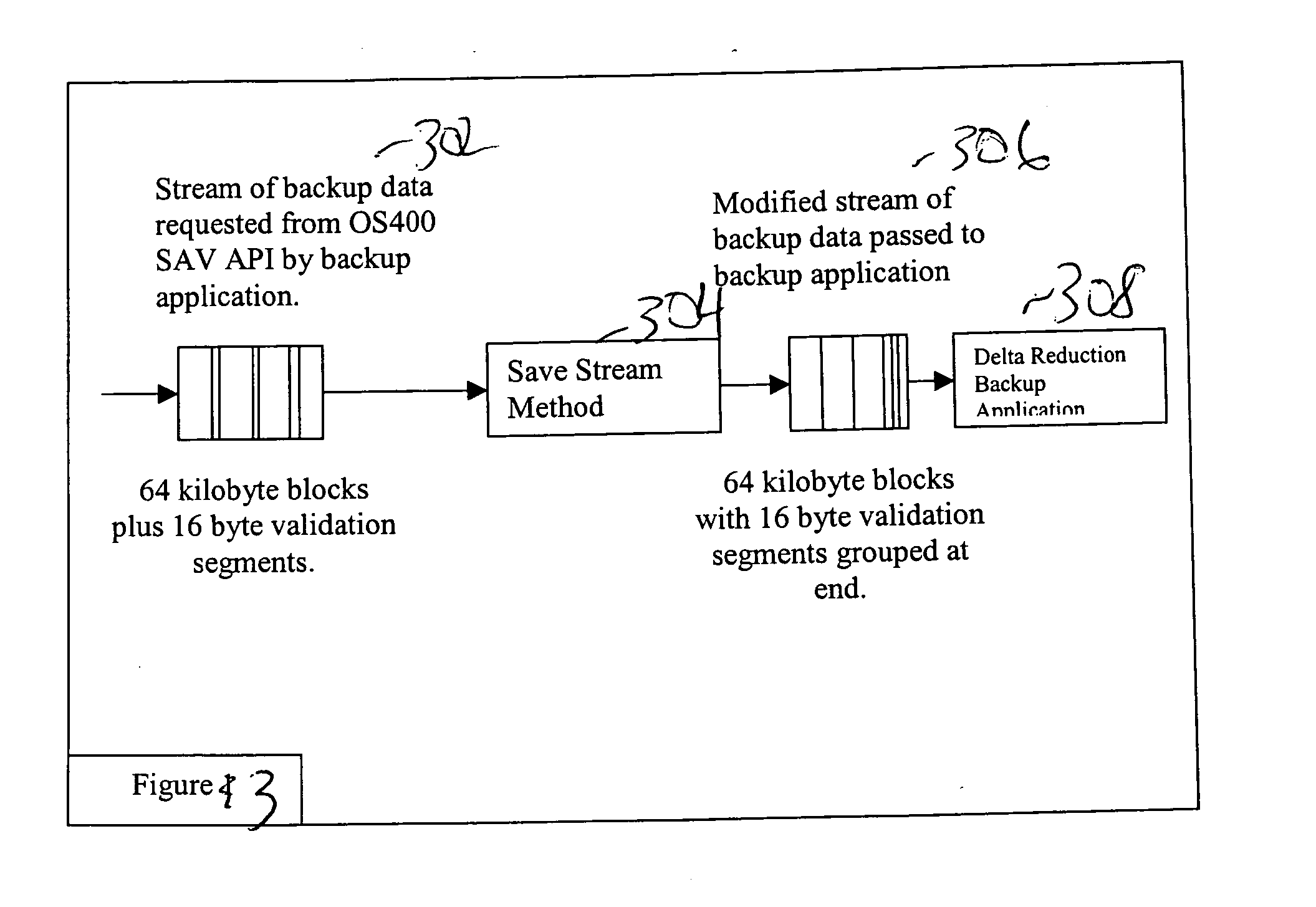

Methods and apparatus for modifying a backup data stream including a set of validation bytes for each data block to be provided to a fixed position delta reduction backup application

ActiveUS20070179998A1Minimizing amount of dataQuantity minimizationDigital data processing detailsError detection/correctionData streamByte

Methods and apparatus for modifying a data stream of backup data to be provided to a fixed position delta reduction backup method are disclosed. When the data stream is received, at least a portion of the data stream is parsed into a plurality of data blocks and a plurality of sets of validation bytes, wherein each of the plurality of data blocks corresponds to one of the plurality of sets of validation bytes. One or more modified data streams are then generated such that the plurality of data blocks are separate from the plurality of sets of validation bytes.

Owner:CARBONITE GMBH

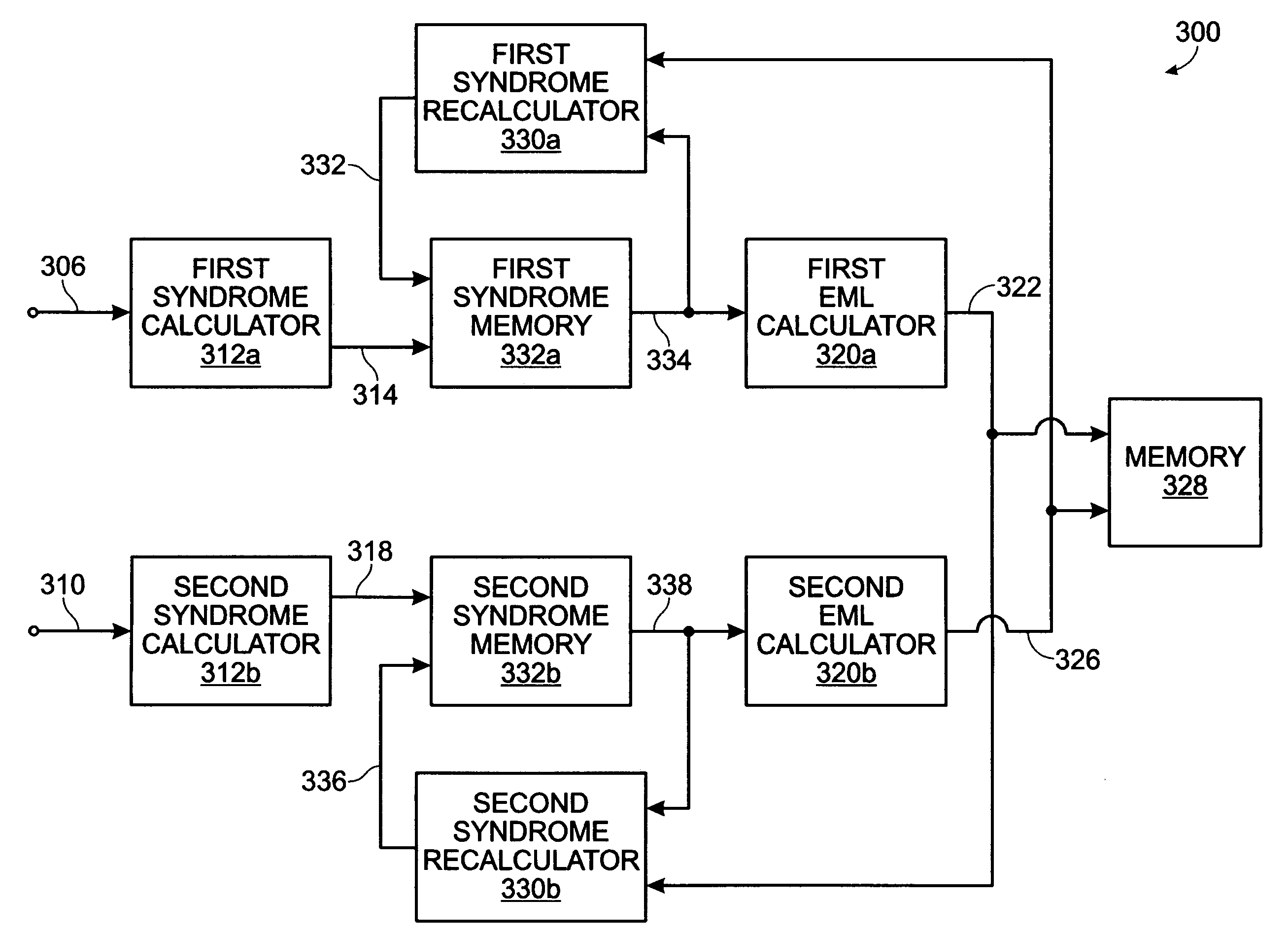

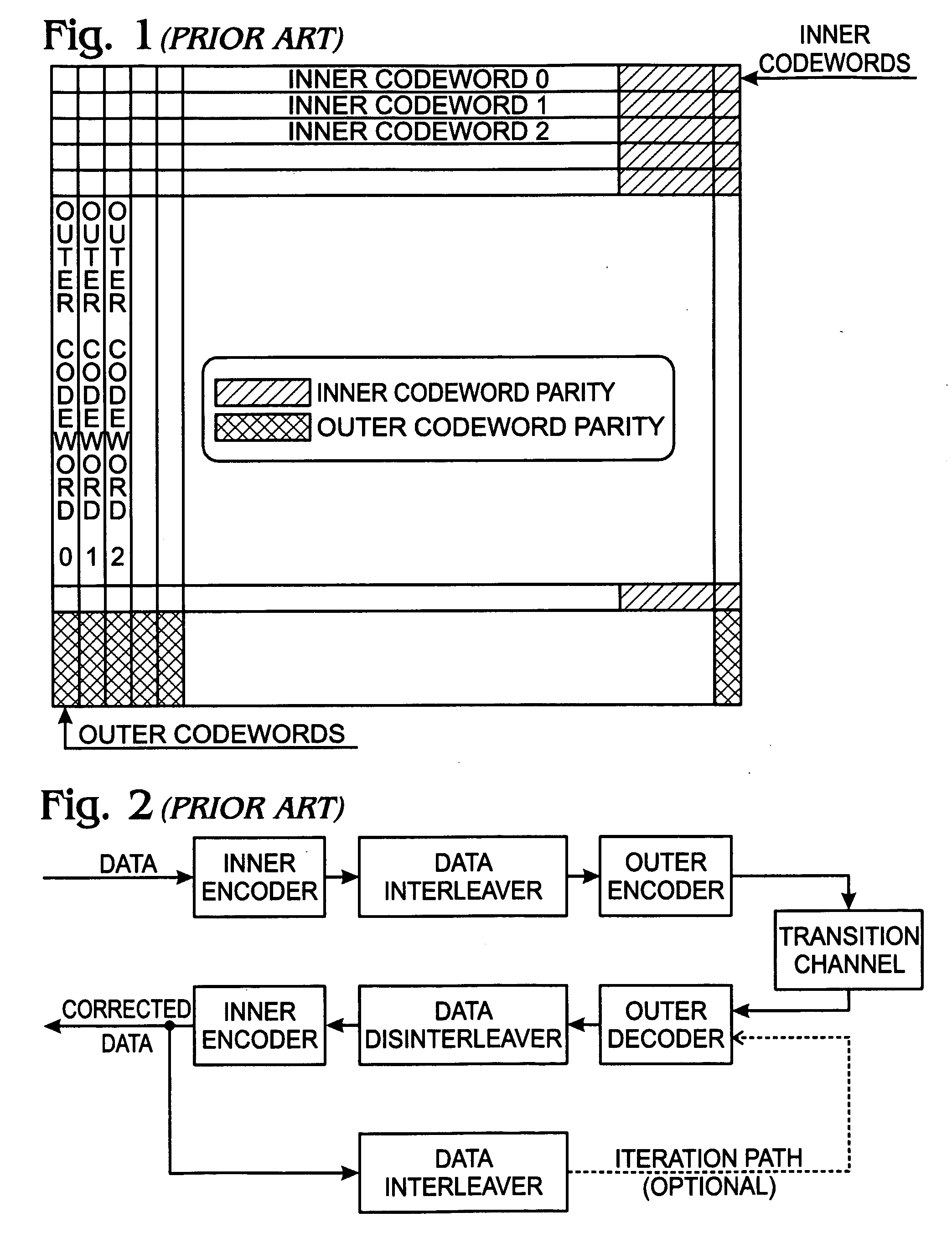

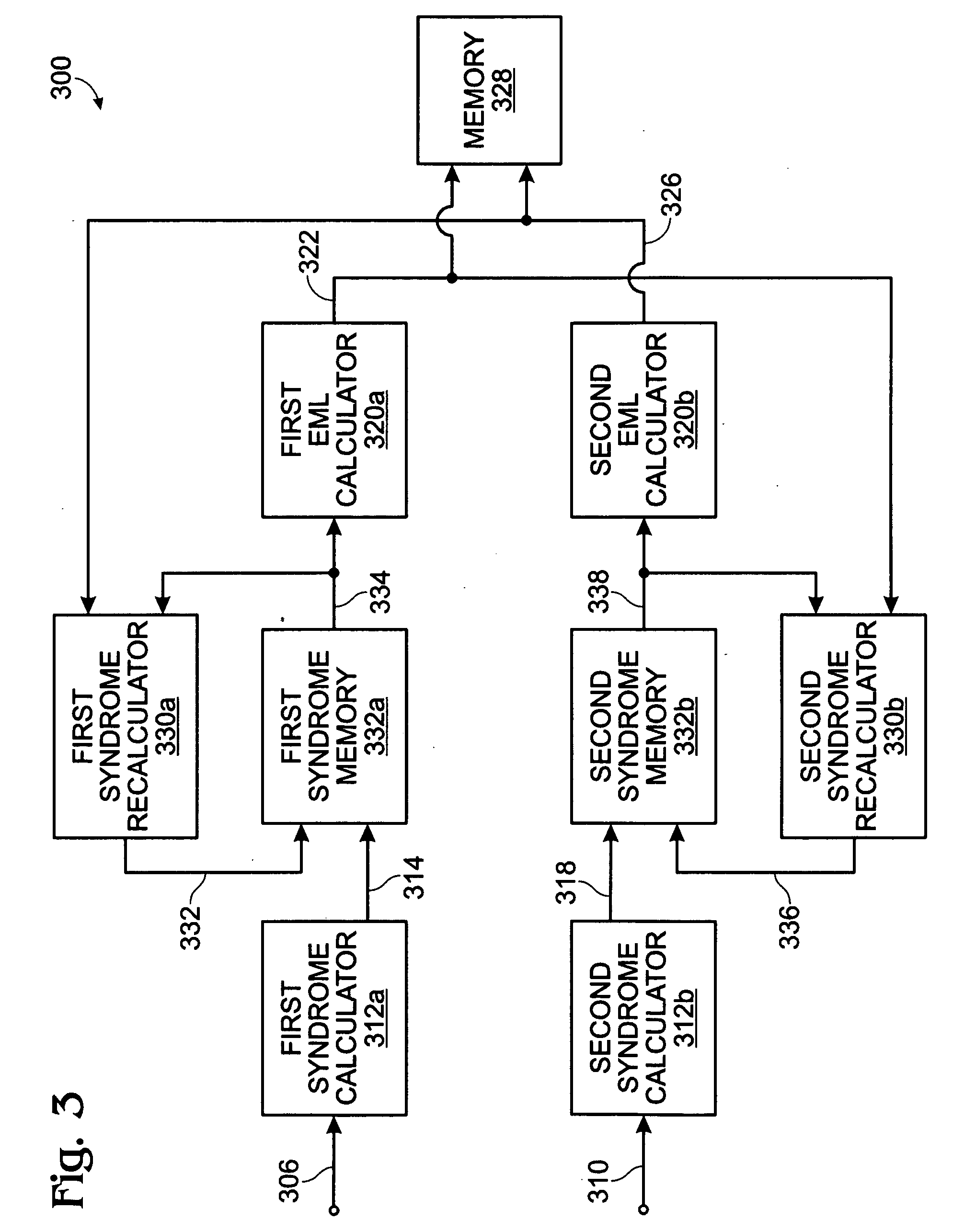

Parallel Forward Error Correction with Syndrome Recalculation

A system and method are provided for parallel processing data that is forward error correction (FEC) protected with multiple codewords. The method accepts an electrical waveform representing a digital wrapper frame of interleaved FEC codewords. Typically, the codeword encoding is solved using an algorithm such as linear block codes, cyclical block codes, Hamming, Reed-Solomon, or Bose-Chaudhuri-Hocquenghem (BCH). The method calculates a first set of syndromes for a first codeword. In parallel with the calculation of the first set of syndromes, a second set of syndromes is calculated for a second codeword with a data component shared with the first codeword. Using the first set of syndromes, an error magnitude and location (EML) of the first codeword is performed. Using the second set of syndromes, an EML of the second codeword is performed in parallel with the EML of the first codeword.

Owner:MACOM CONNECTIVITY SOLUTIONS LLC

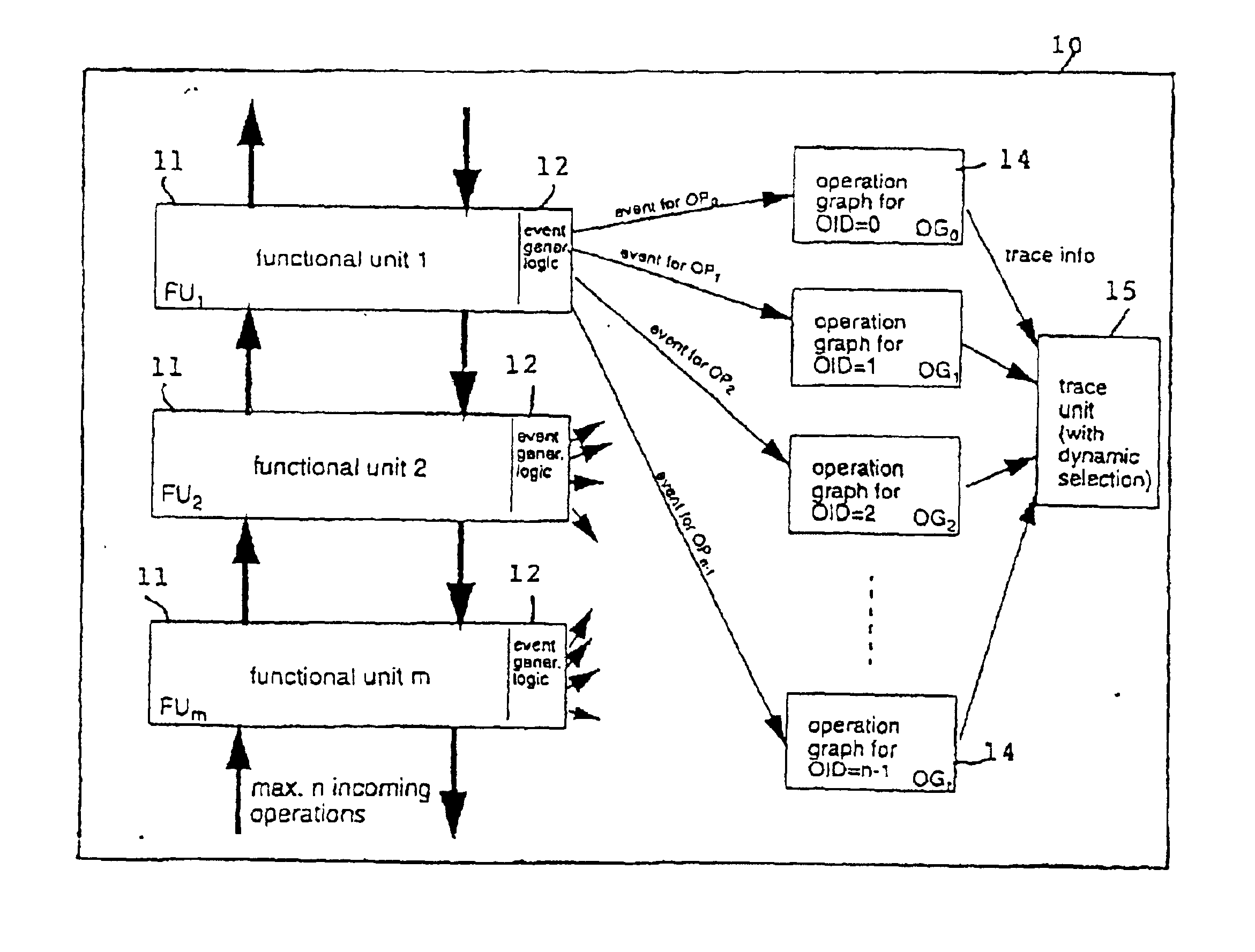

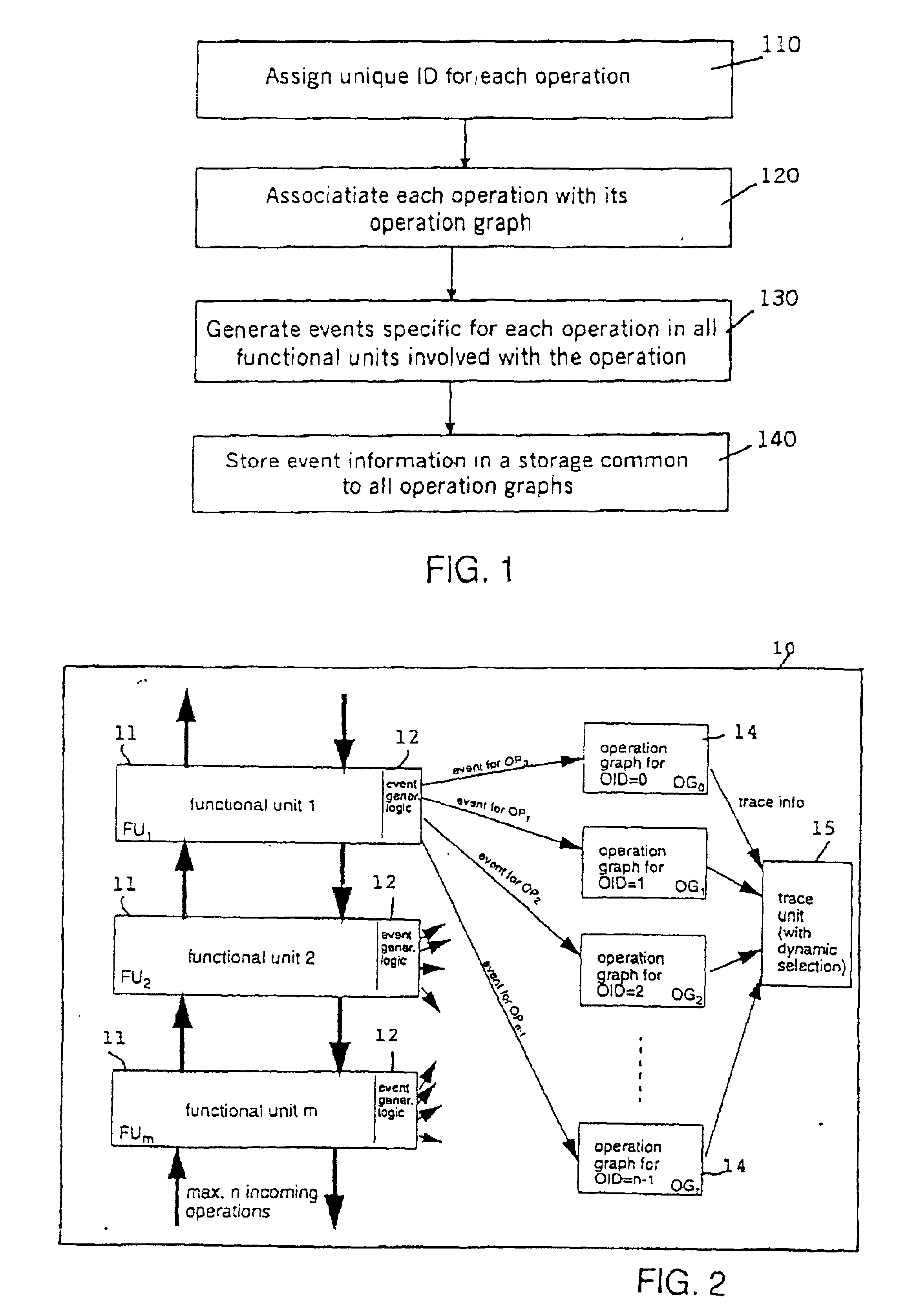

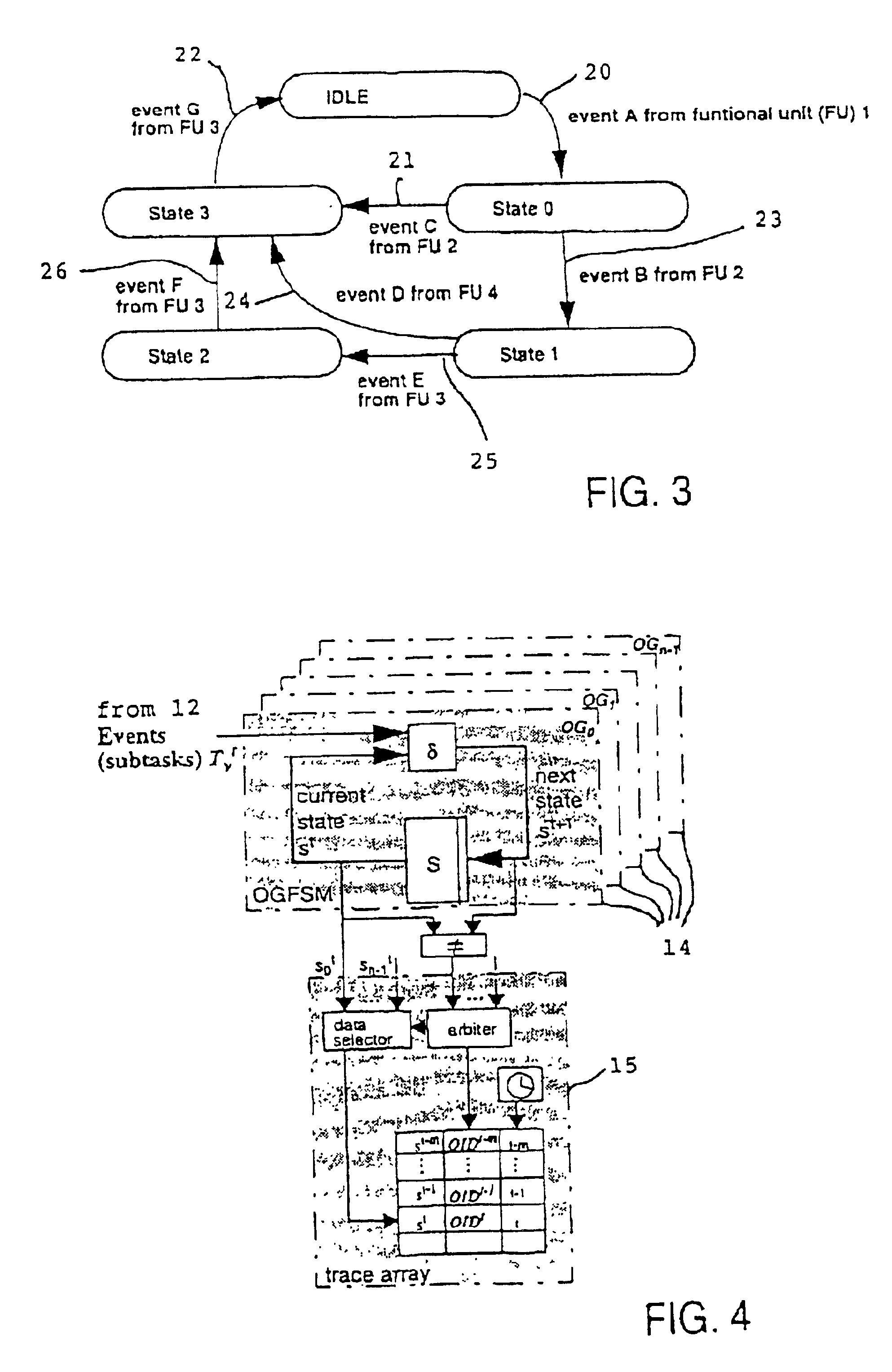

Operation graph based event monitoring system

InactiveUS6874105B2Effective trackingMinimizing amount of dataError detection/correctionSpecific program execution arrangementsConcurrent computingConcurrent computation

Owner:INT BUSINESS MASCH CORP

Efficient encoding and decoding methods for representing schedules and processing forward error correction codes

InactiveUS8006160B2Efficient interpretationMinimizing amount of dataError detection/correctionCode conversionComputer hardwareForward error correction

A sequence of symbol operations (a “schedule representation”) within a data storage device, wherein the operations are those used to process encoding or decoding operations of a forward error correction code (an “FEC code”) upon an arbitrary block of data of a given size (where size can be measured in numbers of symbols). The method is such that the schedule representation can be used to direct the processing of these operations upon a block of data in a way that is computationally efficient. Preferably, the same method can be applied to represent schedules derived from multiple different algorithms for the encoding or decoding of a code or for multiple different codes.

Owner:QUALCOMM INC

Updating positioning data

InactiveUS20170276760A1Reduce power consumptionMinimising bandwidthPosition fixationLocation information based serviceObservation dataData validation

In a mobile positioning system, mobile user devices carry out data validation on locally stored positioning data, regulating the positioning data provided to a positioning module and selectively requesting updated positioning data from a central database. A controller receives requests for updated positioning data and selectively responds with updates. The mobile user devices store observations data concerning measurements of signals from electromagnetic signal sources and transmit data about the locally stored observations data to the controller. The controller then selectively requests transmission of the locally stored observations data and the mobile user device determines when and whether to transmit that data. The amount of positioning data which must be transmitted to and from the mobile user device and the overall power consumption of the mobile user device is reduced. The decision as to what observations data to transmit to the controller is distributed between the mobile user device and the controller.

Owner:HUAWEI TECH CO LTD

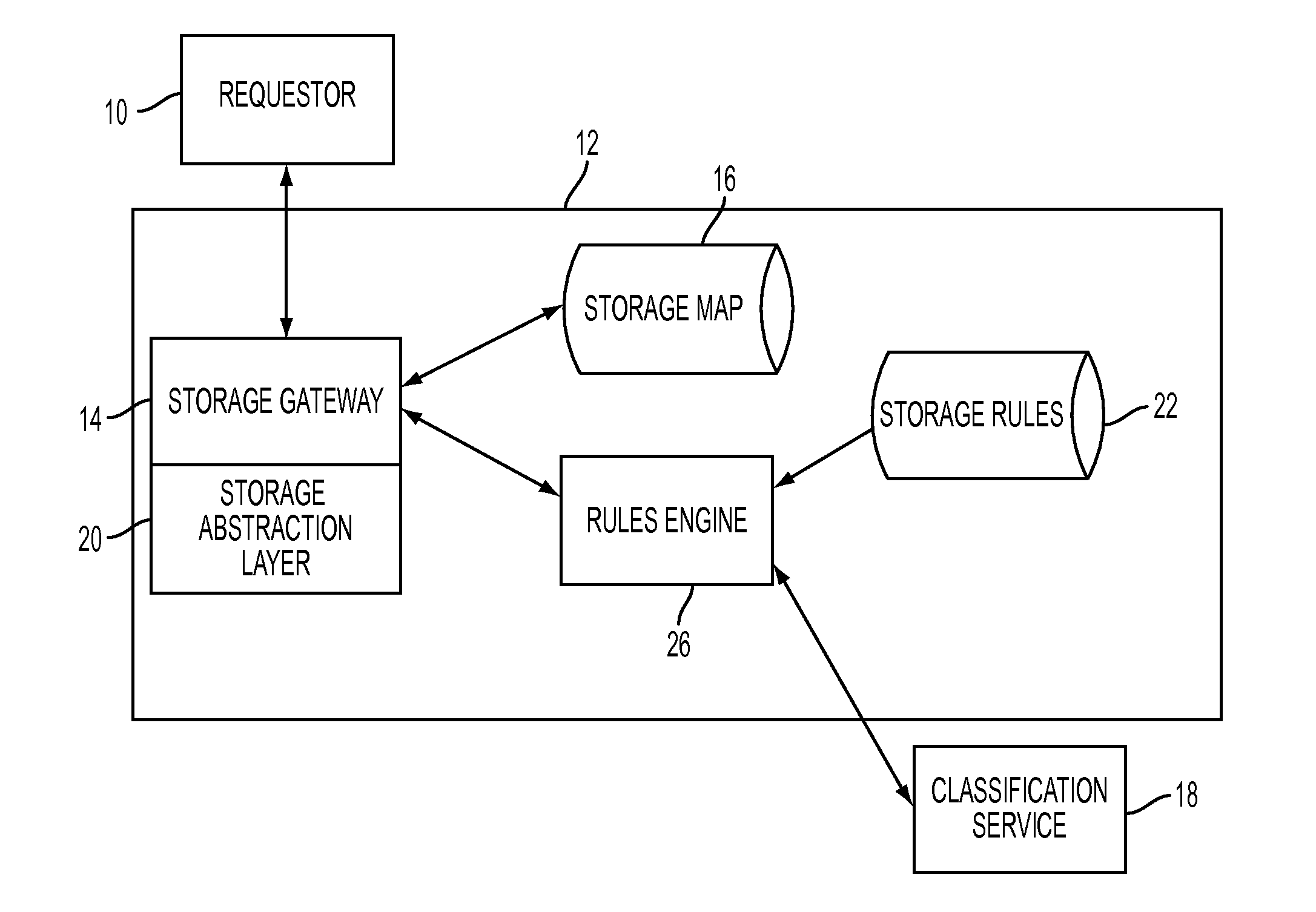

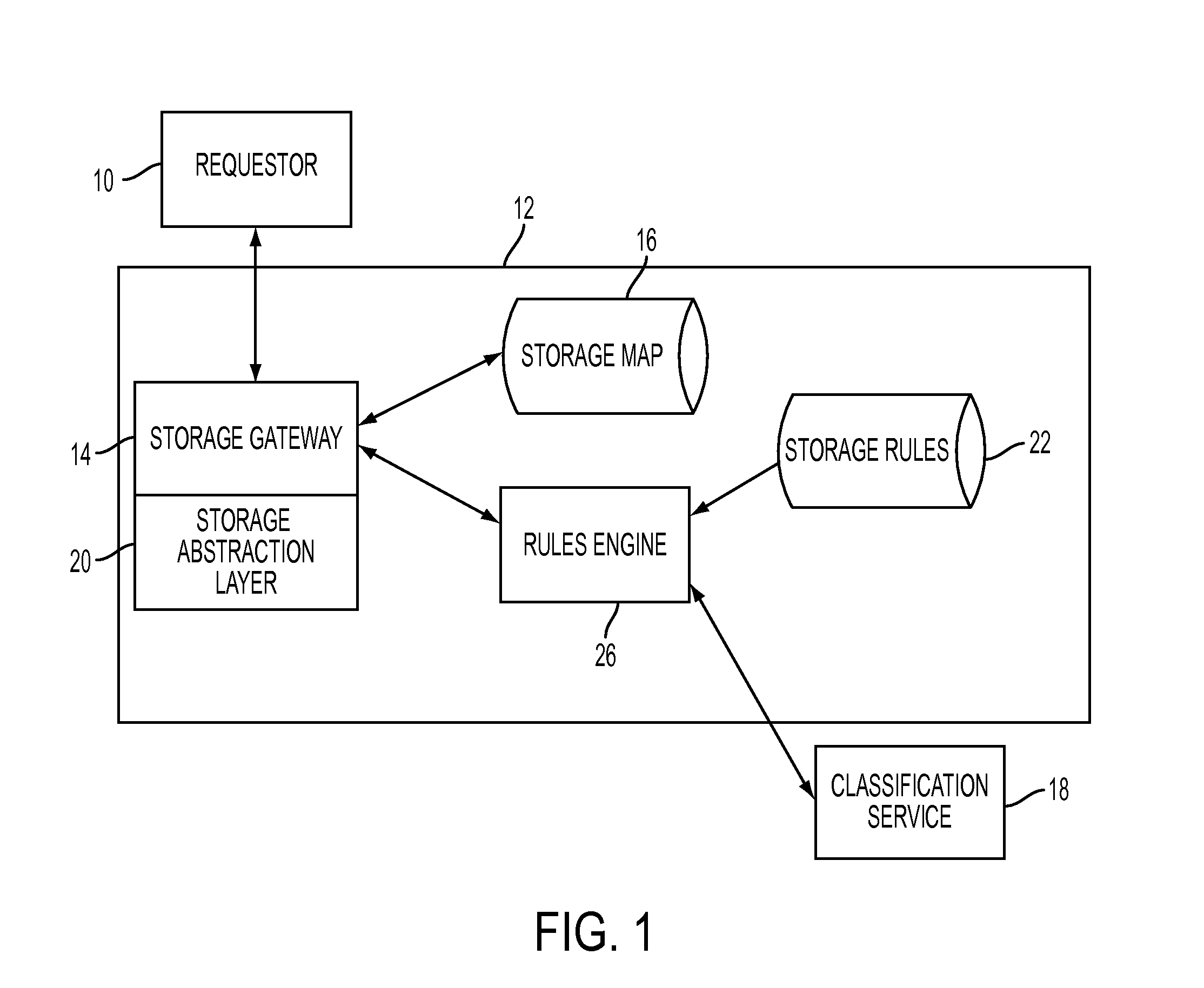

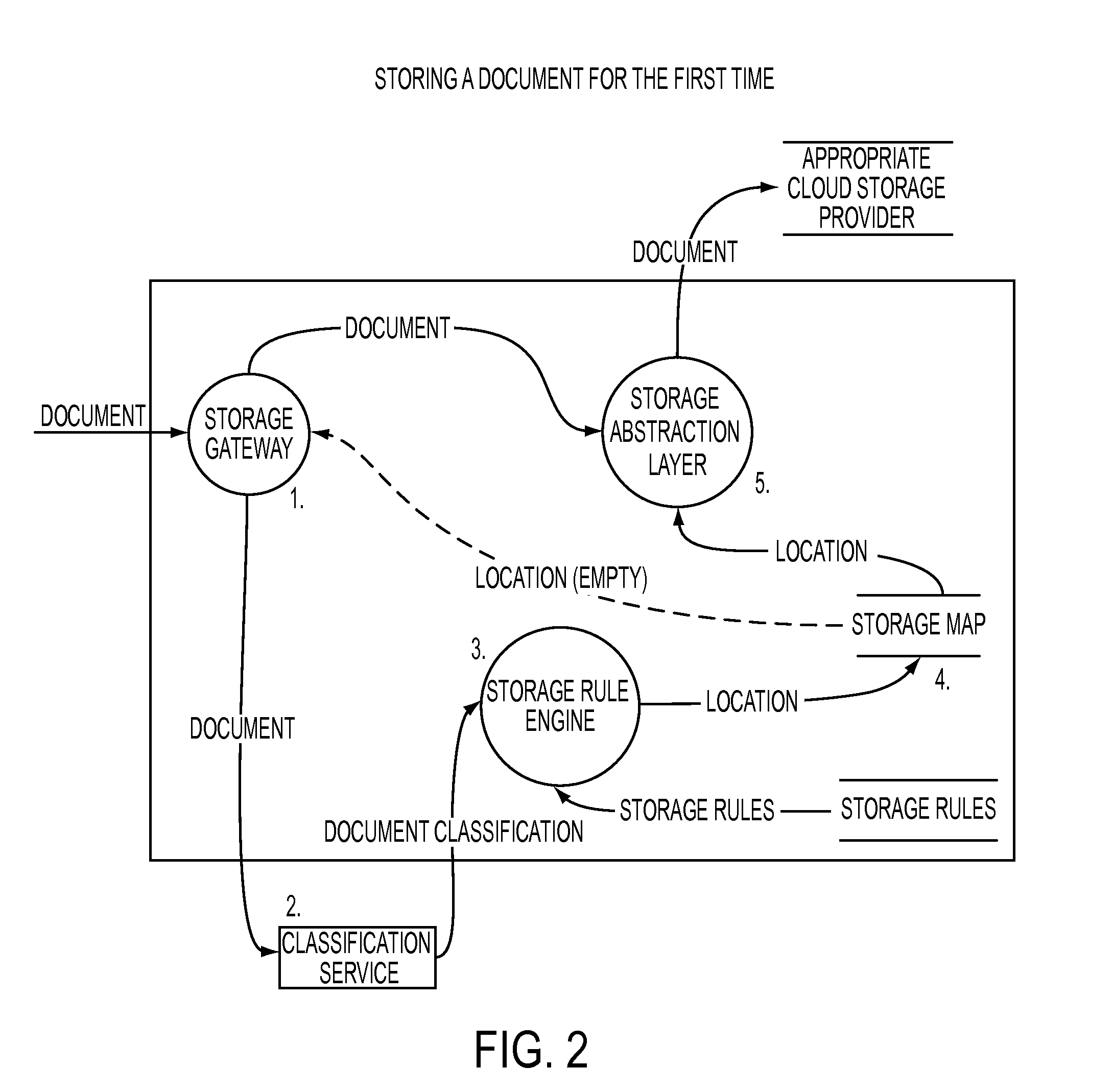

System and method for automatically routing and managing stored documents based on document content

InactiveUS20120323976A1Minimizing amount of dataPreventing consequential storageDigital data processing detailsSpecial data processing applicationsAutomatic routingDocumentation

A system and method for routing and managing documents based on document content comprises obtain a document, determine a classification for the document based on the document content, determine a storage location for the document based on the document classification, determine whether the document is stored in the determined storage location, when the document is stored in the determined storage location, update the document in the determined storage location, when the document is not stored in the determined storage location, determine whether the document is stored in another storage location, when the document is stored in another storage location, add the document in the determined storage location and delete the document from the other storage location, and when the document is not stored in the other storage location, add the document to the determined storage location.

Owner:CA TECH INC

Features

- R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

Why Patsnap Eureka

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Social media

Patsnap Eureka Blog

Learn More Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com