Patents

Literature

365 results about "IOPS" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Input/output operations per second (IOPS, pronounced eye-ops) is an input/output performance measurement used to characterize computer storage devices like hard disk drives (HDD), solid state drives (SSD), and storage area networks (SAN). Like benchmarks, IOPS numbers published by storage device manufacturers do not directly relate to real-world application performance.

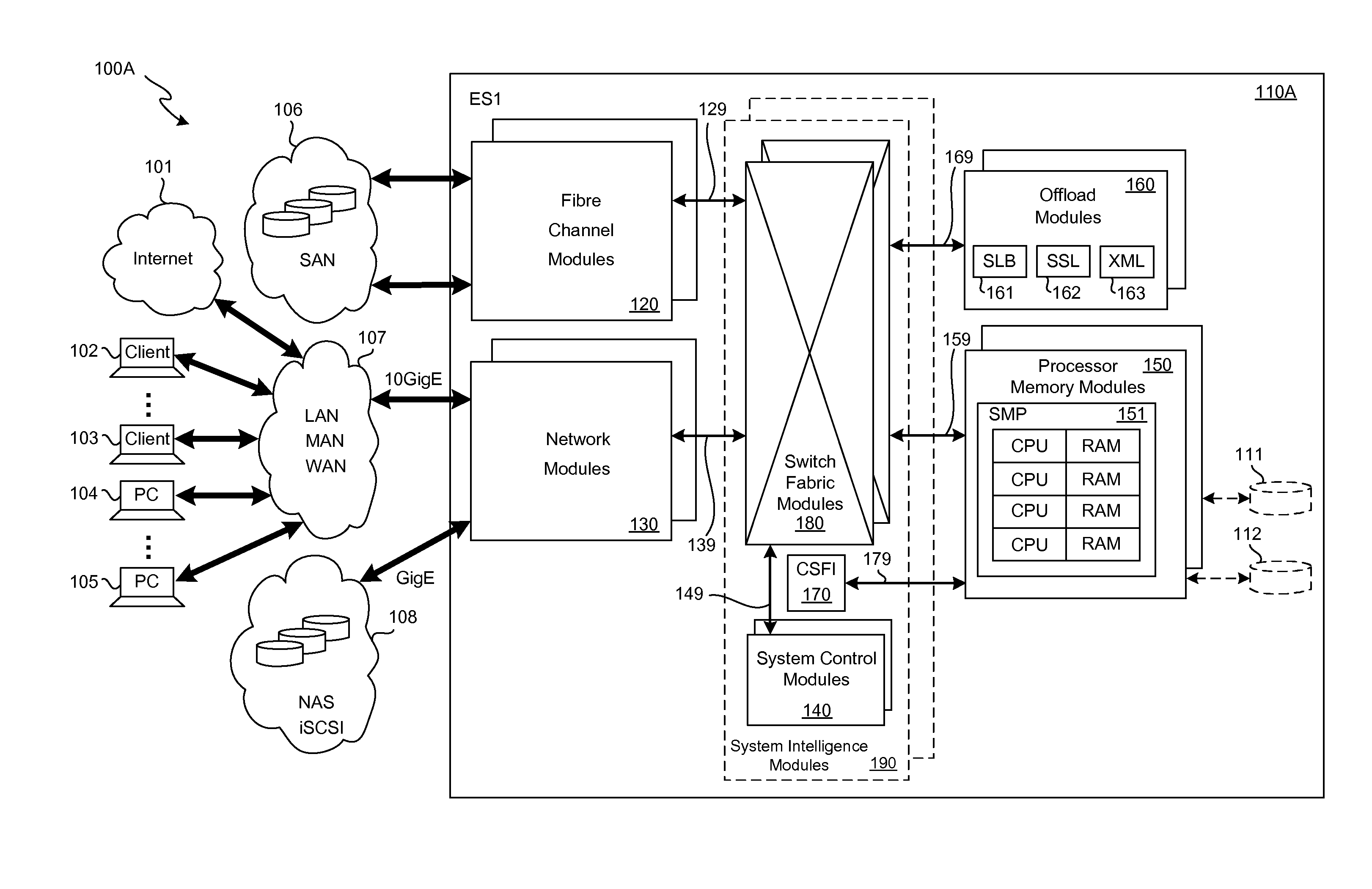

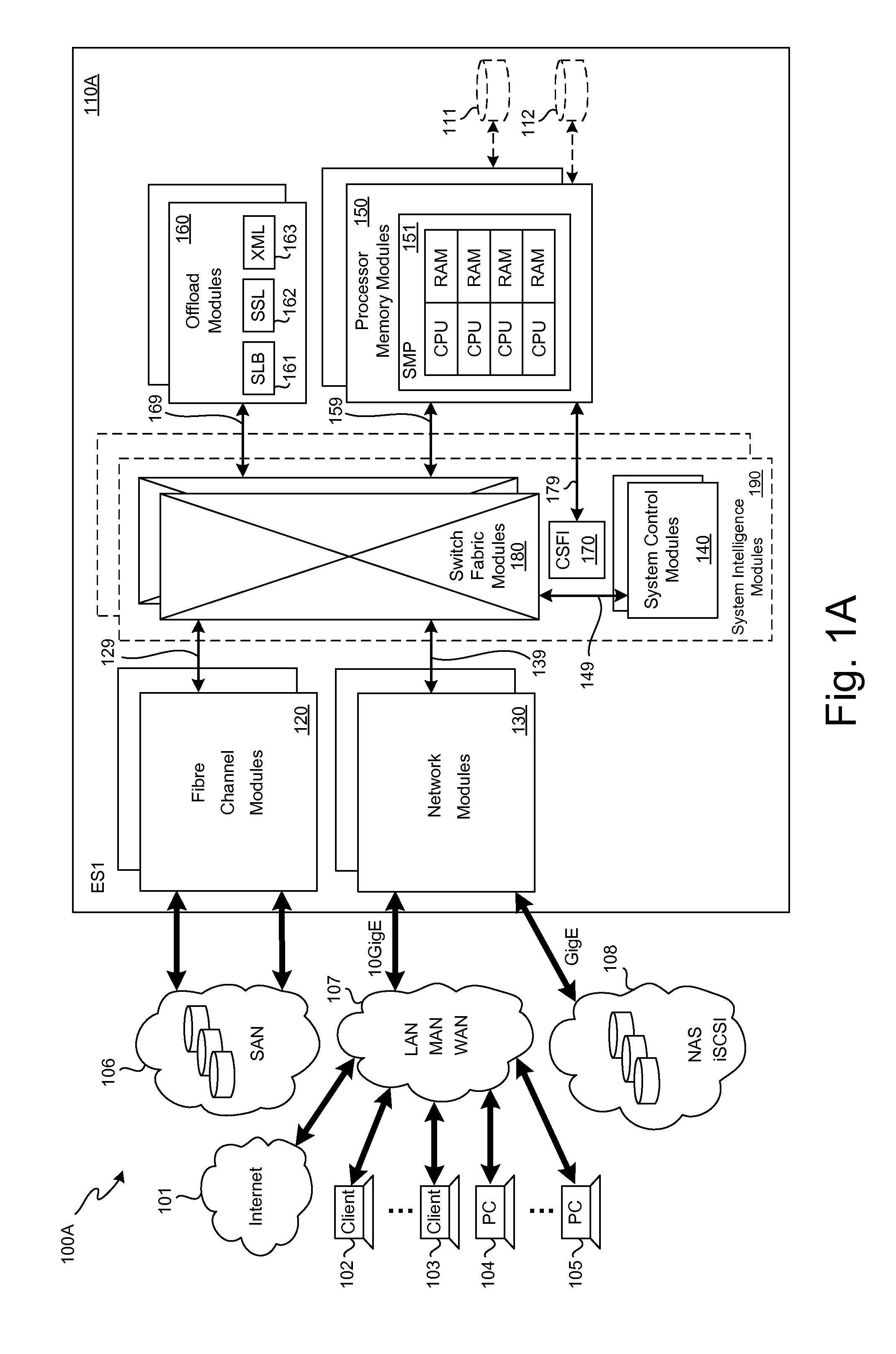

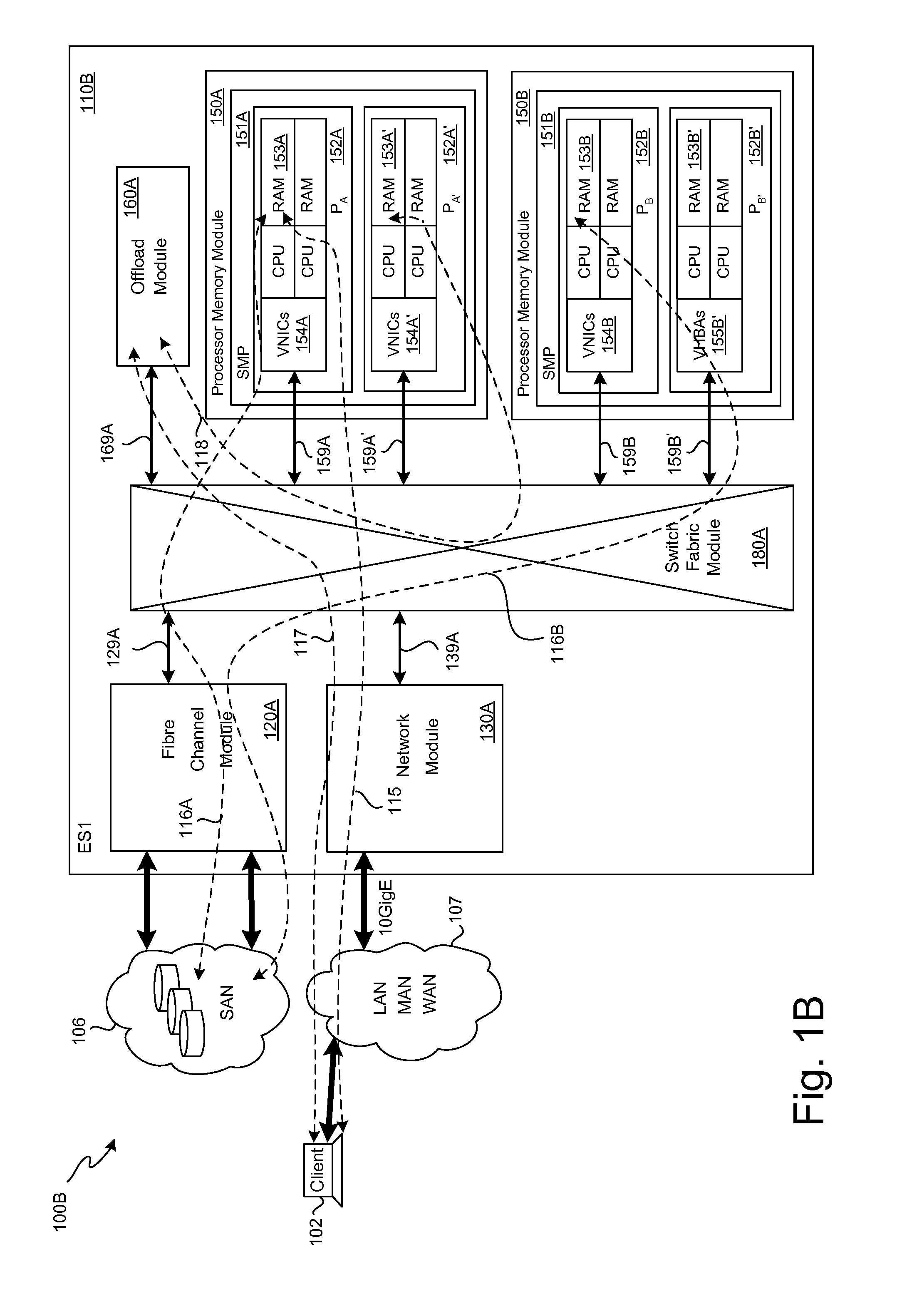

Storage traffic communication via a switch fabric in accordance with a VLAN

ActiveUS20130151646A1Improve performanceImprove efficiencyDigital computer detailsTransmissionTraffic capacityControl store

A plurality of SMP modules and an IOP module communicate storage traffic via respective corresponding I / O controllers coupled to respective physical ports of a switch fabric by addressing cells to physical port addresses corresponding to the physical ports. One of the SMPs executes initiator software to partially manage the storage traffic and the IOP executes target software to partially manage the storage traffic. Storage controllers are coupled to the IOP, enabling communication with storage devices, such as disk drives, tape drives, and / or networks of same. Respective network identification registers are included in each of the I / O controller corresponding to the SMP executing the initiator software and the I / O controller corresponding to the IOP. Transport of the storage traffic in accordance with a particular VLAN is enabled by writing a same particular value into each of the network identification registers.

Owner:ORACLE INT CORP

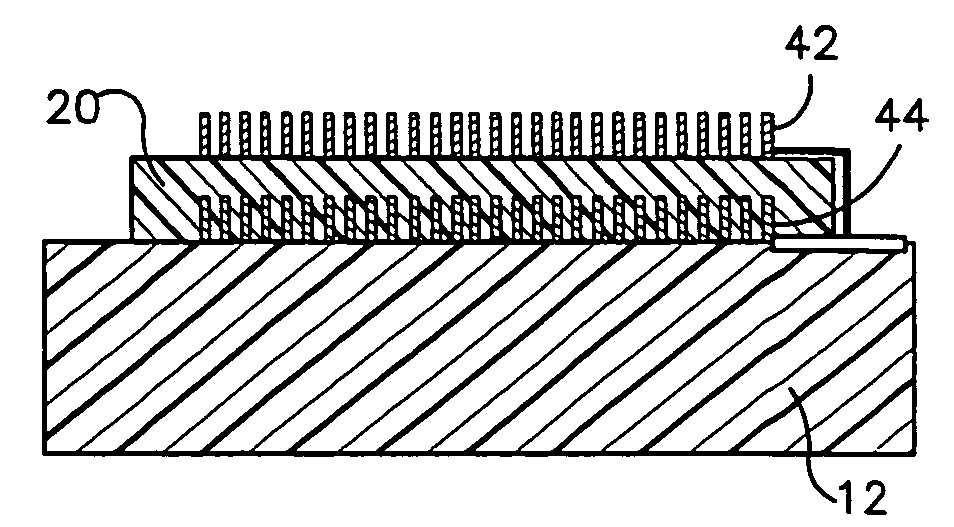

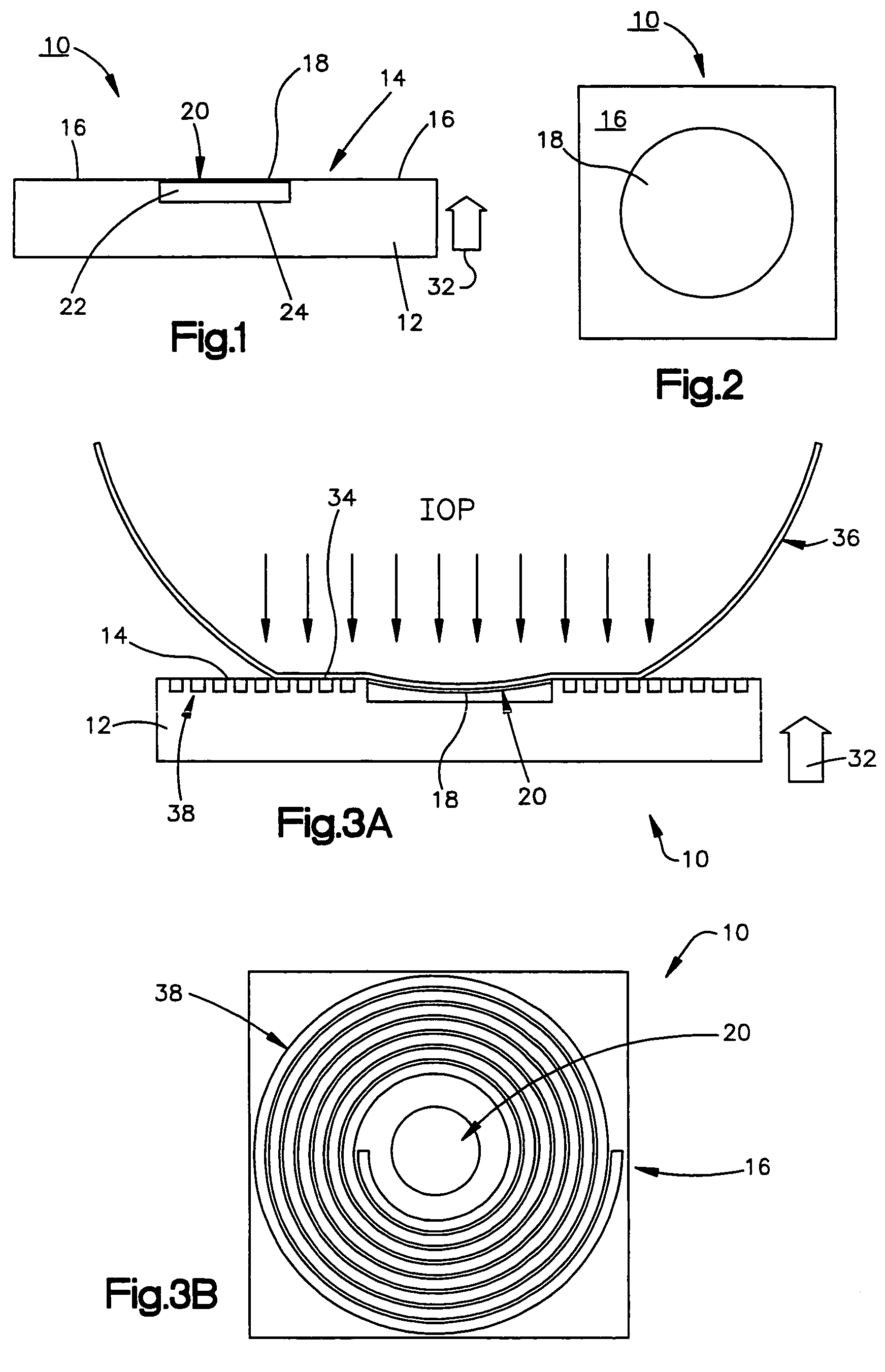

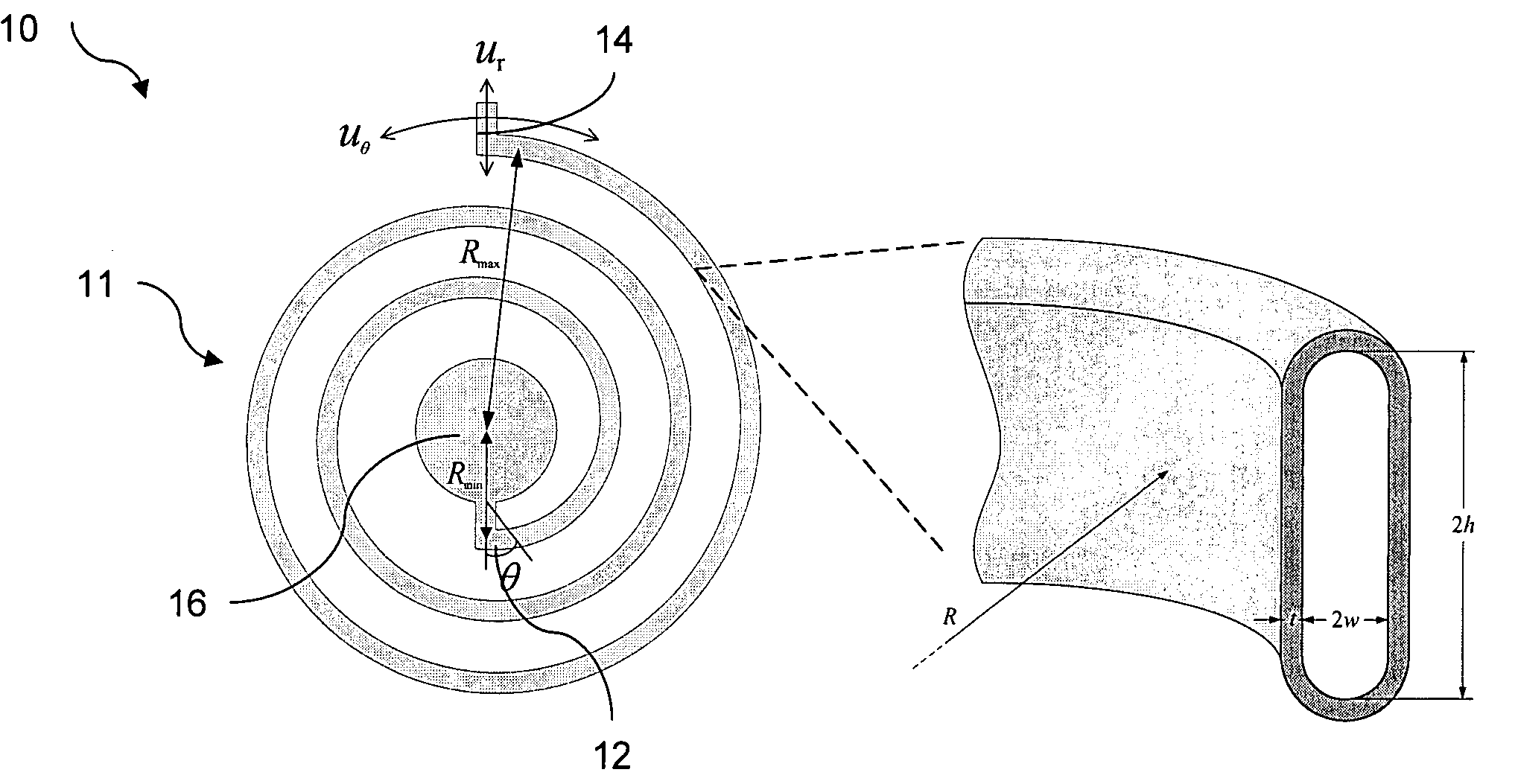

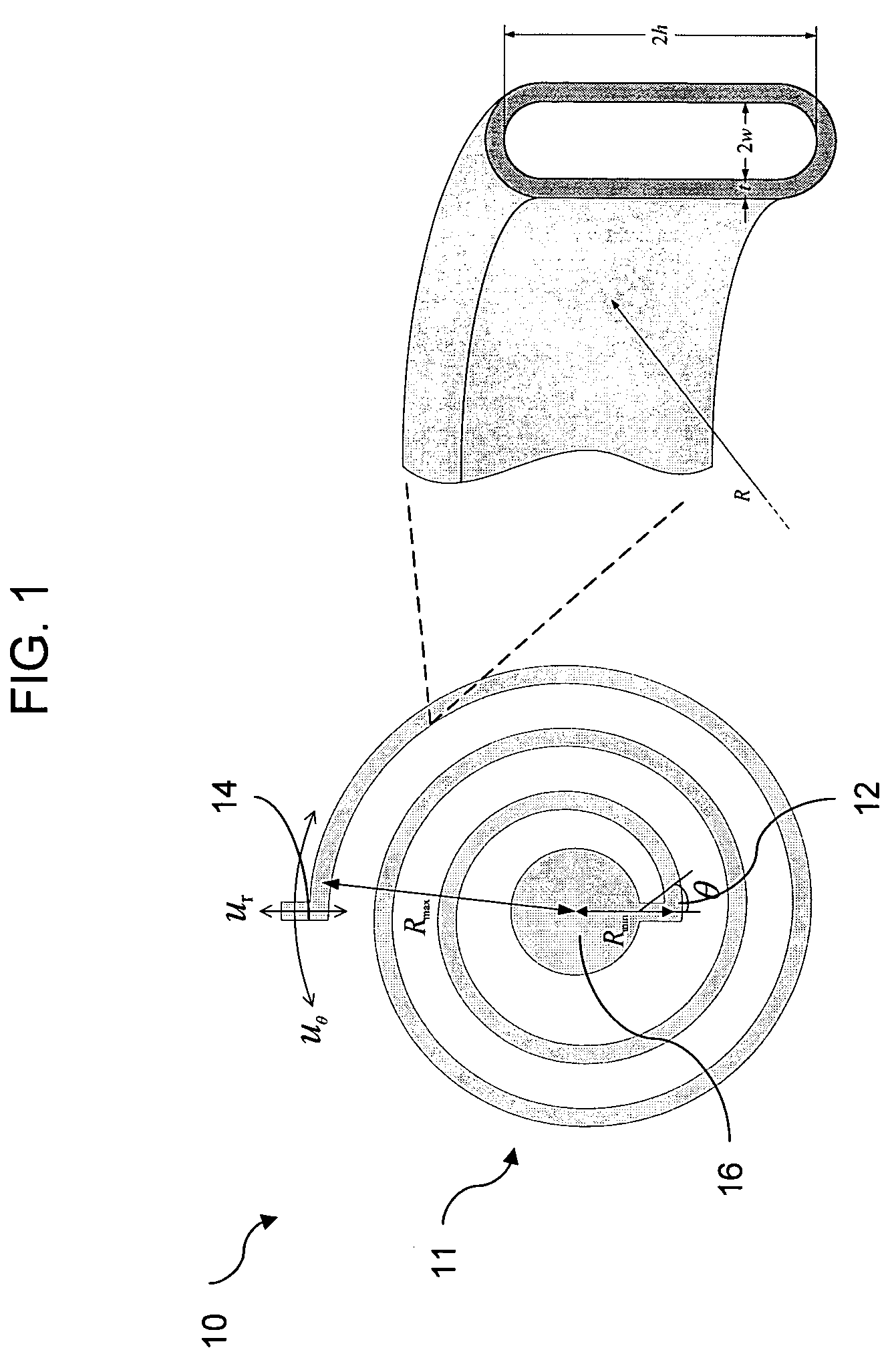

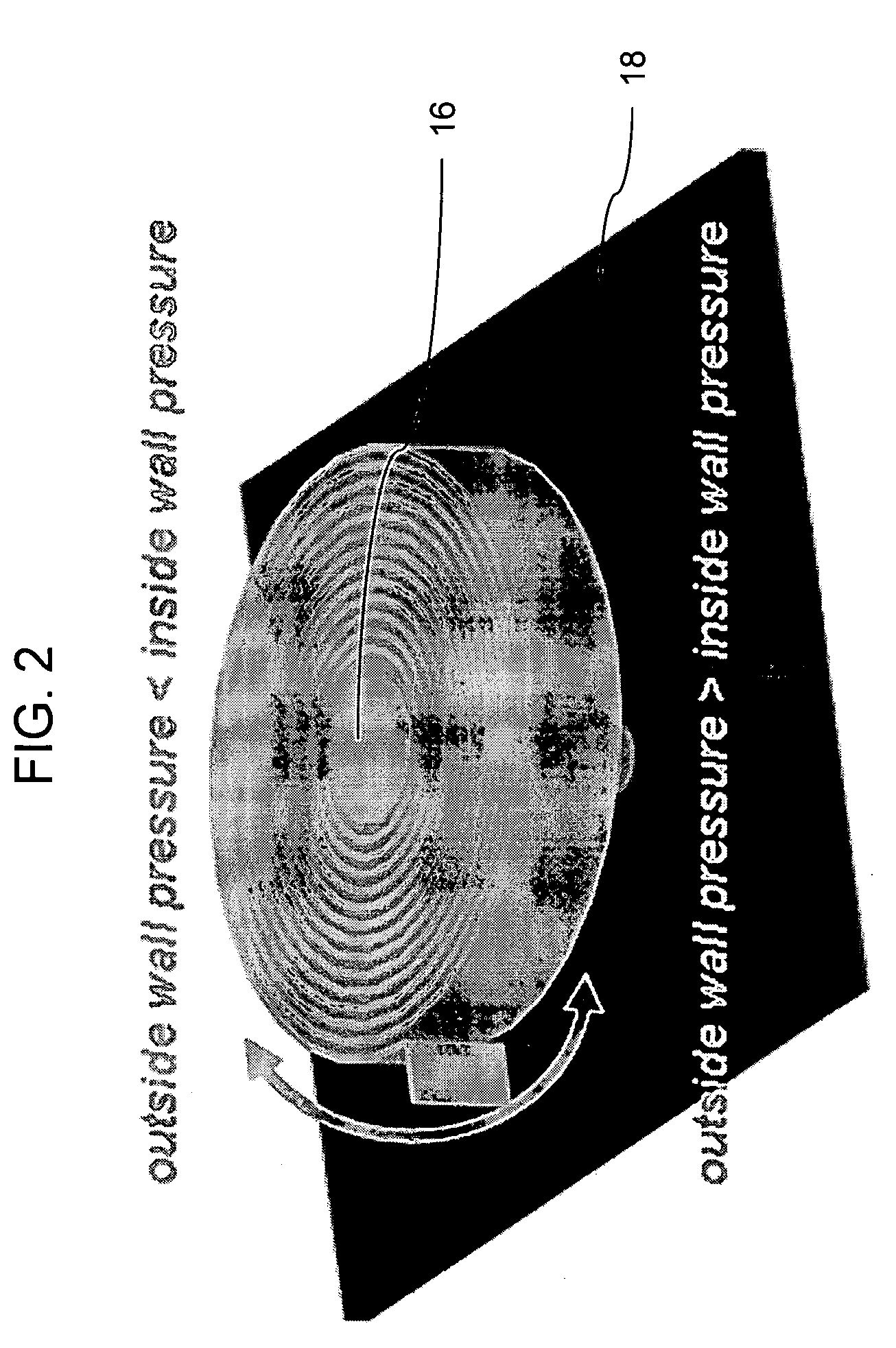

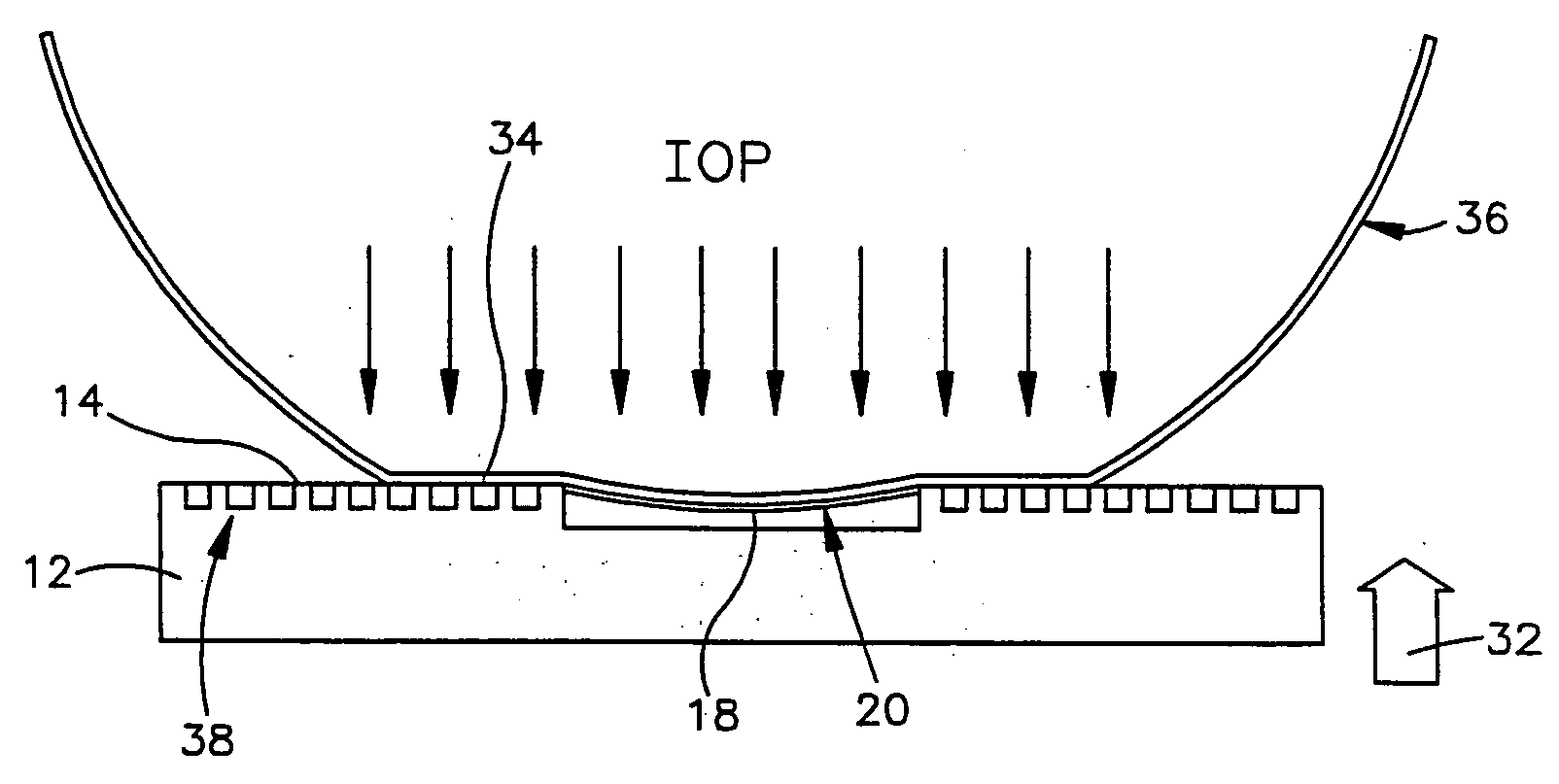

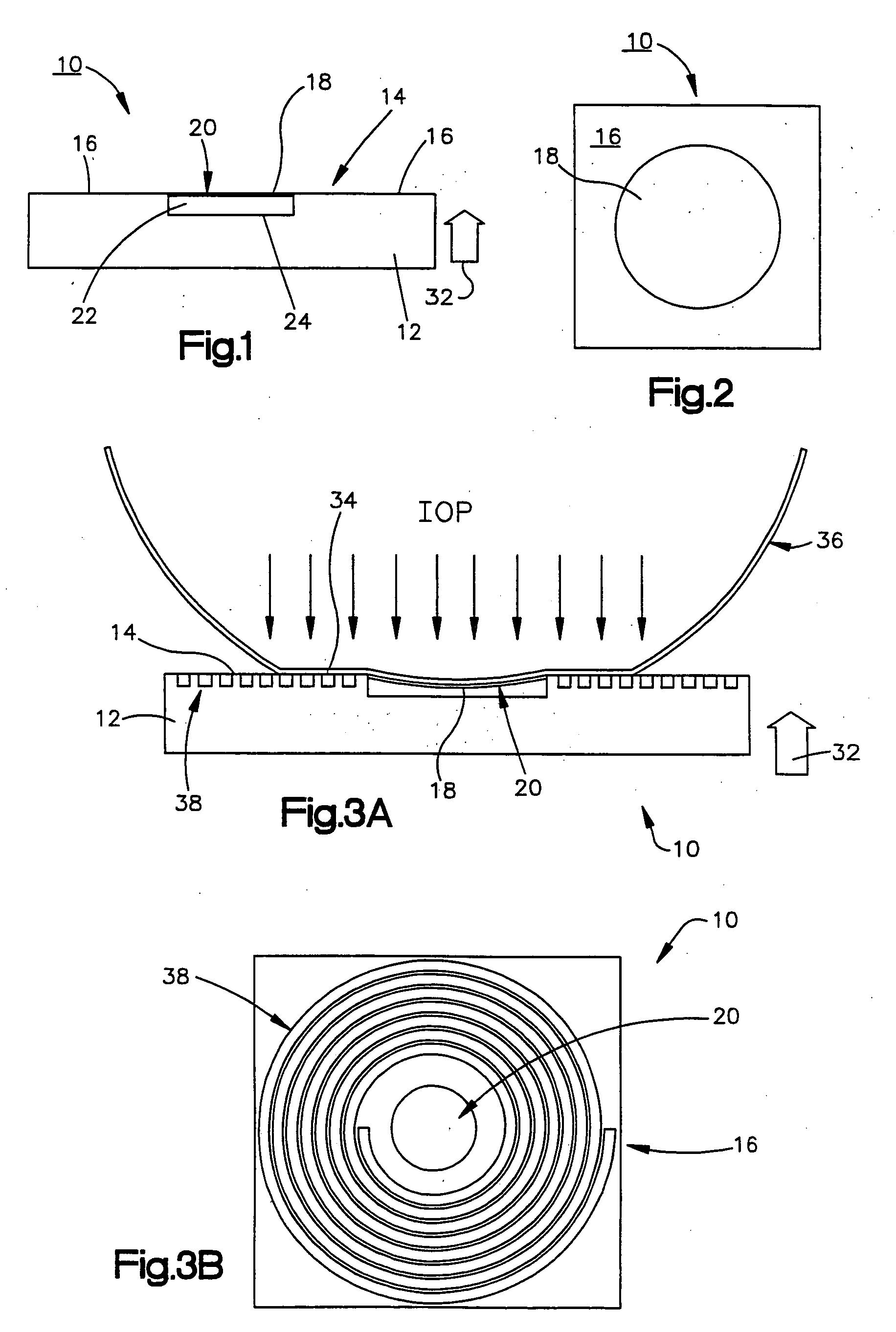

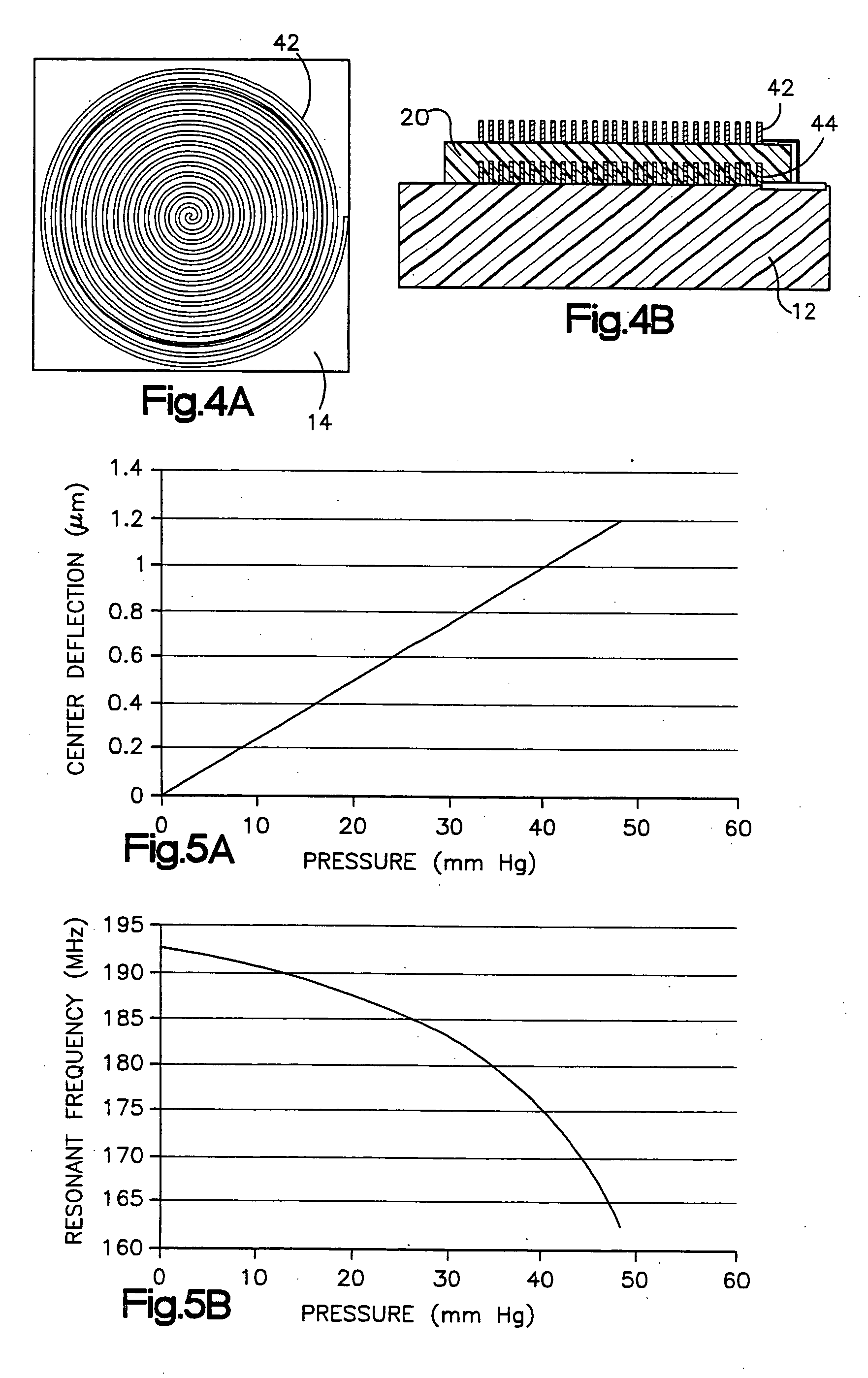

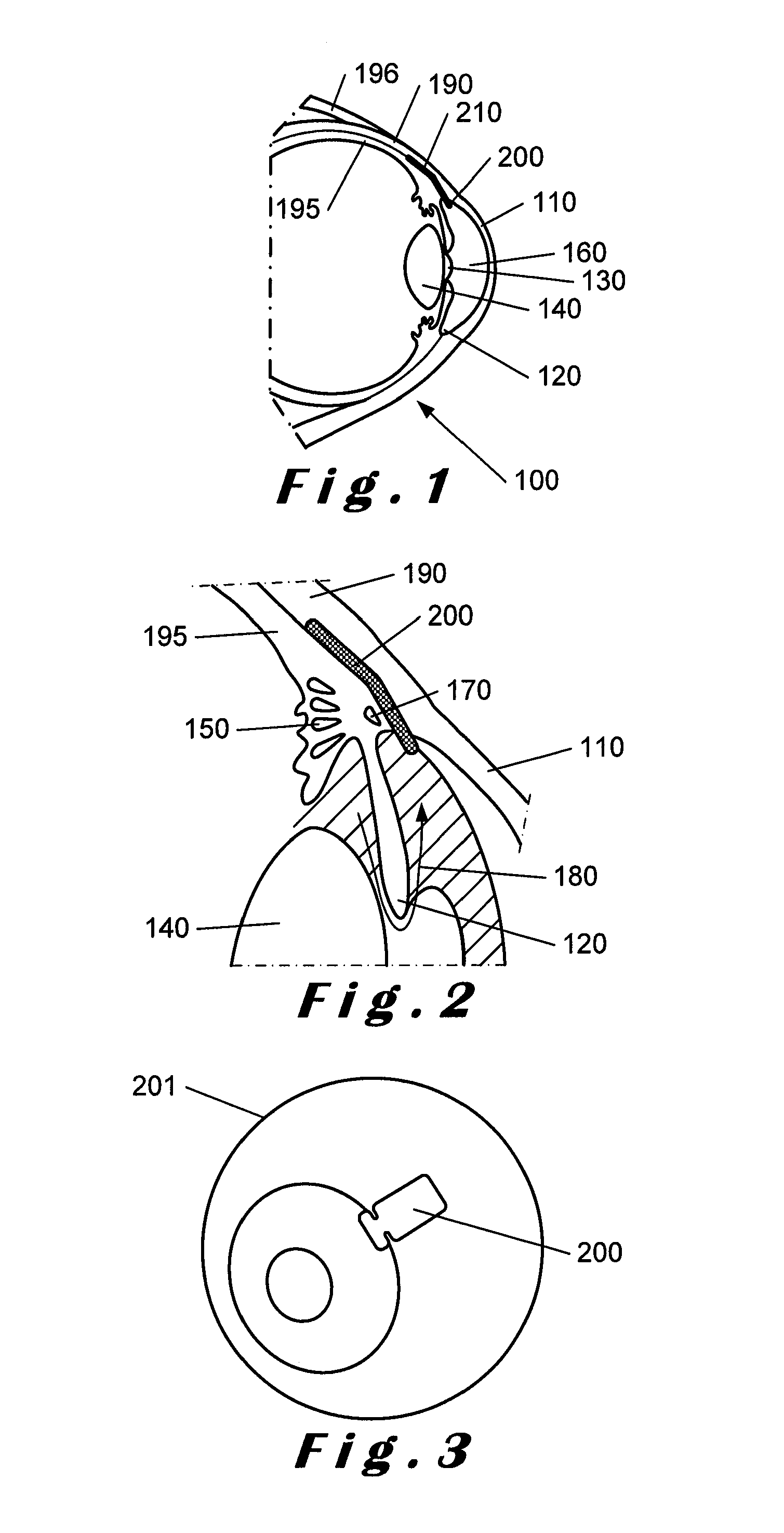

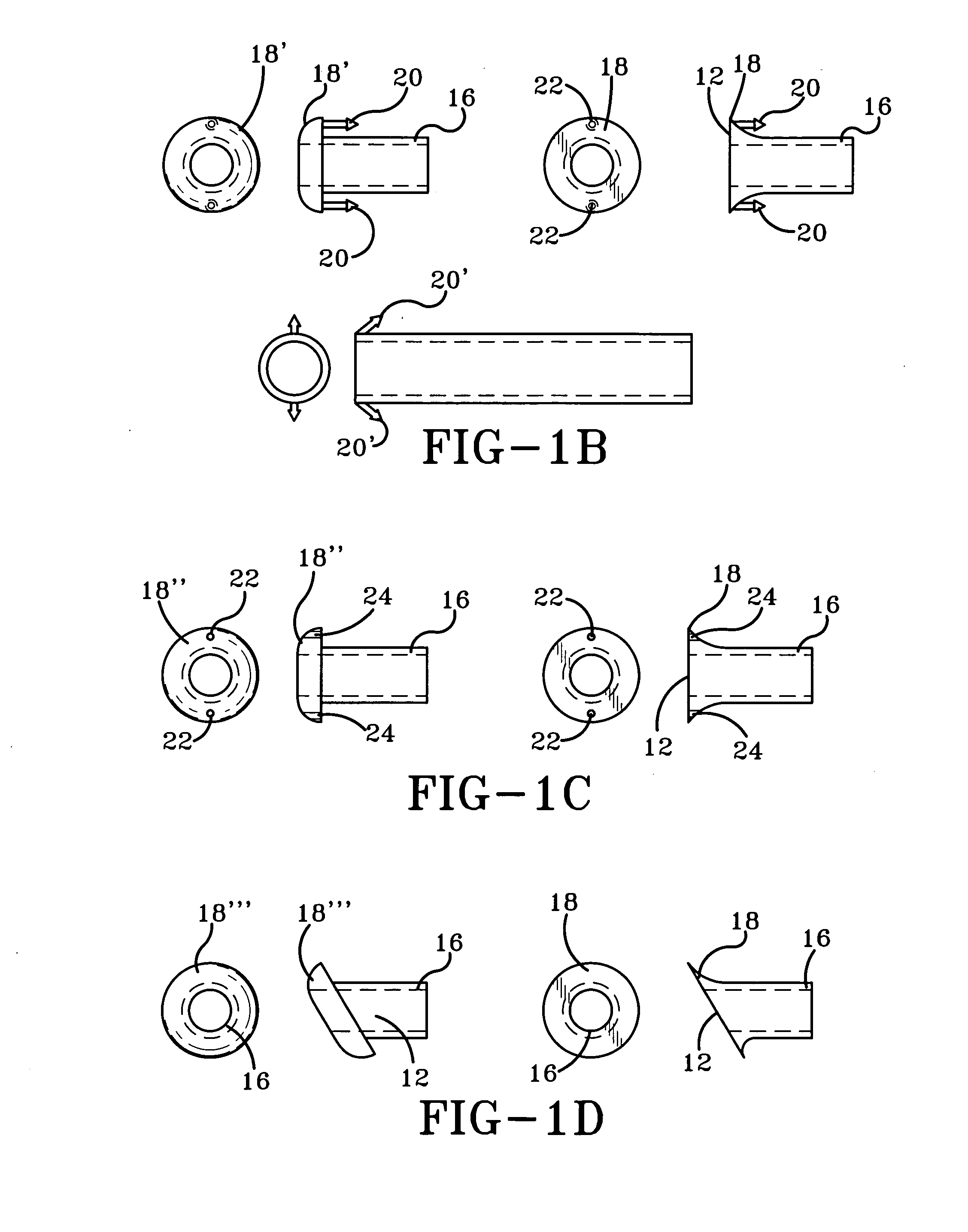

Intraocular pressure measurement system including a sensor mounted in a contact lens

An apparatus (180) for measuring intraocular pressure (IOP) comprises a contact lens (40) including an inner surface (42) contoured to a surface portion (34) of an eye (36) and a sensor (10) disposed in the contact lens. The sensor (10) comprises a contact surface (14) for making contact with the surface portion (34) of the eye (36). The contact surface (14) includes an outer non-compliant region (16) and an inner compliant region (18) fabricated as an impedance element that varies in impedance as the inner compliant region changes shape. The sensor (10) further comprises a region of conductive material (38) electrically coupled to the impedance element of the compliant region (18) and responsive to an external signal for energizing the impedance element so that the IOP may be determined.

Owner:THE CLEVELAND CLINIC FOUND

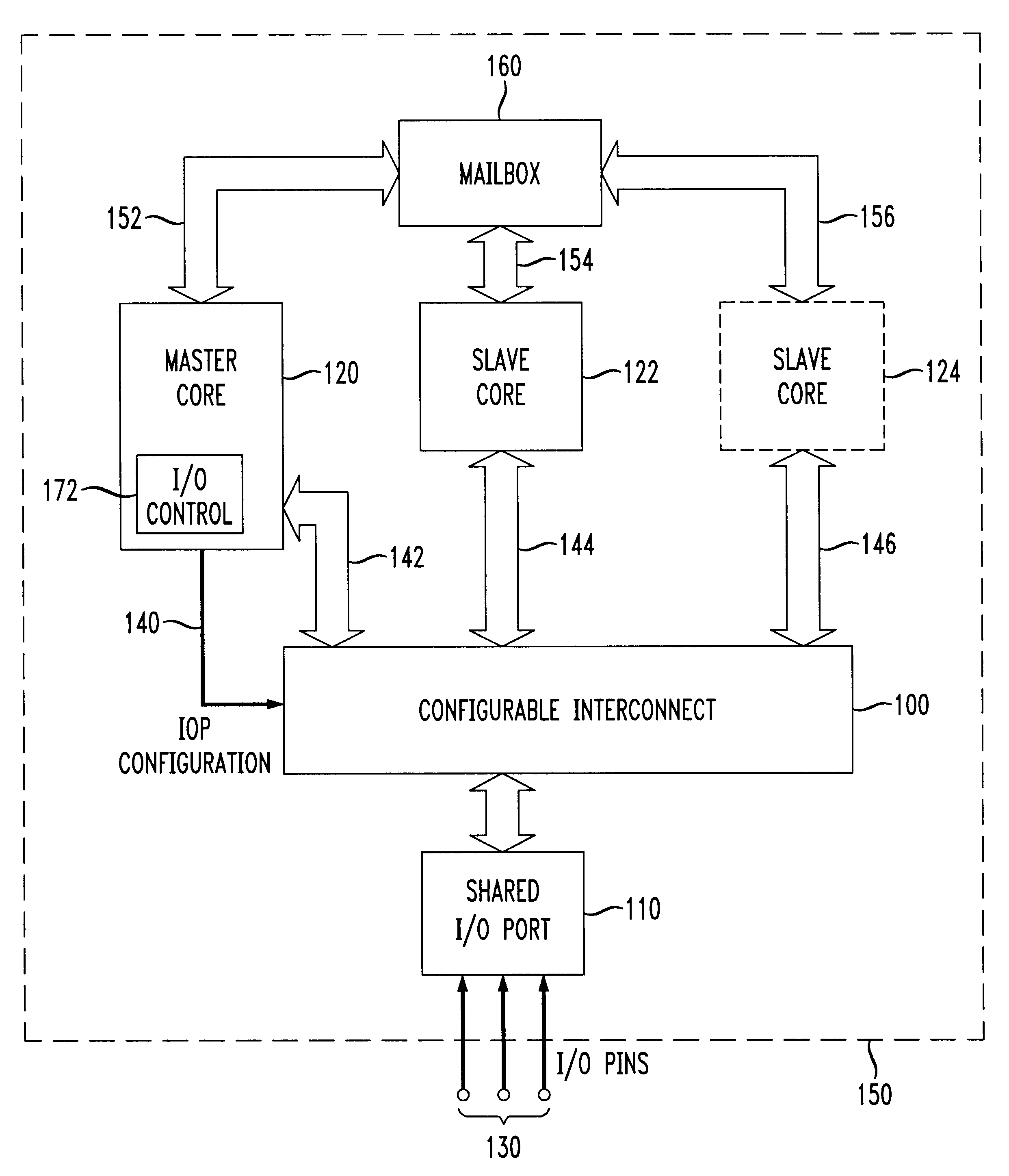

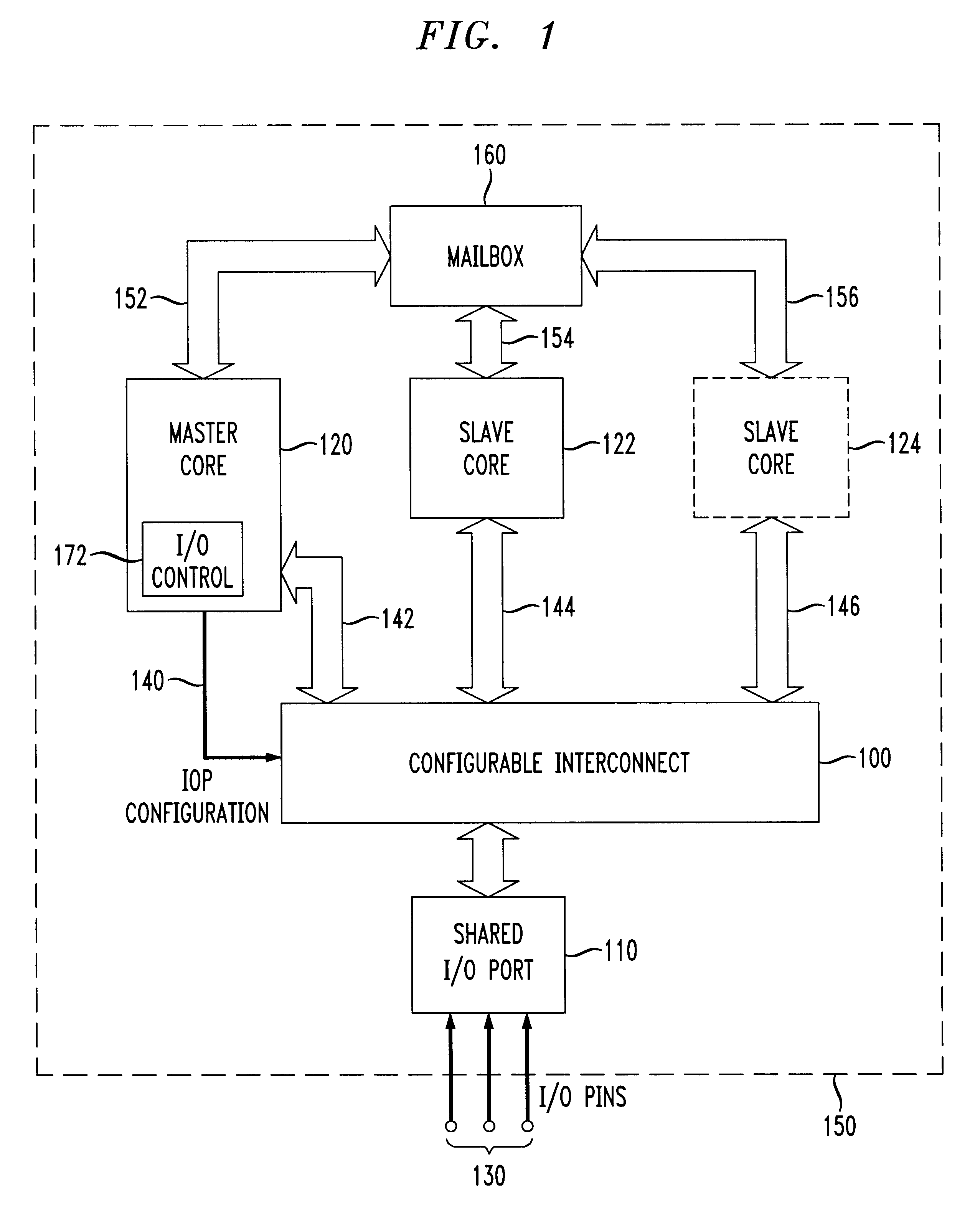

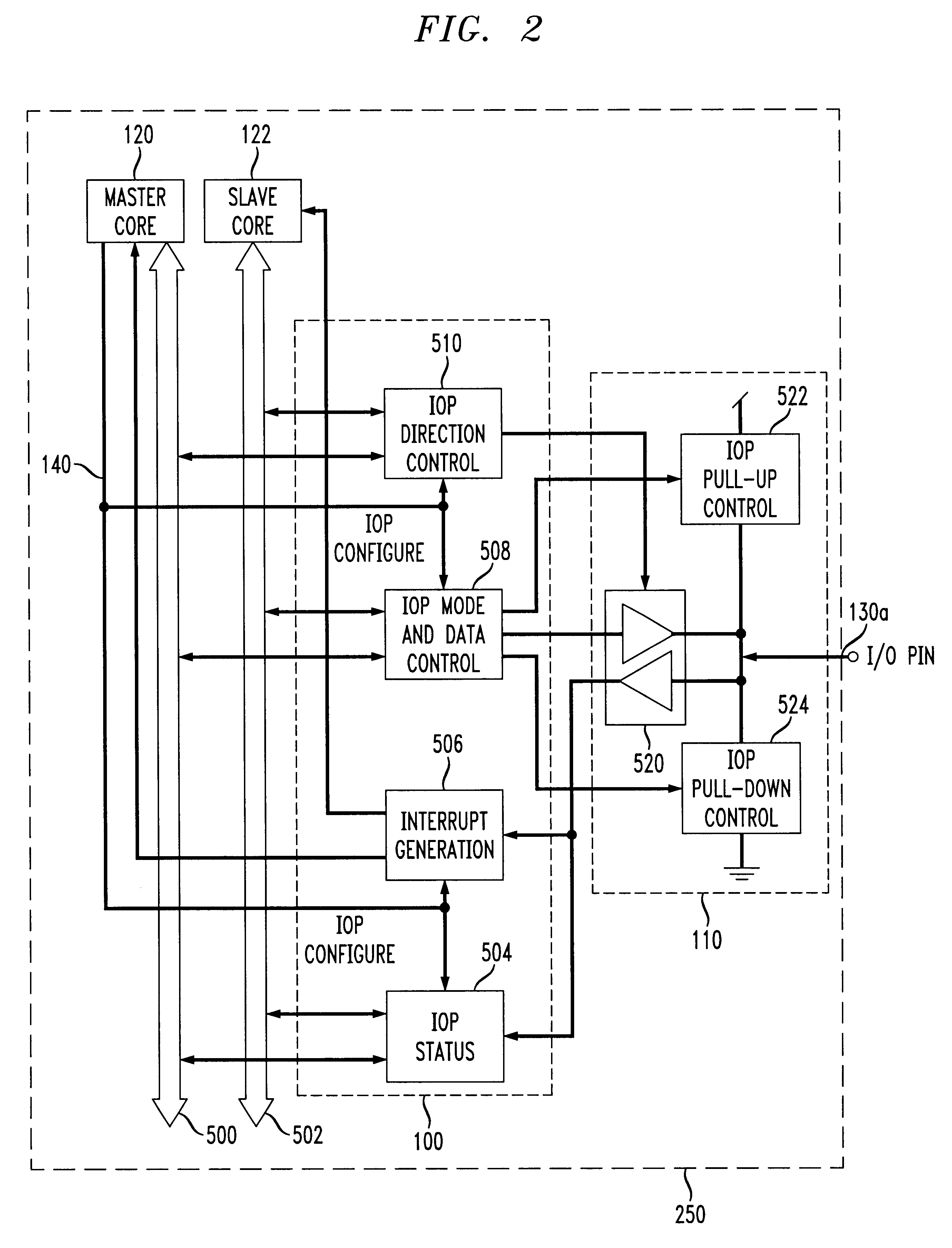

Shared I/O ports for multi-core designs

InactiveUS6496880B1Digital data processing detailsInput/output processes for data processingComputer architectureProcessor register

The present invention provides a shared I / O port and a configurable interconnect allowing any of a plurality of cores to access any pin of a shared I / O port. Preferably, one of the plurality of cores is designated as a master core at least with respect to the configuration of the shared I / O port(s), and the remaining cores desiring to gain access to the shared I / O port(s) are designated as non-master or slave cores. It is the responsibility of the master core to reassign chip resources such as the shared I / O port(s) for use by either the master core or by any of the shared cores. Preferably, all shared I / O ports are controlled by default by the master core. The slave cores communicate with the master core through a suitable internal messaging system. If a slave core requires use of a particular I / O pin or I / O port not already configured appropriately for its use, the slave core will send an appropriate message to the master core through the messaging system, e.g., a dual port memory mailbox. Preferably, the master core will then pass a message back to the requesting slave core indicating completion of the requested reconfiguration. The master core preferably keeps track of which core currently has control of each I / O pin or port using appropriate internal registers. The master core communicates with the relevant I / O pin or port using its I / O data bus, while the slave core communicates with the relevant I / O pin or port using its I / O data bus. IOP configuration signals from the master core configure and thus determine which core in the multi-core integrated circuit or hybrid circuit has access to I / O control modules or registers to control the direction, mode, interrupt generation capability, and / or status of the shared I / O port(s).

Owner:LUCENT TECH INC

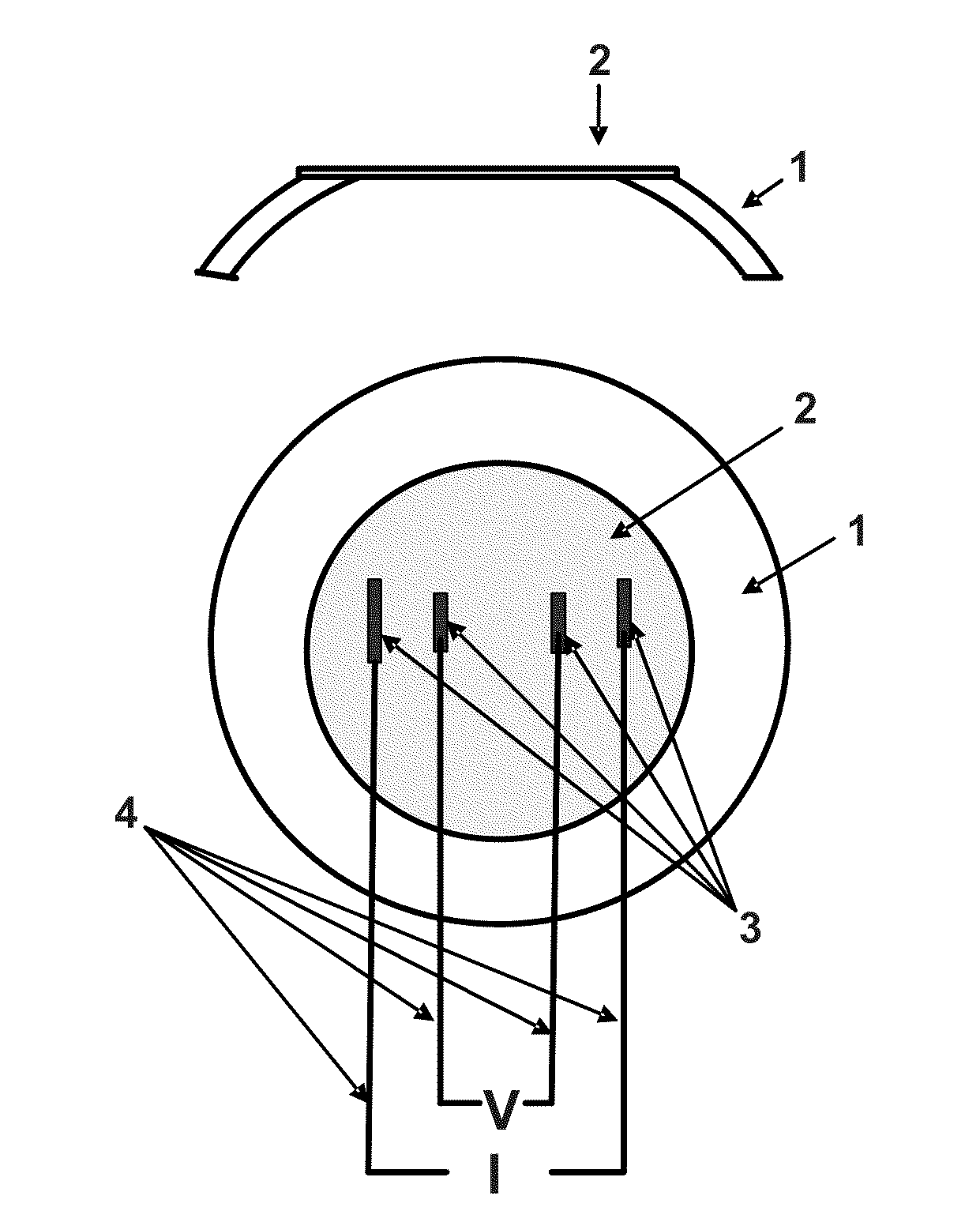

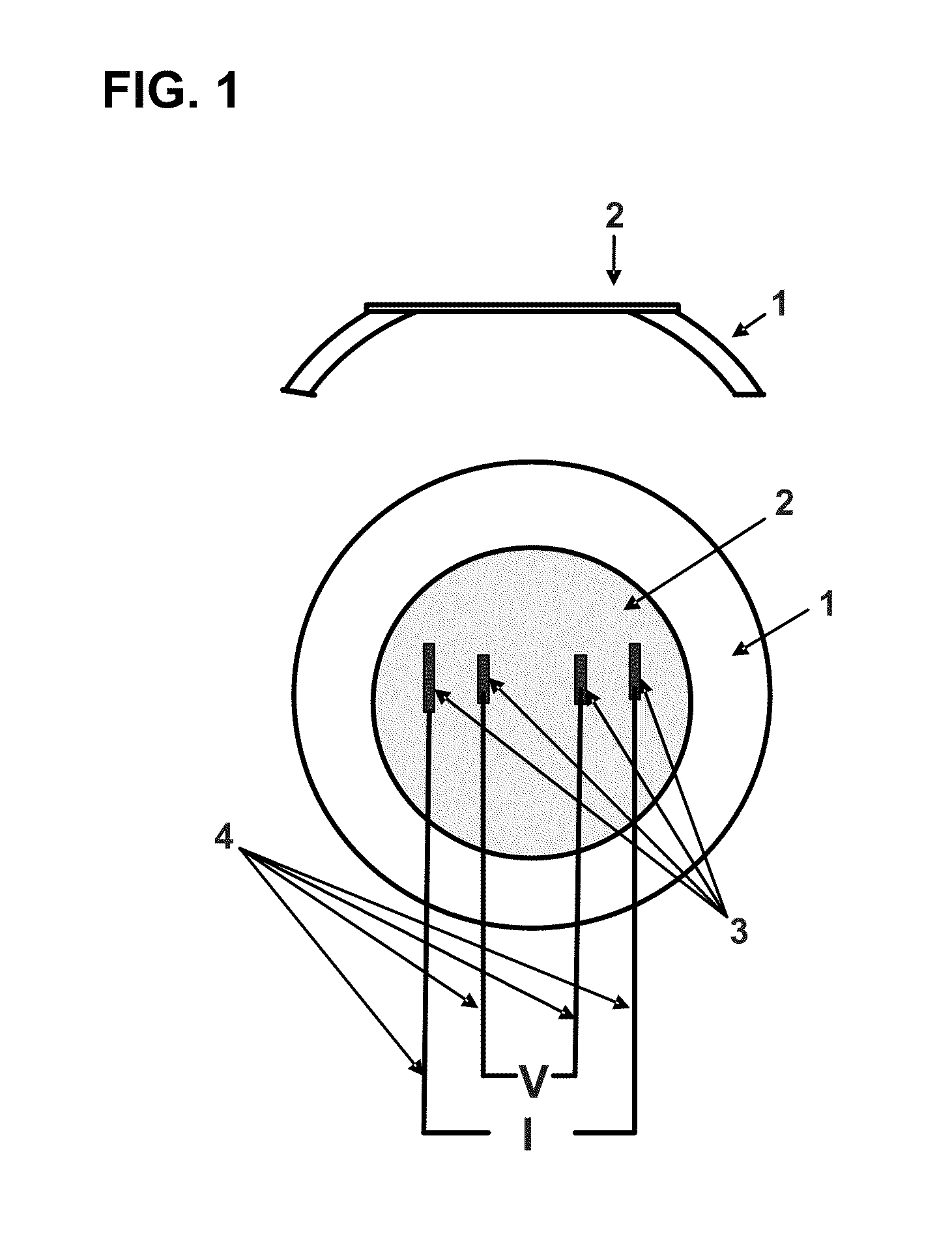

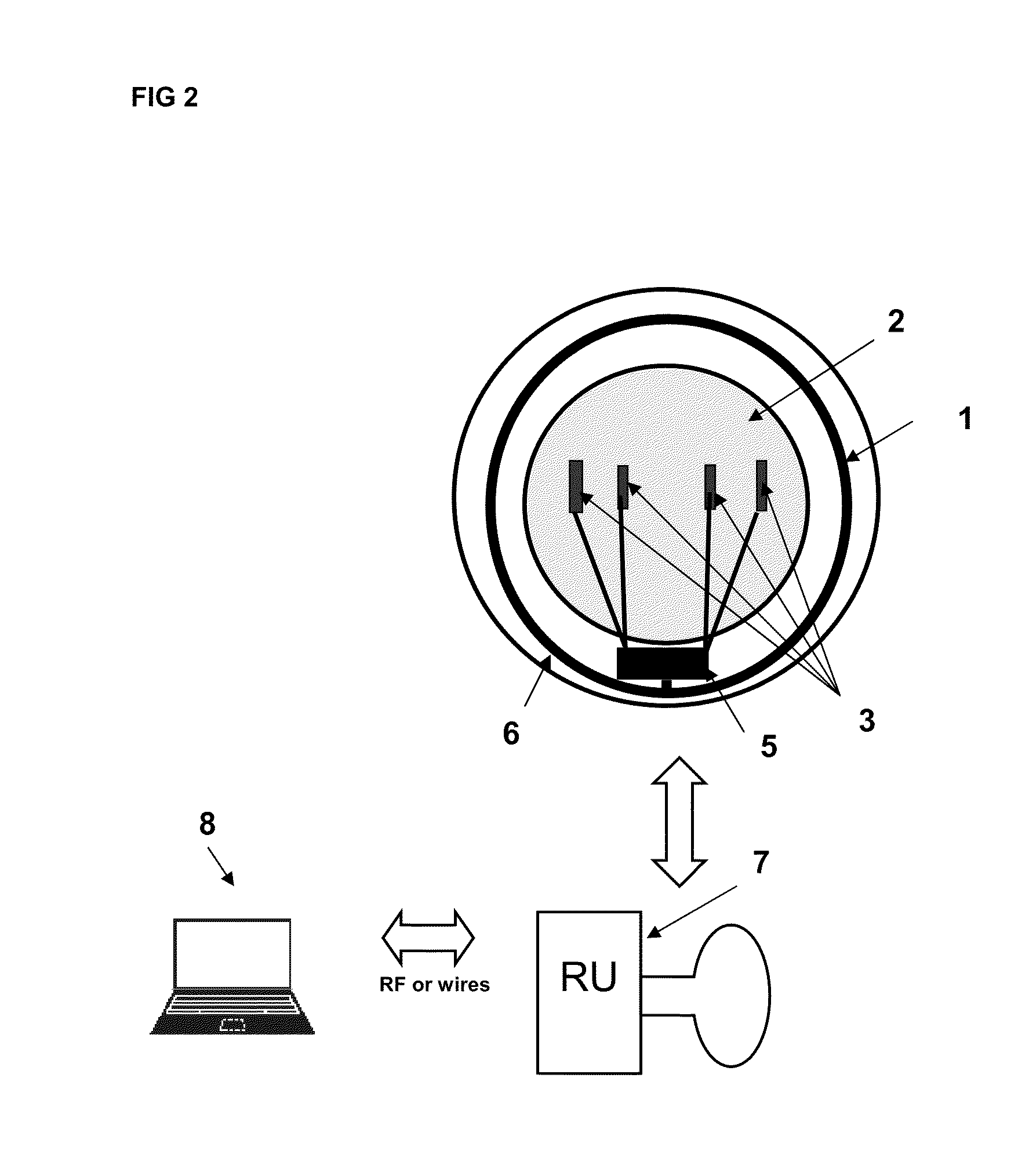

Sensor contact lens, system for the non-invasive monitoring of intraocular pressure and method for measuring same

The invention is characterized in that it comprises a truncated contact lens (1), whose truncation plane is parallel to the base of said contact lens, and a polymeric nanocomposite material (2) centrally disposed and attached to the perimeter of the truncated area, said material being sensitive to pressure changes, biocompatible and transparent, and including contact electrodes (3), and in that it also comprises means for transmitting IOP measurement data to an external system. The invention also relates to a method for measuring IOP using said lens comprising: i) placing said sensor contact lens in the eye to determine its intraocular pressure; ii) providing a direct current value between external electrodes; iii) ΔV measurement between internal electrodes; and iv) identifying whether the value obtained is outside the linear response, expressed in changes of resistivity, of the polymeric nanocomposite material. The invention also relates to a telemetry system comprising said lens.

Owner:CONSEJO SUPERIOR DE INVESTIGACIONES CIENTIFICAS (CSIC) +4

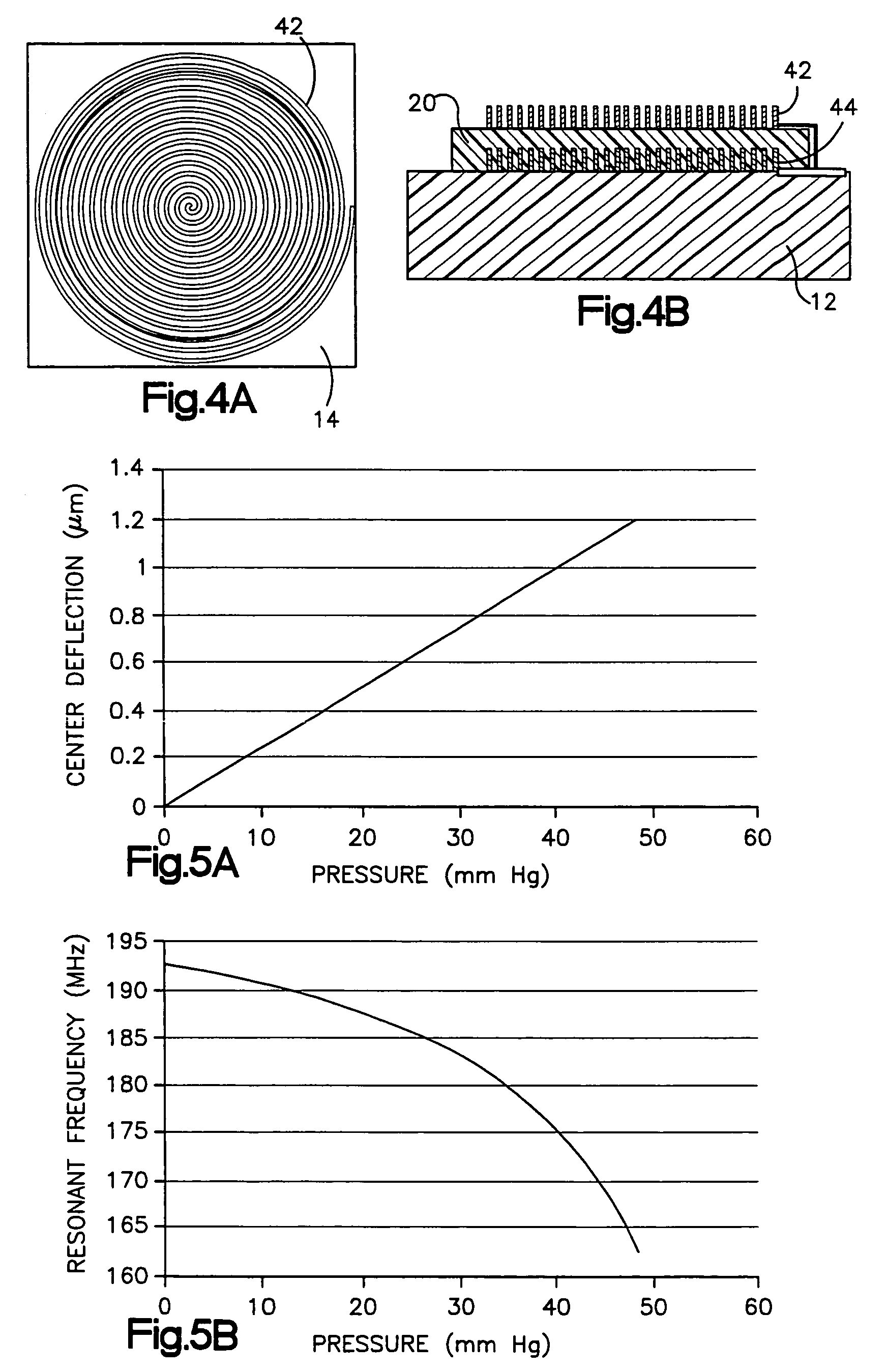

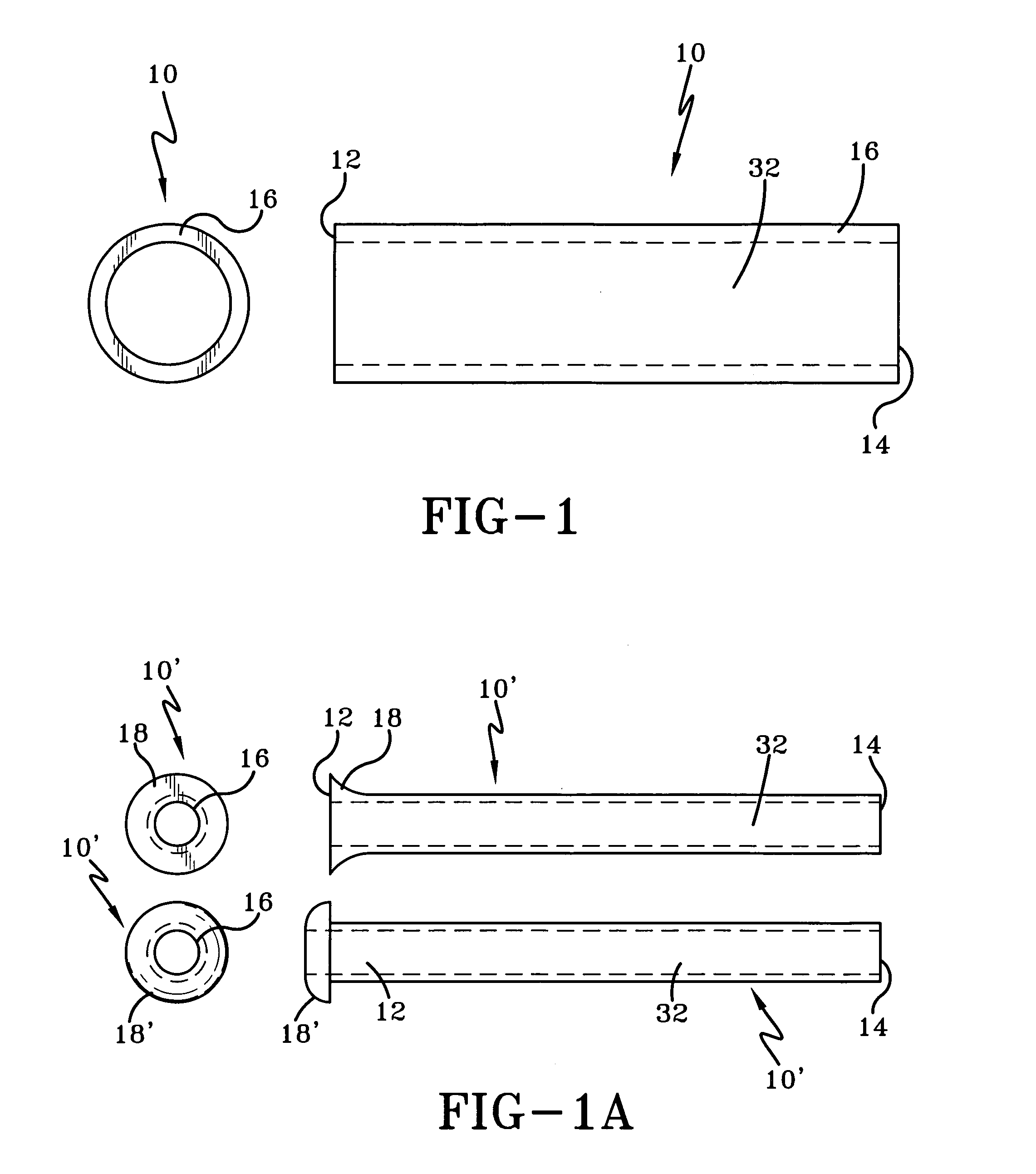

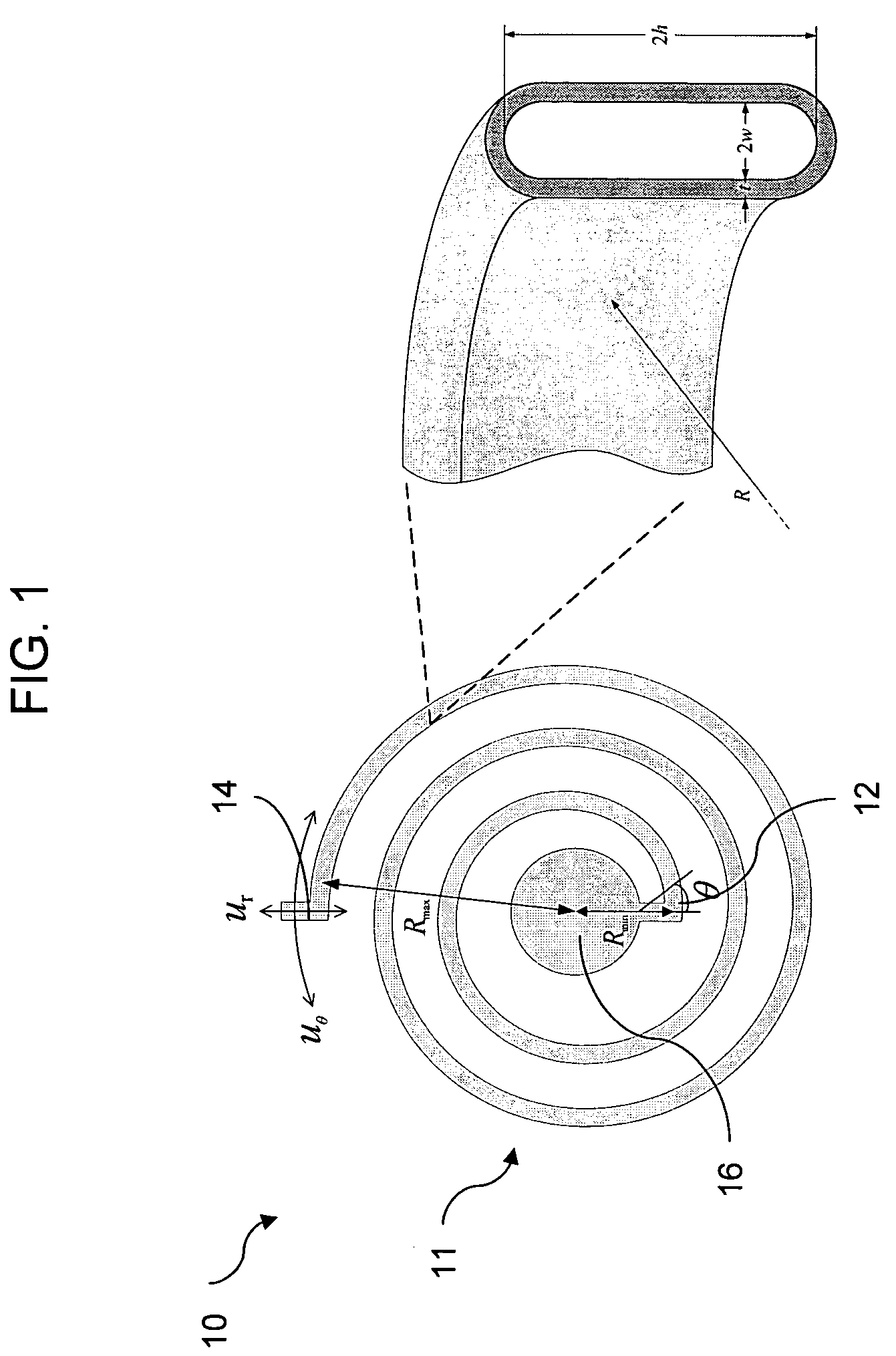

Implantable mechanical pressure sensor and method of manufacturing the same

InactiveUS7252006B2Fluid pressure measurement using elastically-deformable gaugesFluid pressure measurement by electric/magnetic elementsIn planeGlaucoma

A biocompatible, mechanical, micromachined pressure sensor and methods of manufacturing such a pressure sensor are provided. The pressure sensor of the current invention includes a high-aspect-ratio curved-tube structure fabricated through a one-layer parylene process. The pressure sensor of the current invention requires zero power consumption and indicates the pressure variation by changes of the in situ in-plane motion of the sensor, which can be gauged externally by a direct and convenient optical observation. In one embodiment, the pressure sensor of the current invention has been shown to work as an IOP sensor for eye implantation where the intraocular in-plane motion of the sensor can be recorded from outside of the eye, such that the intraocular pressure in glaucoma patients can be constantly monitored.

Owner:CALIFORNIA INST OF TECH

Intraocular pressure measurement system including a sensor mounted in a contact lens

Owner:THE CLEVELAND CLINIC FOUND

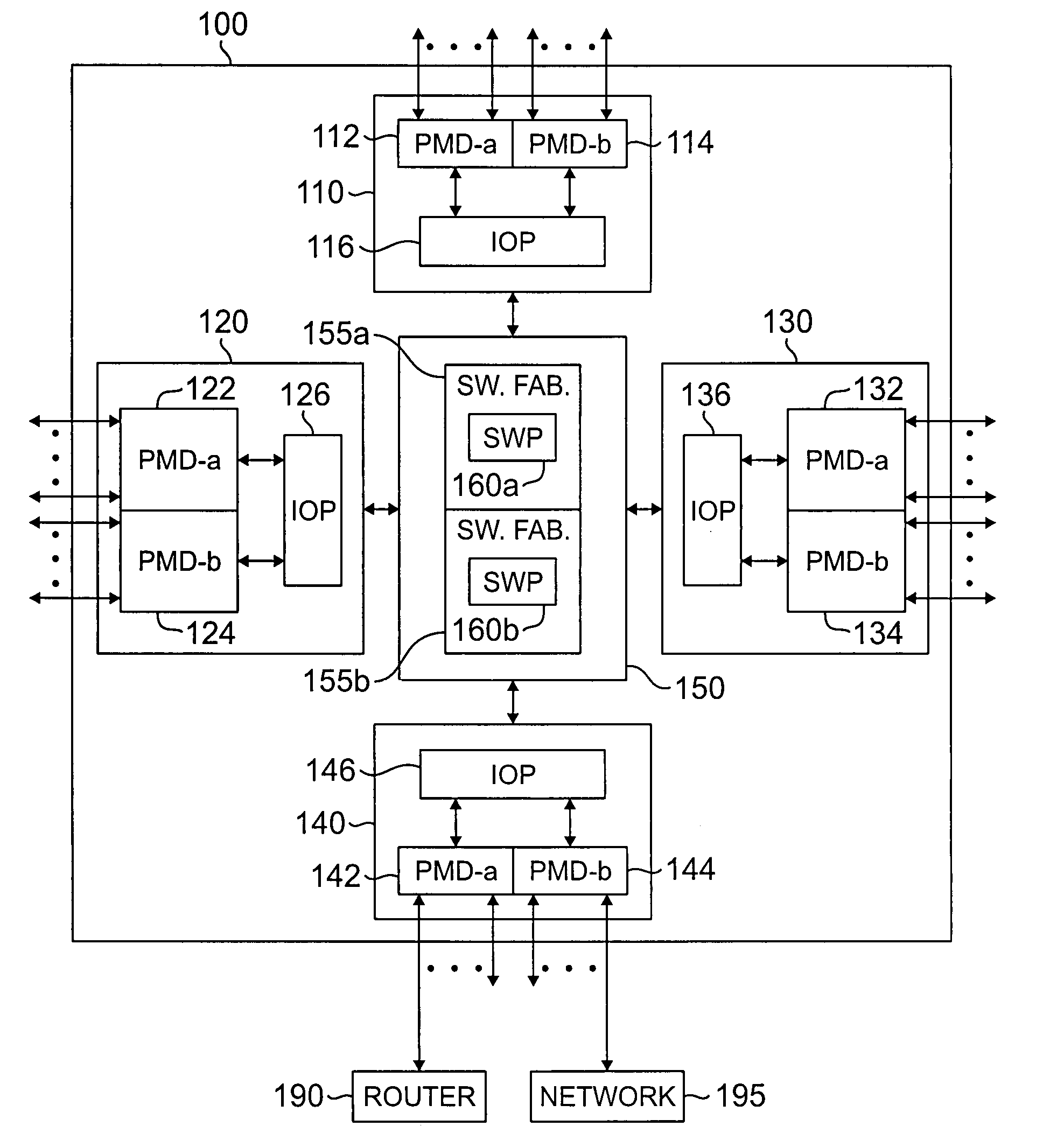

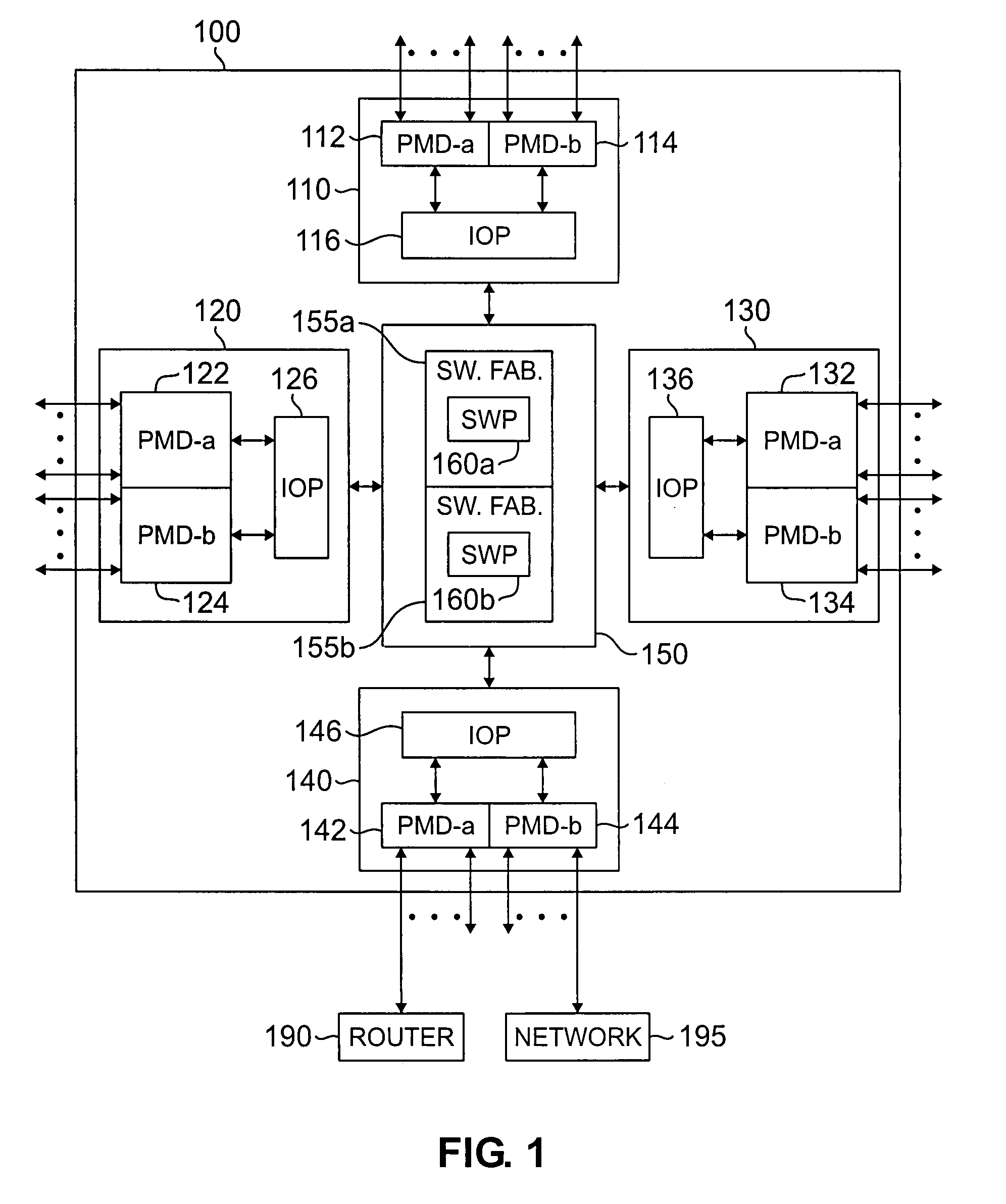

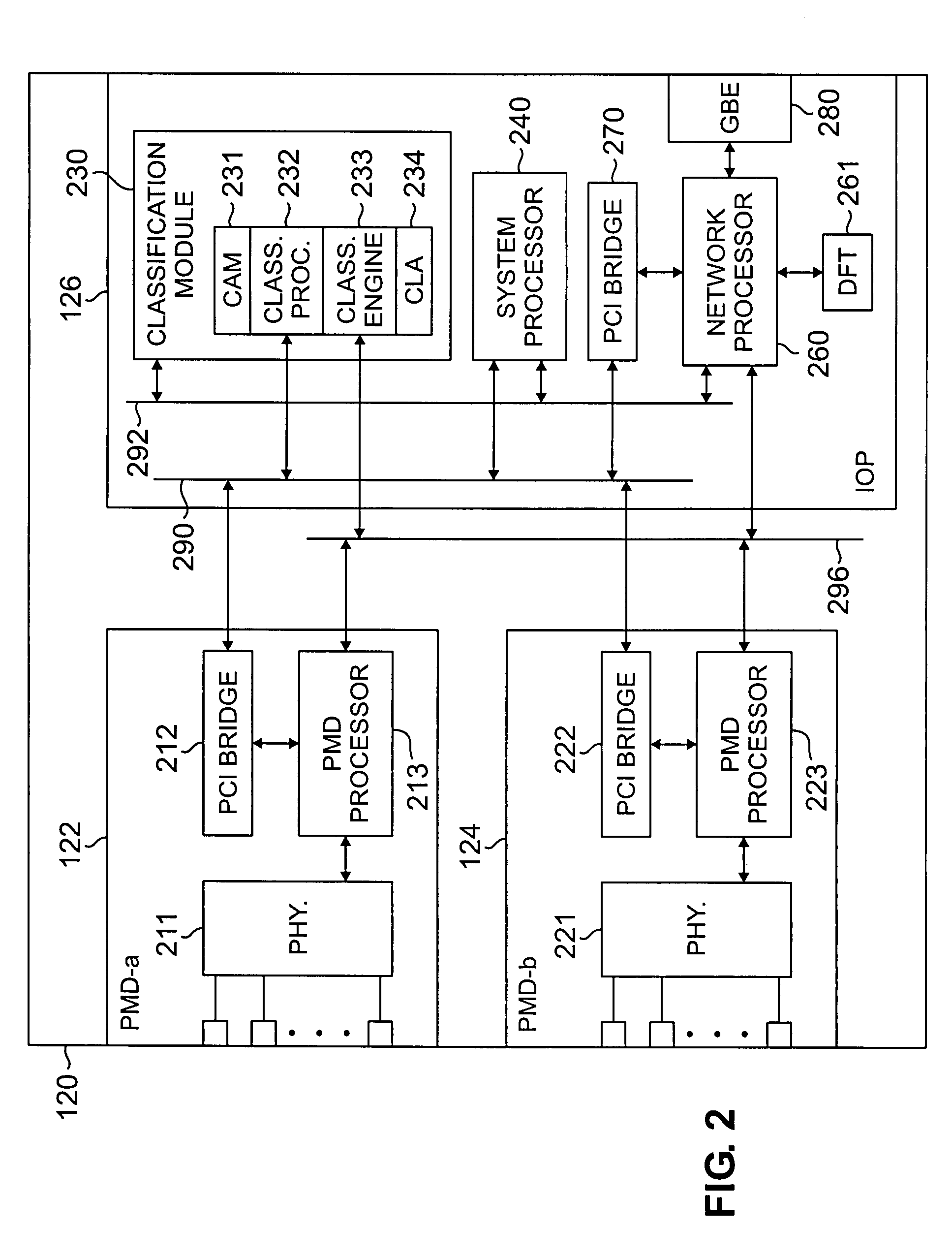

Apparatus and method for classifying traffic in a distributed architecture router

A router for interconnecting N interfacing peripheral devices. The router comprises a switch fabric and routing nodes coupled to the switch fabric. Each routing node comprises: i) a plurality of physical medium device (PMD) modules for transmitting data packets to and receiving data packets from selected ones of the N interfacing peripheral devices; ii) an input-output processing (IOP) module coupled to the PMD modules and the switch fabric for routing the data packets between the PMD modules and the switch fabric and between the PMD modules; and iii) a classification module associated with the IOP module for classifying a first data packet received from the IOP module. The classification module causes the IOP module to forward the first data packet based on the classification. The router architecture incorporates streams-based billing support, firewall capabilities, and data surveillance functionality.

Owner:SAMSUNG ELECTRONICS CO LTD

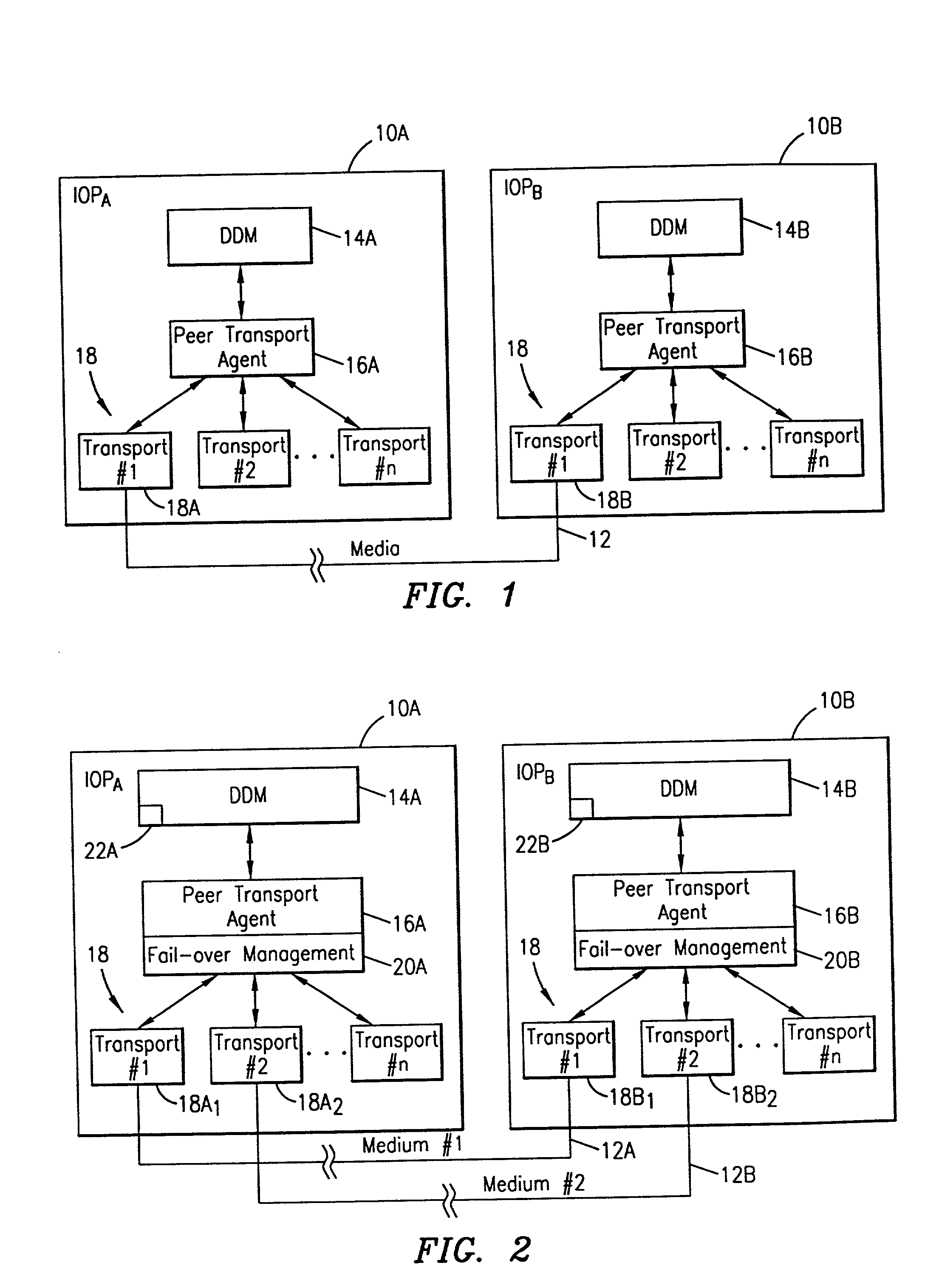

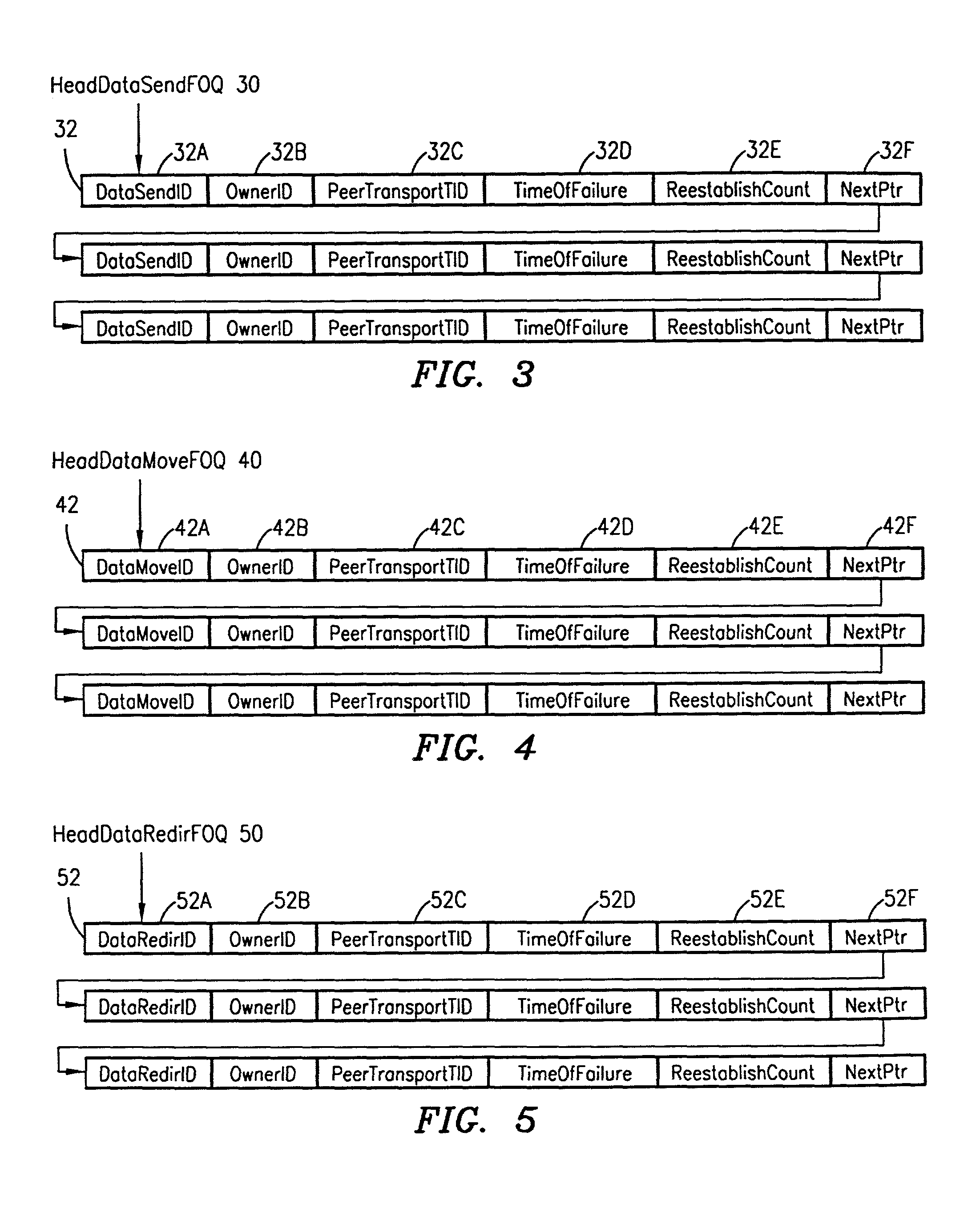

System and method for fail-over data transport

InactiveUS20010014954A1Digital computer detailsRedundant hardware error correctionFailoverComputerized system

A system and method for maintaining a communications within a computer system after a data transport failure across a first link. Fail-over capability is attained by re-establishing communications across a secondary link using different transport mechanisms. Between two Input / Output Processors (IOPs) within a computer system, such as a server, a series of data transactions therebetween are queued until transaction completion. Upon detection of a failure condition between the IOPs across the first link, the IOPs engage fail-over mechanisms to preserve uncompleted data transactions until communications are re-established across the secondary link.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

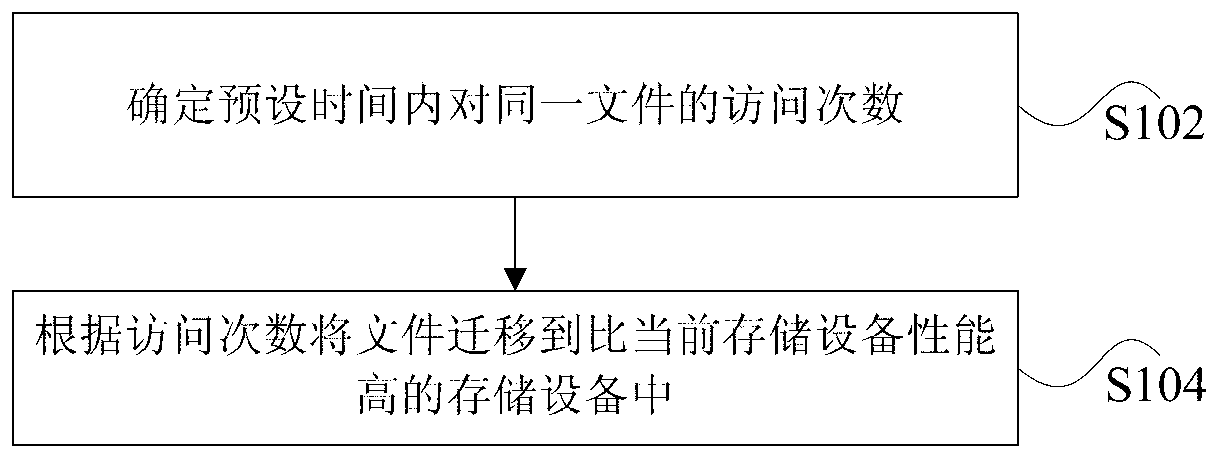

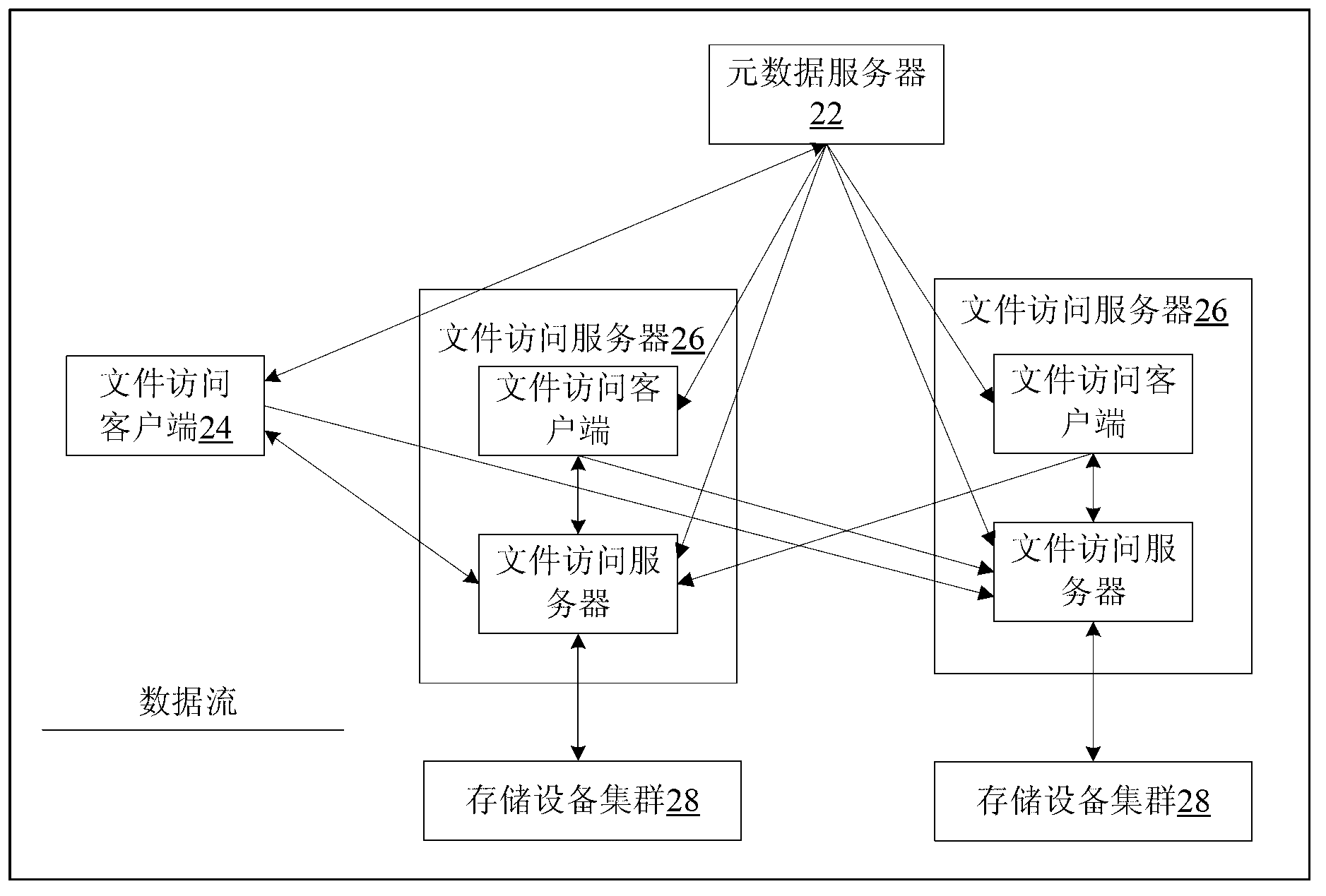

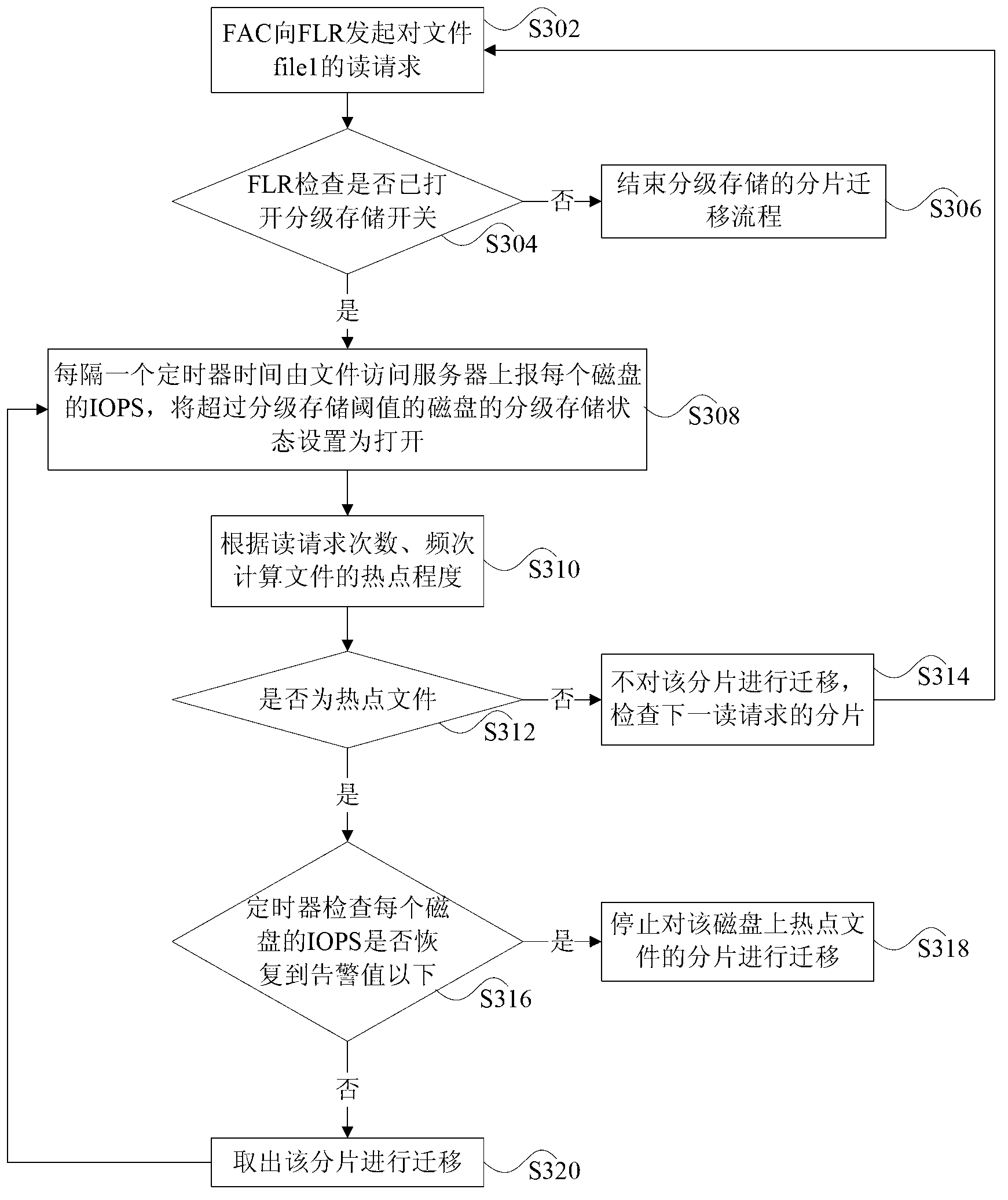

Storage method and storage device of distributive-type file system

InactiveCN102841931AIOPS pressure equalizationImprove performanceDigital data information retrievalProgram control using stored programsAccess timeFile system

Owner:ZTE CORP

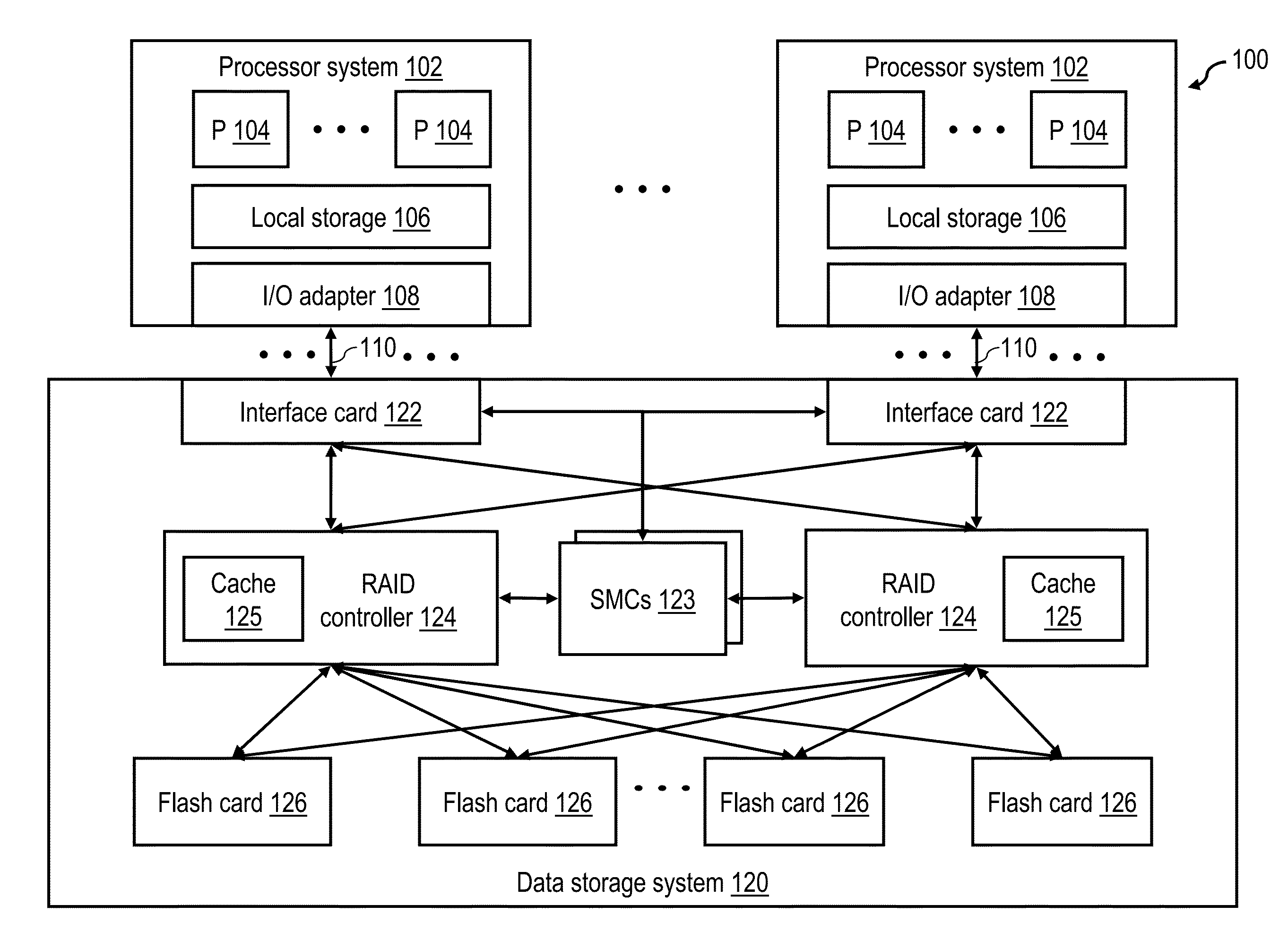

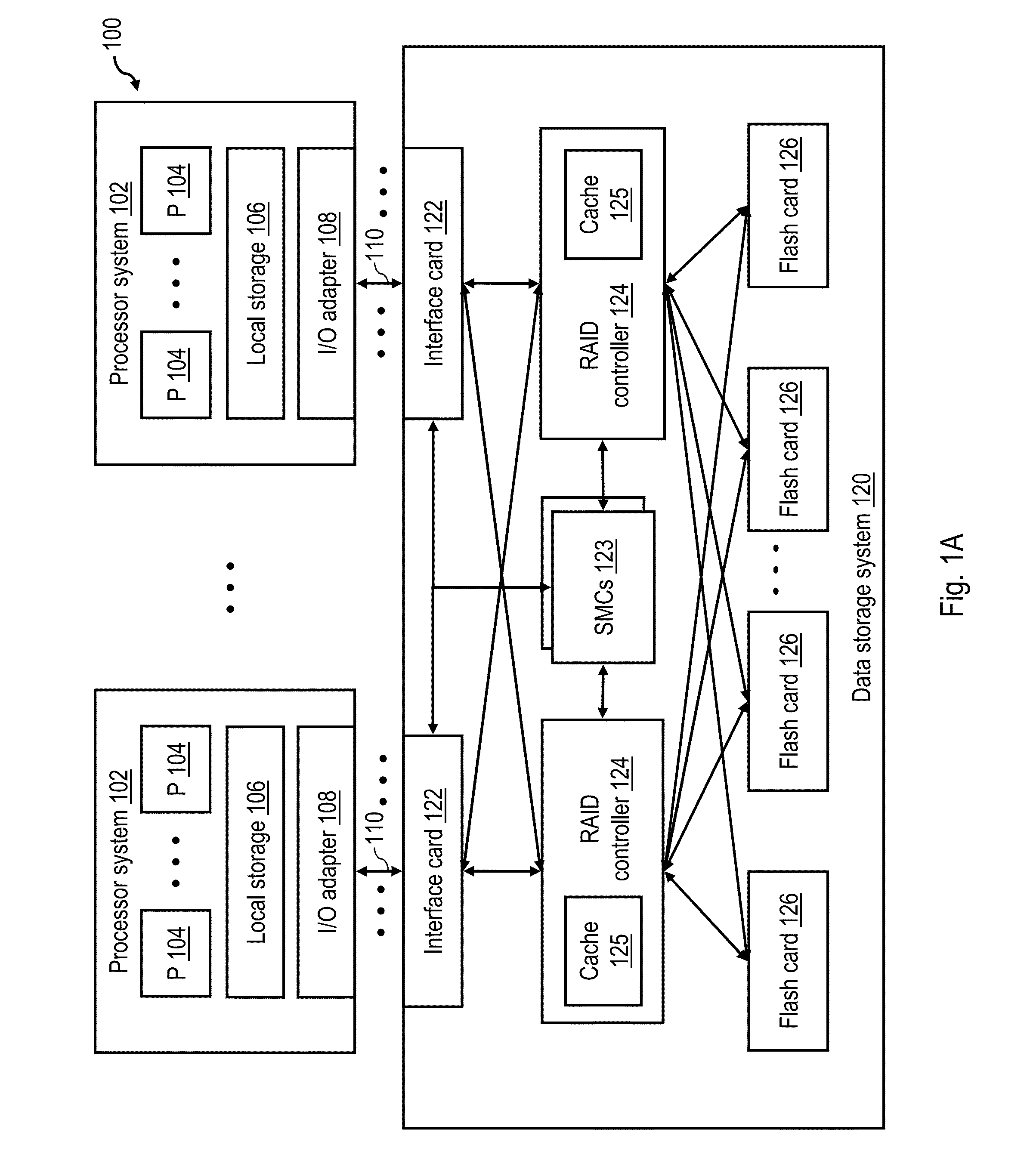

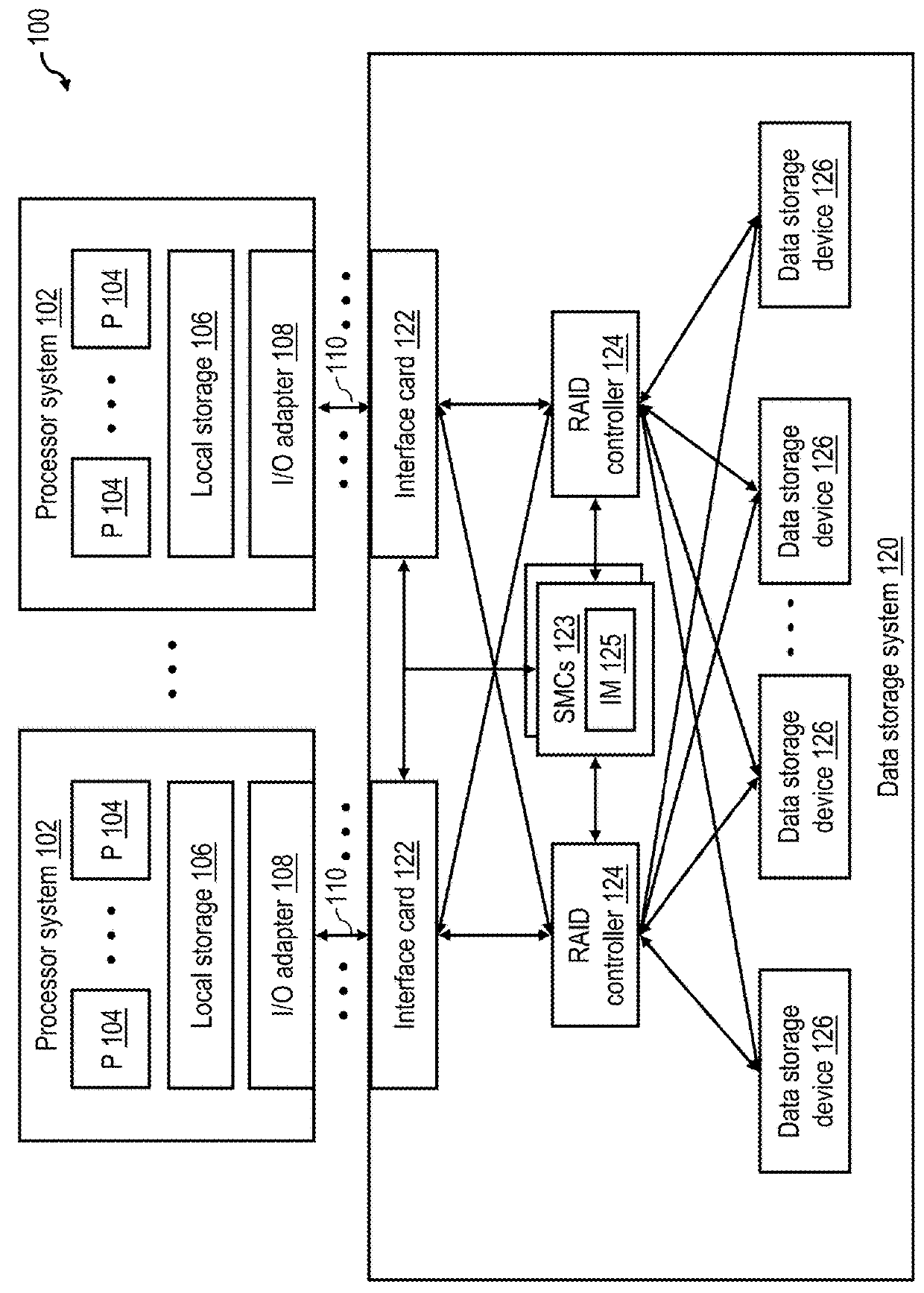

Promoting consistent response times in a data storage system having multiple data retrieval mechanisms

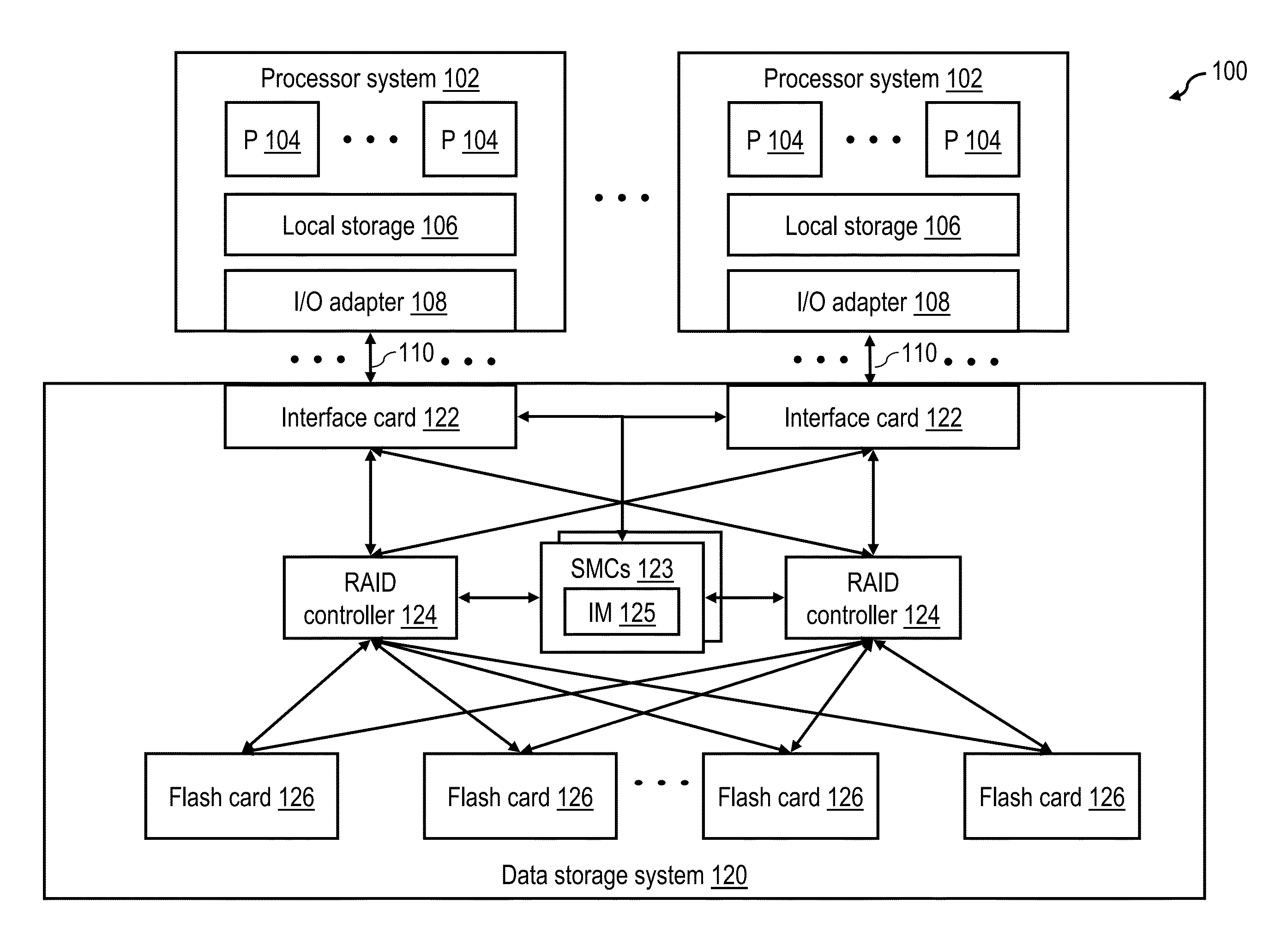

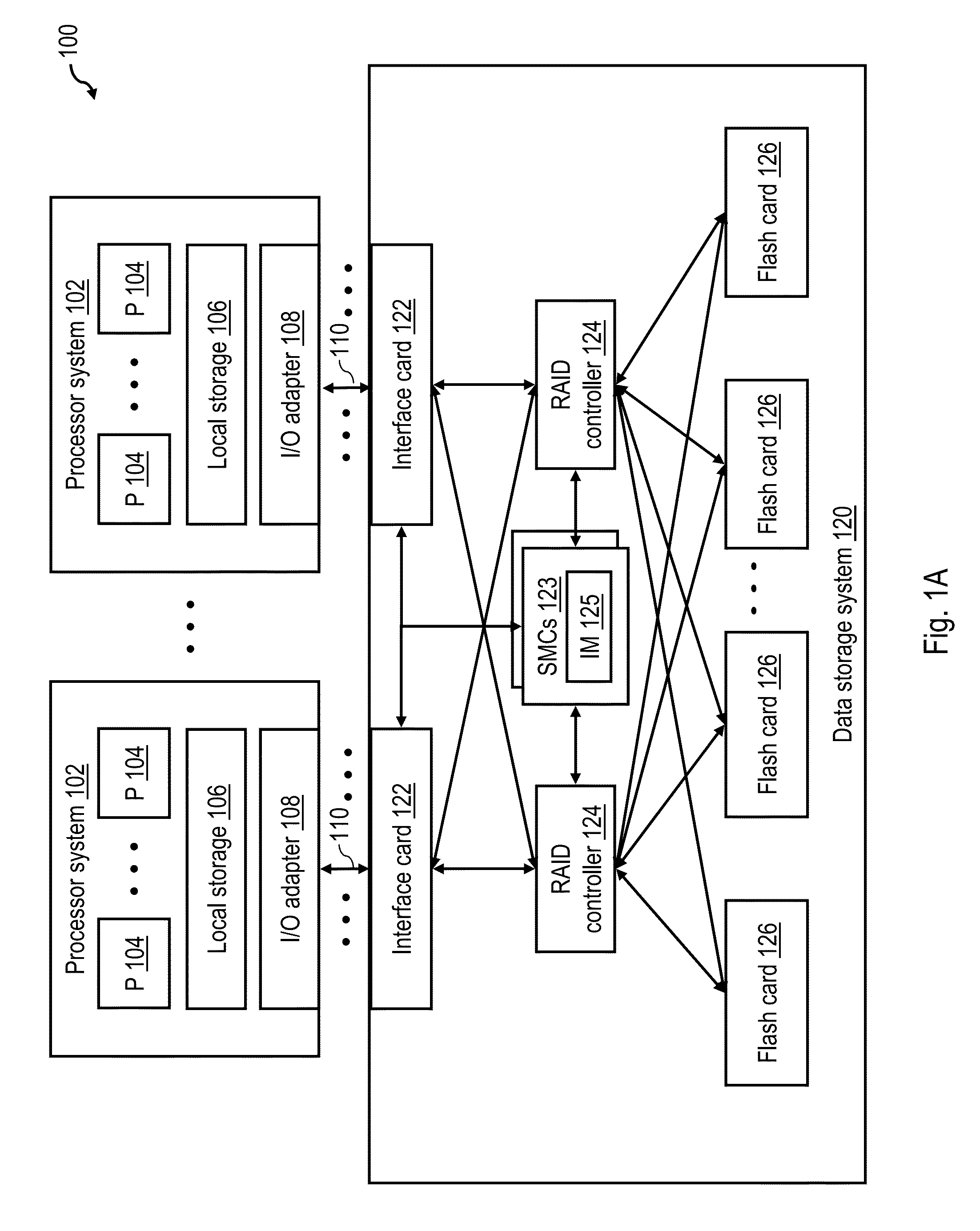

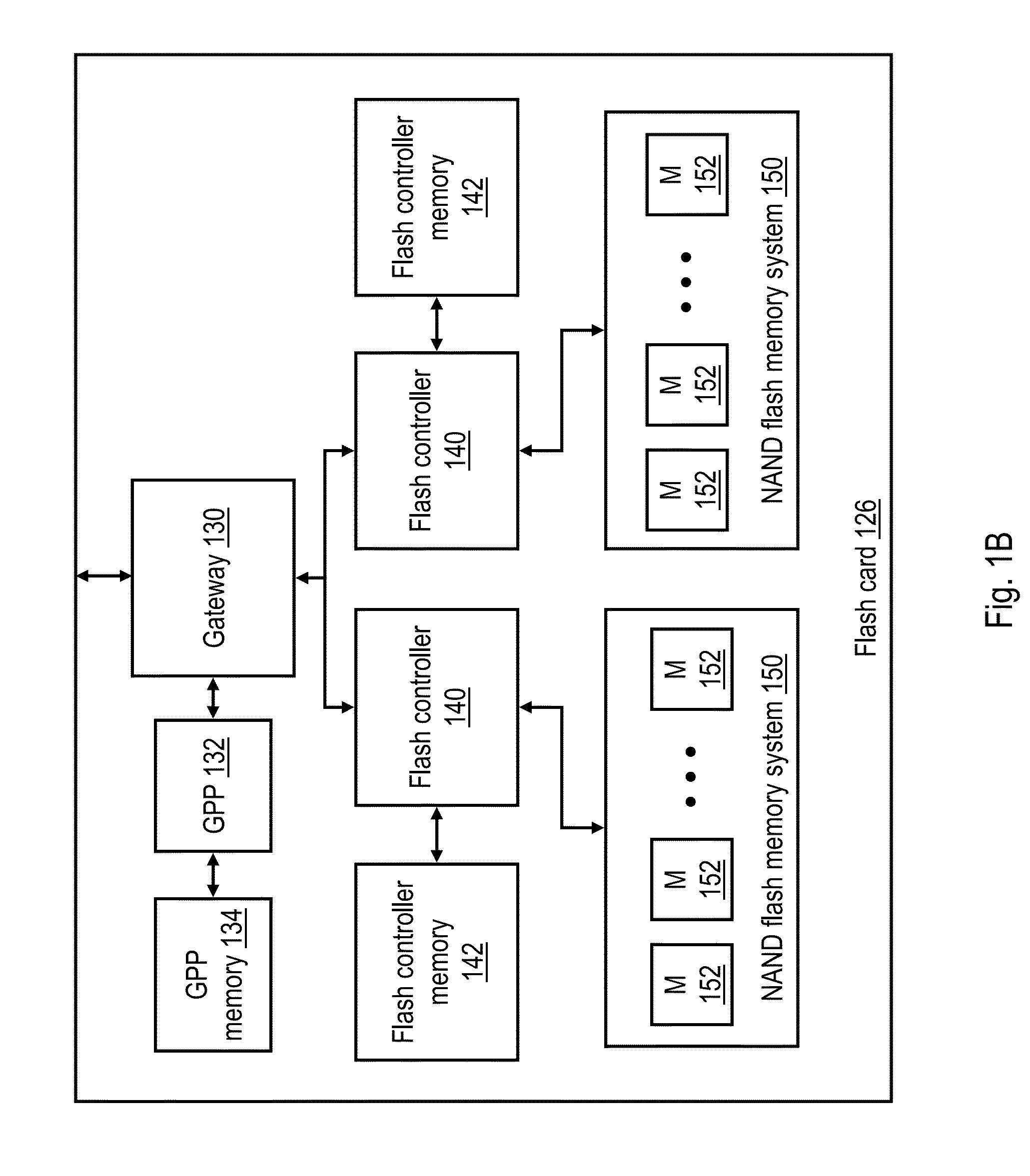

InactiveUS20160188223A1Memory architecture accessing/allocationInput/output to record carriersData errorData storing

A data storage system includes a higher level controller, a lower level controller, and a plurality of storage components including a particular storage component. Data is stored within the data storage system utilizing at least one level of striping across the plurality of storage components. Latencies of input / output operations (IOPs) requesting access to the data stored within the data storage system are monitored. In response to determining that a latency of a read IOP requesting read data stored in the particular storage component exceeds a latency threshold and in absence of a data error, the read IOP is serviced by reconstructing the read data from storage components among the plurality of storage components other than the particular storage component. The lower level controller also provides feedback to the higher level controller to cause the higher level controller to reduce IOPs directed to at least the particular storage component.

Owner:IBM CORP

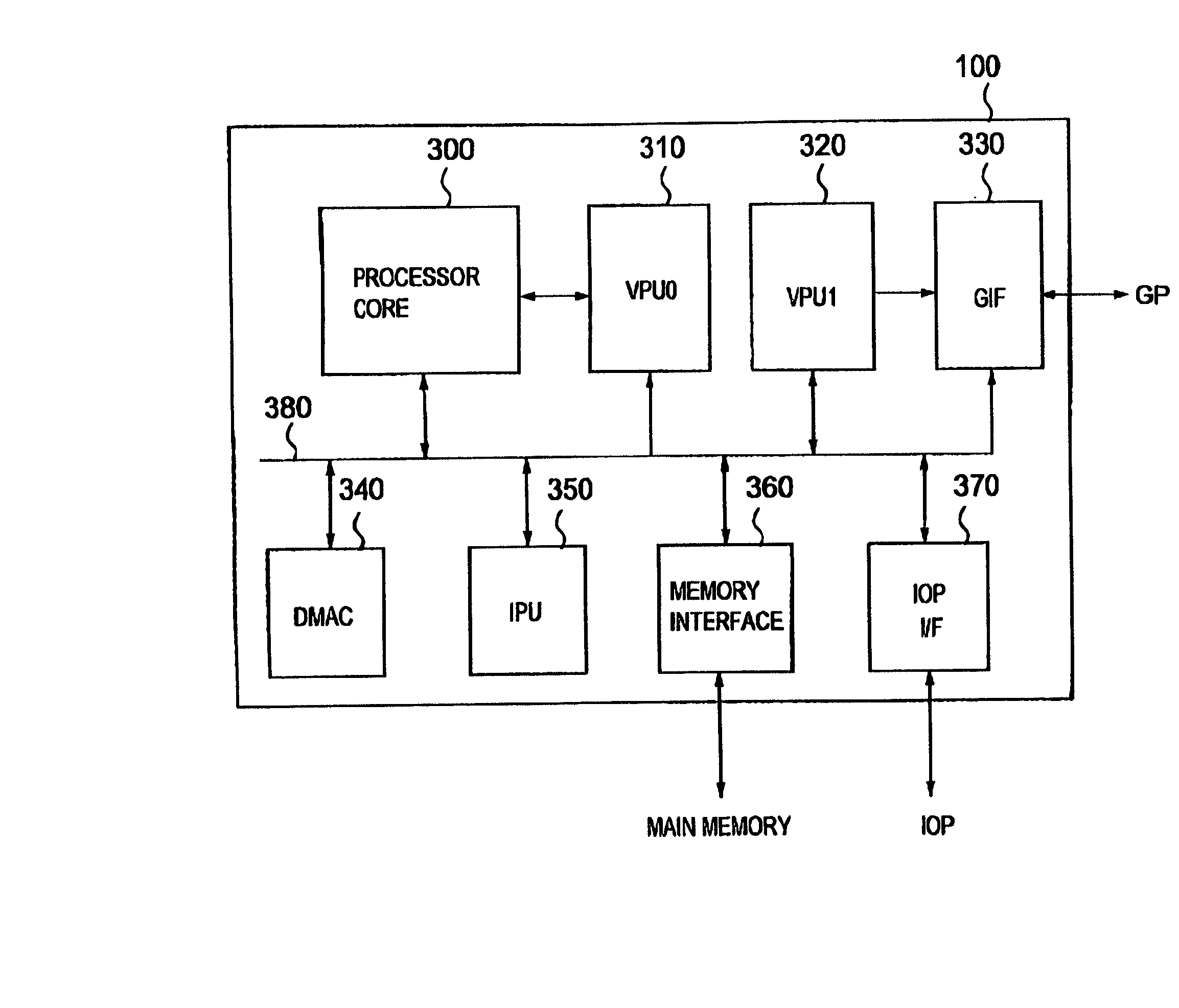

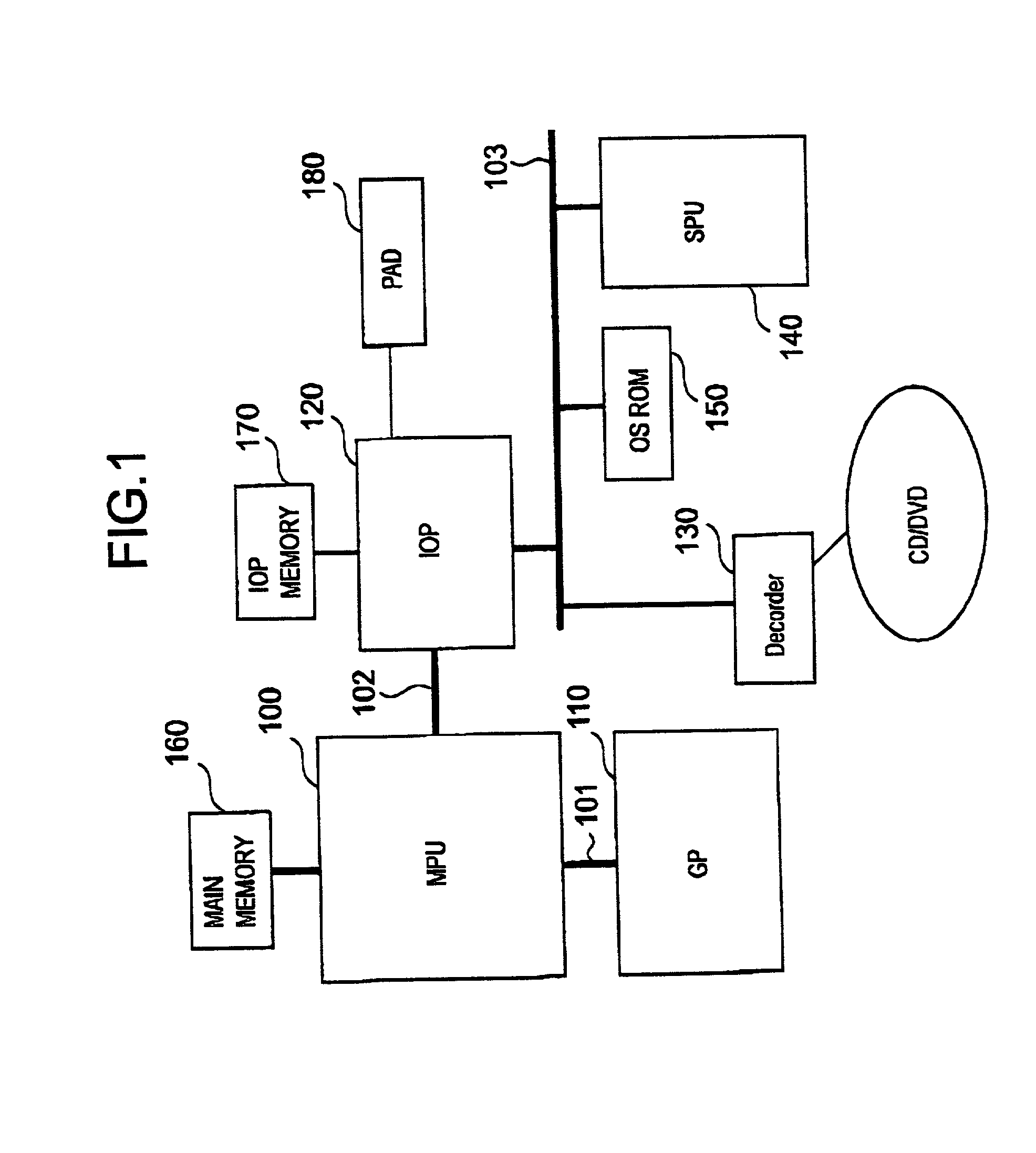

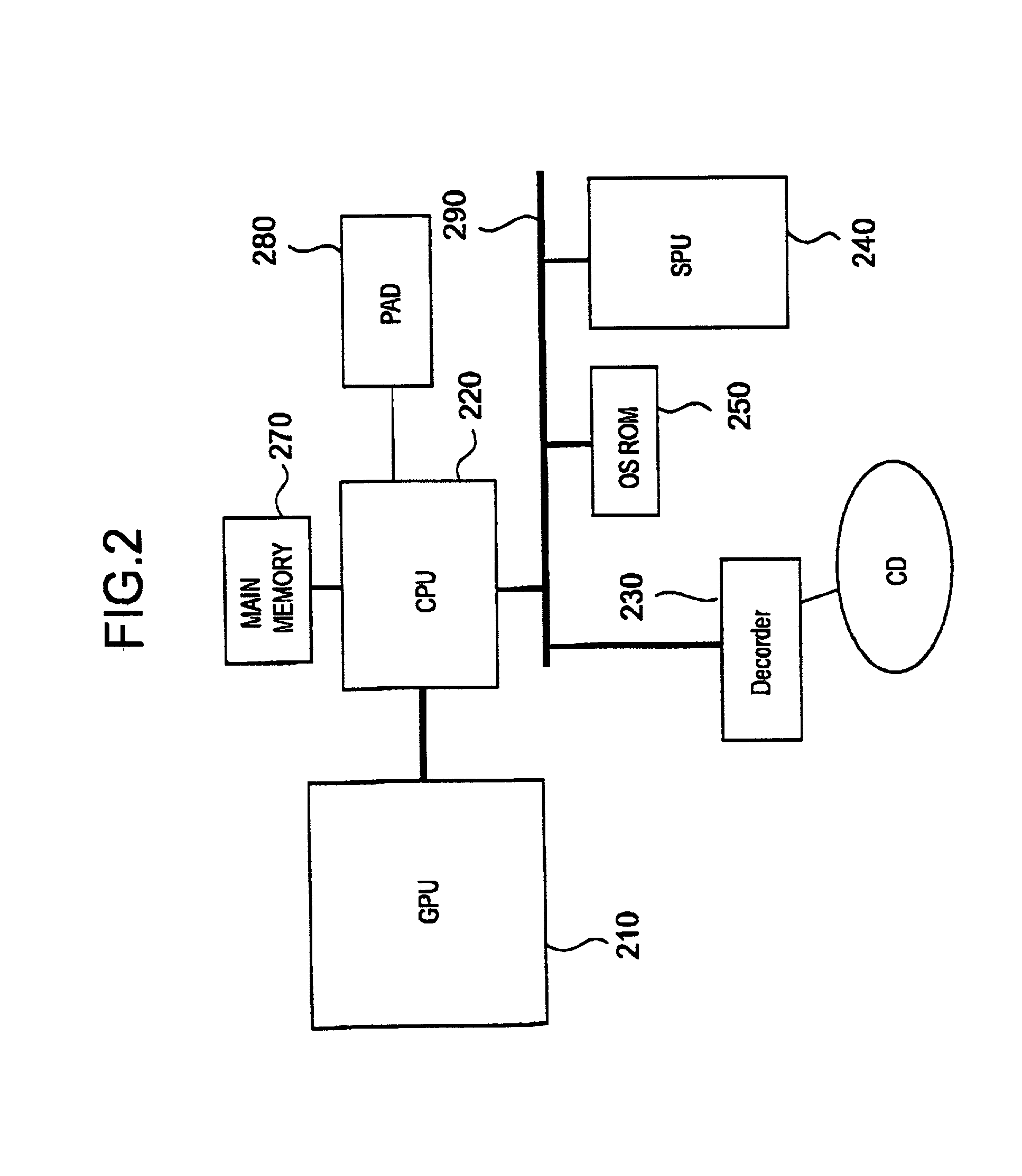

Entertainment apparatus having compatibility and computer system

InactiveUS20020046229A1Multiprogramming arrangementsMultiple digital computer combinationsGraphicsNormal mode

There is disclosed an entertainment apparatus on which a program for an older version of the apparatus can be executed. In a normal mode, an MPU(100) operates as a main CPU:and a GP(110) operates as a graphics processor, and an IOP(120) operates as a subprocessor for input and output. In a compatible mode in which a program for an older version of the apparatus is executed, the IOP(120) capable of executing the program for the older version of the apparatus operates as a main CPU, and the MPU(100) and GP(110) emulate a graphics processor for the older version of the apparatus.

Owner:SONY COMPUTER ENTERTAINMENT INC

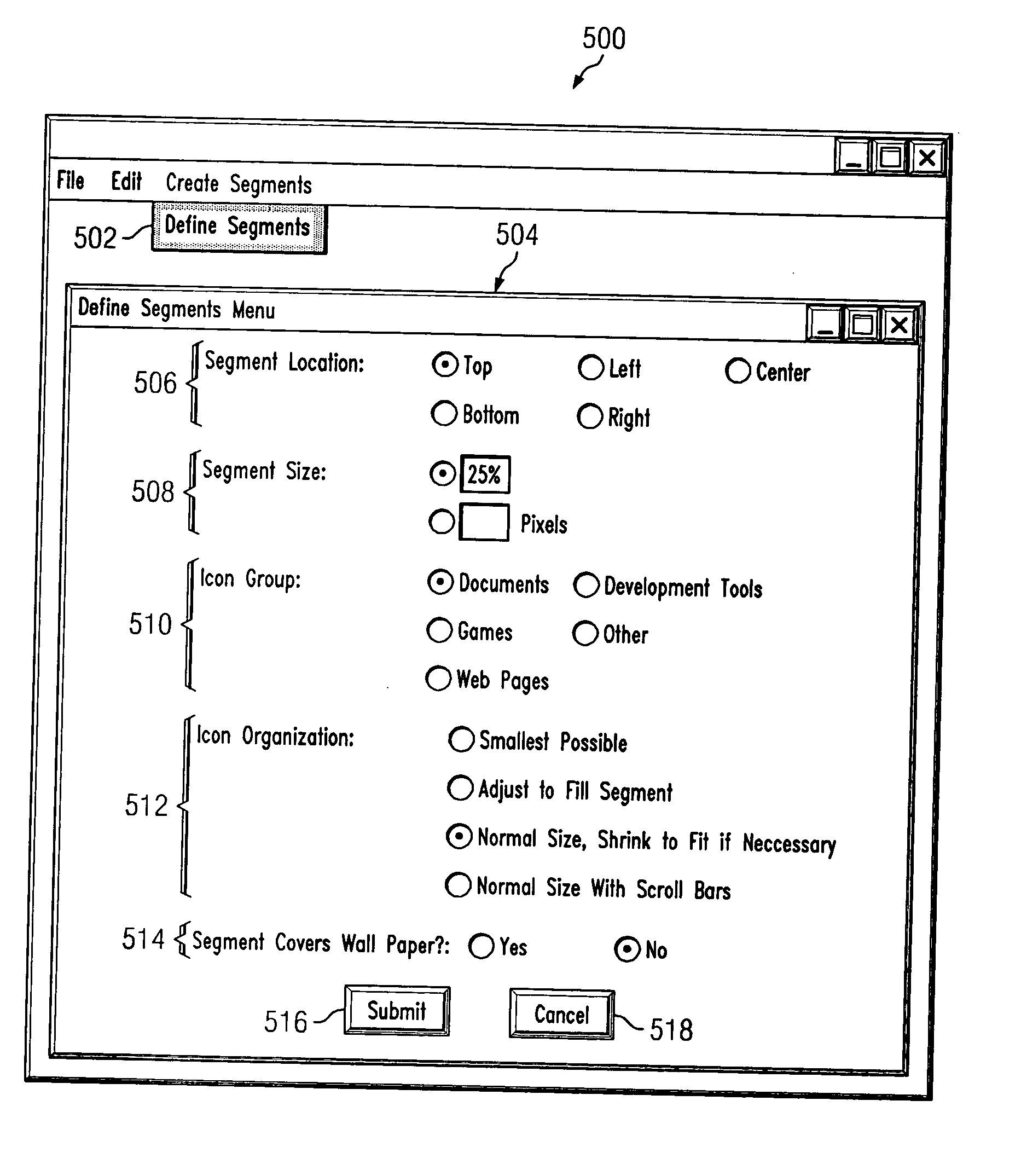

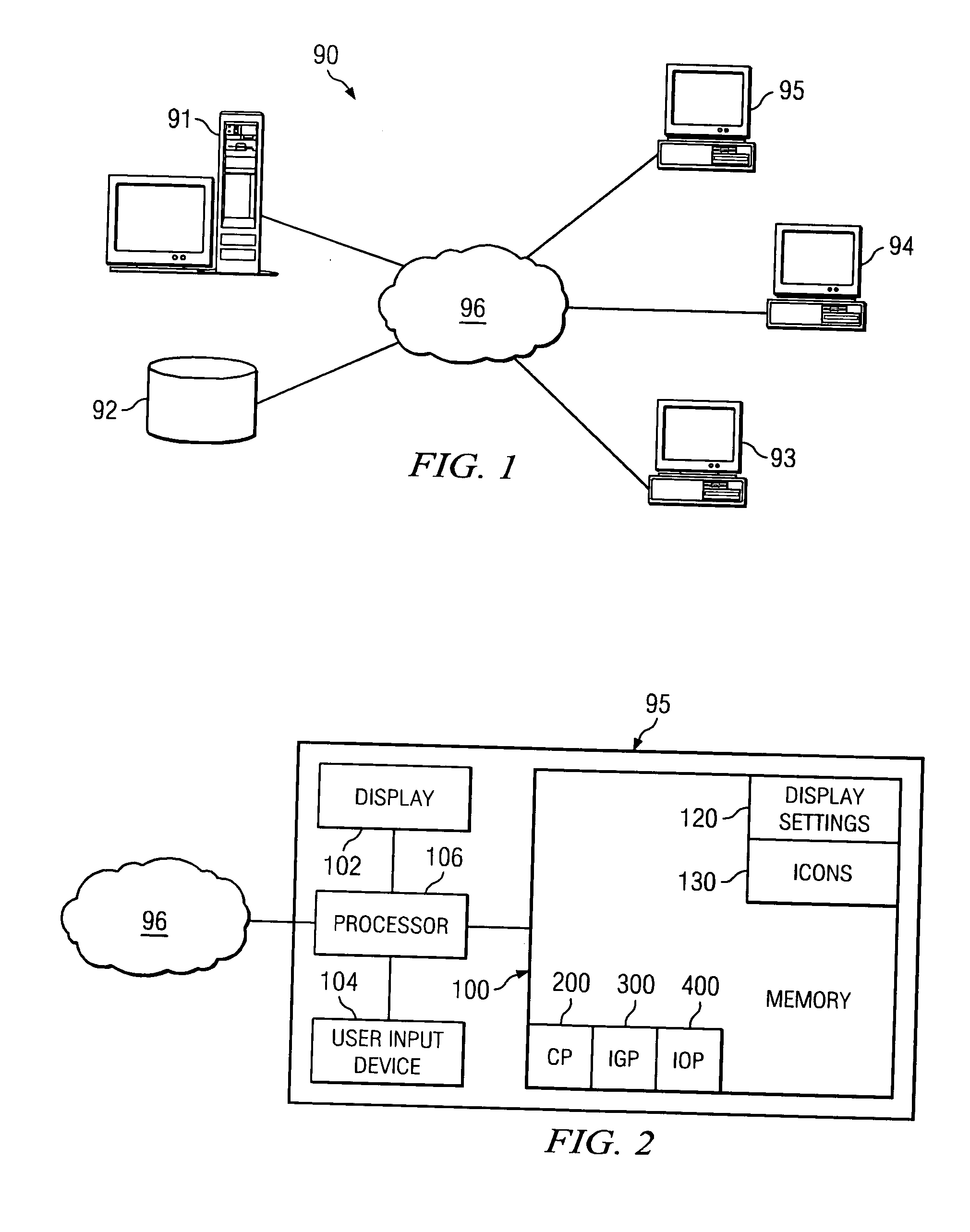

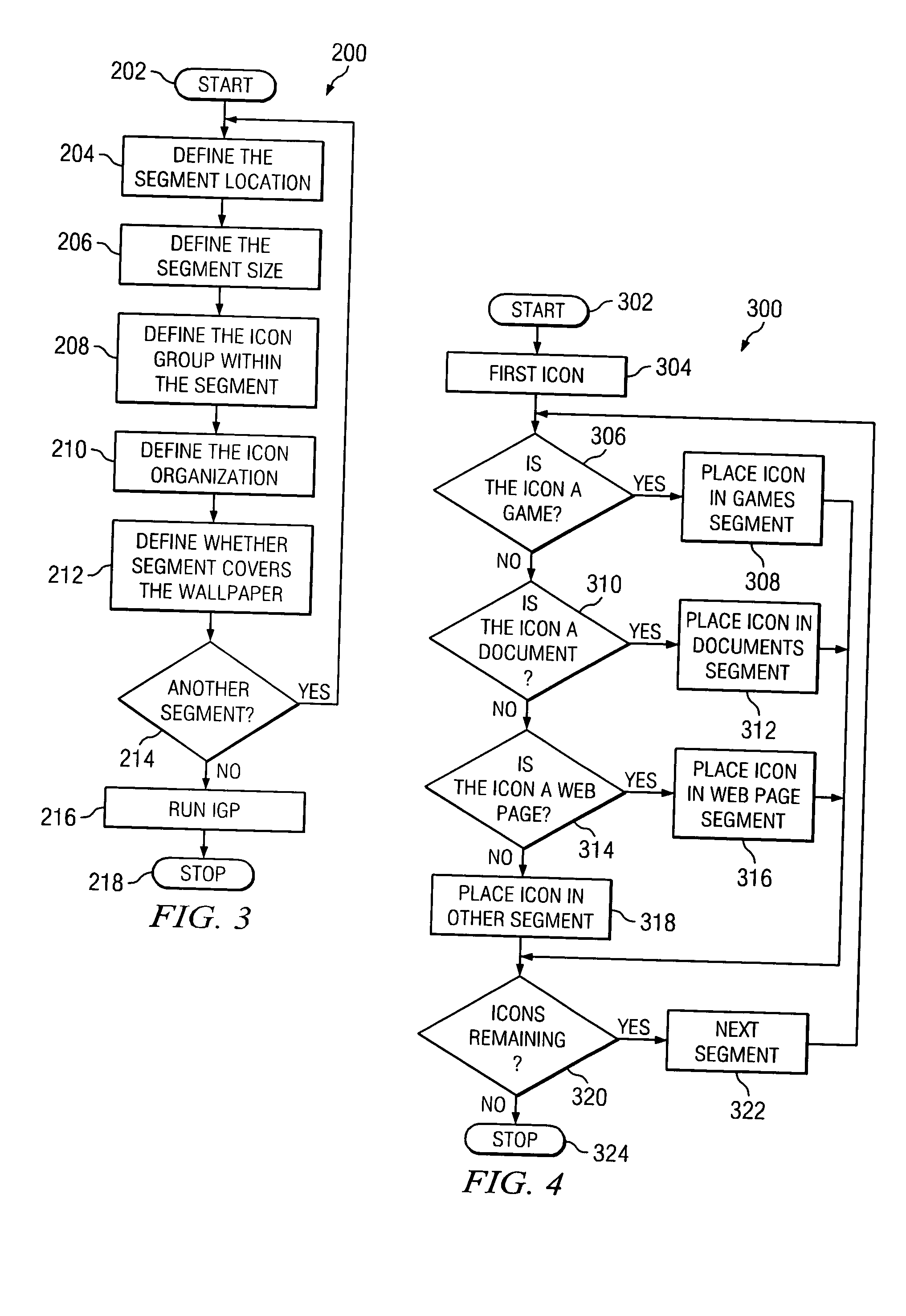

Personalized desktop workspace icon organizer

A method of organizing icons on a desktop into groups and displaying the icon groups in segments on the desktop. The present invention comprises a Configuration Program (CP), an Icon Grouping Program (IGP), and an Icon Organization Program (IOP). The CP allows a user to define at least one segment on the desktop. The user defines the segment location, the segment size, the types of icons associated with the segment, the icon organization within the segment, and whether the segment covers the desktop wallpaper. The IGP analyzes the icons and places the icons into the proper segments based on the type of application associated with the icon. The IOP organizes the icons within each segment using the icon organization specified by the user in the CP. The IOP also organizes new icons that are added to the desktop. The present invention may also be applied to a web portal.

Owner:IBM CORP

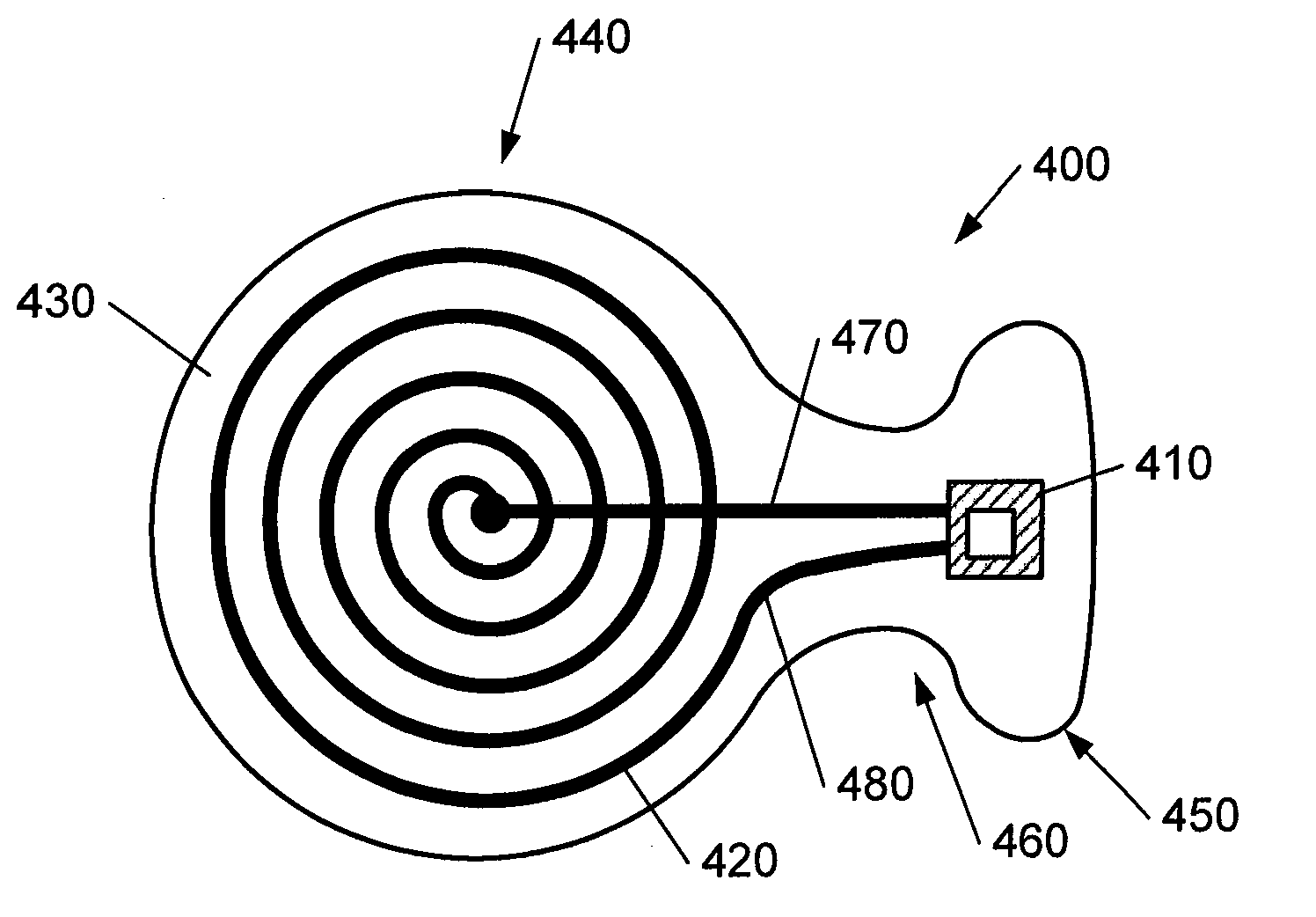

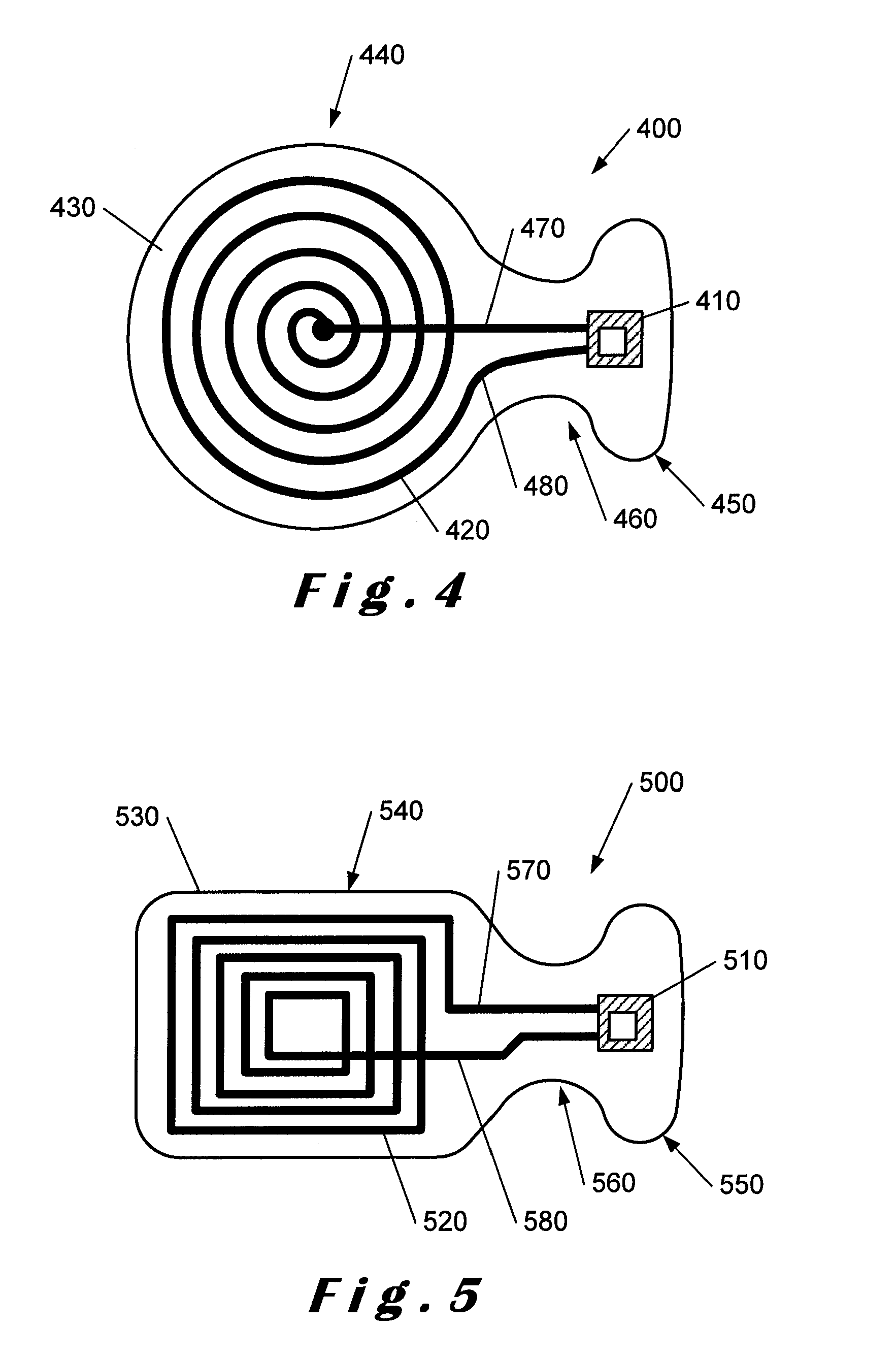

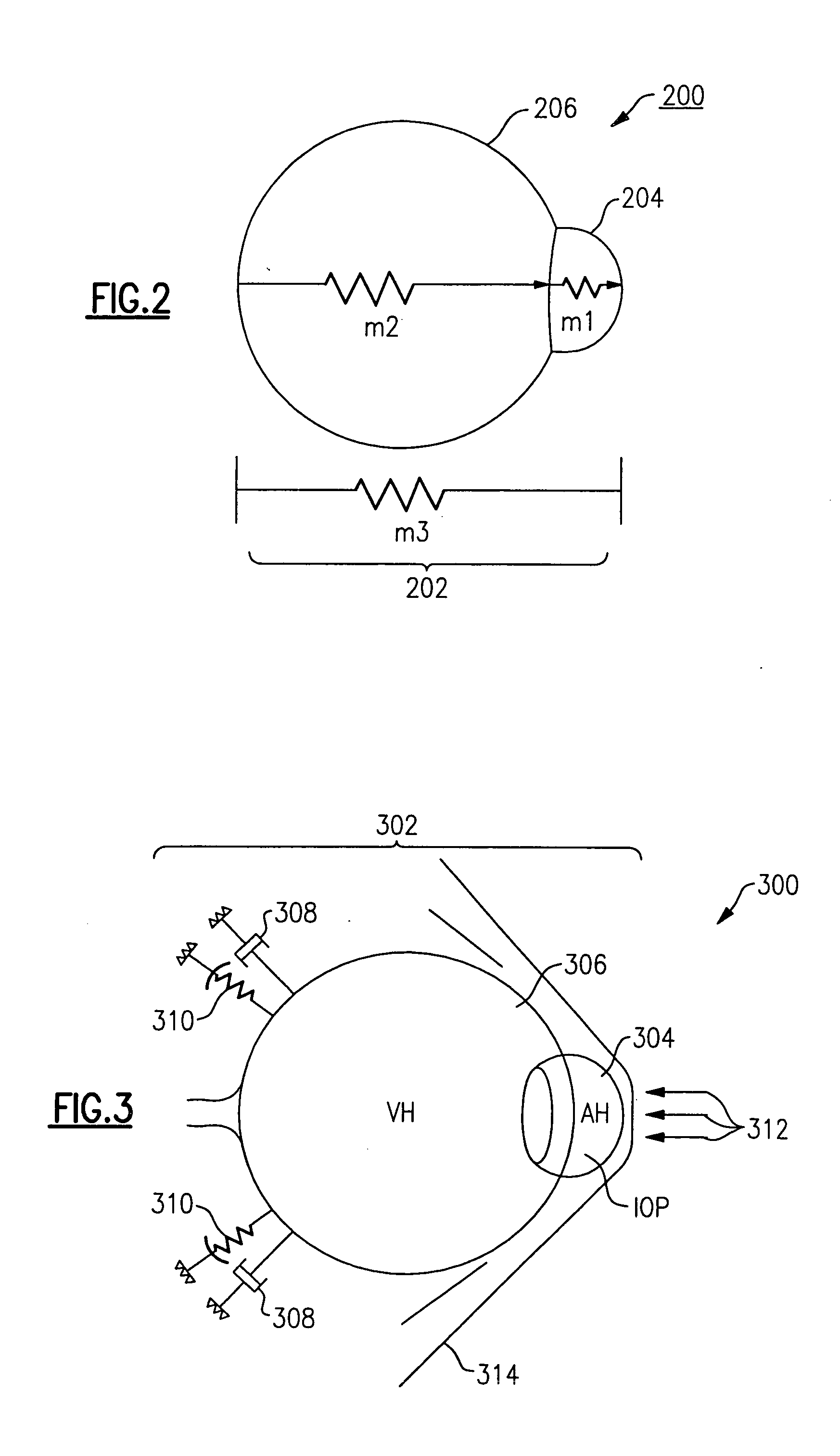

Device and method for glaucoma management and treatment

ActiveUS20120302861A1Readily conform to eye contourMinimize traumaEye surgeryDiagnostic recording/measuringAqueous humourIOPS

Described herein is a device for glaucoma treatment and monitoring that comprises a combination of an intraocular pressure (IOP) sensor and a glaucoma drainage device. The device comprises an IOP sensor and an inductive antenna mounted within a porous biocompatible material that forms the drainage path. The IOP sensor is mounted in a footplate portion of the device and is mountable in the anterior chamber of an eye. The footplate portion is connected to a body portion that houses the spiral antenna by a neck portion which retains the footplate portion in a suitable position within the anterior chamber. Due to its size, the footplate portion housing the IOP sensor can readily be inserted into the anterior chamber with the body portion housing the spiral antenna located outside of the anterior chamber in a sub-scleral space to disperse the aqueous humour.

Owner:ISTAR MEDICAL

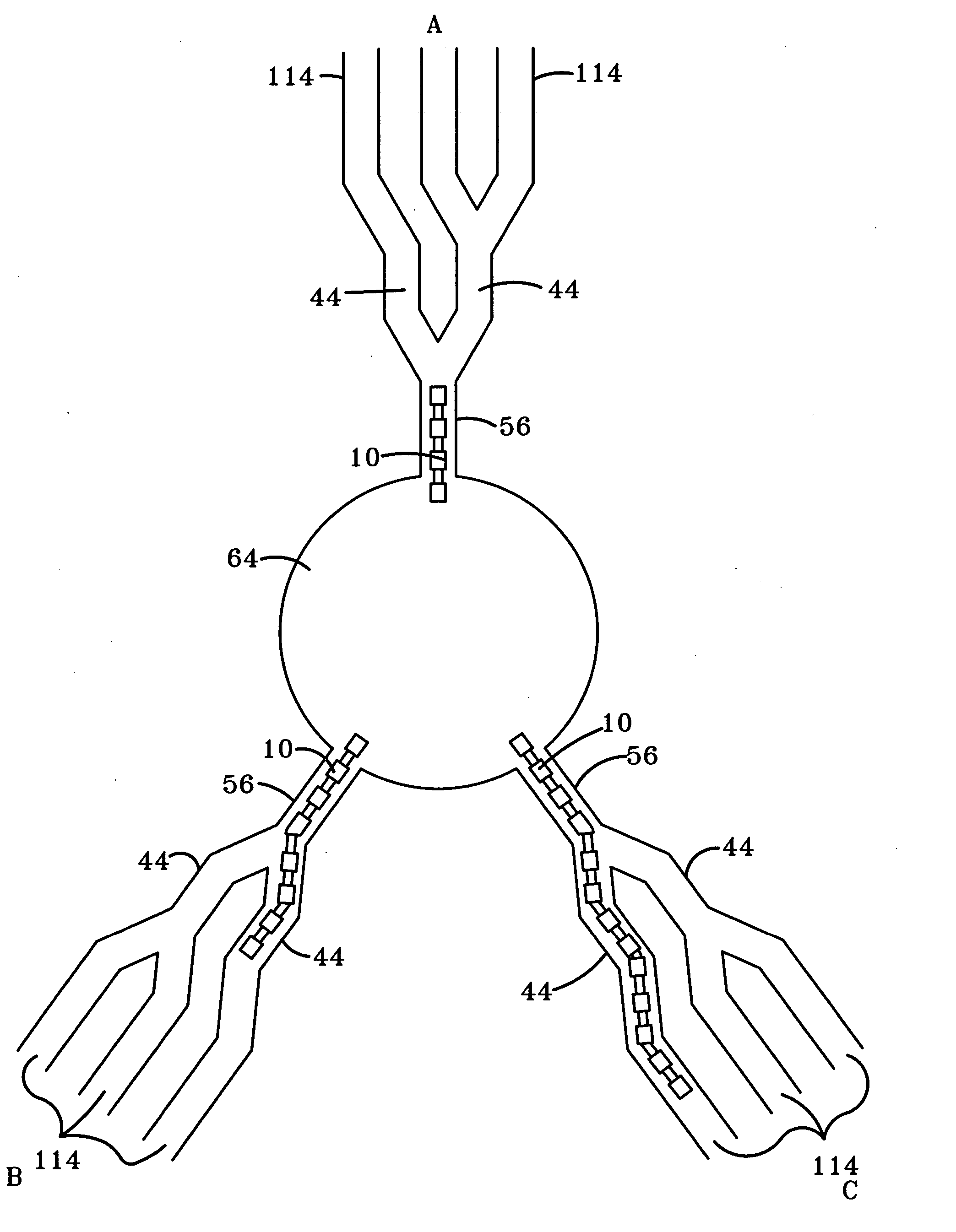

Apparatus and method for non-pharmacological treatment of glaucoma and lowering intraocular pressure

An apparatus and method for treating glaucoma and lowering IOP is herein disclosed. A method for draining aqueous includes creating an incision in the sclera, opening a scleral flap, and inserting a drainage tube between an associated anterior chamber and at least one aqueous vein. The device has a tube with proximal and distal ends that connects between the anterior chamber and the aqueous veins, collector channels, veins, or distal veins.

Owner:SAVAGE JAMES A

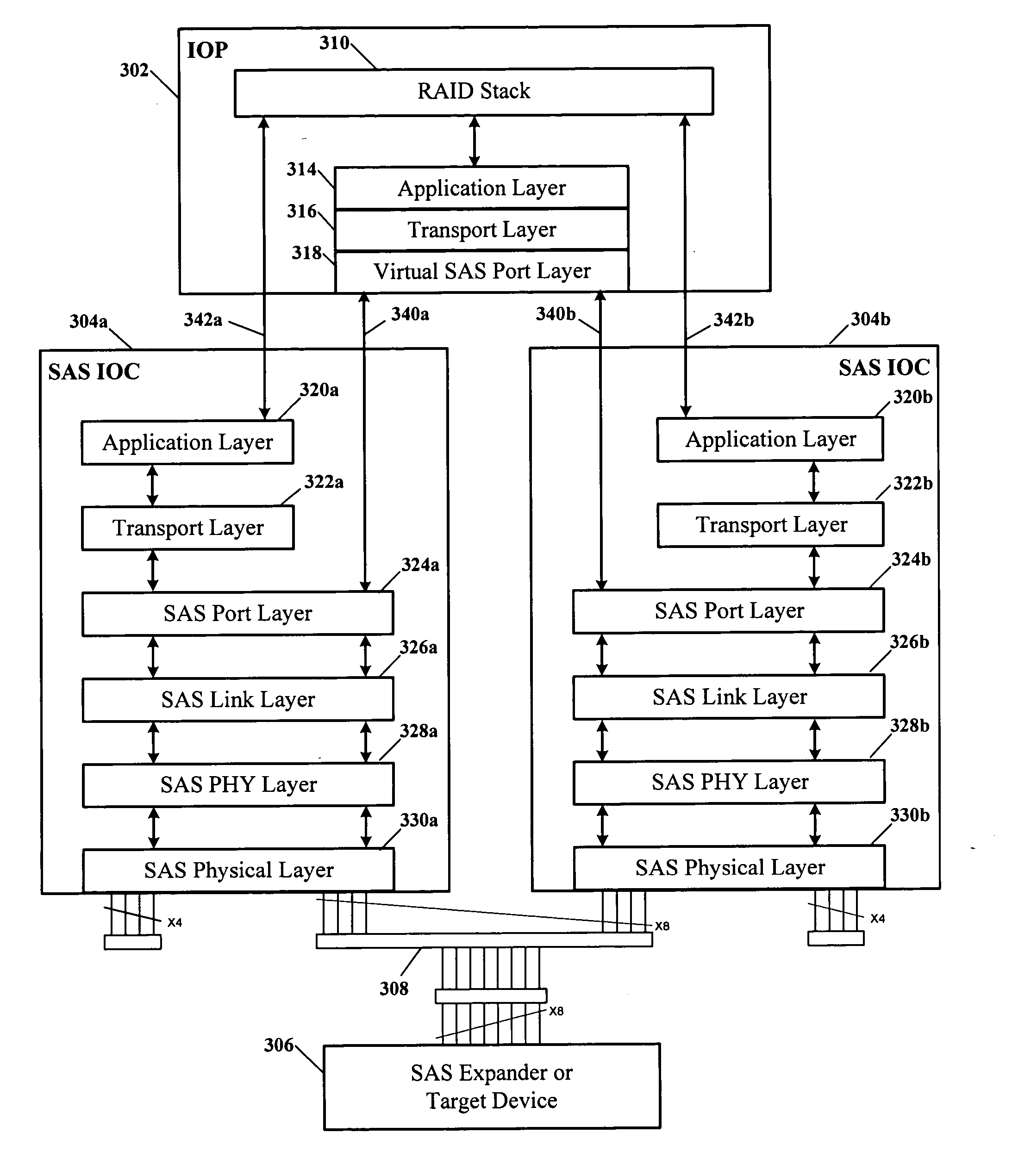

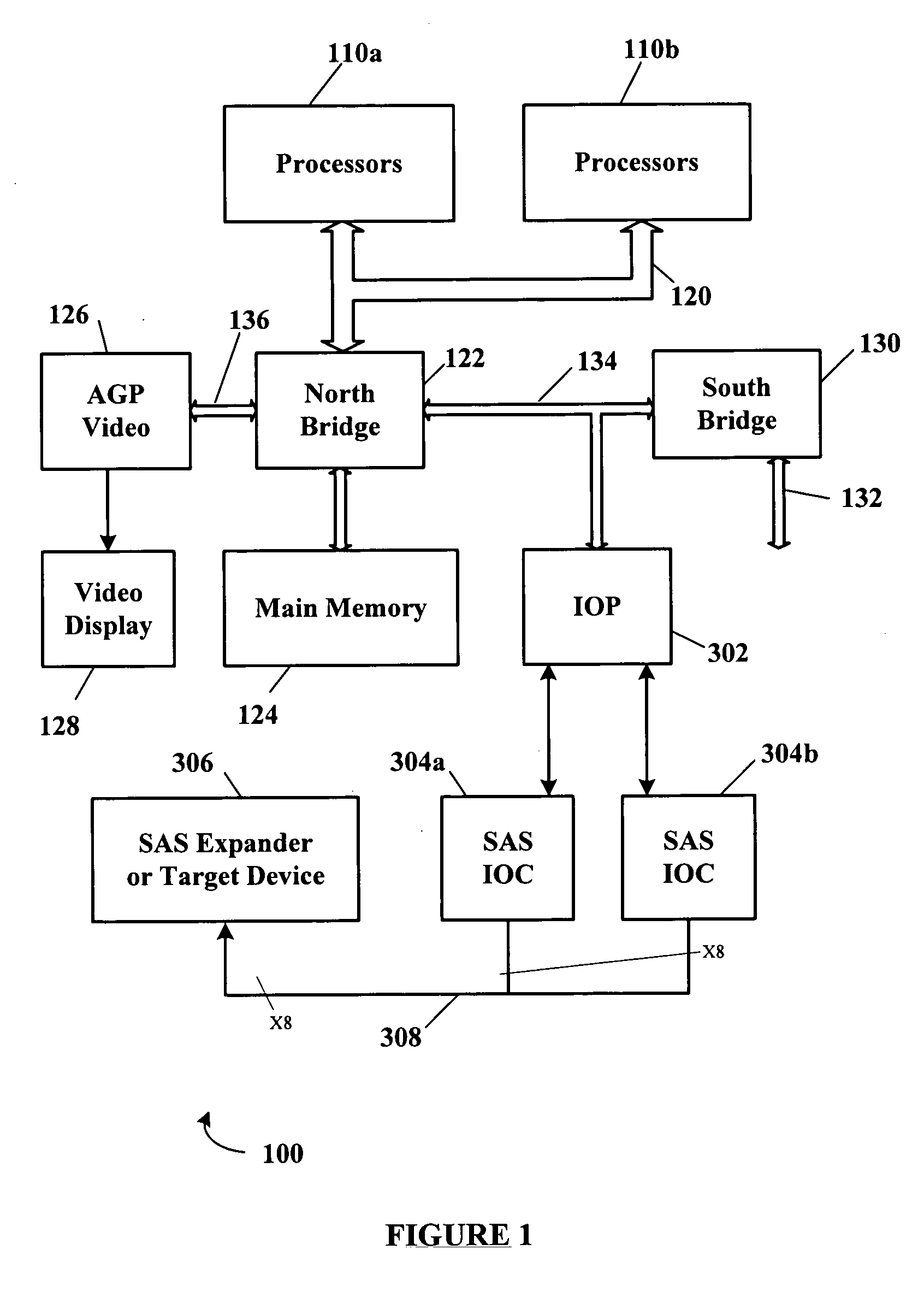

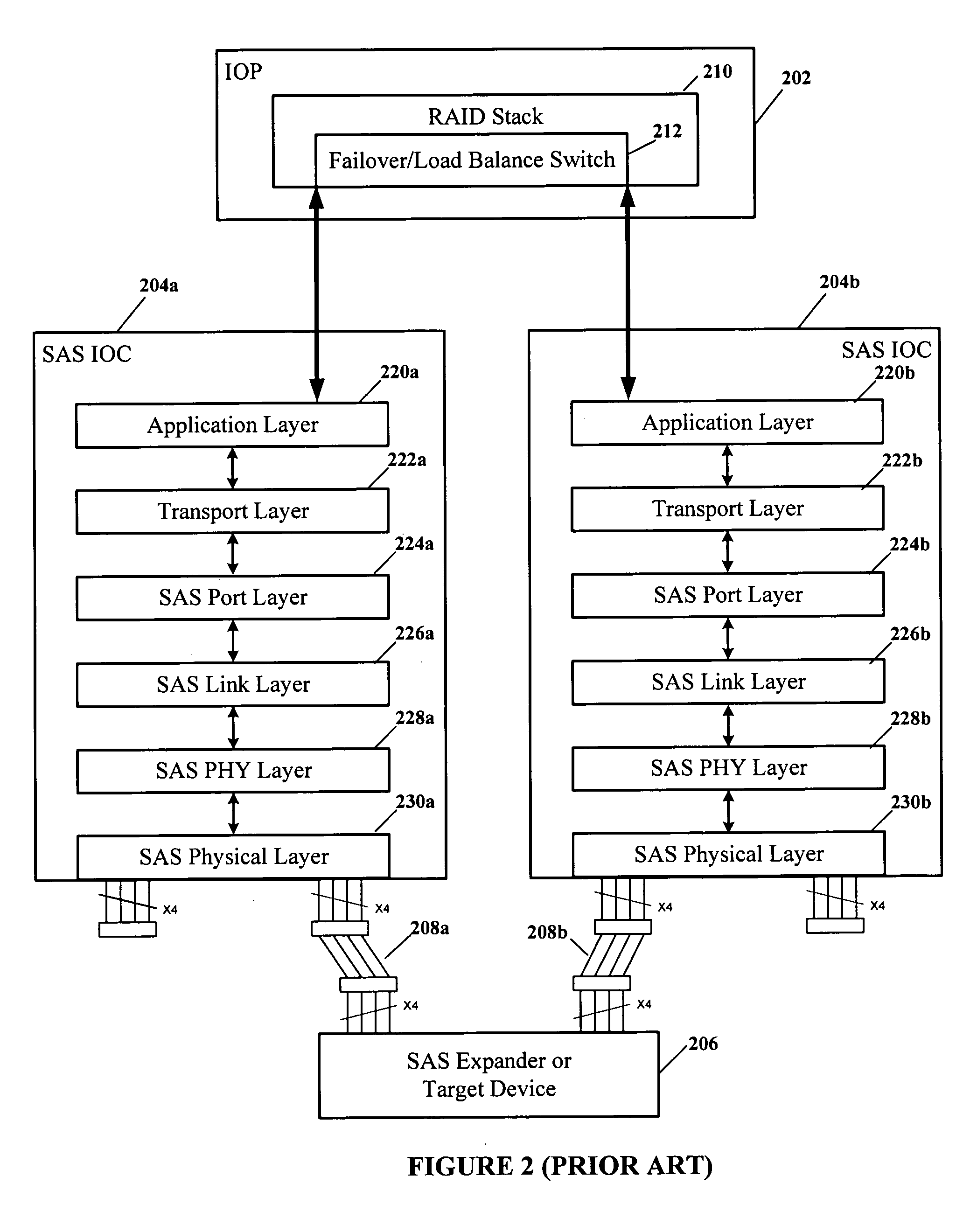

Method and apparatus for supporting port aggregation of serial attached SCSI wide ports via virtual ports

InactiveUS20060194386A1Improve performanceLower latencyError detection/correctionSemiconductor/solid-state device manufacturingRAIDFailover

An SAS RAID adapter comprises an input-output processor (IOP) and at least two SAS input-output controllers (IOCs). Wherein SAS links coupled to each of the IOCs form “virtual ports” in order to increase performance and maintain availability. The virtual ports across the at least two IOCs have wide port SAS link capability so as to provide performance enhancements similar to a standard SAS wide port. Even if a single IOC failure occurs, downshifting to N / 2 links is provided with degraded aggregated bandwidth (data throughput) instead of a failover and / or system shutdown.

Owner:DELL PROD LP

Data storage system employing a hot spare to proactively store array data in absence of a failure or pre-failure event

ActiveUS20180165169A1Input/output to record carriersRedundant hardware error correctionComputer hardwareData store

A data storage system includes a controller, a hot spare storage device and a plurality of primary storage devices. The controller utilizes the hot spare storage device to mirror only a subset of each stripe of logical pages written across the data storage array, where the subset includes a logical page determined by a write input / output operation (IOP) policy. In response to receipt of a write IOP, the controller writes a stripe including a plurality of logical data pages and a logical data protection page across the plurality of primary storage devices and mirrors the logical page determined by the write IOP policy on the hot spare storage device. In response to a failure of a storage device among the plurality of primary storage devices, contents of the failed storage device not already mirrored on the hot spare storage device are rebuilt on the hot spare storage device.

Owner:IBM CORP

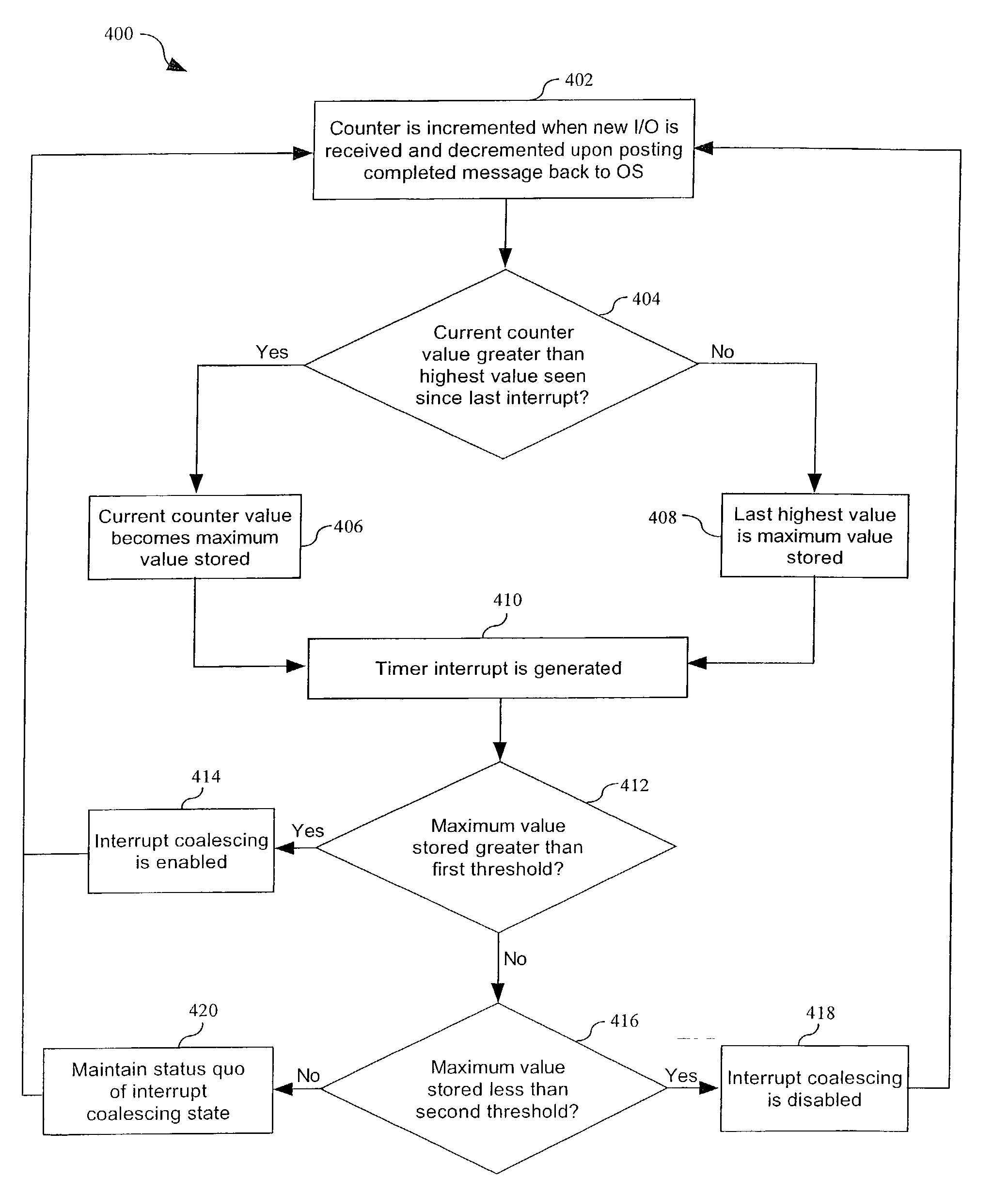

Apparatus and method for dynamically enabling and disabling interrupt coalescing in data processing system

ActiveUS7054972B2Input/output processes for data processingData conversionData processing systemTimer

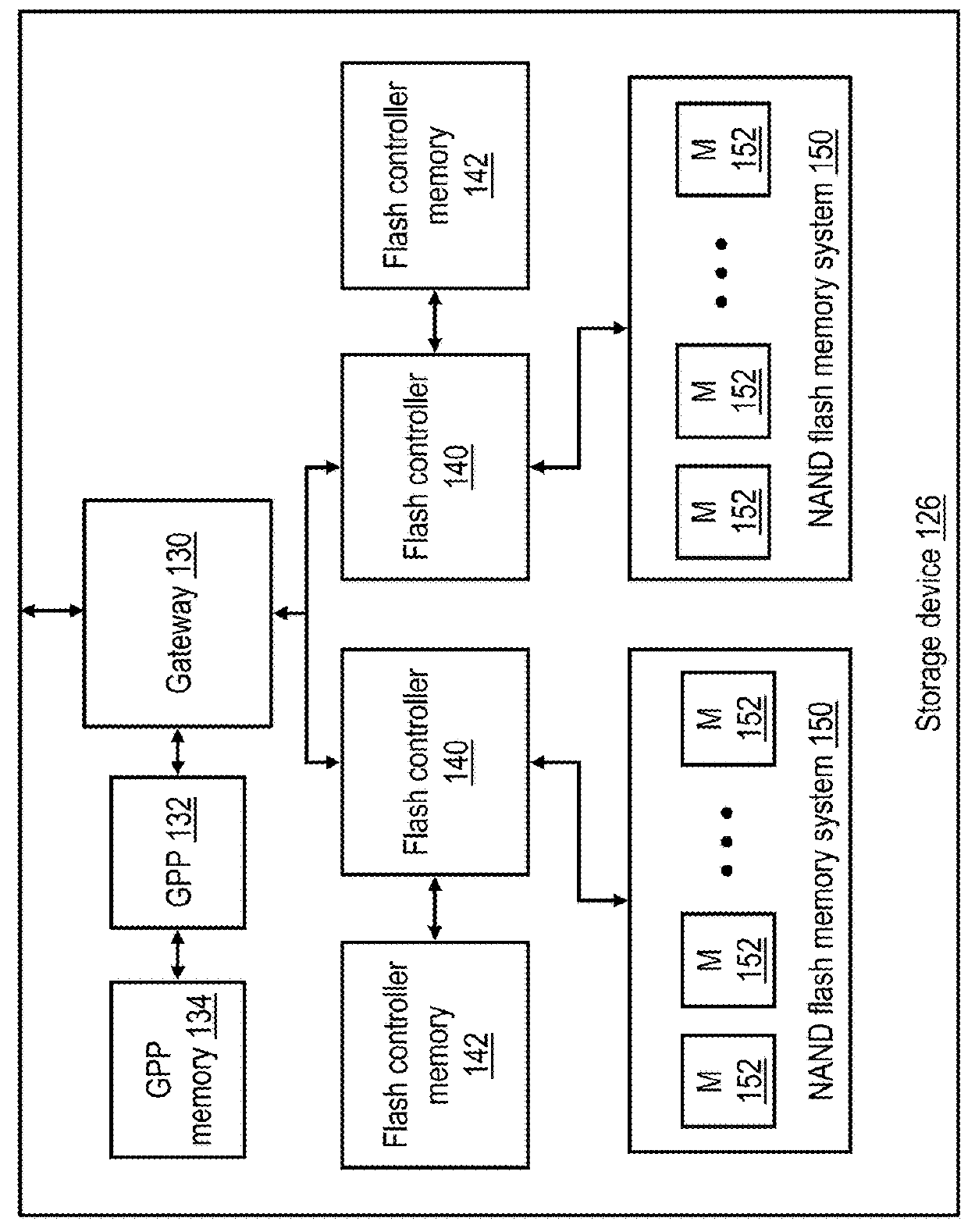

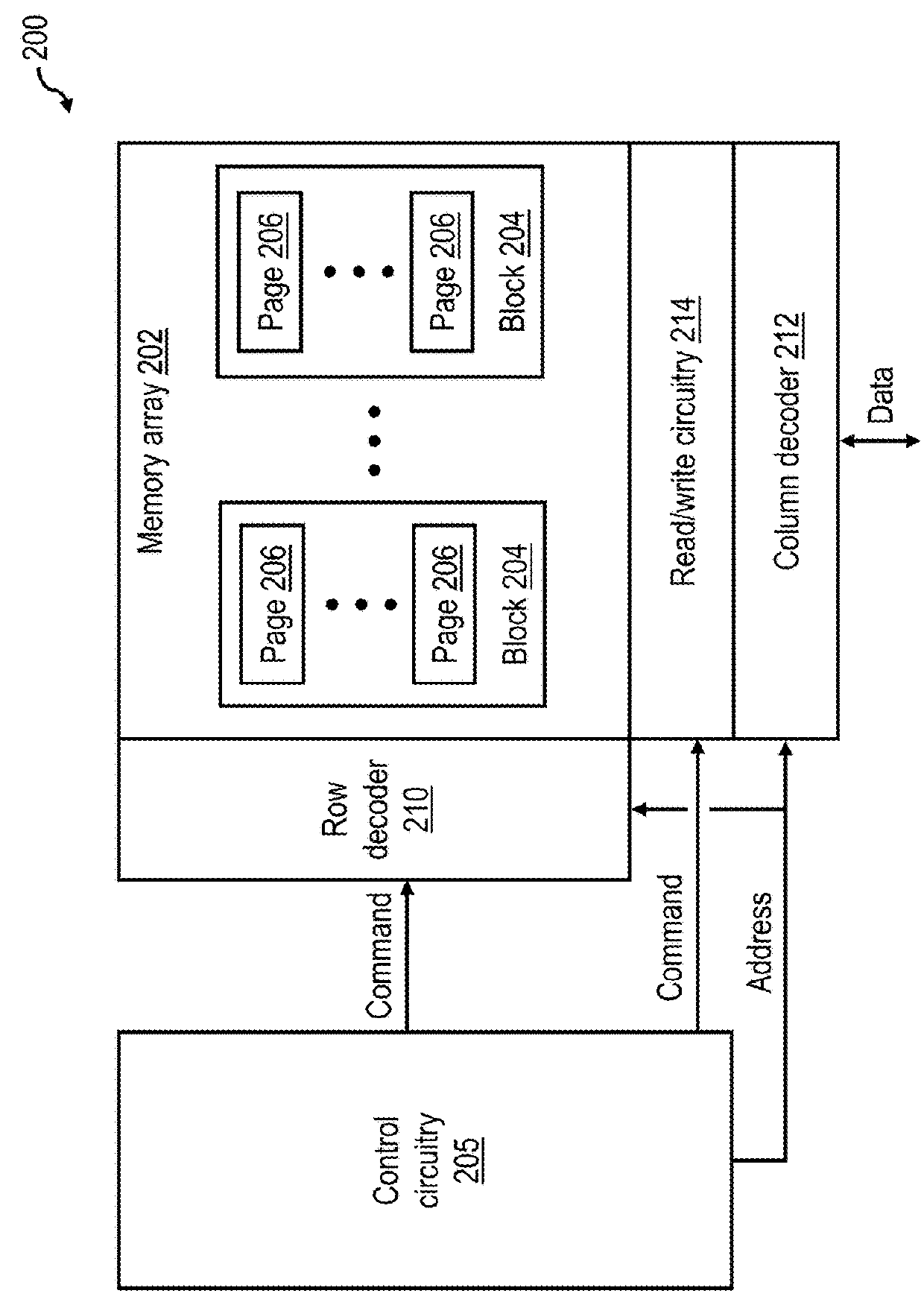

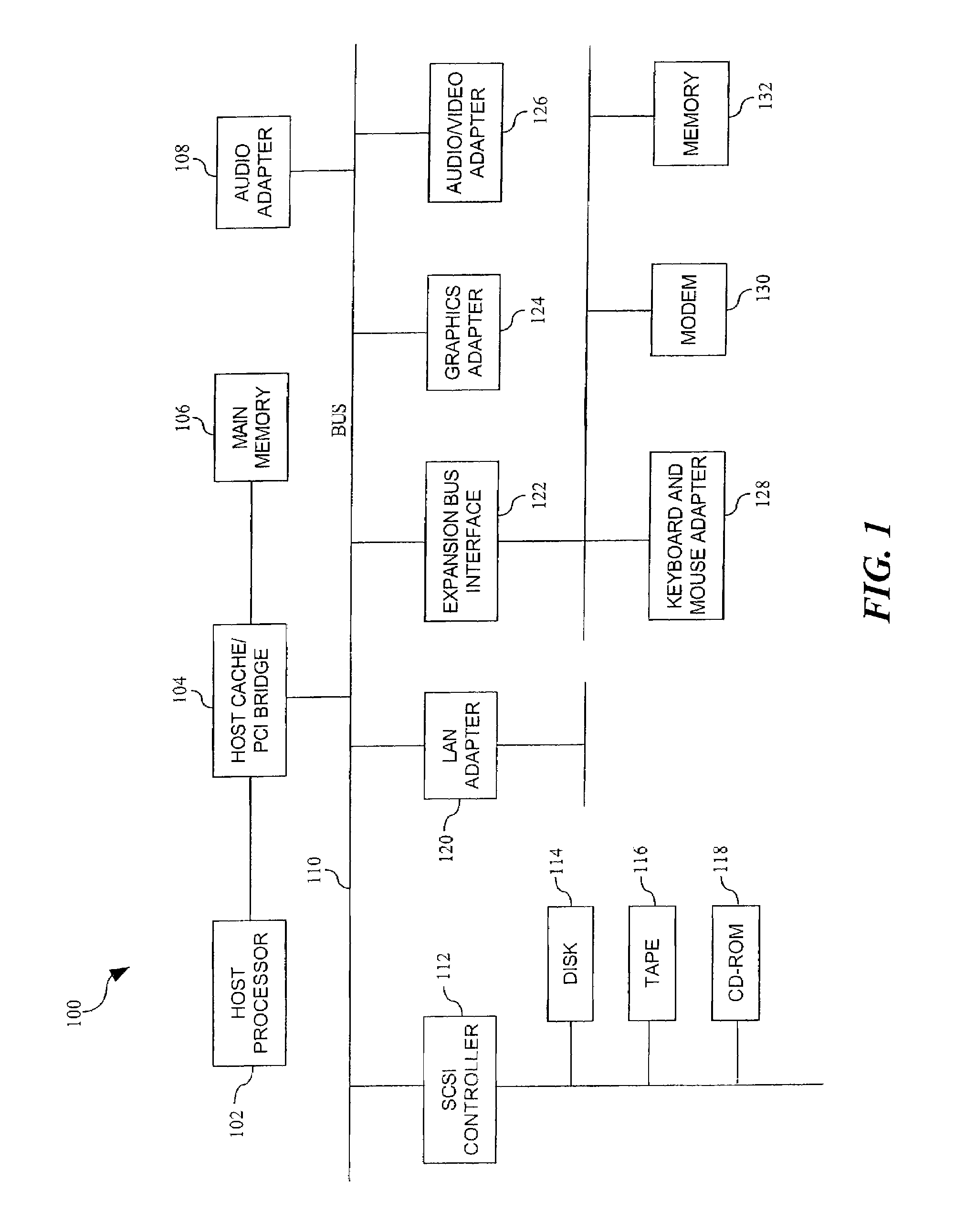

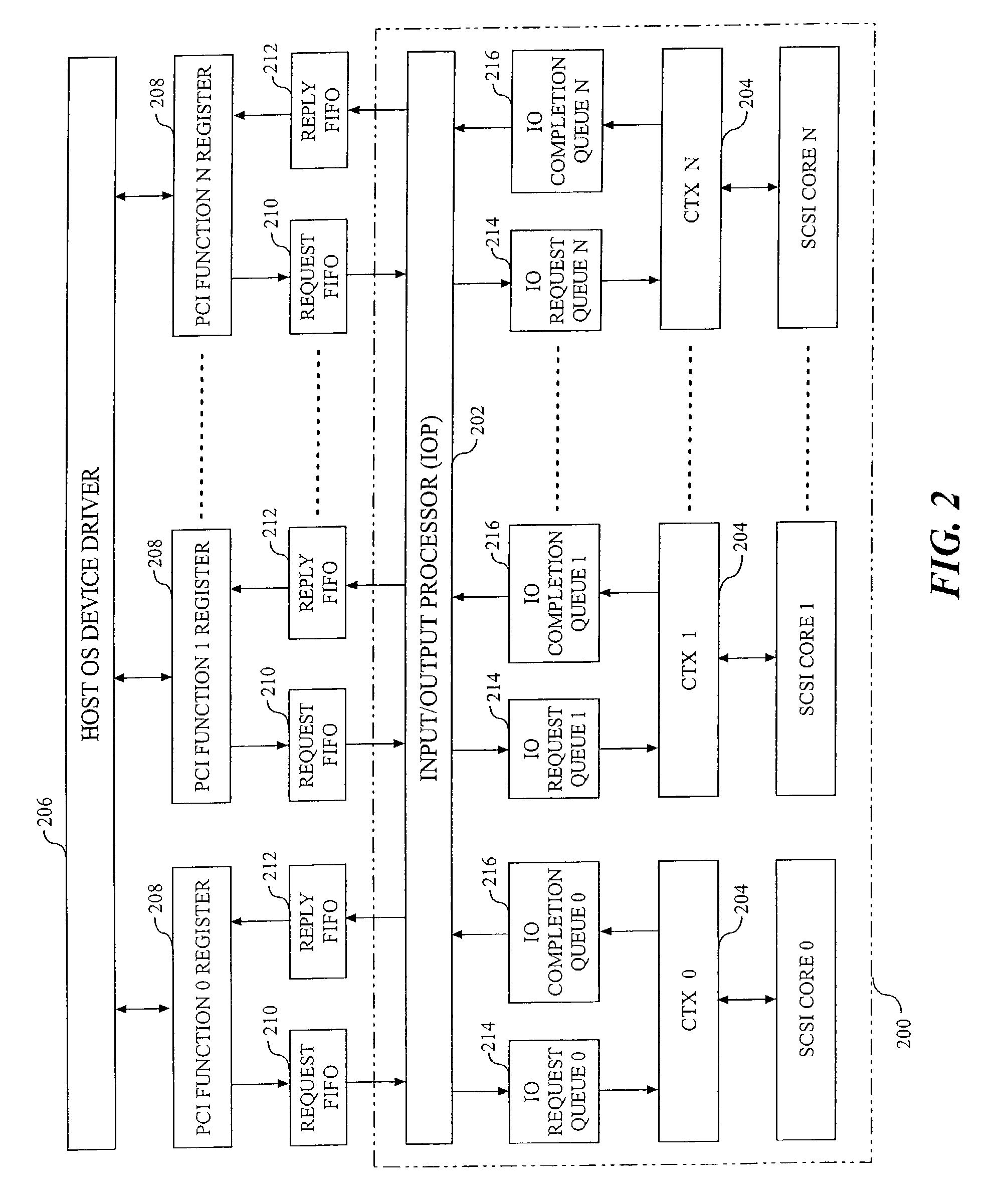

An apparatus and method for dynamically enabling and disabling interrupt coalescing in a data processing system. The present invention involves consistently monitoring IO load on an IOP of an IO adapter. The firmware on the IO adapter may have a global variable that stores counters for PCI function registers. Each counter tracks the number of outstanding IOs of a corresponding PCI function register. The counter is incremented whenever a new IO is received and is decremented upon posting the completed message back to the OS. A timer interrupt is generated periodically so that an ISR may be periodically performed. In the ISR, the maximum value stored of each counter seen since last timer interrupt is analyzed. When the maximum value stored is greater than a predetermined threshold value, the interrupt coalescing is enabled.

Owner:AVAGO TECH INT SALES PTE LTD

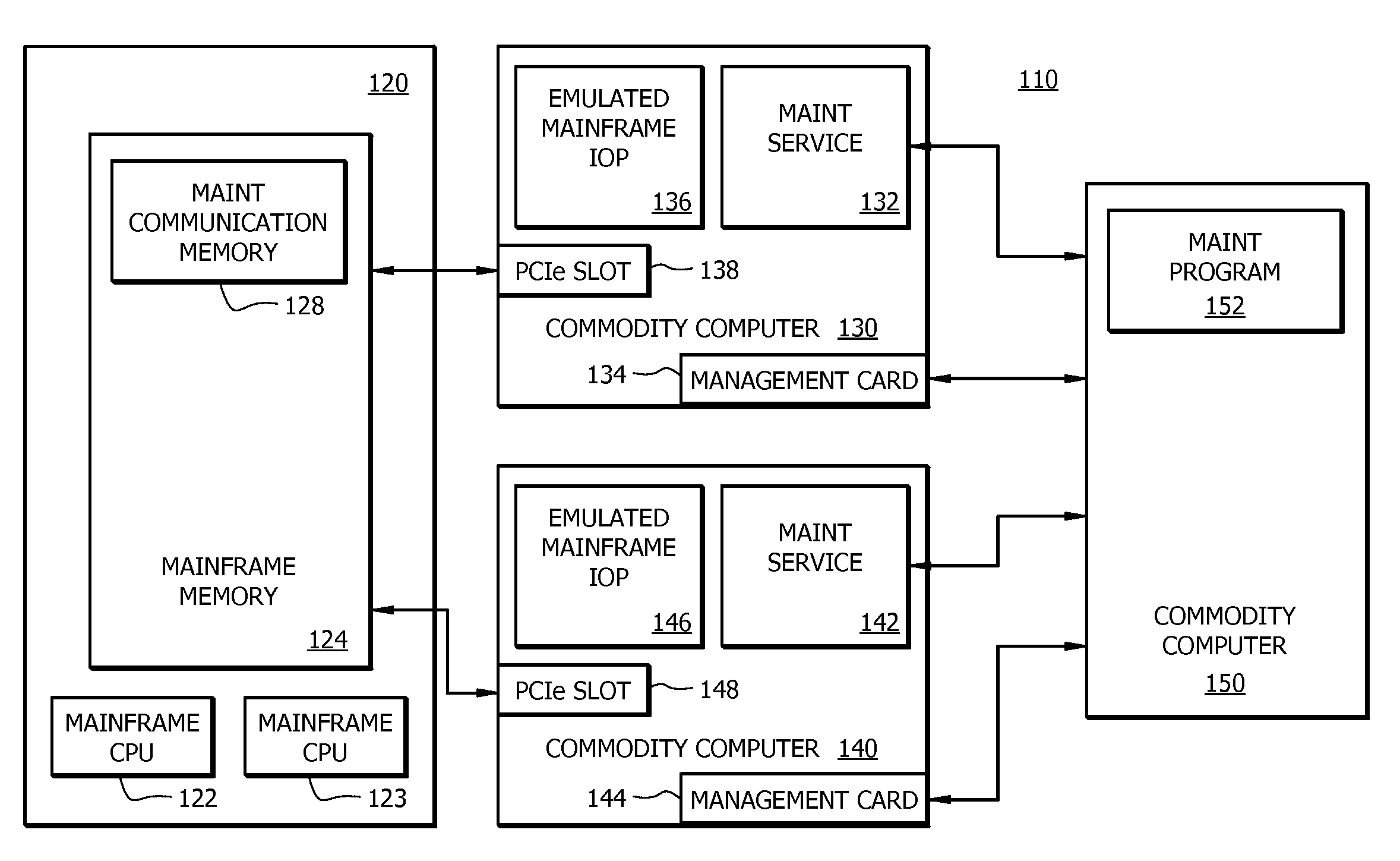

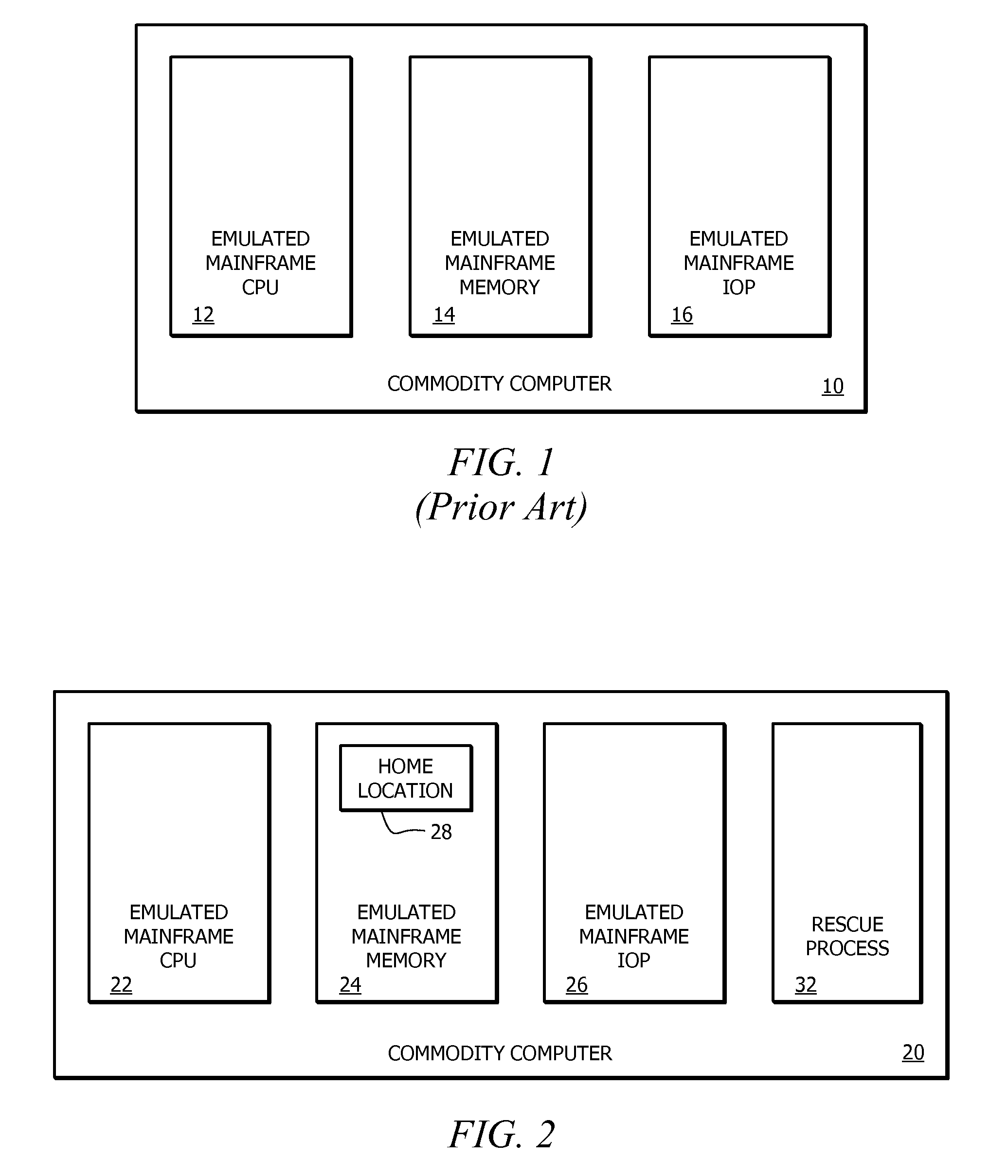

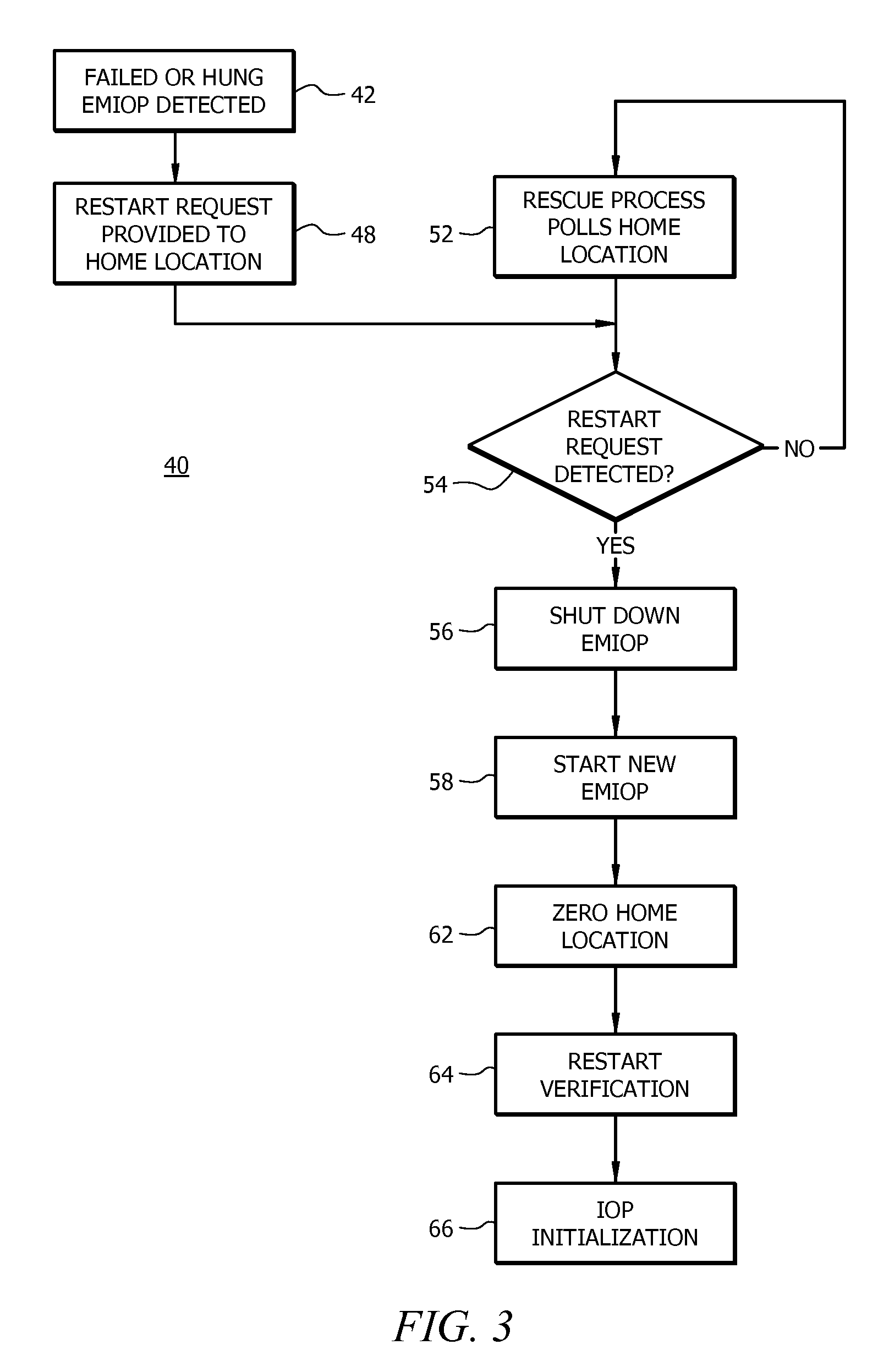

Method, apparatus and system for restarting an emulated mainframe iop

A method, apparatus and system for restarting an emulated mainframe IOP, such as a failed or hung emulated mainframe IOP within an emulated mainframe commodity computer. The method includes a rescue process that polls a home location for Restart Request information. In response to receiving Restart Request information, the rescue process is configured to shut down the existing emulated mainframe IOP, start a new emulated mainframe IOP, and reset the home location. The Restart Request information can be provided to the home location by the mainframe computer being emulated. Alternatively, the rescue mechanism can use an interface management card instructed to restart the commodity computer hosting the failed or hung IOP, e.g., from a maintenance service and / or a maintenance program residing in an active commodity computer coupled to the commodity computers hosting one of several emulated mainframe IOPs.

Owner:RUSS CRAIG F +1

Data storage system employing a hot spare to store and service accesses to data having lower associated wear

ActiveUS20160188424A1Reduce access latencyReduce wear rateRedundant hardware error correctionData setAccess frequency

A controller monitors access frequencies of address ranges mapped to a data storage array. Based on the monitoring, the controller identifies frequently accessed ones of the address ranges that have lower associated wear, for example, those that are read more often than written. In response to the identifying, the controller initiates copying of a dataset associated with the identified address ranges from the data storage array to a spare storage device while refraining from copying other data from the data storage array onto the spare storage device. The controller directs read input / output operations (IOPs) targeting the identified address ranges to be serviced by access to the spare storage device. In response to a failure of a failed storage device among the plurality of primary storage devices, the controller rebuilds contents of the failed storage device on the spare storage device in place of the dataset associated with the identified address ranges.

Owner:IBM CORP

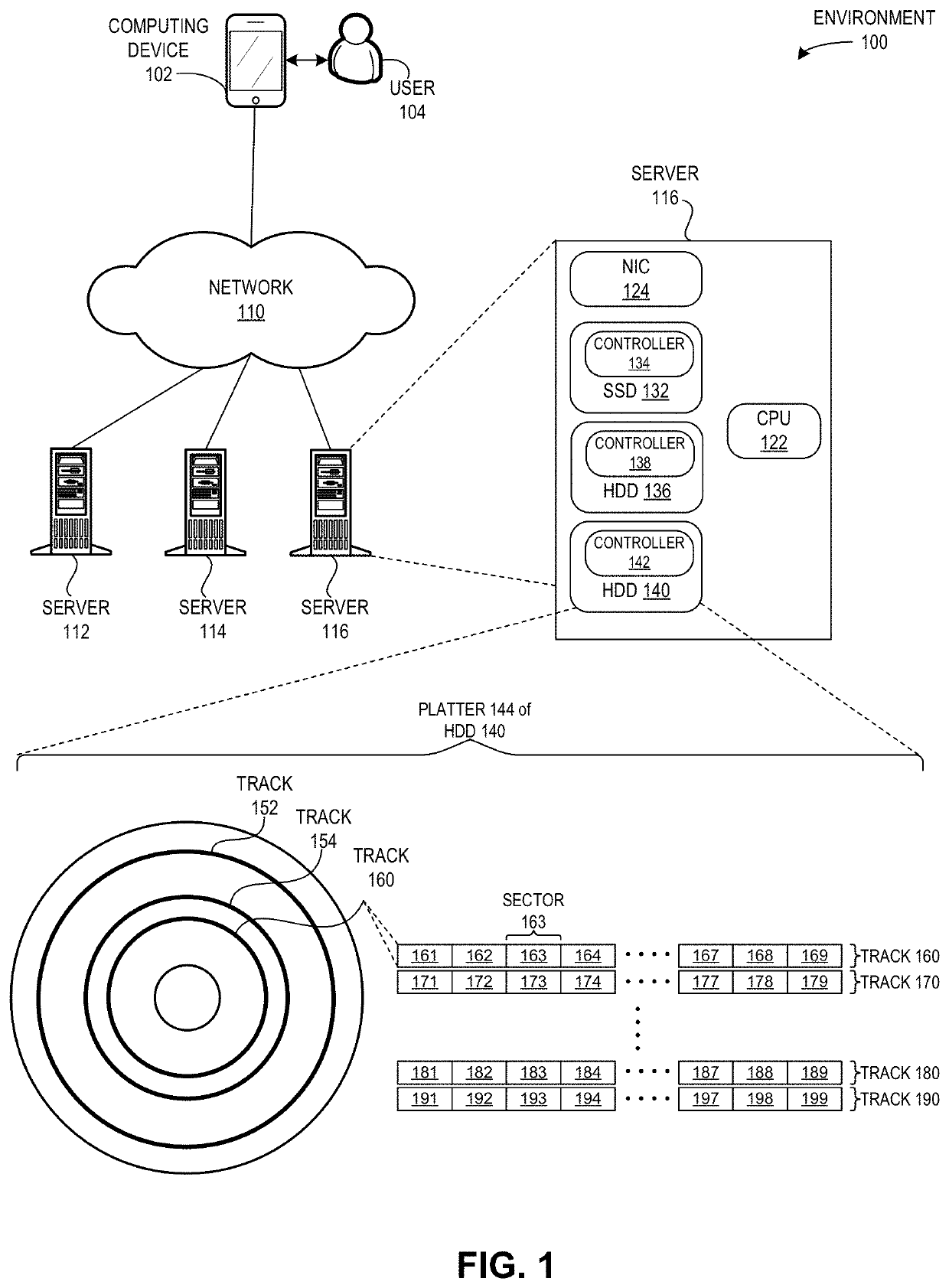

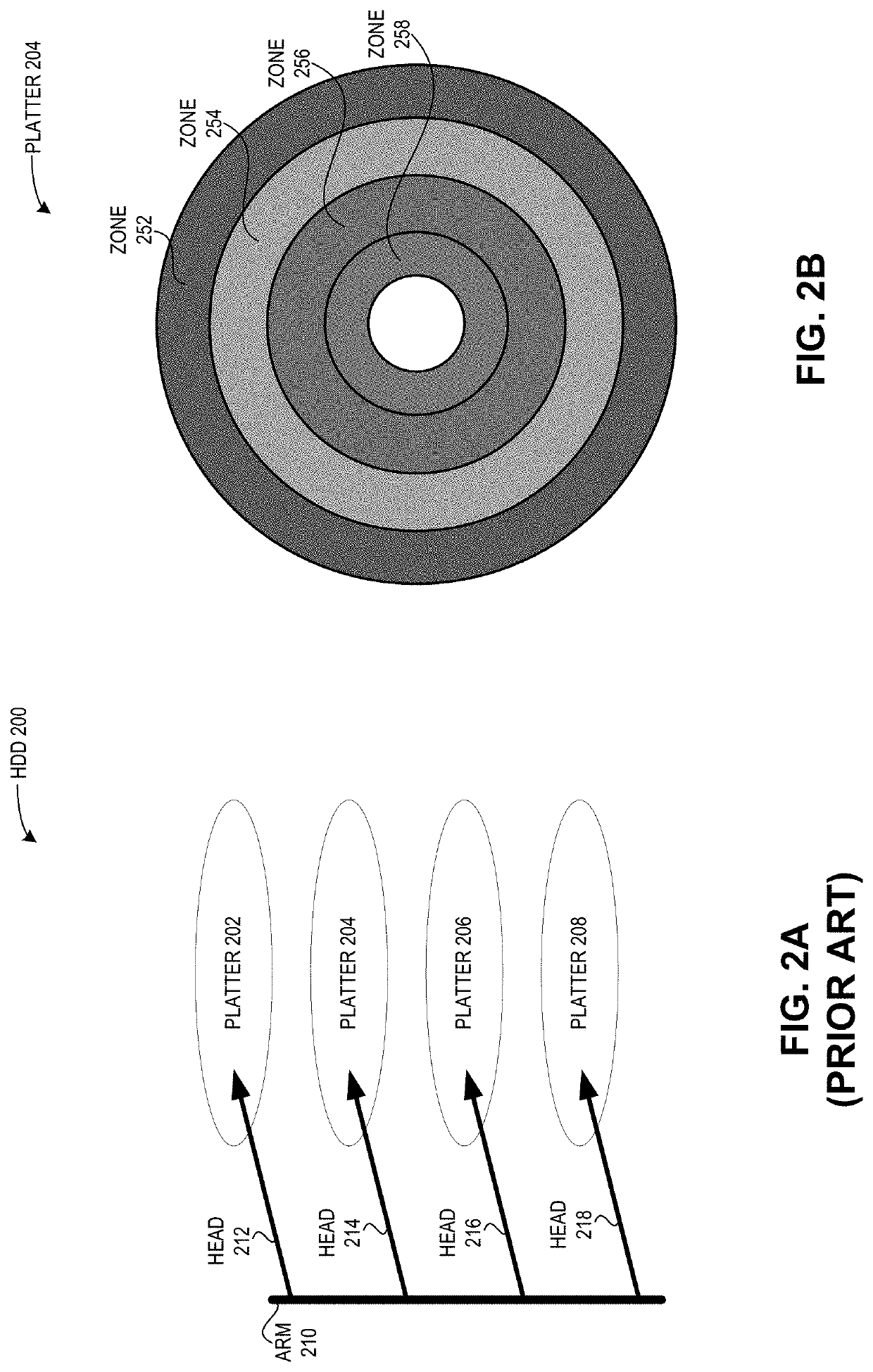

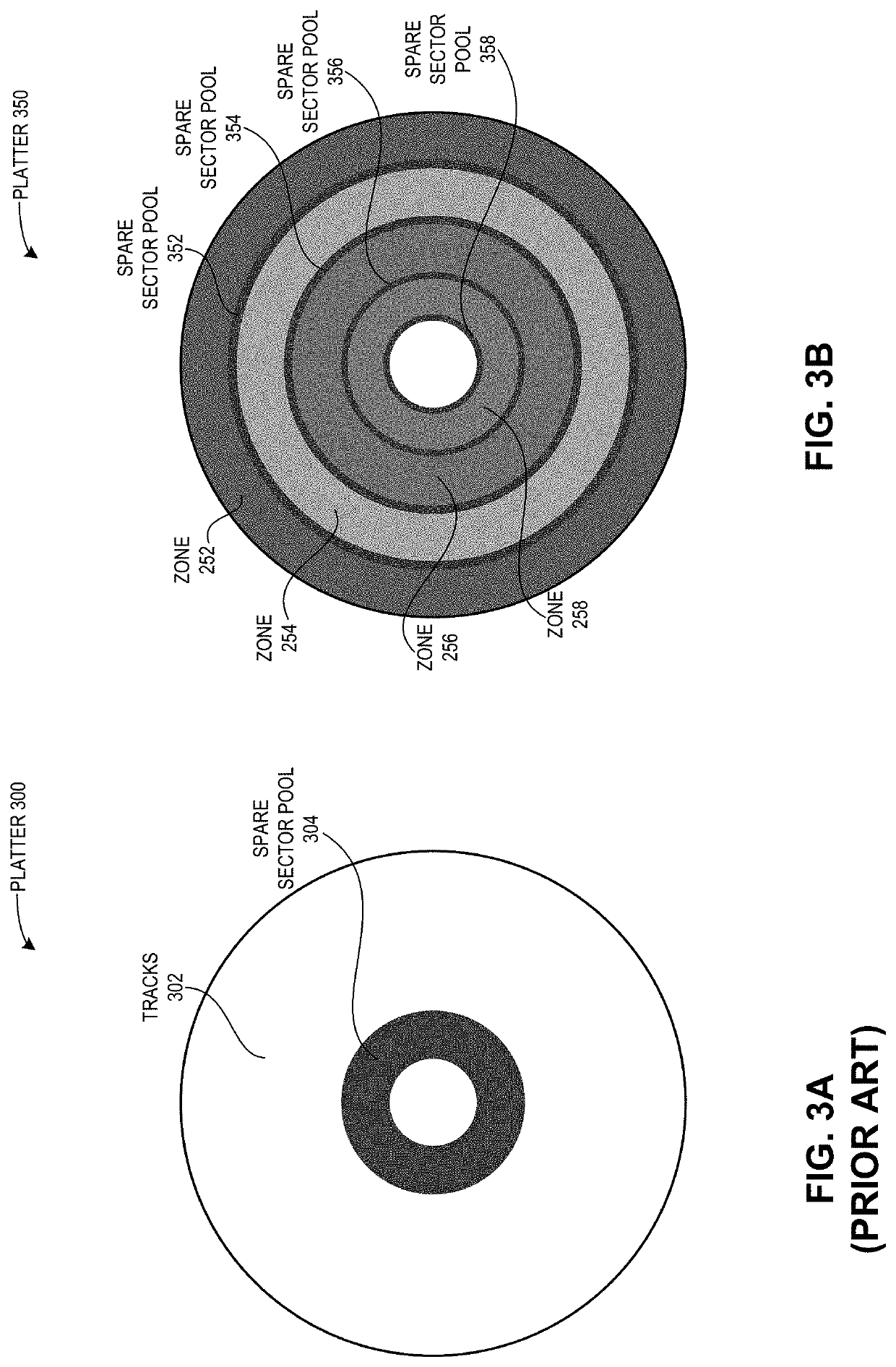

Method and system for data placement in a hard disk drive based on access frequency for improved iops and utilization efficiency

ActiveUS20190391748A1Facilitates data placementEnhanced data placementMemory architecture accessing/allocationInput/output to record carriersShingled magnetic recordingHard disc drive

One embodiment facilitates a write operation in a shingled magnetic recording device. During operation, the system receives, by the storage device, data to be written to the storage device and access-frequency information associated with the data, wherein the storage device includes a plurality of concentric tracks. The system distributes a plurality of spare sector pools among the plurality of concentric tracks. The system selects a track onto which to write the data based on the access-frequency information, wherein data with a highest access-frequency is written to an outer track. The system appends the data at a current write pointer location of the selected track, thereby facilitating an enhanced data placement for subsequent access in the storage device.

Owner:ALIBABA GRP HLDG LTD

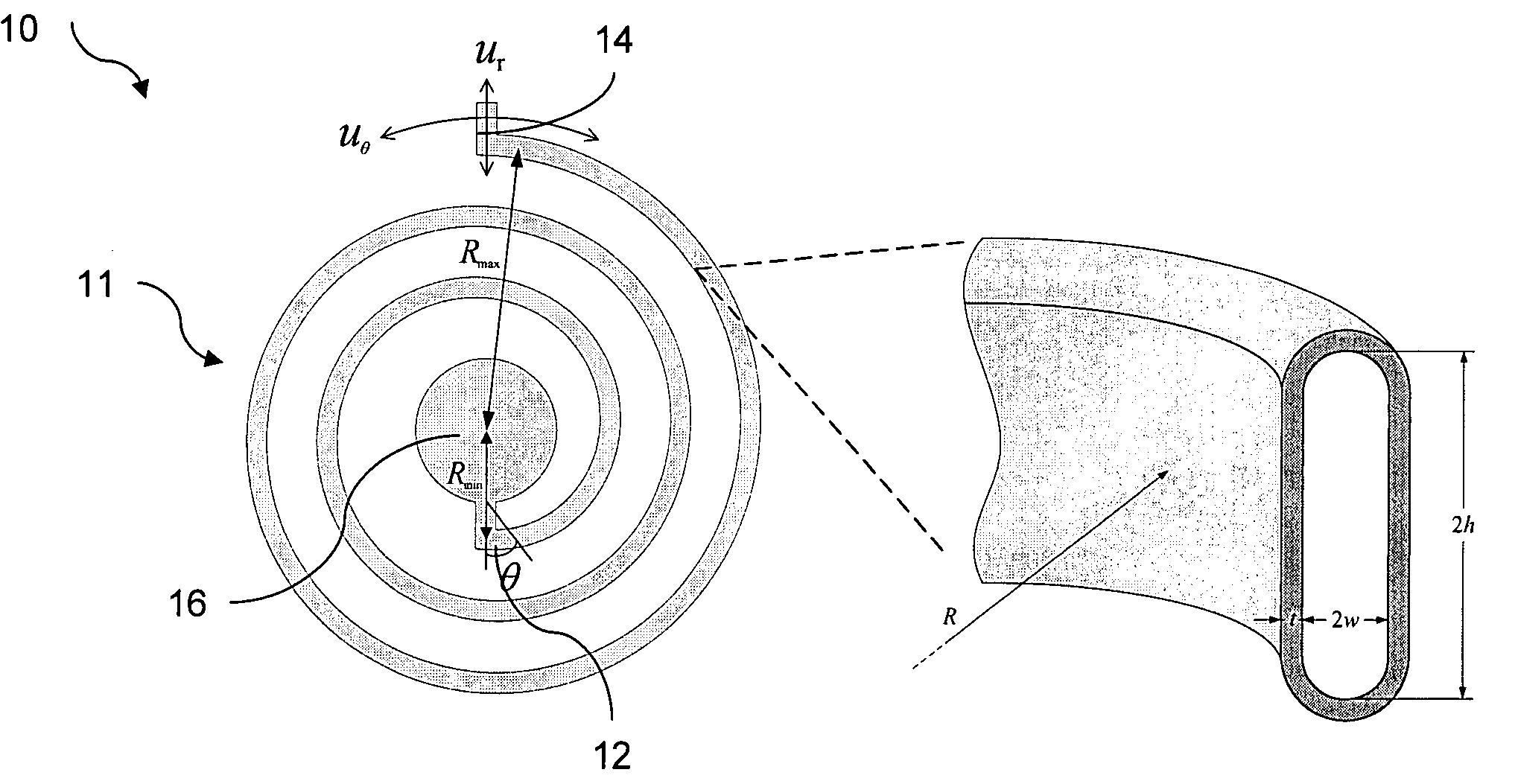

Implantable mechanical pressure sensor and method of manufacturing the same

InactiveUS20050268722A1Fluid pressure measurement using elastically-deformable gaugesCatheterIn planeParylene

A biocompatible, mechanical, micromachined pressure sensor and methods of manufacturing such a pressure sensor are provided. The pressure sensor of the current invention comprises a high-aspect-ratio curved-tube structure fabricated through a one-layer parylene process. The pressure sensor of the current invention requires zero power consumption and indicates the pressure variation by changes of the in situ in-plane motion of the sensor, which can be gauged externally by a direct and convenient optical observation. In one embodiment, the pressure sensor of the current invention has been shown to work as an IOP sensor for eye implantation where the intraocular in-plane motion of the sensor can be recorded from outside of the eye, such that the intraocular pressure in glaucoma patients can be constantly monitored.

Owner:CALIFORNIA INST OF TECH

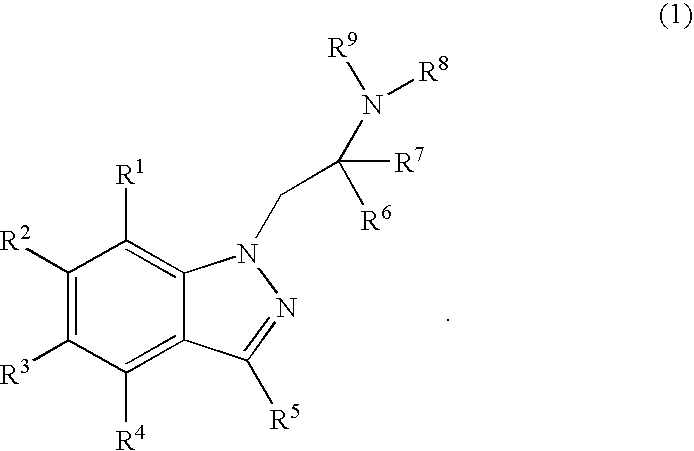

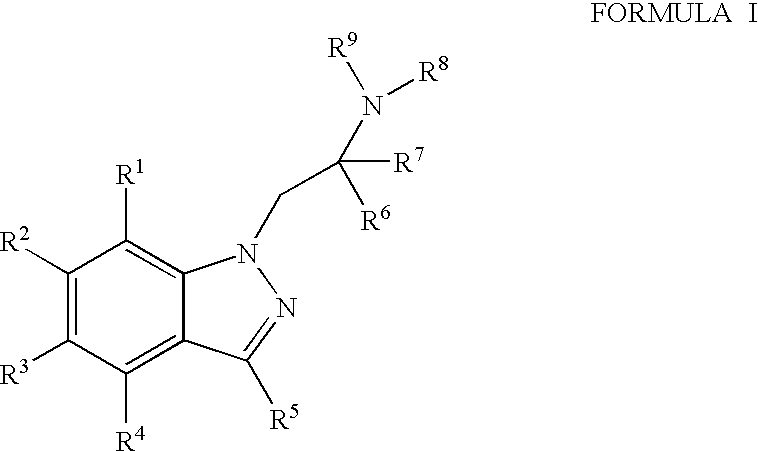

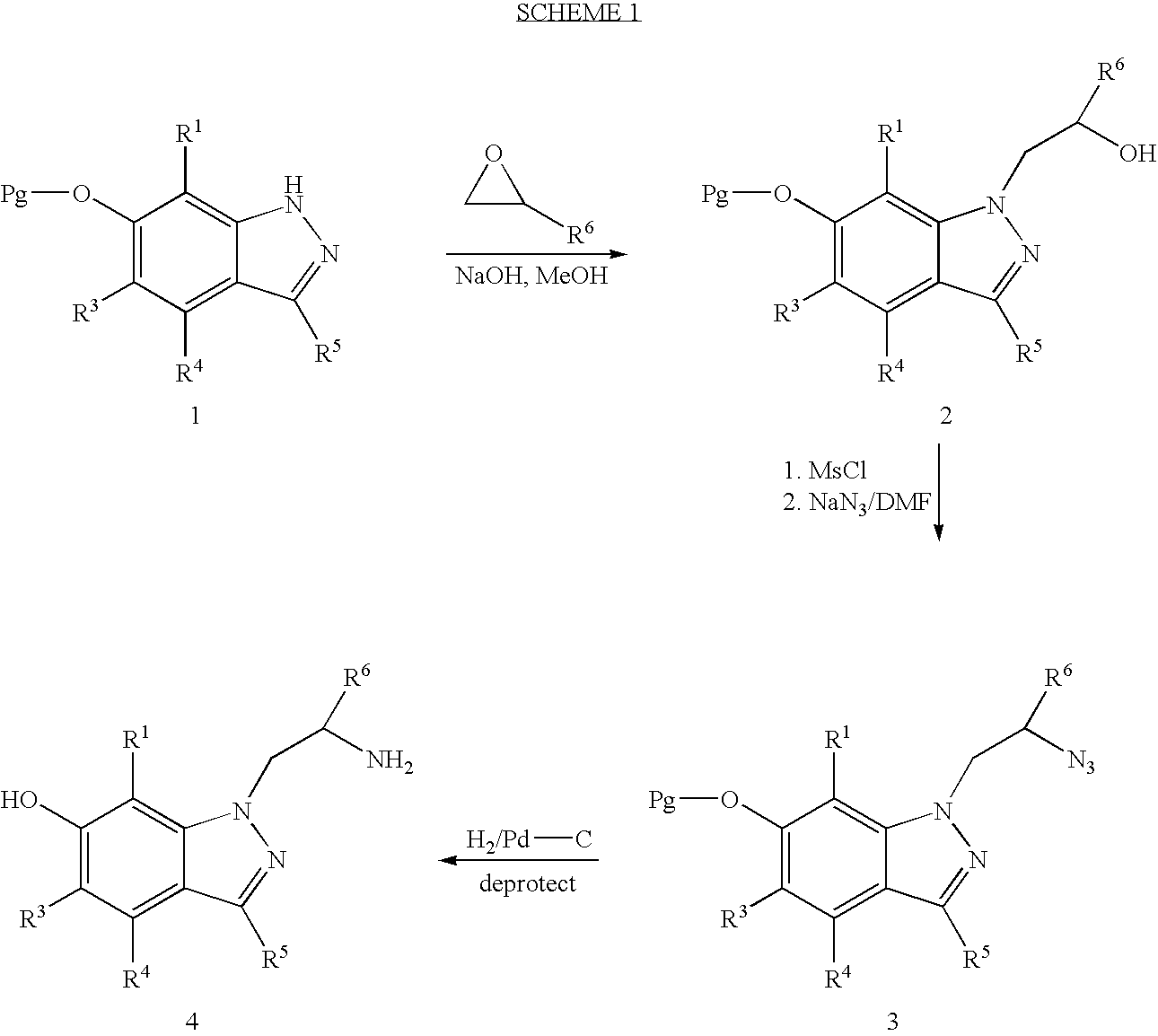

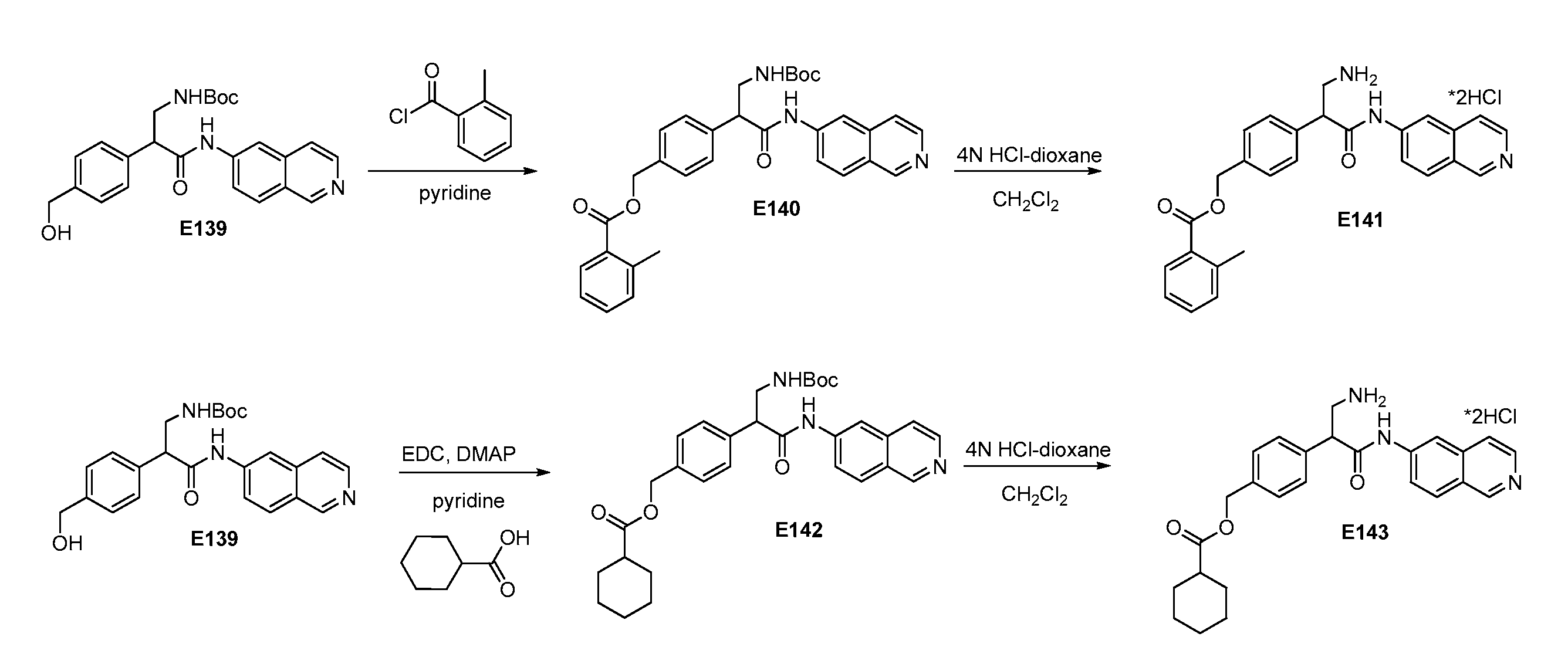

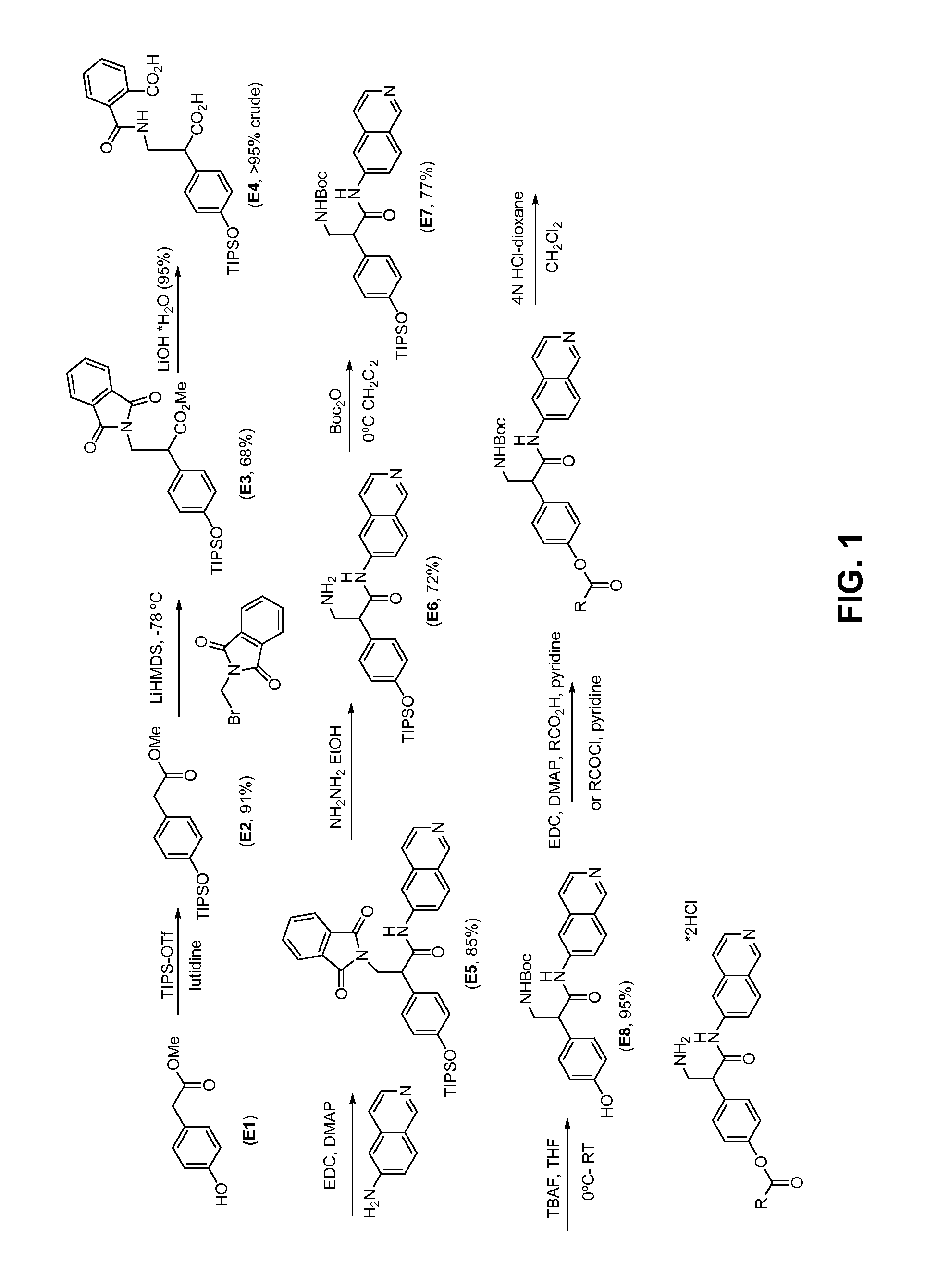

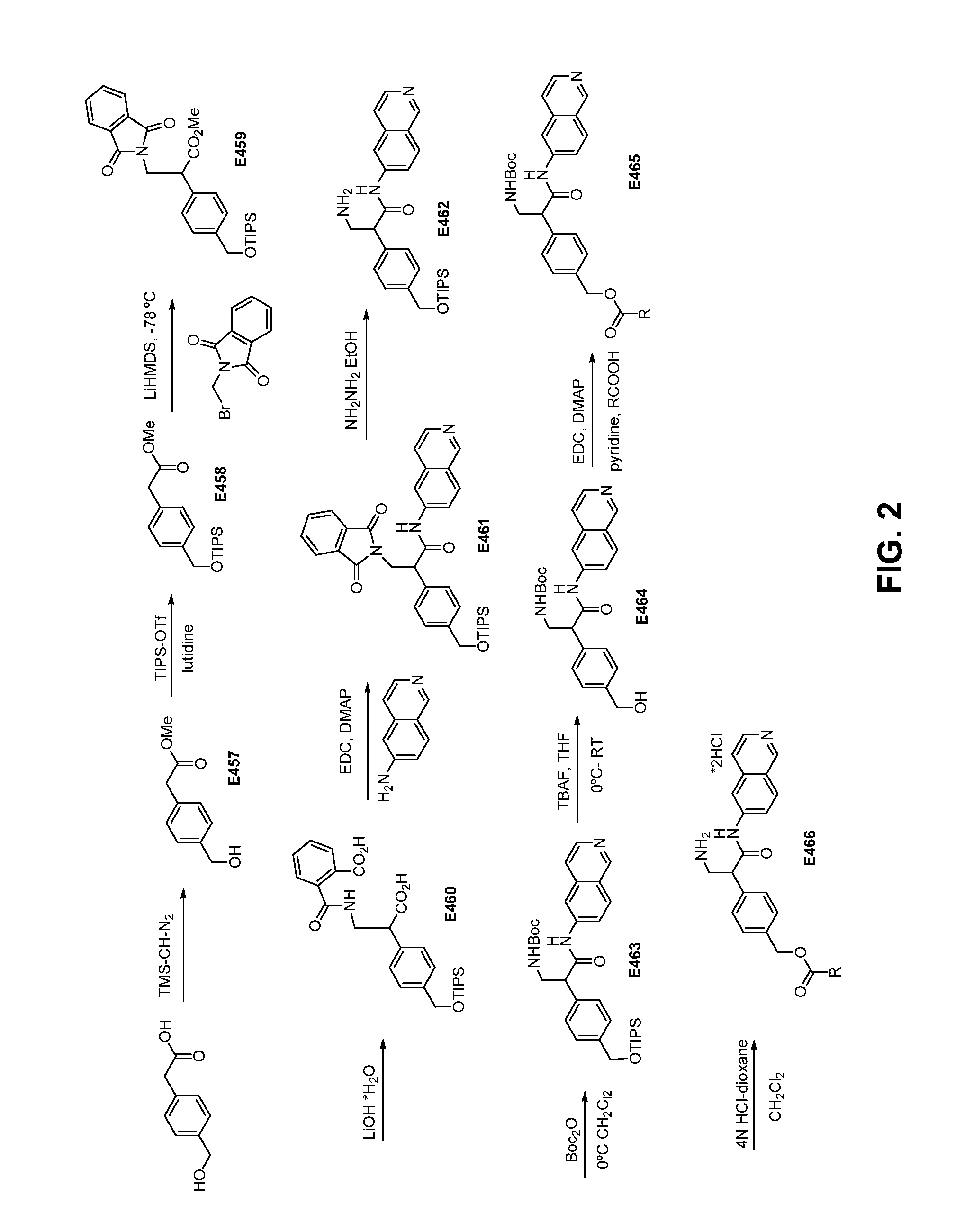

Dual mechanism inhibitors for the treatment of disease

Provided are compounds that are inhibitors of both rho kinase and of a monoamine transporter (MAT) act to improve the disease state or condition. Further provided are compositions comprising the compounds. Further provided are methods for treating diseases or conditions, the methods comprising administering compounds according to the invention. One such disease may be glaucoma for which, among other beneficial effects, a marked reduction in intraocular pressure (IOP) may be achieved.

Owner:AERIE PHARMA

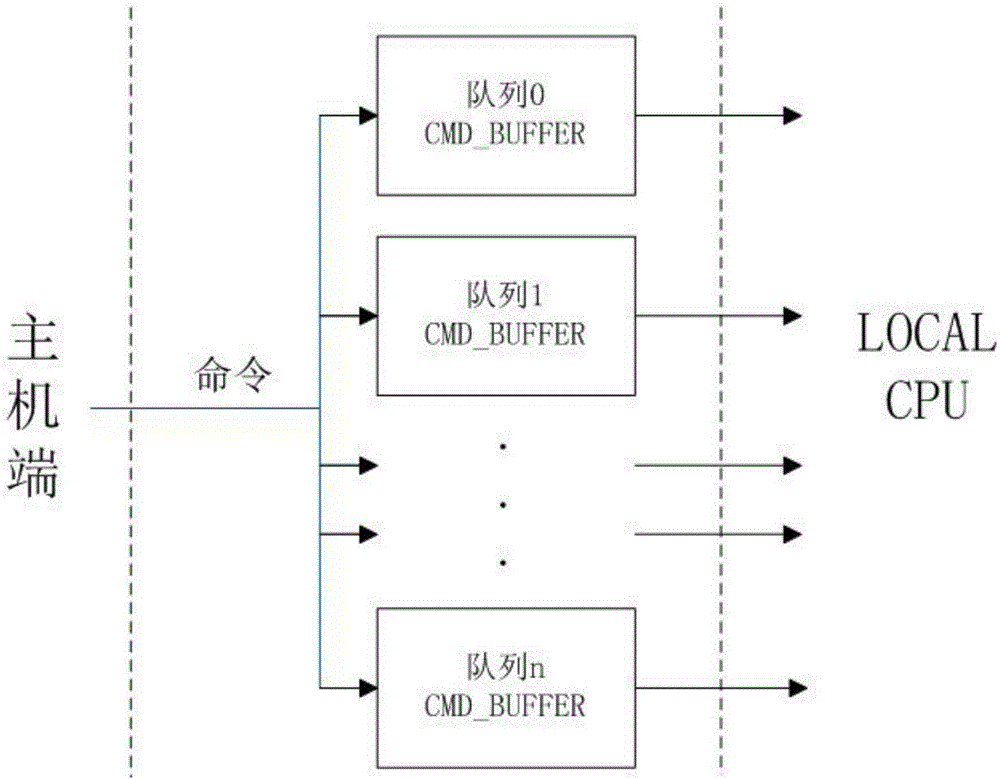

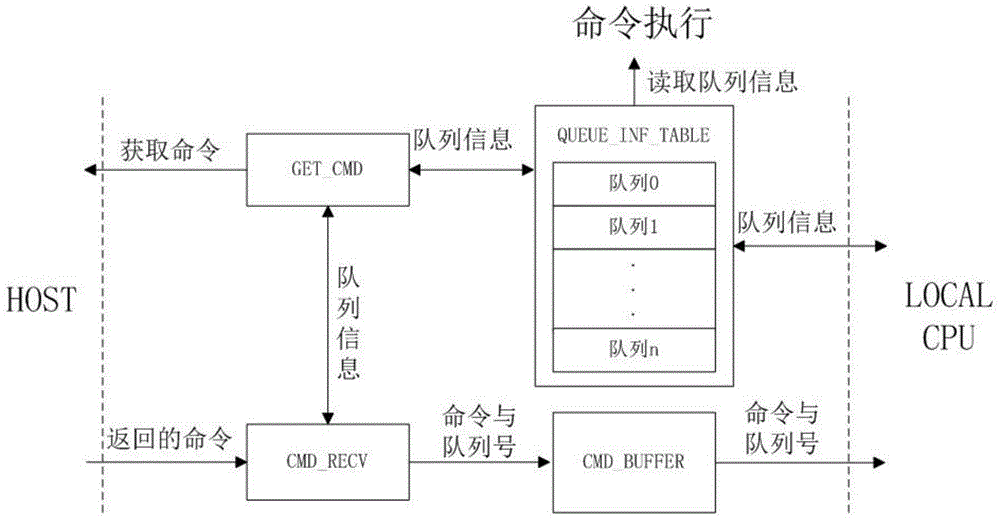

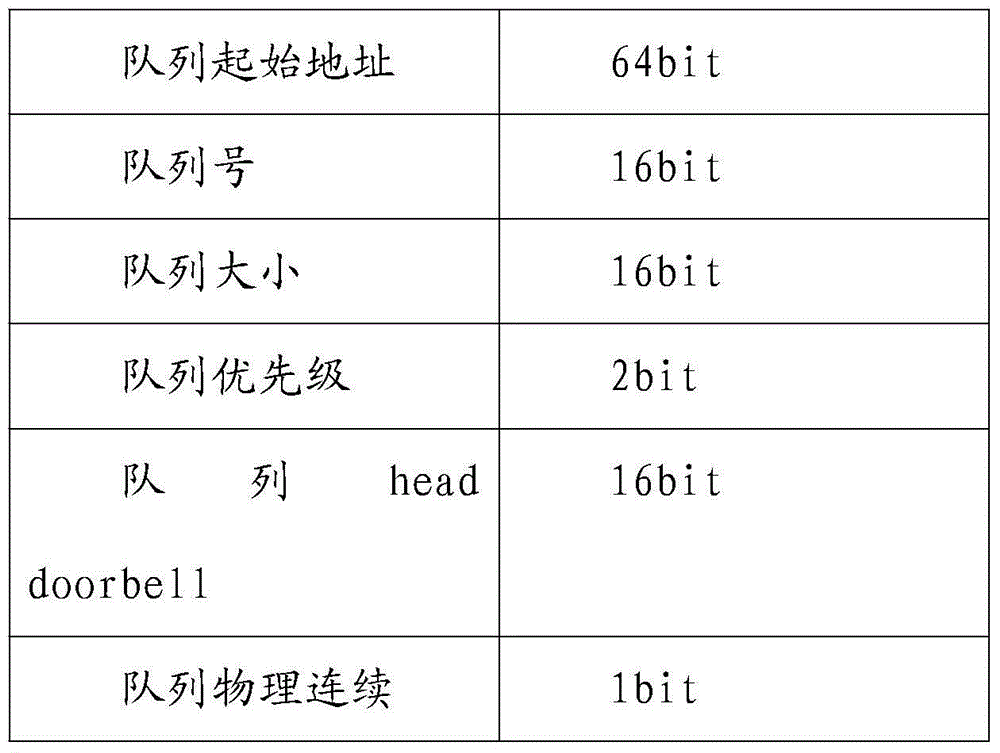

Realizing method and system for NVME protocol multi-command queues

ActiveCN104536701AThe number of command queues is smallThe number of command queues is largeInput/output to record carriersIOPSQueue number

The invention discloses a realizing method for NVME protocol multi-command queues. The method includes the steps that commands and queue information of the command queues are stored separately; uniform command storage caches are set to store the concrete commands corresponding to elements of all the command queues and queue numbers corresponding to the commands; a queue information table is set to store the queue information of all the queues existing at the Host end at present; when an SSD controller executes the concrete commands according to the sequence, the corresponding queue information is searched for from the queue information table according to the queue numbers corresponding to the concrete commands. The invention discloses a realizing system for the NVME protocol multi-command queues. As the commands are actively read from the command queues at the Host end, the uniform command storage areas are opened up in the controller to store the commands, and the command queue information is obtained by searching the table when the commands are executed; the realizing method has the advantages that few storage resources are consumed when one item of command queue support is added to a control chip, a large number of command queues can be supported, and IOPS can be improved greatly.

Owner:RAMAXEL TECH SHENZHEN

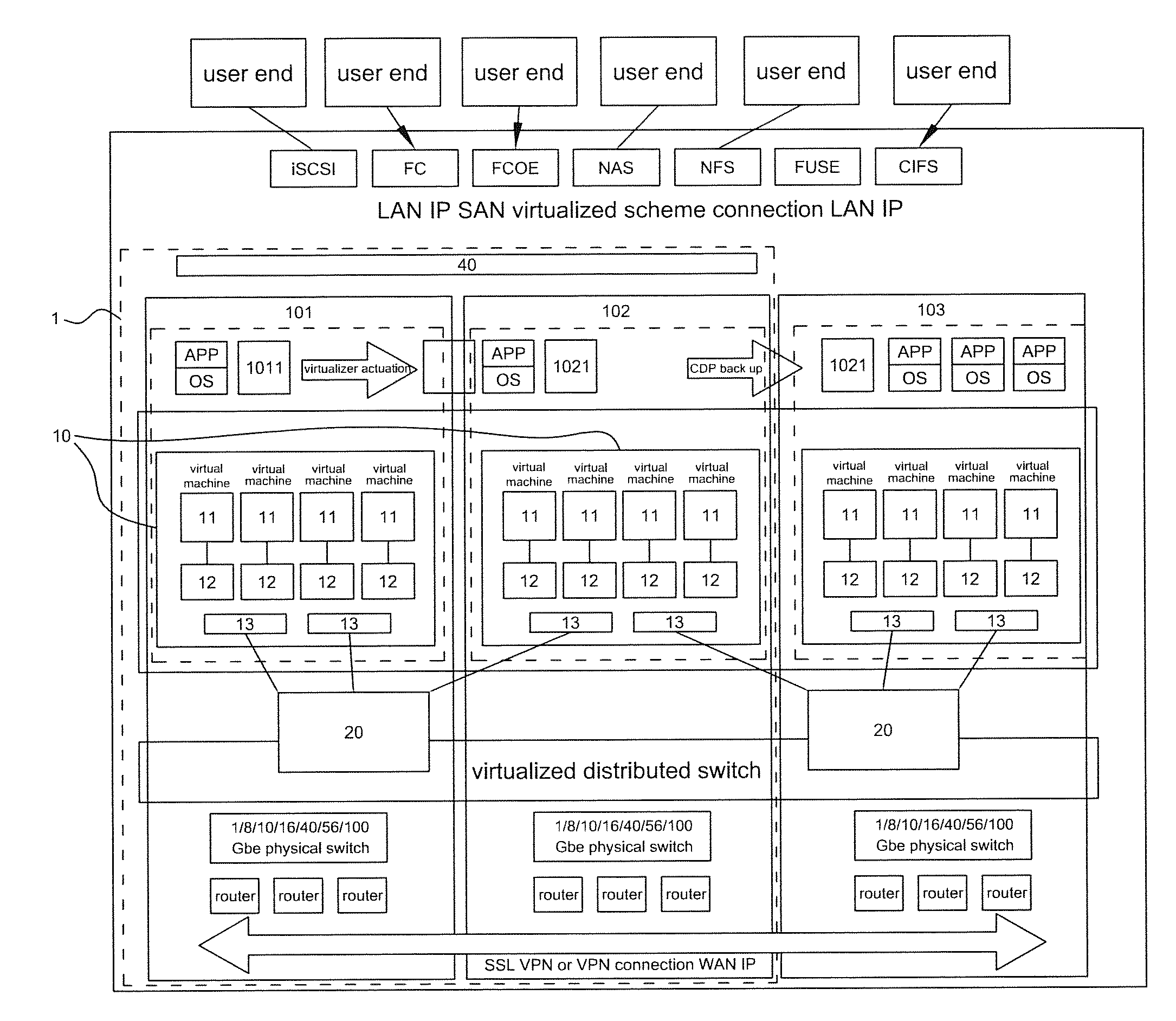

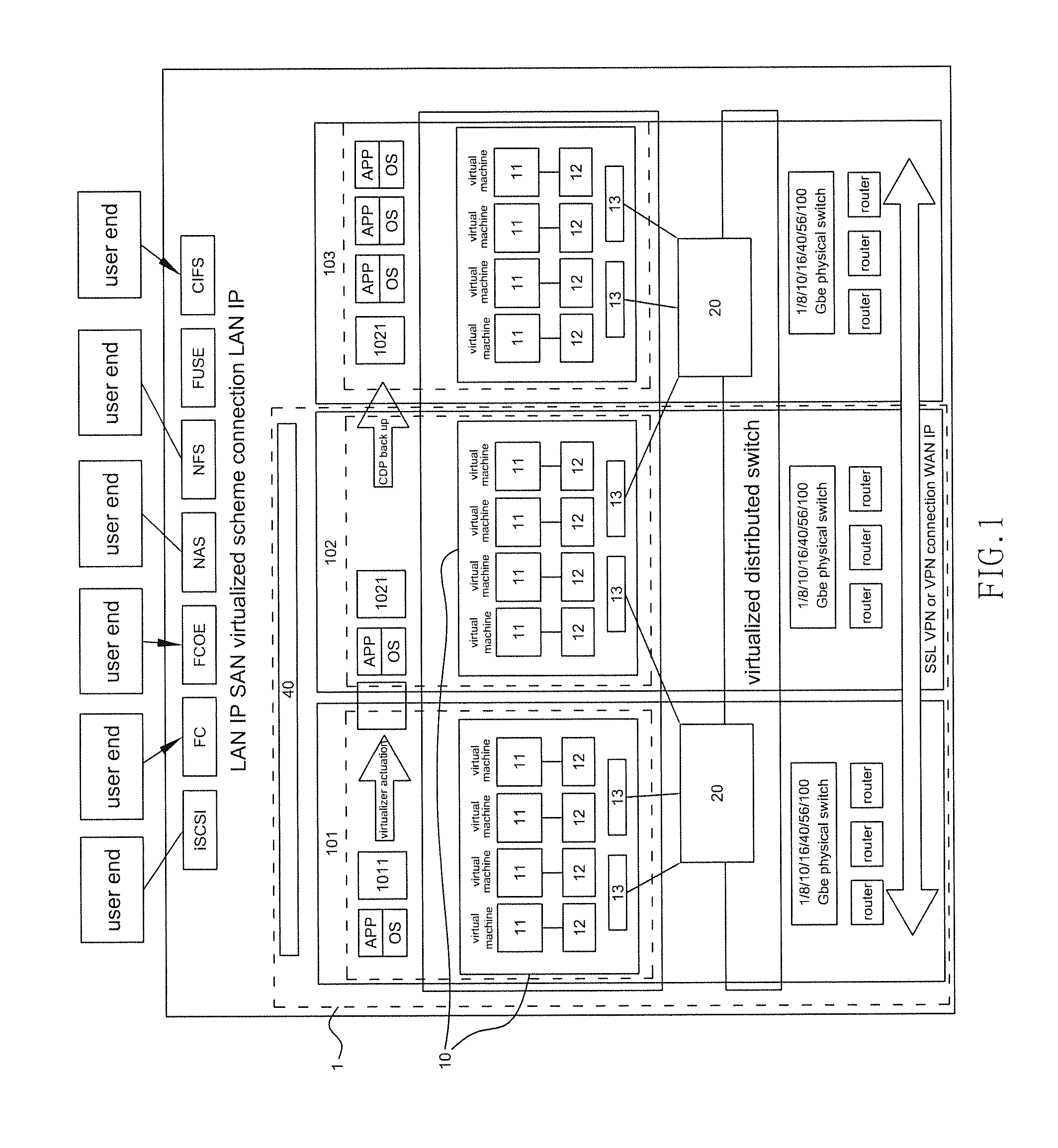

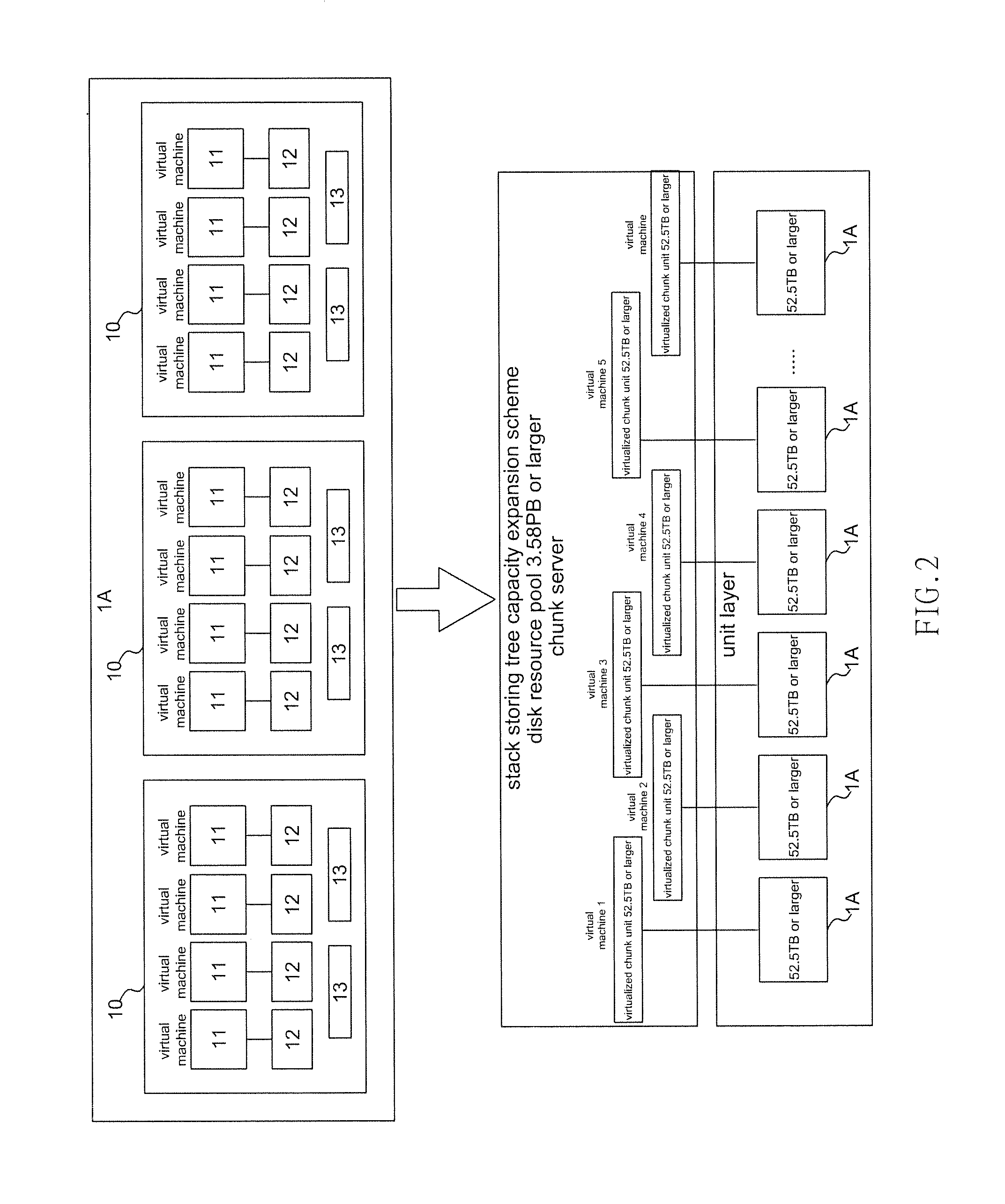

Operation method of distributed memory disk cluster storage system

ActiveUS20150160872A1Improve disadvantagesIncrease the number ofInput/output to record carriersMemory systemsDistributed memoryData center

The present invention relates to anoperation method of distributed memory disk cluster storage system, a distributed memory storage system is adopted thereby satisfying four desired expansions which are the expansion of network bandwidth, the expansion of hard disk capacity, the expansion of IOPS speed, and the expansion of memory I / O transmitting speed. Meanwhile, the system can be cross-region operated, data center and WAN, so the user's requirements can be collected through the local memory disk cluster for being provided with the corresponding services, the capacity of the memory disk cluster can also be gradually expanded for further providing cross-region or cross-country data service.

Owner:CHEN HSUN YUAN

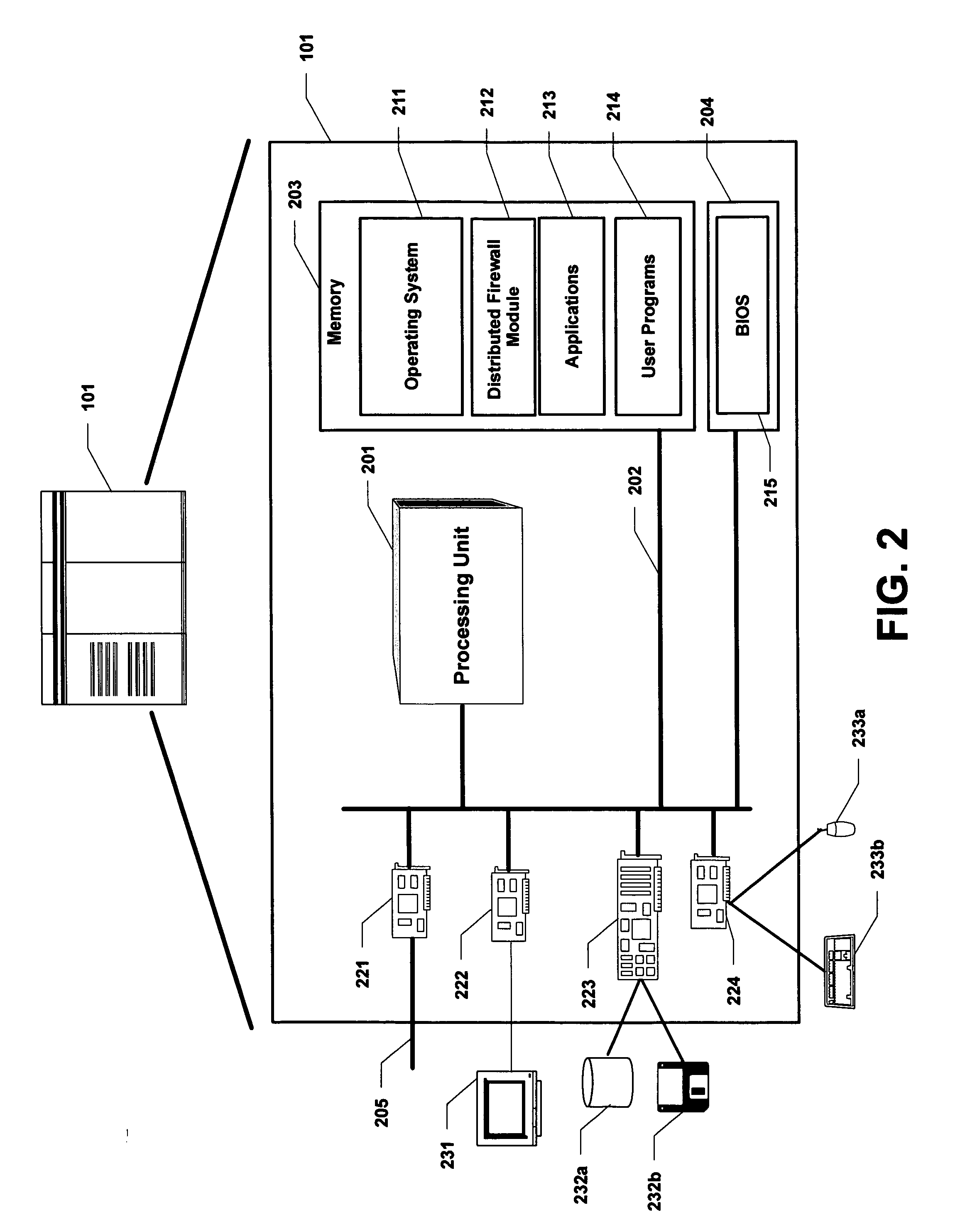

System and method for providing dynamic network firewall with default deny

InactiveUS20070255861A1TransmissionInput/output processes for data processingNetwork packetNetwork data

A computing system having host computer and an I / O processor (IOP) provides firewall services to the host computer. When the host computer and the IOP are initialized, all of the communication ports are reset to a closed state. Application programs are loaded into memory of the host computer for execution and provide the identity of communication ports to be used by the application. The identity of the requested communication ports are used to instruct the IOP to open the communication port to accept network data packets that use the particular port. When the application terminates operation, the communication ports used by the application are closed to provide dynamic control over communication ports. This process ensures that only ports currently used by applications currently executing within the host computer are open without administrator action.

Owner:UNISYS CORP

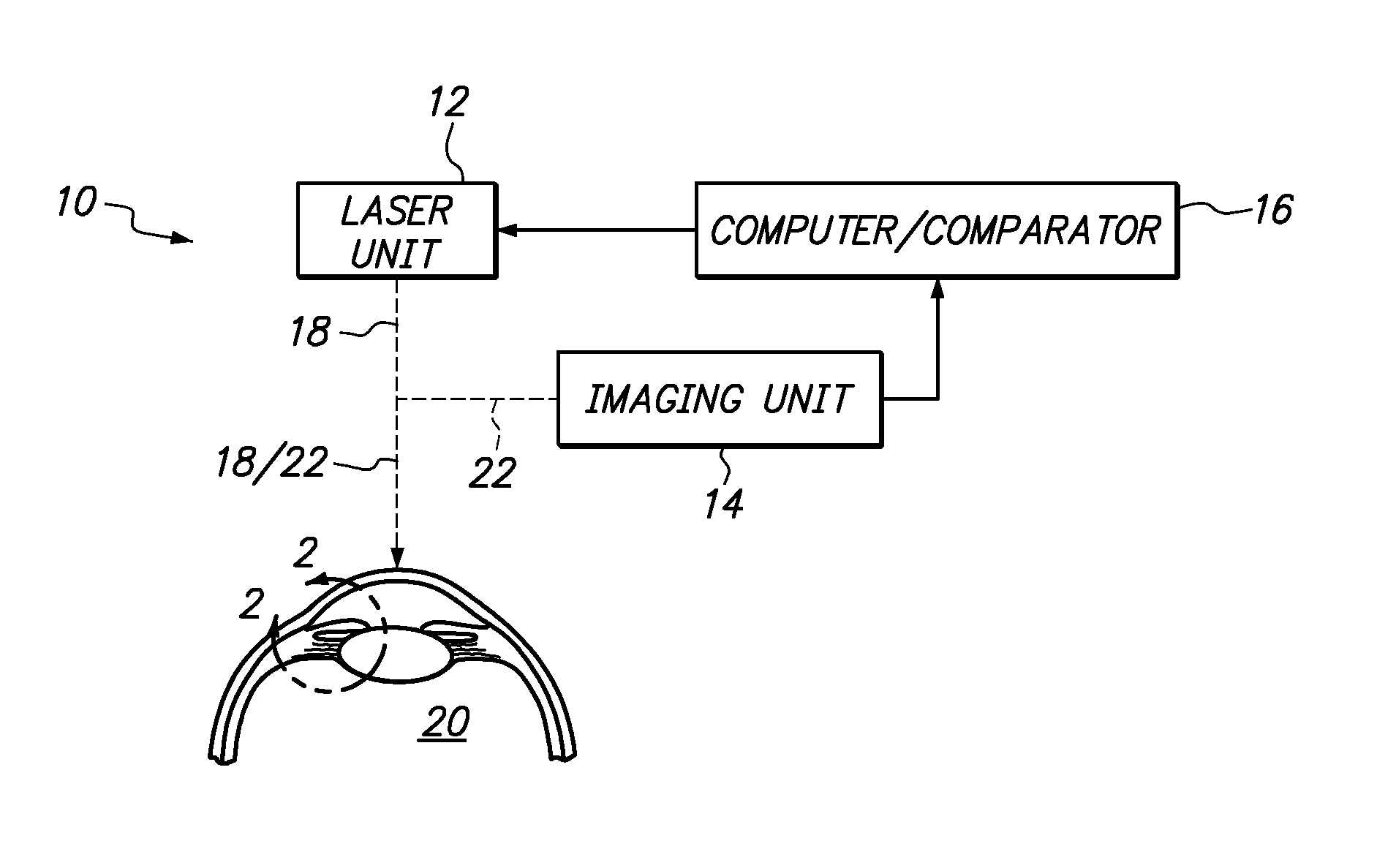

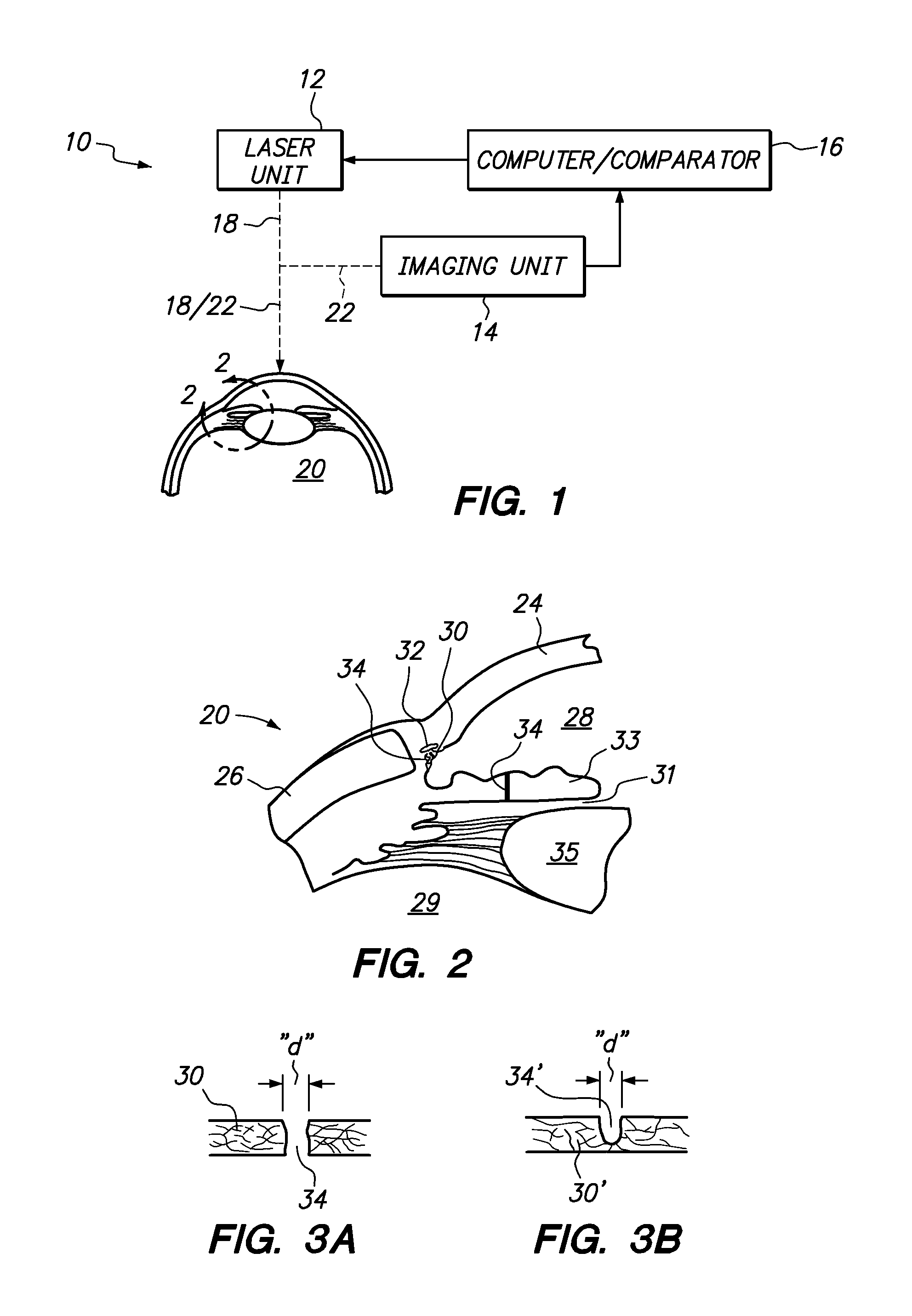

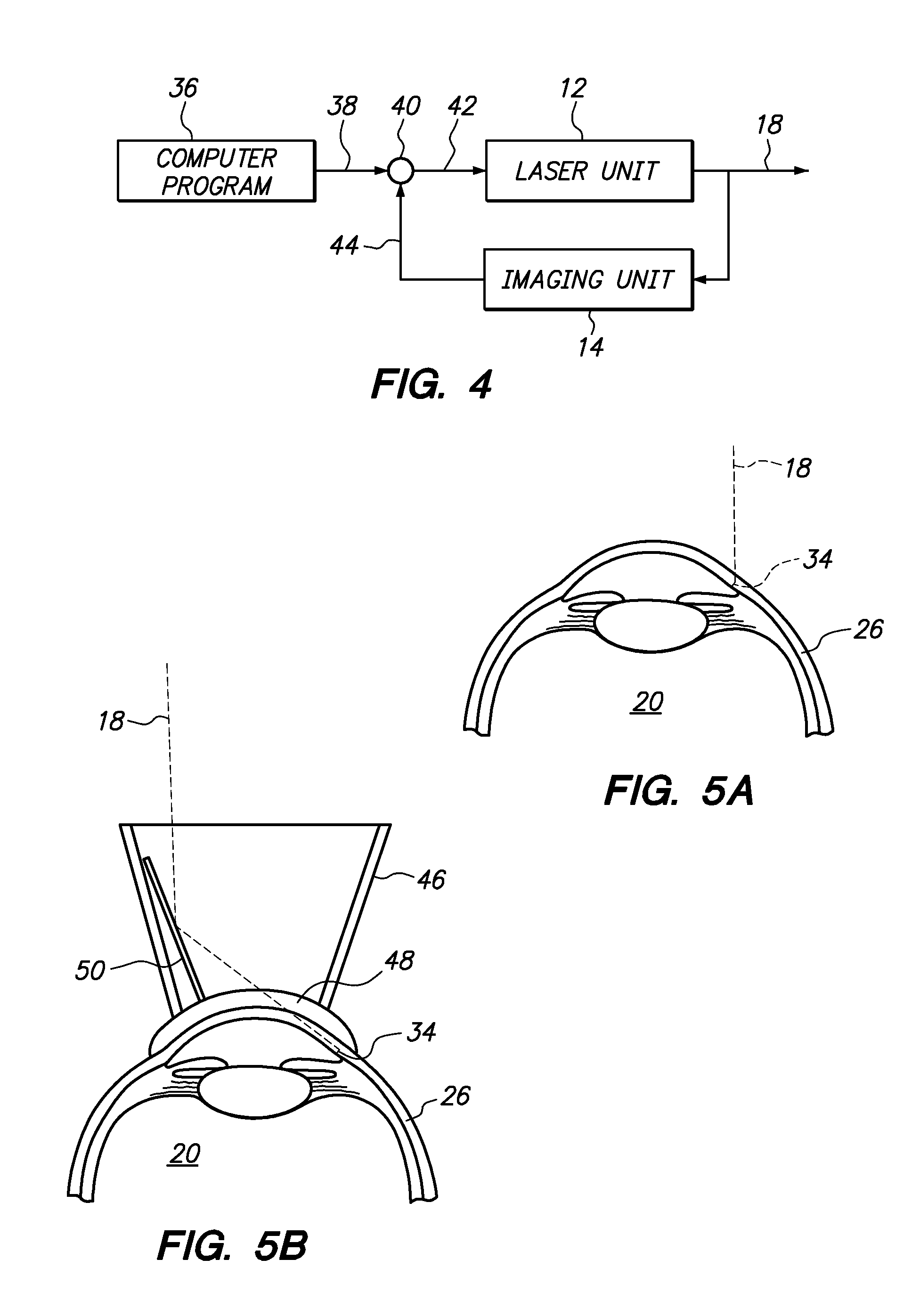

System and Method for Lowering IOP by Creation of Microchannels in Trabecular Meshwork Using a Femtosecond Laser

InactiveUS20130103011A1Function increaseIncrease outflowLaser surgerySurgical instrument detailsFemto second laserOptoelectronics

A system and its method for creating a microchannel in the trabecular meshwork of an eye include a laser unit for generating a laser beam, and an imaging unit for creating an image of the trabecular meshwork. The system also includes a computer which defines the microchannel. A comparator that is connected with the computer then controls the laser unit to move the focal point of the laser beam. This focal point movement is accomplished to create the microchannel, while minimizing deviations of the focal point from the defined microchannel.

Owner:BAUSCH & LOMB INC

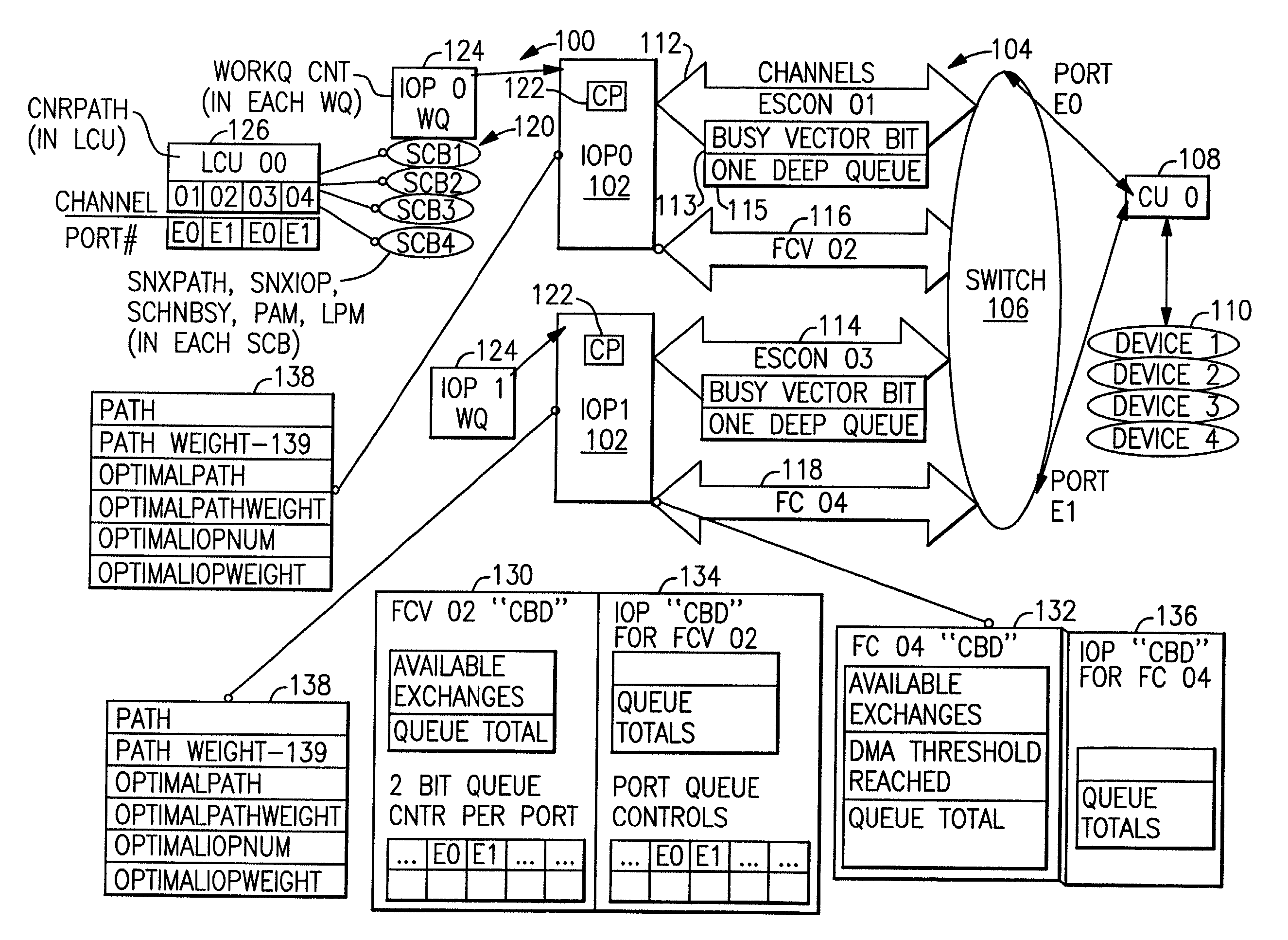

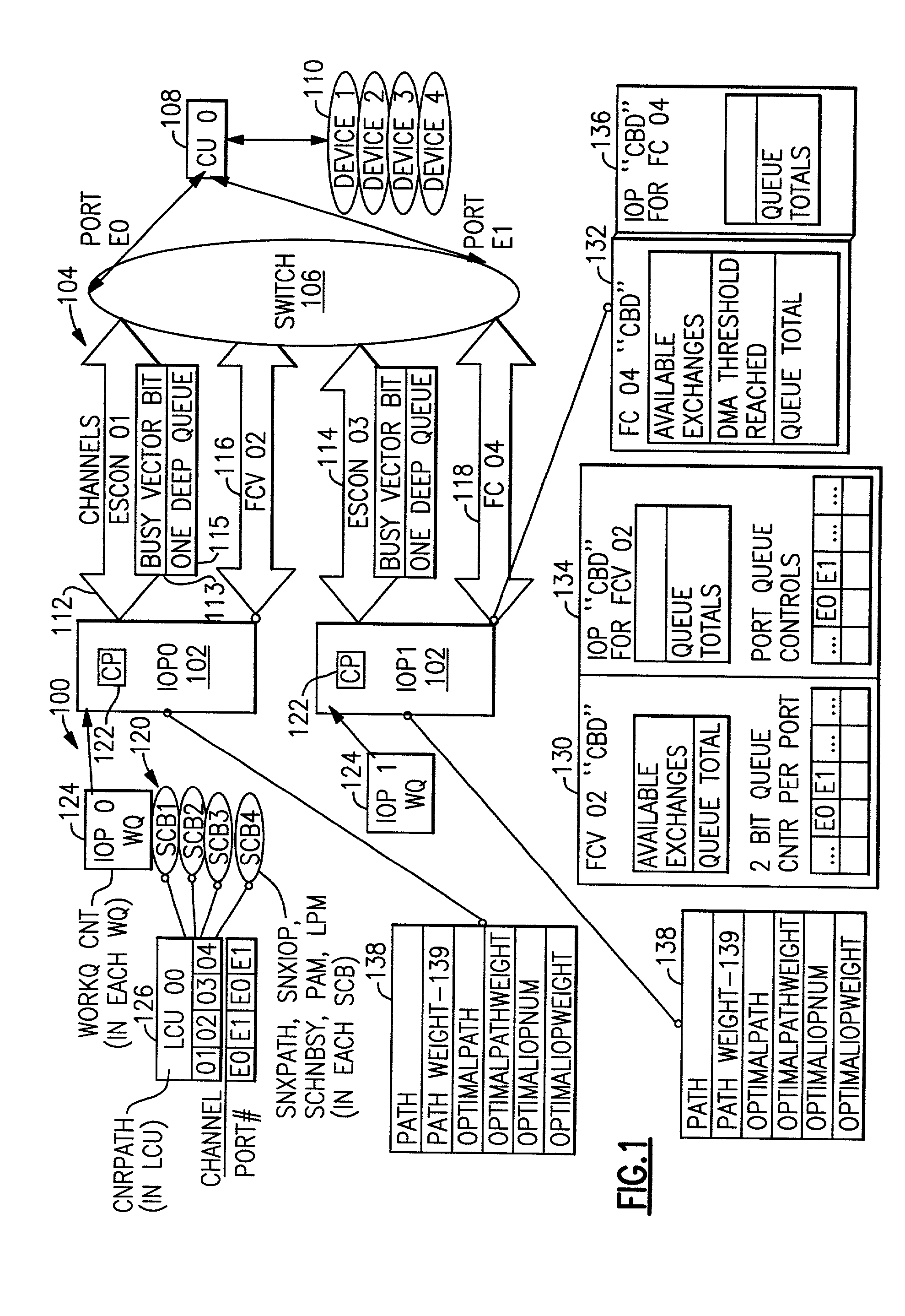

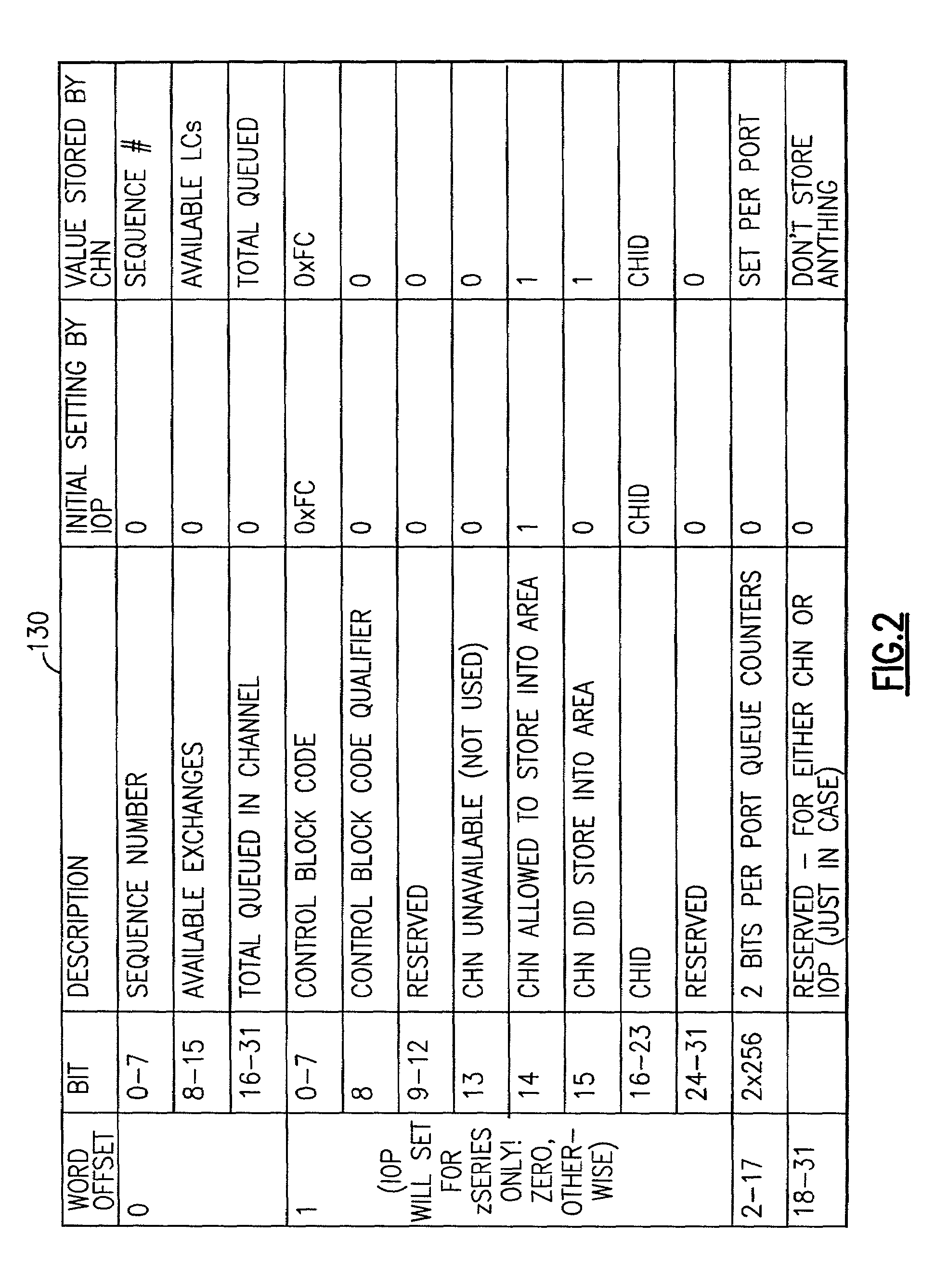

Multiple I/O path selection among disparate channel paths

InactiveUS6973529B2Less likelihoodLess ping-pongingDigital computer detailsInput/output processes for data processingData processing systemChannel types

An apparatus, method and program product for selecting paths between a main memory and I / O devices in a data processing system having a main memory for storing data, one or more I / O devices for receiving data from or sending data to the main memory, and an I / O processor (IOP) for controlling I / O operations for sending data between the main memory and the I / O devices. The data processing system includes disparate channels between the IOP and the I / O devices. The disparate channels carry data between the main memory and the I / O devices during the I / O operations. Included is a computer program executed by the IOP for assigning a path weight to selected ones of the disparate channel paths to be used in selecting the next channel path to carry data between the main memory and I / O devices. Each disparate channel type has a different set of criteria for evaluating the path weight.

Owner:IBM CORP

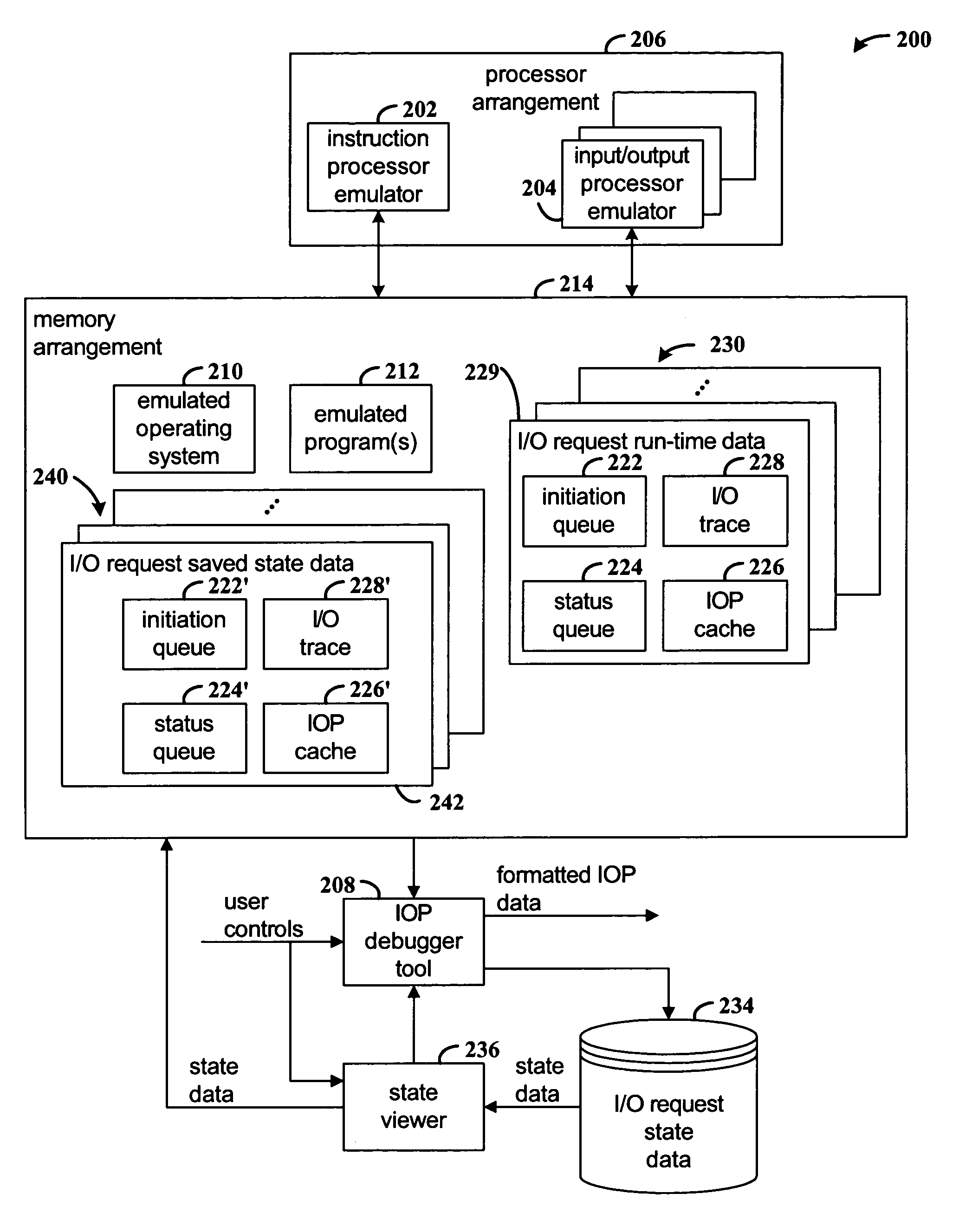

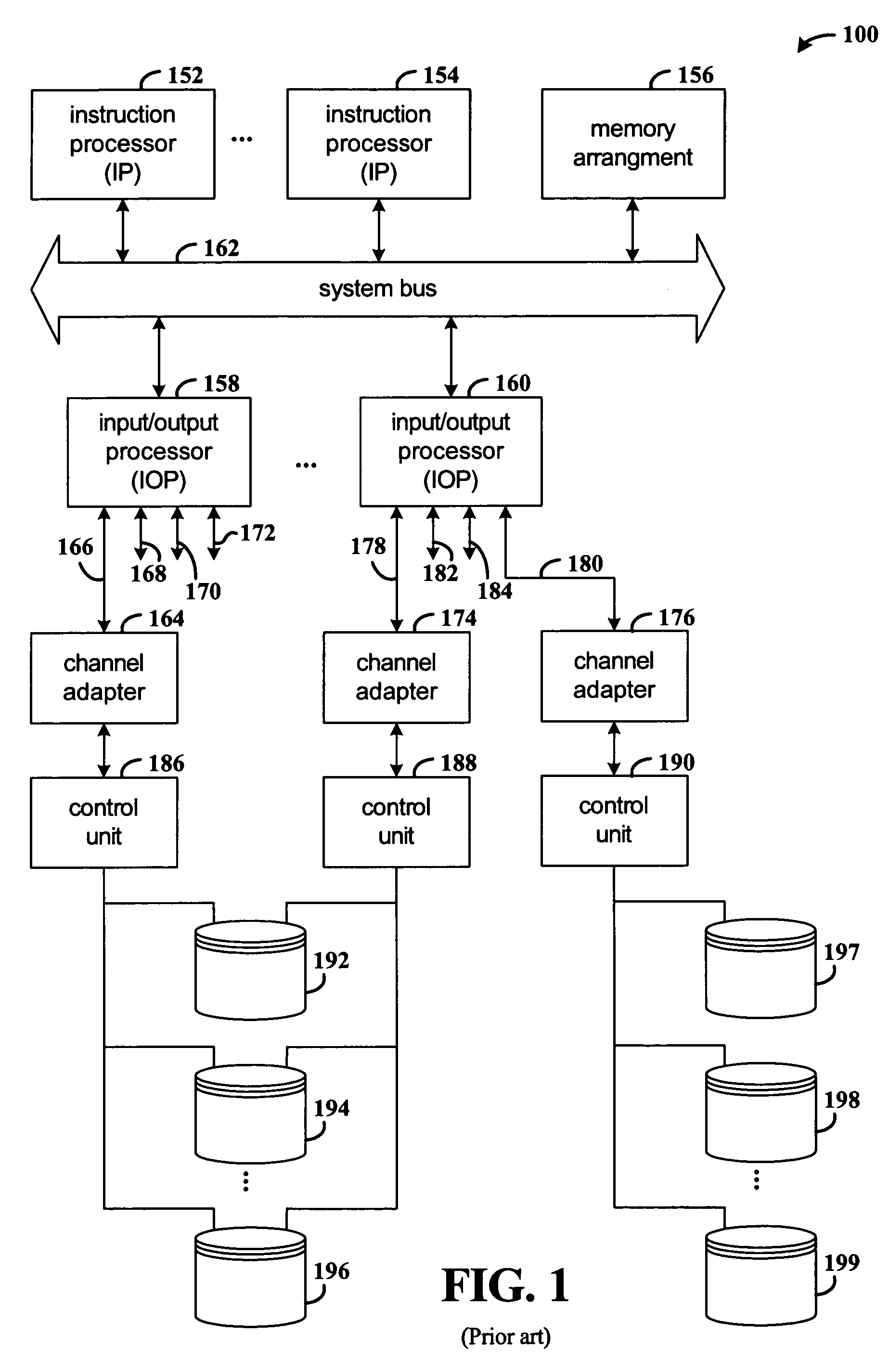

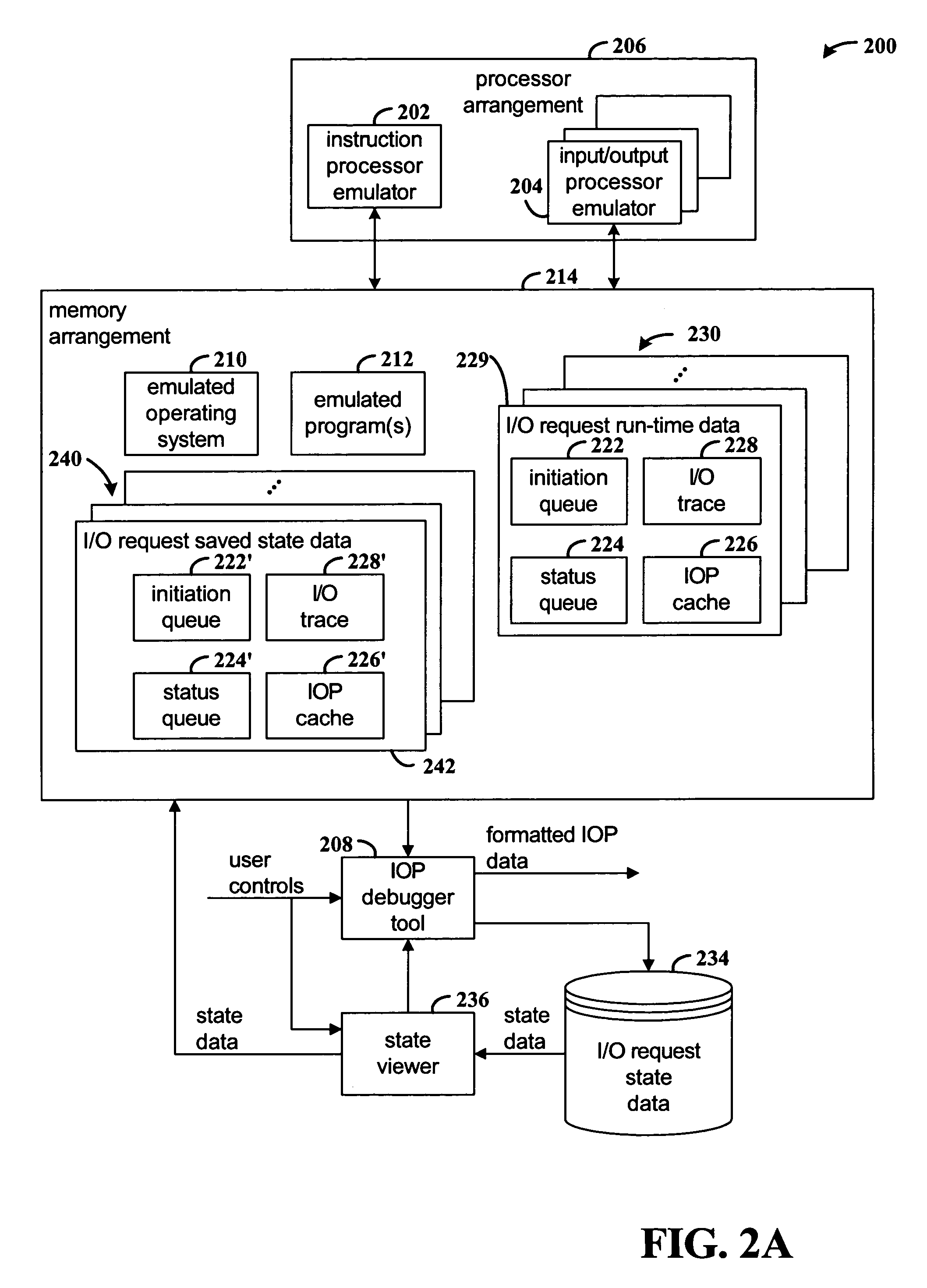

Offline emulated input/output processor debugger

ActiveUS7177791B1Error detection/correctionSoftware simulation/interpretation/emulationOperational systemUser input

The various embodiments of the invention relate to analyzing operations of an emulated input-output processor. Instructions native to the first type of instruction processor are emulated on a second-type instruction processor. The instruction processor emulator executes an operating system that includes instructions native to the first type of instruction processor. The operating system includes instructions that write input / output (IO) requests to the memory arrangement in response to IO functions invoked by a program. An IOP emulator that is executable on the second-type processor emulates IOP processing of IO requests from the memory arrangement. The IOP emulator maintains in the memory arrangement a first set of data structures used in processing the IO requests. State data currently contained in the data structures is stored on a retentive storage device, and in response to user input controls, the state data is read from retentive storage and displayed.

Owner:UNISYS CORP

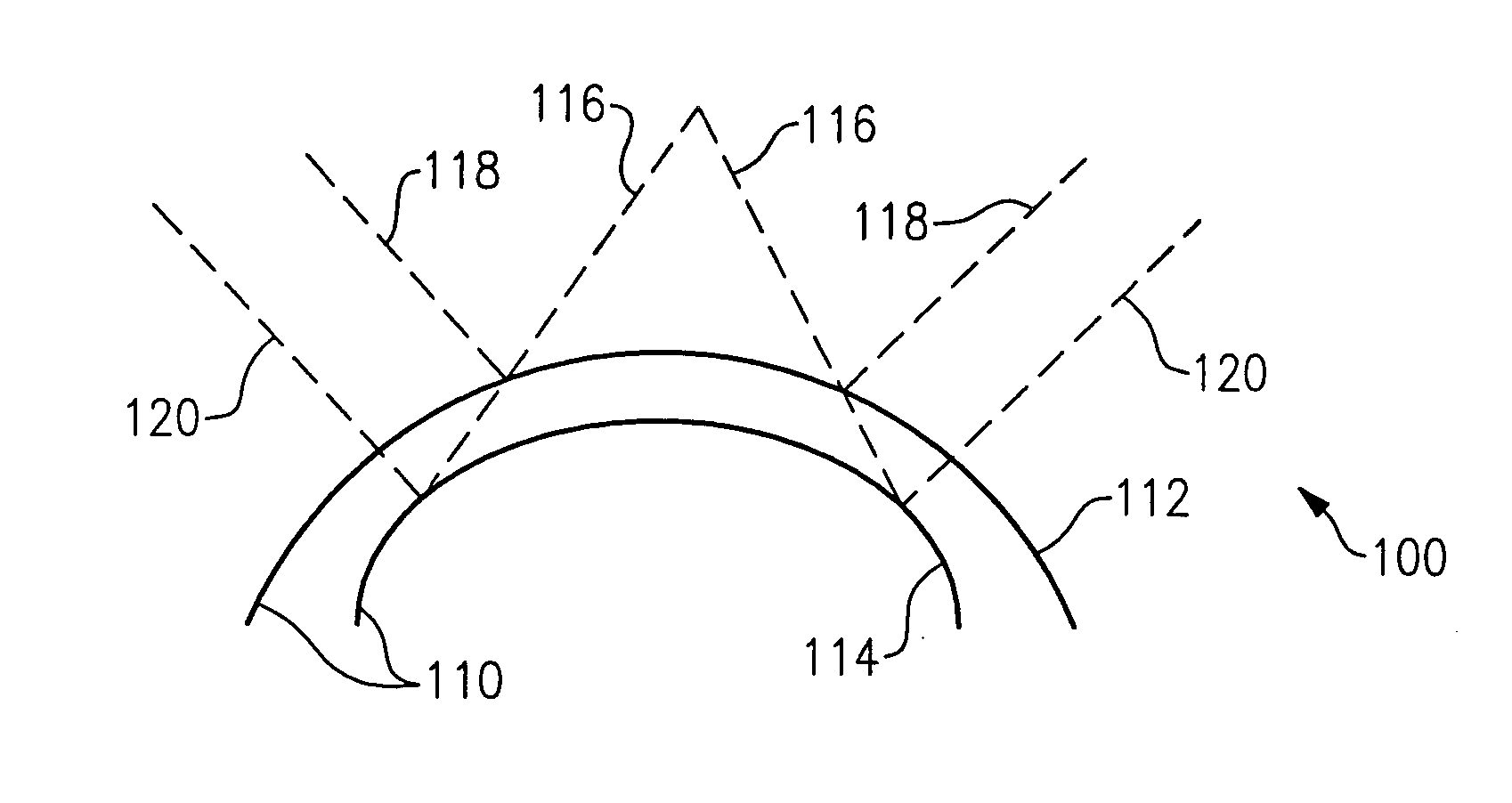

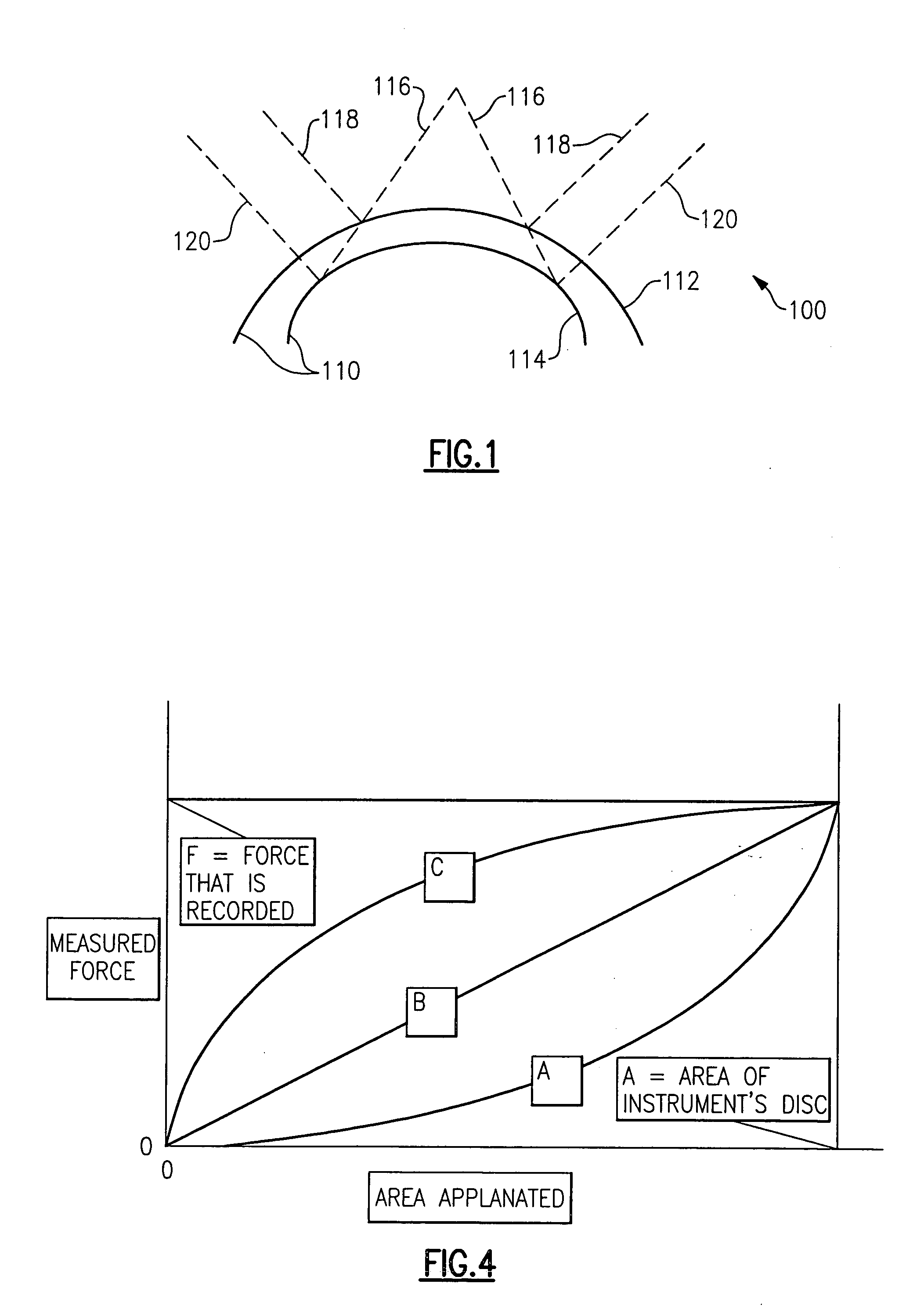

Apparatus and method for determining intraocular pressure and corneal thickness

The invention includes methods and apparatus for measuring (Intraocular Pressure) IOP and (Corneal Thickness) CT for diagnosis and for monitoring a condition of health of an eye. The apparatus uses measurements selected from at least one of IOP and a CT, and a plurality of IOP measurements to deduce an interpretive result indicative of a condition of an eye. In another embodiment, the apparatus measures a relationship between an applanated area of variable size and a selected one of an applied force and an applied pressure. The relationship is used to deduce an interpretive result indicative of the condition of an eye. The result can be displayed to a practitioner. The practitioner uses the result to determine a course of treatment as necessary, and to monitor the effect of a course of treatment on the state of health of the eye over time.

Owner:WELCH ALLYN INC