Technique for inter-procedural memory address space optimization in GPU computing compiler

a technology of inter-procedural memory address space and compiler, which is applied in the direction of program control, architecture with multiple processing units, instruments, etc., can solve the problems of wasting gpu resources, relying on the tagging approach described above, and wasting resources, so as to accelerate the execution of program code and save resources. , the effect of accelerating the execution of the application

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0020]In the following description, numerous specific details are set forth to provide a more thorough understanding of the present invention. However, it will be apparent to one of skill in the art that the present invention may be practiced without one or more of these specific details.

System Overview

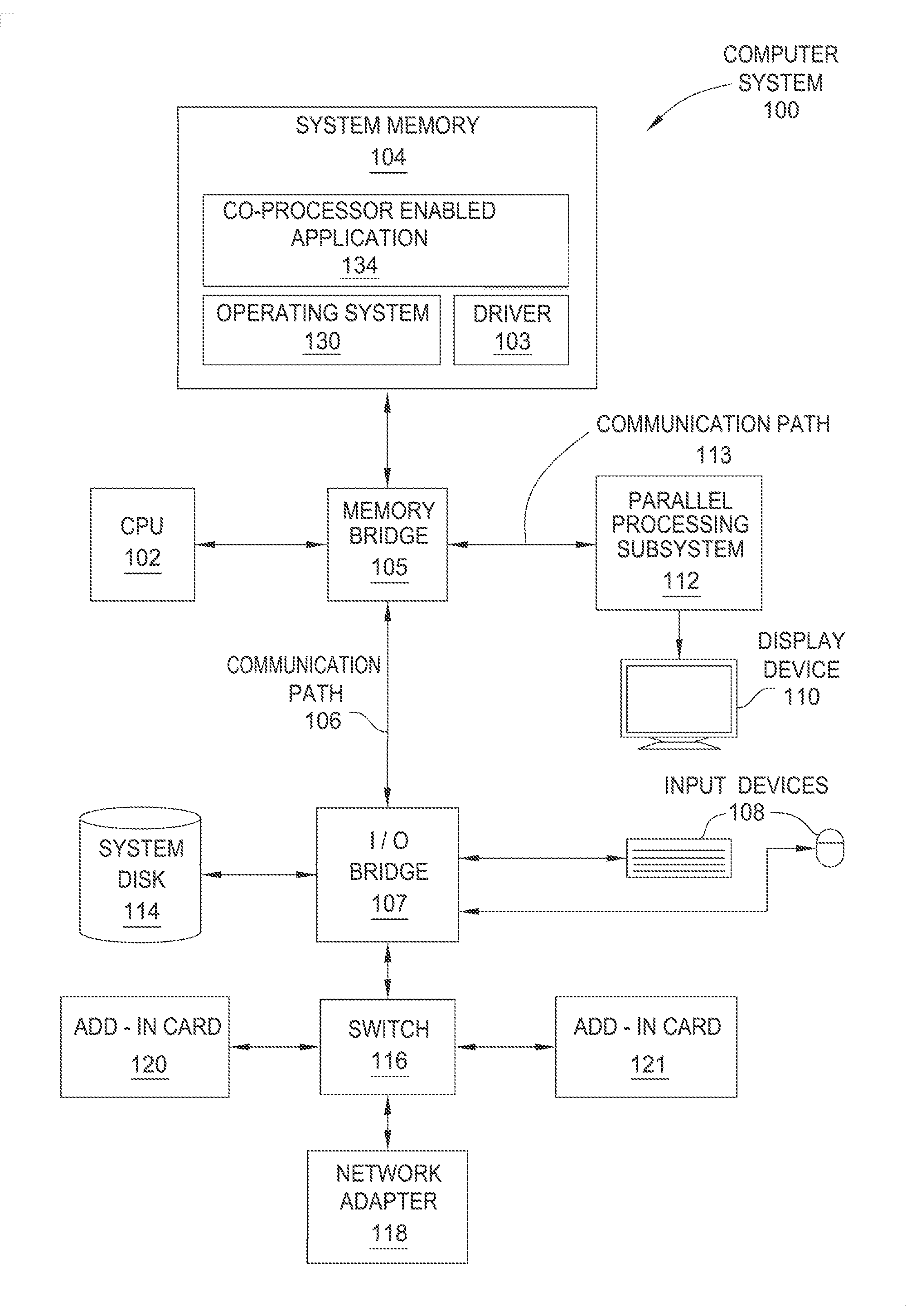

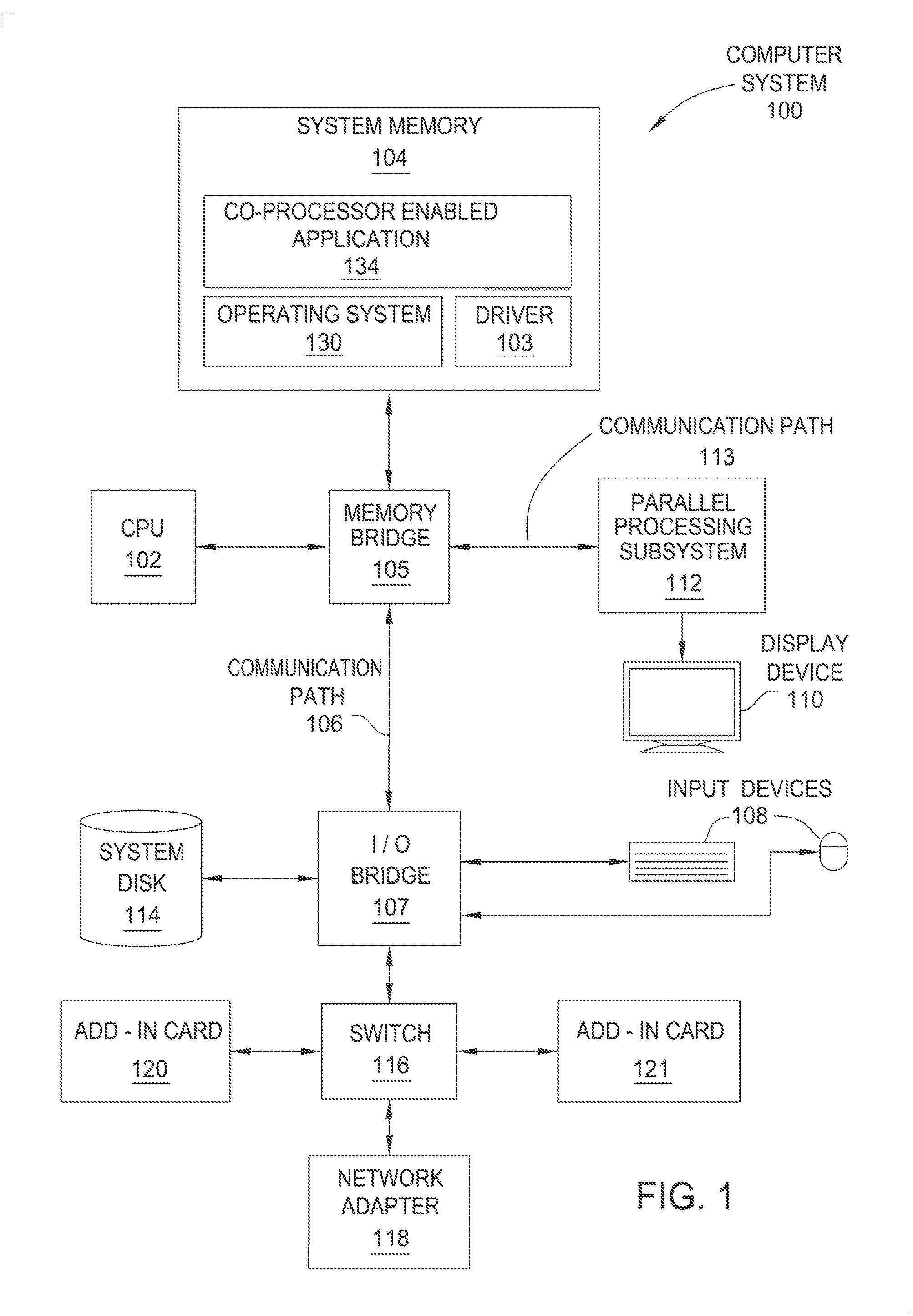

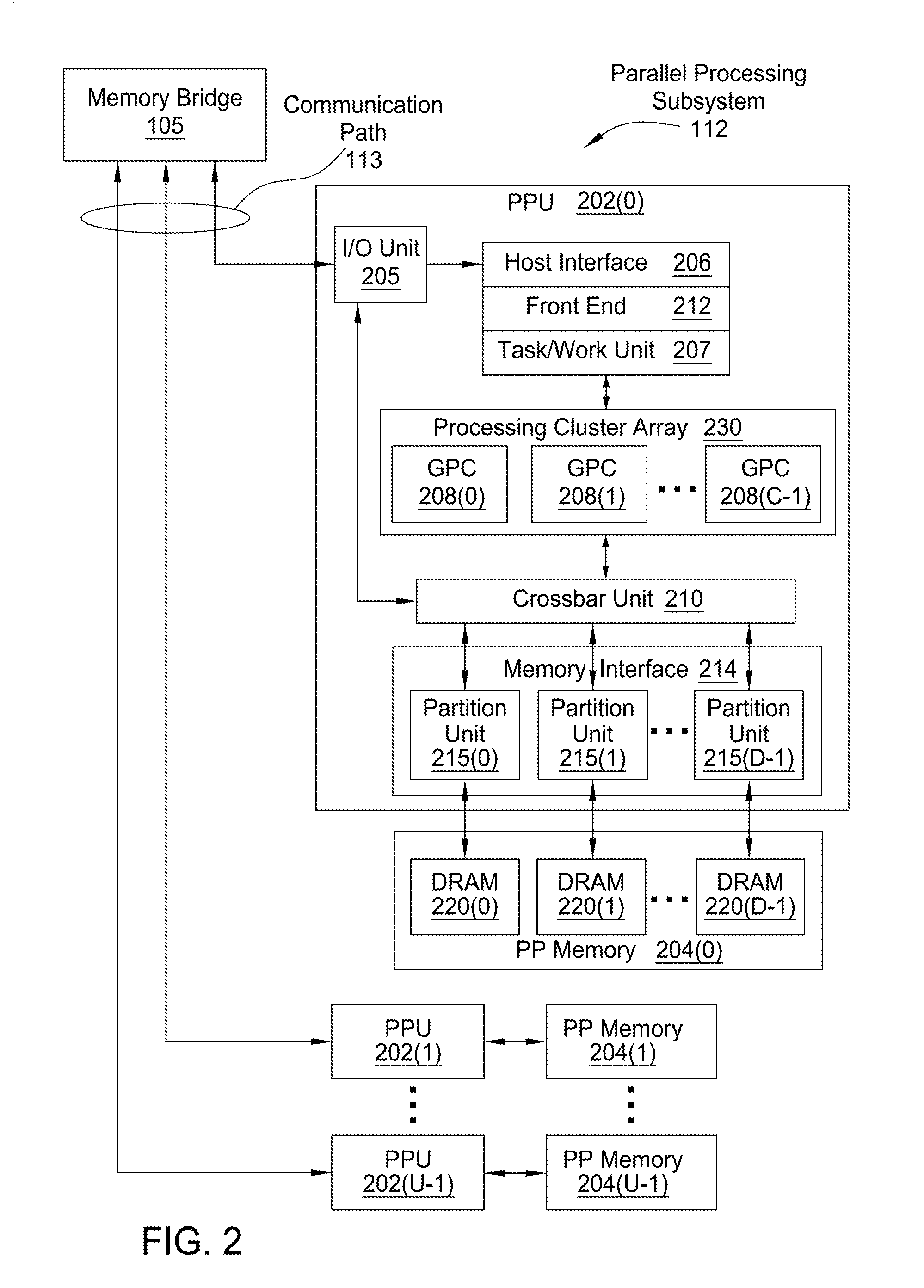

[0021]FIG. 1 is a block diagram illustrating a computer system 100 configured to implement one or more aspects of the present invention. Computer system 100 includes a central processing unit (CPU) 102 and a system memory 104 communicating via an interconnection path that may include a memory bridge 105. System memory 104 includes an image of an operating system 130, a driver 103, and a co-processor enabled application 134. Operating system 130 provides detailed instructions for managing and coordinating the operation of computer system 100. Driver 103 provides detailed instructions for managing and coordinating operation of parallel processing subsystem 112 and one or more parallel p...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More