Patents

Literature

1689results about "Resistors" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

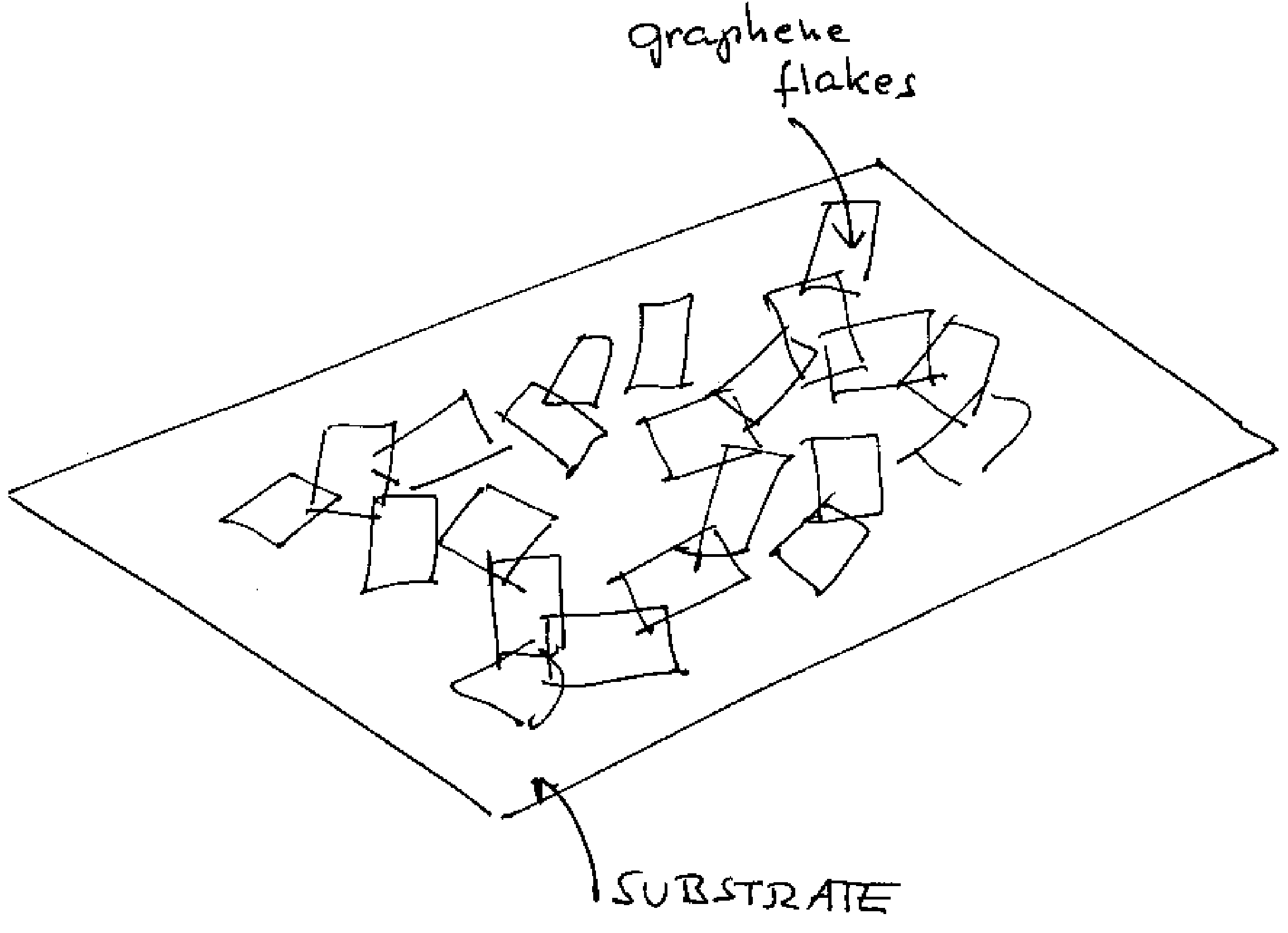

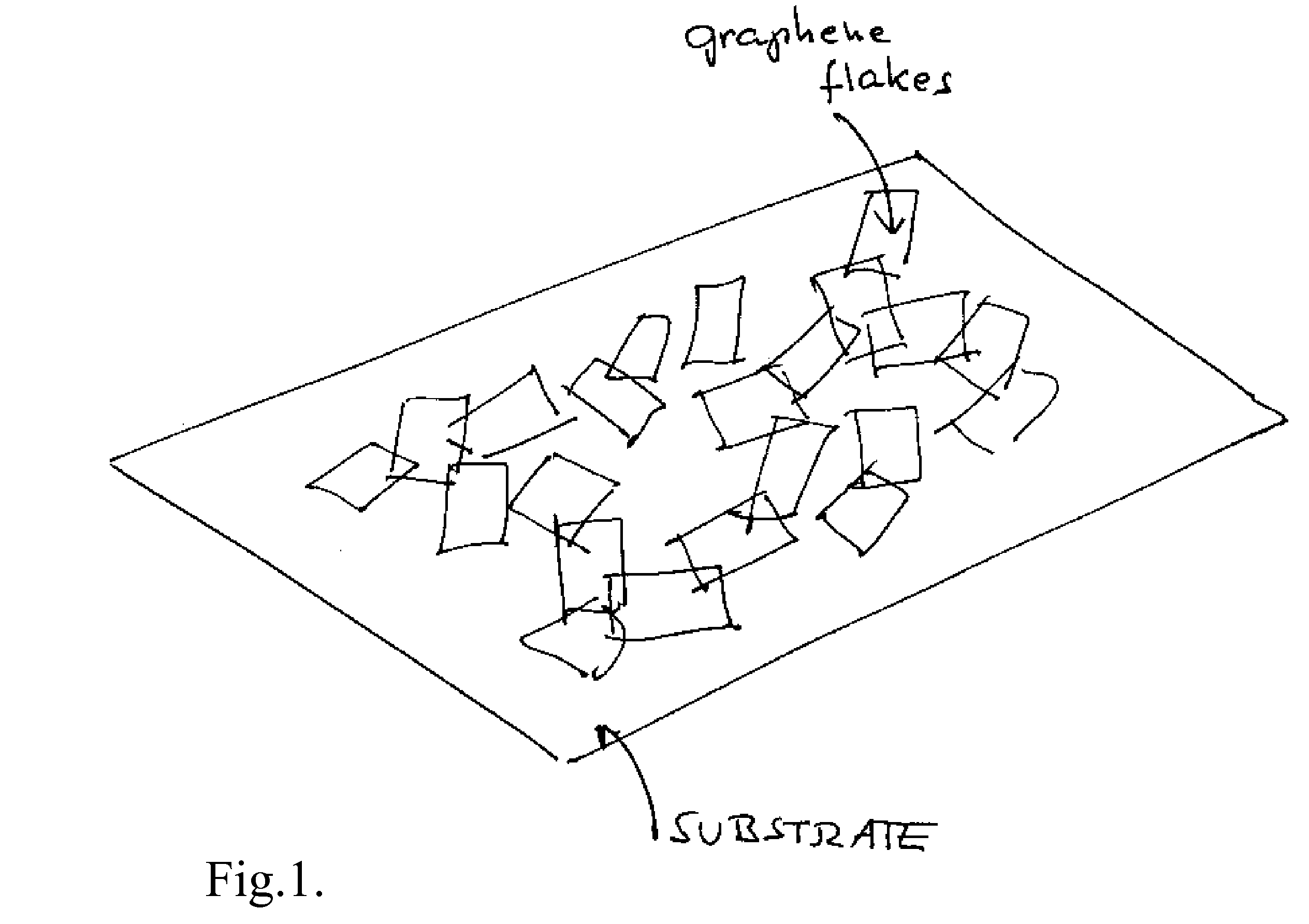

Graphene film as transparent and electrically conducting material

ActiveUS20070284557A1Material nanotechnologyConductive materialGraphene flakeTransparent conducting film

A transparent and conductive film comprising at least one network of graphene flakes is described herein. This film may further comprise an interpenetrating network of other nanostructures, a polymer and / or a functionalization agent(s). A method of fabricating the above device is also described, and may comprise depositing graphene flakes in solution and evaporating solvent therefrom.

Owner:SAMSUNG ELECTRONICS CO LTD

Programmable Resistive Ram and Manufacturing Method

ActiveUS20070173019A1Large sectionSolid-state devicesSemiconductor/solid-state device manufacturingElectrical resistance and conductanceReduced size

Programmable resistive RAM cells have a resistance that depends on the size of the contacts. Manufacturing methods and integrated circuits for lowered contact resistance are disclosed that have contacts of reduced size.

Owner:MACRONIX INT CO LTD

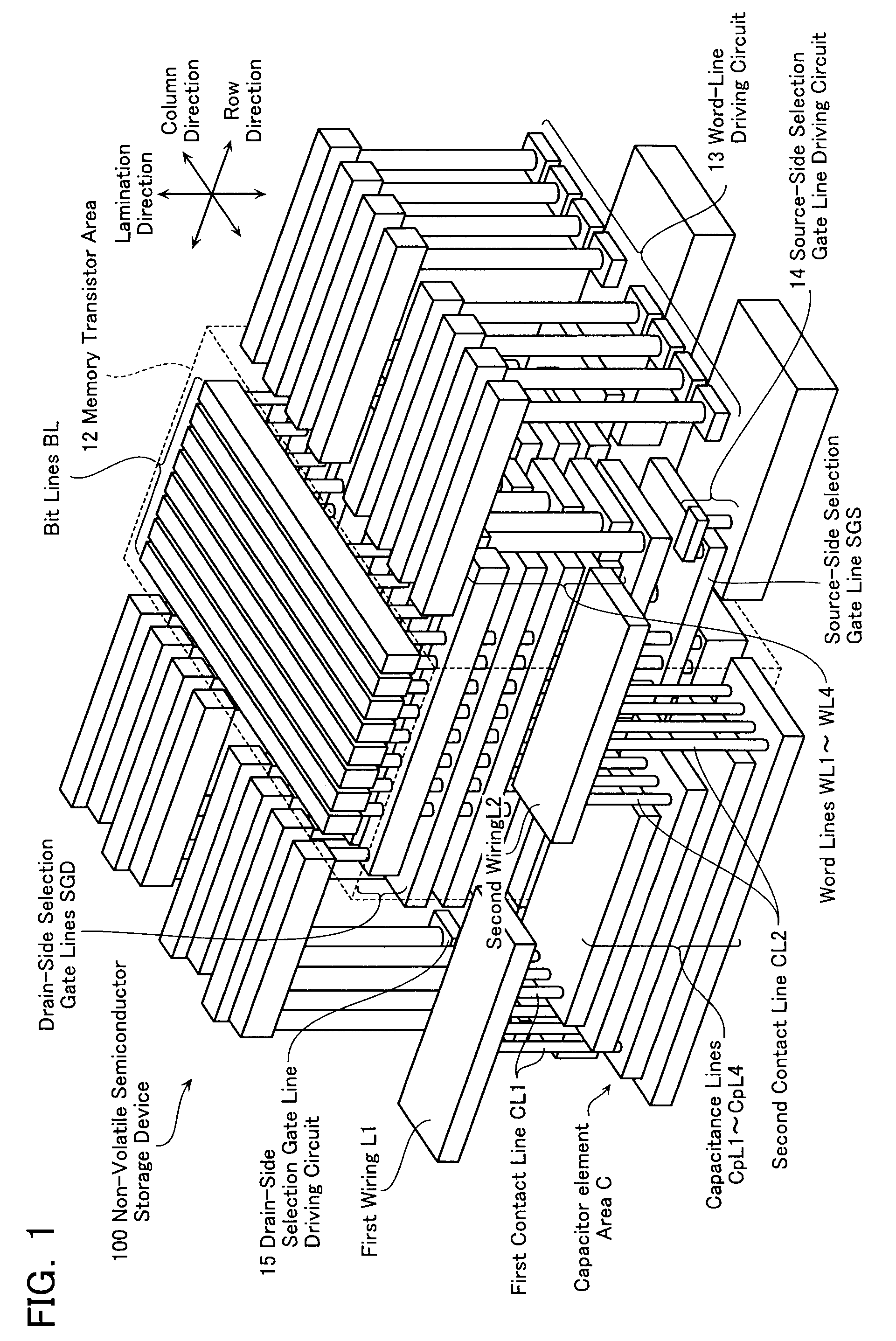

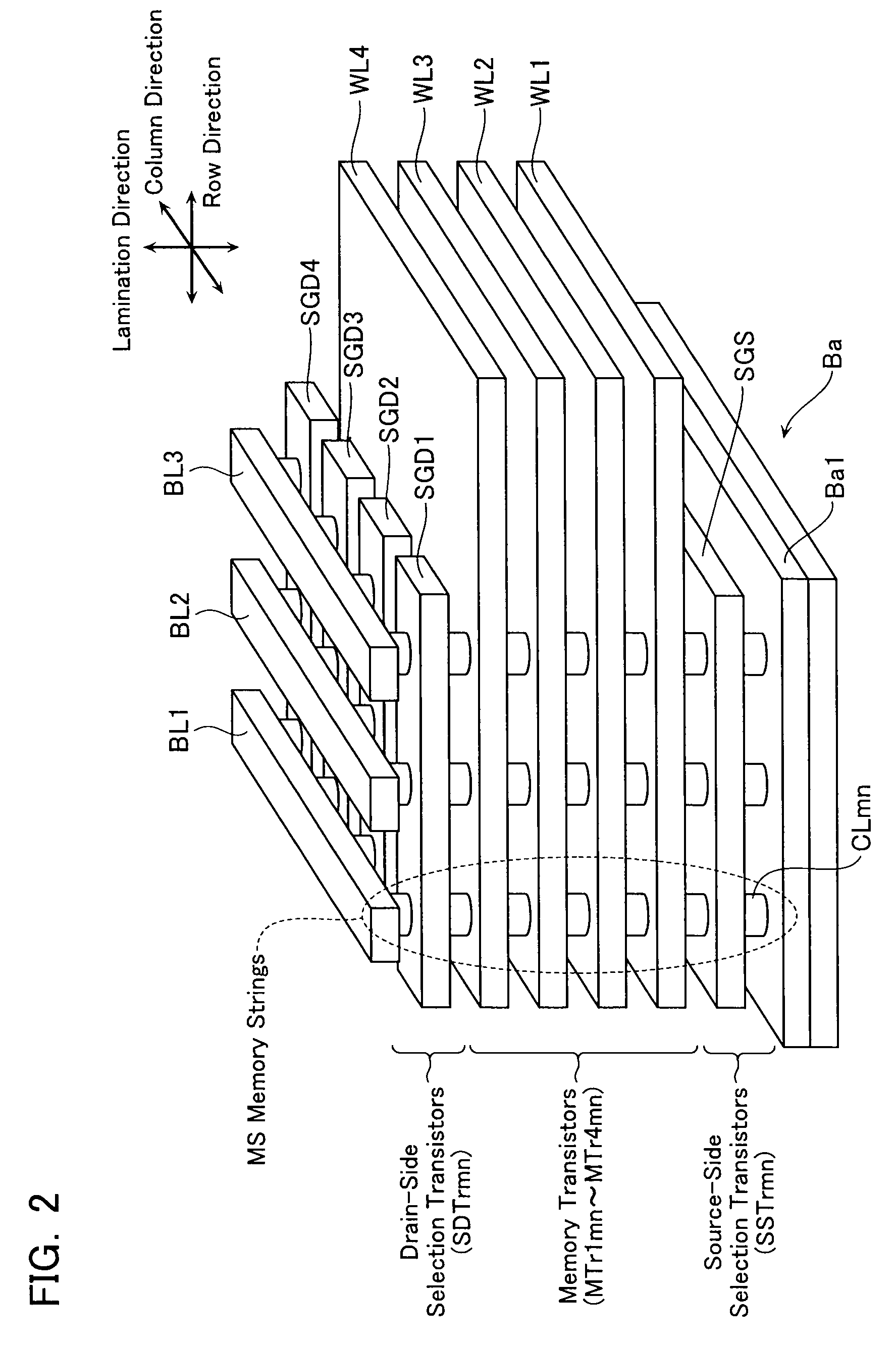

Semiconductor storage device

A non-volatile semiconductor storage device has: a plurality of memory strings with a plurality of electrically rewritable memory cells connected in series; and a capacitor element area including capacitor elements. Each of the memory strings includes: a plurality of first conductive layers laminated on a substrate; and a plurality of first interlayer insulation layers formed between the plurality of first conductive layers. The capacitor element area includes: a plurality of second conductive layers laminated on a substrate and formed in the same layer as the first conductive layers; and a plurality of second interlayer insulation layers formed between the plurality of second conductive layers and formed in the same layer as the first interlayer insulation layers. A group of the adjacently-laminated second conductive layers is connected to a first potential, while another group thereof is connected to a second potential.

Owner:KK TOSHIBA

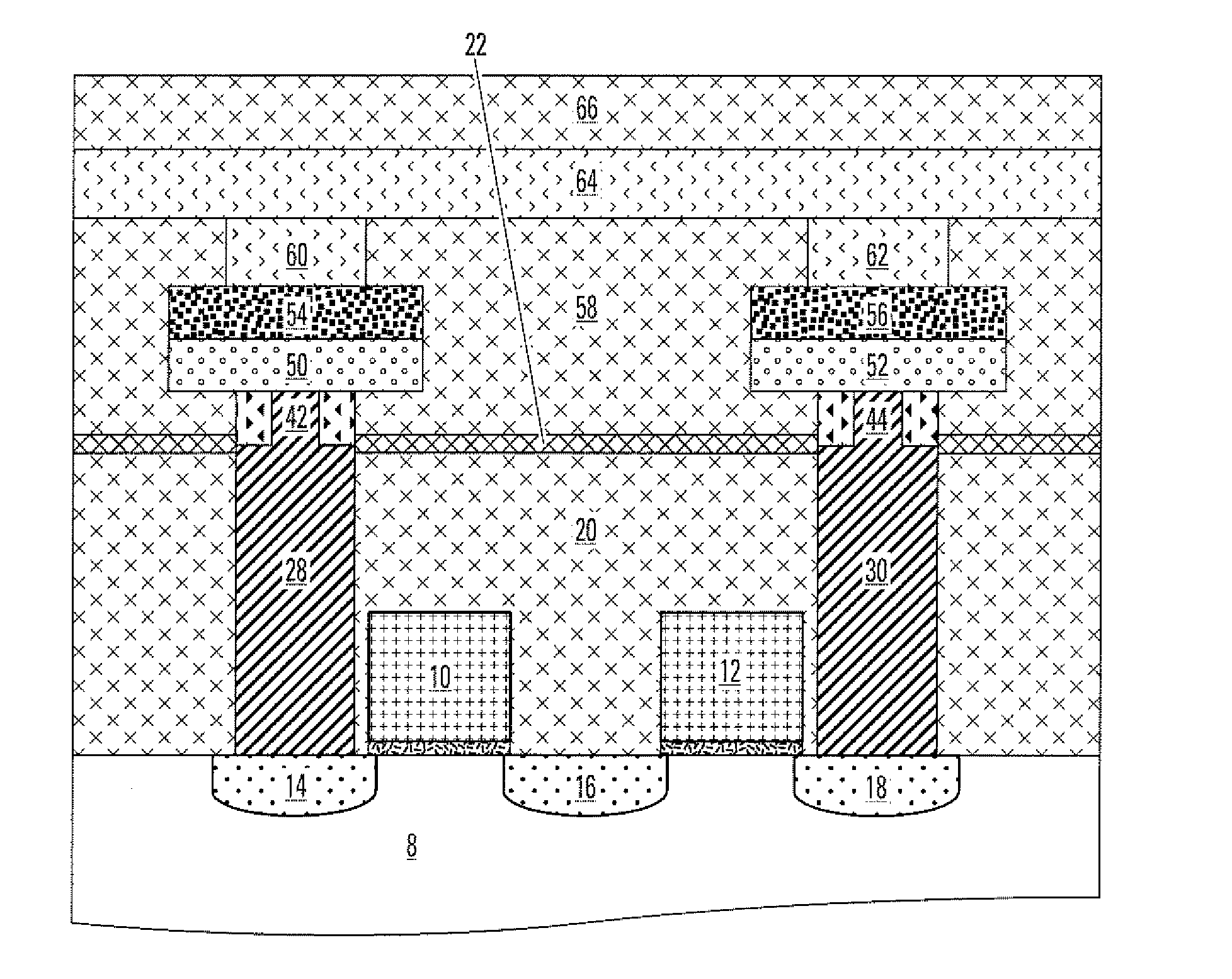

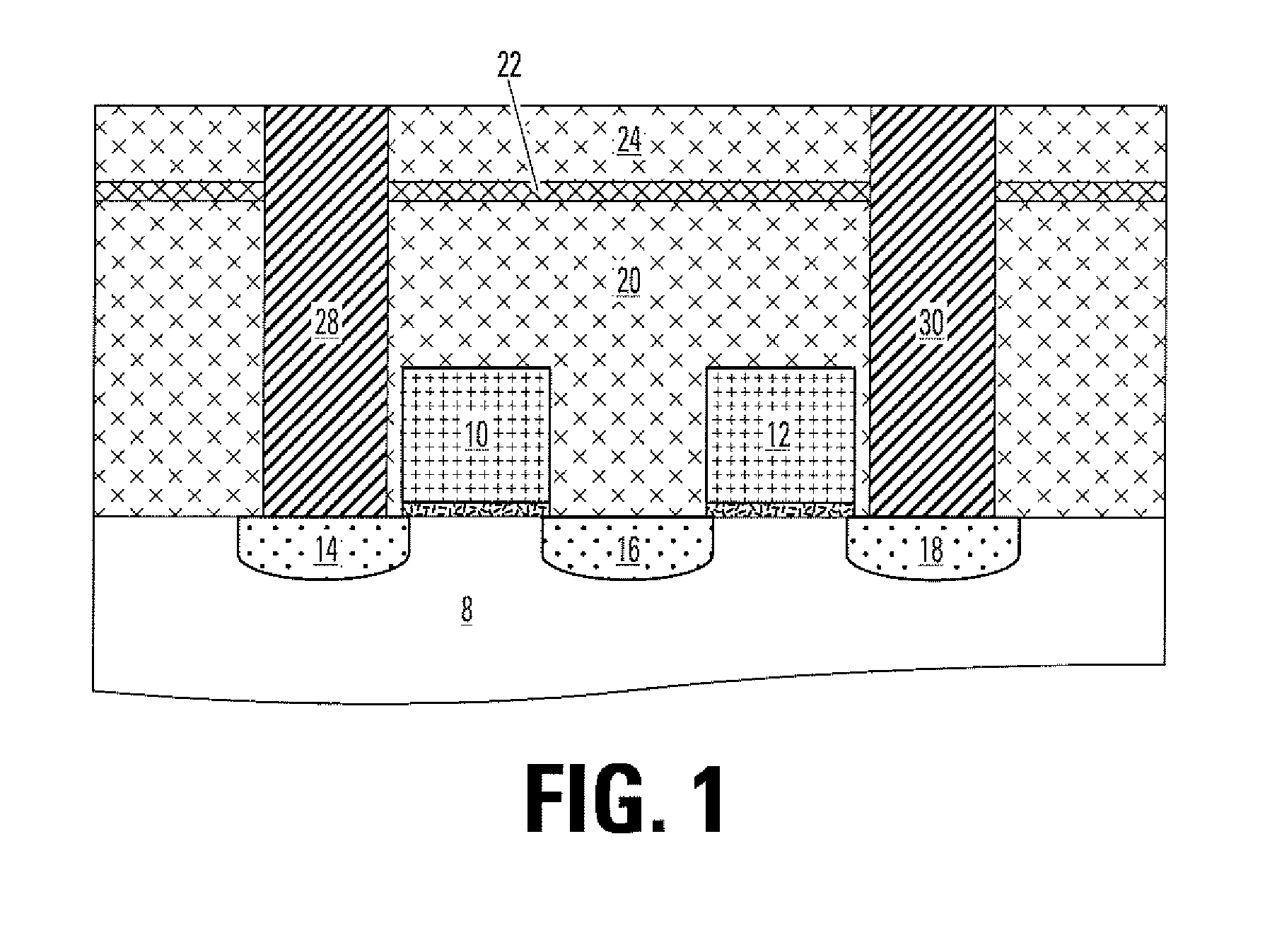

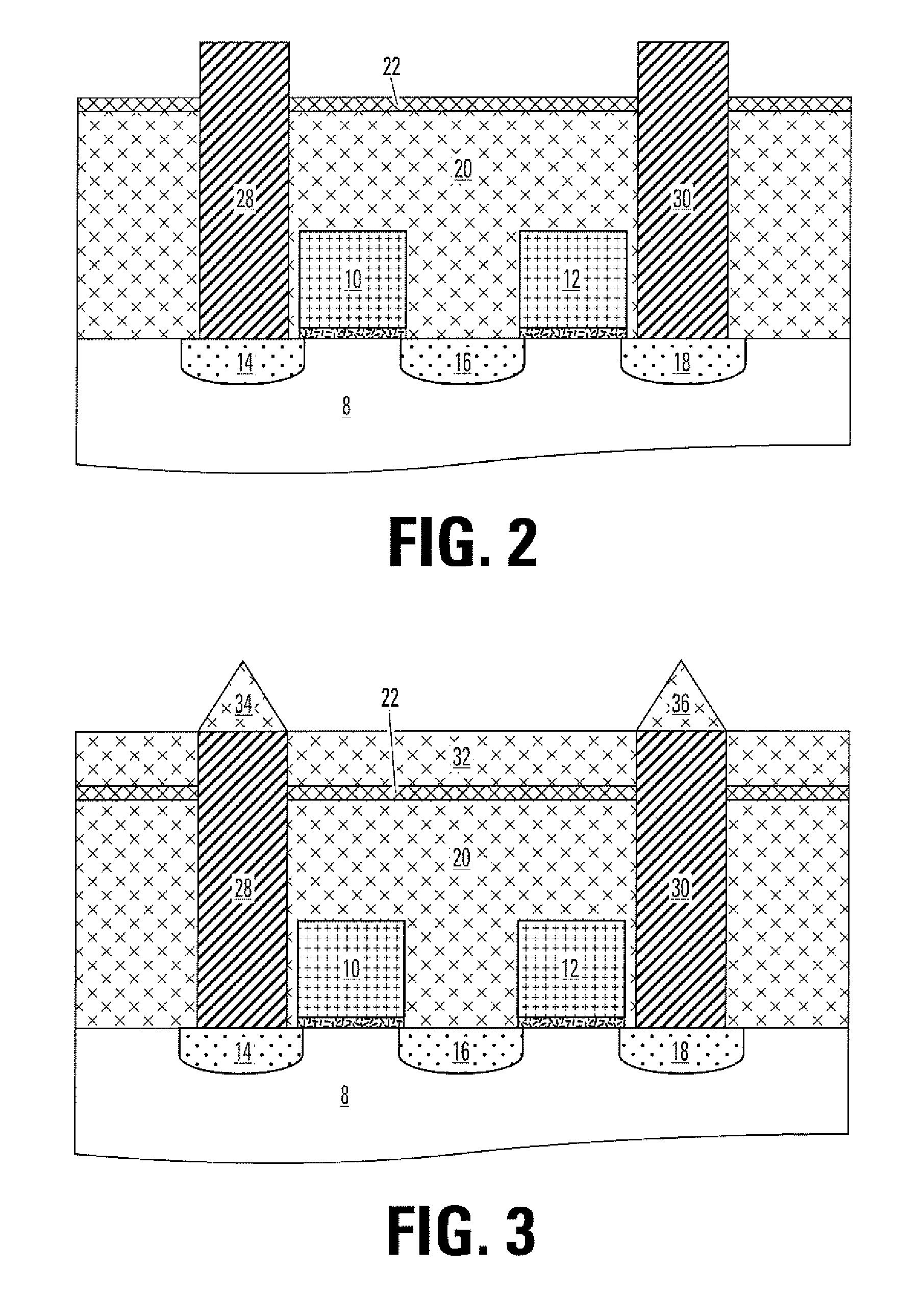

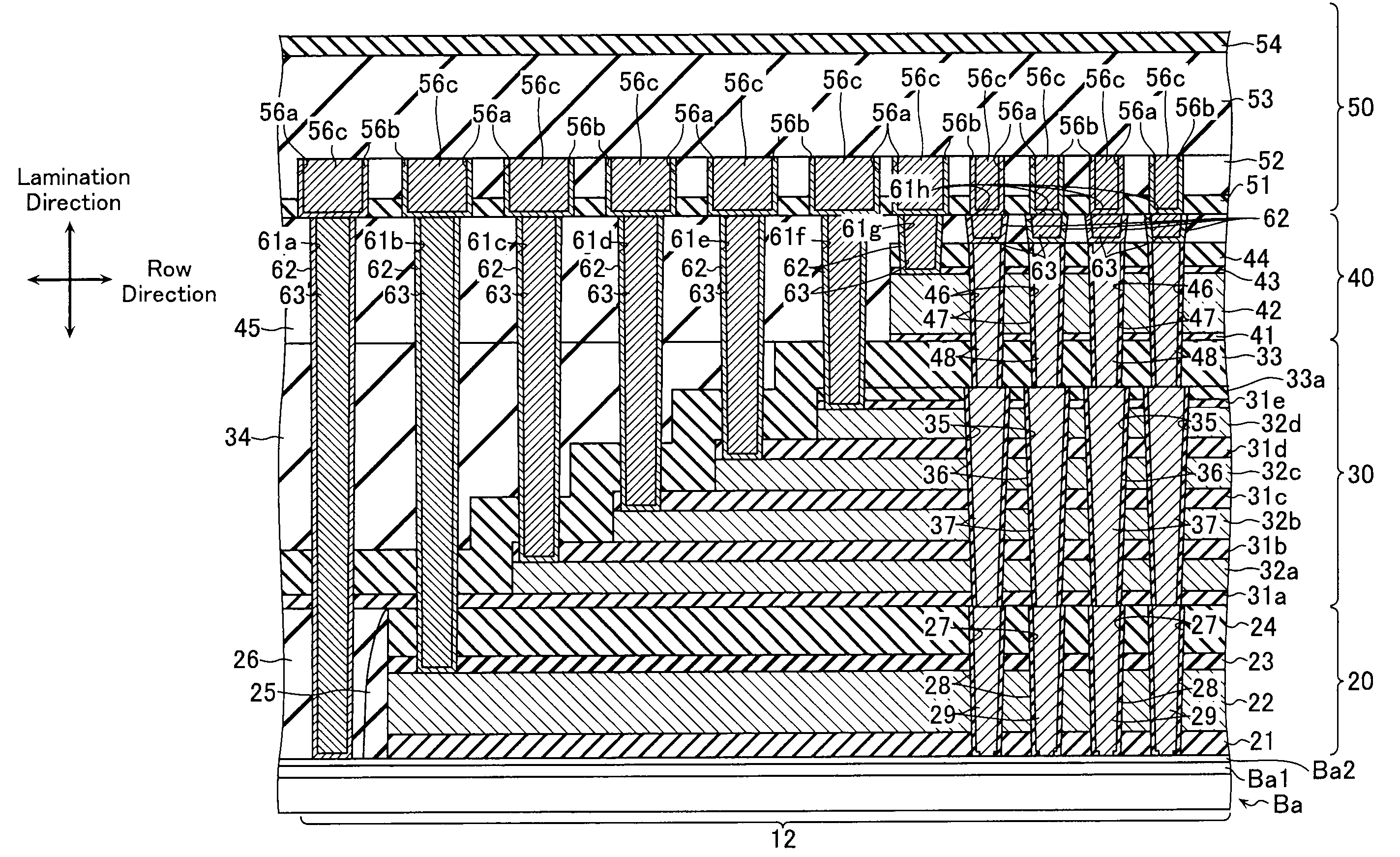

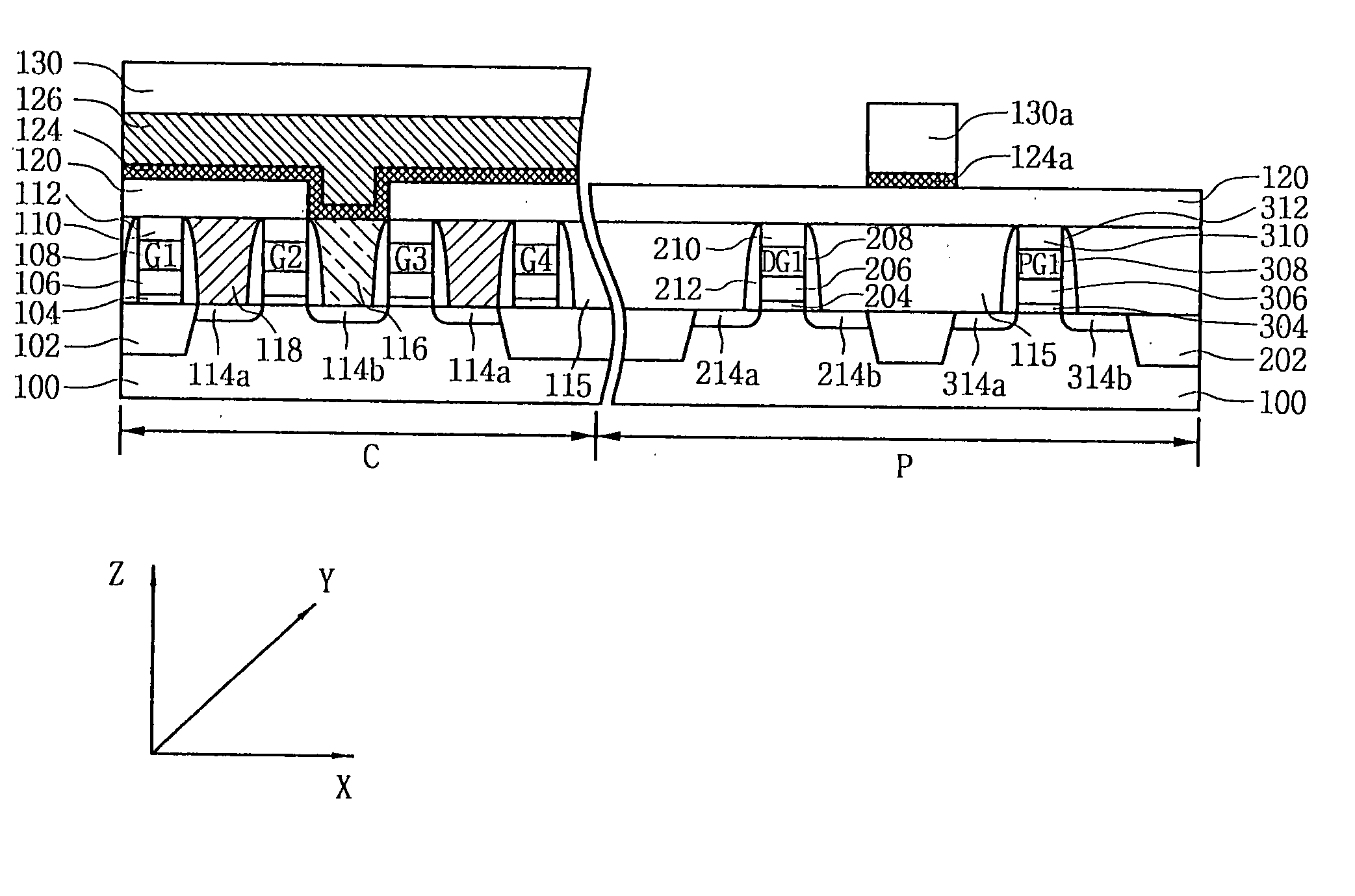

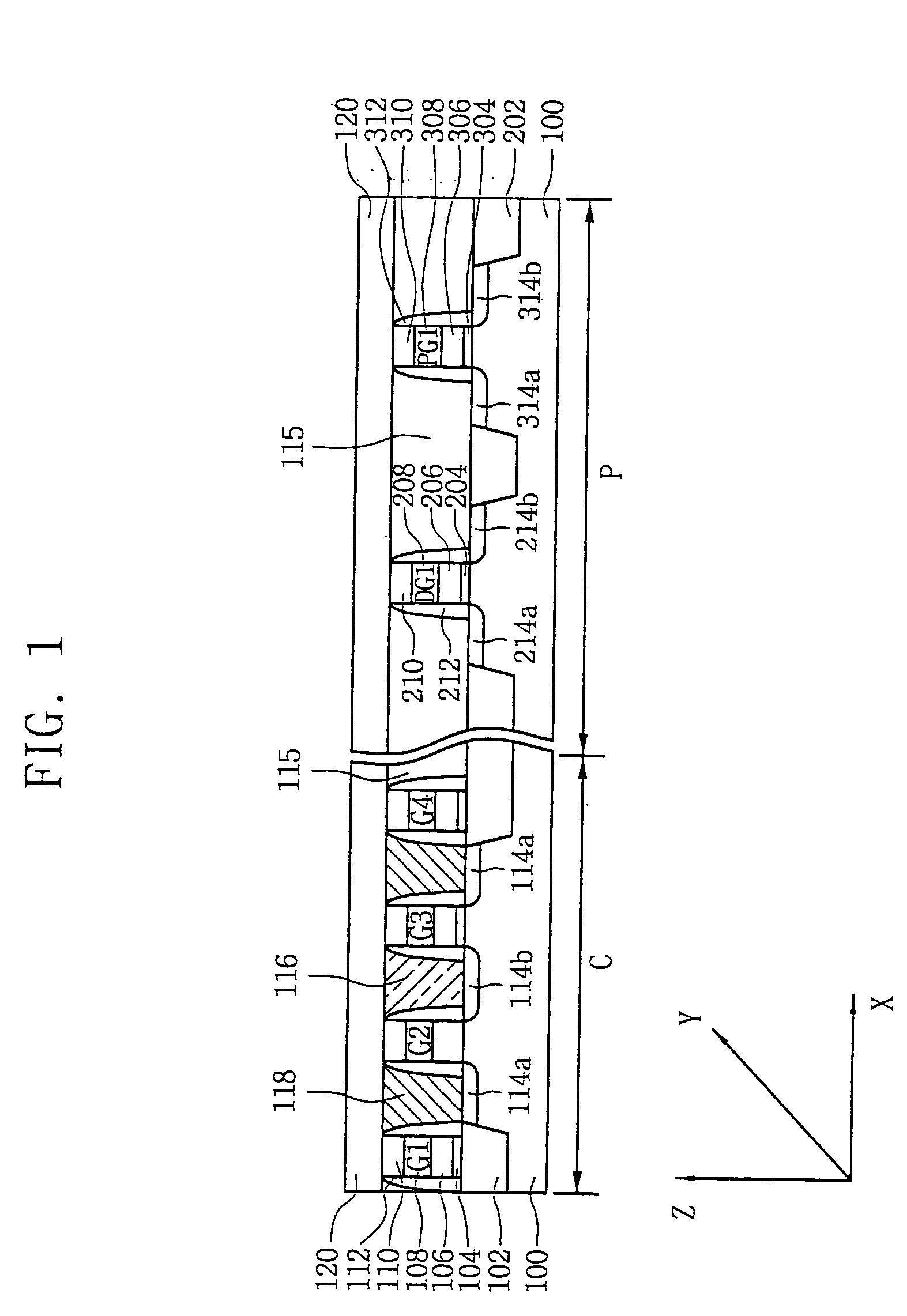

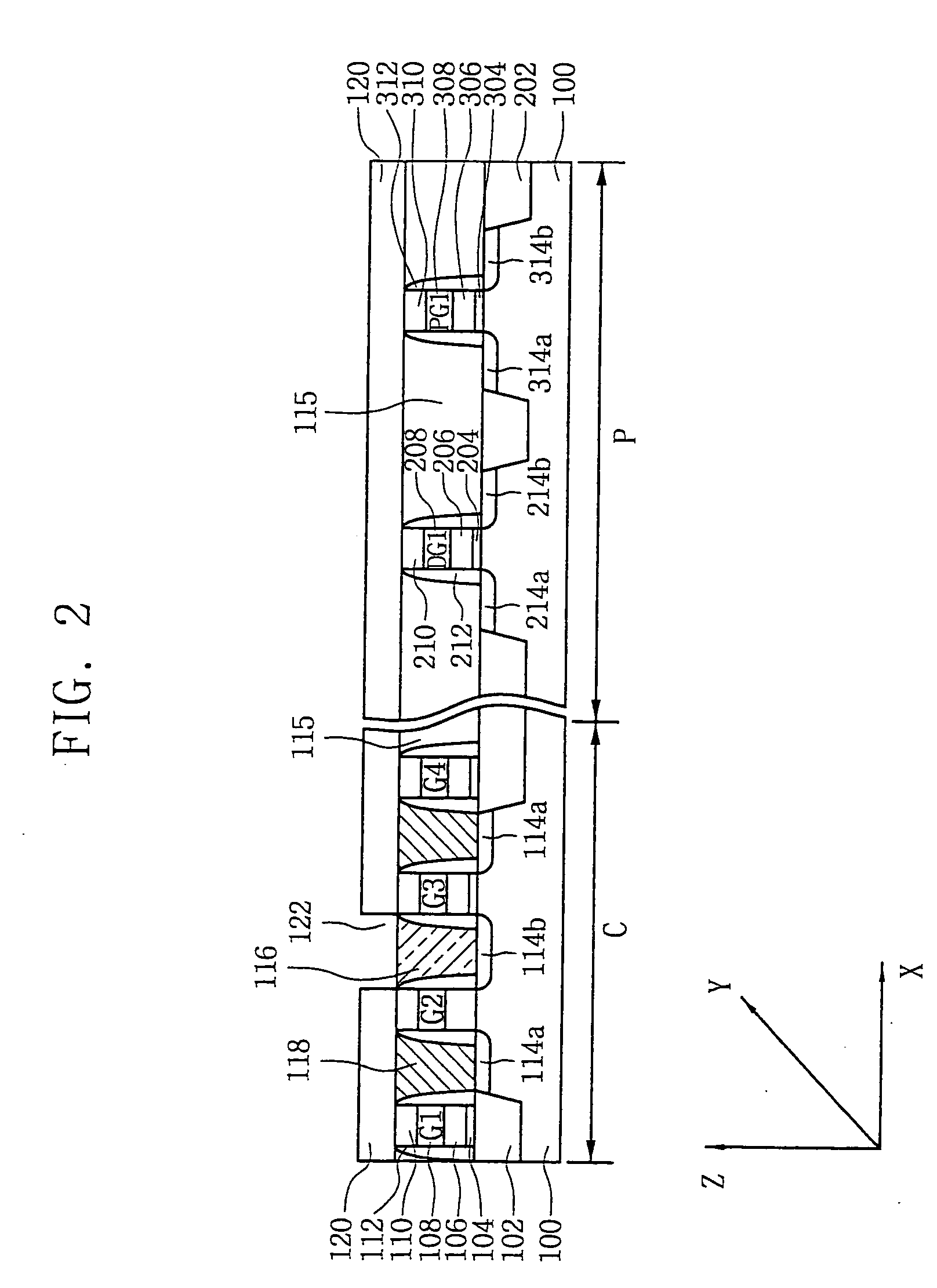

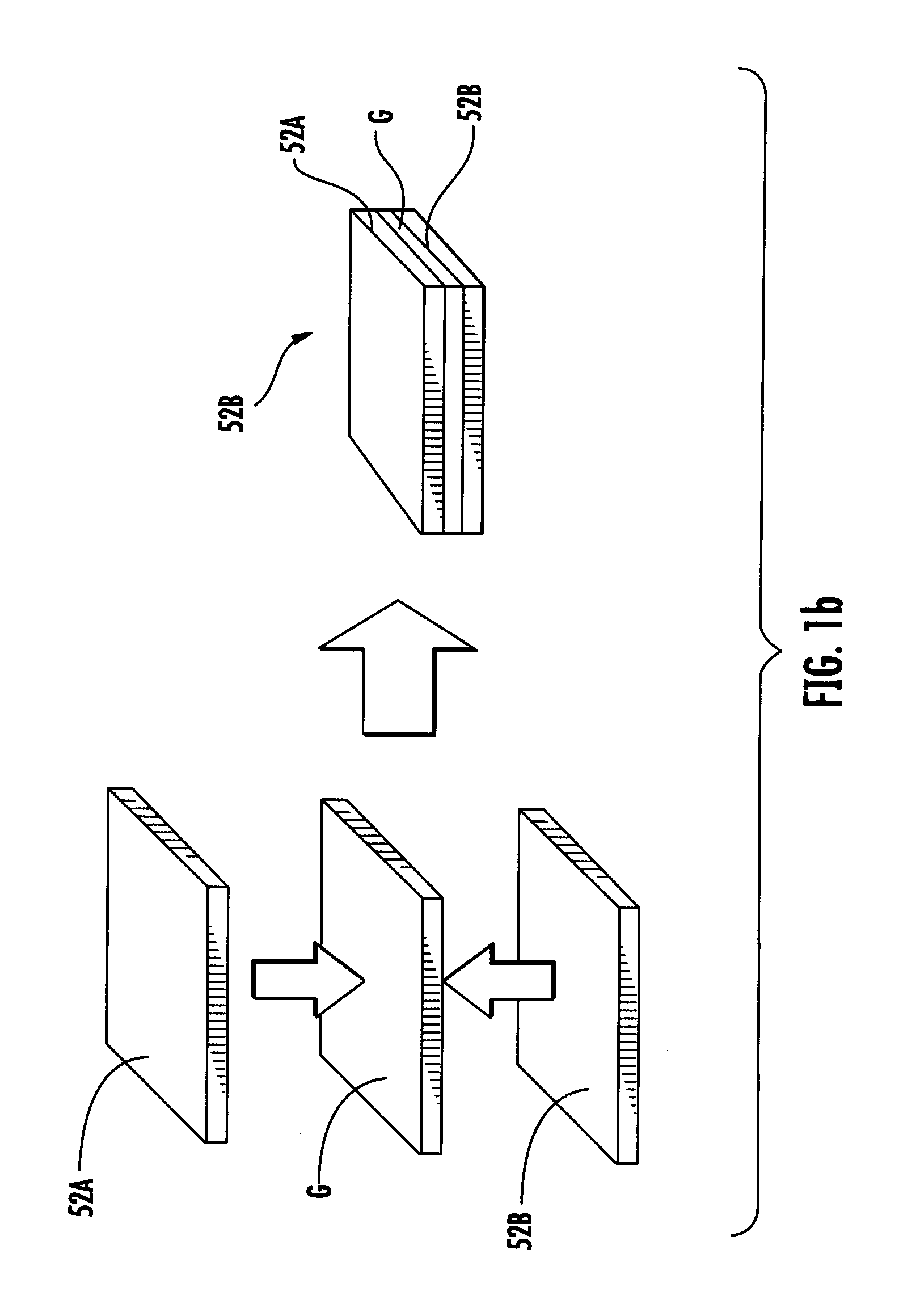

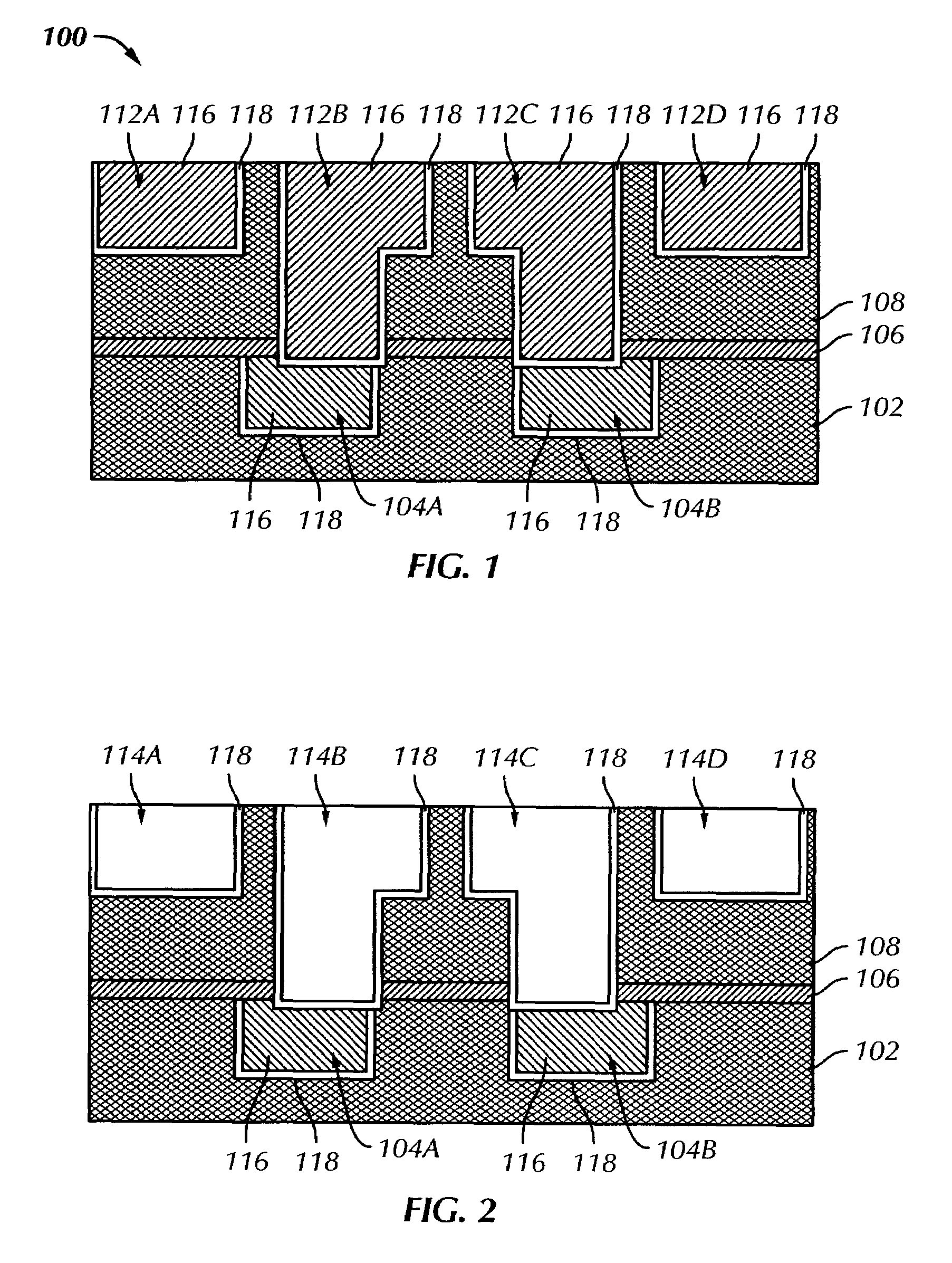

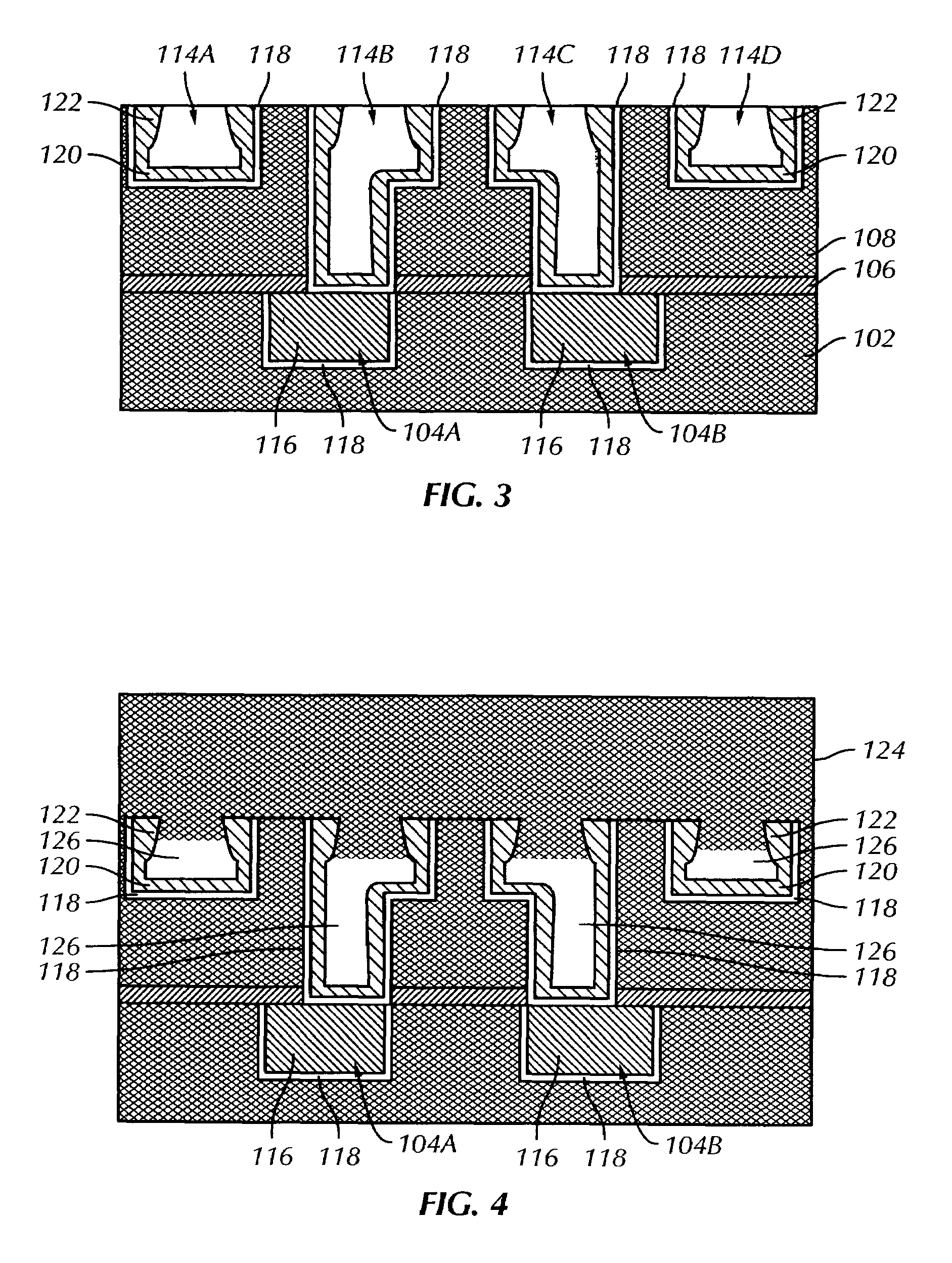

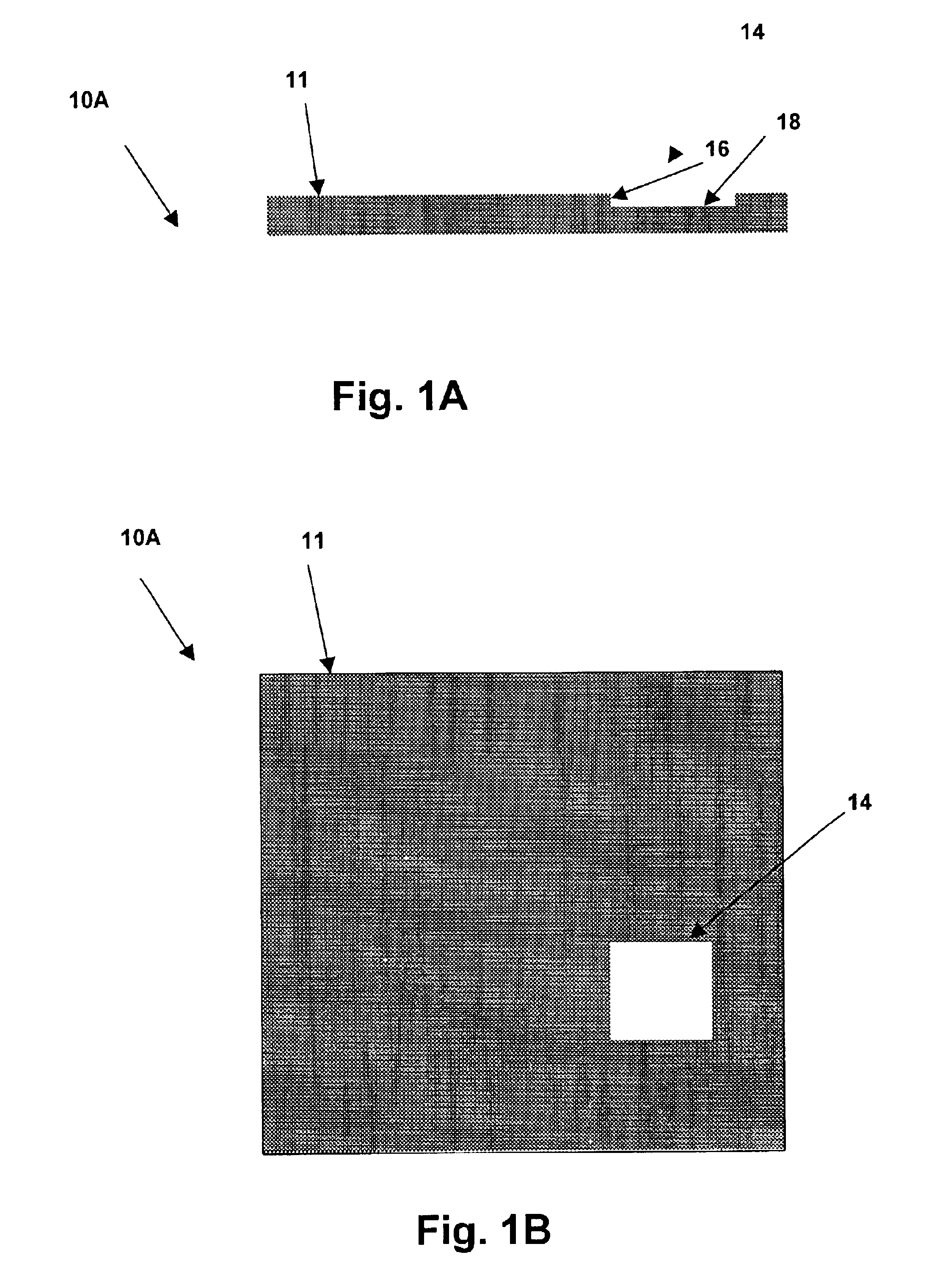

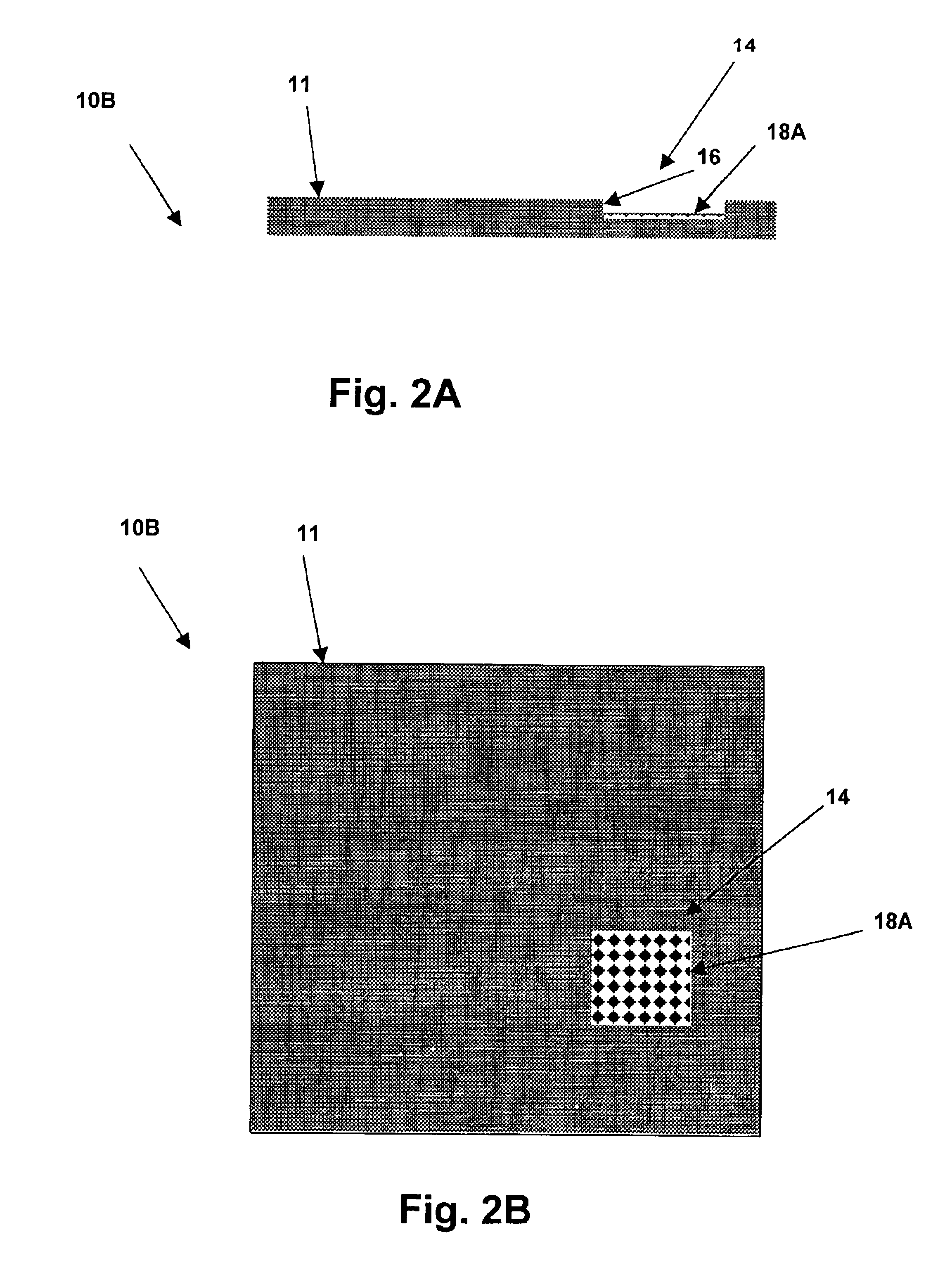

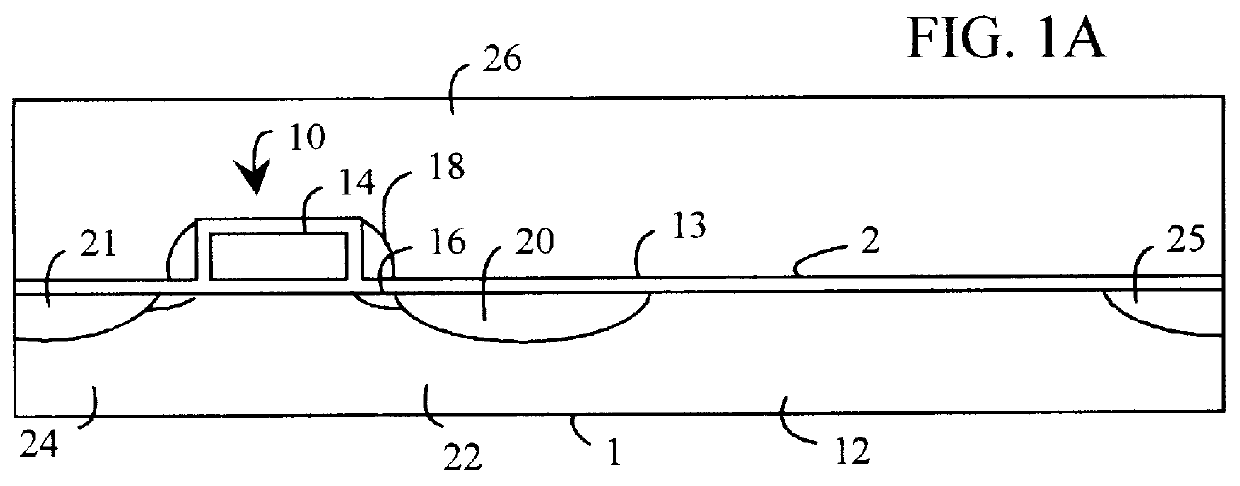

Methods for forming resistors for integrated circuit devices

ActiveUS20050095779A1Easy to manufactureReduce defectsTransistorSemiconductor/solid-state device detailsEngineeringIntegrated circuit

Methods of forming an integrated circuit device may include forming an insulating layer on an integrated circuit substrate, forming a first conductive layer on the insulating layer, and forming a second conductive layer on the first conductive layer so that the first conductive layer is between the second conductive layer and the insulating layer. Moreover, the first conductive layer may be a layer of a first material, the second conductive layer may be a layer of a second material, and the first and second materials may be different. A hole may be formed in the second conductive layer so that portions of the first conductive layer are exposed through the hole. After forming the hole in the second conductive layer, the first and second conductive layers may be patterned so that portions of the first and second conductive layers surrounding portions of the first conductive layer exposed through the hole are removed while maintaining portions of the first conductive layer previously exposed through the hole.

Owner:SAMSUNG ELECTRONICS CO LTD

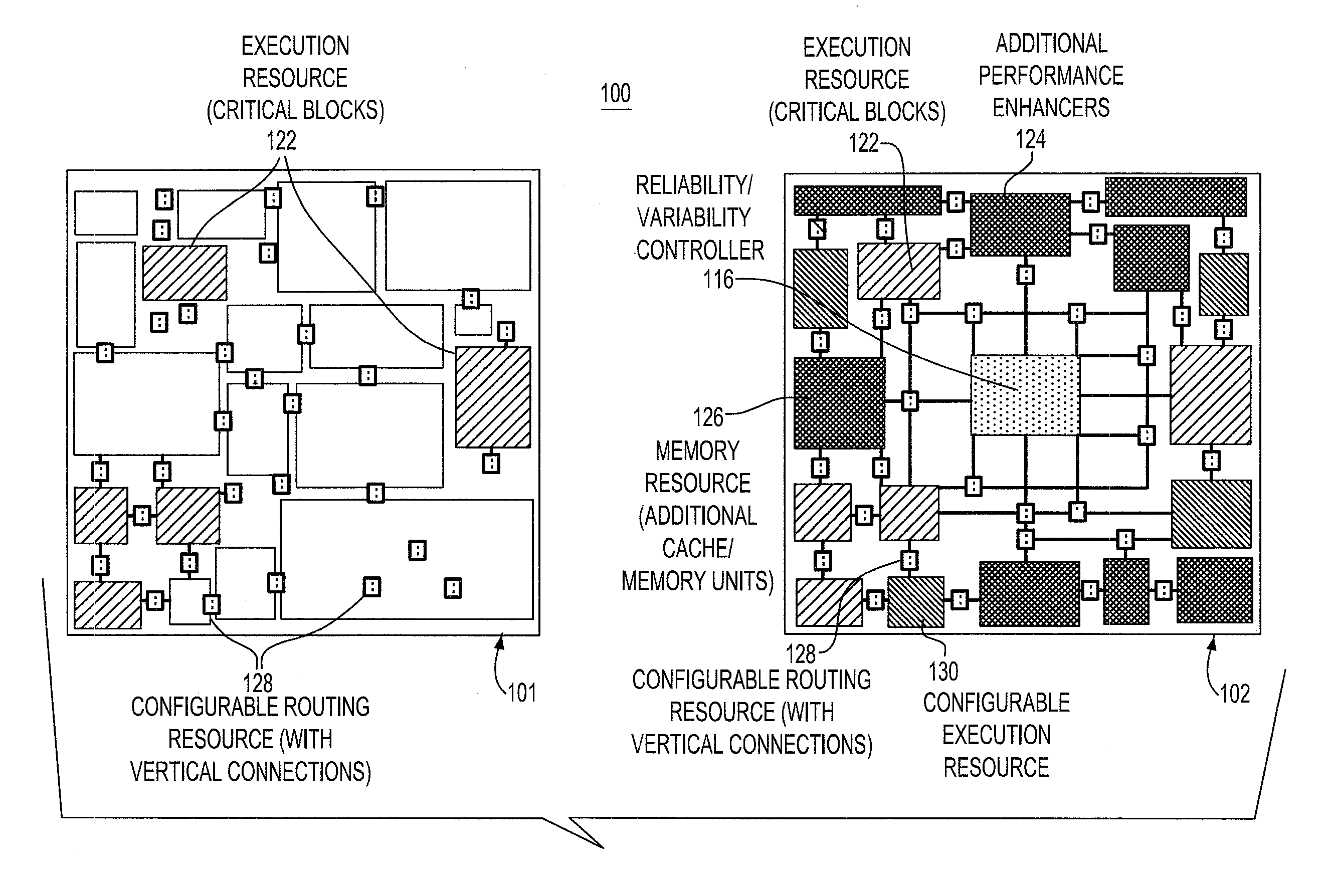

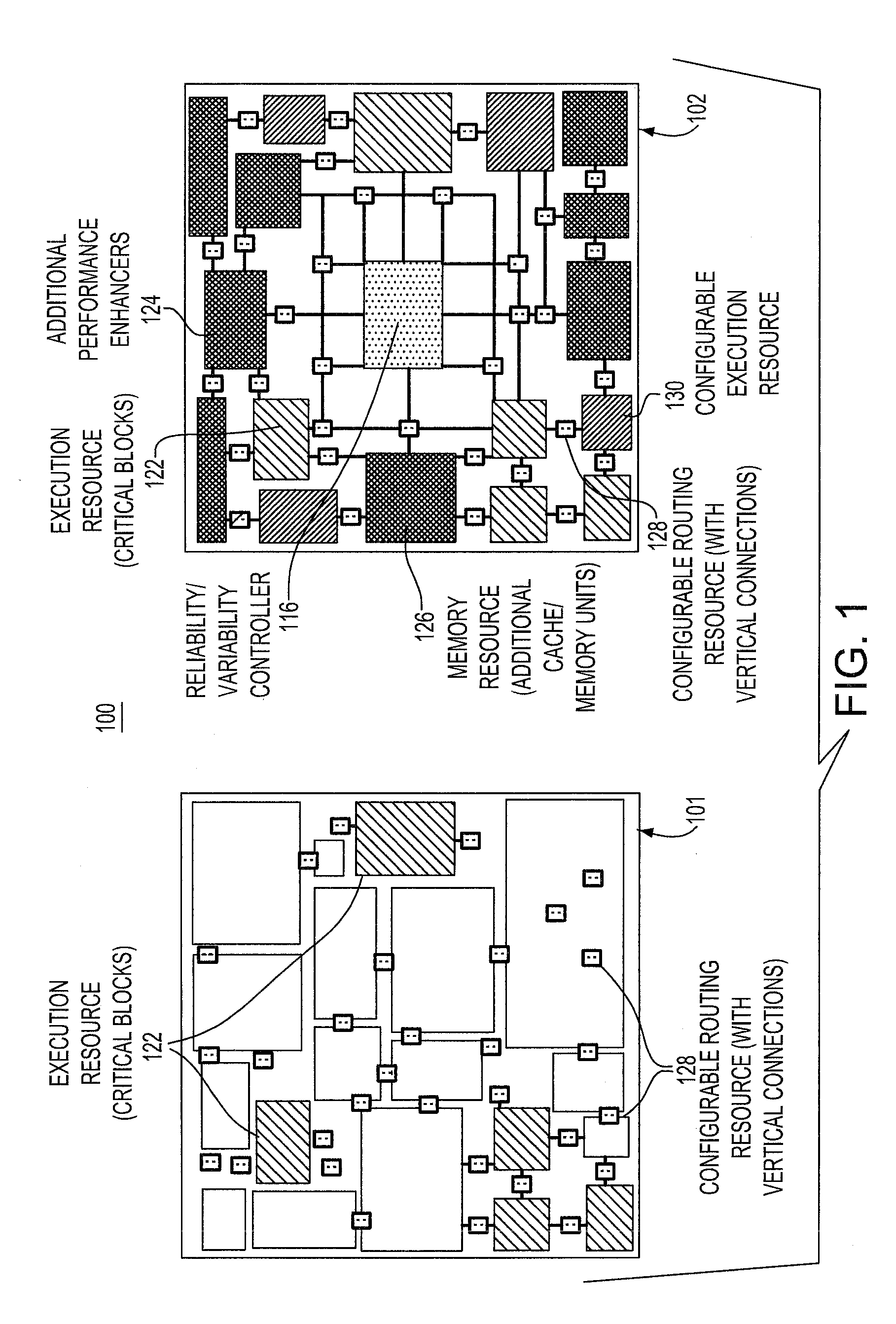

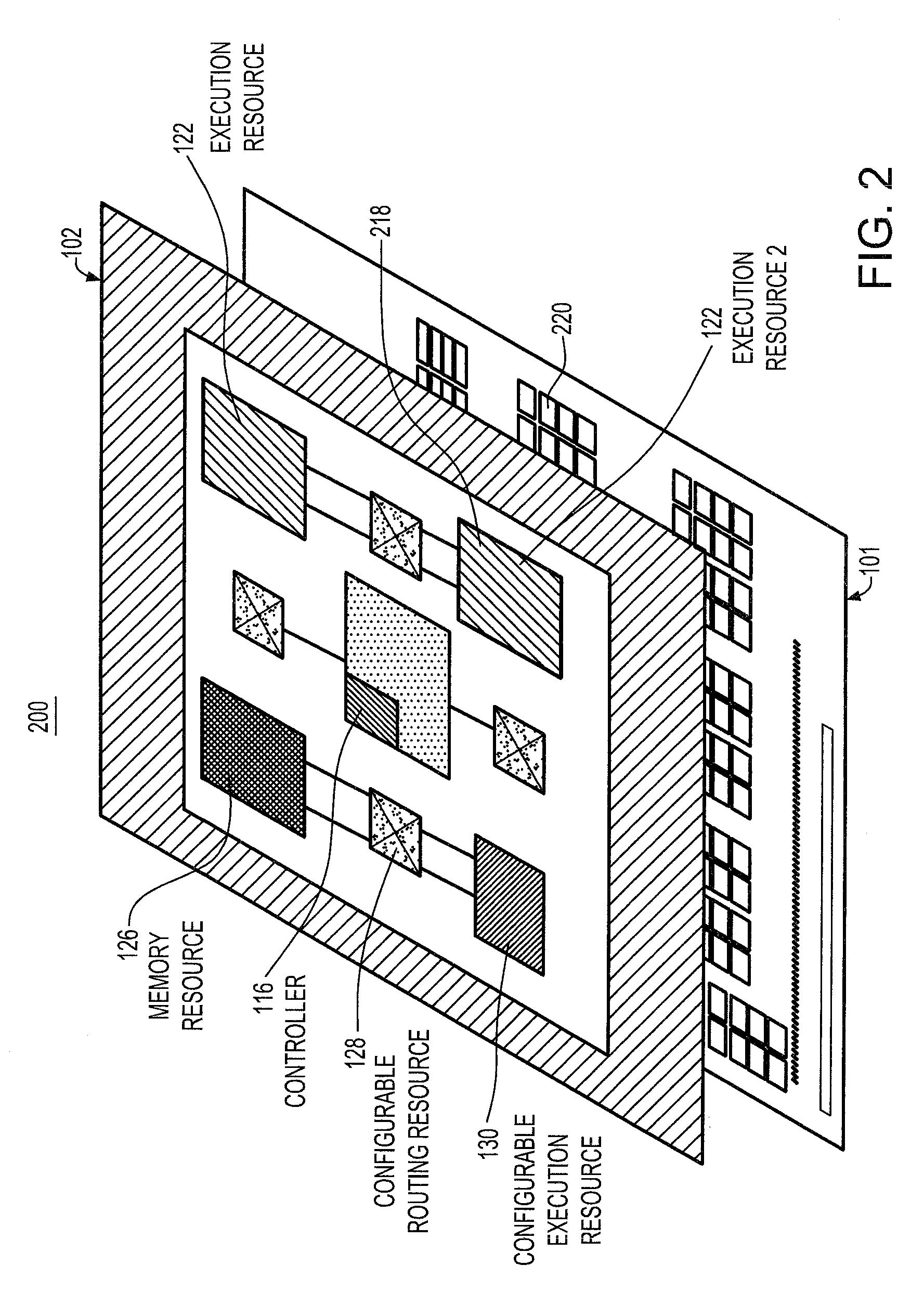

Method and arrangement for enhancing process variability and lifetime reliability through 3D integration

InactiveUS20090144669A1Improve lifetime reliabilityEnhancing process variabilitySolid-state devicesWork holdersSemiconductor chipDependability

A method of enhancing semiconductor chip process variability and lifetime reliability through a three-dimensional (3D) integration applied to electronic packaging. Also provided is an arrangement for implementing the inventive method.

Owner:IBM CORP

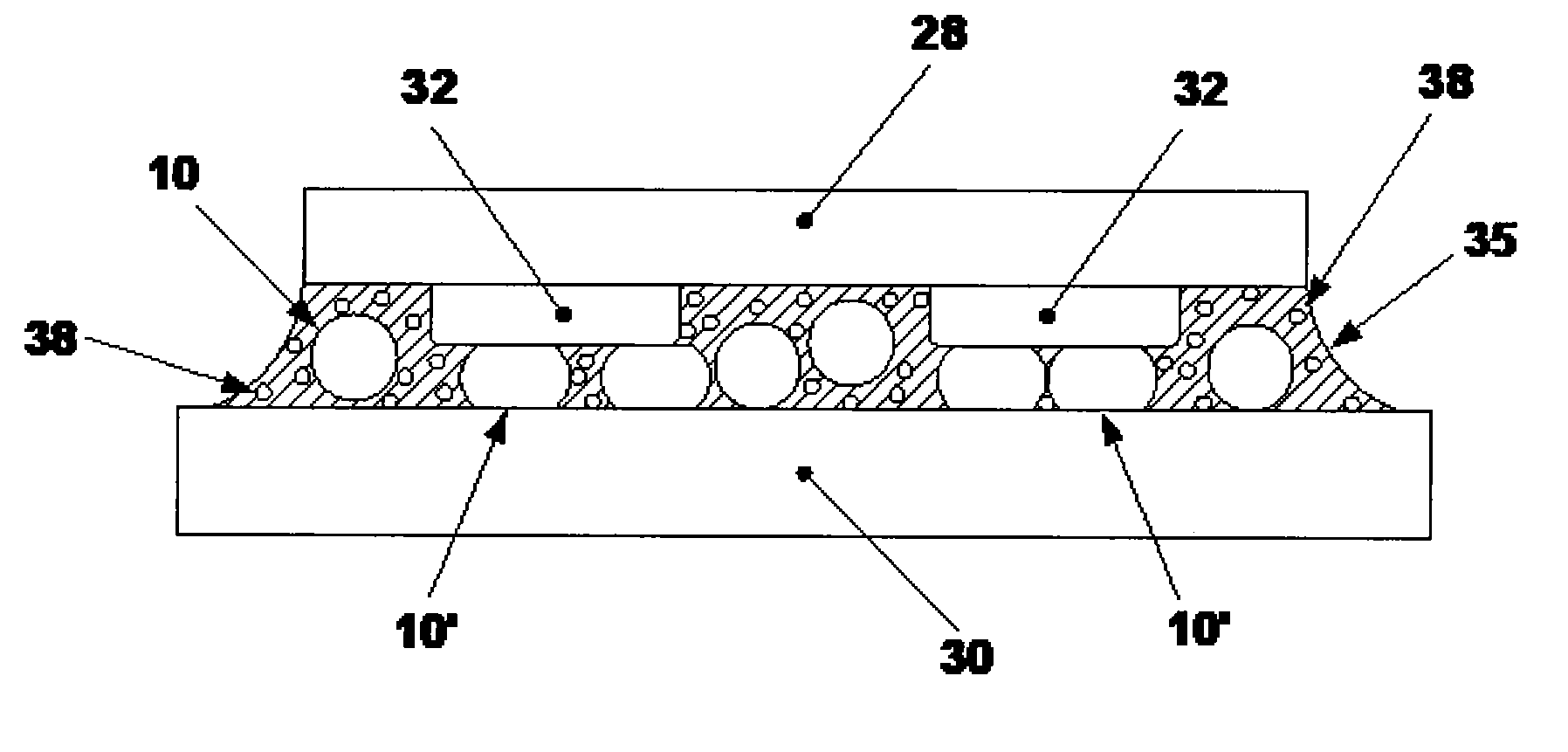

Adhesive bonding composition and method of use

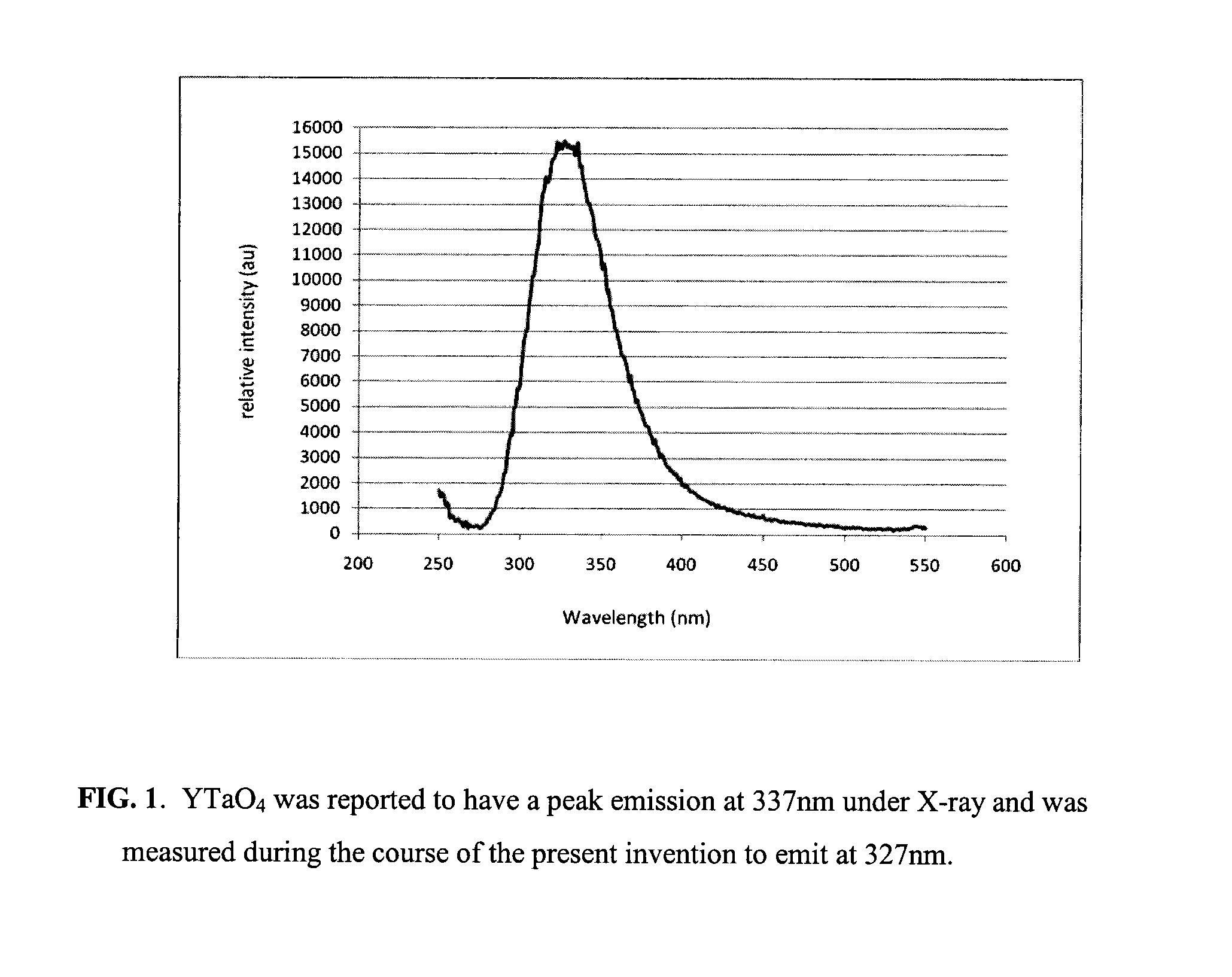

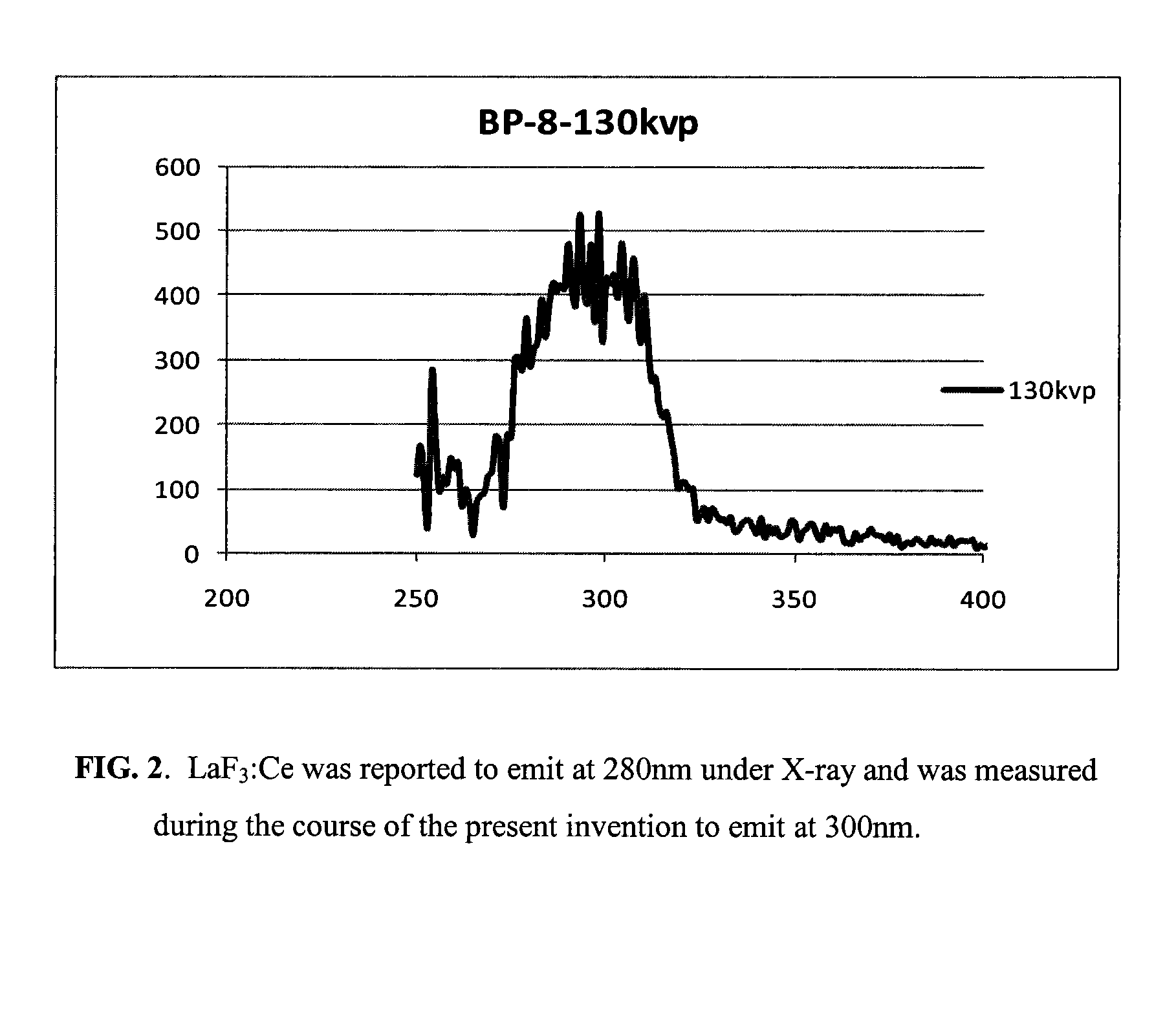

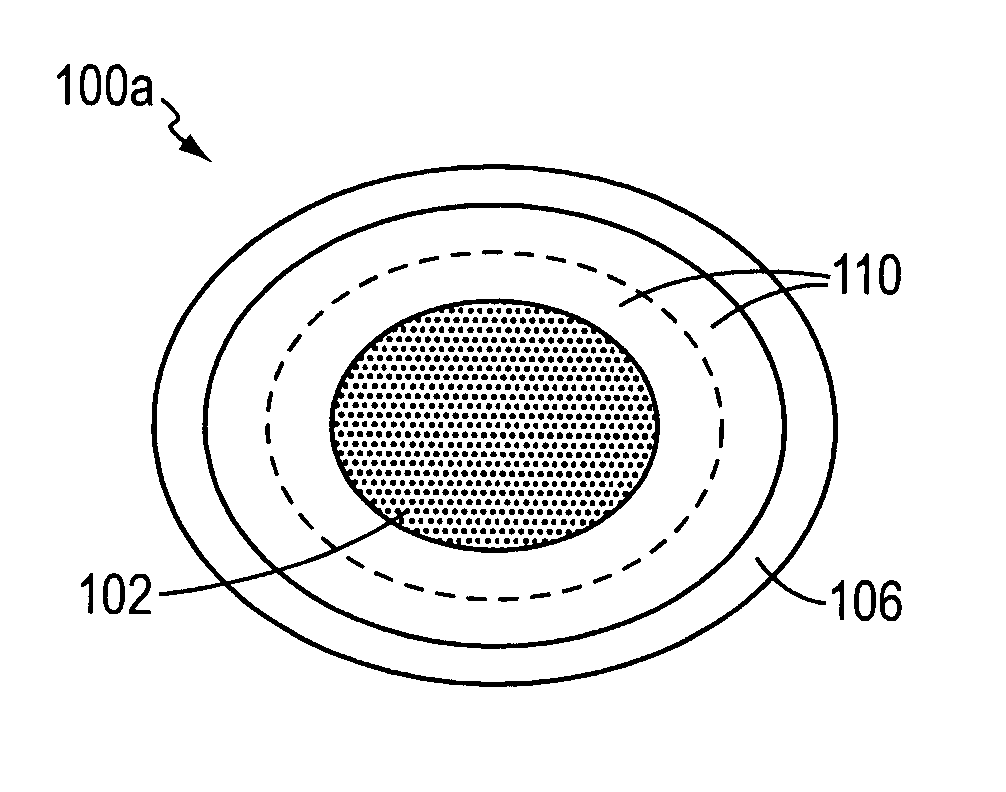

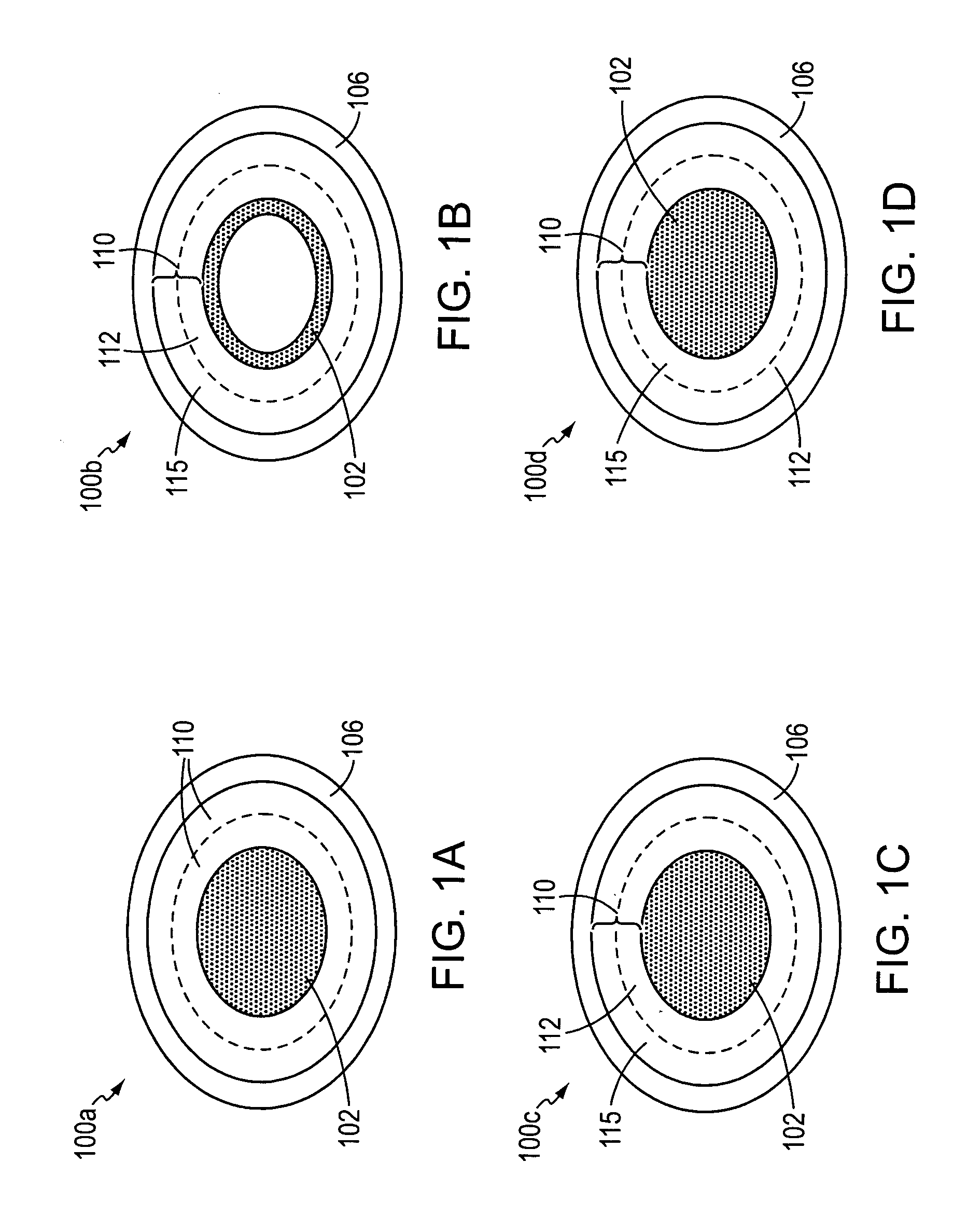

A polymerizable composition includes at least one monomer, a photoinitiator capable of initiating polymerization of the monomer when exposed to light, and a phosphor capable of producing light when exposed to radiation (typically X-rays). The material is particularly suitable for bonding components at ambient temperature in situations where the bond joint is not accessible to an external light source. An associated method includes: placing a polymerizable adhesive composition, including a photoinitiator and energy converting material, such as a down-converting phosphor, in contact with at least two components to be bonded to form an assembly; and, irradiating the assembly with radiation at a first wavelength, capable of conversion (down-conversion by the phosphor) to a second wavelength capable of activating the photoinitiator, to prepare items such as inkjet cartridges, wafer-to-wafer assemblies, semiconductors, integrated circuits, and the like.

Owner:IMMUNOLIGTHT LLC +1

Photovoltaic fibers

InactiveUS20050040374A1Easy to manufactureLight-sensitive devicesFinal product manufactureFiberCell fabrication

Owner:MERCK PATENT GMBH

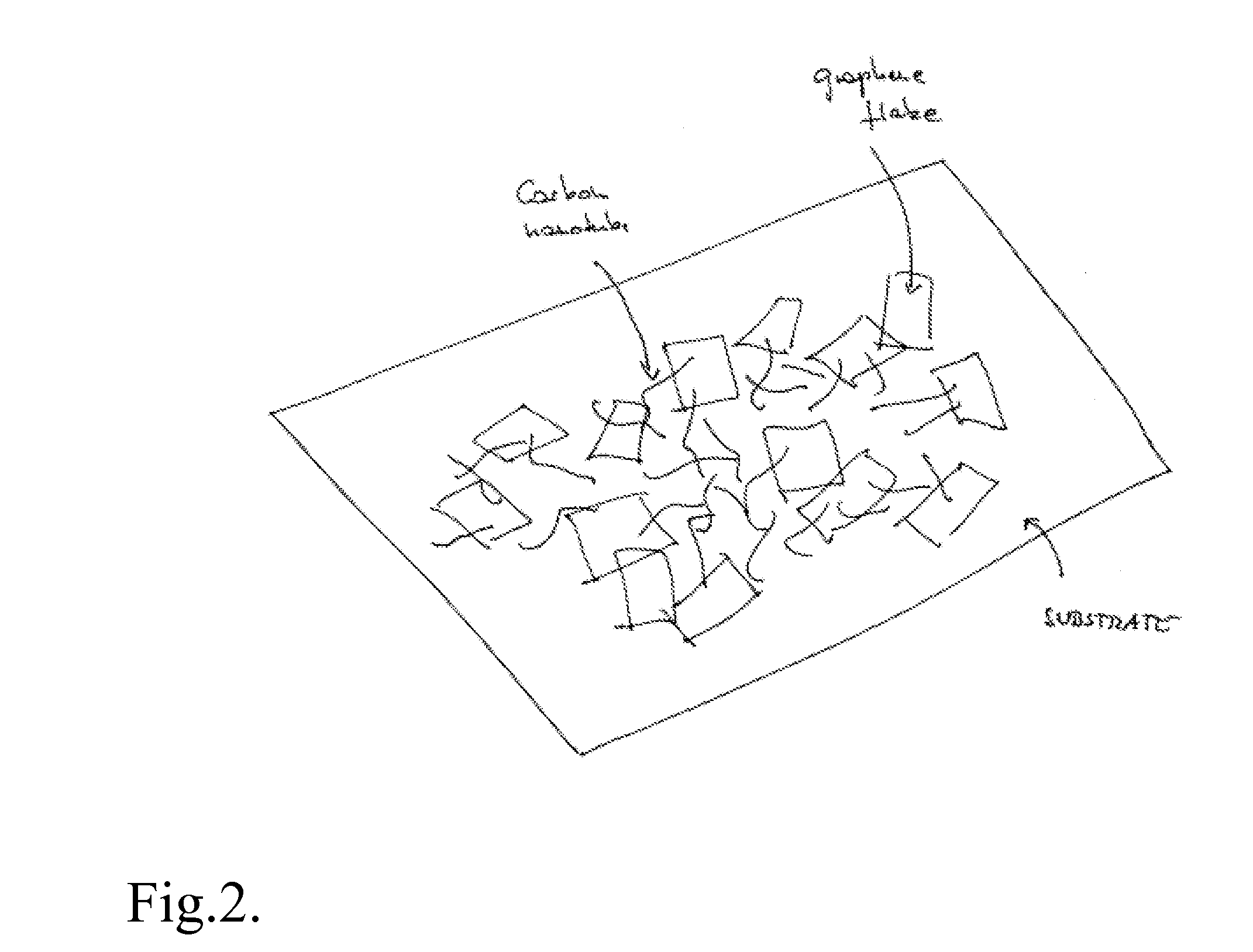

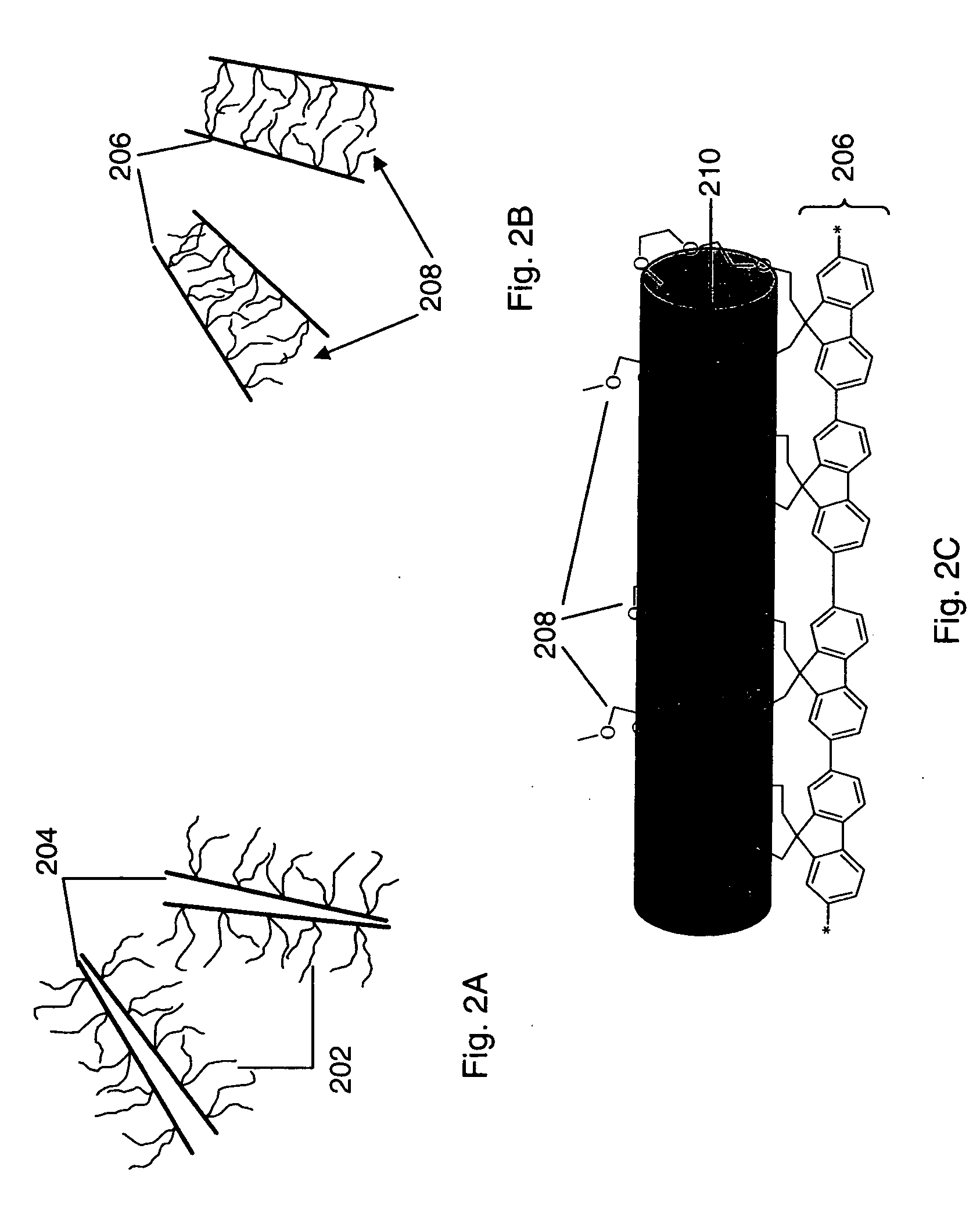

Carbon nanotube polymer composition and devices

A thin film device and compound having an anode, a cathode, and at least one light emitting layer between the anode and cathode, the at least one light emitting layer having at least one carbon nanotube and a conductive polymer.

Owner:RGT UNIV OF CALIFORNIA

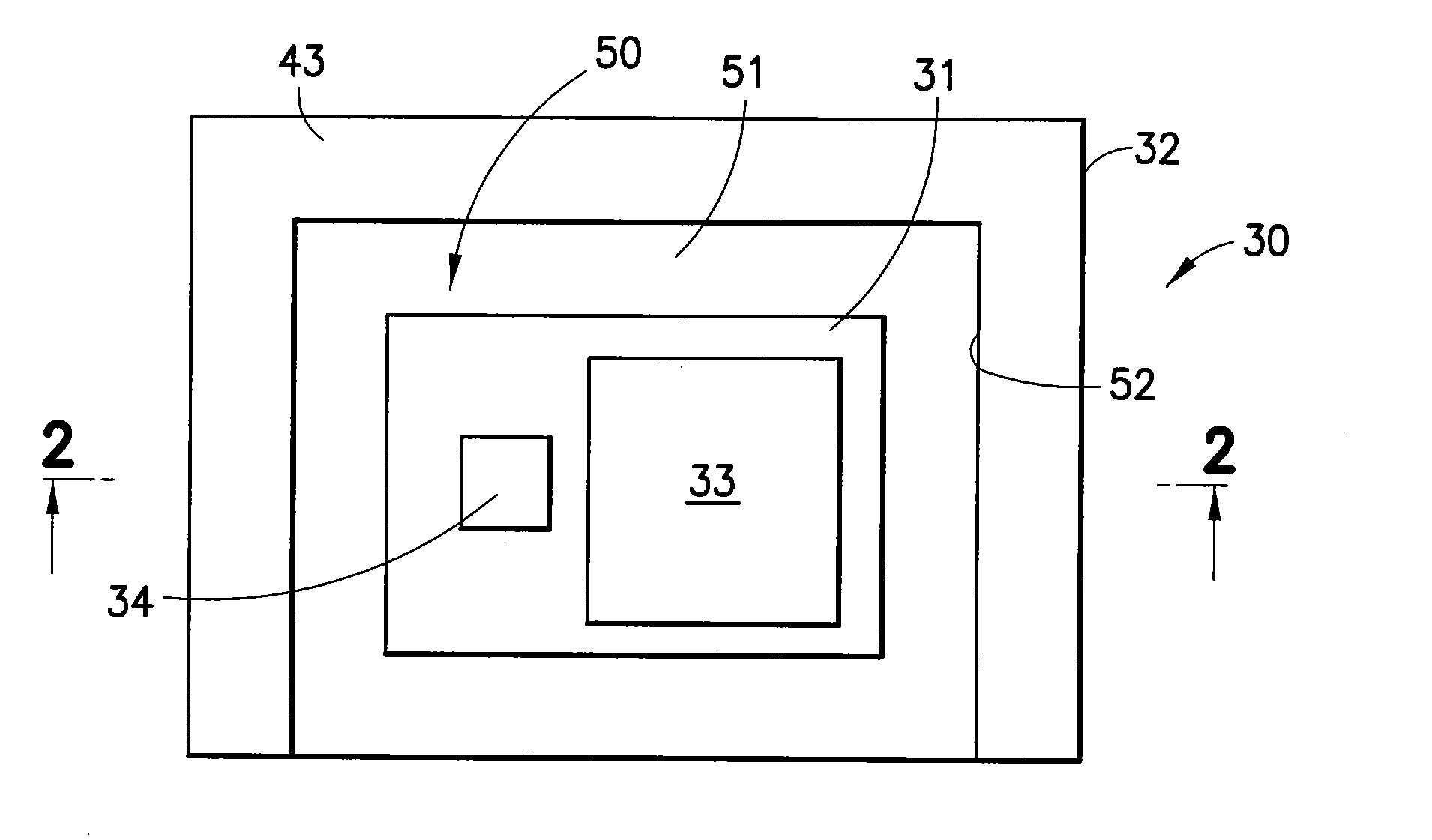

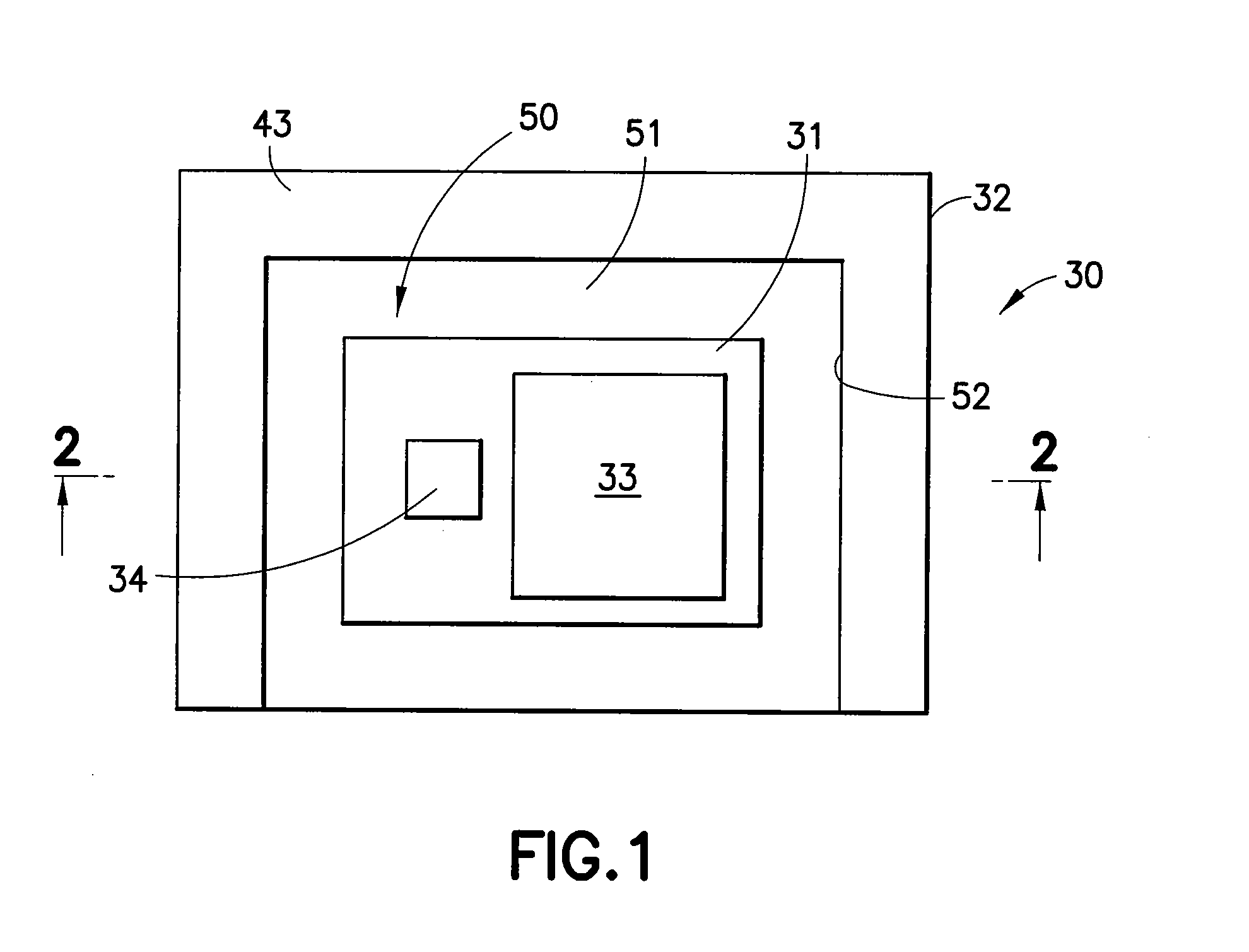

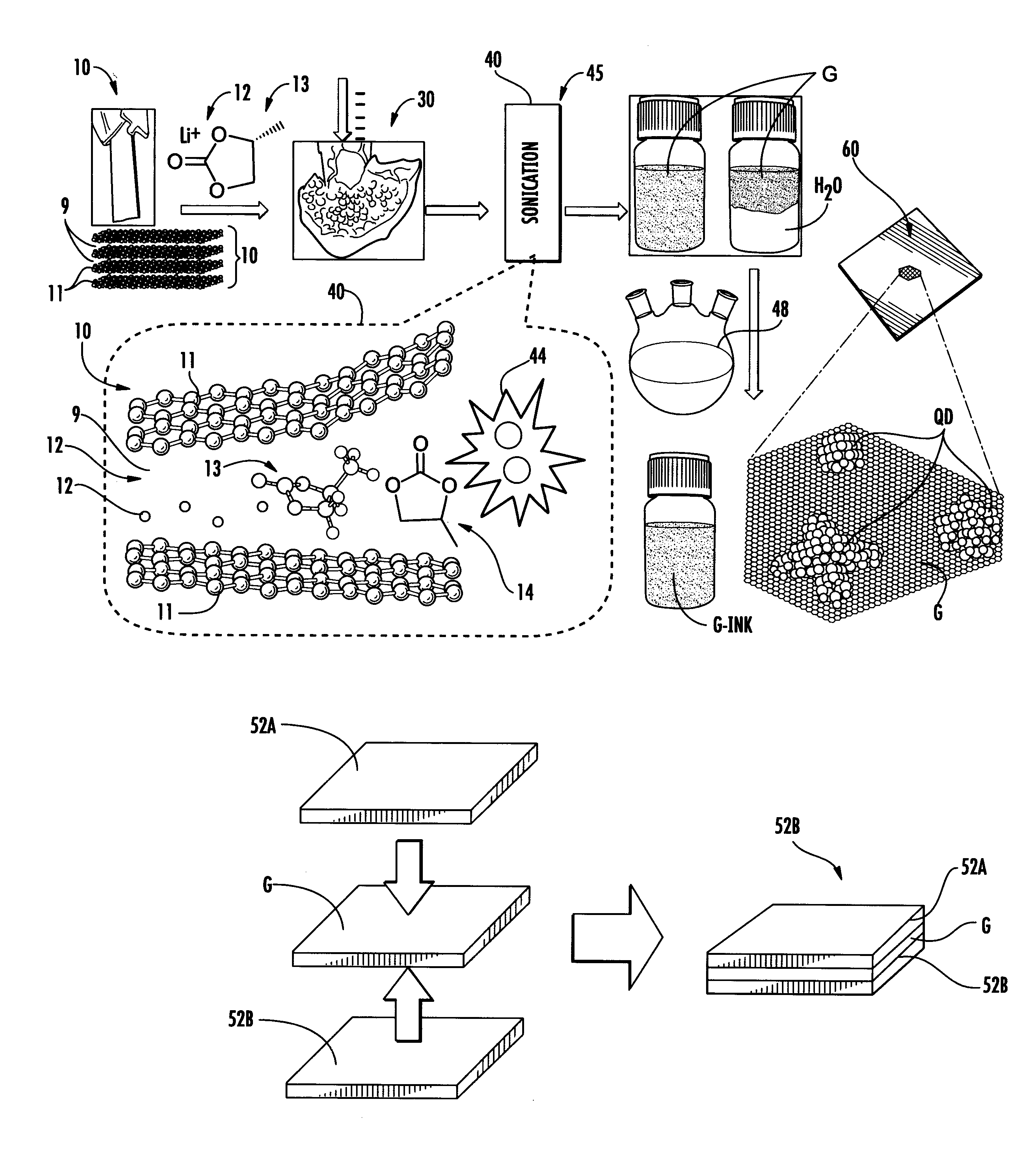

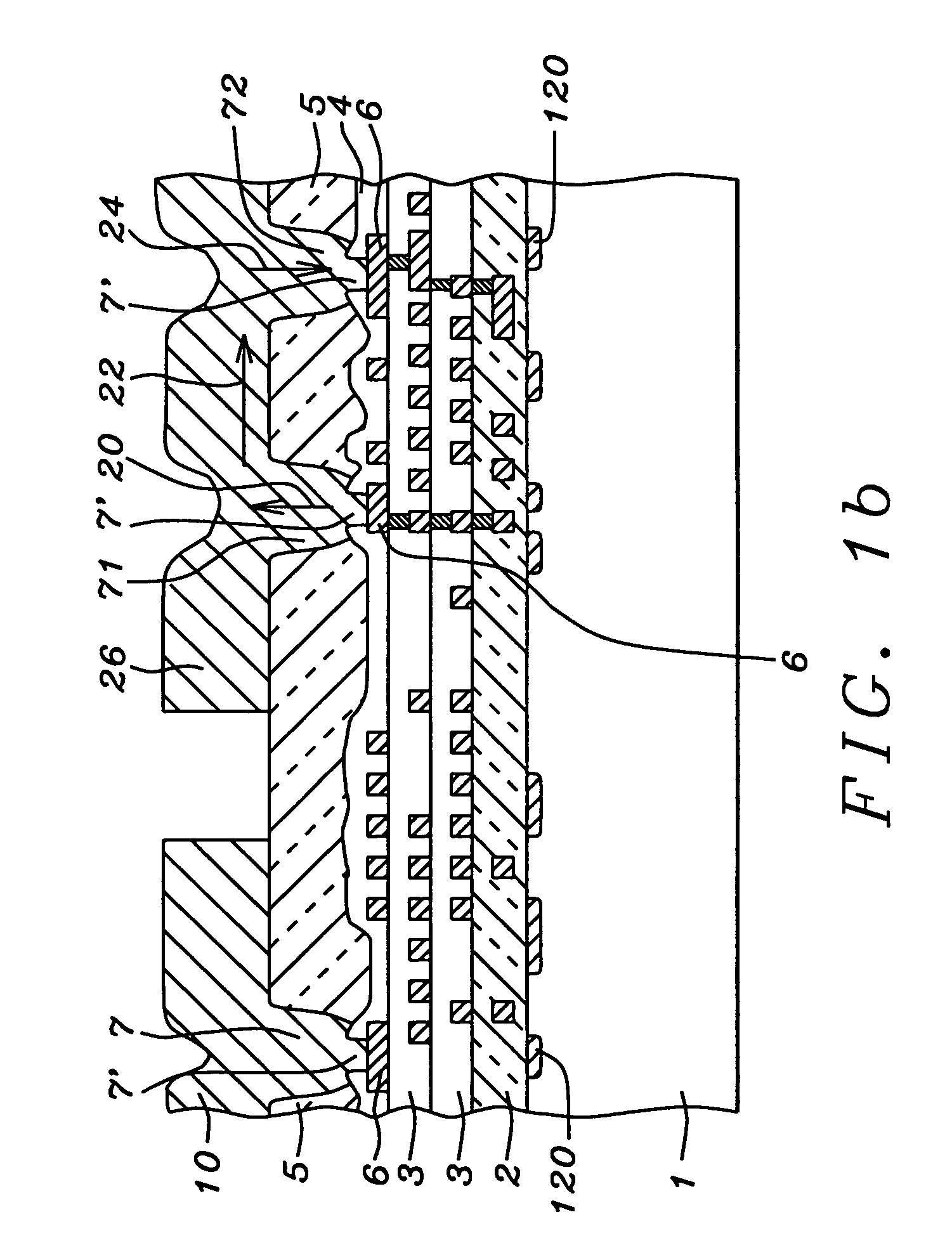

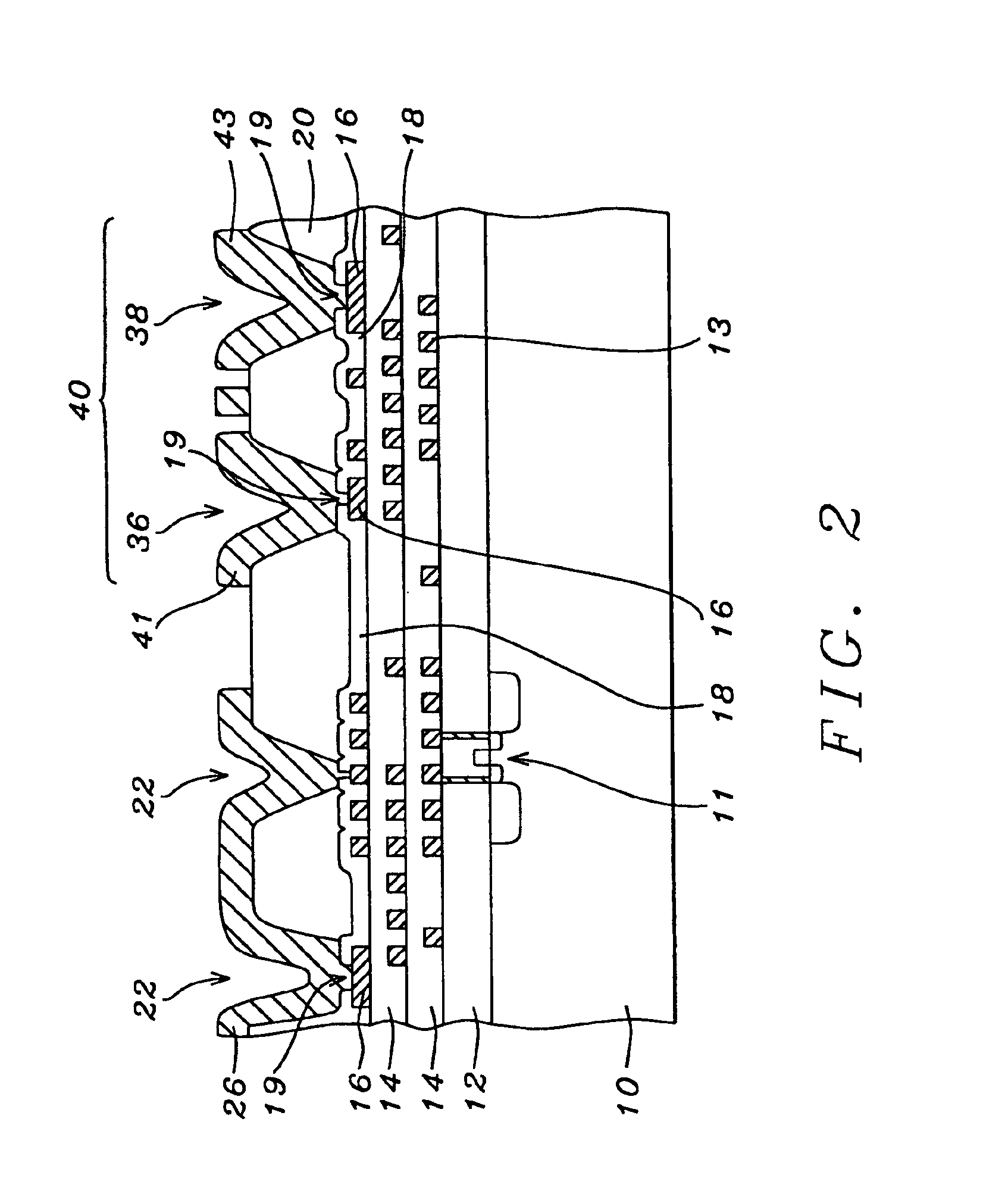

Package for high power density devices

ActiveUS20070138651A1Improve reliabilityIncrease flexibilitySemiconductor/solid-state device detailsSolid-state devicesDBcInsulation layer

A semiconductor device package is formed of DBC in which thinned MOSgated and / or diode die are soldered to the bottom of an etched depression in the upper conductive layer. A via in the insulation layer of the DBC is filled with a conductive material to form a resistive shunt. Plural packages may be formed in a DBC card and may be separated individually or in clusters. The individual packages are mounted in various arrays on a support DBC board and heat sink. Integrated circuits may be mounted on the assembly and connected to the die for control of the die conduction.

Owner:INFINEON TECH AMERICAS CORP

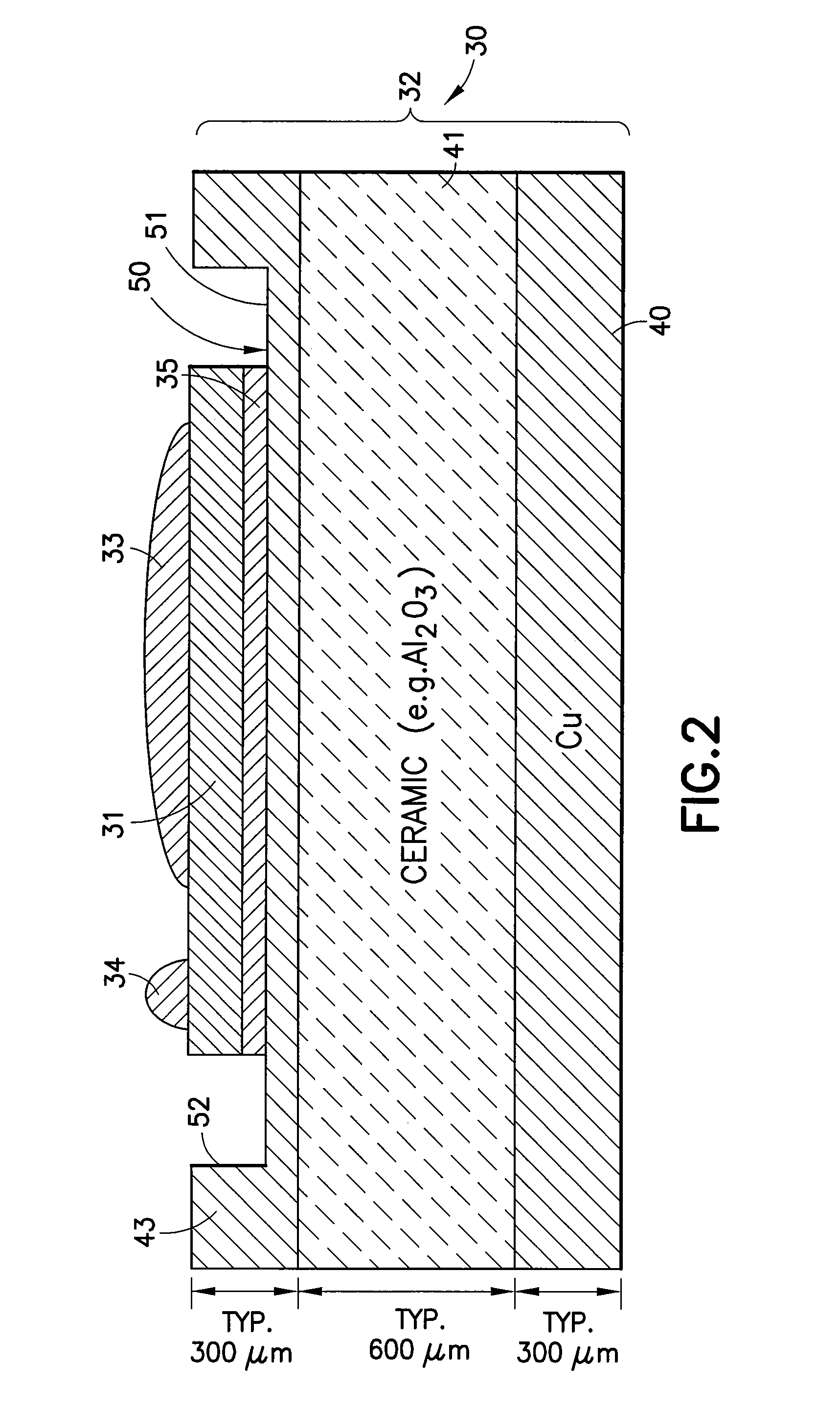

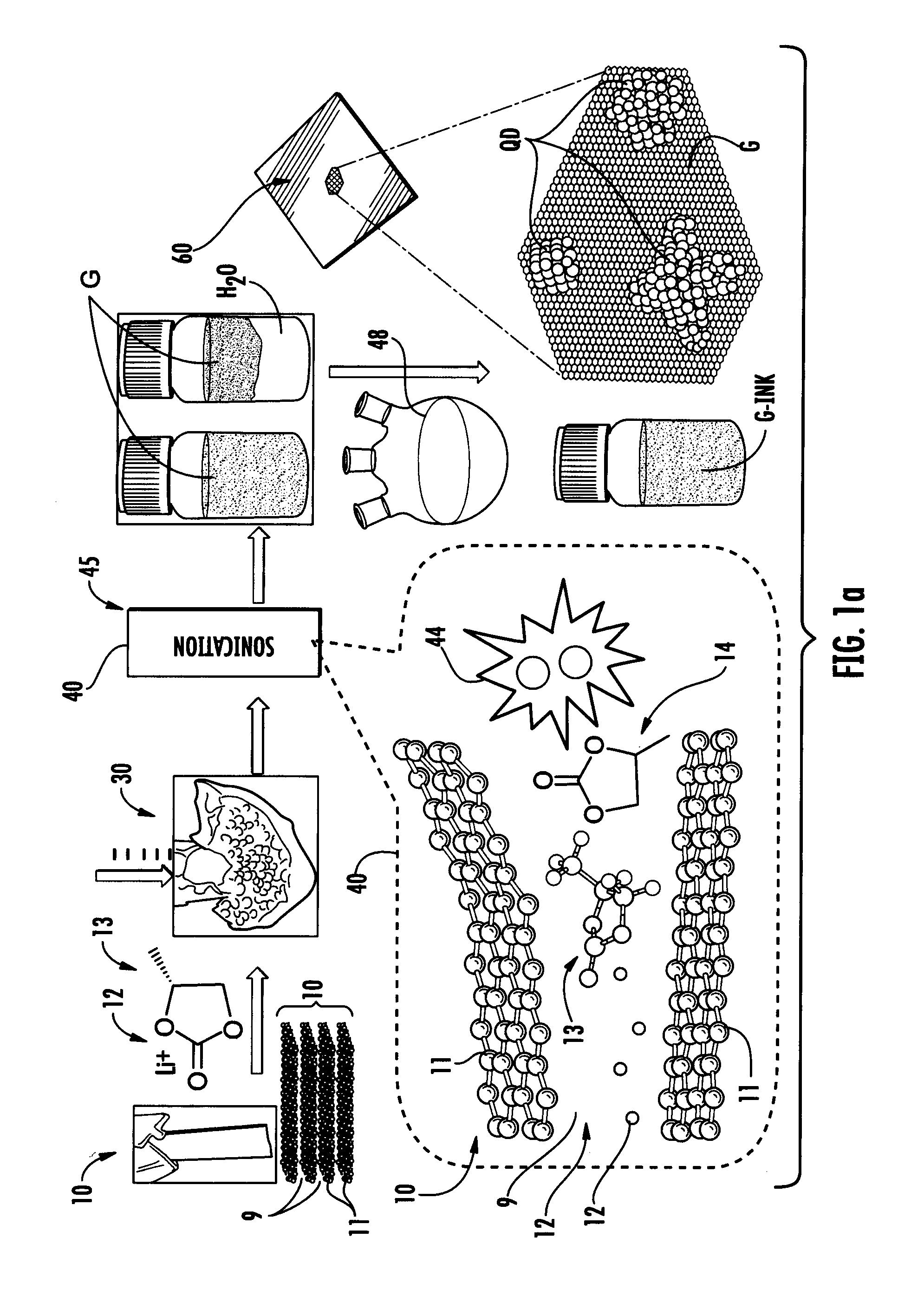

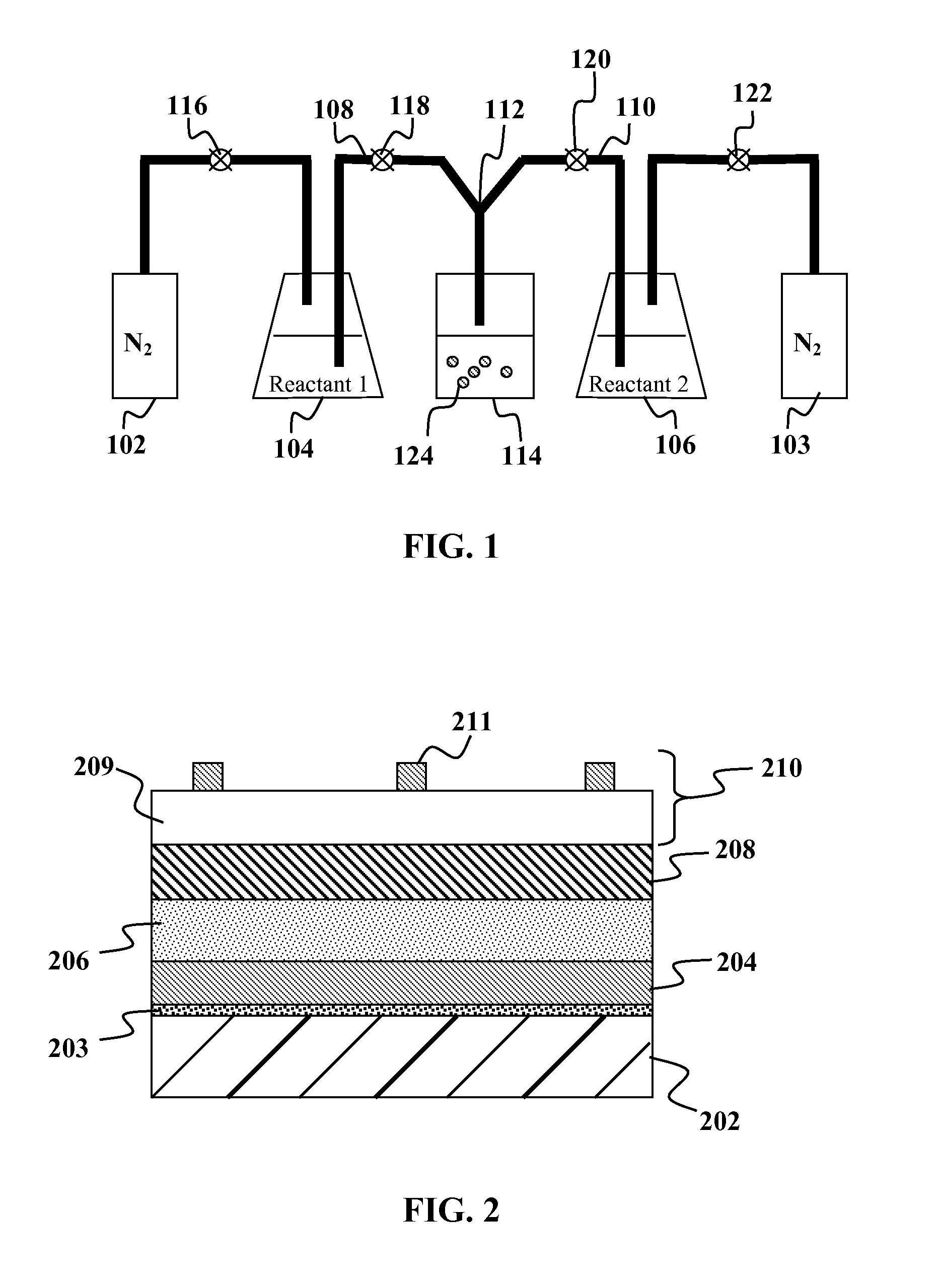

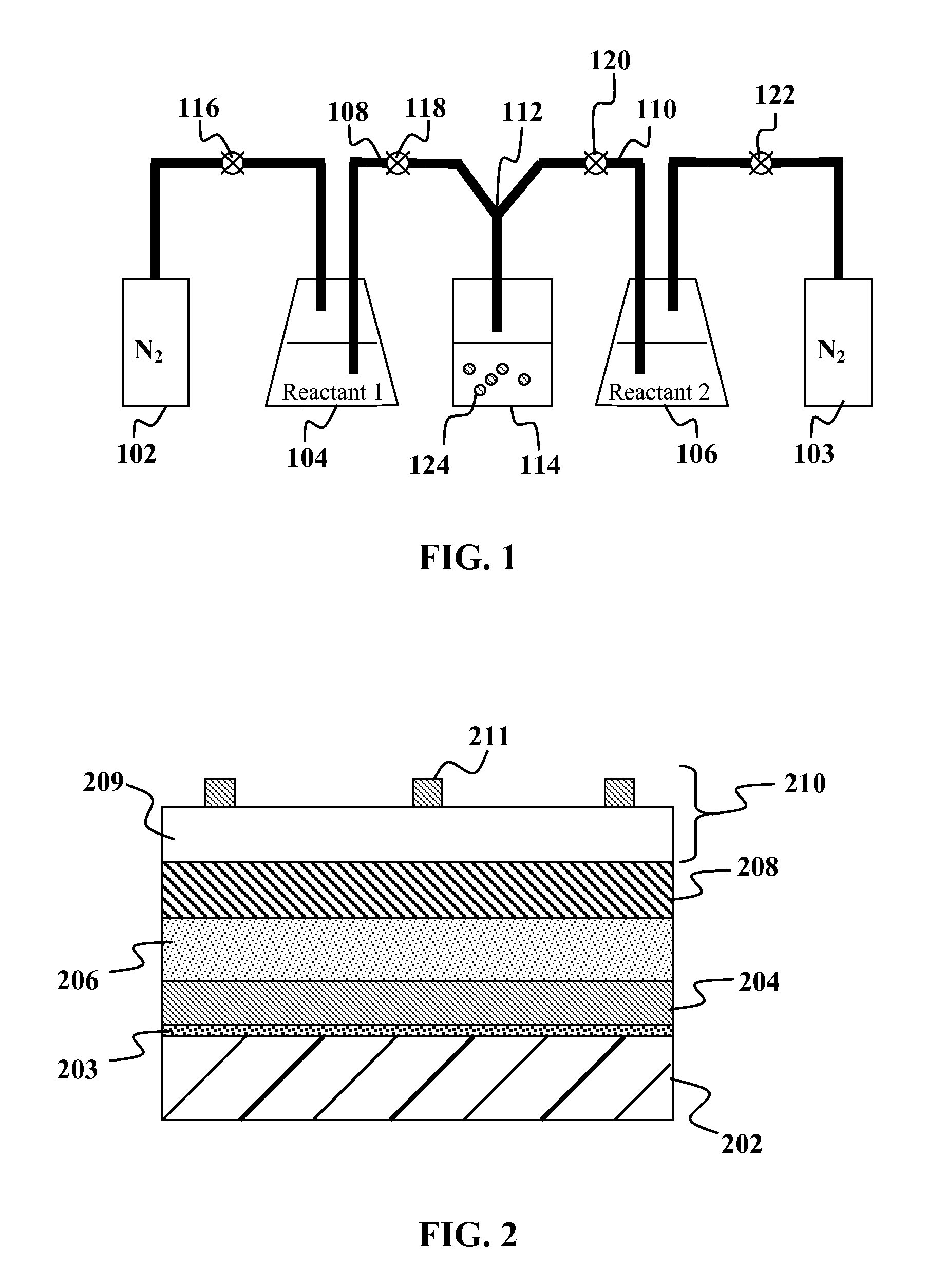

Methods of forming graphene by graphite exfoliation

ActiveUS20130102084A1Promote recoveryEasy to manufactureMaterial nanotechnologyElectrolysis componentsGraphiteSolar cell

Methods of forming graphene by graphite exfoliation, wherein the methods include: providing a graphite sample having atomic layers of carbon; introducing a salt and a solvent into the space between the atomic layers; expanding the space between the atomic layers using organic molecules and ions from the solvent and the salt; and separating the atomic layers using a driving force to form one or more sheets of graphene; the graphene produced by the methods can be used to form solar cells, to perform DNA analysis, and for other electrical, optical and biological applications.

Owner:NAT UNIV OF SINGAPORE

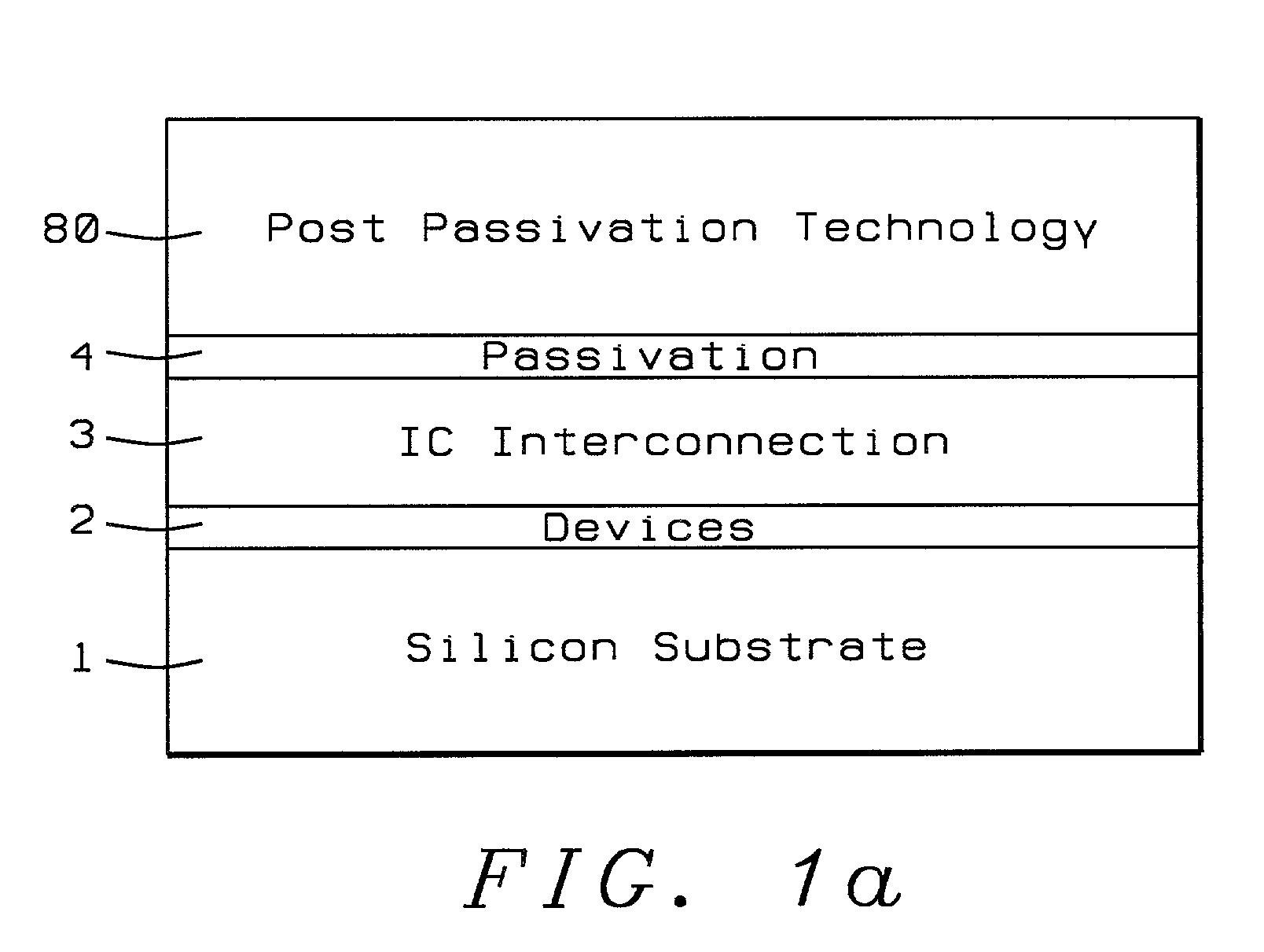

Top layers of metal for integrated circuits

ActiveUS20060063378A1Improve performanceReduce resistive voltage dropSemiconductor/solid-state device detailsSolid-state devicesCritical signalSemiconductor

The present invention adds one or more thick layers of polymer dielectric and one or more layers of thick, wide metal lines on top of a finished semiconductor wafer, post-passivation. The thick, wide metal lines may be used for long signal paths and can also be used for power buses or power planes, clock distribution networks, critical signal, and re-distribution of I / O pads.

Owner:QUALCOMM INC

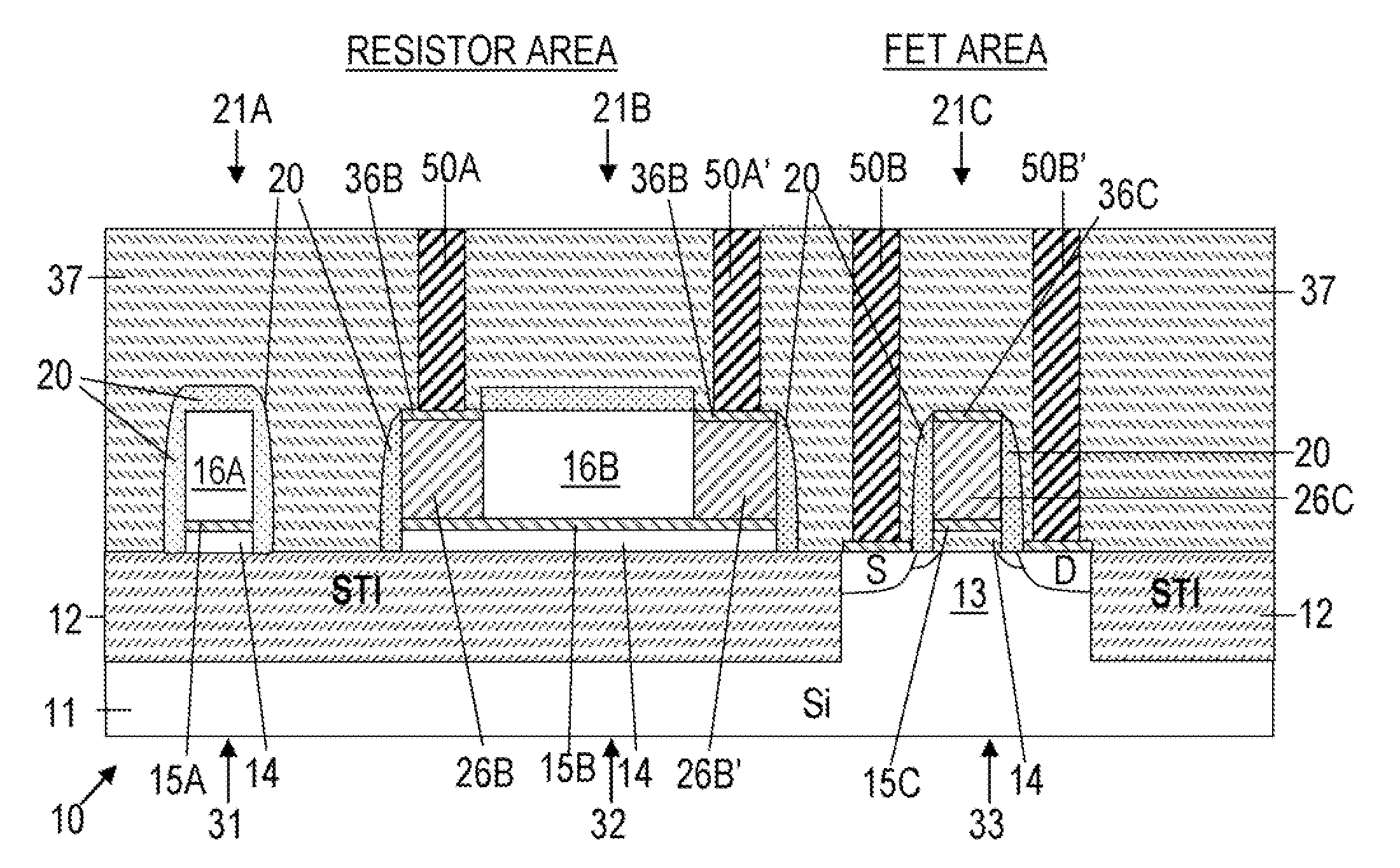

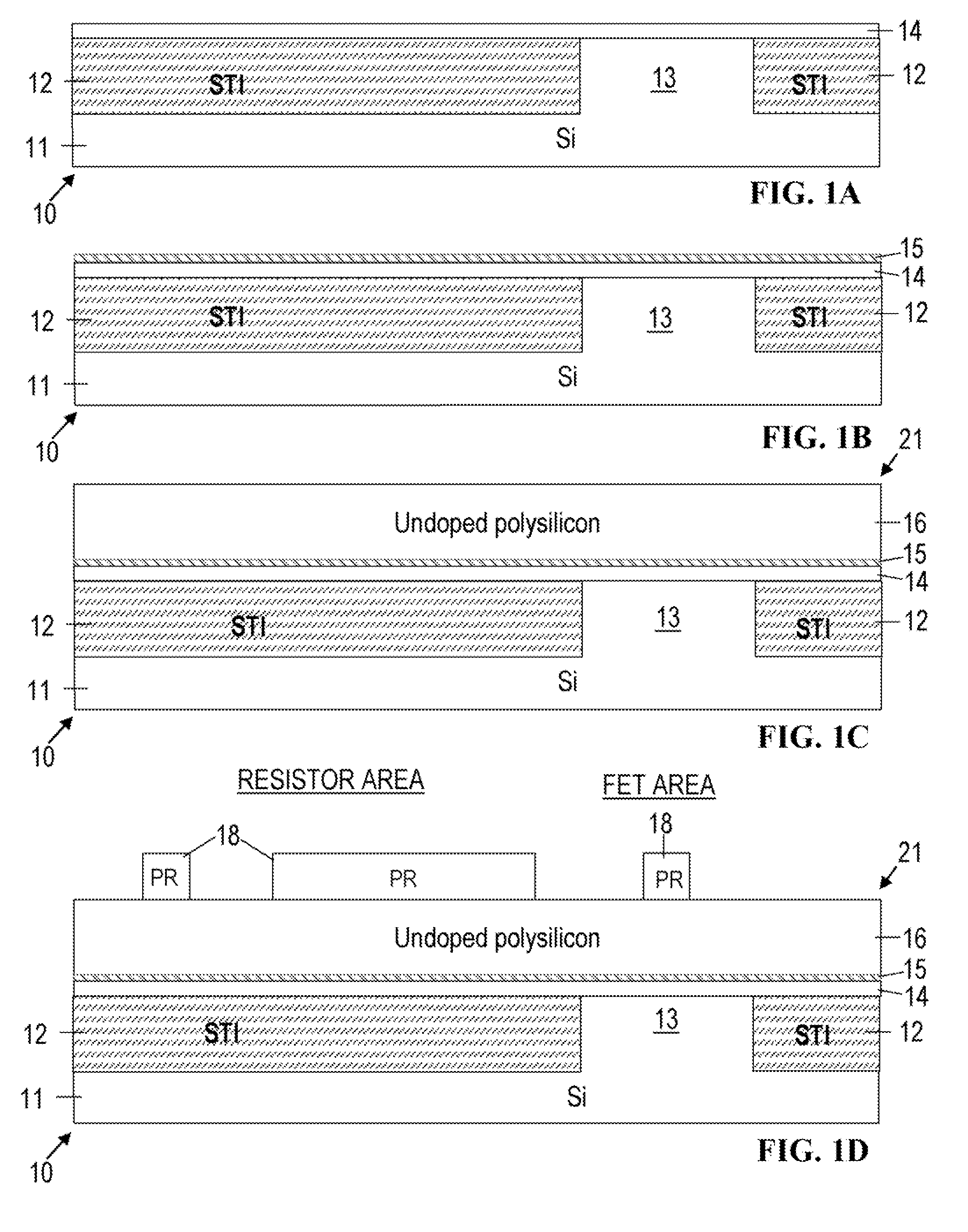

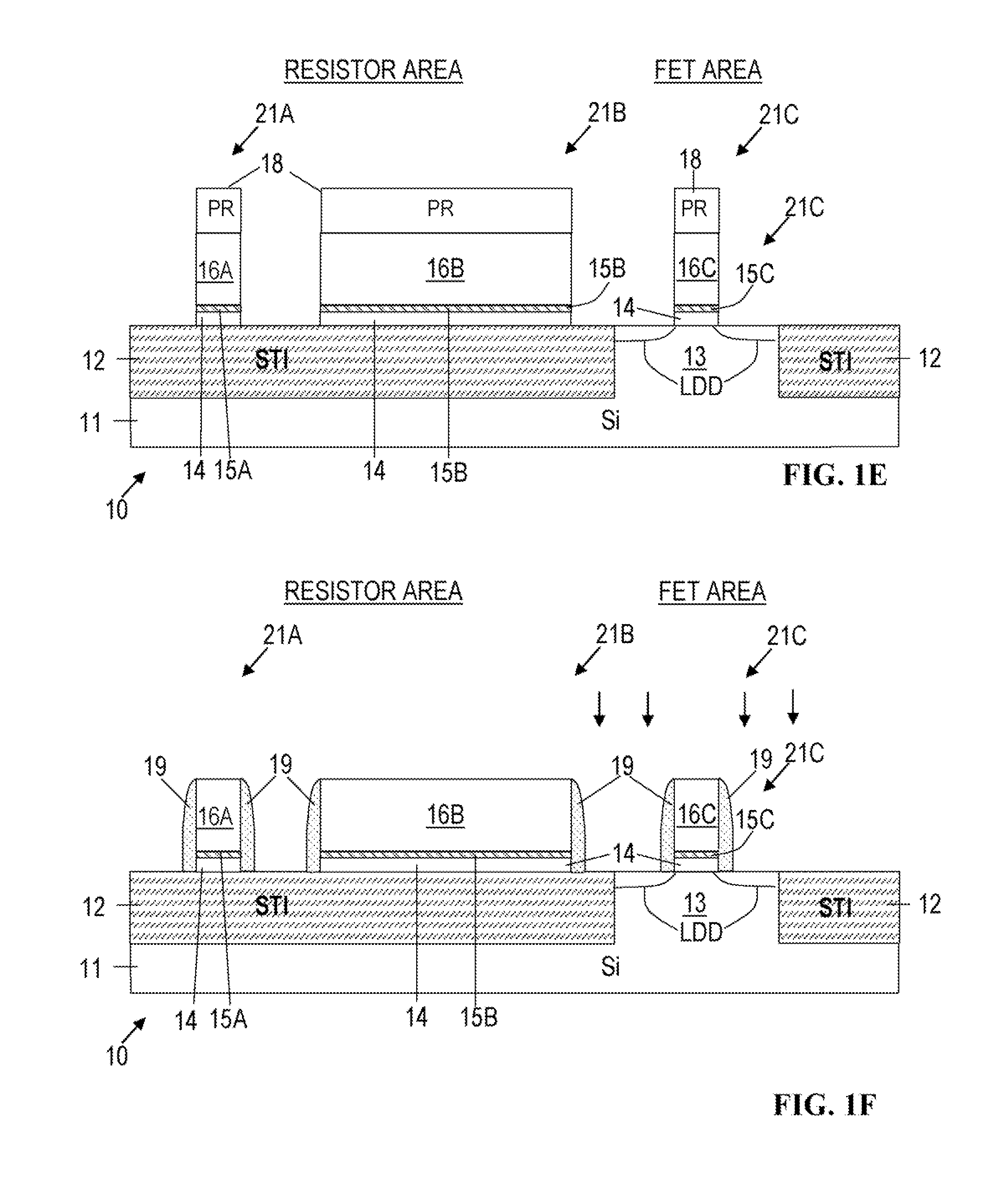

Resistor and fet formed from the metal portion of a mosfet metal gate stack

ActiveUS20090090977A1Improve toleranceNo additional costTransistorSolid-state devicesMOSFETElectrical conductor

An integrated semiconductor device includes a resistor and an FET device formed from a stack of layers. The stack of layers includes a dielectric layer formed on a substrate; a metal conductor layer having lower electrical resistance formed on the dielectric layer; and a polysilicon layer formed on the metal conductor layer. A resistor stack is formed by patterning a portion of the original stack of layers into a resistor. An FET stack is formed from another portion of the original stack of layers. The FET stack is doped to form a gate electrode and the resistor stack is doped aside from the resistor portion thereof. Then terminals are formed at distal ends of the resistor in a doped portion of the polysilicon layer. Alternatively, the polysilicon layer is etched away from the resistor stack followed by forming terminals at distal ends of the metal conductor in the resistor stack.

Owner:TWITTER INC

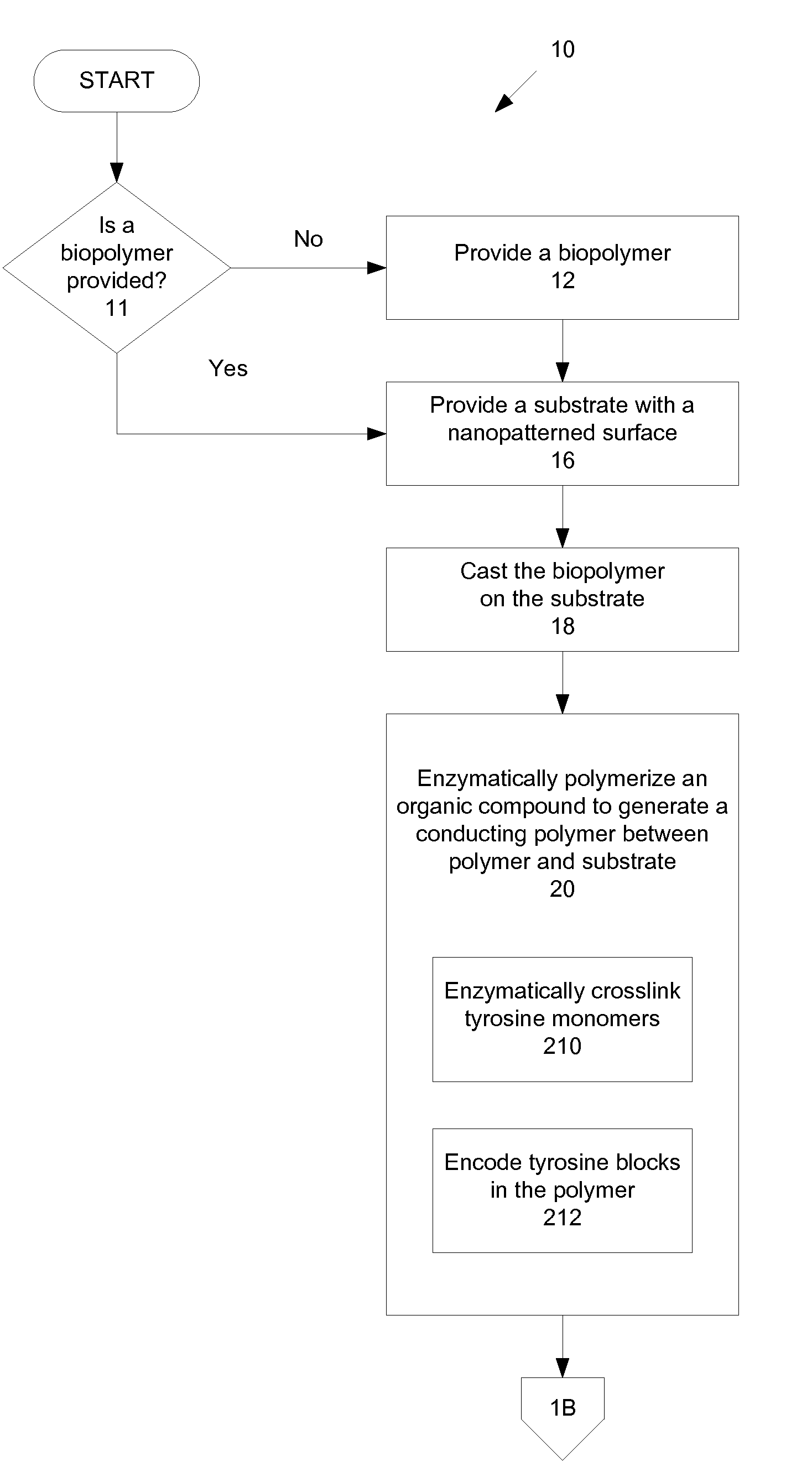

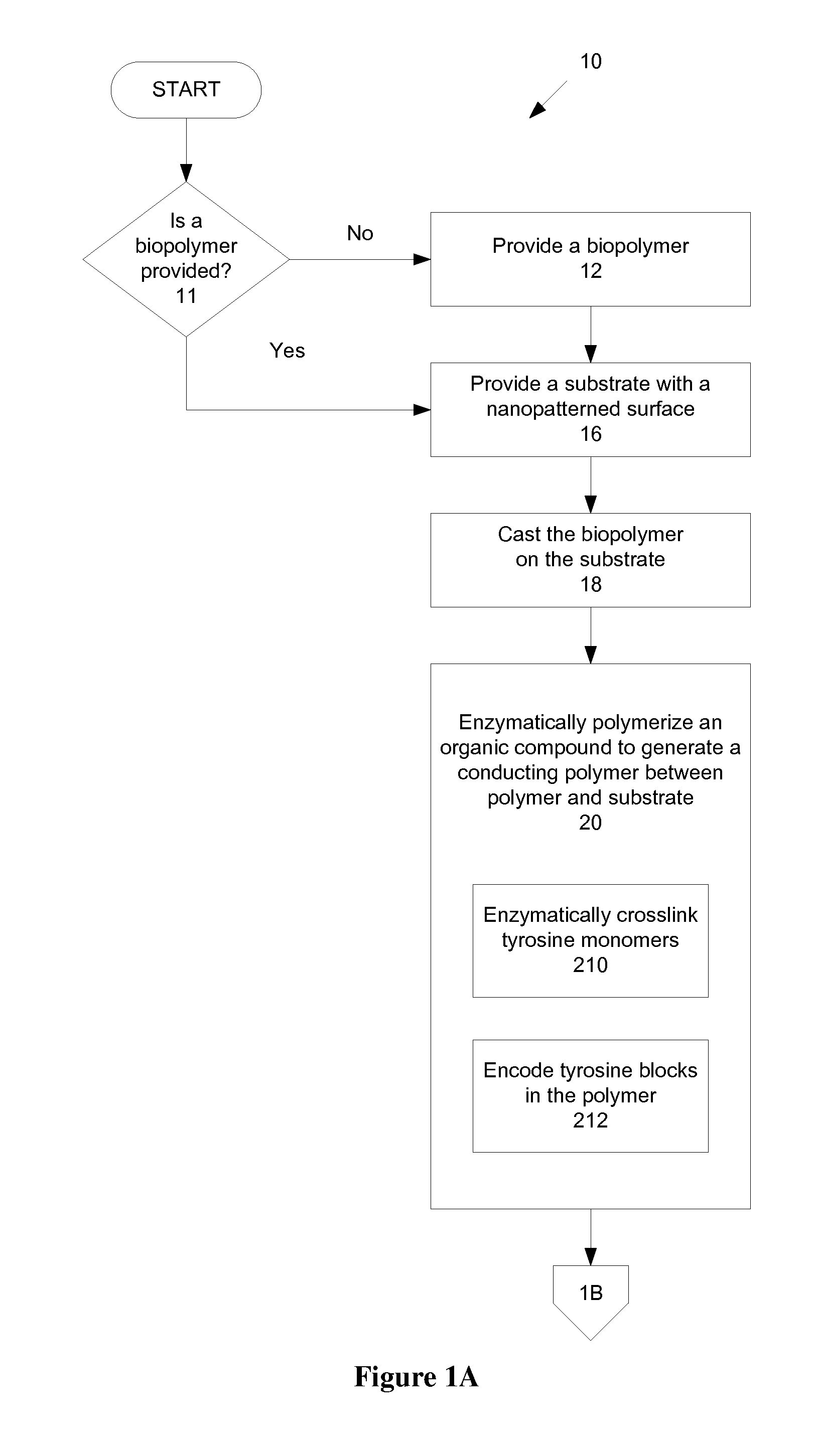

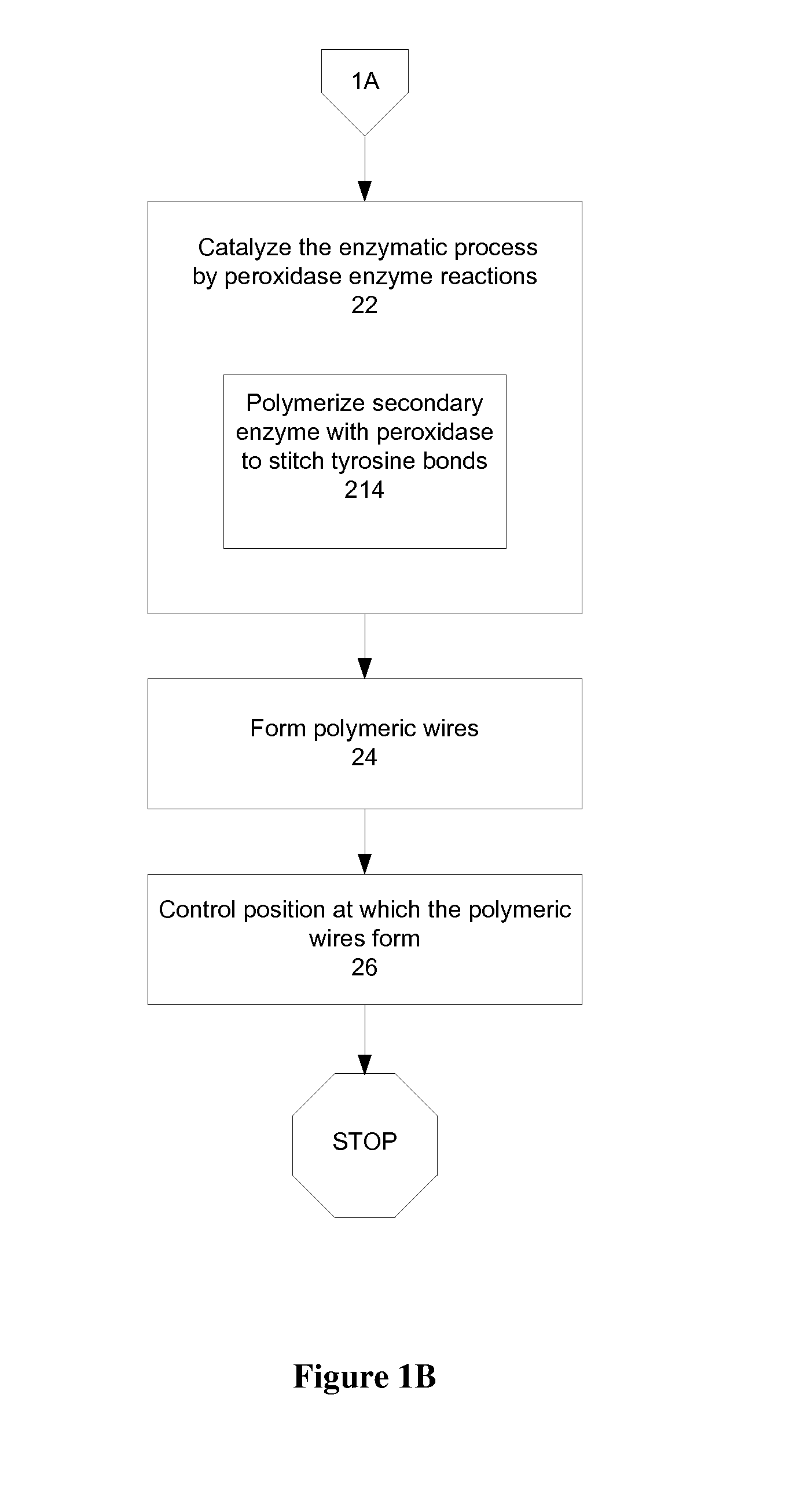

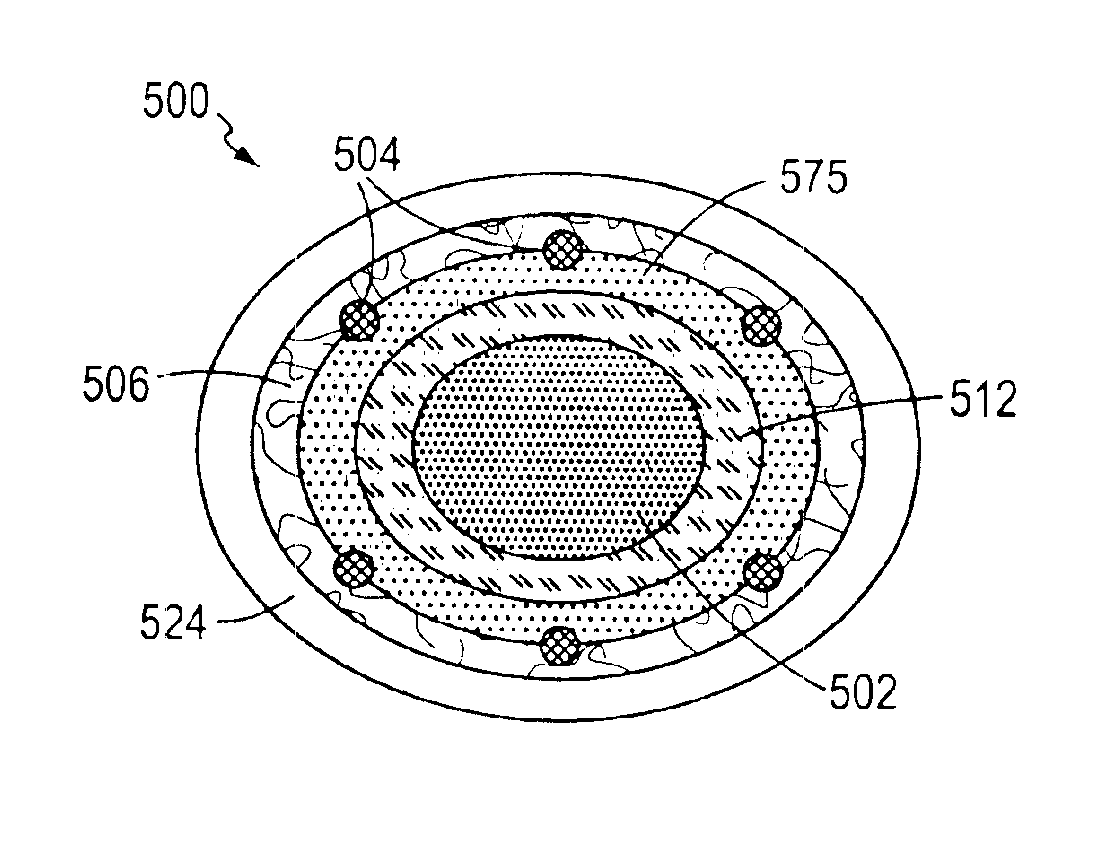

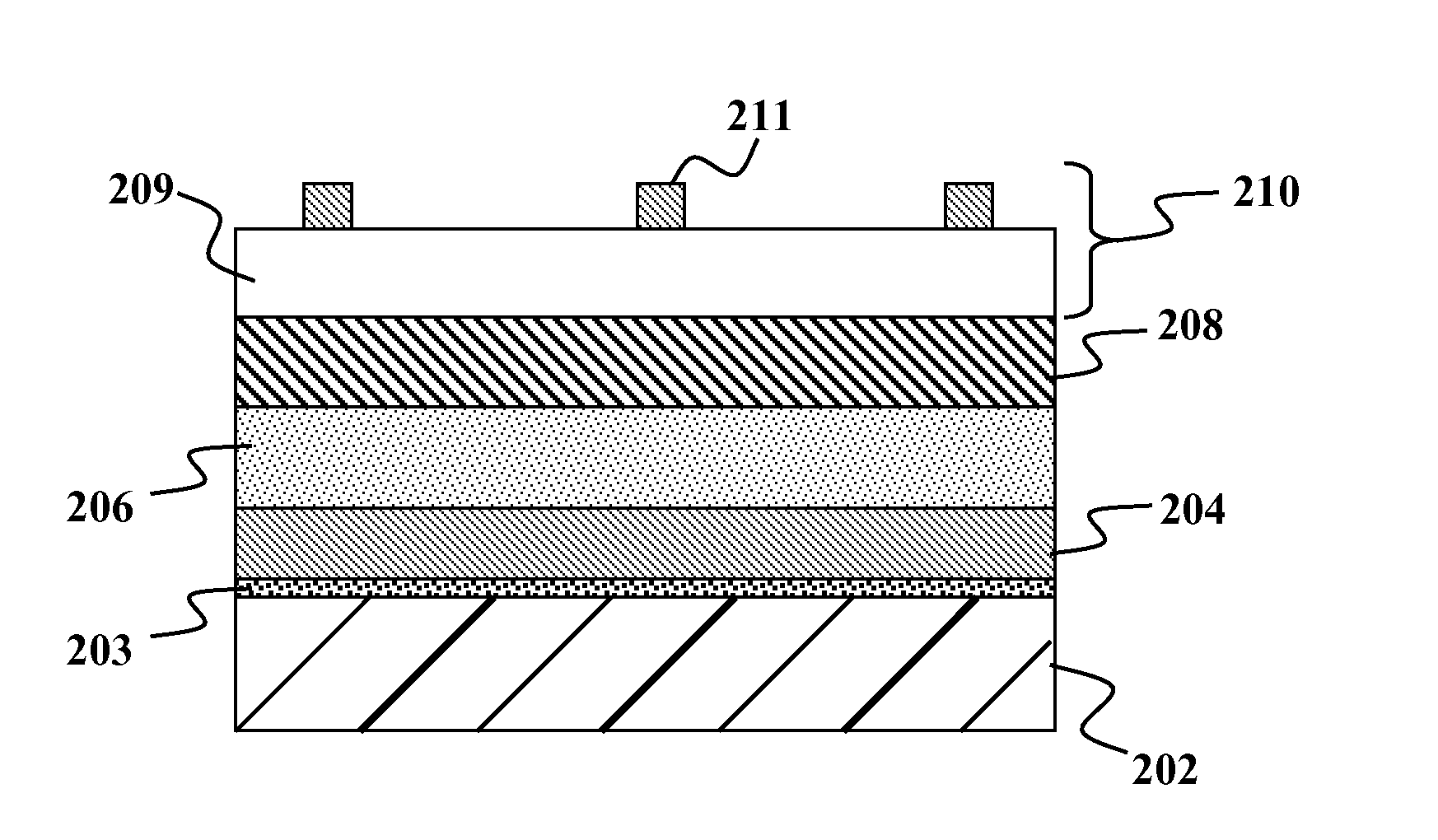

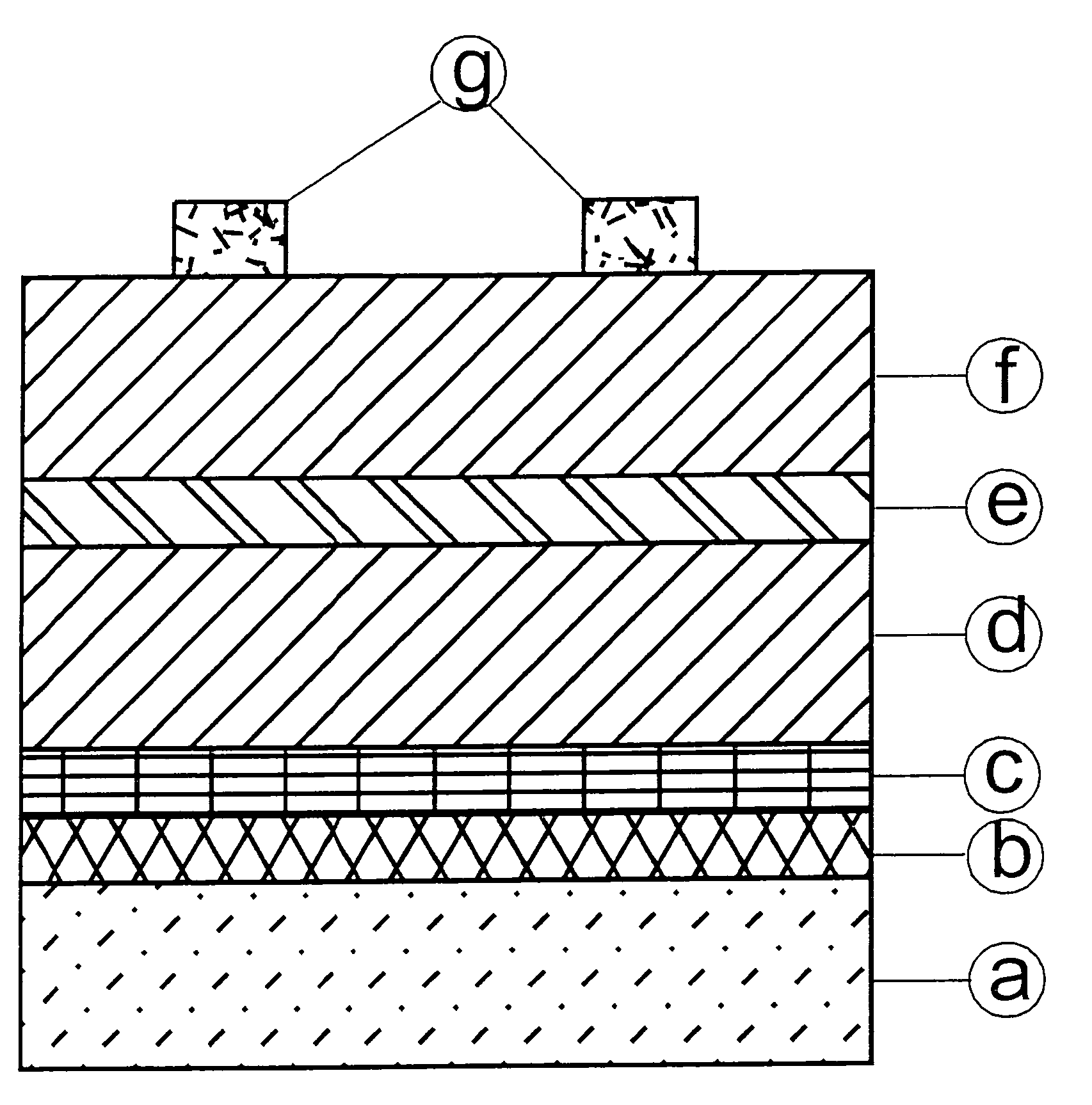

Electroactive biopolymer optical and electro-optical devices and method of manufacturing the same

ActiveUS20100065784A1Minimize negative impactImprove functional propertiesPowder deliveryConductive materialPolymer scienceBiopolymer

A method of manufacturing a biopolymer optical device includes providing a polymer, providing a substrate, casting the polymer on the substrate, and enzymatically polymerizing an organic compound to generate a conducting polymer between the provided polymer and the substrate. The polymer may be a biopolymer such as silk and may be modified using organic compounds such as tyrosines to provide a molecular-level interface between the provided bulk biopolymer of the biopolymer optical device and a substrate or other conducting layer via a tyrosine-enzyme polymerization. The enzymatically polymerizing may include catalyzing the organic compound with peroxidase enzyme reactions. The result is a carbon-carbon conjugated backbone that provides polymeric “wires” for use in polymer and biopolymer optical devices. An all organic biopolymer electroactive material is thereby provided that provides optical functions and features.

Owner:TRUSTEES OF TUFTS COLLEGE

Photovoltaic fibers

Owner:MERCK PATENT GMBH

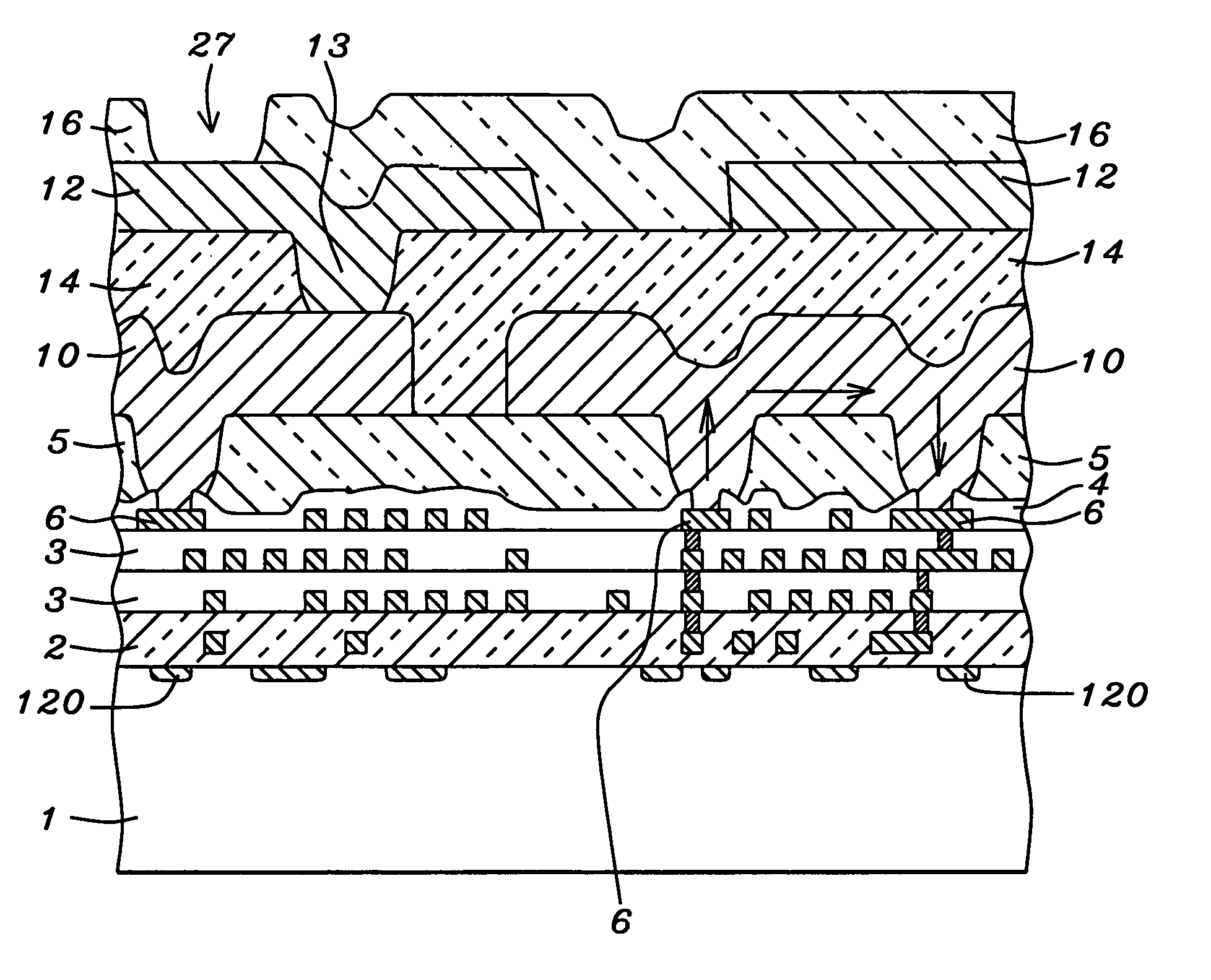

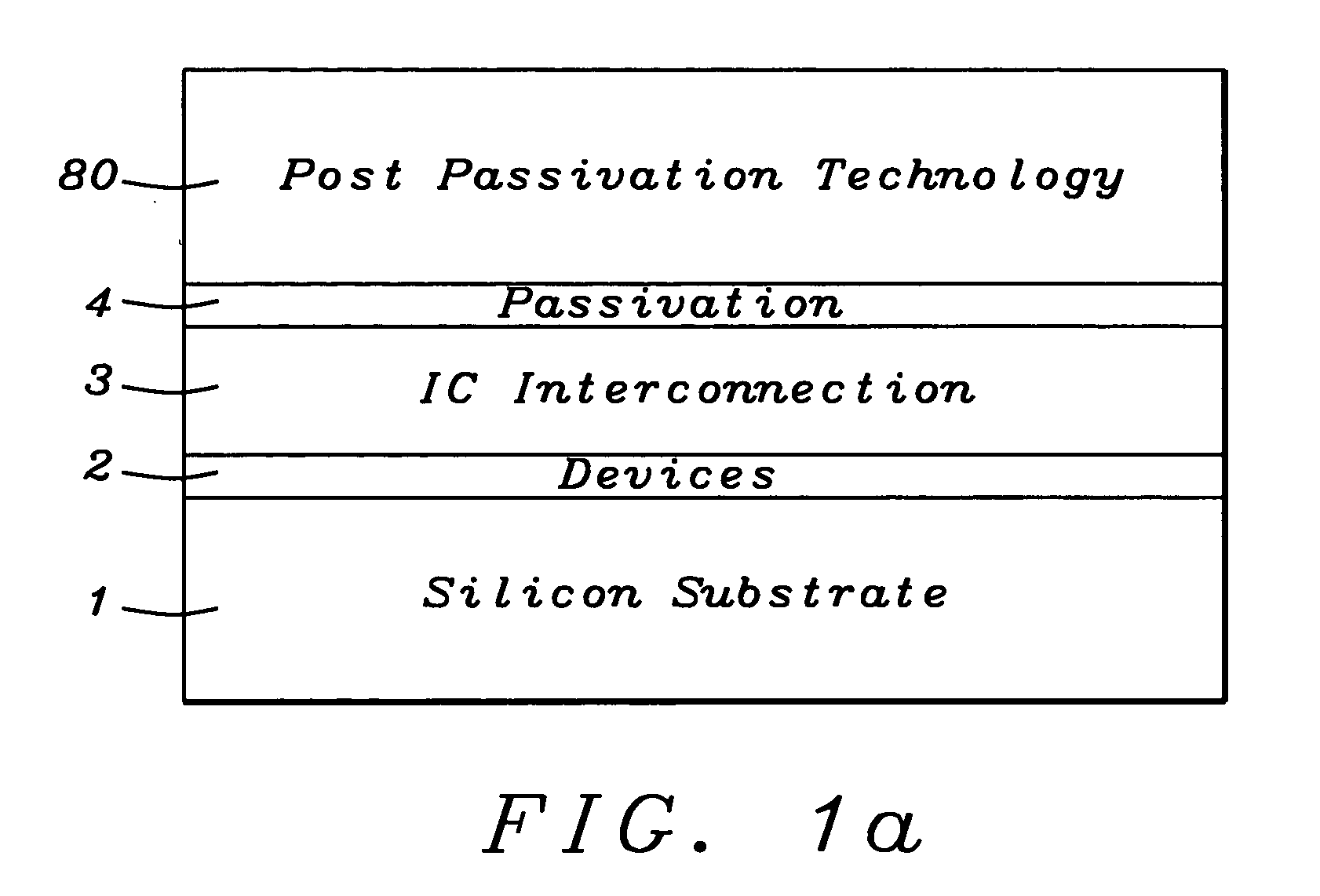

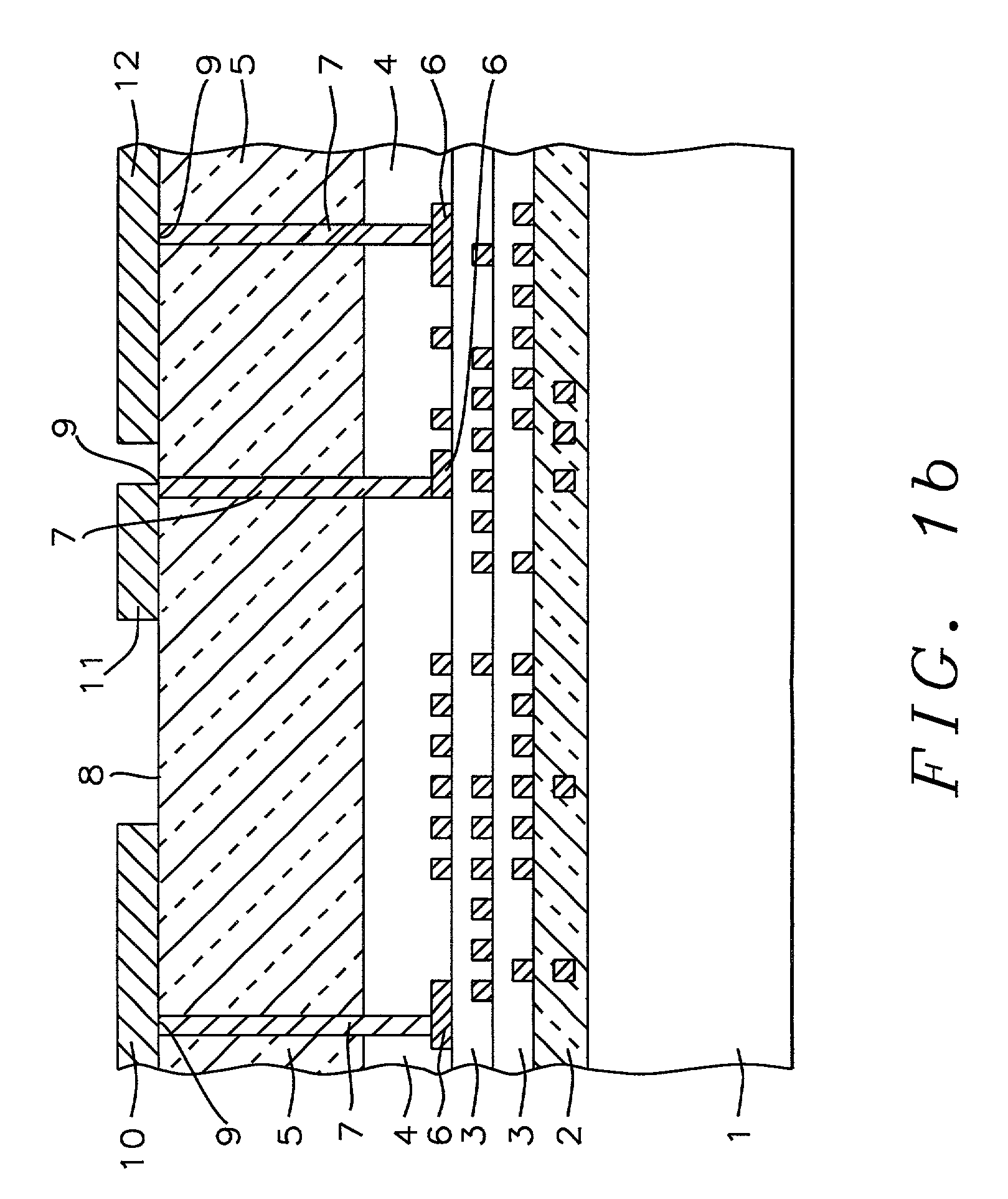

High performance system-on-chip discrete components using post passivation process

InactiveUS6869870B2Improve RF performanceIncreased frequency rangeTransistorSemiconductor/solid-state device detailsHigh performance systemMaterials science

A system and method for forming post passivation discrete components, is described. High quality discrete components are formed on a layer of passivation, or on a thick layer of polymer over a passivation layer.

Owner:QUALCOMM INC

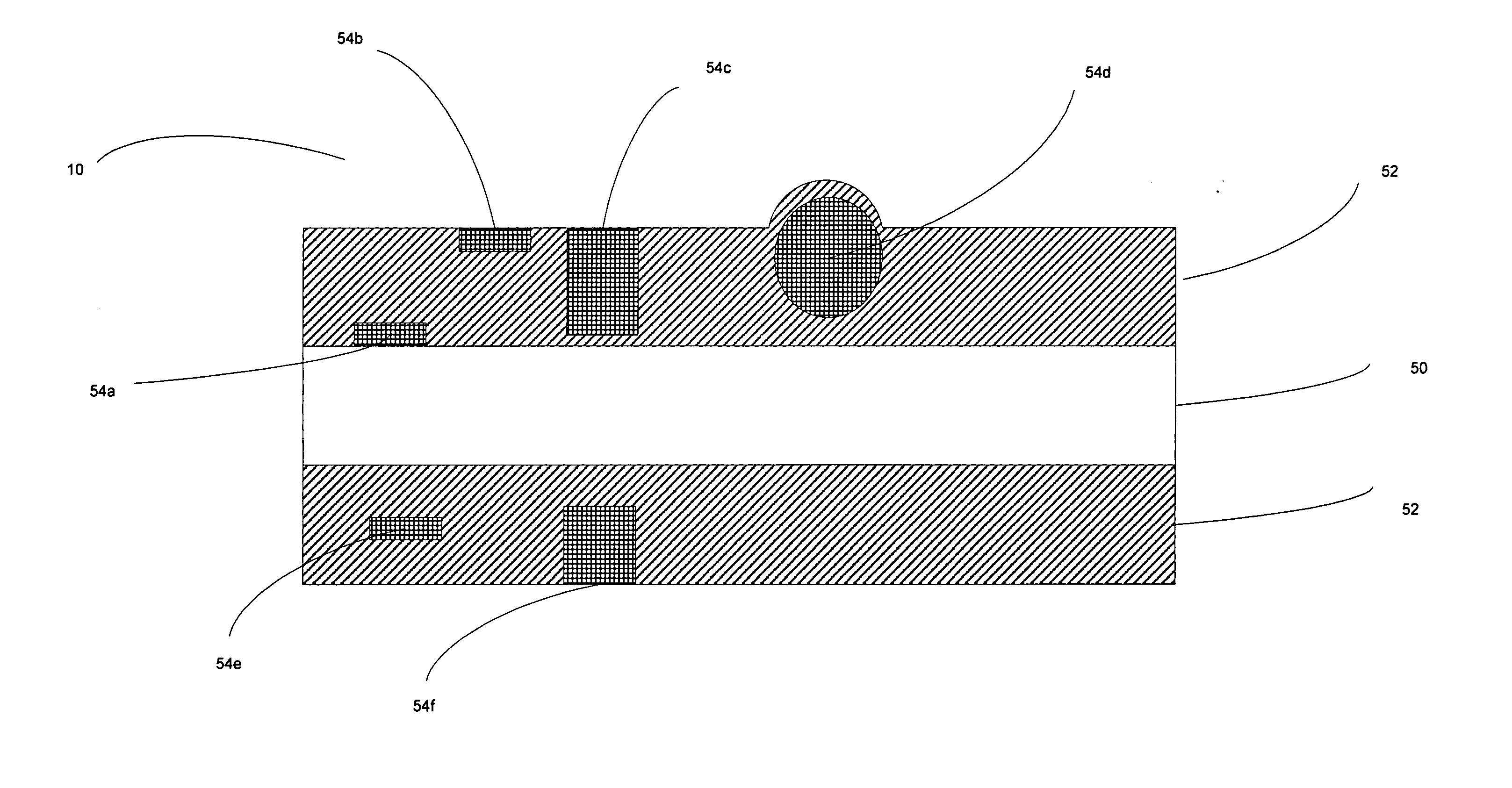

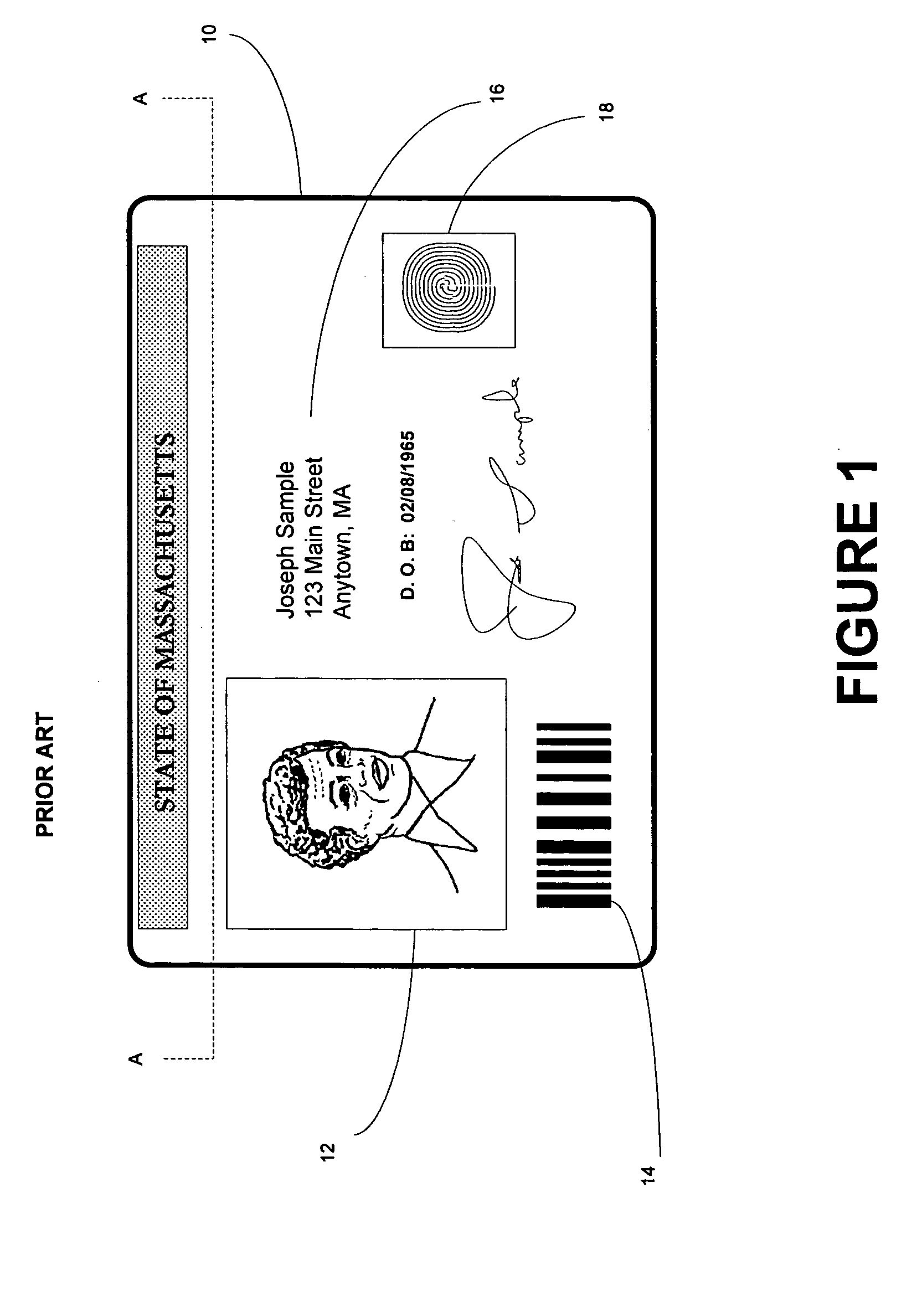

Laser engraving methods and compositions, and articles having laser engraving thereon

ActiveUS20050095408A1Not easy to counterfeitDifficult to alterRadiation applicationsDecorative surface effectsThioester synthesisBarium sulphide

The invention provides a composition having laser engraving properties, comprising a host material and an effective amount of a laser enhancing additive. The laser enhancing additive comprises a first quantity of least one of copper potassium iodide (CuKI3) or Copper Iodide (CuI), and a second quantity at least one substance selected from the group consisting of zinc sulfide (ZnS), barium sulfide (BaS), alkyl sulfonate, and thioester. The composition can be engraved with grayscale images by an Nd:Yag laser and can be added to laminates or coatings. The composition can be used during the manufacture of many articles of manufacture, including identification documents.

Owner:L 1 SECURE CREDENTIALING

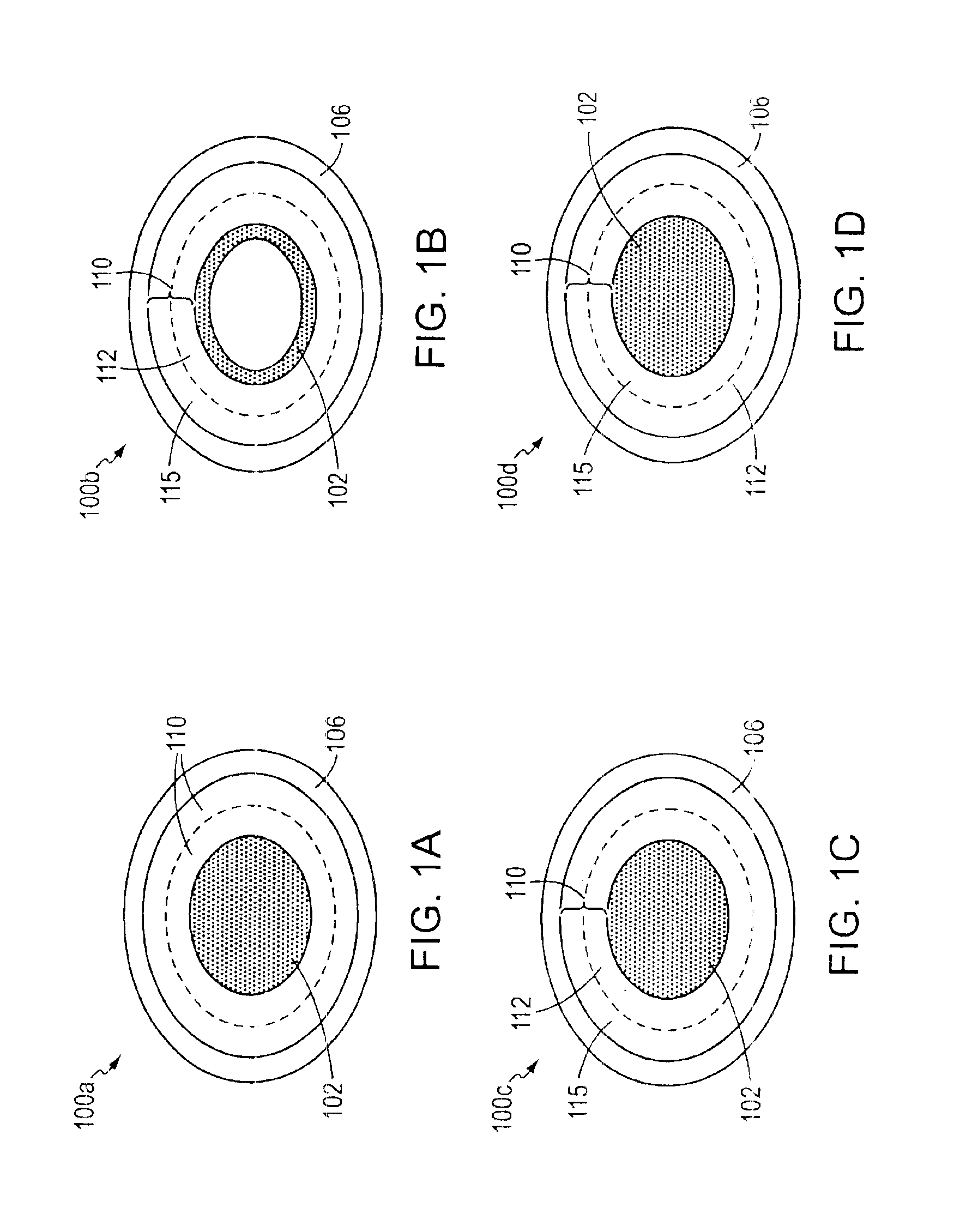

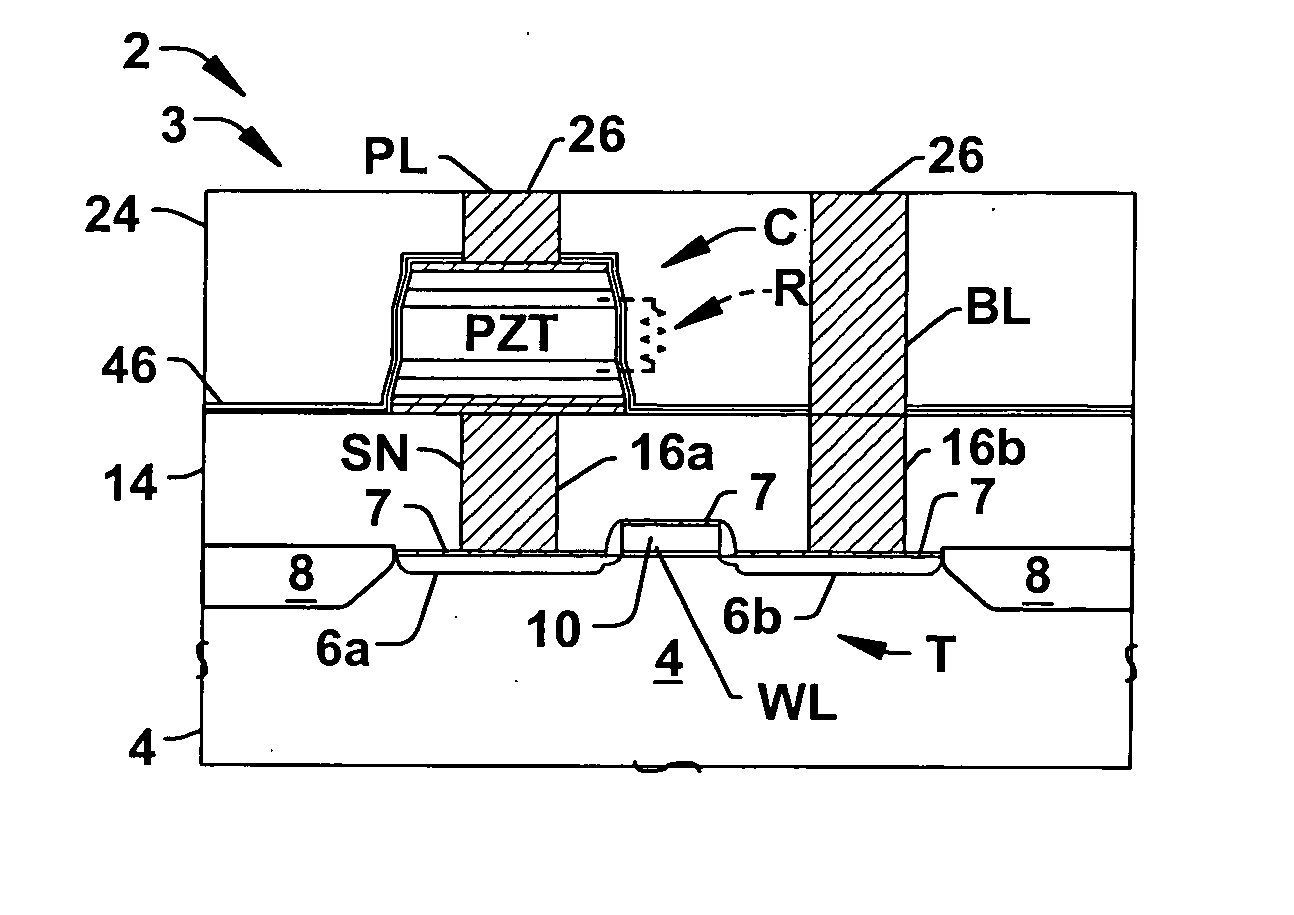

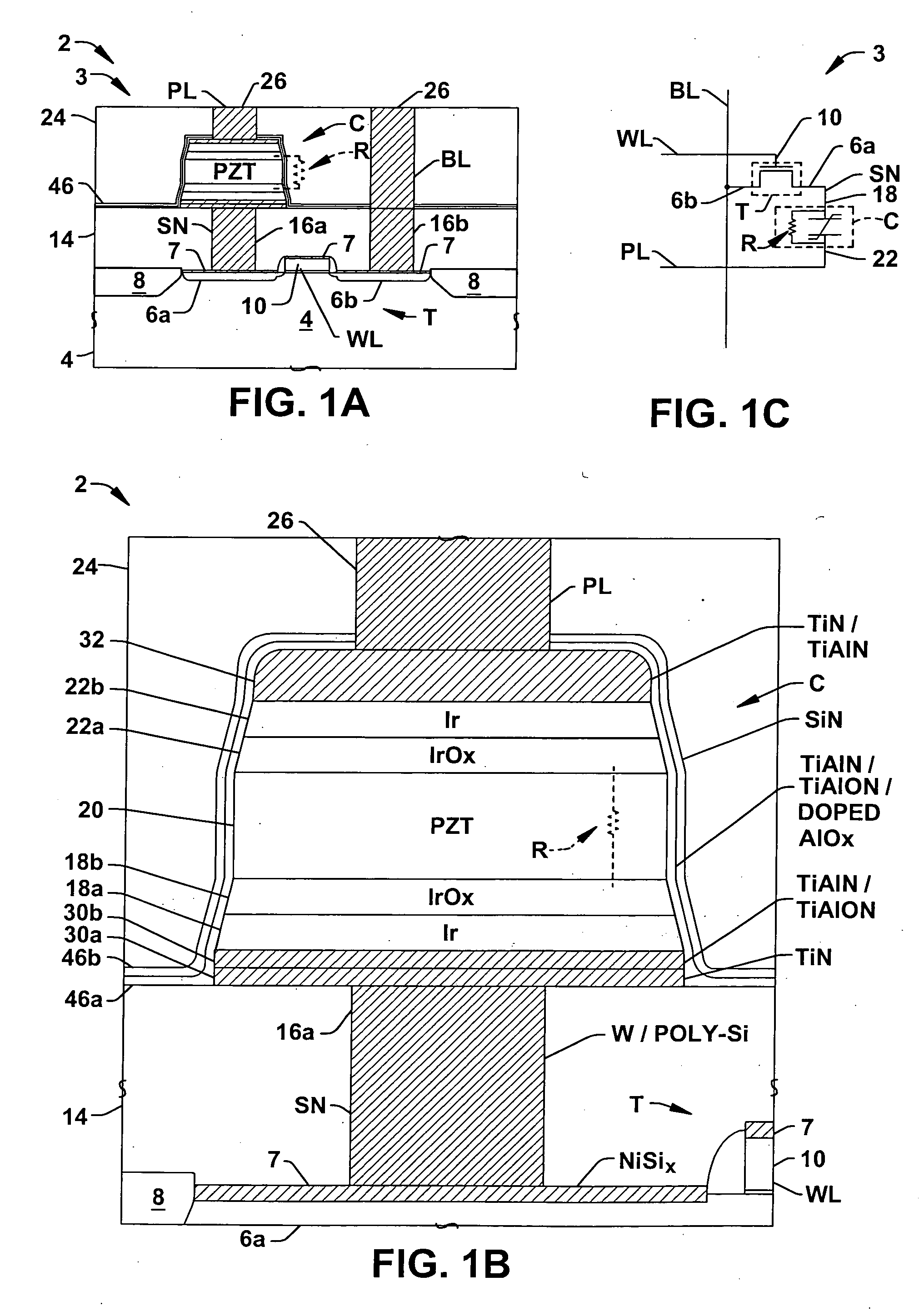

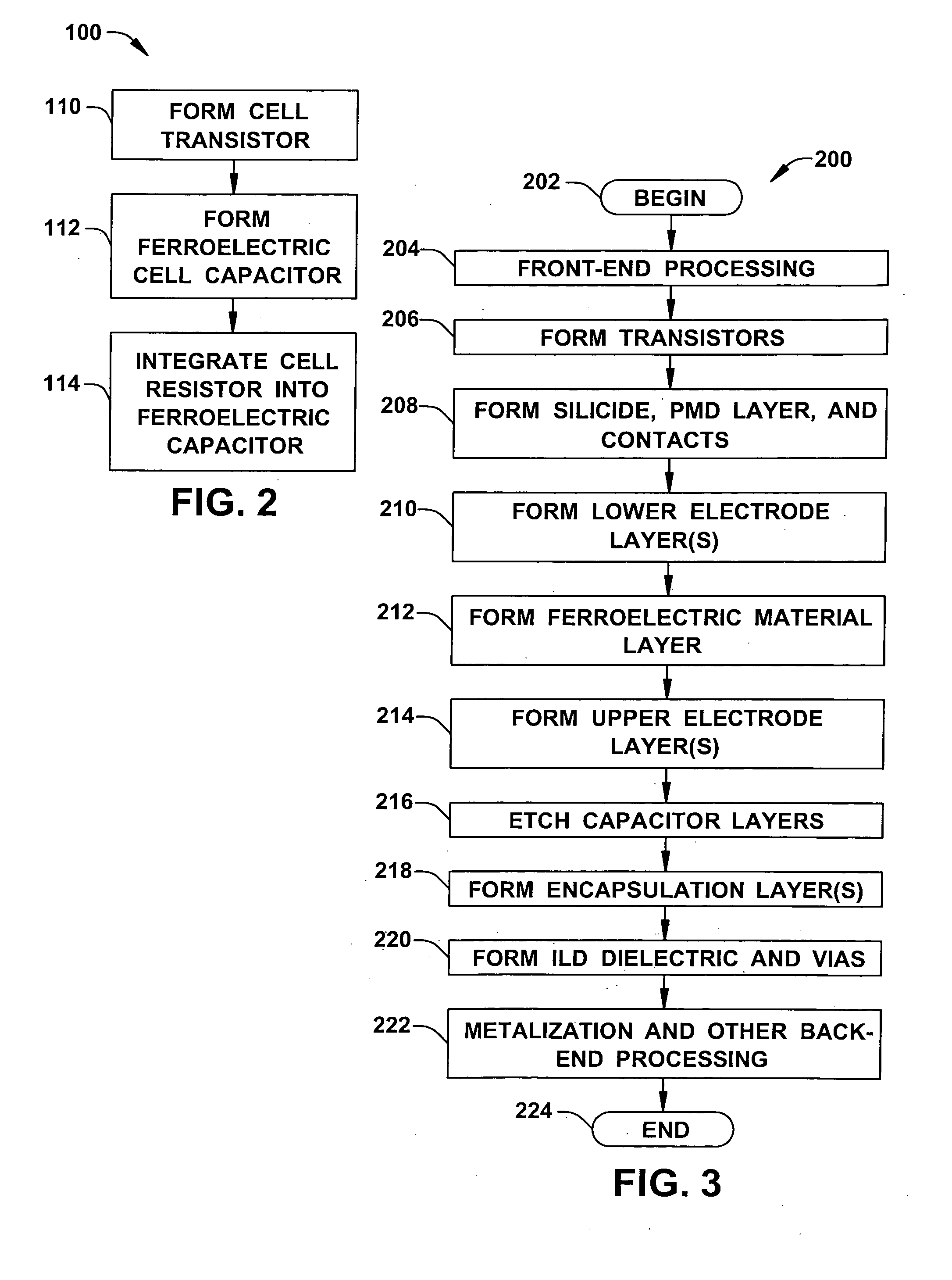

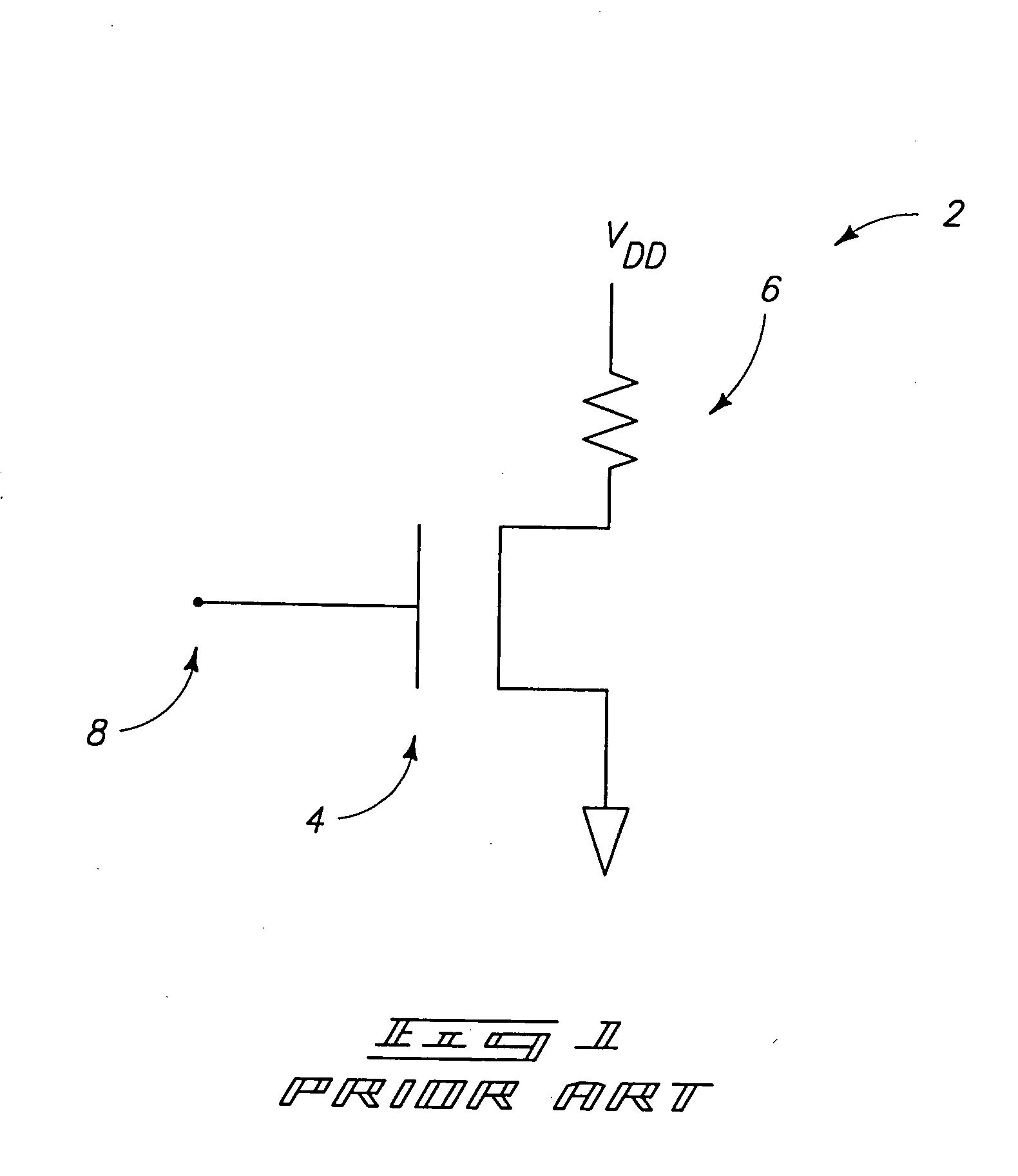

Ferroelectric capacitor with parallel resistance for ferroelectric memory

ActiveUS20060118841A1Avoid charge accumulationInhibits charge charge lossSolid-state devicesSemiconductor/solid-state device manufacturingEngineeringCharge loss

Ferroelectric memory cells (3) are presented, in which a cell resistor (R) is integrated into the cell capacitor (C) to inhibit charge accumulation or charge loss at the cell storage node (SN) when the cell (3) is not being accessed while avoiding significant disruption of memory cell access operations. Methods (100, 200) are provided for fabricating ferroelectric memory cells (3) and ferroelectric capacitors (C), in which a parallel resistance (R) is integrated in the capacitor ferroelectric material (20) or in an encapsulation layer (46) formed over the patterned capacitor structure (C).

Owner:TEXAS INSTR INC

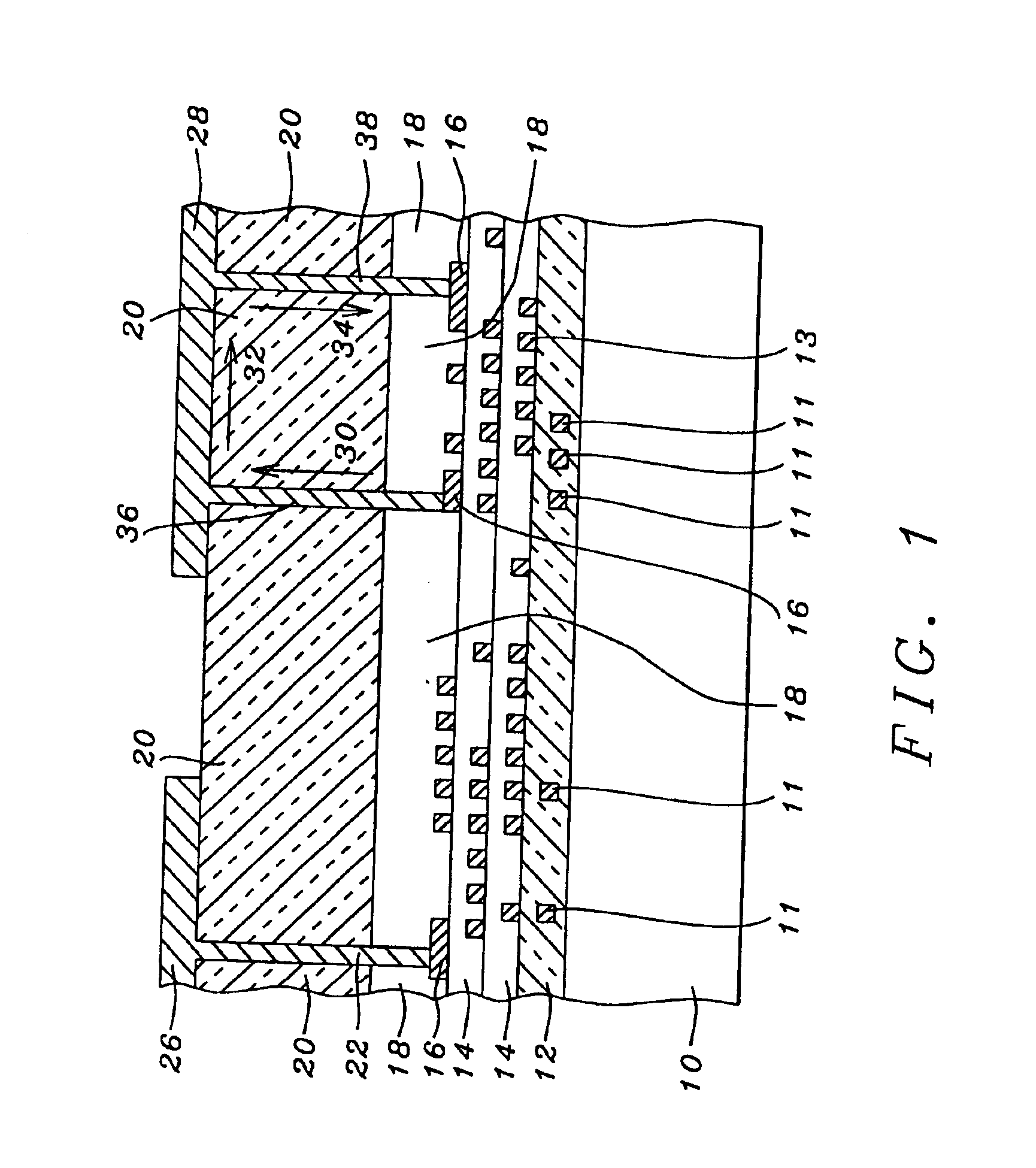

Reversible electric fuse and antifuse structures for semiconductor devices

ActiveUS7557424B2Improve electromigration problemsGood reversibilitySemiconductor/solid-state device detailsSolid-state devicesElectric fusesEngineering

A structure and method of fabricating reversible fuse and antifuse structures for semiconductor devices is provided. In one embodiment, the method includes forming at least one line having a via opening for exposing a portion of a plurality of interconnect features; conformally depositing a first material layer over the via opening; depositing a second material layer over the first material layer, wherein the depositing overhangs a portion of the second material layer on a top portion of the via opening; and depositing a blanket layer of insulating material, where the depositing forms a plurality of fuse elements each having an airgap between the insulating material and the second material layer. The method further includes forming a plurality of electroplates in the insulator material connecting the fuse elements. In another embodiment, the method includes depositing a first and a second material layer on a semiconductor substrate, wherein the second material layer having a higher electrical conductivity than the first material layer; selectively etching the first and second material layer to create at least one constricted region to facilitate electromigration of the second material; wherein the electromigration creates a plurality of micro voids; and forming a plurality of electrical contacts on the second material layer.

Owner:GLOBALFOUNDRIES U S INC

Fast luminescent silicon

There are provided mesoporous silica materials containing in their pores stabilized clusters of silicon atom, of size 2 nanometers or less, and capable of photoluminescence to emit fast photons. They are prepared by chemical vapor deposition of silicon or a silicon precursor such as disilane, under soft conditions such as temperature of 100-150 DEG C., into the mesopores of silicate films which have mesoporous channels prepared by growth of the films using a template to control their sizes, but without removing the template residues from the films prior to the chemical vapor deposition. The template residues serve to limit the size of the silicon clusters which conform. The use of the soft conditions on CVD retains the template residues in an intact, substantially unchanged form. The resultant films have clusters of silicon, of 2 nanometer size or less, anchored to the mesopores, and air stable, so that they can be used in optoelectronic devices in conjunction with standard silicon semiconductors.

Owner:THE GOVERNINIG COUNCIL OF THE UNIV OF TORANTO

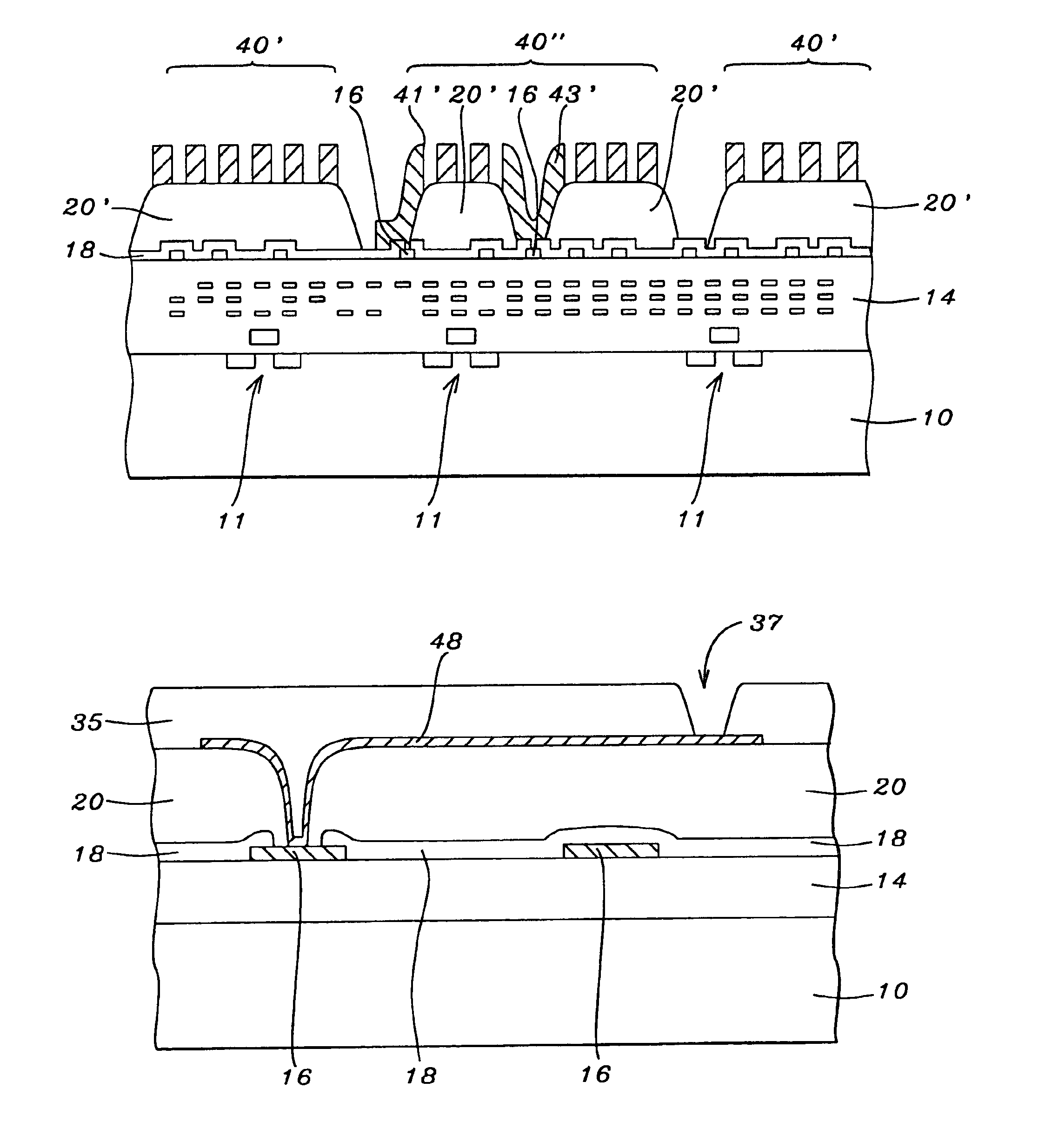

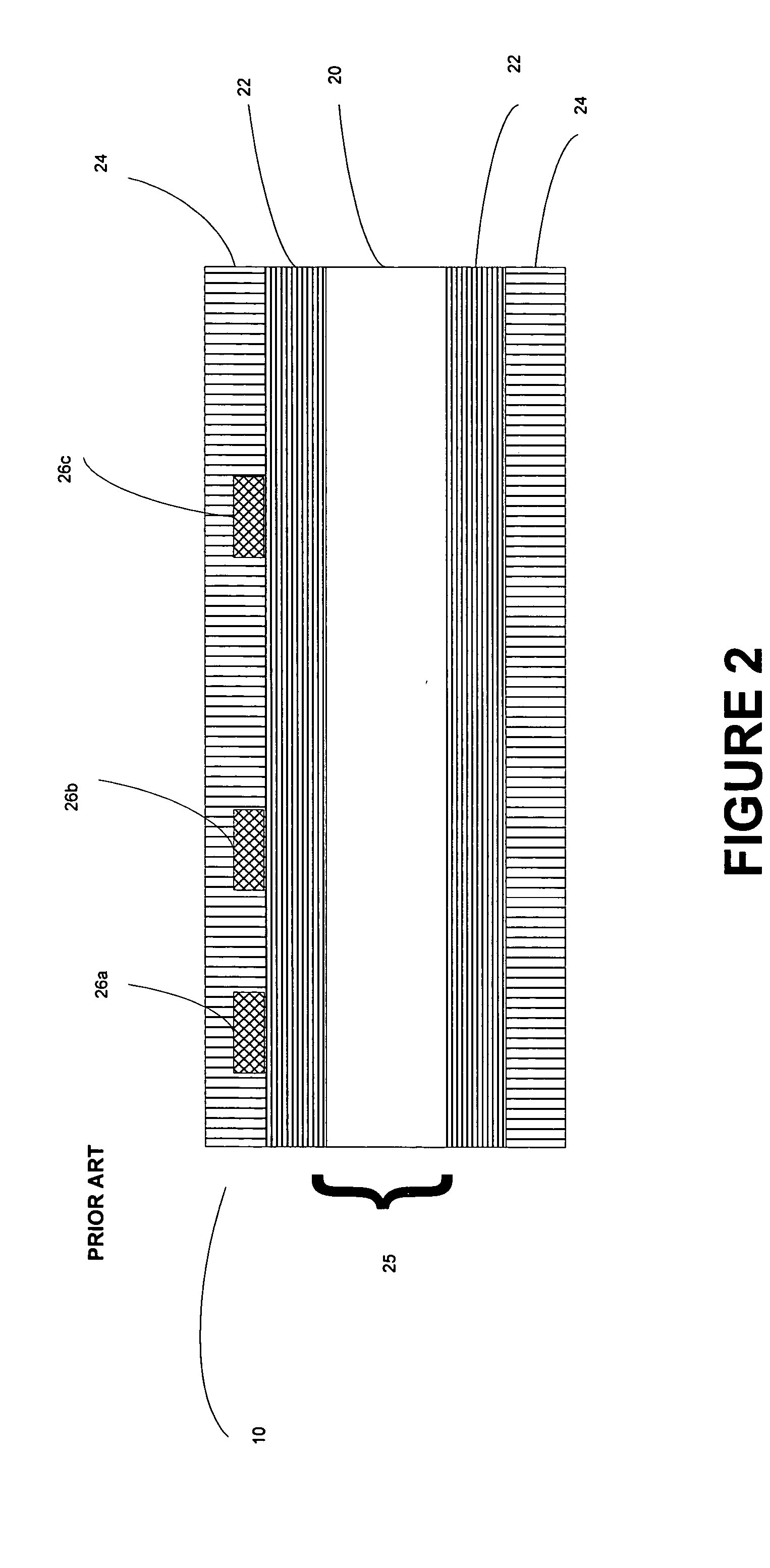

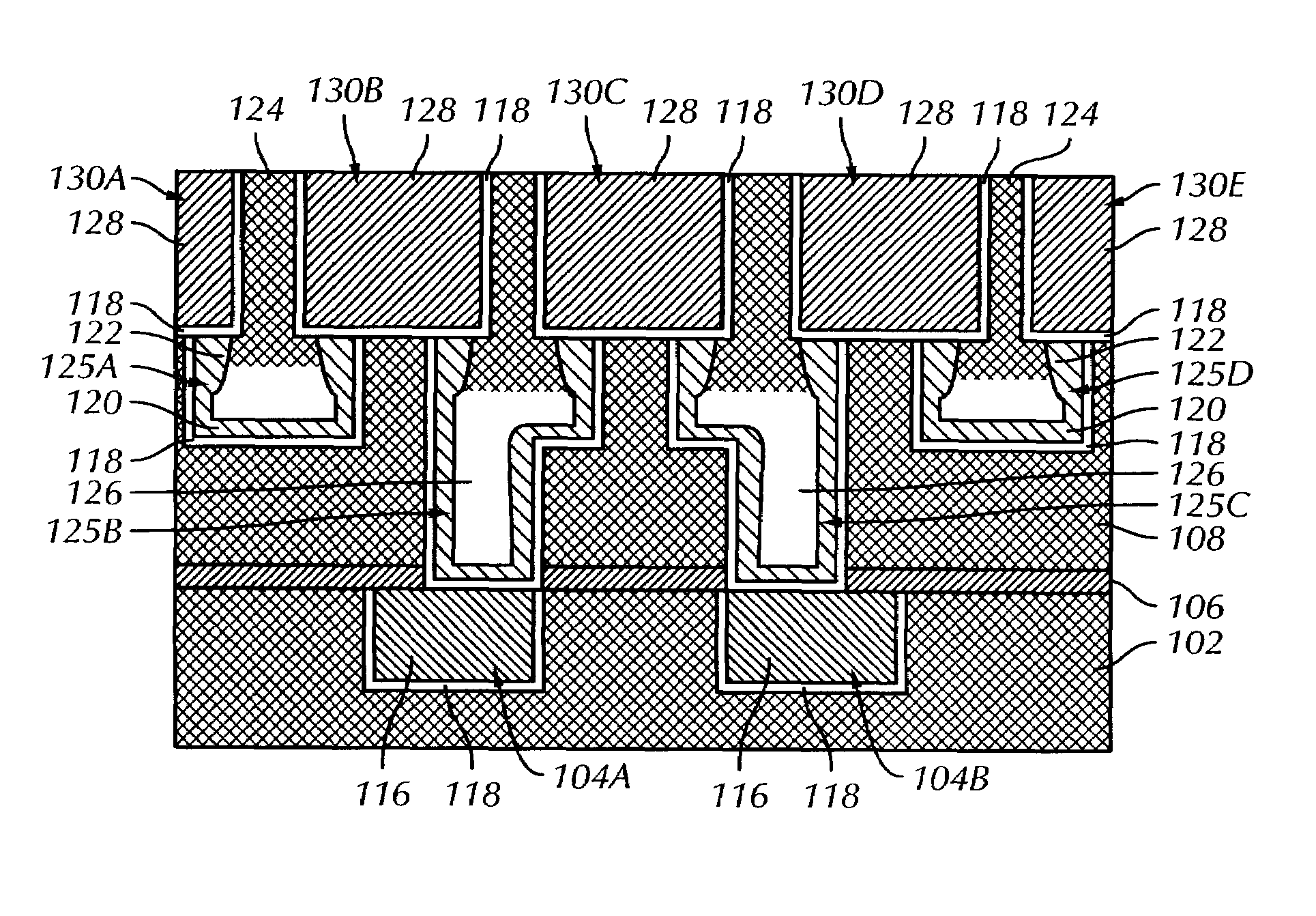

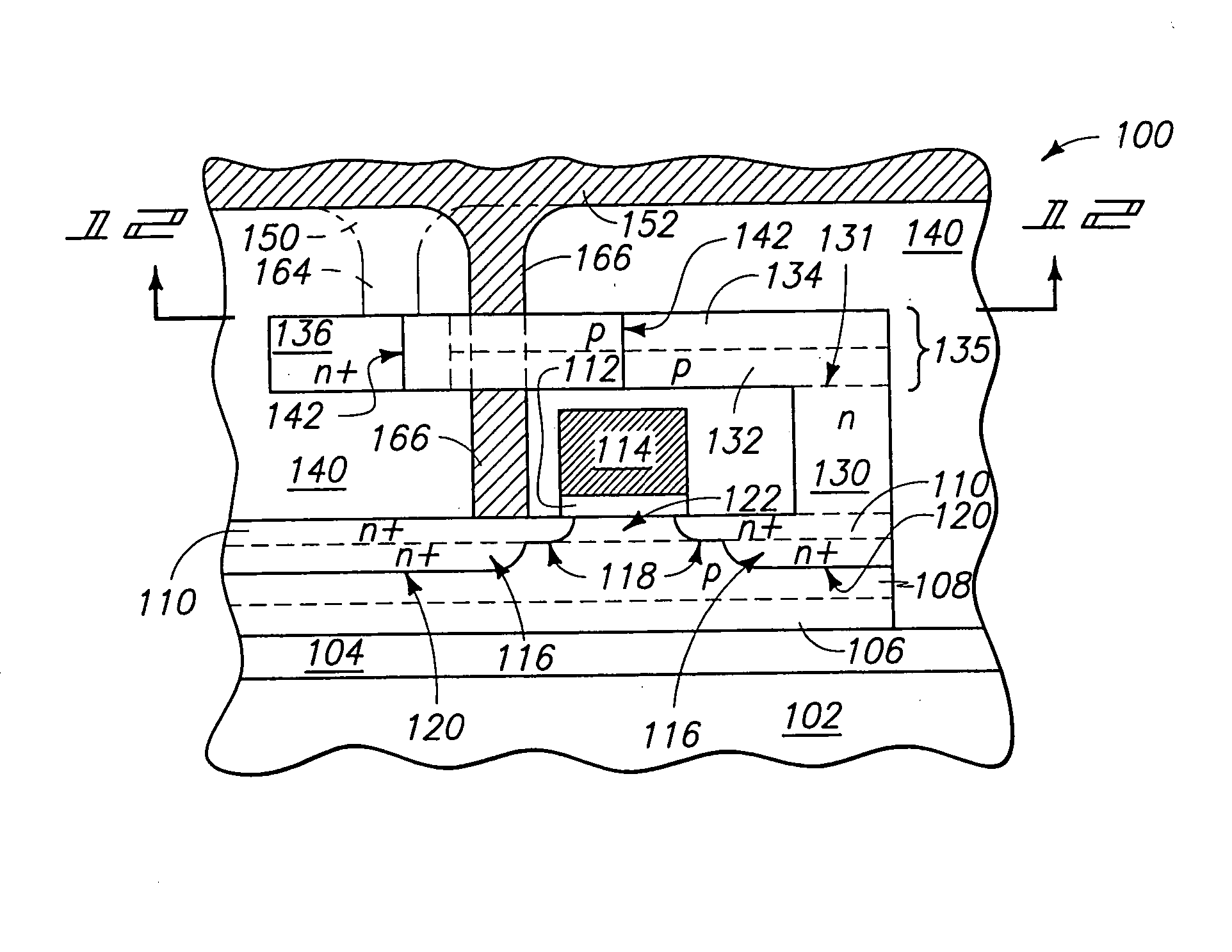

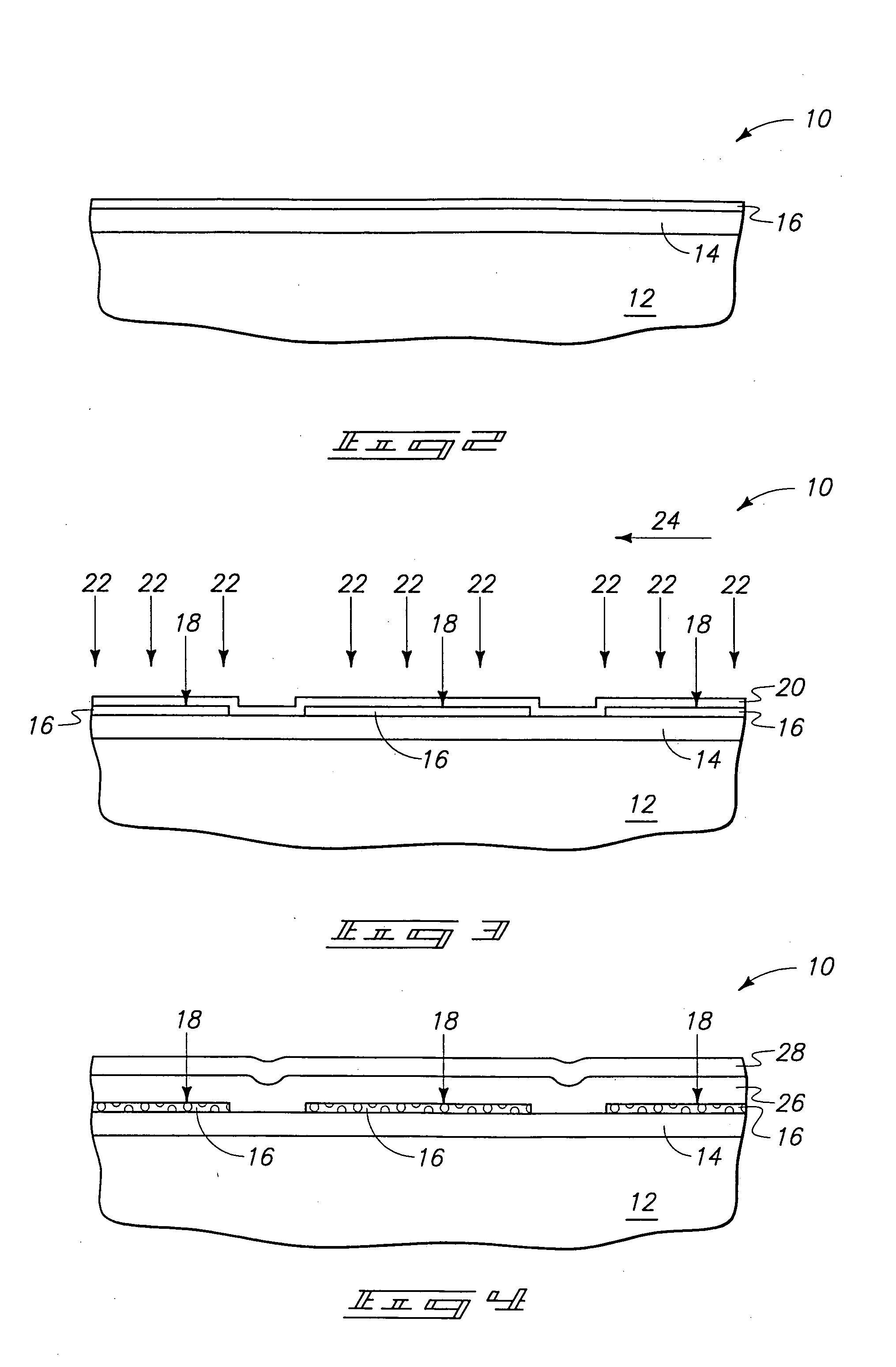

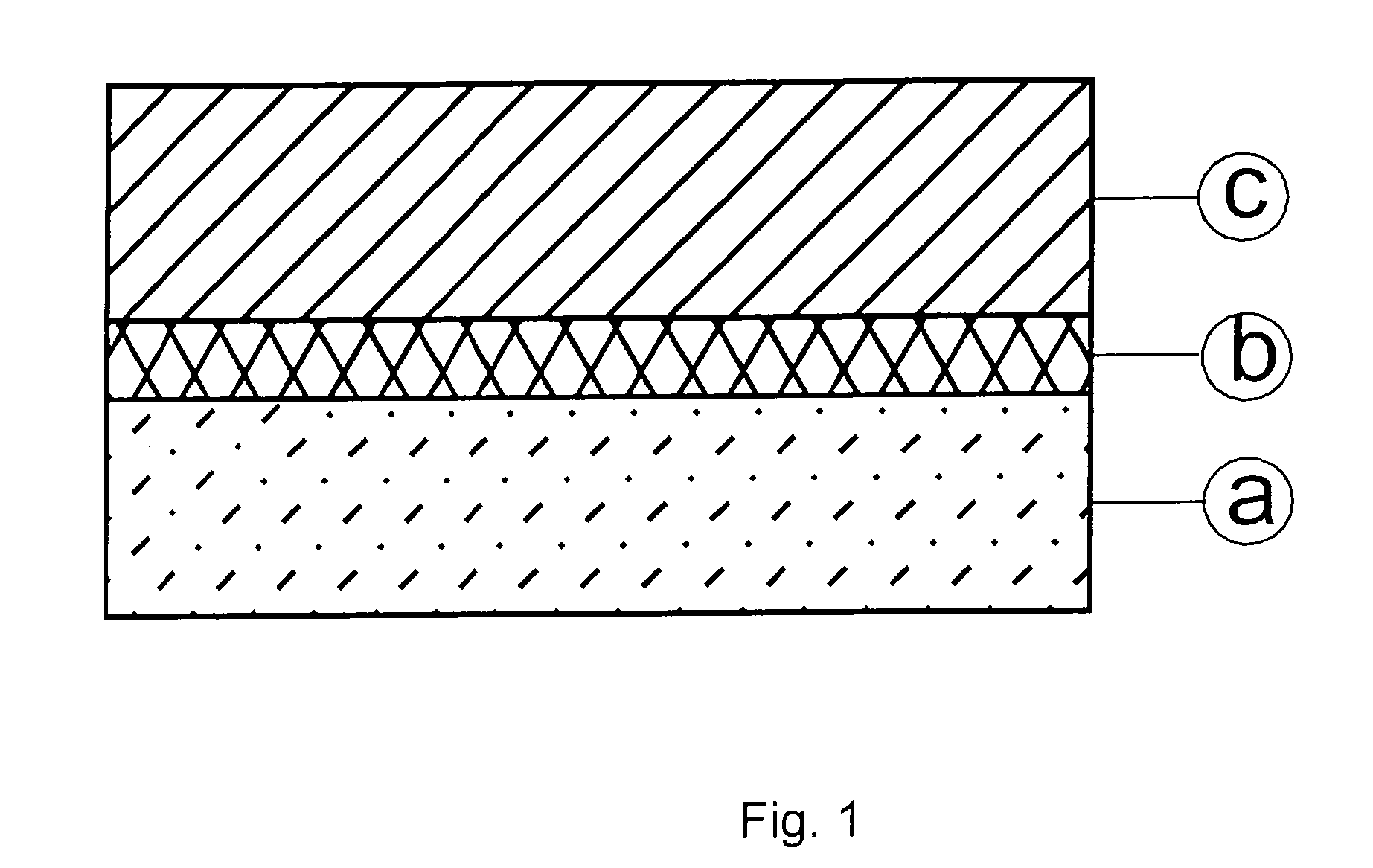

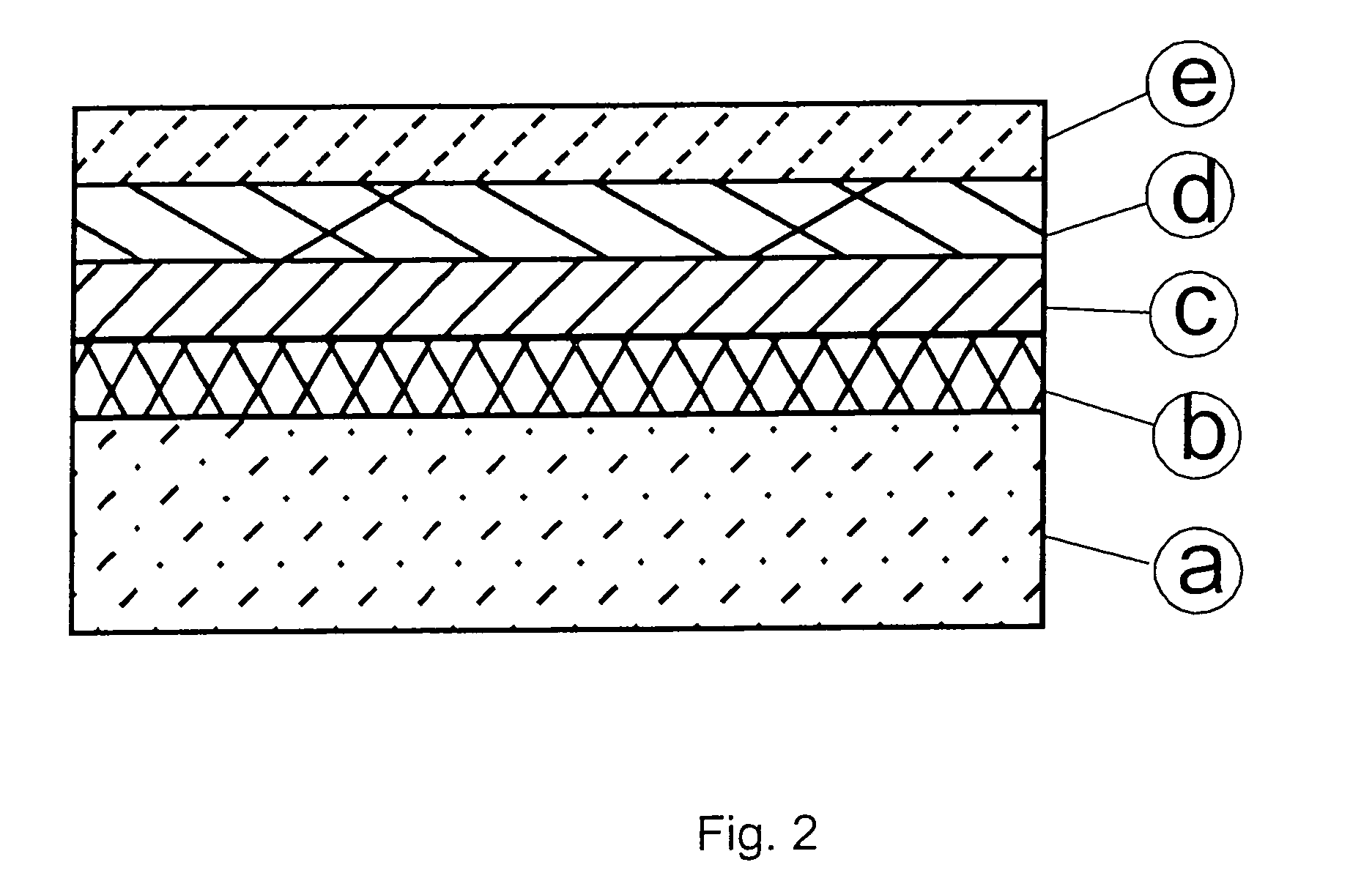

Processes of forming stacked resistor constructions

InactiveUS20050062045A1Semiconductor/solid-state device detailsSolid-state devicesSemiconductor structureElectrical connection

The invention includes semiconductor constructions having a thin film stacked resistor in electrical connection with a source / drain region of a transistor device. The resistor includes first and second crystalline layers which may or may not differ from one another. One of the first and second crystalline layers comprises doped silicon / germanium, and the other comprises doped silicon. The transistor device and resistor can be part of an SOI construction formed over a conventional substrate (such as a monocrystalline silicon wafer) or a non-conventional substrate (such as one or more of glass, aluminum oxide, silicon dioxide, metal and plastic). The invention also includes processes of forming semiconductor constructions, and in particular aspects, includes processes of forming resistor constructions.

Owner:MICRON TECH INC

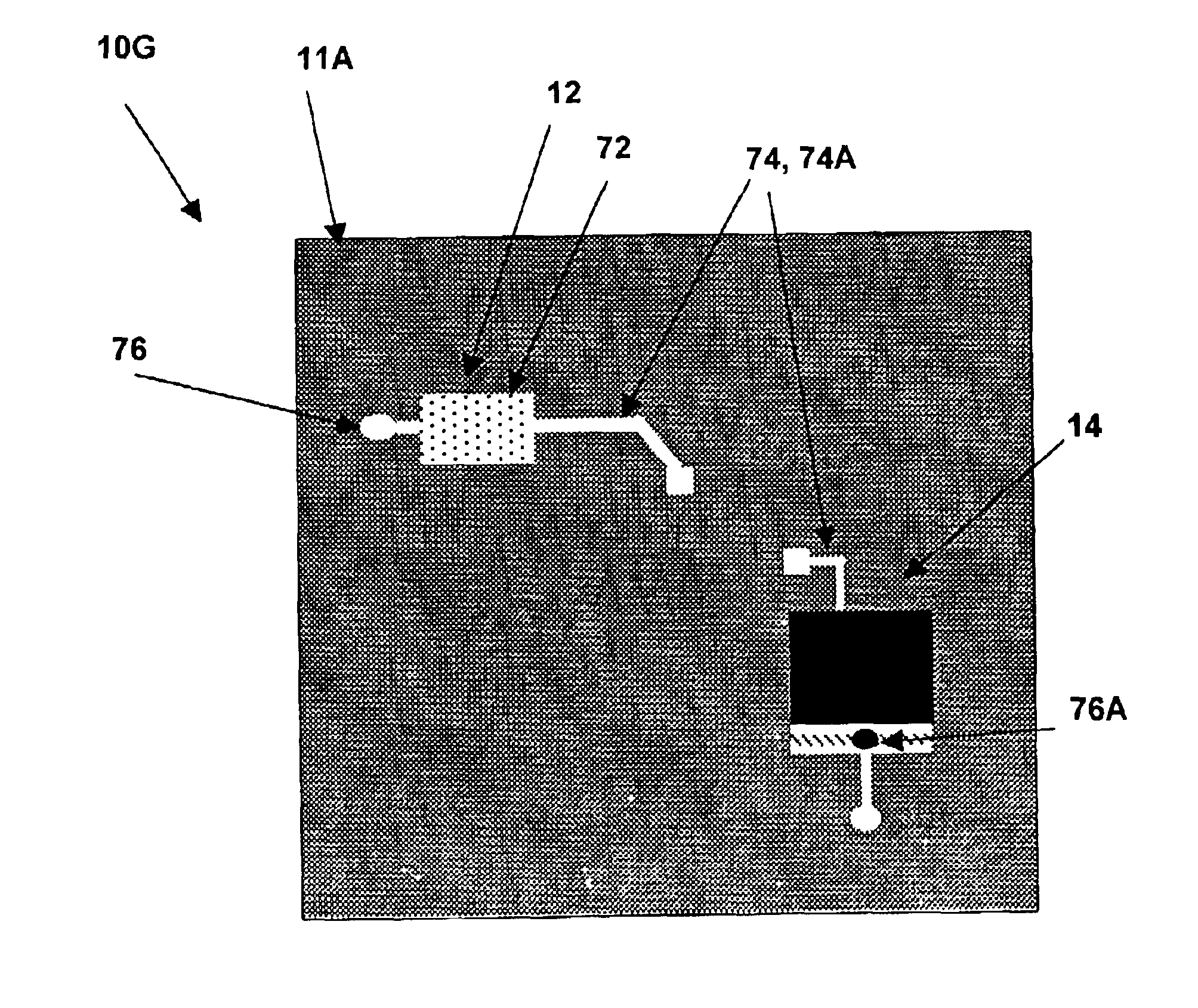

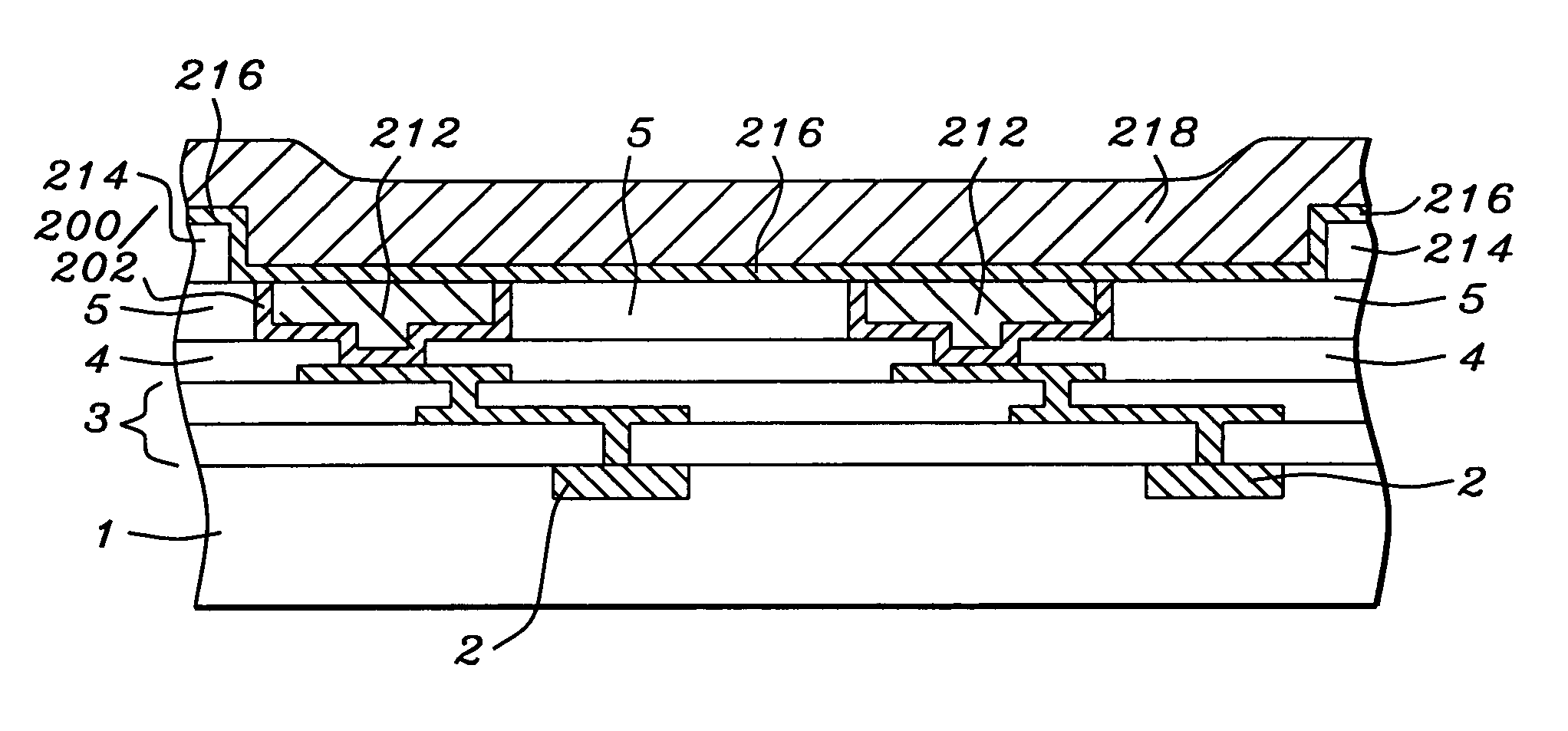

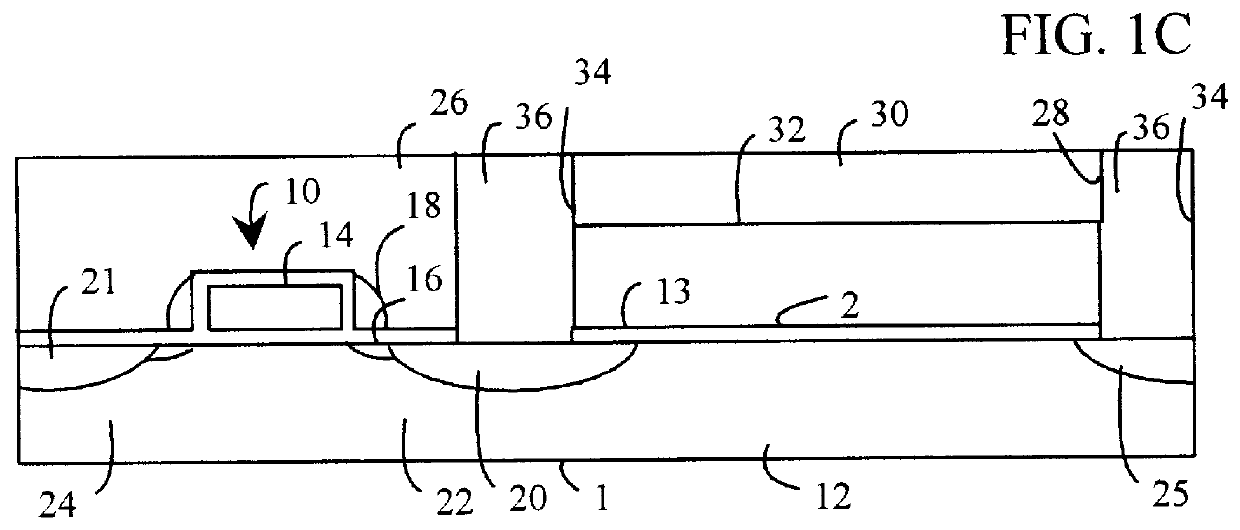

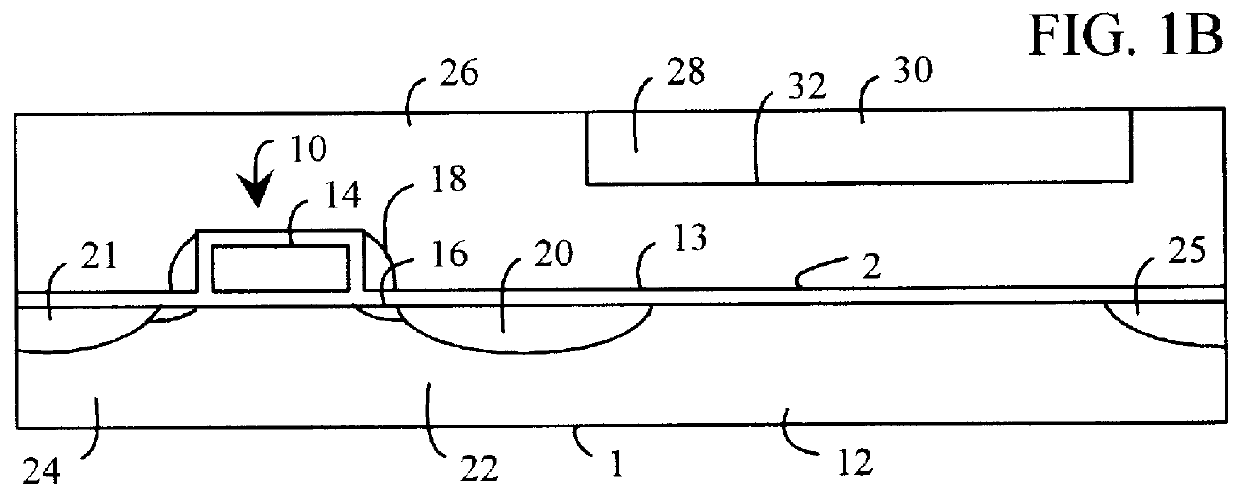

Integrated circuit substrate having embedded passive components and methods therefor

InactiveUS6987661B1Incremental costMultiple fixed capacitorsFixed capacitor dielectricConductive pasteConductive materials

An integrated circuit substrate having embdedded passive components provides a reduced cost and compact package for a die and one or more passive components. An insulating layer of the substrate is embossed or laser-ablated to generate apertures for insertion of a paste forming the body of the passive component. A resistive paste is used to form resistors and a dielectric paste is used for forming capacitors. A capacitor plate may be deposited at a bottom of the aperture by using a doped substrate material and activating only the bottom wall of the aperture, enabling plating of the bottom wall without depositing conductive material on the side walls of the aperture. Vias may be formed to the bottom plate by using a disjoint structure and conductive paste technology. Connection to the passive components may be made by conductive paste-filled channels forming conductive patterns on the substrate.

Owner:AMKOR TECH SINGAPORE HLDG PTE LTD

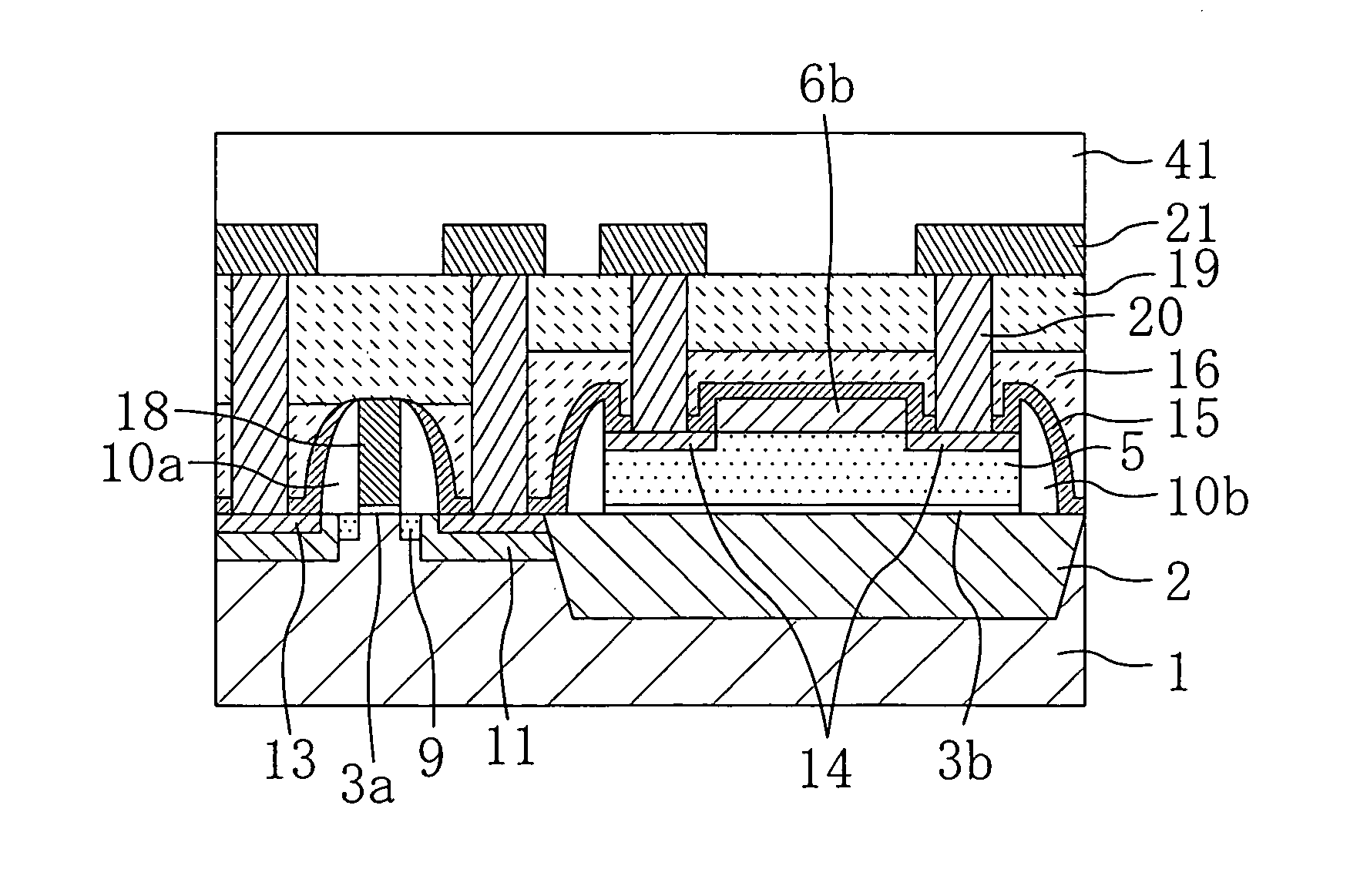

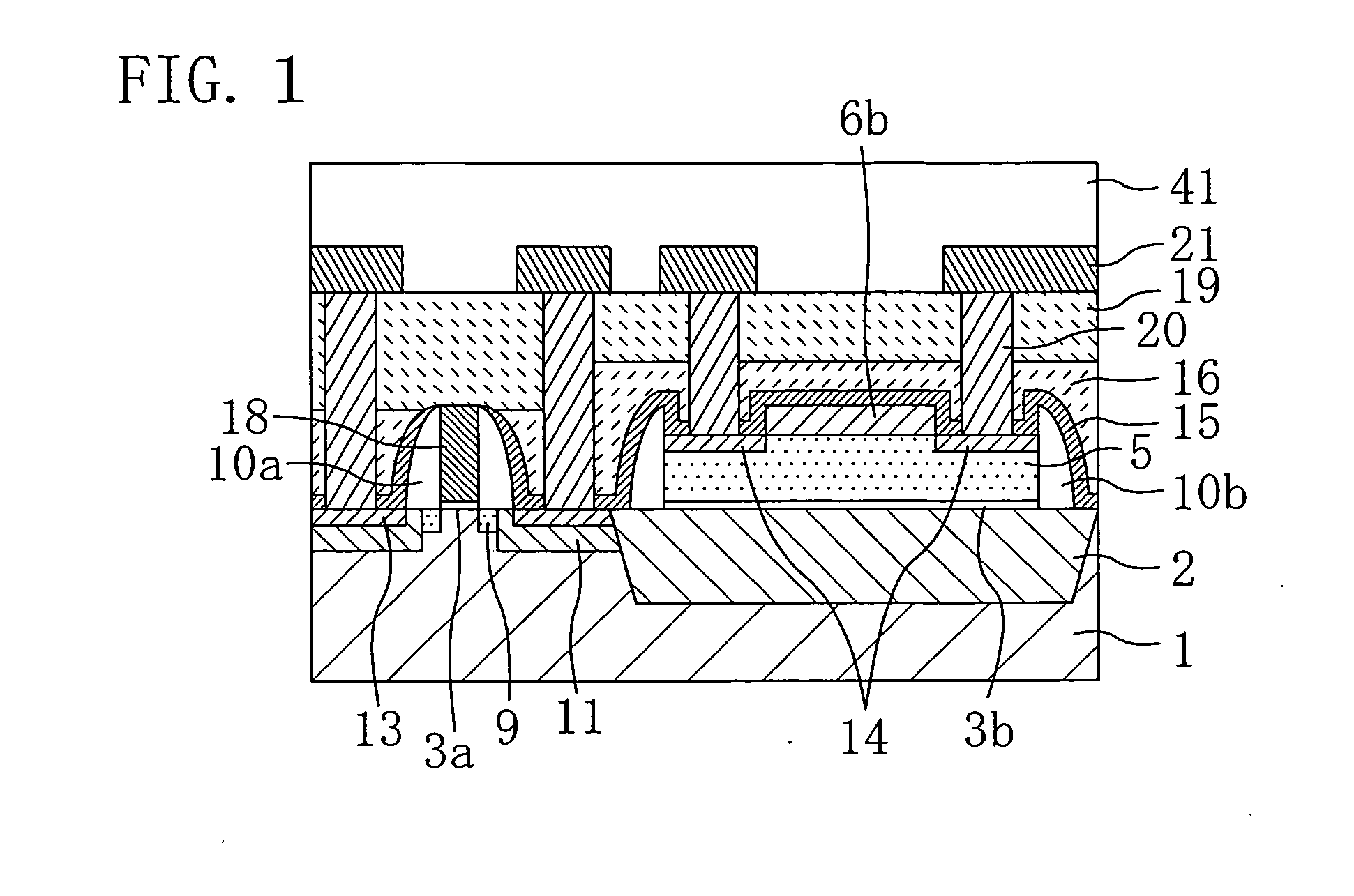

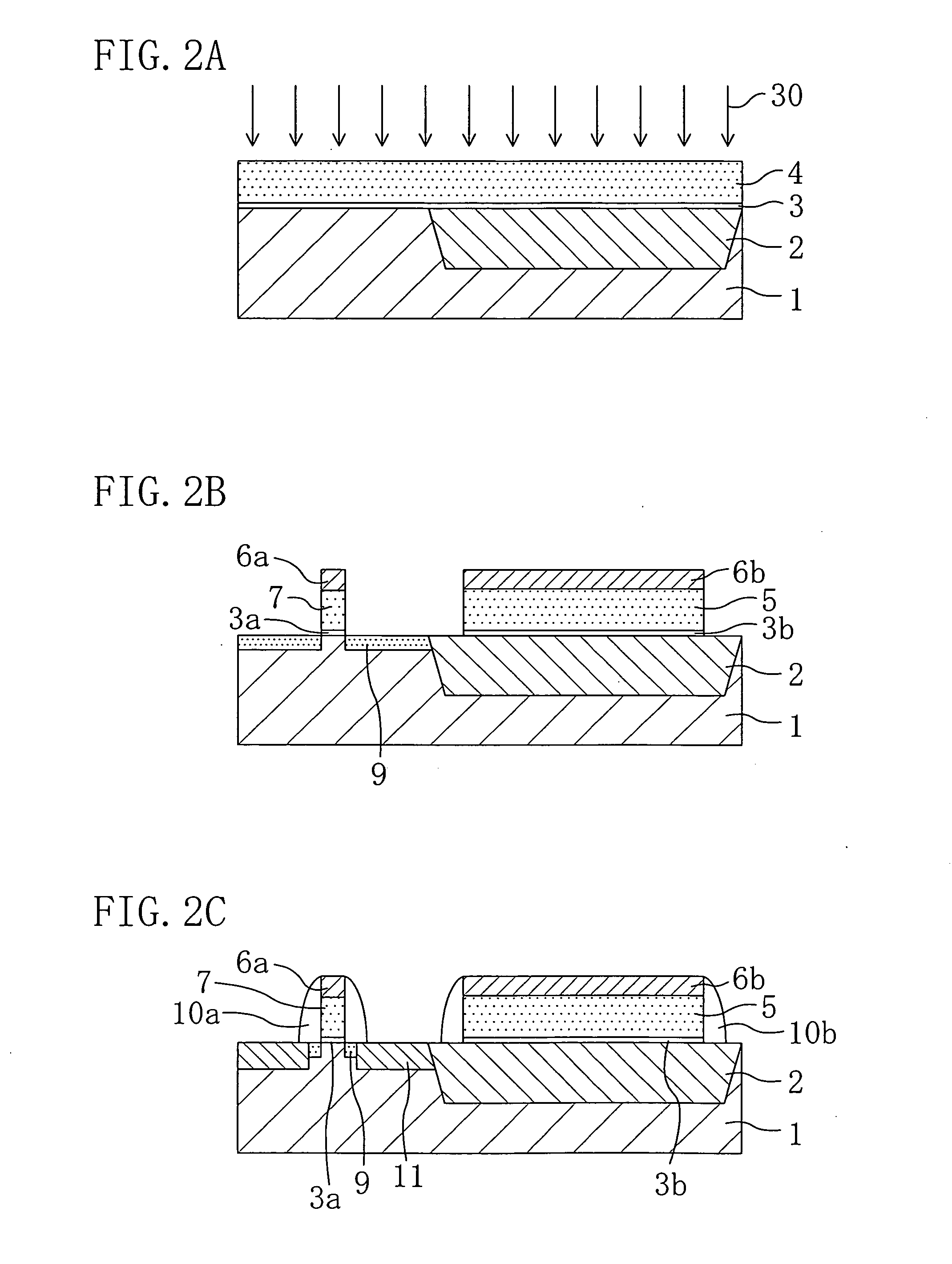

Semiconductor device and method for fabricating the same

InactiveUS20070096183A1Easy to manufactureReduce contact resistanceTransistorSolid-state devicesContact formationDevice material

In a semiconductor device including a MIS transistor with a FUSI gate electrode and a polysilicon resistor, a portion of the polysilicon resistor provided in a contact formation region is silicided simultaneously with the gate electrode or an impurity diffusion region.

Owner:PANASONIC CORP

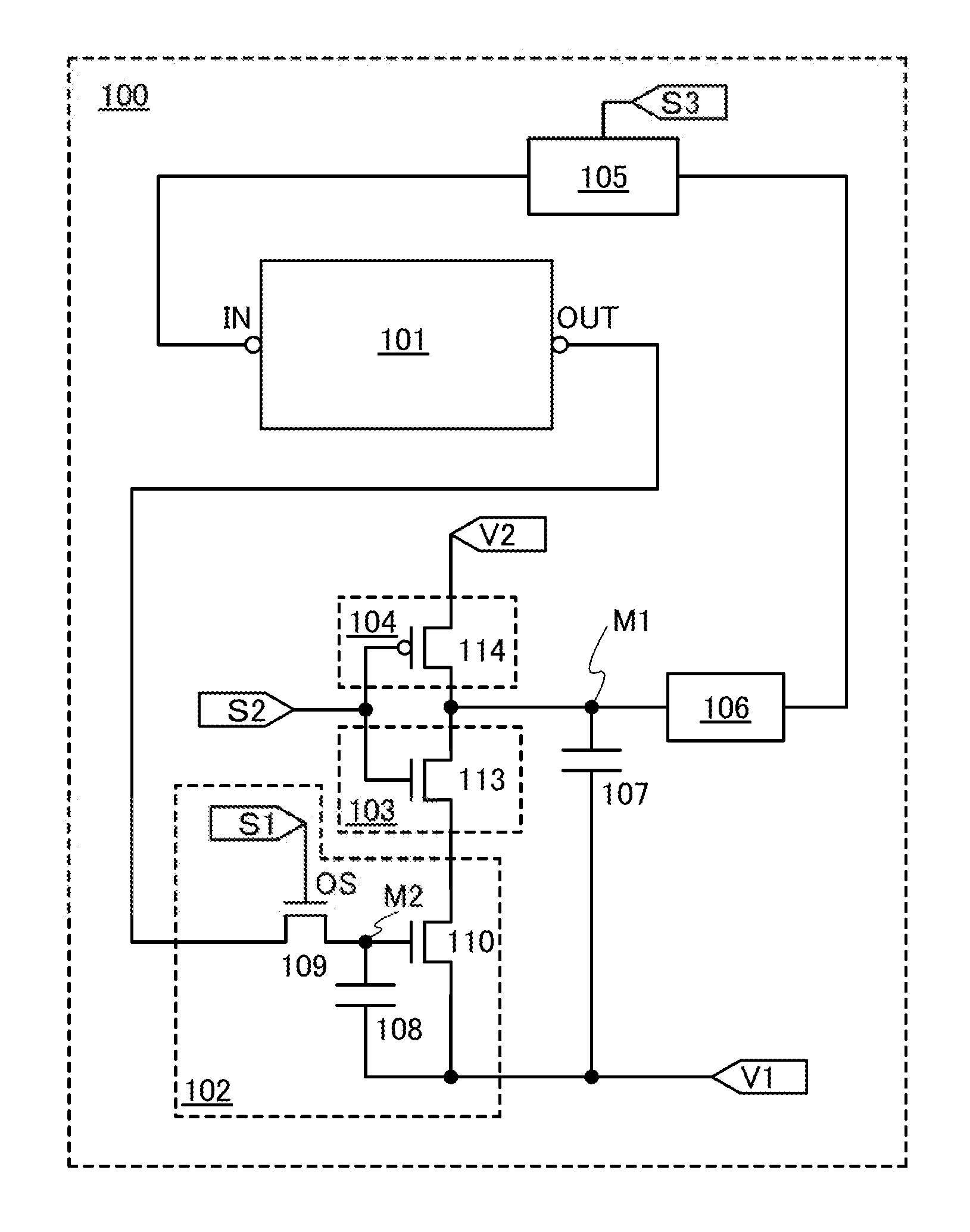

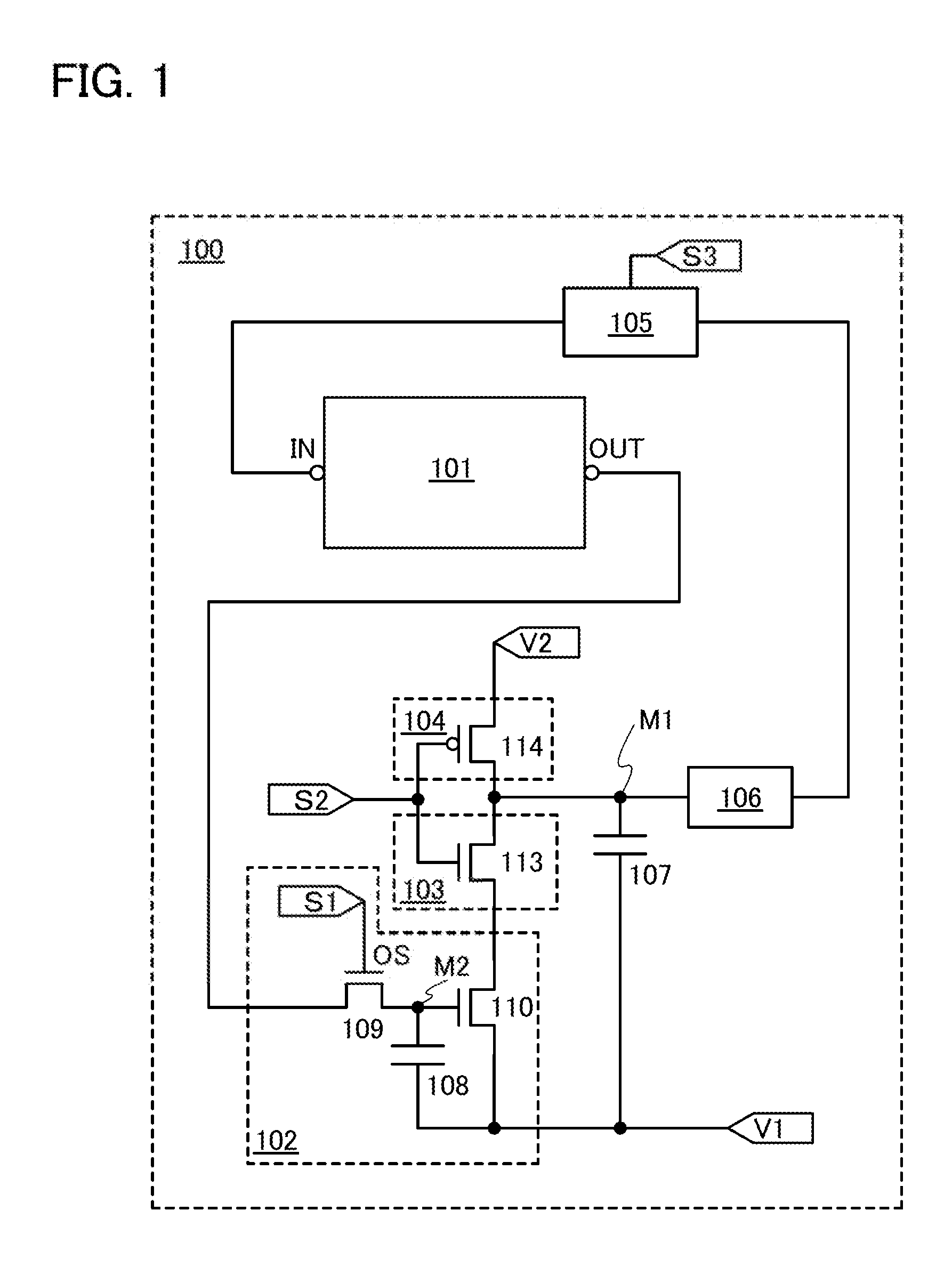

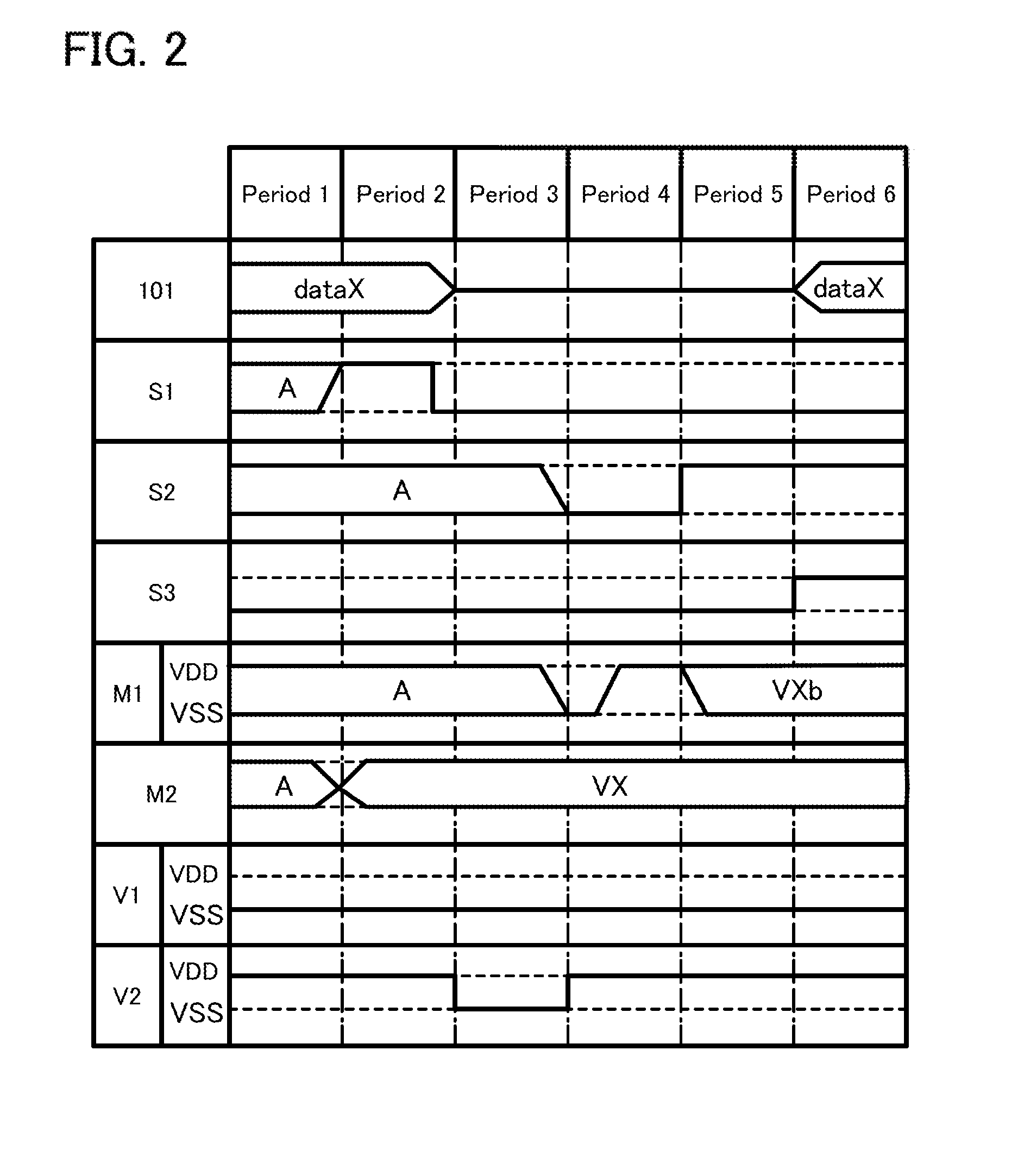

Storage element, storage device, and signal processing circuit

ActiveUS20120170355A1Accurate readingPrevent data storedTransistorEnergy efficient ICTSignal processing circuitsEngineering

A signal processing circuit whose power consumption can be suppressed is provided. In a period during which a power supply voltage is not supplied to a storage element, data stored in a first storage circuit corresponding to a nonvolatile memory can be held by a first capacitor provided in a second storage circuit. With the use of a transistor in which a channel is formed in an oxide semiconductor layer, a signal held in the first capacitor is held for a long time. The storage element can accordingly hold the stored content (data) also in a period during which the supply of the power supply voltage is stopped. A signal held by the first capacitor can be converted into the one corresponding to the state (the on state or off state) of the second transistor and read from the second storage circuit. Consequently, an original signal can be accurately read.

Owner:SEMICON ENERGY LAB CO LTD

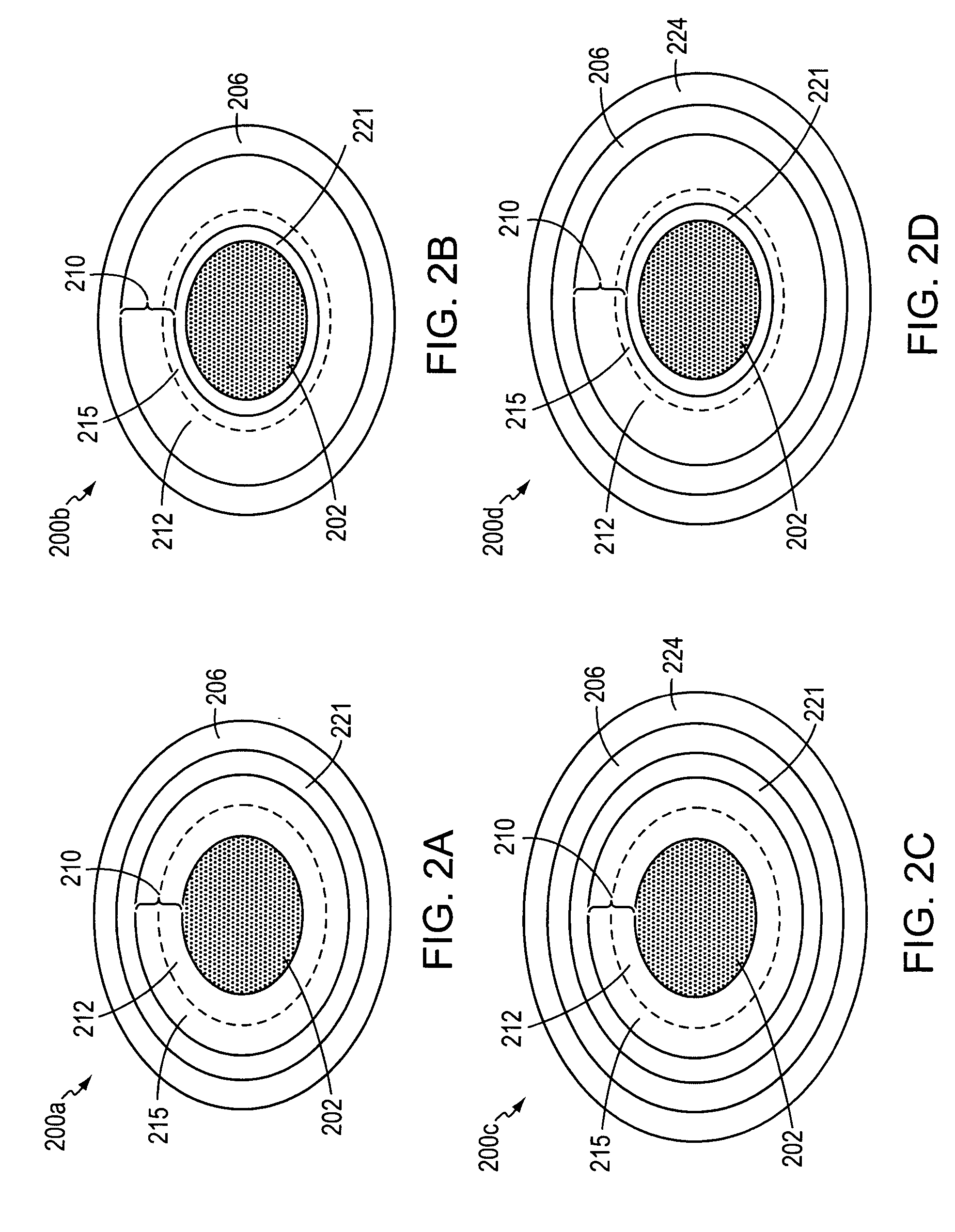

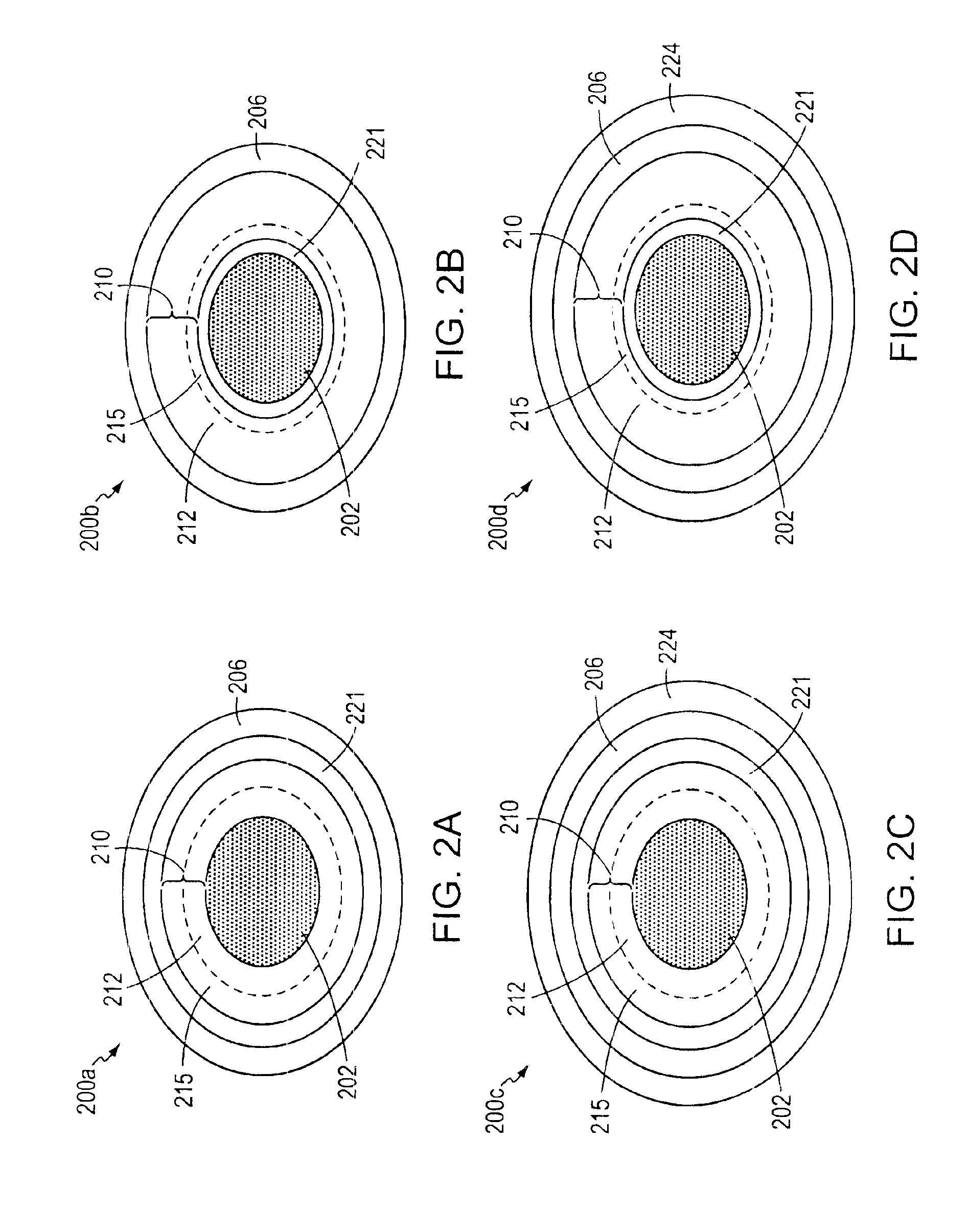

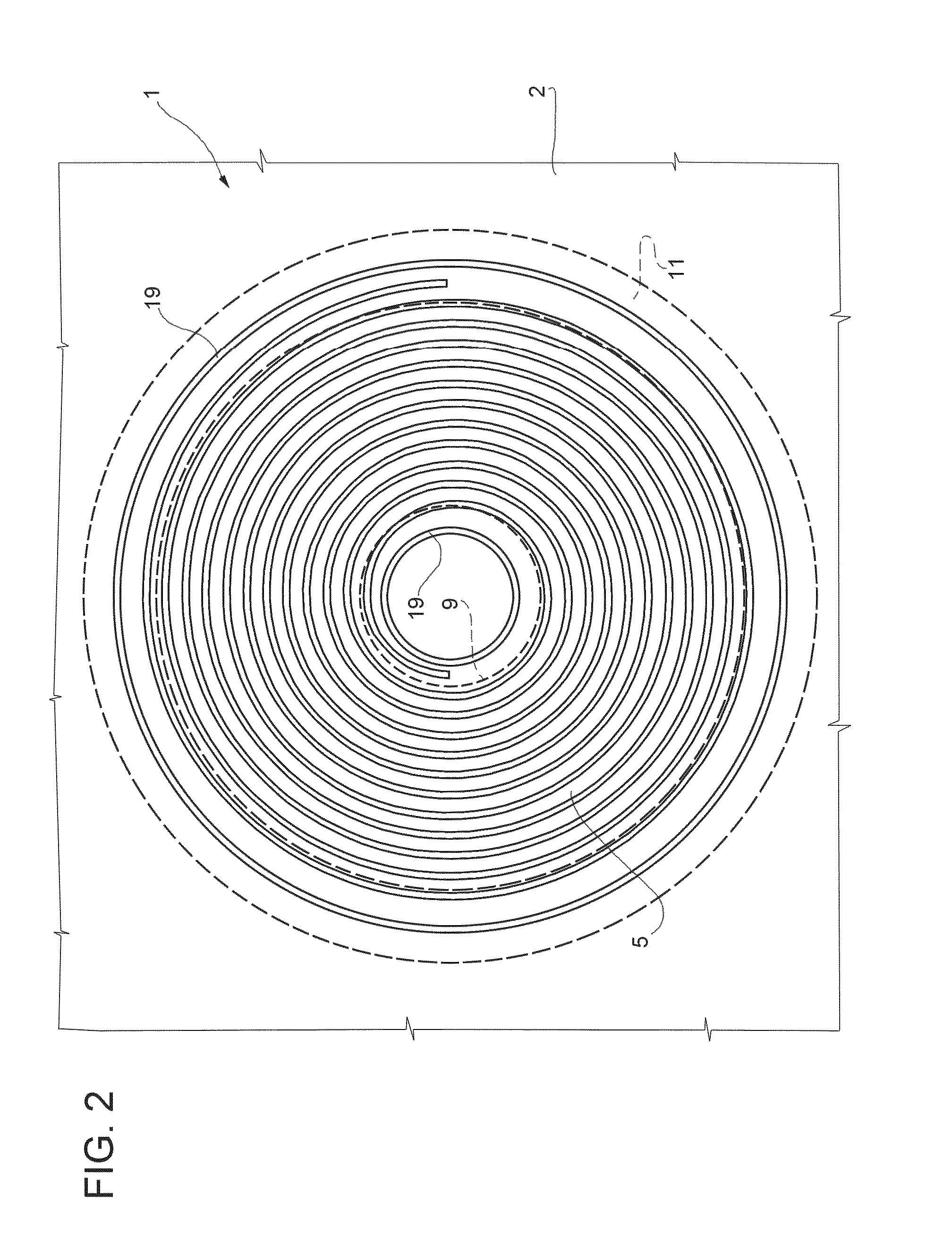

Semiconductor device integrating a voltage divider and process for manufacturing a semiconductor device

A semiconductor device includes: a semiconductor substrate; a high-voltage first resistive structure which extends along a spiral path above the substrate and is separated from the substrate by a first dielectric layer; and a conductive shielding structure, including a plurality of first shielding strips, which are arranged in sequence along respective portions of the first resistive structure and are separated from the first resistive structure by a second dielectric layer.

Owner:STMICROELECTRONICS INT NV

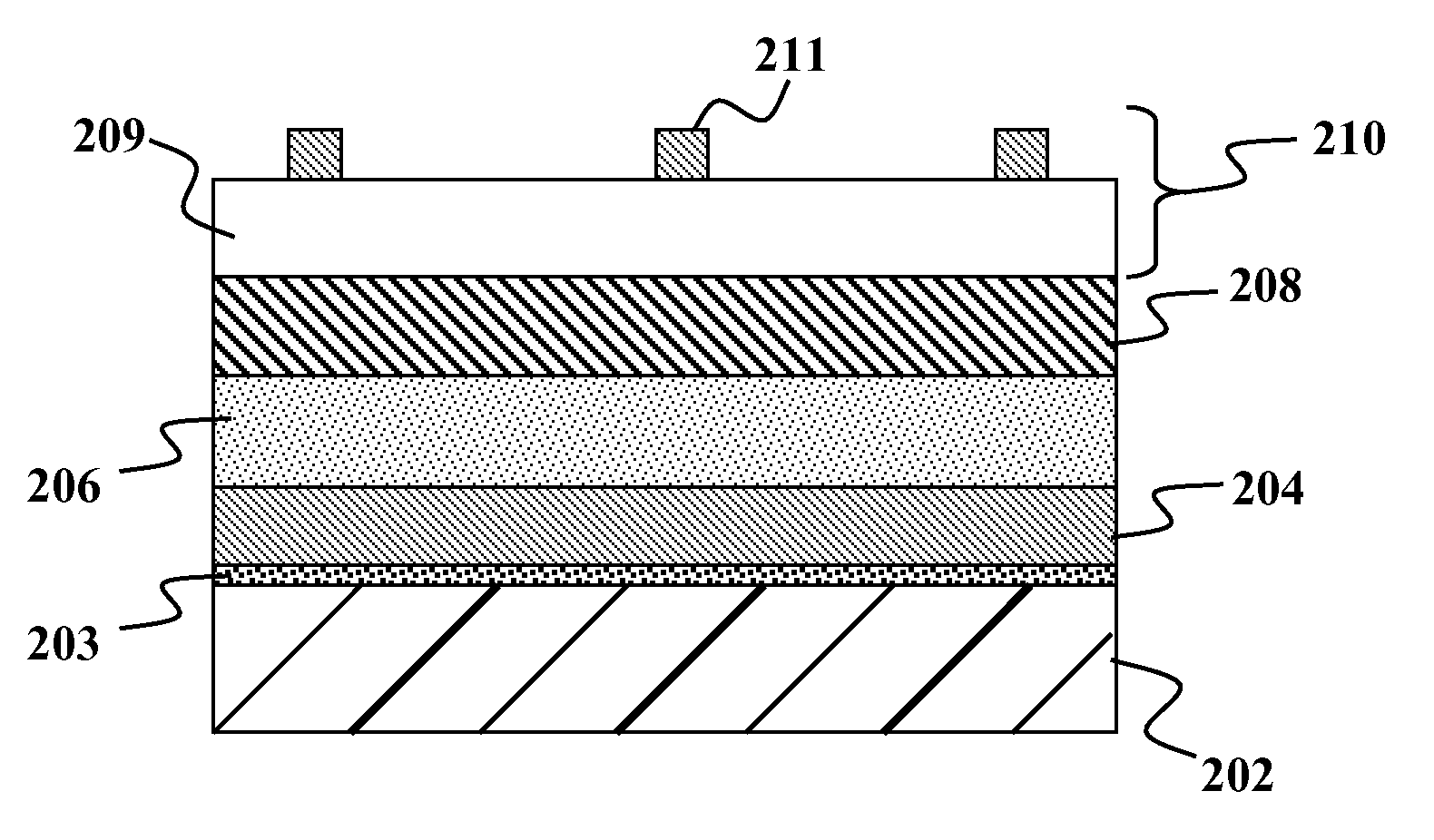

Solution-based fabrication of photovoltaic cell

InactiveUS20080135811A1Improve overall utilizationLow costMaterial nanotechnologyNanostructure manufactureNanoparticleSolar cell

An ink for forming CIGS photovoltaic cell active layers is disclosed along with methods for making the ink, methods for making the active layers and a solar cell made with the active layer. The ink contains a mixture of nanoparticles of elements of groups IB, IIIA and (optionally) VIA. The particles are in a desired particle size range of between about 1 nm and about 500 nm in diameter, where a majority of the mass of the particles comprises particles ranging in size from no more than about 40% above or below an average particle size or, if the average particle size is less than about 5 nanometers, from no more than about 2 nanometers above or below the average particle size. The use of such ink avoids the need to expose the material to an H2Se gas during the construction of a photovoltaic cell and allows more uniform melting during film annealing, more uniform intermixing of nanoparticles, and allows higher quality absorber films to be formed.

Owner:YU DONG +2

Post passivation method for semiconductor chip or wafer

InactiveUS7405149B1Improve performanceReduce resistive voltage dropSemiconductor/solid-state device detailsSolid-state devicesPolymer dielectricsSemiconductor chip

The present invention adds one or more thick layers of polymer dielectric and one or more layers of thick, wide metal lines on top of a finished semiconductor wafer, post-passivation. The thick, wide metal lines may be used for long signal paths and can also be used for power buses or power planes, clock distribution networks, critical signal, and re-distribution of I / O pads for flip chip applications. Photoresist defined electroplating, sputter / etch, or dual and triple damascene techniques are used for forming the metal lines and via fill.

Owner:QUALCOMM INC

Solution-based fabrication of photovoltaic cell

InactiveUS20080138501A1Improve overall utilizationLow costMaterial nanotechnologyNanostructure manufactureNanoparticleSolar cell

An ink for forming CIGS photovoltaic cell active layers is disclosed along with methods for making the ink, methods for making the active layers and a solar cell made with the active layer. The ink contains a mixture of nanoparticles of elements of groups IB, IIIA and (optionally) VIA. The particles are in a desired particle size range of between about 1 nm and about 500 nm in diameter, where a majority of the mass of the particles comprises particles ranging in size from no more than about 40% above or below an average particle size or, if the average particle size is less than about 5 nanometers, from no more than about 2 nanometers above or below the average particle size. The use of such ink avoids the need to expose the material to an H2Se gas during the construction of a photovoltaic cell and allows more uniform melting during film annealing, more uniform intermixing of nanoparticles, and allows higher quality absorber films to be formed.

Owner:YU DONG +2

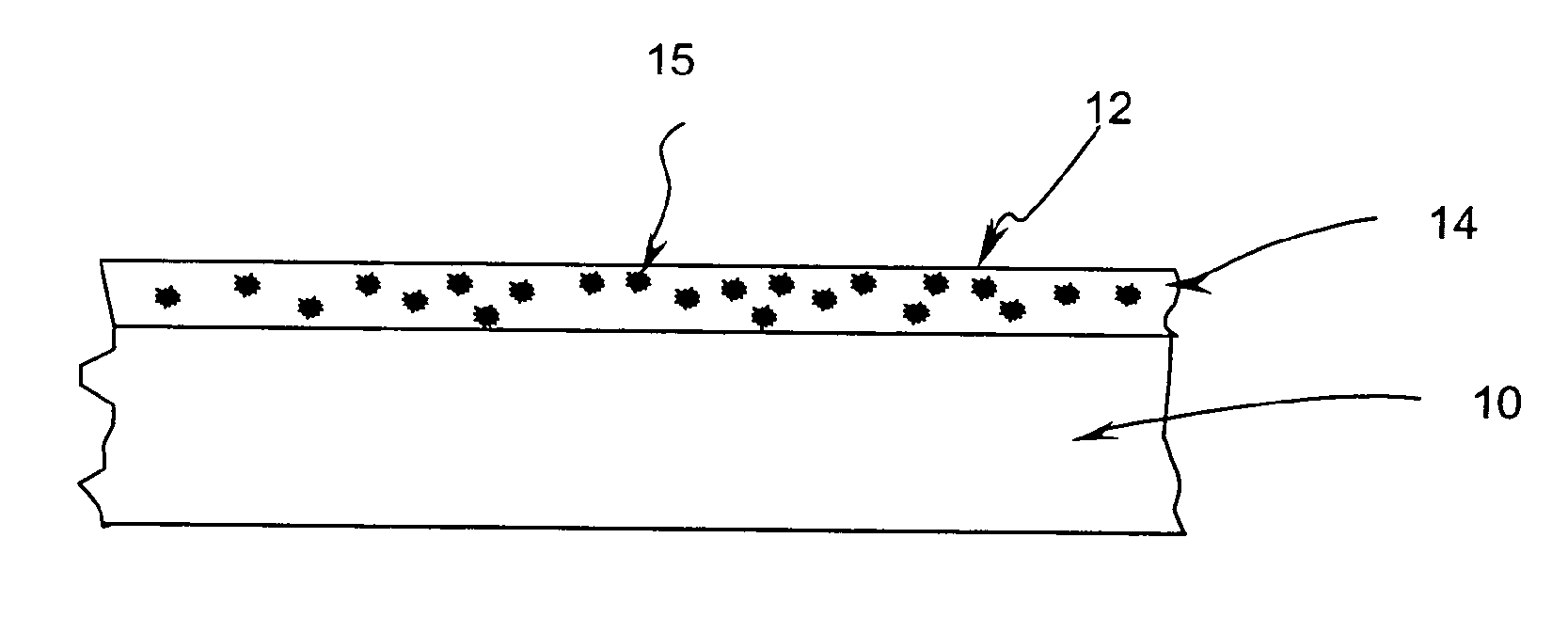

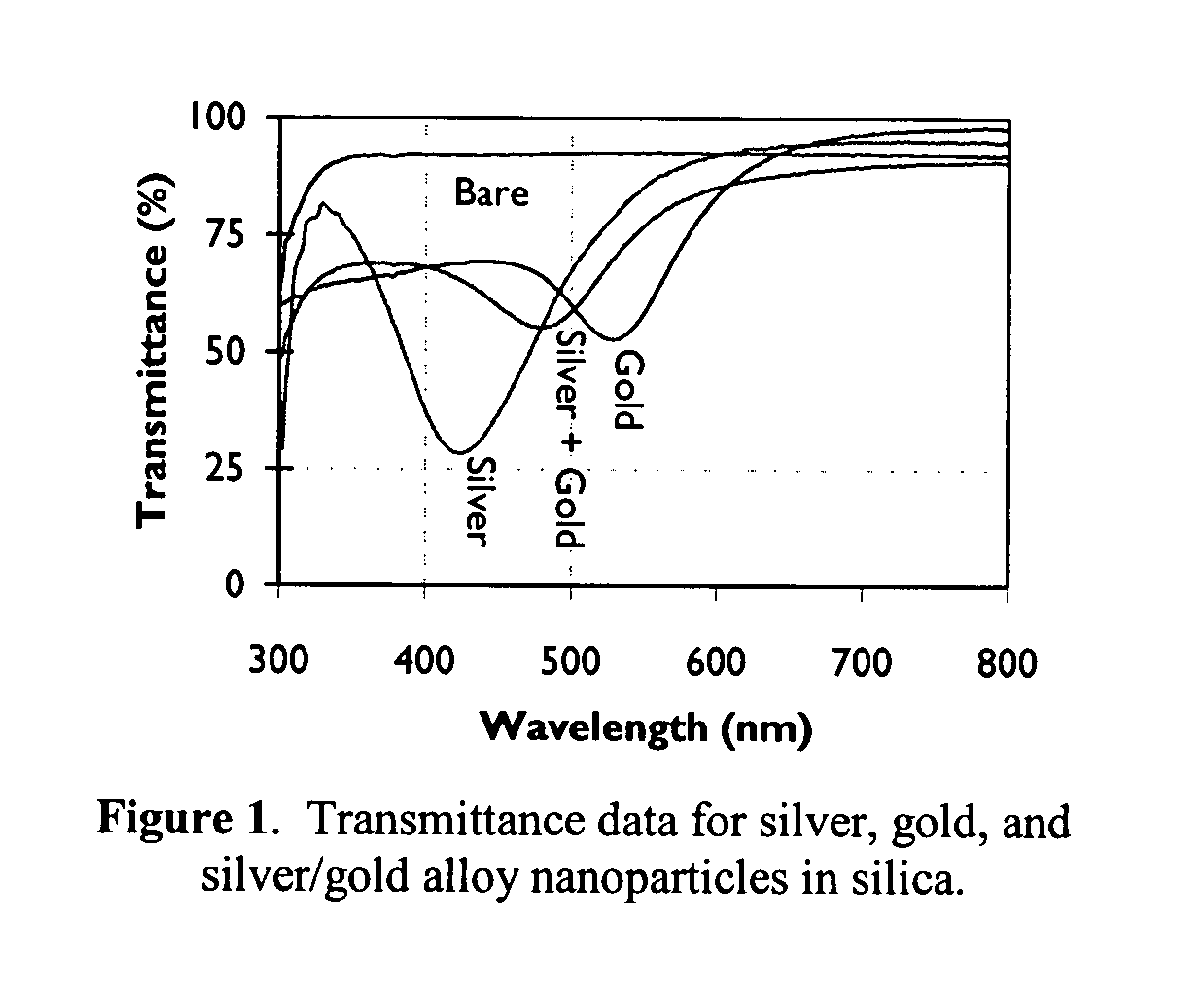

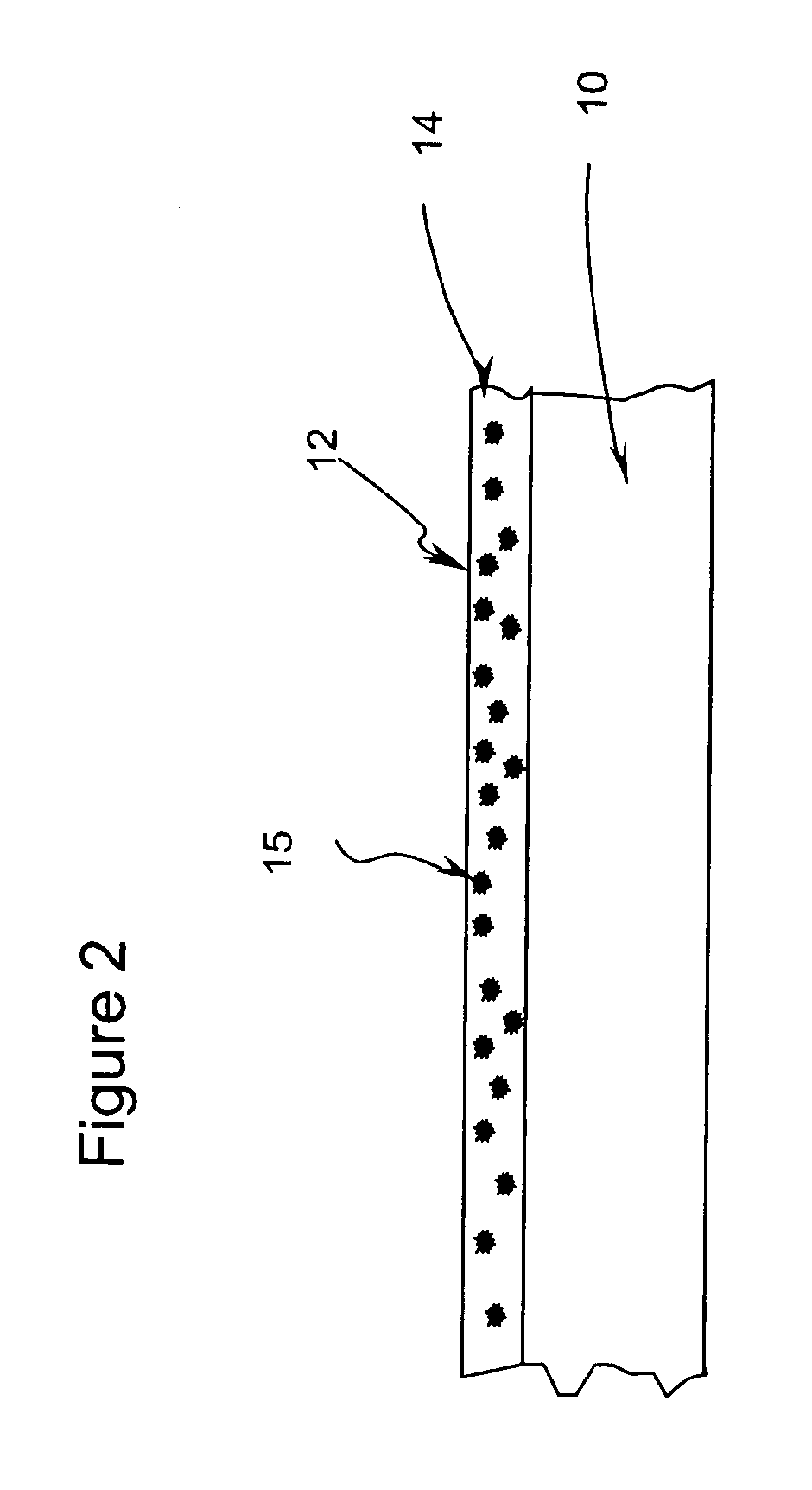

Optical coating

Optical coating materials comprise a transparent matrix material having dispersed nanoparticles comprising between 1 and 20 volume percent of the optical coating material. The coating materials are used to form optical coatings on substrates, such as glass / ceramic, polymer or metal, to alter the color or other optical properties. The nanoparticles are semiconductive material or elemental metals or elemental metal alloys that exhibit surface plasmon resonance.

Owner:POLLEY TODD A +4

Metal Plating Composition and Method for the Deposition of Copper-Zinc-Tin Suitable for Manufacturing Thin Film Solar Cell

InactiveUS20090205714A1Easy to manufactureClear processSemiconductor/solid-state device manufacturingOrganic dyesCopper platingTin plating

To be able to form a copper-zinc-tin alloy which optionally comprises at least one chalcogenide and thus forms a semiconductor without the use of toxic substances a metal plating composition for the deposition of a copper-zinc-tin alloy is disclosed, wherein said metal plating composition comprises at least one copper plating species, at lease one zinc plating species, at least one tin plating species and at least one complexing agent and further, if the alloy contains at least one chalcogen, at least one chalcogen plating species.

Owner:ATOTECH DEUT GMBH

Thin film resistor and fabrication method thereof

A resistor is formed between devices in an integrated circuit by forming a patterned trench in an intralayer dielectric (ILD) deposited over the devices, filling the trench with polysilicon and planarizing the polysilicon. The resistance of the resistor is defined by determining and selecting the size and form of the trench including the width, length, depth and orientation of the trench. In some embodiments, the resistance of the resistor is also controlled by adding selected amounts and species of dopants to the polysilicon. In some embodiments, the resistance is controlled by directly saliciding the polysilicon in the trench.

Owner:GLOBALFOUNDRIES INC