Patents

Literature

189results about "Magnetic-bias transformers" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

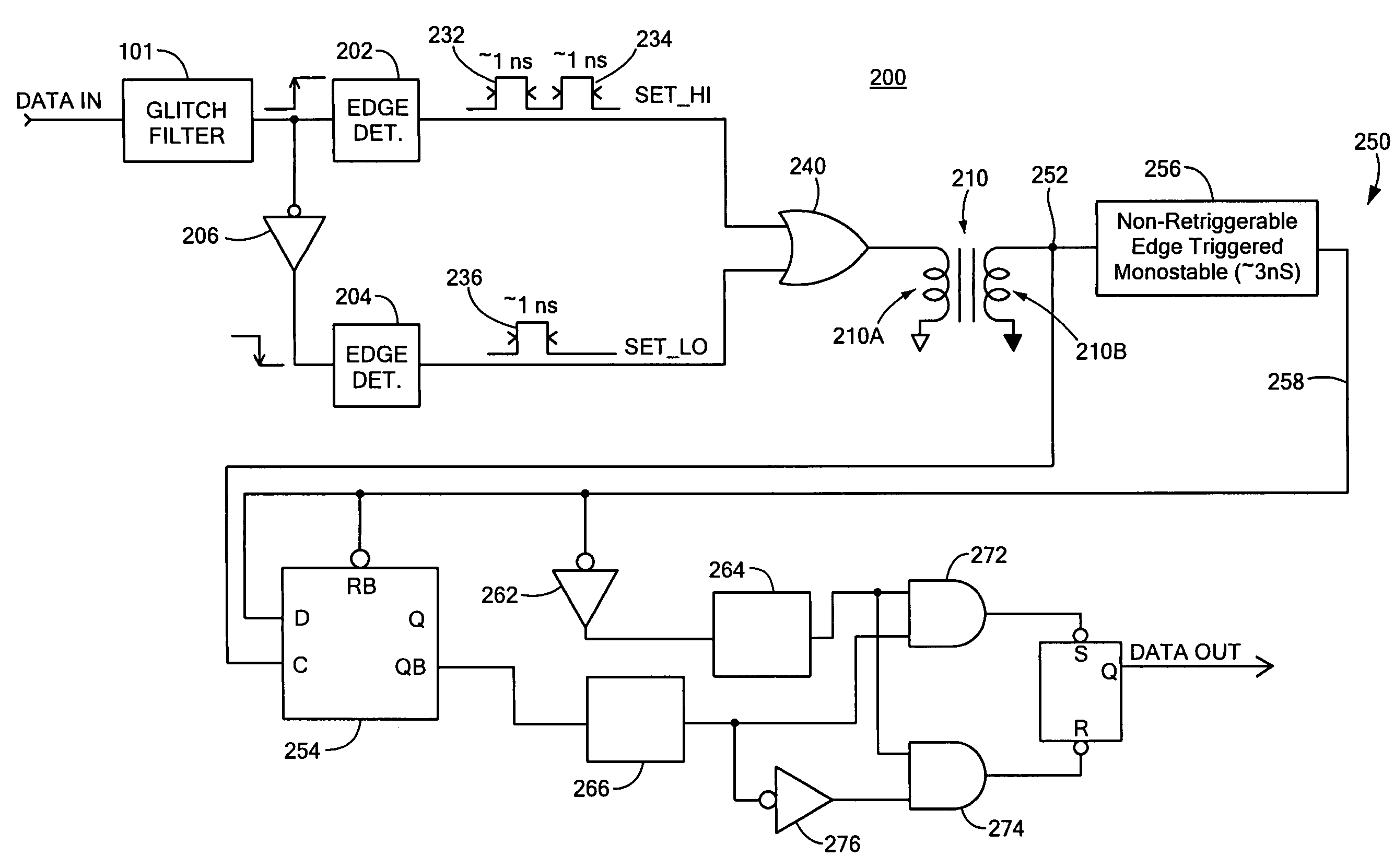

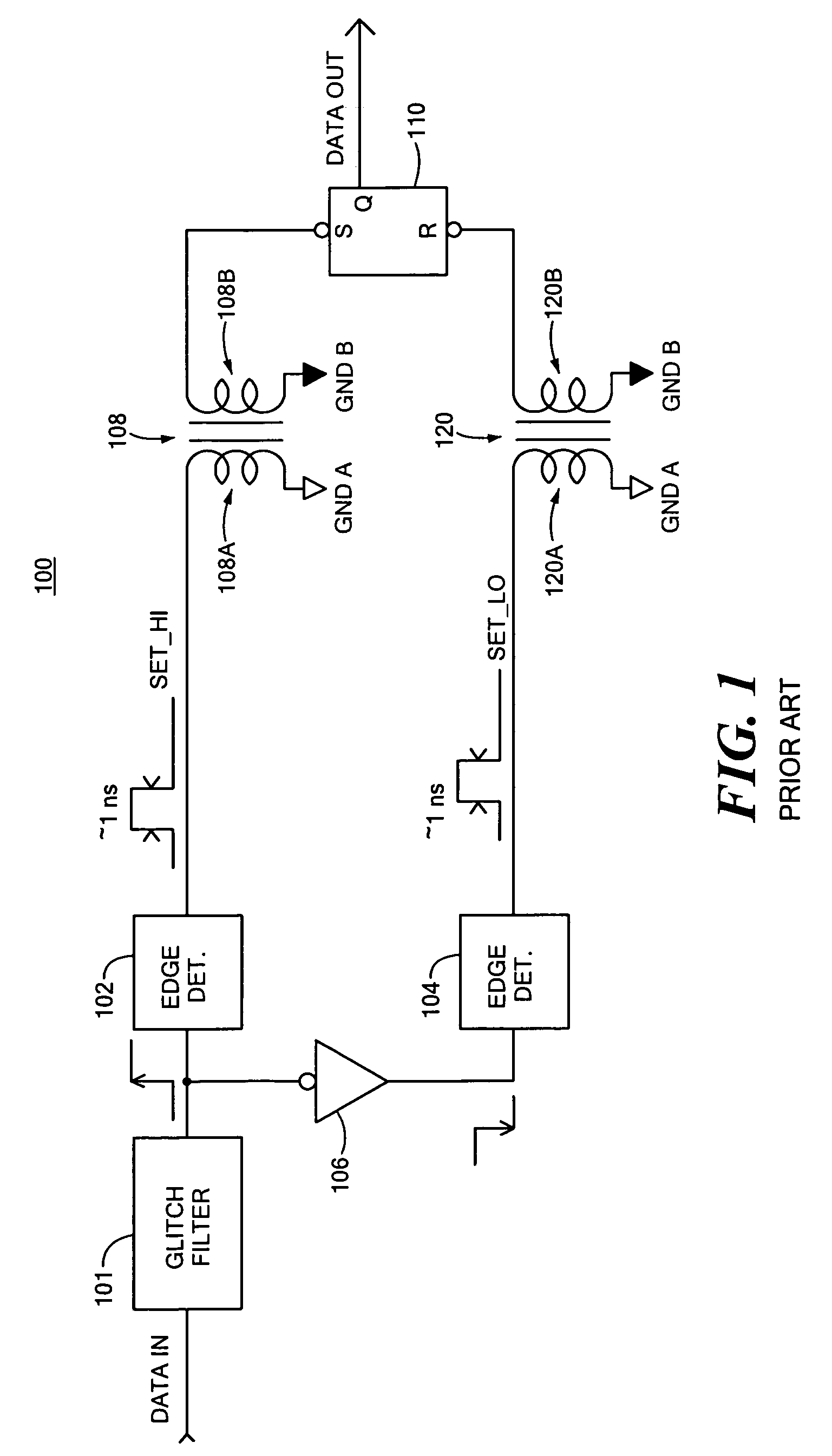

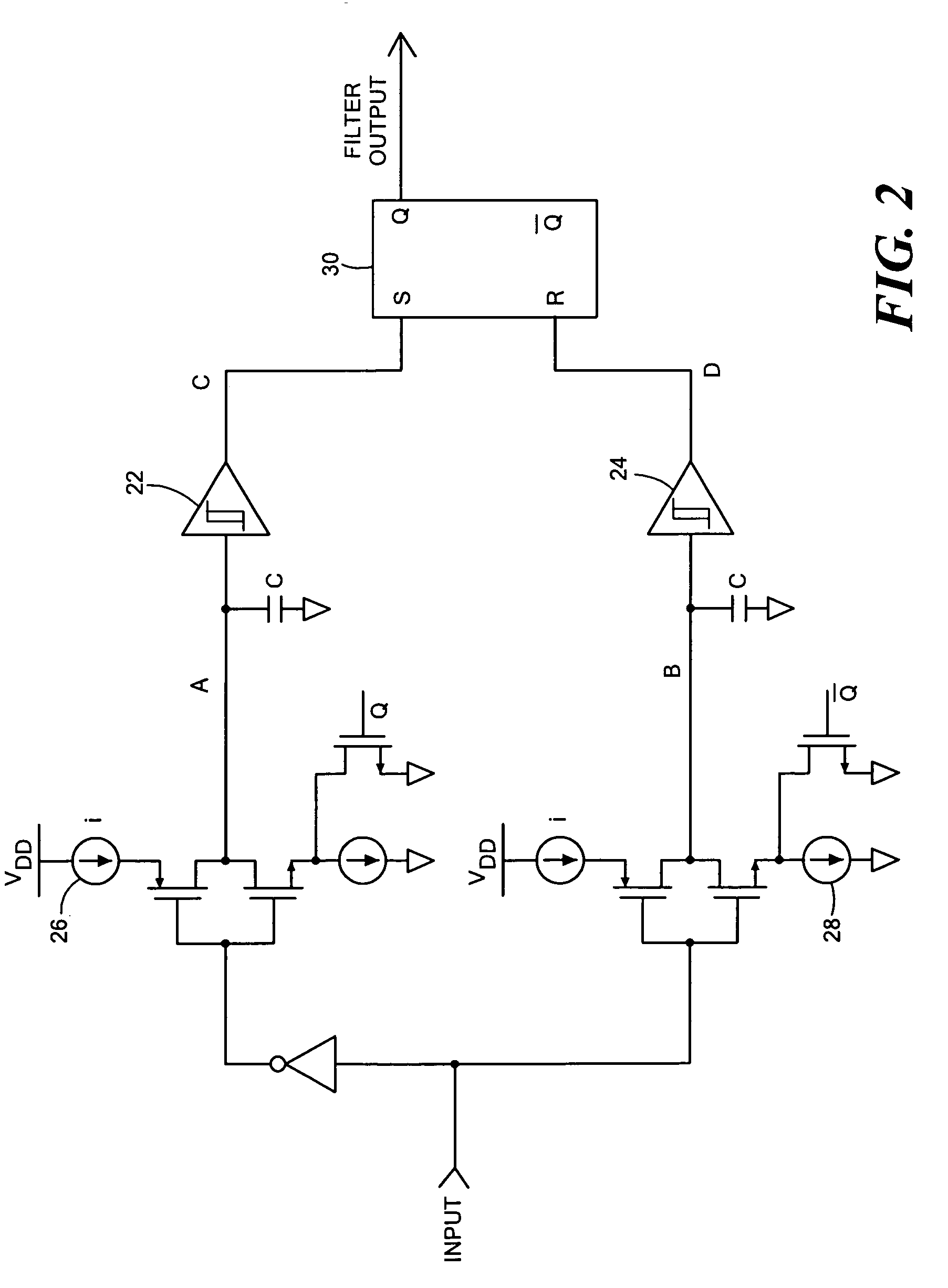

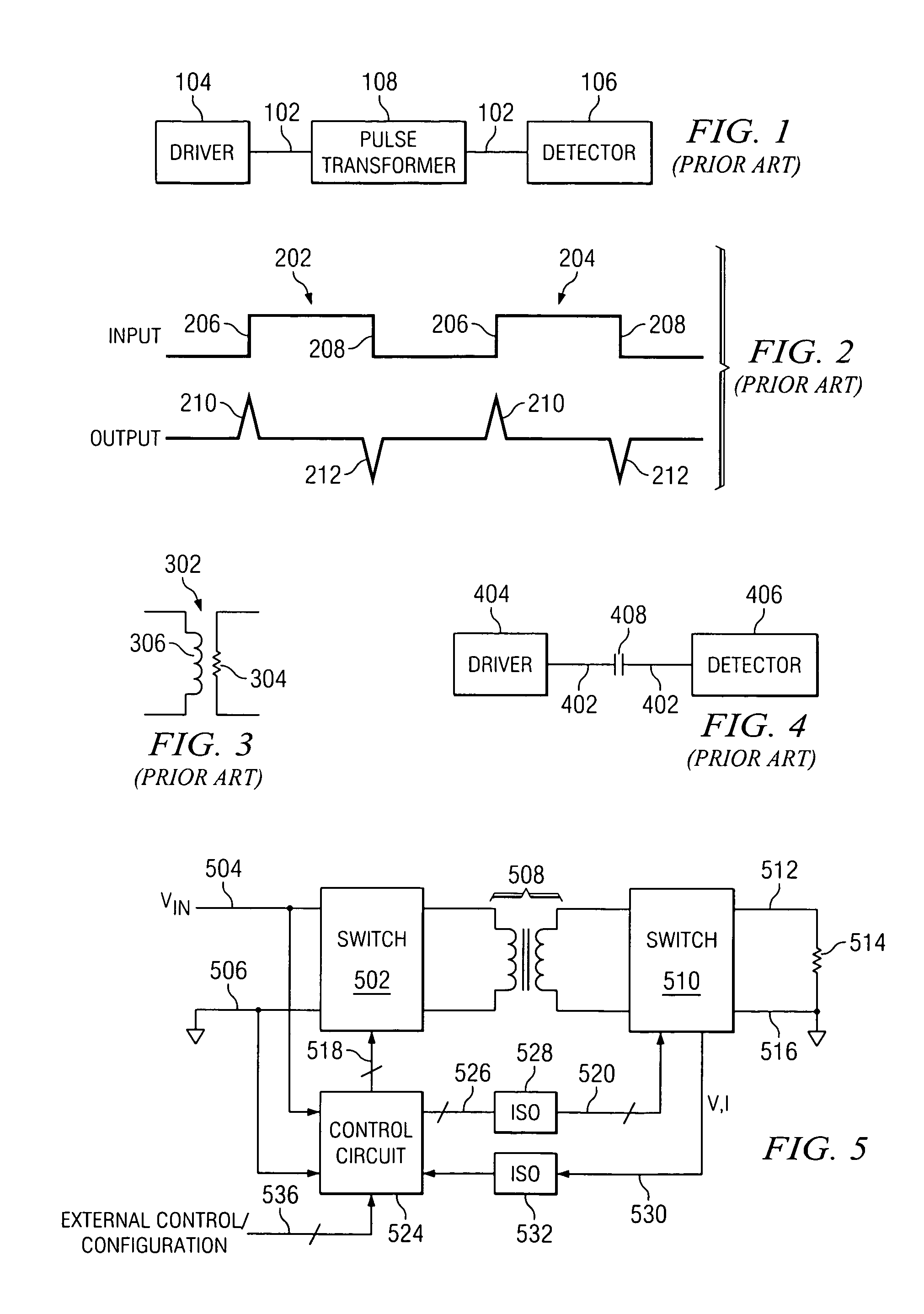

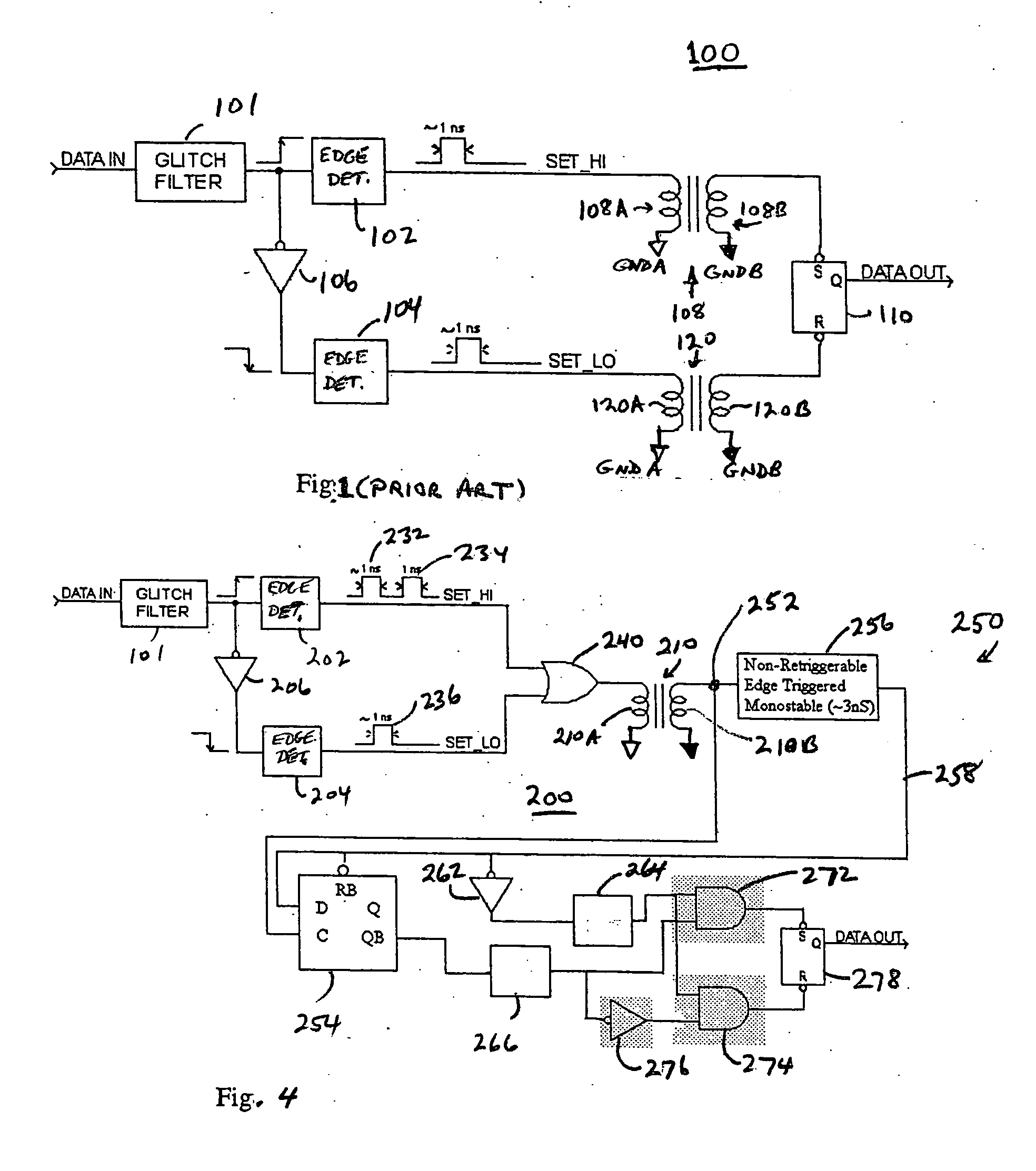

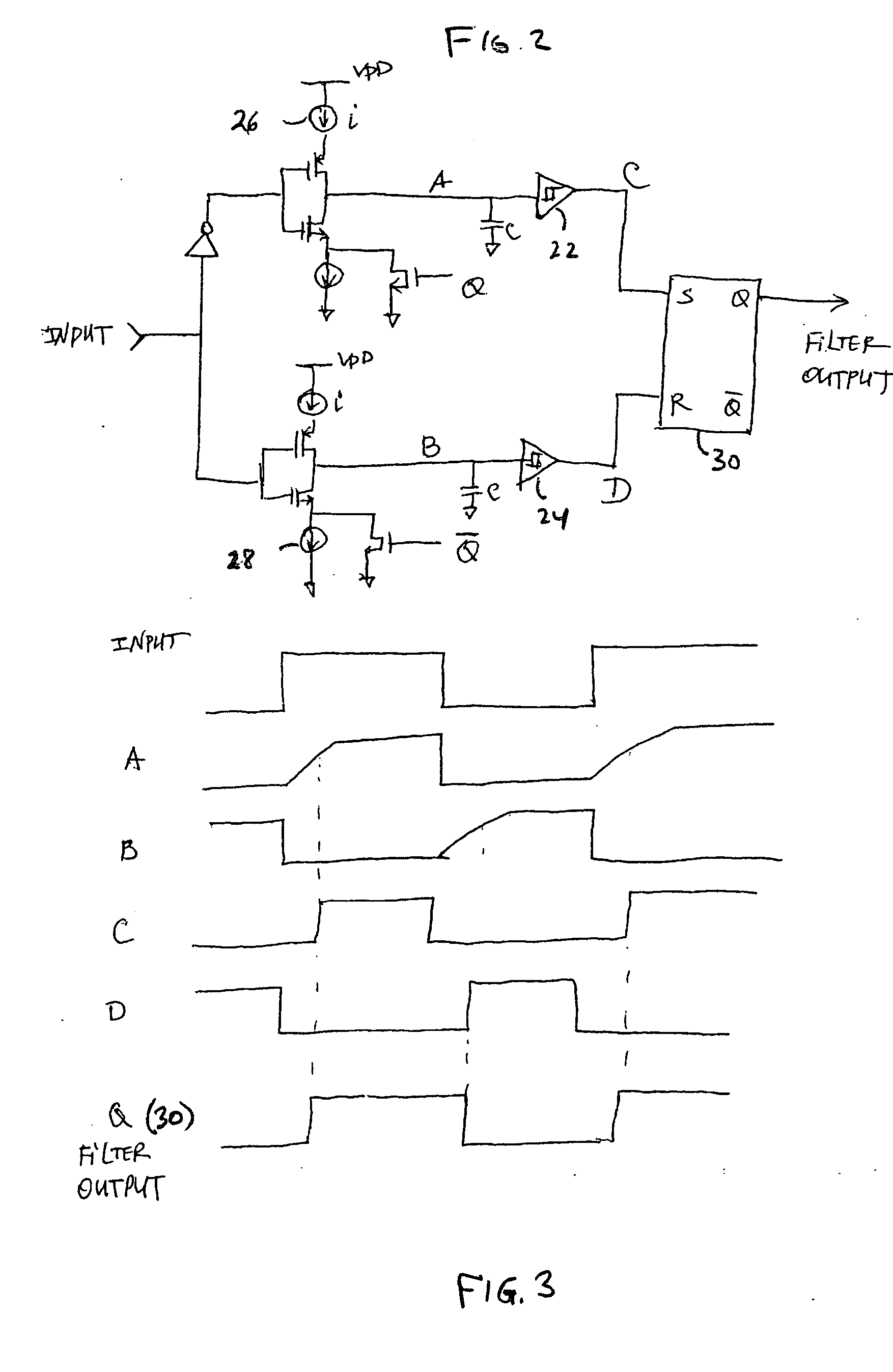

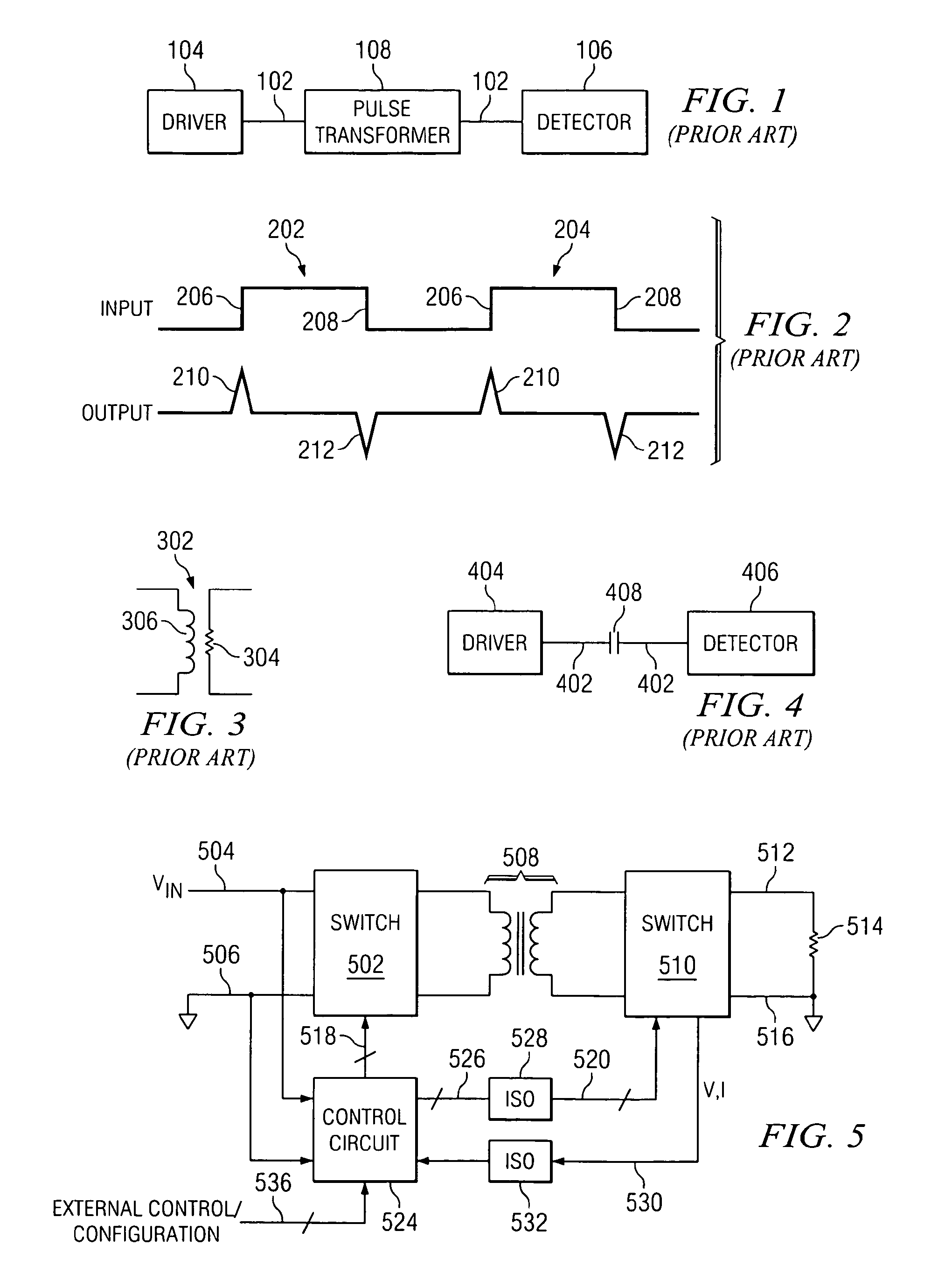

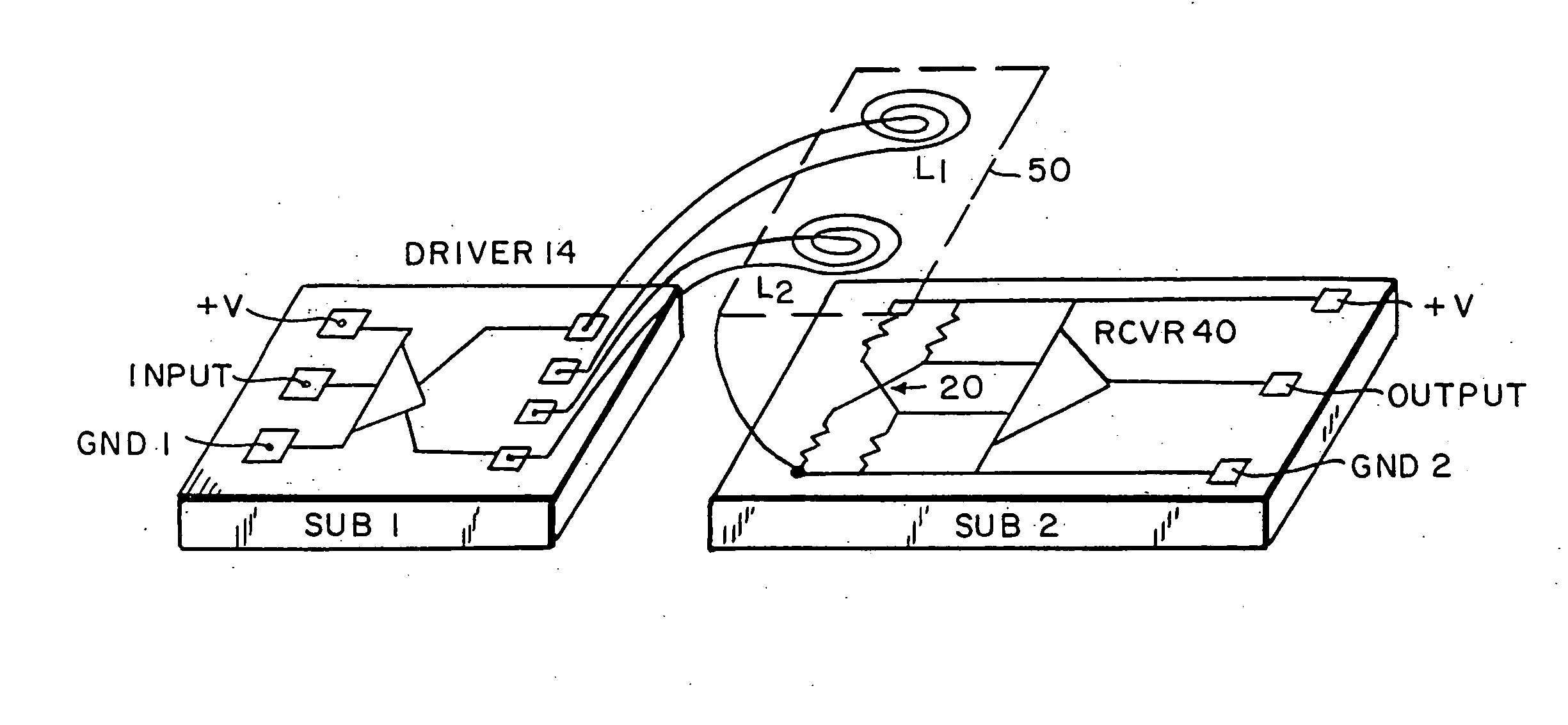

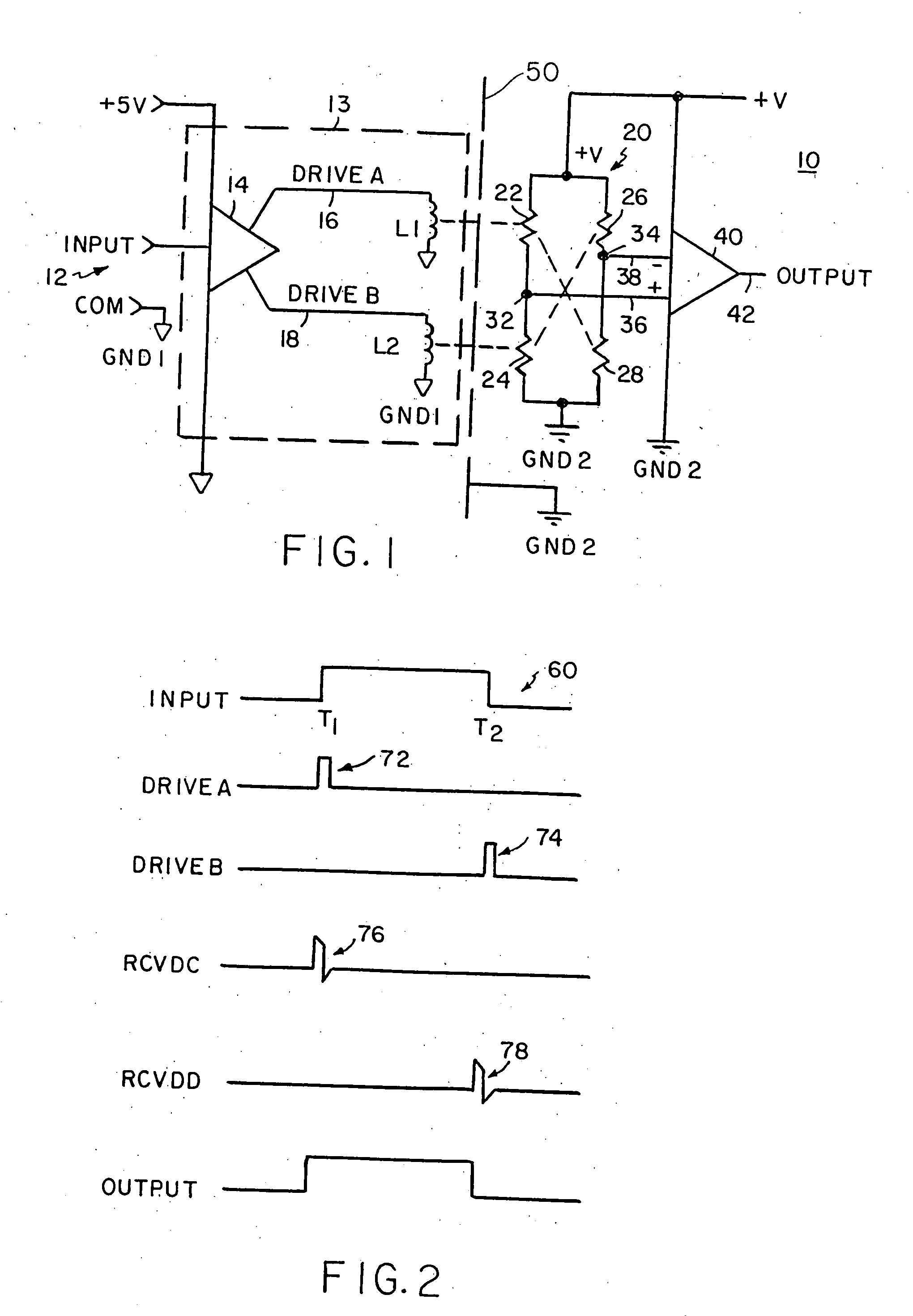

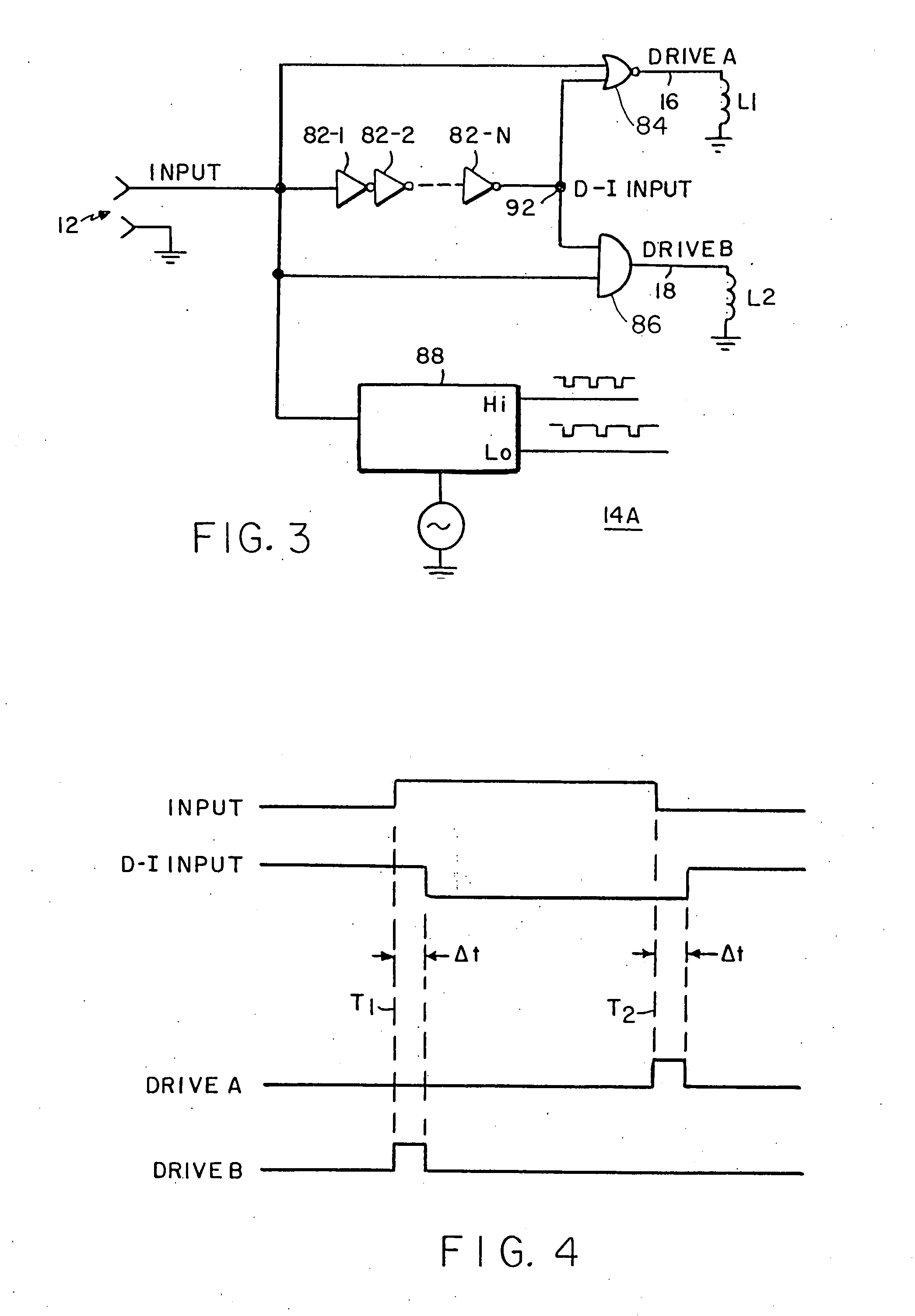

Signal isolators using micro-transformers

ActiveUS7075329B2Reliability increasing modificationsSemiconductor/solid-state device detailsTransformerEngineering

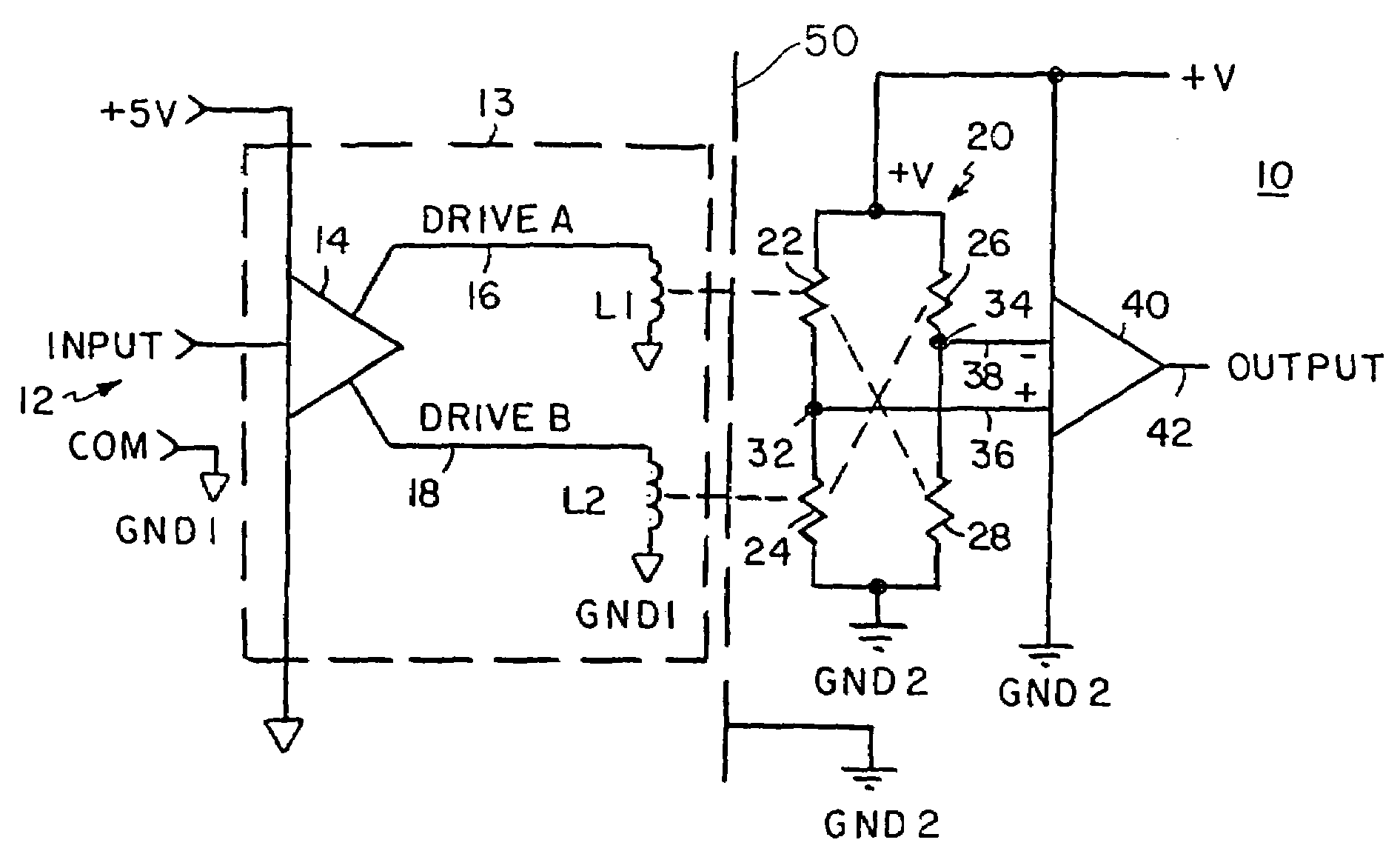

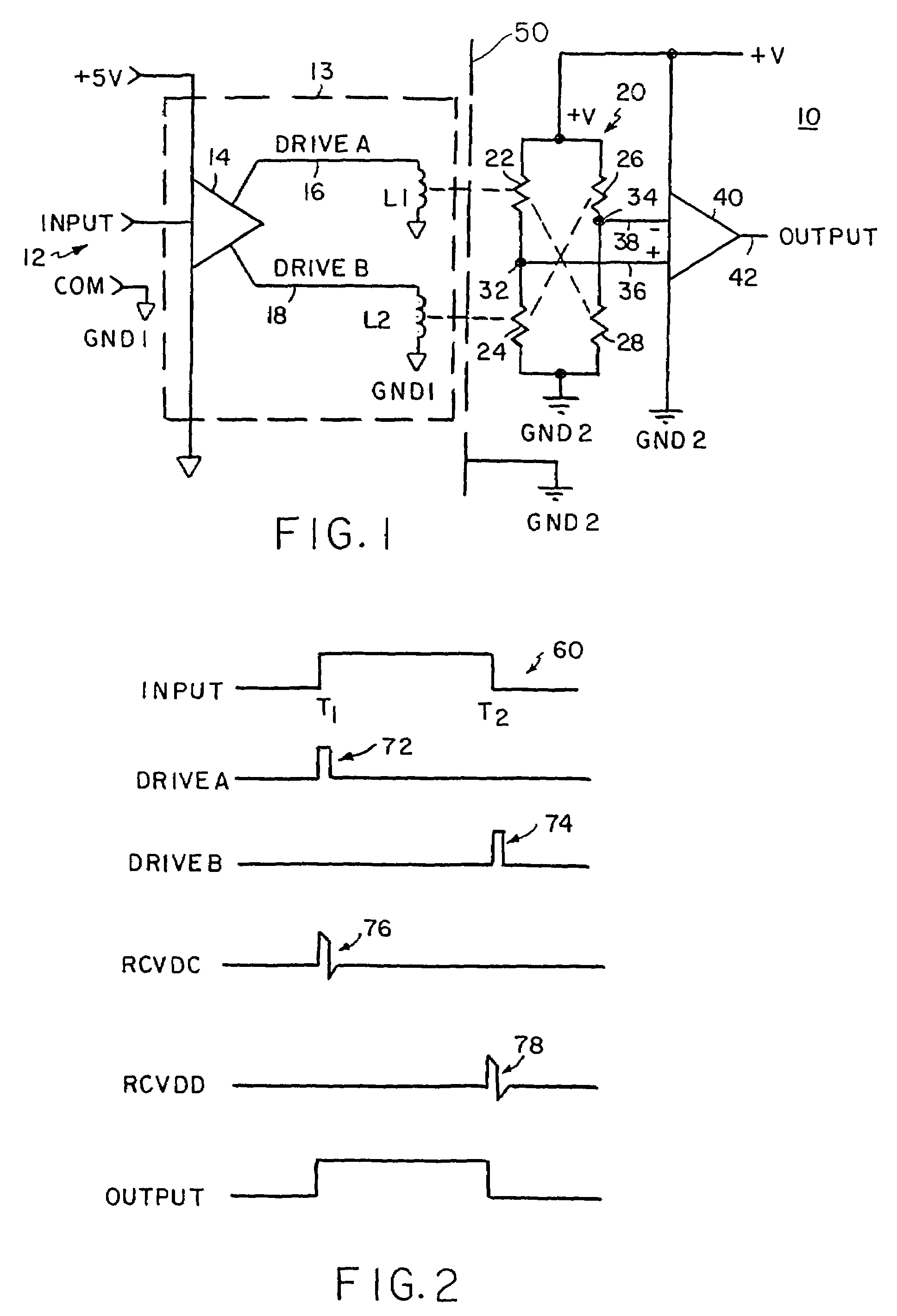

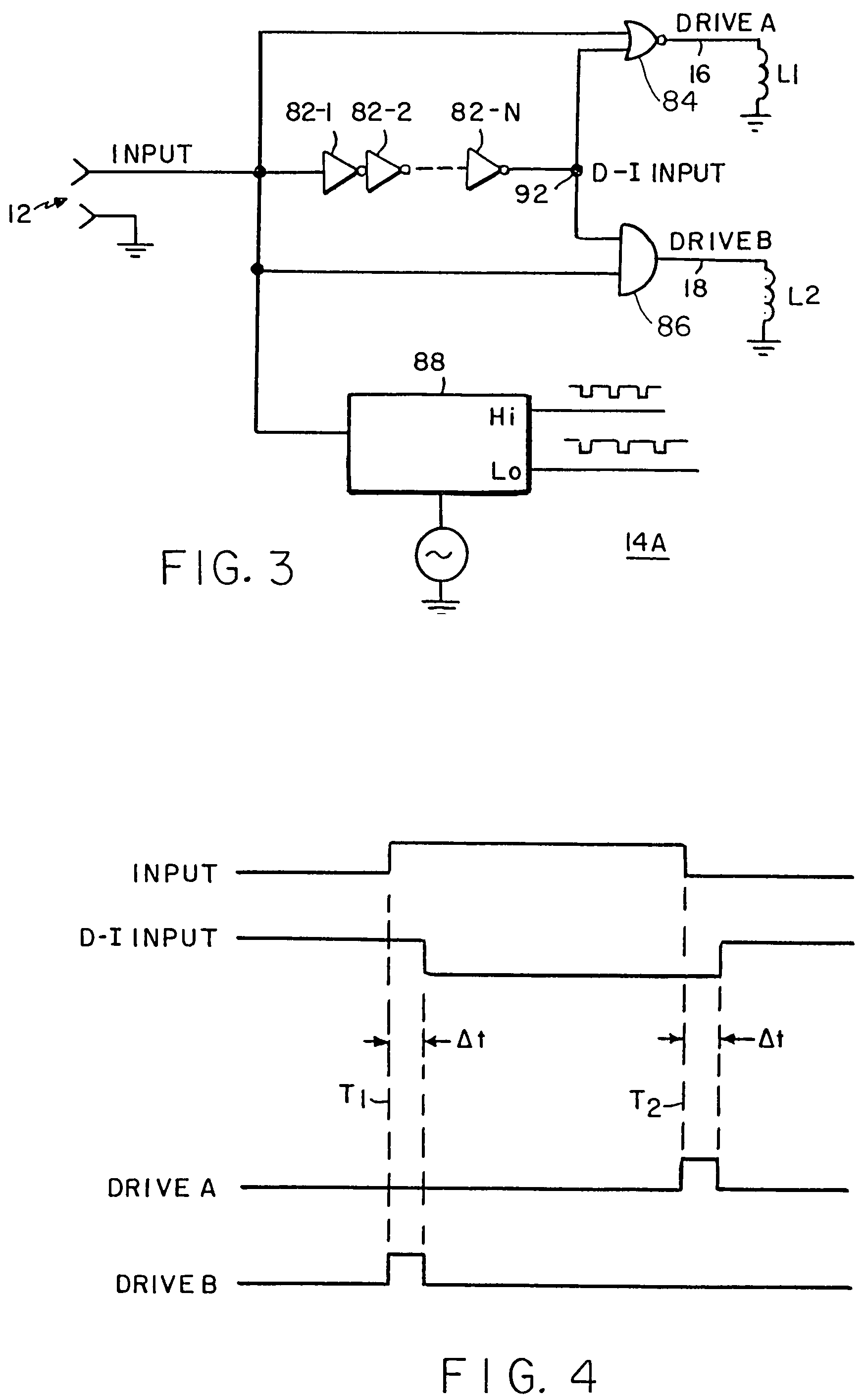

A logic signal isolator comprising a transformer having a primary winding and a secondary winding; a transmitter circuit which drives said primary winding in response to a received logic signal, such that in response to a first type of edge in the logic signal, a signal of a first predetermined type is supplied to the primary winding and in response to a second type of edge in the logic signal, a signal of a second predetermined type is supplied to said primary winding, the primary winding and the transmitter being referenced to a first ground; and the secondary winding being referenced to a second ground which is galvanically isolated from the first ground and said secondary winding supplying to a receiver circuit signals received in correspondence to the signals provided to the primary winding, the receiver reconstructing the received logic signal from the received signals.

Owner:ANALOG DEVICES INC

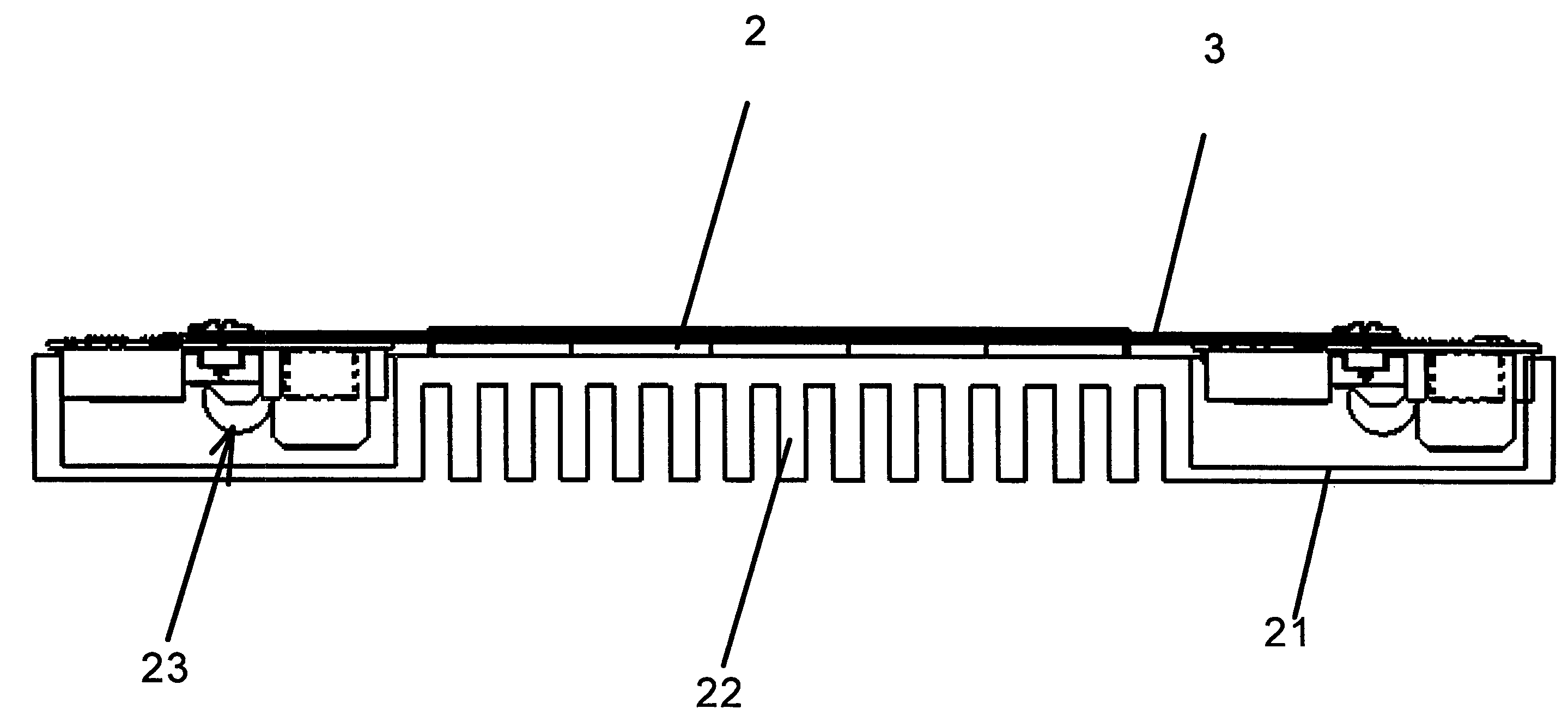

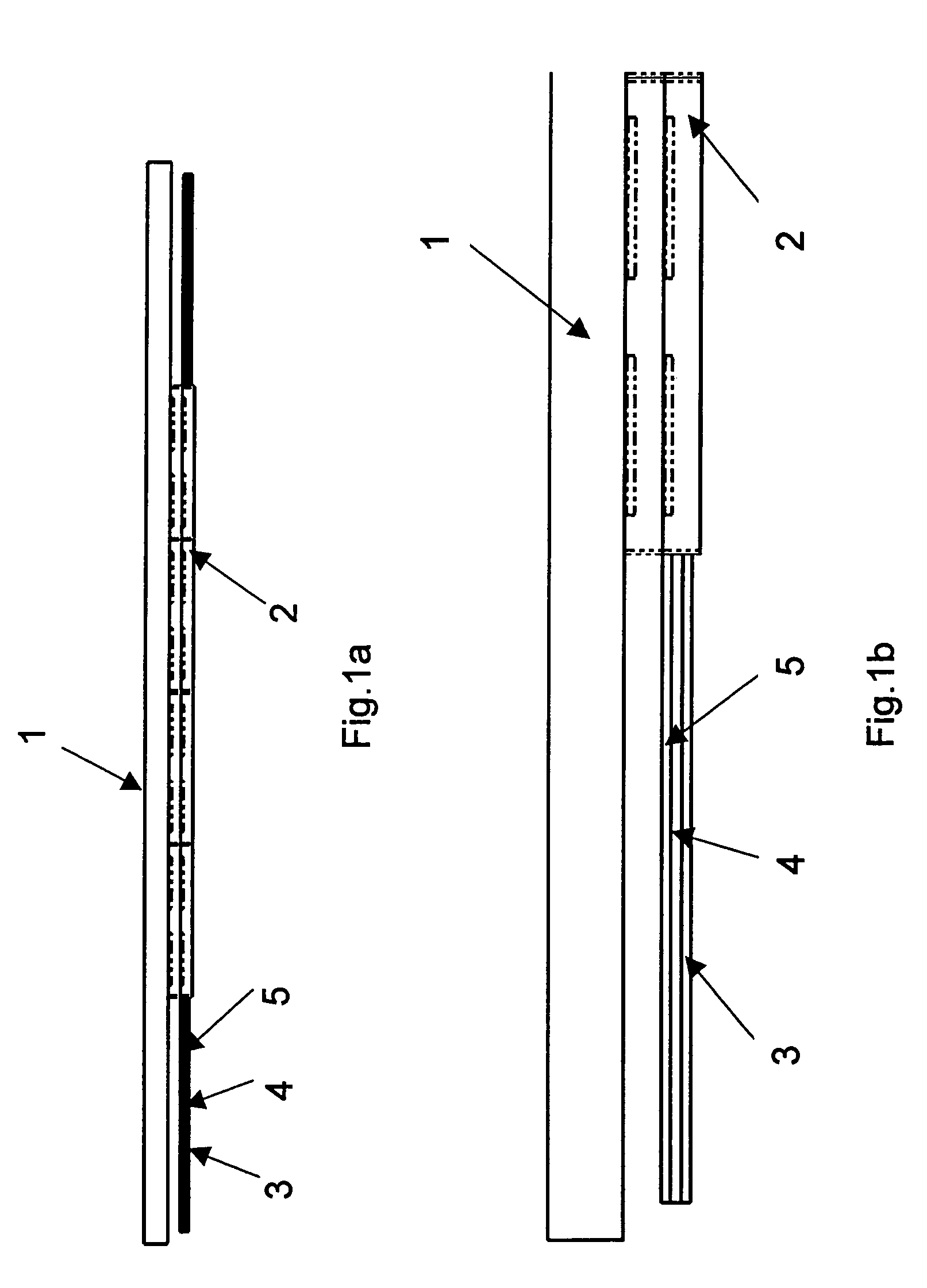

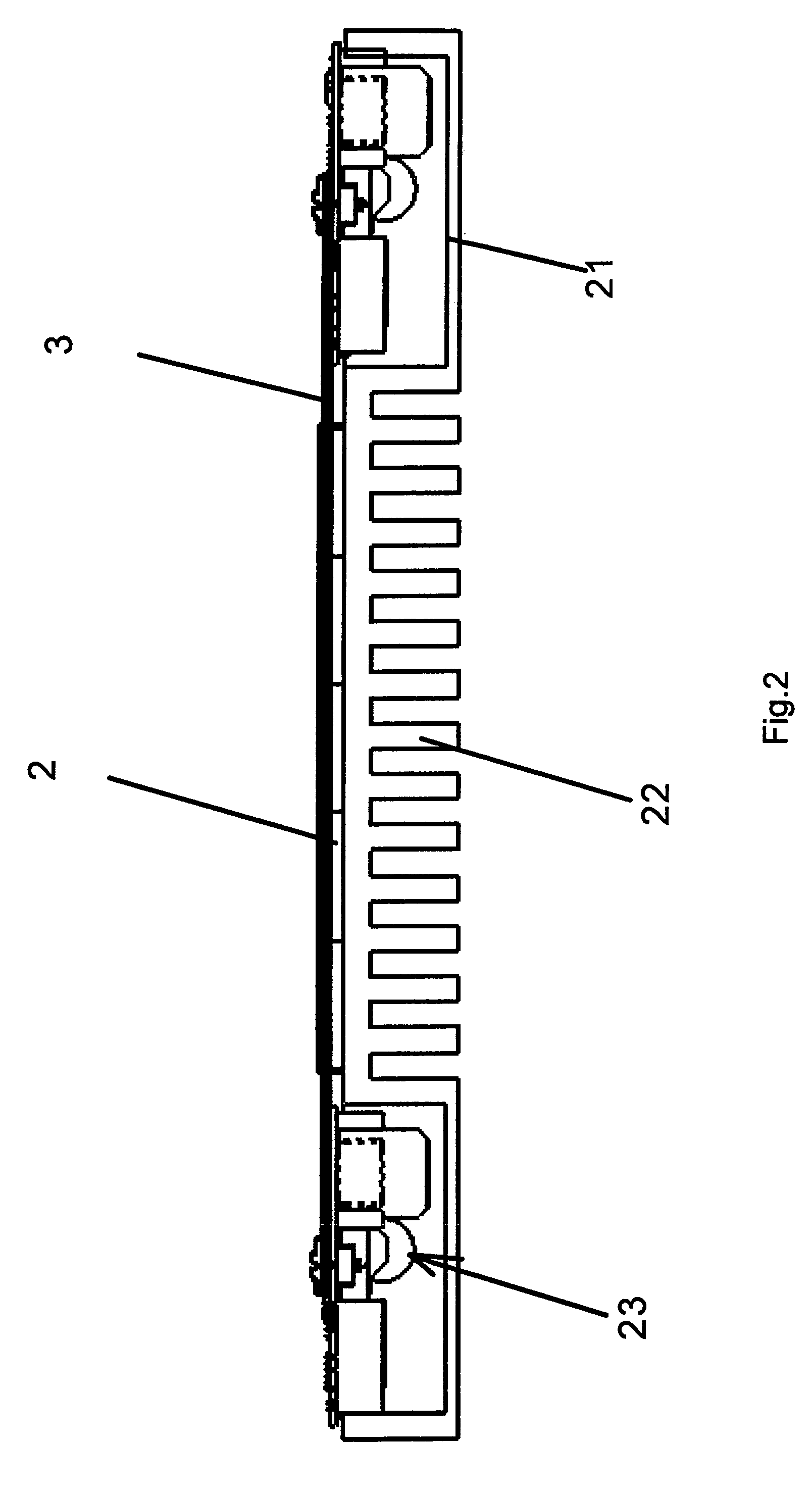

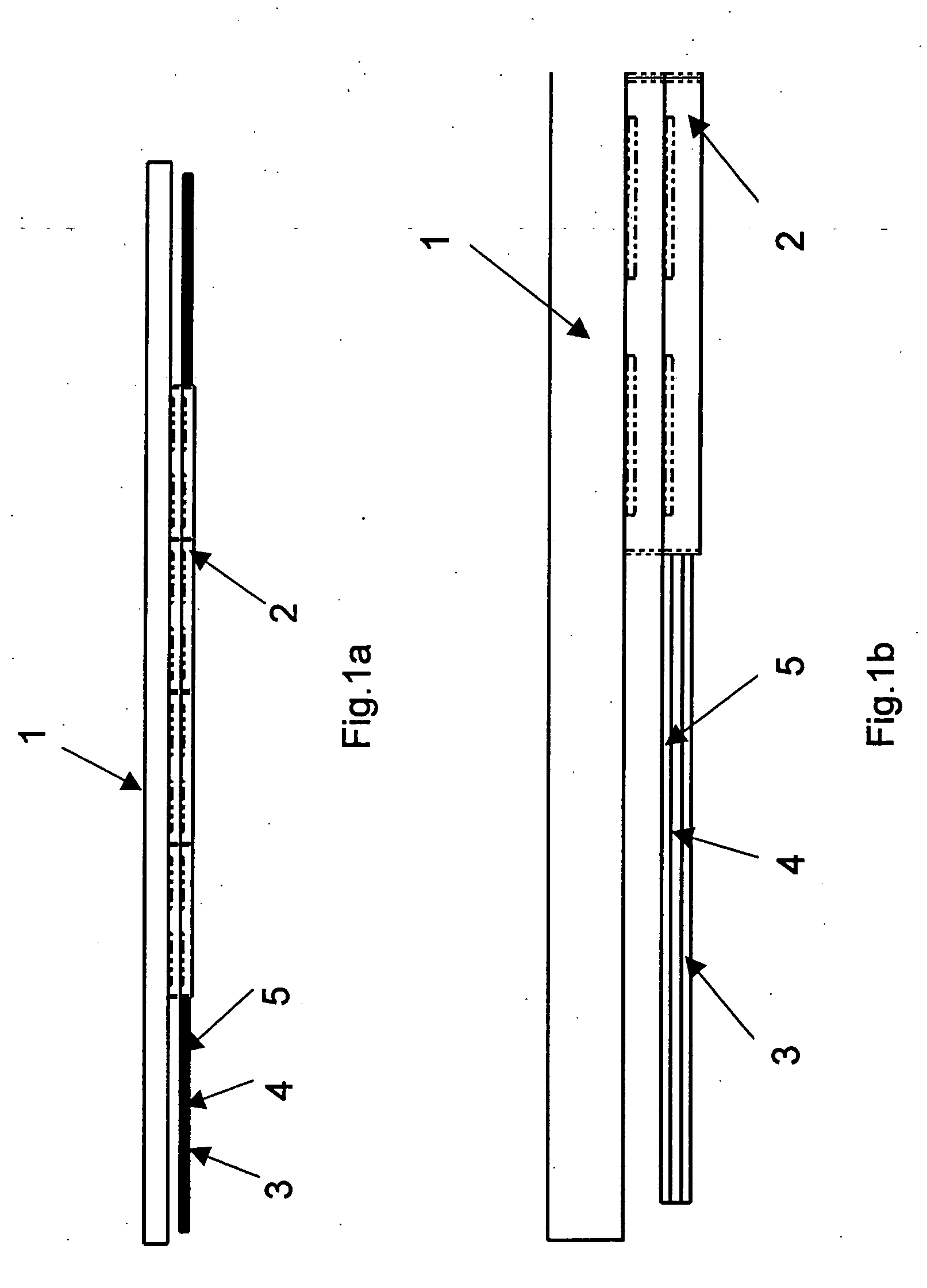

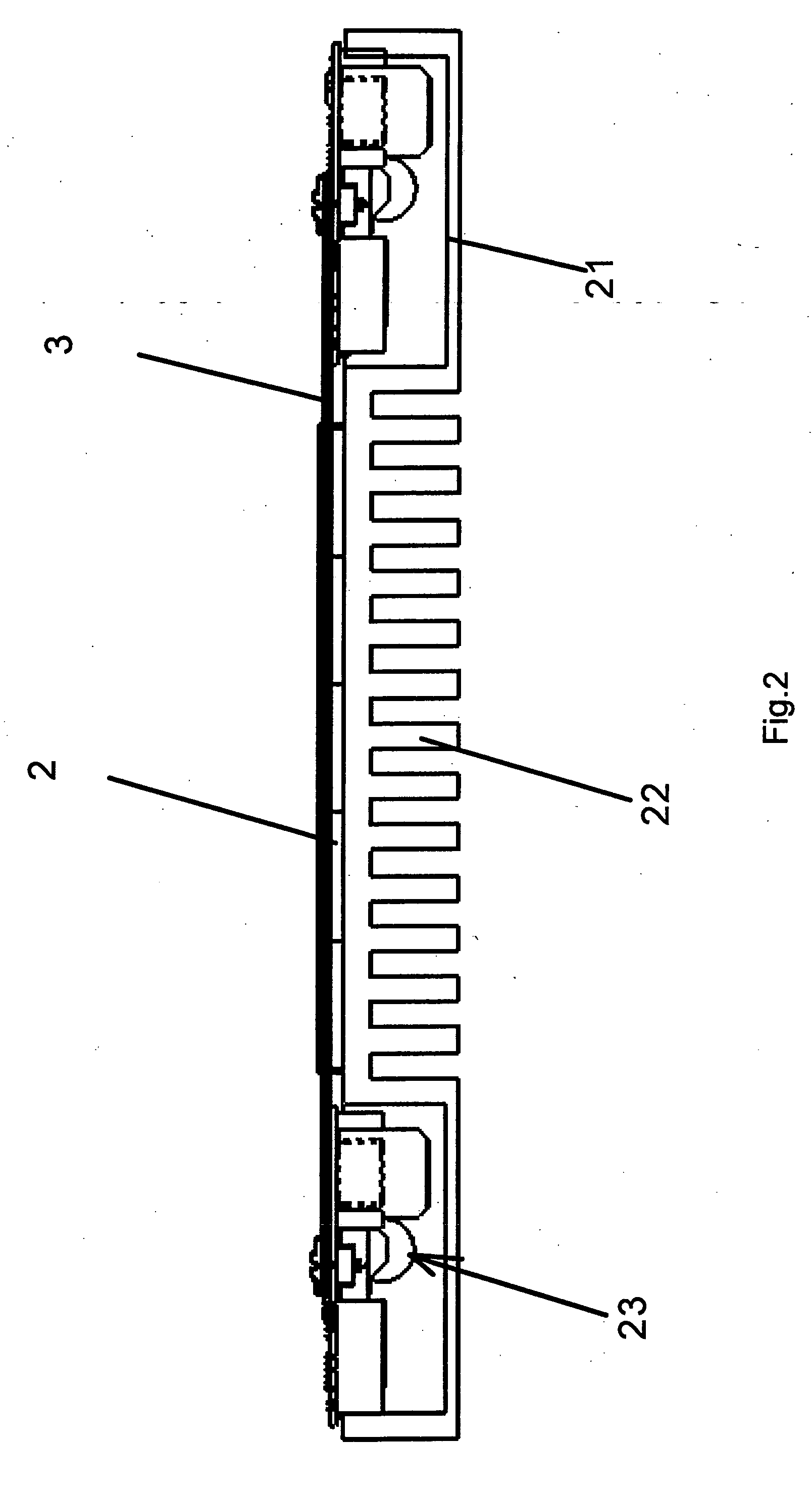

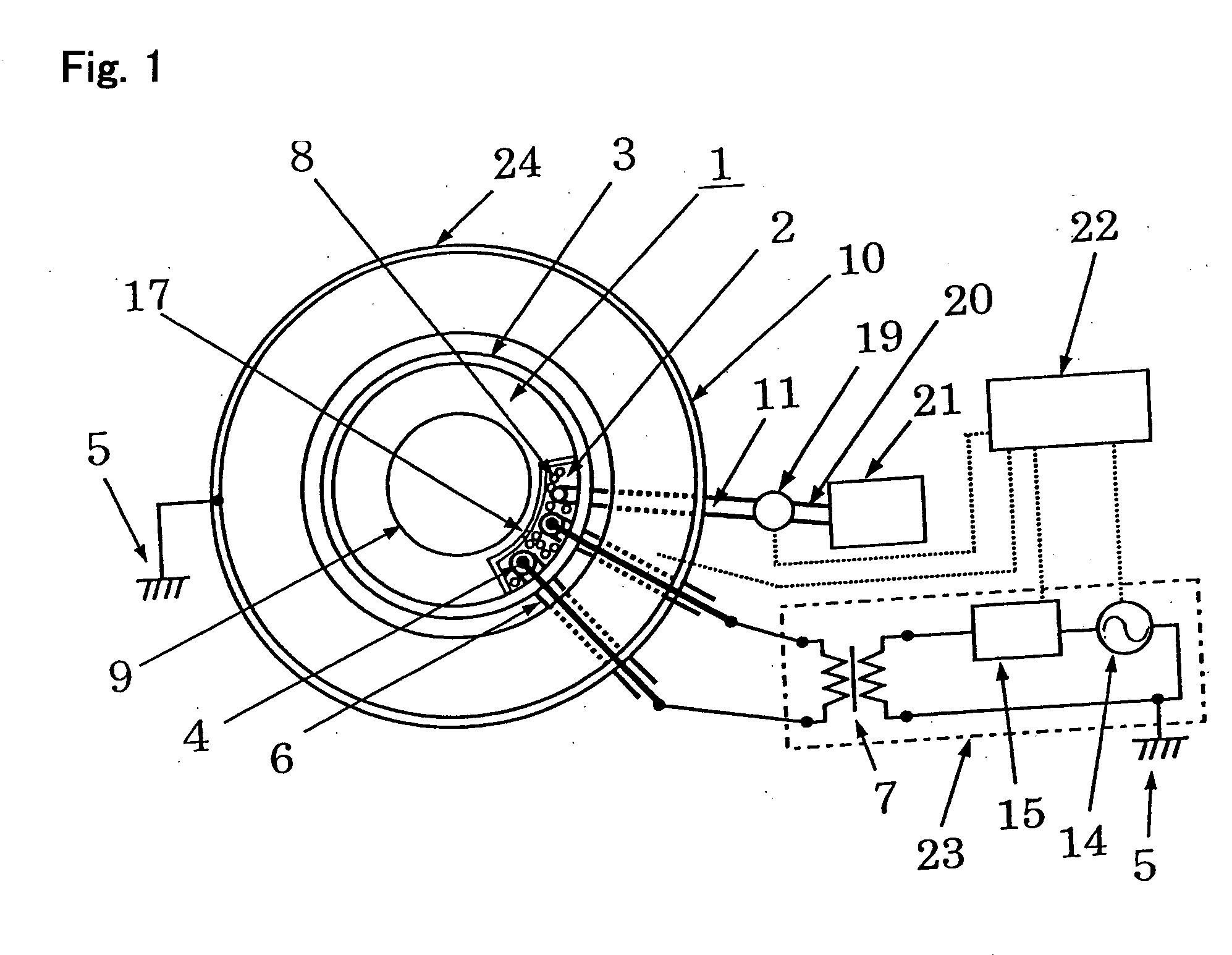

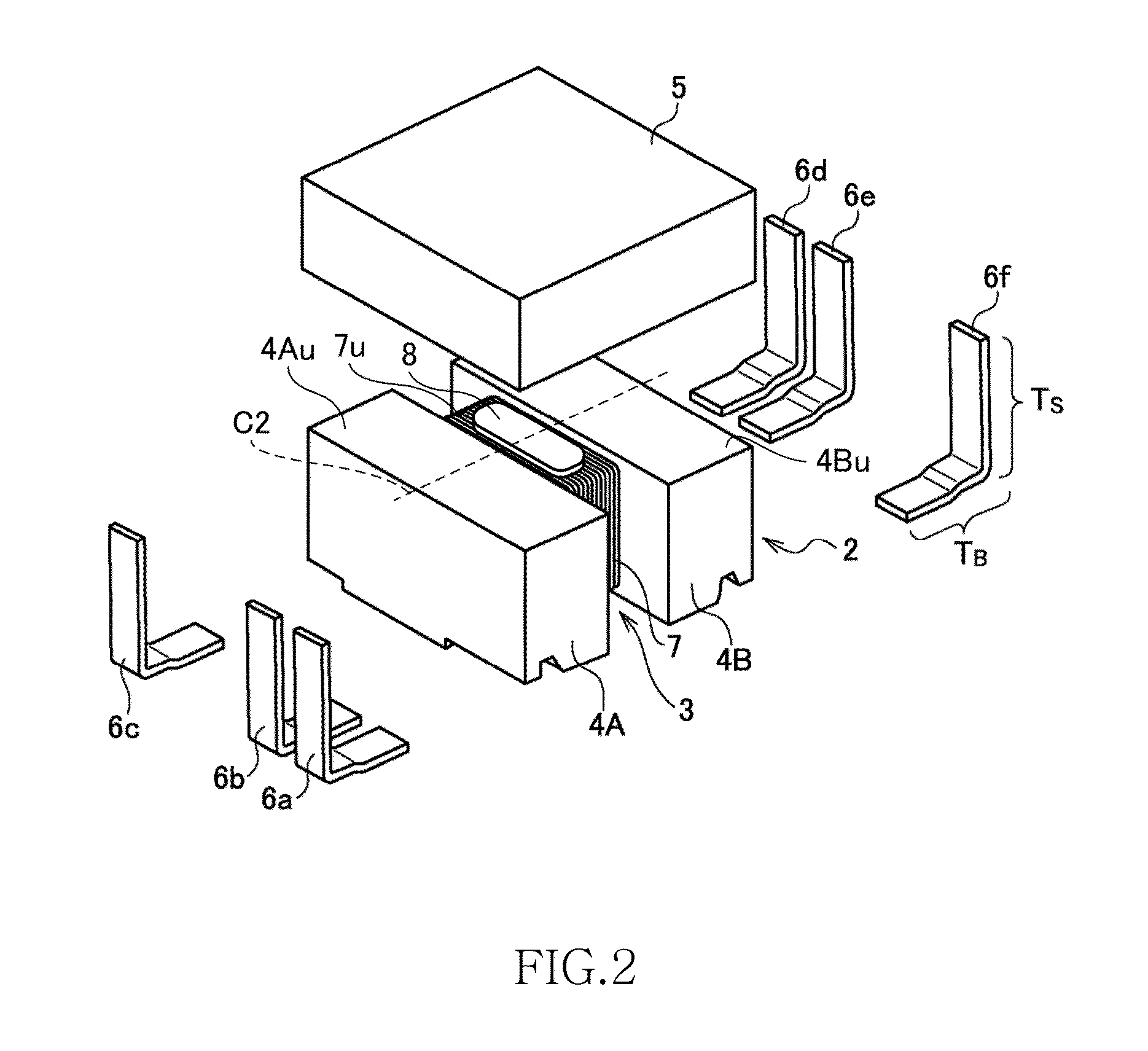

Transmitter head and system for contactless energy transmission

ActiveUS7492247B2Small unit volumeInexpensive and uncomplicated mannerTransformersMagnetic-bias transformersEngineeringConductor Coil

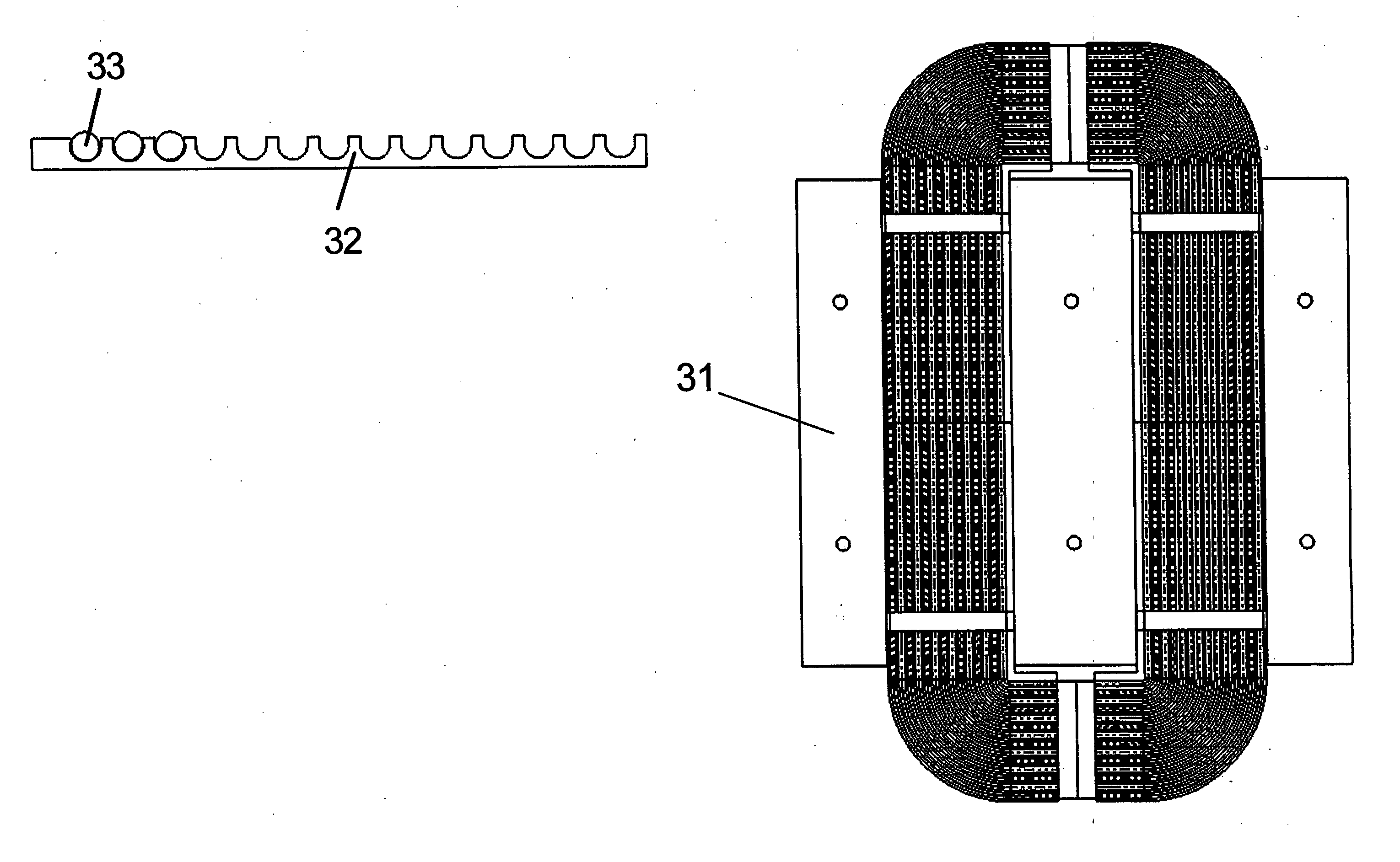

A transmitter head for a system for contactless energy transmission includes a support connected to at least one ferrite core. The ferrite core is embodied at least partially in the E-form and a flat winding is arranged around one leg of the E.

Owner:SEW-EURODRIVE GMBH & CO KG

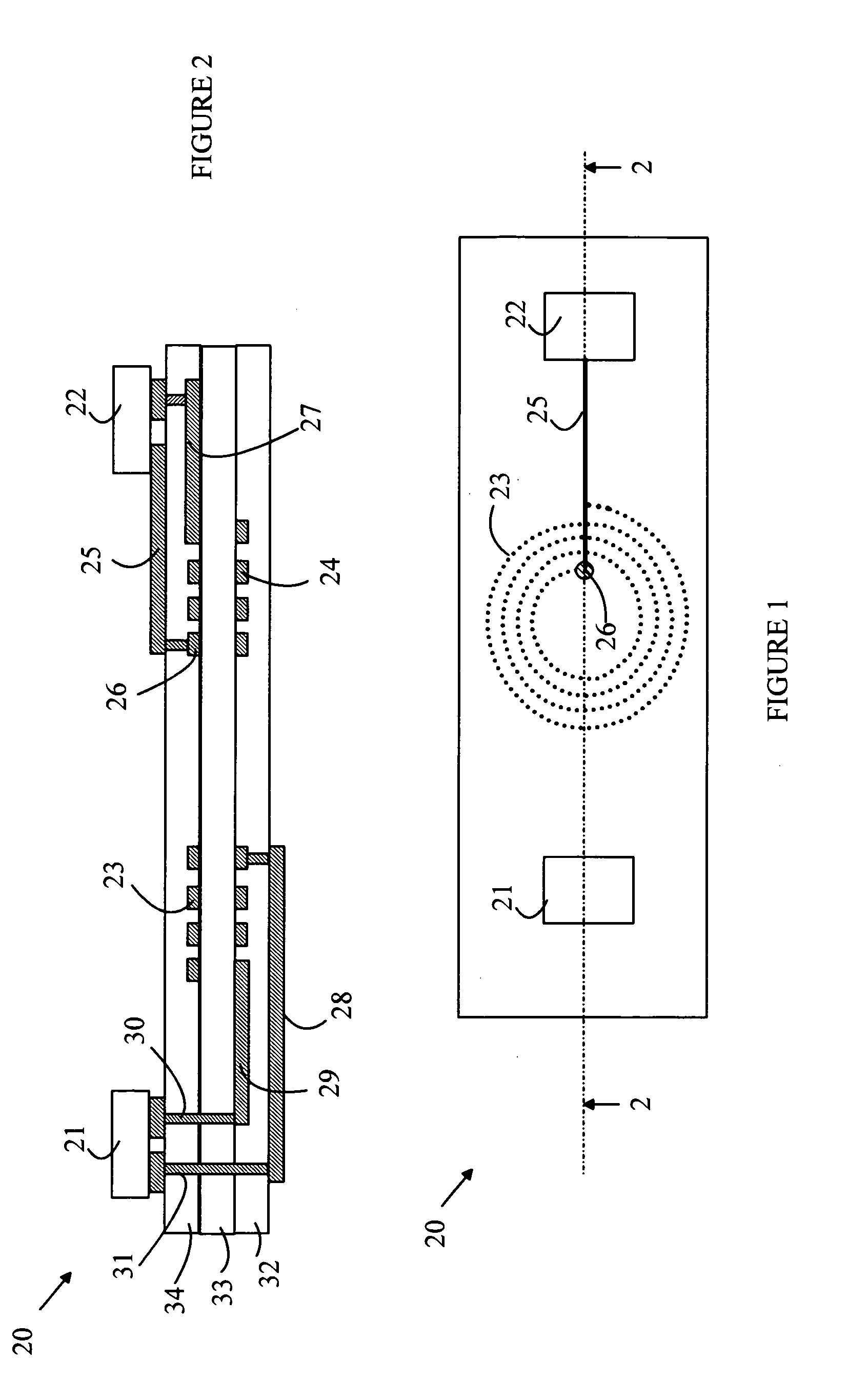

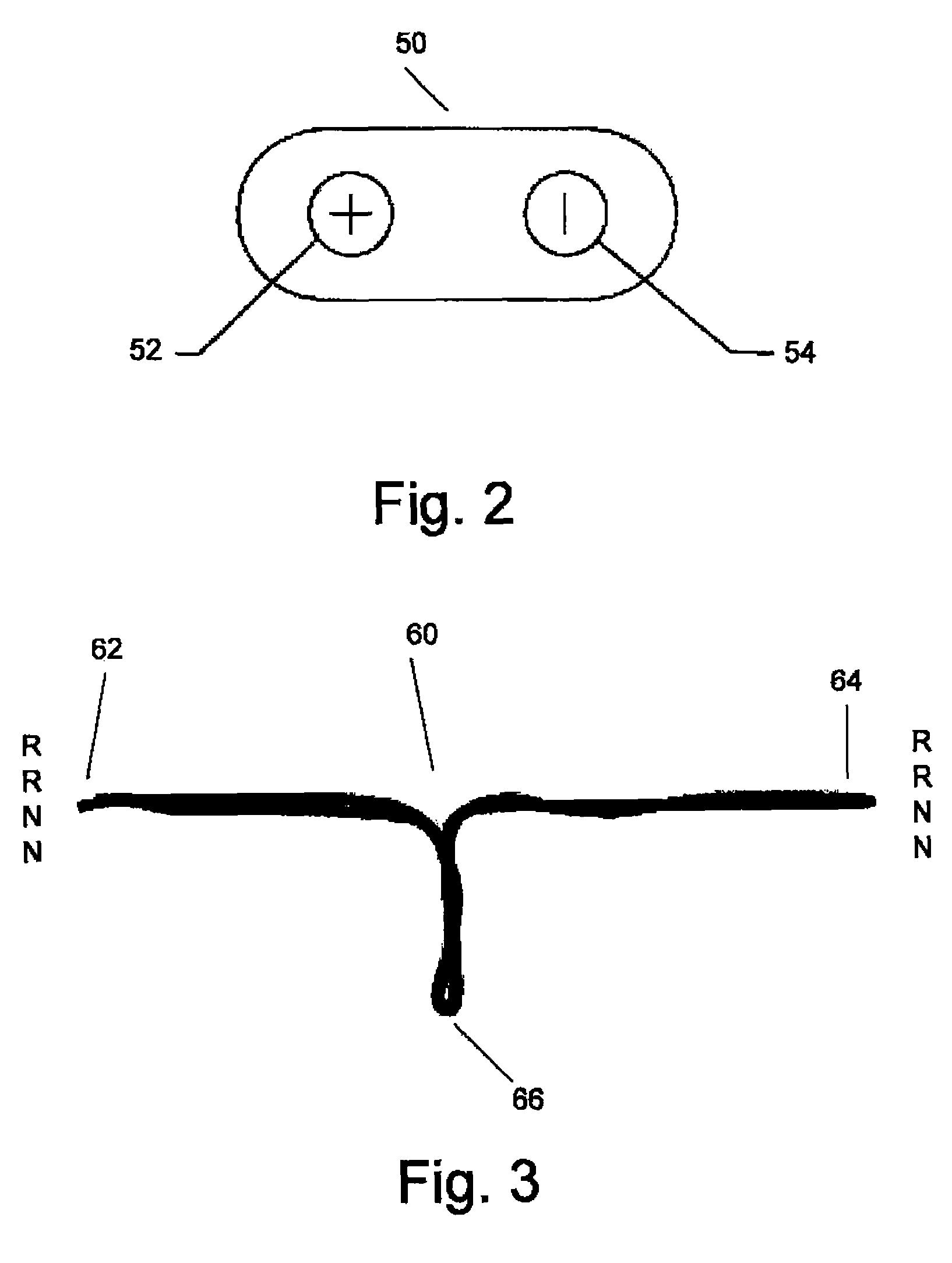

Galvanic isolator

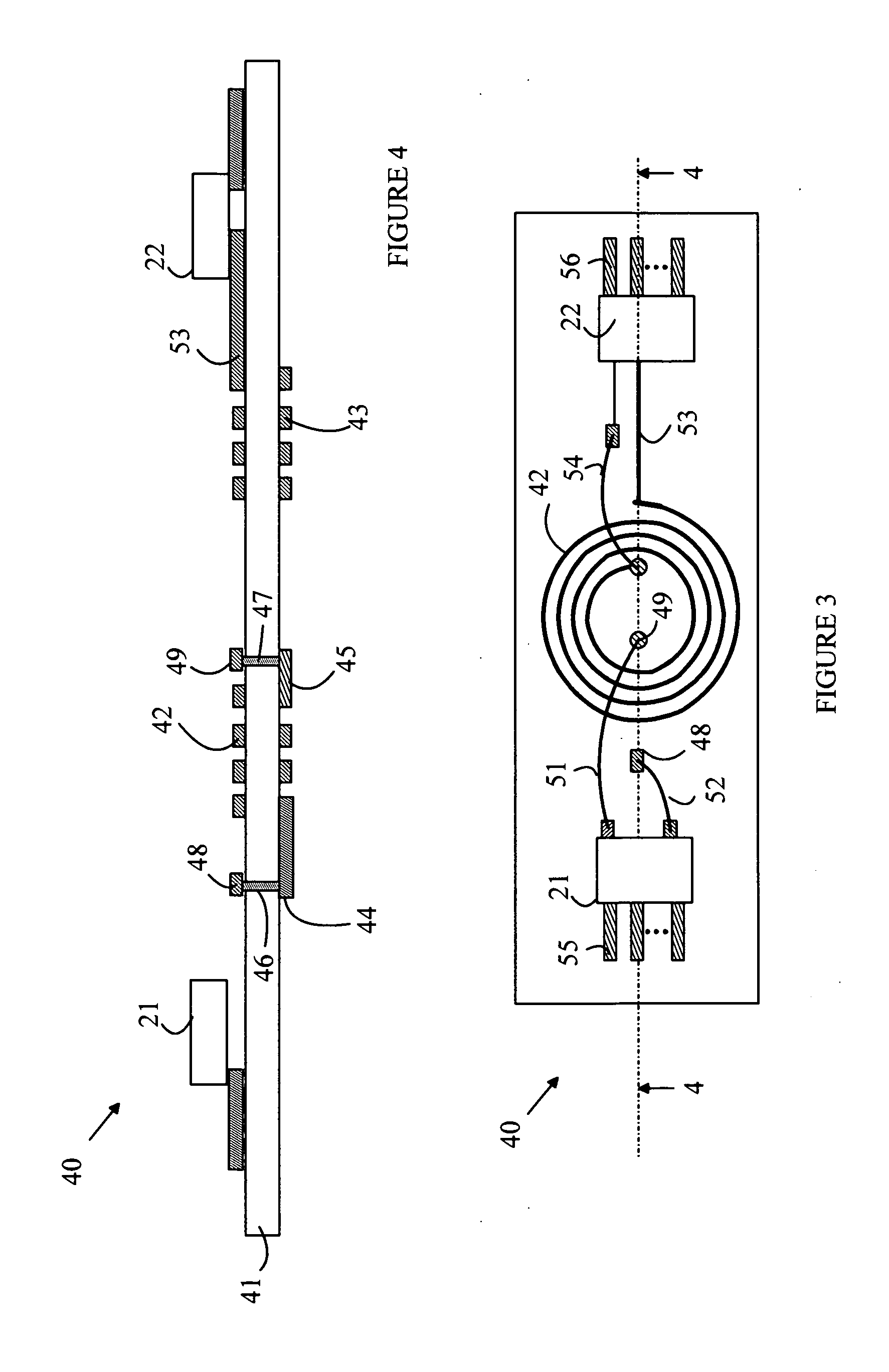

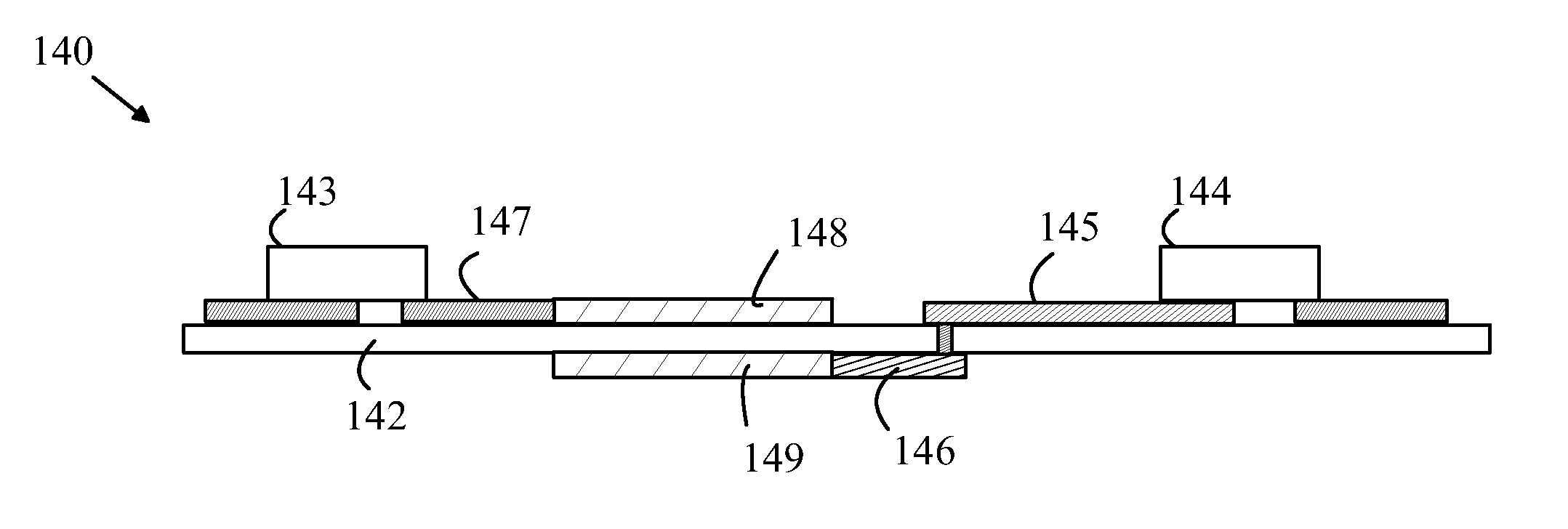

InactiveUS20080061631A1Easy to understandAvoid insufficient thicknessMultiple-port networksNear-field transmissionFlexible circuitsEngineering

A galvanic isolator having a split circuit element, a polymeric substrate, a transmitter and receiver is disclosed. The split circuit element has first and second portions, the first portion being disposed on a first surface of the substrate and the second portion being disposed a second surface of the substrate. The transmitter receives an input signal and couples a signal derived from the input signal to the first portion. The receiver is connected to the second portion of the circuit element and generates an output signal that is coupled to an external circuit. The galvanic isolator can be economically fabricated on conventional printed circuit board substrates and flexible circuit substrates.

Owner:AVAGO TECH INT SALES PTE LTD

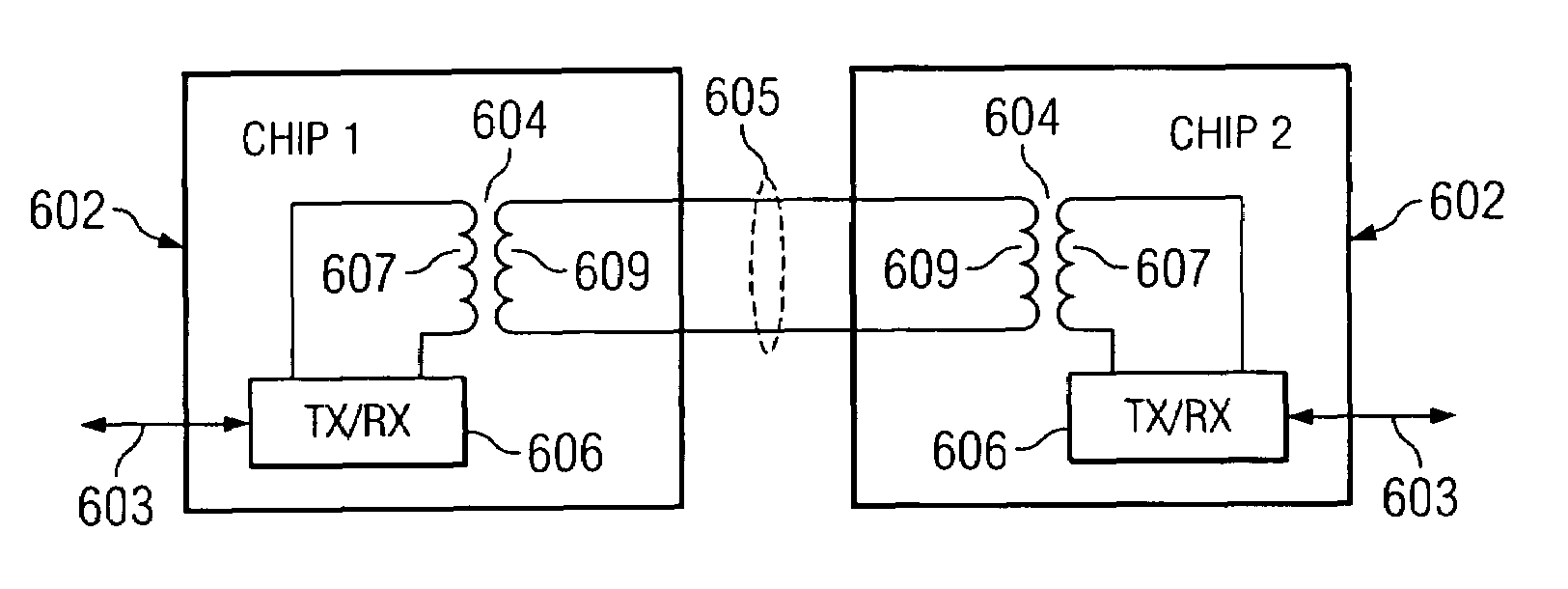

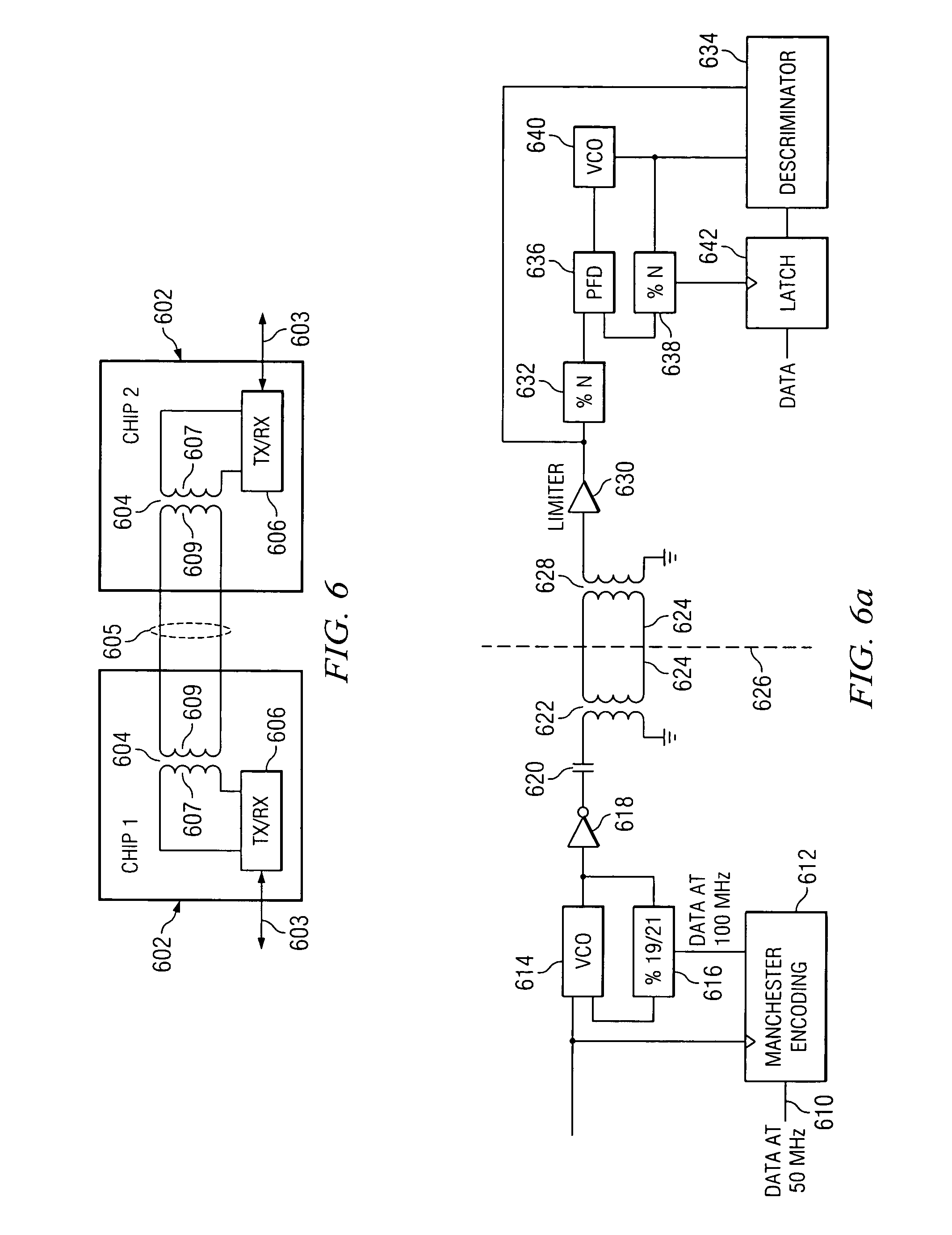

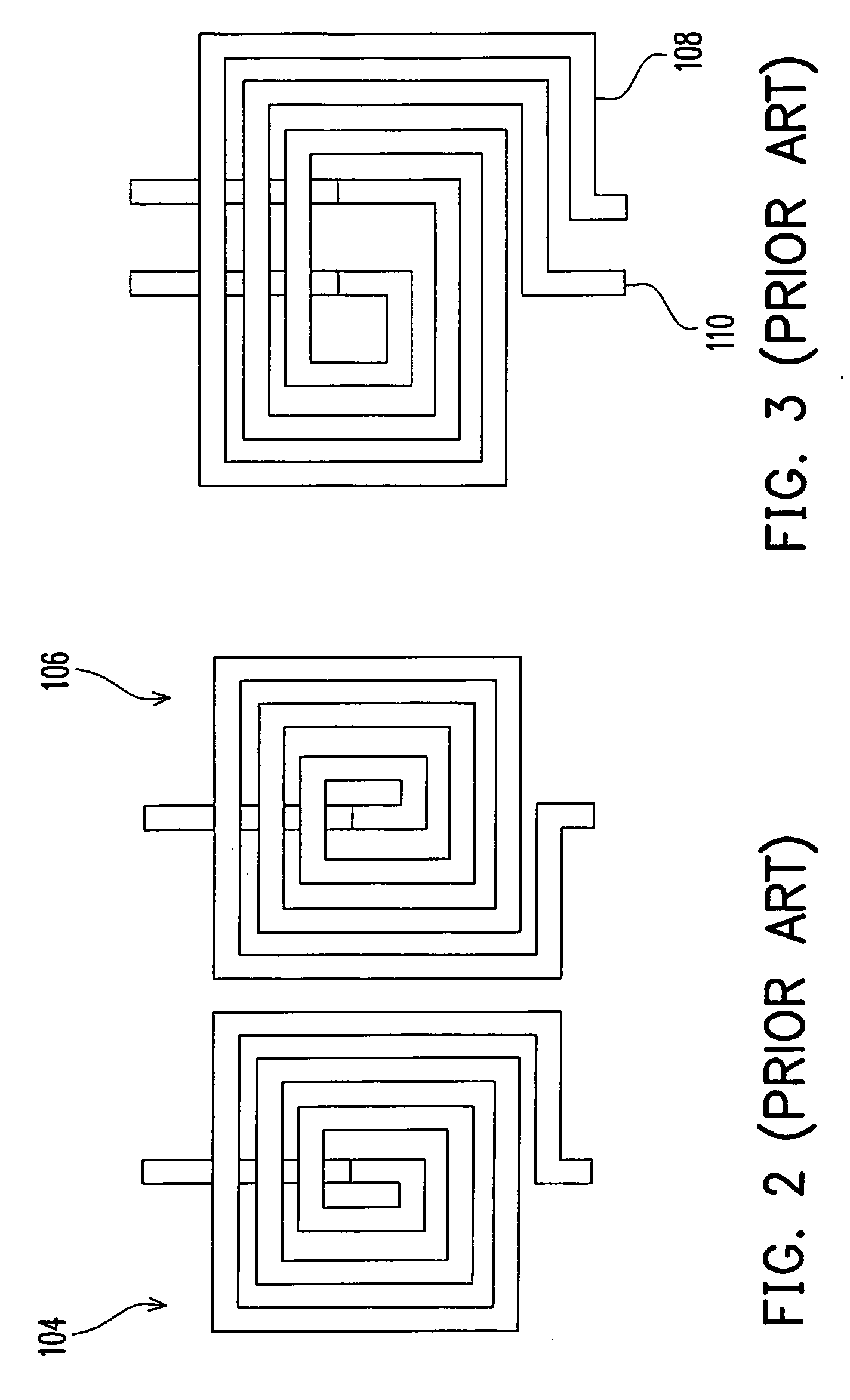

On chip transformer isolator

An integrated circuit having voltage isolation capabilities includes a first area of the integrated circuit containing functional circuitry that is located in the substrate of the integrated circuit. A second area of the integrated circuit contains an integrated RF isolation circuitry for voltage isolating the functional circuitry. The RF isolation circuitry is located in the metal layers of the integrated circuit.

Owner:SKYWORKS SOLUTIONS INC

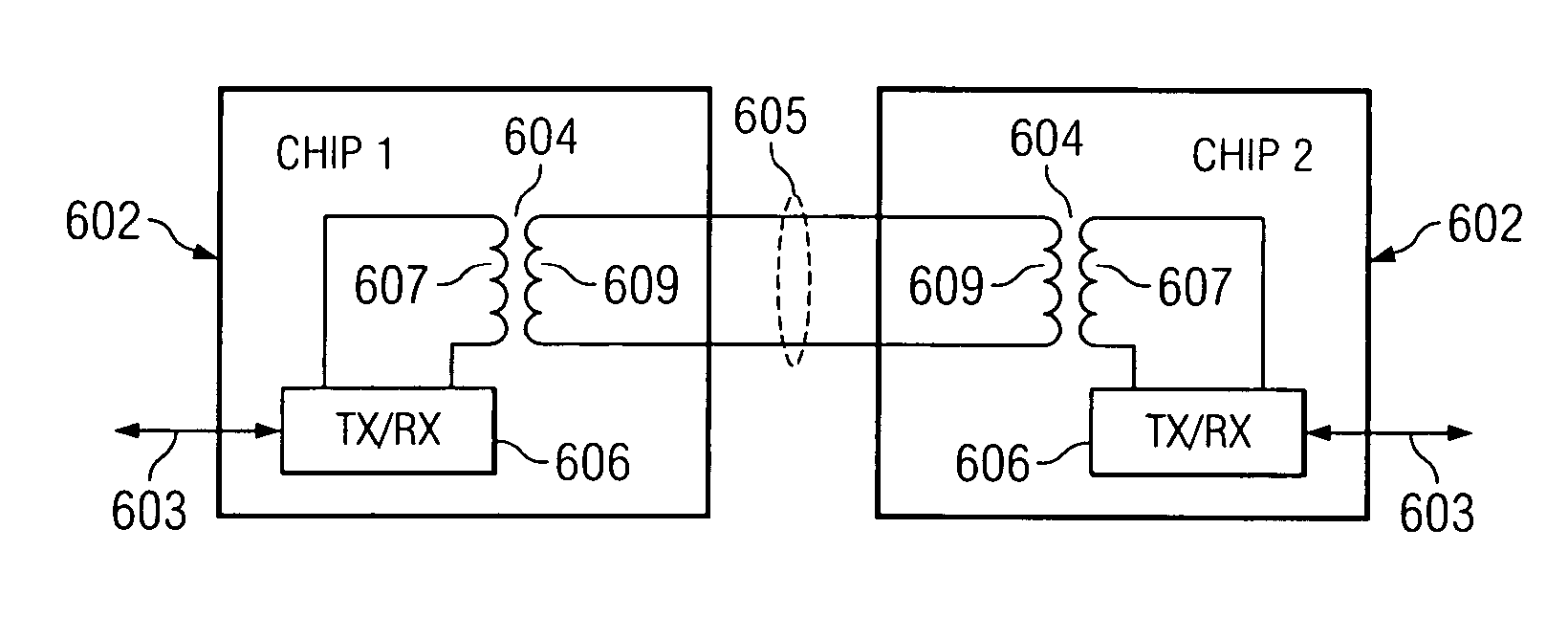

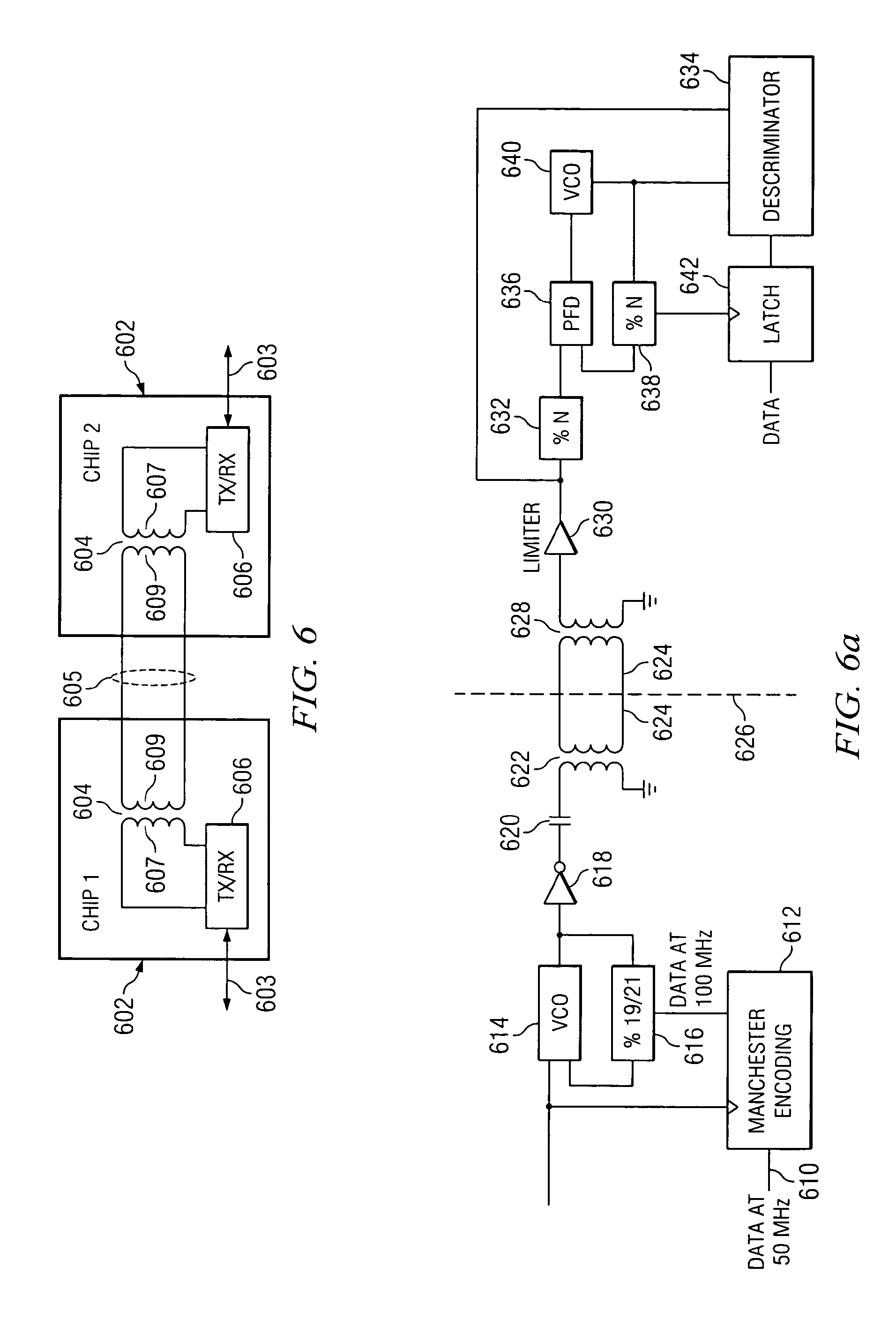

Semiconductor device

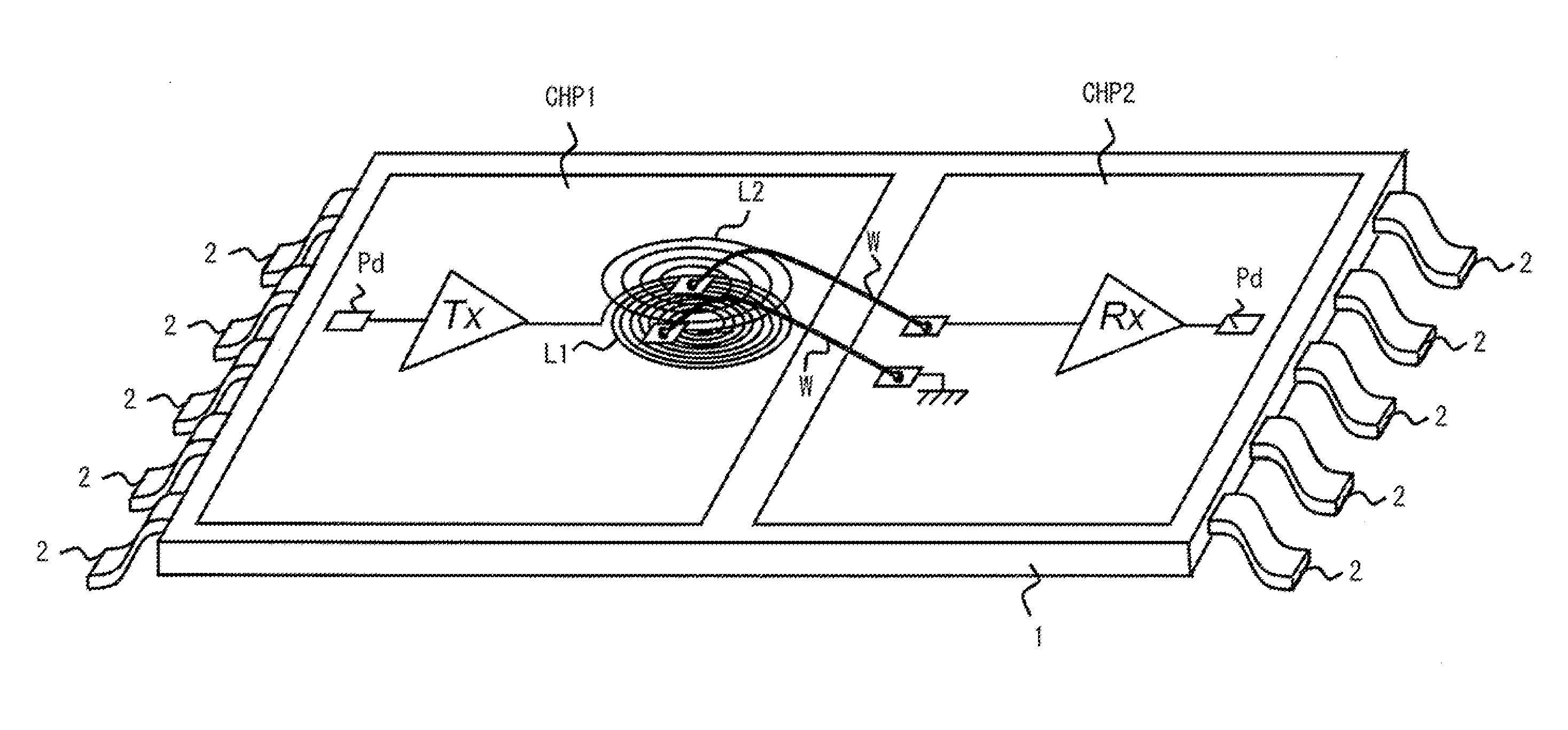

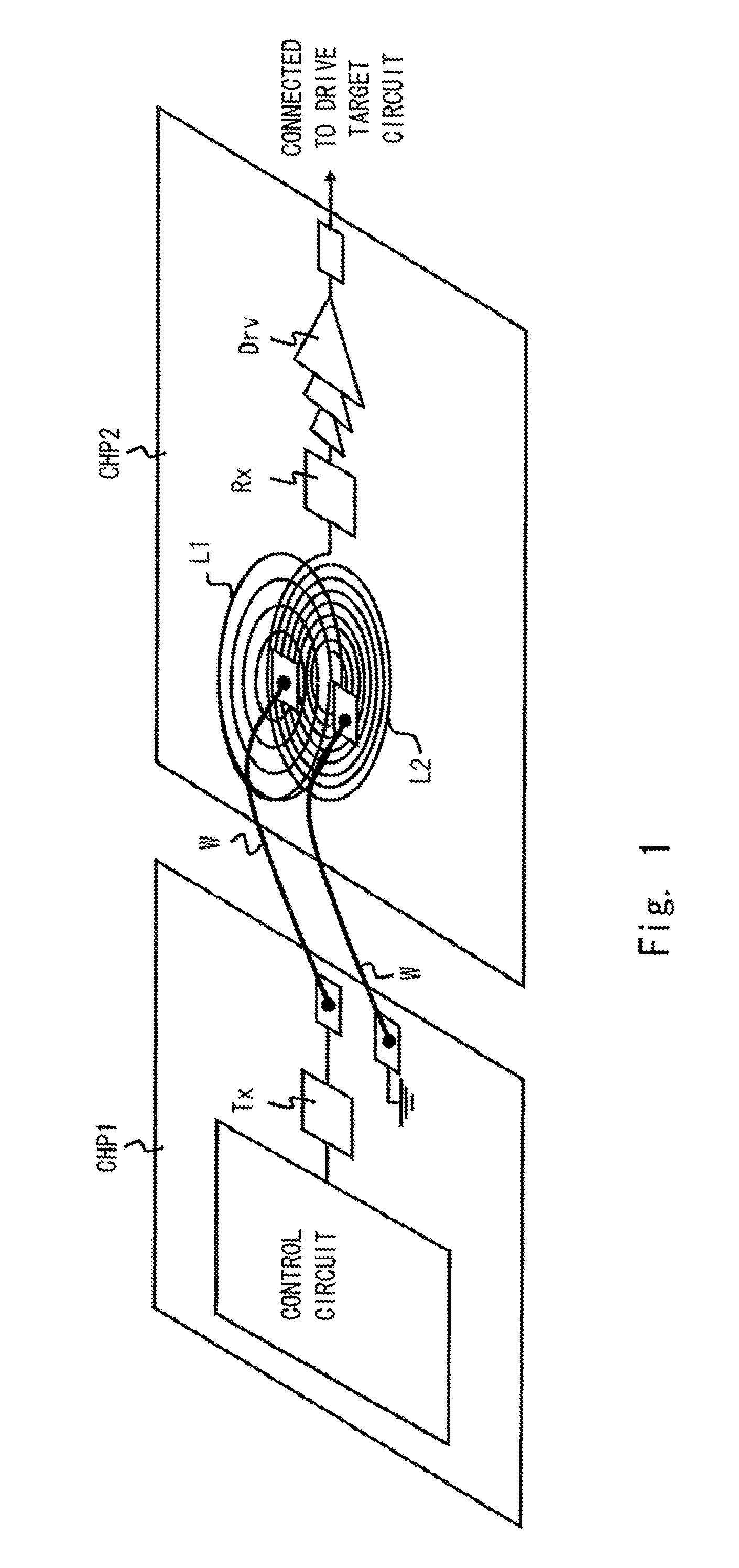

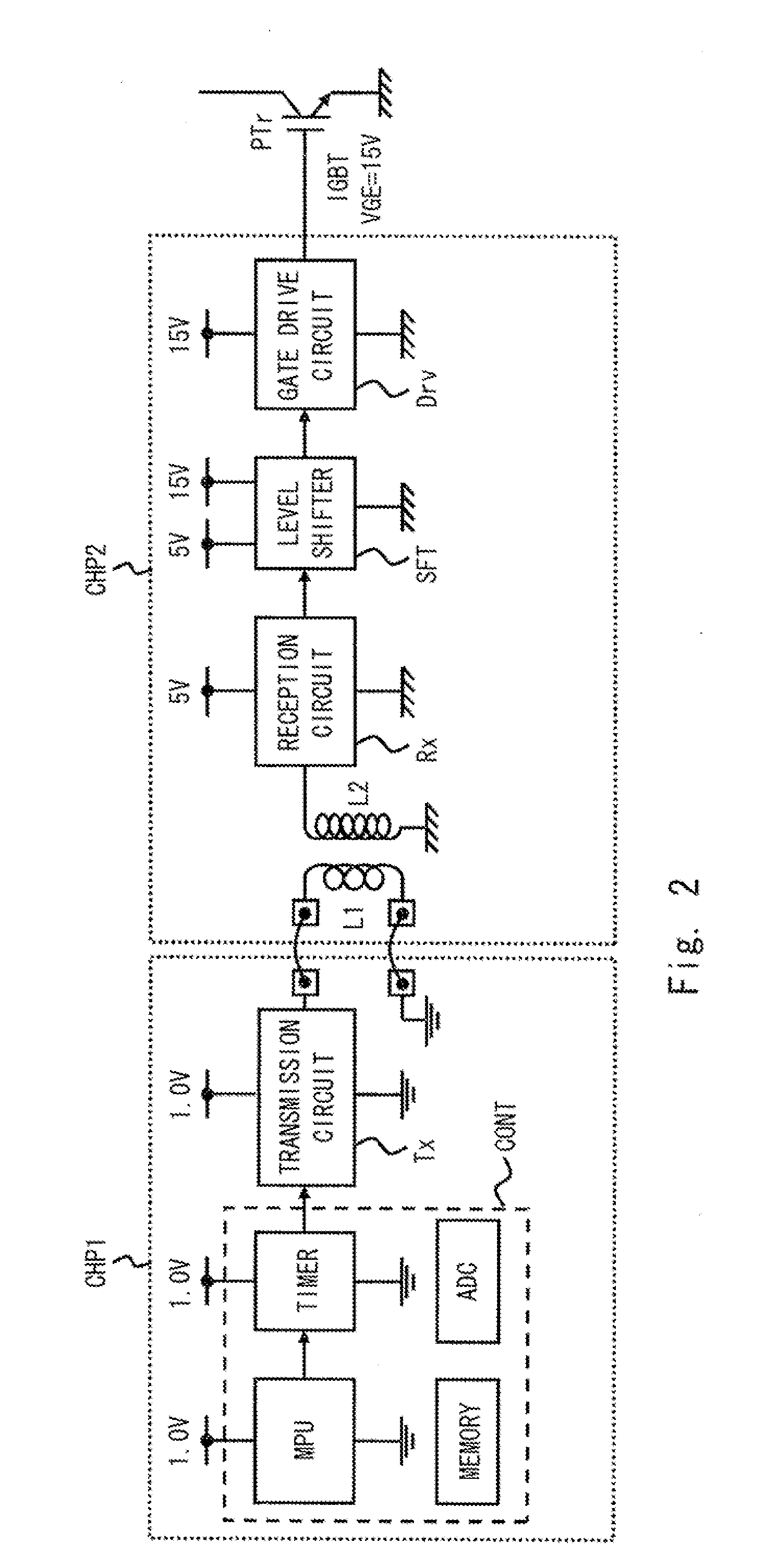

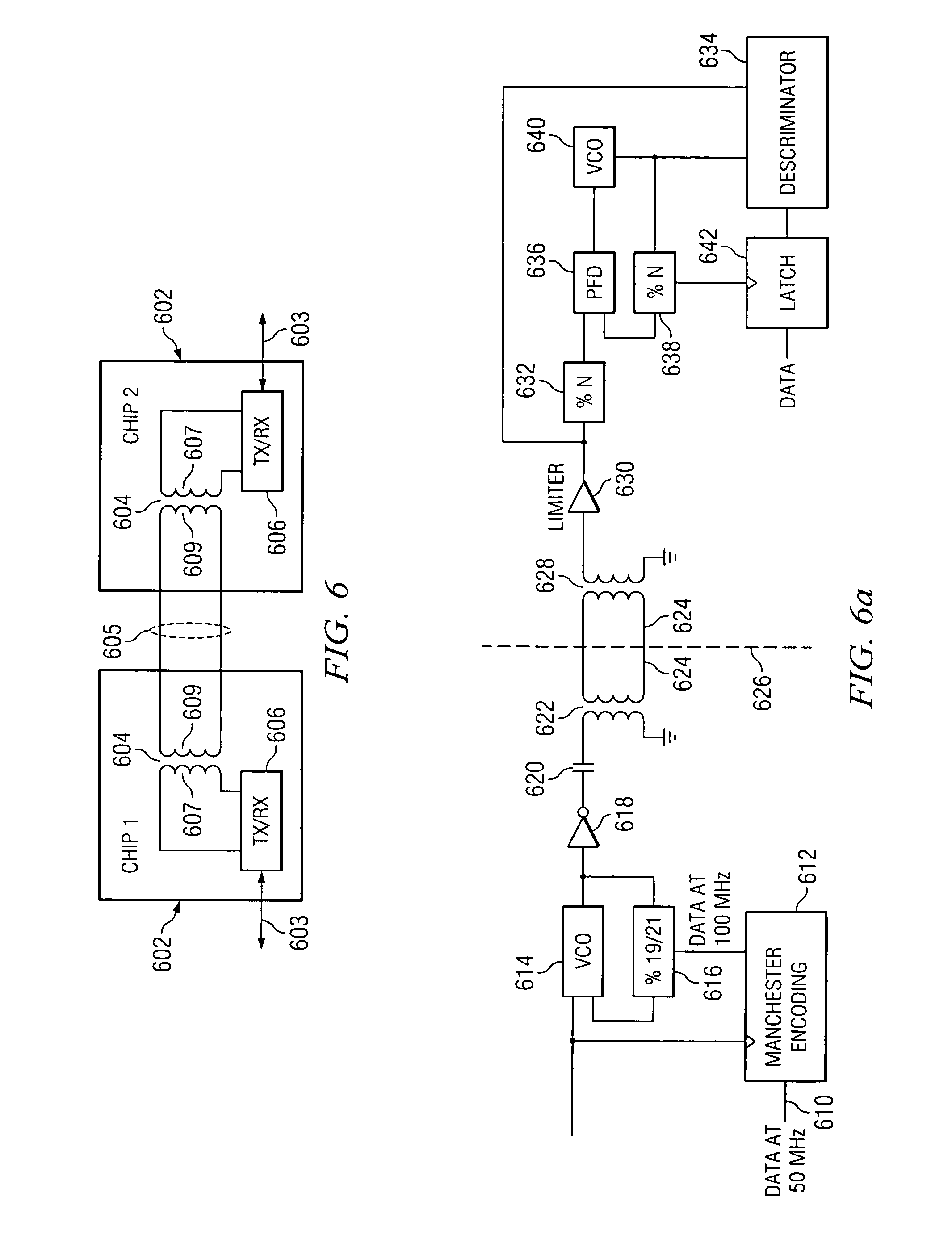

InactiveUS20120020419A1Reduce circuit areaSuppression of increase in mounting areaModulated-carrier systemsSolid-state devicesControl signalCoupling

A semiconductor device according to the present invention includes: a first semiconductor substrate CHP1 including a control circuit that generates a control signal for a control target circuit, and a transmission circuit Tx that modulates the control signal to generate a transmission signal; a second semiconductor substrate CHP2 including a reception circuit Rx that demodulates the transmission signal transmitted from the transmission circuit to reproduce the control signal, and a drive circuit Drv that drives the control target circuit based on the control signal output from the reception circuit, the second semiconductor substrate CHP2 being electrically insulated from the first semiconductor substrate CHP1; an AC coupling element that is formed on a semiconductor substrate and couples the first semiconductor substrate CHP1 and the second semiconductor substrate CHP2 in an alternating manner; and a semiconductor package 20 including the first semiconductor substrate CHP1, the second semiconductor substrate CHP2, and the AC coupling element. This suppresses an increase in circuit area or mounting area.

Owner:NEC CORP

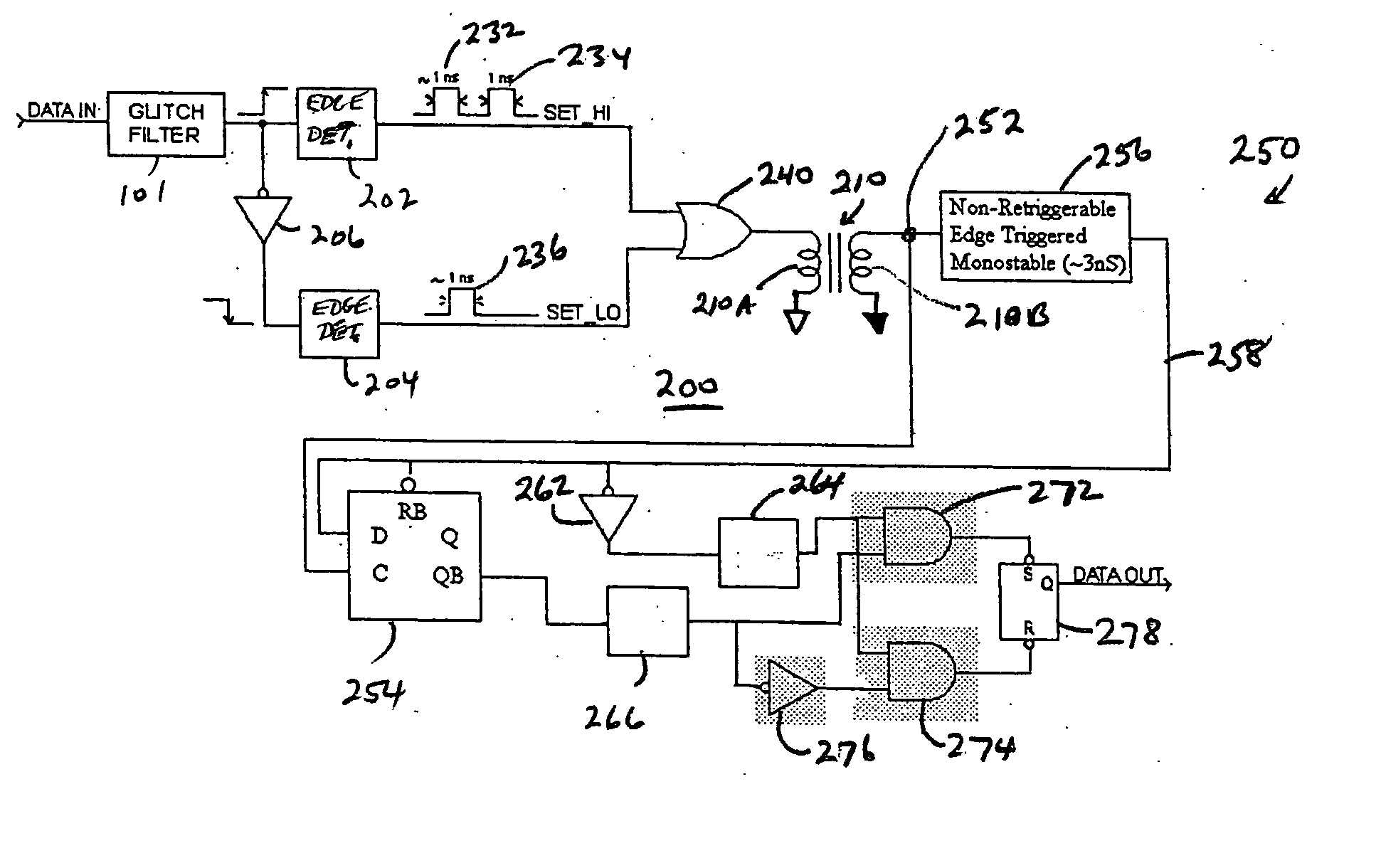

Signal isolators using micro-transformer

A logic signal isolator comprising a transformer having a primary winding and a secondary winding; a transmitter circuit which drives said primary winding in response to a received logic signal, such that in response to a first type of edge in the logic signal, a signal of a first predetermined type is supplied to the primary winding and in response to a second type of edge in the logic signal, a signal of a second predetermined type is supplied to said primary winding, the primary winding and the transmitter being referenced to a first ground; and the secondary winding being referenced to a second ground which is galvanically isolated from the first ground and said secondary winding supplying to a receiver circuit signals received in correspondence to the signals provided to the primary winding, the receiver reconstructing the received logic signal from the received signals.

Owner:ANALOG DEVICES INC

On chip transformer isolator

ActiveUS20050269657A1Semiconductor/solid-state device detailsSolid-state devicesTransformerEngineering

An integrated circuit having voltage isolation capabilities includes a first area of the integrated circuit containing functional circuitry that is located in the substrate of the integrated circuit. A second area of the integrated circuit contains an integrated RF isolation circuitry for voltage isolating the functional circuitry. The RF isolation circuitry is located in the metal layers of the integrated circuit.

Owner:SKYWORKS SOLUTIONS INC

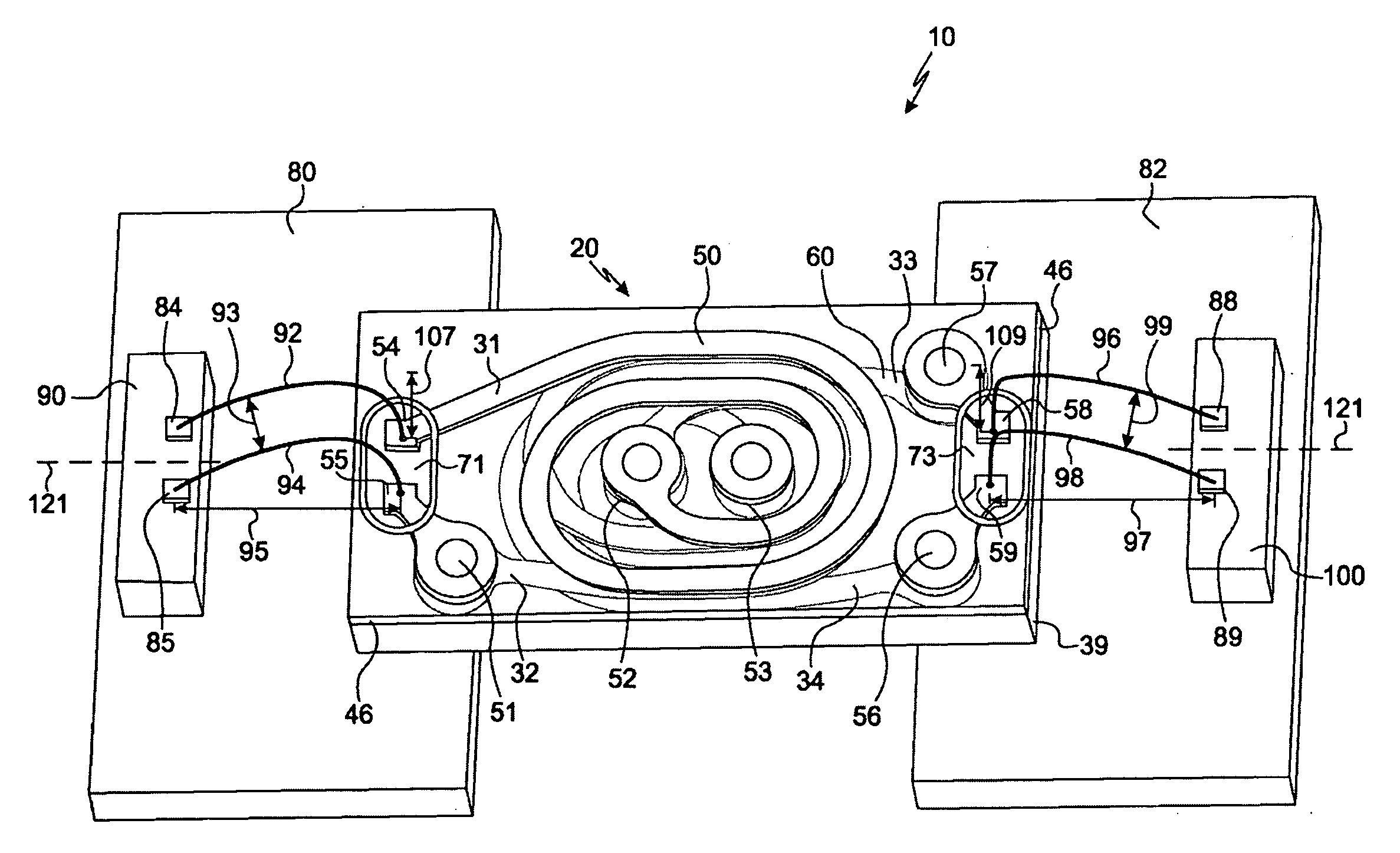

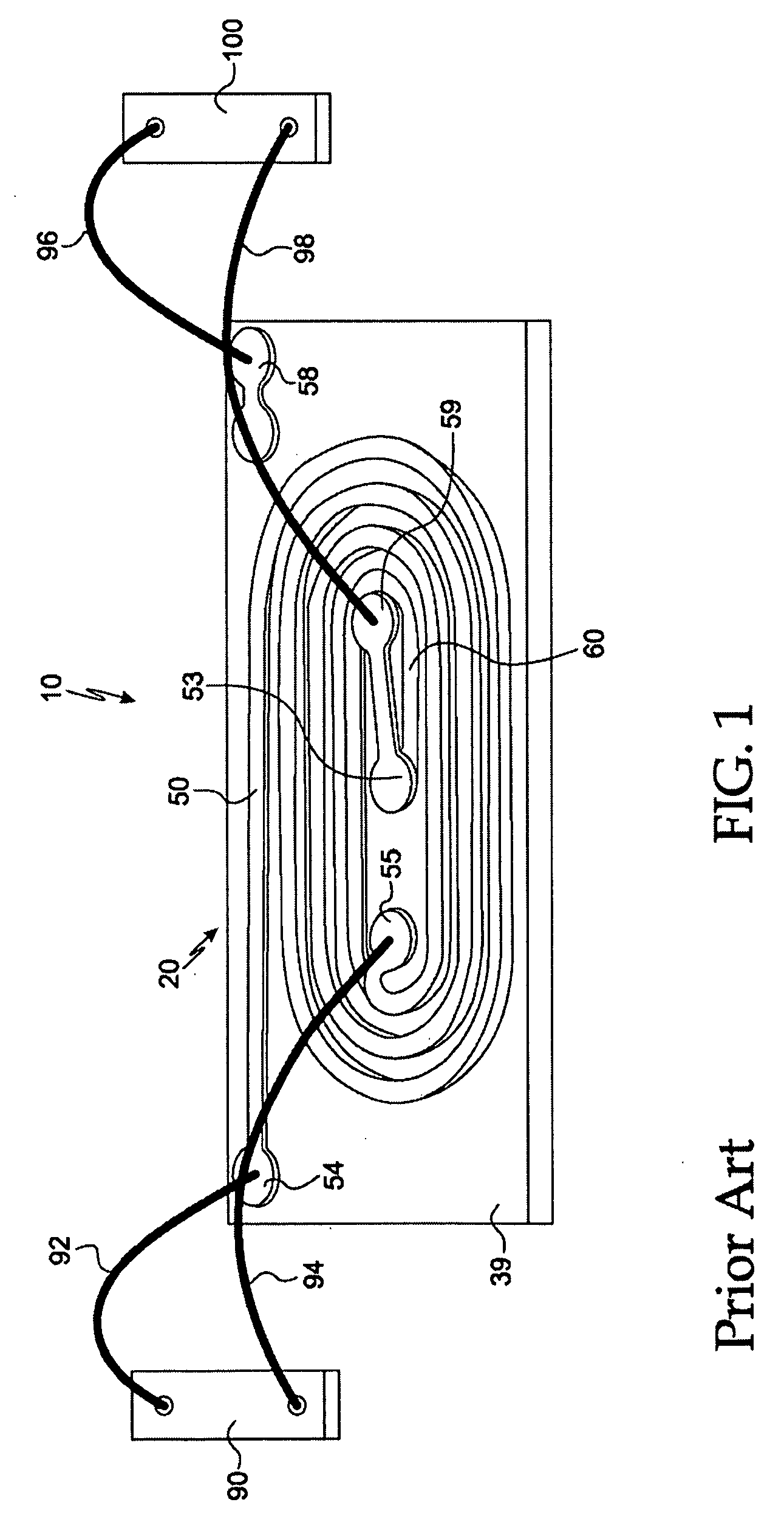

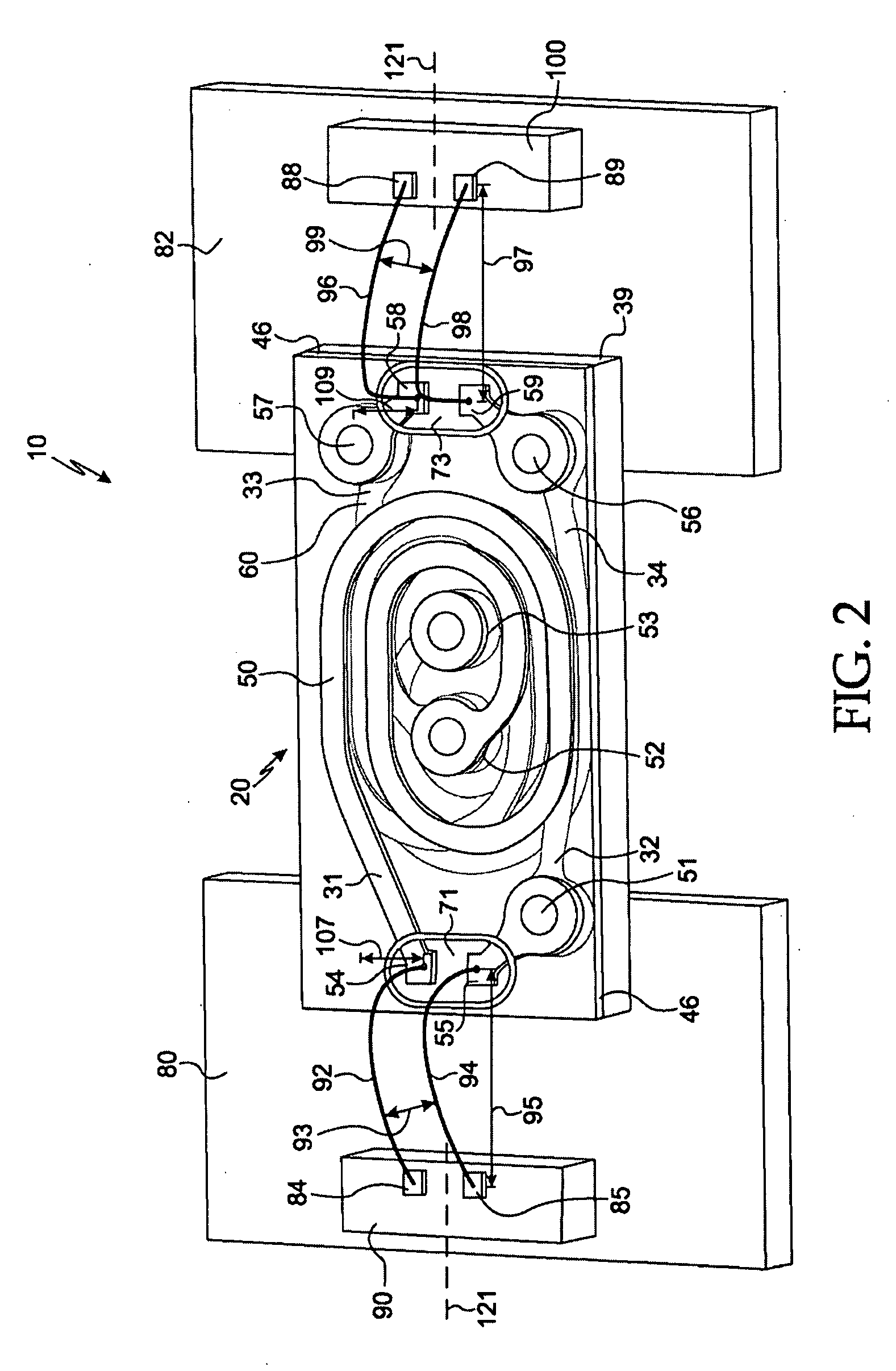

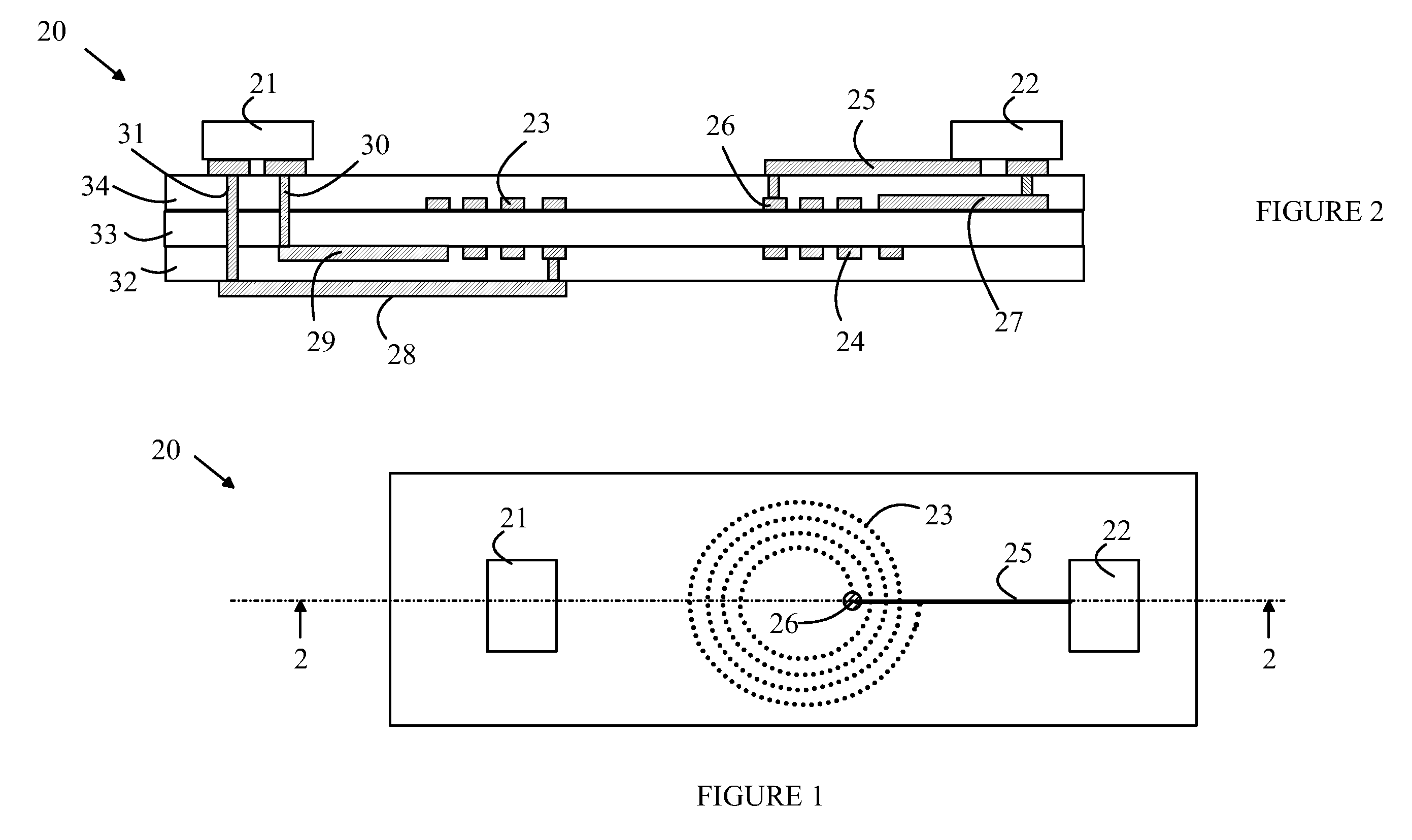

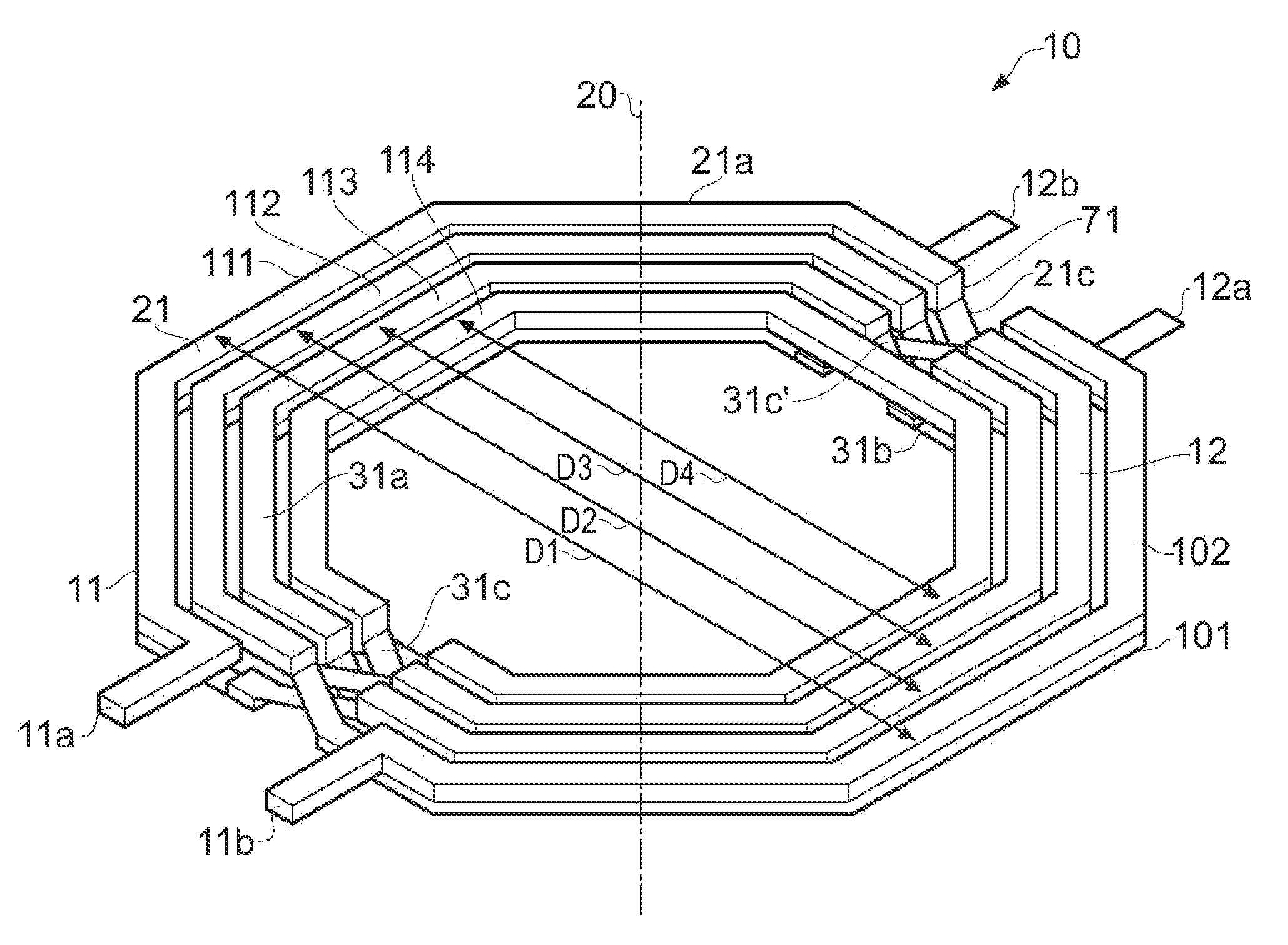

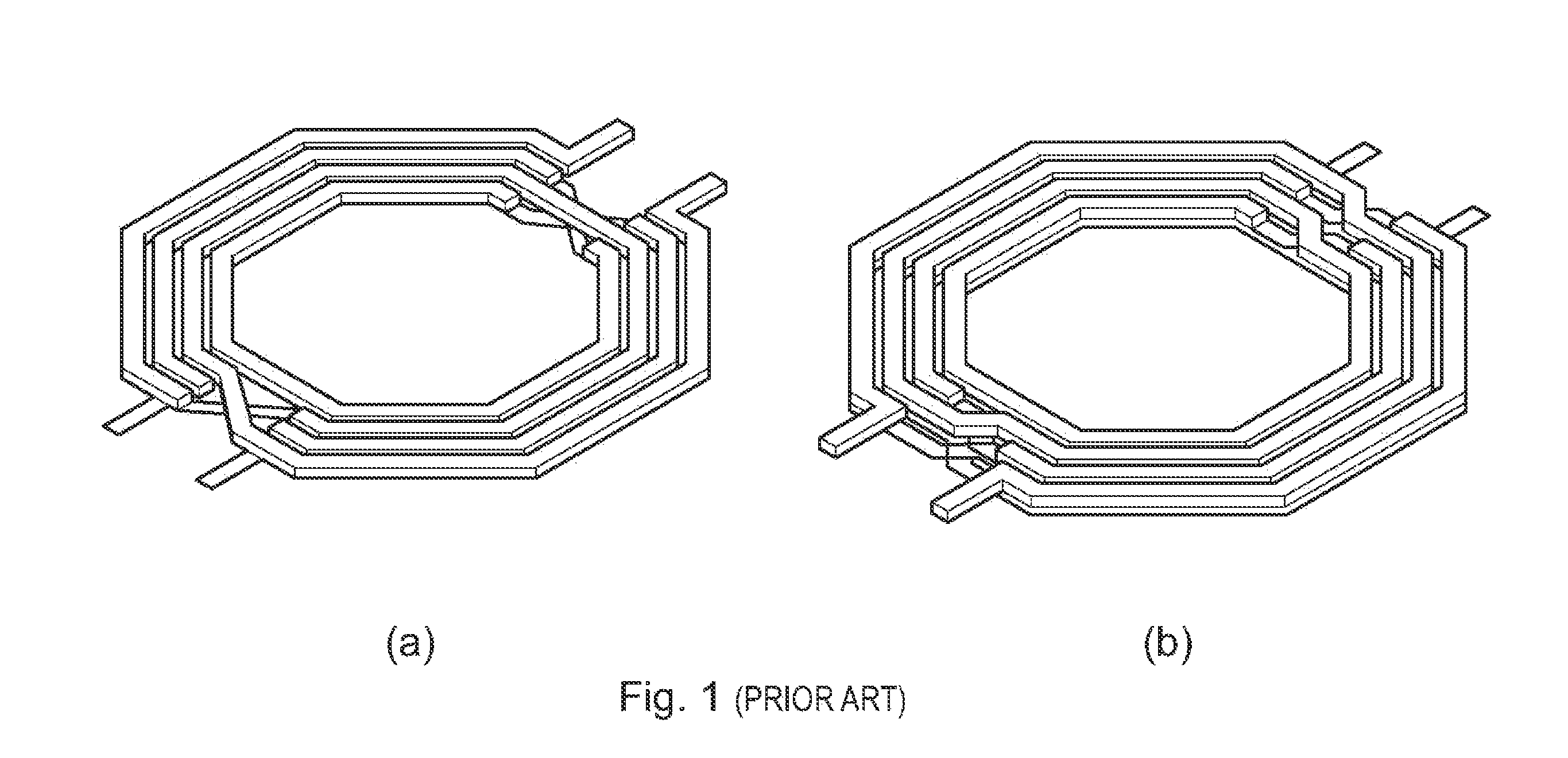

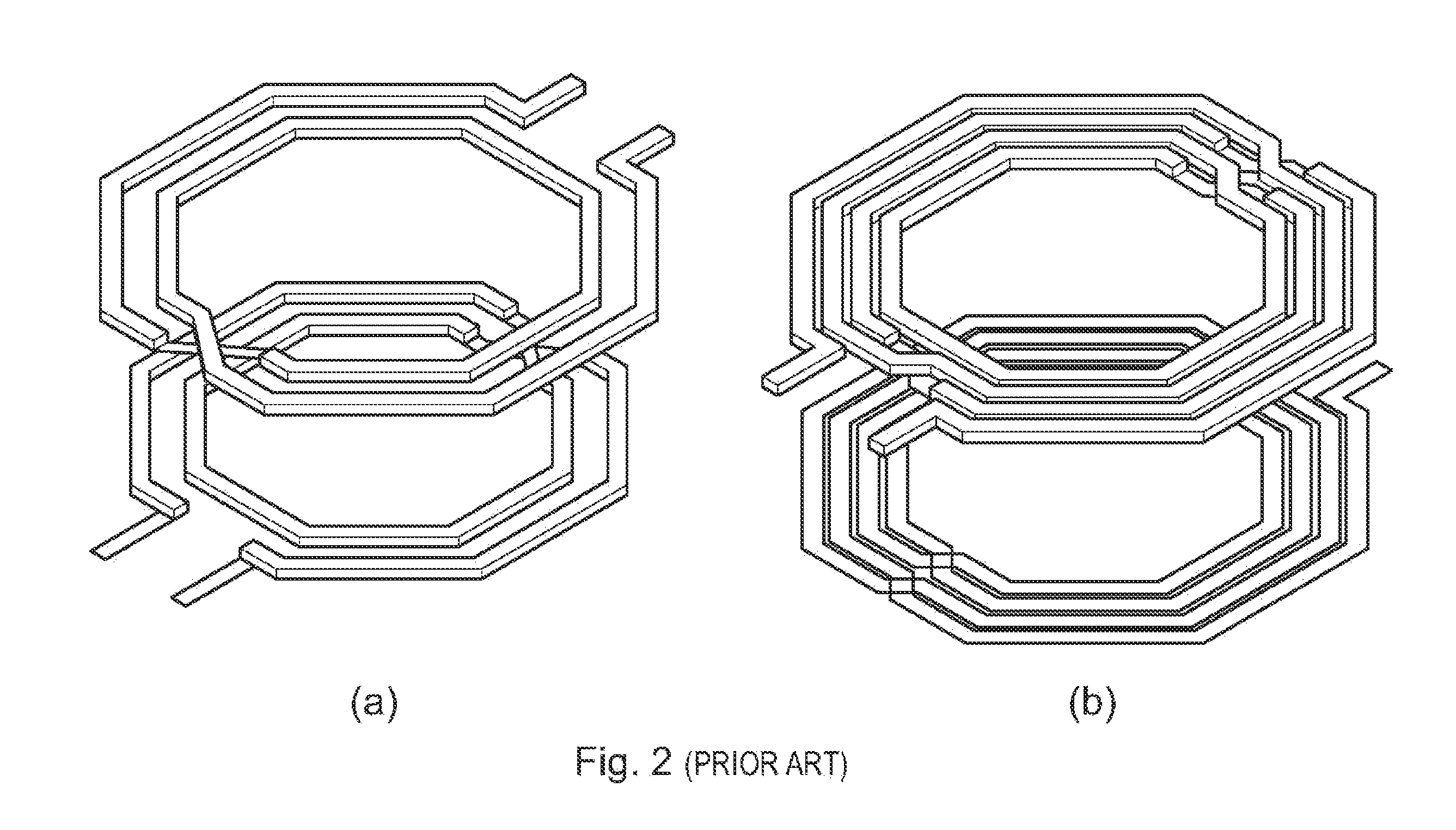

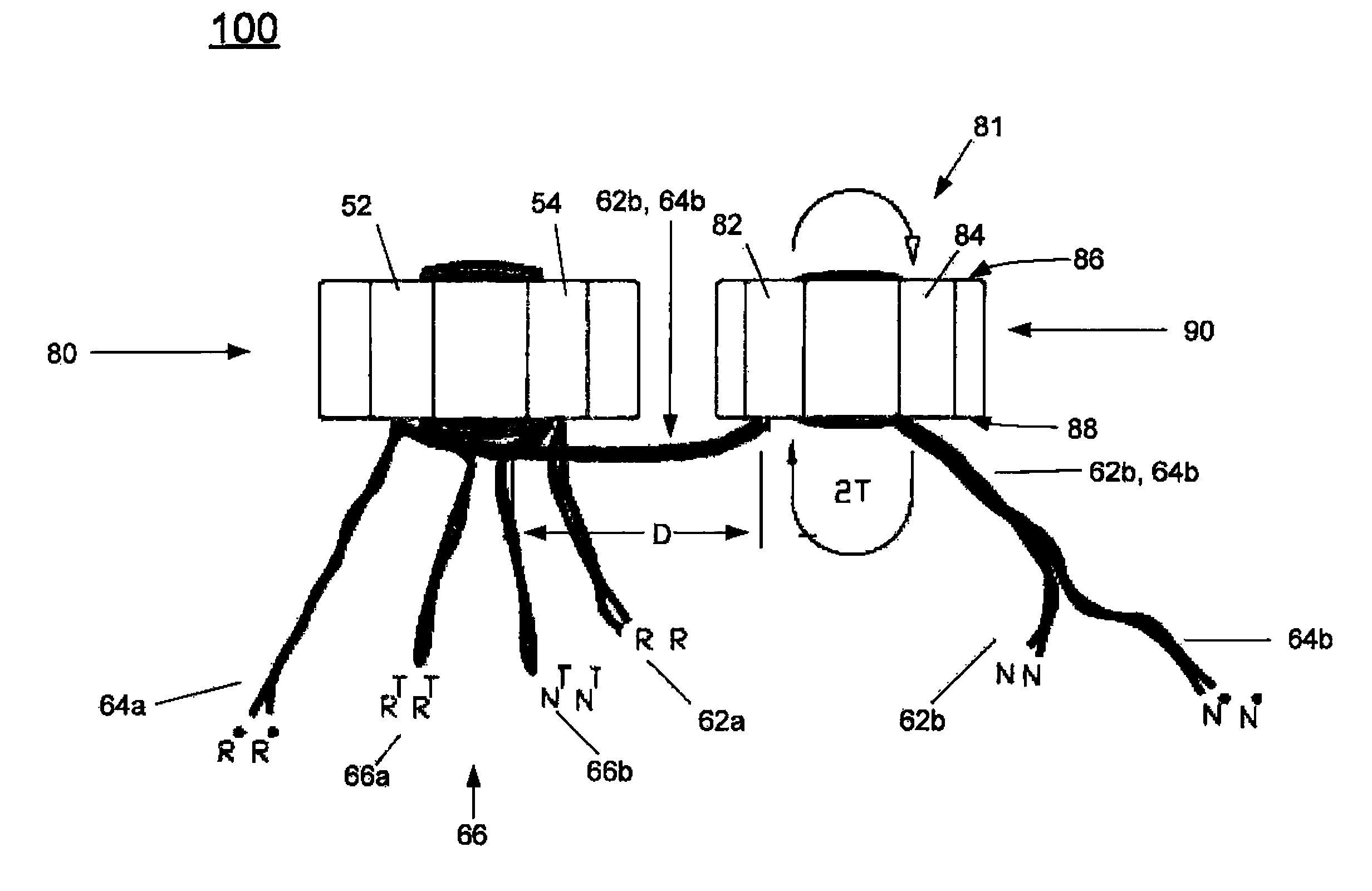

Minimizing Electromagnetic Interference in Coil Transducers

ActiveUS20090243783A1Minimize pick-upTransformers/reacts mounting/support/suspensionNear-field transmissionElectromagnetic interferenceTransducer

Disclosed herein are various embodiments of means and methods for reducing the pick-up of electromagnetic interference (“EMI”) by coil transducers configured to provide high voltage isolation and high voltage breakdown performance characteristics in small packages. In some embodiments, the lengths, heights, and horizontal distances between wires electrically connecting transmitter circuits and receiver circuits to coil transducers are minimized and optimized respecting one another.

Owner:AVAGO TECH INT SALES PTE LTD

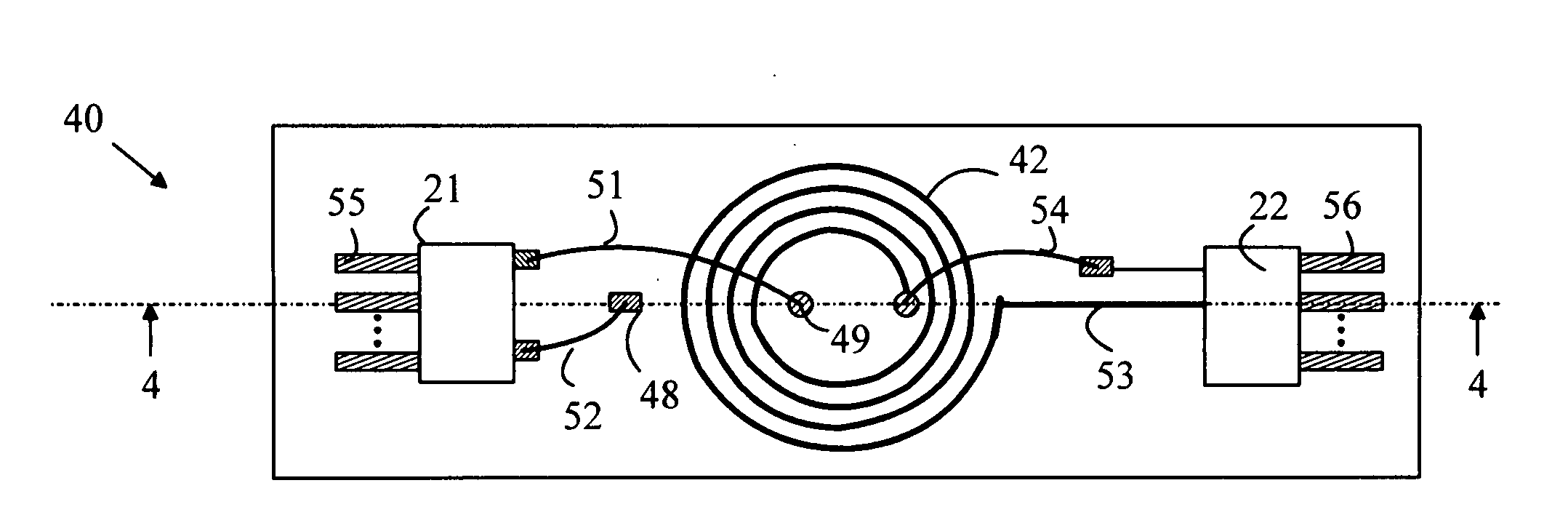

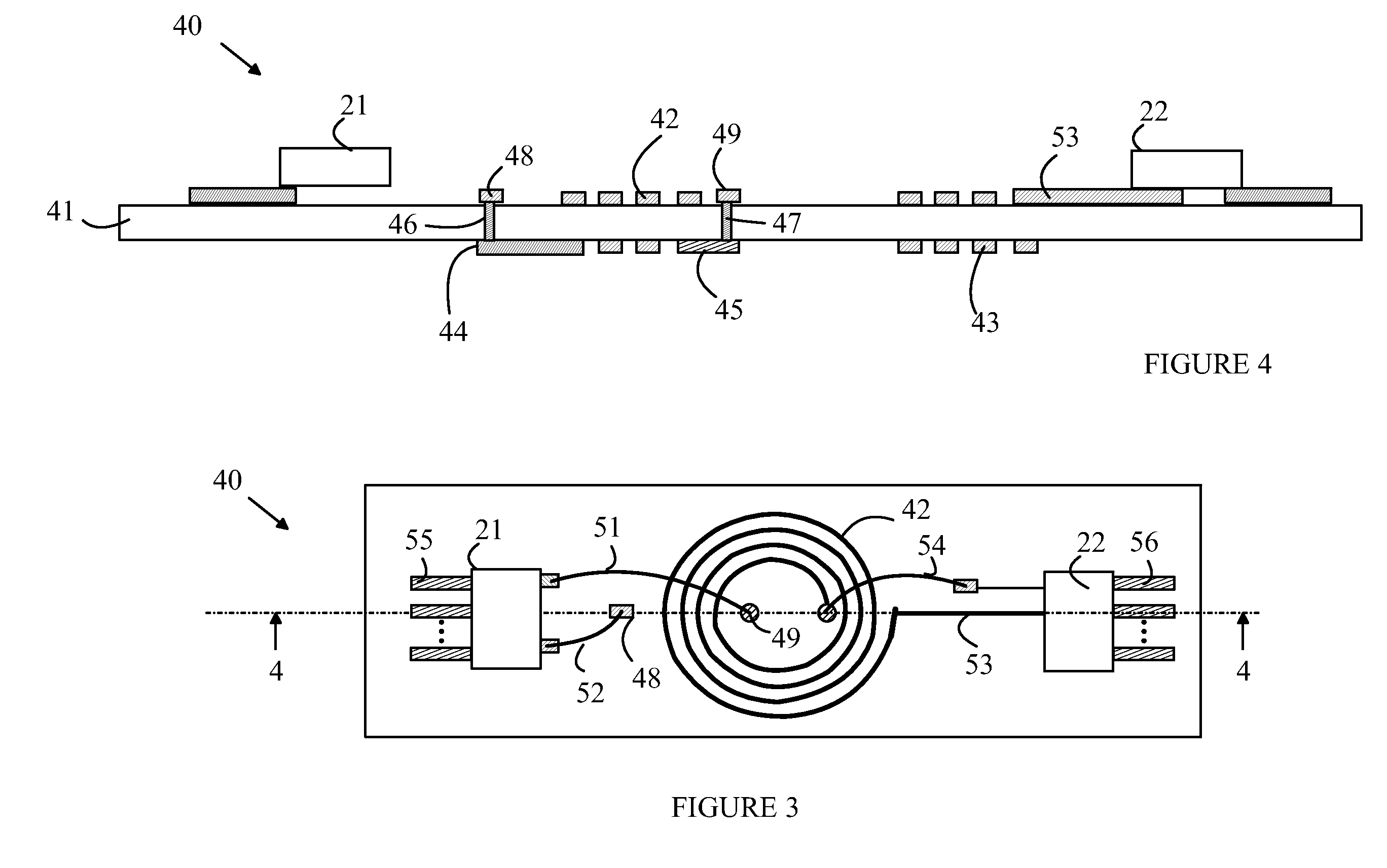

Chip-scale coils and isolators based thereon

InactiveUS7545059B2Improve performanceReduce capacitanceMultiple-port networksNear-field transmissionTransformerEngineering

Coil structures and isolators using them. A coil(s) is (are) used as a magnetic field-generating element(s) paired with another coil(s) or other magnetic field-receiving element(s). The coil(s) is(are) formed in or on a substrate which does not include some or all of the driver (i.e., input) or receiver (i.e., output) circuits. The coil(s) and magnetic field-receiving element(s) thus can be manufactured separately from the driver and / or receiver circuitry, using different processes, instead of subjecting the chip areas containing both input and output circuits to post processing to form the coil(s). Isolators can be assembled using such coils with a resultant lower cost. Isolators also can be assembled using transformers made from such coils wherein the transformers can be driven on either of their windings in order to provide bi-directional isolation with a single transformer.

Owner:ANALOG DEVICES INC

Transmitter head and system for contactless energy transmission

ActiveUS20060209487A1Small unit volumeInexpensive and uncomplicated mannerTransformersMagnetic-bias transformersEngineeringMechanical engineering

A transmitter head for a system for contactless energy transmission includes a support connected to at least one ferrite core. The ferrite core is embodied at least partially in the E-form and a flat winding is arranged around one leg of the E.

Owner:SEW-EURODRIVE GMBH & CO KG

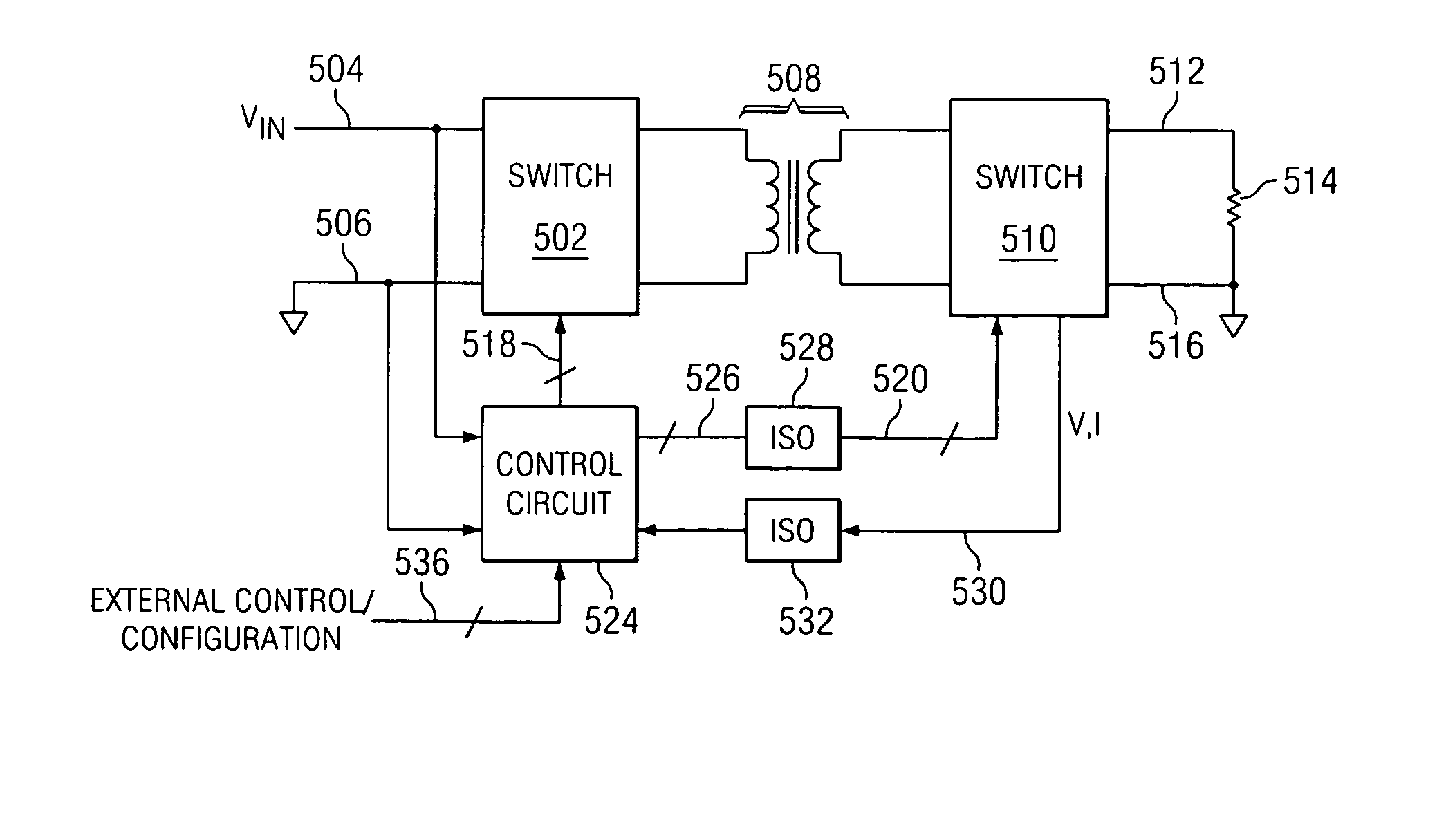

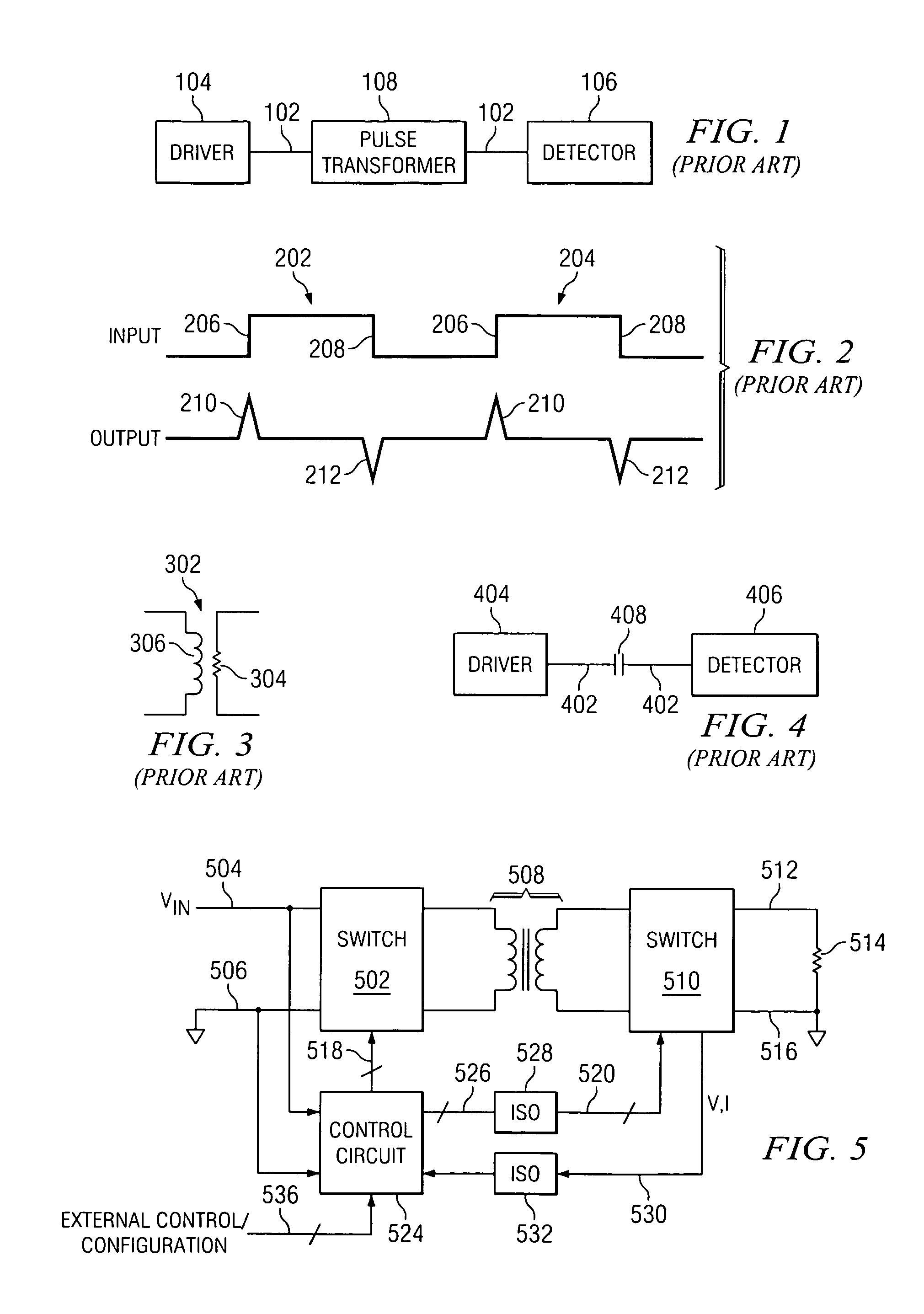

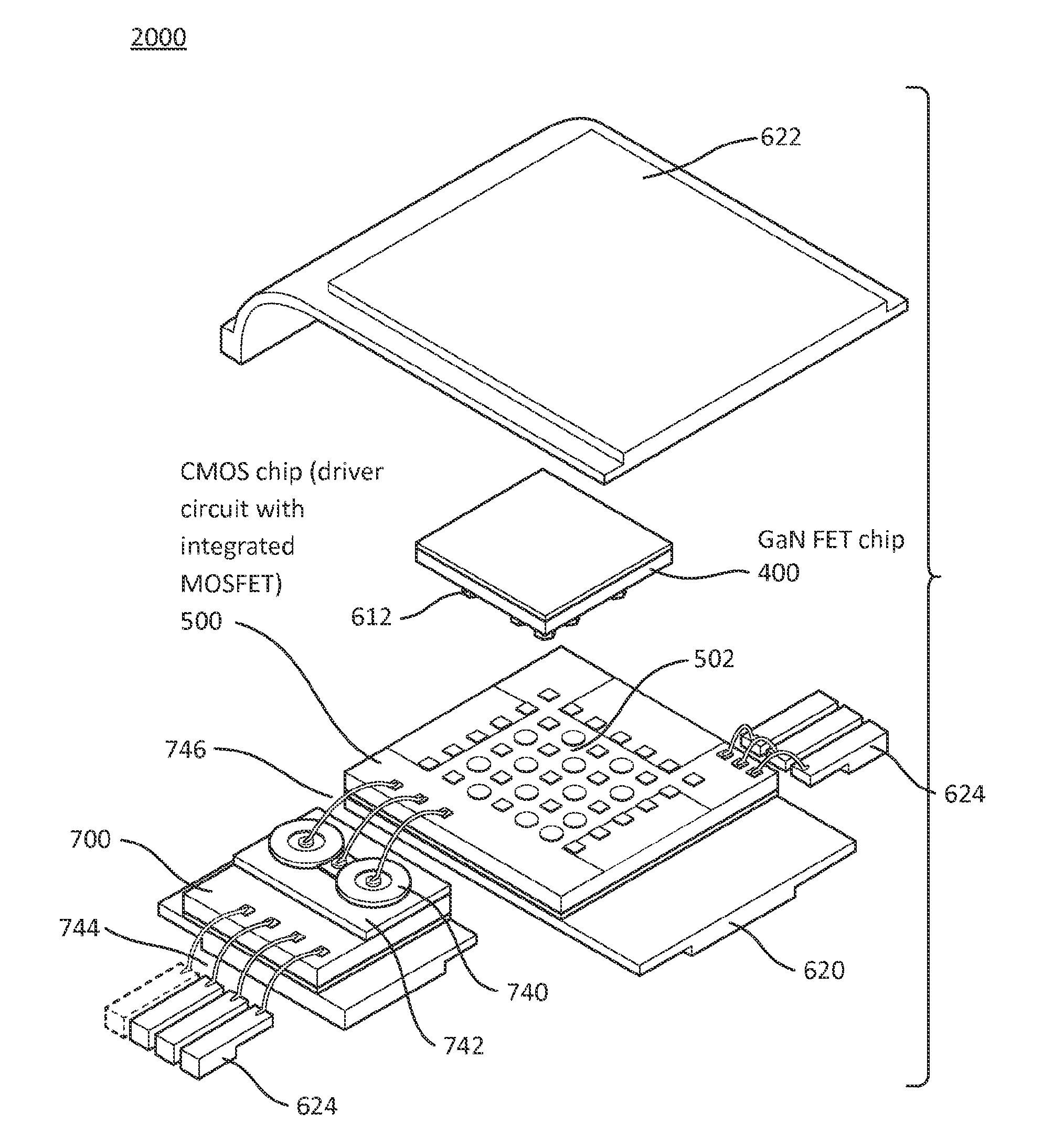

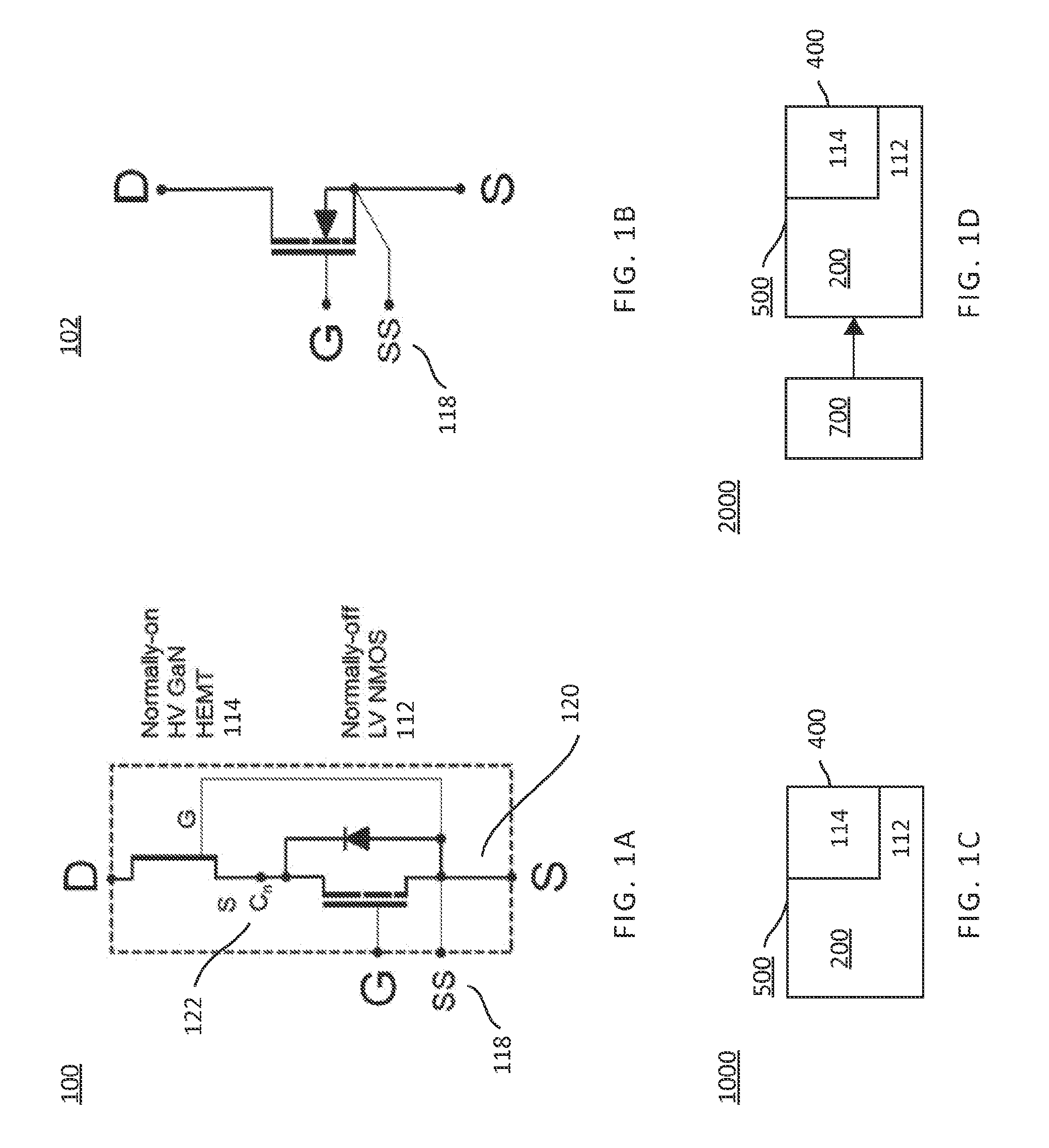

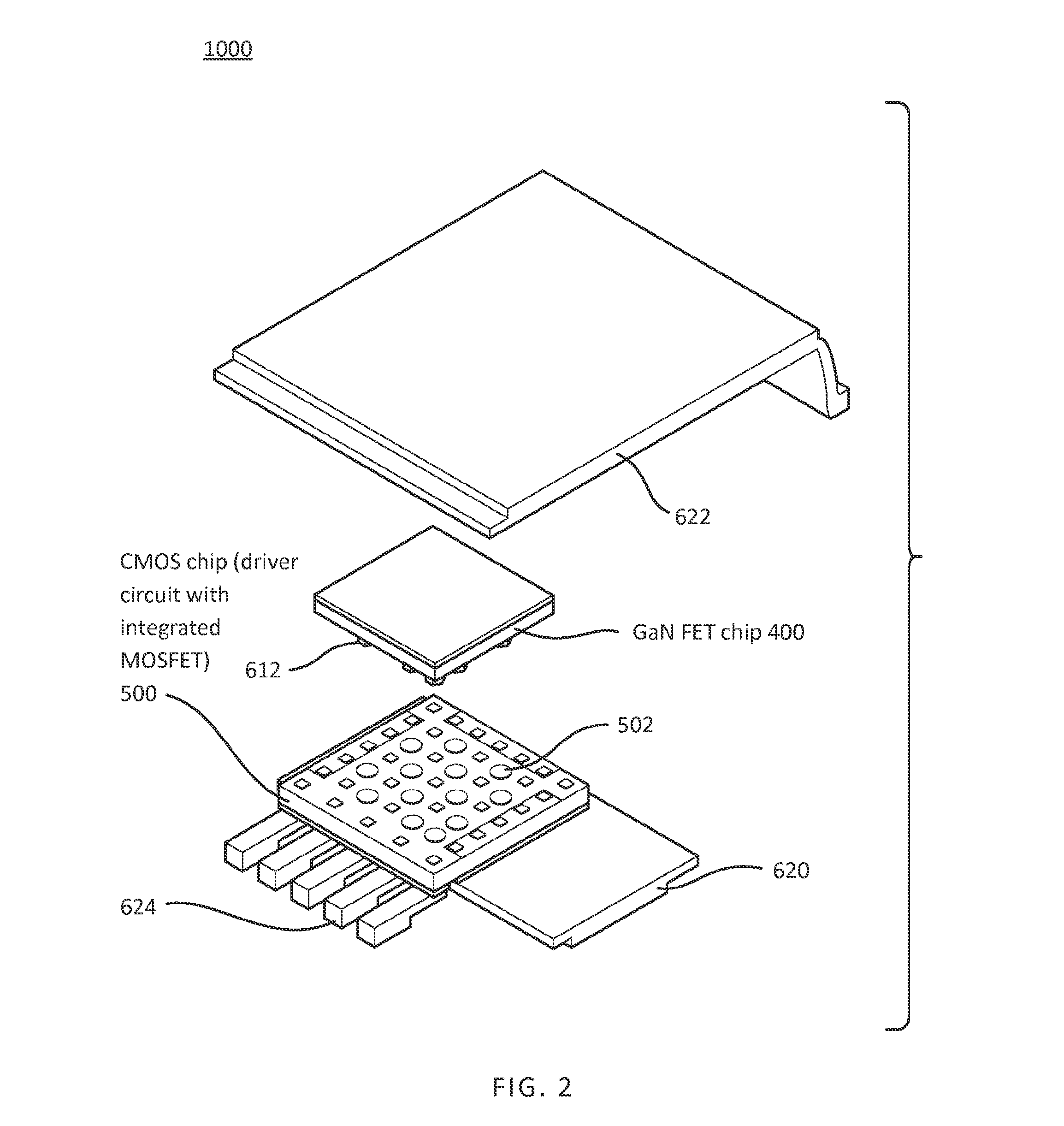

Devices and systems for power conversion circuits

ActiveUS20140175454A1Reduces series inductanceReduce resistanceSemiconductor/solid-state device detailsSolid-state devicesMOSFETLow voltage

Devices and systems comprising driver circuits are disclosed for MOSFET driven, normally-on gallium nitride (GaN) power transistors. Preferably, a low power, high speed CMOS driver circuit with an integrated low voltage, lateral MOSFET driver is series coupled, in a hybrid cascode arrangement to a high voltage GaN HEMT, for improved control of noise and voltage transients. Co-packaging of a GaN transistor die and a CMOS driver die using island topology contacts, through substrate vias, and a flip-chip, stacked configuration provides interconnections with low inductance and resistance, and provides effective thermal management. Co-packaging of a CMOS input interface circuit with the CMOS driver and GaN transistor allows for a compact, integrated CMOS driver with enhanced functionality including shut-down and start-up conditioning for safer operation, particularly for high voltage and high current switching. Preferred embodiments also provide isolated, self-powered, high speed driver devices, with reduced input losses.

Owner:GAN SYST

On chip transformer isolator

ActiveUS8064872B2Semiconductor/solid-state device detailsSolid-state devicesTransformerPhotonic integrated circuit

An integrated circuit having voltage isolation capabilities includes a first area of the integrated circuit containing functional circuitry that is located in the substrate of the integrated circuit. A second area of the integrated circuit contains an integrated RF isolation circuitry for voltage isolating the functional circuitry. The RF isolation circuitry is located in the metal layers of the integrated circuit.

Owner:SKYWORKS SOLUTIONS INC

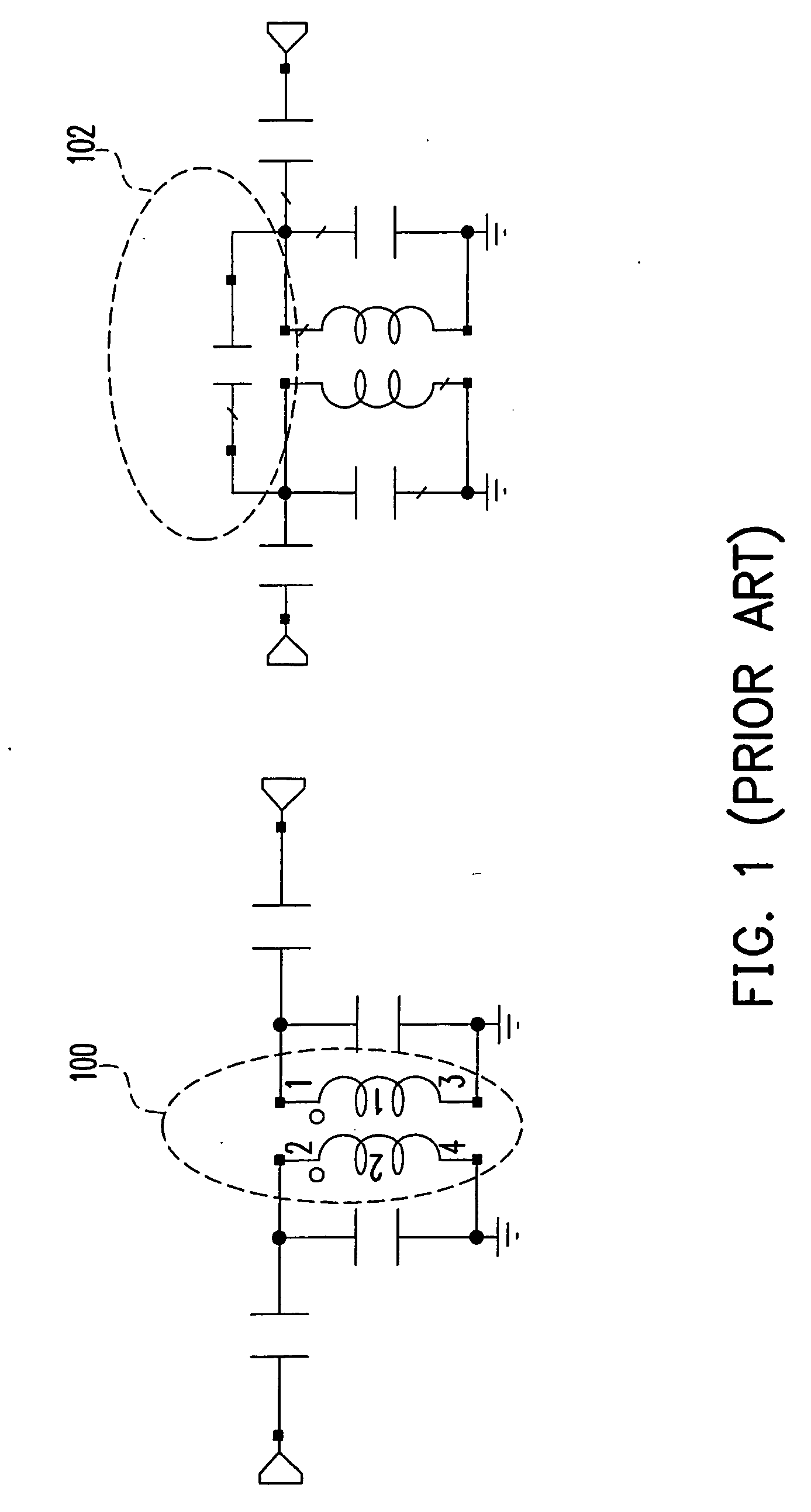

Modular jack for ethernet applications

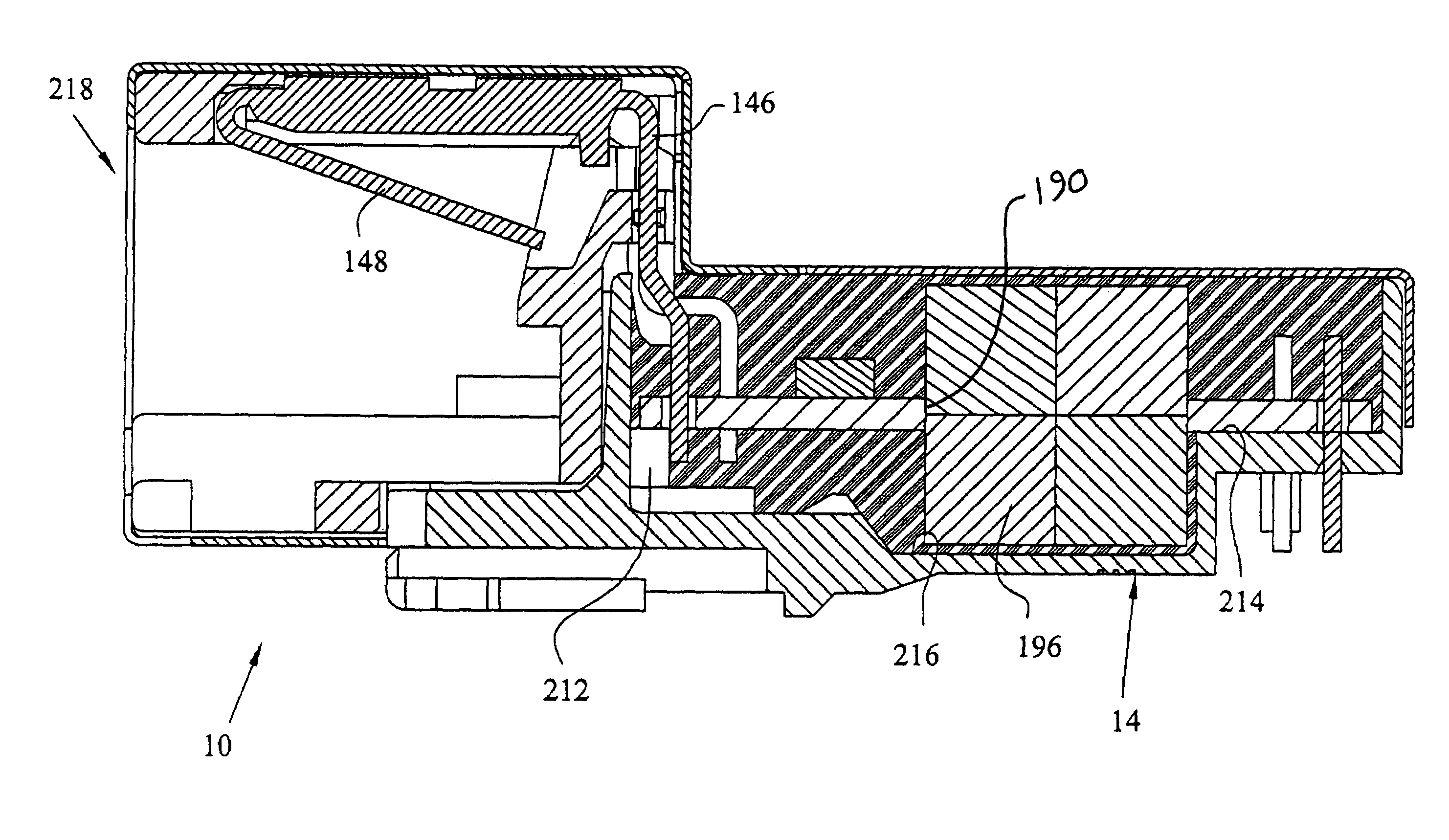

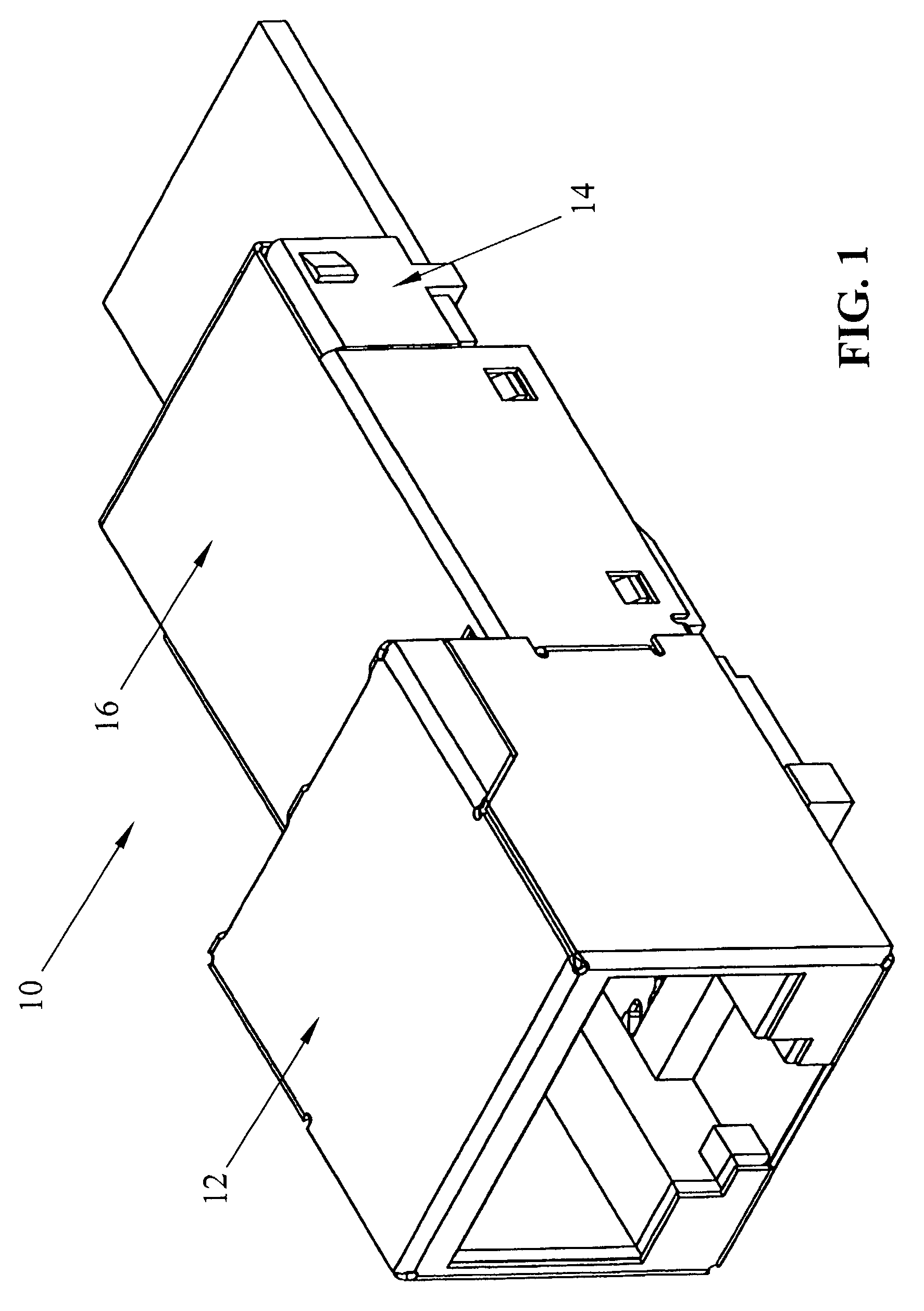

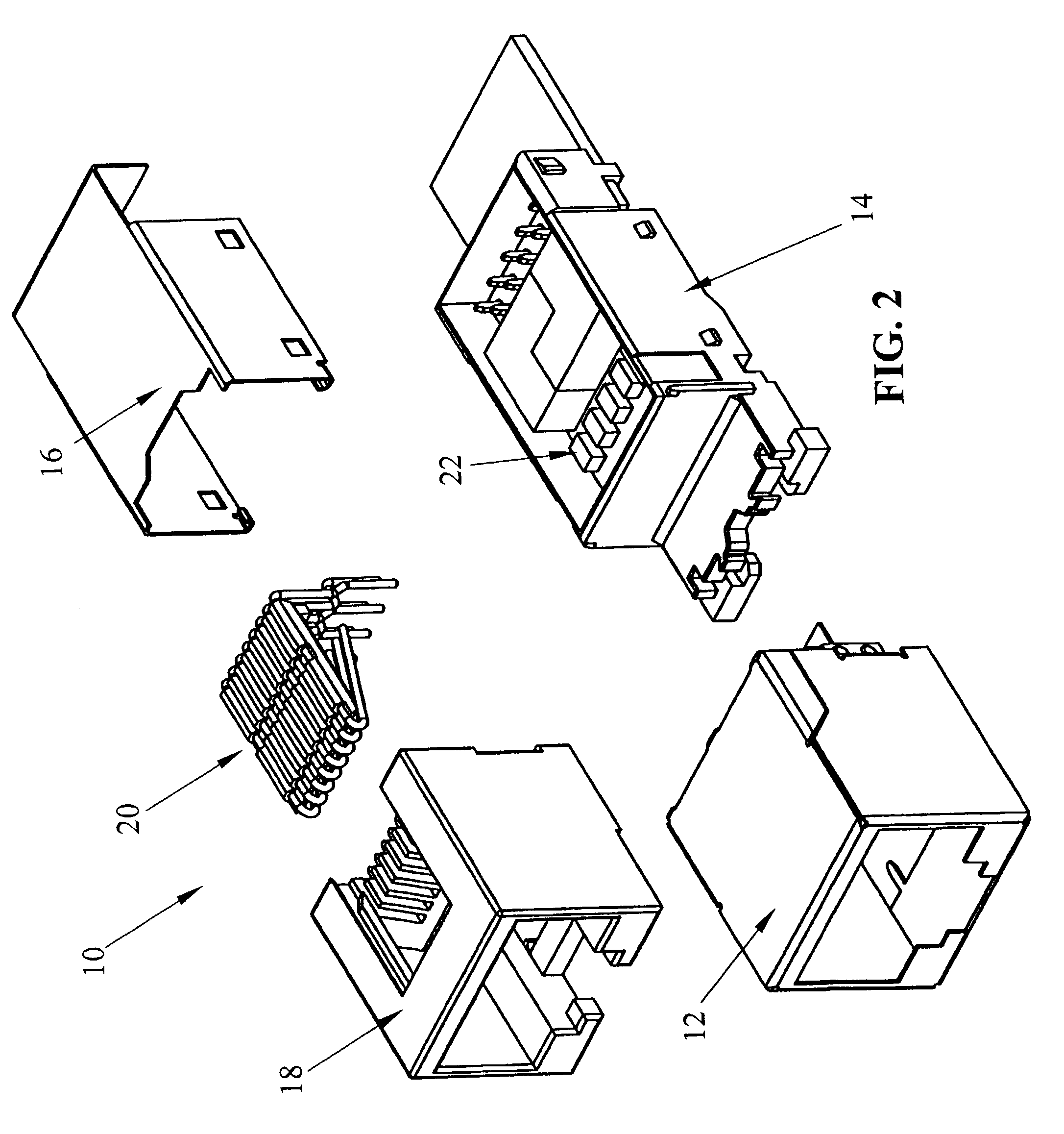

ActiveUS7153163B2Reduced fear of damageCoupling device detailsNetwork connectorsModularityEngineering

A magnetically coupled RJ-45 modular jack assembly for Ethernet applications including a coil pack comprised of a plurality of magnetic circuits. Various numbers of the magnetic circuits may be coupled together in series by way of a variety of wires which may then be soldered directly to a printed circuit board. In order to increase the robustness of the magnetic circuit connection, each group of magnetic circuits coupled together in series, may be encapsulated in an encapsulation material. Additionally, during encapsulation, numerous of the groups of magnet circuits may be encapsulated allowing a plurality of magnetic series to be grouped together further increasing the robustness of the magnetic circuits. Encapsulated coil sets (196, 198) may be fitted together (FIG. 10) and located in notch (190) in the printed circuit board.

Owner:TRP CONNECTOR B V ON BEHALF OF TRP INT

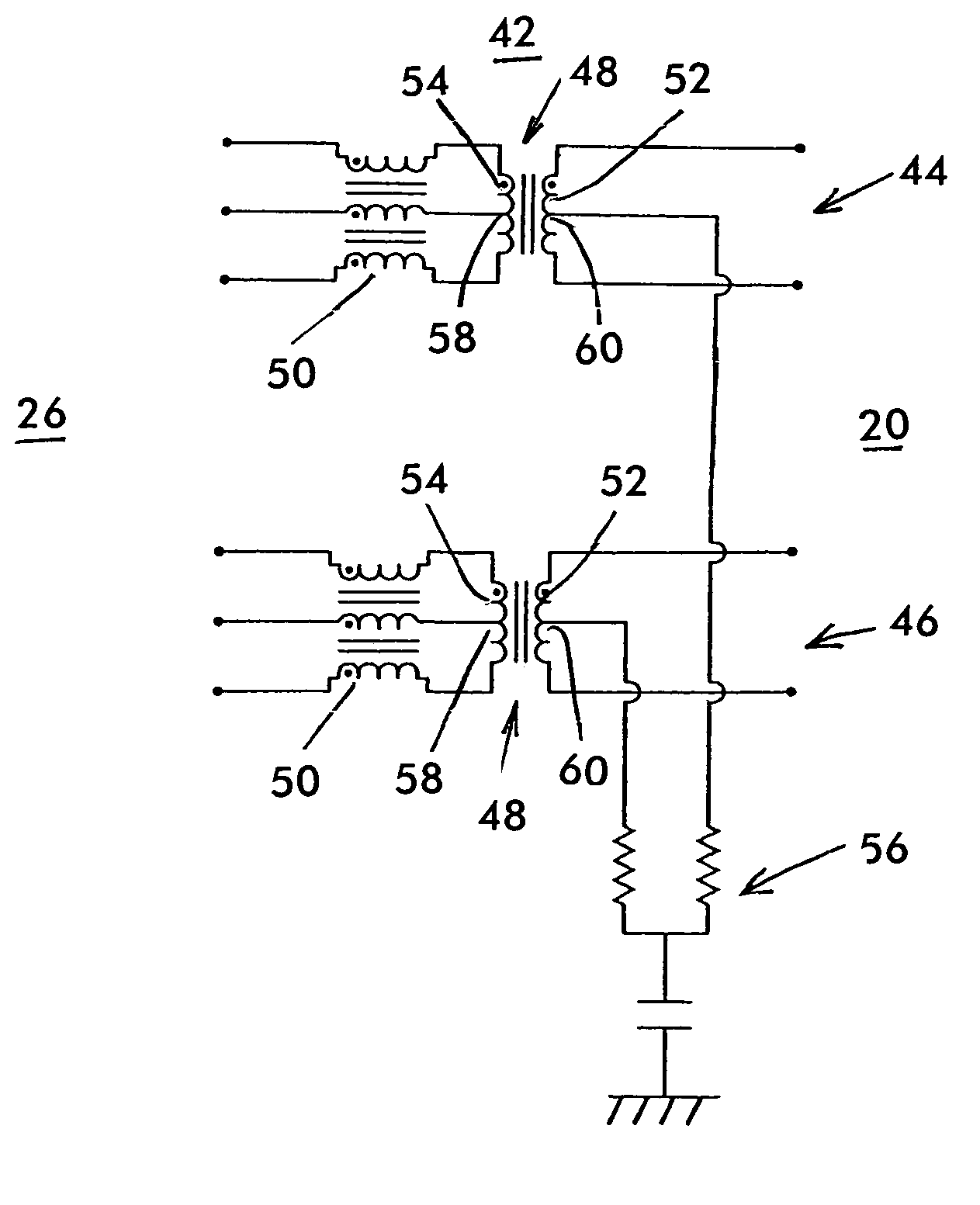

LAN magnetic interface circuit

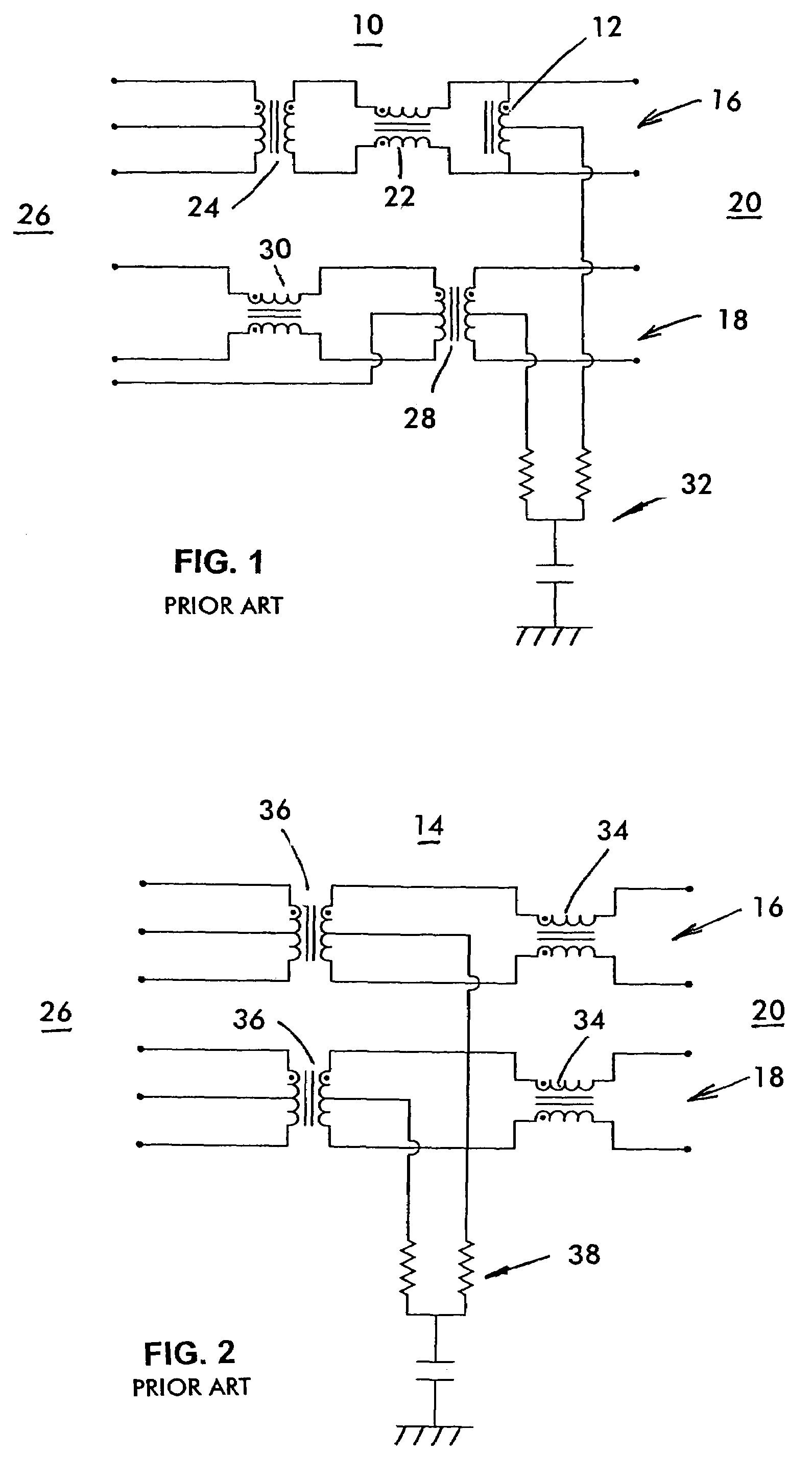

A magnetic interface circuit for a LAN, such as an Ethernet network, includes a transformer having a first winding connected to the line side of the LAN and a second winding connected to the circuit side of the LAN. Each of the first and second windings has two output ports and one of the windings has a center tap port A 3-wire common mode choke having a center winding and two outer windings, the center winding of a 3-wire common mode choke is connected to the center tap of the one winding and the outer windings of the 3-wire common mode choke are respectively connected to the output ports of the one winding.

Owner:BEL FUSE

Planar-like inductor coupling structure

A planar-like inductor coupling structure includes a first planar inductor embedded in an insulating material layer and a second planar inductor also embedded in the insulating material layer. The first planar inductor and the second planar inductor are substantially at the same height, and have a portion in a horizontal distribution serving as a coupled overlapping region with electric insulation from each other. In addition, the first planar inductor and the second planar inductor may be at different heights.

Owner:IND TECH RES INST

Galvanic isolator

ActiveUS20100176660A1Easy to understandAvoid insufficient thicknessMultiple-port networksNear-field transmissionFlexible circuitsEngineering

A galvanic isolator having a split circuit element, a polymeric substrate, a transmitter and receiver is disclosed. The split circuit element has first and second portions, the first portion being disposed on a first surface of the substrate and the second portion being disposed a second surface of the substrate. The transmitter receives an input signal and couples a signal derived from the input signal to the first portion. The receiver is connected to the second portion of the circuit element and generates an output signal that is coupled to an external circuit. The galvanic isolator can be economically fabricated on conventional printed circuit board substrates and flexible circuit substrates.

Owner:AVAGO TECH INT SALES PTE LTD

Chip-scale coils and isolators based thereon

InactiveUS20080030080A1Improved transformer performanceLess substrate lossMultiple-port networksNear-field transmissionTransformerEngineering

Coil structures and isolators using them. A coil(s) is (are) used as a magnetic field-generating element(s) paired with another coil(s) or other magnetic field-receiving element(s). The coil(s) is(are) formed in or on a substrate which does not include some or all of the driver (i.e., input) or receiver (i.e., output) circuits. The coil(s) and magnetic field-receiving element(s) thus can be manufactured separately from the driver and / or receiver circuitry, using different processes, instead of subjecting the chip areas containing both input and output circuits to post processing to form the coil(s). Isolators can be assembled using such coils with a resultant lower cost. Isolators also can be assembled using transformers made from such coils wherein the transformers can be driven on either of their windings in order to provide bi-directional isolation with a single transformer.

Owner:ANALOG DEVICES INC

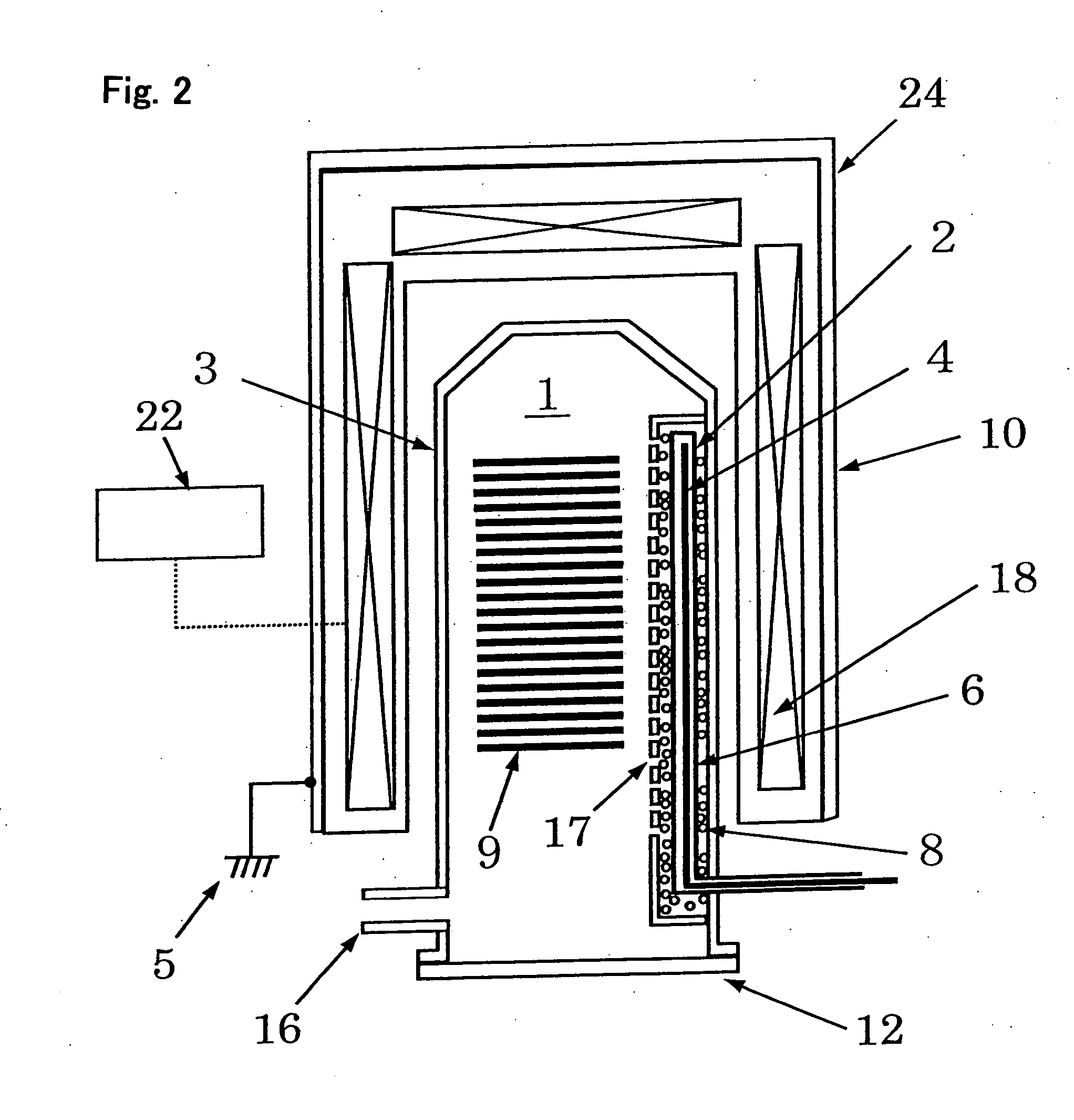

Substrate processing and method of manufacturing device

InactiveUS20060260544A1Electric discharge tubesSemiconductor/solid-state device manufacturingHigh frequency powerRemote plasma

A substrate processor enables realization of a proper process by combining advantages of a remote plasma and a plasma generated in an entire processing chamber. The substrate processor includes a conductive member (10) which is installed surrounding a processing space (1) and grounded to the earth and a pair of electrodes (4) installed inside the conductive member (10). A primary coil of an insularing transformer (7) is connected to a high-frequency power supply unit (14) and a secondary coil is connected to the electrodes (4). A switch (13) is connected to the connection line connecting the secondary coil to the electrodes (4). By setting up / cutting off the connection of the line to the earth with use of the switch (13), the region where the plasma is generated in the processing space (1) can be changed.

Owner:KOKUSA ELECTRIC CO LTD

Pulse transformer

ActiveUS20150084731A1Suppresses magnetic saturationTransformers/inductances coils/windings/connectionsTransformers/inductances magnetic coresEngineeringInductance

Disclosed herein is a pulse transformer that includes a drum core having a winding core portion and first and second flange portions, a plate core connected to the first and second flange portions, and a plurality of wires that are wound around the winding core portion. The first and second flange portions and the plate core are ground such that an inductance of the pulse transformer is 350 μH or more when a bias current of 8 mA is applied to the wires.

Owner:TDK CORPARATION

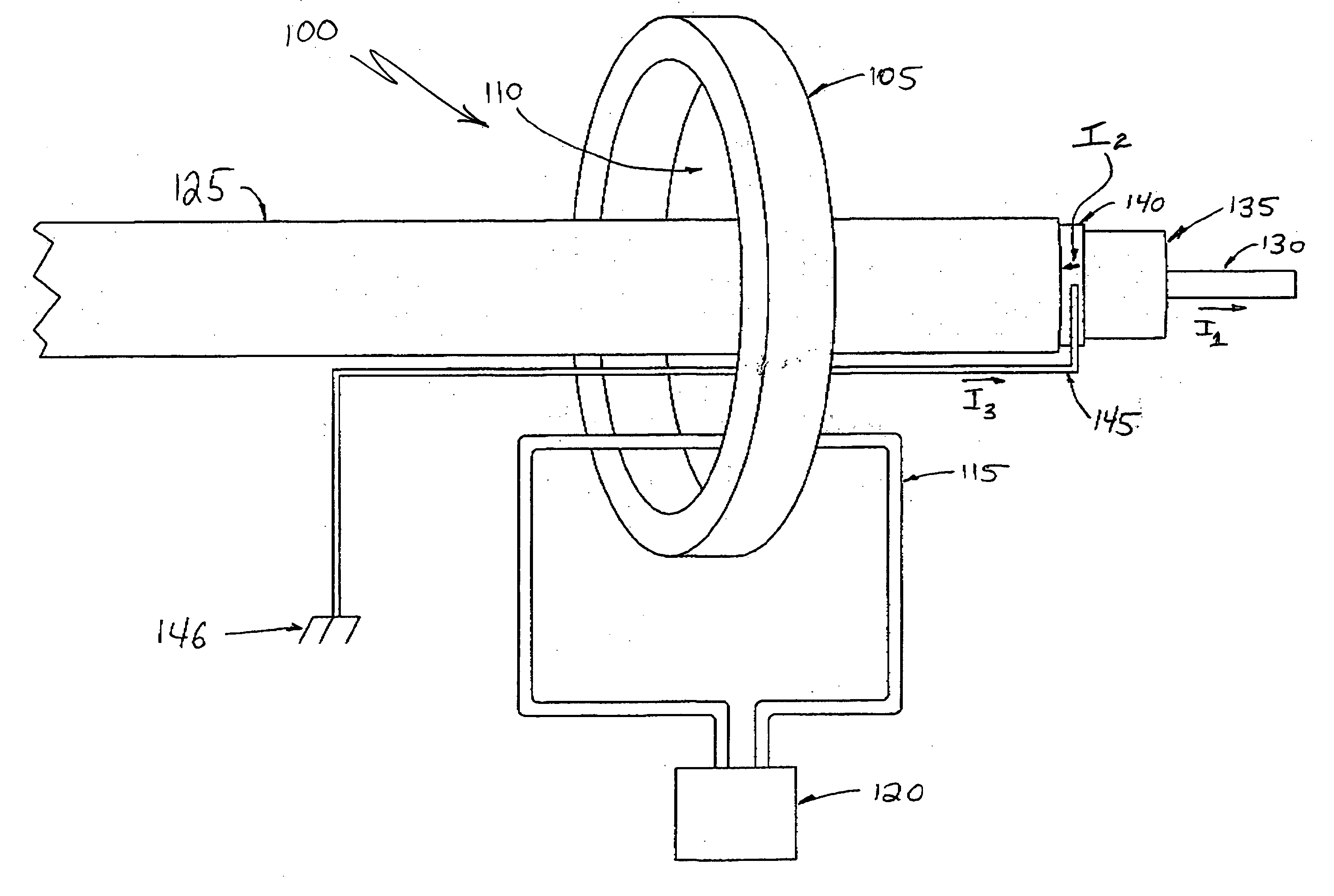

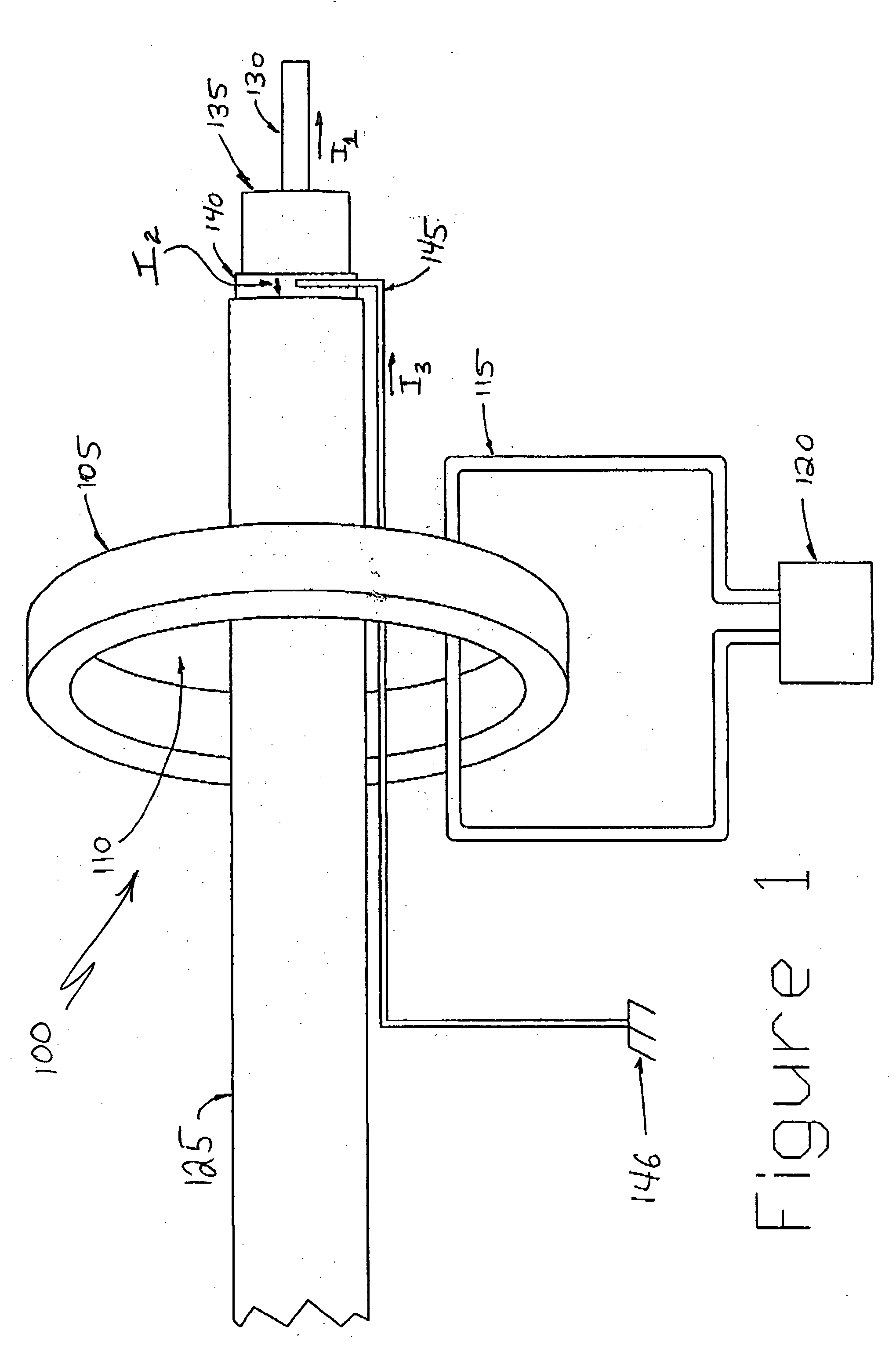

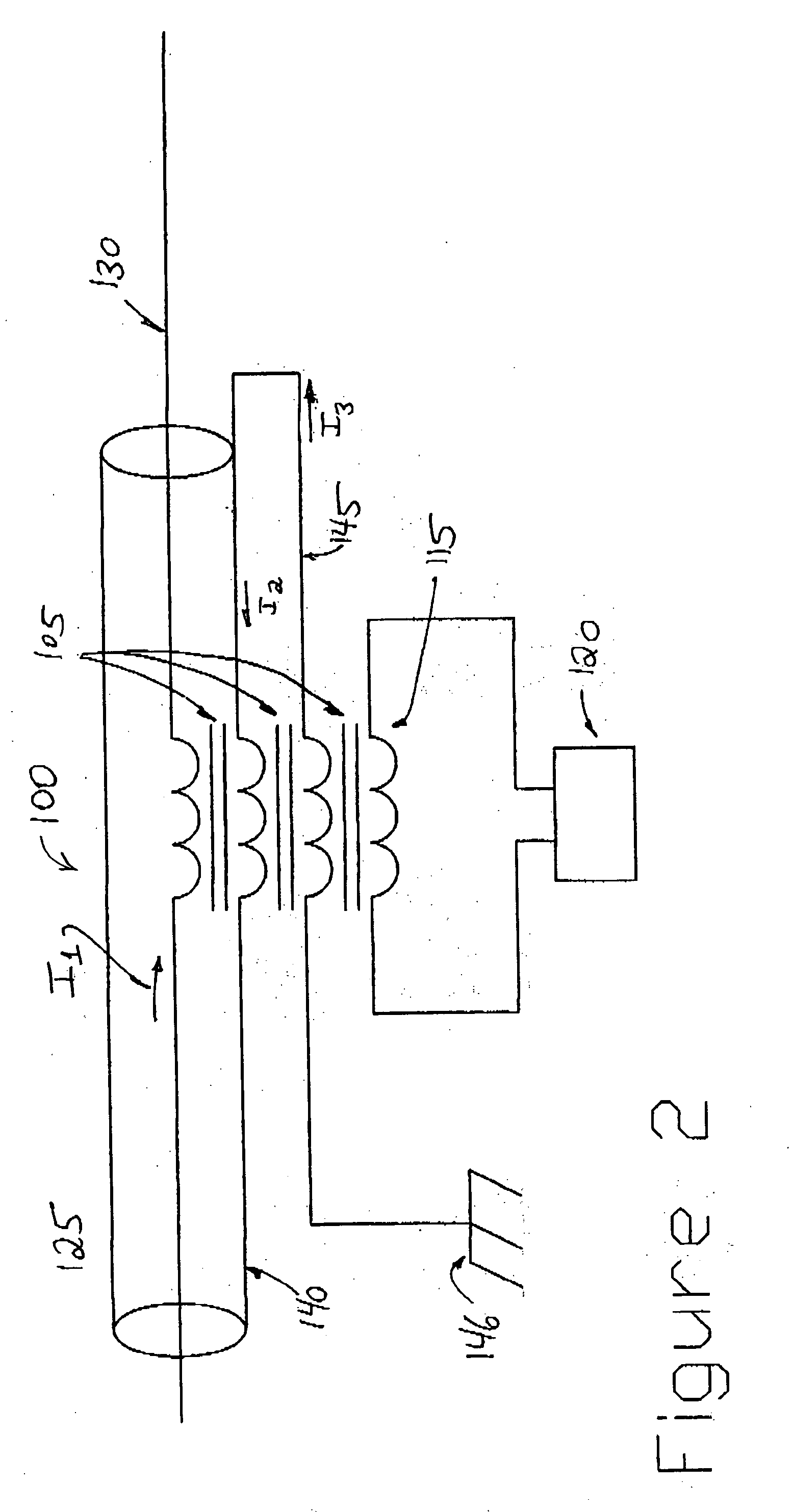

Arrangement of an inductive coupler for power line communications

There is provided an arrangement of components for use in a power line communication system. The arrangement includes (a) an inductive coupler having a core with an aperture through which a coaxial power cable is routed, where the coaxial power cable has a center conductor and an outer conductor; and (b) a lead being routed through the aperture, where the lead connects the outer conductor to a termination.

Owner:ERICSSON INC

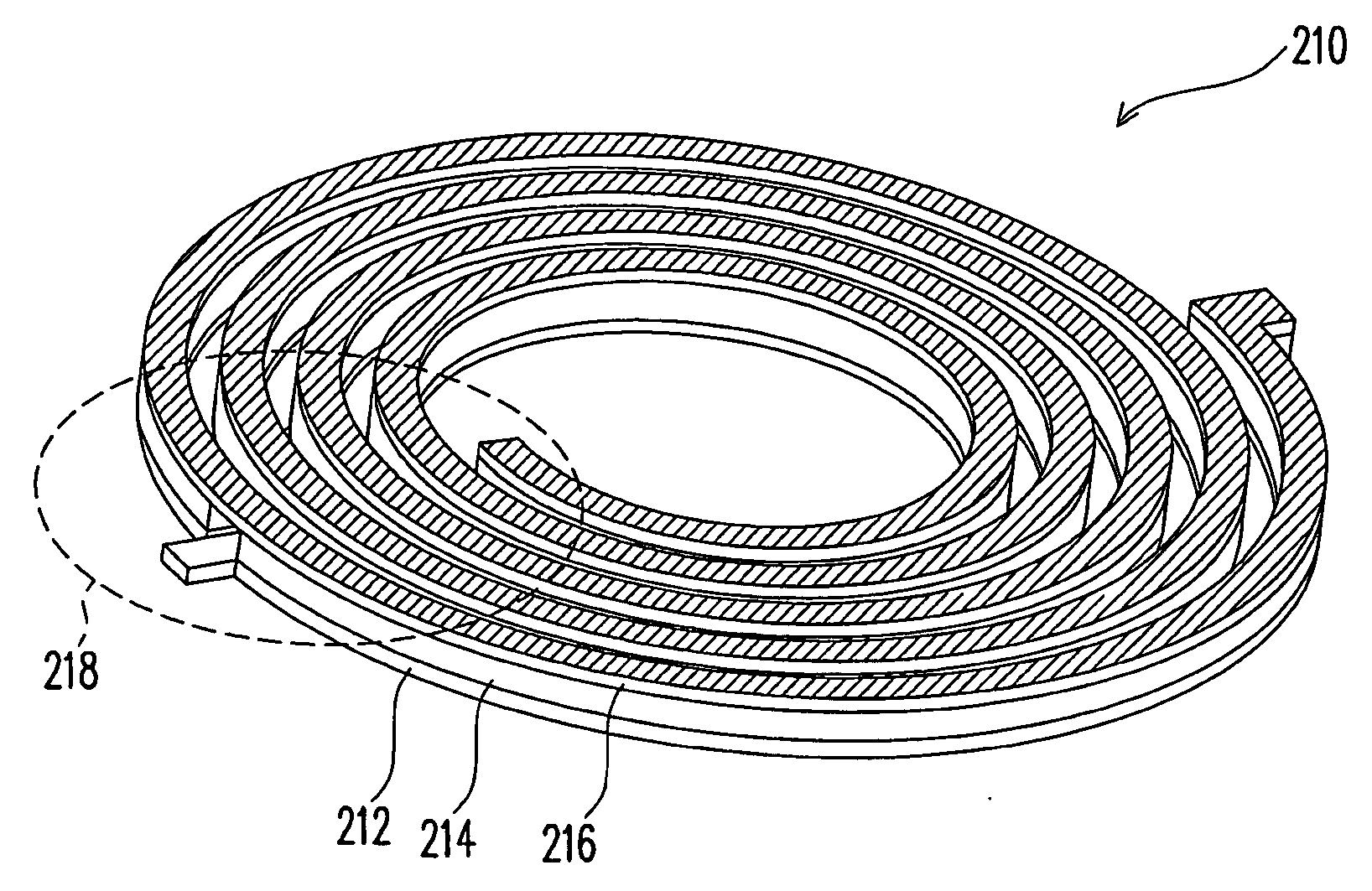

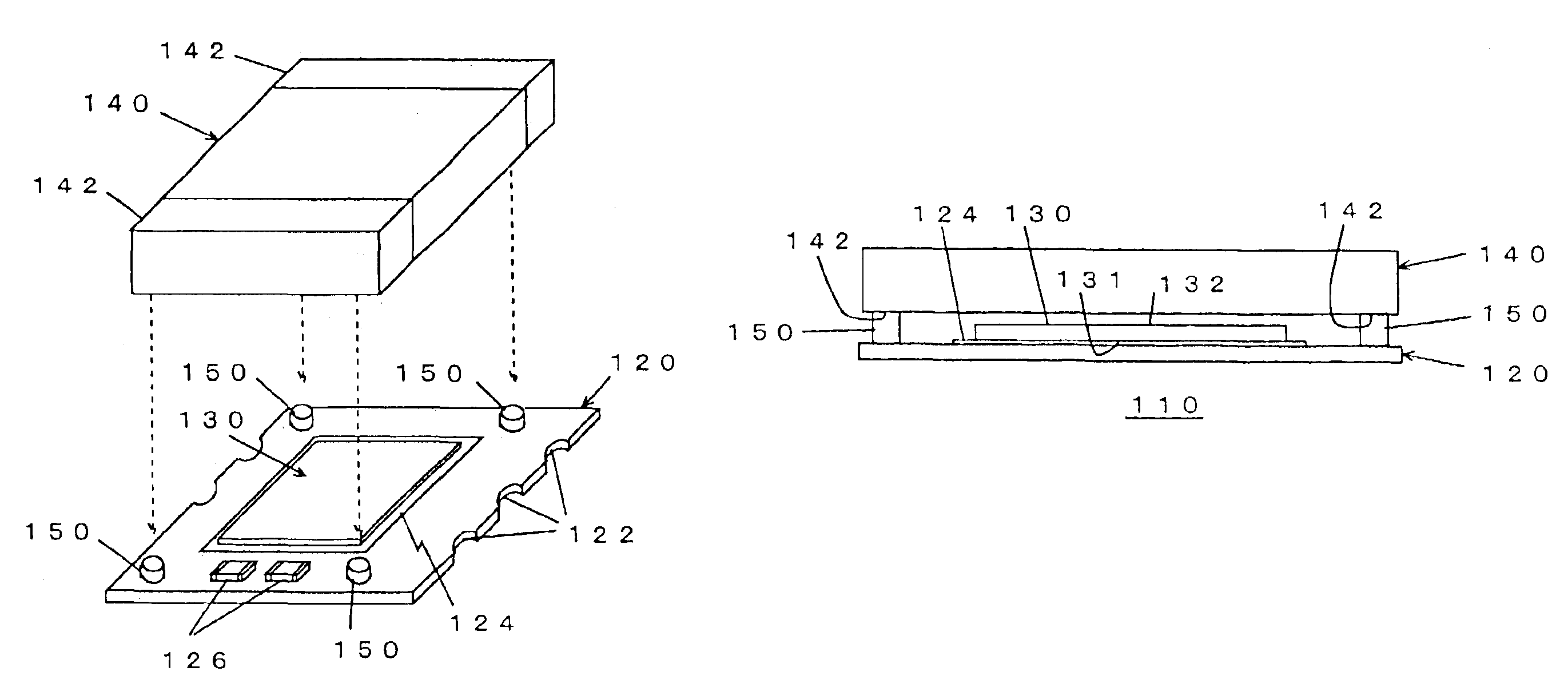

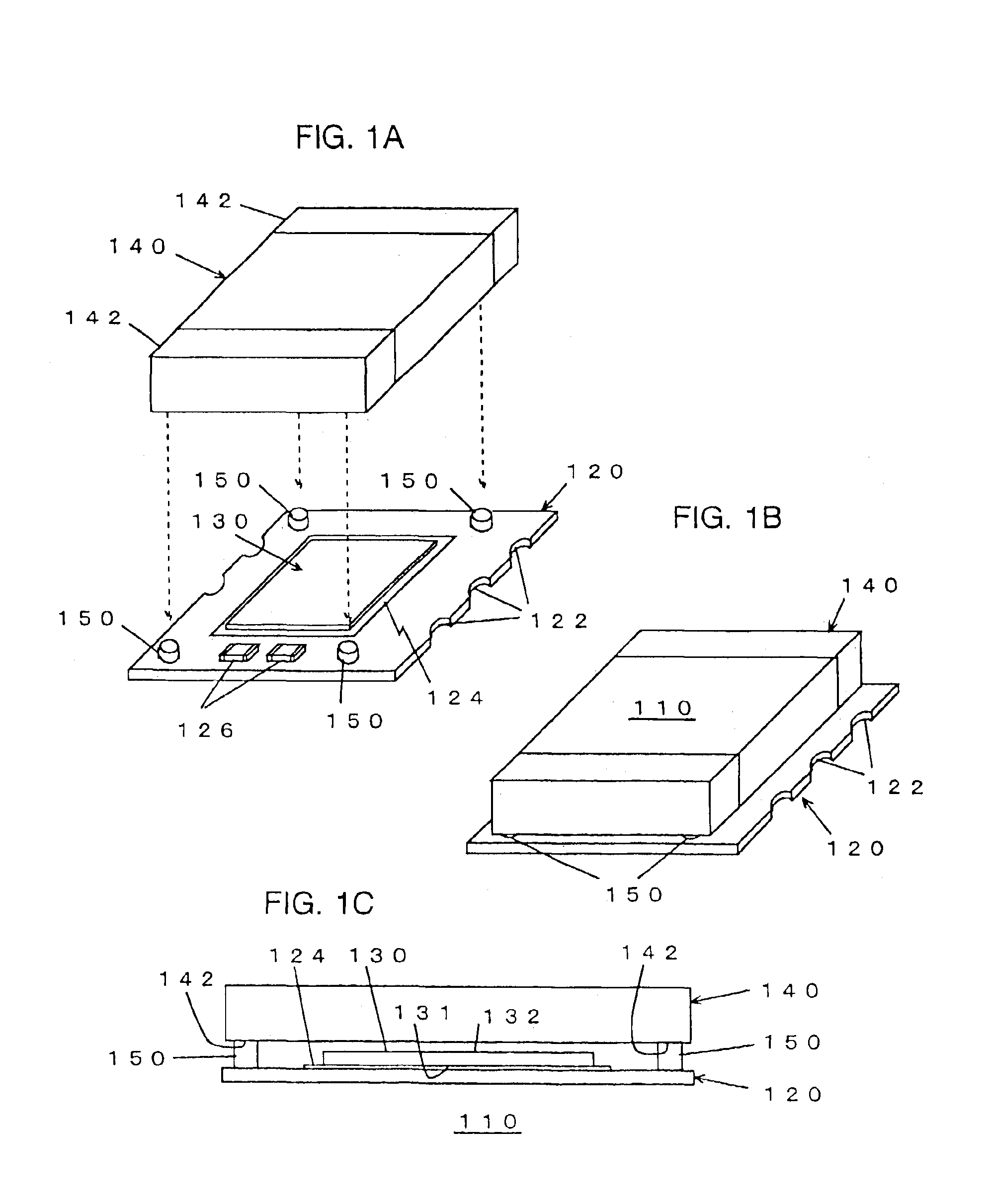

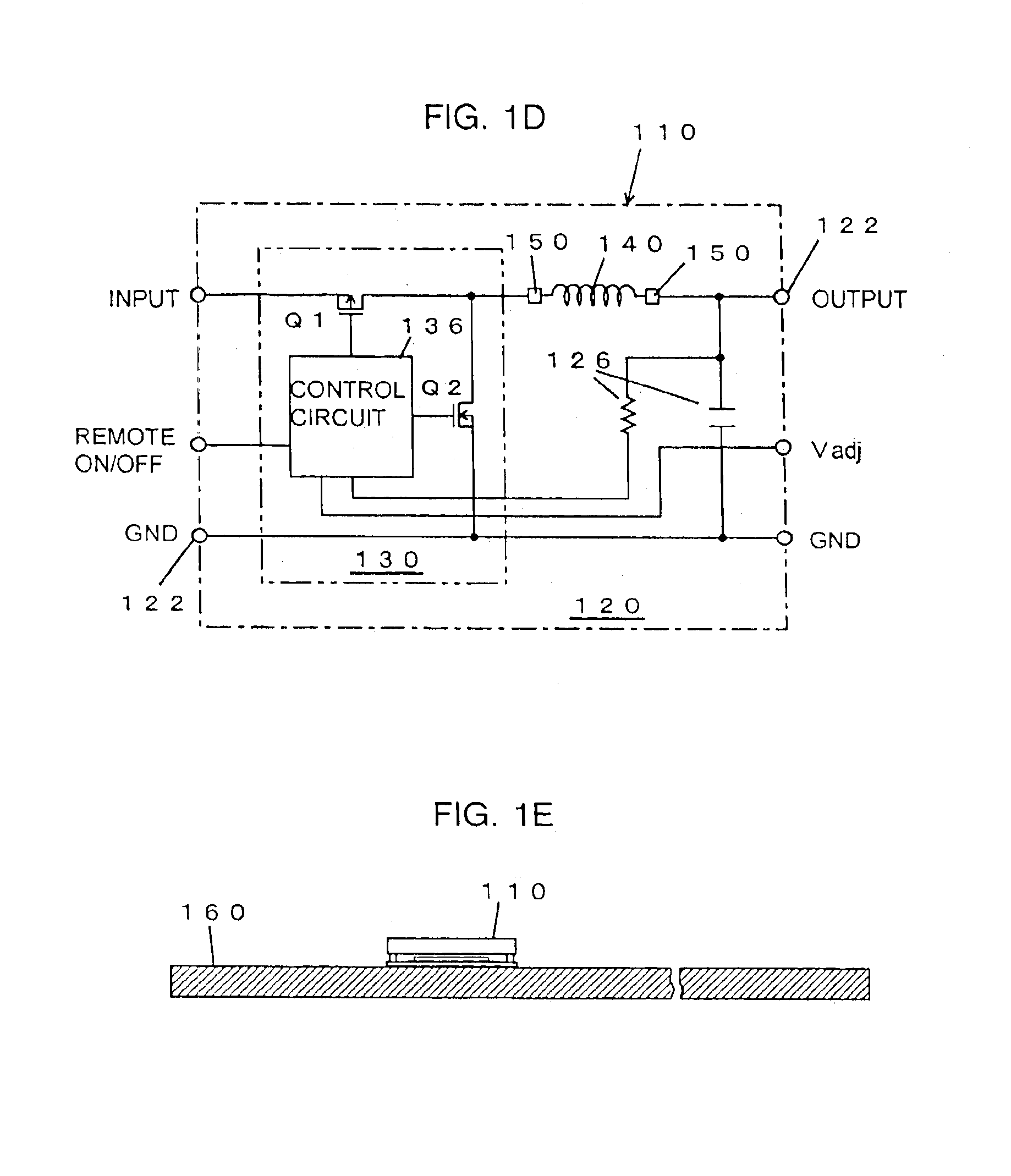

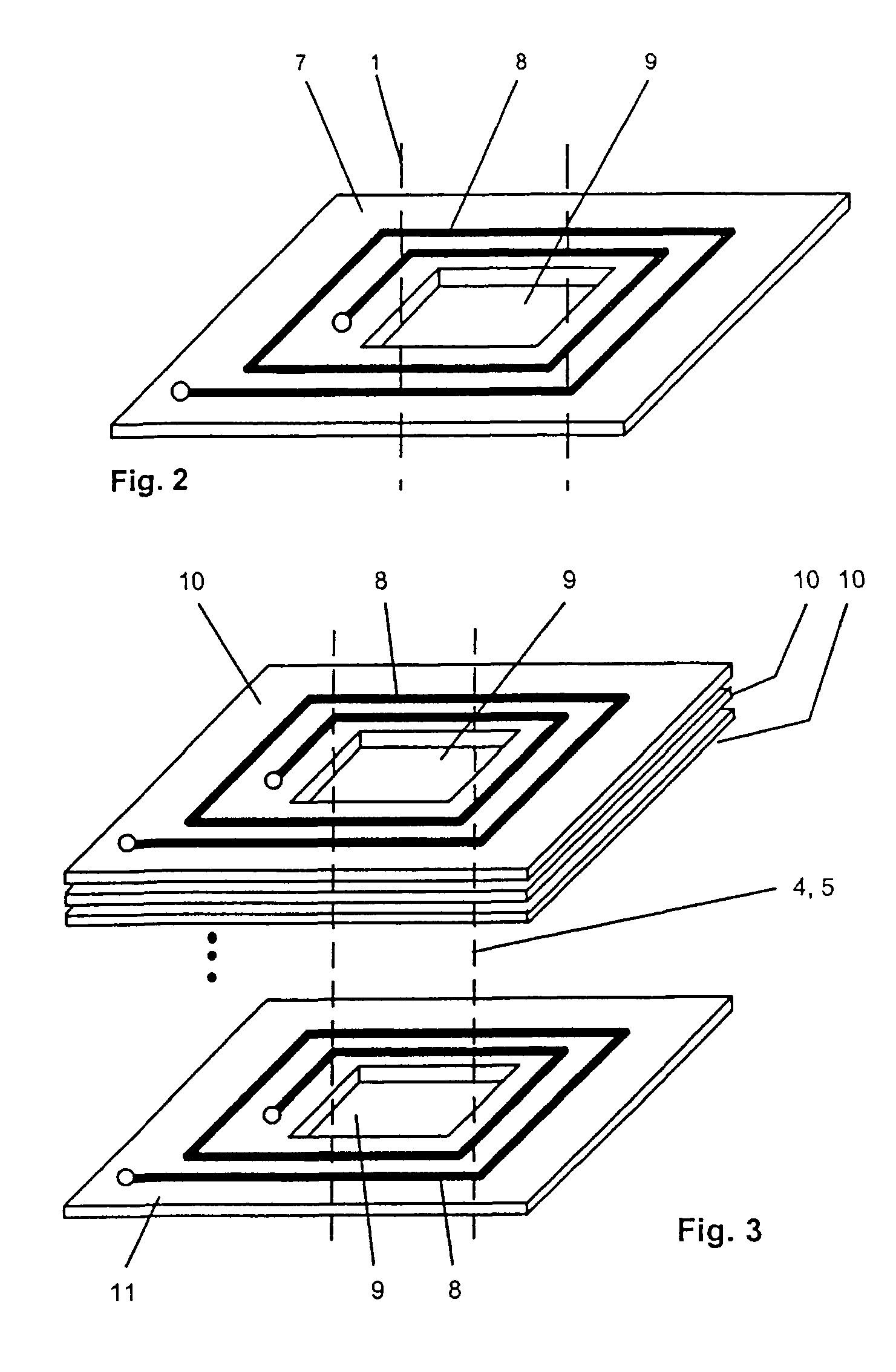

Microconverter and laminated magnetic-core inductor

InactiveUS6885278B2MiniaturizationWide range of variationFinal product manufactureSemiconductor/solid-state device detailsElectrical conductorSurface mounting

A surface-mount microconverter is formed by mounting a microinductor chip and a semiconductor integrated circuit chip on a circuit board. Stud terminals are arranged on the circuit board and the microinductor chip is supported on the stud terminals, and the microinductor chip and the semiconductor integrated circuit chip are superposed on the circuit board. The microconverter has an improved ability and is small and thin. The microconverter includes an effective laminated magnetic-core inductor. The inductor comprises a helical coil formed by uniting alternately superposed insulating magnetic layers and conductive pattern layers, and an annular closed magnetic path formed by the insulating magnetic layers and defining a magnetic field created by the coil. The inductor can be miniaturized in a thin chip, and a wide range in which magnetic flux density varies linearly can be secured by balancing a closed magnetic path for a magnetic field created by the coil.

Owner:FDK CORP

Integrated transformer and method of fabrication thereof

InactiveUS7570144B2Improve power efficiencyEnhanced couplingSemiconductor/solid-state device detailsSolid-state devicesTransverse axisTransformer

An integrated transformer structure includes a first coil element associated with a transverse axis, the first coil element having at least one turn. The first coil element includes a first portion provided on a first lateral level, and a second portion provided on a second lateral level. The first and second lateral levels being mutually spaced apart along said transverse axis. The first and second portions being displaced laterally from said axis by different respective distances. At least one crossover portion of the first coil element, in which the first coil element being configured to provide a conducting path through at least a portion of the first portion of the first coil element to the crossover portion, through the crossover portion and subsequently through at least a portion of the second portion of the first coil element, in which any change of flow direction along said path is less than 90° in a lateral direction.

Owner:CHARTERED SEMICONDUCTOR MANUFACTURING +1

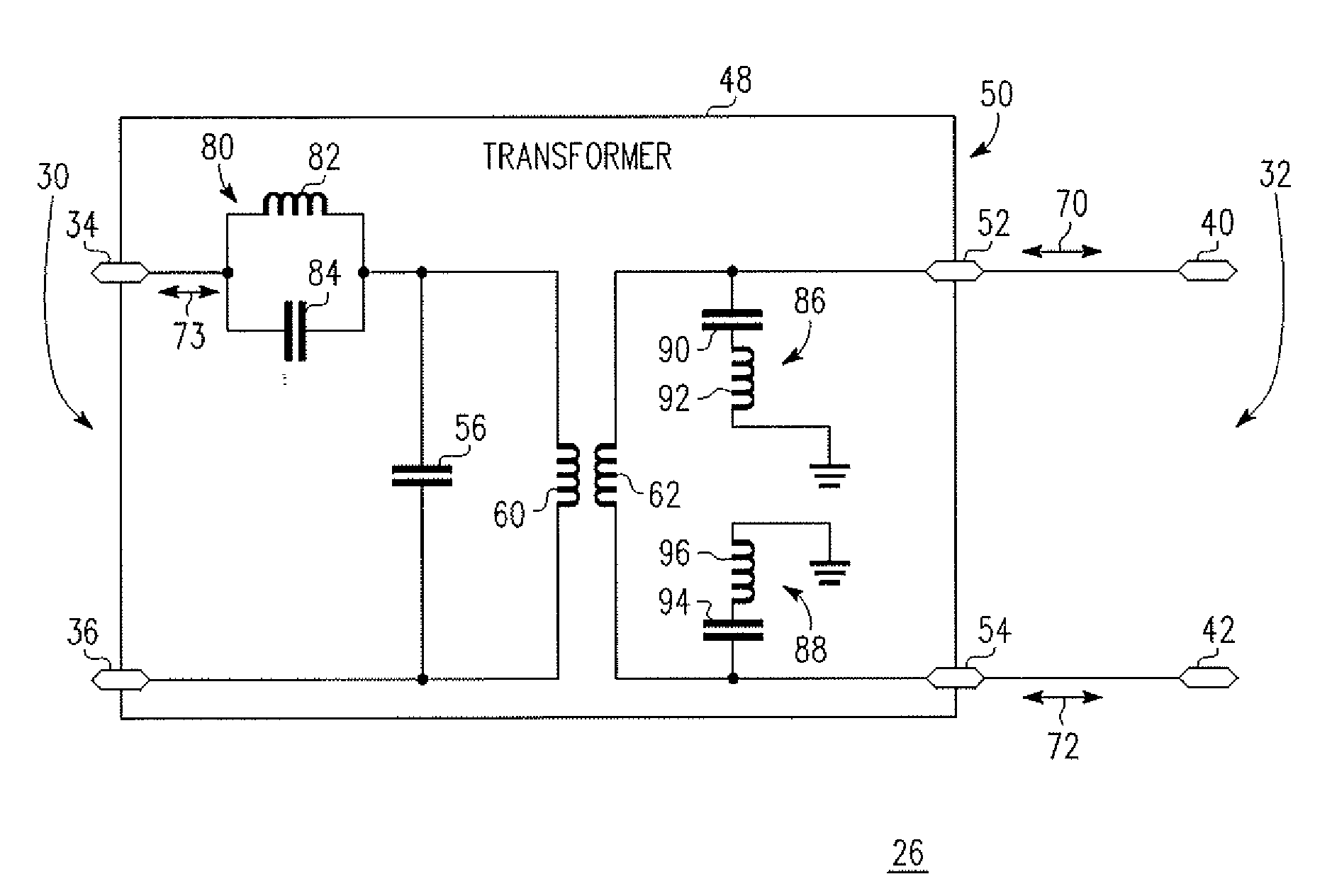

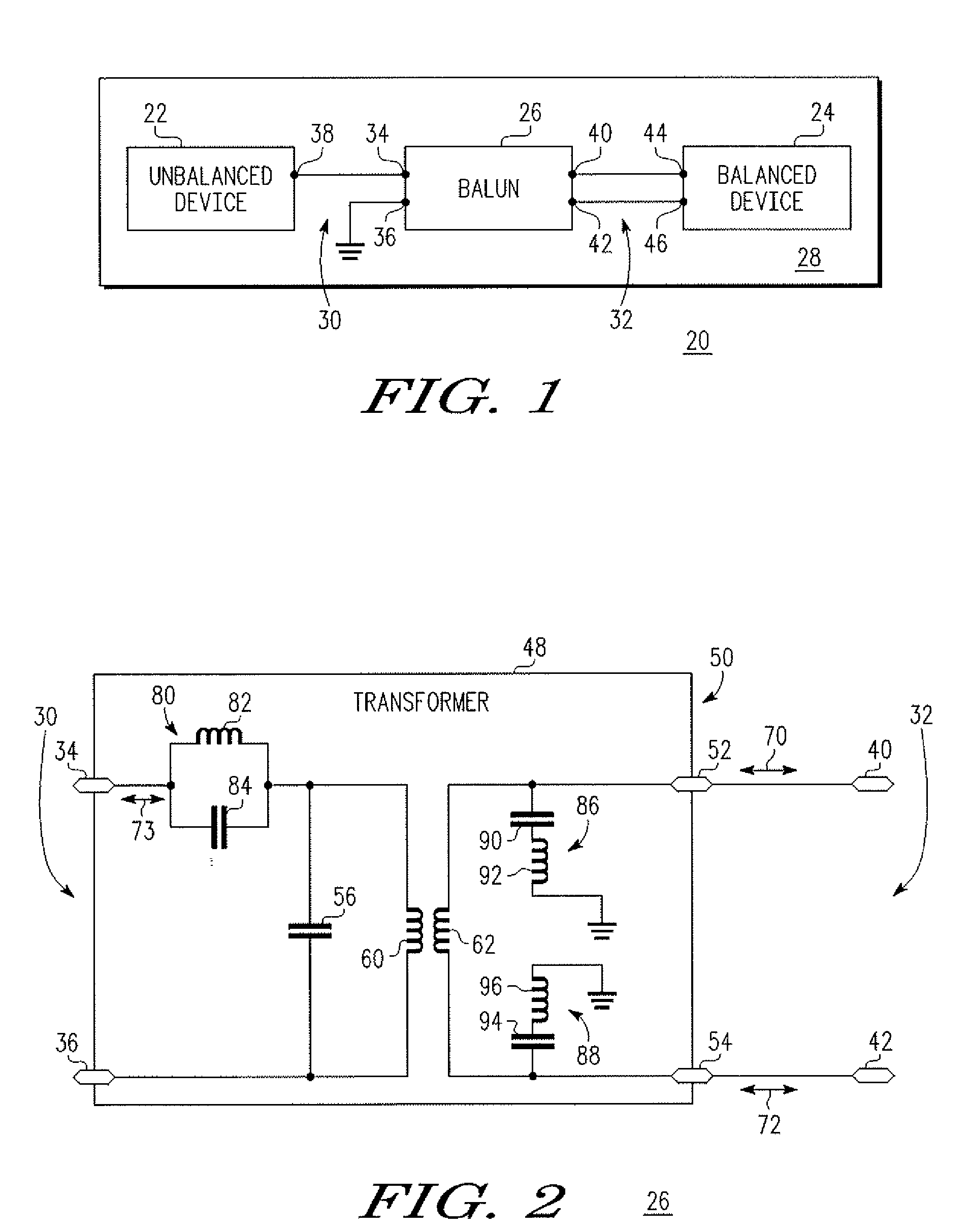

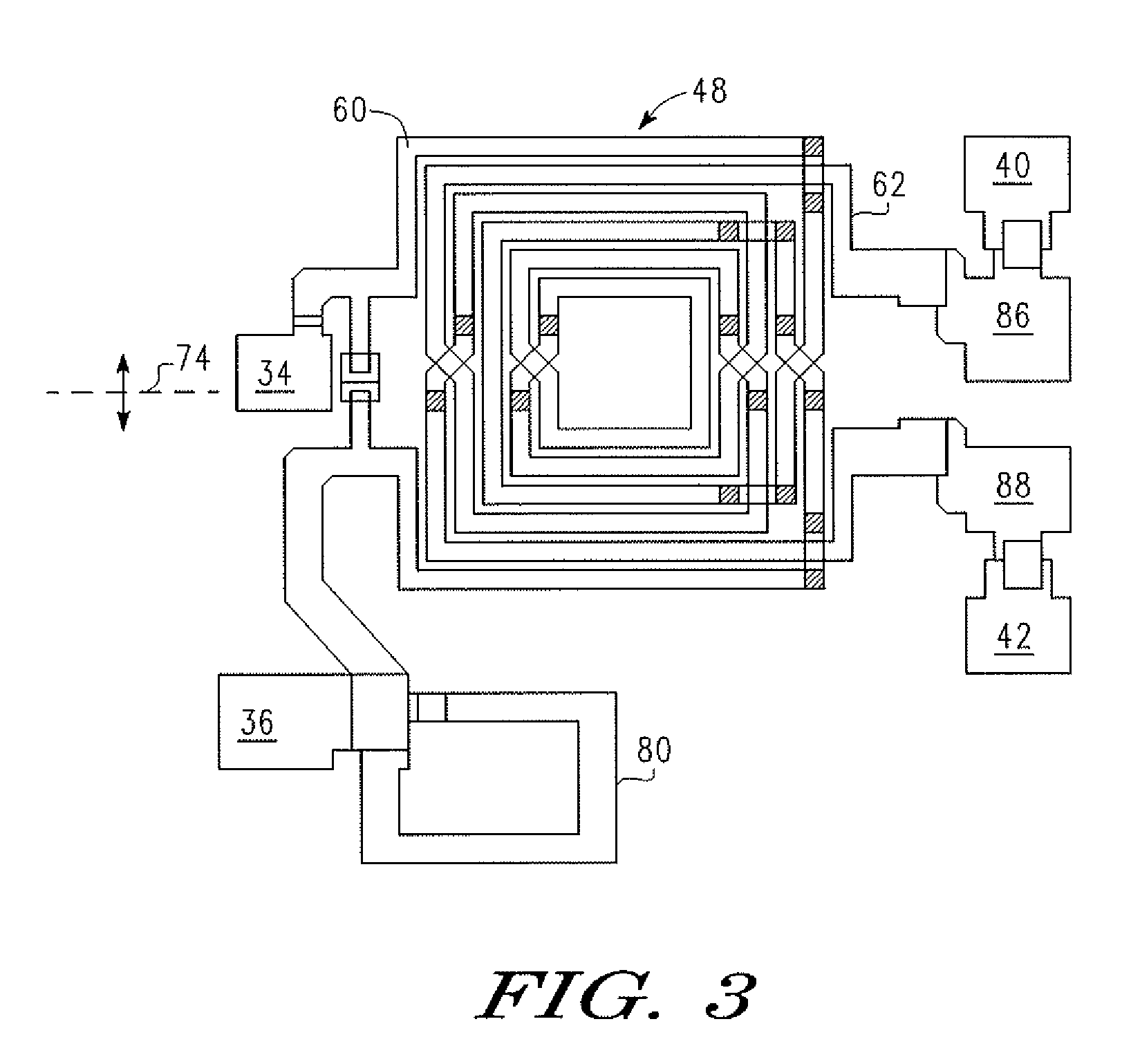

Balun signal transformer and method of forming

A balanced-unbalanced (balun) signal transformer includes an unbalanced port, a balanced port coupled to the unbalanced port, the balanced port comprising a first terminal and a second terminal, a first capacitor coupled to the first terminal, a first inductor coupled to ground and the first capacitor, a second capacitor coupled to the second terminal, and a second inductor coupled to ground and the second capacitor. The transformer may also include a third capacitor coupled to a terminal of the unbalanced port; and a third inductor coupled to the third capacitor and the third terminal.

Owner:NXP USA INC

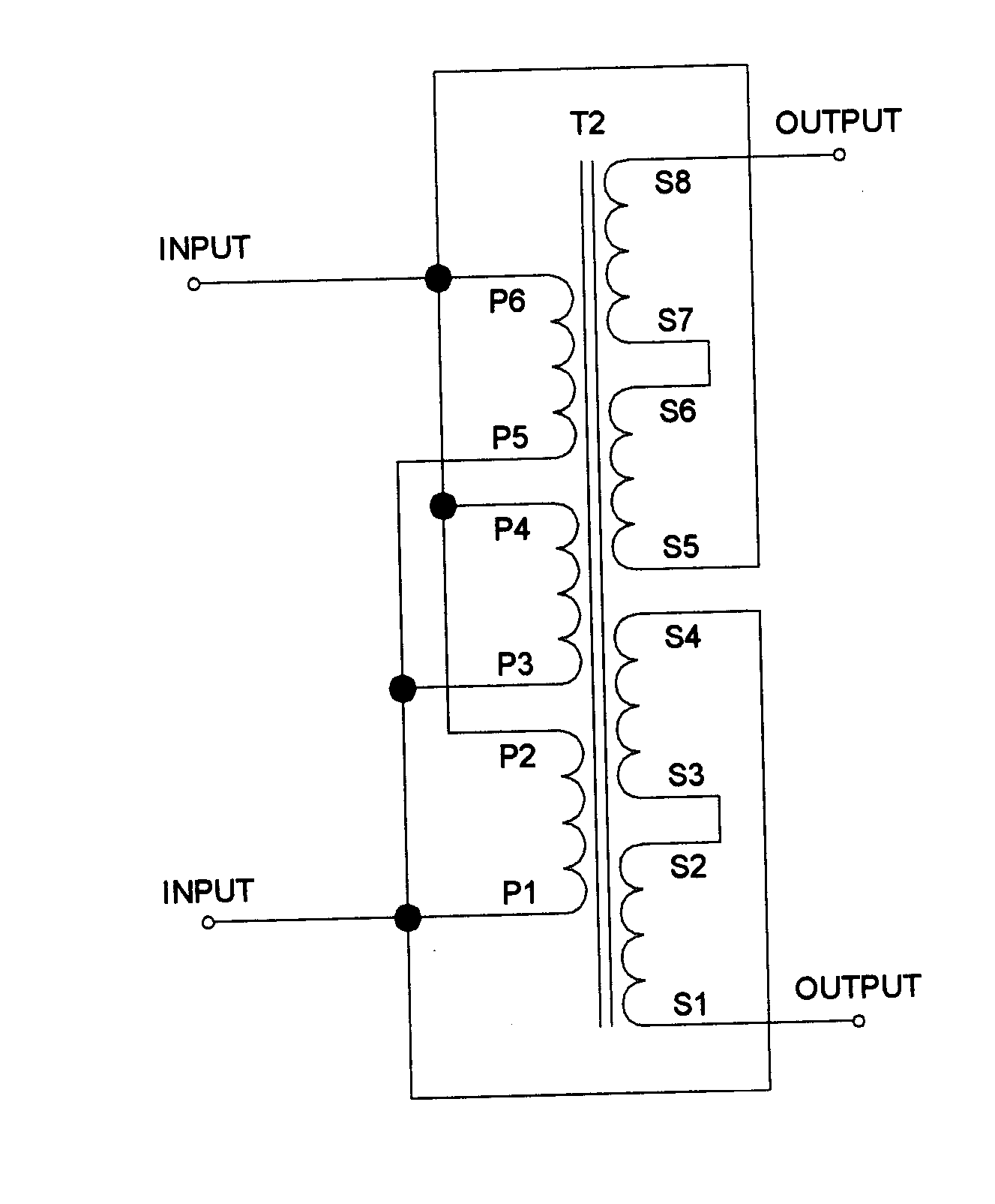

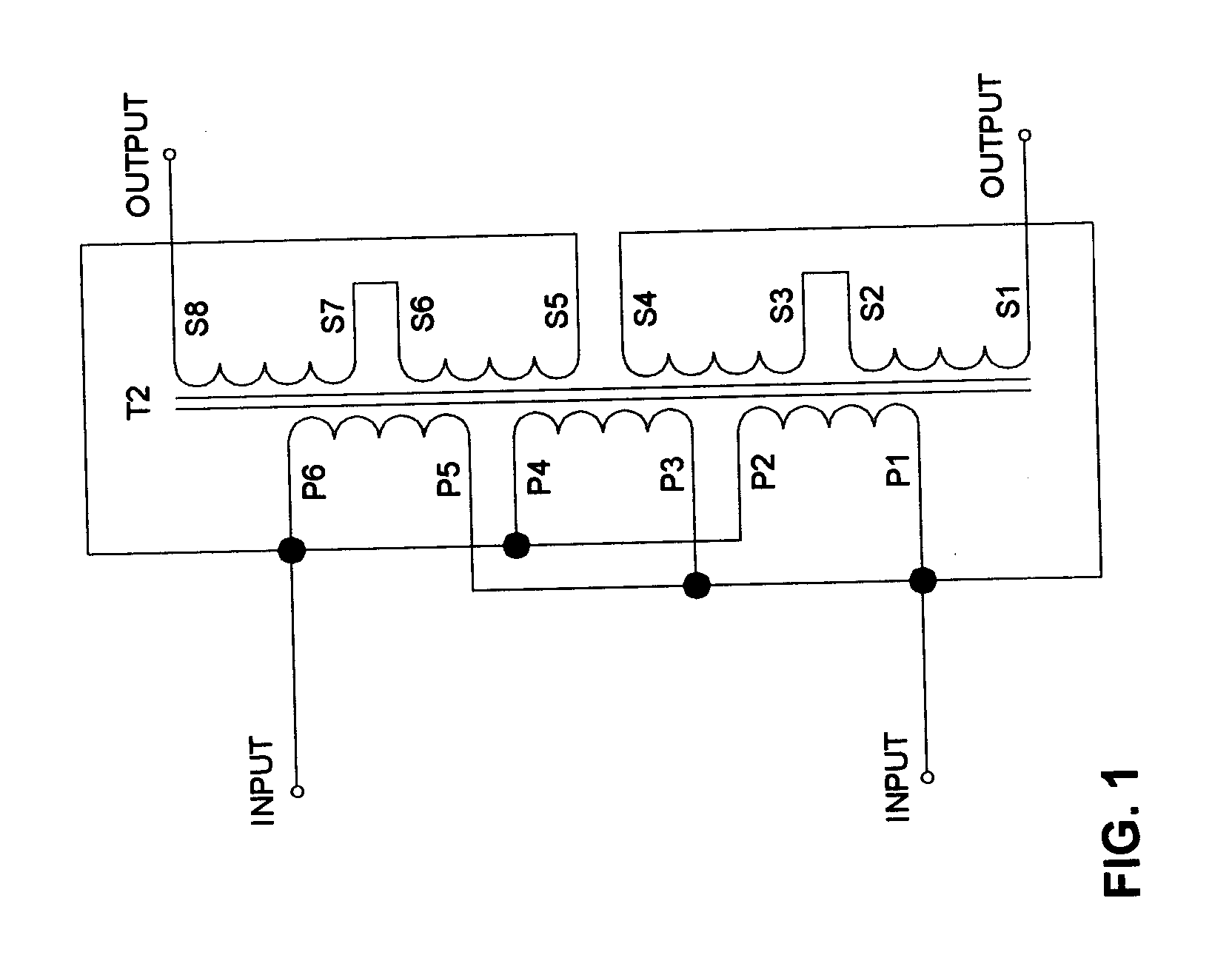

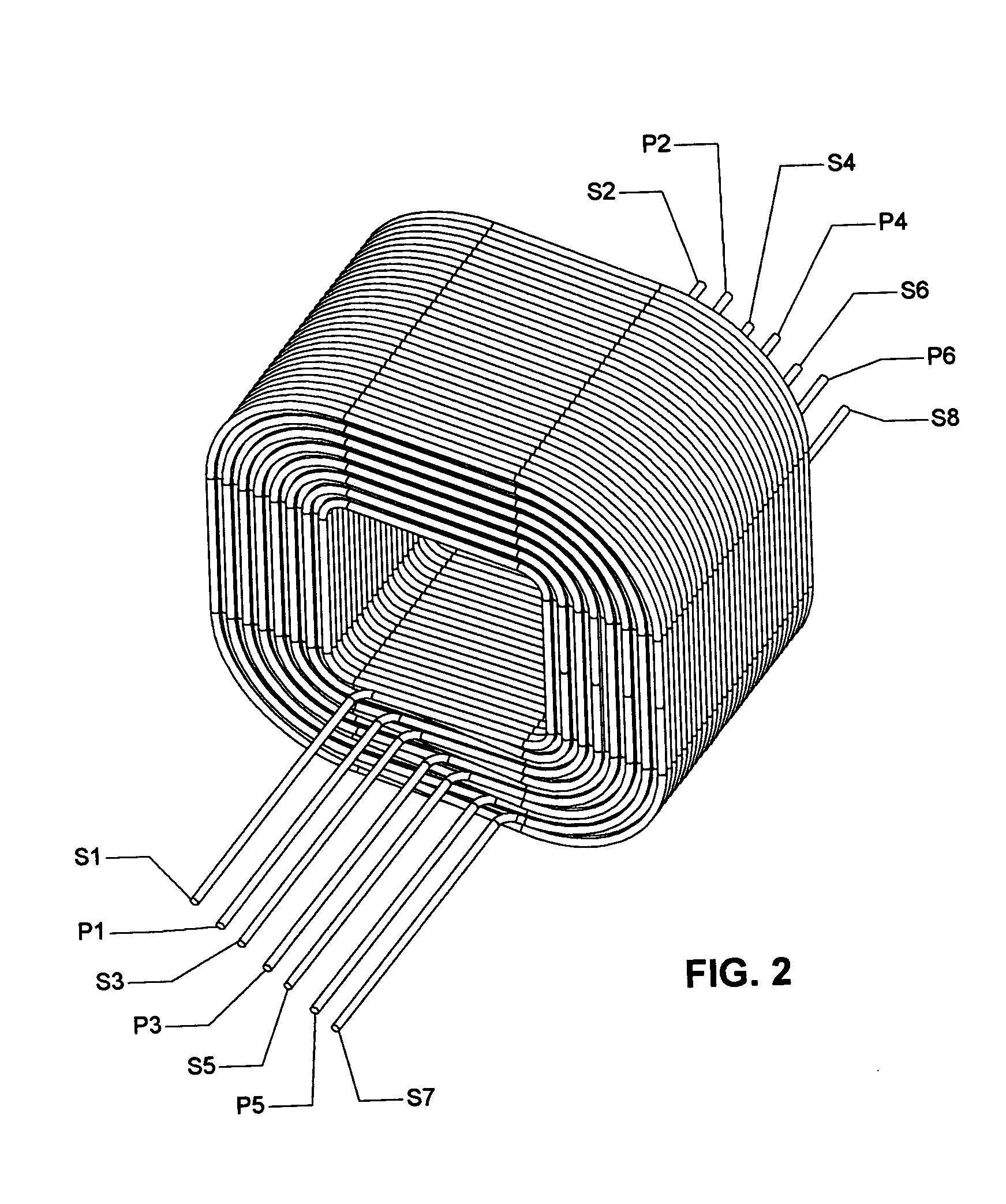

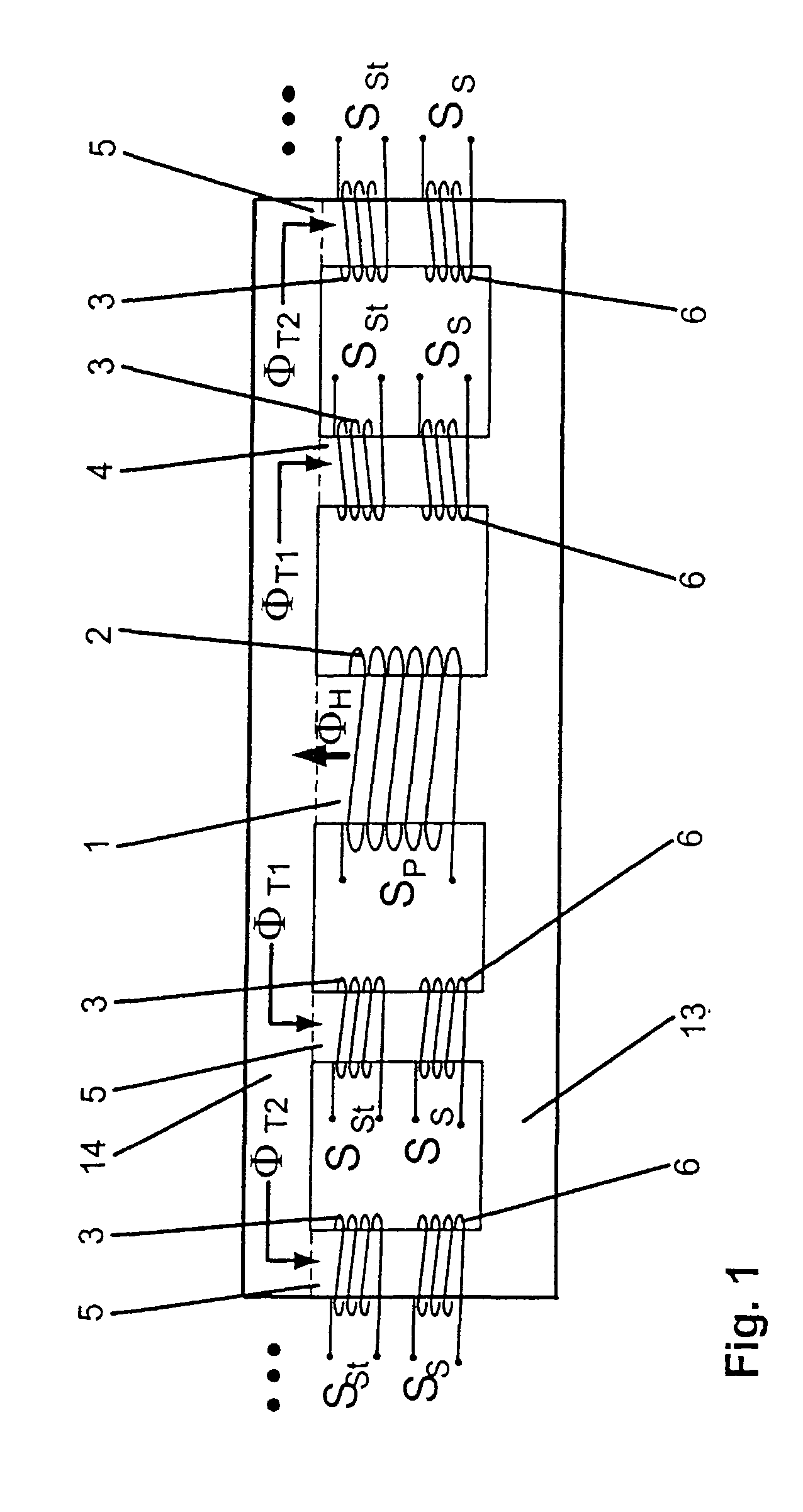

Pulse type transformer with increased coupling coefficient through configuration of plural primary windings

InactiveUS20060049903A1Improve efficiencyLow costTransformers/inductances coils/windings/connectionsVariable inductancesTransformerElectrical connection

The present invention provides a low duty cycle, high current DC pulse type transformer with increased coupling coefficient between the primary and secondary windings by changing the proximity of the primary windings to the secondary windings through a plurality of primary windings separated by layers of secondary windings thus reducing the average distance between the primary windings and secondary windings. In addition to the increased coupling coefficient, the invention provides a reduction in electrical potential between primary windings and secondary windings through an electrical connection between the primary winding and a tap within the secondary winding. The invention significantly increases the coupling coefficient in applications where the transformer's core becomes saturated due to the high peak current typically found in capacitive discharge type circuits such as those used in electric fence controllers, strobe circuits, and high performance ignition systems for automobile, marine, or motorcycle engines.

Owner:WOLFGRAM INDS

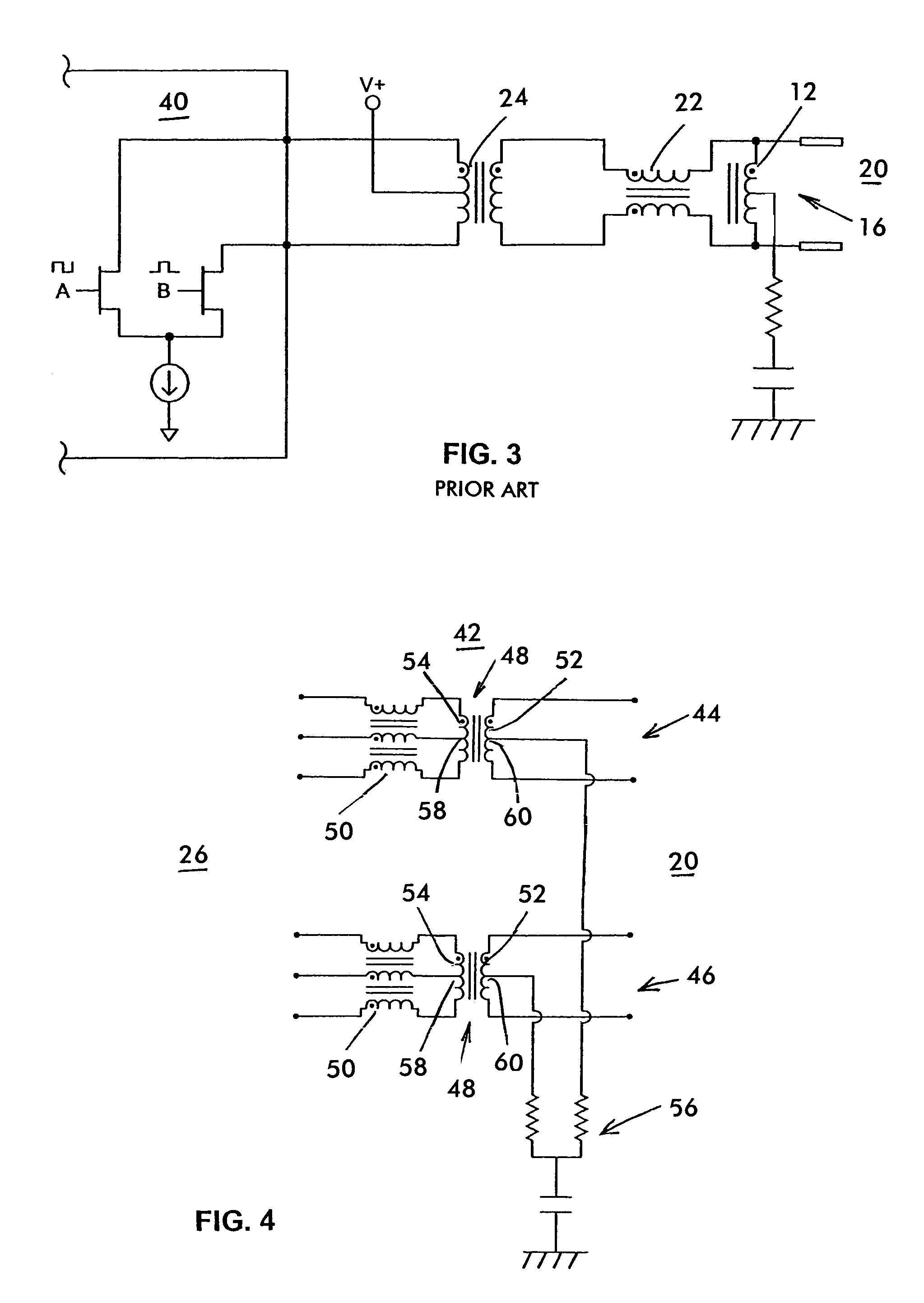

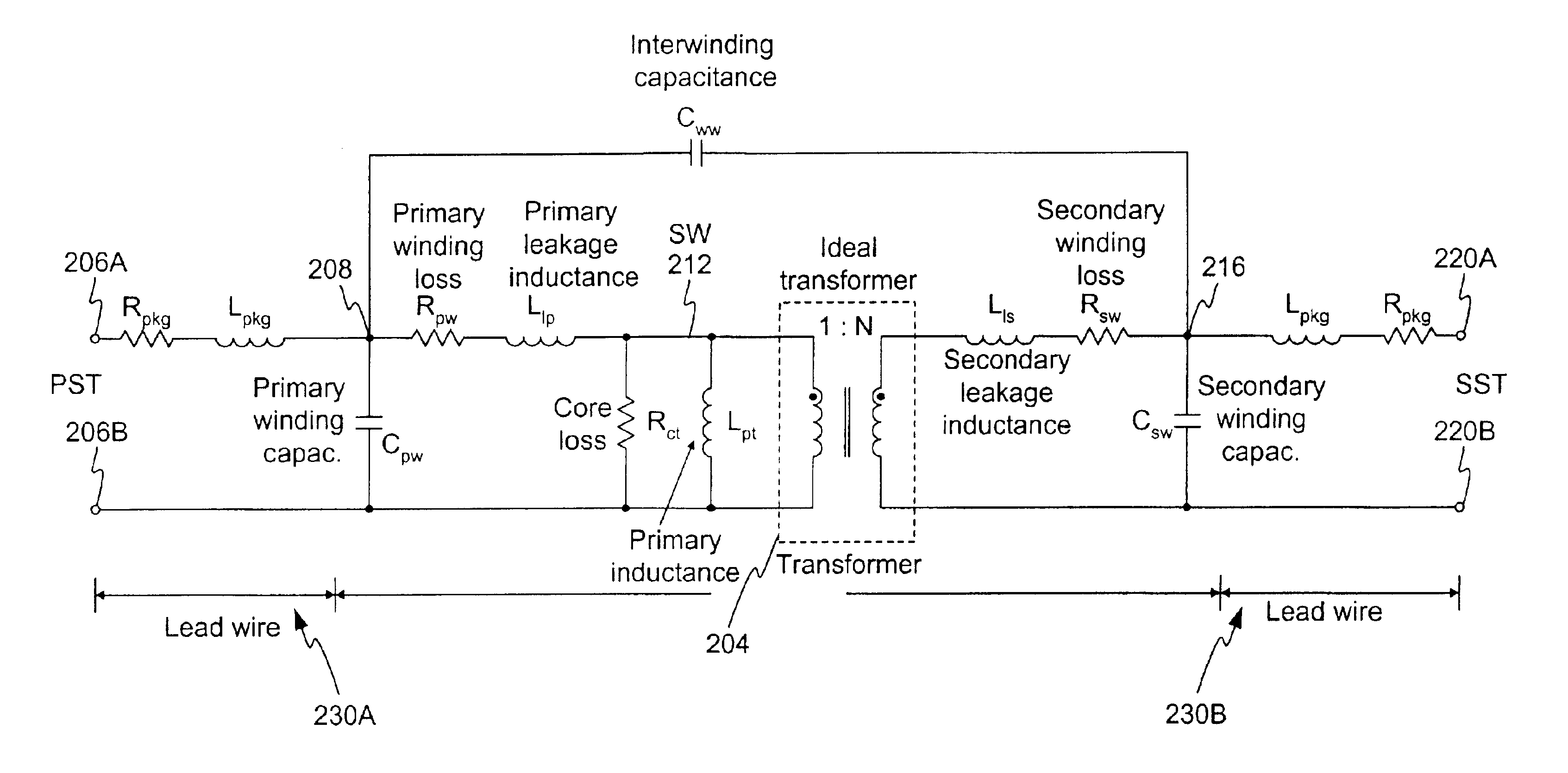

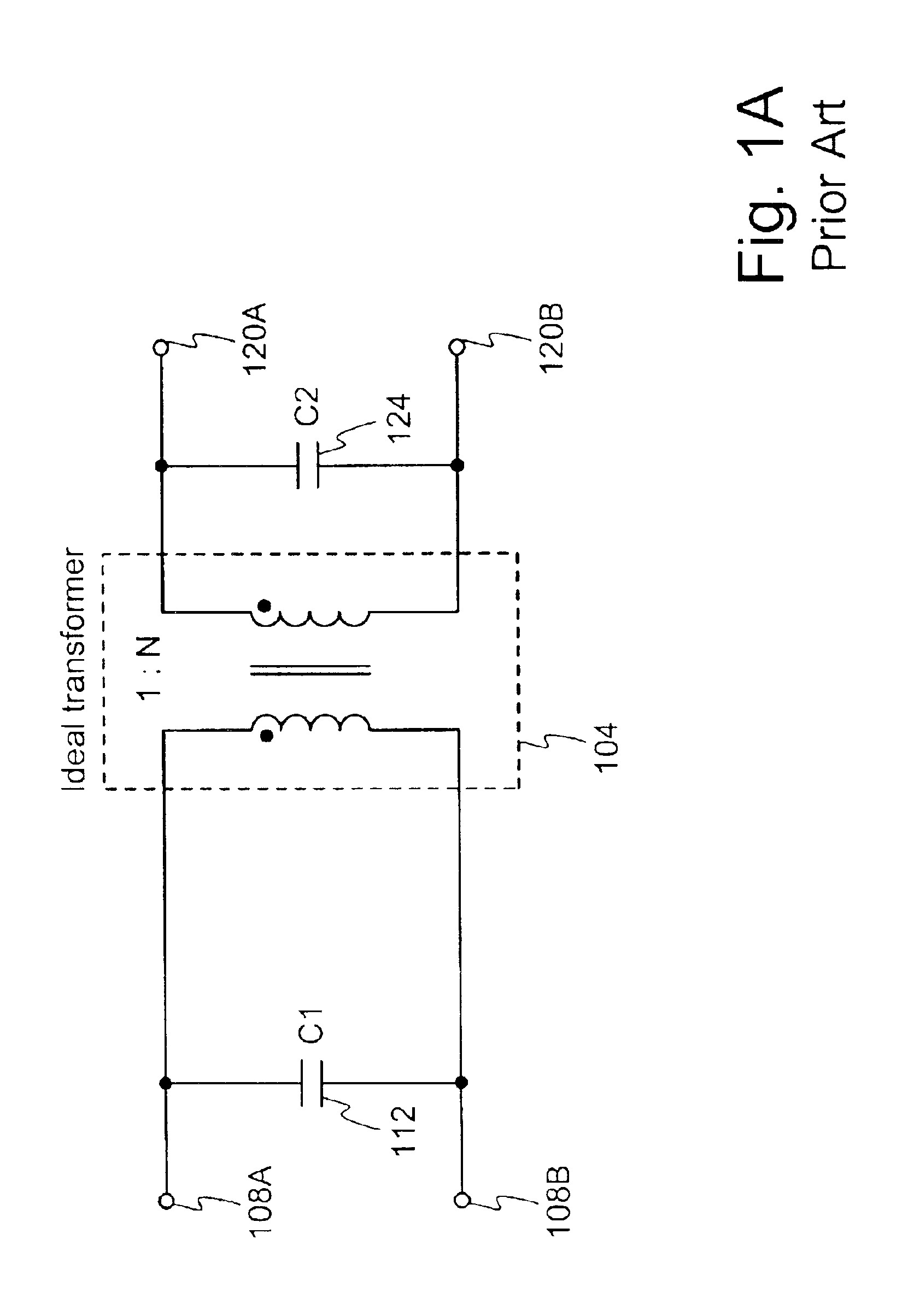

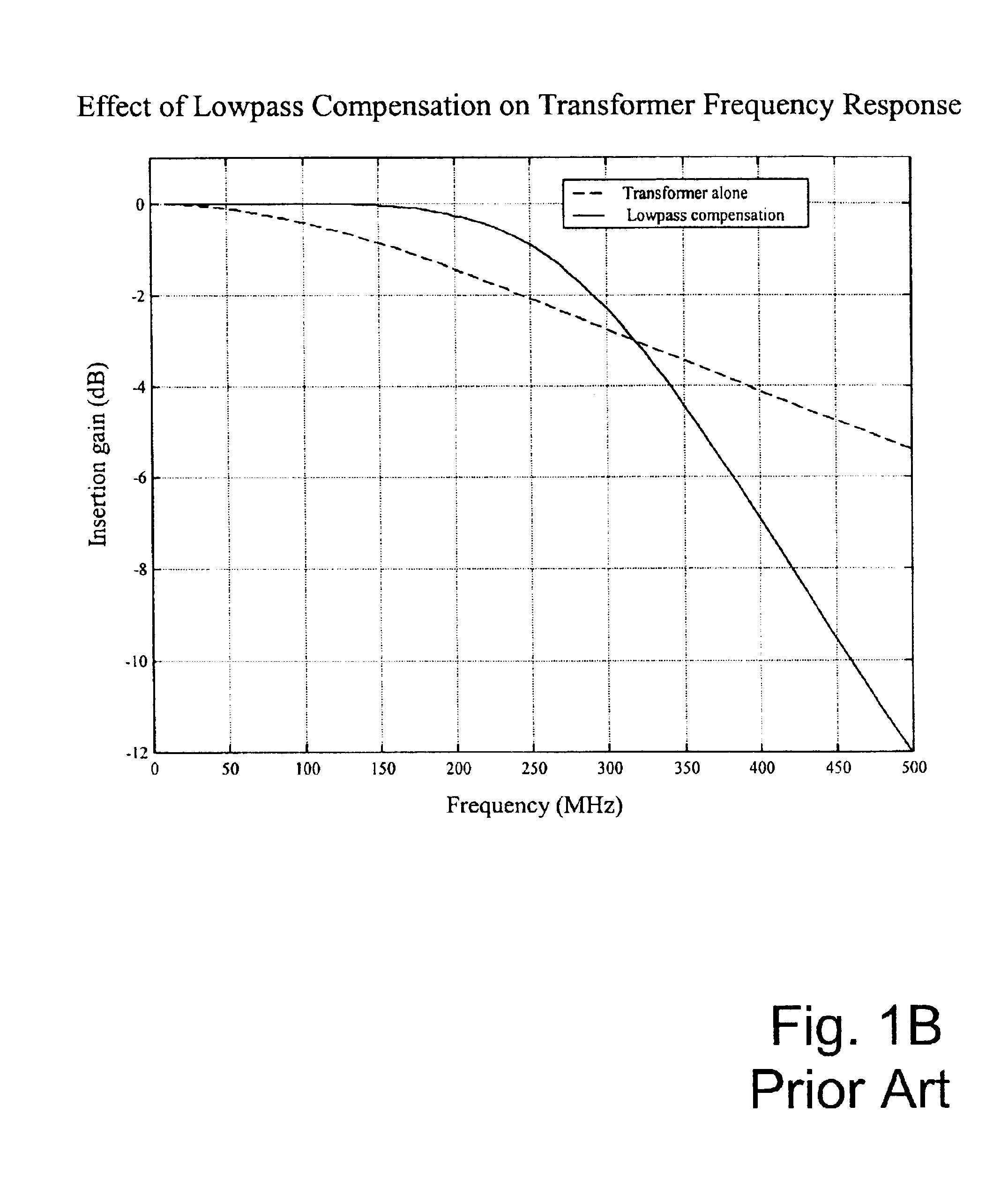

Method and apparatus for transformer bandwidth enhancement

InactiveUS6924724B2Improve communication bandwidthHigh bandwidthTransformers/inductances magnetic coresMagnetic-bias transformersCapacitanceCross connection

A method and apparatus for transformer bandwidth enhancement is disclosed. In one embodiment, a transformer is provided for use in a high frequency communication environment. In one configuration, the transformer is configured with one or more compensation networks to improve high frequency operation and to reduce insertion loss at all frequencies. The compensation networks may be designed, in combination with a transformer, to create an equivalent all-pass symmetric lattice network having a frequency response in the desired range. In one embodiment, the compensation networks comprise a capacitance creating device which, when cross-connected to the transformer, increases transformer bandwidth.

Owner:MARVELL ASIA PTE LTD

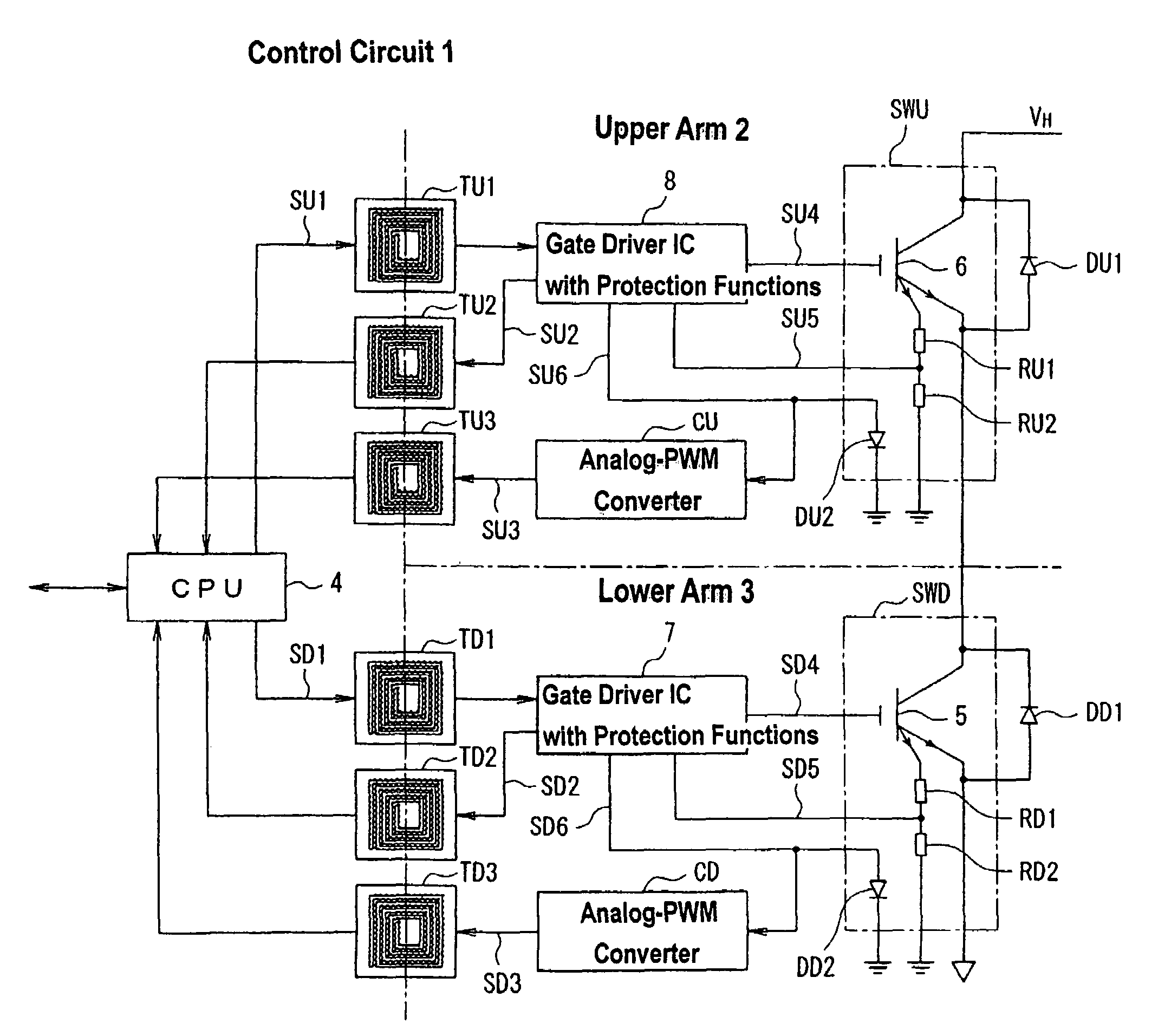

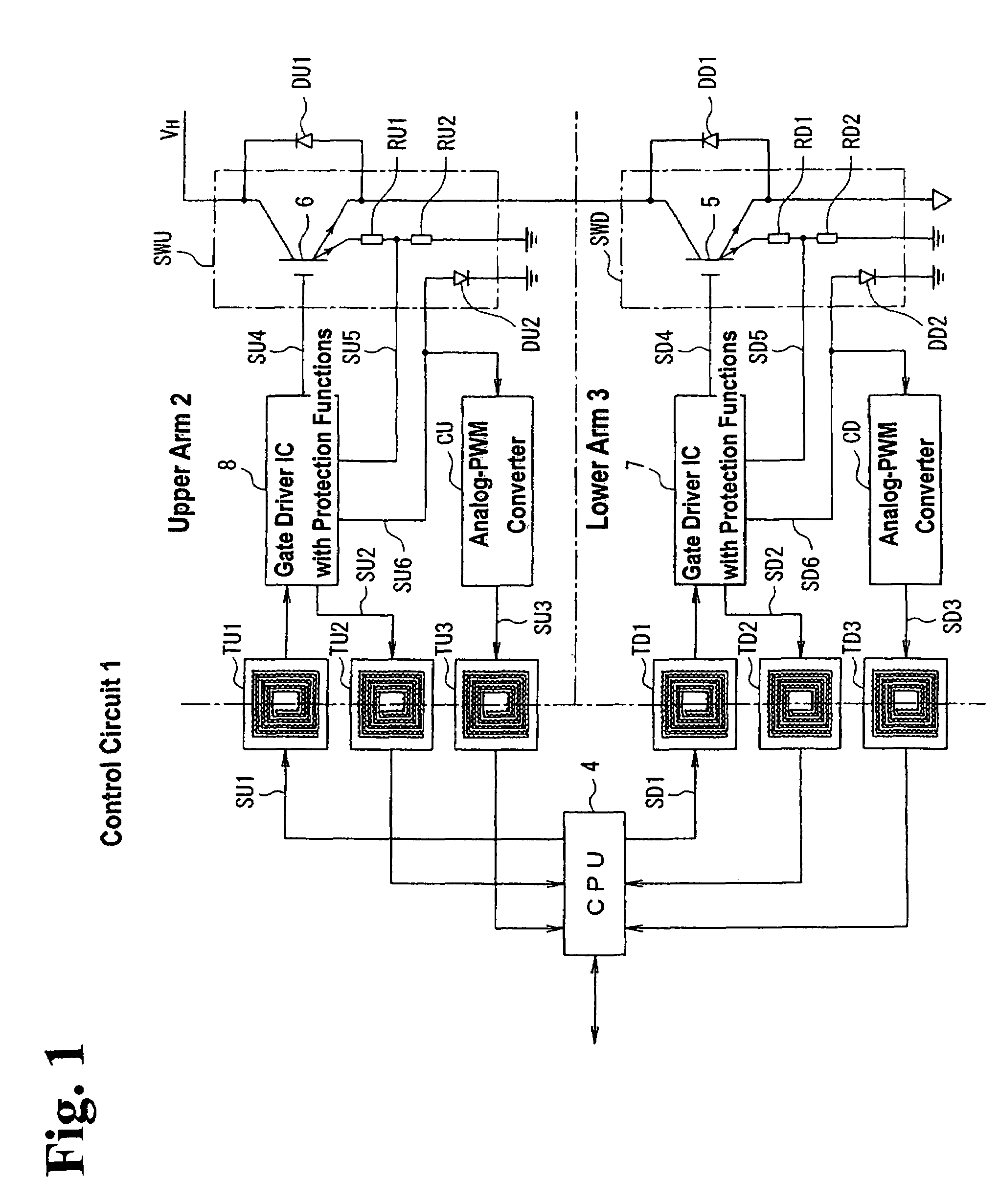

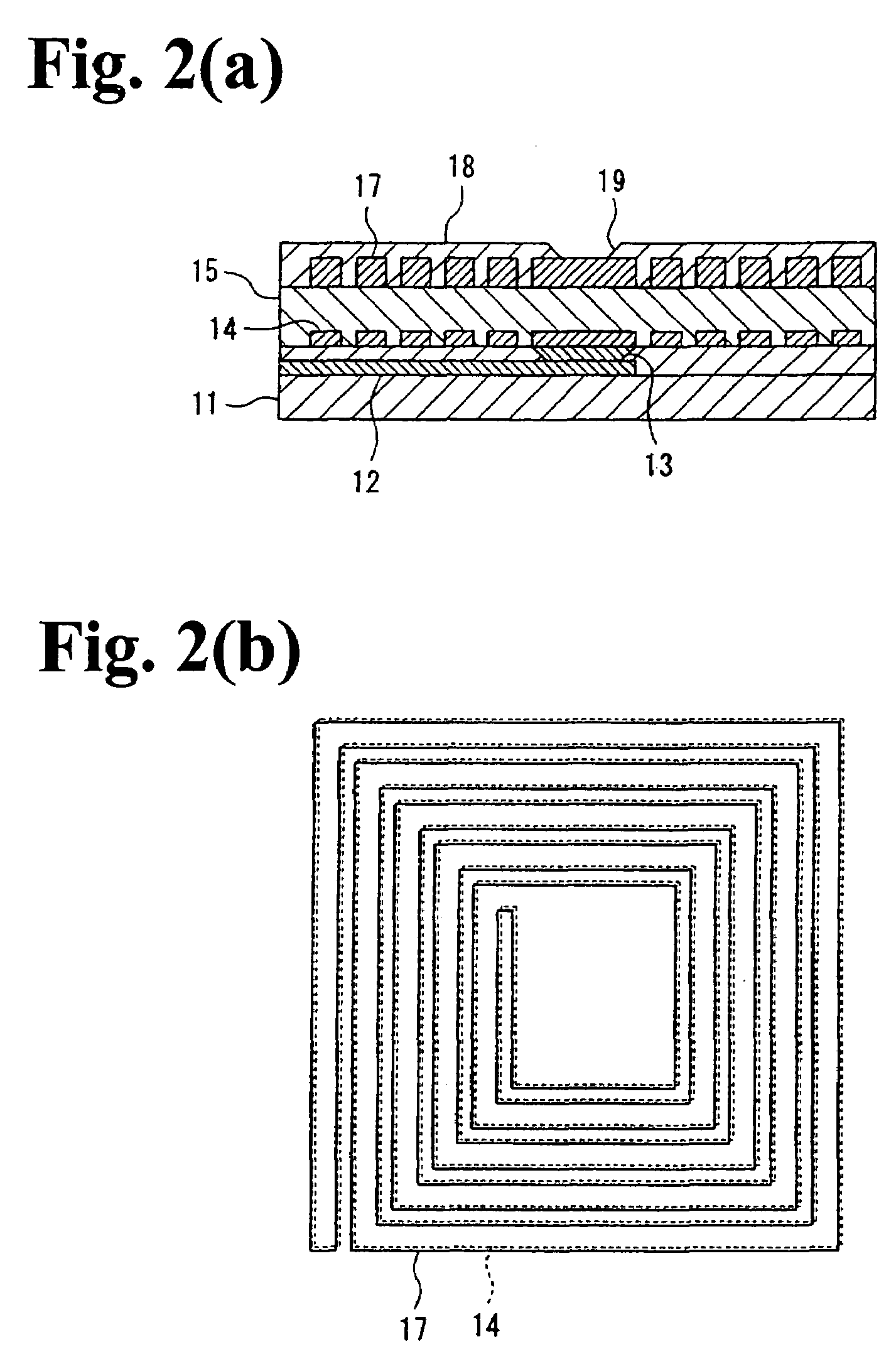

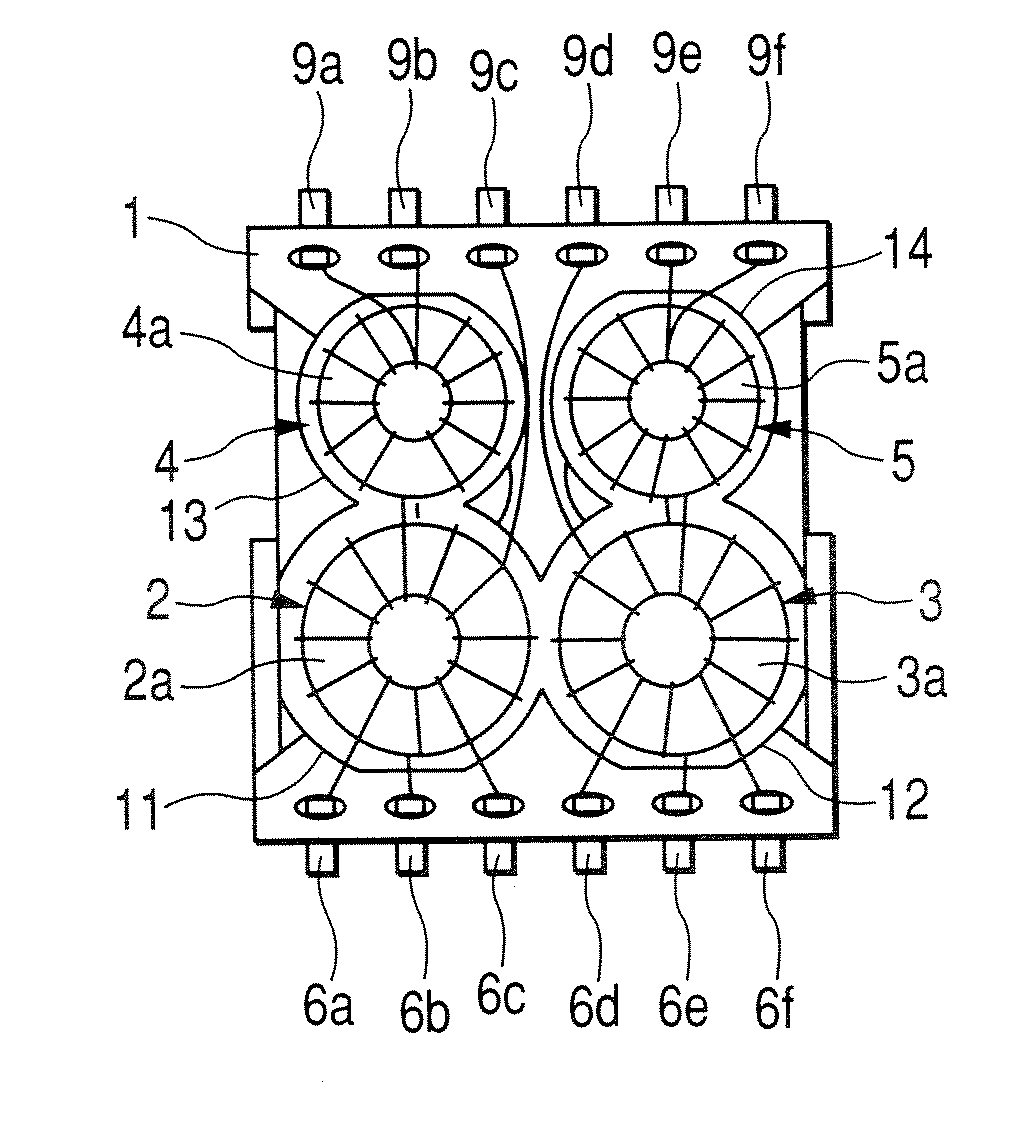

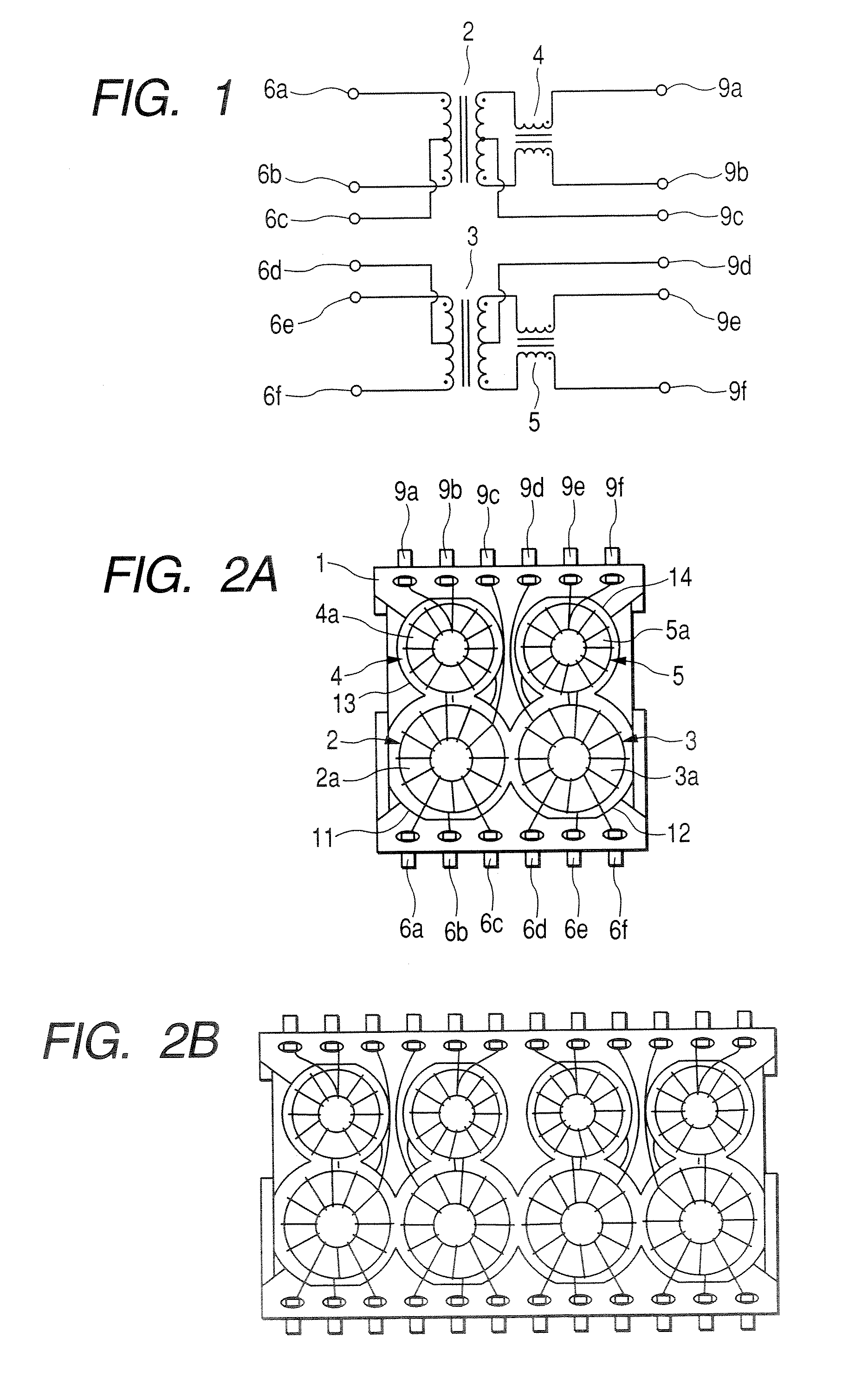

Power electronics equipments

InactiveUS7622887B2Easy to shapeReduce roll diameterMotor/generator/converter stoppersAC motor controlTransformerEngineering

Power electronics equipment includes air-cored insulating transformers inserted between a control circuit grounded to a vehicle body and an upper arm biased at a high voltage, and air-cored insulating transformers between the control circuit grounded to the vehicle body and the lower arm biased at a high voltage. Each of the air-cored insulating transformers includes a primary winding and a secondary facing to each other. The power electronics equipment facilitates improving resistance against hazardous environments, suppressing the deterioration by aging, reducing the adverse effects of noise caused by external magnetic flux, and transmitting and receiving signals while insulating the low and high voltage sides electrically from each other.

Owner:FUJI ELECTRIC CO LTD

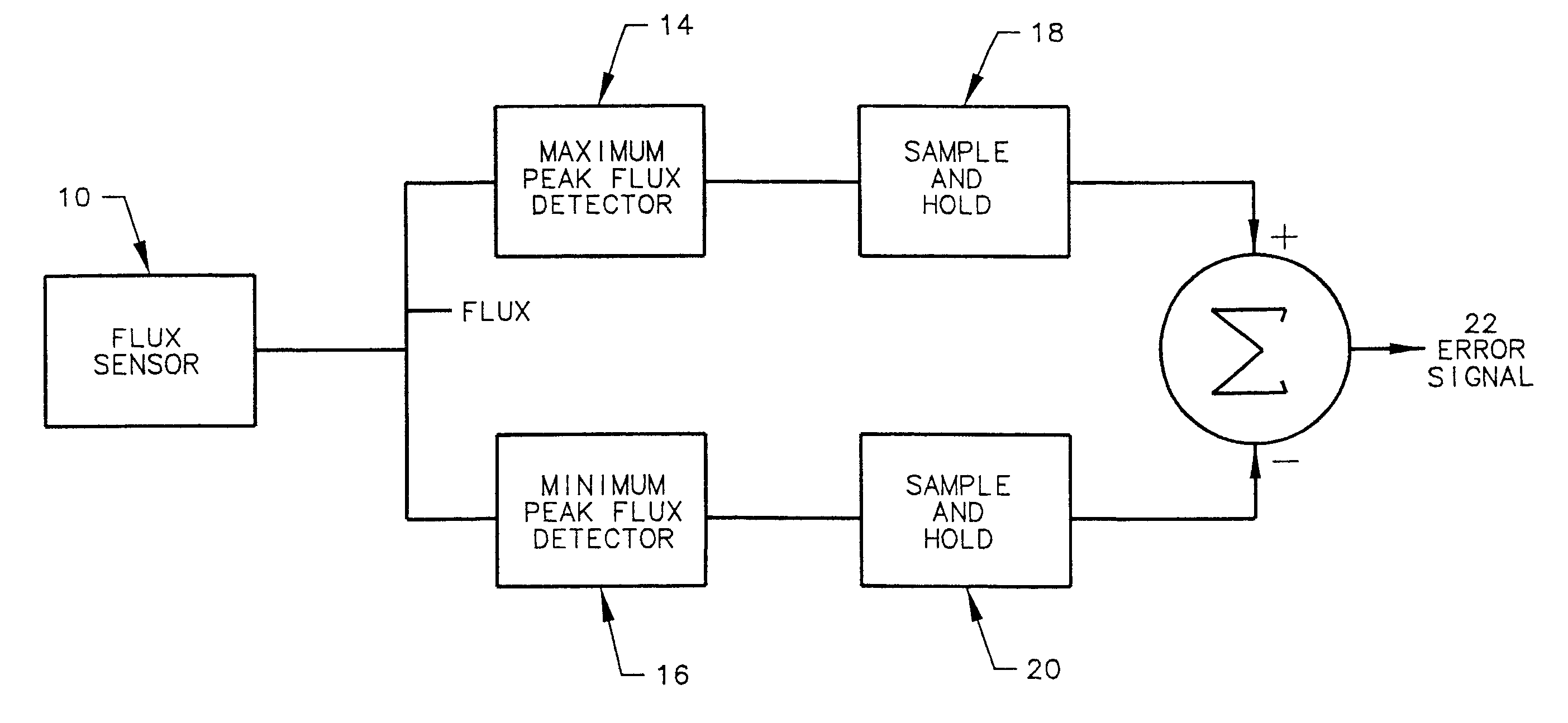

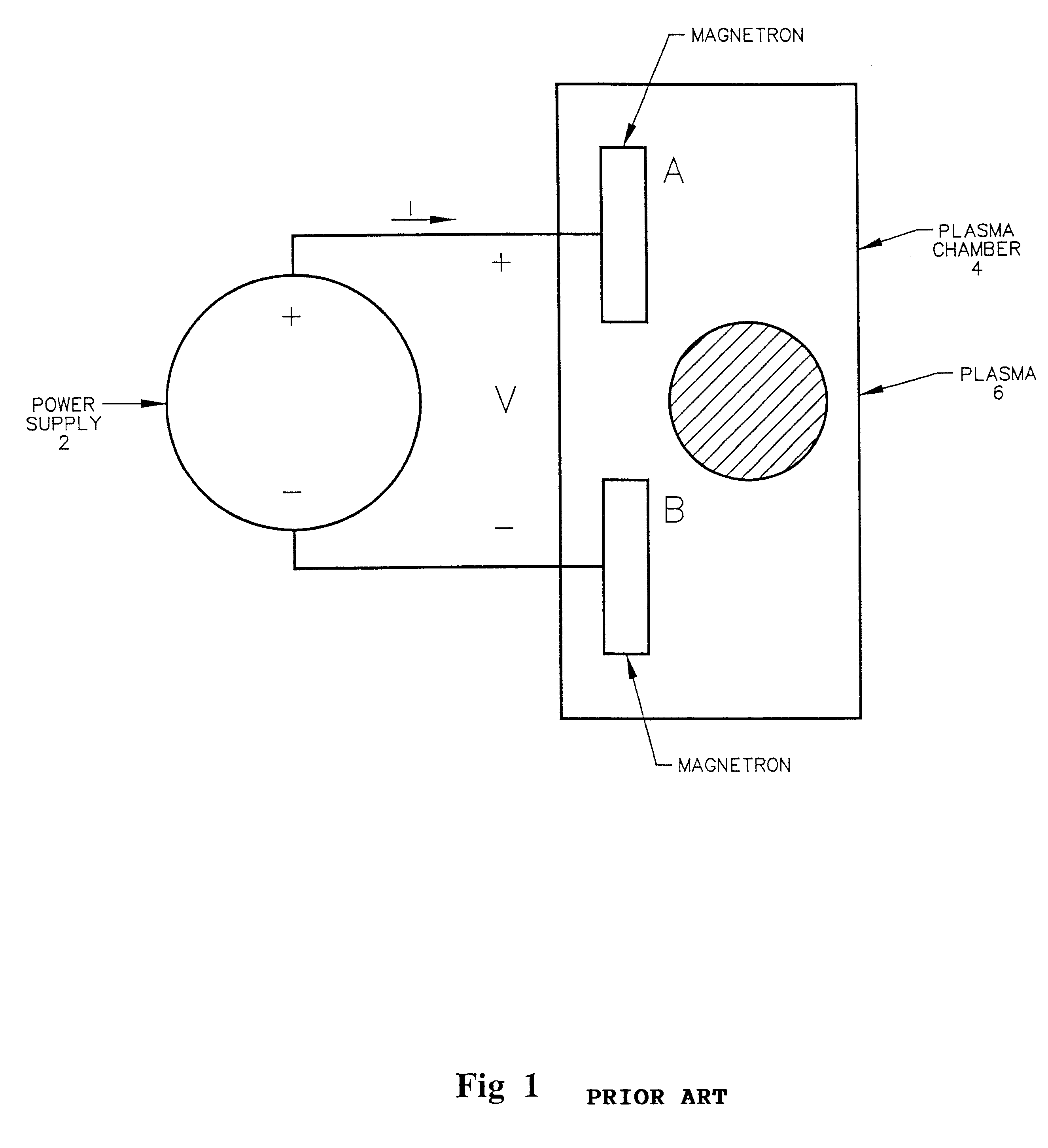

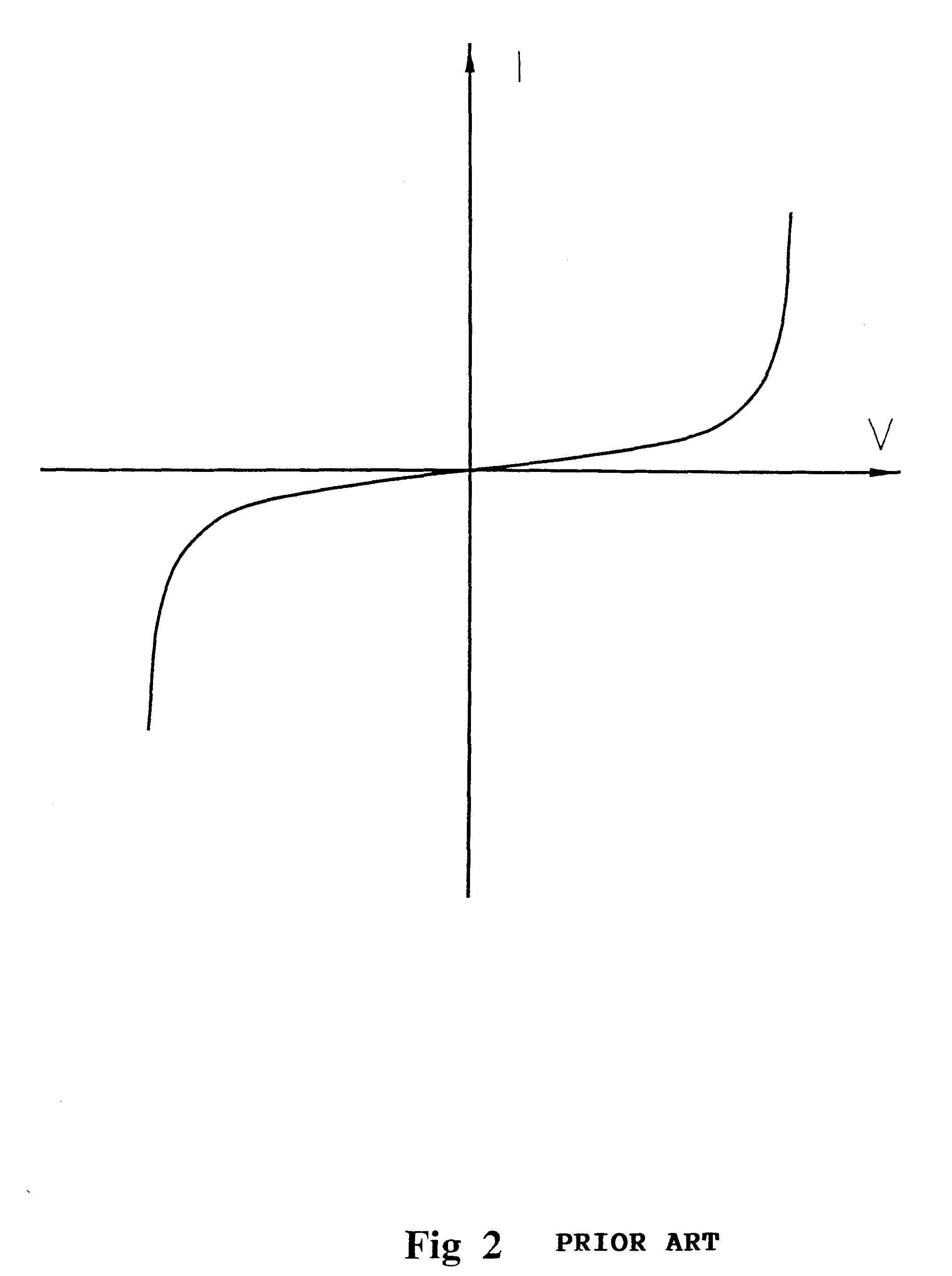

Power supply with flux-controlled transformer

InactiveUS6532161B2Conversion with intermediate conversion to dcEmergency protective circuit arrangementsVoltage pulsePulsed DC

There is provided by this invention an apparatus and method for generating voltage pulses to first and second magnetron devices in a plasma chamber. An isolation transformer is connected to a pulsed DC power supply having a flux sensor, such as a Hall effect sensor, in close proximity to its air gap to monitor the transformer flux. A control circuit is connected to the flux sensor to control the duty cycle of the transformer by controlling the flux of the transformer such that the maximum and minimum peak transformer fluxes are equal in magnitude and opposite in sign to prevent saturation.

Owner:ADVANCED ENERGY IND INC

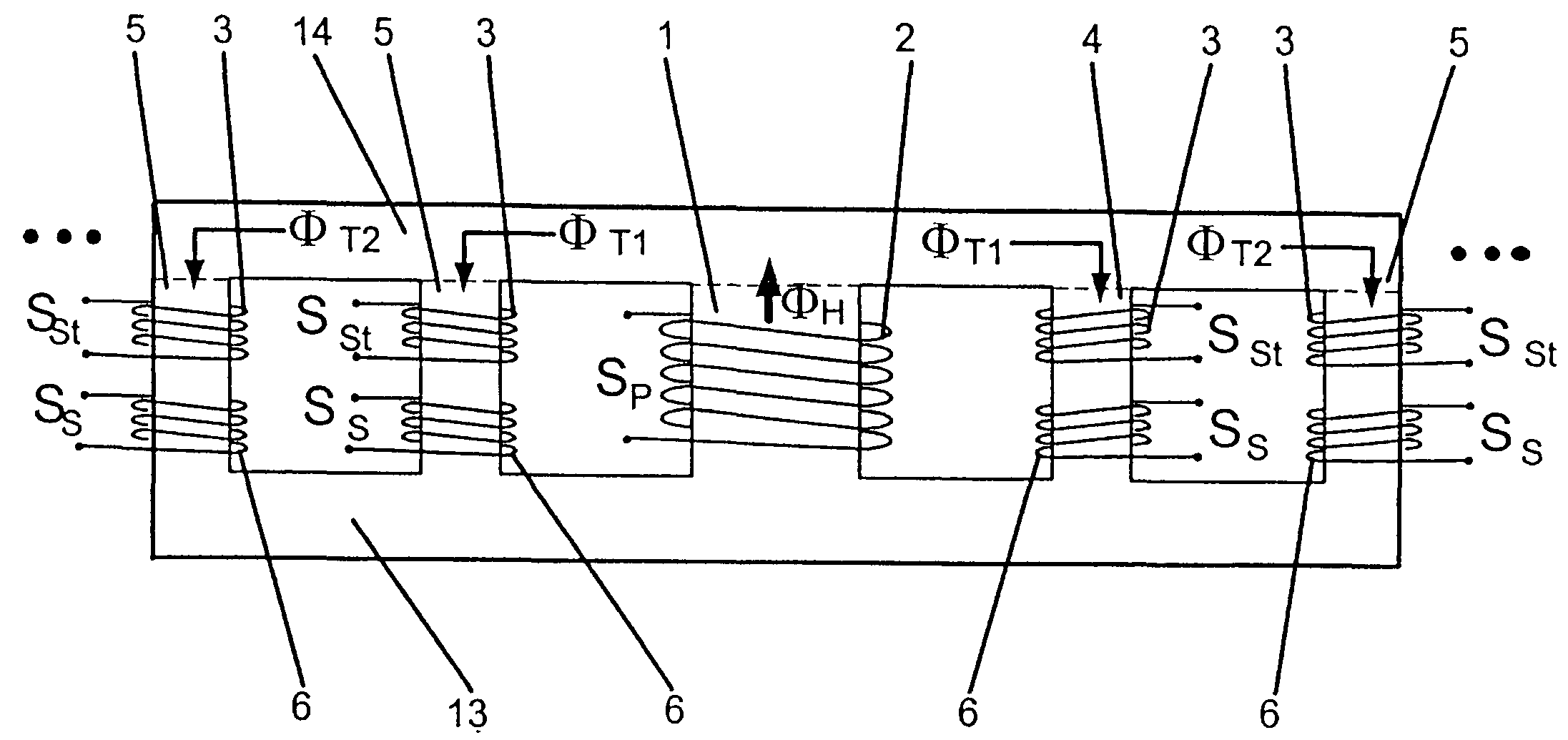

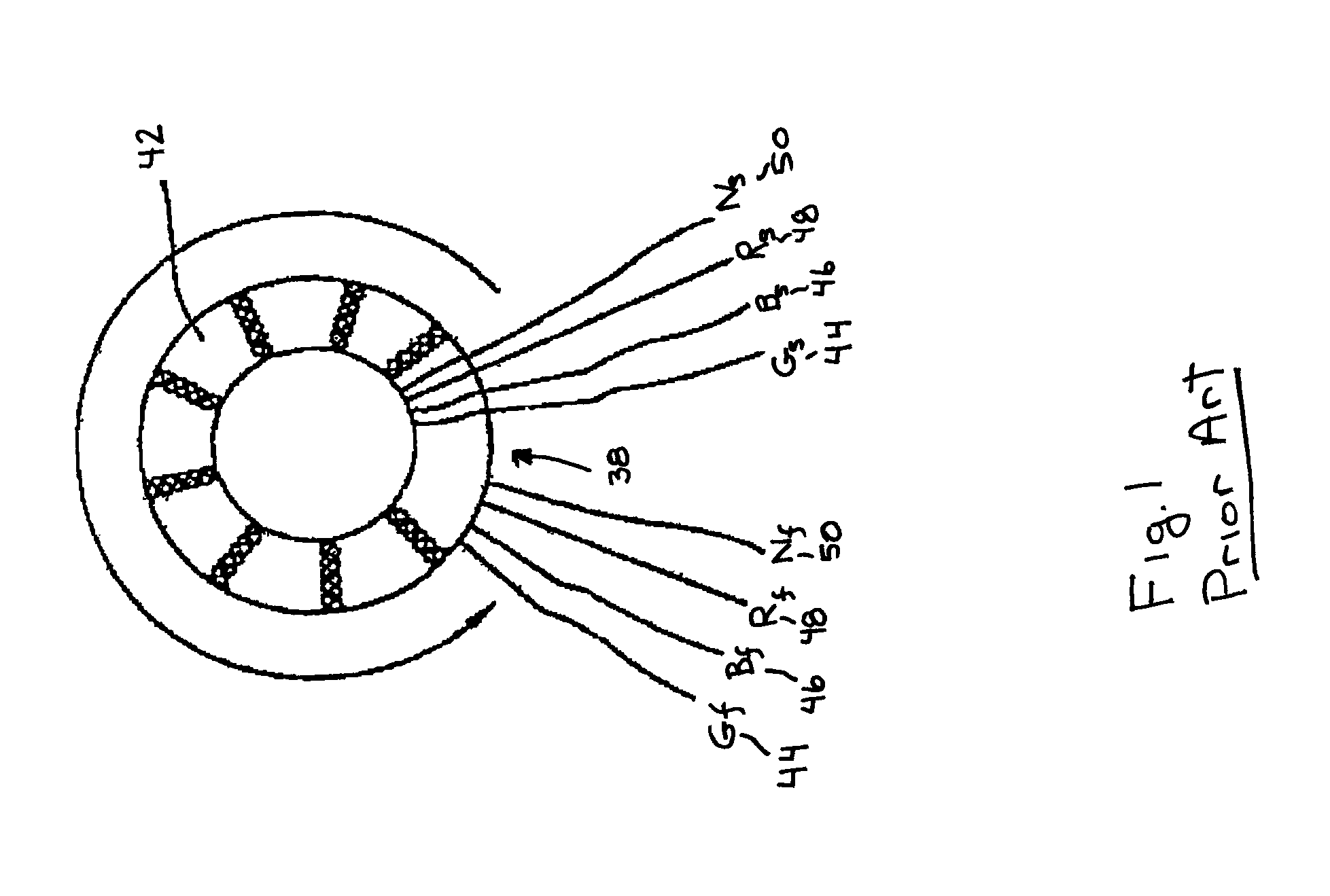

Signal transformer and method for operating such a signal transformer

InactiveUS7042323B2Simple wayPrevent bulk materialTransformers/inductances coils/windings/connectionsVariable inductancesDriver circuitTransformer

A signal transformer having a primary limb and a first secondary limb is specified, a primary winding at least partly enclosing the primary limb and a secondary winding at least partly enclosing the first secondary limb and the primary limb being connected to the first secondary limb. Furthermore, 2n+1 additional secondary limbs are provided, where n=0, 1, 2, 3, . . . , and the additional secondary limbs are connected to the primary limb and the first secondary limb. At least one secondary winding is in each case provided for the additional secondary limbs and for the first secondary limb, the secondary winding at least partly enclosing the respective secondary limb. Moreover, a control winding is provided for each secondary limb, said control winding at least partly enclosing the respective secondary limb. Furthermore, a method for operating such a signal transformer and a driver circuit having such a signal transformer are specified.

Owner:ABB RES LTD

Isolation magnetic devices capable of handling high speed communications

ActiveUS7924130B2Transformers/inductances casingsTransformers/inductances coils/windings/connectionsElectrical and Electronics engineering

Owner:BEL FUSE MACAO COMML OFFSHORE

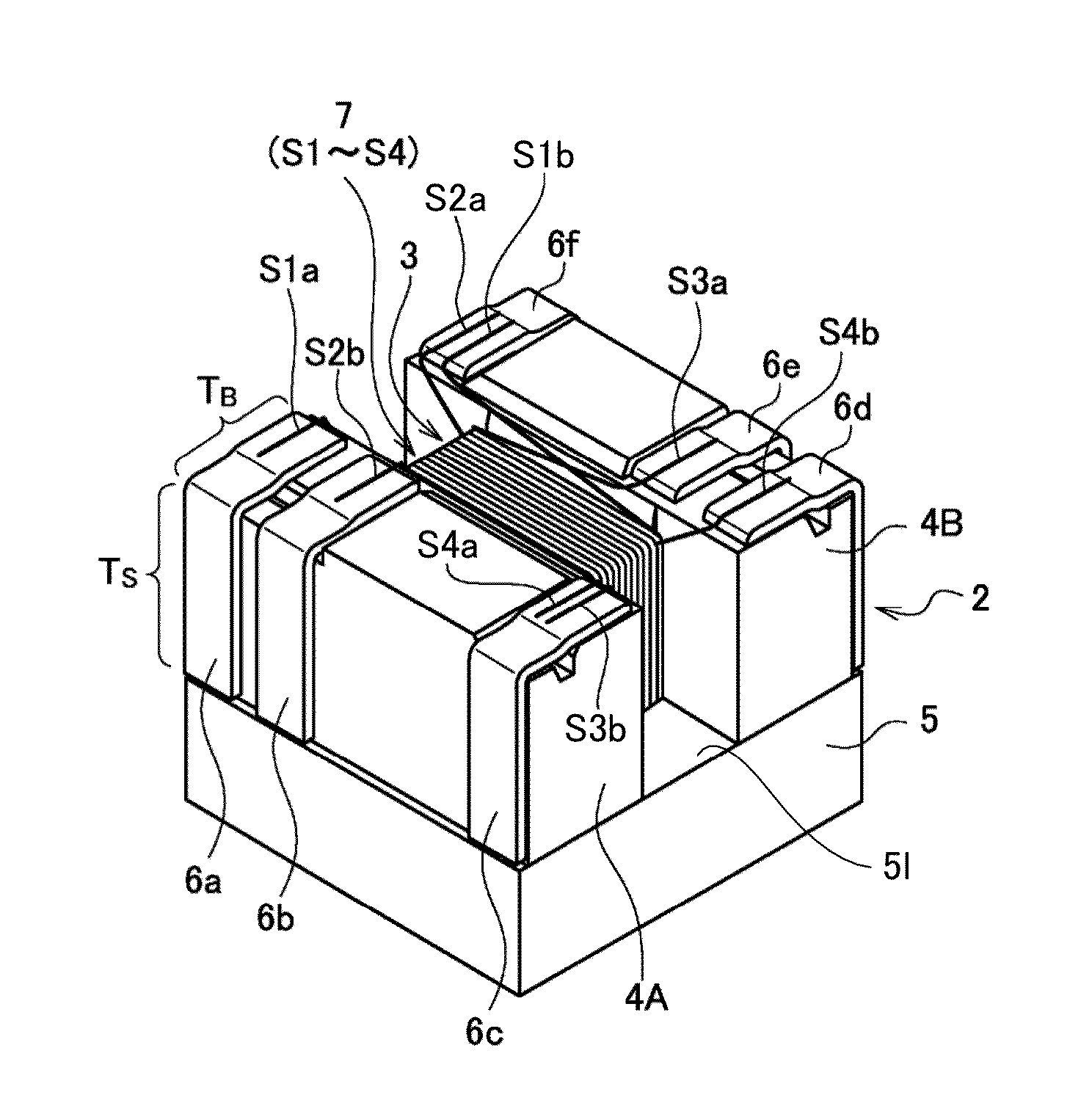

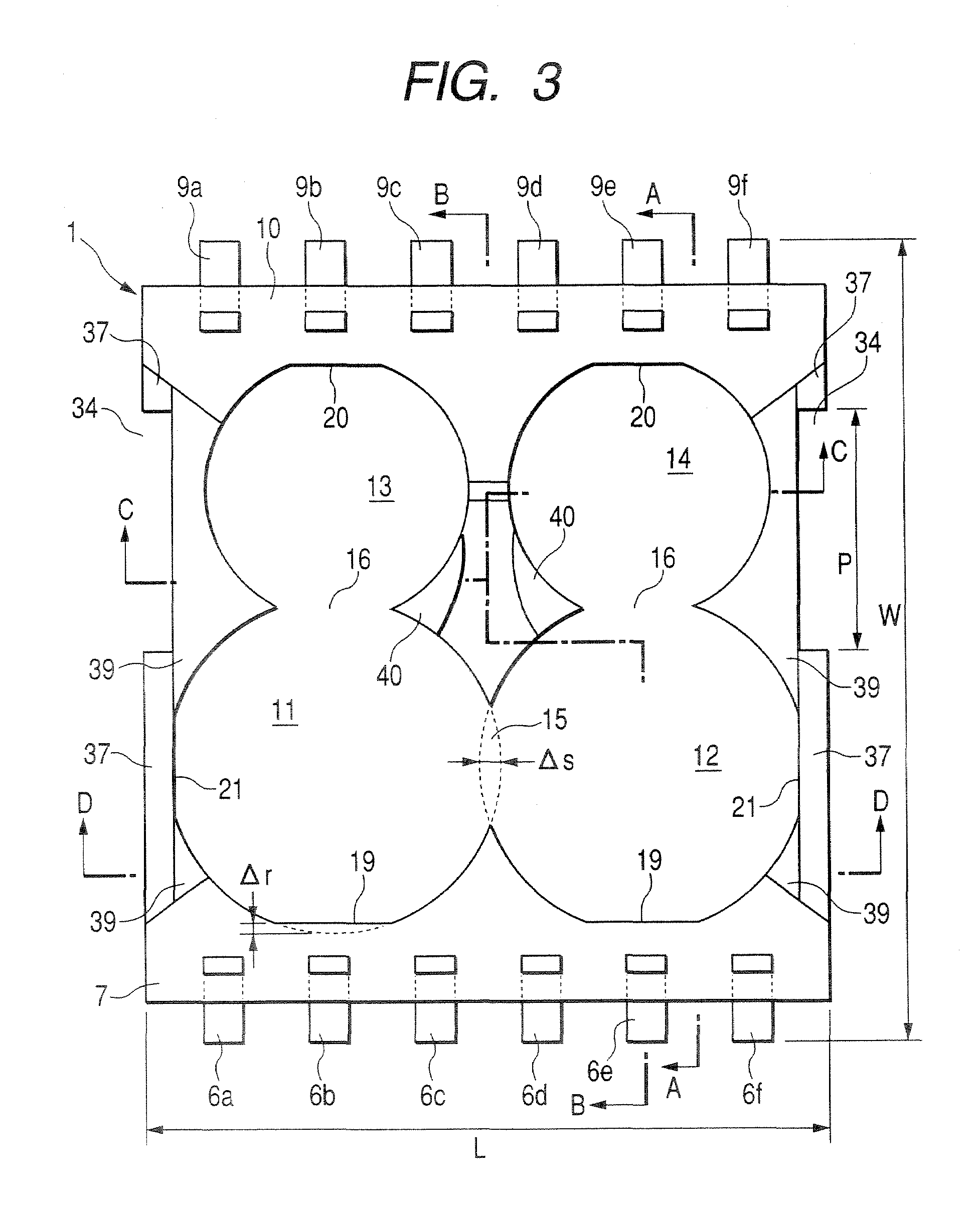

Package for parts for LAN and pulse transformer module for LAN

ActiveUS7230515B2Reduced insertion lossSubstation/switching arrangement detailsTransformers/inductances casingsPulse transformerInsertion loss

A resin-made base body 1 has first recessed portions 11 and 12 for respectively accommodating a plurality of pulse transformers as well as second recessed portions 13 and 14 for accommodating common mode choke coils which are respectively connected to the pulse transformers. The first recessed portions 11 and 12 are formed on one terminal fixing edge 7 side of the base body 1. The second recessed portions 13 and 14 are formed on the other terminal fixing edge 10 side. The first recessed portions 11 and 12 and the second recessed portions 13 and 14 are arranged by being longitudinally connected in a direction from the one terminal fixing edge 7 toward the other terminal fixing edge 10. The adjacent first recessed portions 11 and 12 are connected at one end portion, and the adjacent second recessed portions 13 and 14 are also formed by being connected at one end portion. Thus, provided are a package for parts for LAN and a module for LAN which is miniaturized, and the insertion loss is reduced.

Owner:TDK CORPARATION