Fully differential comparator and fully differential amplifier

A technology of amplifying circuits and differential amplifiers, which is applied to electric pulse generator circuits, amplifiers using switched capacitors, multiple input and output pulse circuits, etc. High-quality fully differential analog signal processing, improved offset reduction effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0056] Hereinafter, embodiments of the present invention will be described with reference to the drawings.

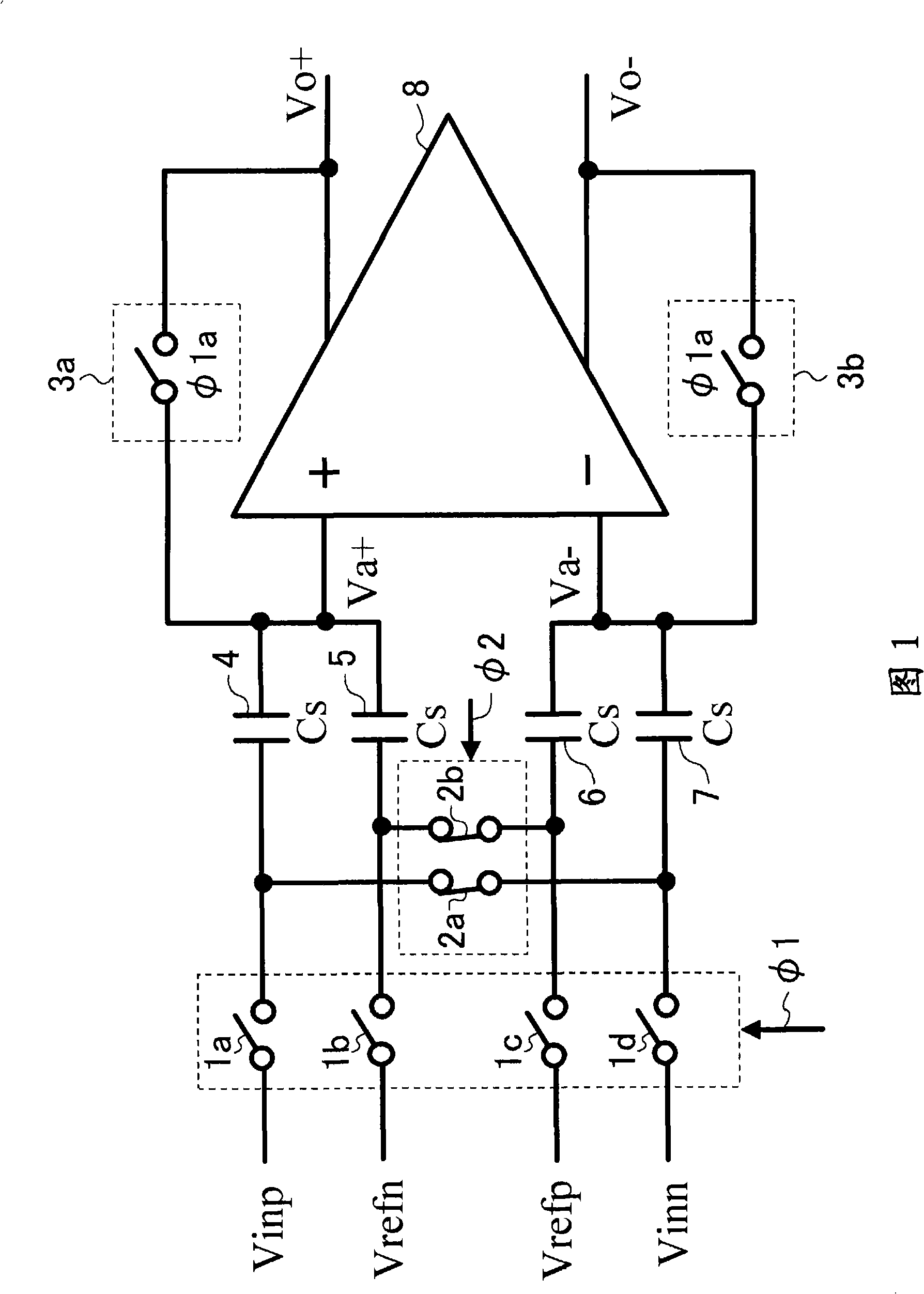

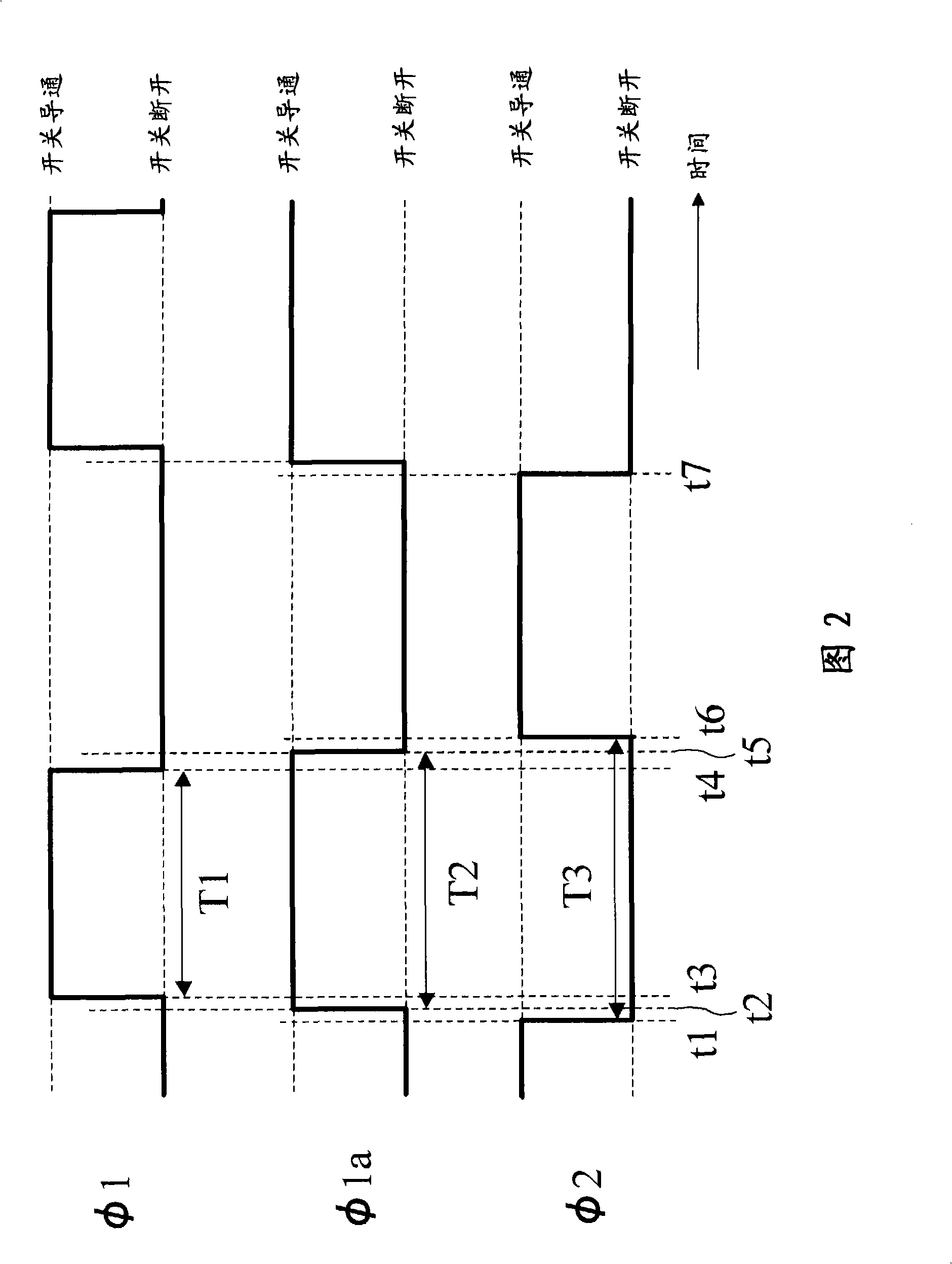

[0057] FIG. 1 shows a configuration example of a fully differential comparator according to the present invention. In Fig. 1, 1a, 1b, 1c, 1d are the first to fourth sampling switches, 2a, 2b are the first charge redistribution switch and the second charge redistribution switch, 3a, 3b are the first reset switch and the second Reset switch, 4, 5, 6, 7 are first to fourth sampling capacitors, 8 is a differential amplifier. In addition, Vinp and Vinn are differential input signal voltages, Vrefp and Vrefn are differential comparison reference voltages, Va+ and Va- are positive and negative polarity input terminals of the differential amplifier 8, and Vo+ and Vo- are differential amplifier 8 input terminals. Positive and negative polarity output terminals. The first to fourth sampling capacitors 4 to 7 substantially have the same capacitance value Cs. Φ1, Φ1a, and Φ2 are...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com