Patents

Literature

130 results about "Associative processor" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Associative processor. [ə′sō·sē‚ād·iv ′präs‚es·ər] (computer science) A digital computer that consists of a content-addressable memory and means for searching rapidly changing random digital data stored within, at speeds up to 1000 times faster than conventional digital computers.

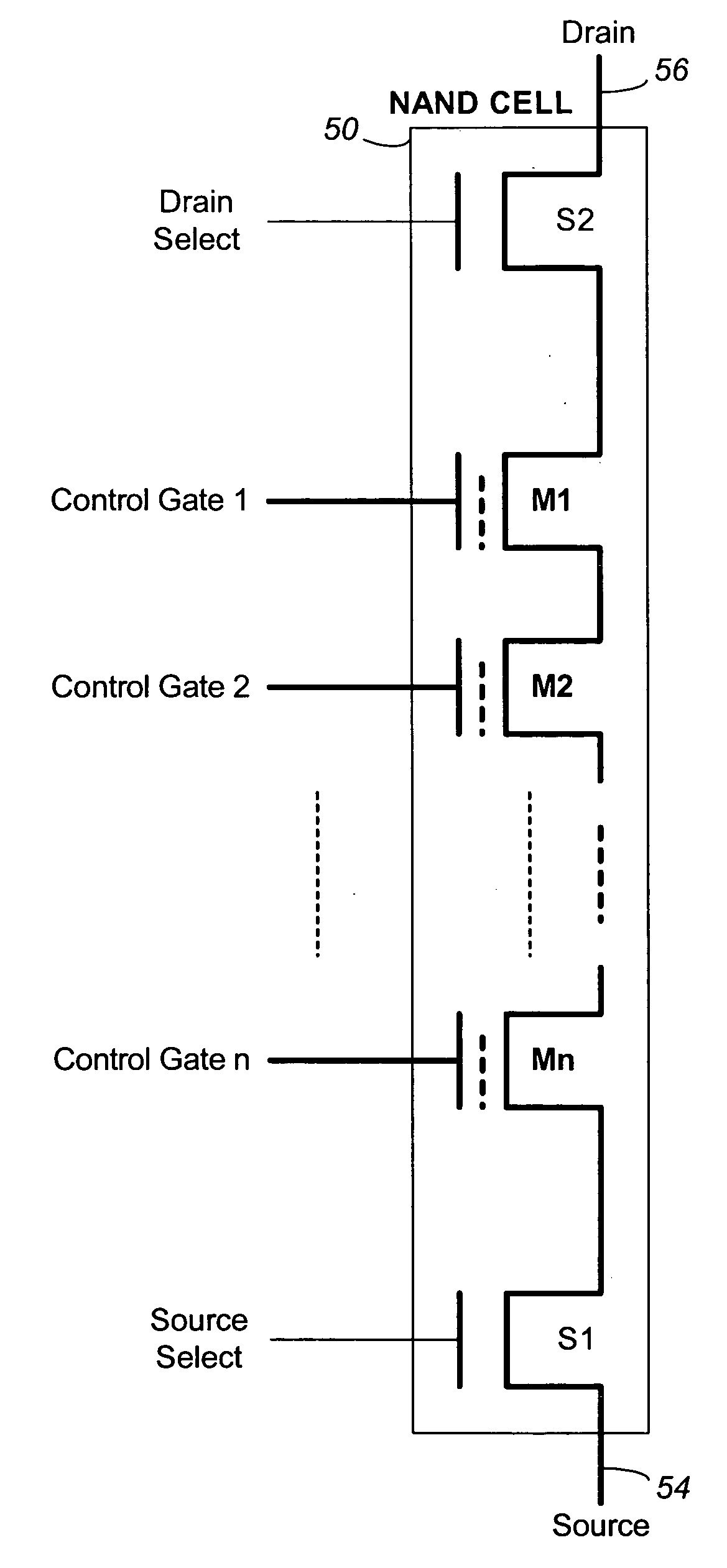

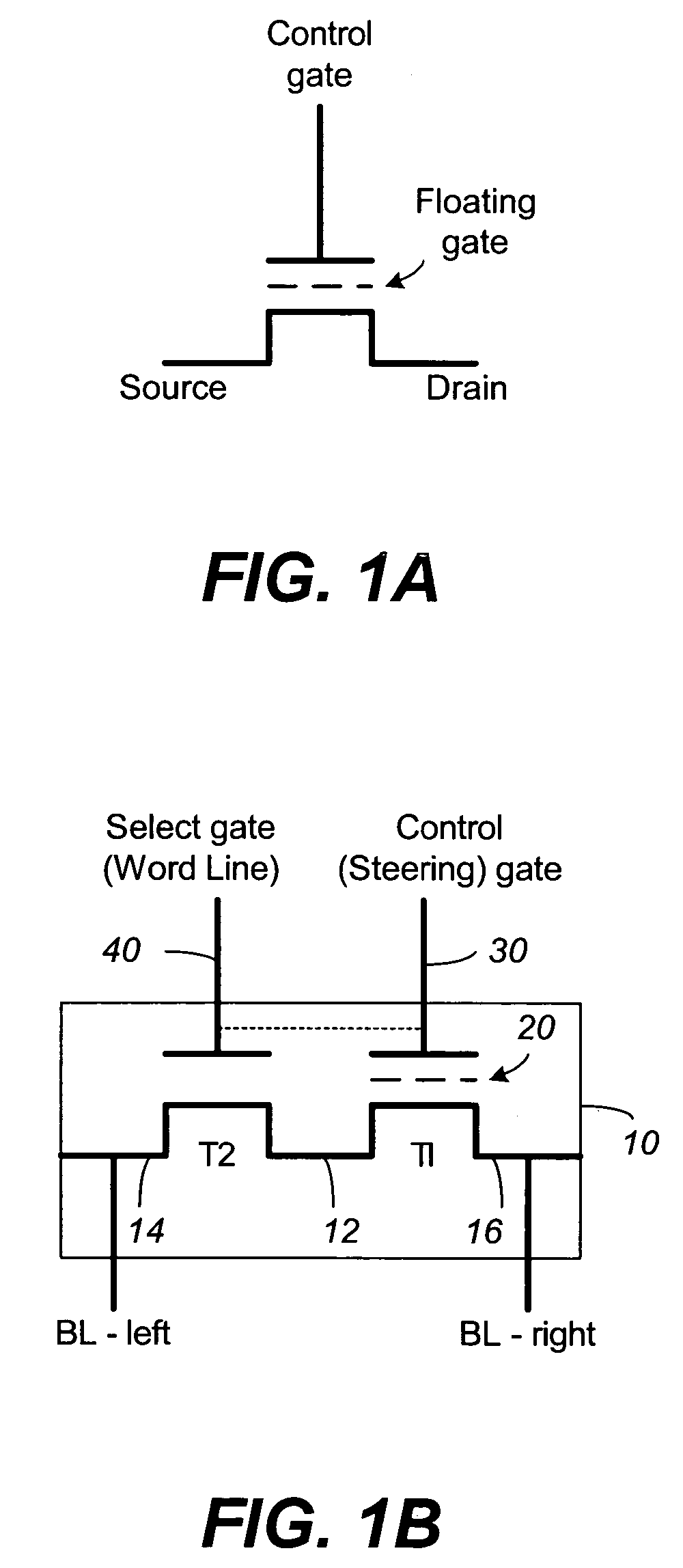

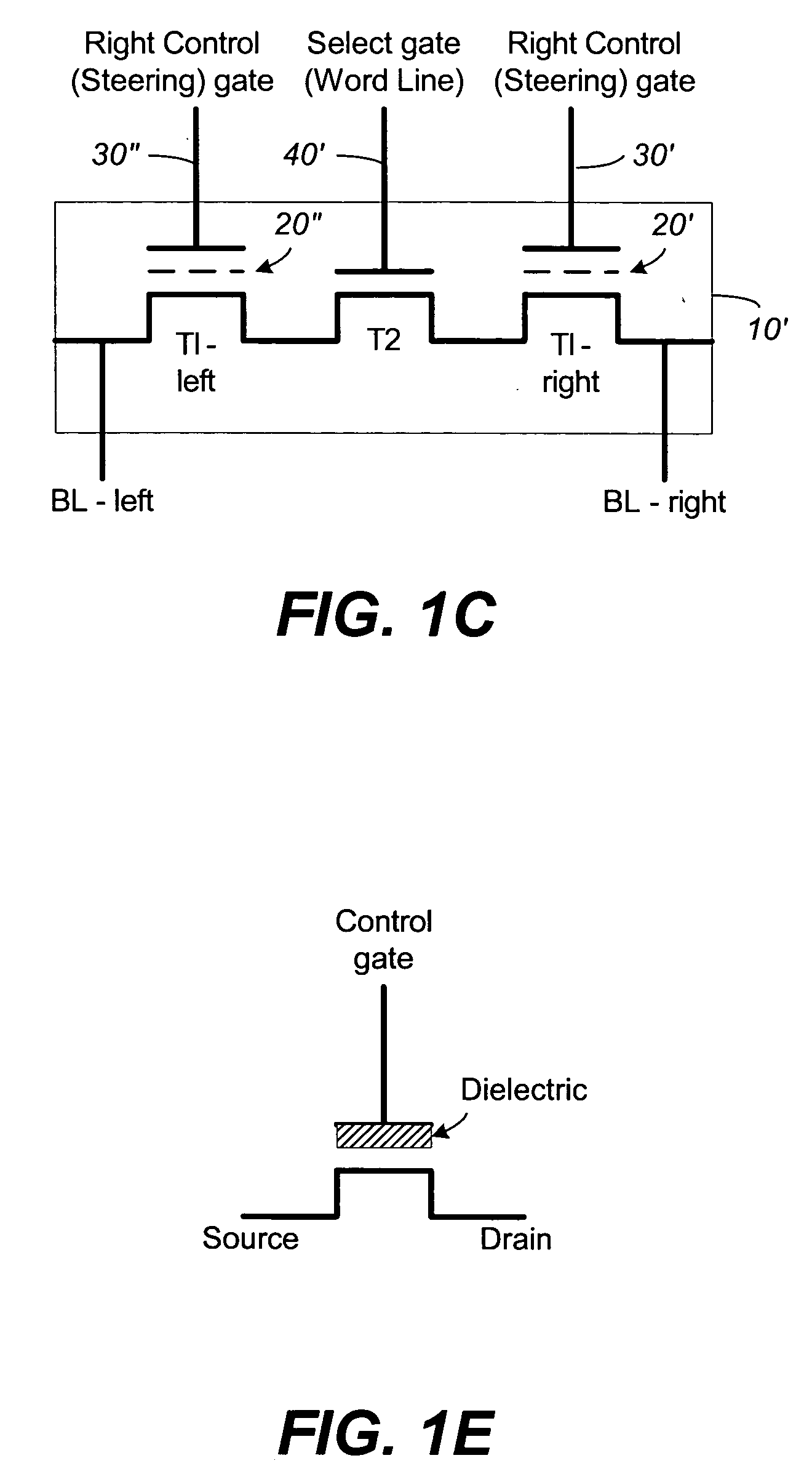

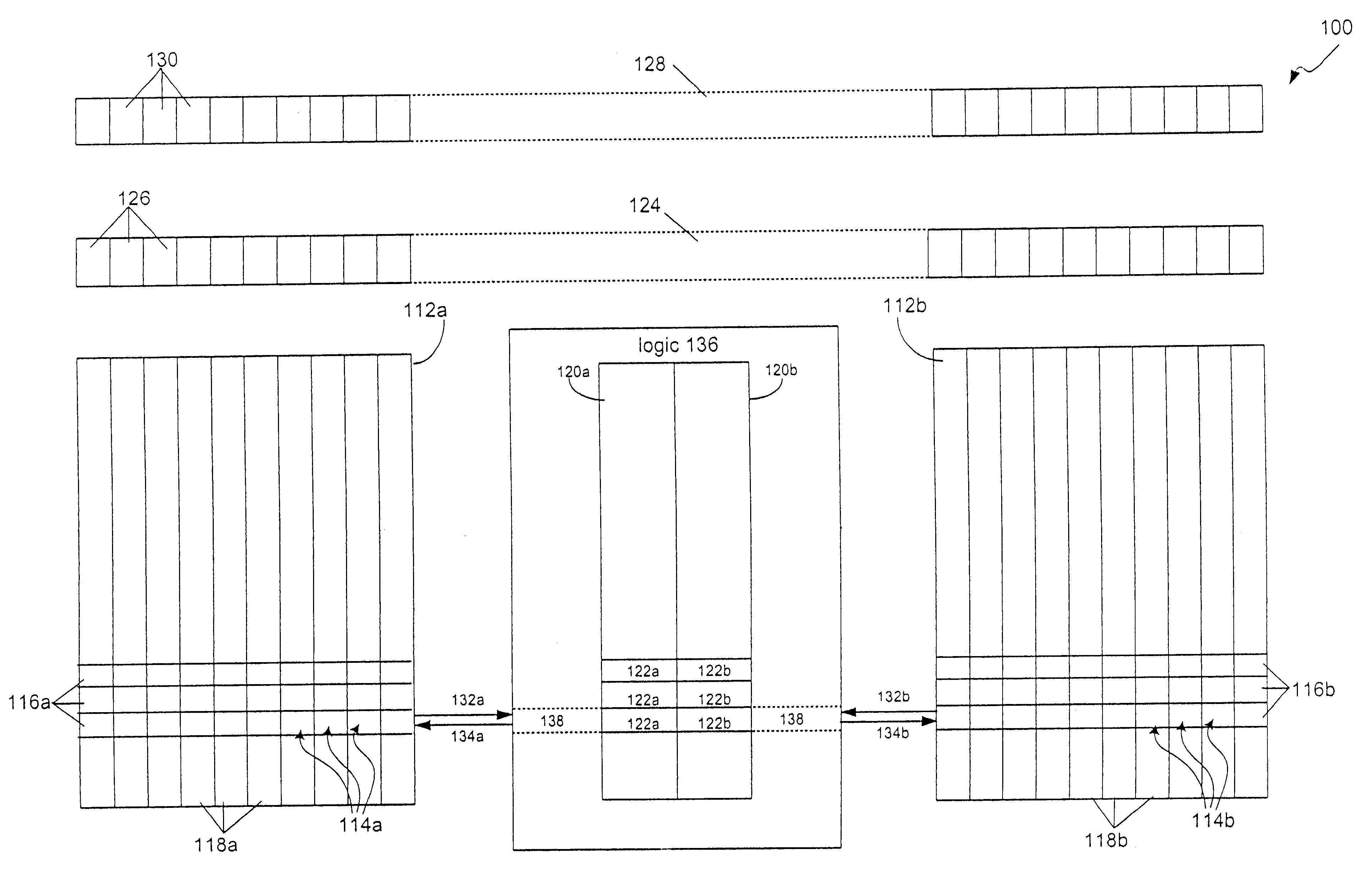

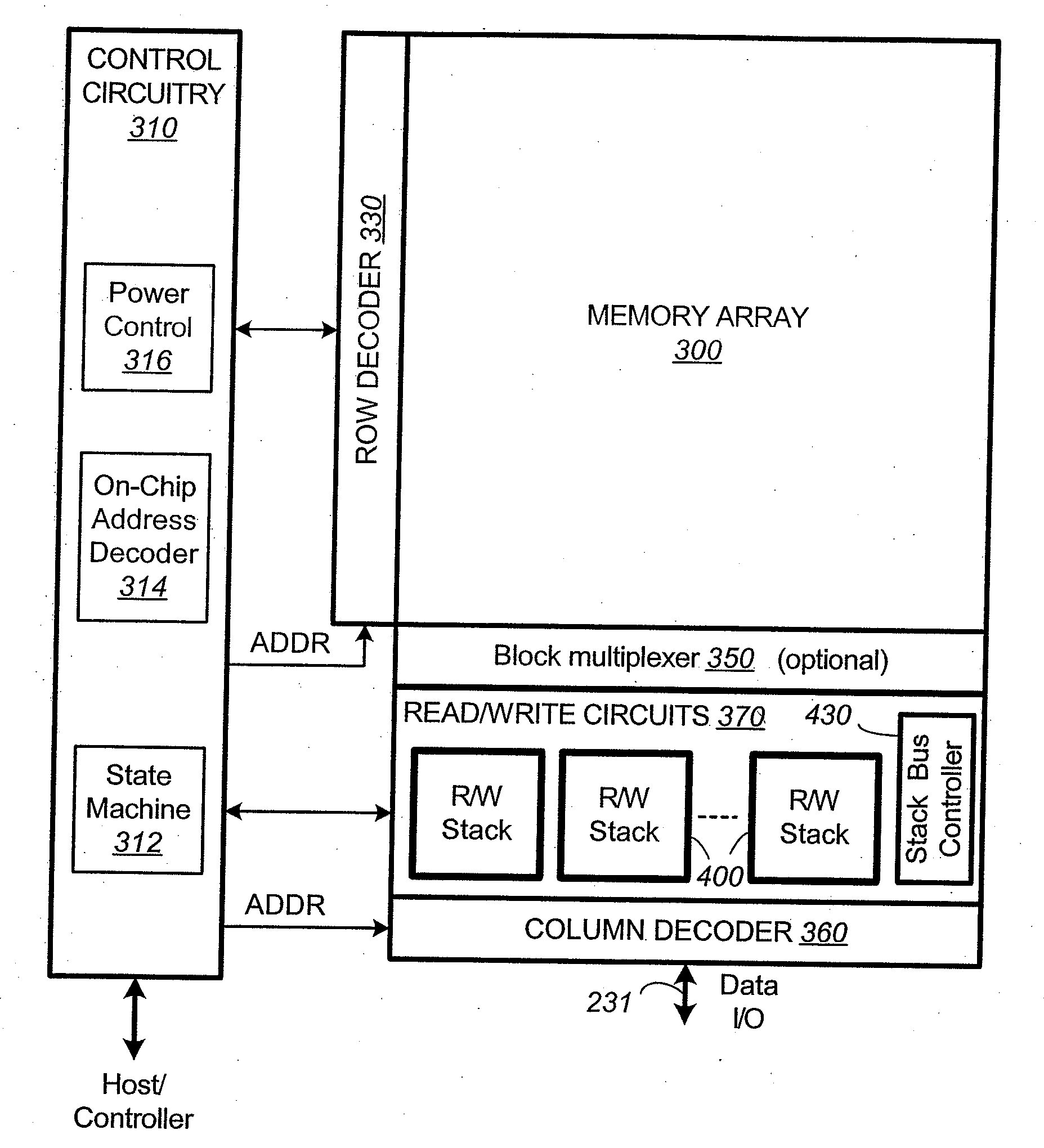

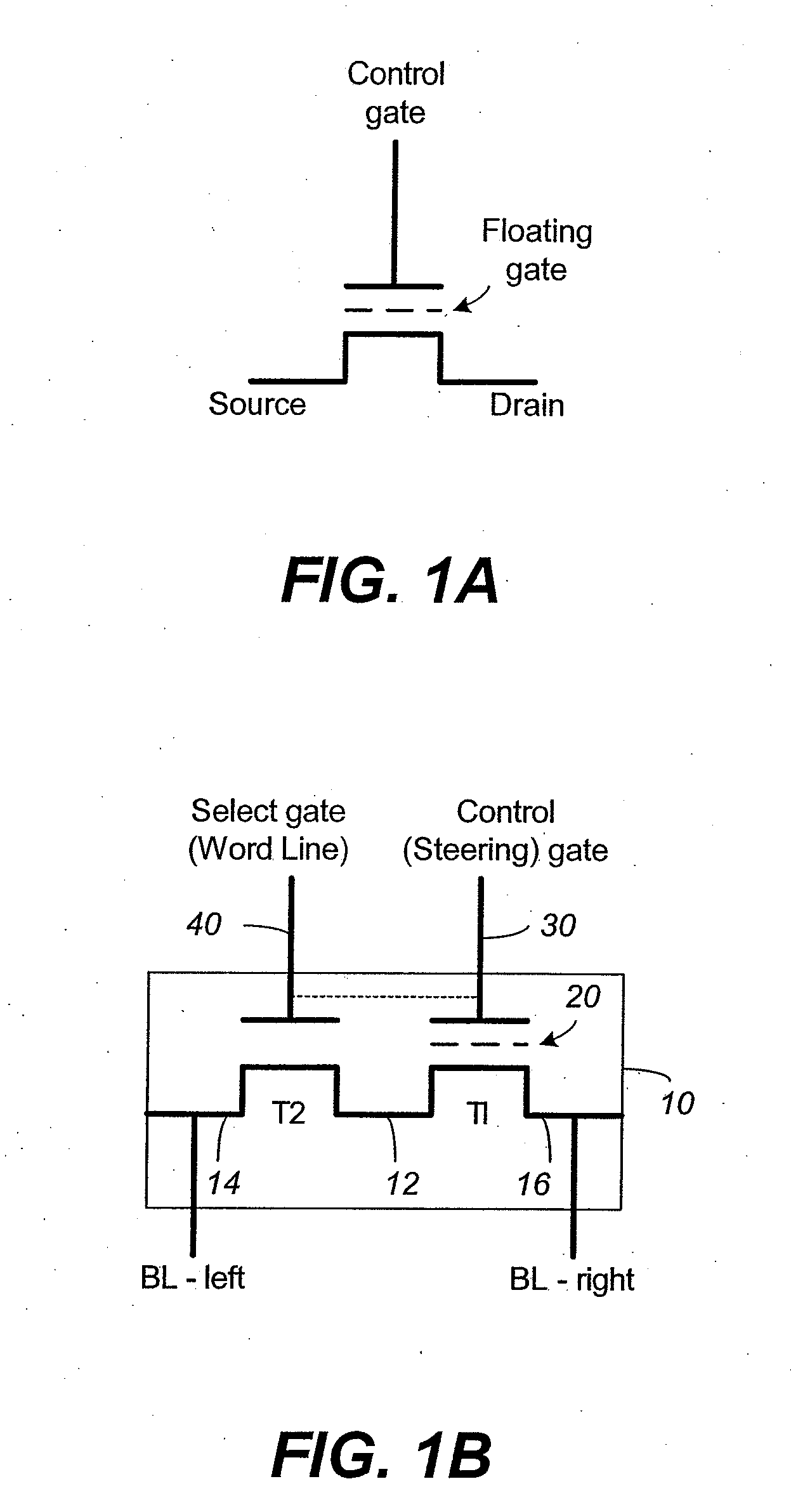

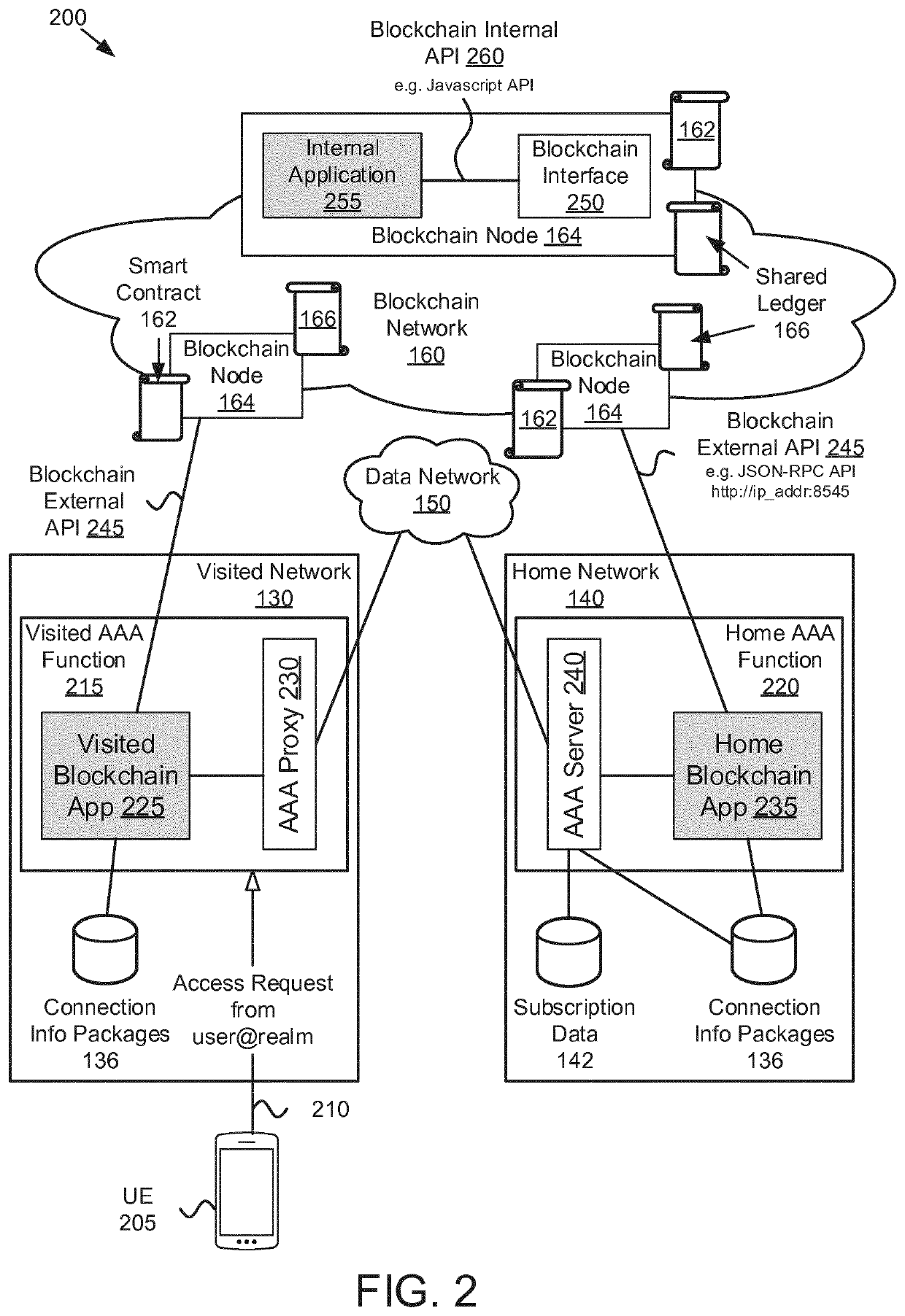

Non-volatile memory and method with shared processing for an aggregate of read/write circuits

InactiveUS20060140007A1Maximum versatilityMinimal componentRead-only memoriesDigital storageAudio power amplifierAssociative processor

A non-volatile memory device capable of reading and writing a large number of memory cells with multiple read / write circuits in parallel has an architecture that reduces redundancy in the multiple read / write circuits to a minimum. The multiple read / write circuits are organized into a bank of similar stacks of components. Redundant circuits such as a processor for processing data among stacks each associated with multiple memory cells are factored out. The processor is implemented with an input logic, a latch and an output logic. The input logic can transform the data received from either the sense amplifier or the data latches. The output logic further processes the transformed data to send to either the sense amplifier or the data latches or to a controller. This provides an infrastructure with maximum versatility and a minimum of components for sophisticated processing of the data sensed and the data to be input or output.

Owner:SANDISK TECH LLC

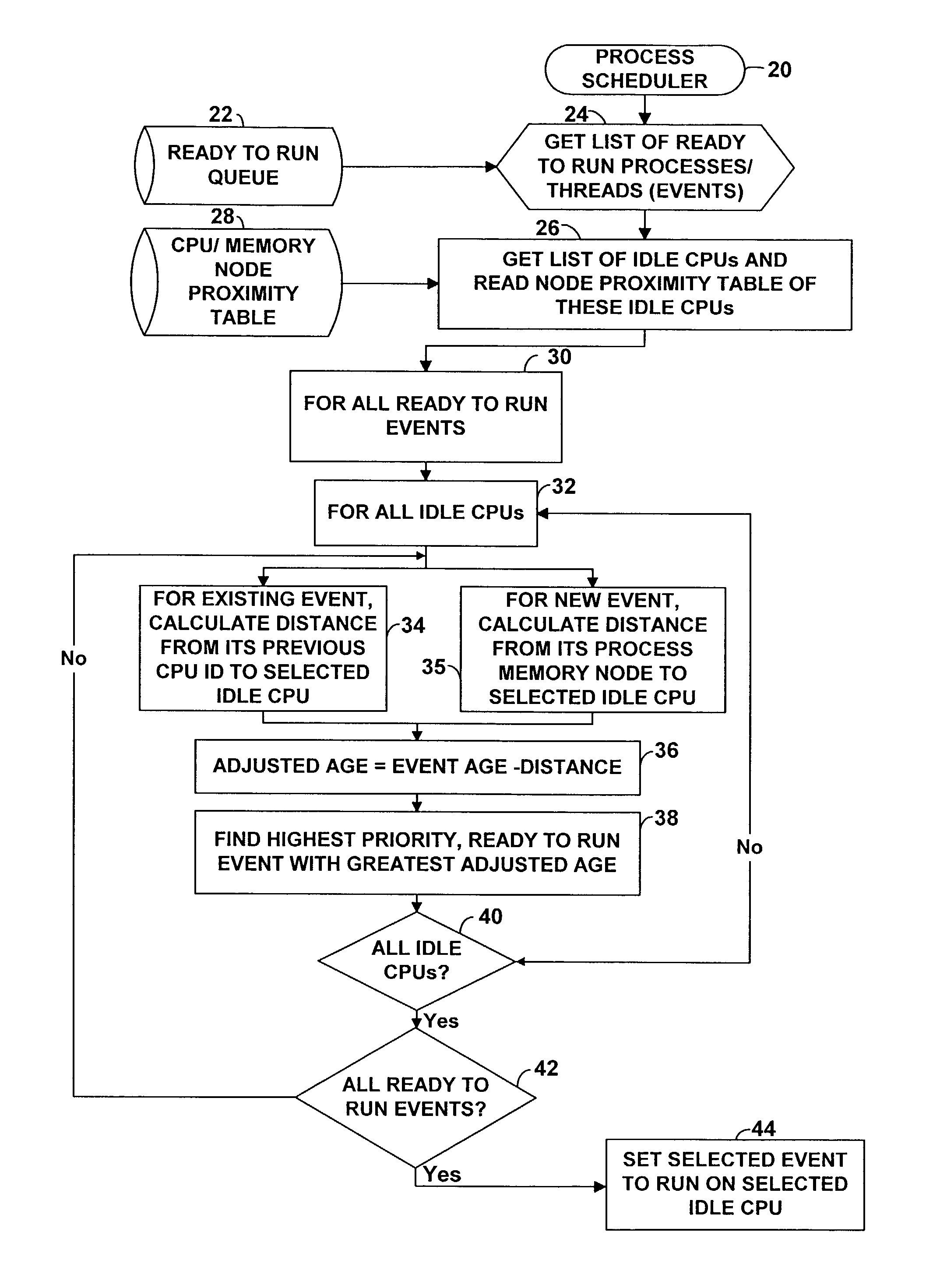

Method and apparatus for optimizing performance in a multi-processing system

InactiveUS7143412B2Interprogram communicationDigital computer detailsError processingThread scheduling

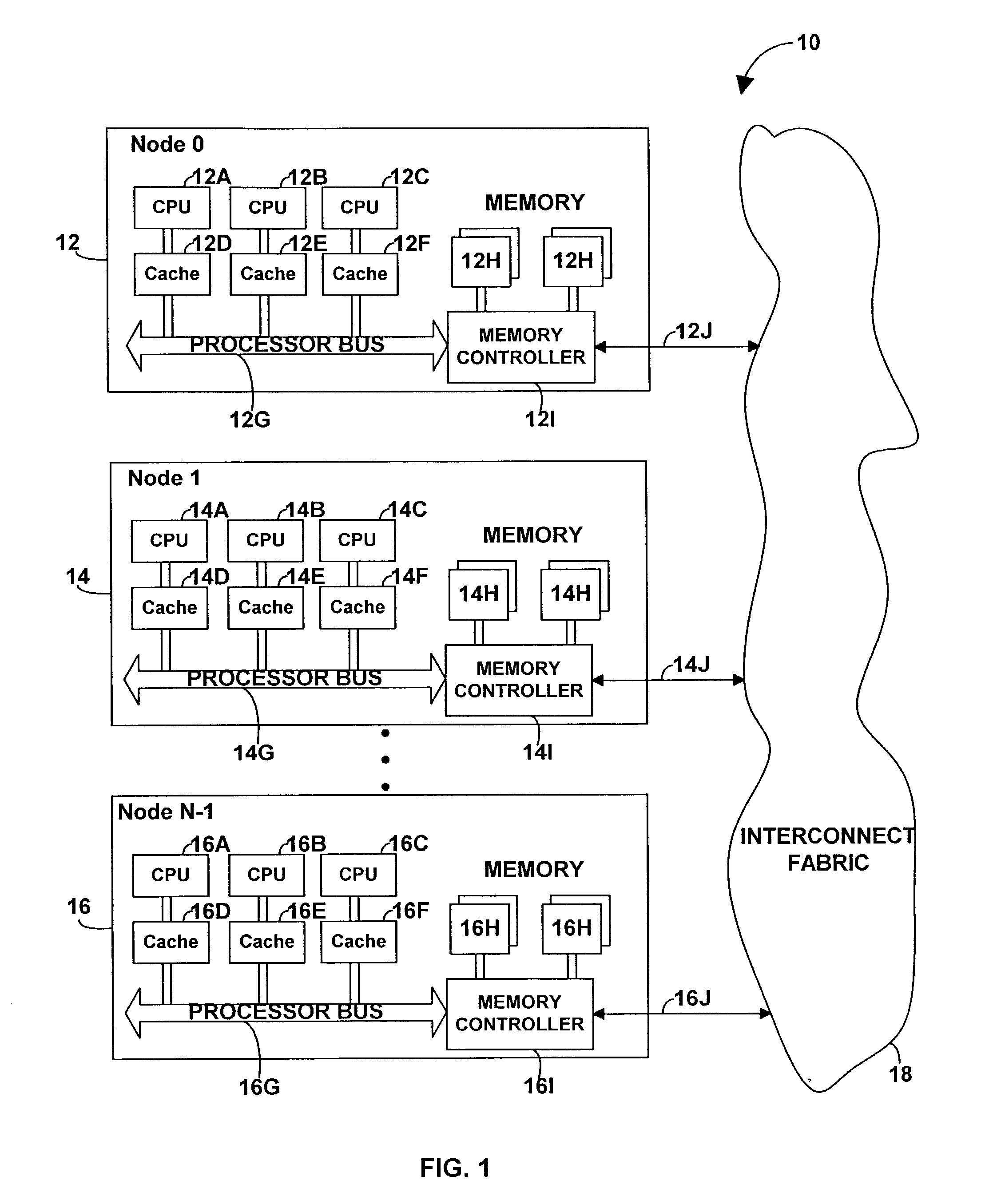

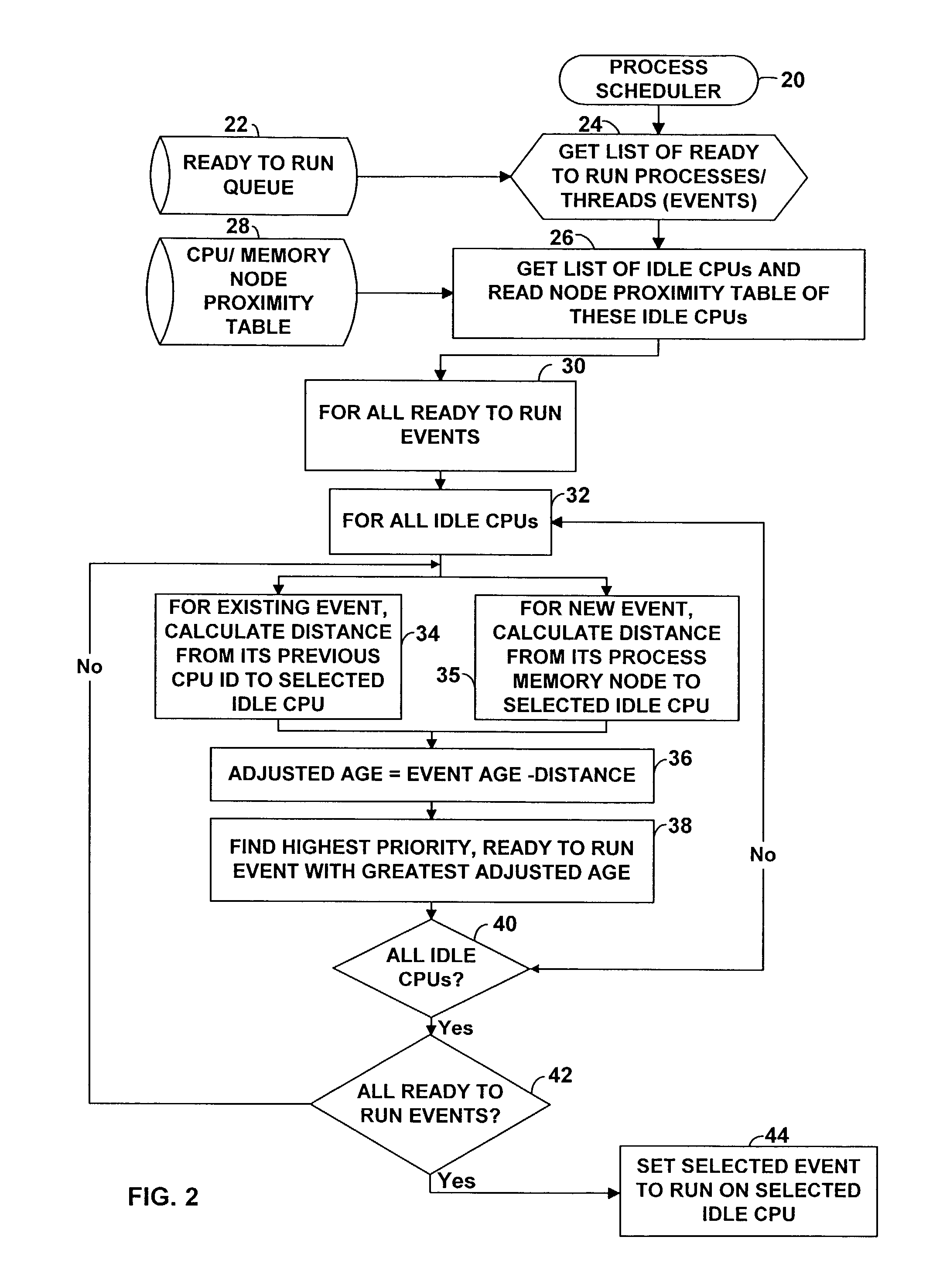

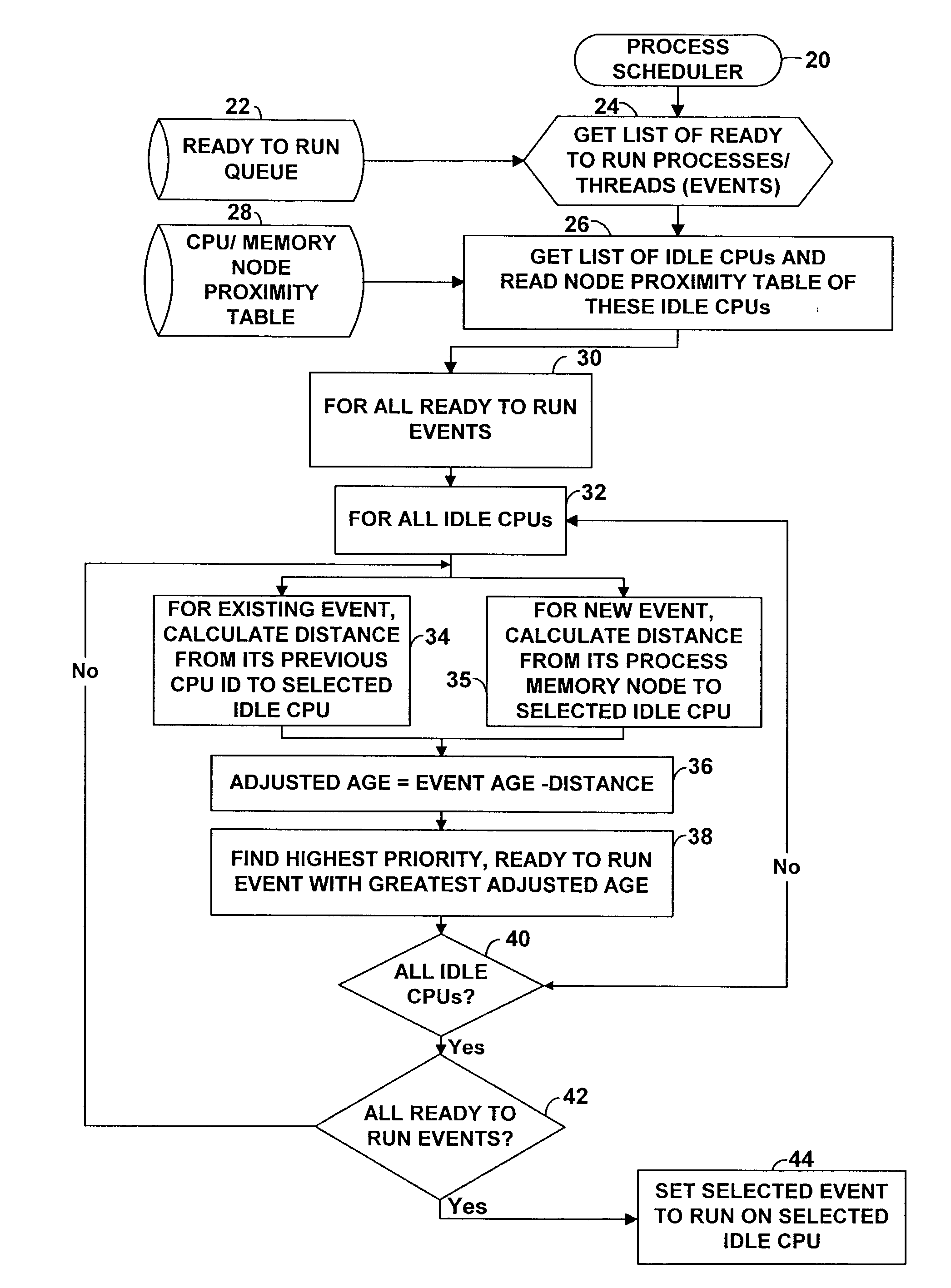

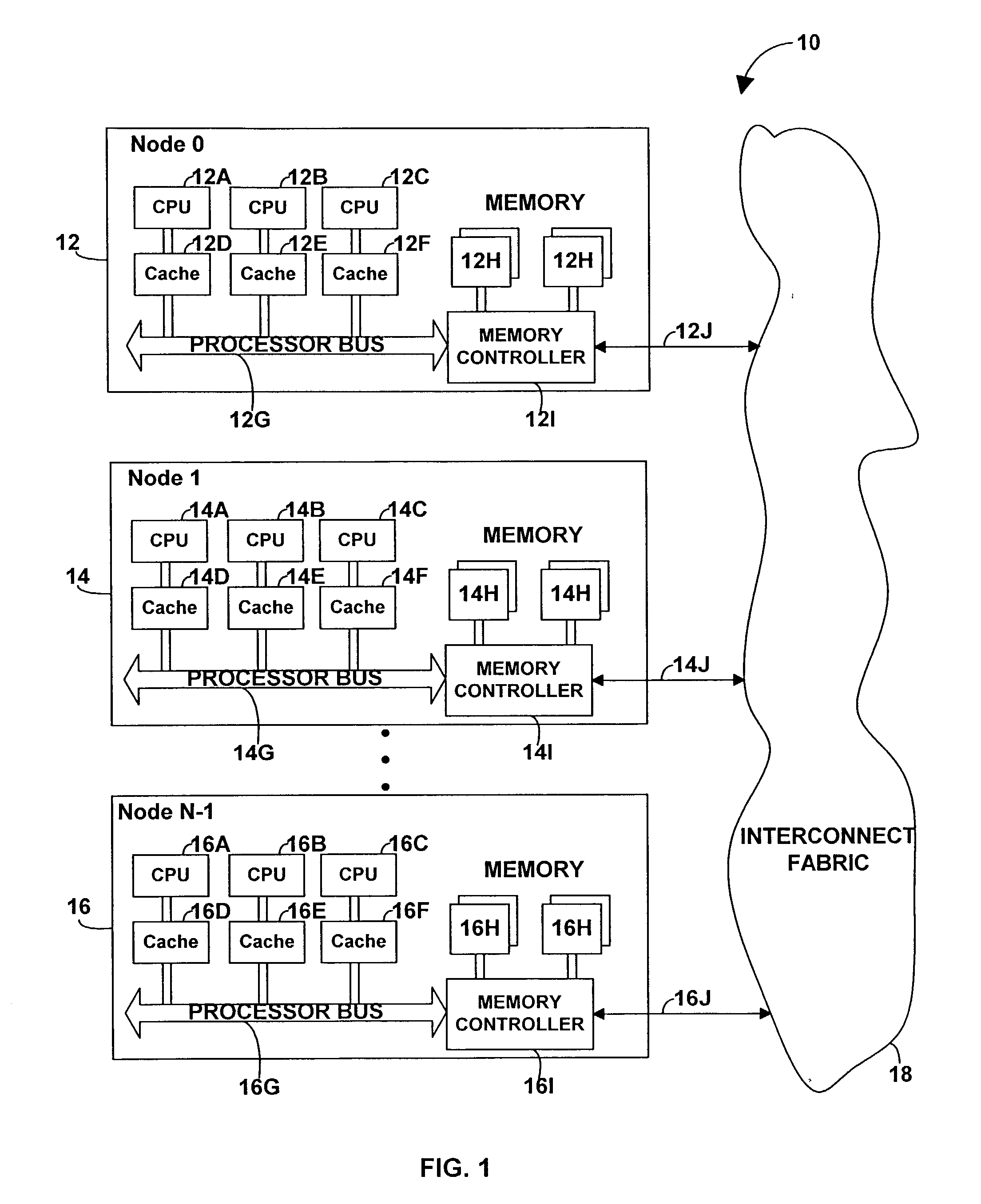

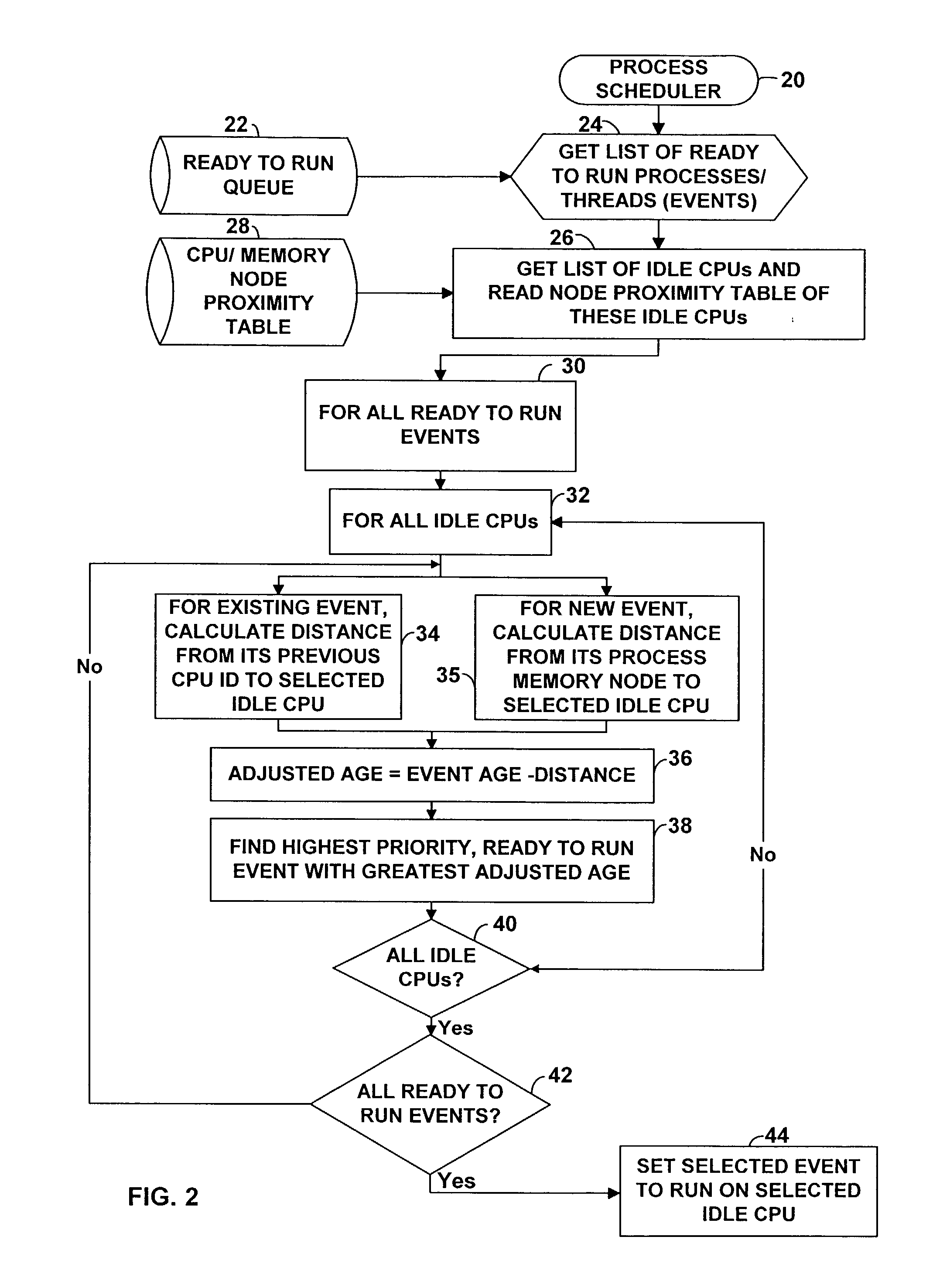

A technique for improving performance in a multi-processor system by reducing access latency by correlating processor, node and memory allocation. Specifically, a Process / Thread Scheduler is modified such that system mapping and node proximity tables may be referenced to help determine processor assignments for ready-to-run processes / threads. Processors are chosen to minimize access latency. Further, the Page Fault Handler is modified such that free memory pages are assigned to a process based partially on the proximity of the memory with respect to the processor requesting memory allocation.

Owner:HEWLETT PACKARD DEV CO LP

Method and apparatus for optimizing performance in a multi-processing system

InactiveUS20040019891A1Interprogram communicationDigital computer detailsError processingThread scheduling

A technique for improving performance in a multi-processor system by reducing access latency by correlating processor, node and memory allocation. Specifically, a Process / Thread Scheduler is modified such that system mapping and node proximity tables may be referenced to help determine processor assignments for ready-to-run processes / threads. Processors are chosen to minimize access latency. Further, the Page Fault Handler is modified such that free memory pages are assigned to a process based partially on the proximity of the memory with respect to the processor requesting memory allocation.

Owner:HEWLETT PACKARD DEV CO LP

Bacteriorhodopsin Protein Variants and Methods of Use for Long Term Data Storage

ActiveUS20090268511A1High through-put storageEnhanced protein performanceNanoinformaticsPeptide preparation methodsLong term dataWild type

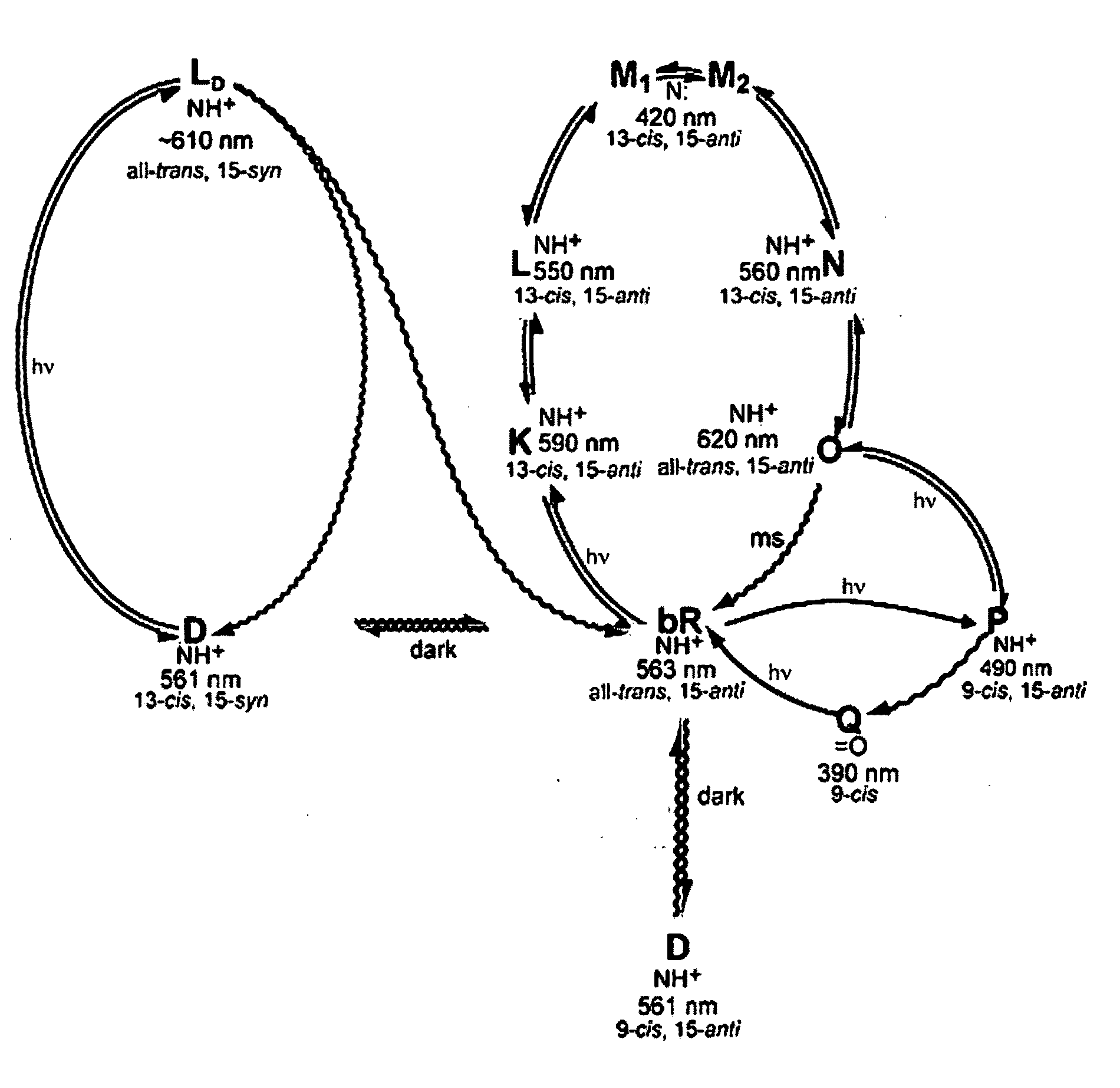

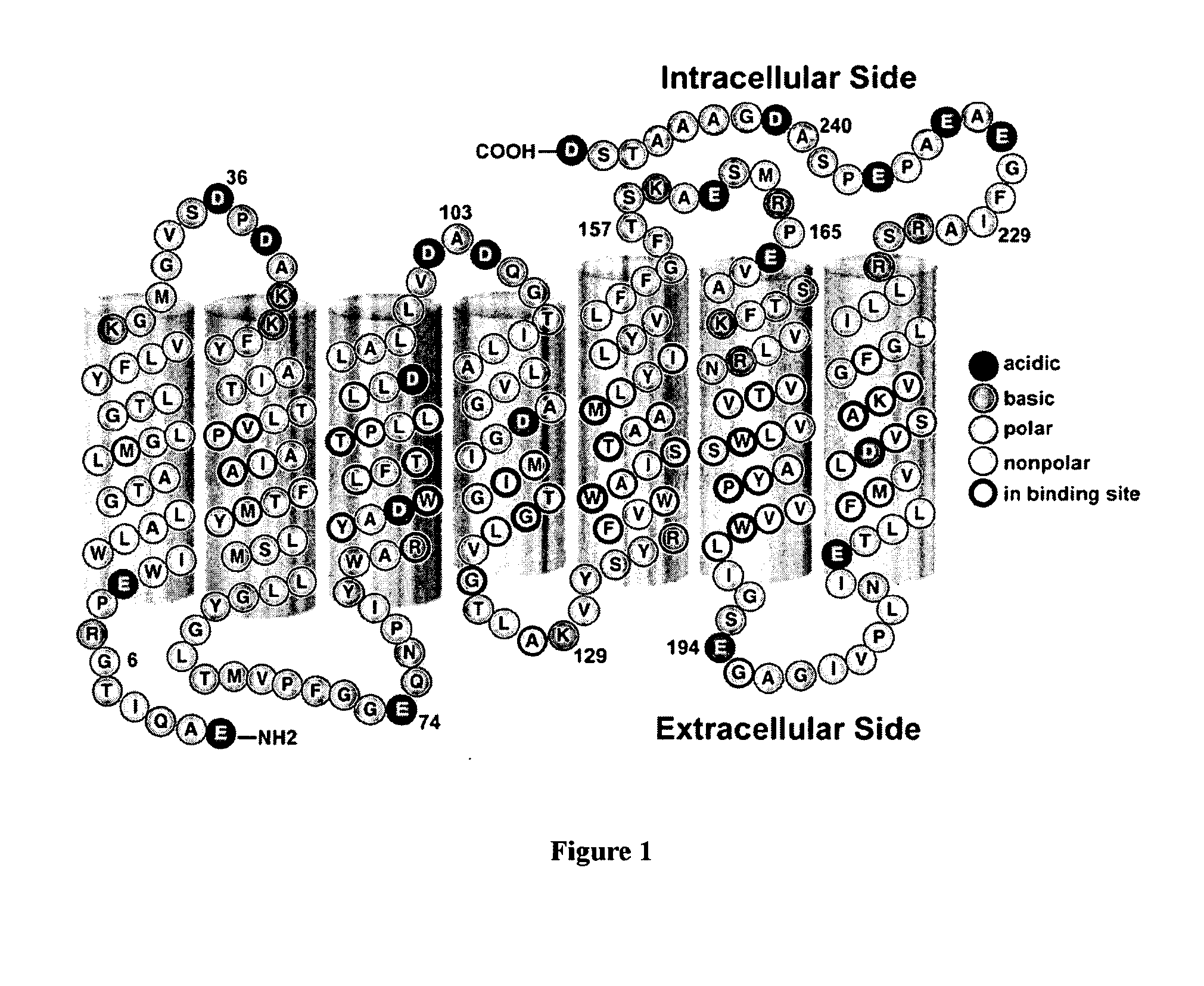

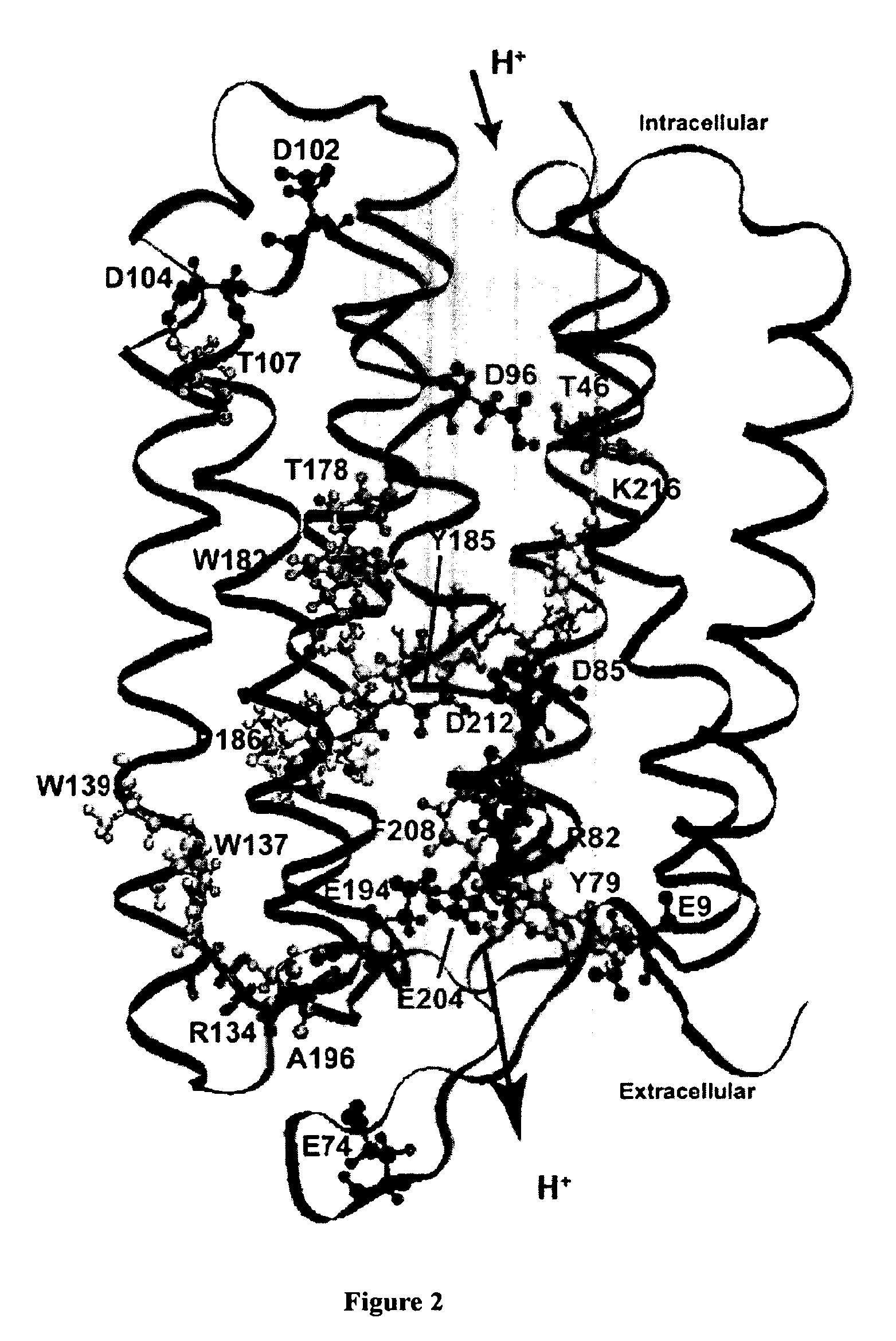

Bacteriorhodopsin protein variants and methods using the bacteriorhodopsin variants for performance in holographic and three-dimensional (3D) memory storage devices are described. The amino acid and chemical modifications of bacteriorhodopsin provided herein achieve greatly enhanced protein performance. The memory storage devices write, read and erase data proficiently. The bacteriorhodopsin protein variants are useful in optical memory storage and associative processor systems. Irradiation of the light-sensitive protein with light of known wavelength causes the protein to switch between different states. The variants enter the branched photocycle via a single or a two photon process and form the permanent ‘Q’ state more efficiently than the wild-type bacteriorhodopsin protein. This branching photocycle of the variants is exploited in the fabrication of 3D memory storage devices.

Owner:UNIV OF CONNECTICUT

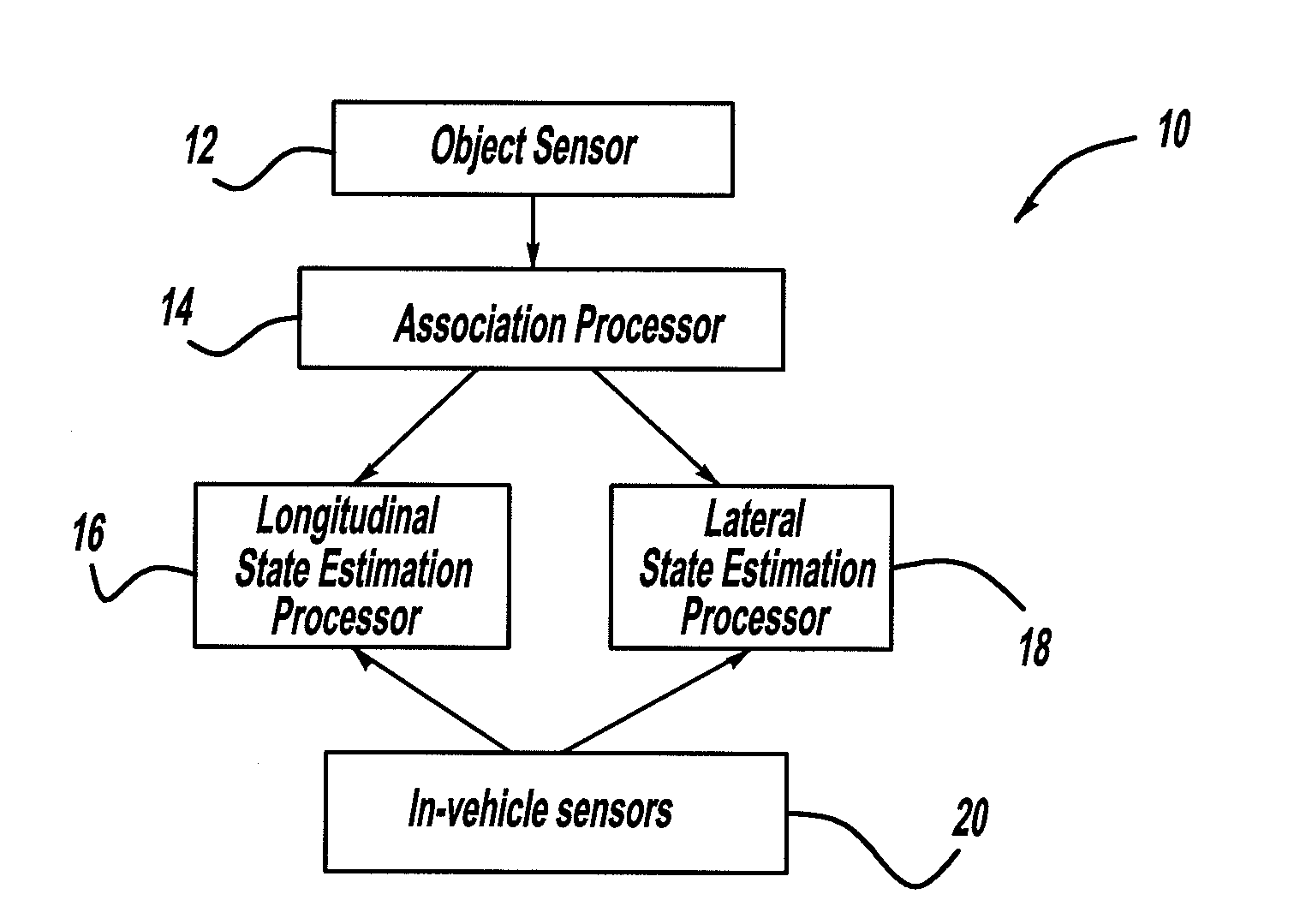

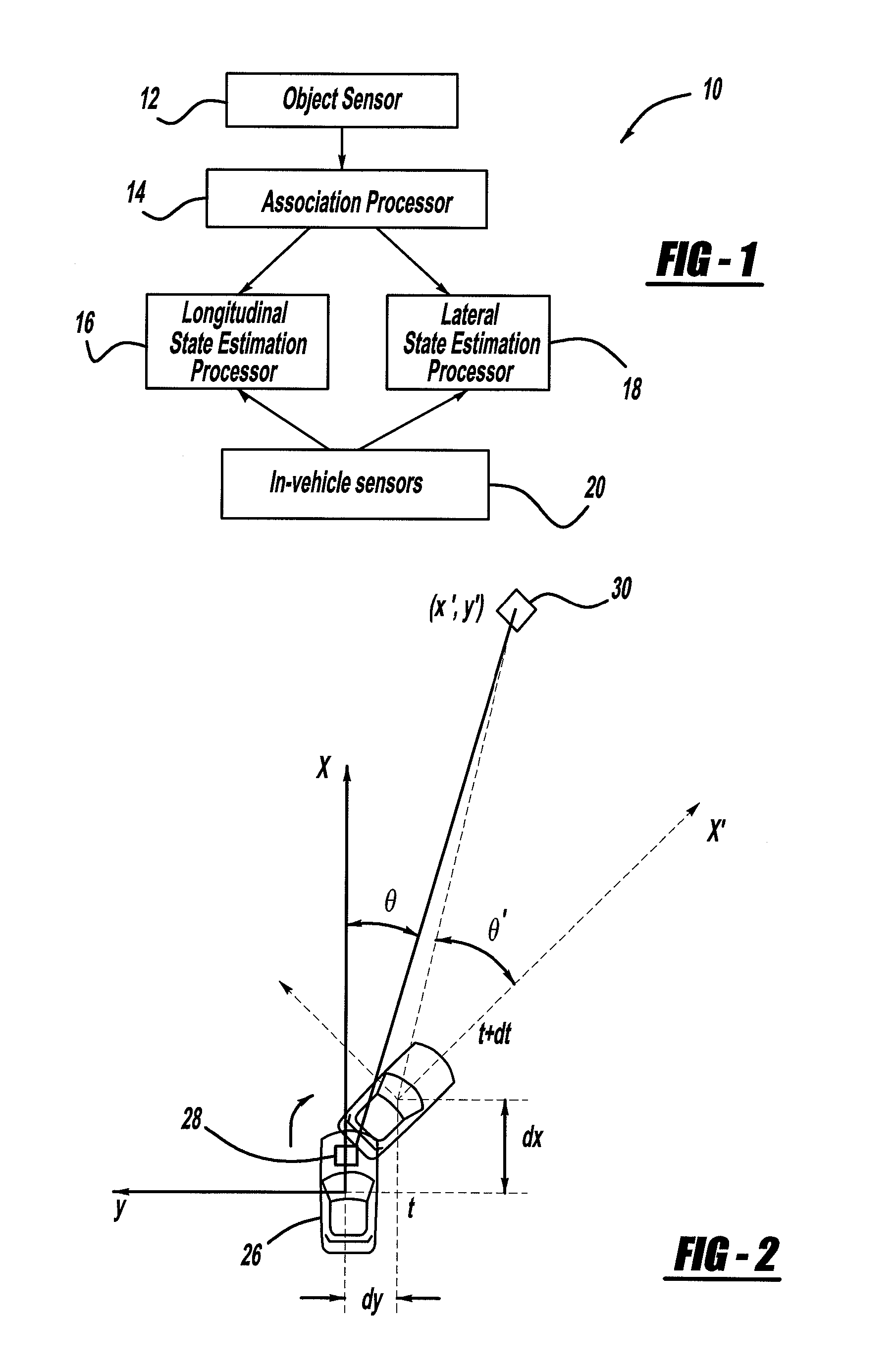

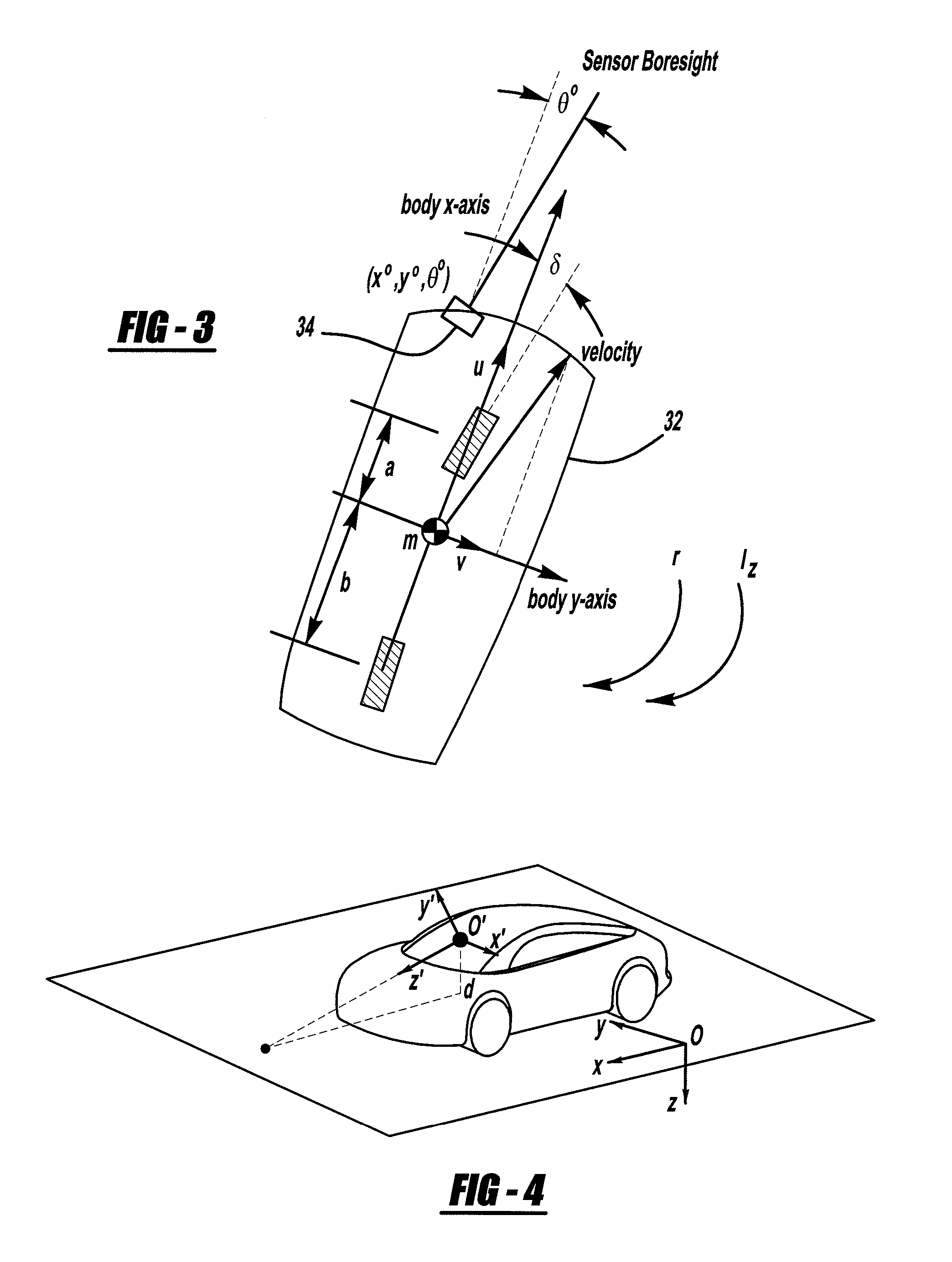

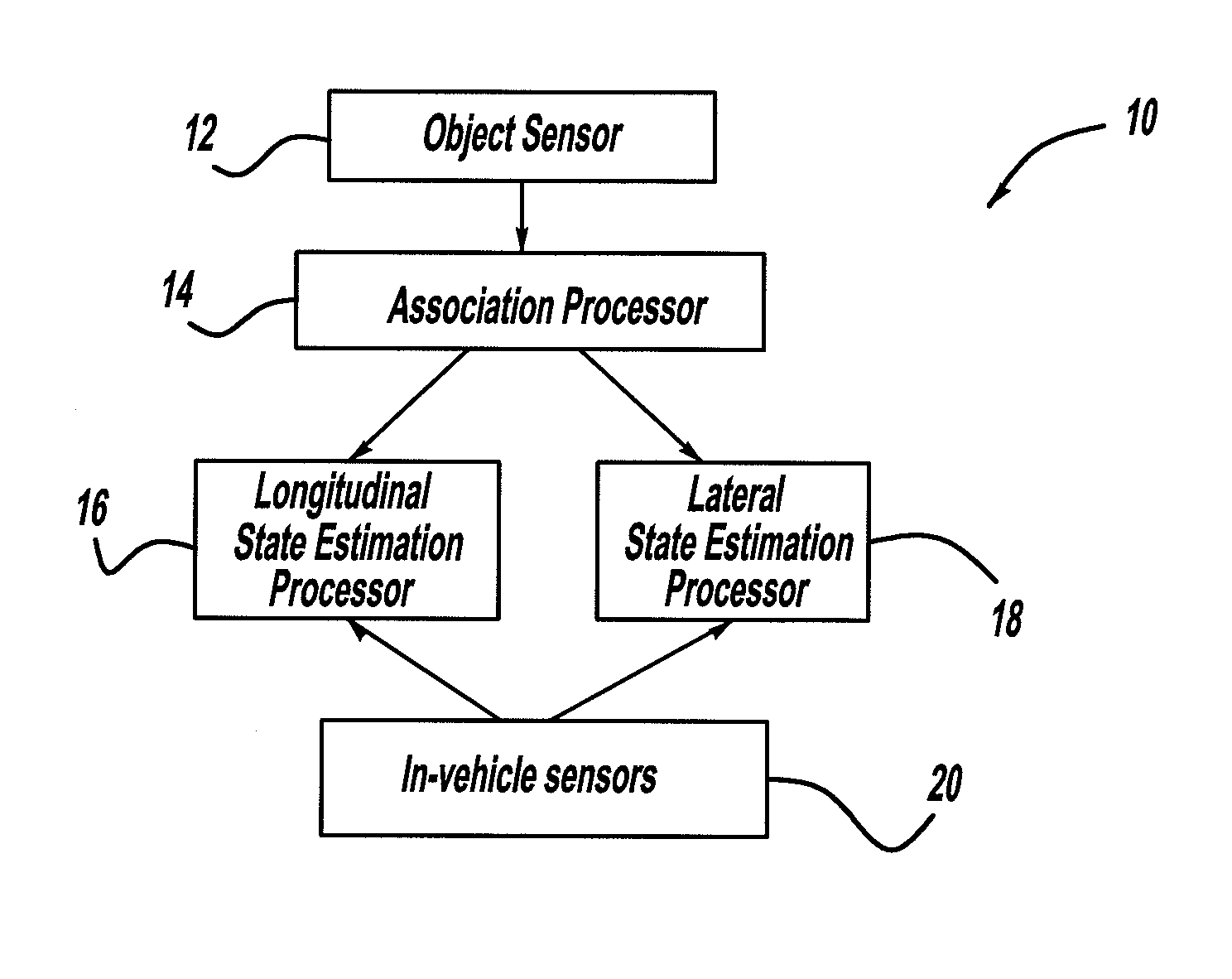

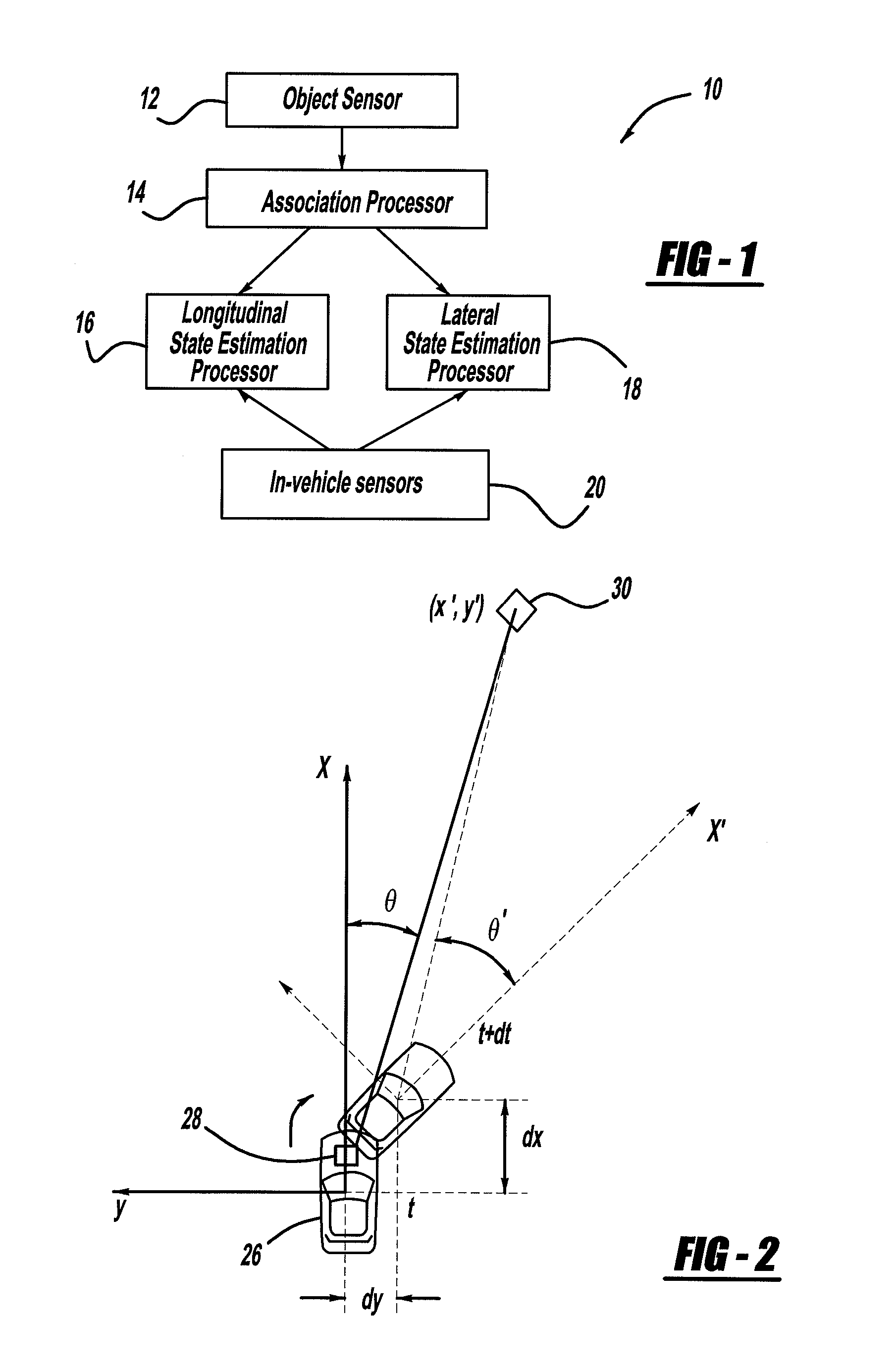

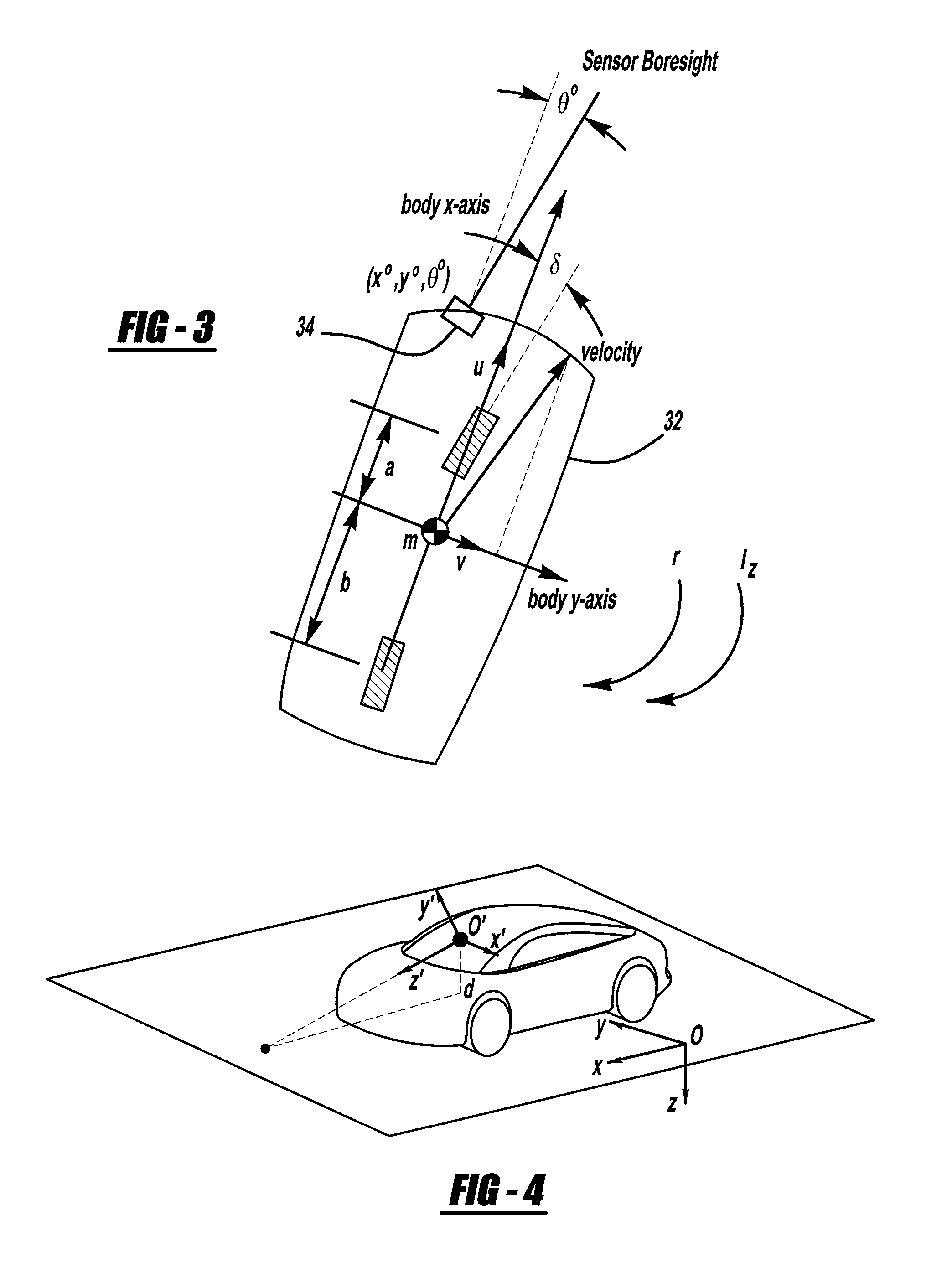

Radar, Lidar and camera enhanced methods for vehicle dynamics estimation

ActiveUS20100017128A1Anti-collision systemsComplex mathematical operationsVehicle dynamicsMultiple frame

A system for estimation vehicle dynamics, including vehicle position and velocity, using a stationary object. The system includes an object sensor that provides object signals of the stationary object. The system also includes in-vehicle sensors that provide signals representative of vehicle motion. The system also includes an association processor that receives the object signals, and provides object tracking through multiple frames of data. The system also includes a longitudinal state estimation processor that receives the object signals and the sensor signals, and provides a correction of the vehicle speed in a forward direction. The system also includes a lateral state estimation processor that receives the object signals and the sensor signals, and provides a correction of the vehicle speed in the lateral direction.

Owner:GM GLOBAL TECH OPERATIONS LLC

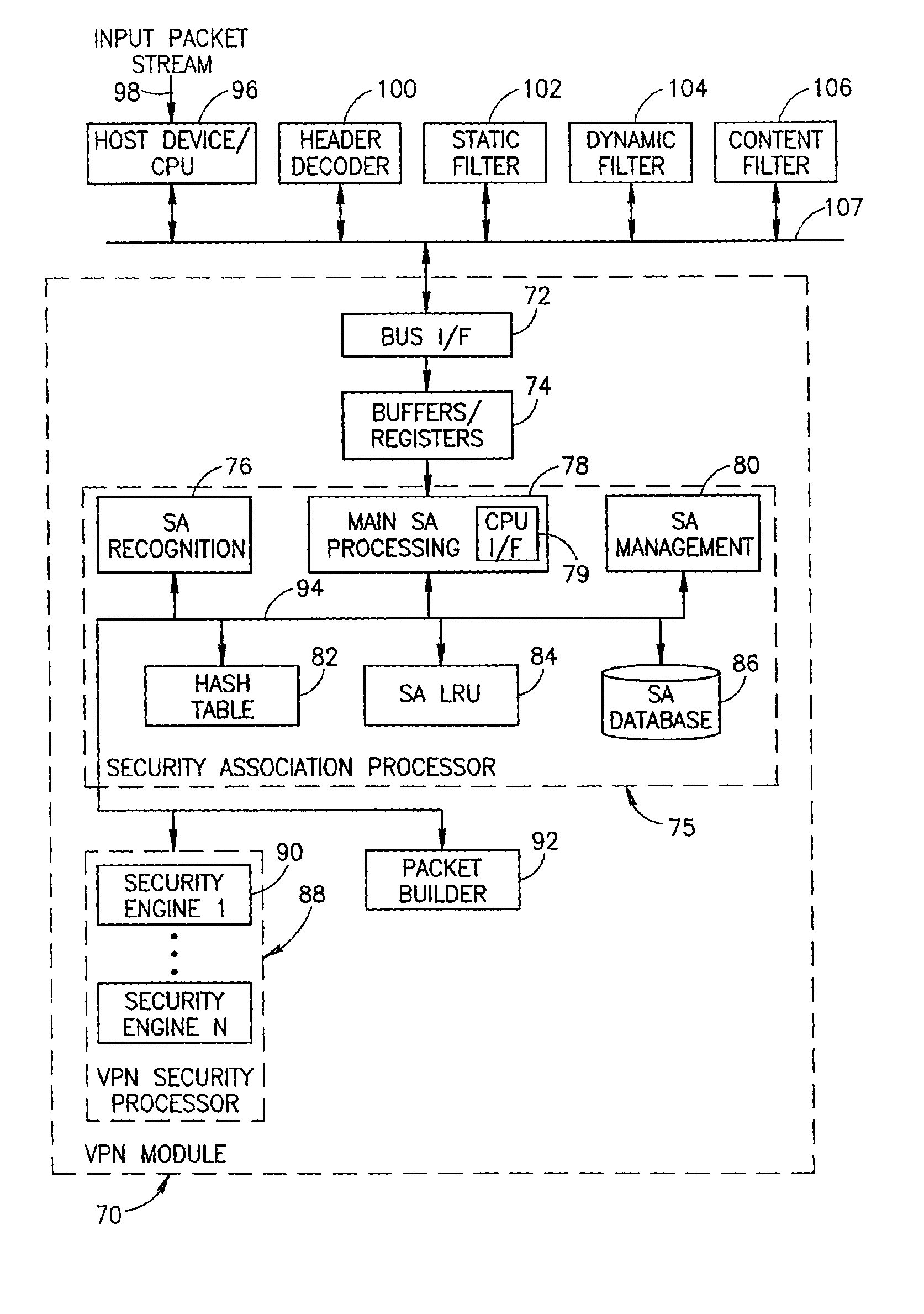

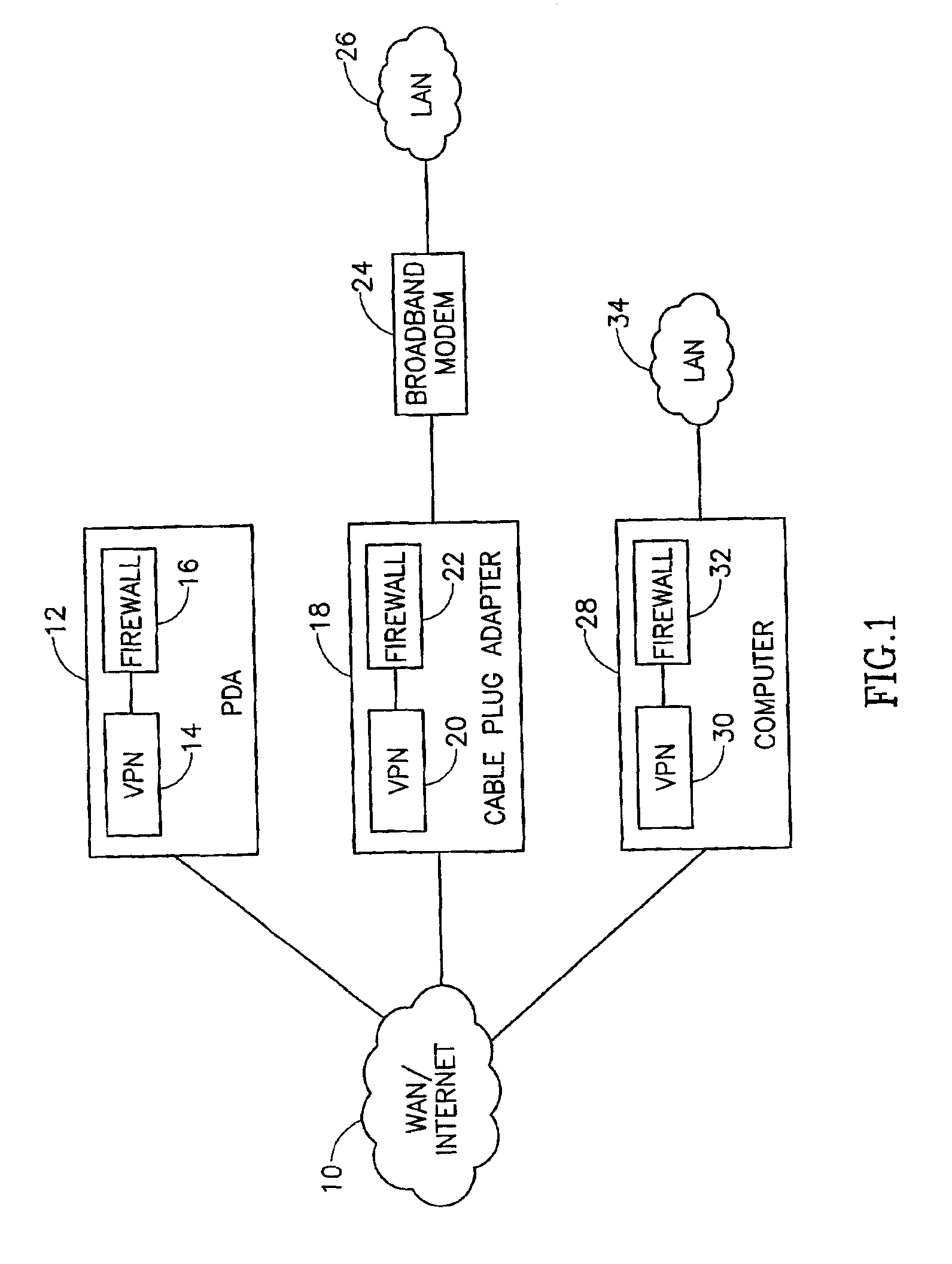

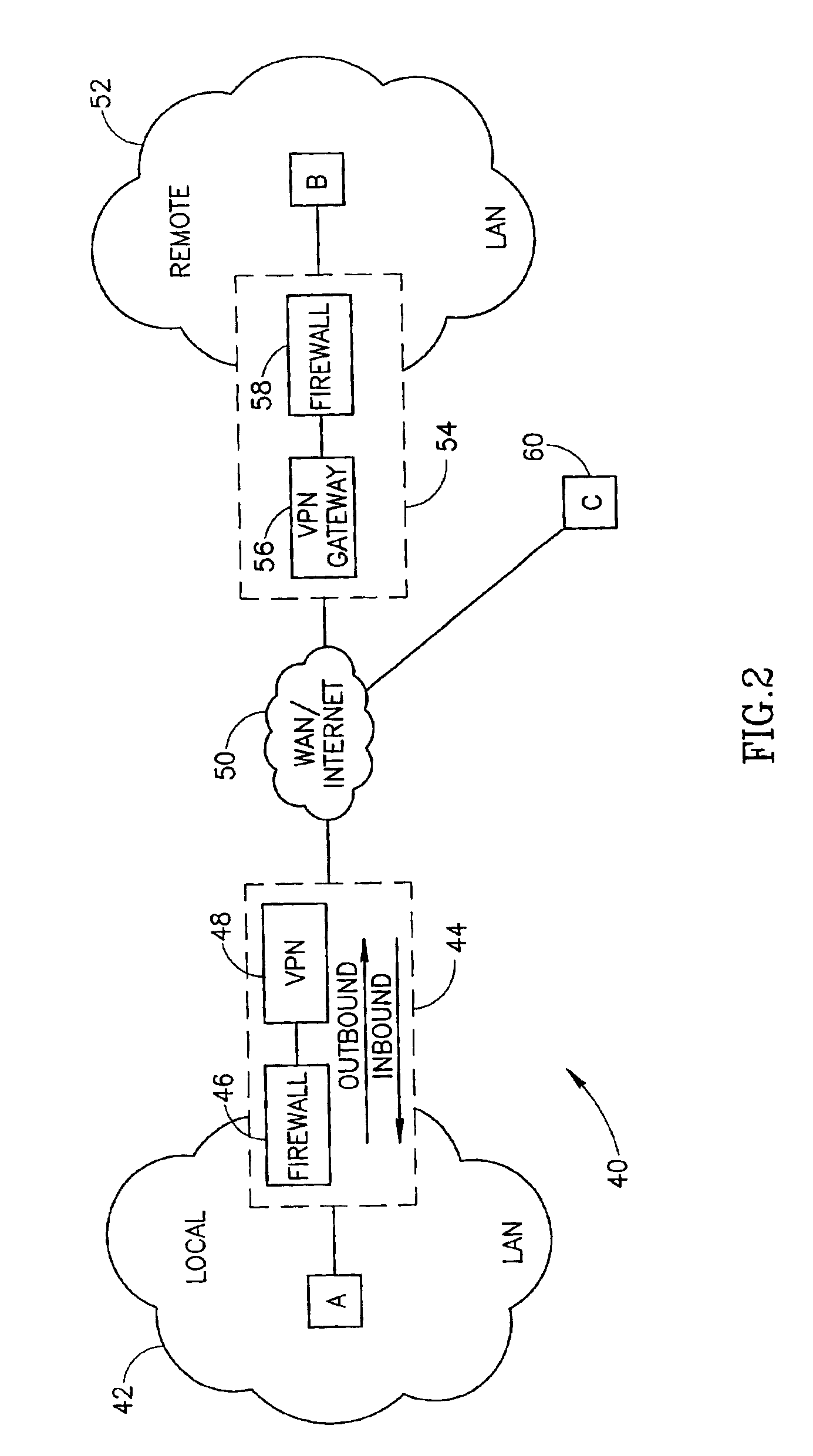

Virtual private network mechanism incorporating security association processor

ActiveUS7107464B2Low costLow-cost implementationMultiple digital computer combinationsProgram controlSecurity associationPrivate network

A novel and useful virtual private network (VPN) mechanism and related security association processor for maintaining the necessary security related parameters to perform security functions such as encryption, decryption and authentication. A security association database (SAD) and related circuitry is adapted to provide the necessary parameters to implement the IPSec group of security specifications for encryption / decryption and authentication. Each security association (SA) entry in the database comprises all the parameters that are necessary to receive and transmit VPN packets according to the IPSec specification.

Owner:TELECOM ITALIA SPA

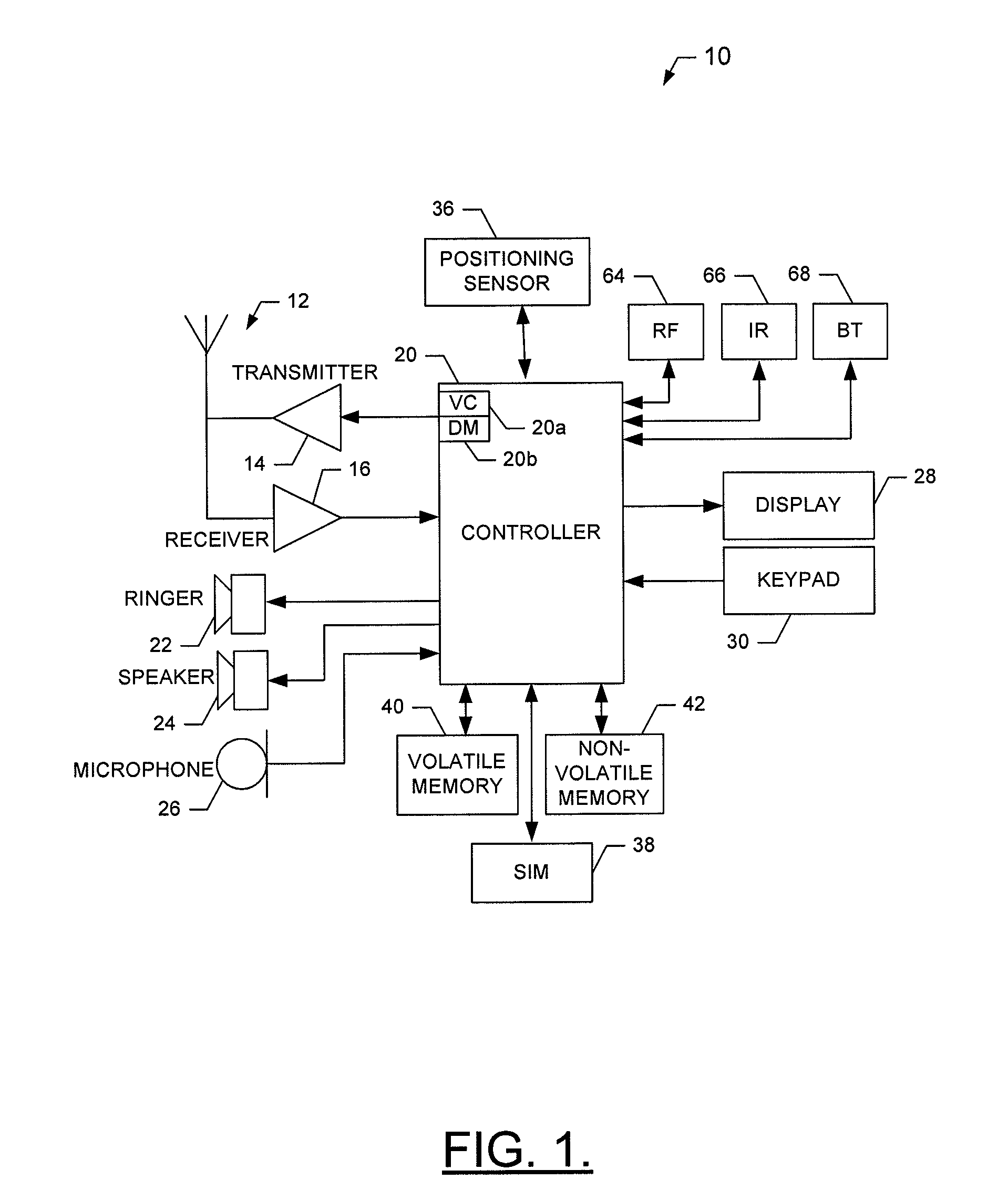

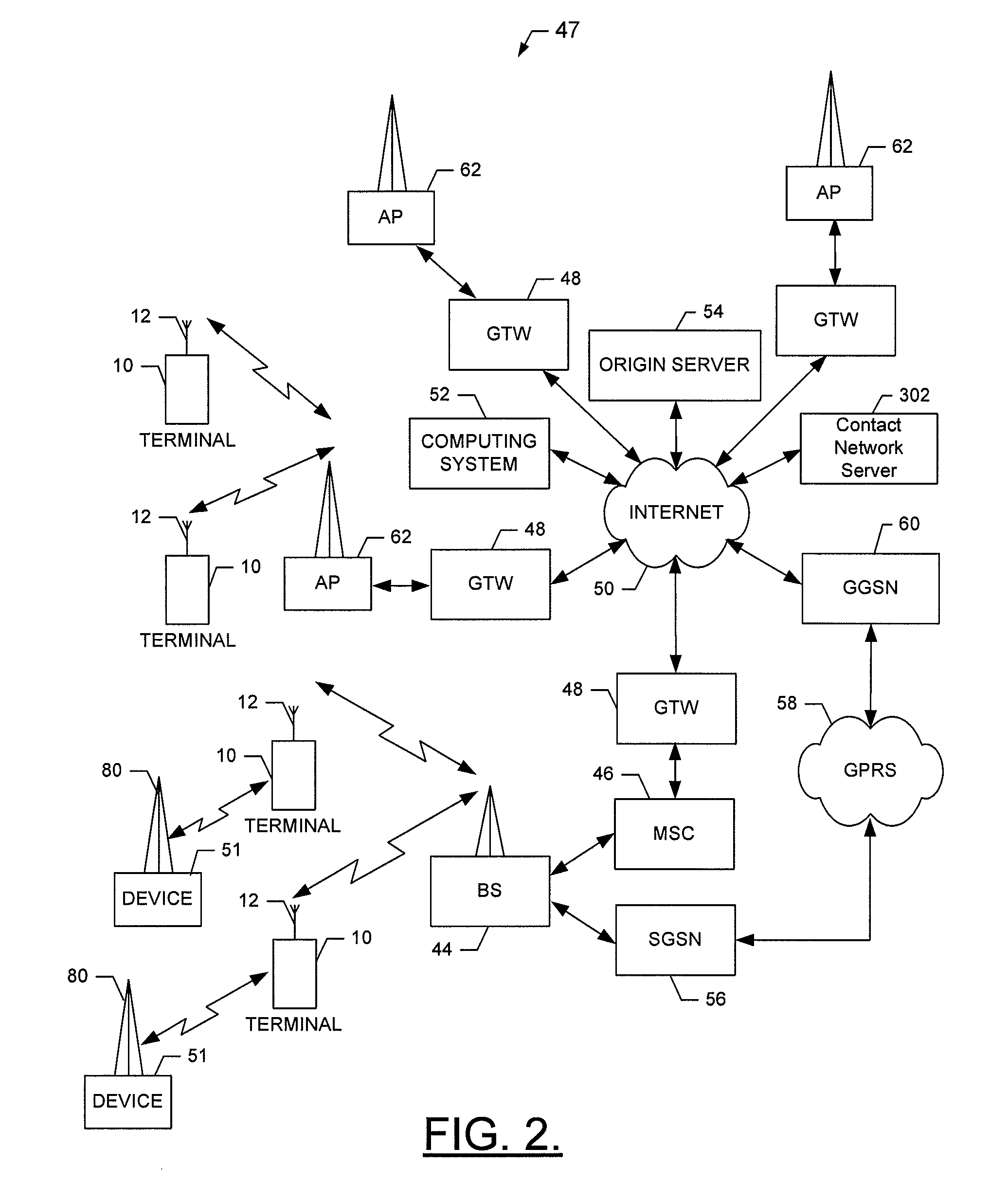

Methods, apparatuses, and computer program products for modeling contact networks

InactiveUS20090228513A1Improve user experienceImproved ability to provide userDigital data information retrievalOffice automationContact networkSimulation

An apparatus for modeling a contact network may include a processor. The processor may be configured to store a plurality of contacts lists, which collectively comprise a contact network. Each contacts list may be comprised of a plurality of contact entries and may be associated with a user of a remote device. The processor may further be configured to model the contact network using one or more modeling parameters. The processor may be configured to generate a plurality of suggested contact entries for a user based at least in part upon the one or more modeling parameters used to model the contact network. The suggested contact entries may be extracted from contact entries stored in the contacts network. Corresponding methods, systems, and computer program products are also provided.

Owner:NOKIA CORP

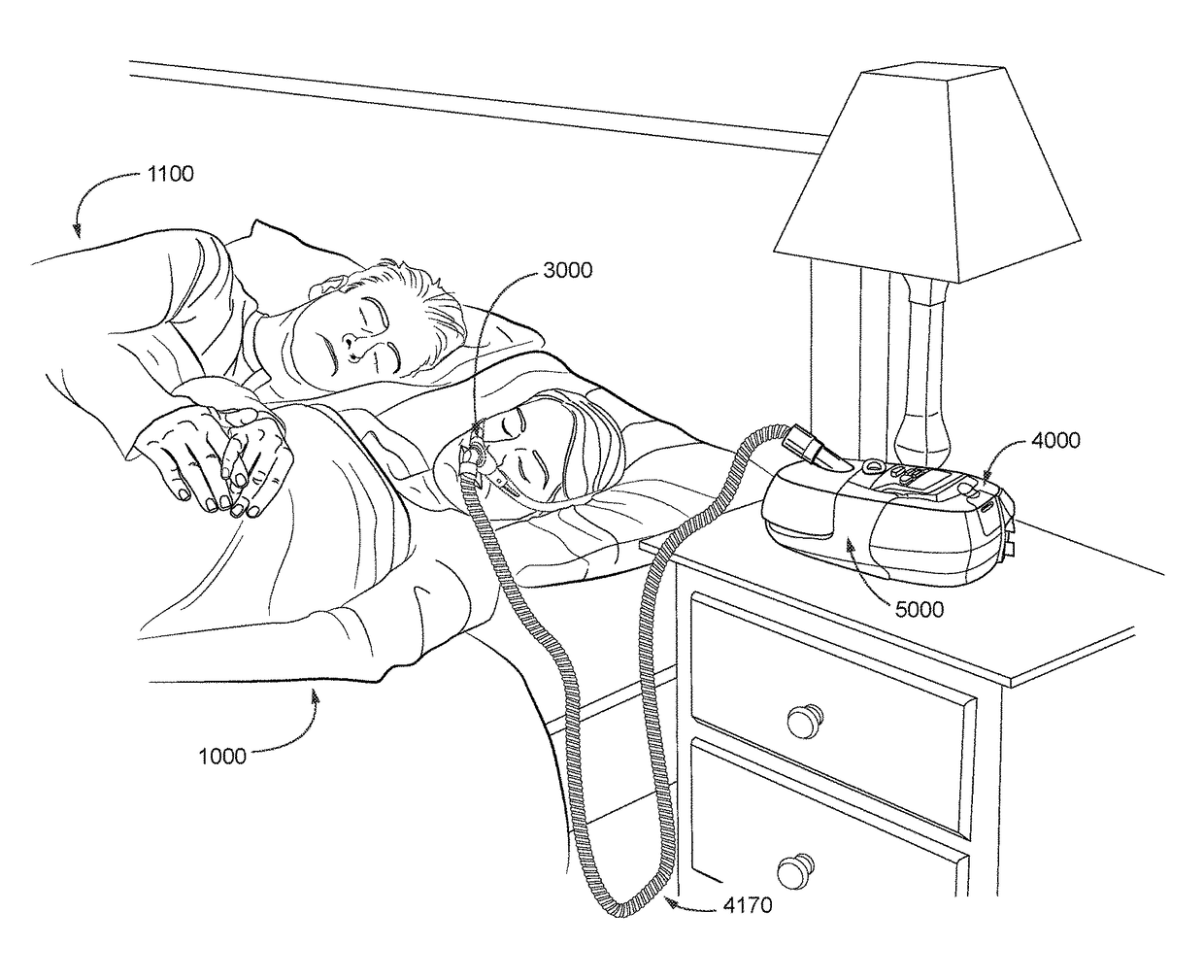

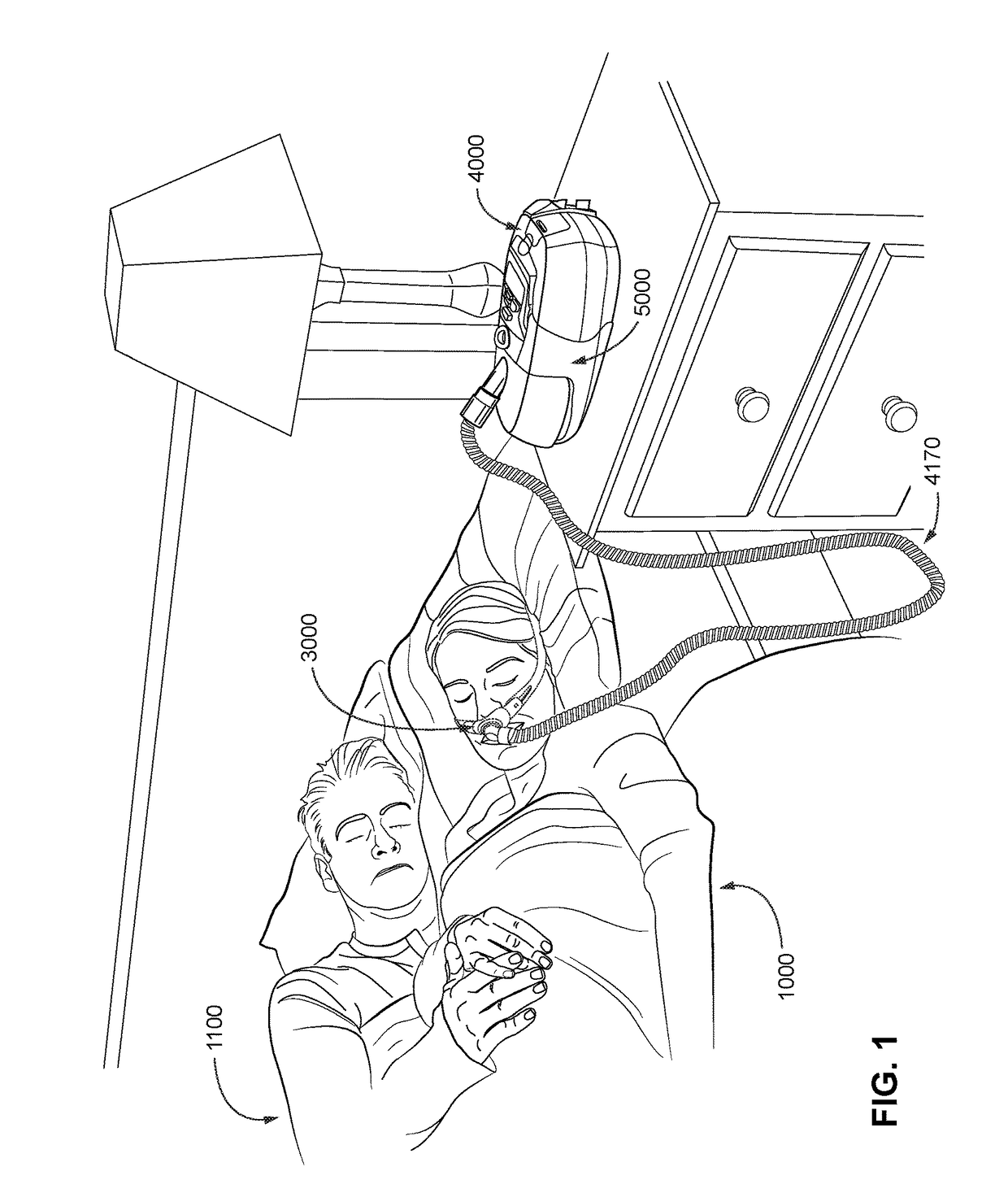

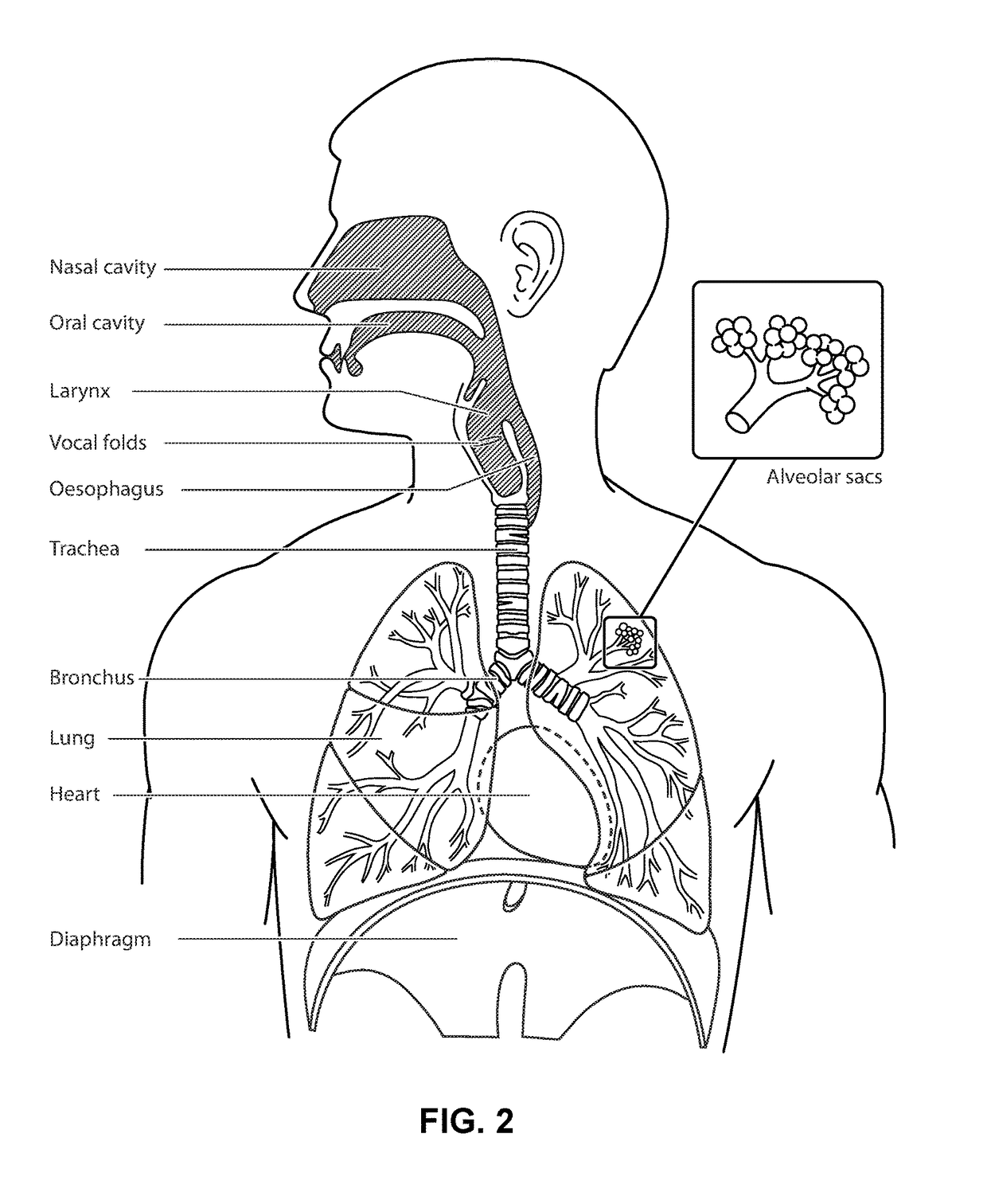

Respiratory pressure therapy system

ActiveUS20170311879A1Improve comfortIncrease costRespiratorsMechanical/radiation/invasive therapiesManagement toolPatient compliance

Apparatus and methods provide compliance management tools such as for respiratory pressure therapy. In some versions, a respiratory pressure therapy system may include one or more processors, such as of a data server, configured to communicate with a computing device and / or a respiratory pressure therapy device. The respiratory pressure therapy device may be configured to deliver respiratory pressure therapy to a patient for a session. The computing device may be associated with the patient. The processor(s) may be further configured to compute a therapy quality indicator of the session from usage data relating to the session. The therapy quality indicator may be a number derived from contributions of a plurality of usage variables for the session in the usage data. The processor(s) may be further configured to present, such as by transmitting, the therapy quality indicator to the computing device. The therapy quality indicator may promote patient compliance.

Owner:RESMED INC

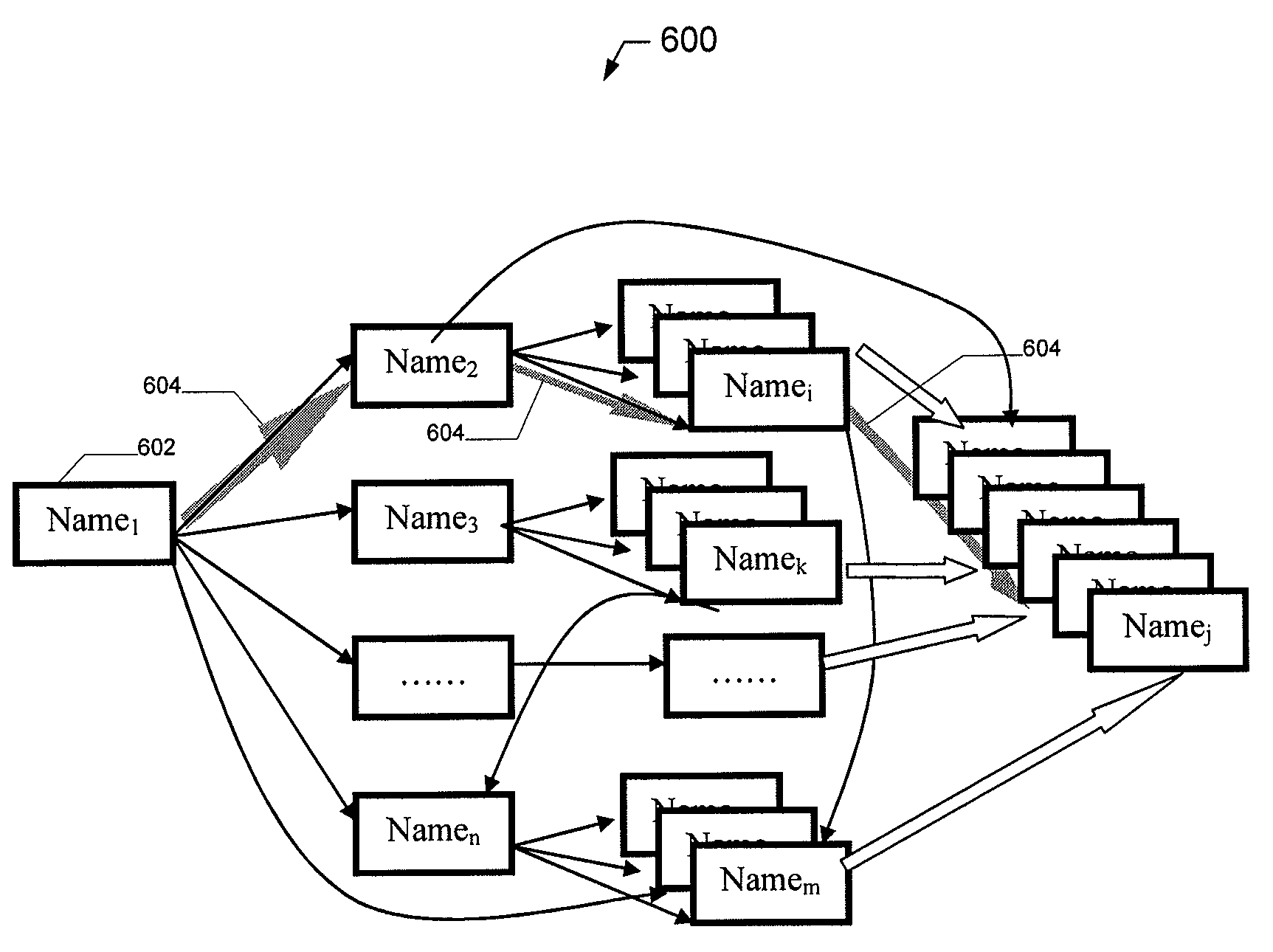

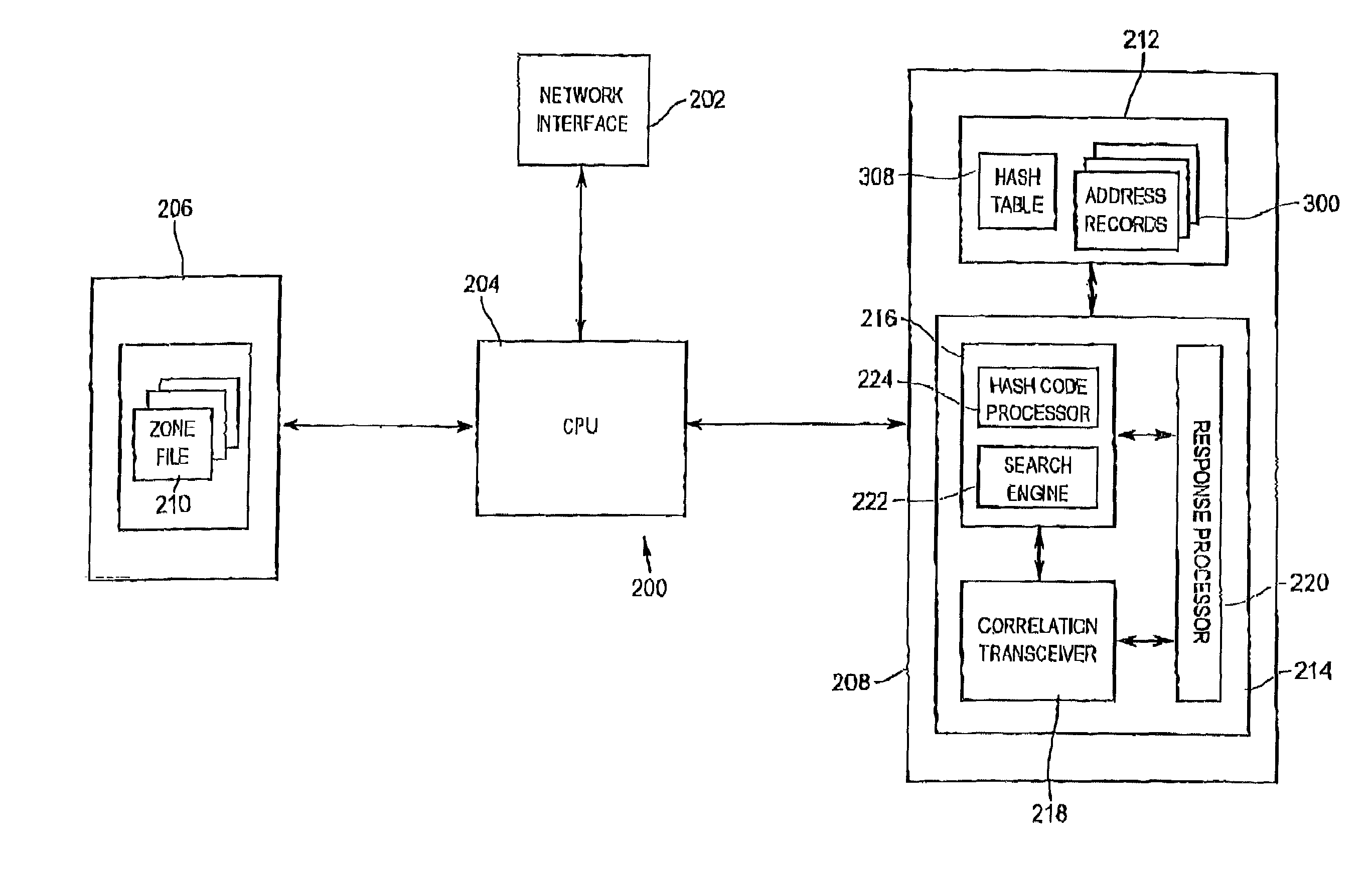

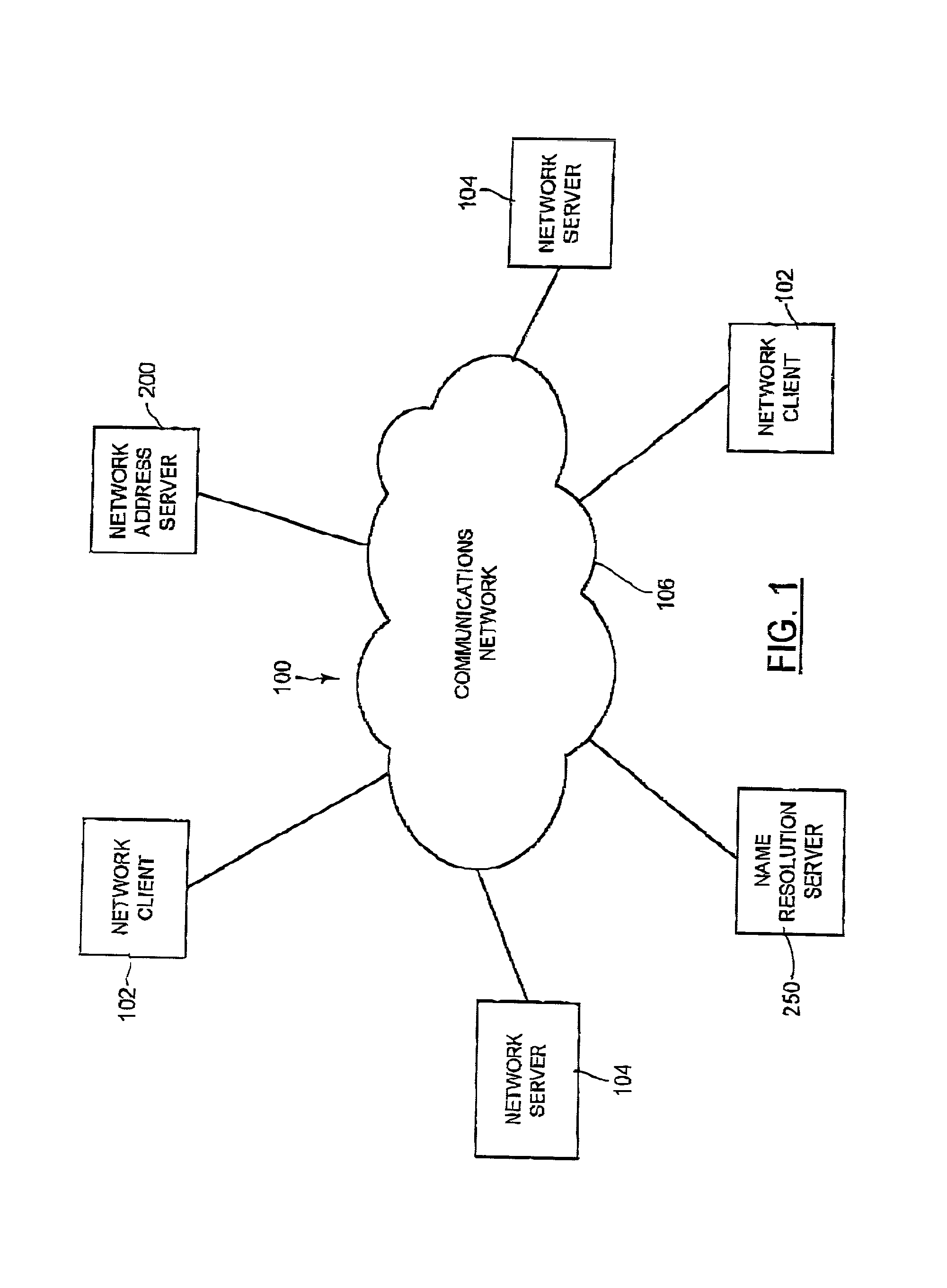

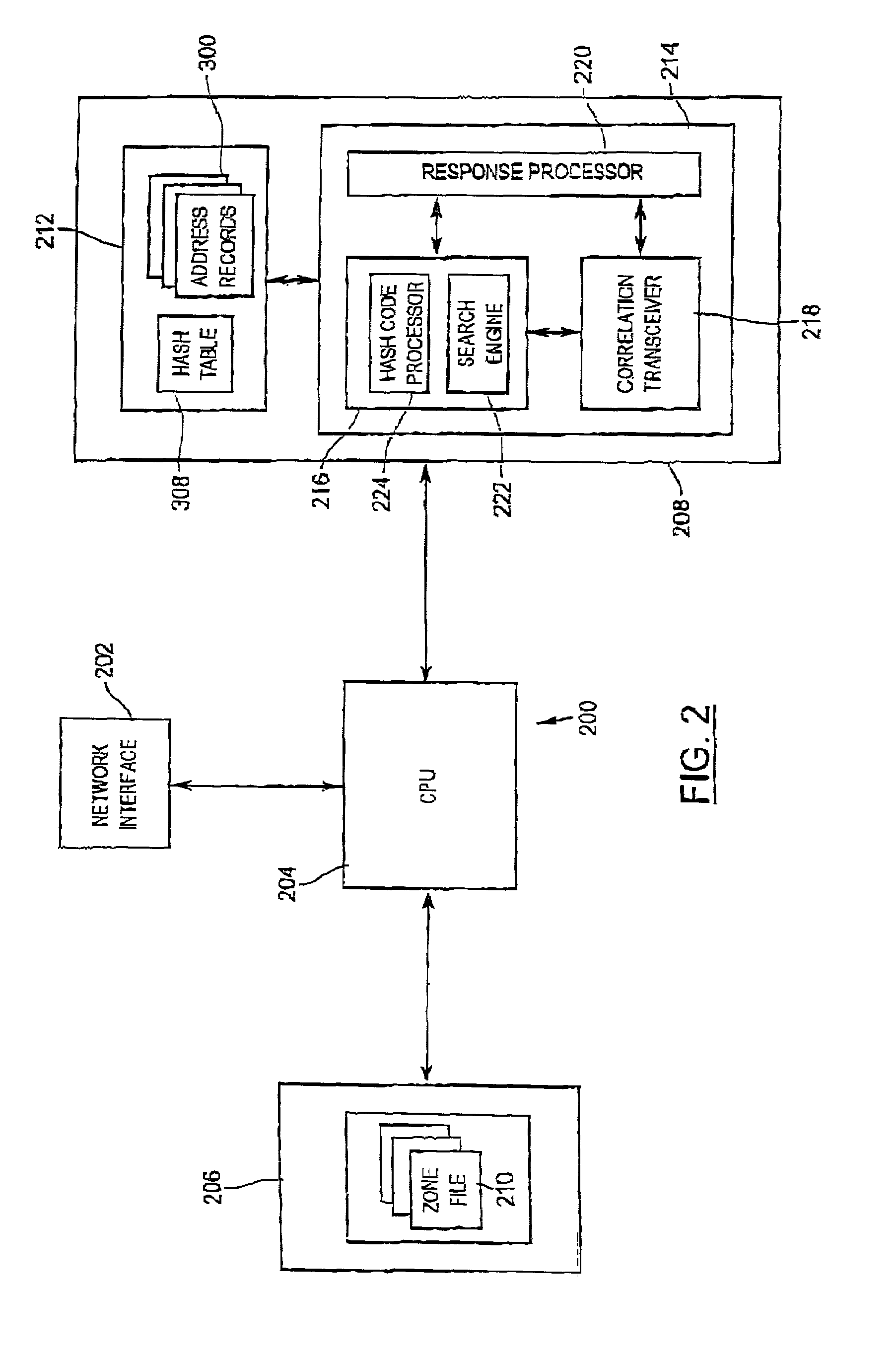

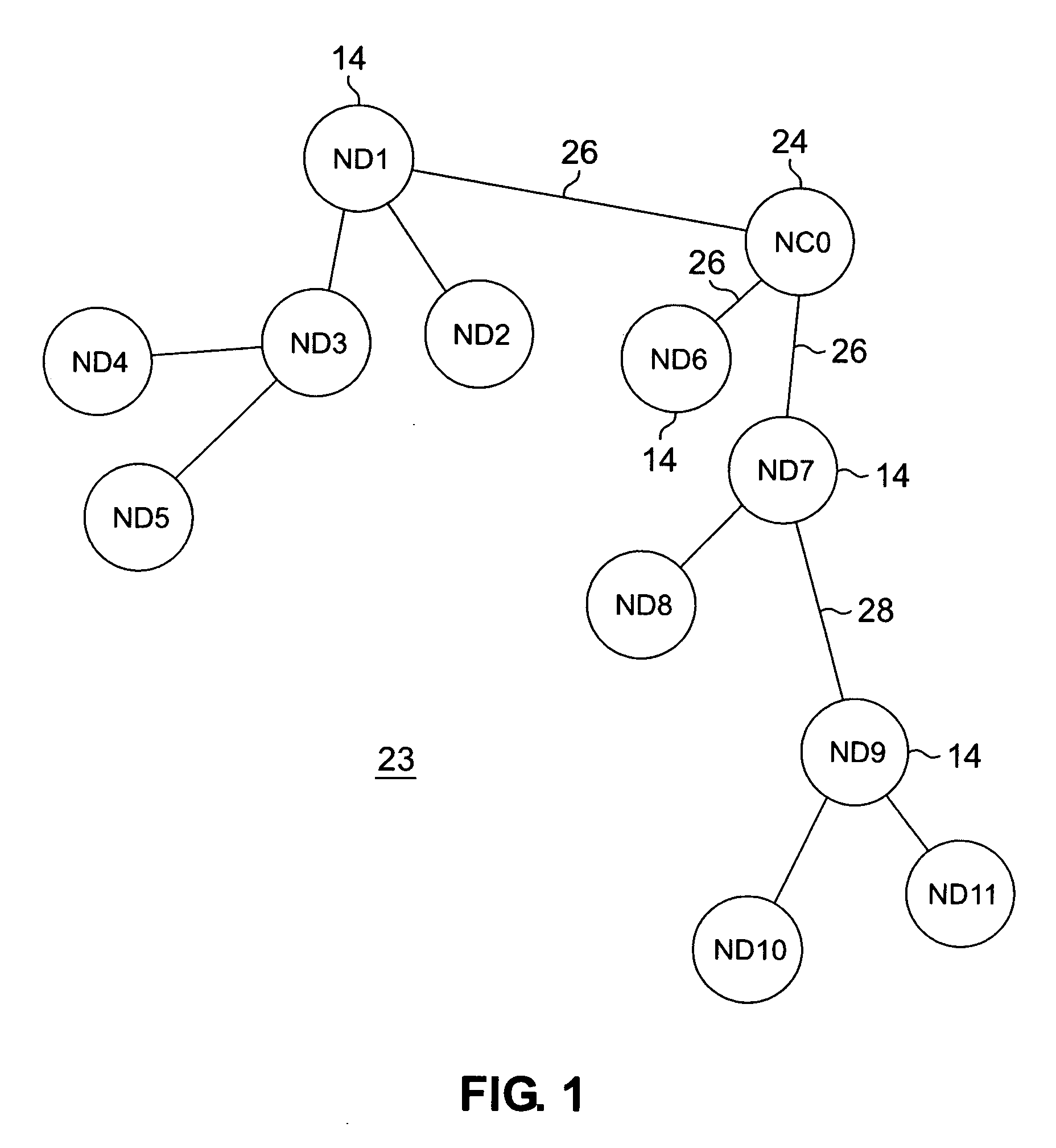

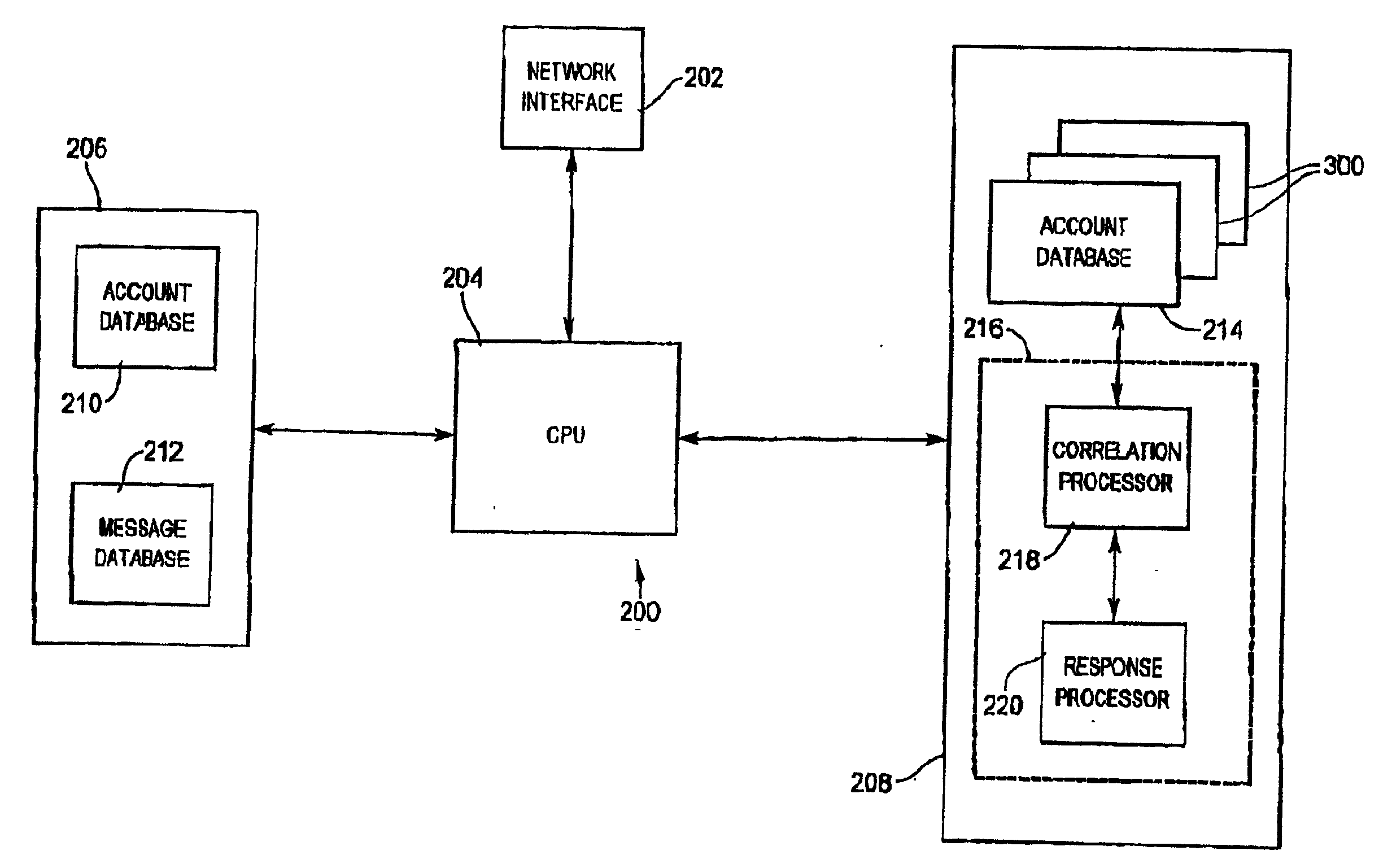

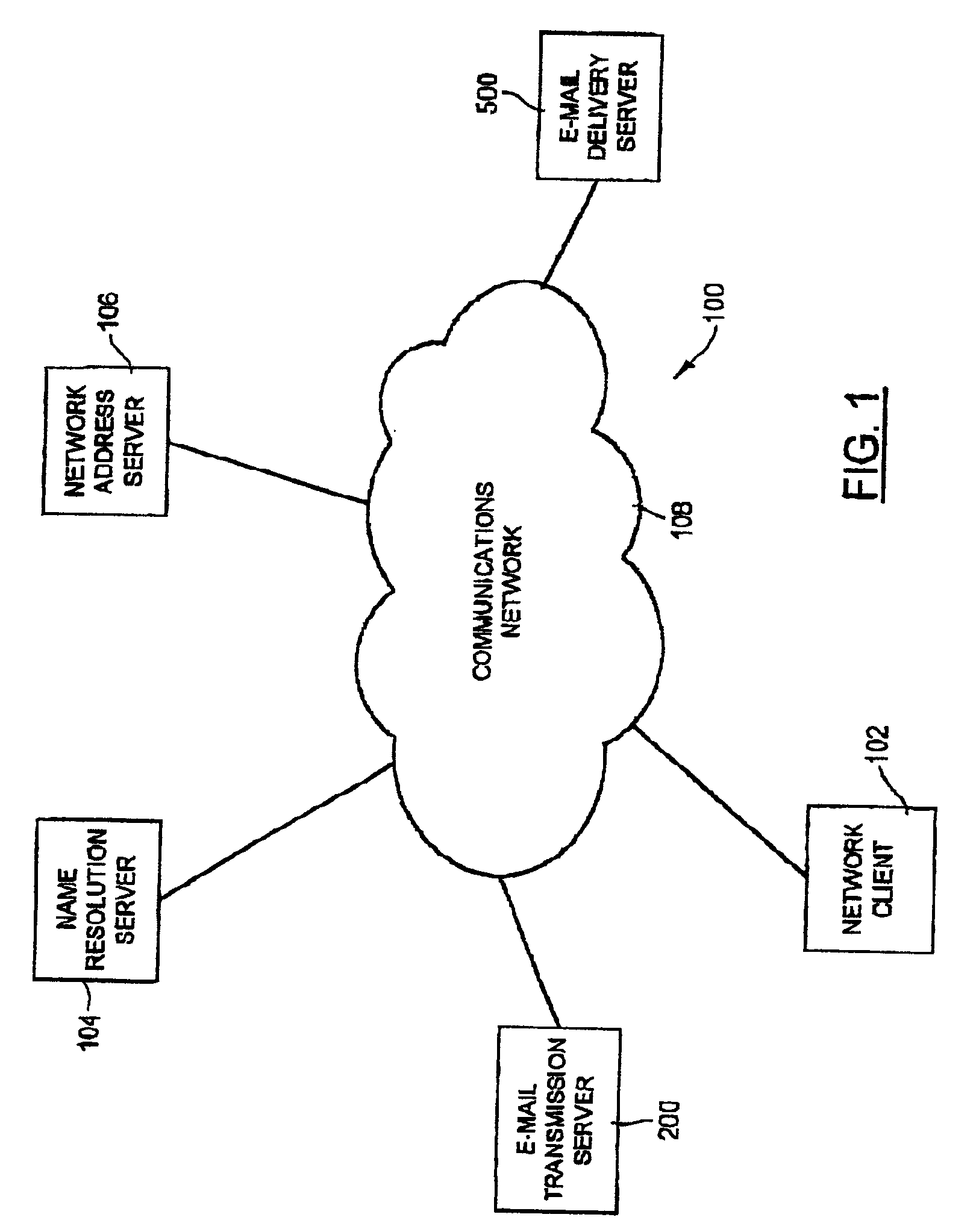

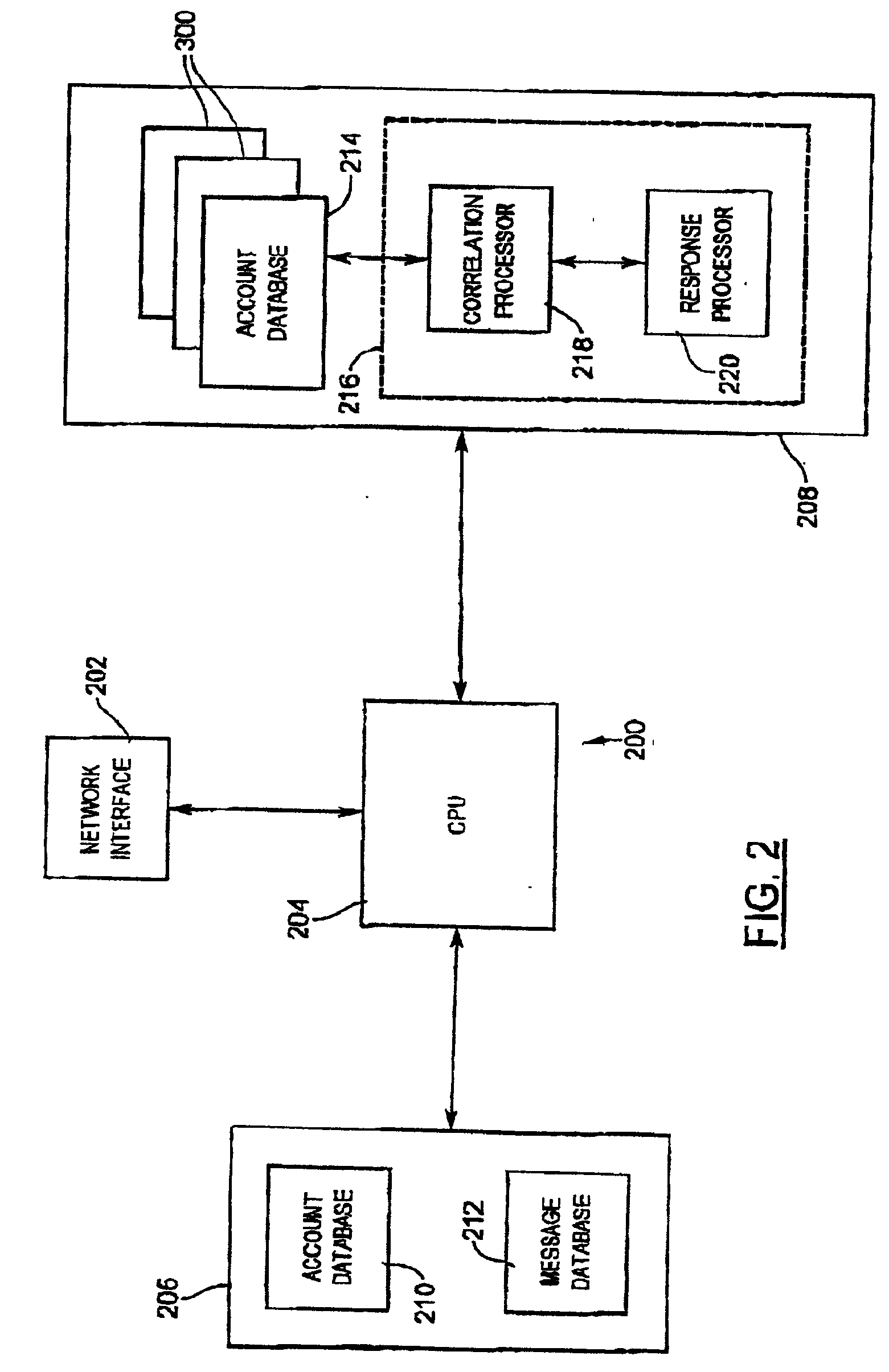

Network address server

InactiveUS7280999B2Data processing applicationsDigital data processing detailsUnique local addressTransceiver

A network address server is configured to resolve a target network address name label with a network address, with the target address name label defining a branch of one level of a multi-level network address name space. The network address server is one of a plurality of network address servers each being uniquely associated with a respective region of the address name space level. The network server includes an address name database, and an address name processor in communication with the address name database for providing a response to a query for the network address corresponding to the target address name label. The address name database includes a number of database records, each identifying a unique address name label and a network address uniquely associated with the address name label. The address name processor includes a correlation processor, a correlation transceiver in communication with the correlation processor, and a response processor in communication with the correlation processor and the correlation transceiver. The correlation processor is configured to determine a correlation between the target address name label and the respective unique address name region. The correlation transceiver is configured to provide the other network address servers with a respective indication of the determined correlation and for receiving a corresponding correlation indication from at least one of the other network address servers. The response processor is configured to provide a response to the query in accordance with the correlation indications.

Owner:AFILIAS LTD

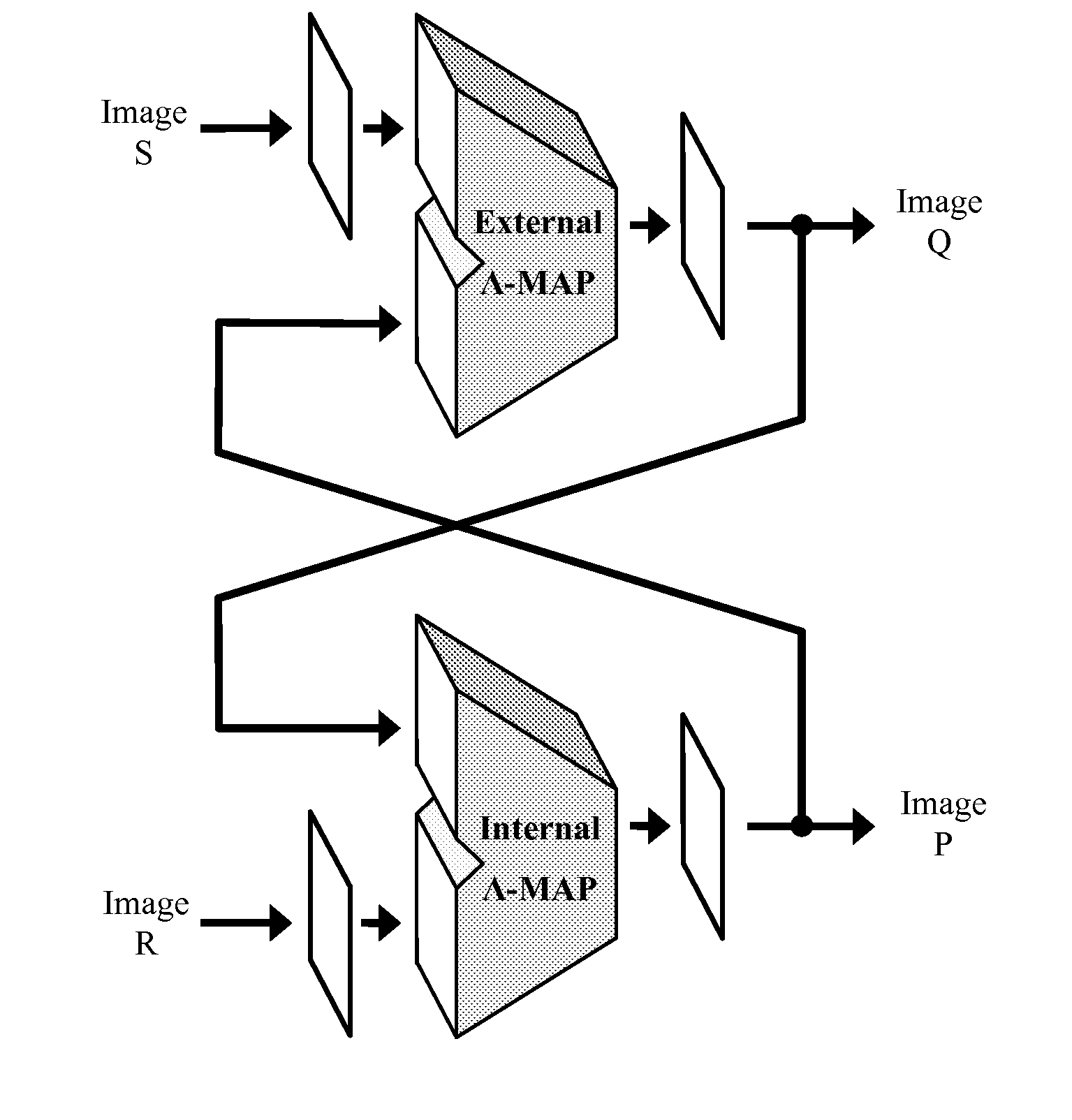

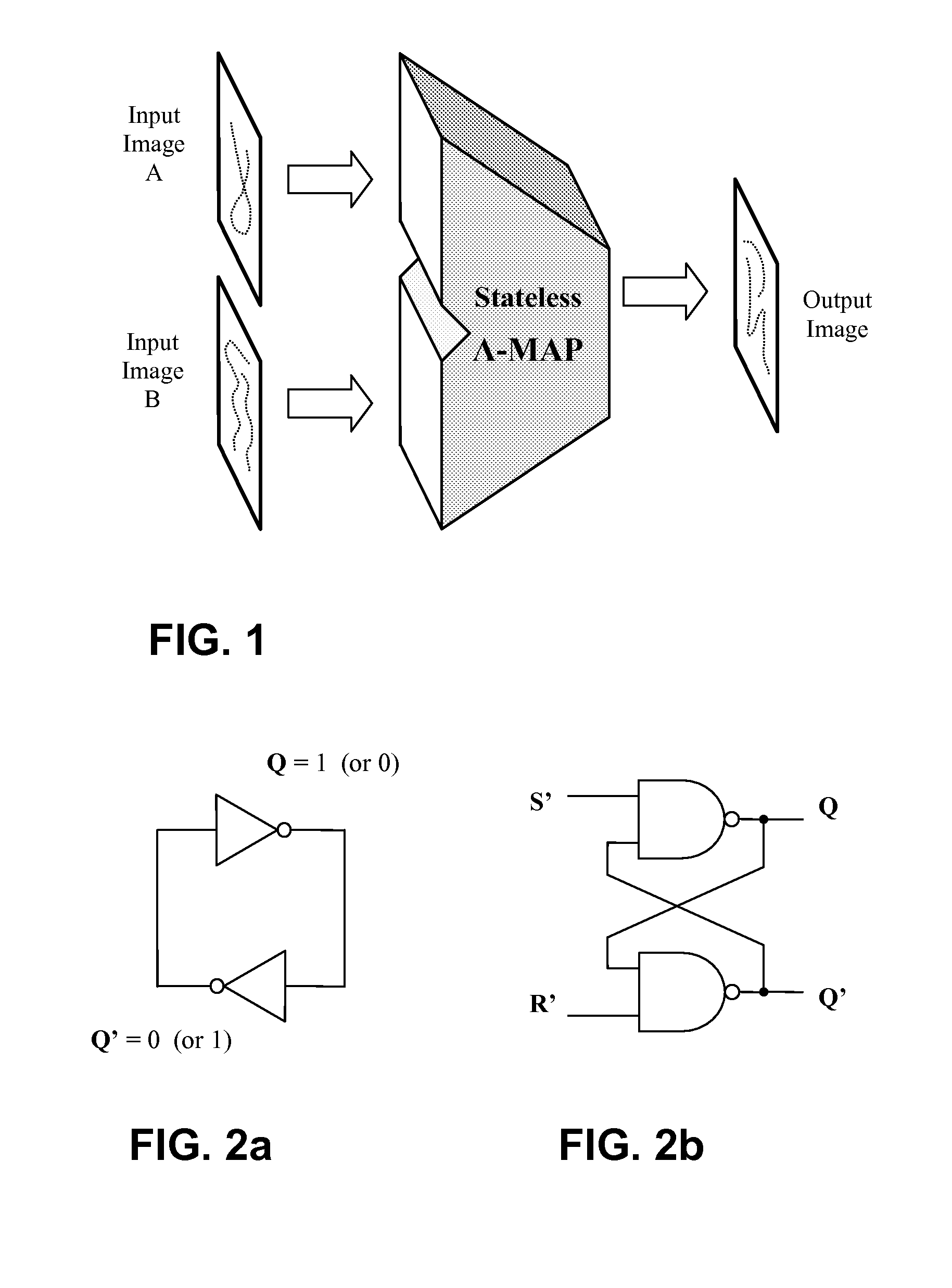

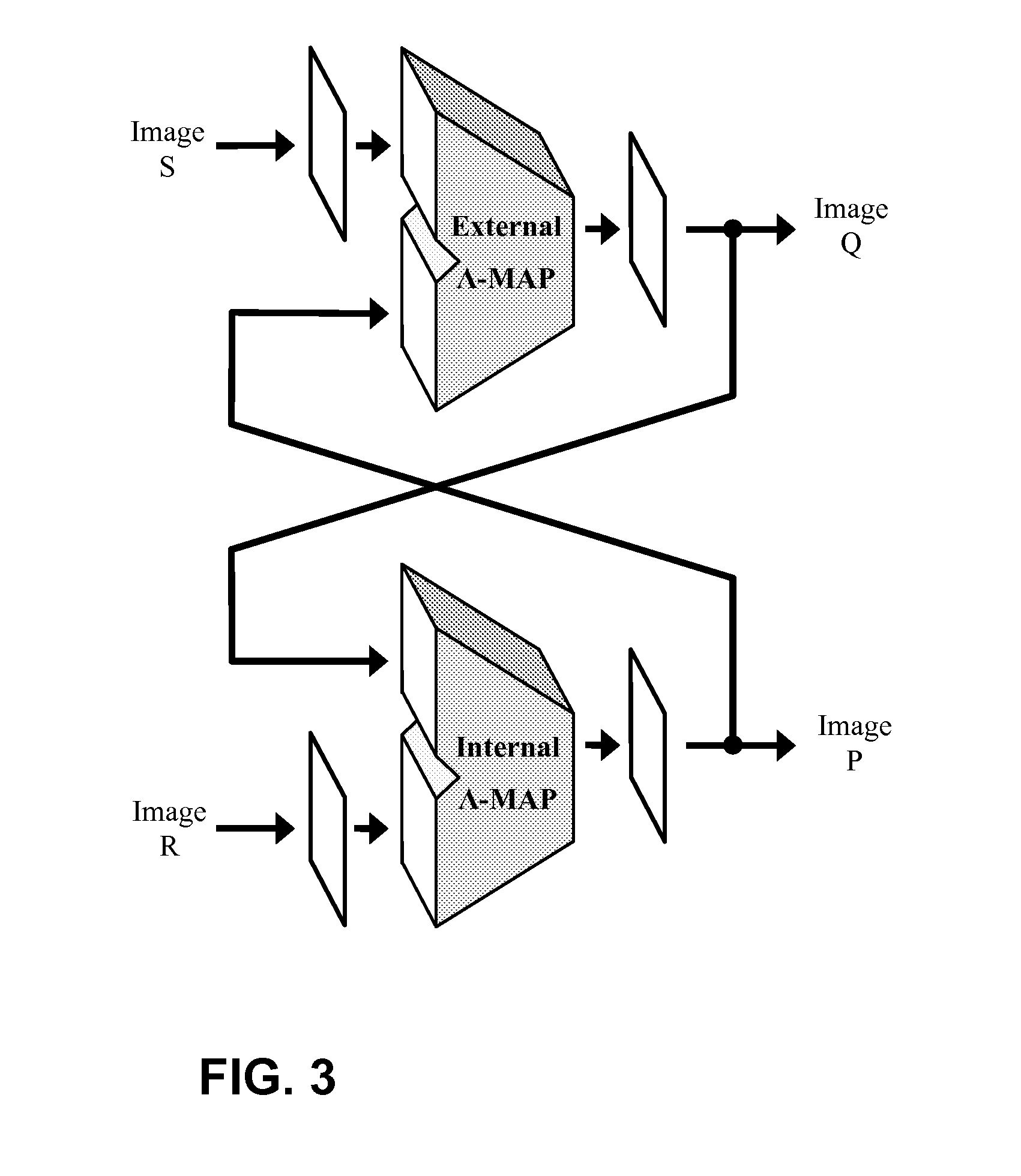

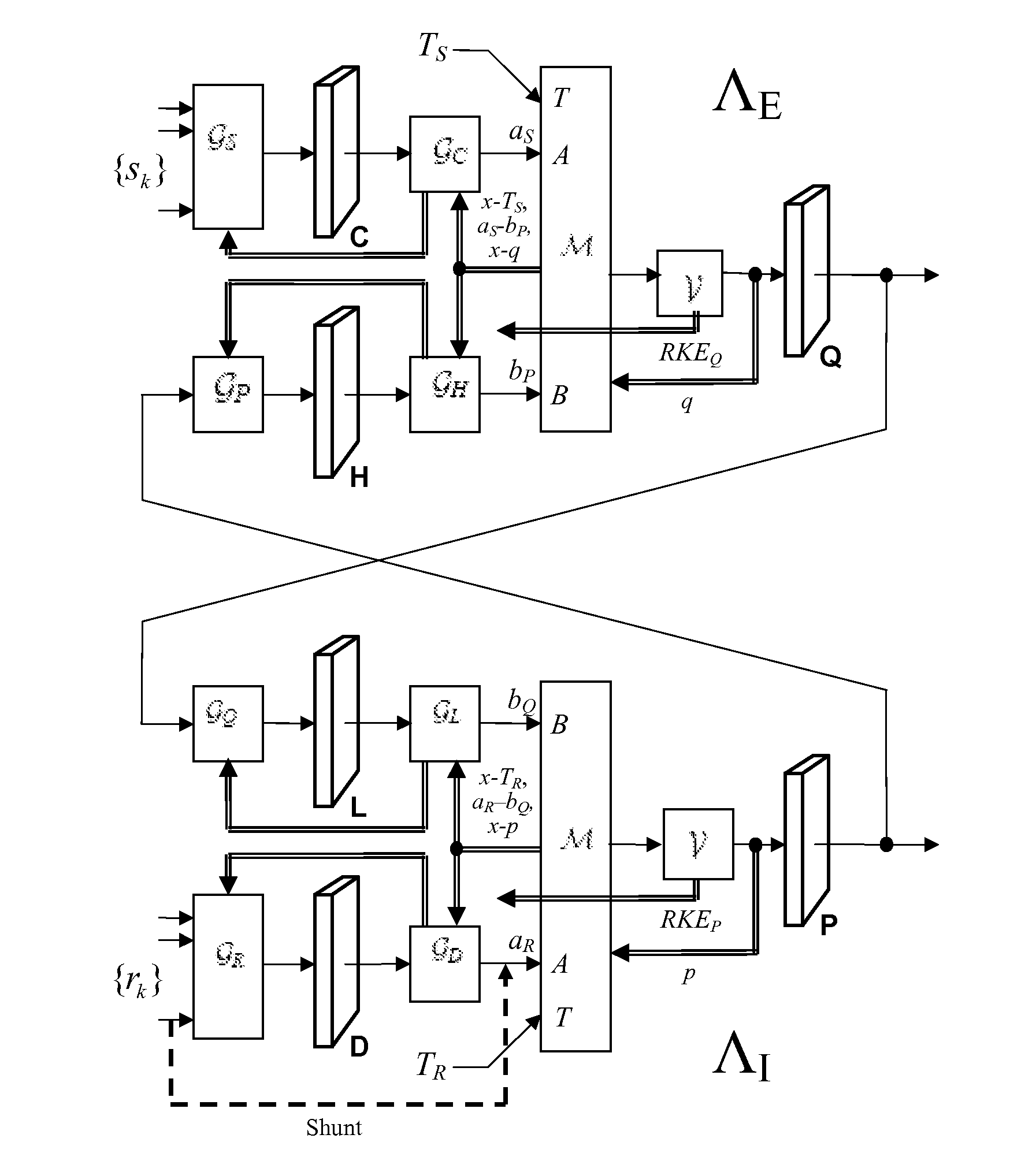

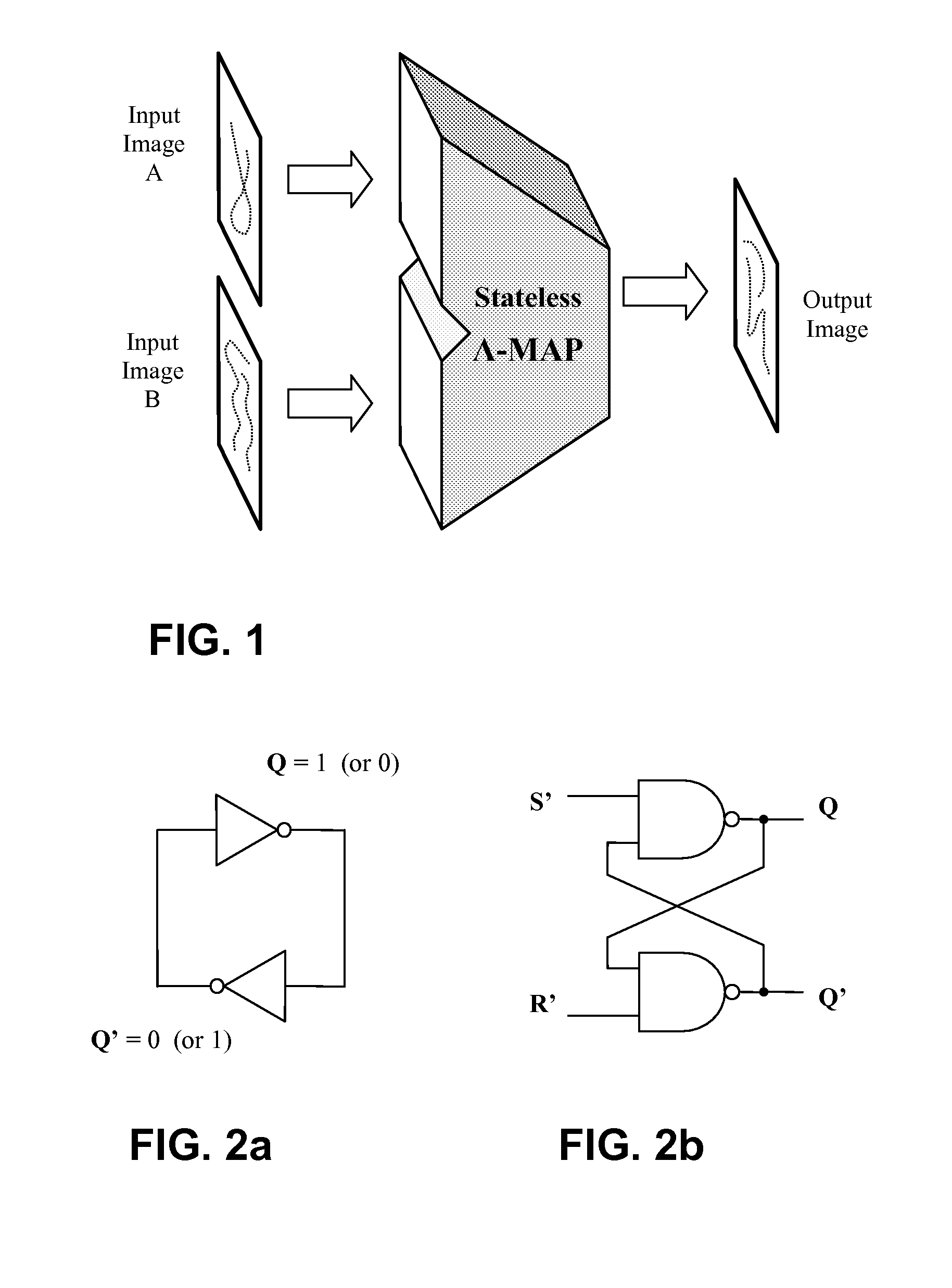

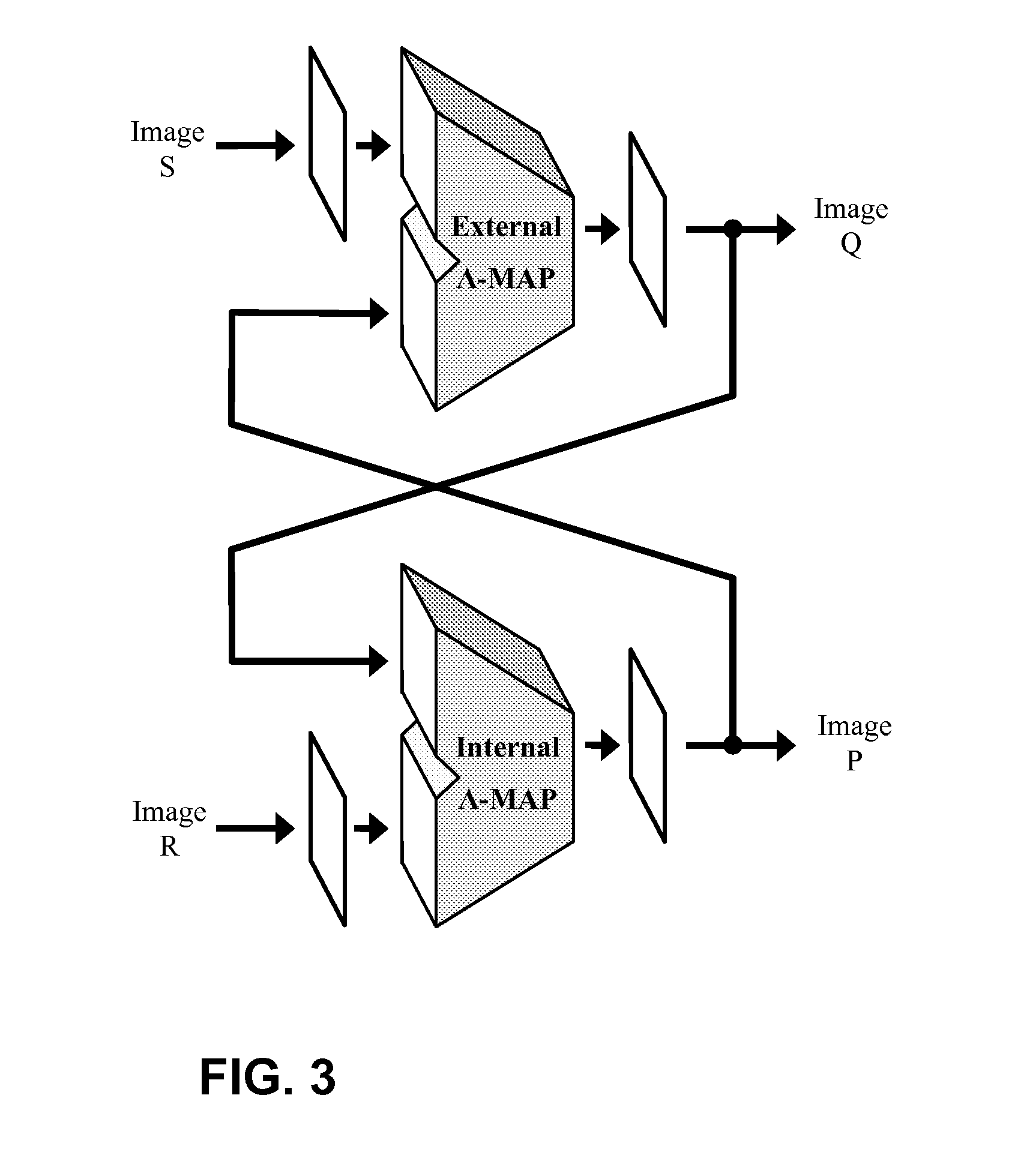

Method of generating an encoded output signal using a manifold association processor having a plurality of pairs of processing elements trained to store a plurality of reciprocal signal pairs

A processor architecture for a learning machine is presented which uses a massive array of processing elements having local, recurrent connections to form global associations between functions defined on manifolds. Associations between these functions provide the basis for learning cause-and-effect relationships involving vision, audition, tactile sensation and kinetic motion. Two arbitrary images hold each other in place in a manifold association processor and form the basis of short-term memory.

Owner:GENERAL MANIFOLDS LLC

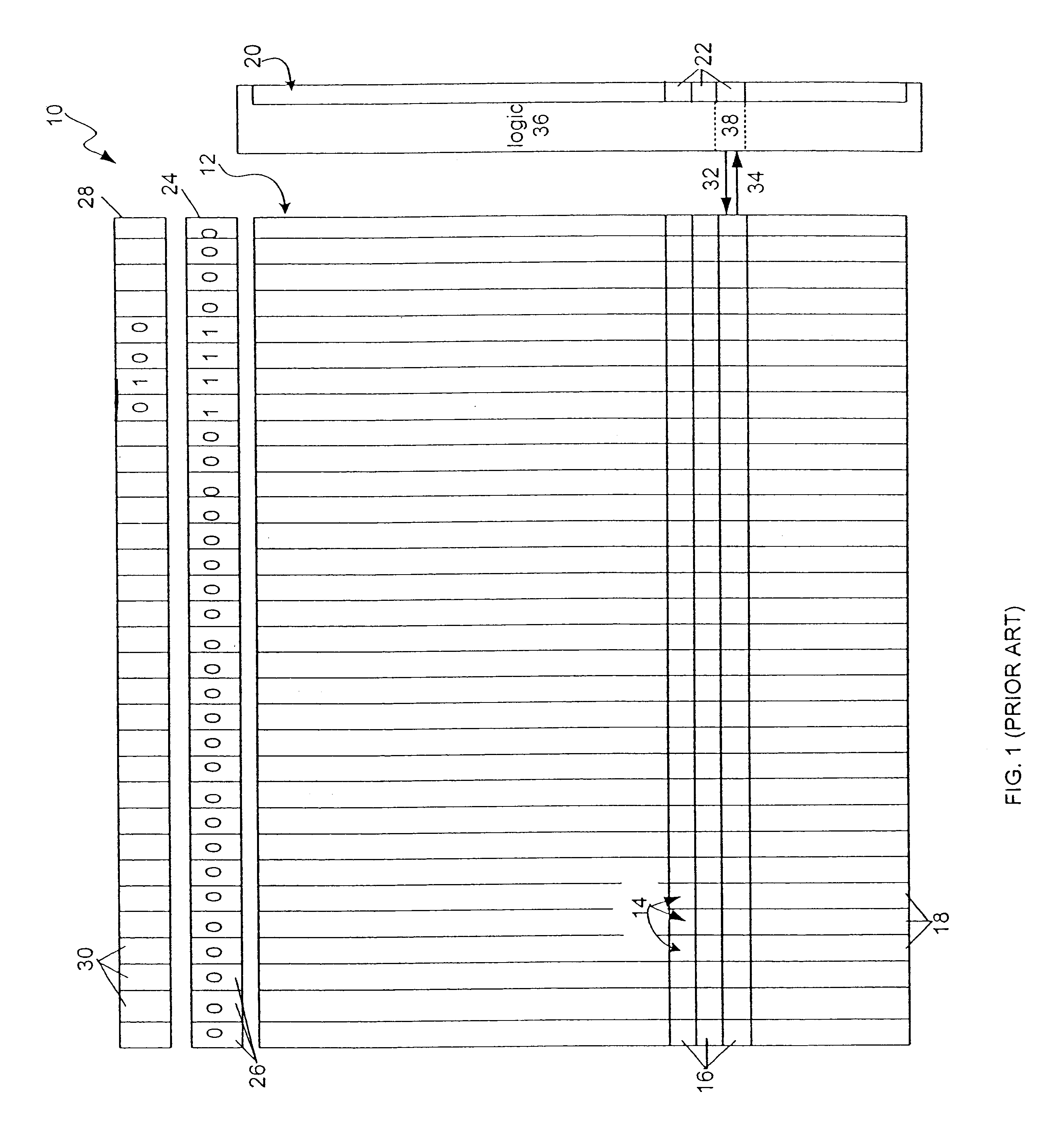

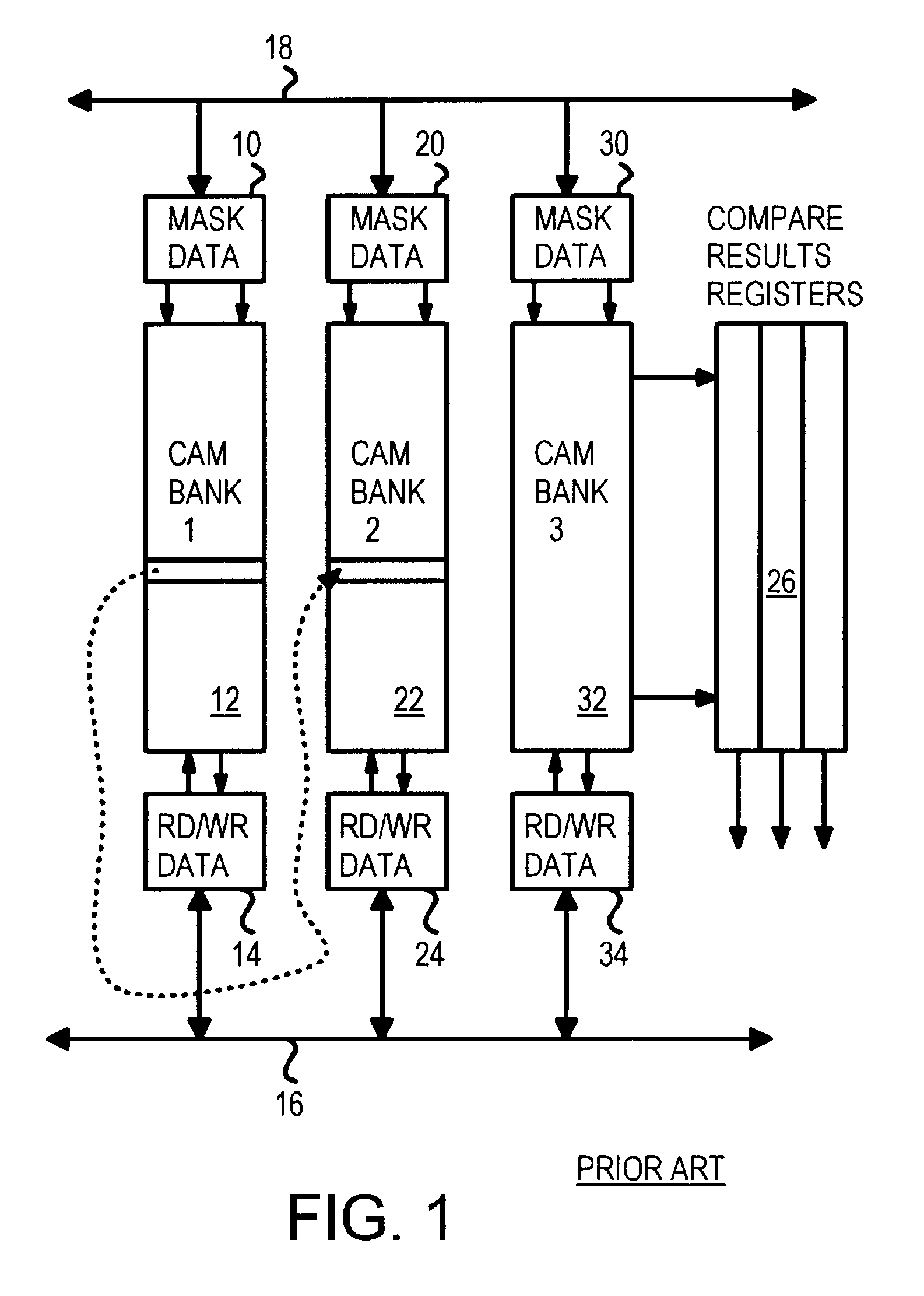

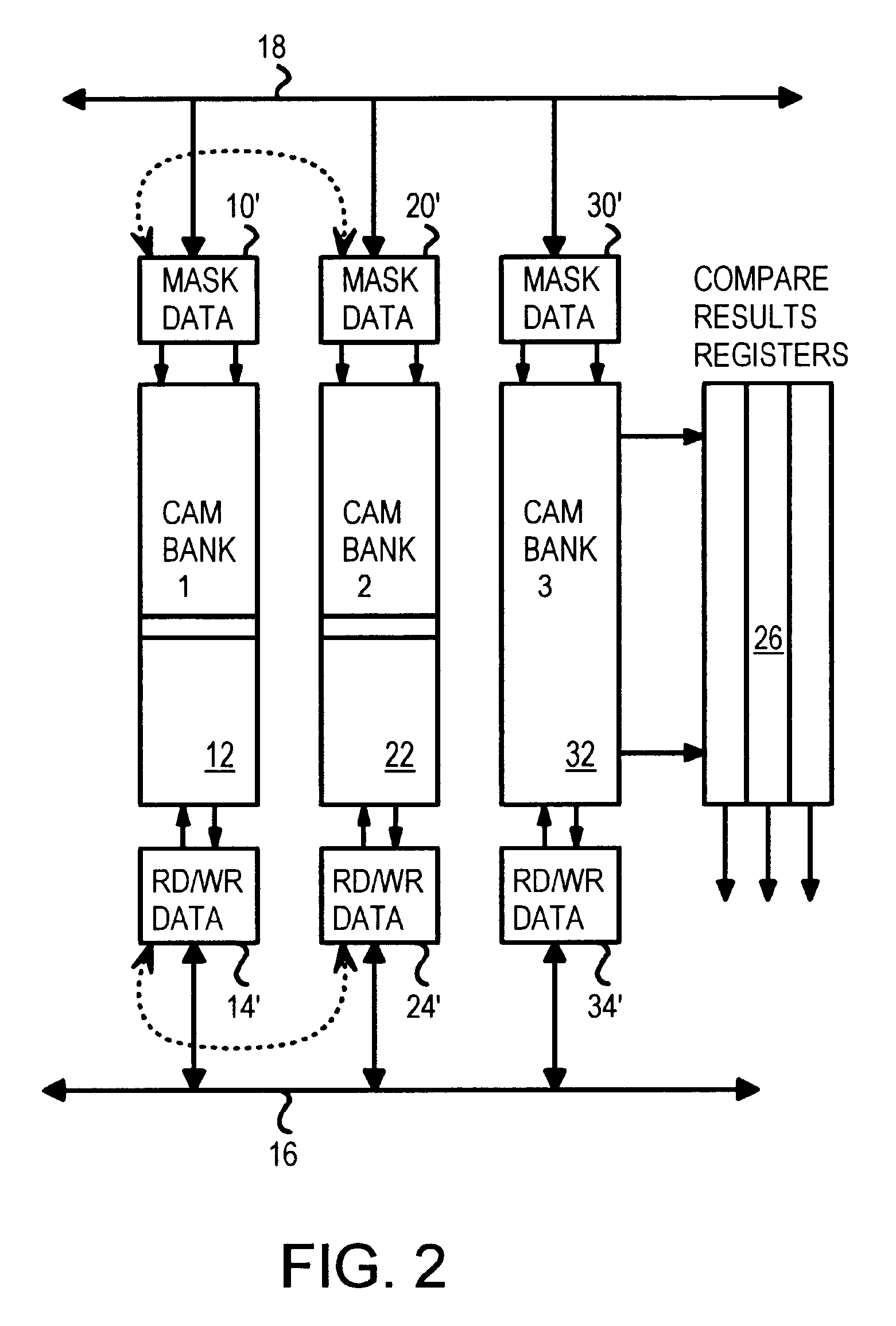

Input/output methods for associative processor

InactiveUS6405281B1Increase speedImprove efficiencyAssociative processorsMemory systemsProcessor registerParallel computing

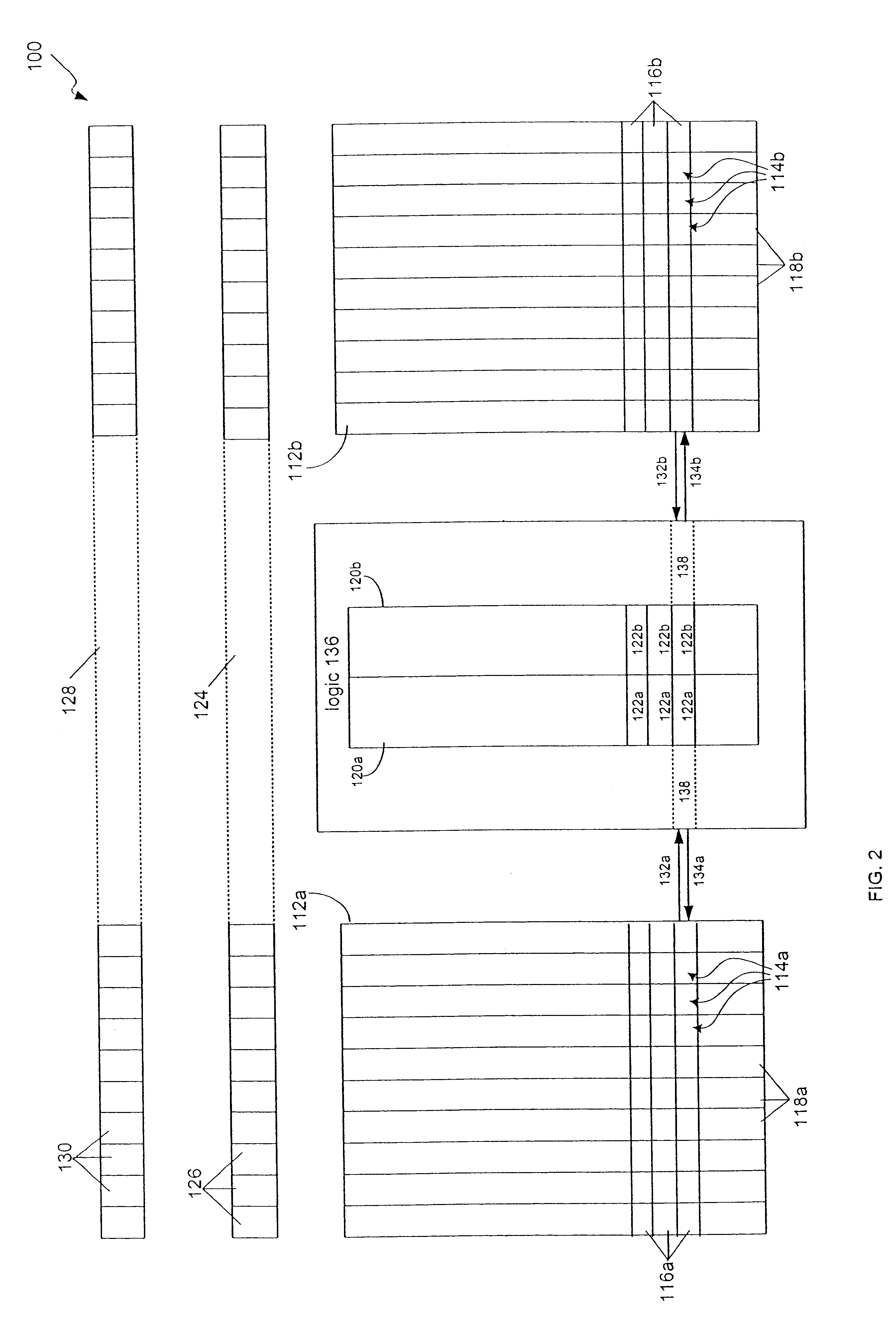

A data processing device includes an associative processor that in turn includes one or more arrays of content addressable memory (CAM) cells and two or more tags registers. The device also includes a memory for storing the data and a bus for exchanging the data with the associative processor. During input and output operations, data are exchanged in parallel, via one of the tags registers. Another tags register is used to select rows of CAM cells for input or output. By appropriately shifting the bits in the buffer tags register between write or compare operation cycles, entire words are exchanged between the selected CAM cell rows and the buffer tags register. During arithmetical operations, in an embodiment with multiple CAM cell arrays, different tags registers are associated with different CAM cell arrays at will. If, in the course of performing arithmetical operations using one of the CAM cell arrays, so many columns of intermediate data are produced that insufficient columns remain for subsequent arithmetical operations, the columns of intermediate data are written to the memory, via the buffer tags registers. These columns of intermediate data are retrieved subsequently from the memory as needed, also via the buffer tags register.

Owner:GSI TECH ISRAEL LTD

System and method for modeling the neocortex and uses therefor

InactiveUS20080152217A1Digital computer detailsCharacter and pattern recognitionLearning machineShort-term memory

A processor architecture for a learning machine is presented which uses a massive array of processing elements having local, recurrent connections to form global associations between functions defined on manifolds. Associations between these functions provide the basis for learning cause-and-effect relationships involving vision, audition, tactile sensation and kinetic motion. Two arbitrary images hold each other in place in a manifold association processor and form the basis of short-term memory.

Owner:GENERAL MANIFOLDS LLC

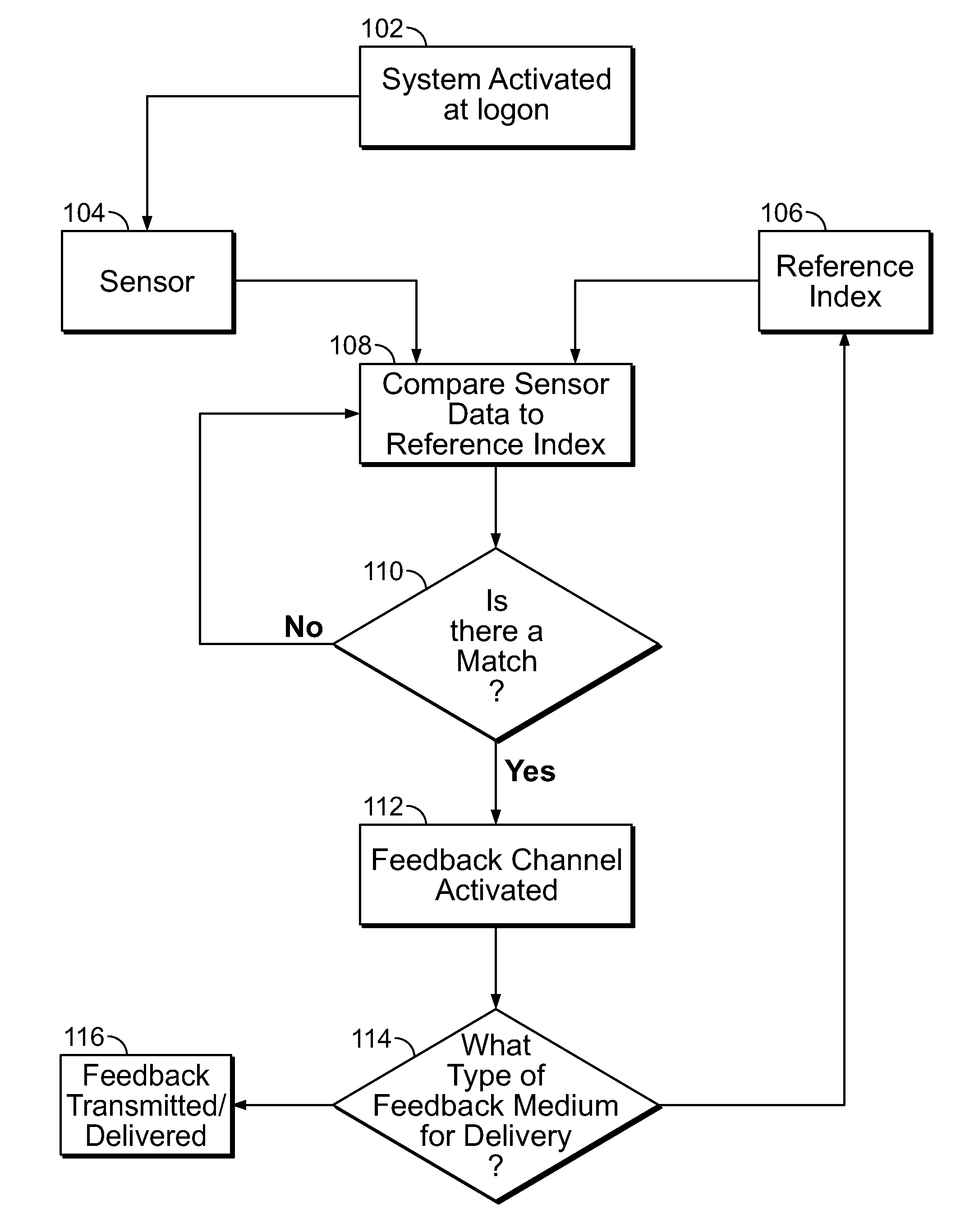

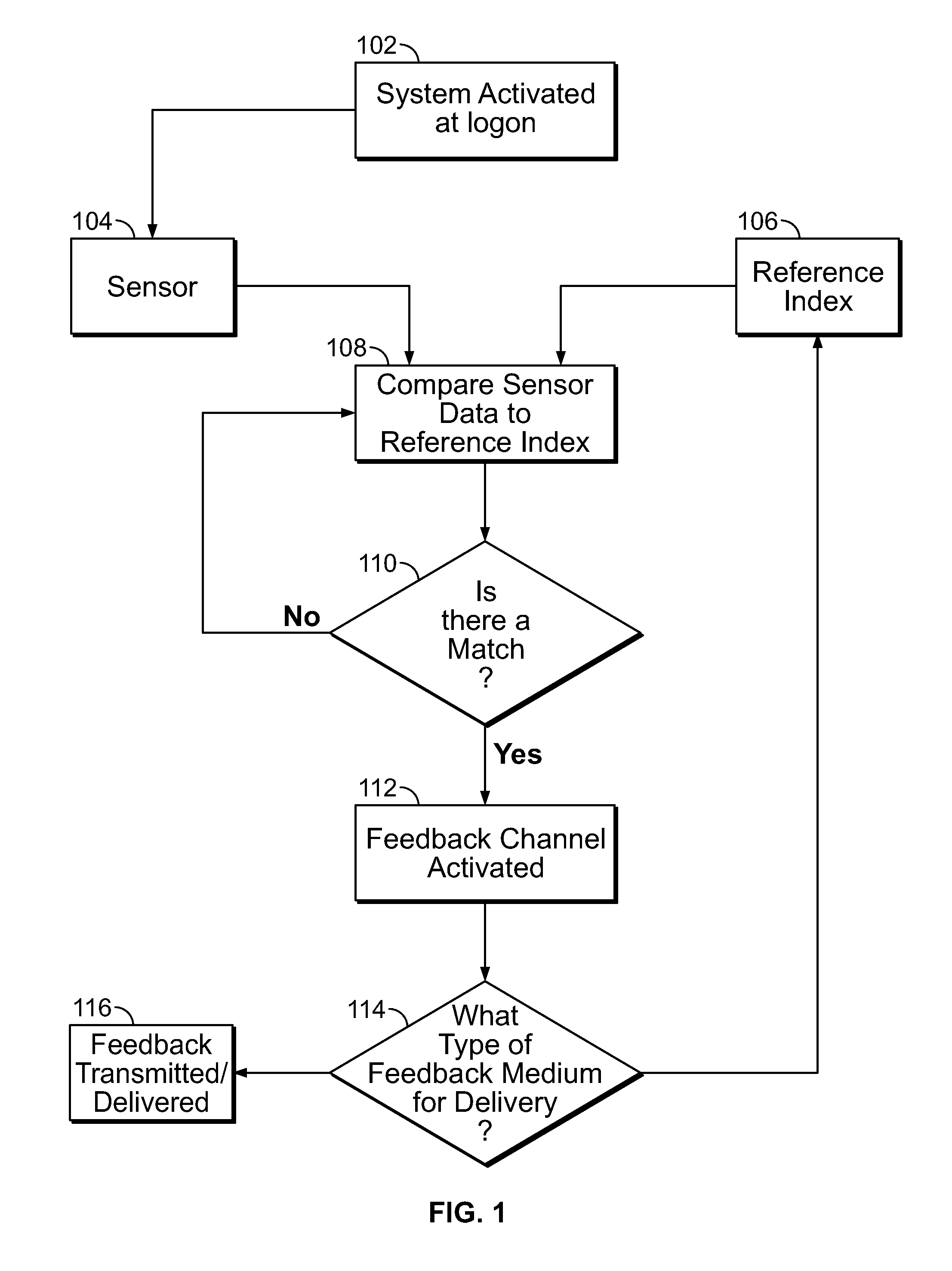

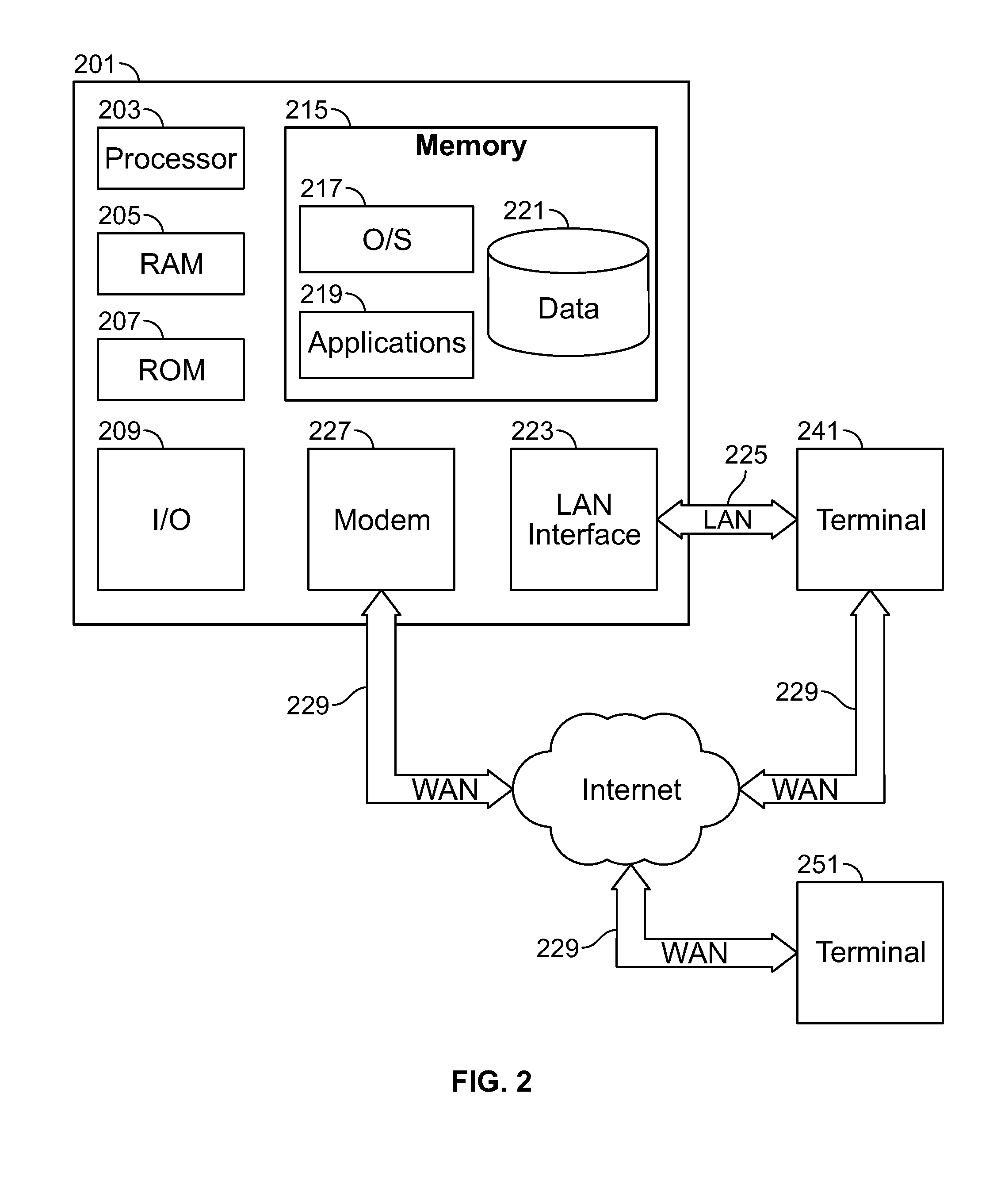

Systems for inducing change in a human physiological characteristic

Systems and methods for inducing a change in a human physiological characteristic. The physiological characteristic may correspond to an emotional state of a dialogue participant. The dialogue participant may be an individual participating in a conversation. The outcome of the conversation may be related to a business objective, such as providing high quality call center services. A sensor may monitor the physiologic characteristic. A processor may relate the physiologic characteristic to an emotional state. The processor may provide feedback to the individual based on the emotional state. The feedback may be formulated to change the individual's emotional state.

Owner:BANK OF AMERICA CORP

Sustainability ratings for legal entities with data inspection

A computer implemented rating system for rating a company using at least one non-economic factor stored in a database populated with hierarchical data and metadata. The system displays at least a portion of the hierarchical data and a formula that generates a sustainability score, the sustainability score defining a rating of the company incorporating the at least one non-economic factor. The user can input at weightings into the system which associates each weighting with a respective non-economic factor. A processor computes the sustainability score using the formula by mathematically applying each associated user-input weighting to the respective non-economic factor. The system displays the sustainability score, and, in response to a user interaction, displays at least a portion of the hierarchical data including the metadata. The hierarchical data can include a second level of data which is used to compute the first level by applying weightings in a formula.

Owner:THOMSON REUTERS ENTERPRISE CENT GMBH

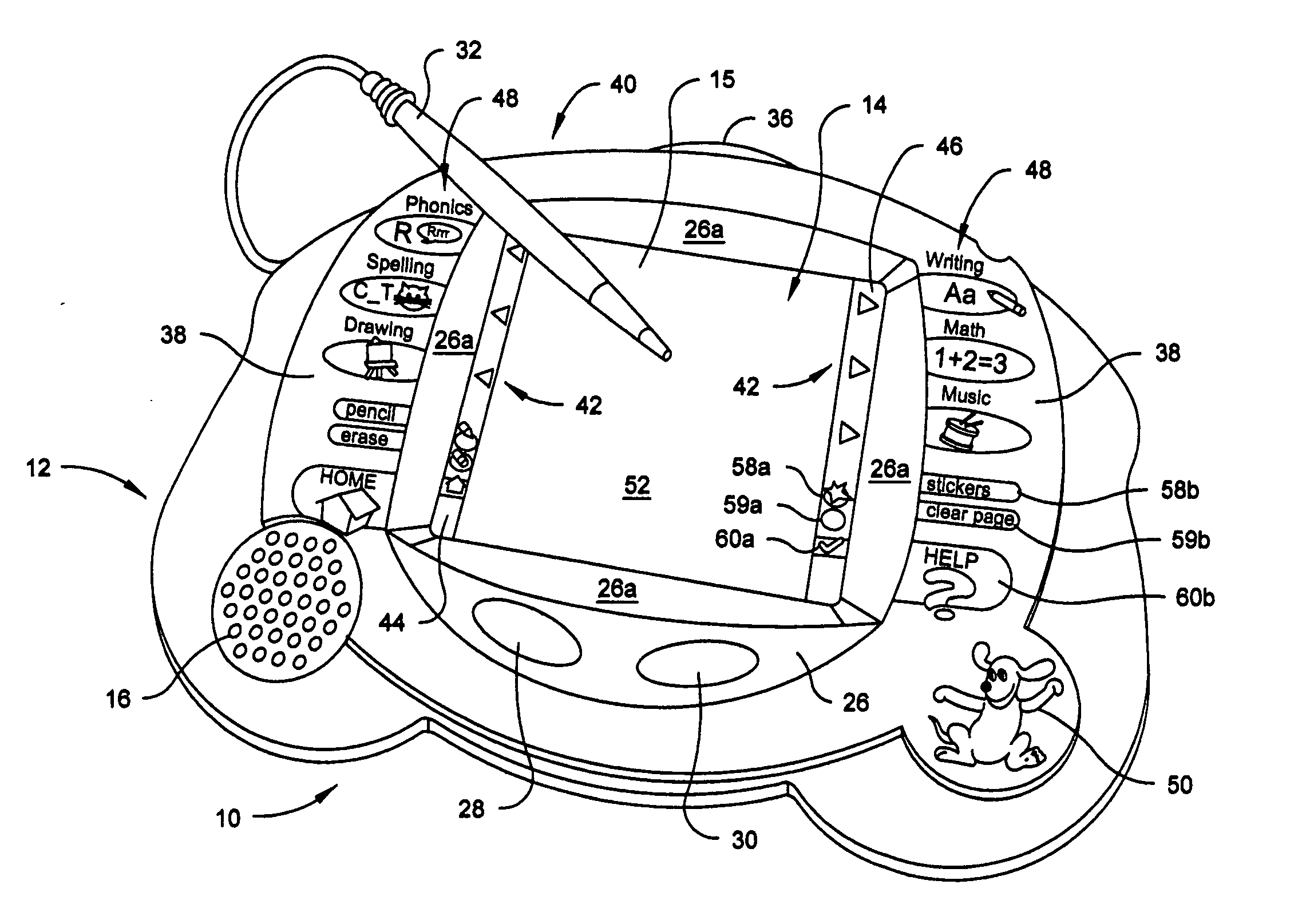

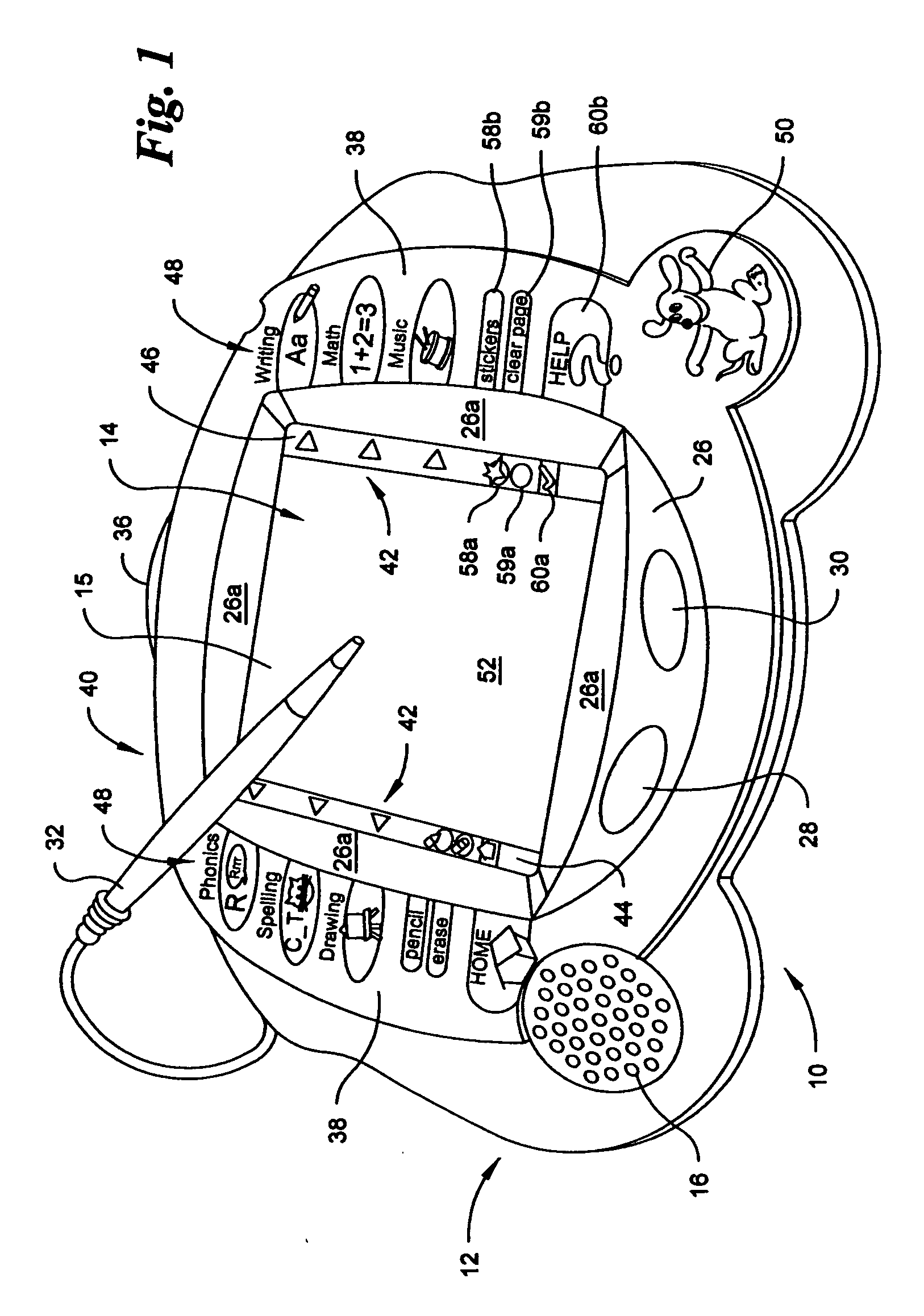

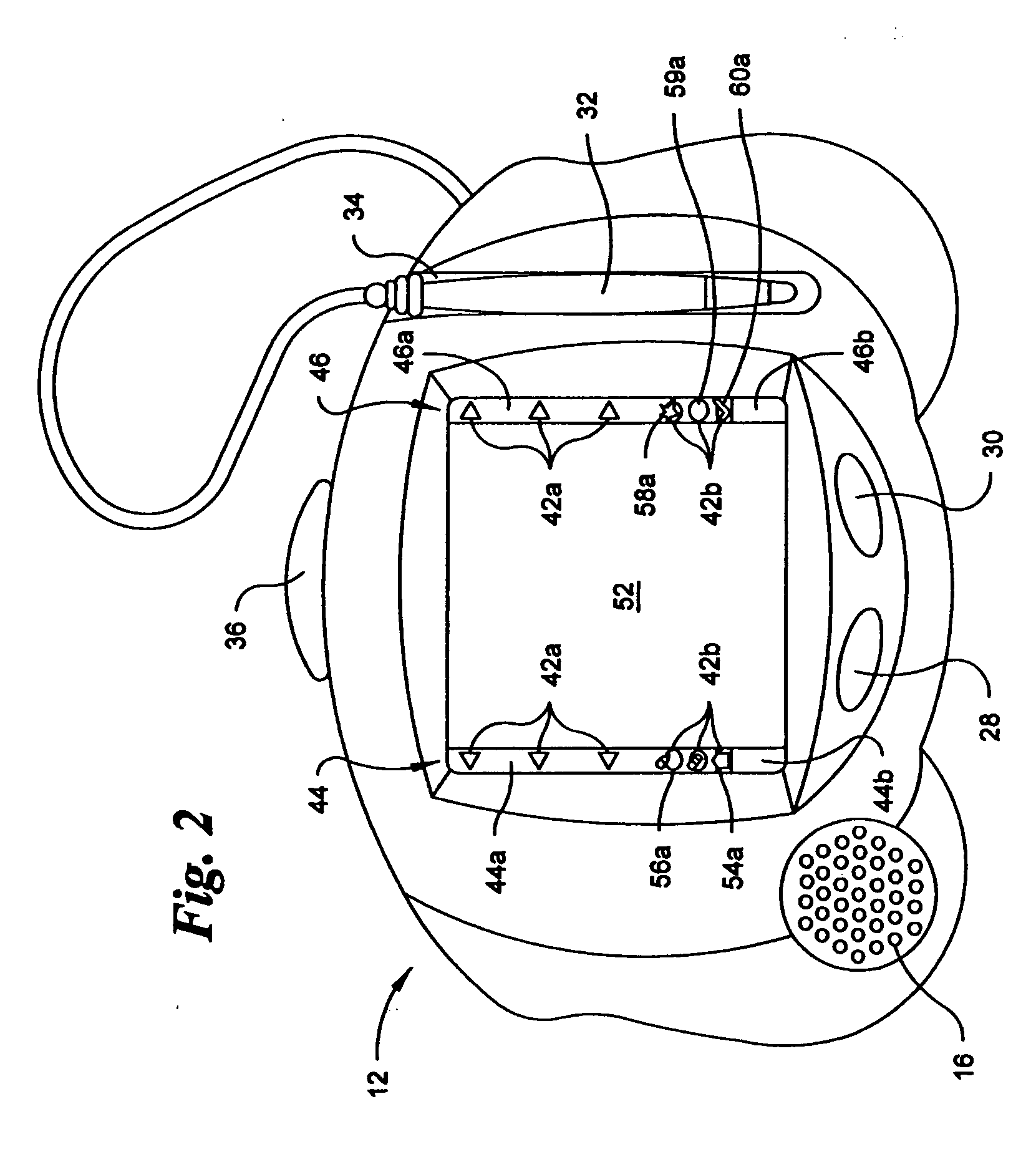

Hand-held interactive electronic device

InactiveUS20060050061A1Digital data processing detailsCathode-ray tube indicatorsDisplay deviceAssociative processor

Owner:MATTEL INC

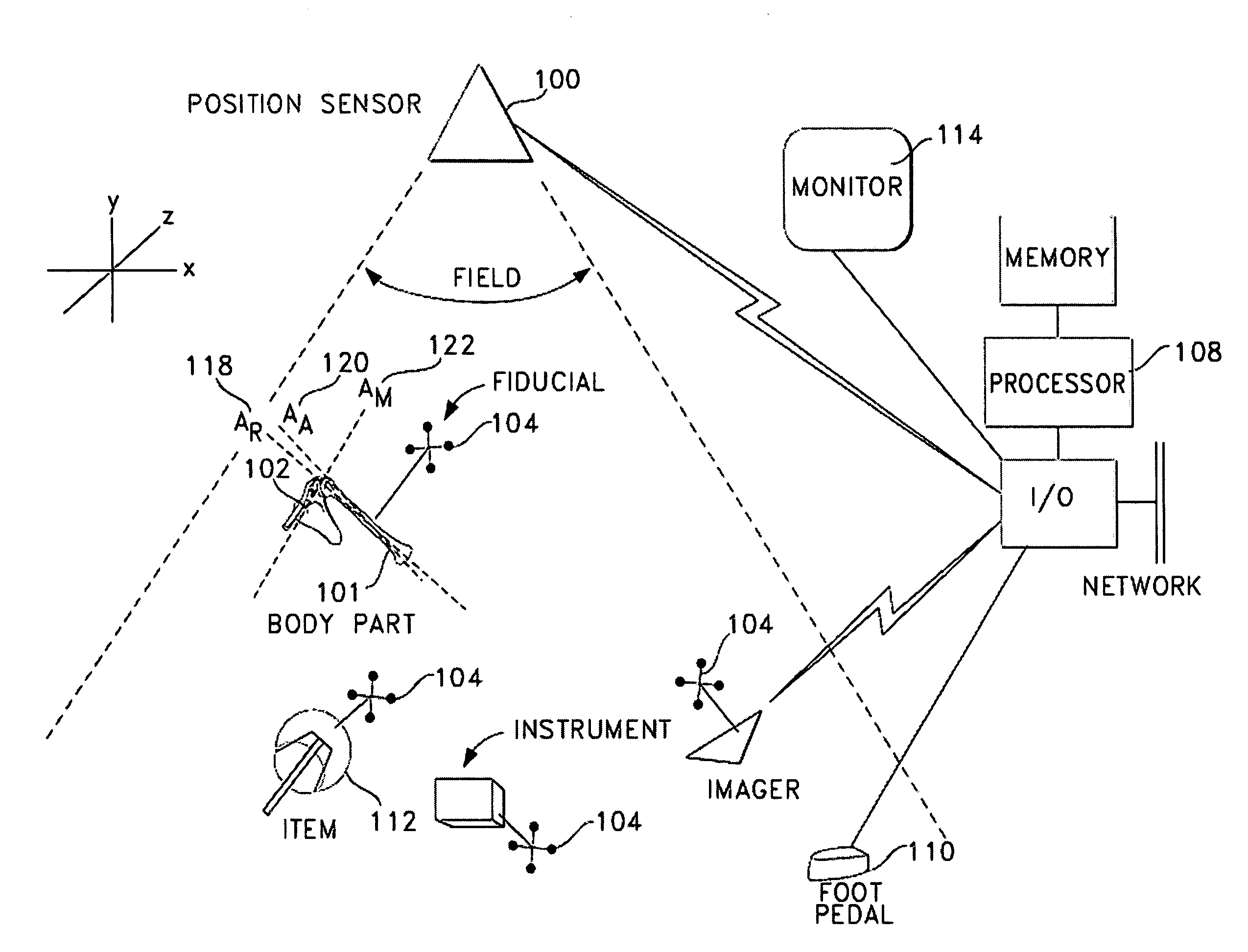

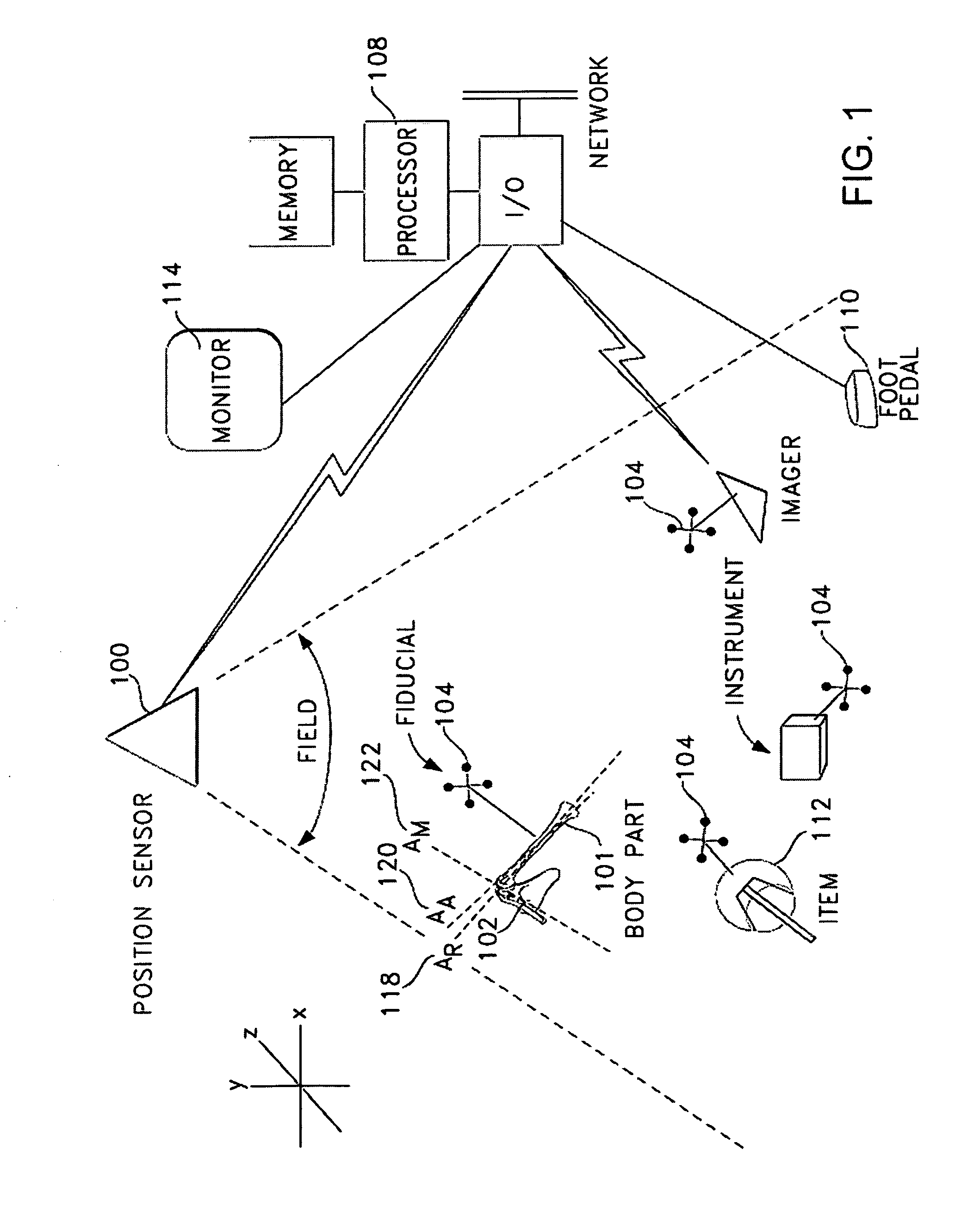

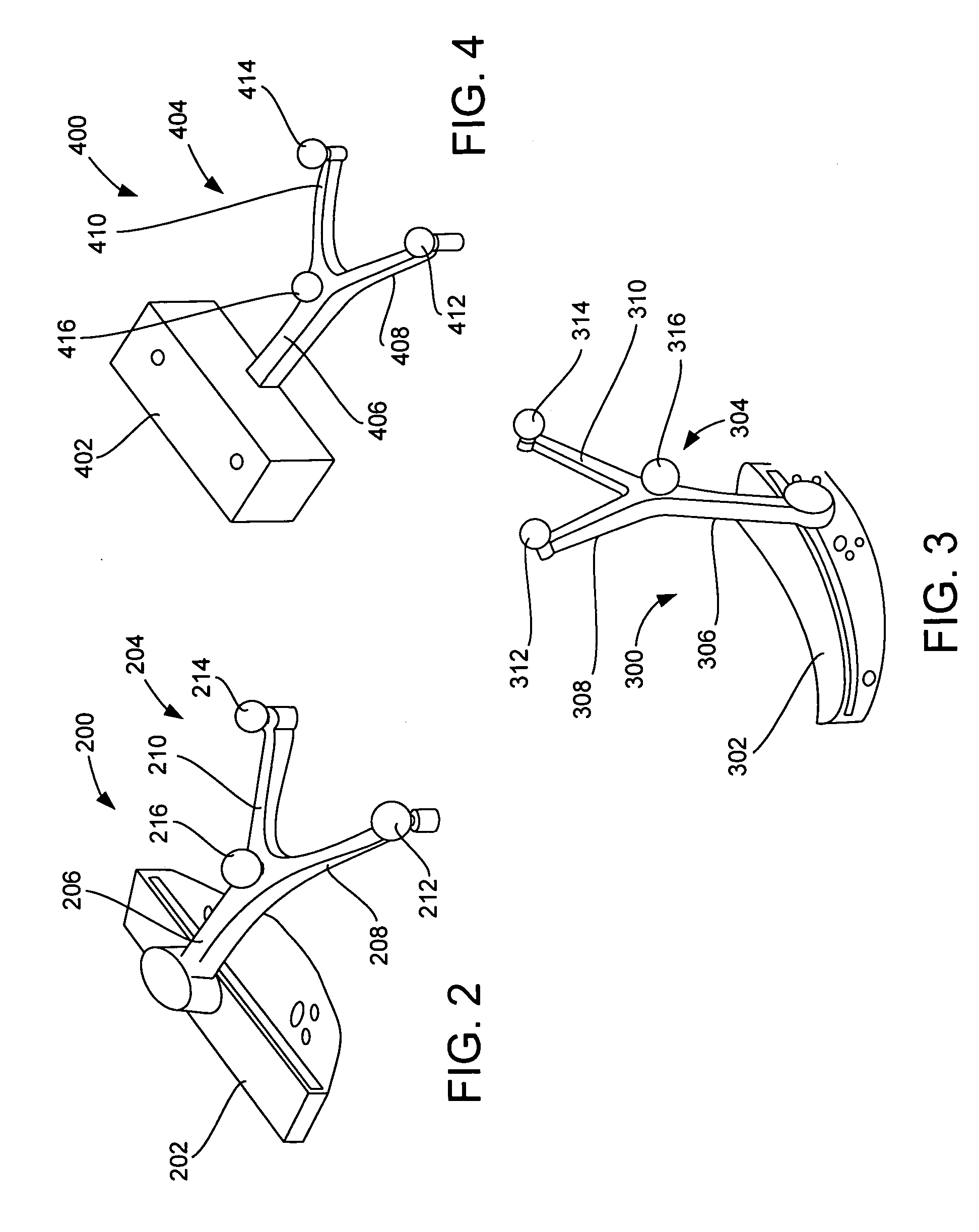

Systems, methods, and apparatus for automatic software flow using instrument detection during computer-aided surgery

InactiveUS20060200025A1Automate software flowAutomate the processSurgical navigation systemsDiagnostic markersComputer aidComputer-aided

Owner:SMITH & NEPHEW INC

Non-Volatile Memory and Method with Shared Processing for an Aggregate of Read/Write Circuits

ActiveUS20070263450A1Maximum versatilityMinimal componentRead-only memoriesDigital storageAudio power amplifierAssociative processor

A non-volatile memory device capable of reading and writing a large number of memory cells with multiple read / write circuits in parallel has an architecture that reduces redundancy in the multiple read / write circuits to a minimum. The multiple read / write circuits are organized into a bank of similar stacks of components. Redundant circuits such as a processor for processing data among stacks each associated with multiple memory cells are factored out. The processor is implemented with an input logic, a latch and an output logic. The input logic can transform the data received from either the sense amplifier or the data latches. The output logic further processes the transformed data to send to either the sense amplifier or the data latches or to a controller. This provides an infrastructure with maximum versatility and a minimum of components for sophisticated processing of the data sensed and the data to be input or output.

Owner:SANDISK TECH LLC

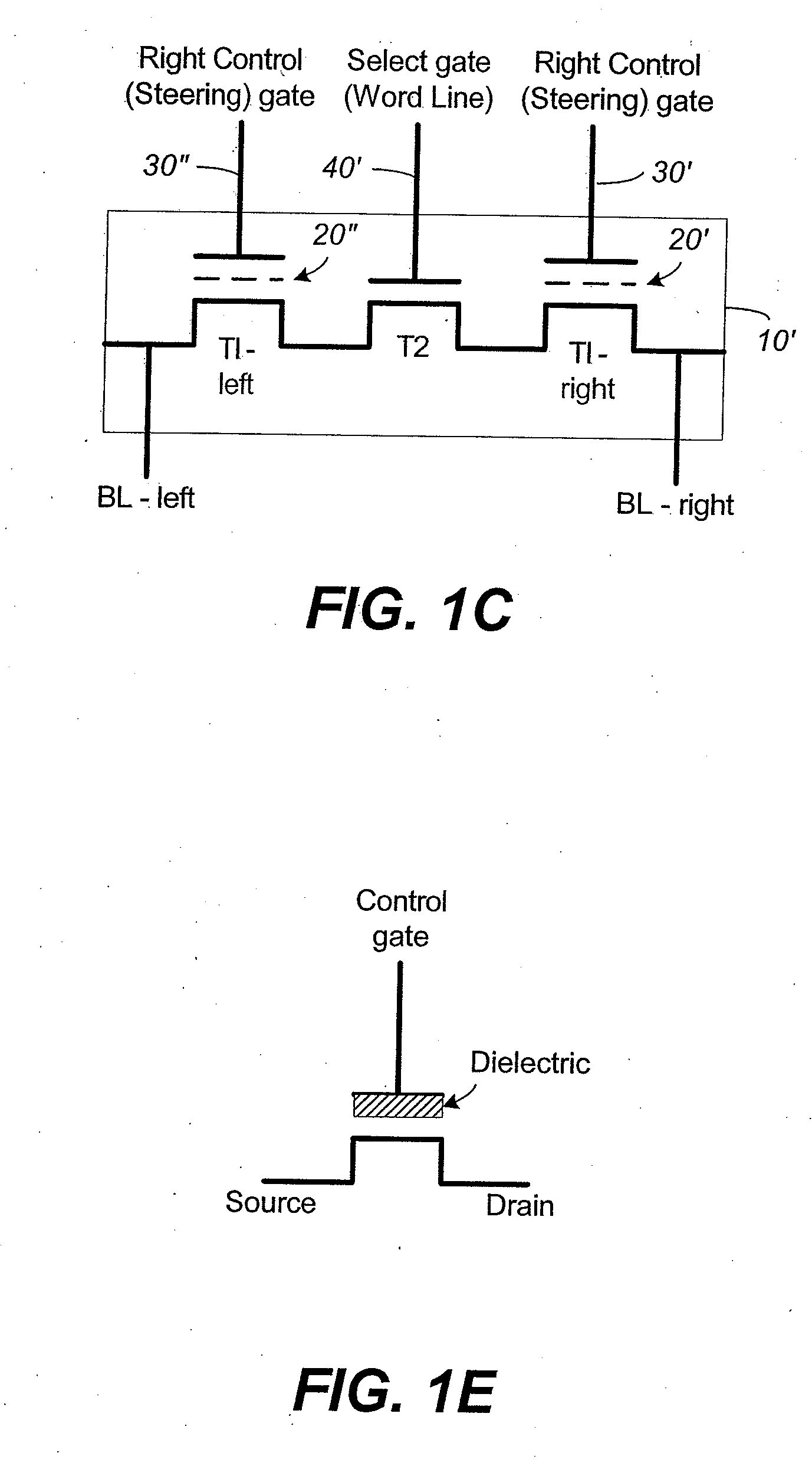

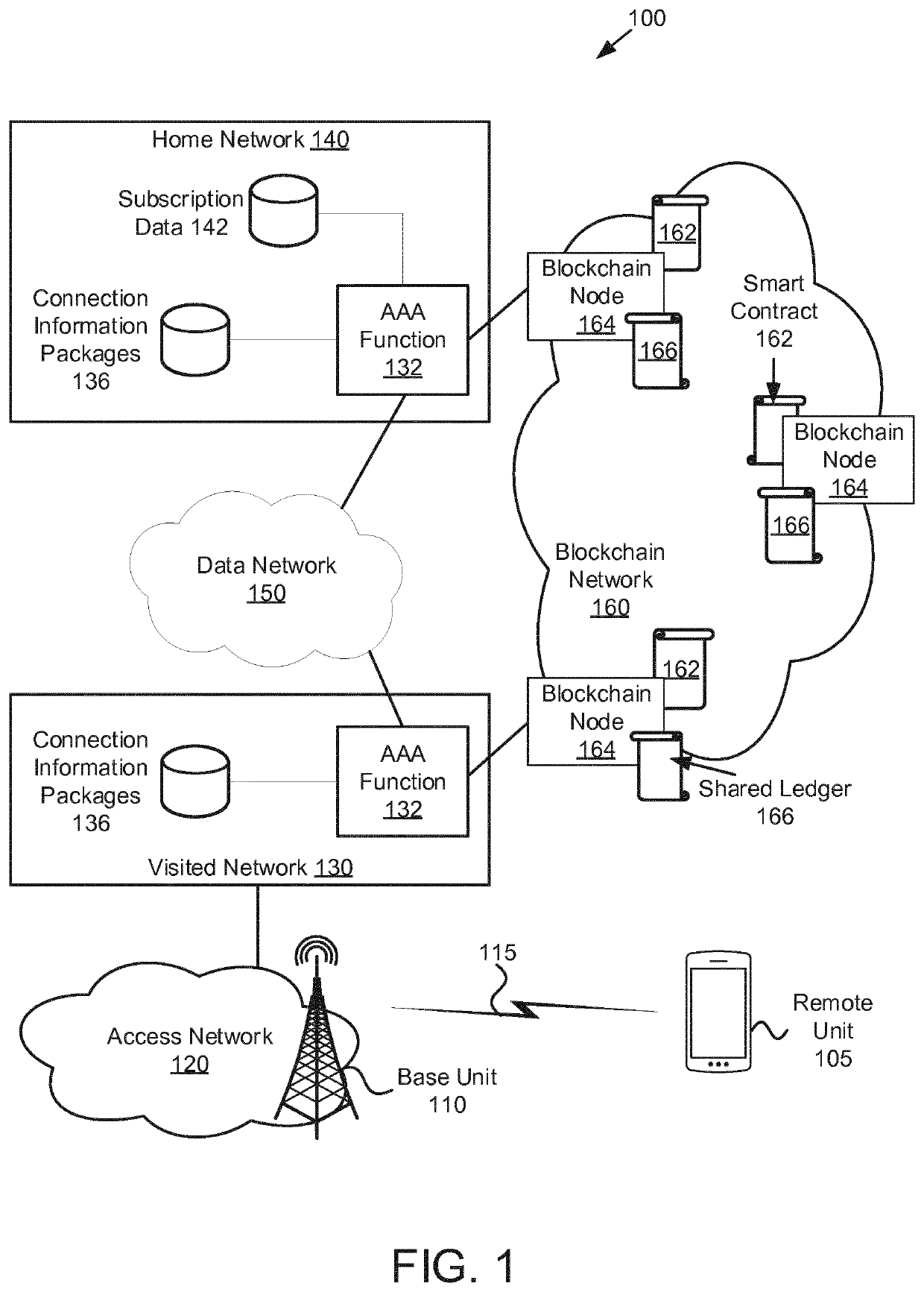

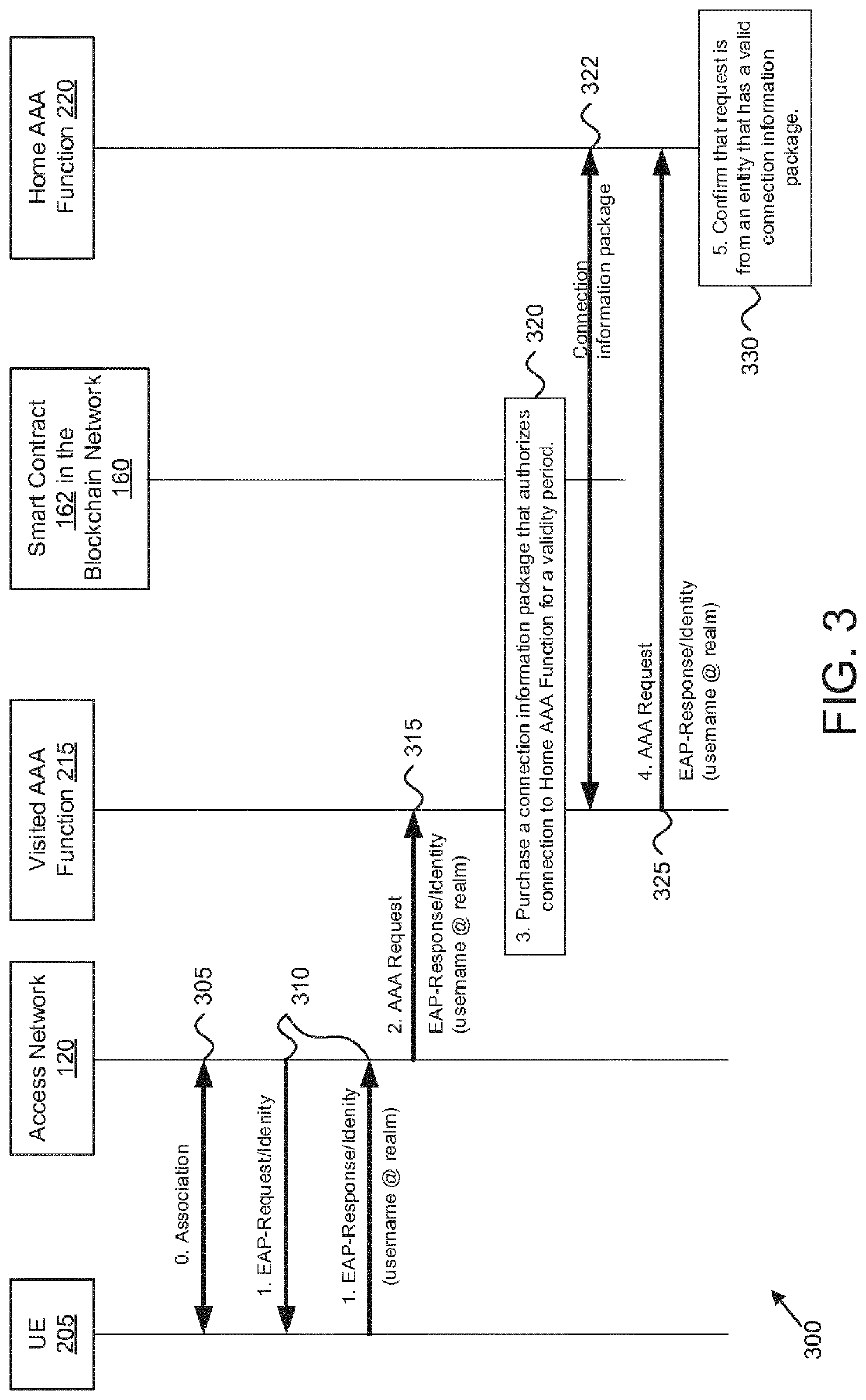

User authentication using connection information provided by a blockchain network

Apparatuses, methods, and systems are disclosed for user authentication using a connection information package provided by a blockchain network. One apparatus includes a processor and a transceiver that receives, from a first address on a blockchain network, a plurality of connection information packages and also receives, from a first function, a request to authenticate a user. The processor determines whether the first function is associated with one of the plurality of connection information packages. In response to the first function being associated with a valid one of the plurality of connection information package, the processor accepts the request to authenticate a user.

Owner:LENOVO (SINGAPORE) PTE LTD +1

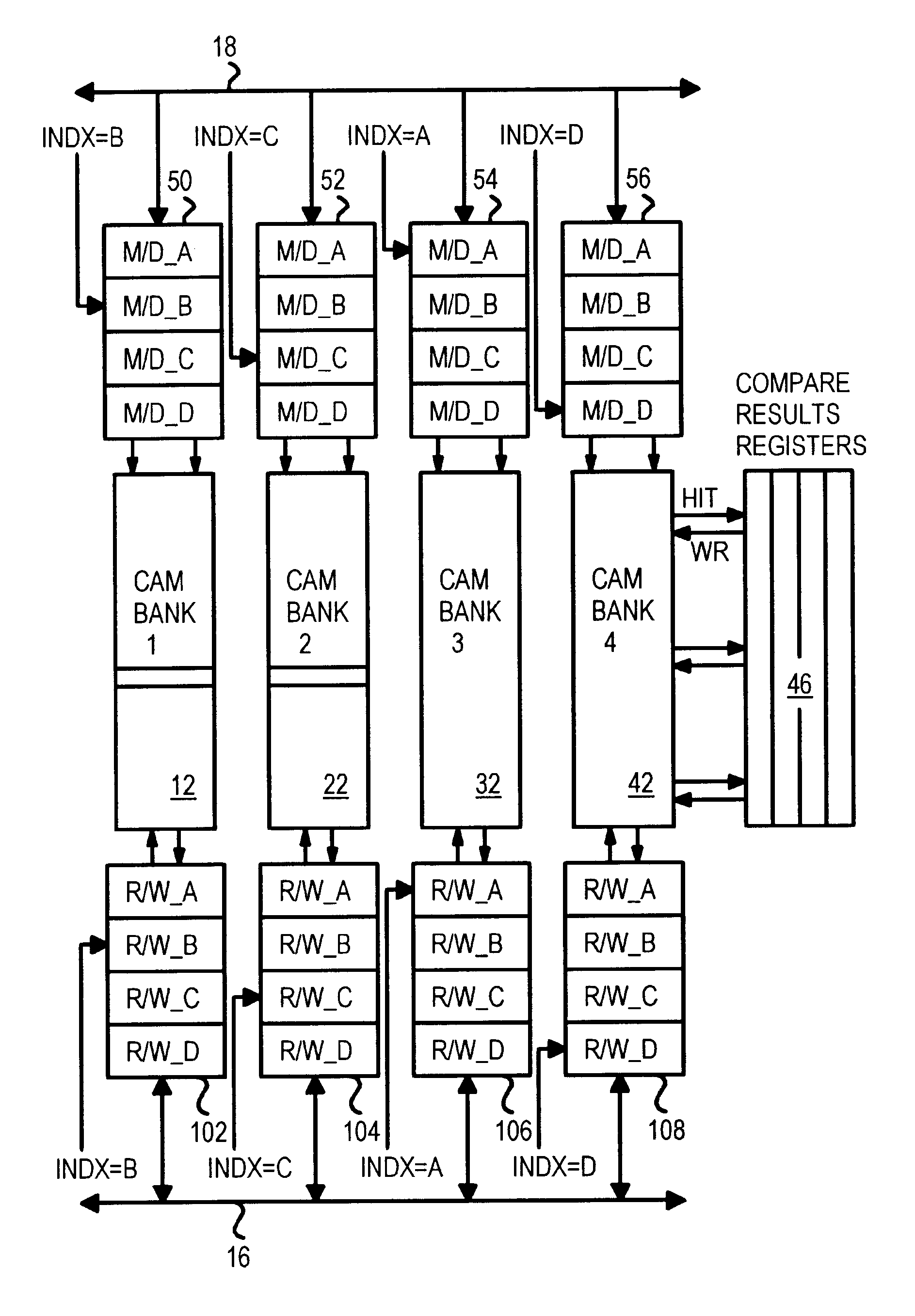

Hardware-assisted fast bank-swap in a content-addressable-memory (CAM) processor

An associative processor uses a content-addressable memory (CAM) array to operate on data. The array has several CAM banks that store data in CAM memory cells. Each CAM bank has a register file that stores compare data that drives compare bit lines to the CAM cells, which activate row-match signals for rows with matching data. Each CAM bank has a register file with copies of compare data for all CAM banks. An index value identifies which of the compare registers drives the bank's compare bit lines. When a bank-swap instruction is executed, the index values of two banks are swapped, causing the compare data to be used for a different CAM bank. The physical data in the CAM banks is not swapped, but the compare data used for comparisons is swapped. Since the register files contain all banks' compare data, the compare data does not have to be physically moved.

Owner:NEOMAGIC

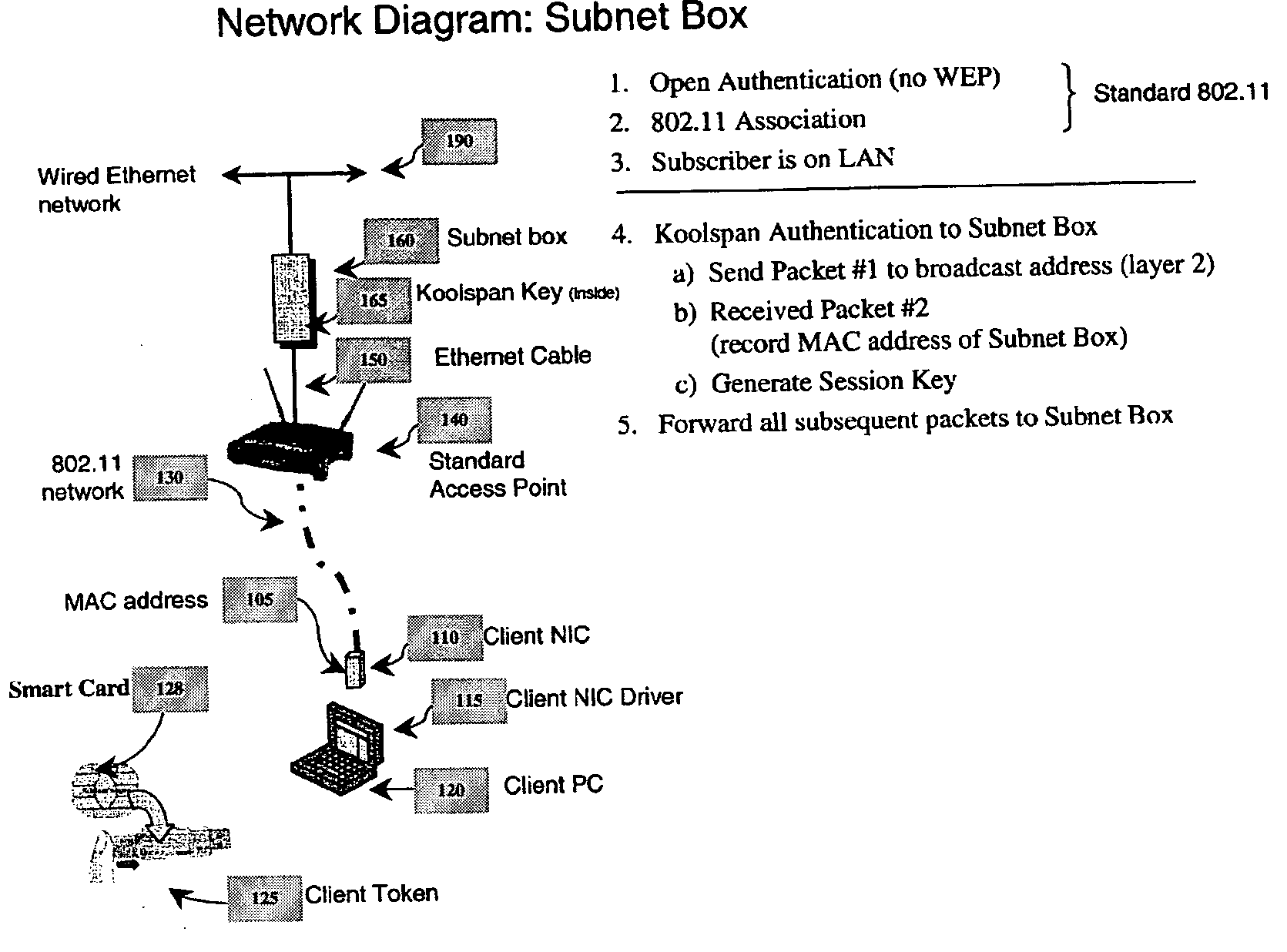

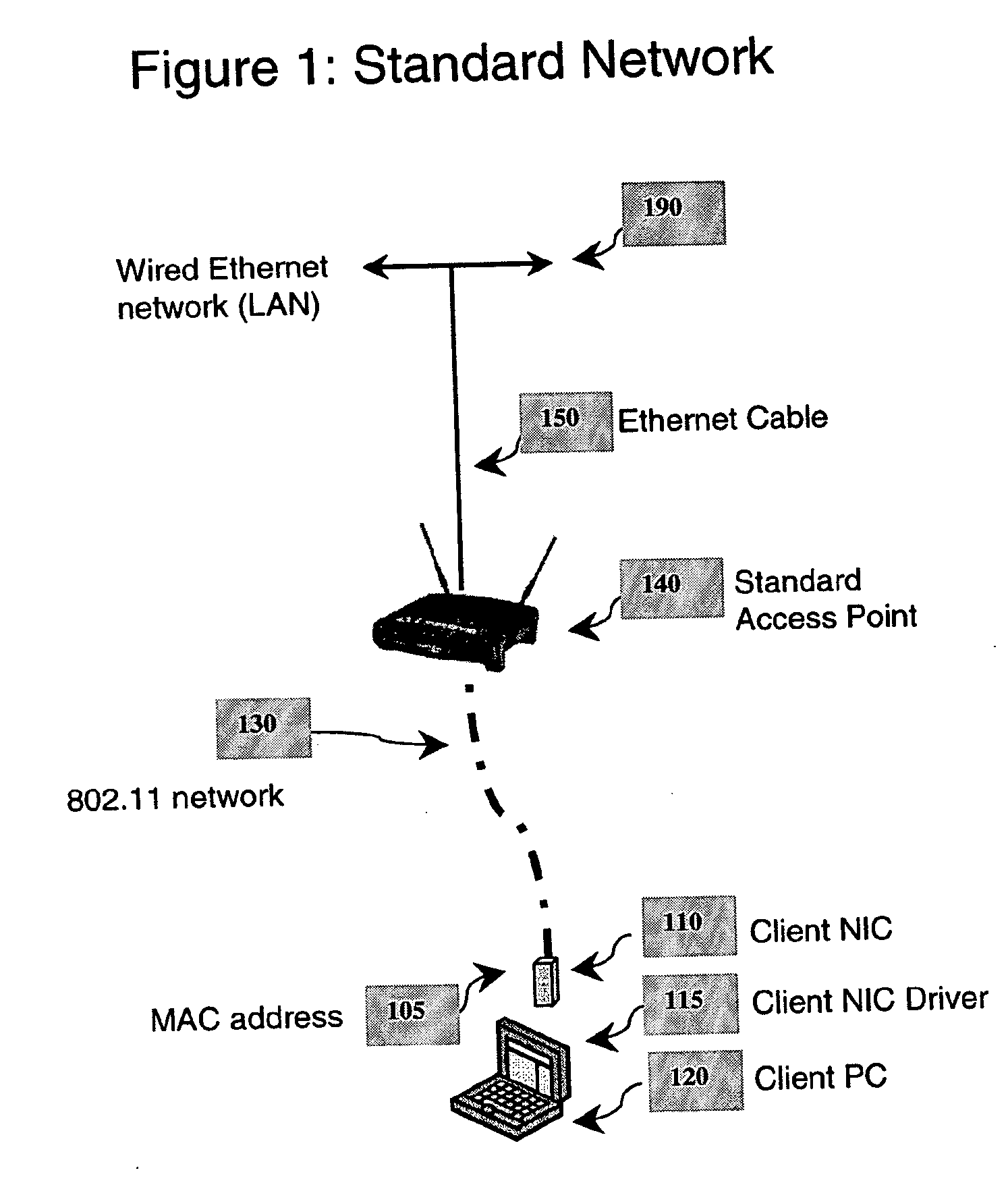

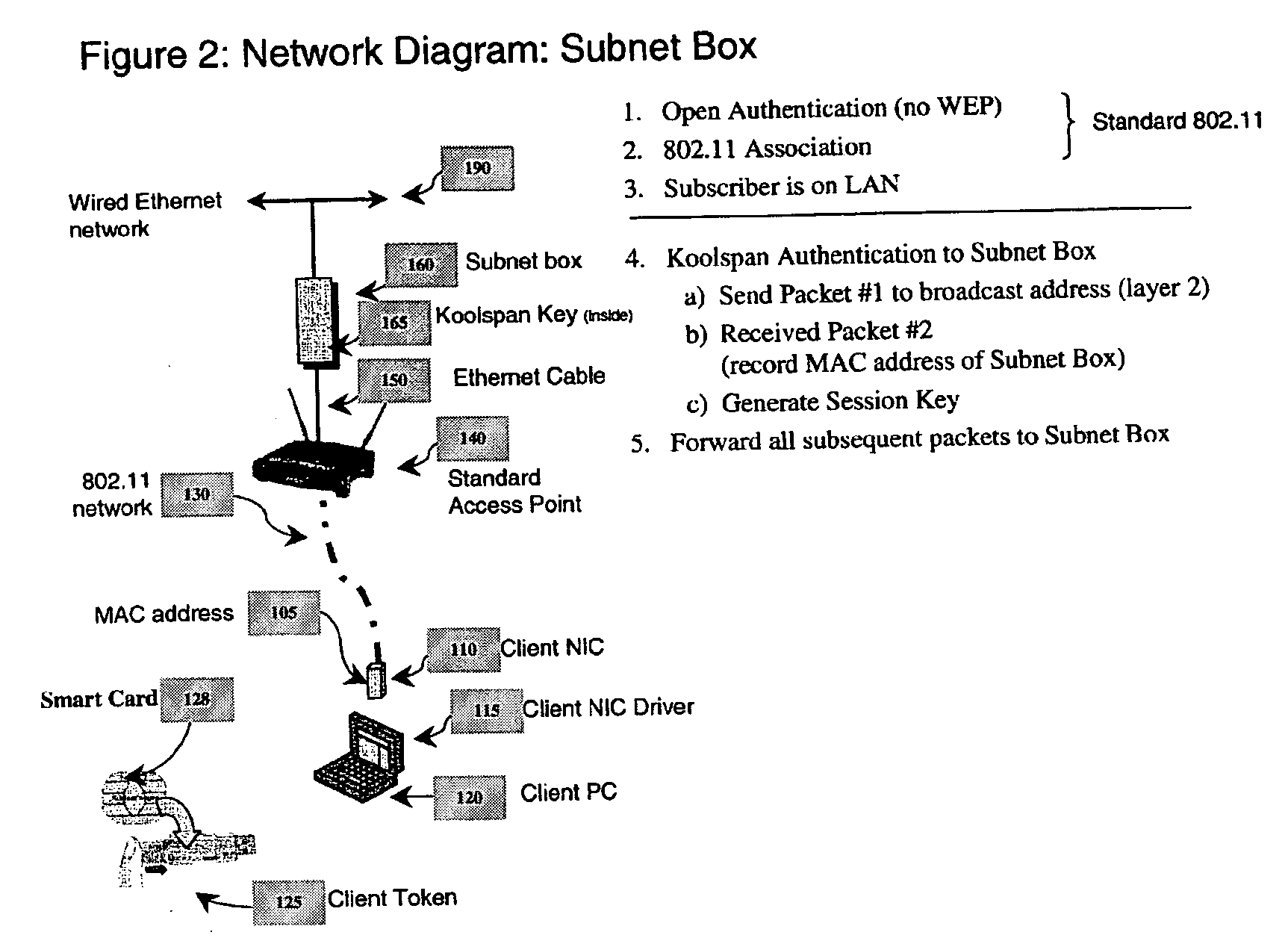

Subnet box

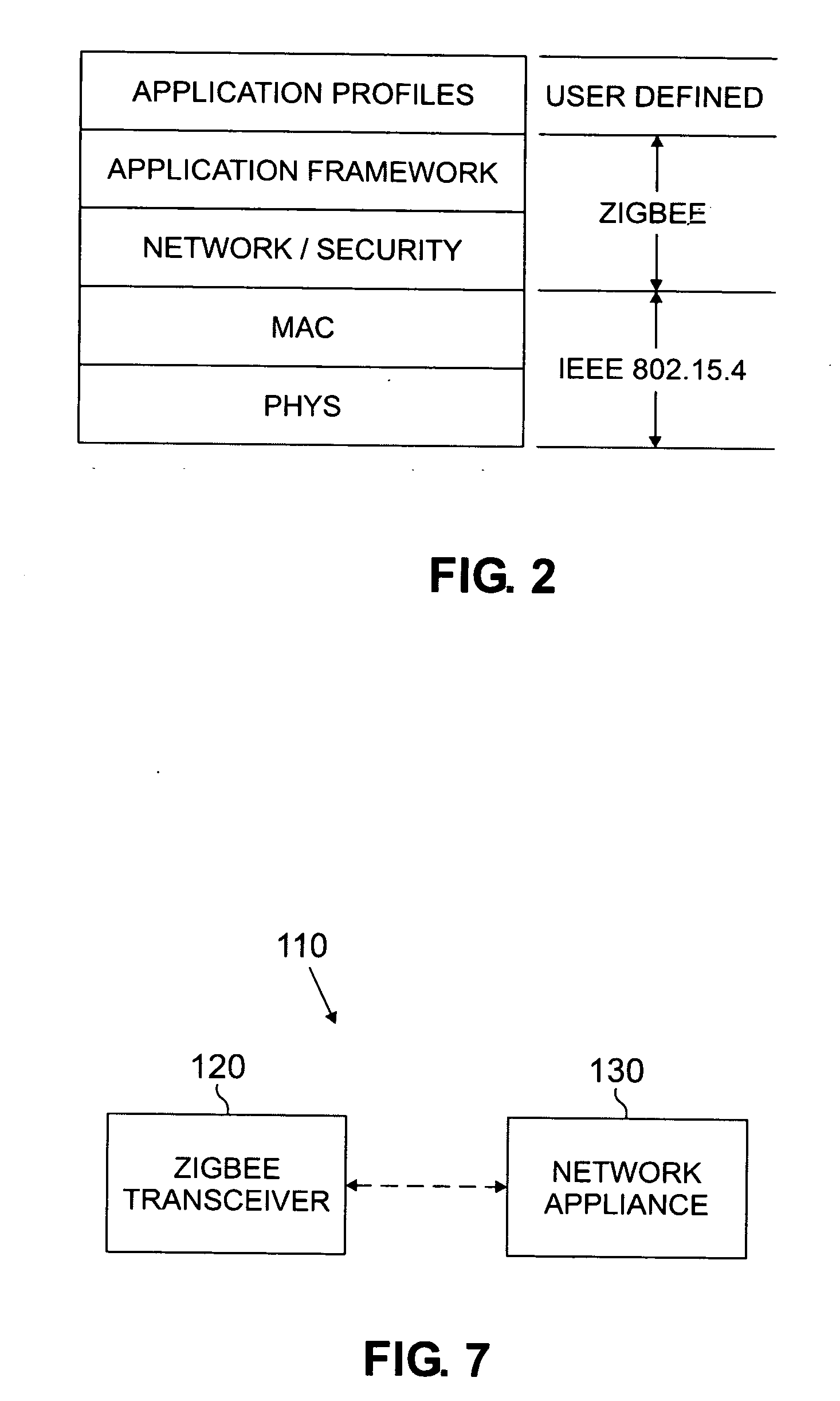

InactiveUS20050091483A1Secure transmissionDigital data processing detailsNetwork topologiesWi-FiWired communication

The invention provides an external in-line device (“Subnet Box”) placed between a network and an access point to achieve secure Wi-Fi communications without needing to modify the access point. The Subnet Box comprises an embedded token and will authenticate users based on pre-stored access rights. In at least one embodiment of the invention, the Subnet Box comprises: a first communications port for intercepting data packets communicated to and from a wired communications network; a second communications port for intercepting data packets communicated to and from a wireless access point, wherein the wireless access point is an edge device of the wired communications network; a database comprising a number of serial numbers each associated with a client token and a secret cryptographic key; and a processor for determining whether a computing device having a client token can access the wired communications network via the wireless access point. The processor establishes a secure tunnel between the computing device and the first communications port.

Owner:KOOLSPAN

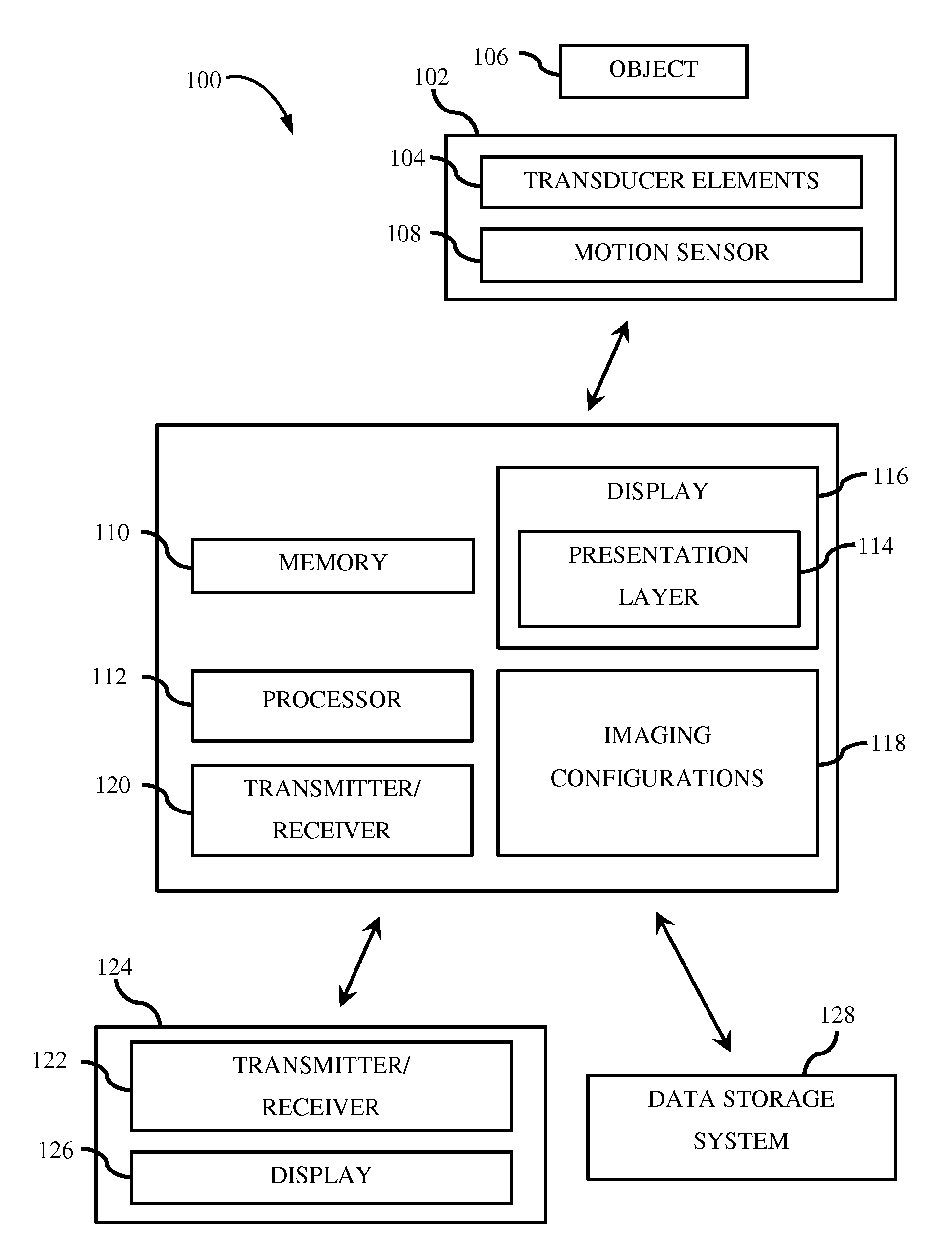

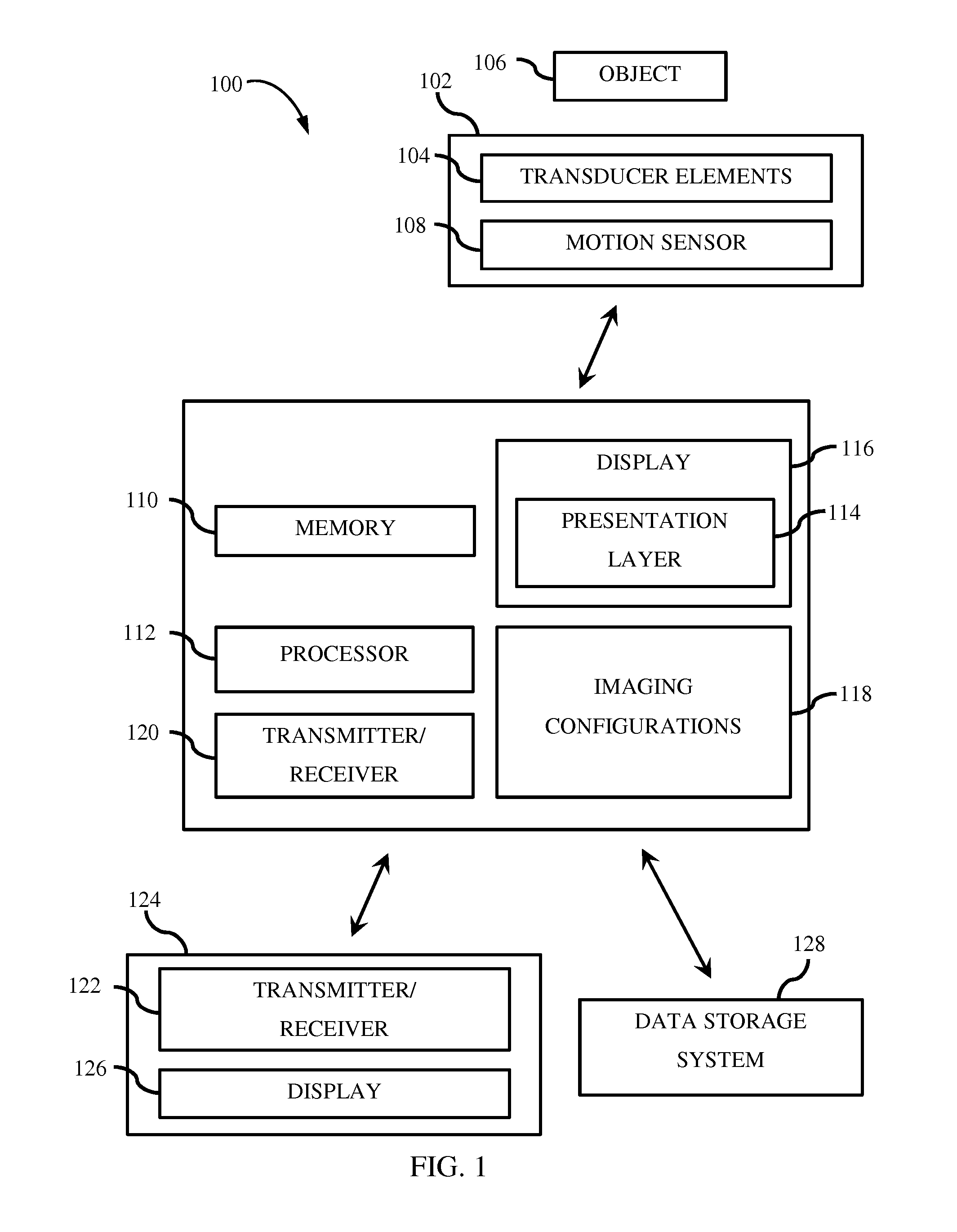

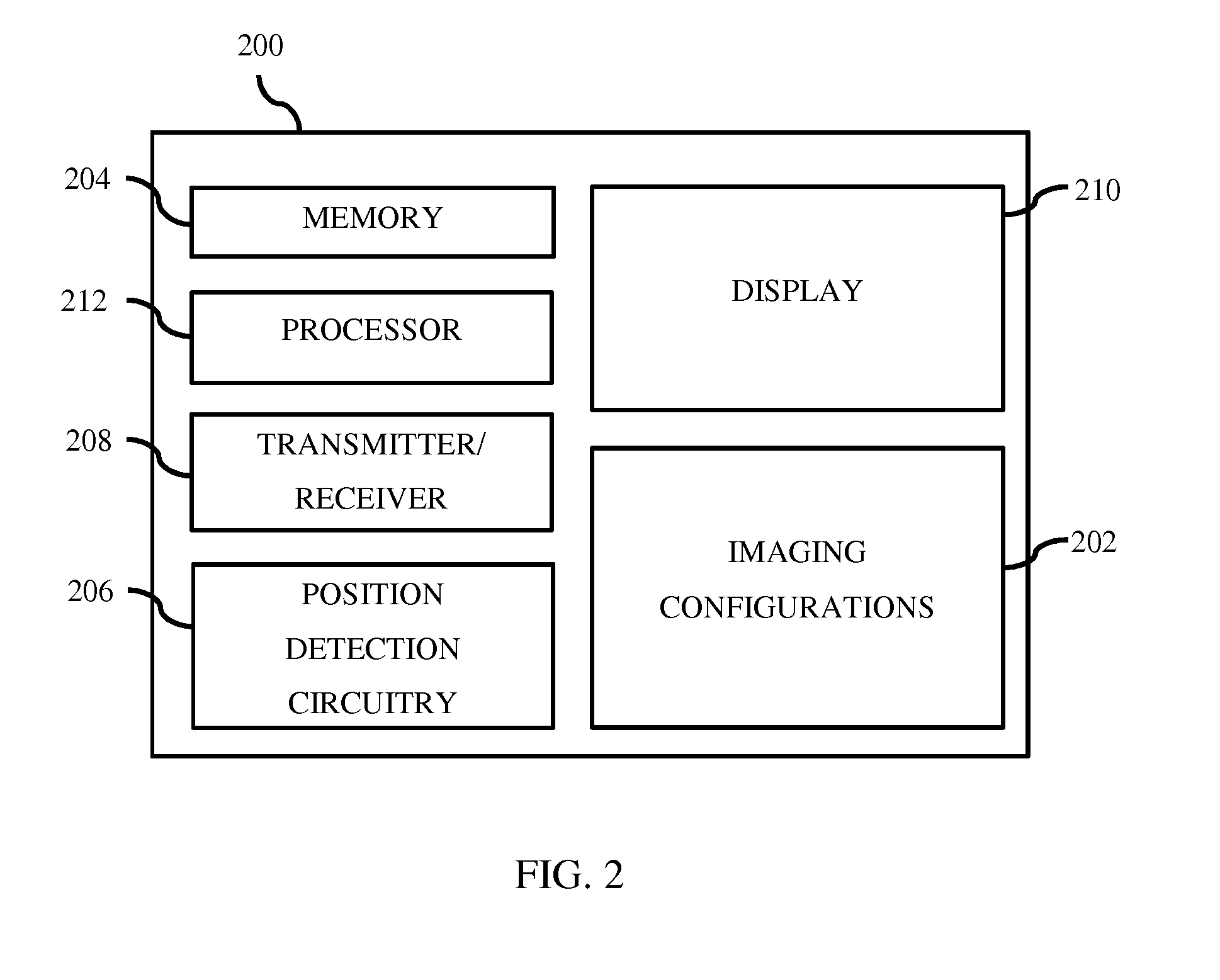

Medical imaging system and a portable medical imaging device for performing imaging

InactiveUS20140121489A1Ultrasonic/sonic/infrasonic diagnosticsRadiation diagnostics testing/calibrationAssociative processorMedical imaging

A portable medical imaging device for performing imaging procedures. The portable medical imaging device comprises a processor configured to analyze location information associated with the portable medical imaging device and determine whether the location information is linked to a location of the performing an imaging procedure. The processor selects an imaging configuration from a plurality of imaging configurations associated with an imaging procedure to be performed in the location, wherein each imaging configuration of the plurality of imaging configurations is associated with a type of imaging procedure. The processor is further configured to load the imaging configuration to perform the imaging procedure. The portable medical device (200) for performing medical procedures further comprises at least one memory communicably coupled to the processor for storing the plurality of imaging configurations.

Owner:GENERAL ELECTRIC CO

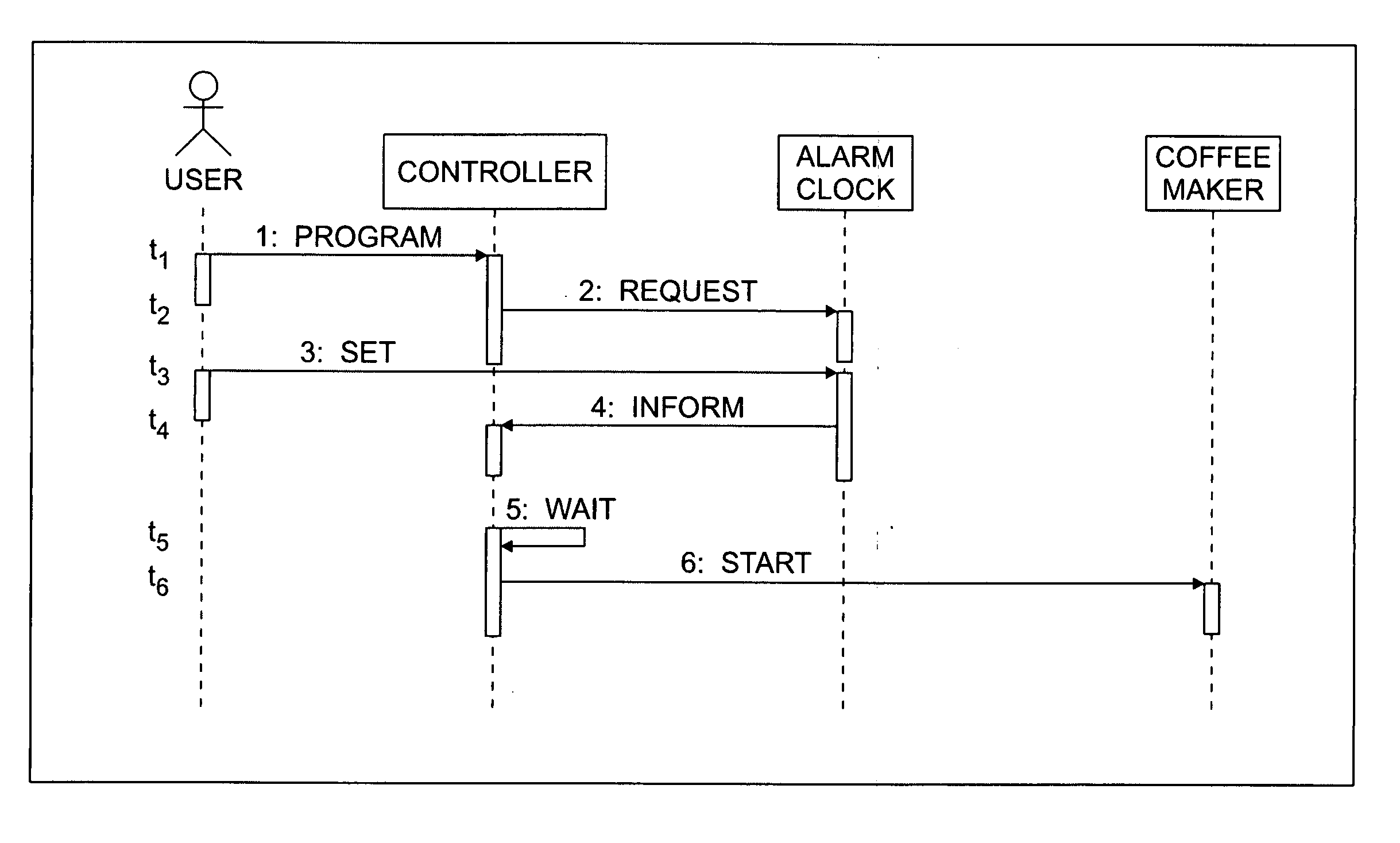

Network alarm clock communicating alarm settings over a wireless or other local area network

InactiveUS20070067300A1Special data processing applicationsHome automation networksAssociative processorNetwork control

A network controller is provided. The controller includes a network interface for transmitting and receiving messages over a network between the networked controller and each of a plurality of networked devices. A first of the networked devices has a time of day event notification indicator. A processor is operatively associated with the network interface. The processor is configured to perform a method including the step of receiving a first message over the network from the first networked device. The message includes a time of day at which the event notification indicator is set. A second message is transmitted over the network to a second of the networked devices instructing the second networked device to perform a prescribed function at a desired time based on the time of day at which the event notification indictor is set. A user interface is operatively associated with the processor for adjusting user-controllable parameters.

Owner:GENERAL INSTR CORP

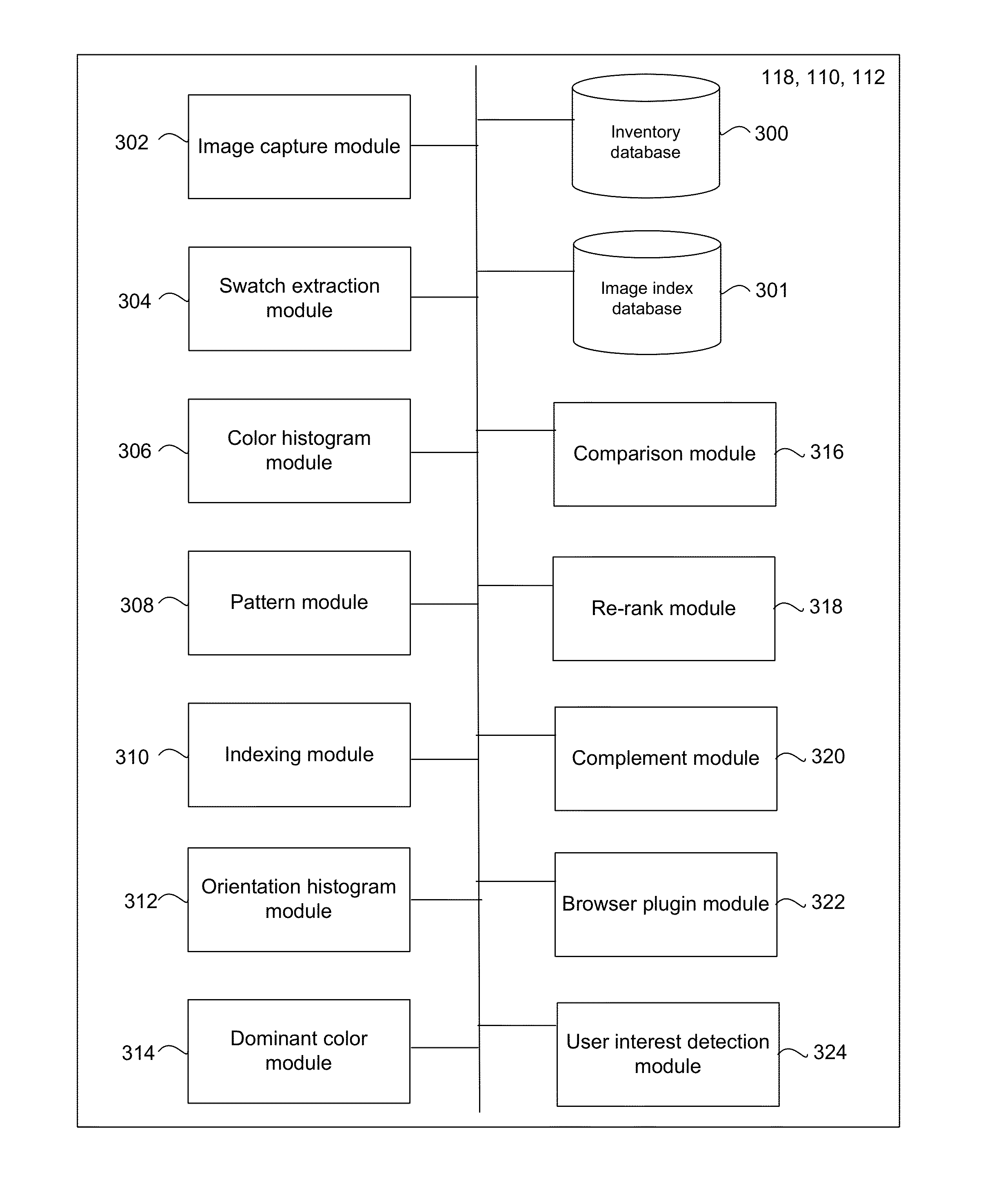

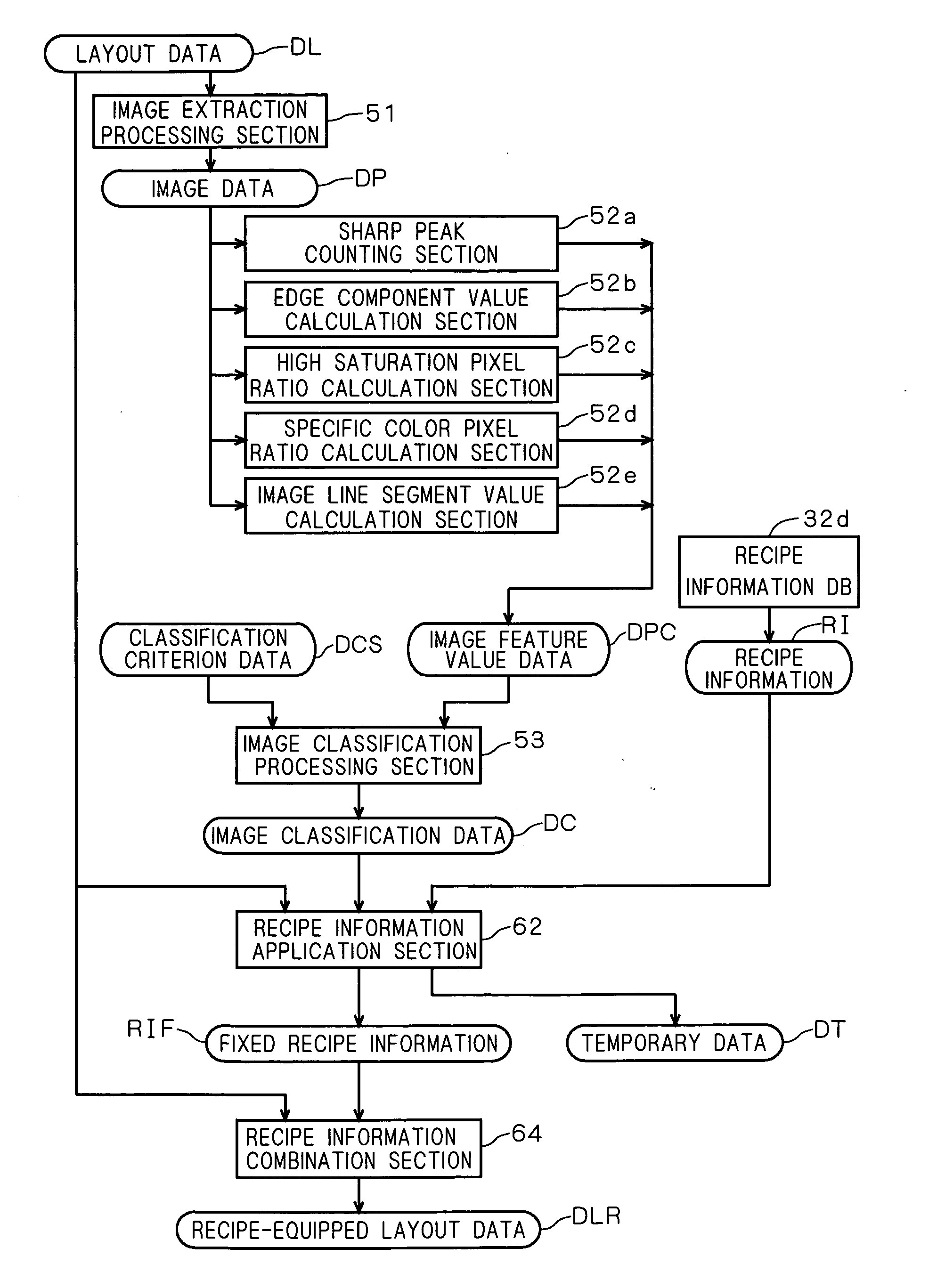

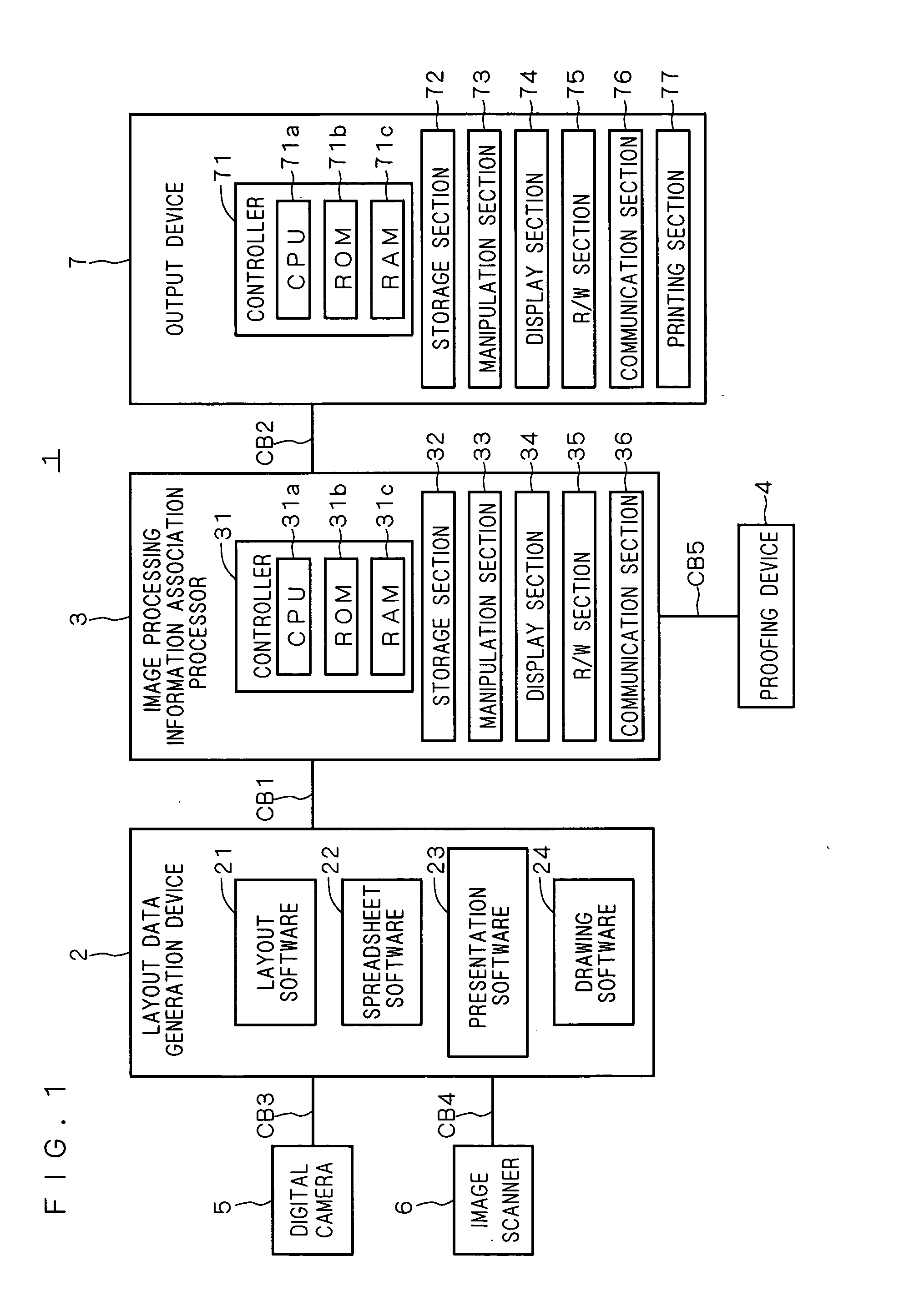

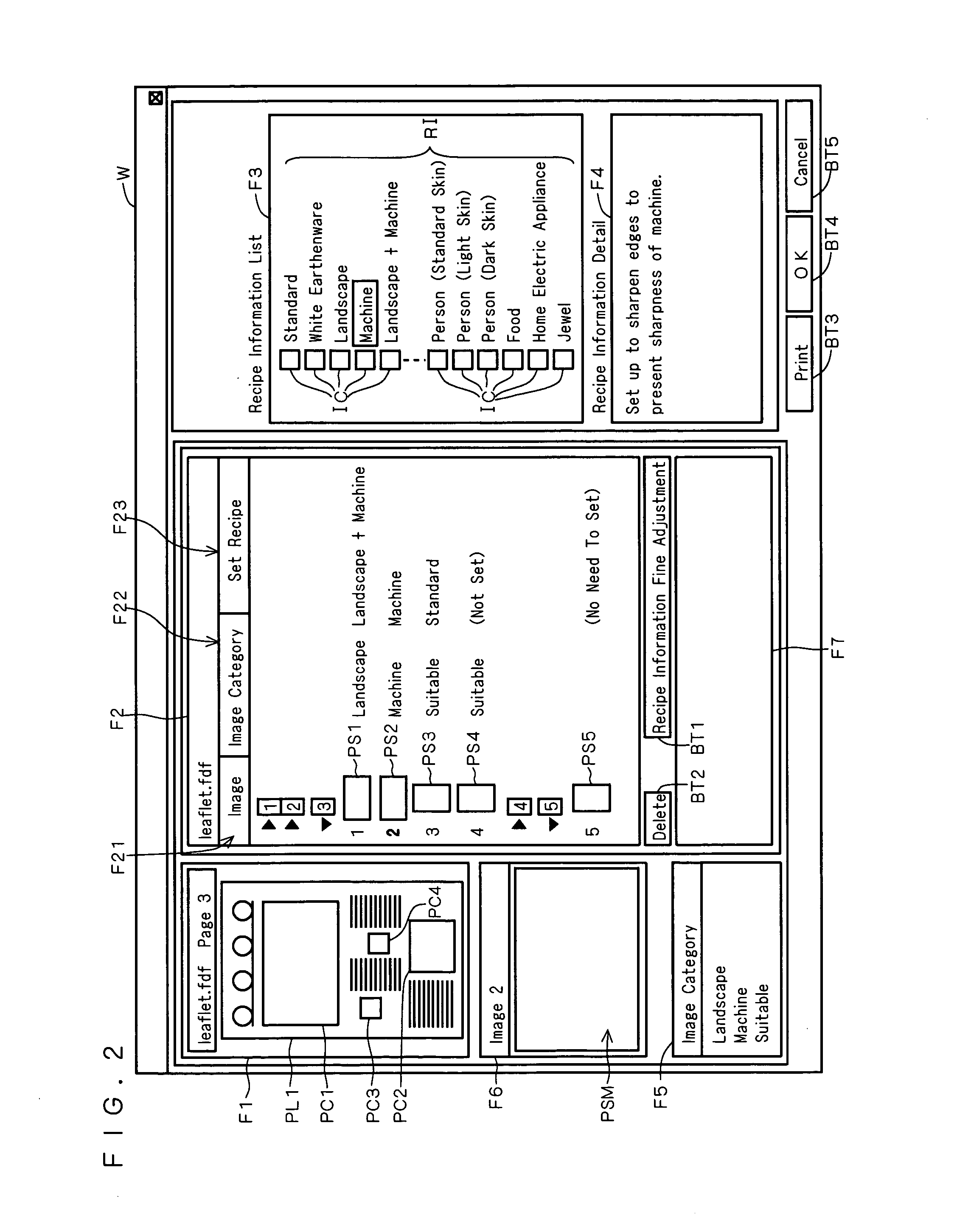

Image processing information association processor, printing system, method of enabling layout data output, and program

ActiveUS20050057776A1Good colorHigh color reproductionImage enhancementDigitally marking record carriersPattern recognitionImaging processing

Image features of a plurality of RGB images arranged for layout are extracted, and the RGB images are classified into image categories determined by the commonality of the image features. Recipe information previously set in accordance with the image features is added to layout data while being associated with RGB images for each image category. This enables an output device to perform an optimization process by reference to the added recipe information, thereby outputting good-quality printed matter excellent in color reproduction and the like if information for the process of optimizing RGB image data is not previously provided during the generation of the layout data.

Owner:DAINIPPON SCREEN MTG CO LTD

Radar, lidar and camera enhanced methods for vehicle dynamics estimation

A system for estimation vehicle dynamics, including vehicle position and velocity, using a stationary object. The system includes an object sensor that provides object signals of the stationary object. The system also includes in-vehicle sensors that provide signals representative of vehicle motion. The system also includes an association processor that receives the object signals, and provides object tracking through multiple frames of data. The system also includes a longitudinal state estimation processor that receives the object signals and the sensor signals, and provides a correction of the vehicle speed in a forward direction. The system also includes a lateral state estimation processor that receives the object signals and the sensor signals, and provides a correction of the vehicle speed in the lateral direction.

Owner:GM GLOBAL TECH OPERATIONS LLC

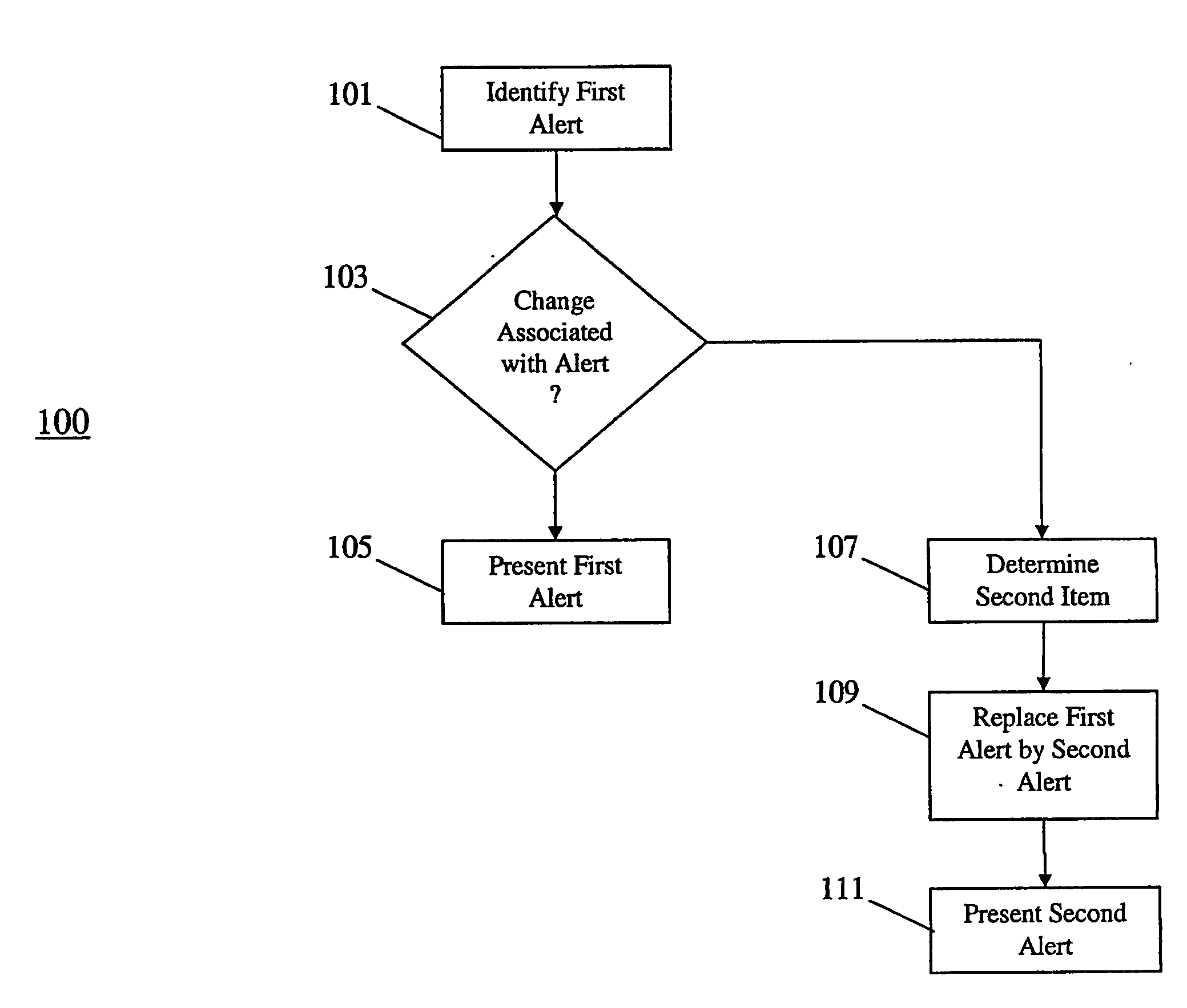

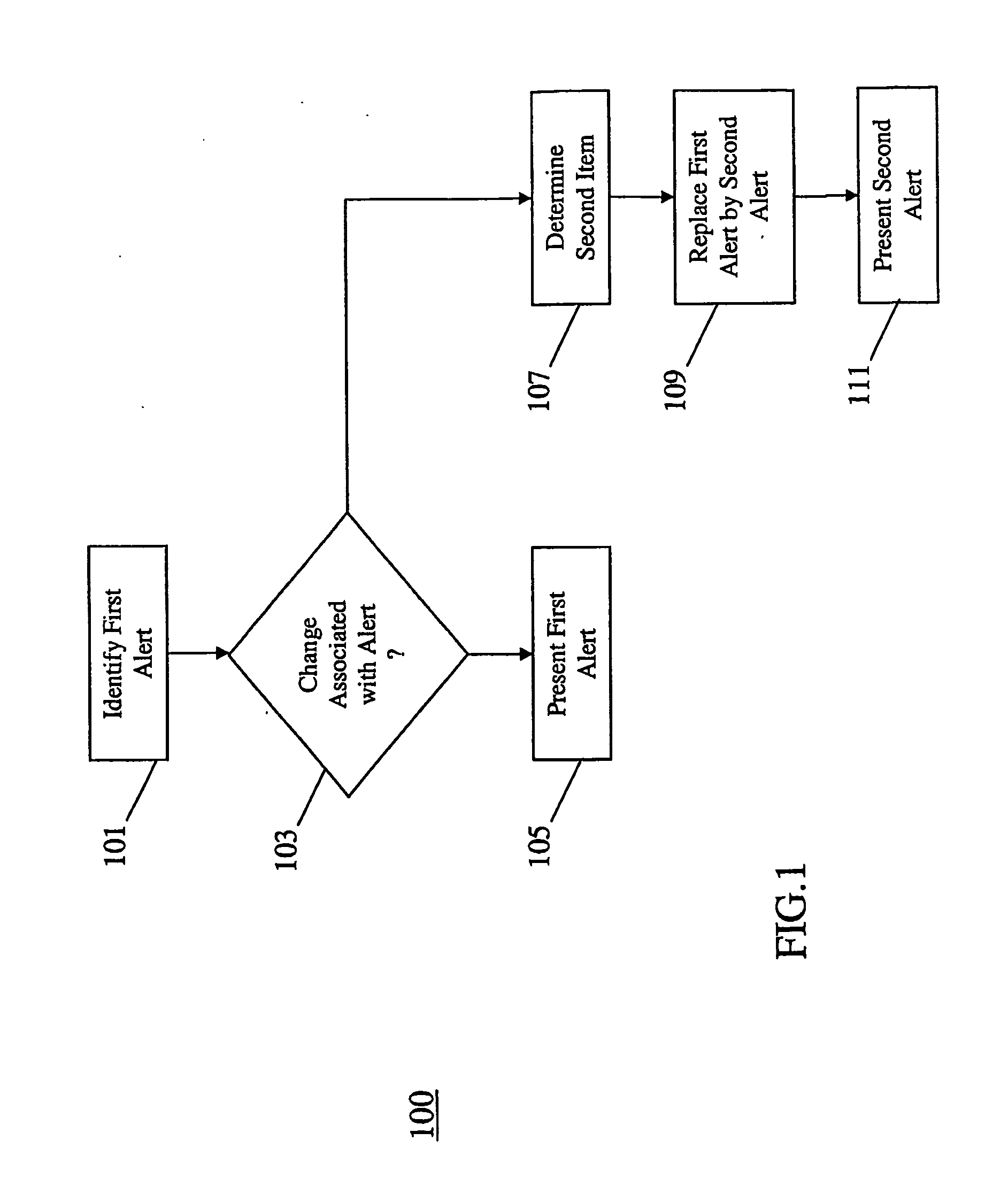

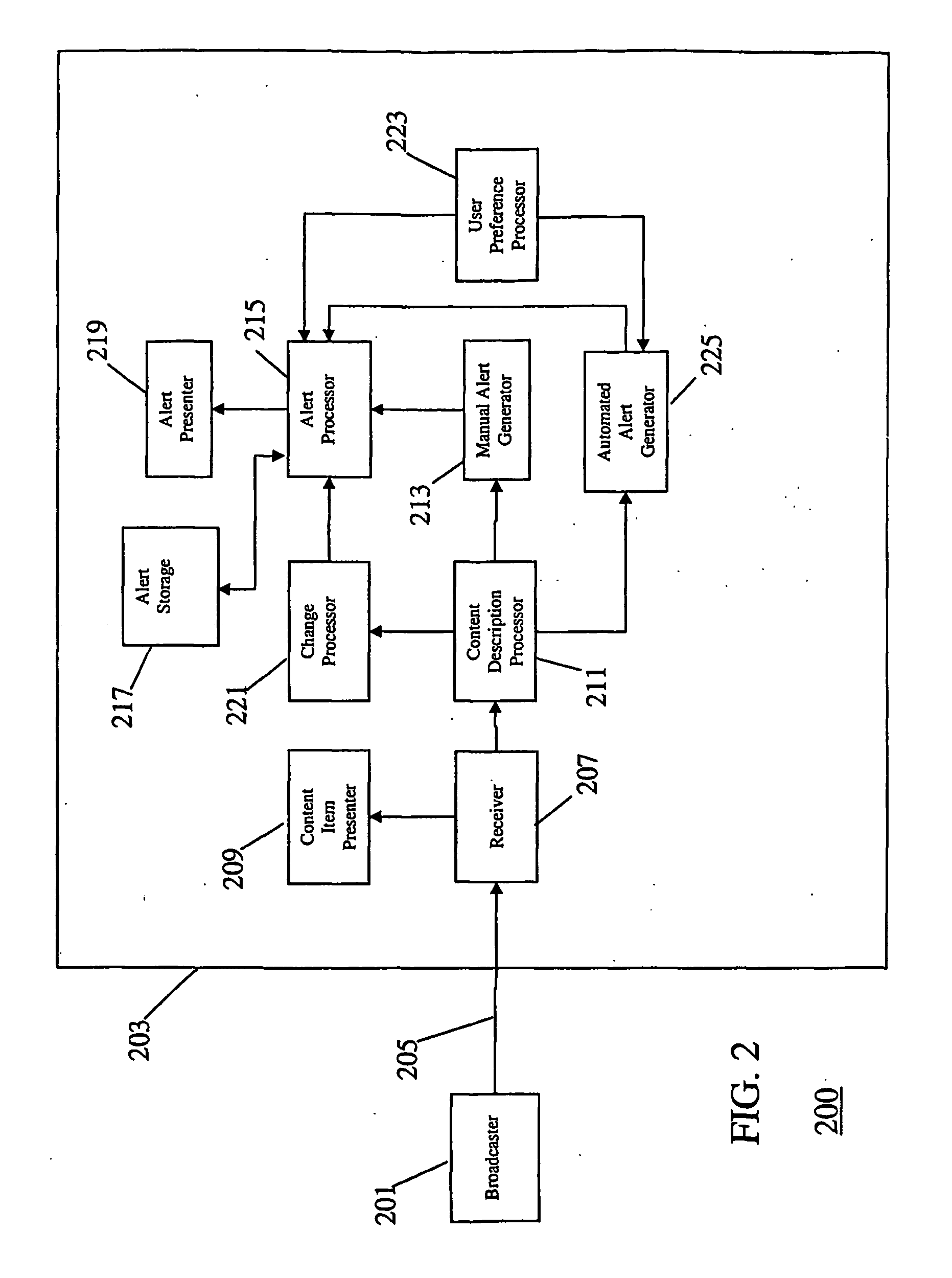

Method and apparatus for alert management

InactiveUS20090231128A1Complex implementationReduce complexityTelevision system detailsColor television detailsAlert managementAssociative processor

An alert management apparatus (100) comprises a presentation item data store (107) providing first description data associated with a plurality of presentation items, such as audio clips. The alert management apparatus (100) further comprises an alert data store (103) storing second description data associated with an alert, such as an alert for a content item. An association processor (109) is coupled to the presentation item data store (107) and the alert data store (103) and is arranged to select a presentation item of the plurality of presentation items for the alert in response to the first description data and the second description data. For example, a presentation item matching the genre, artist and or title of a content item of the alert may be selected. A presentation processor (111) then presents the selected presentation item to a user when the alert is activated. The invention may allow an automatic customisation of alert notifications.

Owner:MOTOROLA INC

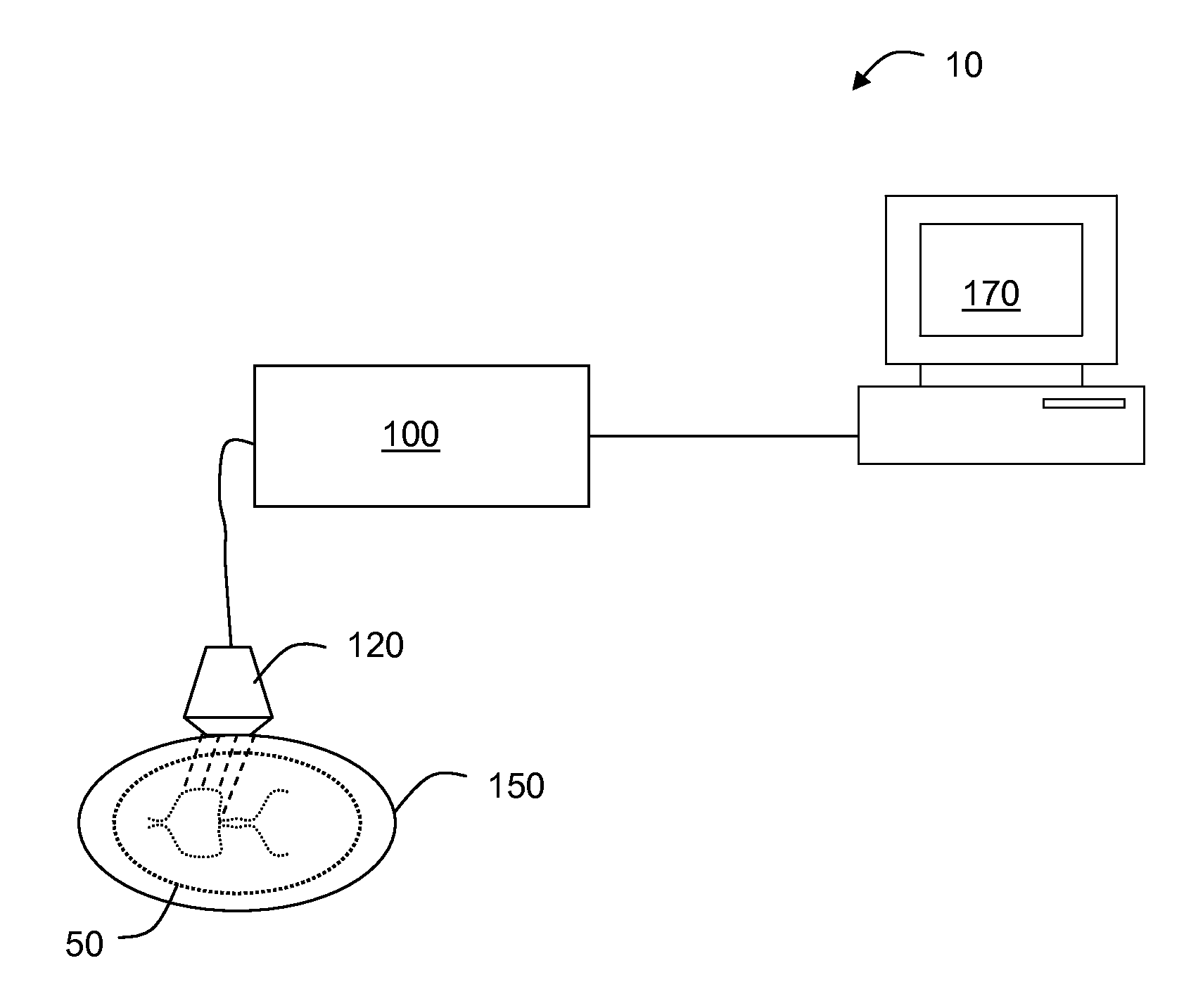

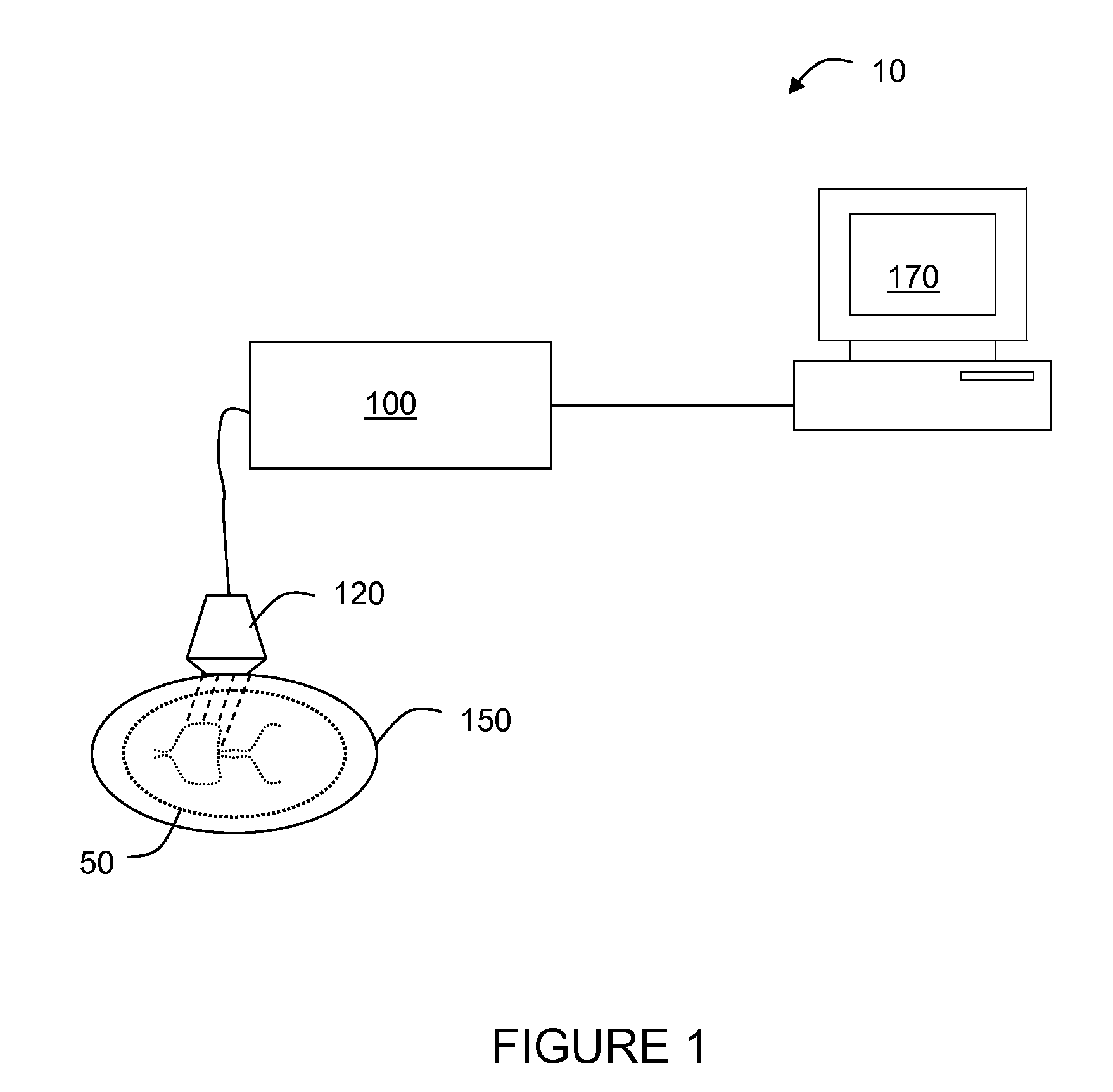

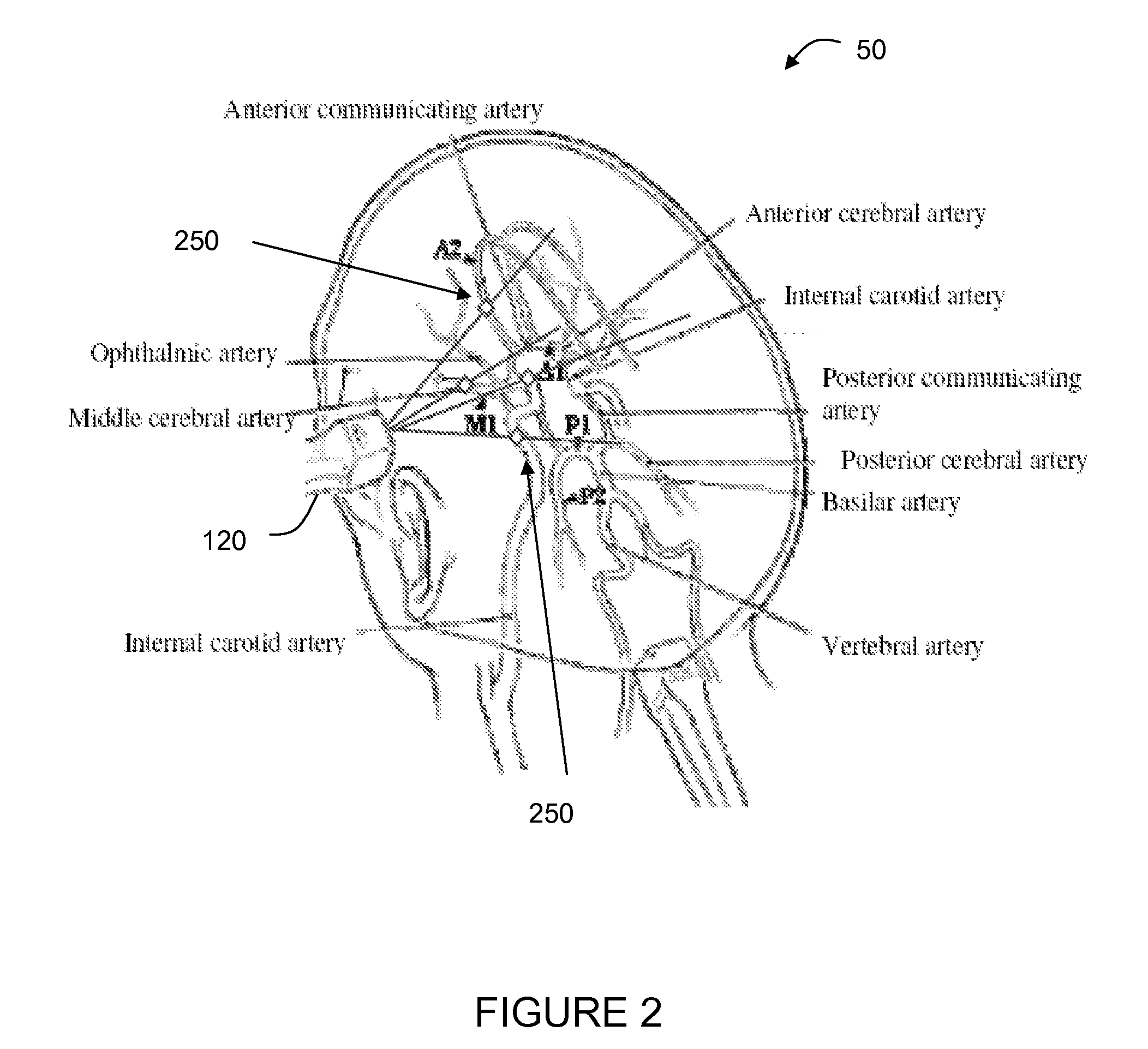

Method and system for imaging vessels

InactiveUS20100249597A1Reducing and eliminating stressReducing and eliminating and injuryDiagnostic probe attachmentBlood flow measurement devicesBlood flowTransducer

A method and system of imaging of a vessel is provided. The system can include a matrix transducer array (120) for transmitting ultrasonic waves into a region of a body having a vessel and receiving echoes in response, where the echoes are associated with blood flow through the vessel; and a processor (100) operably coupled to the matrix transducer array. The processor can adjust positions of sample volumes (250) associated with the echoes. The processor can electronically steers the ultrasonic waves at one or more of the positions of the sample volumes. The processor can determine a wall of the vessel at each of the positions of the sample volumes based on a Doppler spectrum captured at each of the positions of the sample volumes. Other embodiments are disclosed.

Owner:KONINKLIJKE PHILIPS ELECTRONICS NV

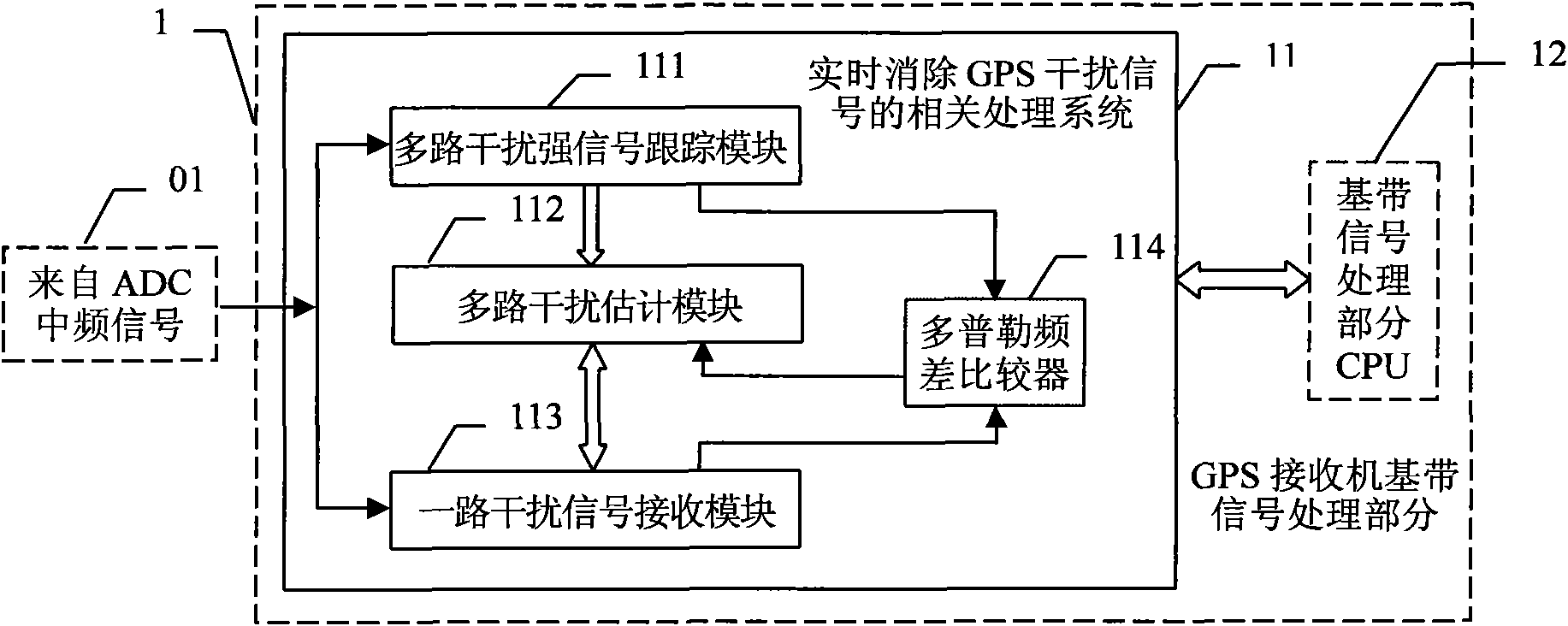

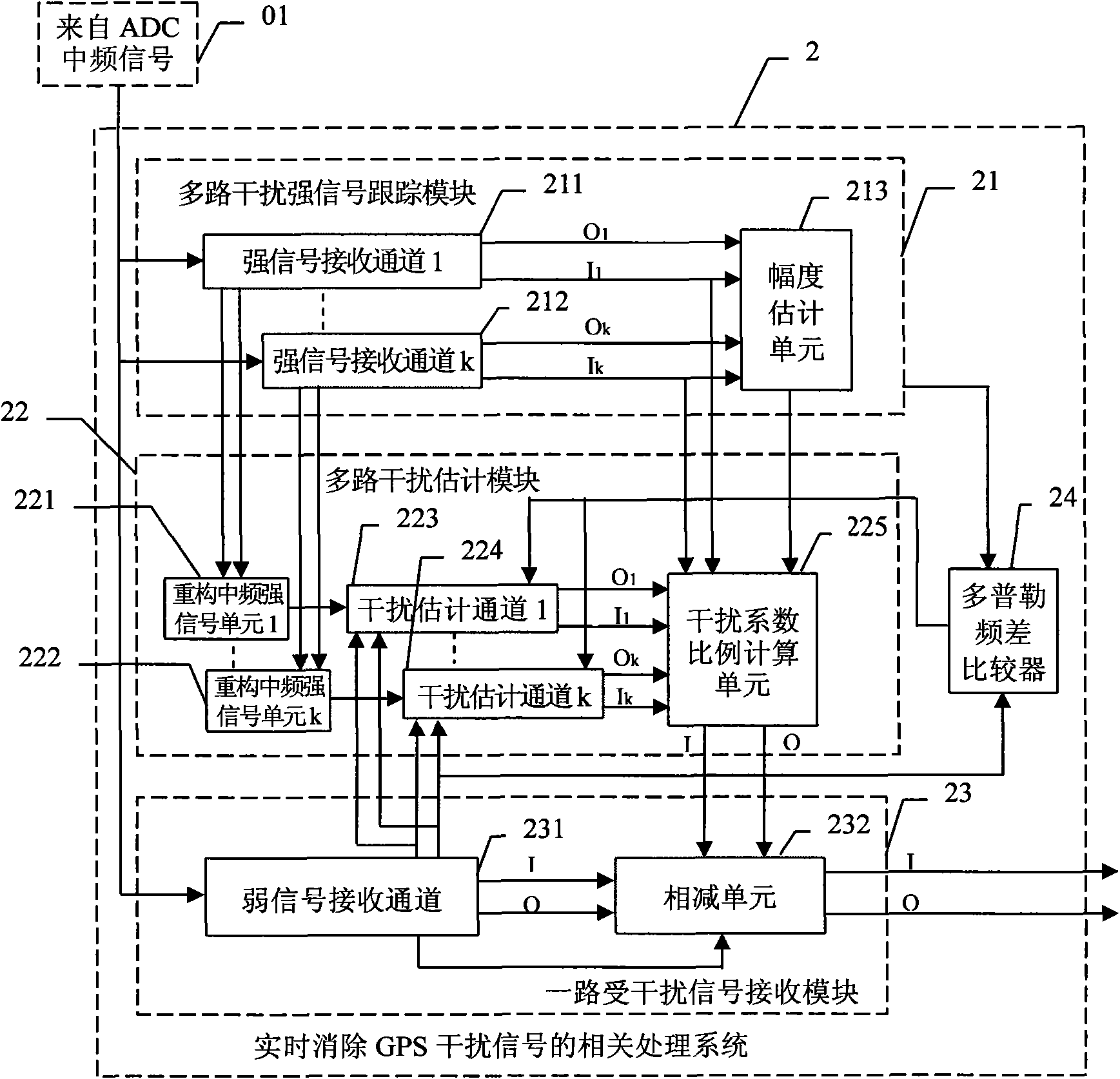

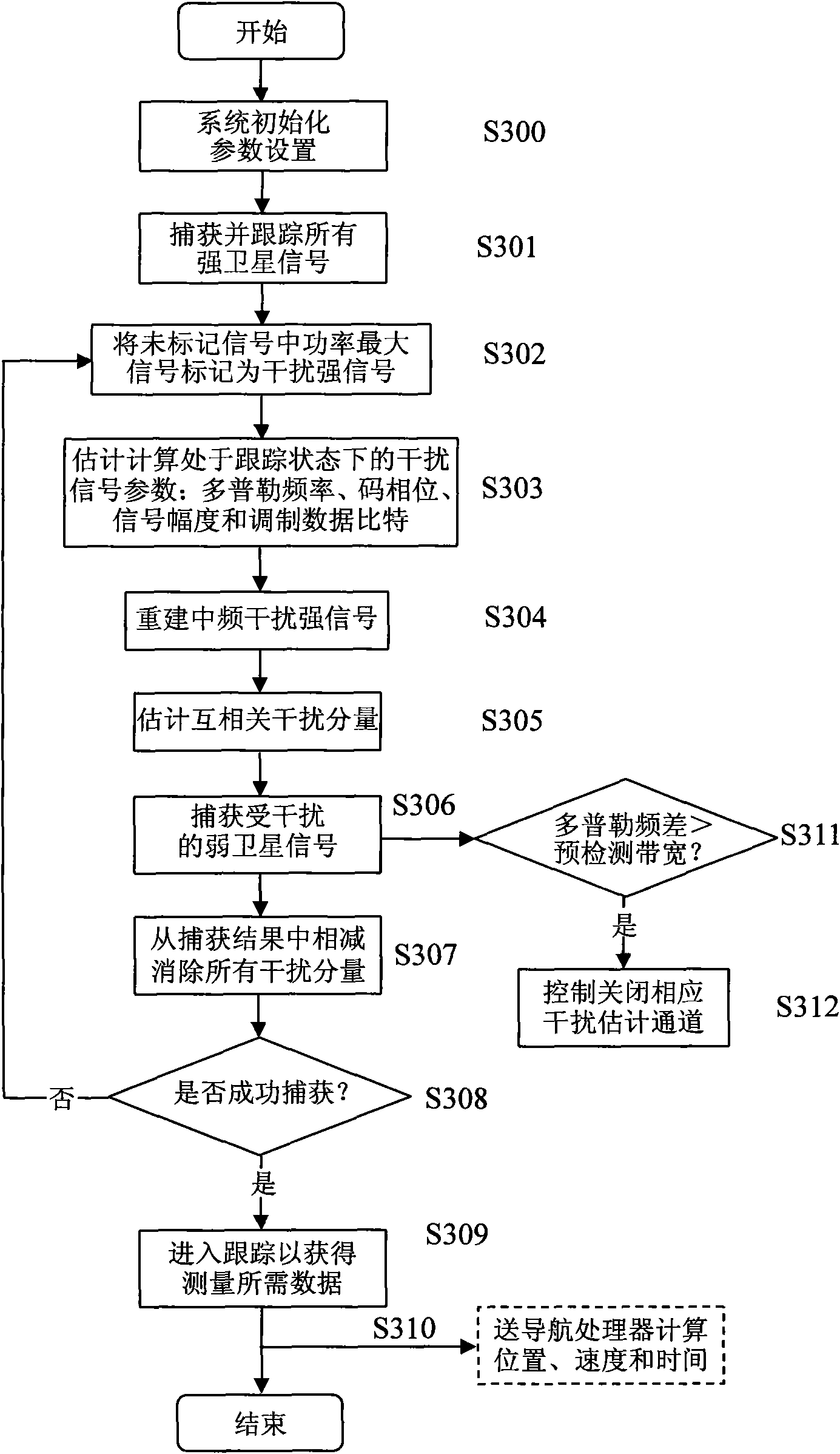

Method for eliminating interference signal of GPS receiver and system thereof

ActiveCN101571585AReduce processing power consumptionAvoid massive pre-storesBeacon systems using radio wavesCode division multiple accessGps positioning system

The invention discloses a method for eliminating an interference signal of a GPS receiver and a related processing system for eliminating the GPS interference signal in real time. A baseband signal processing part of a GPS positioning system is collocated with the related processing system, and a CPU of the baseband signal processing part is collocated with interrelated manipulation program; the related processing system is provided with multiple paths of associative processor channels which are used for parallel processing at least four positioning signals, and the associative processor channels in the related processing system are selectively collocated, so that various disturbing influence on the positioning signal which is caught and tracked can be eliminated, the signal-to-noise is reduced, and the precise catching, tracking and positioning solution for weak satellite signals can be realized, thus improving the positioning coverage rate and precision of the GPS receiver. The method and the system can be used for the related processing system of a code division multiple access (CDMA) global navigational satellite locating receiver and the GPS receiver can provide accurate information of position, speed and time after being processed by the related processing system.

Owner:杭州中科微电子有限公司

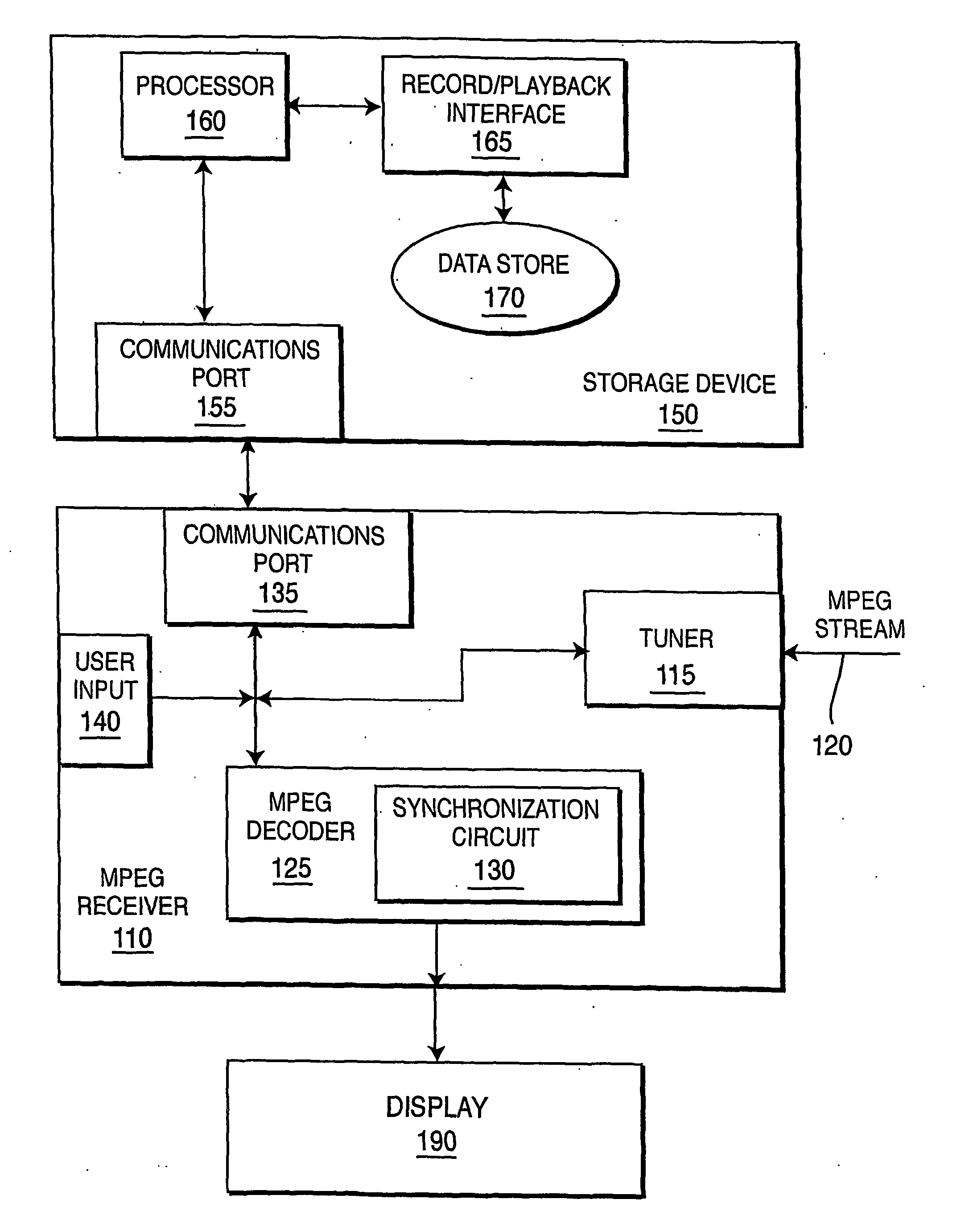

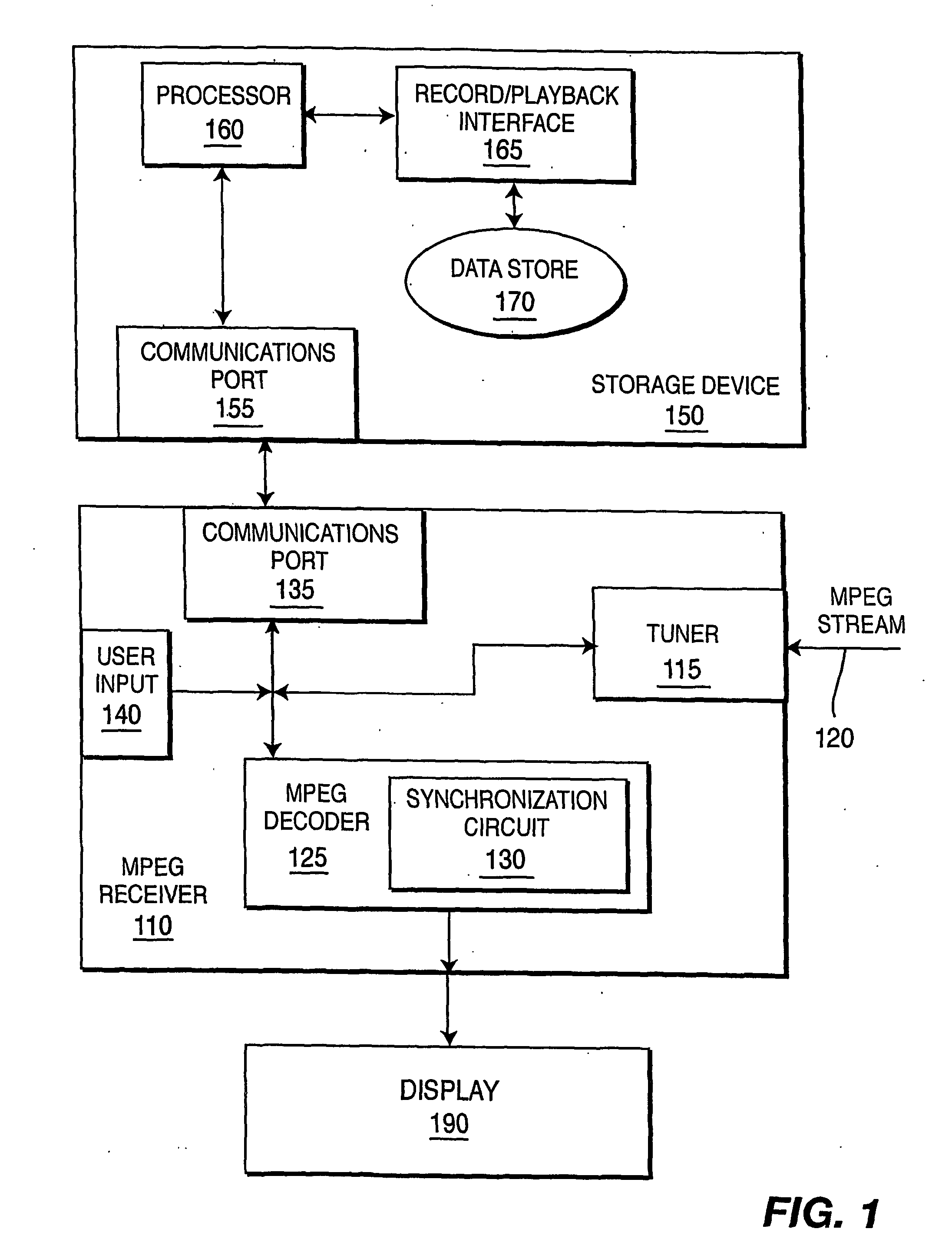

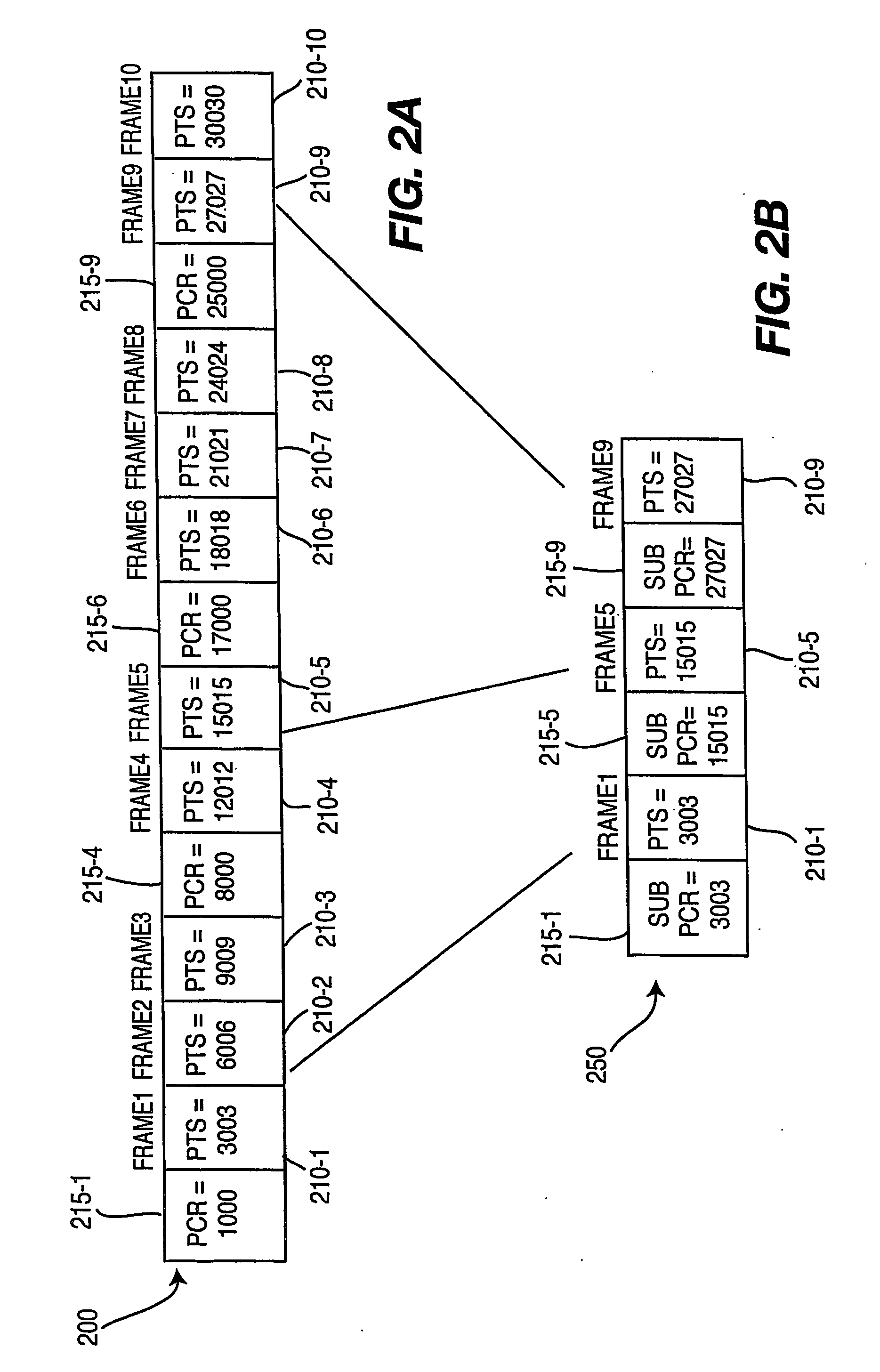

Exploitation of discontinuity indicator for trick mode operation

InactiveUS20060171659A1Television system detailsColor television detailsComputer hardwareProgram clock reference

A system and a method for modifying a stream of multimedia content to implement trick mode playback functions in MPEG receivers that do not follow general MPEG trick mode implementation recommendations. The system can include a processor that sets a discontinuity indicator in an adaptation field associated with a video frame. A substitute program clock reference (PCR) value also can be set in the adaptation field. The substitute PCR value can be set to a value approximately equal to a presentation time stamp (PTS) of the video frame with which the adaptation field is associated. The processor also can insert an adaptation field with at least one video frame with which an adaptation field was not already associated. The processor also can remove at least one video frame from the stream of multimedia content. Adaptation fields associated with the removed video frame also can be removed.

Owner:MAGNOLIA LICENSING LLC

Electronic Mail Server

InactiveUS20070073839A1Special service provision for substationData processing applicationsAssociative processorData mining

An electronic mail server is provided to facilitate e-mail communication over a network. The electronic mail server includes an account name database and an account name processor in communication with the account name database for providing a response to a message received over the network. Typically, the message includes an e-mail account name label comprising at least one account name character (having an account name character set type), with the character set type including a non-ASCII compatible character set. The account name database includes a number of database records, each identifying an e-mail account name comprising at least one record character having a record character set type, and a record character set identifier identifying the record character set type. The account name processor includes a correlation processor and a response processor. The correlation processor is configured to determine the correlation between the received e-mail account name / label and the respective e-mail account names in accordance with the associated character set type. The response processor is in communication with the correlation processor and provides the response to the message in accordance with the correlation indication.

Owner:CHUNG EDMON +2