Pipeline ADC (analog to digital converter) and error calibration method thereof

An analog-to-digital converter and pipeline technology, applied in the direction of analog-to-digital converters, analog/digital conversion calibration/testing, etc., can solve problems such as capacitance mismatch errors, and achieve the effect of simplifying the design

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0035] The specific structure of the pipeline analog-to-digital converter and the specific steps of the error calibration method of the embodiment of the present invention will be described in detail below in conjunction with the accompanying drawings.

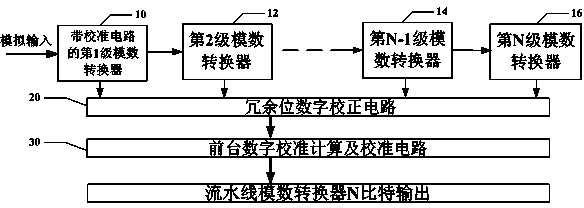

[0036] Such as figure 1 As shown, in one embodiment of the present invention, a pipelined analog-to-digital converter includes at least two stages of analog-to-digital converters (for example, figure 1 10, 12, 14, 16 etc. in) and the front digital calibration calculation and calibration circuit 30.

[0037] In the embodiment of the present invention, a calibration circuit is provided, and the calibration circuit may be set in the preceding one or several stages of the at least two-stage analog-to-digital converters.

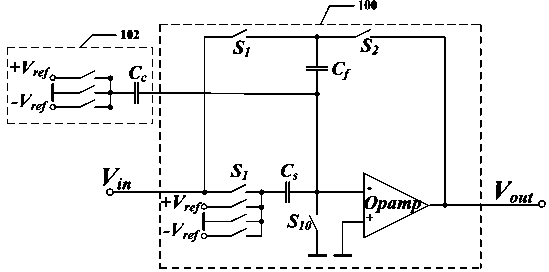

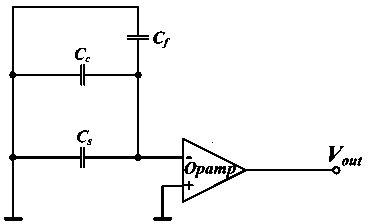

[0038] For example, if figure 1 and figure 2 As shown, at least the first-stage analog-to-digital converter 10 includes a calibration circuit 102 and an MDAC (Multiplying Digital to Analog Converter, multiply...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More