Implementing asynchronous first-in first-out data transmission by double-port direct access storage device

An asynchronous data, dual-port technology, applied in the direction of static memory, digital memory information, information storage, etc., can solve the problems of unfavorable data transmission performance, can not fully and accurately reflect the internal state of FIFO, and achieve the effect of improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

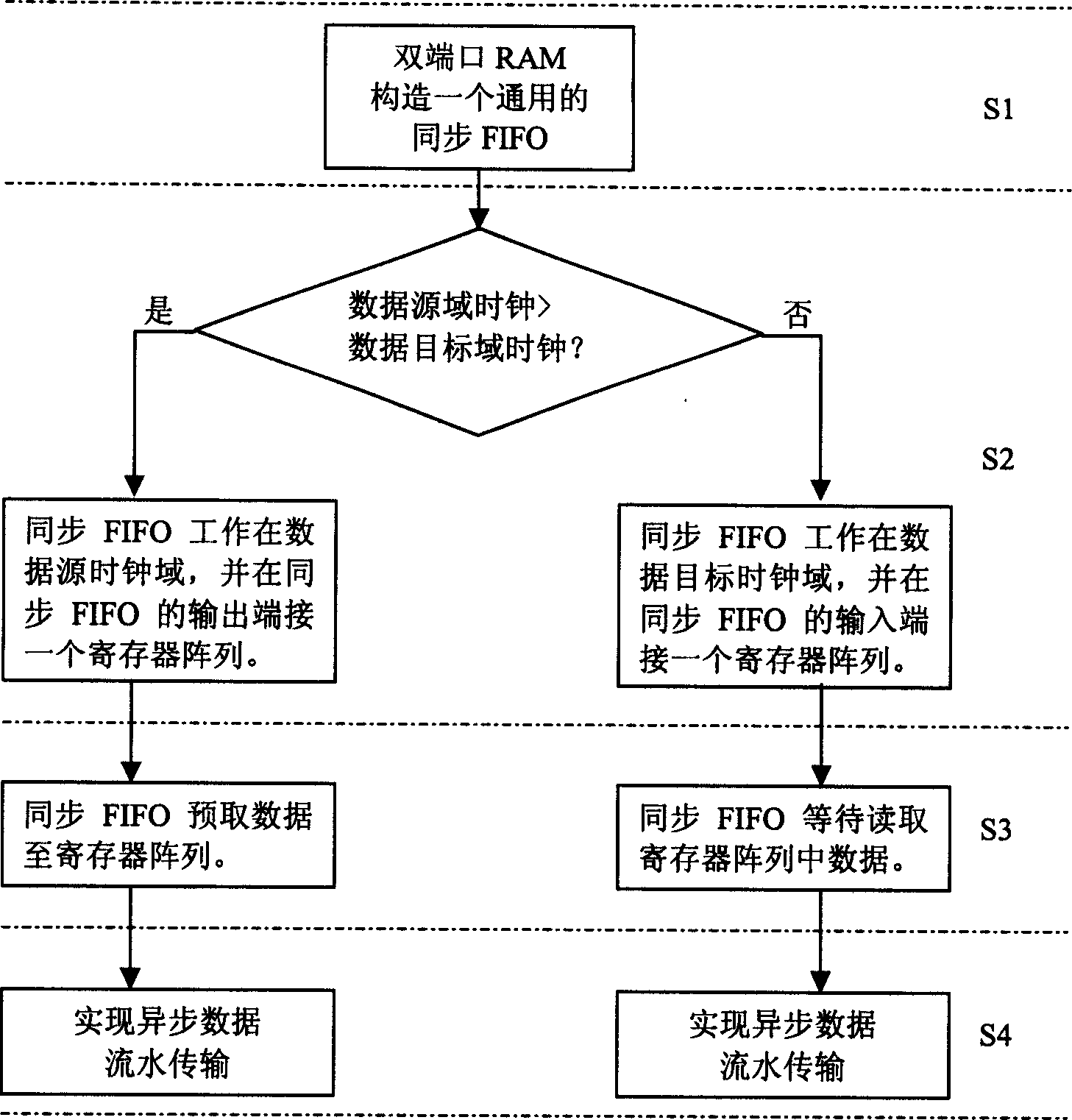

[0011] Using dual-port RAM to construct bridge FIFO in asynchronous data transmission can be divided into two steps to realize asynchronous FIFO.

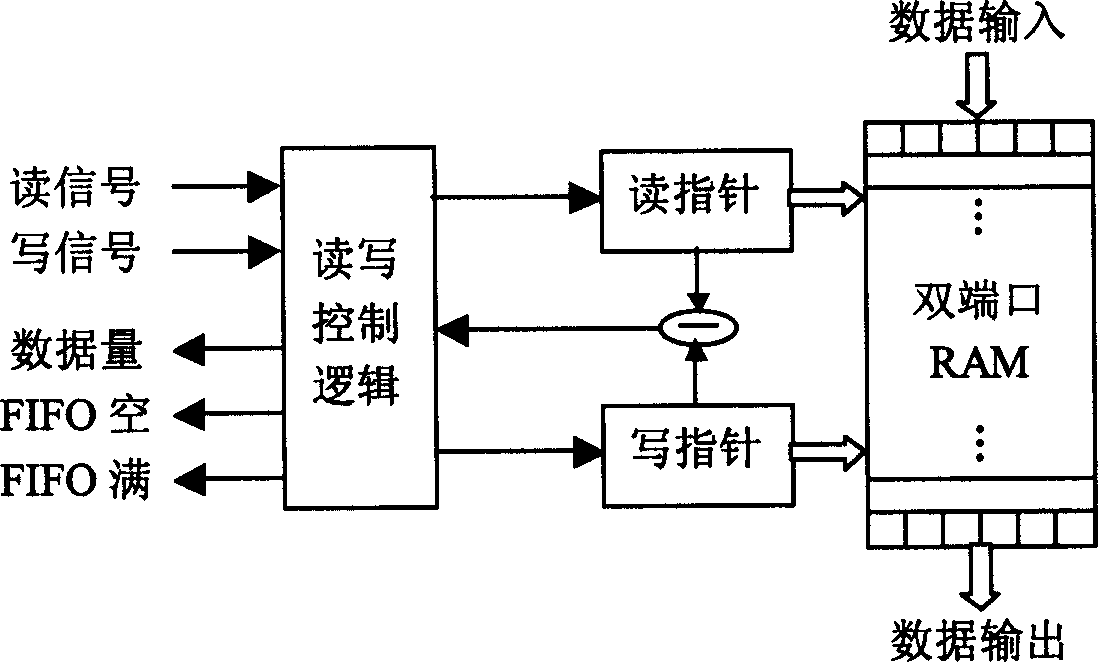

[0012] The first step is to construct a general-purpose synchronous FIFO with dual-port RAM, such as Figure 1 As shown, all the signals in the figure work in one clock domain, and the clock domain is the same as the higher speed of the two external clock sources (both sides of data transmission).

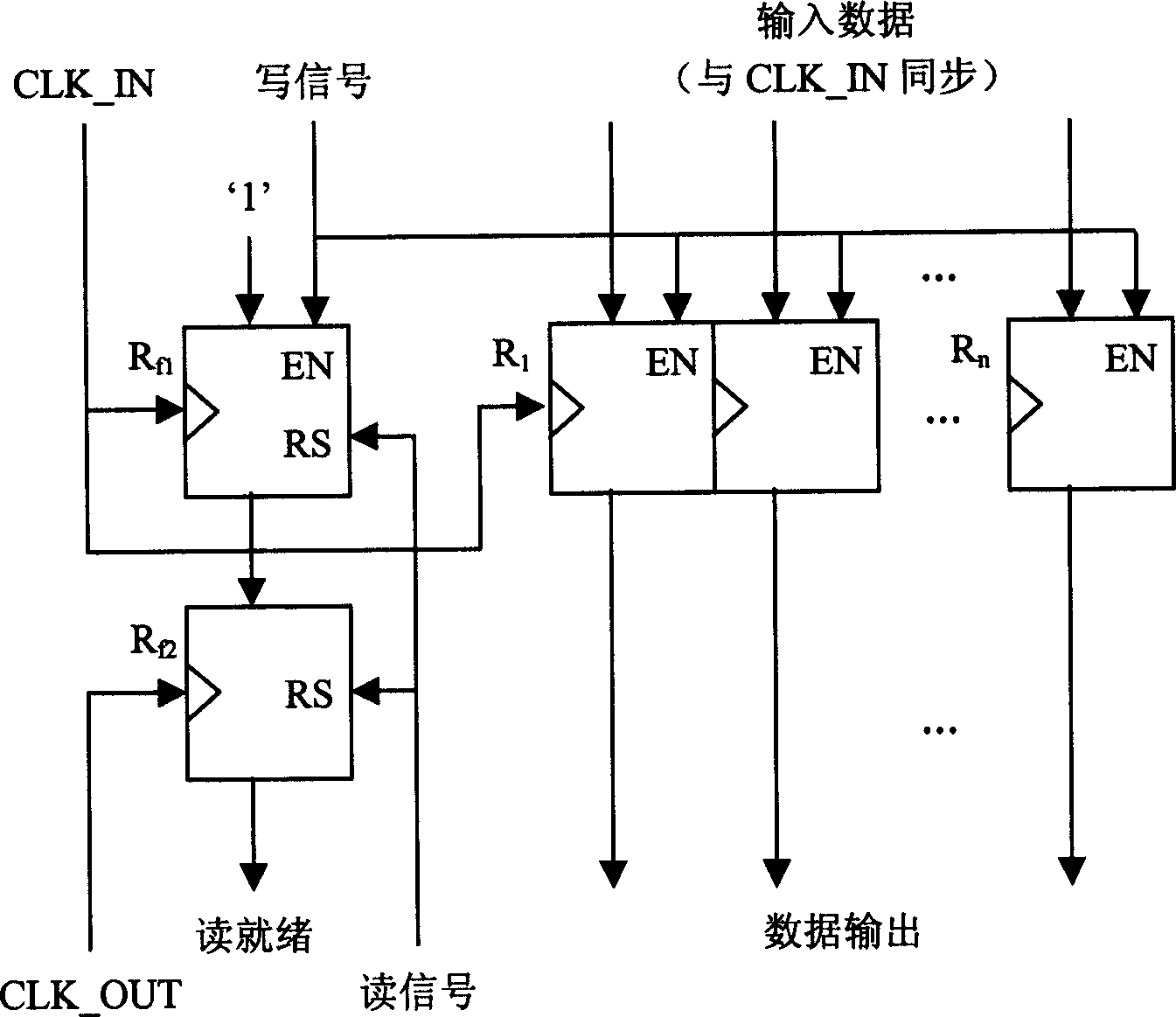

[0013] The second step is to use a smaller register array to form an asynchronous interface on top of the common synchronous FIFO. The width of the register array is equal to the data width of the FIFO, and a status flag register is added; the depth of the register array is determined according to the gap ratio of the asynchronous clock domain. In fact, a register array with a depth of n is a small FIFO formed by connecting n register arrays with a depth of 1 in series. Therefore, the register array with a depth of 1 is defined as a reg...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More