Full digital time-delay locking loop circuit

A delay-locked loop, all-digital technology, applied in digital memory information, electrical components, static memory, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0022] Below in conjunction with accompanying drawing, the technical scheme of invention is described in detail:

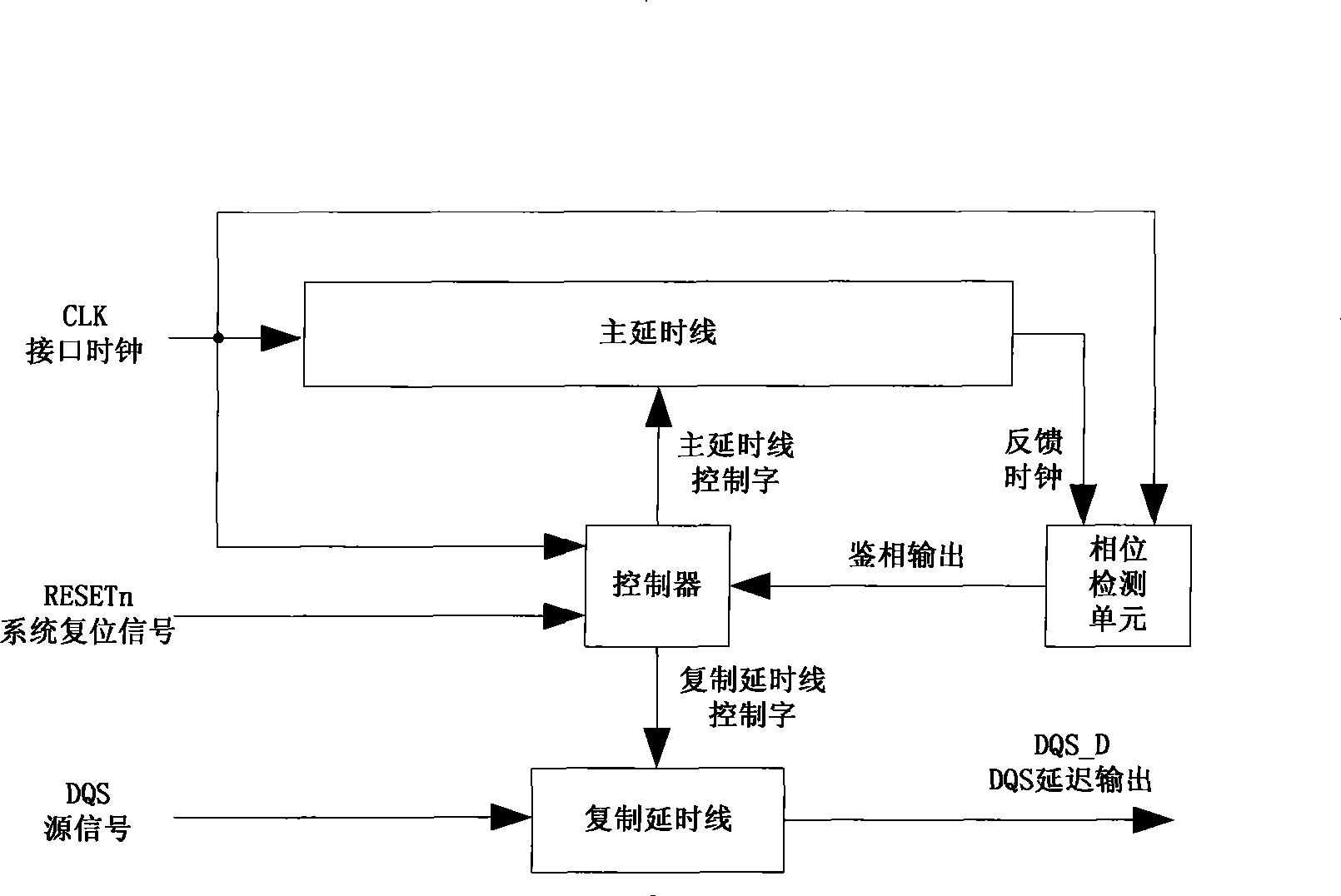

[0023] Such as figure 1 A system block diagram of an all-digital delay-locked loop is shown. In the figure, CLK is input to the main delay line, and the output of the main delay line is named the feedback clock. CLK and the feedback clock perform phase detection, and the controller samples the result of the phase comparison, adjusts the main delay line and the copy delay control word, respectively Control the two delay lines to produce the appropriate amount of delay. The main delay line is responsible for locking the CLK cycle, and the copy delay line is responsible for DQS phase shifting. Phase detection usually includes two links of coarse phase detection and fine phase detection, therefore, the controller also includes a coarse adjustment controller and a fine adjustment controller.

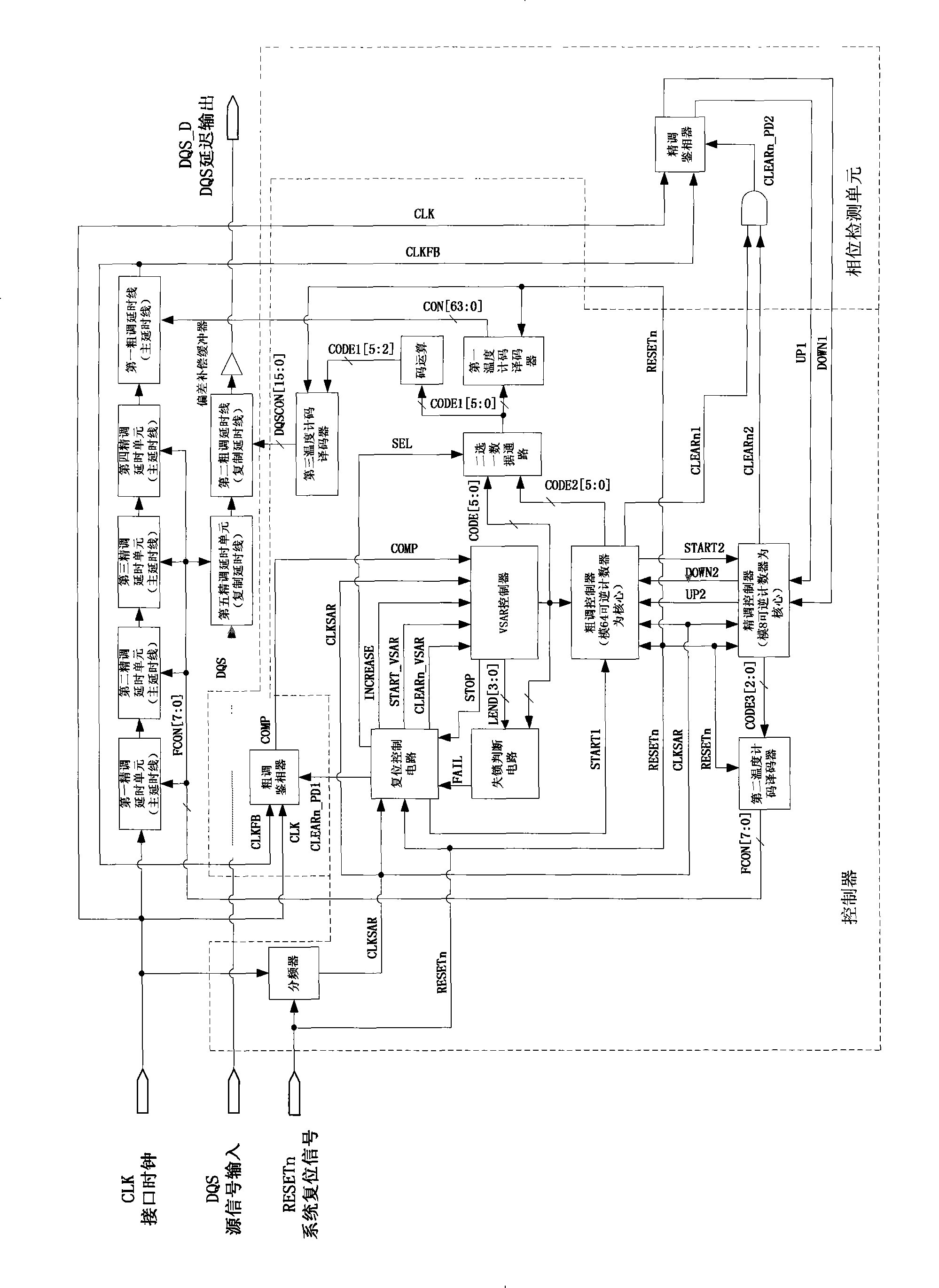

[0024] Such as figure 2 Shown is the complete circuit block diagram of ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More