Clock frequency dividing method based on trigger ring and clock frequency dividing circuit thereof

A clock frequency dividing and frequency dividing circuit technology, applied in the synchronous pulse counter, continuous cycle pulse counter, etc., can solve the problems of inaccurate frequency dividing number, large scale of multi-stage frequency dividing circuit, and inoperable frequency dividing circuit, etc. Achieve the effect of small delay and reduced scale

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

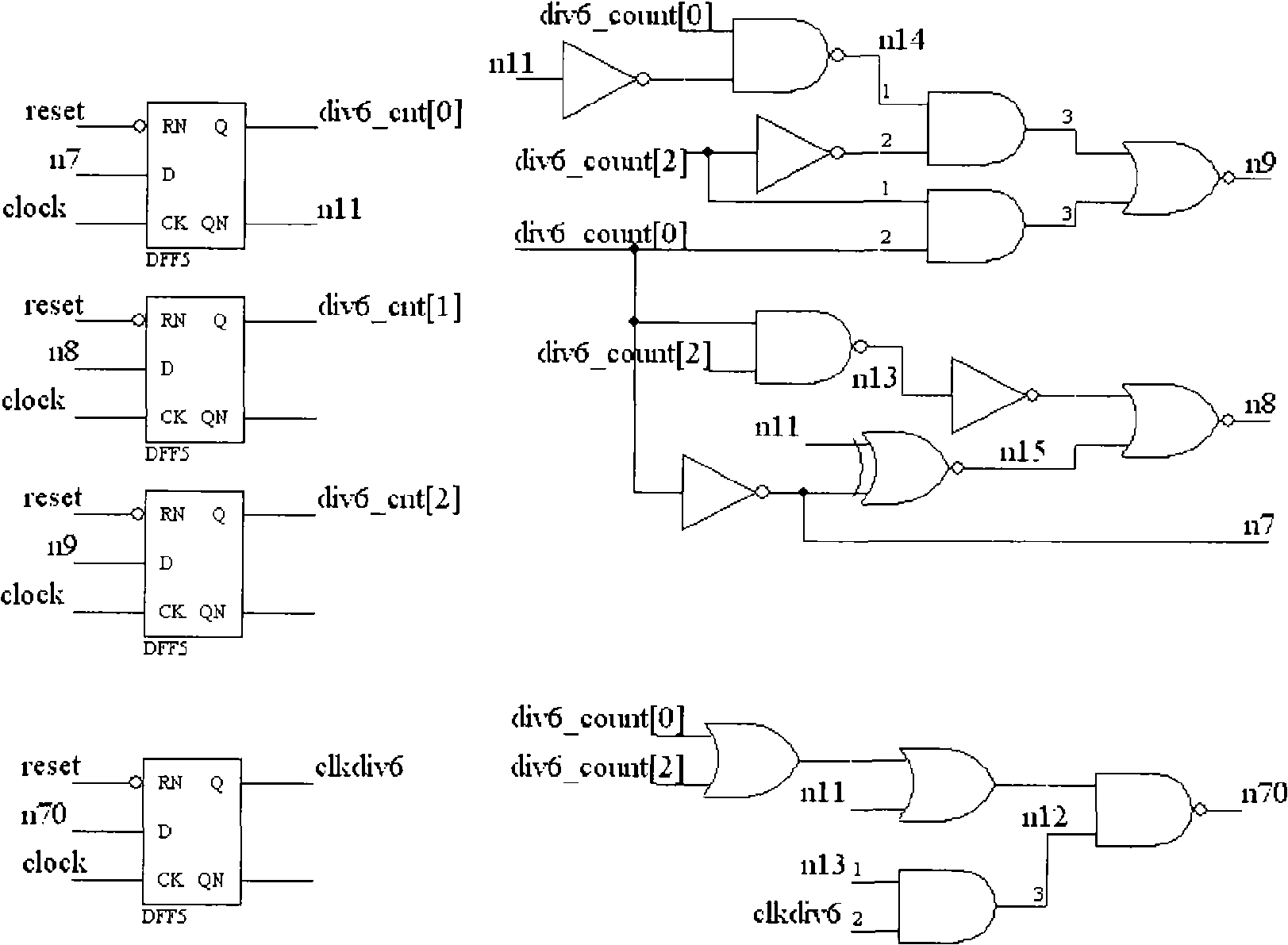

[0041] The present invention will be described in detail below with reference to the accompanying drawings.

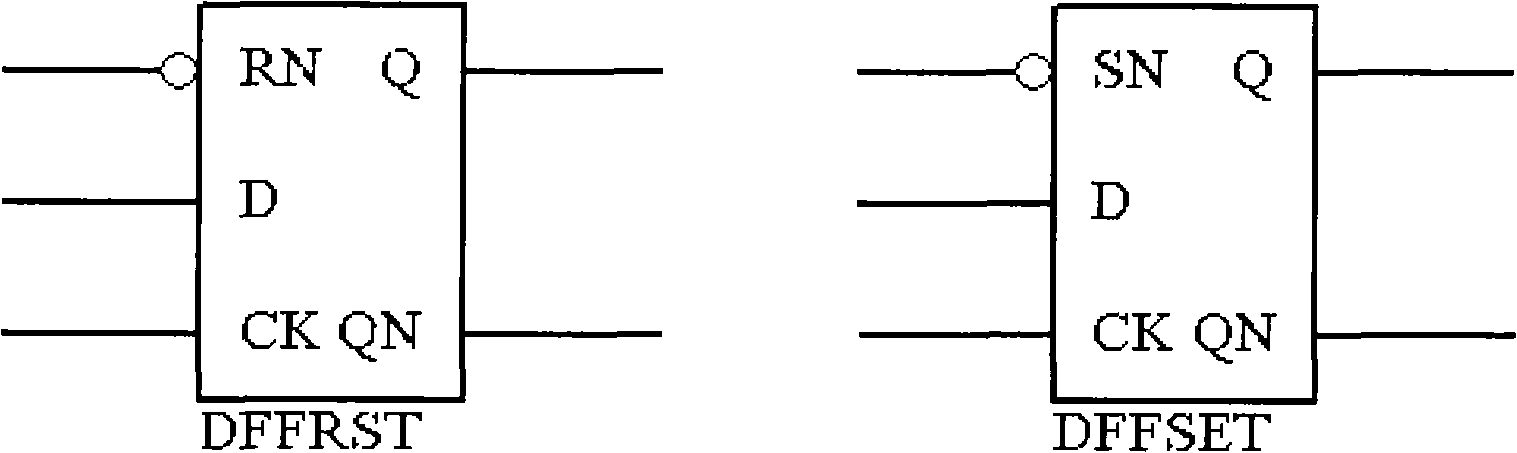

[0042] A flip-flop is a memory device in a circuit. The structure of a common flip-flop with a reset terminal / set terminal is as follows: figure 2 shown. D is the data input terminal, CK is the clock terminal, RN / SN is the reset terminal / set terminal, and Q / QN is the data output terminal. The basic function of the flip-flop is that when RN / SN is 0, the output of Q remains 0 / 1. When RN is not 0, the value of D is latched into Q at the rising edge of each CK. , while QN remains the inverse of Q at all times. Different initial values can be achieved by selecting flip-flops with set or reset terminals.

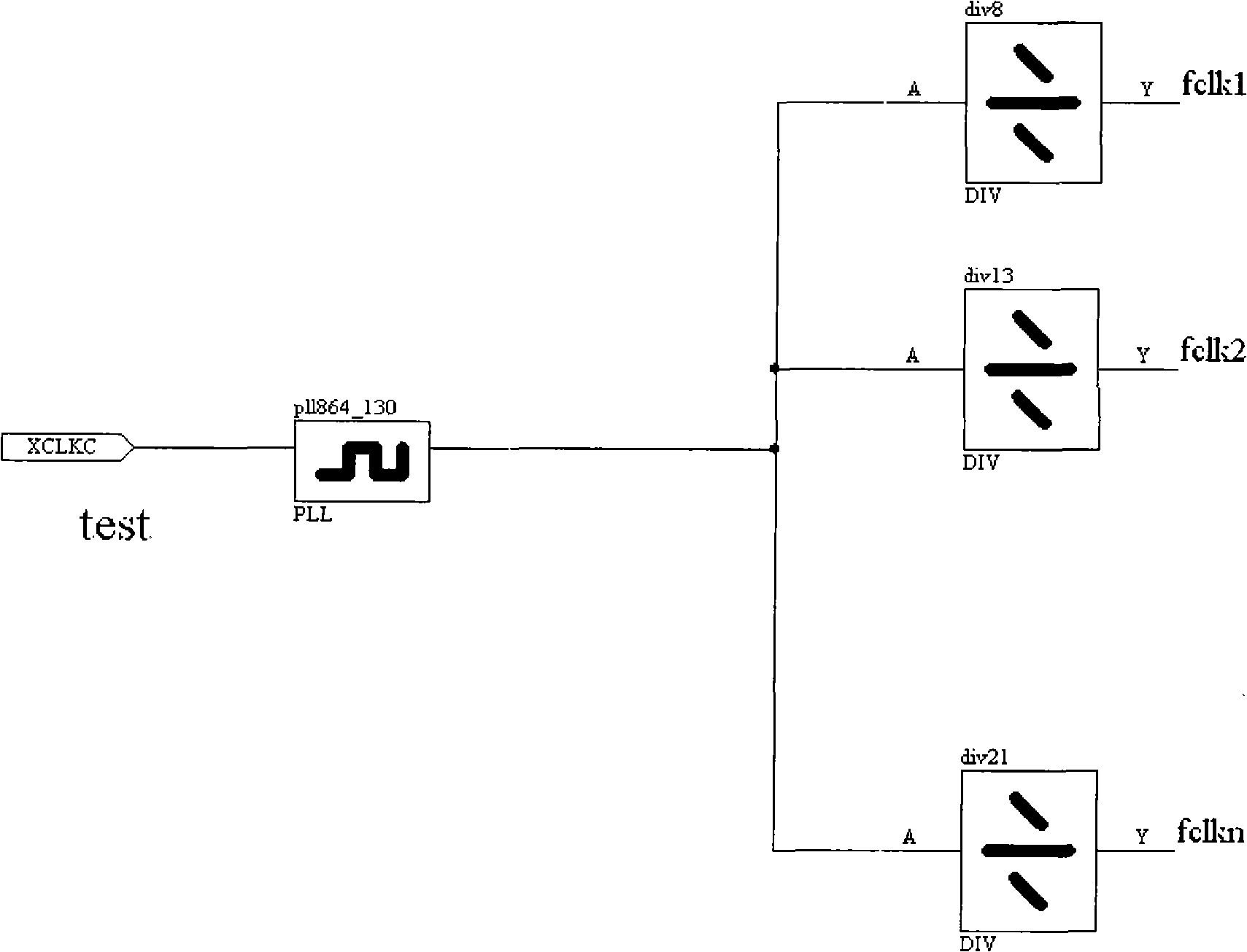

[0043] The clock frequency dividing method based on the flip-flop loop provided by the present invention is to connect the D terminals and Q terminals of several flip-flops in sequence, and the Q terminal of the last flip-flop is connected to the D terminal of the fi...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More