Patents

Literature

232results about "Frequency-changer modifications" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

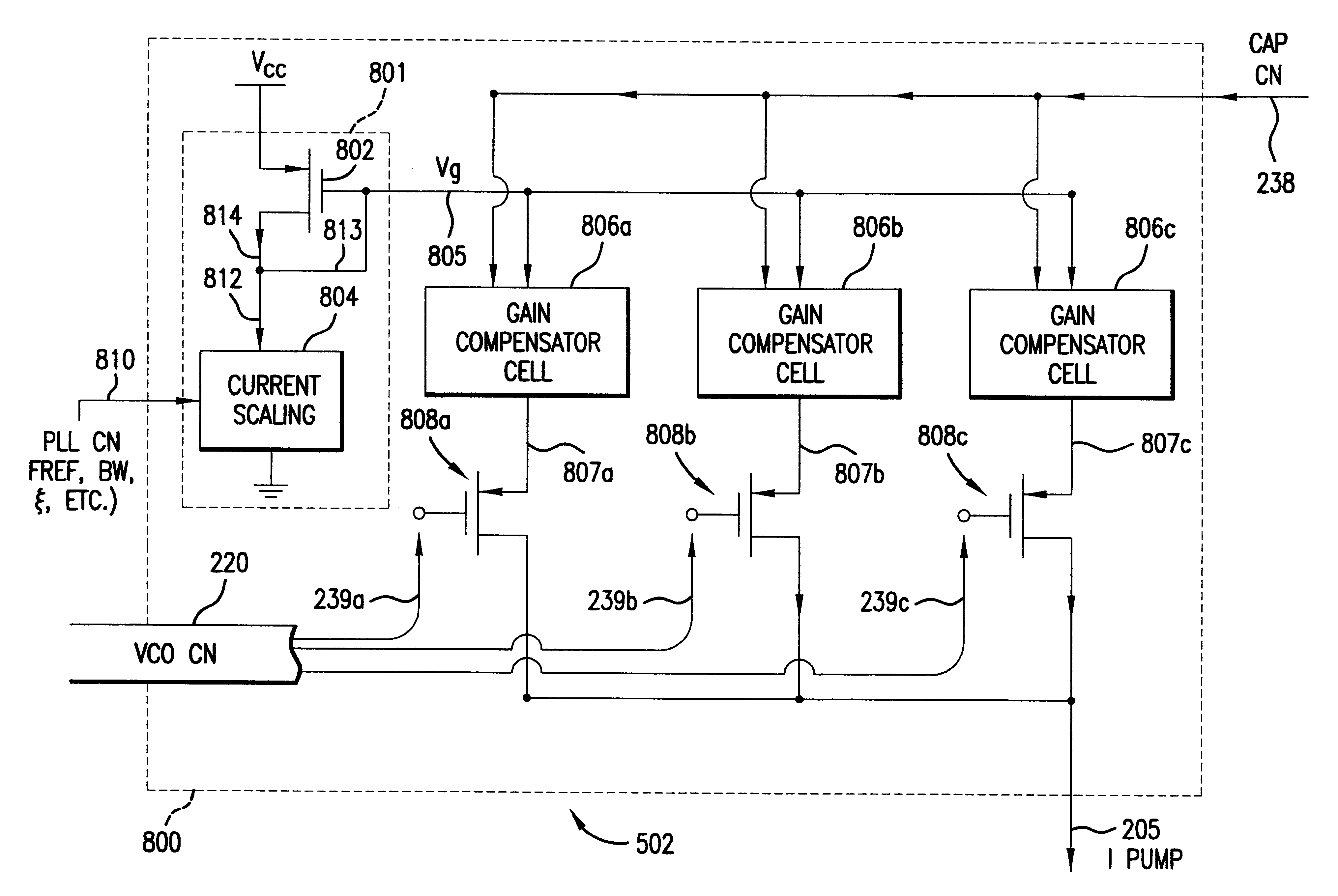

Apparatus and method for phase lock loop gain control using unit current sources

InactiveUS6583675B2Pulse automatic controlDiscontinuous tuning for band selectionFixed capacitorReference current

A gain compensator compensates for the gain variation of a varactor-tuned voltage tuned oscillator (VCO) in a phase lock loop (PLL). The VCO includes a parallel LC circuit having multiple fixed capacitors that can be switched-in or switched-out of the LC circuit according to a capacitor control signal to perform band-select tuning of the VCO. The gain compensator compensates for the variable VCO gain by generating a charge pump reference current that is based on the same capacitor control signal that controls the fixed capacitors in the LC circuit. The gain compensator generates the charge pump reference current by replicating a reference scale current using unit current sources. The number of times the reference scale current is replicated is based on the fixed capacitance that is switched-in to the LC circuit and therefore the frequency band of the PLL. The reference scale current is generated based on a PLL control that specifics certain PLL characteristics such as reference frequency, loop bandwidth, and loop damping. Therefore, the reference pump current can be efficiently optimized for changing PLL operating conditions, in addition to compensating for variable VCO gain.

Owner:AVAGO TECH INT SALES PTE LTD

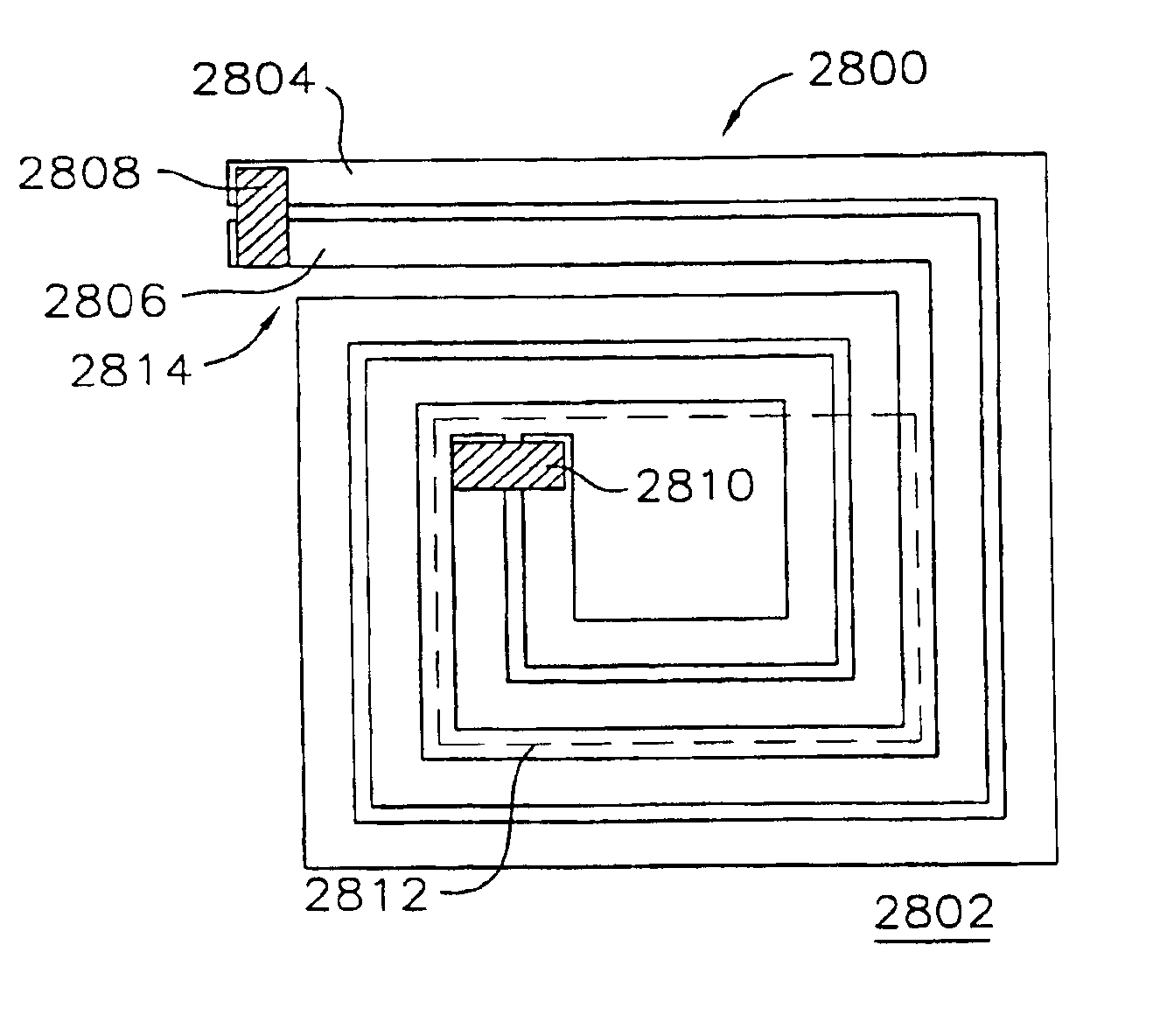

Multi-track integrated spiral inductor

InactiveUS6885275B1Resonant circuit detailsSemiconductor/solid-state device detailsSpiral inductorEngineering

An integrated circuit inductor includes a spiral pattern disposed upon a substrate. The track of the spiral is divided into multiple tracks to form a multi-track inductor. The individual tracks are disposed side by side and in different layers. Tracks that are aligned vertically are coupled by feed throughs, or vias. Multiple vias are used along the length of each of the multiple tracks. Tracks disposed in the same layer are joined together at their beginning, and at their termination. A patterned shield is fabricated from conductive fingers of n+ salicided material that is separated by non conducting polysilicon that fills the gaps between the fingers. The conductive fingers are coupled together in groups, which are in turn tied to a single point ground. In tying the groups together, a gap in the conducting path is provided to prevent ground loop currents. The shield is disposed between the multi-track inductor and the substrate.

Owner:AVAGO TECH INT SALES PTE LTD

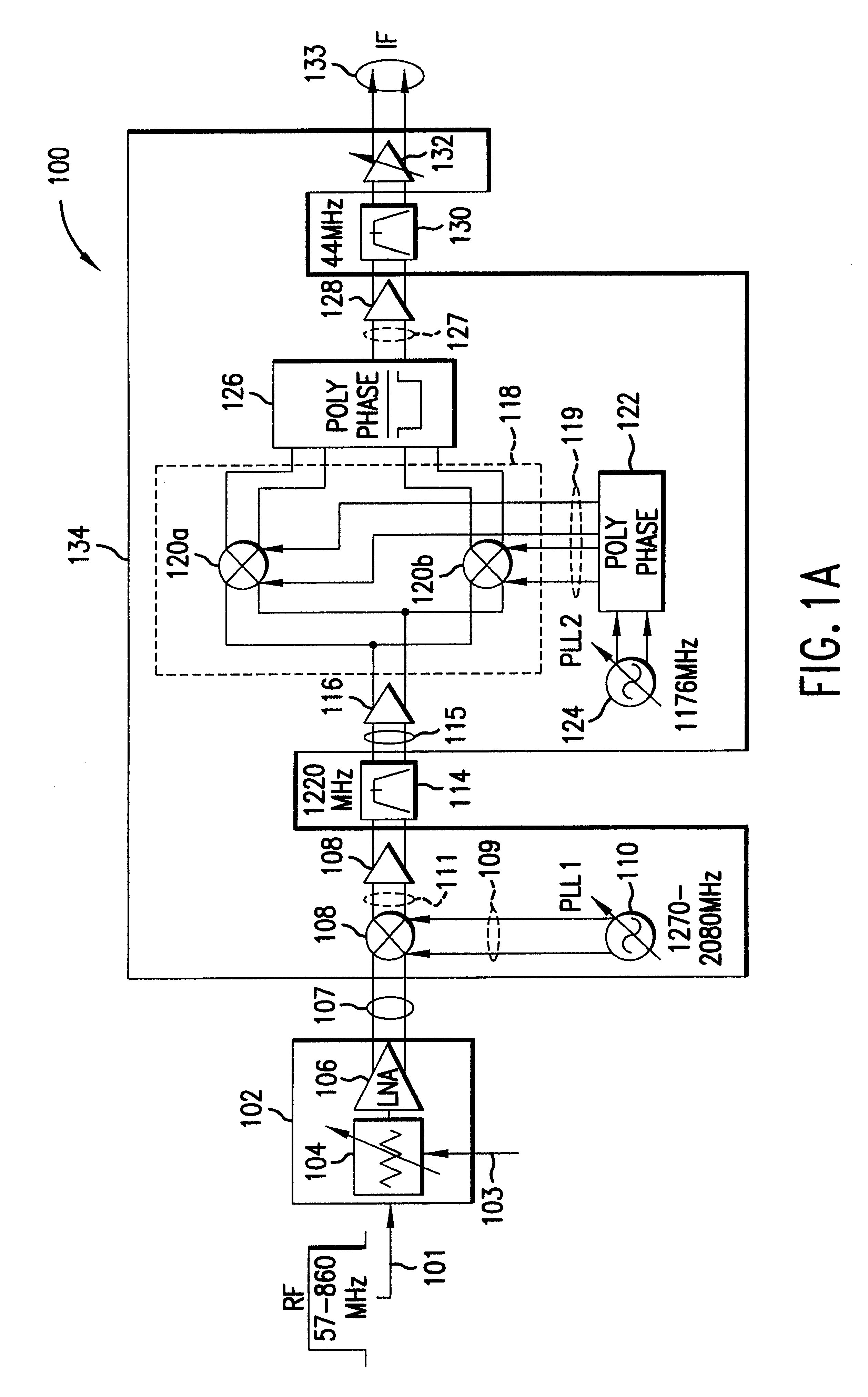

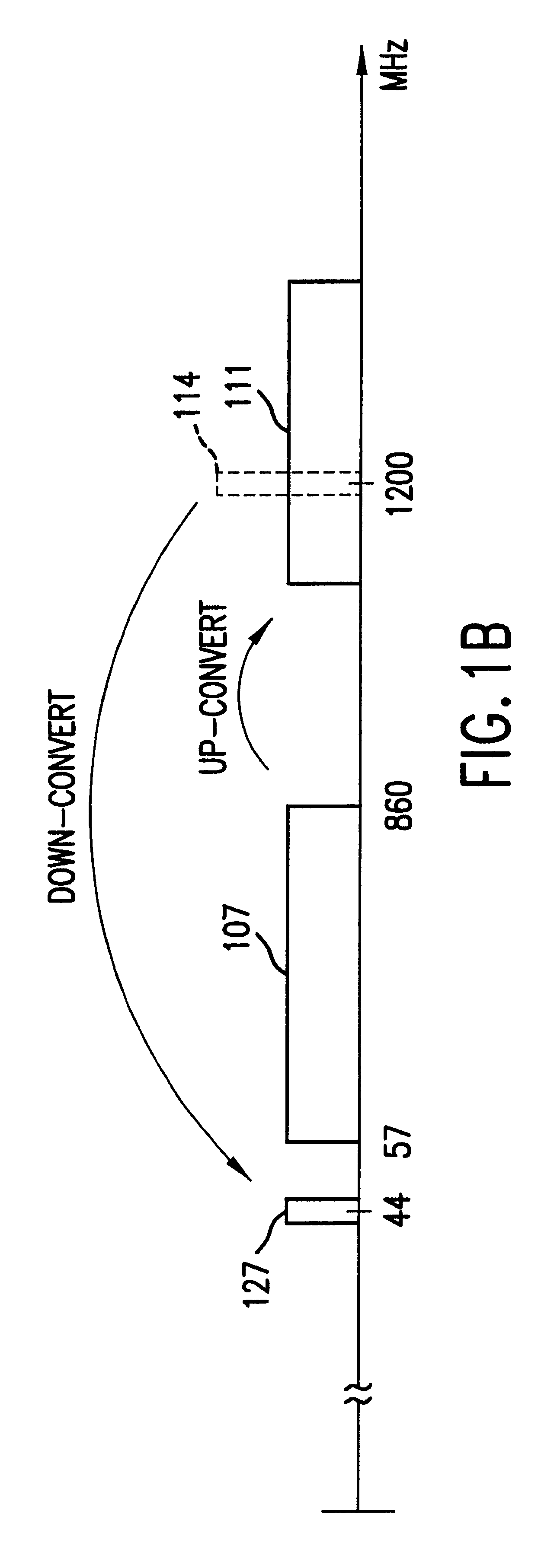

Integrated switchless programmable attenuator and low noise amplifier

InactiveUS6879816B2Multiple-port active networksSwitched capacitor networksCapacitanceLocal oscillator signal

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programmable attenuation and a programmable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

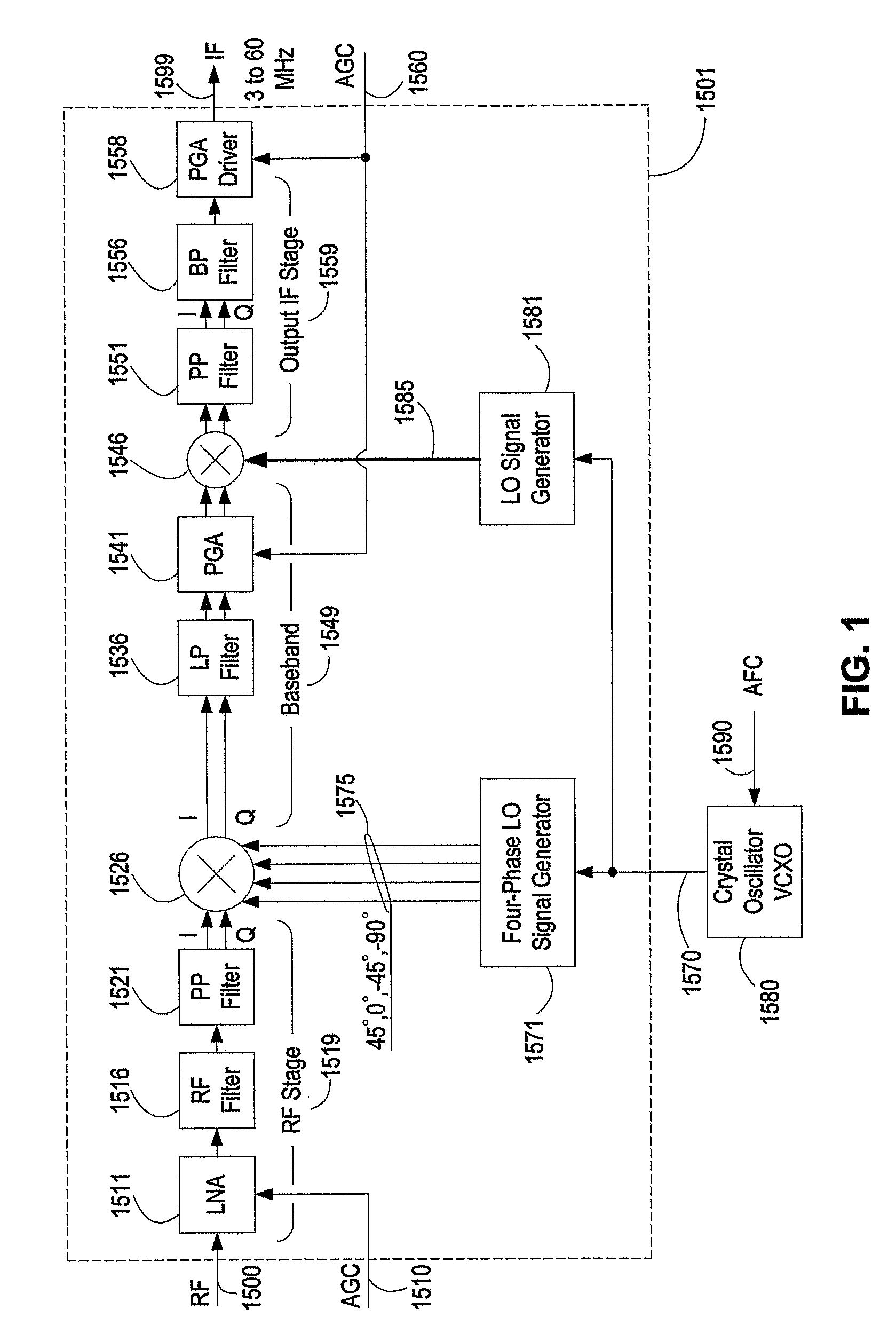

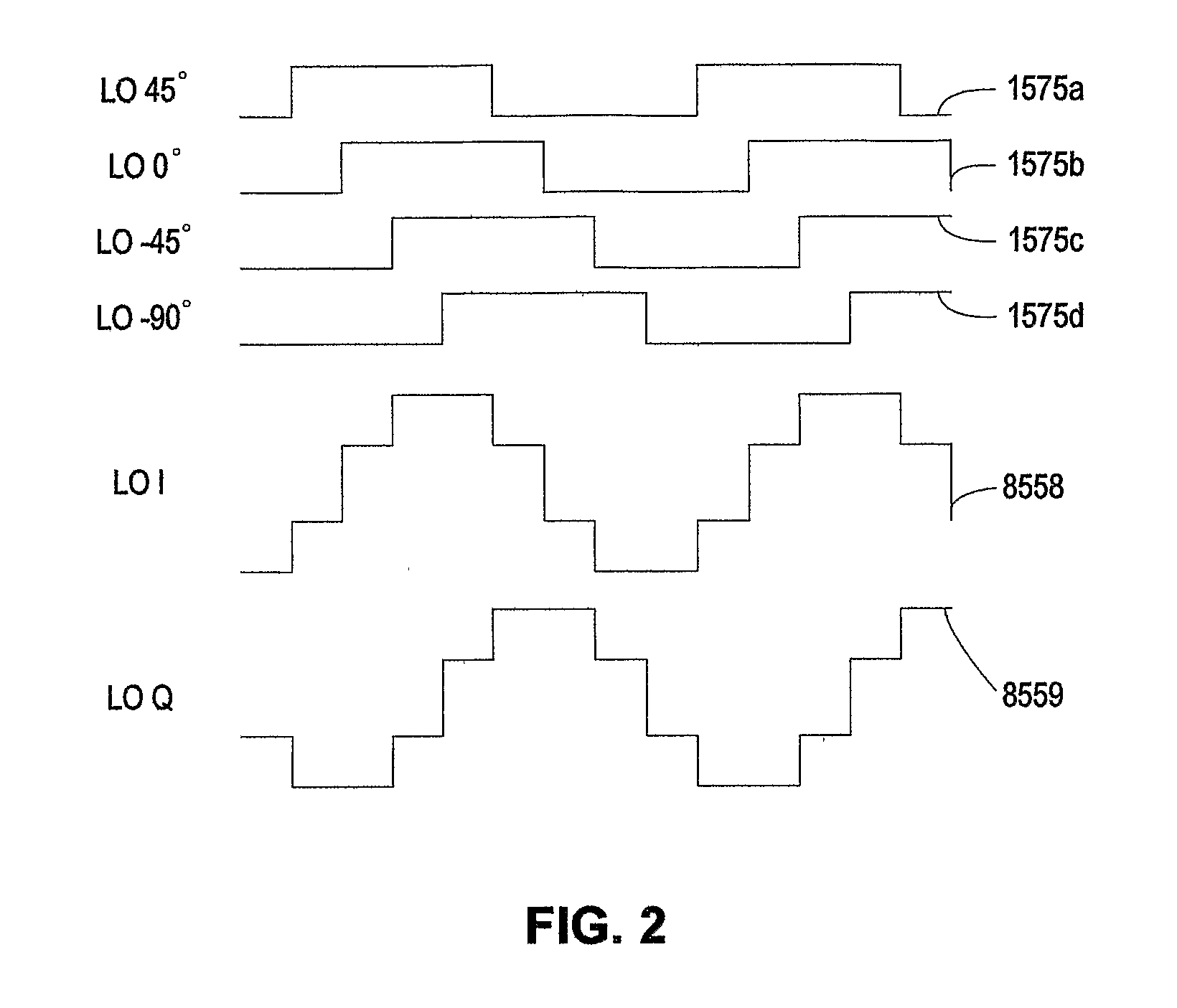

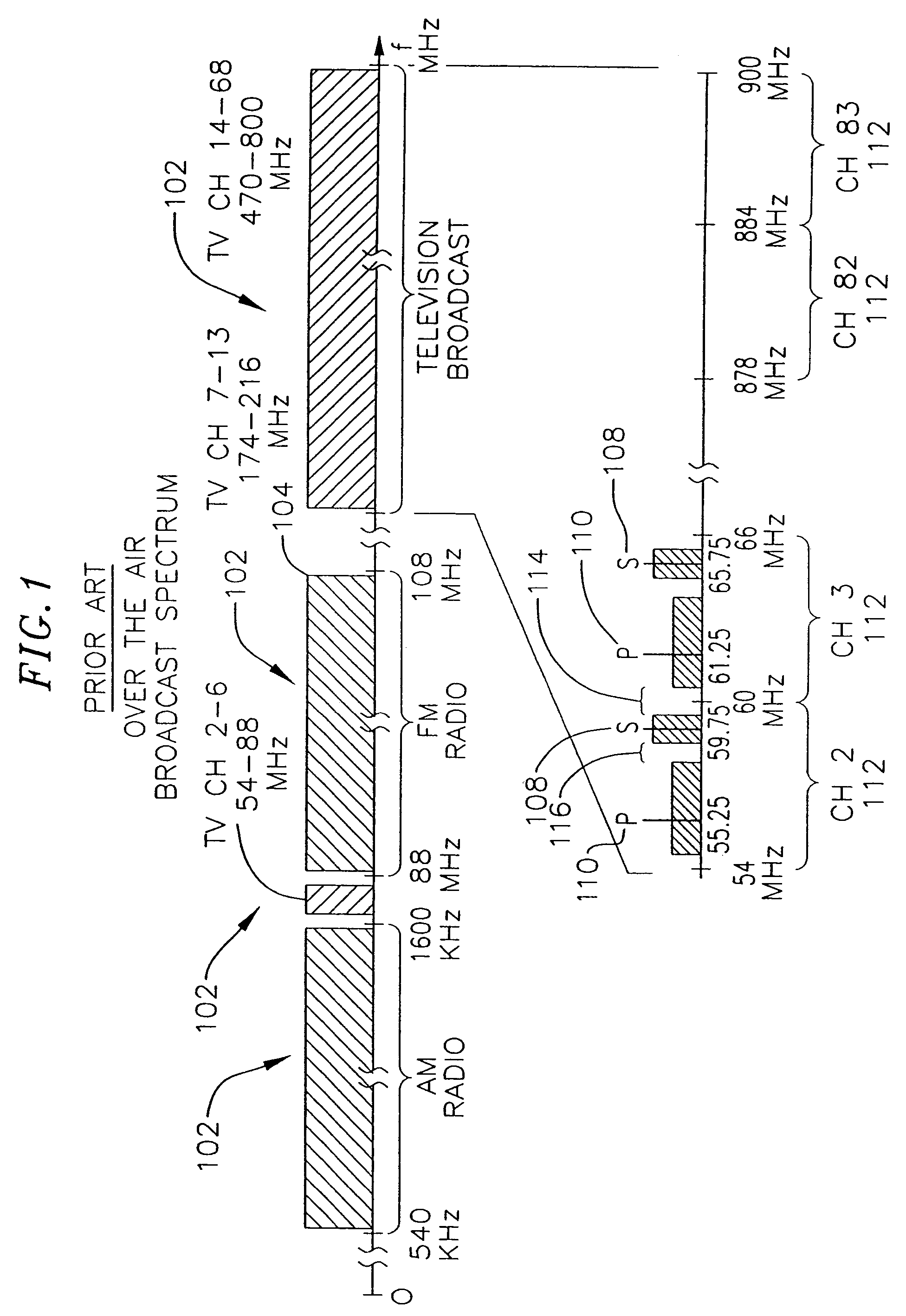

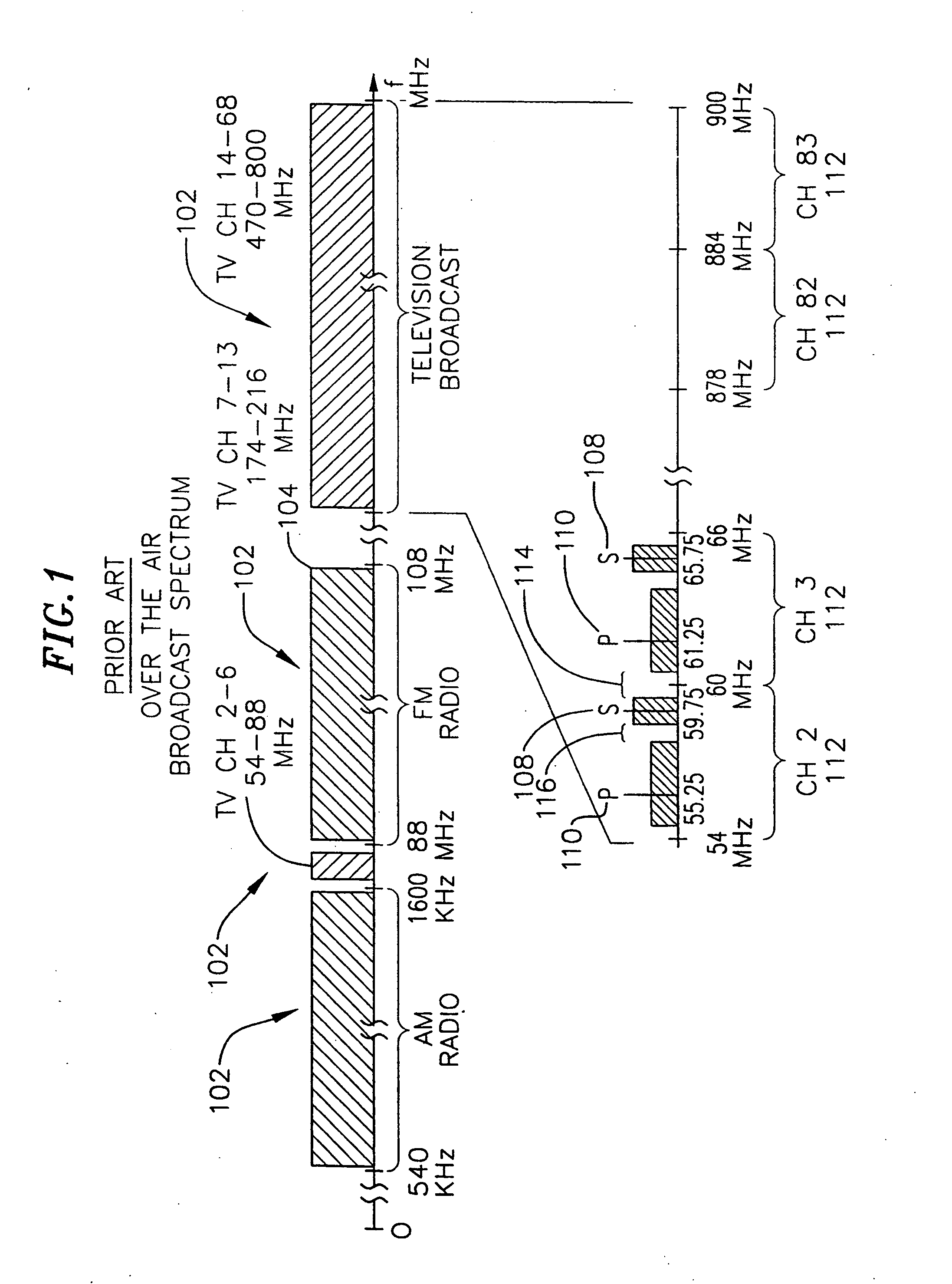

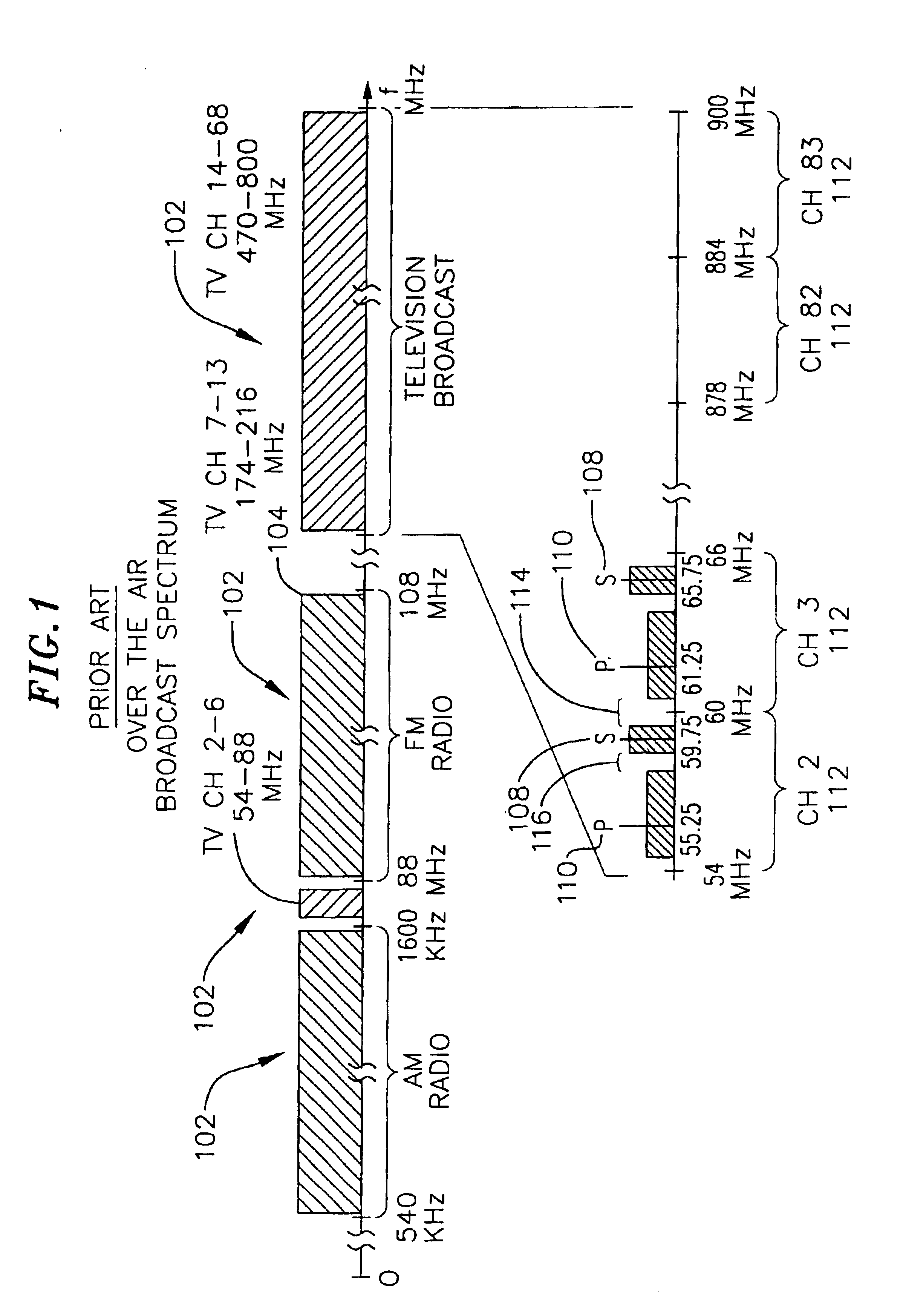

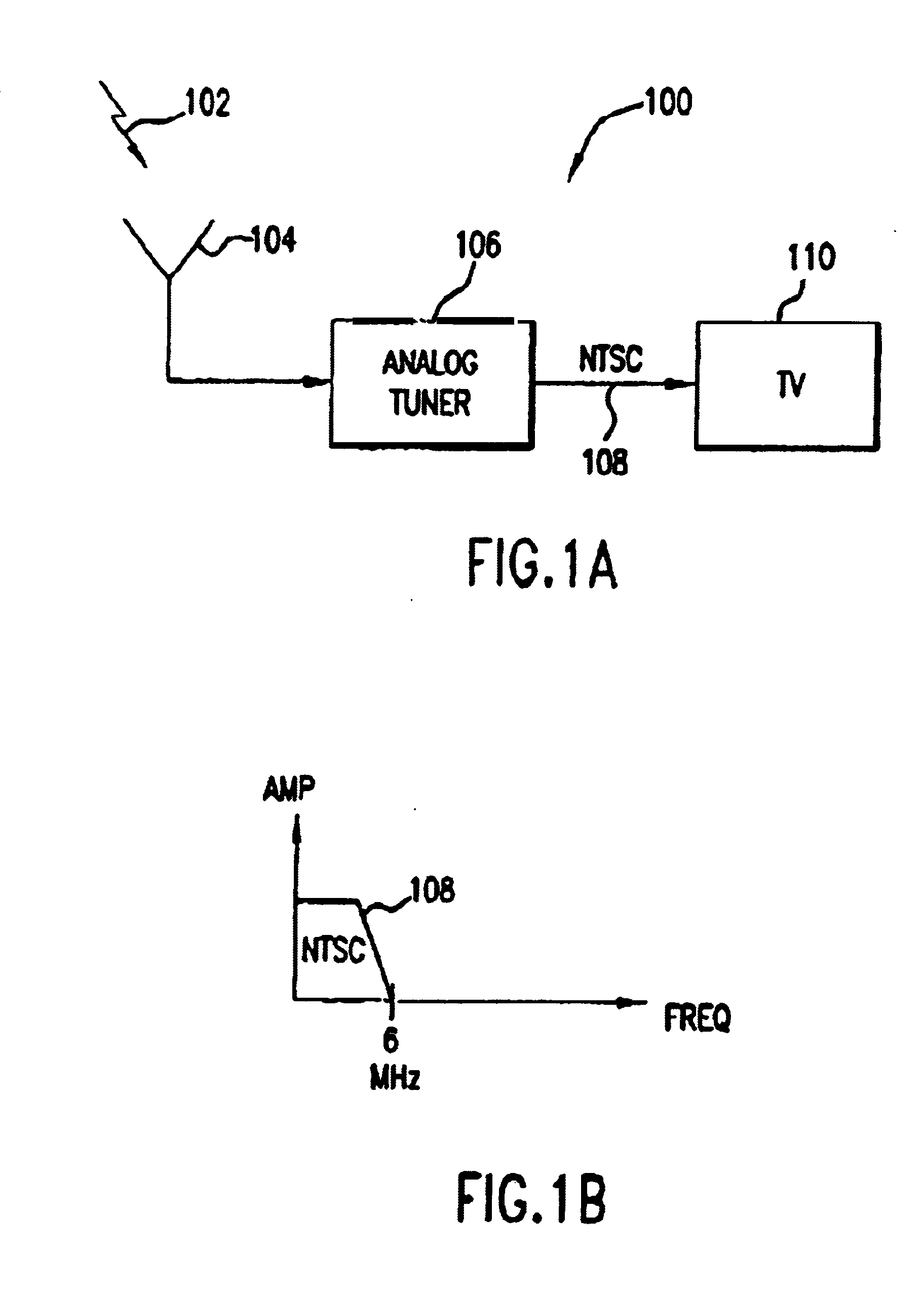

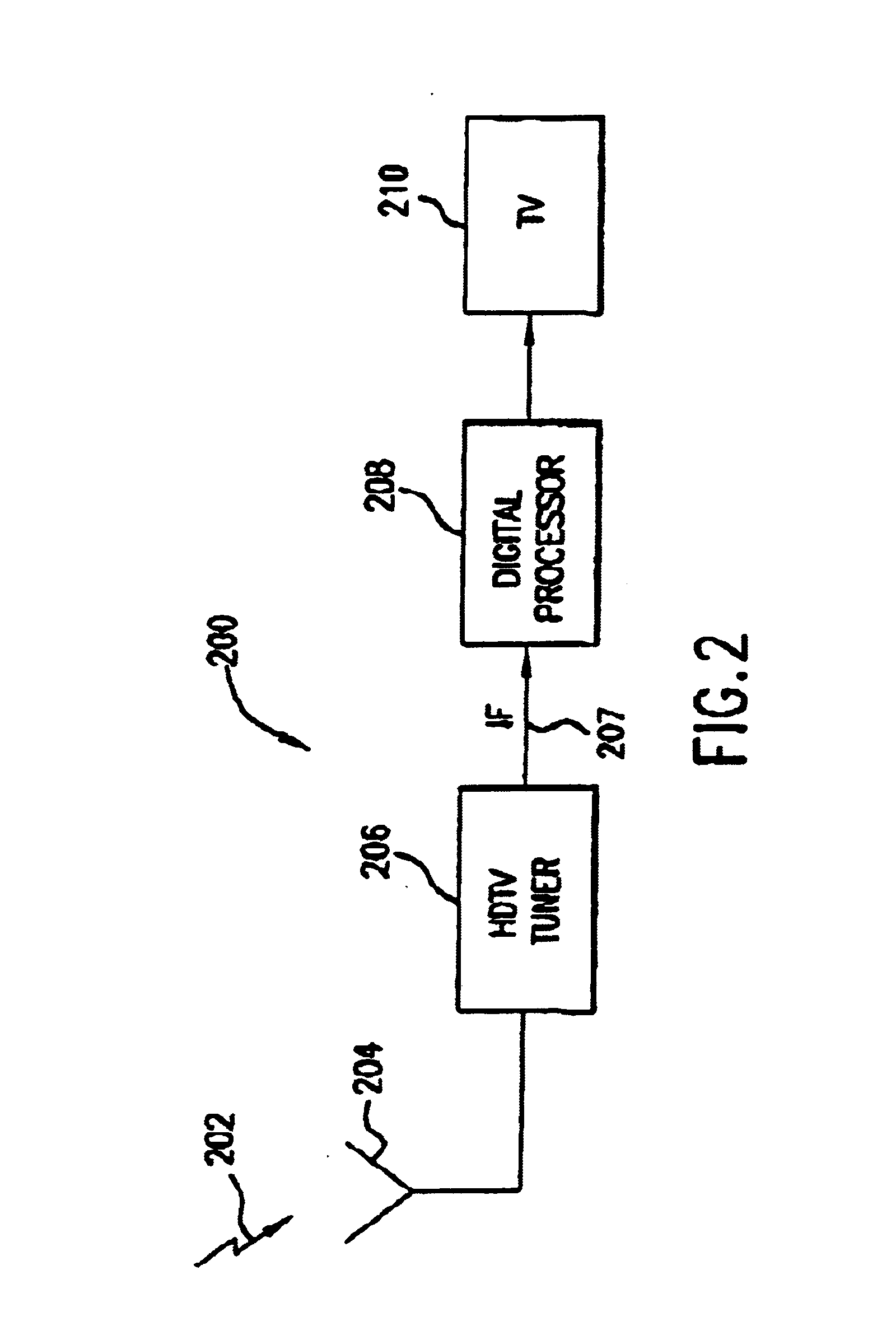

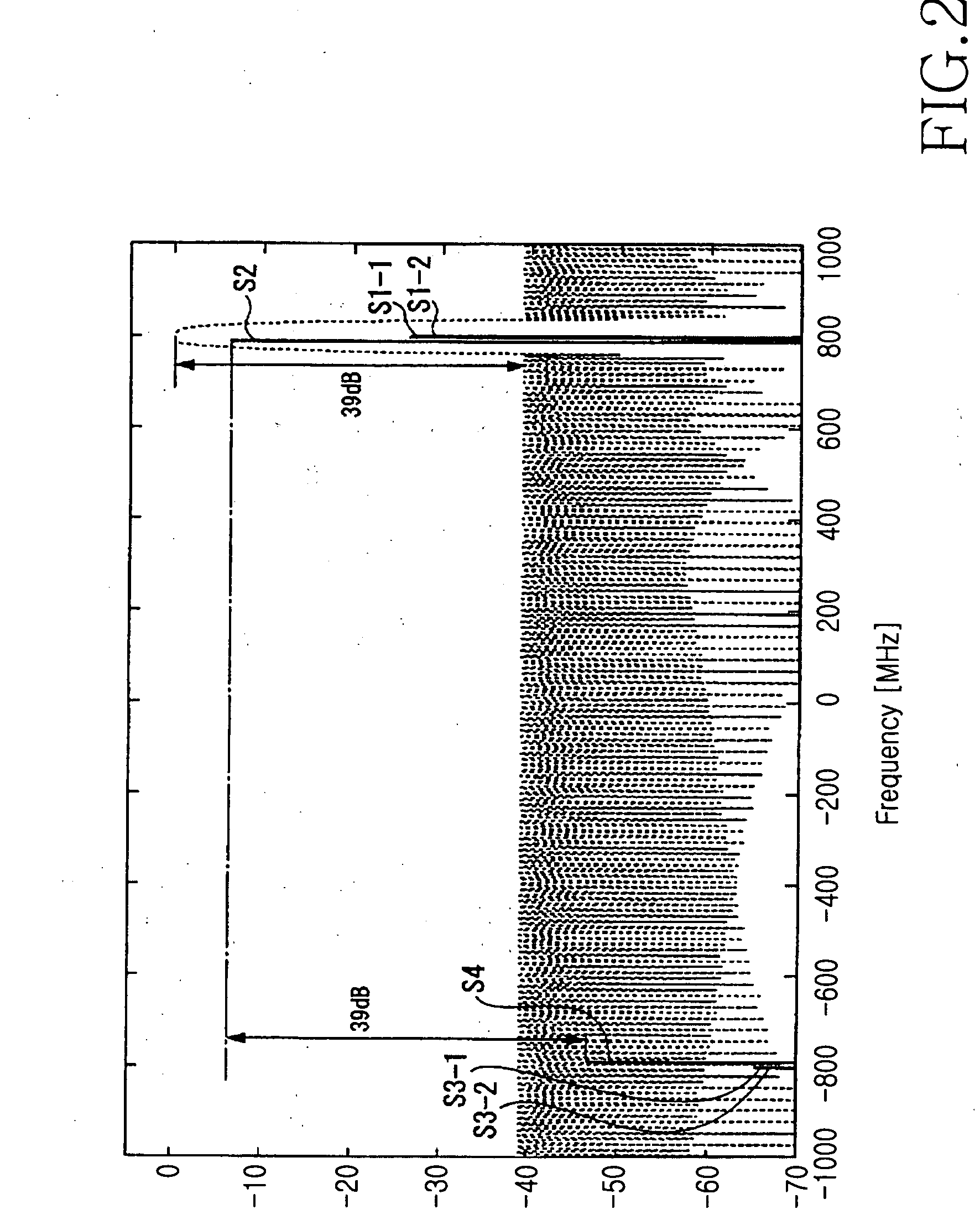

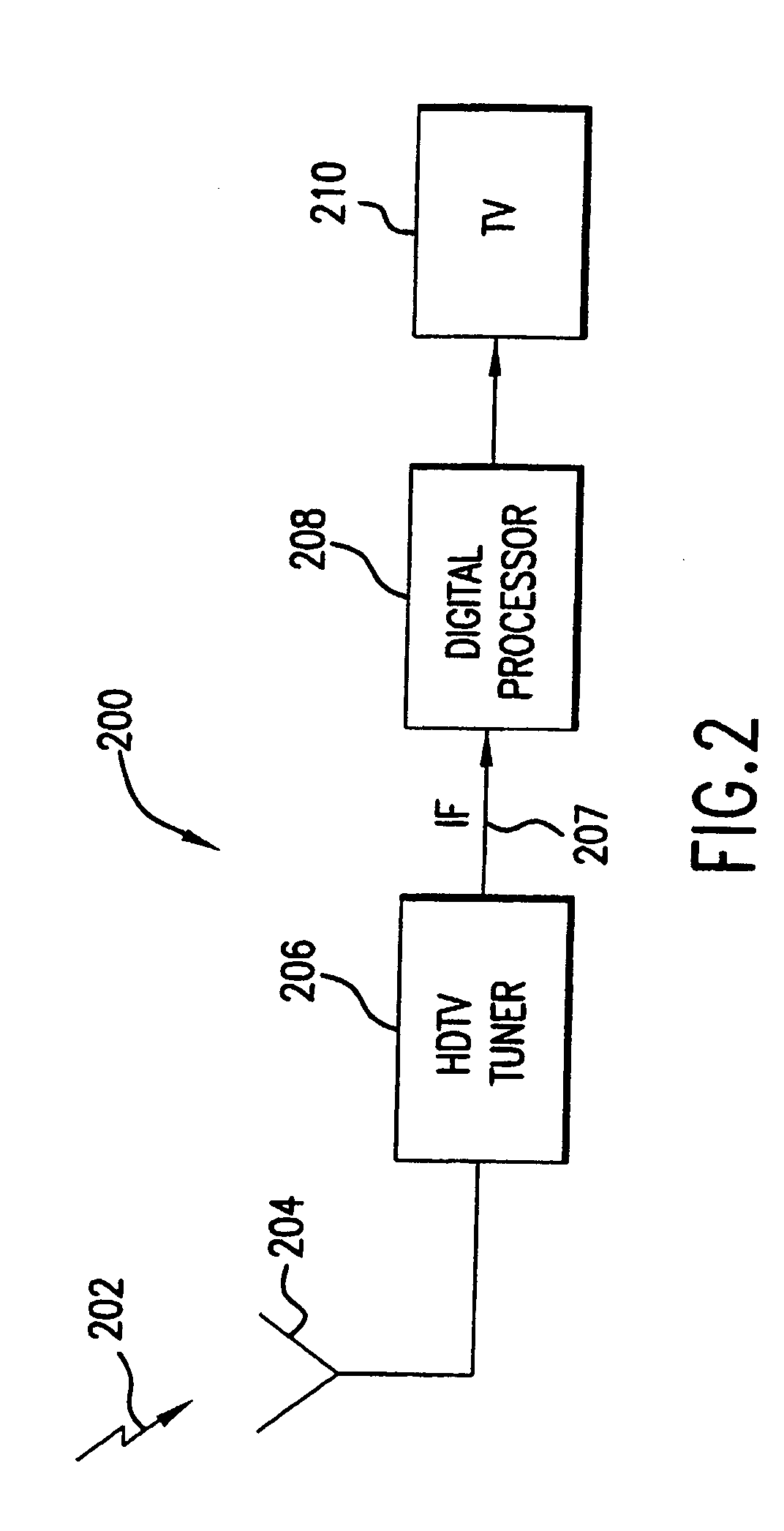

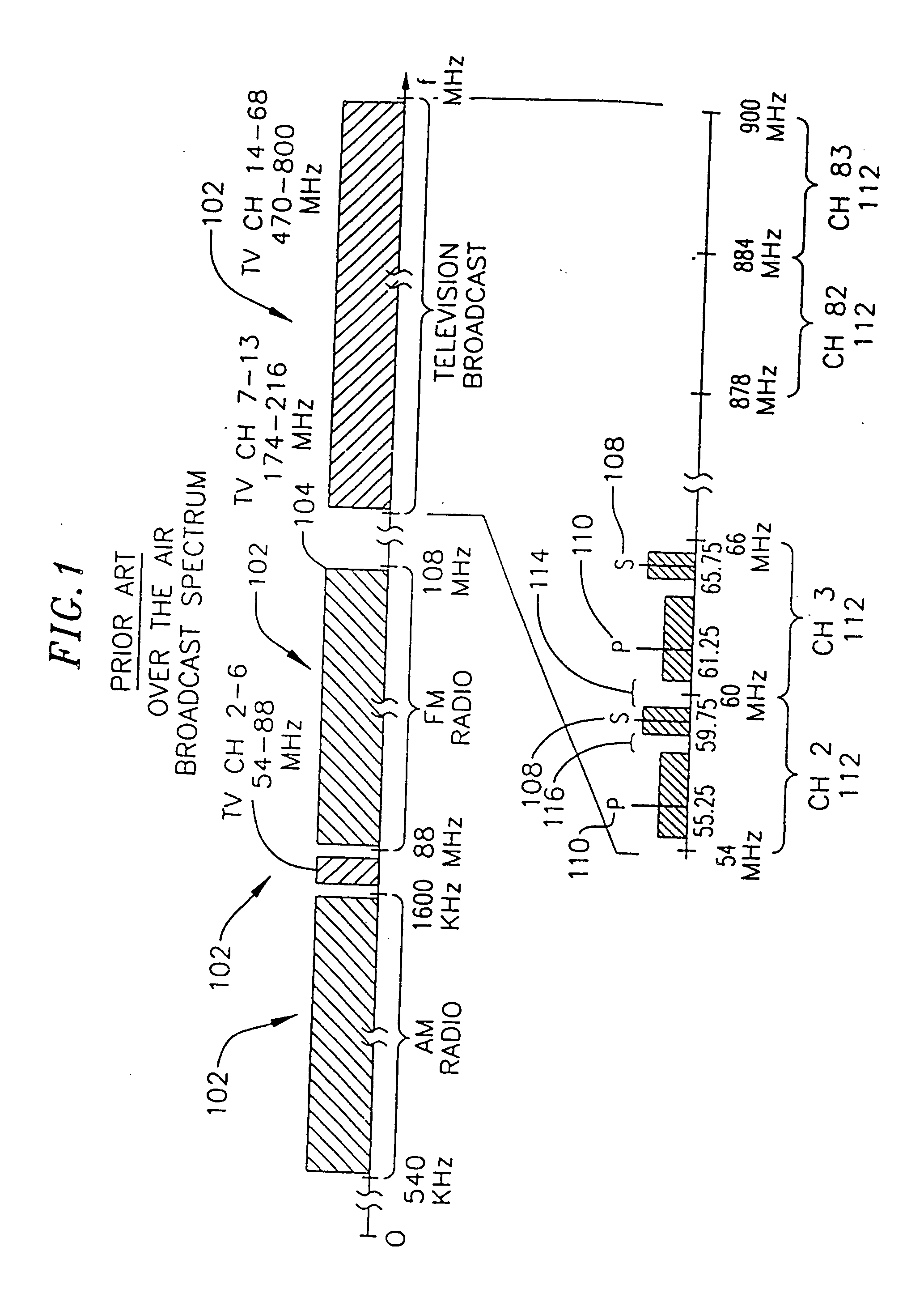

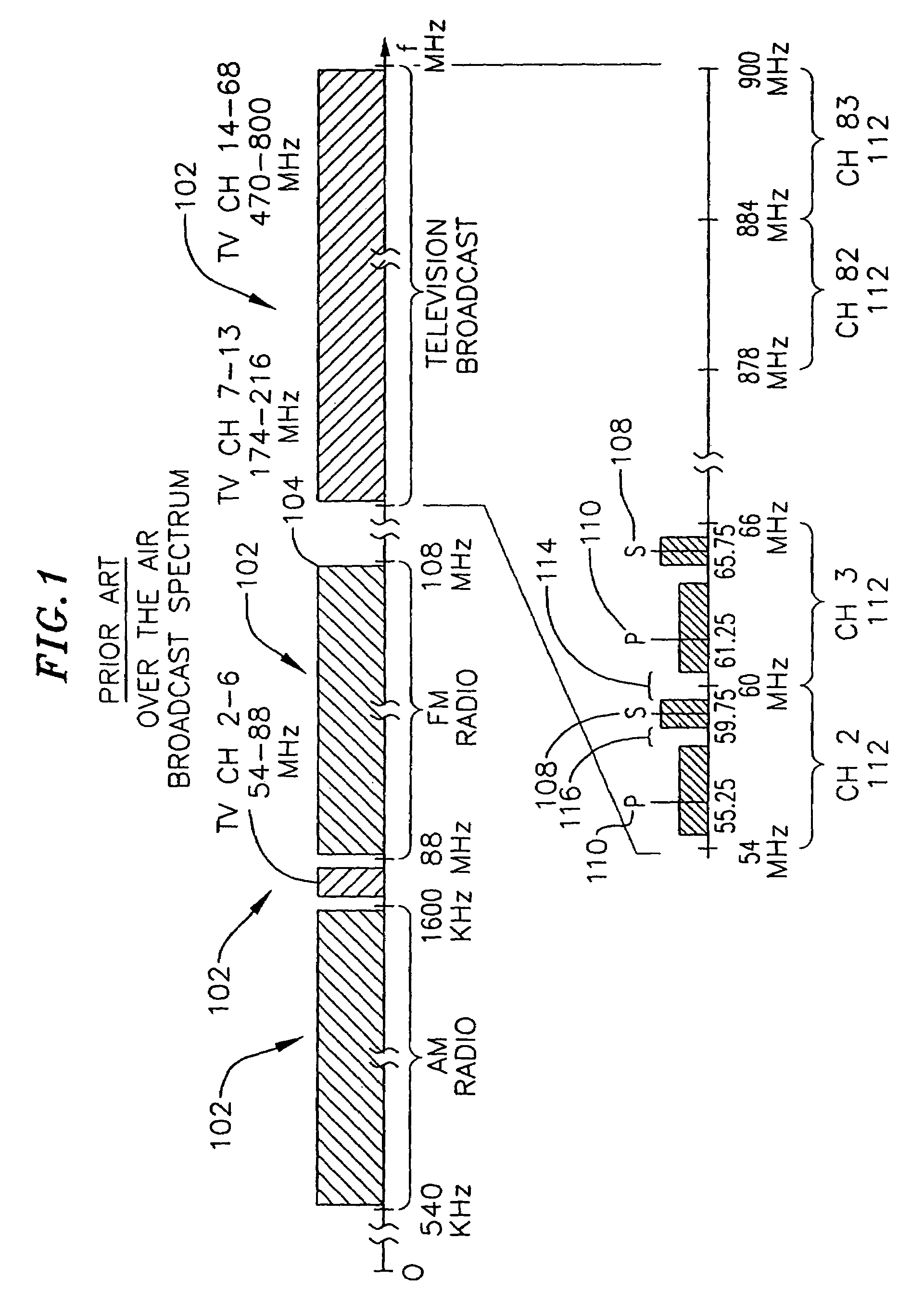

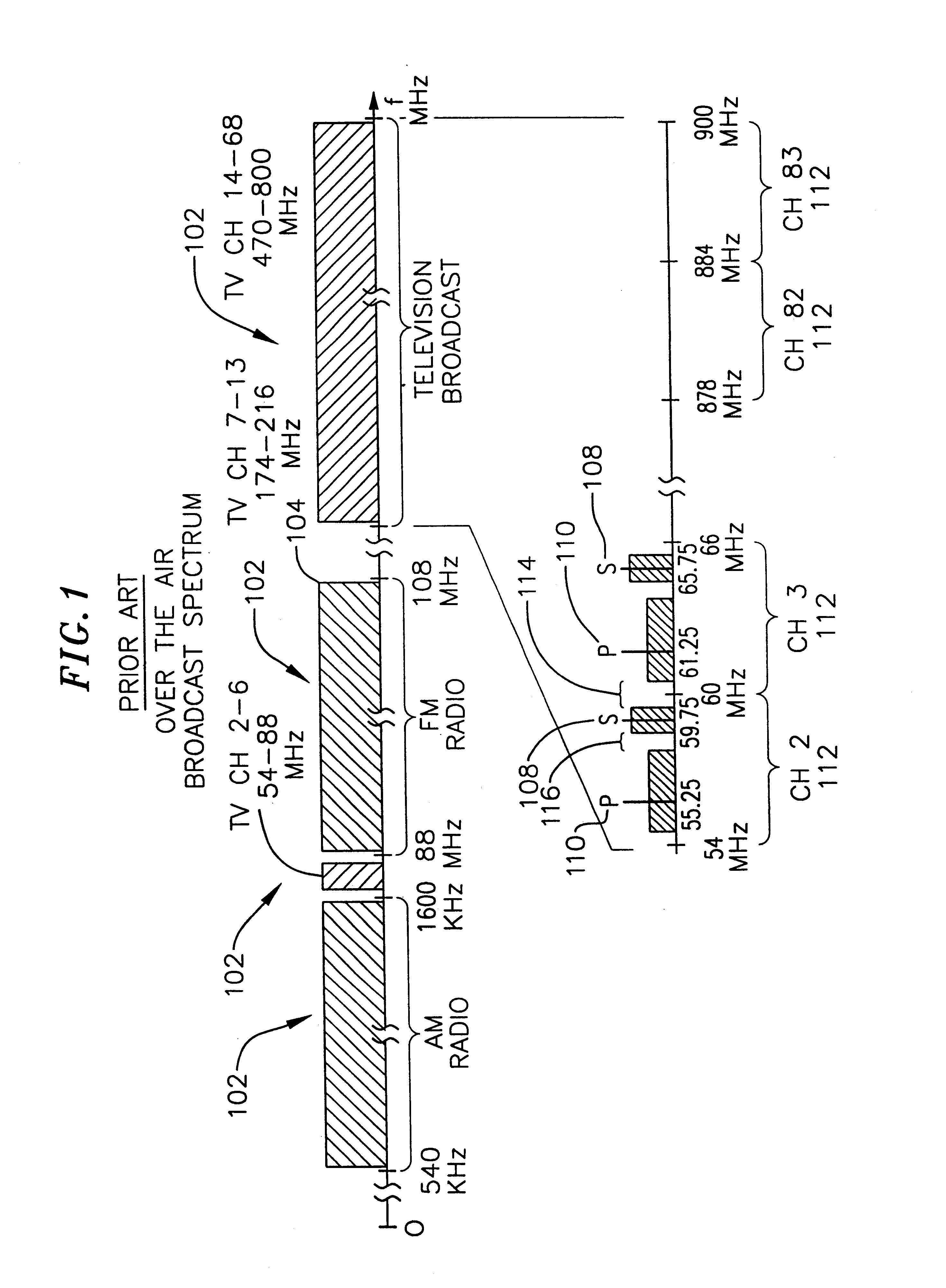

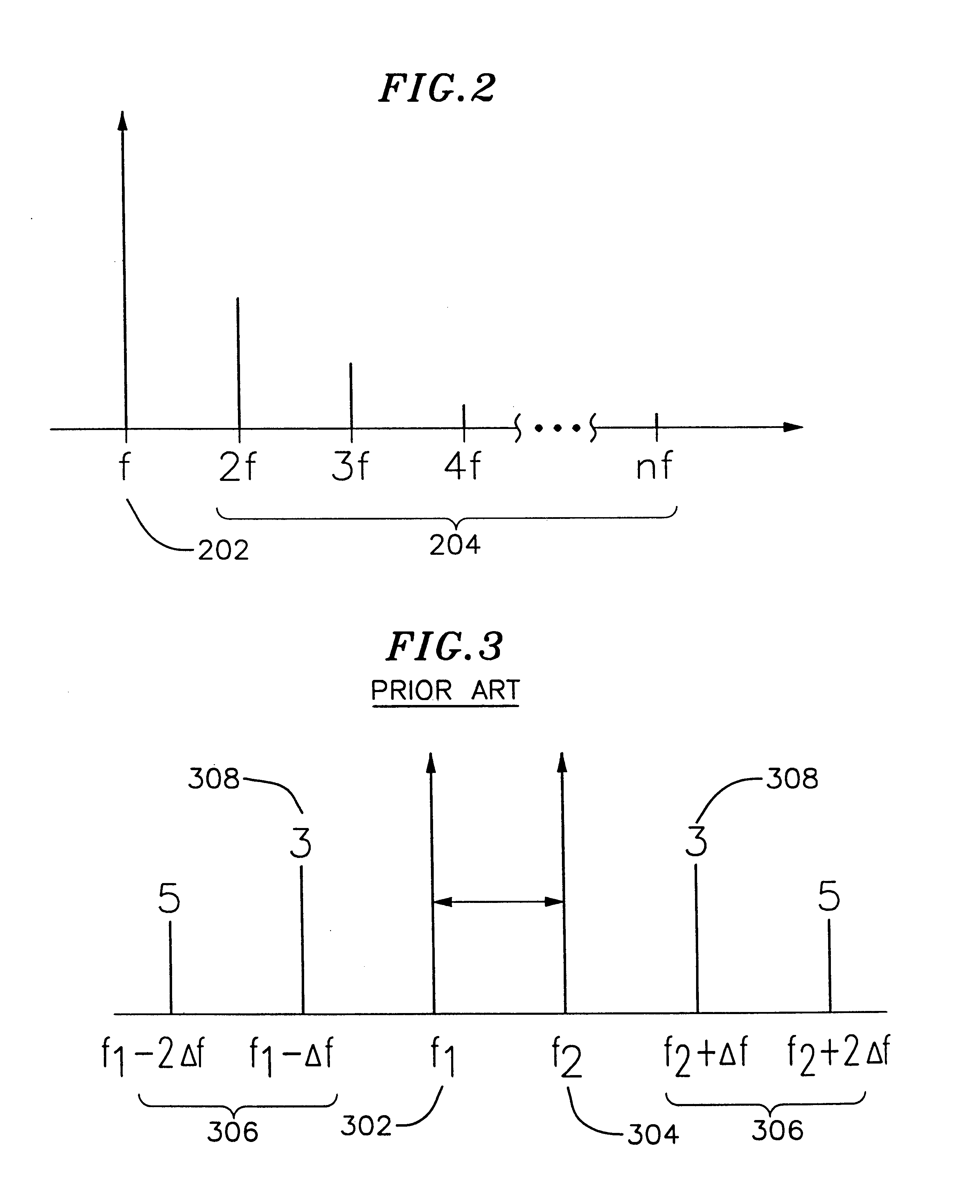

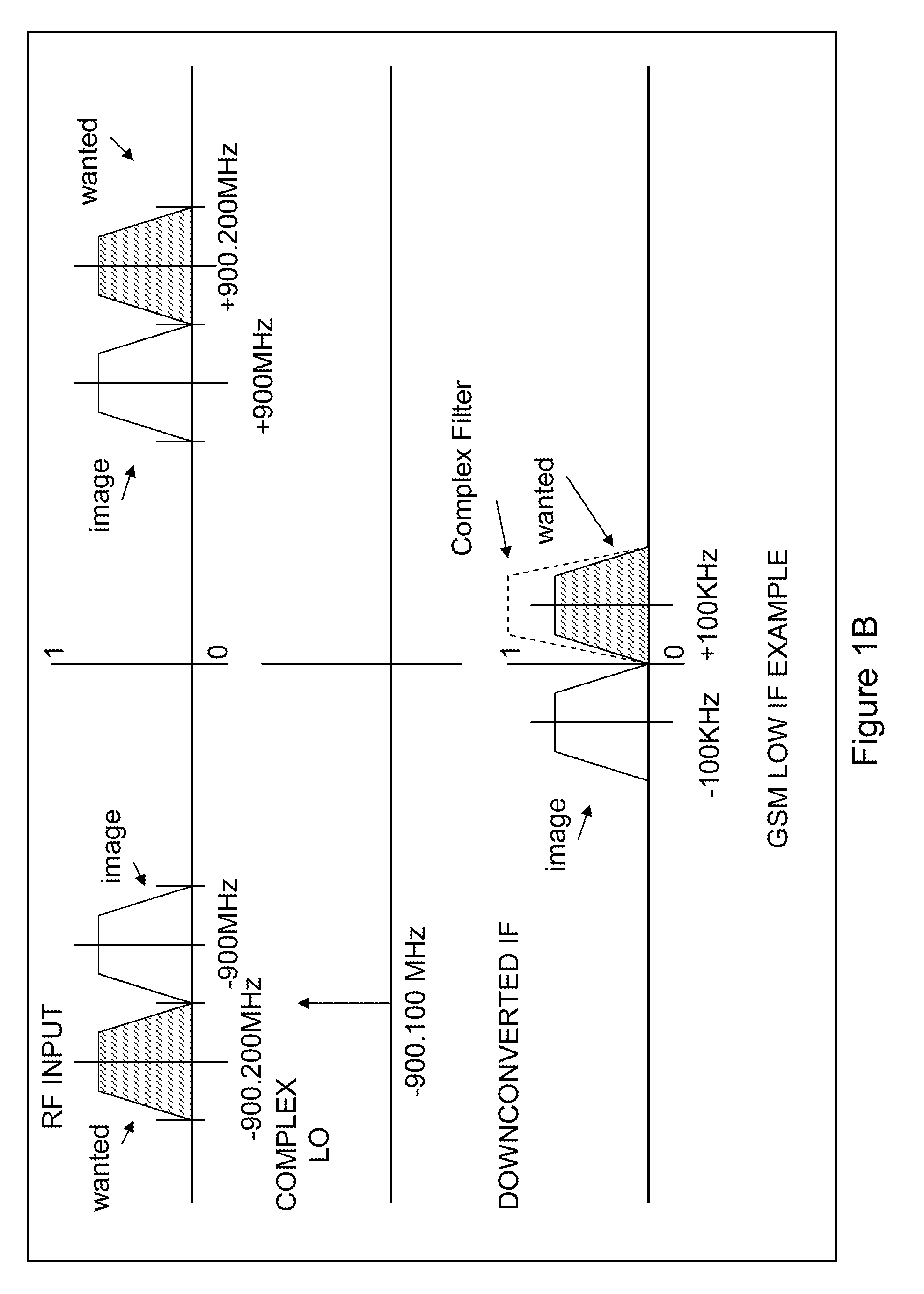

Integrated Tuner for Terrestrial and Cable Television

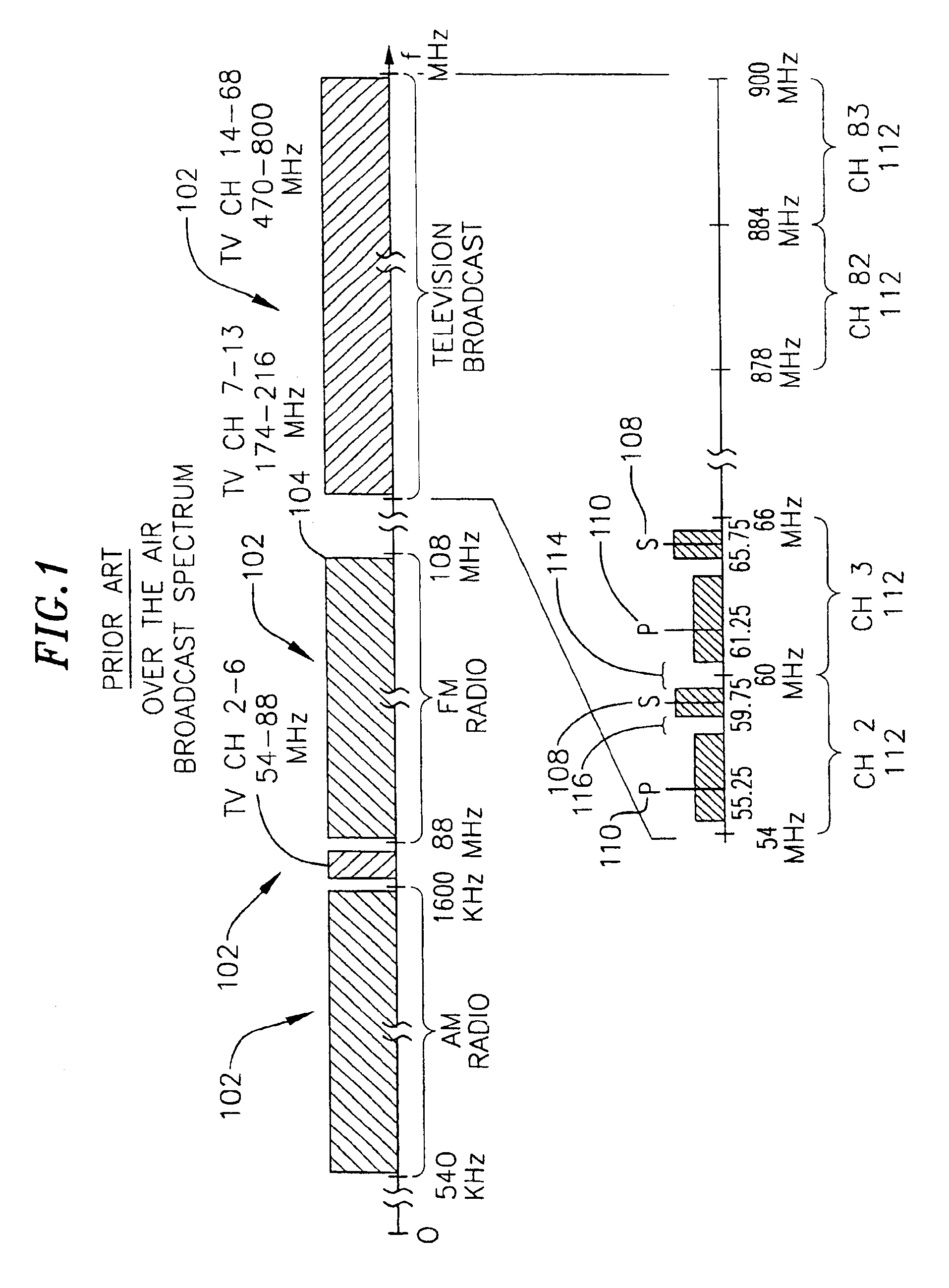

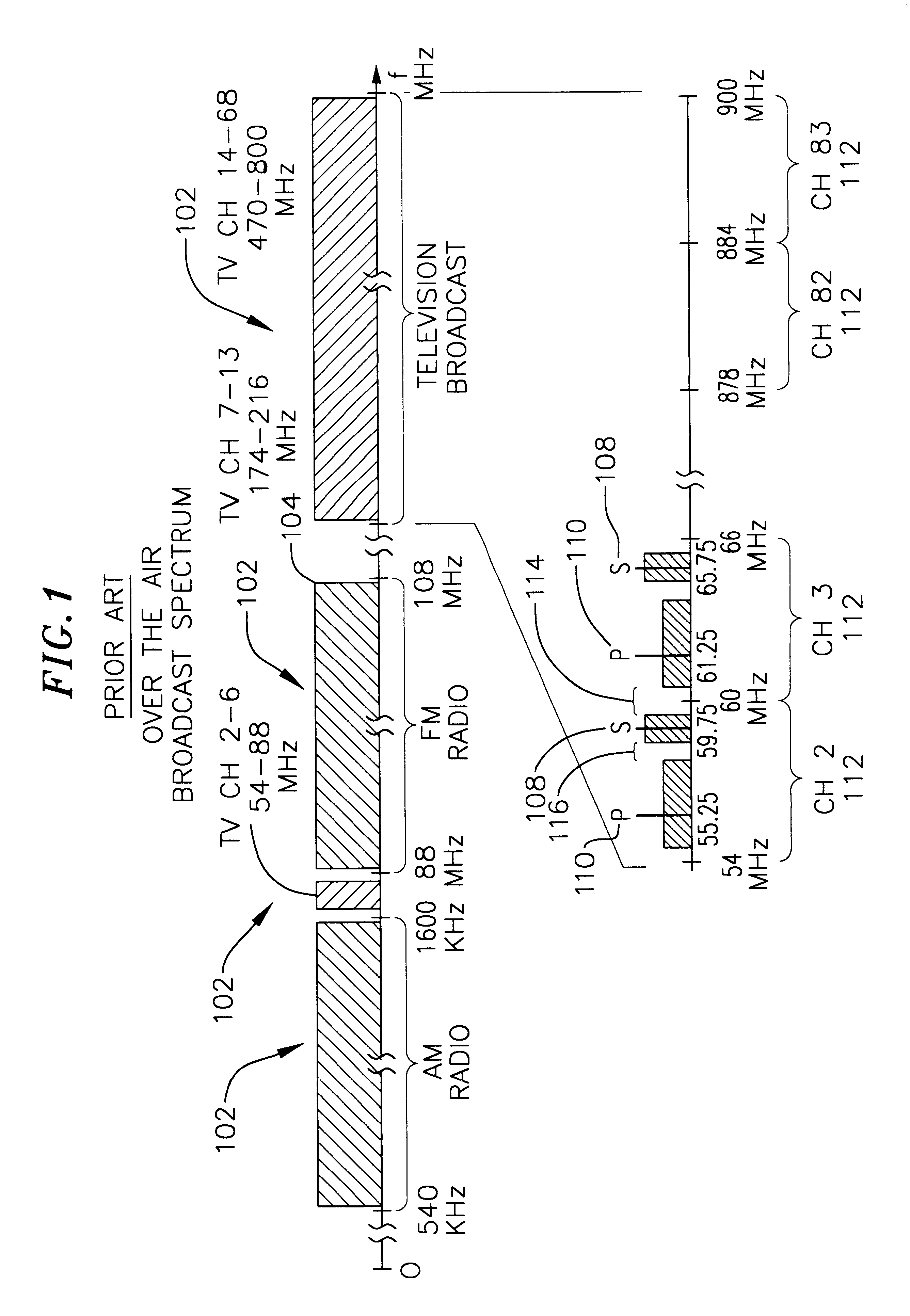

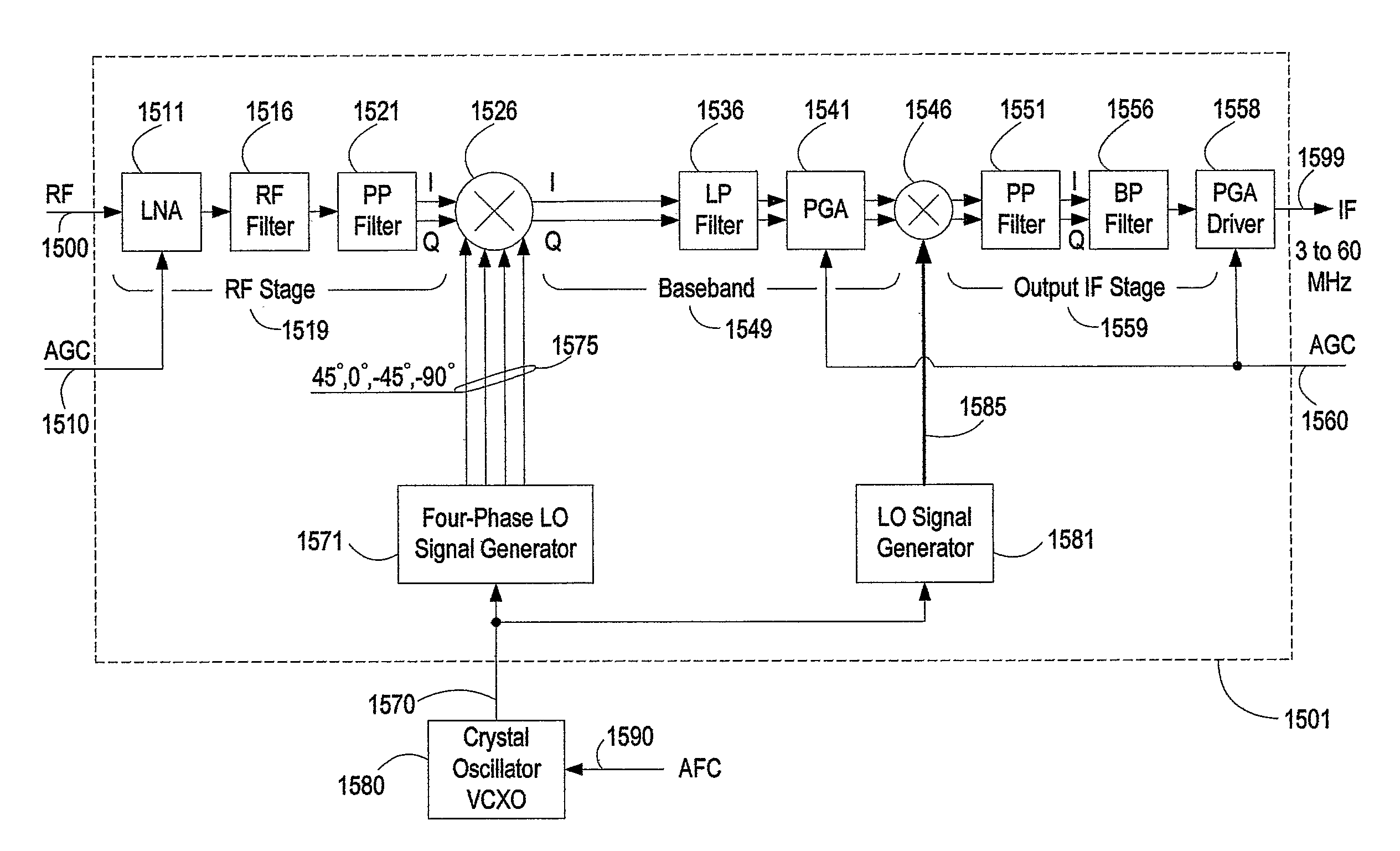

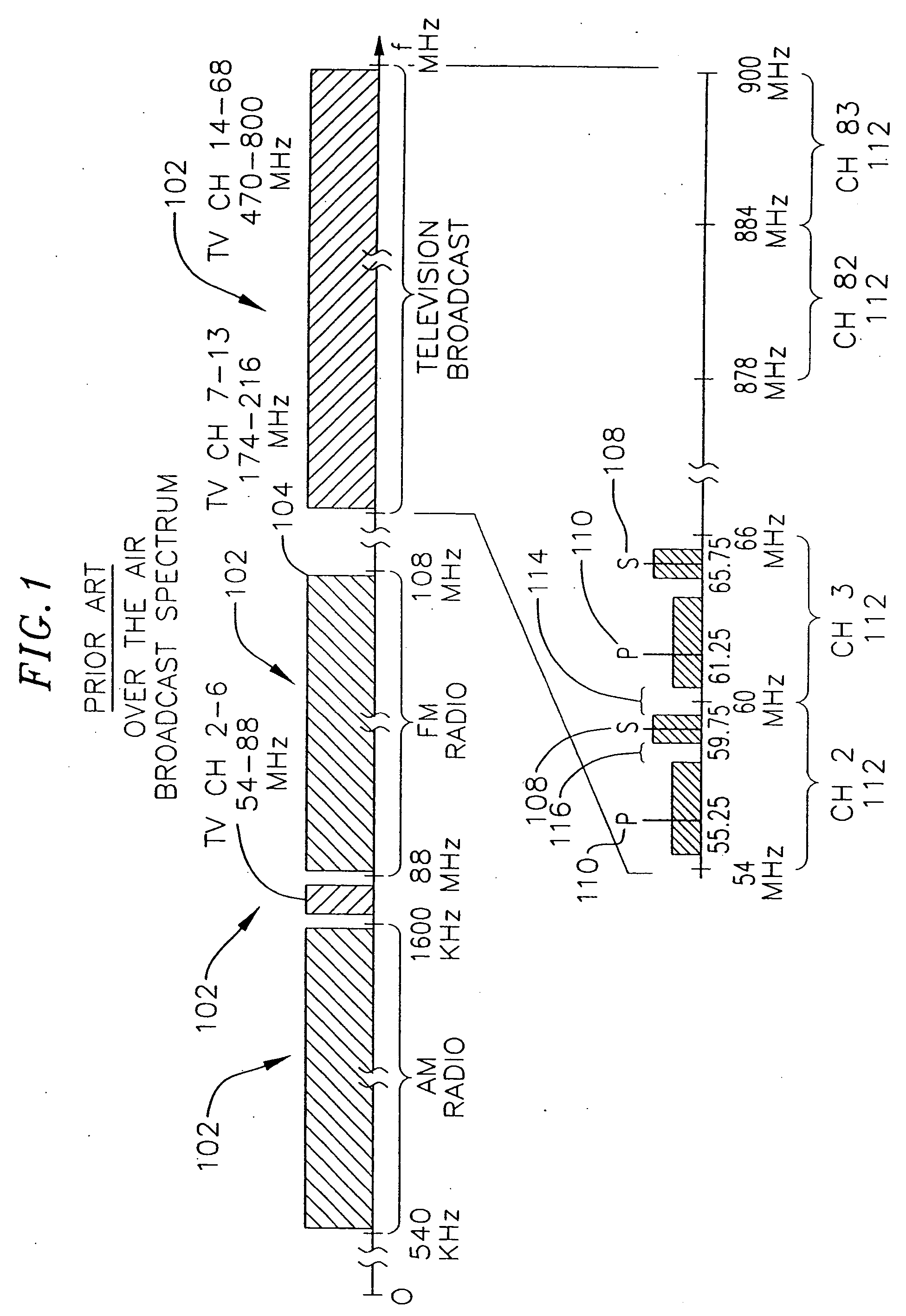

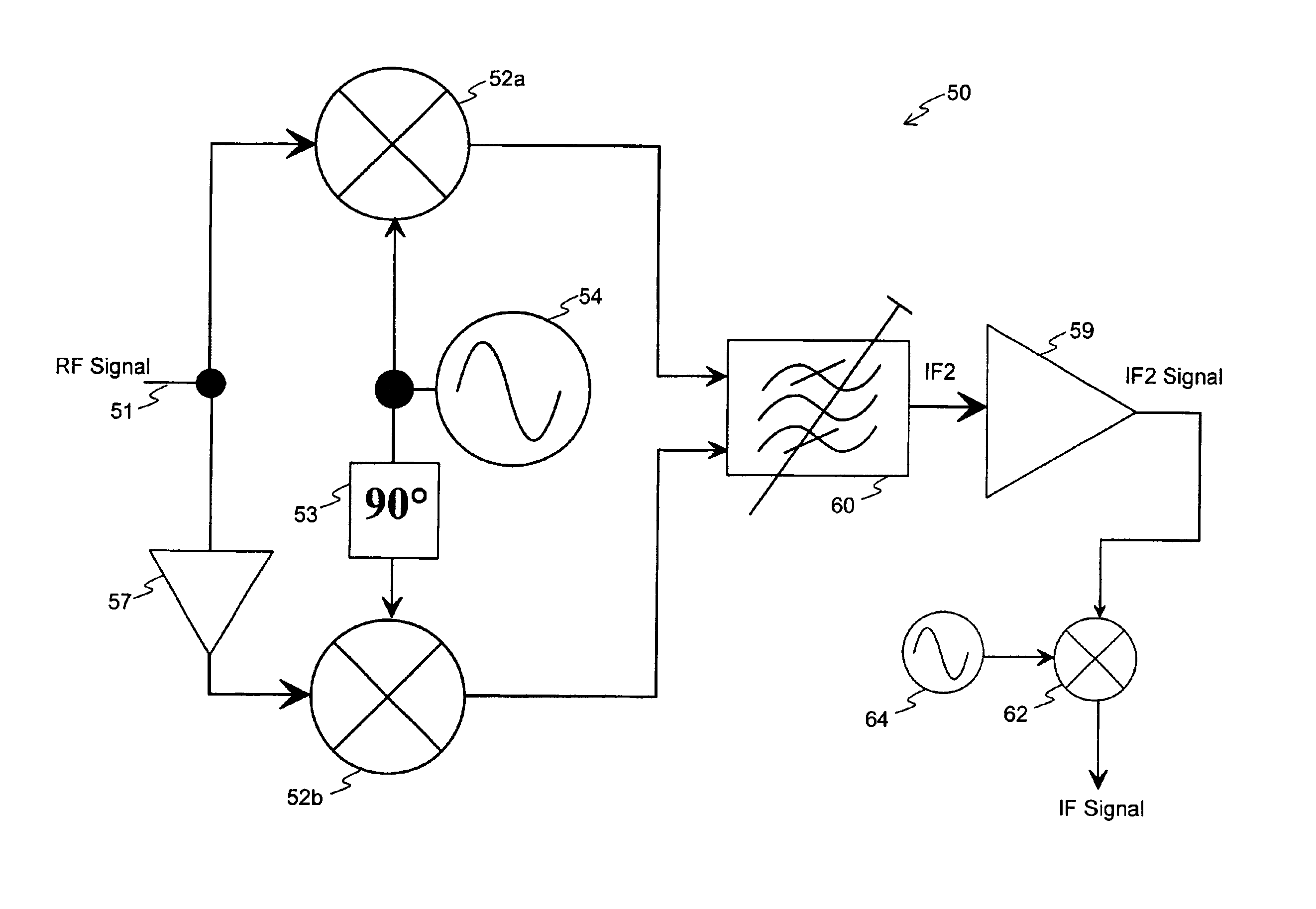

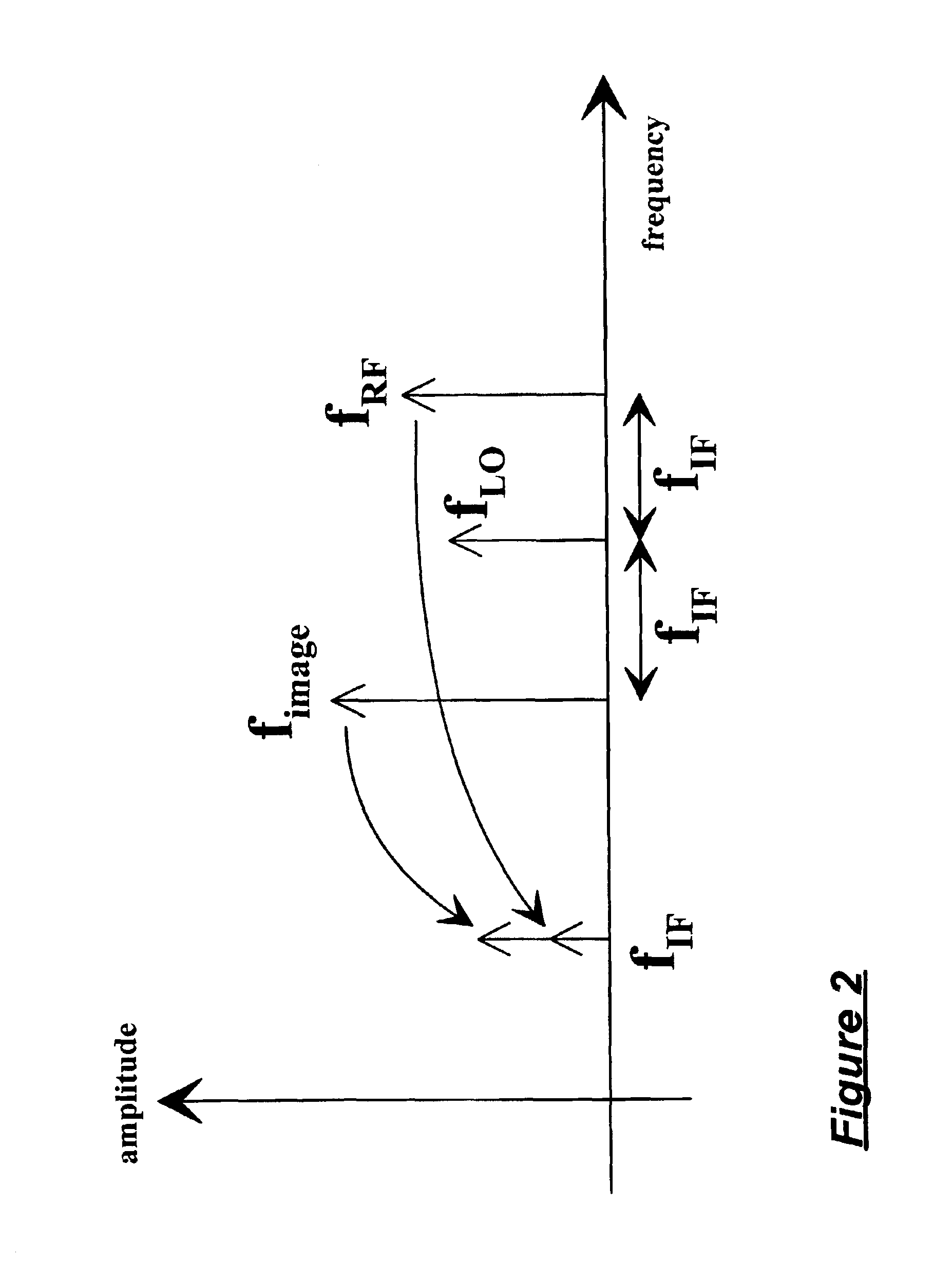

InactiveUS20070218850A1Simple designTransmissionElectrial characteristics varying frequency controlSingle stageIntermediate frequency

A highly integrated terrestrial and cable tuner for receiving digital and analog television signals is disclosed. It achieves high performances in sensitivity, image rejection, dynamic range, channel selectivity and power consumption. A major-images rejection converter disclosed rejects third- and fifth-order images. Thus it significantly relaxes RF filter design in a tuner of a single-stage or a first-stage zero-IF / low-IF downconversion architecture. Different architectures and frequency planning are disclosed in accordance with specifications of TV standards to improve the overall performance of the tuner with a different or configurable IF output. The tuner is integrated by using standard processes, with minimal off-chip components excluding SAW and LC filters. Small tuner modules cost less than discrete (can) tuners. They can be used in digital / analog TV sets and portable and handheld TV devices and for mobile-phone TV reception.

Owner:PAN JIANPING

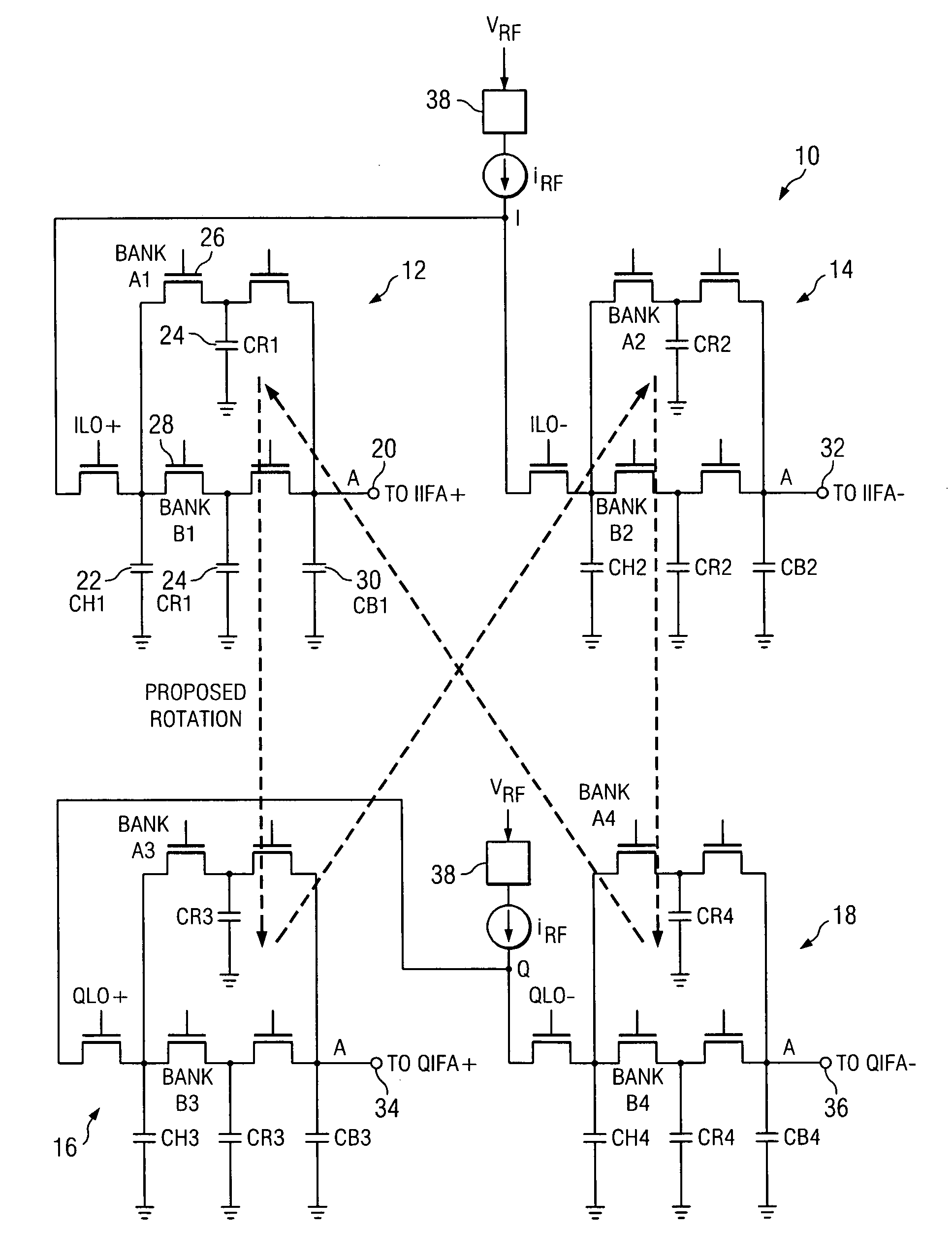

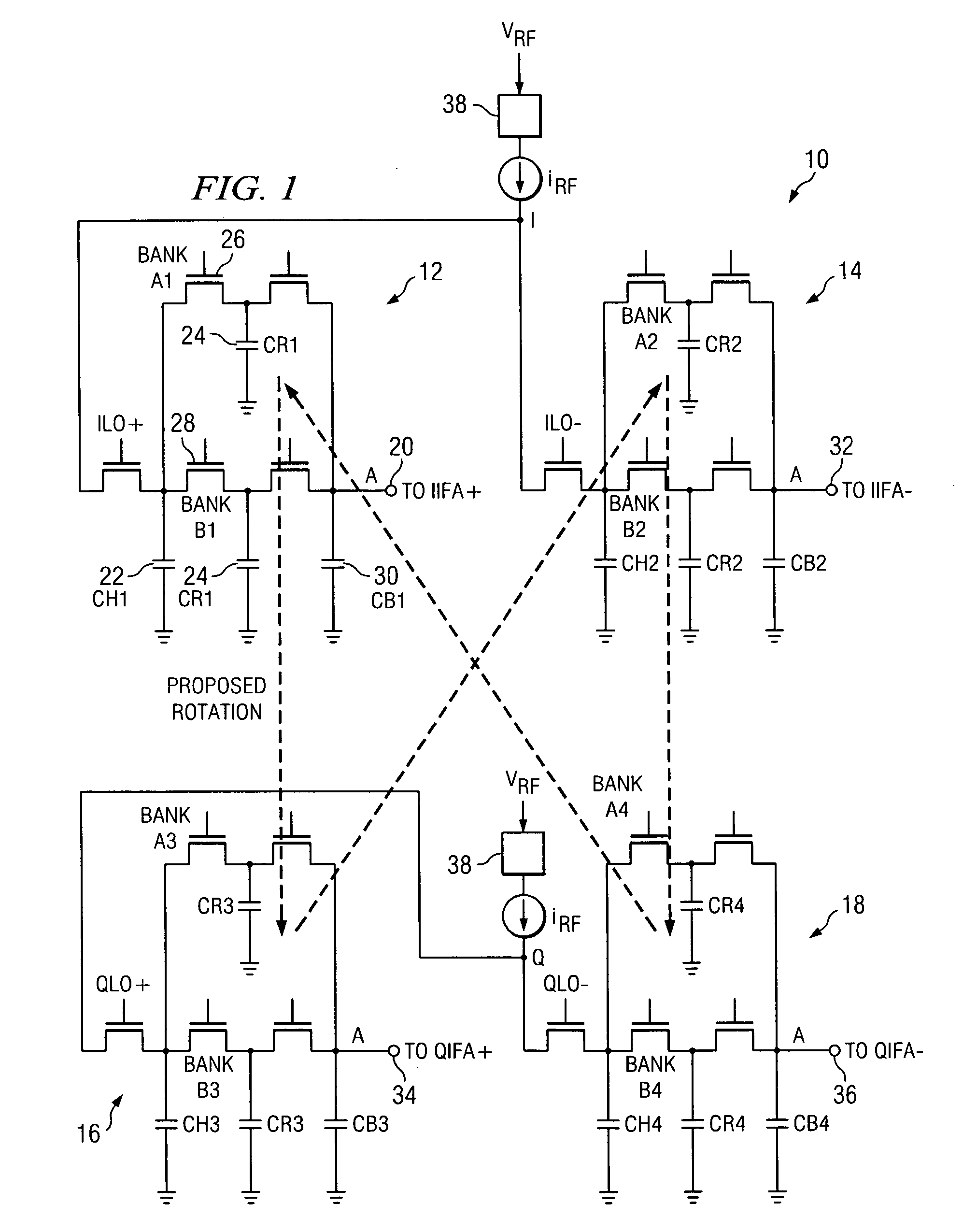

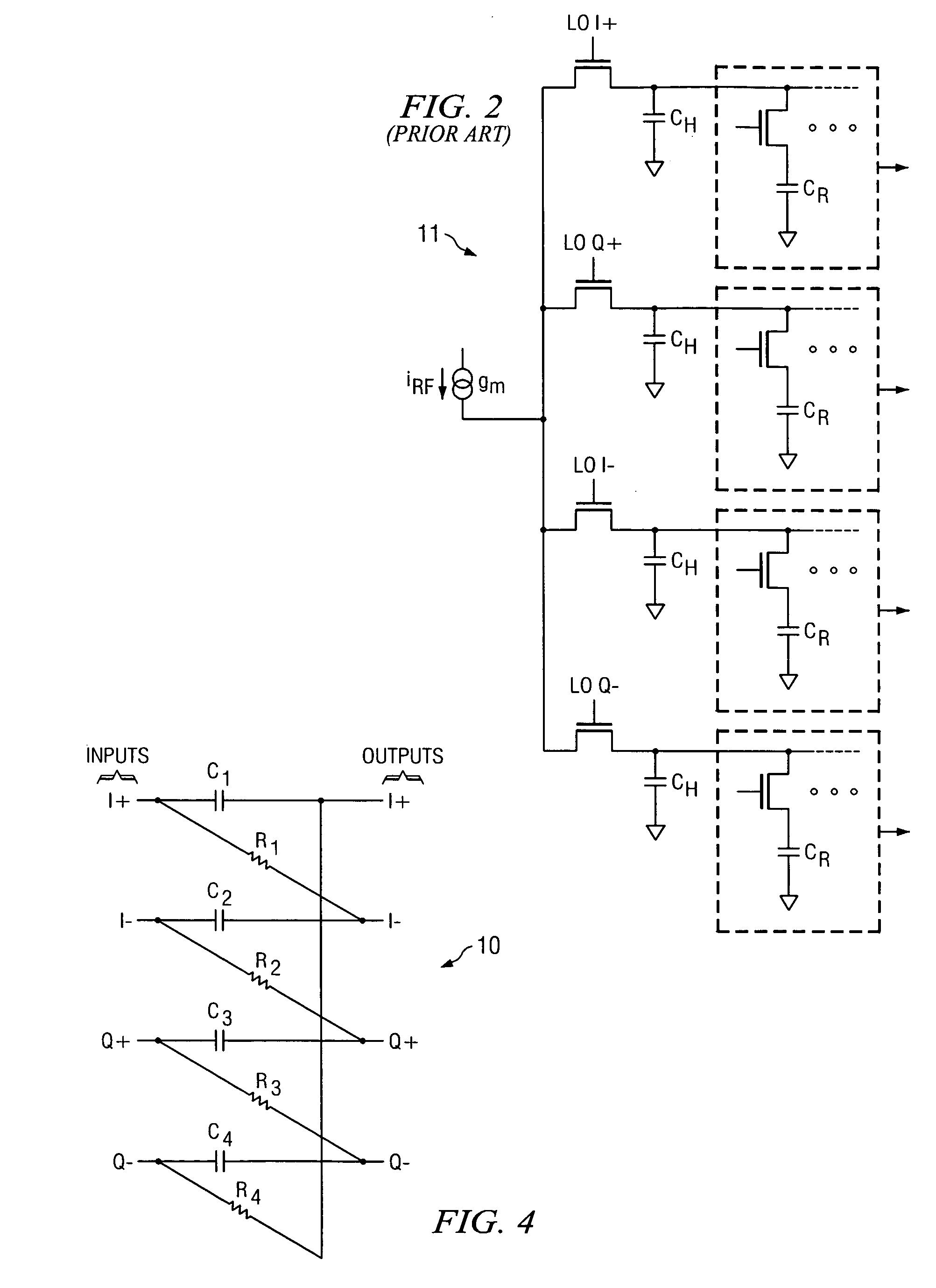

Image reject filtering in a direct sampling mixer

InactiveUS20050233725A1Reduced dynamic rangeReduce areaMultiple-port networksSwitched capacitor networksPattern recognitionFrequency mixer

Disclosed are methods, circuits and systems for image reject filtering in a multi-tap direct sampling mixer (MTDSM) of an IF or RF system. Disclosed is the use of rotating capacitors among the in-phase and quadrature branches of a signal processing system. The exchange of information among the branches of the I and Q channels is used in the implementation of a complex filter. Embodiments using cascaded multiple stages of the complex filter to provide higher order complex filters are also disclosed.

Owner:TEXAS INSTR INC

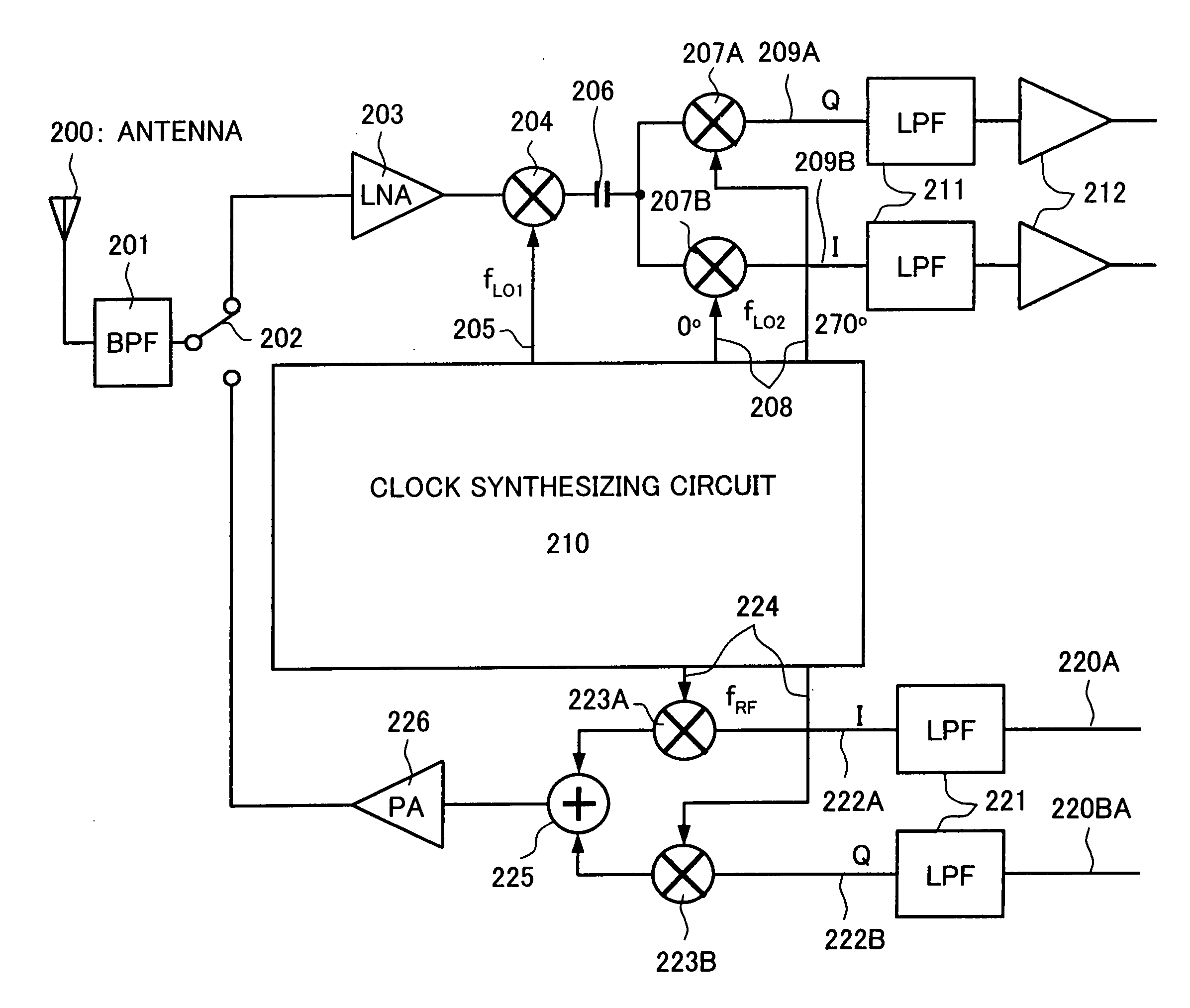

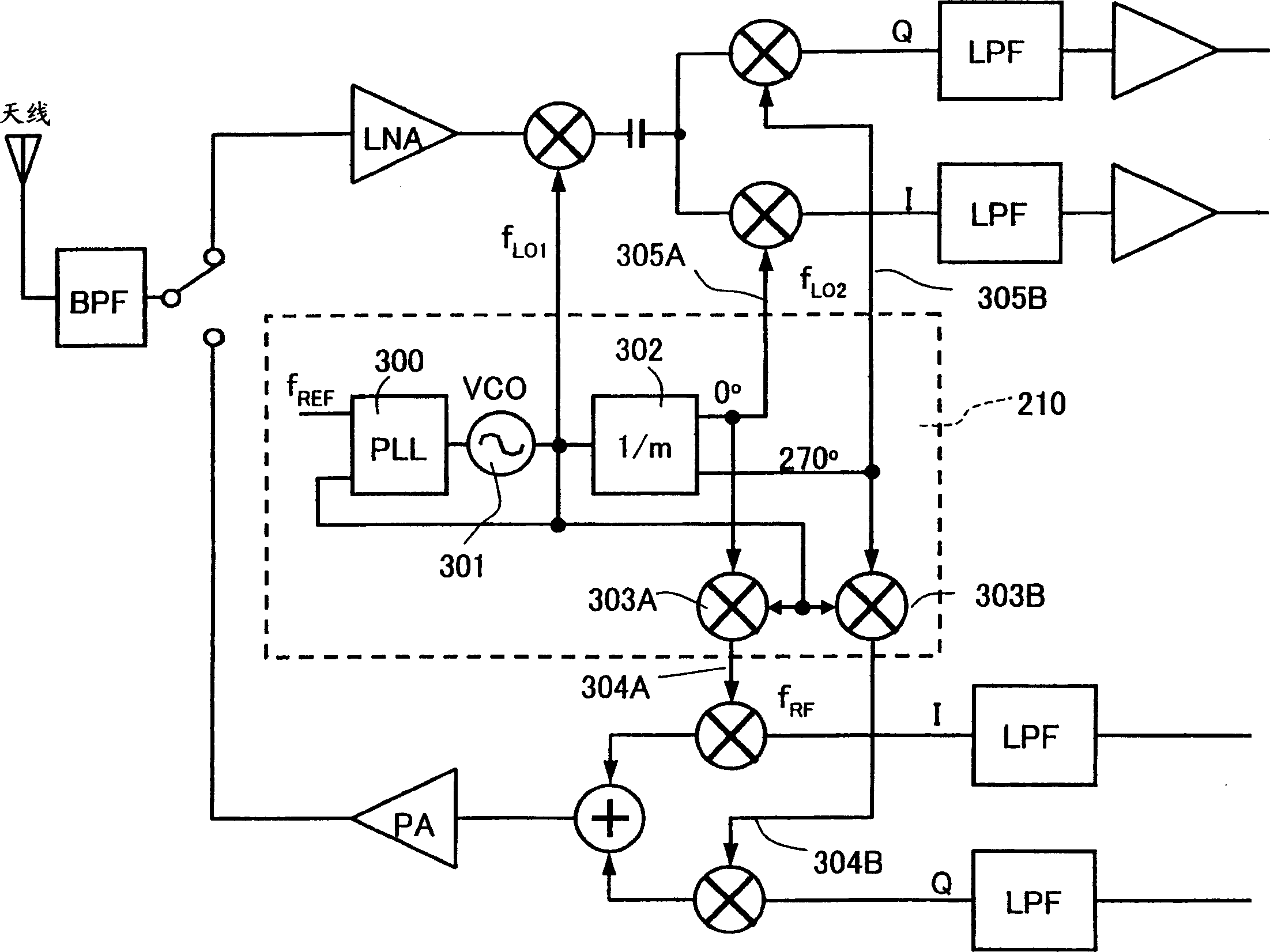

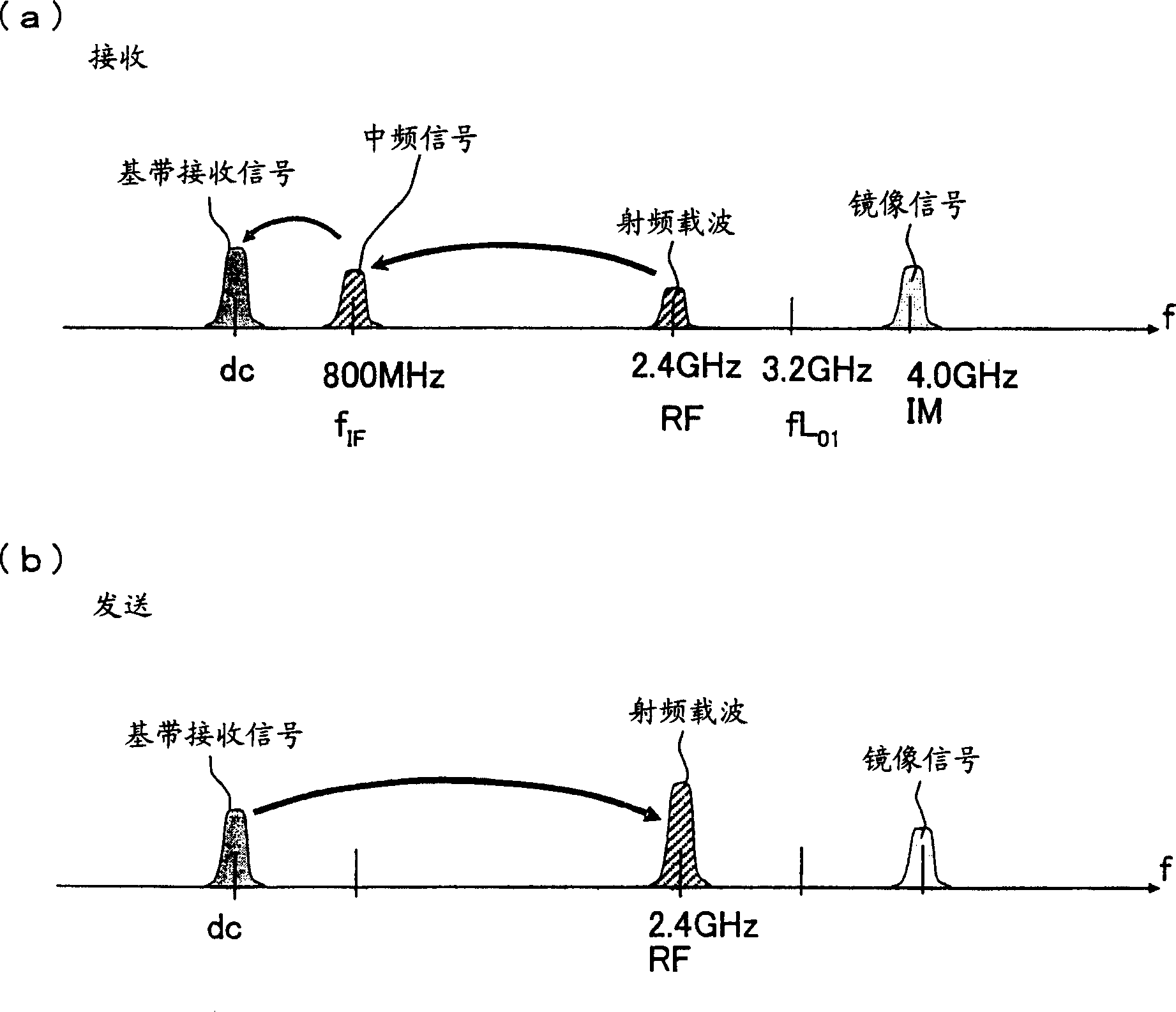

Frequency conversion circuit, radio frequency wave receiver, and radio frequency transceiver

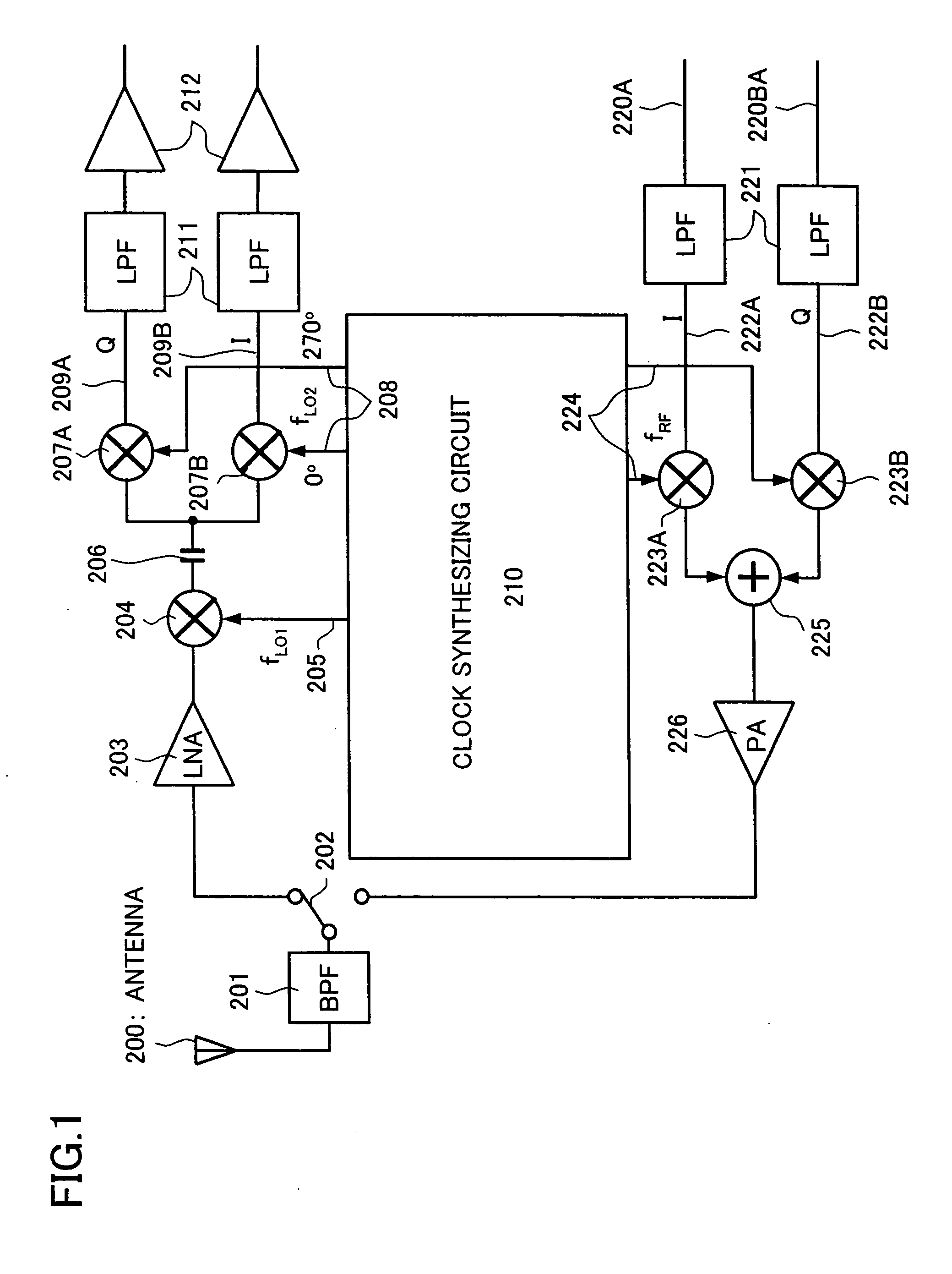

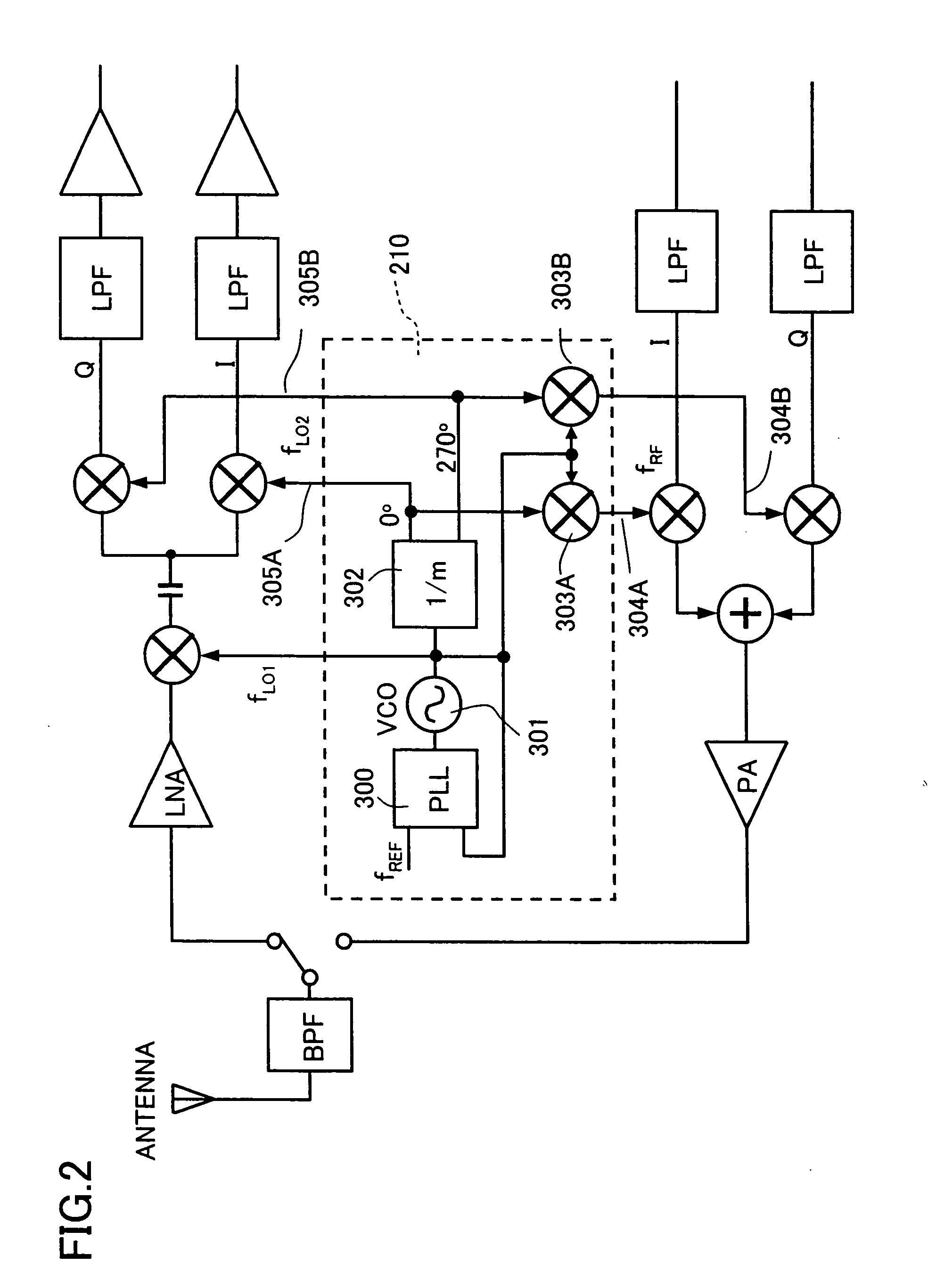

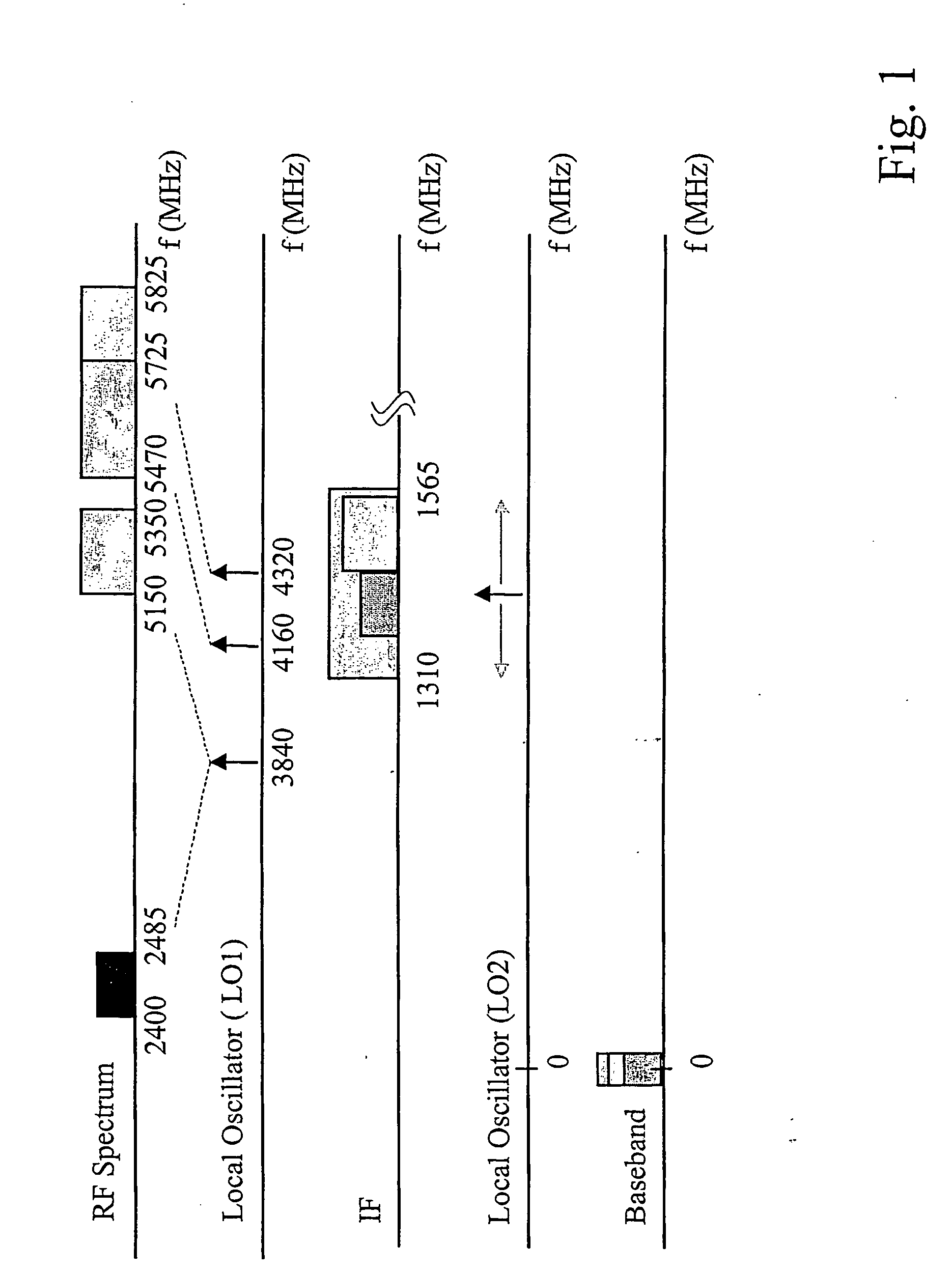

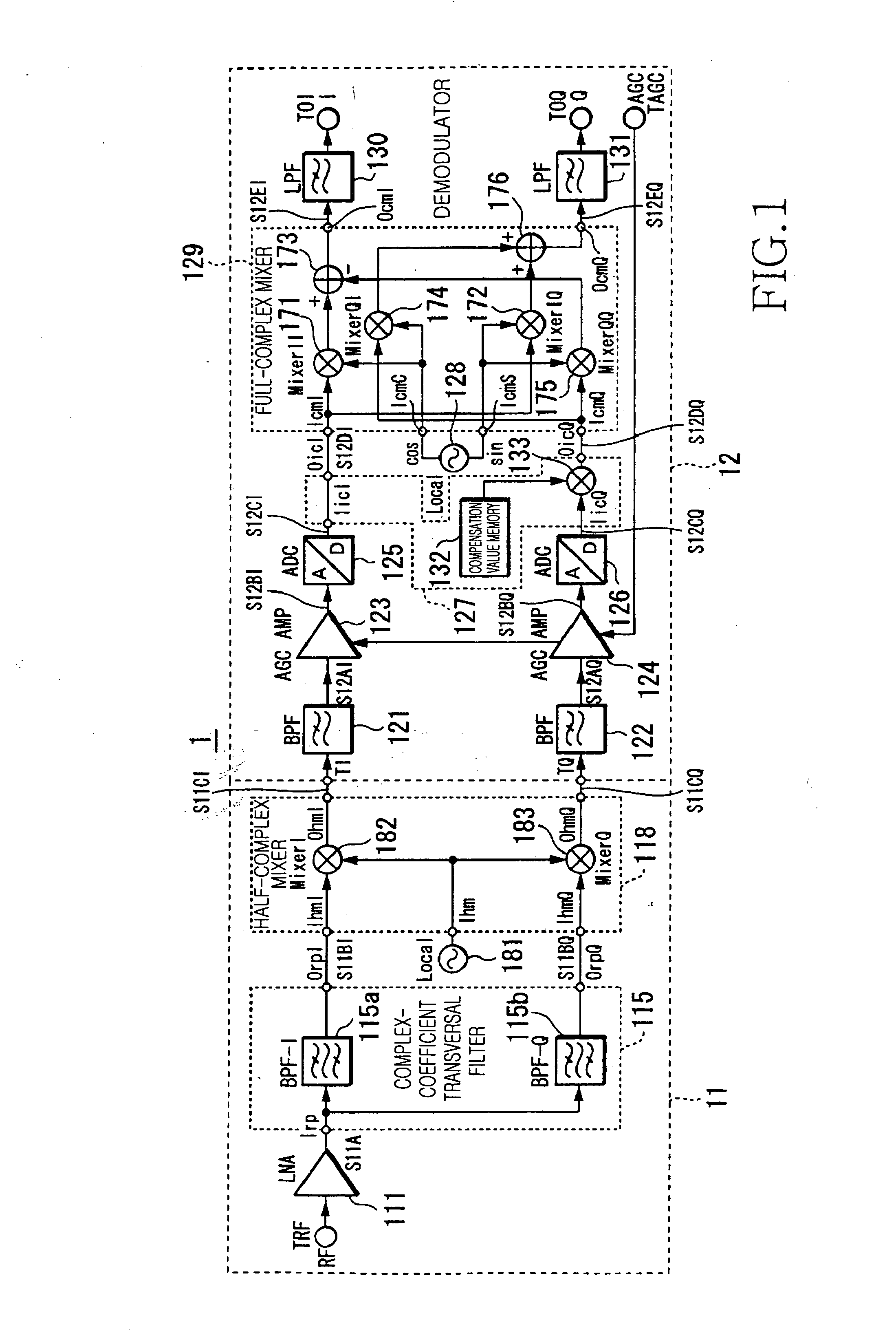

InactiveUS20050117664A1Reduce power consumptionModulation transference balanced arrangementsModulated-carrier systemsTuned radio frequency receiverFrequency conversion

A frequency conversion circuit of the present invention includes: (i) a first mixer for mixing the radio frequency signal having a frequency fRF with a first oscillation signal having a frequency fLO1 so that the radio frequency signal is downconverted into an intermediate frequency signal; and (ii) a second mixer for mixing the intermediate frequency signal sent from the first mixer with two local oscillation signals so that the intermediate frequency signal is downconverted into two base-band signals having different phases. The second local oscillation signals have phases of 0° and 270°, respectively. These frequencies satisfies: fLO1=k×fRF(k>1) fLO2=fLO1 / m, (m>1) k=m / (m−1). This arrangement ensures (i) a small frequency conversion circuit that can be mounted on an integrated circuit, (ii) a radio frequency receiver including the frequency conversion circuit, and (iii) a radio frequency transceiver including the radio frequency receiver.

Owner:SHARP KK

Integrated VCO having an improved tuning range over process and temperature variations

InactiveUS7019598B2Angle modulation by variable impedenceResonant circuit detailsState variableControl circuit

An integrated VCO having an improved tuning range over process and temperature variations. There is therefore provided in a present embodiment of the invention an integrated VCO. The VCO comprises, a substrate, a VCO tuning control circuit responsive to a VCO state variable that is disposed upon the substrate, and a VCO disposed upon the substrate, having a tuning control voltage input falling within a VCO tuning range for adjusting a VCO frequency output, and having its tuning range adjusted by the tuning control circuit in response to the VCO state variable.

Owner:AVAGO TECH INT SALES PTE LTD

Integrated spiral inductor

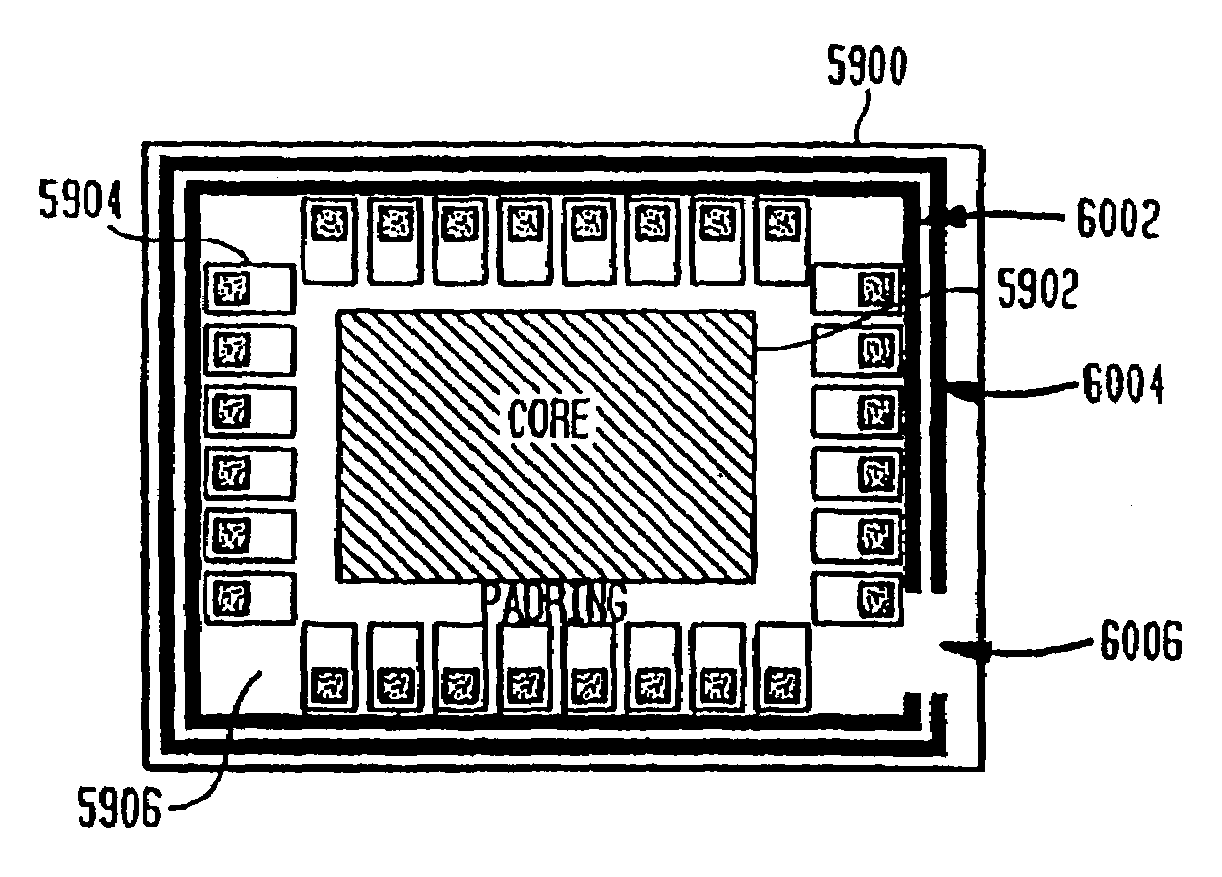

InactiveUS20050156700A1Resonant circuit detailsSemiconductor/solid-state device detailsCapacitanceShunt Device

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors with shields to increase circuit Q. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH INT SALES PTE LTD

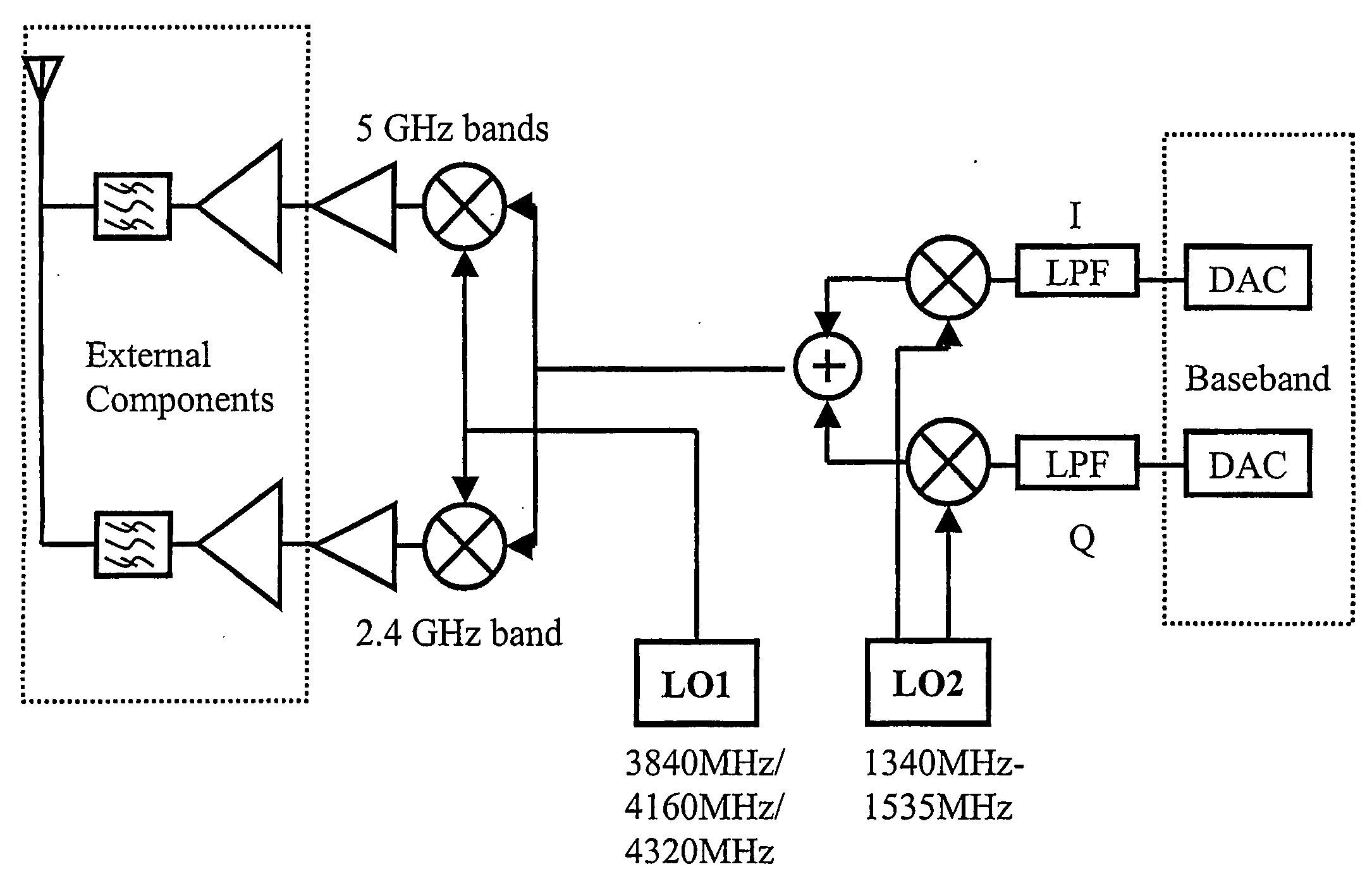

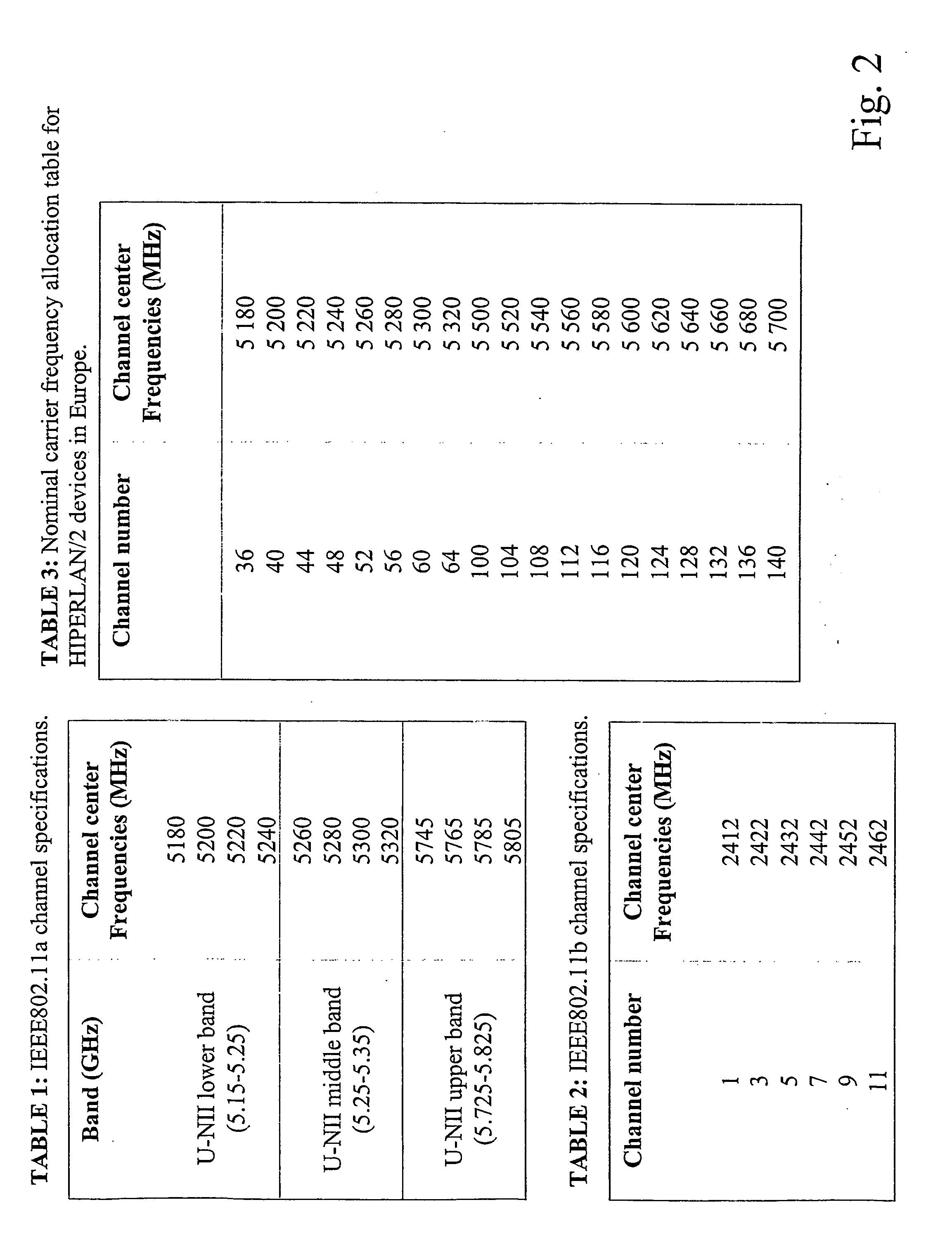

Multi standard transceiver architecture for wlan

InactiveUS20040259518A1Smooth transitionArea minimizationNetwork topologiesInformation formatIntermediate frequencyLocal oscillator

The present invention relates to a radio front end transceiver and methods of operating the transceiver. A transceiver is employed consisting of a first and second receive path and a first and second transmit path. Each first path and second path can handle signals of a first and a second modulation format and a first and a second radio frequency band respectively. The transceiver comprises circuitry for conversion between the respective radio frequency bands and an intermediate frequency. The transceiver is arranged with intermediate frequency circuitry for conversion between the respective intermediate frequencies and basebands. At least some of the intermediate frequency circuitry is common to both receive paths and at least some of the intermediate frequency circuitry is common to both transmit paths. A frequency synthesizer is arranged to derive overlapping local oscillator frequencies suitable for use by the intermediate frequency circuitry on each of the paths.

Owner:FIRSTPASS SEMICON AB

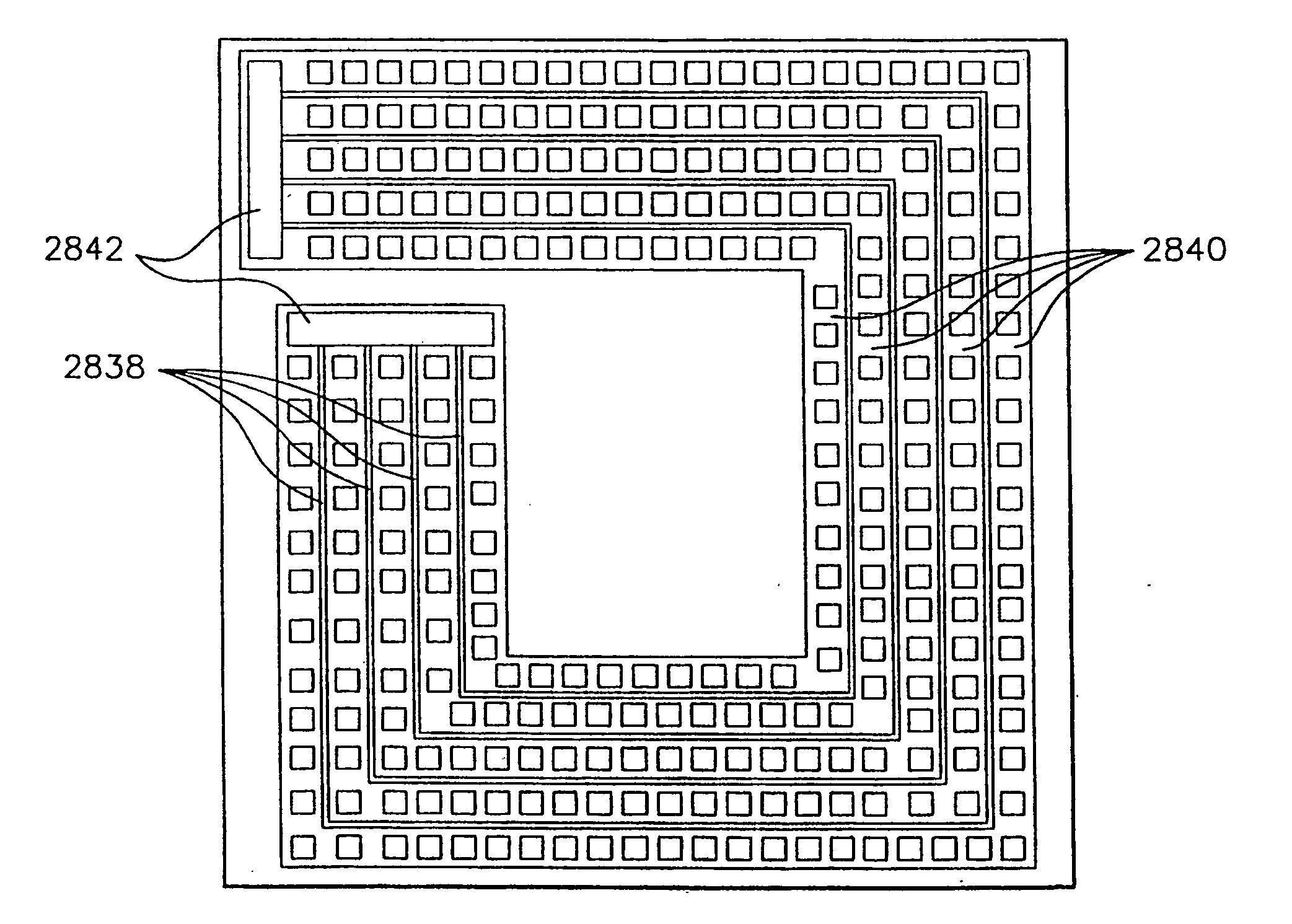

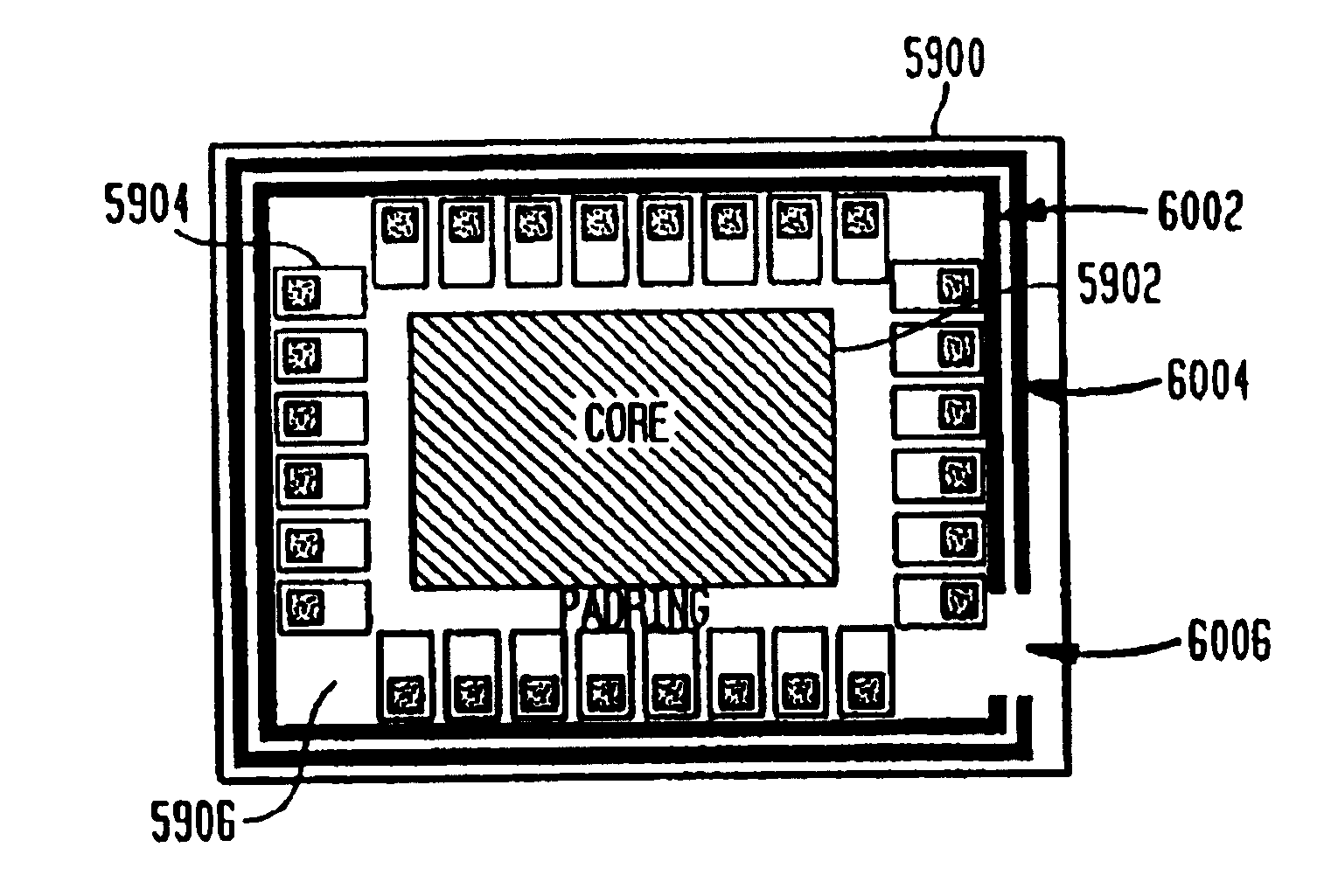

System and method for ESD protection

InactiveUS6963110B2Reduce areaReduce capacitanceResonant circuit detailsSemiconductor/solid-state device detailsShunt DeviceCapacitance

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

Frequency circuit, radio frequency receiver and radio receiving-transmitting machine

InactiveCN1612490AGood choiceHigh sensitivityModulation transference balanced arrangementsTransmissionTuned radio frequency receiverFrequency conversion

A frequency conversion circuit of the present invention includes: (i) a first mixer for mixing the radio frequency signal having a frequency fRF with a first oscillation signal having a frequency fLO1 so that the radio frequency signal is downconverted into an intermediate frequency signal; and (ii) a second mixer for mixing the intermediate frequency signal sent from the first mixer with two local oscillation signals so that the intermediate frequency signal is downconverted into two base-band signals having different phases. The second local oscillation signals have phases of 0° and 270°, respectively. These frequencies satisfies: <?in-line-formulae description="In-line Formulae" end="lead"?>fLO1=kxfRF(k>1) <?in-line-formulae description="In-line Formulae" end="tail"?> <?in-line-formulae description="In-line Formulae" end="lead"?>fLO2=fLO1 / m, (m>1)<?in-line-formulae description="In-line Formulae" end="tail"?> <?in-line-formulae description="In-line Formulae" end="lead"?>k=m / (m-1).<?in-line-formulae description="In-line Formulae" end="tail"?> This arrangement ensures (i) a small frequency conversion circuit that can be mounted on an integrated circuit, (ii) a radio frequency receiver including the frequency conversion circuit, and (iii) a radio frequency transceiver including the radio frequency receiver.

Owner:SHARP KK

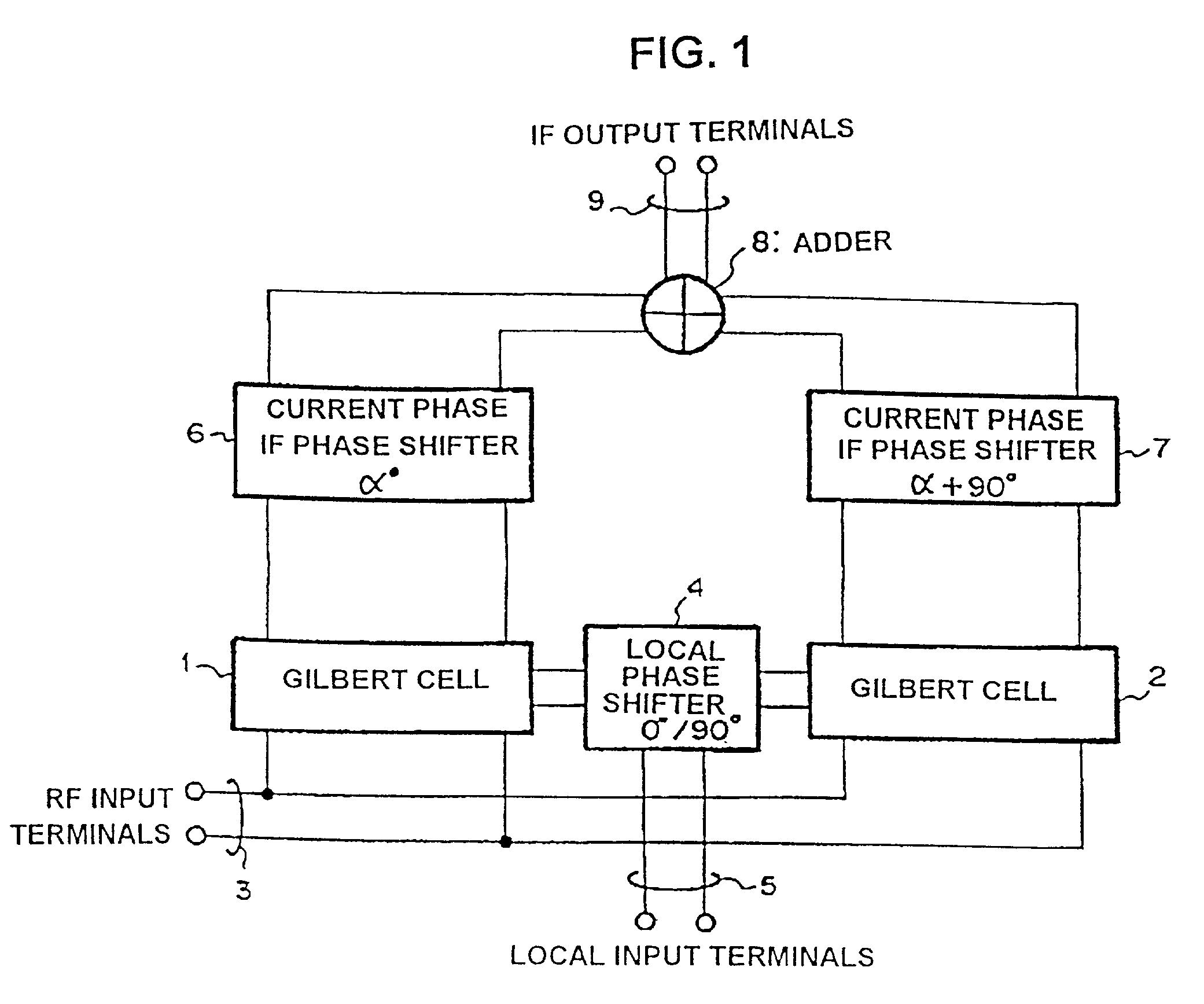

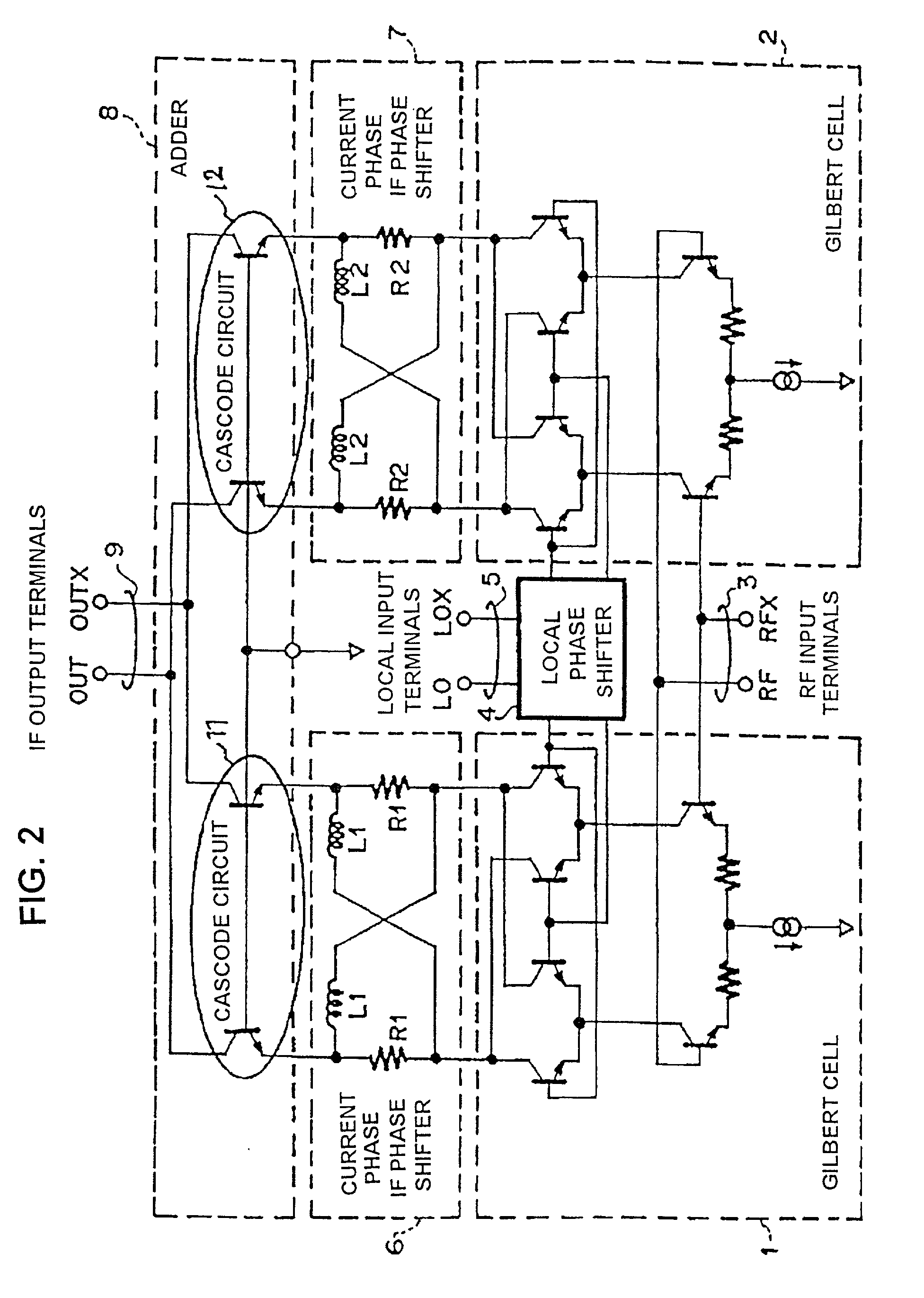

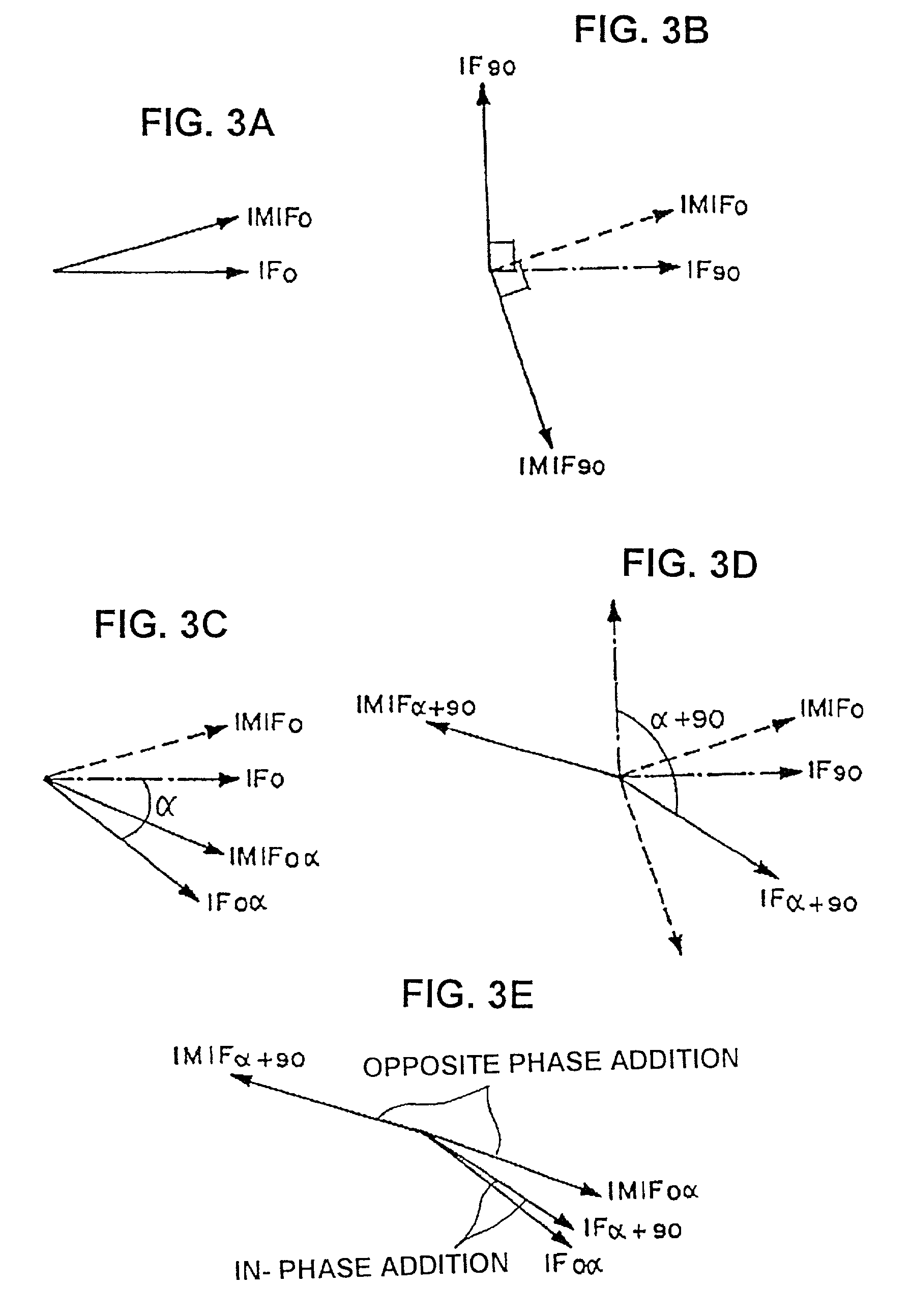

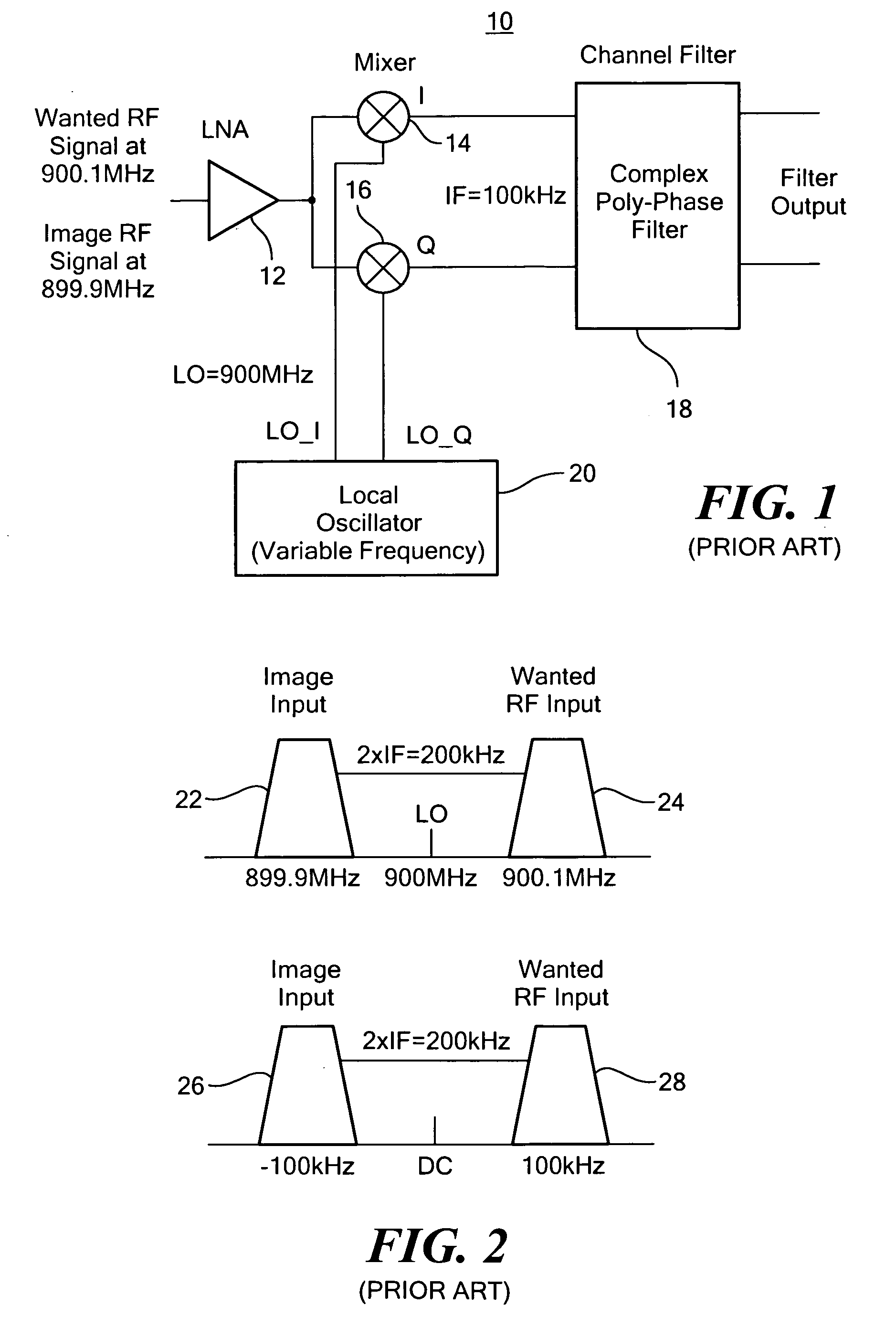

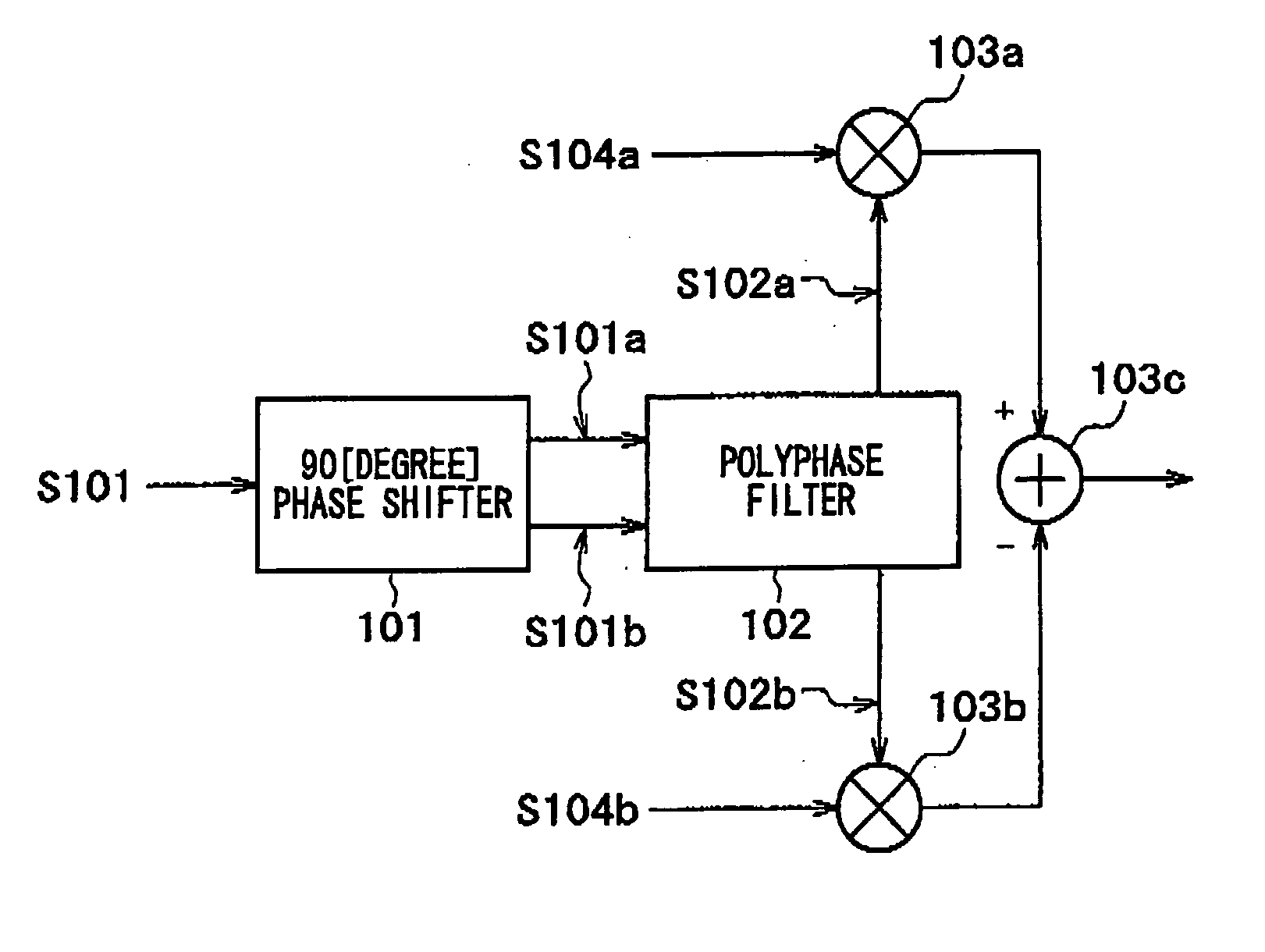

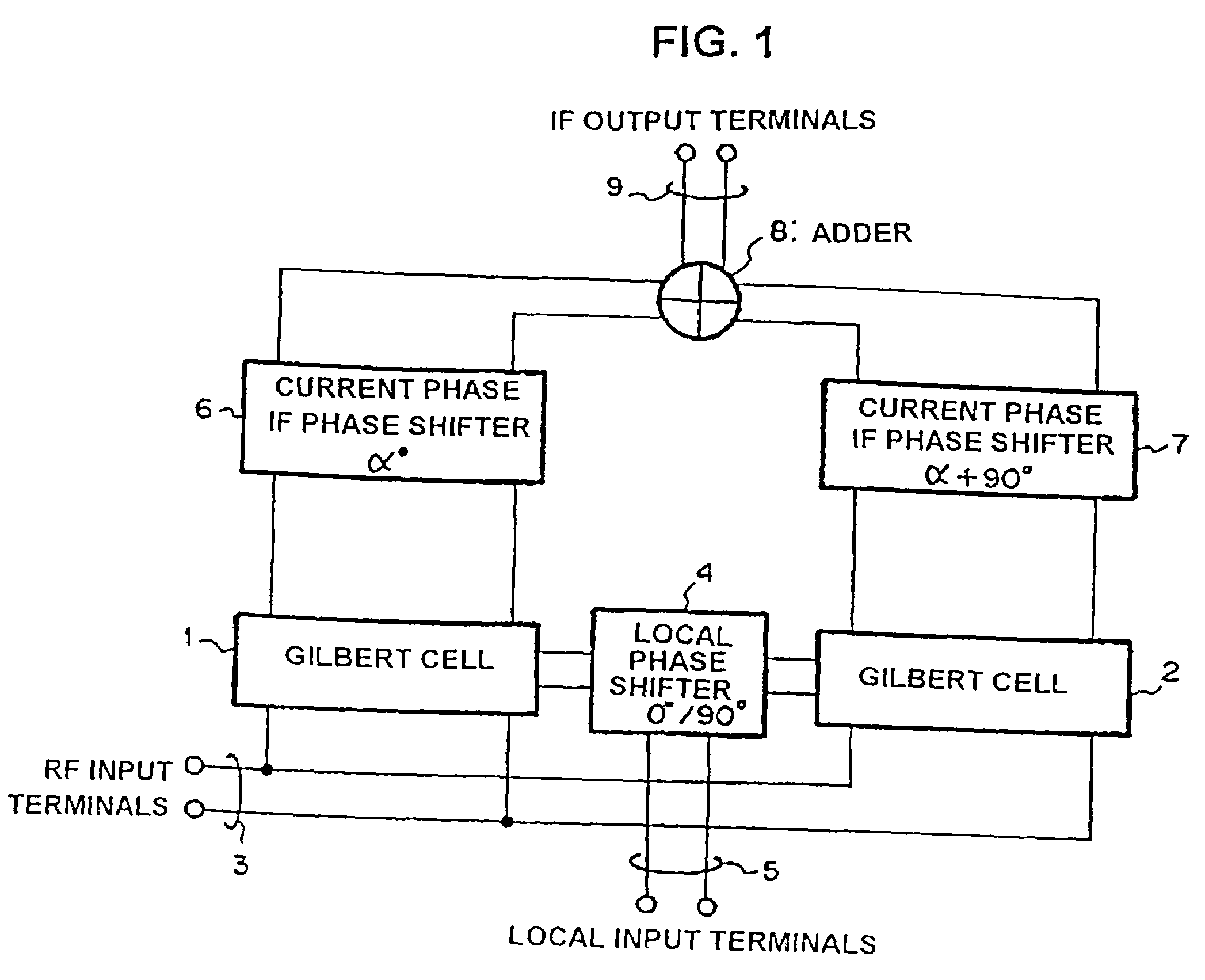

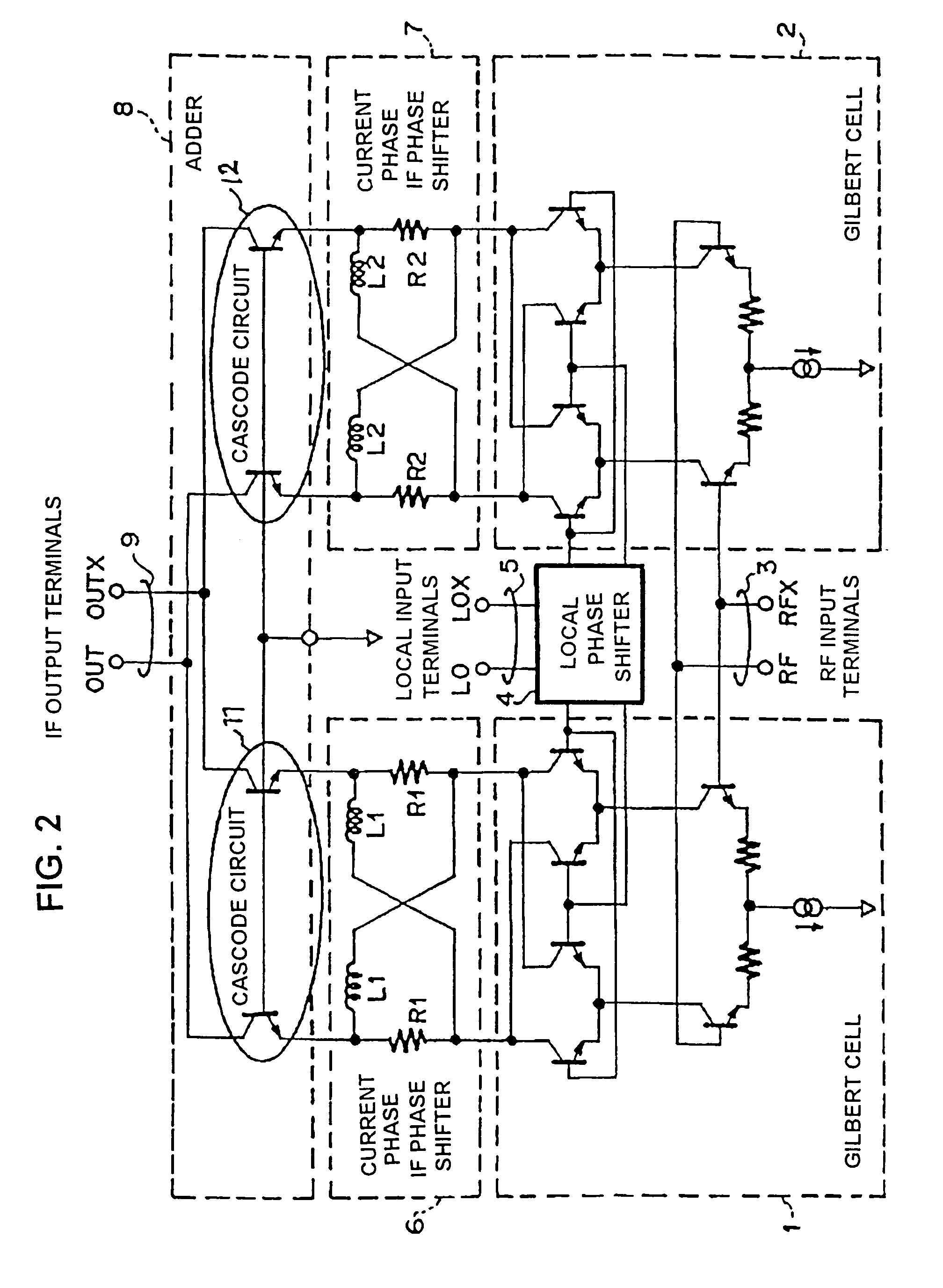

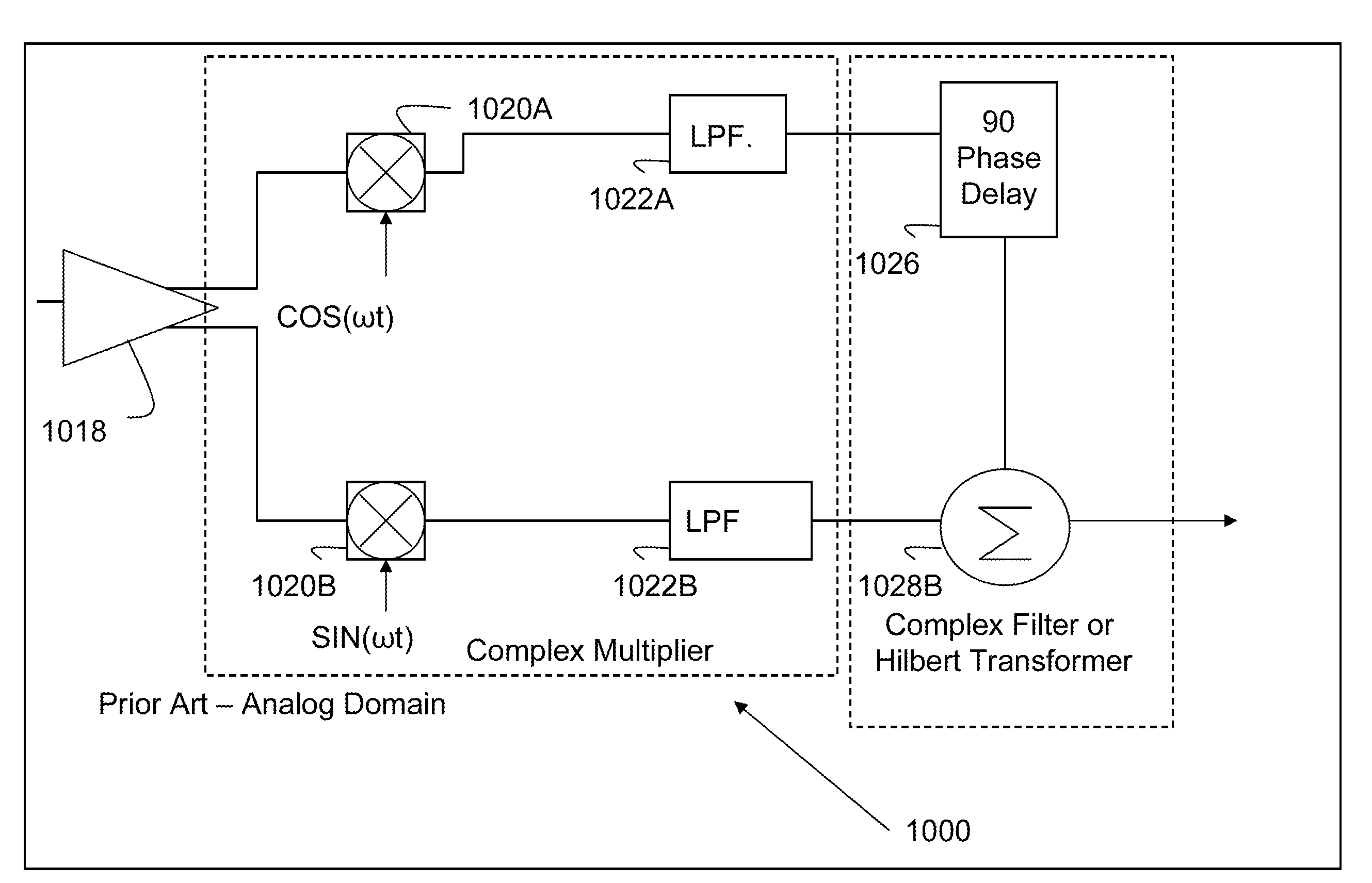

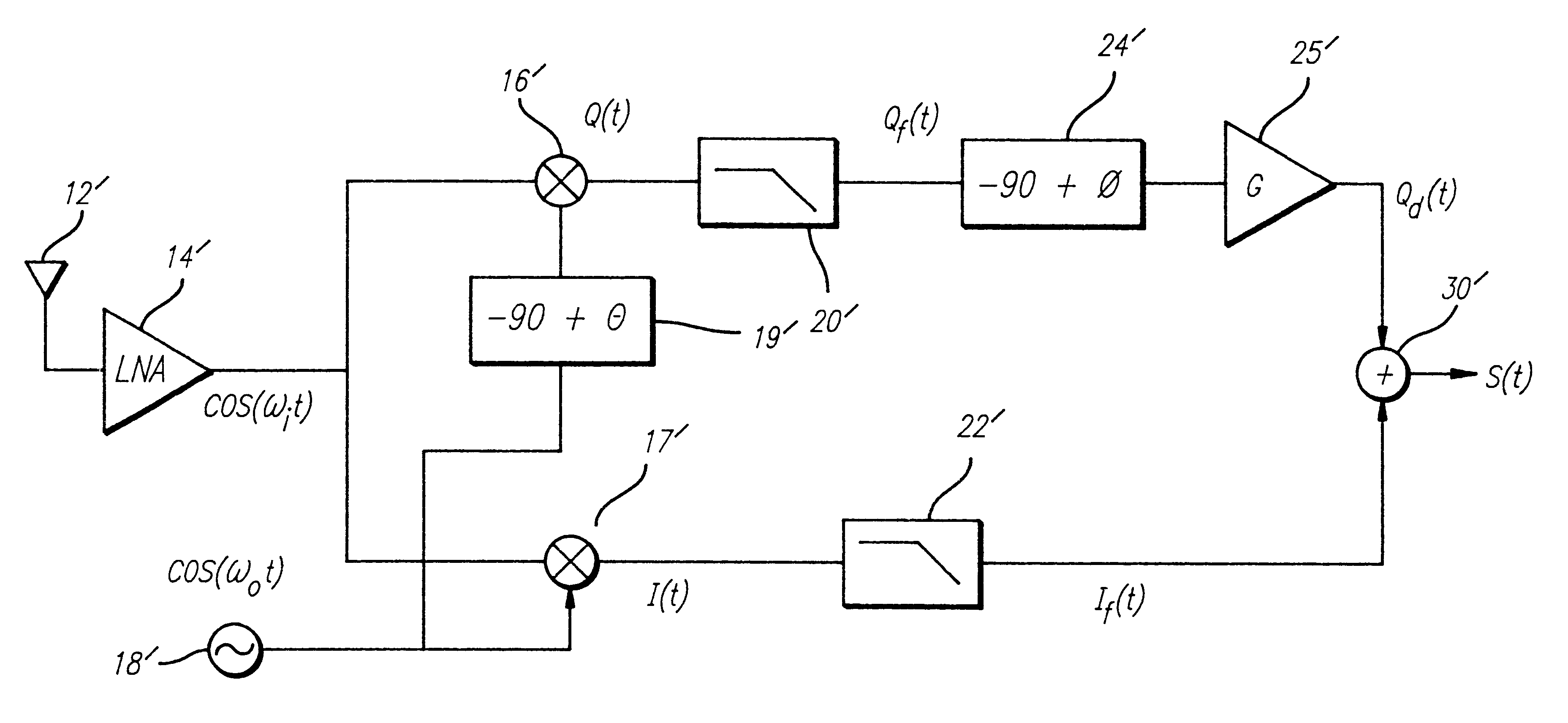

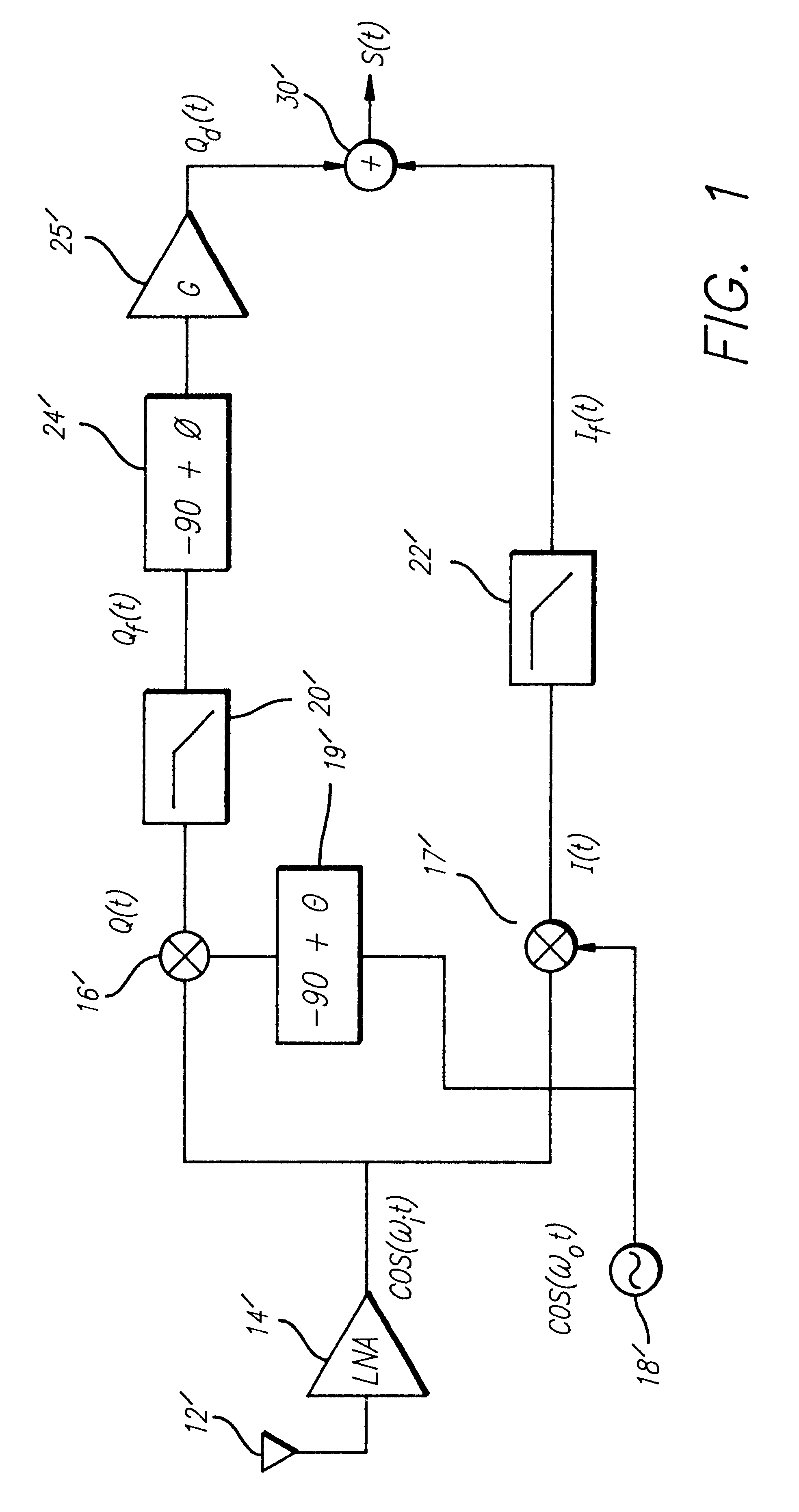

Image rejection mixer

An object of the present invention is to lower the power dissipation of the image rejection mixer. The image rejection mixer includes distribution means supplied with local signals having a phase difference to distribute the local signals, first and second mixing means for mixing the distributed local signals and RF signals having a phase difference and outputting respective IF current signals, phase shift means for shifting in phase the respective mixed IF current signals so as to provide them with a relative phase difference of 90 degrees, and addition means for adding the respective phase shifted intermediate frequency current signals. The phase shift means shifts the phases of the respective IF current signals outputted from the first and second mixing means.

Owner:RENESAS ELECTRONICS CORP

Direct conversion turner

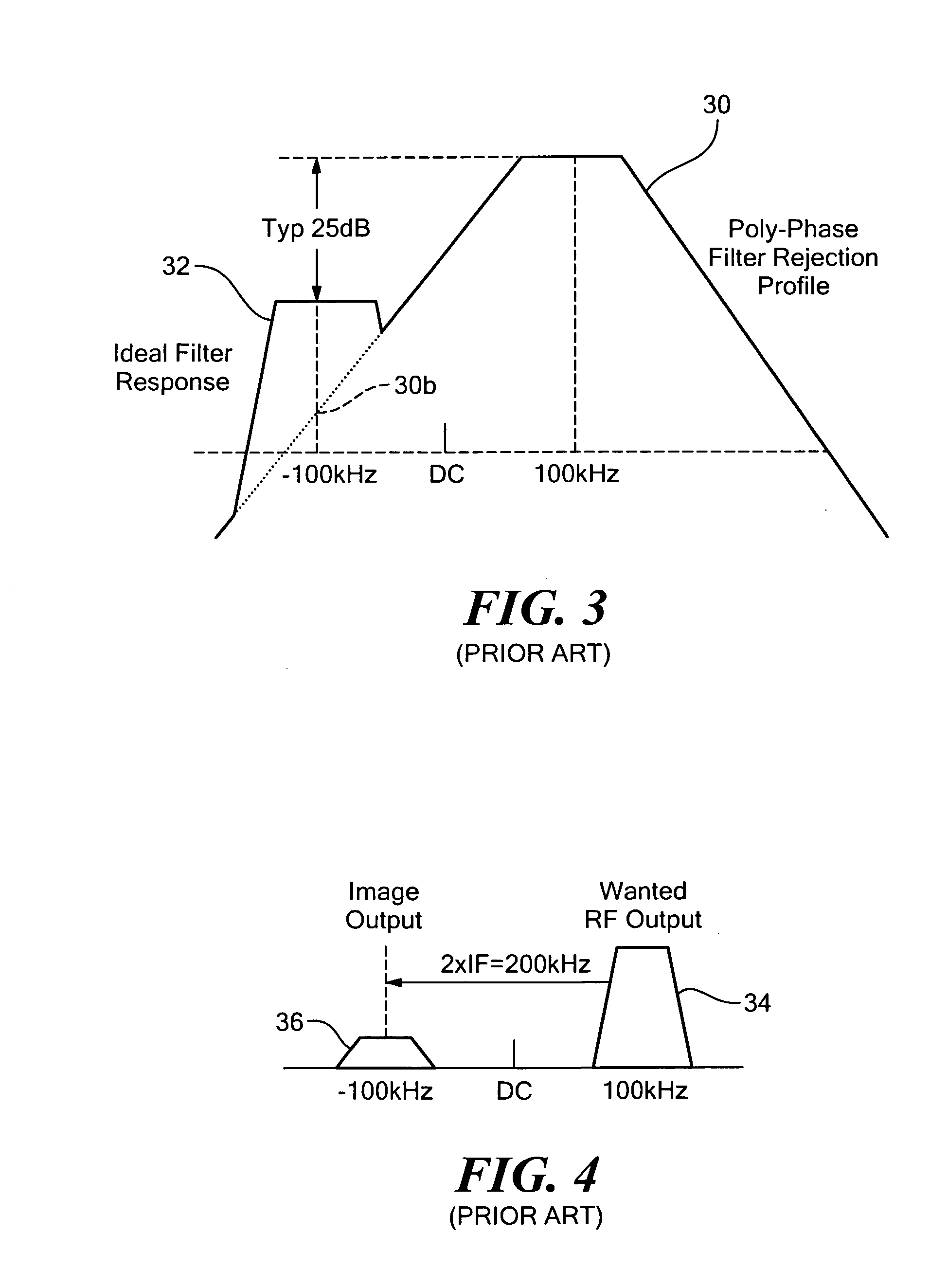

InactiveUS7050778B1Reduced Power RequirementsHigh image rejectionTransmission monitoringTransmission noise suppressionFrequency mixerPhase filter

A direct conversion tuner down-converts television signals, cable signals, or other signals directly from an RF frequency to an IF frequency and / or baseband, without an intermediate up-conversion step for image rejection. The direct conversion tuner includes a pre-select filter, an amplifier, an image reject mixer, and a poly-phase filter. The pre-select filter, amplifier, and the image reject mixer can be calibrated to provide sufficient image rejection to meet the NTSC requirements for TV signals. The entire direct conversion tuner can be fabricated on a single semiconductor substrate without requiring any off-chip components. The tuner configuration described herein is not limited to processing TV signals, and can be utilized to down-convert other RF signals to an IF frequency or baseband.

Owner:AVAGO TECH INT SALES PTE LTD

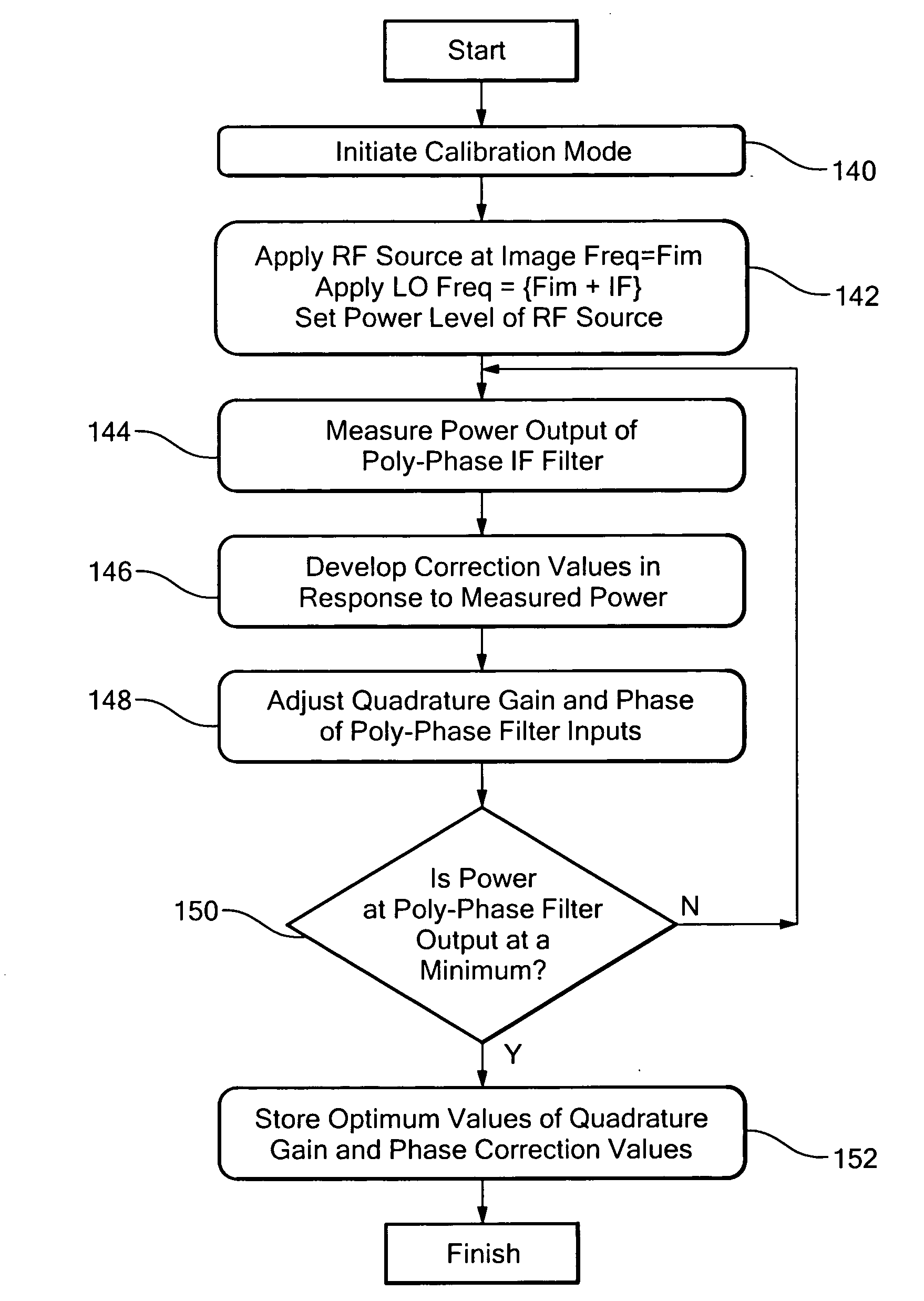

Image rejection calibration system

ActiveUS20080132191A1Improved image rejectionRadio transmissionFrequency-changer modificationsPhase filterLocal oscillator

Image rejection calibration includes initializing the calibration mode by applying to quadrature mixers, in place of the wanted RF input, an RF source in the frequency range of the wanted RF input, sensing the power output from the poly-phase filter, developing gain adjust and phase adjust correction values in response to the power output and adjusting in accordance with the correction values the gain of the quadrature signals from the quadrature mixers to the poly-phase filter and the phase of local oscillator quadrature signals from the local oscillator to the quadrature mixers to reduce the power output.

Owner:ANALOG DEVICES INC

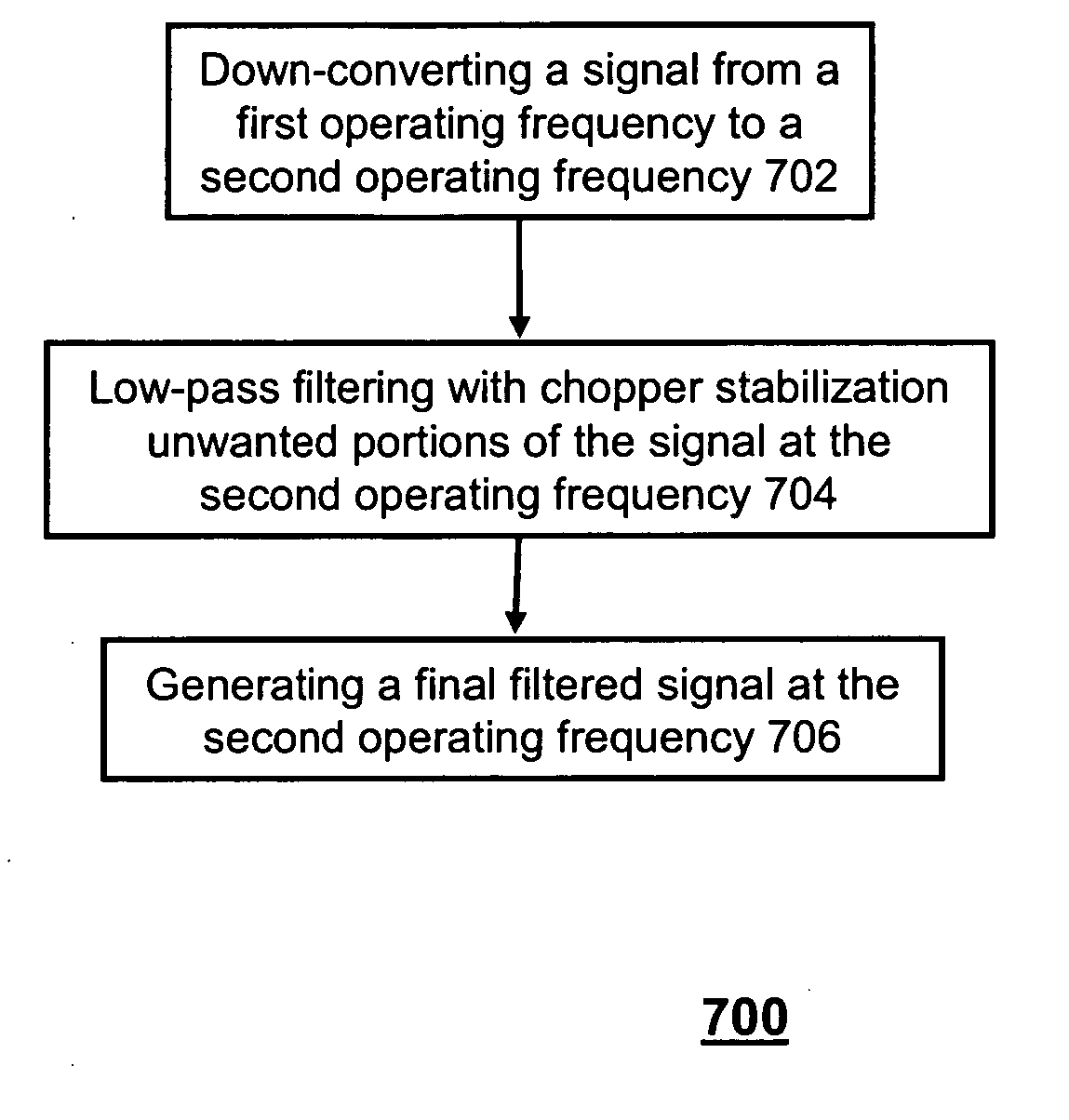

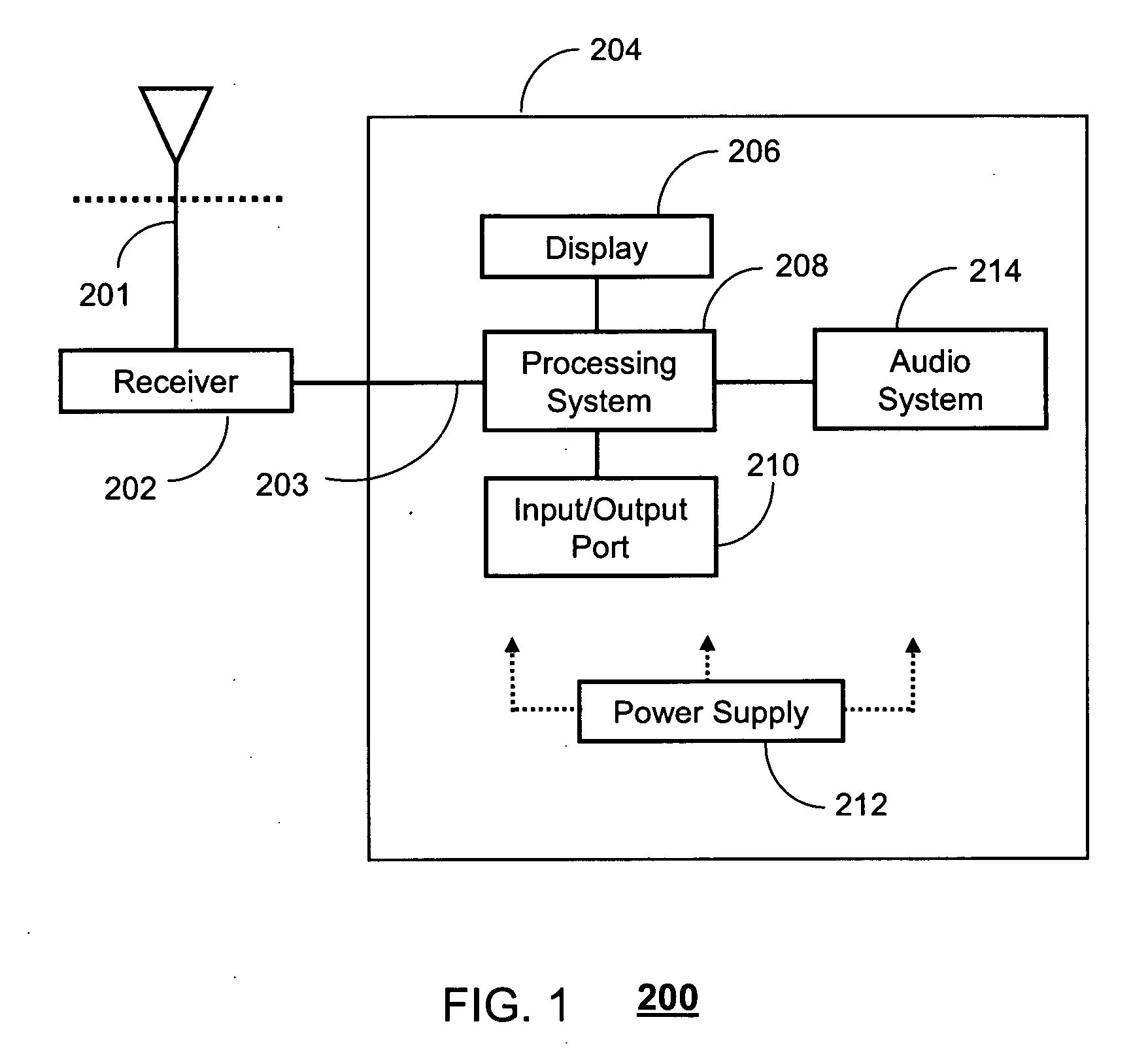

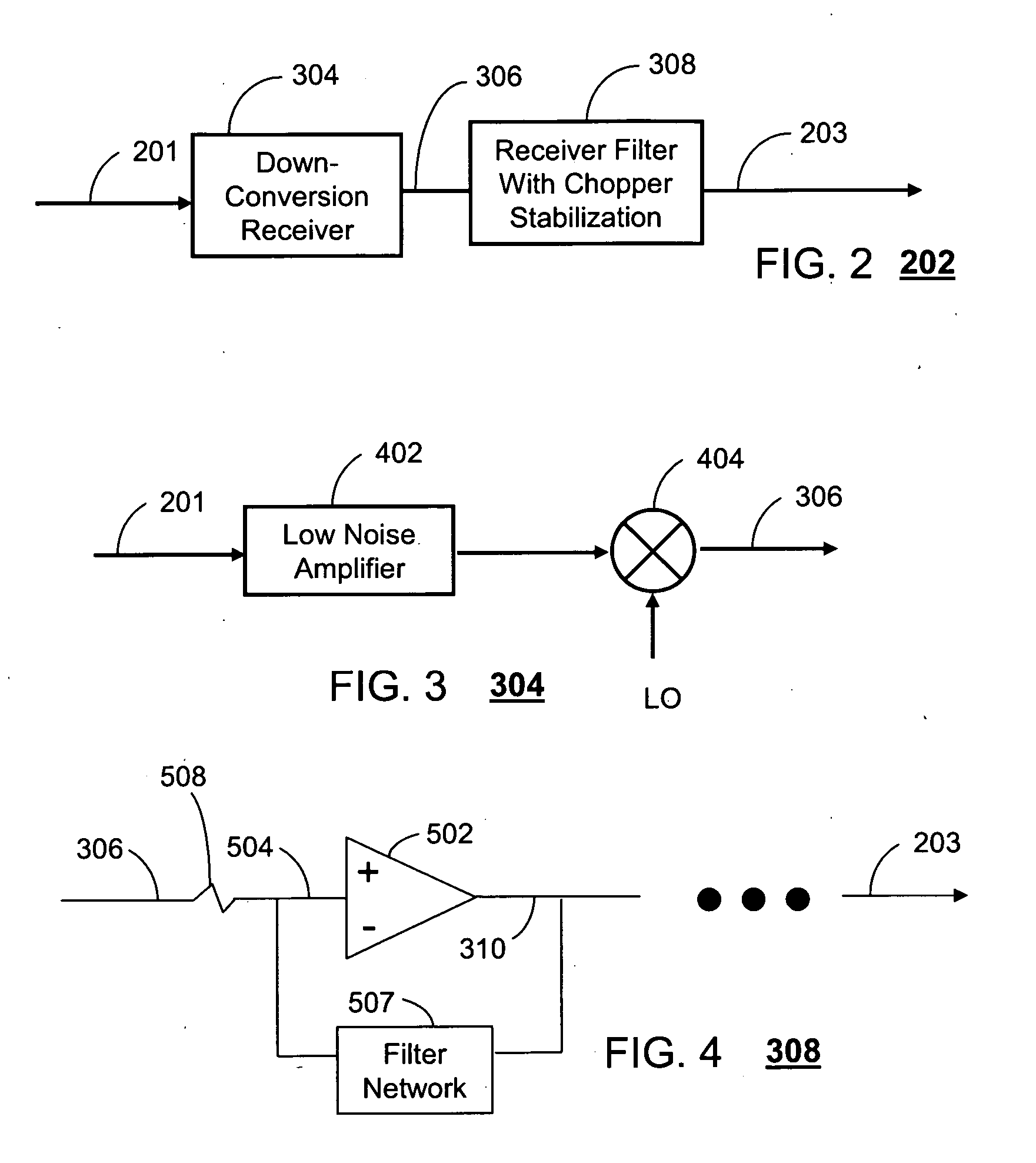

Receiver with chopper stabilization and method thereof

ActiveUS20060133550A1Error preventionLine-faulsts/interference reductionEngineeringOperating frequency

A receiver (202) has a down-conversion receiver (304) for transforming a signal (201) from a first operating frequency to a second operating frequency that is lower than the first operating frequency, and a receiver filter (308) with chopper stabilization for filtering unwanted portions of the signal (306) at the second operating frequency and for generating a final filtered signal (203) at the second operating frequency.

Owner:GOOGLE TECH HLDG LLC

Integrated VCO having an improved tuning range over process and temperature variations

InactiveUS20050030108A1Resonant circuit detailsSemiconductor/solid-state device detailsState variableControl circuit

An integrated VCO having an improved tuning range over process and temperature variations. There is therefore provided in a present embodiment of the invention an integrated VCO. The VCO comprises, a substrate, a VCO tuning control circuit responsive to a VCO state variable that is disposed upon the substrate, and a VCO disposed upon the substrate, having a tuning control voltage input falling within a VCO tuning range for adjusting a VCO frequency output, and having its tuning range adjusted by the tuning control circuit in response to the VCO state variable.

Owner:AVAGO TECH INT SALES PTE LTD

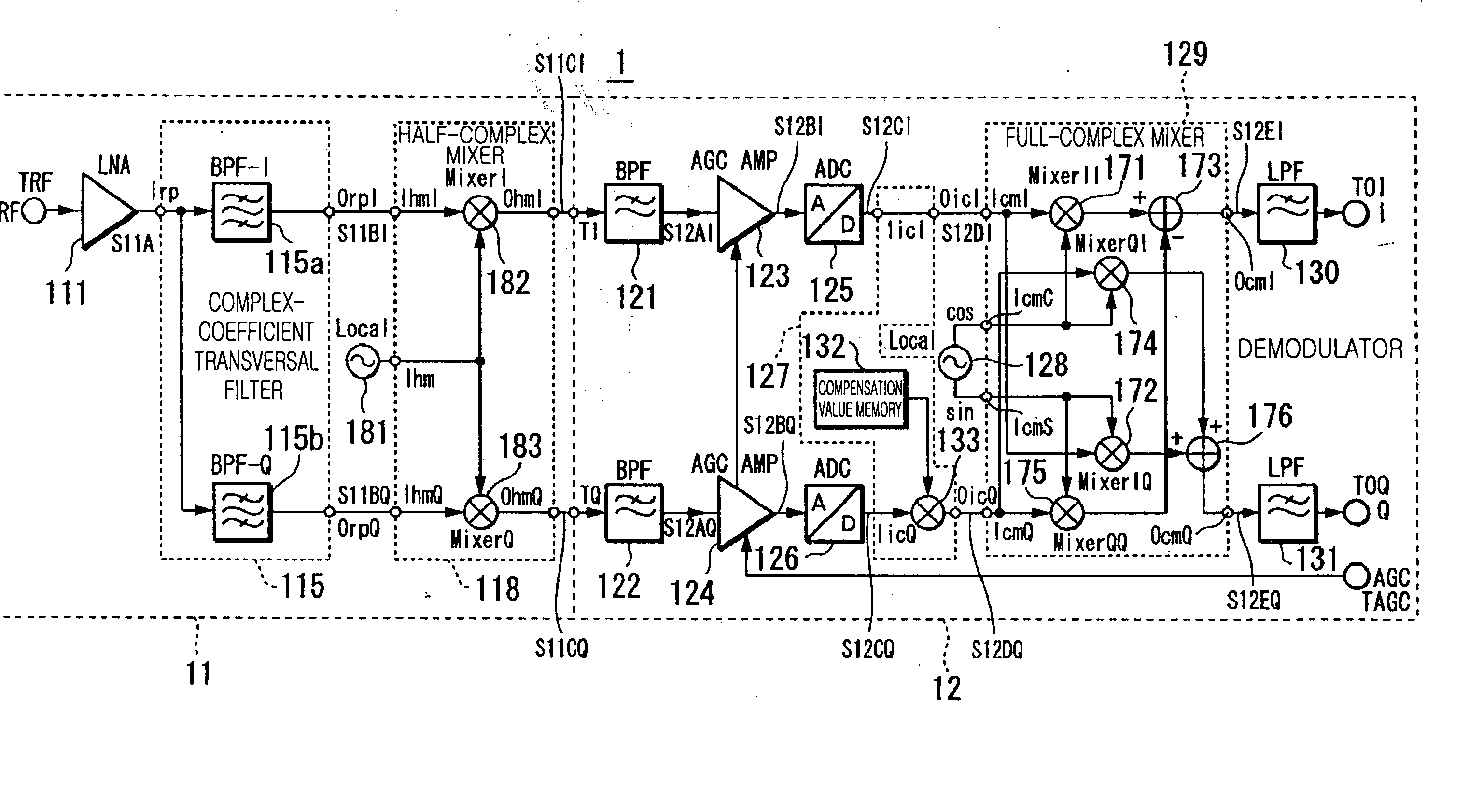

Downconverter and upconverter

InactiveUS20060256216A1Reduce power consumptionSufficient image rejection ratioTelevision system detailsModulated-carrier systemsFrequency changerIntermediate frequency

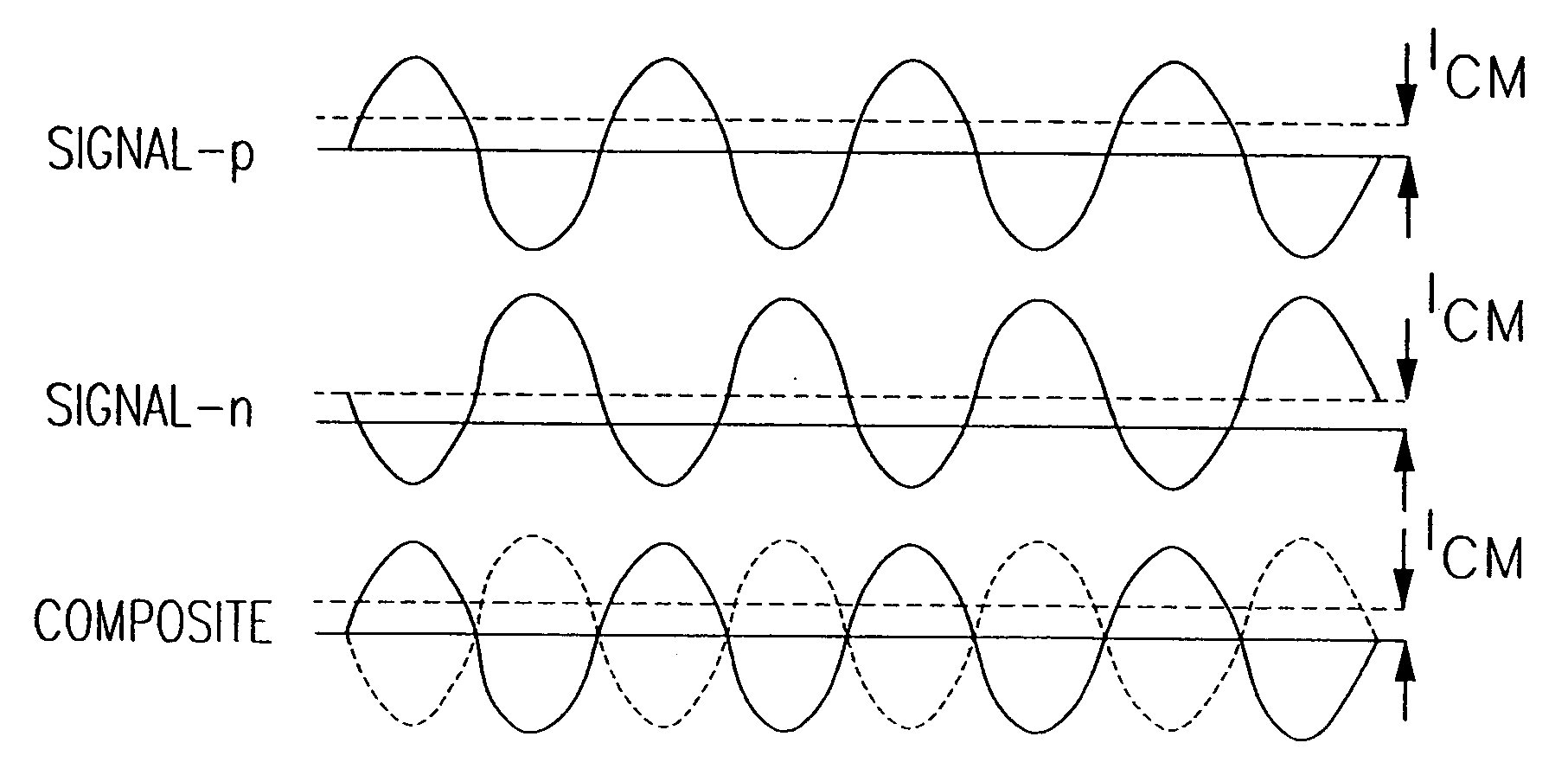

A downconverter and upconverter are provided which can obtain a sufficient image rejection ratio in a low-Intermediate Frequency (IF) scheme while reducing power consumption and can suppress Error Vector Magnitude (EVM)-related degradation in a zero-IF scheme. A complex-coefficient transversal filter rejects one side of a positive or negative frequency, and converts a Radio Frequency (RF) signal to a complex RF signal configured by real and imaginary parts. A local oscillator outputs a real local signal with a set frequency. A half-complex mixer, connected to the complex-coefficient transversal filter and the local oscillator, performs a frequency conversion process by multiplying the complex RF signal output from the complex-coefficient transversal filter and the real local signal output from the local oscillator, and outputs a complex signal of a frequency separated by the set frequency from a frequency of the RF signal.

Owner:SAMSUNG ELECTRONICS CO LTD

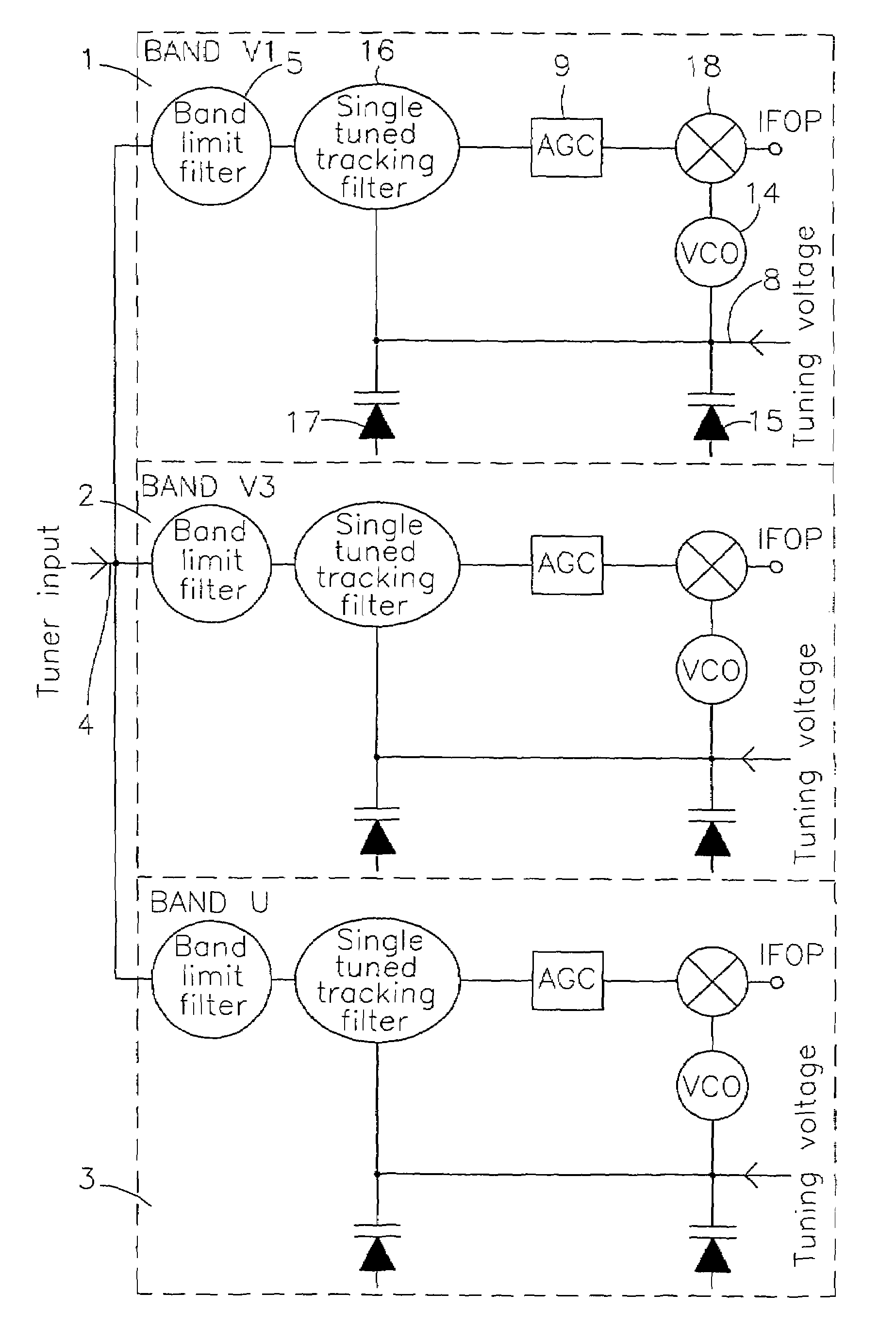

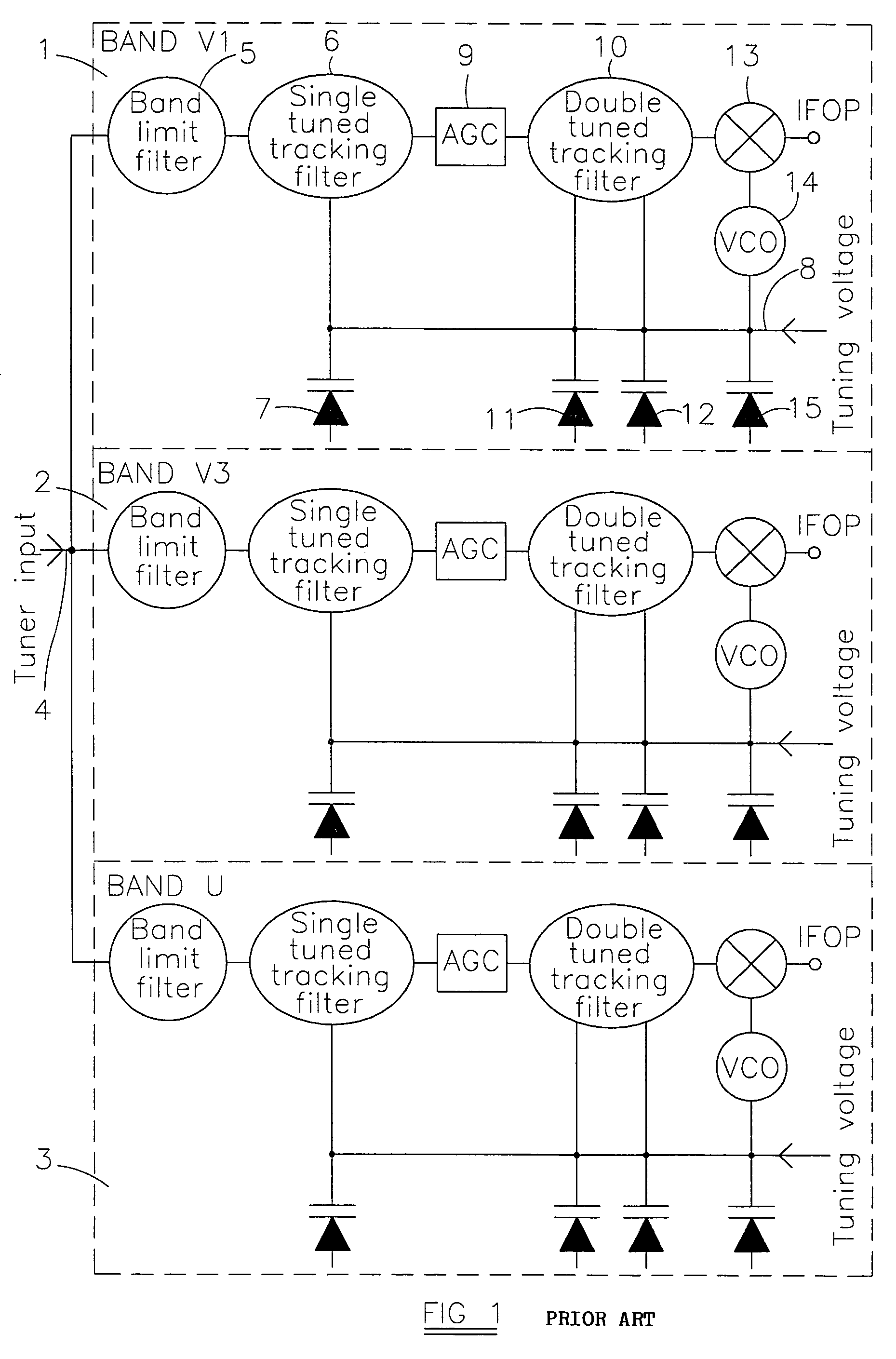

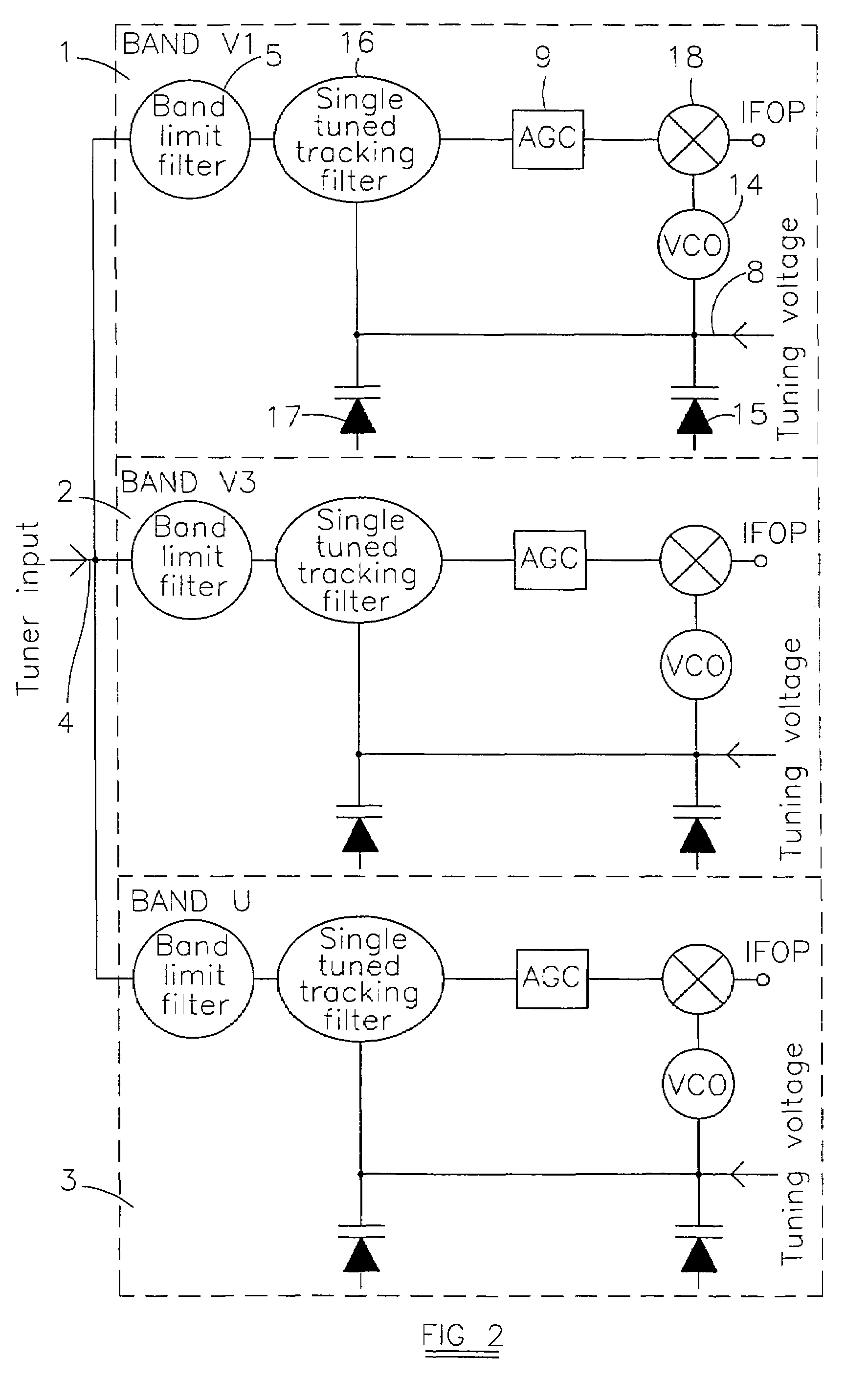

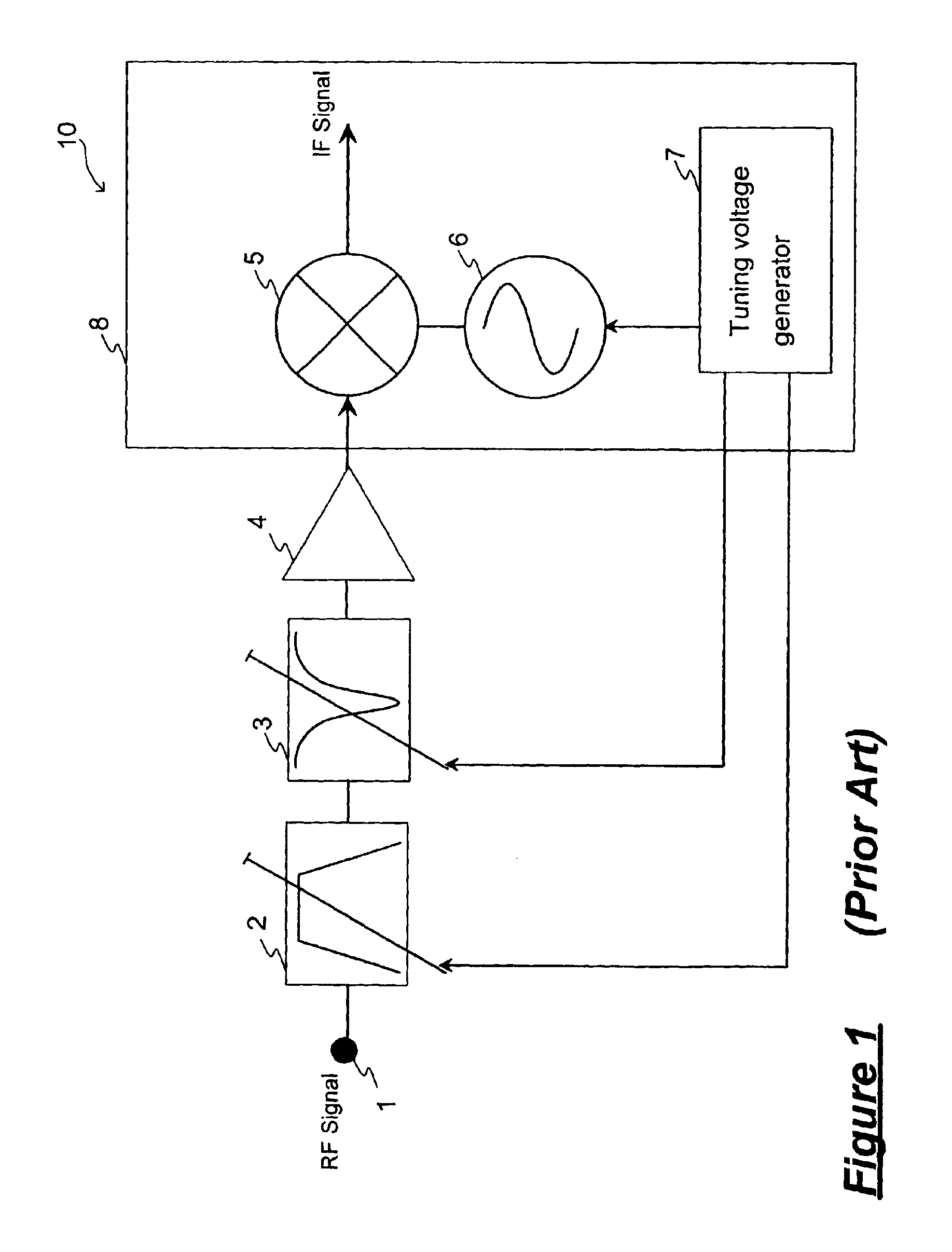

Tuner

InactiveUS7006162B2Easy constructionLow costTelevision system detailsContinuous tuning detailsEngineering

Owner:INTEL CORP

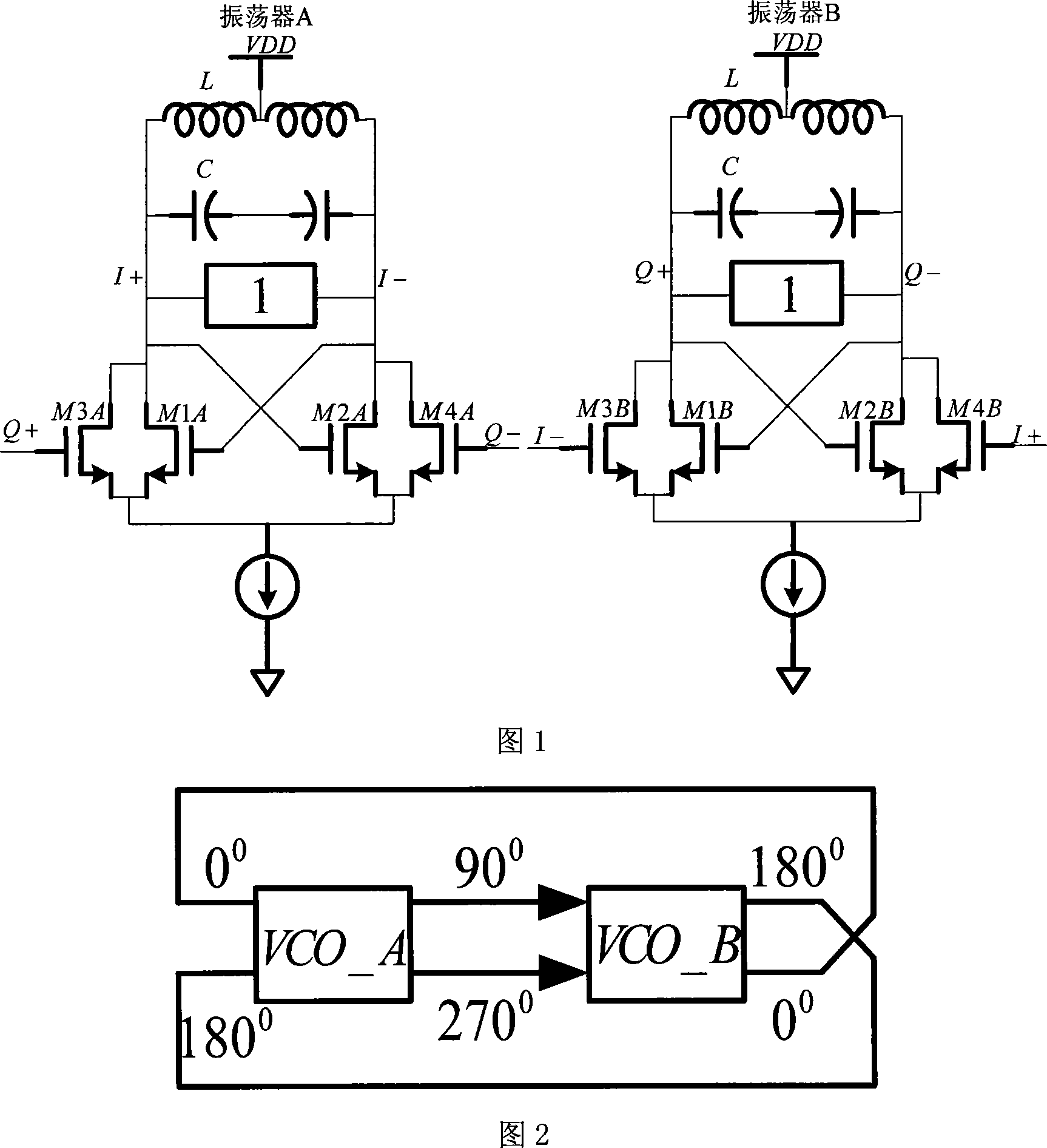

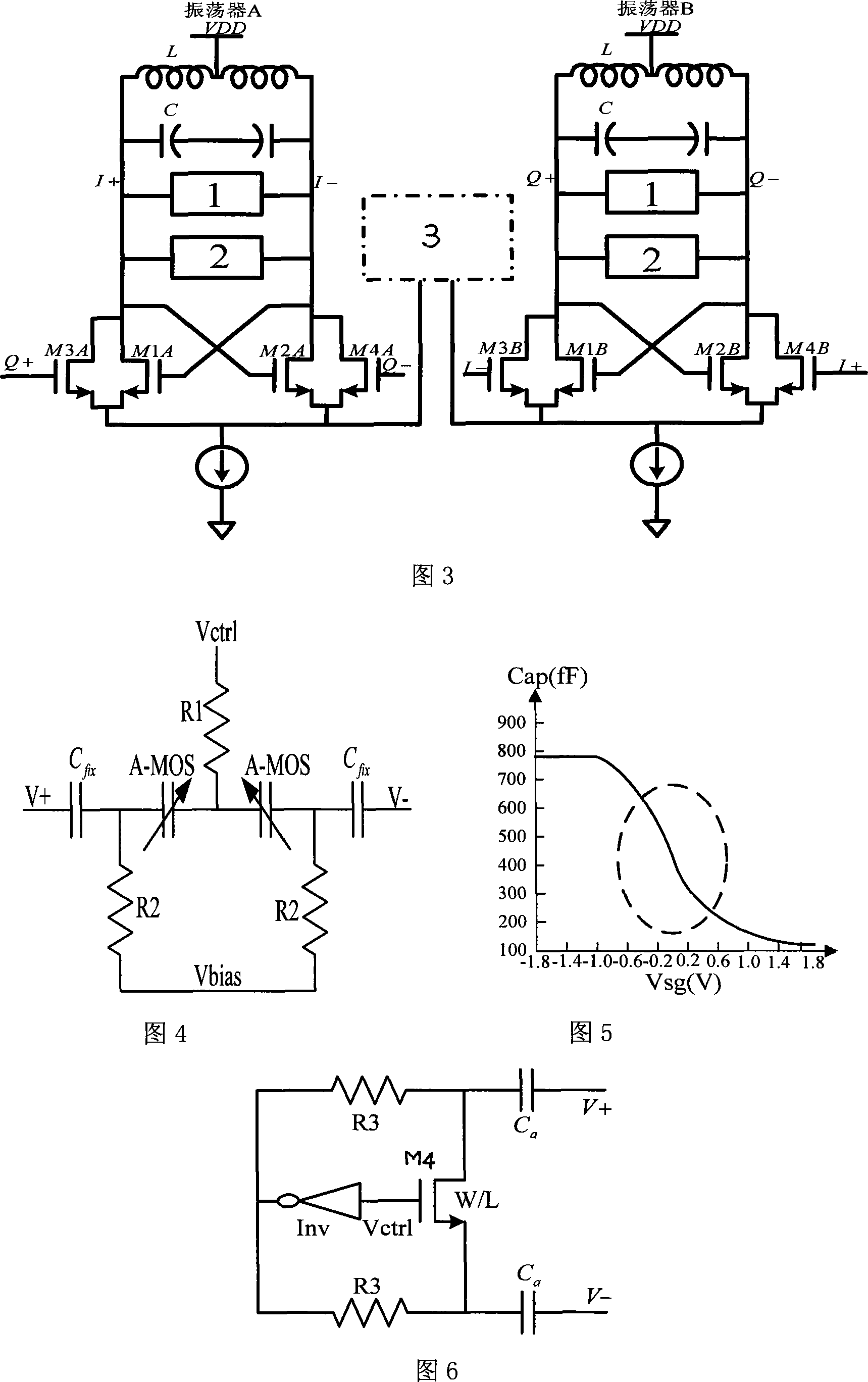

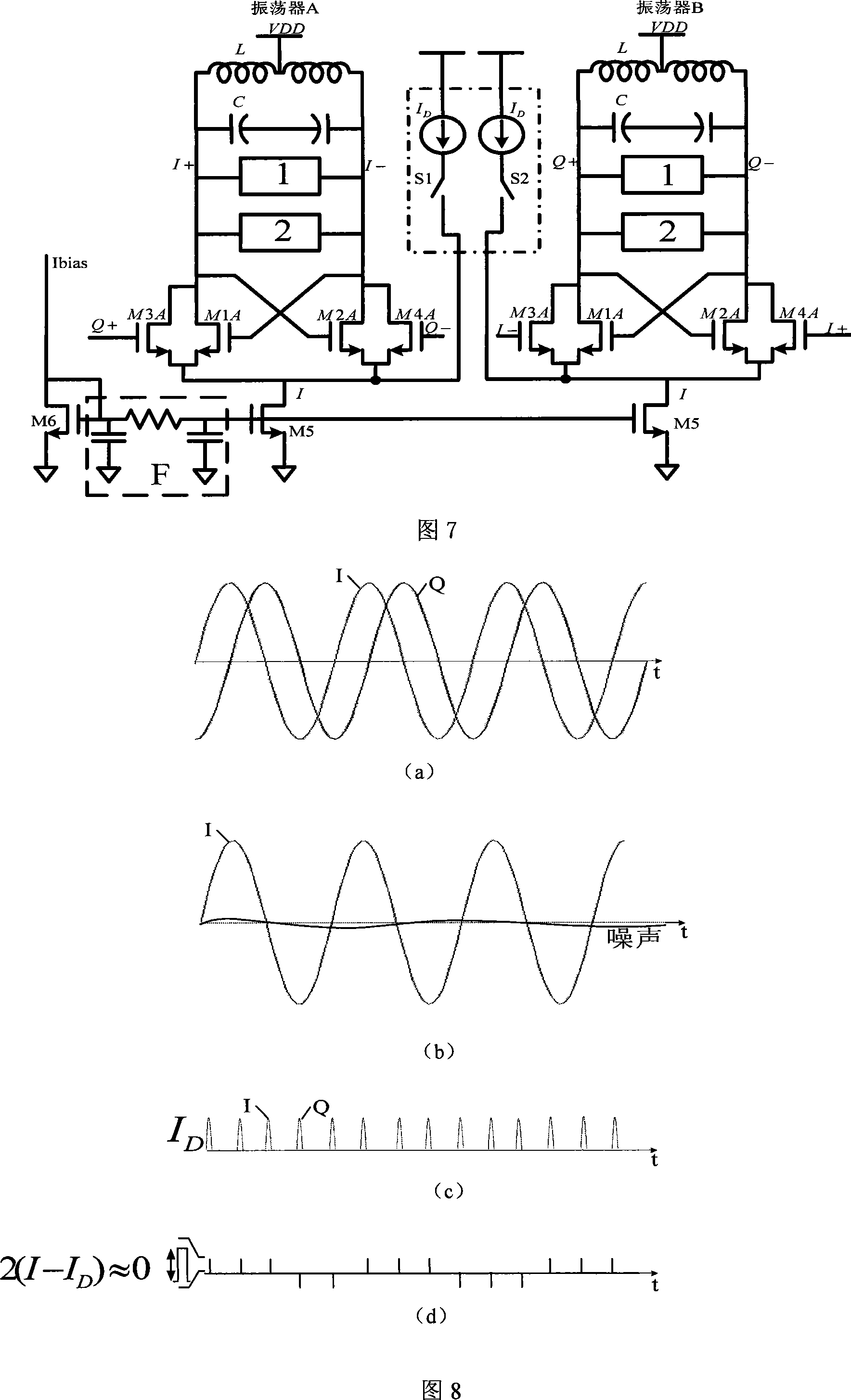

LC orthogonal voltage controlled oscillator capable of reducing flicker noise

InactiveCN101183851AReduce 1/f noiseOscillations generatorsFrequency-changer modificationsPhase noiseQuadrature oscillator

The invention relates to an LC quadrature VCO (voltage controlled oscillator) which can reduce the intermittent noise, belonging to the technical field of integrated circuit, . The invention is characterized in that two negative resistance oscillators are connected together with a quadrature coupler to output quadrature signals; the reduced phase noise is implemented by using a more linear narrow-band turning variable capacitor structure, multiband switching digital array with a lower parasitic capacitance and an intermittent noise eliminating circuit reducing the intermittent noise getting into the LC oscillator when inputting voltage crossing the zero point.

Owner:FUDAN UNIV

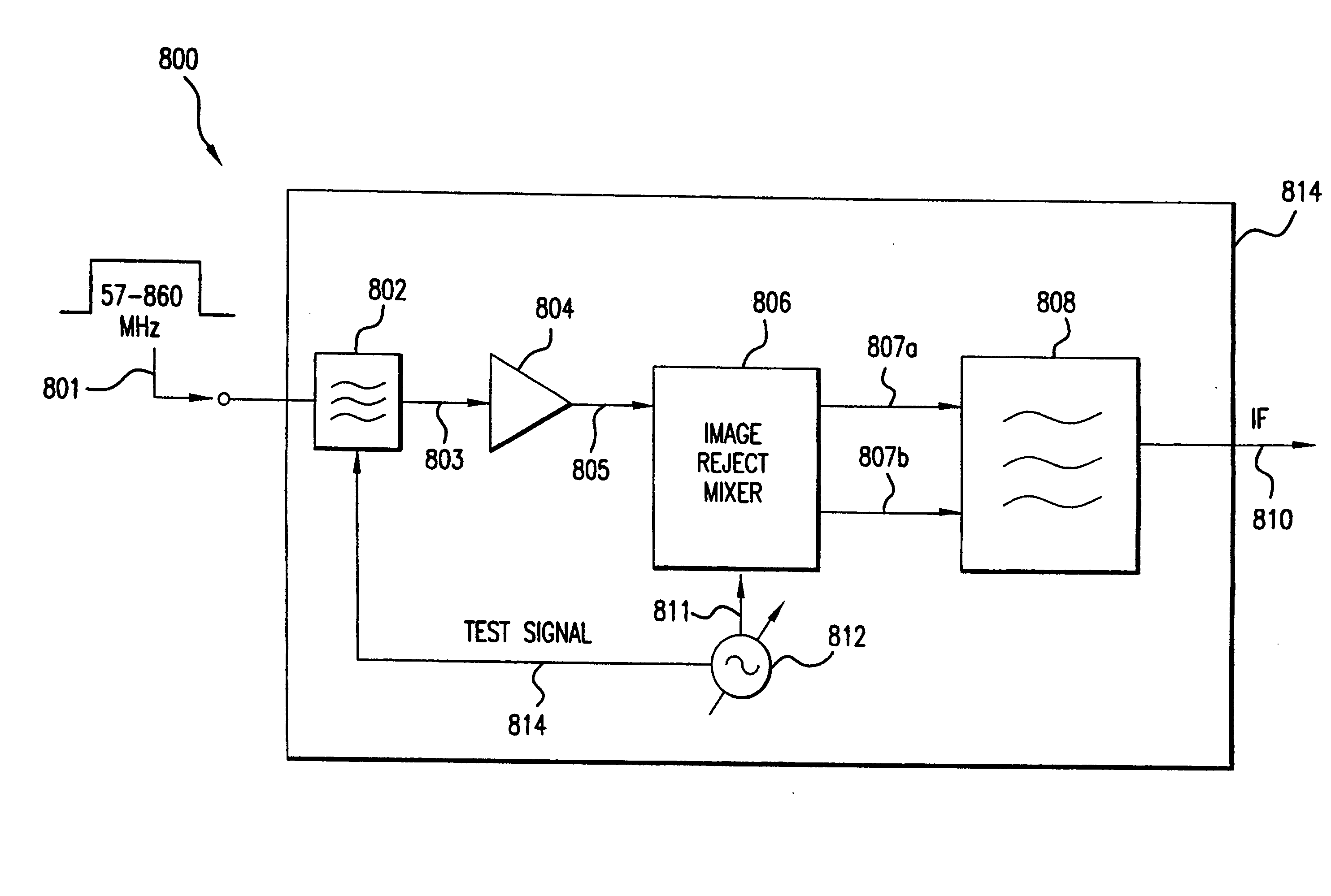

Image rejection mixer for broadband signal reception

ActiveUS6985710B1Radio transmissionFrequency-changer modificationsLocal oscillator signalFrequency mixer

An image rejection mixer includes an input terminal for receiving an input radio frequency (RF) signal, a mode selector coupled to the input terminal generating an output signal for either high side mixing or low side mixing, a first mixer coupled to receive the input RF signal and a signal from a local oscillator providing a signal having a local oscillator frequency, a phase converter coupled to convert the phase of the signal from the local oscillator, a second mixer coupled to receive the output signal from the mode selector and the phase-converted local oscillator signal, and a tunable polyphase filter coupled to receive output signals from the first mixer and the second mixer, the tunable polyphase filter providing an output signal having a variable intermediate frequency. In one embodiment, the variable intermediate frequency the tunable polyphase filter is implemented as a switchable intermediate frequency.

Owner:CR CRESPE LLC +1

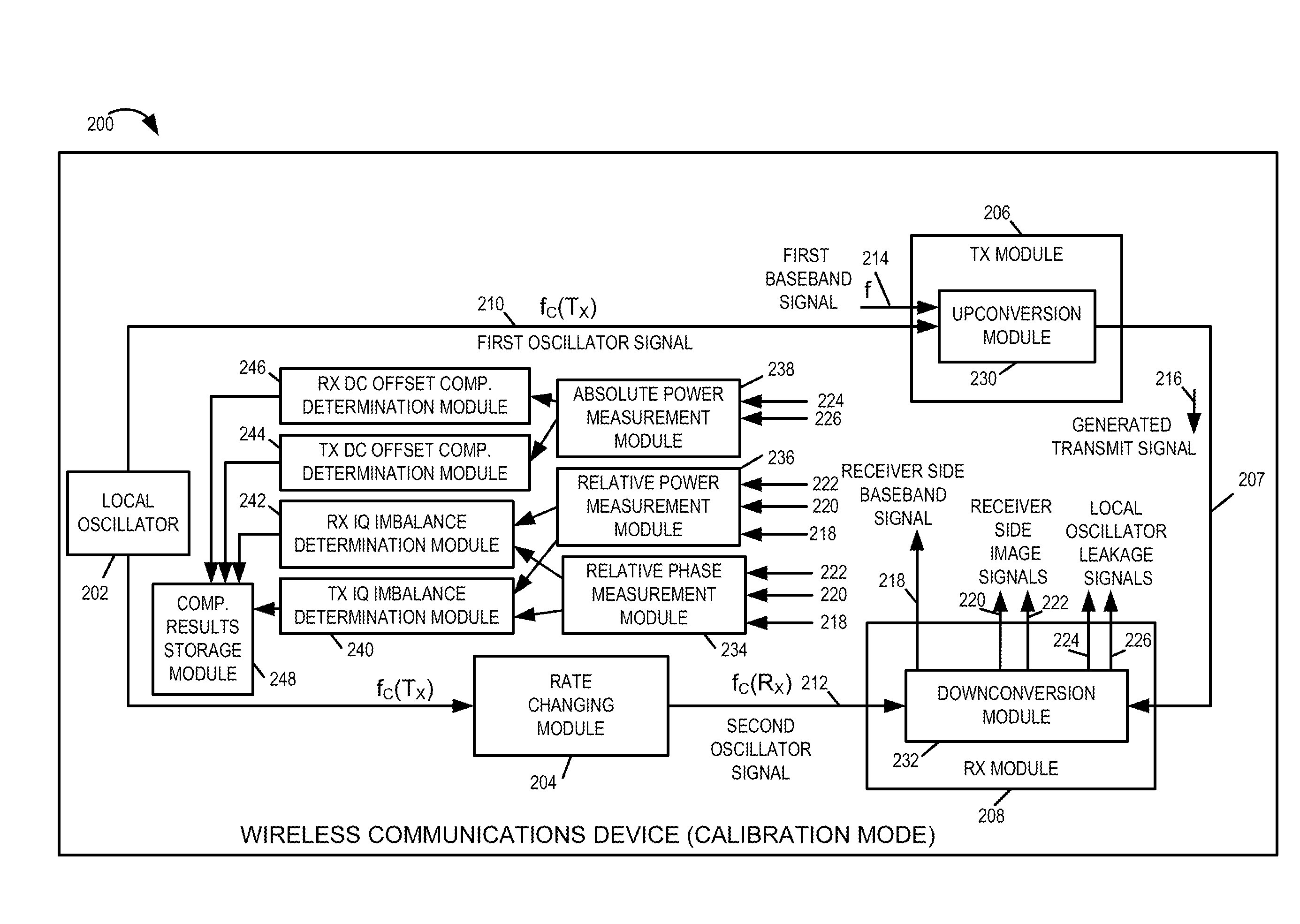

Methods and apparatus for measuring and/or using transmitter and/or receiver iq imbalance information and/or DC offset information

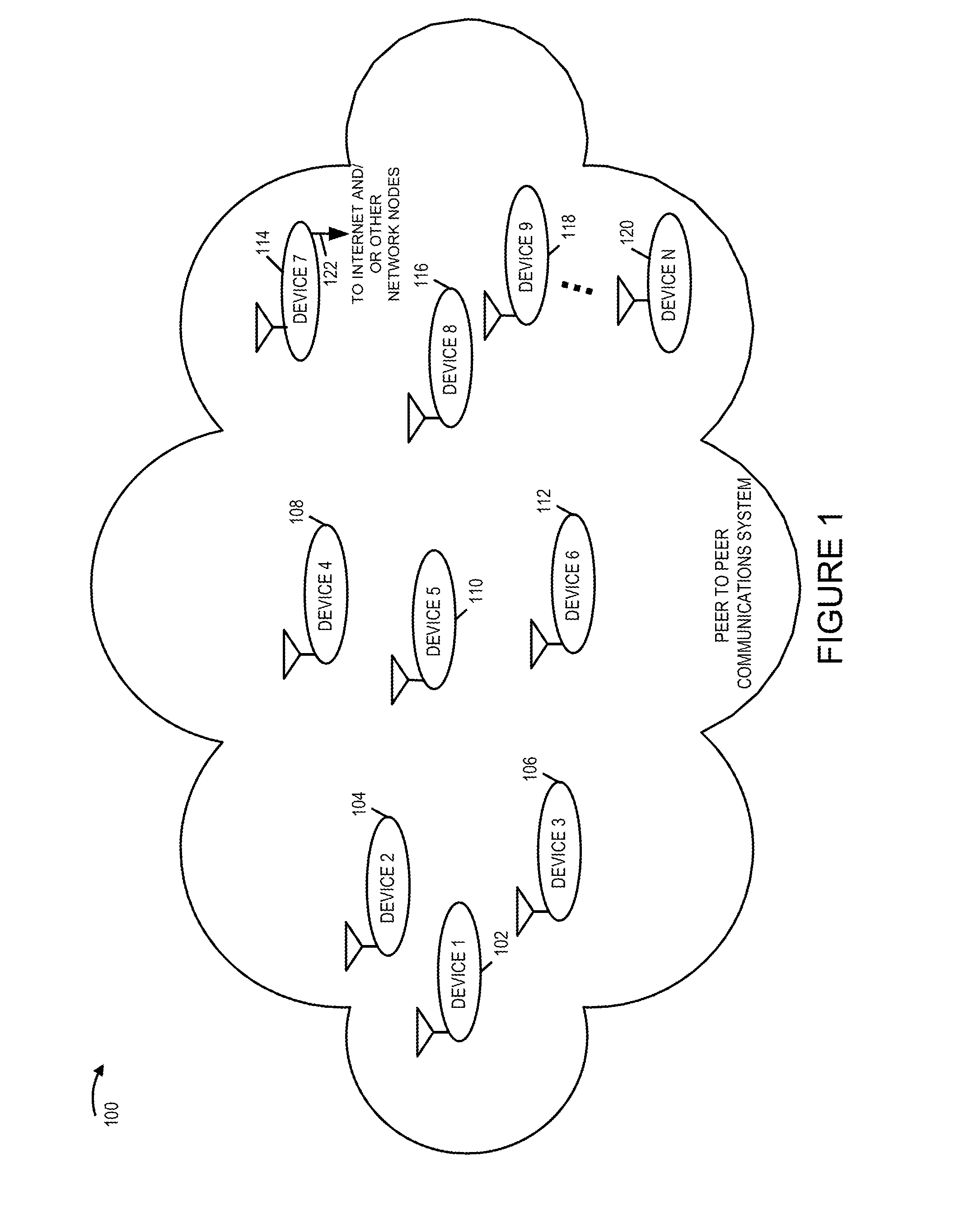

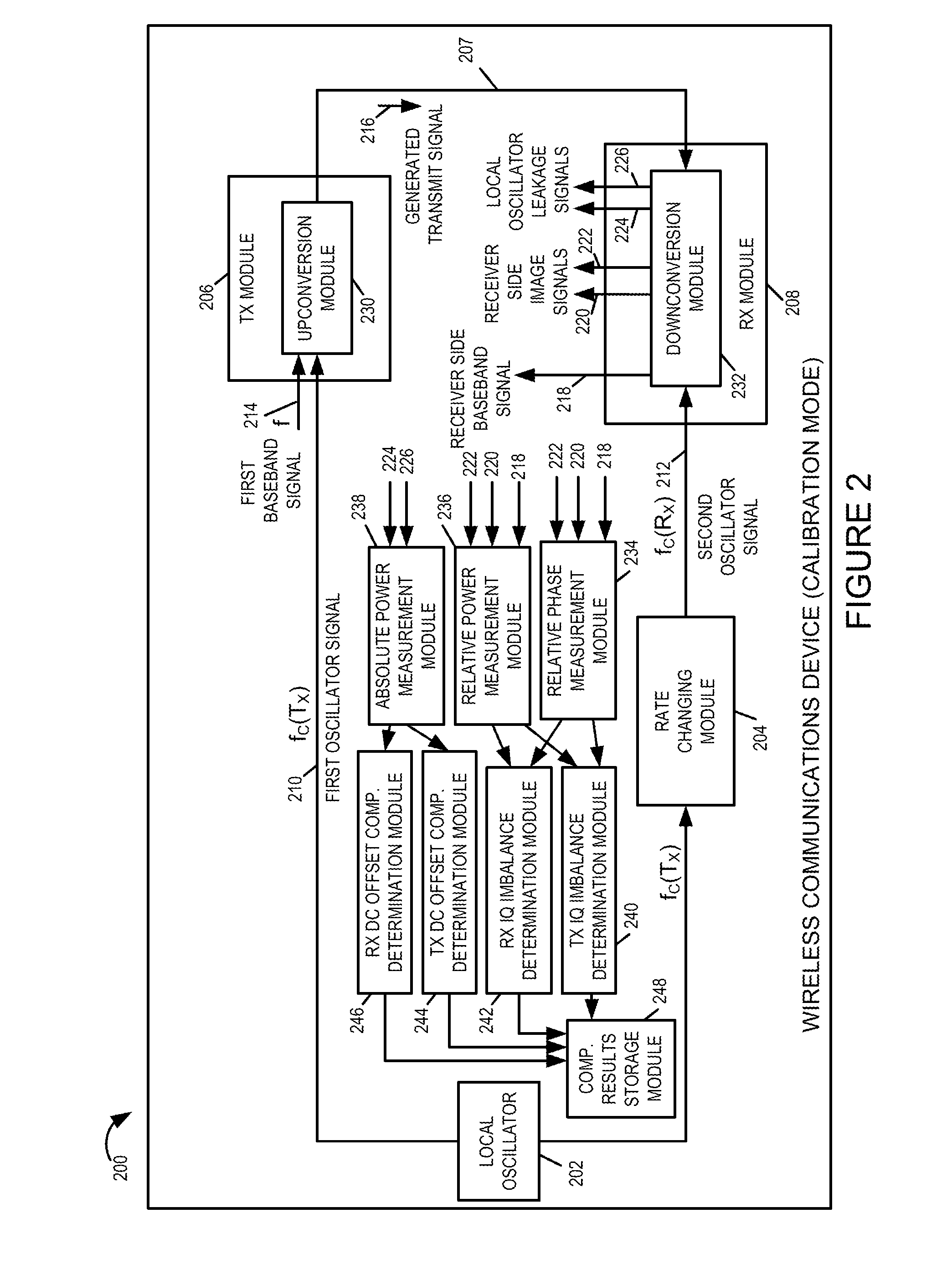

A wireless communications device, e.g., a mobile node supporting direct peer to peer communications, performs a self-calibration of one or more of: receiver IQ imbalance, transmitter IQ imbalance, receiver DC offset, and transmitter DC offset. The wireless communications device, operating in calibration mode, intentionally sets the oscillator frequency used for downconversion in its receiver module to a different frequency than the oscillator frequency used for upconversion in its transmitter module. A first baseband signal, e.g., a single tone test signal, is input to the transmitter module and an upconverted transmit signal is generated. The transmit signal is routed via a feedback loop to the receiver, which performs a downconversion operation. Power and / or phase measurements of the signals output from the downcoversion are used to determine IQ imbalance compensation information and DC offset compensation information. The determined compensation information is used subsequently when operating in a communications mode of operation.

Owner:QUALCOMM INC

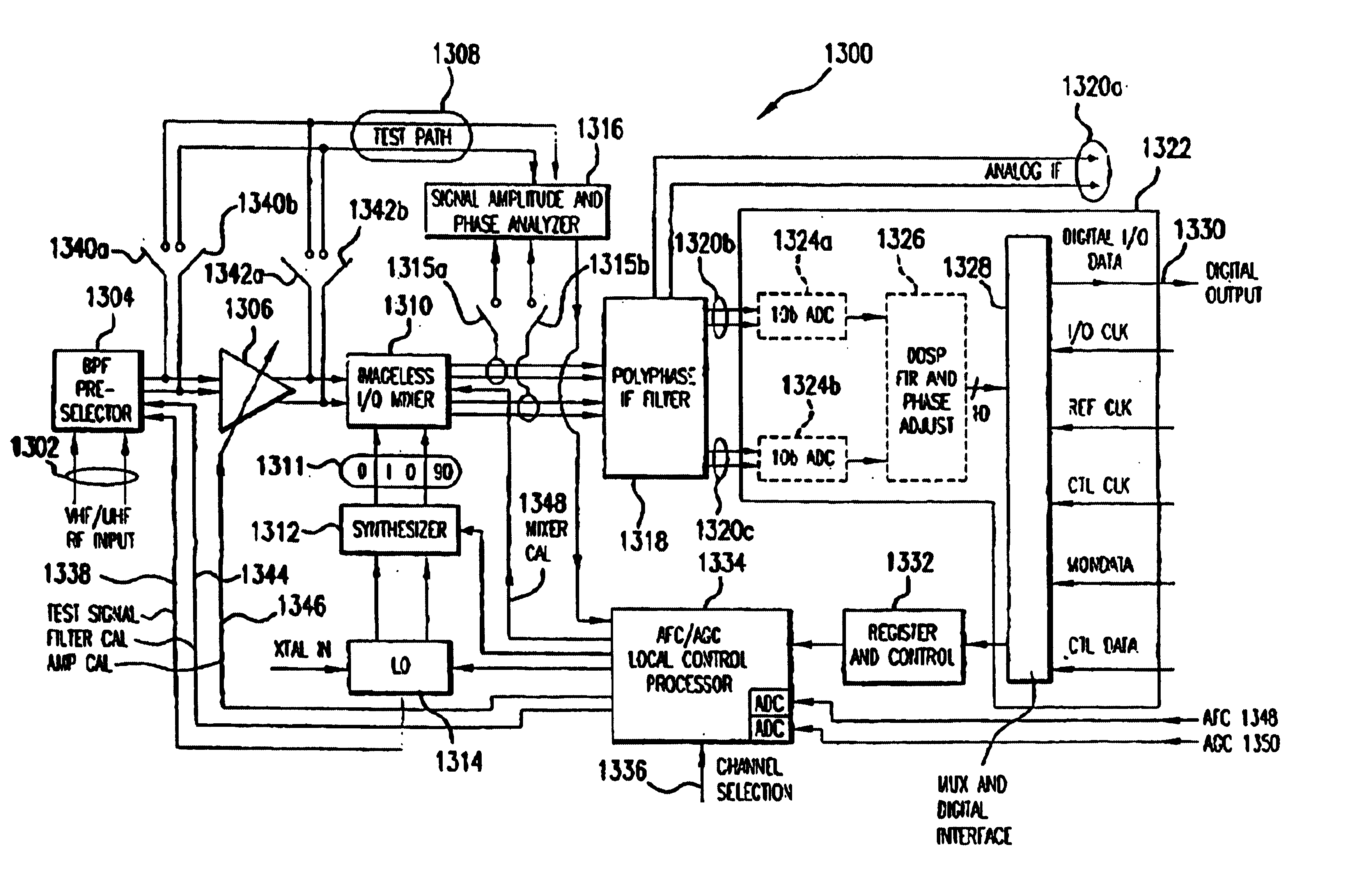

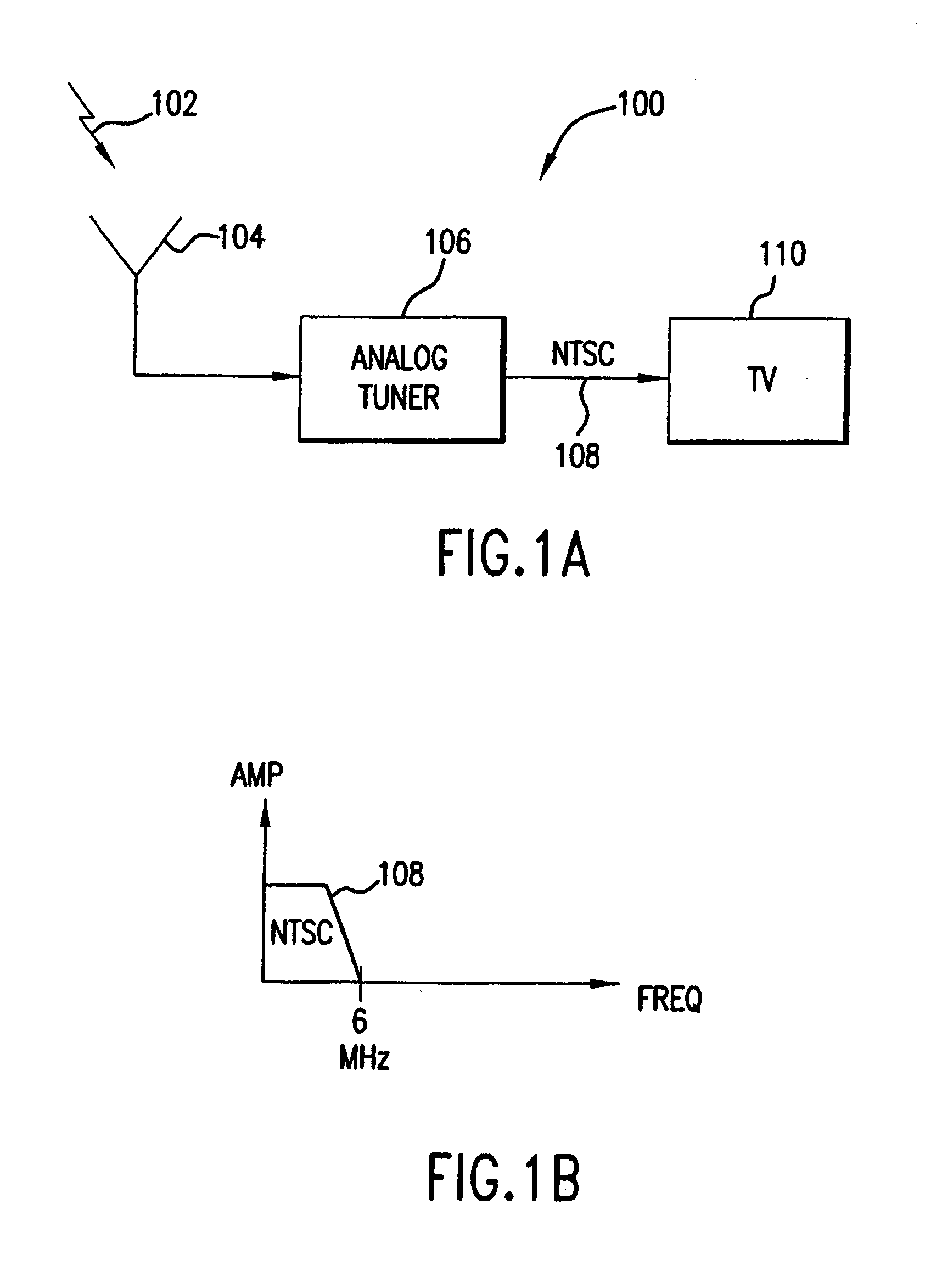

Direct conversion tuner

InactiveUS20060189290A1Reduced Power RequirementsHigh image rejectionTransmission monitoringFrequency-changer modificationsAudio power amplifierPhase filter

A direct conversion tuner down-converts television signals, cable signals, or other signals directly from an RF frequency to an IF frequency and / or baseband, without an intermediate up-conversion step for image rejection. The direct conversion tuner includes a pre-select filter, an amplifier, an image reject mixer, and a poly-phase filter. The pre-select filter, amplifier, and the image reject mixer can be calibrated to provide sufficient image rejection to meet the NTSC requirements for TV signals. The entire direct conversion tuner can be fabricated on a single semiconductor substrate without requiring any off-chip components. The tuner configuration described herein is not limited to processing TV signals, and can be utilized to down-convert other RF signals to an IF frequency or baseband.

Owner:AVAGO TECH INT SALES PTE LTD

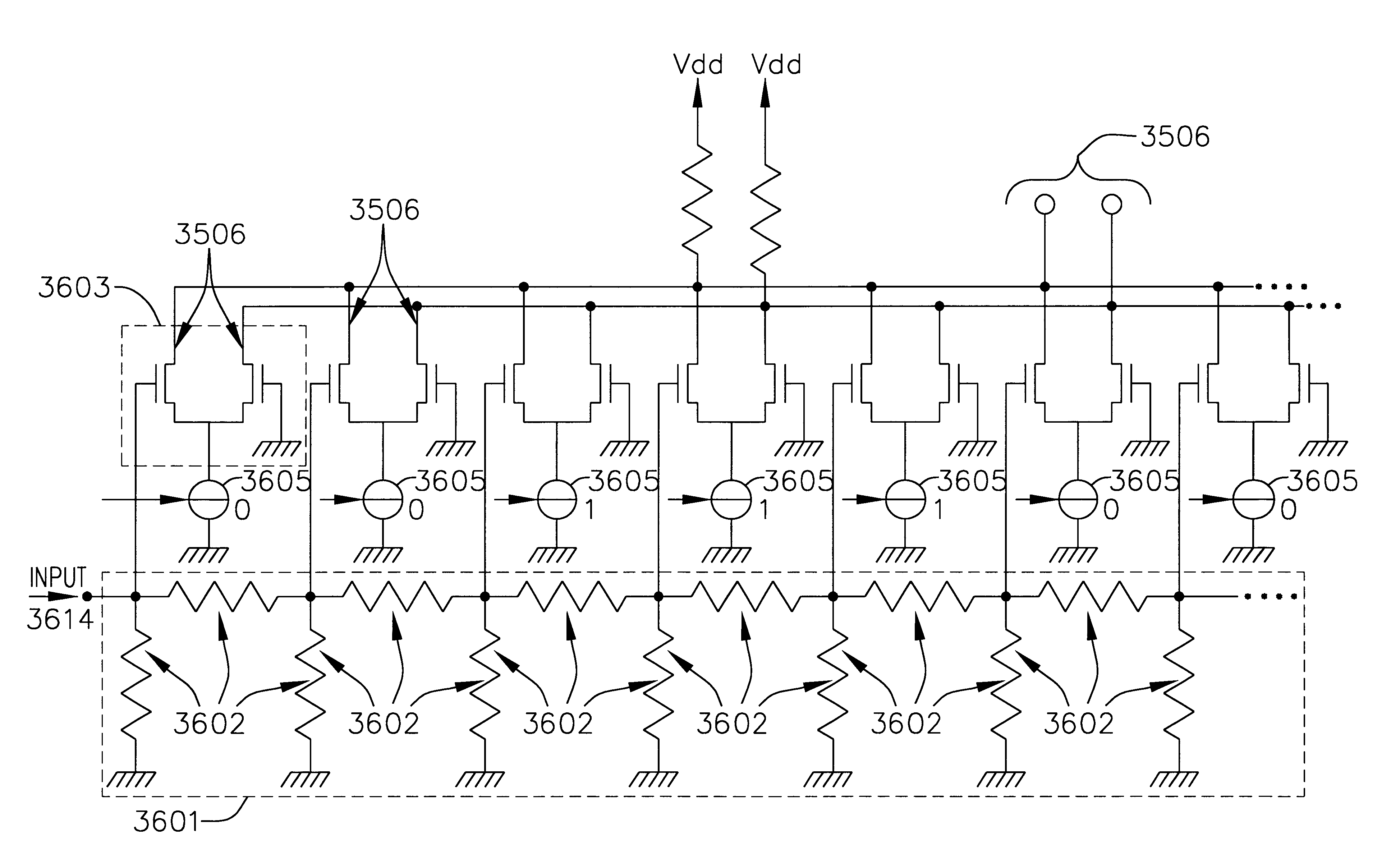

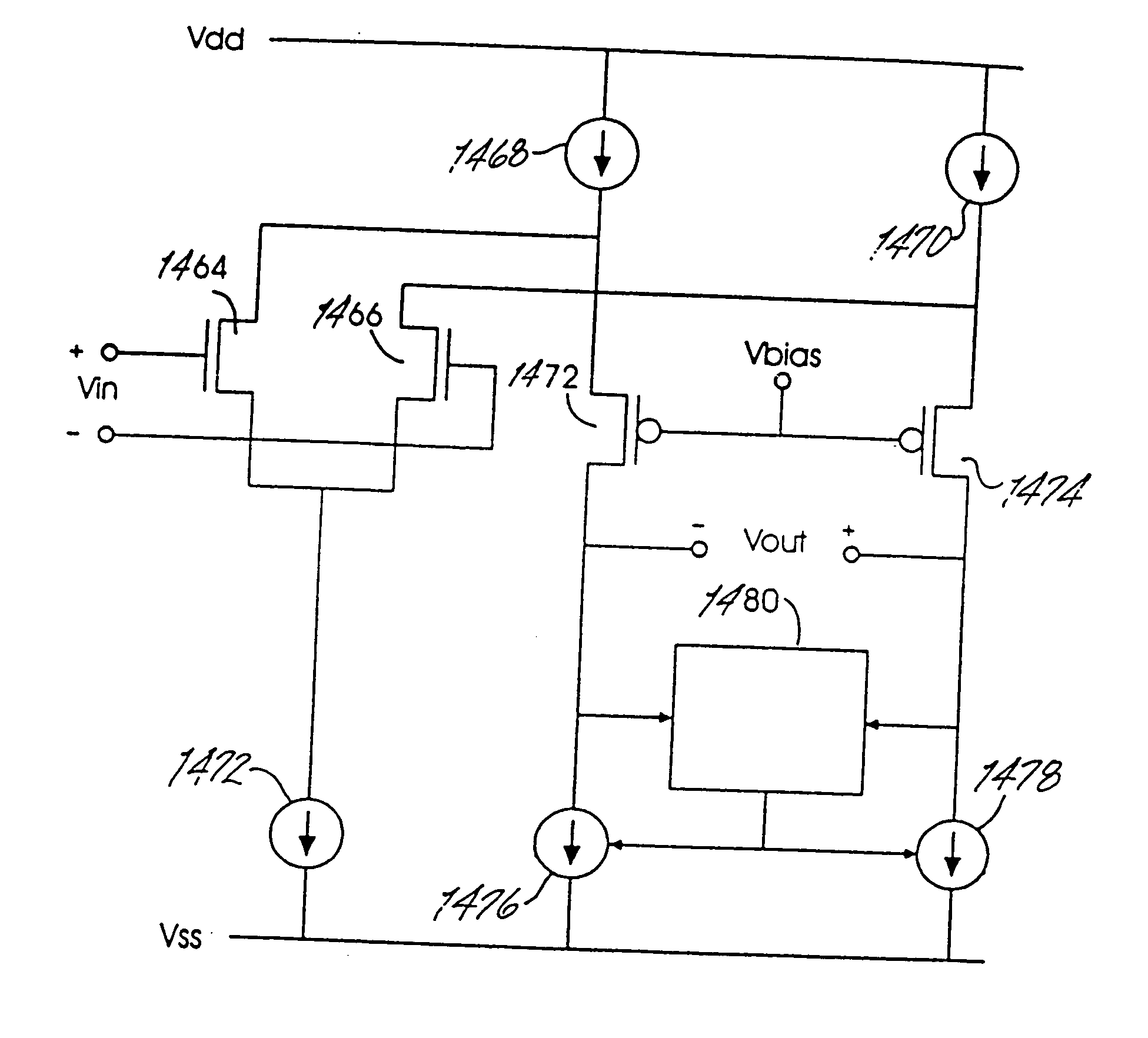

System and method for linearizing a CMOS differential pair

InactiveUS20050258901A1Resonant circuit detailsSemiconductor/solid-state device detailsShunt DeviceFilter tuning

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit. A receiver front end provides programable attenuation and a programable gain low noise amplifier. LC filters integrated onto the substrate in conjunction with image reject mixers provide image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. Active filters utilize multi track spiral inductors with shields to increase circuit Q. The filters incorporate a gain stage that provides improved dynamic range through the use of cross coupled auxiliary differential pair CMOS amplifiers to cancel distortion in a main linearized differential pair amplifier. Frequency planning provides additional image rejection. Local oscillator signal generation methods on chip reduce distortion. A PLL generates needed out of band LO signals. Direct synthesis generates in band LO signals. PLL VCOs are centered automatically. A differential crystal oscillator provides a frequency reference. Differential signal transmission throughout the receiver is used. ESD protection is provided by a pad ring and ESD clamping structure. Shunts utilize a gate boosting at each pin to discharge ESD build up. An IF VGA utilizes distortion cancellation achieved with cross coupled differential pair amplifiers having their Vds dynamically modified in conjunction with current steering of the differential pairs sources.

Owner:AVAGO TECH INT SALES PTE LTD

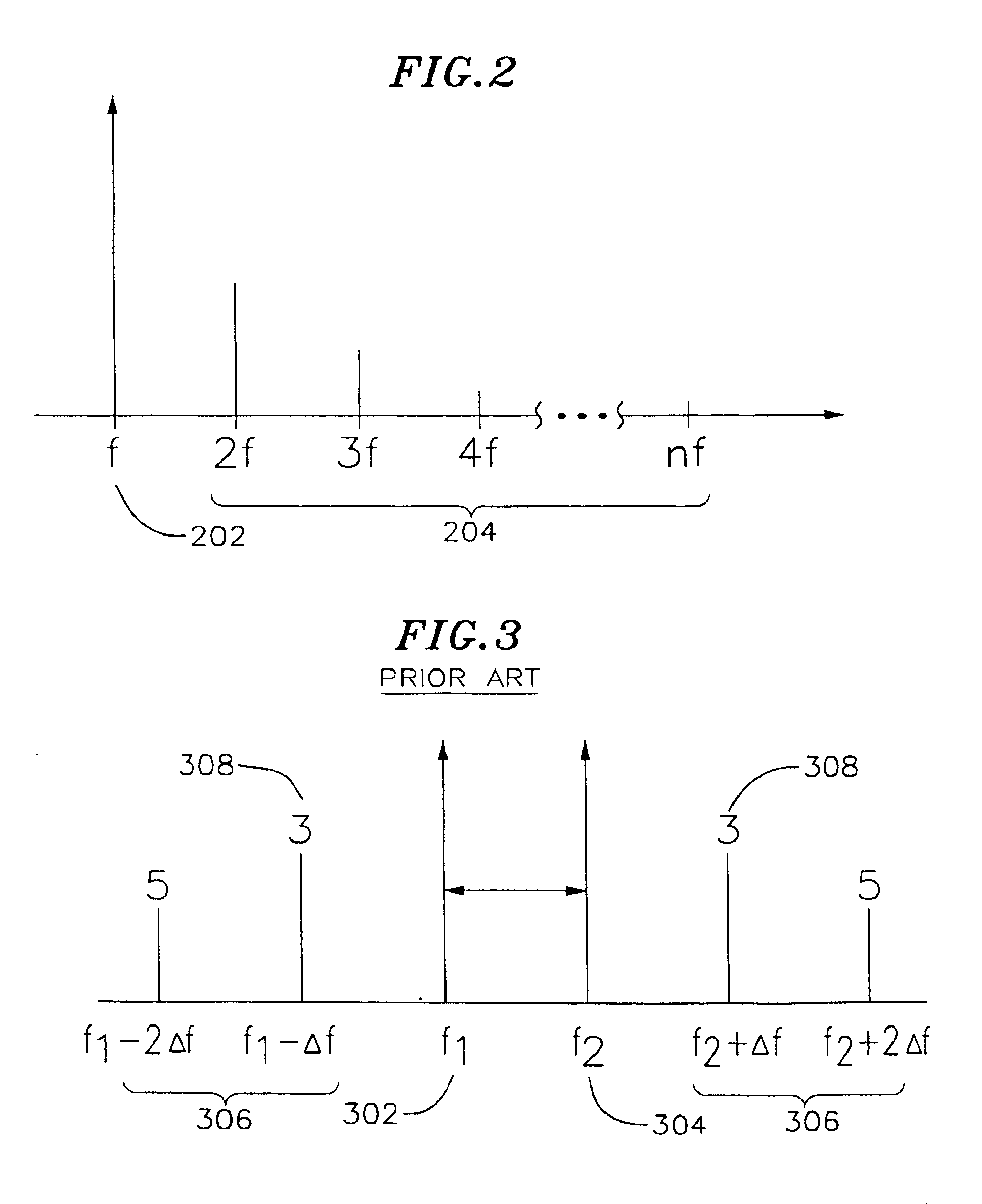

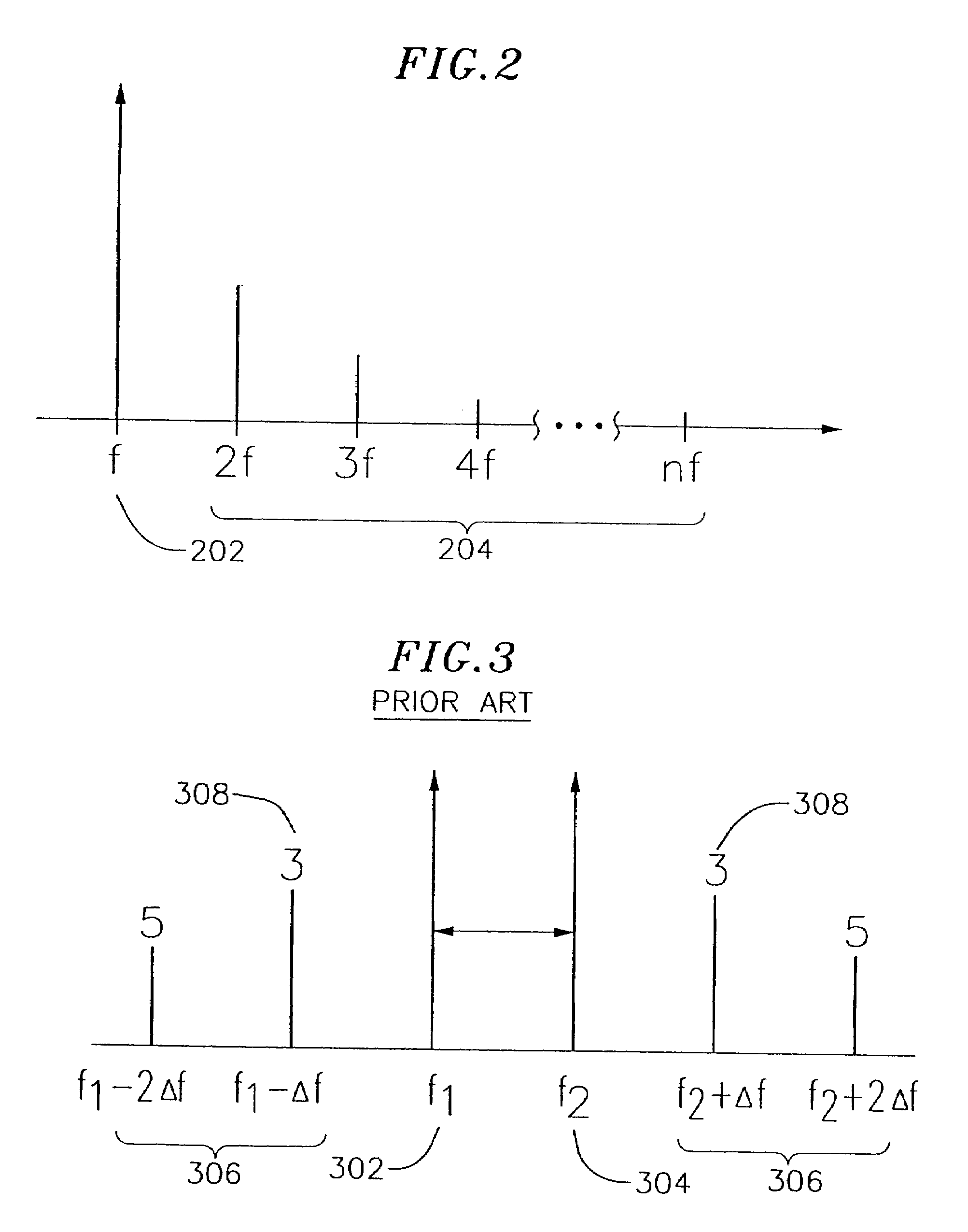

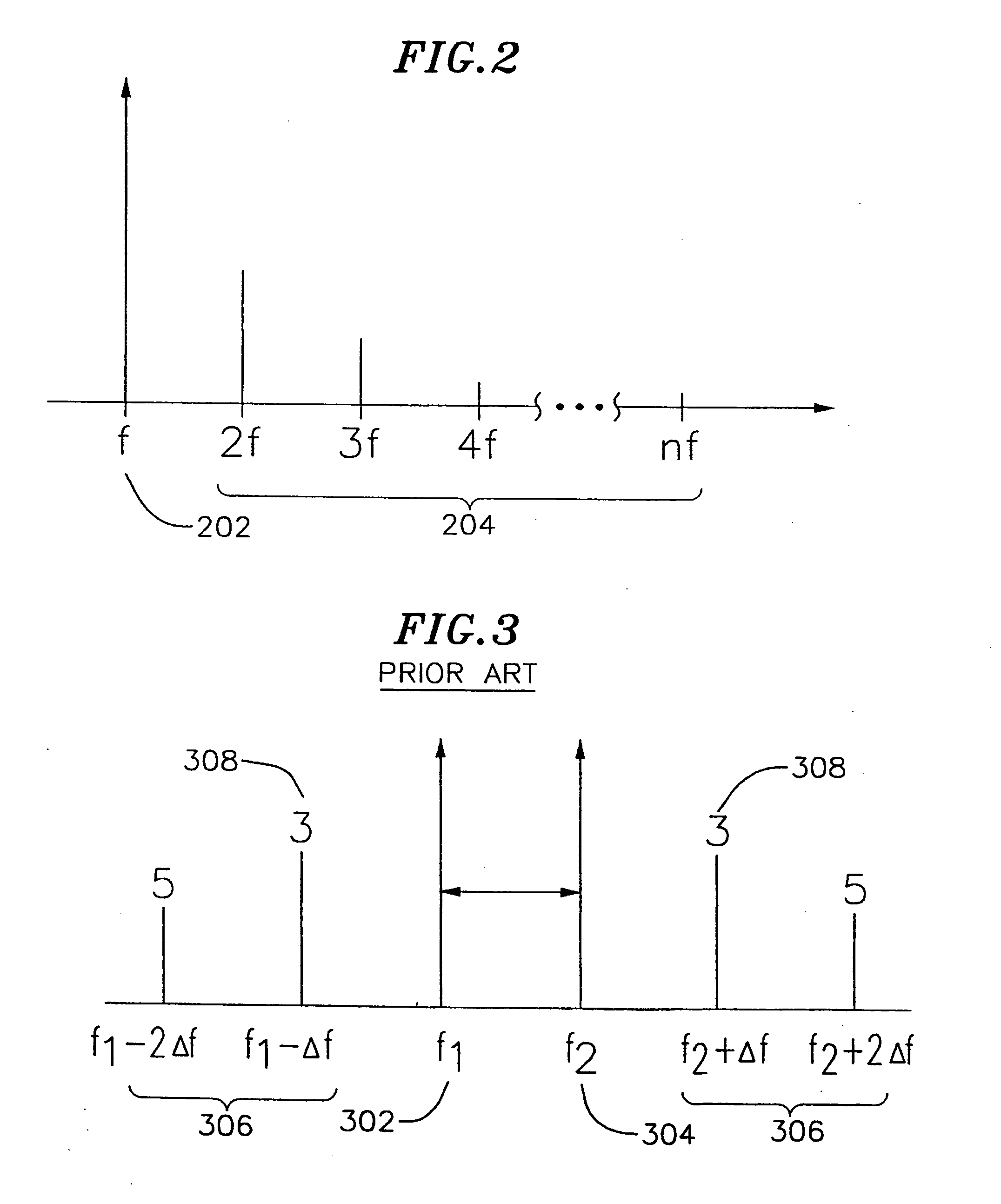

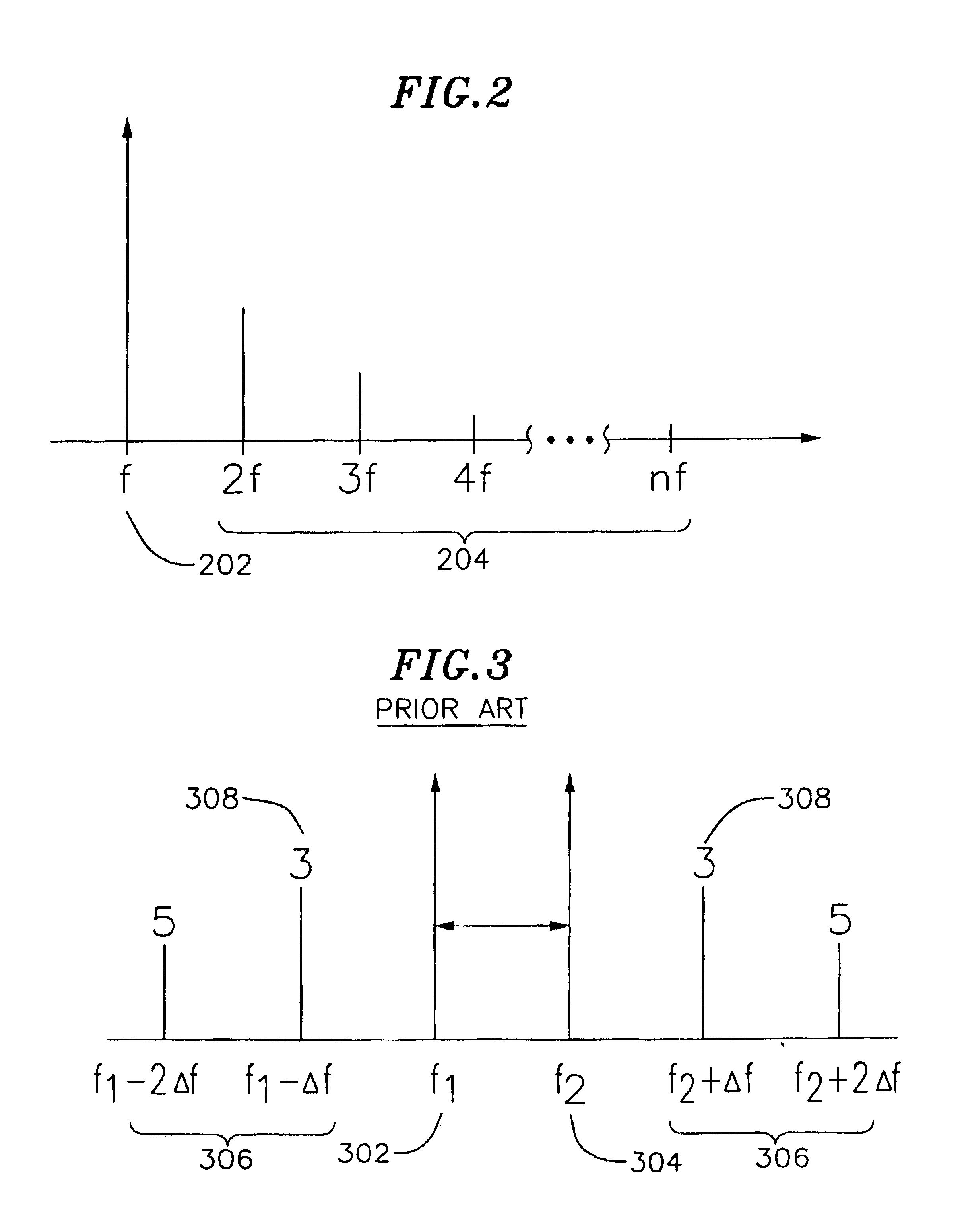

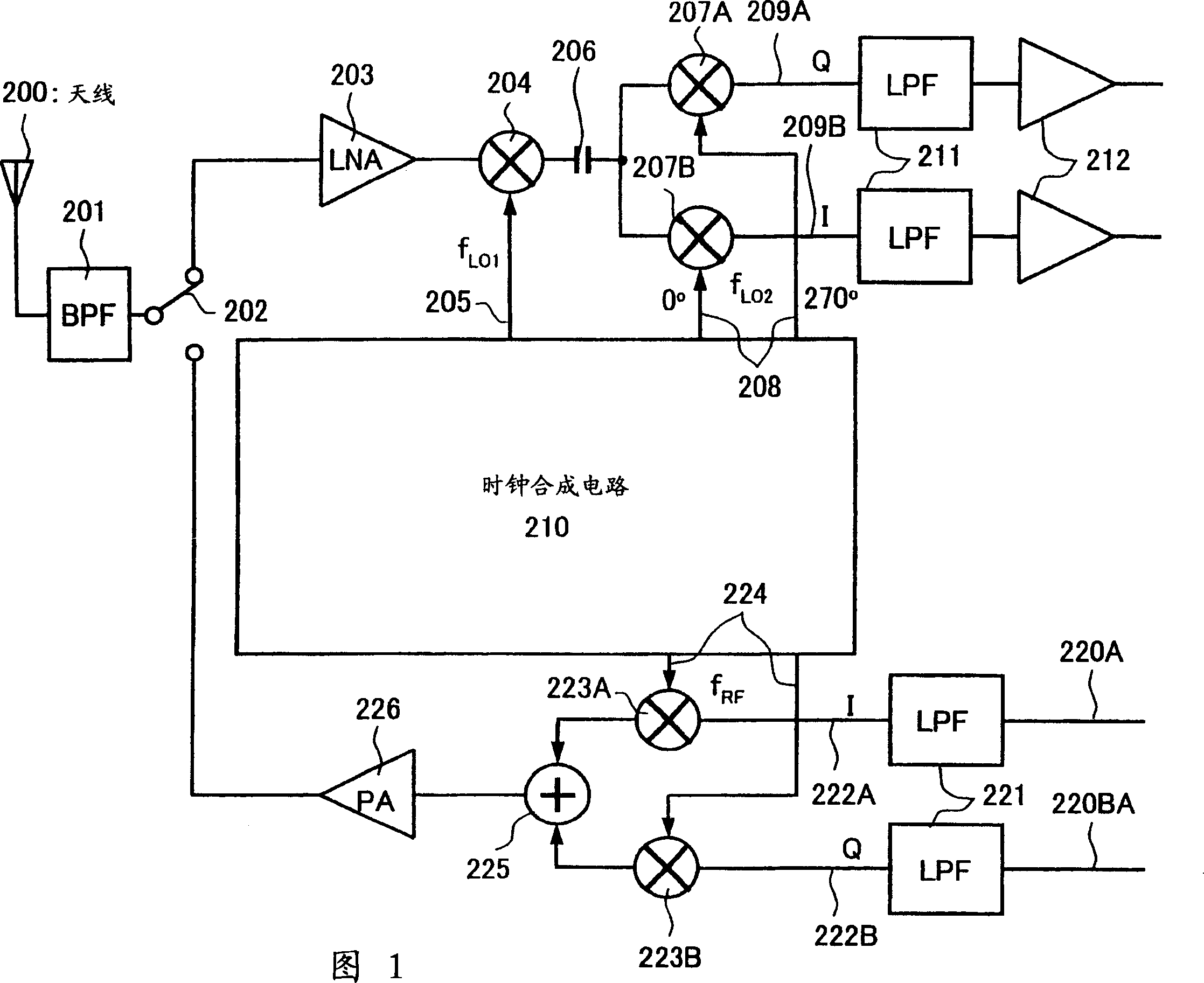

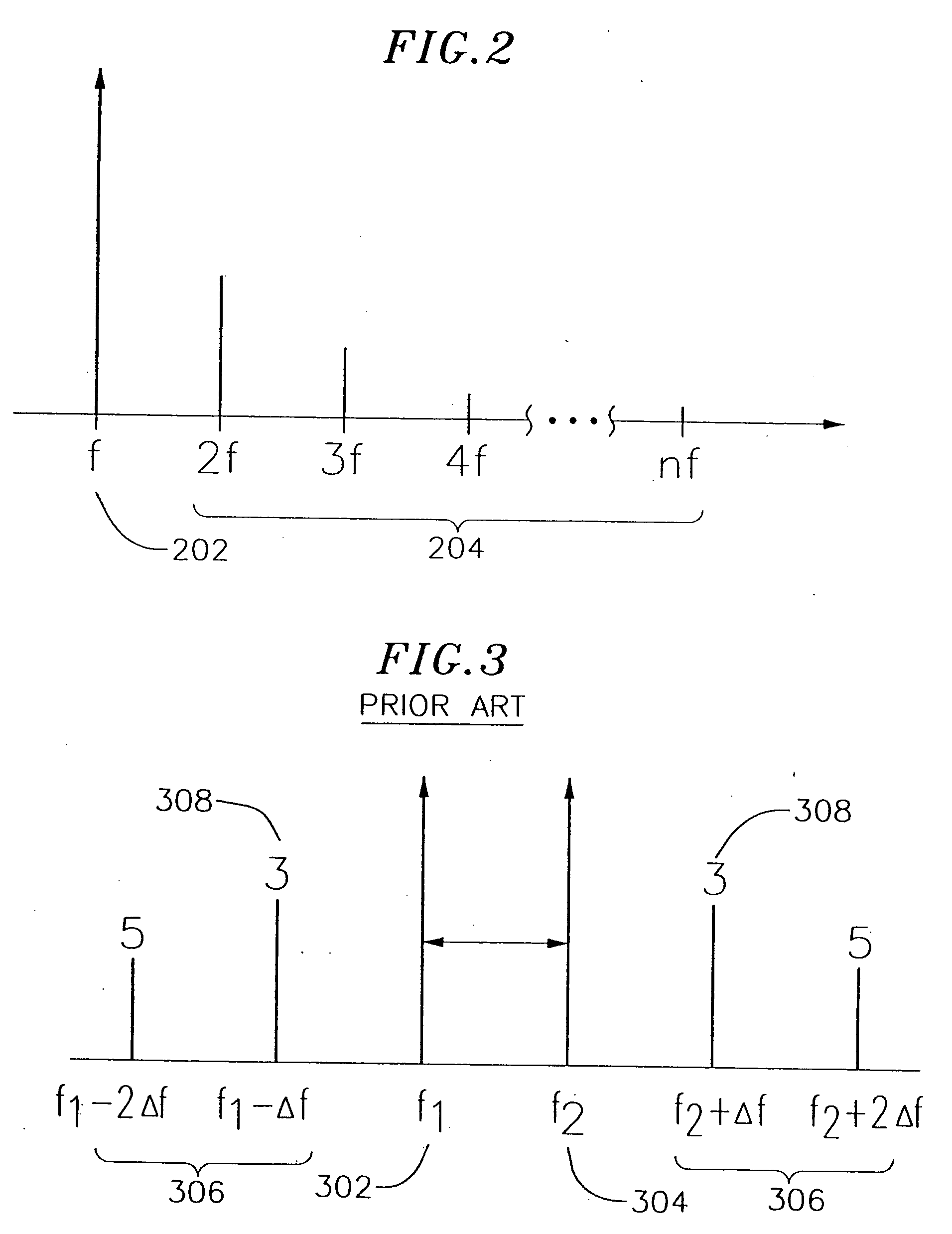

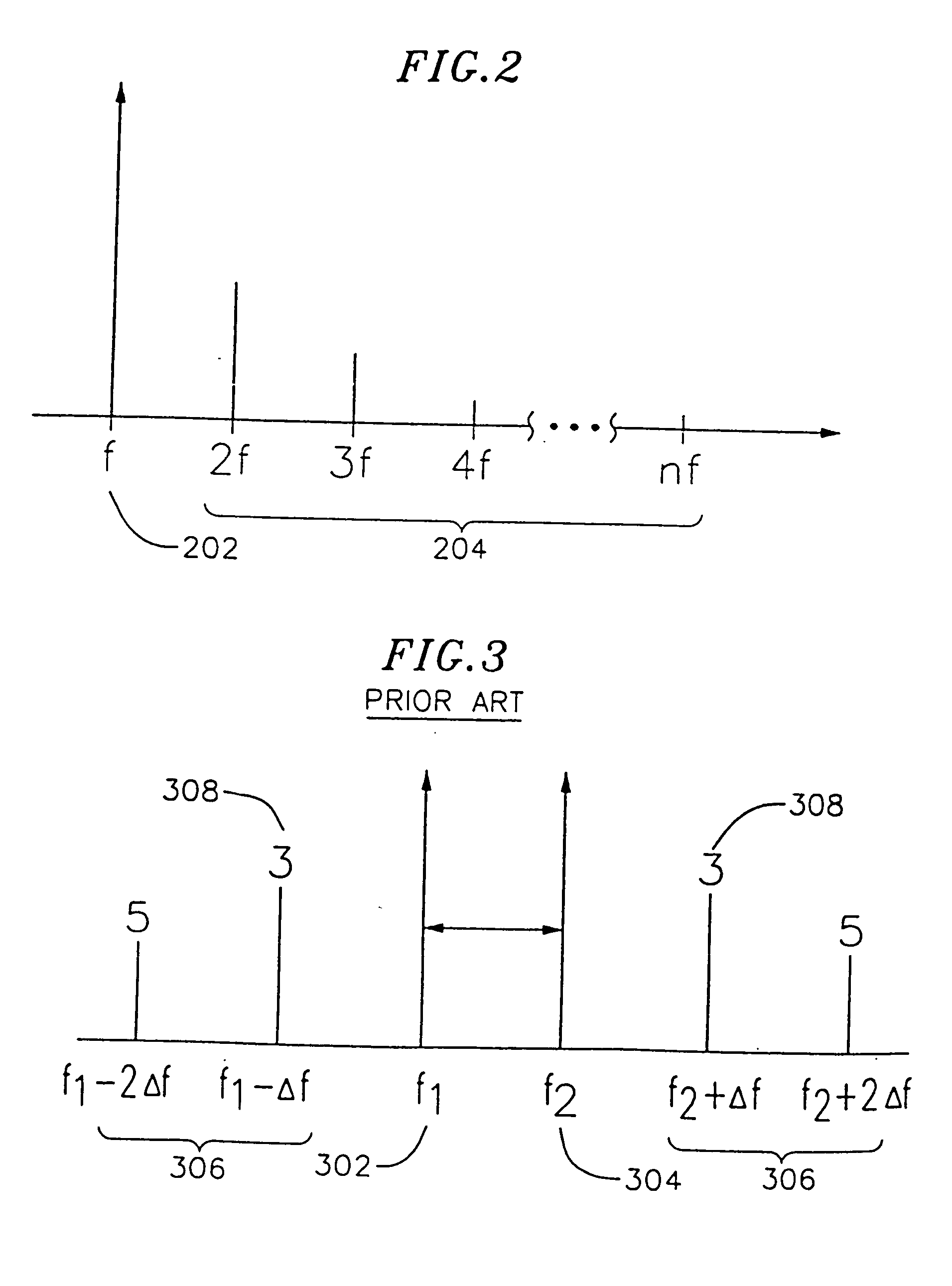

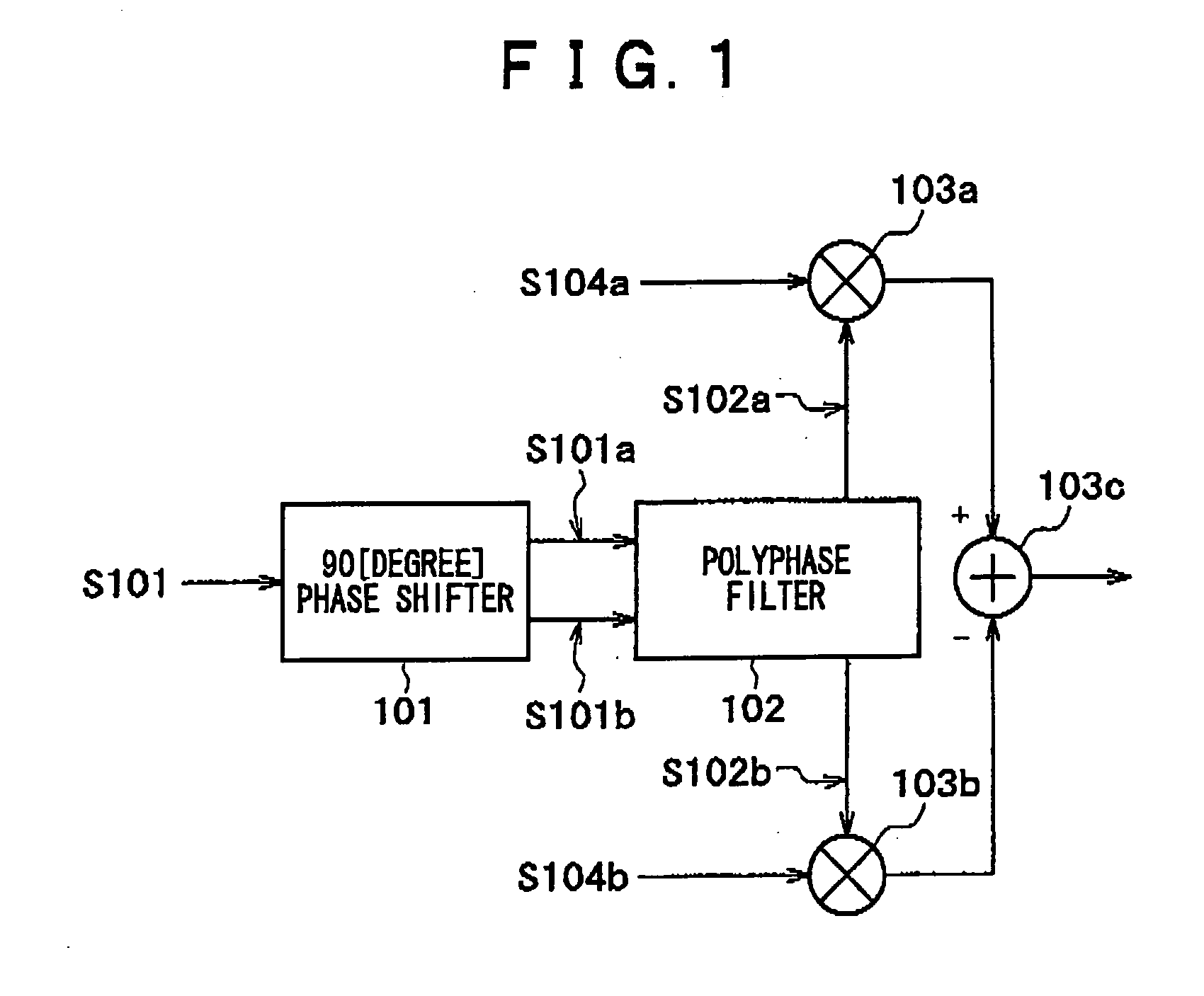

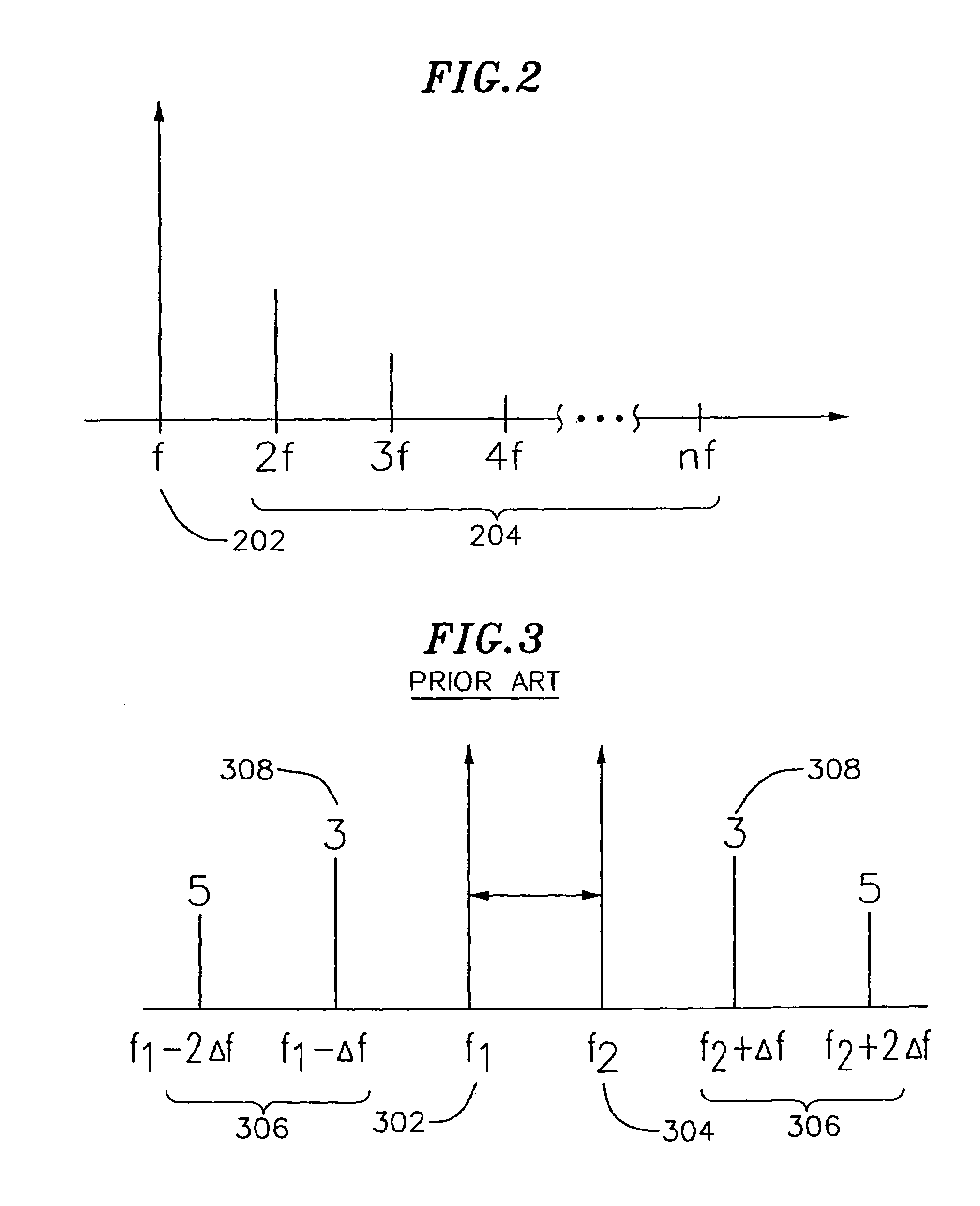

Image rejection mixer and multiband generator

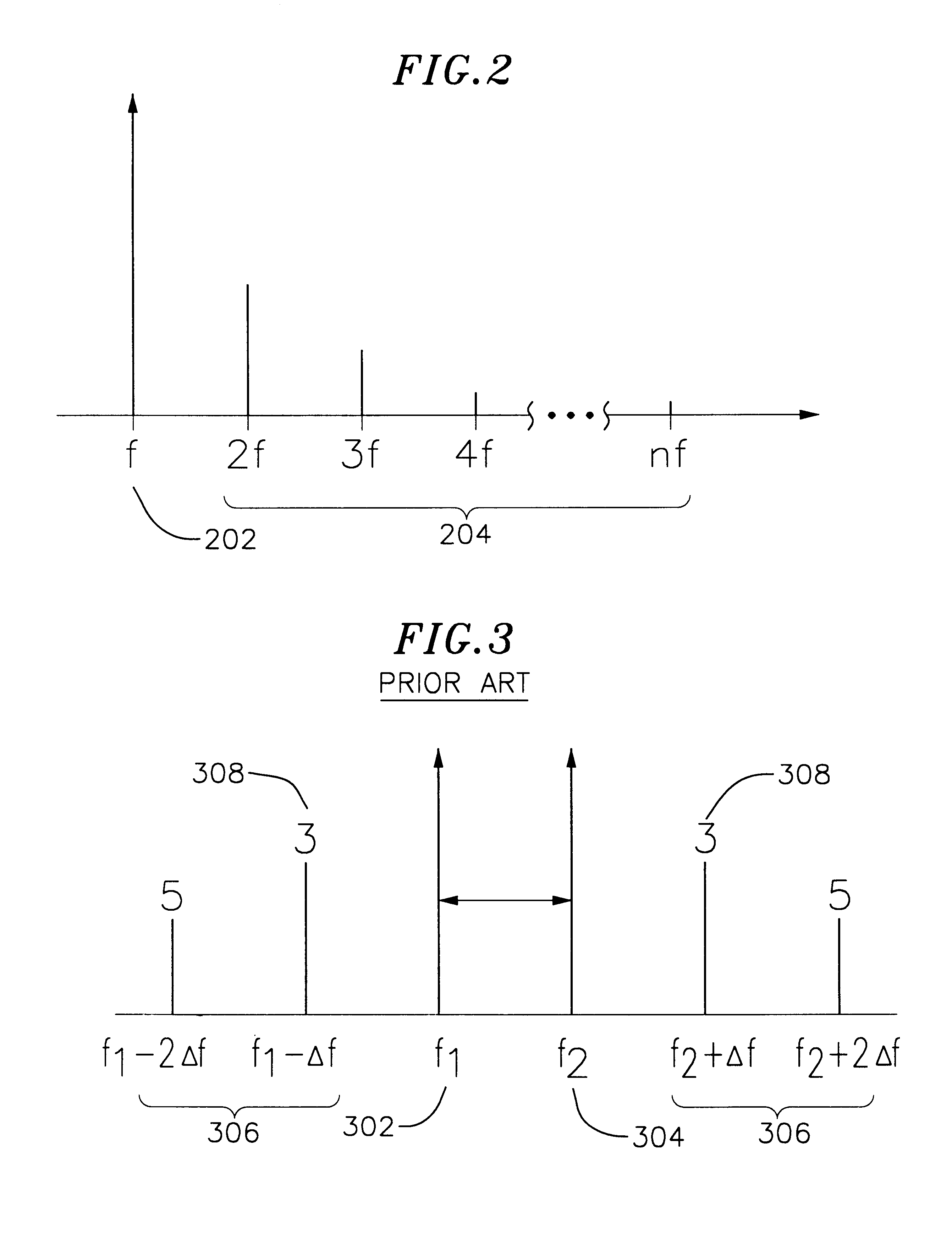

InactiveUS20050159129A1Enhanced inhibitory effectMultiple-port networksDigital computer detailsHarmonicPhase difference

The present invention suppresses a harmonic component without impairing the phase orthogonality of a pair of complex signals. A polyphase filter is configured so that K pieces of filter circuits, each of which comprises a resistor and a capacitor, are connected and +360 / K degrees out of phase with a preceding one. Since counterclockwise rotation occurs when expression is given in terms of the complex plane, a notch occurs in a negative frequency region. A RC value is set so that a notch occurs in a specified frequency band to suppress a (4N+1)-order harmonic component. Since the polyphase filter has a symmetrical structure, an unbalanced component contained in an input signal is eliminated at a frequency that agrees with a pole determined by the RC value. This action improves the orthogonality.

Owner:SONY CORP

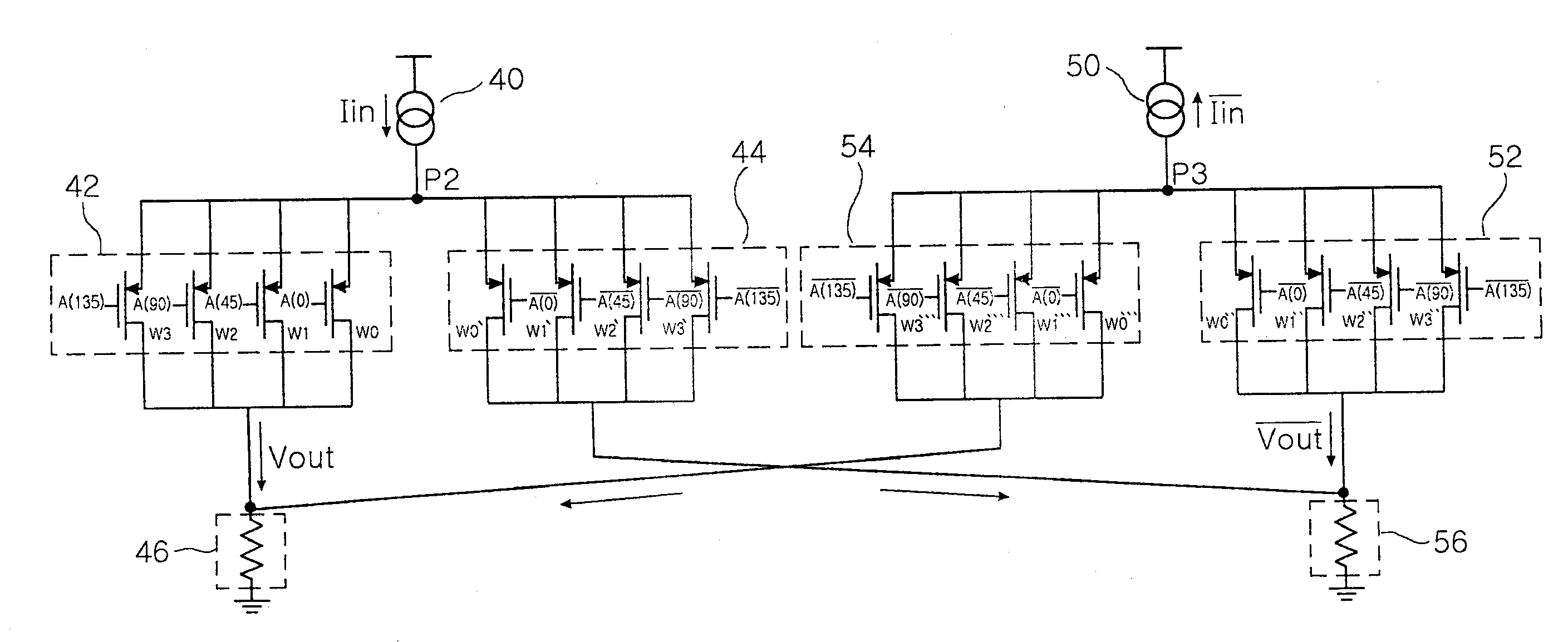

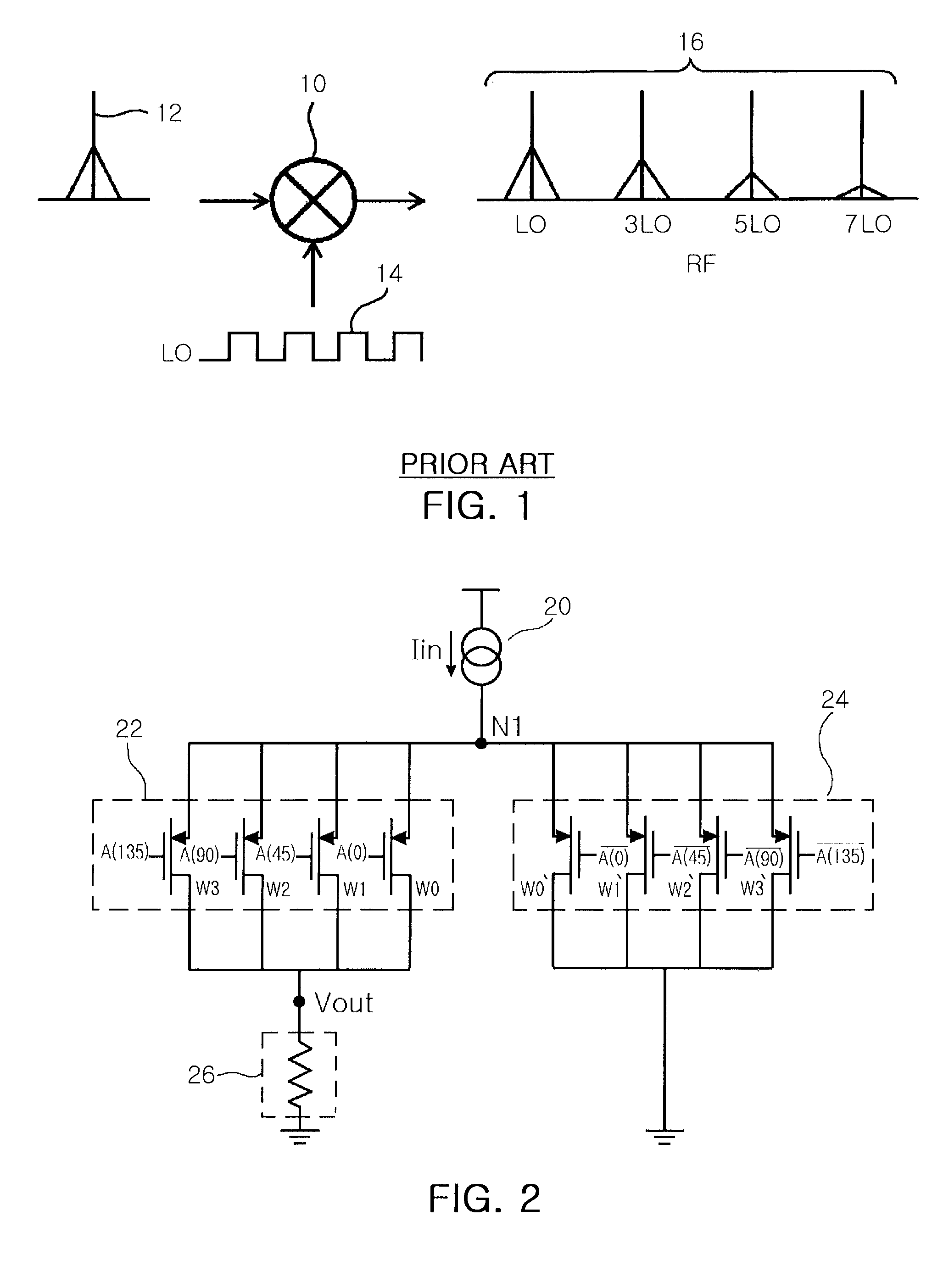

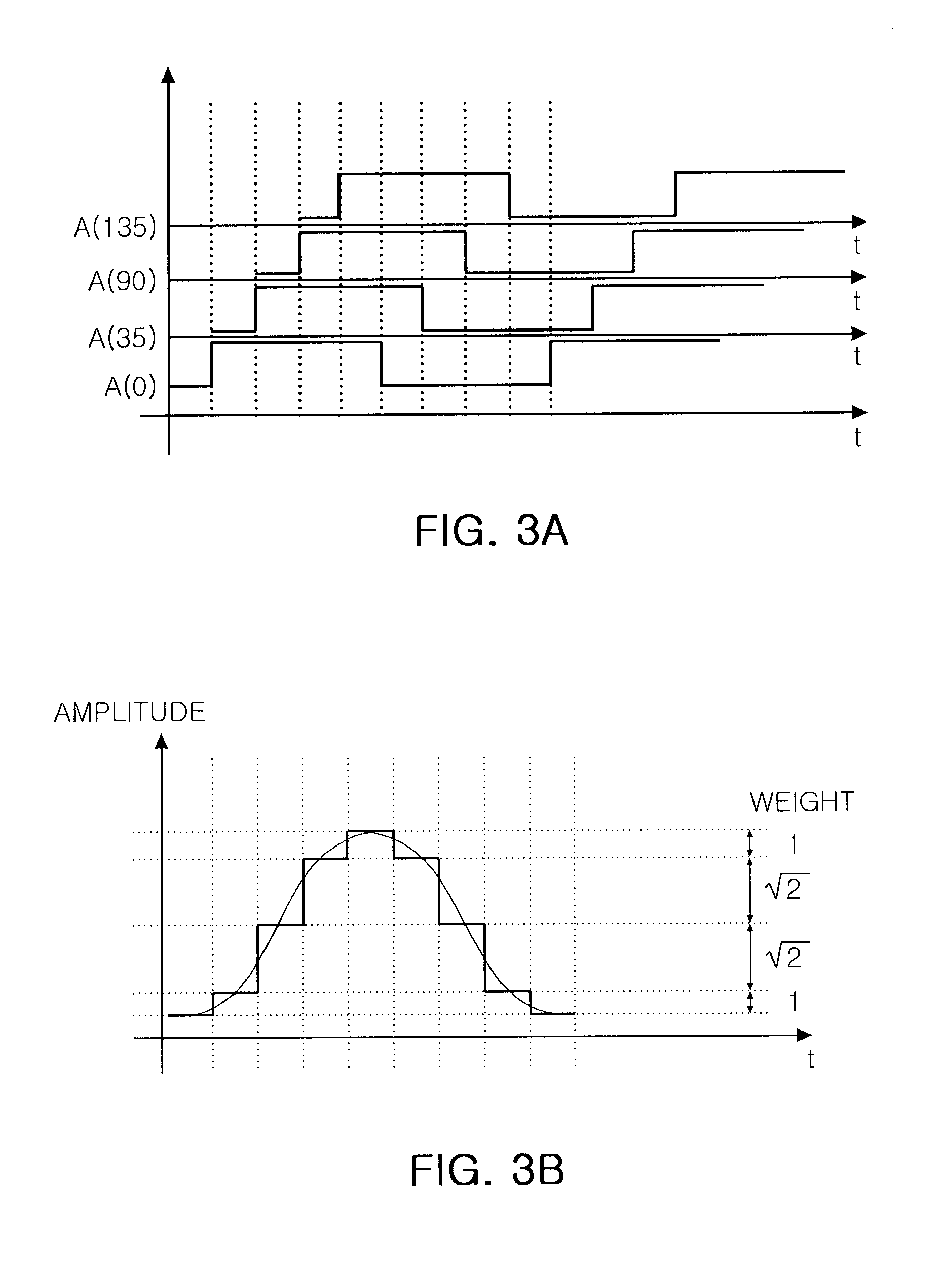

High-order harmonic rejection mixer using current steering technique

InactiveUS20090280762A1TransmissionFrequency-changer modificationsLocal oscillator signalPhase shifted

A mixer includes, an input current generation unit generating an input current; a first path circuit unit including n number of transistors having sources connected in common to an output node of the input current generation unit; and a second path circuit unit including n number of transistors having sources connected in common to the output node of the input current generation unit, and respectively corresponding to the n number of transistors included in the first path circuit unit. Local oscillator signals sequentially phase-shifted by 180° / n are individually input to gates of the n number of transistors included in the first path circuit unit, and local oscillator signals having opposite phases to the local oscillator signals input to the gates of the corresponding transistors included in the first path circuit unit are individually input to gates of the n number of transistors included in the second path circuit unit.

Owner:SAMSUNG ELECTRO MECHANICS CO LTD

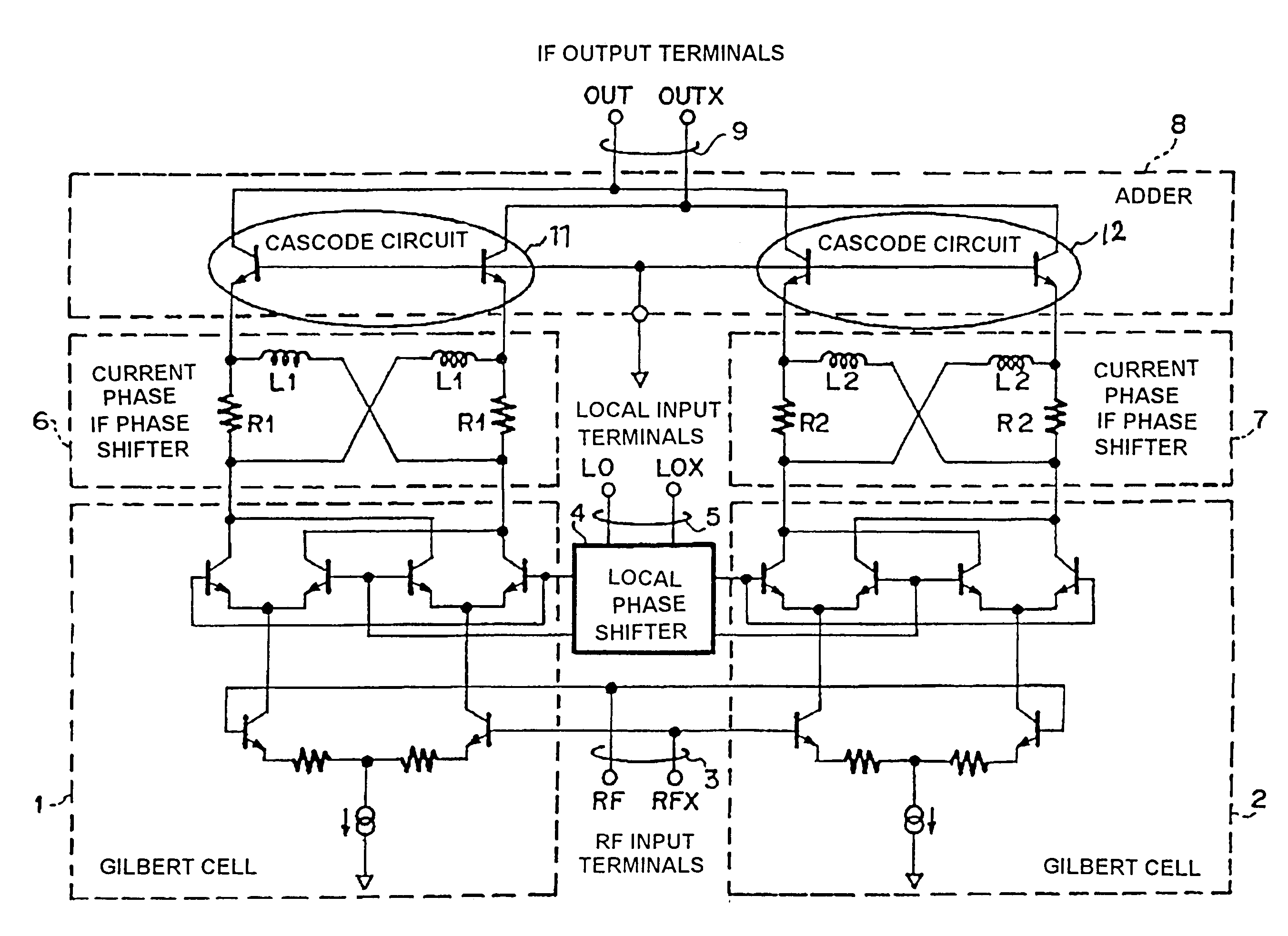

Image rejection mixer

InactiveUS6999746B2Reduce power consumptionReduced in noise and distortionMultiple-port networksTelevision system detailsPhase shiftedRelative phase

An image rejection mixer of reduced power dissipation includes a signal distributor supplied with local signals having a phase difference to distribute the local signals, a first and a second signal mixer for mixing the distributed local signals and RF signals having a phase difference and outputting respective IF current signals, a phase shifter for shifting in phase the respective mixed IF current signals so as to provide them with a relative phase difference of 90 degrees, and a signal adder for adding the respective phase shifted intermediate frequency current signals. The shifter shifts the phases of the respective IF current signals outputted from the first and the second signal mixers.

Owner:RENESAS ELECTRONICS CORP

System and method for ESD protection

InactiveUS7115952B2Reduce areaReduce capacitanceResonant circuit detailsSemiconductor/solid-state device detailsCapacitanceShunt Device

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver. ESD protection is provided by a pad ring and ESD clamping structure that maintains signal integrity. Also provided are shunts at each pin to discharge ESD build up. The shunts utilize a gate boosting structure to provide sufficient small signal RF performance, and minimal parasitic loading.

Owner:AVAGO TECH INT SALES PTE LTD

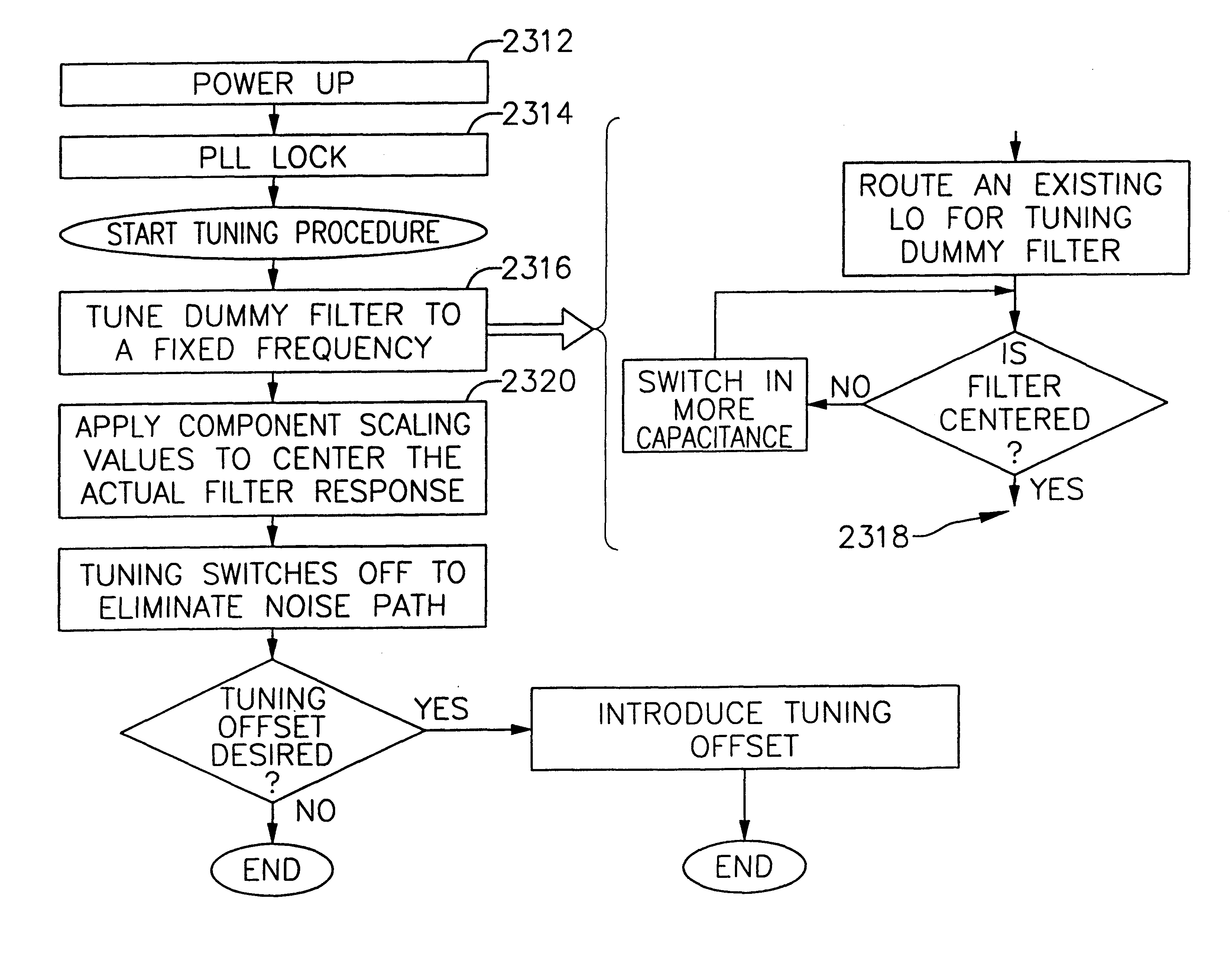

System and method for on-chip filter tuning

InactiveUS6865381B2Low selectivityMultiple-port active networksSolid-state devicesCapacitanceFilter tuning

An integrated receiver with channel selection and image rejection substantially implemented on a single CMOS integrated circuit is described. A receiver front end provides programable attenuation and a programable gain low noise amplifier. Frequency conversion circuitry advantageously uses LC filters integrated onto the substrate in conjunction with image reject mixers to provide sufficient image frequency rejection. Filter tuning and inductor Q compensation over temperature are performed on chip. The filters utilize multi track spiral inductors. The filters are tuned using local oscillators to tune a substitute filter, and frequency scaling during filter component values to those of the filter being tuned. In conjunction with filtering, frequency planning provides additional image rejection. The advantageous choice of local oscillator signal generation methods on chip is by PLL out of band local oscillation and by direct synthesis for in band local oscillator. The VCOs in the PLLs are centered using a control circuit to center the tuning capacitance range. A differential crystal oscillator is advantageously used as a frequency reference. Differential signal transmission is advantageously used throughout the receiver.

Owner:AVAGO TECH INT SALES PTE LTD

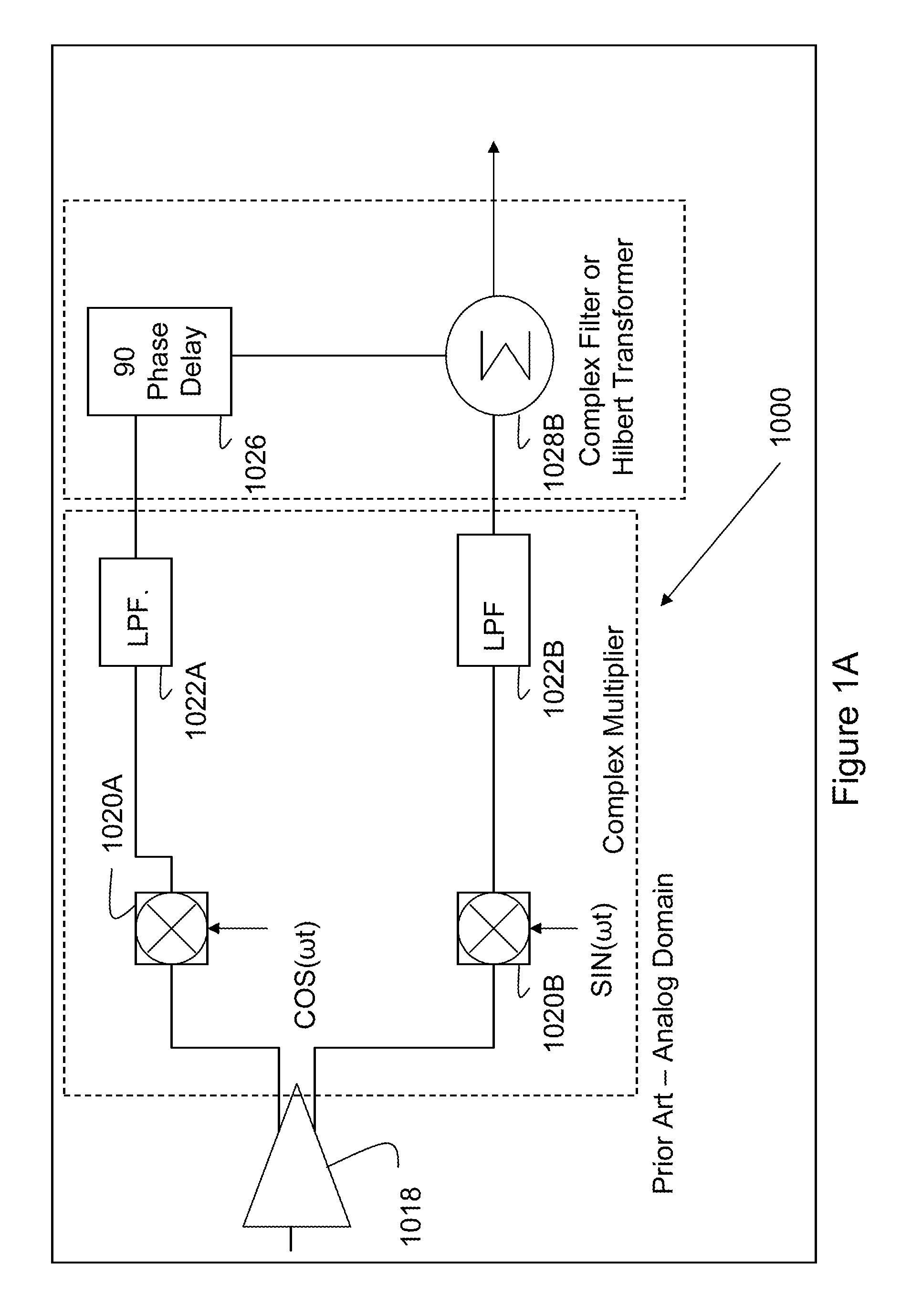

Transceiver development in vhf/uhf/gsm/gps/bluetooth/cordless telephones

ActiveUS20090147884A1Efficient separationAmplitude-modulated carrier systemsPulse demodulatorCMOSTransceiver

A digital communication circuit can be implemented can be implemented in a CMOS, or other IC structure. The digital circuit can utilize negative frequency removers or image frequency removers in the digital domain. The circuit can include mixers, switches, a complex filter, a low noise amplifier and summers. The image frequency can be removed digitally.

Owner:ORCA SYST

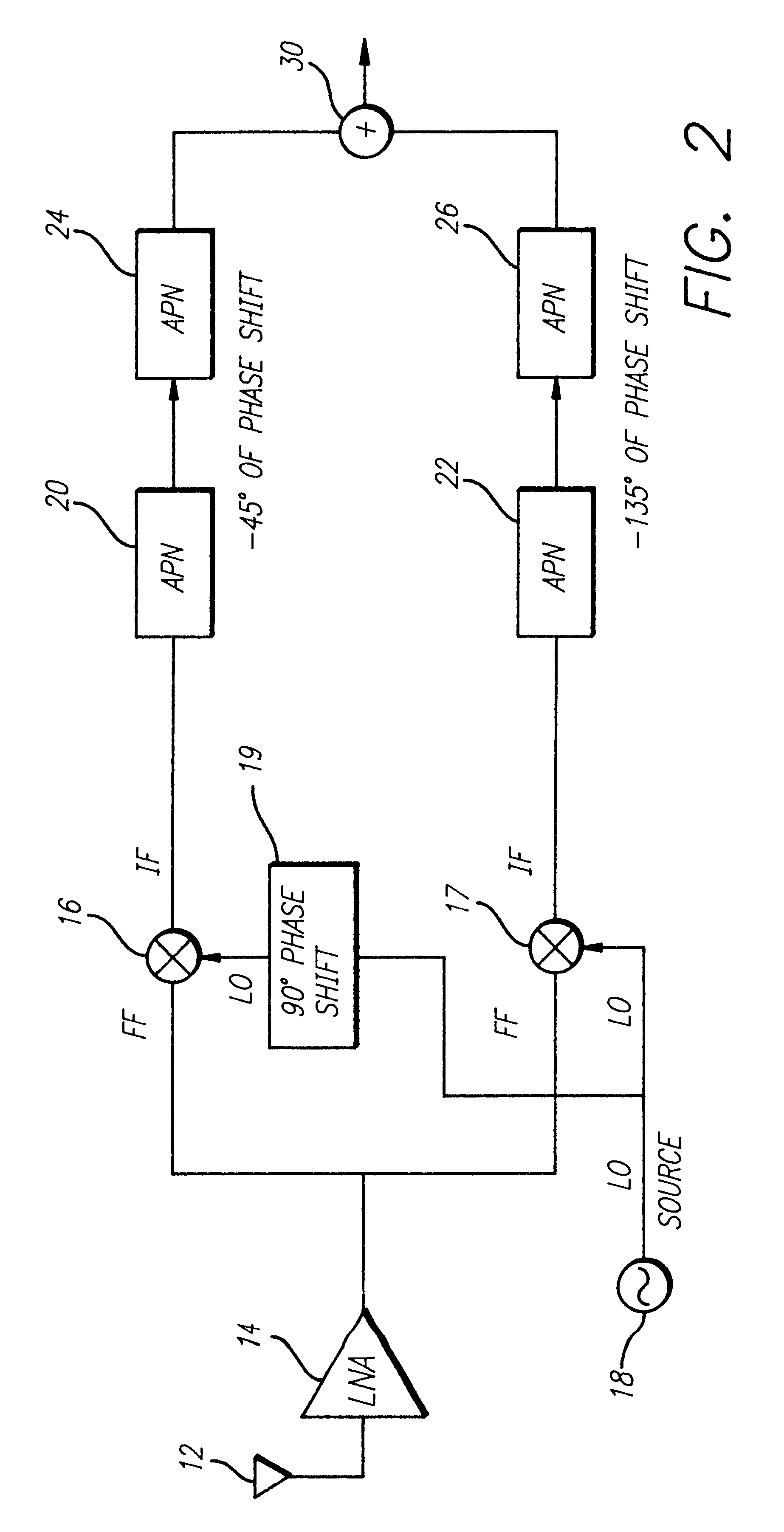

Wideband IF image rejecting receiver

InactiveUS6636730B2Transmission noise suppressionMultiple carrier systemsCapacitanceDifferential amplifier

A system and method for effecting wideband image rejection. In a receiver implementation, the inventive method includes the steps of receiving a first signal in a first frequency band and generating in-phase and quadrature signals therefrom. The phase of the in-phase signal is shifted to provide a second signal and the phase of the quadrature signal is shifted to provide a third signal. A predetermined phase relationship is thereby effected between the second and the third signals. The second and third signals are then summed to provide an output signal which has minimal interference from a mixing signal. In an illustrative receiver application, the phase shifting is achieved via the use of all pass networks. Each of the all pass networks include a differential amplifier having first and second input terminals. The first and the second terminals are connected to a first end of first and second resistive elements, respectively. The second ends of the first and second resistive elements are connected to a common input terminal for the network. The first input terminal is a negative terminal and is connected to an output terminal of the network. The second terminal is a positive terminal and is connected to a source of ground potential via a capacitive element.

Owner:MICROELECTRONICS TECH INC

Popular searches

Variable inductances/transformers Printed inductances Semiconductor devices Amplification control details Frequency selective two-port networks Multi-frequency-changing modulation transference Coils Network modifications to reduce temperature Angle demodulation by phase difference detection Amplifier modifications to reduce noise influence