Patents

Literature

346results about How to "Reduce skew" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

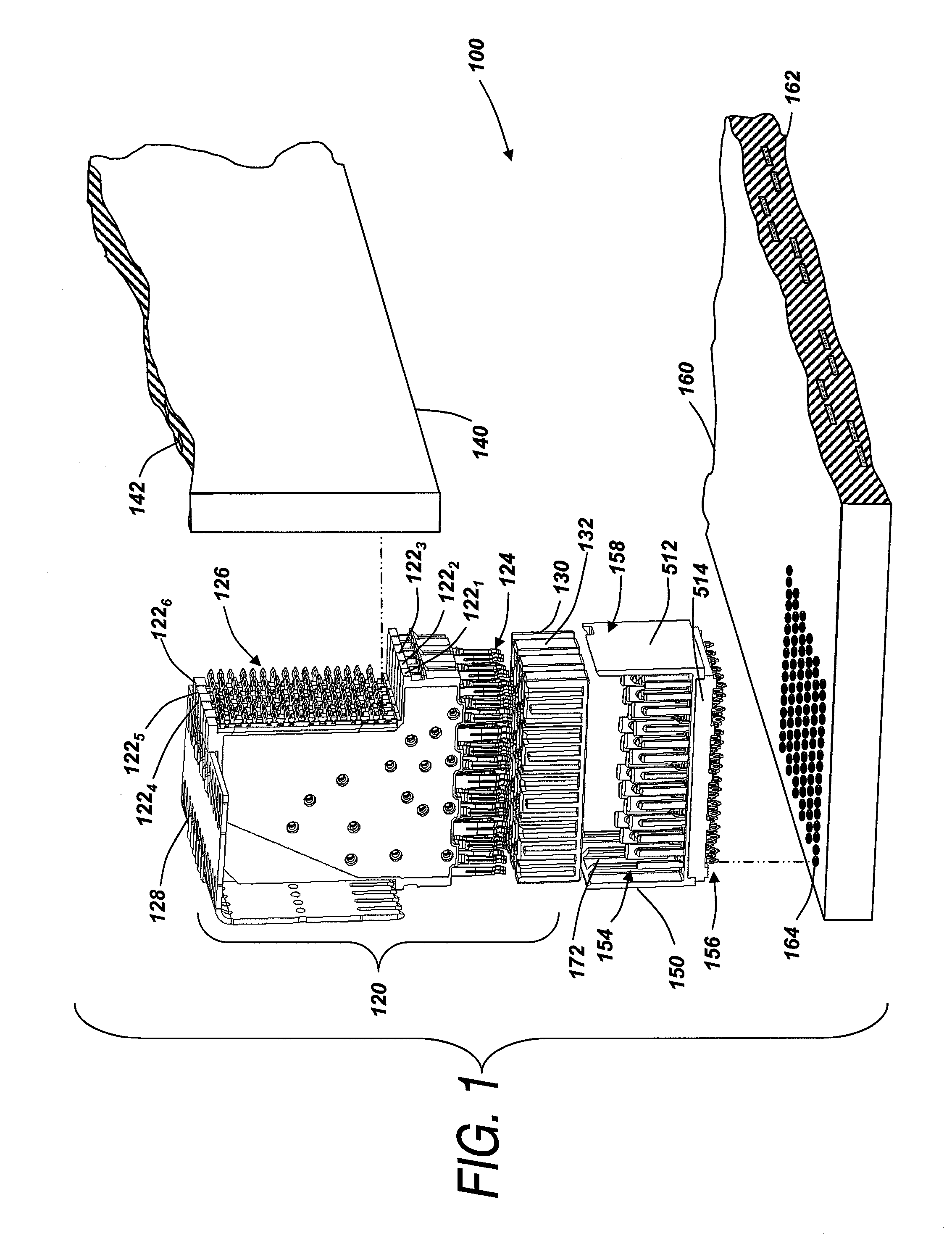

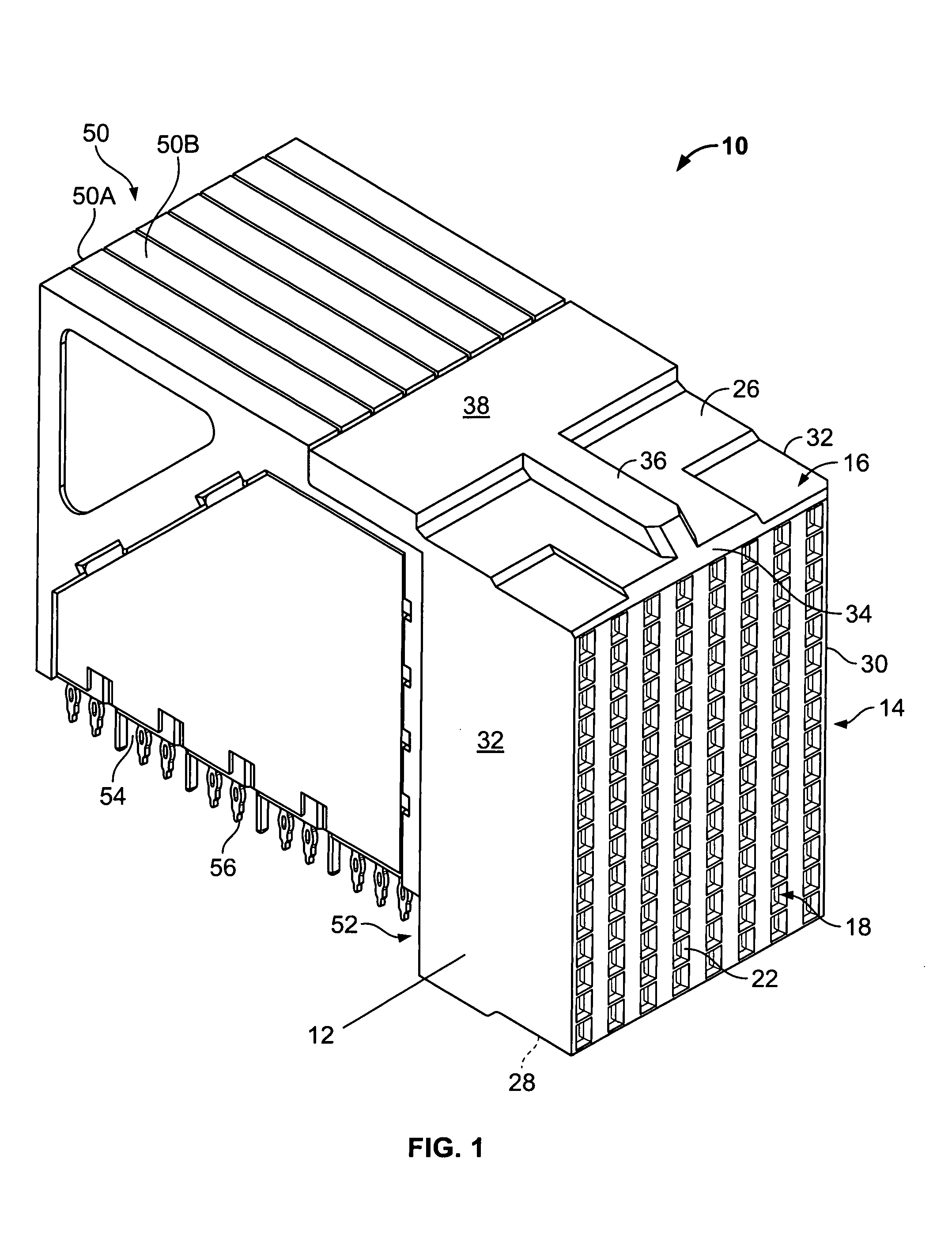

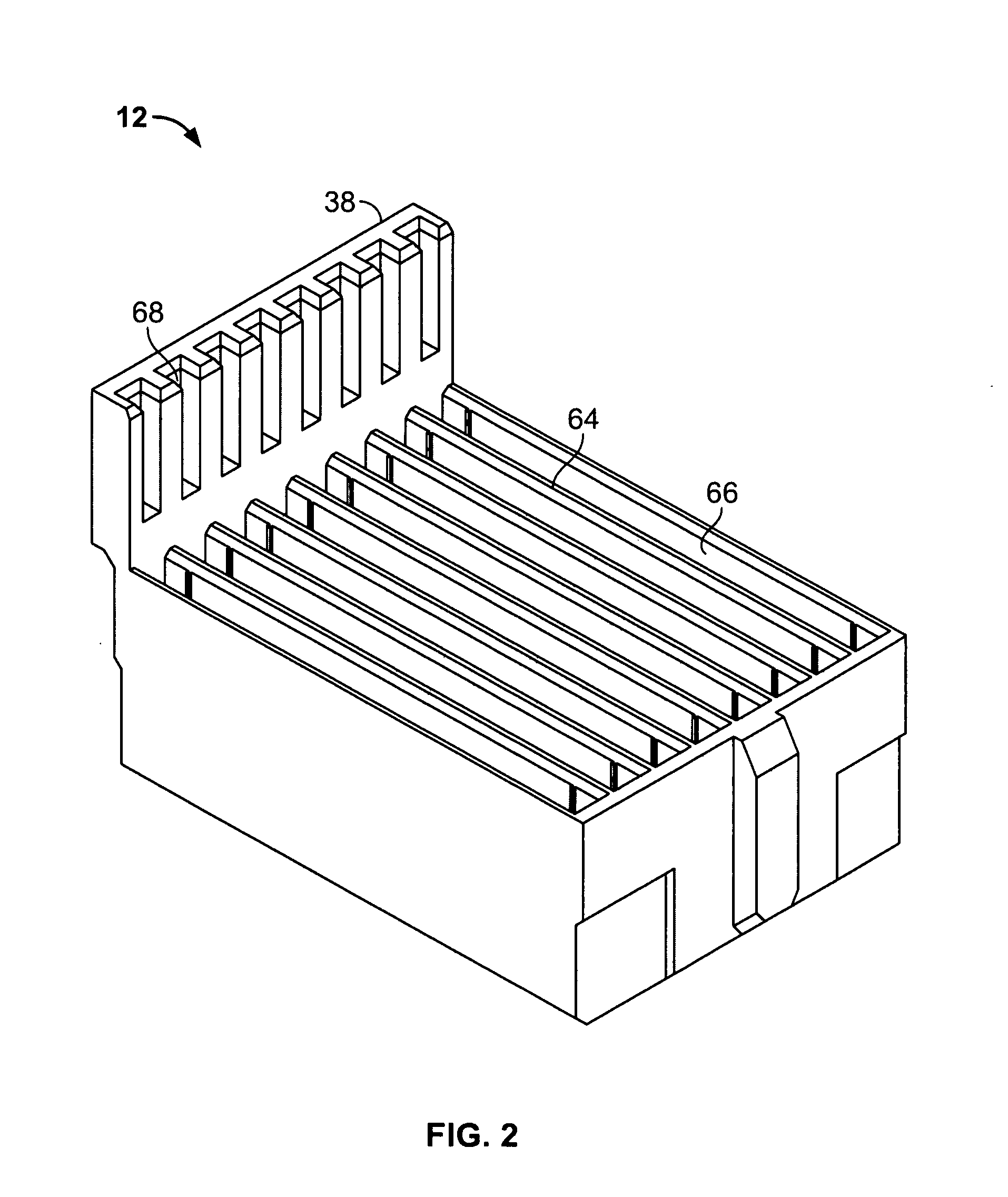

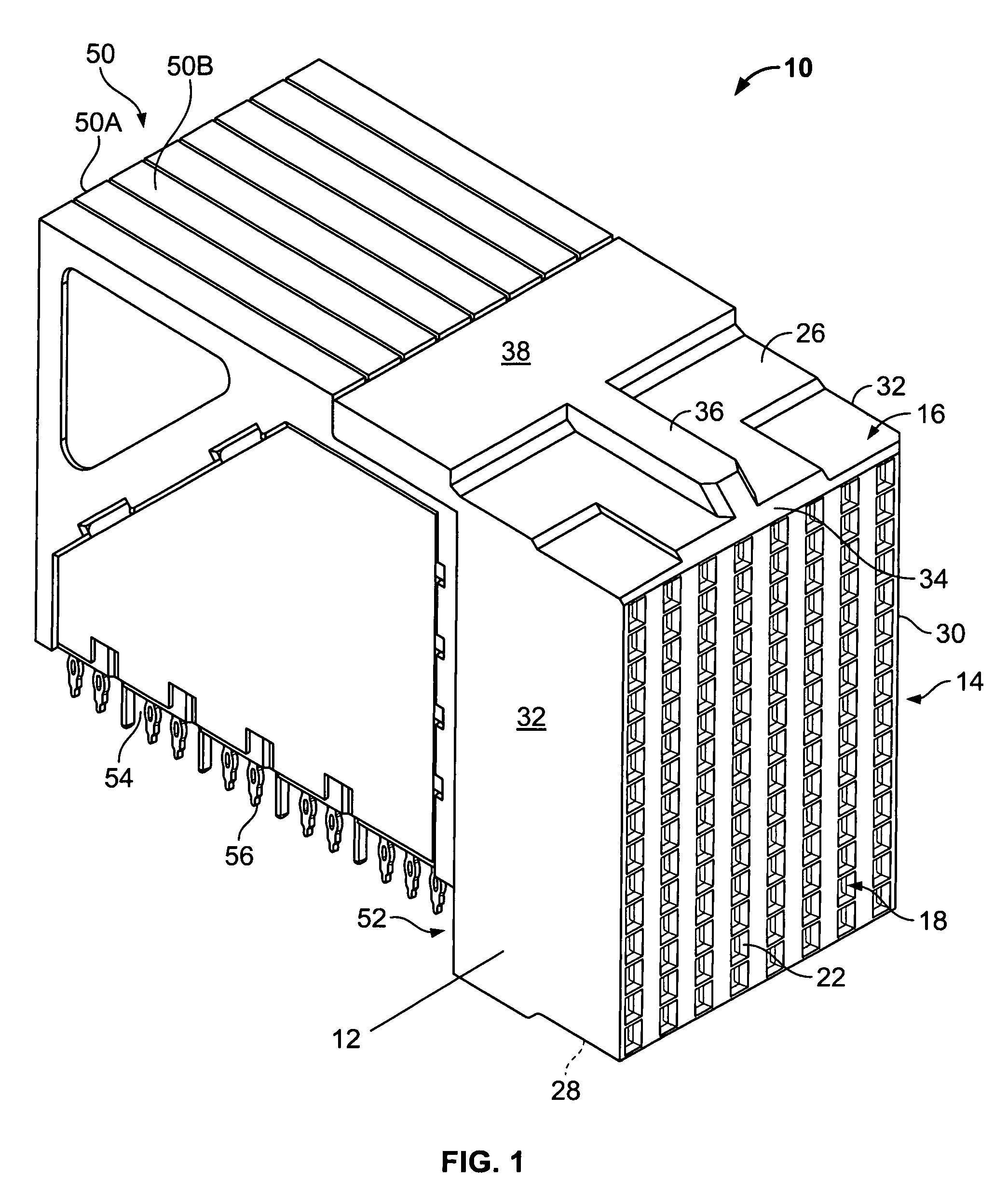

Differential electrical connector with improved skew control

ActiveUS20100291803A1Reduce skewIncrease electrical lengthElectric discharge tubesTwo-part coupling devicesElectricityEngineering

An electrical interconnection system with high speed, differential electrical connectors. The connector is assembled from wafers each containing a column of conductive elements, some of which form differential pairs. Skew control is provided for at least some of the pairs by providing a profile on an edge of the shorter signal conductor of the pair. The profile may contain multiple curved segments that effectively lengthen the signal conductor without significantly impacting its impedance. For connectors in which ground conductors are included between adjacent pairs of signal conductors, patterned segments of varying parameters may be included on edges of the signal conductors and ground conductors to equalize electrical lengths of all edges in a set of edges for which there is common mode or differential mode coupling as a signal propagates along each pair. Such features for skew control may be used in combination with other skew control features. The features used may vary depending on the location of the pair within the column.

Owner:AMPHENOL CORP

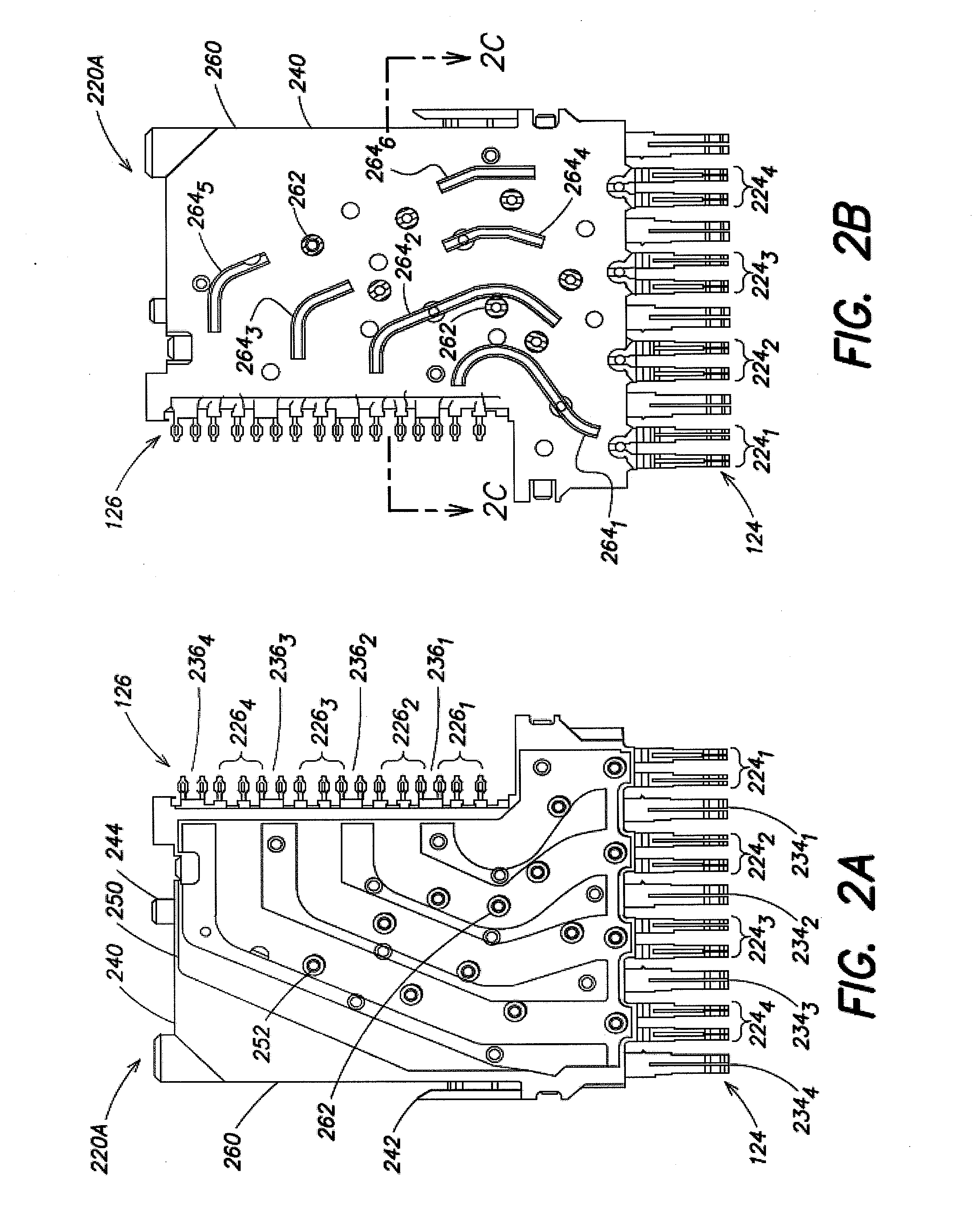

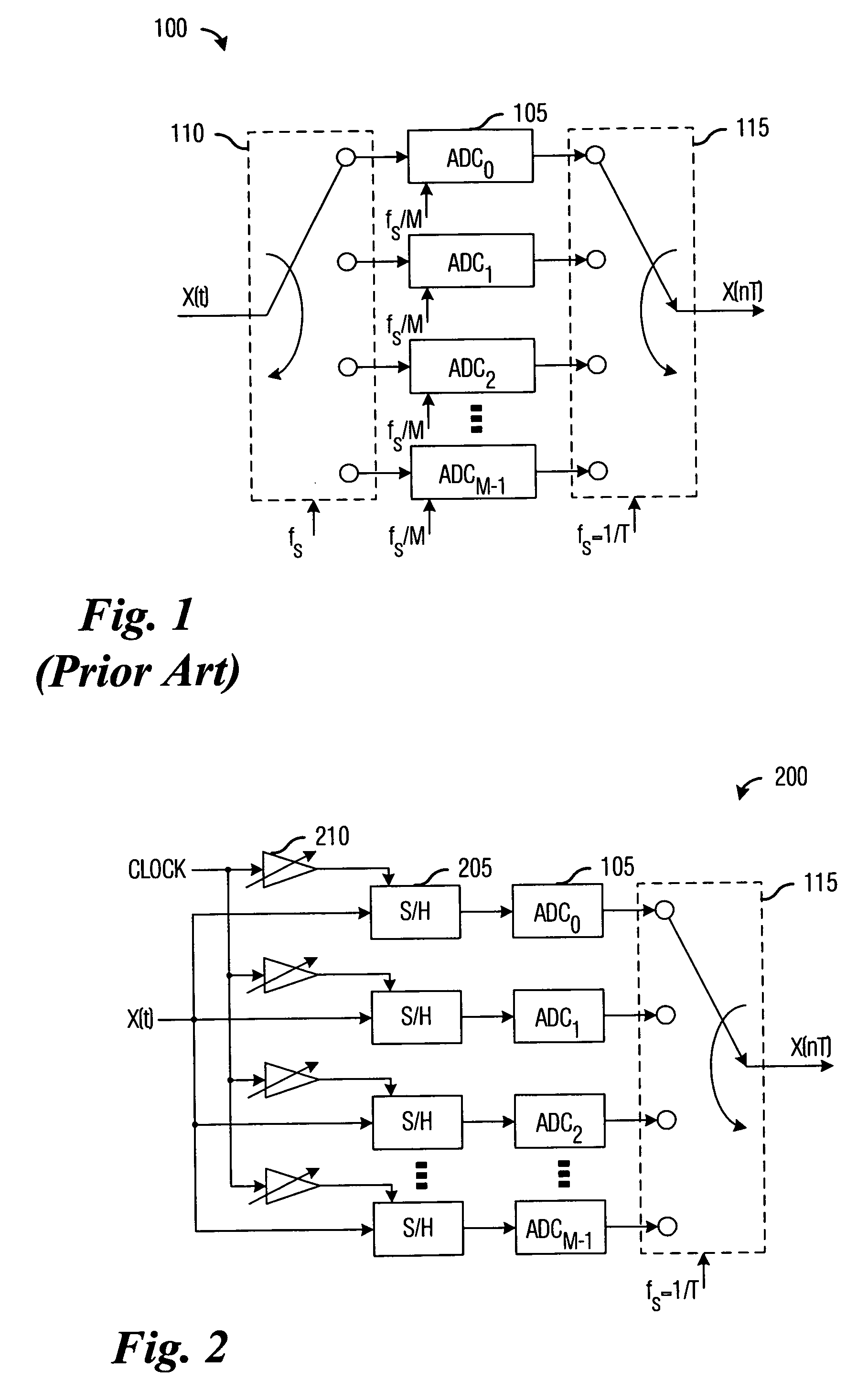

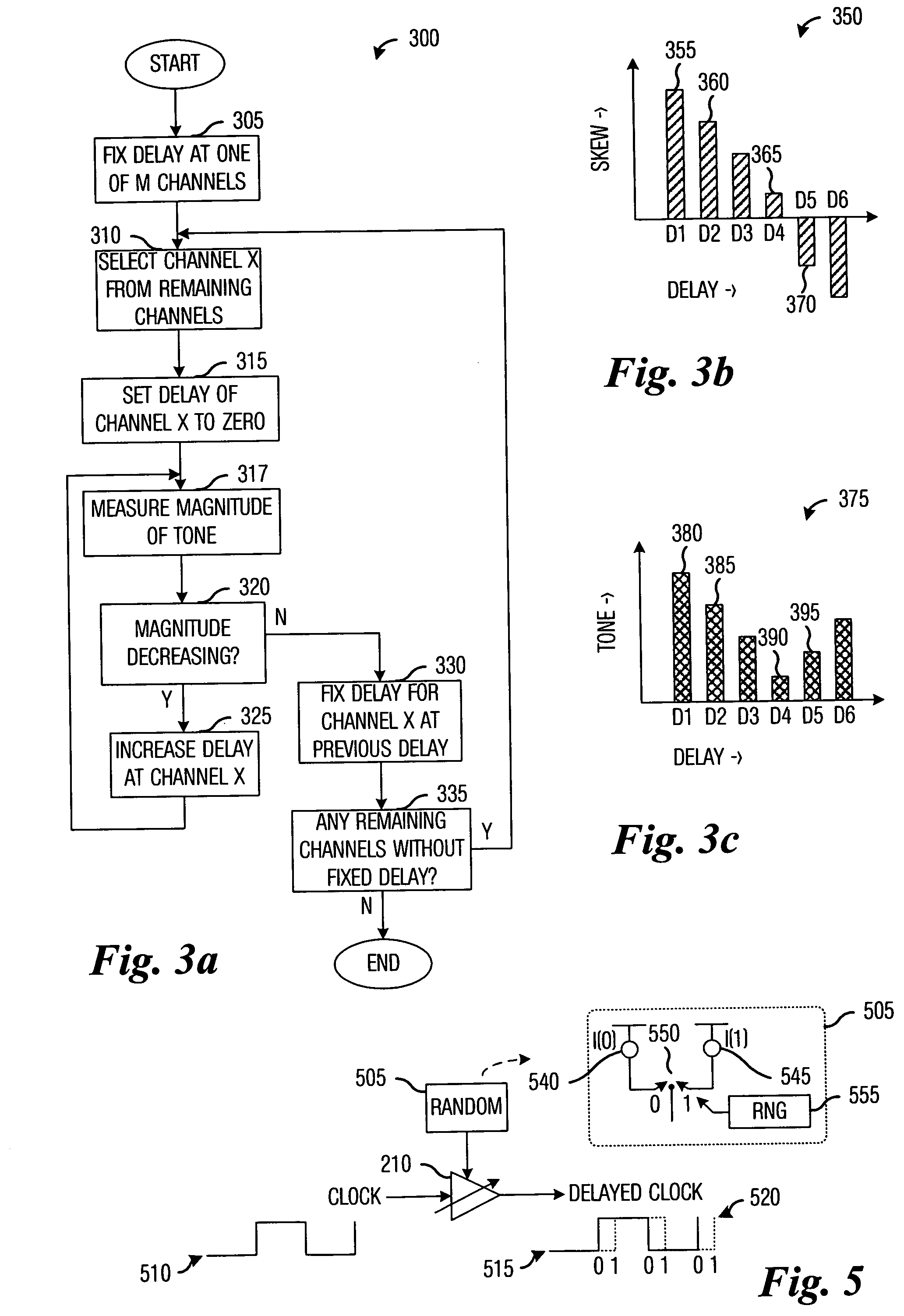

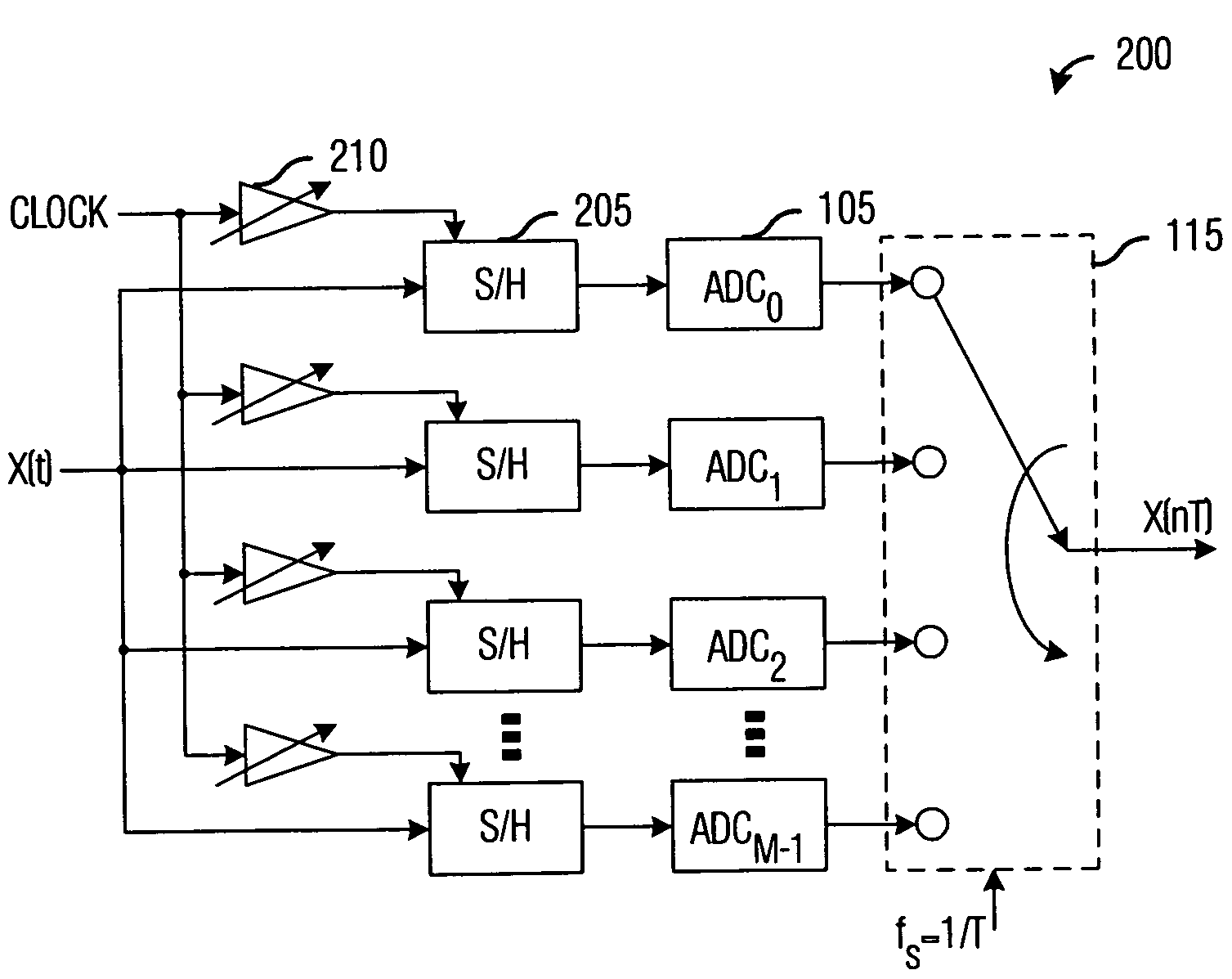

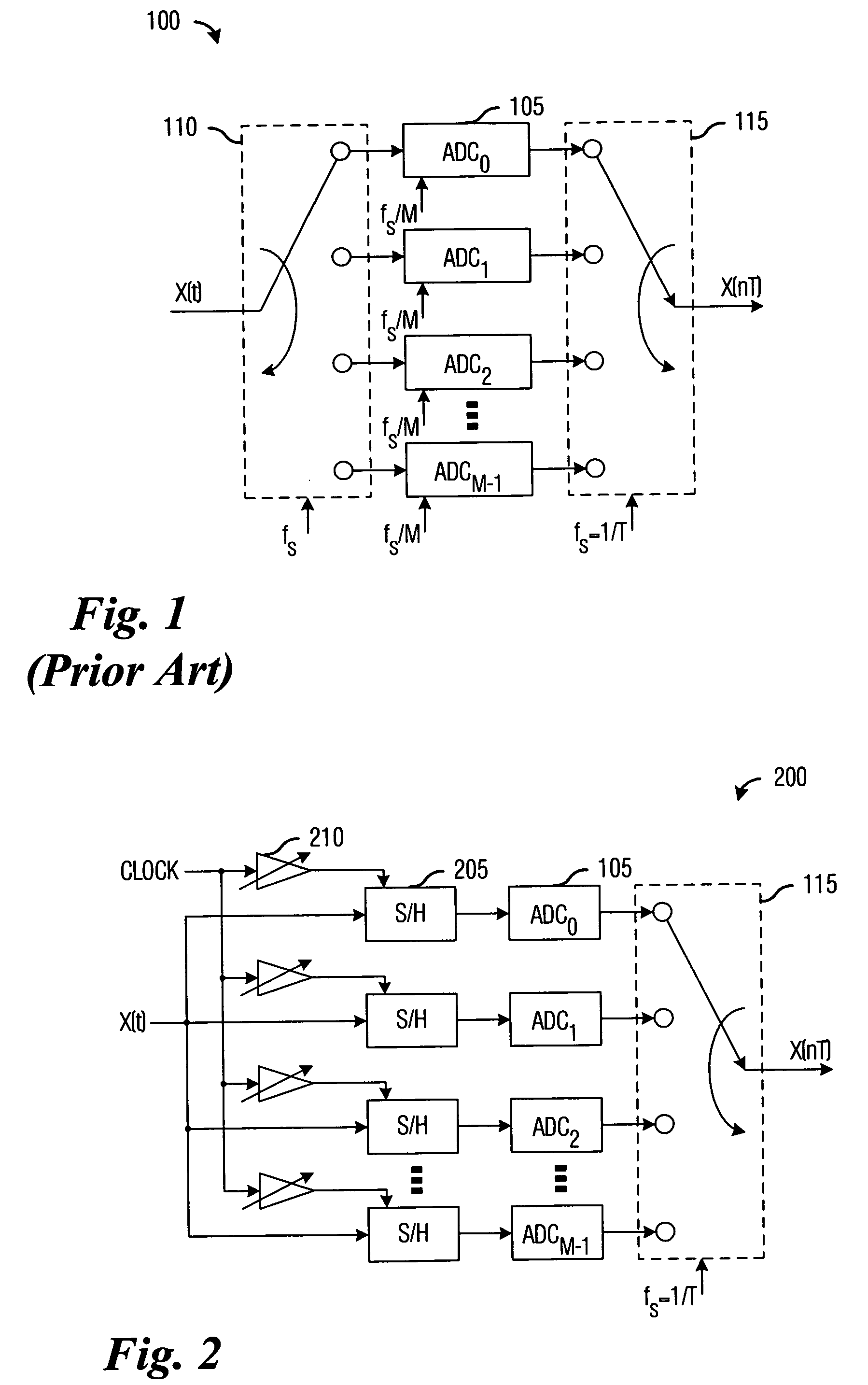

System and method for improved time-interleaved analog-to-digital converter arrays

ActiveUS20060279445A1Reduce distortionReduce distortion problemsElectric signal transmission systemsAnalogue-digital convertersA d converterDistortion

System and method for improved time-interleaved analog-to-digital converter arrays which reduces sampling mismatch distortion found in prior art arrays. There may be two causes of non-uniform sampling mismatch in a TI-ADC array, a mismatch due to skew and a mismatch due to clock jitter. To minimize non-uniform sampling mismatch, the mismatch due to skew can be addressed. A preferred embodiment comprises adjusting a delay imparted on the sampling clock by an adjustable delay in each channel of a plurality of channels in the TI-ADC array to minimize skew and randomly switching between two delays that span a zero-skew delay to reduce residual skew in each channel and thus eliminate (or reduce) frequency domain tones caused by non-uniform sampling mismatch.

Owner:TEXAS INSTR INC

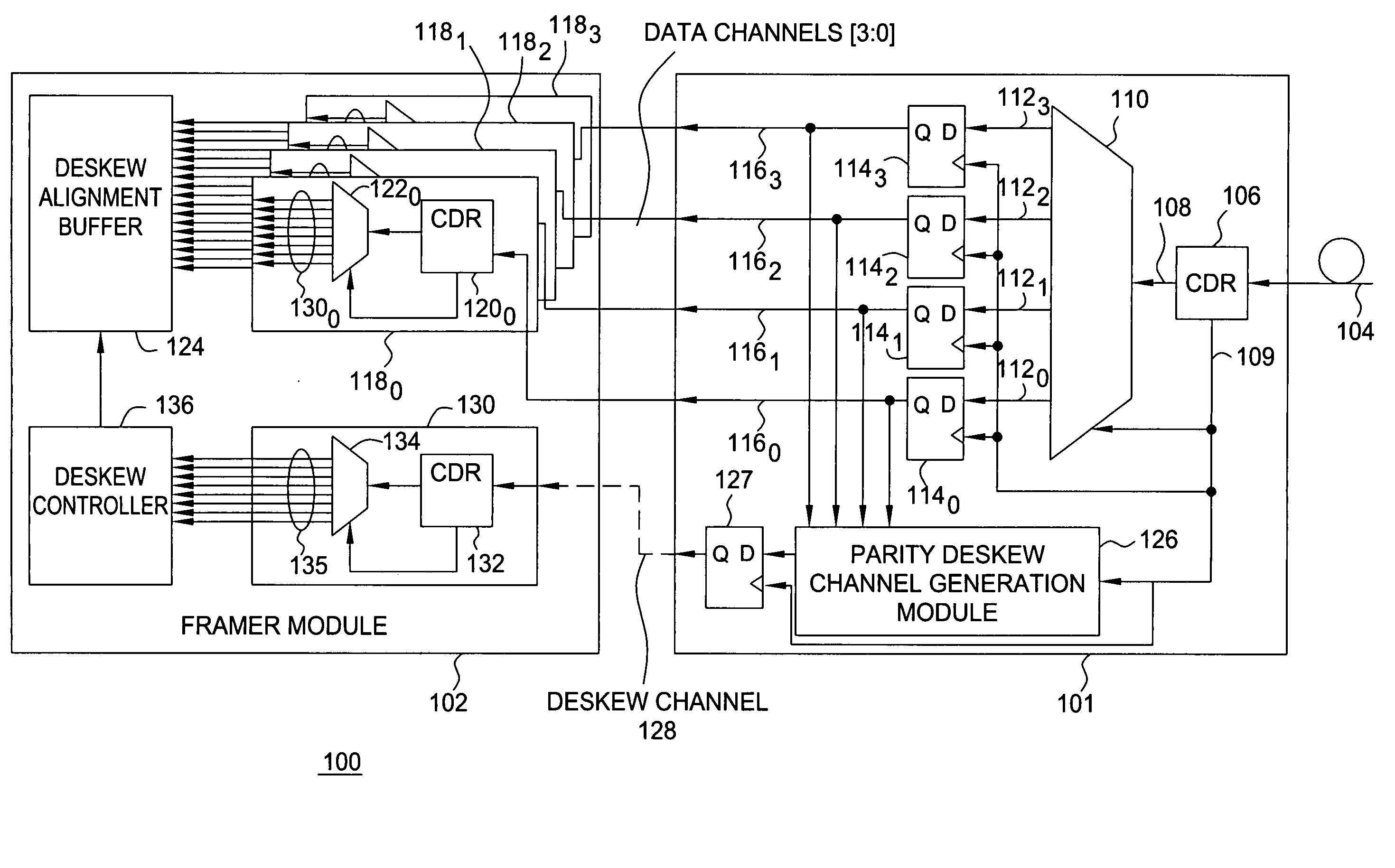

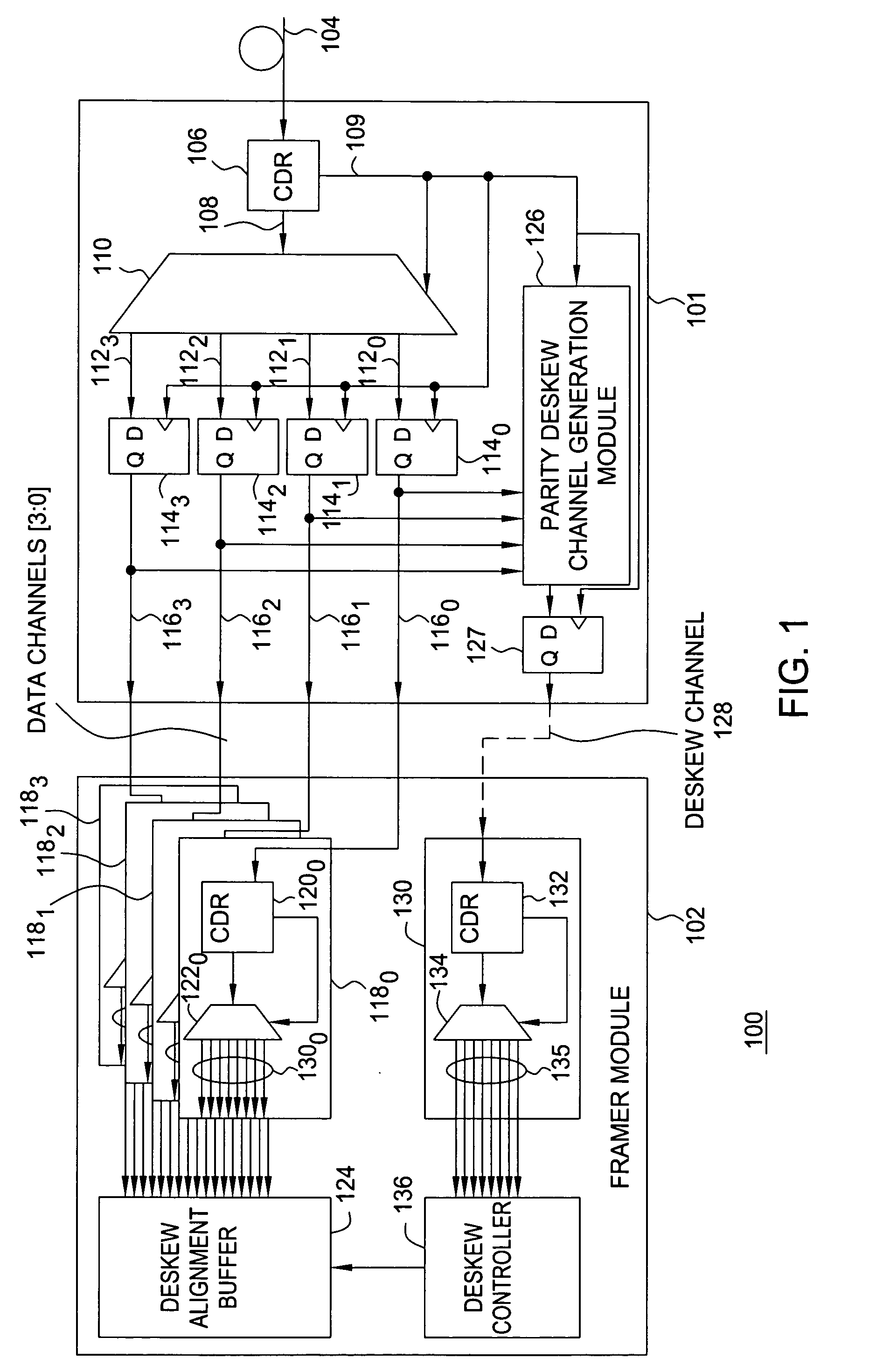

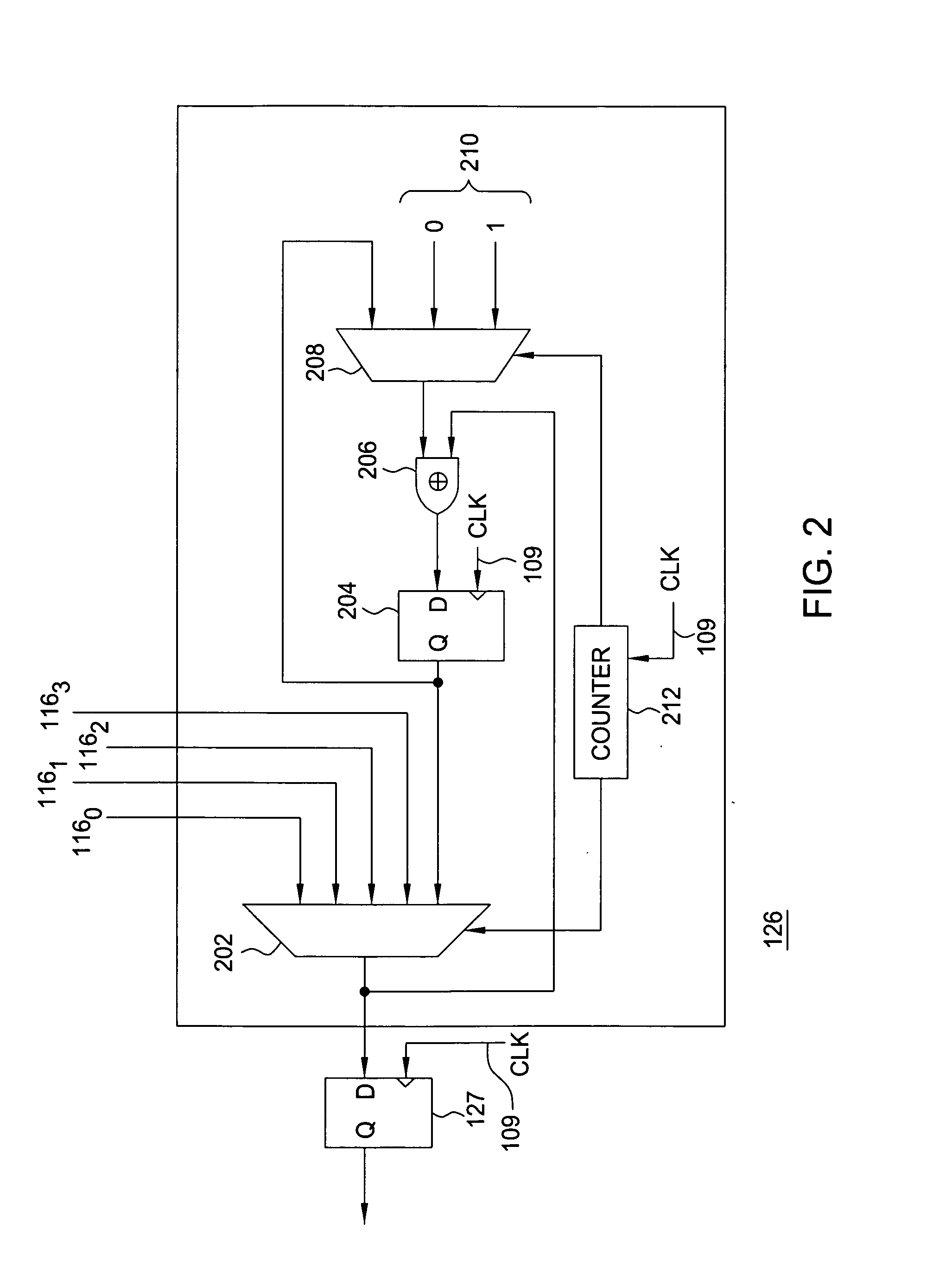

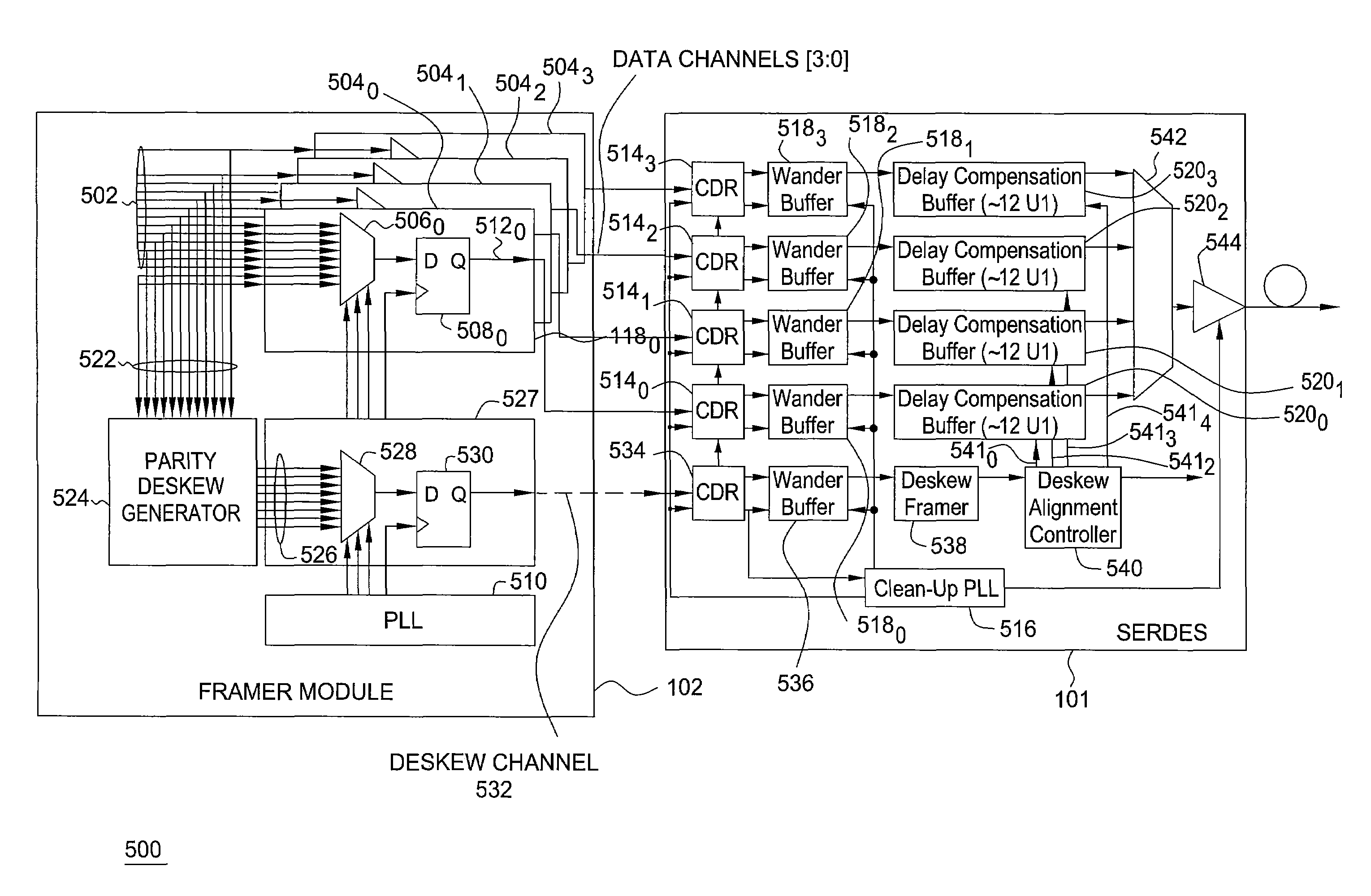

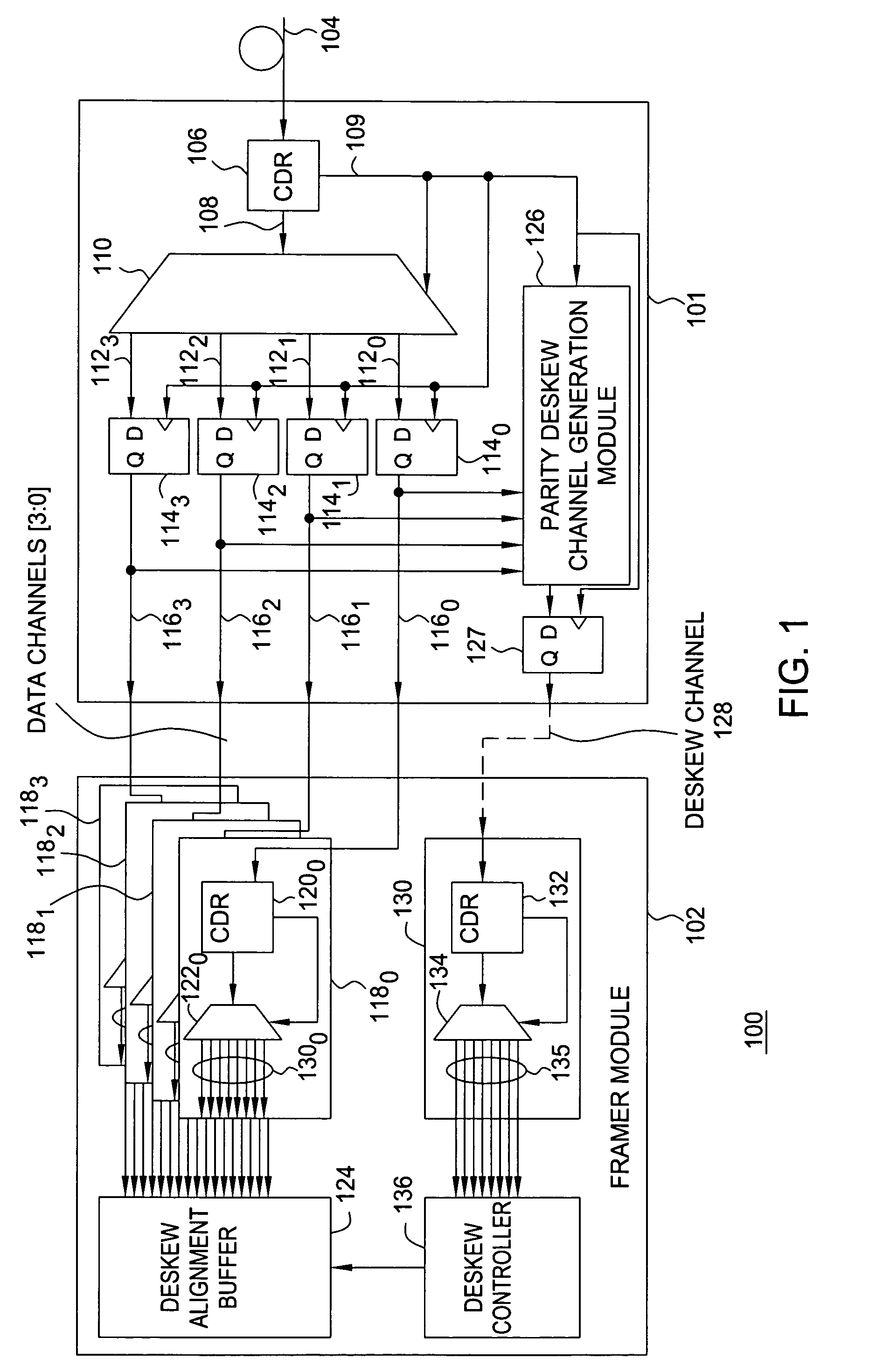

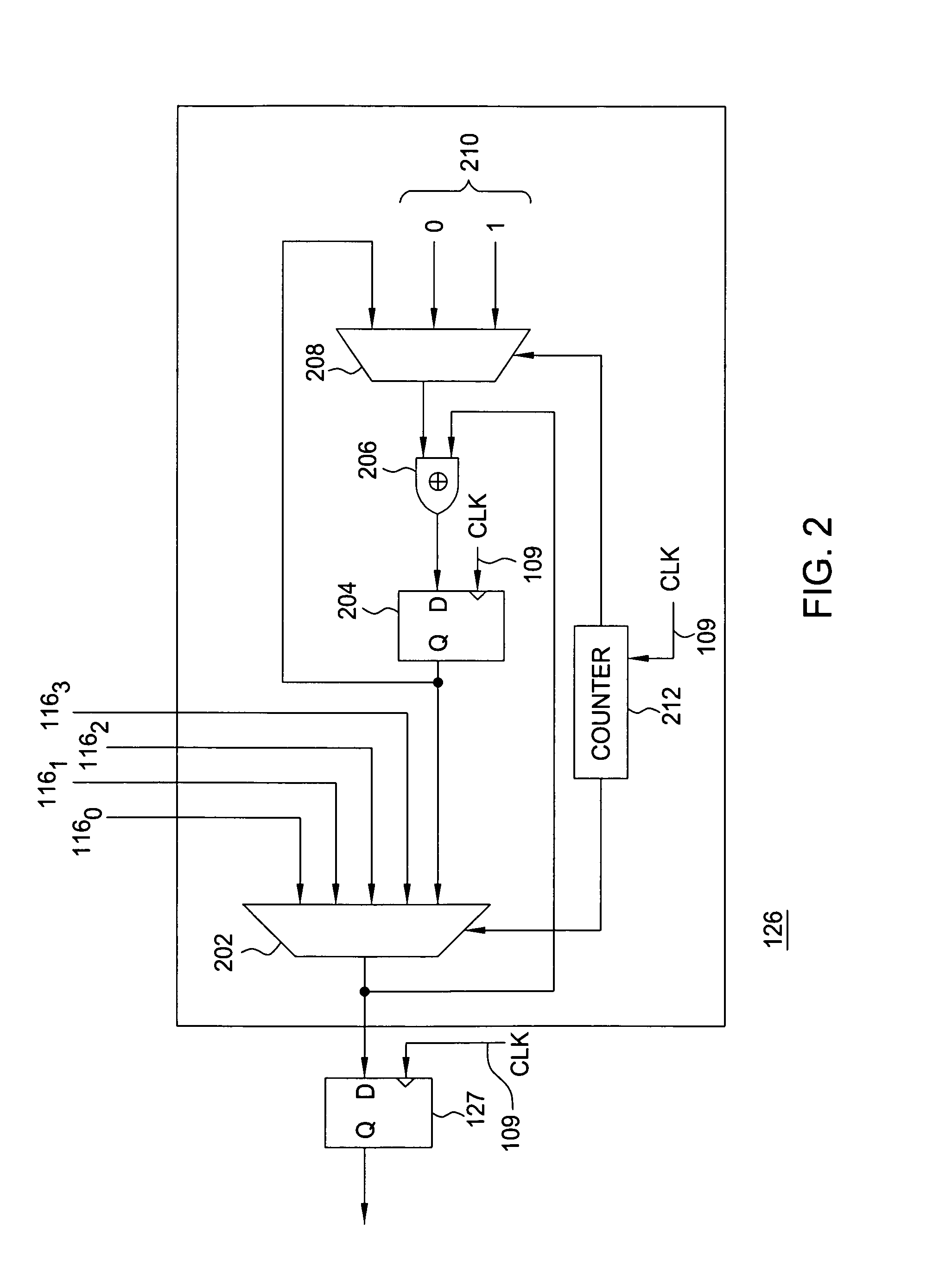

Method and apparatus for synchronizing data channels using an alternating parity deskew channel

ActiveUS20070006053A1Reduce skewSimpler and efficient and reliable and cost-effectiveChannel dividing arrangementsError detection/correctionChannel useParity bit

The invention includes a method and apparatus for aligning a plurality of data channels using a deskew bitstream. The method includes receiving the deskew bitstream, identifying an aligned deskew frame by processing the deskew bitstream, identifying a data channel alignment position associated with each of the plurality of data channels by comparing a deskew channel comparison bit from the aligned deskew frame to a data channel comparison bit from each of the plurality of data channels, and selecting the plurality of data channel alignment positions associated with the respective plurality of data channels for aligning the plurality of data channels. The plurality of data channels are aligned in a manner for substantially reducing skew associated with the data channels. The deskew bitstream comprises a plurality of data bits associated with the data channels and a plurality of parity bits generated using at least a portion of the data bits.

Owner:ALCATEL-LUCENT USA INC

Method and apparatus for synchronizing data channels using an alternating parity deskew channel

ActiveUS7467335B2Reduce skewSimpler and efficient and reliable and cost-effectiveChannel dividing arrangementsError detection/correctionChannel correlationChannel use

The invention includes a method and apparatus for aligning a plurality of data channels using a deskew bitstream. The method includes receiving the deskew bitstream, identifying an aligned deskew frame by processing the deskew bitstream, identifying a data channel alignment position associated with each of the plurality of data channels by comparing a deskew channel comparison bit from the aligned deskew frame to a data channel comparison bit from each of the plurality of data channels, and selecting the plurality of data channel alignment positions associated with the respective plurality of data channels for aligning the plurality of data channels. The plurality of data channels are aligned in a manner for substantially reducing skew associated with the data channels. The deskew bitstream comprises a plurality of data bits associated with the data channels and a plurality of parity bits generated using at least a portion of the data bits.

Owner:ALCATEL-LUCENT USA INC

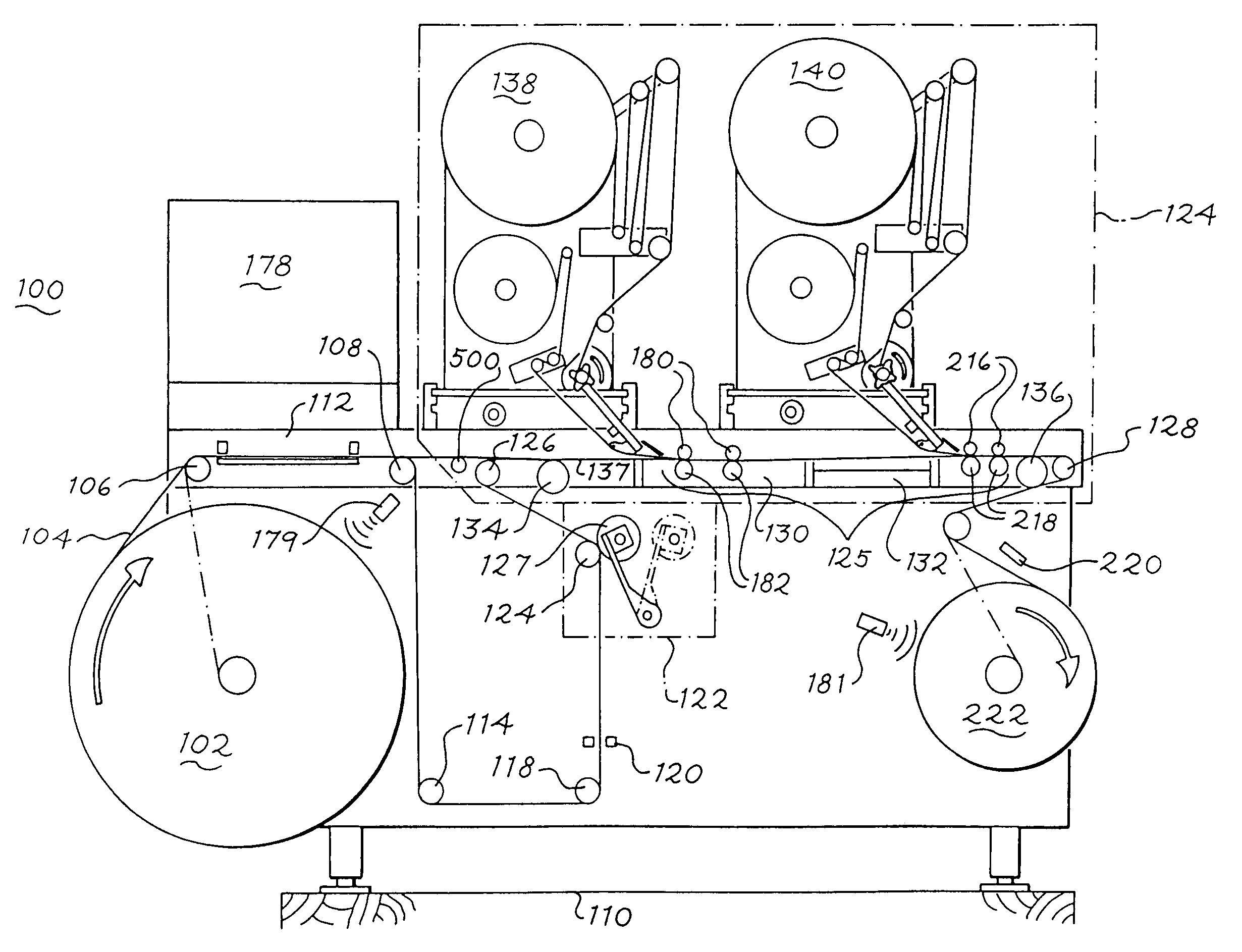

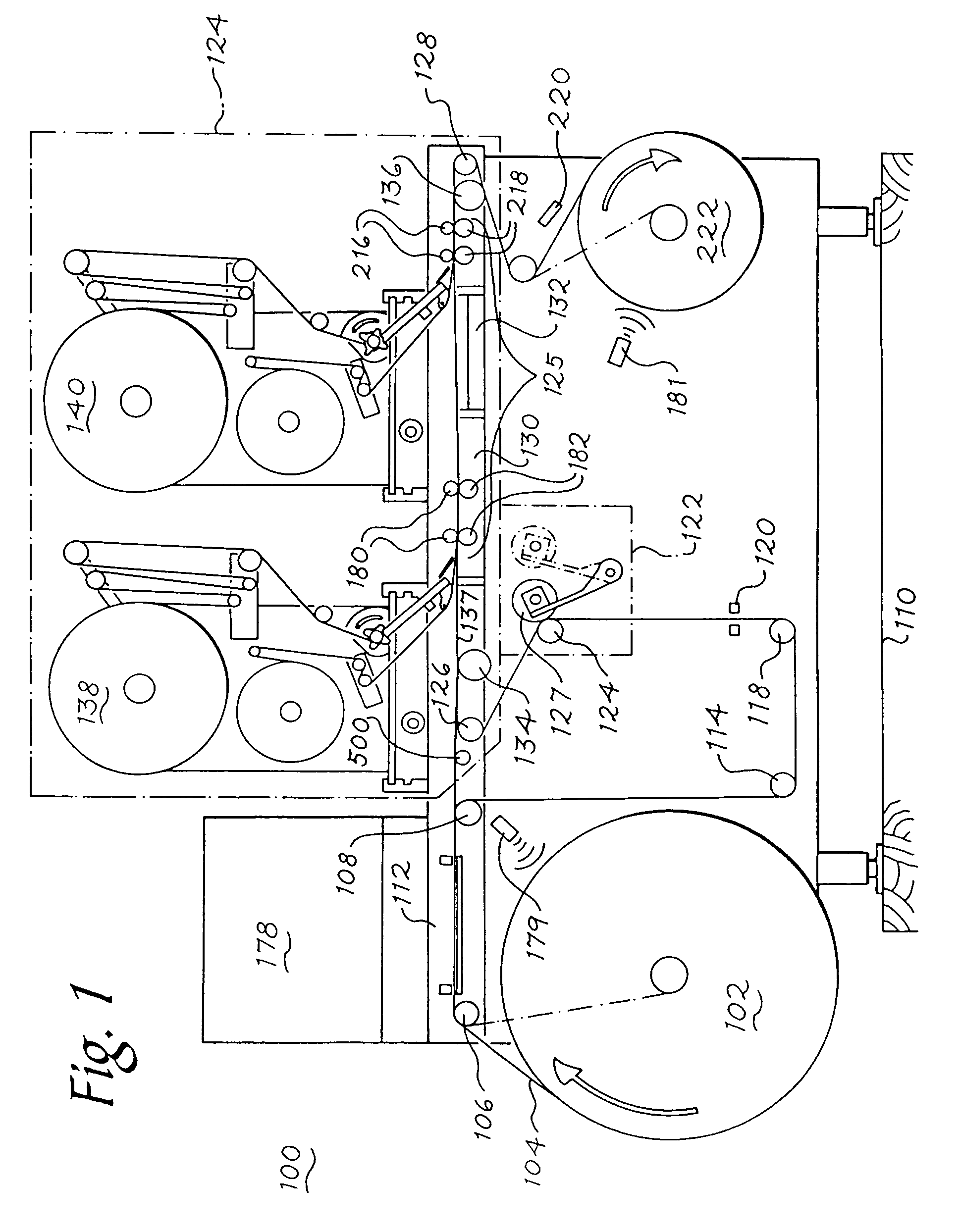

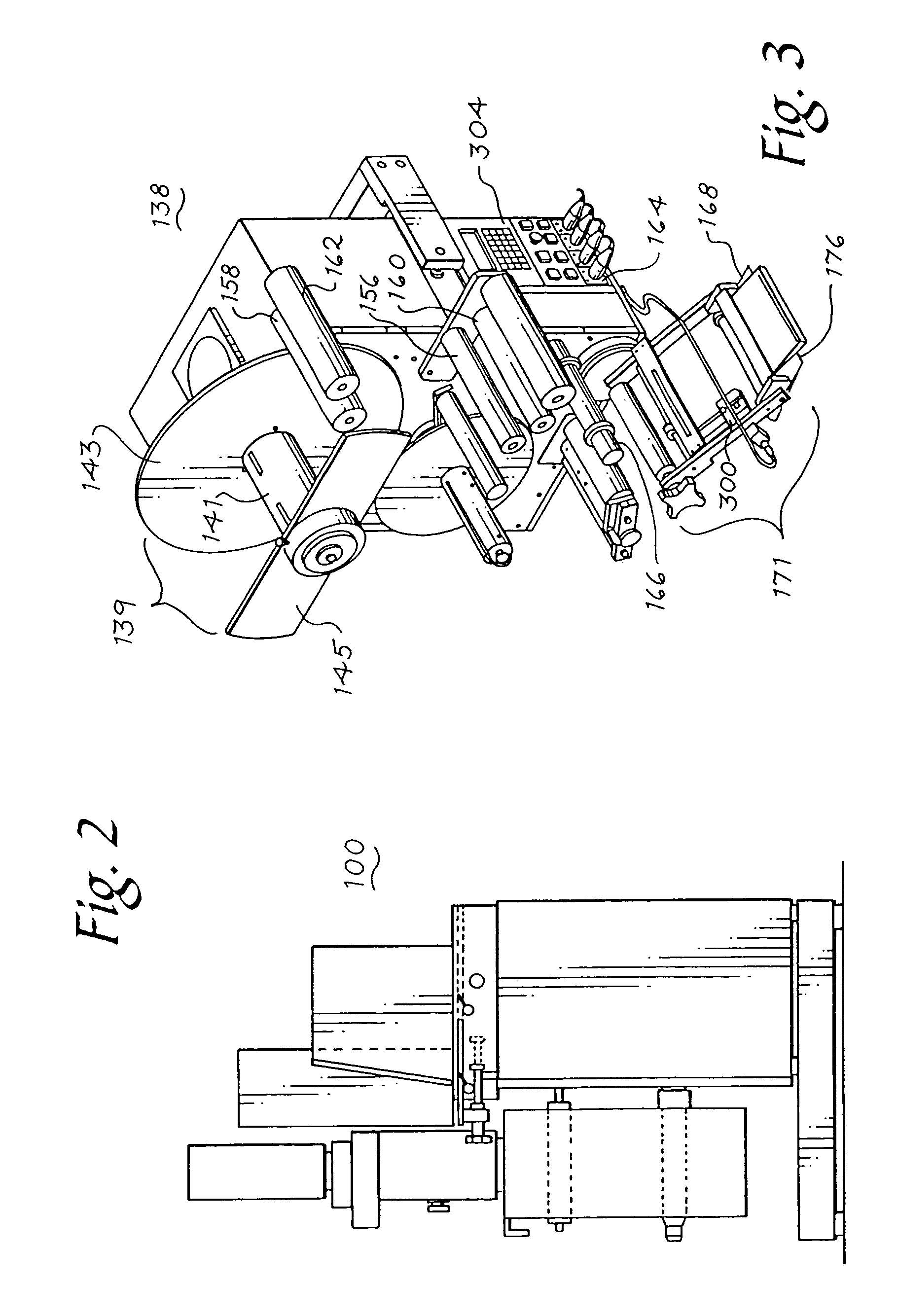

Machine and process for manufacturing a label with a security element

InactiveUS7017820B1Reduce skewImprove efficiencyPaper/cardboard articlesRecord carriers used with machinesEngineeringMechanical engineering

A process for manufacturing a label that includes moving a web of a substrate along a first direction, placing a label upon a portion of the web, pressing the label onto the portion of the web so as to attach the label to the portion of the web and diminishing skewing of the portion of the web during the pressing.

Owner:BRUNNER JAMES

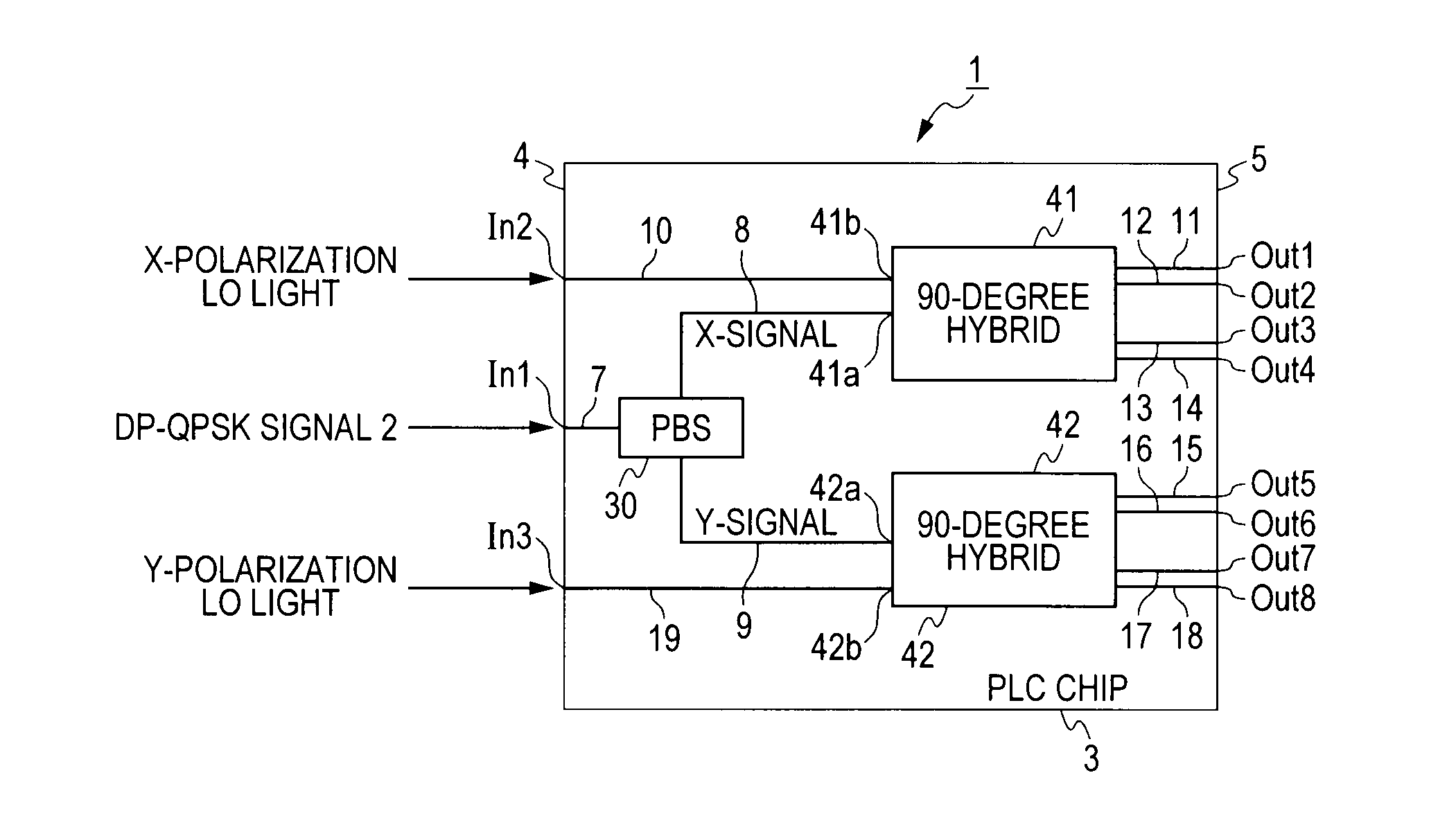

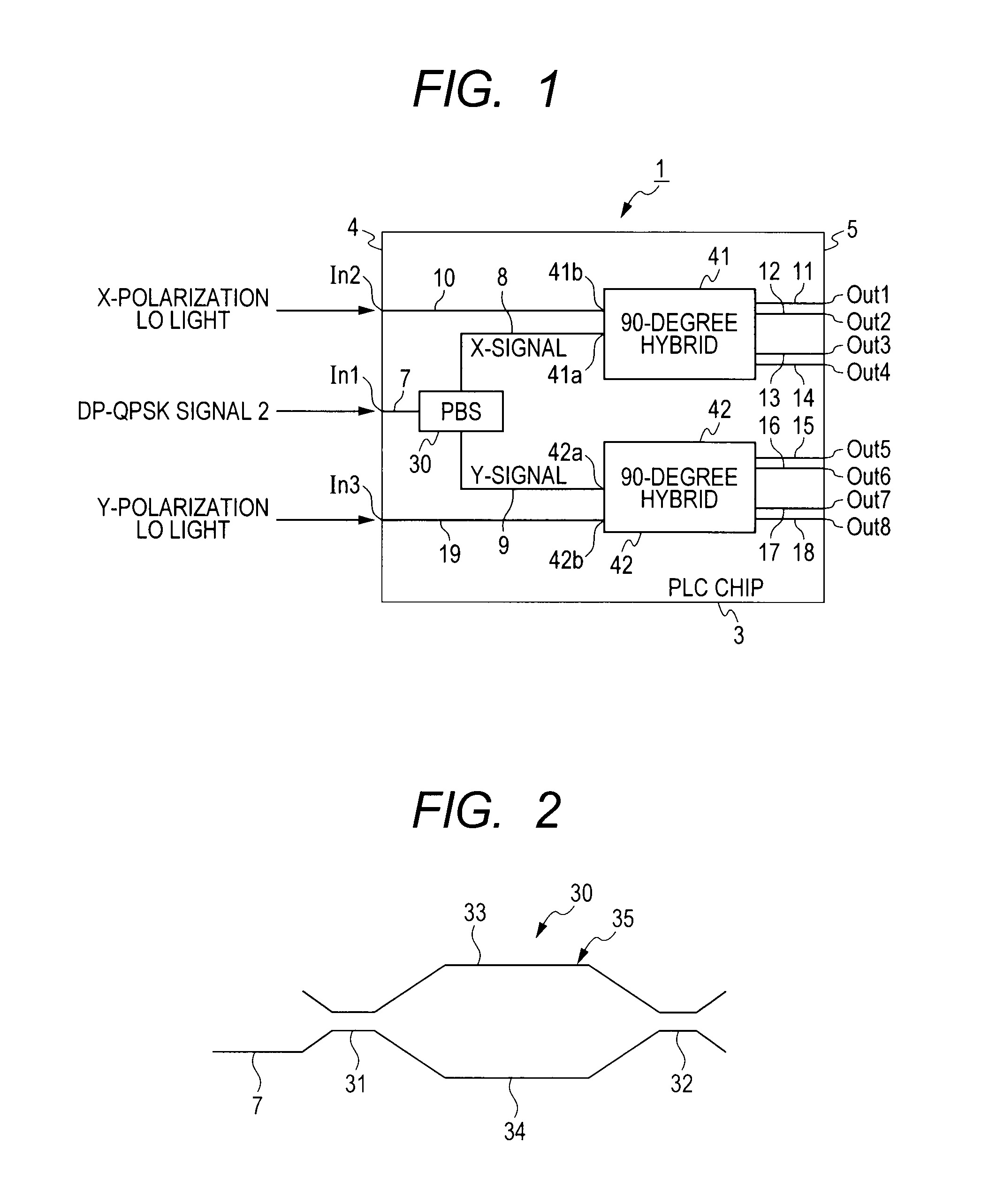

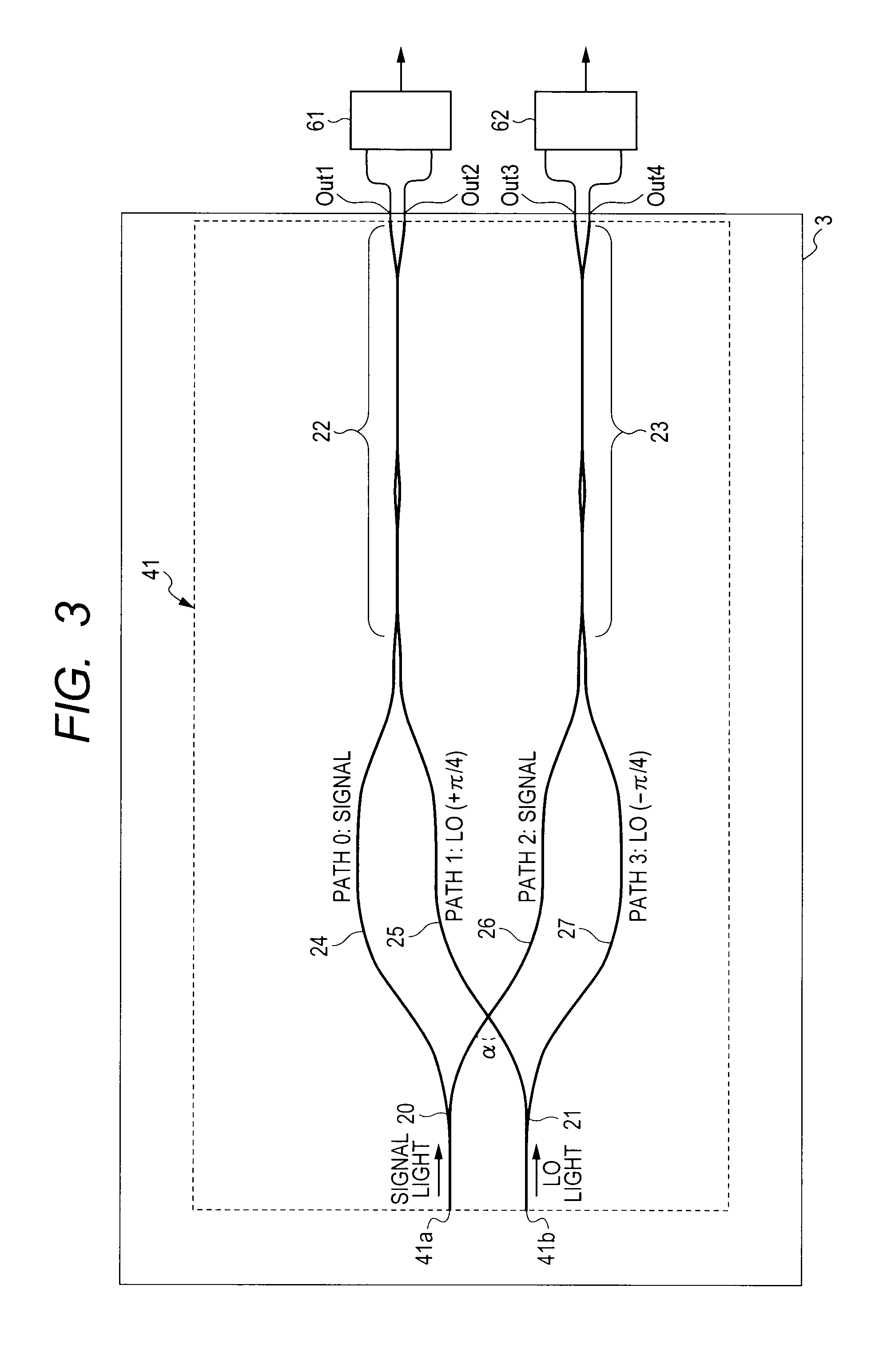

Plc-type demodulator and optical transmission system

ActiveUS20120207474A1Eliminates connection lossReduce manufacturing costPolarisation multiplex systemsCoupling light guidesManufacturing cost reductionPolarization beam splitter

The invention provides a PLC-type DP-QPSK demodulator that reduces connection loss between a polarization beam splitter and a 90-degree hybrid circuit and aims at reducing the manufacturing cost and an optical transmission system using the same. In an embodiment of the invention, a PLC-type DP-QPSK demodulator that receives a DP-QPSK signal includes one PLC chip having a planar lightwave circuit. Input ports and output ports of signal light are provided at an input end and at an output end of the PLC chip, respectively. Within the planar lightwave circuit, there are integrated a polarization beam splitter that splits the DP-QPSK signal into an X-polarization QPSK signal and a Y-polarization QPSK signal, and two 90-degree hybrid circuits that mix the X-polarization QPSK signal and local oscillation light and the Y-polarization QPSK signal and local oscillation light, respectively, split each QPSK signal into orthogonal components I, Q and output them.

Owner:FURUKAWA ELECTRIC CO LTD

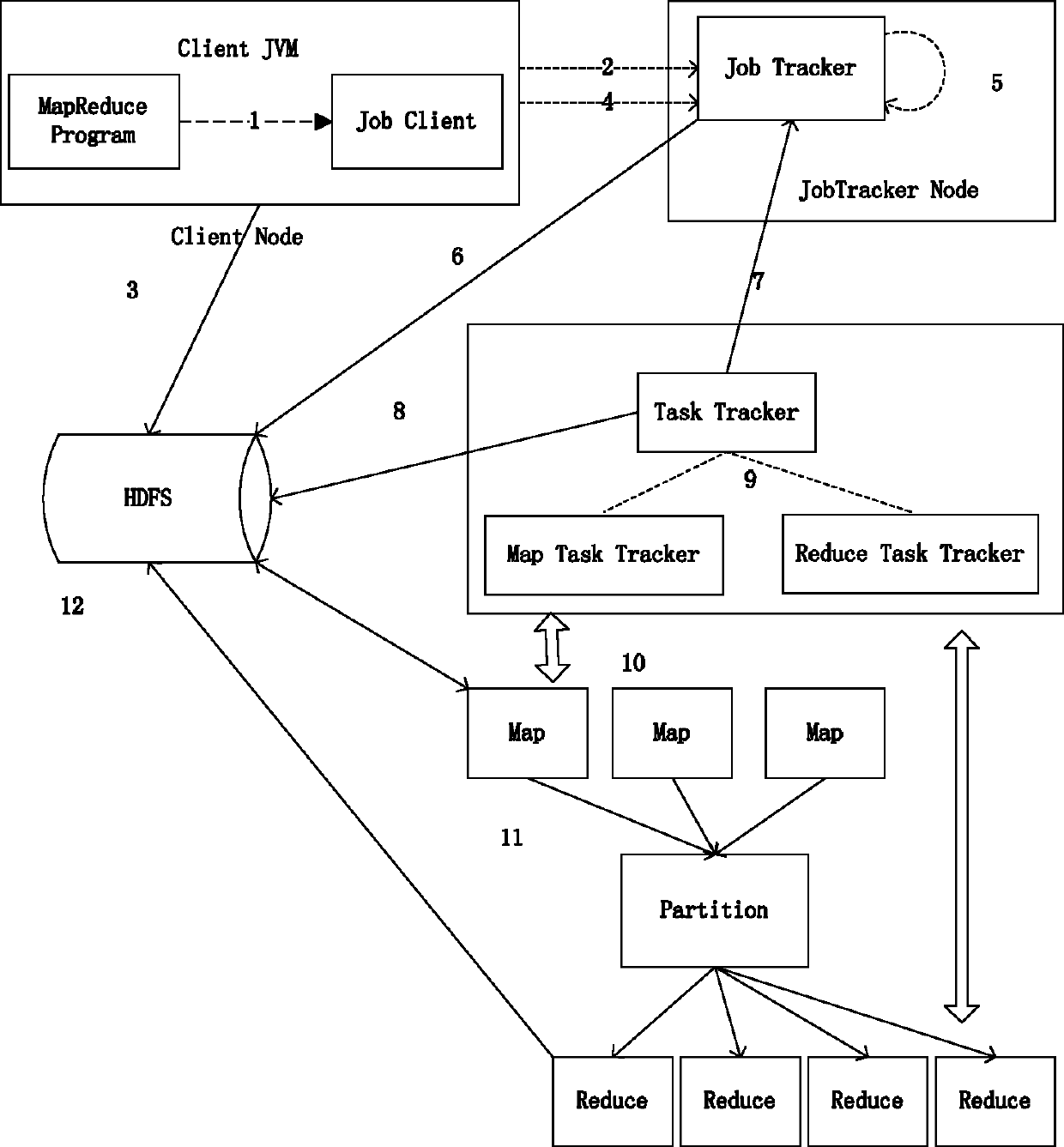

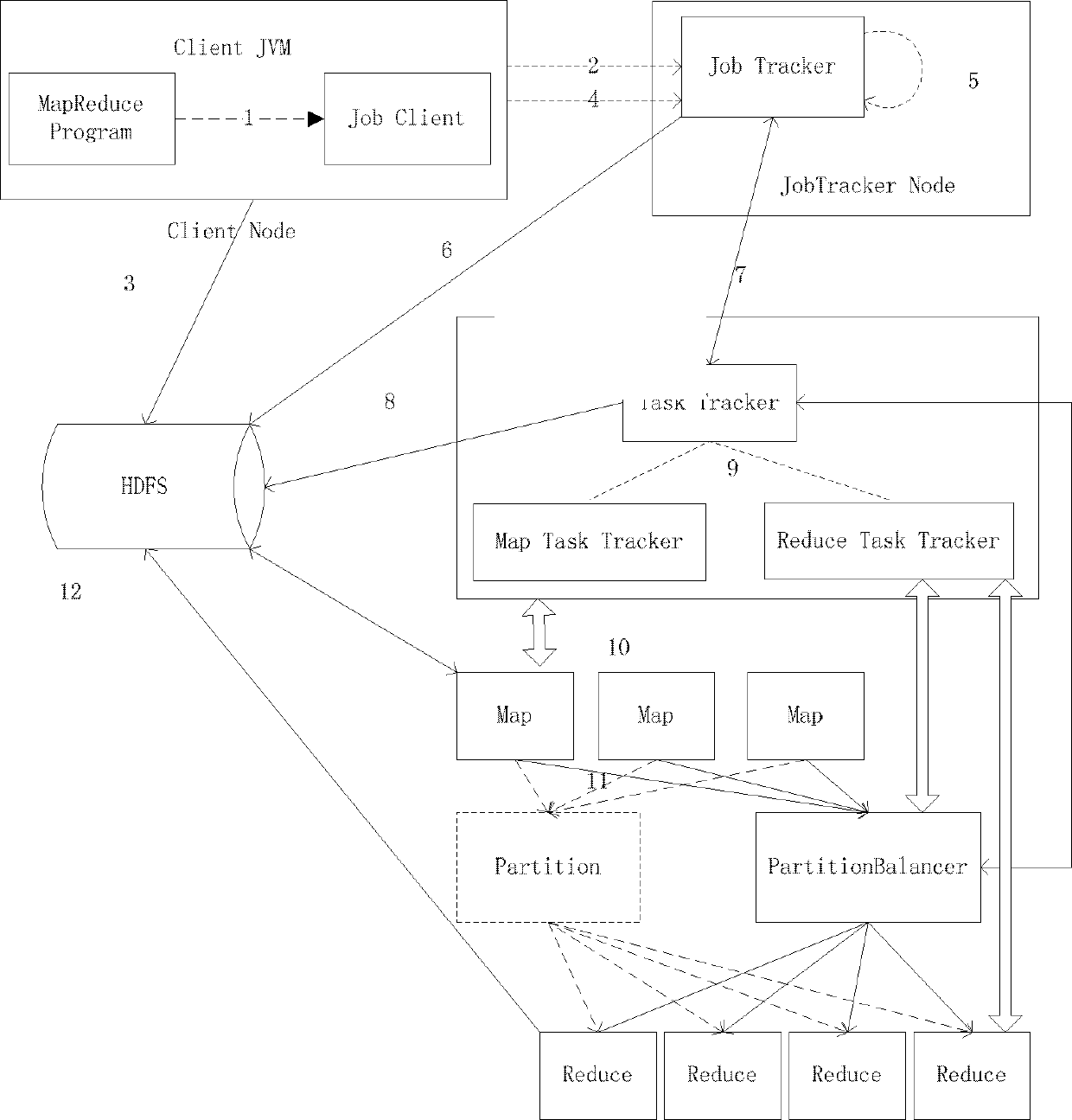

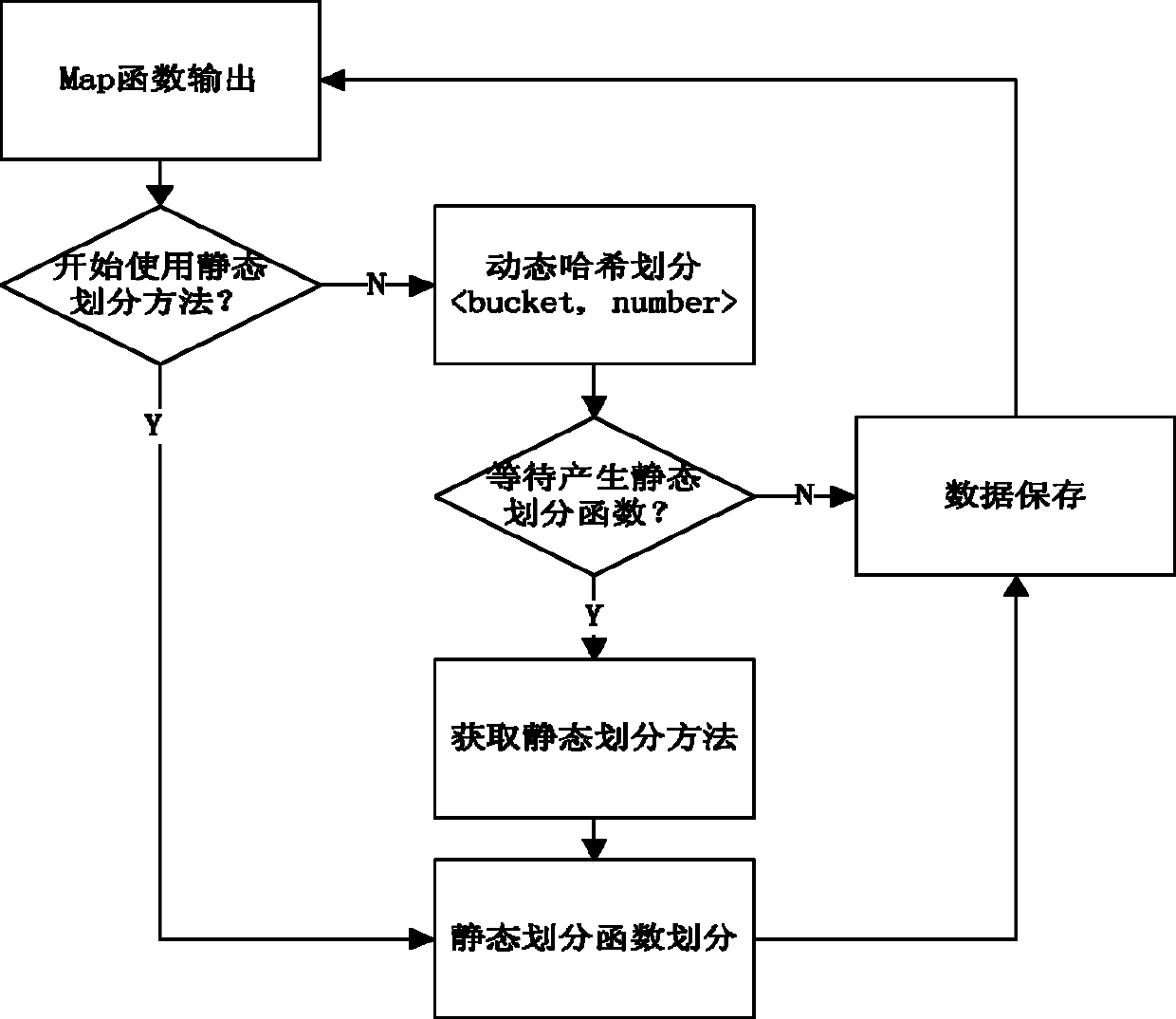

Self-adaptive load balancing method for Reduce ends in parallel computing framework

InactiveCN102629219ASolve load balancingReduce skewResource allocationHash functionDistribution characteristic

The invention relates to a self-adaptive load balancing method for Reduce ends in a parallel computing framework. The distribution of data input by tasks is predicted through adopting a dynamic hash function division method; and a static hash function is produced according to the distribution characteristics of the predicted data, so that under the effect of the static hash function, all data can be evenly distributed into corresponding computing nodes as much as possible. Therefore, during task scheduling, the allocation of the data and computing resources can be dynamically and self-adaptively adjusted according to the data distribution condition, the deflection occurring during the computation is reduced and the efficiency is improved.

Owner:PEKING UNIV

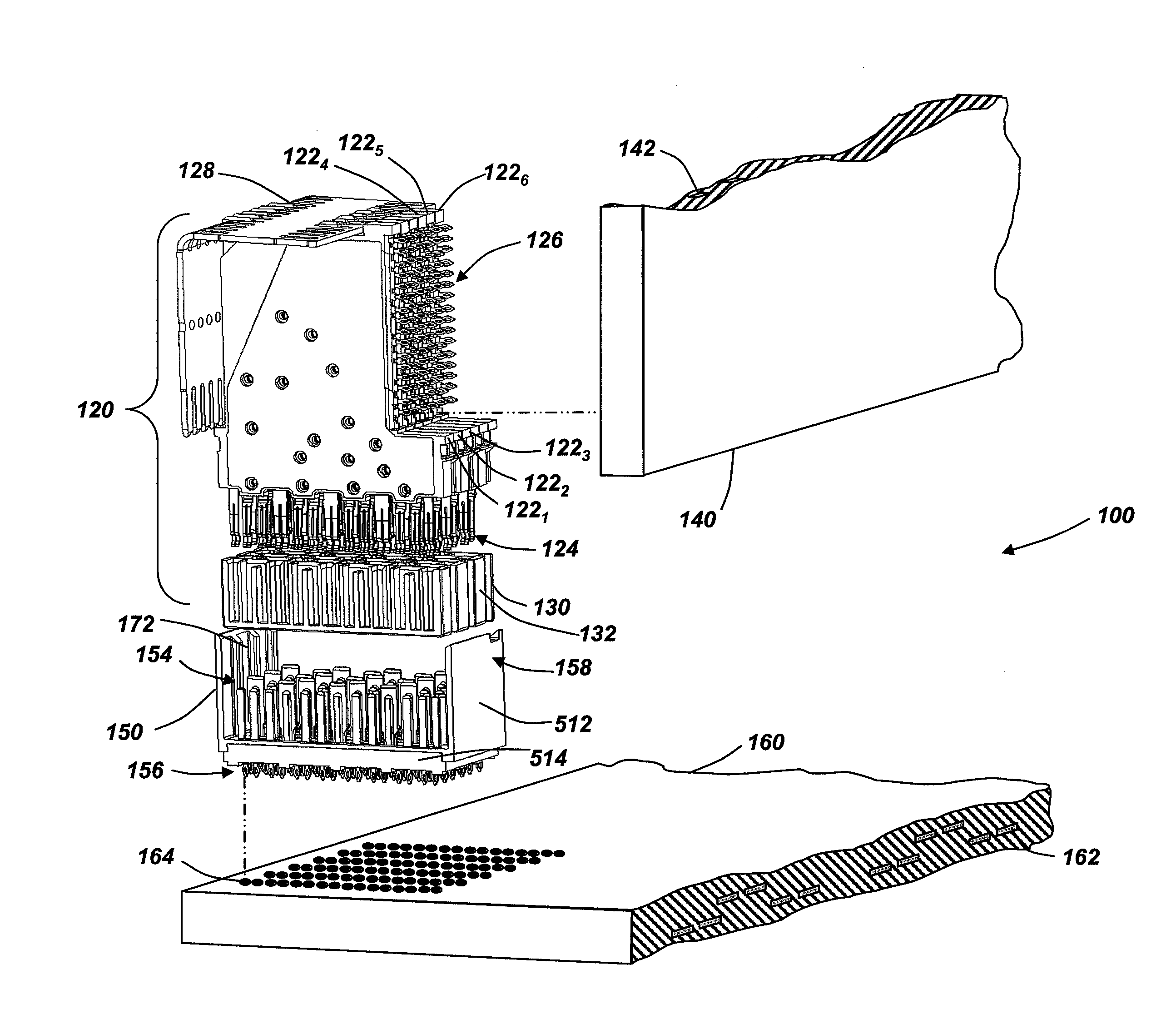

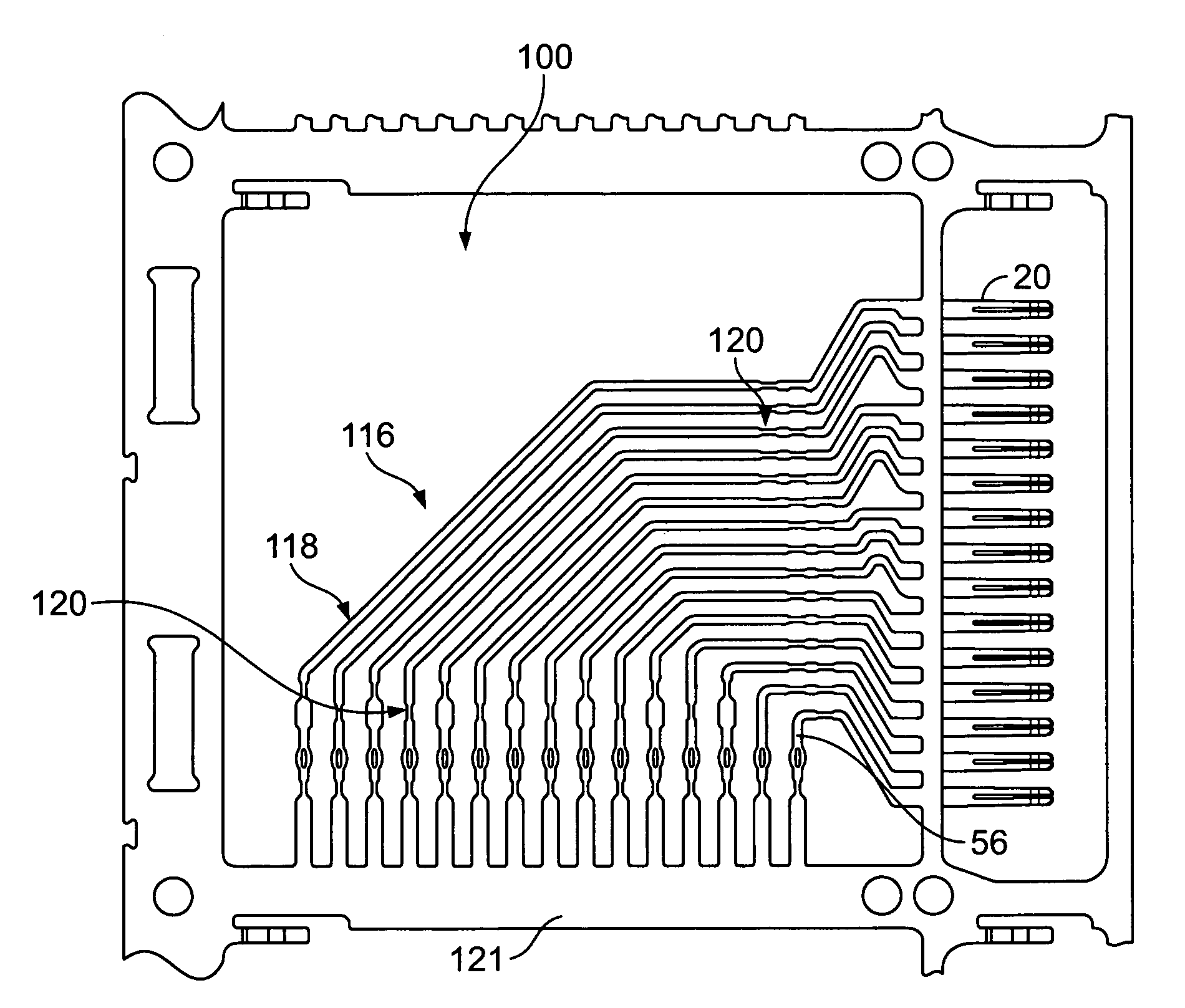

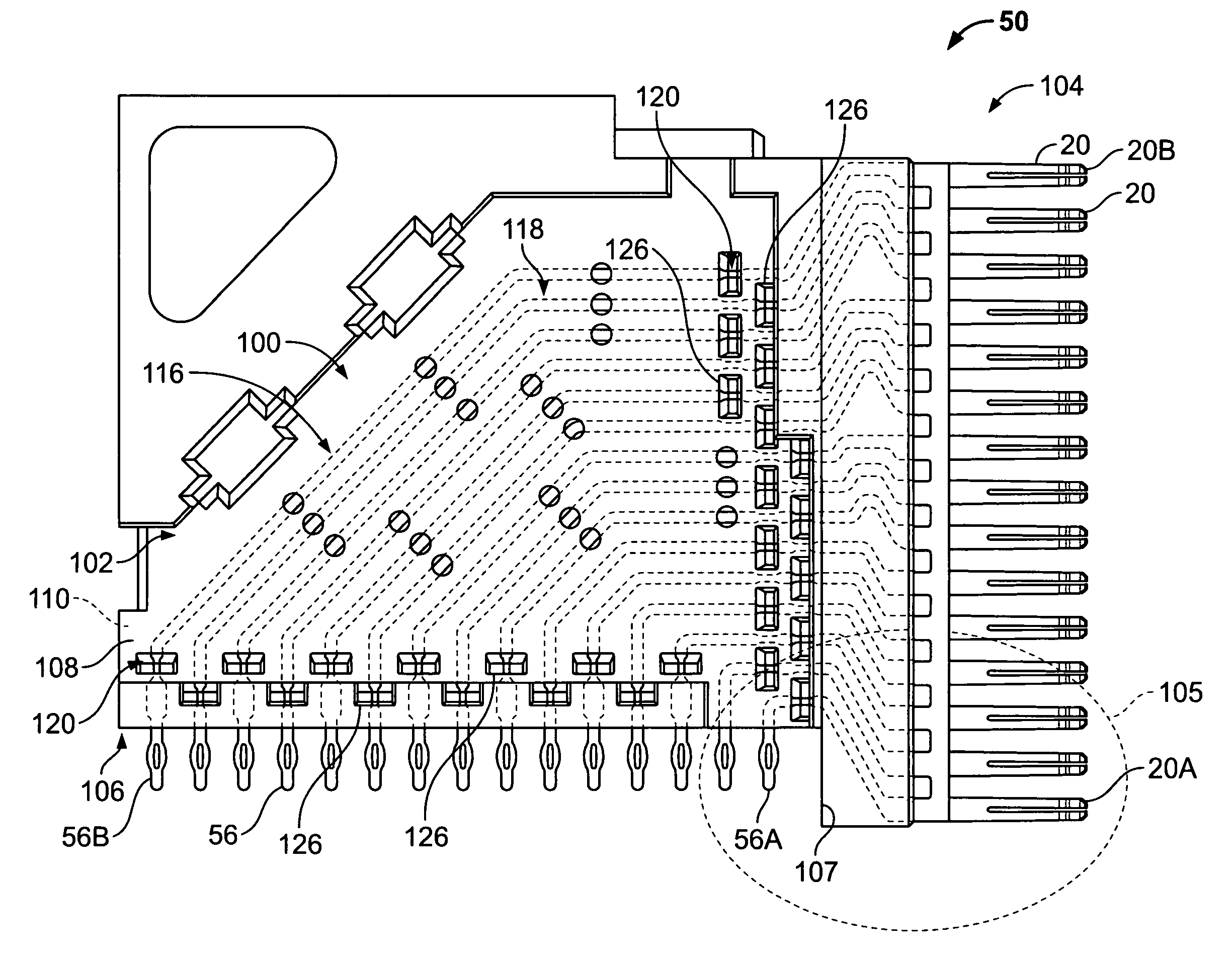

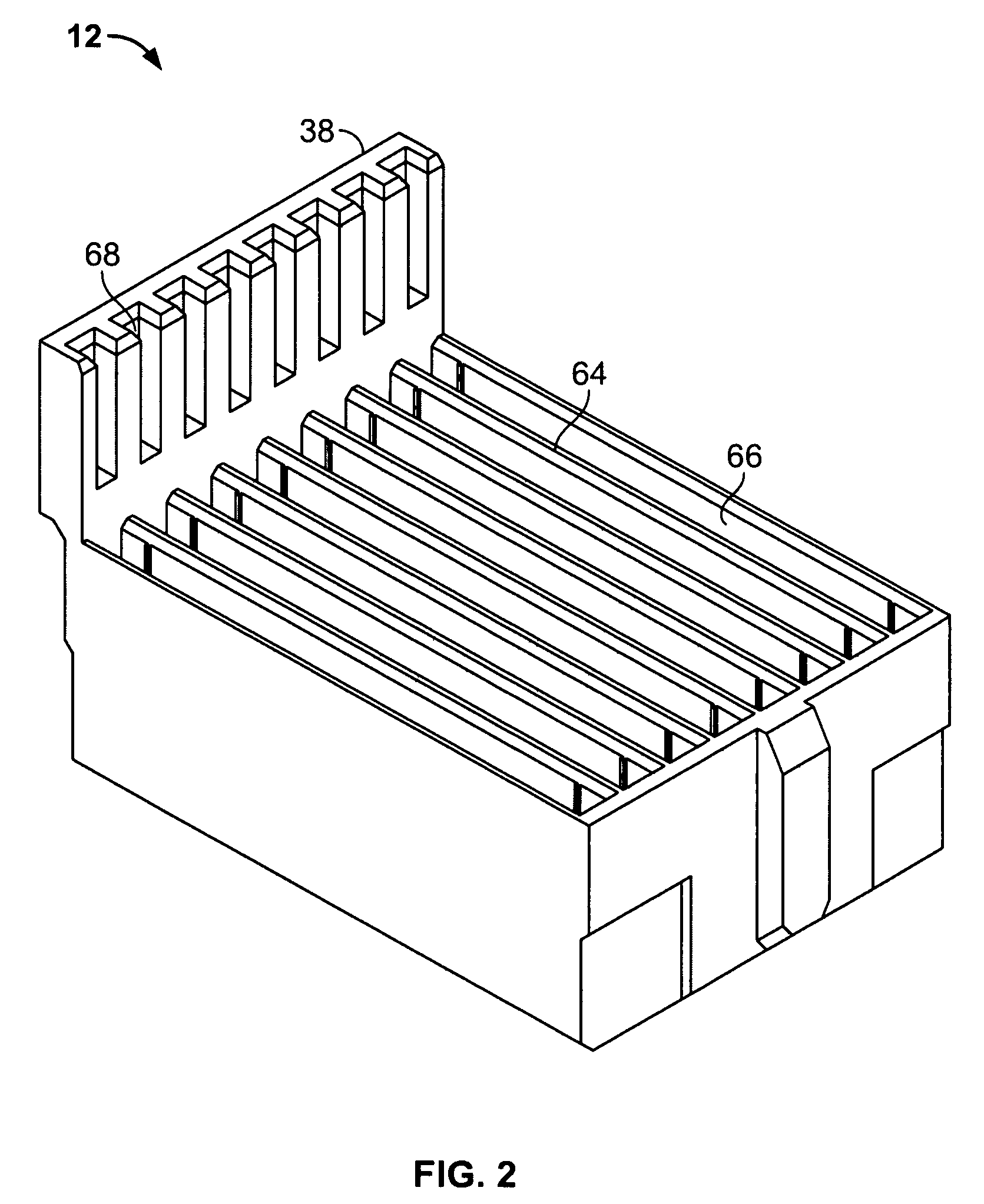

Skew controlled leadframe for a contact module assembly

ActiveUS20080316729A1Reduce skewCasings/cabinets/drawers detailsRack/frame constructionEngineeringGround pattern

A leadframe for a contact module assembly includes a terminal set having first, second and third terminals configured to operate in one of a signal-signal-ground pattern and a ground-signal-signal pattern. Each of the terminals have a length that extends between a mating end and a mounting end, wherein a difference in lengths between the first terminal and the second terminal is the same as a difference in lengths between the second terminal and the third terminal such that the terminal set has the same amount of skew between the terminals defining signal contacts in both the signal-signal-ground pattern and the ground-signal-signal pattern.

Owner:TYCO ELECTRONICS LOGISTICS AG (CH)

System and method for improved time-interleaved analog-to-digital converter arrays

ActiveUS7292170B2Reduce distortion problemsReducing non-uniform sample mismatchElectric signal transmission systemsAnalogue conversionEngineeringTime interleaved

System and method for improved time-interleaved analog-to-digital converter arrays which reduces sampling mismatch distortion found in prior art arrays. There may be two causes of non-uniform sampling mismatch in a TI-ADC array, a mismatch due to skew and a mismatch due to clock jitter. To minimize non-uniform sampling mismatch, the mismatch due to skew can be addressed. A preferred embodiment comprises adjusting a delay imparted on the sampling clock by an adjustable delay in each channel of a plurality of channels in the TI-ADC array to minimize skew and randomly switching between two delays that span a zero-skew delay to reduce residual skew in each channel and thus eliminate (or reduce) frequency domain tones caused by non-uniform sampling mismatch.

Owner:TEXAS INSTR INC

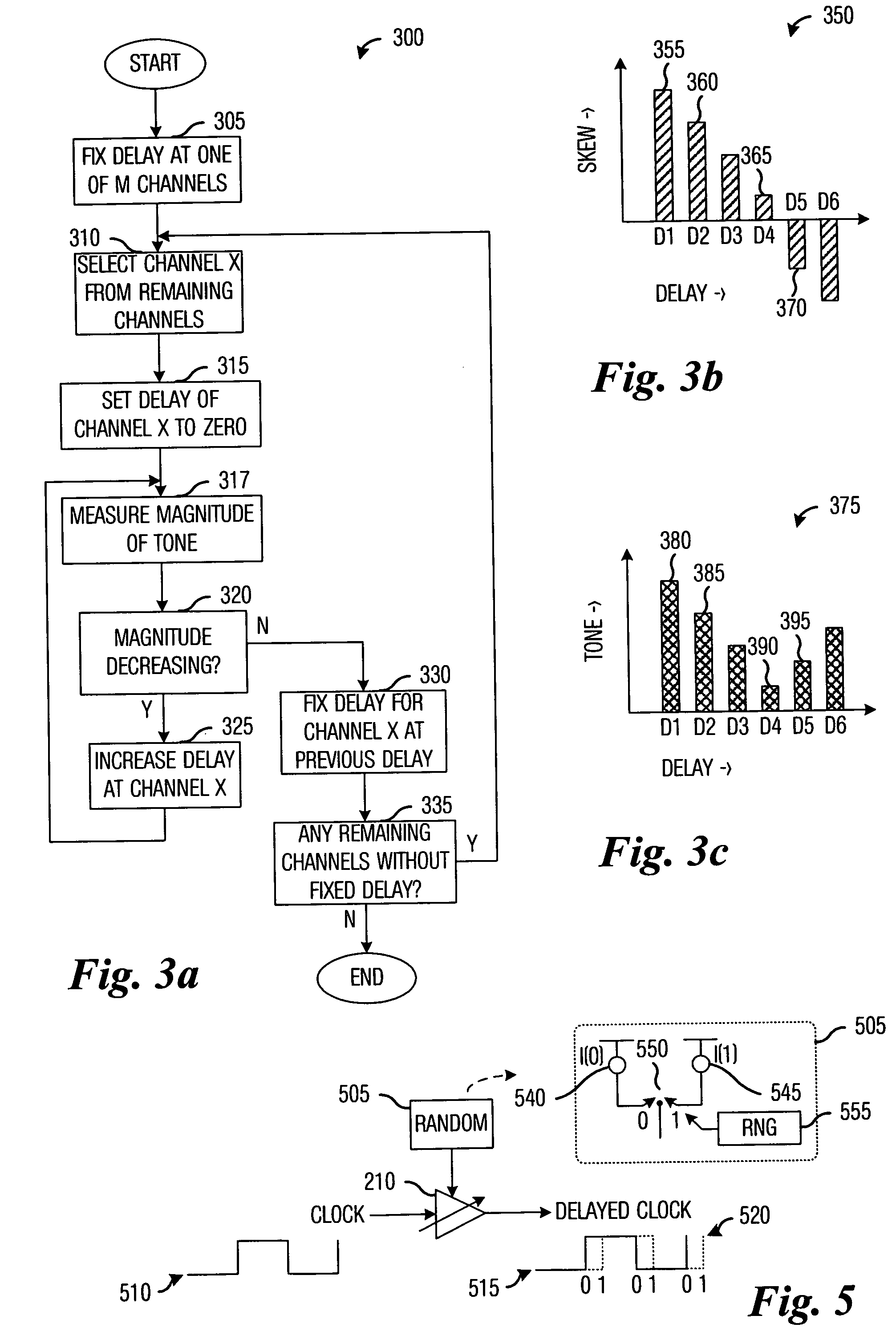

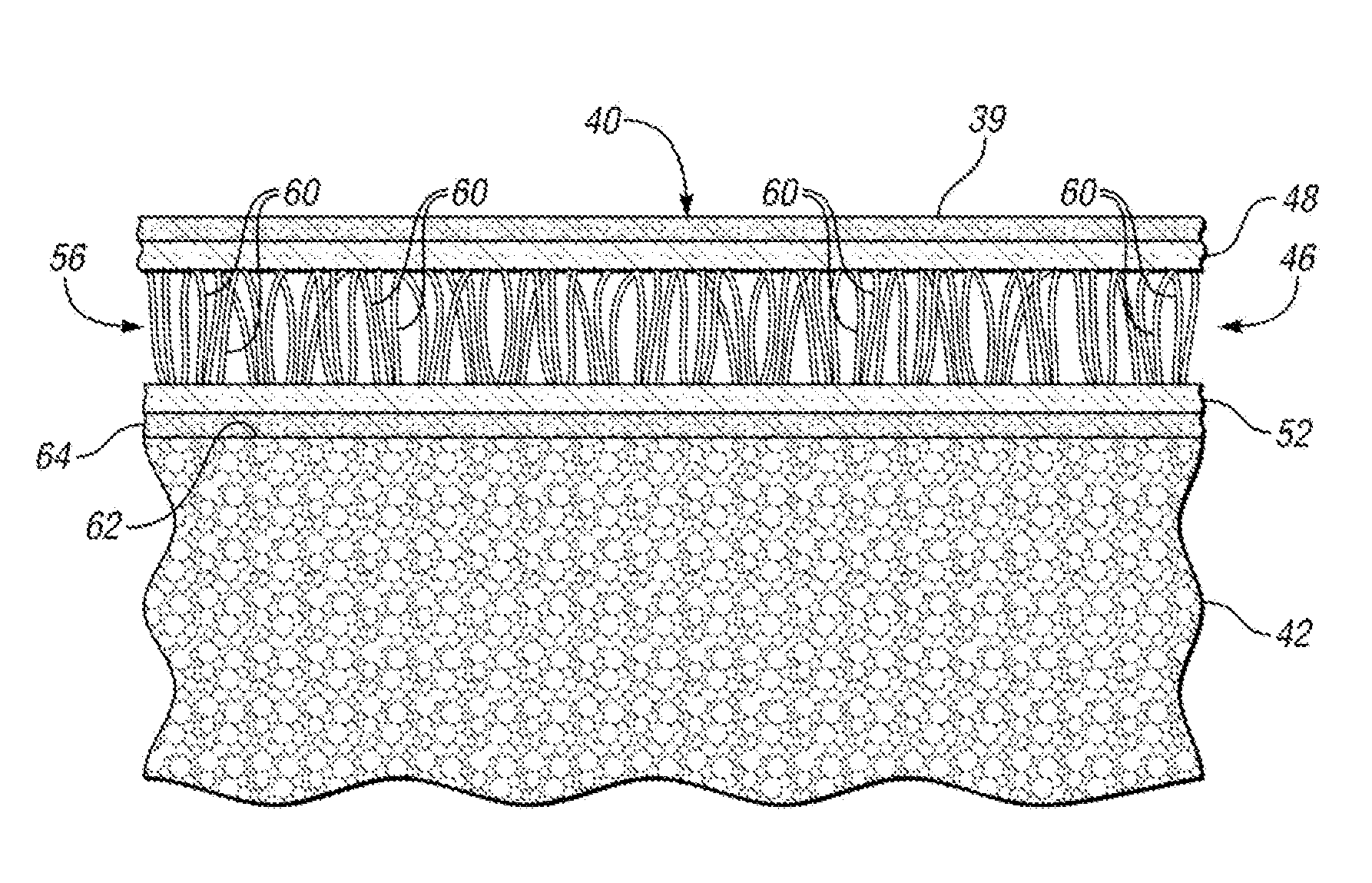

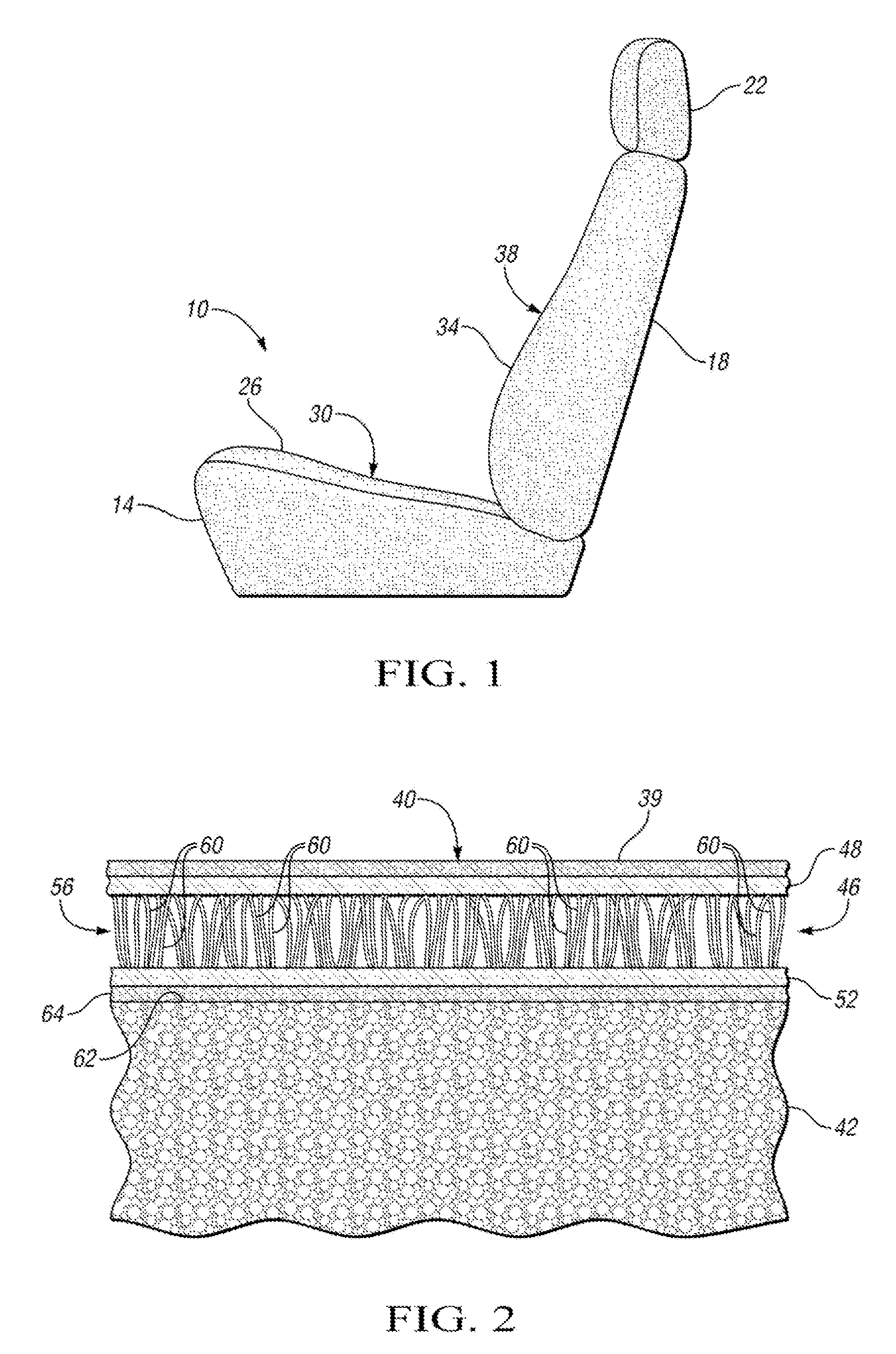

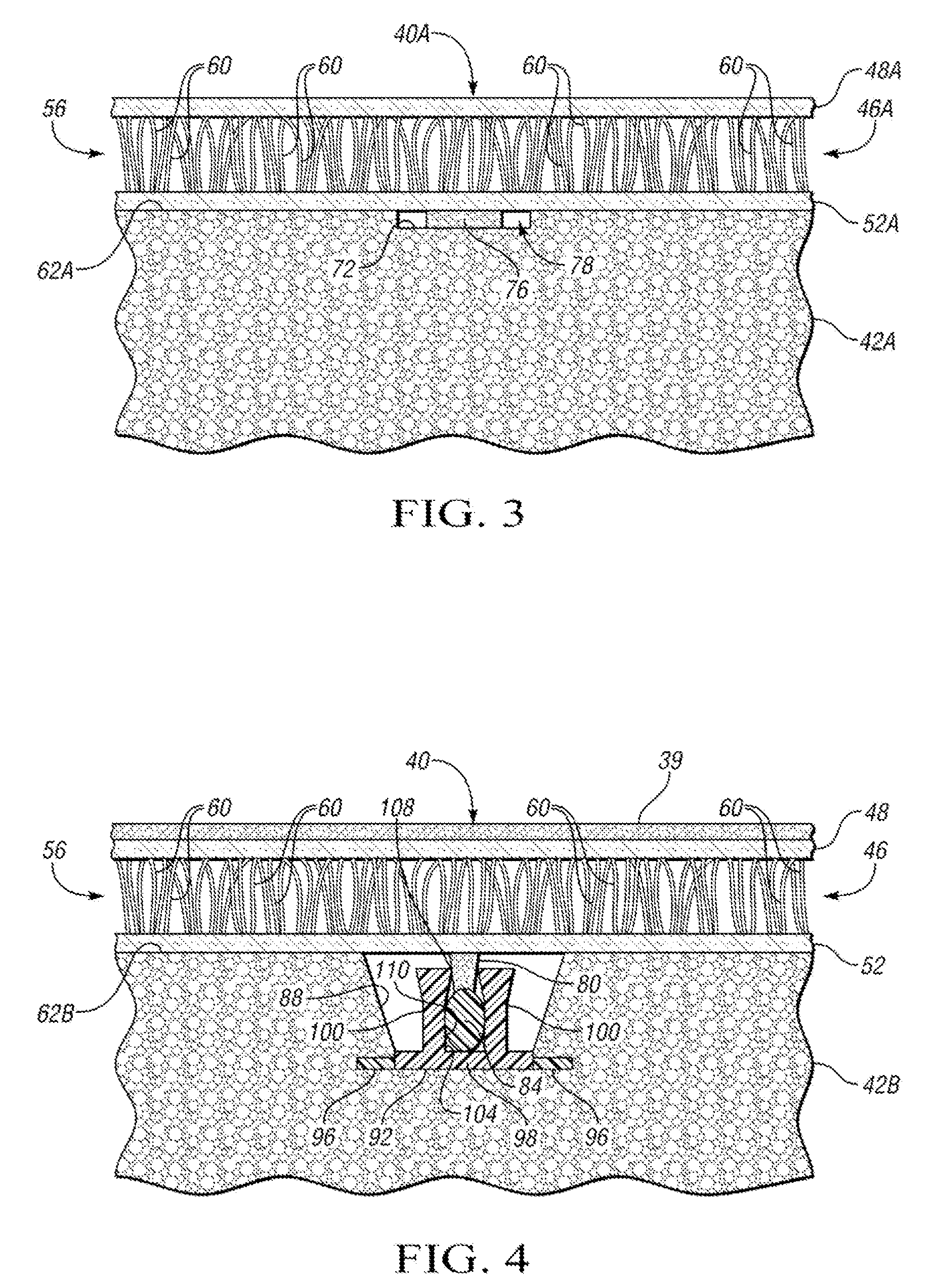

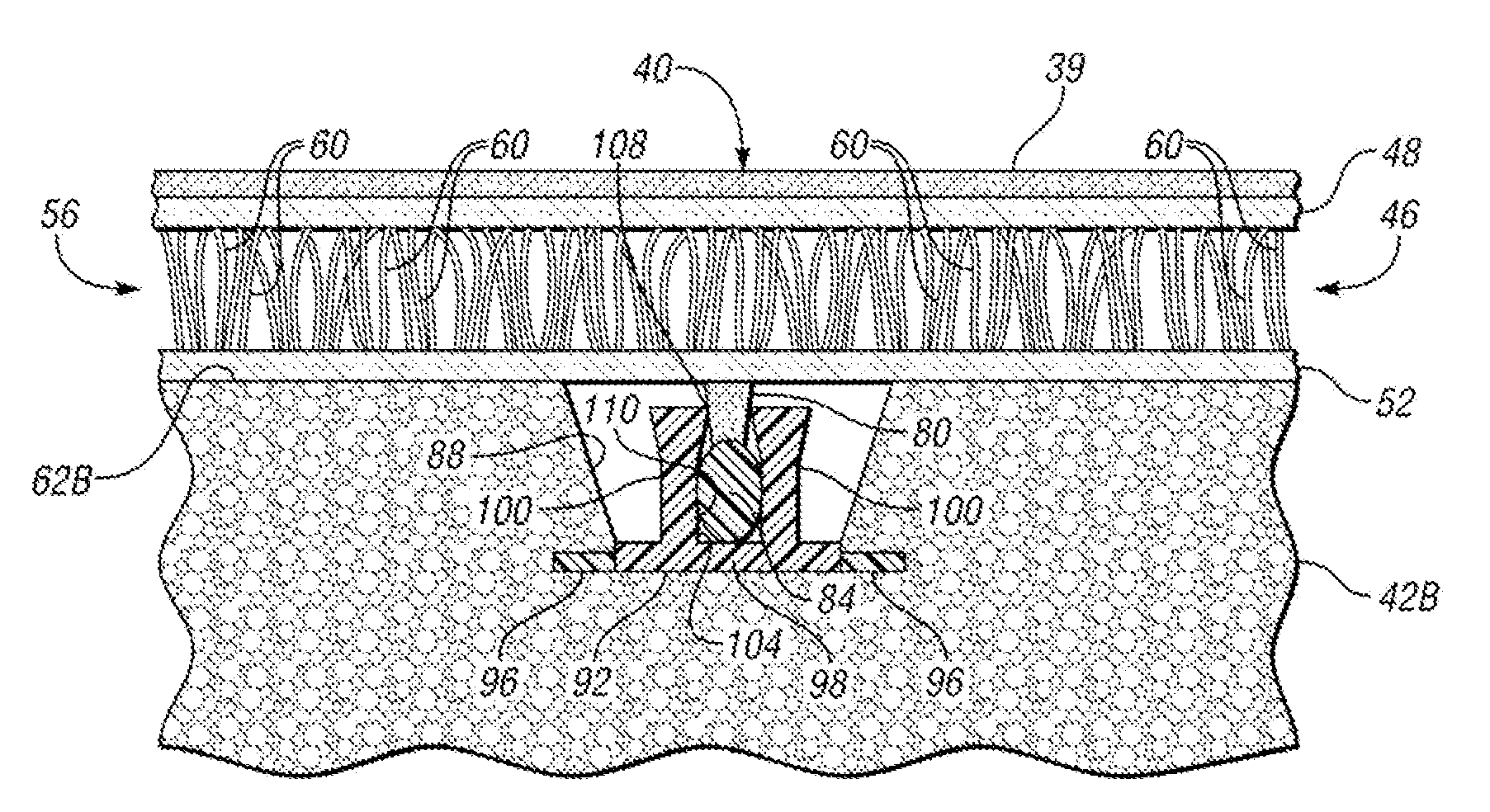

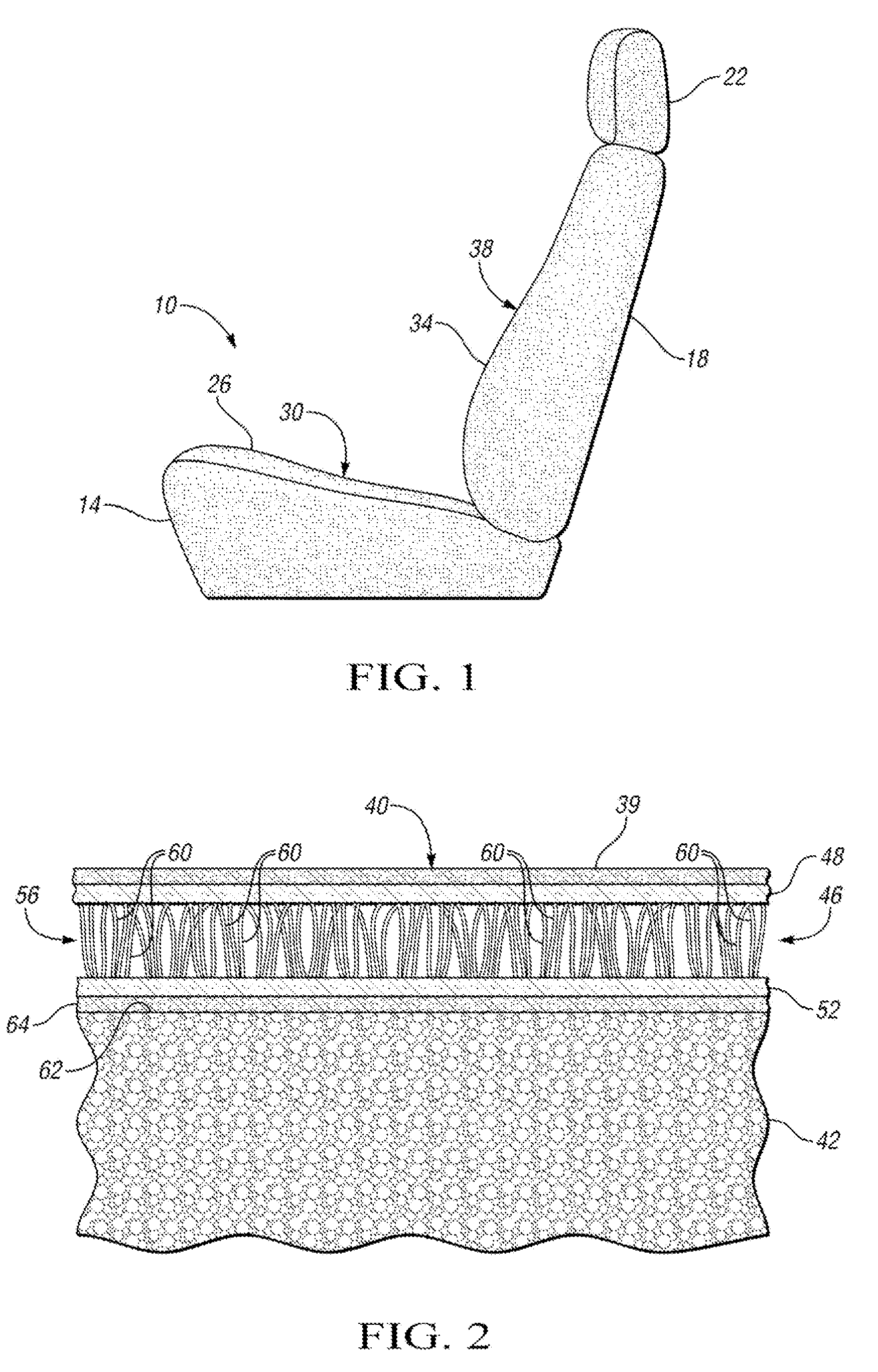

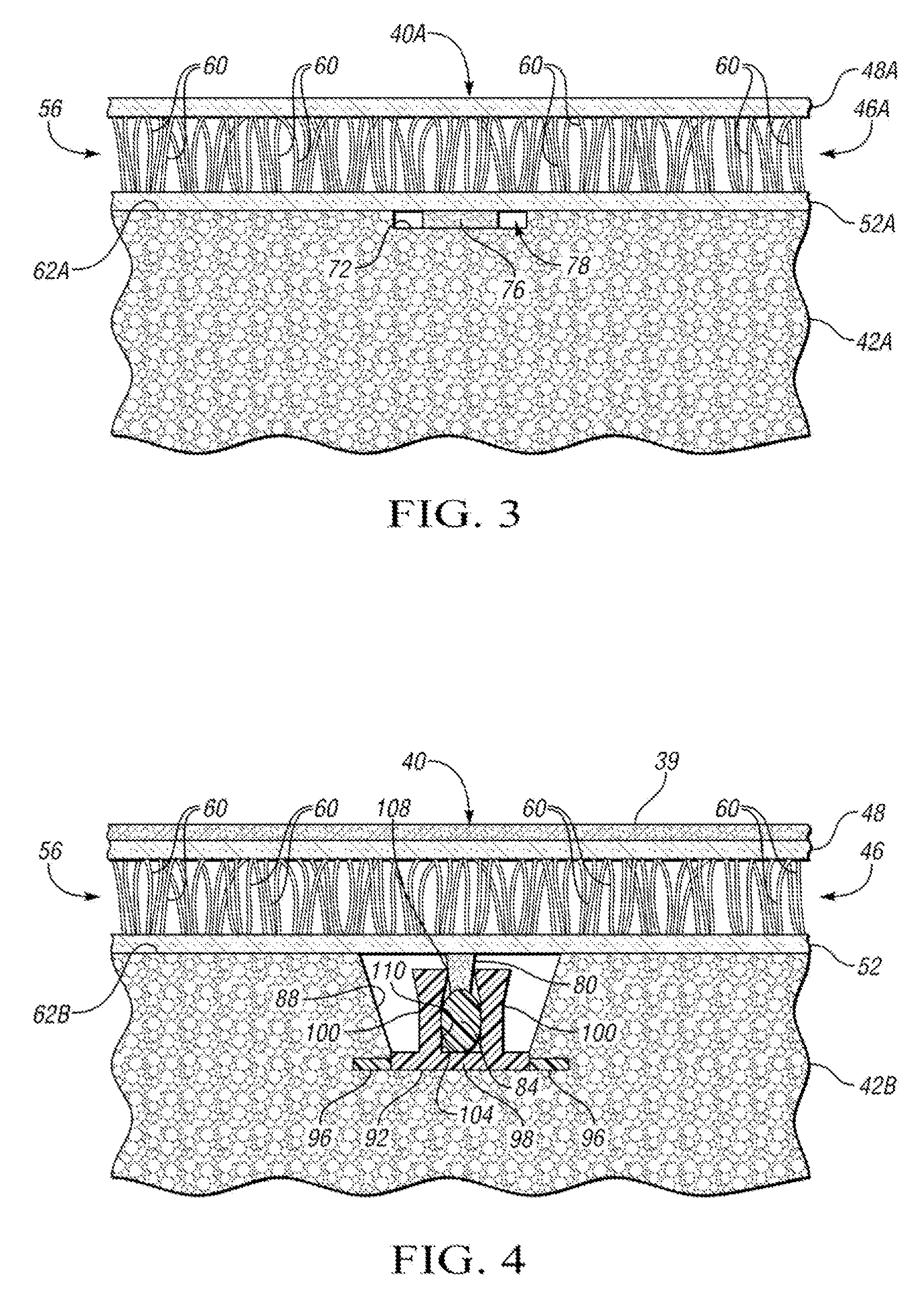

Vehicle Seat Construction

A vehicle seat includes a foam cushion, a flexible cover at least partially defining the outer surface of the vehicle seat, and a spacer fabric. The spacer fabric includes a first fabric panel operatively connected to the flexible cover, a second fabric panel operatively connected to the foam cushion, and an interconnecting layer. The interconnecting layer resiliently interconnects the first and second fabric panels.

Owner:GM GLOBAL TECH OPERATIONS LLC

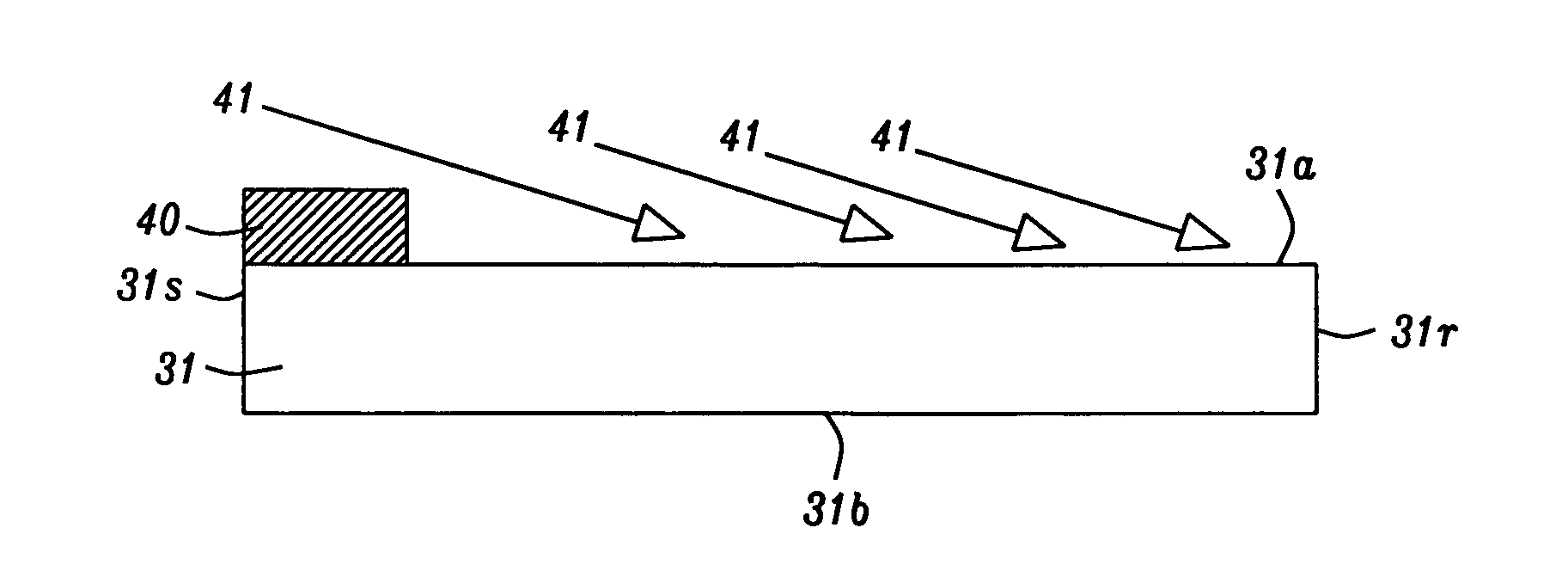

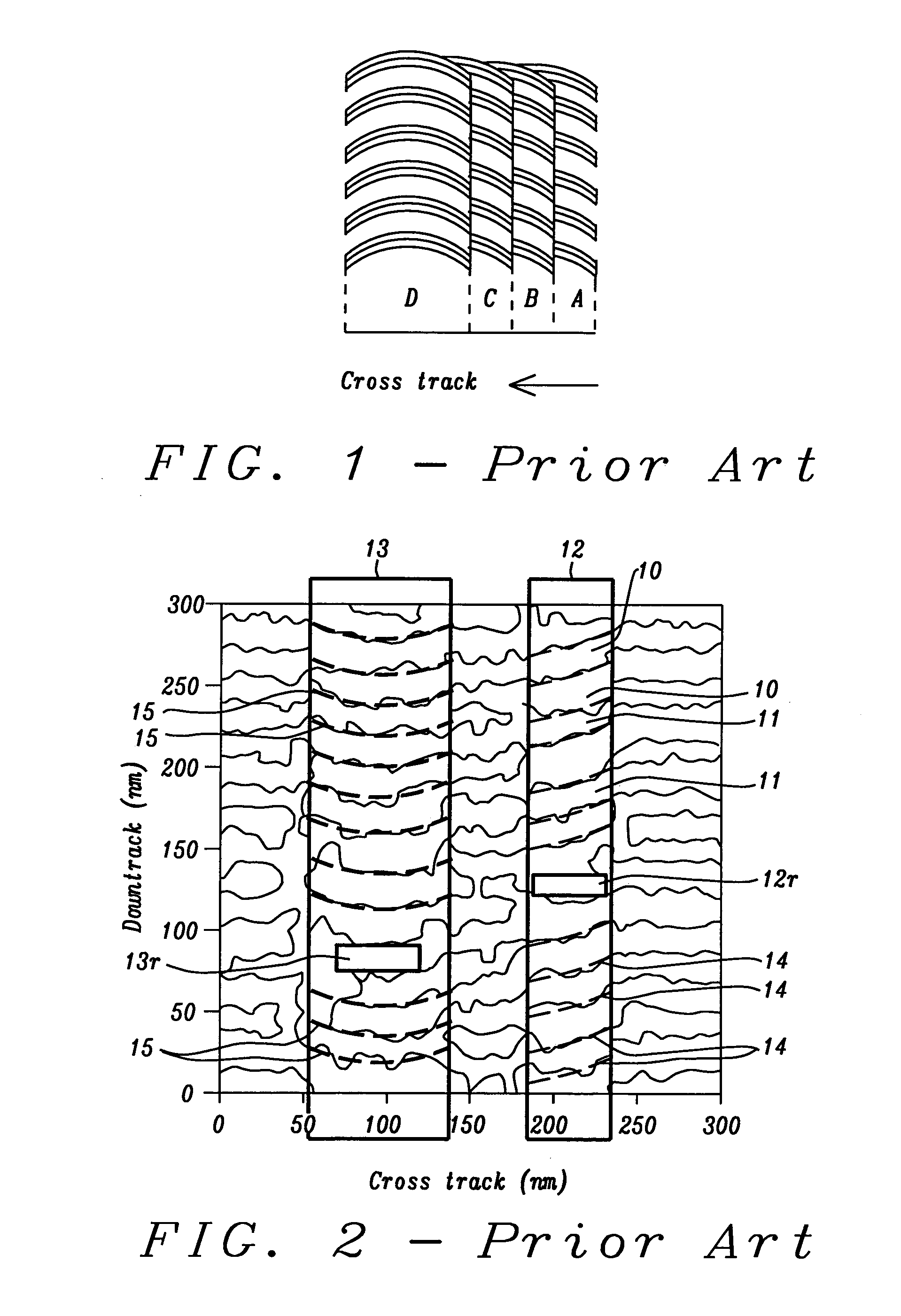

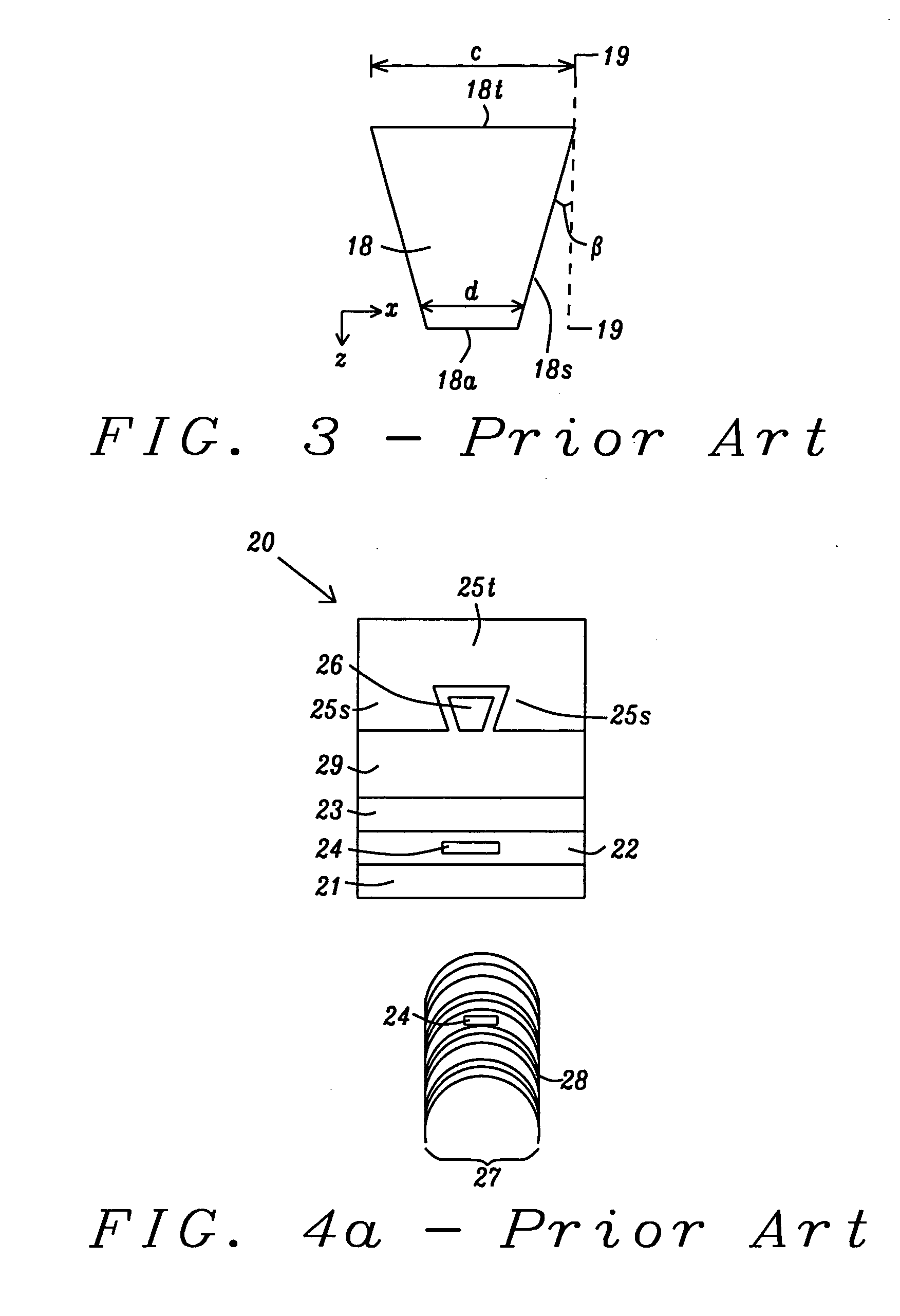

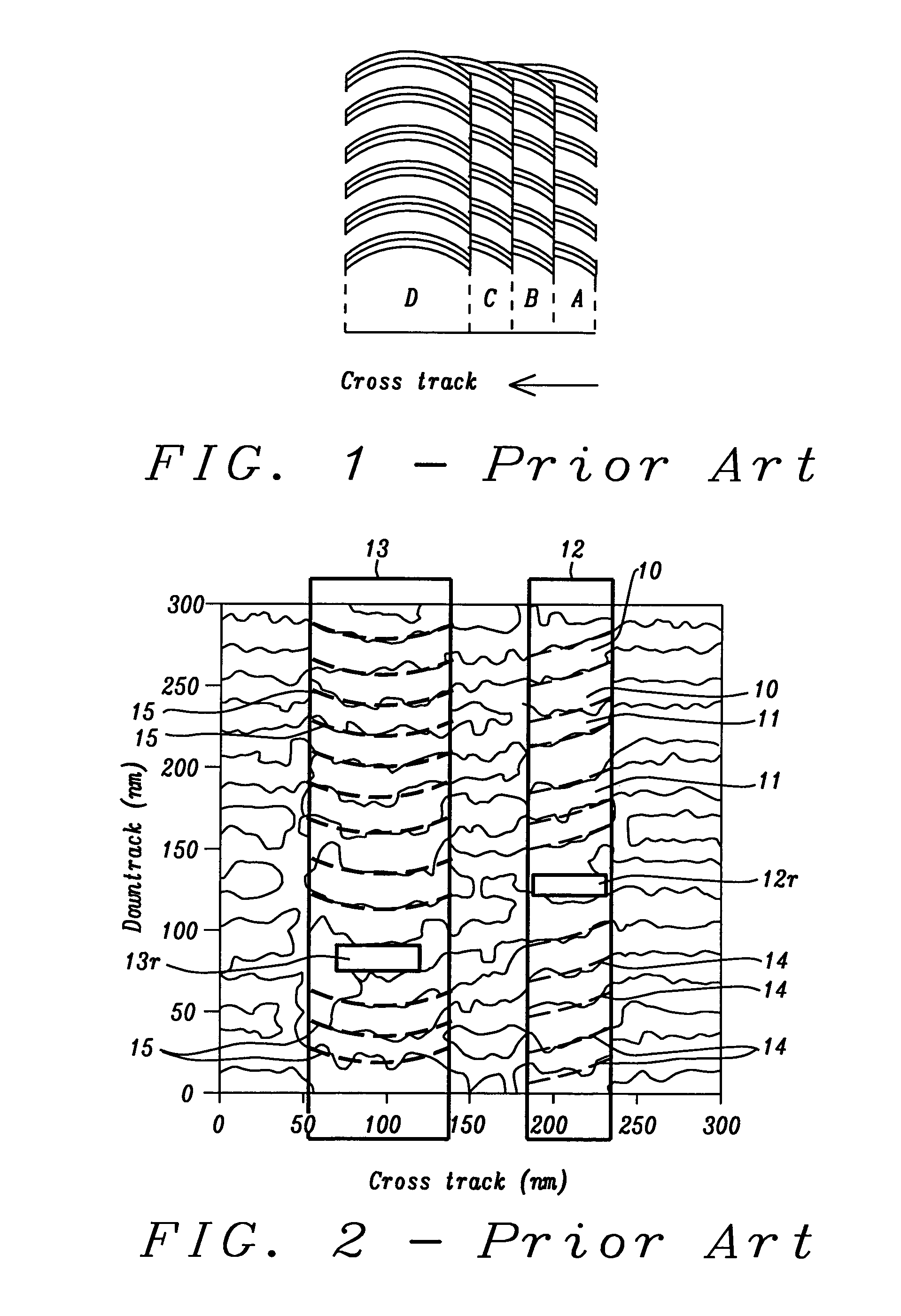

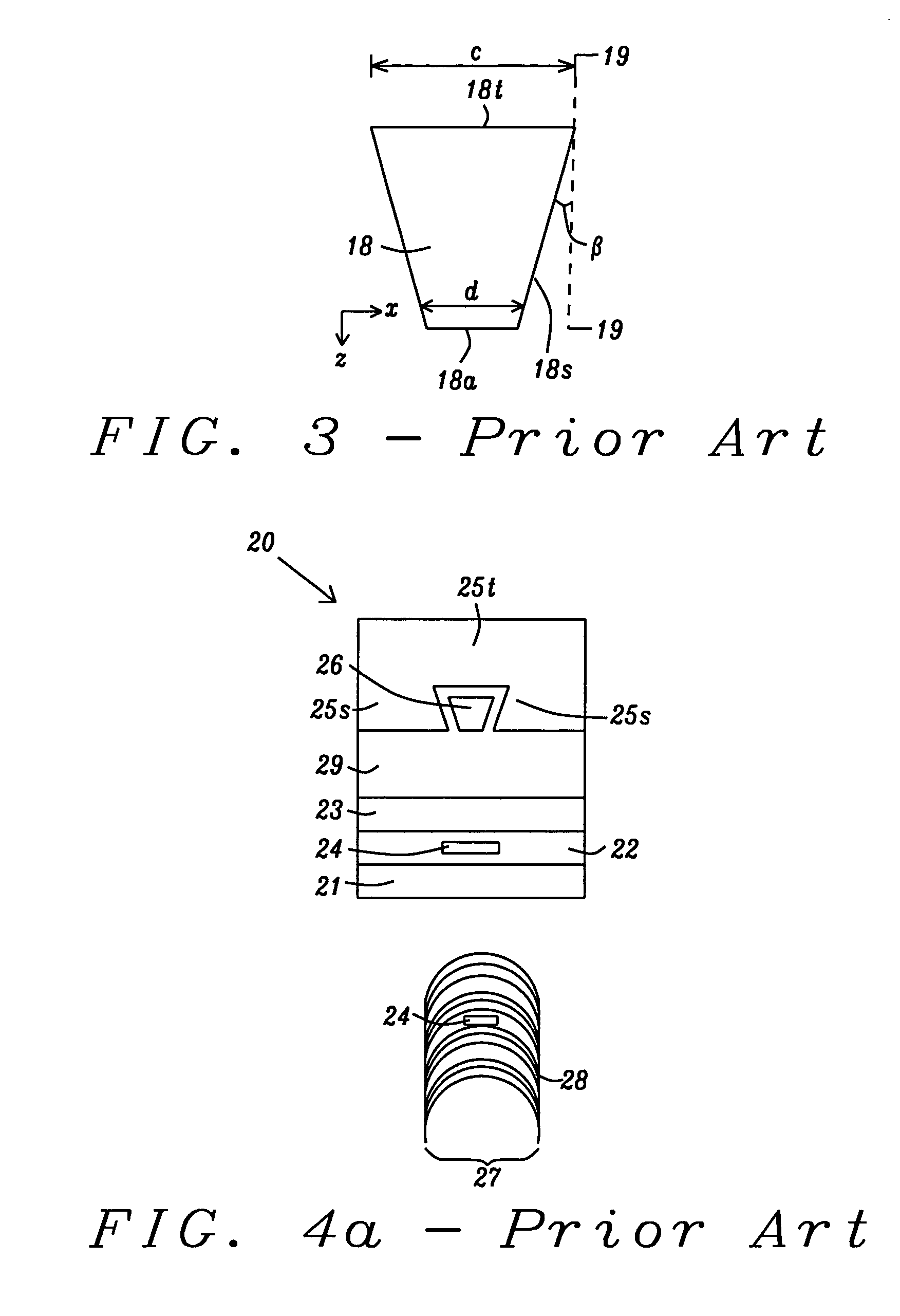

Writer and reader arrangements for shingled writing

ActiveUS20110102942A1Reduce transition curvatureDelay transitionDecorative surface effectsRecord information storageSlope angleEngineering

A sloped reader is disclosed that reduces skew between reader and written transitions in shingled writing. The reader is formed between surfaces of S1 and S2 shields that are aligned parallel to the sloped reader. A PMR writer is described that straightens transition curvature and reduces signal-to-noise ratio in shingled writing. In one embodiment, a symmetrical writer with a bowed trailing edge where two corners have a greater pole height than a center portion may be used for either right corner or left corner shingled writing. In a second embodiment, an asymmetrical writer is formed with a straight and sloped trailing edge such that the write corner has a greater pole height than the opposite corner on the trailing edge. The bowed angle in the symmetrical writer and slope angle in the asymmetrical writer is between 5 and 45 degrees and preferably between 10 and 30 degrees.

Owner:HEADWAY TECH INC

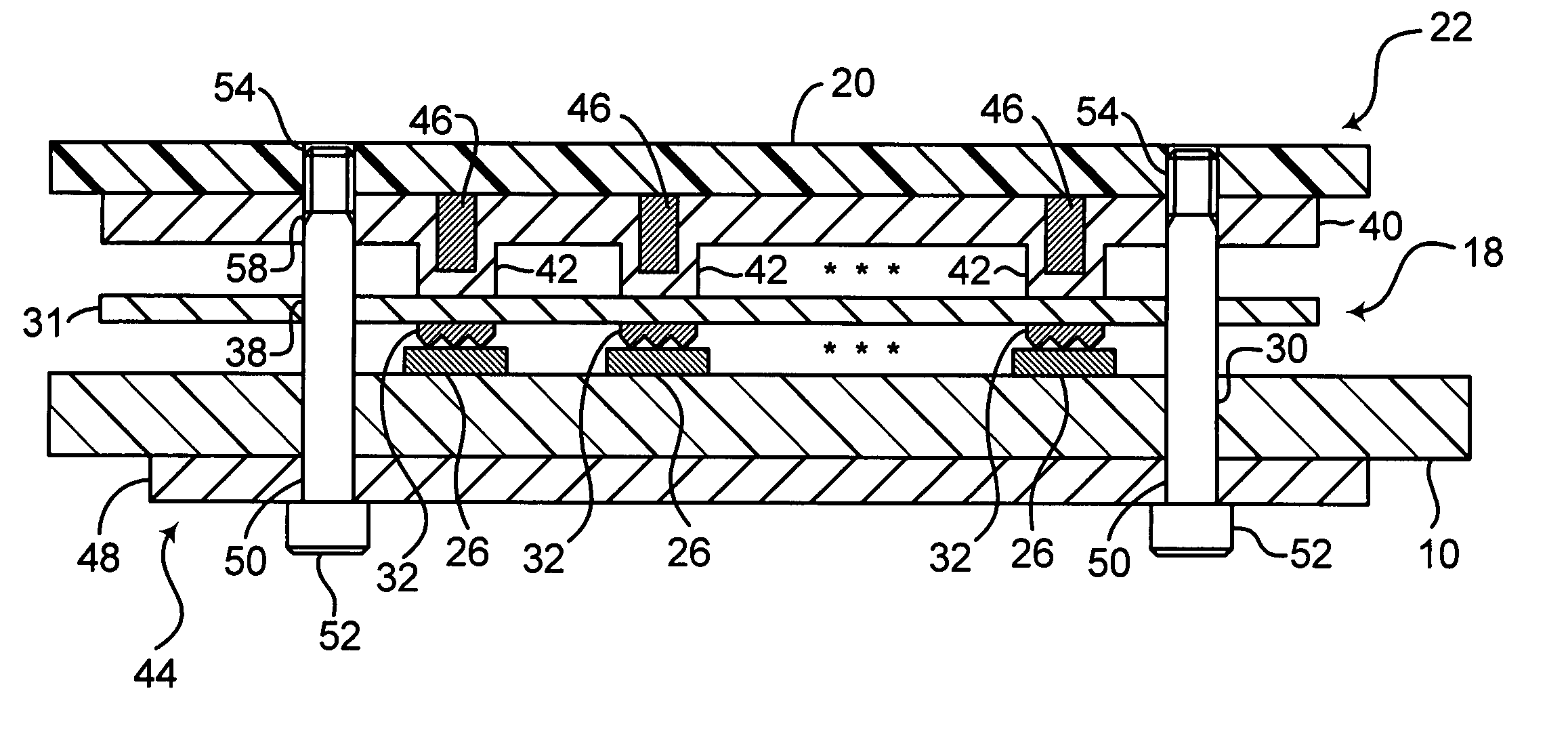

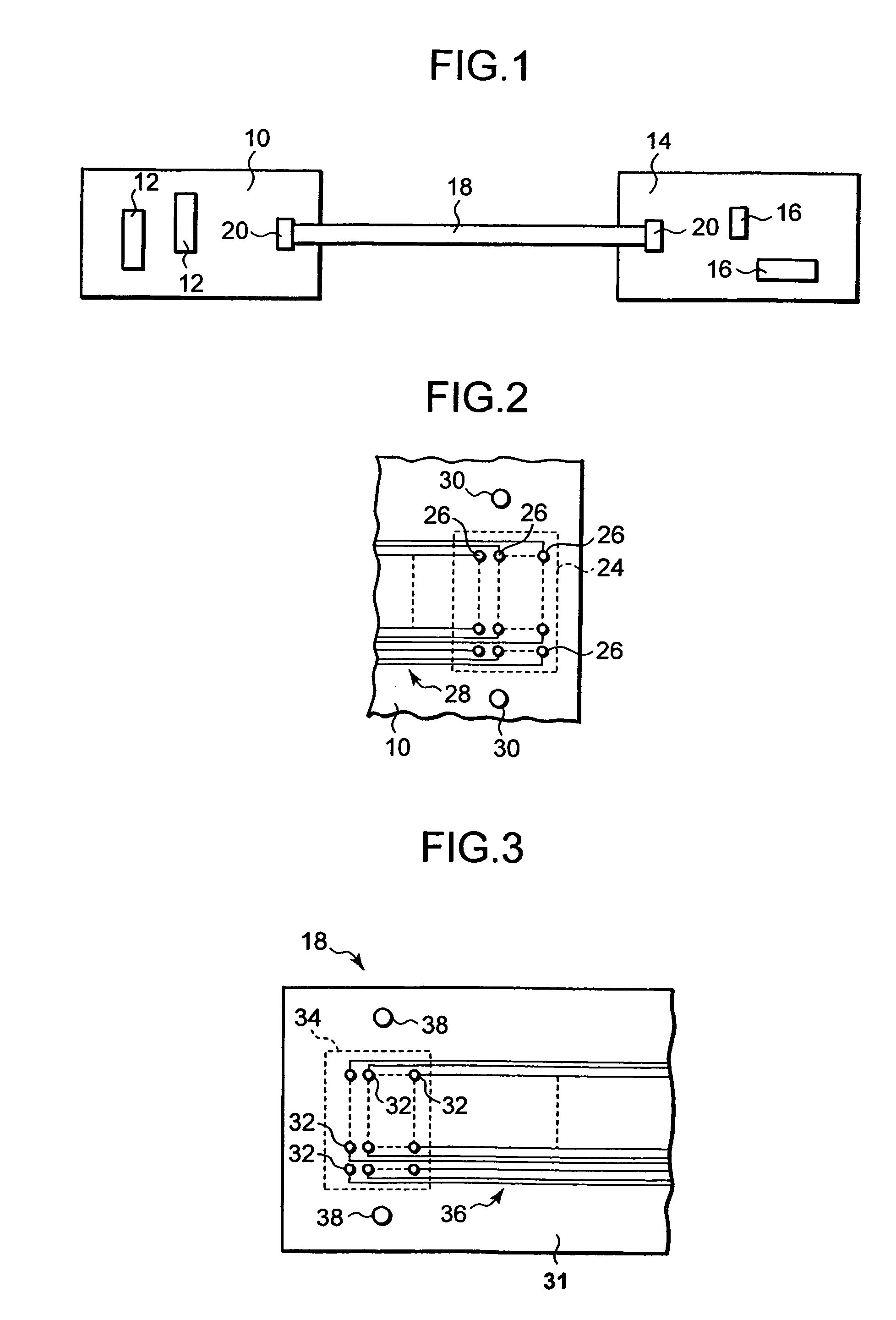

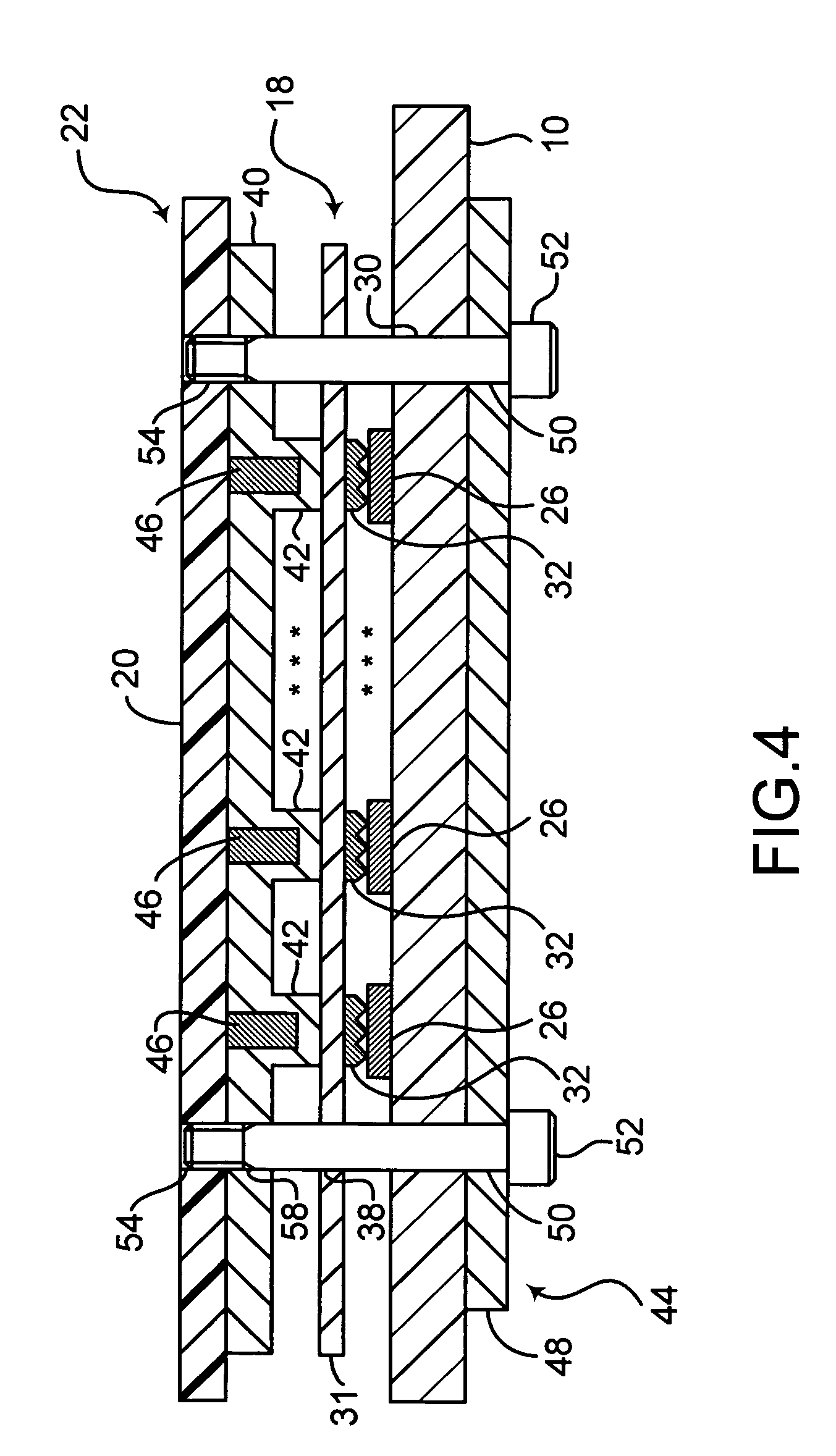

Electrical connector with elastomeric pad having compressor fingers each including a filler member to mitigate relaxation of the elastomer

InactiveUS6991473B1Improve reliabilityReduce skewPrinted circuit aspectsCoupling contact membersContact padPrinted circuit board

An electrical connector includes connector pads on a printed circuit board and contact members on an insulating substrate. The contact members are pressed against the contact pads by a compression mat having compressor fingers. A clamping arrangement forces the compressor fingers against the substrate and thereby presses the contact members against the contact pads. To counteract the inherent tendency of the compressor fingers to undergo stress relaxation after the compressor mat has been clamped, the connector also includes filler members disposed at least partially within the compressor fingers, essentially a “button-within-a-button” arrangement. Optionally, a filler deflection member may be interposed between the compression mat and a clamping plate of the clamping arrangement so that the filler deflection member abuts against the filler members. Alternatively, the filler members may be integral features of the deflection member.

Owner:IBM CORP

Writer and reader arrangements for shingled writing

ActiveUS8134802B2Delay transitionReduce skewRecord information storageHeads for perpendicular magnetisationsSlope angleTrailing edge

Owner:HEADWAY TECH INC

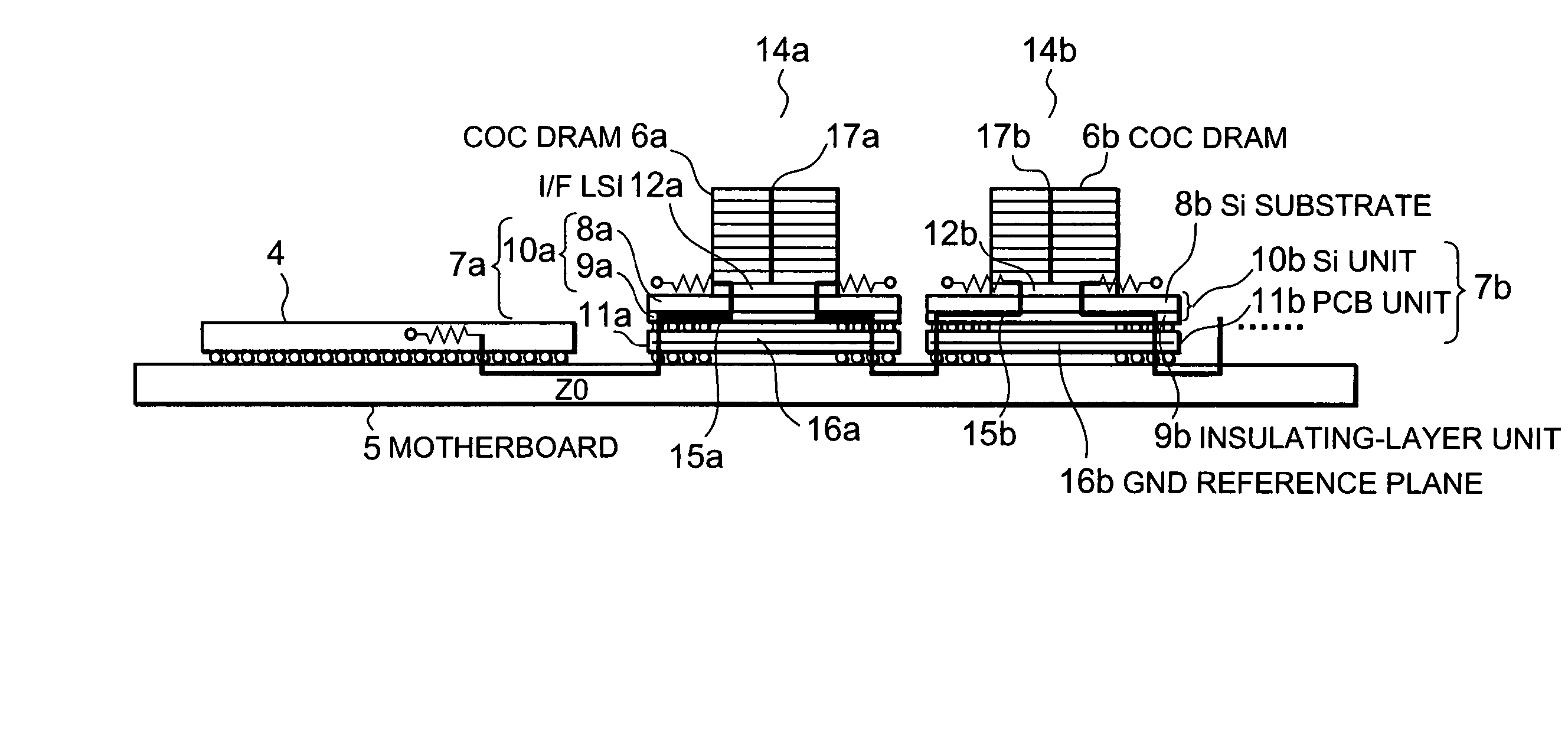

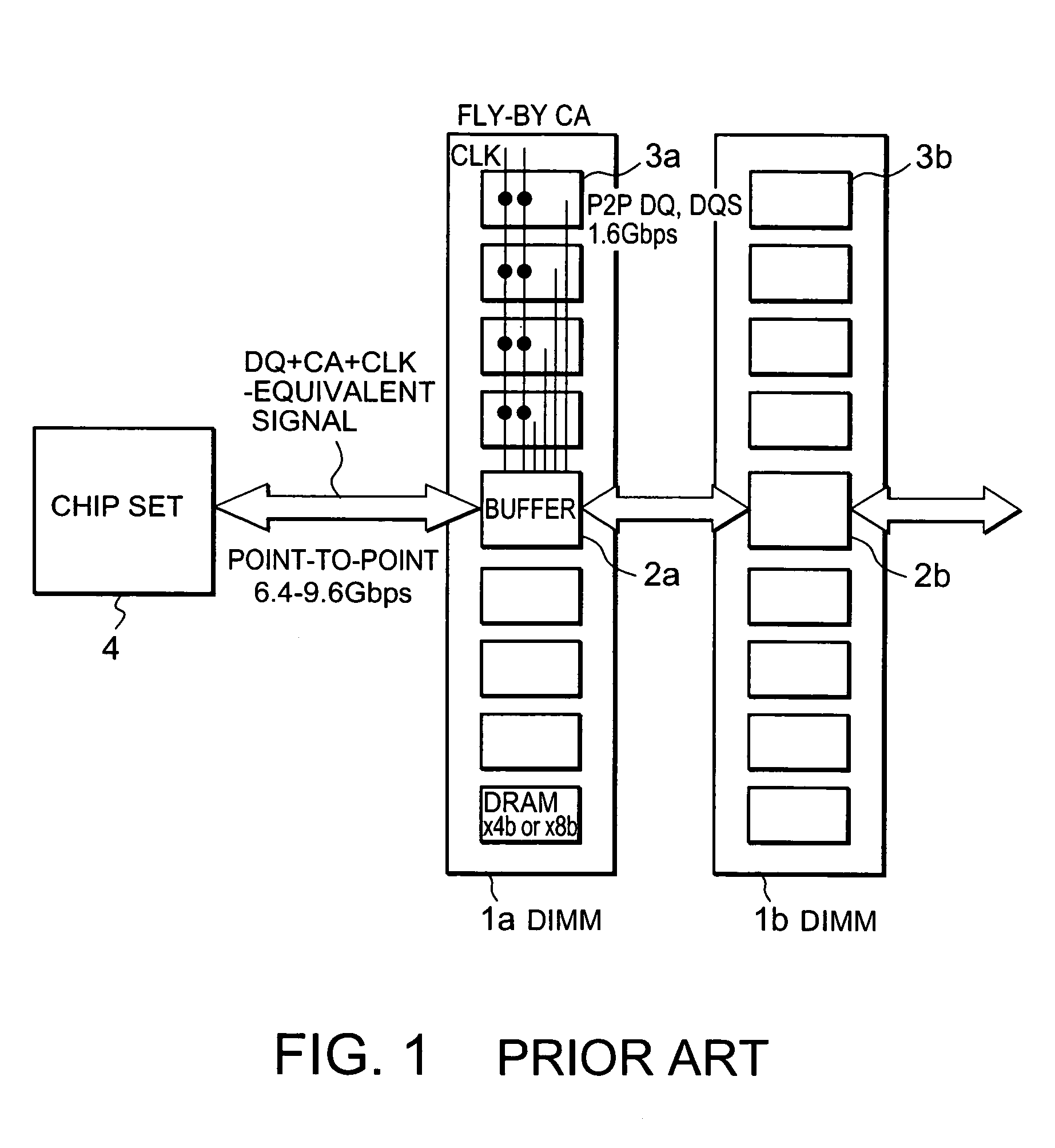

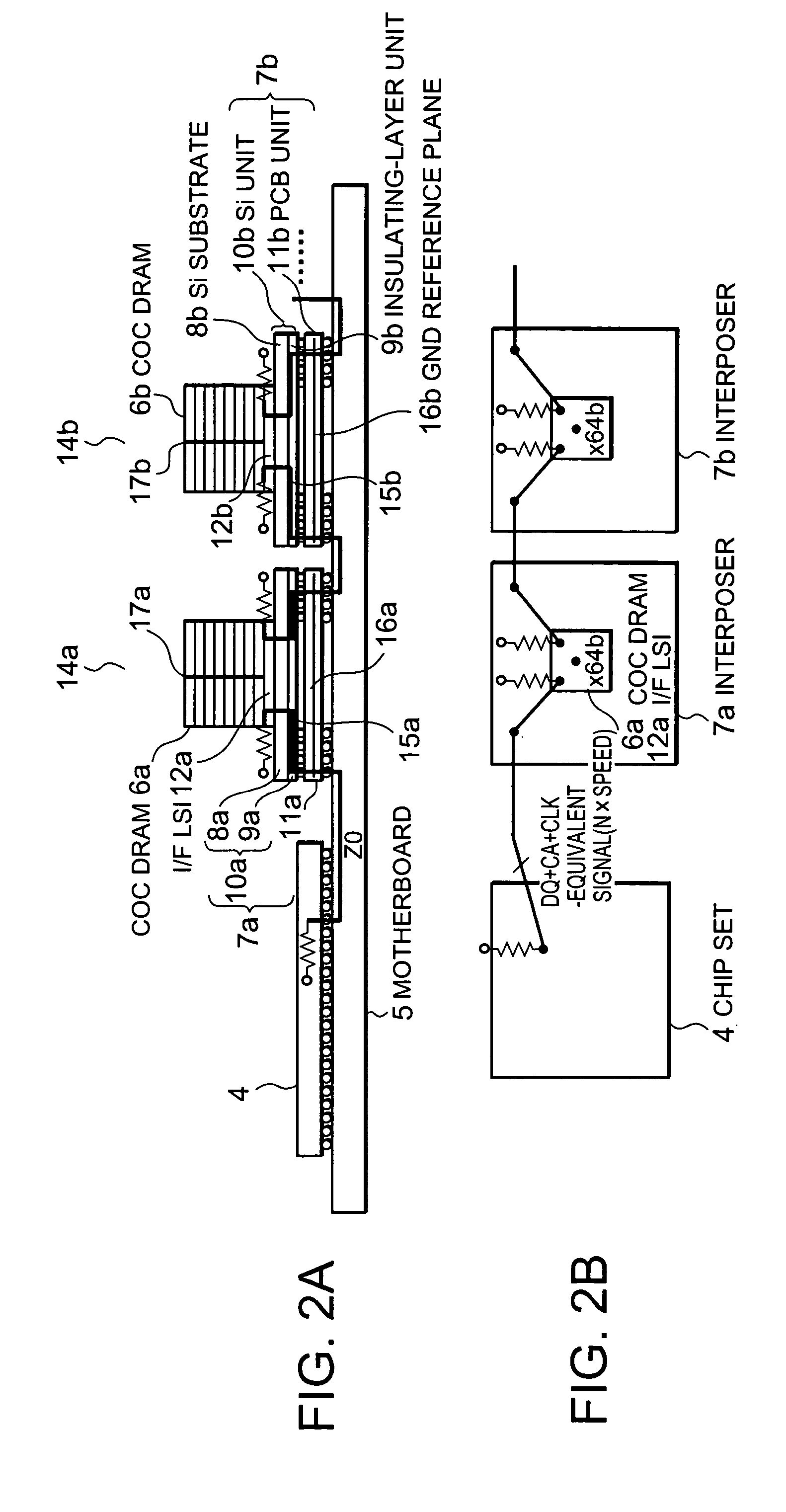

Semiconductor integrated circuit device

InactiveUS7385281B2Run at high speedReduce power consumptionTransistorSemiconductor/solid-state device detailsInterposerEngineering

A COC DRAM including a plurality of stacked DRAM chips is mounted on a motherboard by using an interposer. The interposer includes a Si unit and a PCB. The Si unit includes a Si substrate and an insulating-layer unit in which wiring is installed. The PCB includes a reference plane for the wiring in the Si unit. The wiring topology between a chip set and the COC DRAM is the same for every signal. Accordingly, a memory system enabling a high-speed operation, low power consumption, and large capacity is provided.

Owner:PS4 LUXCO SARL

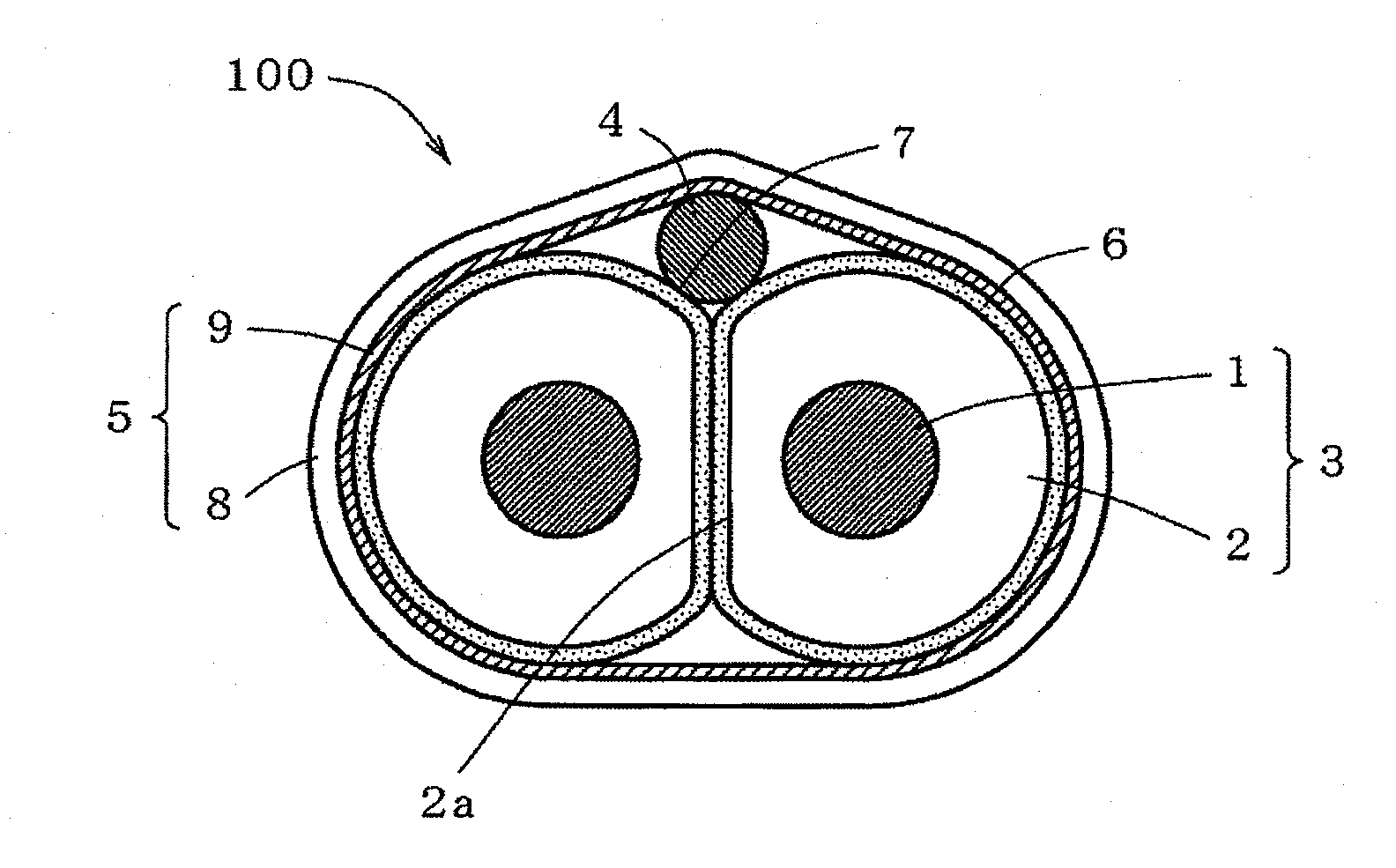

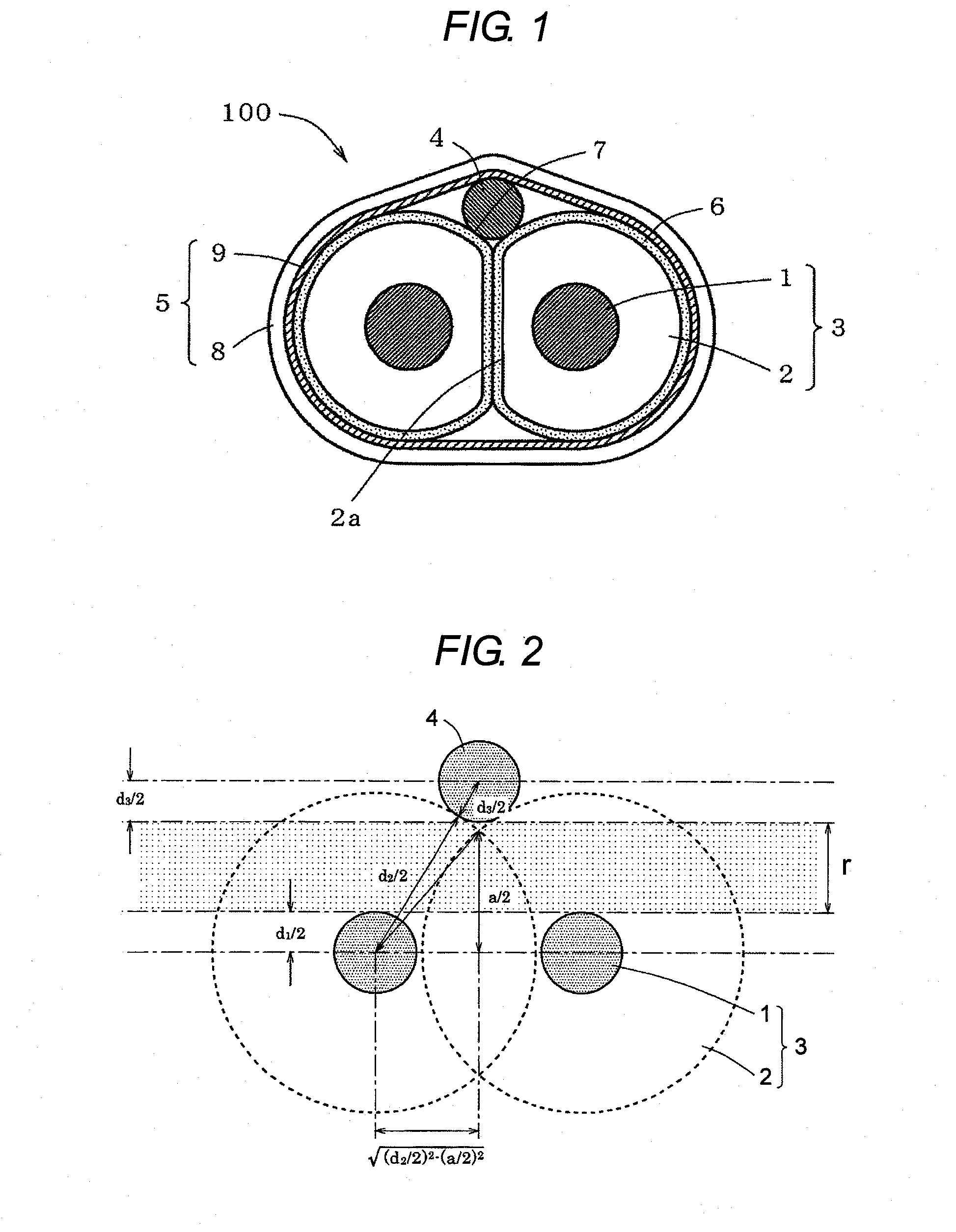

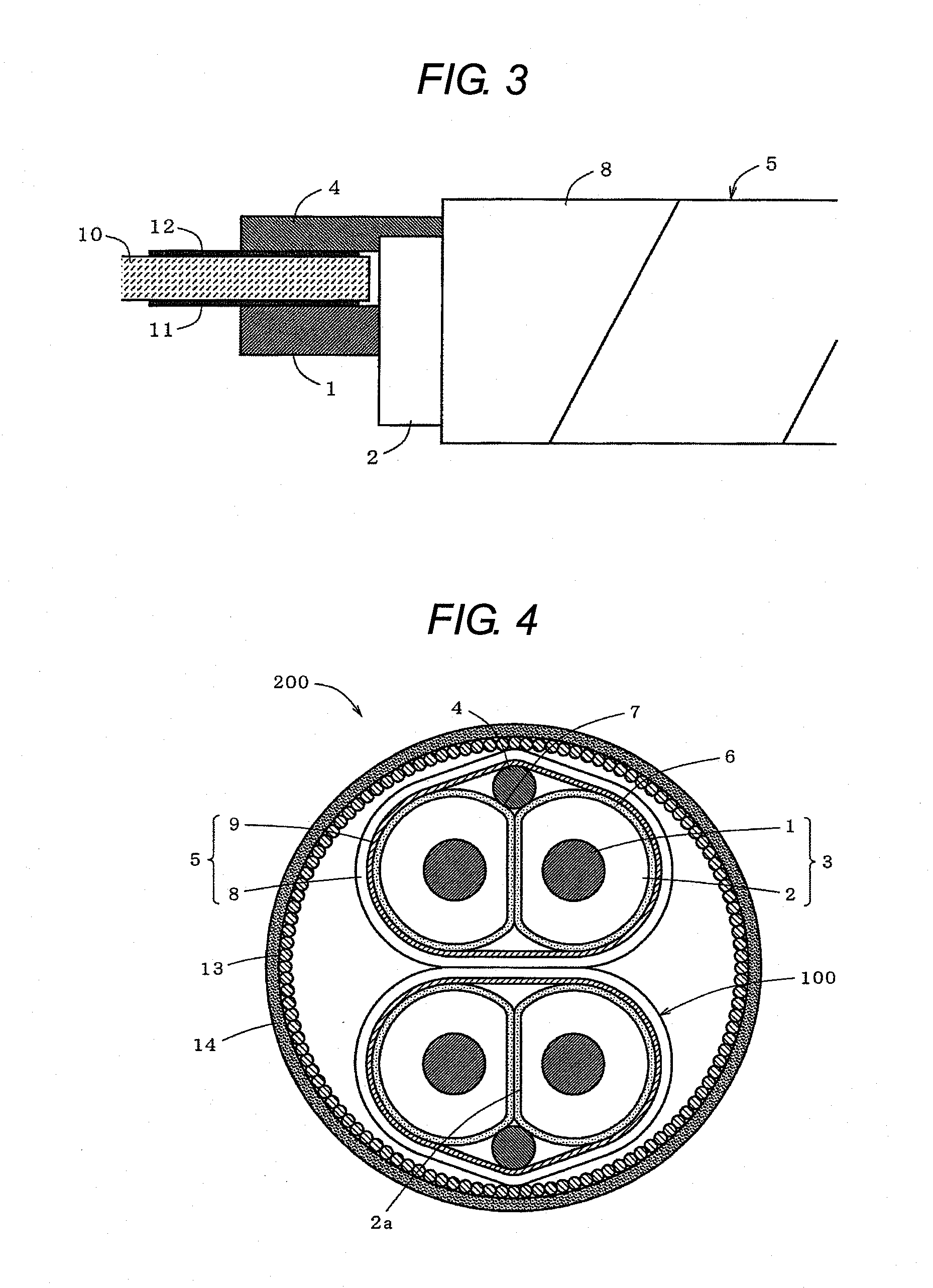

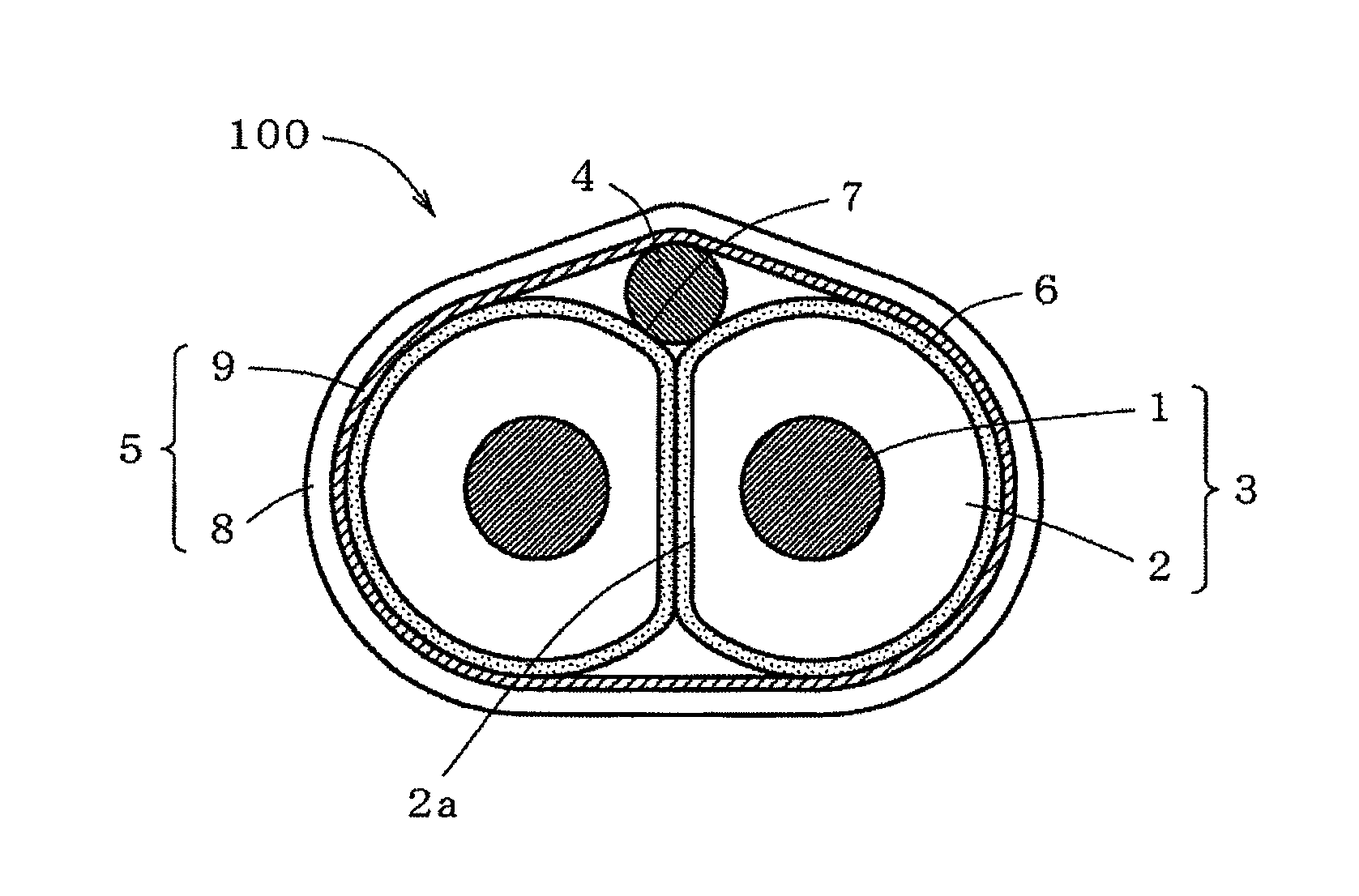

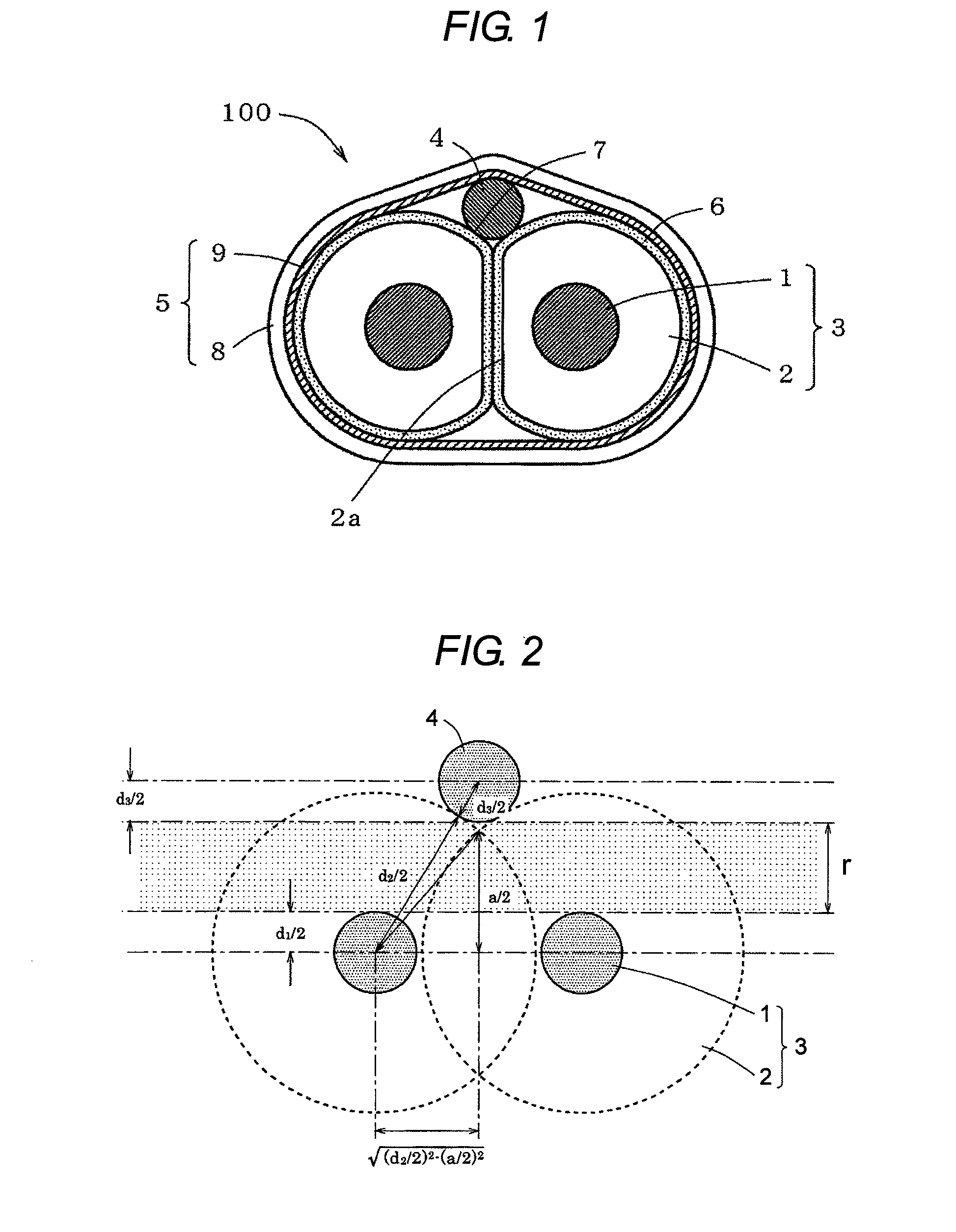

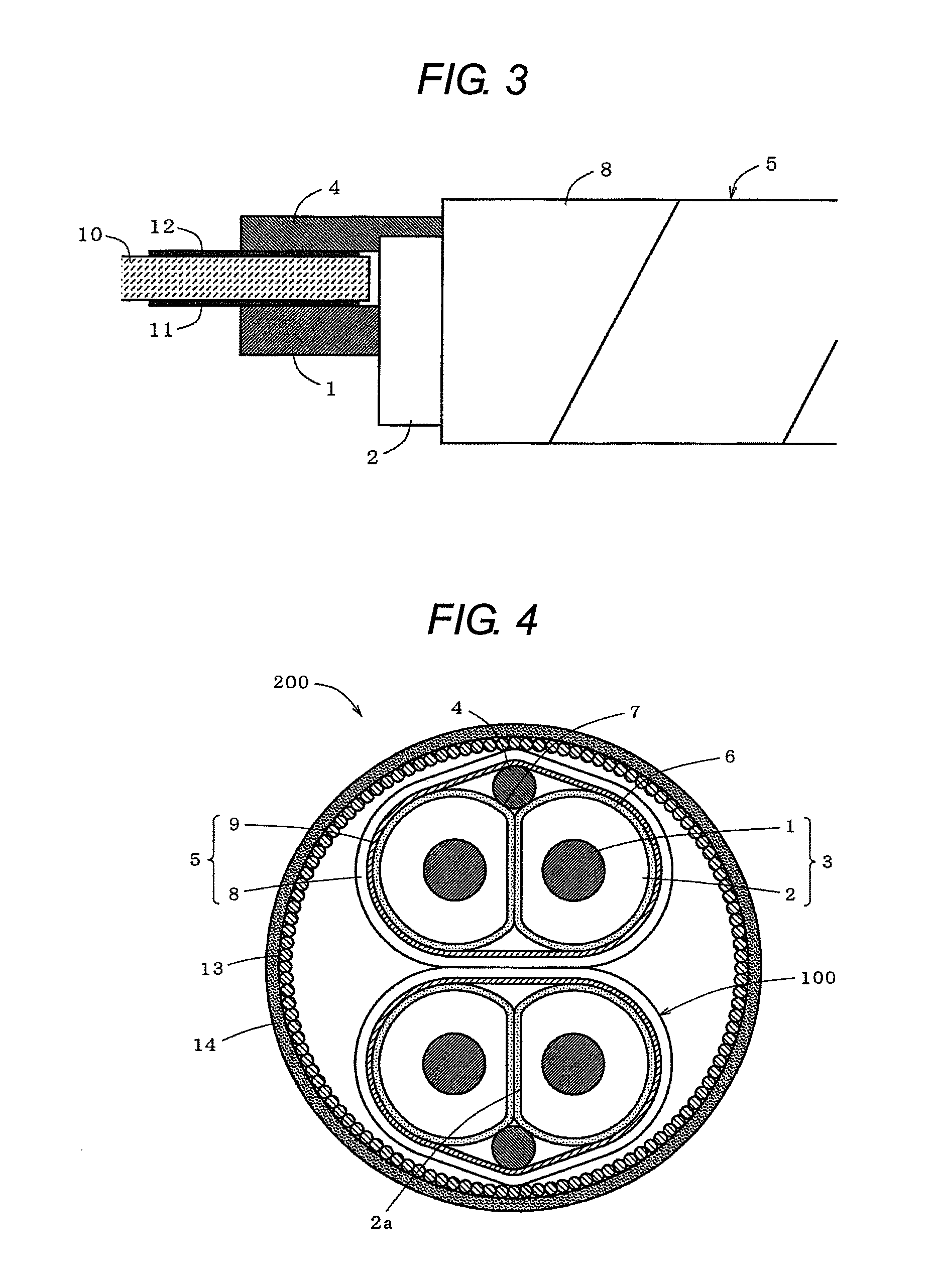

Differential signal cable, and cable assembly and multi-pair differential signal cable using the same

ActiveUS20110232941A1Minimizing characteristic impedance mismatchImprove skewPower cables with screens/conductive layersInsulated cablesElectrical conductorDifferential signaling

A differential signal cable for transmitting high-speed digital differential signals of several Gbit / s or more is provided to minimize characteristic impedance mismatch and to repress increase in the skew, or increase in disturbance due to differential-mode to common-mode conversion. A differential signal cable comprises two insulated wires arranged parallelly in a contact, each of said two insulated wires comprising a conductor and an insulator jacketing the conductor; a fusion layer provided on the surface of each of said two insulated wires; a drain wire placed longitudinally in a recess created in the interstice between said two insulated wires; and a shield tape lapping around said two insulated wires and said drain wire together, wherein a surface of said insulator of each of said two insulated wires is partially deformed so as to have a flat portion and said two insulated wires are fused each other at said flat portions.

Owner:HITACHI CABLE +1

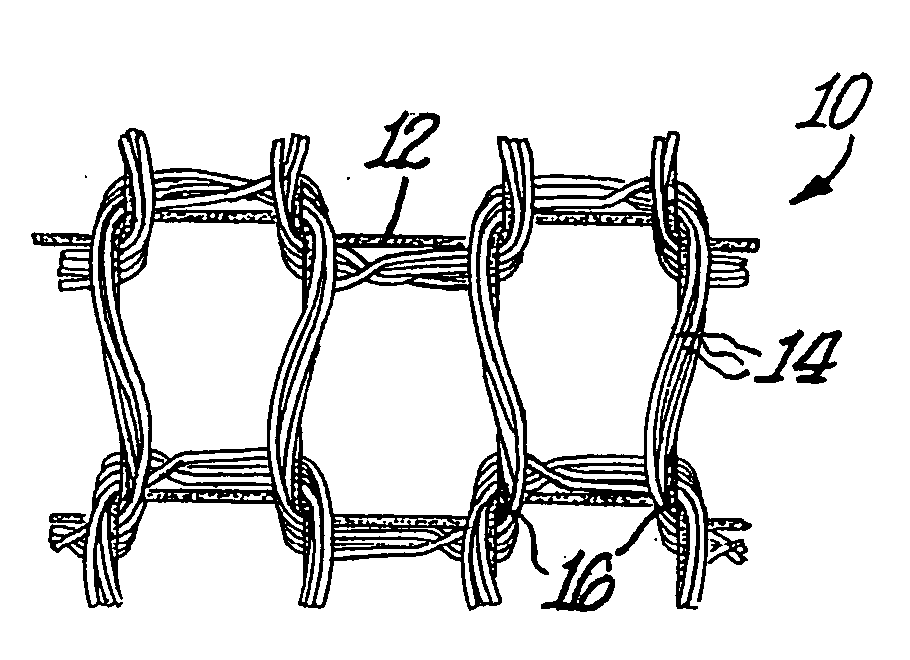

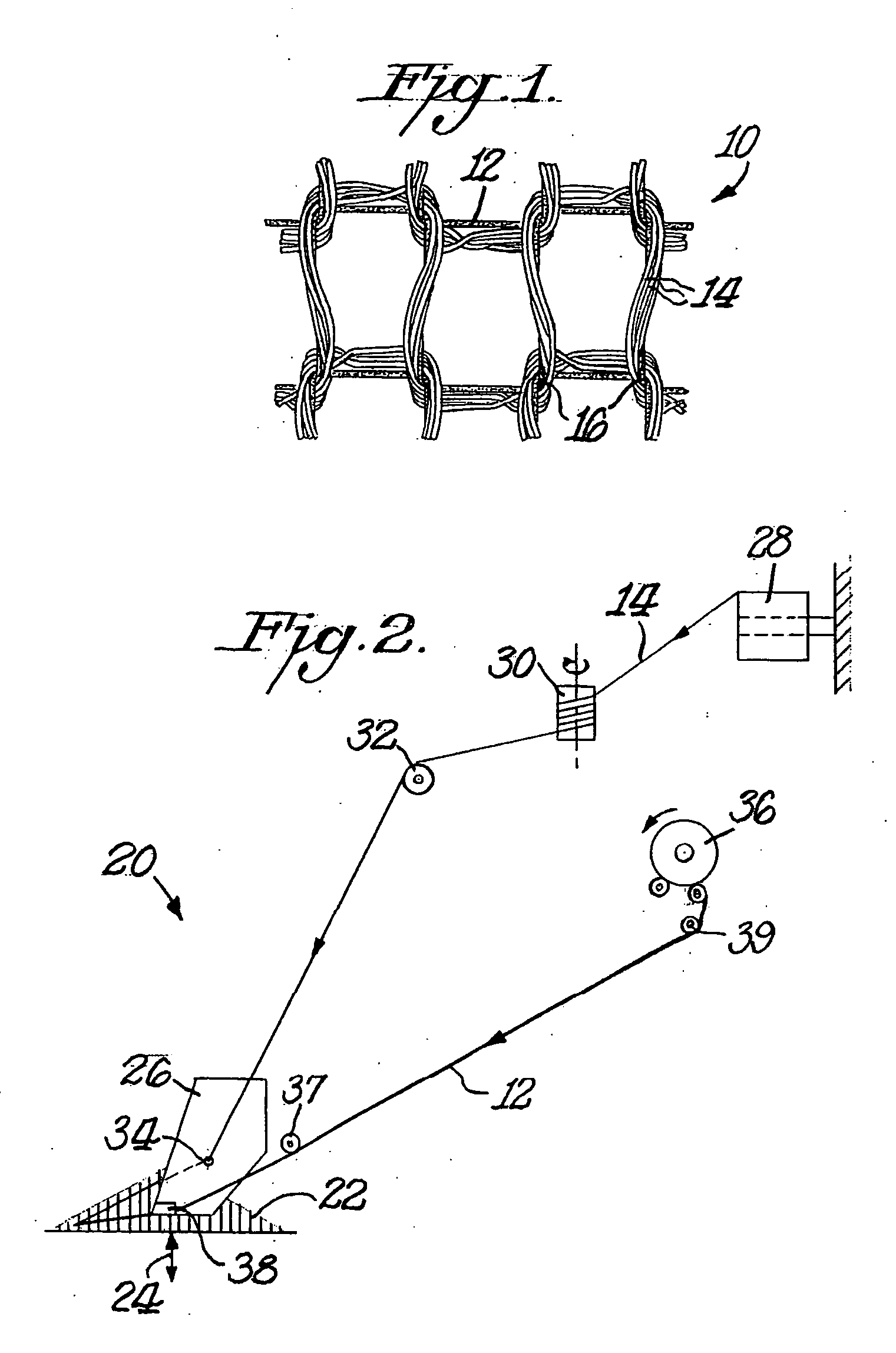

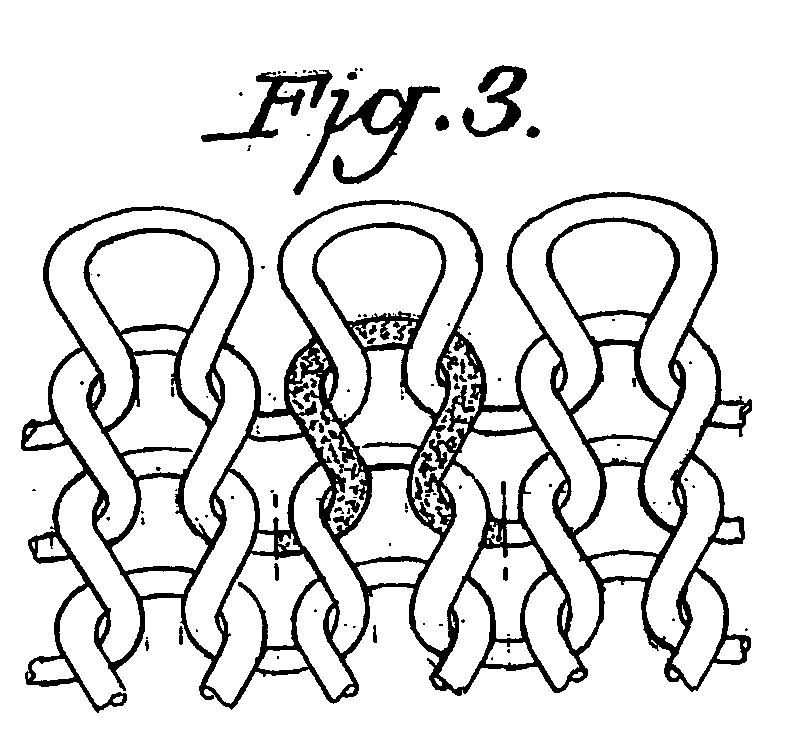

Knit by design method and fabric

InactiveUS20060010929A1Increase productionImprove skewOrnamental textile articlesCircular knitting machinesElastomerEngineering

Circular knit, elastic fabrics of at least one of single jersey, French terry, and fleece are disclosed that include a bare elastomeric material plated with spun and / or continuous filament hard yarns. The circular knit, elastic fabrics of at least one of single jersey, French terry, and fleece are manufactured by a method that does not require a dry heat setting step. The method requires drafting the bare elastomeric material no more than about 2.5× its original length when knitting to form the circular knit, elastic fabrics of at least one of single jersey, French terry, and fleece.

Owner:THE LYCRA CO LLC

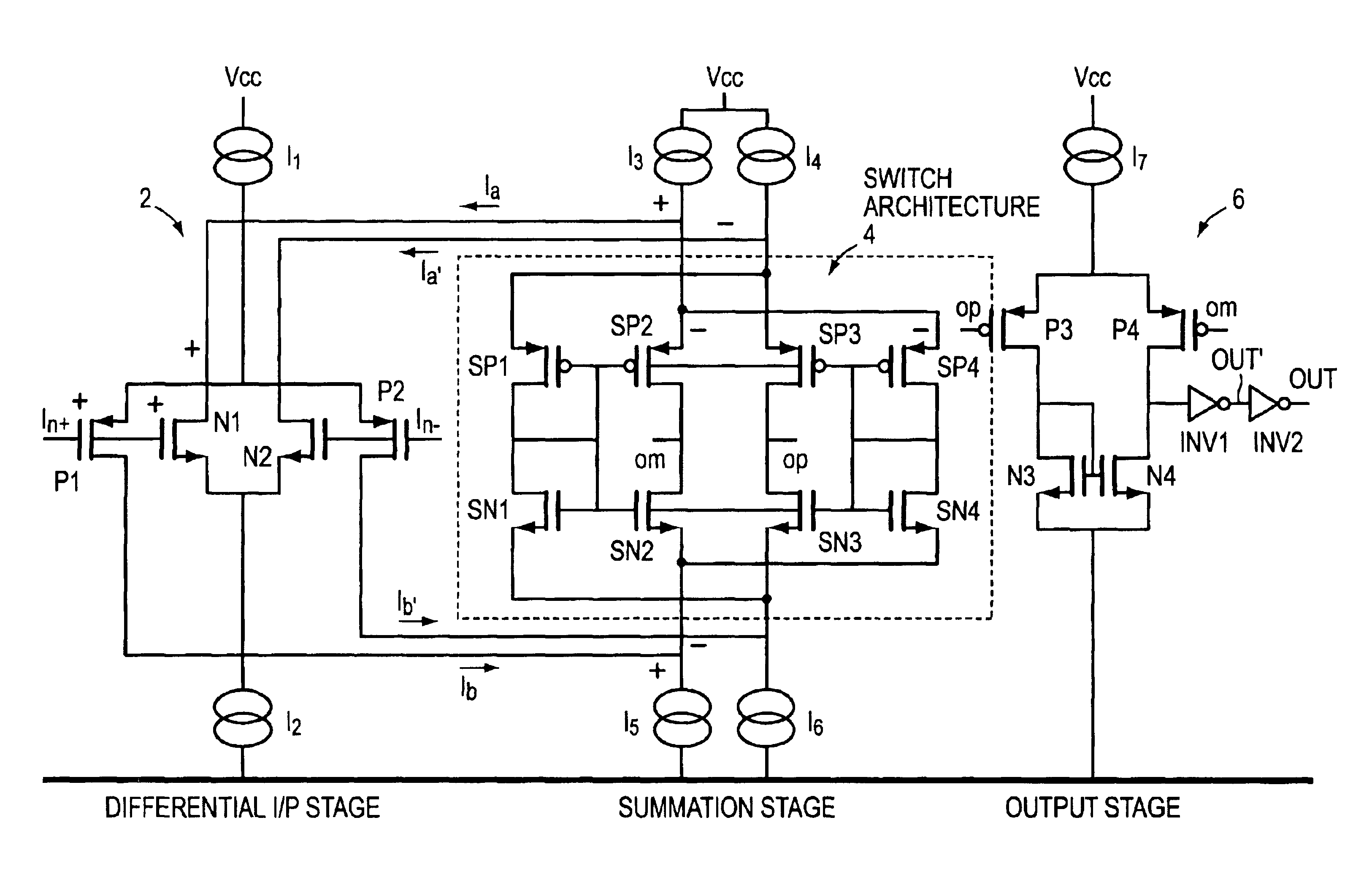

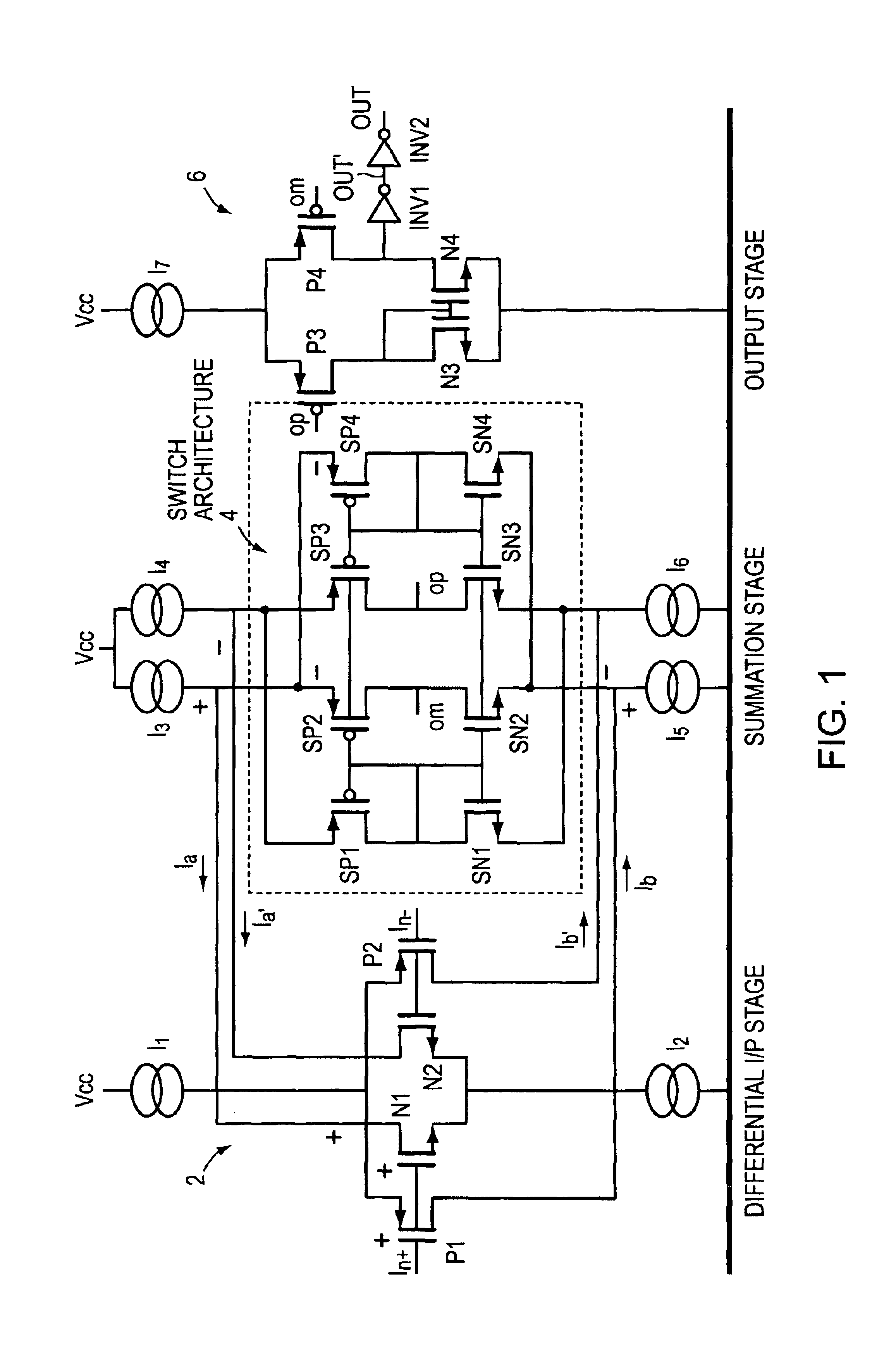

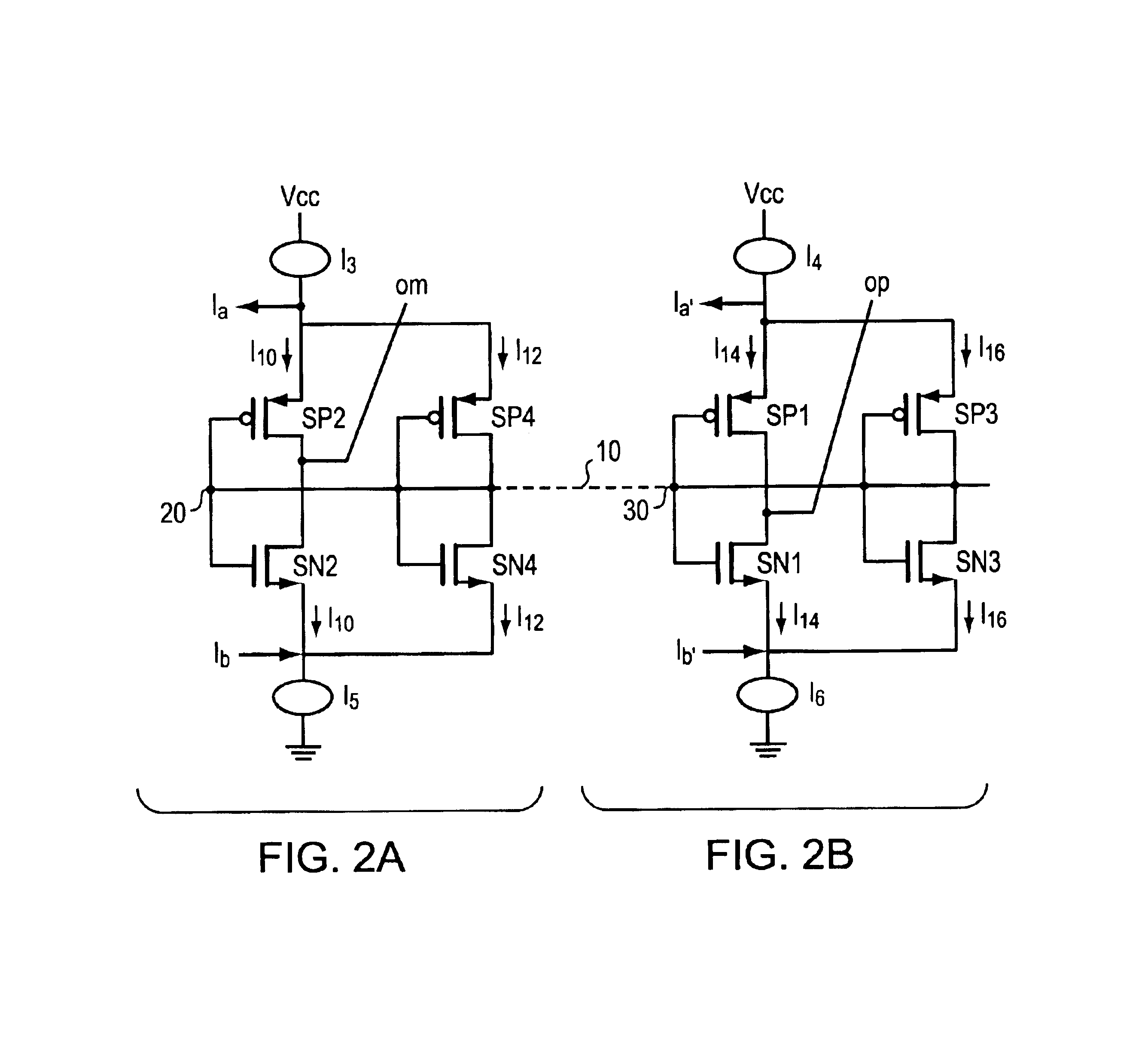

Low voltage, low power differential receiver

InactiveUS6970043B2Improves low Vcc performanceReduce jitterComputations using contact-making devicesComputing operations for multiplication/divisionLow voltageLow jitter

A folded common cascode circuit with symmetric parallel signal paths from the differential inputs to a single ended output provides a low skew, low jitter, low power, high speed differential amplifier. The signal paths on either side of the differential amplifier are made equal with equal loads along each path. Pairs of complementary NMOS and PMOS transistor pairs with parallel complementary biasing current mirroring stacks on the cascode circuitry have all their gates connected together. The layout maintains symmetrical parallel signal paths and symmetrical amplification and impedance loading from differential input to output. Output inverters provide a higher drive capability.

Owner:SEMICON COMPONENTS IND LLC

Differential signal cable, and cable assembly and multi-pair differential signal cable using the same

ActiveUS8378217B2Promote generationUniform impedanceFlat/ribbon cablesPrinted circuitsElectrical conductorDifferential signaling

A differential signal cable for transmitting high-speed digital differential signals of several Gbit / s or more is provided to minimize characteristic impedance mismatch and to repress increase in the skew, or increase in disturbance due to differential-mode to common-mode conversion. A differential signal cable comprises two insulated wires arranged parallelly in a contact, each of said two insulated wires comprising a conductor and an insulator jacketing the conductor; a fusion layer provided on the surface of each of said two insulated wires; a drain wire placed longitudinally in a recess created in the interstice between said two insulated wires; and a shield tape lapping around said two insulated wires and said drain wire together, wherein a surface of said insulator of each of said two insulated wires is partially deformed so as to have a flat portion and said two insulated wires are fused each other at said flat portions.

Owner:HITACHI CABLE +1

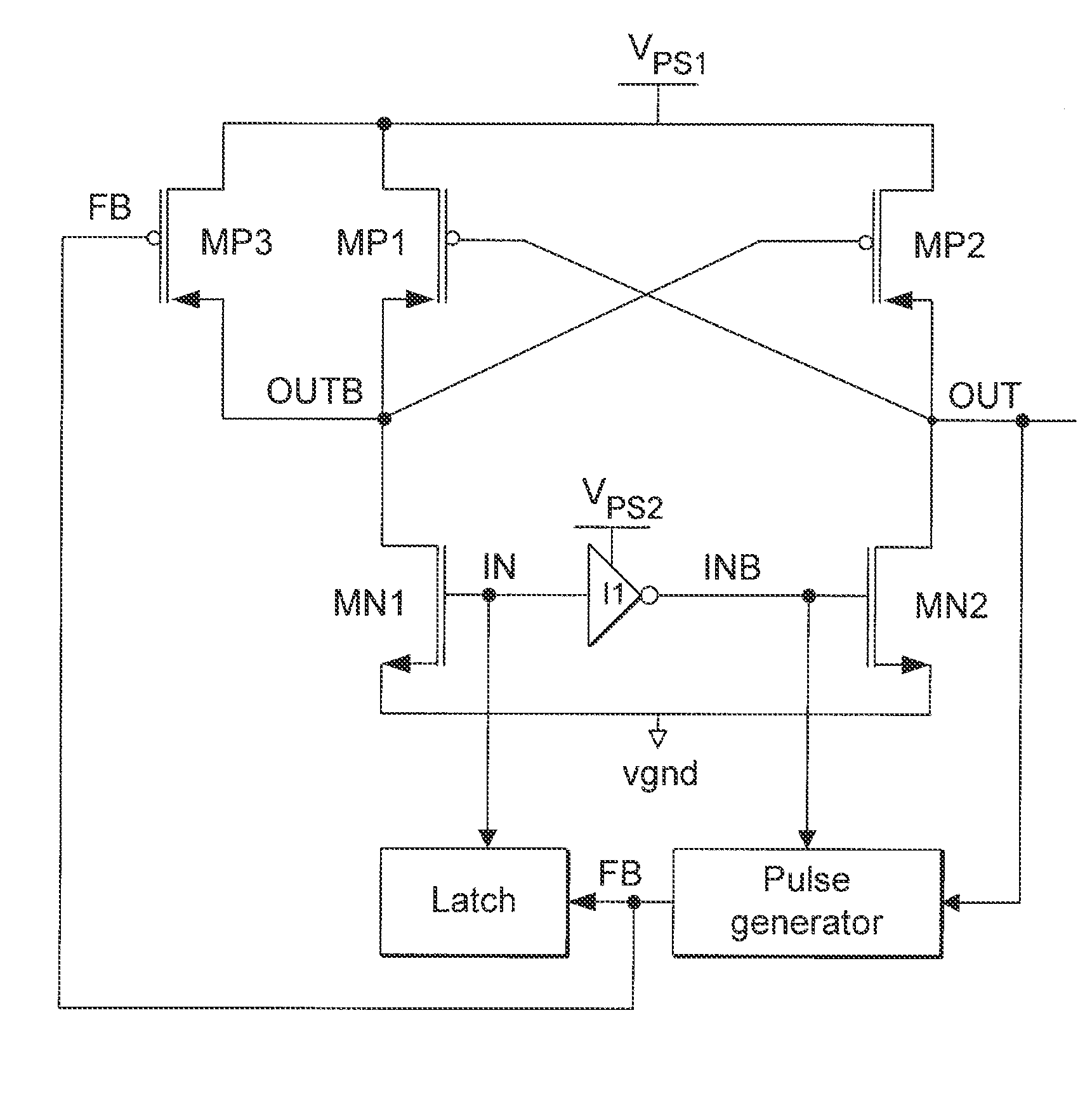

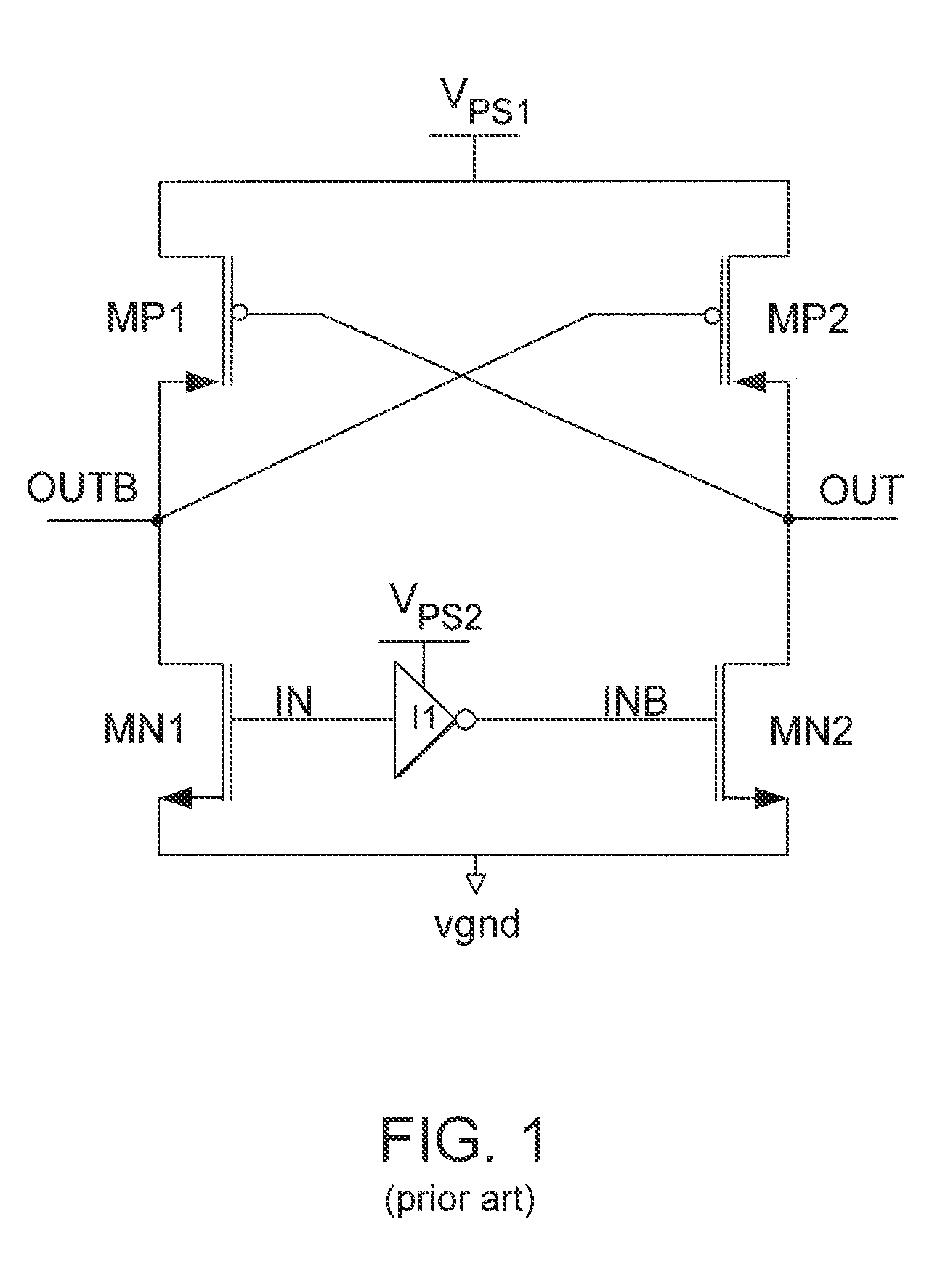

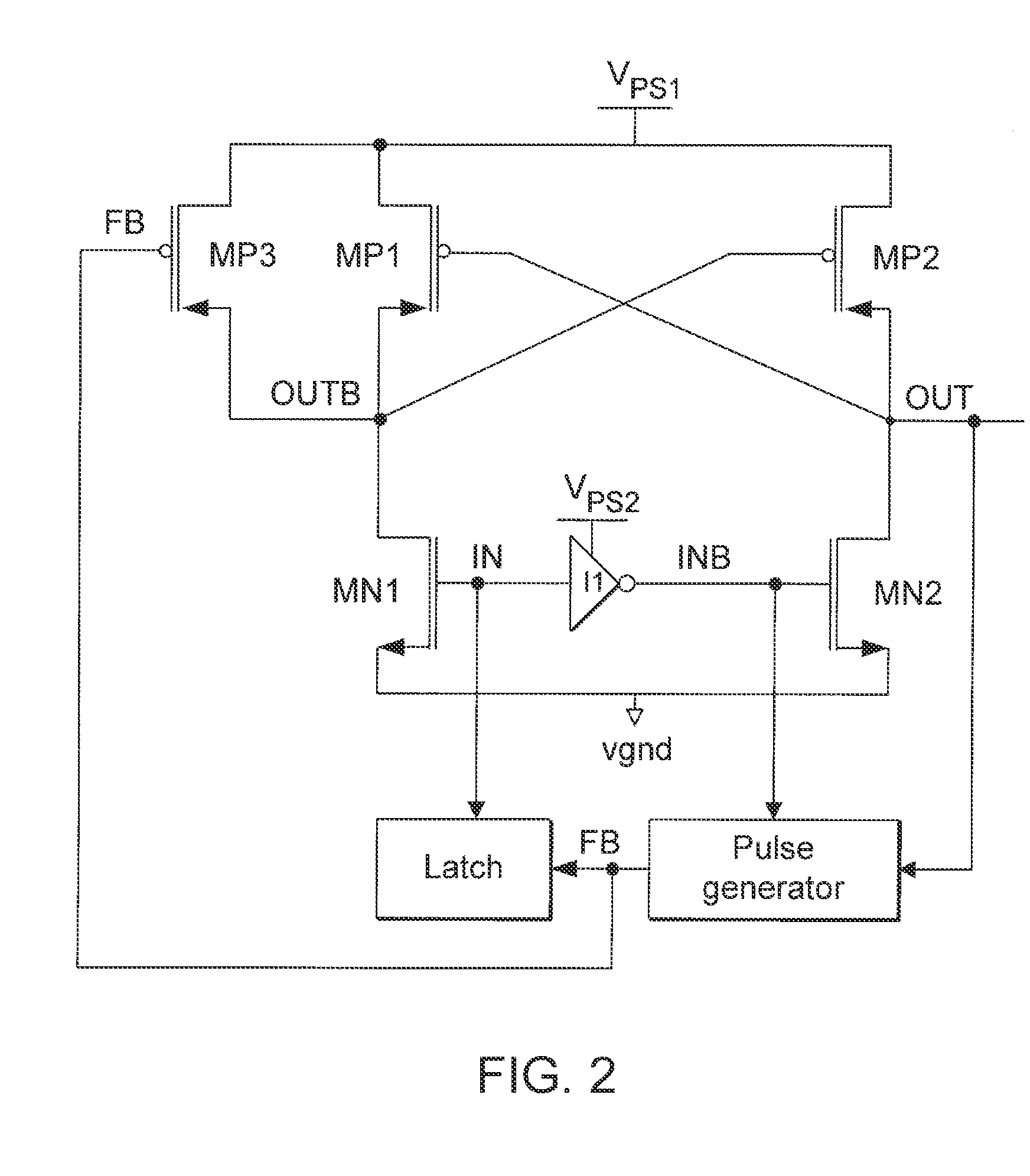

High Speed Level Shift Circuit with Reduced Skew and Method for Level Shifting

InactiveUS20070164789A1Reduce delaysReduced rise and fall propagation delaysLogic circuit coupling/interface arrangementsLevel shiftingShort duration

An improved level shift circuit and method for level shifting is disclosed herein. In general, the improved level shift circuit adds a pulse generator, a feedback transistor and a latch to a conventional cross-coupled level shift circuit configuration. The pulse generator and feedback transistor are configured for reducing a fall delay associated with the level shift circuit. For example, the pulse generator is coupled for supplying a short duration feedback pulse to the feedback transistor during a first time period when input and output signals of the level shift circuit transition to a LOW state. The feedback pulse reduces the fall delay by increasing the speed with which the output signal is pulled LOW. The latch is coupled for preventing the feedback signal from floating when at least one of the input and output signals is HIGH. An integrated circuit comprising at least one level shift circuit is also contemplated herein.

Owner:CYPRESS SEMICON CORP

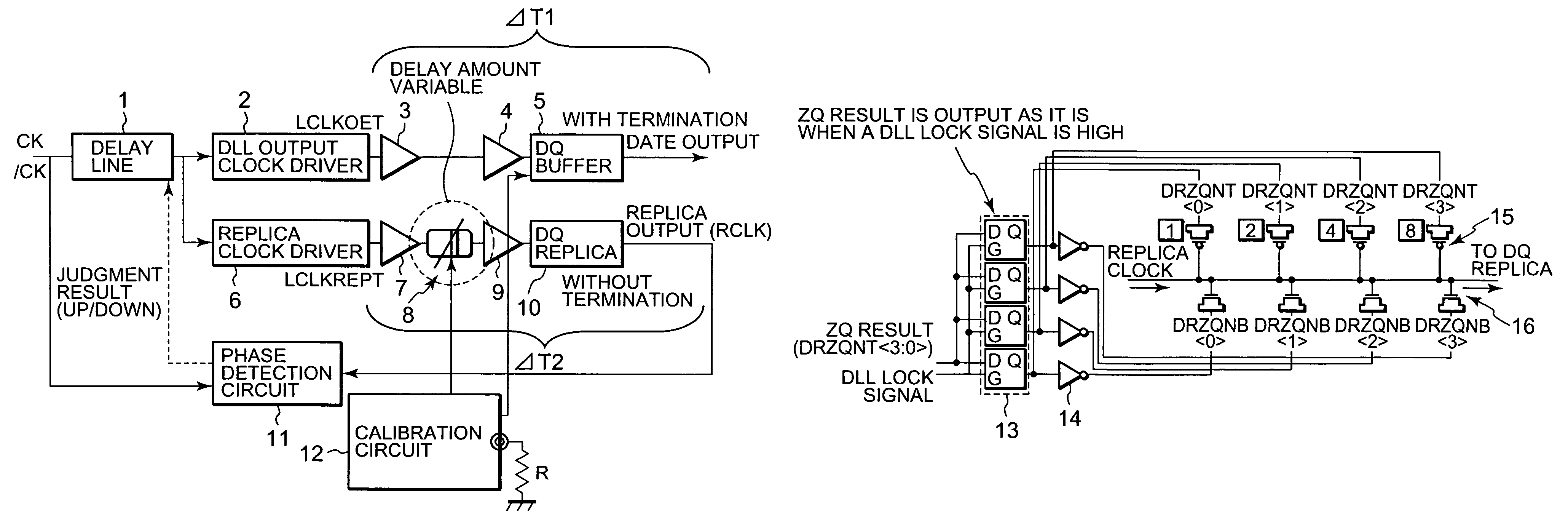

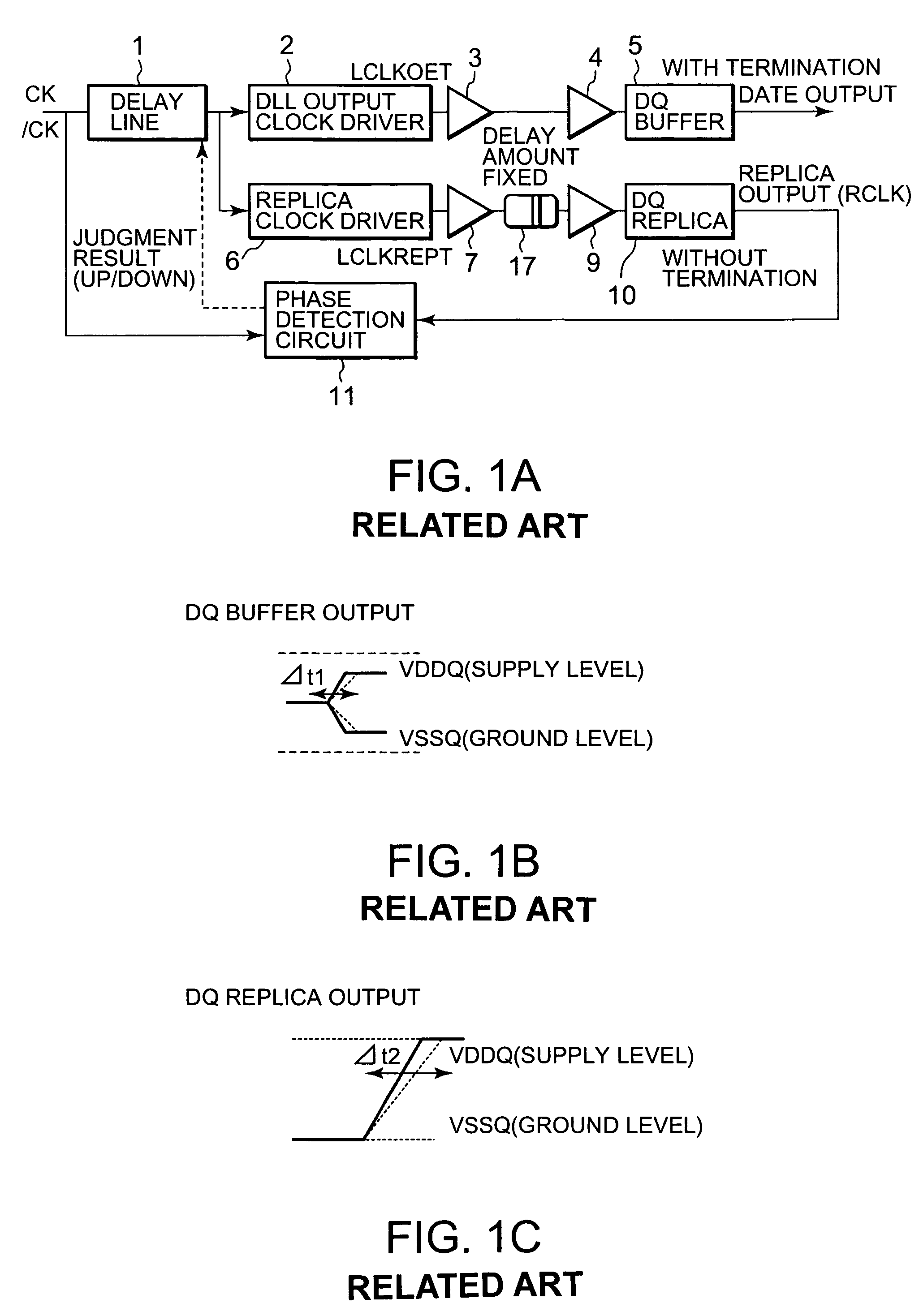

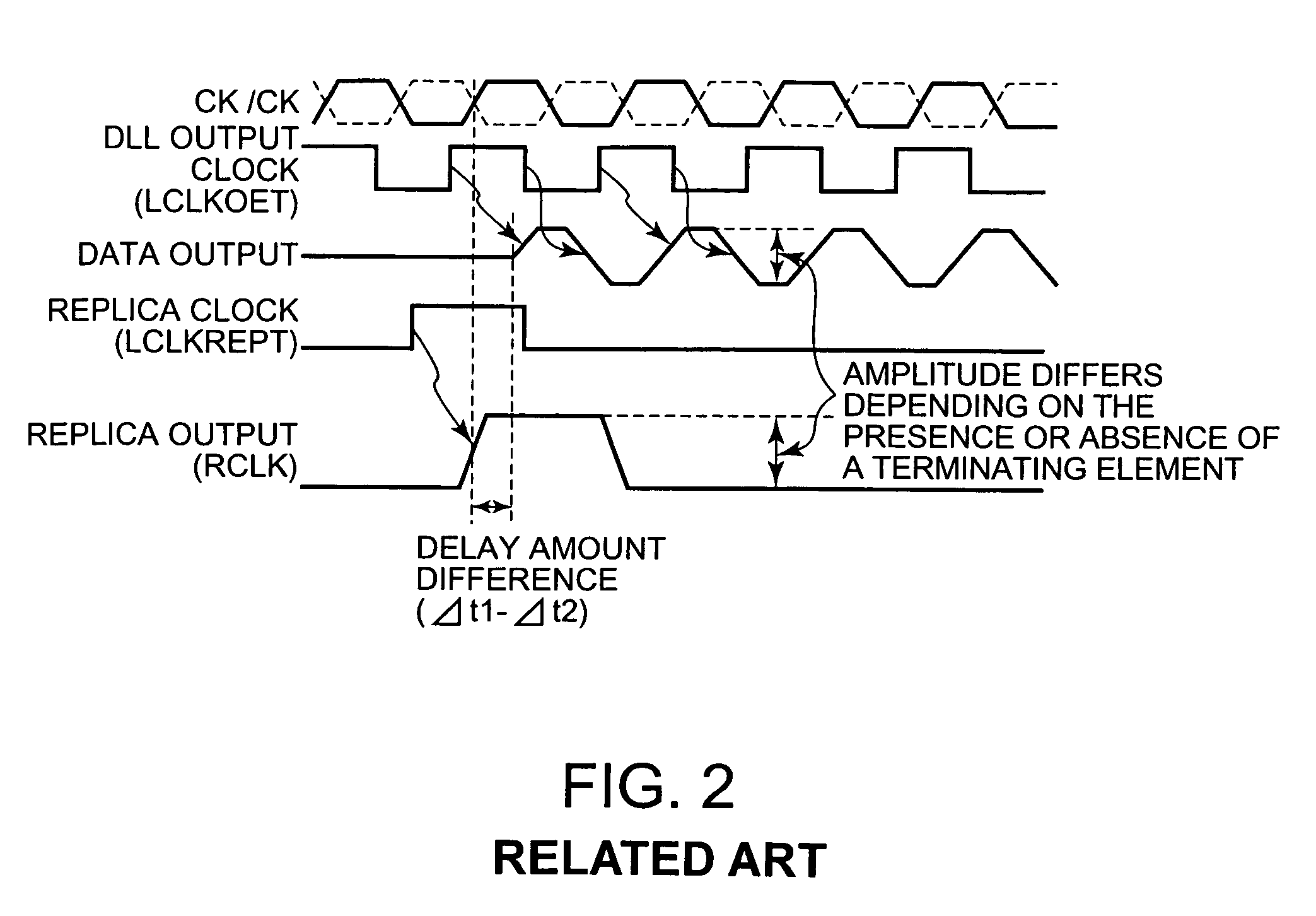

DLL circuit feeding back ZQ calibration result, and semiconductor device incorporating the same

A delay amount variable circuit (8) adapted to change a delay amount according to a ZQ calibration result is inserted in a path of a DQ replica system. The delay amount of the path of the DQ replica system is variable and is adjusted so as to make constant a timing skew difference between a DQ buffer system and the DQ replica system. The ZQ calibration result changes depending on variations in temperature, voltage, and manufacture. Therefore, by obtaining the delay amount corresponding to these variations, there are obtained a DLL circuit with high accuracy that can make the skew difference constant, and a semiconductor device incorporating such a DLL circuit.

Owner:LONGITUDE LICENSING LTD

Skew controlled leadframe for a contact module assembly

ActiveUS7566247B2Reduce skewTwo-part coupling devicesCoupling protective earth/shielding arrangementsGround patternMechanical engineering

Owner:TYCO ELECTRONICS LOGISTICS AG (CH)

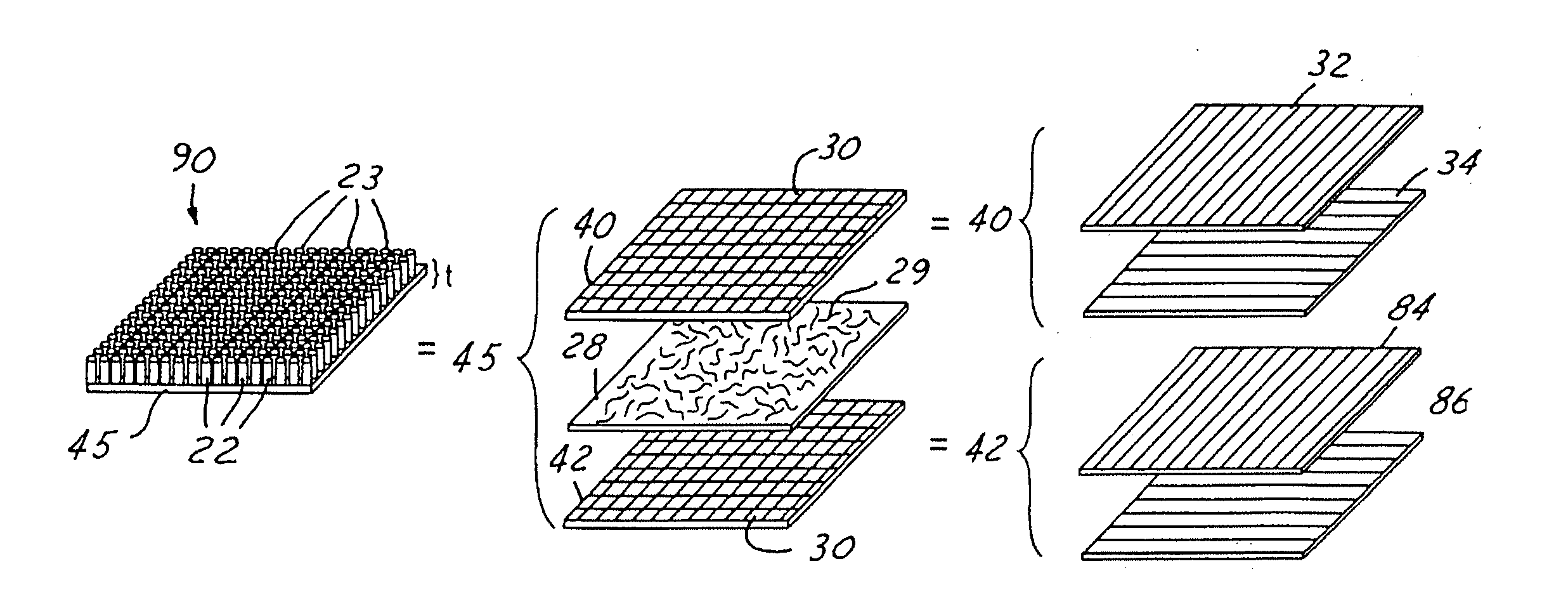

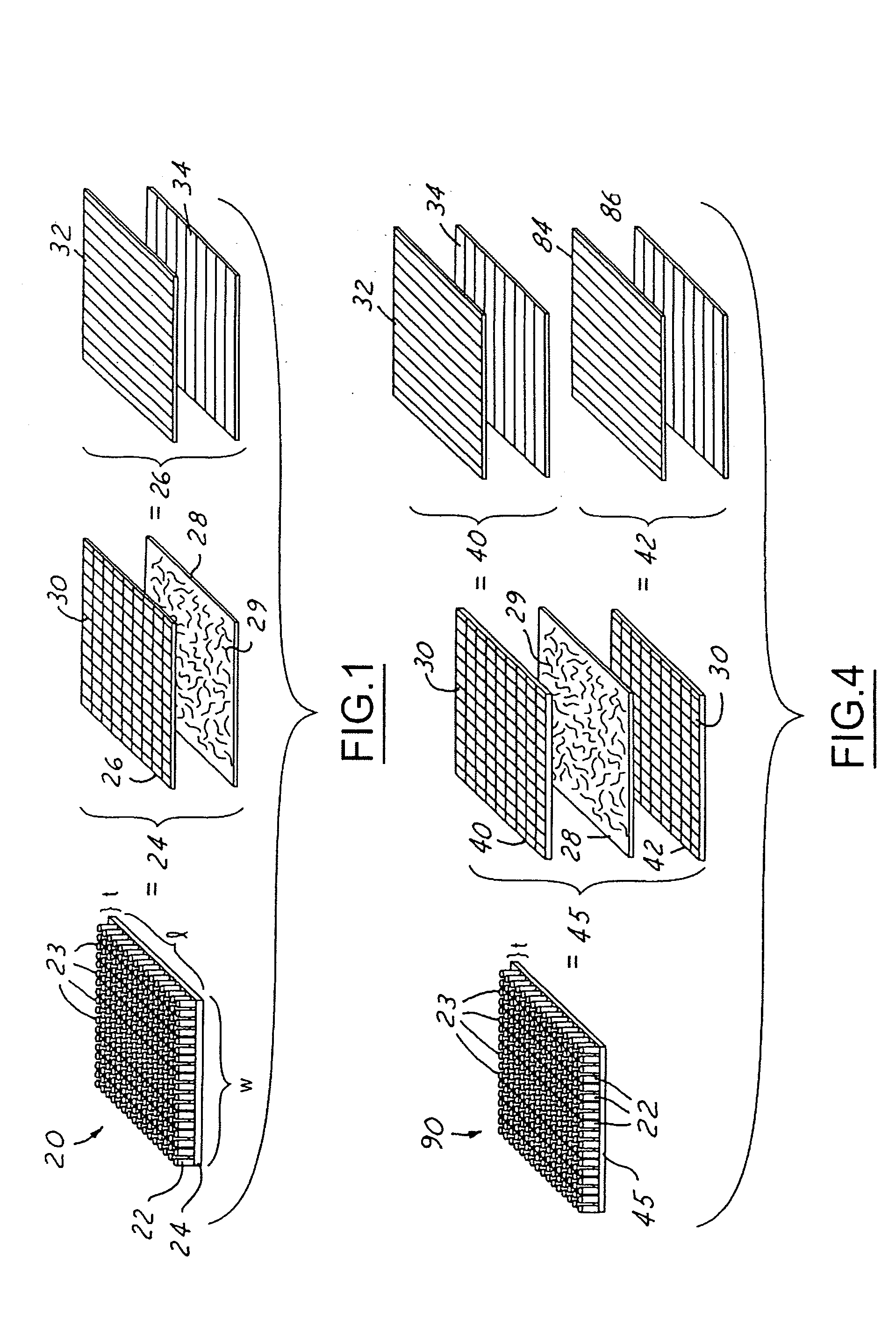

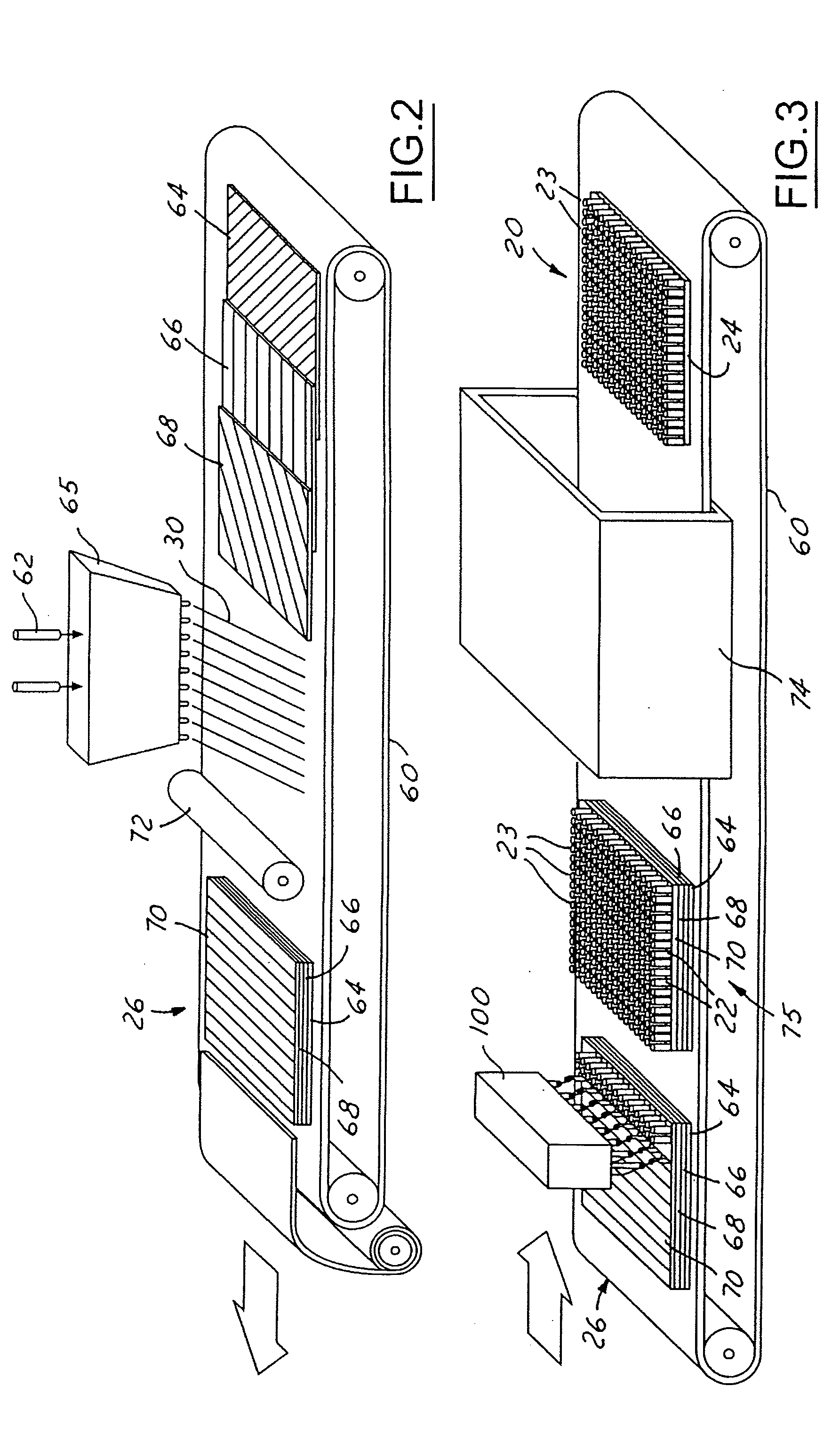

Recyclable tufted carpet with improved stability and durability

InactiveUS20050233107A1Good dimensional stabilityReduce skewTufting apparatusSynthetic resin layered productsGlass fiberWrinkle skin

A recyclable tufted carpet meeting EPA recyclable content standards and having improved dimensional stability that reduces skew, bow, and wrinkles during manufacture and installation is formed by combining prior art primary and secondary backings into a single, fiber-reinforced primary backing layer. Consolidating either a glass fiber fabric layer, a glass veil, or a glass mat with a fiber-reinforced extruded film forms the fiber-reinforced primary backing layer. An additional glass fabric fiber layer can also be introduced to the primary backing to provide additional dimensional stability.

Owner:OCV INTELLECTUAL CAPITAL LLC

Vehicle seat construction

Owner:GM GLOBAL TECH OPERATIONS LLC

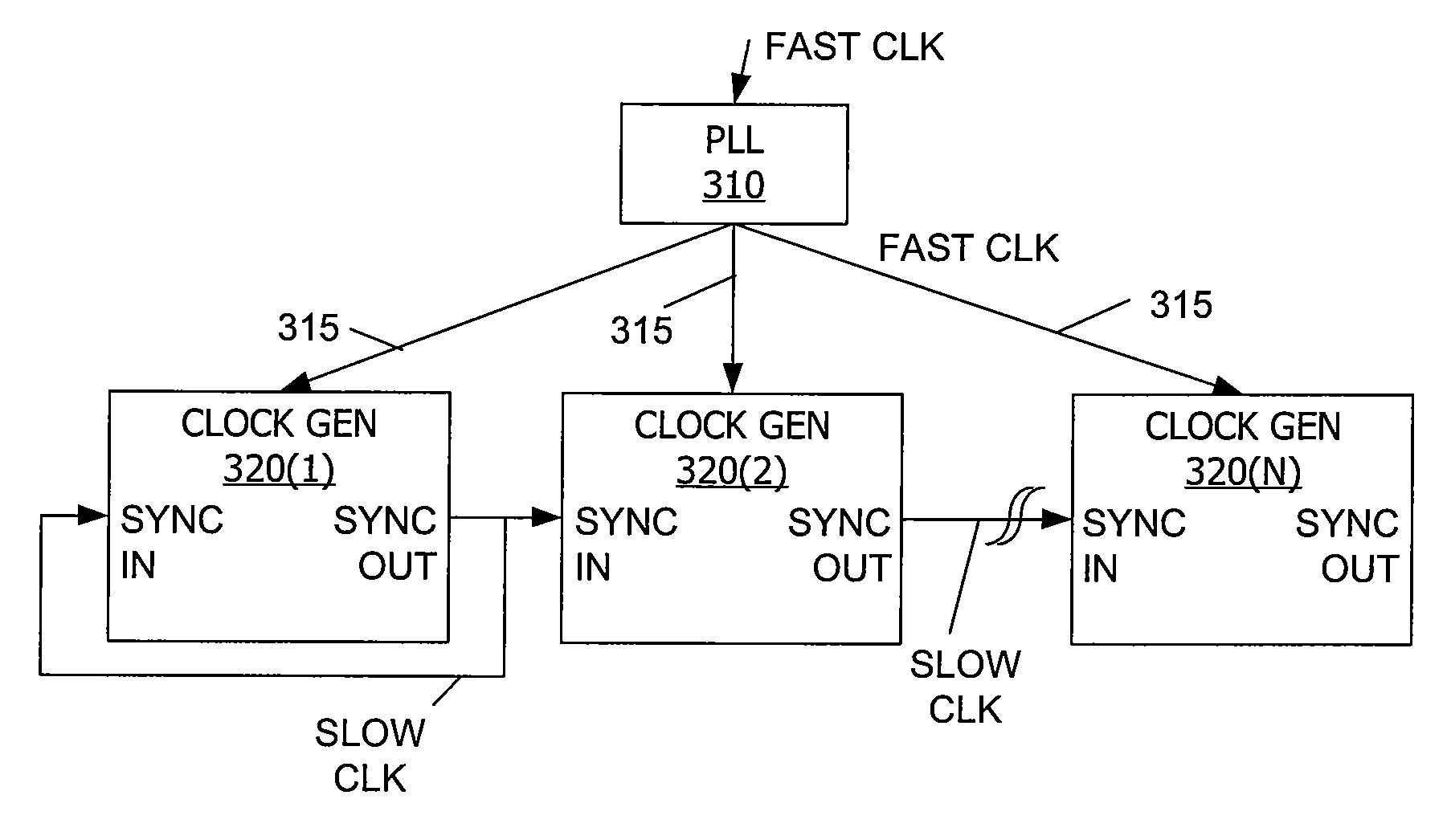

Derived clock synchronization for reduced skew and jitter

ActiveUS7526666B1Reduce amount of timeShorten the timePulse automatic controlError detection/correctionSynchronismIsochronous signal

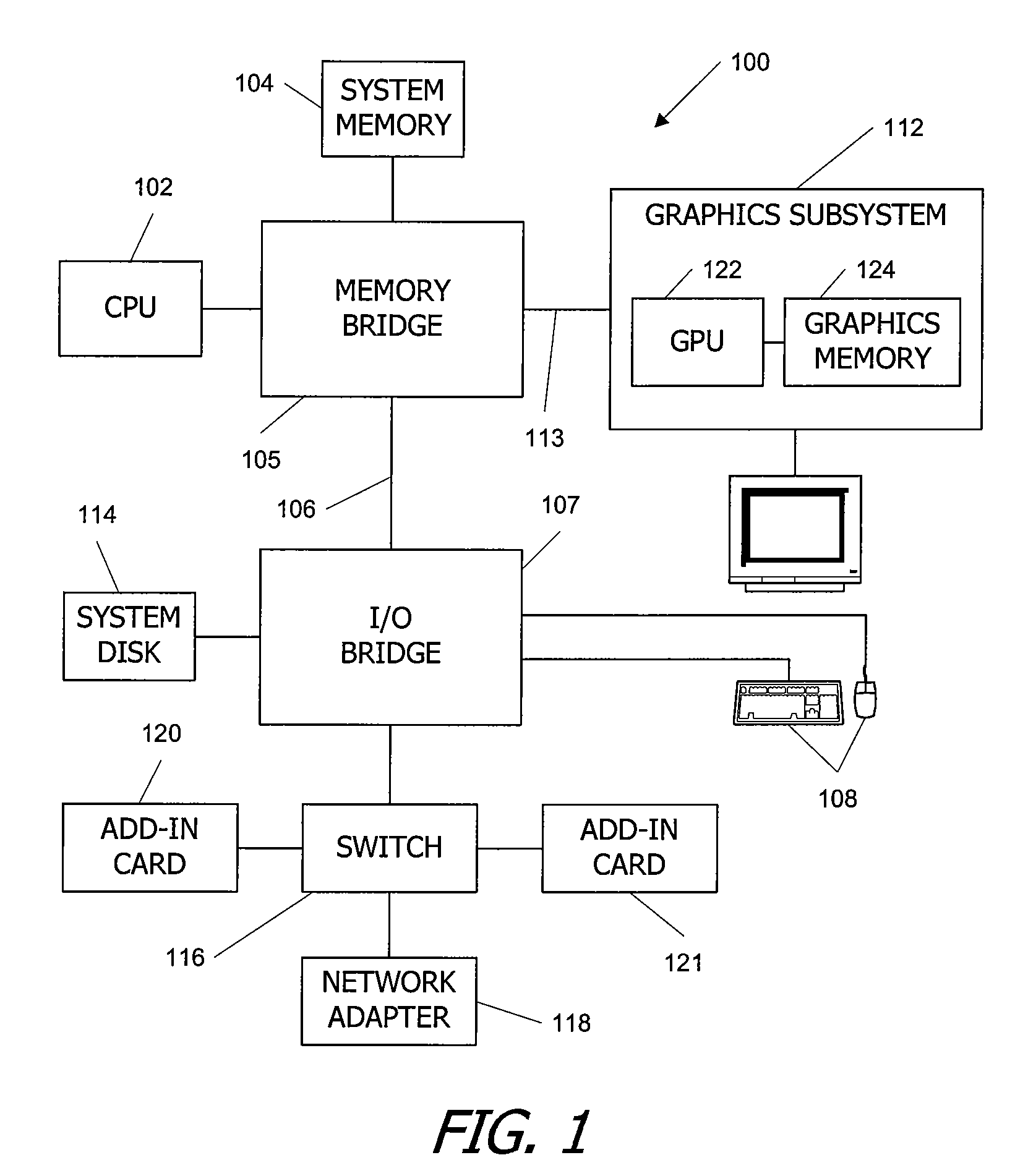

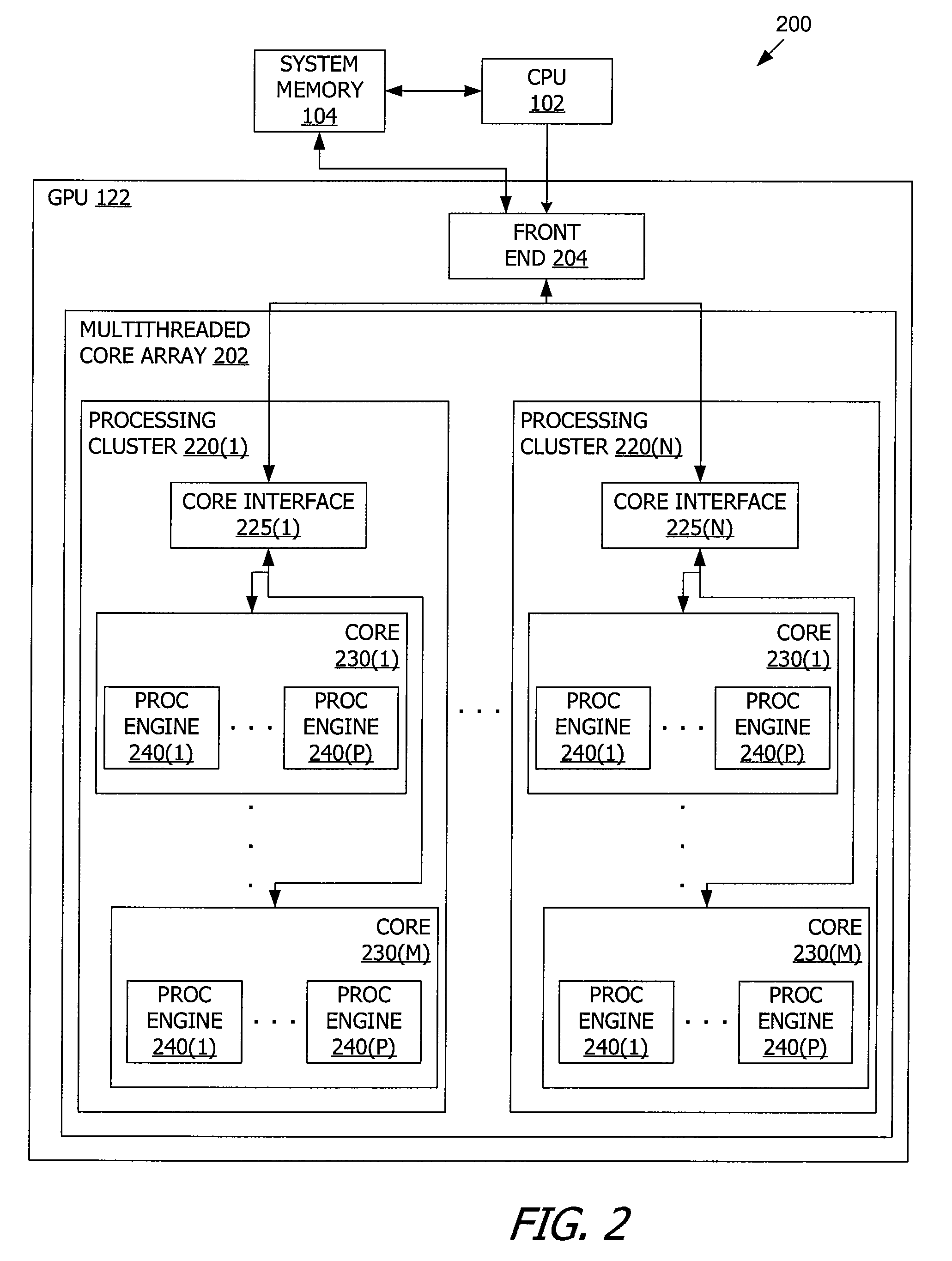

Two or more circuits (e.g. processing cores of a graphics processor) operate synchronously at a fast clock frequency. A core interface to each of the processing cores is designed to communicate in synchronous fashion with one or more other core interfaces at a slow clock frequency. The fast clock is distributed to each processing core in a manner that provides minimized skew and jitter, e.g. with a balanced tree network. The slow clock is locally derived from the fast clock in each core interface. One of the core interfaces is selected to provide a synchronism signal, and the synchronism signal is distributed among the multiple core interfaces to synchronize the locally derived slow clocks.

Owner:NVIDIA CORP

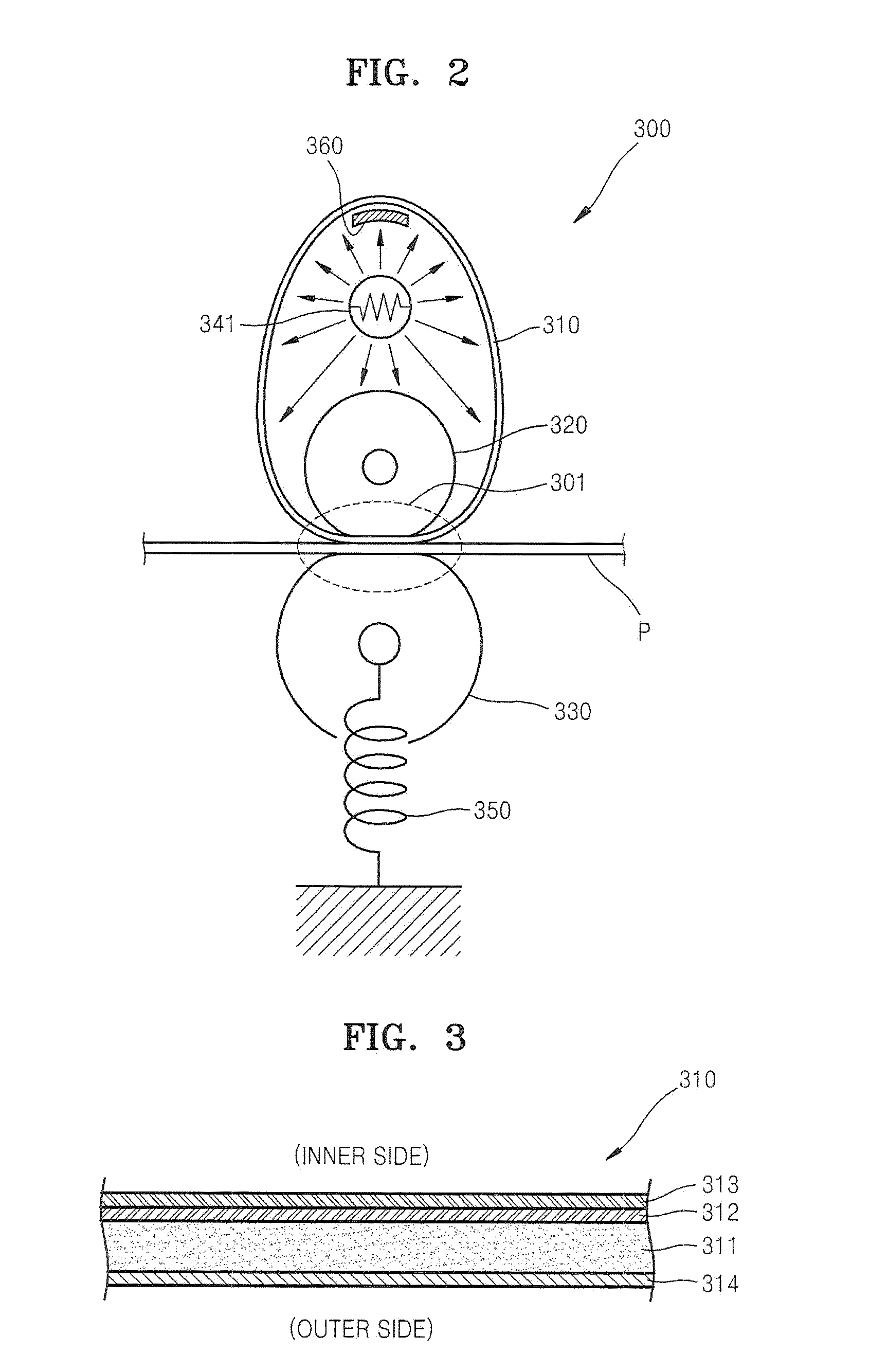

Fusing device and image forming apparatus employing the same

InactiveUS20100098468A1Easy to separateReduce lateral movementElectrographic process apparatusImage formationClosed loop

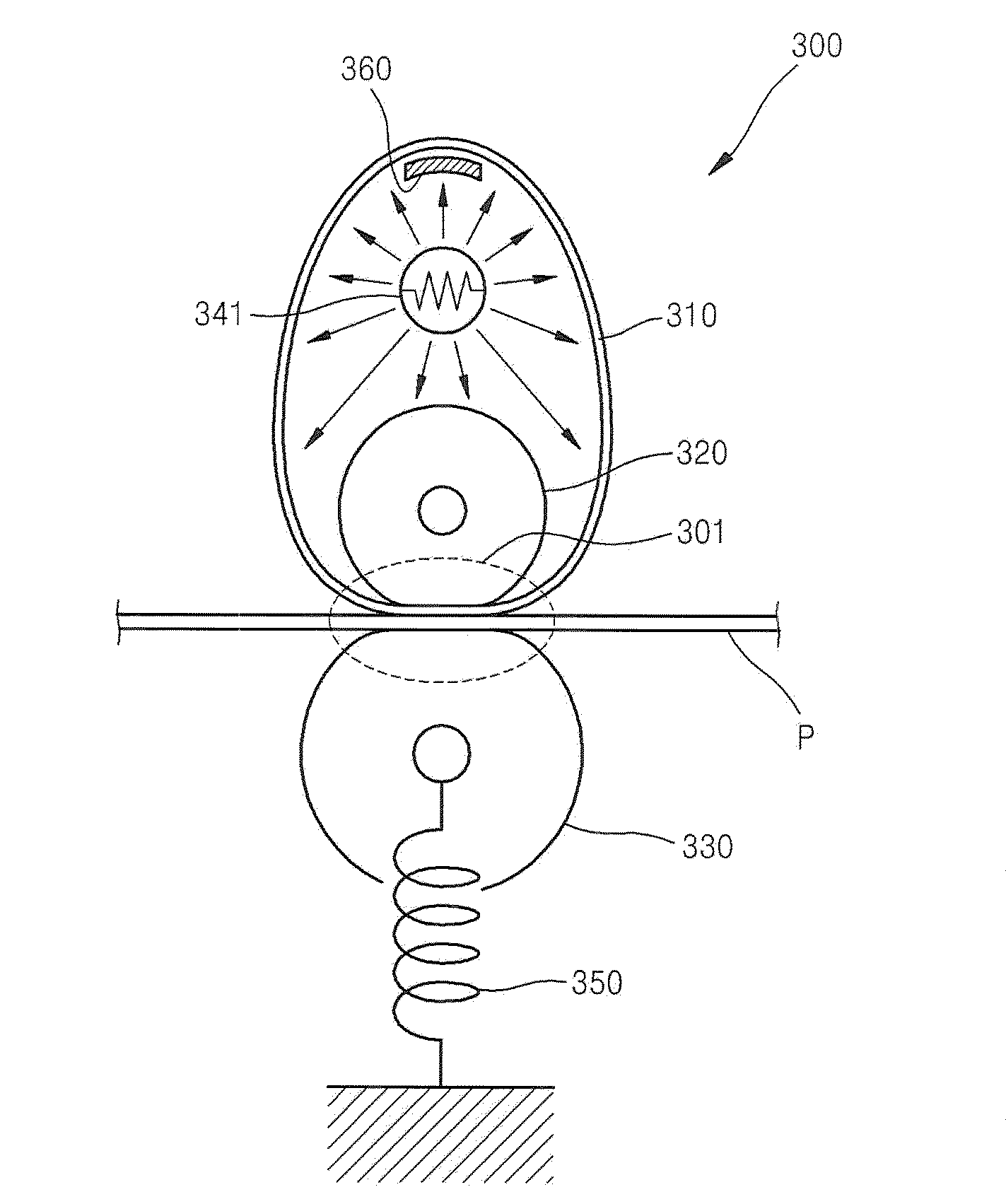

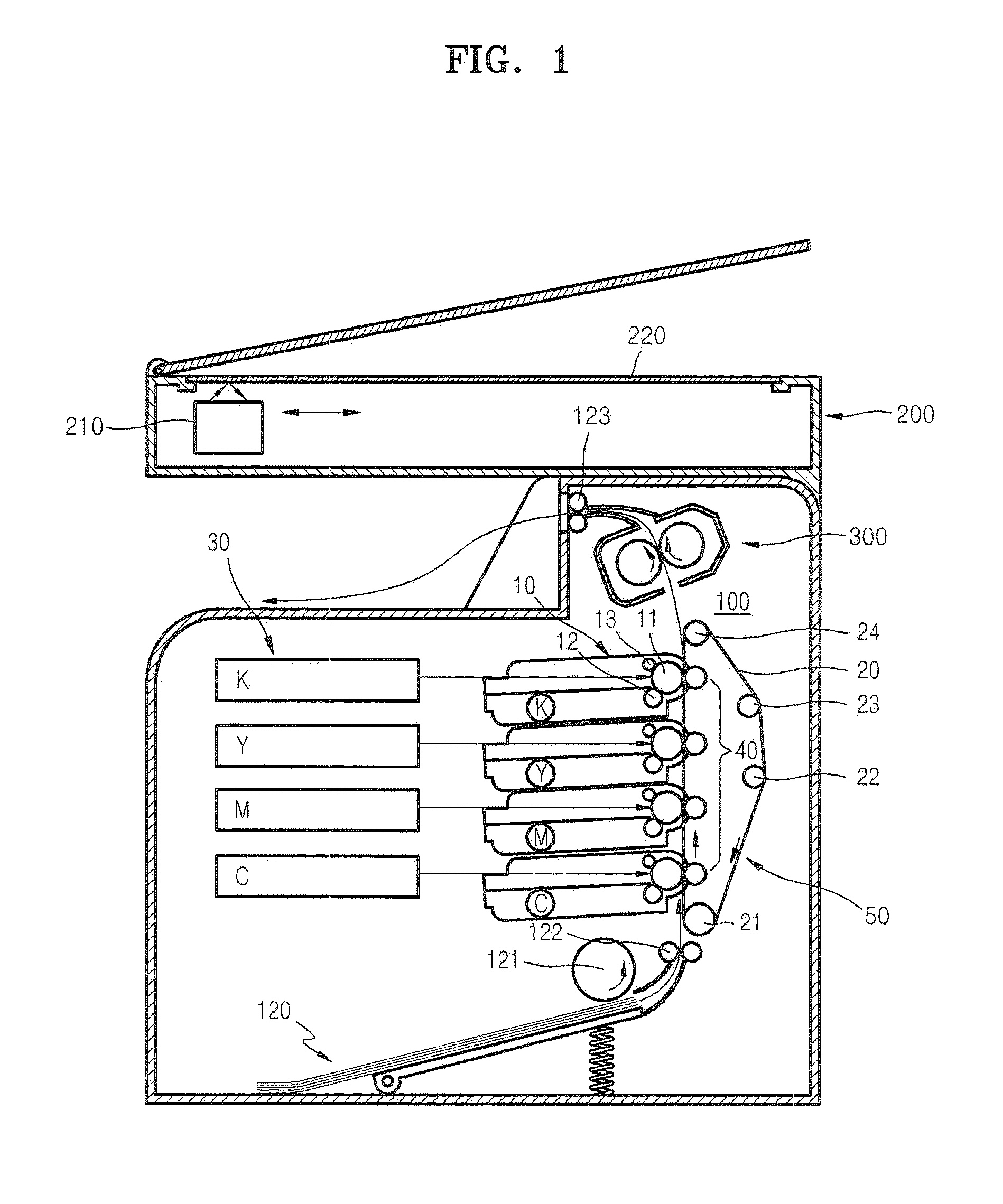

Disclosed are a fusing device and an image forming apparatus employing the fusing device. The fusing device includes a belt having a closed loop configuration, a first roller rotatably disposed inside the loop defined by belt. The first roller includes heat absorbent layer. The fusing device further includes a second roller rotatably disposed outside the loop of the belt, the first and second rollers each make pressing contact with the portion of the belt that passes between them to form the fusing nip. The heat absorbent layer of the first roller provides heat for the fusing nip.

Owner:S PRINTING SOLUTION CO LTD

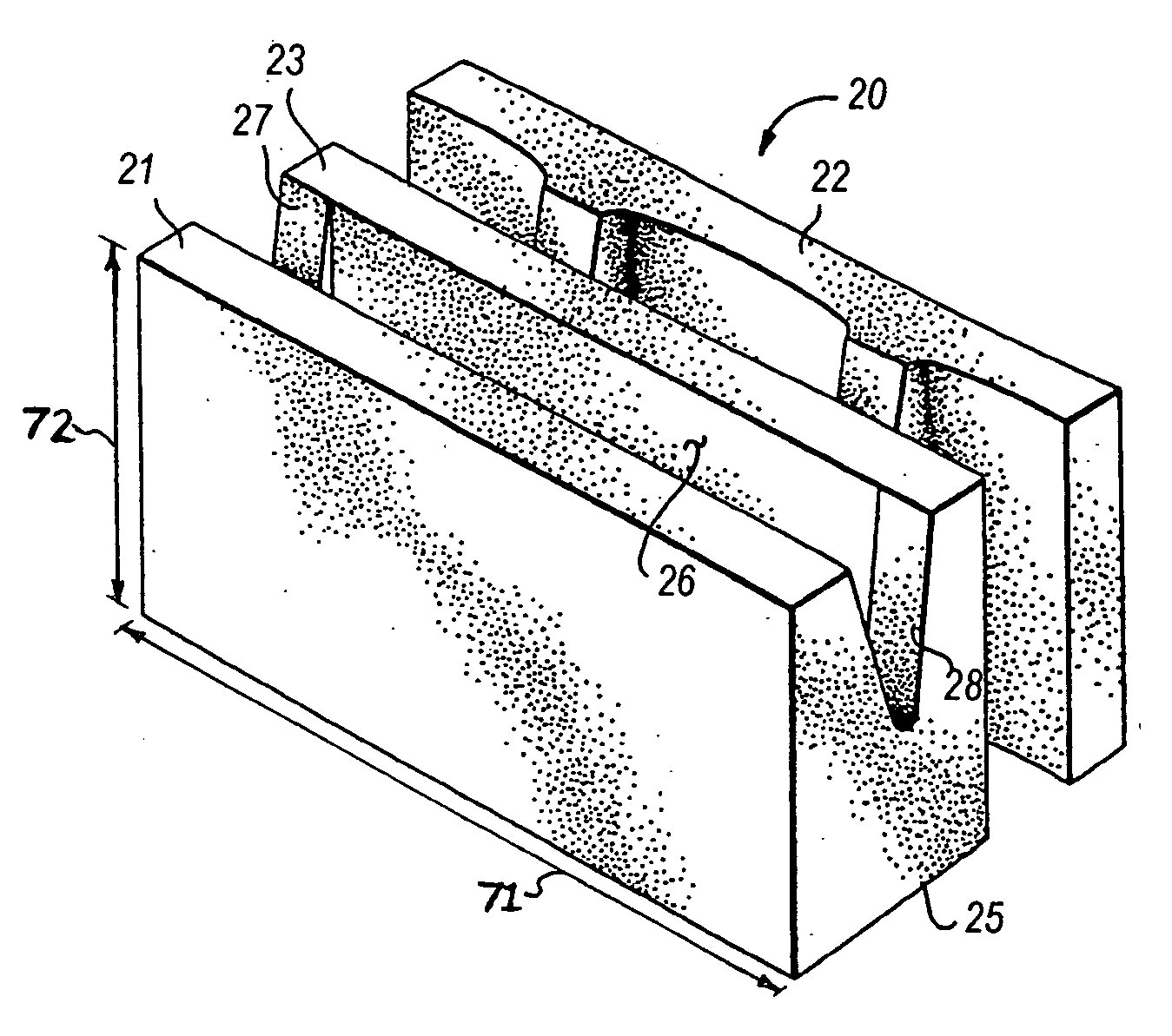

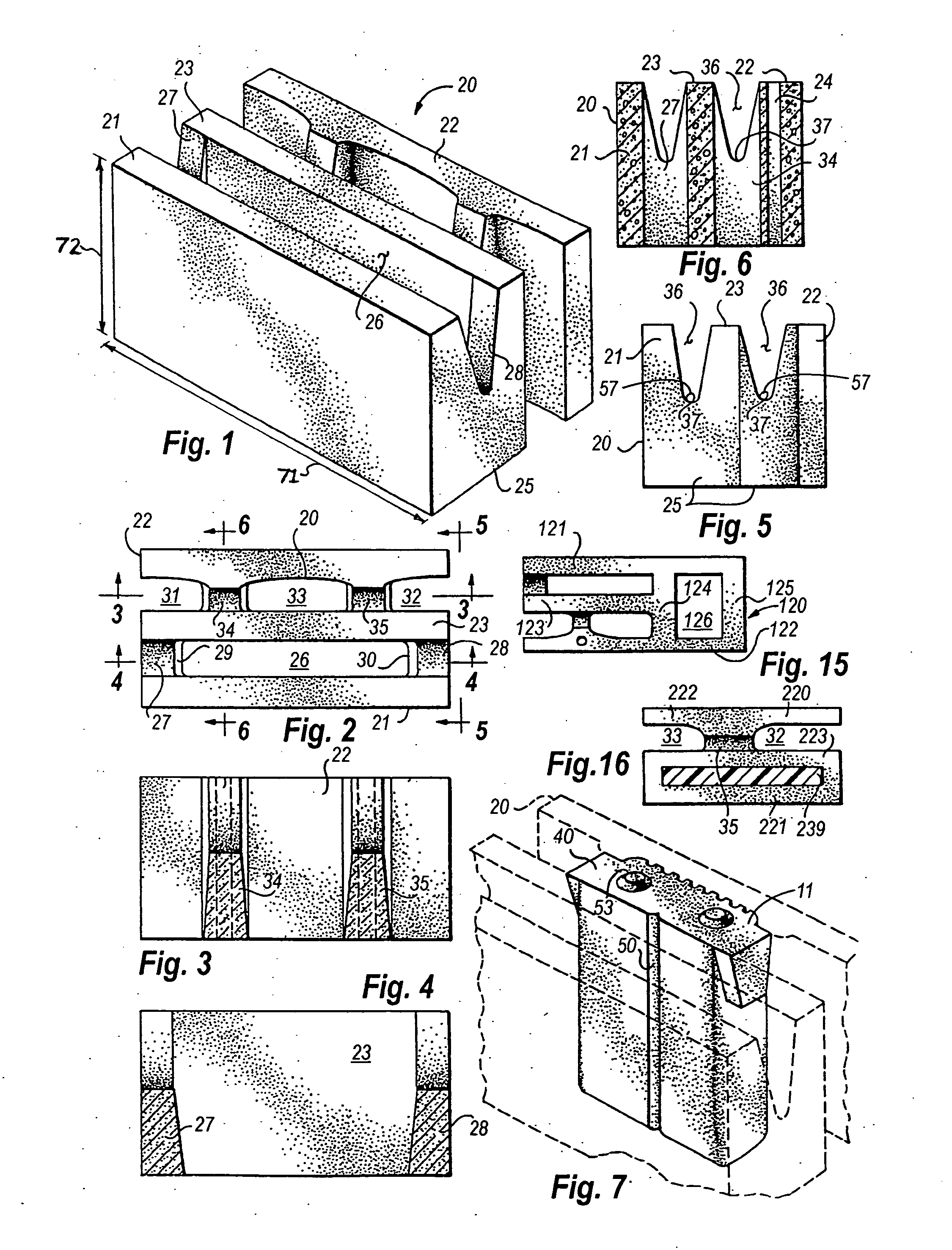

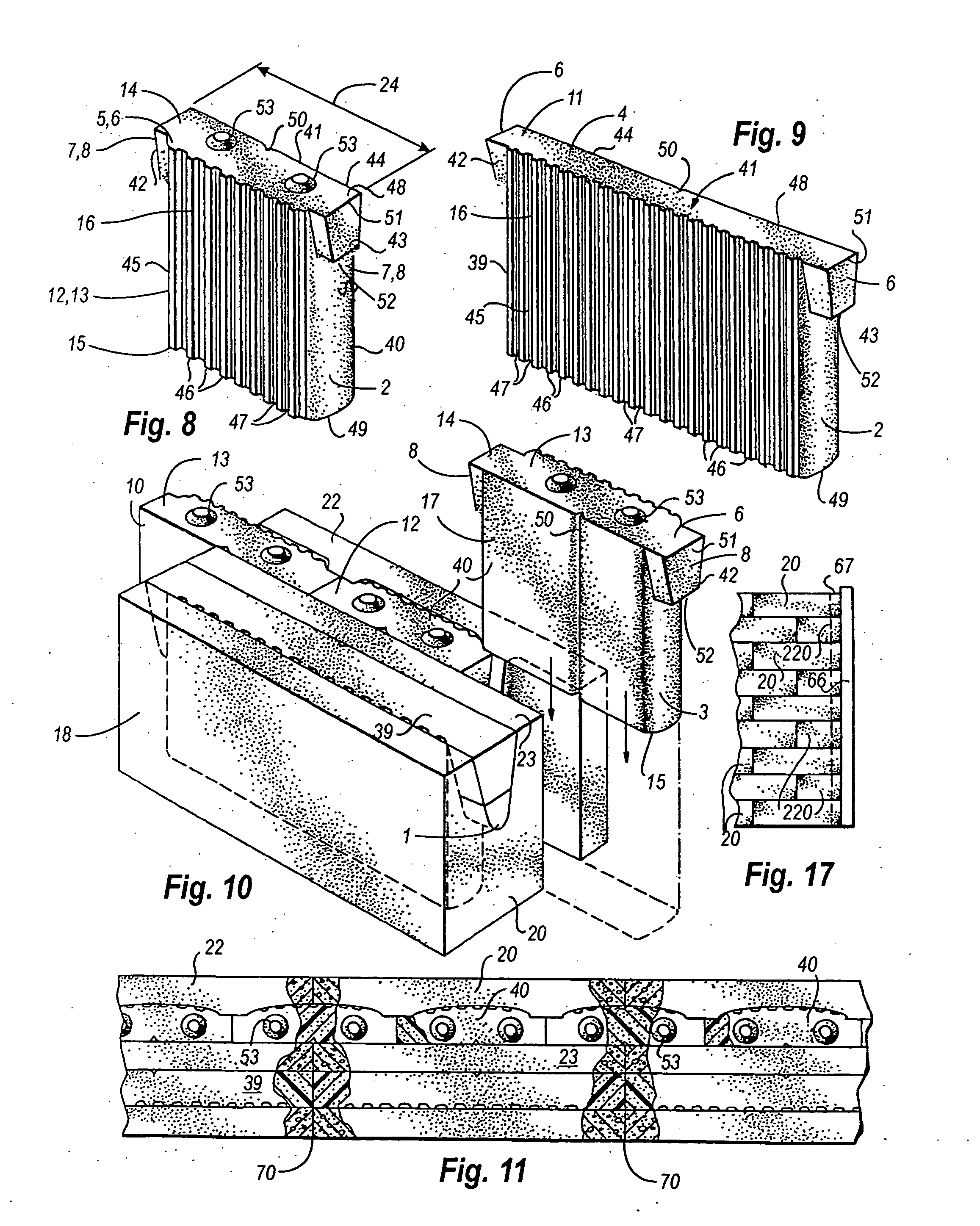

Dry stack insulated building blocks

InactiveUS20080060300A1Improve lateral strengthIncreased shear strengthConstruction materialWallsEngineering

An improved dry stack insulated building block and block wall system, the block having a first and a second side wall, a central web interposed between the side walls, a pair of end transverse webs, and a pair of intermediate transverse webs. The side walls, central web, and transverse webs define a first, a second, and a third cell. A first cell core, second cell core, and a pair of third cell cores of insulative material are inserted in the respective cells. The cell cores have trapezoidal shaped ear members which matingly fit in notches in the transverse webs, the trapezoidal shaped ear members providing for the creation of a notch gap between the base of the ear members and the notch bottom of the respective notches, thereby accommodating crumbing in the notch bottom.

Owner:BRISTOL SYST INT

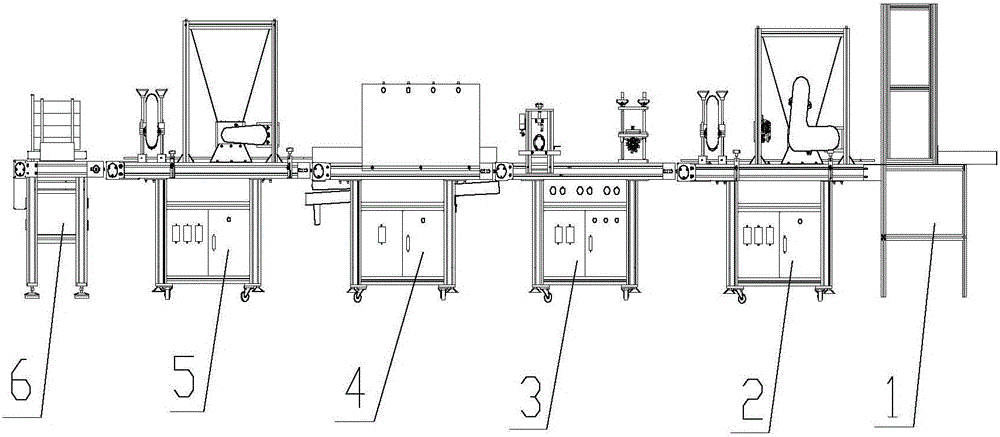

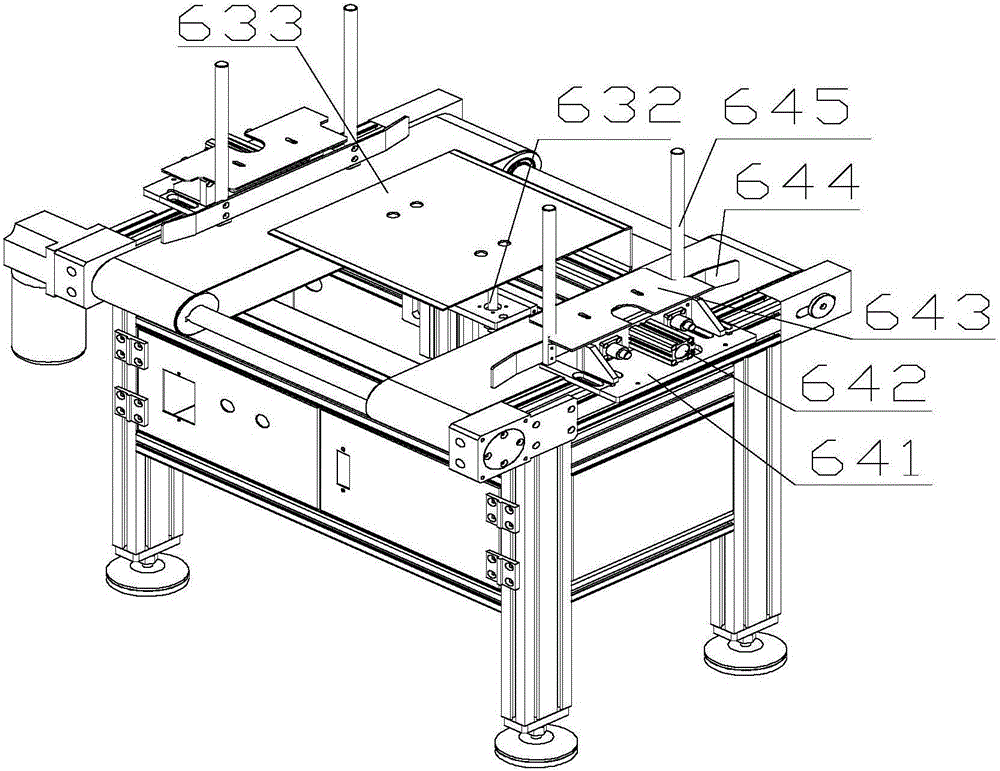

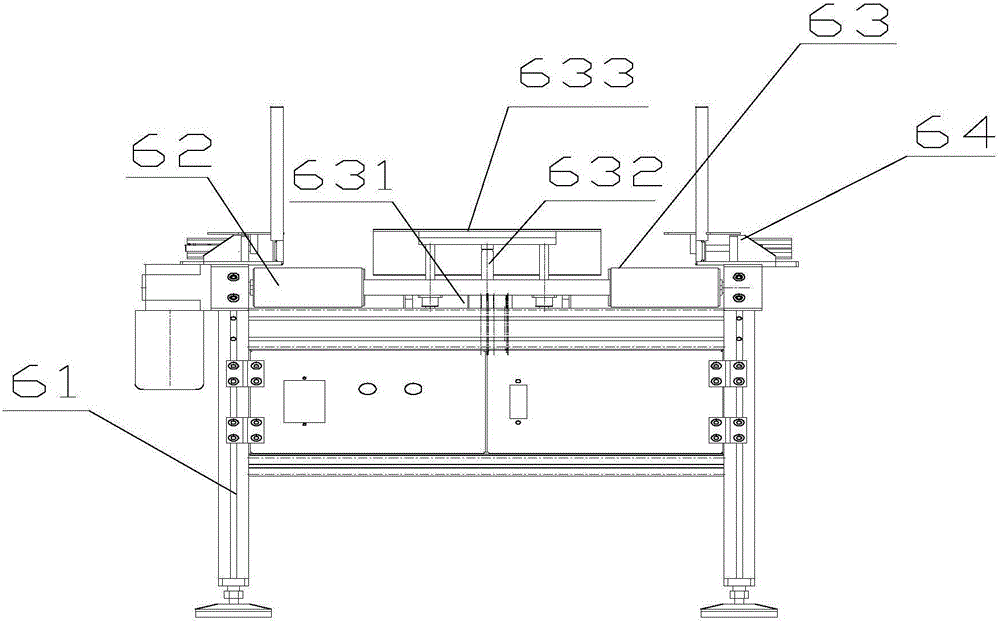

Automated sowing streamline for breeding plug tray

InactiveCN105830592AWith automatic operationImprove work efficiencyCultivating equipmentsSeed depositing seeder partsEngineeringConveyor belt

The invention discloses an automatic seedling tray seeding assembly line. The seeding assembly line is sequentially fixed with a seedling tray upper tray device, a substrate laying device, a precision roller sowing device, a spraying device, a substrate covering device, and a seedling tray stacking device. A seedling raising tray is placed above the seedling raising tray upper plate device, and the seedling raising tray is pushed to the sowing line along the conveyor belt. The working efficiency of the assembly line of the present invention is 10 times that of the traditional artificial seedling raising mode, reduces the labor cost by two-thirds, and can significantly improve the quality of seedling raising. The operation is simpler, the work efficiency and quality are higher, the commonality of parts is better, the reliability and safety are higher, and the market prospect is very broad.

Owner:山东中天盛科自动化设备有限公司

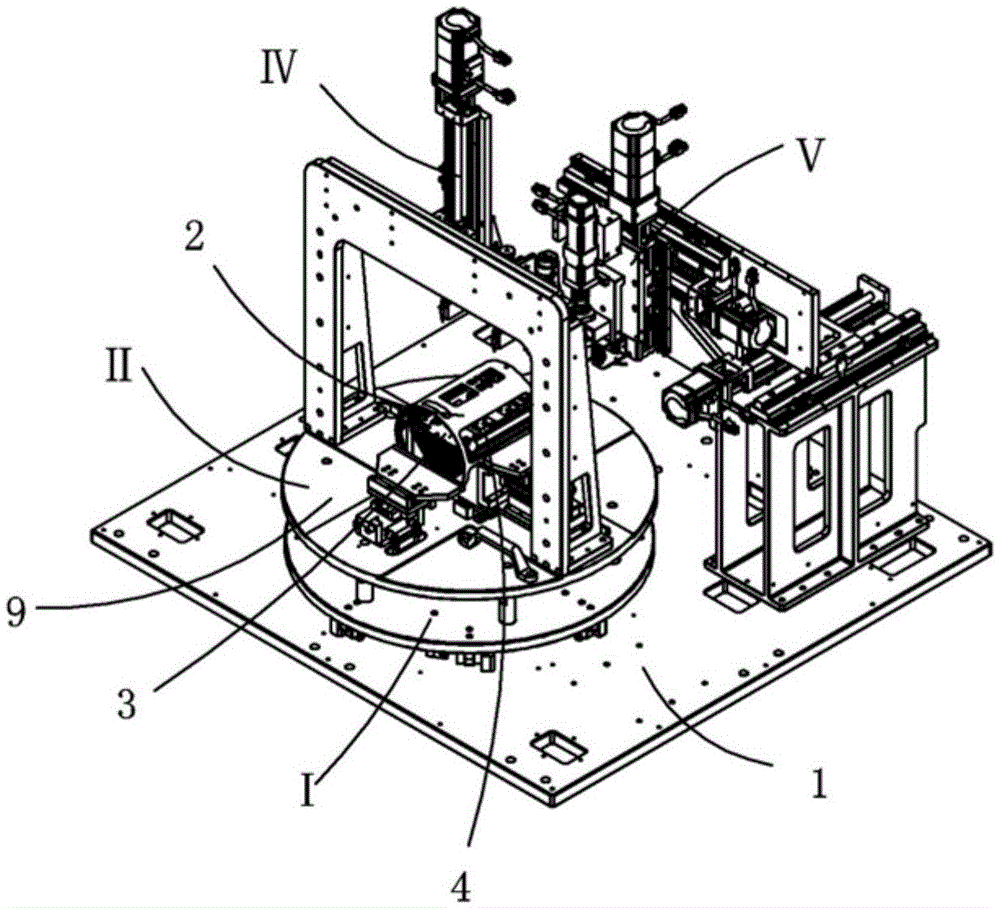

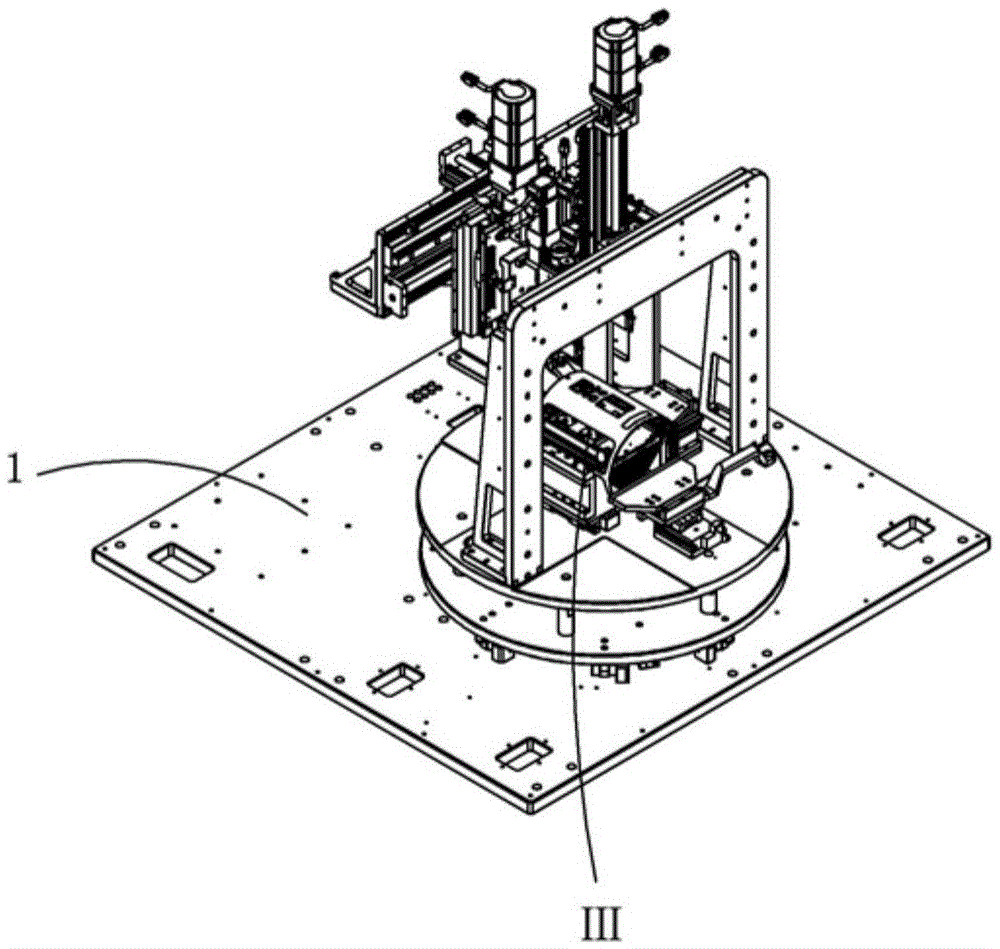

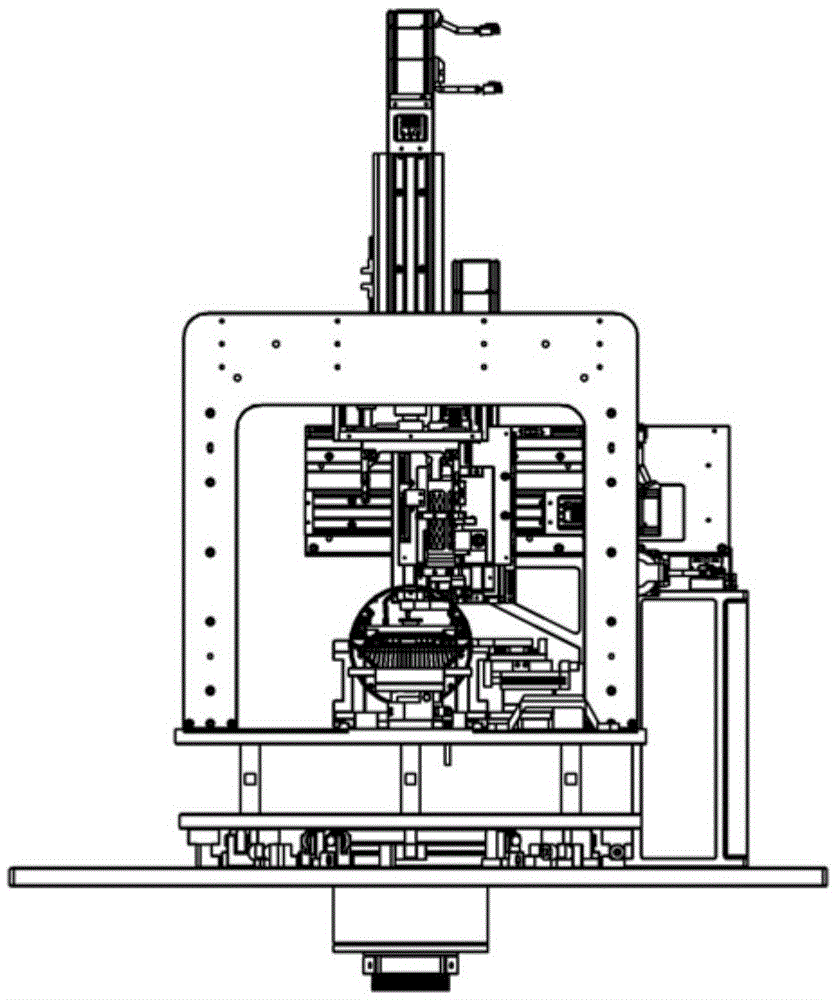

Automatic CPU alignment assembling machine

The invention relates to an automatic CPU alignment assembling machine. The automatic CPU alignment assembling machine comprises a bottom plate. The bottom plate is provided with a rotating mechanism used for facilitating manual feeding and discharging. A rotary disc of the rotating mechanism is provided with a carrier mechanism used for positioning a product. The product is positioned on the carrier mechanism. A CPU is placed in the product. A pressing plate is placed on the CPU. A plurality of sets of screw positioning modules are arranged on the pressing plate and correspond to to-be-locked positions of the product. The bottom plate is provided with a downward pressing mechanism used for downwards pressing the pressing plate. A locking mechanism used for locking the CPU to the product through screws is arranged on the bottom plate. The CPU is locked on a cylinder computer case through the screws, automatic alignment and centering of the left side and the right side of the CPU can be achieved, and accurate screw locking is achieved.

Owner:BOZHON PRECISION IND TECH CO LTD

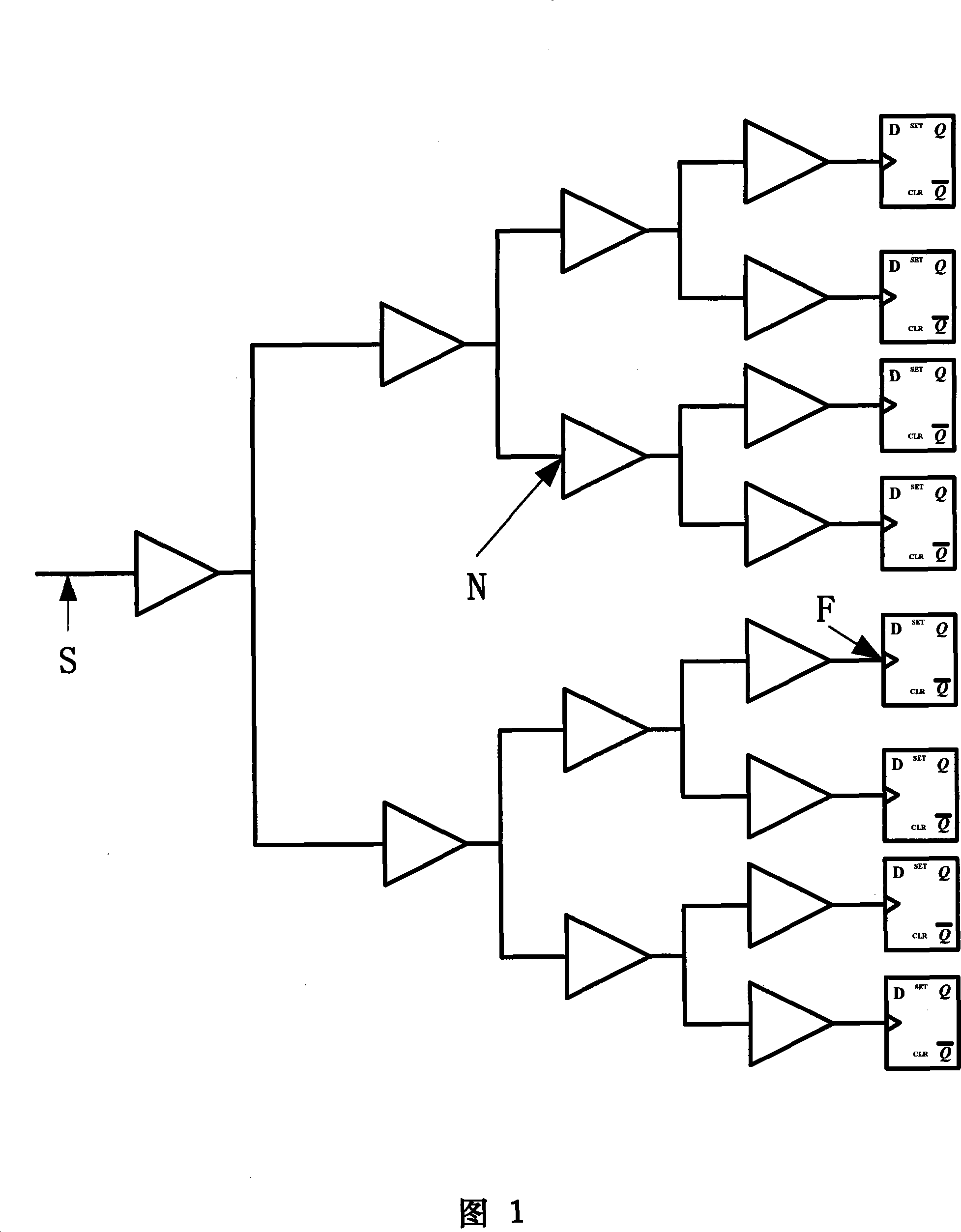

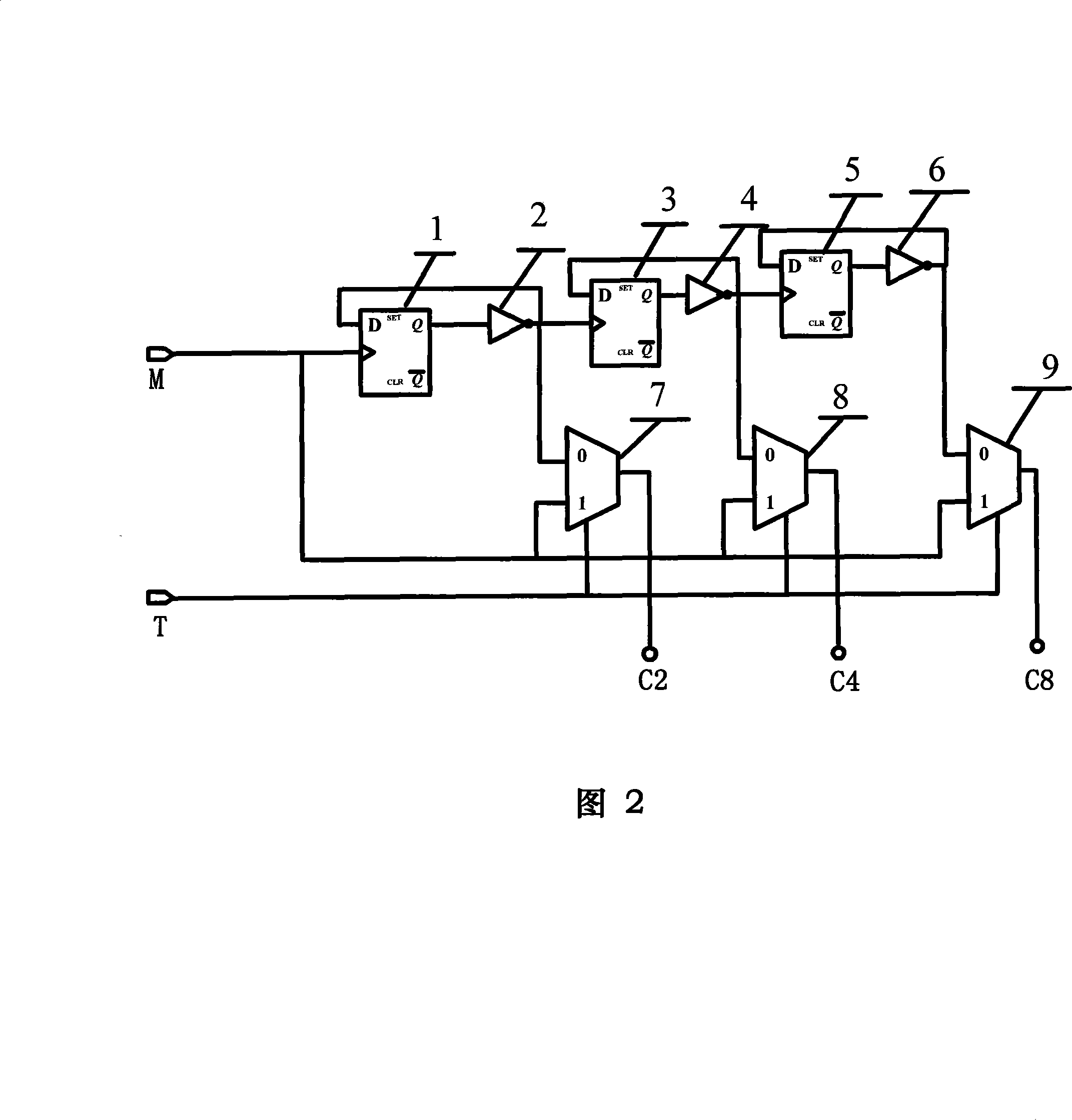

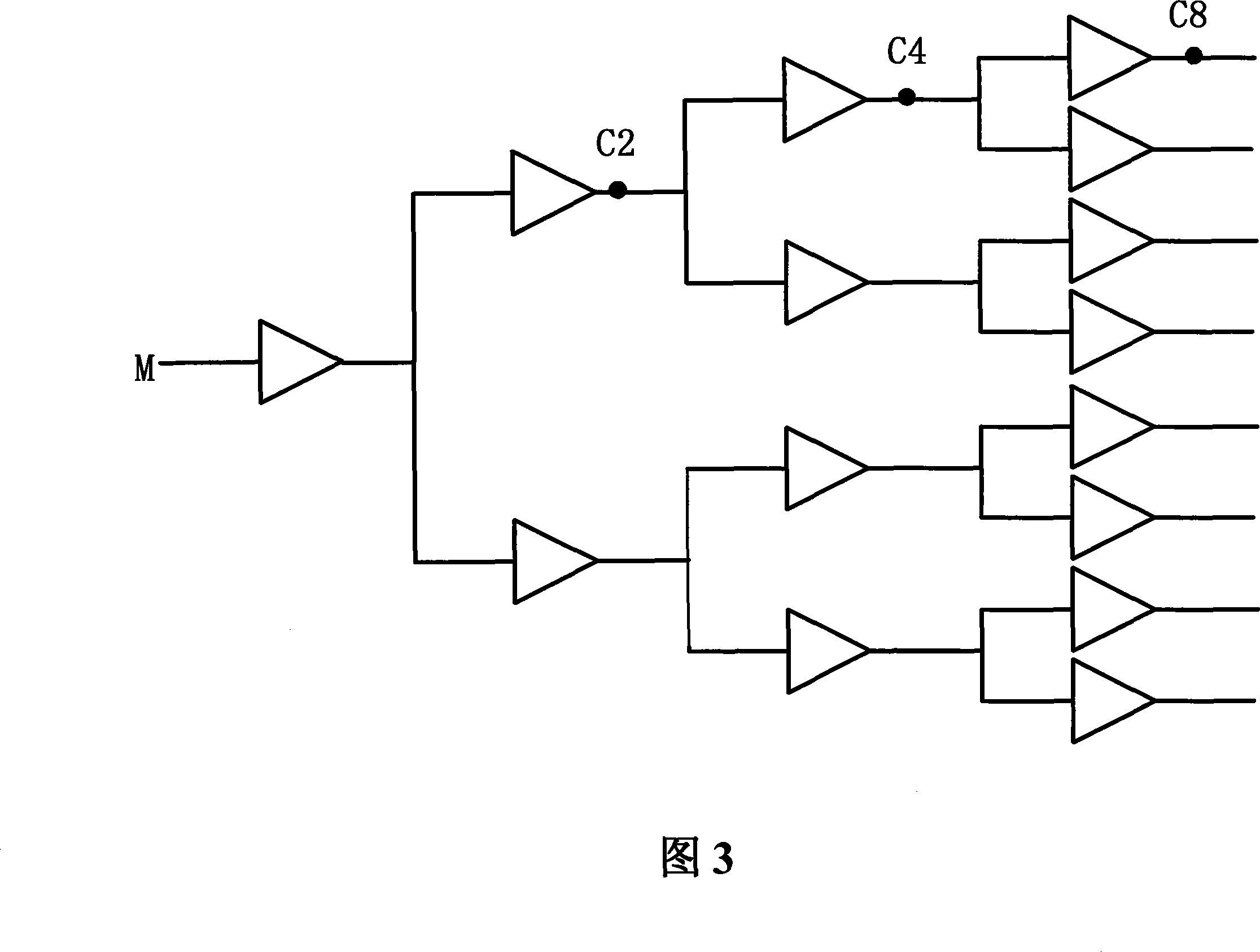

Digital television modulator chip synchronization frequency division clock production devices and method

InactiveCN101216721AReduce skewIncrease clock frequencyTelevision system detailsColor television detailsProcessor registerComputer science

The invention provides a device and a method for generating a synchronous frequency dividing clock in the chip of a digital TV modulator. The invention is used in the chip of the modulator for the multimedia broadcasting base band of a GB20600 ground digital TV and able to divide the main frequency clock signal exponentially. The device includes a main frequency clock signal input end, a testing and enabling signal input end, three basic frequency dividing units in serial connection and three selectors, and, in particular, two flip-latches. The device and the method divide the main frequency clock signal into 2, 4 and 8 sections using a register and an inverter, and meanwhile flip-latching the signal of divided frequency using the main frequency clock signal; the obtained signal of divided frequency becomes the final clock signal of divided frequency after passing through the selector. The invention has the main advantage that each clock signal of divided frequency can be averaged according to the delay in passing the main frequency clock signal so as to reduce the deflection of the synchronous clock signal, thus reducing the deflection of the clock of the whole integrated circuit chip and improving the frequency and performance of the chip.

Owner:BEIHANG UNIV