Method for measuring phase difference of common-period signals based on delay unit dedicated for FPGA

A technology of periodic signal and measurement method, applied in the direction of phase angle between voltage and current, measurement device, measurement of electrical variables, etc., can solve the problems of high filling pulse signal frequency, large measurement error, and low measurement accuracy, and achieve high precision The effect of high, short development cycle and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

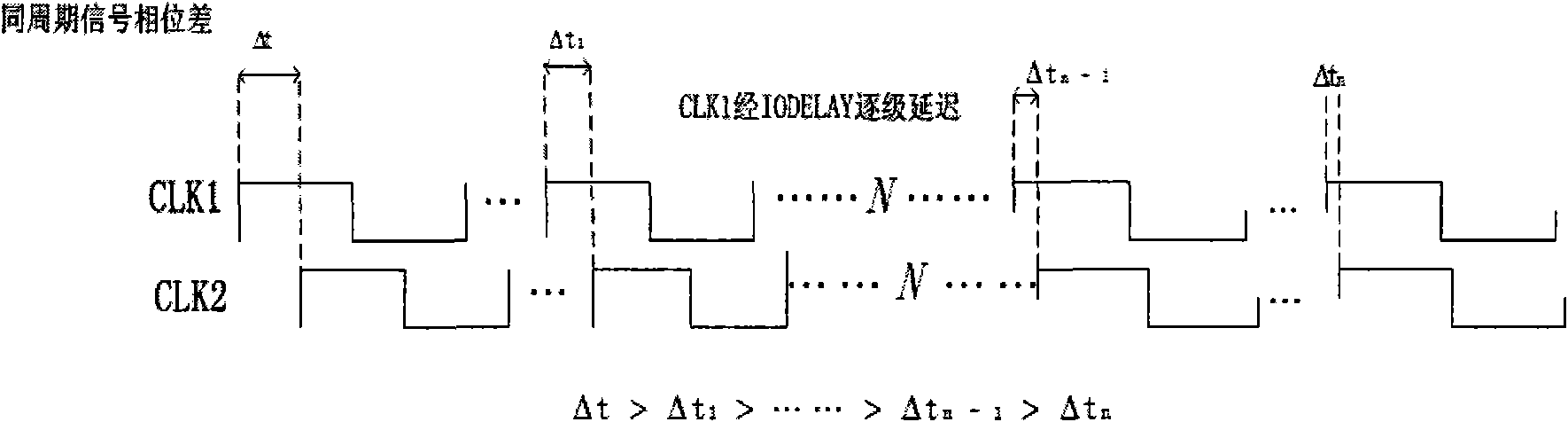

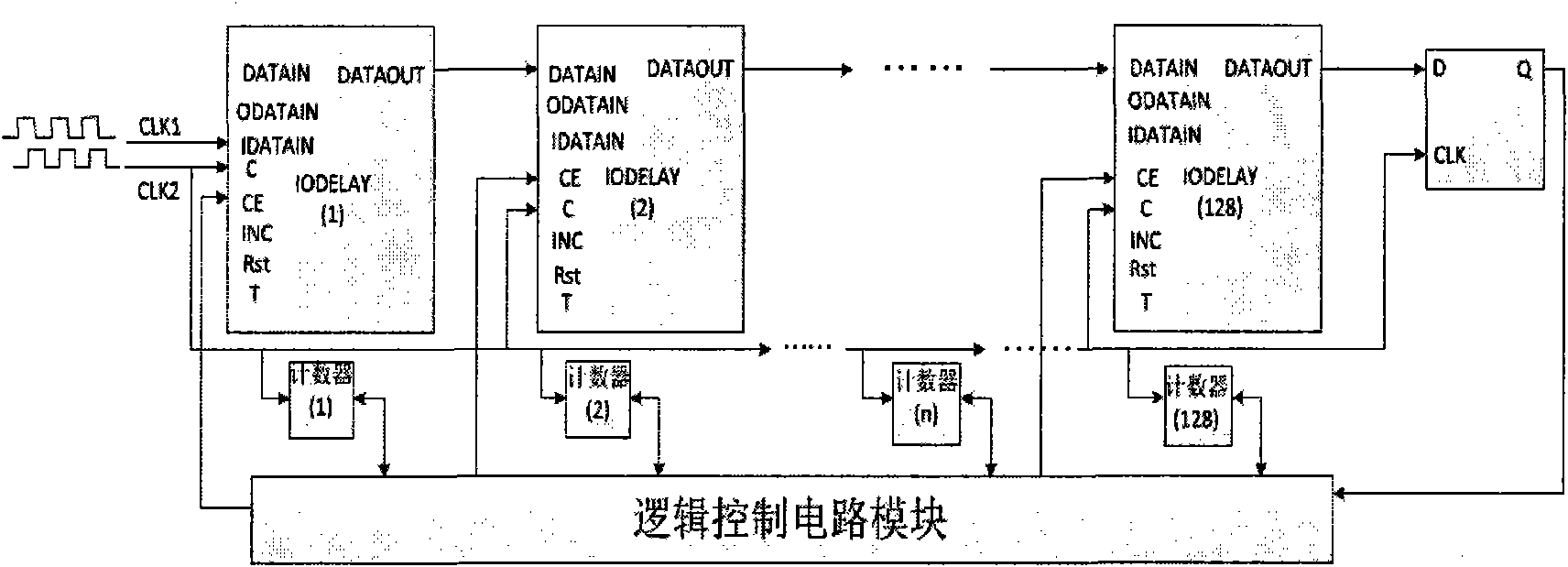

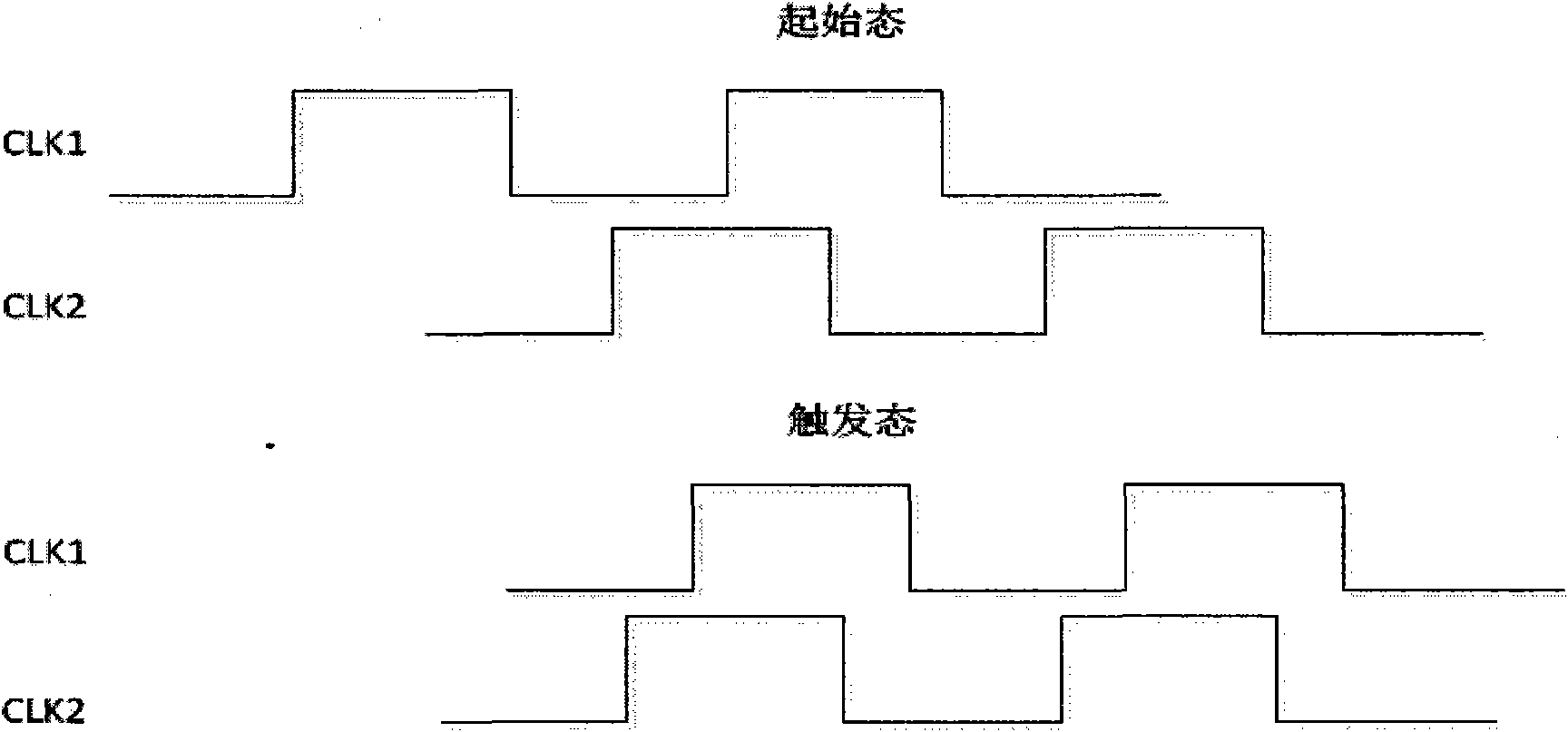

[0018] The invention proposes a Xilinx FPGA-based method for measuring the phase difference of the same period signal with high precision. The measurement method that the present invention adopts is to utilize the tap line of IODELAY, CLK1 is carried out accurate delay, and the D end of input D flip-flop; CLK2 is input to the CLK end of D flip-flop and the CLK end of counter by the global clock network of FPGA; The D flip-flop outputs the change of the Q terminal value, detects the edge coincidence information of the delayed CLK1 and CLK2, and triggers the logic control circuit, so as to control and calculate the phase difference of the same cycle signal.

[0019] Xilinx Virtex-4 and Virtex-5 FPGA devices have a programmable input and output delay unit IODELAY in each IOB. IODELAY is a variable 64-bit delay chain. When used in conjunction with IDELAYCTRL, IODELAY can provide a precise time-delta delay that is not affected by process, temperature, or voltage variations. Each ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More