Digital DLL apparatus for correcting duty cycle and method thereof

a digital dll and duty cycle technology, applied in the field of delay locked, can solve the problems of time delay and the inability of conventional dlls to correct phase delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Benefits of technology

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

Other aspects of the disclosed apparatuses and methods will become apparent from the following description of the embodiments with reference to the accompanying drawings.

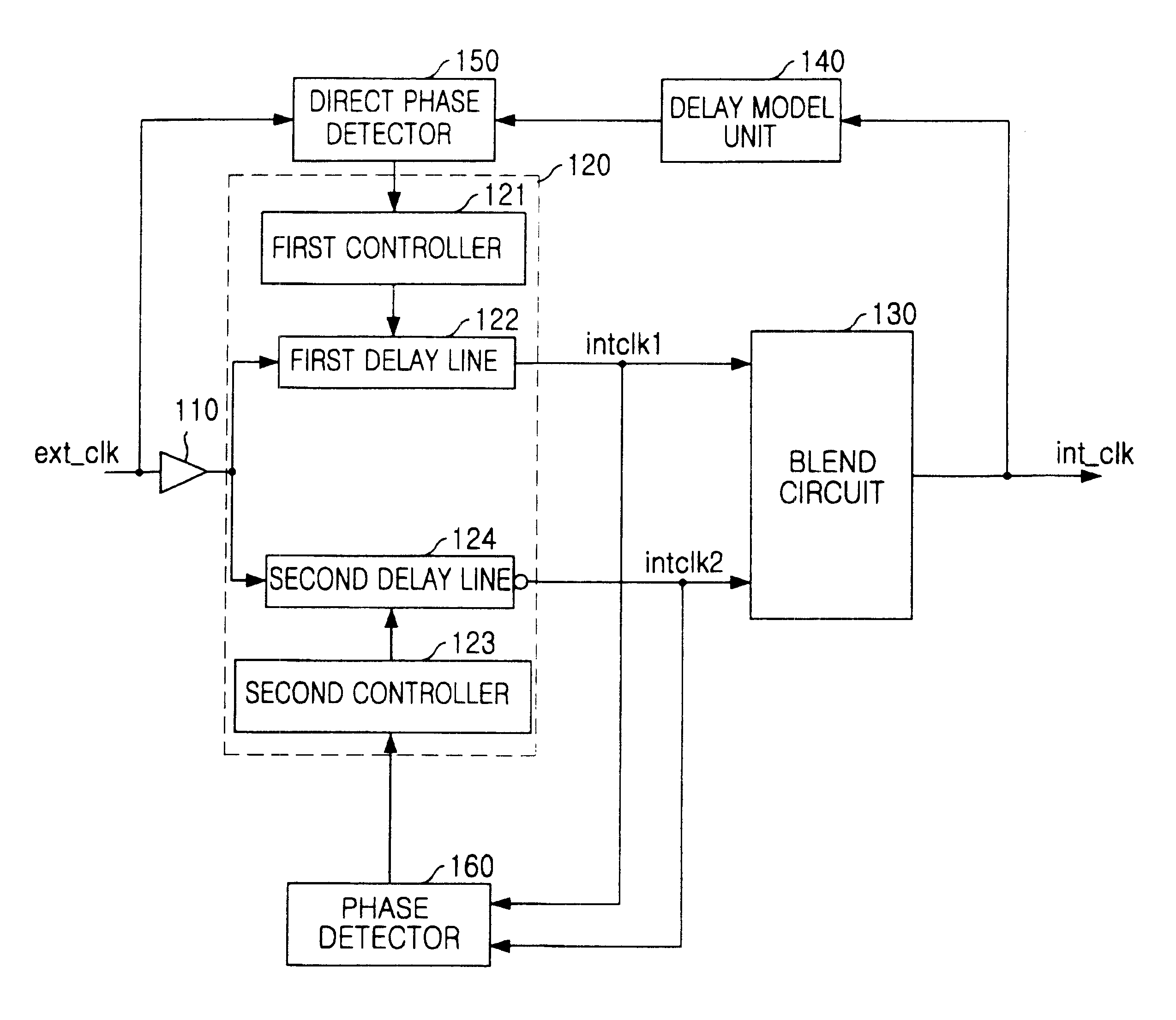

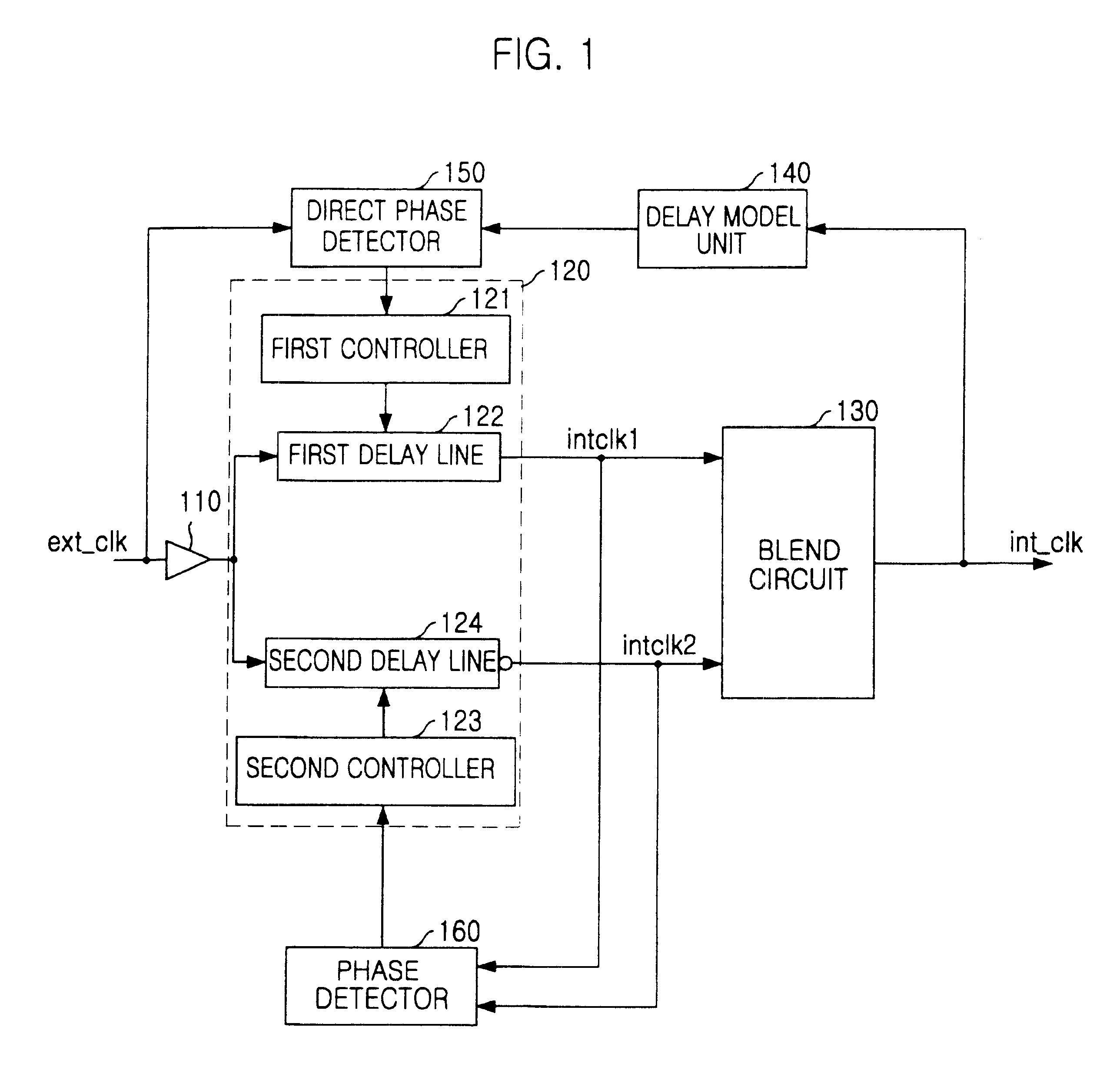

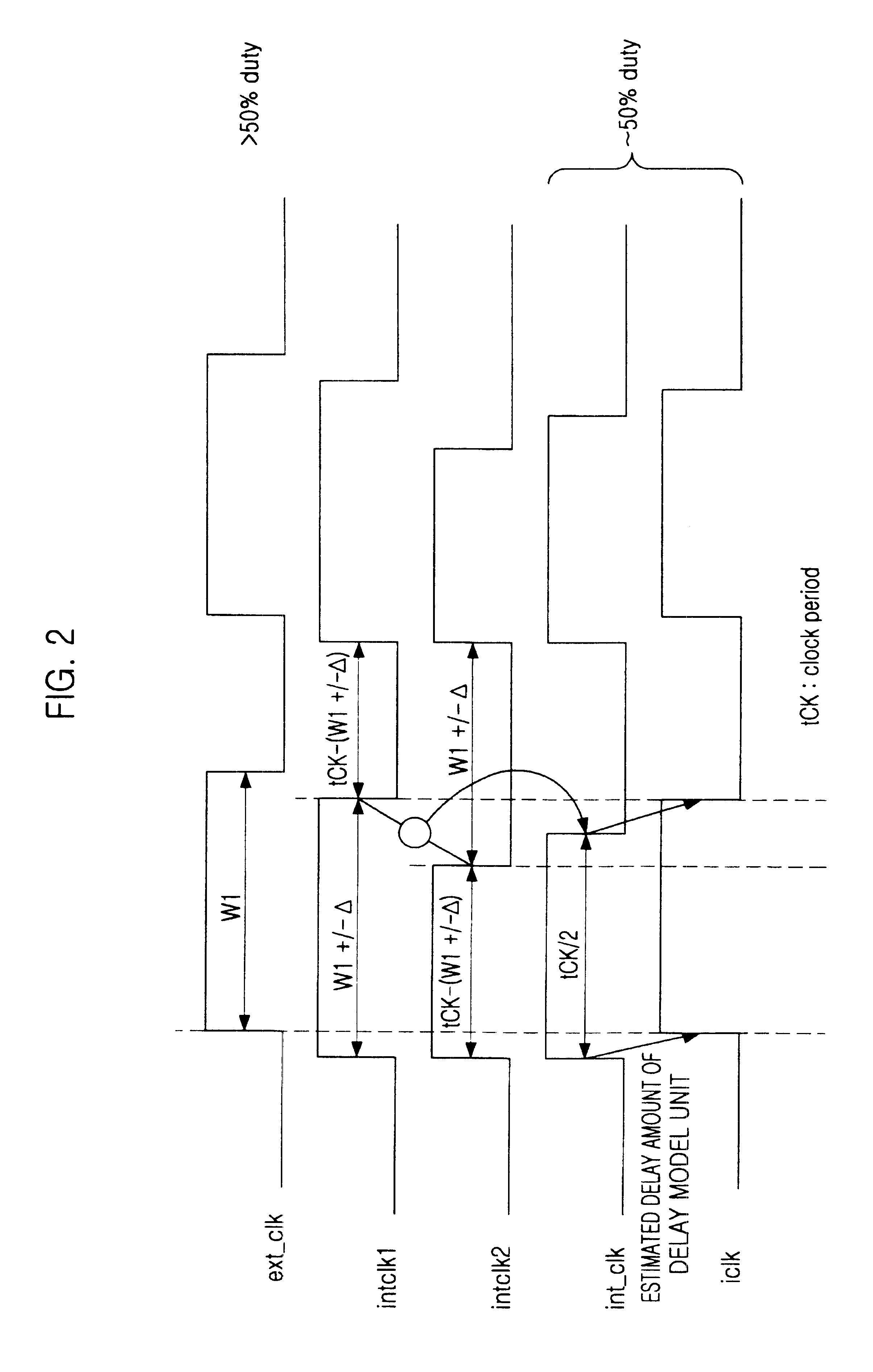

FIG. 1 is a block diagram showing a digital DLL apparatus for correcting a duty cycle in accordance with a preferred embodiment. The digital DLL apparatus includes a buffer 110, a delay line unit 120, a blend circuit 130, a delay model unit 140, a direct phase detector 150 and a phase detector 160.

The buffer 110 receives an external clock signal (ext_clk) and generates a first internal clock signal which becomes activated at an edge of a clock. The first internal clock signal is inputted to the delay line unit 120.

The delay line unit 120 receives the first internal clock signal and also receives a first detection signal and a second detection signal from the direct phase detector 150 and the phase detector 160. The delay line unit 120 delays the first internal clock signal based on the first and second detection sig...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More