Patents

Literature

601results about "Angle demodulation by oscillations conversion" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

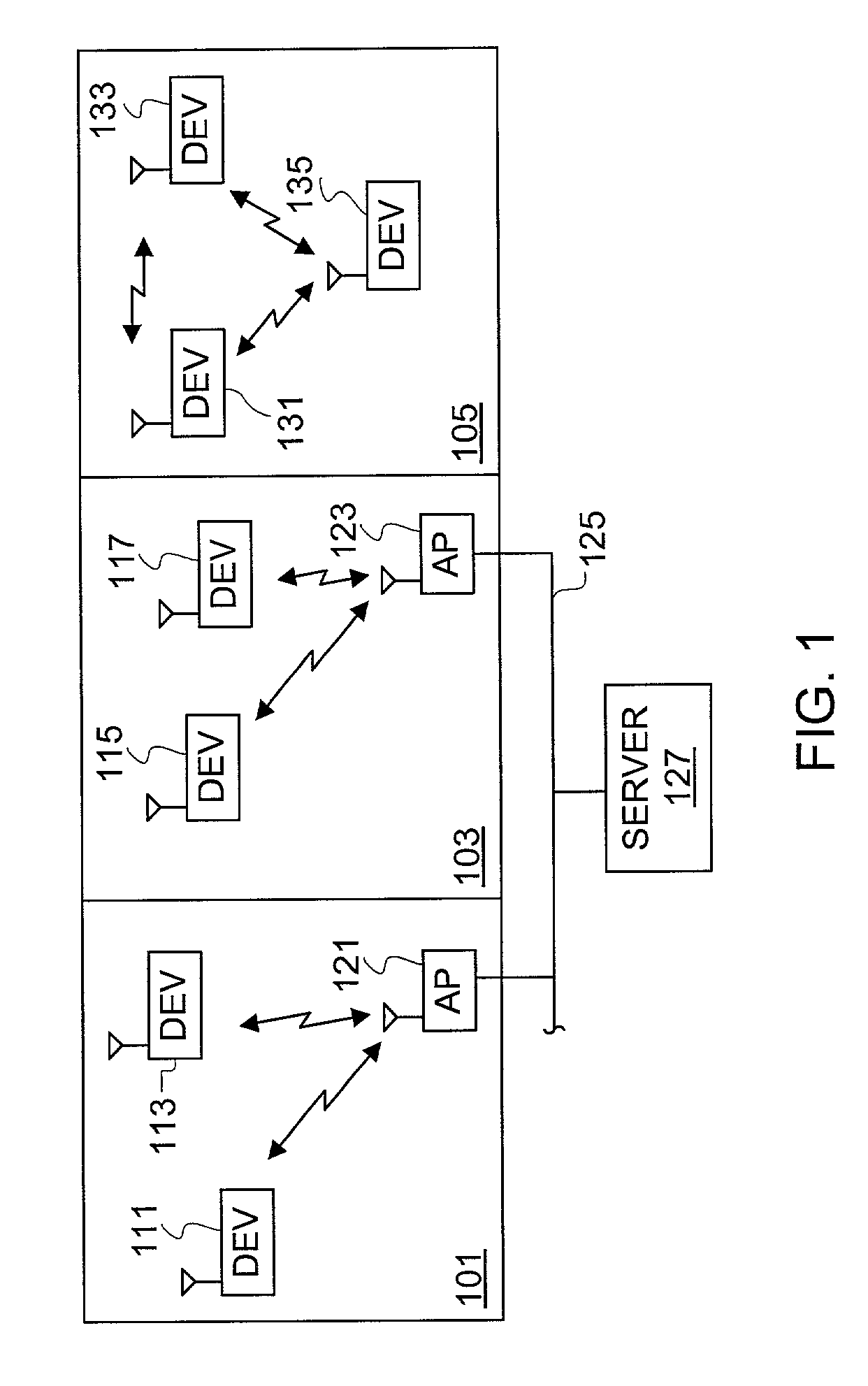

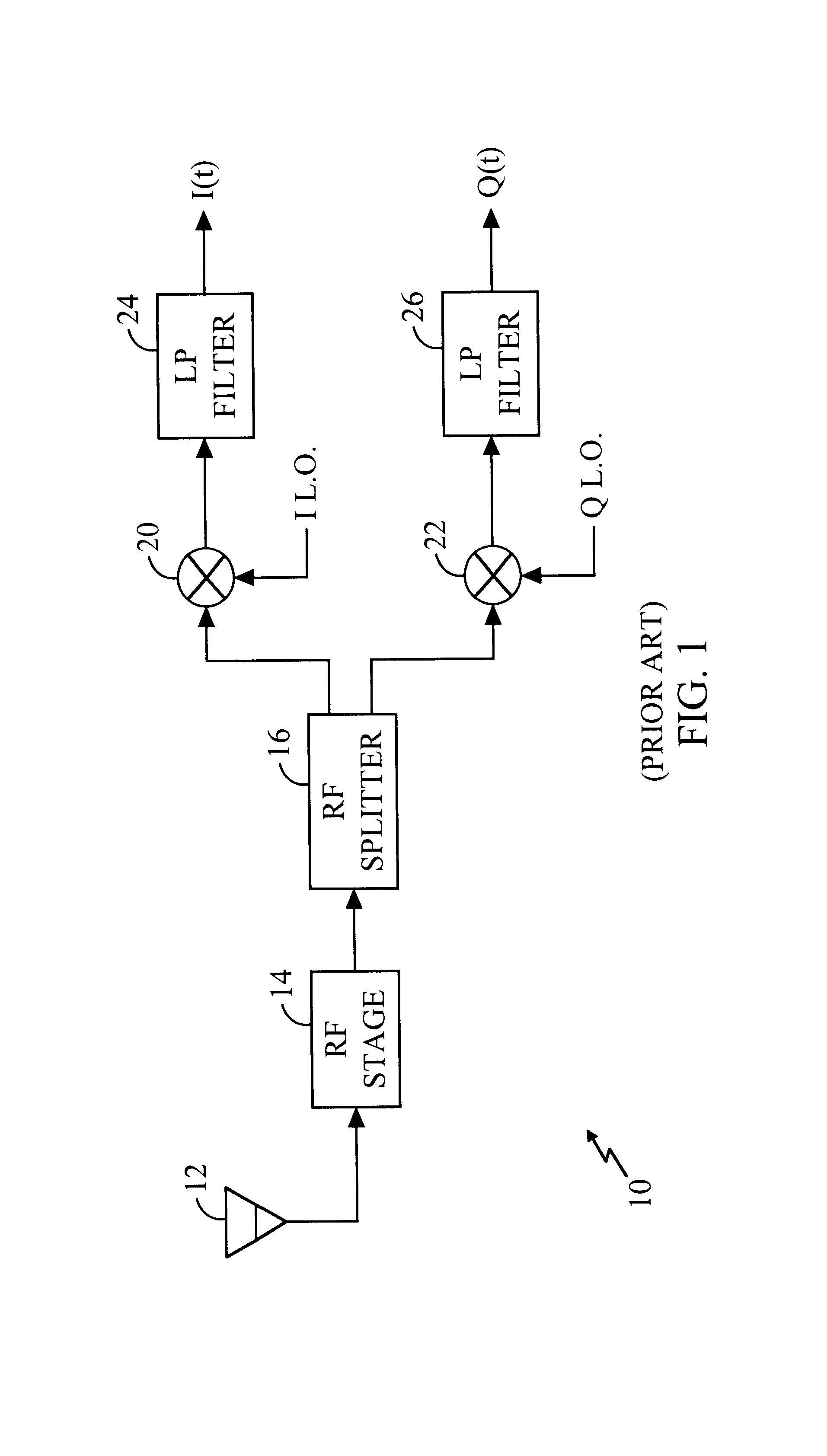

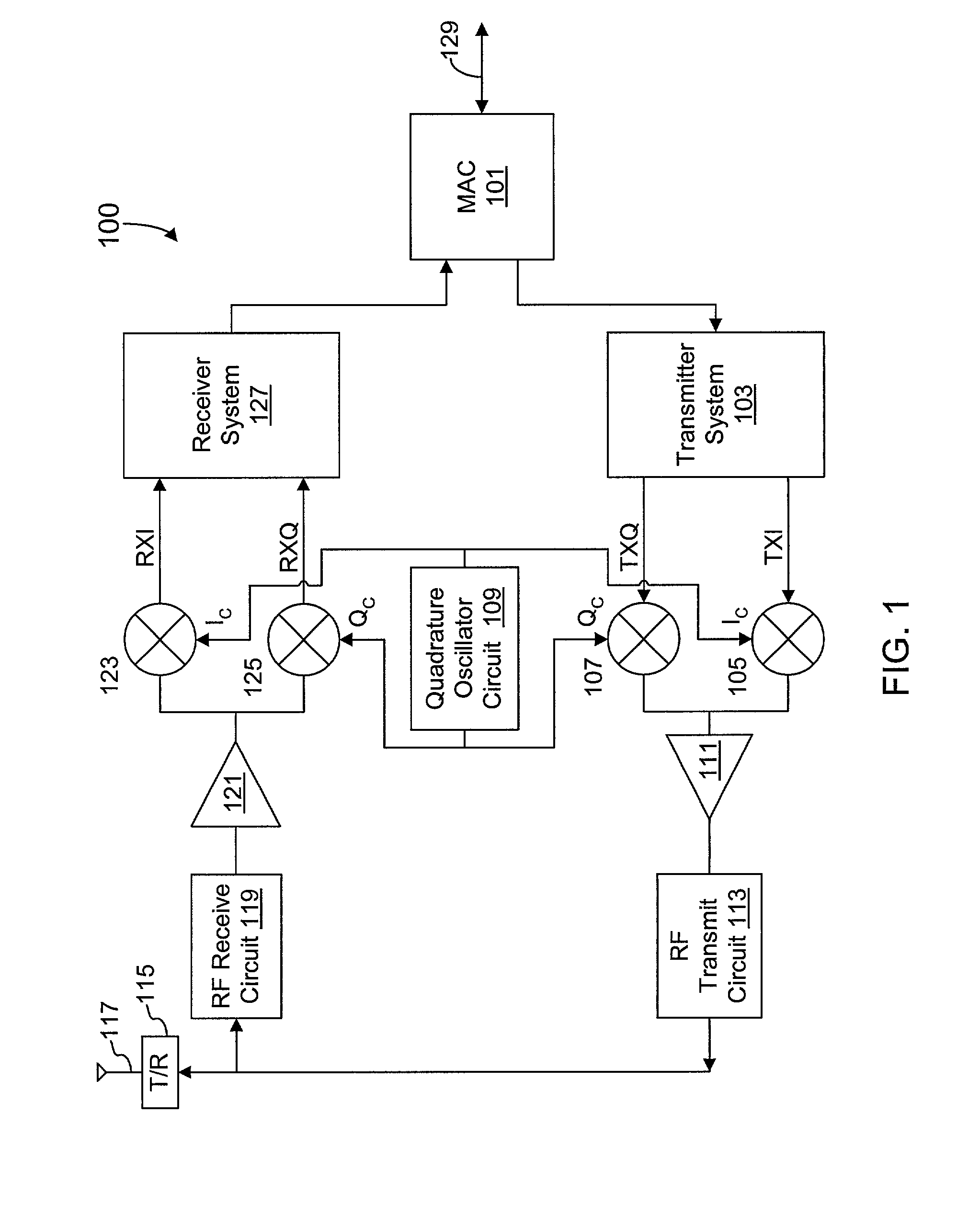

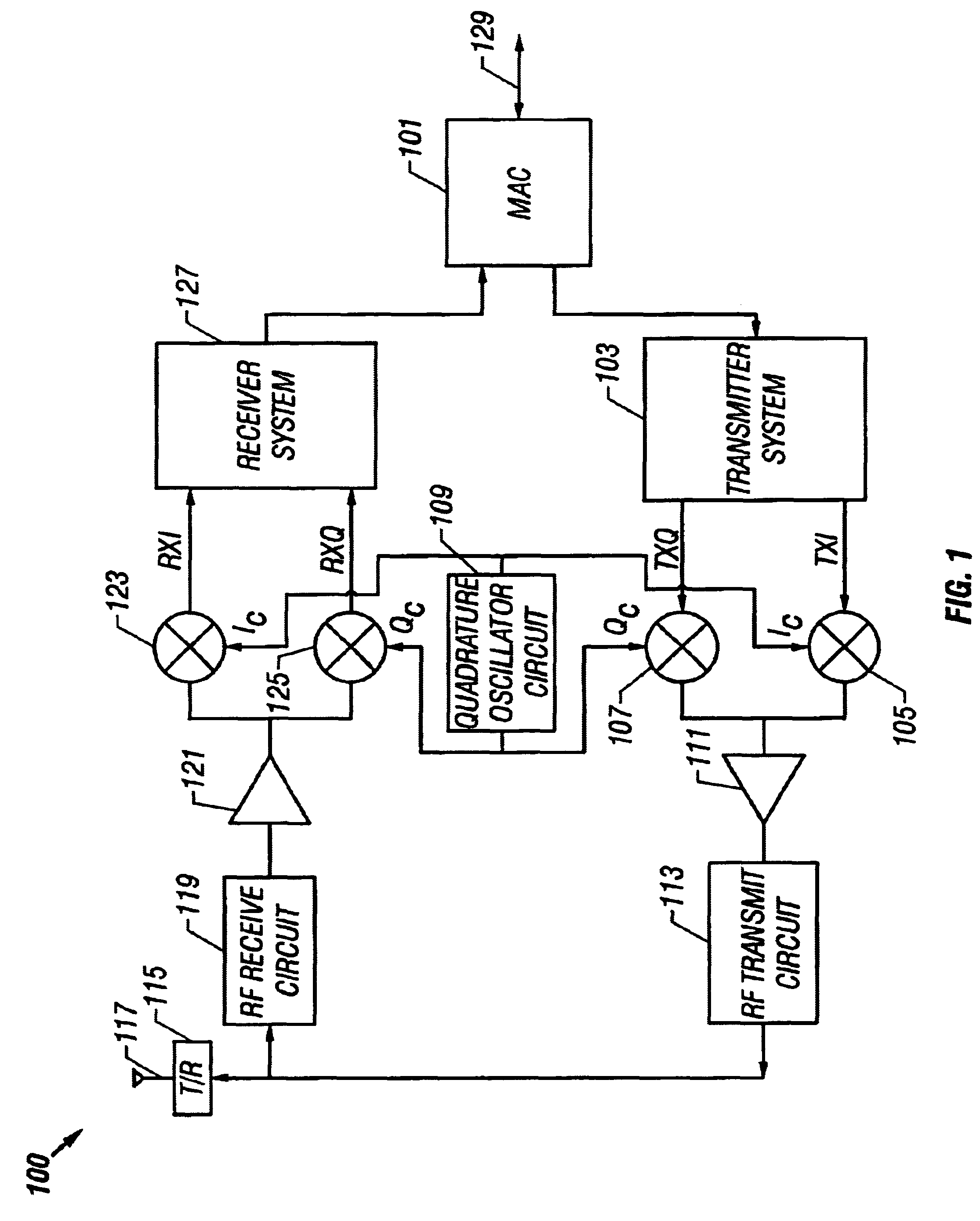

Packet acquisition and channel tracking for a wireless communication device configured in a zero intermediate frequency architecture

A method of controlling operation of a wireless device configured in a zero intermediate frequency architecture including a DC loop and a gain loop. The method includes processing energy in a wireless medium to generate a corresponding receive signal, monitoring the receive signal via a predetermined measurement window, detecting a changed condition in the channel, holding the gain feedback control loop at a constant gain level, and operating the DC loop in an attempt to search a stable DC value for the receive signal while the gain loop is held constant. A first case is DC saturation, where the gain is held constant until DC is controlled. A second case is clear channel assessment, where a prior stored gain setting is applied to the gain loop after detecting the end of the packet. A third case is preparation for receiving an expected acknowledgement packet after transmitting a packet, where again a prior stored gain setting is applied to the gain loop and DC is searched.

Owner:INTELLECTUAL VENTURES I LLC

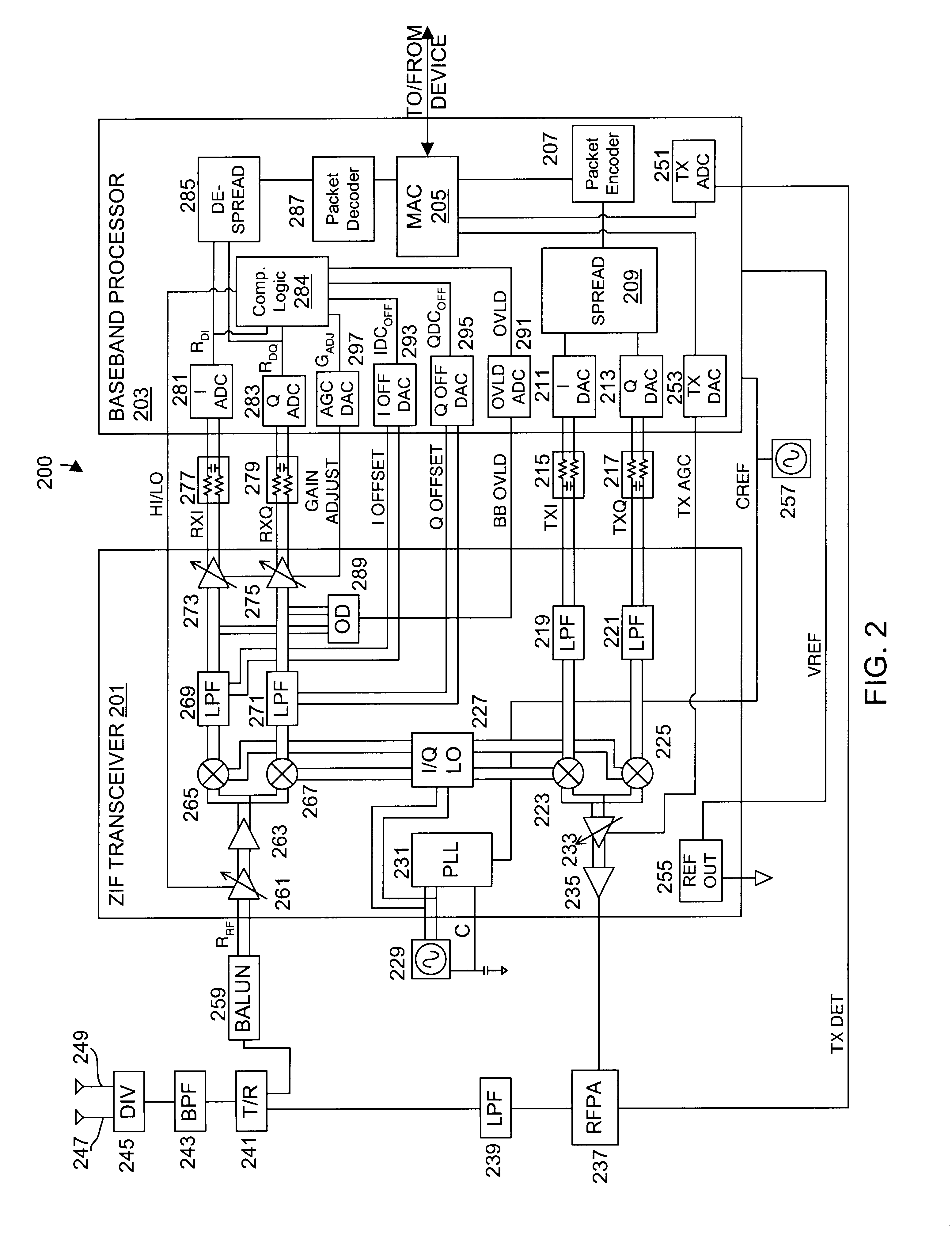

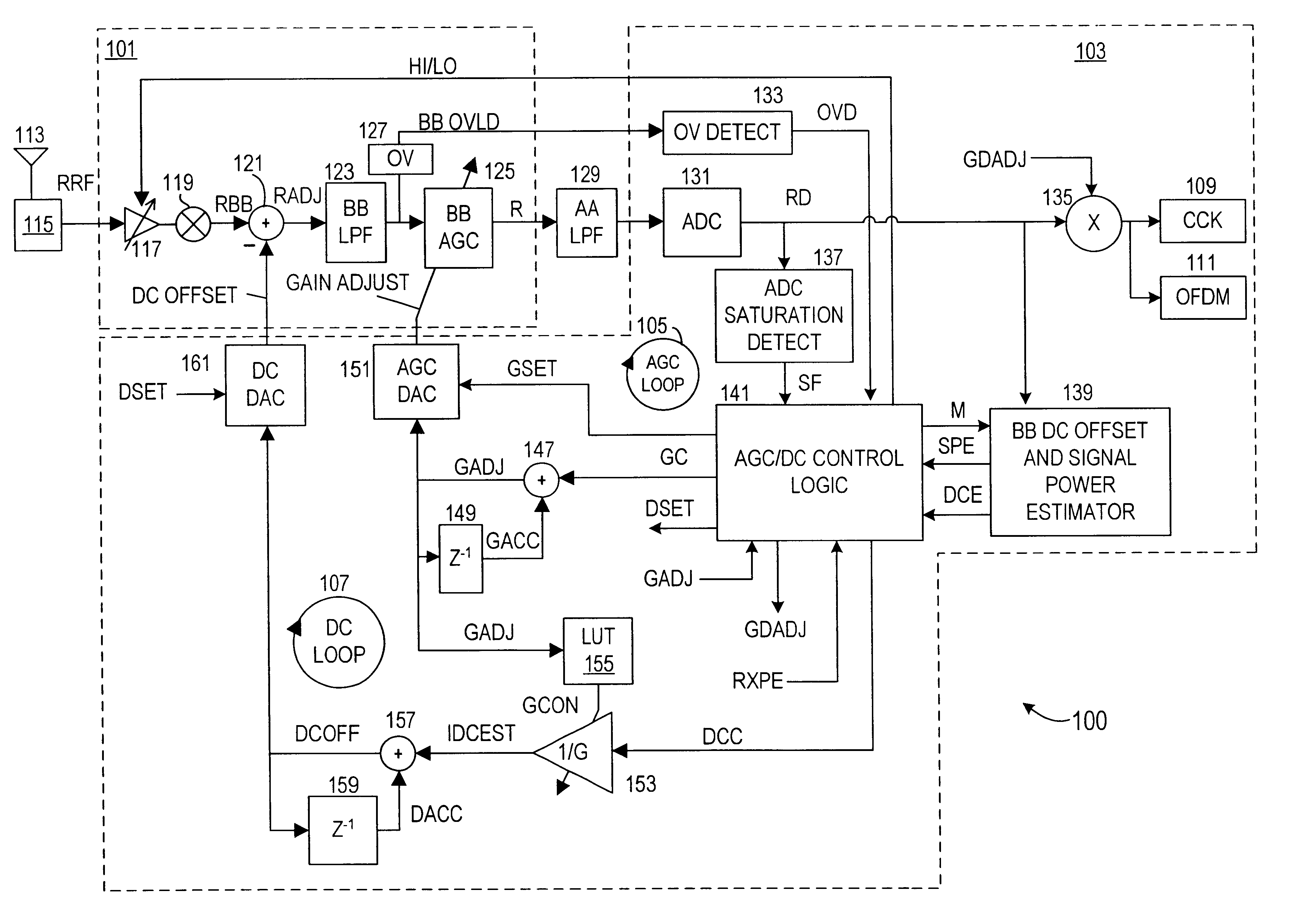

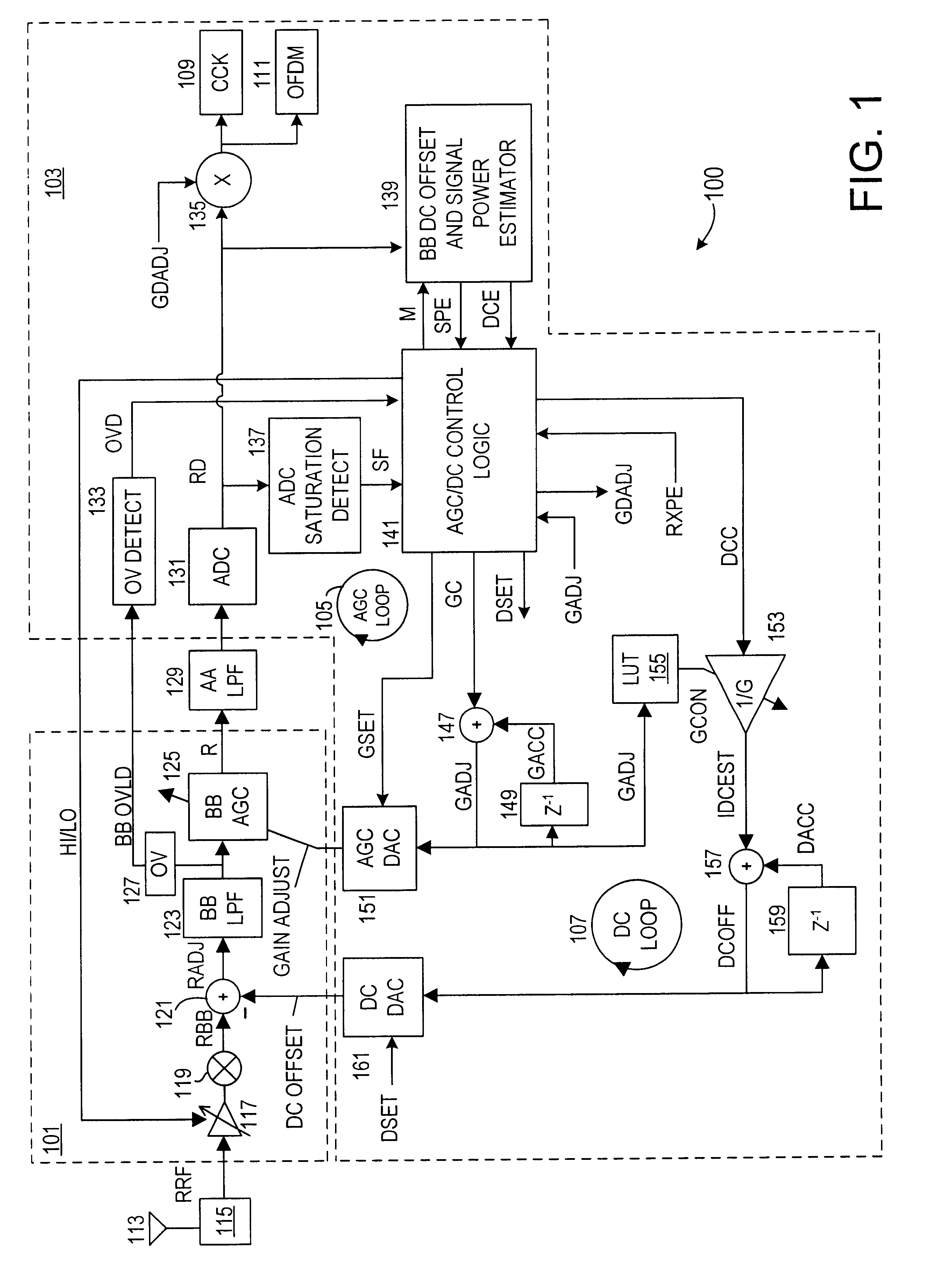

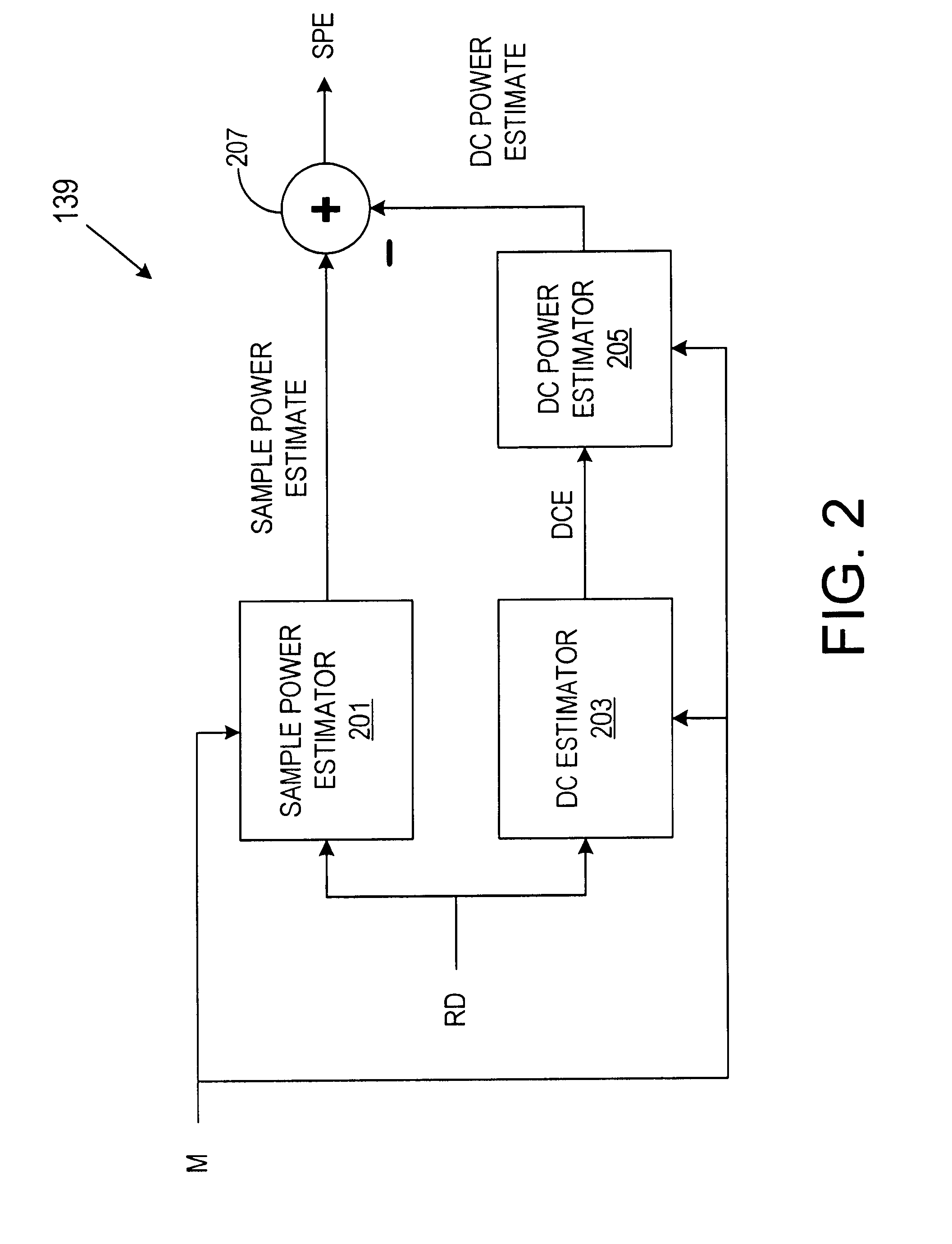

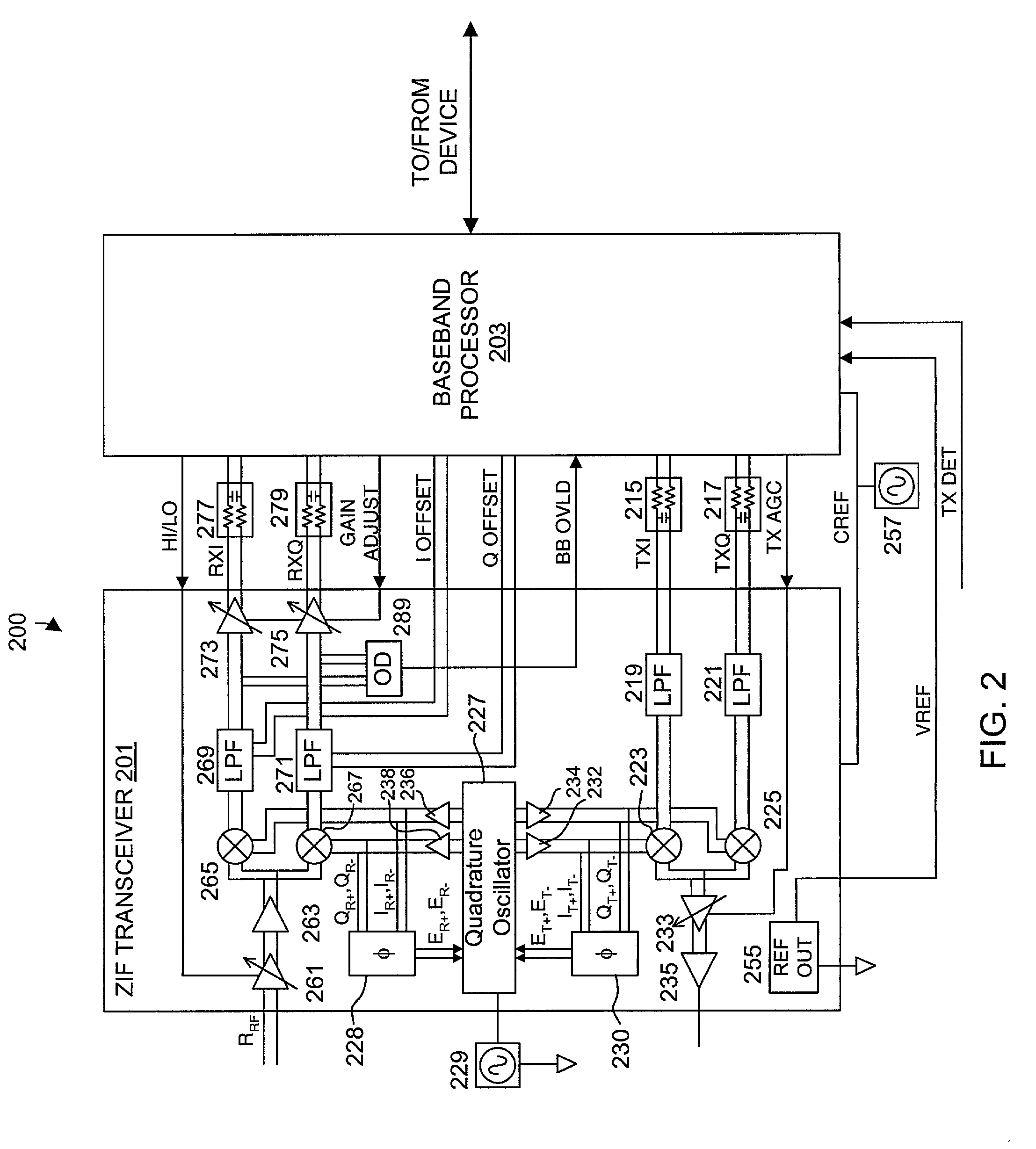

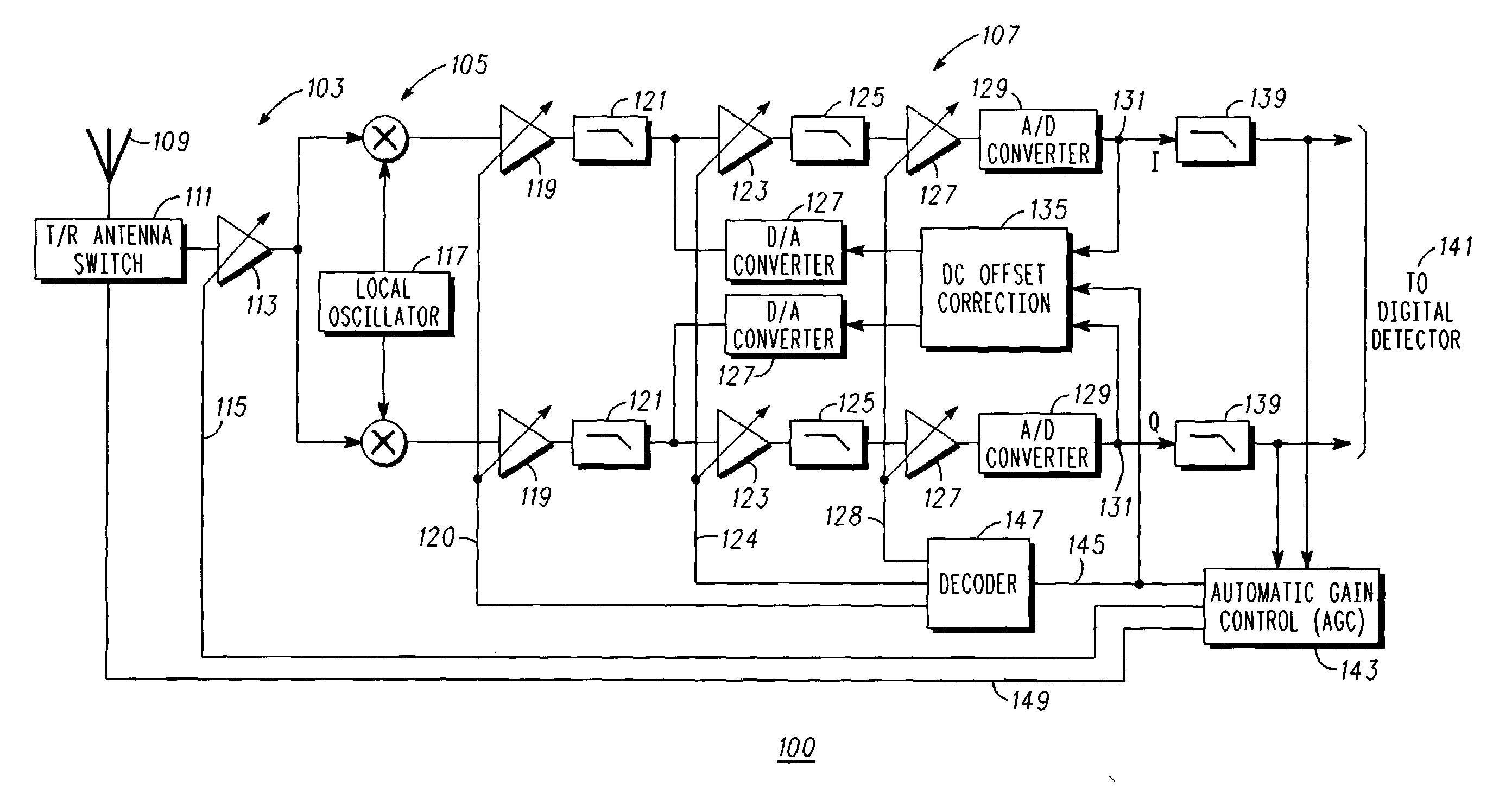

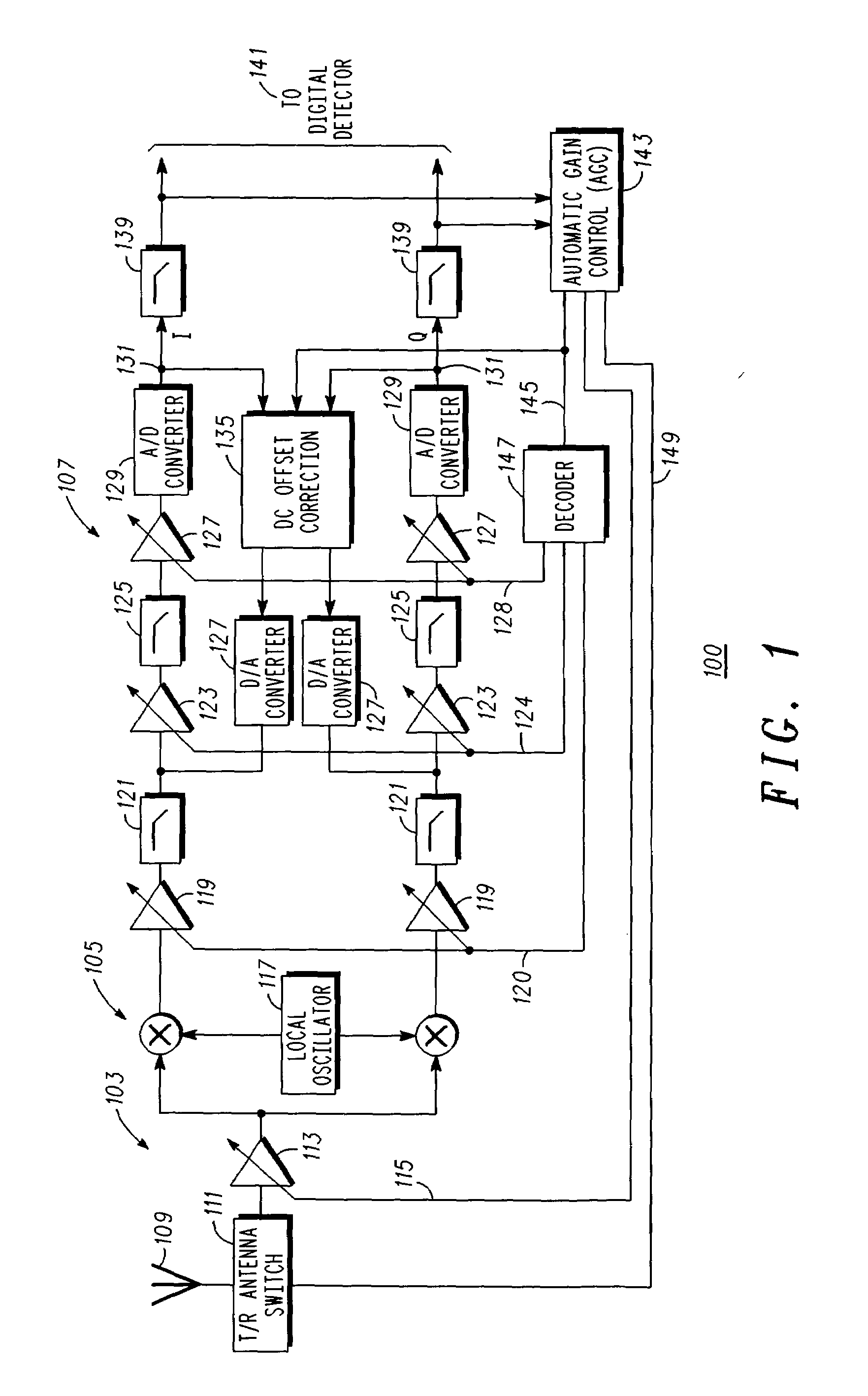

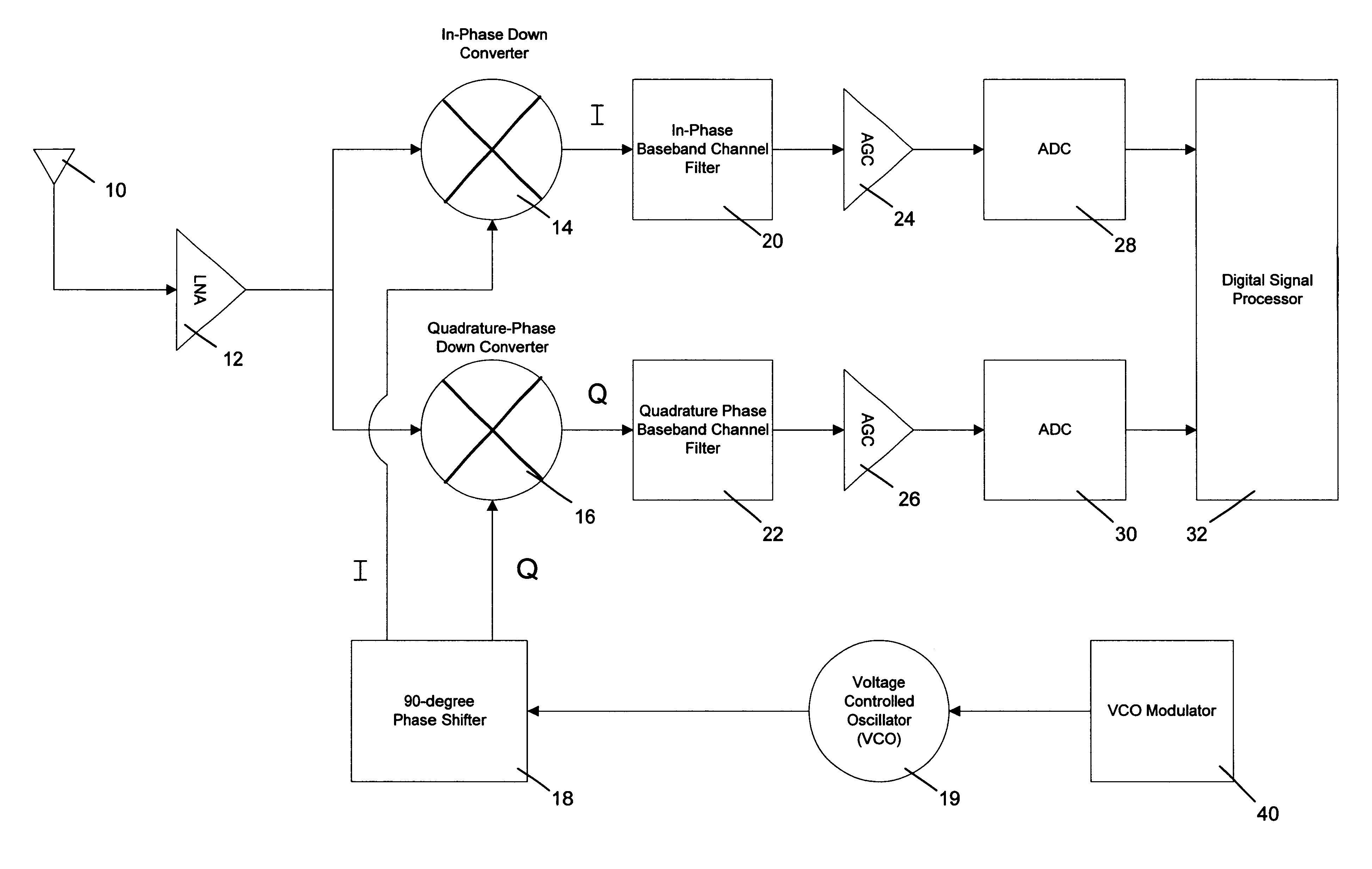

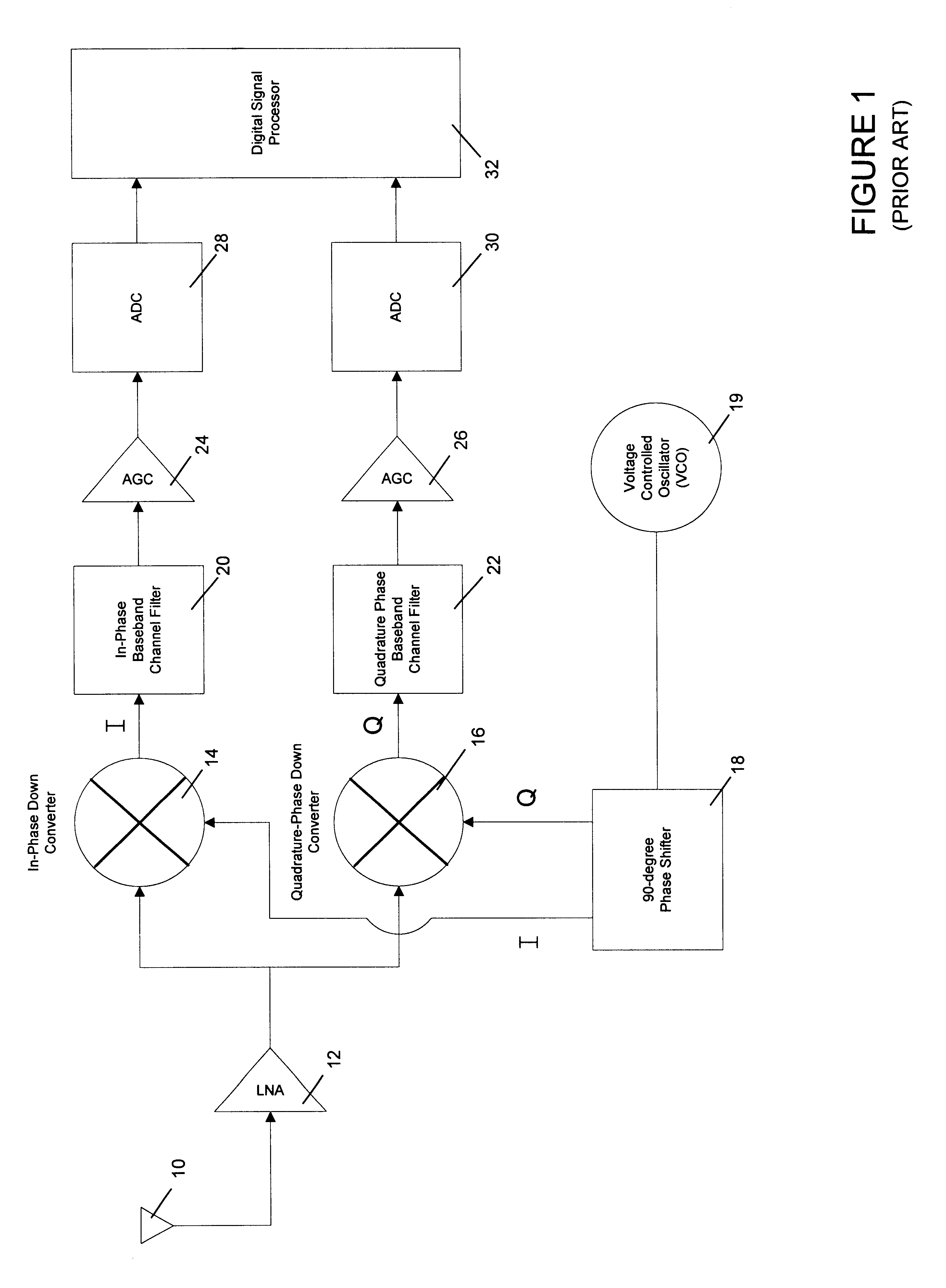

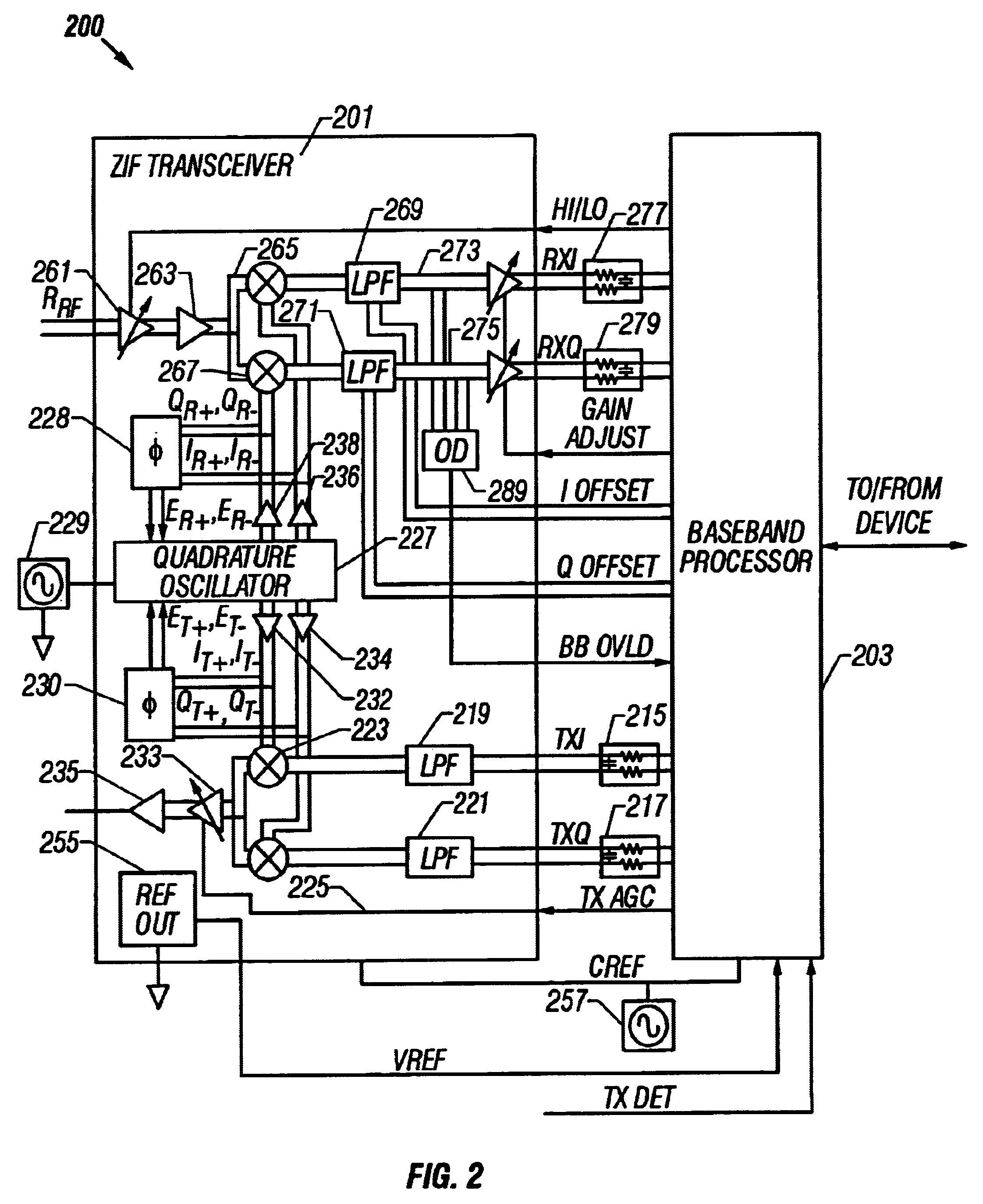

DC compensation system for a wireless communication device configured in a zero intermediate frequency architecture

InactiveUS6560448B1Low costMaximum performanceGain controlAmplitude-modulated carrier systemsTransceiverAudio power amplifier

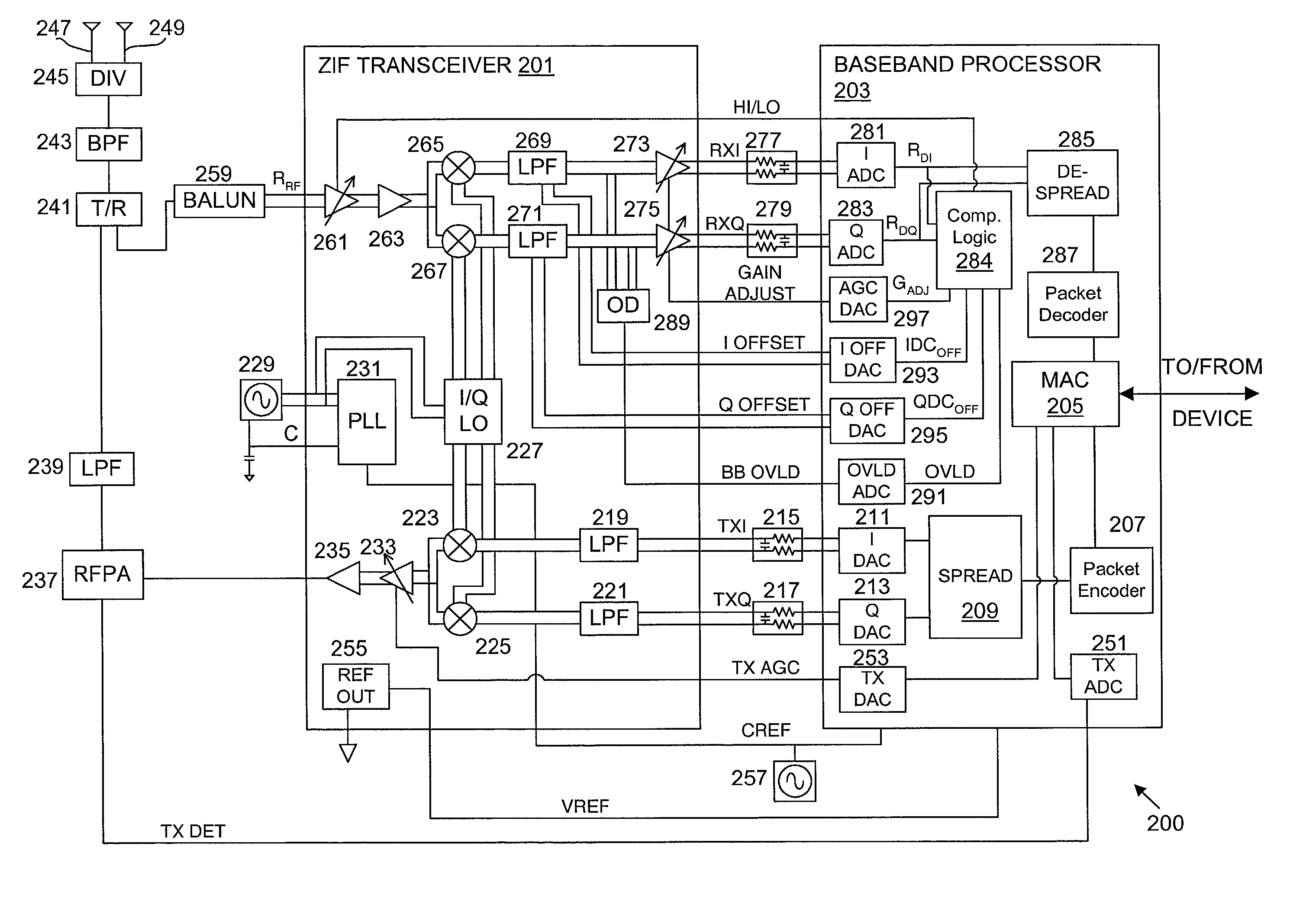

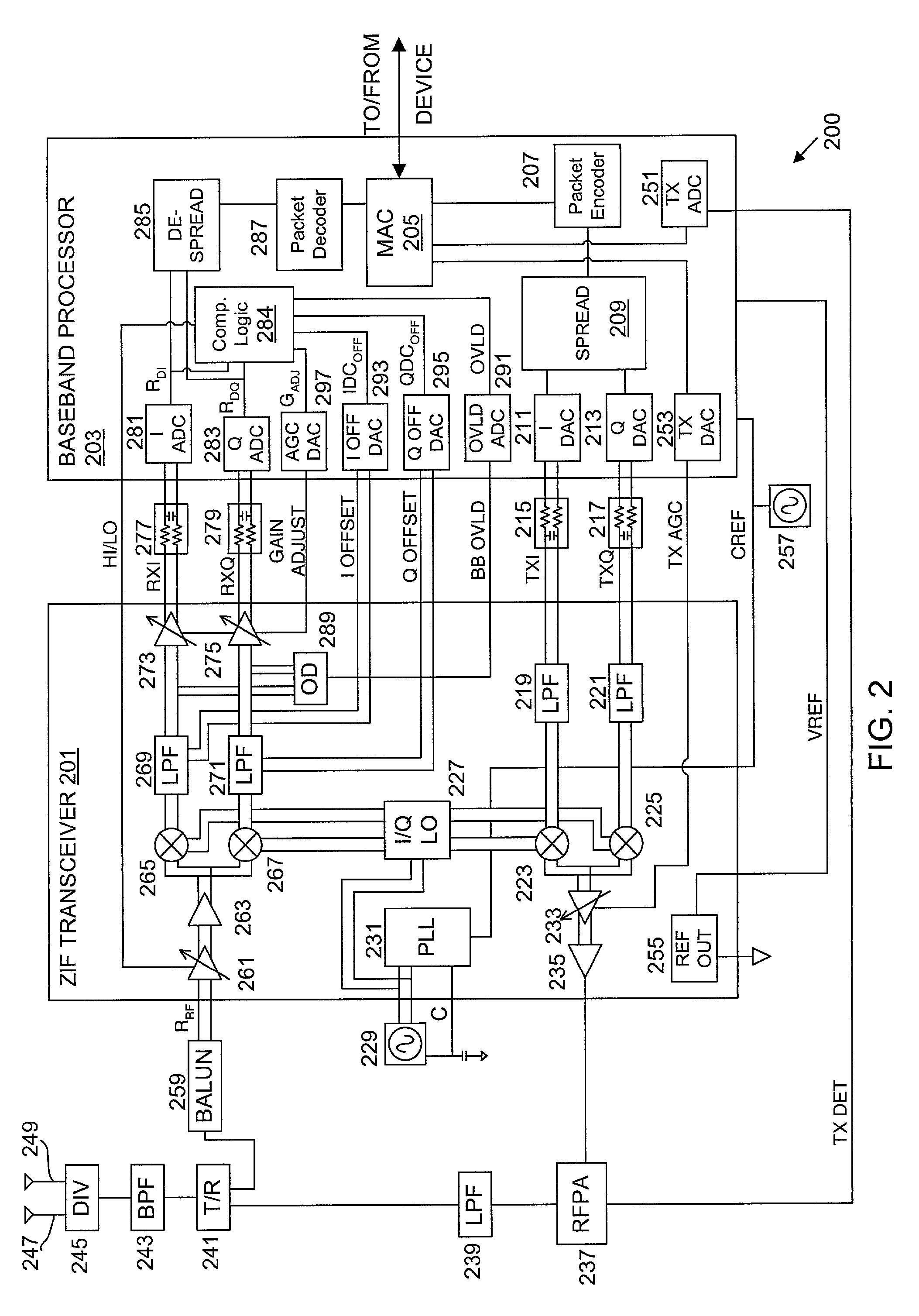

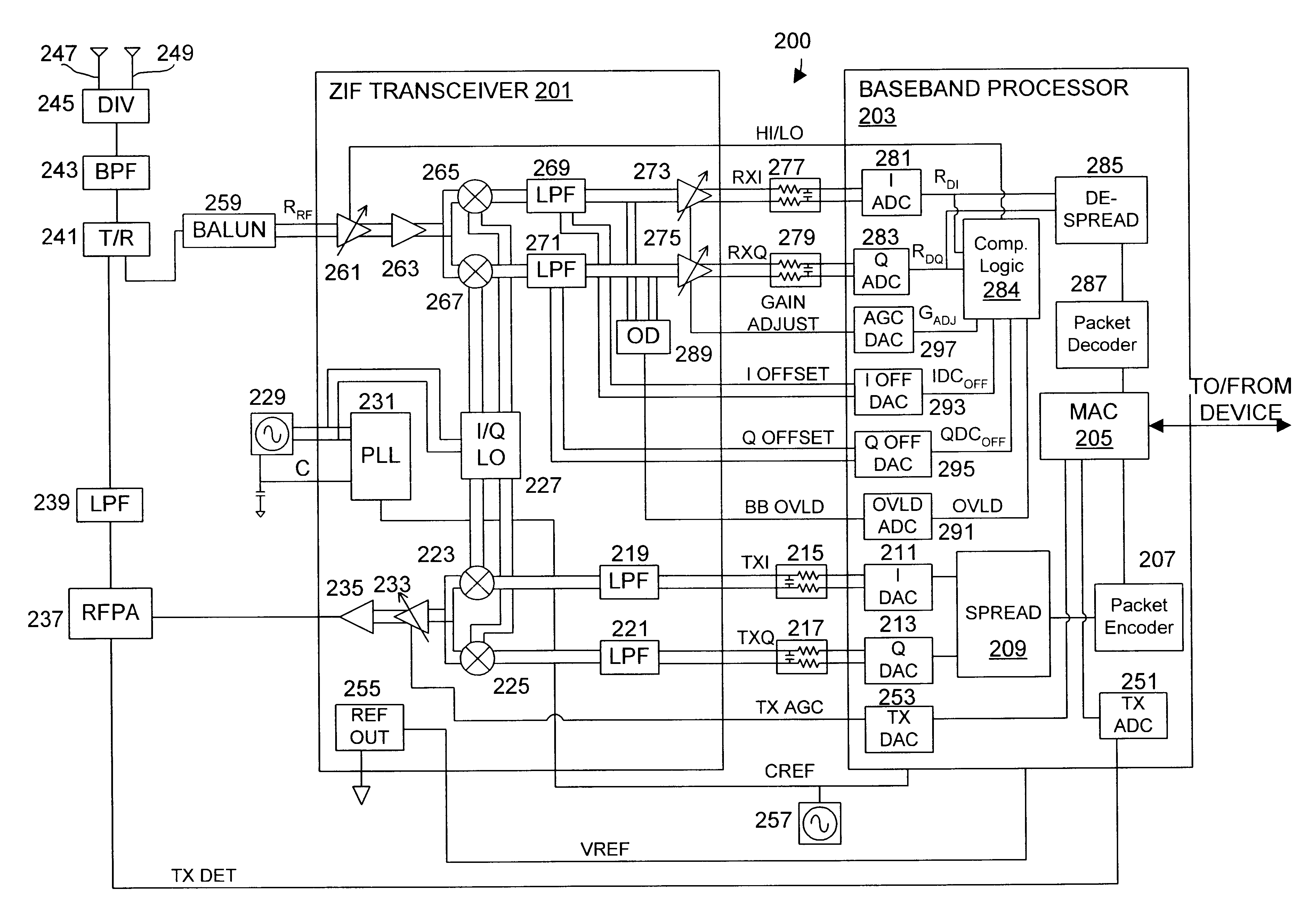

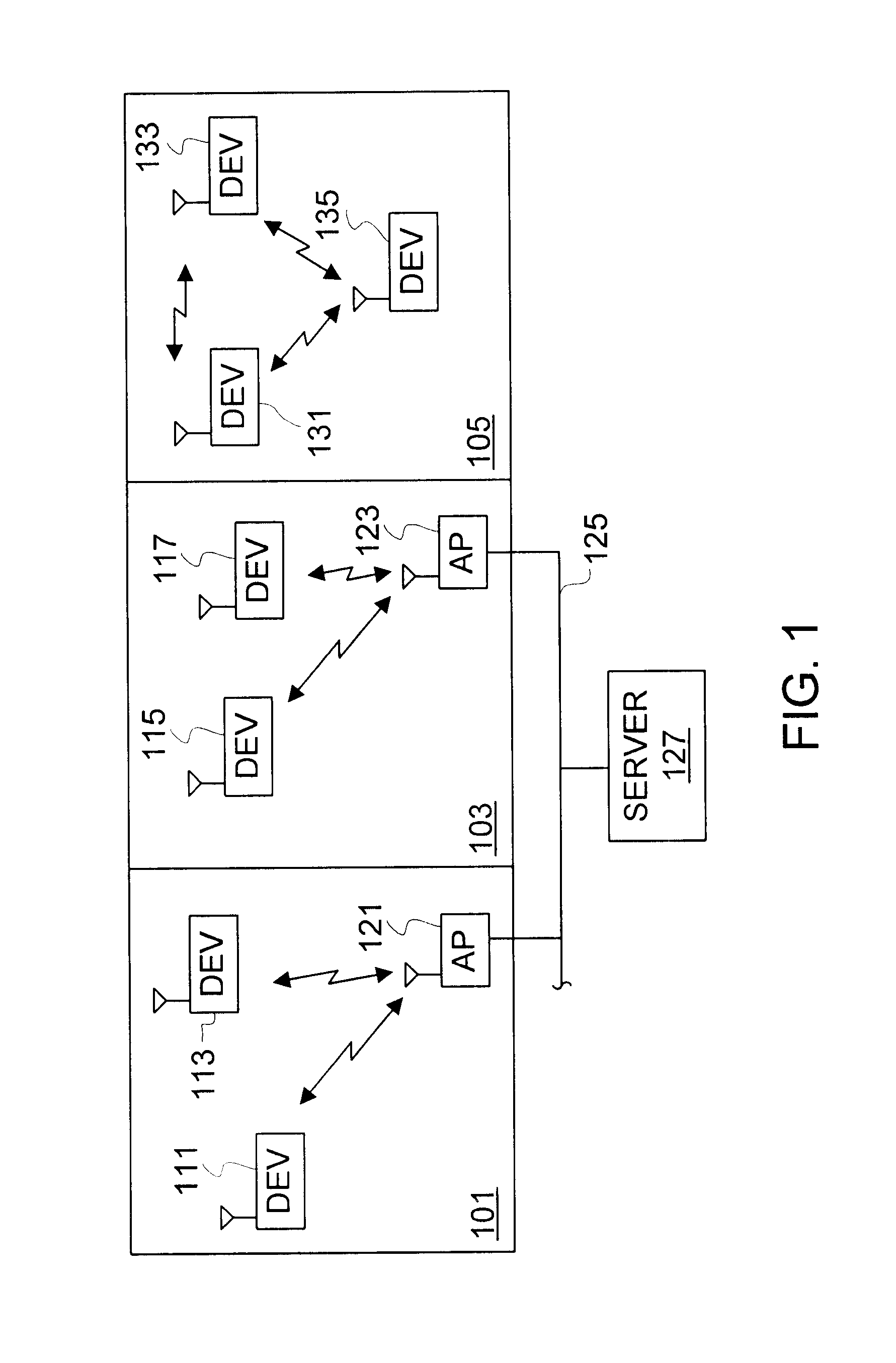

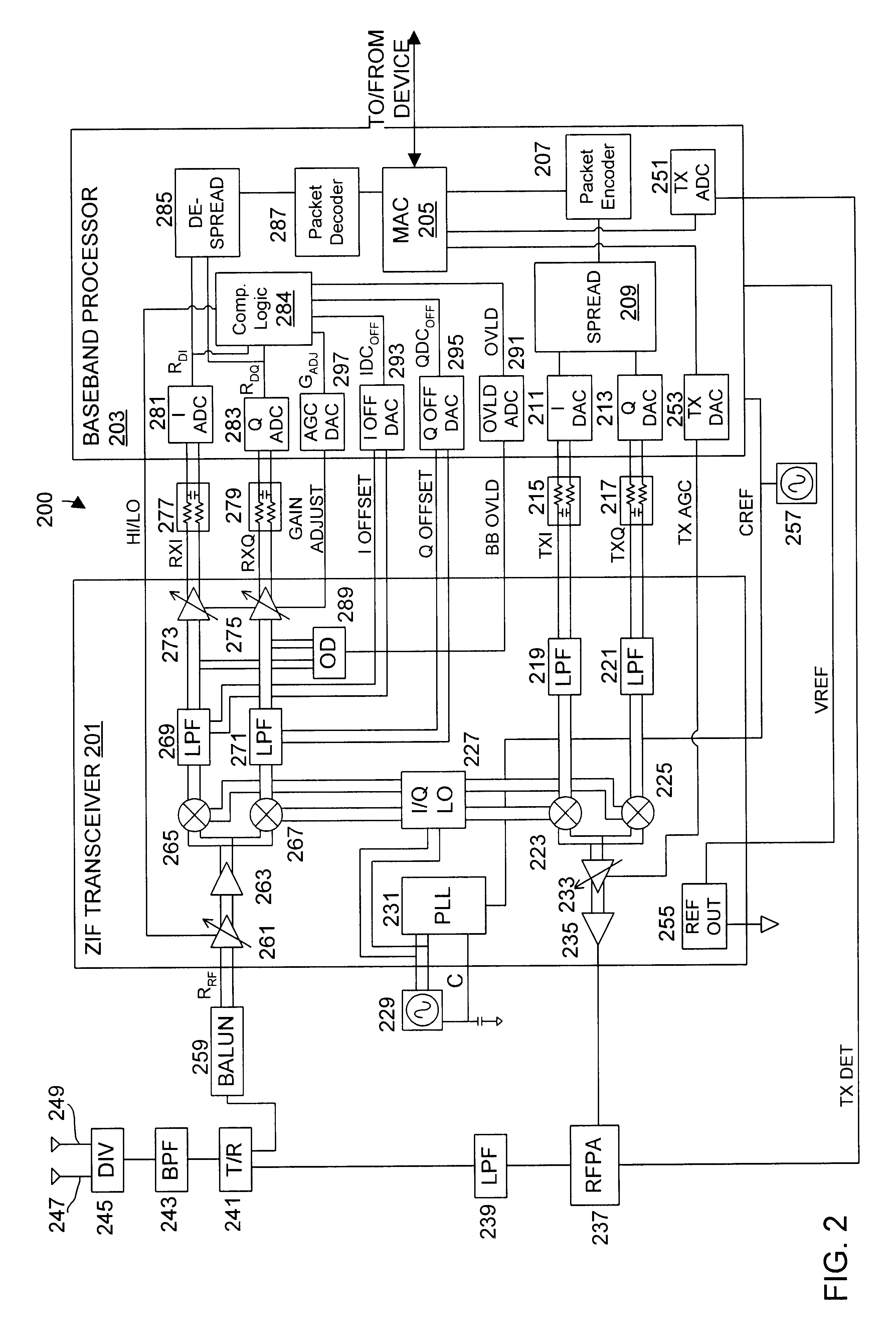

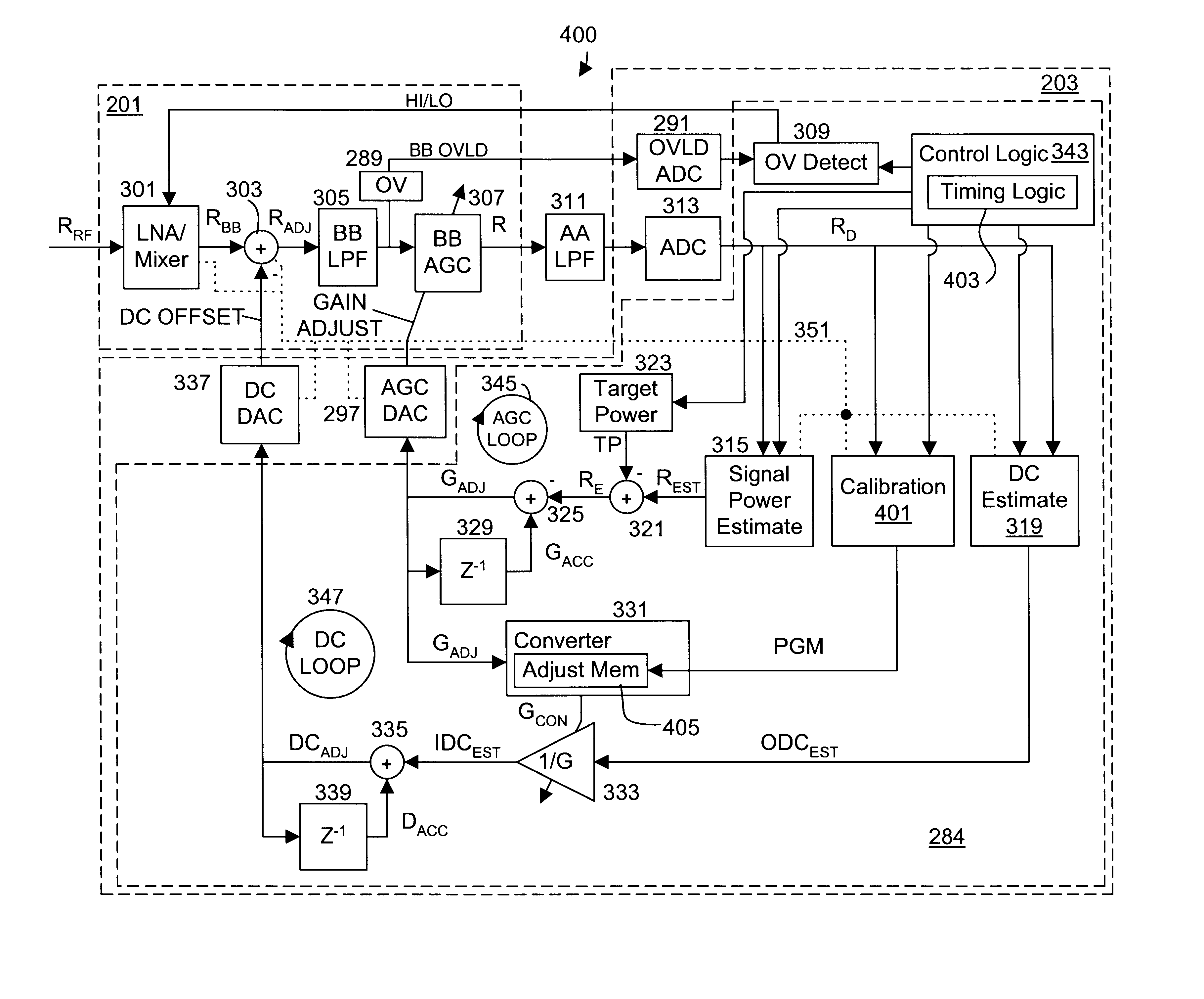

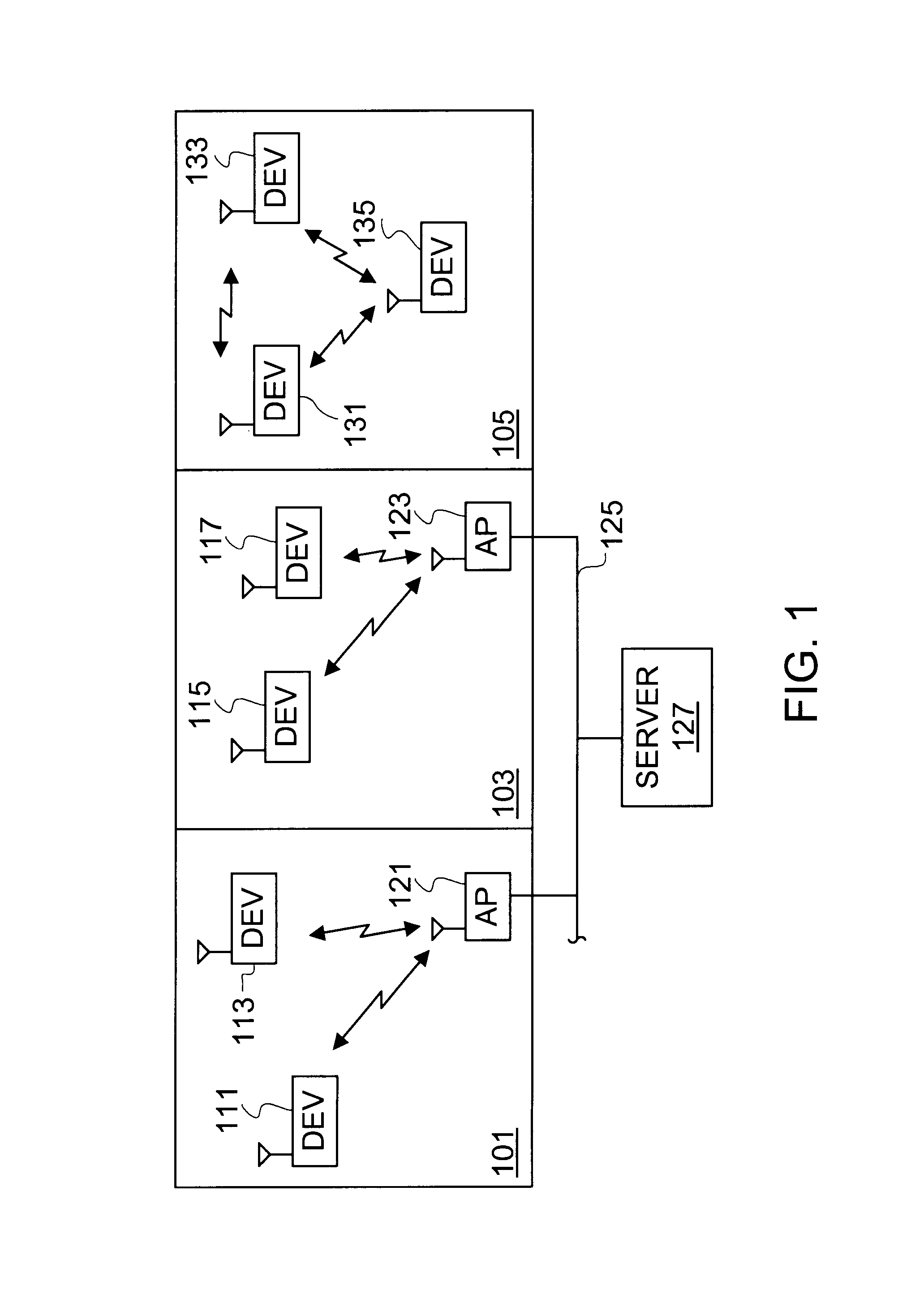

A wireless communication device including a radio frequency (RF) circuit, a ZIF transceiver and a baseband processor. The ZIF transceiver includes an RF mixer circuit that converts the RF signal to a baseband input signal, a summing junction that subtracts a DC offset from the baseband input signal to provide an adjusted baseband input signal, and a baseband amplifier that receives the adjusted baseband input signal and that asserts an amplified input signal based on a gain adjust signal. The baseband processor includes gain control logic, DC control logic and a gain interface. The gain control logic receives the amplified input signal, estimates input signal power and asserts the gain adjust signal in an attempt to keep the input signal power at a target power level. The DC control logic estimates an amount of DC in the amplified input signal and provides the DC offset in an attempt to reduce DC in the amplified input signal. The gain interface converts gain levels between the gain control logic and the DC control logic. The RF signal may include in-phase (I) and quadrature (Q) portions, where the RF mixer circuit splits I and Q baseband input signals from the RF signal. Operation is substantially identical for both I and Q channels. The DC control logic operates to remove or otherwise eliminate DC from the received signal that is provided to decoders in the baseband processor.

Owner:M RED INC

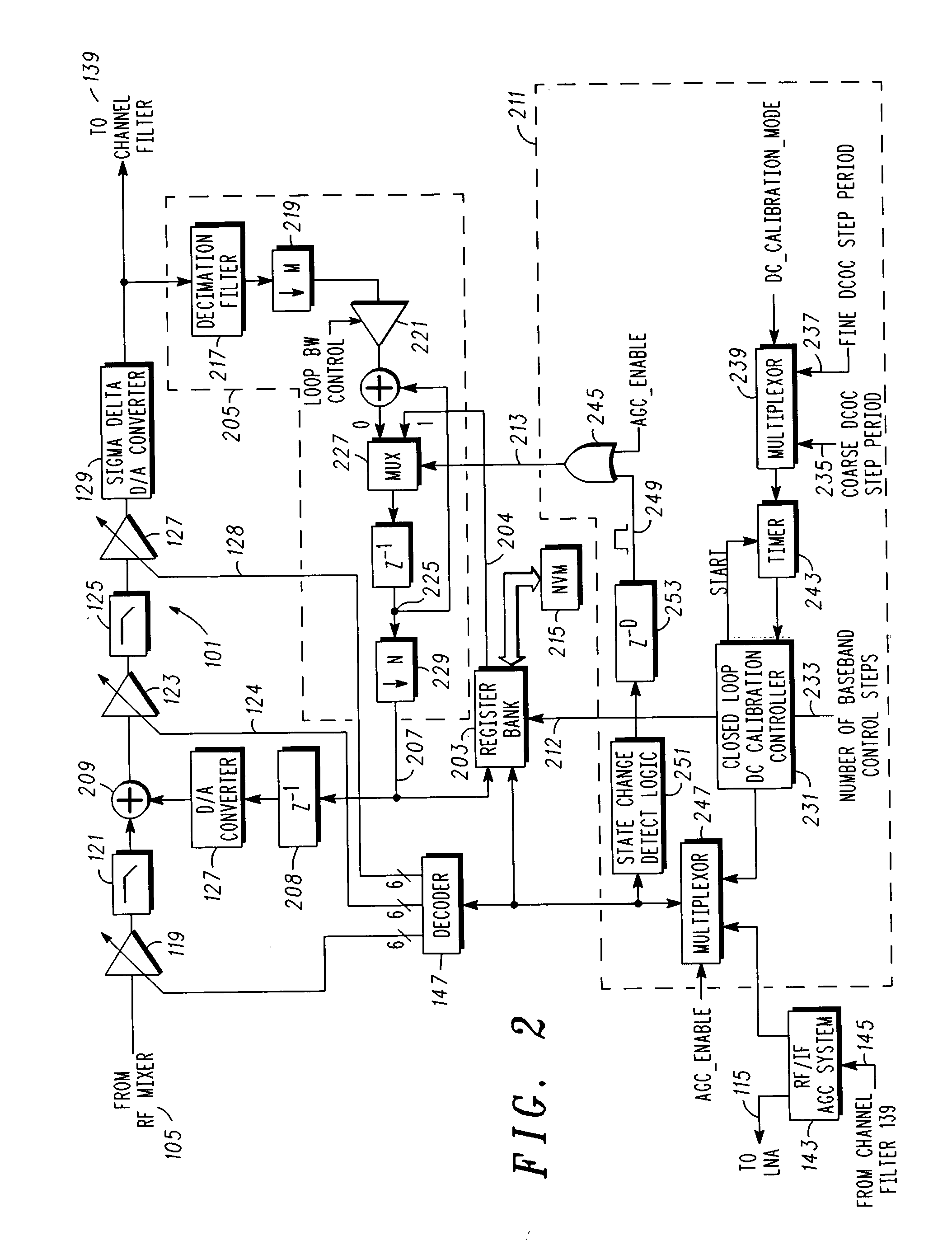

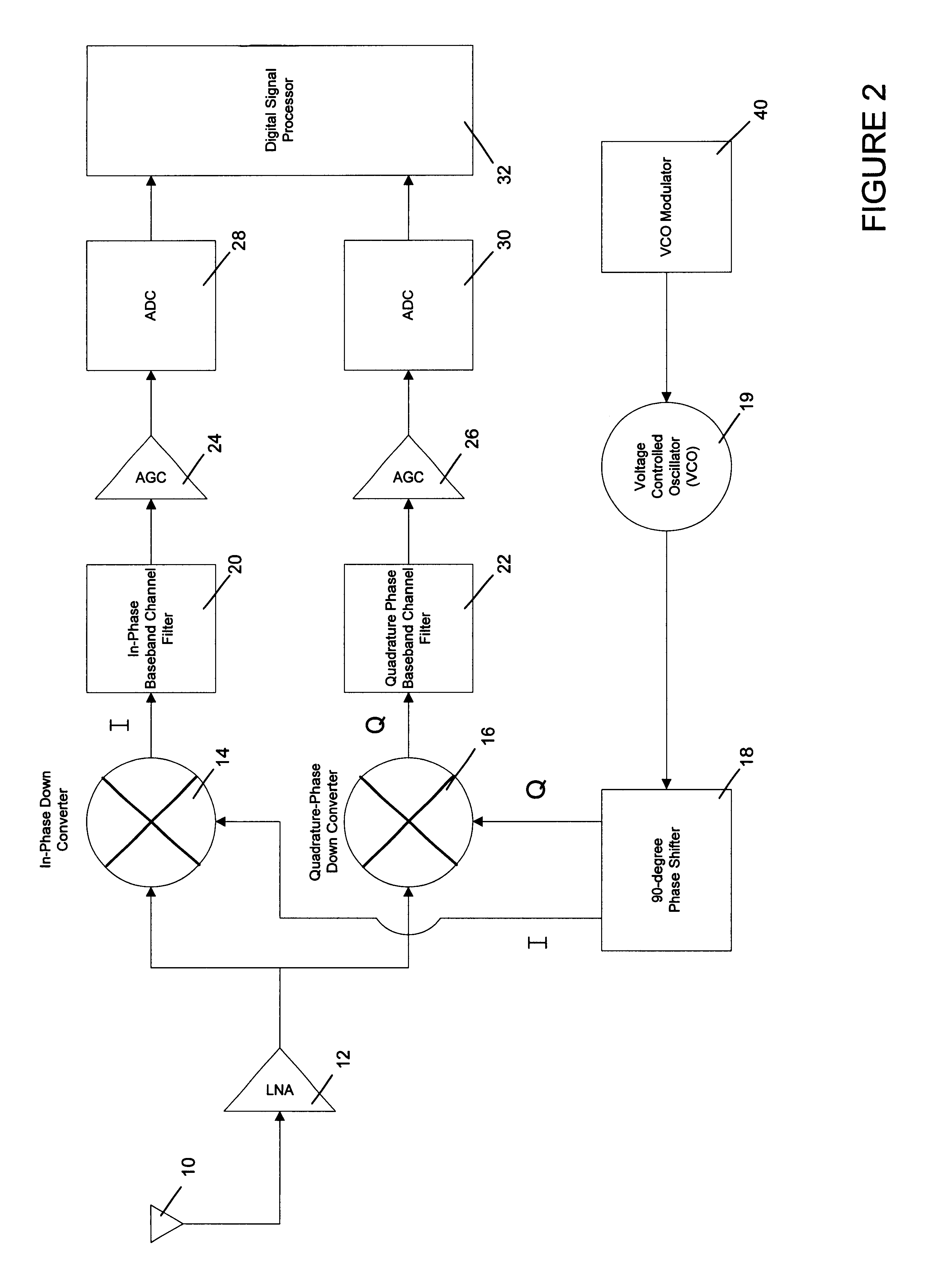

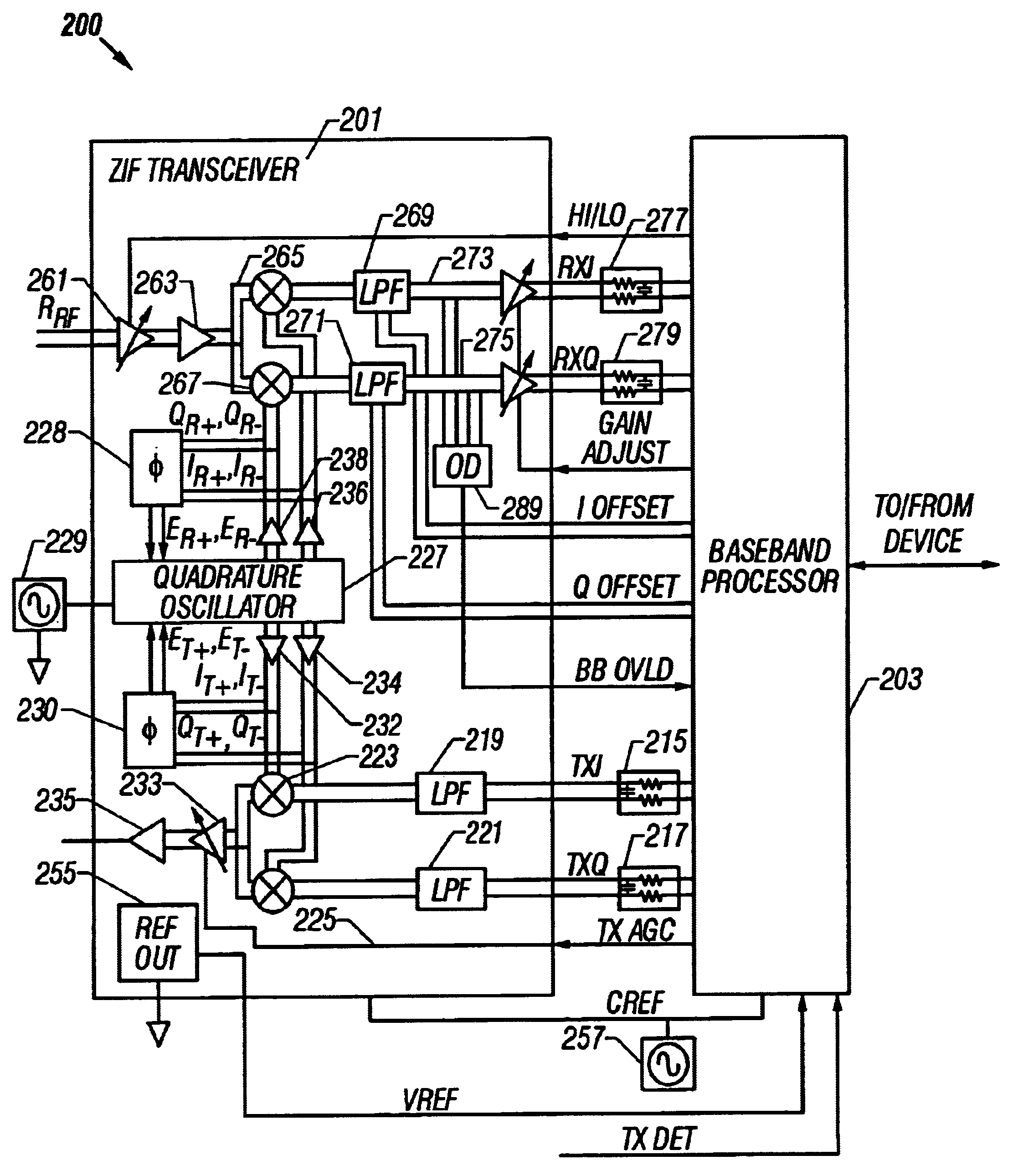

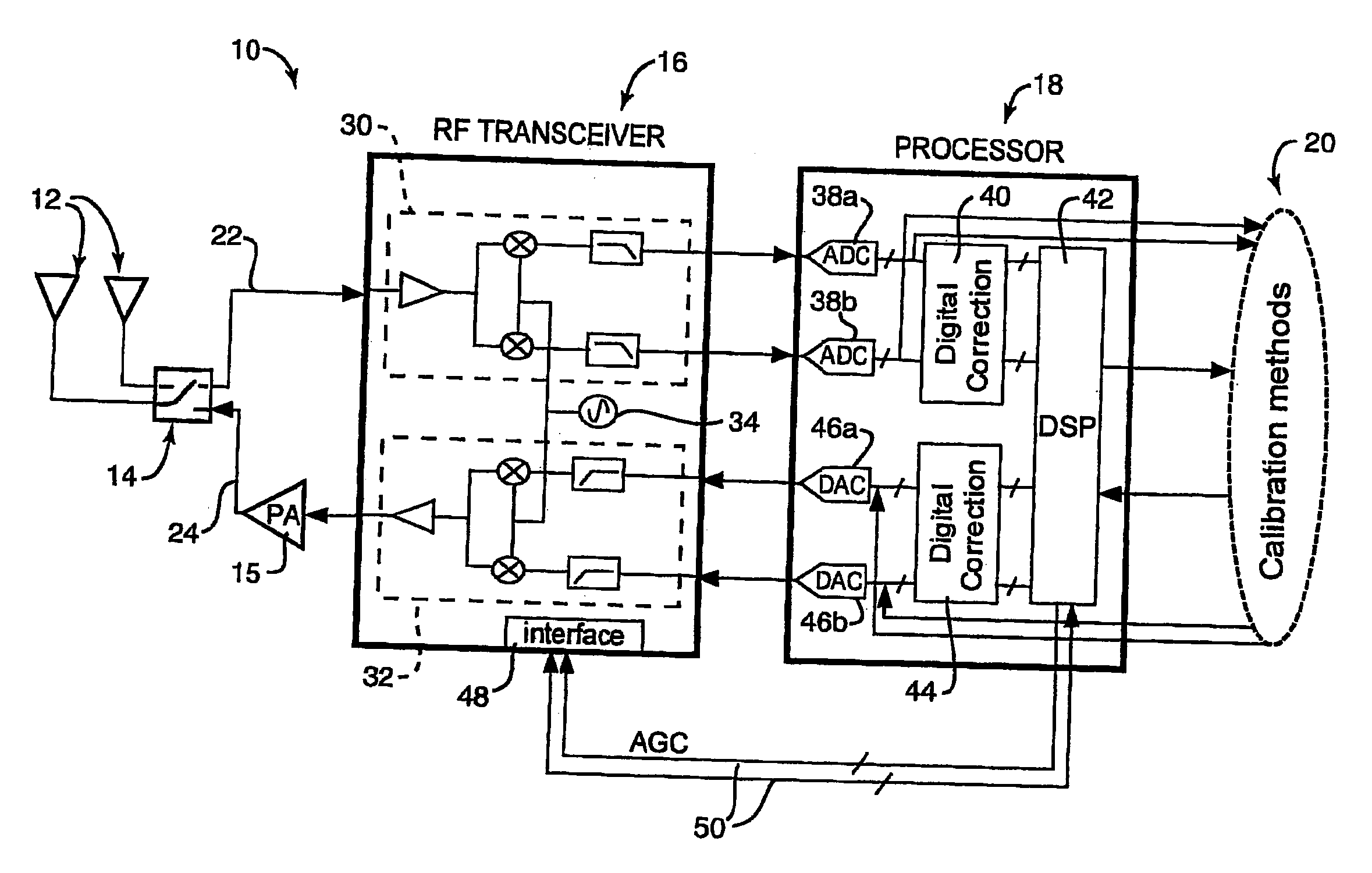

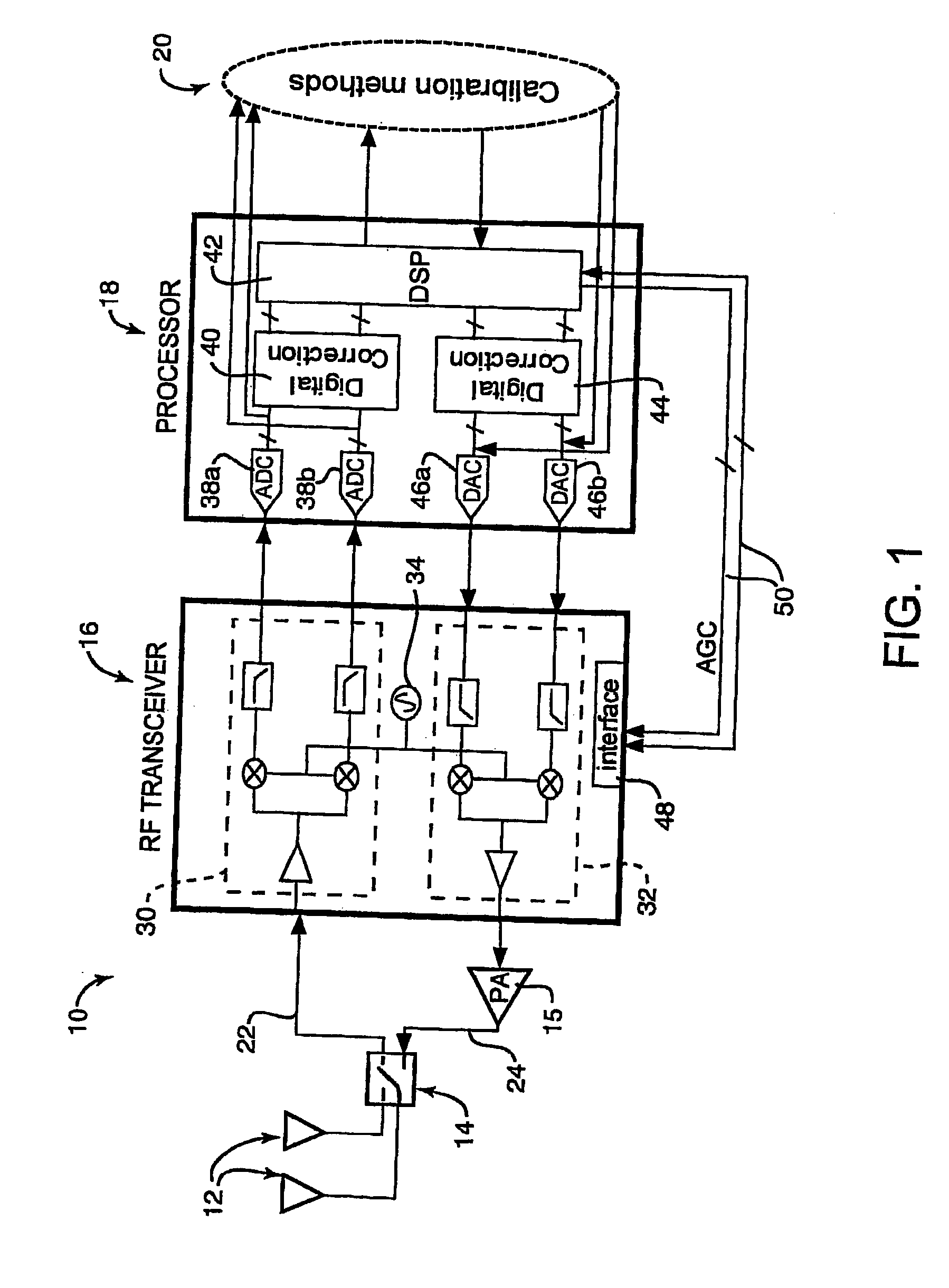

Calibrated DC compensation system for a wireless communication device configured in a zero intermediate frequency architecture

InactiveUS6735422B1Low costMaximum performancePulse automatic controlGain controlTransceiverAudio power amplifier

A calibrated DC compensation system for a wireless communication device configured in a zero intermediate frequency (ZIF) architecture. The device includes a ZIF transceiver and a baseband processor, which further includes a calibrator that periodically performs a calibration procedure. The baseband processor includes gain control logic, DC control logic, a gain converter and the calibrator. The gain converter converts gain between the gain control logic and the DC control logic. The calibrator programs the gain converter with values determined during the calibration procedure. The gain converter may be a lookup table that stores gain conversion values based on measured gain of a baseband gain amplifier of the ZIF transceiver. The gain control logic may further include a gain adjust limiter that limits change of a gain adjust signal during operation based on a maximum limit or on one or more gain change limits. A second lookup table stores a plurality of DC adjust values, which are added during operation to further reduce DC offset. The calibration procedure includes sampling an output signal for each gain step of the baseband amplifier at two predetermined range values and corresponding DC offsets using successive approximation. The data is used to calculate gain, DC offset and DC differential values, which are used to determine the conversion values programmed into the lookup tables or the gain adjust limiter.

Owner:M RED INC

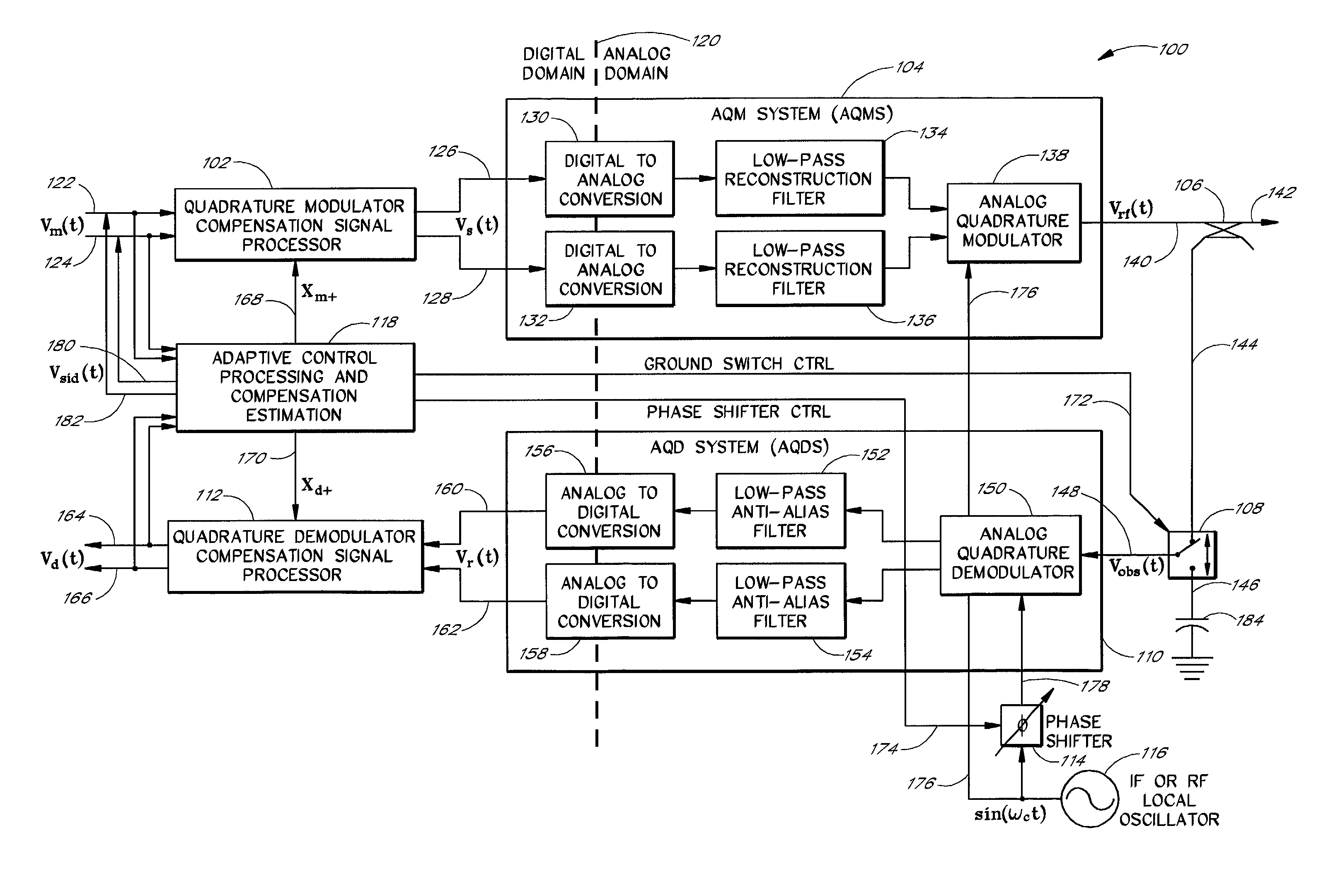

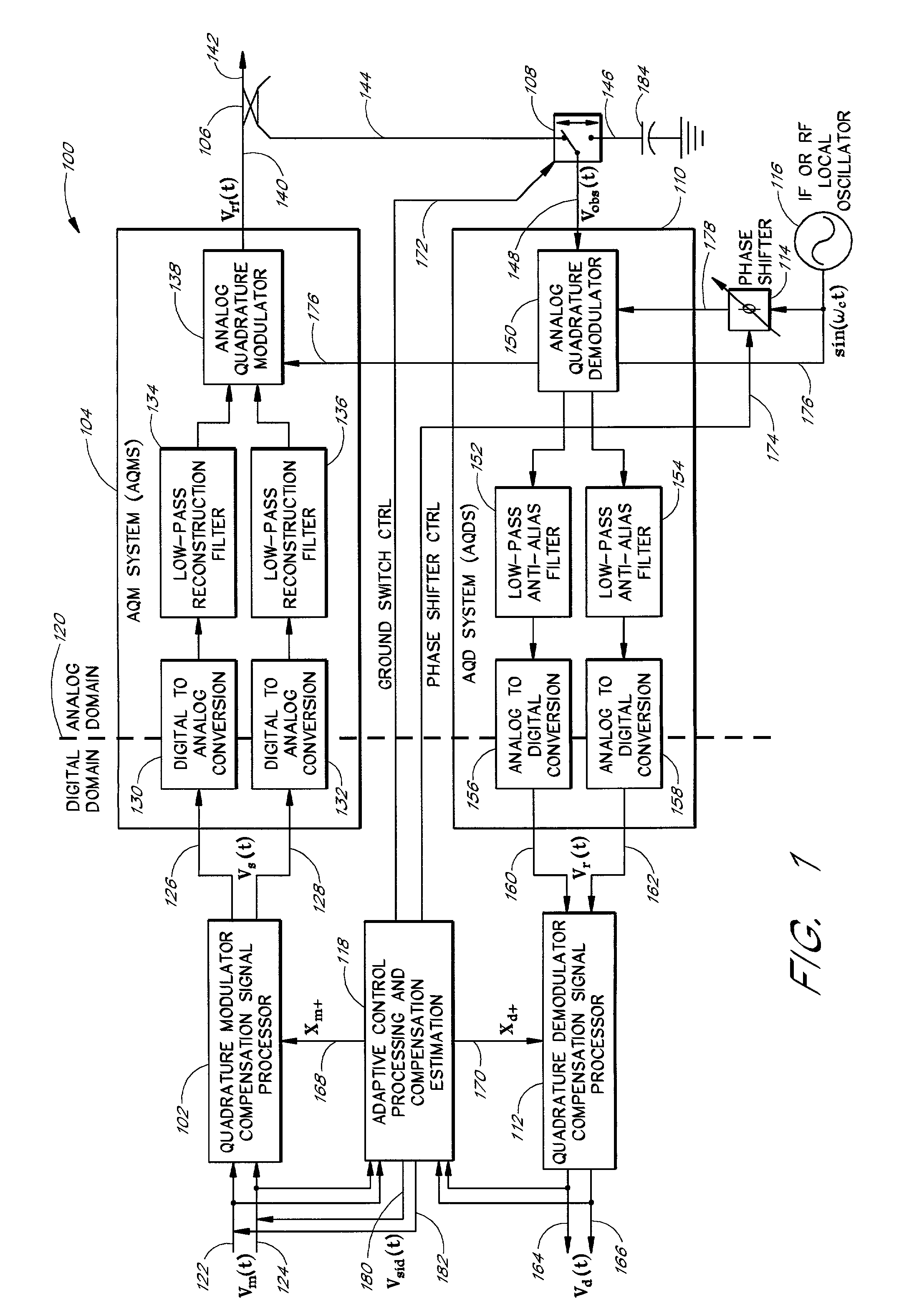

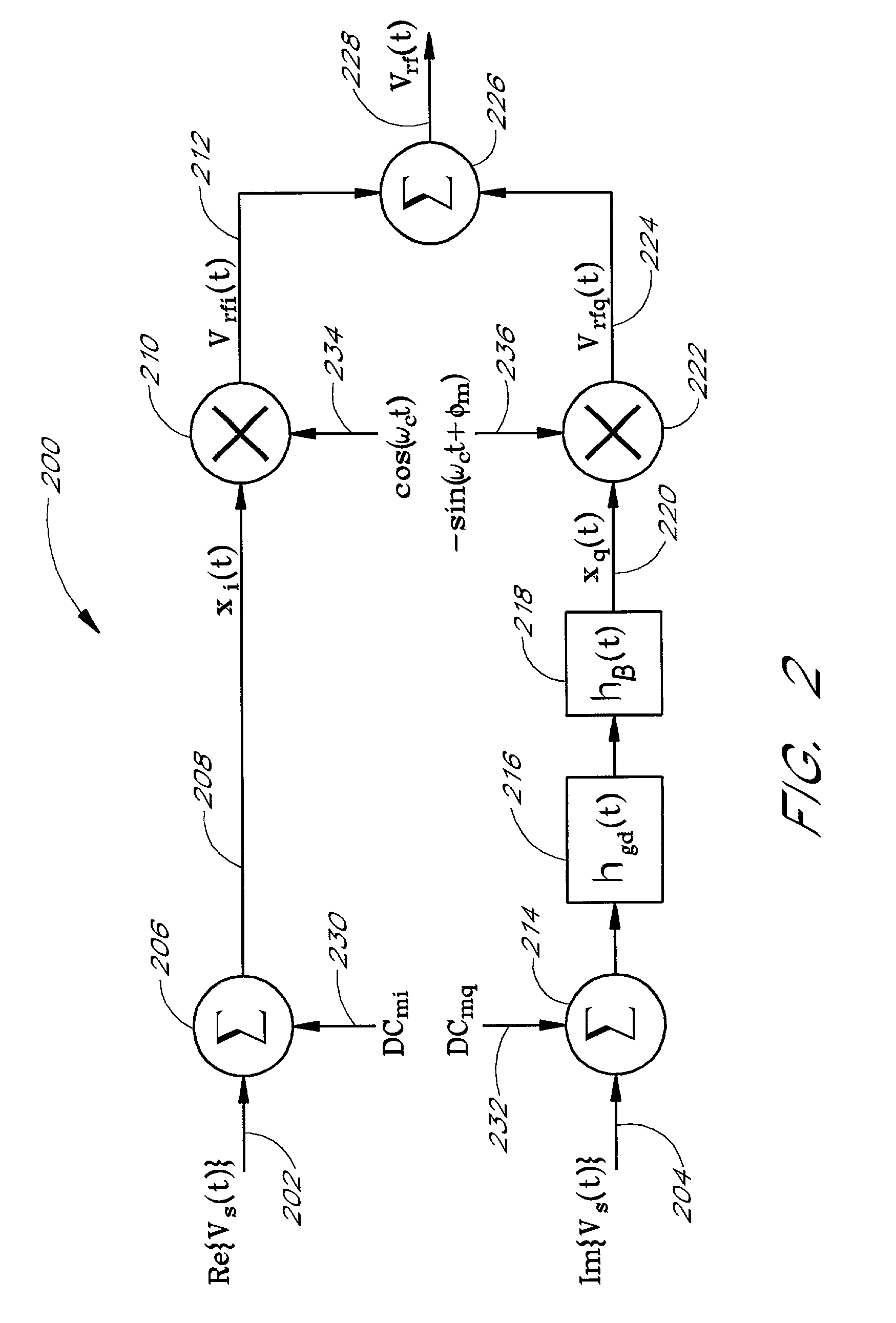

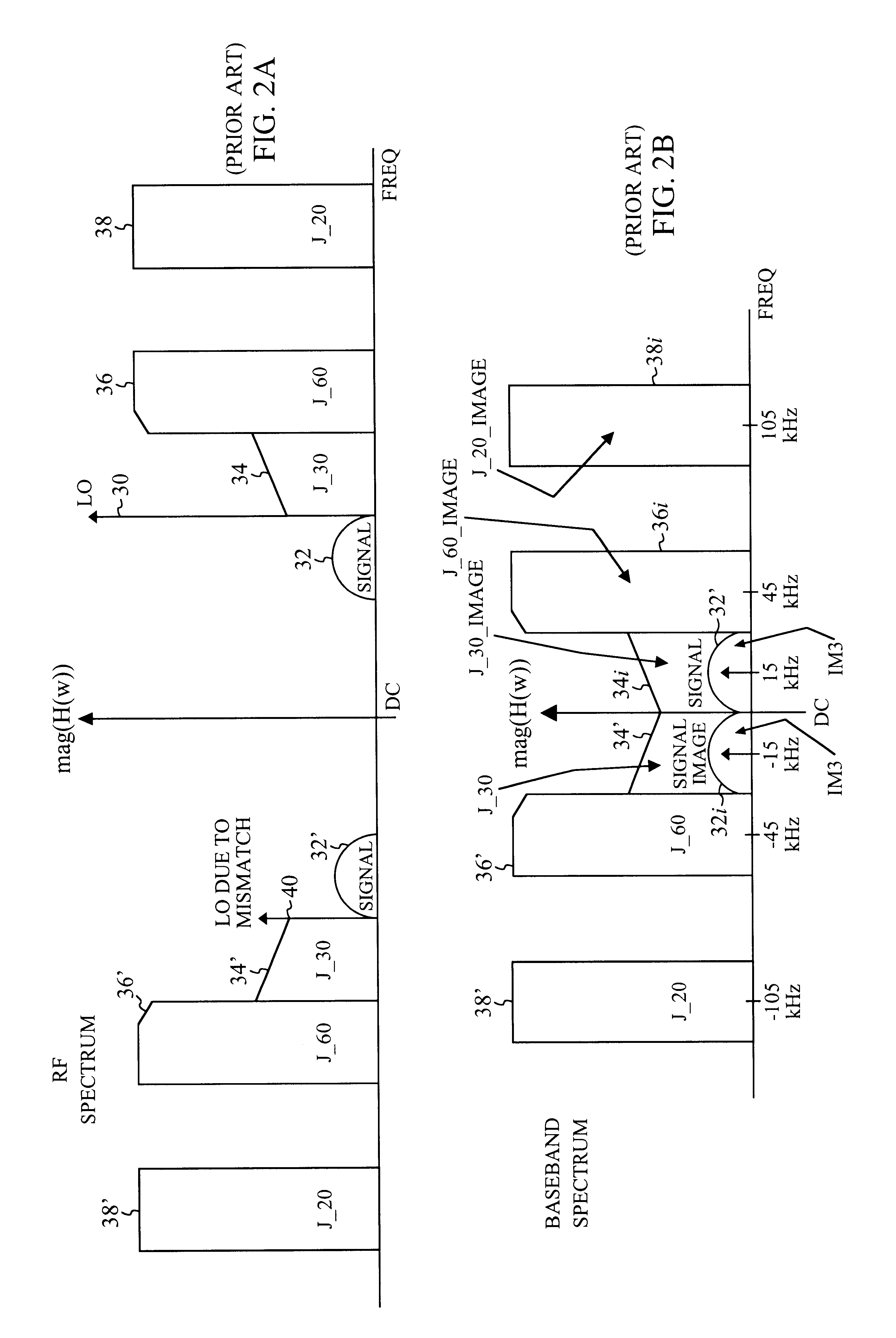

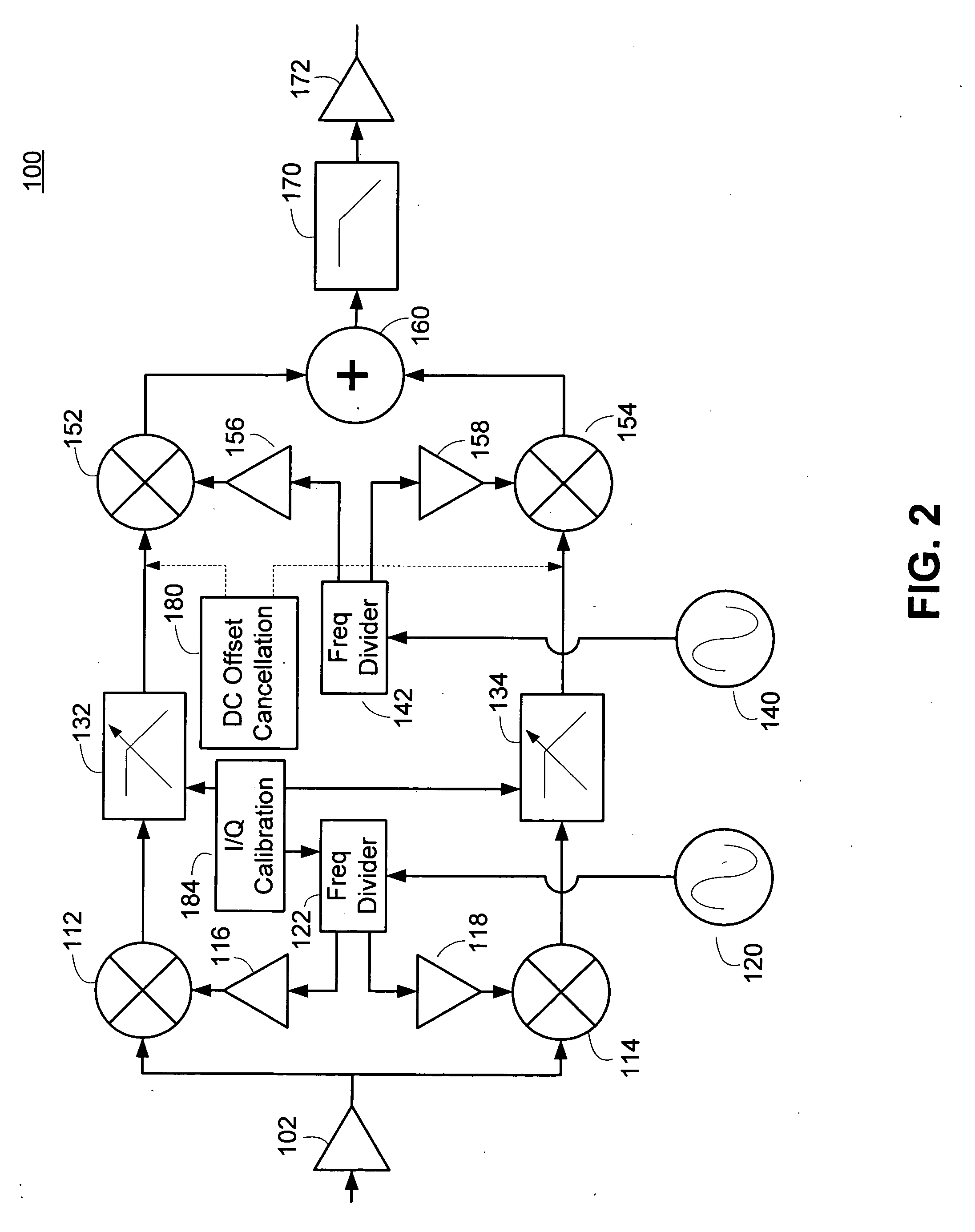

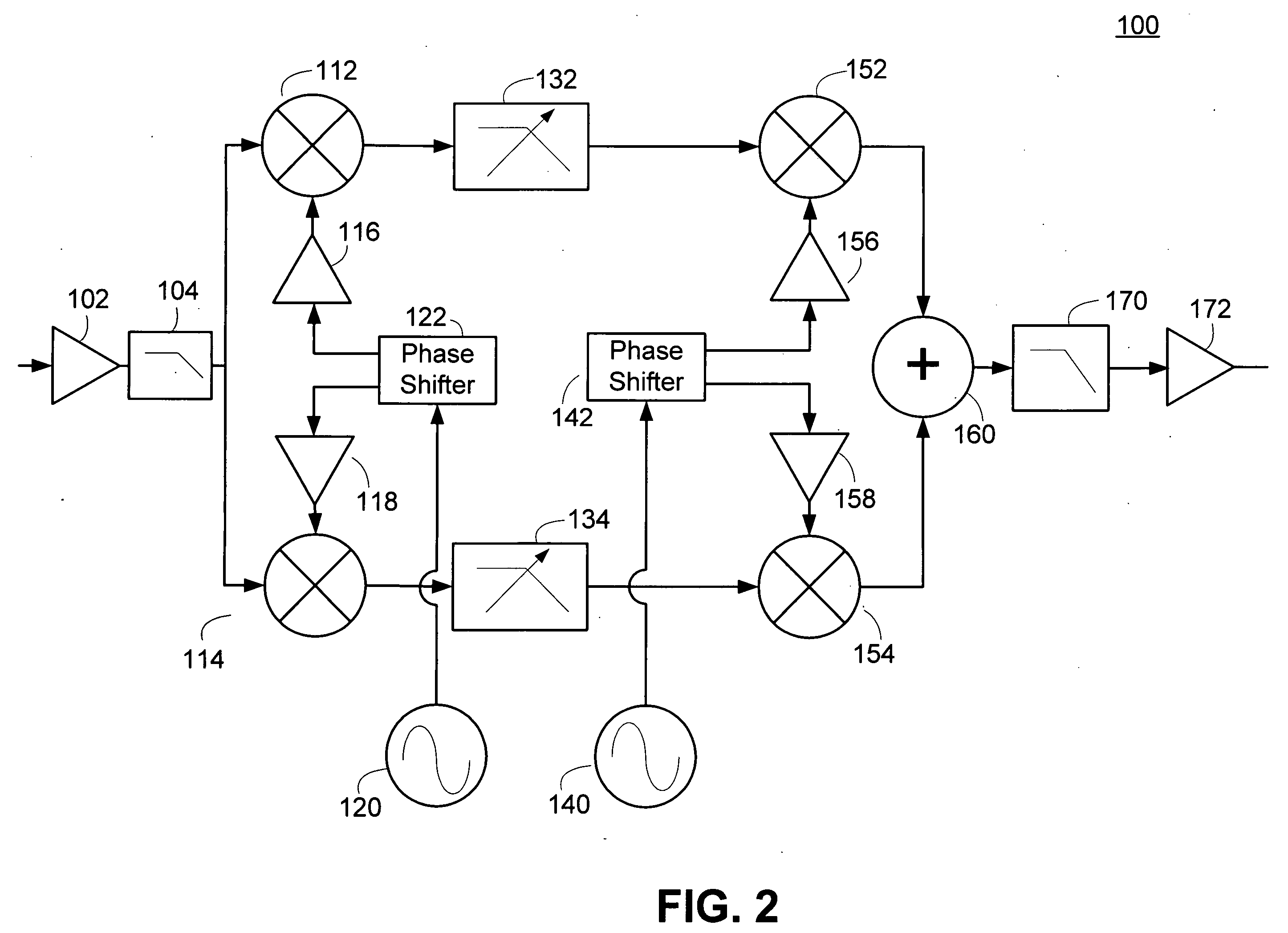

Wideband analog quadrature modulator/demodulator with pre-compensation/post-compensation correction

ActiveUS6940916B1Reduce errorsImproved performance characteristicsCarrier regulationMultiple carrier systemsQuadrature modulatorLocal oscillator signal

The present invention is related to methods and apparatus that compensate for quadrature impairments of an analog quadrature modulator and / or demodulator over a relatively wide signal bandwidth. One embodiment pre-distorts baseband signals in a quadrature modulator compensation signal processor (QMCSP) to negate the quadrature impairment of an analog quadrature modulator and corrects a received baseband signal in a quadrature demodulator compensation signal processor (QDCSP) to cancel the quadrature impairment of an analog quadrature demodulator. The QMCSP and the QDCSP contain adaptive digital filter correction structures that pre-compensate and post-compensate, respectively, for the quadrature impairments introduced by the analog quadrature modulator and the analog quadrature demodulator over a relatively wide bandwidth. A phase shifter advantageously shifts the phase of a local oscillator signal to the analog quadrature demodulator to distinguish quadrature impairments introduced by the modulation path from quadrature impairments introduced by the demodulation path.

Owner:MAXLINEAR ASIA SINGAPORE PTE LTD

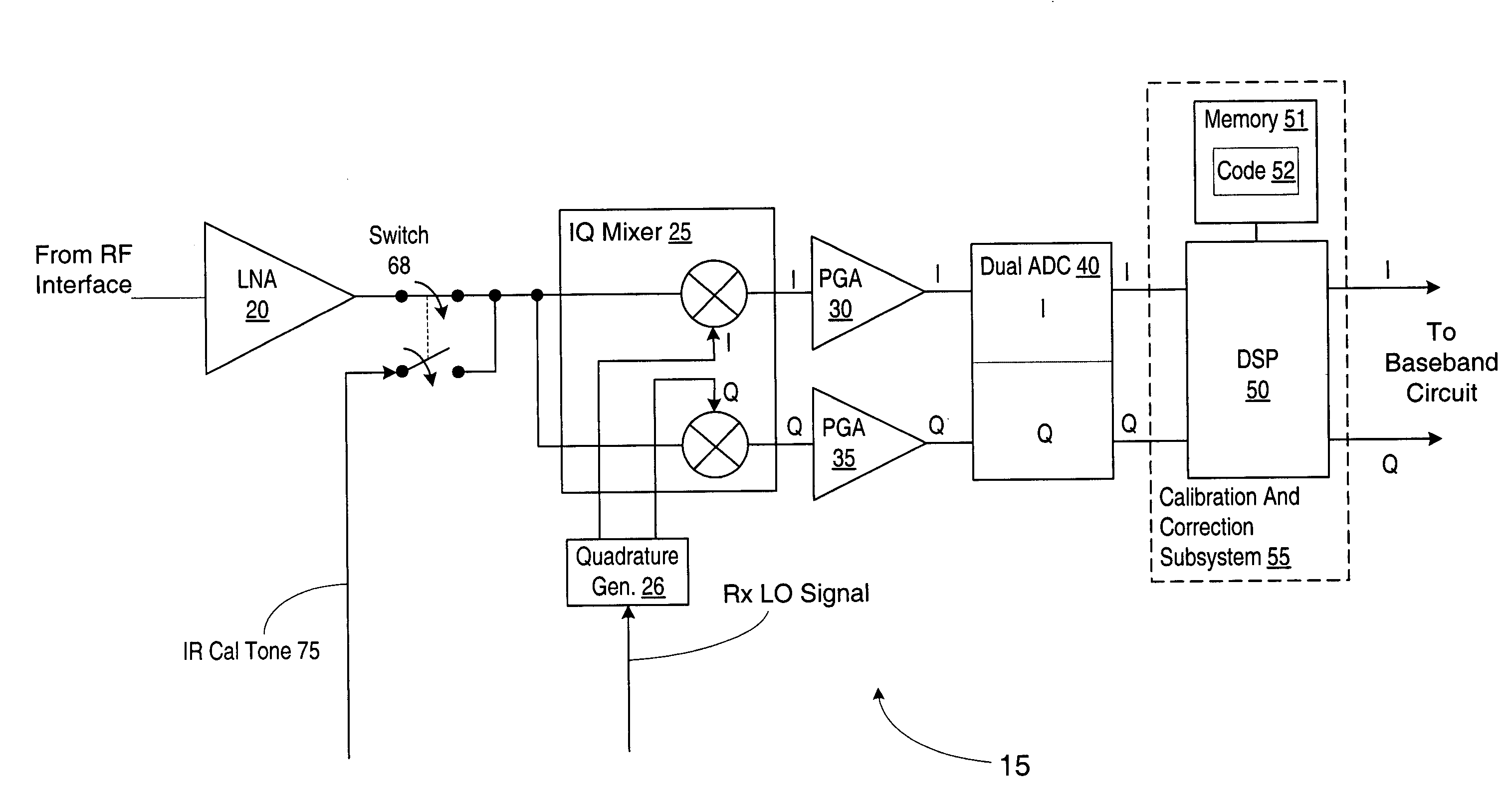

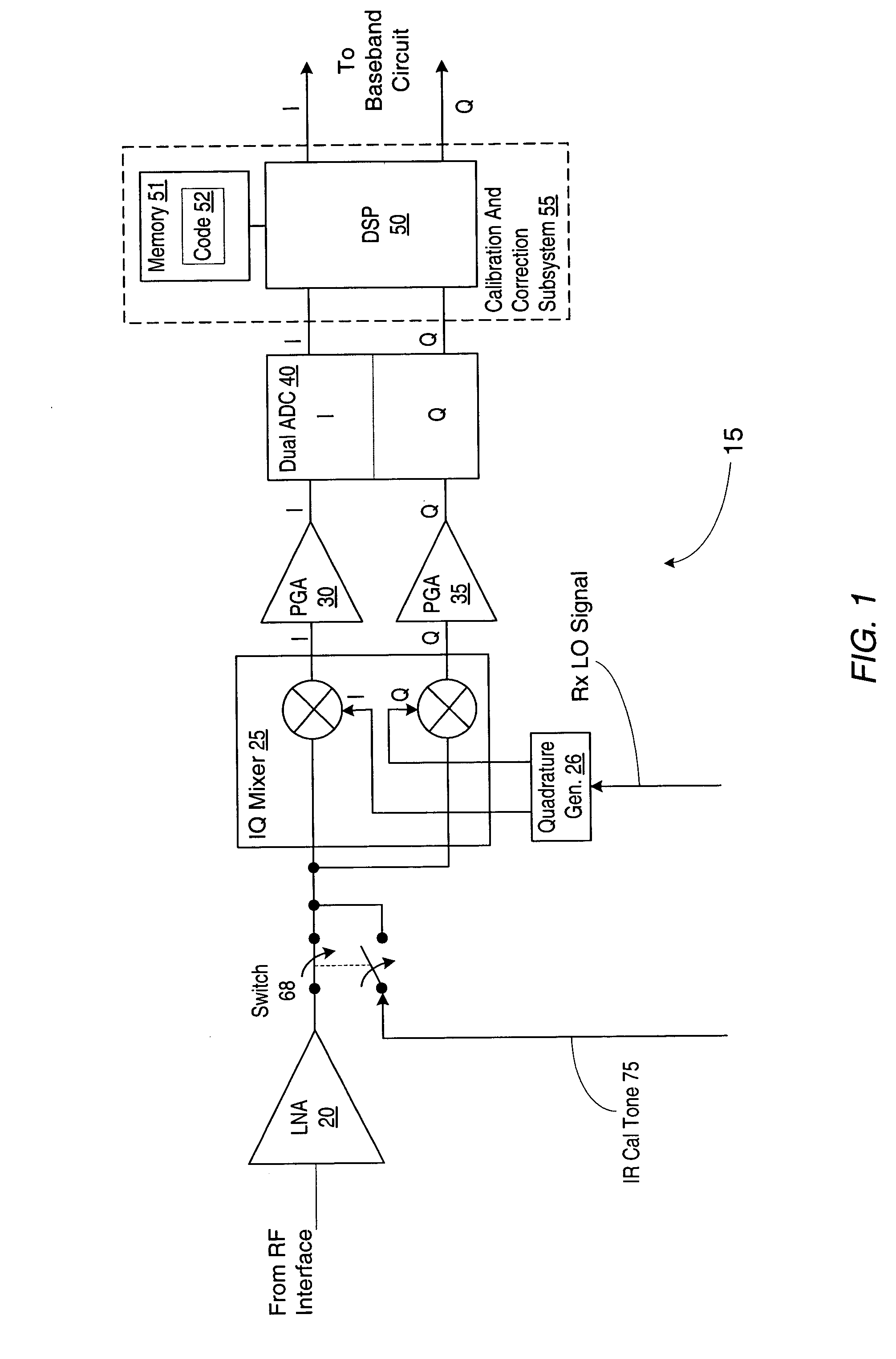

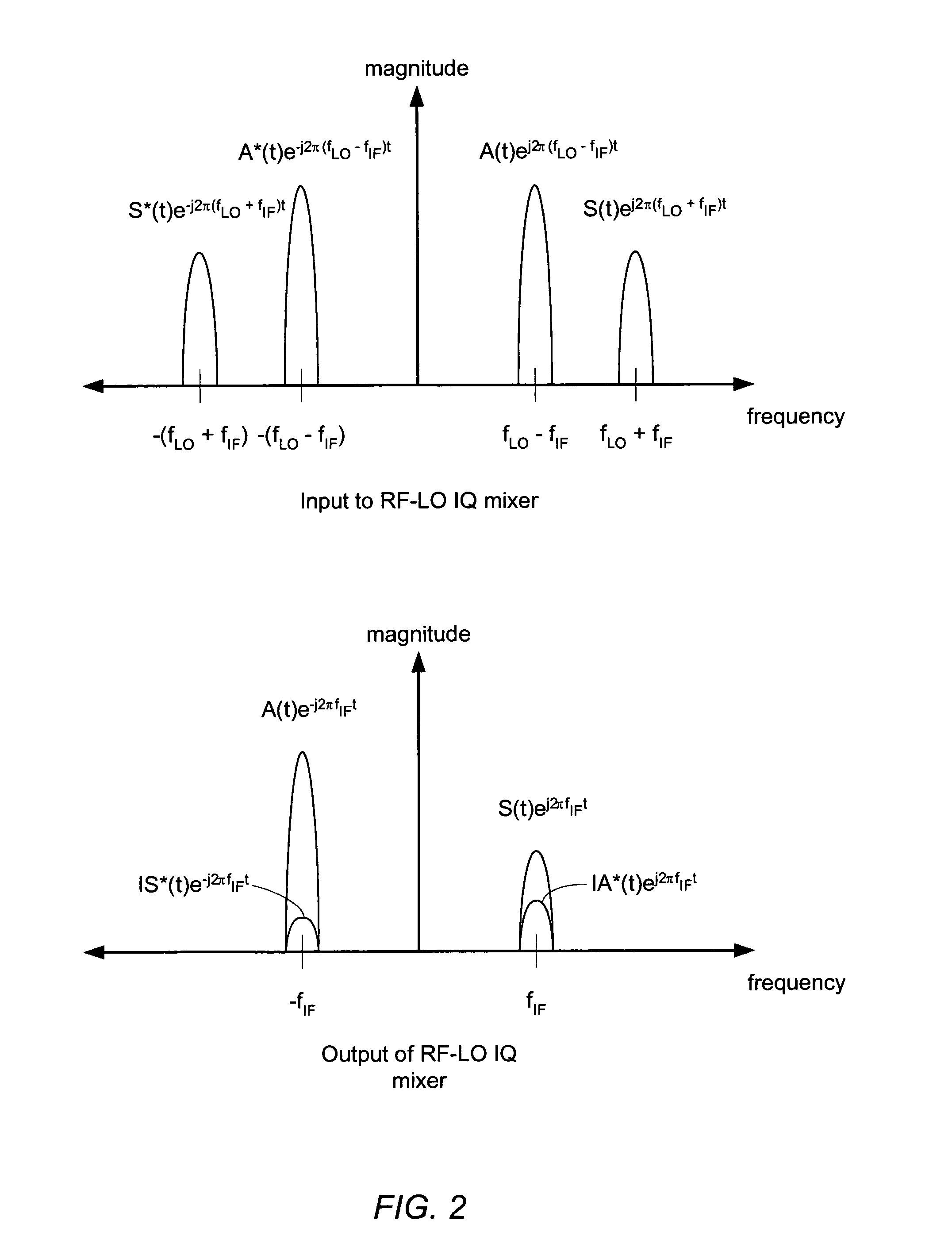

Apparatus and method for digital image correction in a receiver

ActiveUS7142835B2Angle demodulation by oscillations conversionRelay systems monitoringProgram instructionImage correction

An apparatus and method for performing digital image correction in a receiver. In one embodiment, a receiver circuit may include an IQ signal source configured to provide a digital signal comprising in-phase (I) and quadrature (Q) components, such as an IQ mixer in combination with an analog to digital converter, for example. The receiver circuit may also include an image correction unit coupled to the IQ signal source and configured to combine the digital signal with a complex image correction factor. The image correction unit may be implemented using a digital signal processor under the control of associated program instructions, for example. In one specific implementation of the receiver circuit, the image correction unit may be configured to combine the digital signal with the complex image correction factor using a cross-accumulation operation.

Owner:SILICON LAB INC

Automatic gain control system and method for a ZIF architecture

A system and method for controlling amplification of a signal received by a ZIF radio having a power level within a full power range relative to a minimum noise floor. The ZIF radio includes a ZIF receiver front end, an overload detector, an ADC, a saturation detector, a DC and power estimator, and control logic. The control logic utilized full visibility of the ADC to limit gain of the baseband amplifier to a maximum gain setting sufficient to view the minimum noise floor and to view a received signal having a power level within any of several segments of the power spectrum. The segmentation of the power spectrum is based on an overload condition of the ZIF receiver front end and a saturation condition of the ADC. The control logic further employs limited gain stepping of the baseband amplifier to avoid exceeding a DC budget of the ADC.

Owner:M RED INC

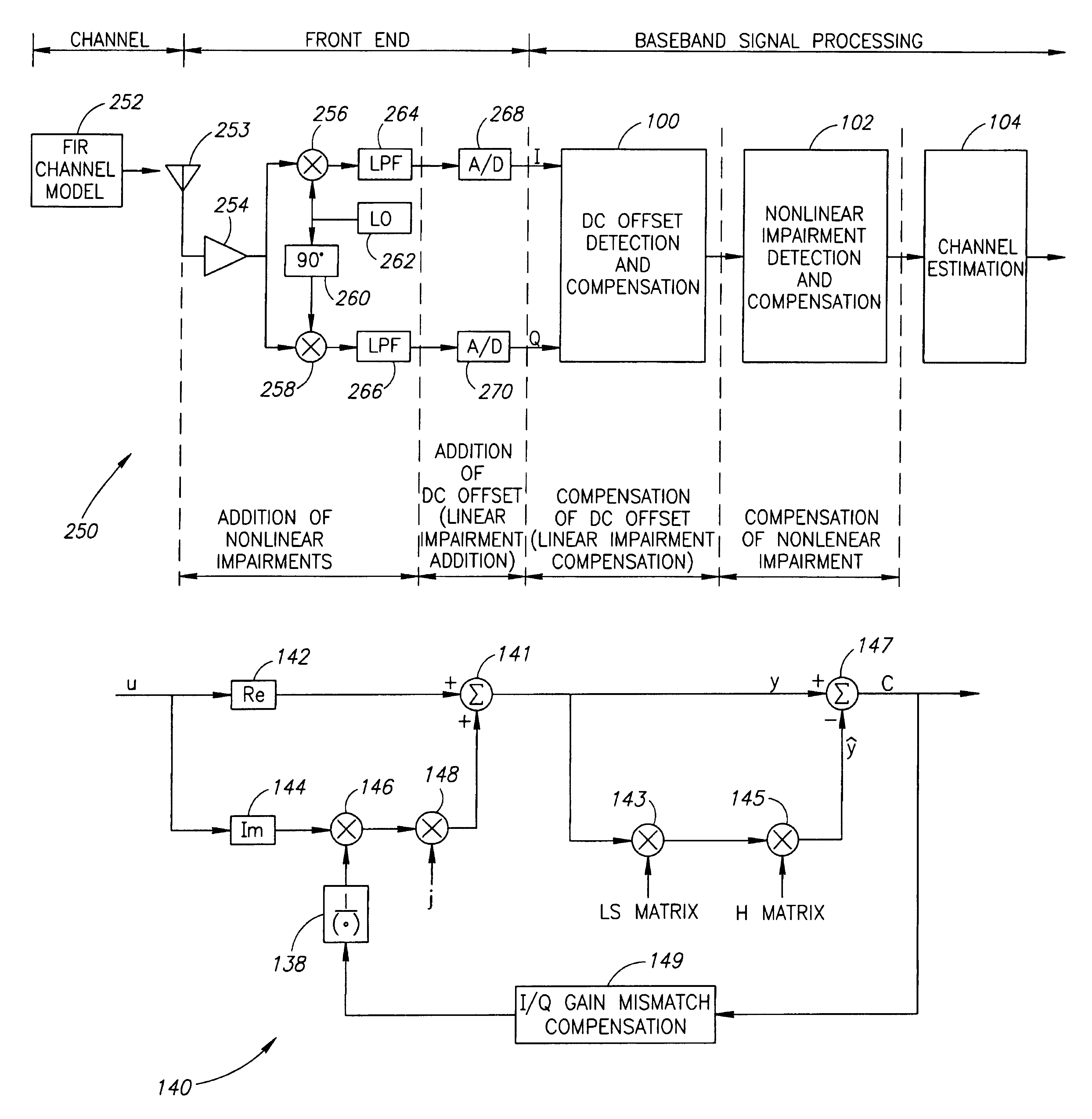

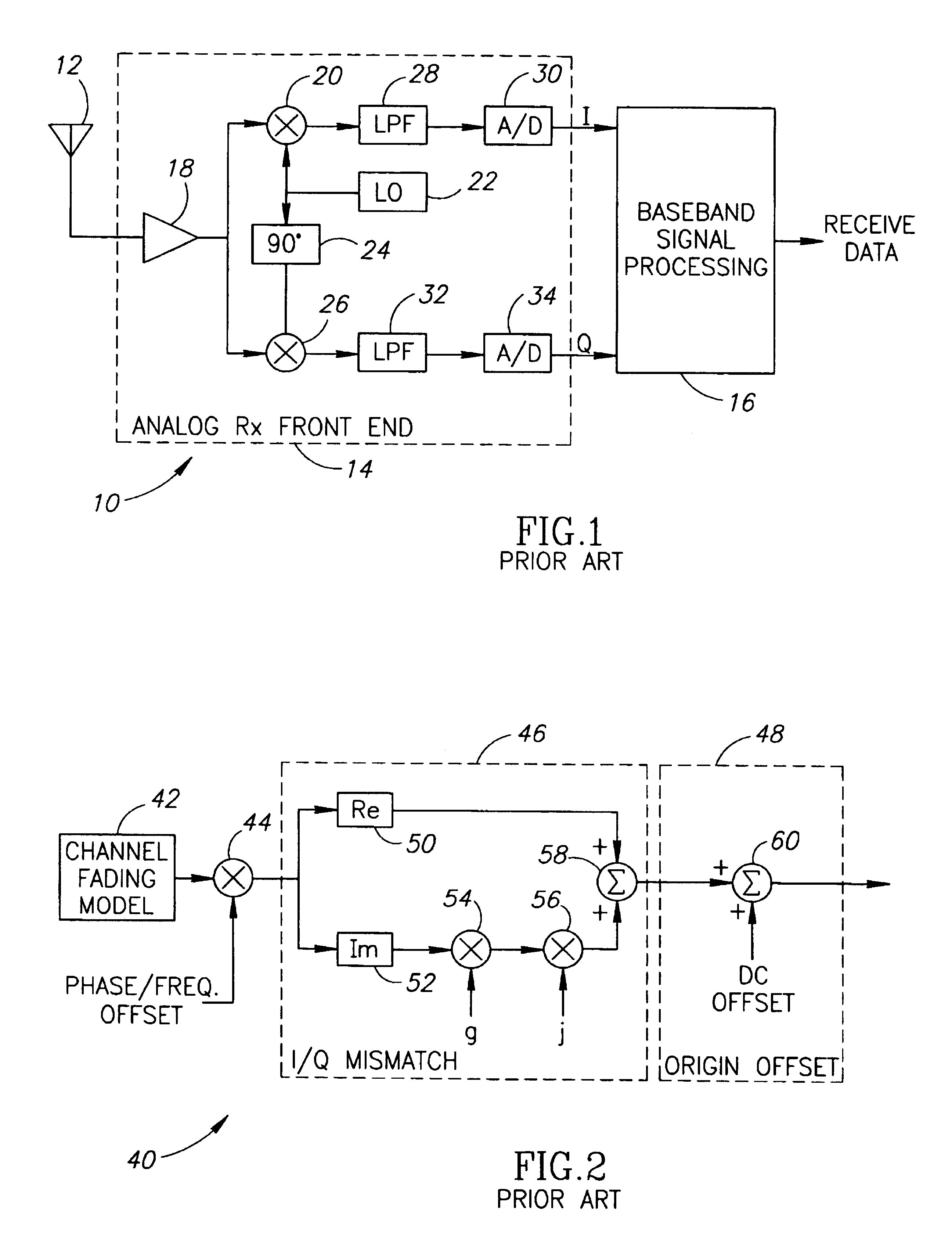

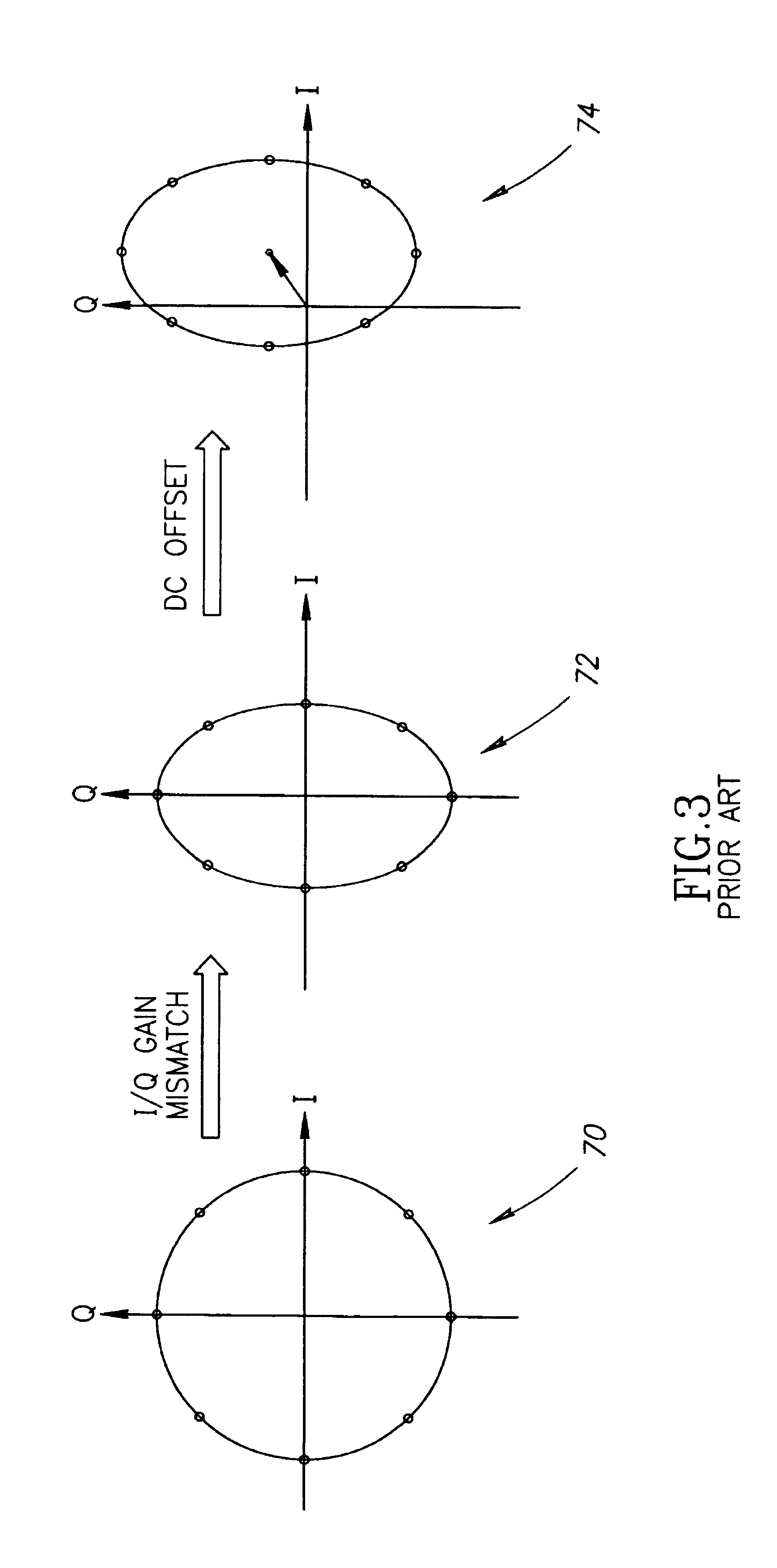

Compensation of I/Q gain mismatch in a communications receiver

A novel and useful apparatus for and method of I / Q gain mismatch compensation for use in a communications receiver. The invention is operative to calculate an estimate of the I / Q gain mismatch. Each input sample is subsequently multiplied by the inverse of the estimate to generate compensated samples. The training sequence portion of the uncompensated input samples is used to generate the I / Q gain mismatch estimate. In accordance with the present invention, the H matrix used in calculating the gain mismatch estimate is pre-calculated for several channel lengths and stored in memory. An estimate of the channel is generated which provides the channel length and the location in the input sample buffer of the first training sequence sample to be used in calculating the gain mismatch estimate. The channel length is used to determine the number of training sequence samples to be used and to select one of the previously calculated H matrices.

Owner:COMSYS COMM & SIGNAL PROC

System and method for I-Q mismatch compensation in a low IF or zero IF receiver

InactiveUS6785529B2Modulated-carrier systemsAngle demodulation by oscillations conversionLocal oscillator signalFrequency mixer

Owner:QUALCOMM INC

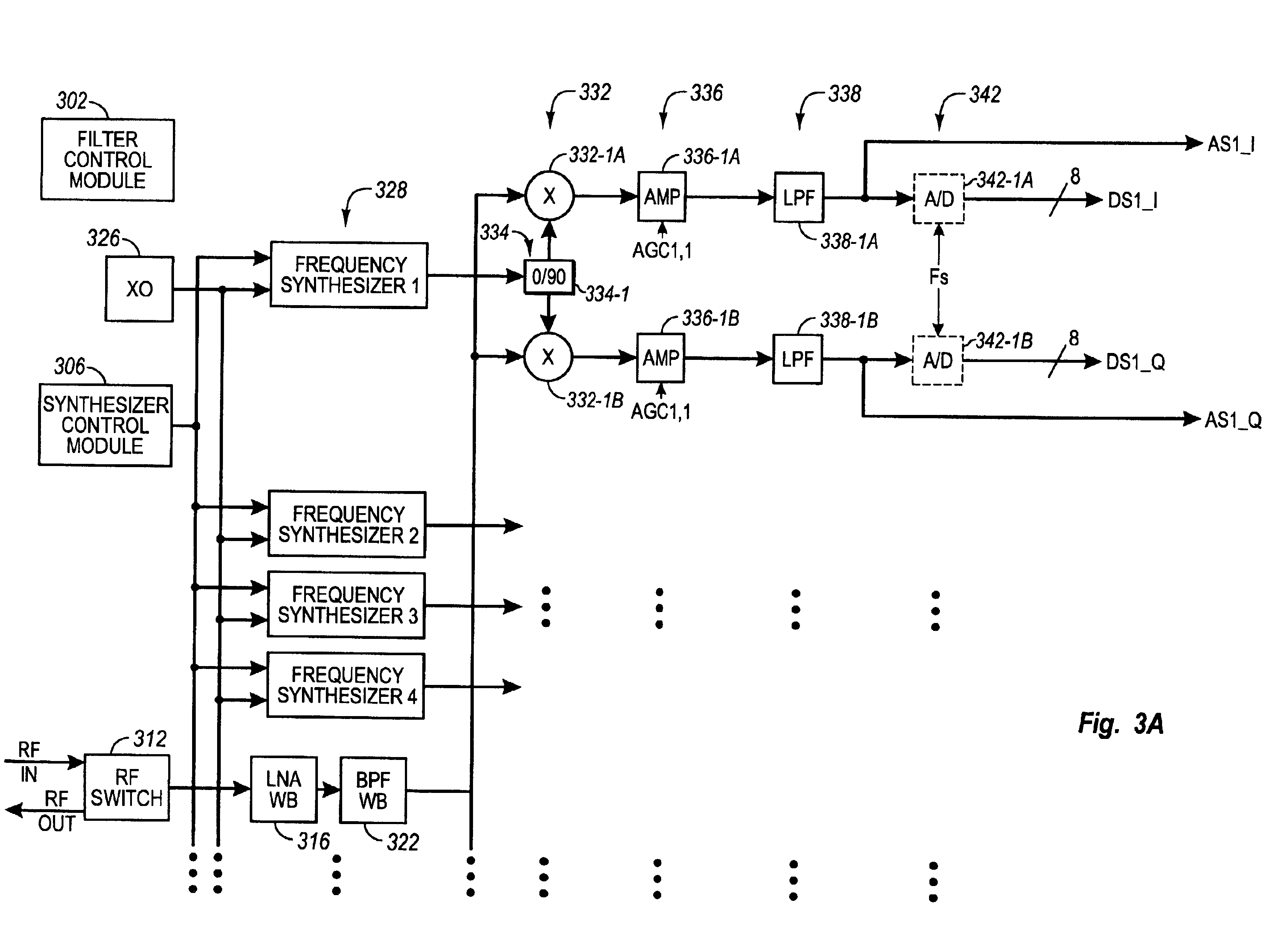

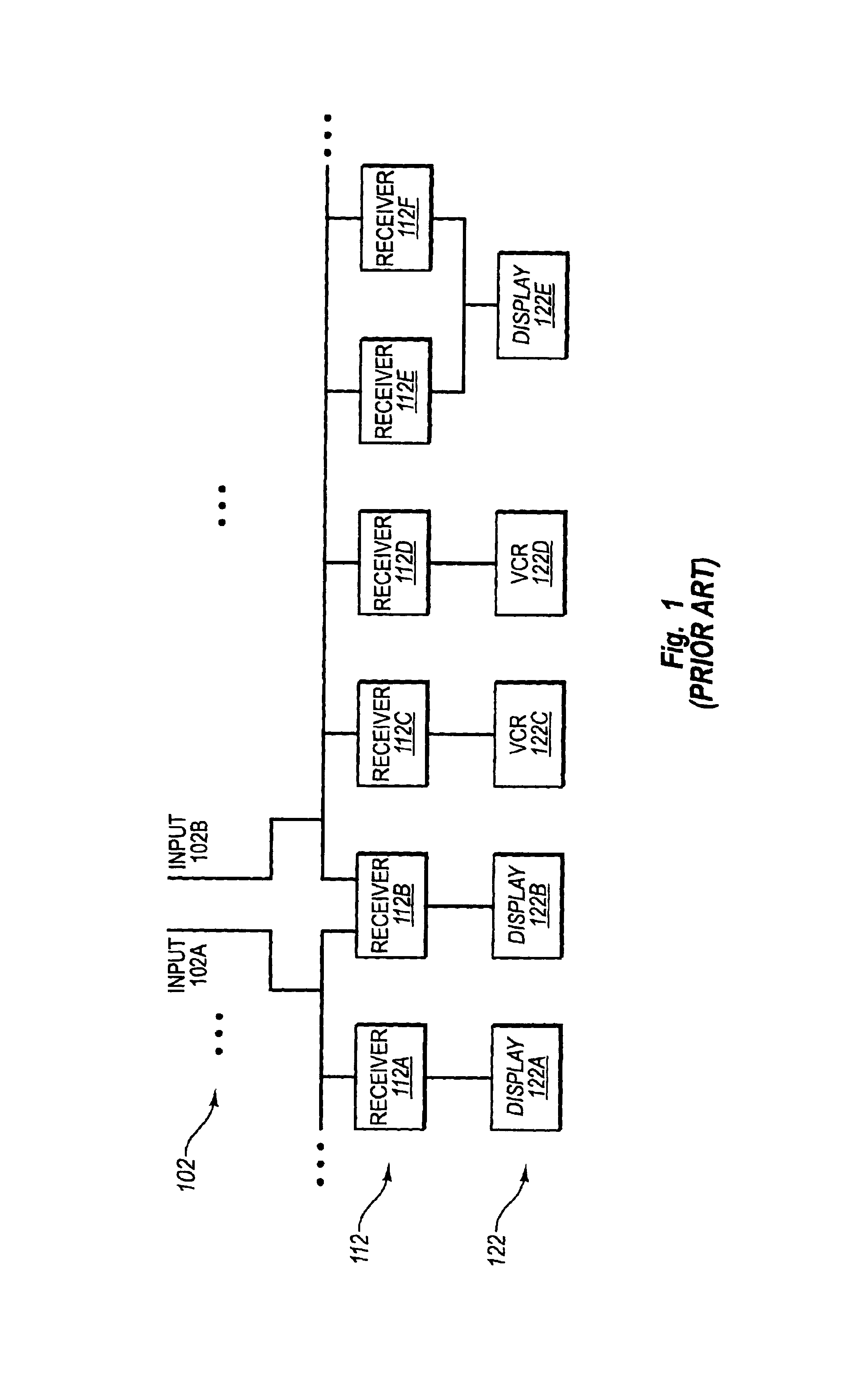

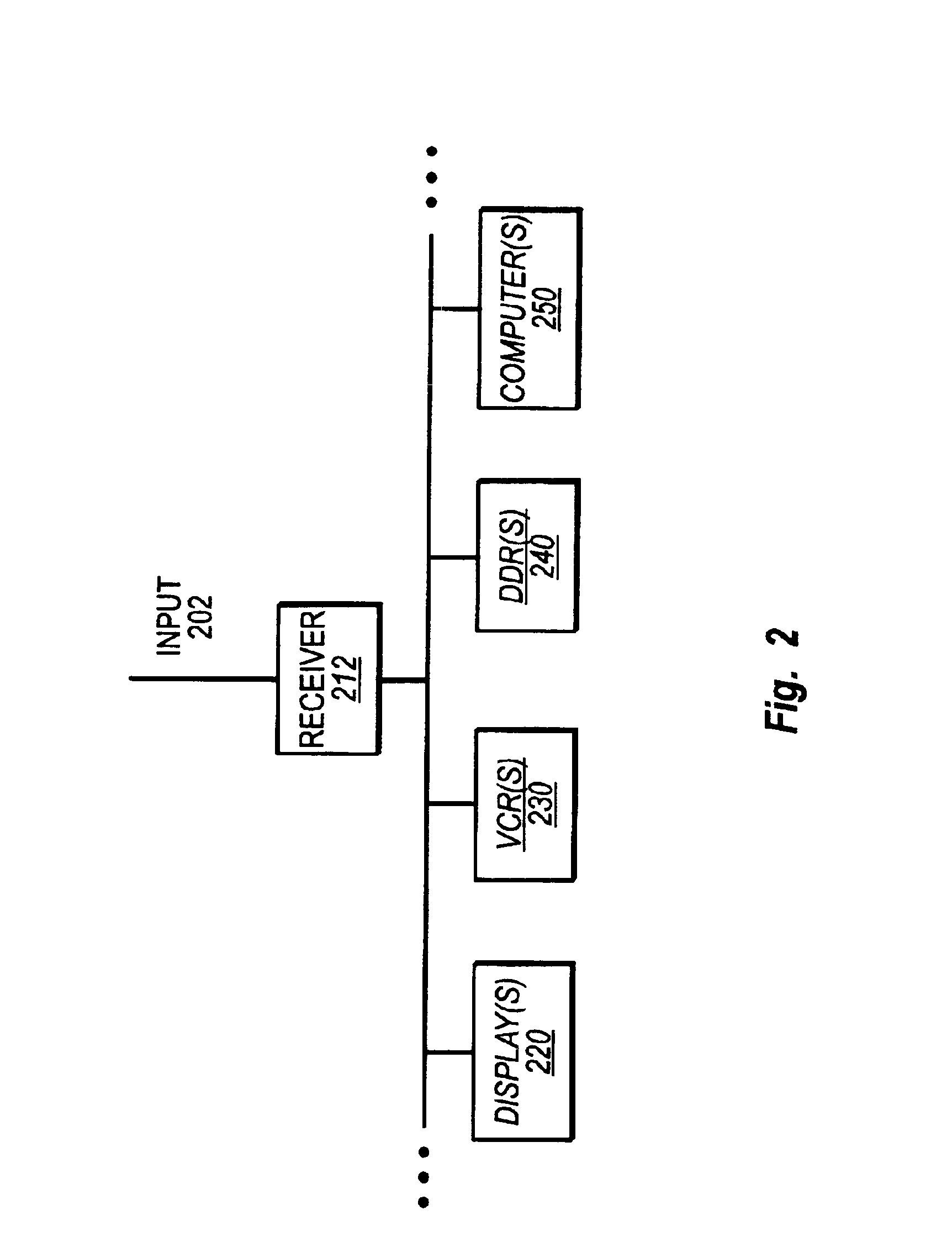

Simultaneous tuning of multiple channels using intermediate frequency sub-sampling

ActiveUS6888888B1Improve cooling effectImprove reliabilityTelevision system detailsPicture reproducers using cathode ray tubesAudio power amplifierIntermediate frequency

Owner:MICROSOFT TECH LICENSING LLC

Local oscillator leakage control in direct conversion processes

InactiveUS6960962B2Automatic scanning with simultaneous frequency displaySpatial transmit diversityIntermediate frequencyLocal oscillator

A system and method for generating a local oscillator (LO) frequency in a zero intermediate frequency (IF) receiver or transmitter is presented. A signal is received from a voltage controlled oscillator (VCO). The signal has a VCO frequency. The VCO frequency is divided by a number N to produce a signal having a divided-down frequency. The signal having the VCO frequency is then mixed with the signal having the divided-down frequency to produce an output signal having an output frequency. Local oscillator leakage is reduced. Thus, the receiver or transmitter may operate in multiple wireless communication bands and modes and meet the associated specifications.

Owner:QUALCOMM INC

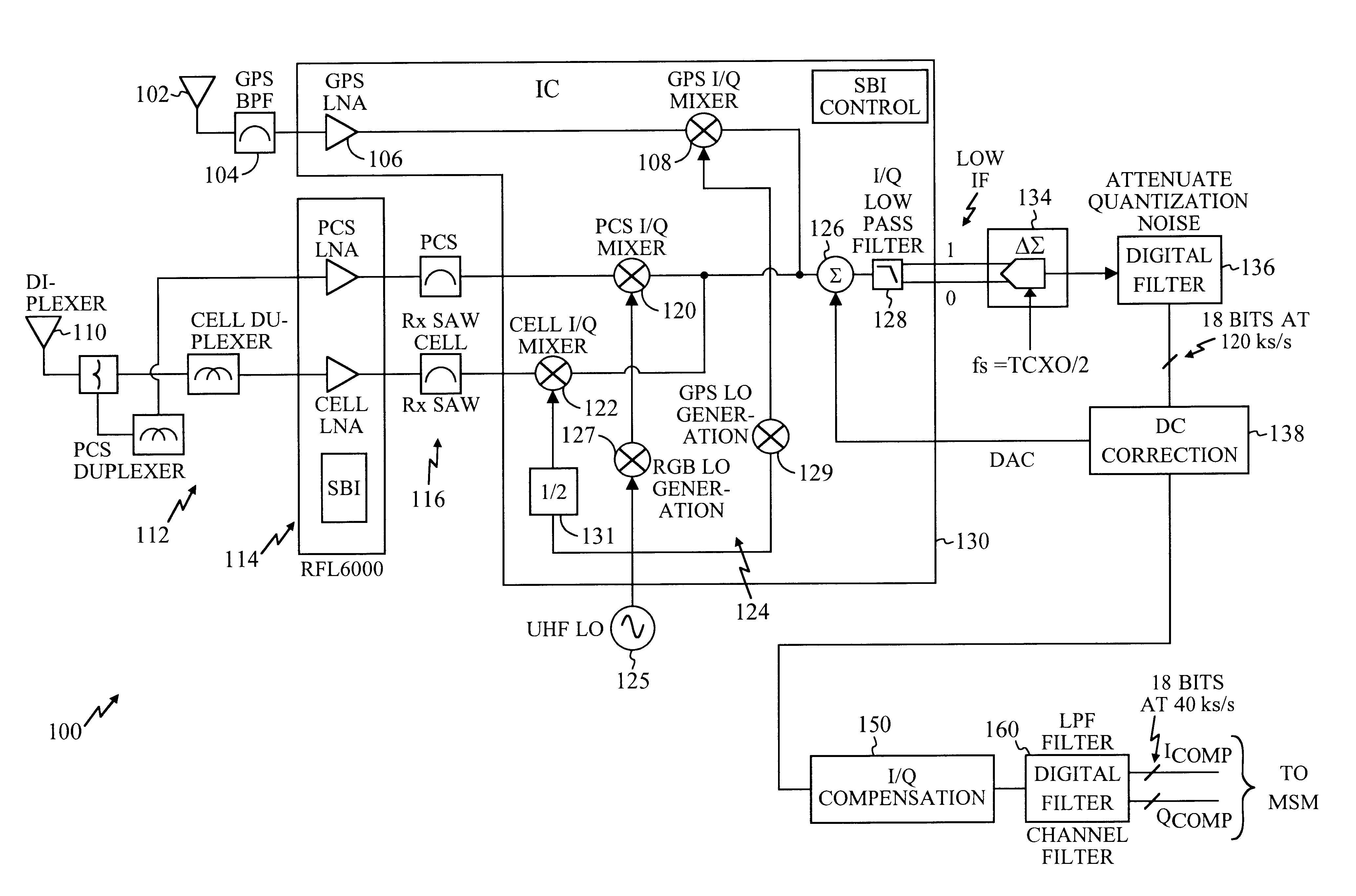

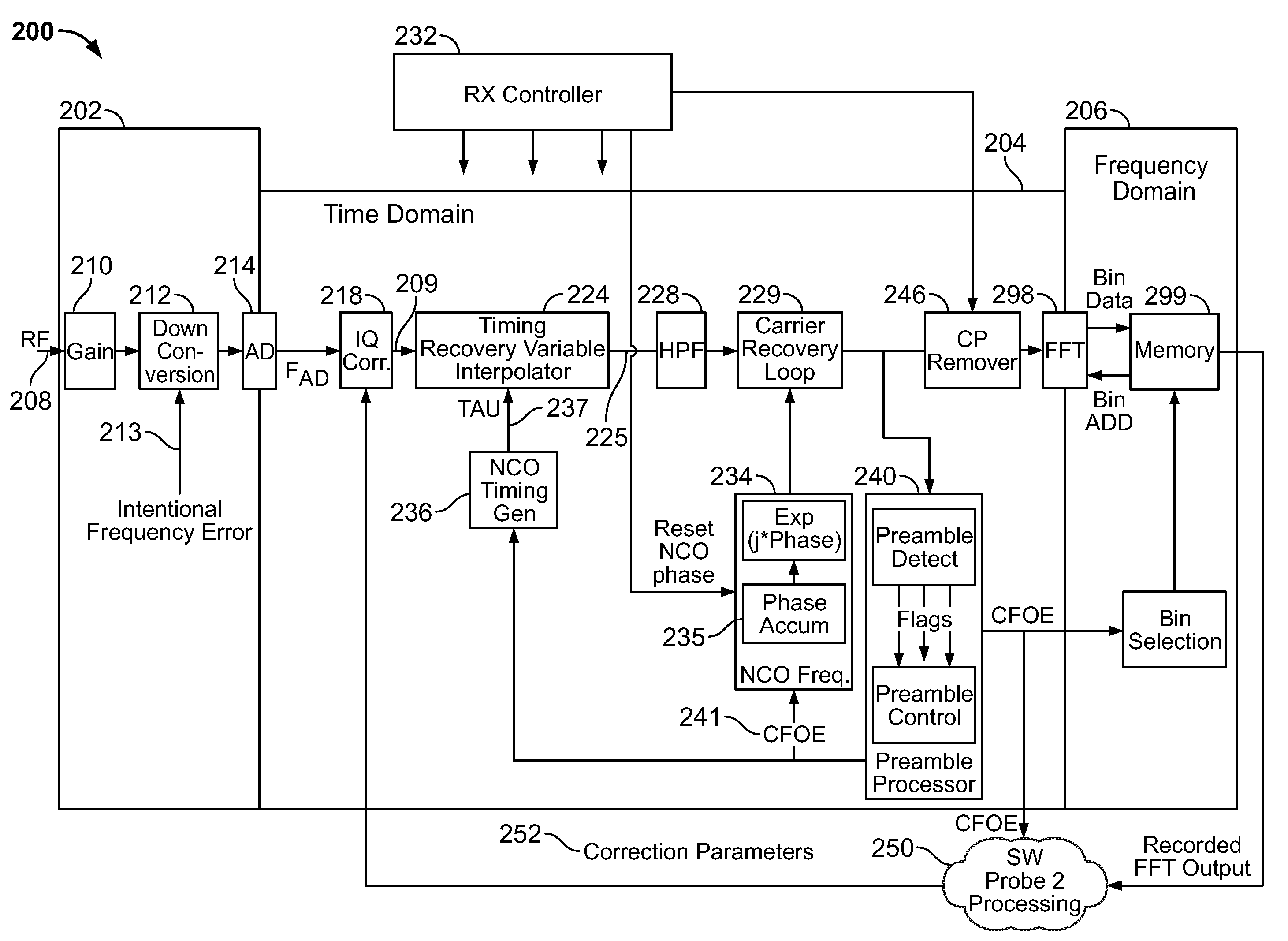

Receiver architecture with digitally generated intermediate frequency

InactiveUS20060083335A1Modulation transferencePhase-modulated carrier systemsRF front endIntermediate frequency

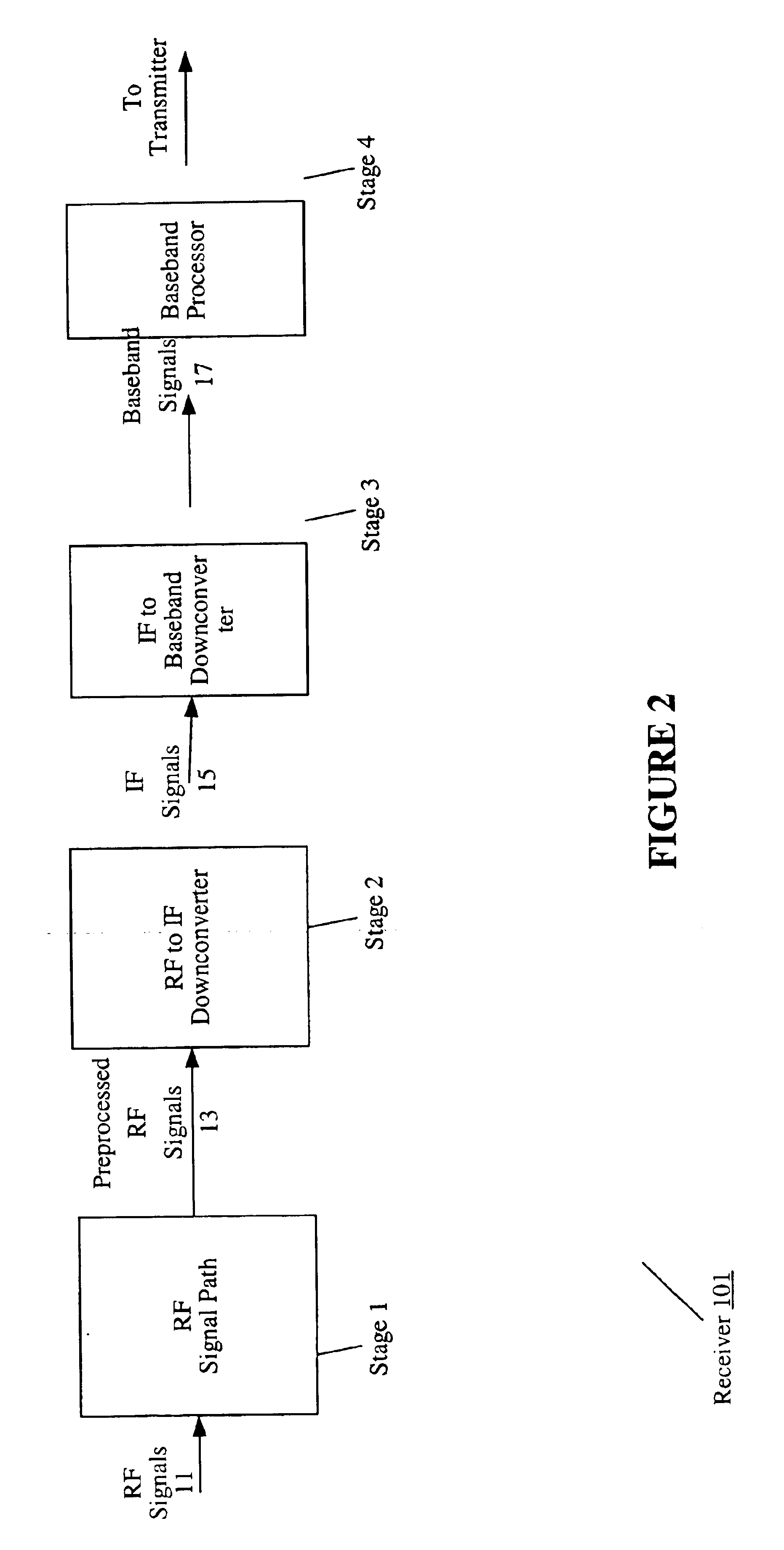

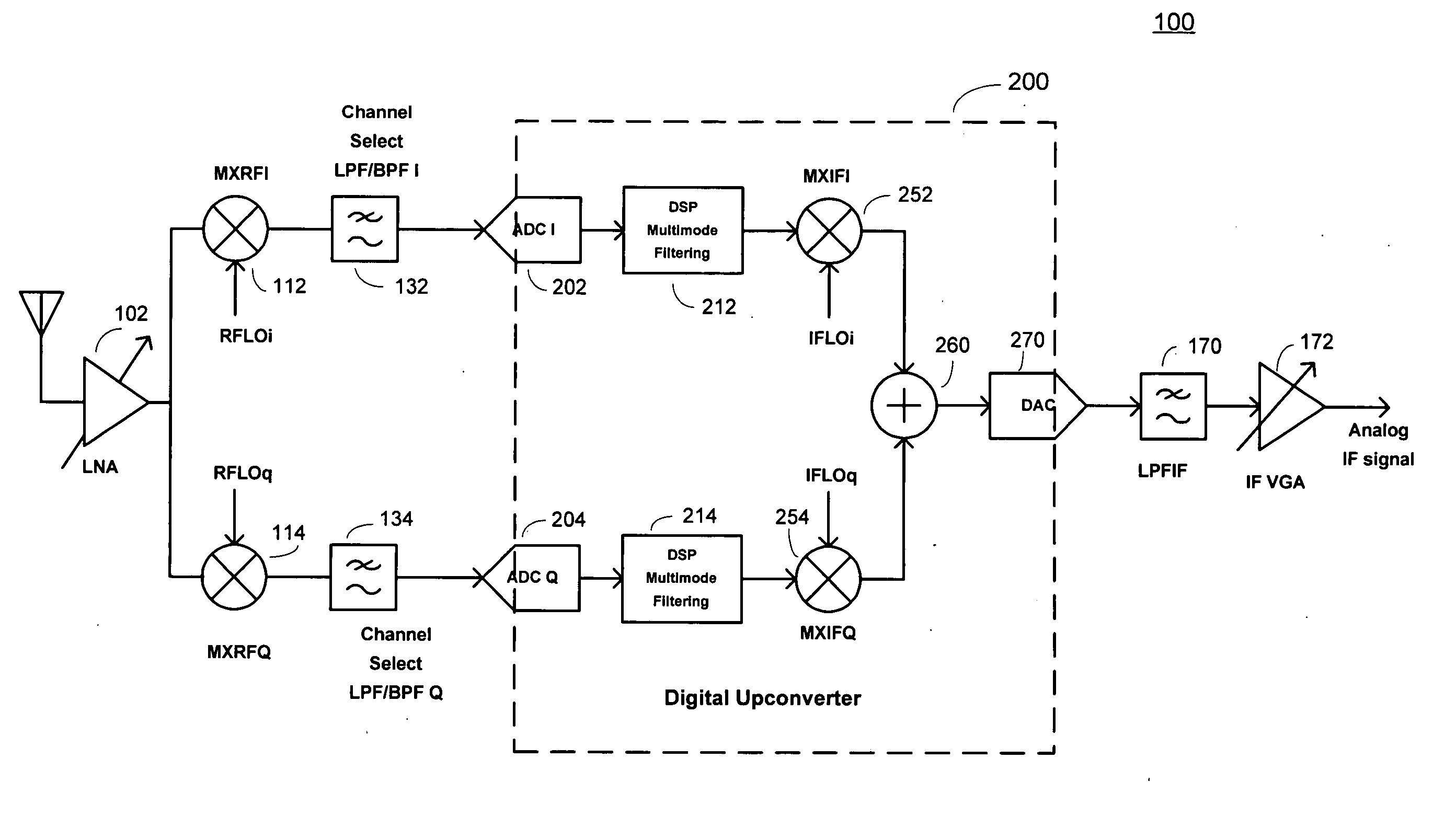

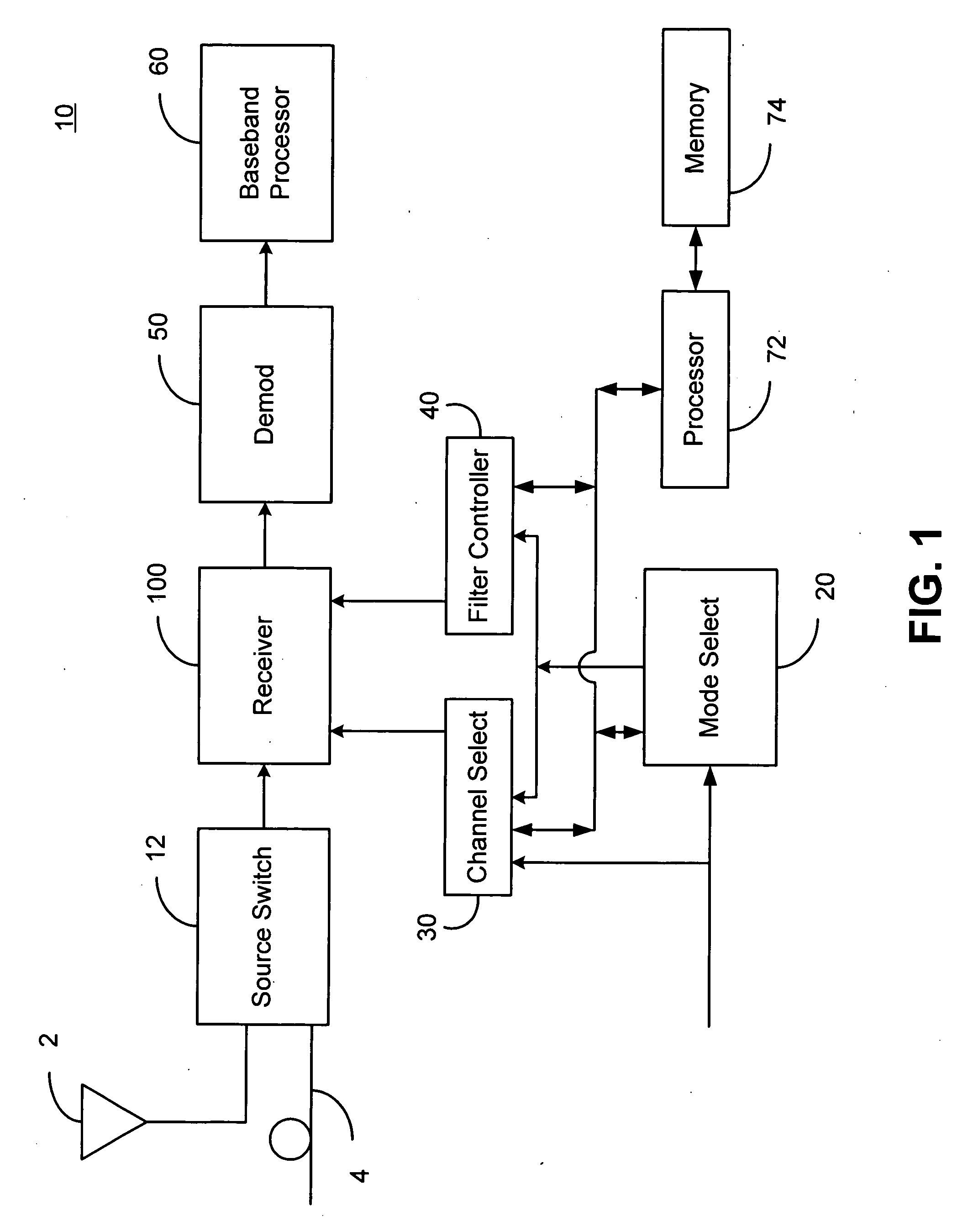

A receiver can be configured to include an RF front end that is configured to downconvert a received signal to a baseband signal or a low Intermediate Frequency (IF) signal. The receiver can downconvert the desired signal from an RF frequency in the presence of numerous interference sources to a baseband or low IF signal for filtering and channel selection. The filtered baseband or low IF signal can be converted to a digital representation. The digital representation of the signal can be upconverted in the digital domain to a programmable IF frequency. The digital IF signal can be converted to an analog IF signal that can be processed by legacy hardware.

Owner:MAXLINEAR INC

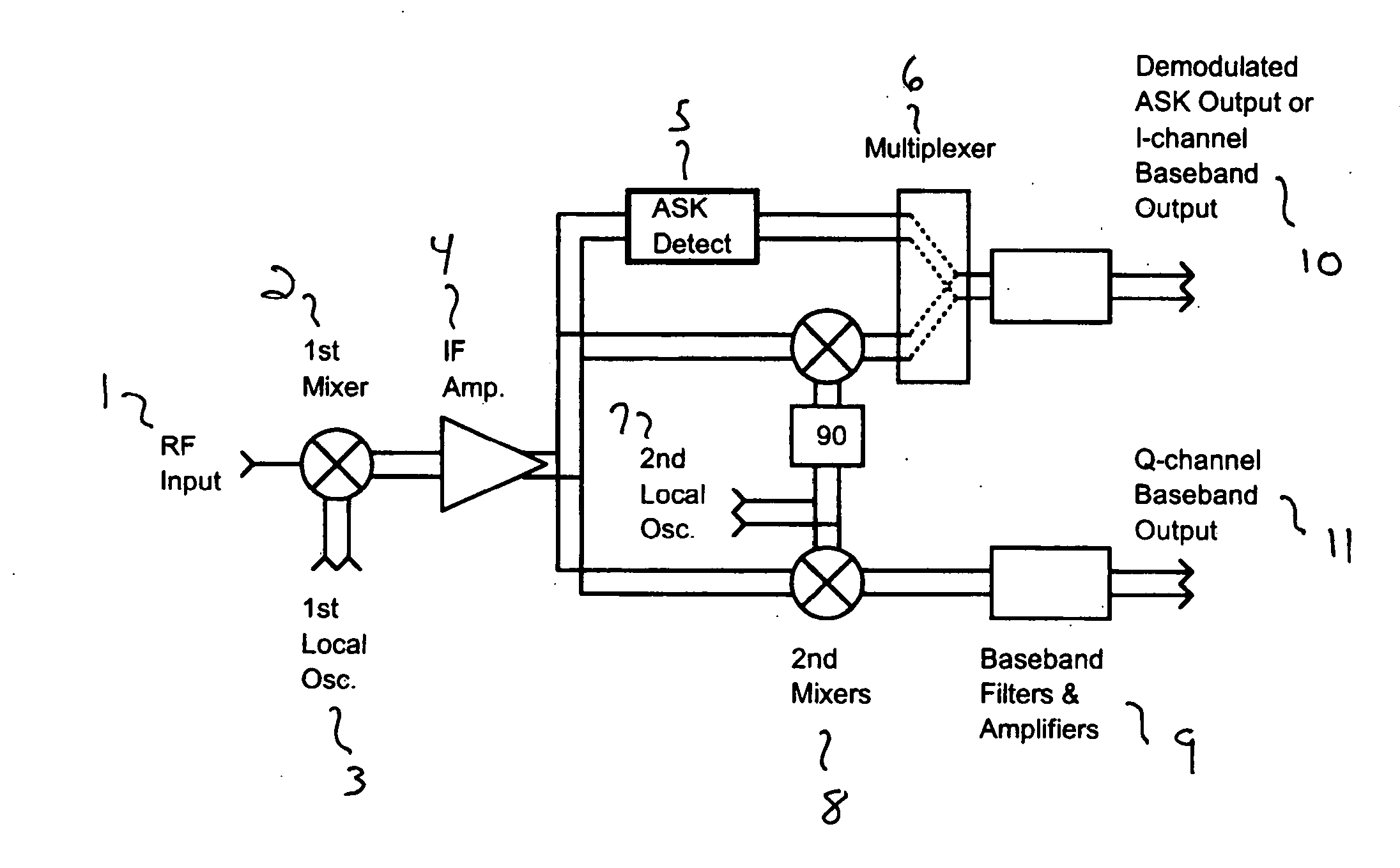

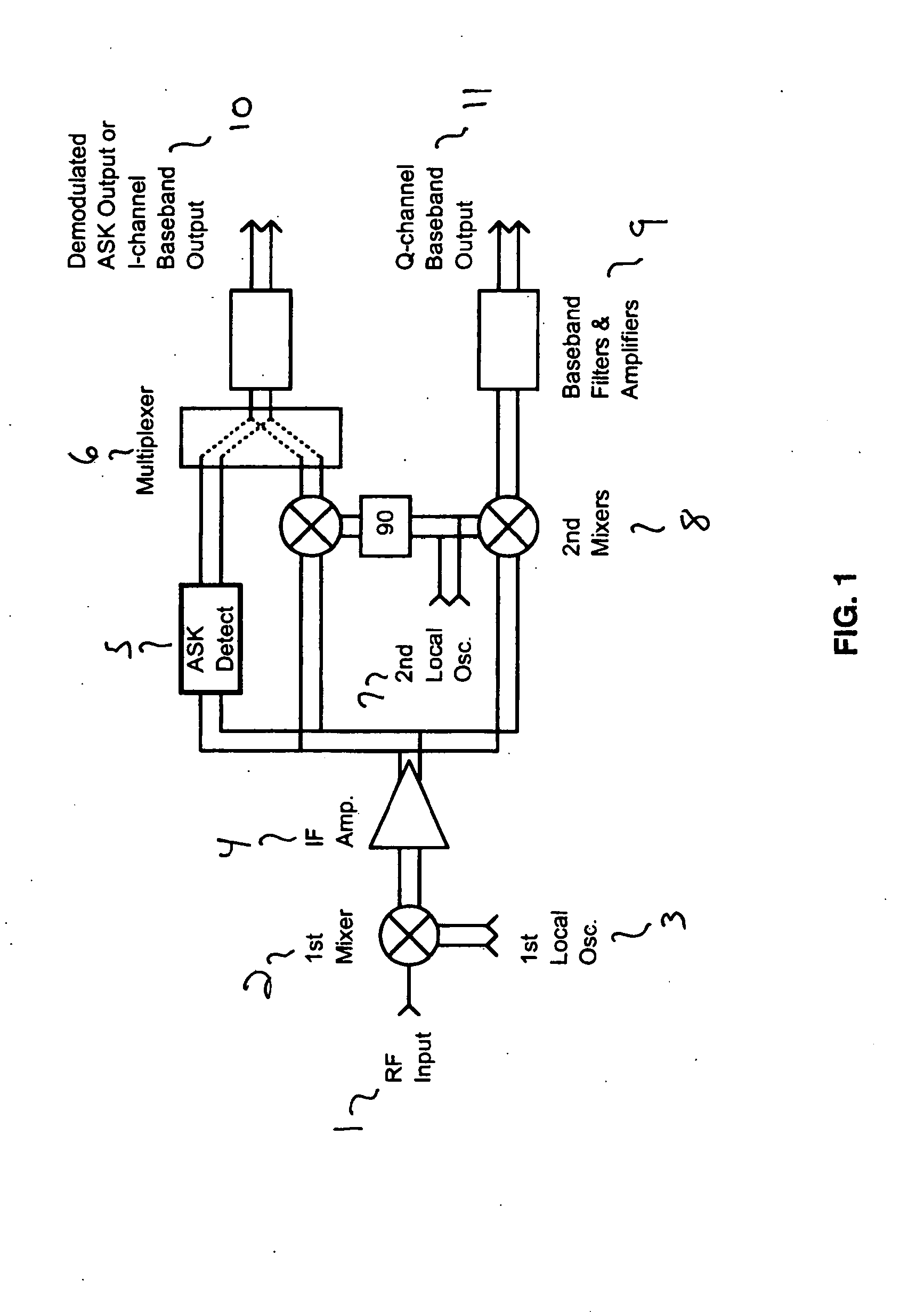

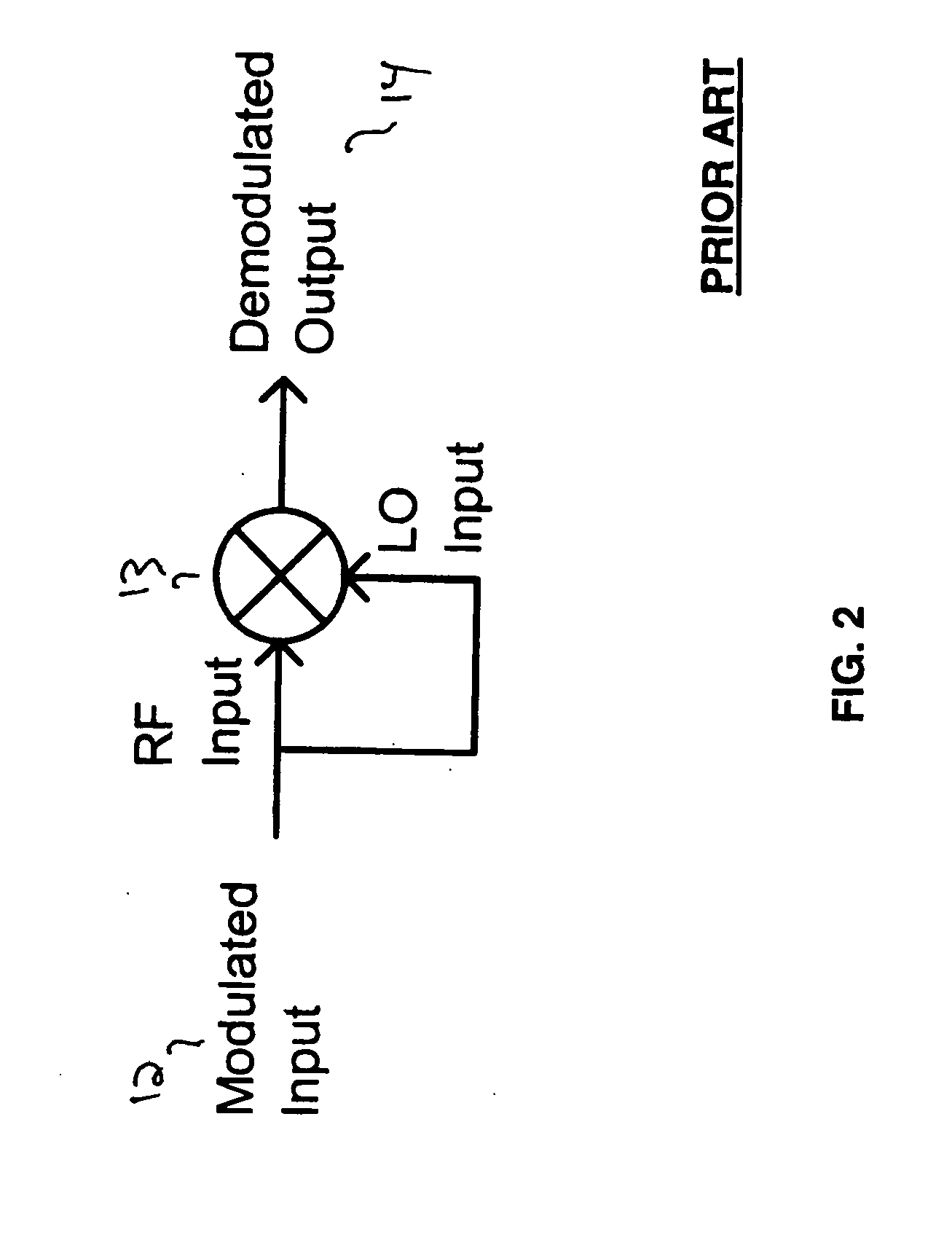

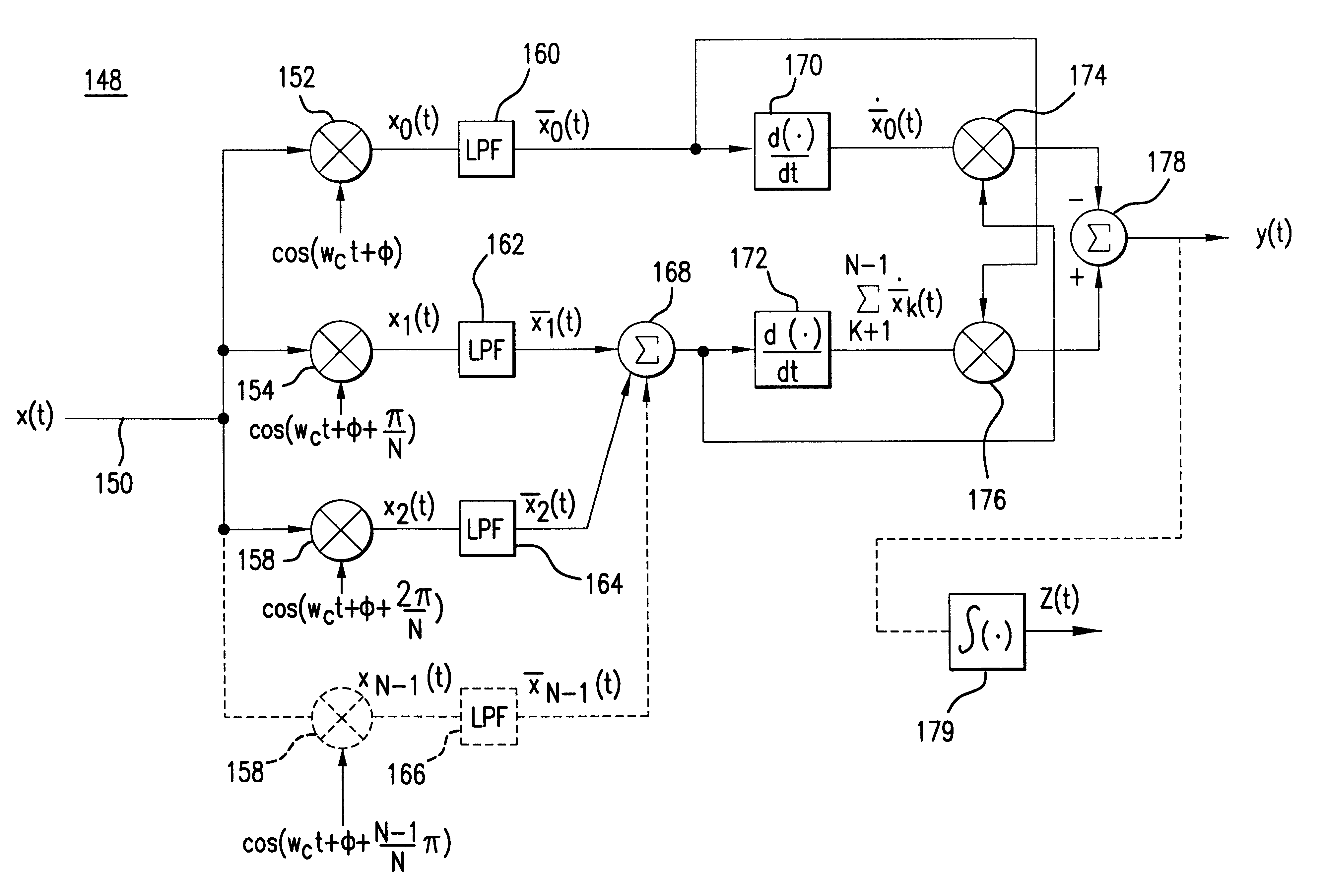

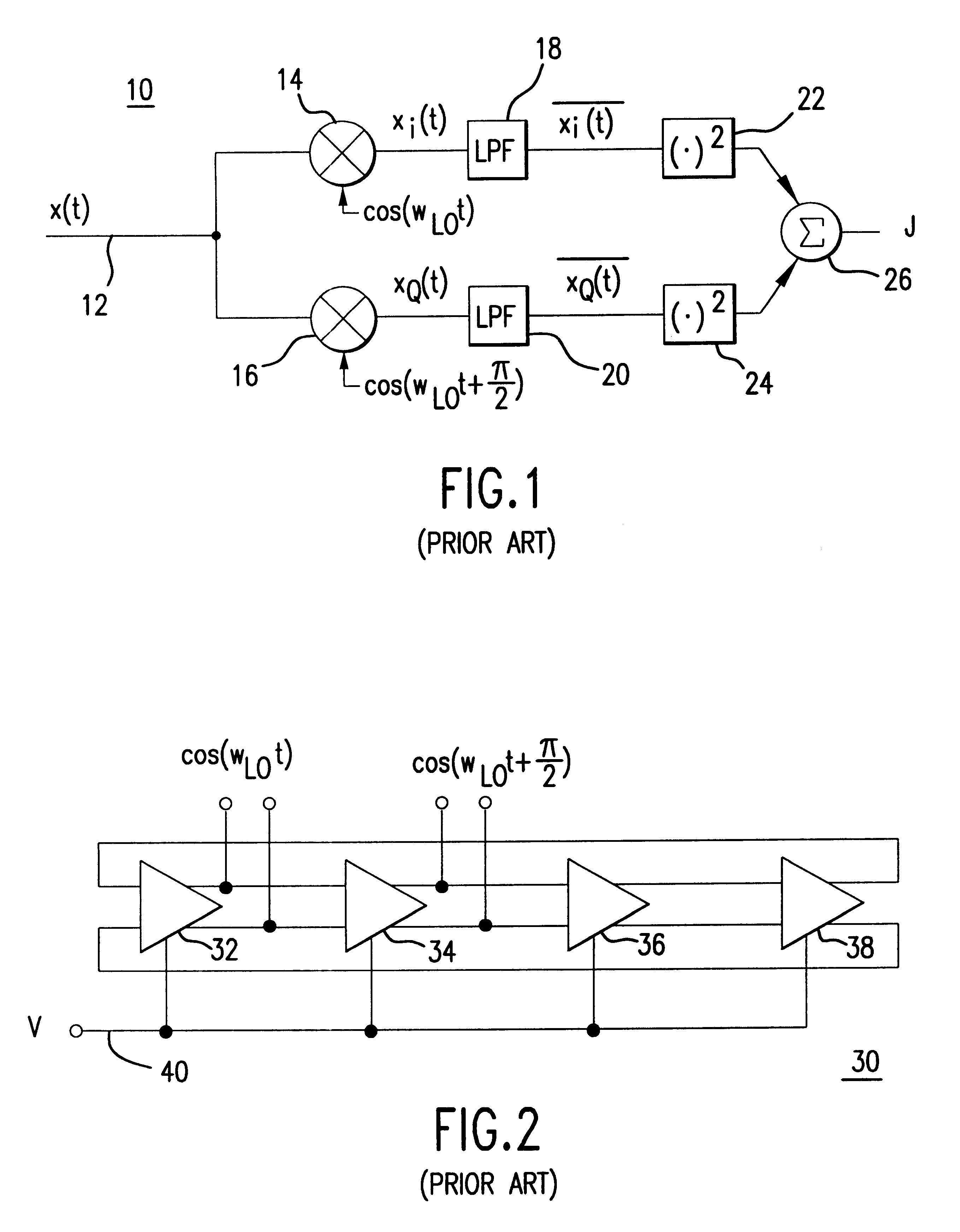

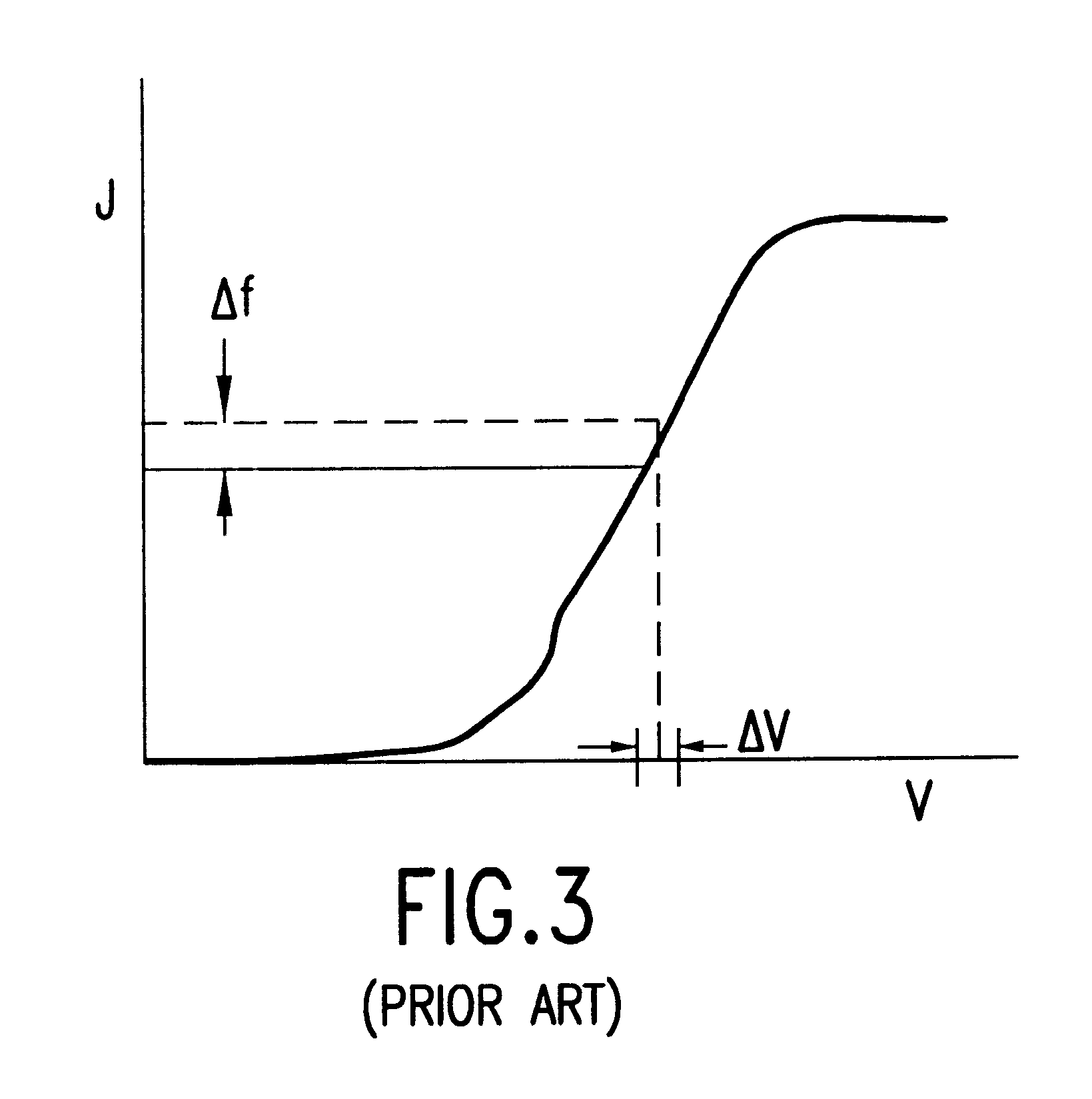

Receiver and integrated am-fm/iq demodulators for gigabit-rate data detection

ActiveUS20080280577A1Easily incorporated into integrated circuit receiver systemSimultaneous amplitude and angle demodulationAmplitude demodulationDiscriminatorDetector circuits

This disclosure addresses providing gigabit-rate data transmission over wireless radio links, using carrier frequencies in the millimeter-wave range (>30 GHz). More specifically, a circuit for detection of amplitude-shift keyed (ASK) or other amplitude modulations (AM) which can be easily incorporated into an integrated circuit receiver system is described, making the receiver capable of supporting both complex IQ modulation schemes and simpler, non-coherent on-off or multiple-level keying signals. Several novel radio architectures are also described which, with the addition of a frequency discriminator network, have the capability of handling frequency shift keyed (FSK) or other frequency modulations (FM), as well as AM and complex IQ modulation schemes. These radio architectures support this wide variety of modulations by efficiently sharing detector hardware components. The architecture for supporting both quadrature down-conversion and ASK / AM is described first, followed by the ASK / AM detector circuit details, then the AM-FM detector architecture, and finally the most general AM-FM / IQ demodulator system concept and the FSK / FM detector circuit details.

Owner:GLOBALFOUNDRIES US INC

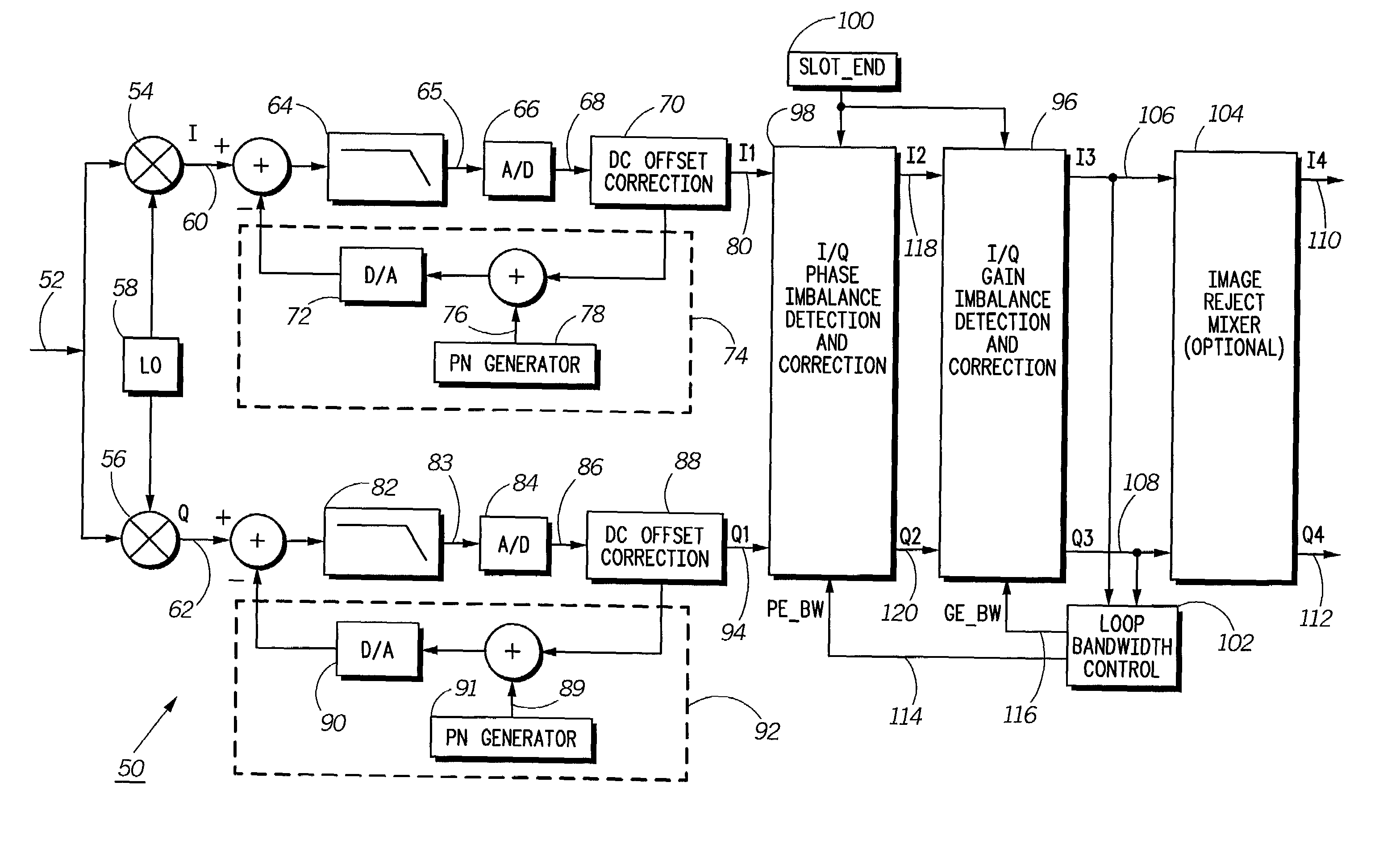

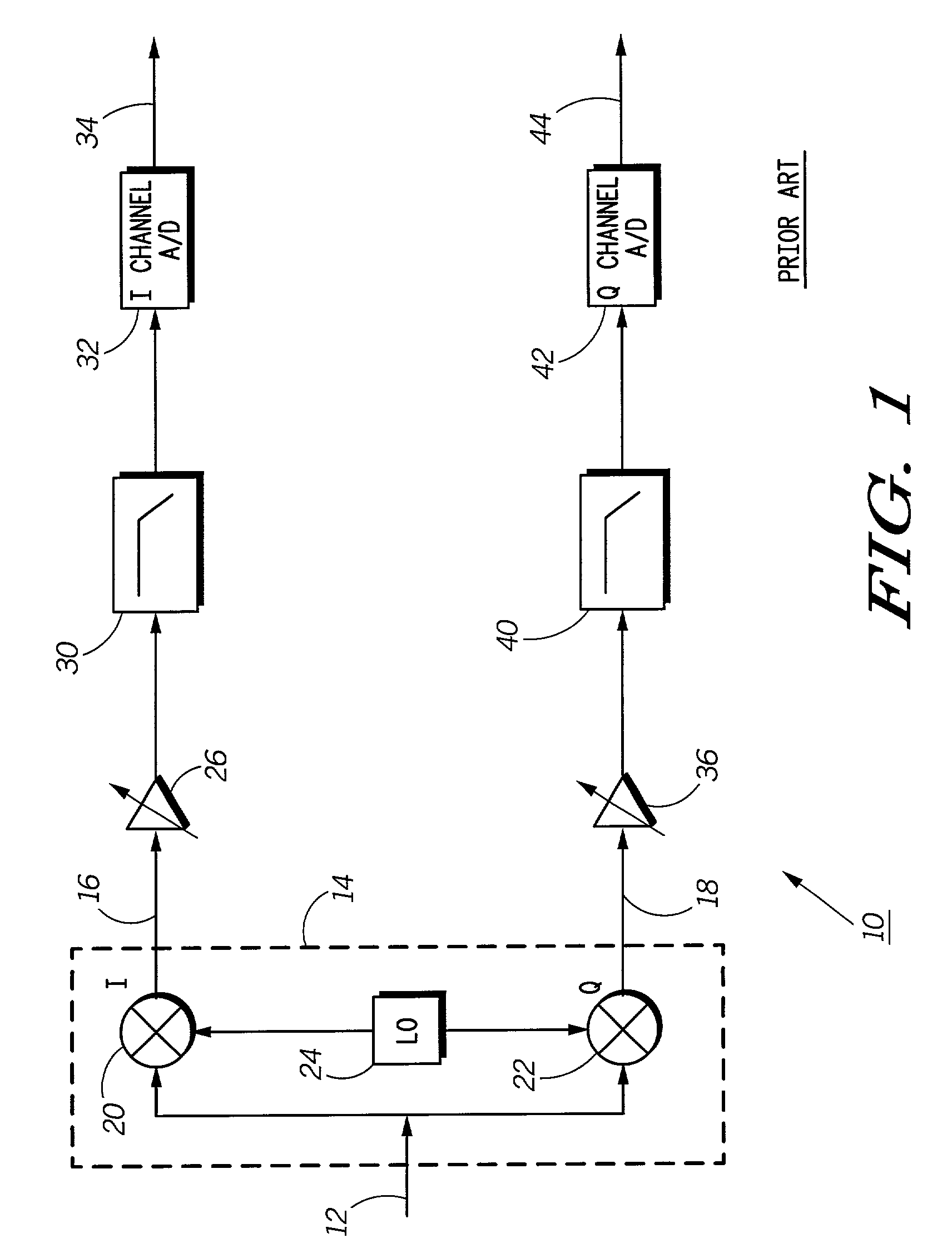

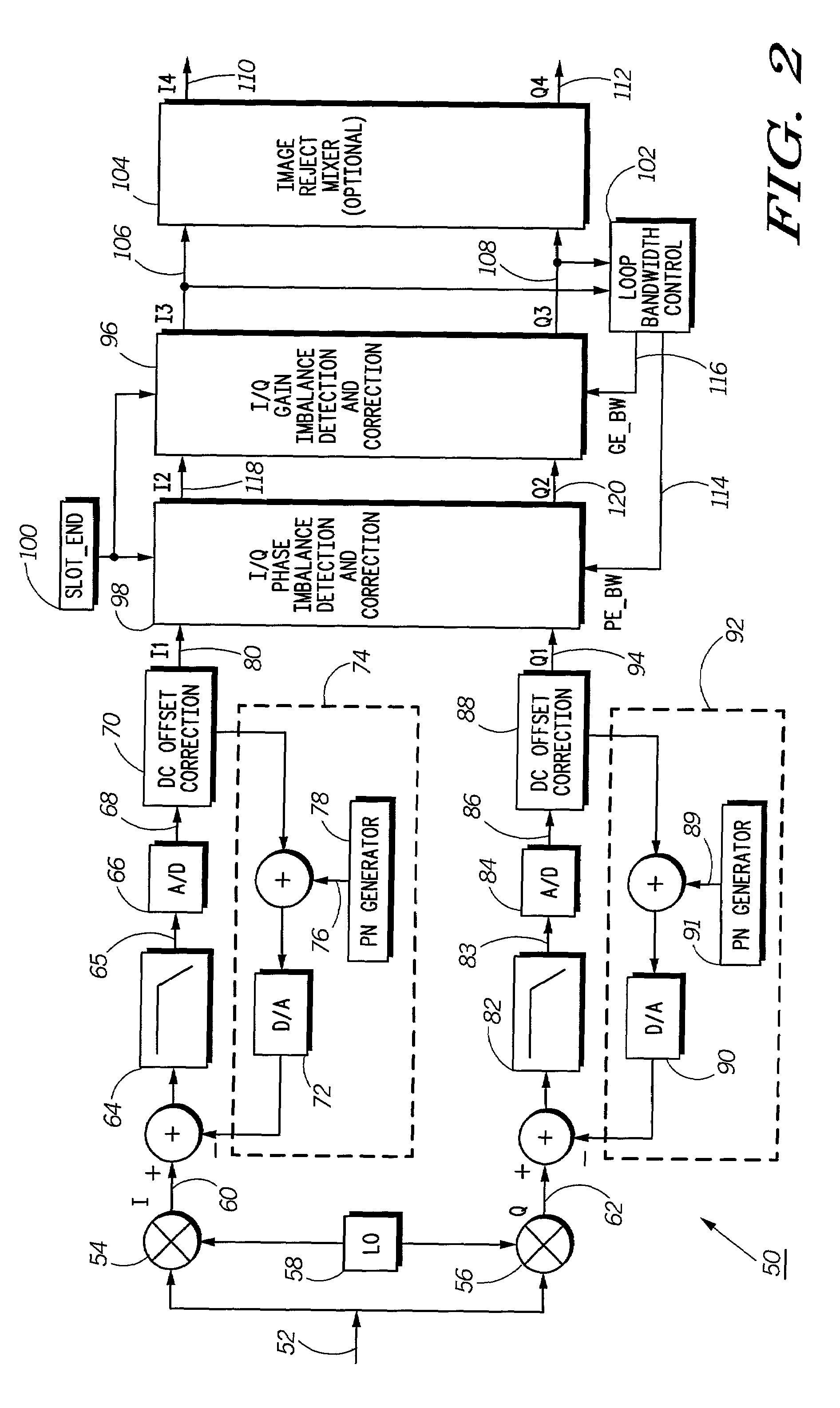

Self calibrating receive path correction system in a receiver

ActiveUS7130359B2Dc level restoring means or bias distort correctionLine balance variation compensationPhase imbalanceRelative phase

A receiver (50) includes a self-calibrating receive path correction system for correction of I / Q gain and phase imbalances in a radio frequency signal. The system includes a signal-processing block (53), an I / Q phase imbalance detection and correction circuit (98), an I / Q gain imbalance detection and correction circuit (96), and an adaptive loop bandwidth control circuit (102). The I / Q phase imbalance detection and correction circuit (98) equalizes for the relative phase imbalance and the I / Q gain imbalance detection and correction circuit (96) equalizes for the relative gain imbalance between the I and Q channels created by the analog portion of a quadrature receiver. The adaptive loop bandwidth control circuit (102) dynamically adjusts at least one loop bandwidth for the I / Q gain imbalance detection and correction circuit (96) and the I / Q phase imbalance detection and correction circuit (98) on a slot boundary.

Owner:GOOGLE TECH HLDG LLC

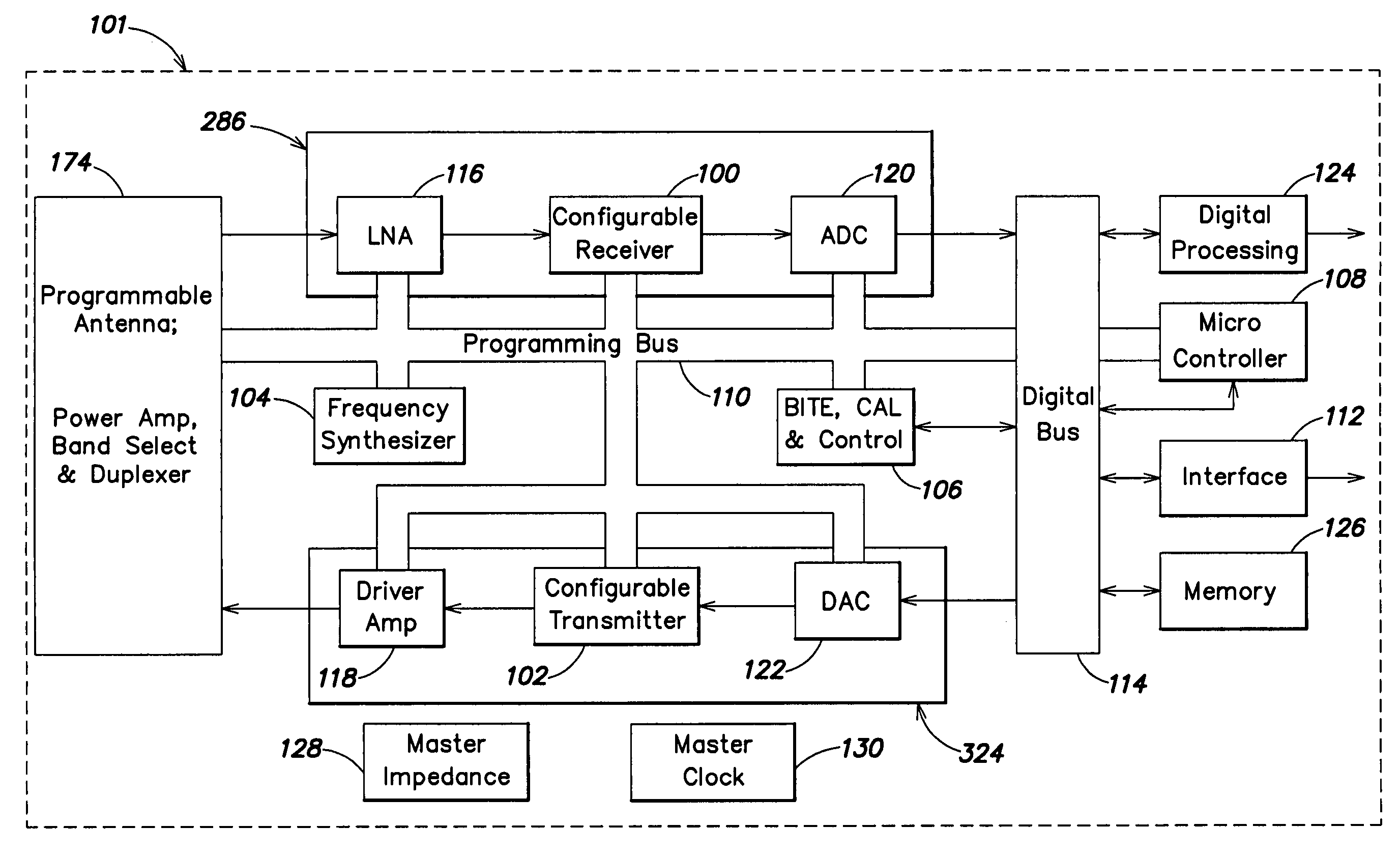

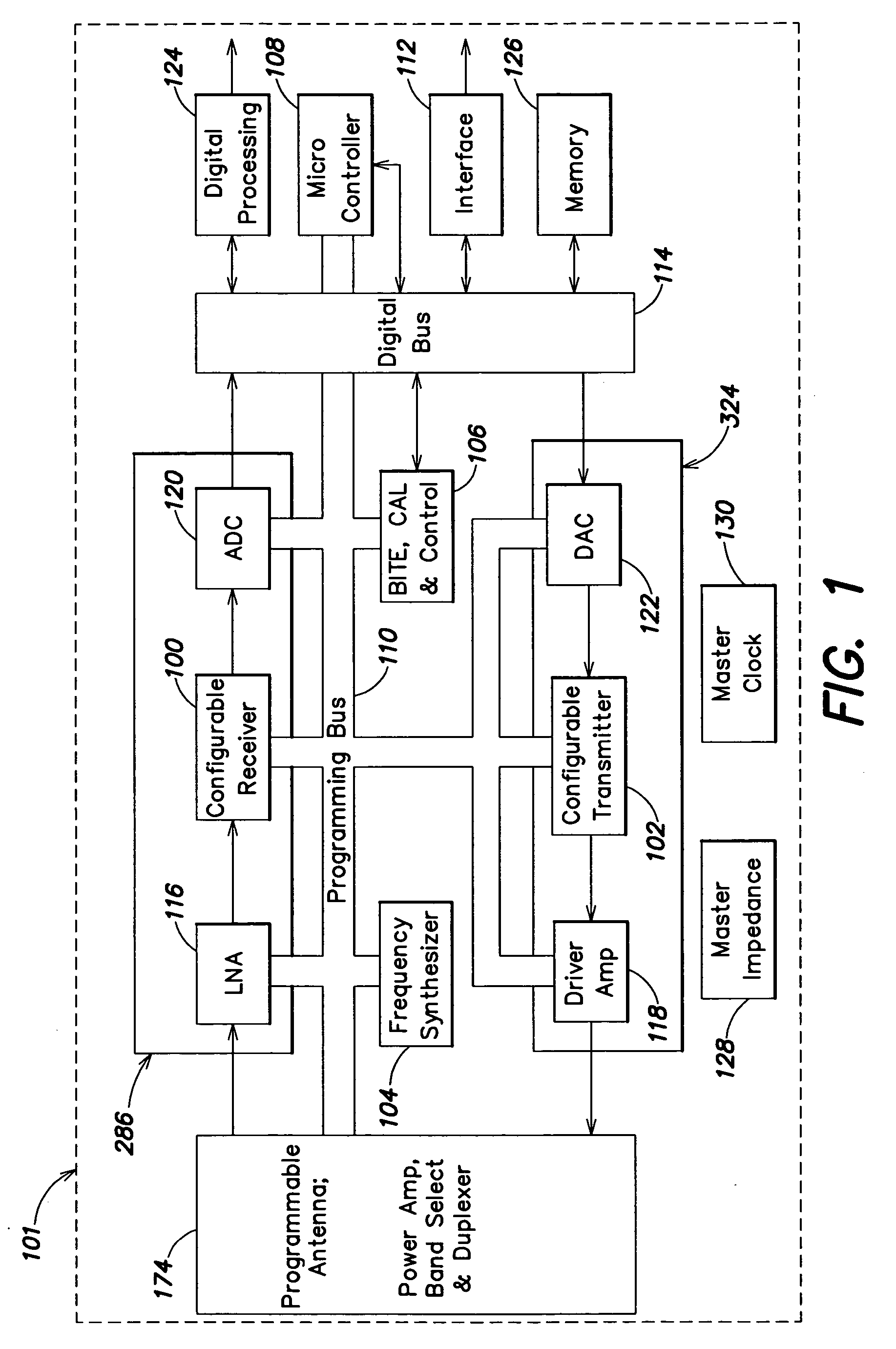

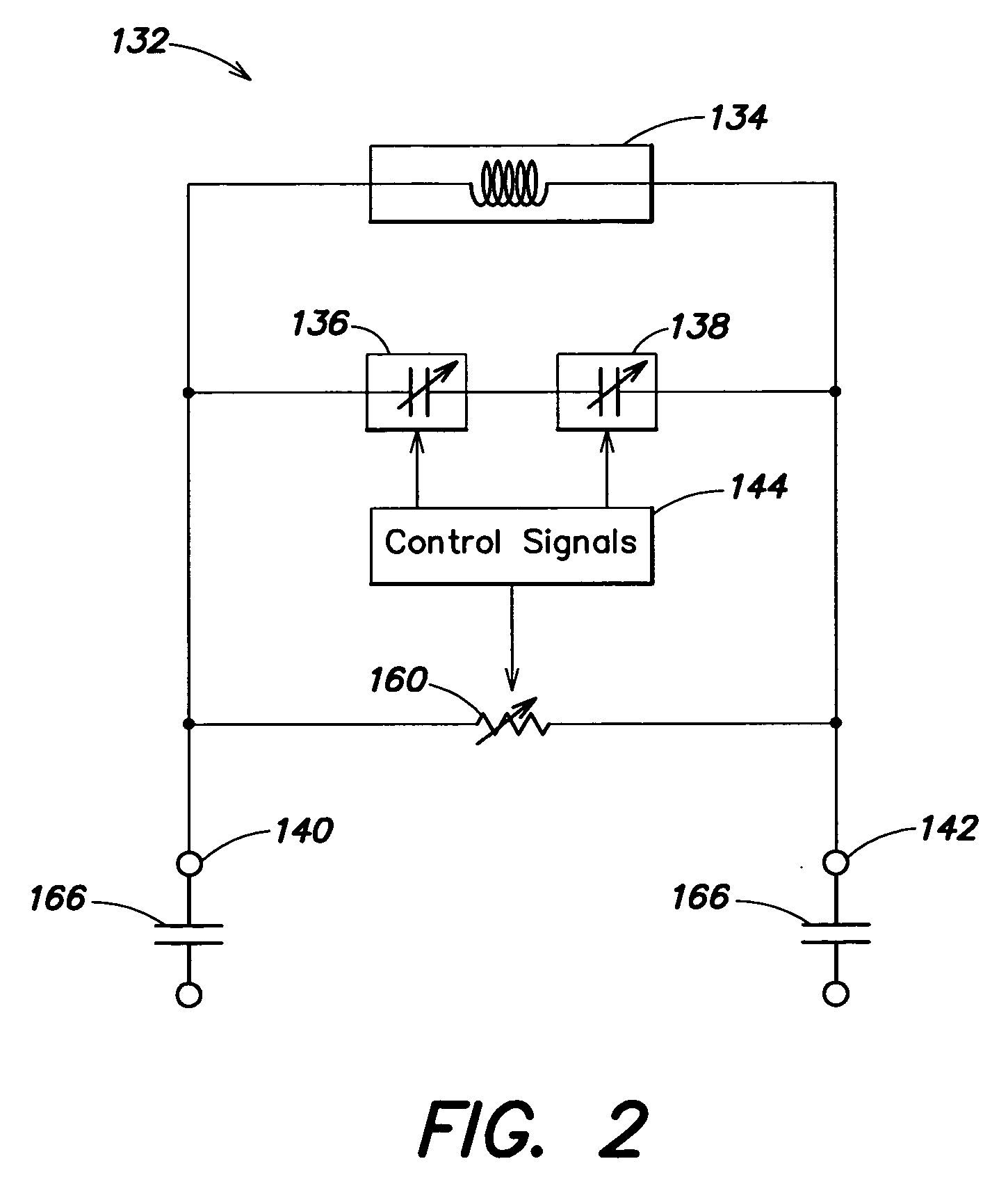

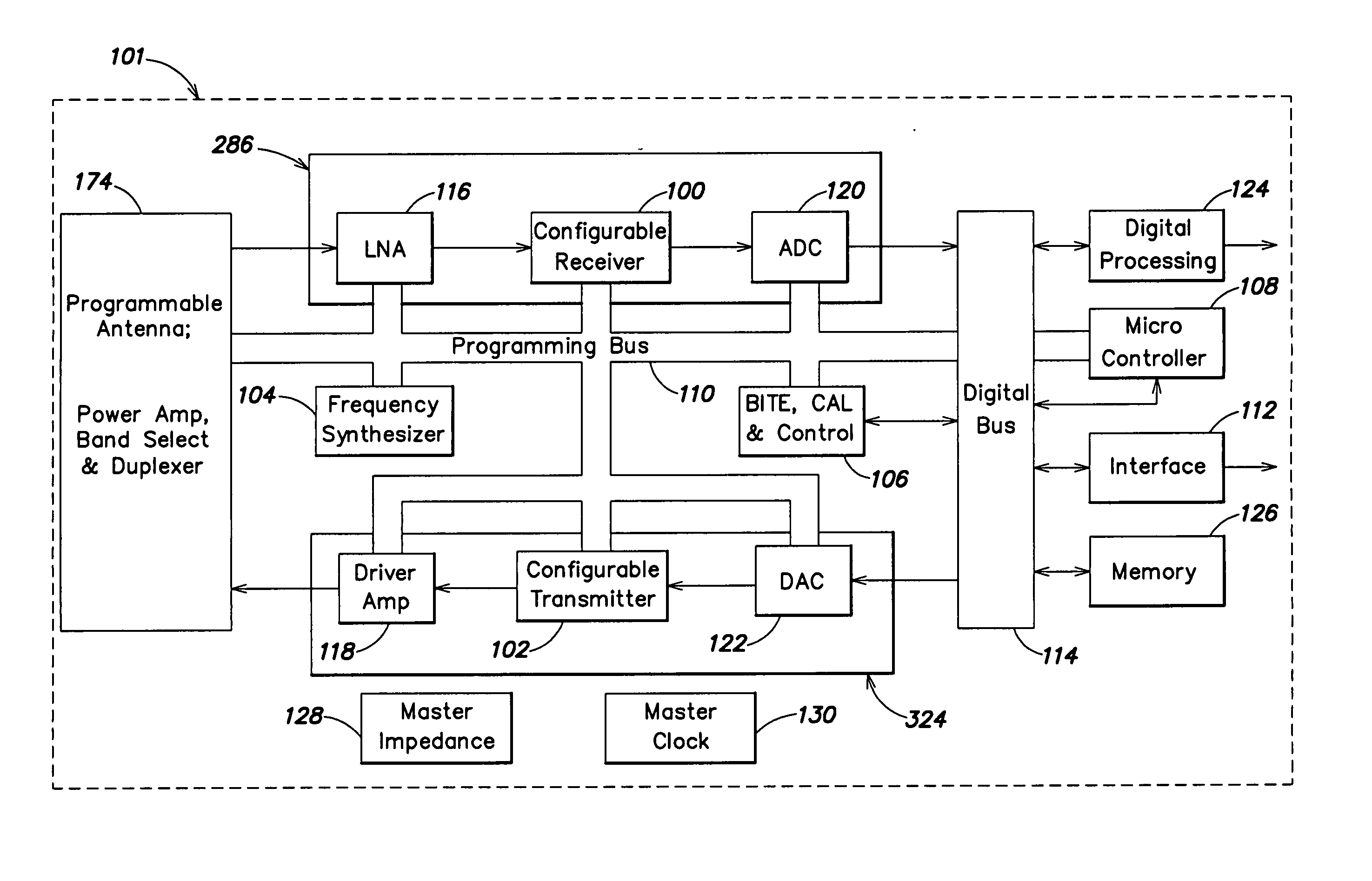

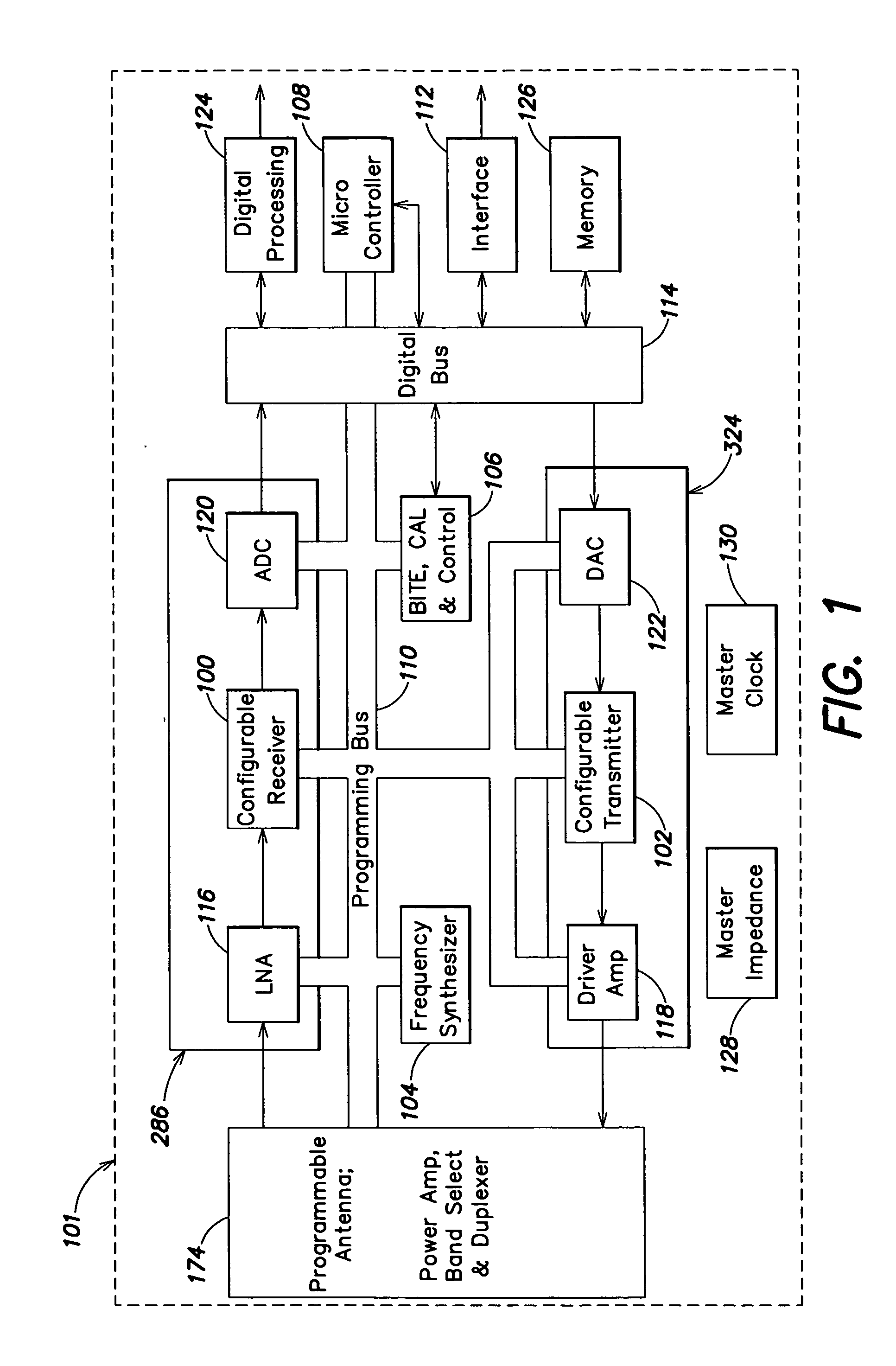

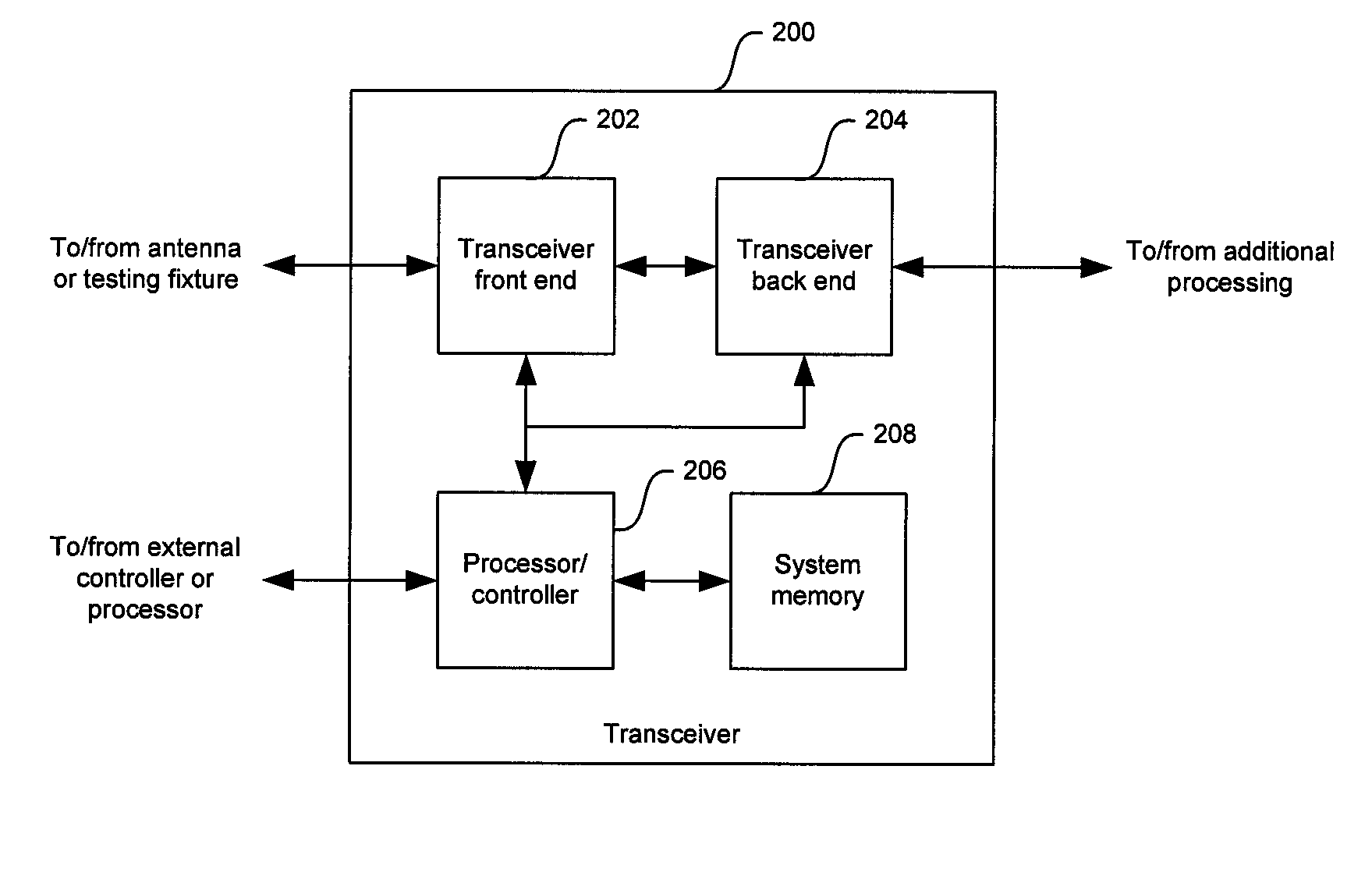

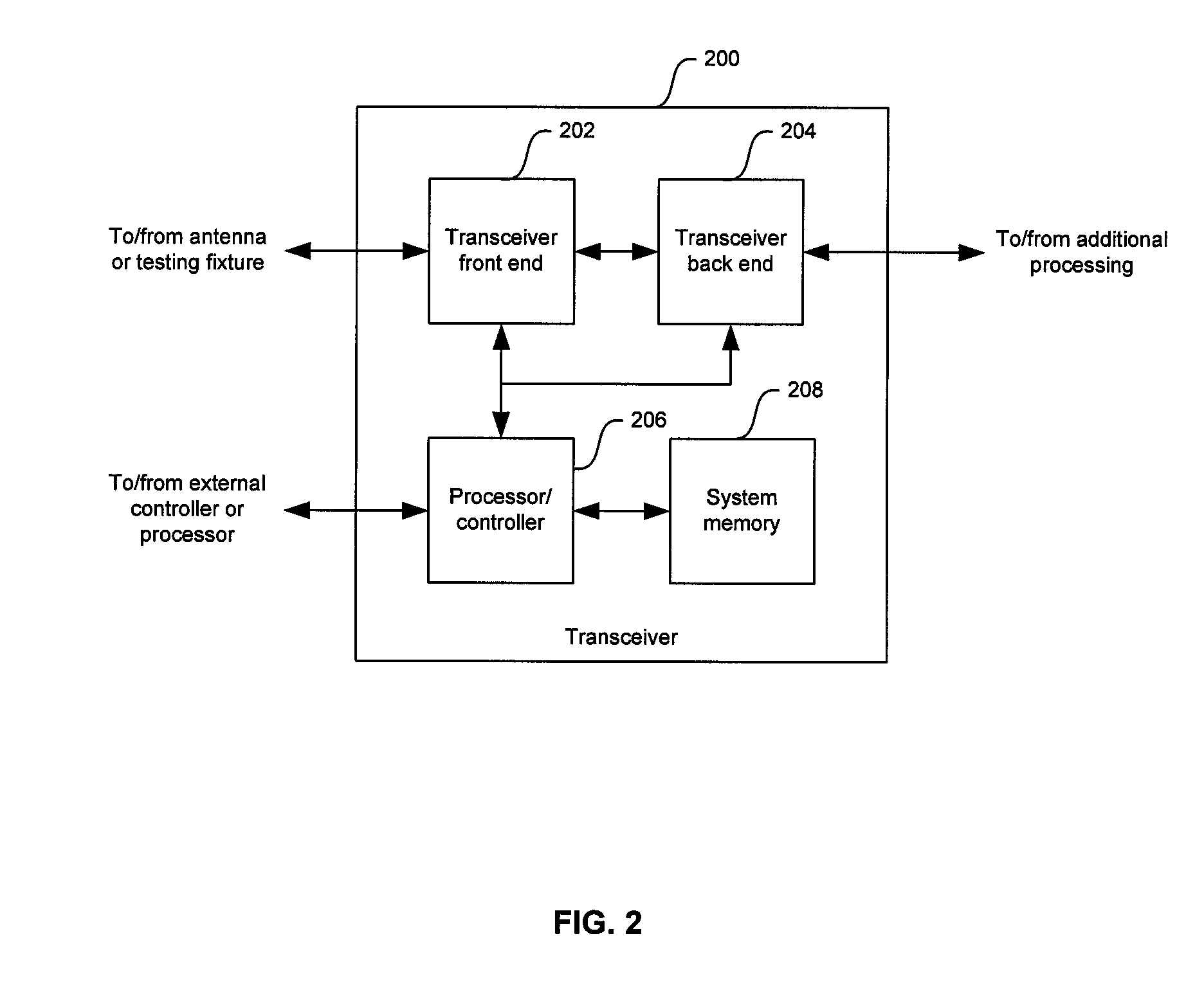

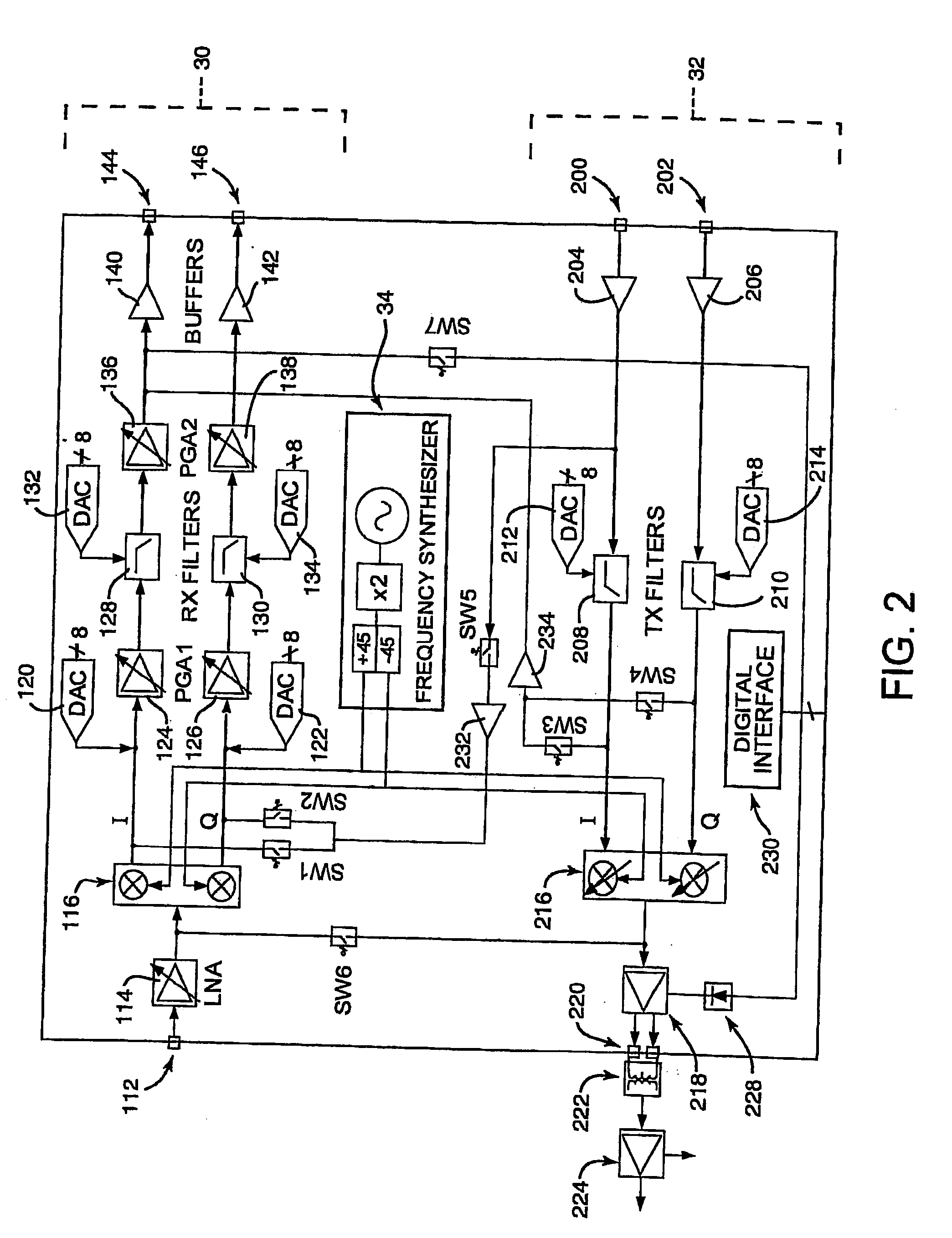

Programmable radio transceiver

ActiveUS20050227627A1Angle modulation by variable impedenceModulated-carrier systemsCapacitanceTransceiver

A fully integrated, programmable mixed-signal radio transceiver comprising a radio frequency integrated circuit (RFIC) which is frequency and protocol agnostic with digital inputs and outputs, the radio transceiver being programmable and configurable for multiple radio frequency bands and standards and being capable of connecting to many networks and service providers. The RFIC includes a tunable resonant circuit that includes a transmission line having an inductance, a plurality of switchable capacitors configured to be switched into and out of the tunable resonant circuit in response to a first control signal, and at least one variable capacitor that can be varied in response to a second control signal, wherein a center resonant frequency of the resonant circuit is electronically tunable responsive to the first and second control signals that control a first capacitance value of the plurality of switchable capacitors and a second capacitance value of the at least one variable capacitor.

Owner:GULA CONSULTING LLC

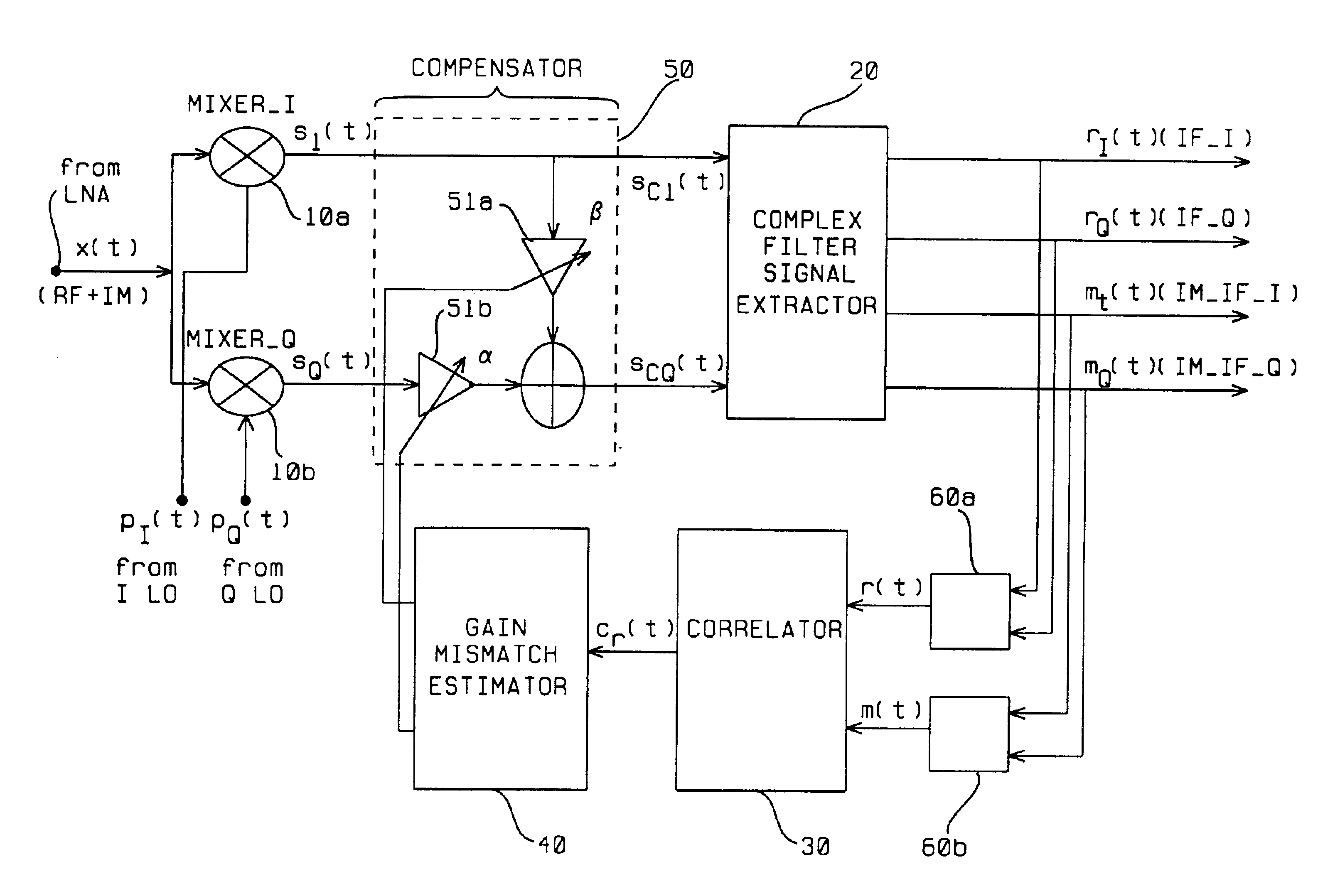

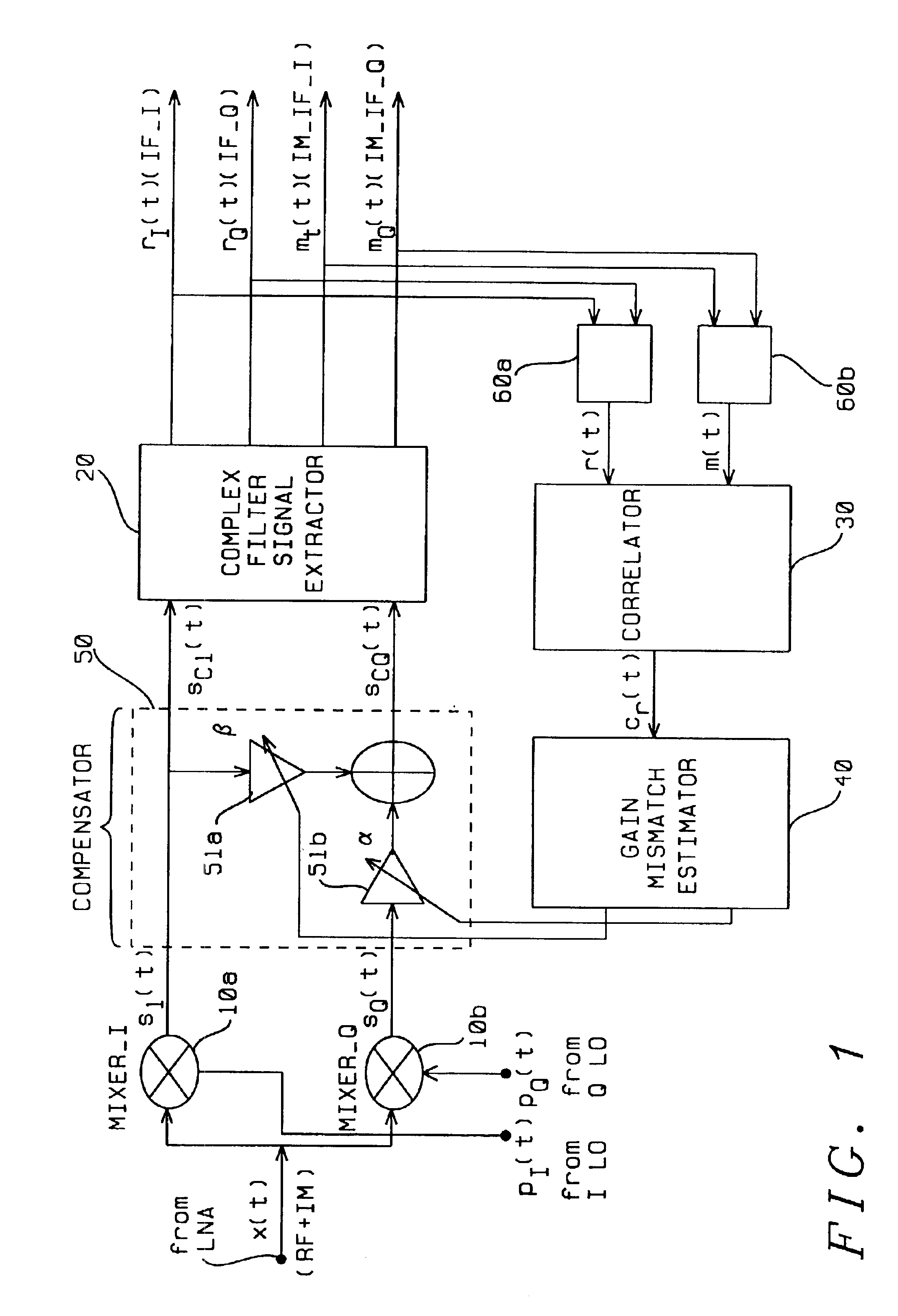

Fully integrated self-tuned image rejection downconversion system

InactiveUS6892060B2Low costEasily integrated into single chip RF+IFError preventionLine-faulsts/interference reductionQuadrature mixerLow IF receiver

A feedback image rejection downconversion system is described, which can be used in low IF receivers with good performance and completely integrated. In the forward path of the system, quadrature mixers and complex filters are used for frequency downconversion and separation of the RF signal from the image signal. In the feedback path, a correlator, a gain mismatch estimator and two VGAs have been used to detect, estimate and compensate the amplitude and phase mismatch between the forward I and Q path signals. The whole system is self-tuned and can operate in both closed and open loop mode. A very high and robust image rejection ratio (over 60 dB) has been achieved.

Owner:INST OF MICROELECTRONICS CHINESE ACAD OF SCI

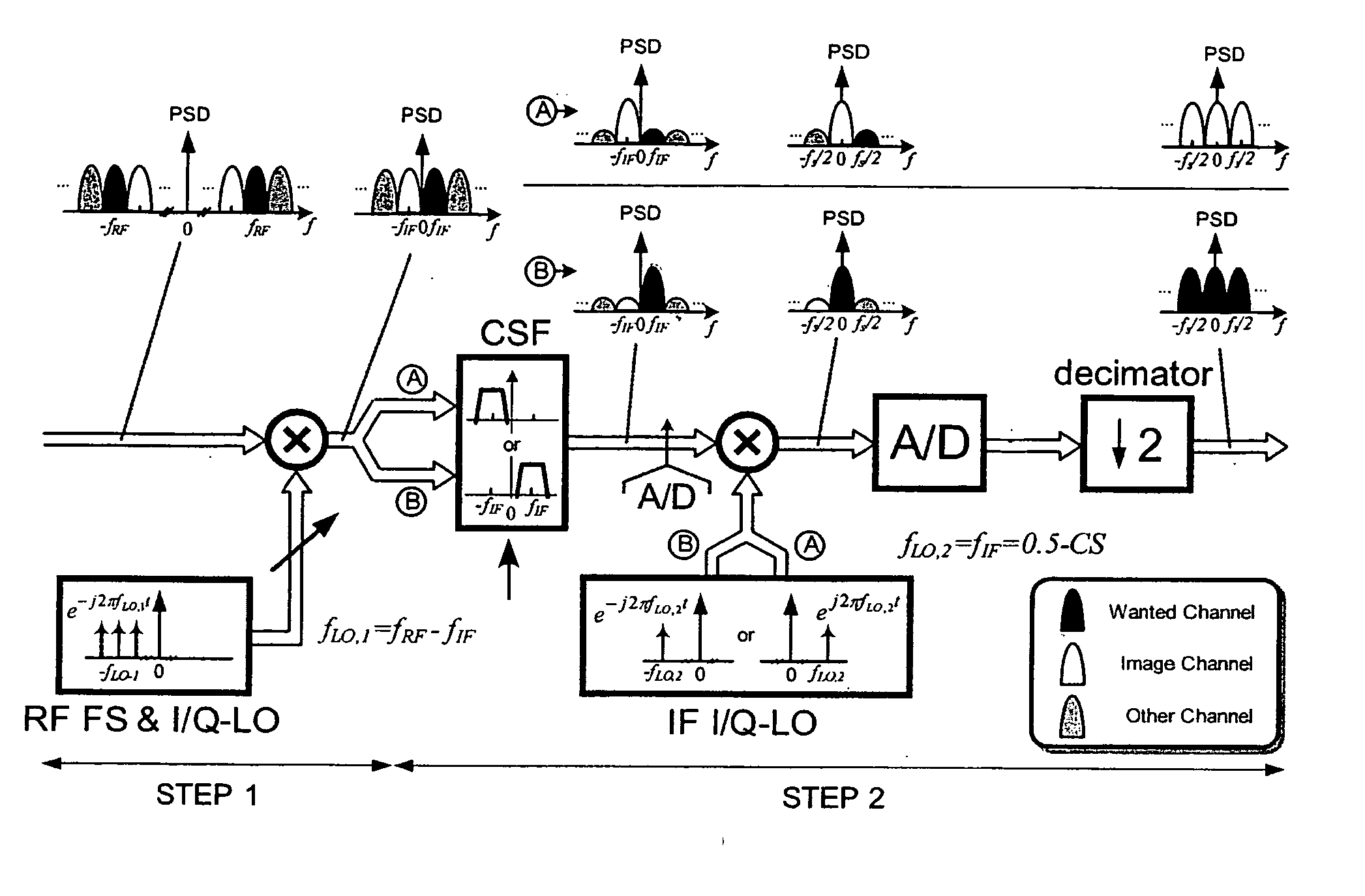

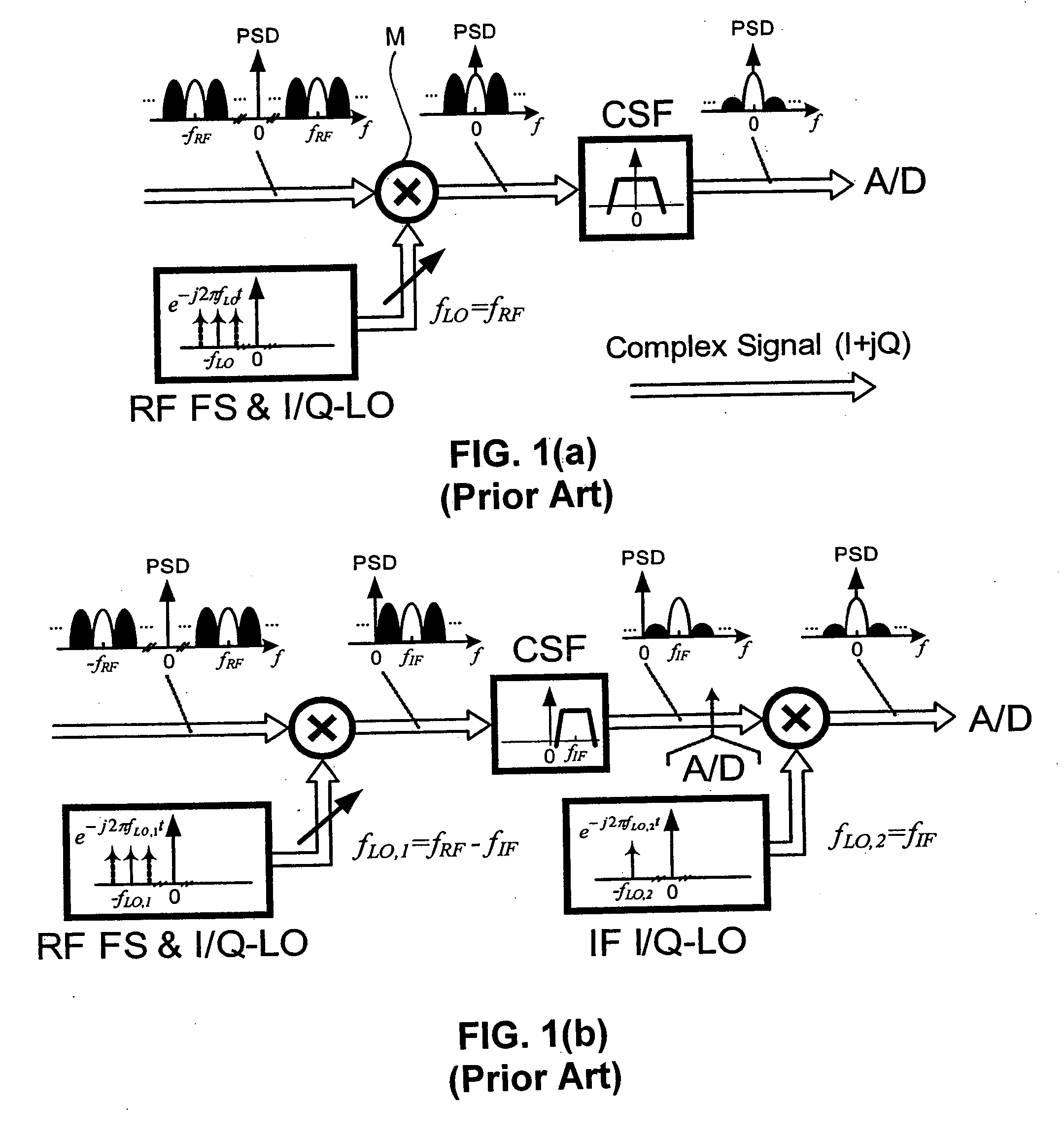

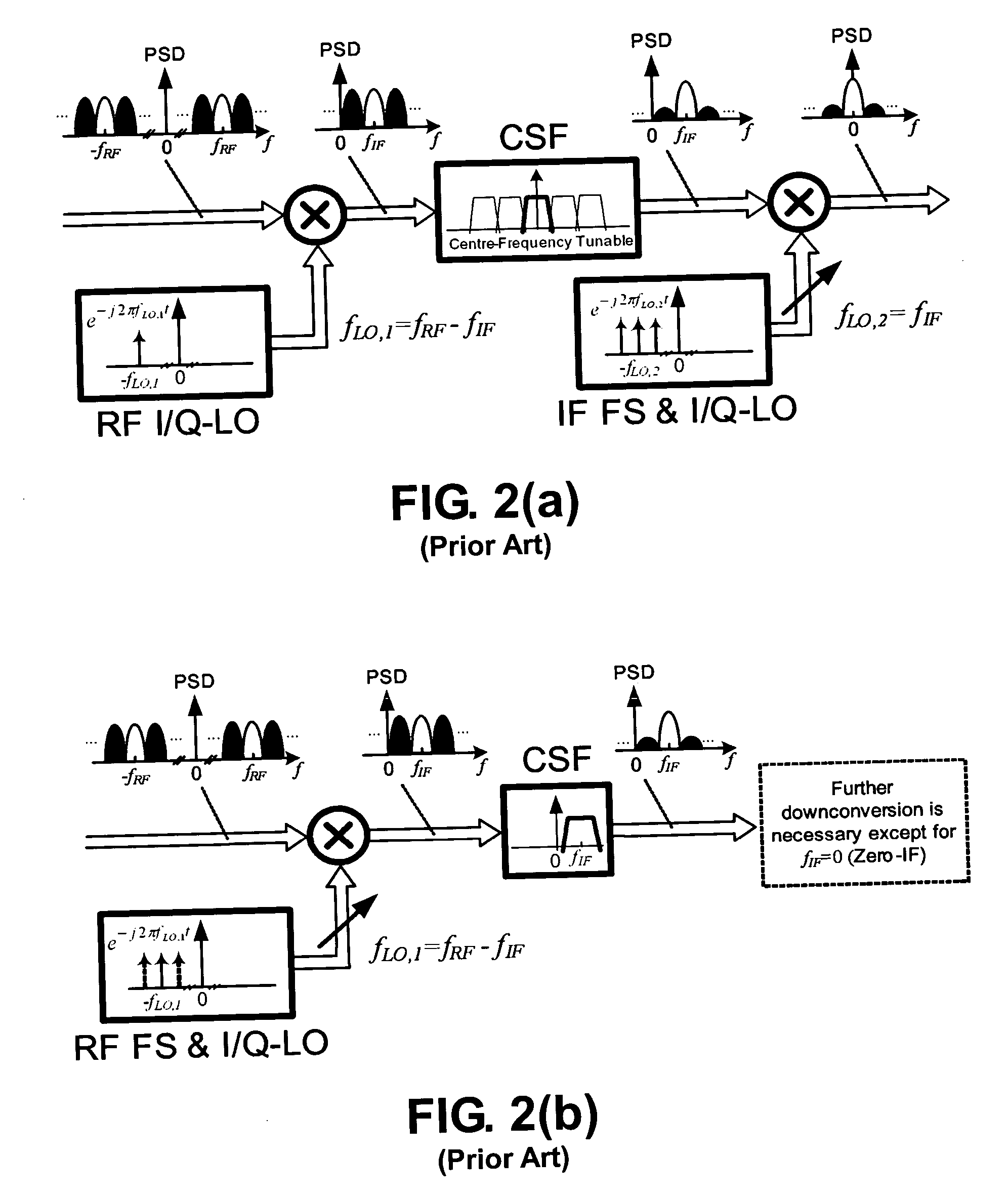

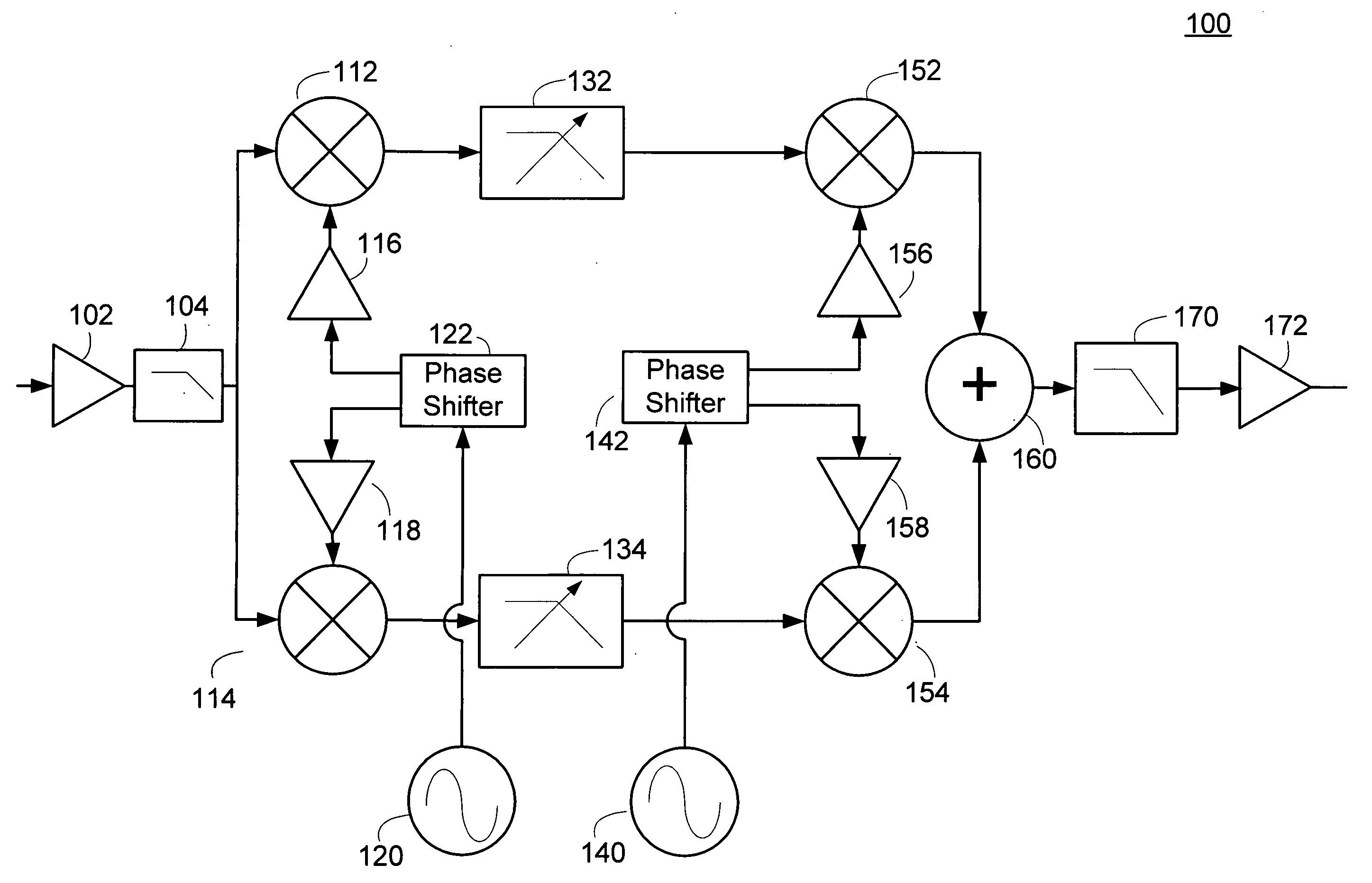

Two-step channel selection for wireless receiver and transmitter front-ends

ActiveUS20070047669A1Easy to implementActive element networkAmplitude-modulated carrier systemsTransceiverIntermediate frequency

A reconfigurable receiver, a reconfigurable transmitter and a multimode receiver are disclosed, operating in accordance with a two-step channel selection. In the receiver, the first step provides for a coarse radio frequency (RF) channel selection, to downconvert a desired channel and an image channel of the desired channel to IF. The second step provides for a fine intermediate frequency (IF) channel selection to select either the desired channel or the image channel. In the transmitter, the first step provides for a fine channel selection and upconversion of a desired channel to either positive or negative IF. The second step is a coarse channel selection and upconversion of a desired channel to the RF. The receiver and transmitter can be used in a transceiver.

Owner:MACAU UNIV OF

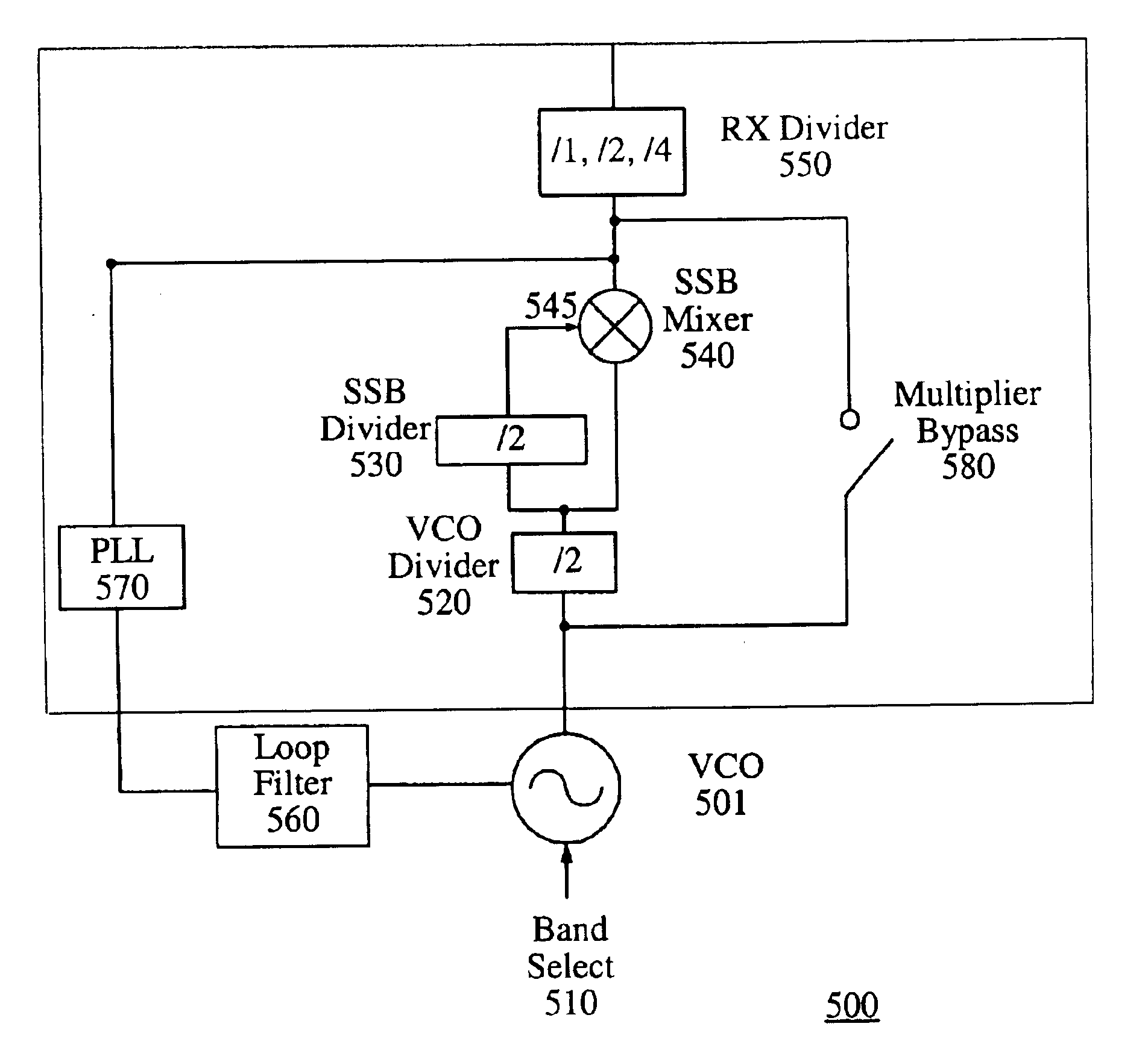

High frequency low noise phase-frequency detector and phase noise reduction method and apparatus

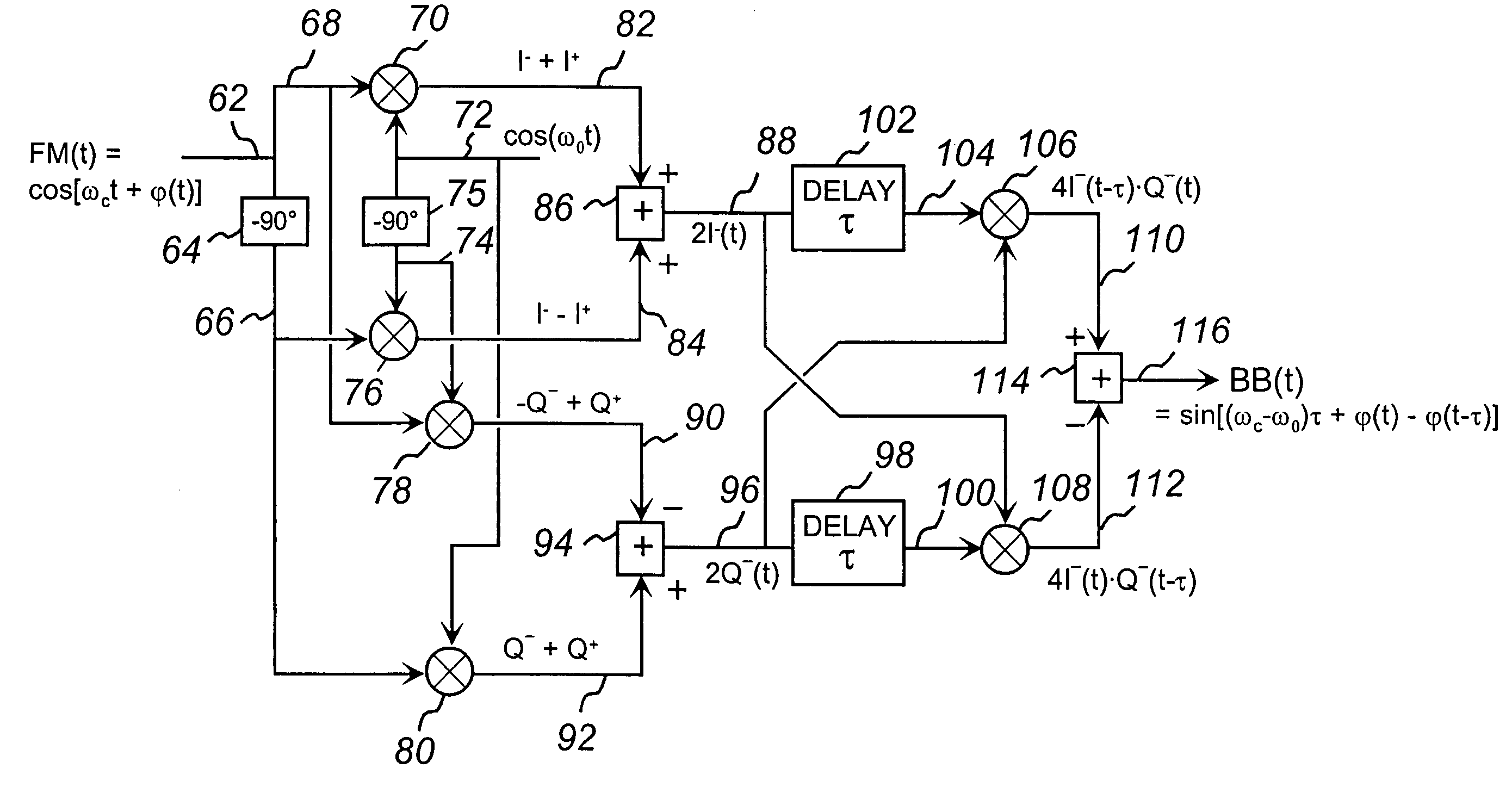

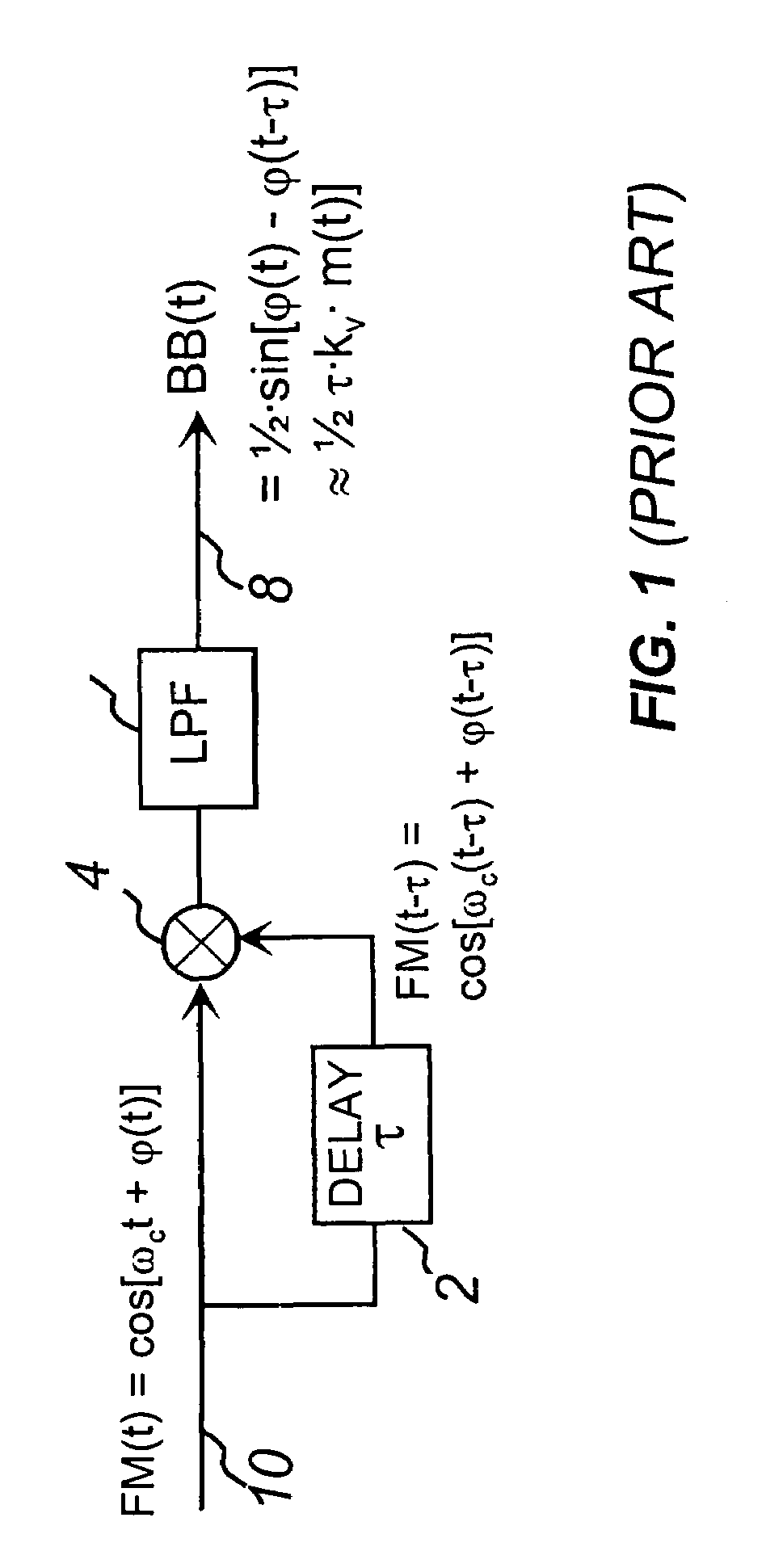

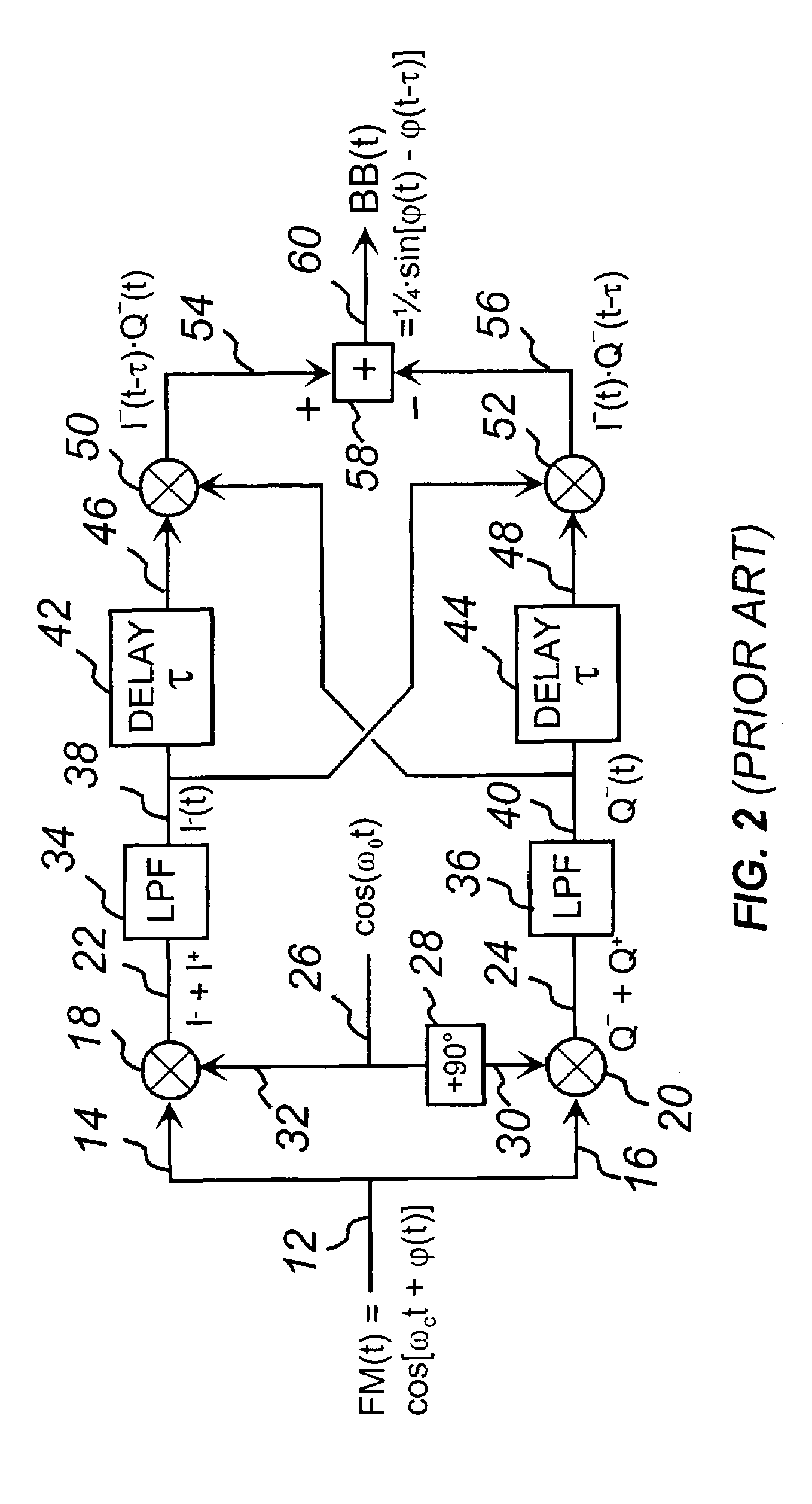

The present invention discloses a new type of extremely low-noise phase-frequency detector (PFD) 500, broadband from DC to multi-GHz RF frequencies for PLL synthesizer applications. Free of any feedback mechanisms, thus inherently fast, it operates close to transition frequency fT of IC processes or frequency limits of discrete mixers. The PFD 500 utilizes complex SSB conversion in both the in-phase and quadrature arms, delaying the in-phase arm in 530, beating the delayed signal 124 with the un-delayed quadrature signal 122 in mixer 126. The output 128 contains both the frequency difference and the phase difference information between the two signals 118 and 520, providing both the frequency-discrimination (FD) and the phase detection (PD) functions. Utilizing standard mixers the PFD 500 can achieve superior CNRs of 180 dBc / Hz at multi-GHz RF. Additionally, utilizing the FD / FM demodulation capability, the present invention improves phase noise of various signals and linearity of FM modulators.

Owner:ARRIS ENTERPRISES LLC

Quadrature oscillator with phase error correction

InactiveUS20020039052A1Increase volumePulse automatic controlGain controlPhase detectorAudio power amplifier

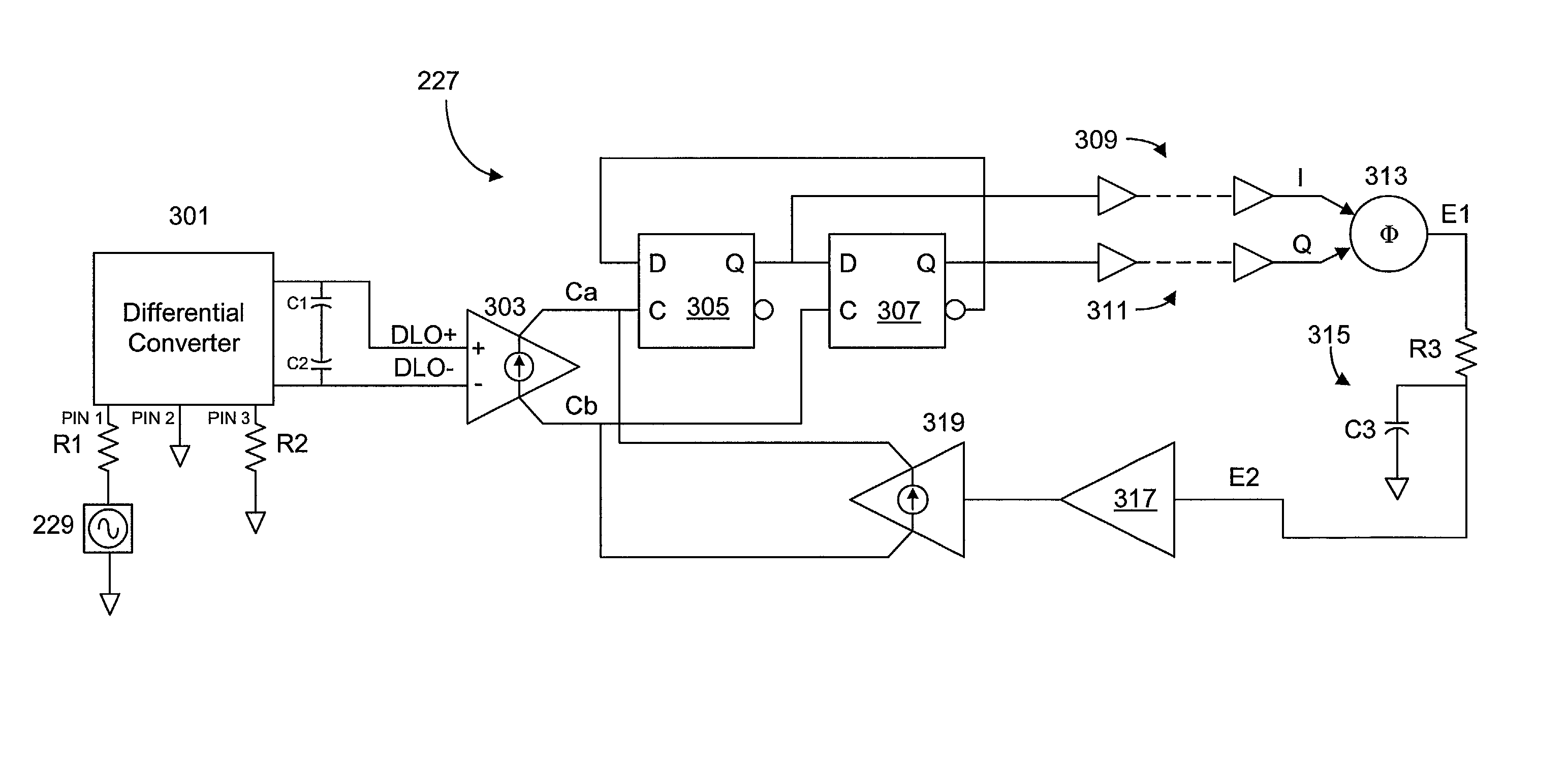

A quadrature oscillator with phase error correction including a local oscillator that generates a single-ended clock signal, a single-ended to differential converter that converts the clock signal to a differential clock signal, a quadrature generator that converts the differential clock signal into I and Q carrier signals, a phase error detector that measures a phase error between the I and Q carrier signals, and a feedback amplifier that modifies the differential clock signal based on measured phase error. The feedback amplifier applies the measured phase error as a DC offset to an AC differential clock signal. A transconductor converts the differential clock voltage signal into two pairs of differential current clock signals, where the quadrature generator generates I and Q current signal outputs from the two pairs of differential current clock signals. The phase error detector generates a phase error voltage, and the feedback amplifier includes a transconductance stage that converts phase error voltage into a DC correction current and that adds the correction current to each of the two pairs of AC differential current clock signals.

Owner:M RED INC

Apparatus and methods for compensating for signal imbalance in a receiver

ActiveUS20080130779A1Diversity/multi-antenna systemsMulti-frequency code systemsData signalCarrier signal

Apparatus, methods and systems for compensating for an I / Q imbalance may include compensating for an imbalance between a first component of a data signal and a second component of the data signal. The data signal may be modulated by a carrier signal having a frequency error. The first component may be characterized by at least one parameter. The method may include receiving the data and carrier signals; selecting a value for the parameter such that the frequency domain energy at negative frequencies is reduced; and modifying at least one of the components based on the value.

Owner:AVAGO TECH INT SALES PTE LTD

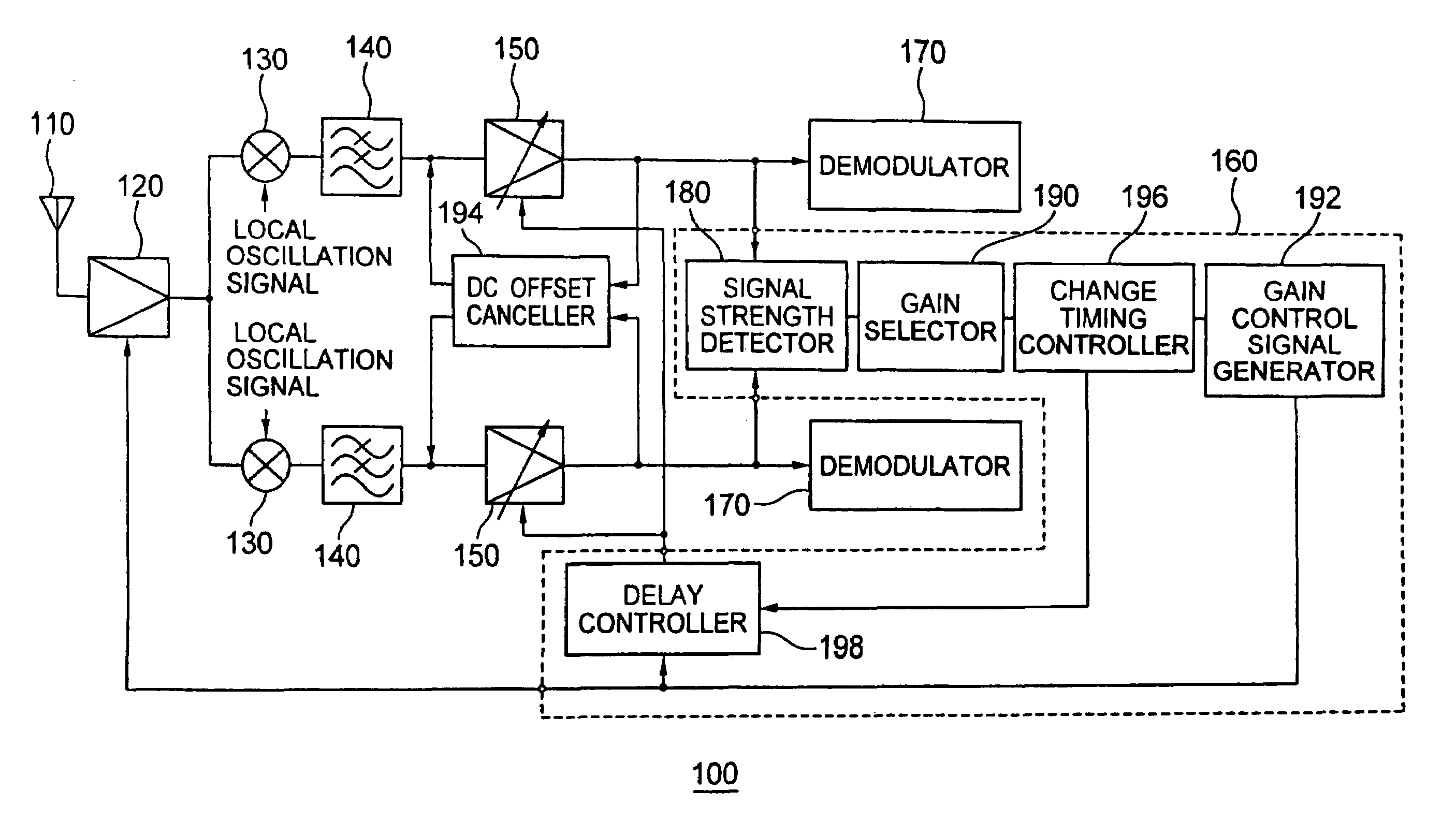

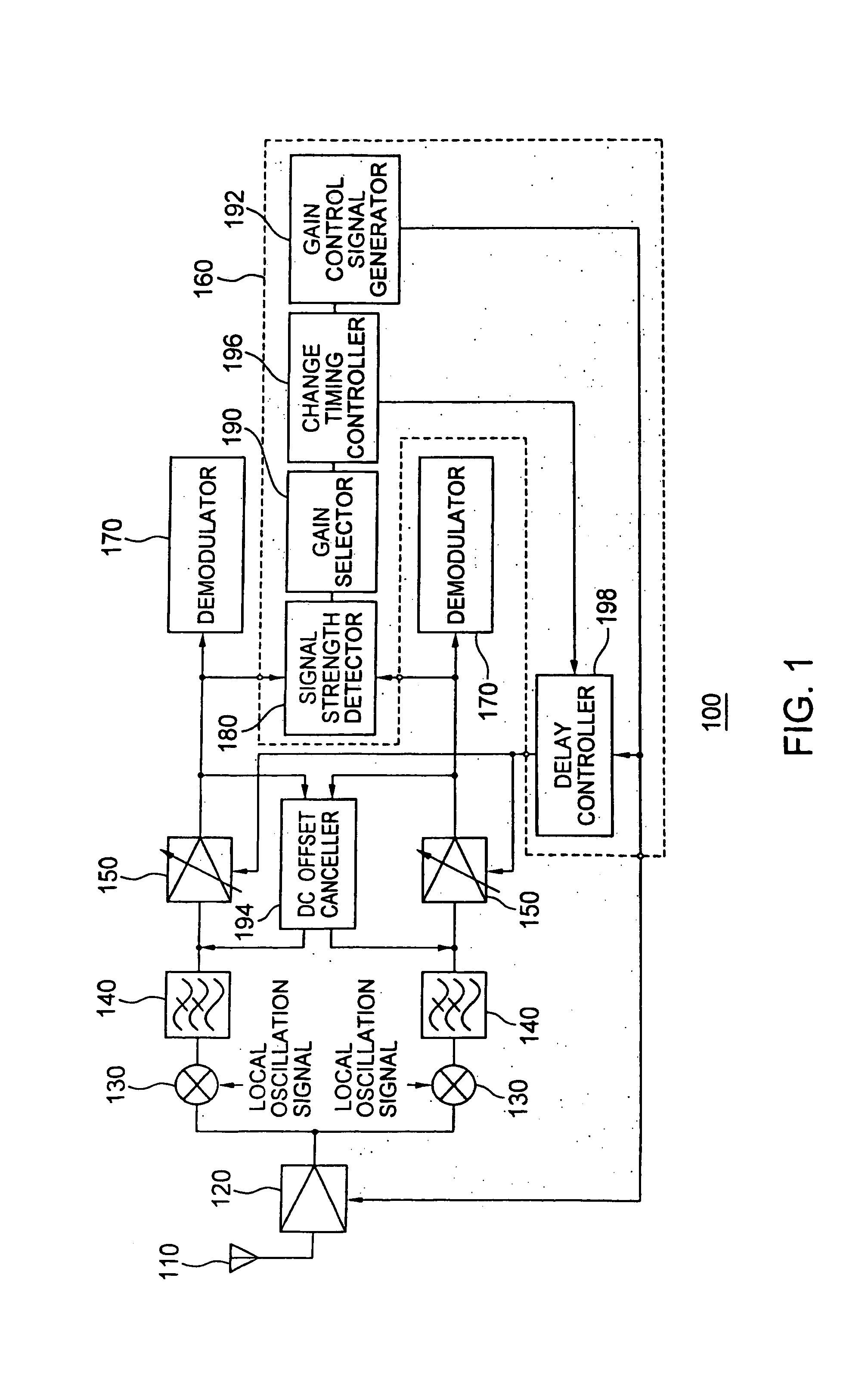

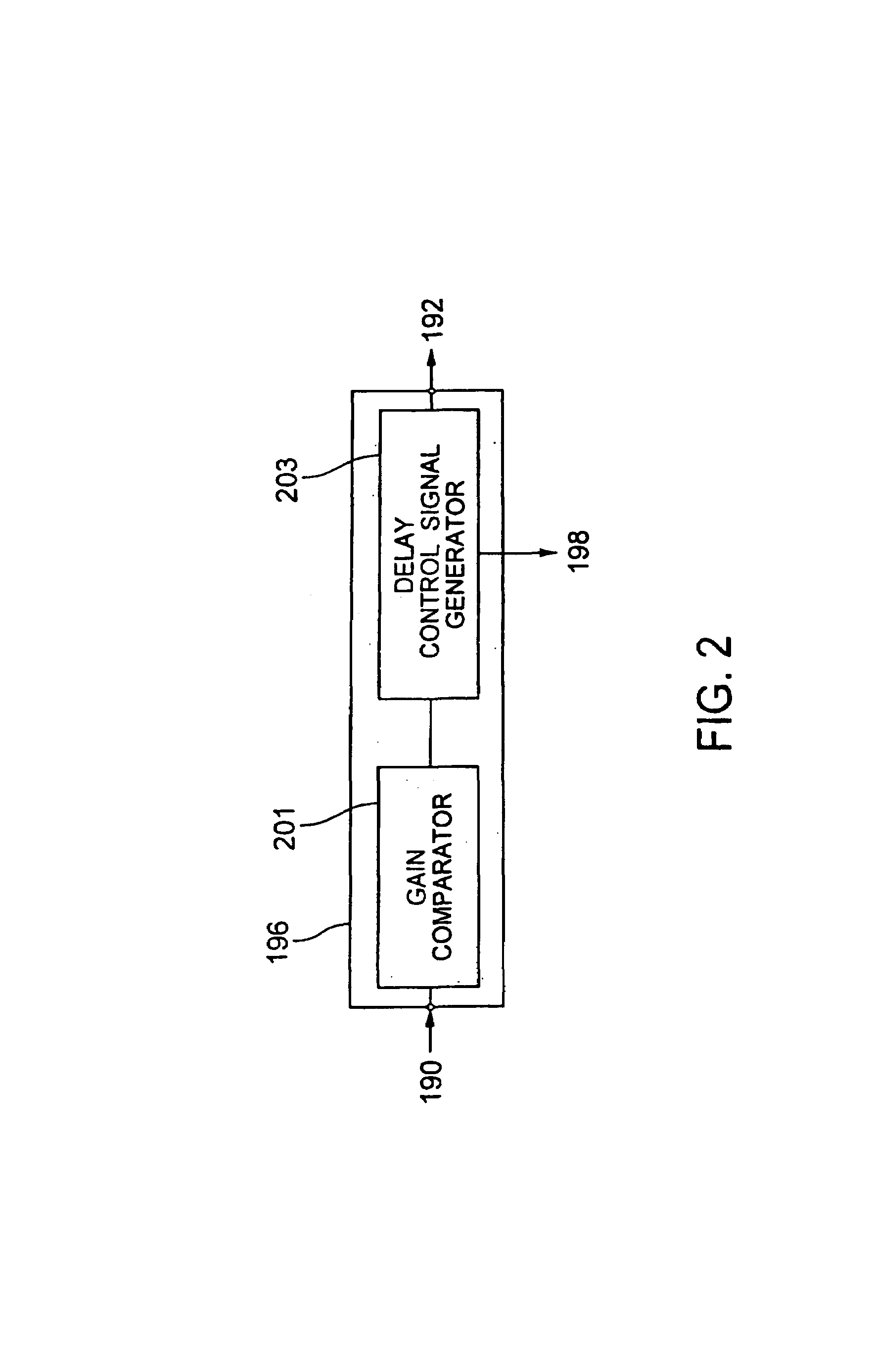

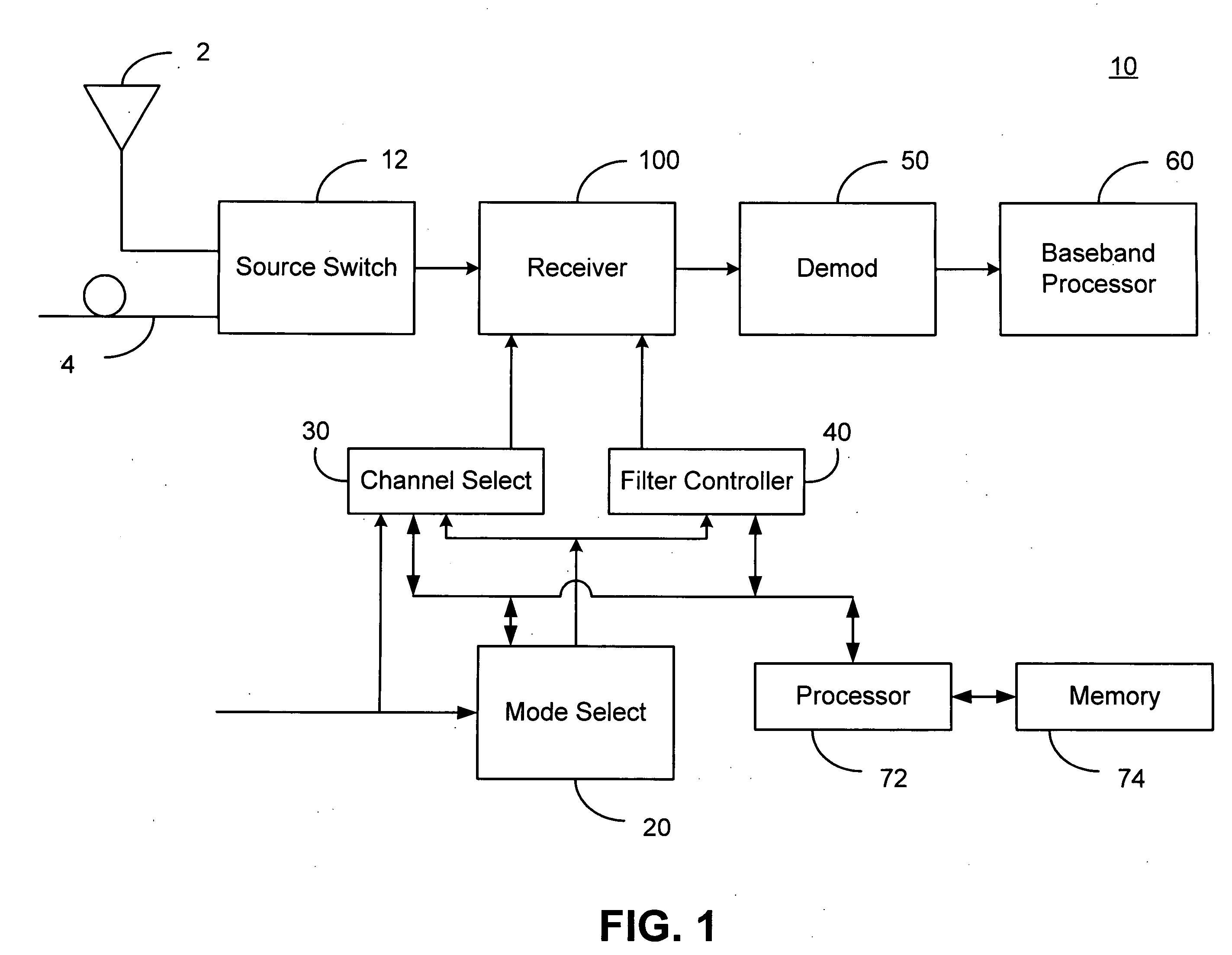

Radio receiver and radio signal processing method with controlling gain

InactiveUS7245894B2Gain controlAmplitude-modulated carrier systemsRadio receiver designAudio power amplifier

A radio receiver comprises a first amplifier to amplify a received radio signal; a quadrature demodulator to demodulate the radio signal amplified by said first amplifier and thereby generate a baseband signal; a second amplifier to amplify the baseband signal; a demodulator to demodulate the baseband signal amplified by said second amplifier; and a gain controller to control timing of a change in a gain of said second amplifier, in case that changing the gain of said first amplifier and the gain of said second amplifier, on the basis of a gain of said first amplifier before and after the change.

Owner:KK TOSHIBA

Multiphase receiver and oscillator

InactiveUS6385442B1Single output arrangementsPulse generation by logic circuitsLocal oscillator signalEngineering

A differential ring oscillator is provided with three differential amplifiers and provides three-phase output signals which can be used for synchronous detection of a received multi-phase modulated signal in a multi-phase receiver, wherein the phase of the local oscillator signals may be in other-than-quadrature relation. Two of the phase outputs of the local oscillator can be combined to provide a signal that is in quadrature with the remaining output. The oscillator is preferably controlled in coarse frequency control steps and using a fine voltage control signal responsive to a phase-locked loop to reduce frequency modulation of the oscillator signal arising out of leakage signals.

Owner:EXTREME NETWORKS INC

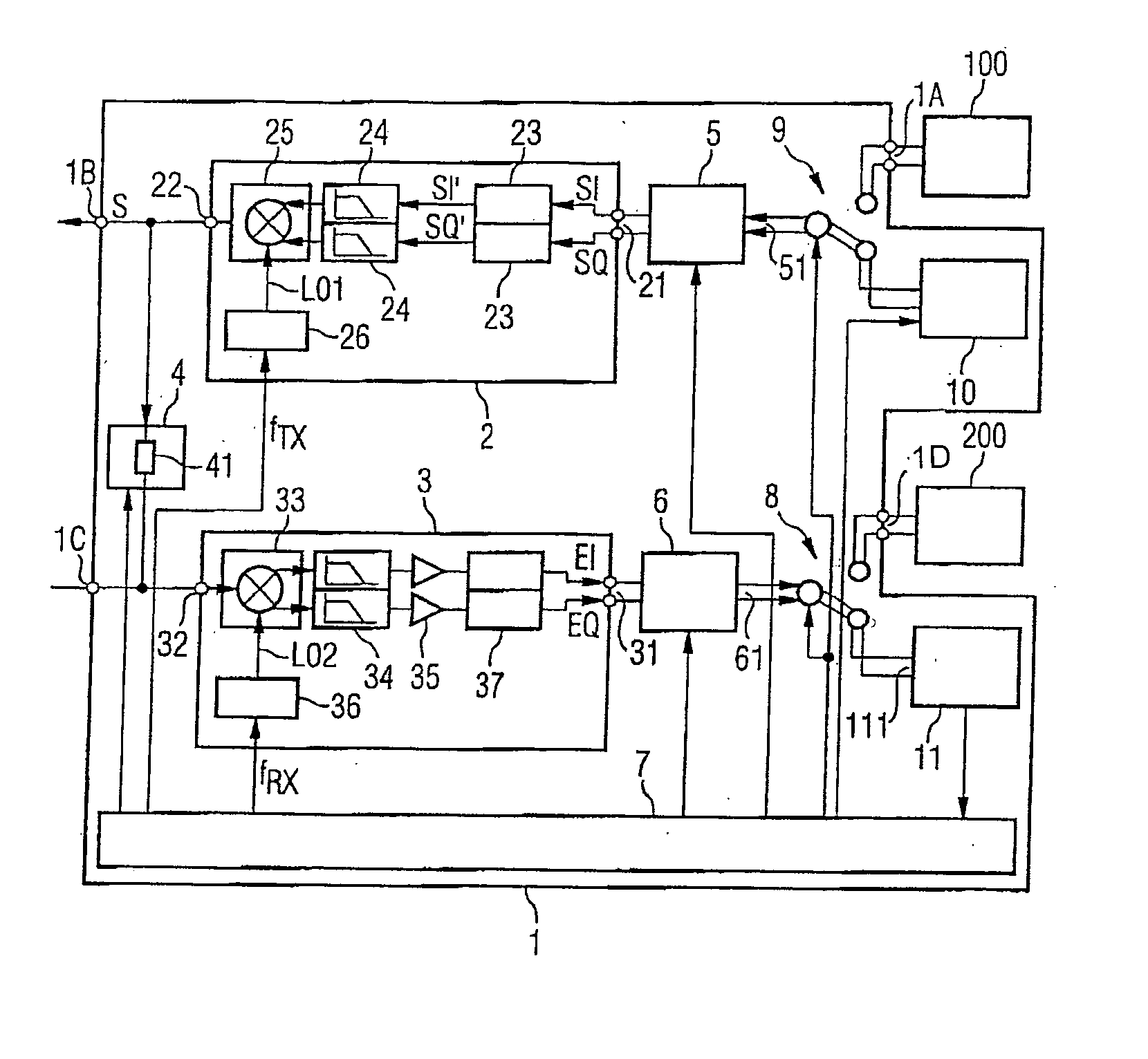

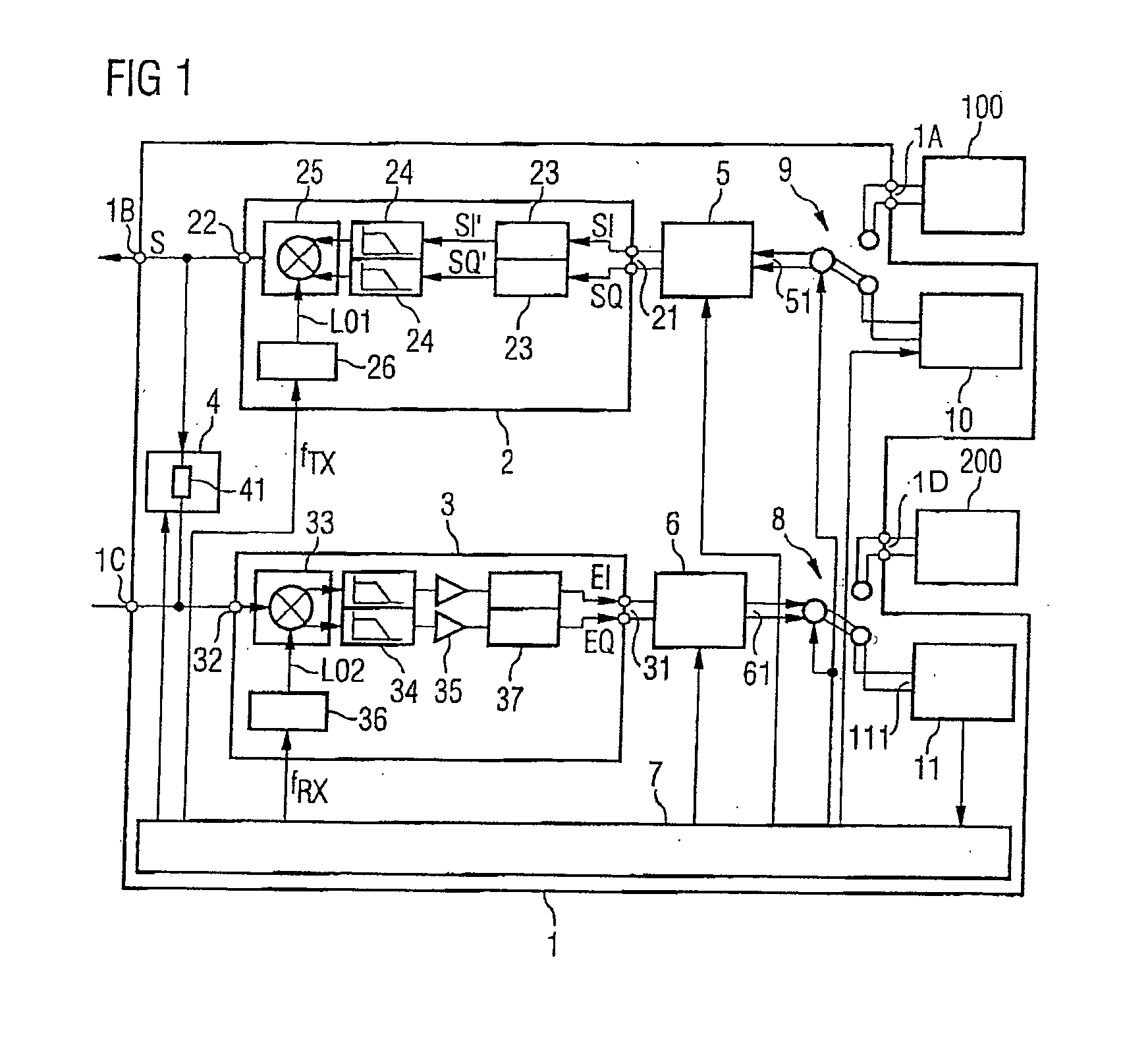

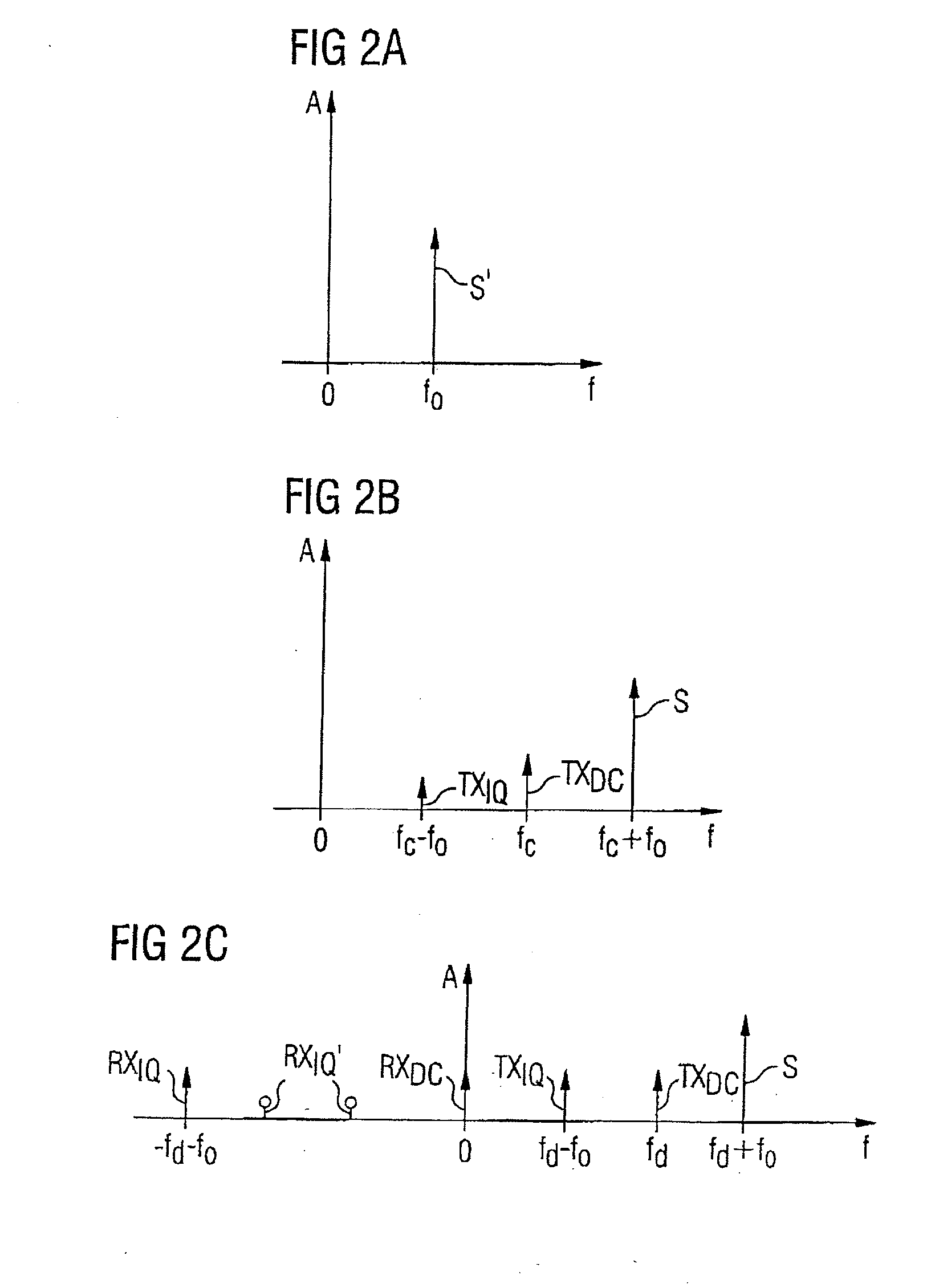

Transmission/reception arrangement and method for reducing nonlinearities in output signals from a transmission/reception arrangement

ActiveUS20060034356A1Easy to produceMismatched componentSecret communicationTransmitter/receiver shaping networksFrequency spectrumSources of error

The invention proposes a transmission / reception arrangement (1) which contains a respective distortion unit (5, 6) for the transmission and reception paths (2, 3) and also a calibration apparatus (7). By sending a test signal in an operating mode for calibration and returning the test signal processed in the transmission path (2) to the reception path, it is possible to evaluate the error signals in the transmission and reception paths. In line with the principle proposed, this is done by evaluating the spectral components of the returned received signal which each represent single sources of error in the transmission or reception path. This allows calculation of calibration parameters for suppressing these errors both in the transmission path and in the reception path.

Owner:APPLE INC

Programmable radio transceiver

ActiveUS20050212604A1Error signalAngle modulation by variable impedenceHigh frequency amplifiersCapacitanceTransceiver

A fully integrated, programmable mixed-signal radio transceiver comprising a radio frequency integrated circuit (RFIC) which is frequency and protocol agnostic with digital inputs and outputs, the radio transceiver being programmable and configurable for multiple radio frequency bands and standards and being capable of connecting to many networks and service providers. The RFIC includes a tunable resonant circuit that includes a transmission line having an inductance, a plurality of switchable capacitors configured to be switched into and out of the tunable resonant circuit in response to a first control signal, and at least one variable capacitor that can be varied in response to a second control signal, wherein a center resonant frequency of the resonant circuit is electronically tunable responsive to the first and second control signals that control a first capacitance value of the plurality of switchable capacitors and a second capacitance value of the at least one variable capacitor.

Owner:GULA CONSULTING LLC

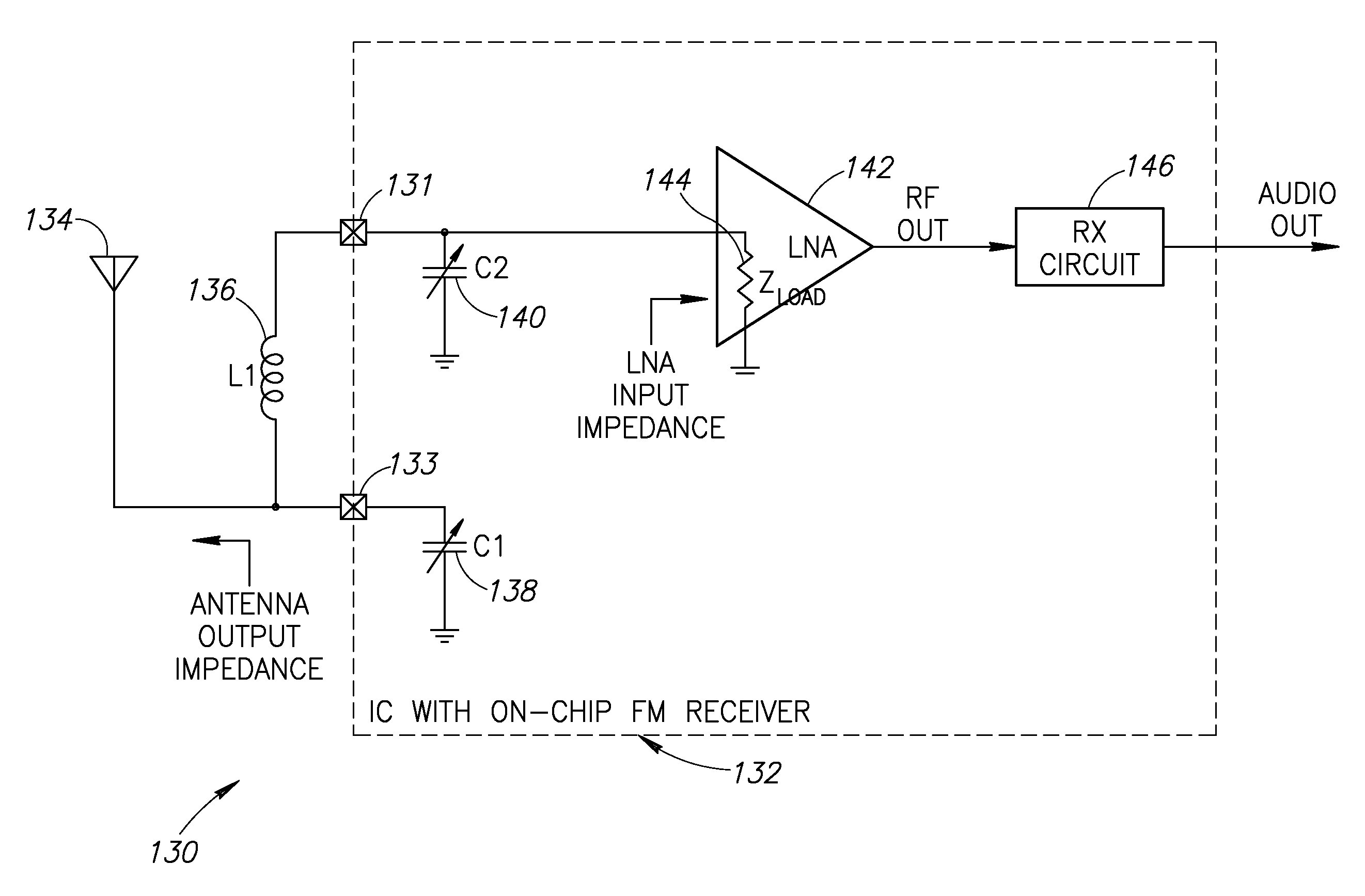

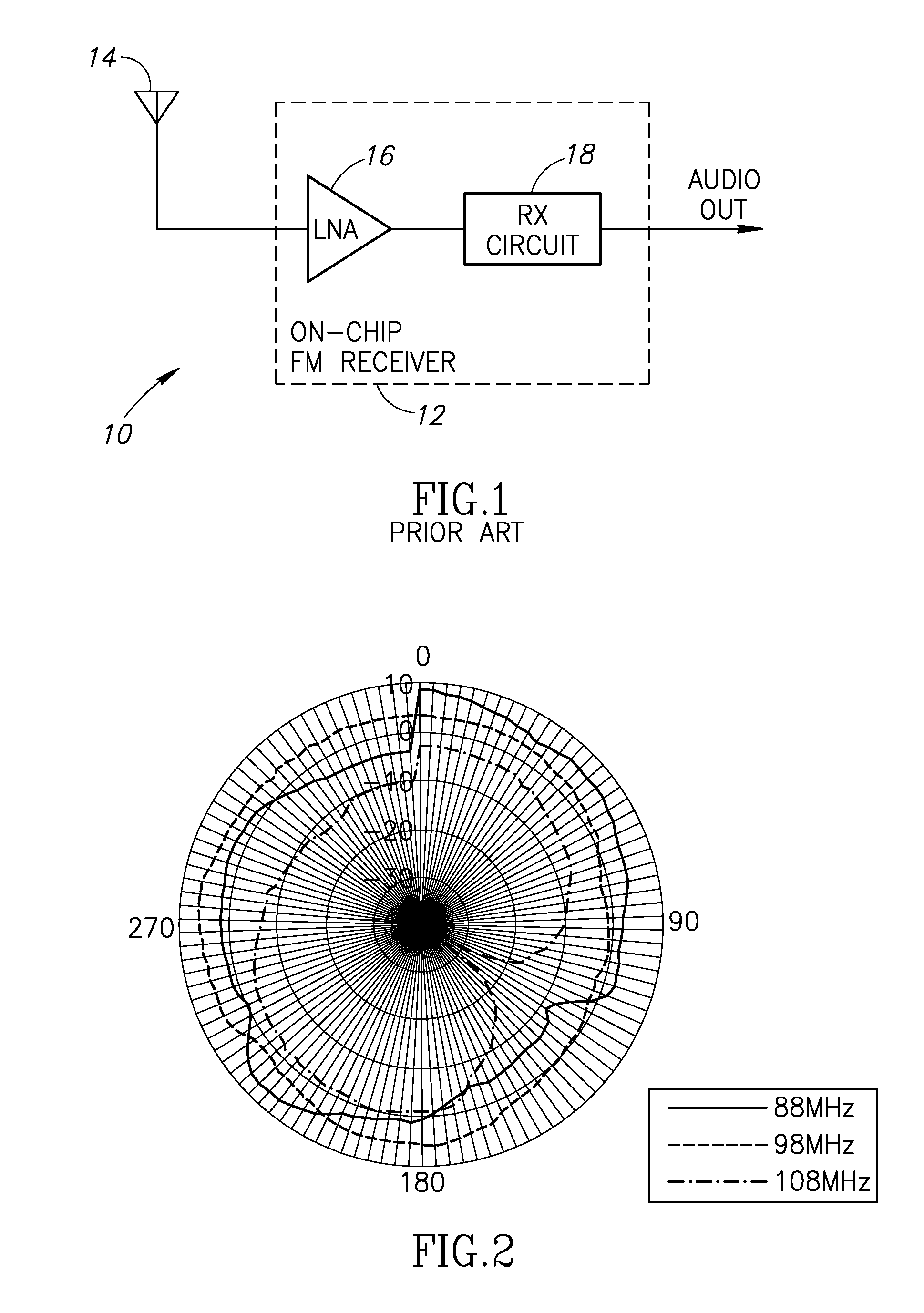

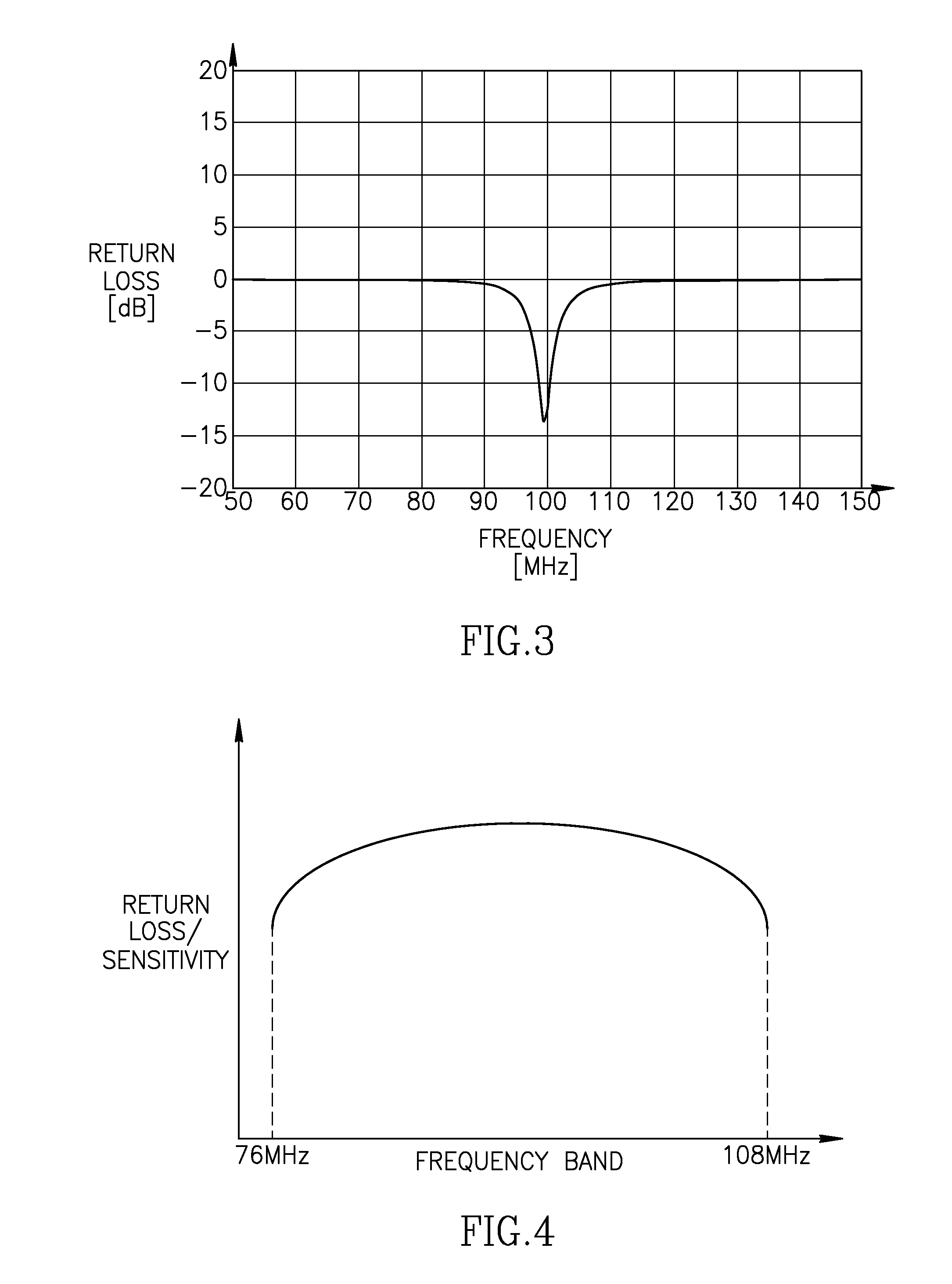

Adaptive antenna matching for portable radio operating at VHF with single-chip based implementation

InactiveUS20080129610A1Low costImprove efficiencyMultiple-port networksReceivers monitoringRadio equipmentClosed loop

A novel and useful apparatus for and method of improving antenna matching and reducing mismatch loss for a VHF receiver such as an FM receiver. The invention can be used in a very low cost implementation of a single chip radio such as used in cellphone applications. The impedance of the low cost VHF antenna in cellphone application can dramatically vary across time, frequency and depending on the human body proximity resulting in a large mismatch loss. The adaptive antenna matching mechanism uses dynamically configurable on-chip variable capacitors to provide a custom matching network with the external inductor in a pi-network configuration. The variable ranges of the on-chip capacitors enable adaptation in a closed loop manner so that the optimum SNR is achieved thus ensuring minimum mismatch loss. The mechanism measures RSSI and SNR and, using a novel adaptive calibration mechanism, adjusts the internal matching network capacitors such that the mismatch loss is minimized.

Owner:TEXAS INSTR INC

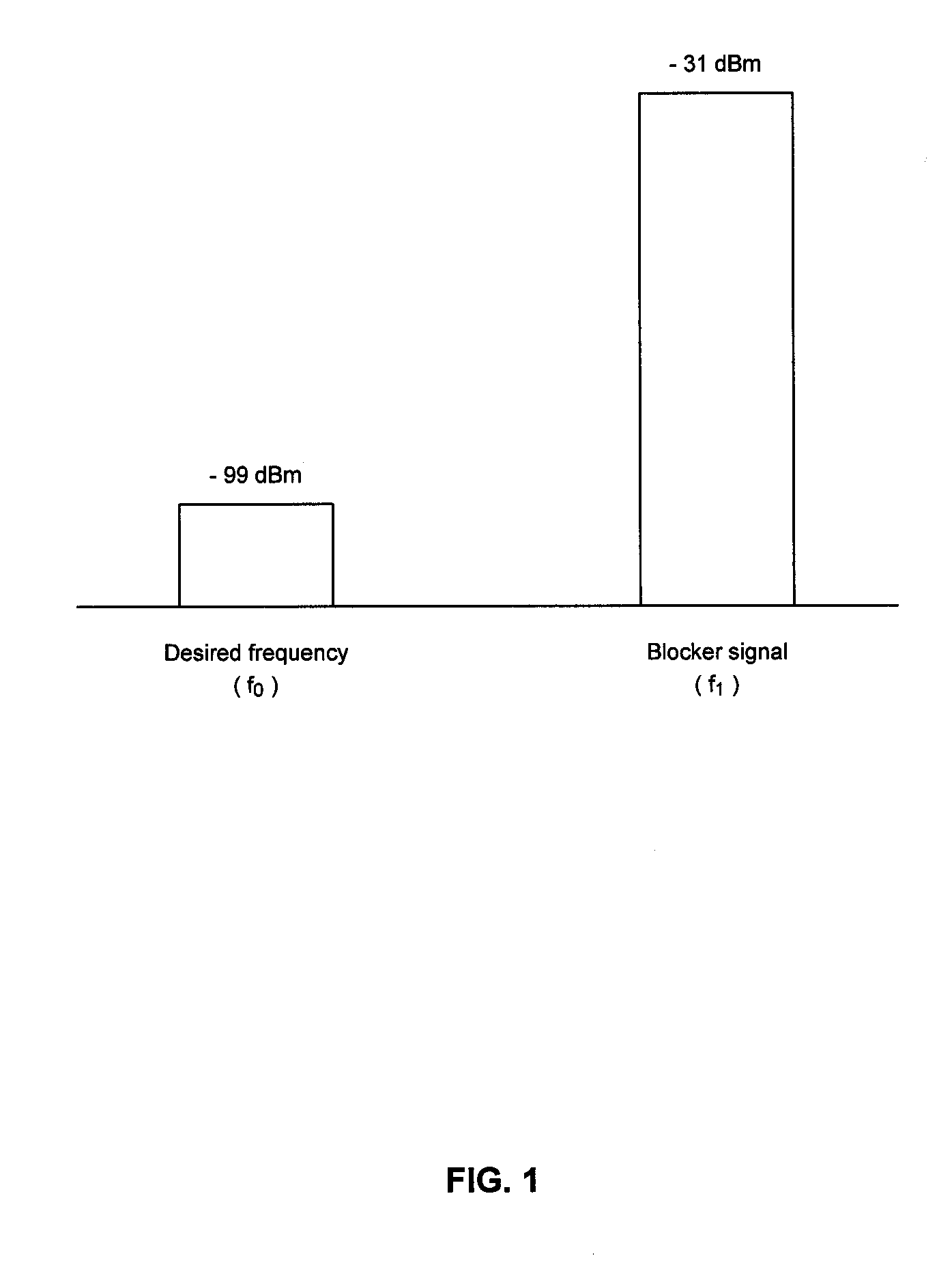

Method and system for a second order input intercept point (IIP2) correction

In RF transceivers, a method and system for a second order input intercept point (IIP2) correction are provided. A DC offset sensor may detect DC offset voltages produced by blocker signals in “I” and “Q” signal component paths in an RF receiver. The DC offset sensor may generate control signals which may be utilized by a first and second injection circuits to generate DC offset currents that compensate for the DC offset voltages in the signal component paths. An injection circuit may utilize current drivers to generate binary weighted currents which may be added together to produce a DC offset current. The polarity of the DC offset current and the selection of which current drivers to use may be determined by the control signals. A calibration voltage may also be utilized to correct or adjust the gain in the injection circuit.

Owner:AVAGO TECH INT SALES PTE LTD

Harmonic reject receiver architecture and mixer

InactiveUS20060160518A1Reducing mixer responseReduced responseModulation transference balanced arrangementsMultiplex with amplitude-modulated carrierLocal oscillator signalFrequency mixer

Receiver architectures and methods of processing harmonic rich input signals employing harmonic suppression mixers are disclosed herein. The disclosed receivers, mixers, and methods enable a receiver to achieve the advantages of switching mixers while greatly reducing the mixer response to the undesired harmonics. A harmonic mixer can include a plurality of mixers coupled to an input signal. A plurality of phases of a local oscillator signal can be generated from a single local oscillator output. Each of the phases can be used to drive an input of one of the mixers. The mixer outputs can be combined to generate a frequency converted output that has harmonic rejection.

Owner:MAXLINEAR INC

DC offset correction for direct conversion receivers

InactiveUS20070293180A1Radio transmissionAngle demodulation by oscillations conversionDirect-conversion receiverClosed loop

A direct current (DC) offset correction system for a direct conversion receiver and corresponding receiver and methods facilitate reduction of DC offsets in such receivers. One method includes calibrating a DC offset correction system in a closed loop configuration over each of a plurality of gain settings to provide a plurality of offset data for an operating mode of the direct conversion receiver; selecting one of the plurality of offset data based on a current gain setting of the direct conversion receiver as supplied, e.g., by an AGC system; and operating the DC offset correction system in an open loop configuration using the one of the plurality of offset data to correct for a DC offset in the direct conversion receiver.

Owner:APPLE INC

Method and apparatus for calibrating DC-offsets in a direct conversion receiver

InactiveUS6868128B1Reduce sizeSmall sizeDc level restoring means or bias distort correctionCarrier regulationDirect-conversion receiverOffset calibration

A novel method and apparatus for calibrating DC offsets in a direct conversion receiver. The present DC offset calibration method and apparatus comprises a direct conversion receiver equipped with a frequency shifter means and a DC offset measurement and correction technique. In accordance with the present invention, DC offsets are calibrated in direct conversion receivers through an inventive method including two steps: a DC offset measurement step and a DC offset correction step. In the DC offset measurement step the frequency of a local oscillation signal (typically generated by a voltage-controlled oscillator (VCO)) is shifted by a selected frequency shift value during the inactive time intervals of the receiver. DC offsets are measured while the frequency of the down-conversion oscillation signal is shifted by the frequency shift value. Before the inactive time interval expires, the frequency of the down-conversion oscillator signal is shifted back to its original value. In the DC offset correction step of the present invention incoming signals are corrected using a correction means that removes the DC offset measured during the DC offset measurement step.

Owner:QUALCOMM INC

System and method for detecting and correcting phase error between differential signals

InactiveUS6674998B2Detect and reduce and otherwise eliminate phase errorIncrease the amount of dataPulse automatic controlGain controlDifferential signalingQuadrature oscillator

A phase error detector that detects phase error between differential signals. A quadrature oscillator provides in-phase (I) and quadrature phase (Q) differential carrier signals and receives a phase error signal from the phase error detector. The oscillator maintains a quarter cycle phase delay between the I and Q carrier signals based on the phase error signal. The phase error detector includes a summing network and first and second bipolar transistor mixer circuits. The summing network develops four sum signals by summing respective pairs of the differential components of the I and Q carrier signals. A bias circuit biases the transistors to turn on at positive base voltages. The mixer circuits may include filter capacitors so that the transistors are responsive to positive base voltages. The mixer circuits develop polarity signals based on the sum signals, and the resulting phase error signal is the differential of the polarity signals.

Owner:M RED INC

Method and system for measuring receiver mixer iq mismatch

InactiveUS20070123188A1TransmissionAngle demodulation by oscillations conversionTransceiverFrequency mixer

Aspects for measuring receiver mixer IQ mismatch in a transceiver are described. The measuring includes providing a training signal for a receiver mixer, the training signal having periodic, uncorrelated I and Q signals. A phase mismatch in the receiver mixer is determined from IQ correlation over a unit period. A gain mismatch in the receiver mixer is determined from a power estimate of both I and Q signal for the unit period.

Owner:AVAGO TECH INT SALES PTE LTD

Popular searches

Amplitude to angle modulation conversion Signal channels Local circuits Amplitude demodulation details Pulse shaping Transmission noise suppression Pulse slope modification Picture reproducers with optical-mechanical scanning Frequency/rate-modulated pulse demodulation Analogue secracy/subscription systems