DDR SDRAM control circuit, DDR SDRAM chip, PCB and electronic equipment

A technology for controlling circuits and clock circuits, applied in the fields of DDRSDRAM control circuits, DDRSDRAM chips, PCB boards and electronic equipment, can solve the problems of multiple clock connections, low clock frequency, unbalanced delay, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

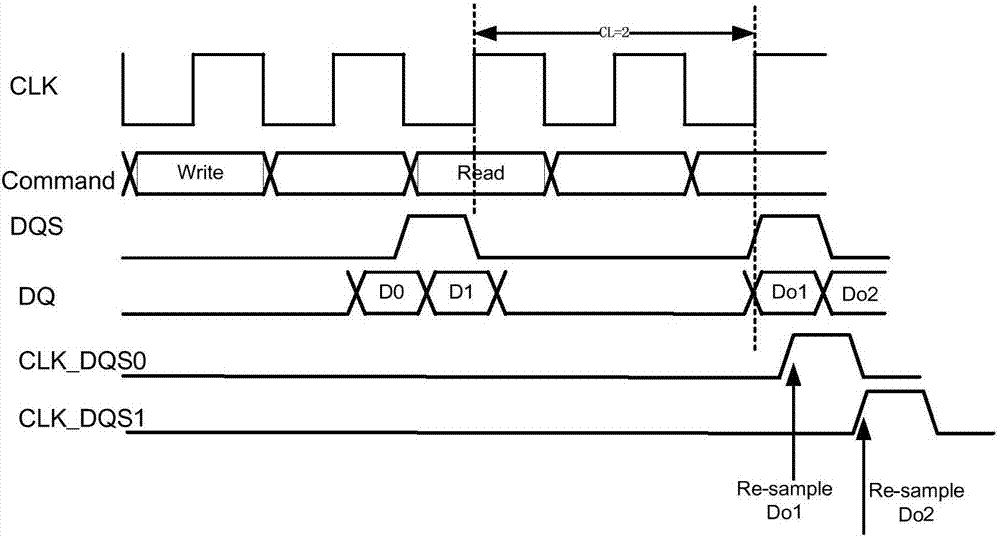

[0035] For a DDR SDRAM memory connected to the chip, it needs to accurately determine the position of the clock signal and the data strobe pulse DQS in the address, control and data signals. Such as figure 1As shown, in a DDR SDRAM clock cycle, there are two data pulses DQ (data signal) per cycle, and one data pulse per half cycle. When the data pulse DQ is stable within a half cycle (for example, in the middle of a half cycle), it is usually necessary to issue a data strobe pulse DQS. Gating a data pulse DQ at a stable point is required to correctly read or write data to the DDR SDRAM memory.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More