Frequency multiplier based on delayed phase-locked loop structure

A phase-locked loop and frequency multiplier technology is applied in the field of frequency multipliers based on a delay phase-locked loop structure, which can solve the problems of increasing the hardware cost of a clock generator and achieve the effect of small hardware cost

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] In order to make the purpose, technical solutions and advantages of the embodiments of the present invention clearer, the technical solutions in the embodiments of the present invention will be clearly described below in conjunction with the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are the Some, but not all, embodiments are invented. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

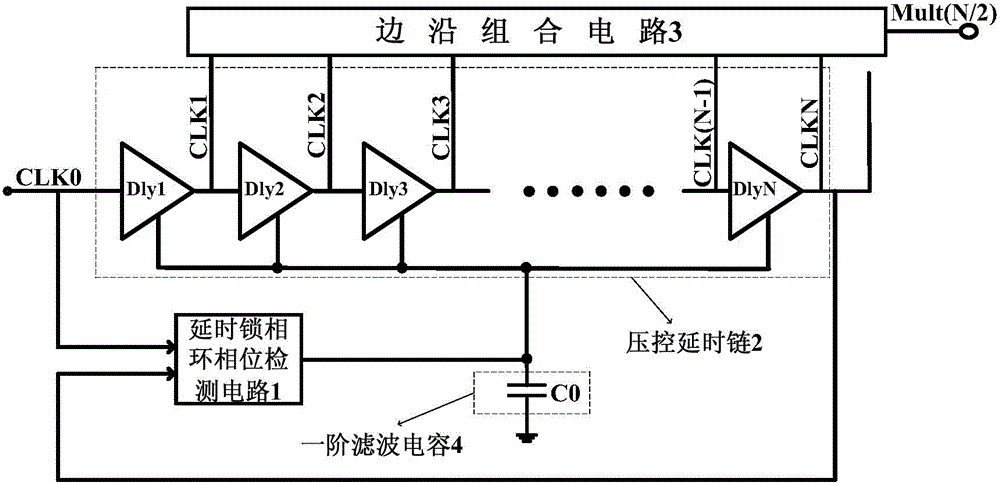

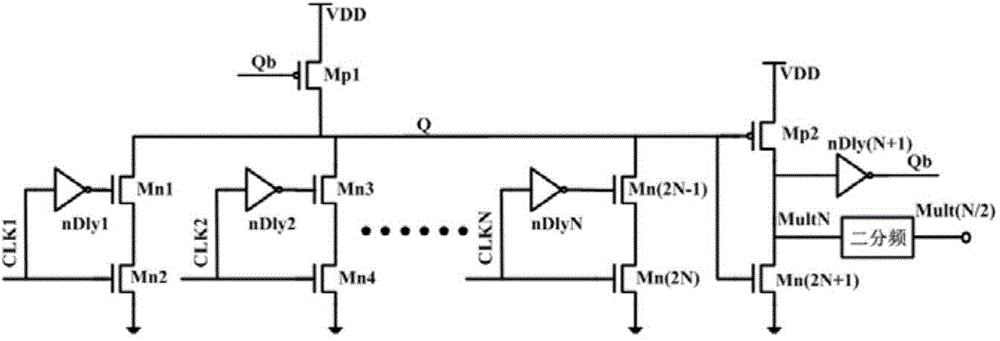

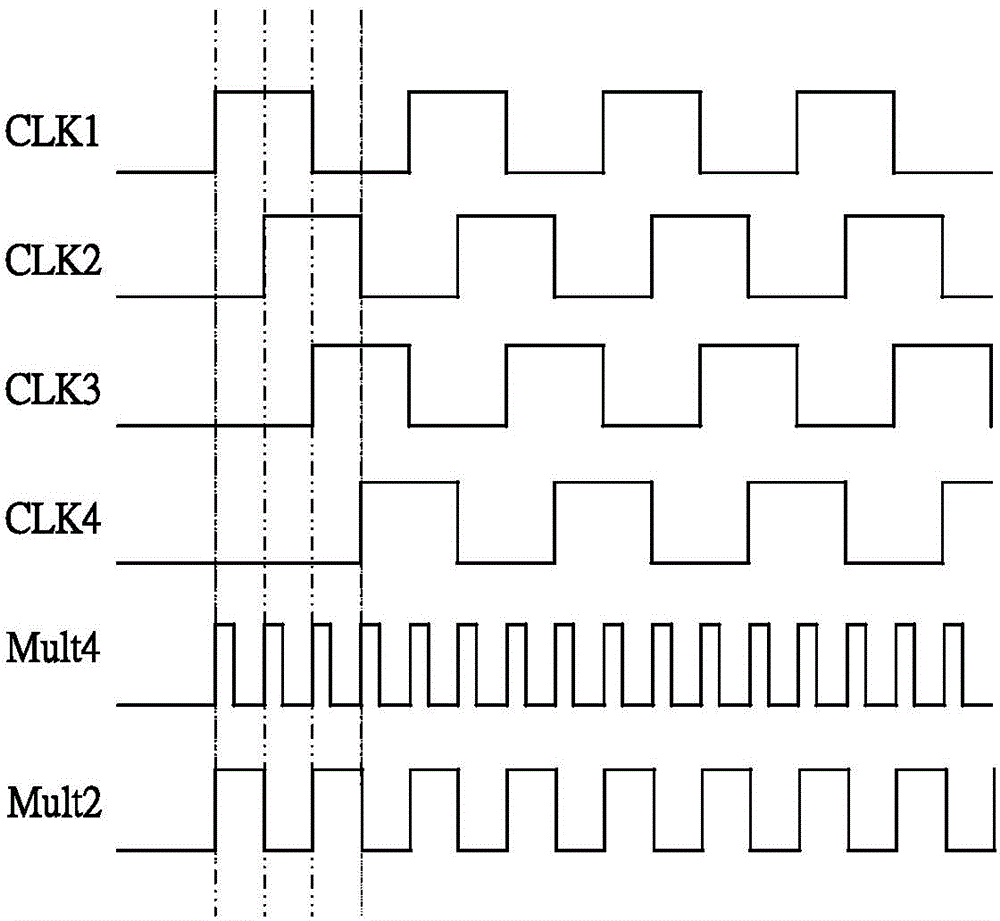

[0019] Such as figure 1 As shown, this embodiment discloses a frequency multiplier based on a delay phase-locked loop structure, including:

[0020] Delay phase-locked loop phase detection circuit 1, voltage-controlled delay chain 2, edge combination circuit 3 and first-order filter capacitor 4;

[0021] Wherein, the input signal of the delay phase-locked loop phase d...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More