Duty degree correction circuit and delayed phase-lock loop having same

A technology for correcting circuits and duty cycles, applied in the field of delay-locked loops, which can solve problems such as occupation, power consumption, and multi-chip area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

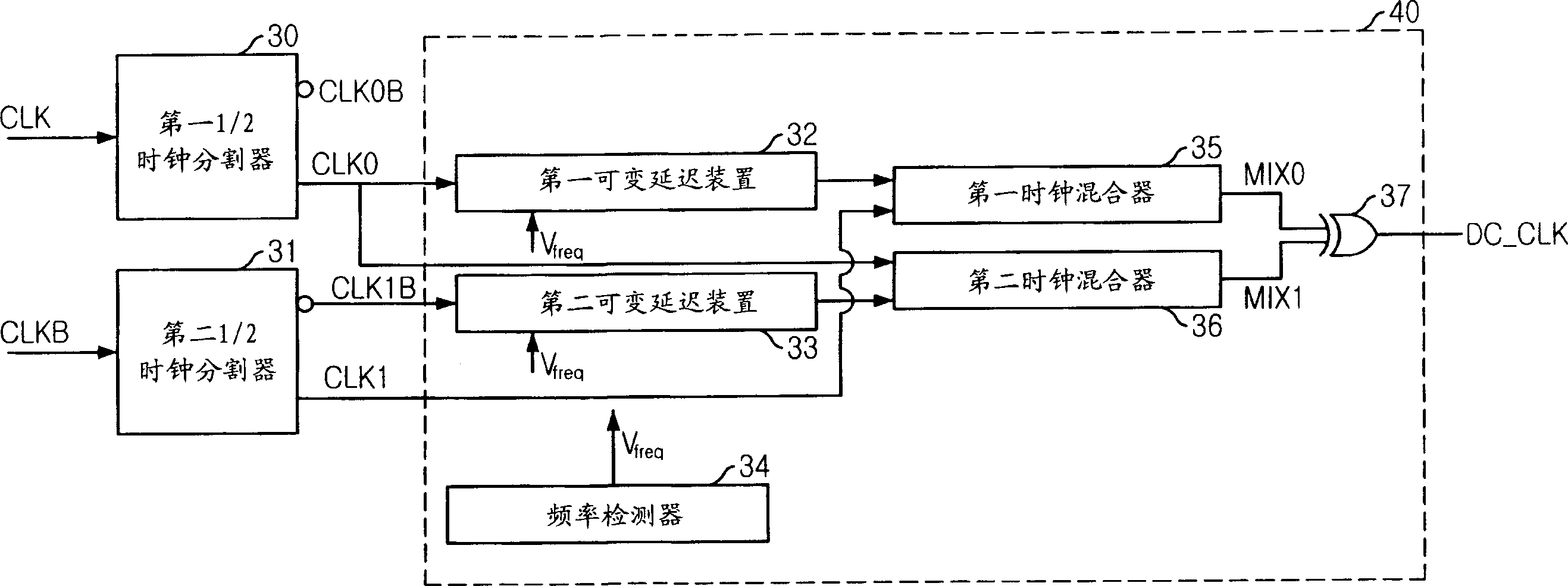

[0025] Hereinafter, a duty cycle correction circuit (DCC) and a delay locked loop (DLL) including the duty cycle correction circuit of the present invention will be described in detail with reference to the accompanying drawings.

[0026] image 3 is a block diagram of a DCC circuit according to a preferred embodiment of the present invention.

[0027] refer to image 3 , the DCC circuit includes: a first 1 / 2 clock divider 30 for generating normal split clocks (CLK0 and CLK0B) by dividing a normal input clock (CLK) by 2; a second 1 / 2 clock divider device 31 for generating clocks (CLK1 and CLK1B) by dividing a sub-normal input clock (CLKB) by 2; and a DCC core circuit 40 for dividing The duty cycle of the output of the device 31 is used to generate a duty cycle corrected clock (DC_CLK) having a corrected duty cycle.

[0028] The core circuit 40 includes: a frequency detector 34, which is used to generate a voltage signal (Vfreq) that varies proportionally to the frequency of...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More