Patents

Literature

250results about How to "Shorten lock time" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

Phase-locked loop and automatic frequency calibration circuit thereof and phase-locked loop self-tuning locking method

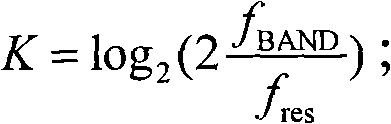

InactiveCN101951259ASpeed up lock timeGuaranteed robustnessPulse automatic controlSelf-tuningLock time

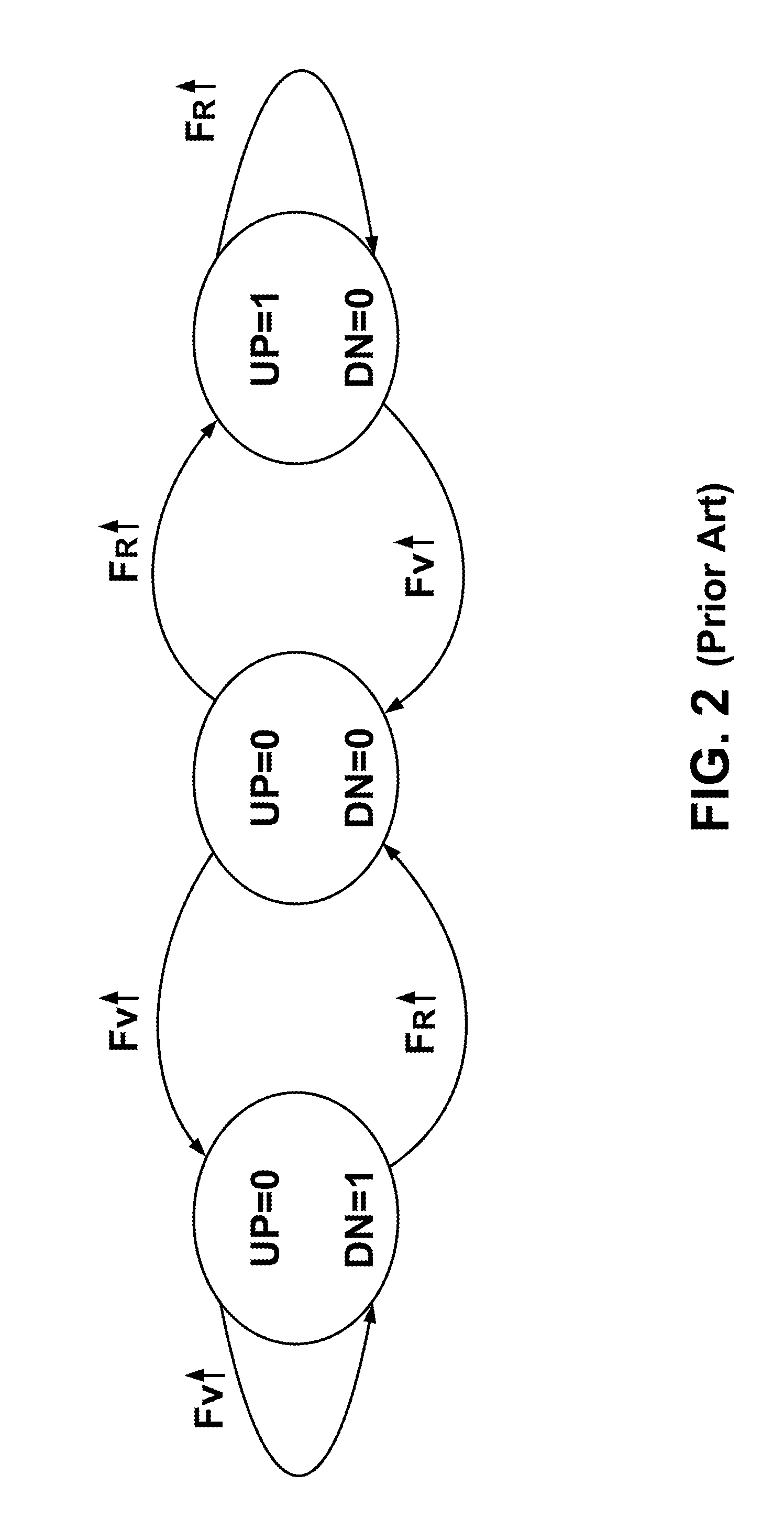

The invention discloses a phase-locked loop and an automatic frequency calibration circuit thereof. The phase-locked loop comprises a phase / frequency detector, a charge pump, a filter, a voltage-controlled oscillator (VCO) and a first frequency divider which are connected in sequence, wherein the phase-locked loop further comprises the automatic frequency calibration circuit; the automatic frequency calibration circuit reduces the oscillation frequency CKV of the VCO when the oscillation frequency CKV of the VCO after undergoing frequency division by the first frequency divider is higher than the reference frequency CKR, and increases the oscillation frequency CKV of the VCO when the oscillation frequency CKV of the VCO is lower than the reference frequency CKR; and a precharging circuit A0 is connected at the input end of the filter and carries out precharging when AFC carries out searching. The phase-locked loop has the rapid self-tuning locking function and ensures the VCO to carry out coarse tuning automatically to approach the final tuning coil, thus reducing the locking time of the phase-locked loop.

Owner:SHANGHAI NATLINEAR ELECTRONICS CO LTD

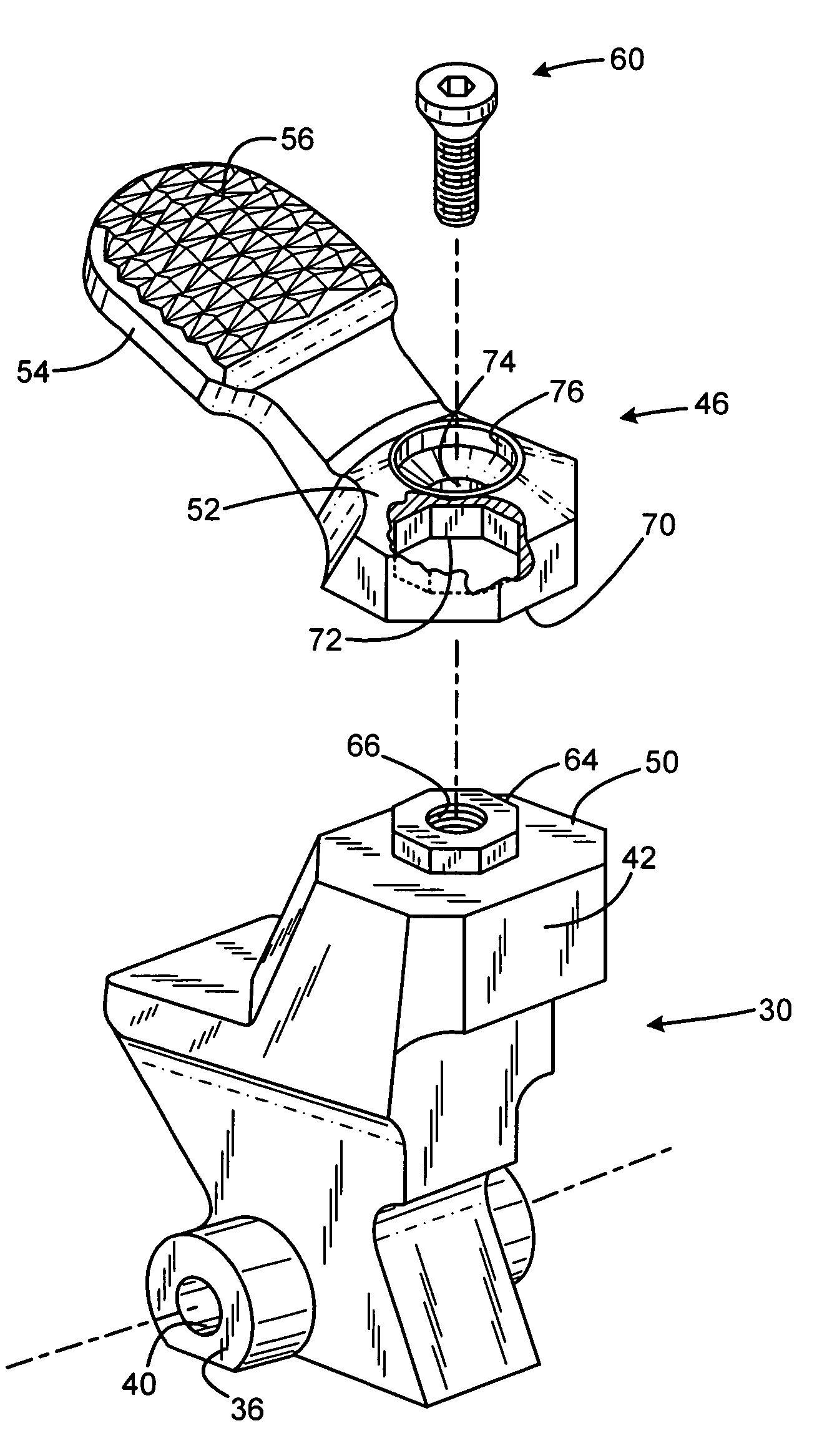

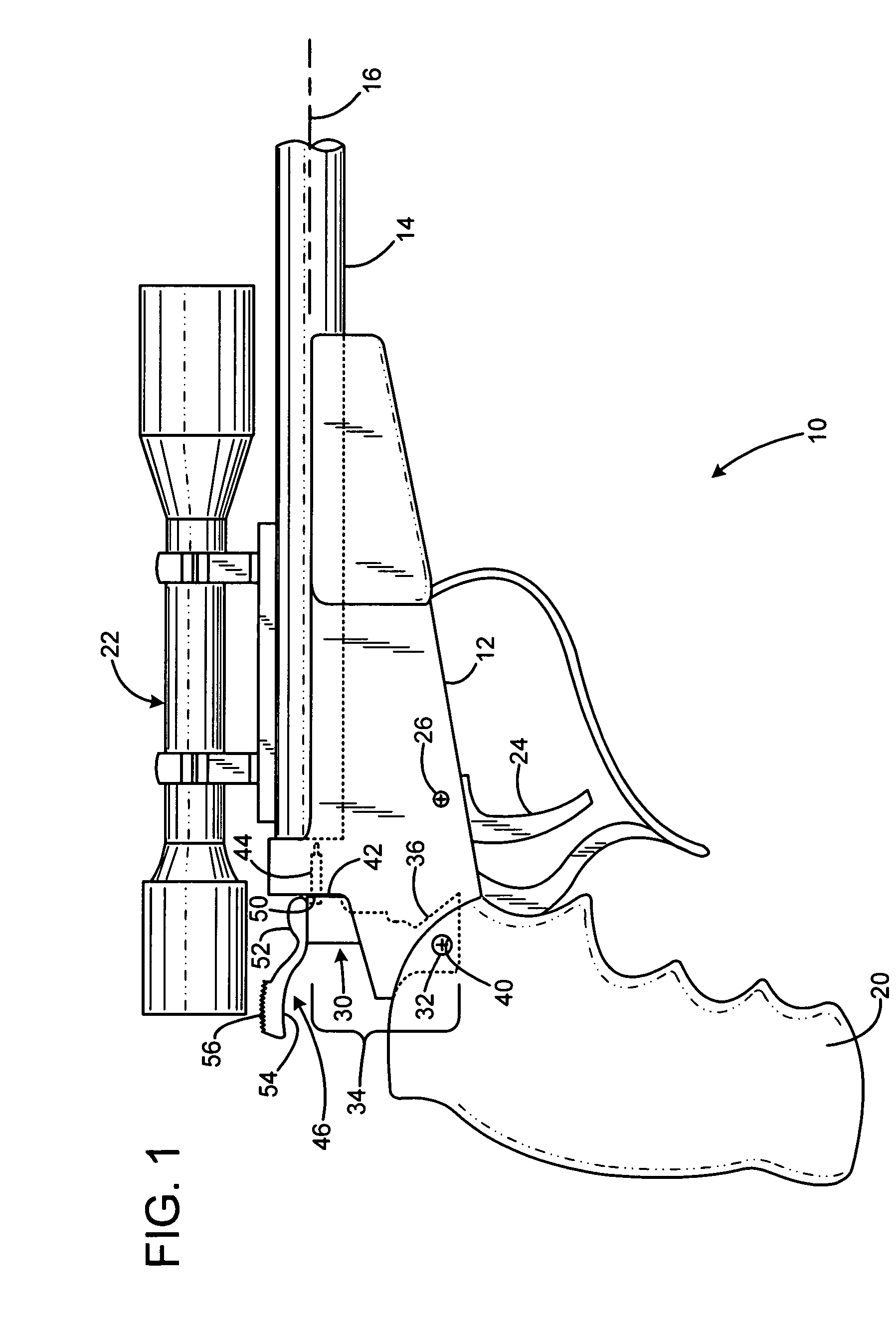

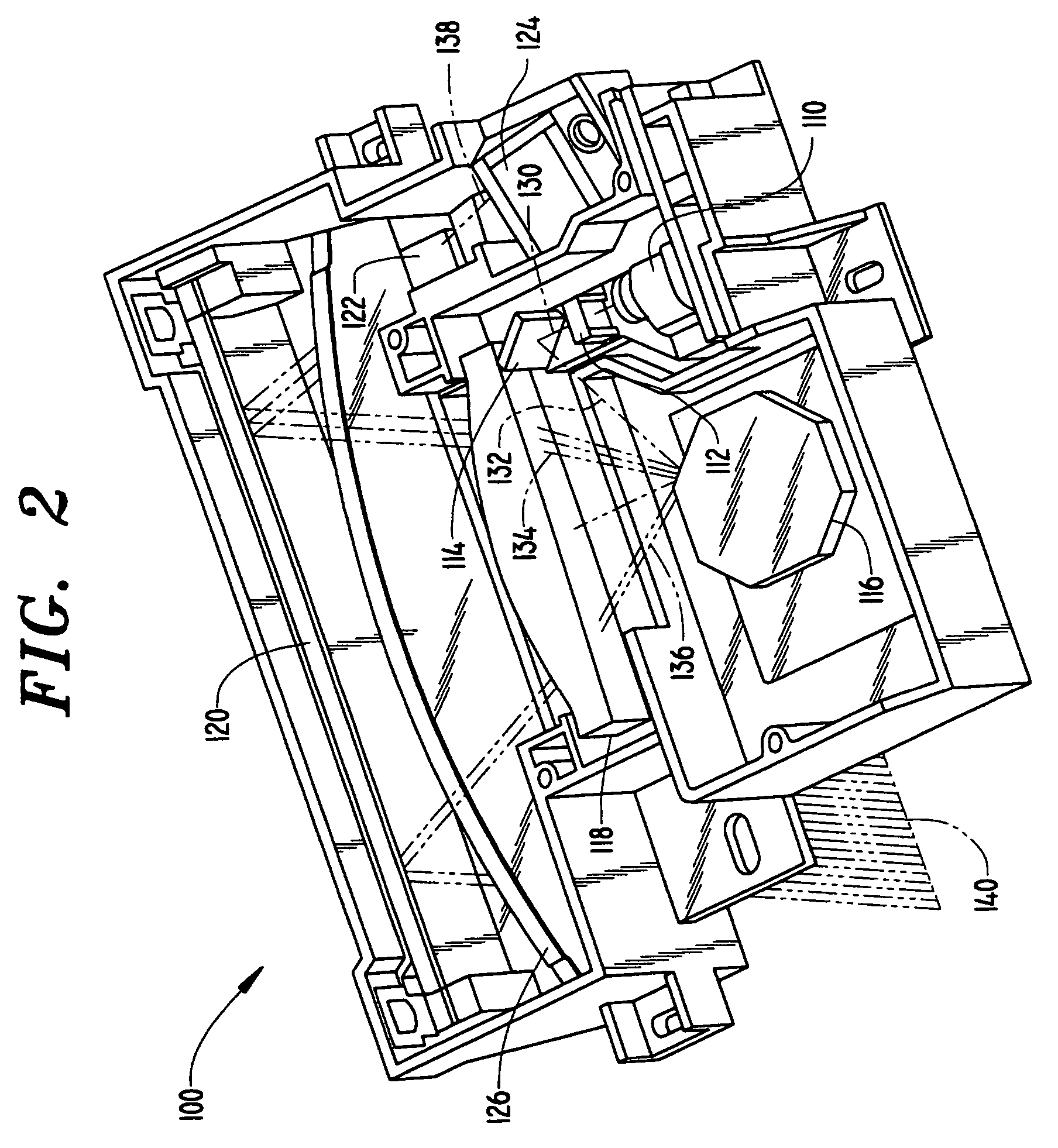

Firearm hammer with adjustable spur

ActiveUS7140138B1Reduces “ lock time ”Convenient and accurateSafety arrangementFiring/trigger mechanismsEngineeringStandard position

A firearm hammer has a hammer body with a hammer pivot axis for attachment to a firearm frame. A spur is connected to the hammer body, and the spur is movable among a number of positions with respect to the hammer body. The spur may be attached in a standard position in which it extends within the medial plane of the hammer body for use without a scope, or offset positions in which it angles away from the medial plane to provide accessibility. The offset angle may be 45 degrees, and a mating feature may provide the several attachment positions, each secure against movement except by deliberate removal of a fastener.

Owner:SMITH & WESSON

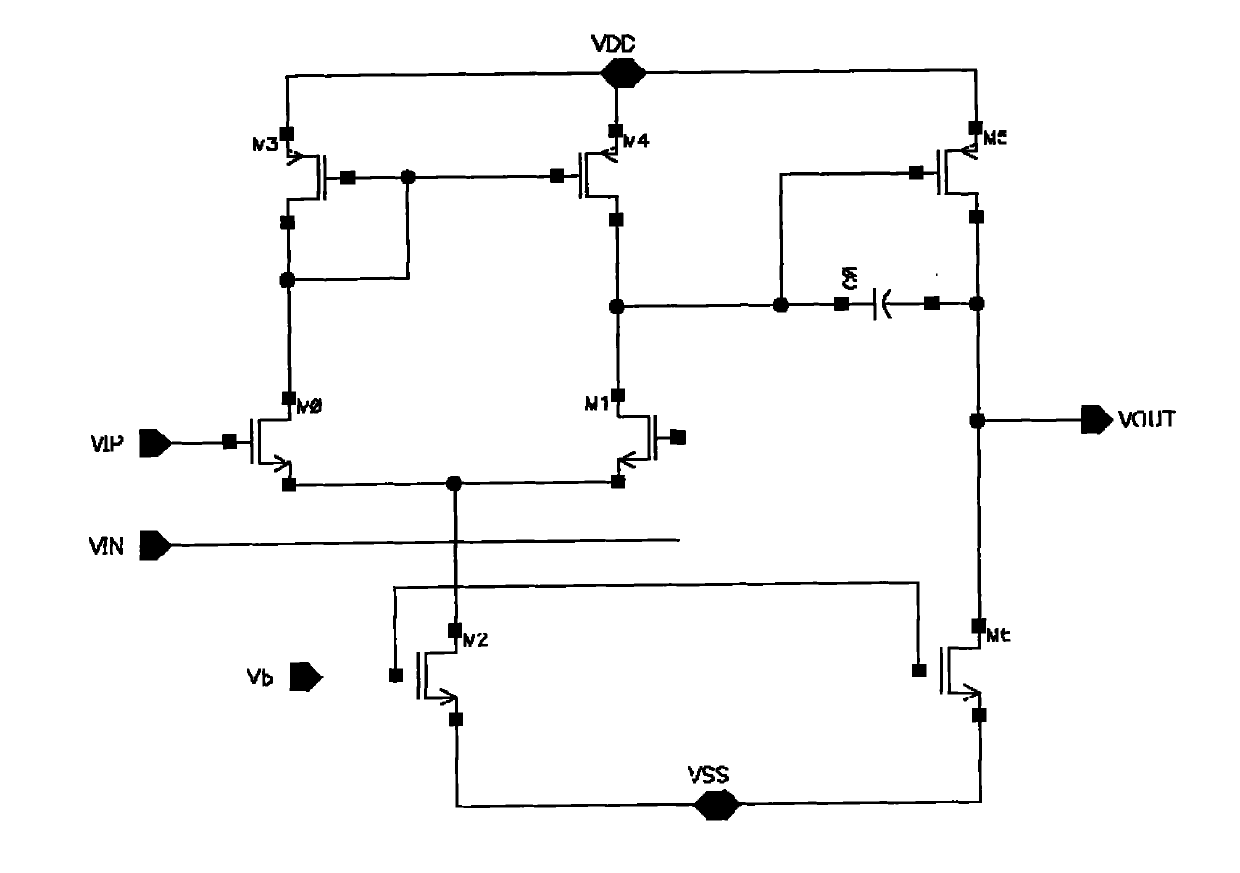

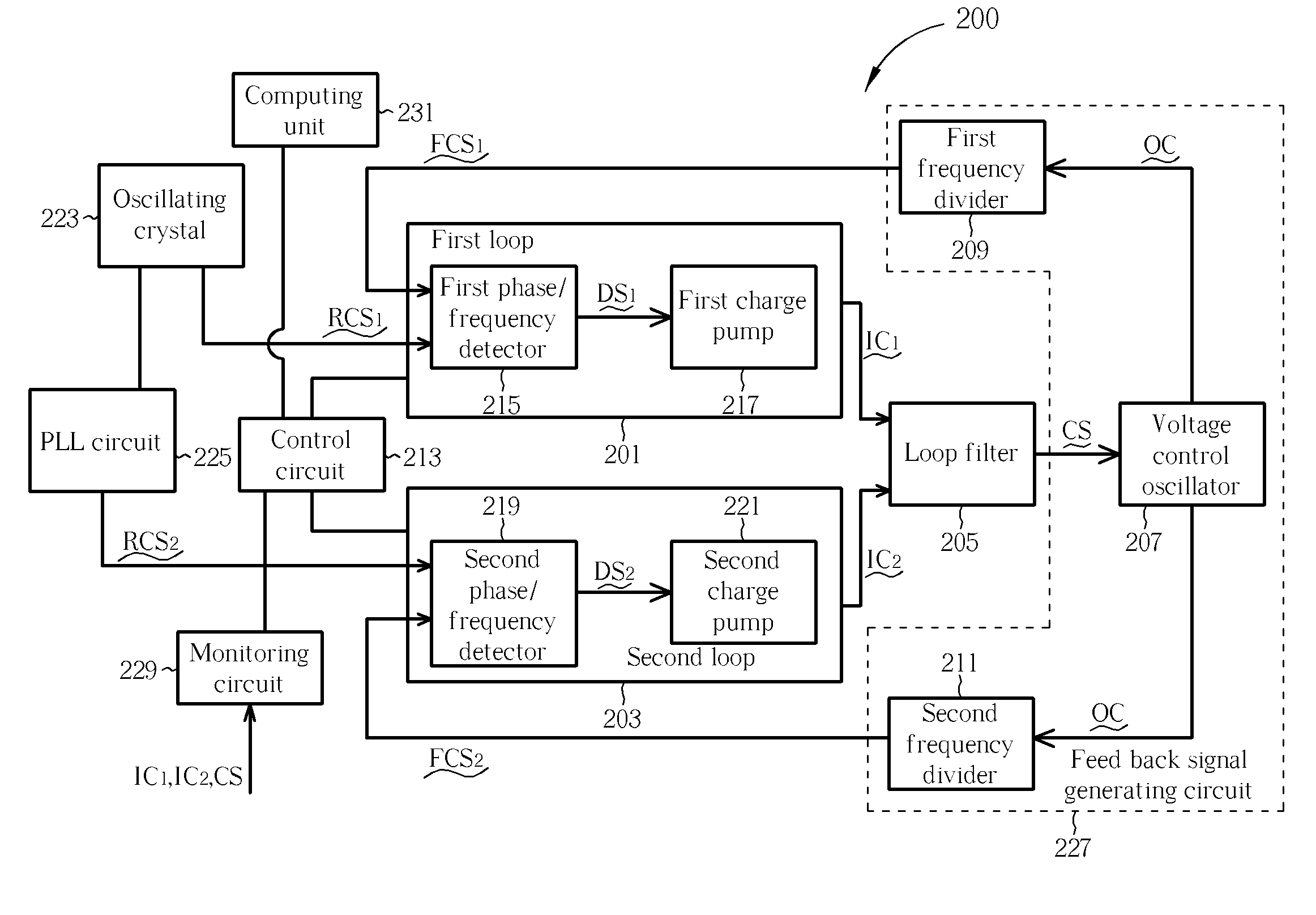

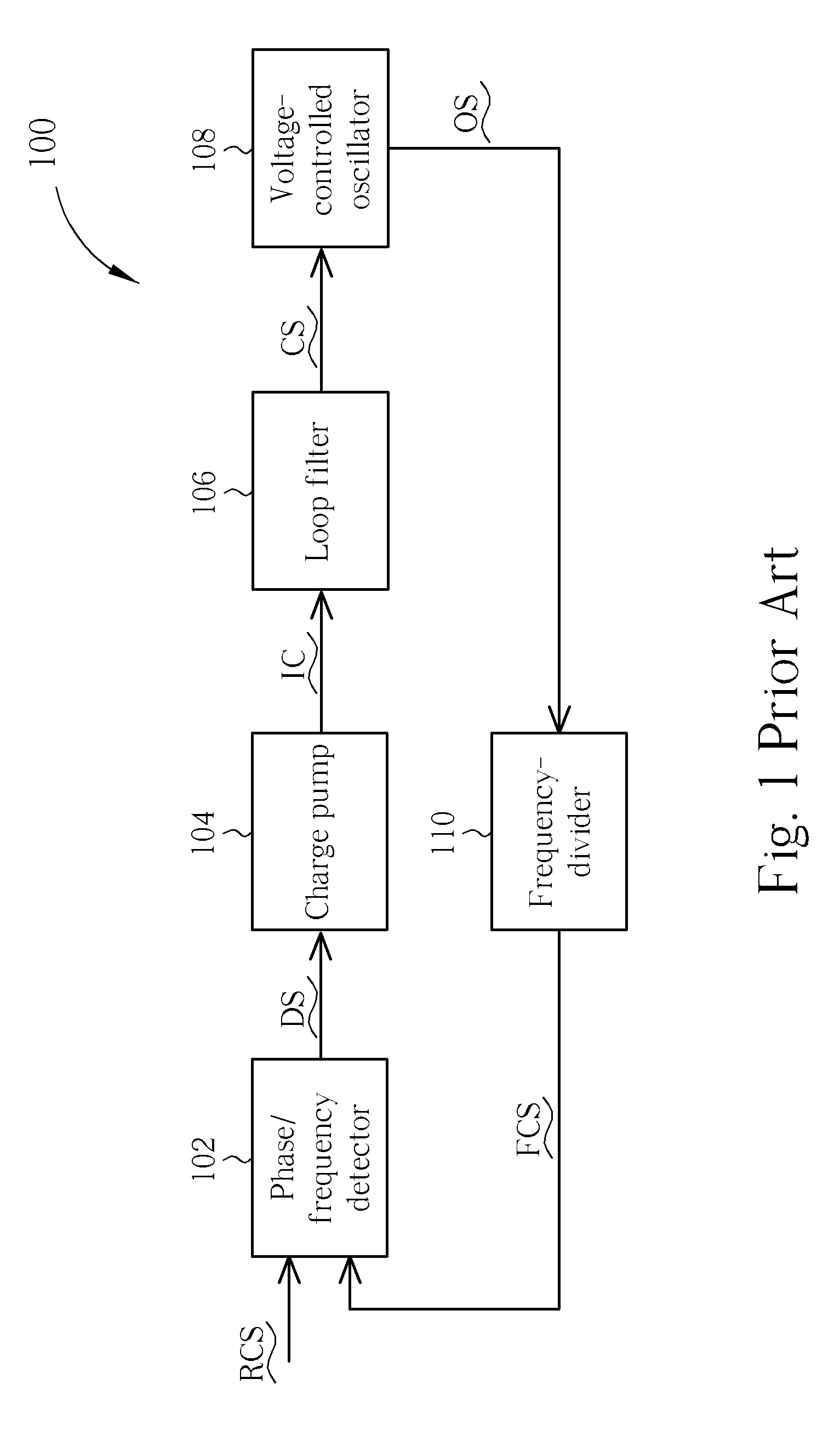

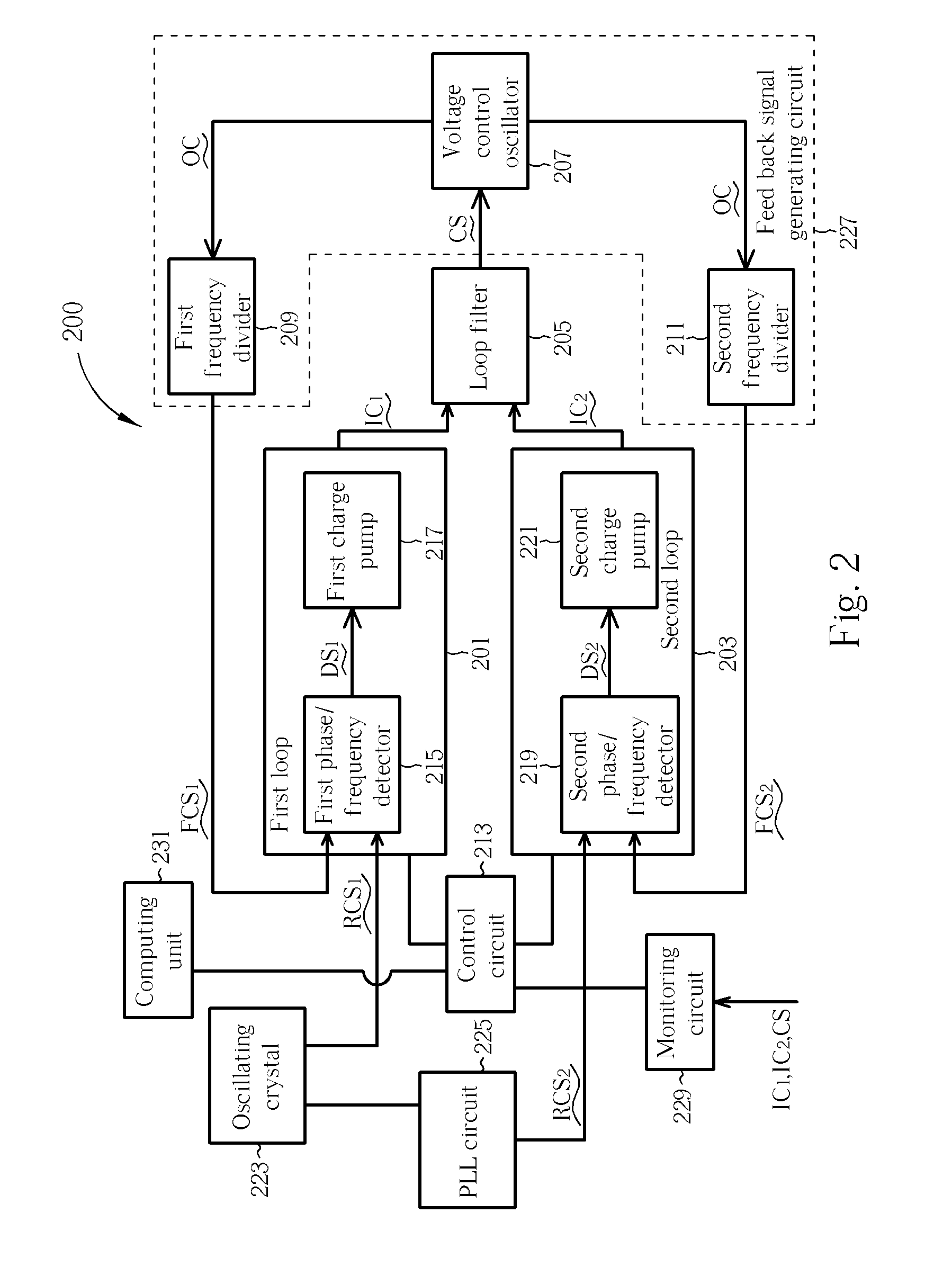

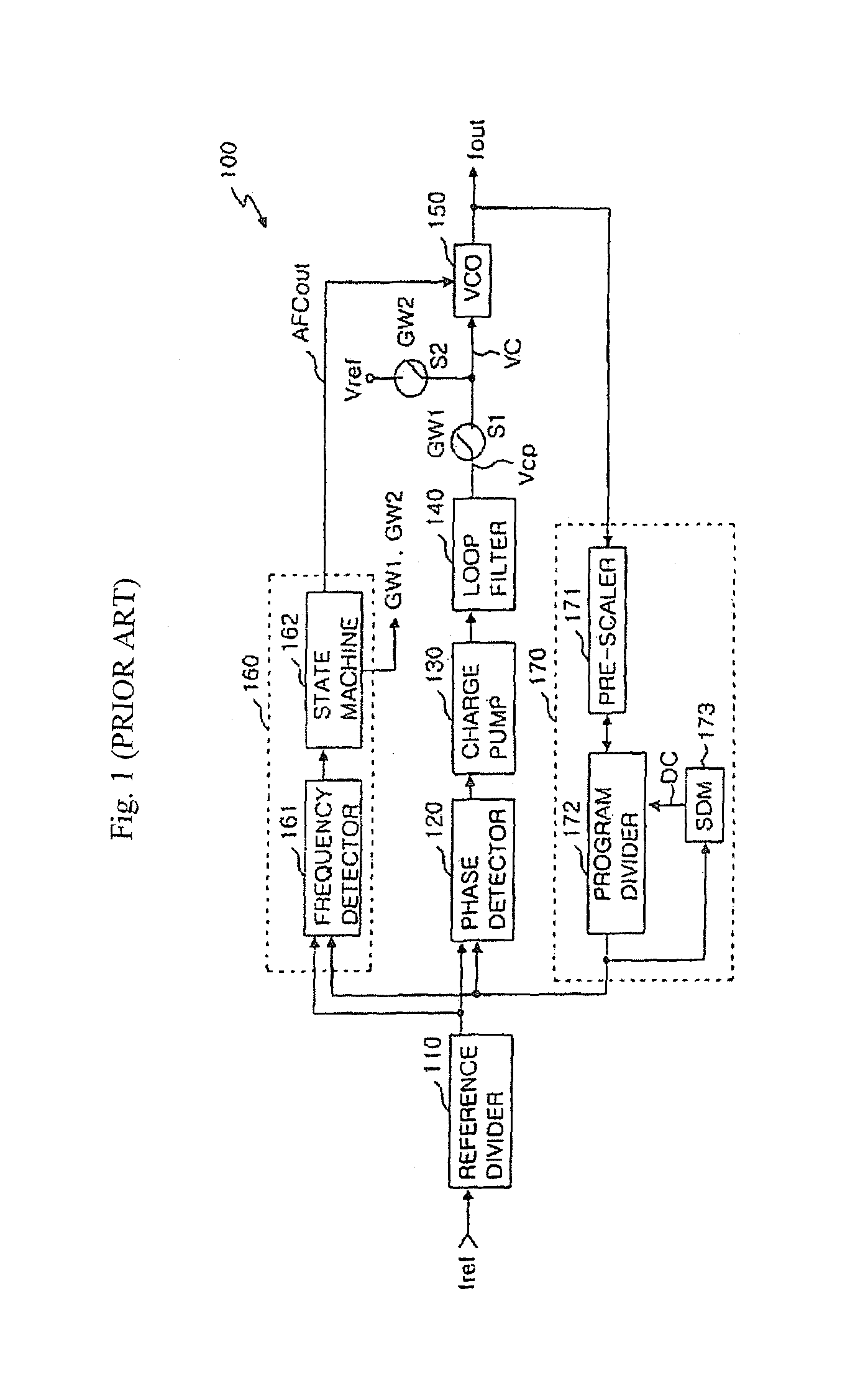

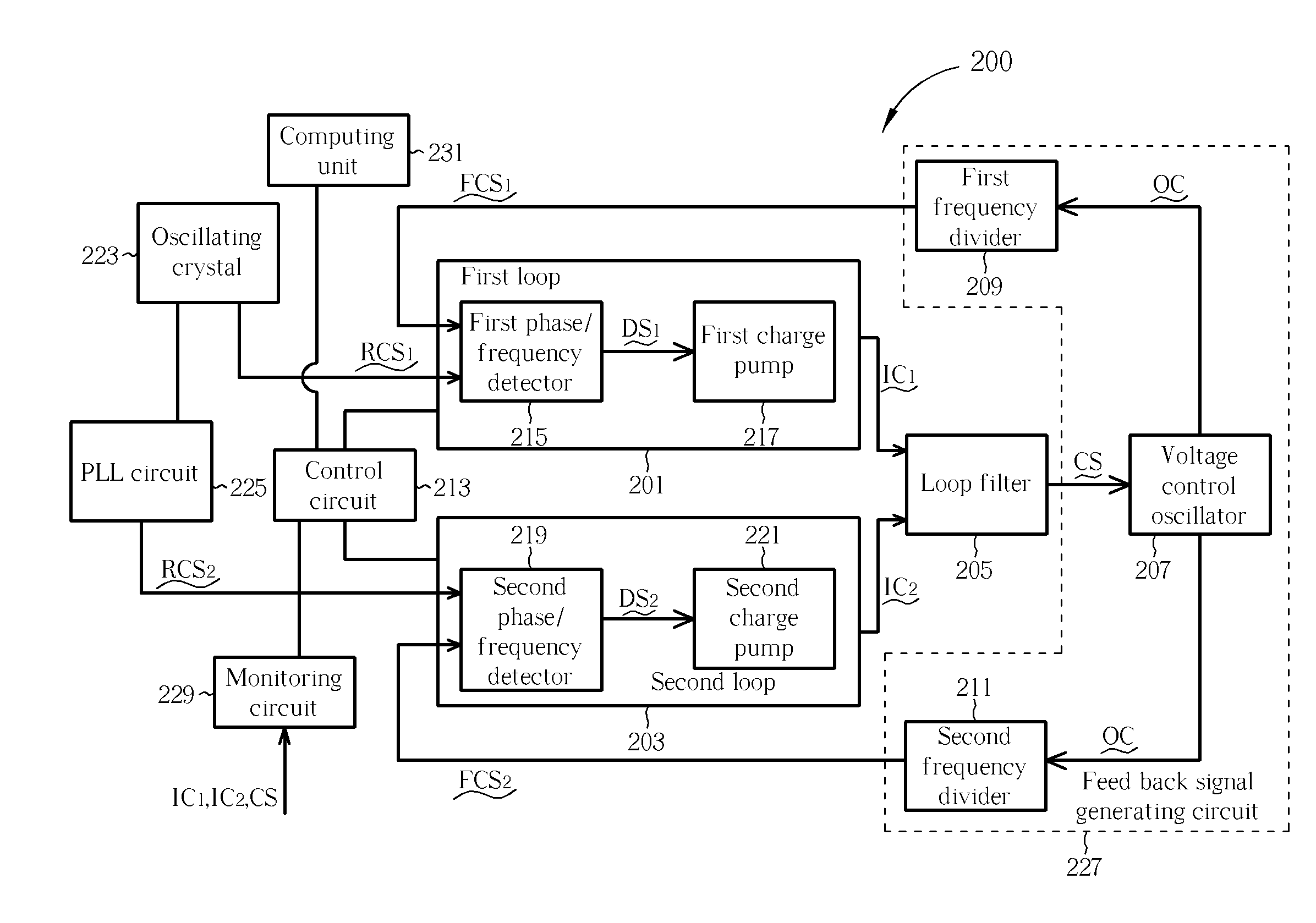

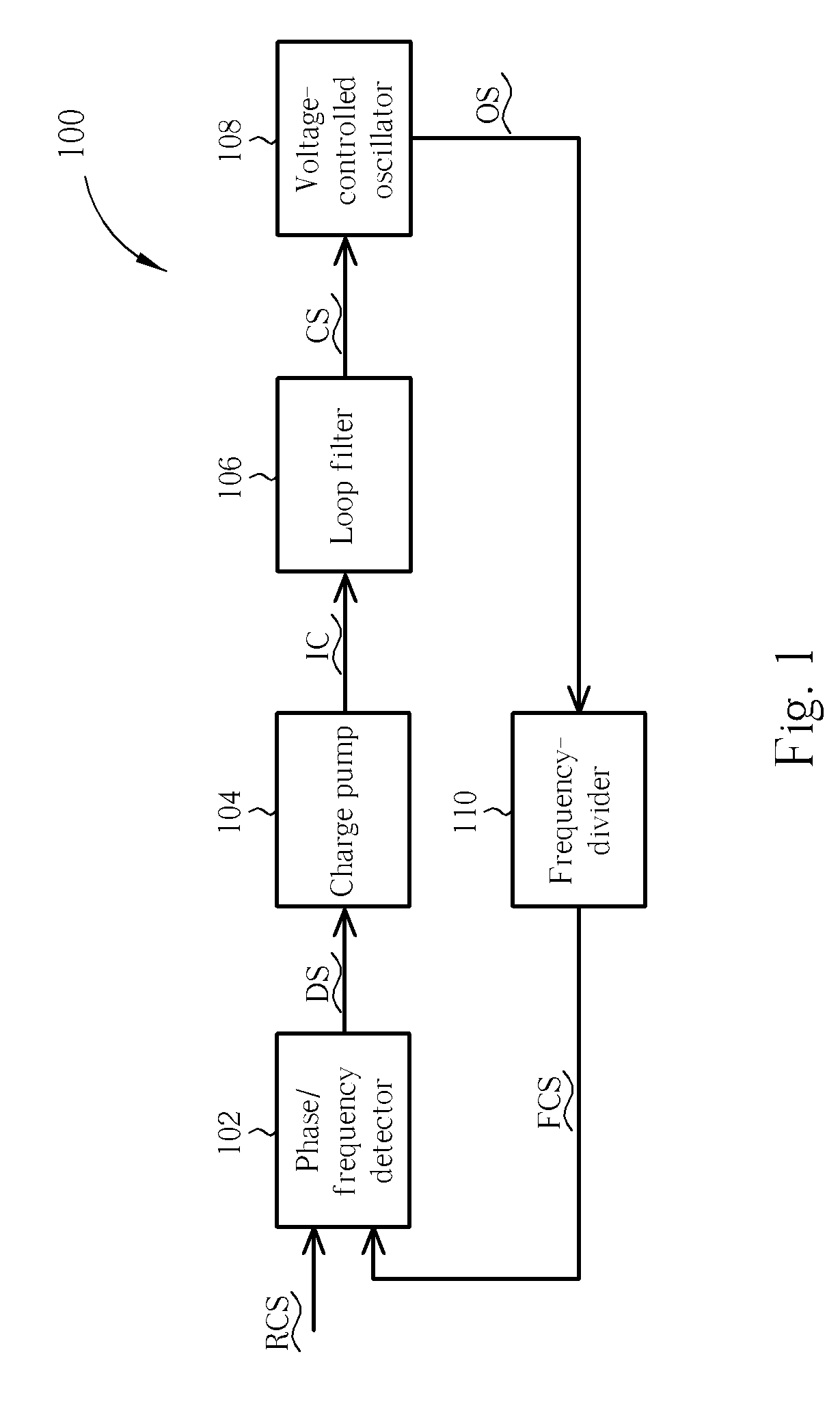

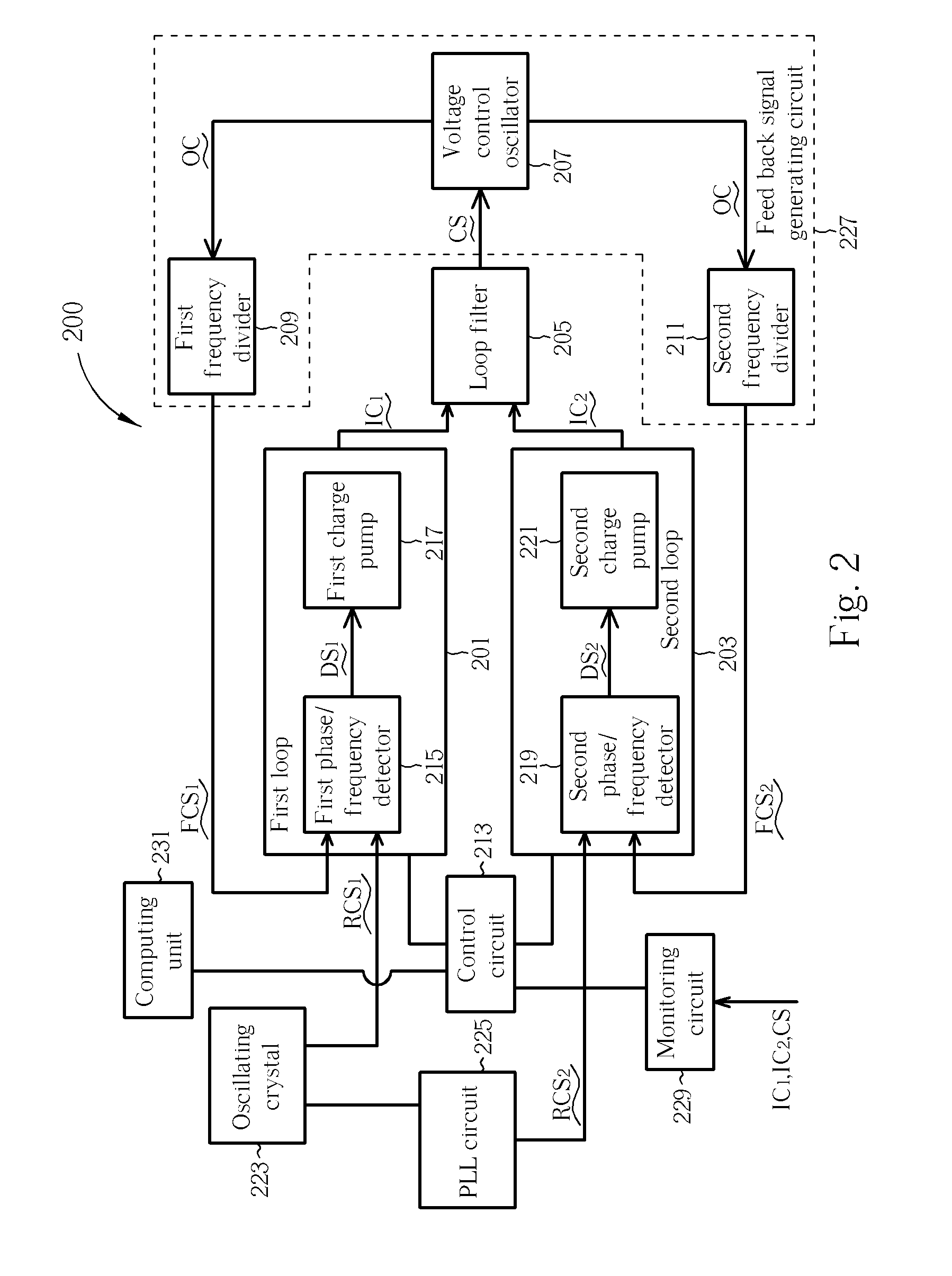

Multi-loop phase locked loop circuit

Disclosed is a multi-loop PLL circuit and a related method of which, the circuit includes: a first loop for generating a first control current; a second loop for generating a second control current; a loop filter for generating a control signal according to the first control current or the second control current; a voltage control oscillator for generating a first oscillating signal or a second oscillating signal according to the control signal; a first frequency divider for generating a first feed back clock signal; a second frequency divider for generating a second feed back clock signal; and a control circuit for switching the first loop or the second loop to generate the control signal. The frequency of the second reference clock signal is higher than which of the first reference clock signal. The control circuit turns on the second loop first and then turns on the first loop.

Owner:REALTEK SEMICON CORP

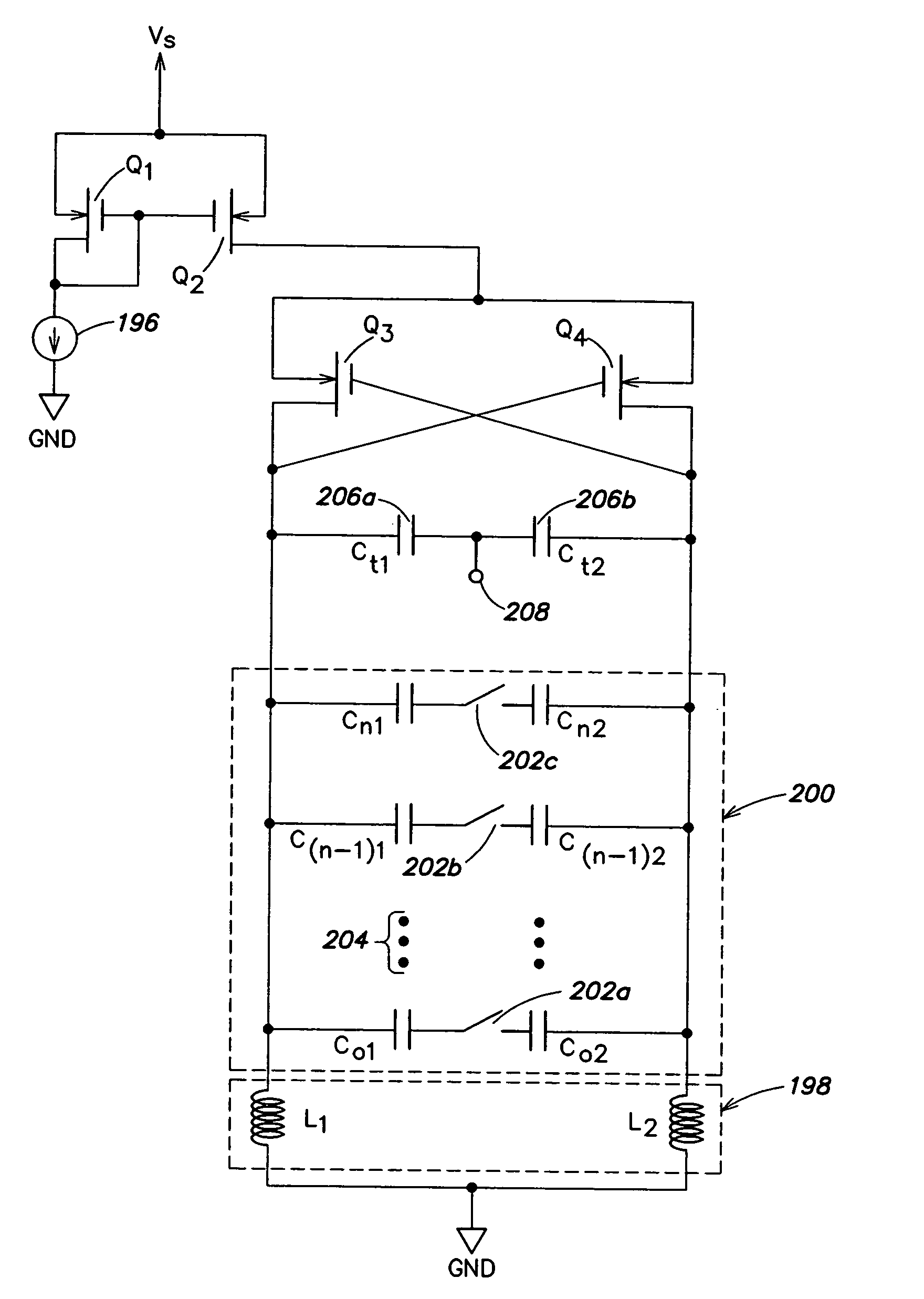

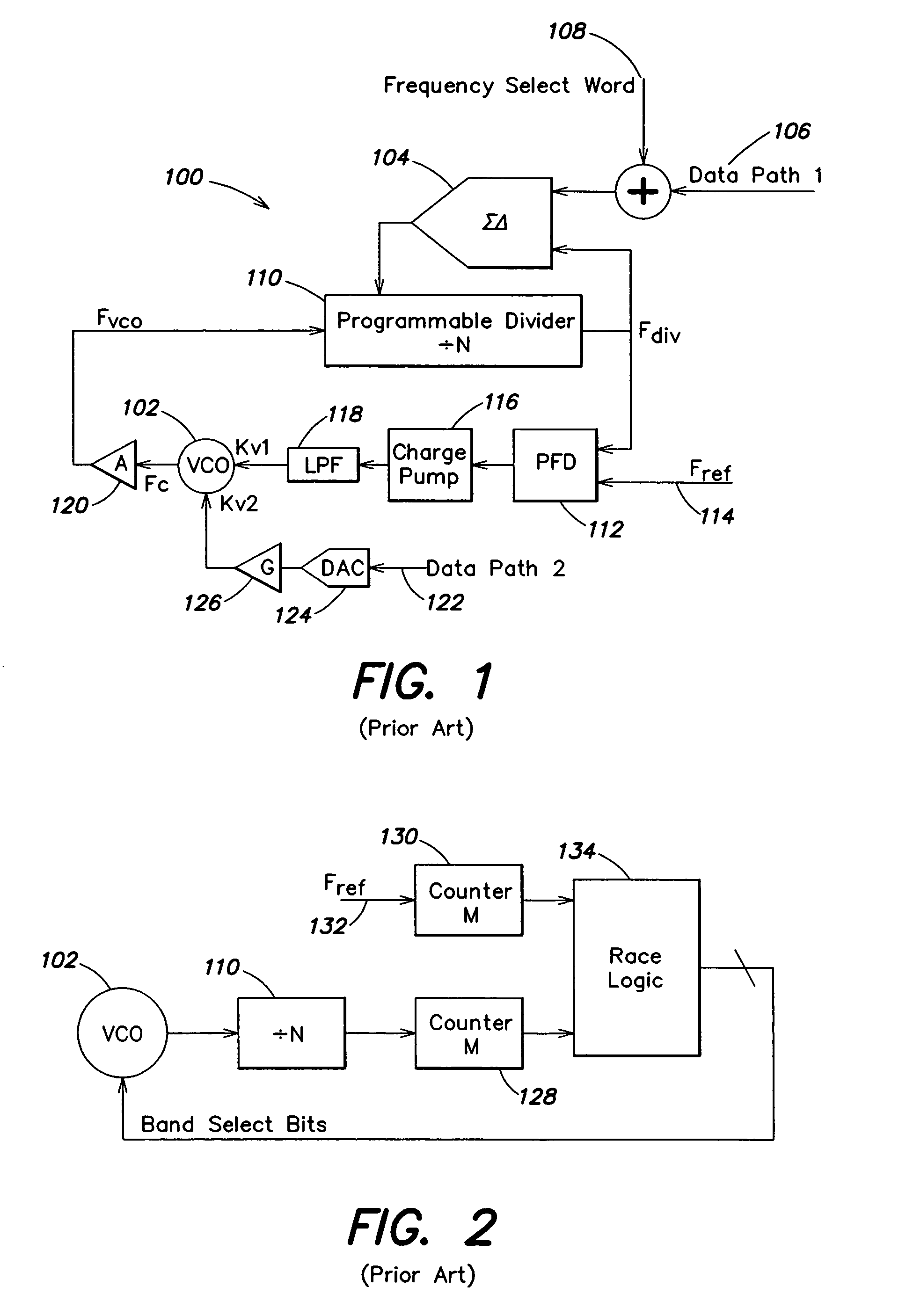

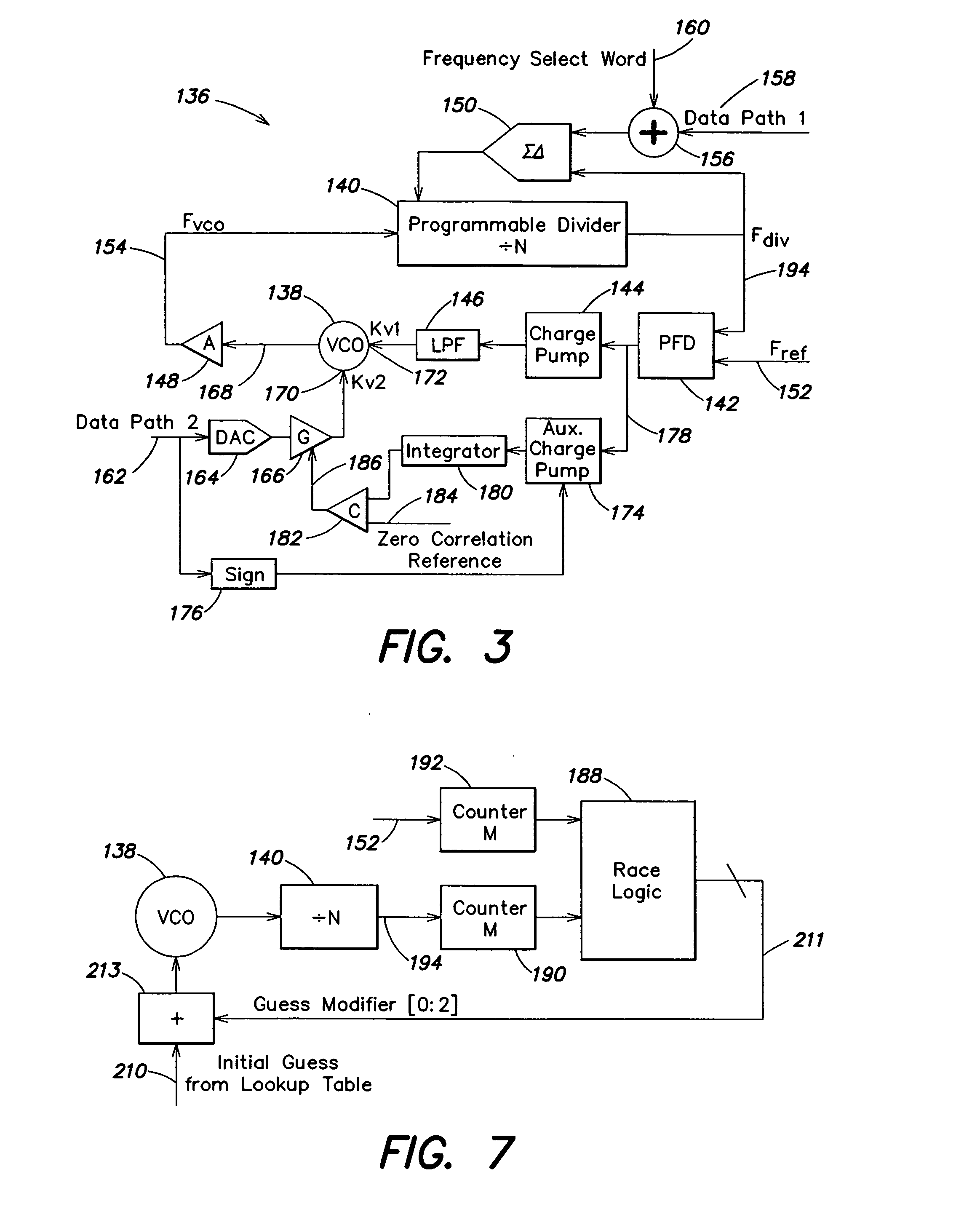

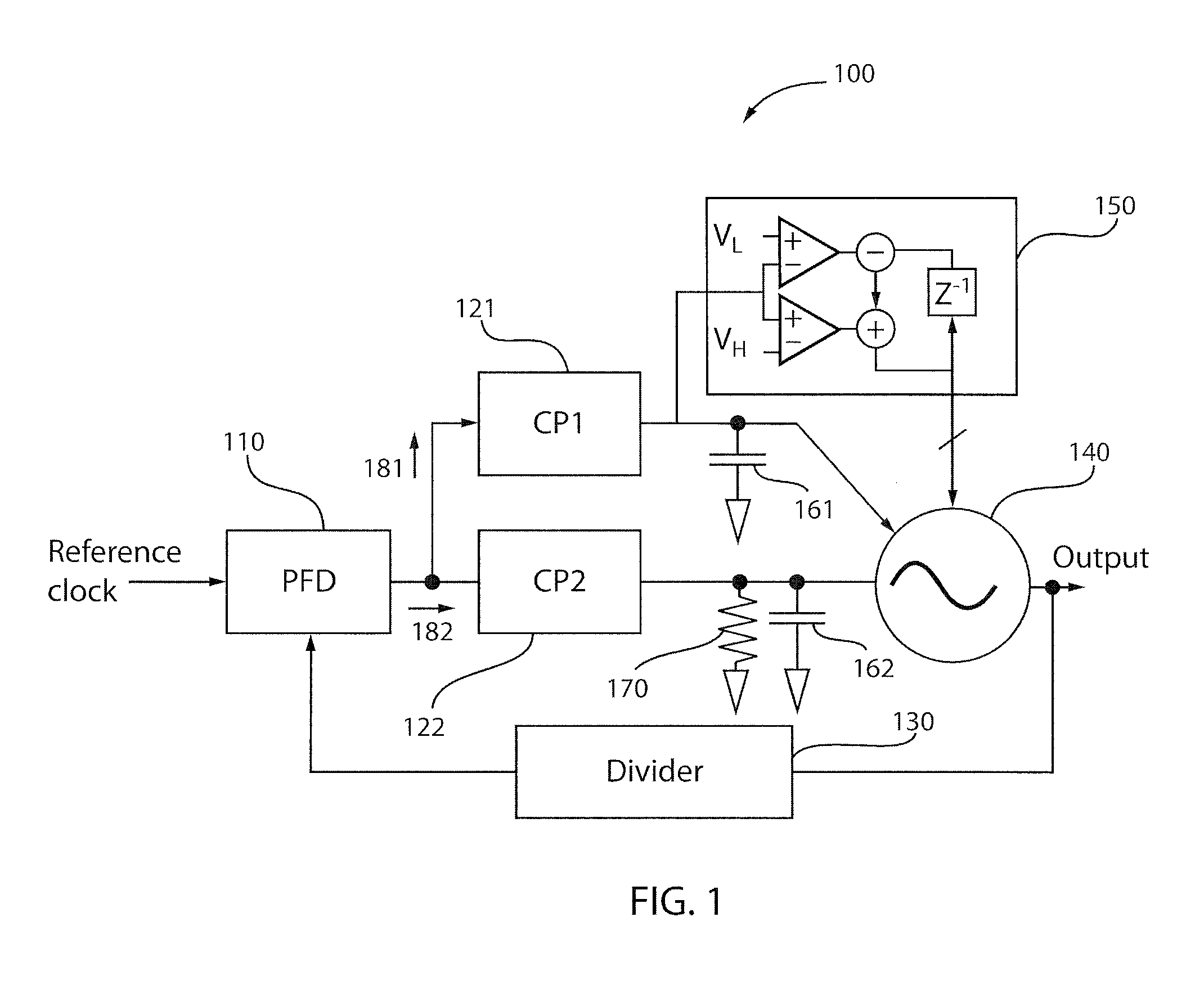

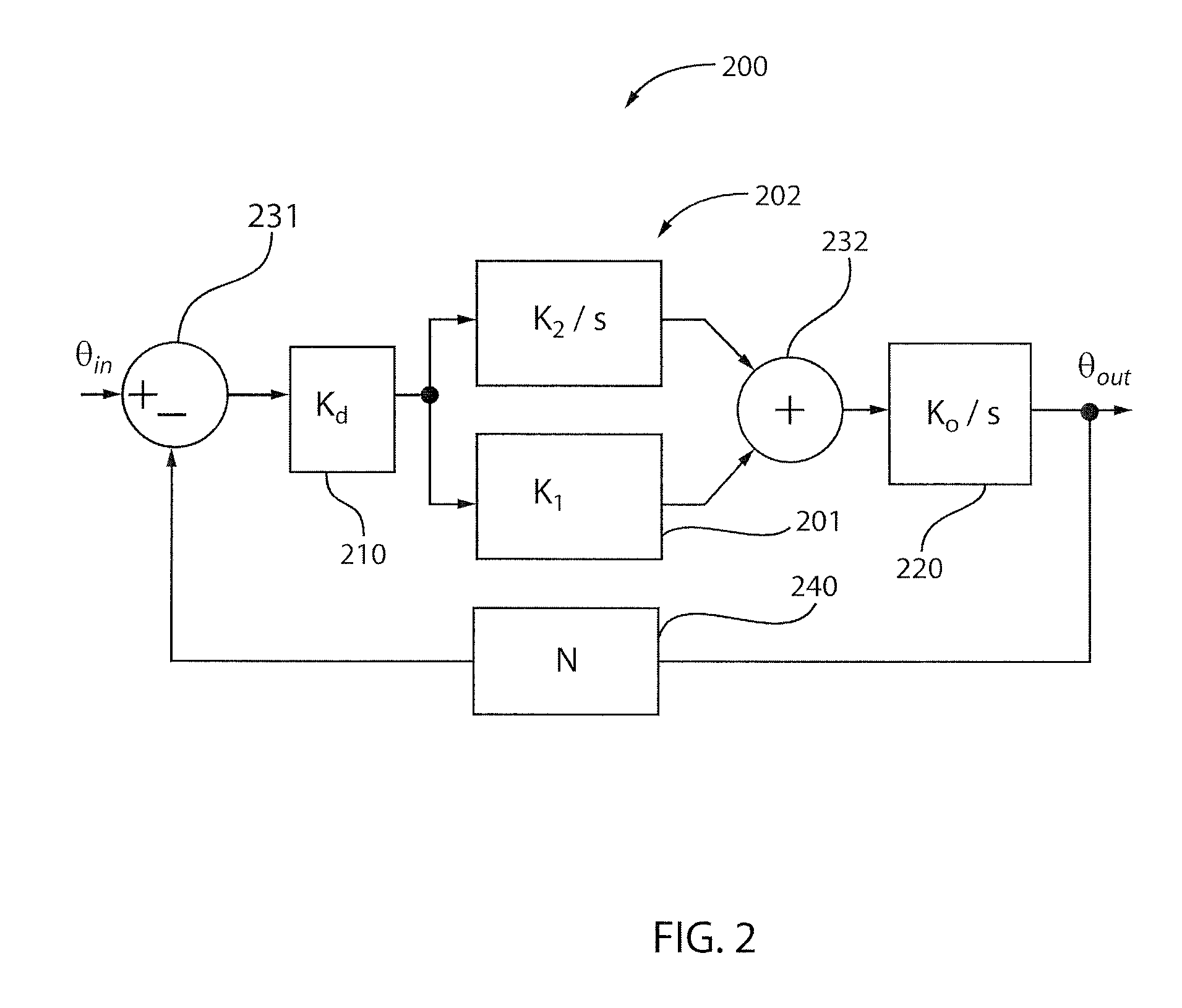

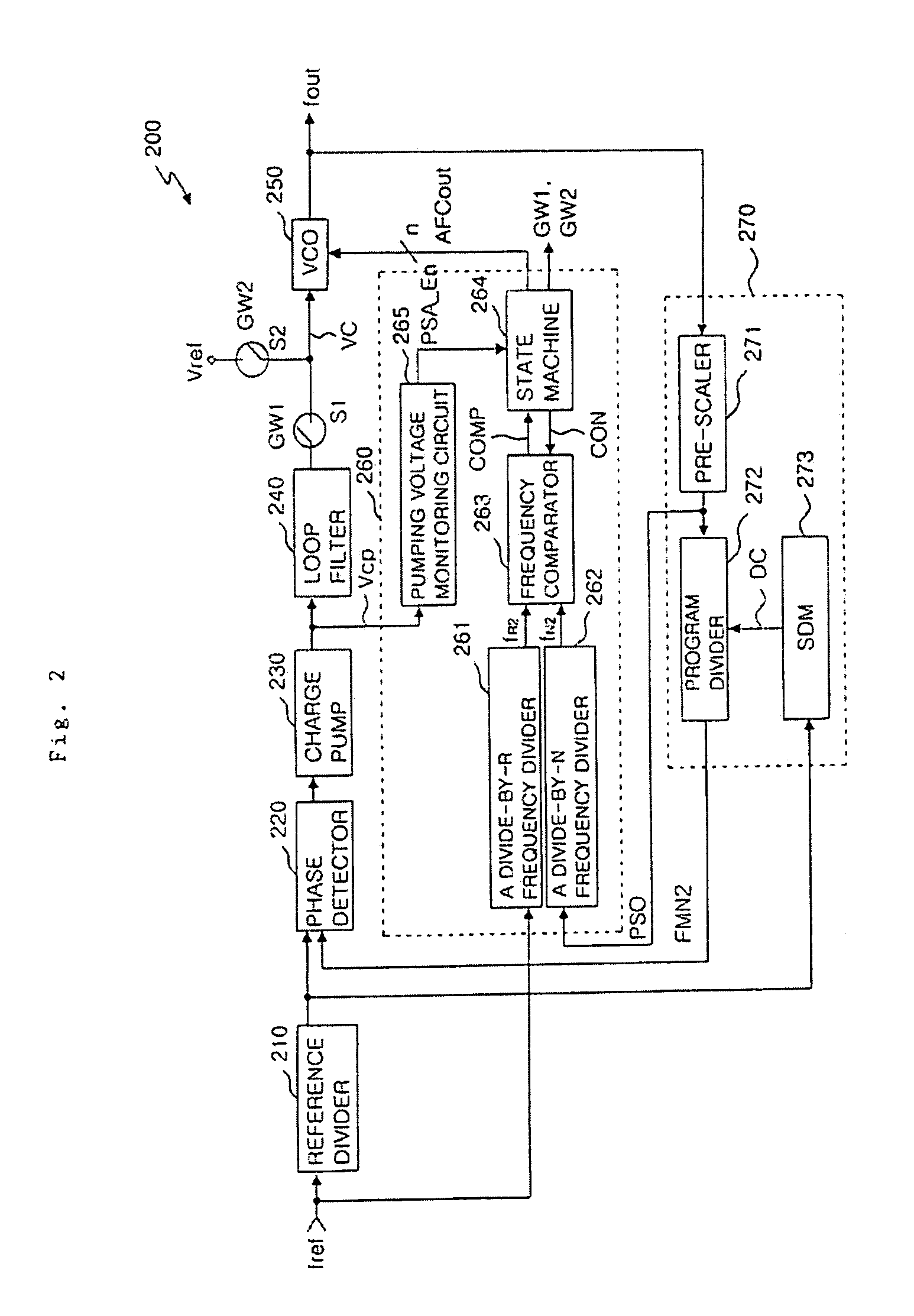

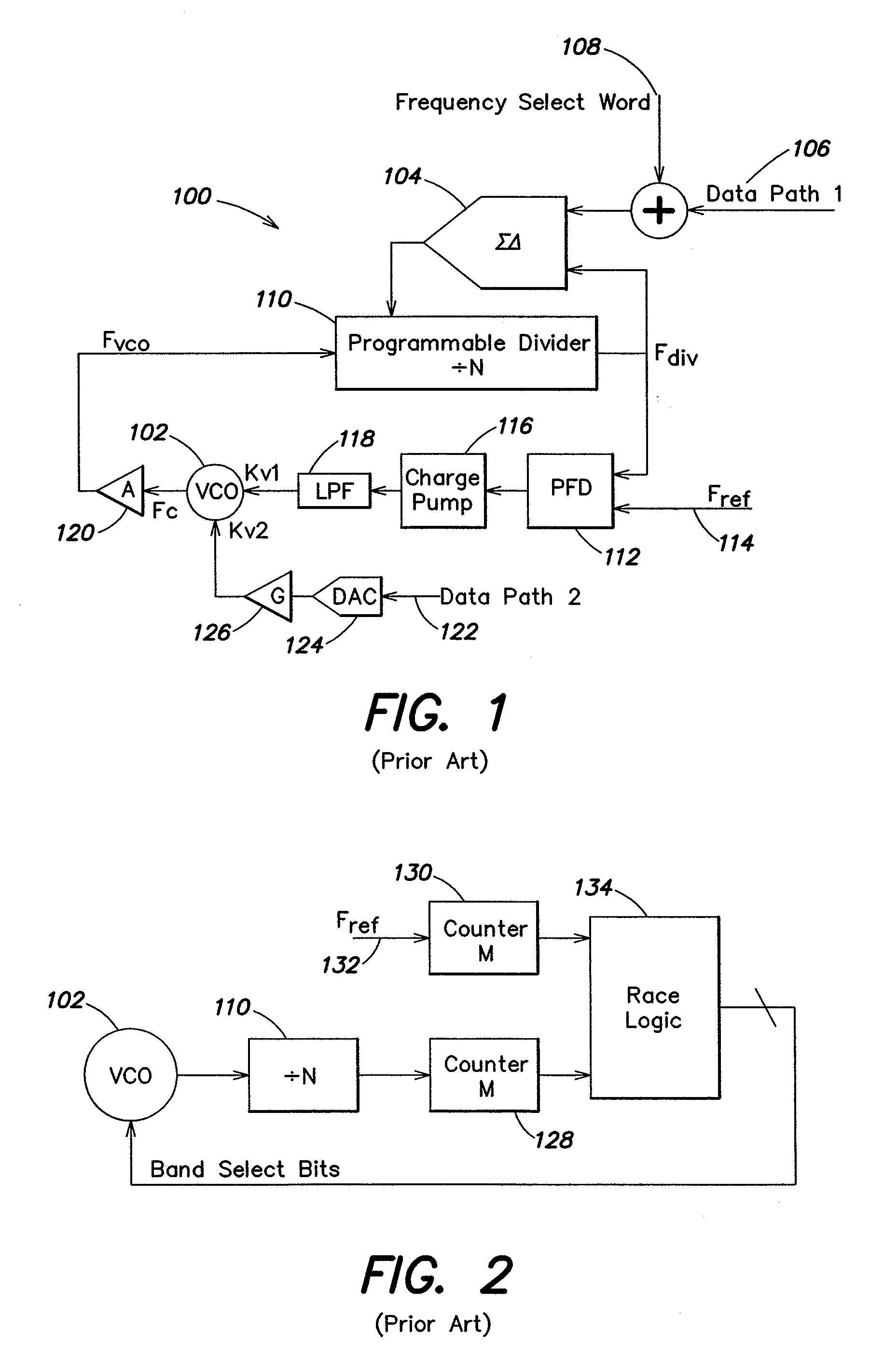

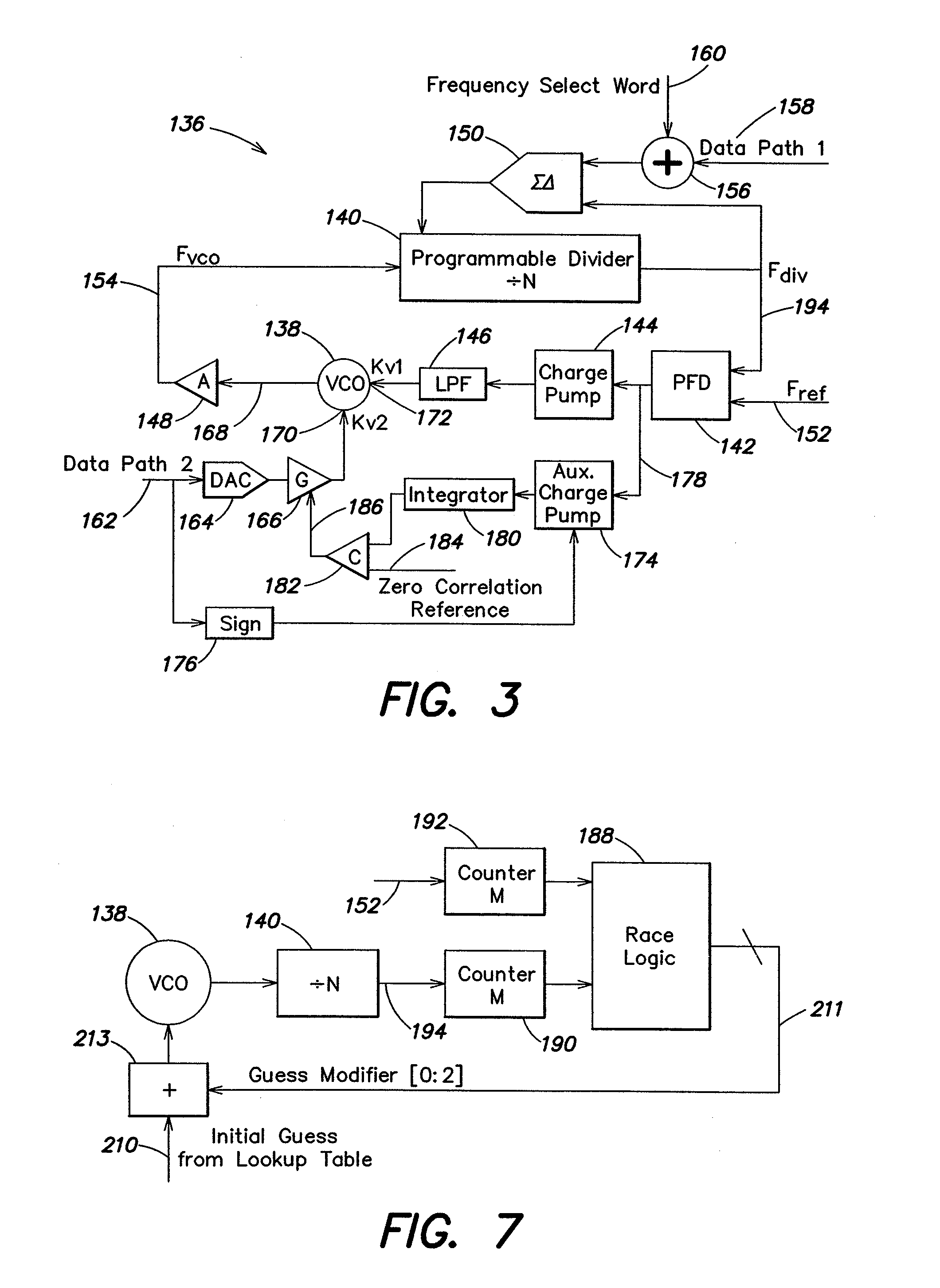

Continuous gain compensation and fast band selection in a multi-standard, multi-frequency synthesizer

InactiveUS20080007365A1Designing can be facilitatedShorten lock timePulse automatic controlAngle modulationMulti bandLoop filter

A frequency synthesizer capable of high speed, low power, wideband operation including a method of gain compensation, and a method of fast voltage controlled oscillator (VCO) band calibration. In addition, the frequency synthesizer may include two or more switchable independent loop filters to facilitate wideband operation. Such a frequency synthesizer may be used in many applications, and in one example, may be particularly suitable for use in a multi-band, multi-standard transmitter or radio transceiver.

Owner:TRIDEV RES

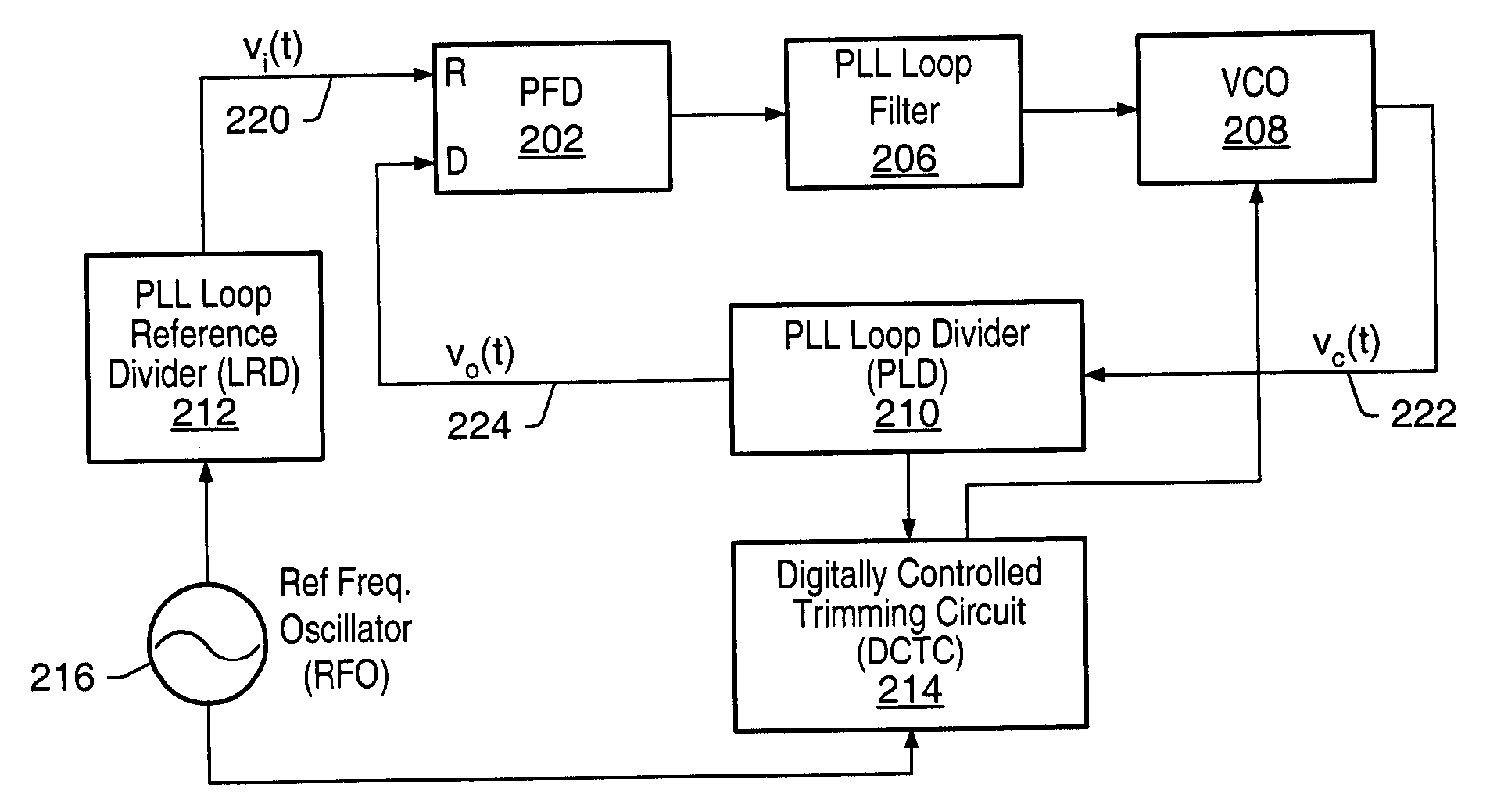

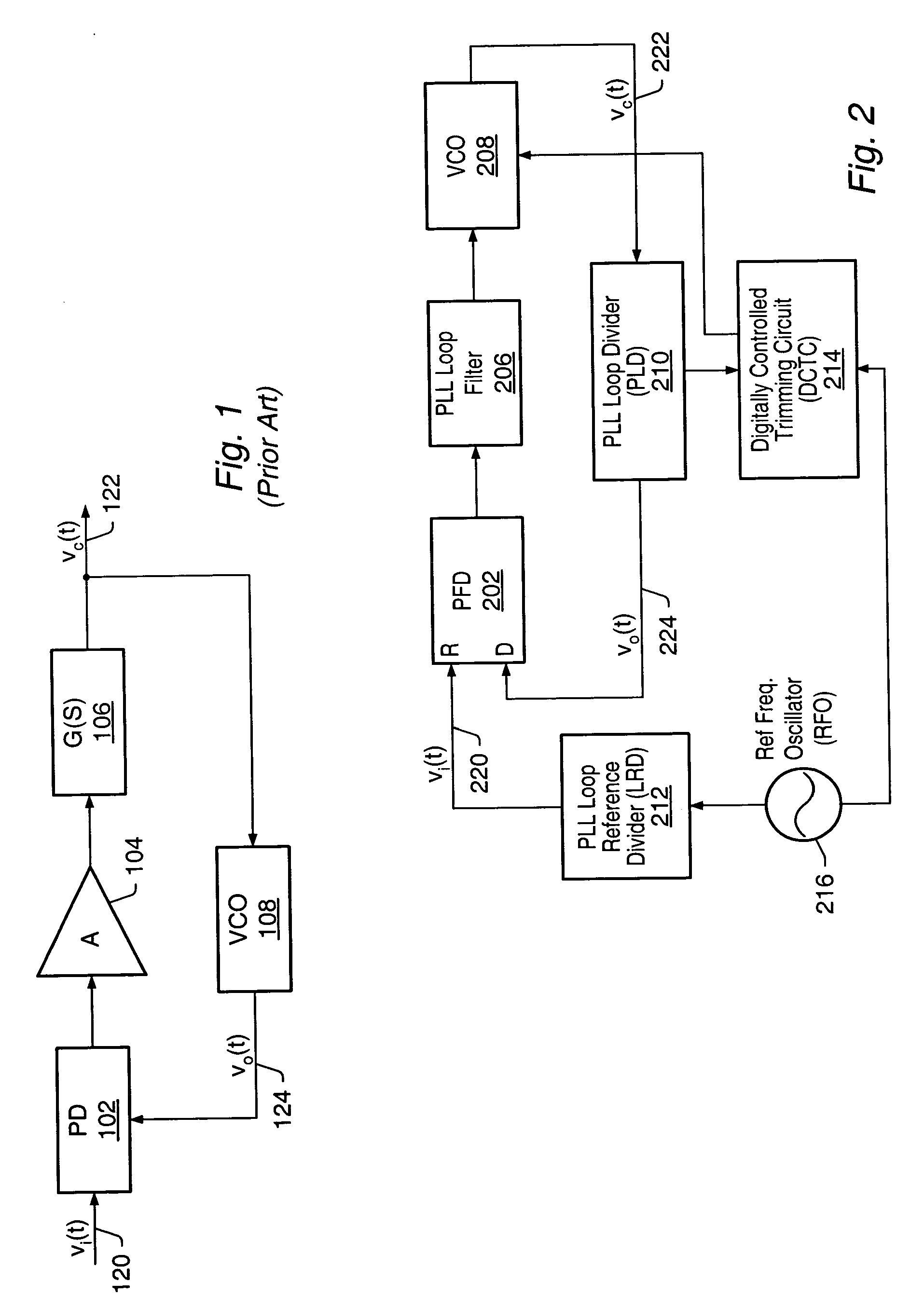

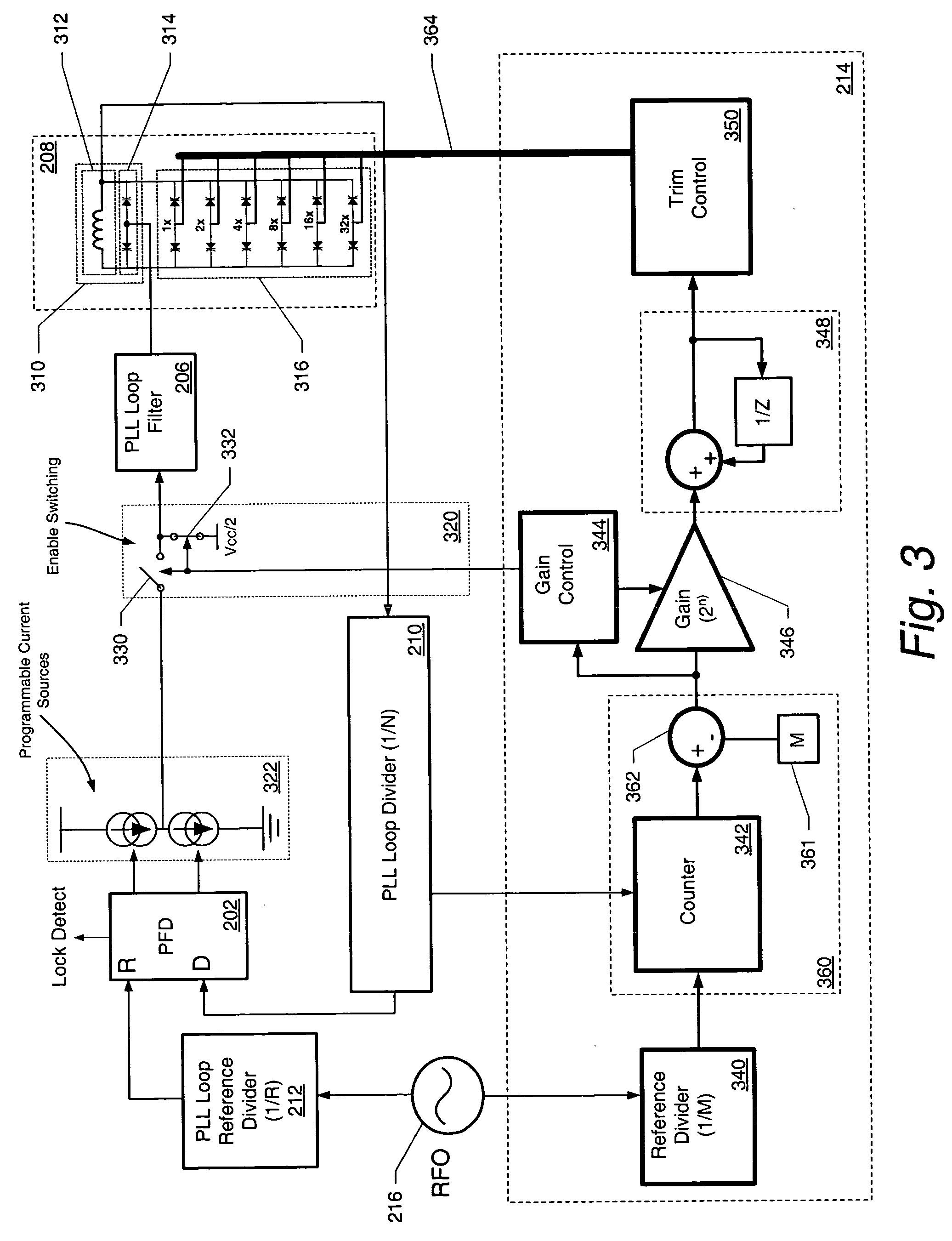

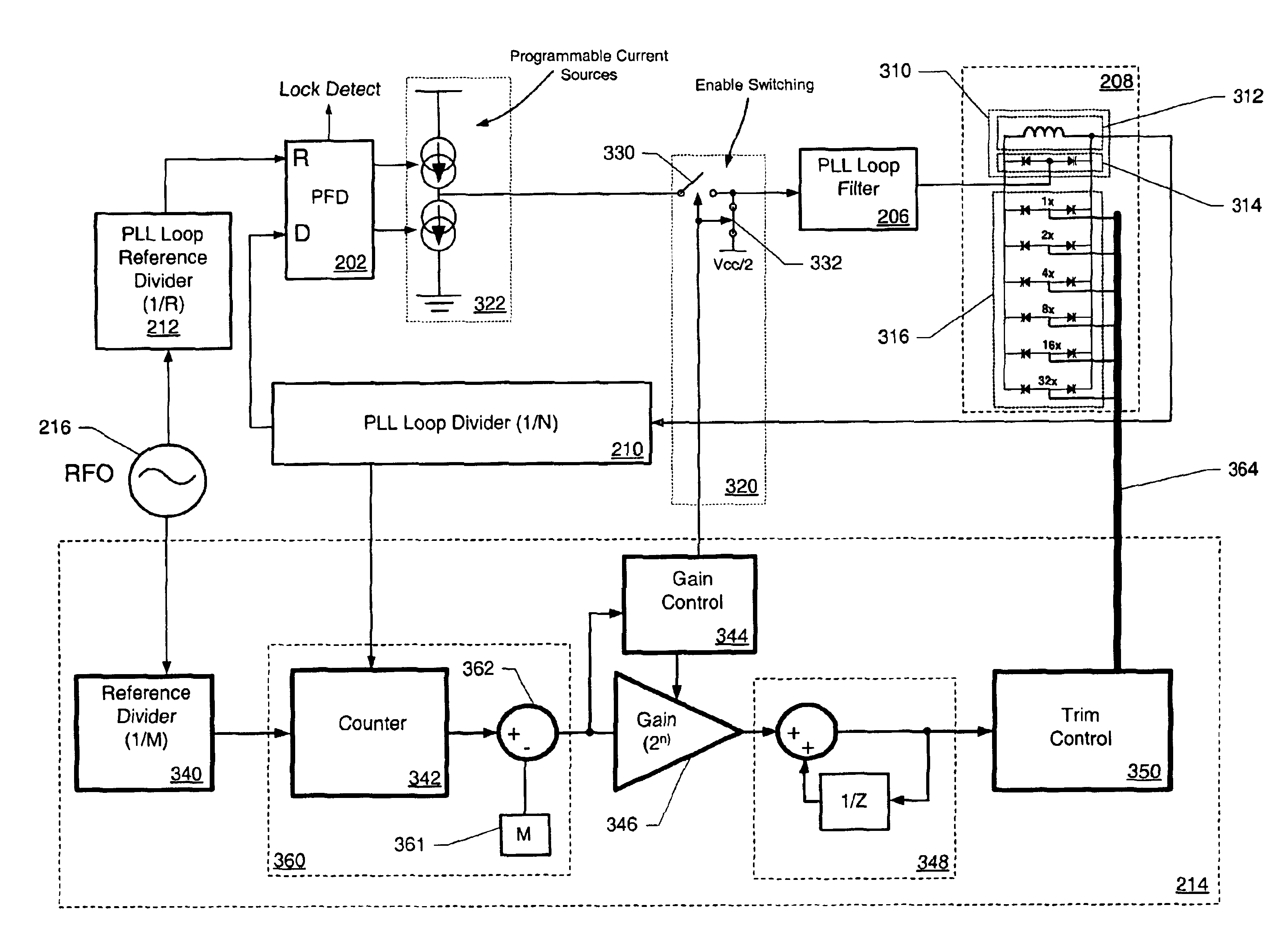

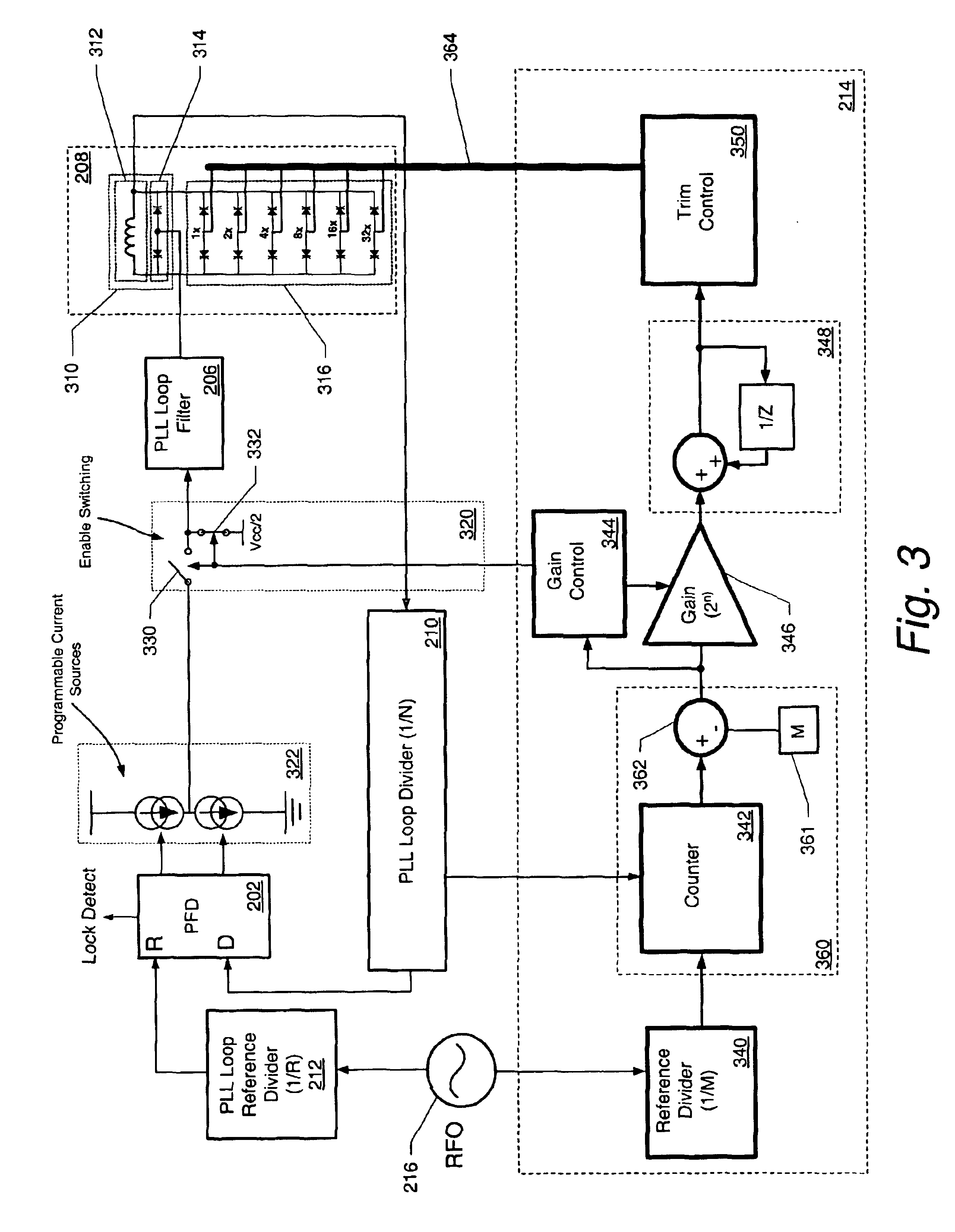

All digital PLL trimming circuit

InactiveUS20050046452A1Shorten lock timeFrequency differencePulse automatic controlPhase detectorClock recovery

In one set of embodiments, the invention comprises a system and method for automatically trimming the center frequency of a VCO in a PLL. The trimming may be performed by a digitally controlled trimming circuit, which may be operated to modify a gain of the VCO and may be used as part of a clock recovery architecture or as part of a high-end PLL. It may also be used by itself in low-end PLLs. In one embodiment, a second loop based solely on the frequency difference between a reference frequency and a divided output frequency of the VCO is introduced into the PLL loop. This frequency loop may be optimized by the inclusion of a gain control stage, which may lower the locking time. A control module may also be introduced to delay the deployment of the phase detector until the frequency loop has fully converged, that is until trimming has been completed, thus preventing the two loops from interfering with each other and compromising each other's performance.

Owner:MICROCHIP TECH INC

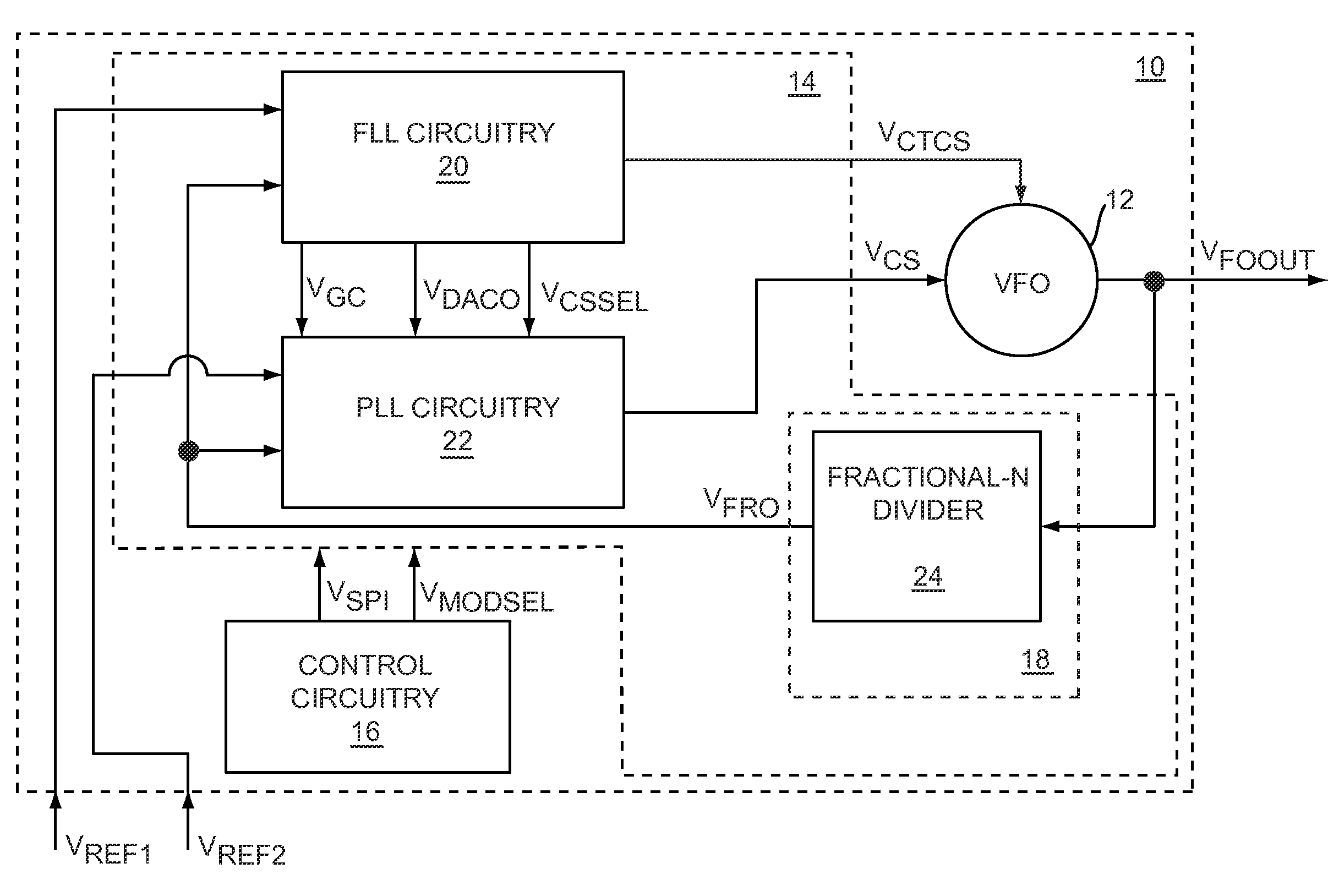

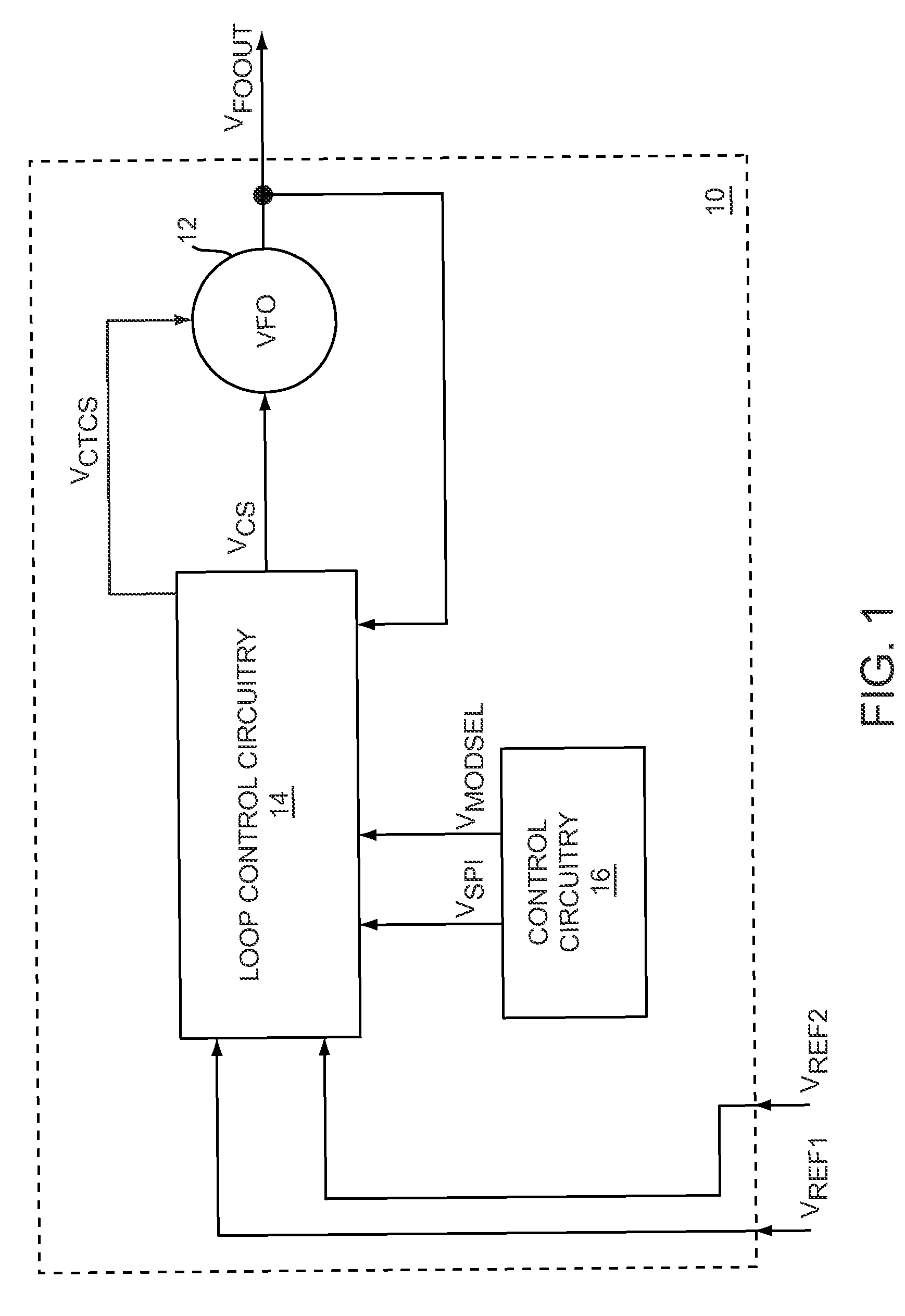

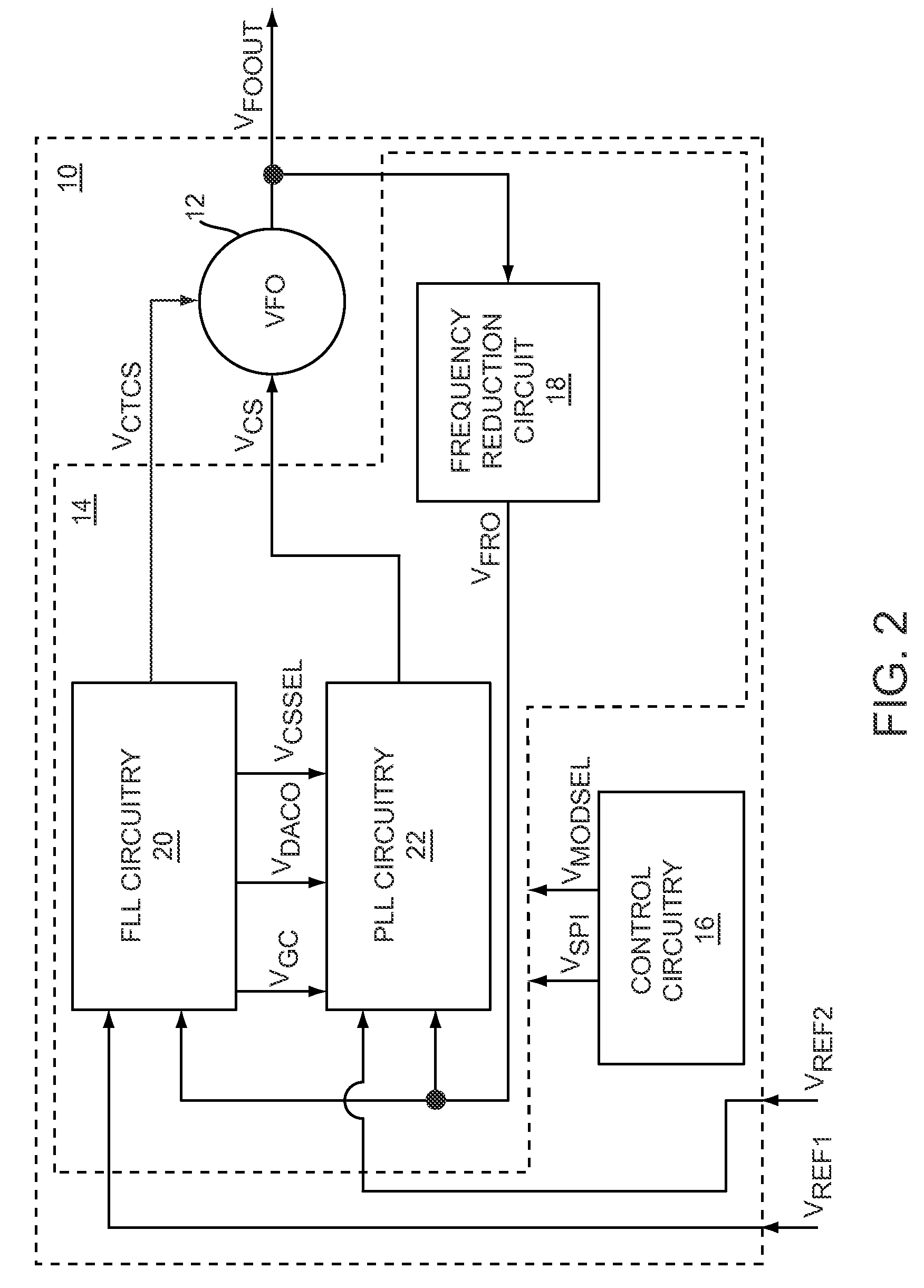

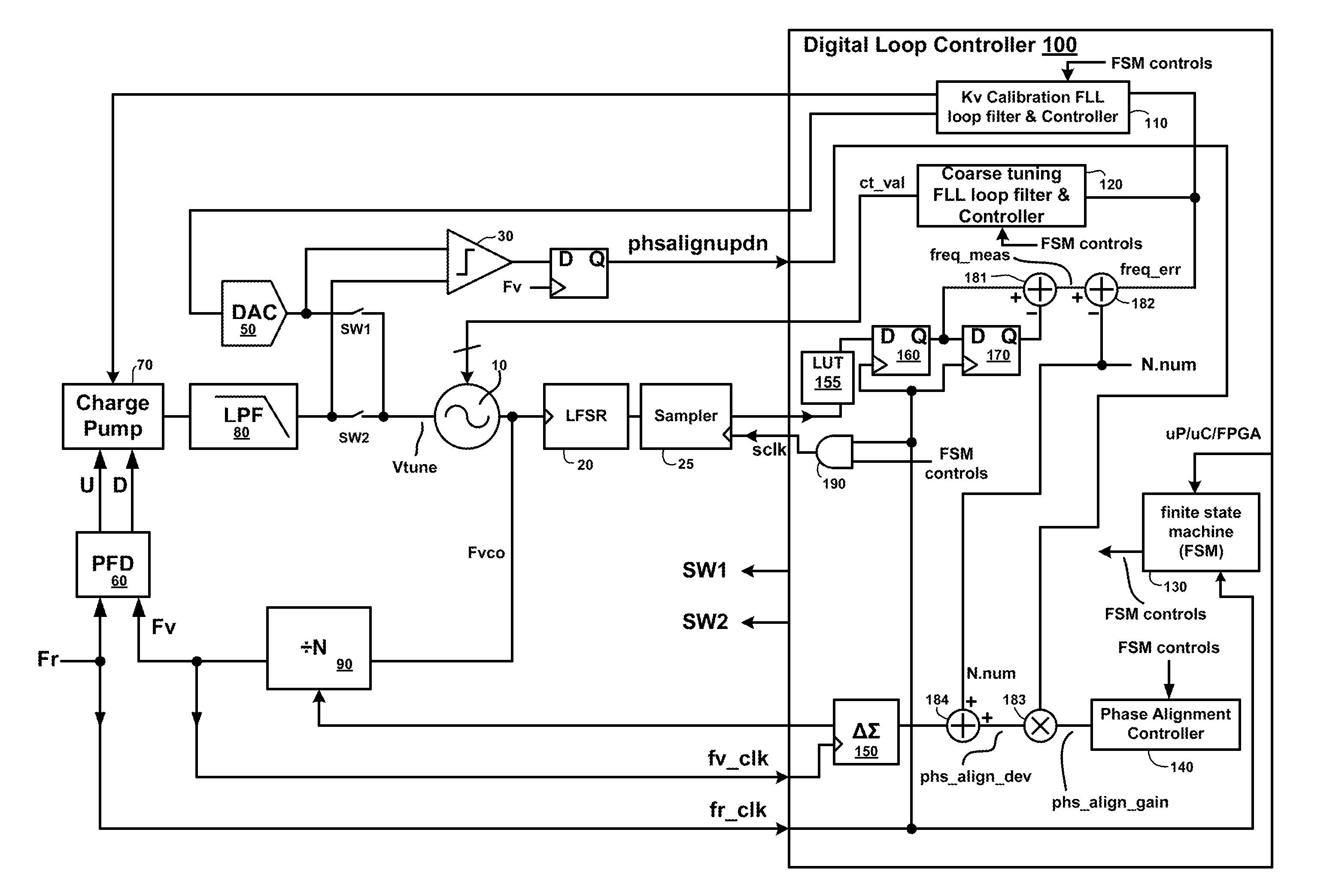

Frequency-locked loop calibration of a phase-locked loop gain

InactiveUS7898343B1Reduce locking timeHigh frequency accuracyPulse automatic controlFrequency analysisNoise spectrumVariable-frequency oscillator

The present invention relates to a calibrated phase-locked loop (PLL), which has a calibration mode for measuring a tuning gain of a variable frequency oscillator (VFO) and a PLL mode for normal operation. Calibration information based on the tuning gain is used during the PLL mode to regulate a PLL loop gain. During the calibration mode, the calibrated PLL operates as a frequency-locked loop (FLL) for low frequency lock times, and during the PLL mode the calibrated PLL operates as a PLL for high frequency accuracy and low noise. By regulating the PLL loop gain, the desired noise spectrum and dynamic behavior of the PLL may be maintained in spite of variations in the operating characteristics or in the characteristics of the PLL components.

Owner:QORVO US INC

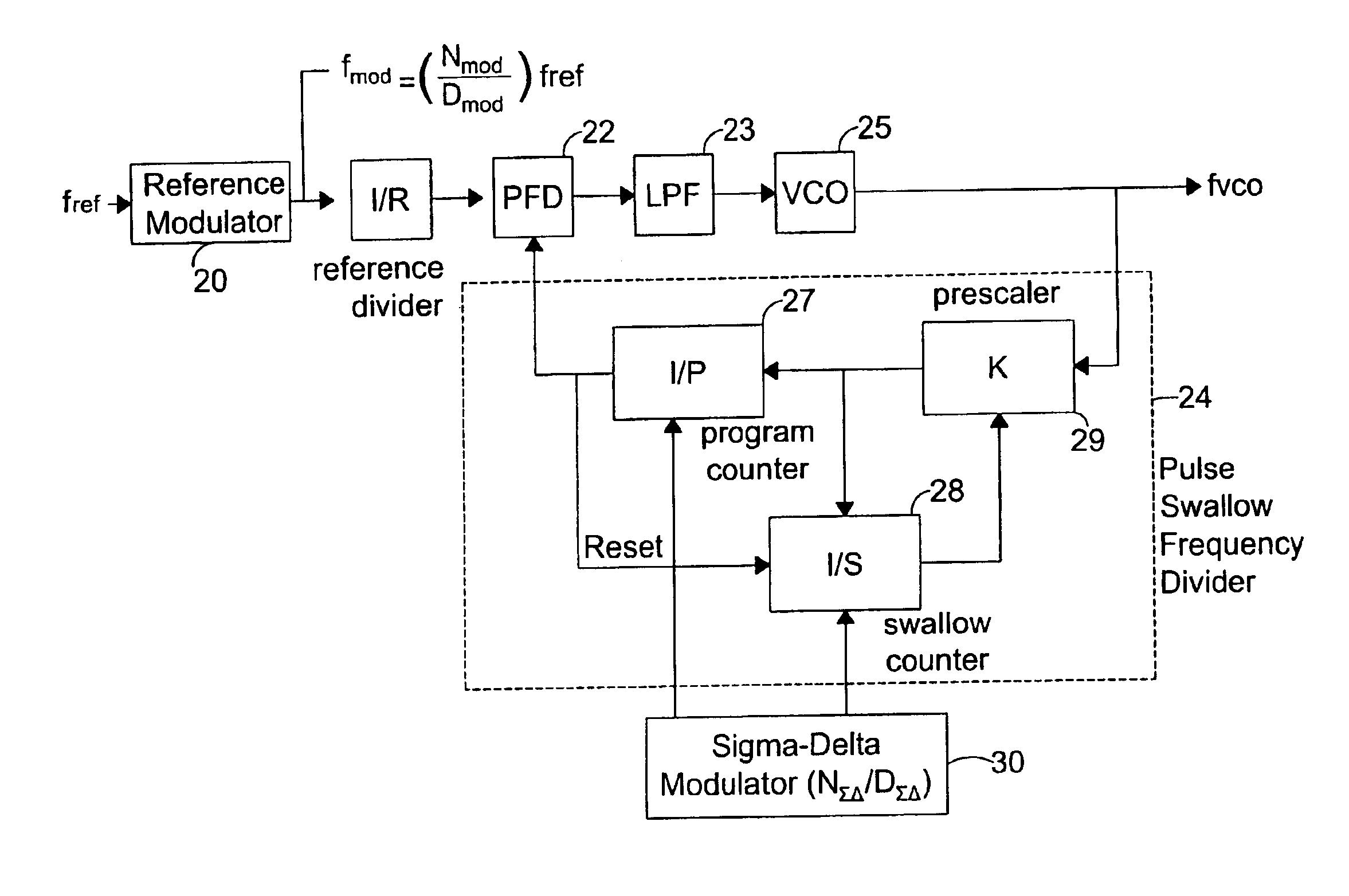

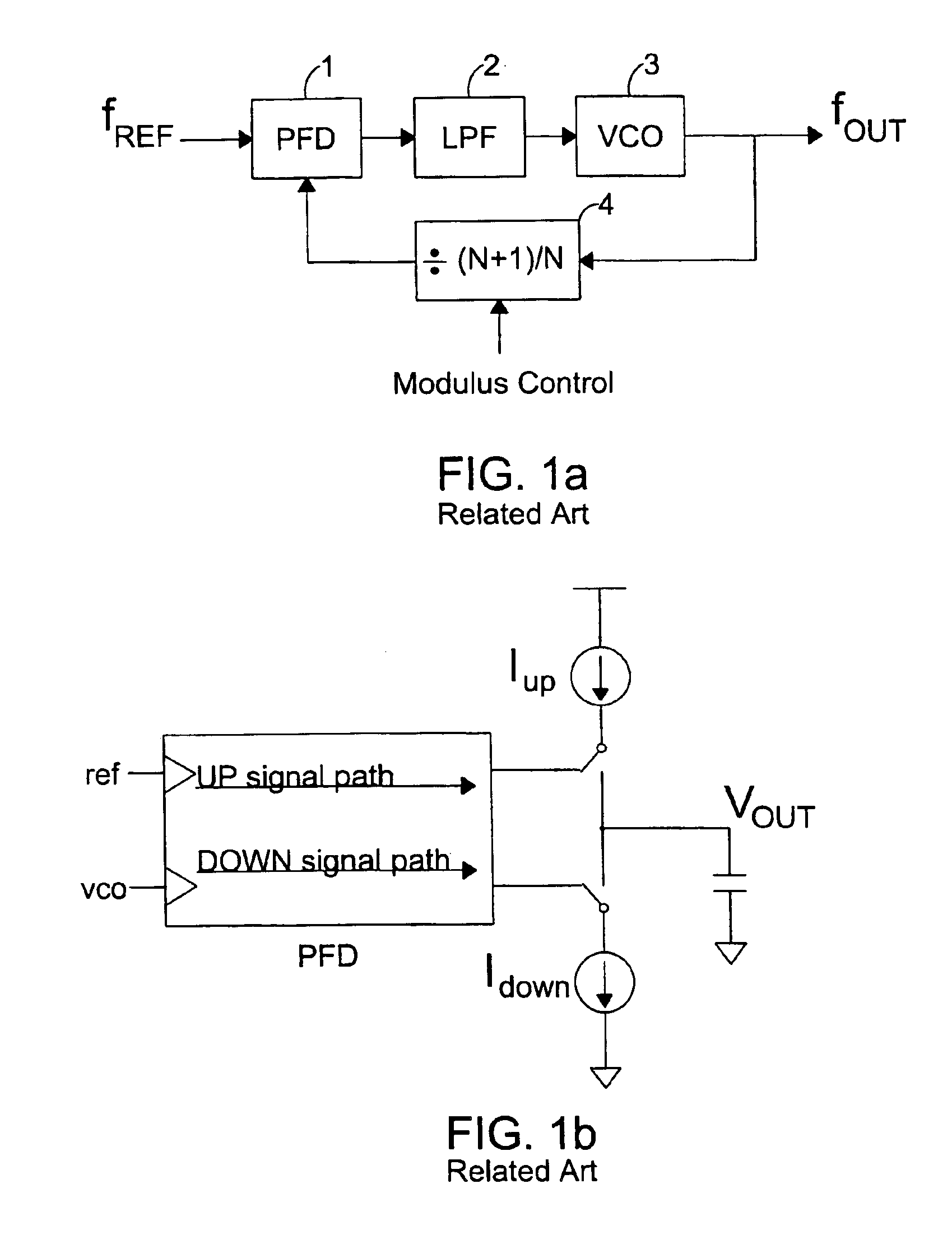

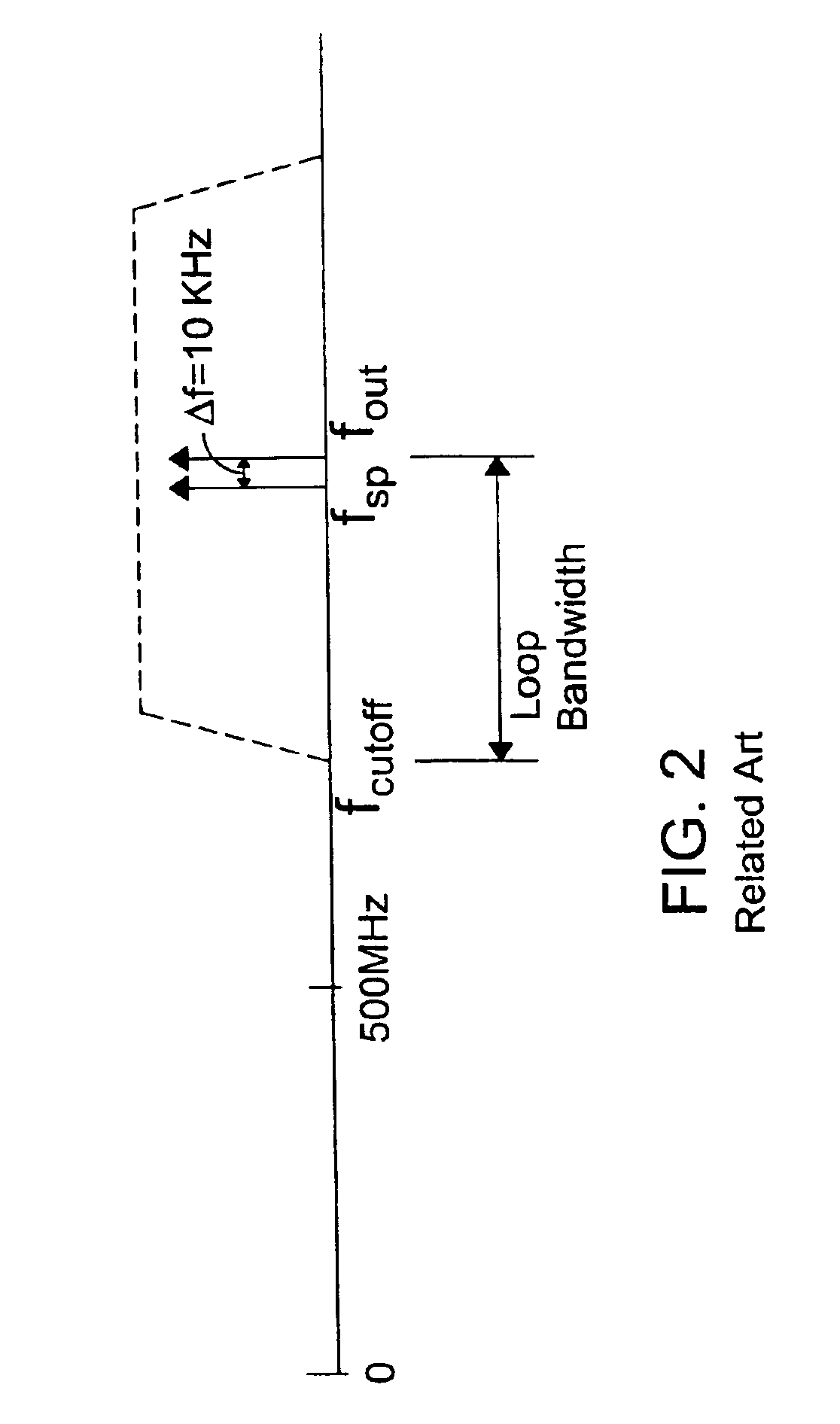

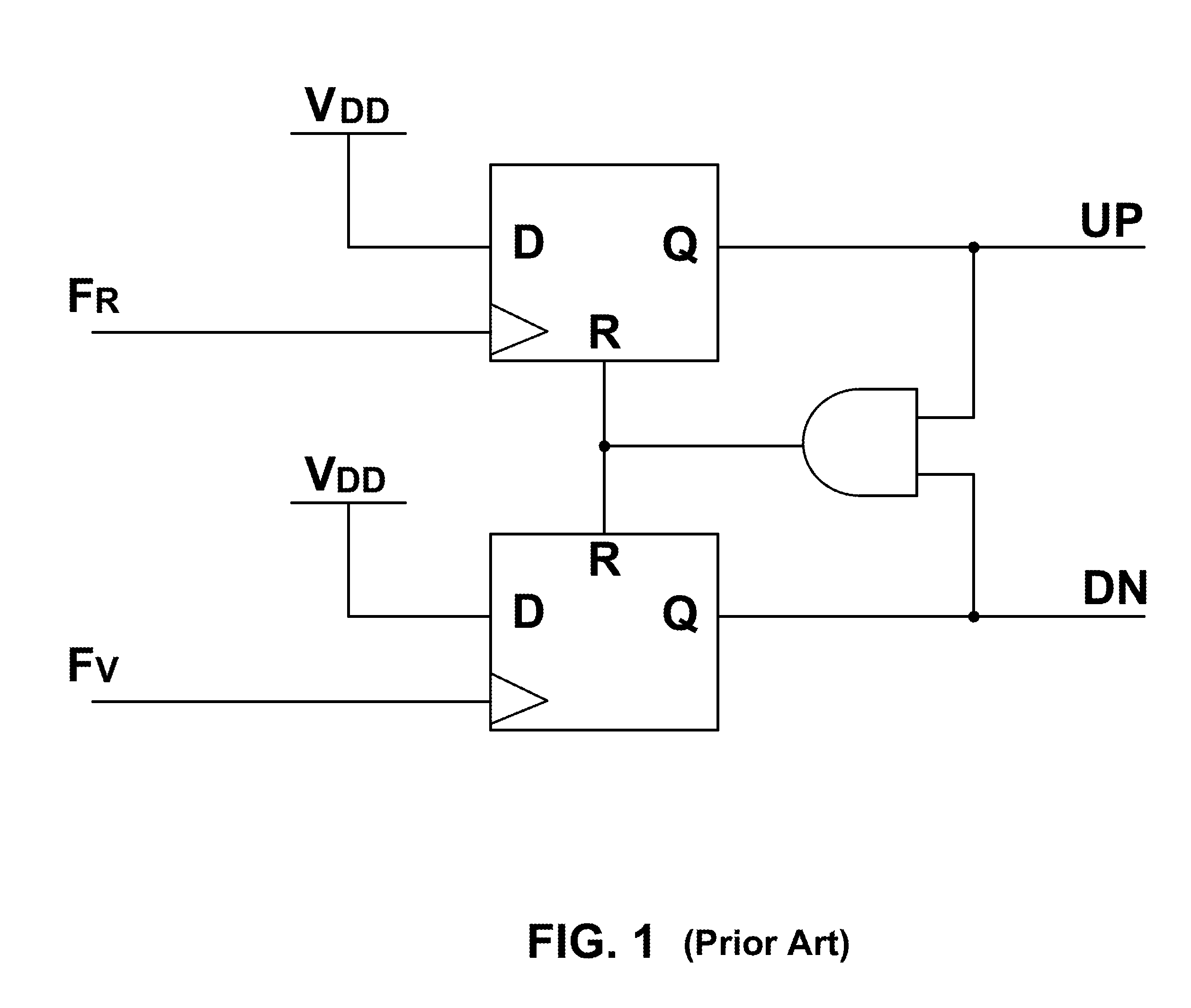

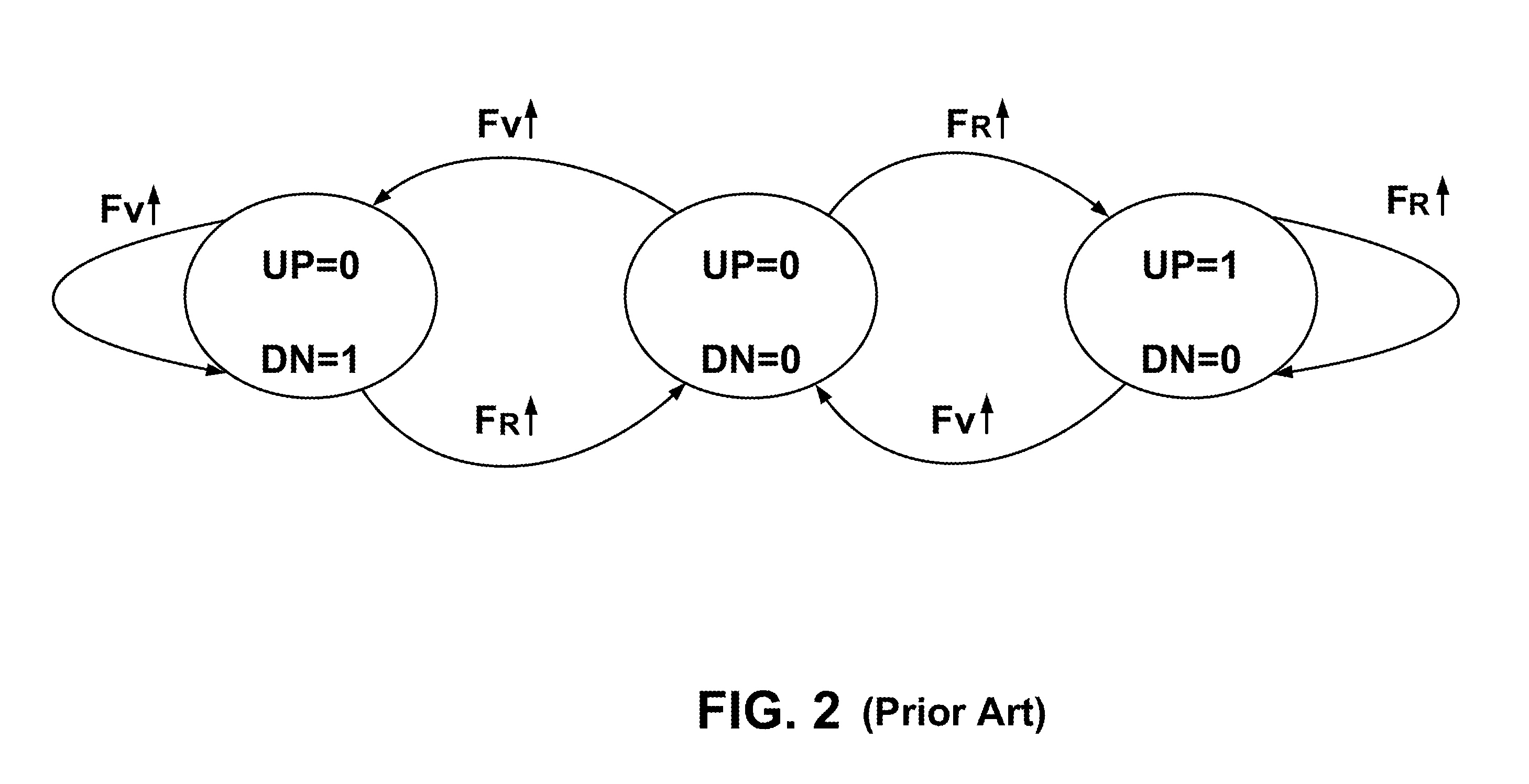

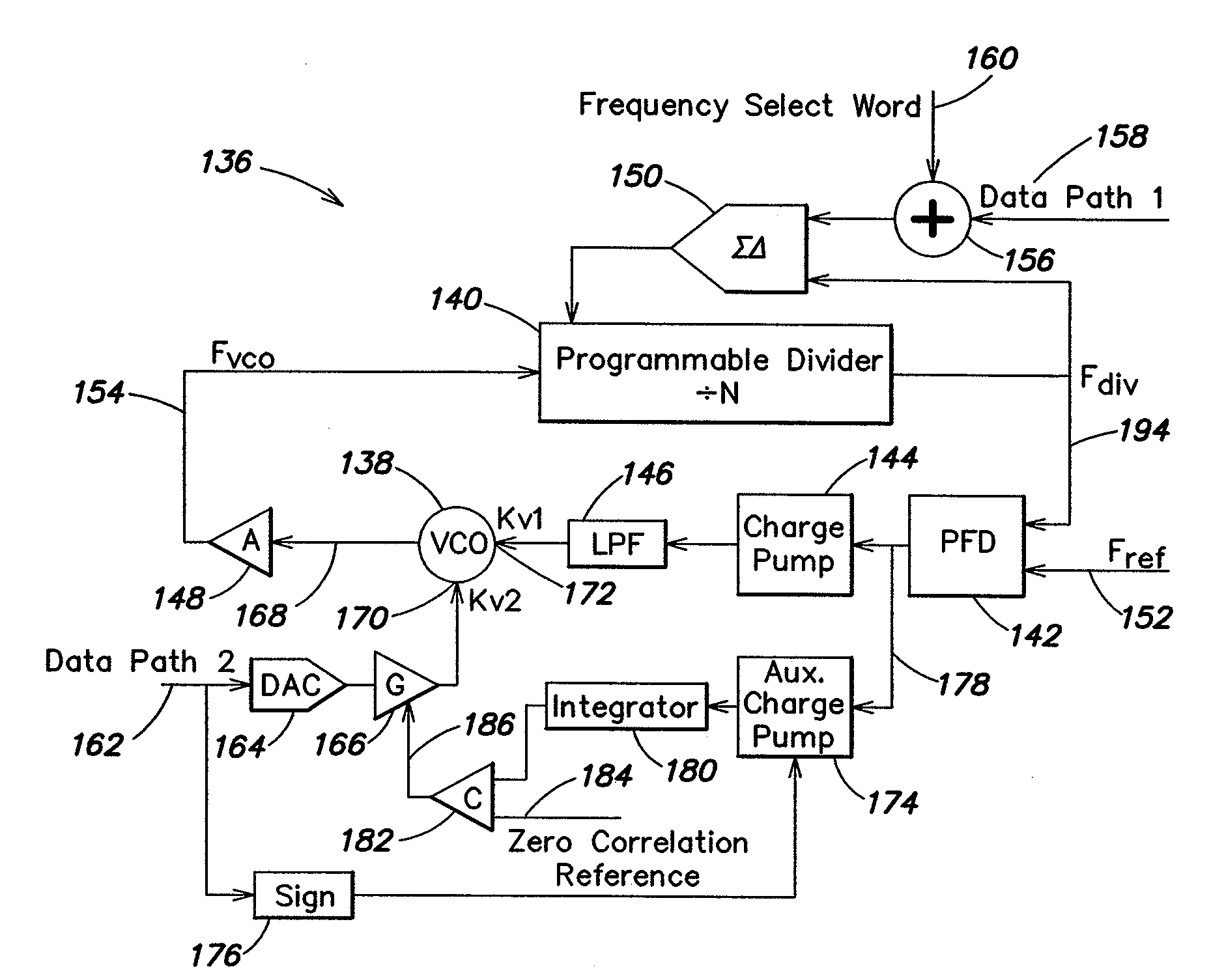

System and method for suppressing noise in a phase-locked loop circuit

InactiveUS6952125B2Suppress noiseShorten lock timePulse automatic controlCounting chain pulse countersSignal-to-noise ratio (imaging)Phase locked loop circuit

A system and method for improving the signal-to-noise ratio of a frequency generator suppresses phase noise and noise generated from mismatches in the internal generator circuits. This is accomplished using a modulation scheme which shifts spurious noise signals outside the loop bandwidth of the generator. When shifted in this manner, the noise signals maybe removed entirely or to any desired degree using, for example, a filter located along the signal path of the generator. In one embodiment, a Sigma-Delta modulator controls the value of a pulse-swallow frequency divider situated along a feedback path of a phase-locked loop to achieve a desired level of noise suppression. In another embodiment, a reference signal input into a phase-locked loop is modulated to effect noise suppression. In another embodiment, the foregoing forms of modulation are combined to accomplish the desired frequency shift. Through these modulation techniques, the signal-to-noise ratio of the frequency generator may be substantially improved while simultaneously achieving faster lock times.

Owner:GCT SEMICONDUCTOR INC

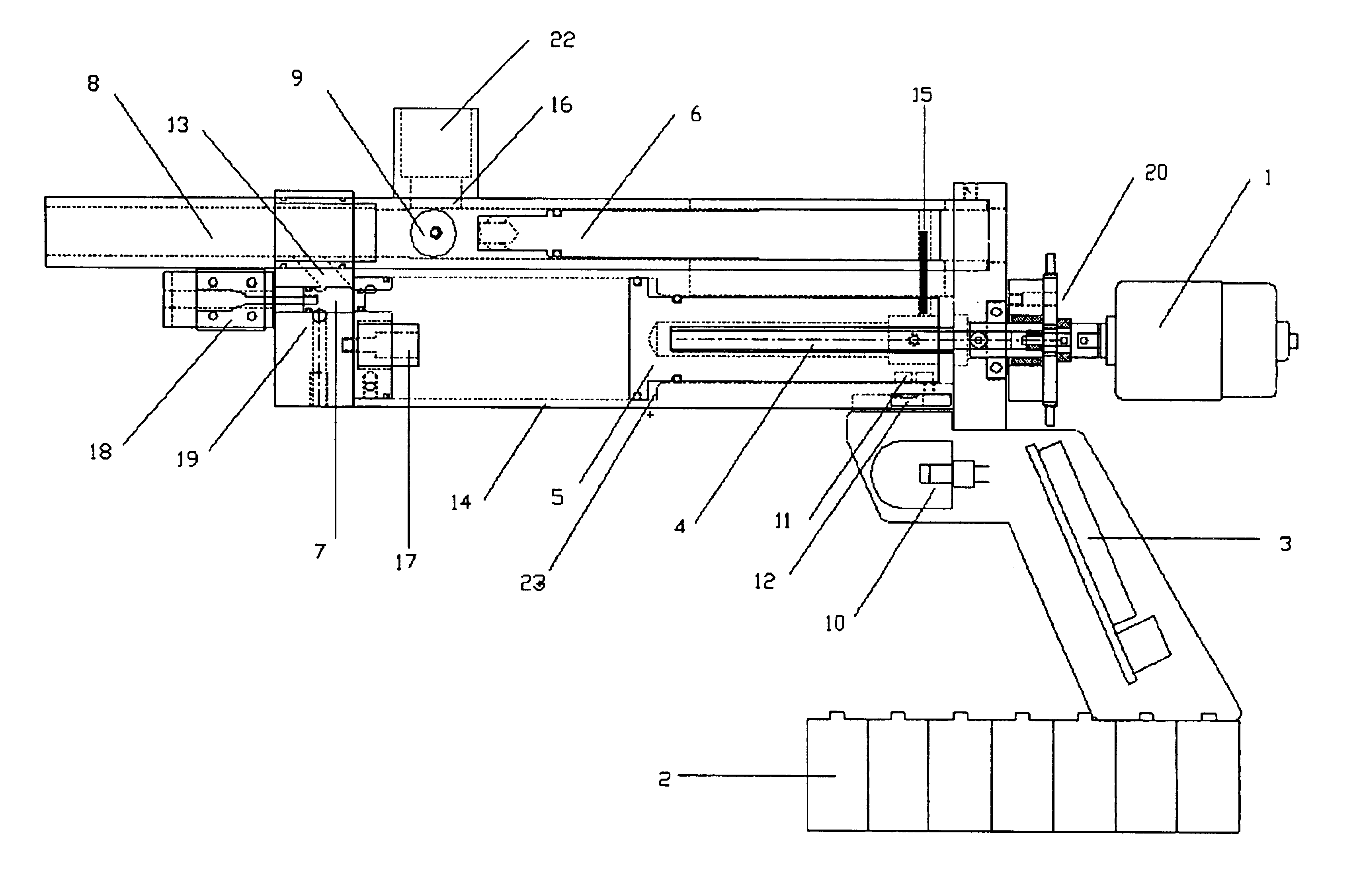

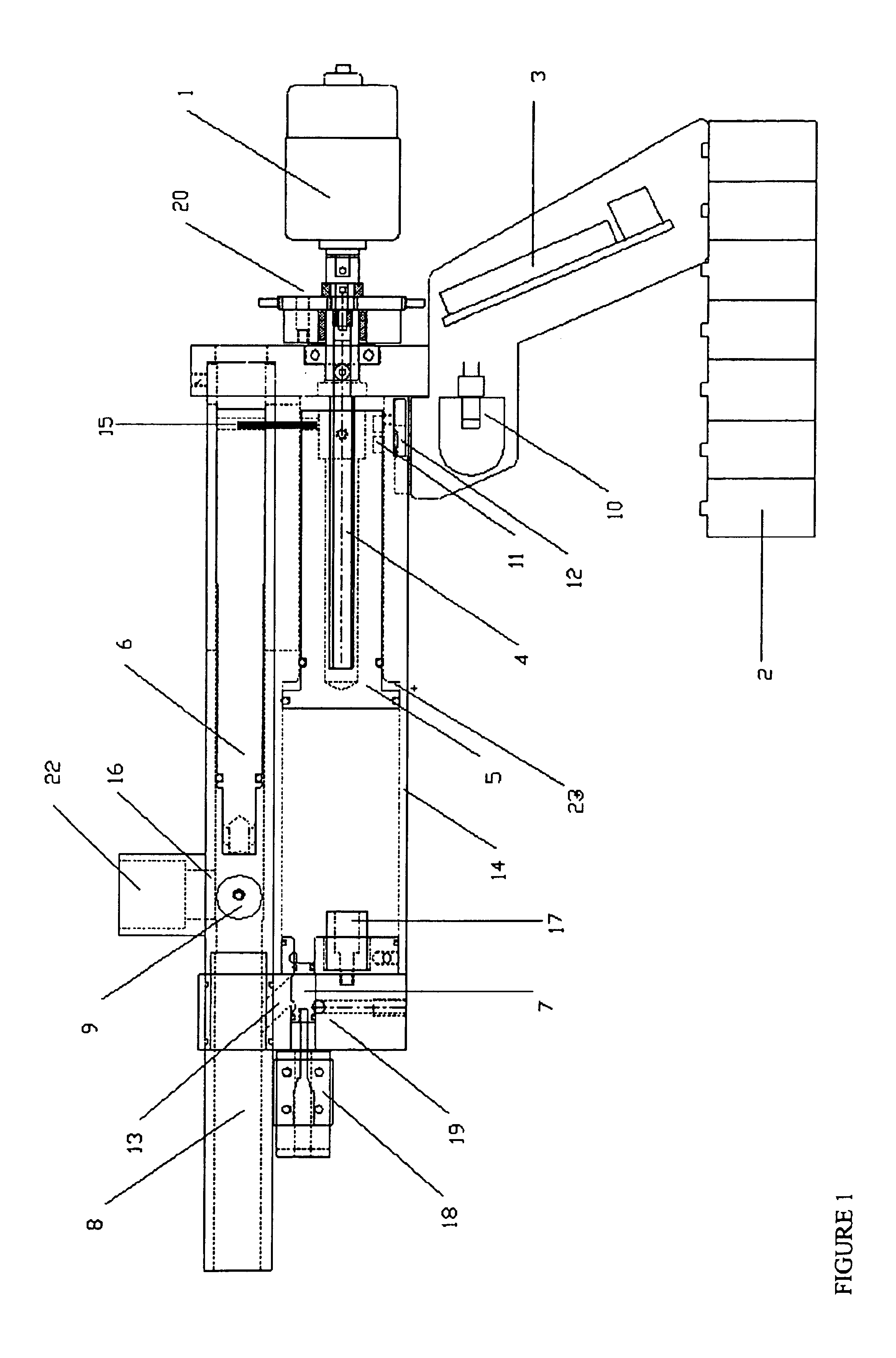

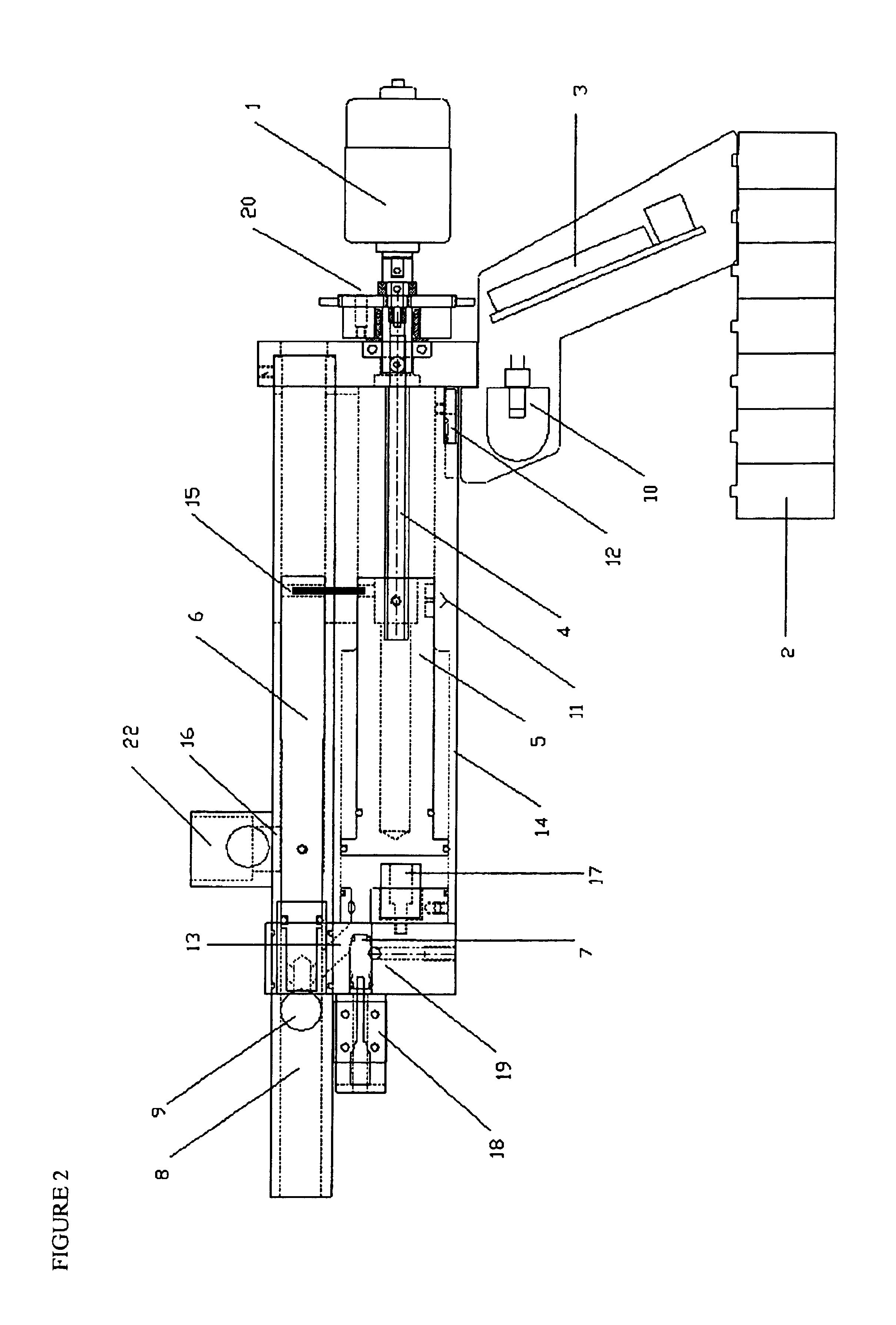

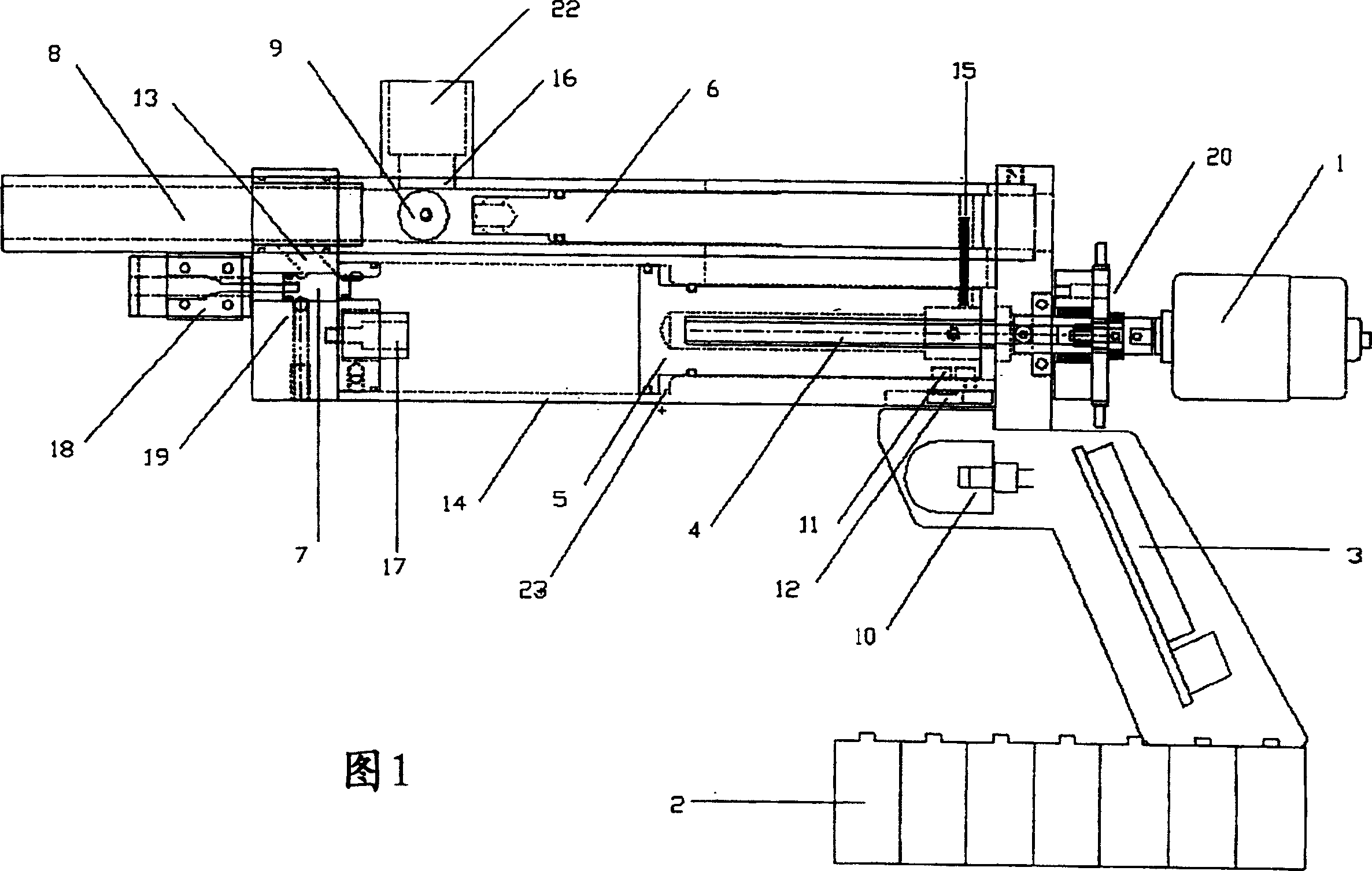

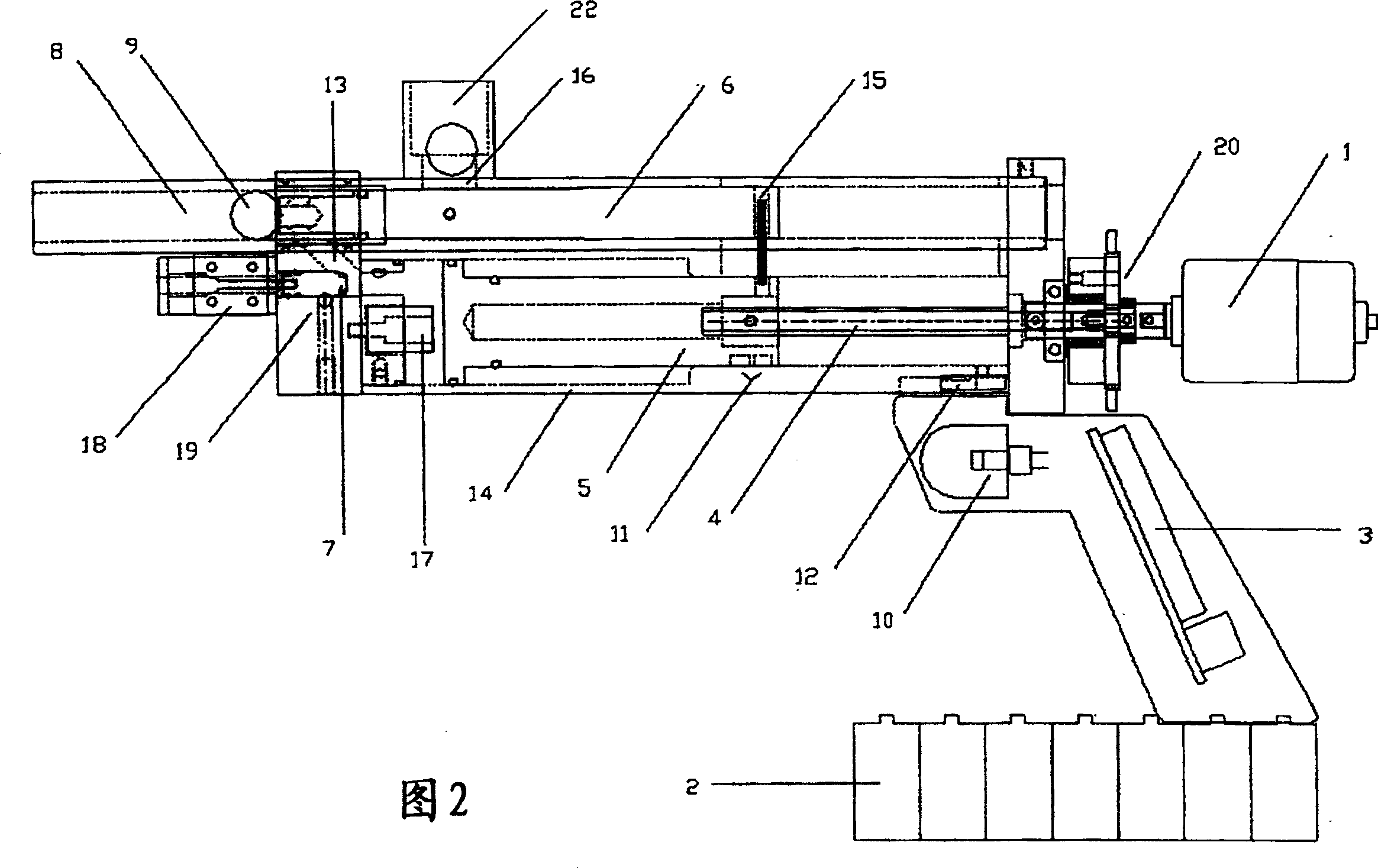

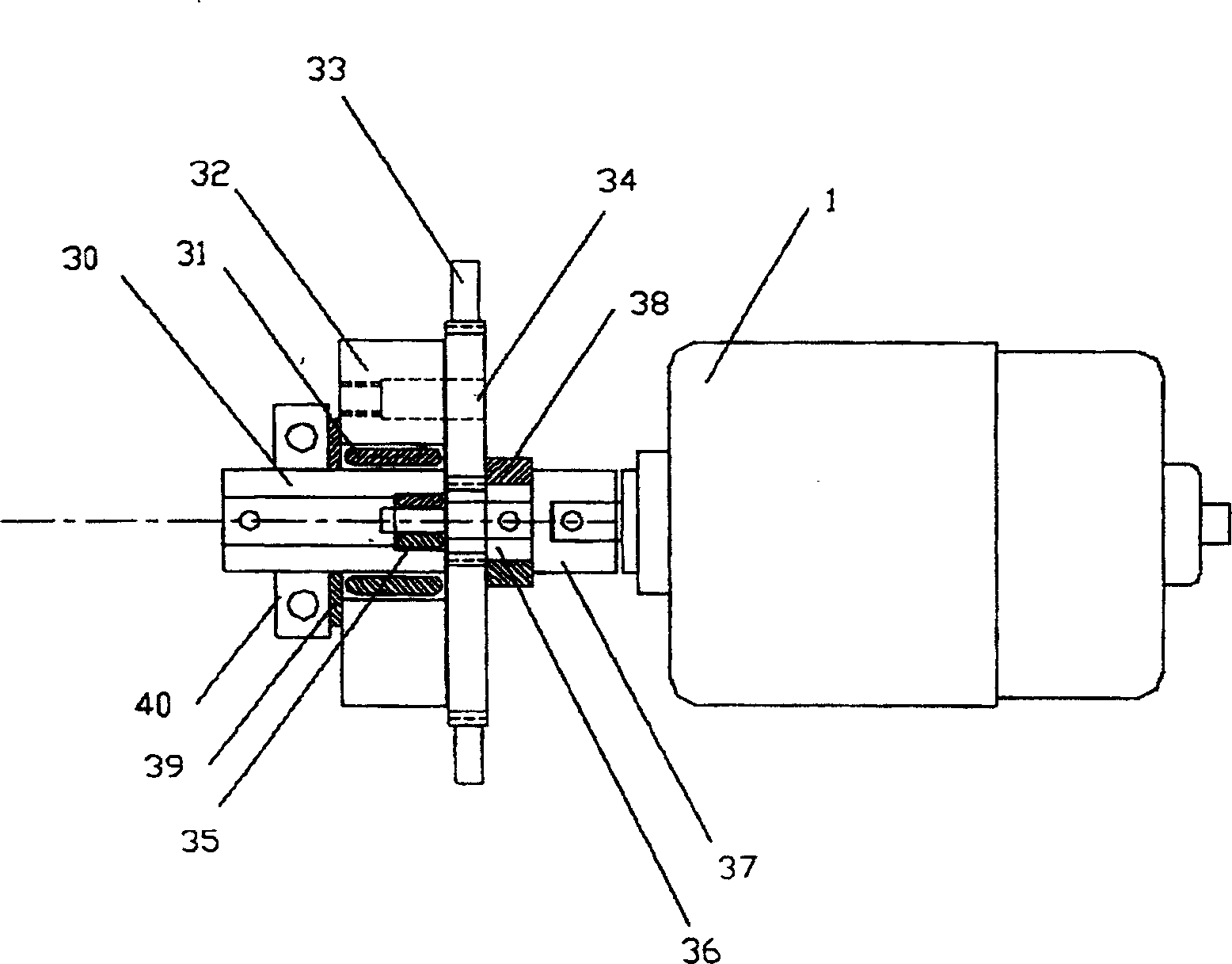

Portable electric driven compressed air gun

ActiveUS6857422B2Robust and simple designImprove securityFiring/trigger mechanismsCompressed gas gunsElectric driveHigh pressure

A portable electric motor driven air gun powered by a power source. The motor is coupled to a lead screw, which drives a piston. The piston compresses air in a chamber producing high-pressure air. When sufficient energy is stored within the air stream by the piston a valve opens which releases the air to act on the projectile. The compressed air is used to push a projectile such as a paintball, an airsoft ball, a “bb”, or a pellet through a barrel. The lead screw is then reversed and the piston is reset for the next shot. The piston is preferably coupled to a feeding mechanism to facilitate positioning of the projectile for firing. The direction speed and operative modes of the gun are preferably controlled with an electric circuit. The power source is preferably rechargeable and allows the air gun to be operated completely independent from either a wall outlet or a compressed air supply.

Owner:TRICORD SOLUTIONS INC

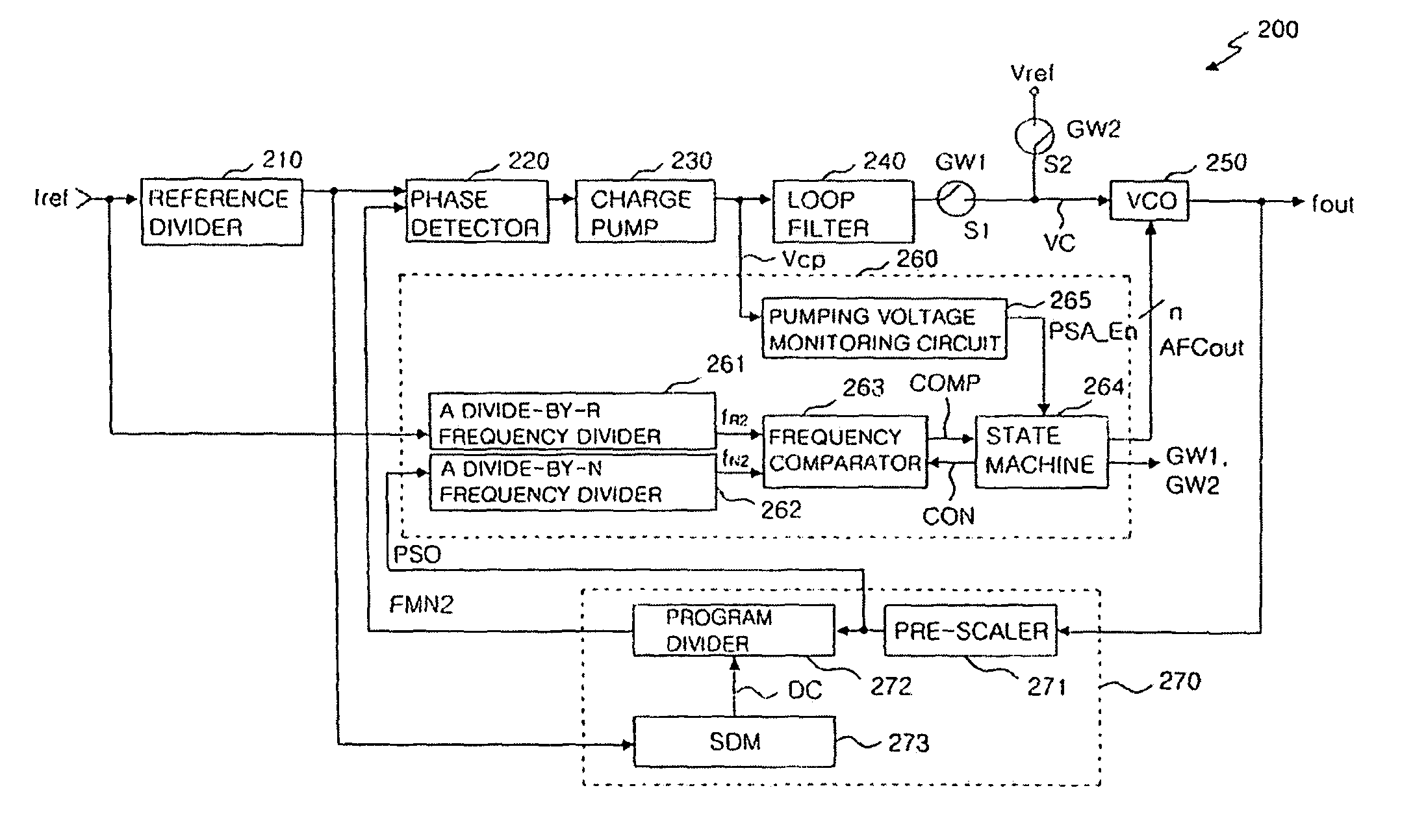

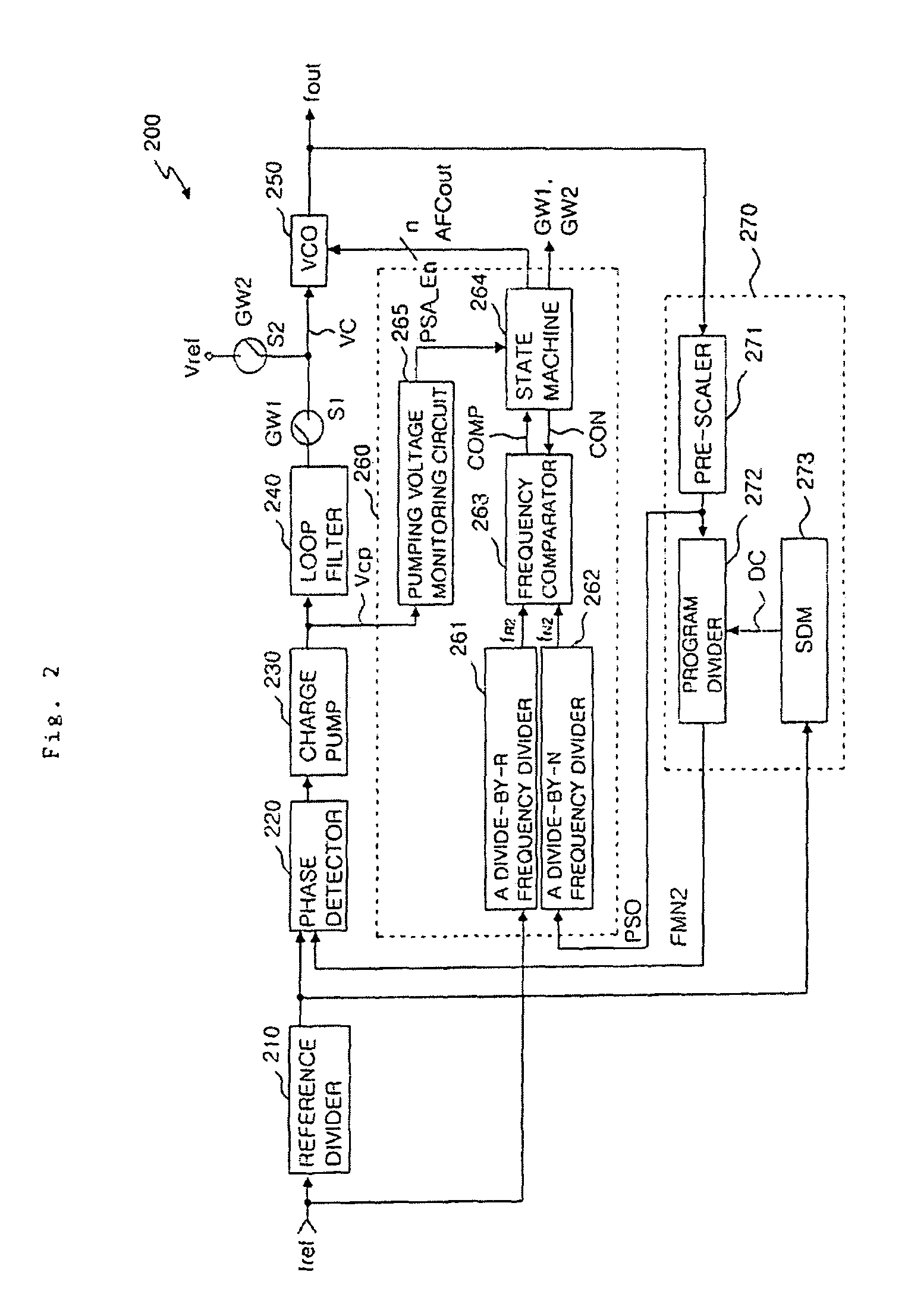

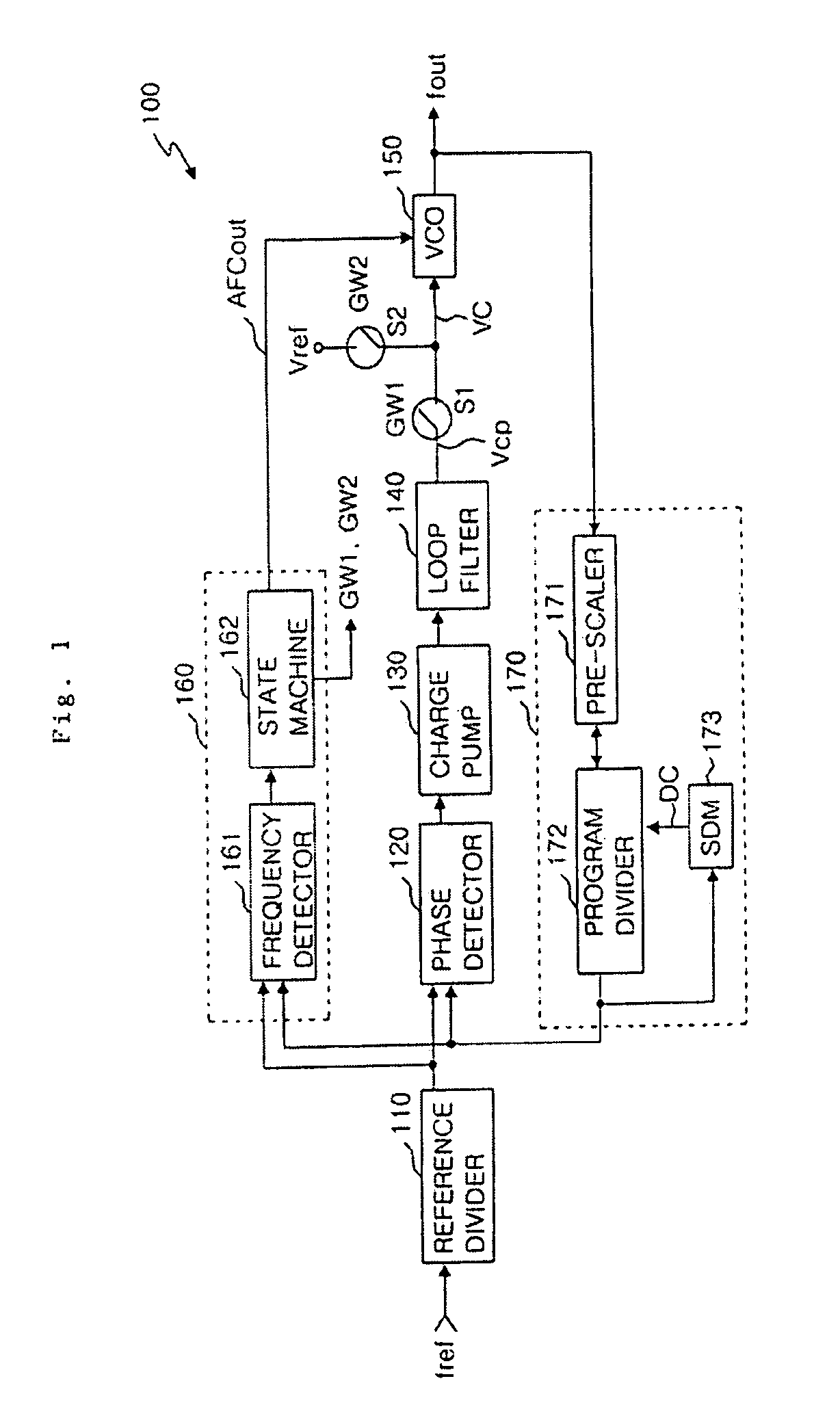

Frequency synthesizer and frequency calibration method

InactiveUS7804367B2Quick calibrationAvoid failurePulse automatic controlFrequency analysisLoop filterPhase detector

A frequency synthesizer capable of using a voltage controlled oscillator (VCO) with a low value of gain Kvco, having a short automatic frequency calibration time and automatically coping with environments and a frequency calibration method are provided. The frequency synthesizer includes a reference divider, a phase detector, a main divider, a charge pump, a loop filter, a first switch, a second switch, a VCO, and an automatic frequency calibration block. The frequency calibration method includes an initialization step, an N-target algorithm step, an auxiliary search algorithm step, and a post search algorithm step.

Owner:DIALOG SEMICON KOREA INC

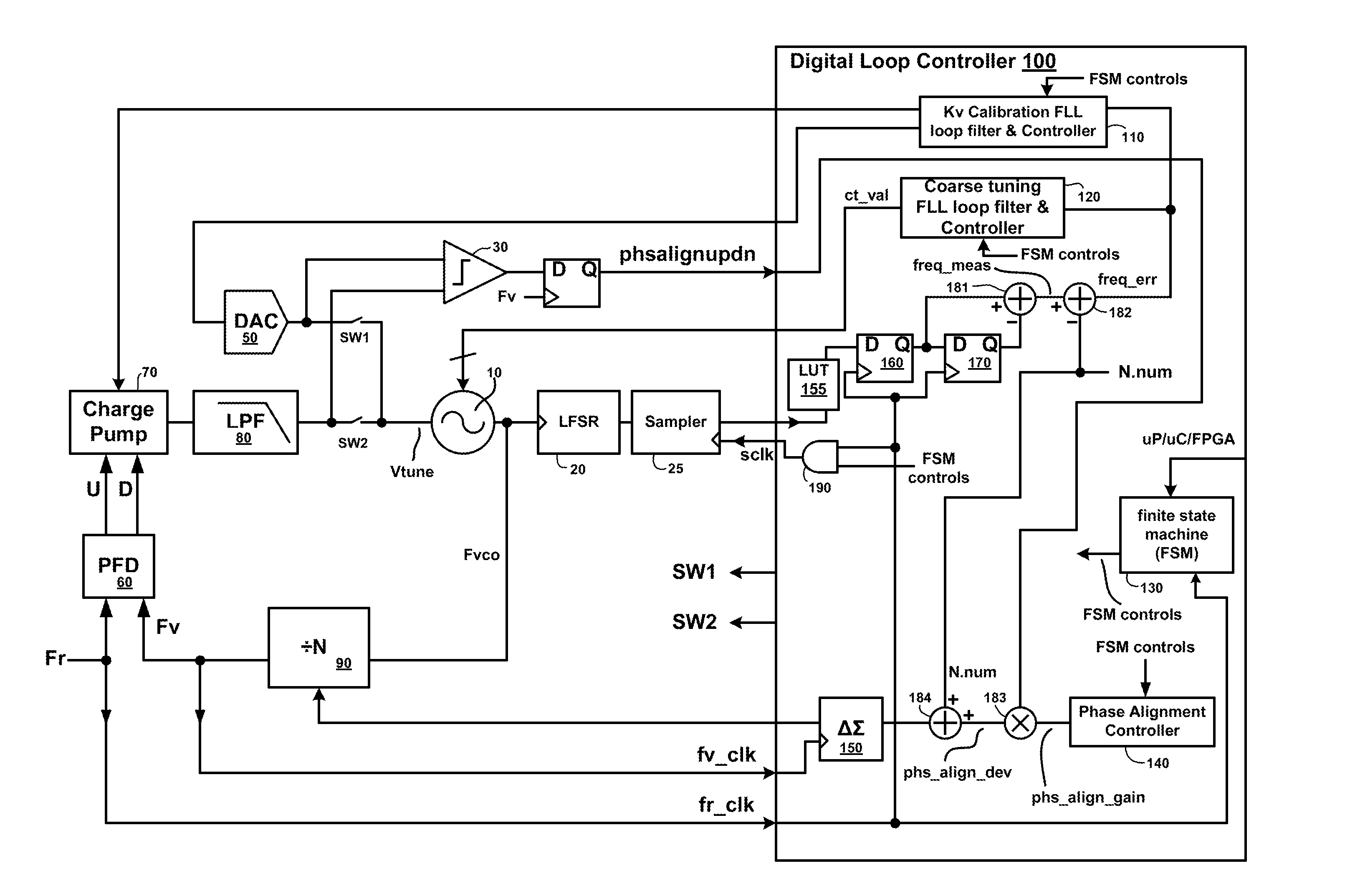

Fast phase locking system for automatically calibrated fractional-N PLL

Owner:MSTAR SEMICON INC +3

Method for generating unique object indentifiers in a data abstraction layer disposed between first and second DBMS software in response to parent thread performing client application

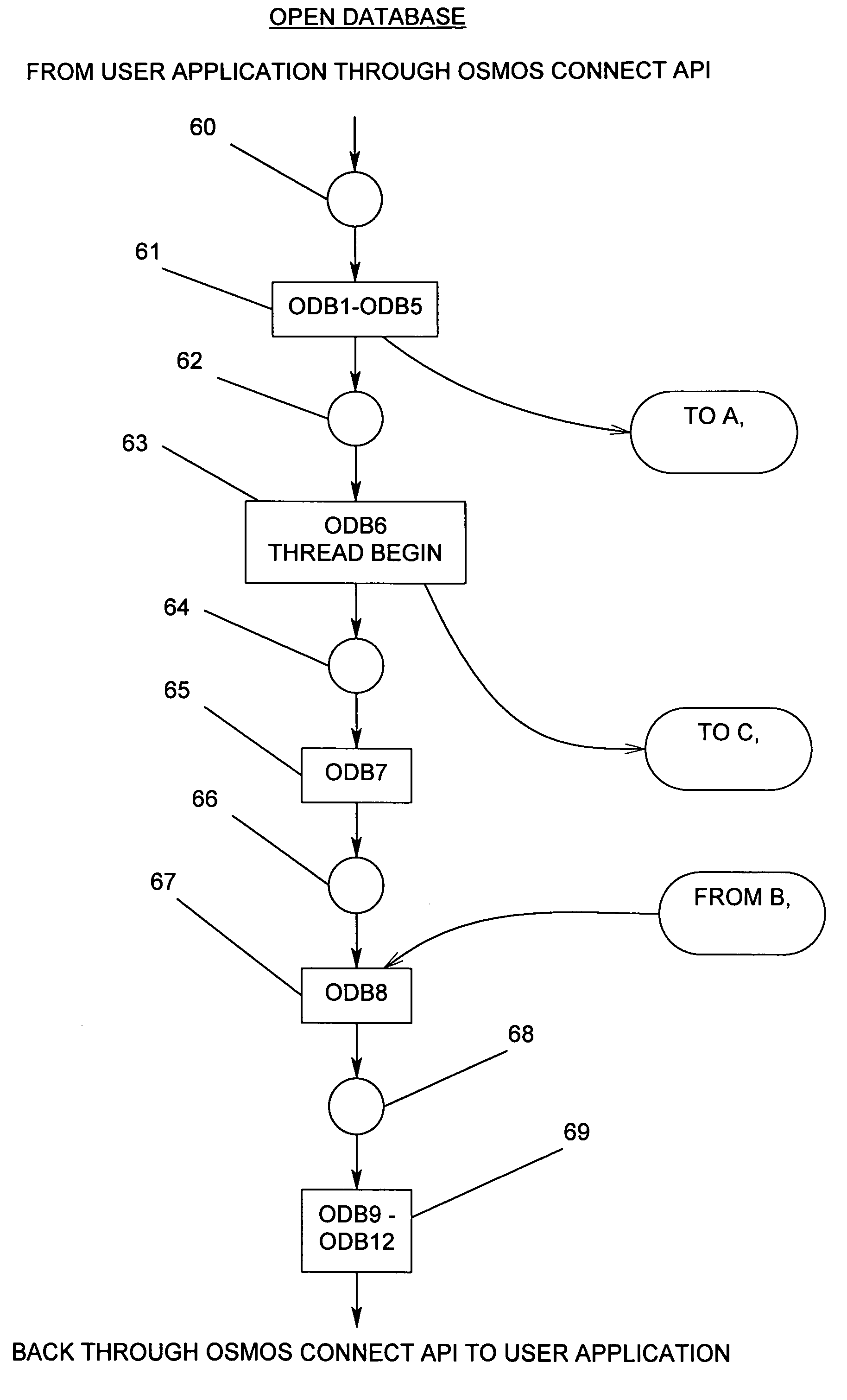

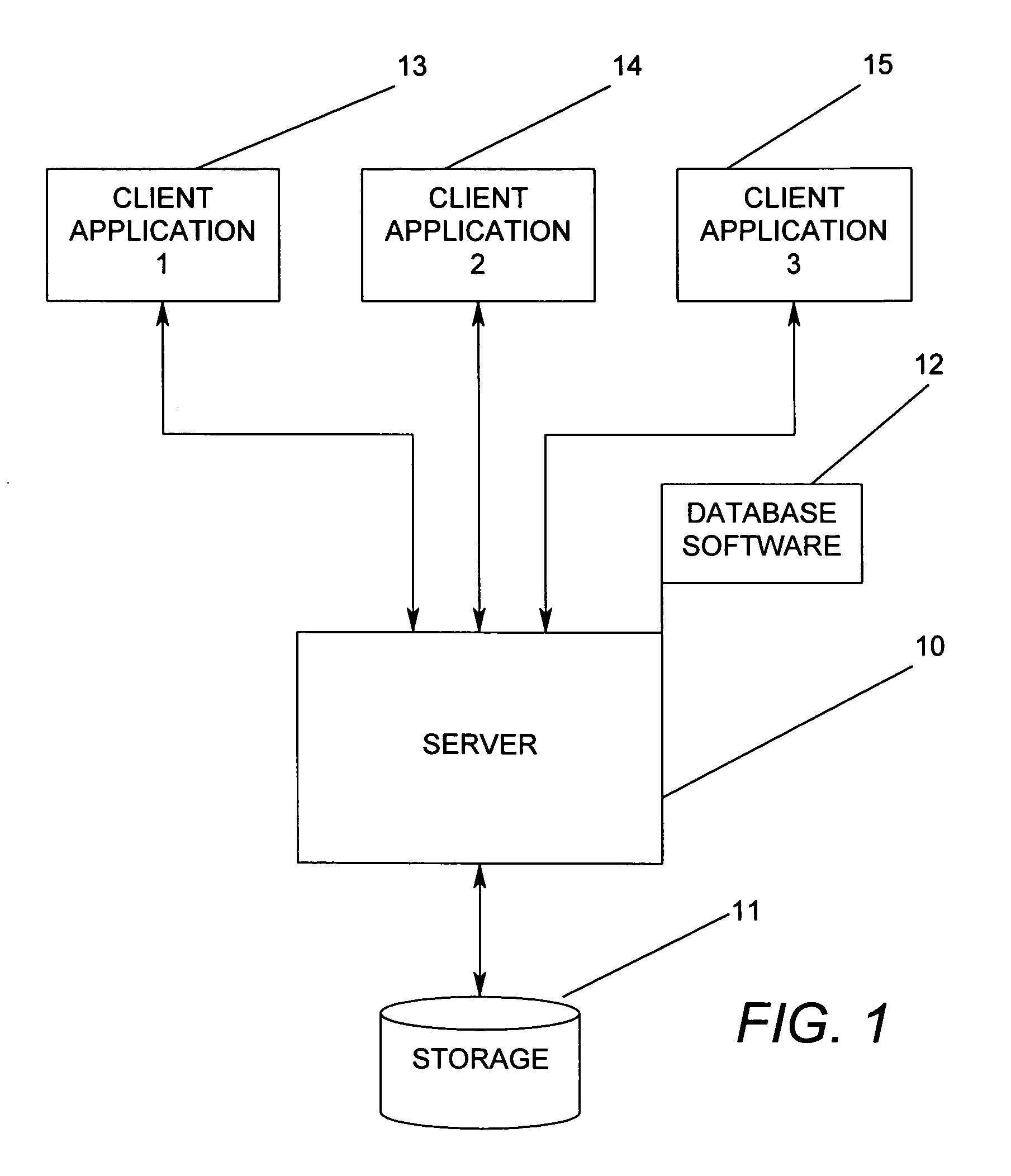

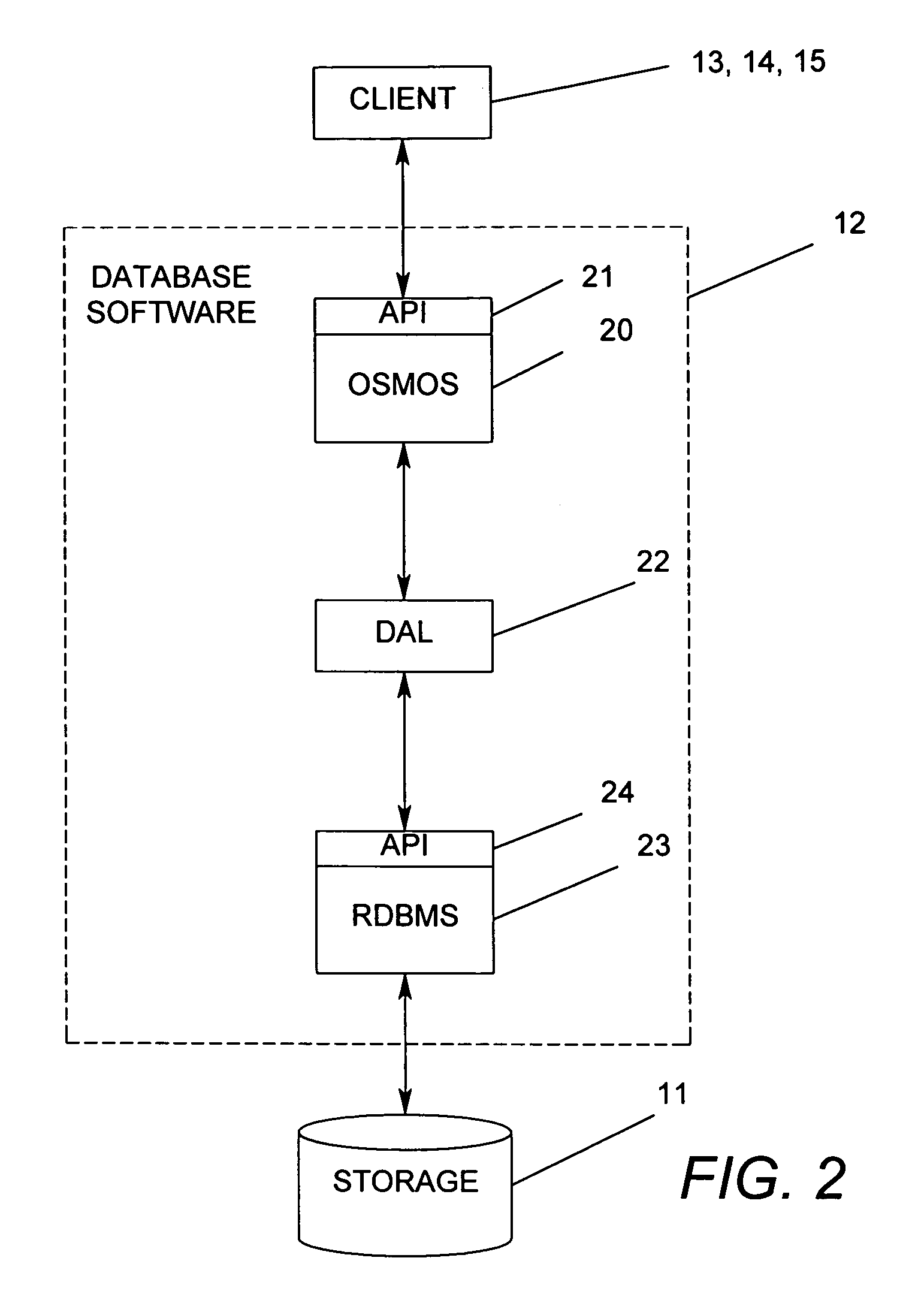

InactiveUS6947952B1Reduce waiting timeOptimize timingData processing applicationsObject oriented databasesAbstraction layerData abstraction

A method in a computer system executing a client application and an OODBMS and an RDBMS software, which system has a storage medium accessible by the RDBMS software and the OODBMS software being accessible by the client application. The method generates unique object identifiers in a data abstraction layer disposed between the OODBMS and the RDBMS software in response to a parent thread created by the client application. The method includes the steps of creating a child thread that has access to the RDBMS software, which child thread is used exclusively for generating object identifier numbers and for returning the same to the parent thread. A unique object identifier table is created, which is maintained by the child thread. In response to a request by the parent thread for a unique object identifier, the child thread generates a finite number of the unique object identifiers and communicates their values to the parent thread. After this, a recording is made in the table of the fact that a finite number of unique object identifiers have been generated.

Owner:UNISYS CORP

Reducing phase locked loop phase lock time

There is provided a method for reducing lock time in a phase locked loop. The method includes detecting a saturation condition on a path within the phase locked loop. The method further includes temporarily applying saturation compensation along the path when the saturation condition is detected.

Owner:GLOBALFOUNDRIES US INC

All digital PLL trimming circuit

InactiveUS6900675B2Shorten lock timeFrequency differencePulse automatic controlPhase detectorClock recovery

Owner:MICROCHIP TECH INC

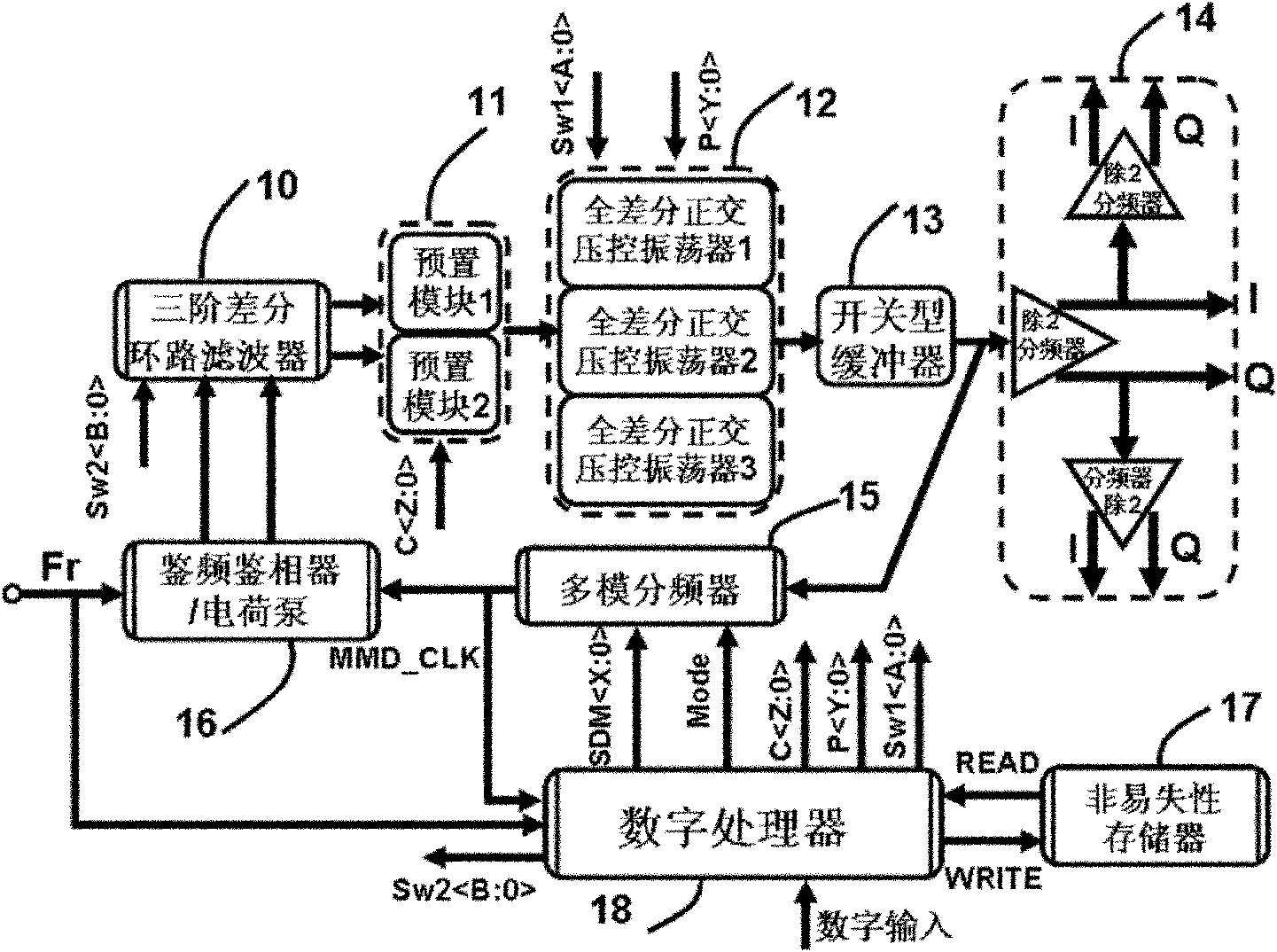

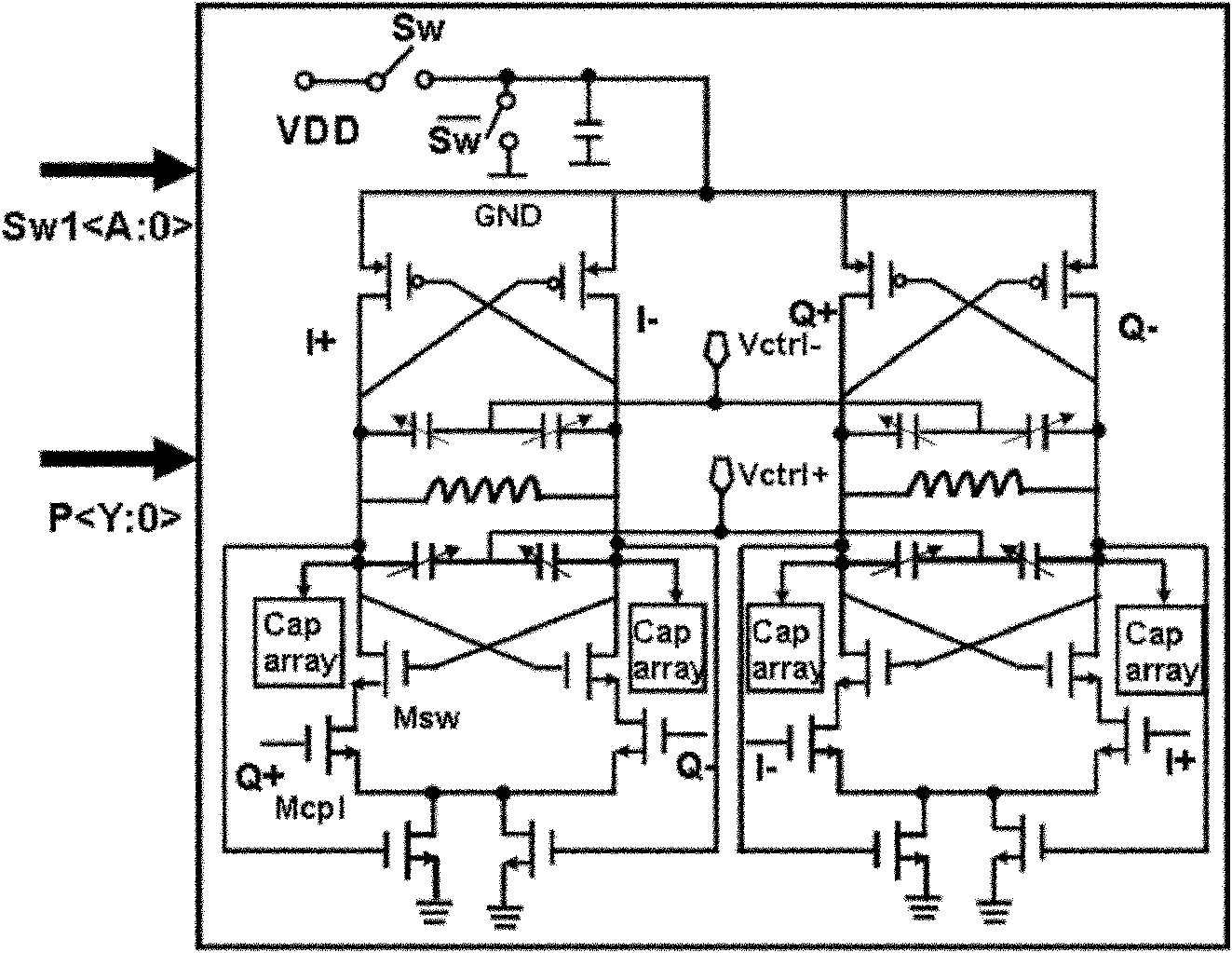

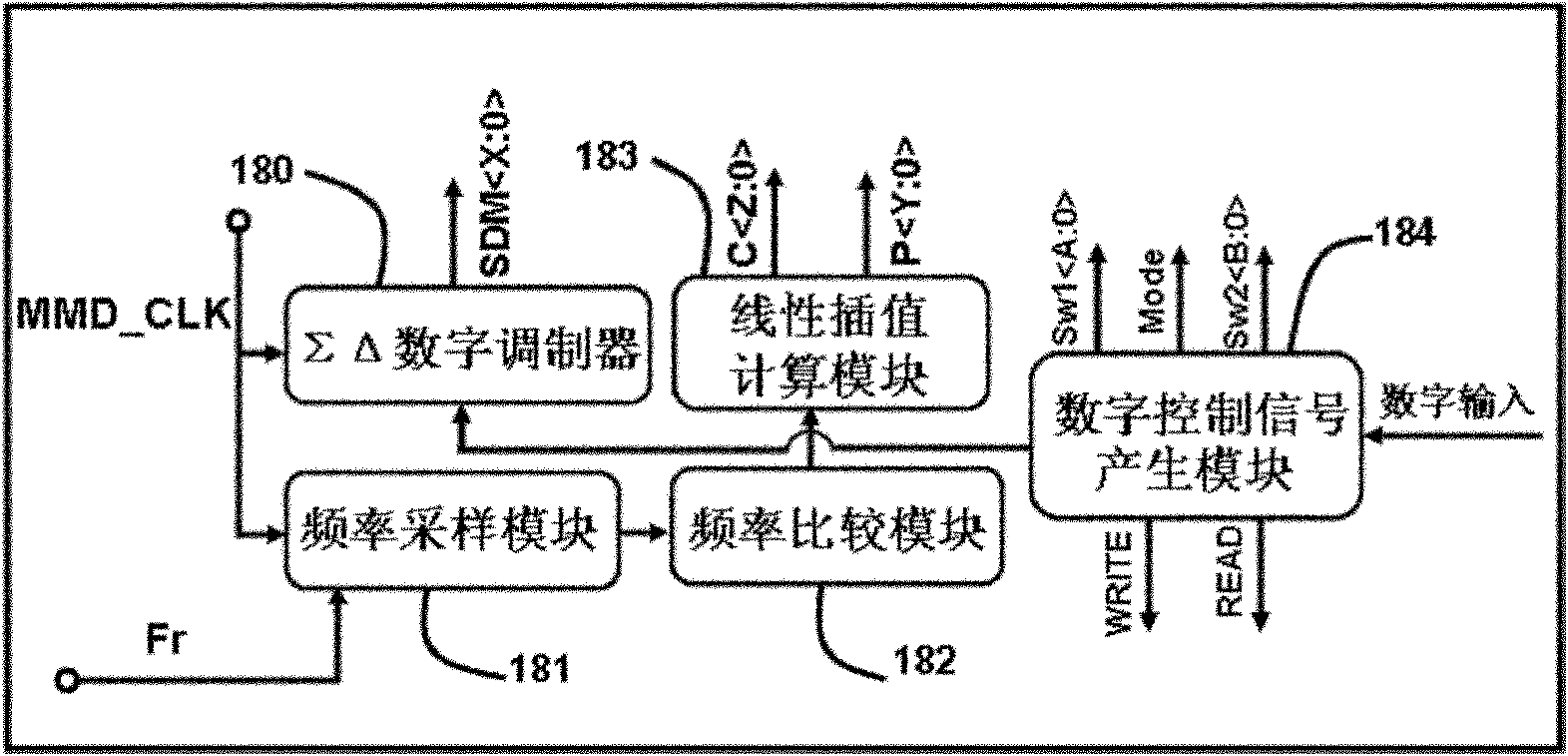

Multistandard I/Q (In-Phase/Quadrature-Phase) carrier generating device based on fractional frequency-dividing frequency synthesizer

ActiveCN102122955AFast frequency hoppingShorten lock timePulse automatic controlDiscriminatorLoop filter

The invention discloses a multistandard I / Q (In-Phase / Quadrature-Phase) carrier generating device based on a fractional frequency-dividing frequency synthesizer. The device comprises a three-order differential loop filter (10), a preset module (11), a full-differential quadrature voltage-controlled oscillator (12), a switch type bumper (13), a continuous two-dividing frequency divider module (14), a multimode frequency divider (15), a frequency and phase discriminator / charge pump (16), a nonvolatile memory (17) and a digital processor (18). By utilizing the invention, the frequency can continuously cover the range from 0.7GHz to 6GHz by reasonable frequency distribution, and the rapid frequency hopping is realized by presetting the frequency by the digital processor with strong function.

Owner:INST OF SEMICONDUCTORS - CHINESE ACAD OF SCI

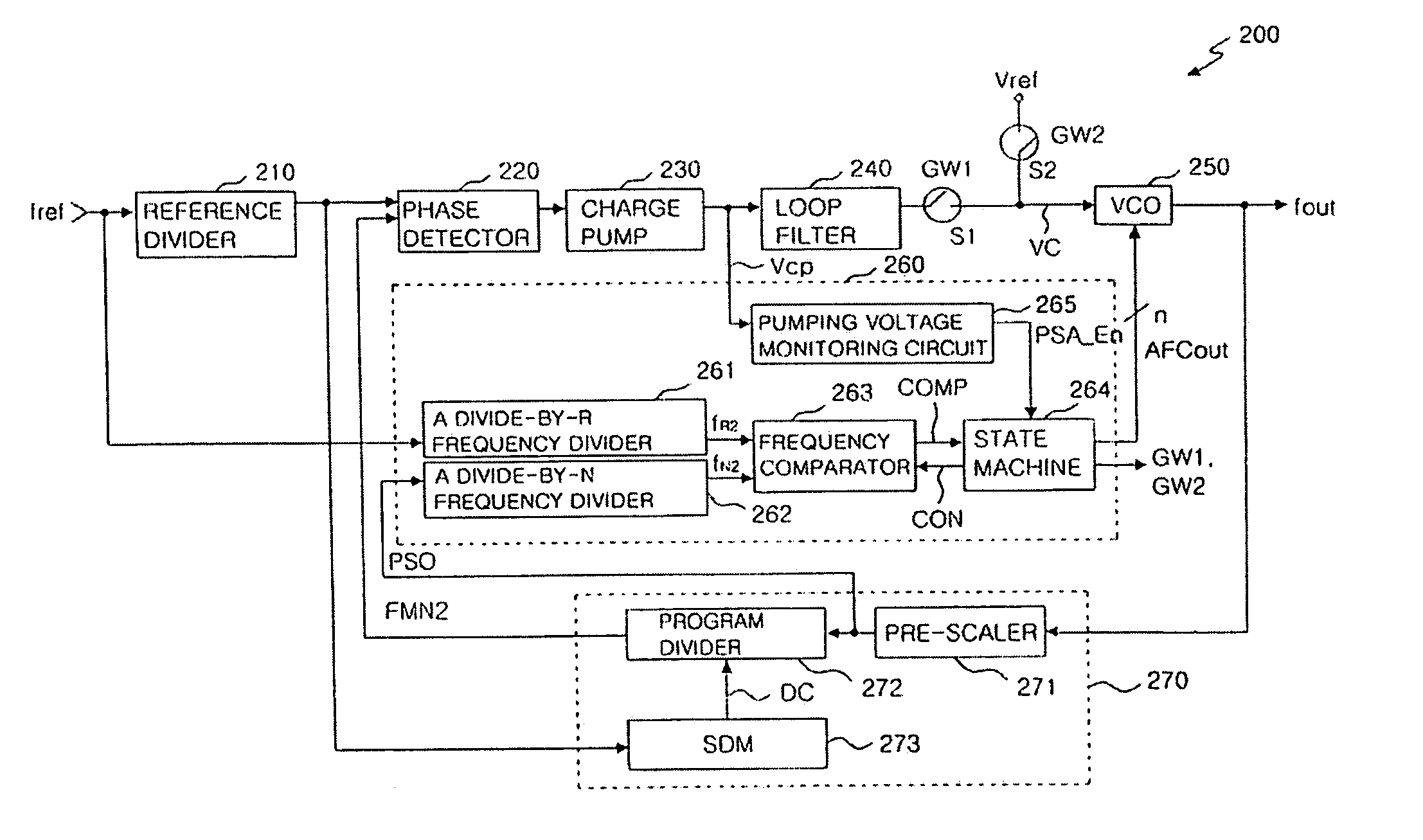

Fast phase locking system for automatically calibrated fractional-n pll

The current invention provides a second feedback loop around the existing FLL, which forces the signal on the route of N-divider (NDIV), PFD, CP, and LPF to essentially reach their desired lock conditions before the FLL is switched off and the system enters PLL mode. This loop works by comparing the output voltage of the FLL DAC to the LPF output voltage, and then using this value to modulate the divider's dividing value. After the secondary feedback loop settles, output voltage from the LPF will be equal to the value that can drive the VCO to the desired lock frequency, and the phase error at the input side of the PFD produces a zero-average current to the charge pump. When this condition is set, the loop is essentially already in phase lock and the lock transient from the FLL mode to the PLL mode will be minimal.

Owner:MSTAR SEMICON INC +3

Frequency synthesizer and frequency calibration method

InactiveUS20080106340A1Quick calibrationAvoid failurePulse automatic controlFrequency analysisPhase detectorLoop filter

A frequency synthesizer capable of using a voltage controlled oscillator (VCO) with a low value of gain Kvco, having a short automatic frequency calibration time and automatically coping with environments and a frequency calibration method are provided. The frequency synthesizer includes a reference divider, a phase detector, a main divider, a charge pump, a loop filter, a first switch, a second switch, a VCO, and an automatic frequency calibration block. The frequency calibration method includes an initialization step, an N-target algorithm step, an auxiliary search algorithm step, and a post search algorithm step.

Owner:DIALOG SEMICON KOREA INC

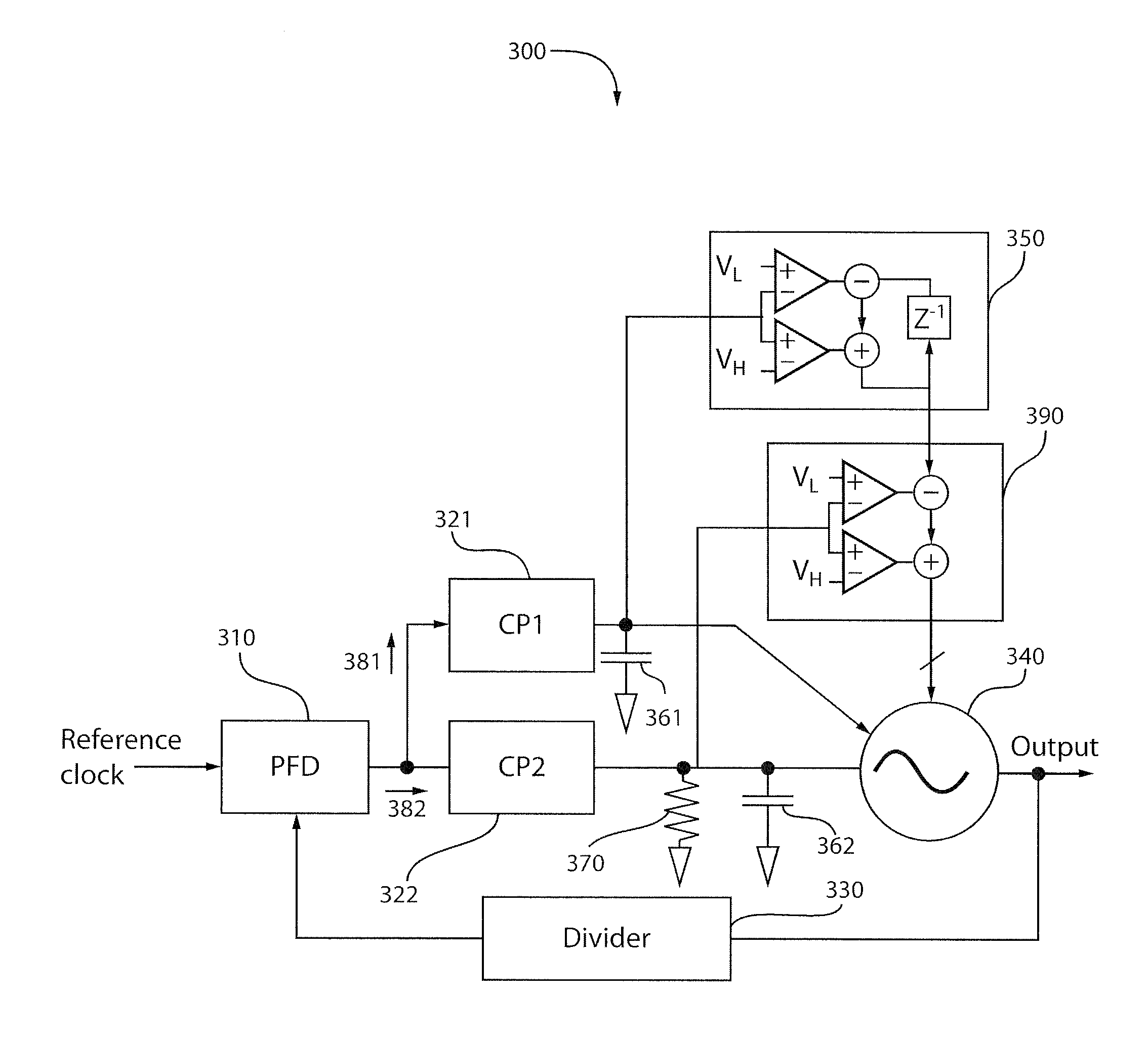

Continuous gain compensation and fast band selection in a multi-standard, multi-frequency synthesizer

InactiveUS20090002079A1Designing can be facilitatedShorten lock timePulse automatic controlAngle modulationLoop filterMulti band

A frequency synthesizer capable of high speed, low power, wideband operation including a method of gain compensation, and a method of fast voltage controlled oscillator (VCO) band calibration. In addition, the frequency synthesizer may include two or more switchable independent loop filters to facilitate wideband operation. Such a frequency synthesizer may be used in many applications, and in one example, may be particularly suitable for use in a multi-band, multi-standard transmitter or radio transceiver.

Owner:TRIDEV RES

Multi-loop phase locked loop circuit

Disclosed is a multi-loop PLL circuit and a related method of which, the circuit includes: a first loop for generating a first control current; a second loop for generating a second control current; a loop filter for generating a control signal according to the first control current or the second control current; a voltage control oscillator for generating a first oscillating signal or a second oscillating signal according to the control signal; a first frequency divider for generating a first feed back clock signal; a second frequency divider for generating a second feed back clock signal; and a control circuit for switching the first loop or the second loop to generate the control signal. The frequency of the second reference clock signal is higher than which of the first reference clock signal. The control circuit turns on the second loop first and then turns on the first loop.

Owner:REALTEK SEMICON CORP

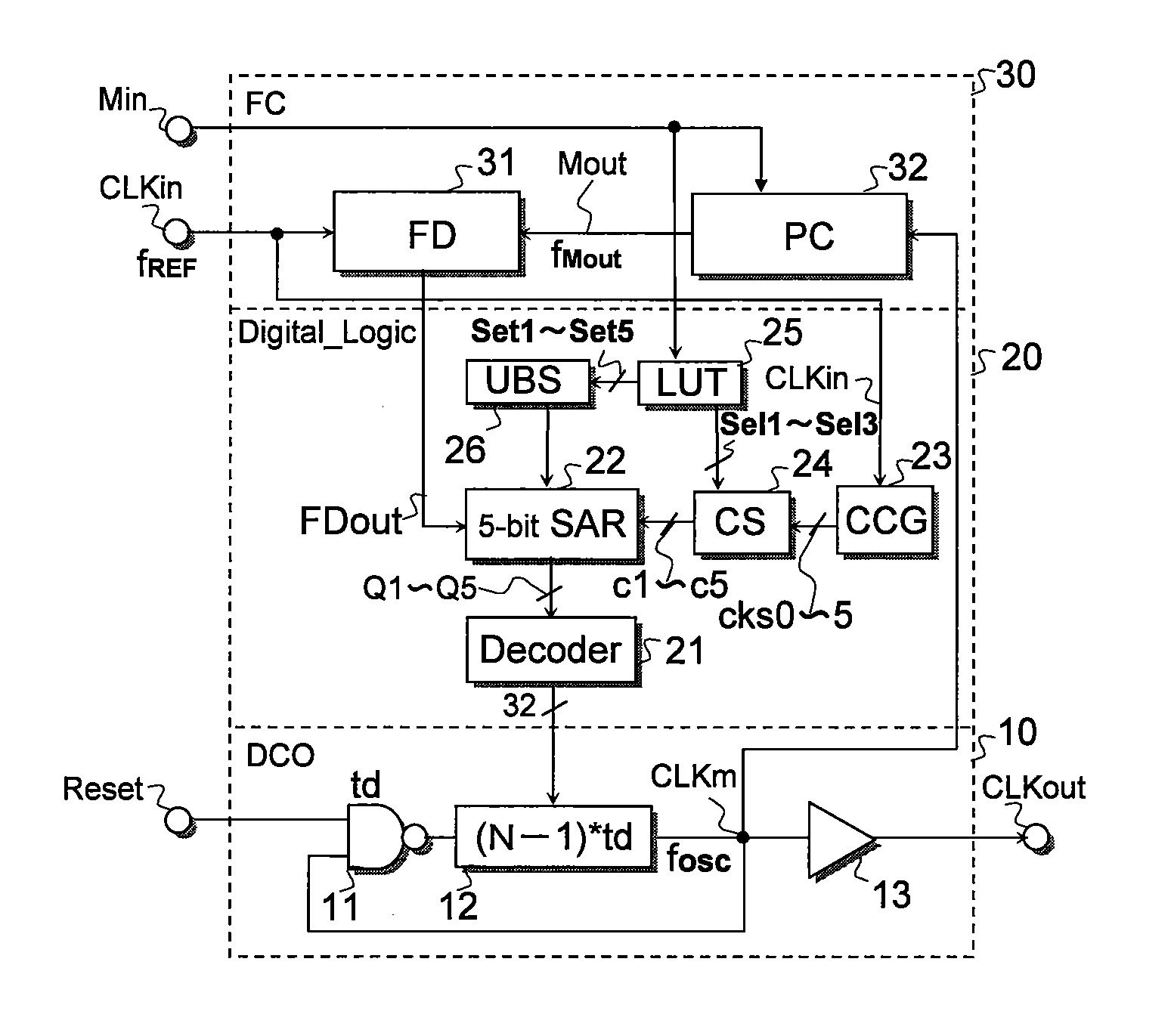

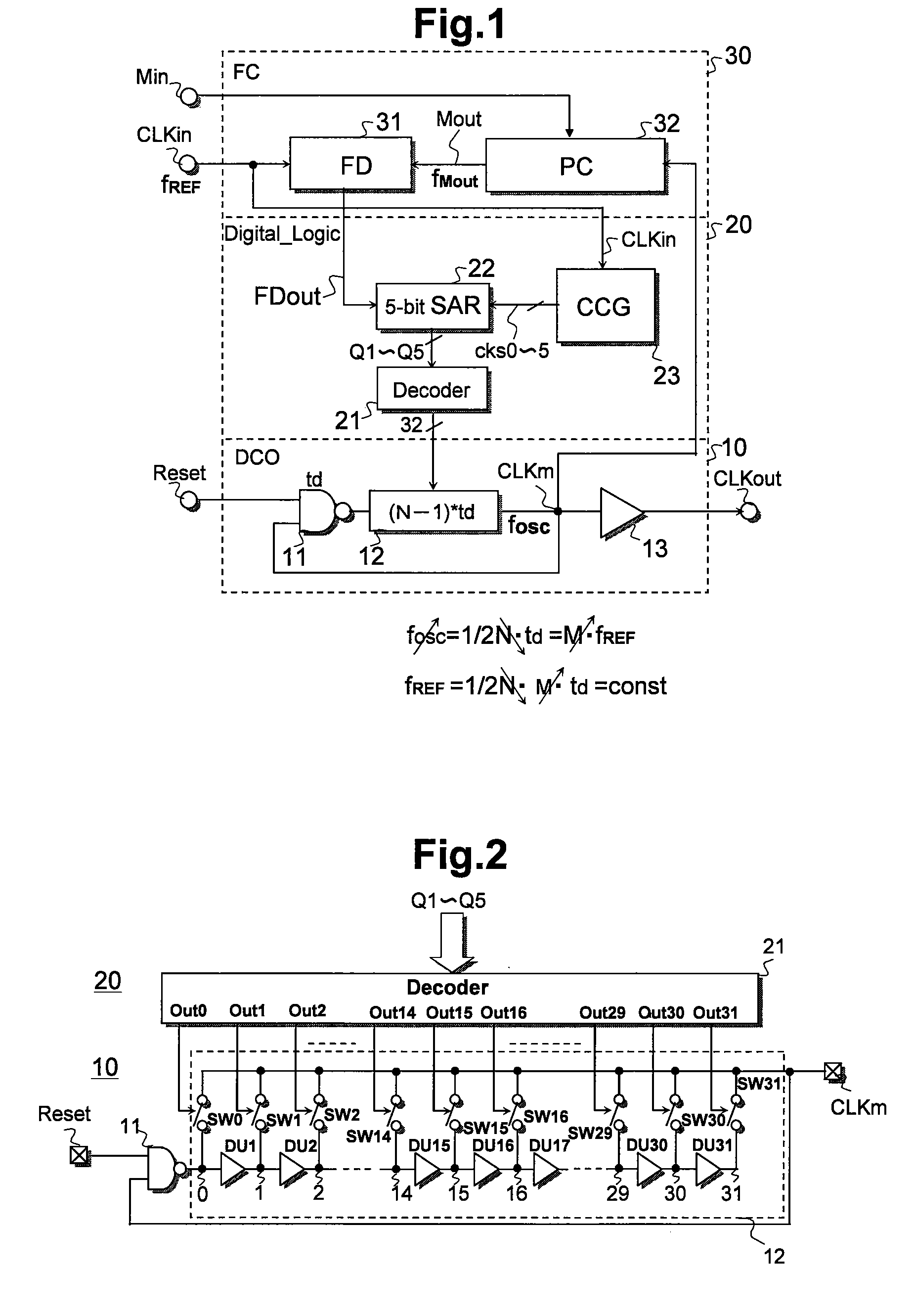

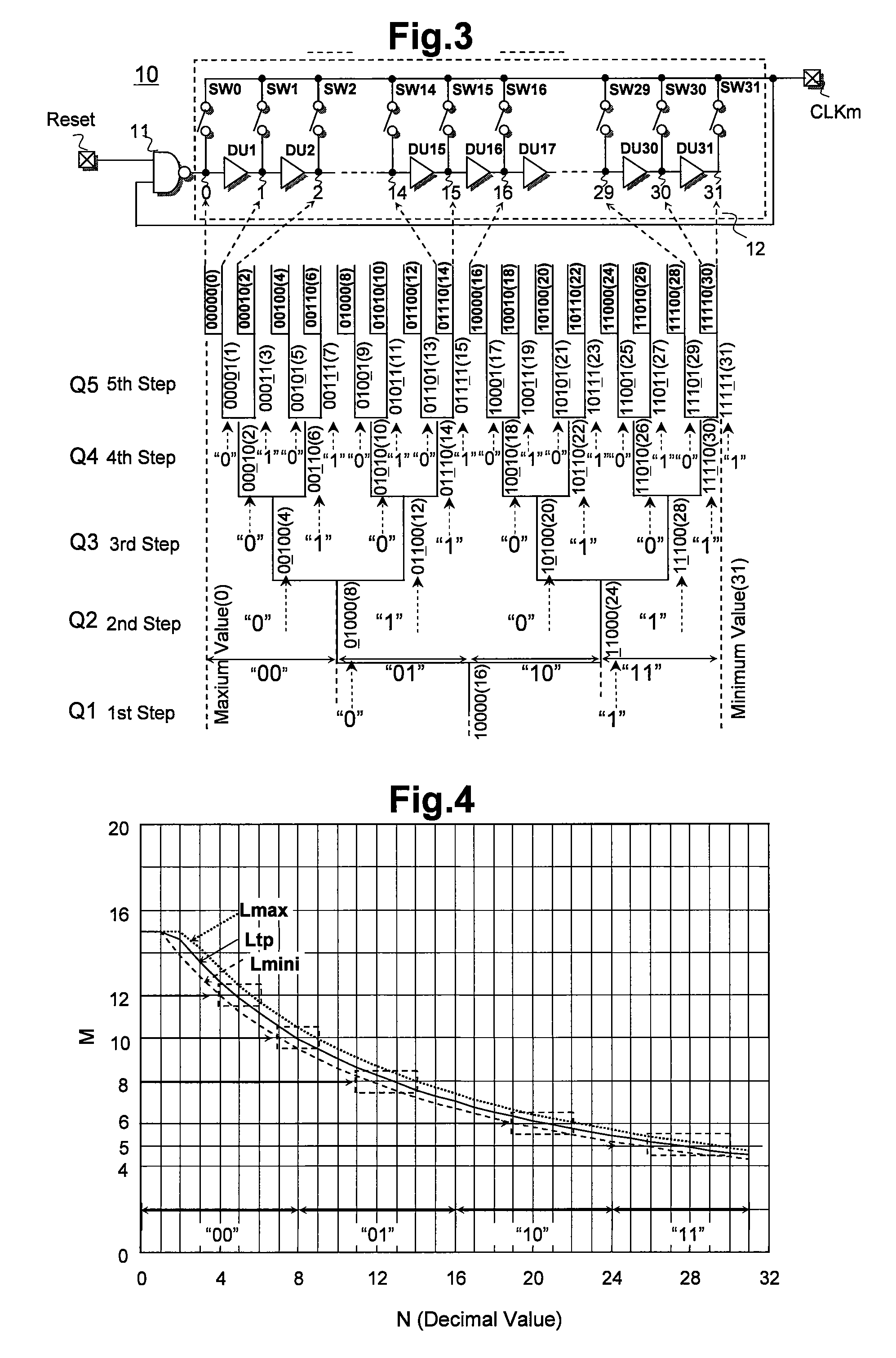

Semiconductor integrated circuit

InactiveUS20090195277A1Shorten lock timeReduce the number of stepsPulse automatic controlControl signalProcessor register

The semiconductor integrated circuit includes a clock generating section having a digital control signal generating part operable to generate a clock signal and a digital control part. The clock generating section further includes a phase-frequency comparator and a control register. The comparator is supplied with a reference signal CLKin and a feedback signal. The control register is supplied with an output signal of the comparator, and stores two or larger bits of digital control information. The clock generating section further includes a control data storing circuit for previously storing sets of initial set data for lock operations. In response to operation select information, initial set data are stored at upper bit of the control register from the control data storing circuit. Thus, it becomes possible to reduce the number of steps to store control information in a register for digitally controlling the clock signal generating part.

Owner:RENESAS ELECTRONICS CORP

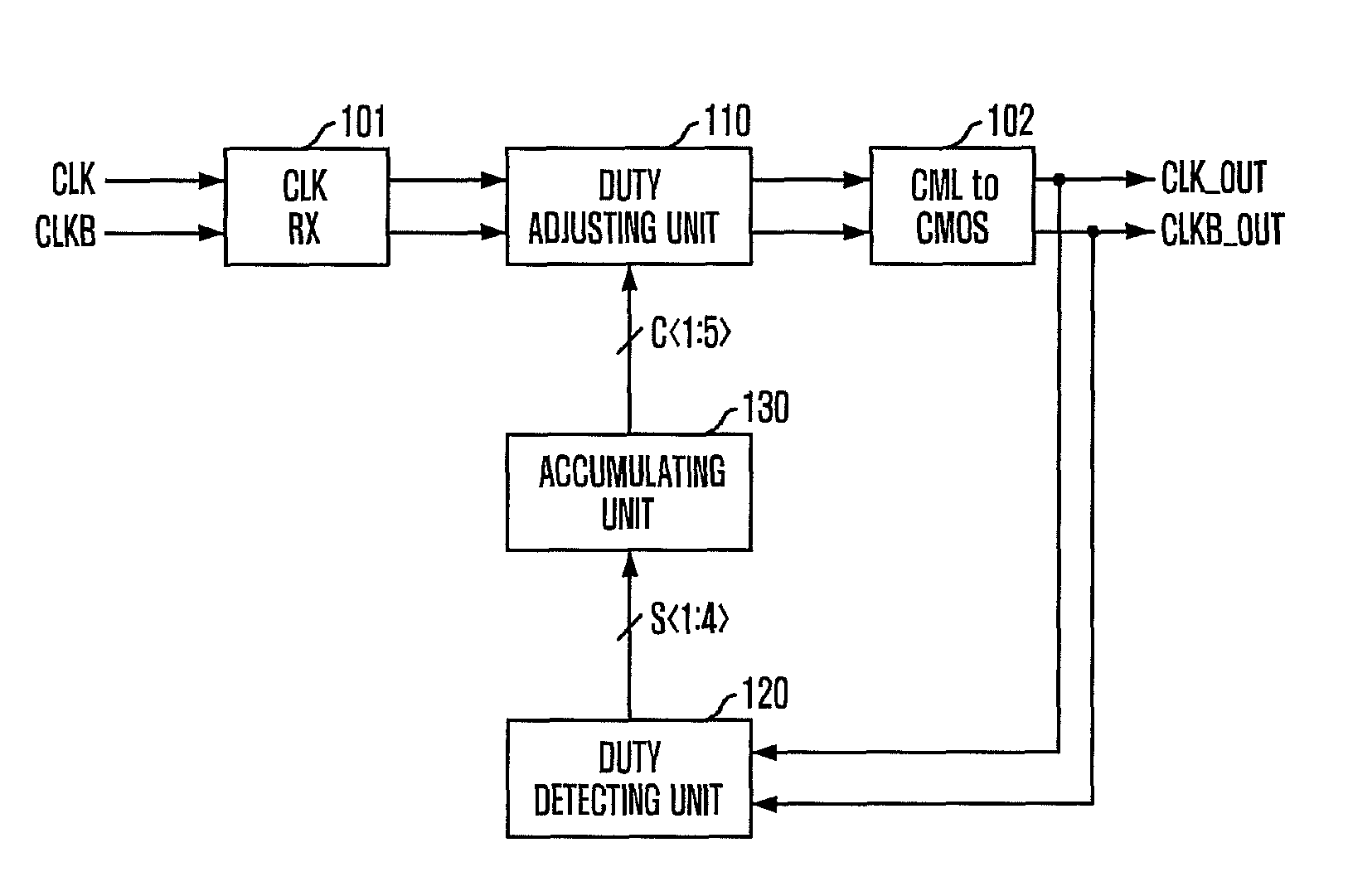

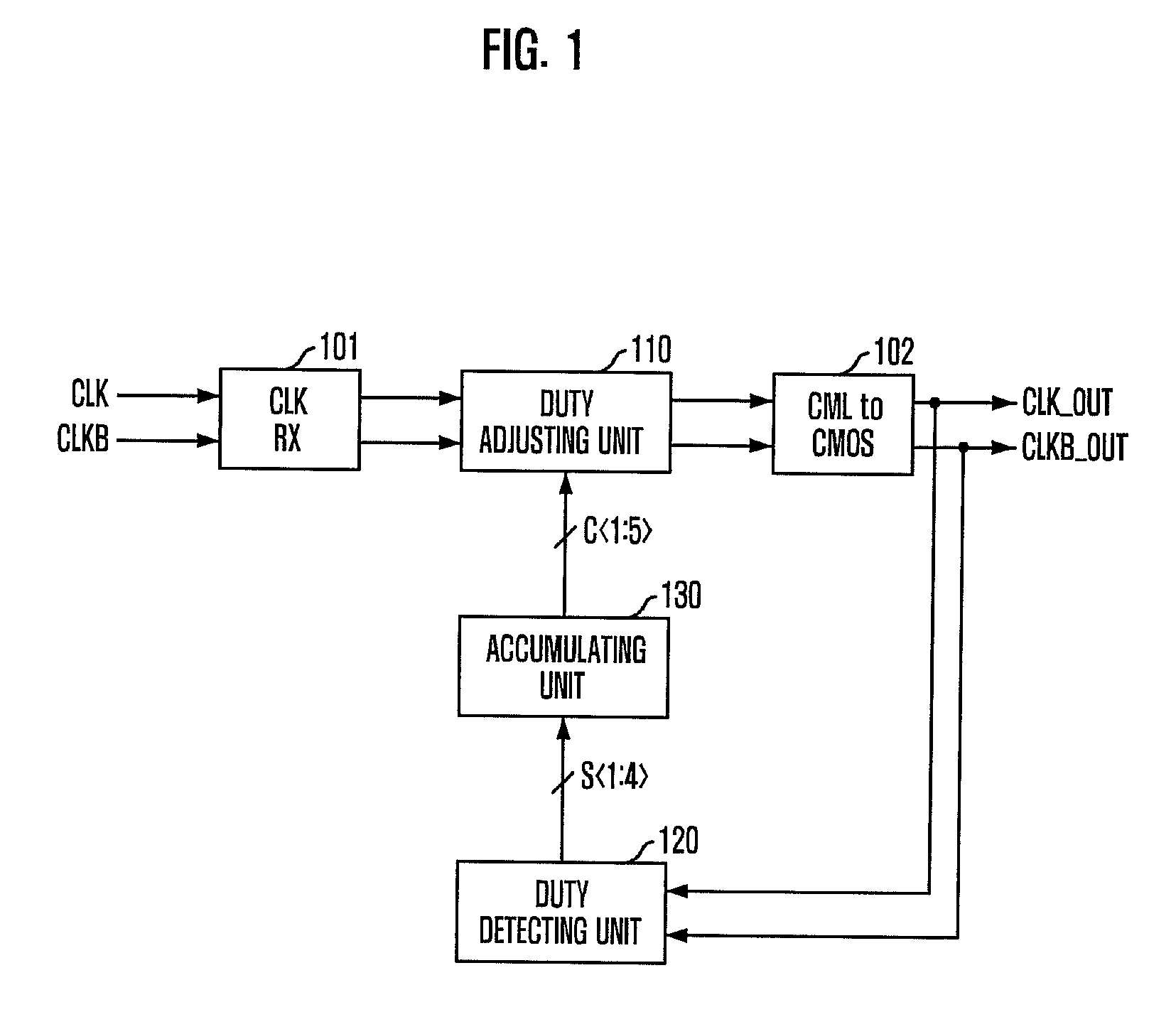

Duty detecting circuit and duty cycle corrector including the same

ActiveUS7847609B2Shorten lock timeAccurate correctionMultiple input and output pulse circuitsDelay line applicationsDuty cycle correctorCorrection code

A duty cycle corrector includes a duty adjusting unit configured to adjust a duty cycle of an input clock in response to a duty correction code and generate an output clock, a duty detecting unit configured to measure a difference between a high pulse width and a low pulse width of the output clock and output a difference value, and an accumulating unit configured to accumulate the difference value to generate the duty correction code.

Owner:SK HYNIX INC

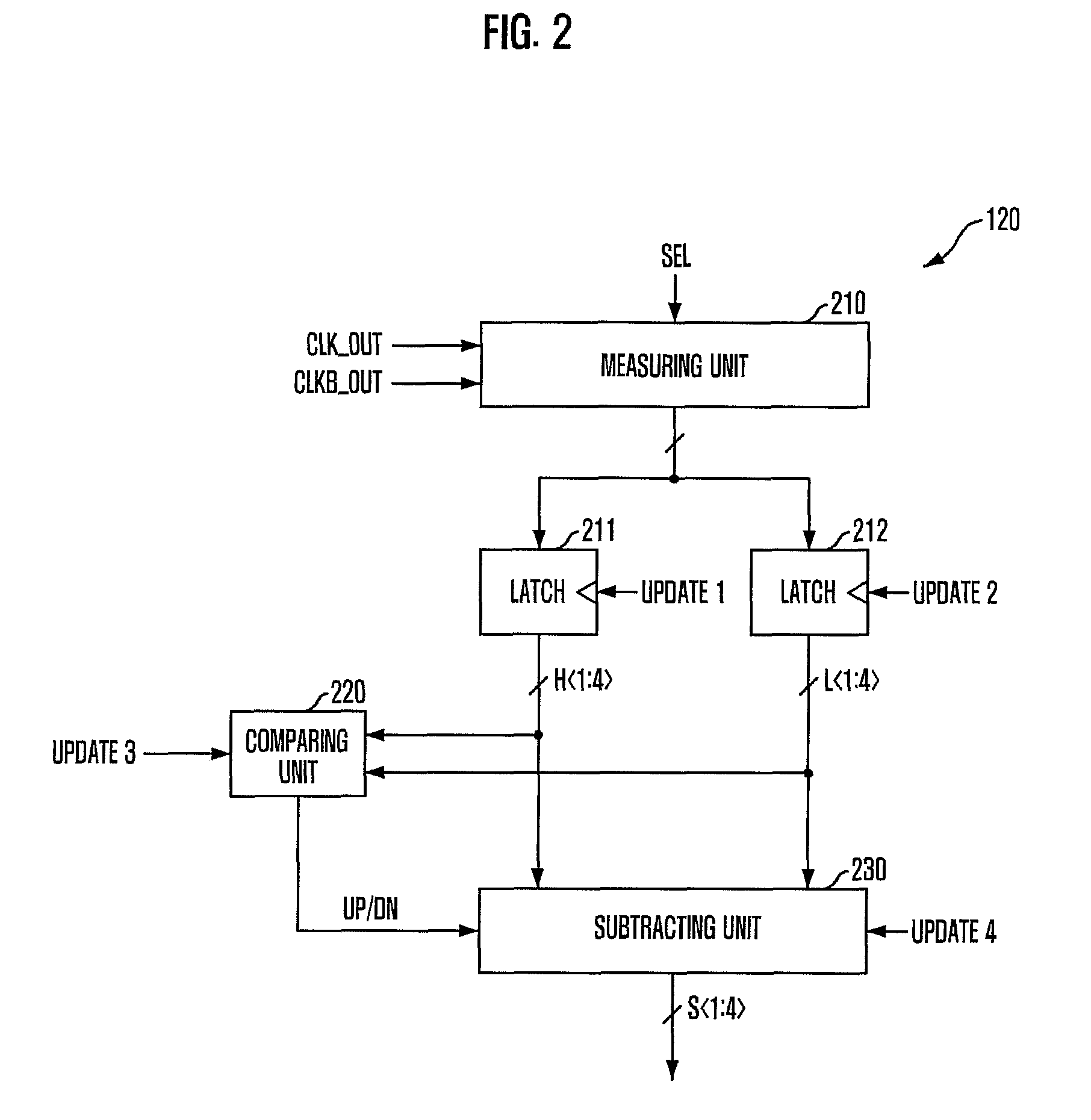

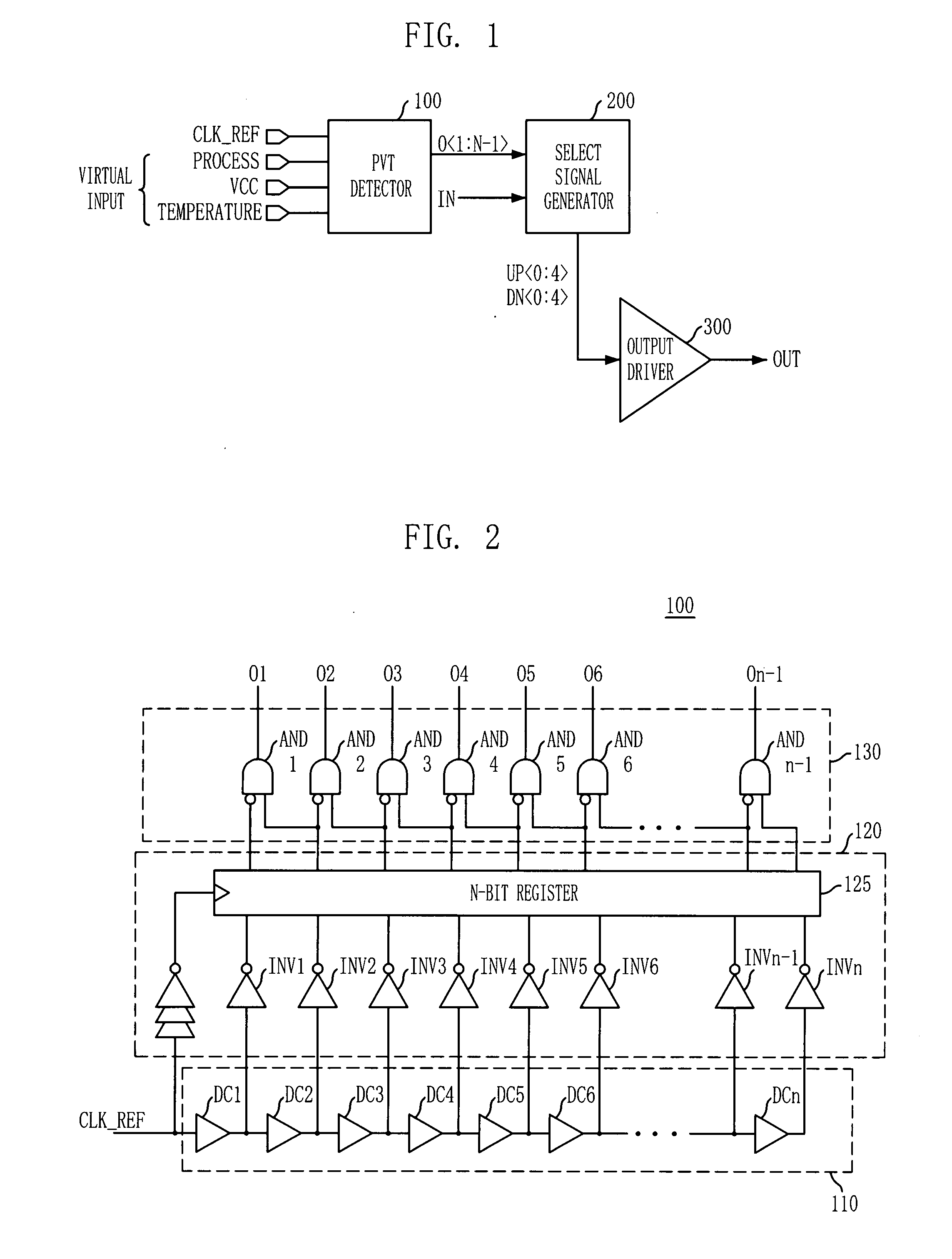

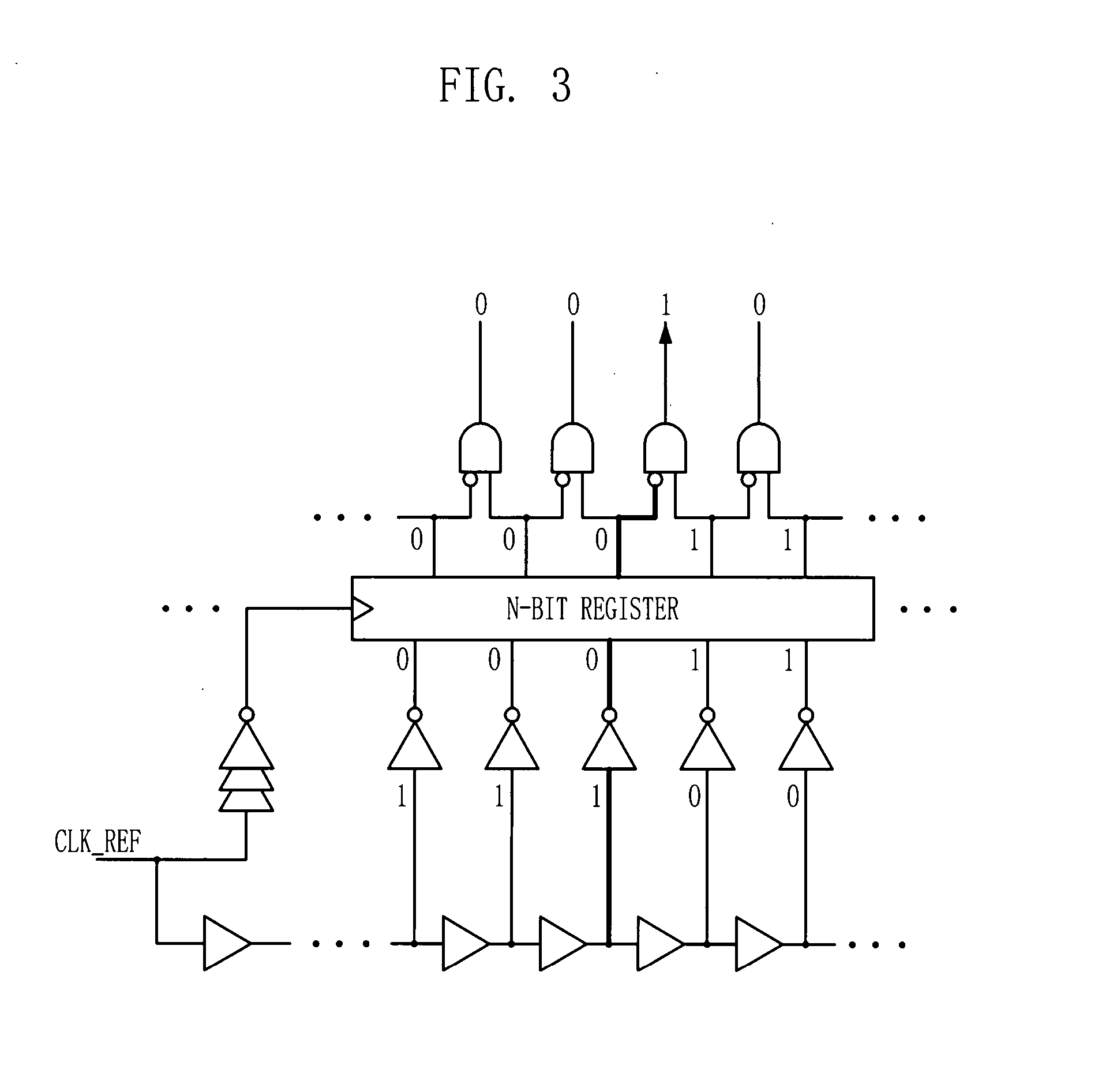

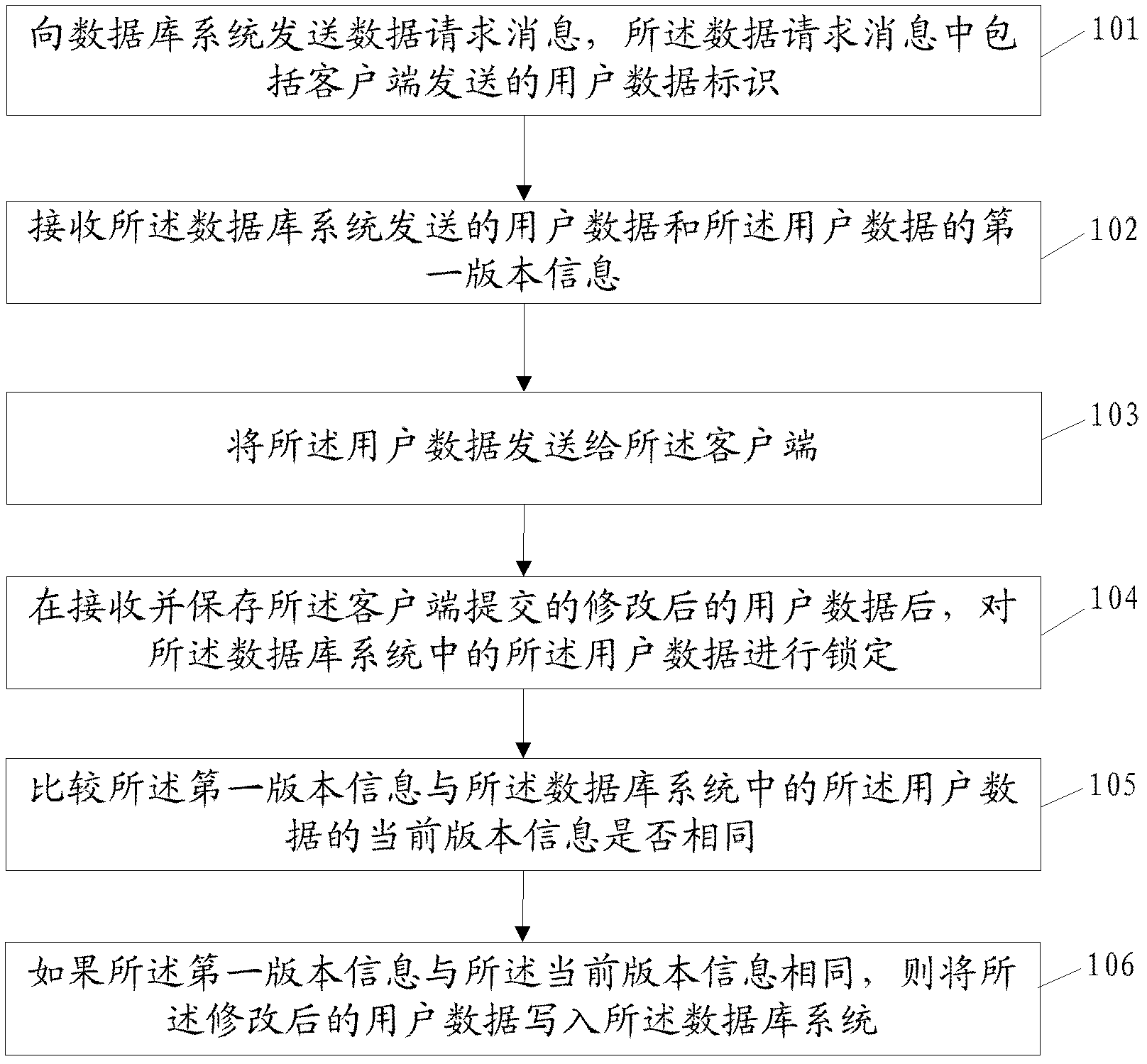

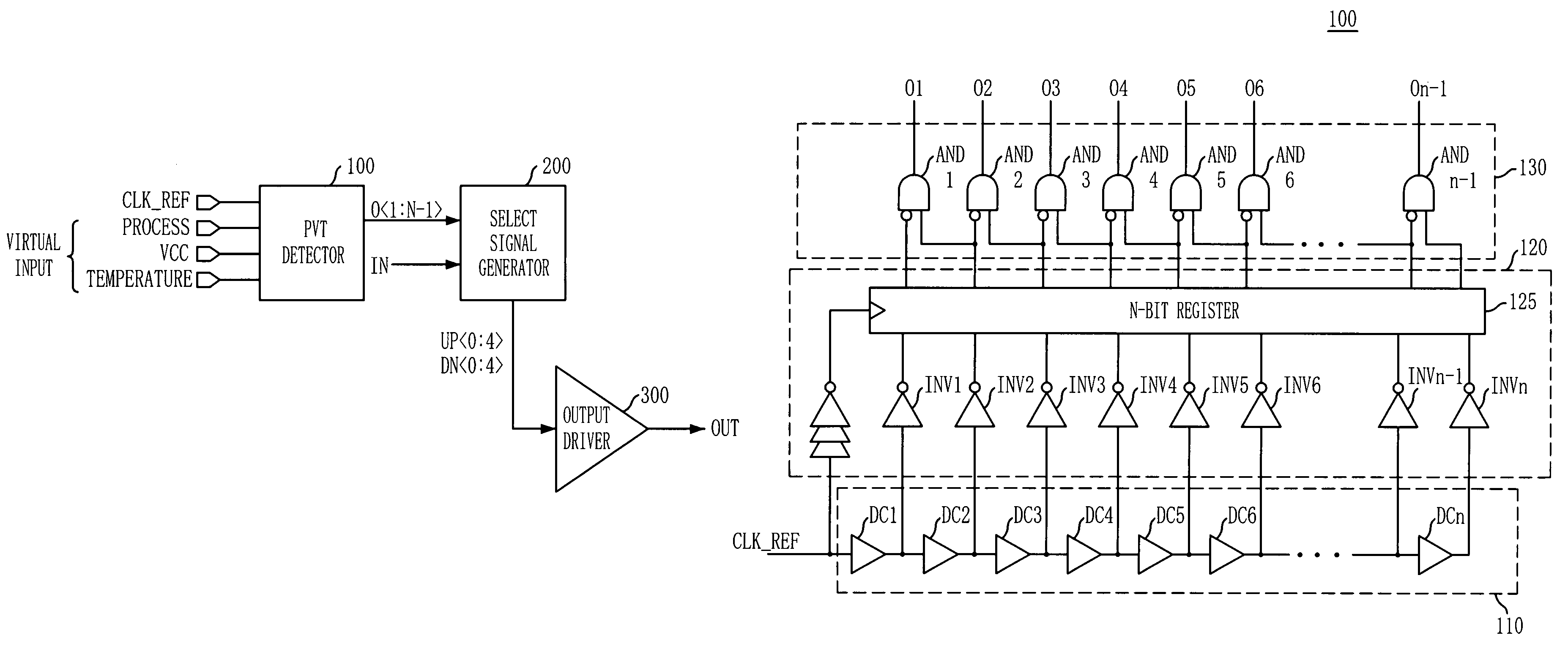

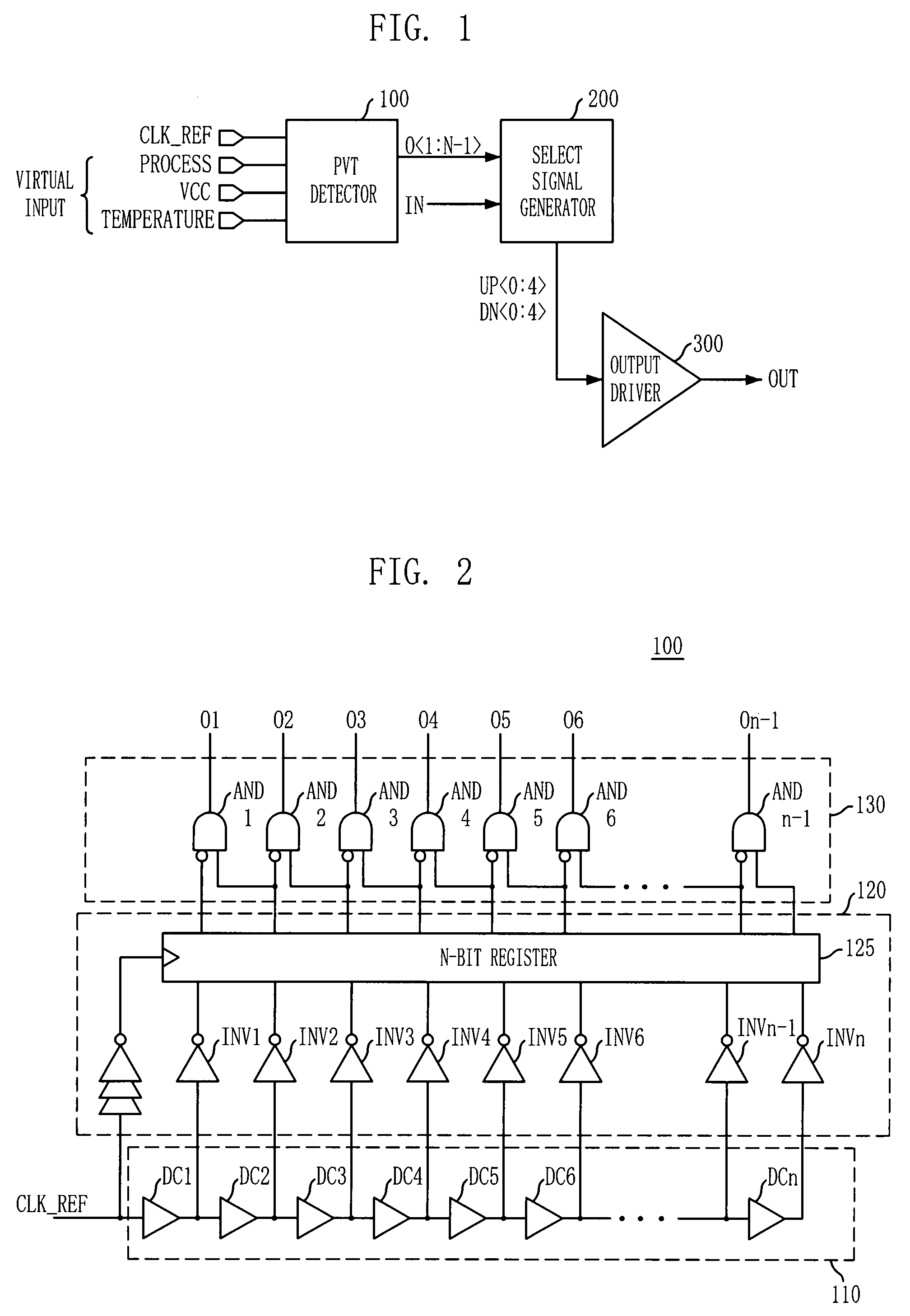

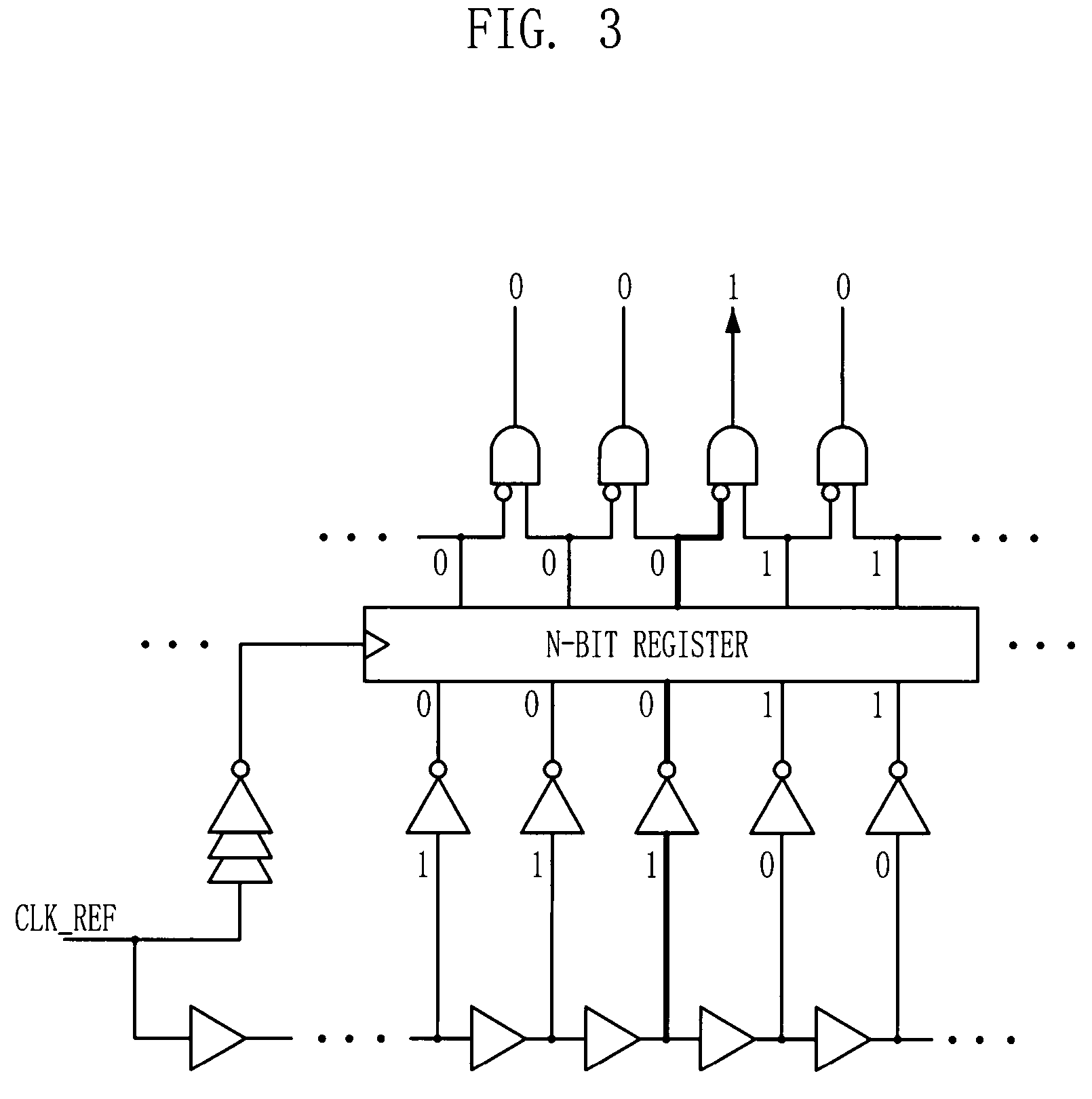

Impedance-controlled pseudo-open drain output driver circuit and method for driving the same

InactiveUS20080079458A1Reduce impedance locking timeMinimize occurrenceReliability increasing modificationsLogic circuits coupling/interface using field-effect transistorsDriver circuitState variation

An impedance-controlled pseudo-open drain output driver circuit includes: a process, voltage, and temperature (PVT) detector configured to have a delay line receiving a reference clock and detect a state variation of the delay line according to PVT conditions to output detection signals; a select signal generator configured to generate a driving select signal based on the detection signals and an output data; and an output driver configured to drive an output terminal, the output driver including a plurality of pull-up / pull-down driving blocks controlled by the driving select signal, each of the pull-up / pull-down driving blocks including a resistor having an intended impedance.

Owner:SK HYNIX INC

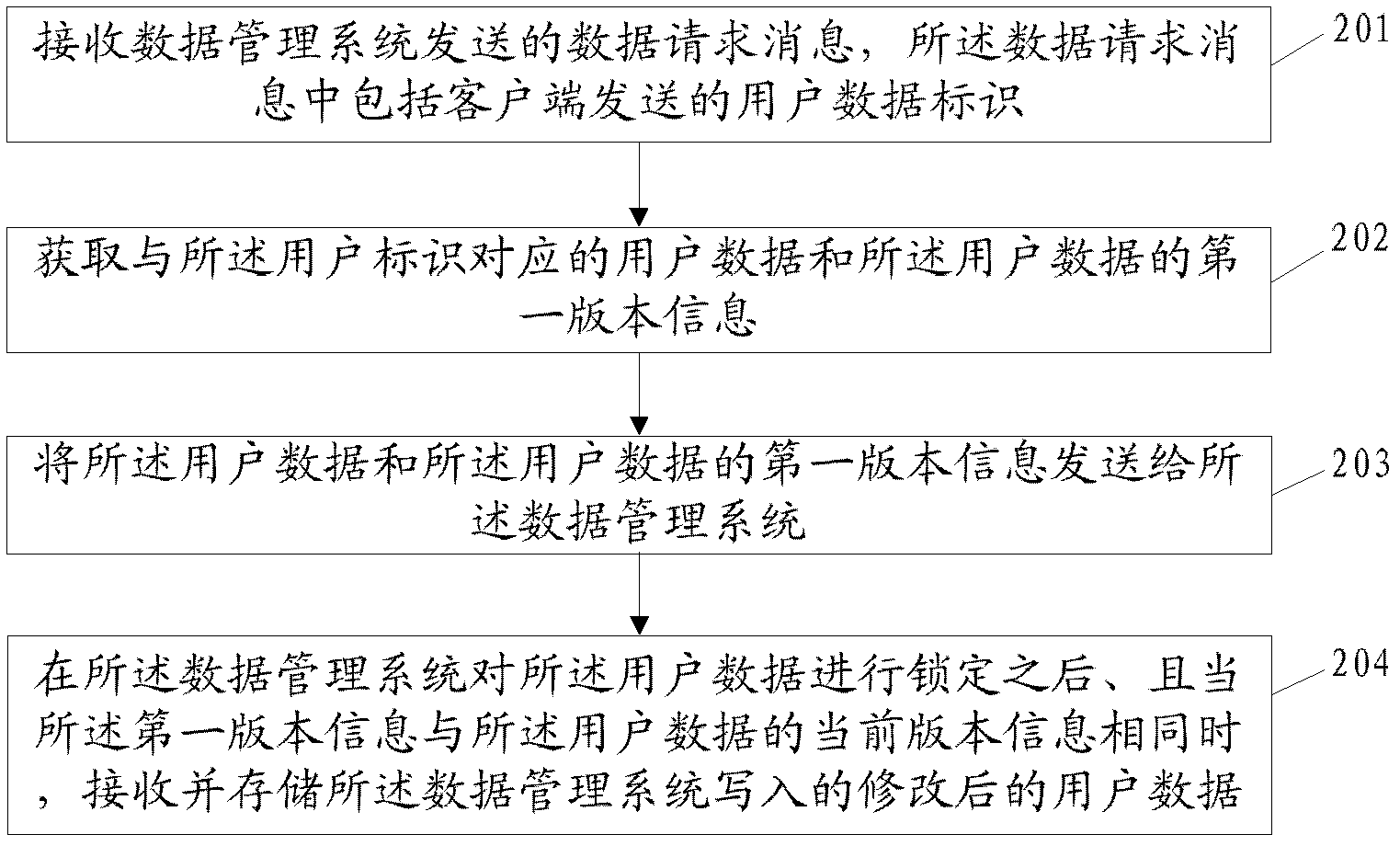

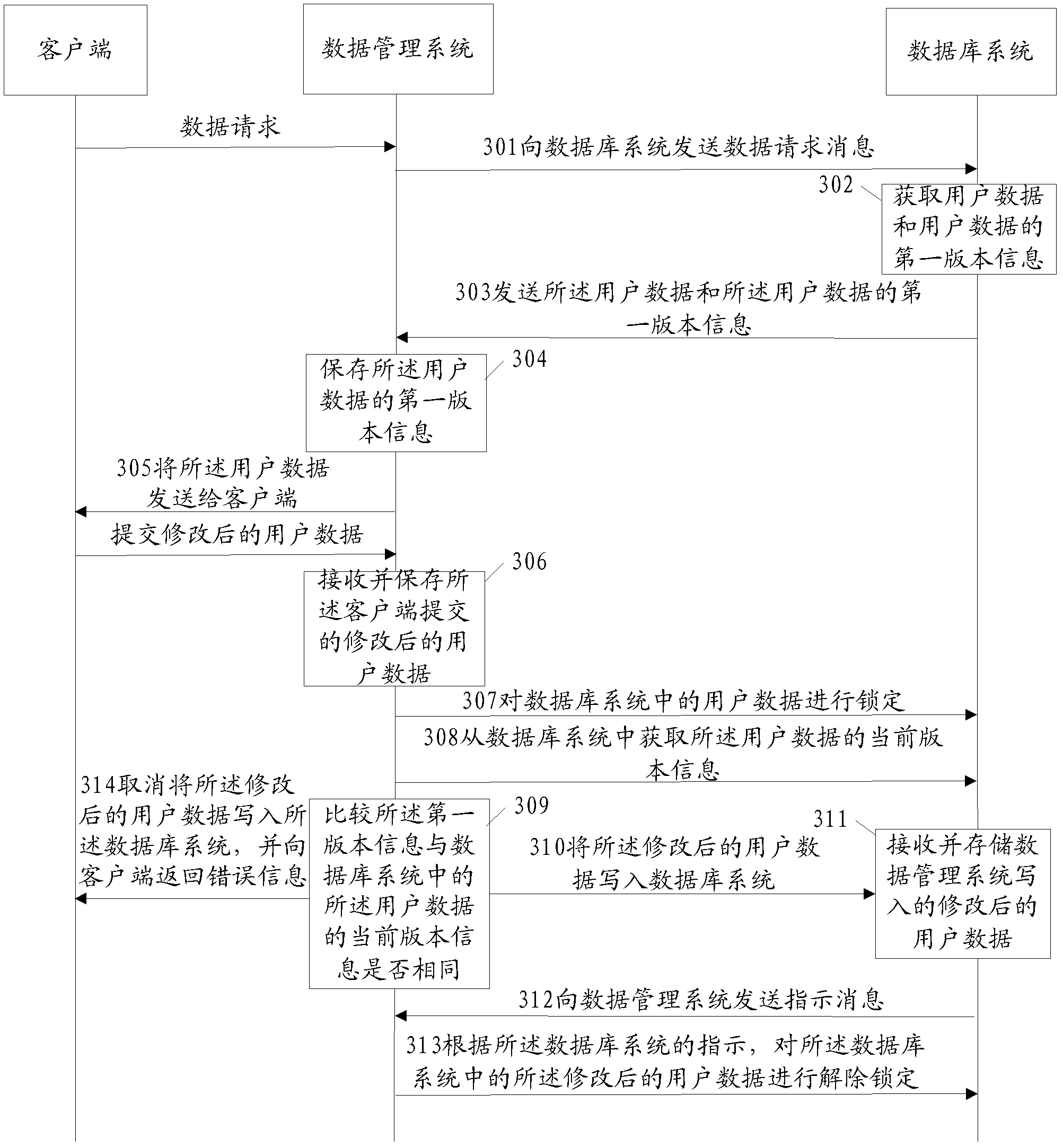

Data management method and system as well as database system

InactiveCN102436633AEnsure consistencyImprove performanceData processing applicationsSpecial data processing applicationsData managementClient-side

The embodiment of the invention discloses a data management method and a system as well as a database system. The method comprises the following steps of: transmitting a data request message to the database system, wherein the data request message contains a user data identification sent by a client; receiving user data and a first version of information of the user data, which are transmitted by the database system; transmitting the user data to the client; receiving and storing the user data which is submitted by the client and is modified, and locking the user data in the database system; comparing whether the first version of information is the same as that the current version of information of the user data in the database system or not; and if so, writing the modified user data into the database system.

Owner:HUAWEI TECH CO LTD

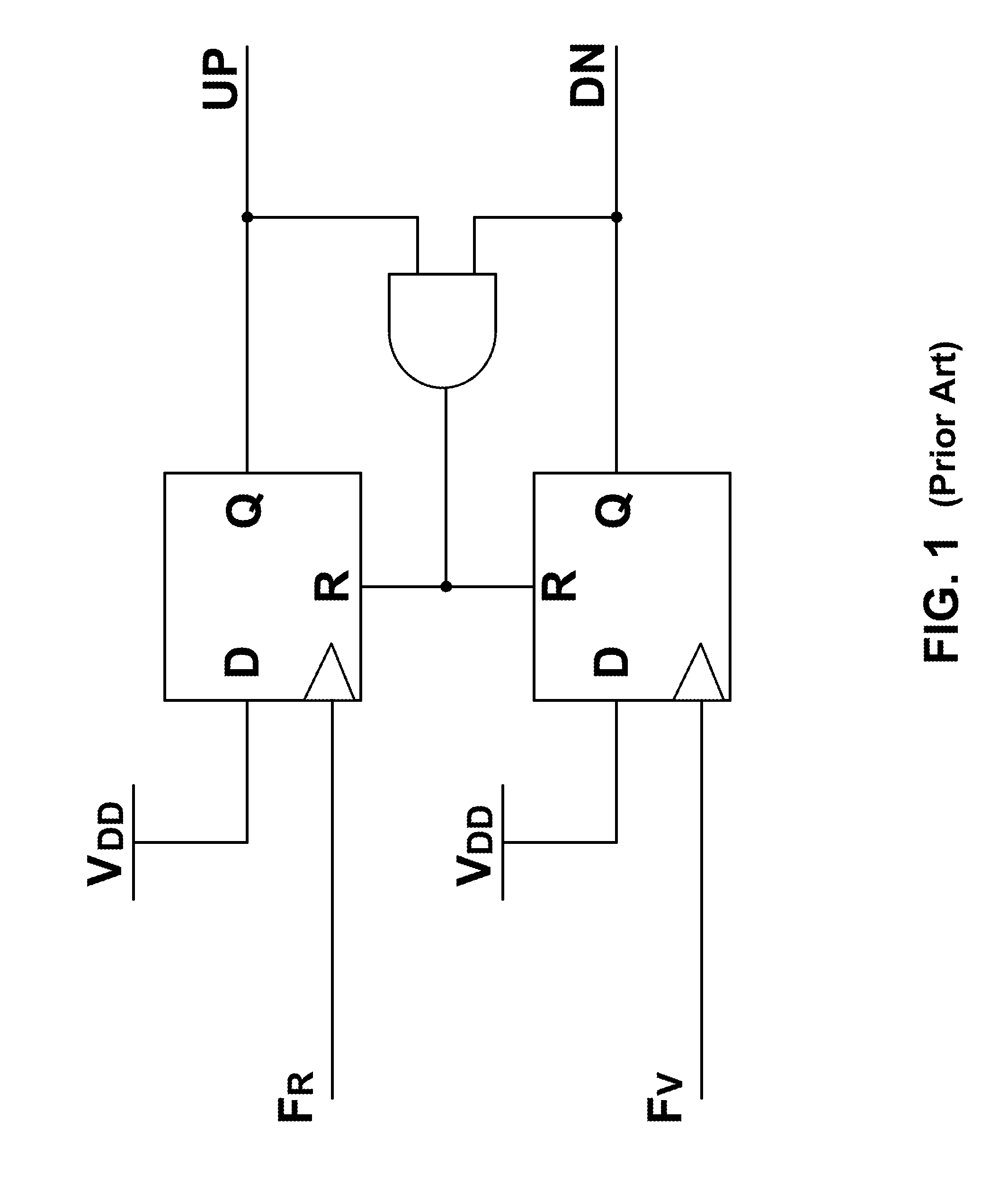

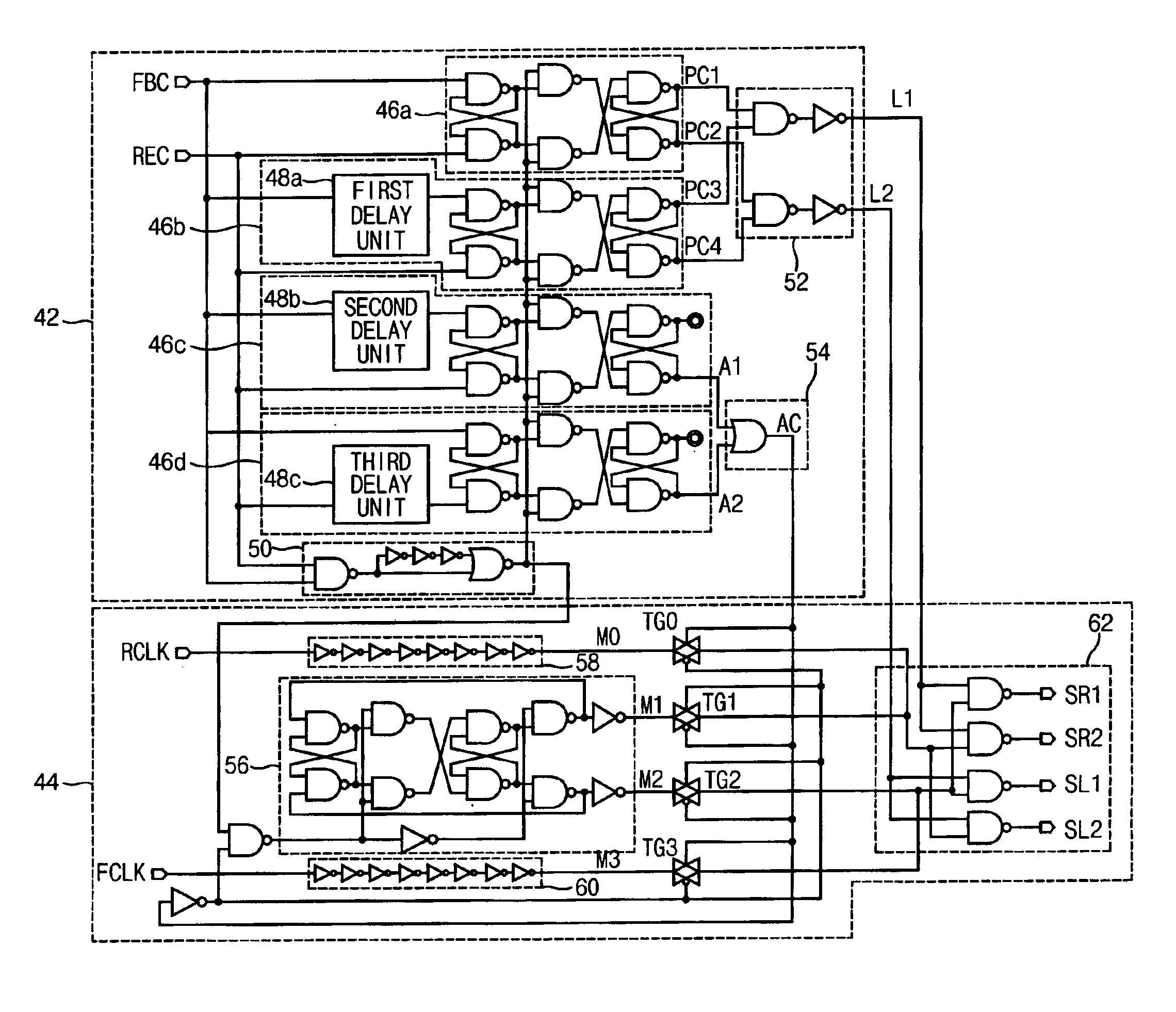

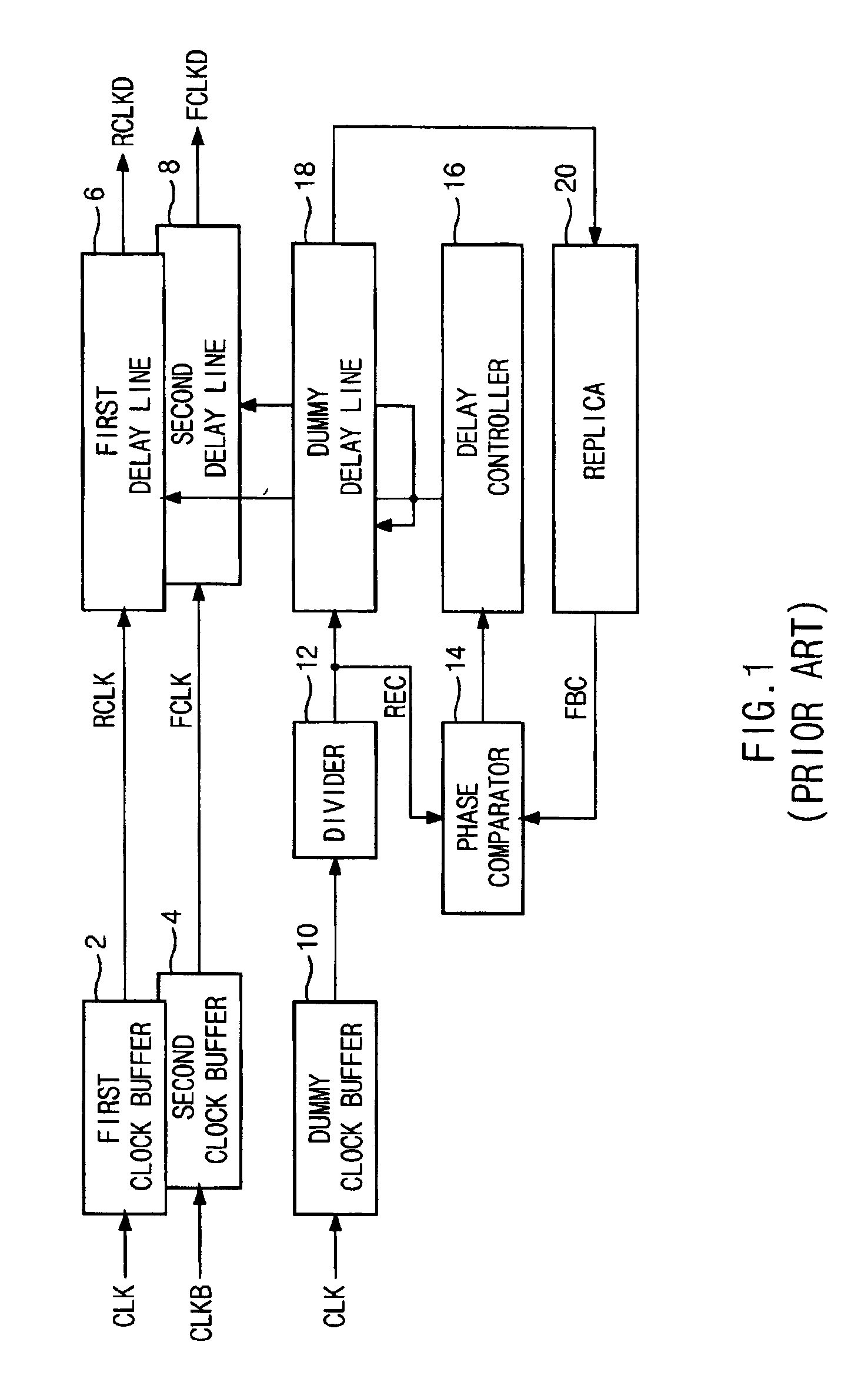

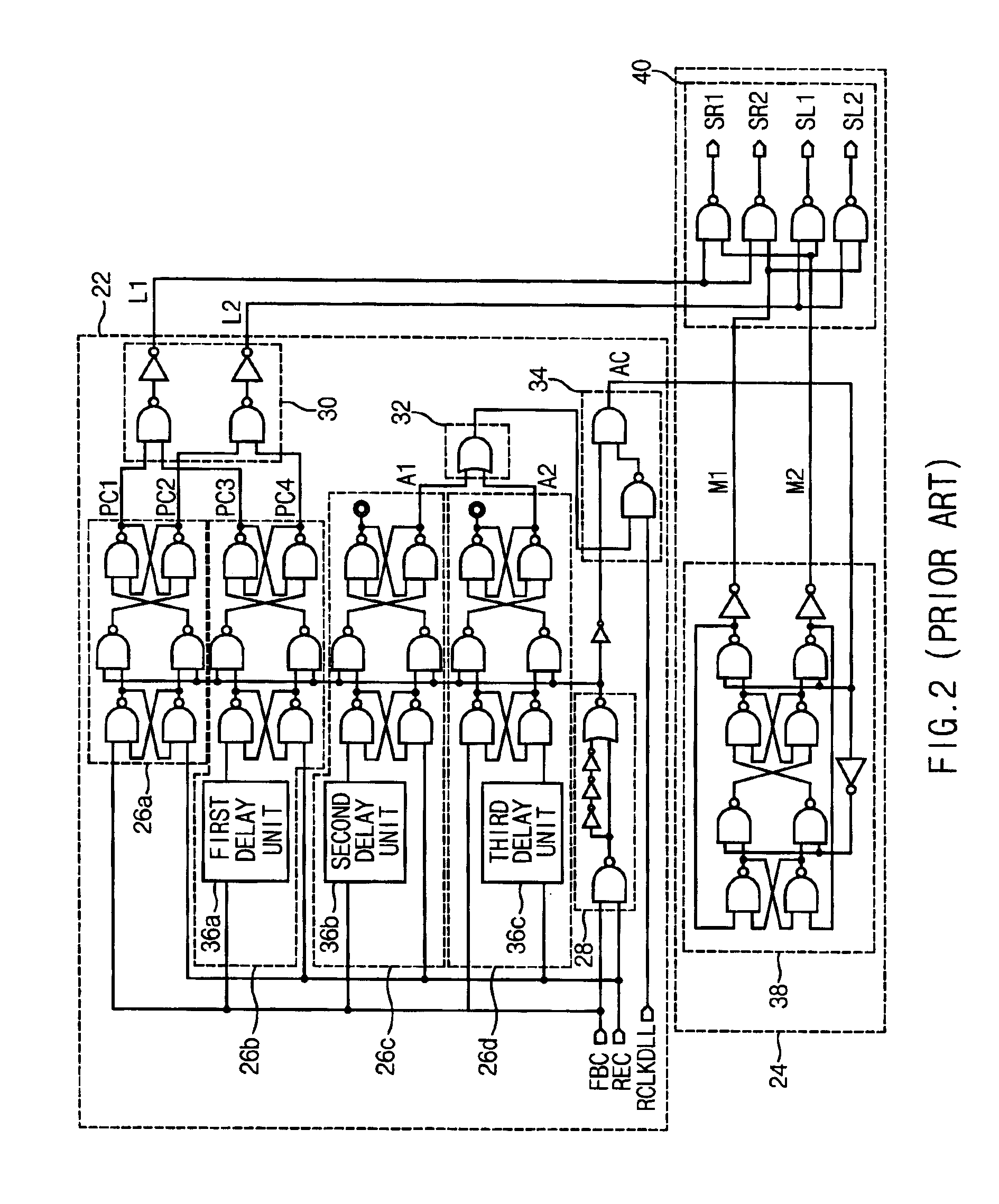

Delay locked loop having phase comparator

ActiveUS6894539B2Shorten lock timePulse automatic controlVoltage-current phase angleShift registerDelay-locked loop

A delay locked loop features a phase comparator. The phase comparator compares a phase of a reference clock signal obtained by dividing a buffered external clock signal with a phase of a feedback clock signal considering delay time of delay lines and inside circuits, and controls a shift register for controlling the delay lines in response not only a rising clock signal outputted from a clock buffer but also a falling clock signal depending on the comparison result, thereby rapidly locking an initial phase and tracking the phase in spite of fast delay variations by external noises.

Owner:SK HYNIX INC

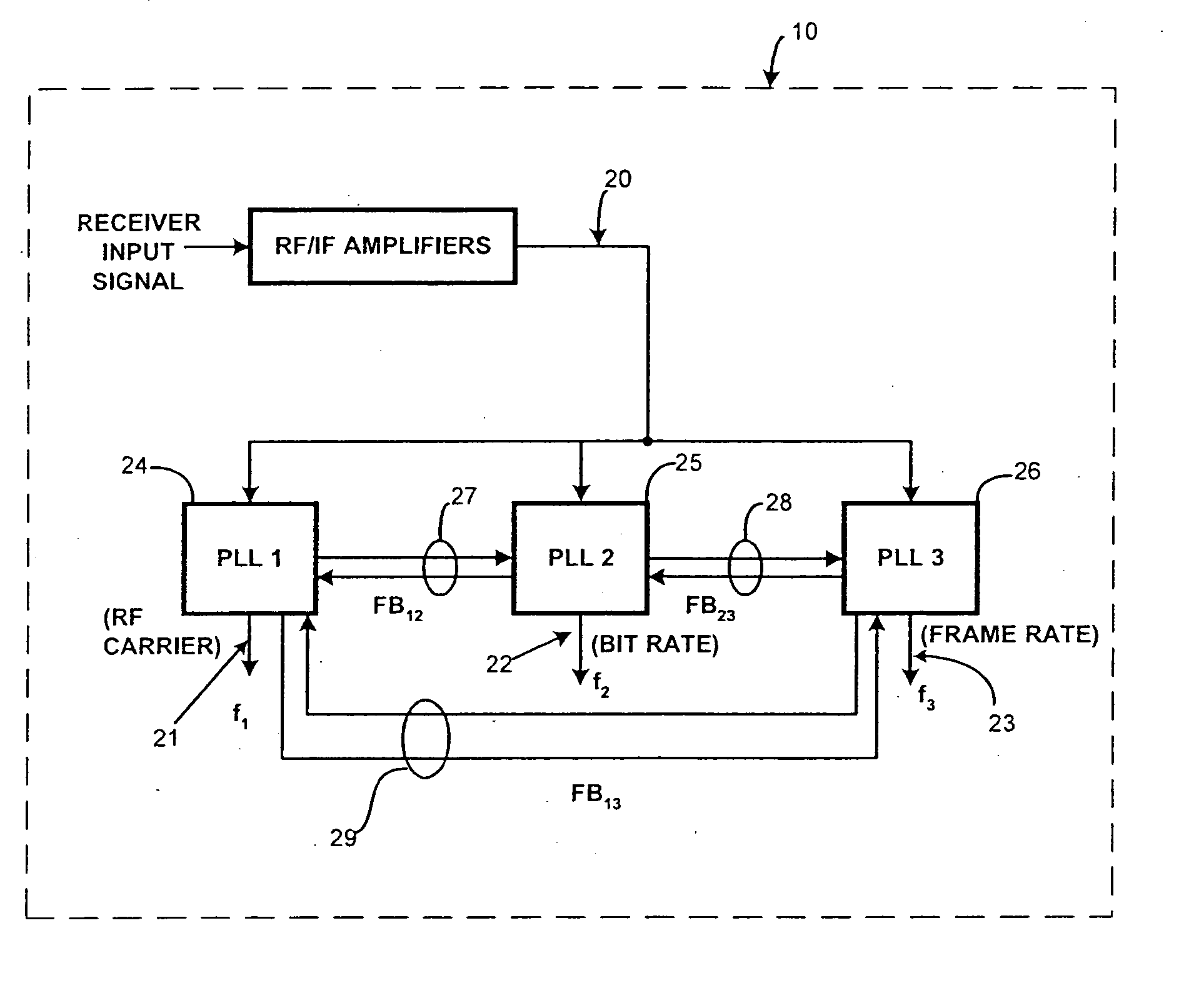

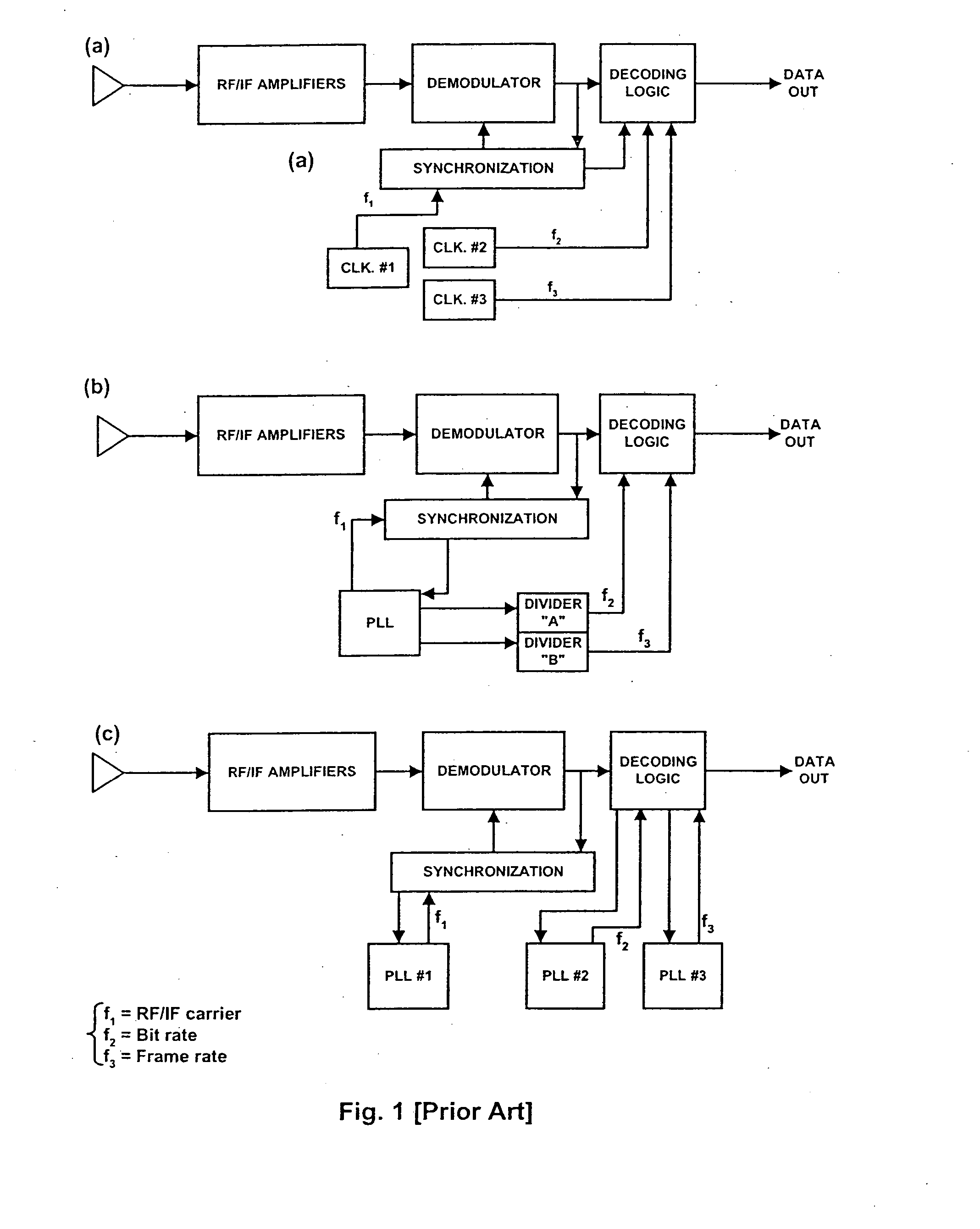

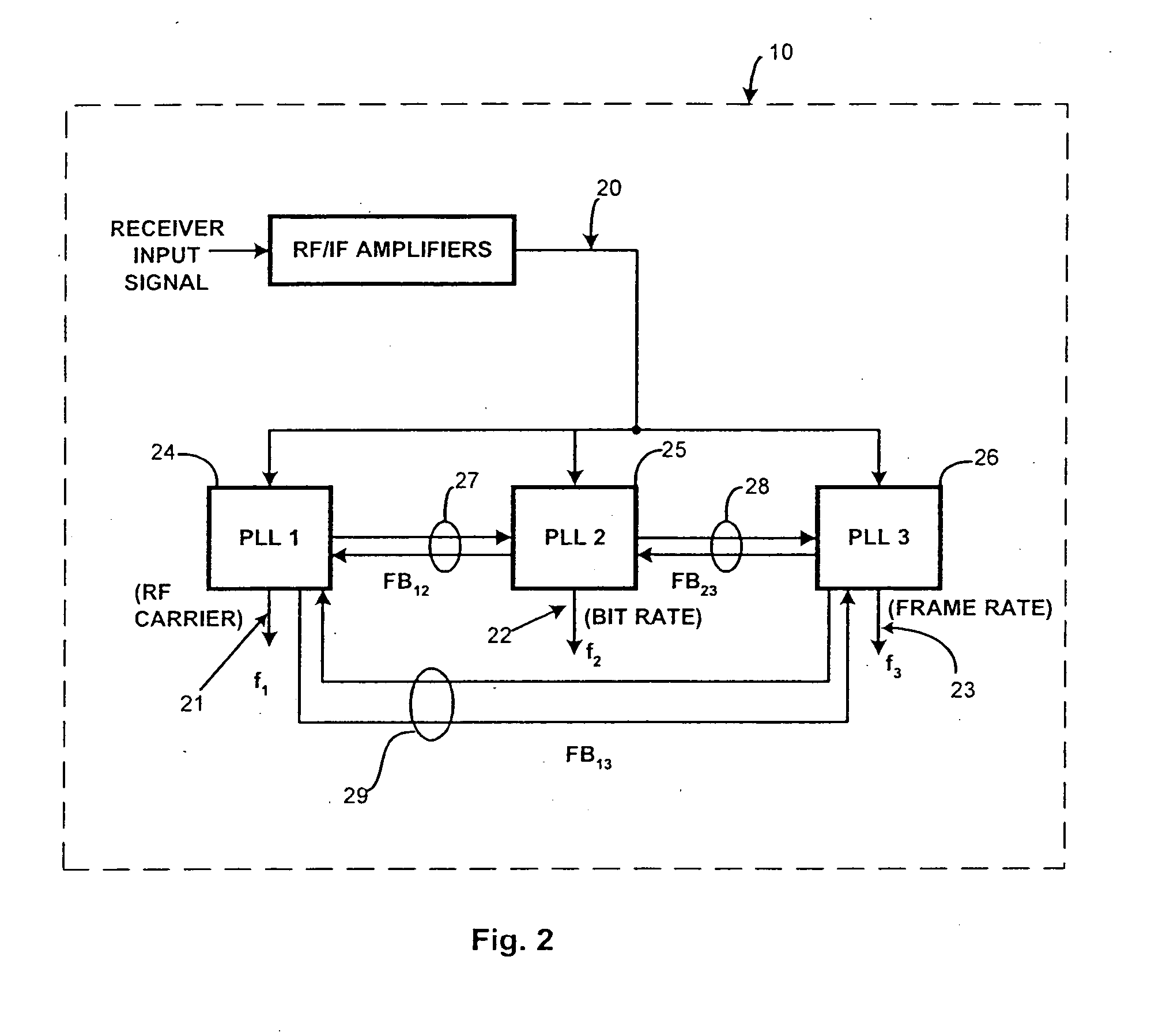

Digital-data receiver synchronization

InactiveUS20040105516A1Fast lock-up timeAvoids loss of lockPulse automatic controlTime-division multiplexDigital dataPhase frequency detector

An improved digital-data receiver synchronization apparatus and method is provided wherein memory devices in the receiver such as phase-lock loops are provided with composite phase-frequency detectors, mutually cross-connected comparison feedback means, or both to provide robust reception of digital data signals. The apparatus and method are preferrably utilized with synchronous architecture wherein a single master clock is used to provide frequency signals to the memory devices, and also can be used with asynchronous architecture. The apparatus and method provide fast lock-up times in moderately to severely noisy conditions and have improved tolerances to clock asymmetries.

Owner:UT BATTELLE LLC

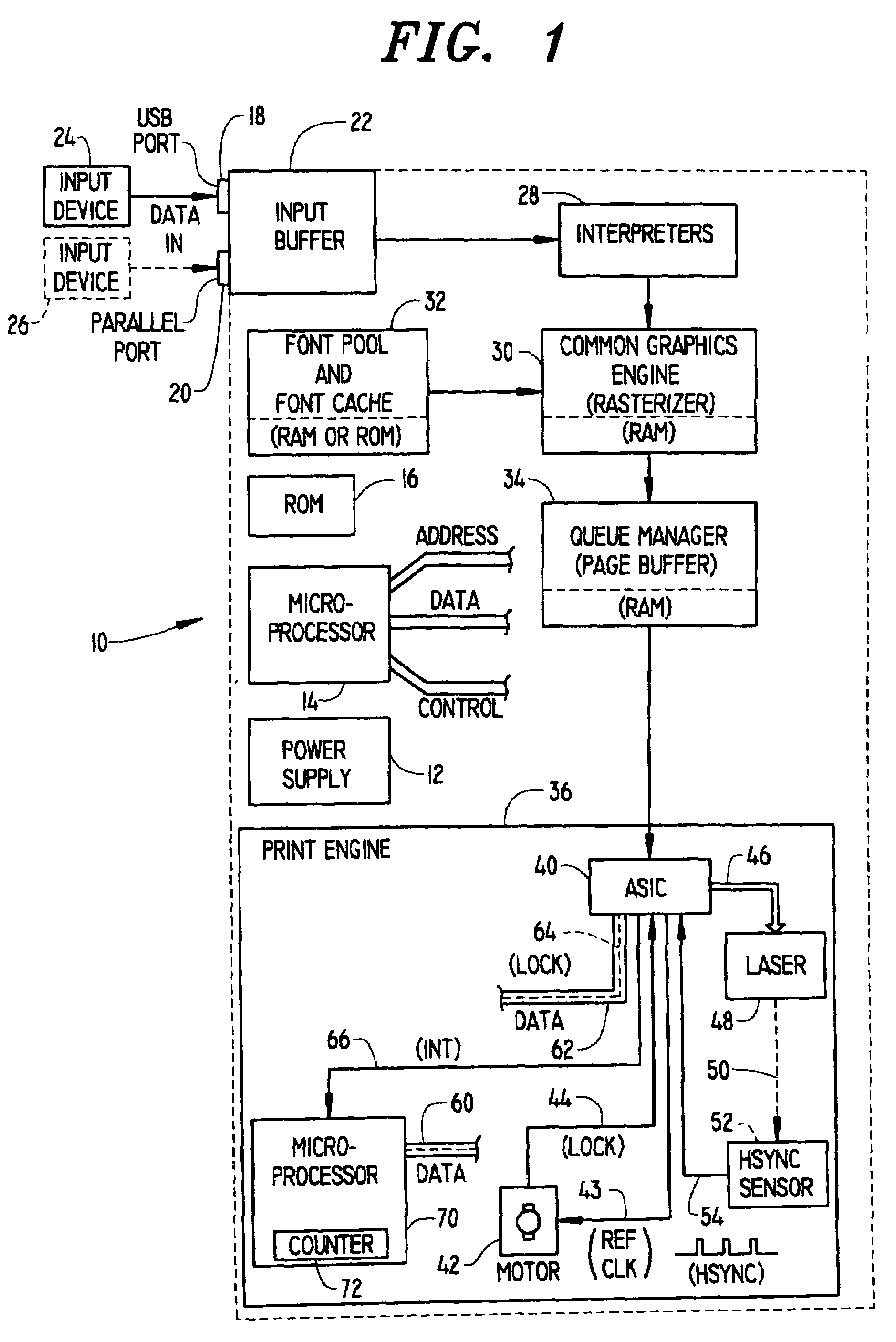

Dynamic time to first print selection

ActiveUS7136089B2Fast timeFaster print timeElectrographic process apparatusOther printing apparatusComputer scienceHigh velocity

Owner:LEXMARK INT INC +1

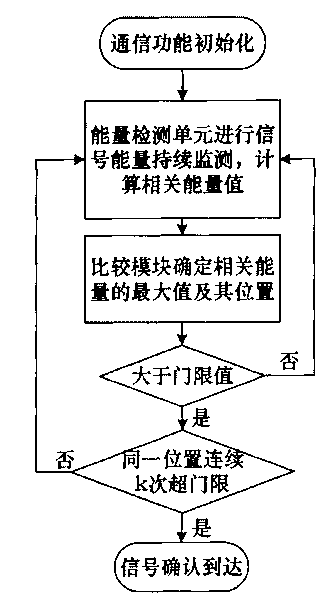

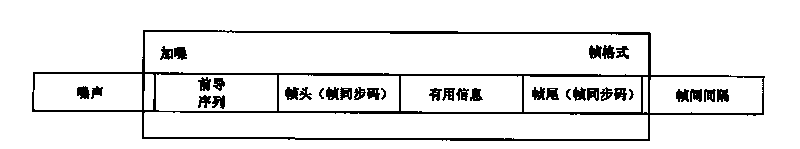

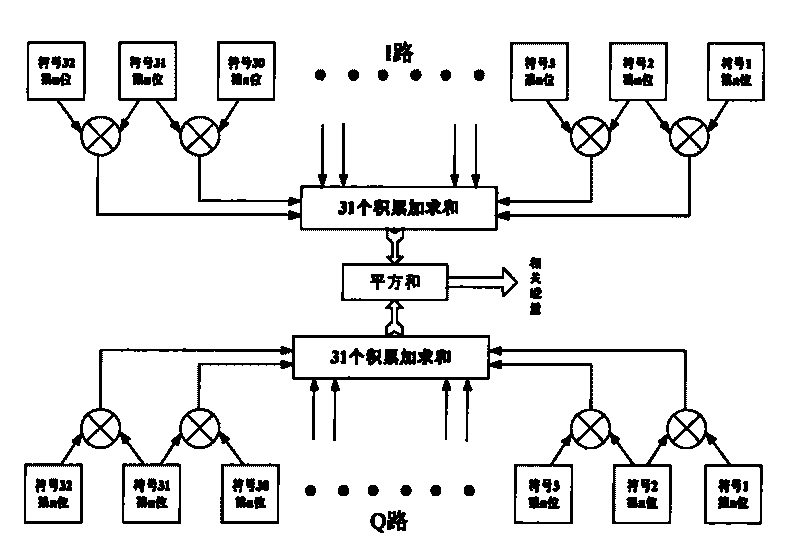

Signal arrival detection method suitable for downlink data link communication of unmanned plane

InactiveCN101707494AShorten lock timeAccurate demodulationRadio transmission for post communicationFunctional moduleDemodulation

The invention discloses a signal arrival detection method suitable for downlink data link communication of an unmanned plane, which comprises the following steps: firstly, initializing functions of a communication system; secondly, performing signal energy continuous monitoring and calculating correlation energy values by an energy detection unit; thirdly, determining the maximum value and the position of correlation energy by a comparison module; and fourthly, confirming the arrival of signals. The signal arrival detection method shortens the time for locking a synchronizing functional module of a demodulation terminal, and determines the optimal initial sampling point on the basis of the arrival of detection signals, and the position of the optimal sampling point is the position of the maximum value of the energy. The signal arrival detection method can ensure accurate demodulation of the signals and reduce the error rate, and has good stability.

Owner:BEIHANG UNIV

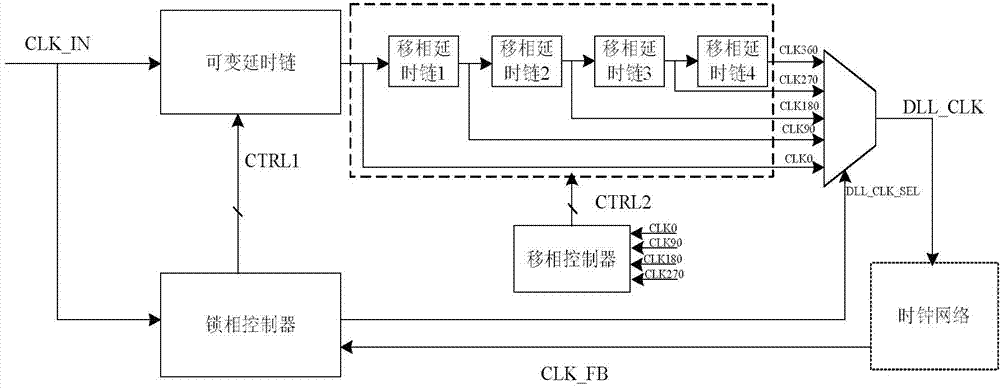

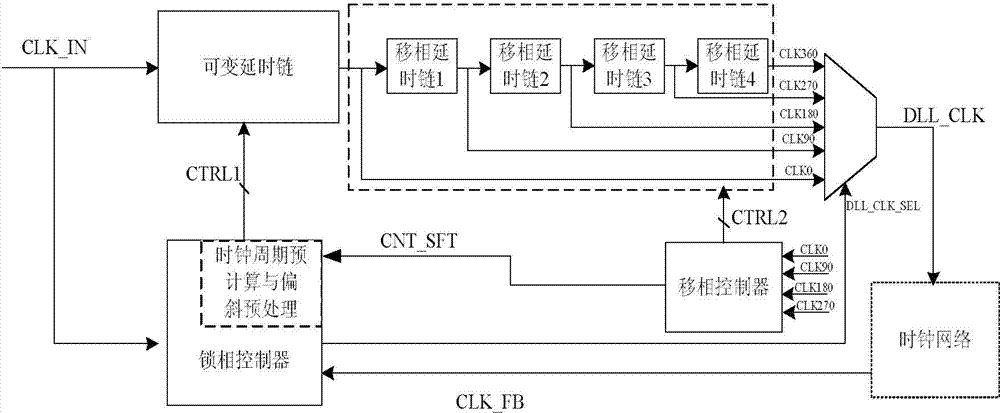

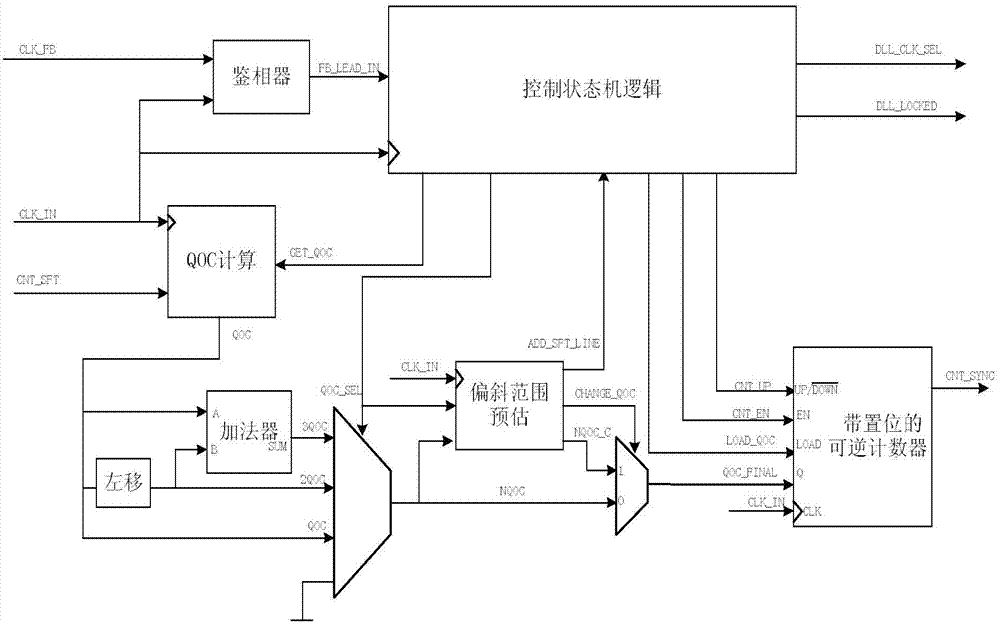

Periodical precomputation and skew compensation circuit and method for delaying locking loop in FPGA chip thereof

InactiveCN103905038AShorten lock timeBalance lock timePulse automatic controlPhase shiftedPhase locking

The invention discloses a periodical precomputation and skew compensation circuit and a method for delaying a locking loop in a FPGA chip of the periodical precomputation and skew compensation circuit. On the basis of an original traditional DLL locking method, the periodical precomputation technology and the skew preprocessing technology are adopted for two-level processing of clock skew in the FPGA chip, and under the conditions that system stability is maintained and hardware expenses are not increased, the clock skew is removed rapidly, and locking is achieved. According to the method, in the phase locking process of a DLL structure, first-level digital logic computes and loads a preprocessed skew value according to periodical information digitized by a phase shift delay link, and then clock locking is completed by means of second-level counting approximation processing based on the preprocessed skew value. By means of the method, locking time can be effectively shortened, the method is particularly suitable for an occasion with a high demand for low-frequency skew compensation, phase locking time within a DLL operating frequency range can be balanced, and FPGA internal clock management performance can be improved.

Owner:SOUTHEAST UNIV

Impedance-controlled pseudo-open drain output driver circuit and method for driving the same

InactiveUS7579861B2Minimize occurrenceShorten lock timeReliability increasing modificationsElectronic switchingDriver circuitState variation

An impedance-controlled pseudo-open drain output driver circuit includes: a process, voltage, and temperature (PVT) detector configured to have a delay line receiving a reference clock and detect a state variation of the delay line according to PVT conditions to output detection signals; a select signal generator configured to generate a driving select signal based on the detection signals and an output data; and an output driver configured to drive an output terminal, the output driver including a plurality of pull-up / pull-down driving blocks controlled by the driving select signal, each of the pull-up / pull-down driving blocks including a resistor having an intended impedance.

Owner:SK HYNIX INC

Portable electric driven compressed air gun

InactiveCN1798954ASimple structureEasy to operateFiring/trigger mechanismsCompressed gas gunsElectricityEngineering

A portable electric motor driven air gun powered by a power source. The motor is coupled to a lead screw, which drives a piston. The piston compresses air in a chamber producing high-pressure air. When sufficient energy is stored within the air stream by the piston a valve opens which releases the air to act on the projectile. The compressed air is used to push a projectile such as a paintball, an airsoft ball, a ''bb'', or a pellet through a barrel. The lead screw is then reversed and the piston is reset for the next shot. The piston is preferably coupled to a feeding mechanism to facilitate positioning of the projectile for firing. The direction speed and operative modes of the gun are preferably controlled with an electric circuit. The power source is preferably rechargeable and allows the air gun to be operated completely independent from either a wall outlet or a compressed air supply.

Owner:TRICORD SOLUTIONS

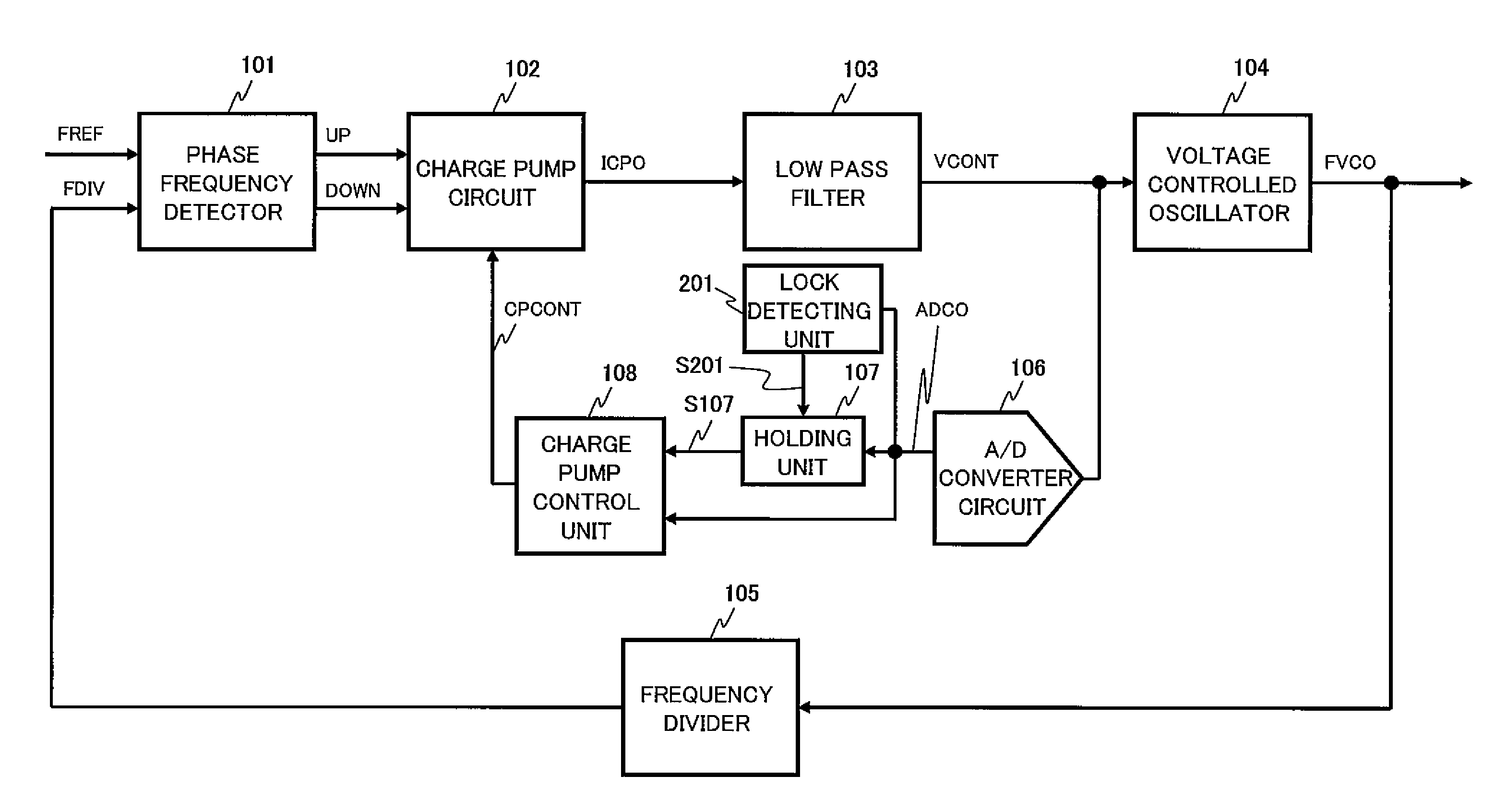

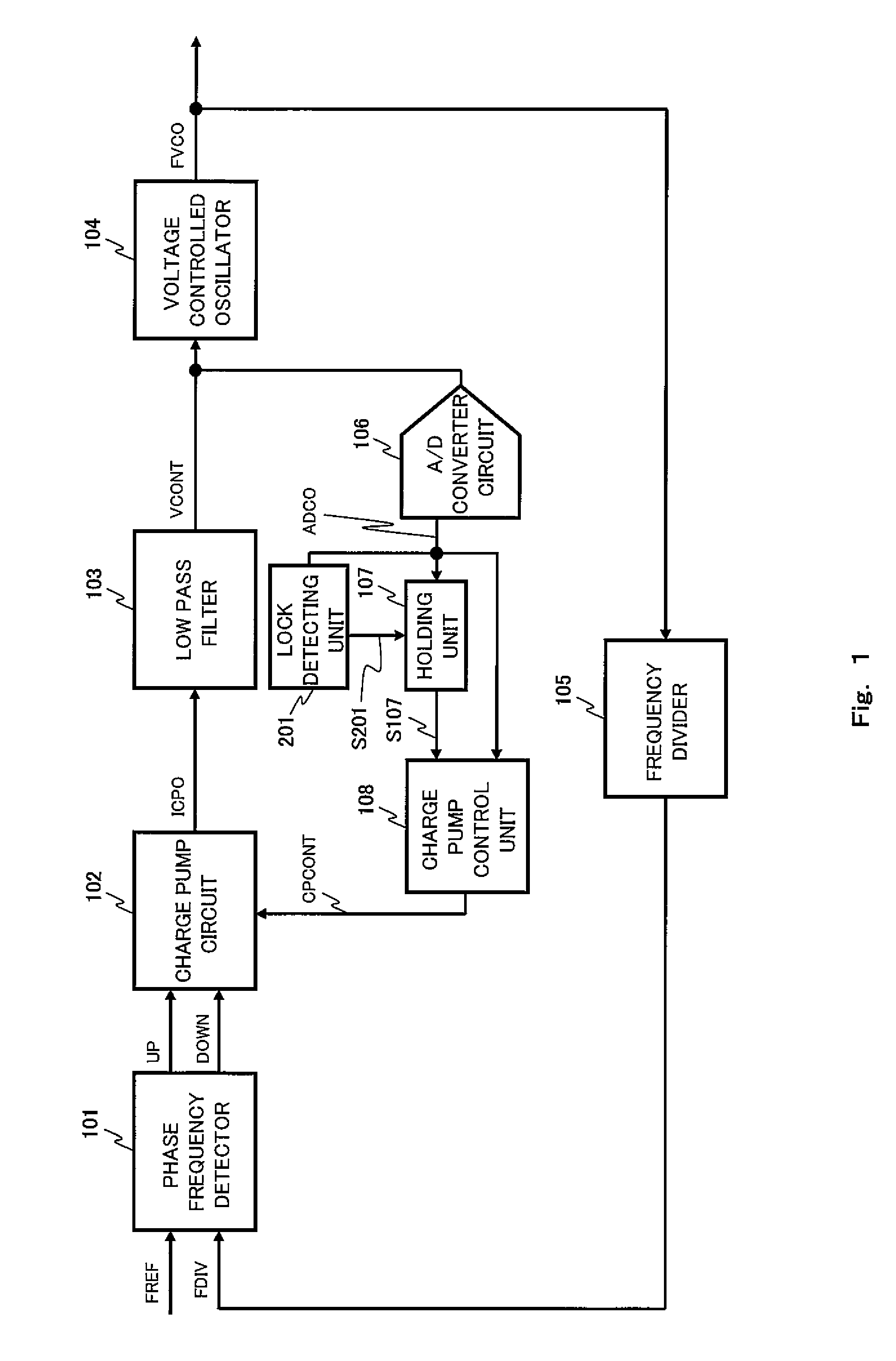

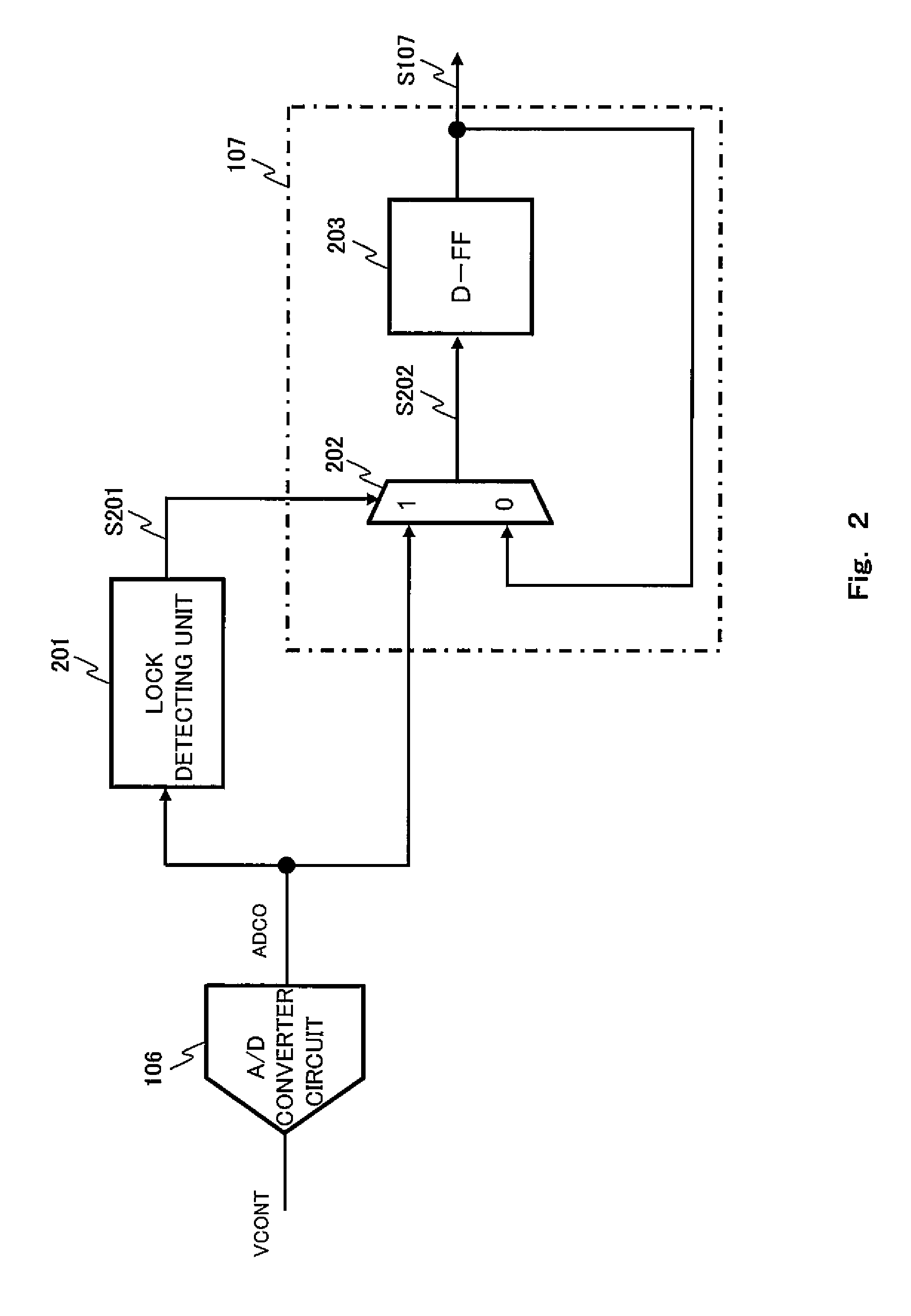

Pll circuit

InactiveUS20110304366A1Shorten lock timeReduced referencePulse automatic controlControl signalPhase difference

A PLL circuit comprises a phase frequency detector configured to output a phase frequency difference signal with a pulse duration according to a phase difference and a frequency difference between a reference clock signal and a feedback clock signal according to an output clock signal; a charge pump circuit configured to output a charge pump current which is an output current according to the phase frequency difference signal and reduce a charge pump current amount in accordance with a charge pump current amount control signal for reducing the charge pump current amount stepwisely; and a lock detecting unit configured to detect whether or not the feedback clock signal is locked to the reference clock signal and output a lock detection signal when detecting a lock of the reference clock signal and the feedback clock signal

Owner:PANASONIC CORP