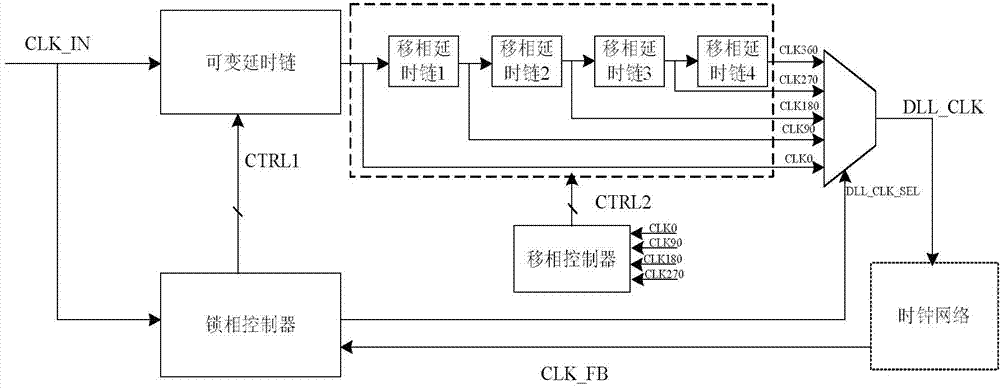

Periodical precomputation and skew compensation circuit and method for delaying locking loop in FPGA chip thereof

A pre-calculation and periodic technology, applied in the direction of electrical components, automatic power control, etc., can solve the problems of large resource consumption and long lock time, and achieve the effect of balancing phase lock time, shortening lock time, and improving clock management performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0067] Below in conjunction with specific embodiment, further illustrate the present invention, should be understood that these embodiments are only used to illustrate the present invention and are not intended to limit the scope of the present invention, after having read the present invention, those skilled in the art will understand various equivalent forms of the present invention All modifications fall within the scope defined by the appended claims of the present application.

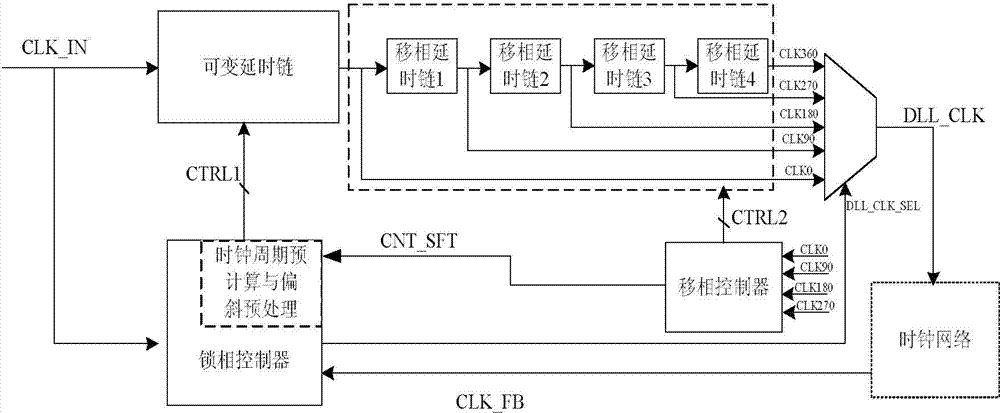

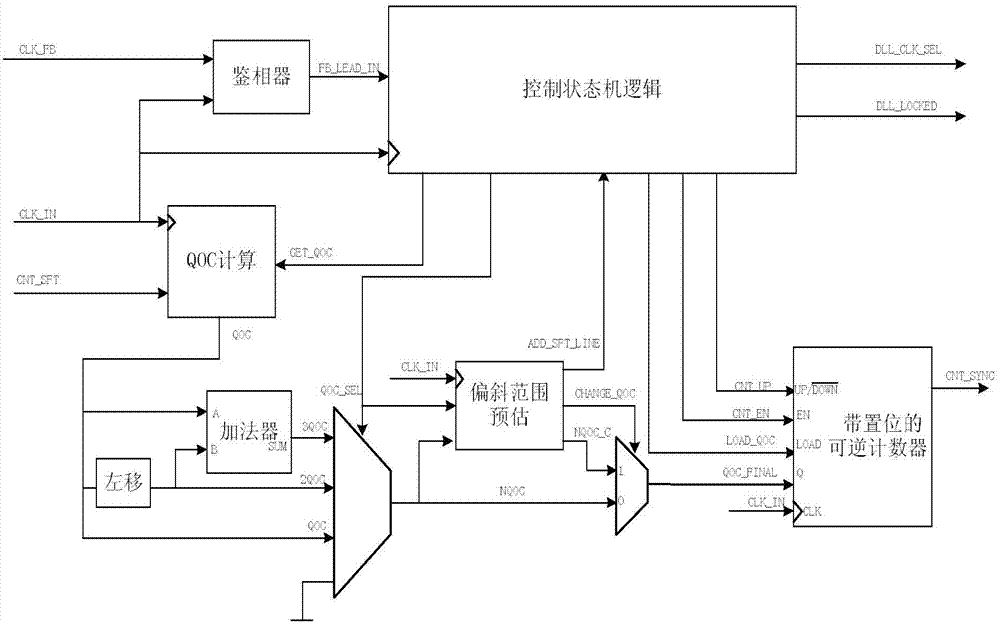

[0068] Such as Figure 2-3 As shown, the DLL is based on the phase-locked controller of the period pre-calculation and skew compensation control circuit inside the DLL. The circuit structure includes: QOC calculation circuit module, left shifter, adder, four-to-one multiplexer, two-to-one multiplexer , Skew range estimation circuit, reversible counter with setting, phase detector and control state machine logic;

[0069]The QOC calculation circuit module inputs the phase-shift delay link input ad...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More