Patents

Literature

929results about "Phase shifting networks" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

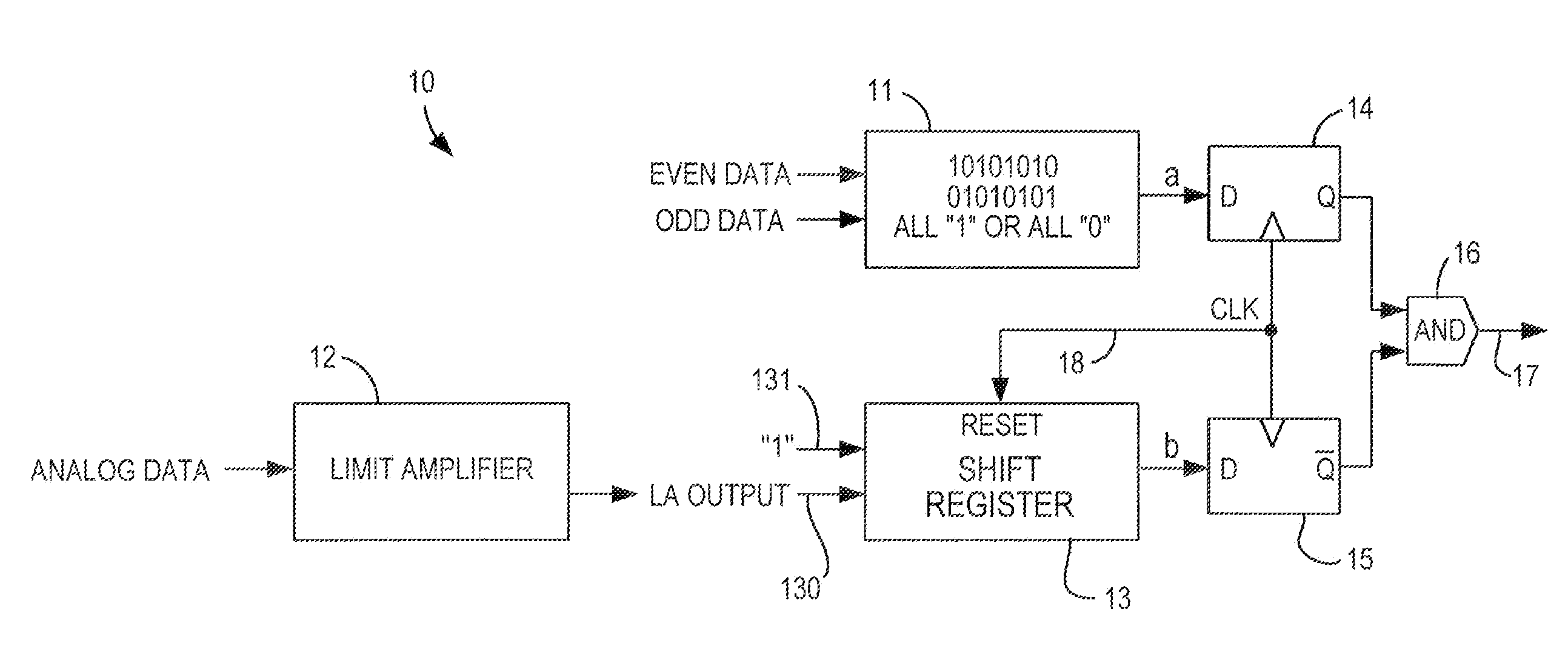

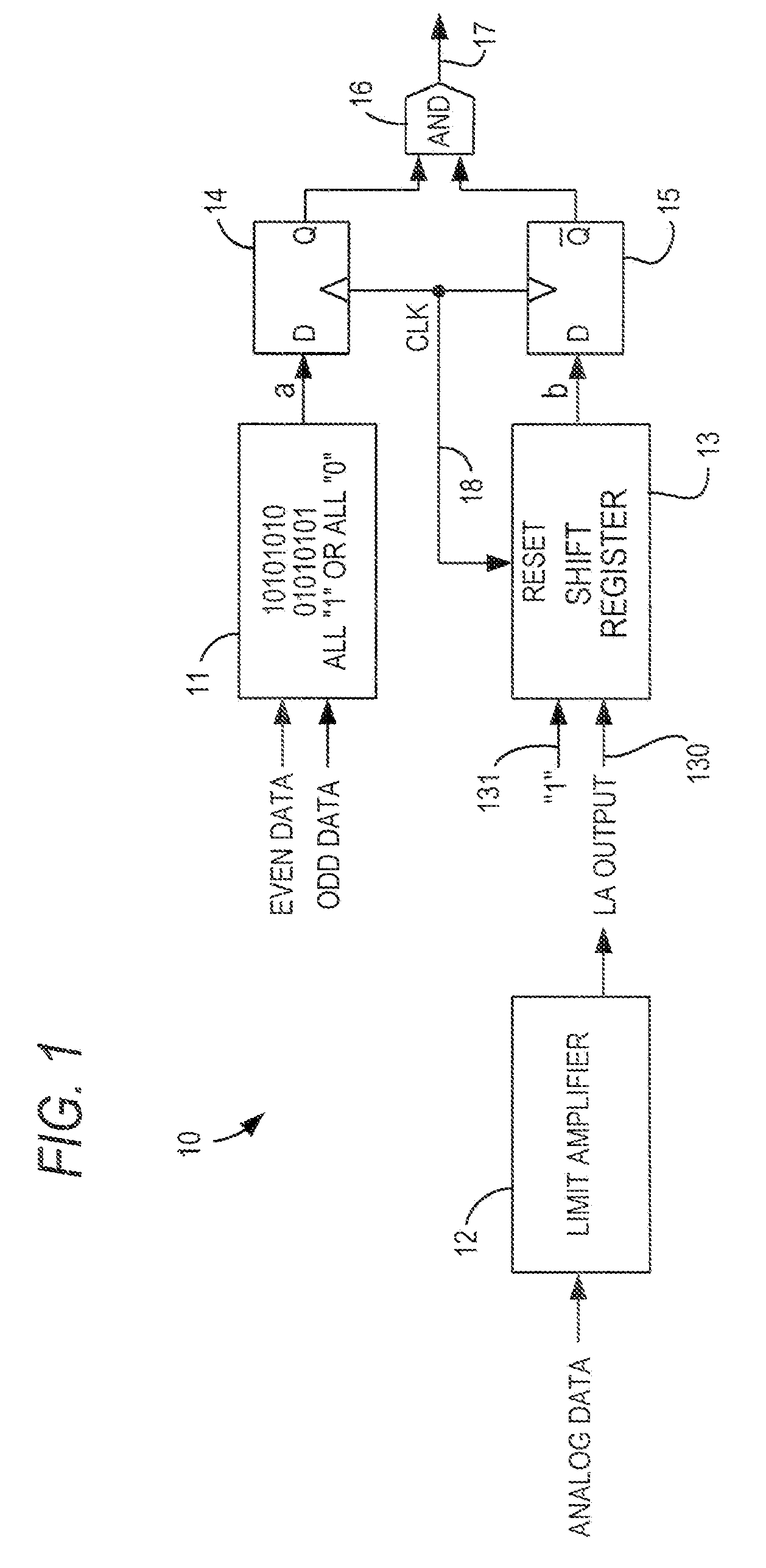

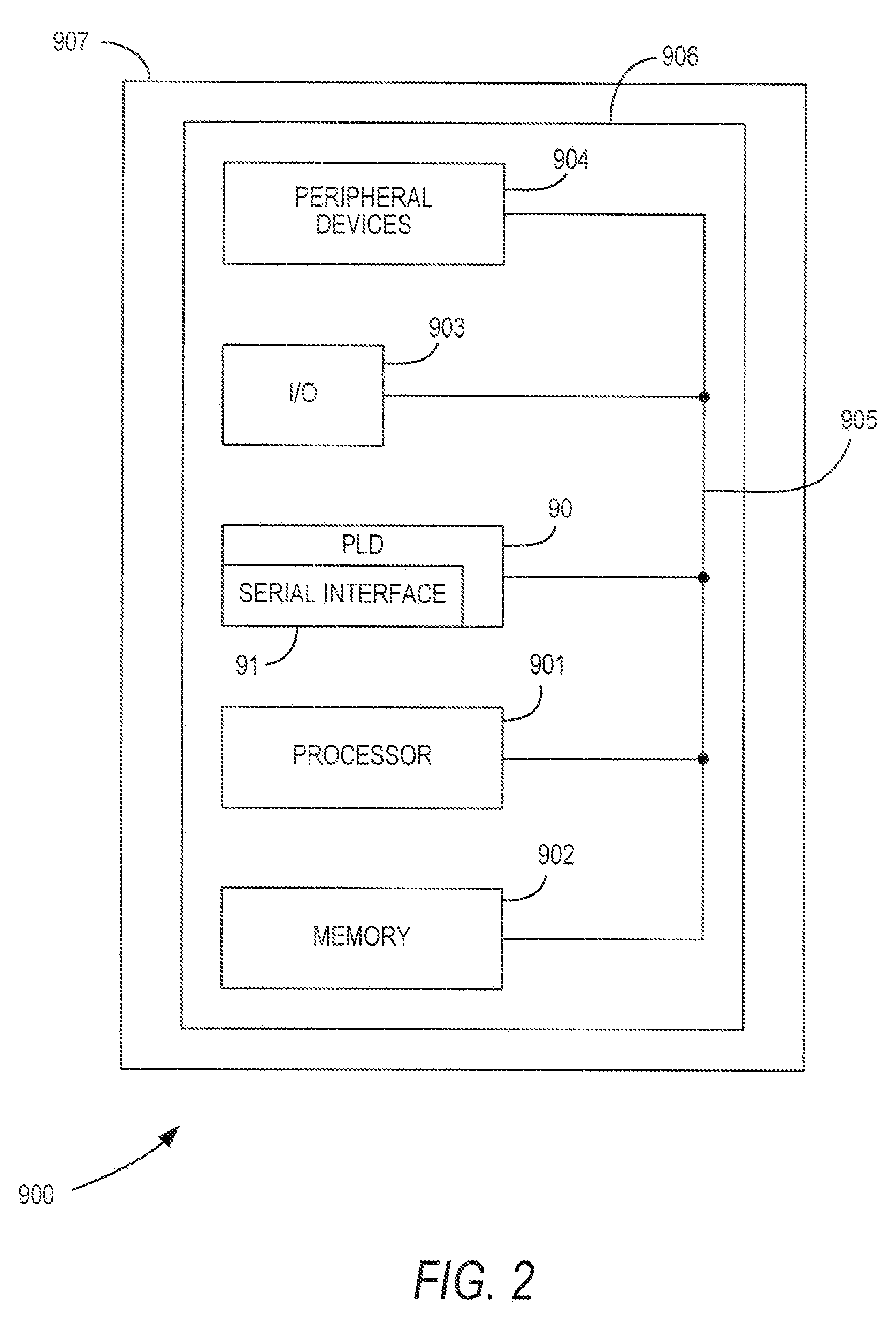

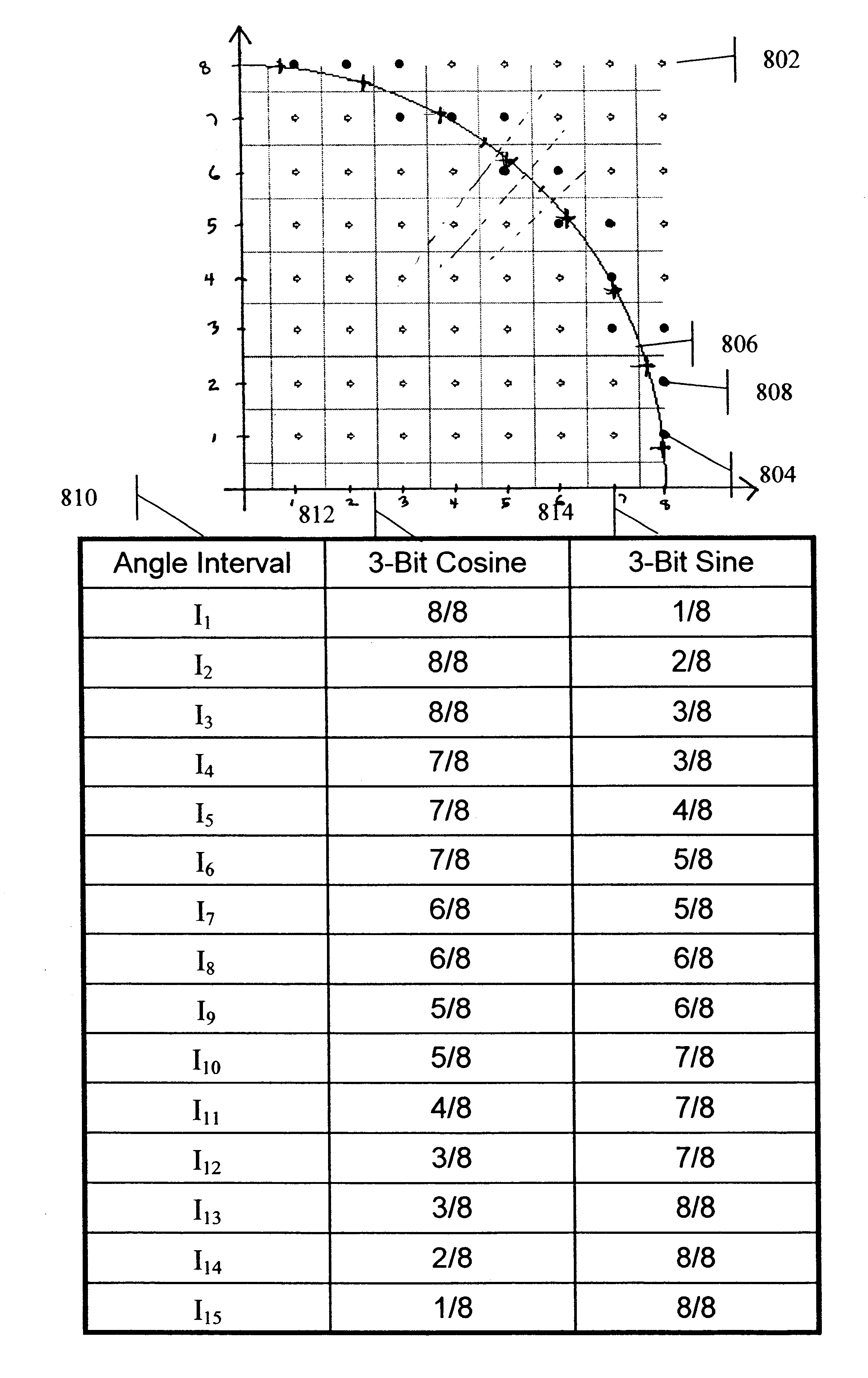

Signal loss detector for high-speed serial interface of a programmable logic device

InactiveUS7996749B2Multiple-port networksData representation error detection/correctionPattern matchingProgrammable logic device

Owner:ALTERA CORP

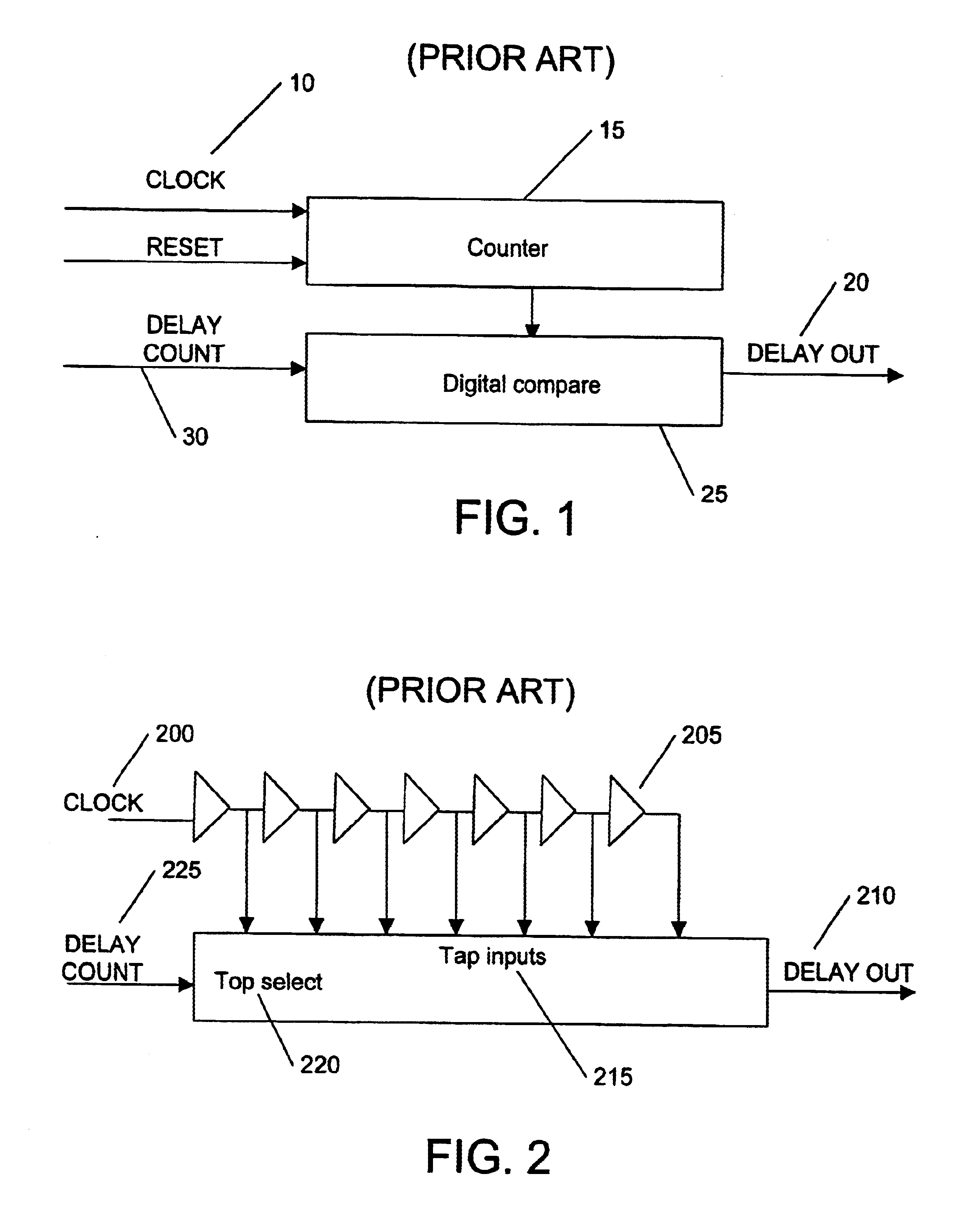

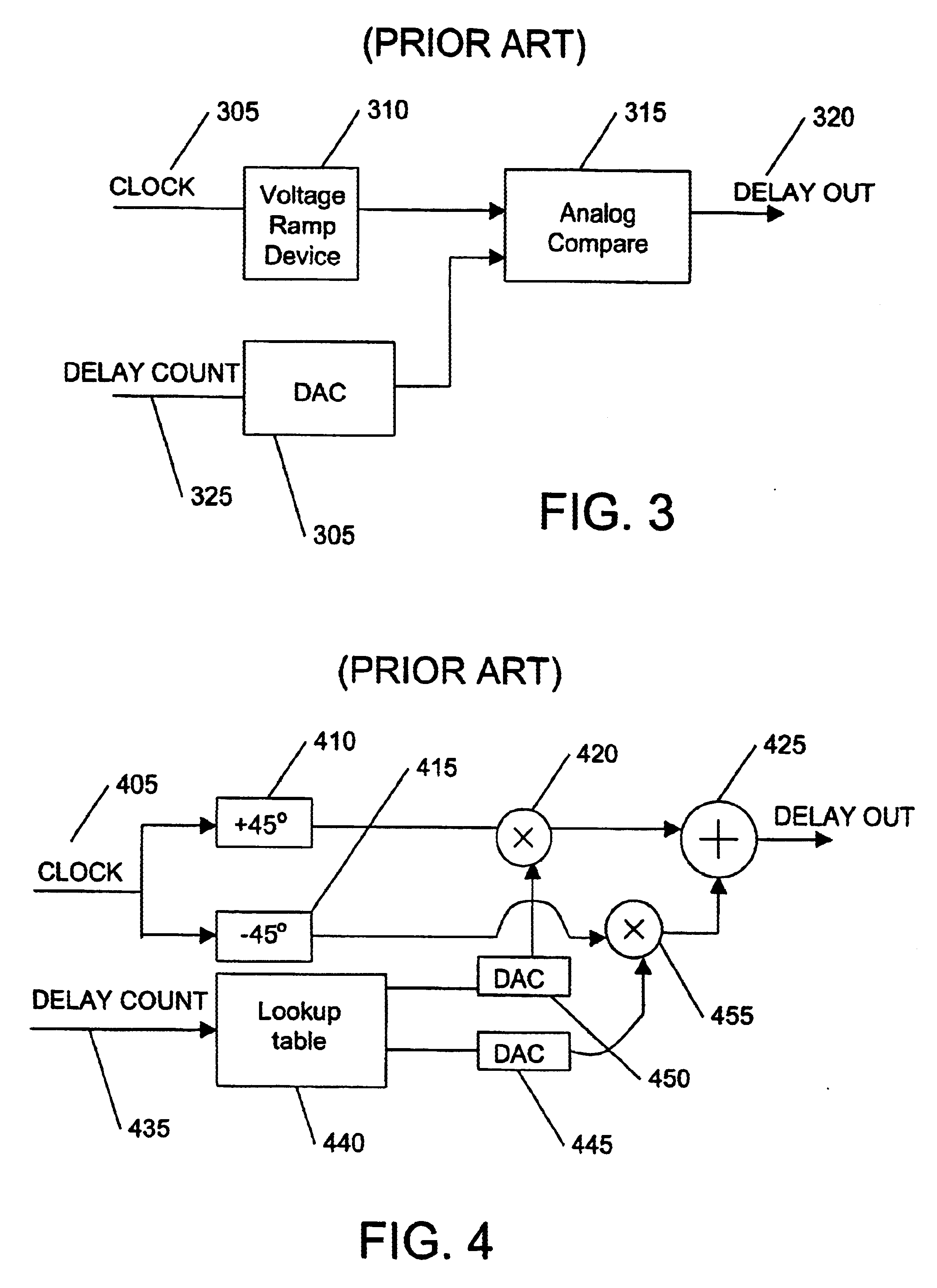

Method and apparatus for implementing precision time delays

Owner:TDC ACQUISITION HLDG

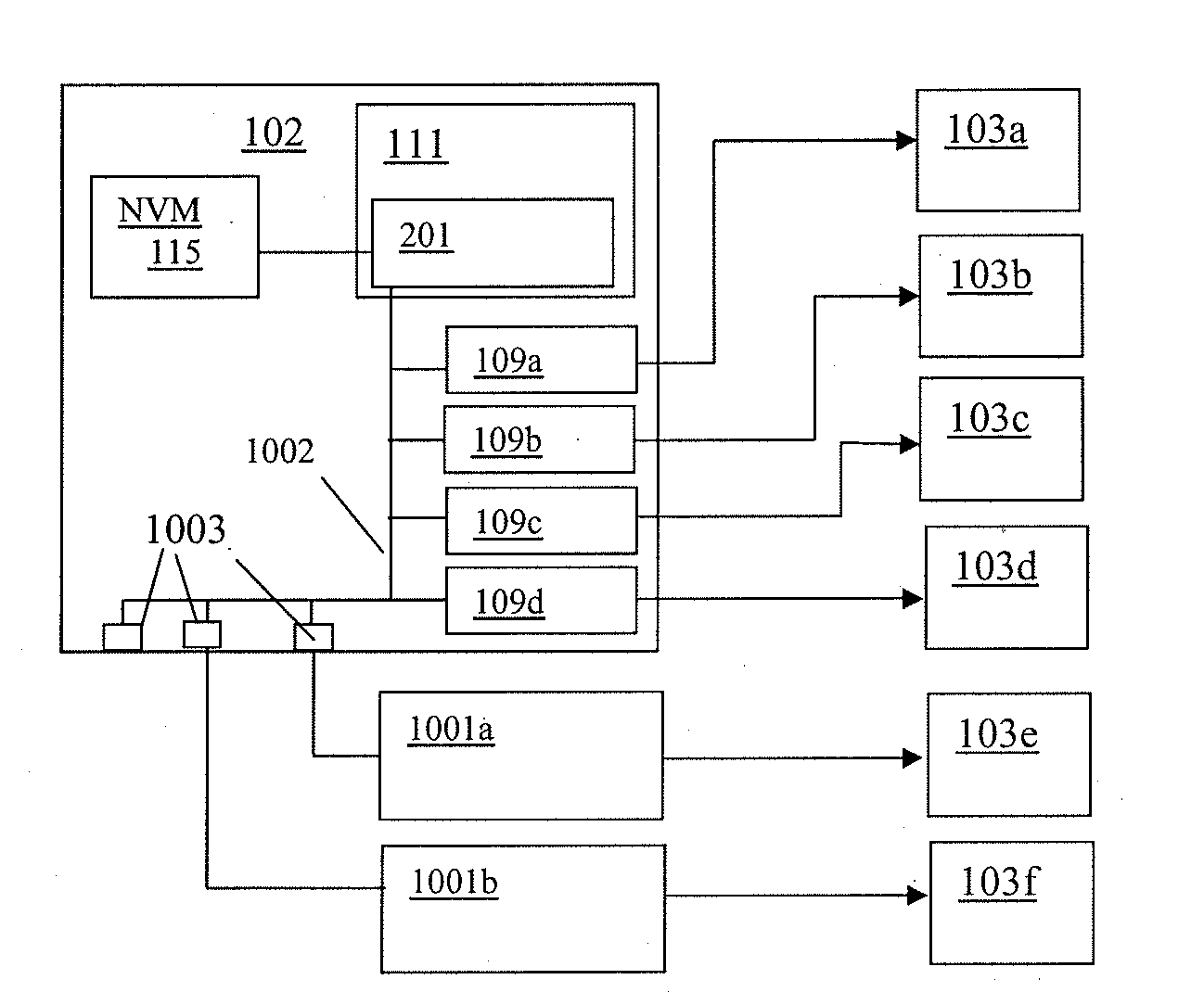

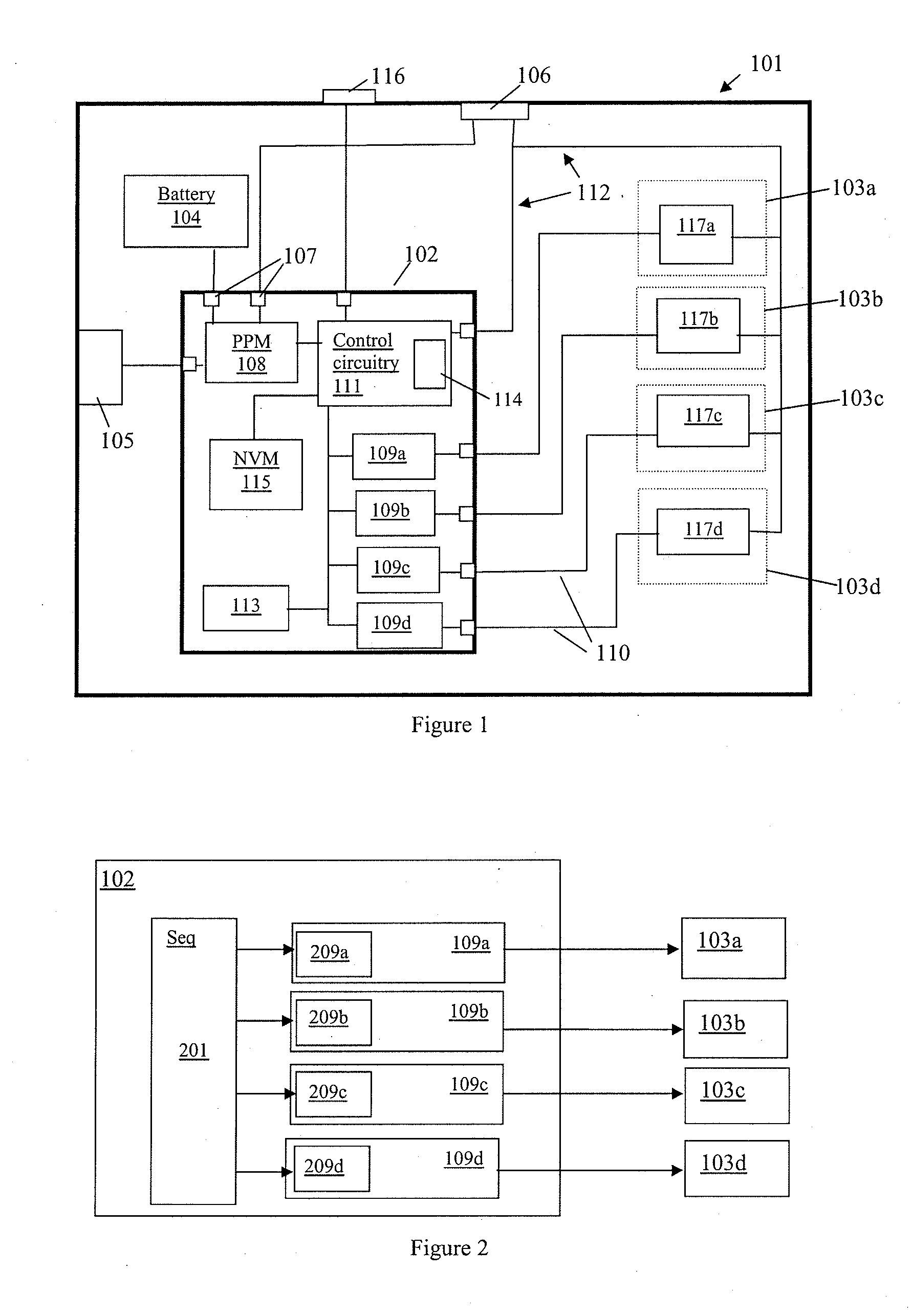

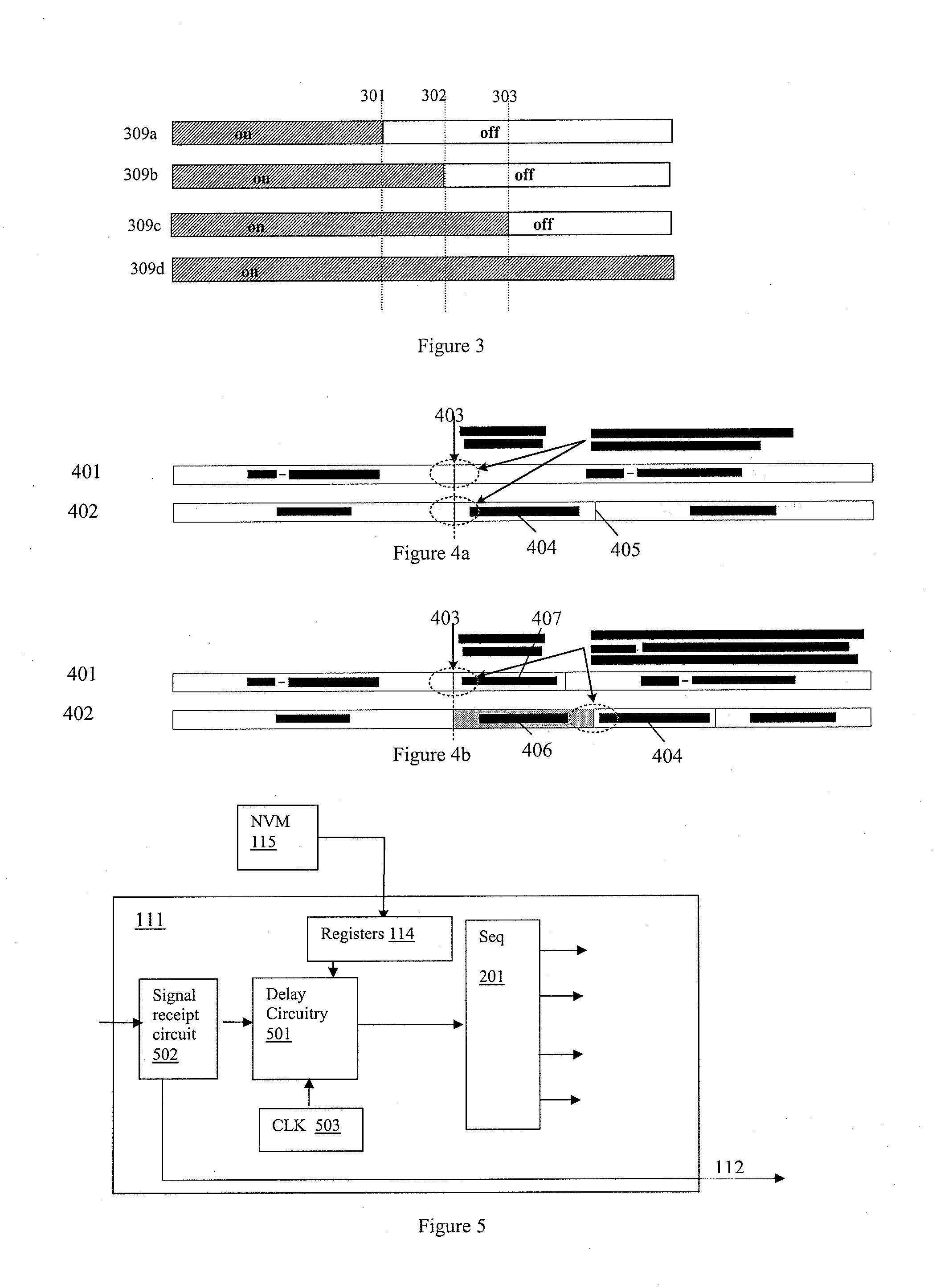

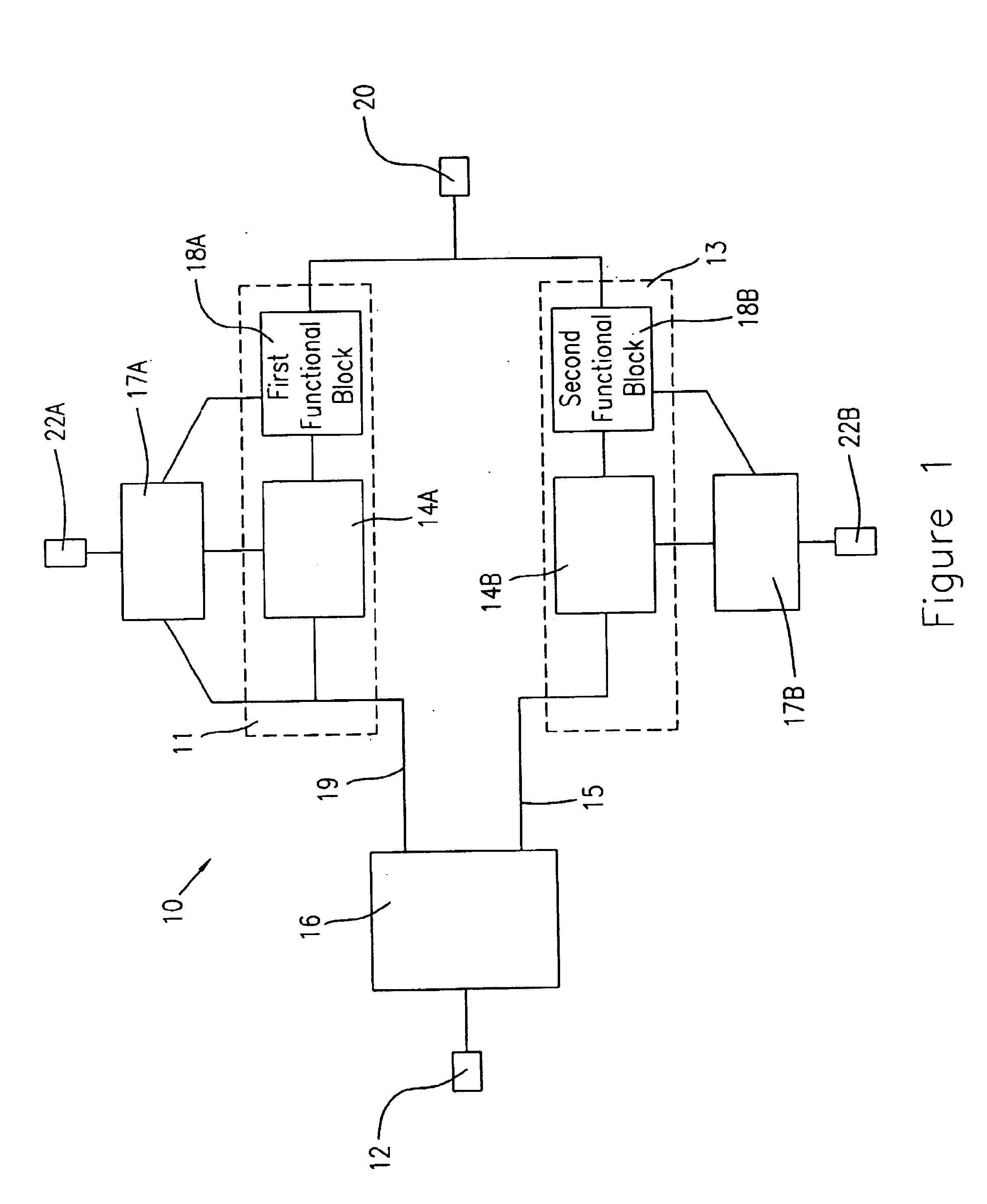

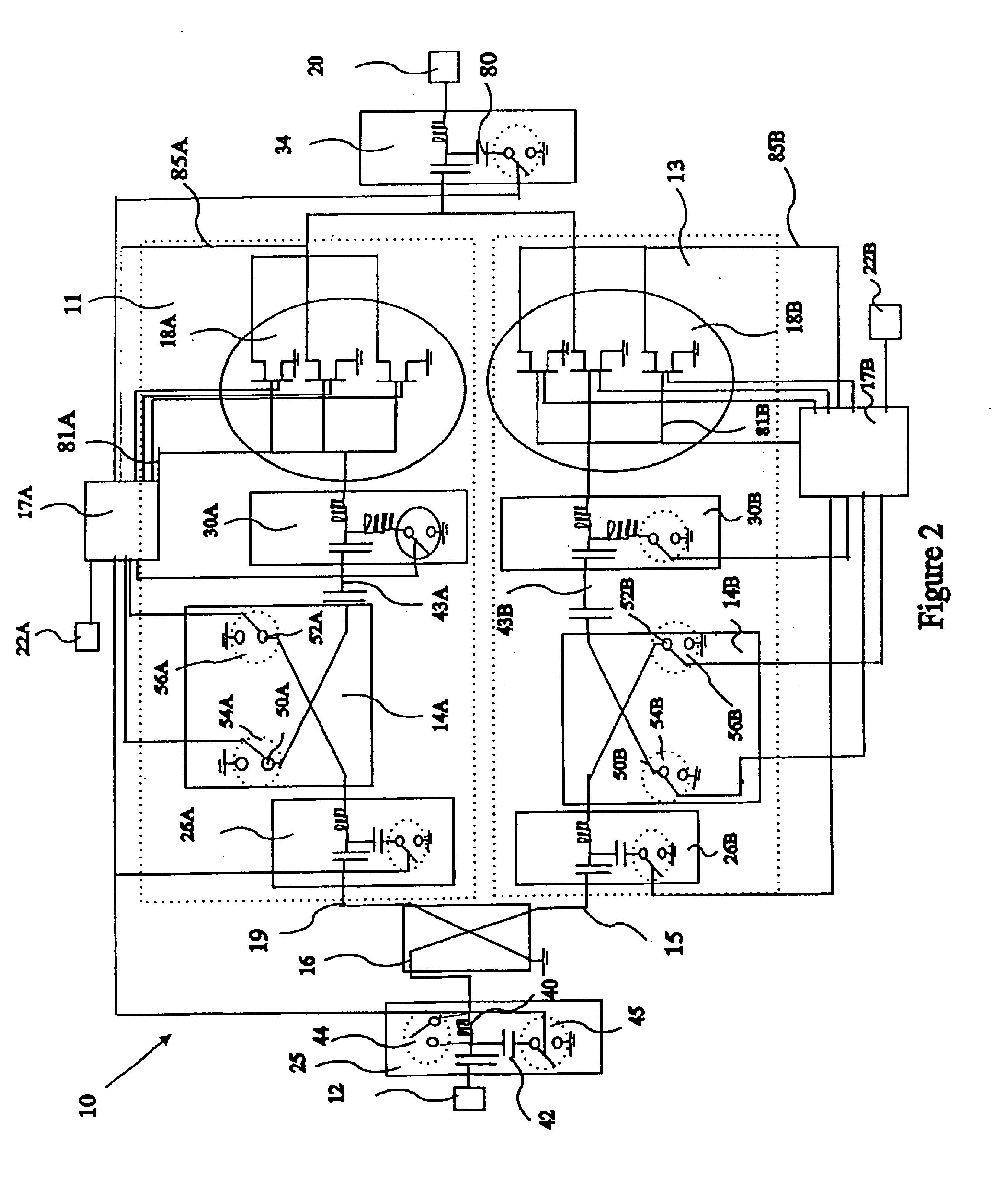

Power management apparatus and methods

ActiveUS20110022859A1Precise processingDc network circuit arrangementsVolume/mass flow measurementControl powerIntegrated circuit

Power management integrated circuits (PMICs) and related methods. In one aspect a PMIC which is operable to provide a plurality of PMIC power states is arranged to provide a predetermined delay before a power state transition. The delay is applied after receipt by the PMIC control circuitry of a power state transition command. Applying a delay allows time for the system powered by the PMIC to perform any necessary shut-down procedures and terminate active processes before power is removed, preventing corruption of the system. The delay is preferably configurable. The PMIC may also be arranged to control power converters which are external to the PMIC. In another aspect the PMIC has translation circuitry for providing the control settings of one power block, e.g. power converter, with any necessary modifications to be used by another power block. This means that only one set of control settings needs to be updated to change the output of both power blocks simultaneously.

Owner:CIRRUS LOGIC INC

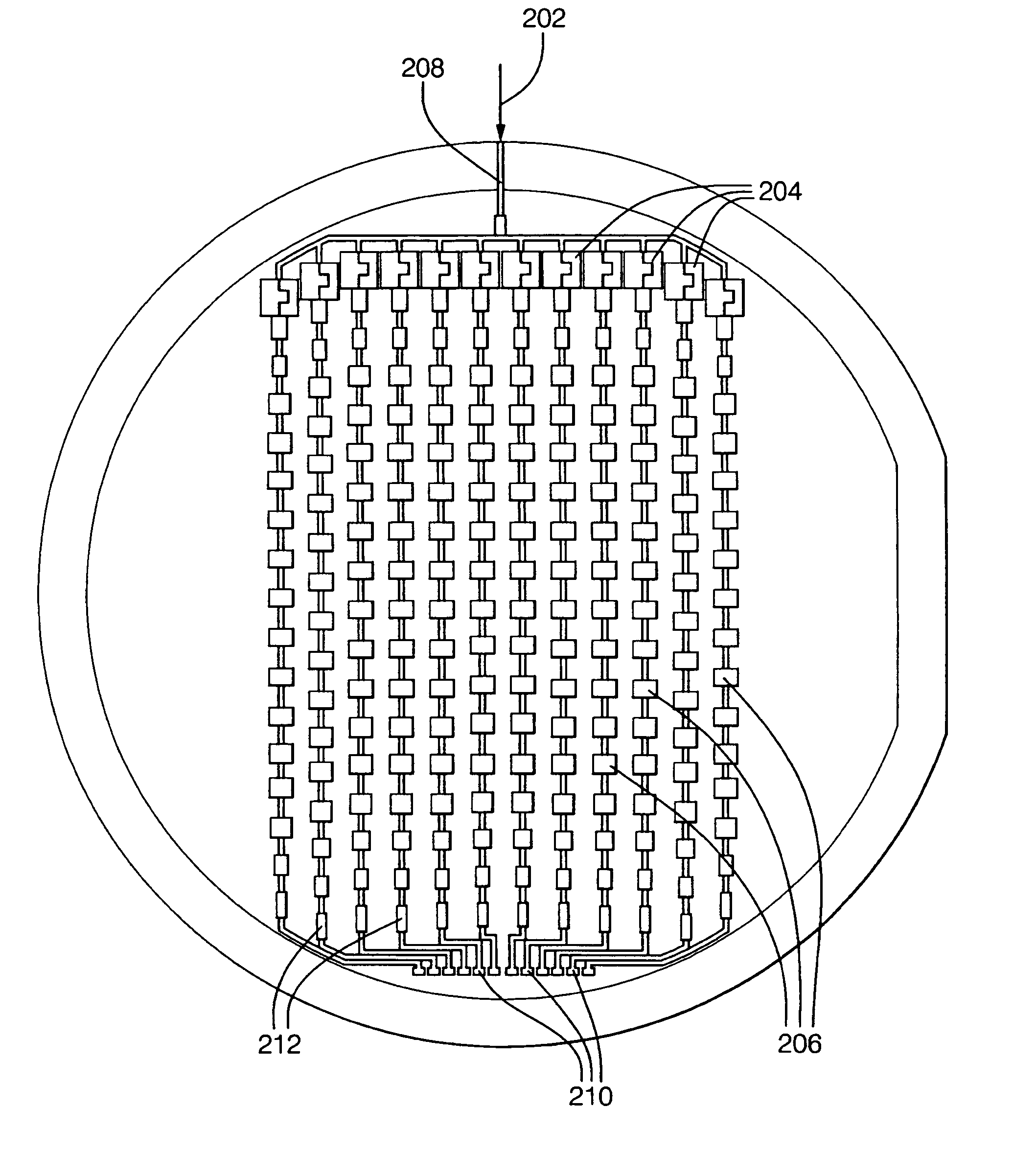

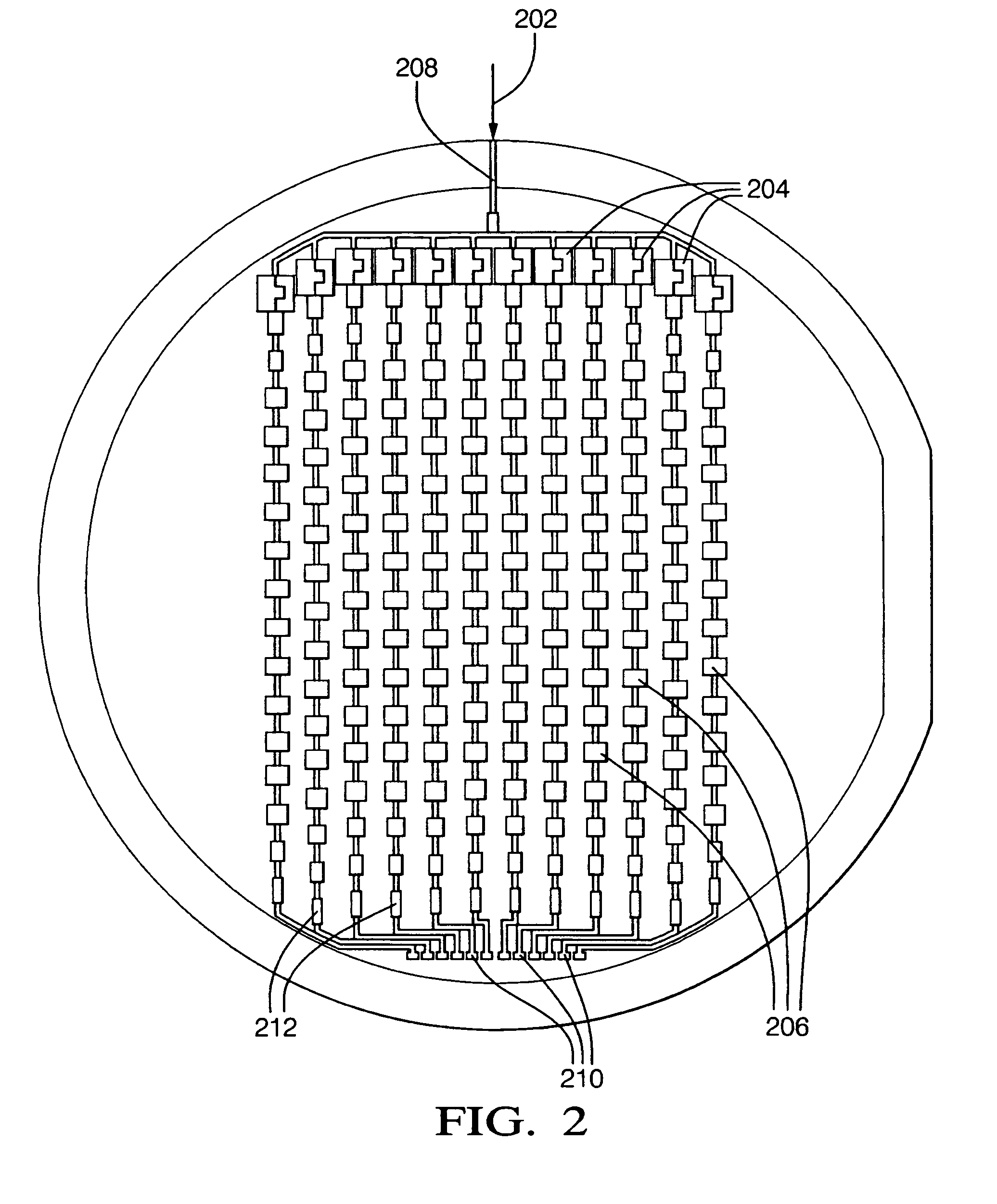

Phase shifters deposited en masse for an electronically scanned antenna

ActiveUS7324043B2Increase processing costPatterning of backsideSimultaneous aerial operationsRadiating elements structural formsDielectricEngineering

A system and method for an electronically scanned antenna is provided in which phase shifters are deposited en masse along with other electronically scanned antenna components on a wafer scale substrate using a thin film process. Alternative wafer scale sizes may be utilized to furnish a required antenna aperture area. Significant processing costs for radar and communication systems are saved utilizing the present invention as compared with contemporary discrete phase shifters that are individually mounted on an antenna. In an aspect, the phase shifter is made up of a base electrode, a barium strontanate titanate (BST) ferroelectric varactor and a top electrode. The BST ferroelectric material is a voltage variable dielectric, which generates a radiation phase. The radiation phase is regulated by a phase shifter control. The radiation phase generates an electromagnetic field about a radiating element and electromagnetic radio waves are radiated from the radiating element.

Owner:APTIV TECH LTD

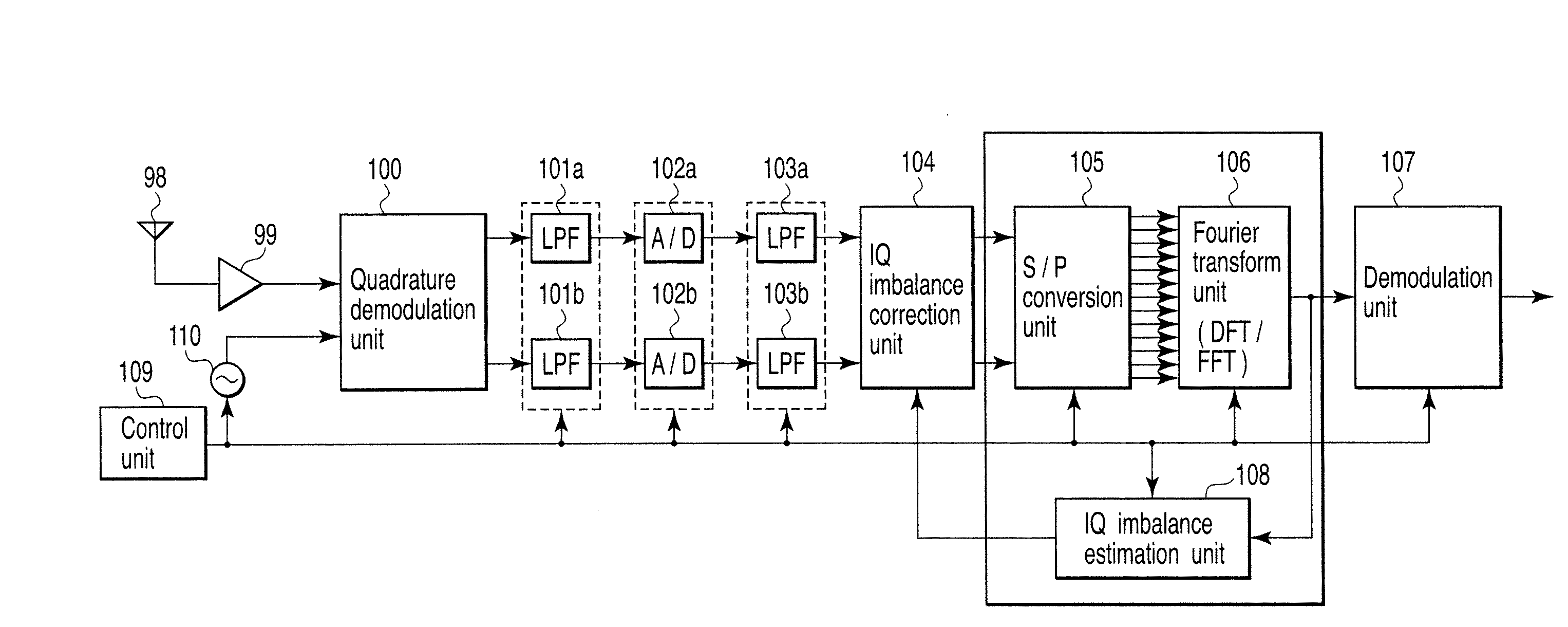

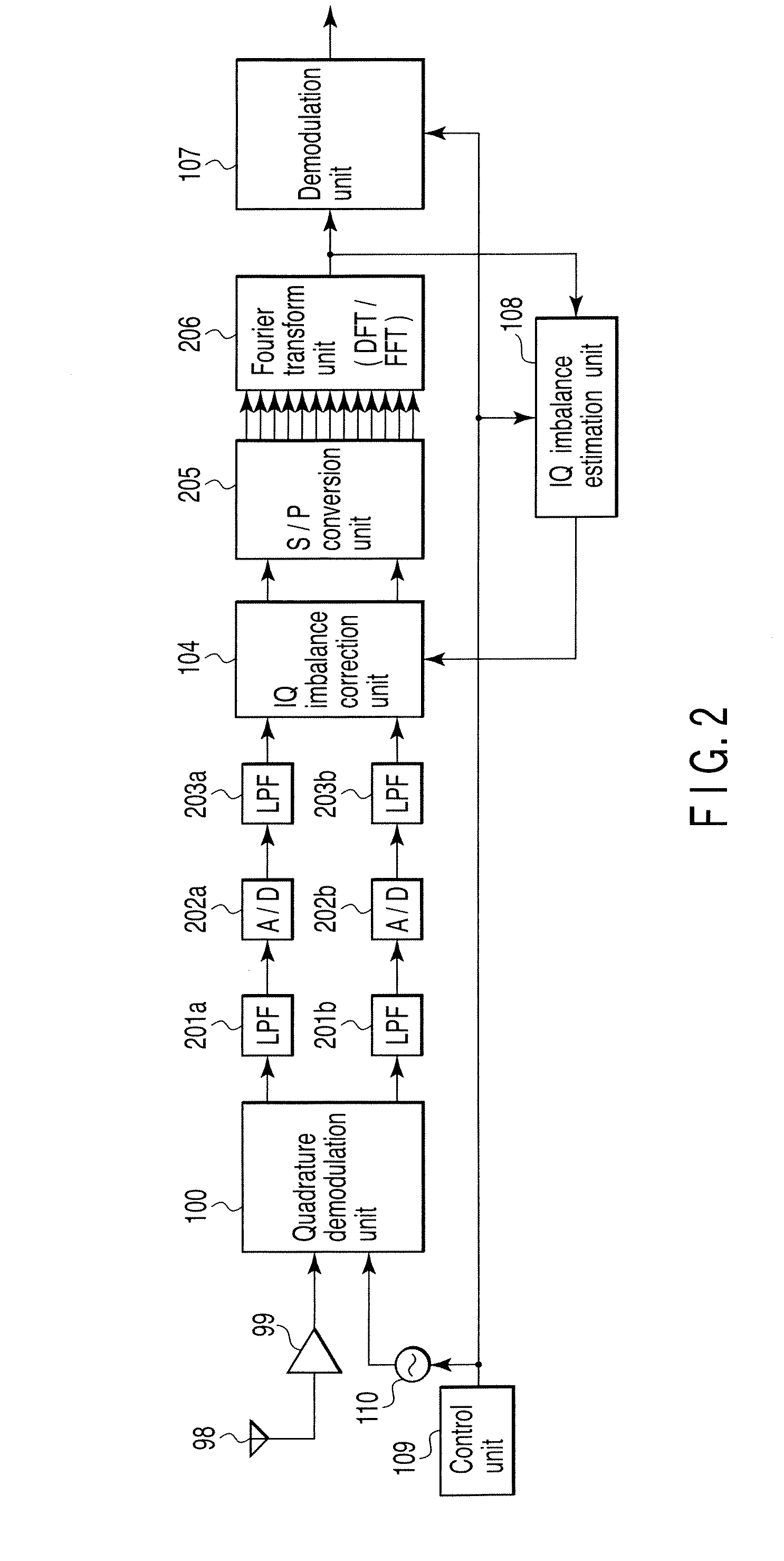

Wireless communication apparatus and receiving method

InactiveUS20080159442A1Single output arrangementsElectric pulse generatorAmplitude distortionTelecommunications

A wireless communication apparatus receives an quadrature modulated signal, generate a local signal having a frequency different from a center frequency of the quadrature modulated signal, performs quadrature demodulation on the quadrature modulated signal by using the local signal, to obtain an I channel signal and a Q channel signal, performs Fourier transform on the I channel signal and the Q channel signal, to obtain signals in a frequency domain, and calculates a first correction coefficient for correcting phase distortion and amplitude distortion caused by the quadrature demodulation by using pairs of signals among the signals, each of the pairs are located at symmetrical frequency positions with respect to the frequency of the local signal.

Owner:KK TOSHIBA

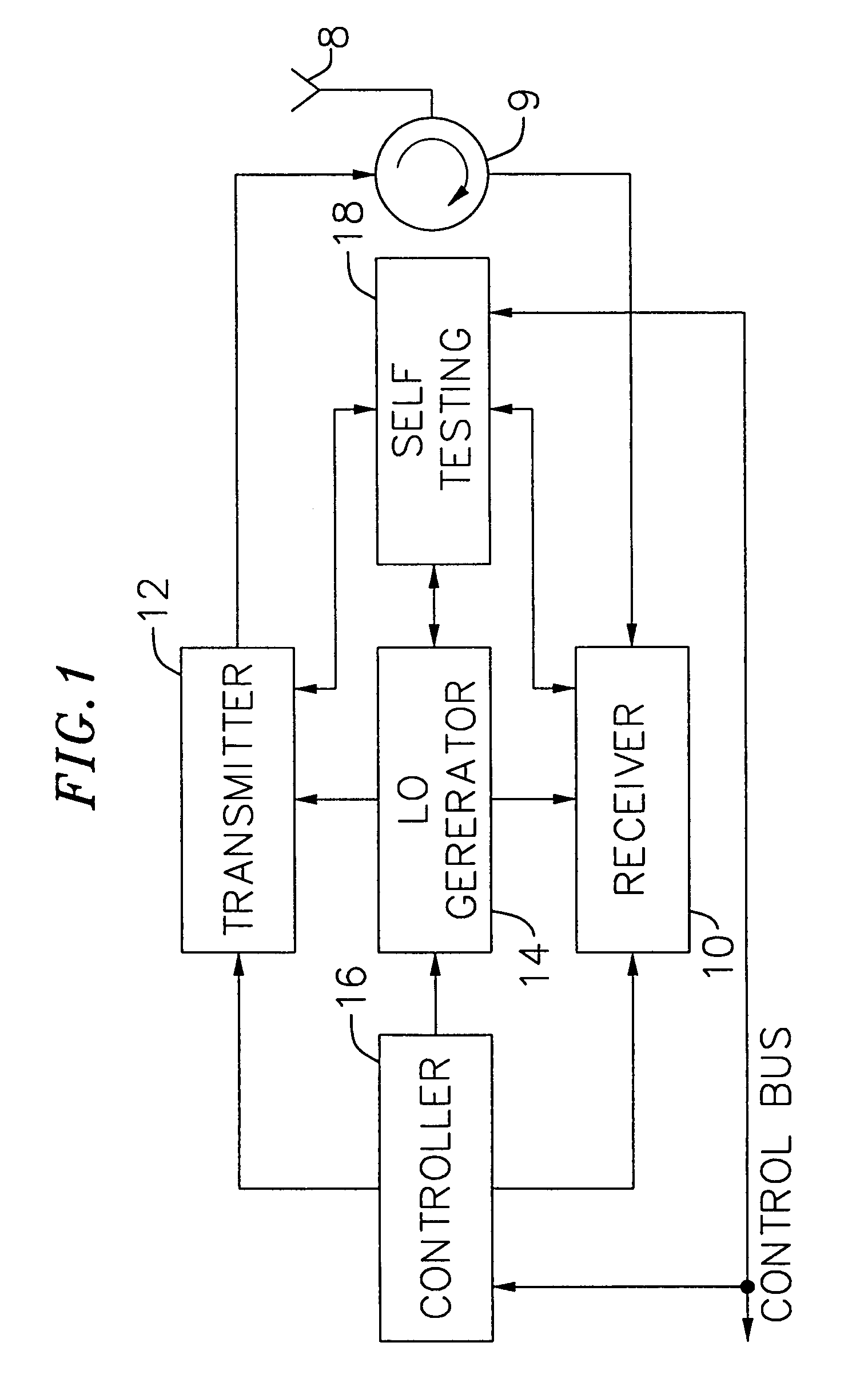

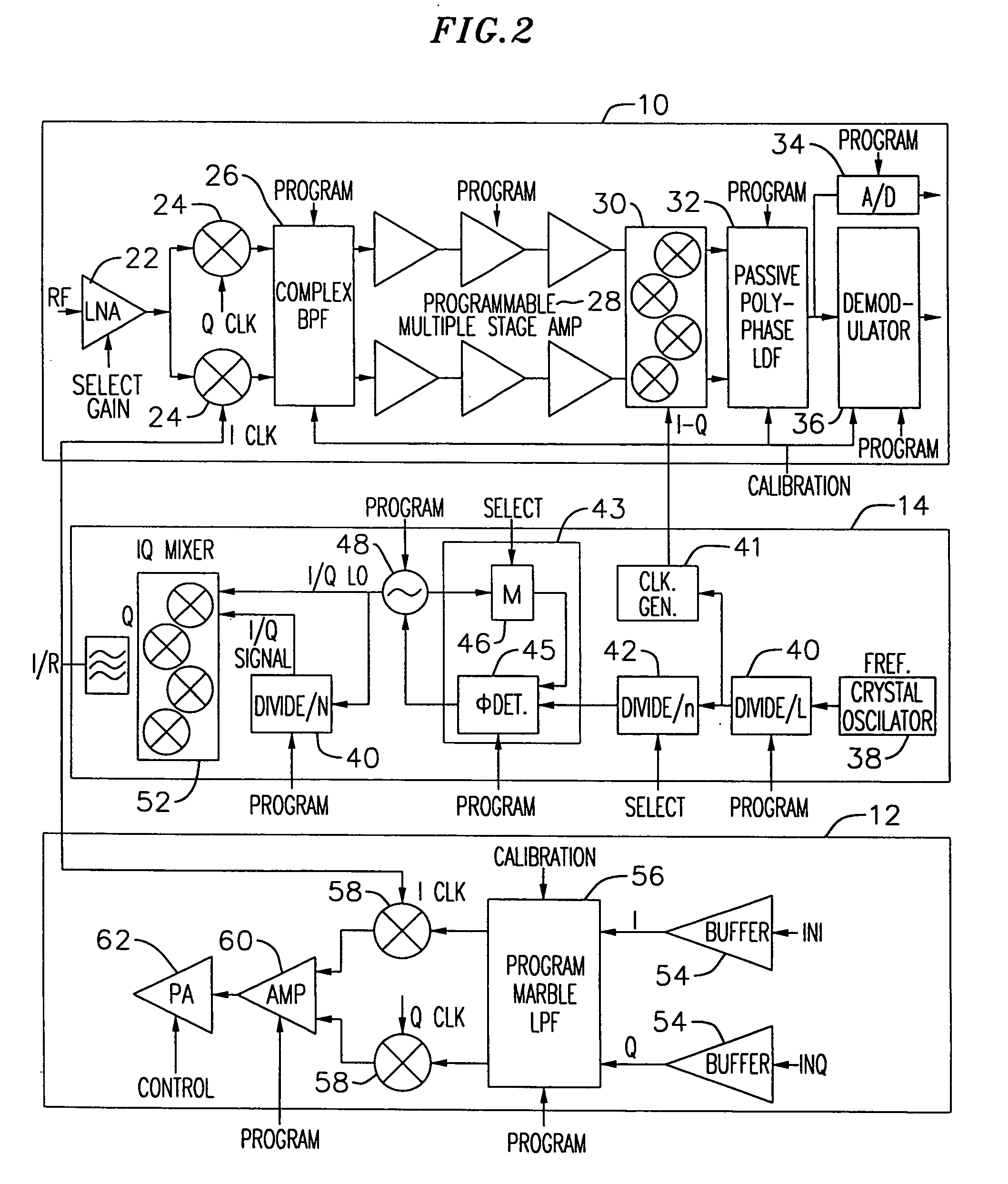

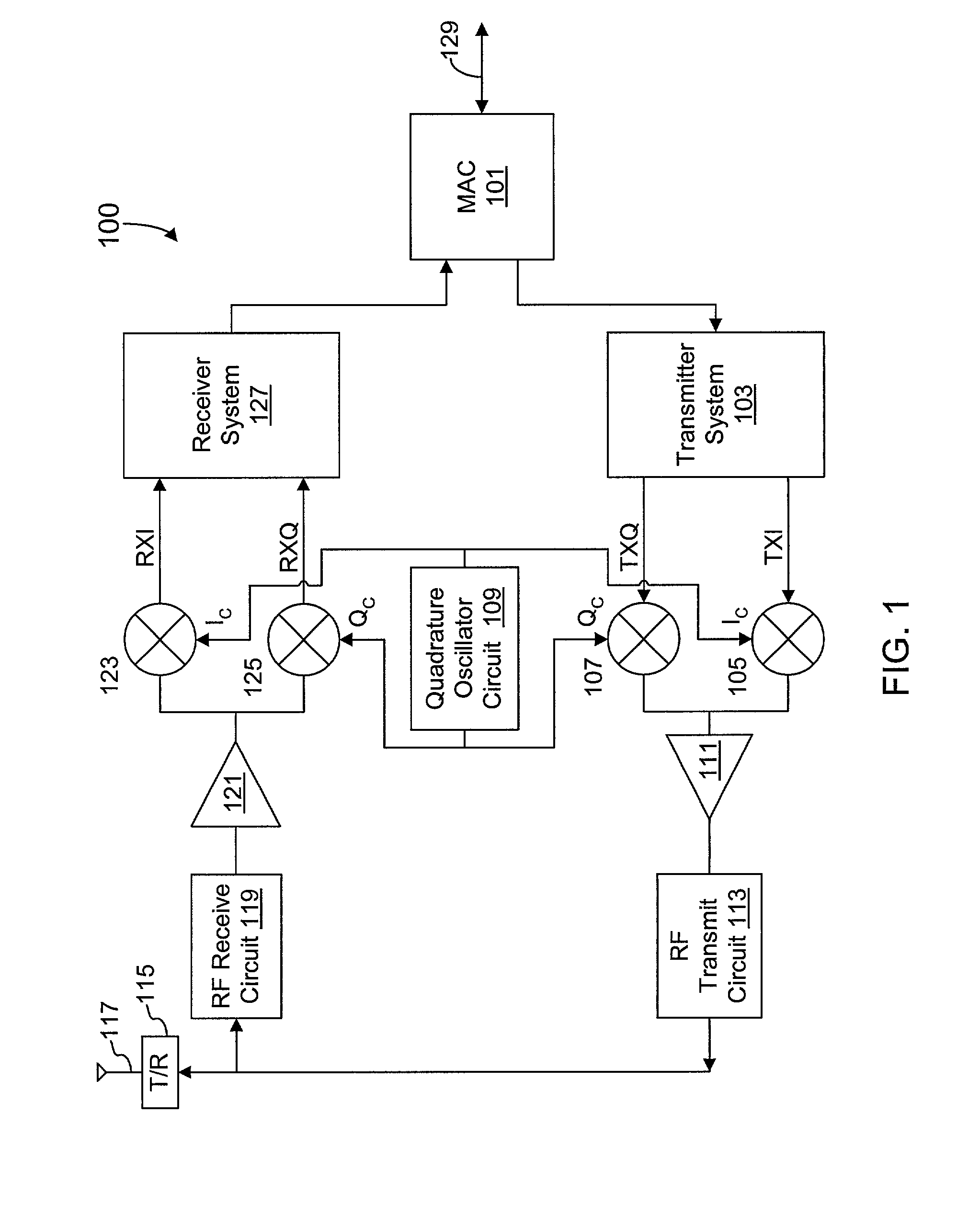

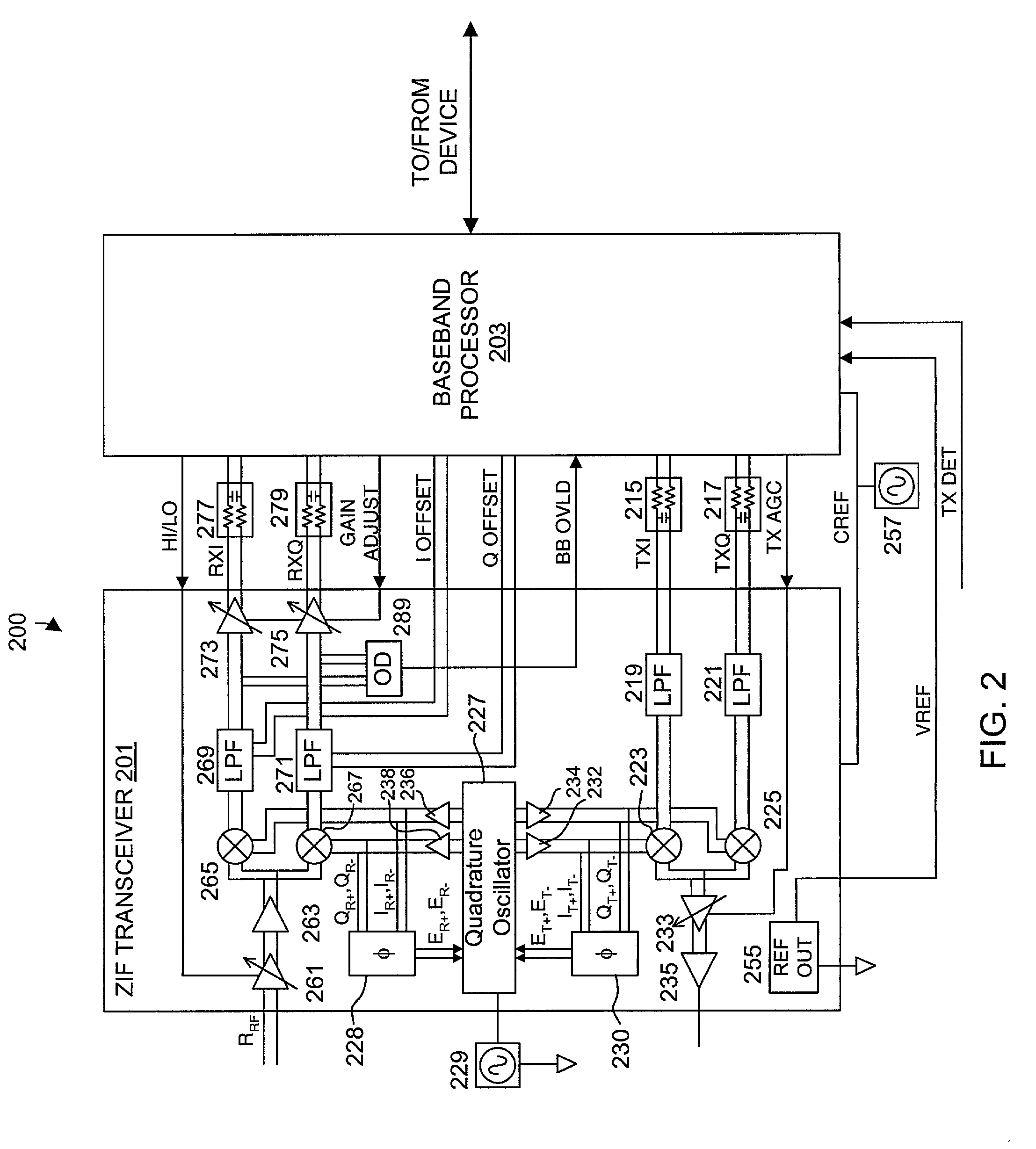

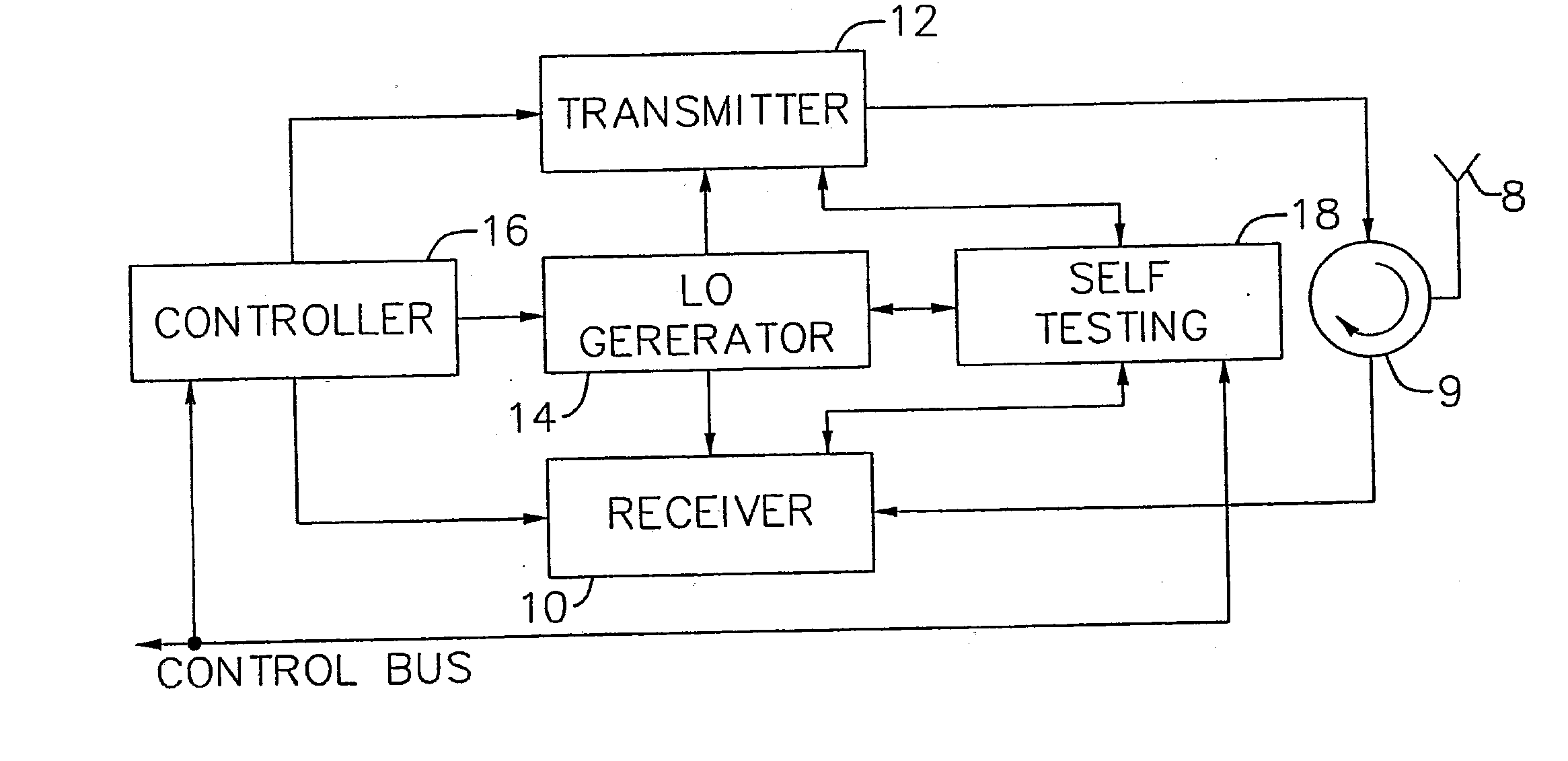

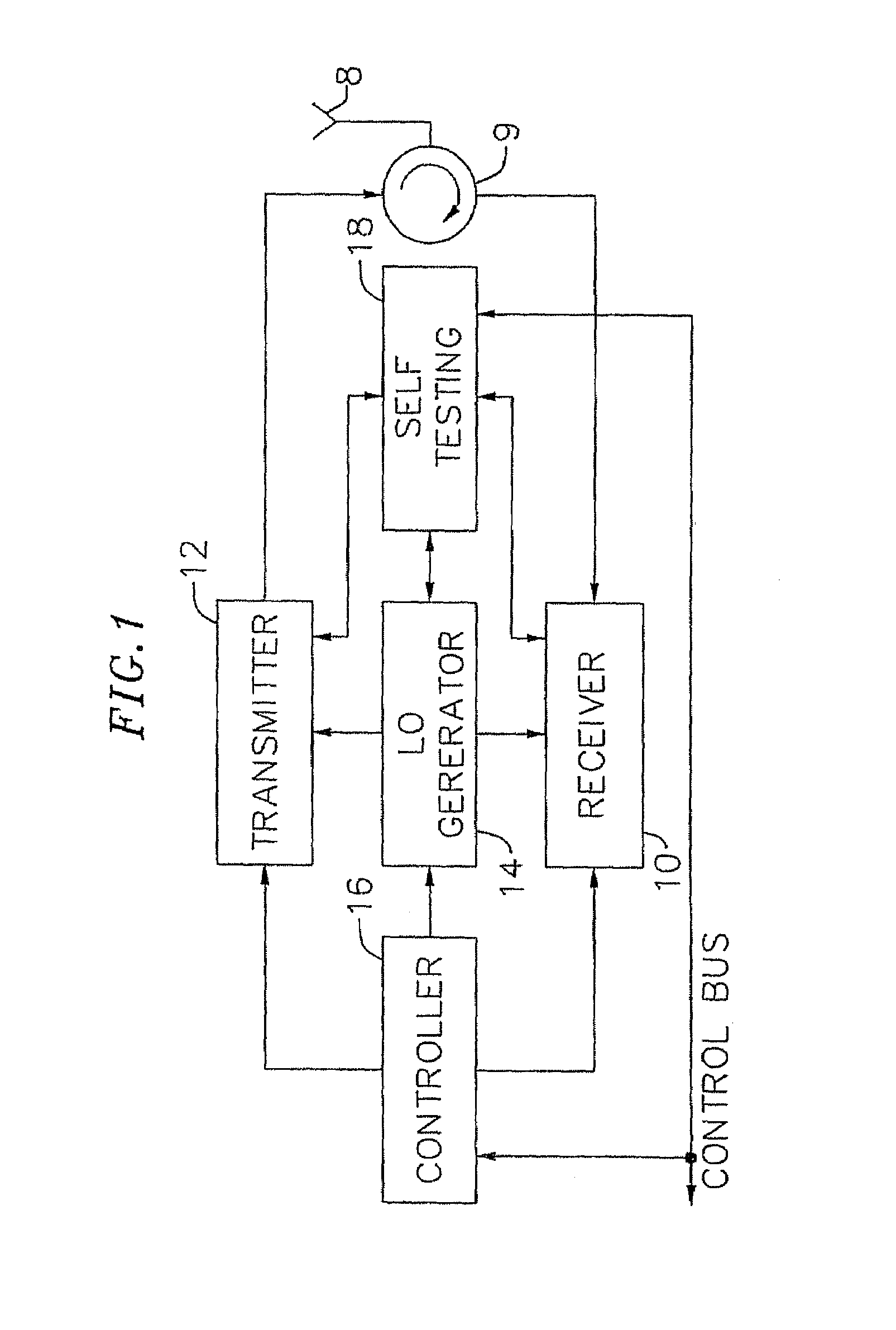

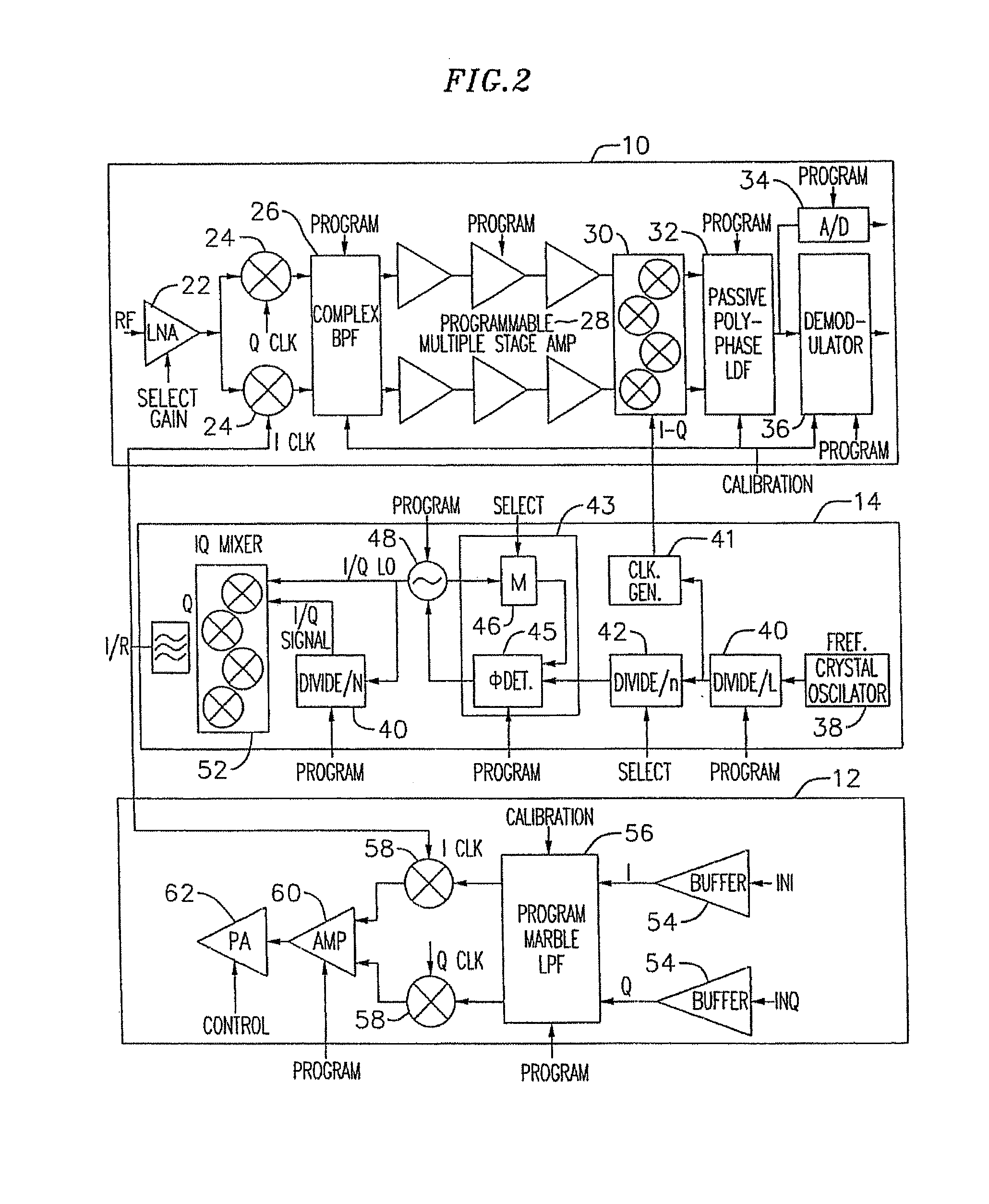

Adaptive radio transceiver with CMOS offset PLL

InactiveUS7082293B1Minimize adverse effectsReduce power consumptionTransmitters monitoringReceivers monitoringCMOSAdaptive programming

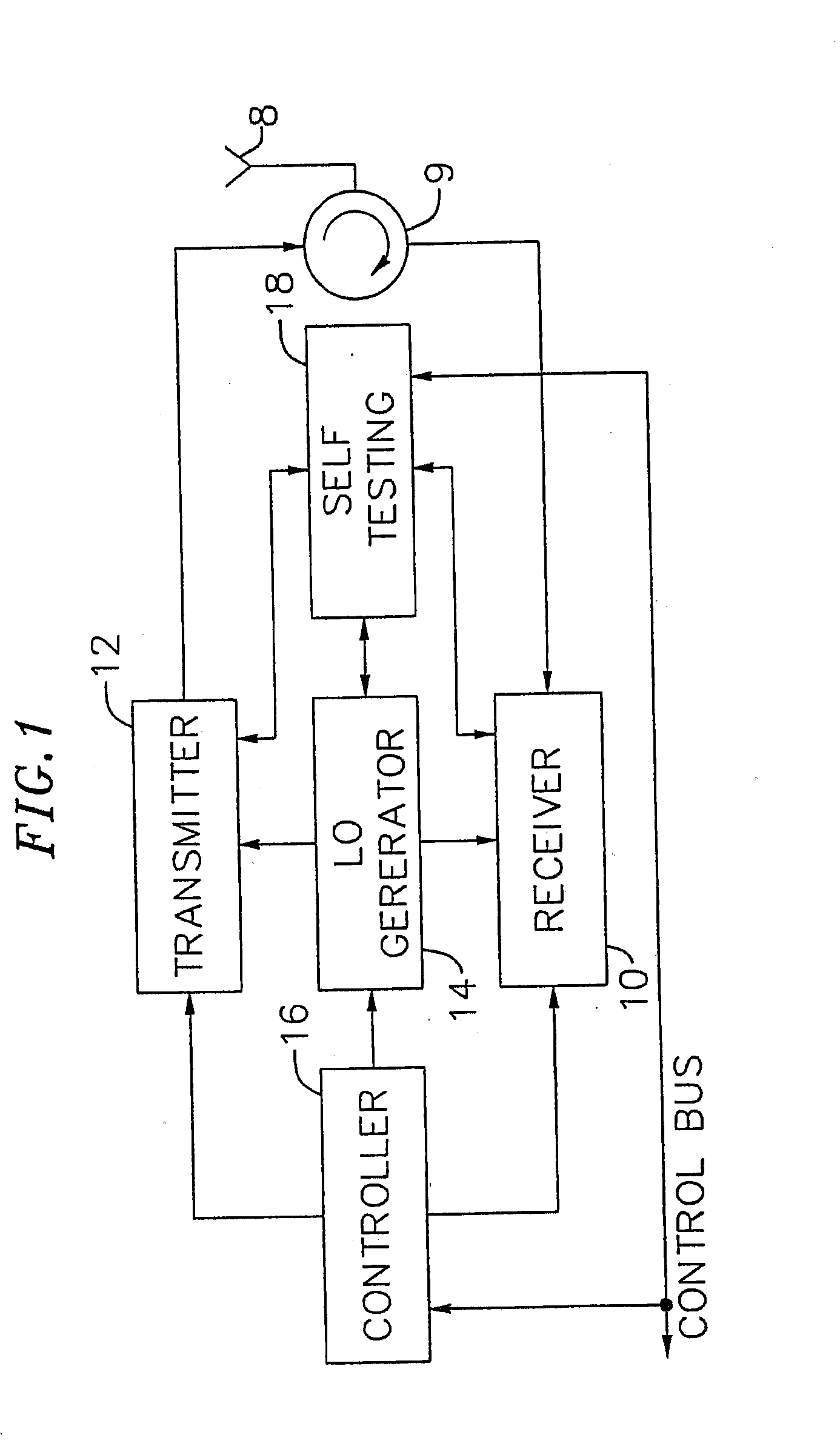

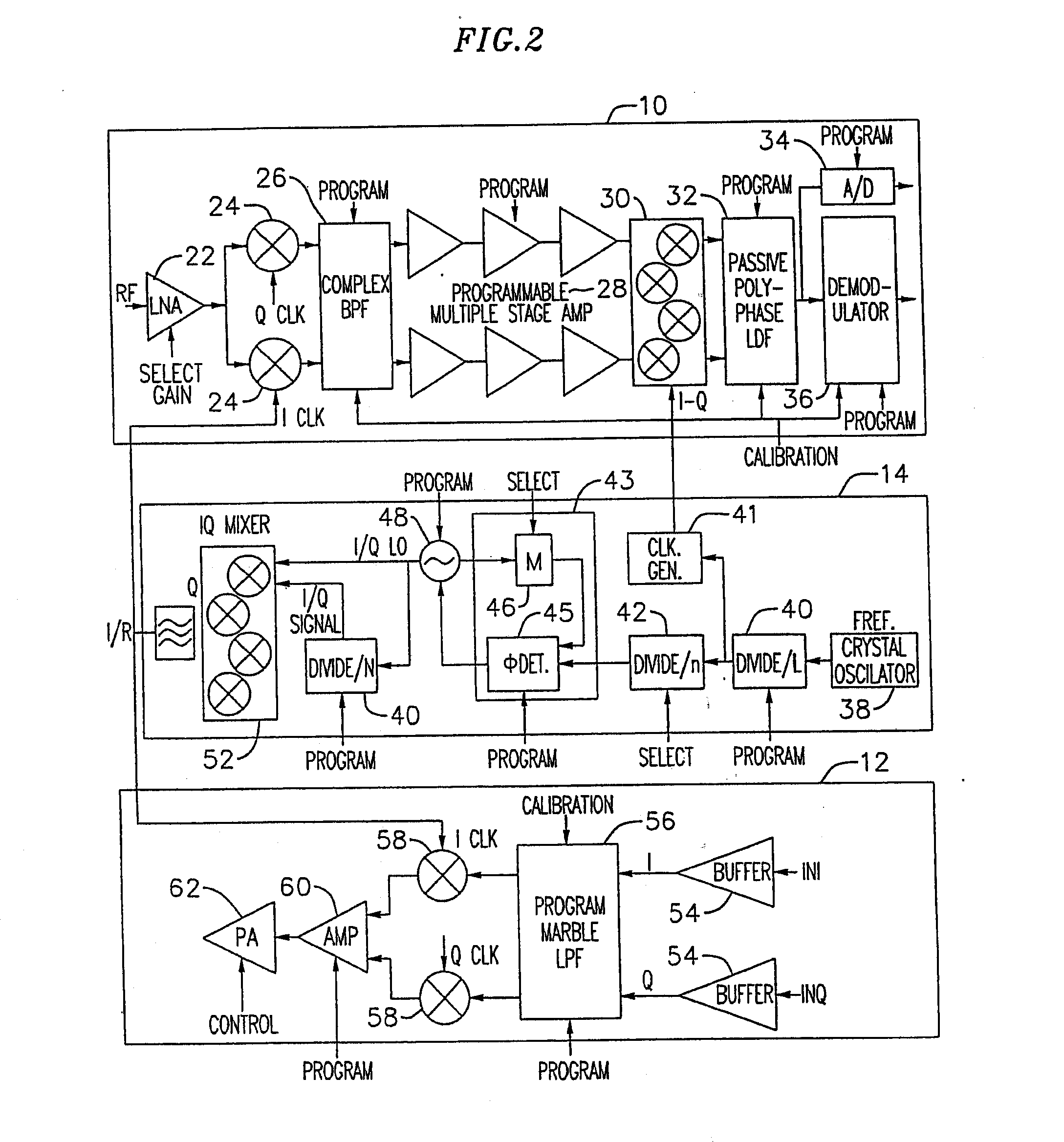

An exemplary embodiment of the present invention described and shown in the specification and drawings is a transceiver with a receiver, a transmitter, a local oscillator (LO) generator, a controller, and a self-testing unit. All of these components can be packaged for integration into a single IC including components such as filters and inductors. The controller for adaptive programming and calibration of the receiver, transmitter and LO generator. The self-testing unit generates is used to determine the gain, frequency characteristics, selectivity, noise floor, and distortion behavior of the receiver, transmitter and LO generator. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or the meaning of the claims.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

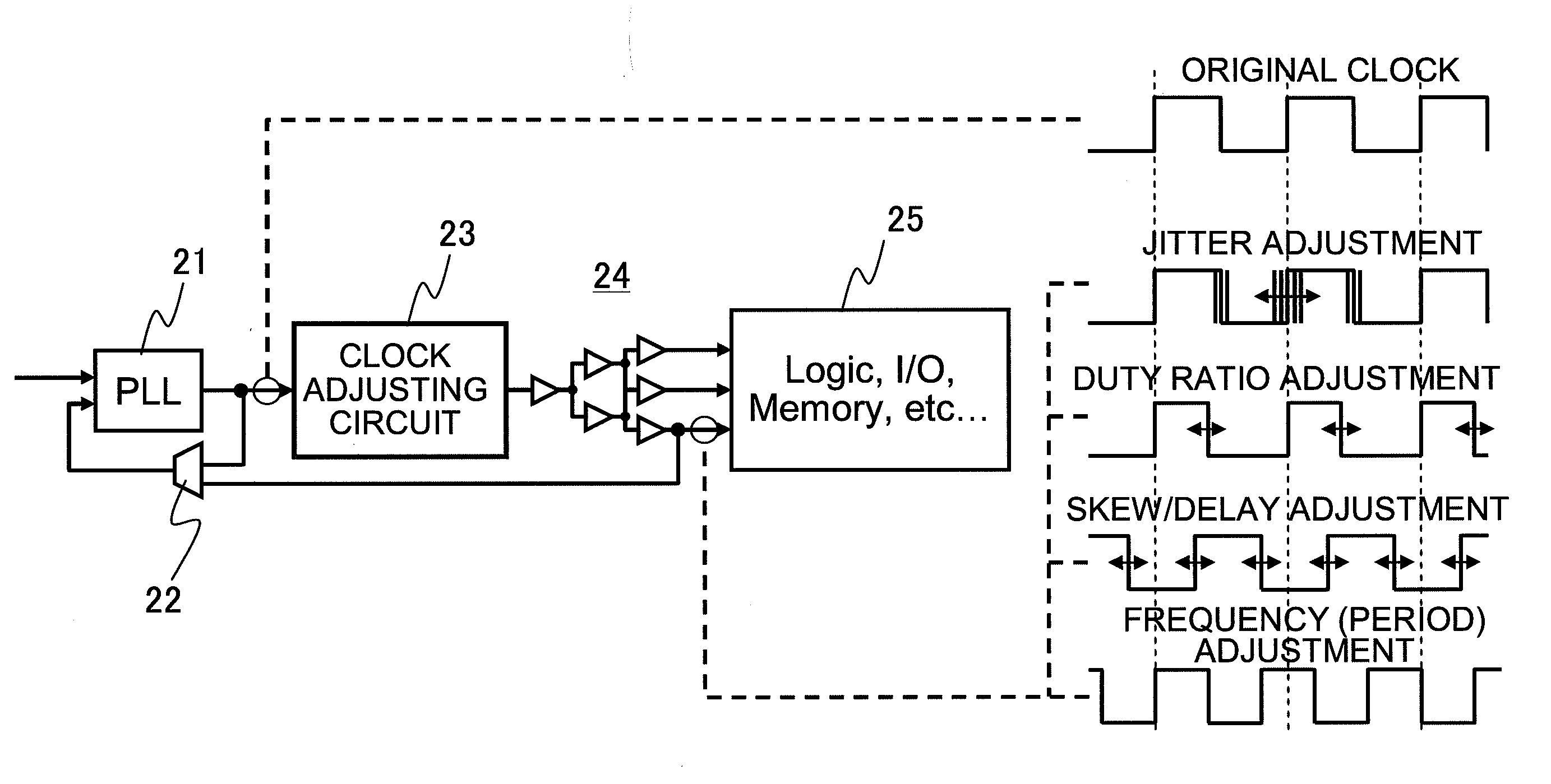

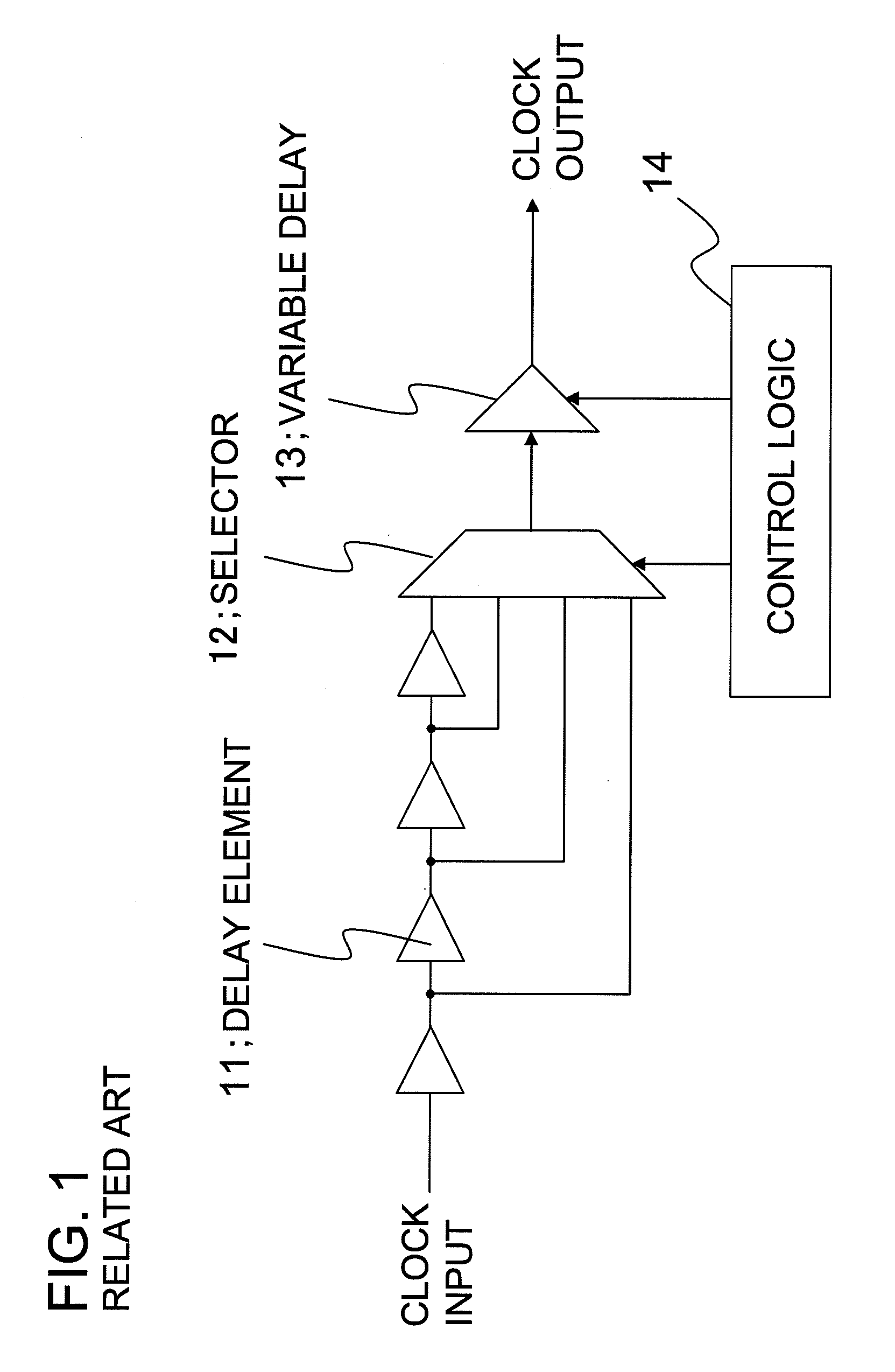

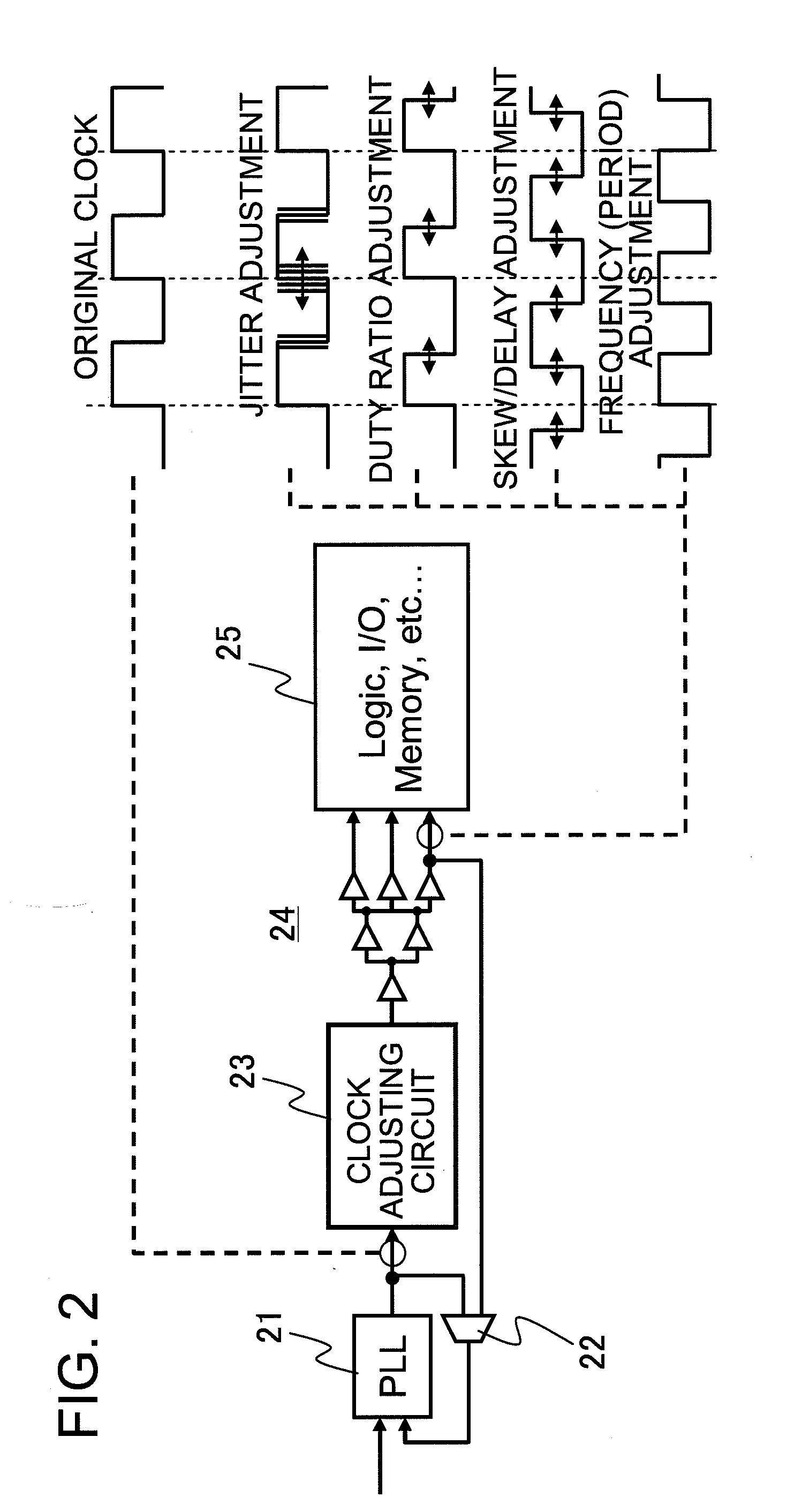

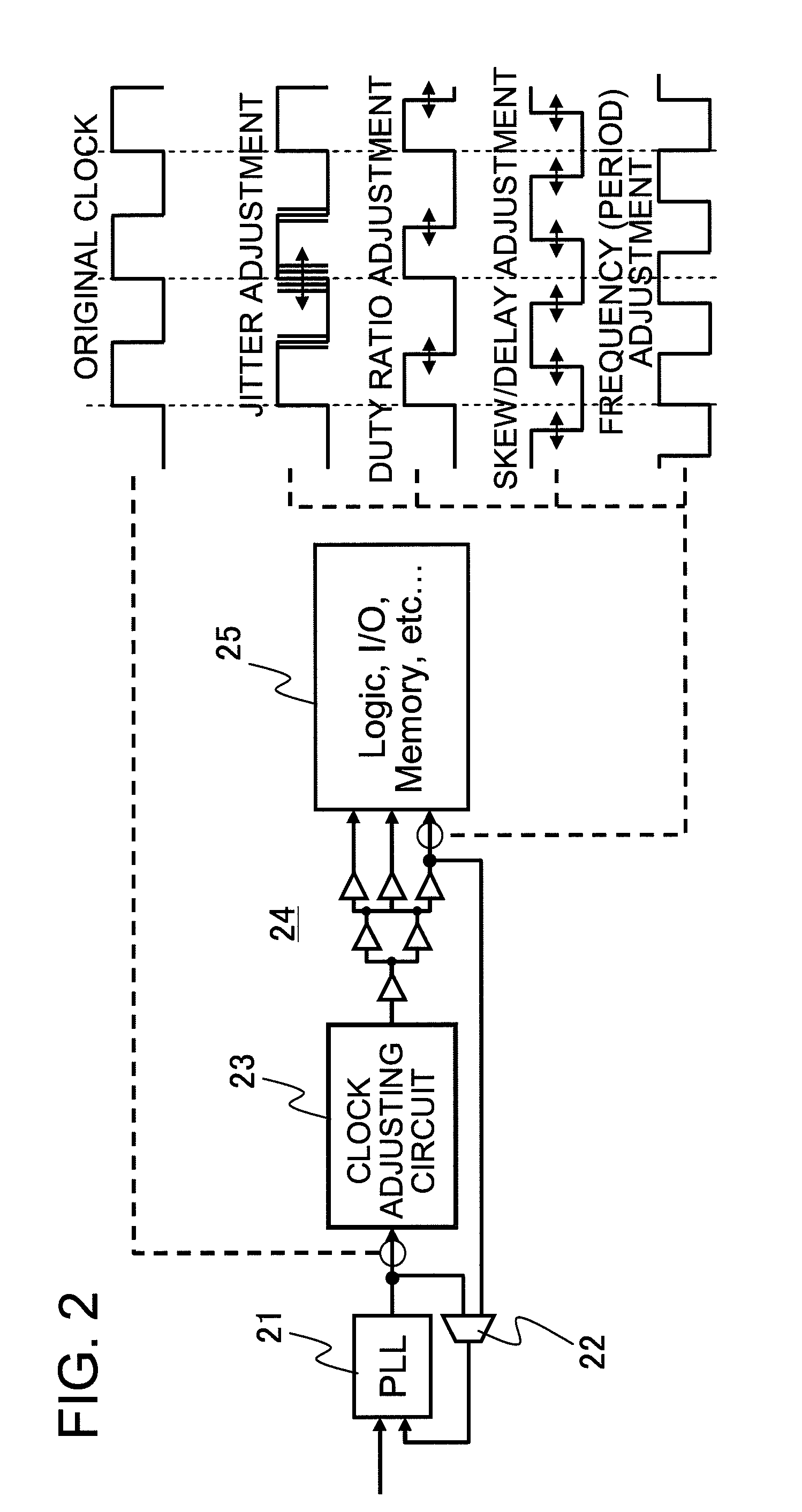

Clock adjusting circuit and semiconductor integrated circuit device

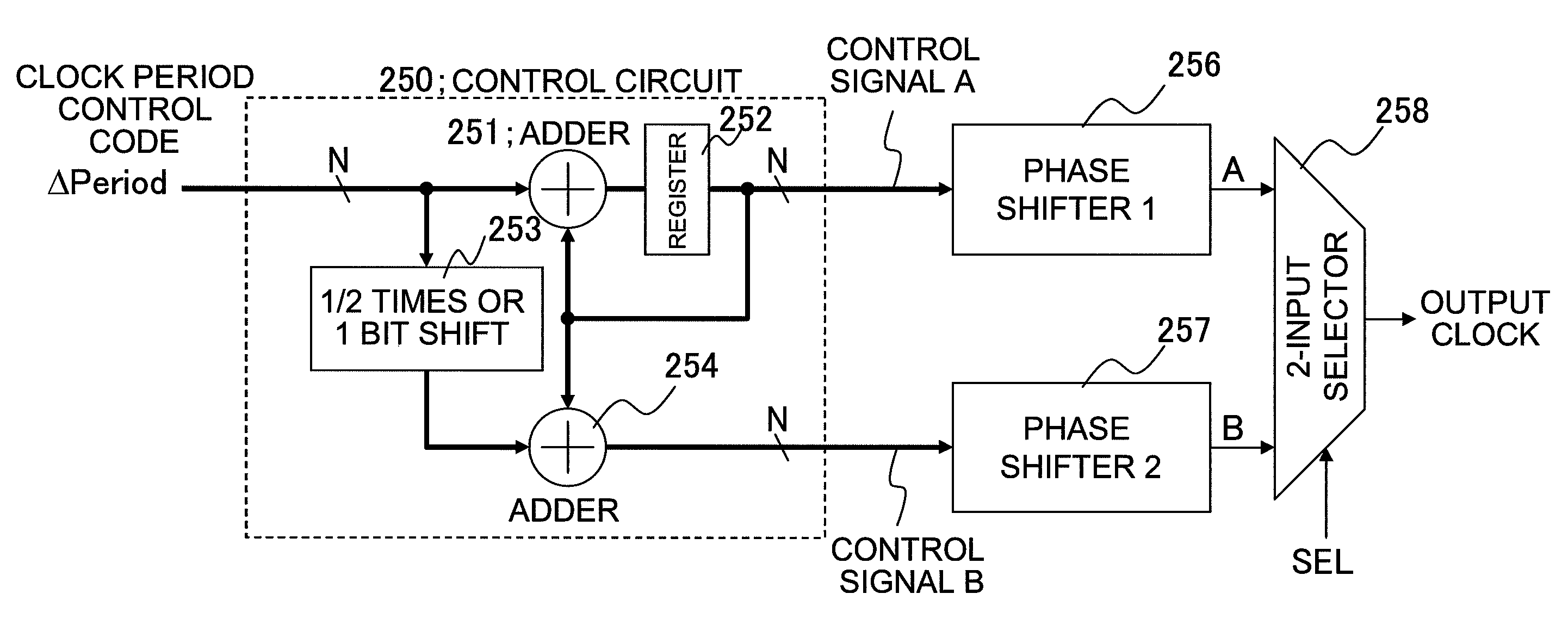

InactiveUS20100039157A1Improve reliabilityLarge marginPulse automatic controlSingle output arrangementsControl signalControl circuit

Disclosed is a clock adjusting circuit comprising a phase shifter that receives a clock signal and variably shifts, based on a control signal, respective timing phases of a rising edge and a falling edge of the clock signal; and a control circuit that supplies the control signal to the phase shifter circuit before each edge is output; wherein the clock signal, in which at least one of a period, a duty ratio, jitter and skew / delay of the input clock signal is changed over an arbitrary number of clock cycles, is output.

Owner:NEC CORP

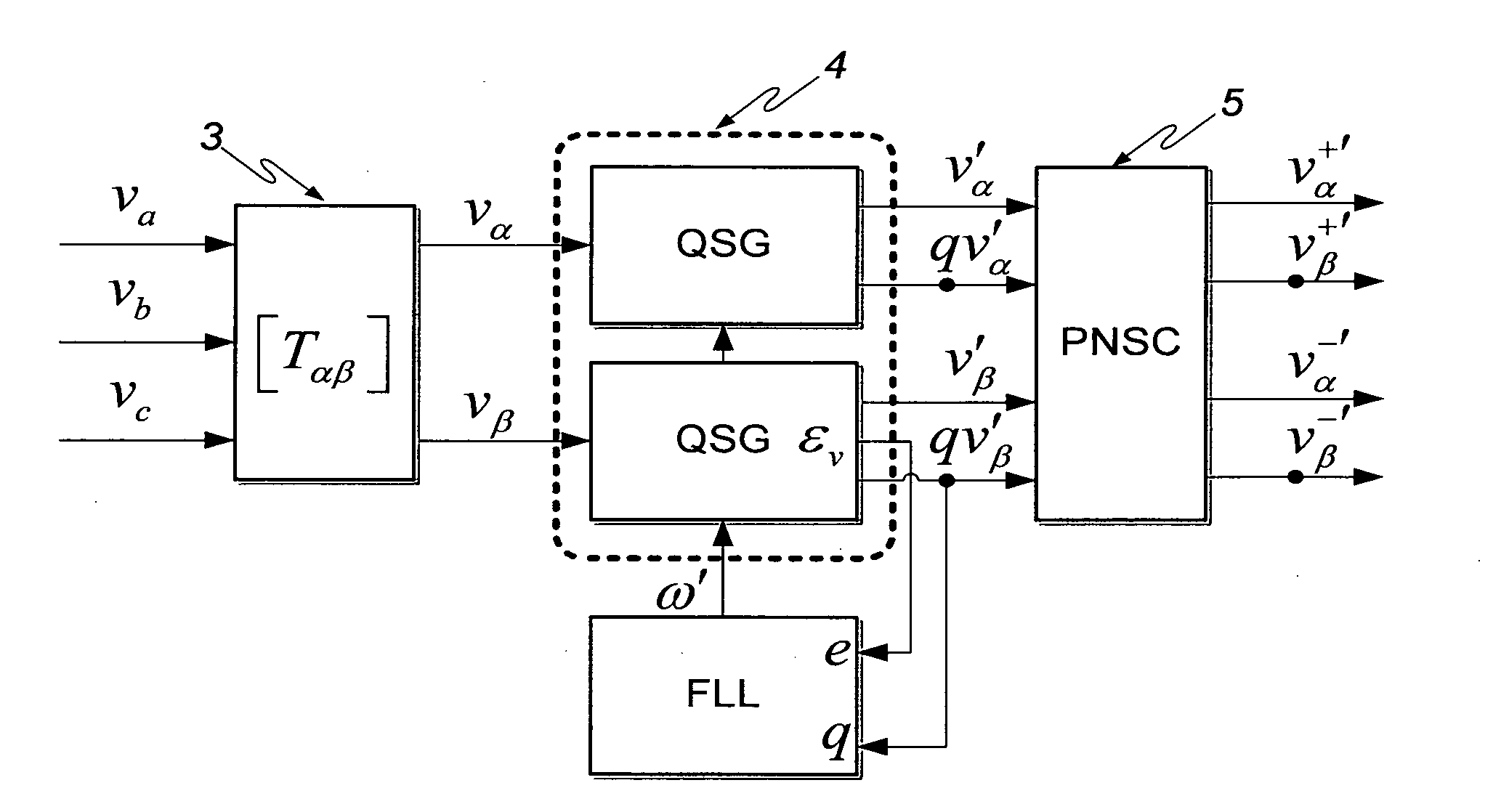

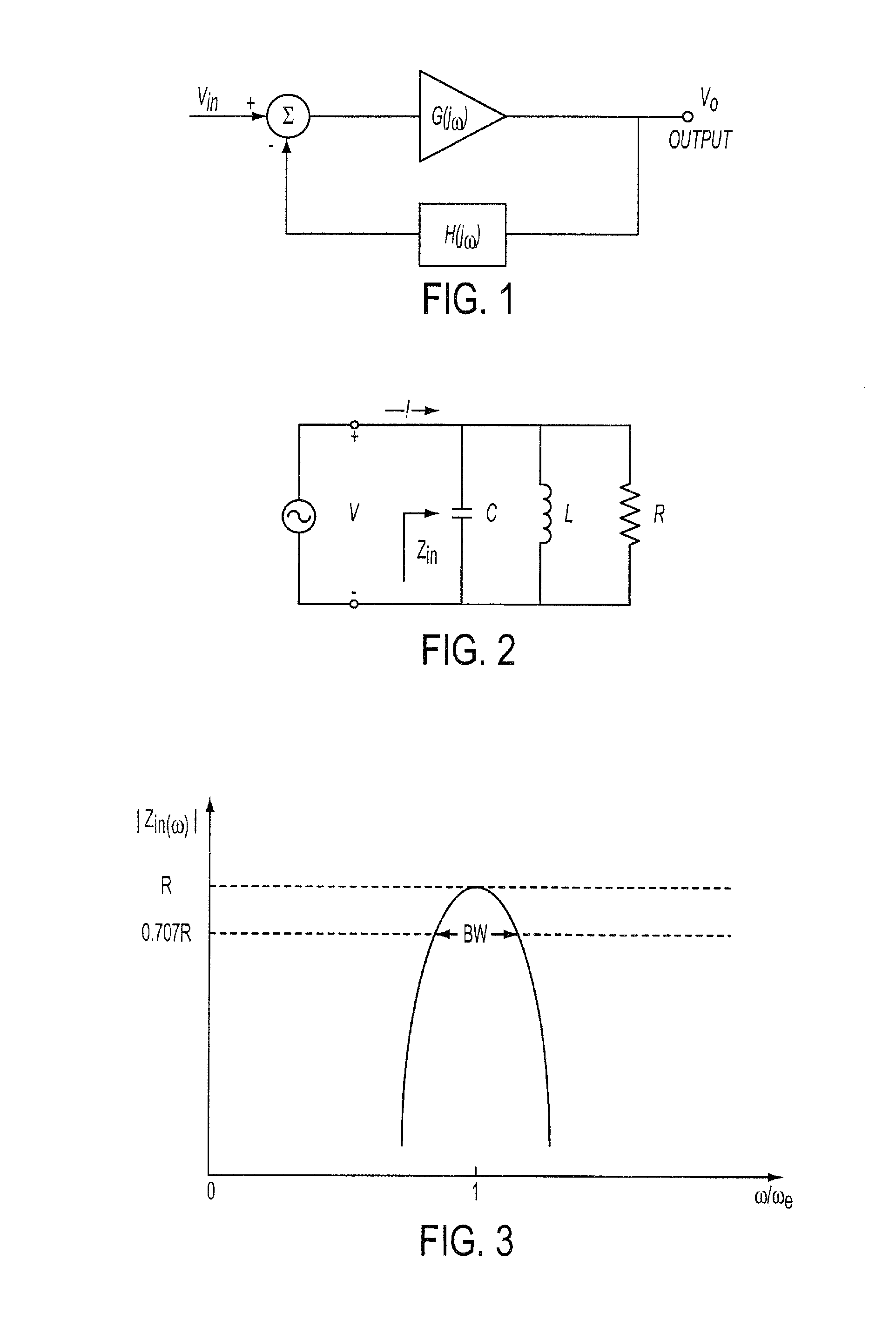

Advanced real-time grid monitoring system and method

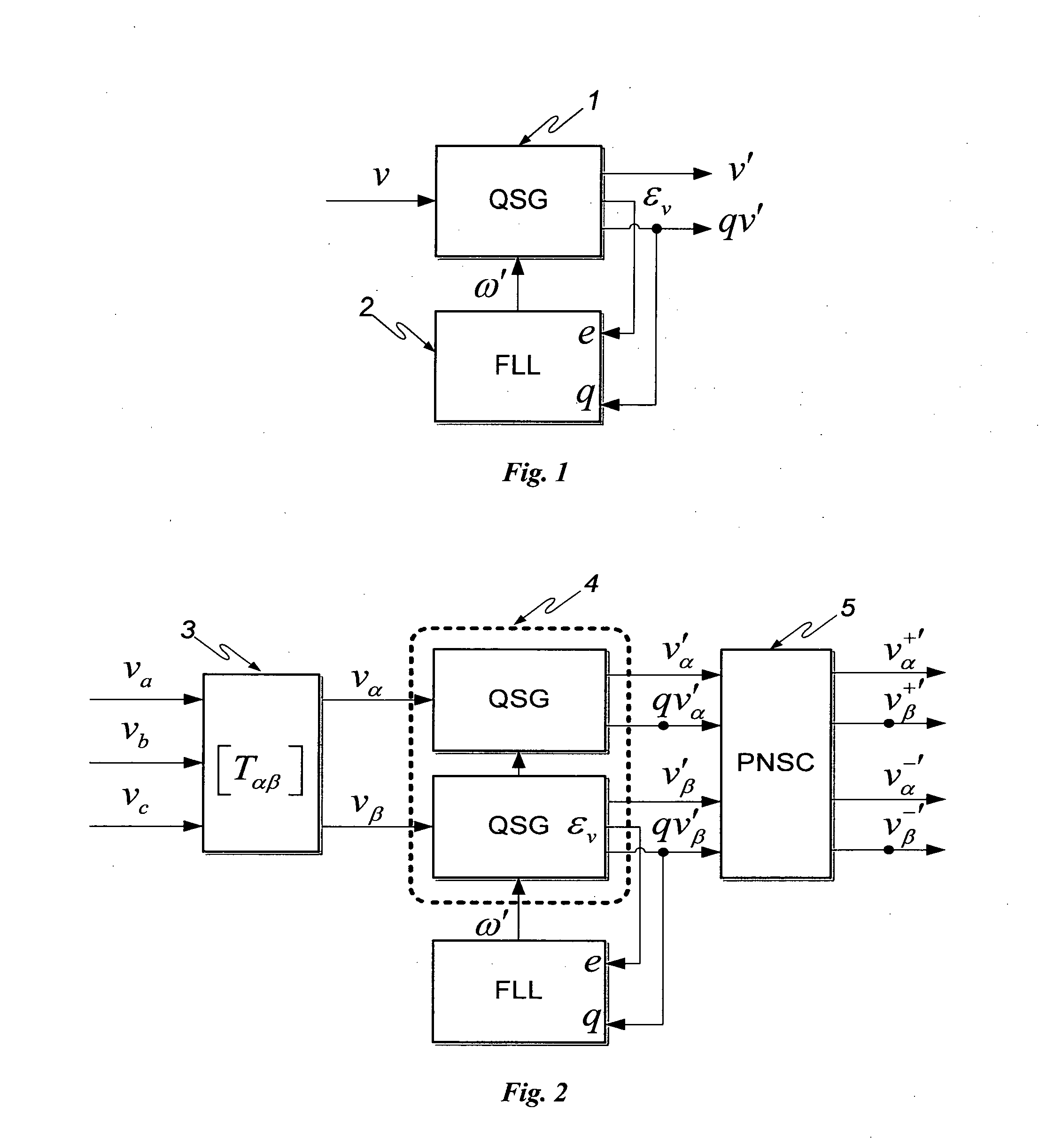

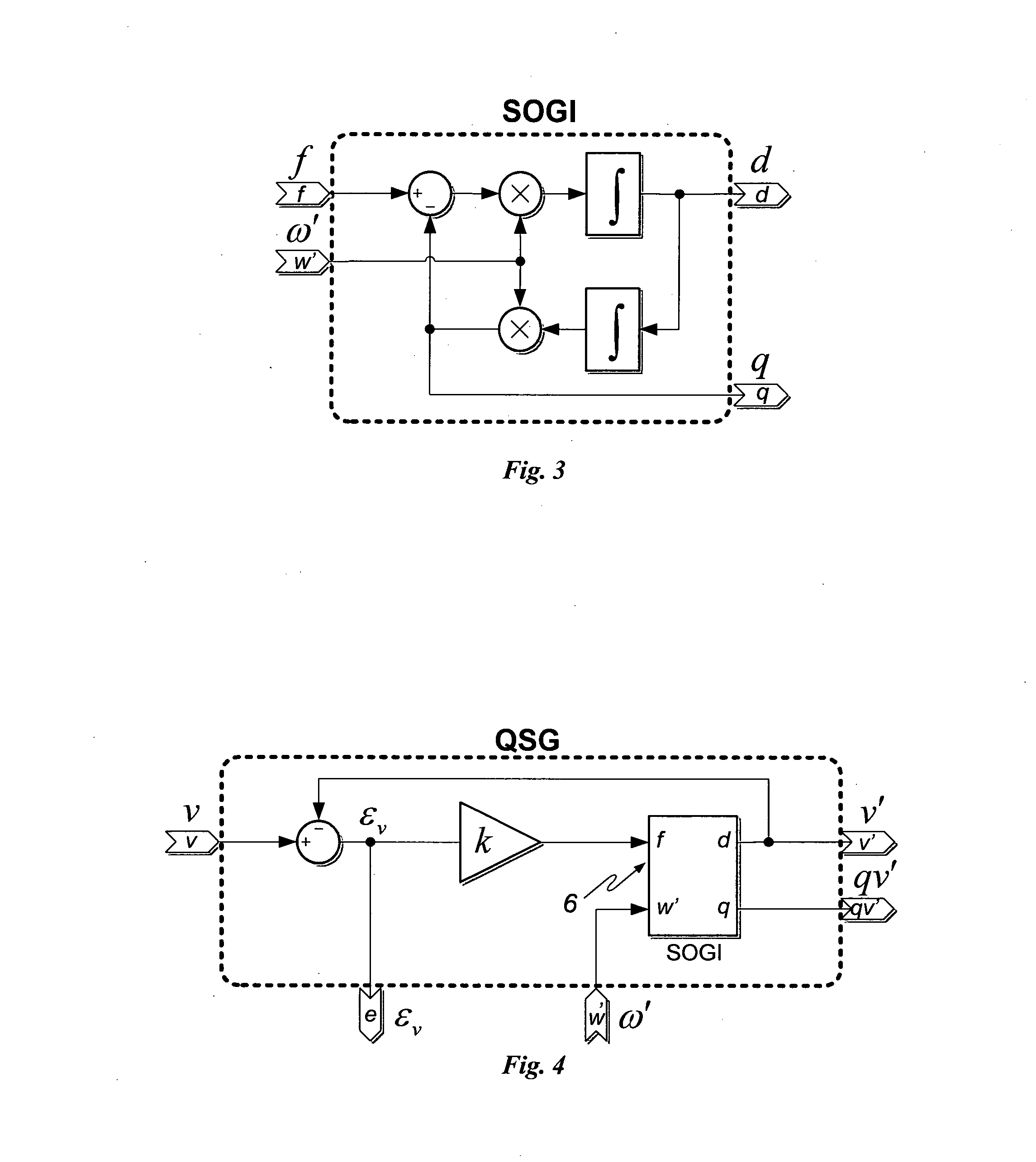

ActiveUS20100213925A1Efficient and robustIncreased computational burdenCurrent/voltage measurementVoltage-current phase anglePower qualityElectric power system

This invention deals with an advanced Real-time Grid Monitoring System (RTGMS) suitable for both single-phase and three-phase electric power systems. This invention provides an essential signal processing block to be used as a part of complex systems either focused on supervising and diagnosing power systems or devoted to control power processors interacting with the grid. This invention is based on a new algorithm very suitable for real-time characterization of the grid variables under distorted and unbalanced grid conditions. The main characteristic of this invention is the usage of a frequency-locked loop, based on detecting the grid frequency, for synchronizing to the grid variables. It results in a very robust system response in relation to existing technique based on the phase-angle detection since grid frequency is much more stable variable than the grid voltage / current phase-angle, mainly during grid faults. Moreover, the algorithm supporting this invention is very efficient and can be implemented in regular industrial microprocessors. These features make the RTGMS object of this invention ideal to be applied in the control of distributed generation systems (DGS), flexible AC transmission systems (FACTS), power quality conditioners (PQC) and uninterruptible power supplies (UPS). In all these systems, the fast and precise real time detection of the voltage and / or current sequence components under grid fault conditions is a crucial matter.

Owner:GAMESA INNOVATION & TECH SA

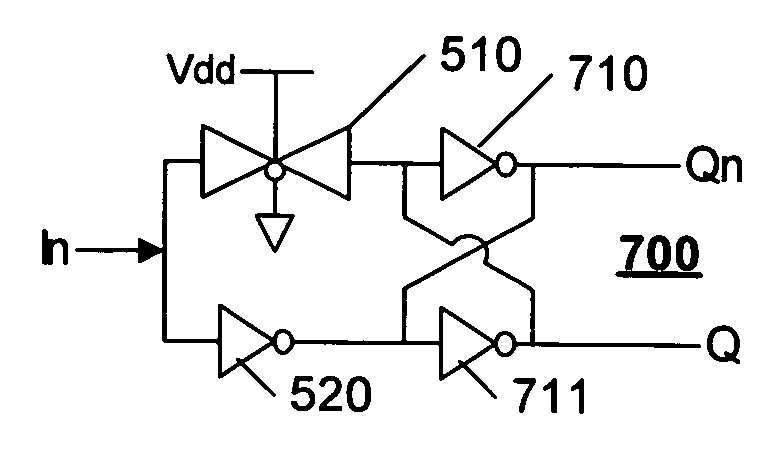

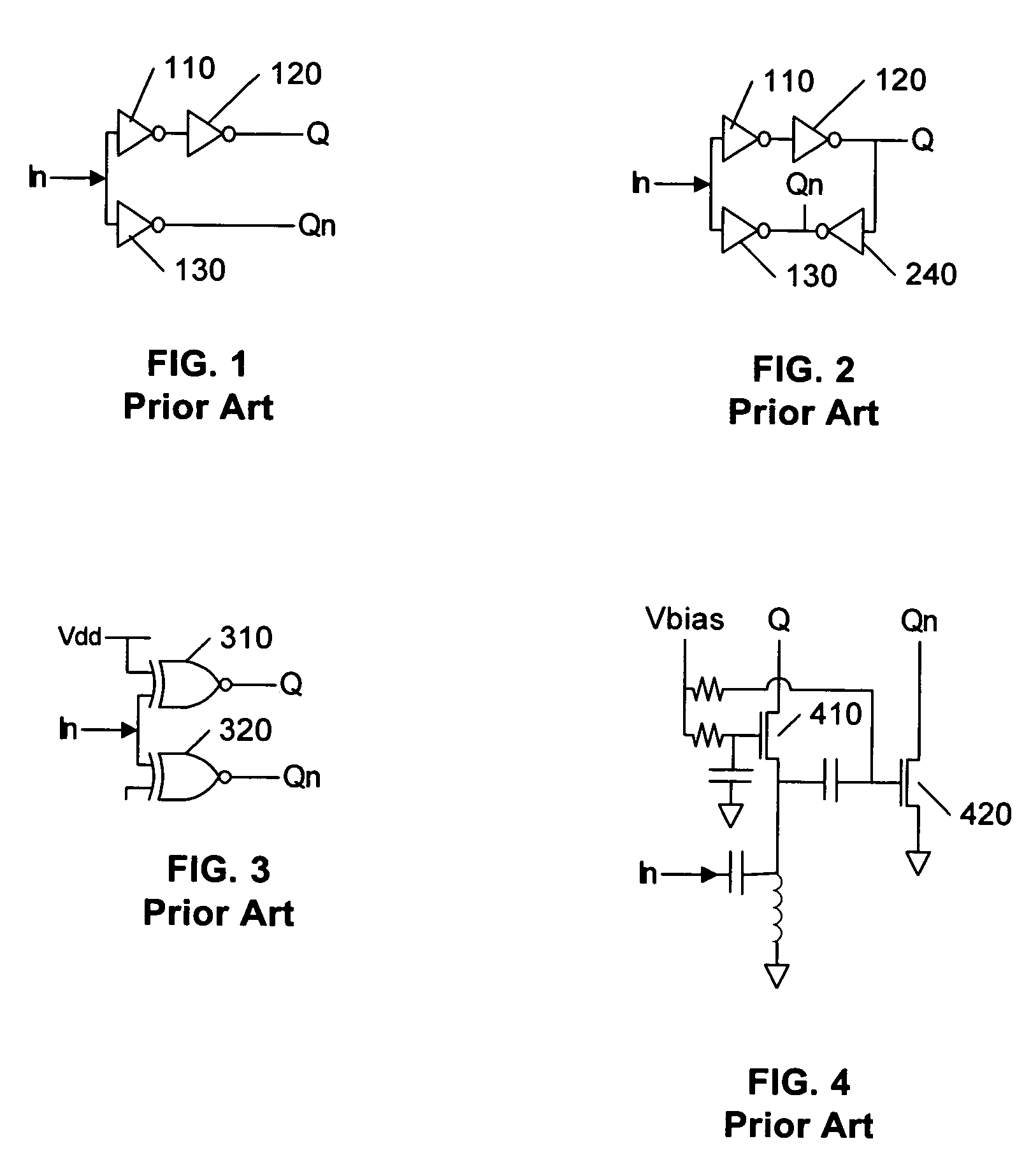

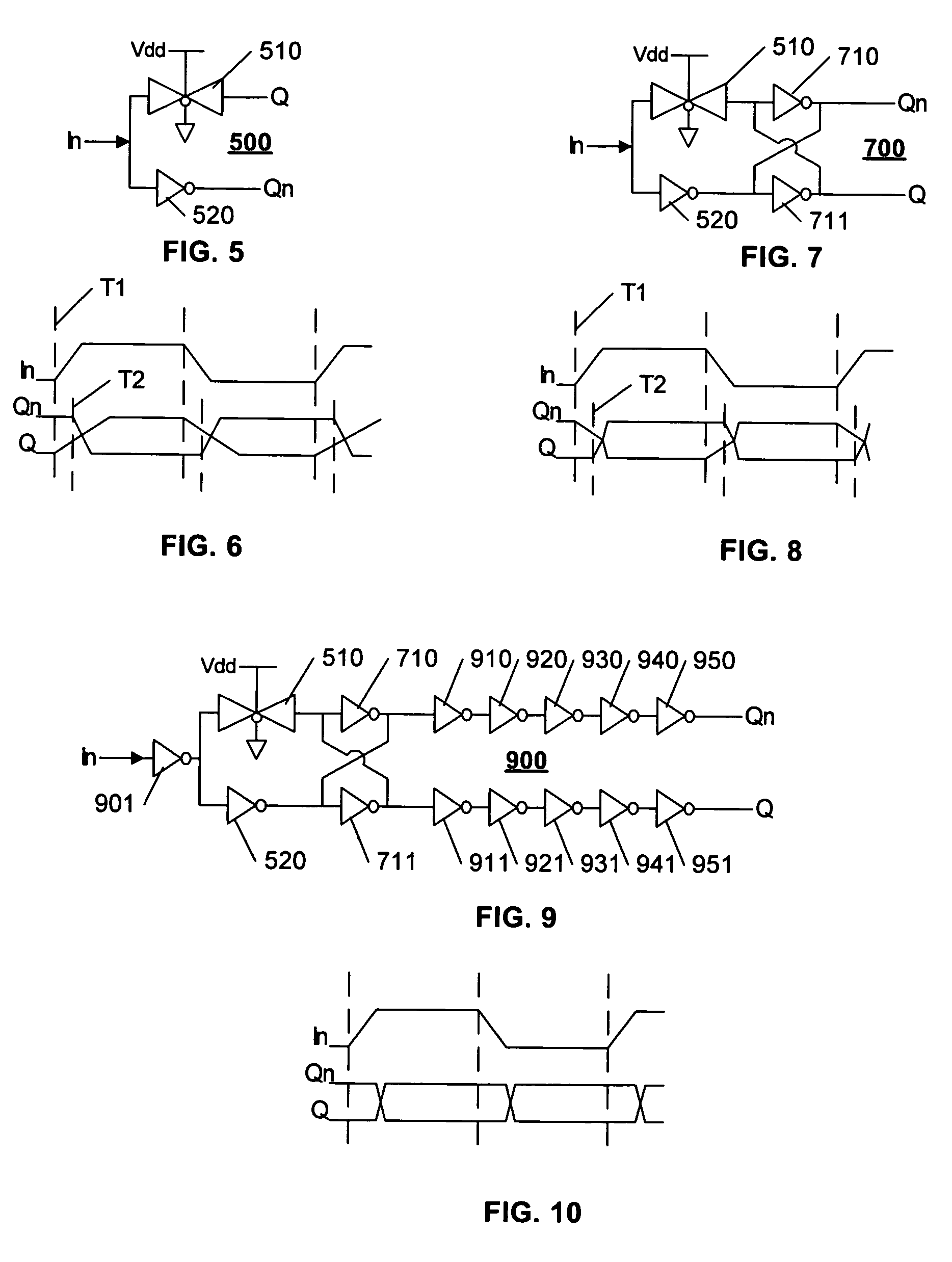

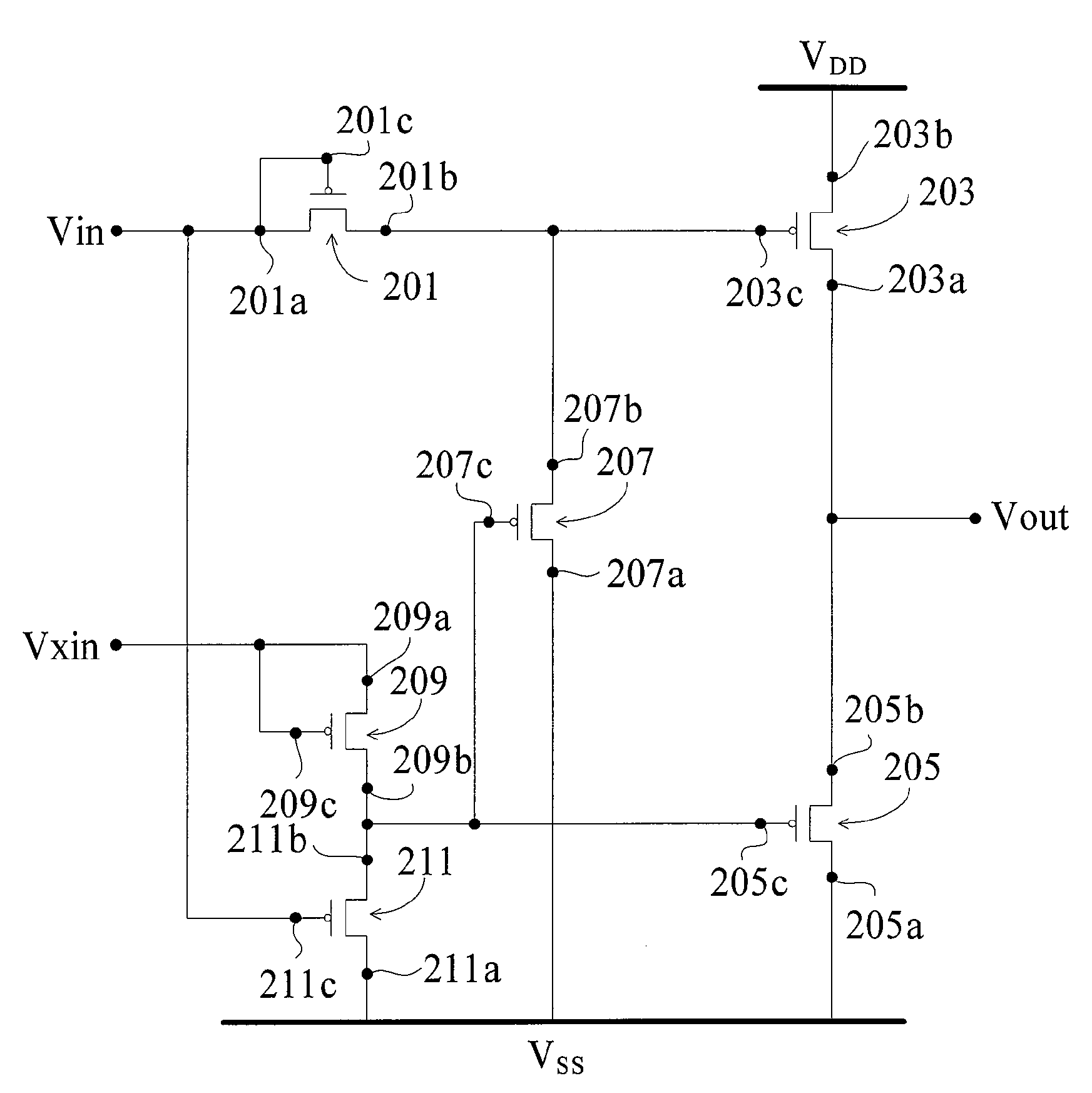

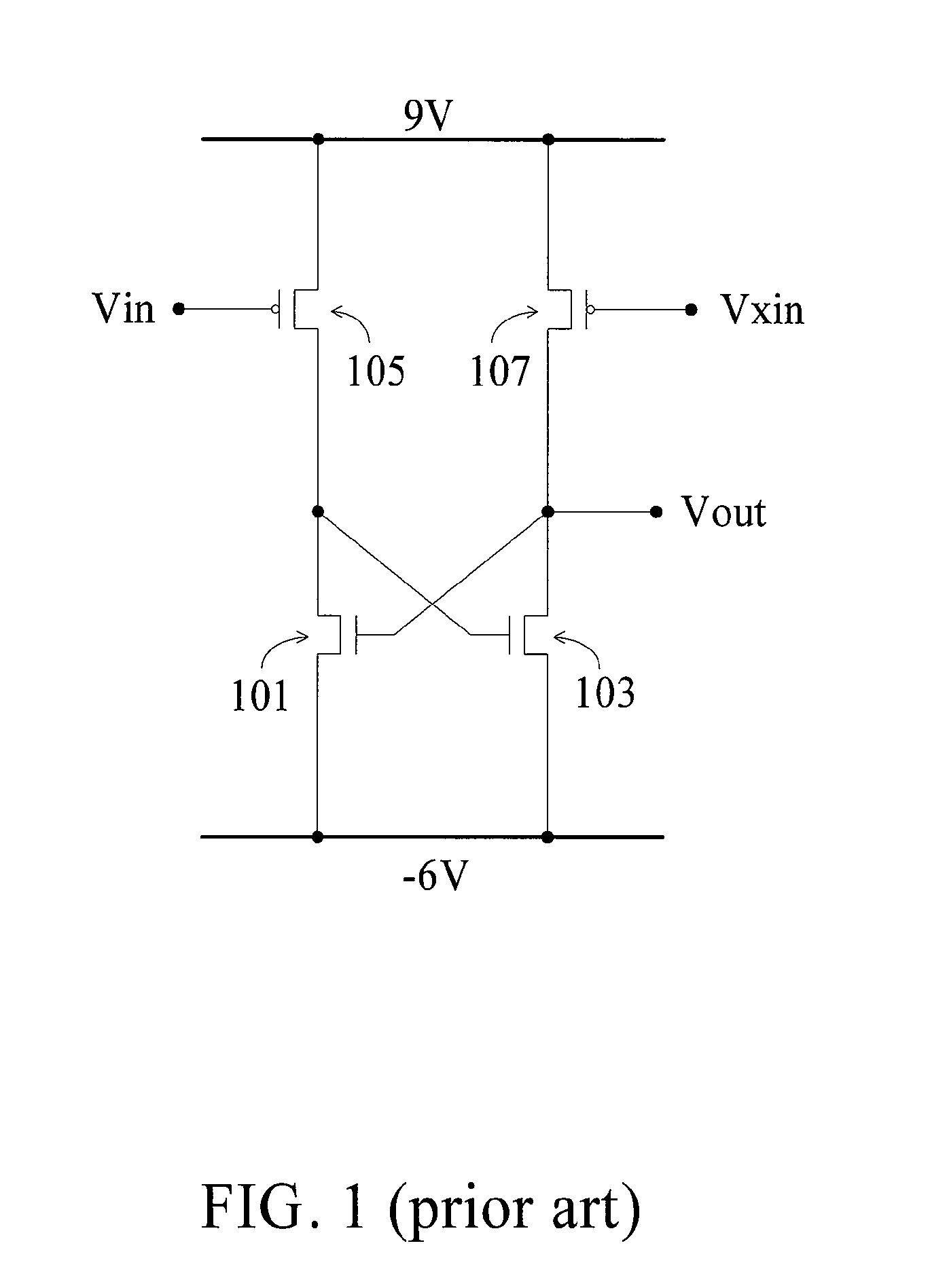

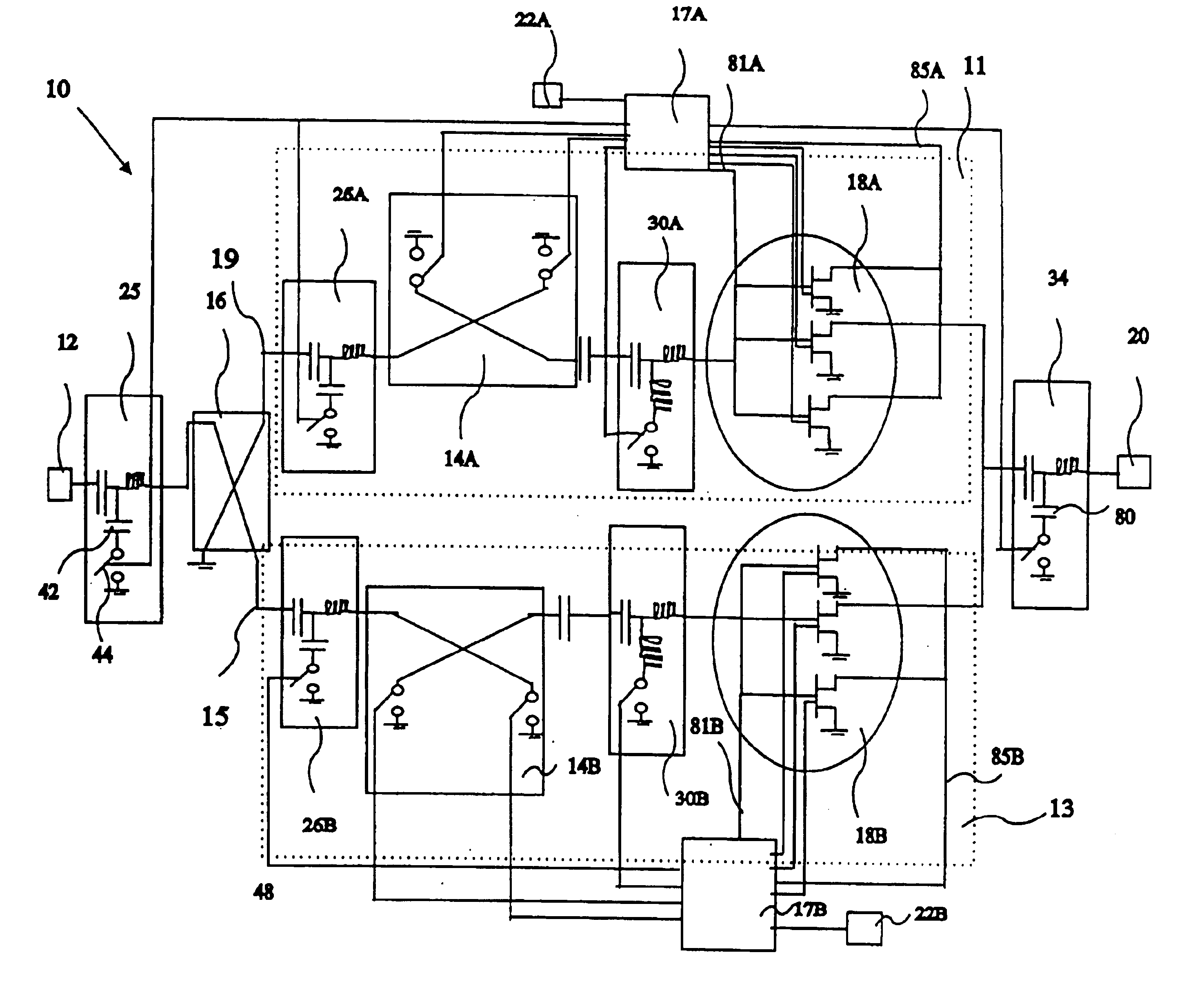

Low-skew single-ended to differential converter

InactiveUS7119602B2Reduce offsetReduce static power consumptionTransistorSingle output arrangementsTransmission gateEngineering

A single-ended to differential converter uses a cross-coupled latch that maximizes the output zero-crossing symmetry and is self compensating over PVT variations. An in-phase driving signal is provided by an always-on transmission gate coupled to the input. An out-of-phase driving signal is provided by an inverter coupled to the input. The in-phase and out-of-phase driving signals each drive an input of the cross-coupled latch. The in-phase driving signal from the always-on transmission gate starts to bring the cross-coupled latch into conduction, and when the out-of-phase driving signal arrives, the simultaneous driving of the cross-coupled latch causes a rapid and symmetric transition of both outputs of the cross-coupled latch.

Owner:TELEFON AB LM ERICSSON (PUBL)

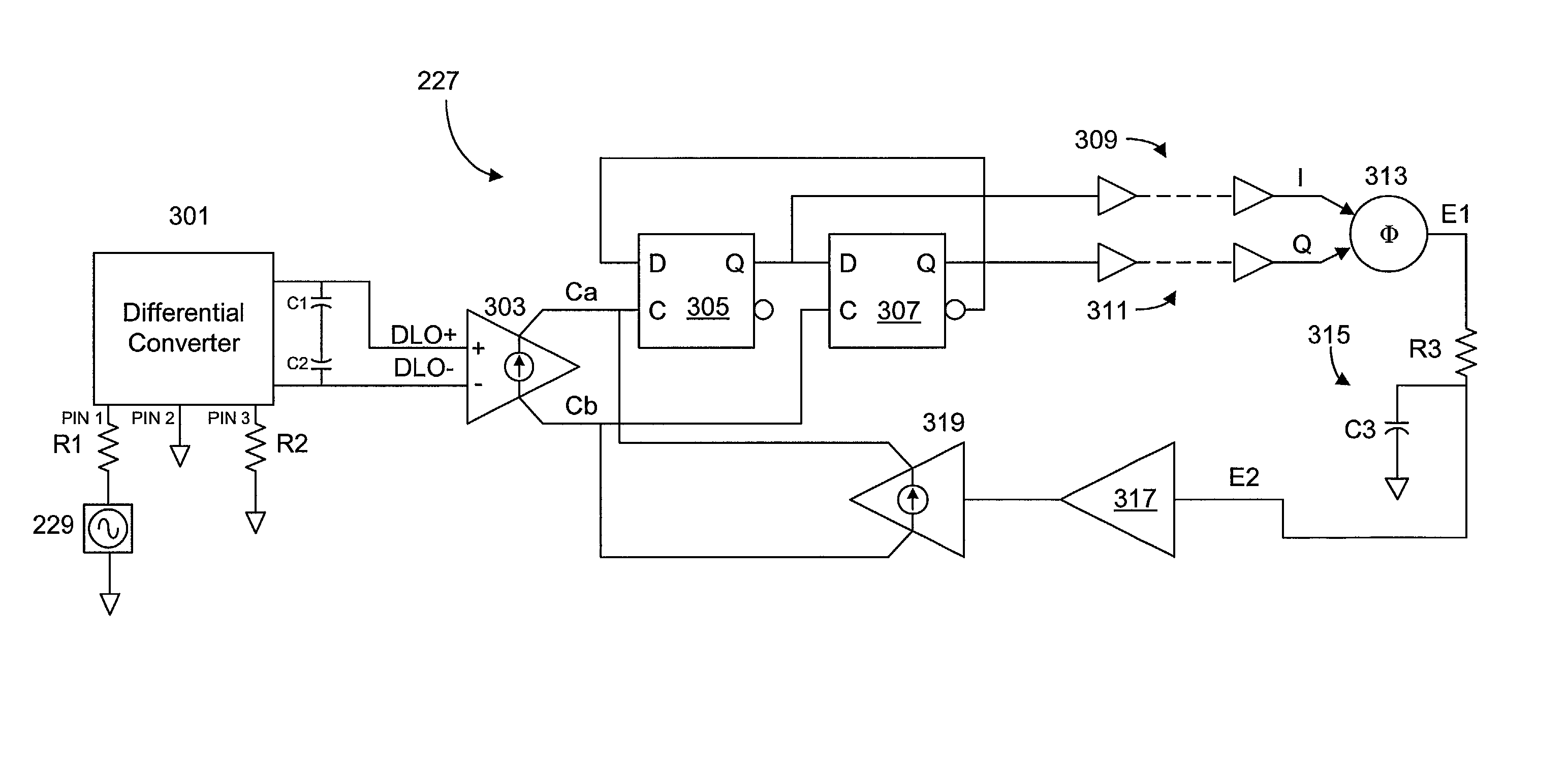

Quadrature oscillator with phase error correction

InactiveUS20020039052A1Increase volumePulse automatic controlGain controlPhase detectorAudio power amplifier

A quadrature oscillator with phase error correction including a local oscillator that generates a single-ended clock signal, a single-ended to differential converter that converts the clock signal to a differential clock signal, a quadrature generator that converts the differential clock signal into I and Q carrier signals, a phase error detector that measures a phase error between the I and Q carrier signals, and a feedback amplifier that modifies the differential clock signal based on measured phase error. The feedback amplifier applies the measured phase error as a DC offset to an AC differential clock signal. A transconductor converts the differential clock voltage signal into two pairs of differential current clock signals, where the quadrature generator generates I and Q current signal outputs from the two pairs of differential current clock signals. The phase error detector generates a phase error voltage, and the feedback amplifier includes a transconductance stage that converts phase error voltage into a DC correction current and that adds the correction current to each of the two pairs of AC differential current clock signals.

Owner:M RED INC

Multiphase receiver and oscillator

InactiveUS6385442B1Single output arrangementsPulse generation by logic circuitsLocal oscillator signalEngineering

A differential ring oscillator is provided with three differential amplifiers and provides three-phase output signals which can be used for synchronous detection of a received multi-phase modulated signal in a multi-phase receiver, wherein the phase of the local oscillator signals may be in other-than-quadrature relation. Two of the phase outputs of the local oscillator can be combined to provide a signal that is in quadrature with the remaining output. The oscillator is preferably controlled in coarse frequency control steps and using a fine voltage control signal responsive to a phase-locked loop to reduce frequency modulation of the oscillator signal arising out of leakage signals.

Owner:EXTREME NETWORKS INC

Adaptive radio transceiver

An exemplary embodiment of the present invention described and shown in the specification and drawings is a transceiver with a receiver, a transmitter, a local oscillator (LO) generator, a controller, and a self-testing unit. All of these components can be packaged for integration into a single IC including components such as filters and inductors. The controller for adaptive programming and calibration of the receiver, transmitter and LO generator. The self-testing unit generates is used to determine the gain, frequency characteristics, selectivity, noise floor, and distortion behavior of the receiver, transmitter and LO generator. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or the meaning of the claims.

Owner:AVAGO TECH INT SALES PTE LTD

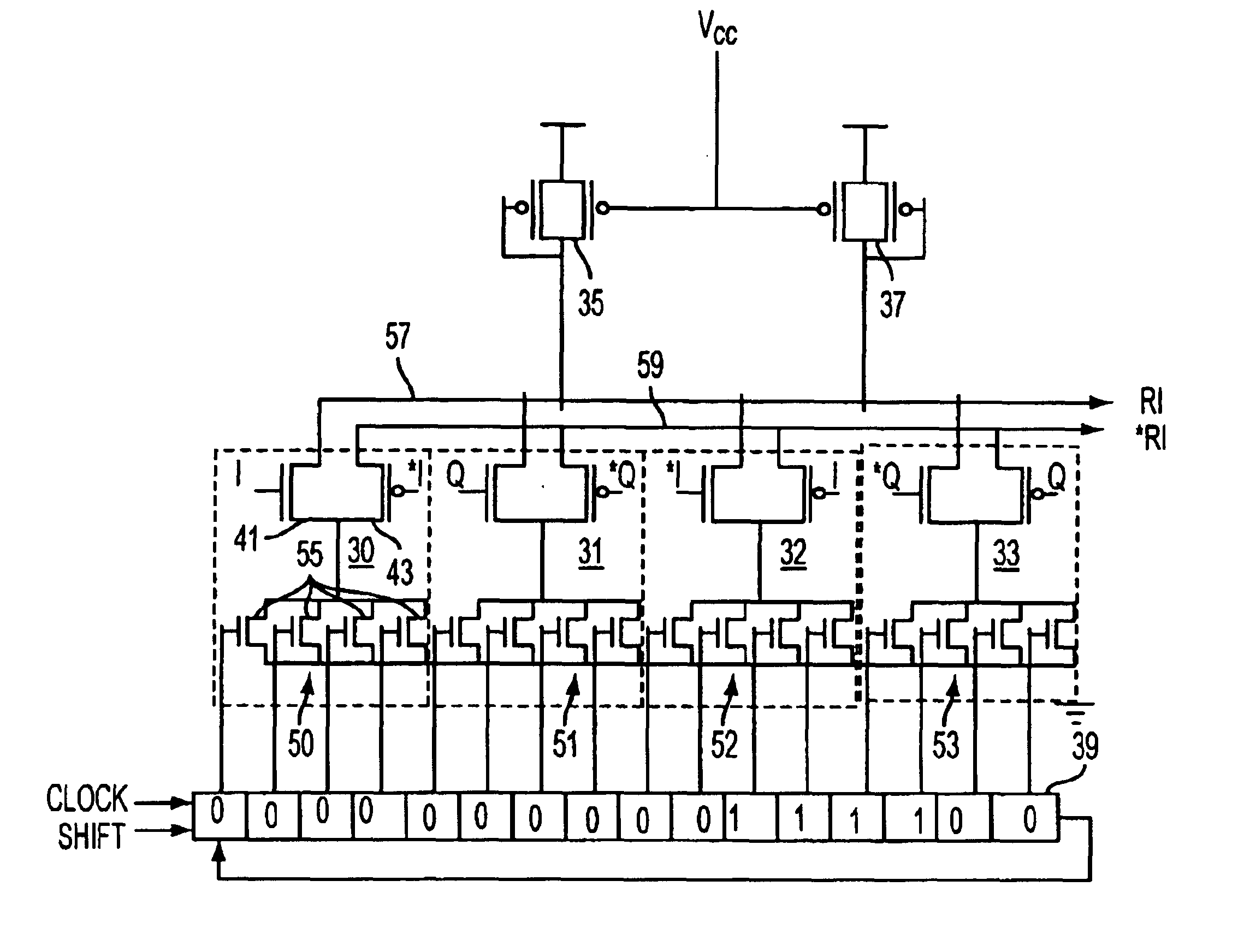

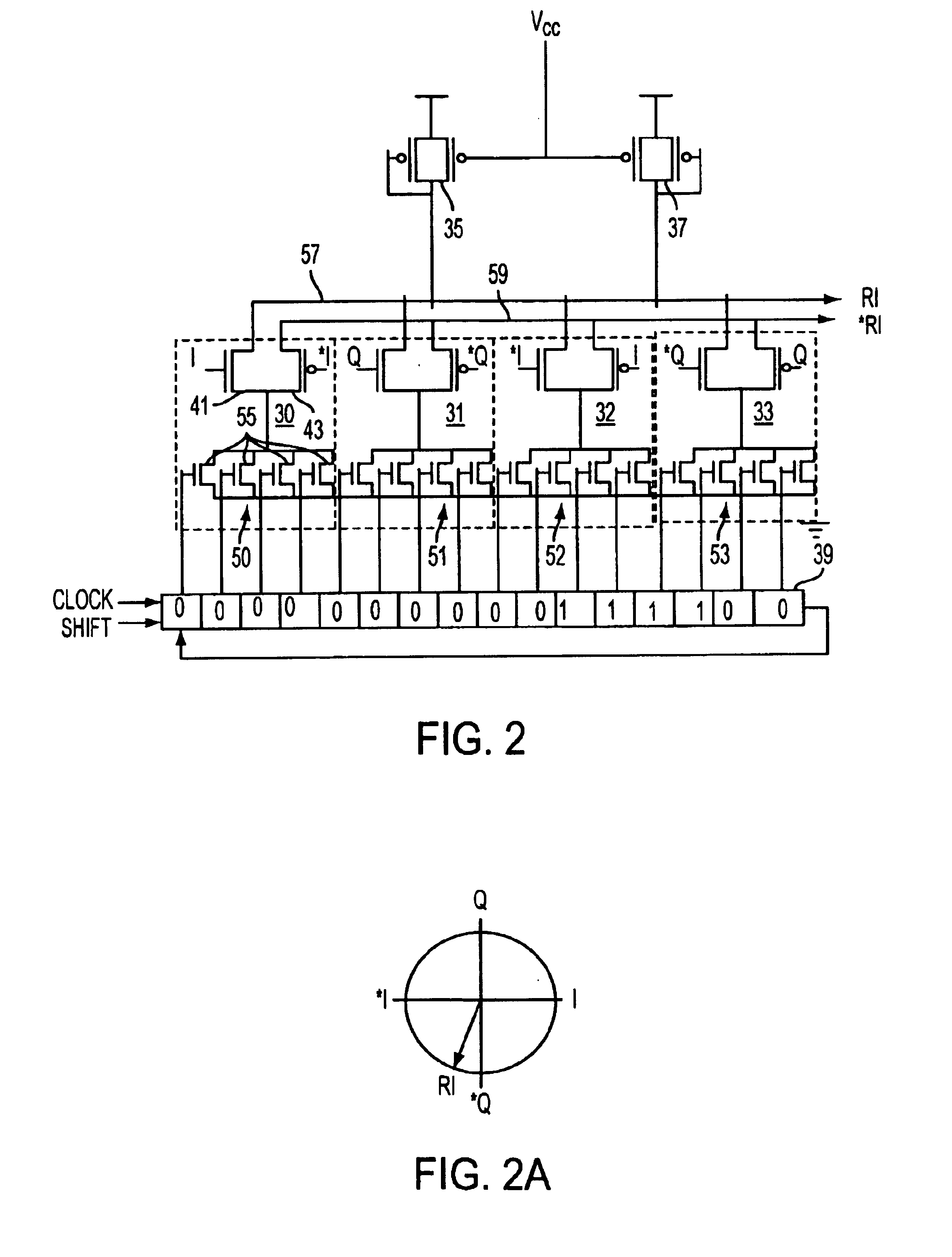

Phase interpolator to interpolate between a plurality of clock phases

A phase interpolator interpolates between a plurality of clock phases using a plurality of switching legs coupled to a common output. Each switching leg includes a pair of differential switching transistors each having a gate and two additional terminals, one of which is coupled to said common output. The gates are coupled to respective ones of the plurality of clock phases and their complements. Tails couple the other terminals of said switching transistors to ground. Each tail made up of a plurality of transistors. A load coupling the common output to a voltage.

Owner:INTEL CORP

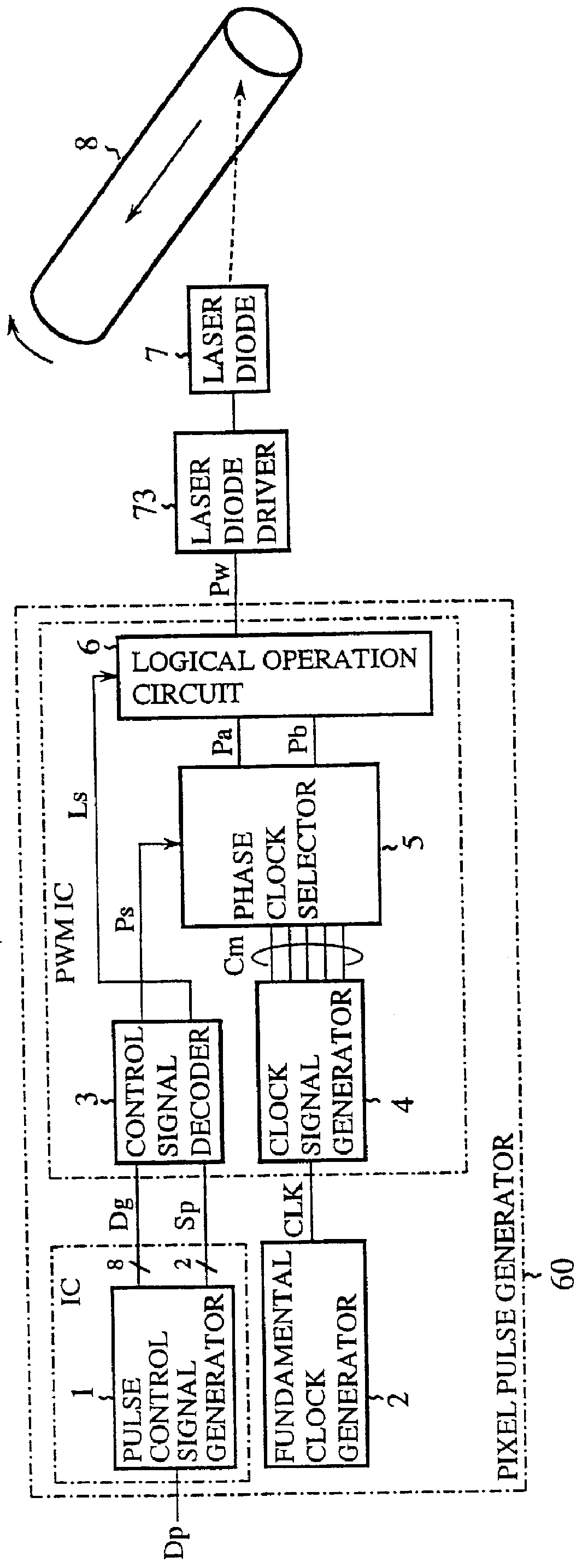

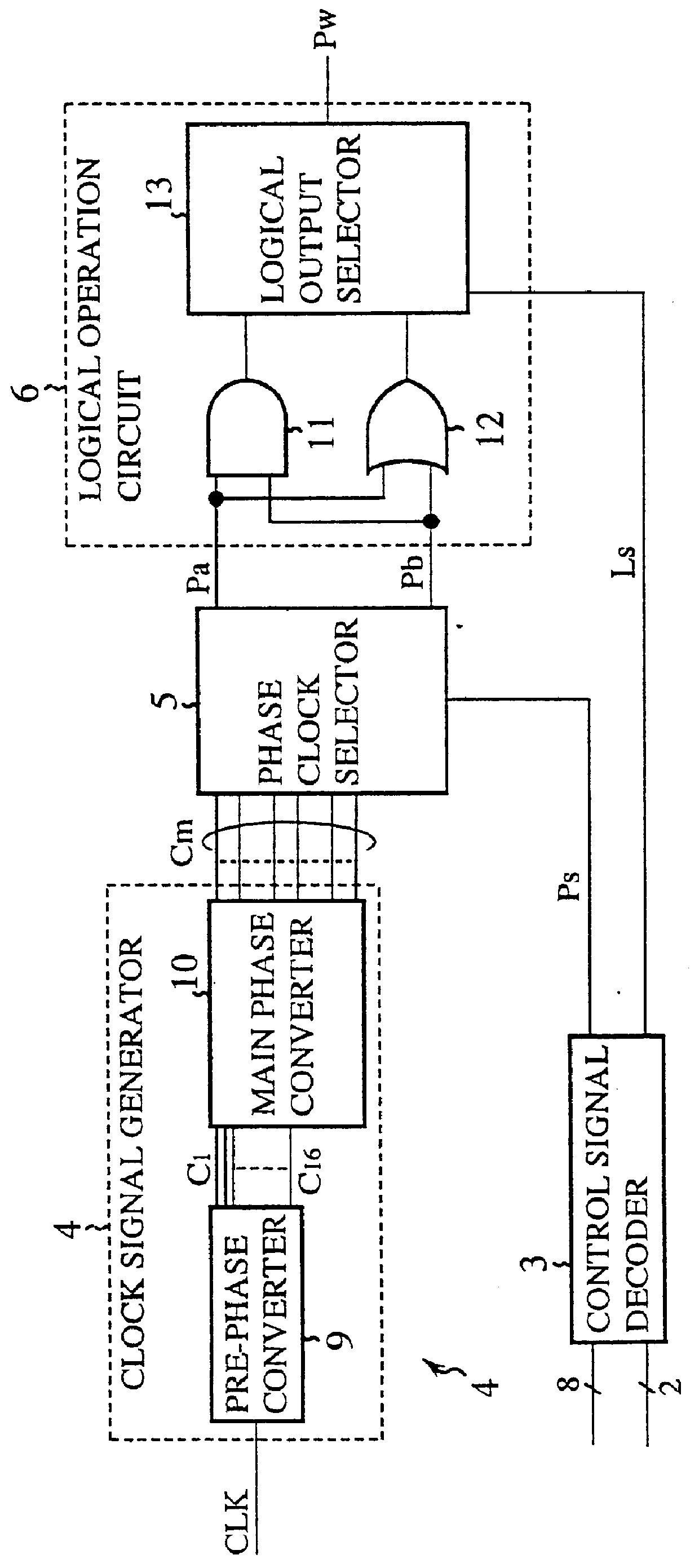

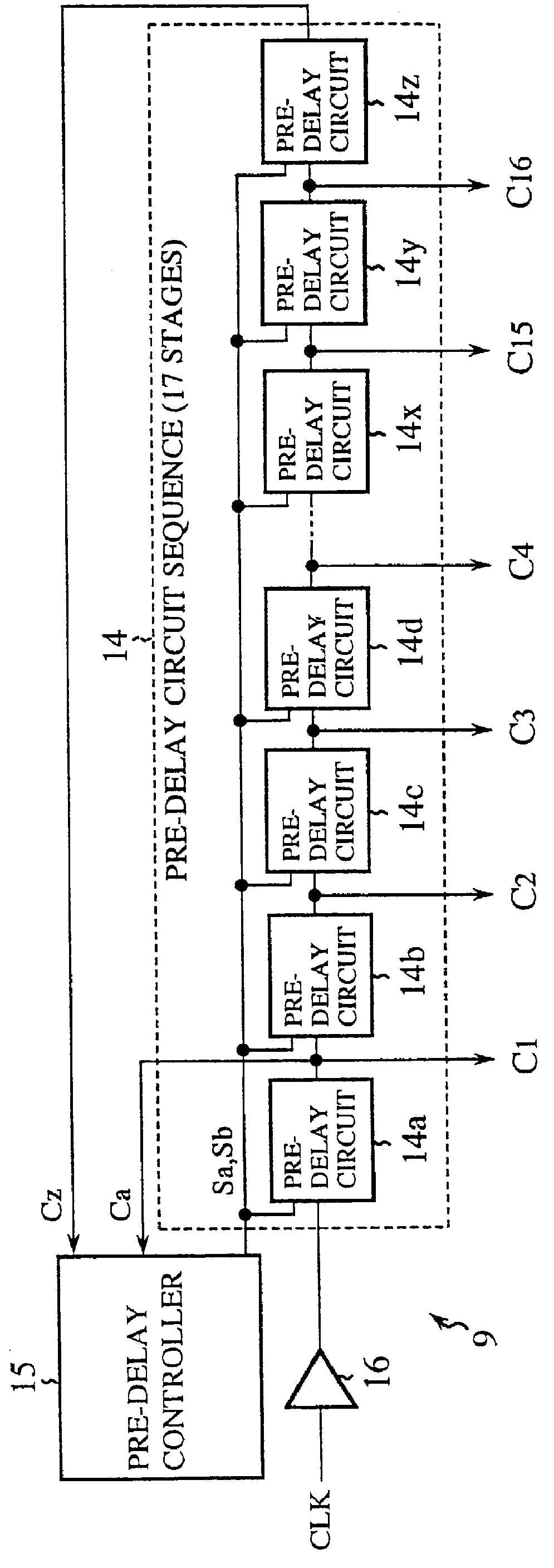

Clock signal generator for generating a plurality of clock signals with different phases, and clock phase controller using the same

A clock signal generator having a pre-phase converter for generating in response to an input clock signal a plurality of pre-delay clock signals with different phases; and main phase converters each of which receives one of the pre-delay clock signals, and generates a plurality of main delay clock signals with their phases different from each other, thereby generating multiple main delay clock signals with their phases different from each other.

Owner:RENESAS ELECTRONICS CORP

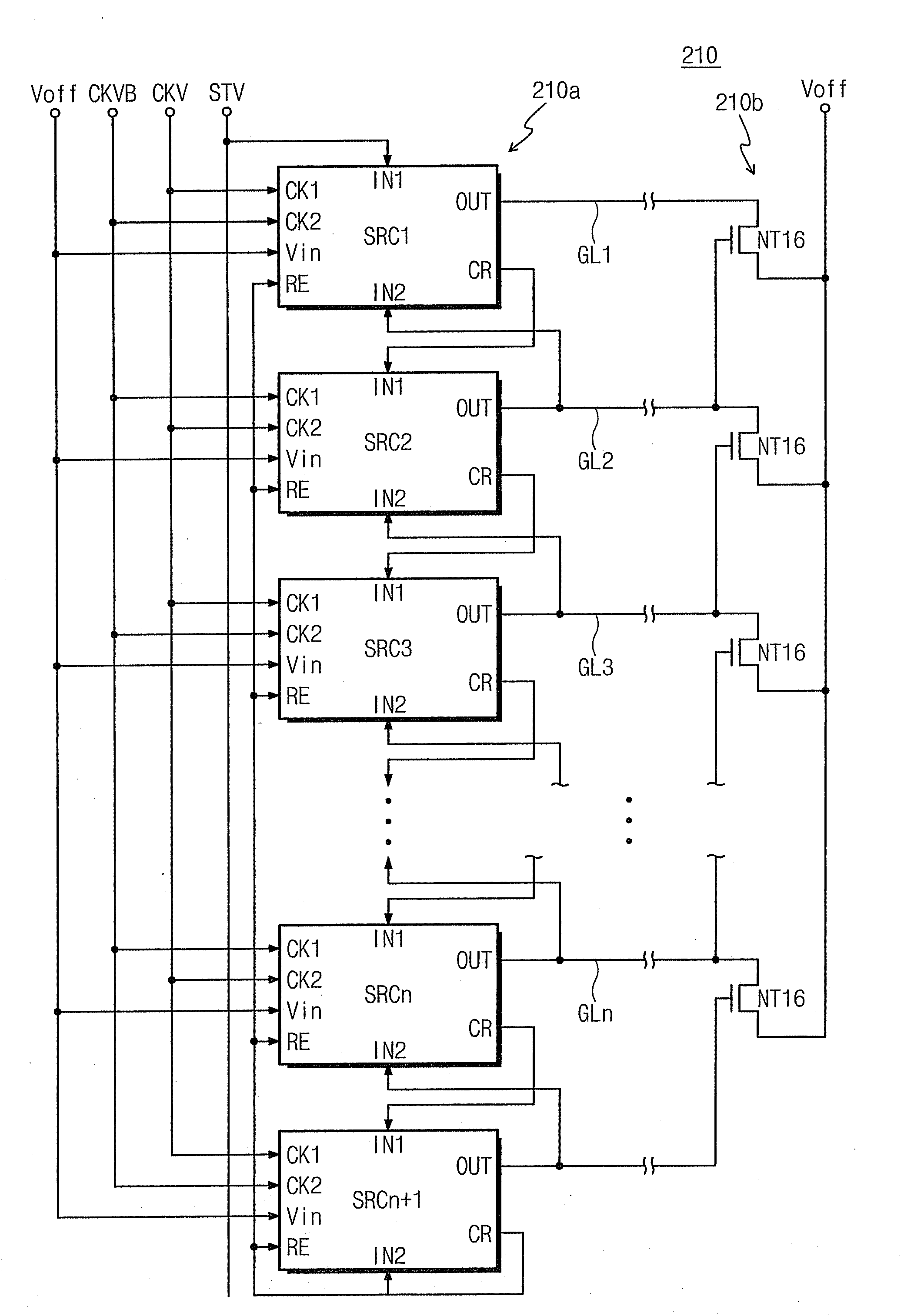

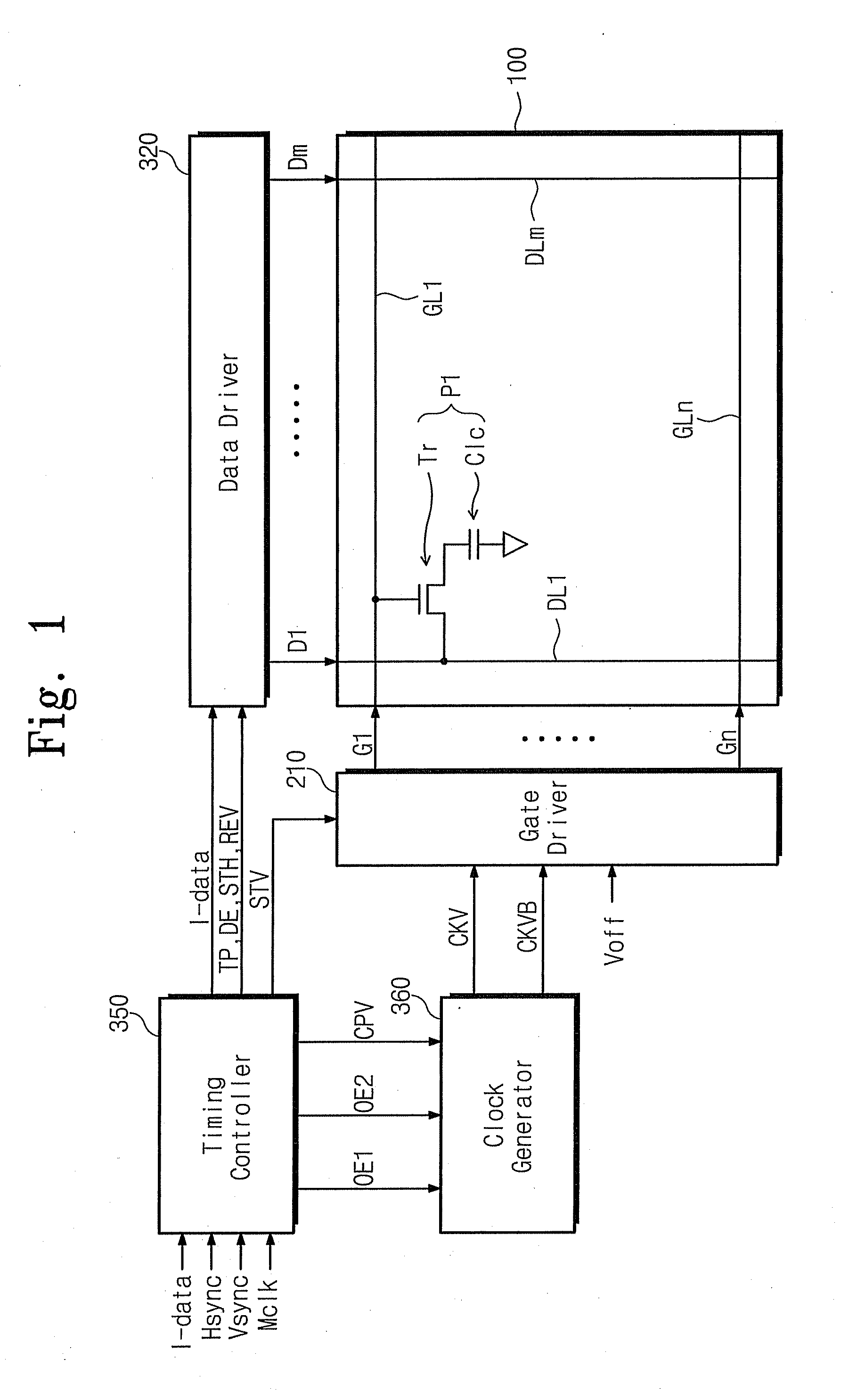

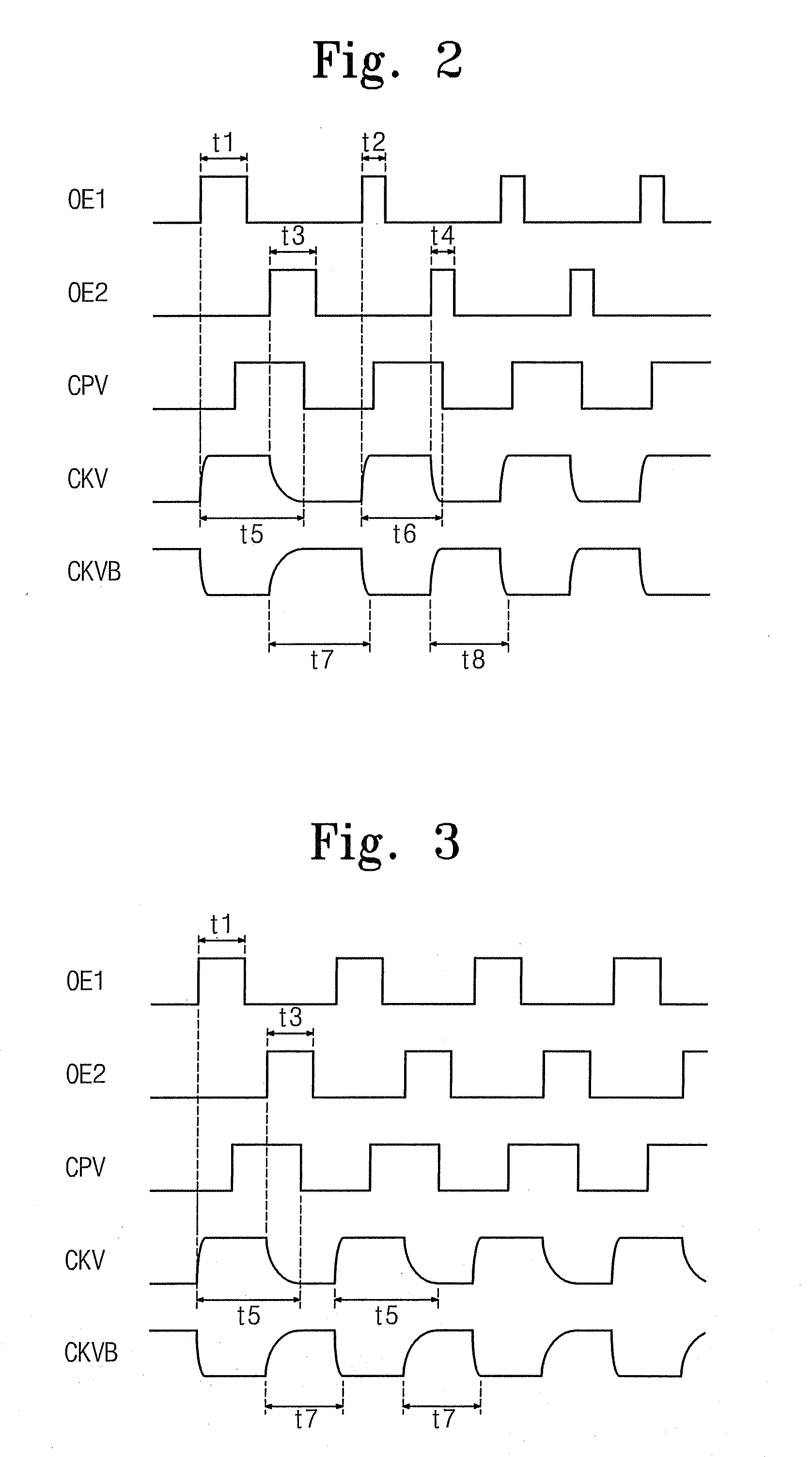

Display apparatus and method of driving the same

ActiveUS20080218502A1Improve display qualityReduce outputSingle output arrangementsCathode-ray tube indicatorsData controlControl signal

A display apparatus includes a gate driver which sequentially outputs a gate signal at a high state in response to a gate control signal and a data driver which converts image data into a data signal in response to a data control signal. The display apparatus further includes a display panel which includes a plurality of gate lines which sequentially receive the gate signal, a plurality of data lines which receive the data signal and a plurality of pixels connected to the gate and data lines and which receive the data signal in response to the gate signal to display an image. The polarity of the data signal is inverted after the gate signal transitions to a low state.

Owner:SAMSUNG DISPLAY CO LTD

Phase interpolator device and method

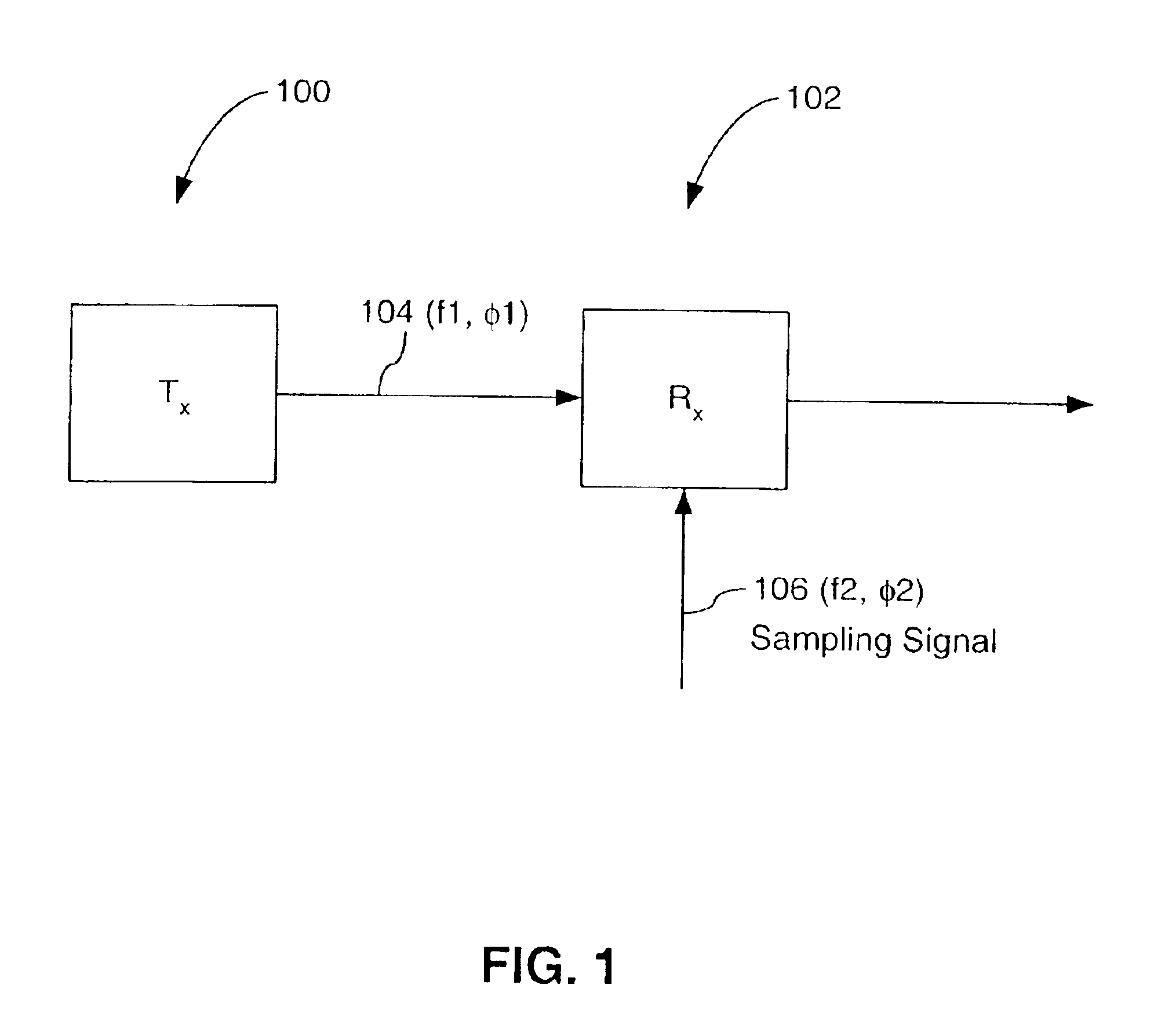

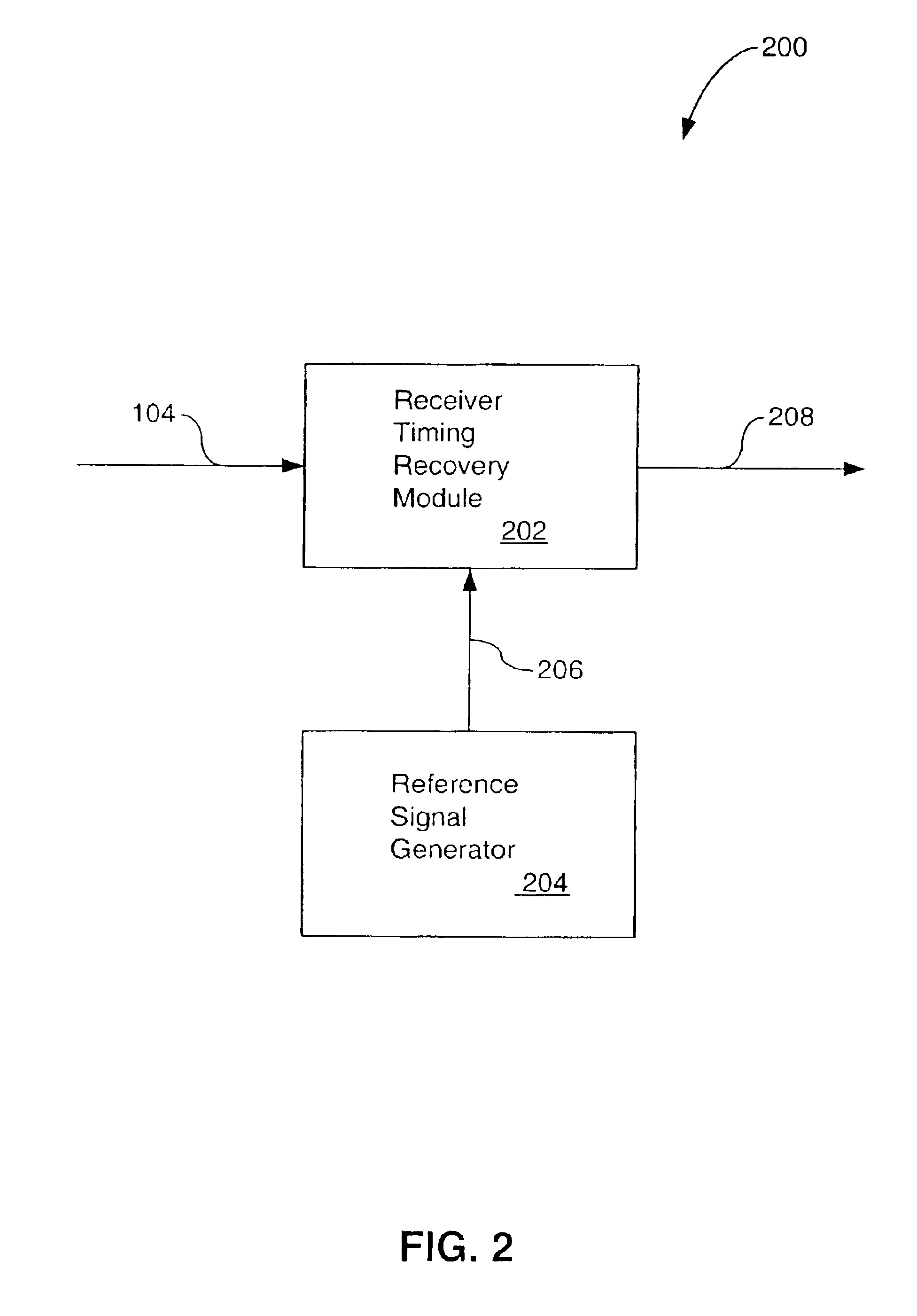

InactiveUS6791388B2Reduce frequency offsetComputations using contact-making devicesPulse automatic controlTransceiverGigabit

A high-speed serial data transceiver includes multiple receivers and transmitters for receiving and transmitting multiple analog, serial data signals at multi-gigabit-per-second data rates. Each receiver includes a timing recovery system for tracking a phase and a frequency of the serial data signal associated with the receiver. The timing recovery system includes a phase interpolator responsive to phase control signals and a set of reference signals having different predetermined phases. The phase interpolator derives a sampling signal, having an interpolated phase, to sample the serial data signal. The timing recovery system in each receiver independently phase-aligns and frequency synchronizes the sampling signal to the serial data signal associated with the receiver. A receiver can include multiple paths for sampling a received, serial data signal in accordance with multiple time-staggered sampling signals, each having an interpolated phase.

Owner:AVAGO TECH WIRELESS IP SINGAPORE PTE

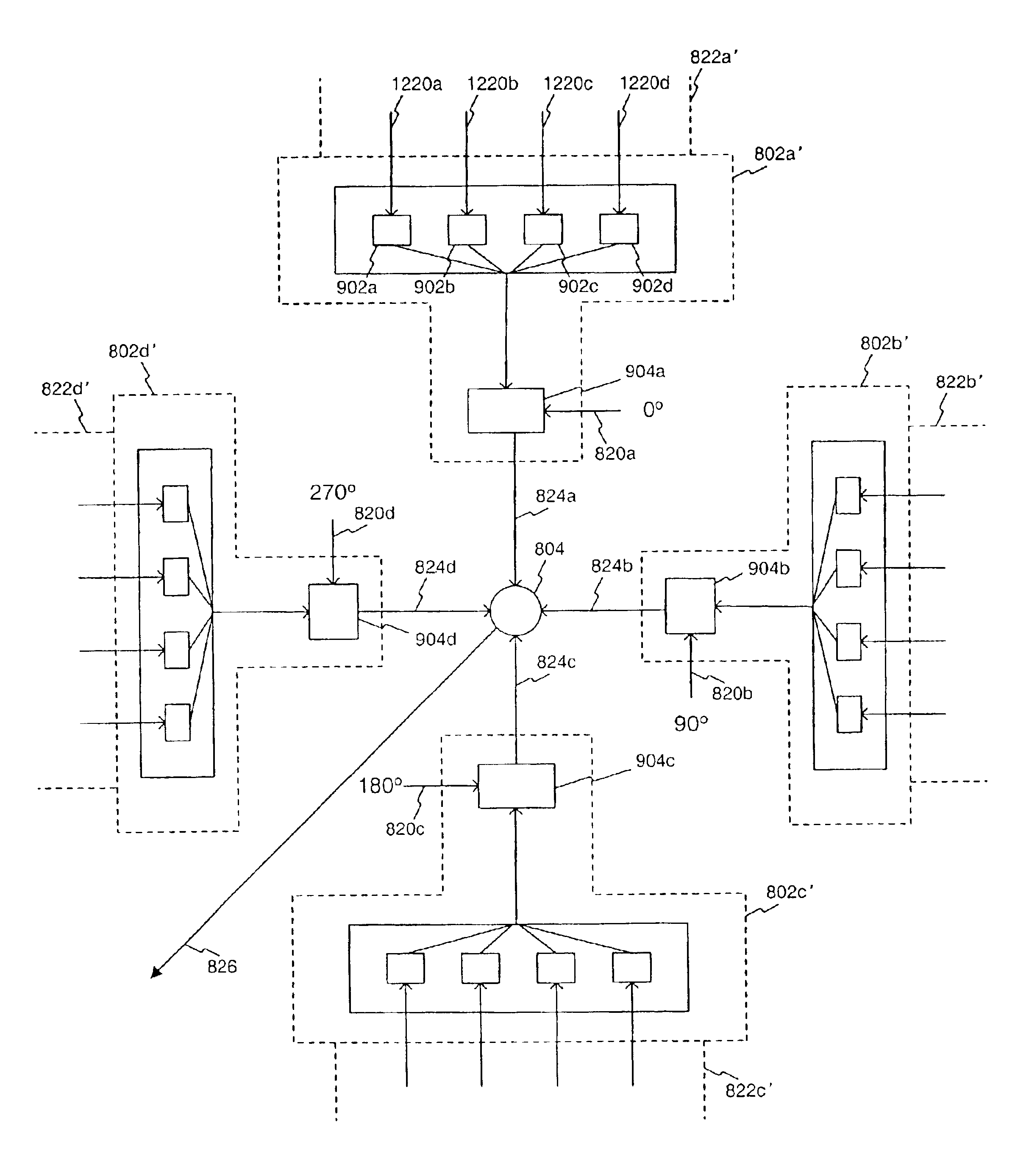

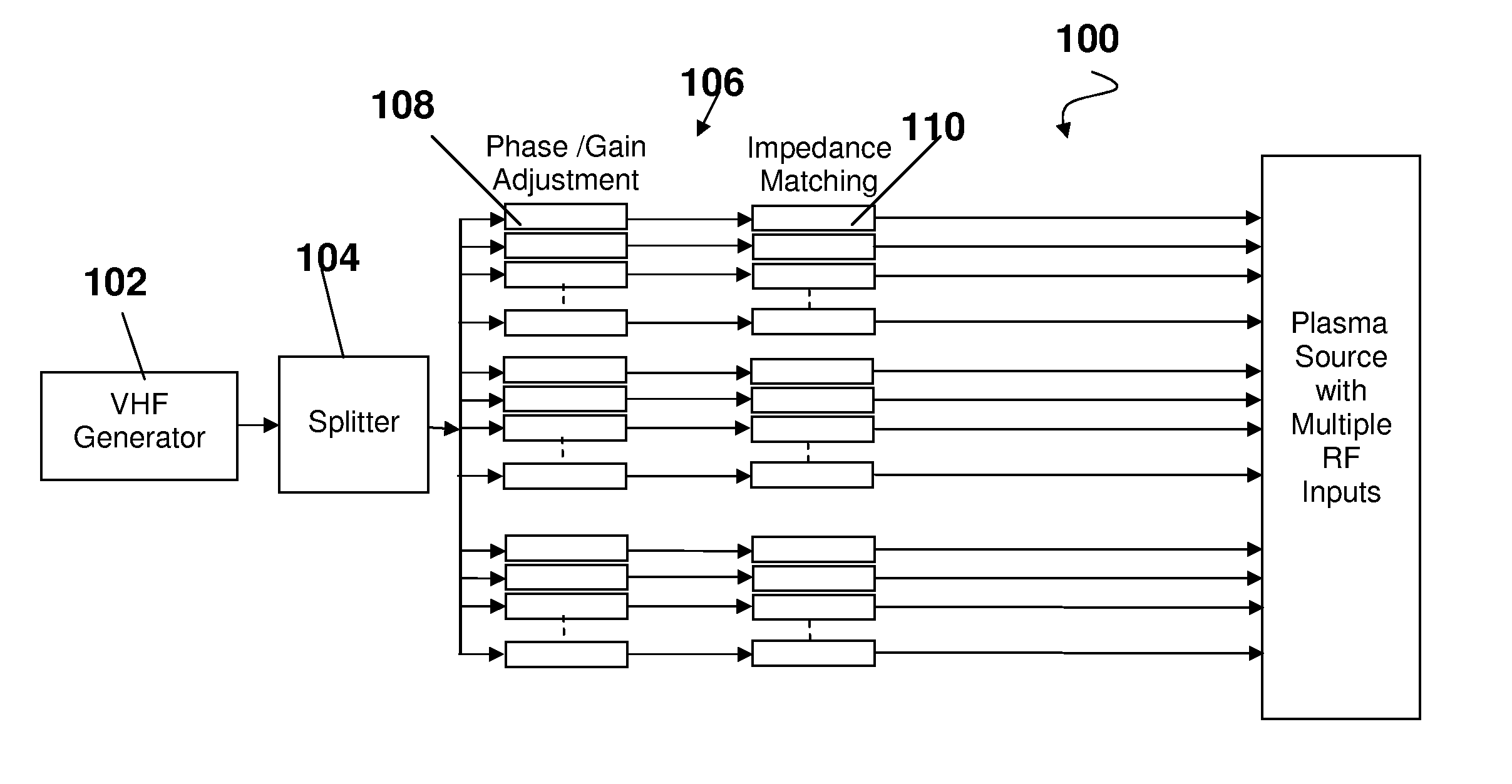

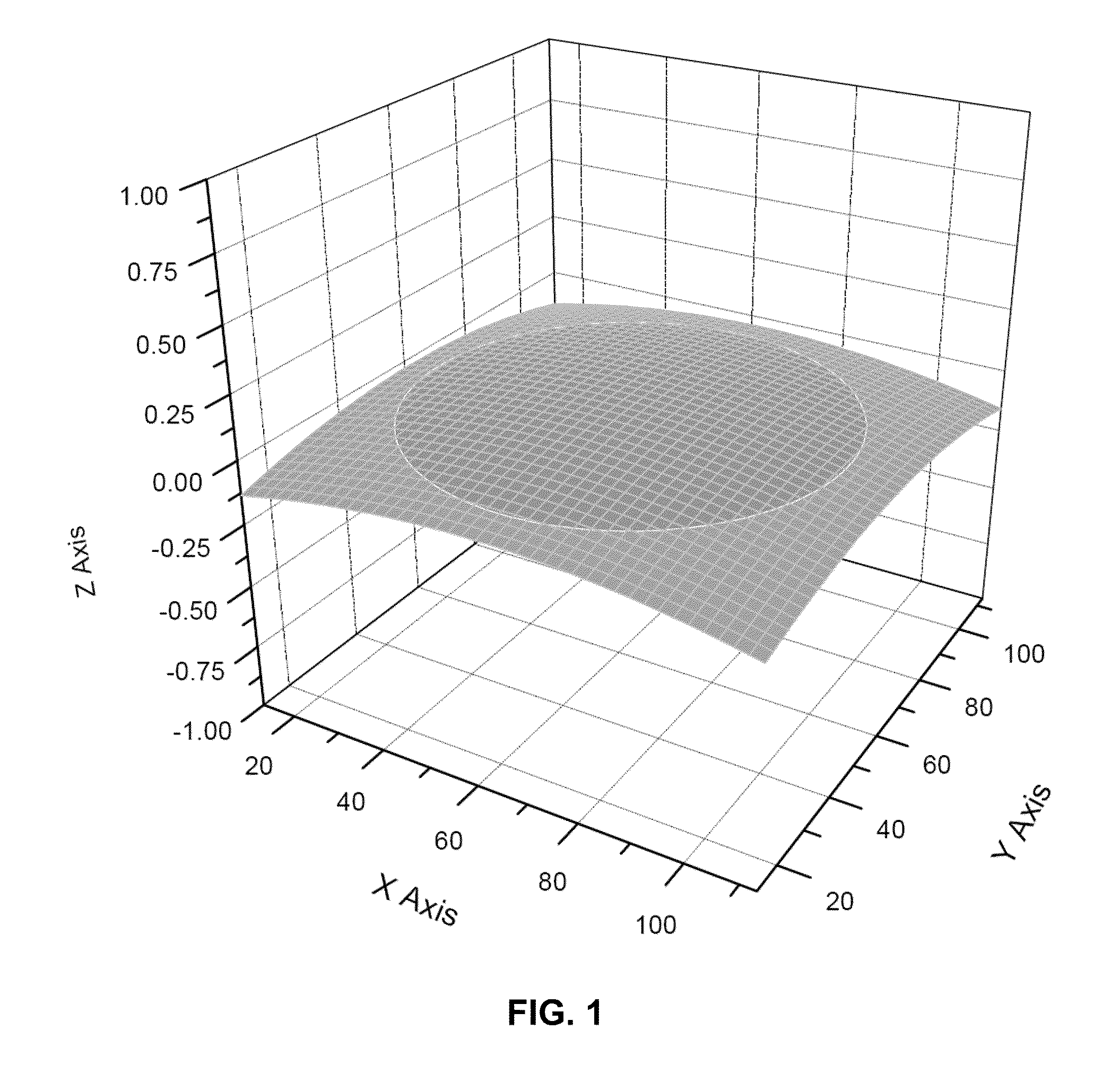

System for providing a substantially uniform potential profile

InactiveUS20100123502A1Uniform potential distributionImpedence matching networksMultiple-port networksEngineeringSignal generator

A system for providing at least two output signals to produce a substantially uniform potential profile includes a signal generator adapted to emit a frequency at least about 30 megahertz, a splitter in communication with the signal generator, and a signal manipulator in communication with the splitter. The splitter is adapted to split the signal of the signal generator into the two output signals, and the signal manipulator is adapted to manipulate a phase, a gain, or an impedance of the two output signals. The signal manipulator manipulates the two output signals so that the two output signals produce the substantially uniform potential profile.

Owner:RENO SUB-SYST INC

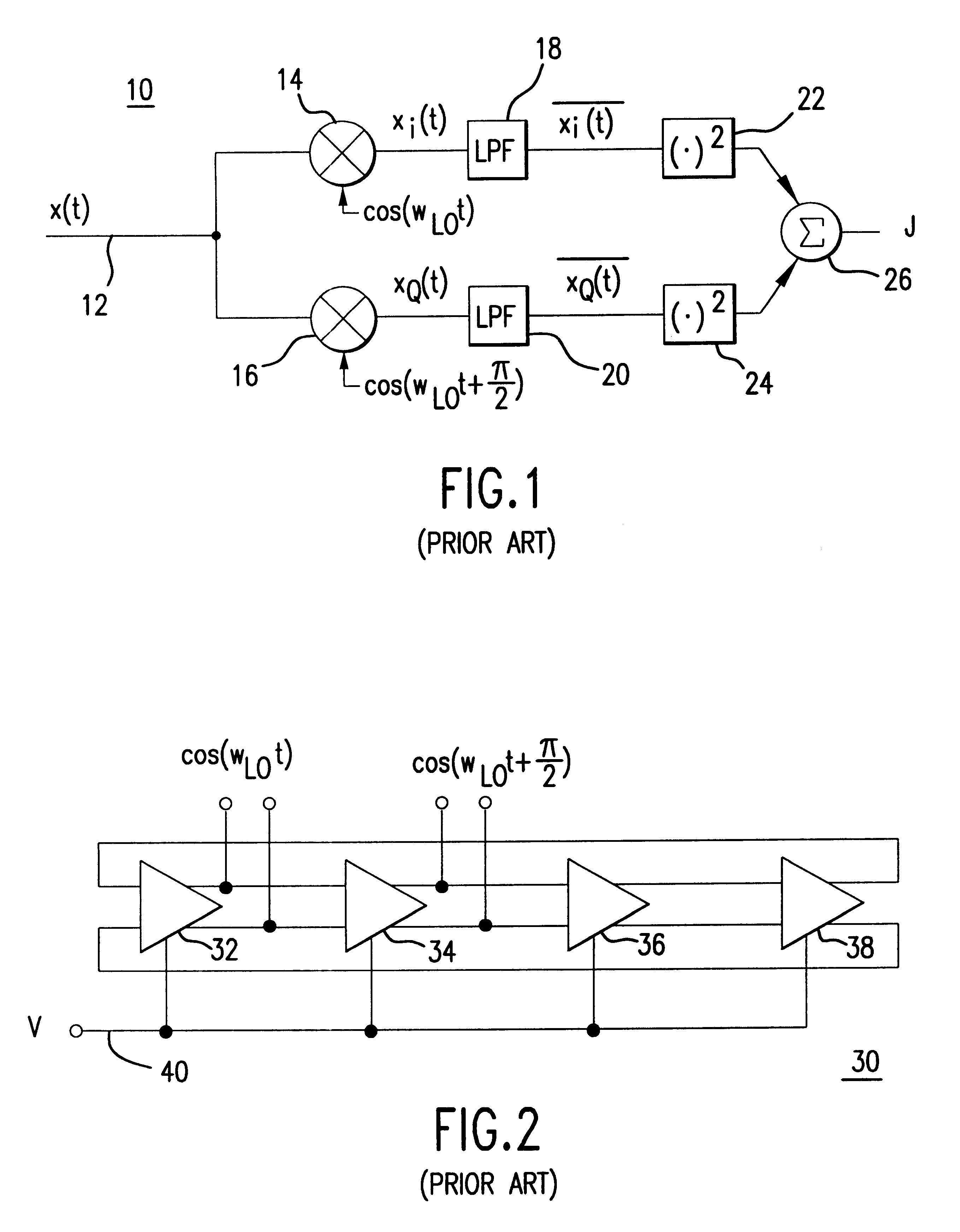

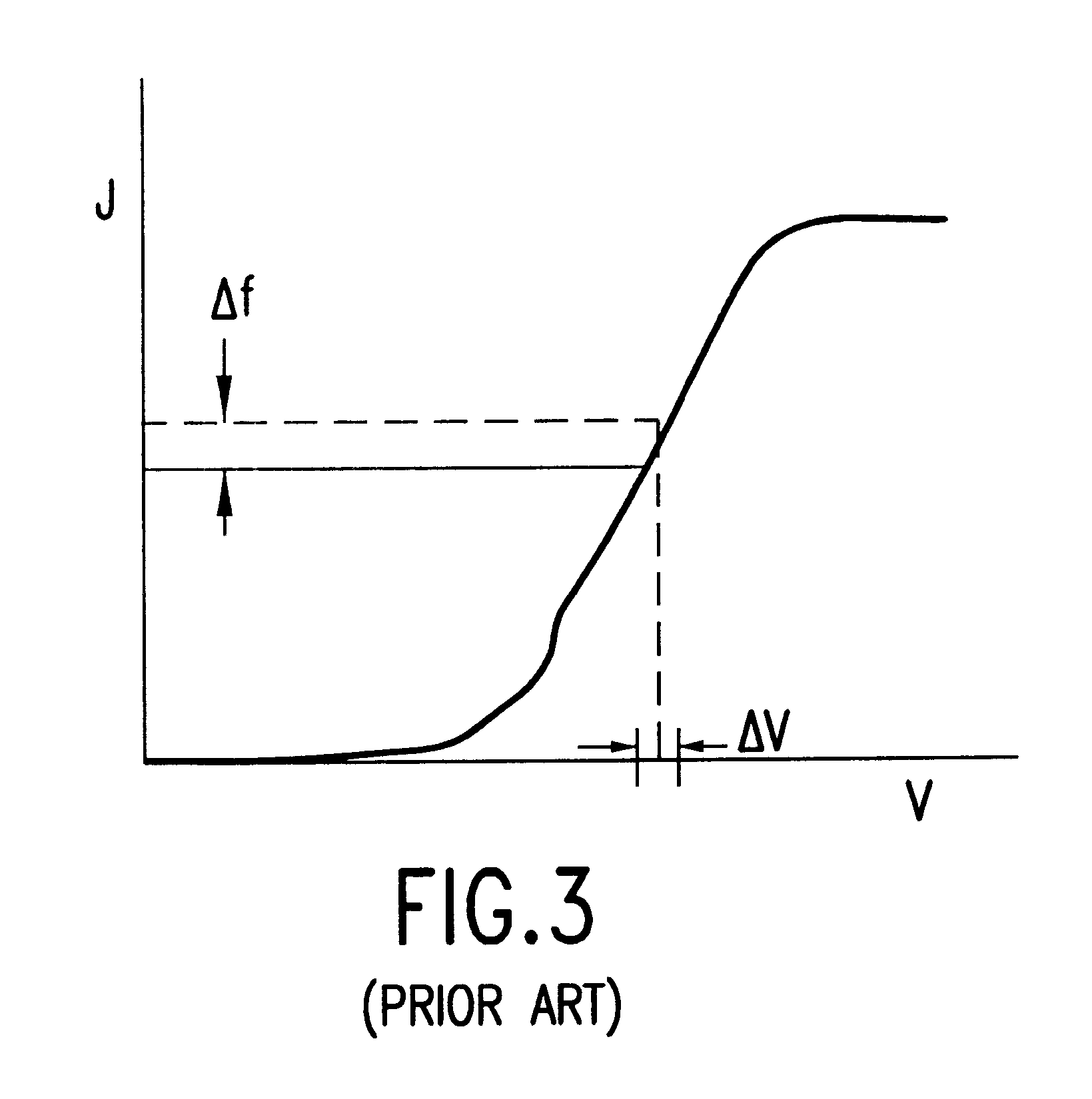

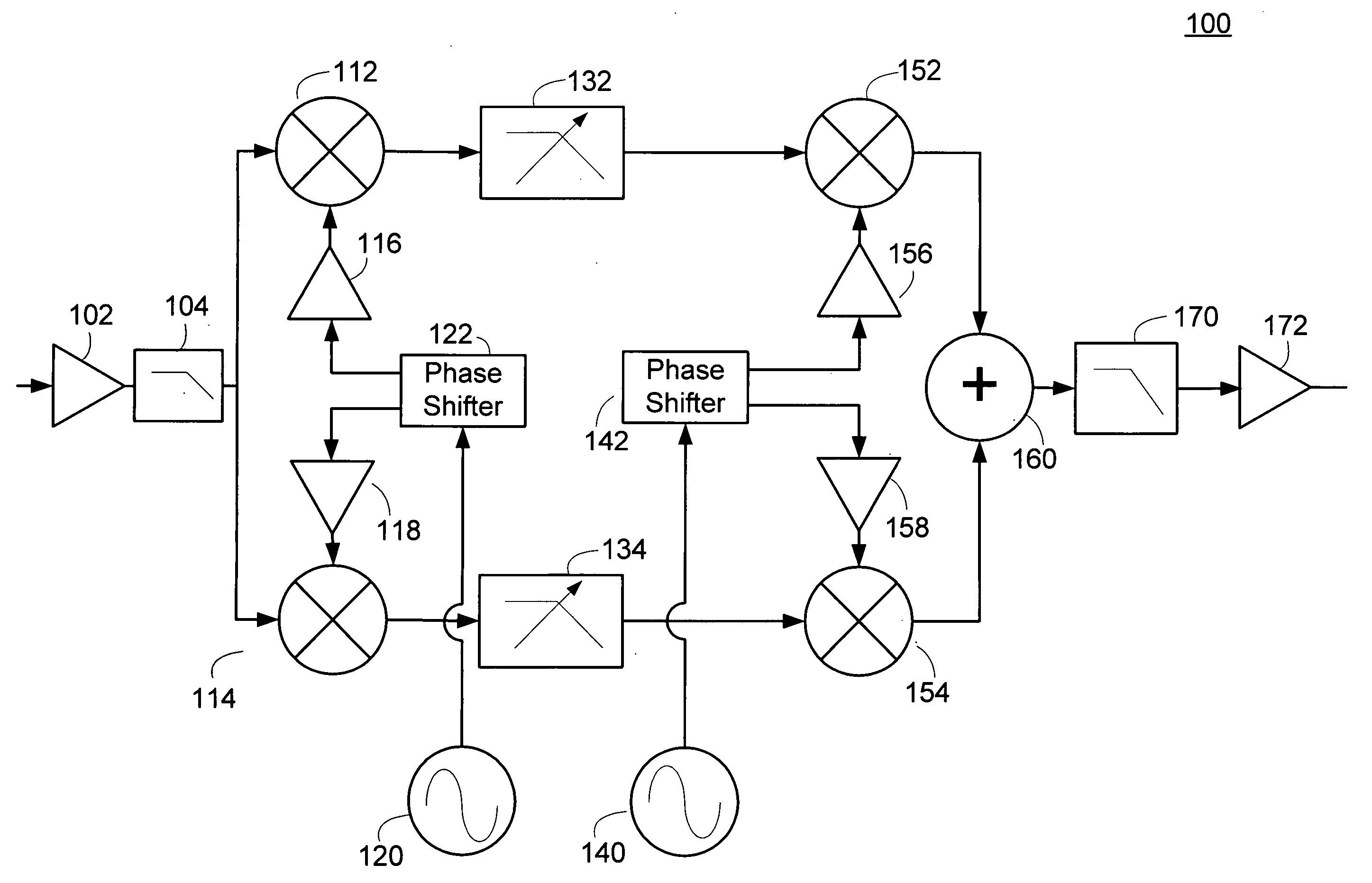

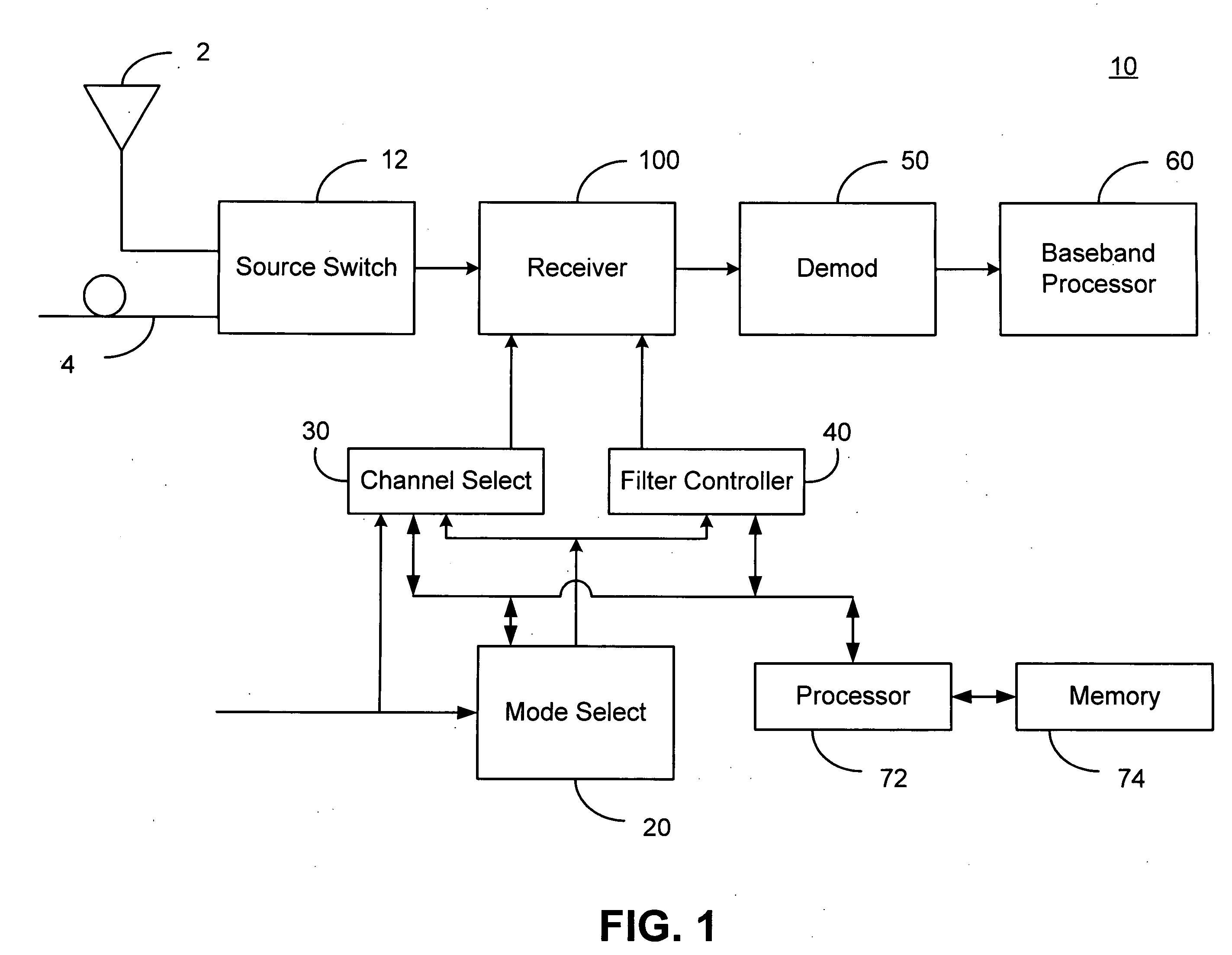

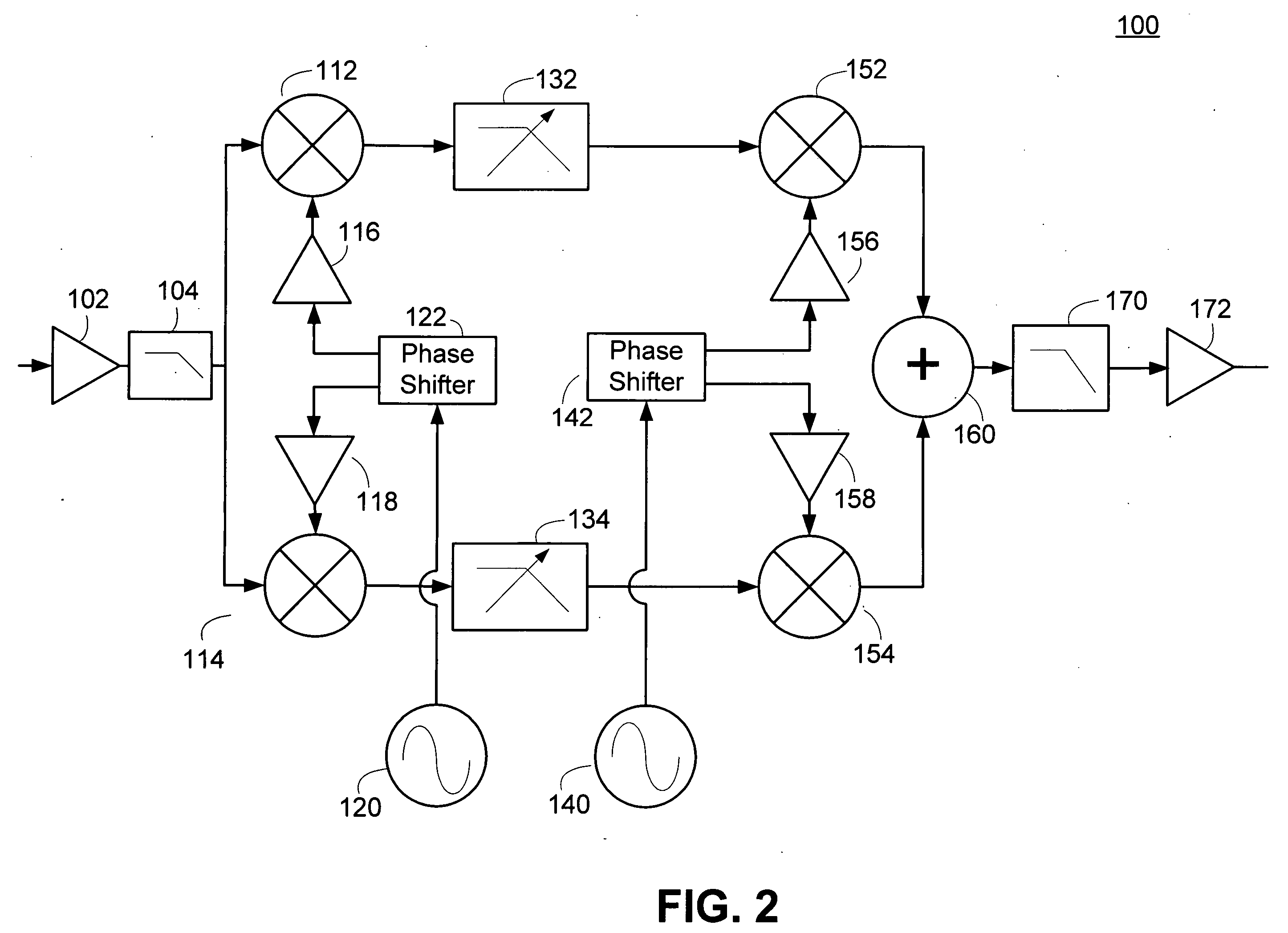

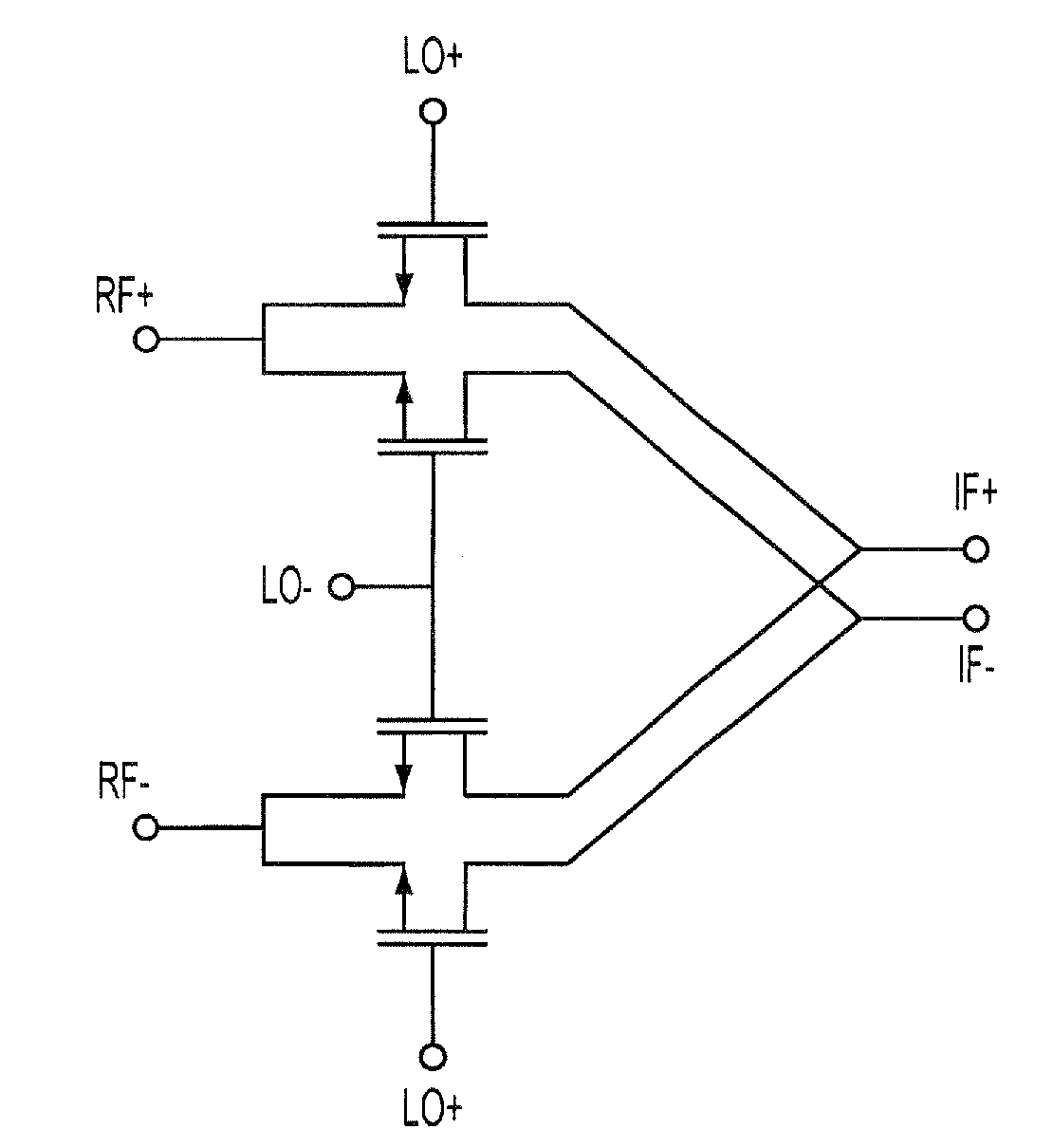

Harmonic reject receiver architecture and mixer

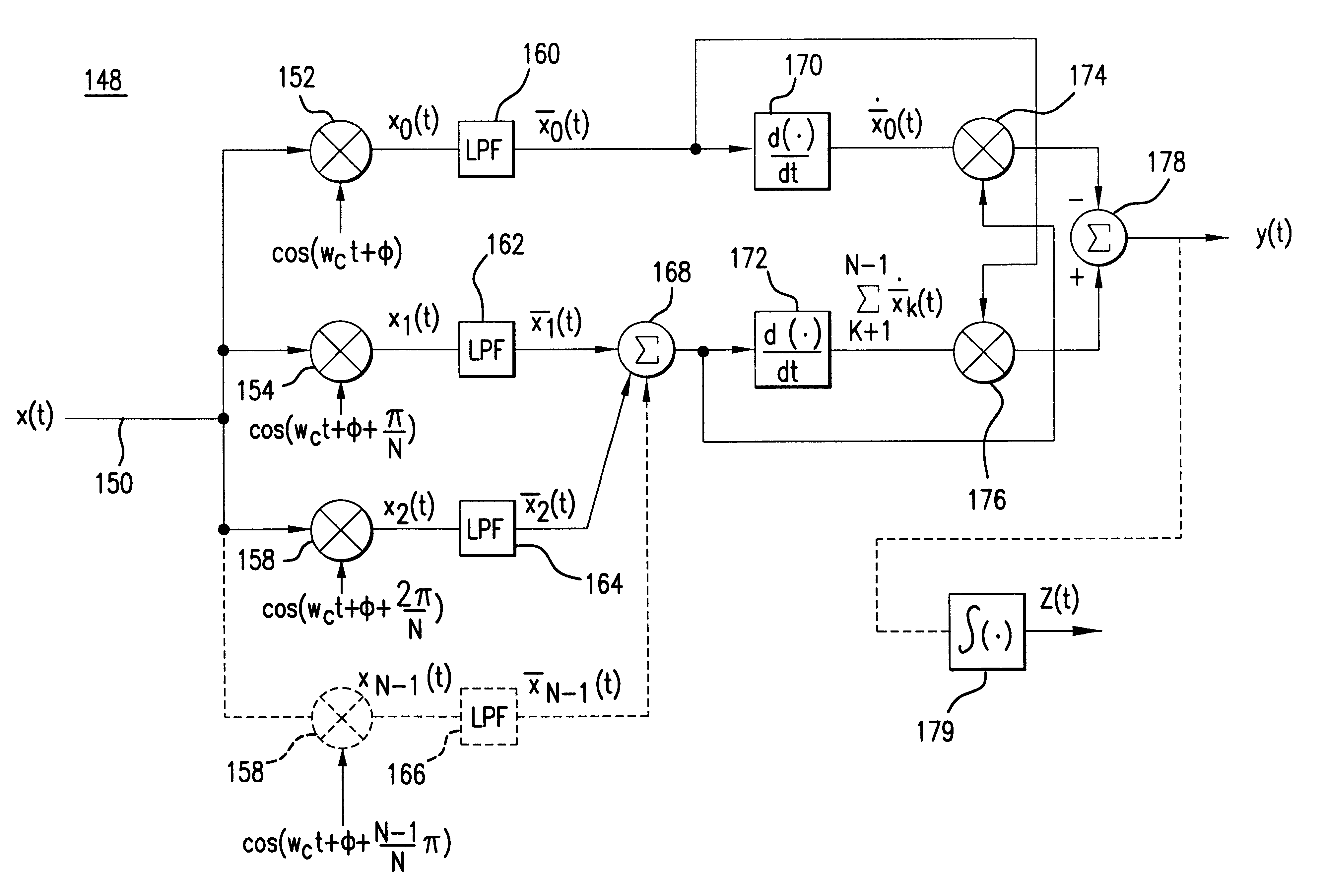

InactiveUS20060160518A1Reducing mixer responseReduced responseModulation transference balanced arrangementsMultiplex with amplitude-modulated carrierLocal oscillator signalFrequency mixer

Receiver architectures and methods of processing harmonic rich input signals employing harmonic suppression mixers are disclosed herein. The disclosed receivers, mixers, and methods enable a receiver to achieve the advantages of switching mixers while greatly reducing the mixer response to the undesired harmonics. A harmonic mixer can include a plurality of mixers coupled to an input signal. A plurality of phases of a local oscillator signal can be generated from a single local oscillator output. Each of the phases can be used to drive an input of one of the mixers. The mixer outputs can be combined to generate a frequency converted output that has harmonic rejection.

Owner:MAXLINEAR INC

Semi-Digital Delay Locked Loop Circuit and Method

ActiveUS20090243679A1High resolutionSmall DLL jitterTelevision system detailsPulse automatic controlPhase detectorPhase locked loop circuit

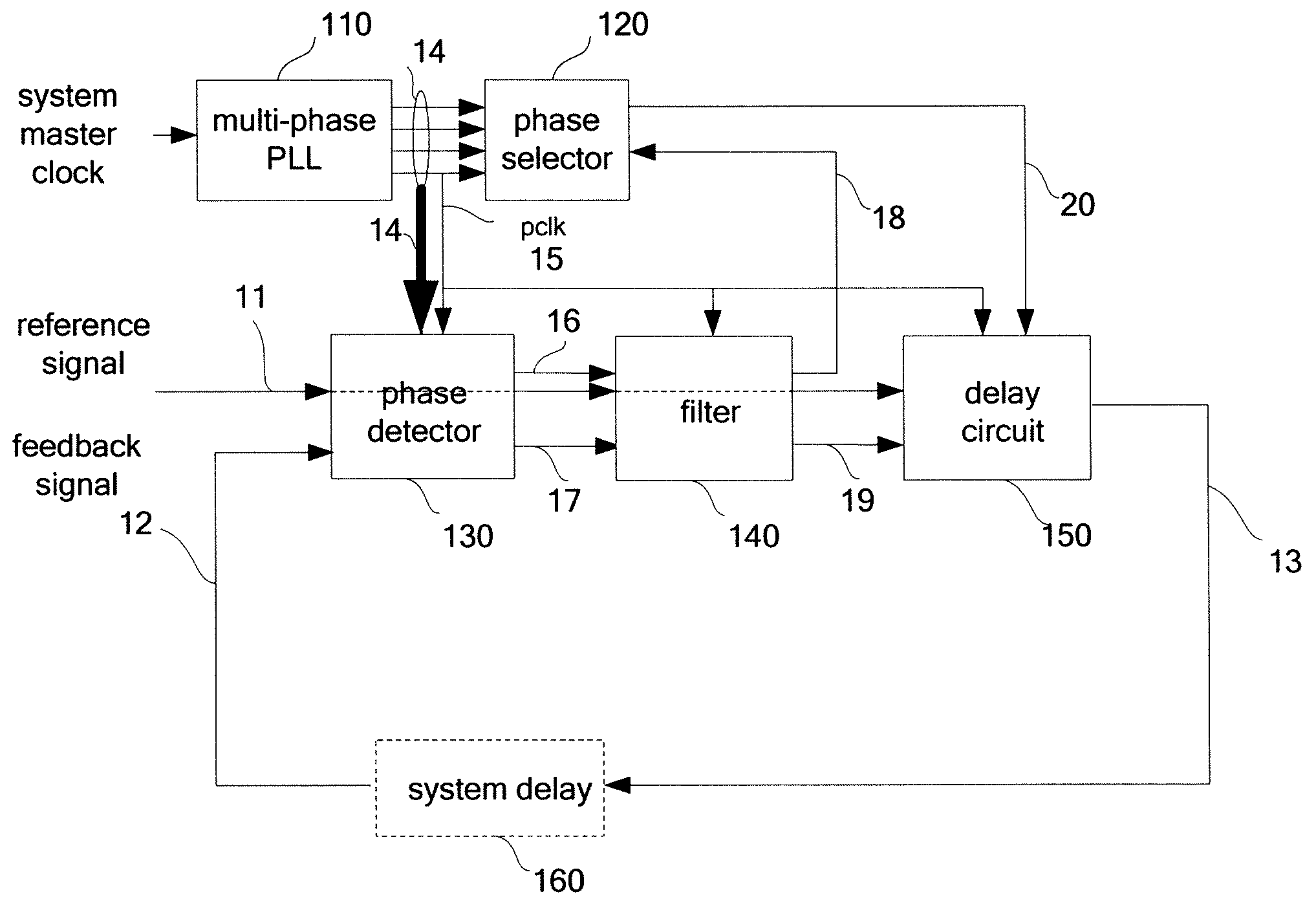

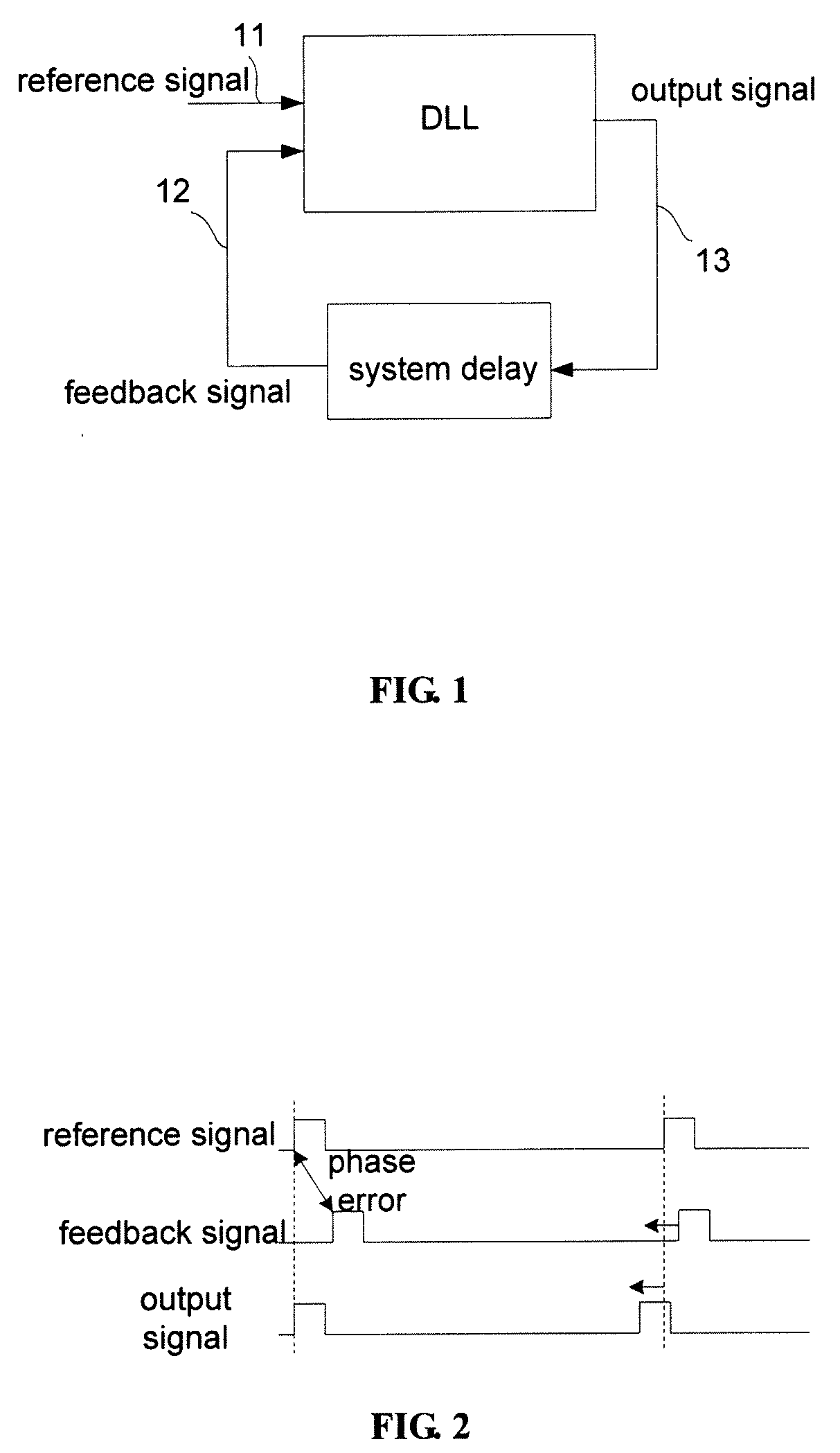

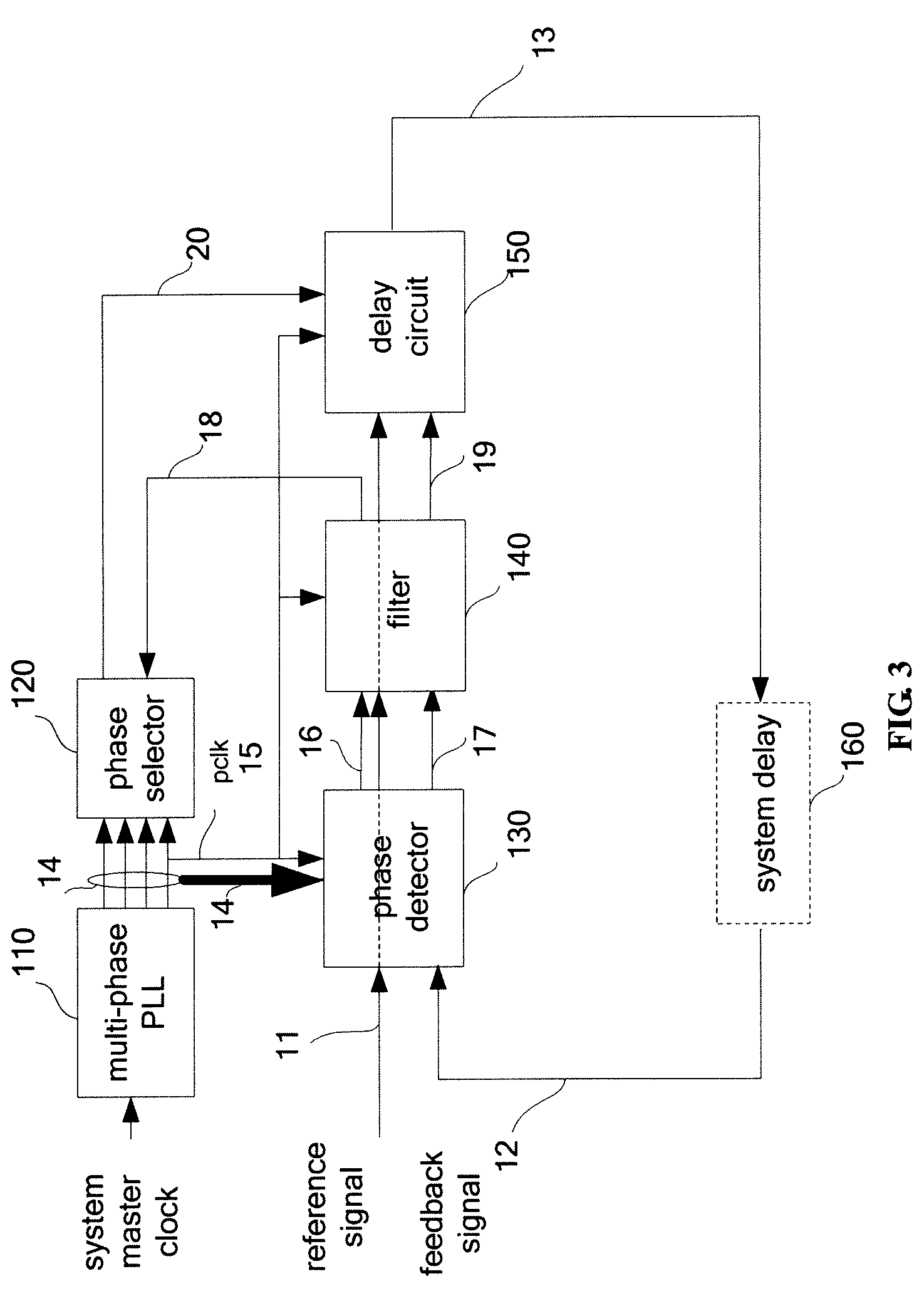

A scalable DLL (delay locked loop) circuit that has a calibration mechanism to auto tune locking precision. The delay locked loop circuit includes a multi-phase phase locked loop circuit for generating a plurality of phase signals according to a system clock, wherein one of the phase signals is a pixel clock; a phase detector for detecting an integral phase error and a fractional phase error between a reference signal and a feedback signal according to the pixel clock; a phase selector for selecting one of the phase signals according to the fractional phase error; and a delay circuit for shifting the phase of the reference signal according to the integral phase error and the selected phase signal to generate an output signal.

Owner:XUESHAN TECH INC

Clock adjusting circuit and semiconductor integrated circuit device

InactiveUS8072253B2Improve reliabilityLarge marginPulse automatic controlSingle output arrangementsControl signalControl circuit

Owner:NEC CORP

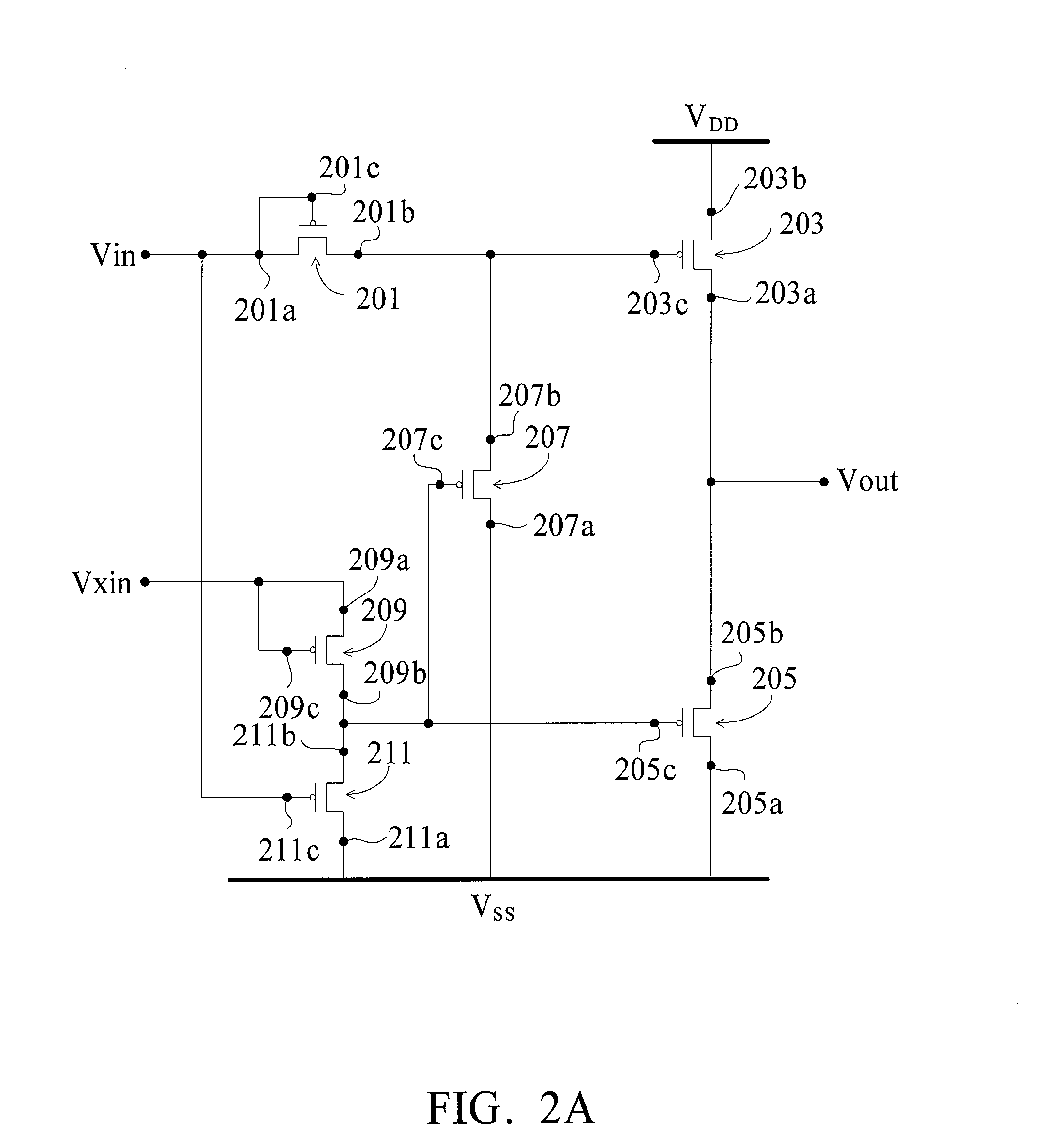

Voltage Level Shifter

ActiveUS20070247412A1Simple manufacturing processSave powerPulse automatic controlCounting chain pulse countersSingle typeLevel converter

A voltage level shifter formed by single-typed transistors comprises two input terminals, two power supply terminals, a plurality of thin-film transistors, and an output terminal. Another voltage level shifter formed by single-typed transistors comprises two input terminals, an output terminal, two power supply terminals, two input units, a first thin-film transistor, a disable unit, a feedback unit, and a second thin-film transistor. The voltage level shifters are formed by single-typed TFTs. When integrating the voltage level shifters into a substrate of a TFT display, the manufacturing processes are simplified. Besides, power is saved.

Owner:AU OPTRONICS CORP

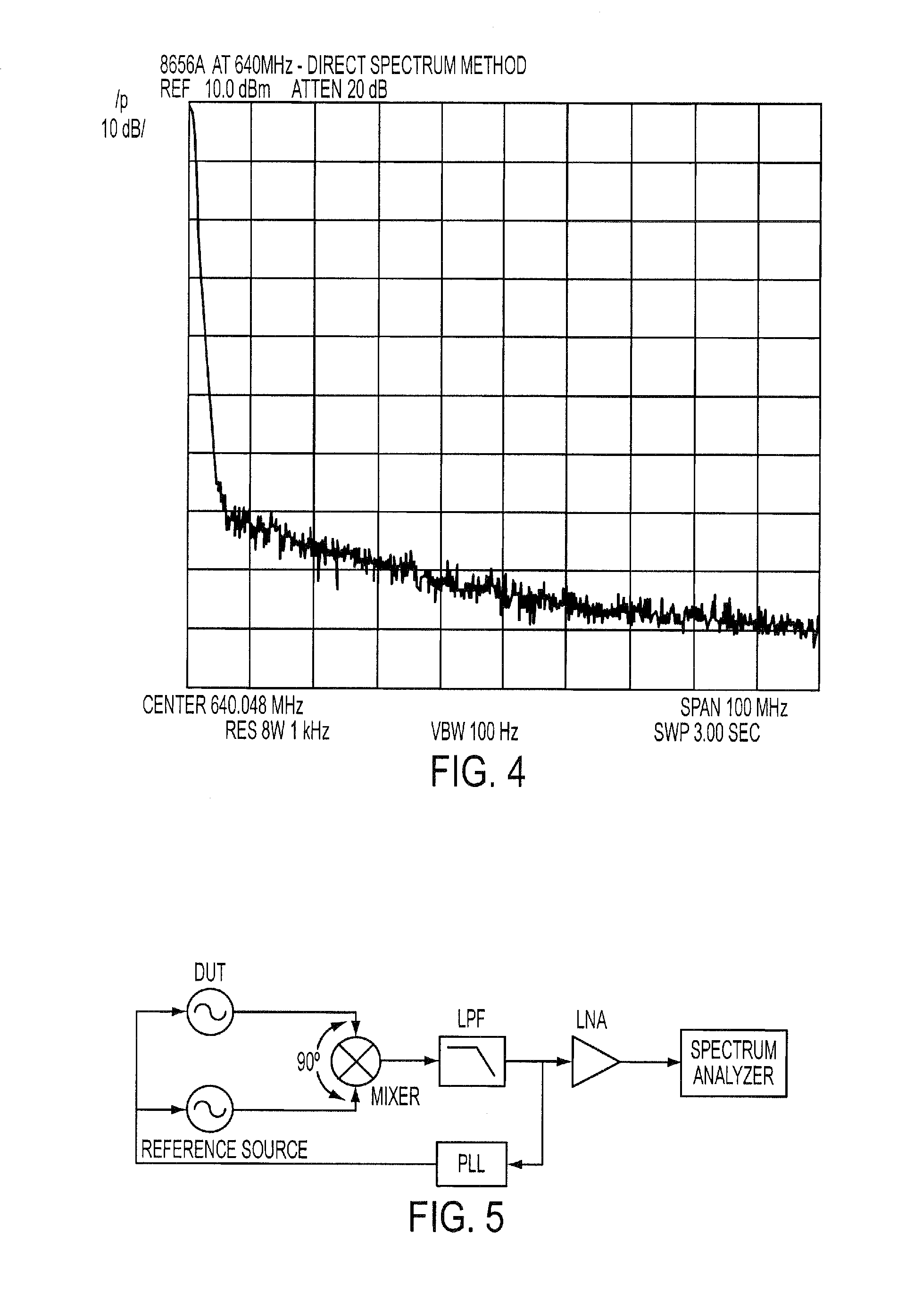

Embedded phase noise measurement system

InactiveUS20100327940A1Improve featuresComputations using contact-making devicesVoltage-current phase anglePhase detectorPhase noise

Phase noise detection systems for a device under test (DUT) are provided that can be embedded within a chip. According to one embodiment, the embedded phase noise detection system can include an active delay line cell, a phase shifter, and a phase detector. The active delay line and phase shifter separately receive the output signal of the DUT. The phase detector can include a double-balanced mixer followed by an active RC filter. The double-balanced mixer receives, as input, the outputs from the active delay line and phase shifter and can produce different dc voltages proportional to the difference from the input phase quadrature. An auto-adjustment circuit can also be included to help the input signal from the phase shifter to the mixer maintain quadrature.

Owner:UNIV OF FLORIDA RES FOUNDATION INC

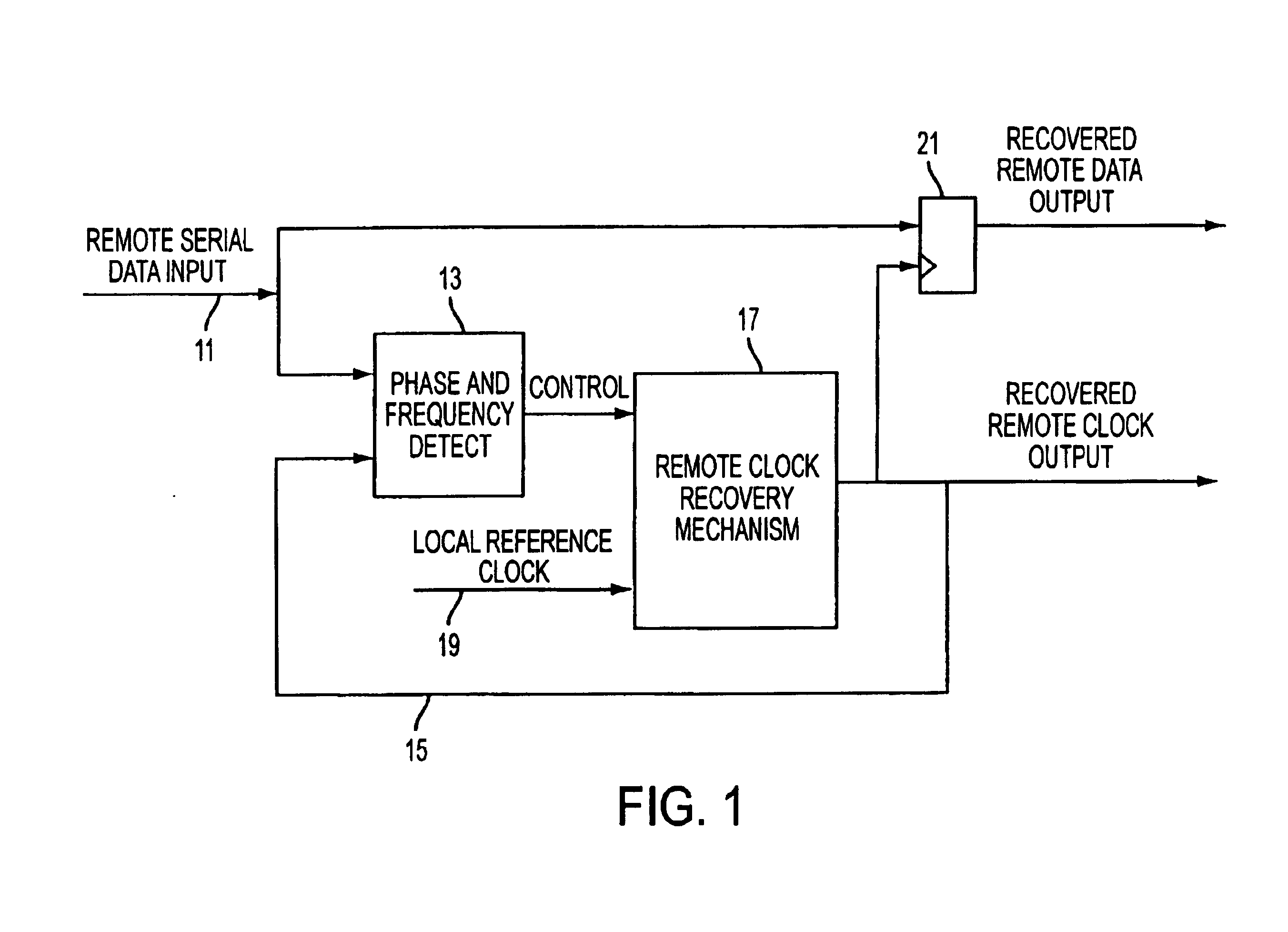

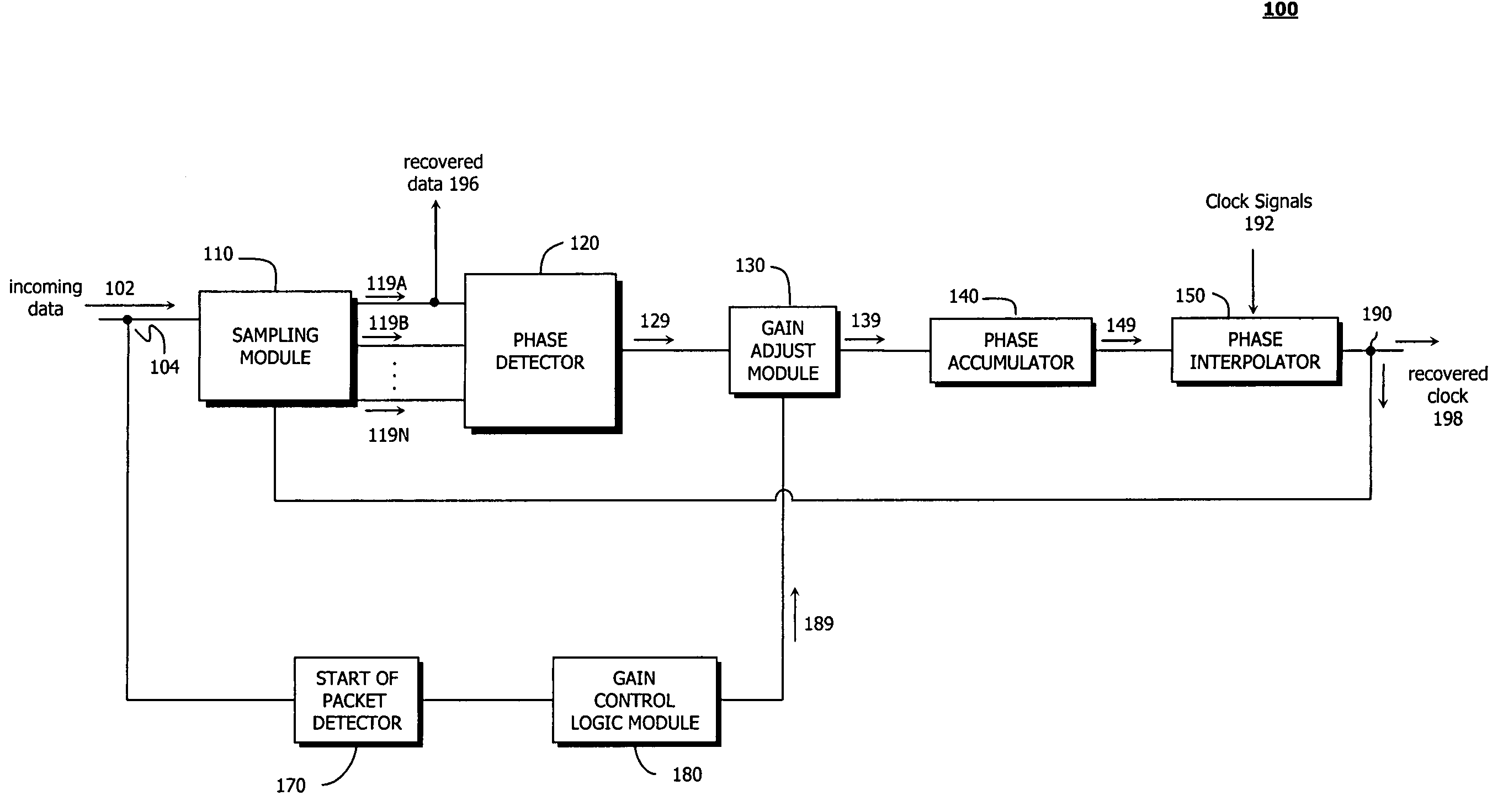

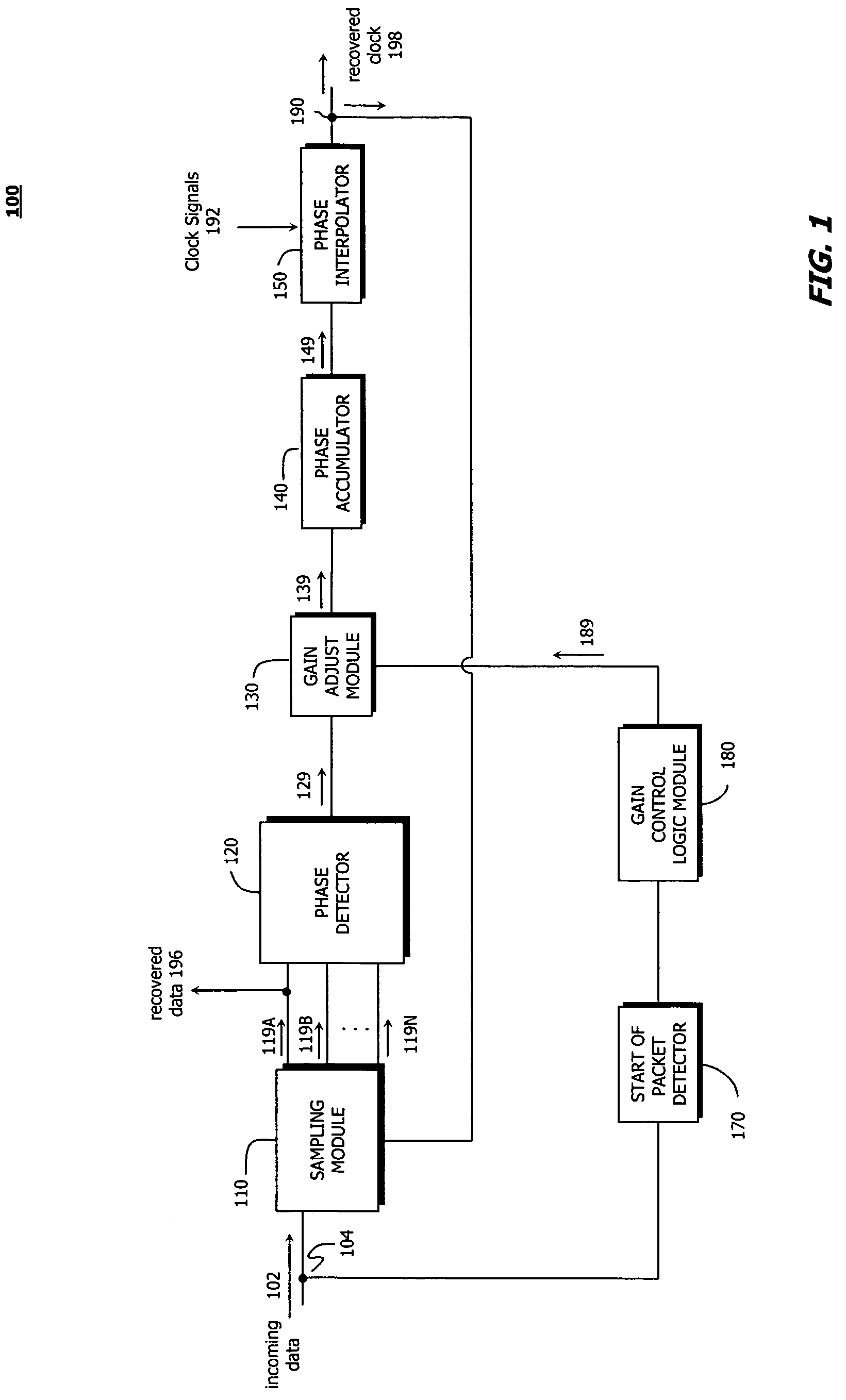

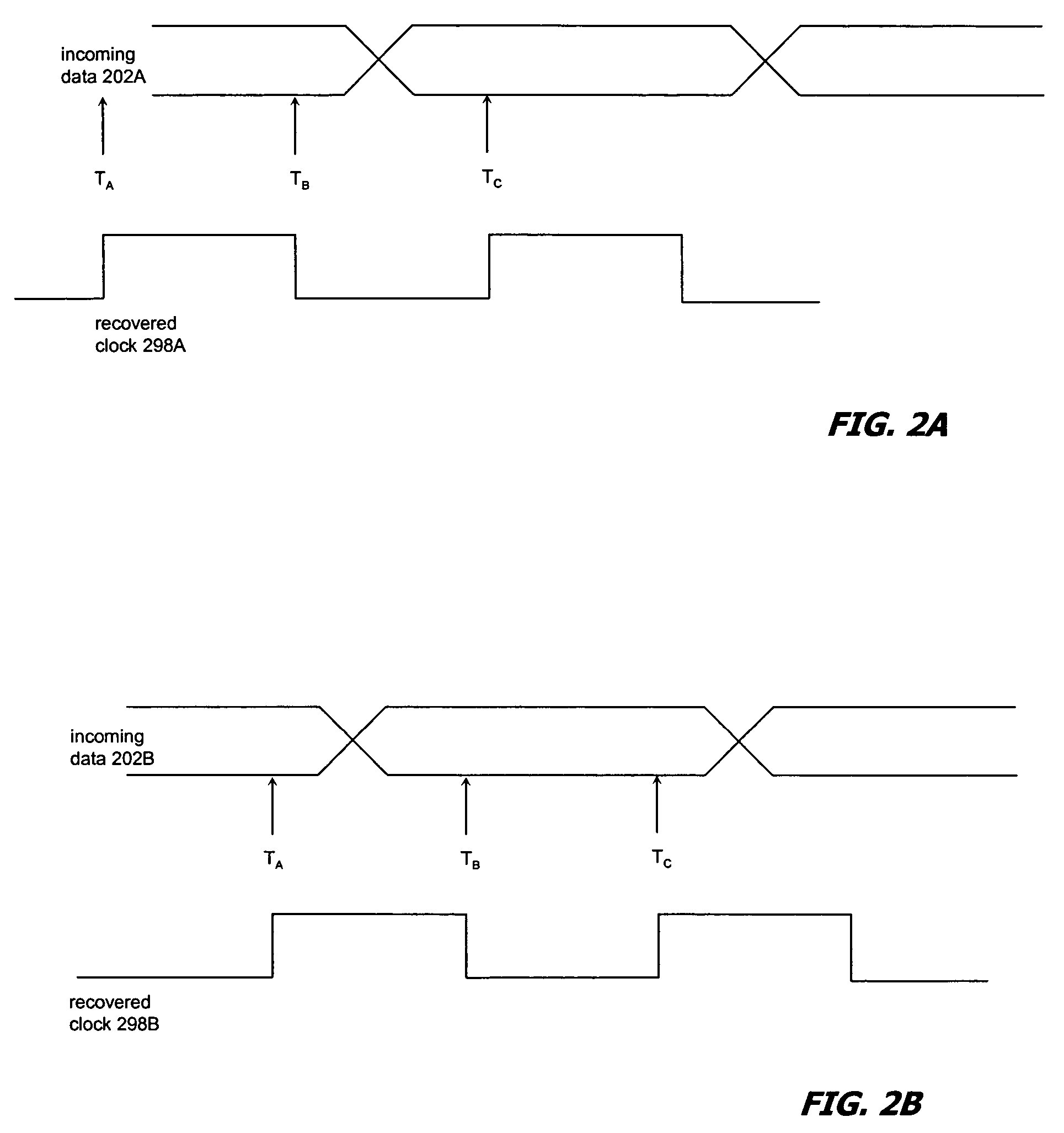

High speed clock and data recovery system

InactiveUS7135905B2Fast decayRemissionTelevision system detailsPulse automatic controlPhase detectorIntegrator

A clock and data recovery system for detecting and resolving meta-stability conditions is provided. The clock and data recovery system includes a phase detector having logic configured to detect a meta-stability condition and to generate an output signal to mitigate the condition. The system can also include a time varying gain adjustment portion. This portion includes a gain control logic configured to determine and adjust system gain during reception of an incoming data stream. The system further includes a phase interpolator having increased linearity. The phase interpolator has a plurality of first branches having a differential transistor pair, a switch, and a current source, coupled between a first output and a first supply voltage and a plurality of second branches having a differential transistor pair, a switch, and a current source, coupled between a second output and the first supply voltage. The phase interpolator can also include an integrator portion.

Owner:AVAGO TECH INT SALES PTE LTD

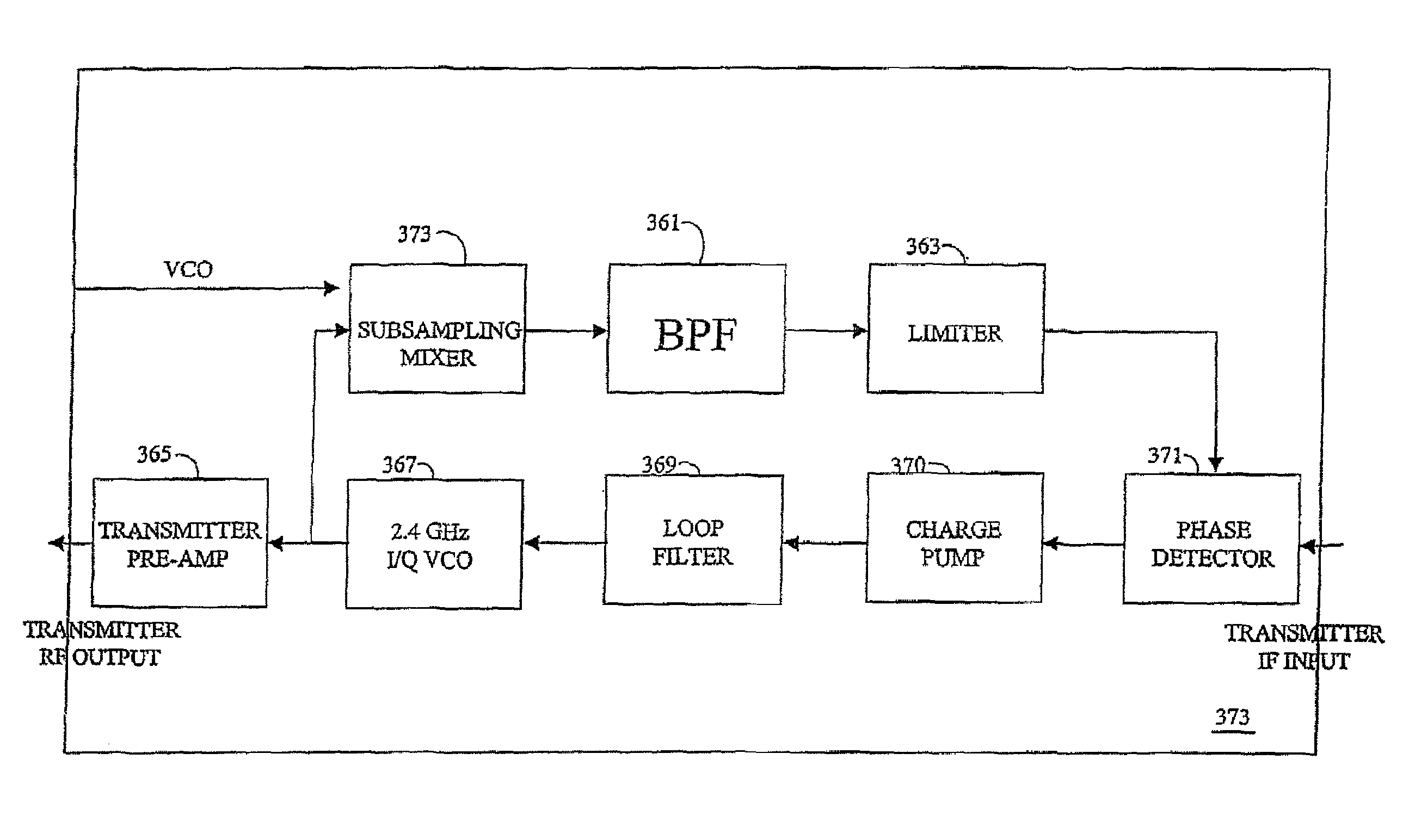

Adaptive radio transceiver with subsampling mixers

InactiveUS7558556B1Minimize adverse effectsReduce power consumptionResonant long antennasResonant circuit tuningAdaptive programmingTransceiver

An exemplary embodiment of the present invention described and shown in the specification and drawings is a transceiver with a receiver, a transmitter, a local oscillator (LO) generator, a controller, and a self-testing unit. All of these components can be packaged for integration into a single IC including components such as filters and inductors. The controller for adaptive programming and calibration of the receiver, transmitter and LO generator. The self-testing unit generates is used to determine the gain, frequency characteristics, selectivity, noise floor, and distortion behavior of the receiver, transmitter and LO generator. It is emphasized that this abstract is provided to comply with the rules requiring an abstract which will allow a searcher or other reader to quickly ascertain the subject matter of the technical disclosure. It is submitted with the understanding that it will not be used to interpret or limit the scope or the meaning of the claims.

Owner:AVAGO TECH INT SALES PTE LTD

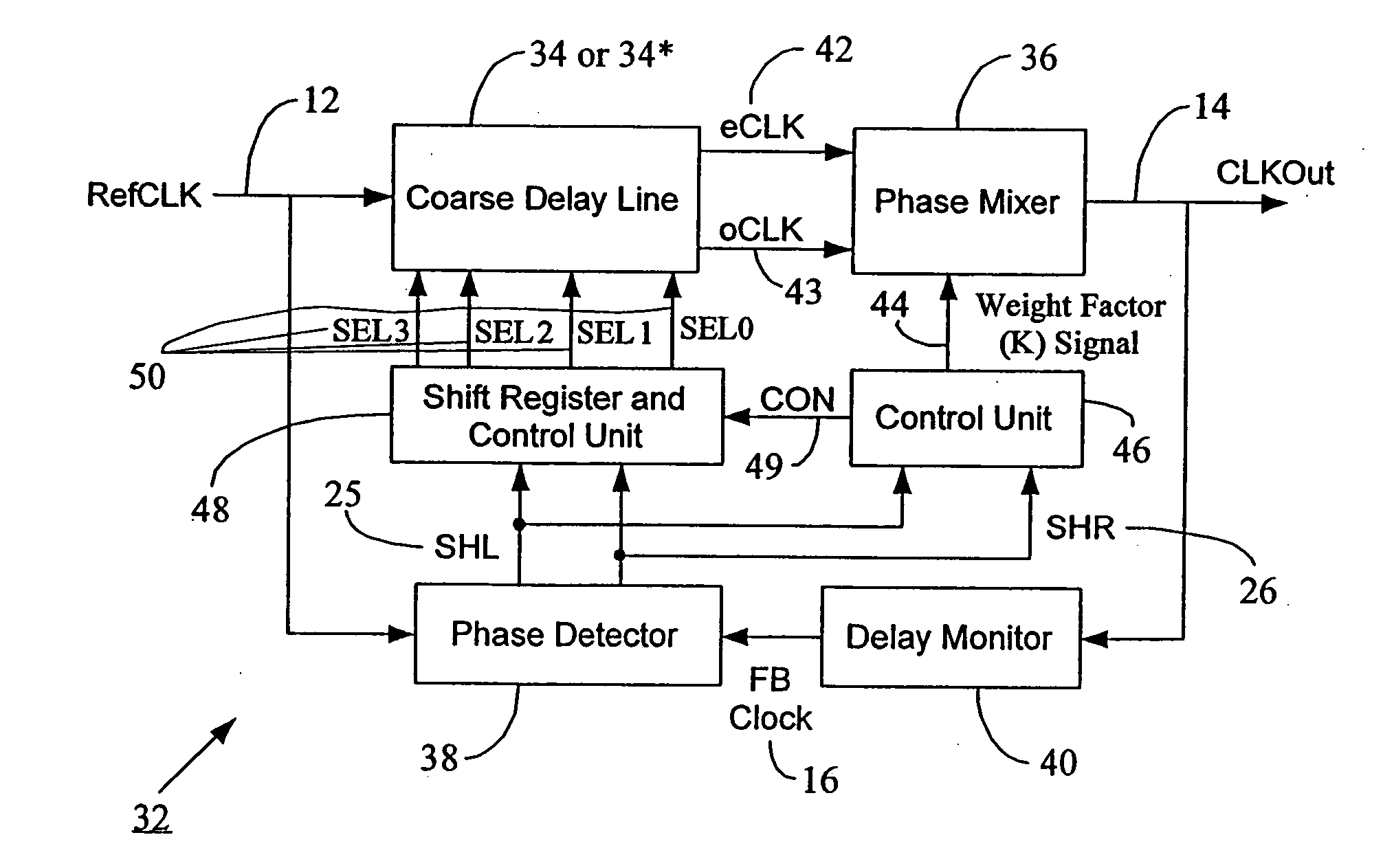

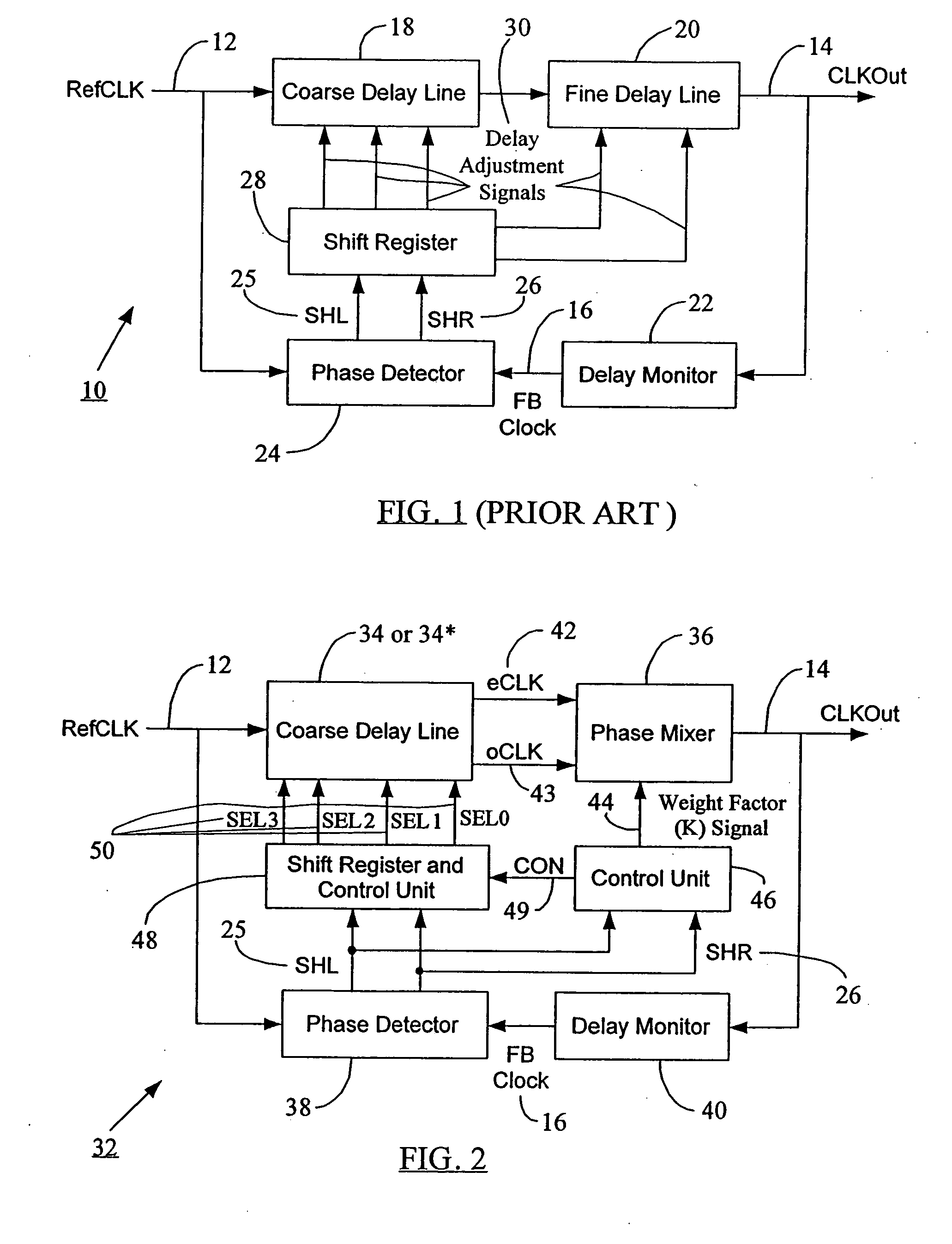

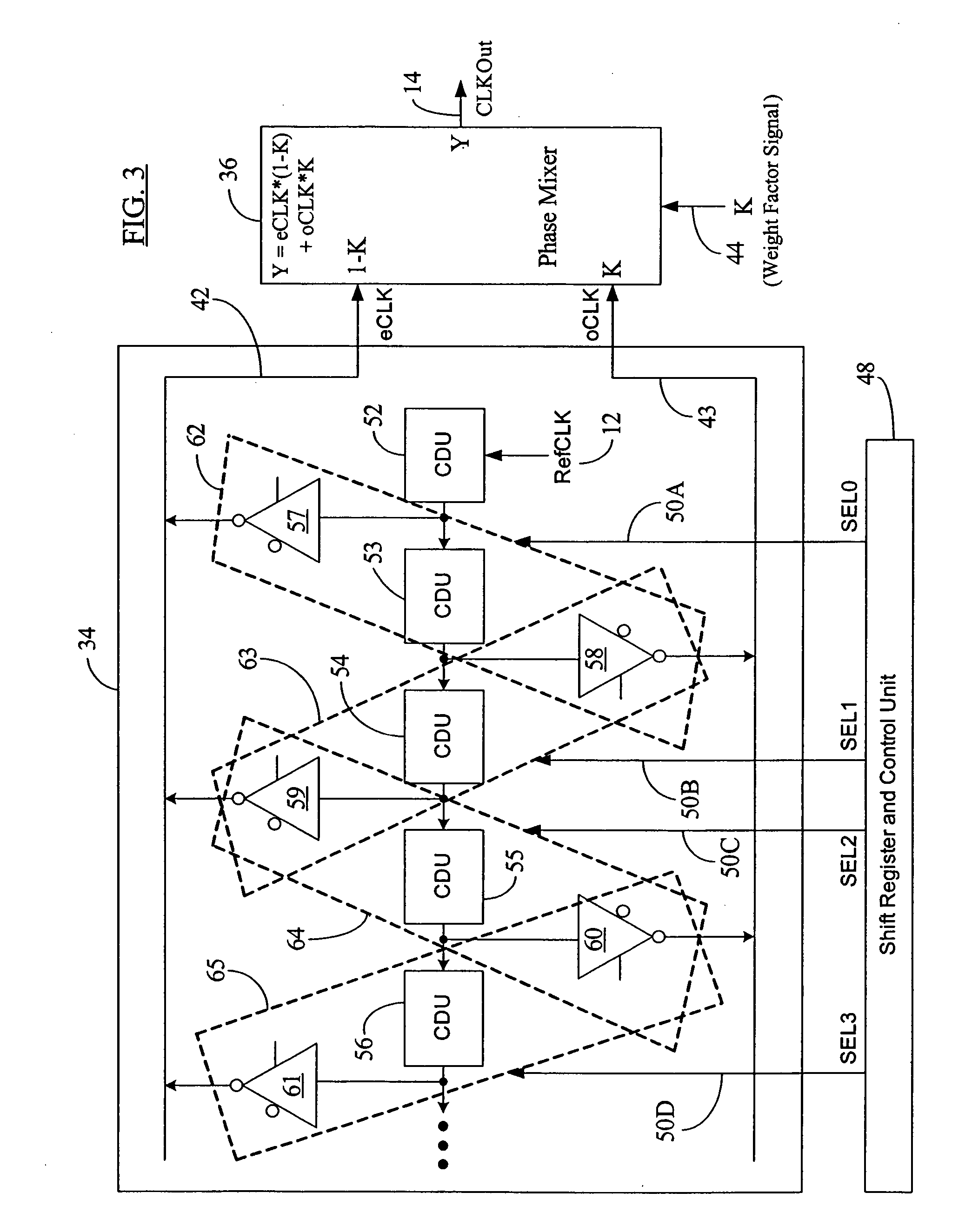

Seamless coarse and fine delay structure for high performance DLL

ActiveUS20070030753A1Smooth phase transitionDelay problemPulse automatic controlCounting chain pulse countersClock timePhase difference

A clock synchronization system and method avoids output clock jitter at high frequencies and also achieves a smooth phase transition at the boundary of the coarse and fine delays. The system may use a single coarse delay line configured to generate two intermediate clocks from the input reference clock and having a fixed phase difference therebetween. The coarse delay line may have a hierarchical or a non-hierarchical structure. A phase mixer receives these two intermediate clocks and generates the final output clock having a phase between the phases of the intermediate clocks. The coarse shifting in the delay line at high clock frequencies does not affect the phase relationship between the intermediate clocks fed into the phase mixer. The output clock from the phase mixer is time synchronized with the input reference clock and does not exhibit any jitter or noise even at high clock frequency inputs. Because of the rules governing abstracts, this abstract should not be used to construe the claims.

Owner:MICRON TECH INC

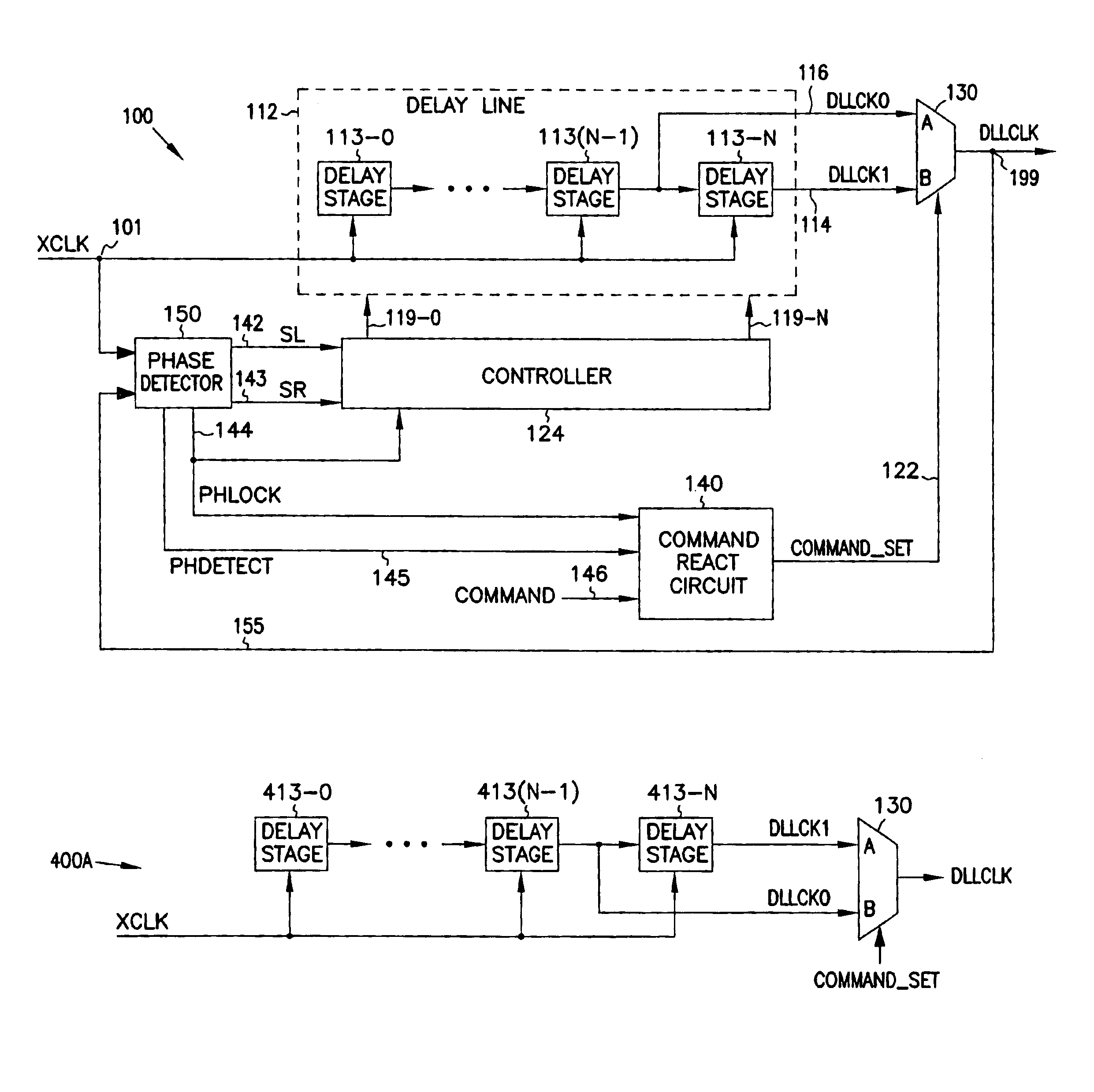

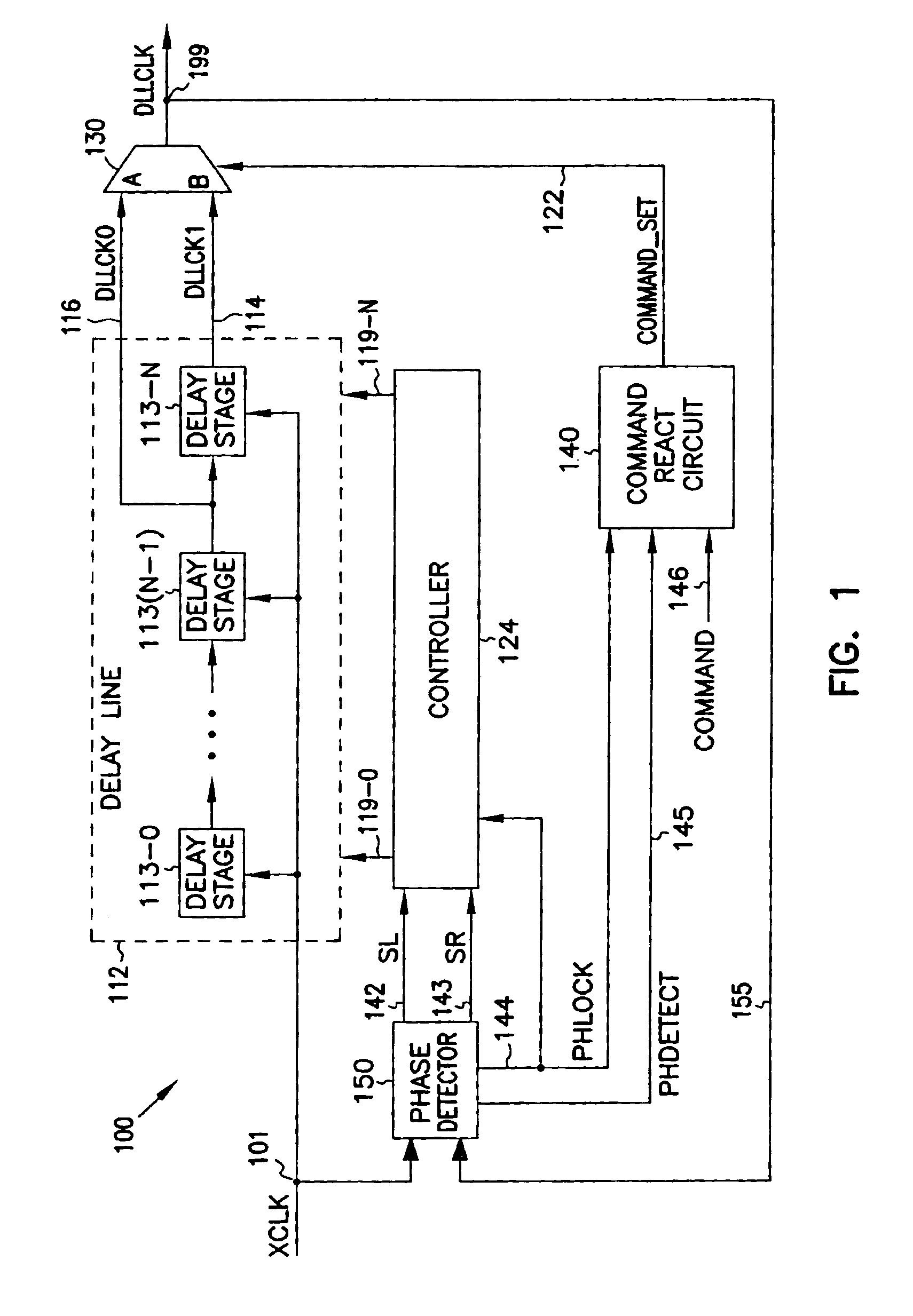

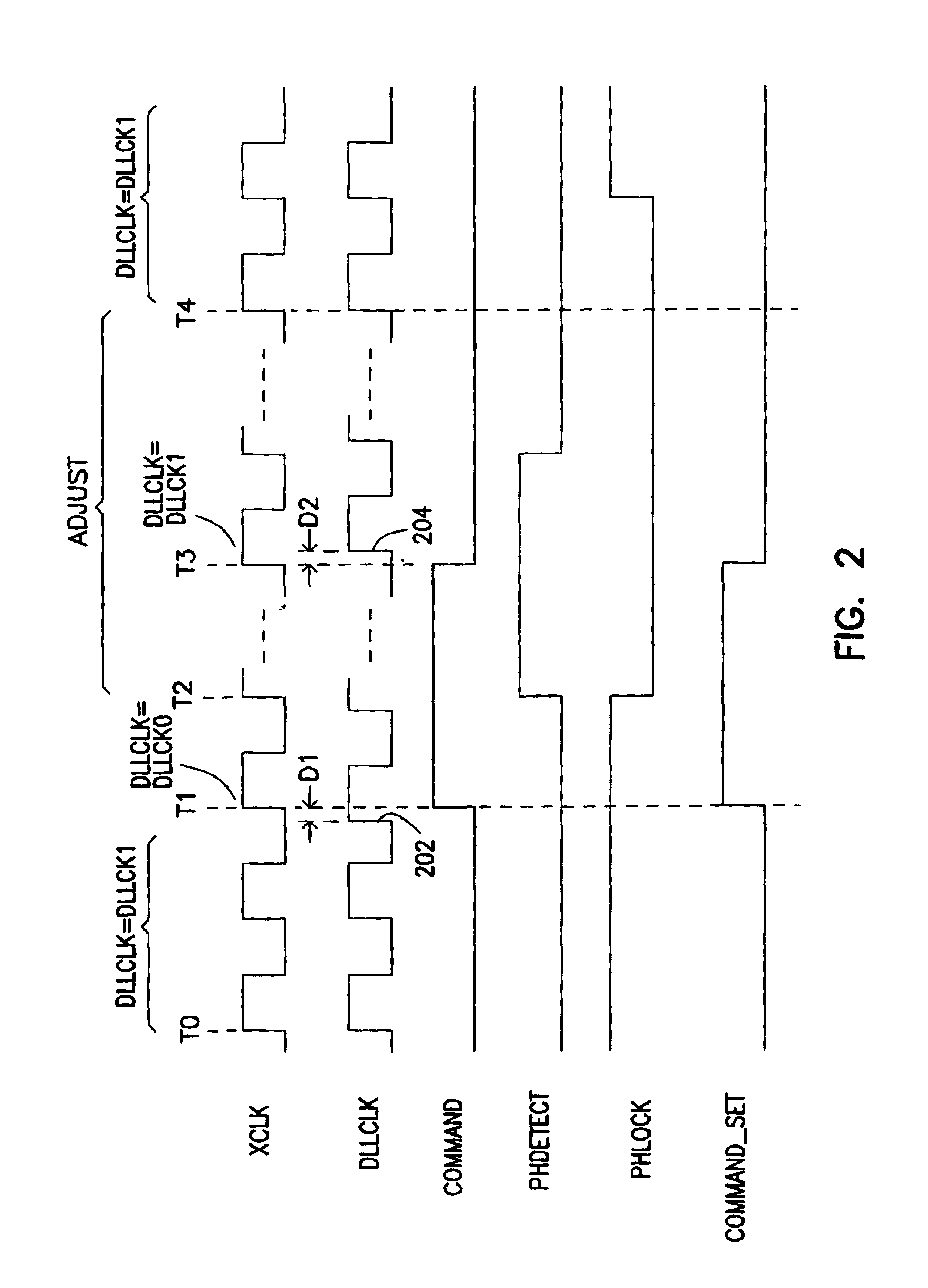

Delay locked loop "ACTIVE command" reactor

A delay locked loop (DLL) that applies an amount of delay to an external clock signal to generate multiple delayed signals. One of the delayed signals is selected as an internal clock signal. The multiple delayed signals have different delays in relation to the external clock signal. If a change in operating condition of the DLL occurs, such as a change in the supply voltage during an operational mode of the memory device such as an ACTIVE, a READ or a REFRESH mode, the DLL immediately selects another delayed signal among the multiple delayed signals as a new internal clock signal to compensate for the change before a phase detector of the DLL detects the change.

Owner:MICRON TECH INC

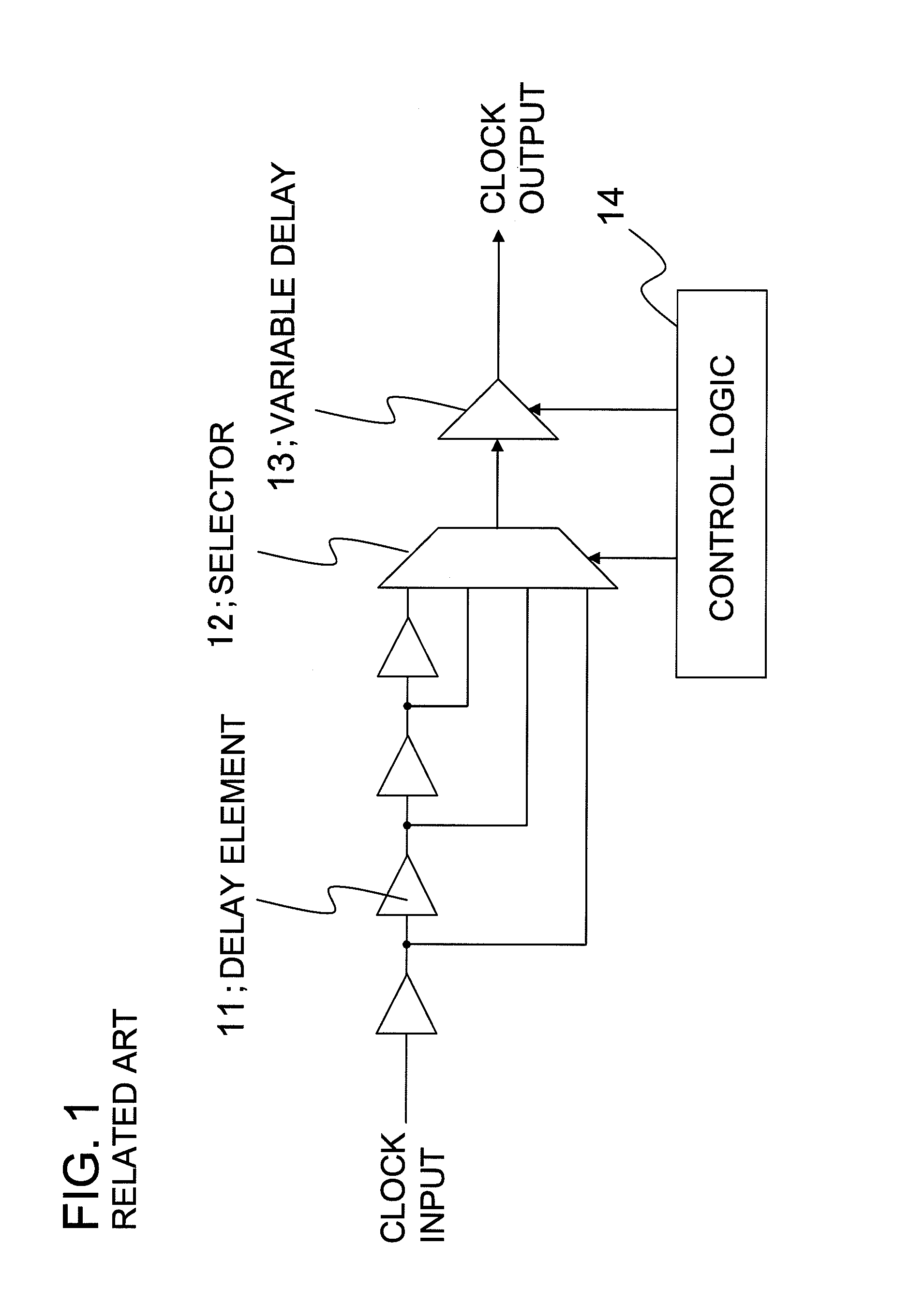

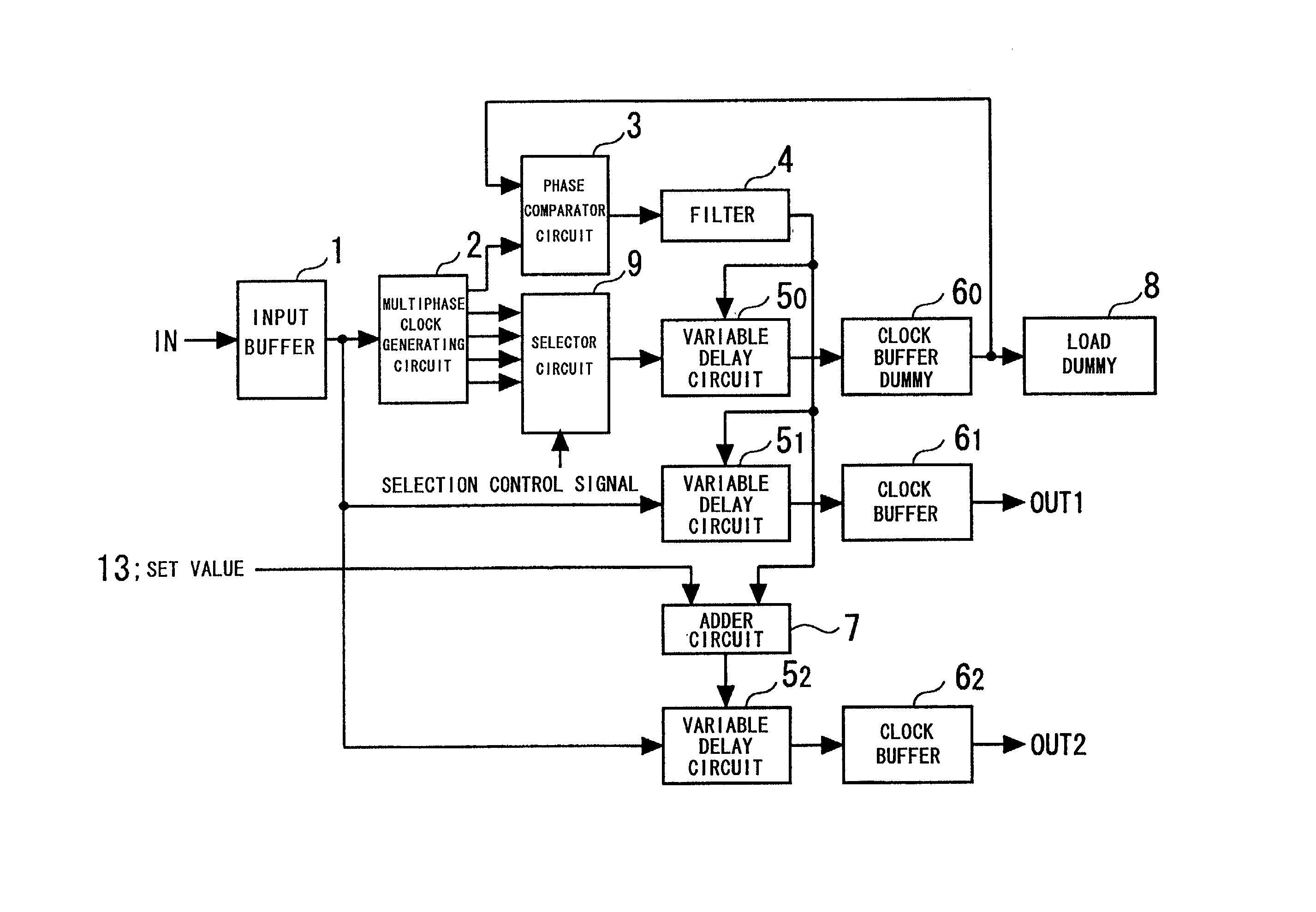

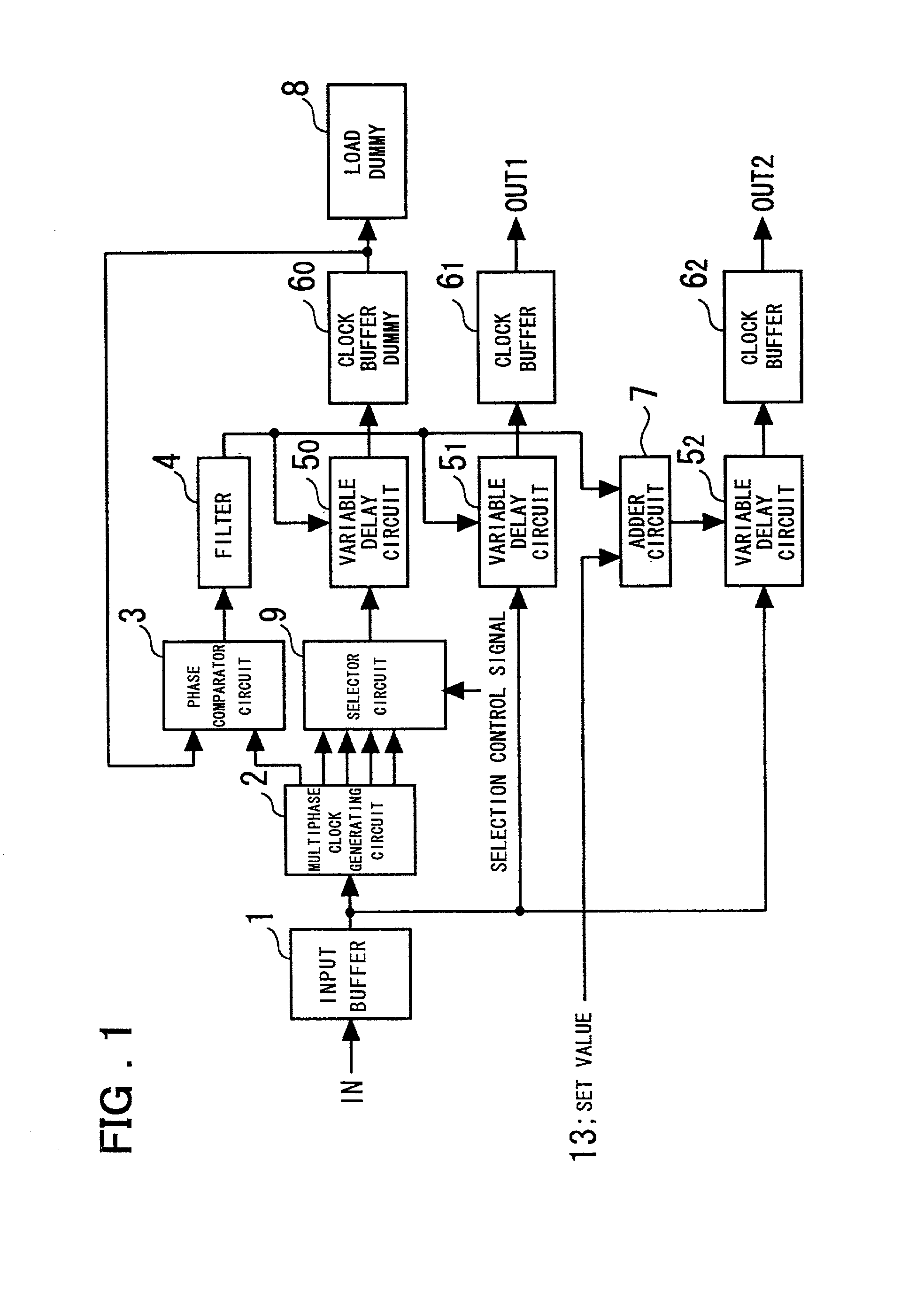

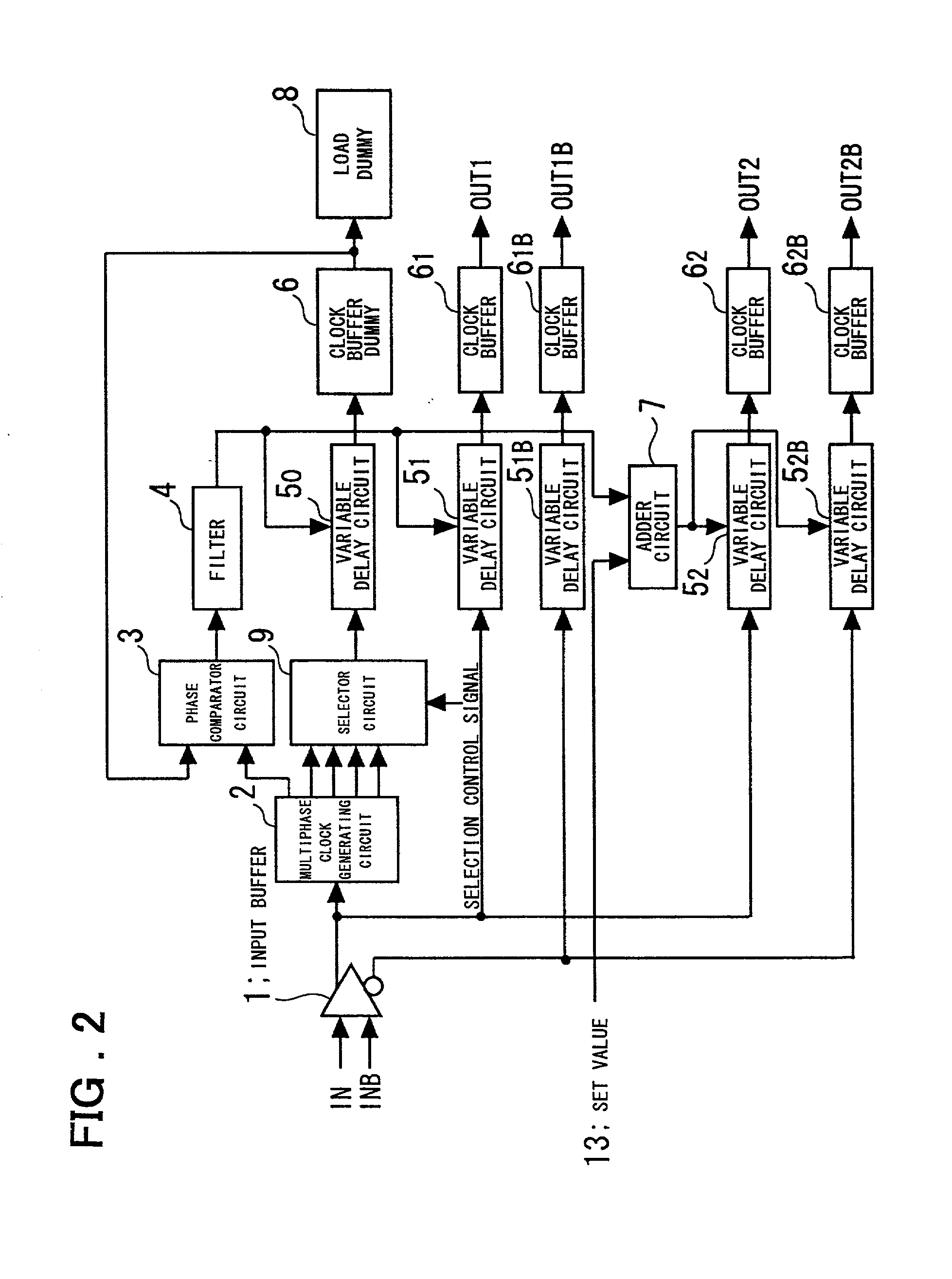

Clock control circuit and method

InactiveUS20020070783A1Generate accuratelyPulse automatic controlSingle output arrangementsPhase differenceComparators circuits

A clock control circuit includes a multiphase clock generating circuit receiving an output signal of a input buffer for generating multiphase clocks; a selector circuit receiving multiphase clocks output from the multiphase clock generating circuit for selecting one of the multiphase clocks; a first variable delay circuit for delaying the output of the selector circuit; a clock buffer dummy receiving the output signal of the variable delay circuit ; a phase comparator circuit for detecting a phase difference between an output from the multiphase clock generating circuit and an output of the clock buffer dummy; and a filter for smoothing the output of the phase comparator circuit. The first variable delay circuit has its delay time varied by the output of the filter. The clock control circuit further includes a second variable delay circuit, receiving the output signal of the input buffer, having its delay time varied by the output of the filter; an adder circuit for adding the filter output and an input set value; a third variable delay circuit, receiving the output signal of the input buffer, having its delay time varied by the output of the adder circuit; and clock buffers receiving output signals of respective ones of the second and third variable delay circuits.

Owner:RENESAS ELECTRONICS CORP

Electronically programmable multimode circuit

Owner:NORTHROP GRUMMAN SYST CORP

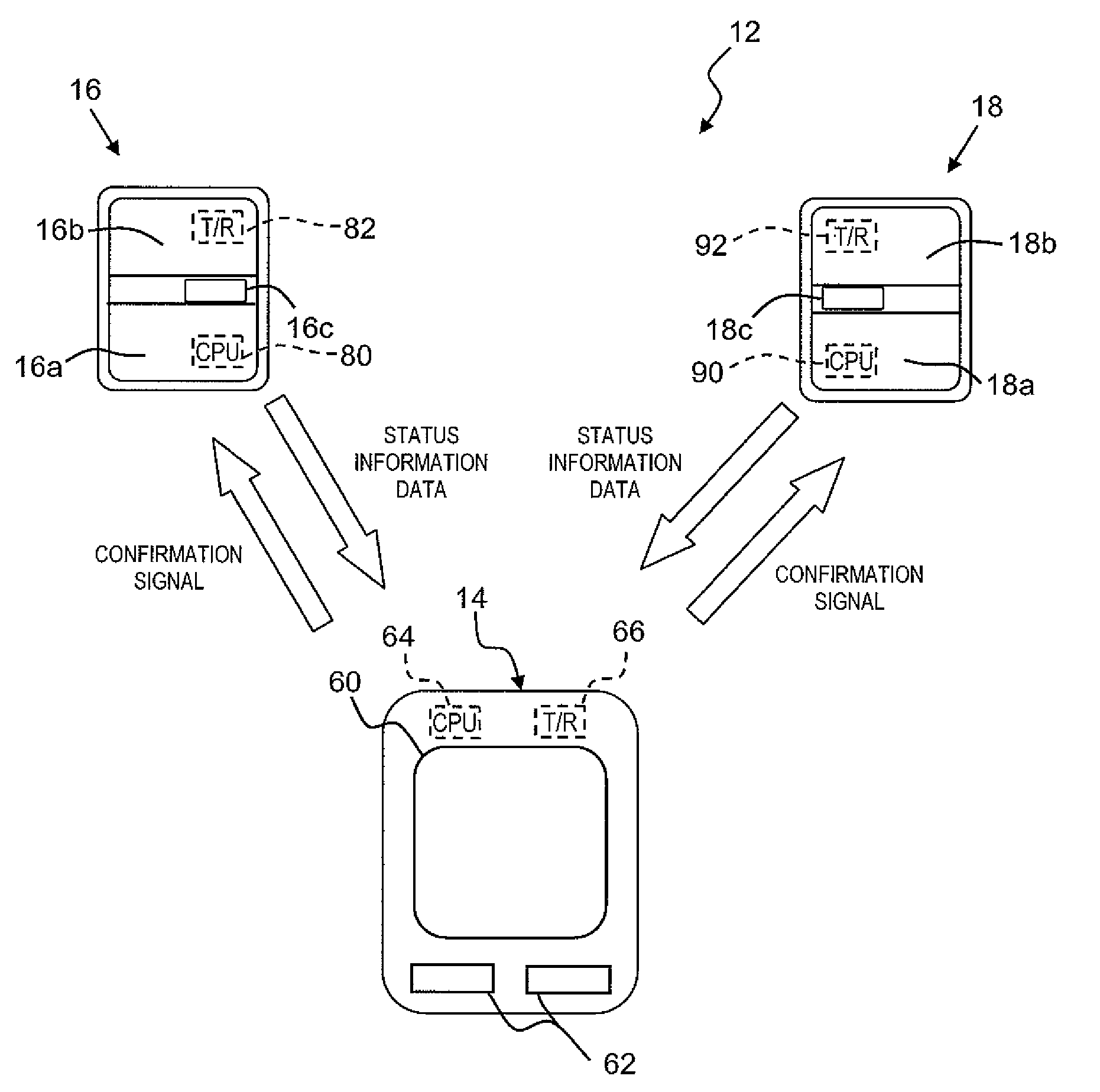

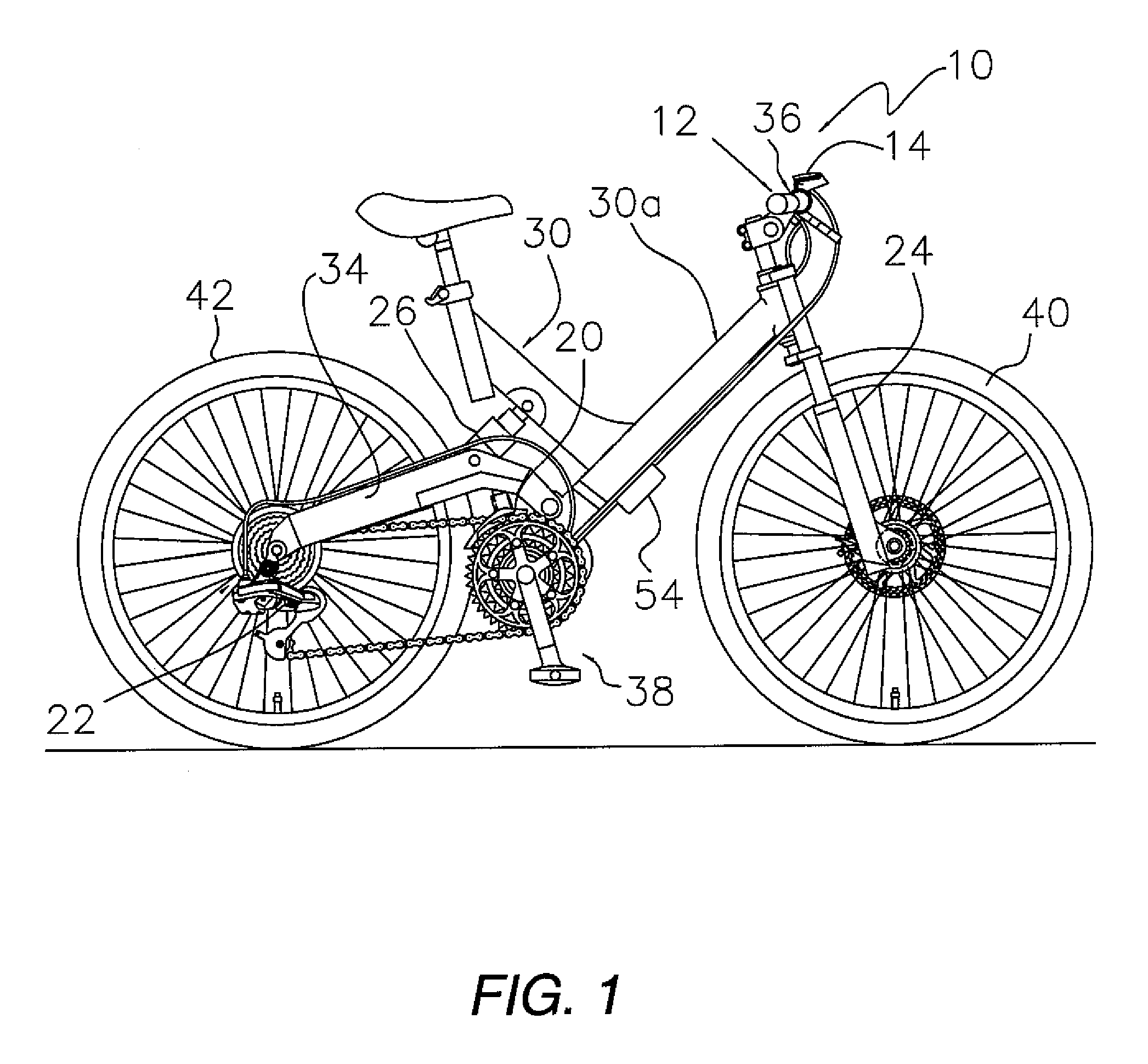

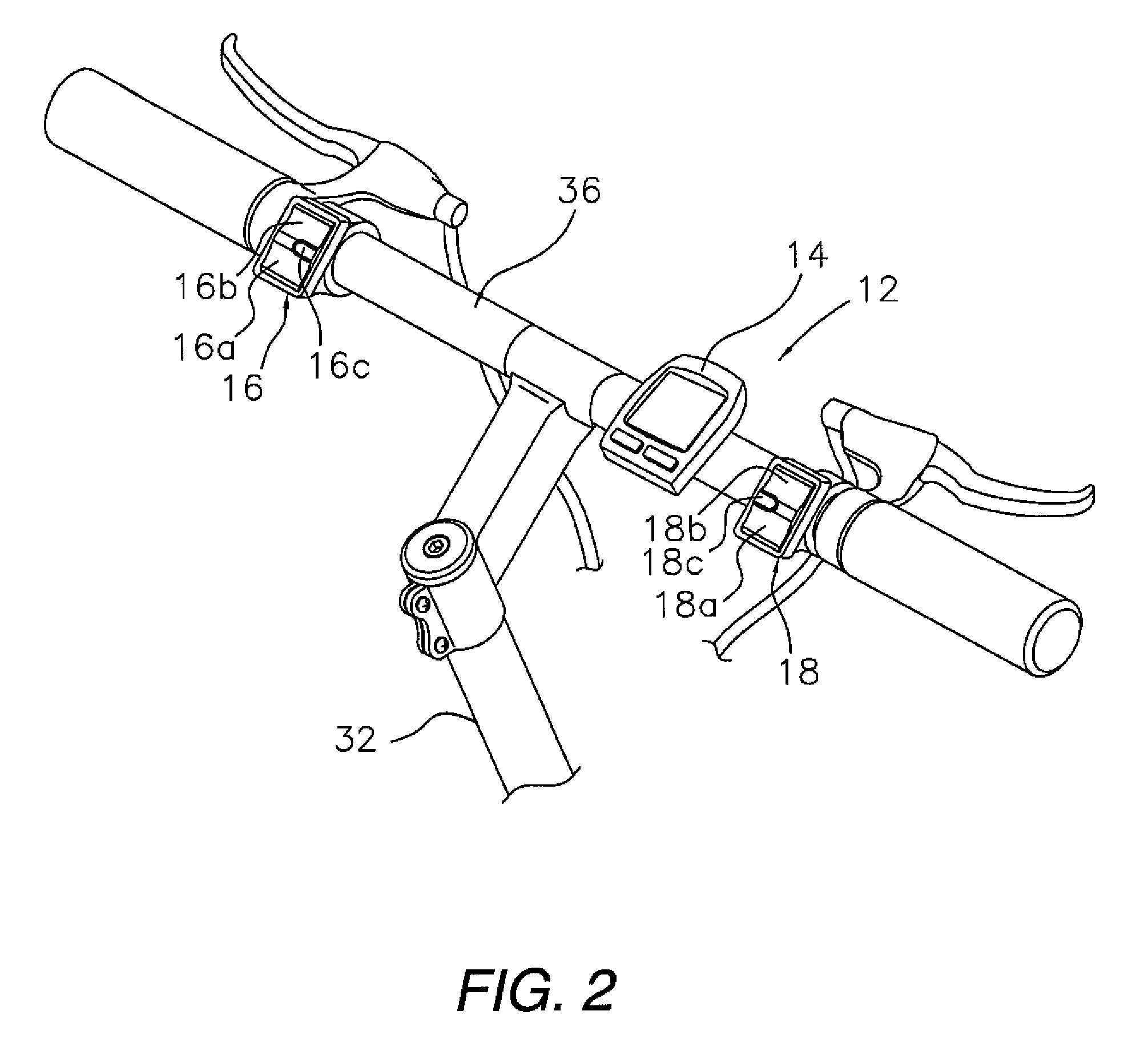

Bicycle control system

ActiveUS20090102628A1Accurate identificationAcoustic signalAnti-theft cycle devicesControl systemEngineering

A bicycle control system is provided with a switch device and a cycle computer. The switch device includes a switch operation member, a sensor arranged relative to the switch operation member to detect operation of the switch operation member, a processing unit operatively coupled to the sensor and a transmitter arranged to transmit an output signal. The processing unit of the switch device includes an identification code generating member, an operating signal generating member and an output member. The identification code generating member generates identification code related to identification of the switch device. The operating signal generating member generates an operation code indicative of operation of the switch operation member. The output member combines the identification code and the operation code as the output signal to be transmitted by the transmitter of the switch device.

Owner:SHIMANO INC

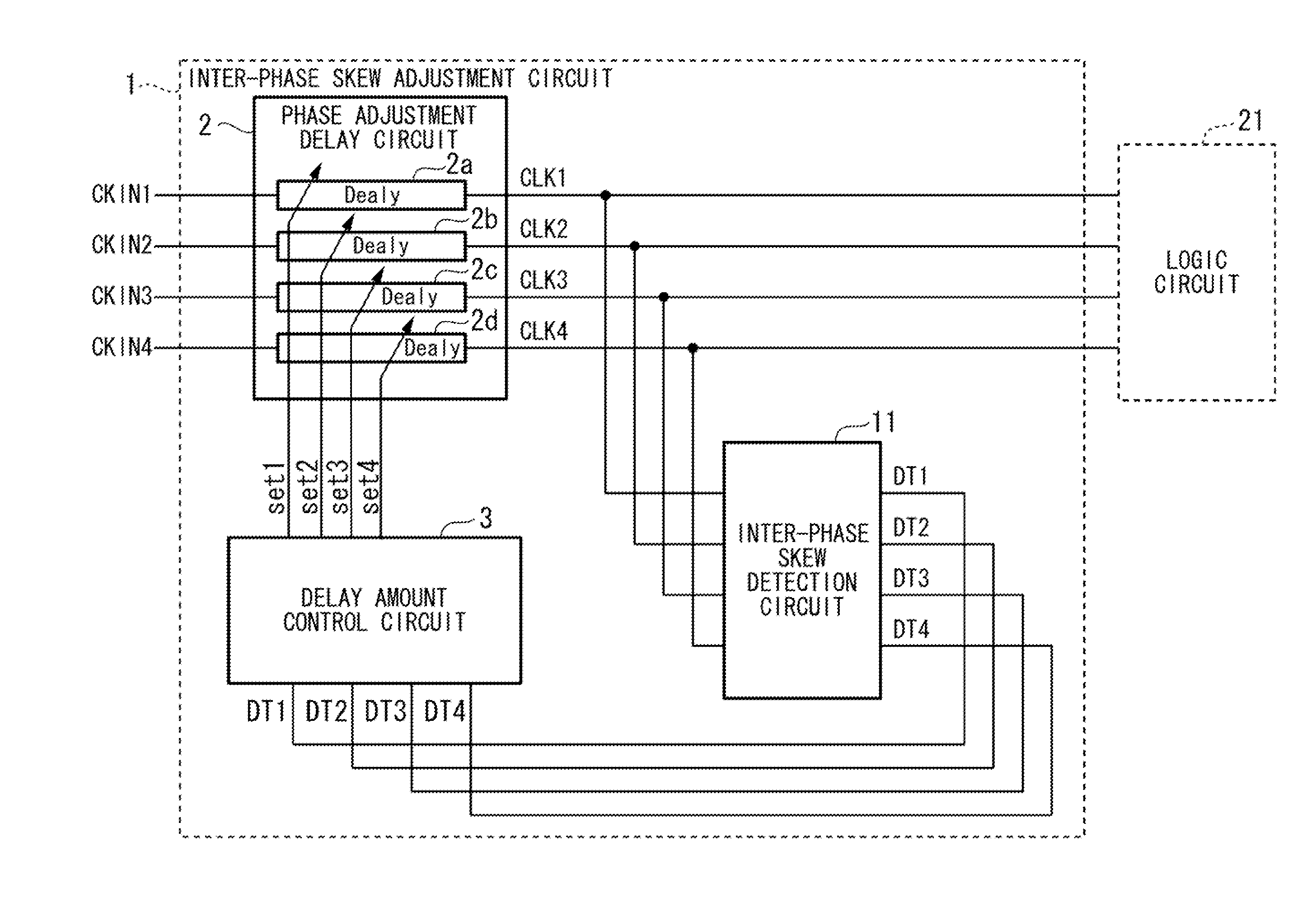

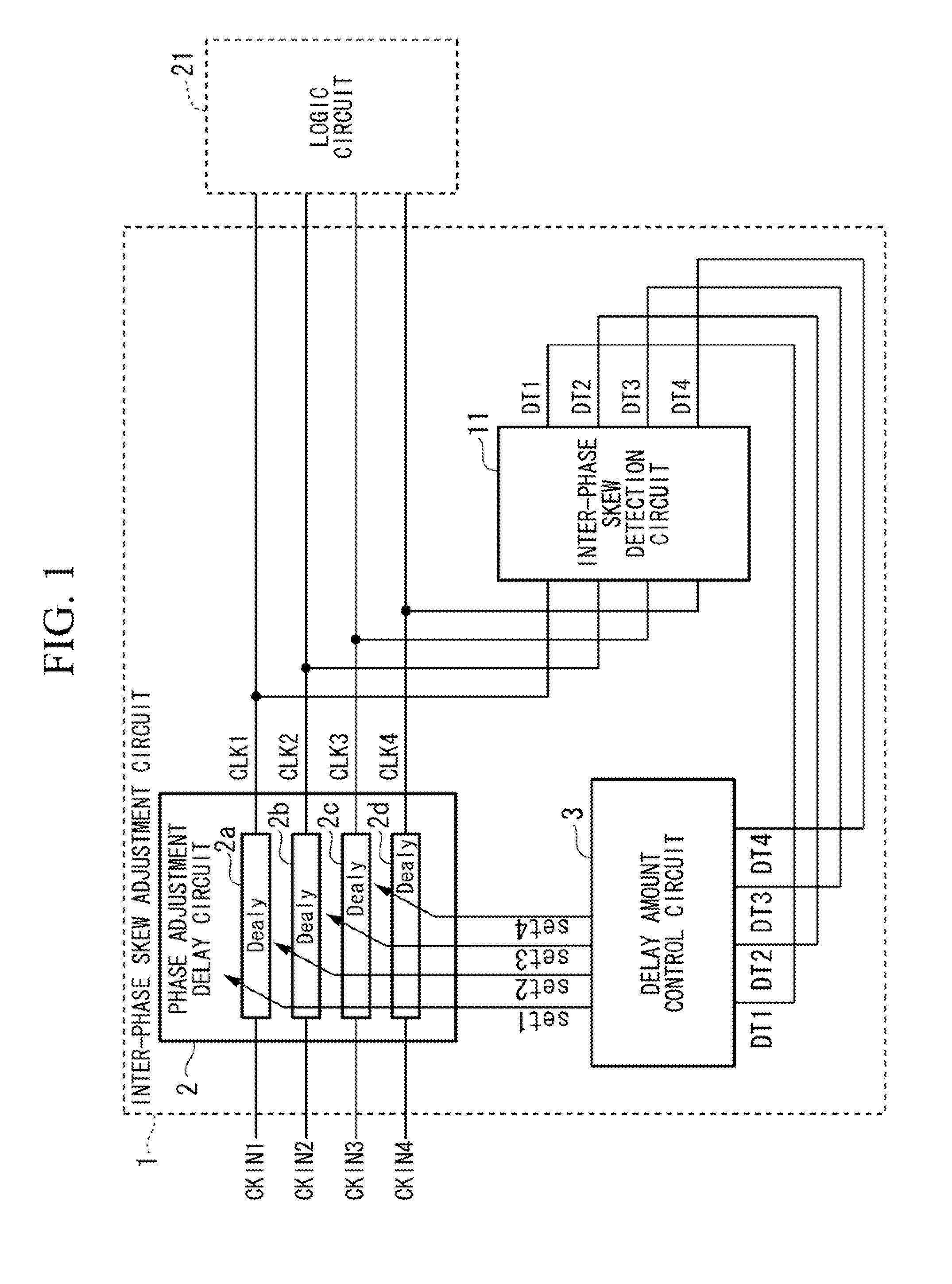

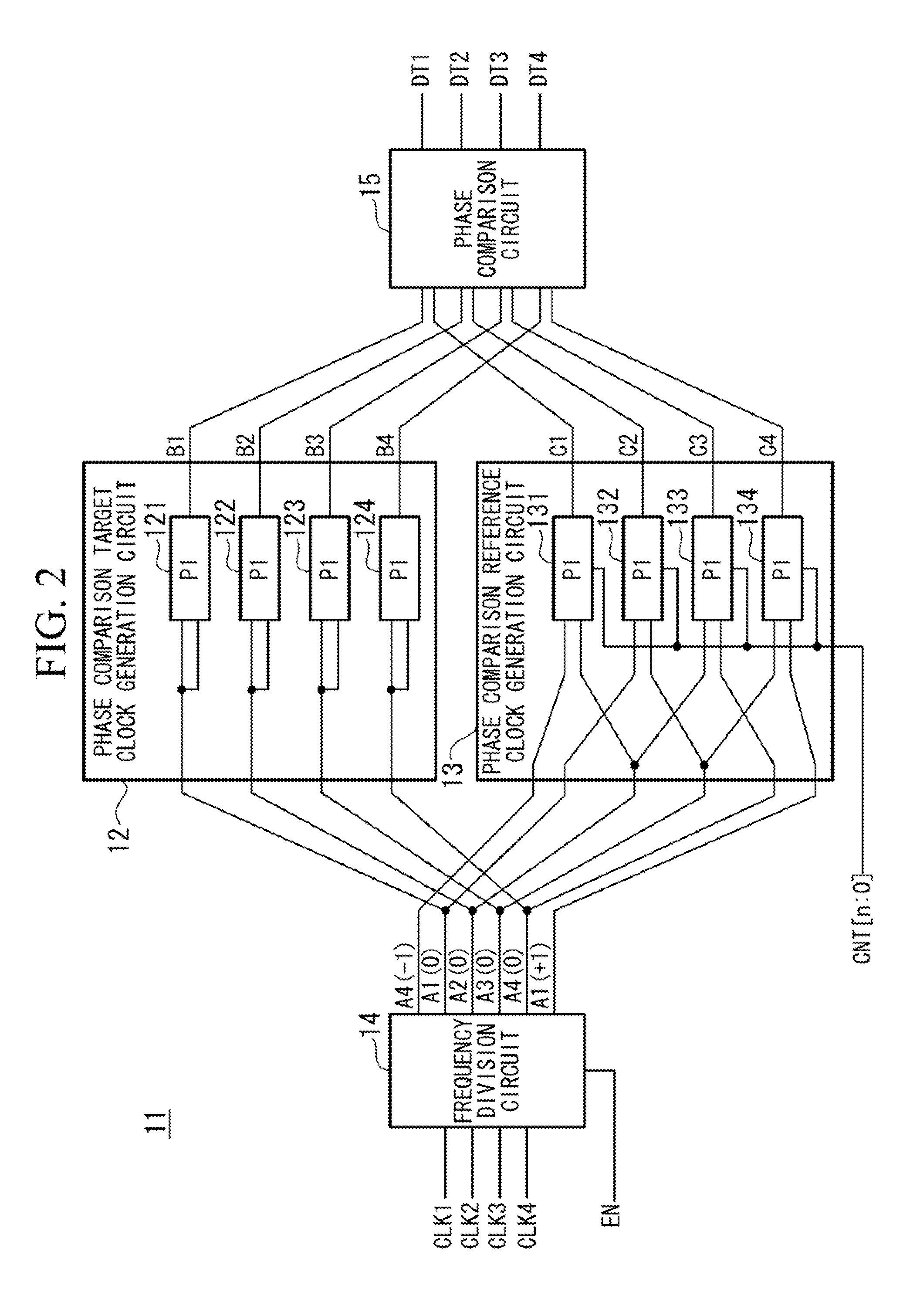

Inter-phase skew detection circuit for multi-phase clock, inter-phase skew adjustment circuit, and semiconductor integrated circuit

InactiveUS20110156757A1Reduce necessityReduce biasPulse automatic controlElectrical testingHemt circuitsEngineering

An inter-phase skew detection circuit includes a frequency division circuit that frequency-divides N-phase clocks to be measured at predetermined timings so as to generate N+2 frequency-divided clocks; a phase comparison target clock generation circuit that generates N phase comparison target clocks by using predetermined N frequency-divided clocks among the N+2 frequency-divided clocks; a phase comparison reference clock generation circuit that generates N reference clocks by using the N+2 frequency-divided clocks, in accordance with predetermined combinations between the N+2 frequency-divided clocks and an operation criterion; and a phase comparison circuit that detects respective phase differences between the N phase comparison target clocks and the corresponding N reference clocks.

Owner:NEC CORP