Low-power-consumption and low-leakage SRAM applied to storage and calculation integrated chip

A low-power, low-leakage technology, applied in information storage, static memory, digital memory information, etc., can solve the problems of SRAM read and write performance decline, SRAM power consumption increase, SRAM power supply voltage is difficult to reduce and other problems, to reduce the minimum work effect of voltage, reduced power consumption, improved static noise margin

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0036] The present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

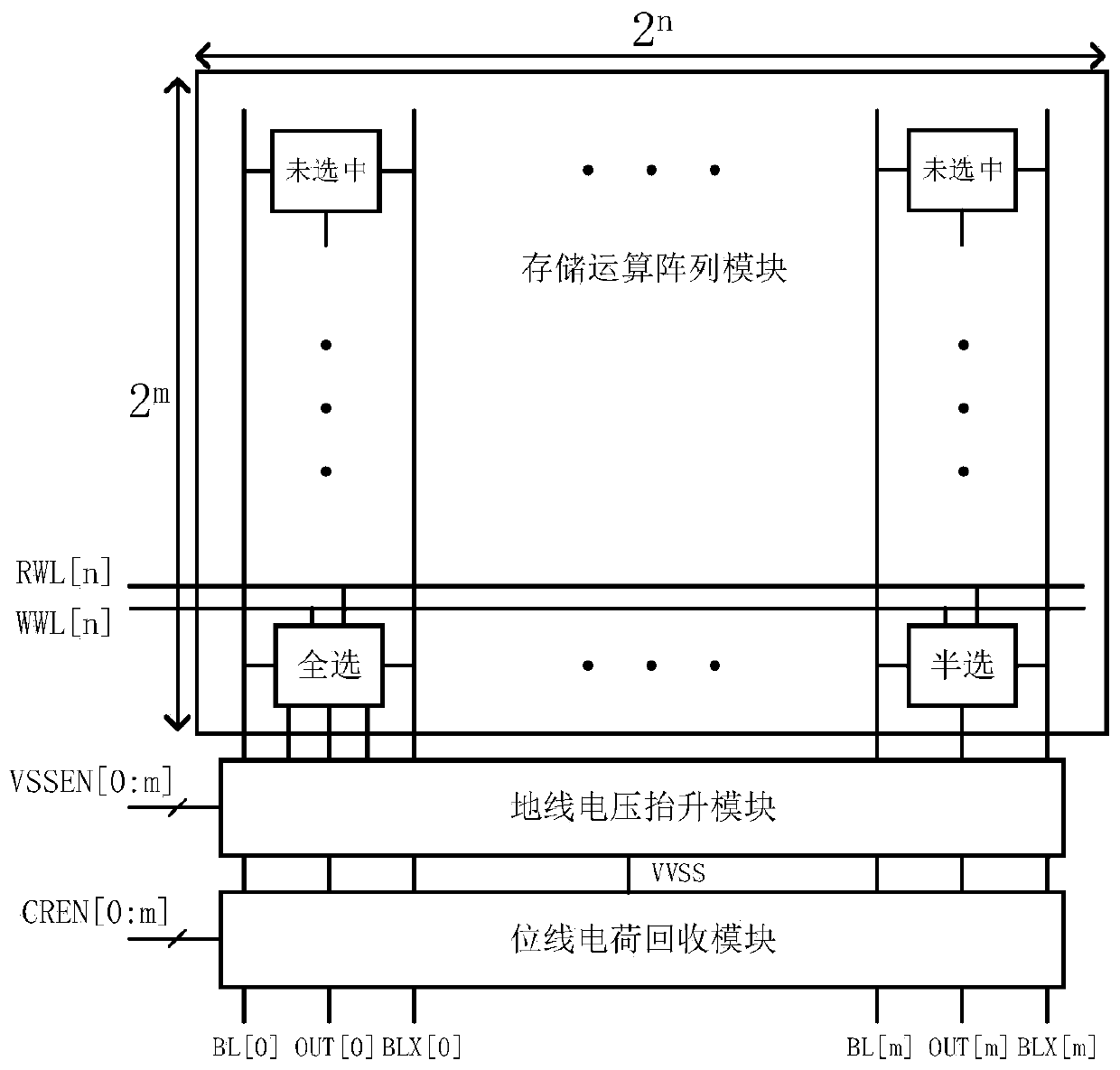

[0037] Such as figure 1 As shown, the low-power and low-leakage SRAM applied to the storage and calculation integrated chip of the present invention is optimized based on the traditional SRAM structure, and will work in a low power supply voltage environment near the threshold to reduce the power consumption of the SRAM, including the storage and calculation unit array, a ground voltage boost module and a bit line charge recovery module.

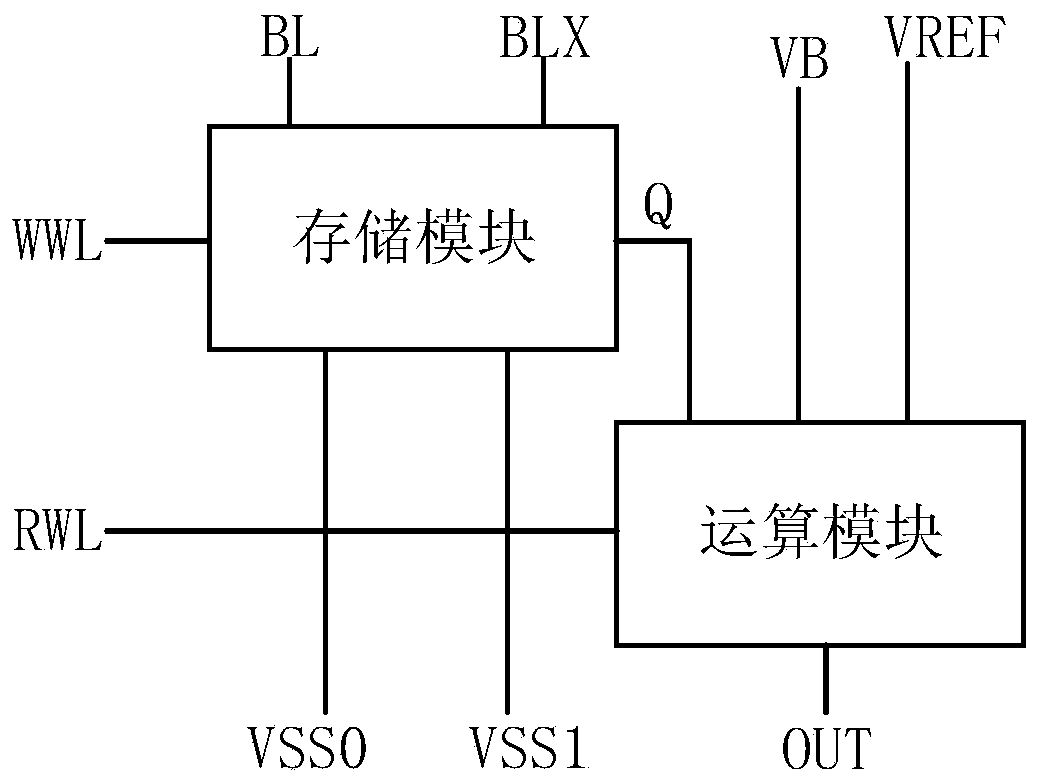

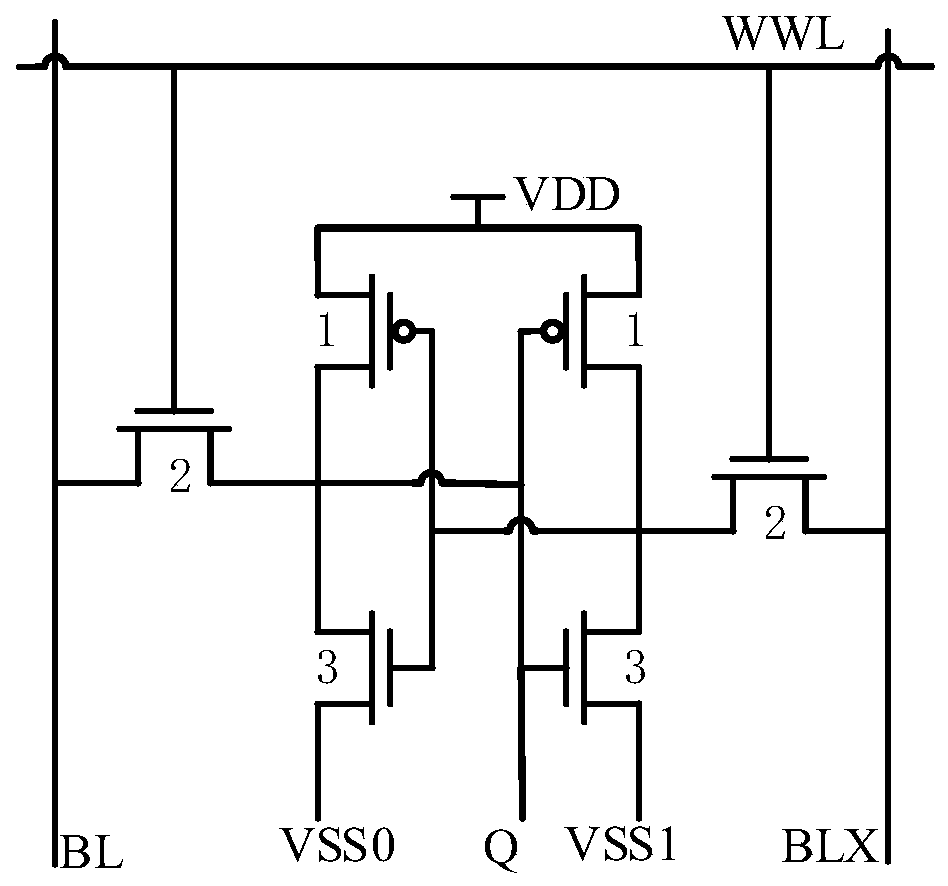

[0038] The SRAM storage operation unit array module is composed of N rows and M columns of storage operation units, each storage operation unit is composed of a storage module and an operation module, the module can realize voltage signal input, and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More