Semiconductor device and forming method thereof

A technology for semiconductors and devices, applied in the field of semiconductor devices and their formation, can solve problems such as increasing the working voltage of semiconductor devices, increasing gate resistance of semiconductor devices, and low permeability, so as to reduce interface resistance, improve uniformity, and enhance penetration. effect of ability

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

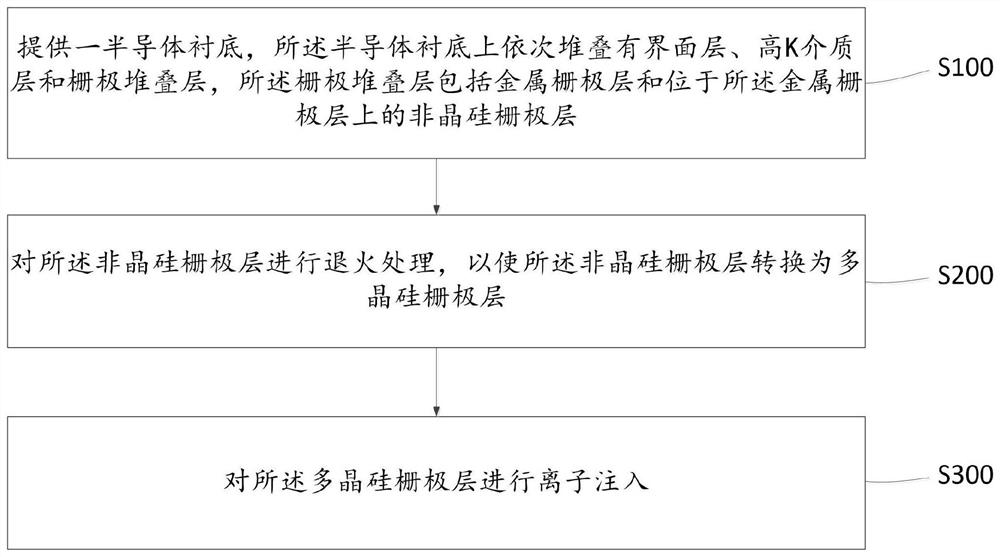

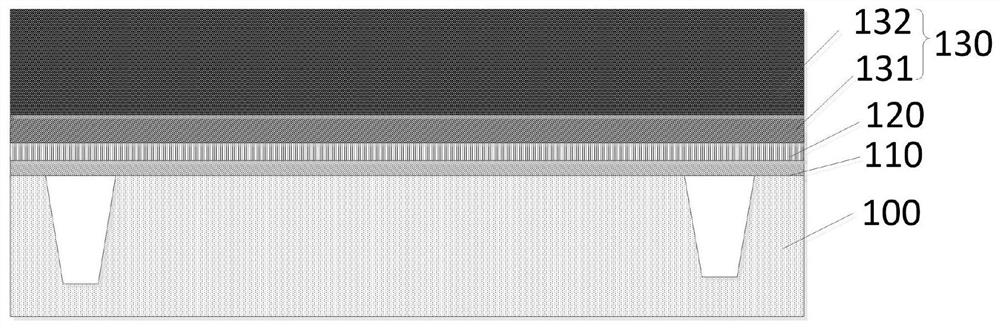

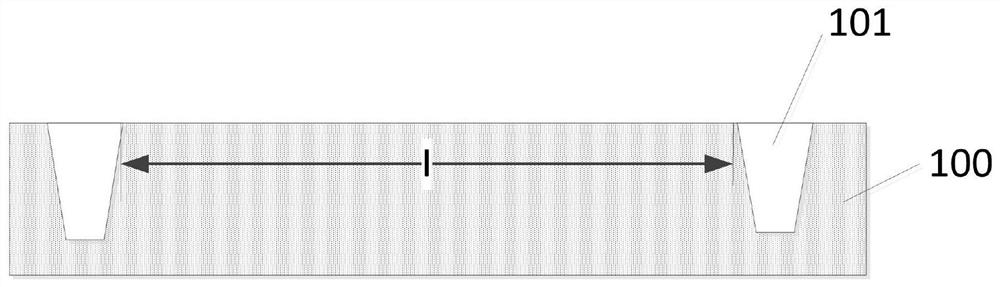

[0042] As mentioned in the background, at present, the gate process is the process method for realizing high-k metal gate in the semiconductor manufacturing process flow, and its manufacturing process flow is similar to the process adopted in the traditional poly / SiON method. The gate electrode is first formed, including a high-k dielectric film and a single-crystal silicon gate, followed by subsequent transistor manufacturing stages, such as the definition of source and drain regions, silicidation of part of the substrate surface, metallization, and so on. However, in the process of forming semiconductor devices using the gate-first process, due to the non-uniformity and low permeability of the single crystal silicon gate to doped boron ions, the gate resistance of the semiconductor device increases, thereby improving the performance of the semiconductor device. Operating Voltage.

[0043] Therefore, the present invention provides a method for forming a semiconductor device, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More