Patents

Literature

45 results about "Intermediate logic" patented technology

Efficacy Topic

Property

Owner

Technical Advancement

Application Domain

Technology Topic

Technology Field Word

Patent Country/Region

Patent Type

Patent Status

Application Year

Inventor

In mathematical logic, a superintuitionistic logic is a propositional logic extending intuitionistic logic. Classical logic is the strongest consistent superintuitionistic logic; thus, consistent superintuitionistic logics are called intermediate logics (the logics are intermediate between intuitionistic logic and classical logic).

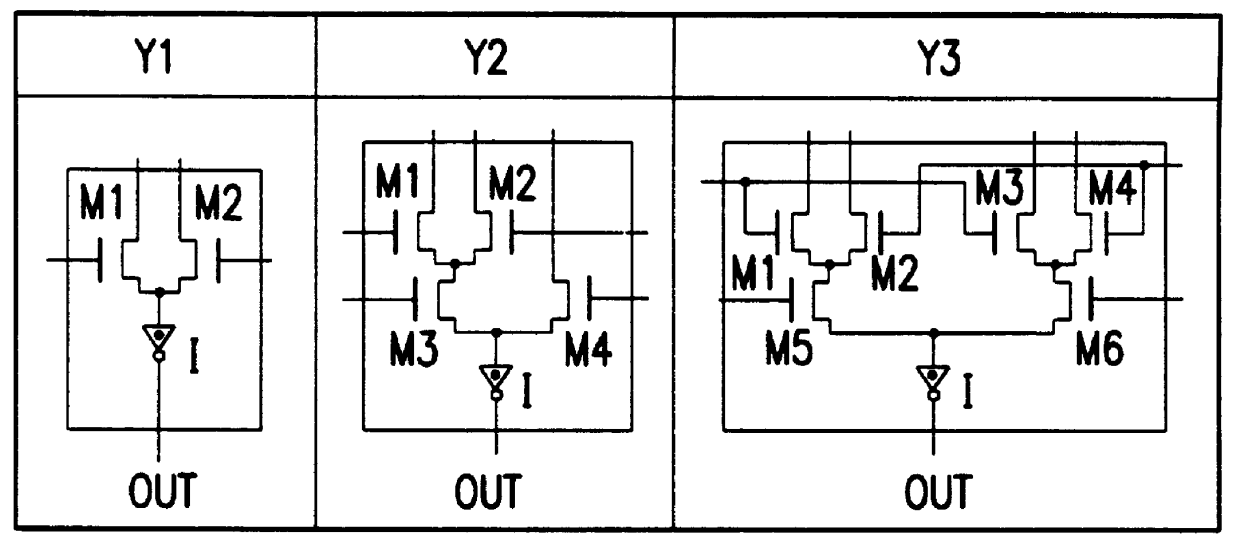

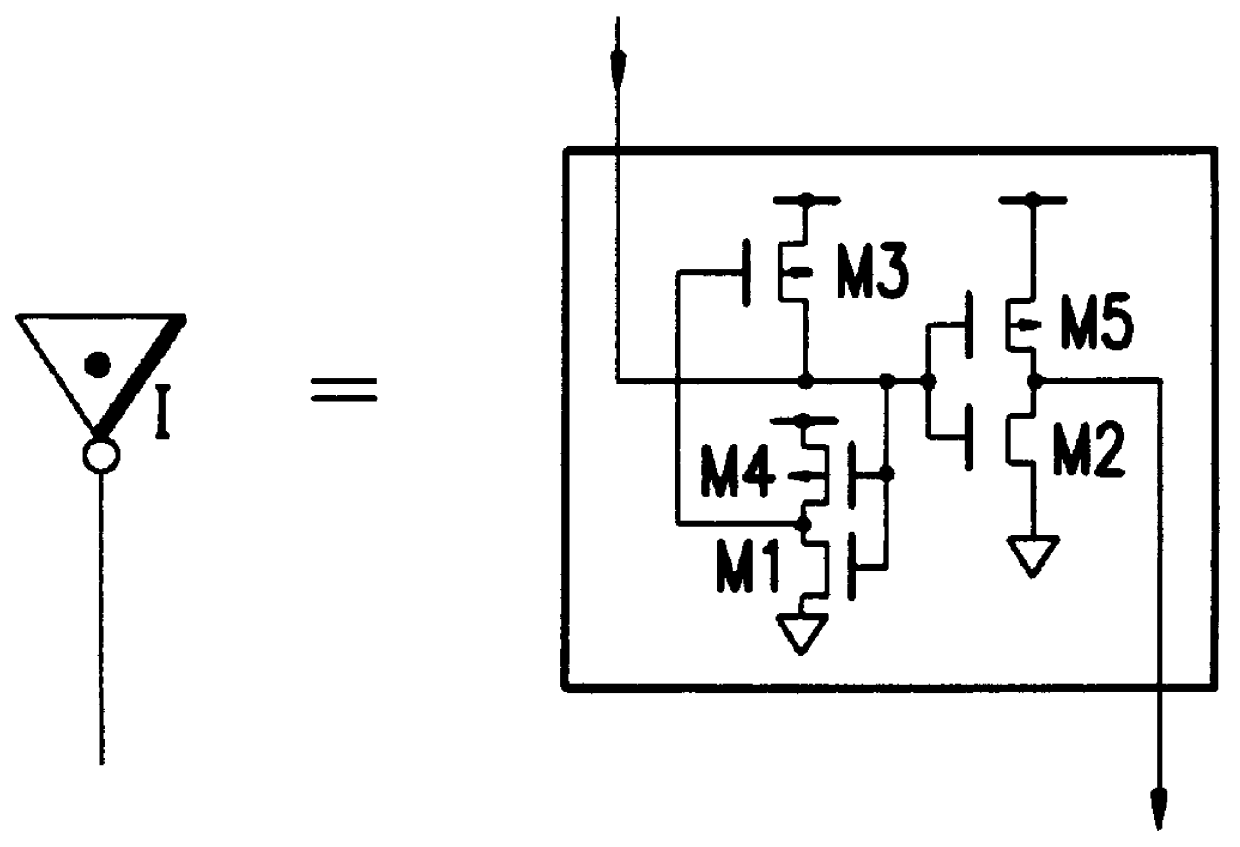

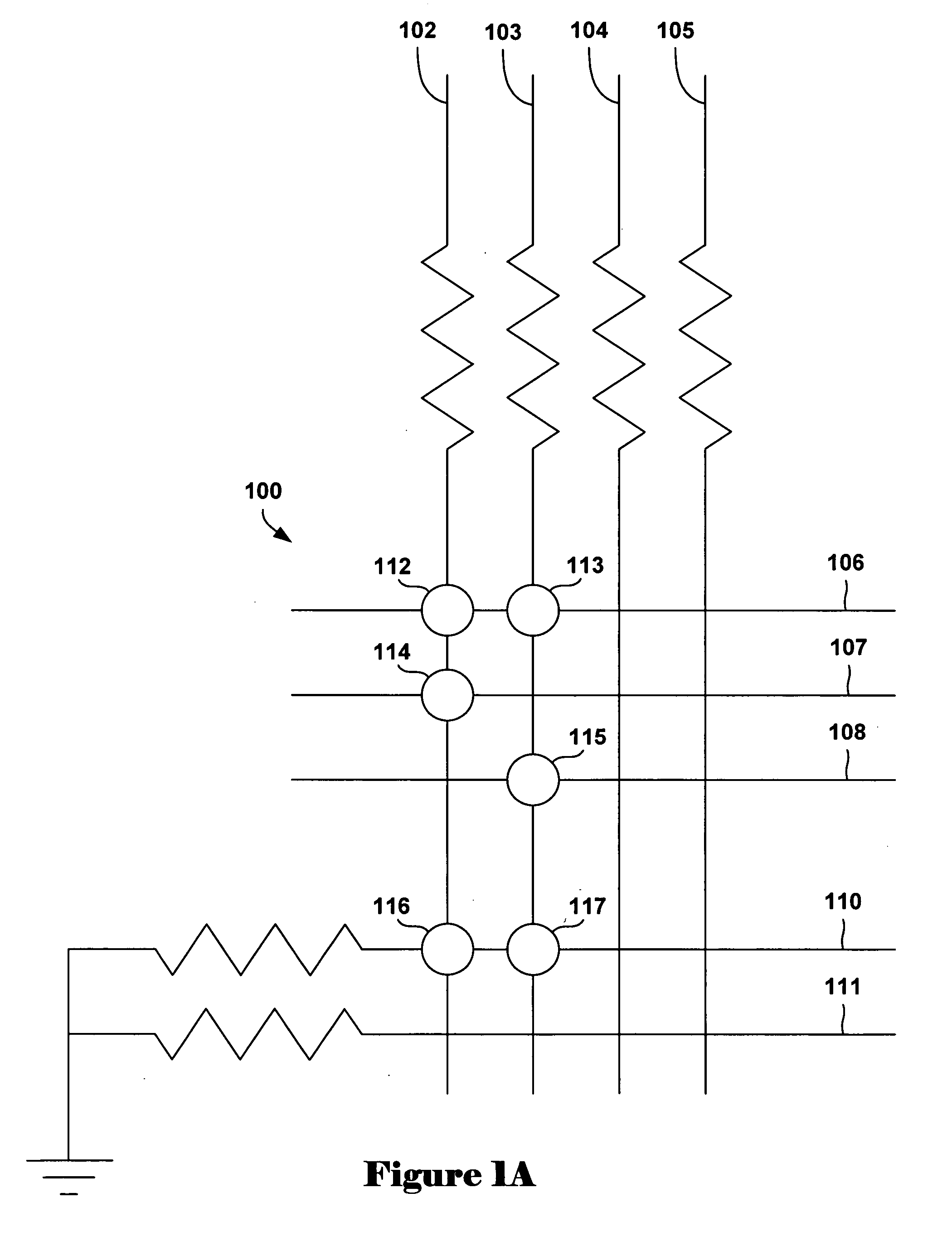

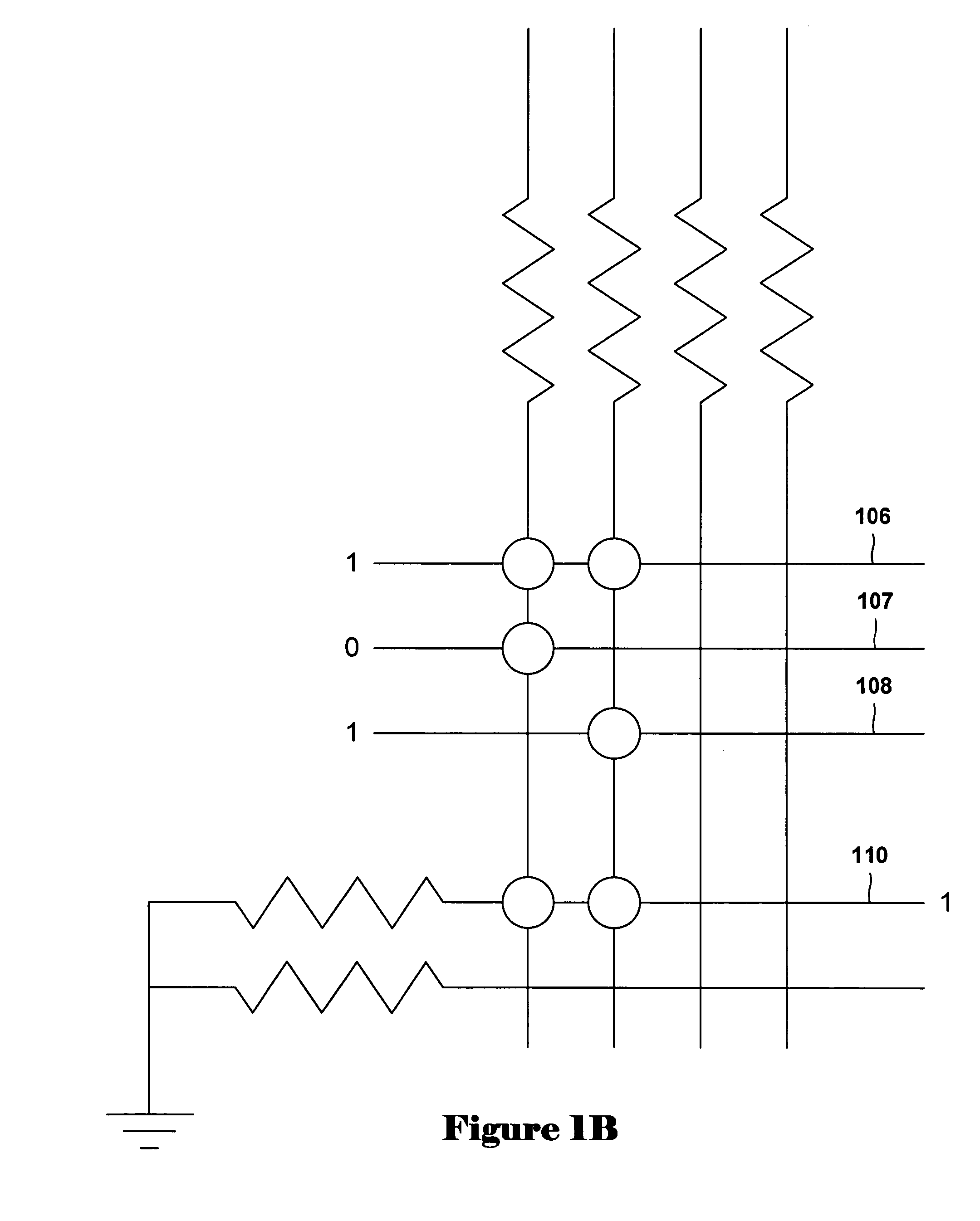

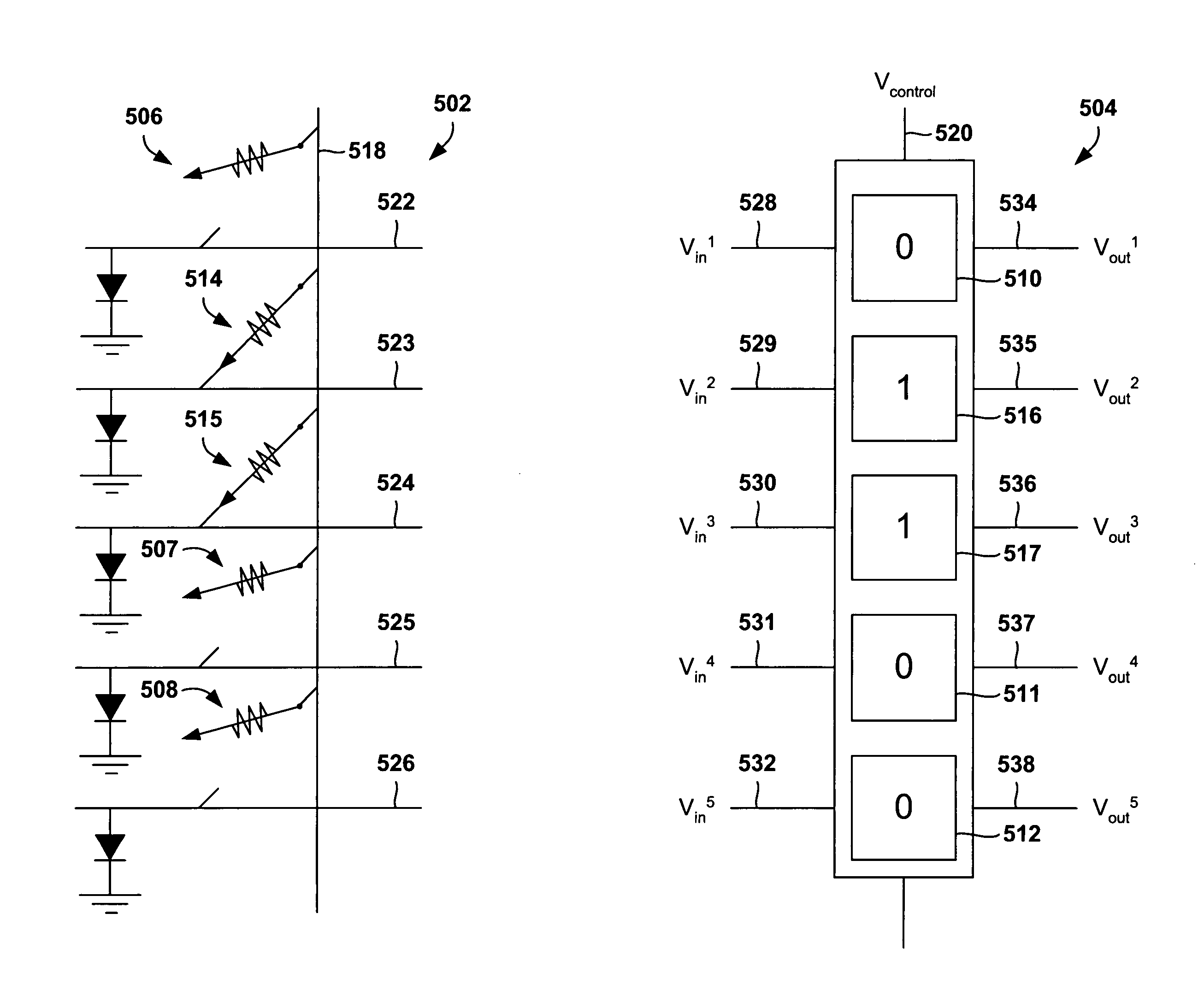

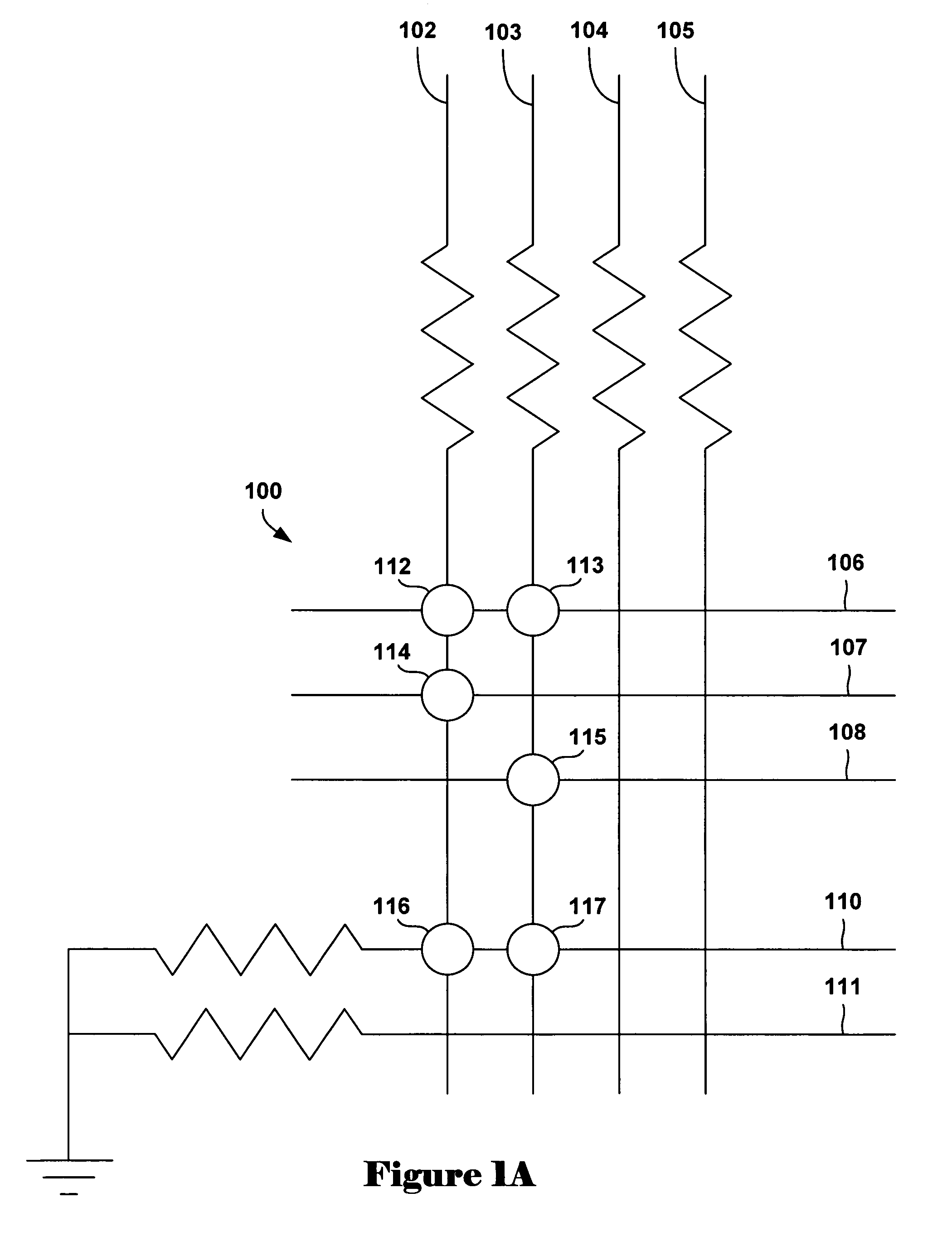

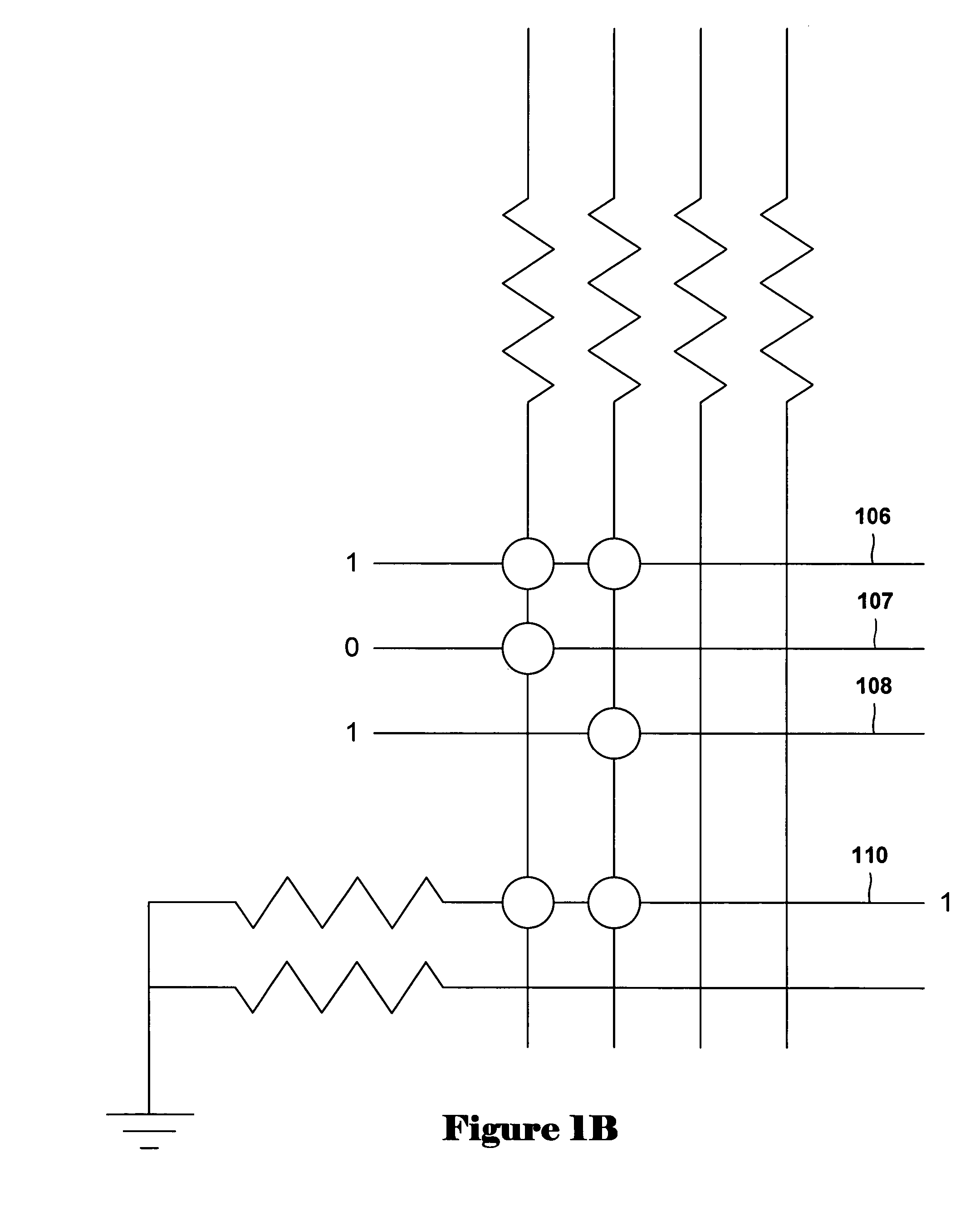

Logic circuit utilizing pass transistors and logic gate

InactiveUS6084437ATransistorReliability increasing modificationsCmos logic circuitsLogical operations

A logic circuit combines a plurality of pass-transistor logic trees and a multiple-input logic gate for receiving intermediate logic signals from the respective pass-transistor logic trees, and can express a complex logical operation while decreasing the number of stages in pass-transistor logic trees and improving operation speed. Even a logical operation that cannot be expressed efficiently by a known or conventional pass-transistor logic circuit can be expressed efficiently with performance higher than that of a known CMOS logic circuit. Furthermore, when a static feedthrough current of the multiple-input logic gate is suppressed, power consumption can be reduced. In some embodiments, since circuitry for suppressing a static feedthrough current of the multiple-input logic gate is arranged so that a probability of occurrence of logical collision with a preceding stage will decrease or will be nil, power consumption can further be reduced.

Owner:KAWASAKI MICROELECTRONICS

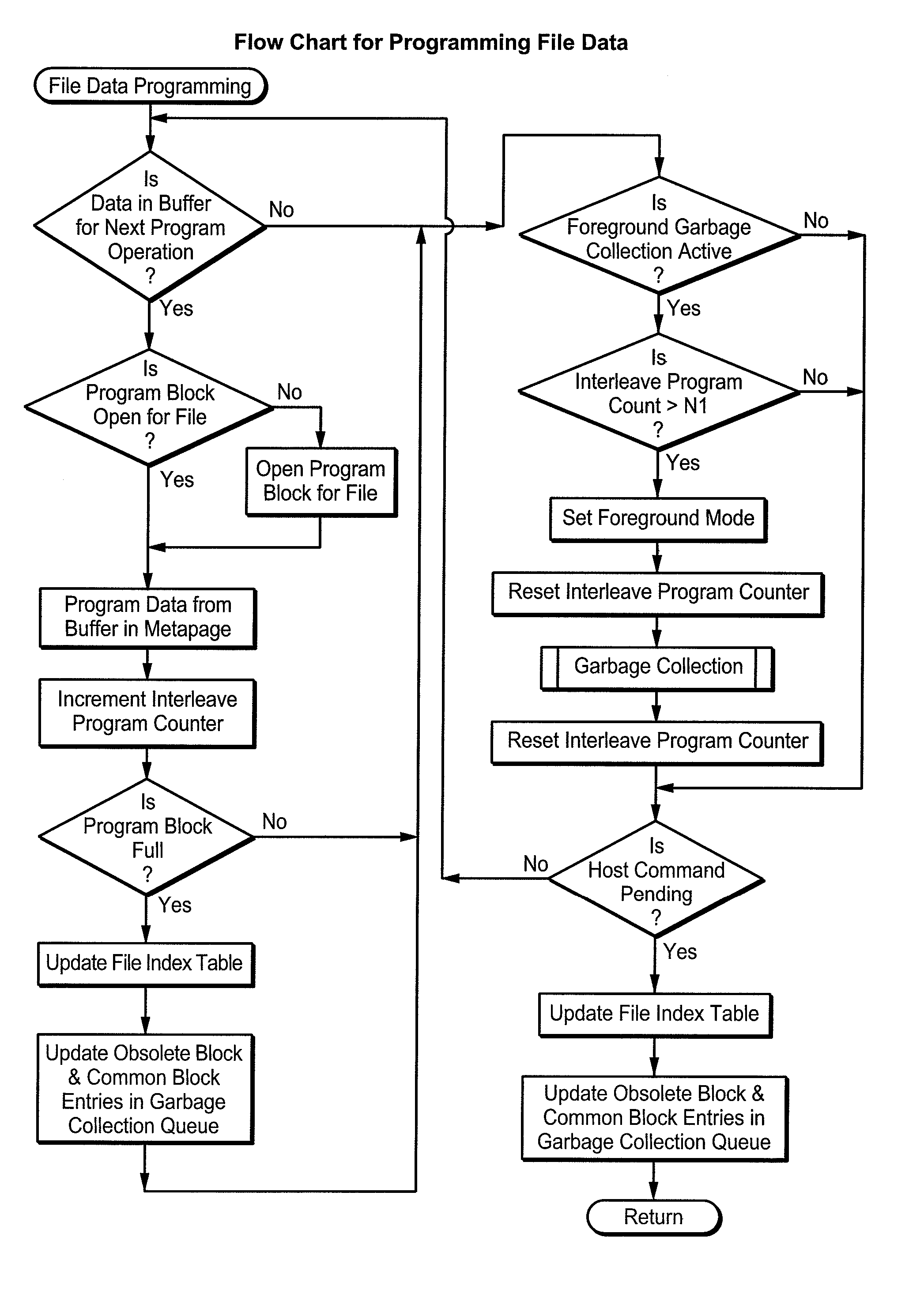

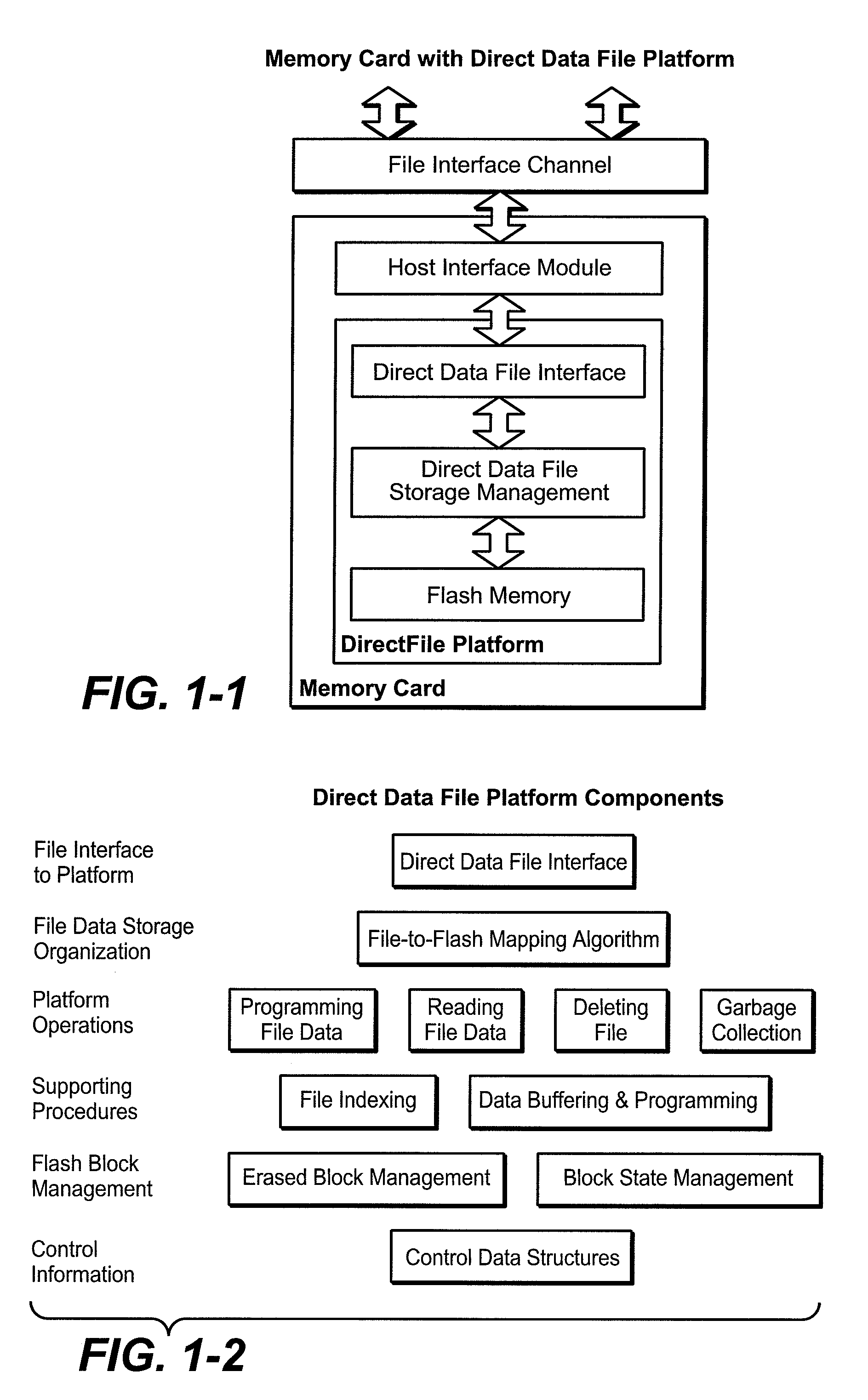

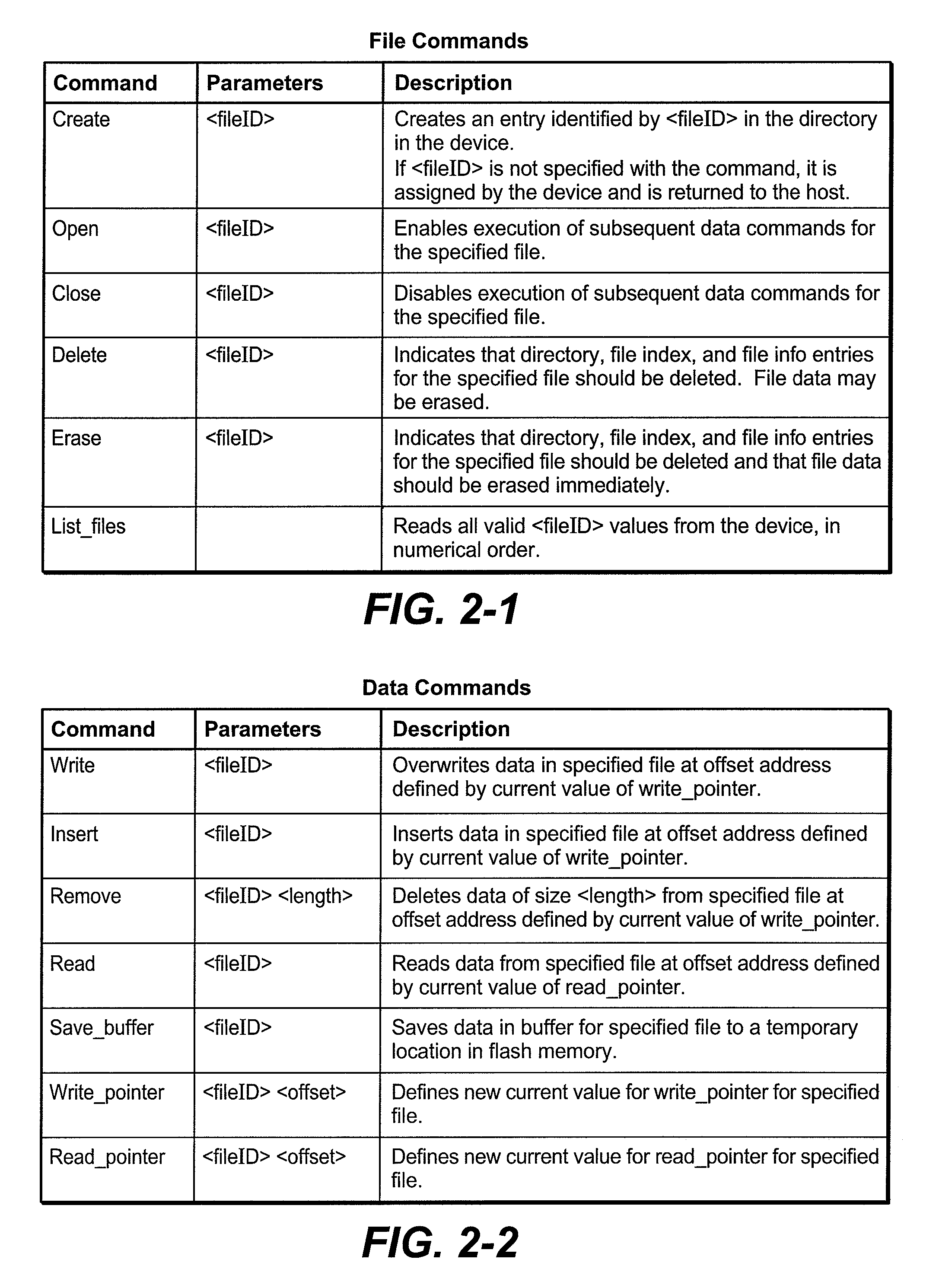

Data Operations in Flash Memories Utilizing Direct Data File Storage

ActiveUS20070033377A1Prevent ConsolidationImprove memory performanceMemory architecture accessing/allocationDigital data information retrievalData operationsData file

Host system data files are written directly to a large erase block flash memory system with a unique identification of each file and offsets of data within the file but without the use of any intermediate logical addresses or a virtual address space for the memory. Directory information of where the files are stored in the memory is maintained within the memory system by its controller, rather than by the host.

Owner:SANDISK TECH LLC

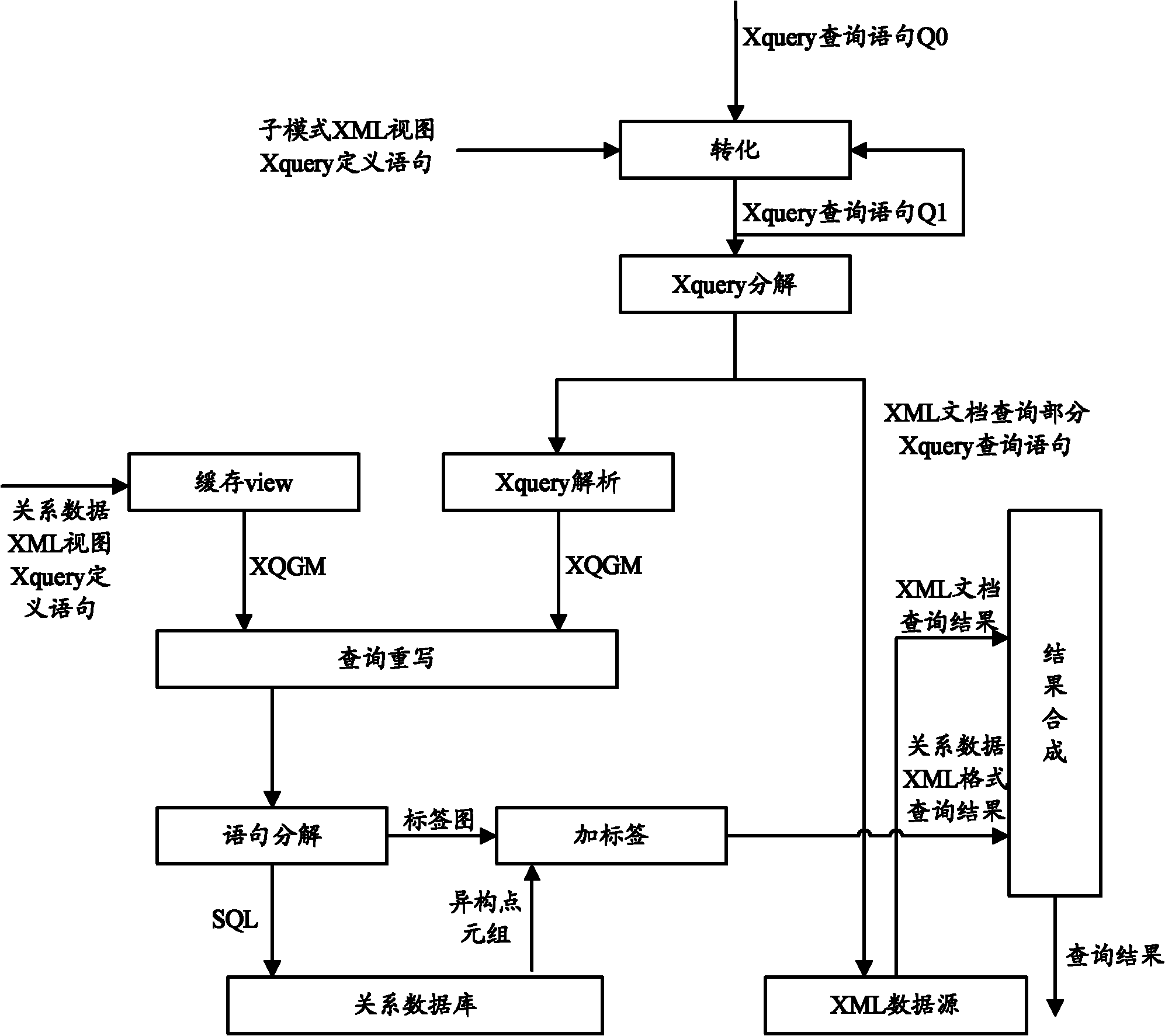

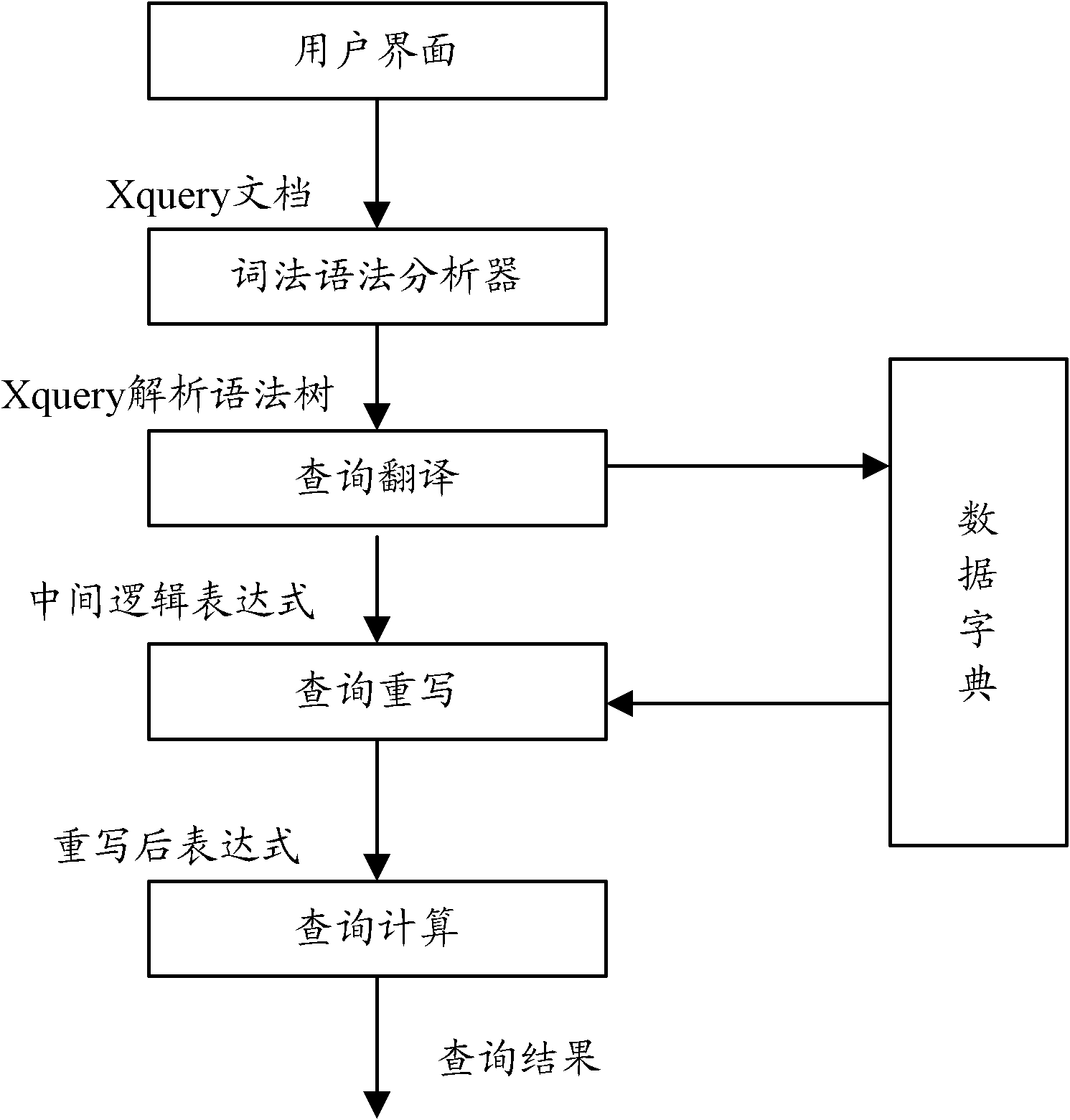

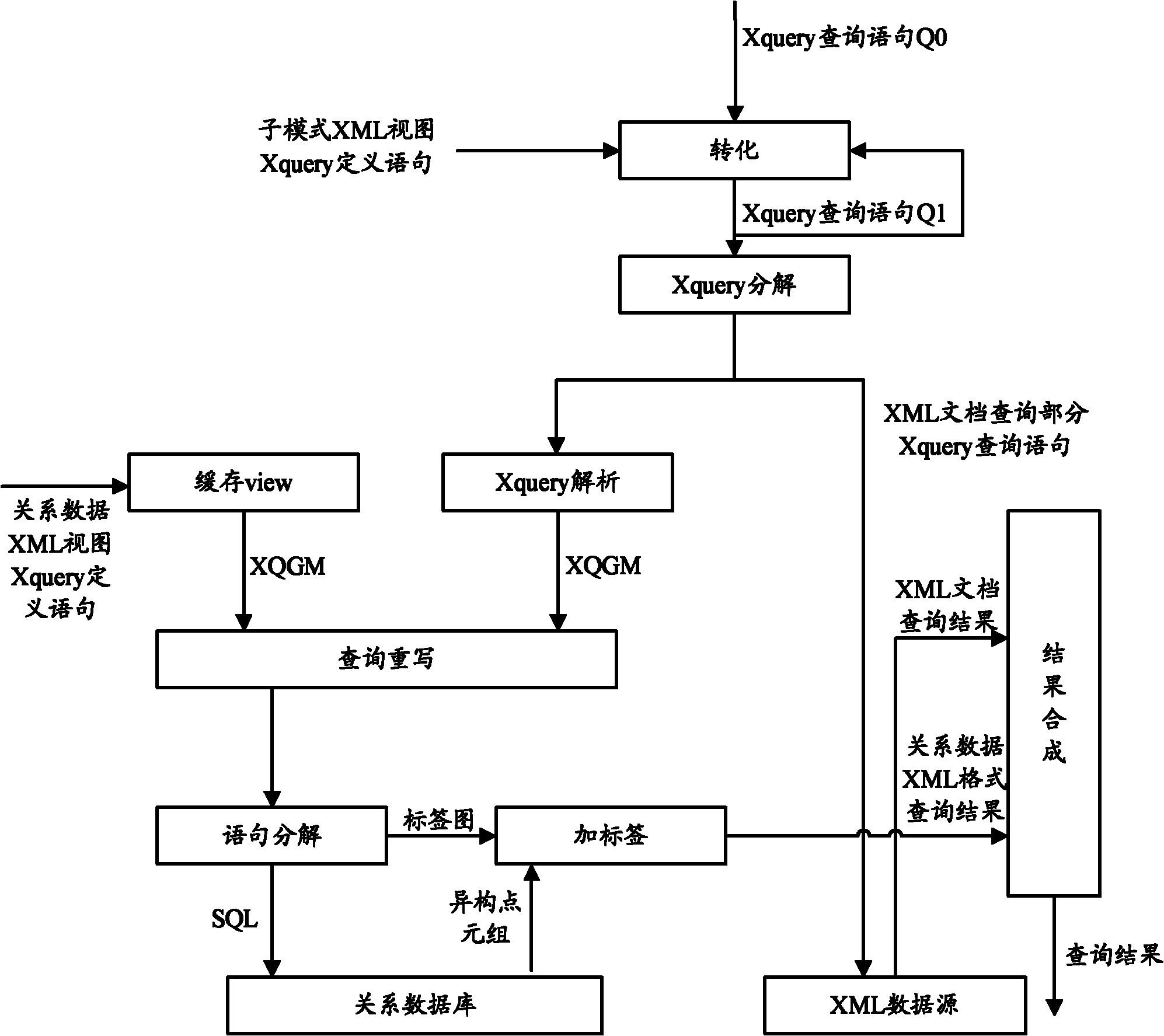

Method for realizing optimization of data source extensive makeup language (XML) query system based on sub-queries

InactiveCN101984439ALess layersEasy to optimizeSpecial data processing applicationsApplicability domainData source

The invention relates to a method for realizing optimization of a data source extensive makeup language (XML) query system based on sub-queries. The method comprises the following steps: receiving corresponding XML query input information; carrying out morphological analysis and syntactic analysis, and verifying the correctness and the validity; if the analysis is successful and the verification is passed, generating an XML analytical syntactic tree; translating the XML analytical syntactic tree, and converting the XML query input information into intermediate logical representation; carrying out rewriting treatment, and generating a target query expression; and calling supported querying and computing engines for querying and computing, and acquiring output query results. By adopting the method for realizing the optimization of the data source XML query system based on the sub-queries, the query rewriting can be used for converting a procedural query into a descriptive query, the sub-queries are optimized, and certain specific sub-queries are rewritten into equivalent attended operation of a plurality of tables by the combination of the sub-queries, thus the levels of query sentences are reduced as much as possible, the treatment of planning optimization can be carried out conveniently, and the method has stable and reliable working performance and wider application range.

Owner:SHANGHAI GONGJIN COMM TECH

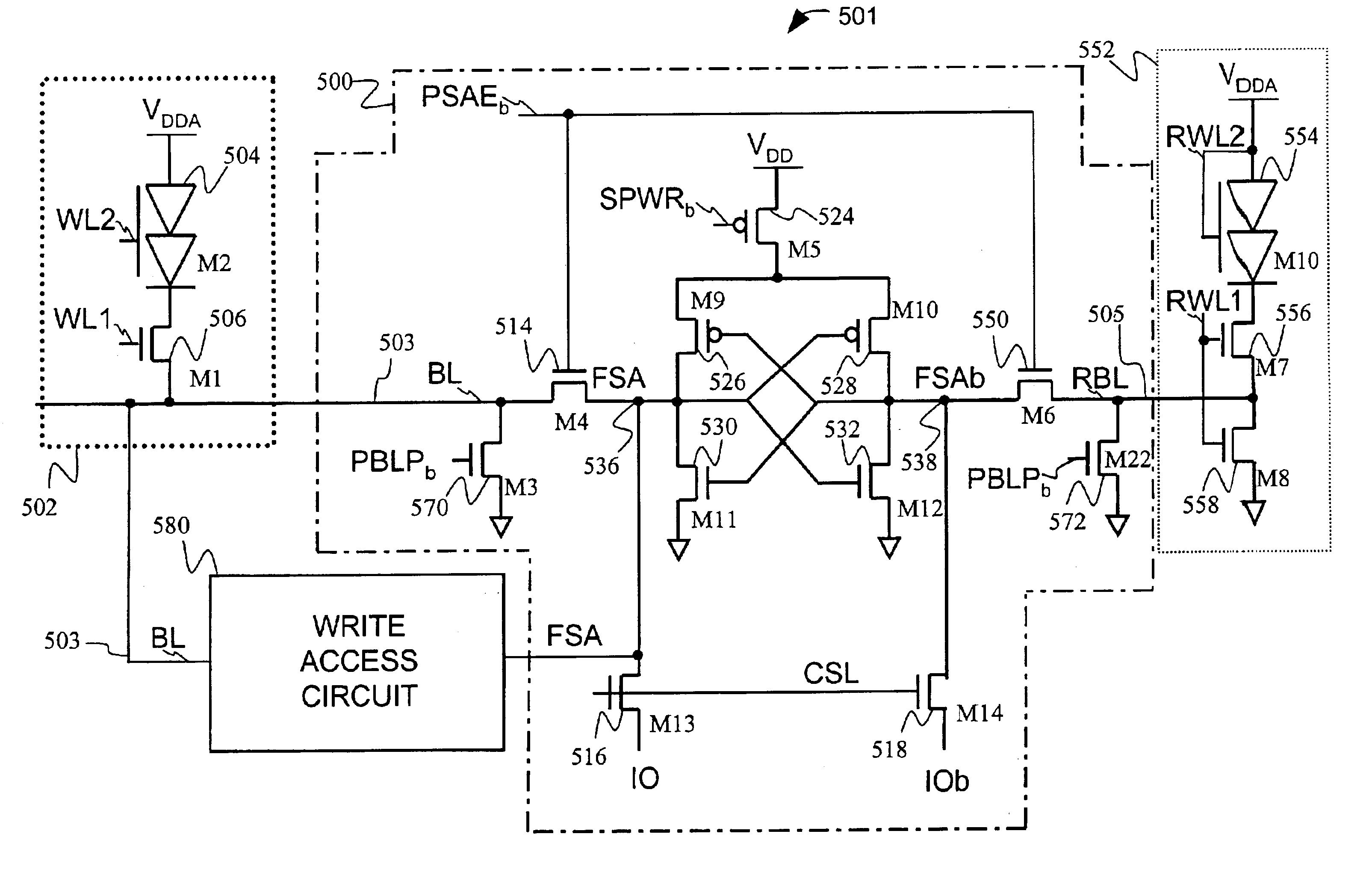

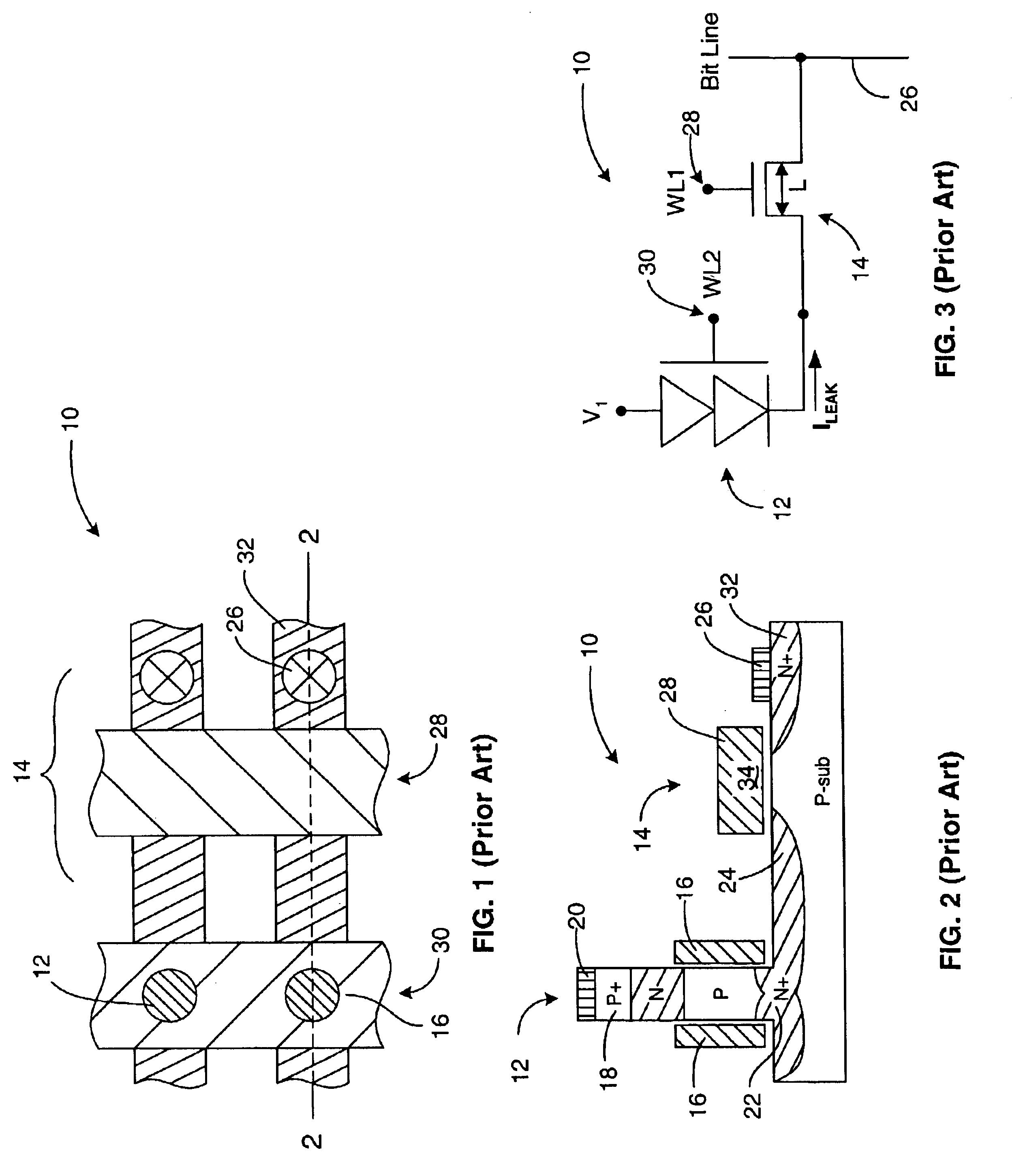

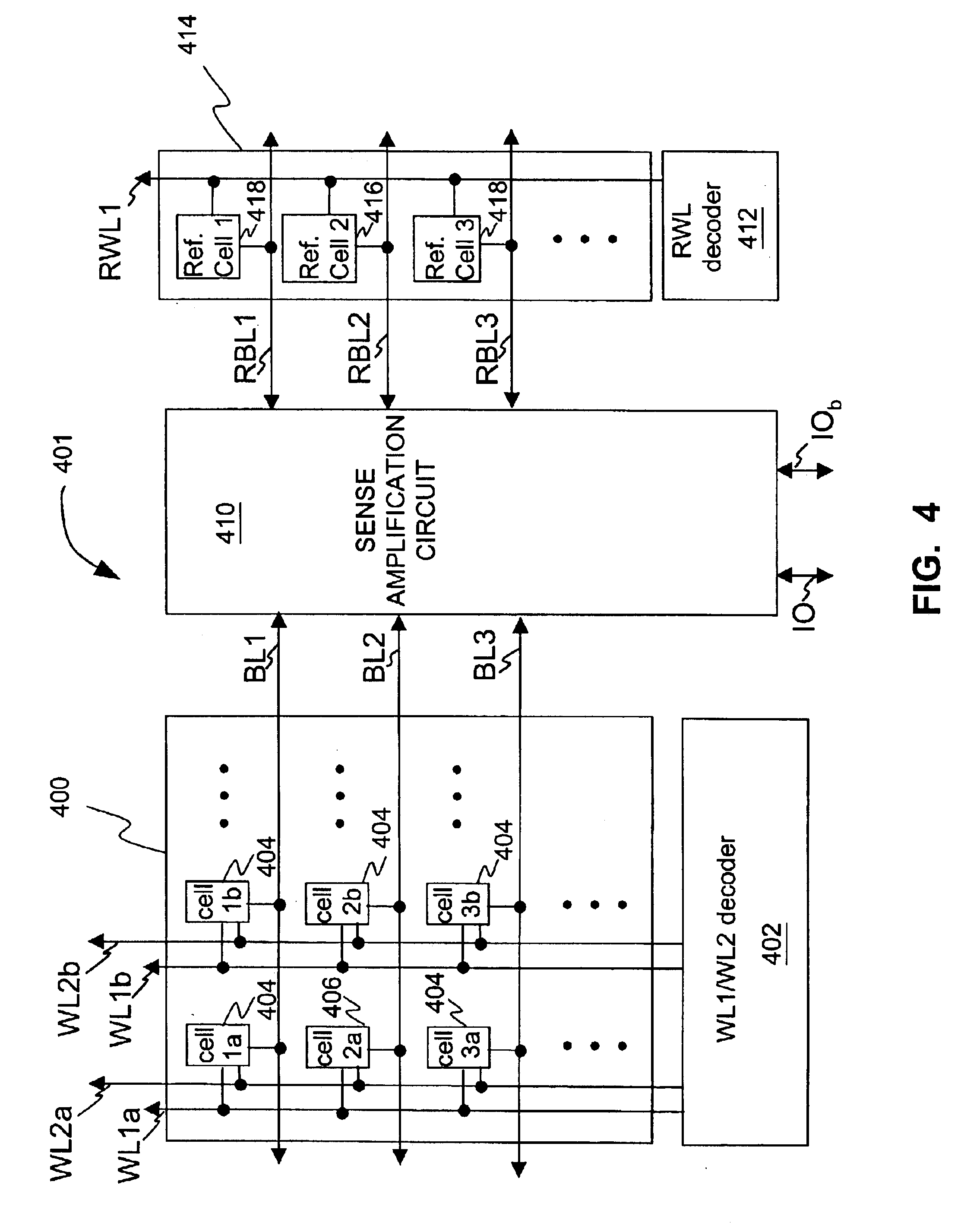

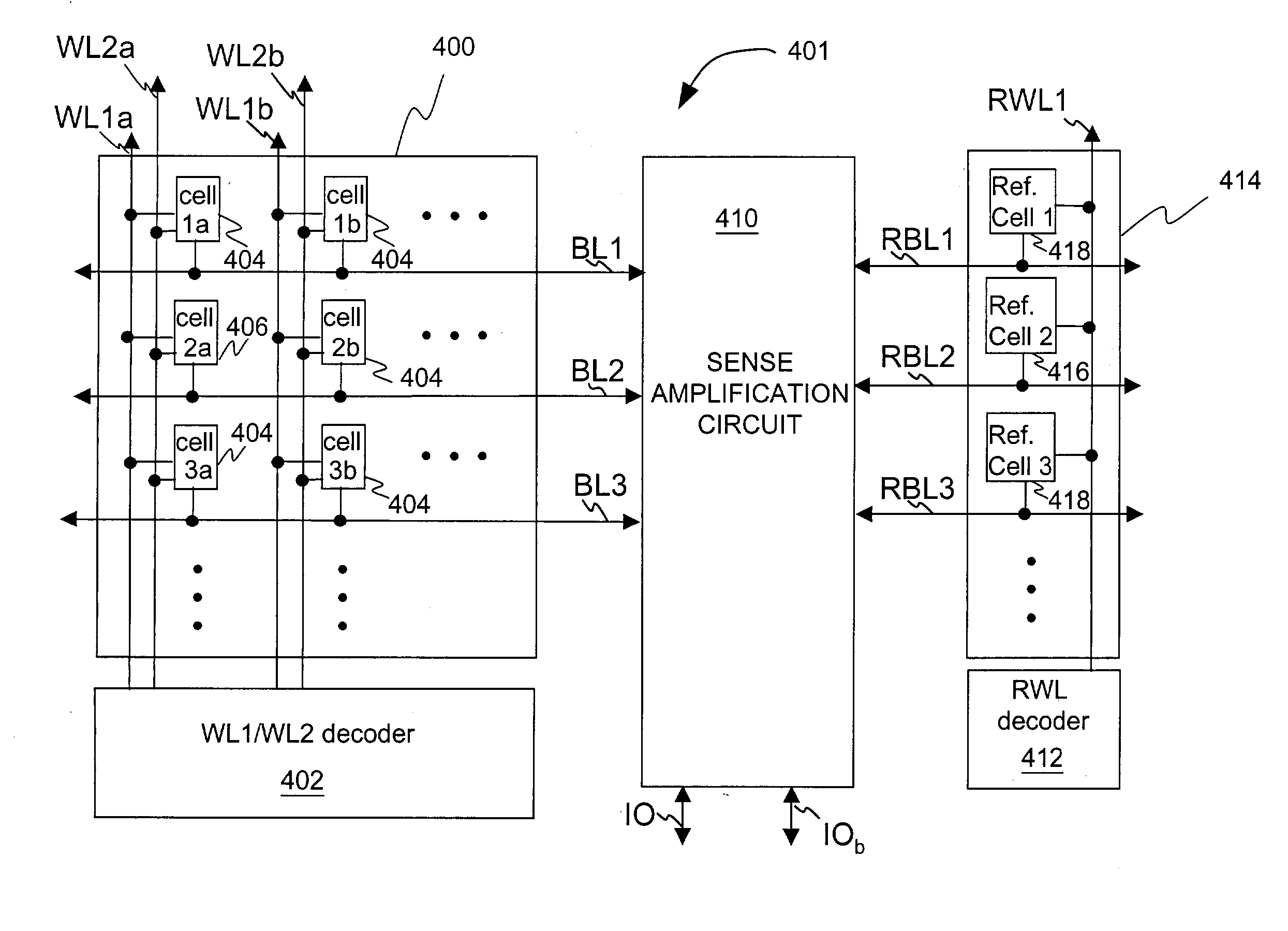

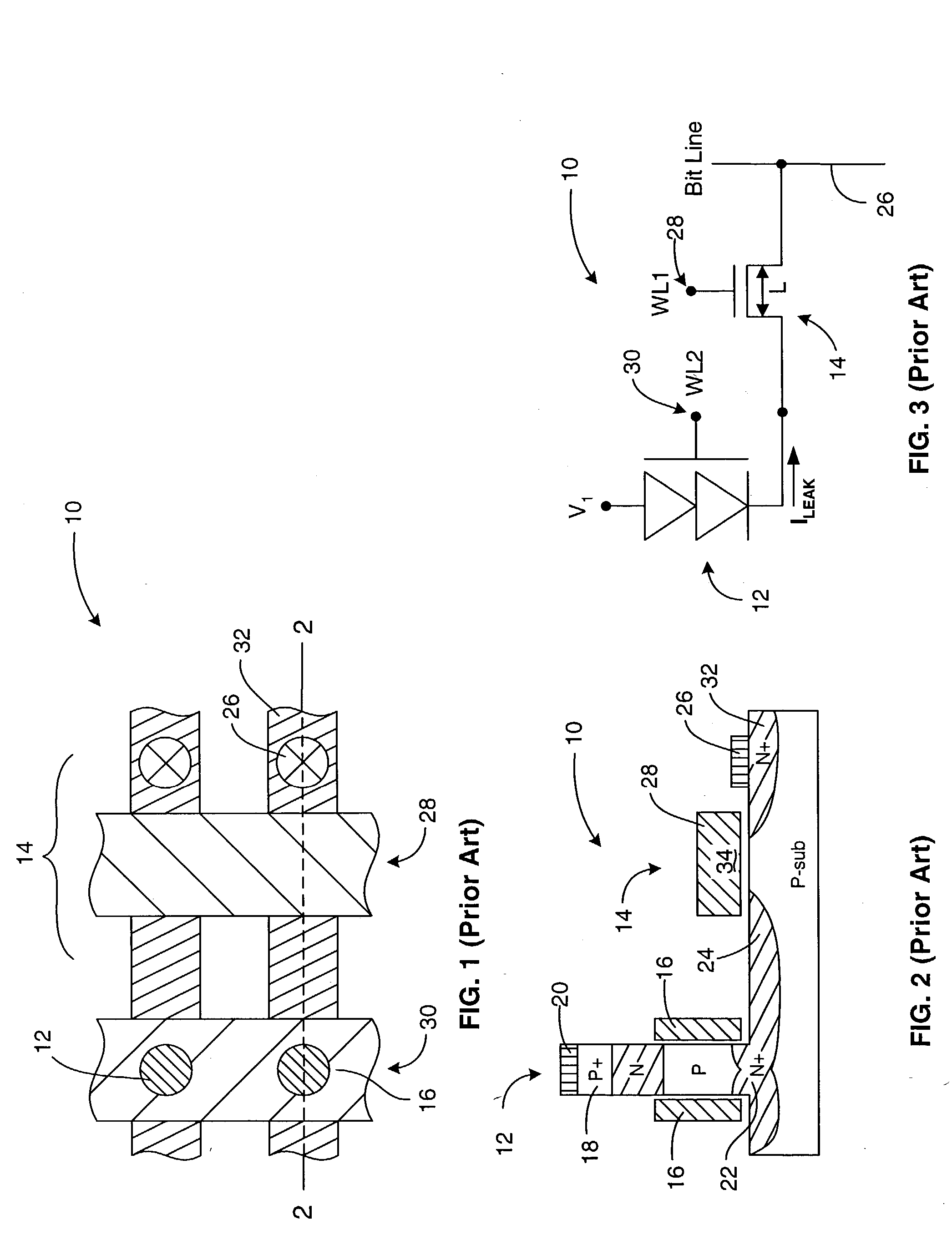

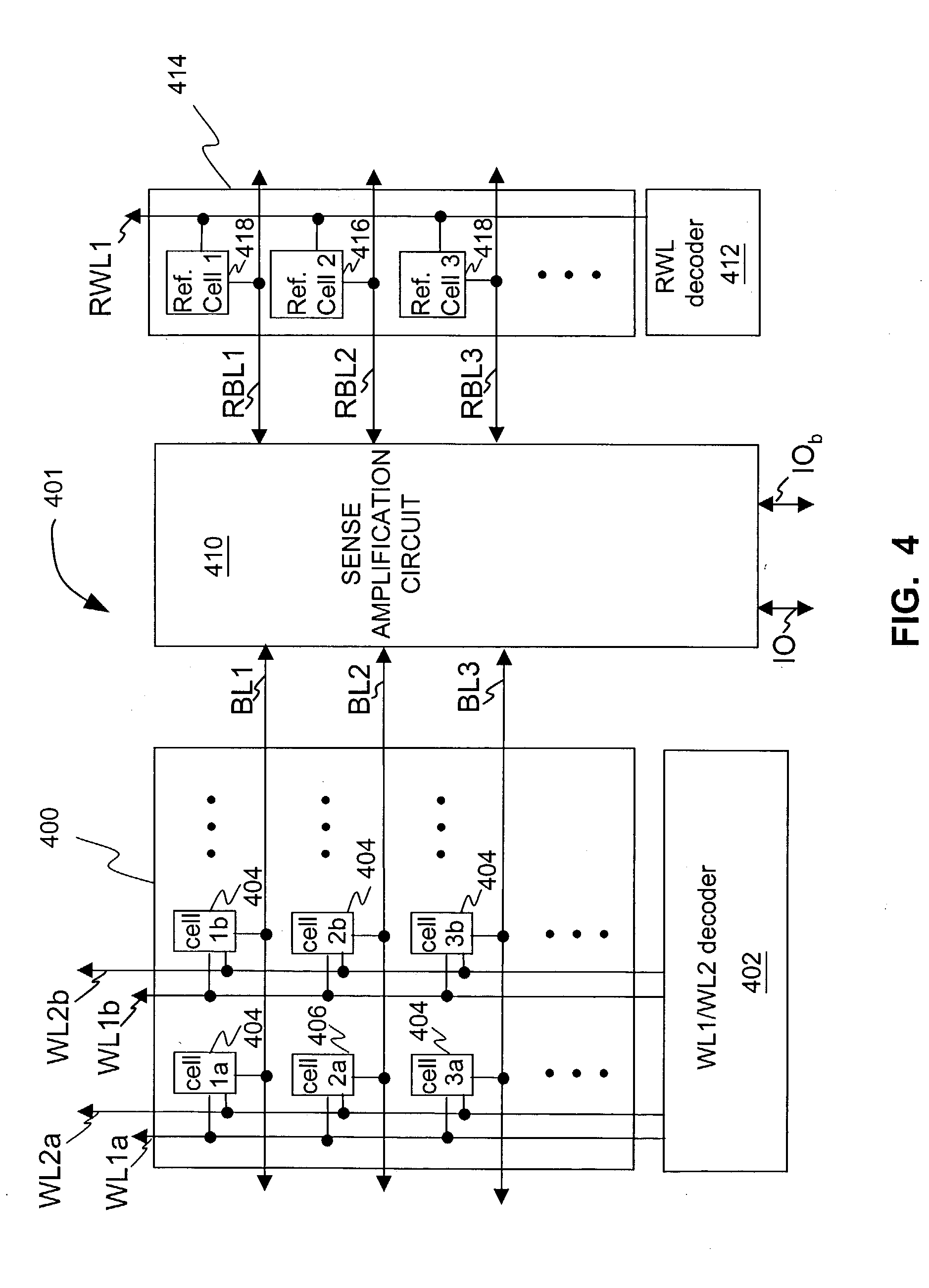

Circuit and method for implementing a write operation with TCCT-based memory cells

The present invention provides a circuit and a method for providing nondestructive write operations and optimized memory access operations with reduced power consumption during memory access, such as during write operations. In one embodiment, a memory device comprises a memory cell configured to store a first data bit. The memory device also comprises a write access circuit coupled to the memory cell for providing a write data bit having a write data bit magnitude. The write access circuit is configured to adjust the write data bit magnitude to an intermediate logic state magnitude in a memory operation.

Owner:MICRON TECH INC +1

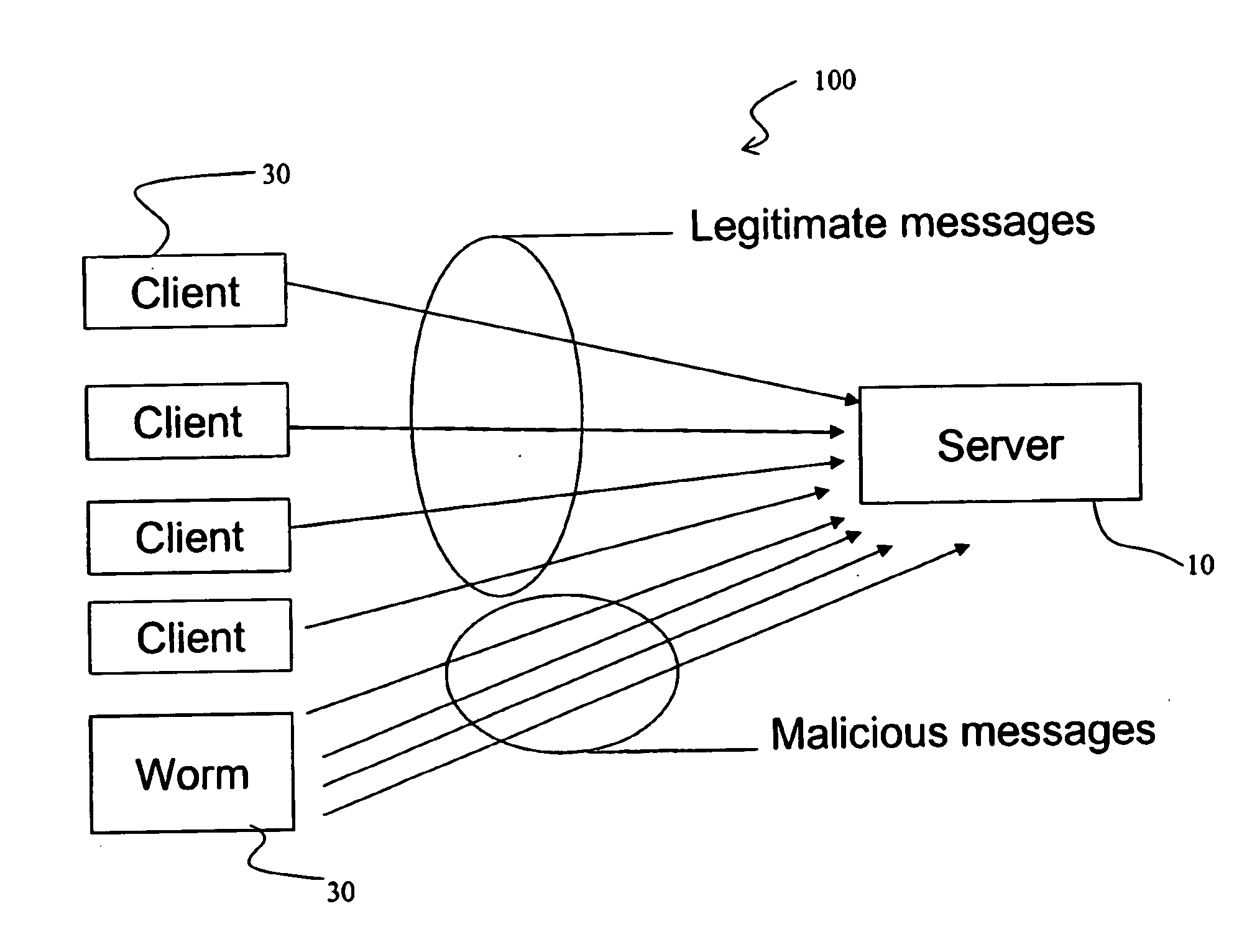

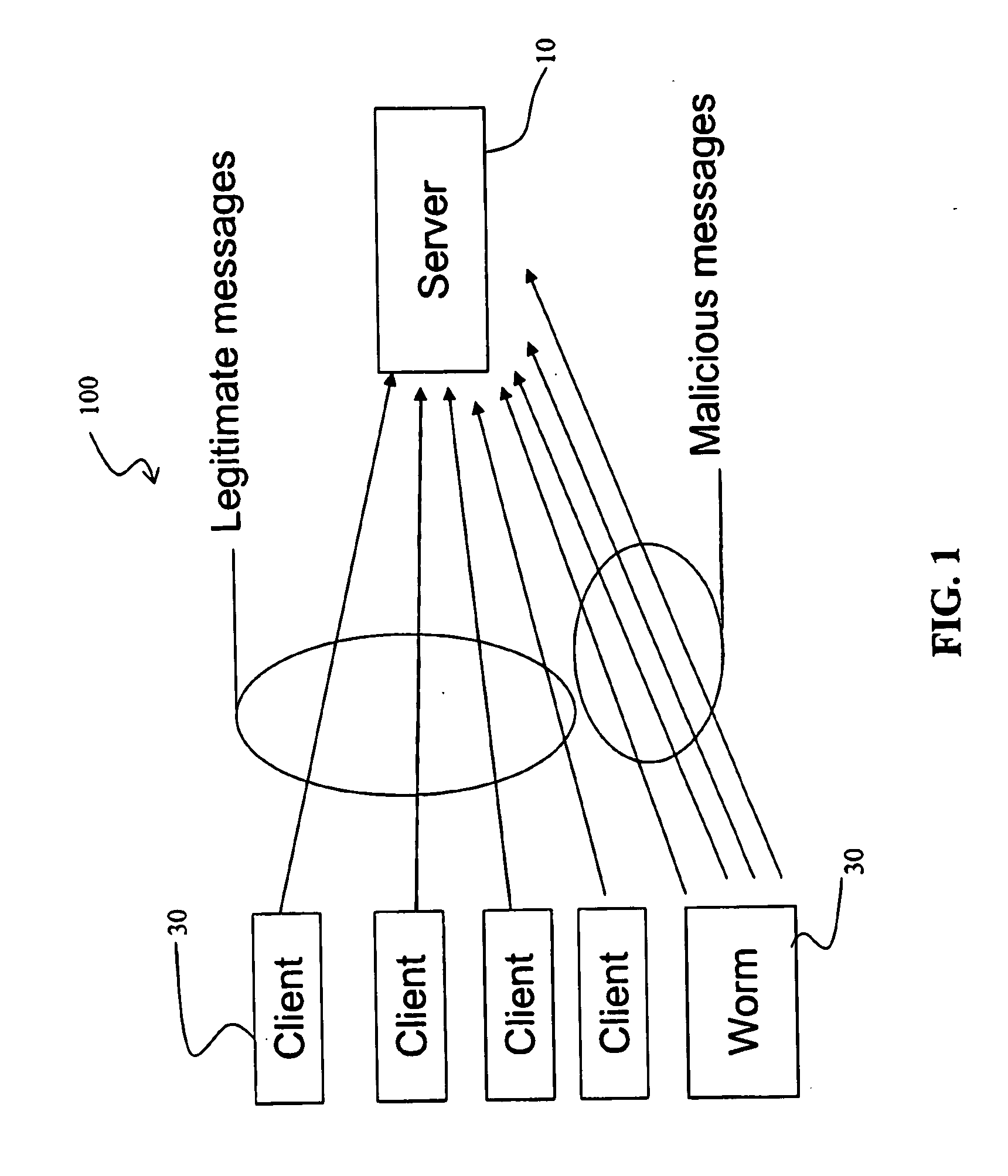

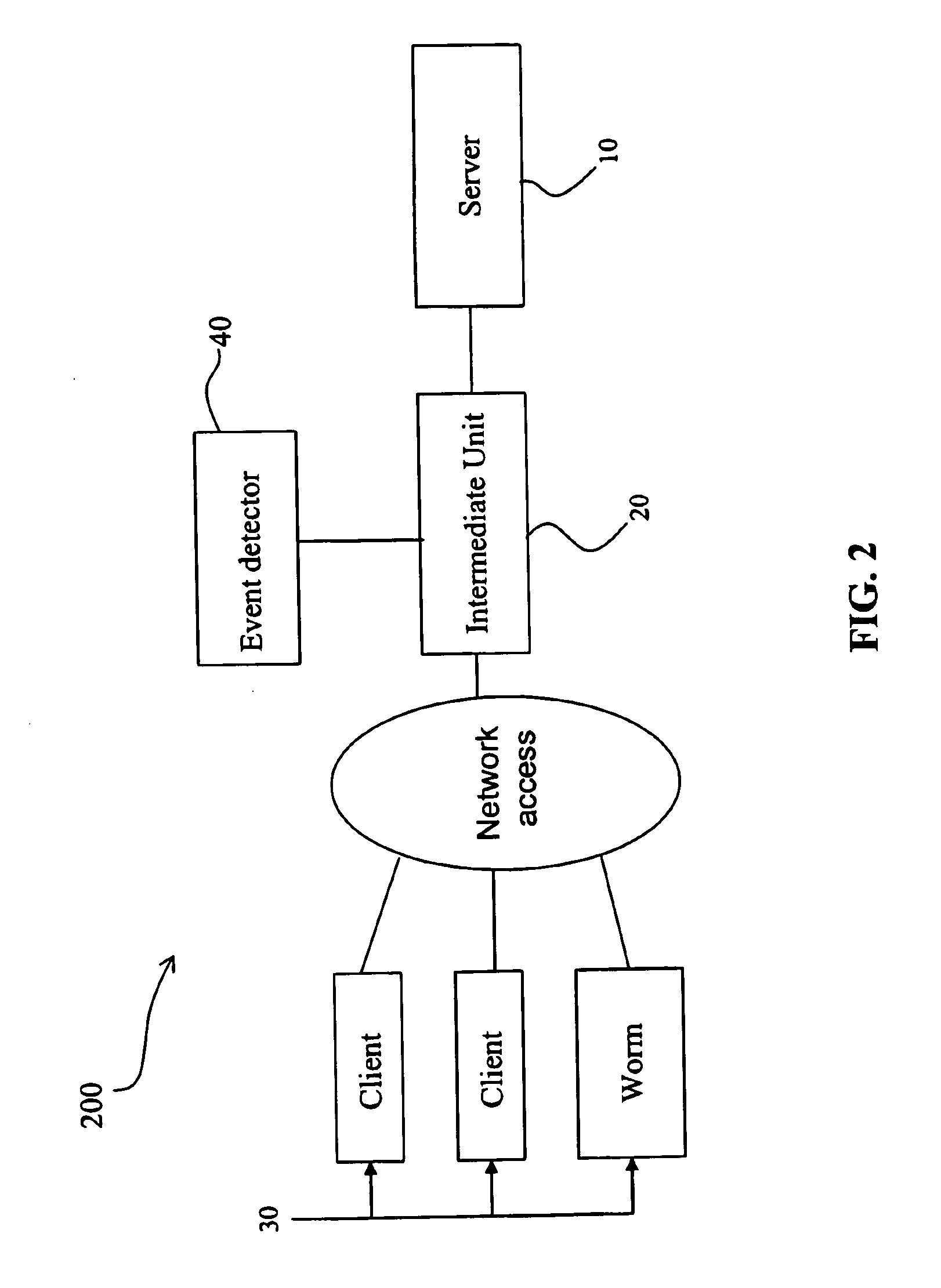

Method and appratus to control application messages between client and a server having a private network address

InactiveUS20110019547A1Avoid burdenLarge amount of processingError preventionFrequency-division multiplex detailsTraffic capacityControl communications

A method to control communication traffic in a communication network. The traffic includes application-level messages between a client and a server having a private network address. The method includes the steps of: sending by the client a request message requesting a service to the server using a first public network address associated with the server; processing the request message at an intermediate logic unit logically positioned between the client and the server; and receiving an alert signal at the intermediate unit. Upon receipt of said alert signal, the method provides for: mapping the private network address of the server to a second public network address associated with the server; and instructing the client to send the request message to the second public network address of the server, routing to the server only request messages directed to the second public network address.

Owner:TELECOM ITALIA SPA

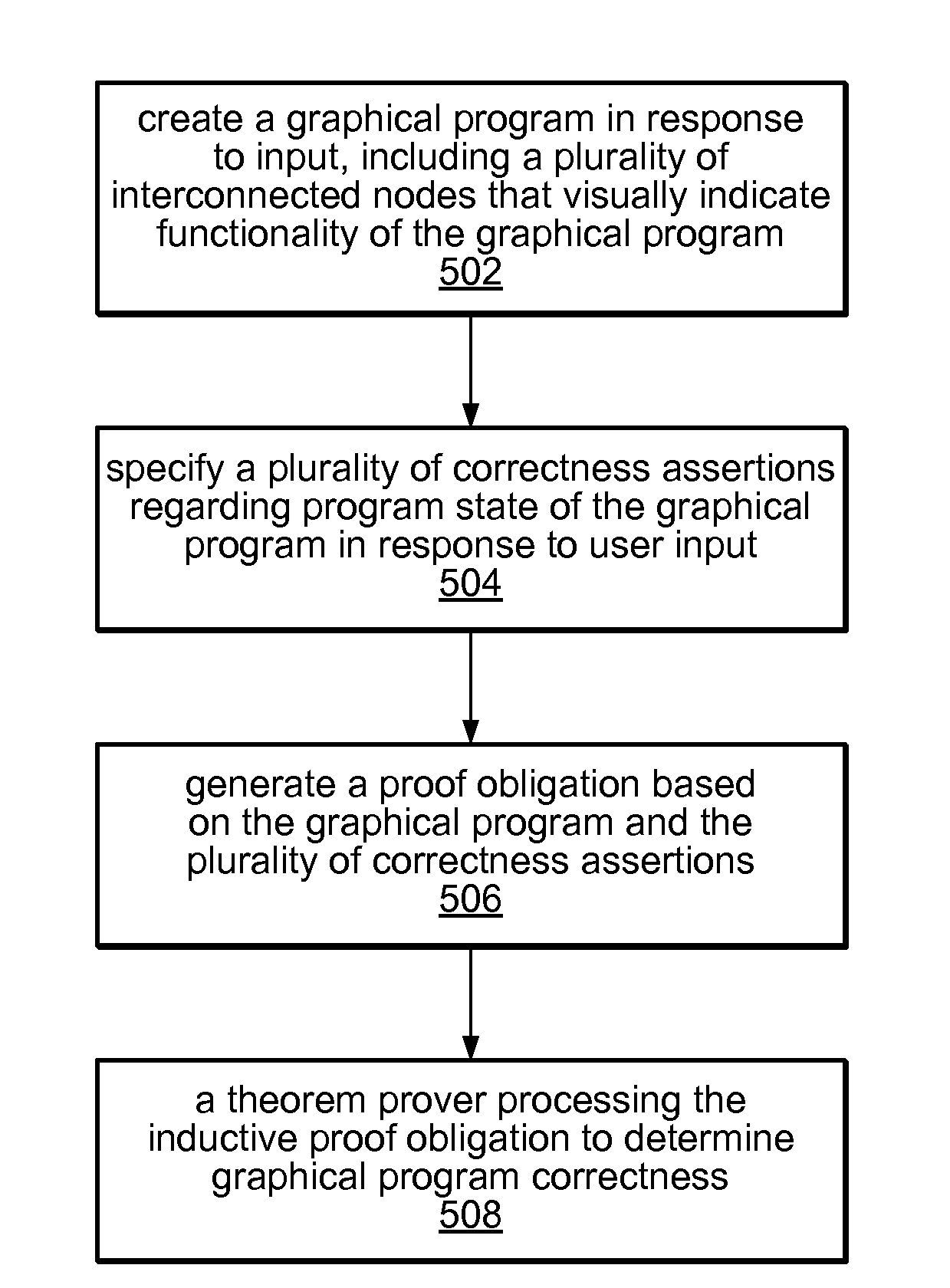

Formal Verification of Graphical Programs

InactiveUS20090064111A1Error detection/correctionVisual/graphical programmingObject levelHuman language

System and method for formal verification of a graphical program. A graphical program comprising a plurality of interconnected nodes is created in response to input. One or more correctness assertions regarding program state of the graphical program are specified in response to user input, and a proof obligation generated based on the graphical program and the correctness assertions, which is usable by a theorem prover to determine correctness of the graphical program. The proof obligation may be generated by compiling the graphical program to generate an object-level diagram, parsing the correctness assertions to generate an intermediate logical form of the one or more correctness assertions, and analyzing the object-level diagram, the intermediate logical form, and / or semantics of the graphical programming language in which the graphical program is written to generate the proof obligation. A theorem prover may then process the proof obligation to determine whether the graphical program is correct.

Owner:NATIONAL INSTRUMENTS

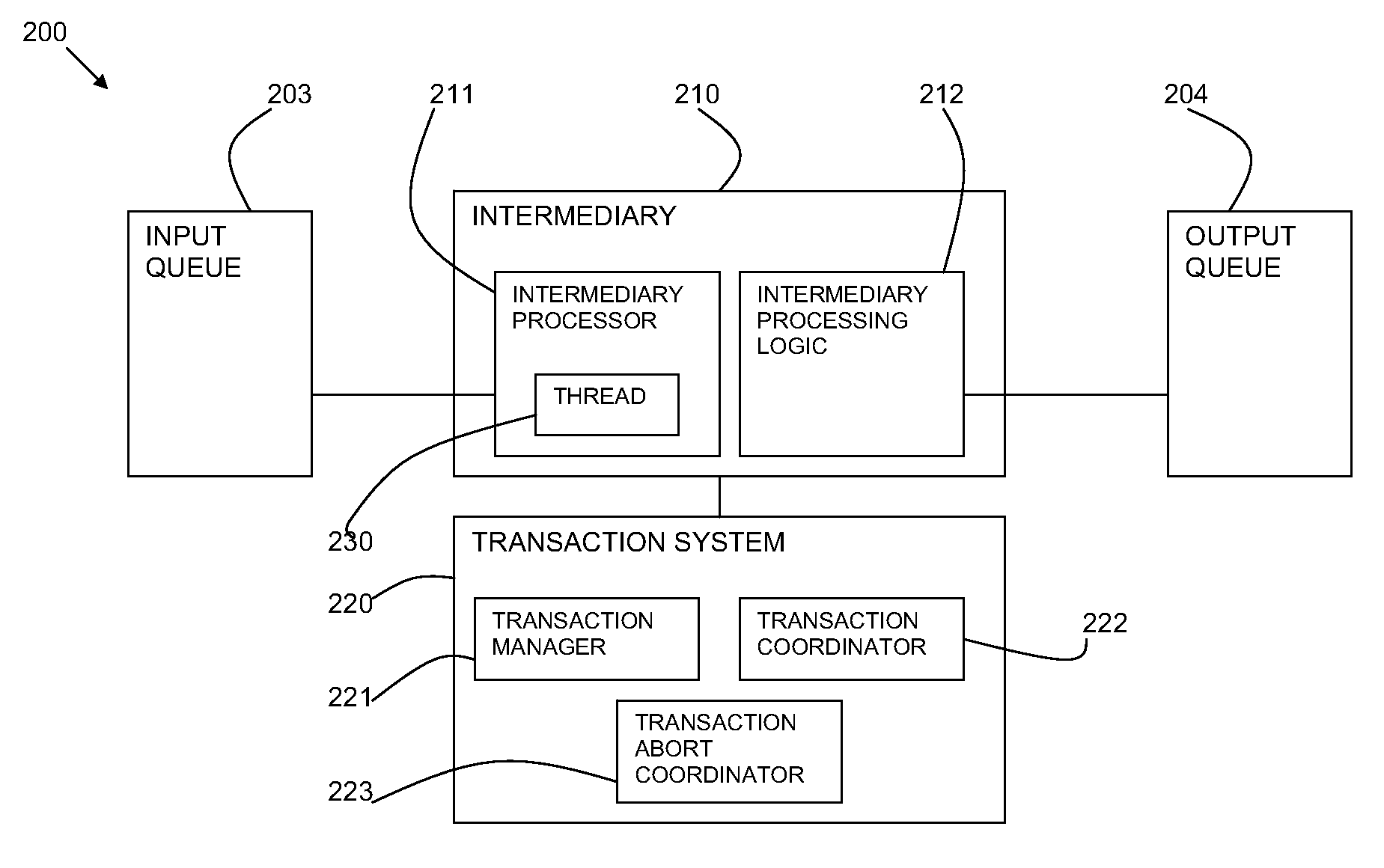

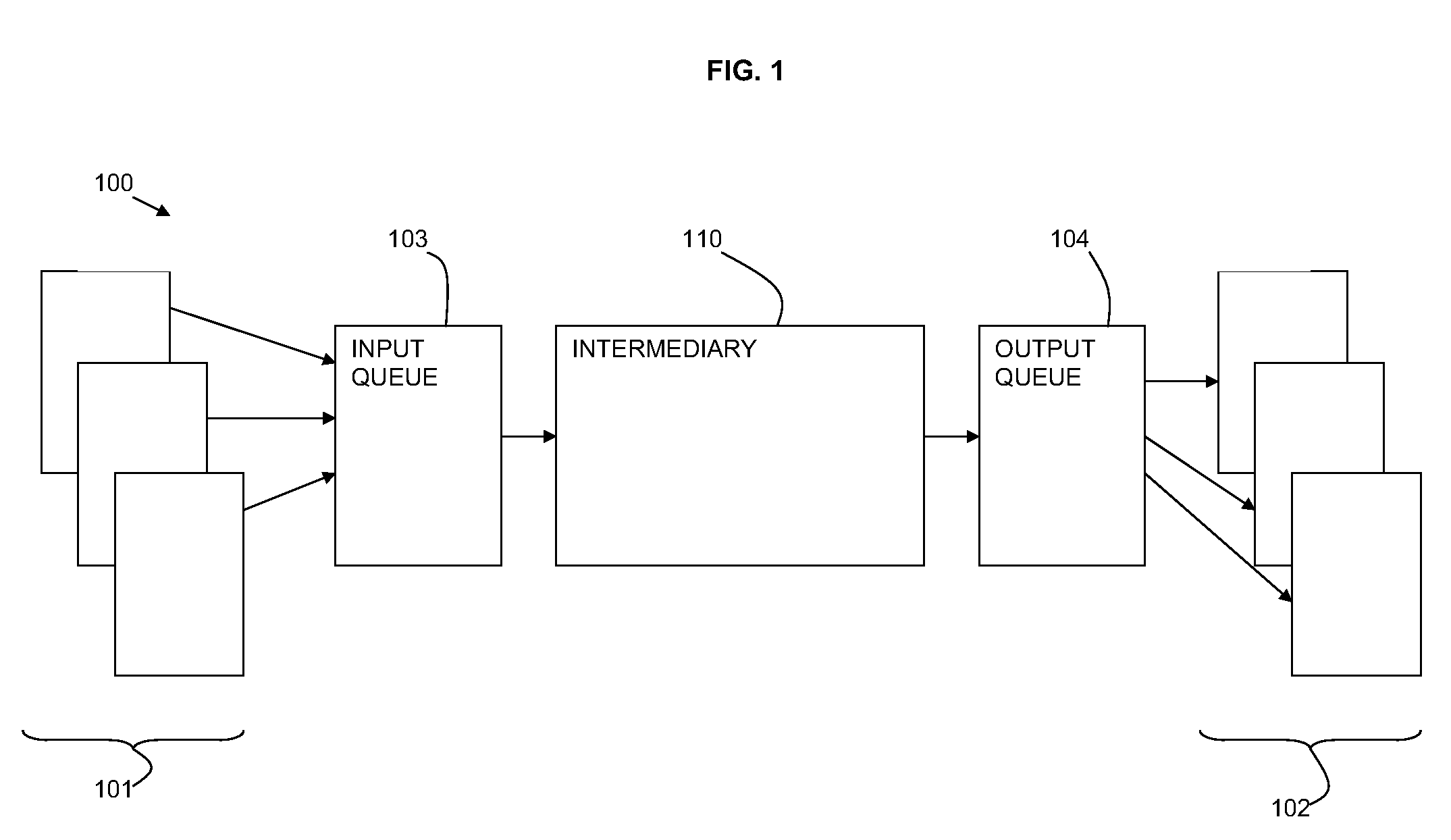

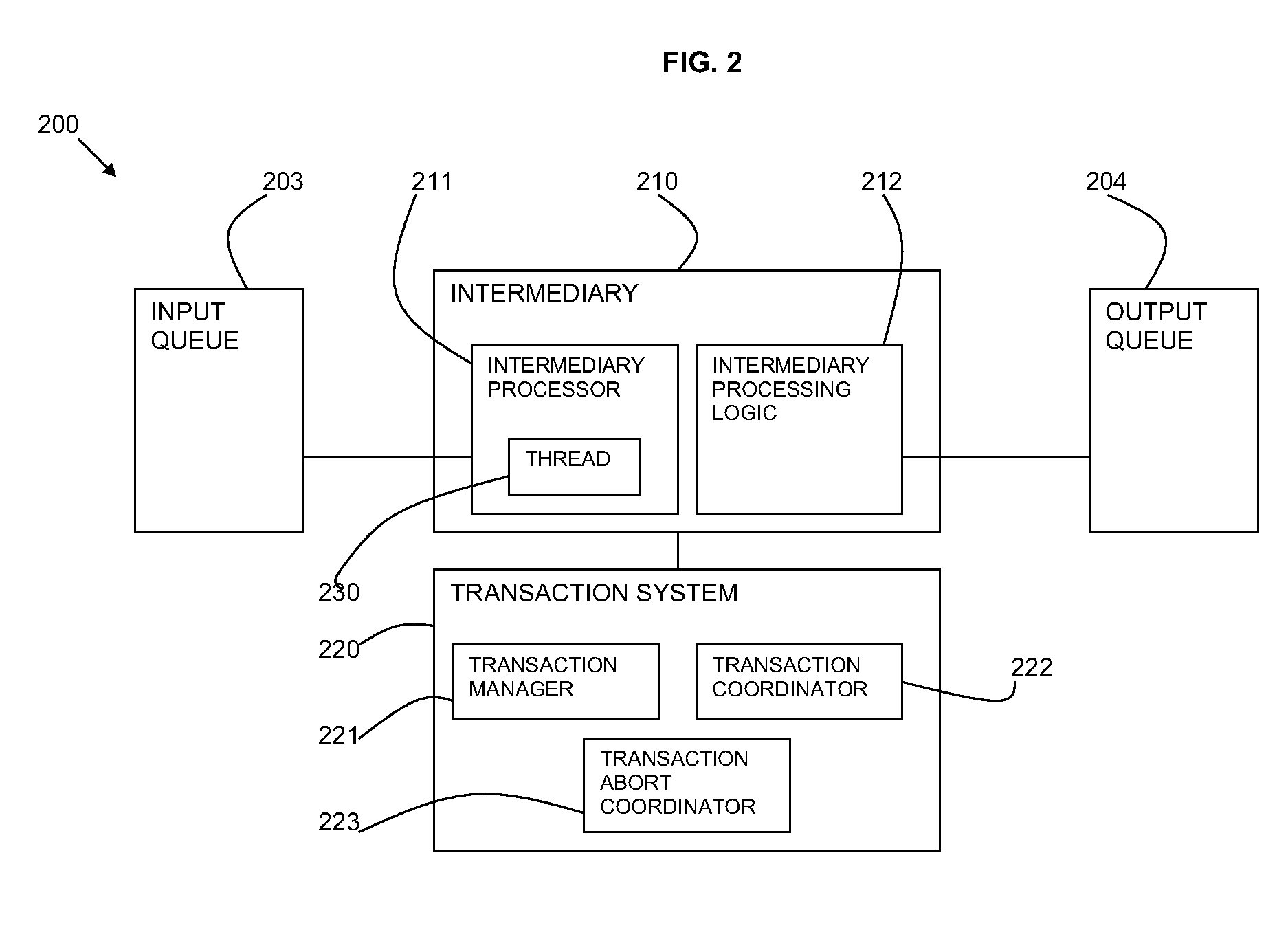

Method and System for Concurrent Message Processing

A method and system are provided for concurrent message processing. The system includes: an input queue capable of receiving multiple messages in a given order; an intermediary for processing the messages; and an output queue for releasing the messages from the intermediary. Means are provided for retrieving a message from an input queue for processing at the intermediary and starting a transaction under which the message is to be processed. The intermediate logic processes the transactions in parallel and a transaction management means ensures that the messages are released to the output queue in the order of the messages in the input queue.

Owner:IBM CORP

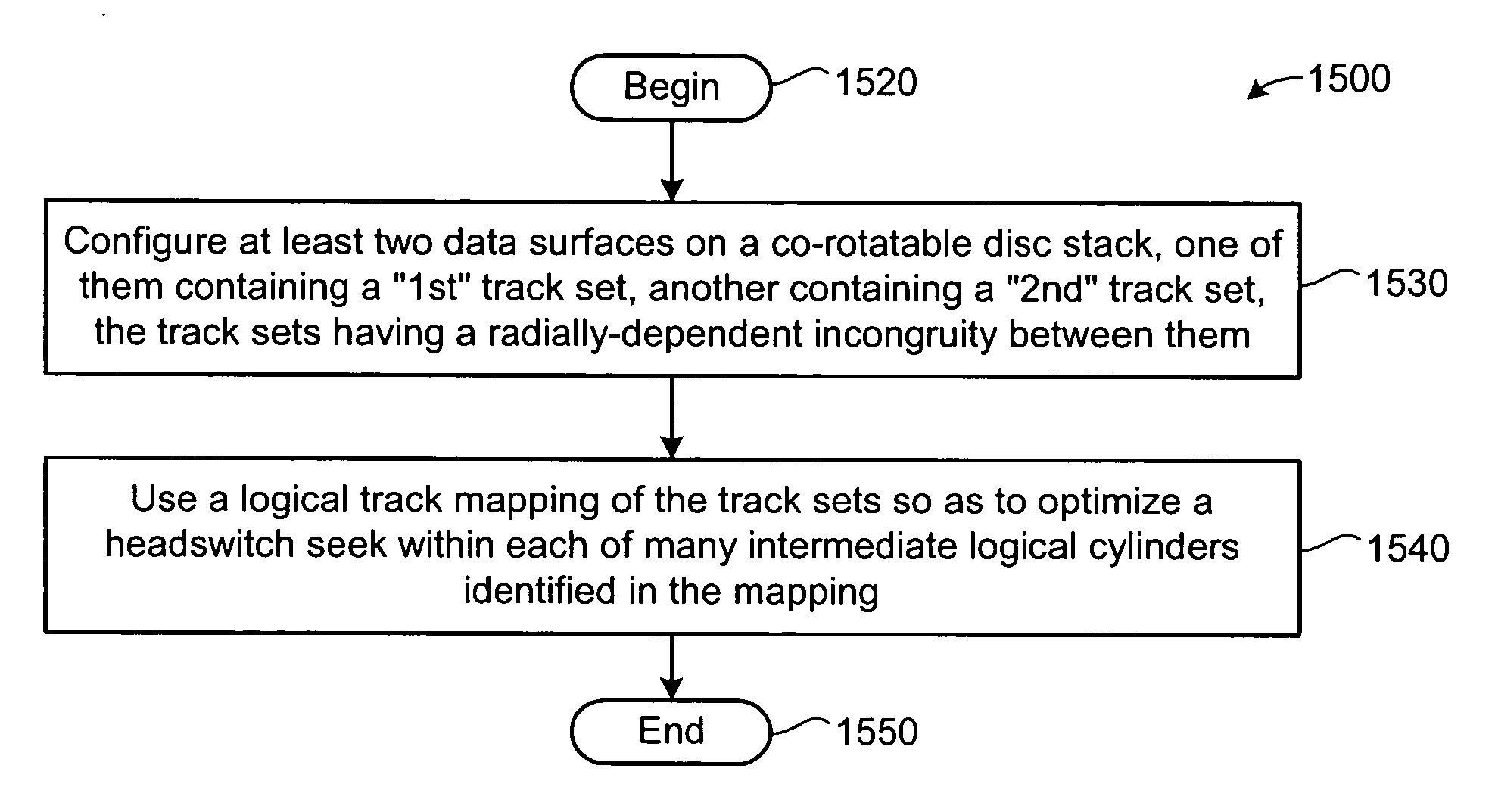

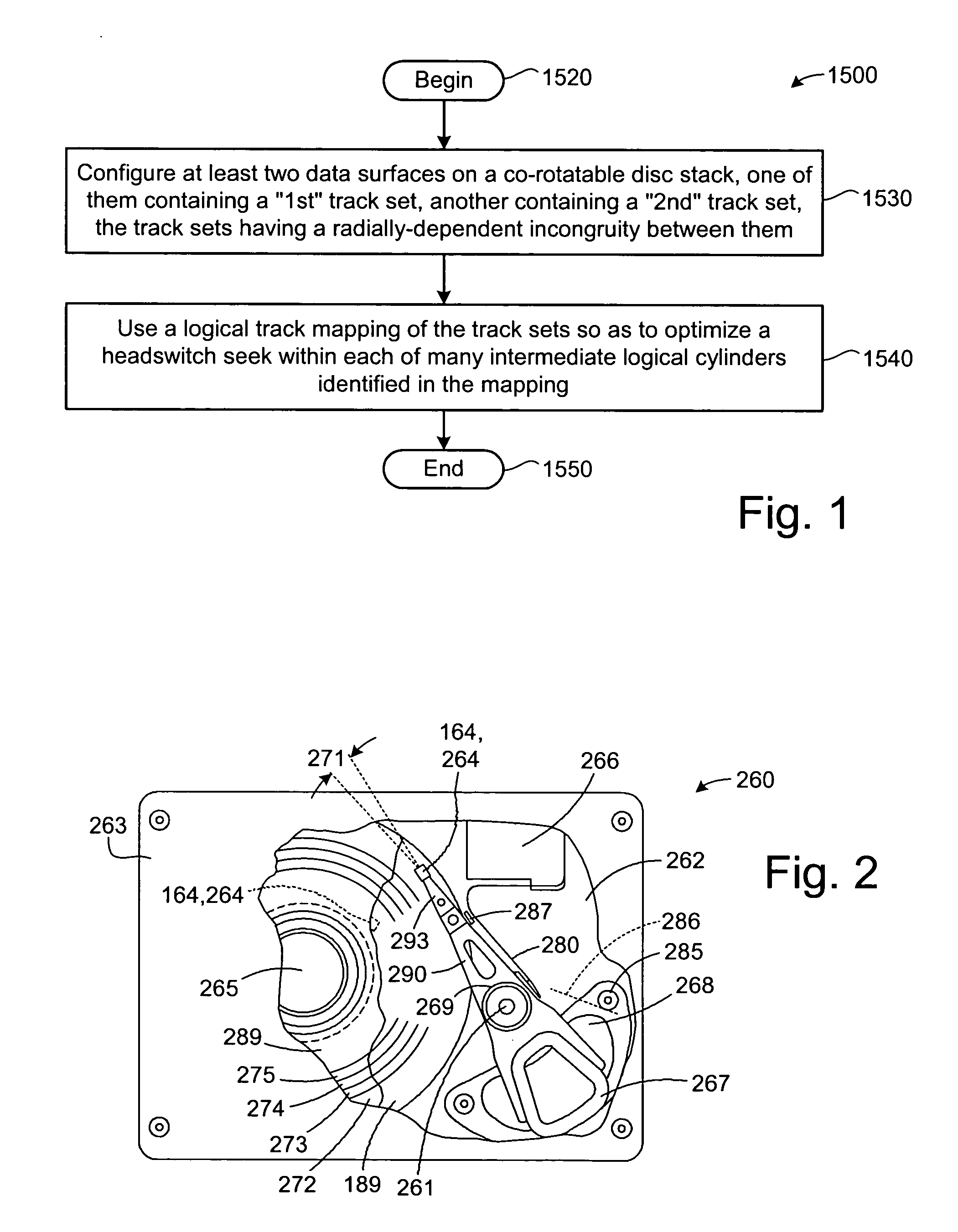

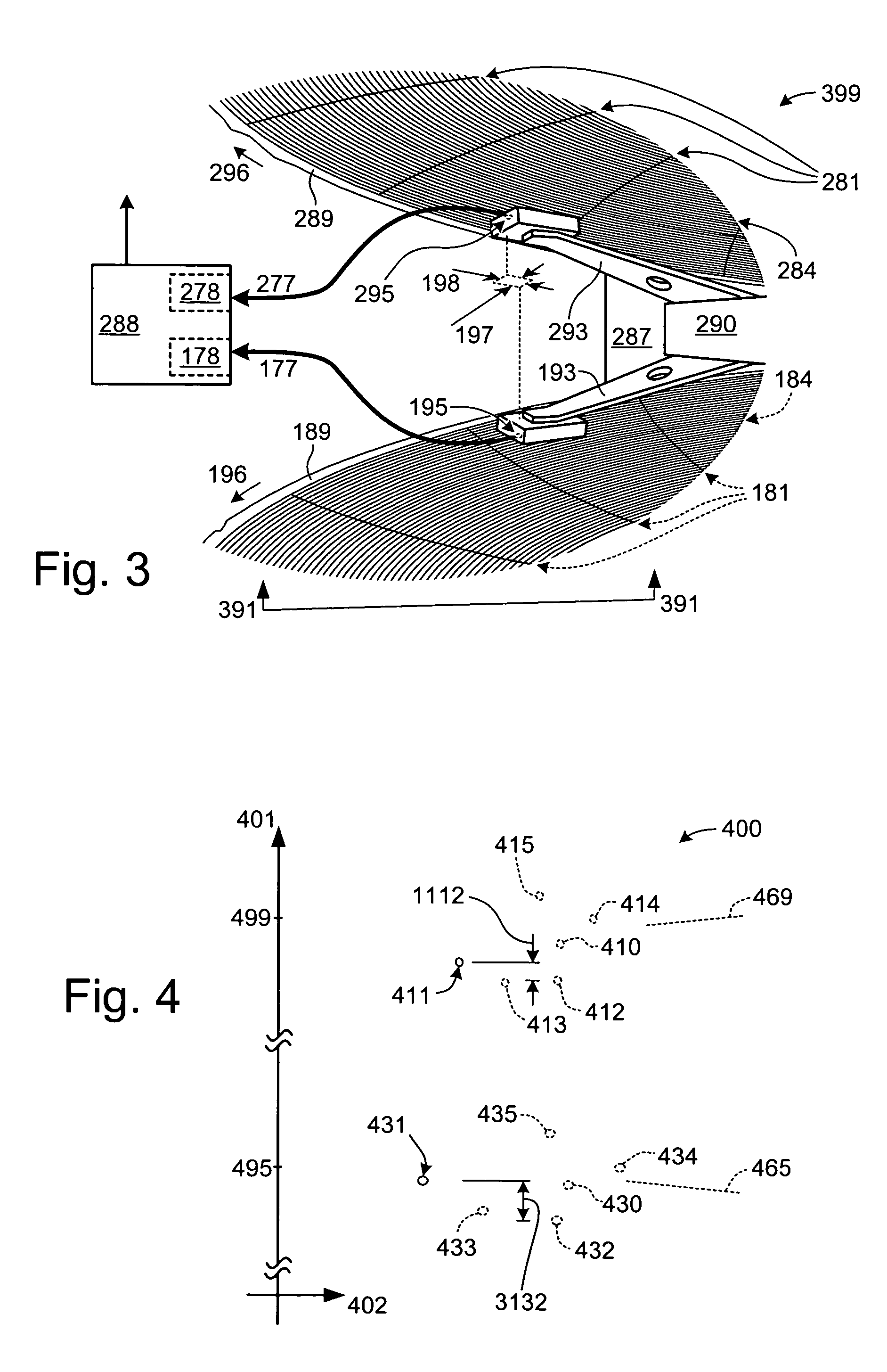

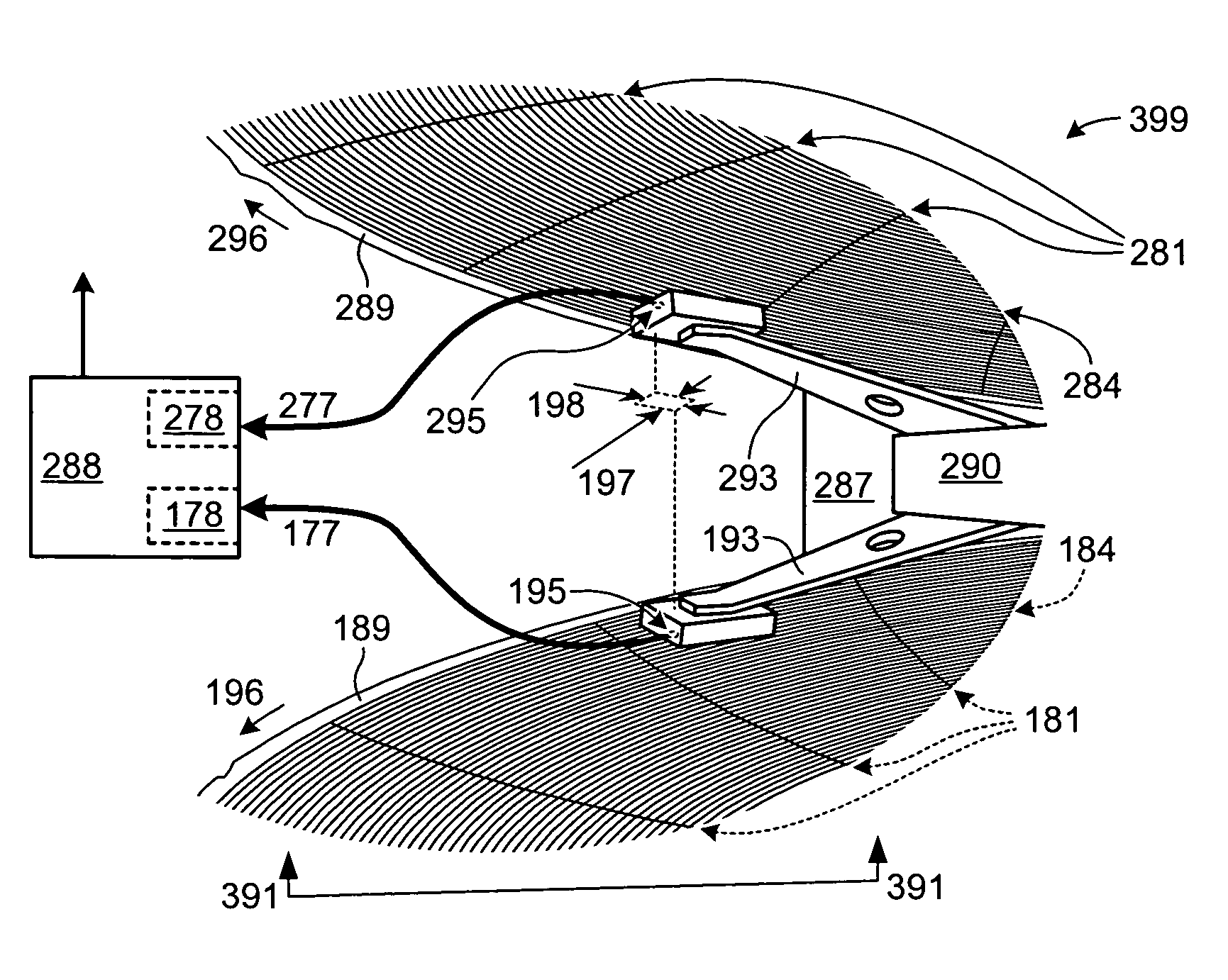

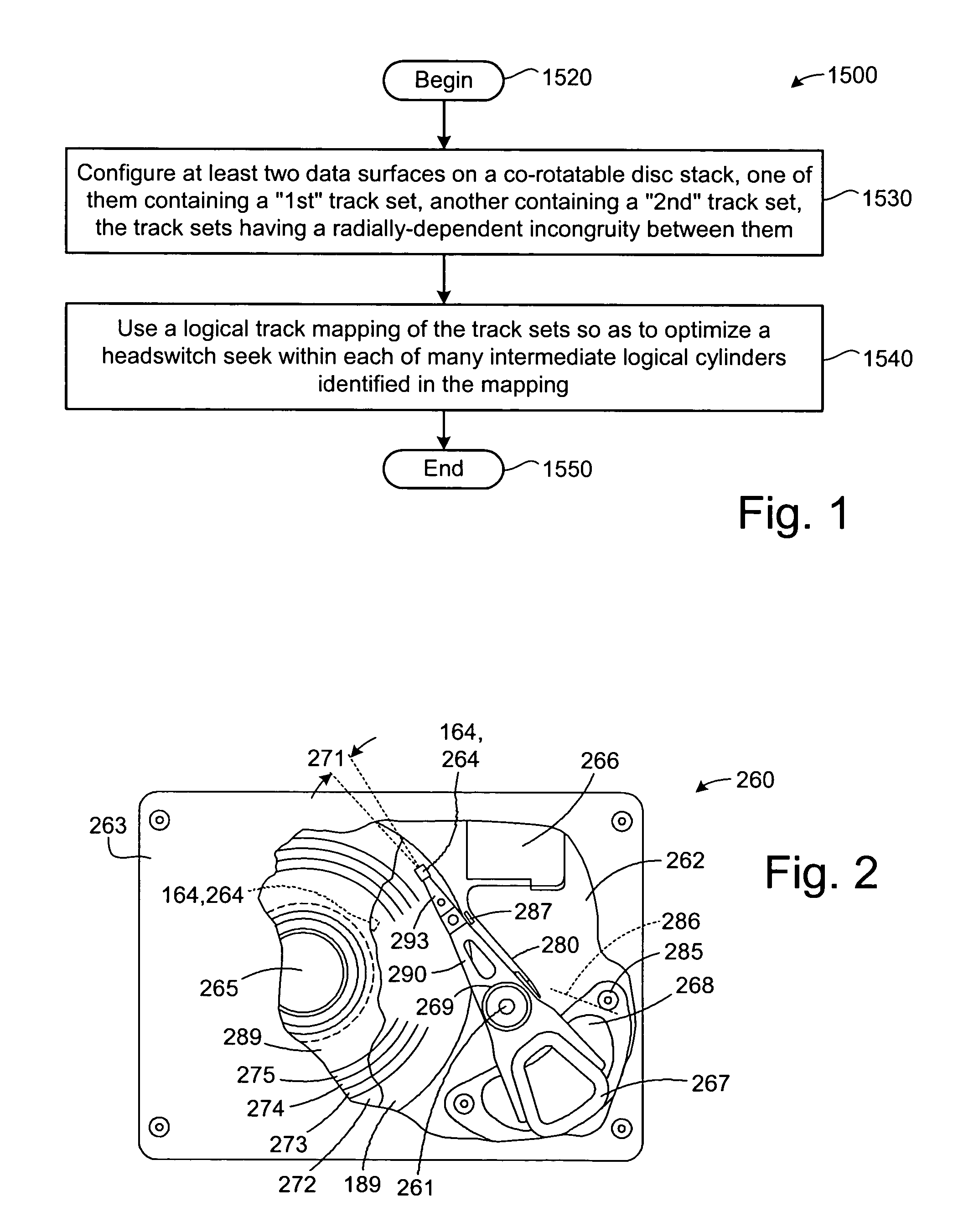

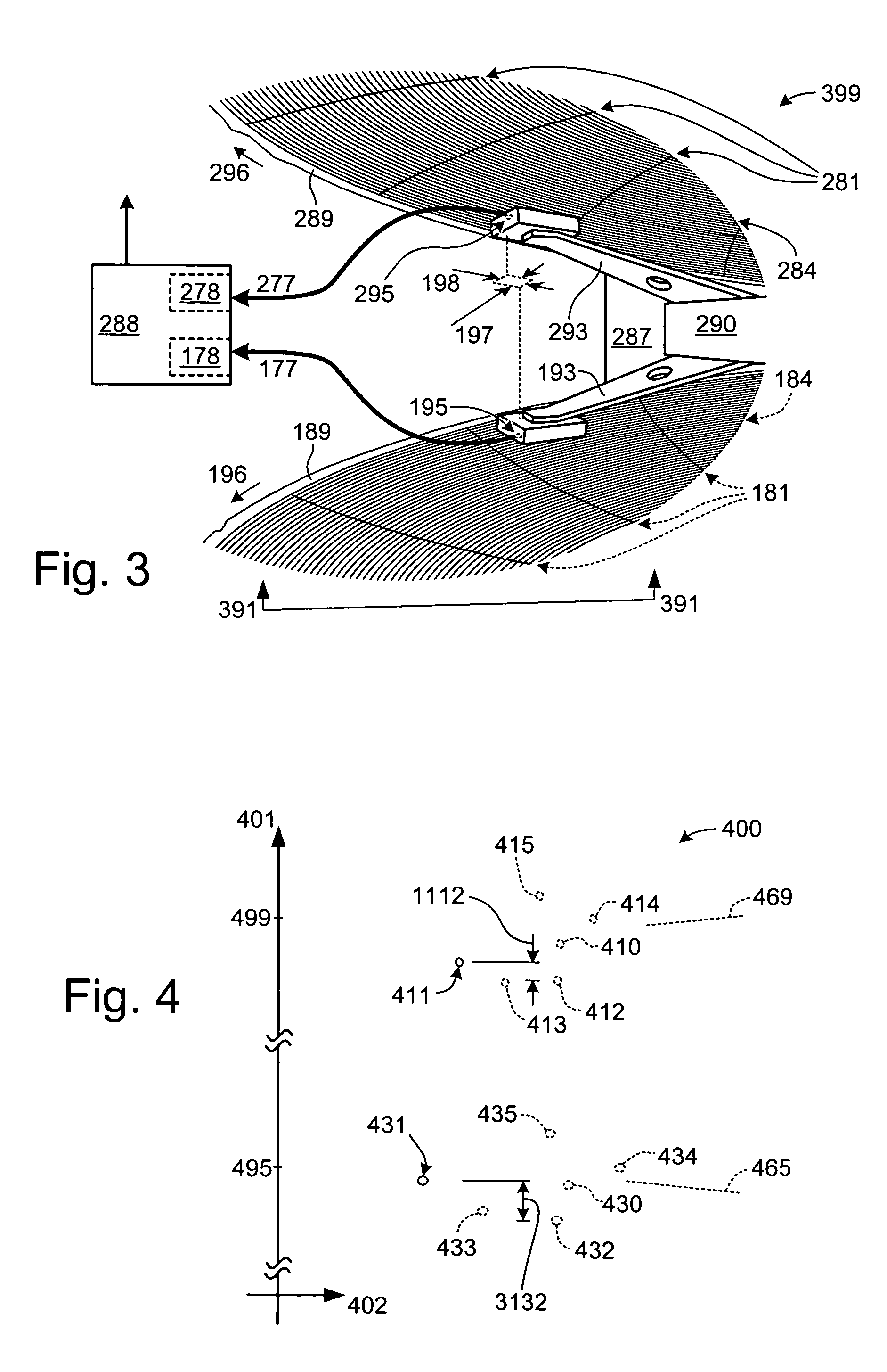

Logical mapping for improved head switching between corresponding tracks in a data handling device

InactiveUS20050078566A1Combination recordingDisposition/mounting of recording headsData processing systemTheoretical computer science

In a data handling system having a radially-dependent track incongruity between data surfaces, at least some tracks are logically mapped so that tracks on different data surfaces correspond with one another. The correspondence is defined by the mapping so as to shorten an average headswitch seek. For example, a logical track mapping of first and second non-coaxial track sets can be defined so as to optimize a headswitch seek within each of many intermediate logical cylinders identified in the mapping.

Owner:SEAGATE TECH LLC

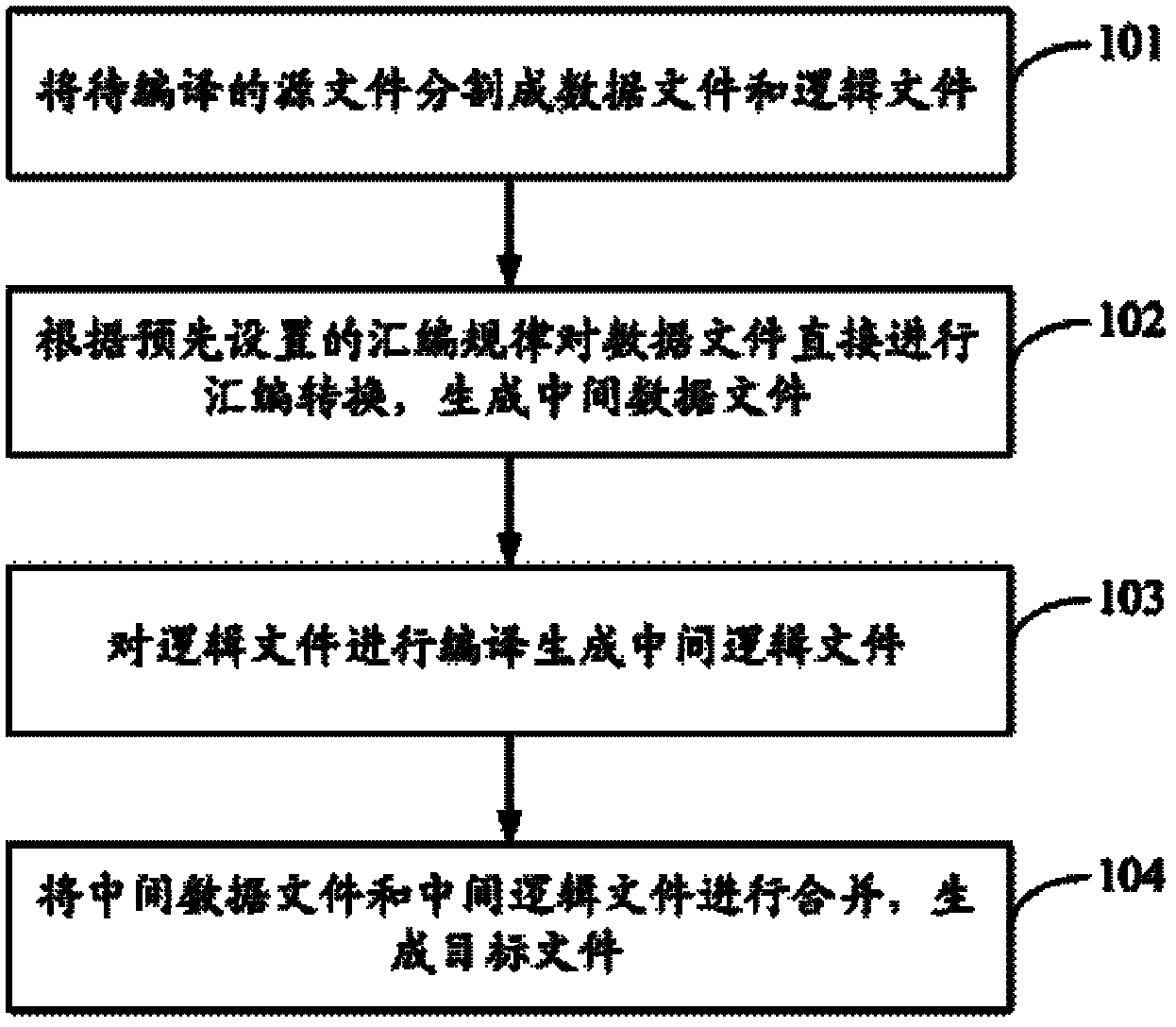

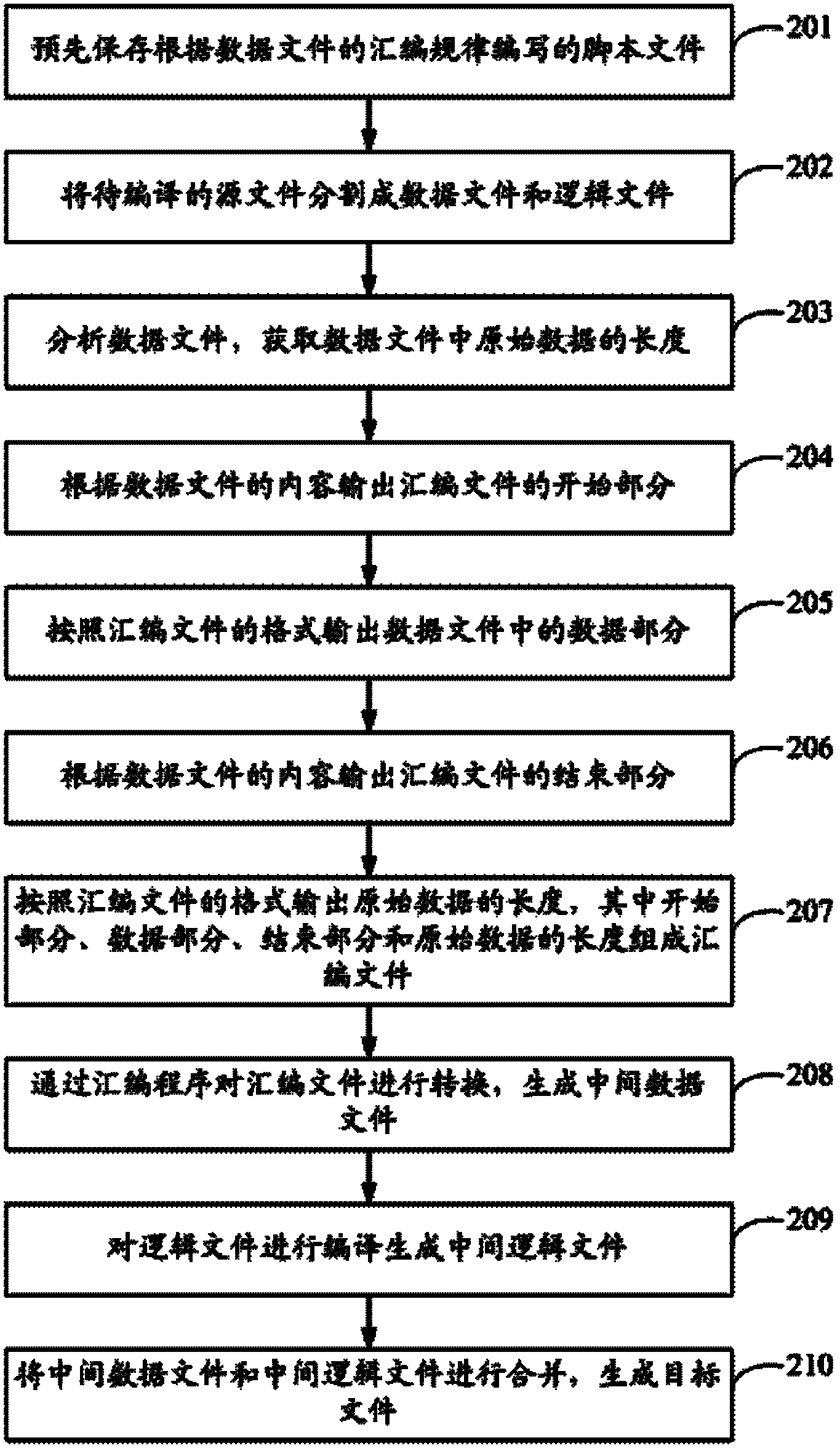

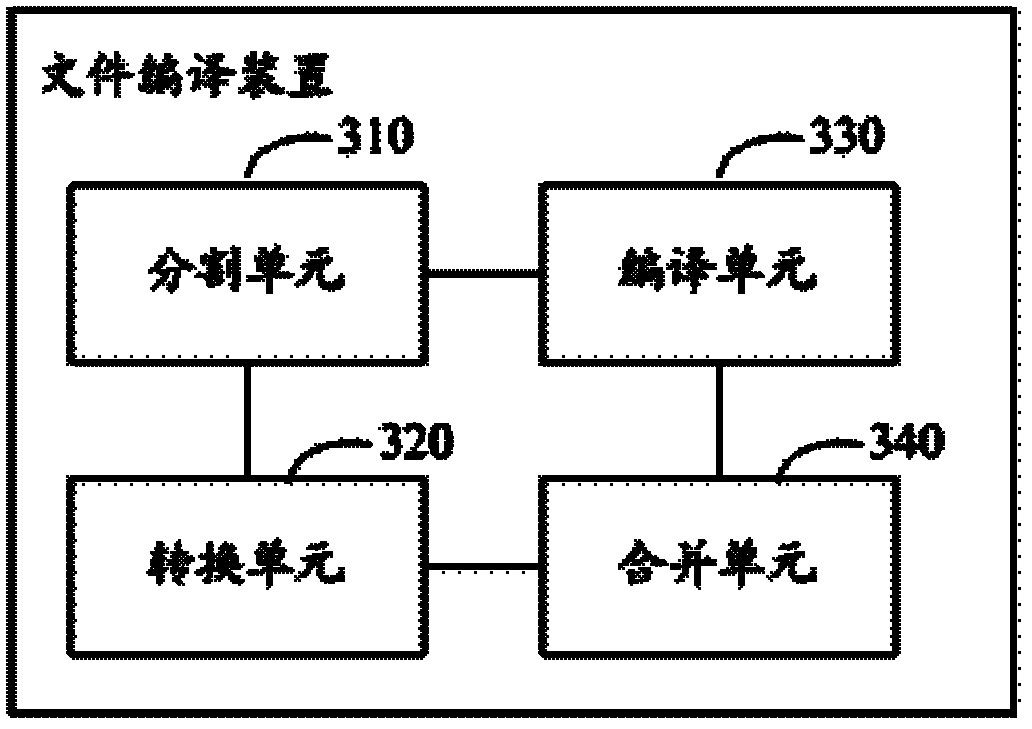

File compiling method and device

InactiveCN102207884AShorten the timeHigh speedProgram controlMemory systemsData fileIntermediate logic

The embodiment of the invention discloses a file compiling method and device. The method comprises the following steps: splitting a source file to be compiled into a data file and a logic file; directly assembling and transforming the data file according to a preset assembling rule to generate an intermediate data file; compiling the logic file to generate an intermediate logic file; and combining the intermediate data file with the intermediate logic file to obtain a target file. According to the embodiment of the invention, the file compiling method can improve the target file generation speed because the data file can be directly transformed according to the preset assembling rule rather than directly compiling the data file, thereby saving the time as well as the system resources consumed by compiling the large amount of data files.

Owner:SHENZHEN IPANEL TECH LTD

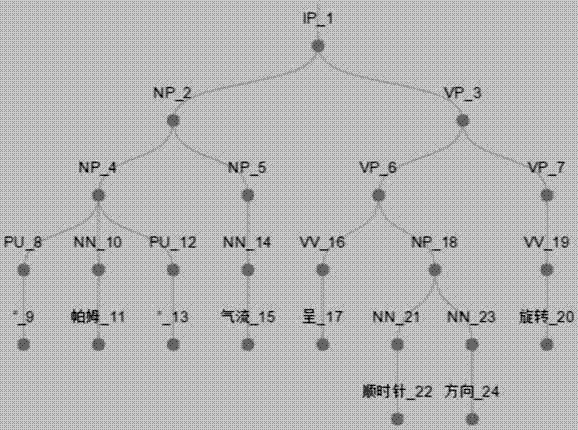

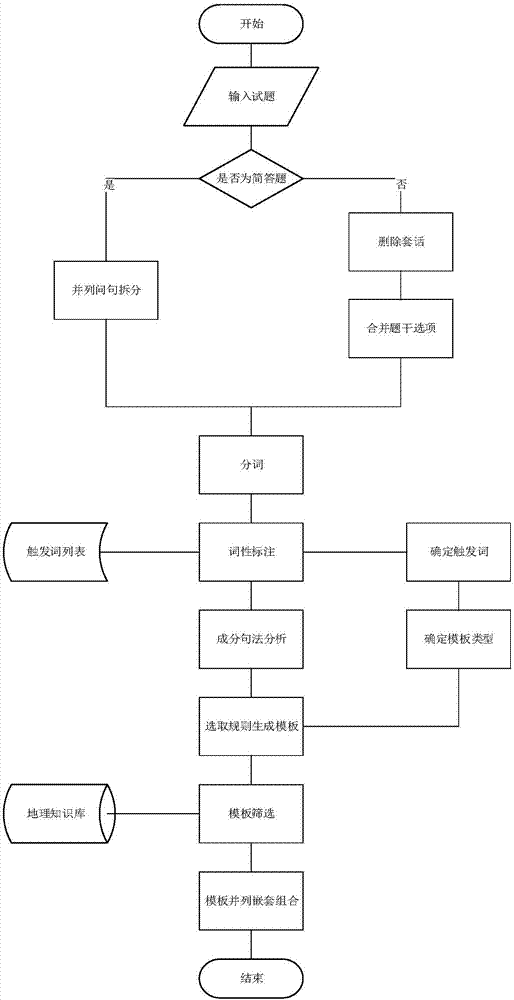

Method for understanding questions in question type automatic question-answer systems on basis of rule

ActiveCN107193798AImprove efficiencyImprove accuracyNatural language data processingSpecial data processing applicationsTemplate basedIntermediate form

The invention discloses a method for understanding questions in question type automatic question-answer systems on the basis of a rule. The method comprises the following steps of: regular expression-based question preprocessing: deleting useless texts such as polite formulas and the like, adding omitted punctuations, completing sentences, and carrying out basic natural language processing such as word segmentation, part of speech tagging and component syntax analysis on the completed sentences; designing a set of type-argument template-based question understanding intermediate forms, and applying a trigger word and a question template conversion rule summarized through manually pre-tagged data; and further verifying the generation result by utilizing a knowledge base so as to obtain a reasonable and complete question logic expression. According to the method, key points of questions can be extracted aiming at intermediate logic forms in question text design, so that proper input is reasonably and effectively provided for the question solution and then the question answering correctness is improved.

Owner:NANJING UNIV

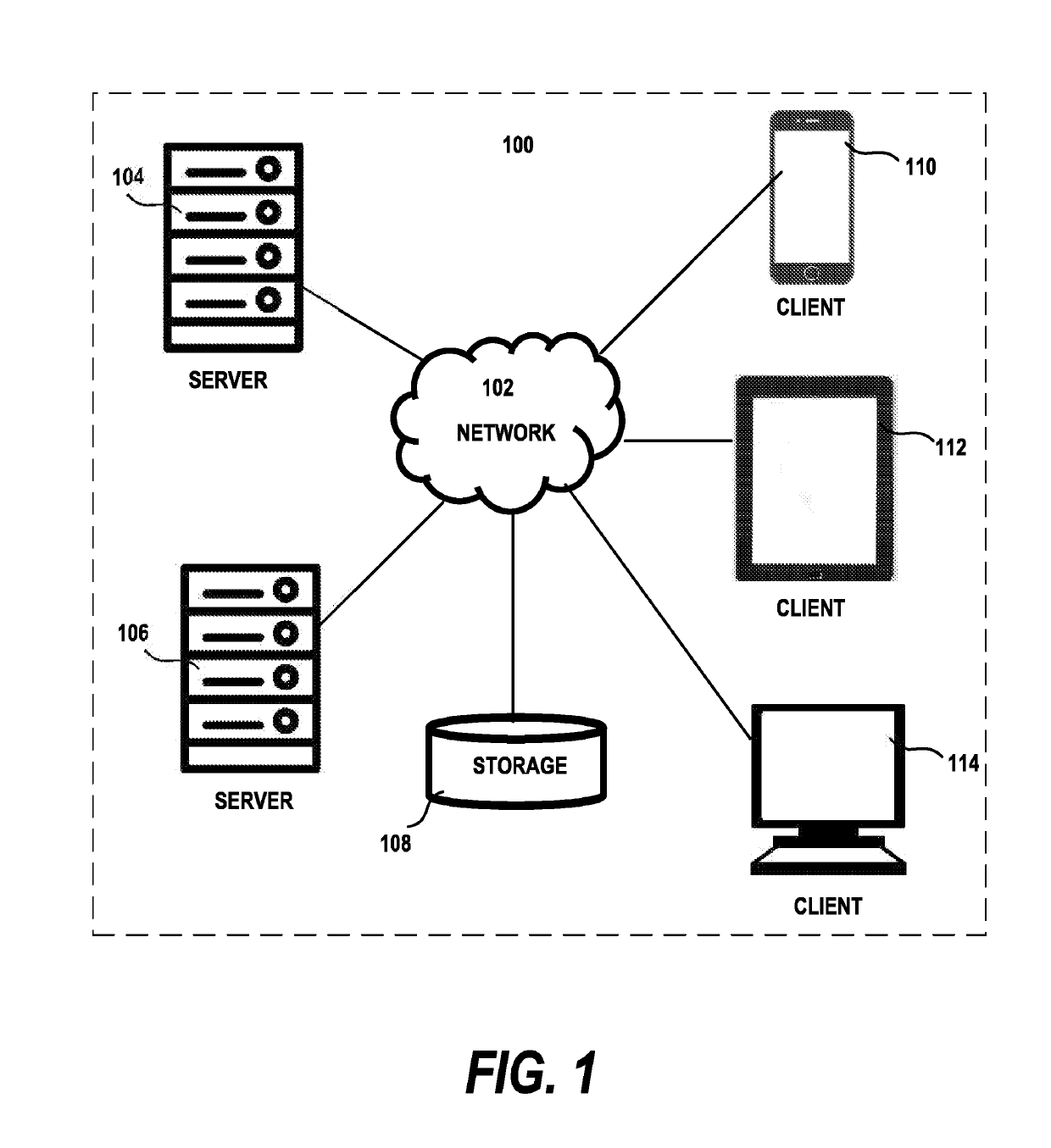

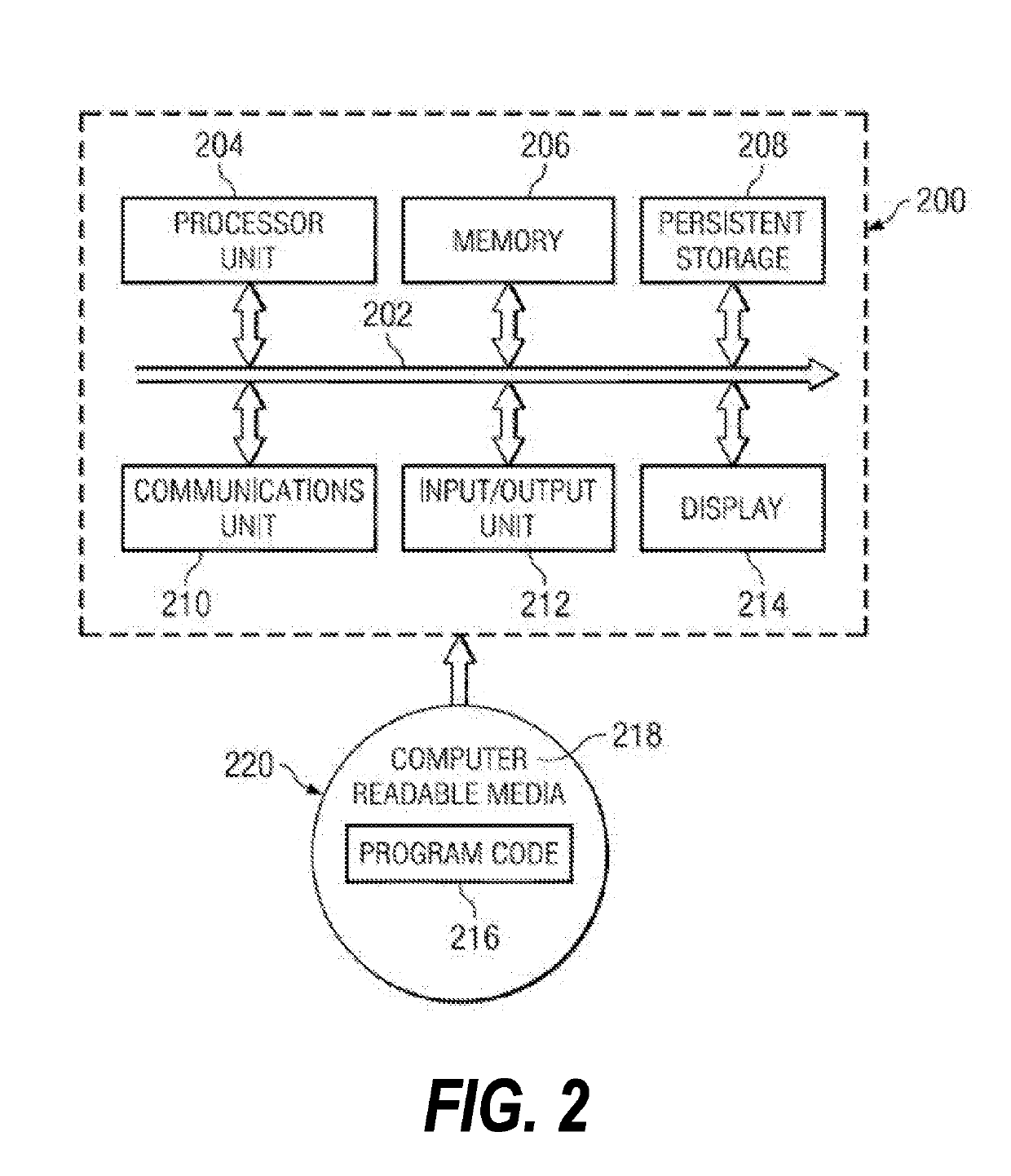

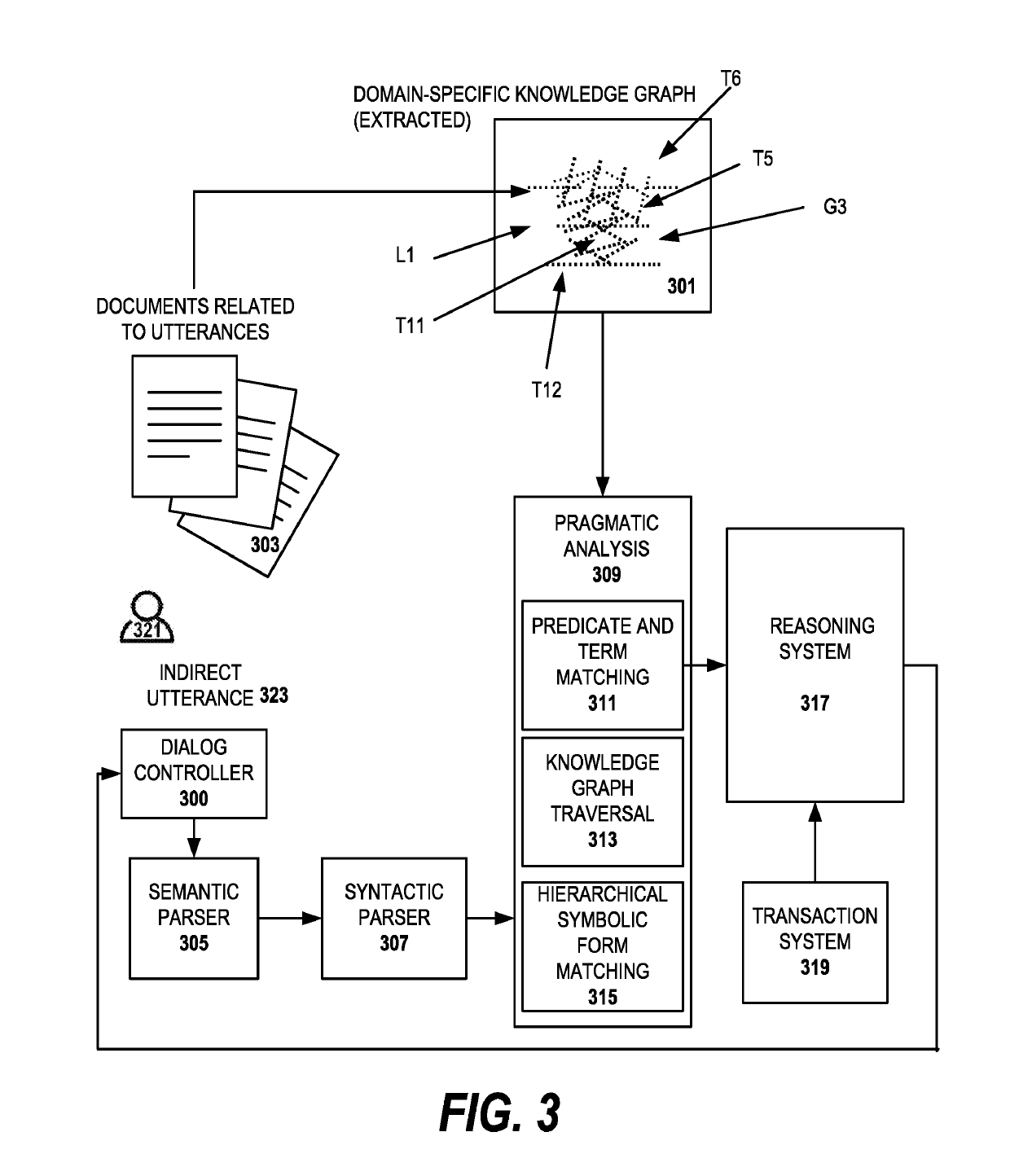

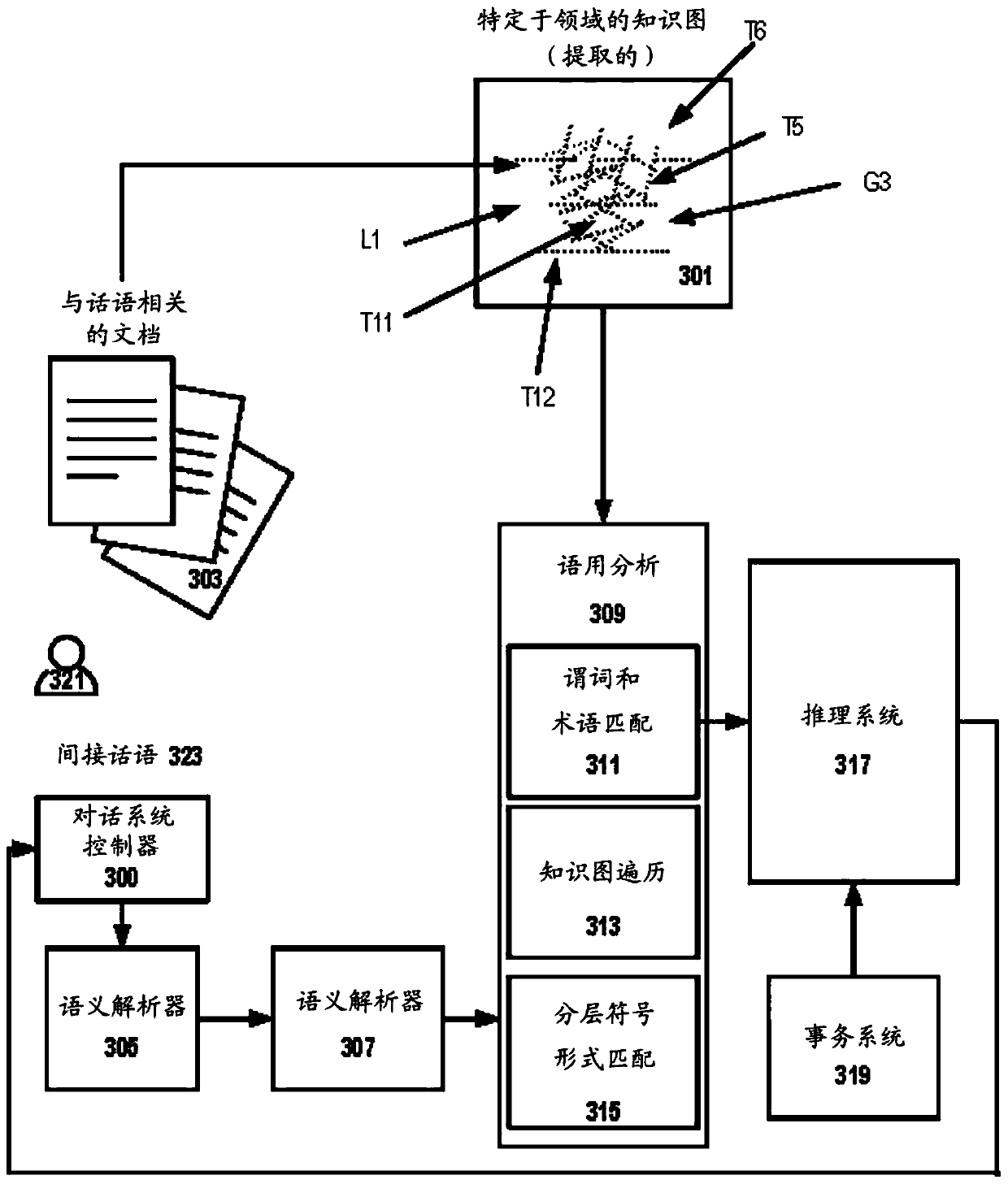

Establishing a logical connection between an indirect utterance and a transaction

A method, apparatus and computer program product for establishing a logical connection between an indirect utterance and a transaction is described. An indirect utterance is received from a user as an input to a conversational system. The indirect utterance is parsed to a first logical form. A first set of predicates and terms is mapped from the first logical form to a first subgraph in a knowledge graph. A second set of predicates and terms is mapped from a second logical form belonging to a transaction to a second subgraph of the knowledge graph. A best path in the knowledge graph between the first subgraph and the second subgraph is searched for while transforming the first logical form using the node and edge labels along the best path to generate an intermediate logical form. A system action is performed for a transaction if a graph structure of the intermediate logical form matches the graph structure of the logical form of the transaction above a threshold.

Owner:IBM CORP

Circuit and method for implementing a write operation with tcct-based memory cells

The present invention provides a circuit and a method for providing nondestructive write operations and optimized memory access operations with reduced power consumption during memory access, such as during write operations. In one embodiment, a memory device comprises a memory cell configured to store a first data bit. The memory device also comprises a write access circuit coupled to the memory cell for providing a write data bit having a write data bit magnitude. The write access circuit is configured to adjust the write data bit magnitude to an intermediate logic state magnitude in a memory operation.

Owner:MICRON TECH INC +1

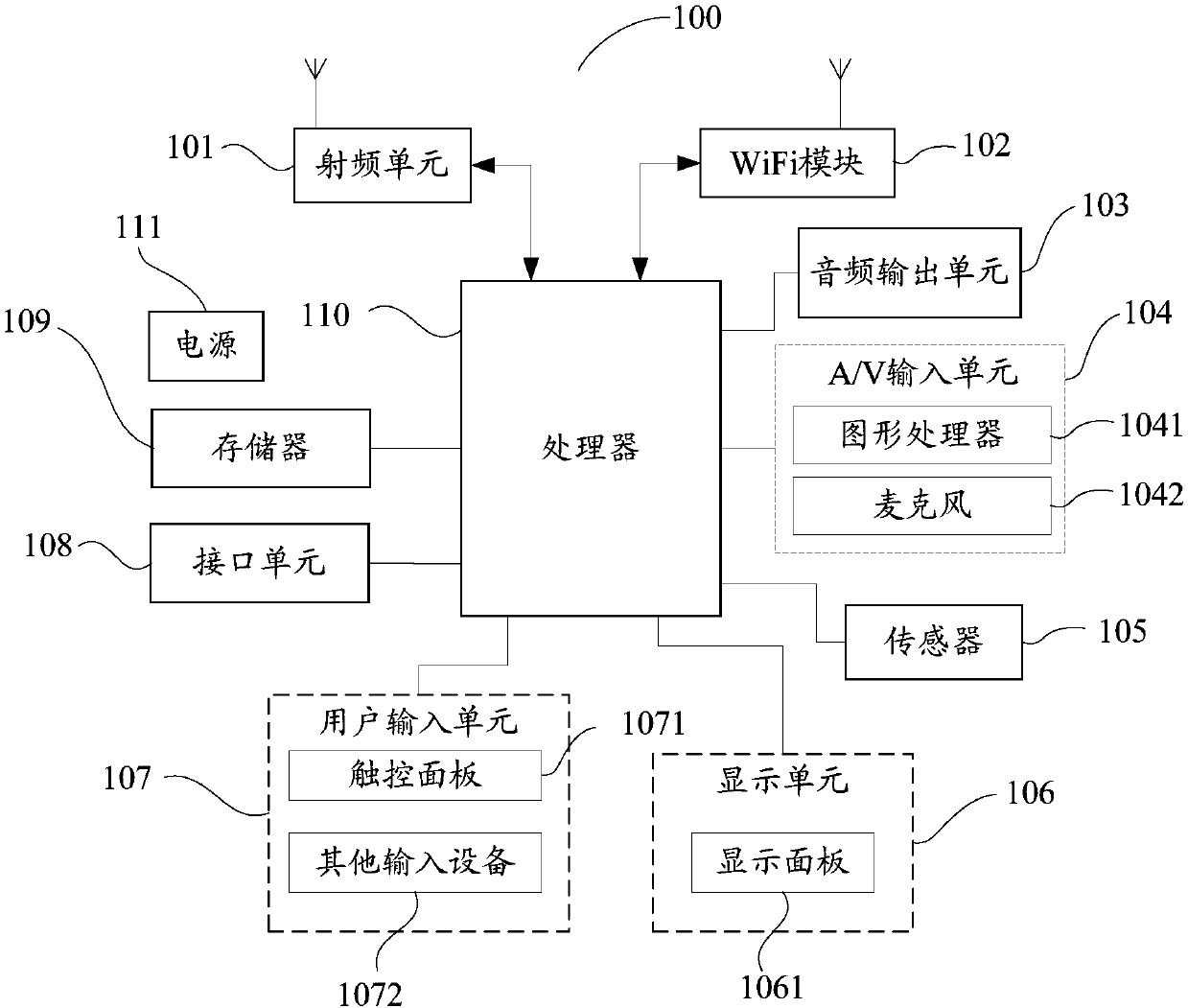

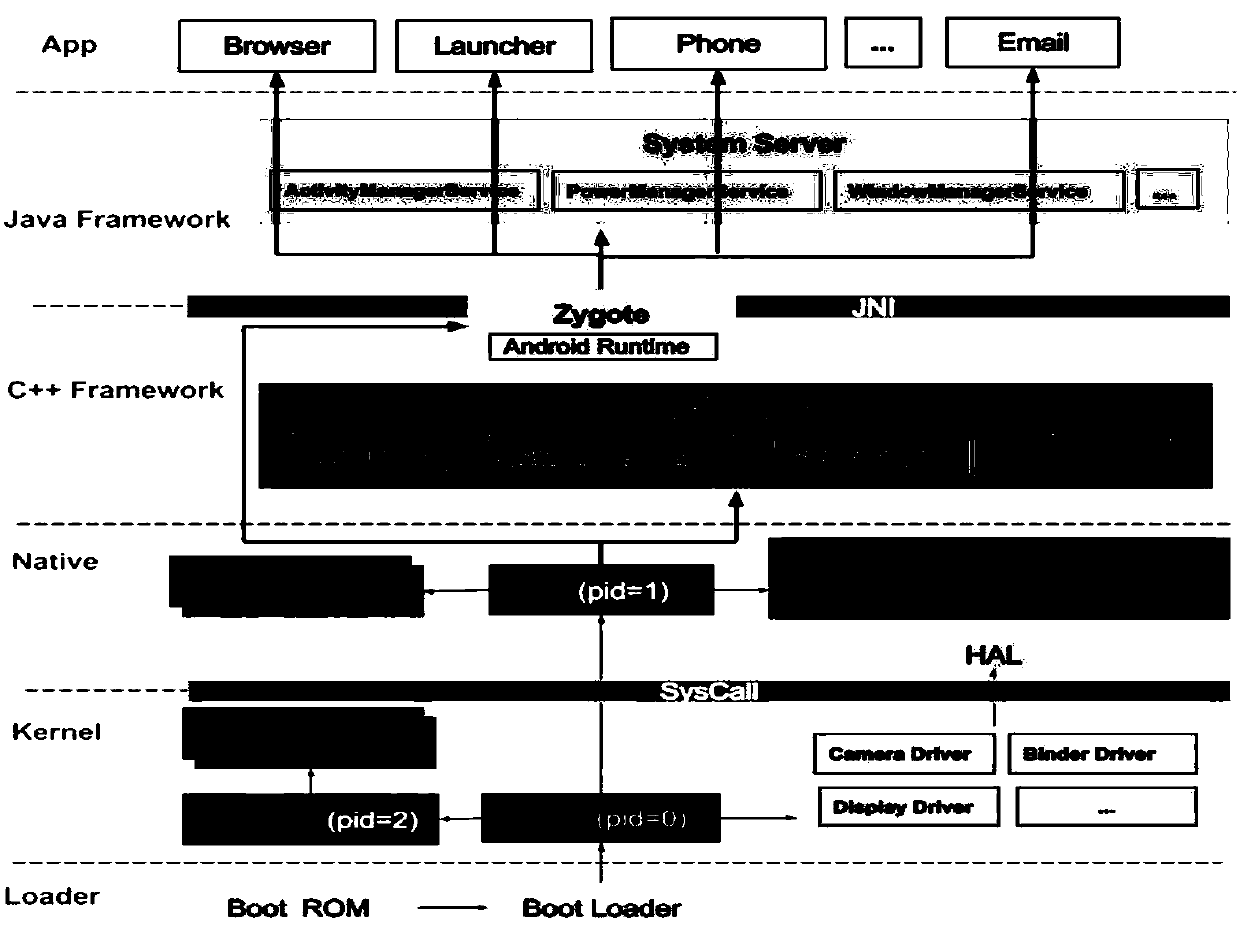

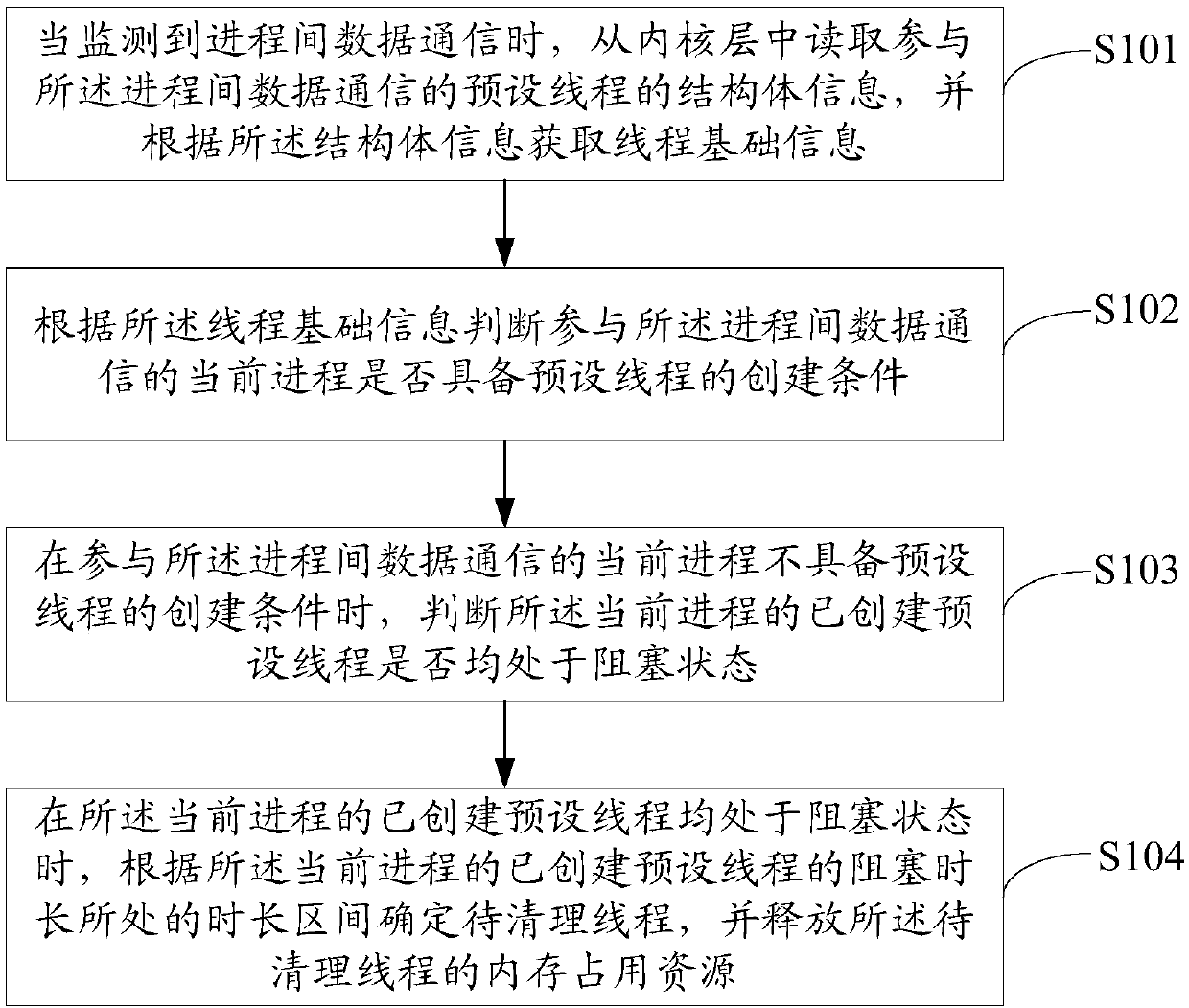

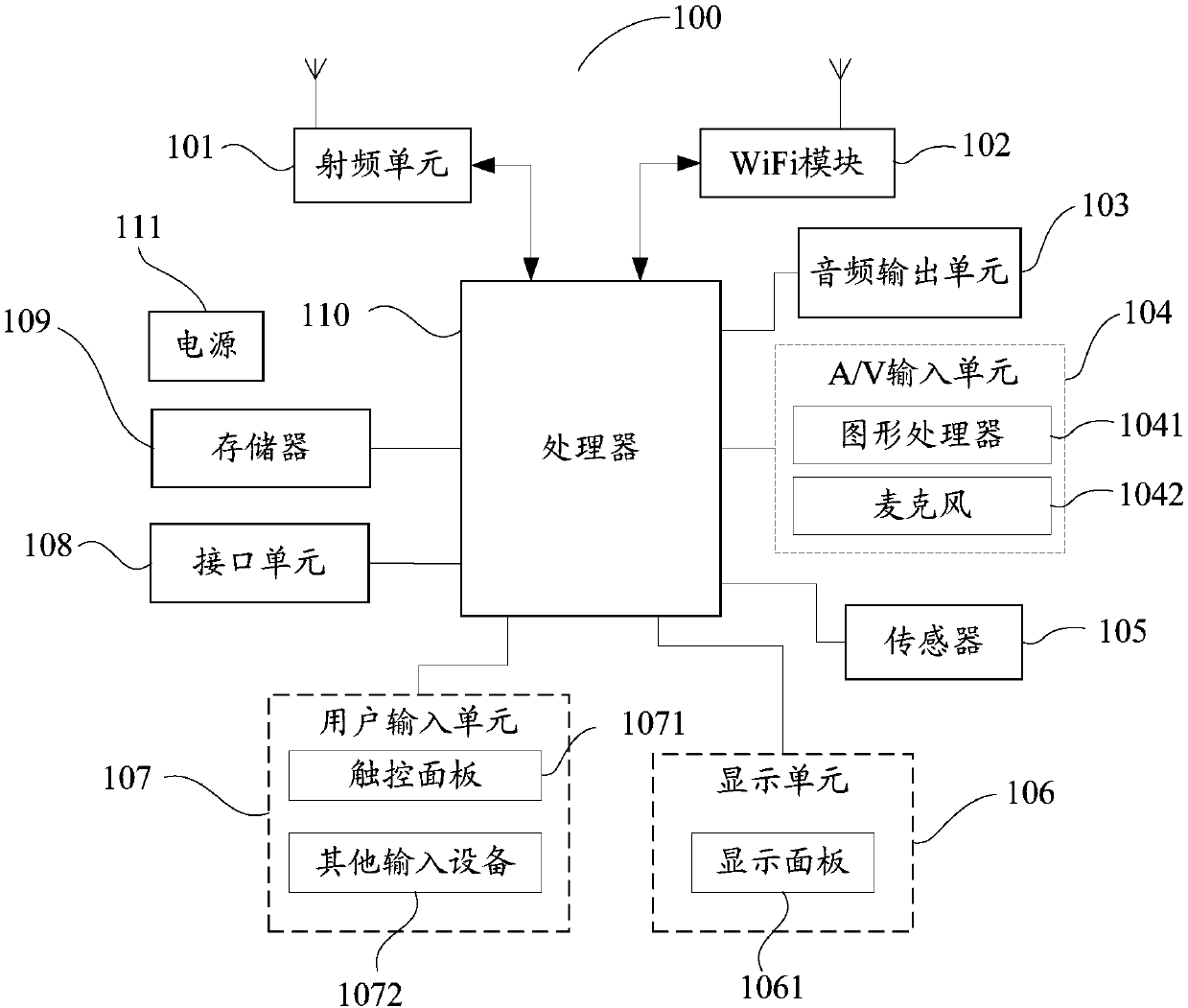

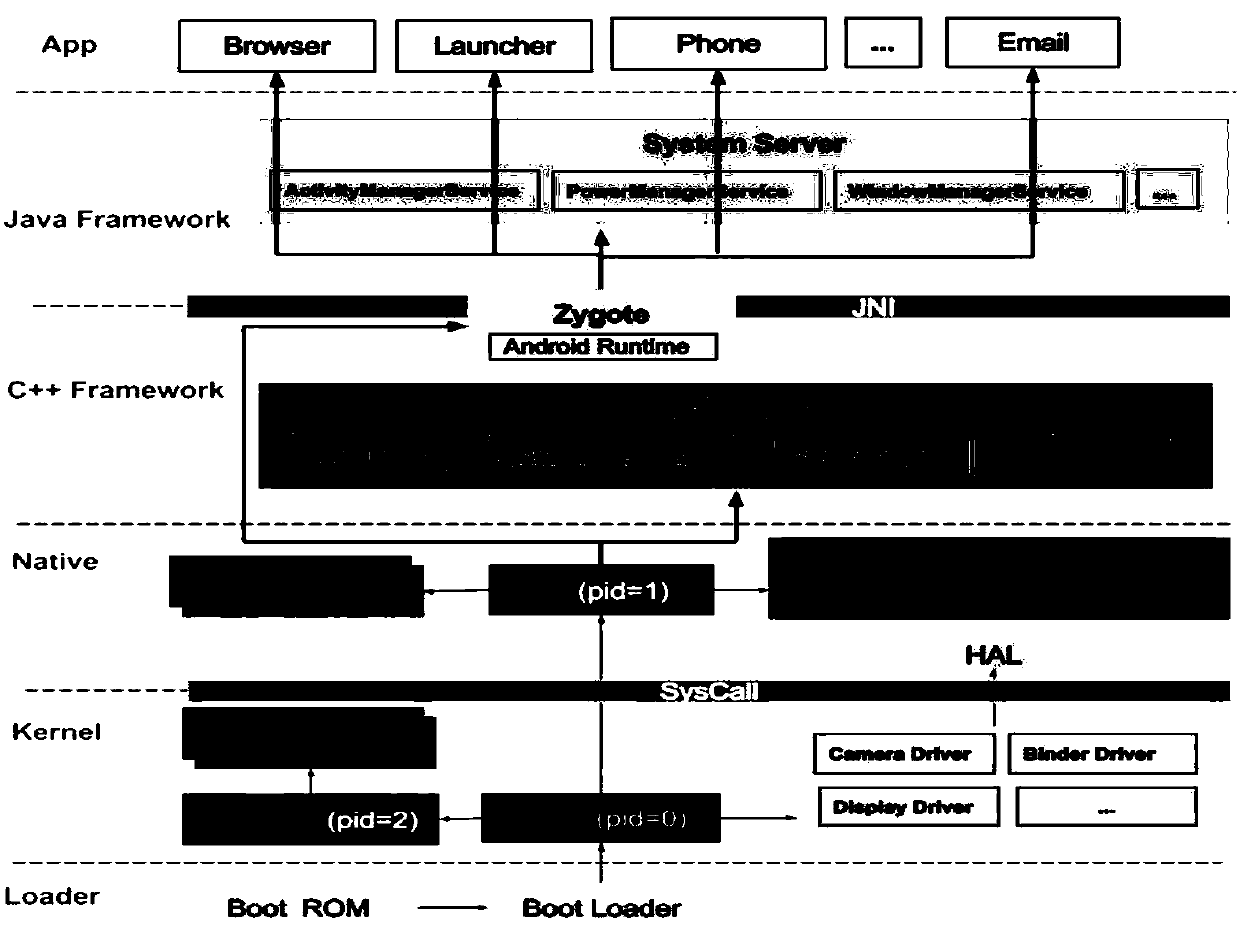

Memory optimization method based on thread blocking, mobile terminal and readable storage medium

ActiveCN107861817AReduce intermediate logic callsAvoid frequent freezesResource allocationInterprogram communicationMemory footprintIntermediate logic

The invention discloses a memory optimization method based on thread blocking, a mobile terminal and a readable storage medium. The method comprises the steps of directly obtaining thread basic information of a preset thread participating in inter-process data communication from a core layer when inter-process data communication is monitored, reducing intermediate logic calling, and quickly obtaining the thread basic information; meanwhile, judging whether the current progress satisfies an establishing condition of the preset thread or not based on the thread basic information, conducting blocking judgment according to the preset thread which is already created in the current progress, when the current progress does not satisfy the establishing condition of the preset thread and the presetthread which is already created is currently in a blocking state, to-be-cleaned progresses are determined according to the blocking duration of the preset thread which is already created, the memoryoccupation resource of the to-be-cleaned thread is released, thus when the preset thread (Binder thread) is clogged, the memory is automatically cleaned, abundant memory is reserved, and the system isprevented from being frequently stuck.

Owner:NUBIA TECHNOLOGY CO LTD

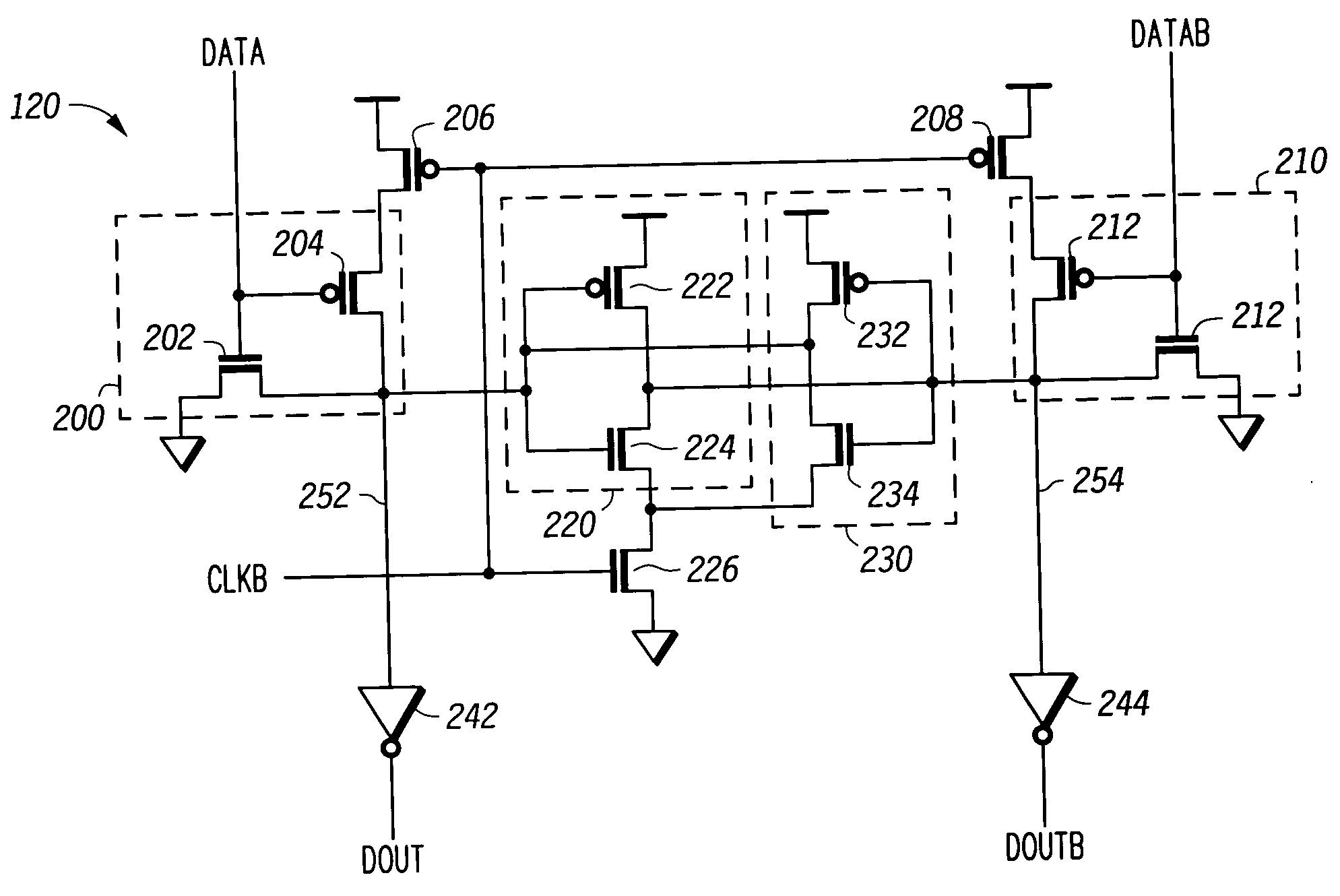

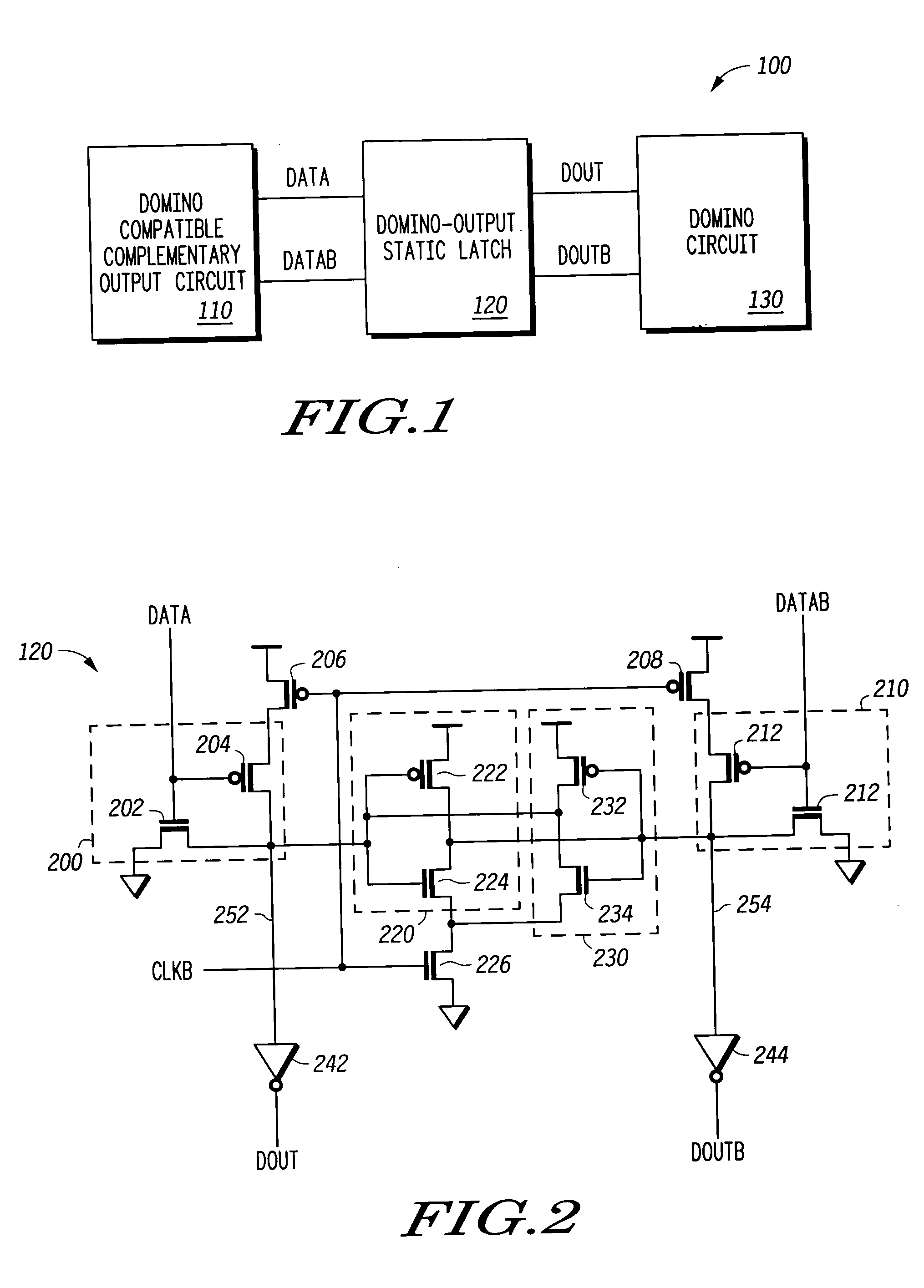

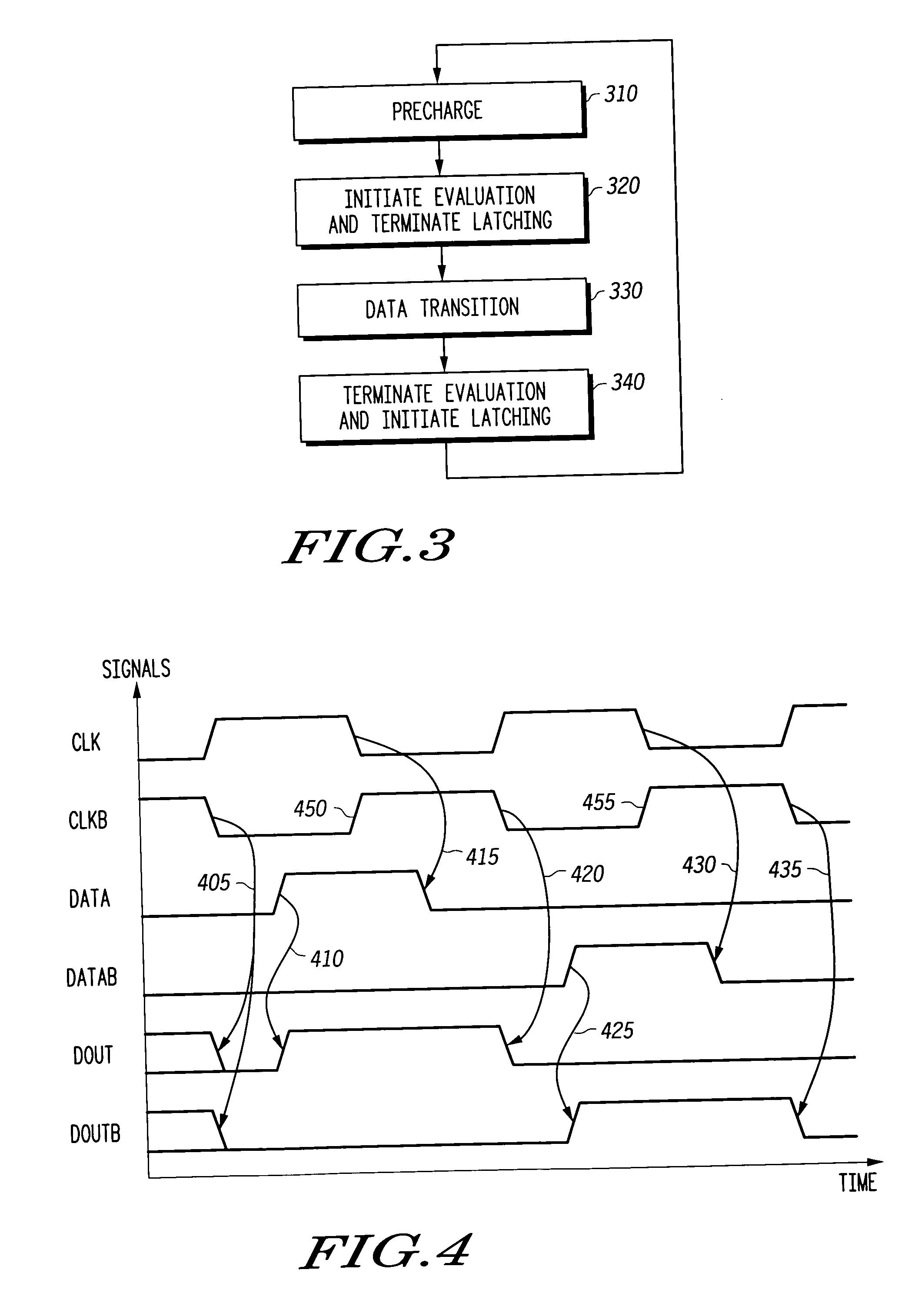

Domino circuitry compatible static latch

A circuit provides latched data in a domino circuit environment. The circuit receives a pair of input signals that are either in complementary logic states, which is data, or in the same logic state, which is the reset condition. The circuit responds to the complementary logic states by providing intermediate signals and output signals in corresponding complementary logic states. The intermediate logic states are latched by cross-coupled clocked inverters prior to the pair of signals switching from data to reset. The intermediate signals are thus latched in the complementary logic states that correspond to data even after the pair of input signals have returned to reset. The output signals are also thus provided in complementary logic states that correspond to data prior to the input signals being reset.

Owner:FREESCALE SEMICON INC

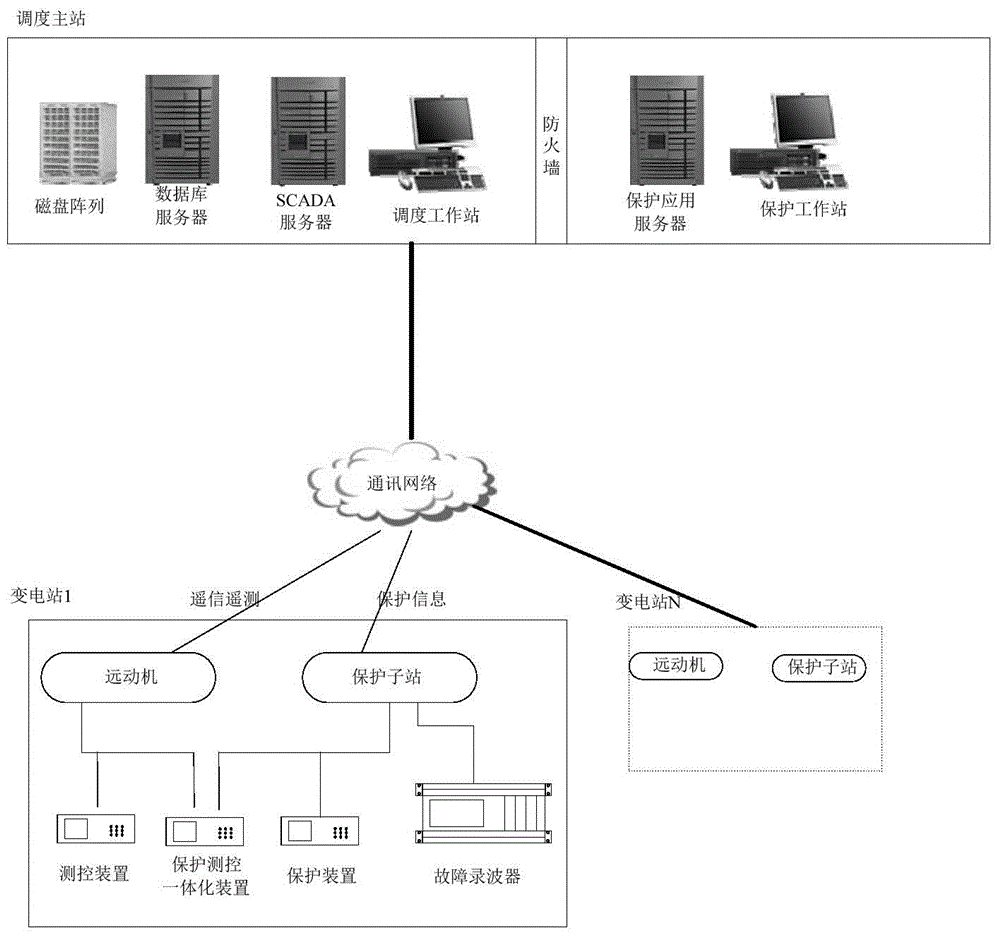

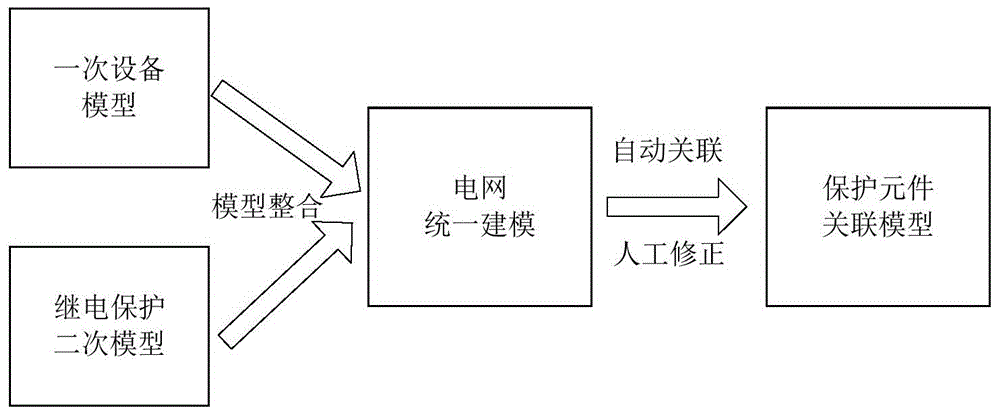

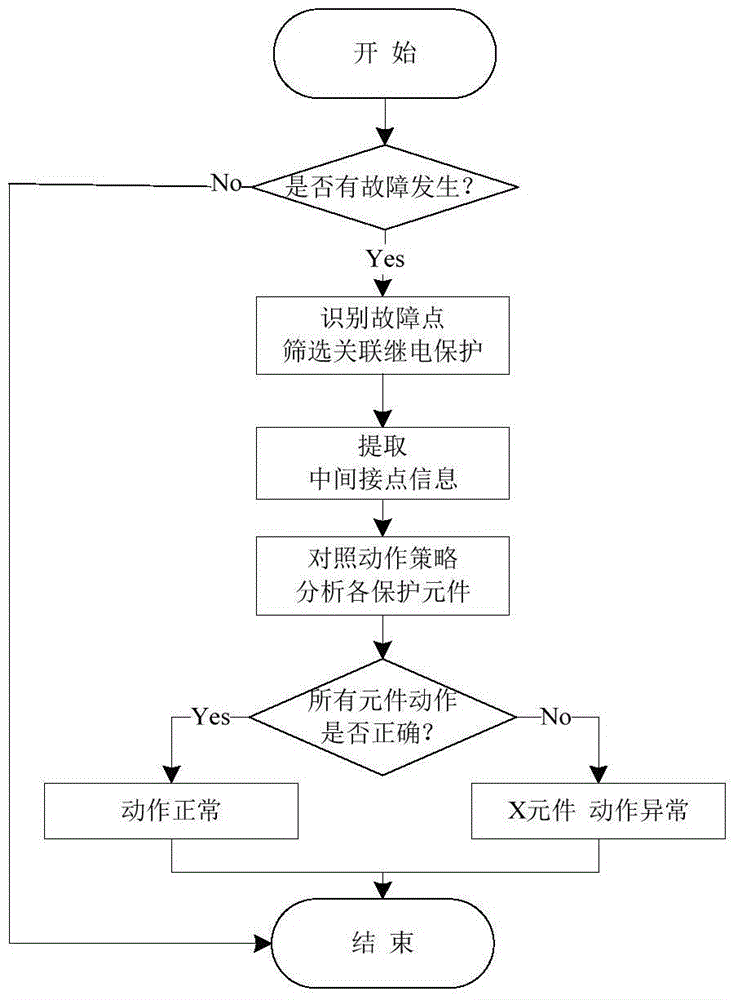

Remote diagnosis method for motion behavior of protection element at dispatching terminal

ActiveCN104880629AFind out the cause of the failure quicklyRestore powerFault locationAssociation modelPower grid

The invention discloses a remote diagnosis method for the motion behavior of a protection element at a dispatching terminal. The remote diagnosis method is characterized in that the method comprises following steps: S01: establishing an association model of primary equipment and relay protection; S02: transmitting and collecting relay protection intermediate logic node information, SOE information, protection motion information, telecommand deflection information, and fault record files from a substation to the dispatching terminal; S03: determining whether a power grid has faults; S04: determining a fault point via protection motion information, breaker deflection, and protection fault range-measuring information and obtaining association relay protection if the power grid has faults; S05: extracting intermediate logic node files of association relay protection; S06: comparing and analyzing each protection member according to self-consistency and consistency of each protection member and motion strategy; and S07: determining whether all the protection member motions are correct. According to the method, hidden problems of the protection members are discovered in advance, and necessary data is provided for remote operation and maintenance of relay protection.

Owner:NARI TECH CO LTD +3

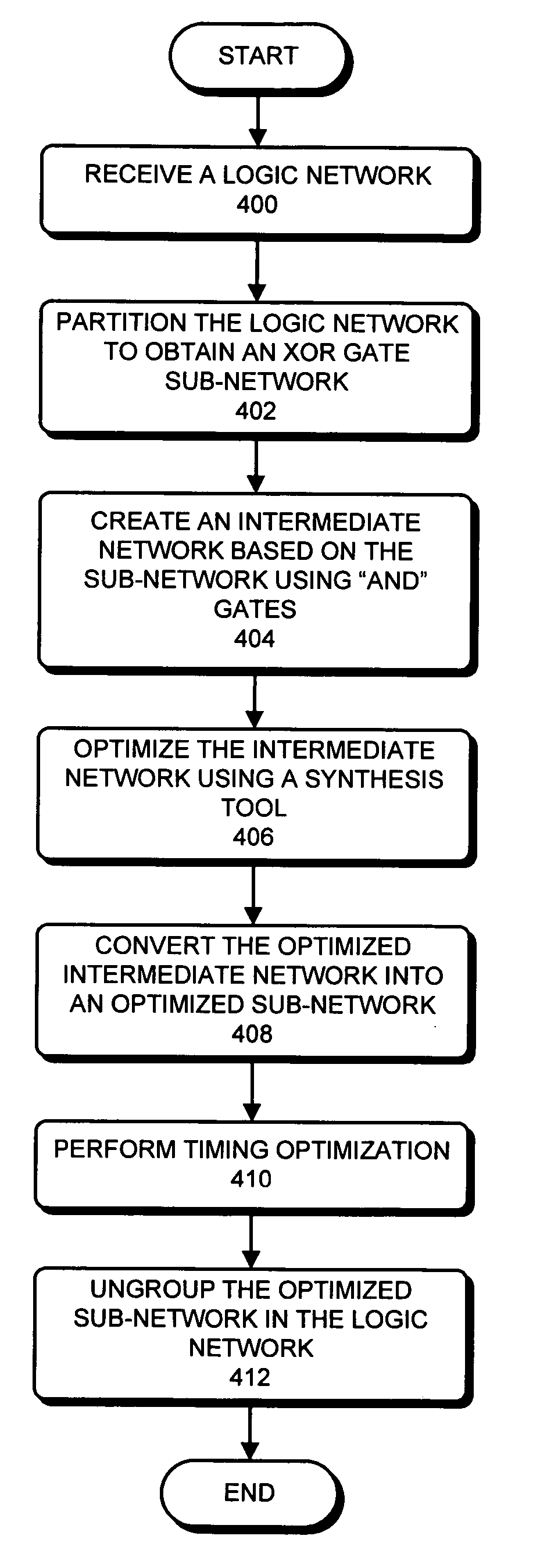

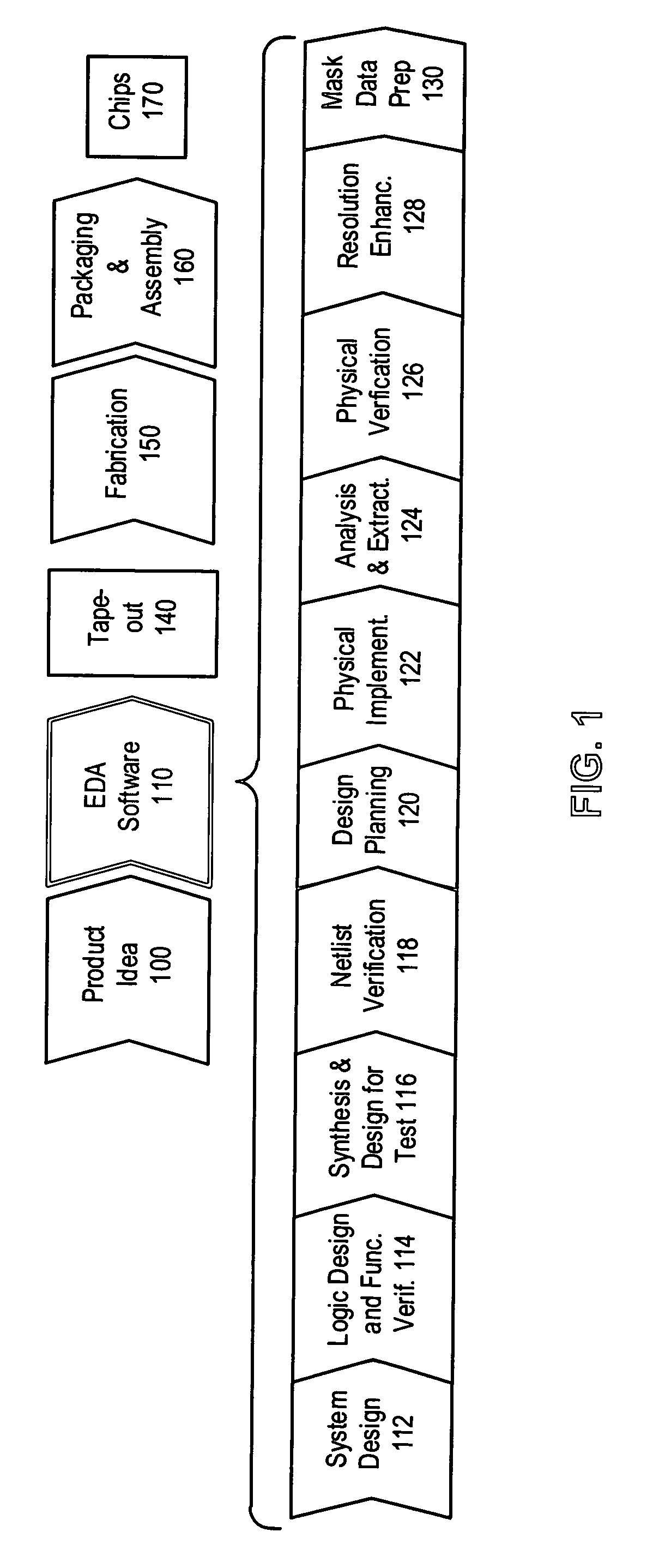

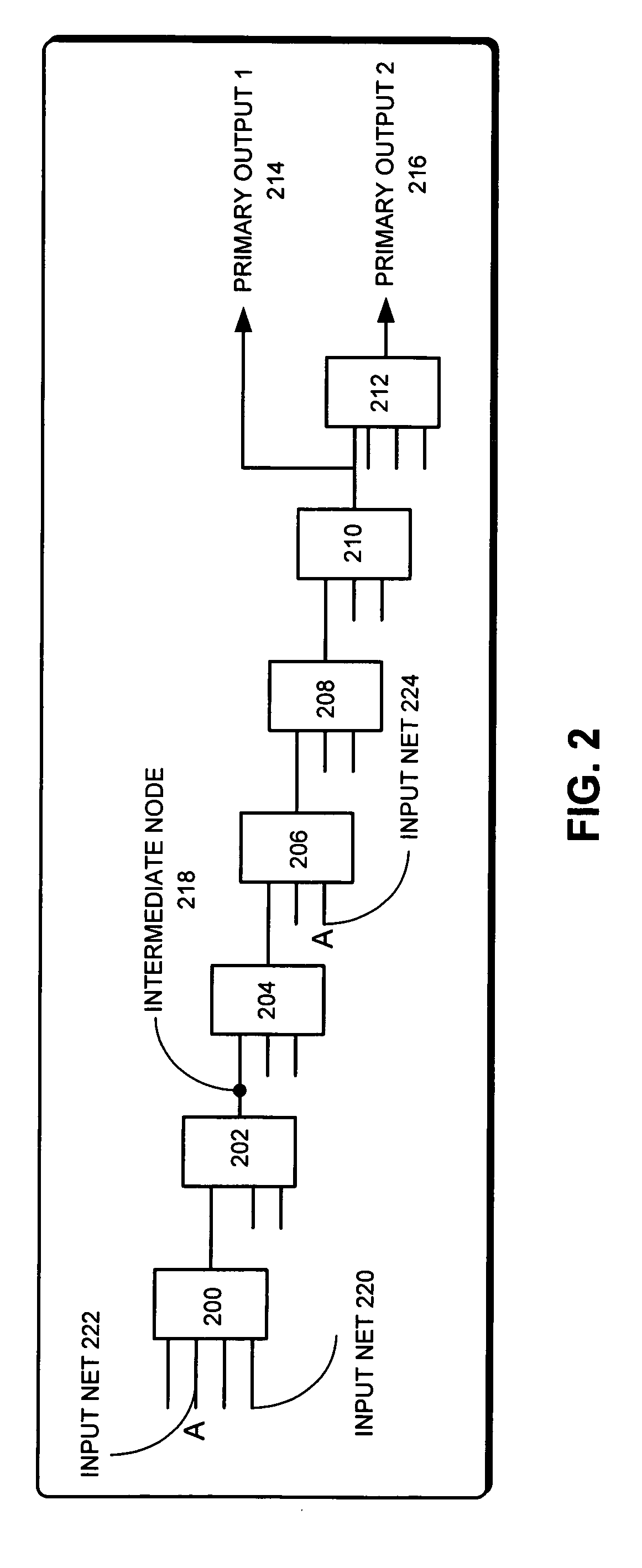

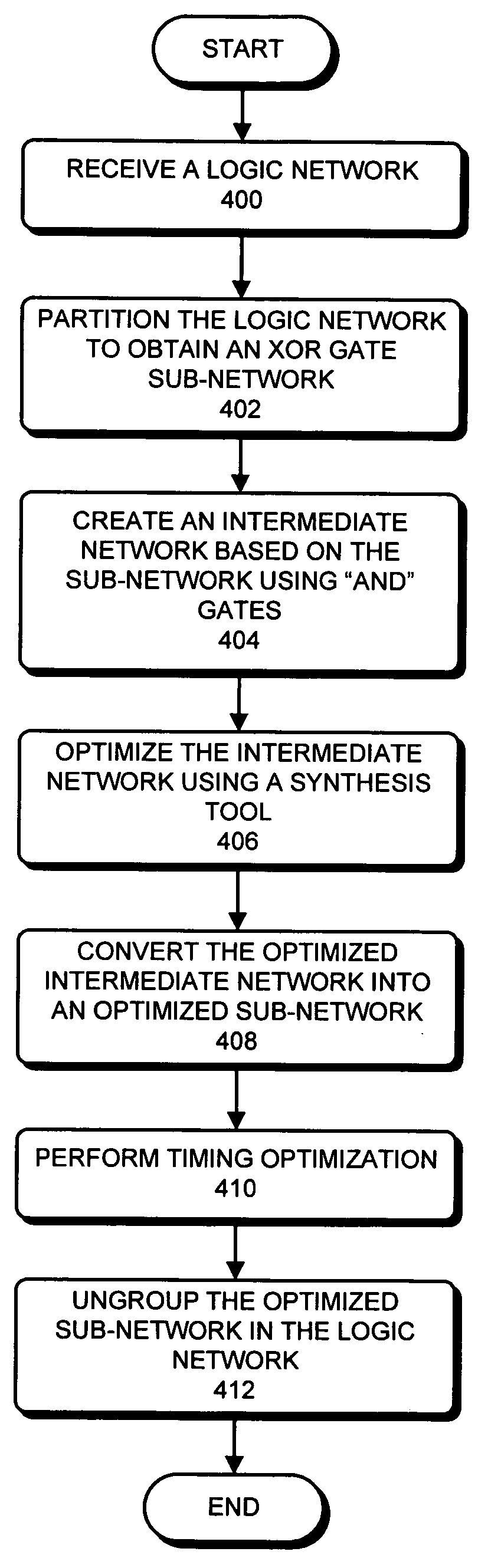

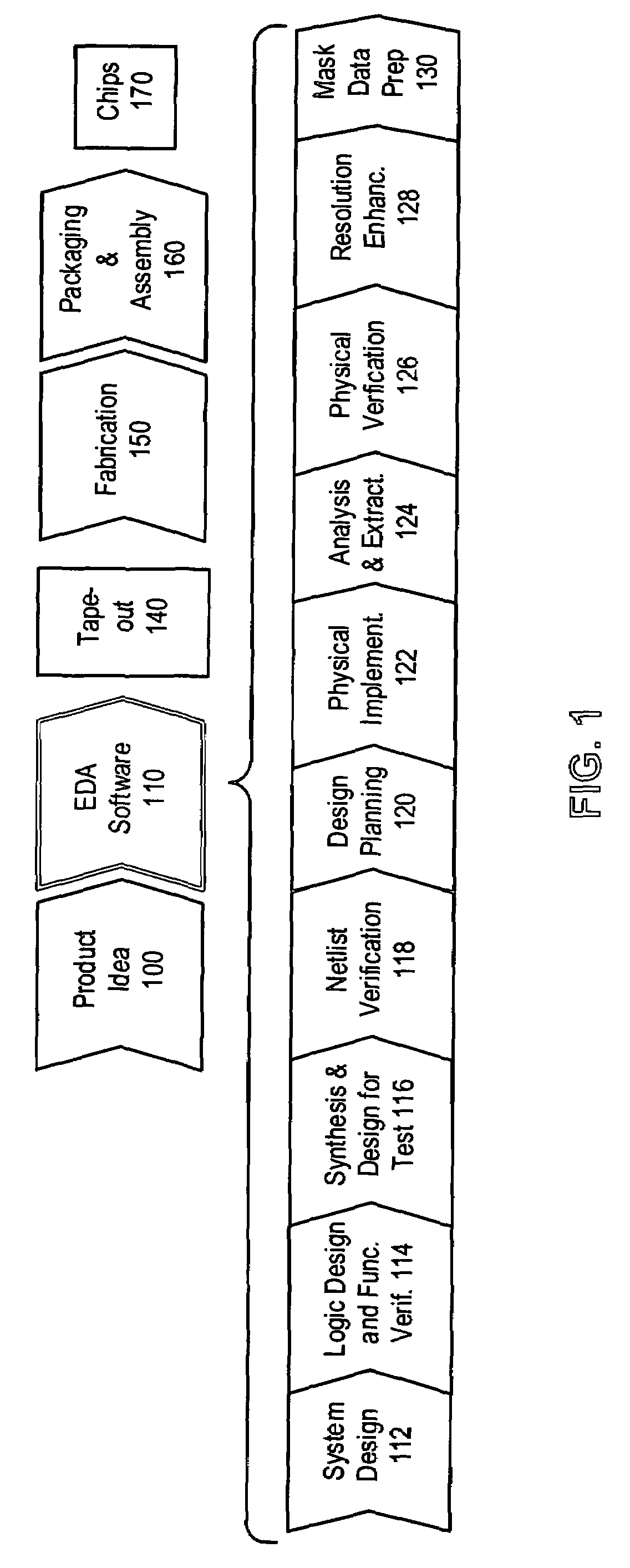

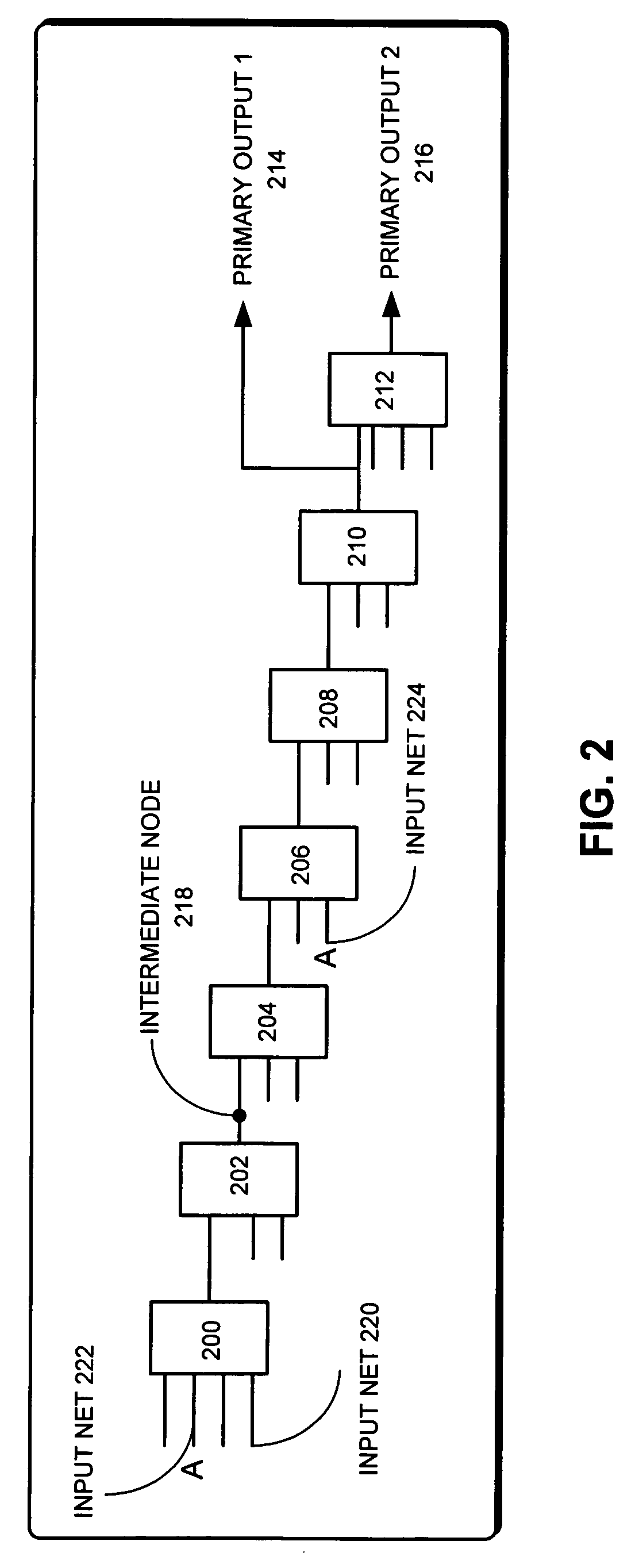

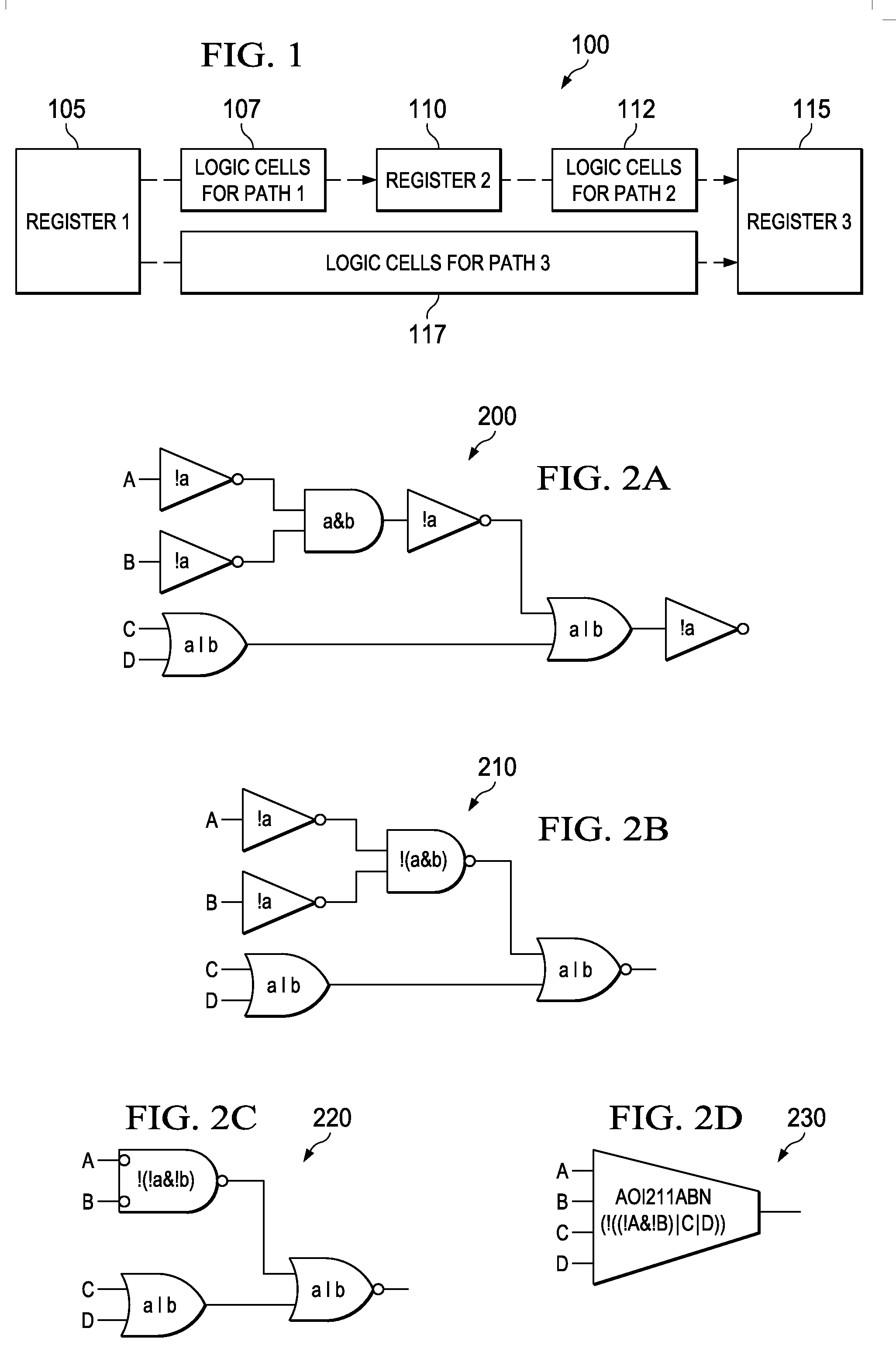

Method and apparatus for optimizing a logic network in a digital circuit

ActiveUS20070044045A1Improve efficiencyOptimize networkComputer aided designSoftware simulation/interpretation/emulationTheoretical computer scienceLogic network

One embodiment of the present invention provides a system that optimizes a logic network. During operation, the system receives a first logic network which defines a logical function, wherein the first logic network cannot be efficiently optimized by directly using an optimization process that preserves the logical function. Next, the system creates an intermediate logic network based on the first logic network, wherein the intermediate logic network defines an intermediate logical function which is different from the logical function, wherein the intermediate logic network can be efficiently optimized using the optimization process. The system then optimizes the intermediate logic network using the optimization process to create an optimized intermediate logic network. Next, the system creates an optimized first logic network based on the optimized intermediate logic network. In this way, the system indirectly uses the optimization process to efficiently optimize the first logic network.

Owner:SYNOPSYS INC

Method and apparatus for optimizing a logic network in a digital circuit

ActiveUS7346862B2Improve efficiencyOptimize networkComputer aided designSoftware simulation/interpretation/emulationTheoretical computer scienceLogic network

One embodiment of the present invention provides a system that optimizes a logic network. During operation, the system receives a first logic network which defines a logical function, wherein the first logic network cannot be efficiently optimized by directly using an optimization process that preserves the logical function. Next, the system creates an intermediate logic network based on the first logic network, wherein the intermediate logic network defines an intermediate logical function which is different from the logical function, wherein the intermediate logic network can be efficiently optimized using the optimization process. The system then optimizes the intermediate logic network using the optimization process to create an optimized intermediate logic network. Next, the system creates an optimized first logic network based on the optimized intermediate logic network. In this way, the system indirectly uses the optimization process to efficiently optimize the first logic network.

Owner:SYNOPSYS INC

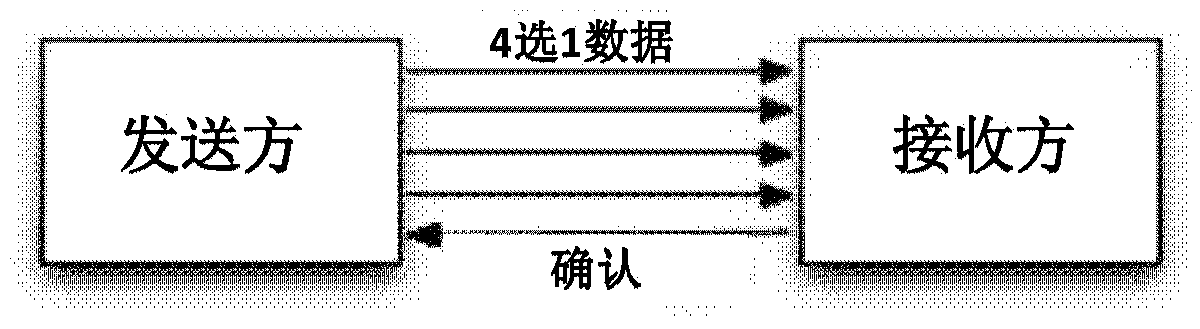

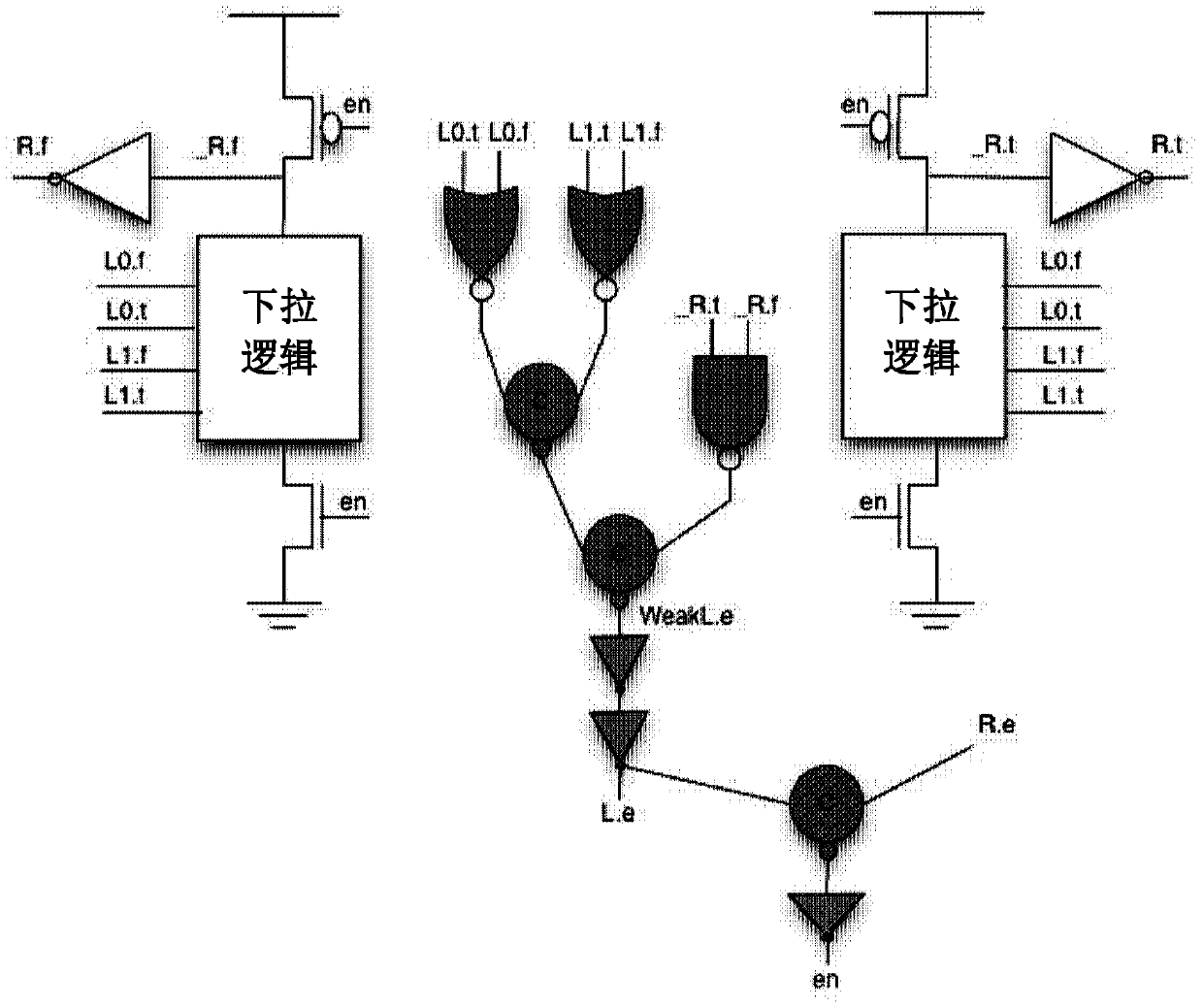

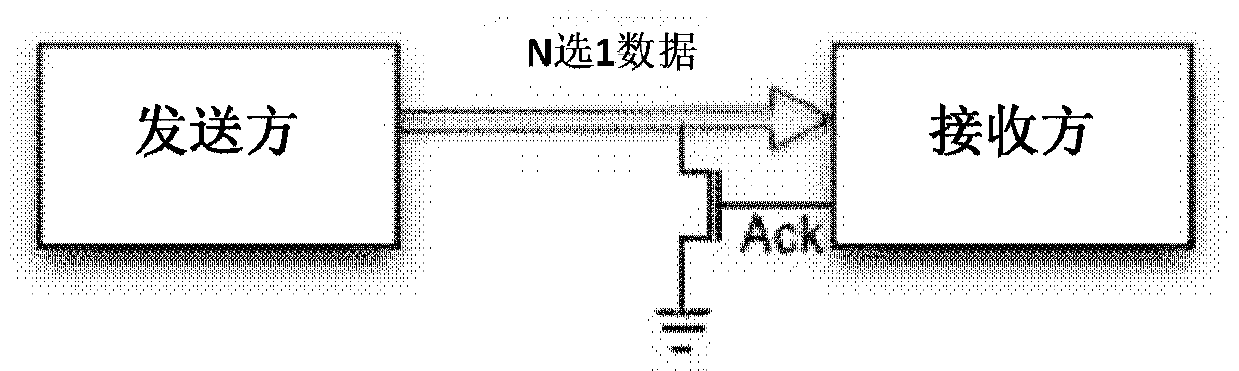

Energy-efficient pipeline circuit templates for high performance asynchronous circuits

InactiveCN103874968AConcurrent instruction executionCAD circuit designAsynchronous circuitParallel computing

Asynchronous circuits and techniques are described for asynchronous processing without synchronization to a common clock. Two specific energy-efficient pipeline templates for high throughput asynchronous circuits are provided as examples based on single-track handshake protocol. Each pipeline contains multiple stages of logic. The handshake overhead is minimized by eliminating validity and neutrality detection logic gates for all input tokens as well as for all intermediate logic nodes. Both of these templates can pack significant amount of logic within each pipeline block, while still maintaining a fast cycle time.

Owner:CORNELL UNIVERSITY

Nanoscale latches and impedance-encoded logic for use in nanoscale state machines, nanoscale pipelines, and in other nanoscale electronic circuits

ActiveUS20060087344A1Prevent degradationLogic circuits characterised by logic functionNanoinformaticsNanowireEngineering

Various embodiments of the present invention are directed to implementation and use of logic-state-storing, impedance-encoded nanoscale, impedance-encoded latches that store logic values as impedance states within nanoscale electronic circuits that employ impedance-driven logic. In certain of these embodiments, use of nanoscale, impedance-encoded latches together with nanoscale electronic circuits that employ impedance-driven logic avoids cumulative degradation of voltage margins along a cascaded series of logic circuits and provides for temporary storage of intermediate logic values, allowing for practical interconnection of nanowire-crossbar-implemented logic circuits through nanoscale, impedance-encoded latches to other nanowire-crossbar-implemented logic circuits in order to implement complex, nanoscale-logic-circuit pipelines, nanoscale-logic-circuit-based state machines, and other complex logic devices with various different interconnection topologies and corresponding functionalities.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Establishing a logical connection between an indirect utterance and a transaction

PendingCN110110053ADigital data information retrievalSemantic analysisKnowledge graphIntermediate logic

A method, apparatus and computer program product for establishing a logical connection between an indirect utterance and a transaction are described. Indirect utterance is received from a user as input to a session system. The indirect utterance is parsed into a first logical form. A first set of predicates and terms are mapped from the first logical form to a first sub-graph in a knowledge graph.A second set of predicates and terms are mapped from a second logical form belonging to a transaction to a second subgraph of the knowledge graph. An optimal path between the first sub-graph and thesecond sub-graph is searched for in the knowledge graph, and simultaneously the first logical form is transformed by using nodes and edge labels along the optimal path to generate an intermediate logical form. If the graph structure of the intermediate logical form matches the graph structure of the logical form of the transaction above the threshold, a system action is performed on the transaction.

Owner:IBM CORP

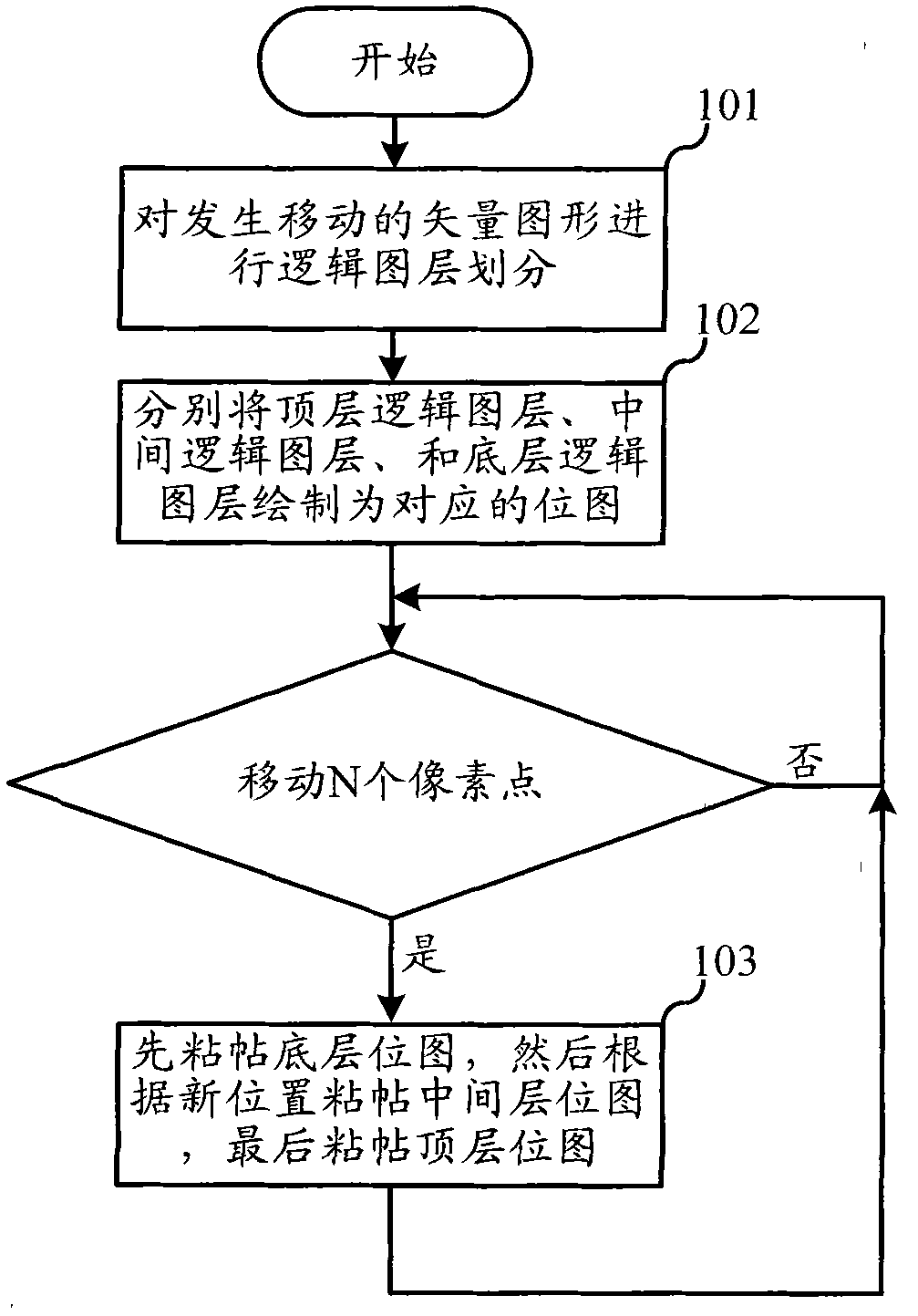

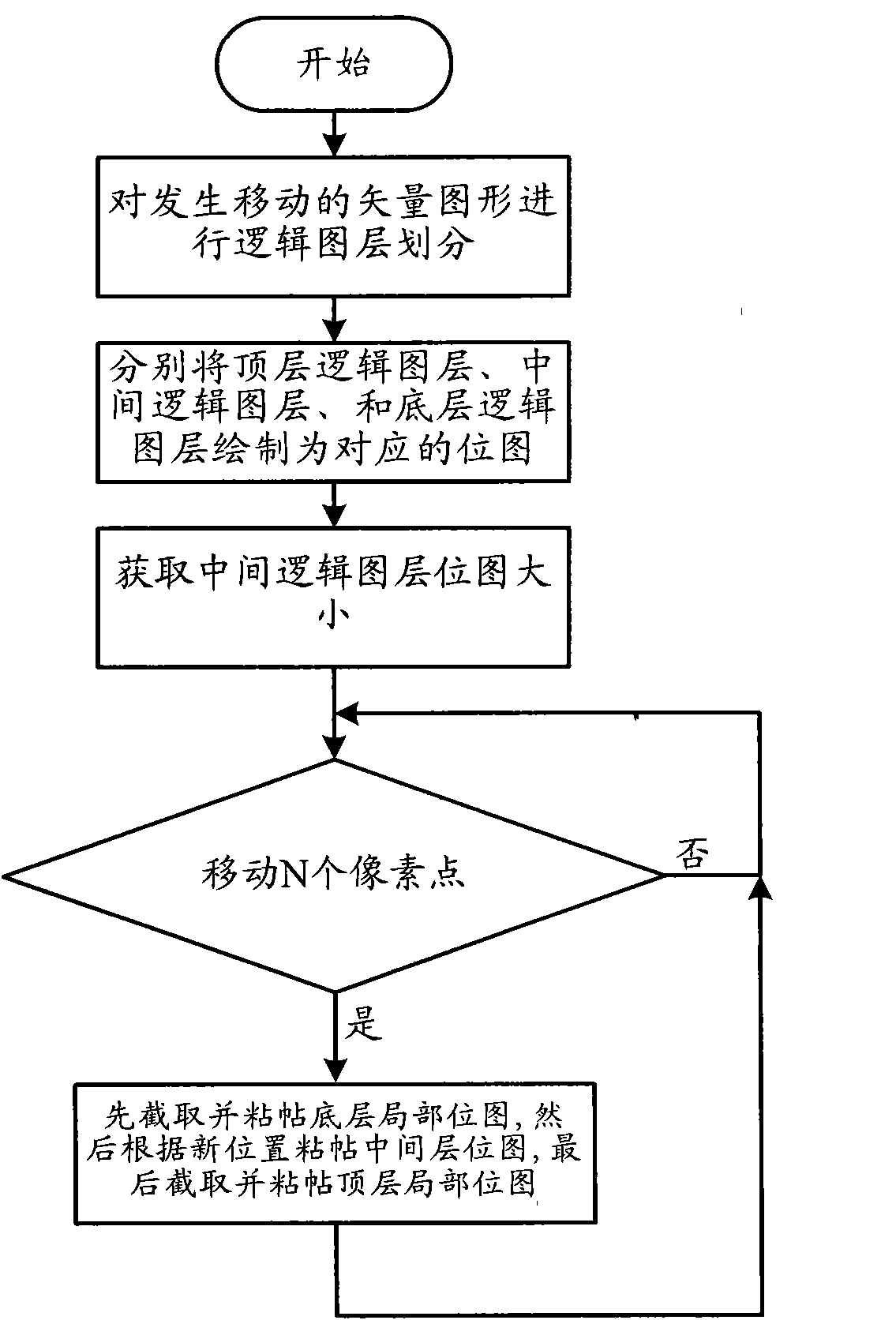

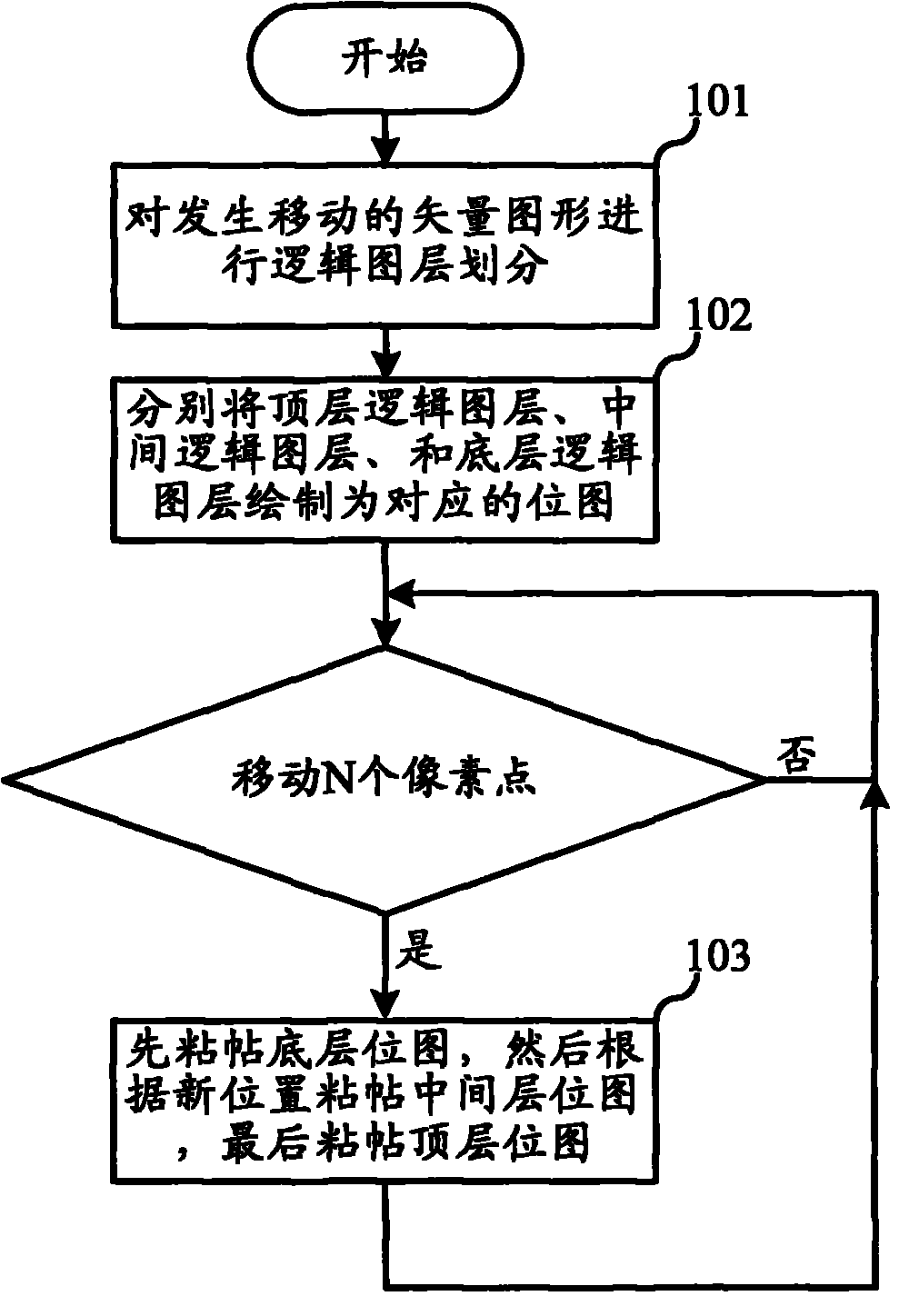

Drawing method used during vector graphics moving process

ActiveCN102214363ASpeed up redrawingMove fastDrawing from basic elementsIntermediate logicVector graphics

The invention discloses a drawing method used during the vector graphics moving process, which comprises the steps of carrying out logic layer division on moved vector graphics, forming pixel objects to be moved into a middle logic layer, forming a top logic layer by all pixel objects positioned on the upper layer, and forming a bottom logic layer by all pixel objects positioned at the lower layer; drawing the three logic layers into corresponding bitmaps respectively; and when pixel objects to be moved are moved at new positions, firstly sticking the bottom logic layer bitmap, then sticking the middle logic layer bitmap according to the newly moved position, and finally sticking the top logic layer bitmap. The whole graphics moving process is realized by a graphics sticking manner and is not influenced by the number and complexity of the vector graphics, thus quickening the graphics redrawing speed, and quickening the visual graphic moving speed. Particularly, when graphics needing to be moved consists of complicated pixel objects, or the pixel objects needing to be moved are filled with more colors, the moving speed can be obviously quickened.

Owner:ASAT CHINA TECH

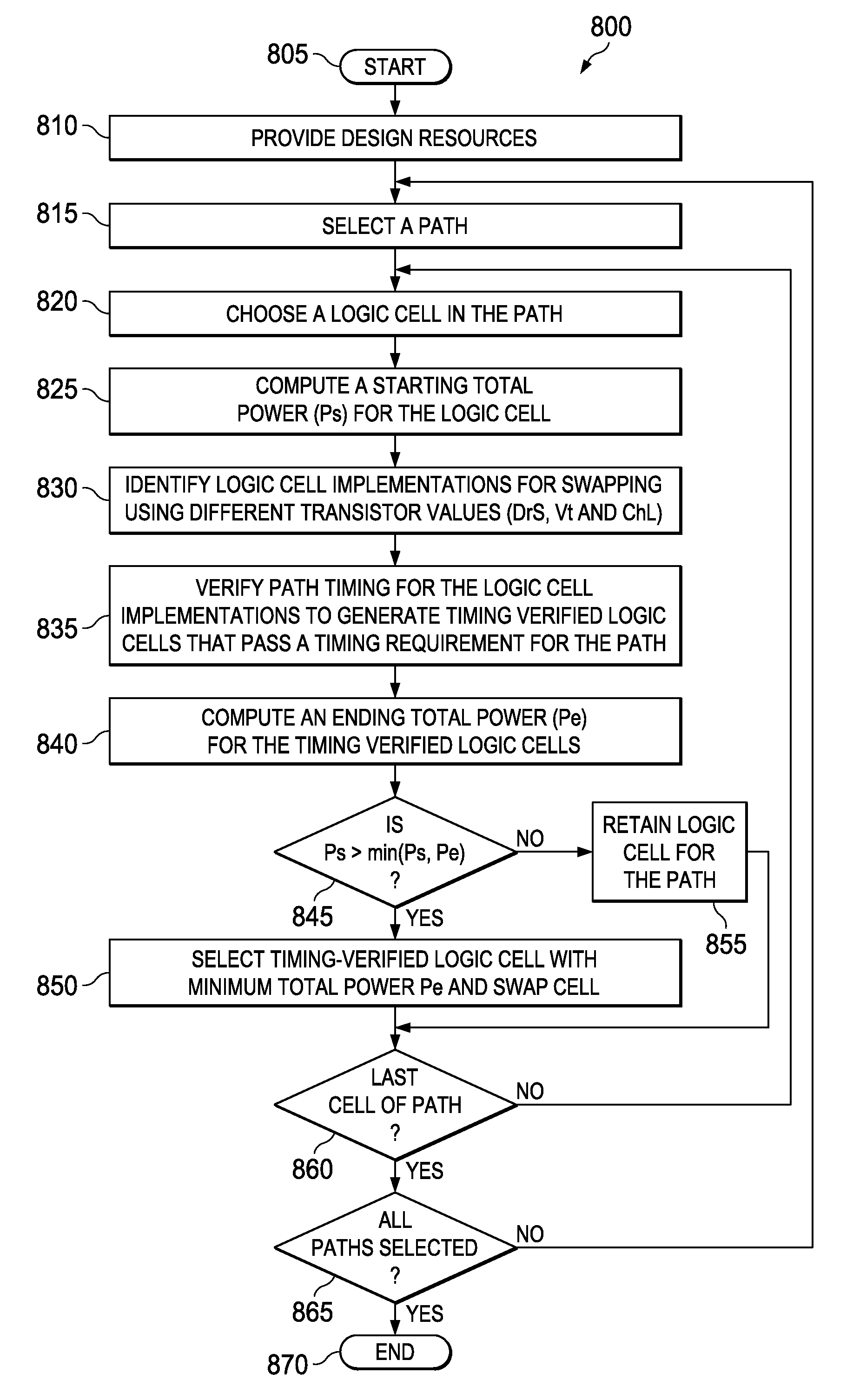

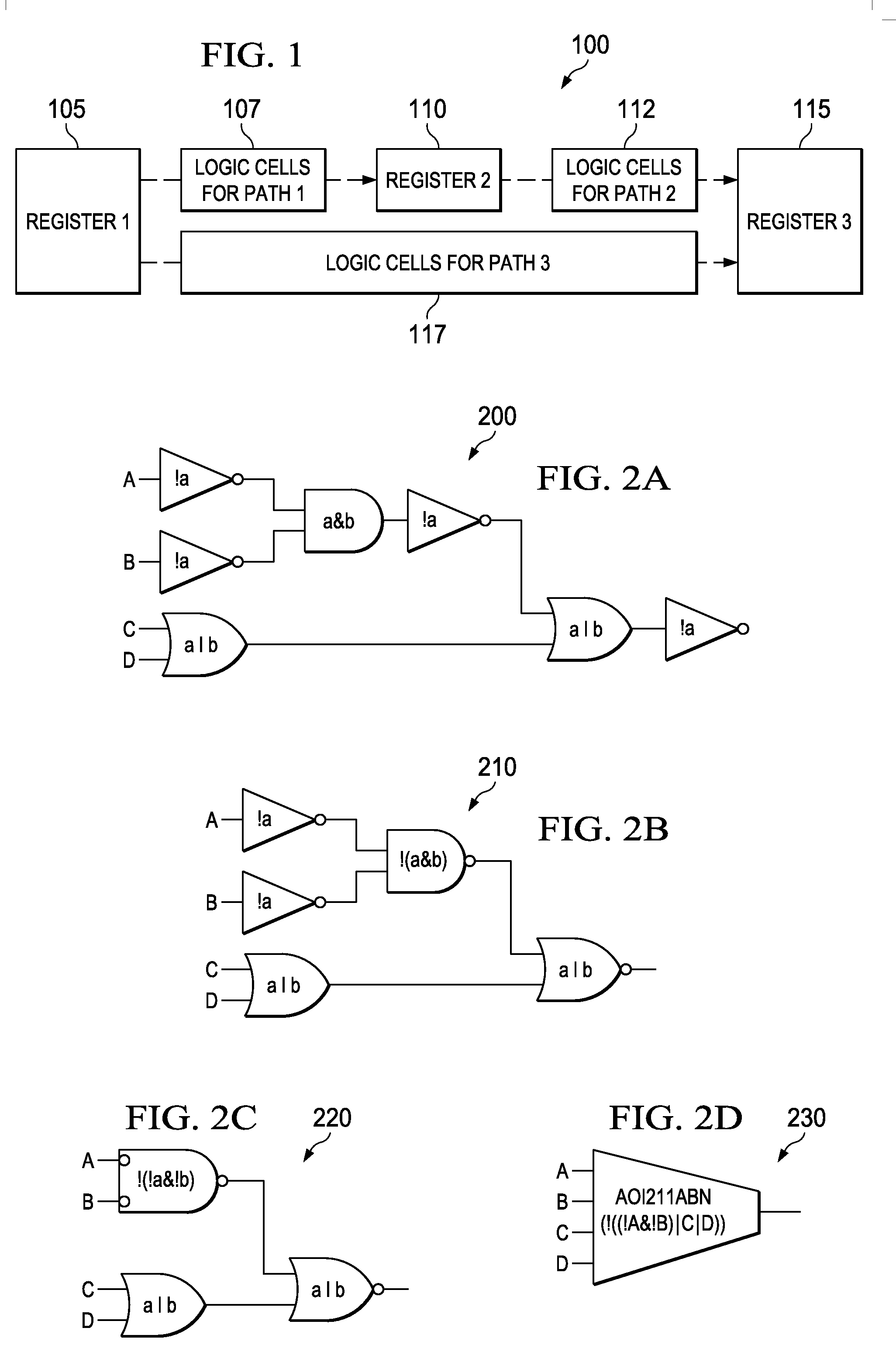

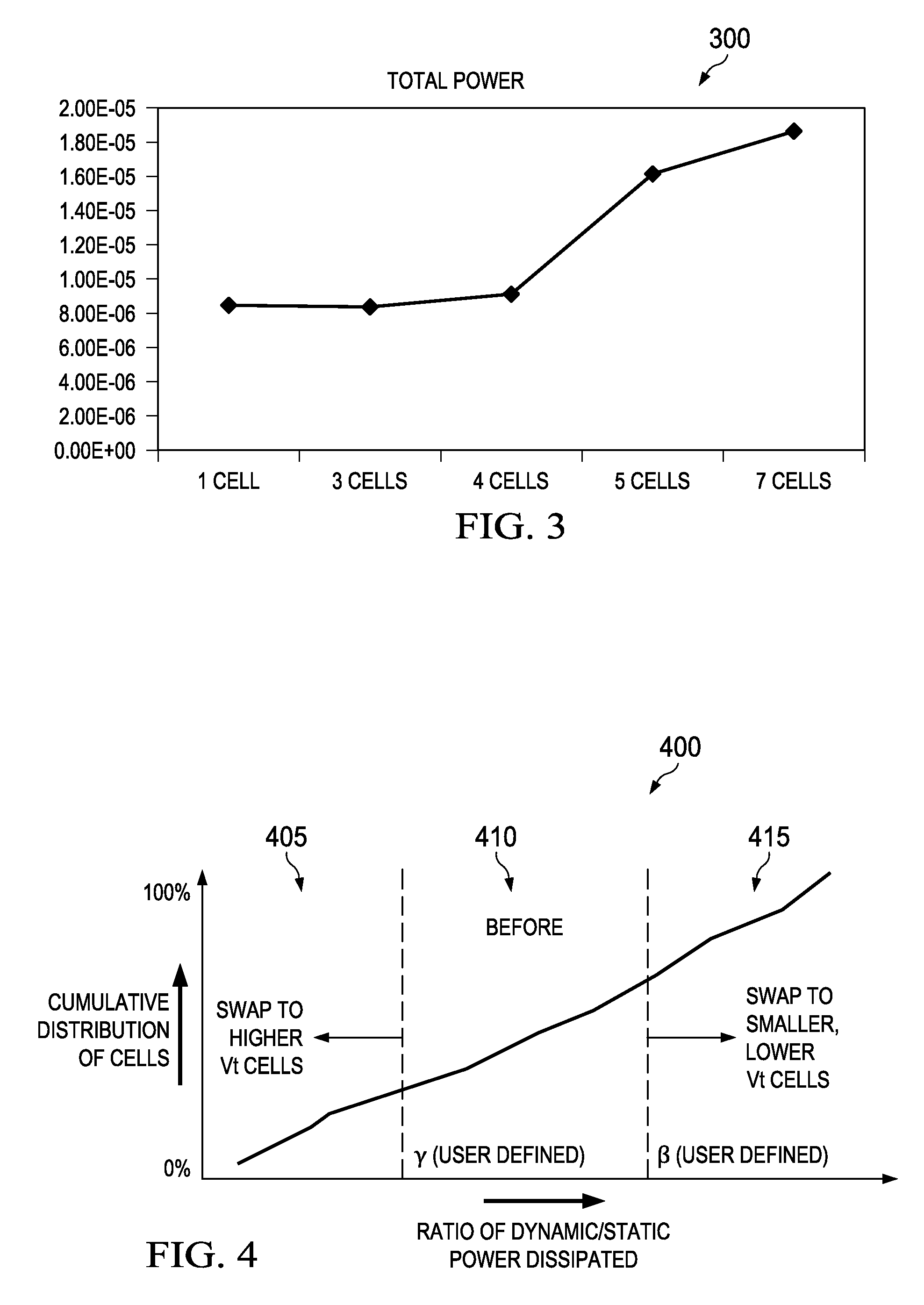

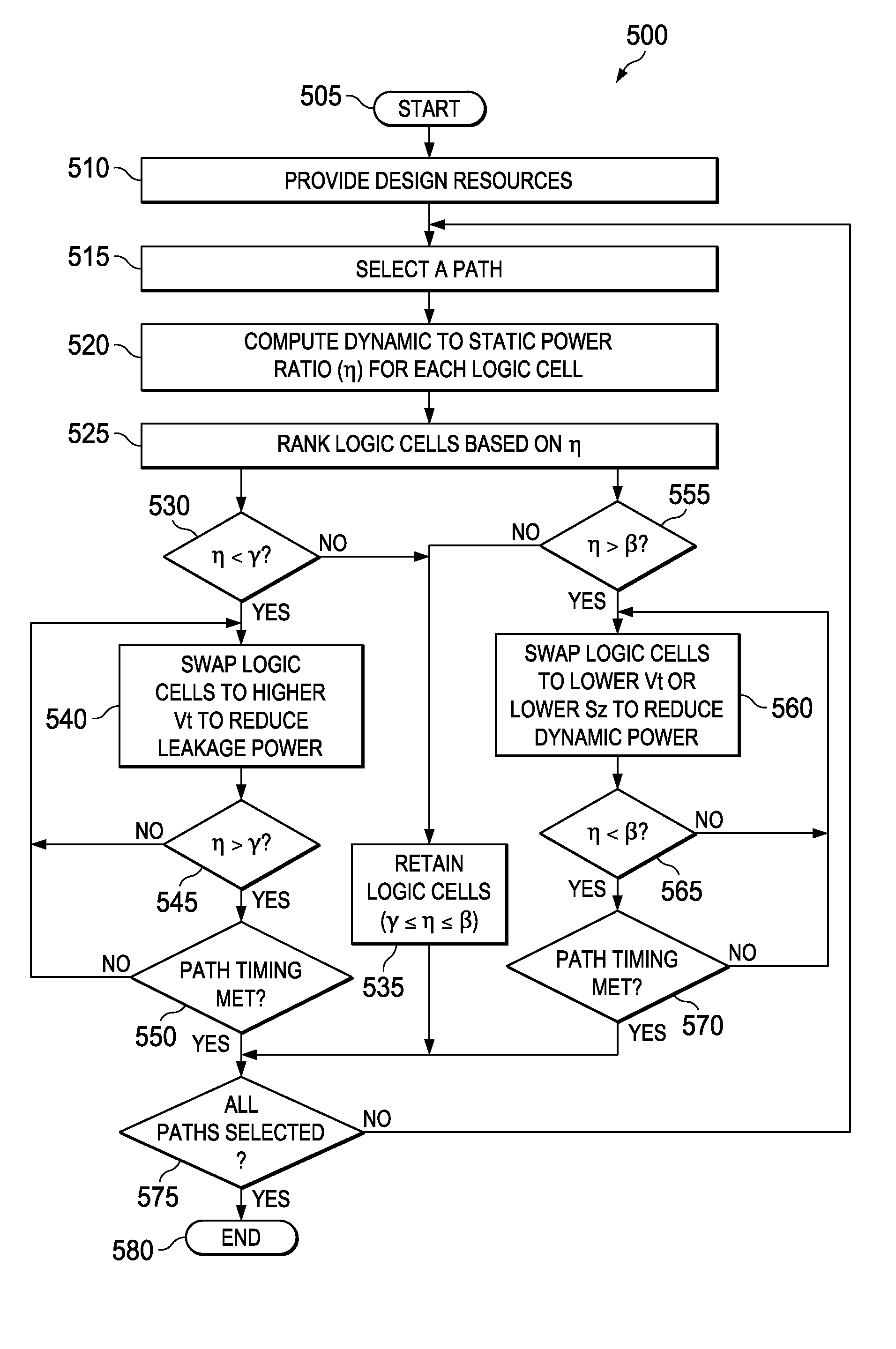

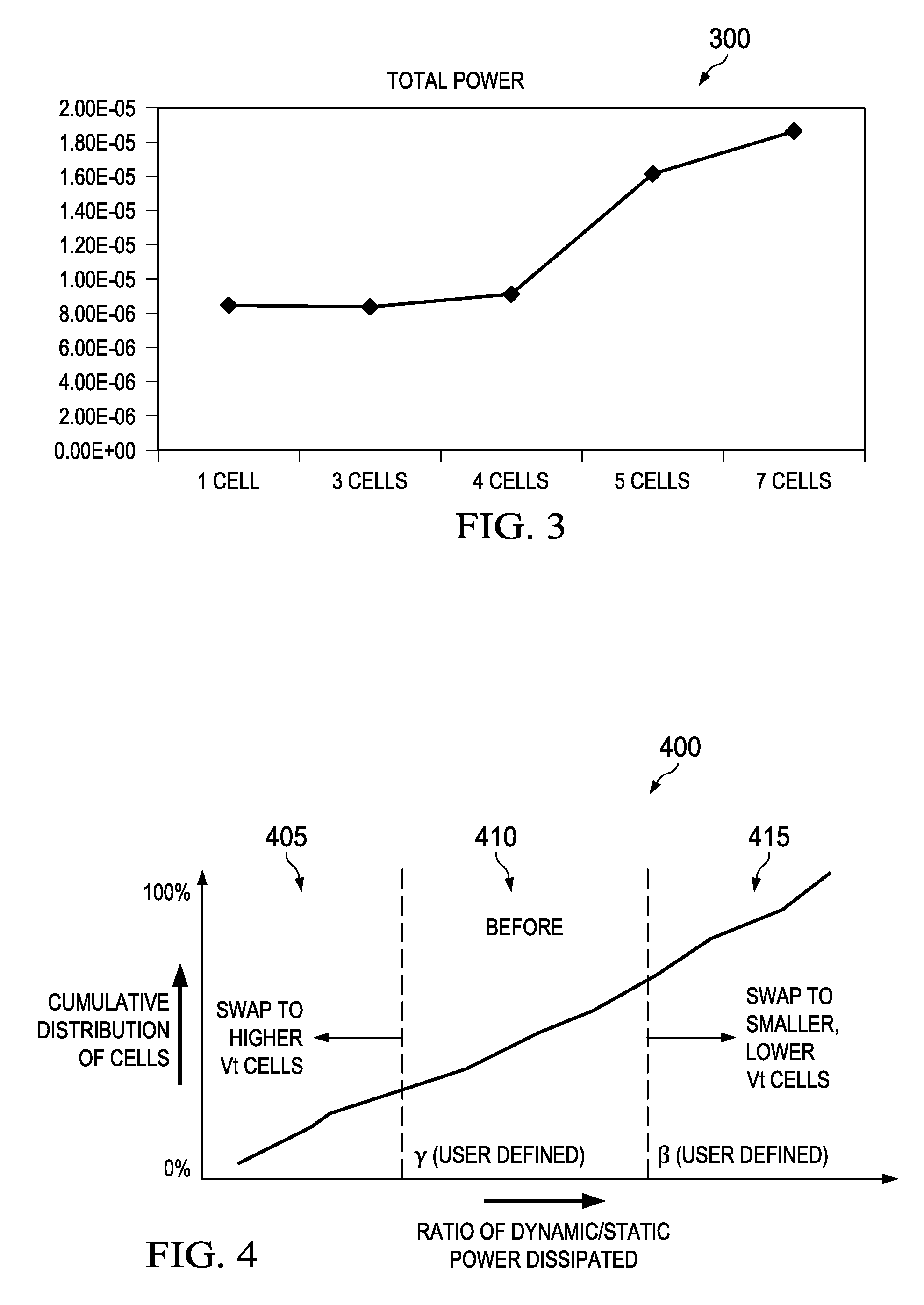

Total power optimization for a logic integrated circuit

InactiveUS20120290994A1Computer aided designSoftware simulation/interpretation/emulationMiddle groupLogic cell

A method of reducing total power dissipation for logic cells includes selecting a distribution of logic cells corresponding to at least one path, computing a dynamic to static power ratio for each logic cell in the distribution of logic cells and ranking the dynamic to static power ratio for each logic cell into a lower group, a middle group and an upper group of logic cells. Additionally, the method includes swapping the lower group of logic cells and the upper group of logic cells for a reconfigured middle group of logic cells and verifying path timing for the reconfigured middle group of logic cells. Methods of reducing total power dissipation using Boolean equations and for logic cell sets are also provided.

Owner:BELL SEMICON LLC

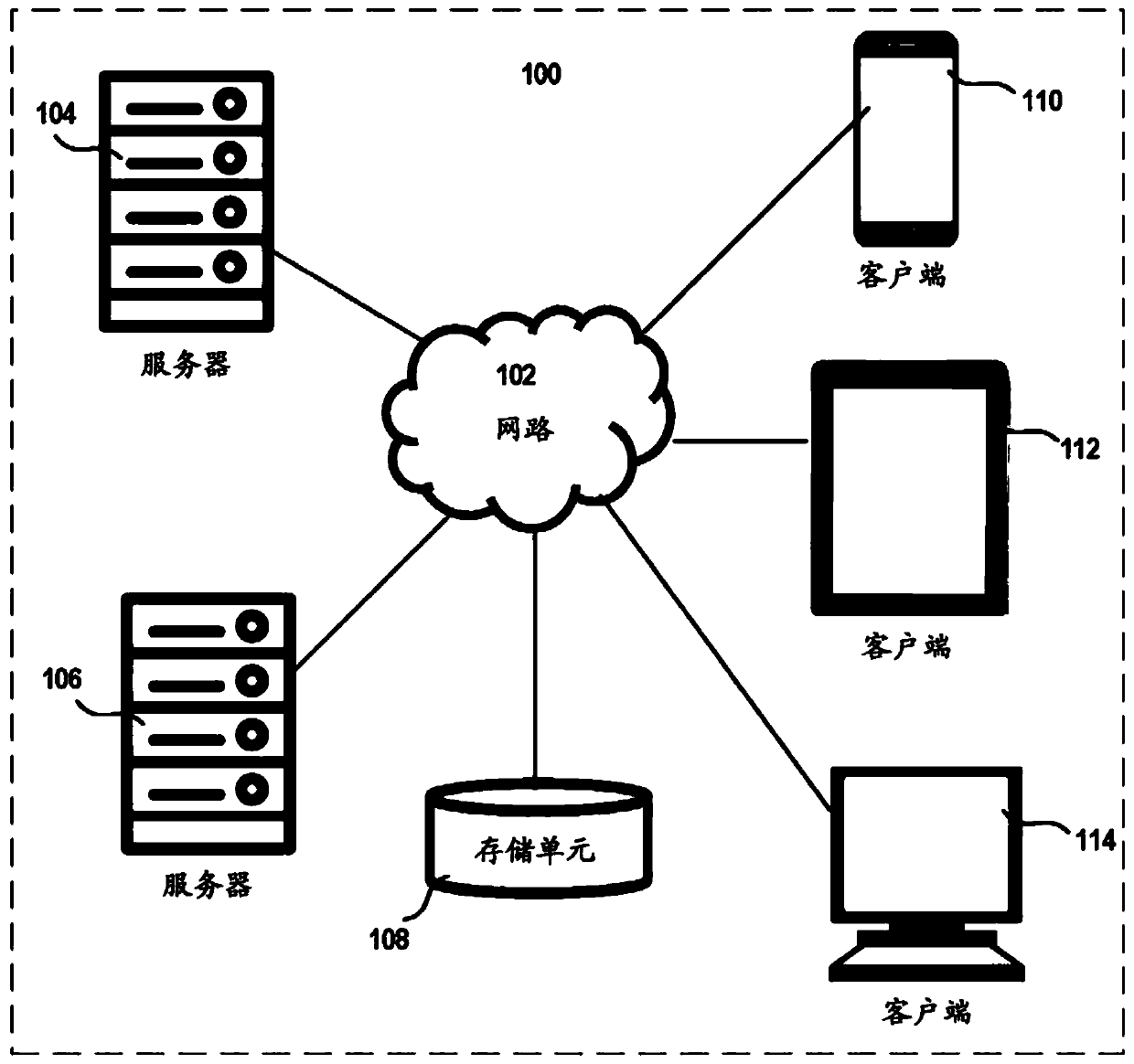

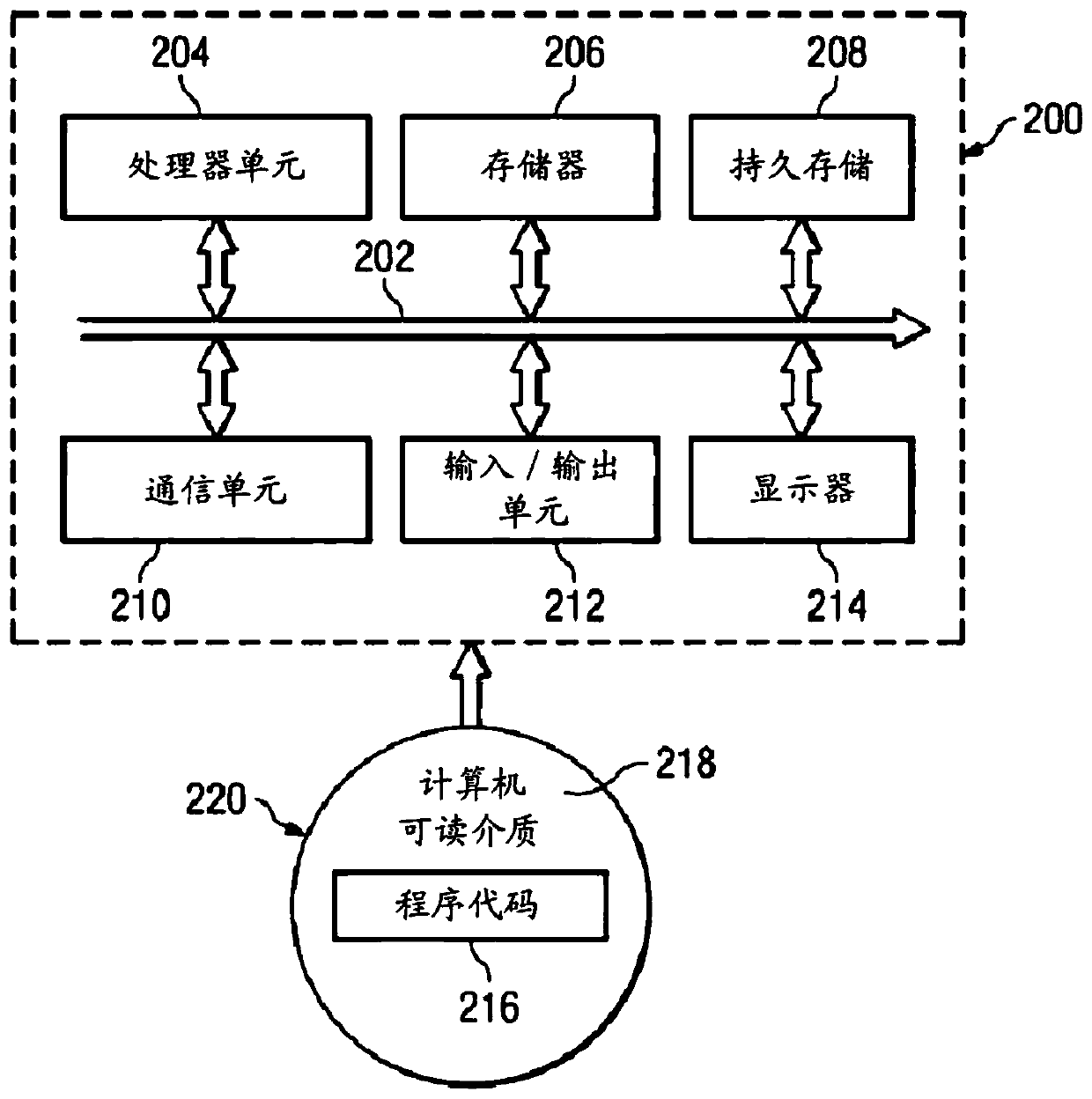

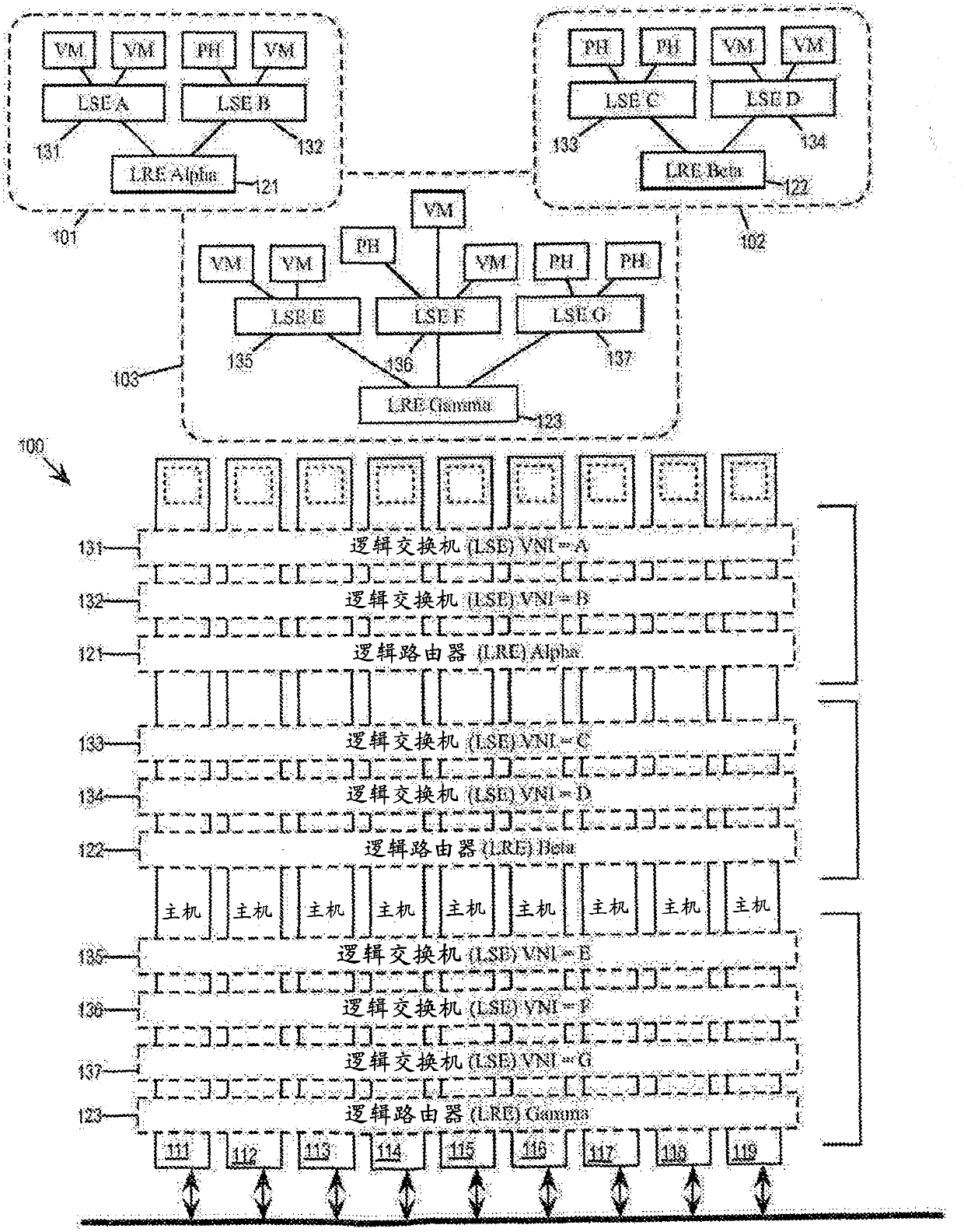

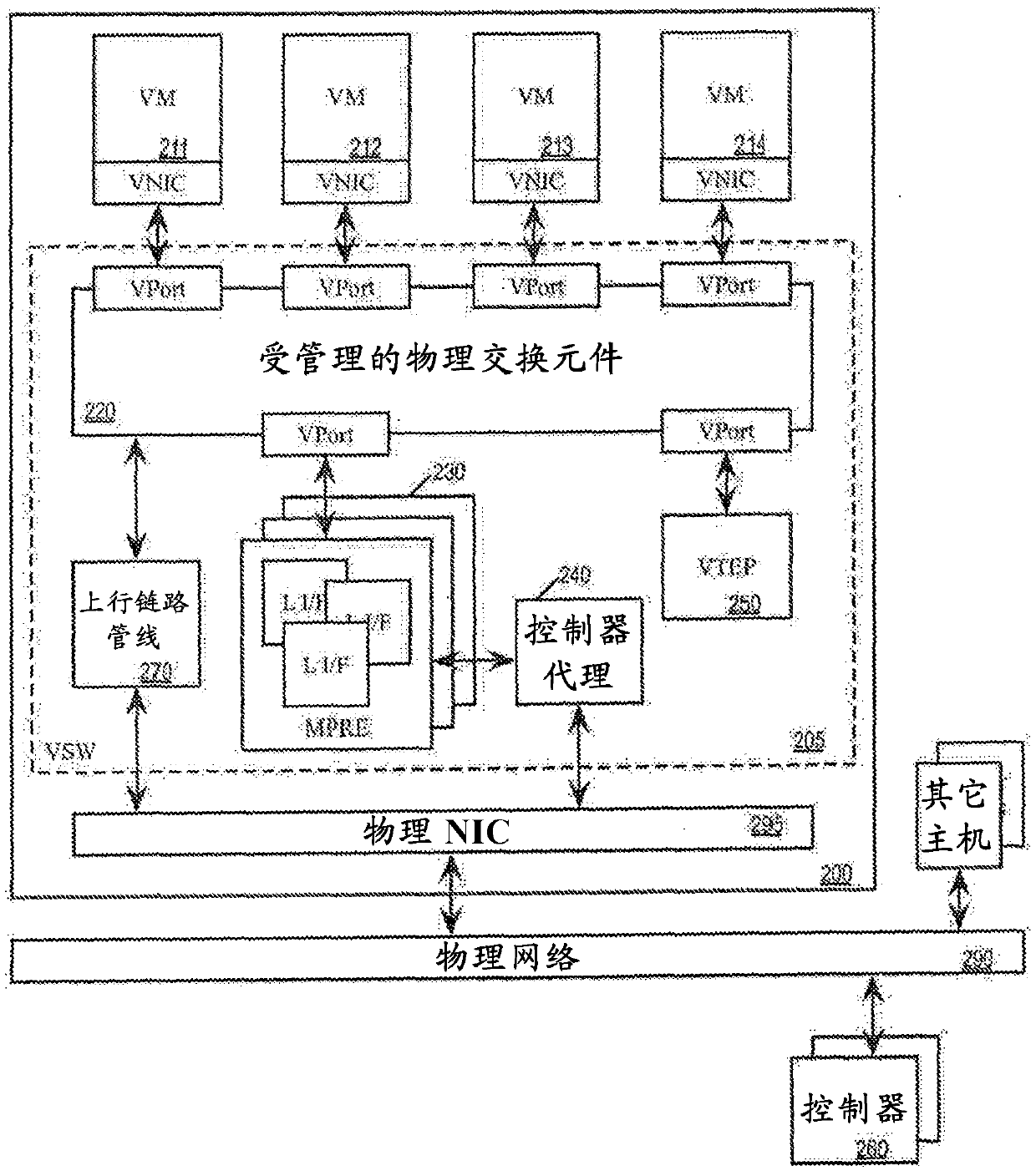

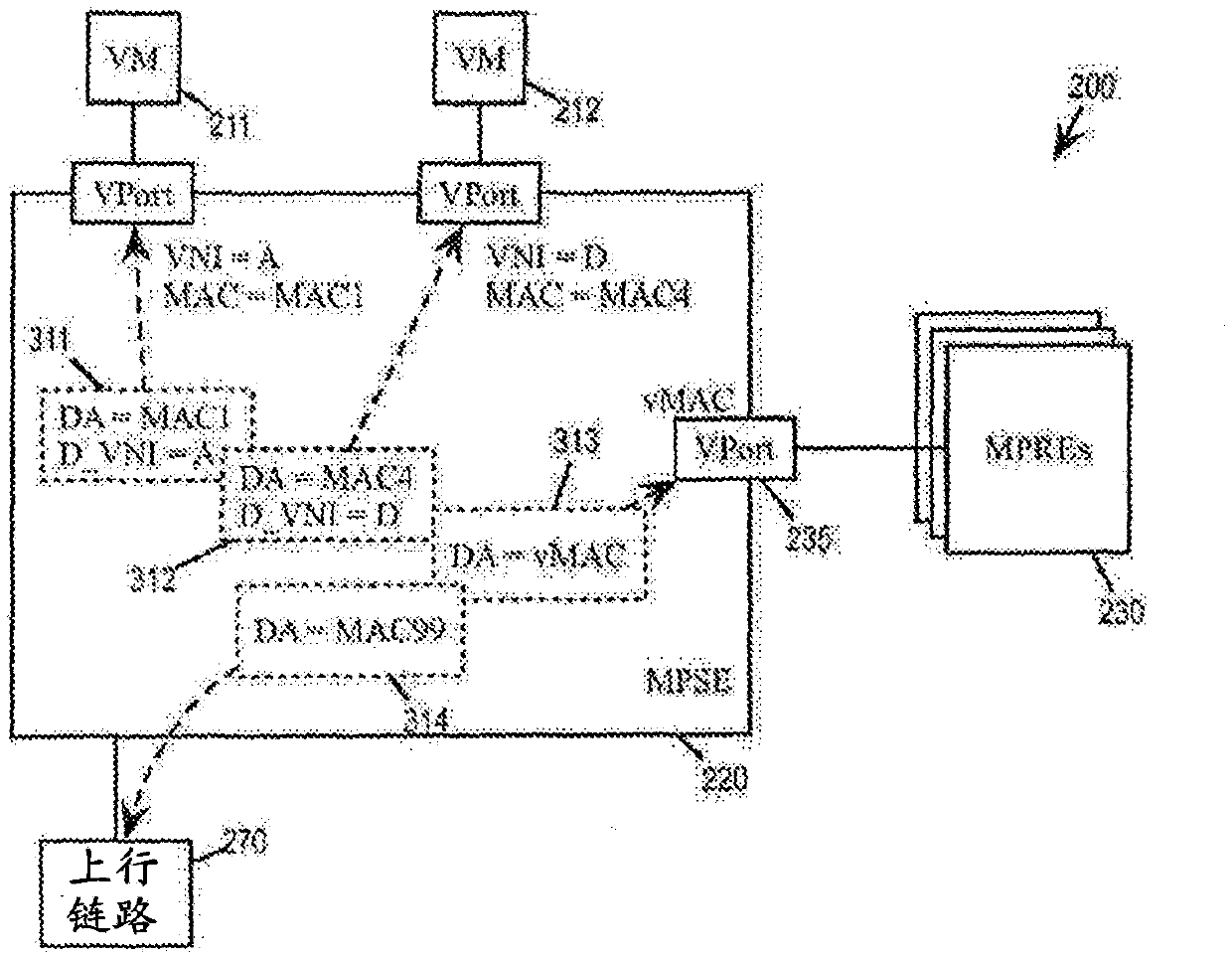

Intermediate logical interfaces in a virtual distributed router environment

ActiveCN107771384ANetworks interconnectionSoftware simulation/interpretation/emulationIntermediate logicDistributed computing

A LRE (logical routing element) that have LIFs that are active in all host machines spanned by the LRE as well as LIFs that are active in only a subset of those spanned host machines is provided. A host machine having an active LIF for a particular L2 segment would perform the L3 routing operations for network traffic related to that L2 segment. A host machine having an inactive LIF for the particular L2 segment would not perform. L3 routing operations for the network traffic of the L2 segment.

Owner:NICIRA

Logical mapping for improved head switching between corresponding tracks in a data handling device

InactiveUS7274530B2Combination recordingDriving/moving recording headsProgramming languageData processing system

In a data handling system having a radially-dependent track incongruity between data surfaces, at least some tracks are logically mapped so that tracks on different data surfaces correspond with one another. The correspondence is defined by the mapping so as to shorten an average headswitch seek. For example, a logical track mapping of first and second non-coaxial track sets can be defined so as to optimize a headswitch seek within each of many intermediate logical cylinders identified in the mapping.

Owner:SEAGATE TECH LLC

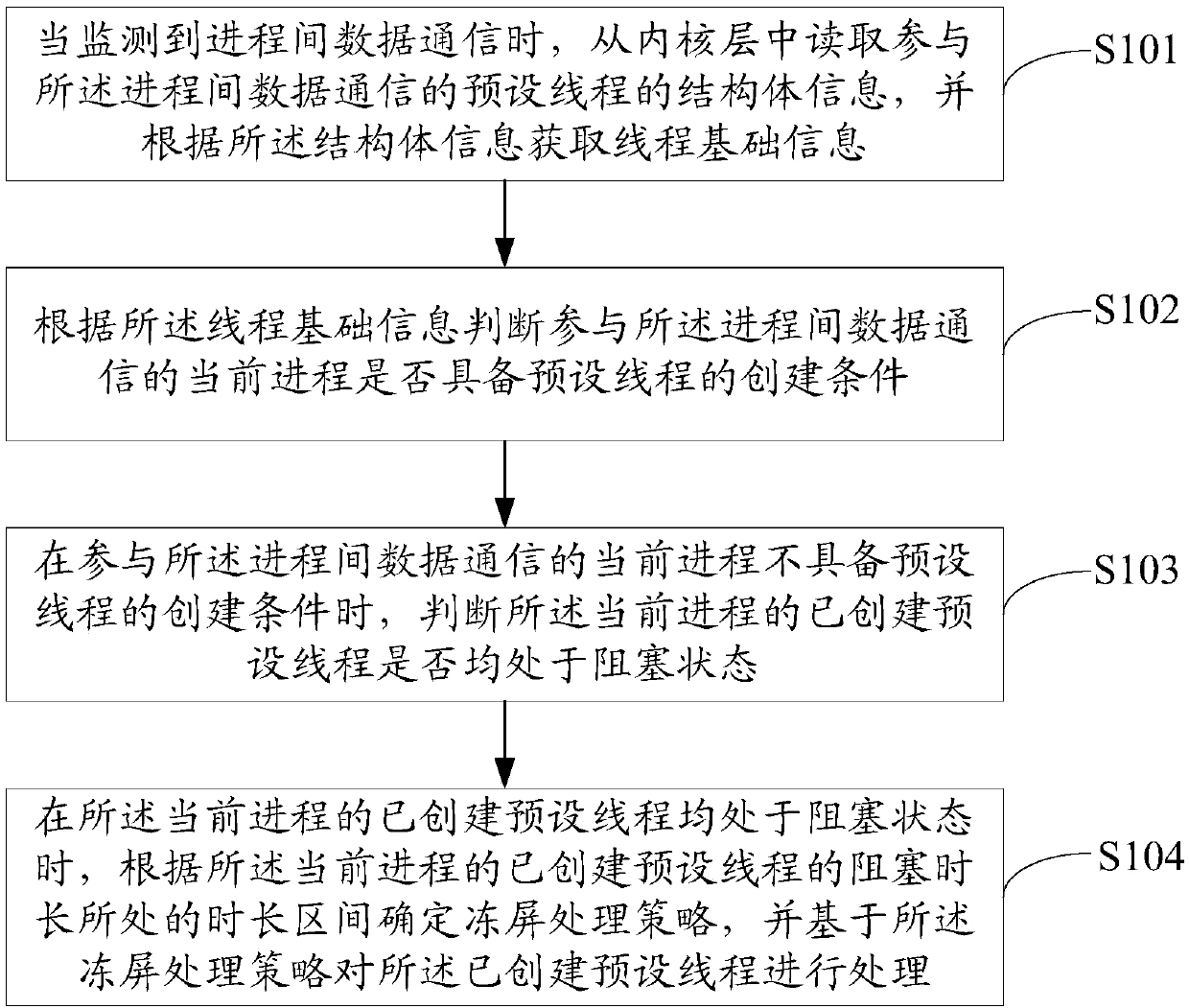

Frozen screen monitoring and solving method, mobile terminal and computer readable storage medium

ActiveCN107908493AReduce intermediate logic callsShorten maintenance timeResource allocationHardware monitoringIntermediate logicReal-time computing

The invention discloses a frozen screen monitoring and solving method, a mobile terminal and a computer readable storage medium. The method includes the following steps: when inter-process data communication is monitored, directly acquiring thread basic information of a preset thread that participates in the inter-process data communication from a kernel layer to reduce intermediate logic calls and quickly acquire the thread basic information; and simultaneously, when determining that current processes do not have creation conditions of the preset thread and the created preset threads in the current processes are in a blocked state based on the thread basic information, determining that the mobile terminal has a frozen screen phenomenon, finally determining a frozen screen processing strategy according to the blocking time of the created preset threads, and processing the created preset threads based on the frozen screen processing strategy. Thereby, the frozen screen phenomenon can bequickly and timely solved, the operation of returning the mobile terminal to a manufacturer for maintenance is not required, the maintenance time can be saved, and the problem of automatically and timely solving the frozen screen phenomenon and saving the maintenance time when the frozen screen phenomenon is monitored can be solved.

Owner:NUBIA TECHNOLOGY CO LTD

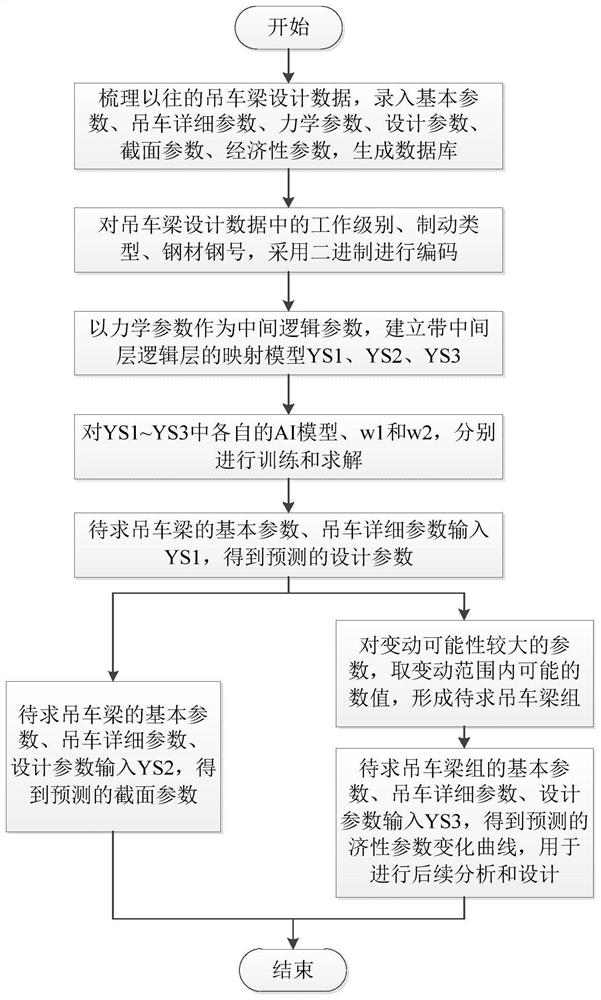

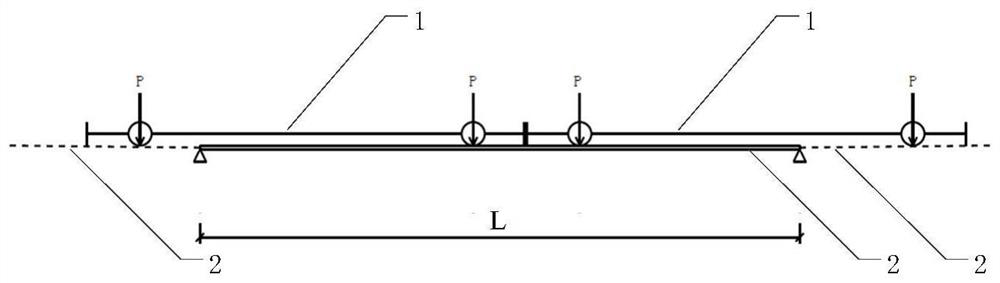

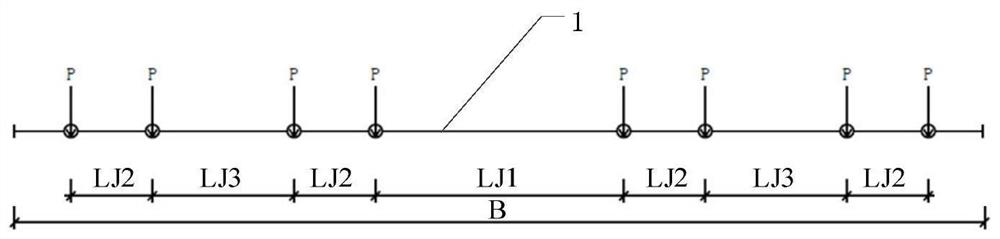

Crane beam rapid estimation method based on mapping model with intermediate logic layer

ActiveCN111651809AScalableStrong correlationGeometric CADDesign optimisation/simulationAlgorithmNetwork model

The invention belongs to the field of civil engineering, and discloses a crane beam rapid estimation method based on the mapping model with the intermediate logic layer. The method comprises the stepsof generating a crane beam design parameter database, carrying out classifying and encoding, establishing the mapping model with the intermediate logic layer, training an AI model, rapidly estimatinga crane beam to be solved and analyzing the influence of parameter change on economy. According to the estimation method provided by the invention, after the intermediate logic layer is added, the theoretical basis of the whole mapping model is stronger than that of a general input-output model, and the solving process can reflect a professional background; the model has expandability and can form a model in which a plurality of intermediate logic layers are connected in parallel; a neural network model with clear logic significance can be formed, the steel number, the braking form, the section size and the weight per unit length suitable for the crane beam can be rapidly evaluated, and the method can be used for analyzing the influence of parameter change on the crane beam design resultso as to optimize the crane beam from the perspective of economy.

Owner:ZHONGCHUAN NO 9 DESIGN & RES INST

Nanoscale latches and impedance-encoded logic for use in nanoscale state machines, nanoscale pipelines, and in other nanoscale electronic circuits

ActiveUS7242215B2Prevent degradationLogic circuits characterised by logic functionNanoinformaticsNanowireInterconnection

Various embodiments of the present invention are directed to implementation and use of logic-state-storing, impedance-encoded nanoscale, impedance-encoded latches that store logic values as impedance states within nanoscale electronic circuits that employ impedance-driven logic. In certain of these embodiments, use of nanoscale, impedance-encoded latches together with nanoscale electronic circuits that employ impedance-driven logic avoids cumulative degradation of voltage margins along a cascaded series of logic circuits and provides for temporary storage of intermediate logic values, allowing for practical interconnection of nanowire-crossbar-implemented logic circuits through nanoscale, impedance-encoded latches to other nanowire-crossbar-implemented logic circuits in order to implement complex, nanoscale-logic-circuit pipelines, nanoscale-logic-circuit-based state machines, and other complex logic devices with various different interconnection topologies and corresponding functionalities.

Owner:HEWLETT-PACKARD ENTERPRISE DEV LP

Total power optimization for a logic integrated circuit

InactiveUS8589853B2Computer aided designSoftware simulation/interpretation/emulationMiddle groupLogic cell

A method of reducing total power dissipation for logic cells includes selecting a distribution of logic cells corresponding to at least one path, computing a dynamic to static power ratio for each logic cell in the distribution of logic cells and ranking the dynamic to static power ratio for each logic cell into a lower group, a middle group and an upper group of logic cells. Additionally, the method includes swapping the lower group of logic cells and the upper group of logic cells for a reconfigured middle group of logic cells and verifying path timing for the reconfigured middle group of logic cells. Methods of reducing total power dissipation using Boolean equations and for logic cell sets are also provided.

Owner:BELL SEMICON LLC

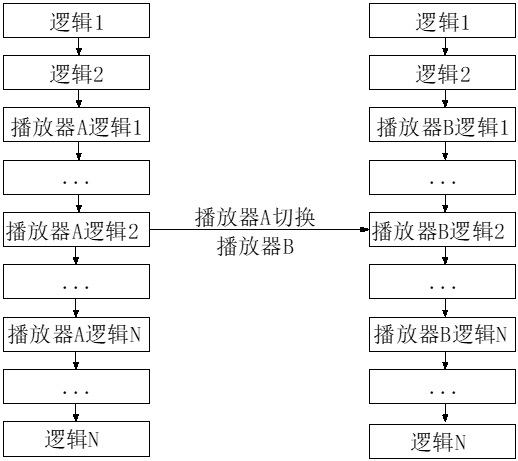

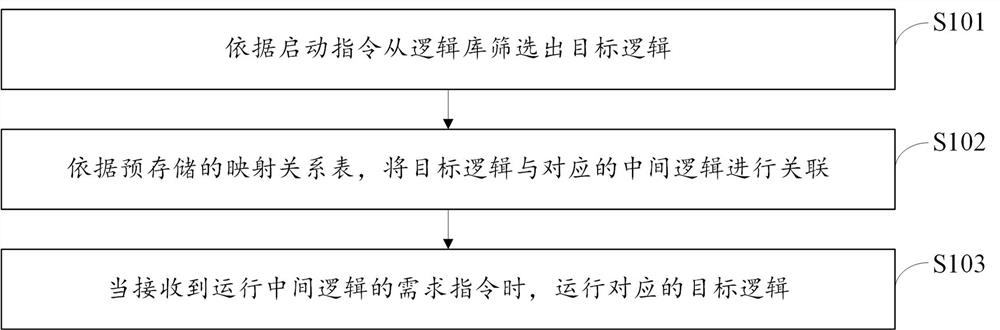

Audio and video player control method and device, storage medium and electronic equipment

ActiveCN112102853AShielding differencesEasy to integrateRecord information storageRecording on magnetic disksComputer hardwareThird party

The invention provides an audio and video player control method and device, a storage medium and electronic equipment, and the method comprises the steps: firstly screening out target logic from a logic library according to a starting instruction, and then associating the target logic with corresponding intermediate logic according to a pre-stored mapping relation table, and when a demand instruction for running the intermediate logic is received, running the corresponding target logic. According to the audio and video player control method provided by the invention, the intermediate logic cancorrespond to the playing logics of different third-party players, different logic architectures do not need to be constructed for each third-party player on a service layer, the logic difference ofthe plurality of third-party players is shielded, and compared with the upper-layer service logic, only unified intermediate logic is provided, so that the debugging time is saved, and a new third-party player can be integrated more conveniently.

Owner:浙江岩华文化科技有限公司

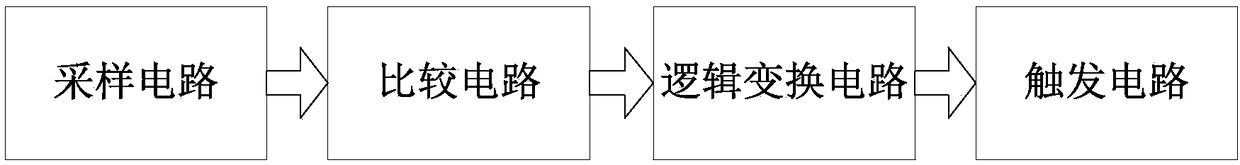

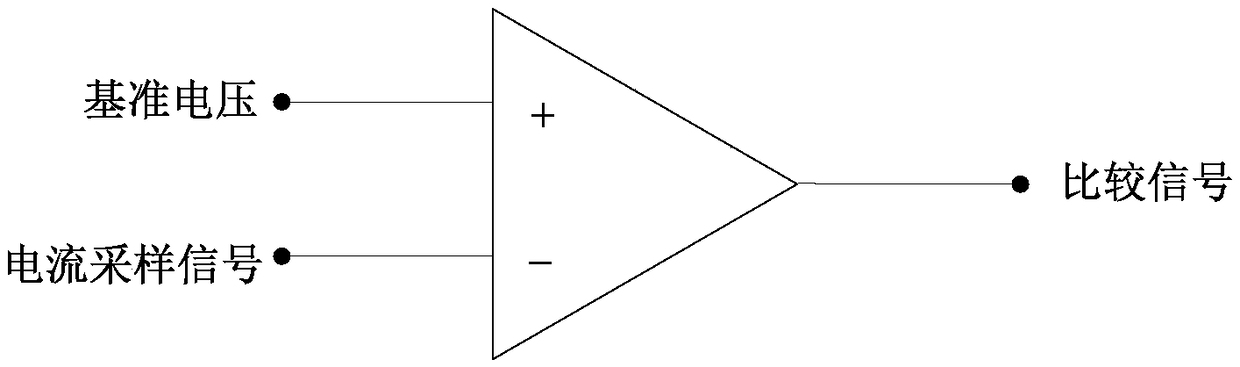

Overcurrent protection circuit and control method therefor, electronic equipment and storage medium

InactiveCN108847652AEasy to controlLow costEmergency protection detectionElectric powerOvercurrentEngineering

The invention provides an overcurrent protection circuit, which comprises a sampling circuit, a comparison circuit, a logic conversion circuit and a trigger circuit, wherein the sampling circuit is connected with a drive circuit in series and connected with the comparison circuit; the comparison circuit is connected with the logic conversion circuit; the logic conversion circuit is connected withthe trigger circuit; the sampling circuit is used for sampling the drive circuit to obtain a current sampling signal and outputting the current sampling signal to the comparison circuit; the comparison circuit is used for receiving the current sampling signal, comparing the current sampling signal to generate a comparison signal and outputting the comparison signal to the logic conversion circuit;the logic conversion circuit is used for carrying out logic conversion on the comparison signal to generate an intermediate logic signal and outputting the intermediate logic signal to the trigger circuit; and the trigger circuit generates an overcurrent protection signal through the intermediate logic signal. The invention further relates to a control method for the overcurrent protection circuit, electronic equipment and a storage medium. Overcurrent protection can be effectively, quickly and stably carried out, the control is simple and the cost is low.

Owner:苏州舜唐新能源电控设备有限公司